|              |                                                                               |

|--------------|-------------------------------------------------------------------------------|

| Title        | SiCショットキーバリアダイオードを用いた高電圧直流電源の設計と高周波応用に関する研究                                   |

| Author(s)    | 野村, 優貴                                                                        |

| Citation     | 大阪大学, 2025, 博士論文                                                              |

| Version Type | VoR                                                                           |

| URL          | <a href="https://doi.org/10.18910/101665">https://doi.org/10.18910/101665</a> |

| rights       |                                                                               |

| Note         |                                                                               |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

博士学位論文

SiC ショットキーバリアダイオードを用いた

高電圧直流電源の設計と高周波応用に関する研究

野 村 優 貴

2025 年 1 月

大阪大学大学院工学研究科

## 論文要旨

本論文は、SiC ショットキーバリアダイオード（SBD）を用いた高電圧直流電源の設計と高周波応用に関する研究を取りまとめたものである。以下に、各章の要点を要約する。

第1章では、高電圧直流電源の産業応用と従来技術の課題について述べている。特に半導体プロセスやプラズマ発生装置において高電圧・高周波電源が求められる背景を説明し、従来の Si パワーデバイスの限界を指摘している。これを克服するために、ワイドバンドギャップ材料である SiC を用いたデバイスが高耐圧、低損失、高速スイッチングを可能にし、小型化と高効率化に寄与することを提案している。

第2章では、SiC SBD モジュールの設計と評価に焦点を当て、直列接続による高耐圧モジュールの開発について述べている。SiC SBD は高耐圧低オン抵抗のユニポーラデバイスが作製できるため、従来の Si デバイスと比較して優れた性能を示す。さらに直列構成による耐圧向上と低損失化の実現メカニズムを明確にし、モジュールの静特性や電圧分担の評価結果を示す。

第3章では、高周波高電圧電源の昇圧回路である Cockcroft-Walton 回路への適用について検討している。高耐圧 SiC SBD モジュールを直列に配置することで、段数と損失評価の最適化を行い、高効率設計を実現する方針を示した。シミュレーションによる解析を通じて、モジュールの性能と電力損失との関係について具体的に論じる。

第4章では、SiC SBD を用いた高周波高電圧電源の動作特性を分析し、寄生成分やスイッチング特性に関する評価を行った。ベクトルネットワークアナライザ（VNA）を用いた回路解析を通じて、回路の寄生インダクタンスを評価した。また SiC SBD モジュールの高周波動作の可能性を実験的に示し、実用化に向けた性能向上を確認した。

第5章では、研究成果の総括と将来展望について述べている。SiC SBD モジュールは、高電圧直流電源の小型化・高効率化・高耐圧化を実現する有効な手段であり、産業応用への影響が期待されると結論付けている。またさらなる研究課題として、大電力化や長期安定動作に関する評価の継続が挙げられている。

本研究は SiC SBD を用いた高電圧電源技術の新たな展開を示すものであり、次世代の電源設計に向けた基盤技術として重要な知見を提供する。

## 目次

|          |                                                       |           |

|----------|-------------------------------------------------------|-----------|

| <b>1</b> | <b>緒論</b>                                             | <b>1</b>  |

| <b>2</b> | <b>高耐圧 SiC ショットキーバリアダイオード（SBD）モジュールの設計と評価</b>         | <b>4</b>  |

| 2.1      | SiC SBD . . . . .                                     | 4         |

| 2.1.1    | 高耐圧および低オン抵抗を実現する SiC SBD の特性 . . . . .                | 4         |

| 2.1.2    | 金属半導体接合のバンド図 . . . . .                                | 8         |

| 2.1.3    | SBD の接合容量 . . . . .                                   | 15        |

| 2.2      | SiC SBD モジュールの開発と評価 . . . . .                         | 18        |

| 2.2.1    | 素子の直列接合による SiC SBD モジュール . . . . .                    | 18        |

| 2.2.2    | SiC SBD モジュールの静特性 . . . . .                           | 19        |

| 2.3      | SiC SBD モジュールの分担電圧の評価 . . . . .                       | 26        |

| 2.3.1    | 定常遮断状態における直列接続された SiC SBD の電圧分担 . . . . .             | 30        |

| 2.3.2    | スイッチング過渡状態における直列接続された SiC SBD の電圧分担 . . . . .         | 32        |

| 2.3.3    | 分担電圧に対するスイッチング速度の影響 . . . . .                         | 35        |

| <b>3</b> | <b>高周波高電圧電源の昇圧方式に関する検討</b>                            | <b>37</b> |

| 3.1      | Cockcroft-Walton 回路の段数と SBD の直列数の関係 . . . . .         | 37        |

| 3.2      | シミュレーションの妥当性の確認 . . . . .                             | 41        |

| 3.3      | モジュール直列数と電力損失の関係 . . . . .                            | 44        |

| <b>4</b> | <b>高耐圧 SiC SBD モジュールを用いた高電圧直流電源の高周波動作</b>             | <b>51</b> |

| 4.1      | ベクトルネットワークアナライザ（VNA）を用いた回路寄生成分の同定 . . . . .           | 51        |

| 4.2      | Cockcroft-Walton 回路への SiC SBD モジュールの適用 . . . . .      | 56        |

| 4.2.1    | SiC SBD モジュールを用いた Cockcroft-Walton 回路の高周波動作 . . . . . | 57        |

| 4.2.2    | 高周波 Cockcroft-Walton 回路の大電力化 . . . . .                | 61        |

| <b>5</b> | <b>結言</b>                                             | <b>63</b> |

| 5.1      | 結論 . . . . .                                          | 63        |

| 5.2      | 産業への影響 . . . . .                                      | 63        |

| 5.3      | 将来の展望 . . . . .                                       | 64        |

|          | <b>謝辞</b>                                             | <b>65</b> |

|          | <b>参考文献</b>                                           | <b>66</b> |

## 1 緒論

高電圧直流電源はプラズマ生成、産機用非破壊検査装置や高電圧直流送配電システムなど、多岐にわたる産業応用分野で用いられている [1, 2, 3, 4]。特にプラズマ生成分野では半導体チップの製造プロセスにおけるドライエッチングや薄膜形成で高精度なパターン形成を行うために、10kV級の高電圧直流電源がプラズマ発生源として不可欠な役割を果たす [5]。電極間に強力な電界を発生させることによりイオン化率が増加し、プラズマ密度の向上及び反応性が高くなるため、パターン形成加工といった用途にはバックパワーとなる高電圧直流電源が必要になる [6]。高電圧電源を利用することで、高密度で高温のプラズマを効率的に生成できる。最近の高電圧・高周波パルス電源では、プラズマ生成の効率と安定性が向上し、成膜やエッチングプロセスの精度が大幅に改善されることも報告されている [6]。

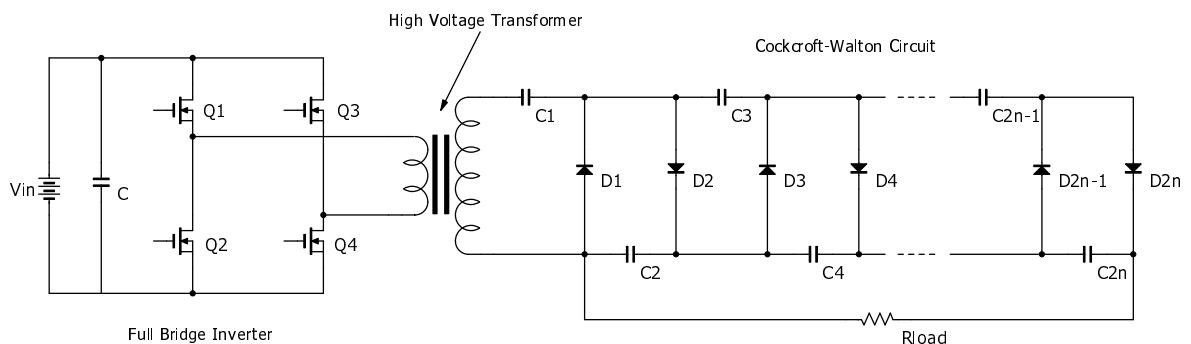

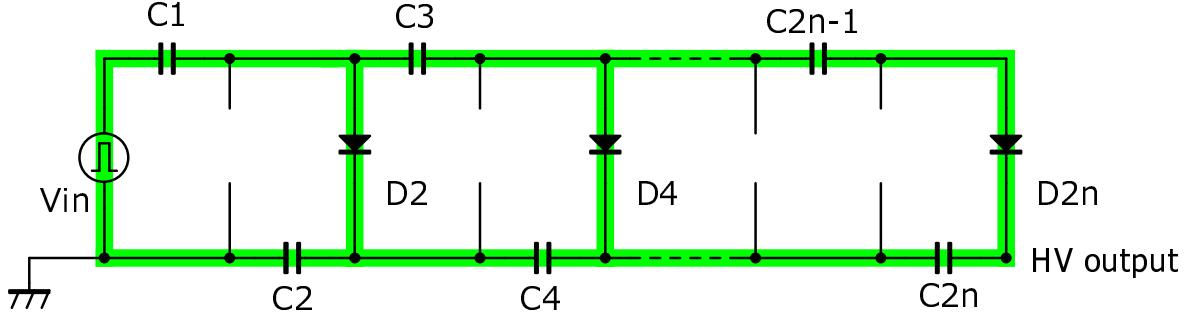

高電圧直流電源の回路構成は図 1.1 に示すようにインバータが出力する交流を高電圧トランスと Cockcroft-Walton 回路 [7] で昇圧する多段昇圧方式が採用される [8, 9, 10]。インバータの周波数を高周波化することで、Cockcroft-Walton 回路のコンデンサや高電圧トランスのコアの小型軽量化が可能であるため、本方式を採用することが通例である [11]。従来の高電圧電源は電源を構成する素子としてシリコン (Si) パワーデバイスを採用してきたが、現行の Si パワーデバイスでは電力損失や冷却装置の大型化などにより今以上の高周波動作を期待することが難しい。

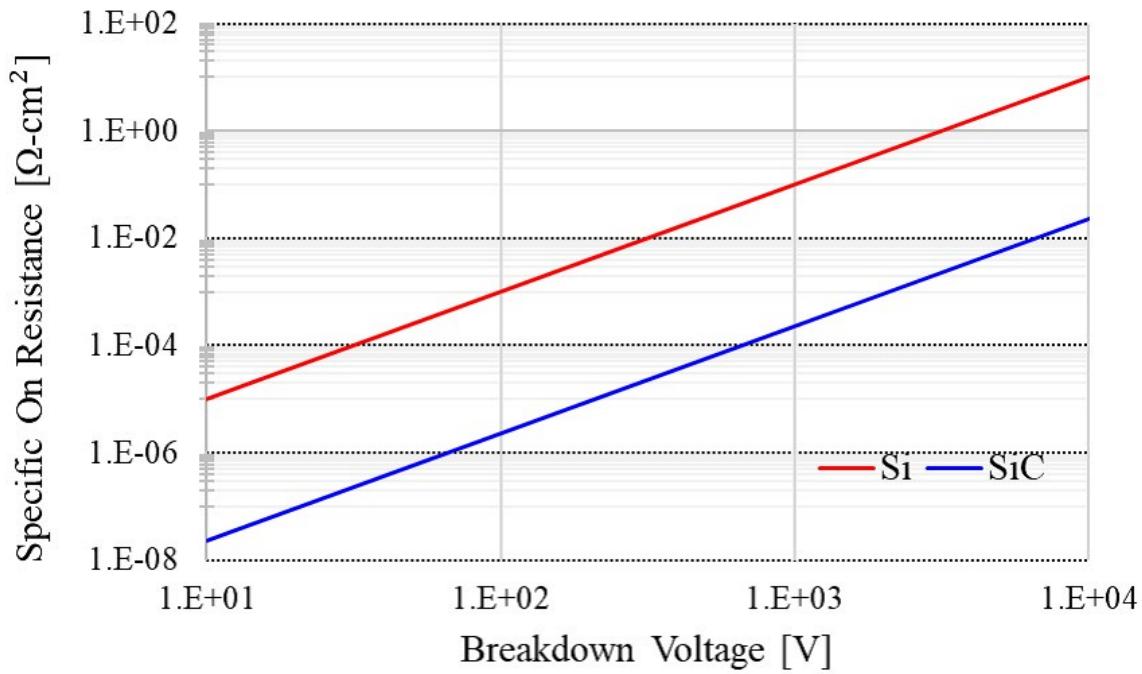

通常、高耐圧のユニポーラデバイスを Si 半導体で作製すると、耐圧を保持するために不純物濃度を低くせざるを得ないため、オン抵抗が大きくなる [12]。このため電源回路の損失低減が難しくなる。従って高耐圧の Si パワーデバイスを用いて電源回路を構成する場合、伝導度変調によりオン抵抗が低くなるバイポーラデバイスが用いられる。ただし、バイポーラデバイスは蓄積少数キャリアの掃き出しによる逆回復時間が存在するためスイッチング速度が遅く、高周波動作に適さない。従って、Si パワーデバイスを高周波高電圧電源の素子として用いることは難しい。そこで、Si よりも優れた物性値を有するワイドバンドギャップ半導体である炭化ケイ素 (SiC) を適用したパワーデバイスに注目し、高電圧直流電源の構成要素として適用することを考えた。表 1.1 は、Si 及び SiC 半導体の代表的な物性値である。SiC

図 1.1 多段式直流高電圧電源の回路構成

は Si よりもバンドギャップが大きく、絶縁破壊電界強度が Si の約十倍であることから、高耐圧で低オシントリクタのユニポーラデバイスを作製することができる [13]。ユニポーラデバイスは原理的に多数キャリアのみで動作するため、バイポーラトランジスタや PiN ダイオード (PiND) で発生する逆回復現象の影響はなく、高速スイッチングが可能である。現行の高電圧電源におけるインバータの駆動周波数はこれまでせいぜい数十 kHz 程度であった [14] が、SiC パワーデバイスを用いることによって数百 kHz で動作させることができるとなり、装置の小型化及び電力変換効率の向上につながることが示されてきた。また SiC は高温耐性があり、200°C 以上の過酷な条件下でも動作することが知られている [15]。このため、高周波スイッチング動作を連続的に行っても熱暴走による素子破壊を回避しやすい。熱伝導率も Si に比べて 3 倍以上大きいため、冷却機構を簡素化することができ、装置の小型化につながる。

高周波 Cockcroft-Walton 回路に用いる高耐圧整流ダイオードについても、従来の Si PiND から逆回復現象が発生しない SiC ショットキーバリアダイオード (SBD) へ変更することで、発生するスイッチング損失を大幅に低減することができる [14, 16, 17]。ただし、ユニポーラデバイスにおいてドリフト相の抵抗は耐圧の 2 乗に比例して大きくなるため、要求される素子耐圧が高い場合には SiC SBD を用いた場合でも導通損失が増加する。素子の自己発熱が問題となる場合には、ヒートシンクなどの冷却器を取り付けて対処するが、高電圧電源では絶縁確保の観点から外部冷却器の使用が容易でなく、素子単体で超高耐圧を実現することは現実的でない。

そこで本研究では、チップを直接直列に積層した構造の SiC-SBD モジュールを開発し、高周波 Cockcroft-Walton 回路の高耐圧ダイオードへの適用を検討した。高電圧分野ではコンデンサやダイオードなどのディスクリート素子を直列に接続することで耐圧を向上させる手法が一般的に用いられている [18, 19] が、高速スイッチング動作させる場合に寄生インダクタンスによる過電圧が発生する課題があった。この手法に着想を得て、チップ自体を直接直列に積層するモジュール構造を採用することで、高速スイッチング動作時に各素子に印加される電圧を低減しながらモジュール全体としての耐電圧を向上させた。また開発モジュールの構造では高耐圧を確保しつつ、従来の外部絶縁を必要とする冷却方式に依存しないシンプルな設計を実現する。

表 1.1 Si と SiC の物性値

|                                     | Si   | 4H-SiC |

|-------------------------------------|------|--------|

| バンドギャップ (eV)                        | 1.1  | 3.3    |

| 熱伝導率 (W/cm · K)                     | 1.5  | 4.9    |

| 絶縁破壊電界 (MV/cm)                      | 0.30 | 2.8    |

| 電子移動度 (cm <sup>2</sup> /Vs)         | 1400 | 900    |

| ホール移動度 (cm <sup>2</sup> /Vs)        | 600  | 100    |

| 飽和ドリフト速度 Vs(cm/s) × 10 <sup>7</sup> | 1.0  | 2.7    |

| 比誘電率 $\epsilon$                     | 12   | 10     |

本論文は次の構成からなる。まず第2章では高周波高電圧電源に用いるSiC SBDの動作原理と直列接続による高耐圧・低損失化のメカニズムを論じる。また開発した超高耐圧SiC SBDモジュールの設計と特性評価を通じて、電圧分担の均衡性や耐圧設計の指針を示した。第3章では、高周波 Cockcroft-Walton回路用途に開発した超高耐圧SiC SBDモジュールの直列数の設計方針に関して論じた。直列数とCockcroft-Walton回路の段数の両方を考慮して損失評価を行うことで、電源仕様に基づいた回路構成の提案をするとともに、高効率設計に向けた検討も行った。第4章では高耐圧SiC SBDモジュールを用いた高周波高電圧直流電源の動作特性を解析し、回路の寄生成分やスイッチングにより生じる電圧サージの影響を評価した。さらに、SiC SBDモジュールの優れたスイッチング特性を実験的に示し、高効率で安定した高周波高電圧電源設計への適用可能性を明らかにした。最後に第5章の結論をもってまとめる。

## 2 高耐圧 SiC ショットキーバリアダイオード (SBD) モジュールの設計と評価

本章では高周波高電圧電源に用いる SiC ショットキーバリアダイオード (SBD) に関する研究を以下の 3 つの観点から論じる。まず、SiC SBD の動作原理および基本的な物理モデルについて詳述する。SiC の物性が Si に比べて優れている点に着目し、高耐圧かつ低オン抵抗を実現する仕組みを、金属-半導体接合モデルにおけるキャリア輸送の観点から説明する。またこれらの特性を活用し、素子を直接直列接続することで 10kV 以上の耐圧を確保しながら低損失デバイスを実現するメカニズムを示す。このメカニズムが高電圧電力変換回路における高周波化と低損失化にどのように寄与するかを明らかにする。

次に、開発した超高耐圧 SiC SBD モジュールの設計と開発について述べる。本研究では耐圧向上と低損失化を両立するため、素子を直接接続する構造を採用し、分圧抵抗やコンデンサを使用しないシンプルな設計を実現した。この構造により、高周波動作時の損失低減が可能となるが、一方で素子を直列接続する際に生じる電圧分担の不均衡が懸念される。素子特性にばらつきがある場合、特定の素子に局所的に過電圧が印加され、最悪の場合、素子破壊に至る可能性がある。本モジュールでは低損失化を重視して分圧素子を使用していないため、素子間の特性ばらつきが電圧分担に直接影響する。

本章後半では、各素子の分担電圧を実験およびシミュレーションの両面から評価し、モジュールの高周波動作の可否を検討した。この評価により、本モジュールの定常状態および過渡状態における電圧印加条件下での挙動を詳細に明らかにし、その結果に基づいて耐圧設計の指針を提示する。

### 2.1 SiC SBD

本節では、金属-半導体接合モデルにおけるキャリア輸送を考え、高耐圧・低損失の SiC SBD が実現できる原理について詳述する。SiC SBD の耐圧とオン抵抗の関係から、素子の直列接続によって 10kV 以上の超高耐を確保しながら低損失・高周波動作を実現するメカニズムを示す。

#### 2.1.1 高耐圧および低オン抵抗を実現する SiC SBD の特性

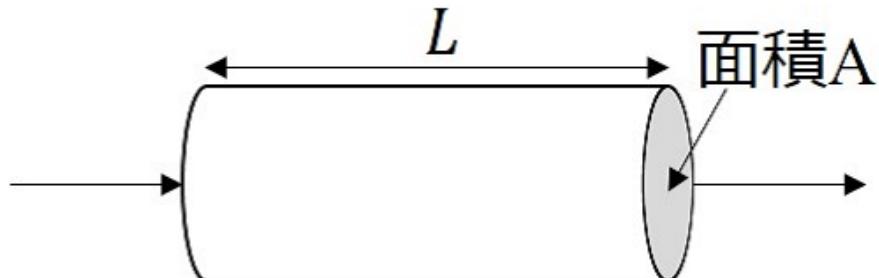

図 2.1 の棒状の n 型半導体モデルについて、外部から印加された電界によるキャリアの移動を考える。断面積  $A$ 、長さ  $L$ 、電子密度  $n$  の半導体に電界  $E$  を与えた場合の電流密度  $J_n$  は、電子の電荷  $-q$  と速度  $v_i$  の積を単位体積中の全電子について加え合わせることによって求めることができる [20]。

$$J_n = \frac{I_n}{A} = \sum_{i=1}^n (-qv_i) = -qn\mu_n E \quad (2.1)$$

ただし、 $\mu_n$  は電子移動度である。ホールに関して同様に考えれば、全電流は式 (2.2) で表現することができる。

$$J = J_n + J_p = (qn\mu_n + qp\mu_p)E \quad (2.2)$$

ただし、 $\mu_p$ はホールの移動度、 $p$ はホール密度である。また、電子密度 $n$ とホール密度 $p$ は真性キャリア密度 $n_i$ を用いて式(2.3)の関係がある。

$$n_i^2 = np \quad (2.3)$$

従って、棒状半導体モデルの導電率 $\sigma$ 及び抵抗率 $\rho$ はそれぞれ式(2.4)、(2.5)で与えられる。

$$\sigma = q(n\mu_n + p\mu_p) \quad (2.4)$$

$$\rho = \frac{1}{\sigma} = \frac{1}{q(n\mu_n + p\mu_p)} \quad (2.5)$$

一般にn型半導体の電子密度 $n$ は、室温下では不純物密度 $N_d$ に等しく、真性キャリア密度 $n_i$ より十分大きく設計される。従って、式(2.3)よりn型半導体中におけるホールキャリア密度は十分小さくなり、多数キャリアのみのキャリア輸送として扱うことが可能である。このため、逆回復現象が原理的に発生しない。

$$p = \frac{n_i^2}{n} \approx \frac{n_i^2}{N_d} \ll n \quad (2.6)$$

2種のキャリア密度の差異より、n型半導体においては式(2.5)を式(2.7)で近似することができる。

$$\rho = \frac{1}{qn\mu_n} = \frac{1}{qN_d\mu_n} \quad (2.7)$$

すなわち、半導体のオン抵抗はドリフト層の不純物濃度 $N_d$ 及び電子移動度 $\mu_n$ に反比例する。

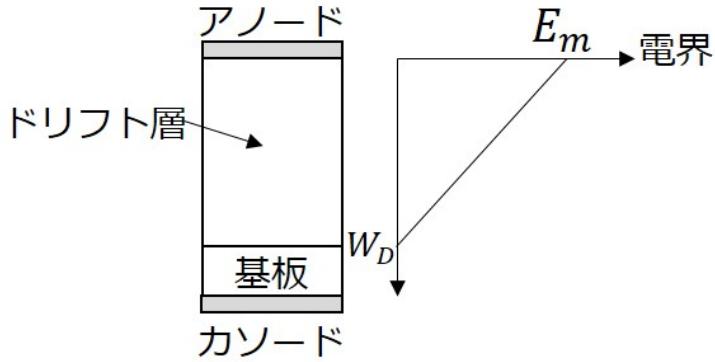

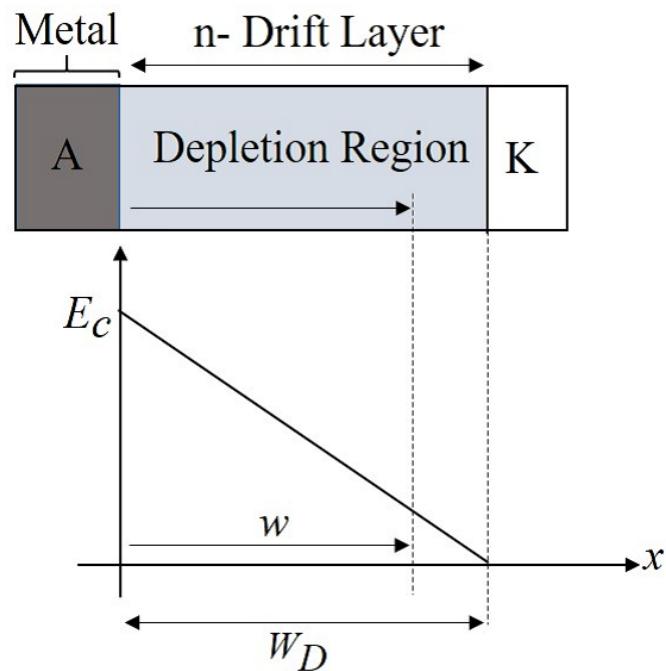

図2.1の不純物密度 $N_d$ が一様な棒状半導体モデルに対して金属を接合した片側階段接合を仮定すると、式(2.8)の1次元Poisson方程式より、図2.2に示すようにドリフト層に沿って単調に減少する電界分布となる[20]。ただし、 $\varepsilon$ は誘電率である。

$$\frac{dE}{dx} = \frac{qN_d}{\varepsilon} \quad (2.8)$$

式(2.8)を1回積分すると、式(2.9)が得られ、2回積分すると、式(2.10)が得られる。ただし、 $W_D$ は耐圧 $BV$ を得るために必要なドリフト層の厚さである。式(2.9)より、片側階段状接合において電界

図2.1 棒状半導体における電気伝導

図2.2 ドリフト層と電界分布

は接合面で最大となり接合面から離れるにつれて単調減少する。また式(2.10)より、絶縁破壊電圧  $BV$  は図2.2の電界分布の三角形の面積に相当することになる。

$$E = \frac{qN_d}{\varepsilon}(x - W_D) \quad (2.9)$$

$$V = \frac{1}{2} \cdot \frac{qN_d}{\varepsilon}(x^2 - 2W_Dx) \quad (2.10)$$

$$BV = \frac{1}{2} \cdot E_m W_D \quad (2.11)$$

式(2.11)より、ドリフト層の厚さは次式で与えられる。

$$W_D = \frac{2BV}{E_m} \quad (2.12)$$

また式(2.10)より、 $x = W_D$  の時の電圧  $V$  が絶縁破壊電圧  $BV$  に相当する。

$$BV = \frac{2qN_d}{\varepsilon} \frac{BV^2}{E_c^2} \quad (2.13)$$

従って、不純物濃度  $N_d$  は式(2.14)で示される。

$$N_d = \frac{\varepsilon E_c^2}{2qBV} \quad (2.14)$$

半導体中における抵抗率は式(2.7)で表されることから、ドリフト層の抵抗  $R_{sp}$  は式(2.15)となる。

$$R_{sp} = \frac{W_D}{qN_d \mu_n} \quad (2.15)$$

式(2.12), (2.14), (2.15)から式(2.16)が得られる。

$$R_{sp} = \frac{4BV^2}{\varepsilon \mu_n E_m^3} \quad (2.16)$$

式(2.16)より、ショットキー接合におけるドリフト層の抵抗  $R_{sp}$  は素子の絶縁破壊電圧  $BV$  の2乗に比例する。すなわち高耐圧のSBDを作製する場合はオン抵抗  $R_{sp}$  は耐圧  $BV$  に対して2乗に比例し、

図 2.3 オン抵抗と素子の耐電圧の関係

絶縁破壊電界  $E_m$  の 3 乗に反比例する。

表 1.1 に示したように SiC の絶縁破壊電界  $E_m$  は Si と比較して約 10 倍のため、オン抵抗が大幅に低減する。図 2.3 は Si と SiC のドリフト層のオン抵抗と耐電圧の関係である。濃度、デバイスサイズが同じ条件下では、高耐圧パワーデバイスの抵抗成分はドリフト層の抵抗が支配的であるため、SiC では単位面積当たりのオン抵抗が非常に低く抑えられ、高耐圧 SBD が実現できる。式 (2.16) より、同耐圧であれば Si と比較してドリフト層の抵抗を 1/1000 に低減できる。汎用の SiC SBD の電圧定格は 600V～1.2kV の高耐圧 SiC SBD であり、同耐圧の Si SBD よりも大幅にオン抵抗を低減できている。

図2.4 接合前の金属と半導体のバンド図

### 2.1.2 金属半導体接合のバンド図

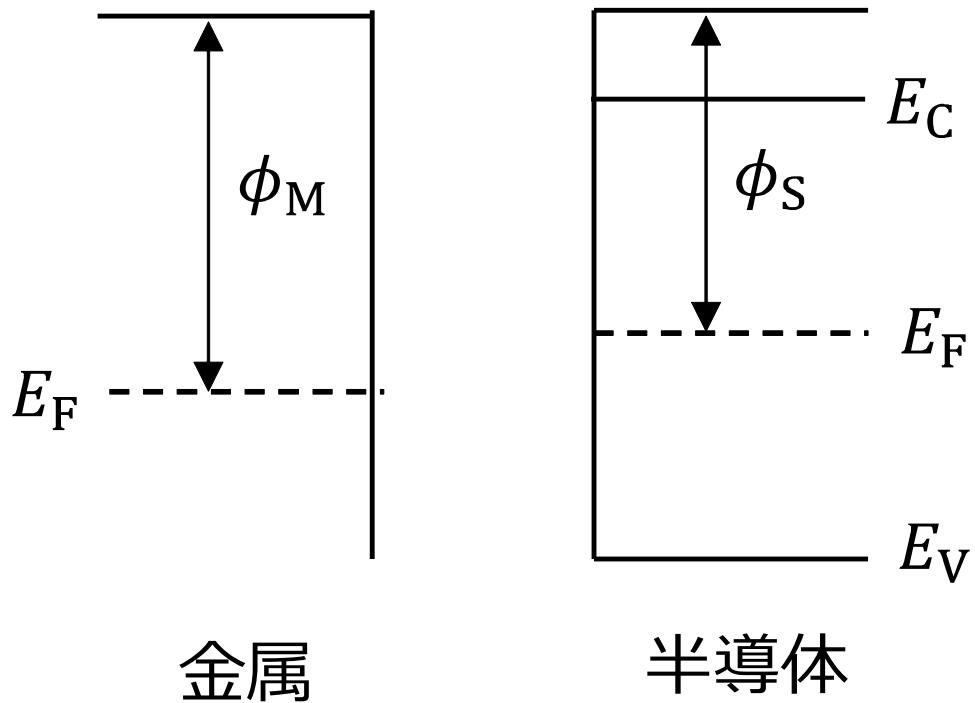

金属と半導体を接触させた場合のバンド構造について考える。ただし、n型半導体を仮定する。図2.4は接合前の金属と半導体のエネルギー-band図である。ただし、 $E_C$ : 伝導帯、 $E_F$ : フェルミ準位、 $E_V$ : 値電子帯である。金属の仕事関数  $q\phi_M$  は一般に半導体の仕事関数  $q\phi_S$  とは異なり、その大きさの違いでオーム接合( $\phi_M < \phi_S$ )かショットキー接合( $\phi_S < \phi_M$ )かが決まる。

オーム接合のエネルギー-band図を図2.5に示す。金属側のフェルミ準位が半導体側のフェルミ準位よりも高いため、金属側の電子が半導体側へ拡散することで電位勾配が形成される。半導体側の伝導帯が金属側に対して高いため、印加電圧に応じて電子が流れることになり、オーム性を示す。

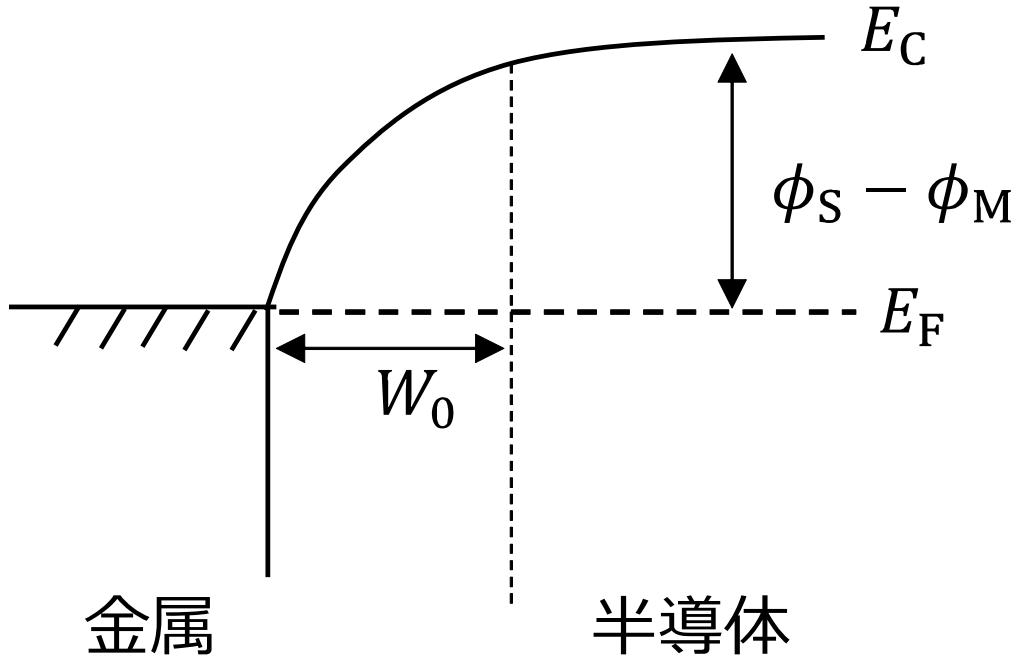

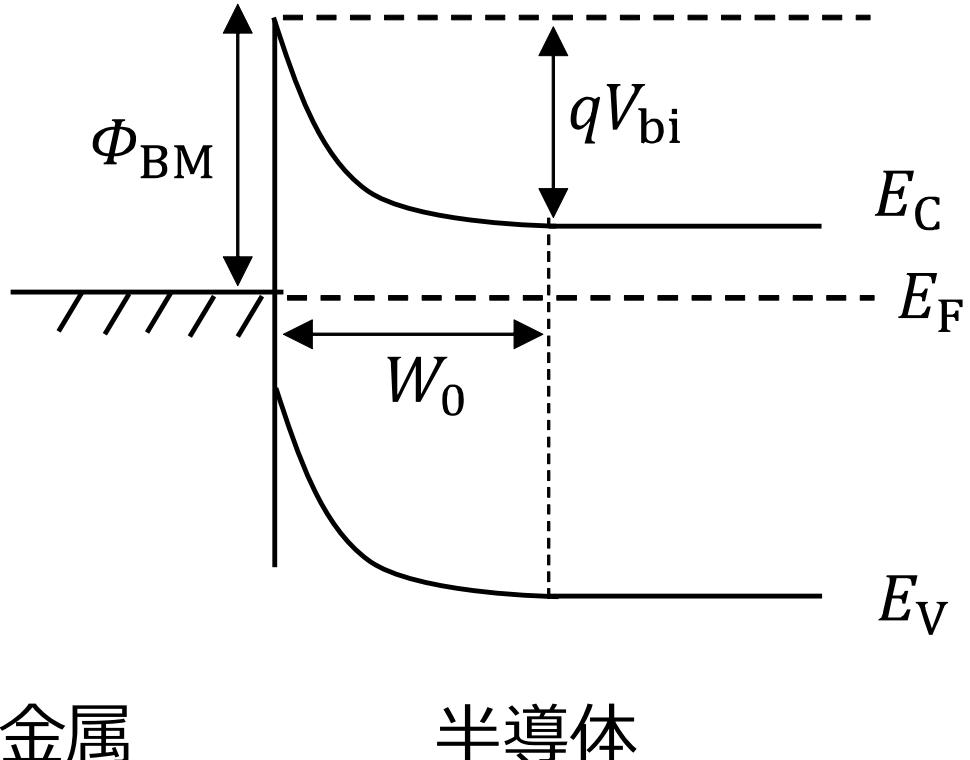

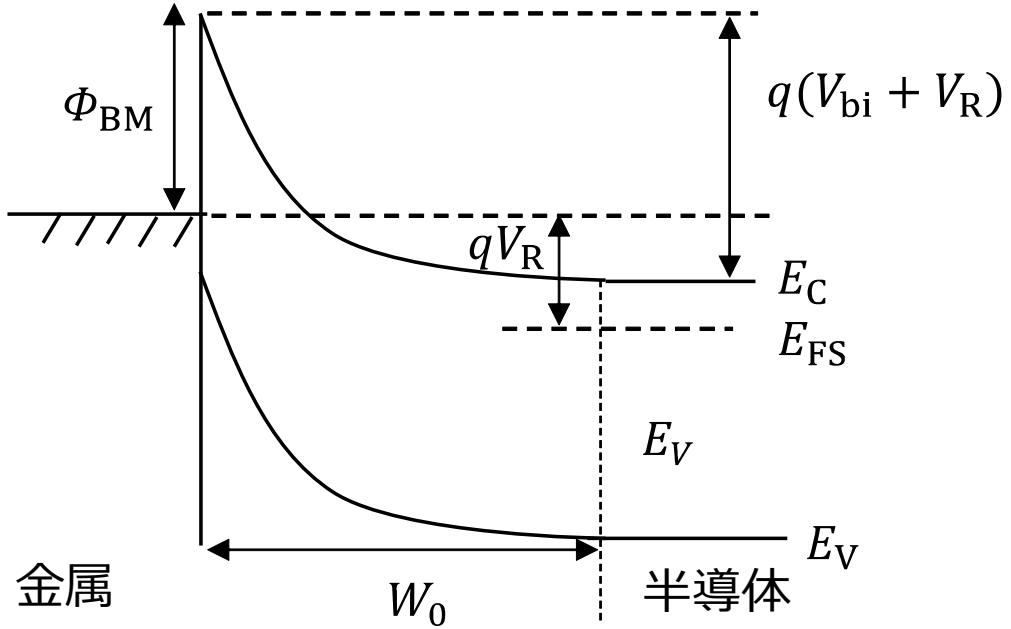

次にショットキー接合のエネルギー-band図を図2.6に示す。半導体側のフェルミ準位が金属側のフェルミ準位より高いため、半導体と金属を接触させると熱平衡状態を満たすように半導体の電子が金属へと流れ込む。このため半導体表面に正の空間電荷が現れてキャリアの存在しない空乏層が生じる。図2.6に示すように空乏層によって半導体側から見るとポテンシャル障壁ができるため、整流性を示す。このポテンシャル障壁をビルトイン電圧  $V_{bi}$  と呼び、この時の接合部における障壁高さは、ビルトイン電圧  $V_{bi}$  を用いて式(2.17)で定義される。またゼロバイアス時の半導体中の空乏層幅  $W_0$  はビルトイン電圧

図 2.5 オーム接觸によるバンド構造の変化

$V_{bi}$  によって生じるため、式 (2.10) より式 (2.18) の関係を得る。

$$\Phi_{BN} = qV_{bi} + (E_C - E_F) \quad (2.17)$$

$$W_0 = \sqrt{\frac{2\epsilon_s V_{bi}}{qN_d}} \quad (2.18)$$

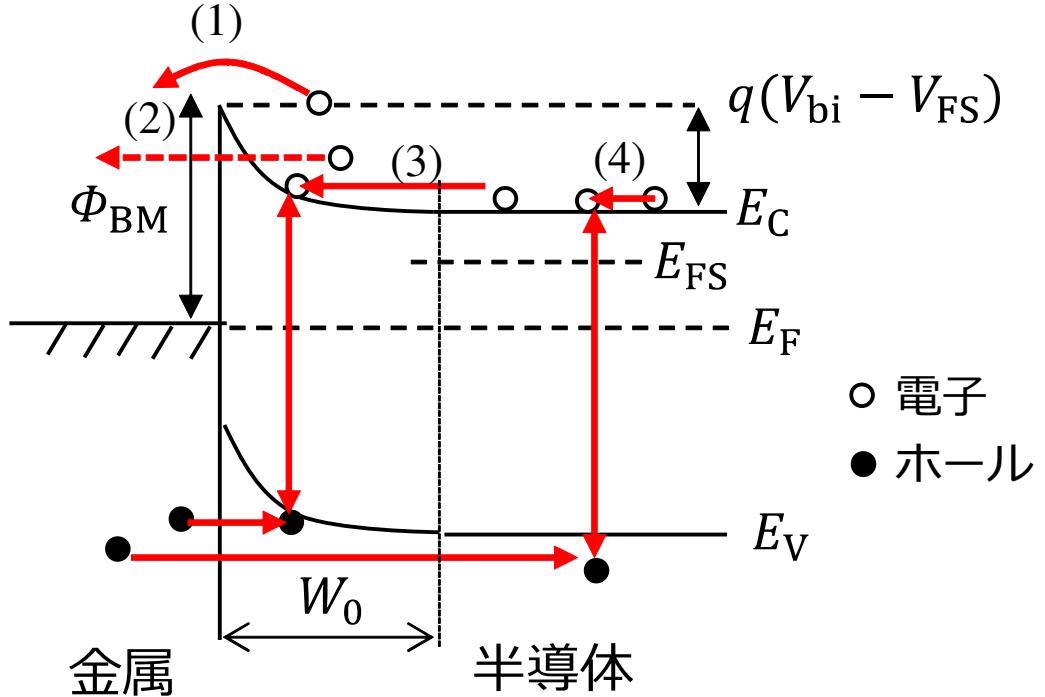

図 2.7 は順方向バイアスにおける金属-半導体接合のバンド構造である。順方向バイアス時はキャリアの輸送には以下の 4 つの過程が存在する [12]。

過程 (1) ポテンシャル障壁を乗り越えて半導体側から金属へと流れ込む電子の輸送 (熱電子電流)

過程 (2) 量子トンネル効果によりポテンシャル障壁を通り抜けて流れ込む電子の輸送

過程 (3) 空乏層内での電子とホールの再結合

過程 (4) 再結合による金属から半導体側へと流れ込むホールの輸送

SBD では逆電圧に耐えるため、ドリフト層は比較的低いドーピング濃度に設定されている。また過程 (2) のトンネル効果を防ぐために十分な長さの空乏層を確保して、鋭く細いポテンシャル障壁を避けるように設計されている。

空間電荷領域における再結合による電流は非常に小さく、少数キャリアのホールが半導体へ流れ込むことによって生じる電流も十分な障壁高さの下では無視することができるため、順方向バイアス時でのキャ

図 2.6 ショットキー接觸によるバンド構造の変化

リア輸送は過程 (1) によるものが支配的である。ポテンシャル障壁を乗り越えて流れる電流は式 (2.19) で表される [15]。ただし  $T$ : 絶対温度,  $k$ : Boltzmann 定数,  $V$ : 印加電圧である。また,  $A$ : Richardson 定数であり, n型 Si 半導体及び SiC 半導体はそれぞれ,  $A = 110, 146$  ( $\text{Acm}^{-2}\text{K}^{-2}$ ) である。

$$J = AT^2 e^{-(q\phi_{BM}/kT)} (e^{qV/kT} - 1) \quad (2.19)$$

順バイアス時は、式 (2.19) 中の第 1 項が支配的とみなせるから、式 (2.20) のように近似することができる。

$$J = AT^2 e^{-(q\phi_{BM}/kT)} e^{qV_{FS}/kT} \quad (2.20)$$

ただし、 $V_{FS}$  はショットキー接合面における順方向電圧降下である。

SBD における全順方向電圧降下  $V_F$  は、式 (2.20) の  $J$  を用いることで式 (2.21) のように表すことができる。

$$V_F = V_{FS} + V_R = \frac{kT}{q} \ln \left( \frac{J}{J_s} \right) + R_{sp} J \quad (2.21)$$

ただし  $R_{sp}$  はドリフト層、基板、オーム接触などの抵抗値の合算値である。また  $J_s$  は飽和電流密度であり、式 (2.22) で与えられる。

$$J_s = AT^2 e^{-(q\phi_{BM}/kT)} \quad (2.22)$$

図 2.7 順方向バイアス時のバンド構造

Si SBD では 100V 程度の耐圧が限界であったが、SiC では数 kV 耐圧のデバイスを作製することができるため、大電力下での高速スイッチングが可能となり、電力変換回路の小型化及び高効率化に寄与する。

逆方向バイアス時におけるバンド構造を図 2.8 に示す。図 2.8 のように逆電圧が印加されると障壁の高さが大きくなり、空乏層が半導体方向に広がる。これにより、電子はポテンシャルの壁を乗り越えることが難しくなり、電流は流れない。またこの時のドリフト層における電界は式 (2.9) より、接合面で最大となる。

SBD における漏れ電流は、式 (2.19) で示される熱電子放出によるものが支配的であり、式 (2.19) 中に  $V = -V_R$  を代入することで求められる。

$$J = AT^2 e^{-(q\phi_{BM}/kT)} (e^{-qV_R/kT} - 1) \quad (2.23)$$

一般的に、逆電圧  $V_R$  は熱エネルギー  $kT/q$  よりも十分に大きいため、 $e^{-qV_R/kT} \ll 1$  の関係があり、式 (2.23) は式 (2.24) と近似することができる。

$$J = -AT^2 e^{-(q\phi_{BM}/kT)} = -J_S \quad (2.24)$$

式 (2.24) より、熱電子放出による漏れ電流は、ショットキー障壁高さと温度に強く依存する。漏れ電流は、OFF 状態における損失につながる。漏れ電流による損失が支配的な場合、温度の上昇によって、

図2.8 逆バイアス時のバンド構造

さらに漏れ電流が増加し、熱暴走に至る可能性がある。これを避けるために十分に高いポテンシャル障壁 $\Phi_{BM}$ でデバイスは設計される。高いポテンシャル障壁 $\Phi_{BM}$ はオン電圧降下を増大させる一方で、デバイスの信頼性を保証するため、適切な値が求められる。

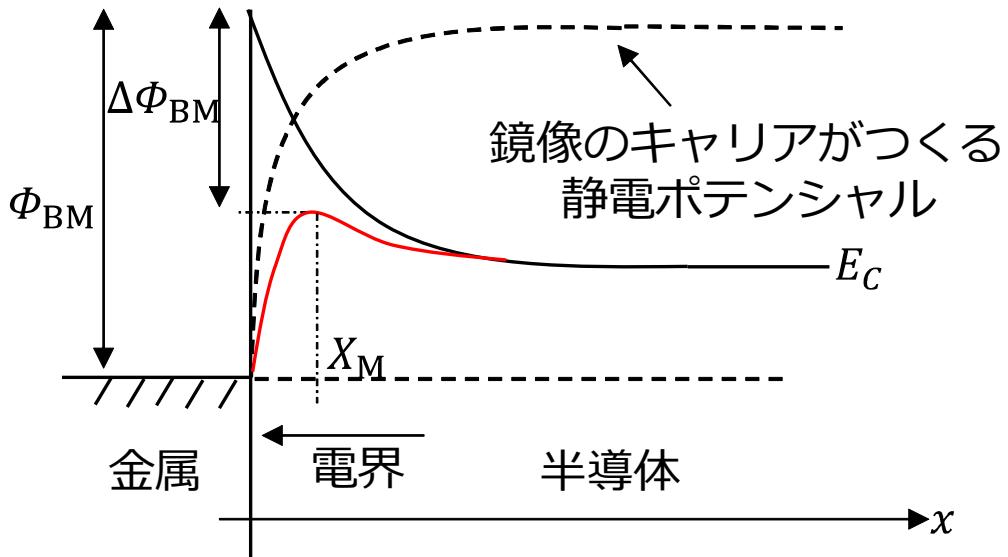

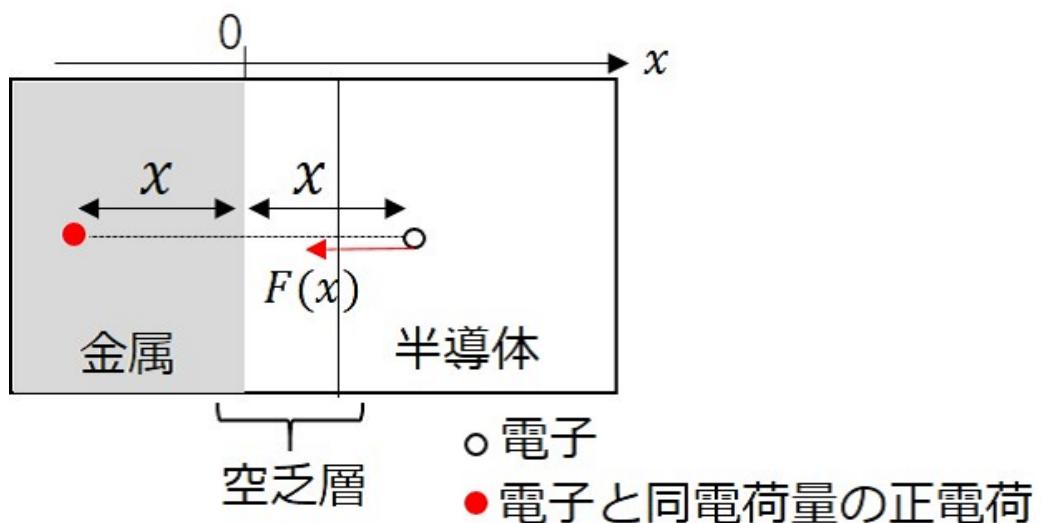

実際のSBDにおいては、印加する逆電圧の増加に従って、漏れ電流も増加する。これは印加電圧によってショットキー障壁高さが低下することに起因する。図2.9はダイオードに逆電圧が印加された場合のバンド図である。ショットキー接合から位置 $x$ だけ離れた半導体中の電子は、図2.10に示すように金属中に存在する鏡像の正電荷による静電気力を受ける。この時の静電気力は式(2.25)で与えられる。

$$F(x) = -\frac{q^2}{4\pi\varepsilon(2x)^2} \quad (2.25)$$

この粒子間に働く静電気力によって発生するポテンシャルは、静電気力を無限遠から位置 $x$ まで積分することによって得られる。

$$V(x) = \int_x^\infty E(x)dx = -\frac{q}{16\pi\varepsilon x} \quad (2.26)$$

正味のポテンシャルは、式(2.26)で表されるポテンシャルエネルギーとショットキー接合によるポテンシャルエネルギーの和であるため、式(2.27)で与えられる。

$$U(x) = q\phi(x) = -\frac{q^2}{16\pi\varepsilon x} - qE_m x \quad (2.27)$$

式(2.27)及び図2.9から明らかなように、電界はショットキー接合面から $X_M$ だけ離れた位置で最大電界 $E_m$ となる。式(2.26)において $x = X_M$ における静電ポテンシャルは、空乏層内のポテンシャル降

図2.9 ショットキーバリア障壁の低下

下に等しく、

$$E_m X_M = -\frac{q^2}{16\pi\epsilon X_M} \quad (2.28)$$

となる。式(2.27)と式(2.28)により、障壁高さの低下分は、 $\Delta\Phi_{BM} = 2E_m X_M$  で与えられ、式(2.28)で  $X_M$  を消去すると、

$$\Delta\Phi_{BM} = \sqrt{\frac{qE_m}{4\pi\epsilon}} \quad (2.29)$$

を得る。式(2.29)より、最大電界  $E_m$  が増加するにつれて、障壁高さの低下量  $\Delta\Phi_{BM}$  は増大する。

SiC SBDにおけるドリフト層の不純物濃度はSiに比較して数百倍であるため、式(2.29)より印加電圧に対するショットキー障壁の低下は、Si SBDよりも顕著になる。従ってSiC SBDにおいては、オン電圧降下は1~1.5VとSi SBDよりも高めに設計されることになる。

図 2.10 鏡像電荷がつくる静電気力

### 2.1.3 SBD の接合容量

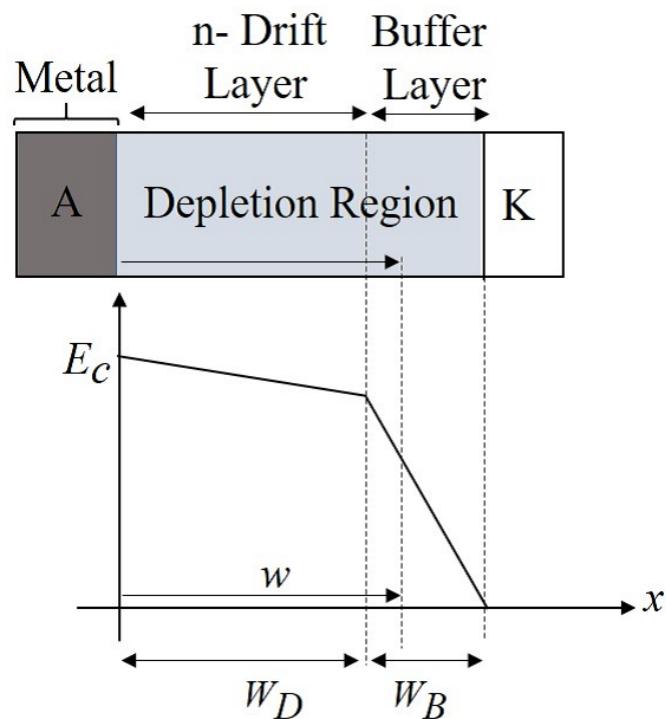

片側階段状接合を仮定したときのSBDの物理モデルを図2.11に示す。図2.11(a)はパンチスルーフ構造をとらないSBD(NPT-SBD)の1次元モデル及びその電界分布である。また、図2.11(b)はパンチスルーフ構造のSBD(PT-SBD)の1次元モデル及びその電界分布である。パンチスルーフ構造のデバイスは不純物濃度の低いドリフト層と不純物濃度の高いバッファ層によって構成される。式(2.16)より、ドリフト層の抵抗と耐圧はトレードオフの関係にあり、PT-SBDではNPT-SBDに比べ、同耐圧下でドリフト層を薄く設計することが可能である[21]。図2.11(a)のNPT-SBDの物理モデルにおいて、式(2.10)及び(2.18)より、逆バイアス電圧 $V_R$ を印加したときの空乏層 $W_D$ は、式(2.30)で与えられる。ただし、不純物濃度 $N_d$ はドリフト層内で一様であるとする。

$$w = \sqrt{\frac{2\varepsilon_s}{qN_d}(V_{bi} + V_R)} \quad (2.30)$$

一般に印加する逆バイアス電圧 $V_R$ はビルトイン電圧 $V_{bi}$ より十分に大きいことから式(2.31)で近似することができる。

$$w \simeq \sqrt{\frac{2\varepsilon_s}{qN_d}V_R} \quad (2.31)$$

逆電圧 $V_R$ を印加した際、単位面積当たりの空乏層電荷量 $Q$ はドリフト層の電荷密度 $qN_d$ 、空乏層幅 $w$ を用いて次式で表される。

$$Q = qN_d w = \sqrt{2\varepsilon_s q N_d (V_R + V_{bi})} \quad (2.32)$$

式(2.32)より、SBDの接合容量 $C_j$ は式(2.33)で表される。

$$C_j = \frac{dQ}{dV_R} = \sqrt{\frac{\varepsilon_s q N_d}{2(V_{bi} + V_R)}} \simeq \sqrt{\frac{\varepsilon_s q N_d}{2V_R}} \quad (2.33)$$

次に図2.11(b)のPT-SBDの物理モデルについて考慮する。図2.11(b)において $x = 0$ から $x = W_D$ でPoisson方程式を立式し、両辺を位置 $x$ に関して積分すると次式が得られる。ただし、 $N_b$ はバッファ層の不純物濃度であり、 $N_d \ll N_b$ である。

$$E(x) = -\frac{q}{\varepsilon_s} \{N_d(x - W_D) + N_b(W_D - w)\} \quad (0 \leq x \leq W_D) \quad (2.34)$$

同様に $x = W_D$ から $x = w$ でPoisson方程式を立式し、両辺を位置 $x$ に関して積分すると次式が得られる。

$$E(x) = -\frac{q}{\varepsilon_s} N_b (x - W_D + W_B) \quad (W_D \leq x \leq W_D + W_B) \quad (2.35)$$

式(2.34)及び(2.35)を位置 $x$ で積分することで、逆電圧 $V_R$ は式(2.36)で表される。

$$V_R(x) + V_{bi} = - \left[ \int_0^{W_D} \frac{q}{\varepsilon_s} \{N_d(x - W_D) + N_b(W_D - w)\} dx + \int_{W_D}^w \frac{q}{\varepsilon_s} \{N_b(x - w)\} dx \right] \quad (2.36)$$

$N_d \ll N_b$ であるため、式(2.36)は式(2.37)で近似できる。

$$V_R(x) \simeq \frac{q}{2\varepsilon_s} \{(N_d - N_b)W_d^2 + N_b w^2\} \quad (2.37)$$

式(2.37)より、空乏層幅  $w$  は逆電圧  $V_R$  の関数として式(2.38)で与えられる。

$$w = \sqrt{\frac{2\varepsilon_s}{qN_b} V_R + \left(1 - \frac{N_d}{N_b}\right) W_D^2} \quad (2.38)$$

ショットキー接合面で電界は最大値  $E_m$  をとるので、式(2.34)で  $x = 0$  を代入することで式(2.39)の関係式が成立する。

$$E_m = E(0) = -\frac{q}{\varepsilon_s} (N_b - N_d) W_D + \frac{qN_b}{\varepsilon_s} w \quad (2.39)$$

$w = W_D + W_B$  で空乏層幅は最大値となり、式(2.39)を変形すると次式を得る。

$$W_D + W_B = \frac{N_b - N_d}{N_b} W_D + \frac{\varepsilon_s}{qN_b} E_c \quad (2.40)$$

したがって絶縁破壊電圧  $BV$  は式(2.38)及び式(2.40)より、式(2.41)で与えられる。

$$BV = \frac{q}{\varepsilon_s} \left\{ W_D^2 N_d \left( -1 + \frac{N_d}{N_b} \right) + 2(N_b - N_d) W_D \frac{\varepsilon_s E_c}{qN_b} + \frac{\varepsilon_s^2 E_c^2}{q^2 N_b} \right\} \quad (2.41)$$

$0 \leq x \leq W_D$  における空乏層電荷量は式(2.42)で与えられる。

$$Q(V) = qN_d w = \sqrt{2\varepsilon_s q N_d (V_R + V_{bi})} \quad (2.42)$$

$W_D \leq x \leq w$  における空乏層電荷量は式(2.43)で与えられる。

$$\begin{aligned} Q(V) &= qN_d W_D + qN_B(w - W_D) \\ &= (N_d - N_b)qW_D + \sqrt{2\varepsilon_s q N_b (V_R + V_{bi}) + (N_b - N_d)N_b q^2 W_D^2} \end{aligned} \quad (2.43)$$

従って、パンチスルーコンタクト構造SBDの接合容量  $C_j$  は式(2.44)で表される。ただし、 $V_{pt}$  はパンチスルーエレメント電圧である。

$$\begin{aligned} C_j(V_R) &= \sqrt{\frac{\varepsilon_s q N_d}{2V_R}} \quad (0 \leq V_R \leq V_{pt}) \\ C_j(V_R) &= \sqrt{\frac{\varepsilon_s^2 q N_d}{2\varepsilon_s V_R + (N_b - N_d)q W_D^2}} \quad (V_{pt} \leq V_R \leq BV) \end{aligned} \quad (2.44)$$

(a) NPT-SBD の構造と電界分布

(b) PT-SBD の構造と電界分布

図 2.11 SBD の物理モデル

図 2.12 開発した高耐圧 SiC SBD モジュール

## 2.2 SiC SBD モジュールの開発と評価

### 2.2.1 素子の直列接合による SiC SBD モジュール

高周波 Cockcroft-Walton 回路に用いる高耐圧整流ダイオードを従来はオン抵抗低減のため、バイポーラデバイスである Si PiND が用いられてきた。Si PiND はスイッチング時に少数キャリアの注入・掃きだしに時間を要するため、スイッチング損失による自己発熱が問題となり、高周波化に限界があった。SiC パワーデバイスは Si では不可能な高耐圧で低オン抵抗のユニポーラデバイスを作製することができるため、高周波の Cockcroft-Walton 回路への適用で、これまでの動作限界を超えることができる [16]。ただし、ユニポーラデバイスではドリフト層の抵抗は耐圧の 2 乗に比例して大きくなるため、要求される素子耐圧が高い場合は SiC SBD を用いた場合でも素子単体で超高耐圧を実現することは現実的でない。しかしながら、SiC SBD のペアチップを複数個直列に接続した超高耐圧 SBD モジュールは、耐圧とオン抵抗の両方がペアチップの直列数倍となるため、高耐圧化においてオン抵抗は耐圧に比例となり、低オン抵抗化を両立できる。

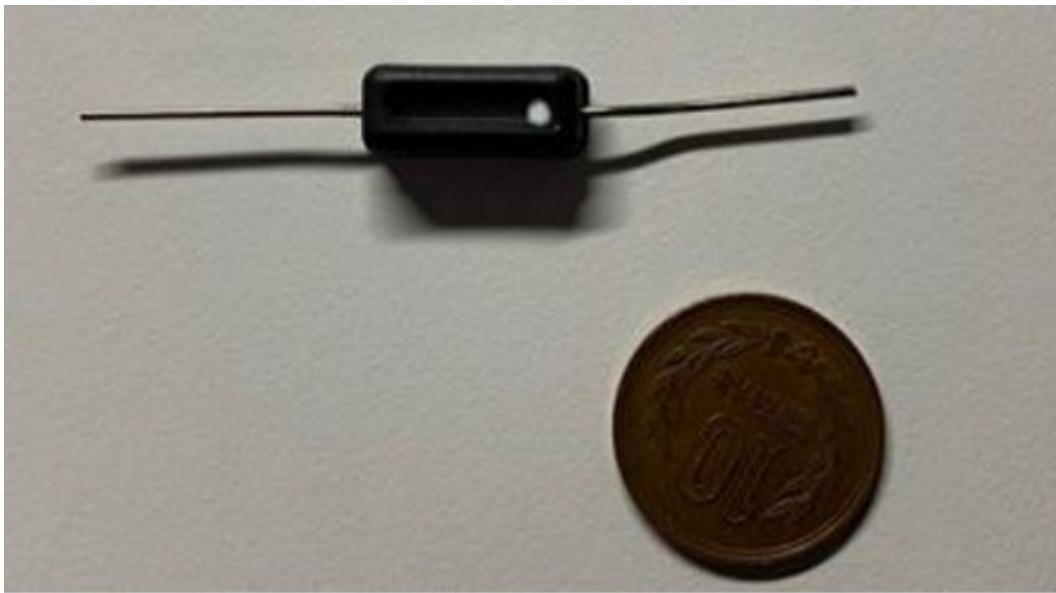

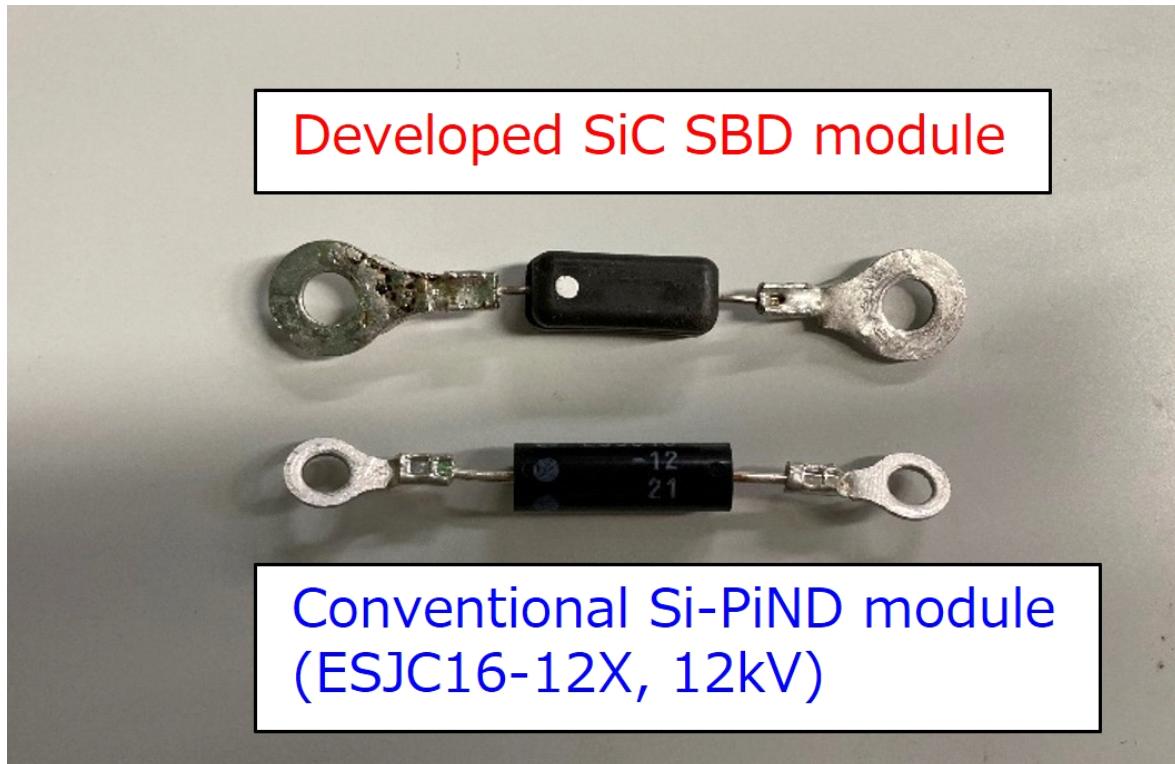

本研究では 10kV 級の Cockcroft-Walton 回路への適用を考え、定格電圧 12kV の超高耐圧 10 直列 SiC SBD モジュールを開発した。図 2.12 に開発した SiC SBD モジュールを、図 2.13 に本モジュールの内部構造を示す。SiC SBD のチップ S5301(Rohm, 1.2kV, 5A) を 10 直列しており、チップ間ははんだ及び導電性接着剤を用いて接合した。また周囲をエポキシ樹脂でモールド封止することで絶縁を確保している。SiC SBD モジュールのサイズは縦 10mm、横 25mm、厚み 5mm であり、小型化及び低損失化を図るため分圧素子を使用しないものとした。モジュール自体が小型のため、Cockcroft-Walton 回路のような多数のダイオードモジュールが必要になる回路でもコンパクトに設計することができる。

図 2.13 開発した高耐圧 SiC SBD モジュールの内部構造

表 2.1 SiC SBD 単体と SiC SBD モジュールのオン抵抗  $R_s$ , 立ち上がり電圧  $V_f$  及び漏れ抵抗 ( $T = 25^\circ\text{C}$ )

| Extracted Parameter                    | Single SiC SBD | SiC SBD module(developed) |

|----------------------------------------|----------------|---------------------------|

| $V_f$ (V)                              | 1.2            | 11                        |

| $R_s$ ( $\Omega$ )                     | 0.10           | 1.2                       |

| $R_{\text{leak}}$ ( $\text{G}\Omega$ ) | 0.28           | 3.2                       |

### 2.2.2 SiC SBD モジュールの静特性

本節ではモジュールの基礎特性として、開発した SiC SBD モジュールと SiC SBD 単体の静特性をそれぞれ比較し、耐圧とオン抵抗の両方がベアチップの直列数倍となるかを実験的に確認する。また同サイズで同定格の Si PiND とも比較し、静特性での優劣関係を評価した。

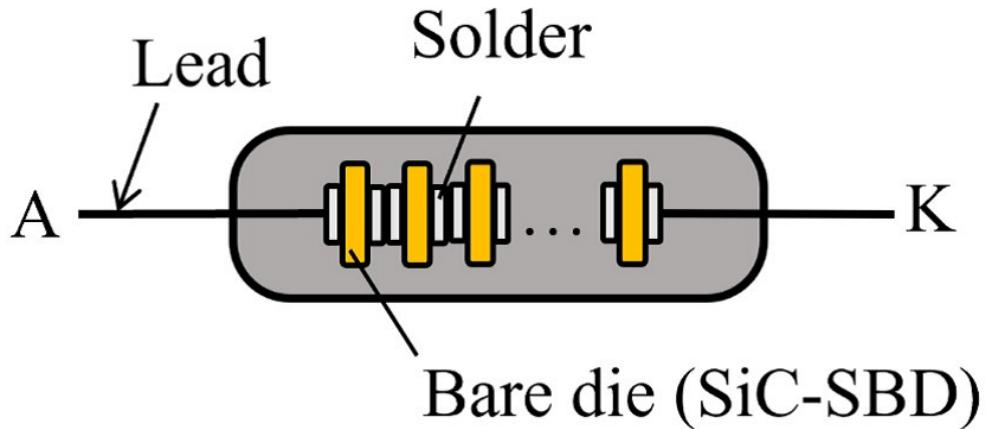

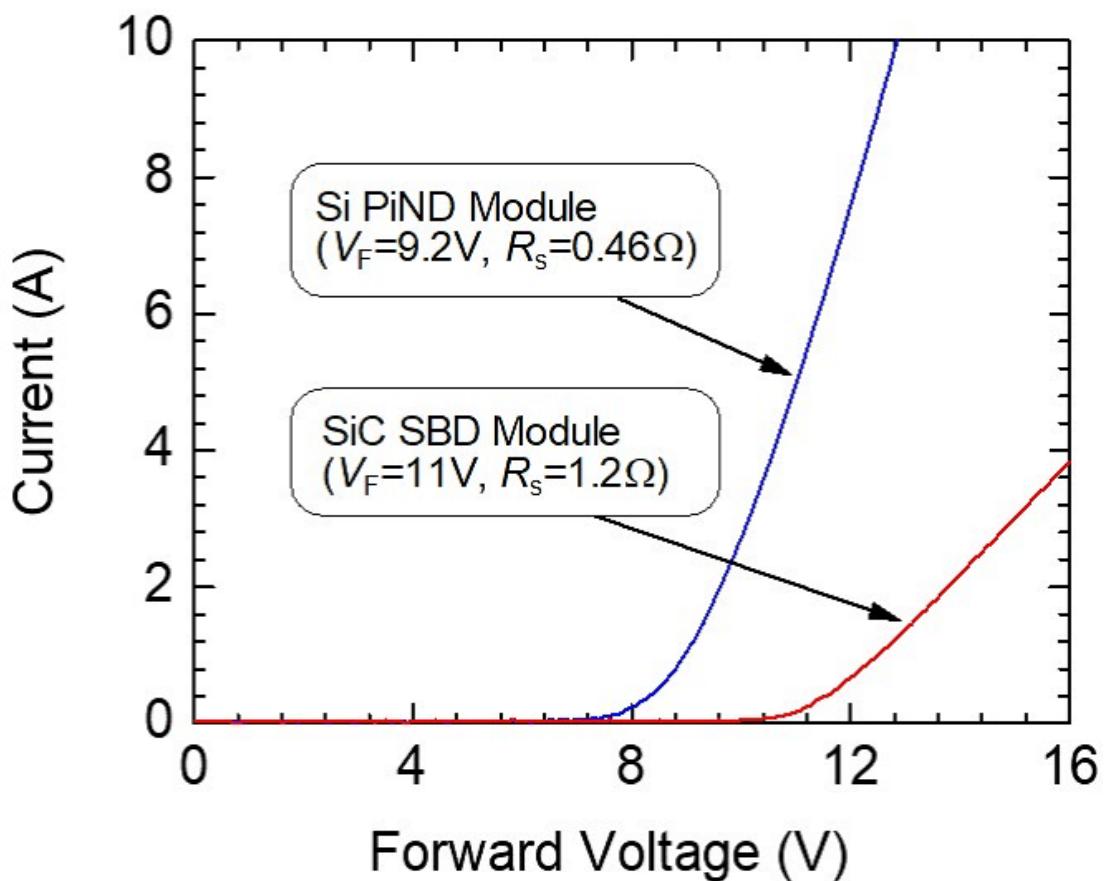

モジュールの順方向 IV 特性は、半導体カーブトレーサ B1505A (Agilent) を用いた 4 端子測定により得る。図 2.14 に開発した SiC SBD モジュールと SiC SBD 単体の順方向 IV 特性をそれぞれ示す。ただし、室温での測定とする。1A 以上の大電流領域において、一次近似した直線の傾きと  $x$  切片から等価直列抵抗  $R_s$  及び立ち上がり電圧  $V_f$  をそれぞれ求めた。表 2.1 に同定した  $R_s$ ,  $V_f$  を示す。10 直列の SiC SBD モジュールの立ち上がり電圧  $V_f$  及び等価直列抵抗  $R_s$  は共に SiC SBD 単体のほぼ 10 倍となっている。

逆方向 IV 特性は SiC SBD モジュール及び SBD 単体に直流高電圧を印加して評価する。SBD 単体は半導体カーブトレーサ B1505A で 1kV 印加したときの IV 特性から、10 直列した SiC SBD モジュールは絶縁抵抗計 KEW3123A (KYORITSU) によって得られた絶縁抵抗からそれぞれ漏れ抵抗を算出した。結果を表 2.1 に示す。素子の直列化により、本モジュールは素子単体に比べて漏れ抵抗が約 10 倍と

図 2.14 開発した SiC SBD モジュールと SBD 単体の順方向 IV 特性

なっている。

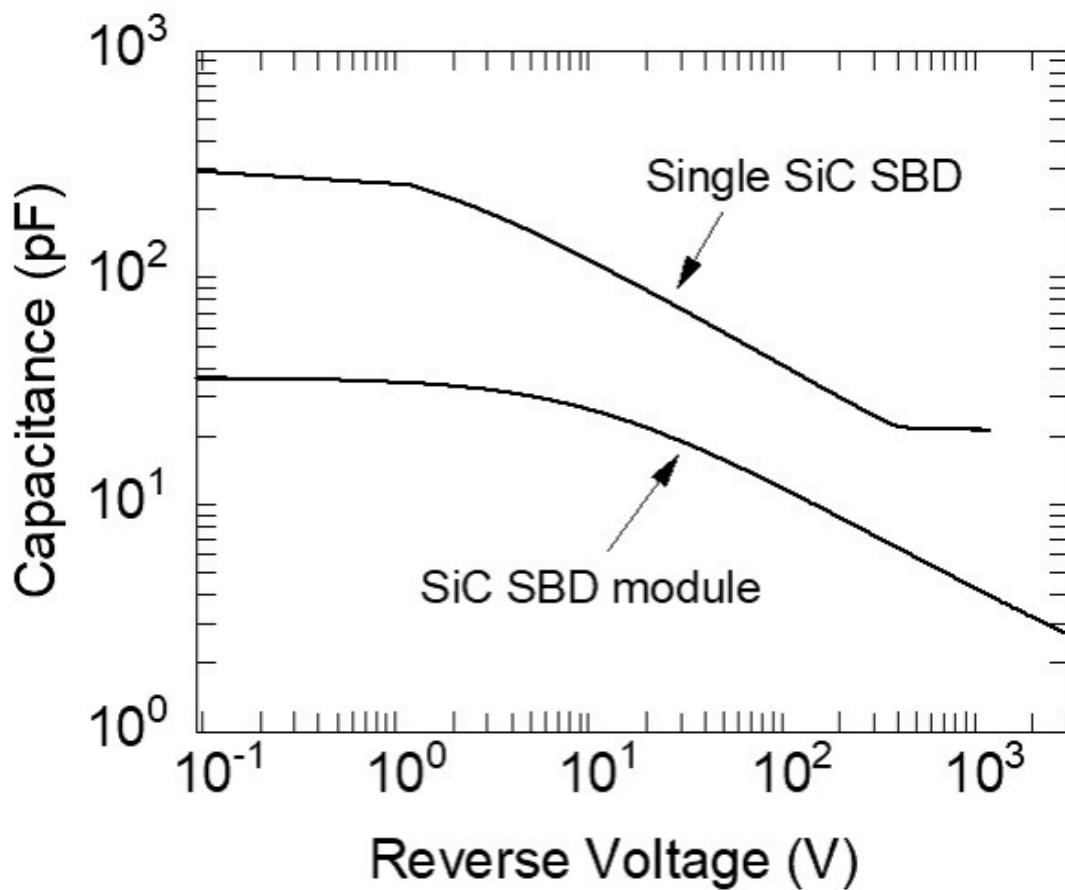

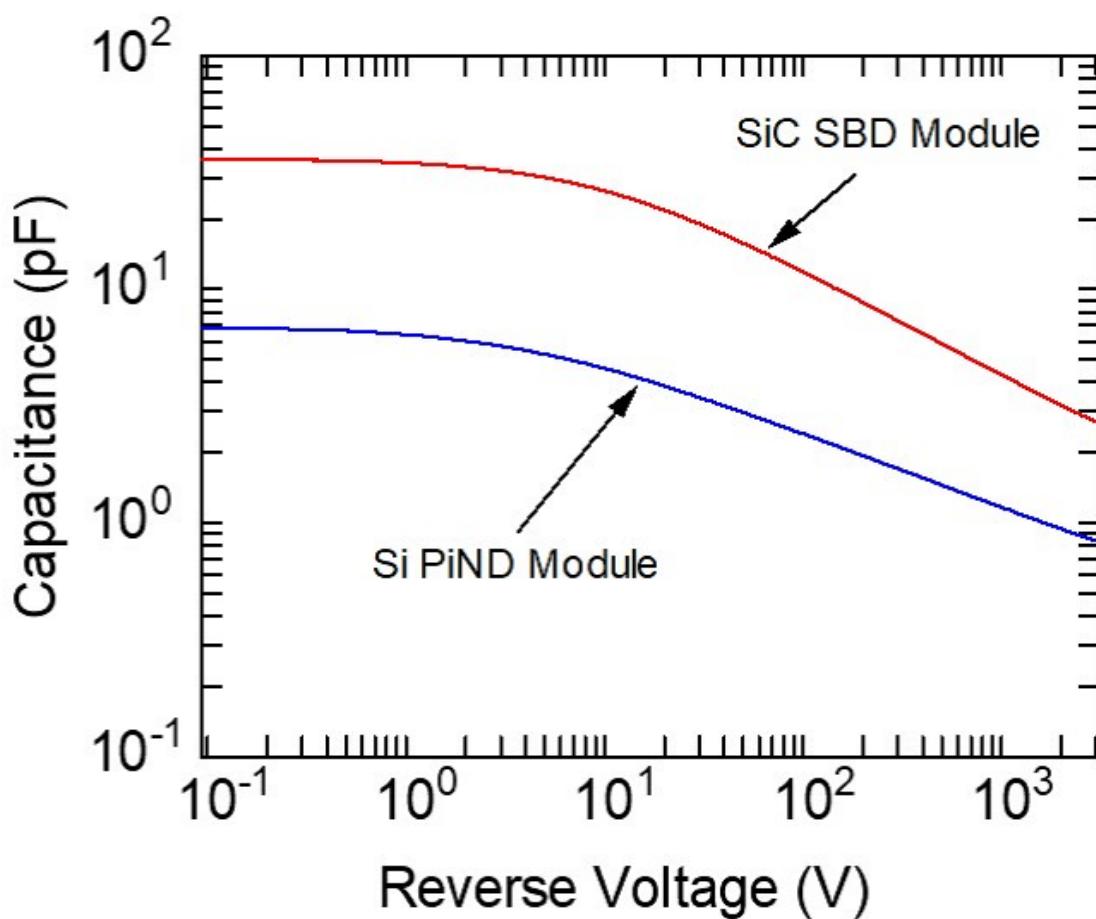

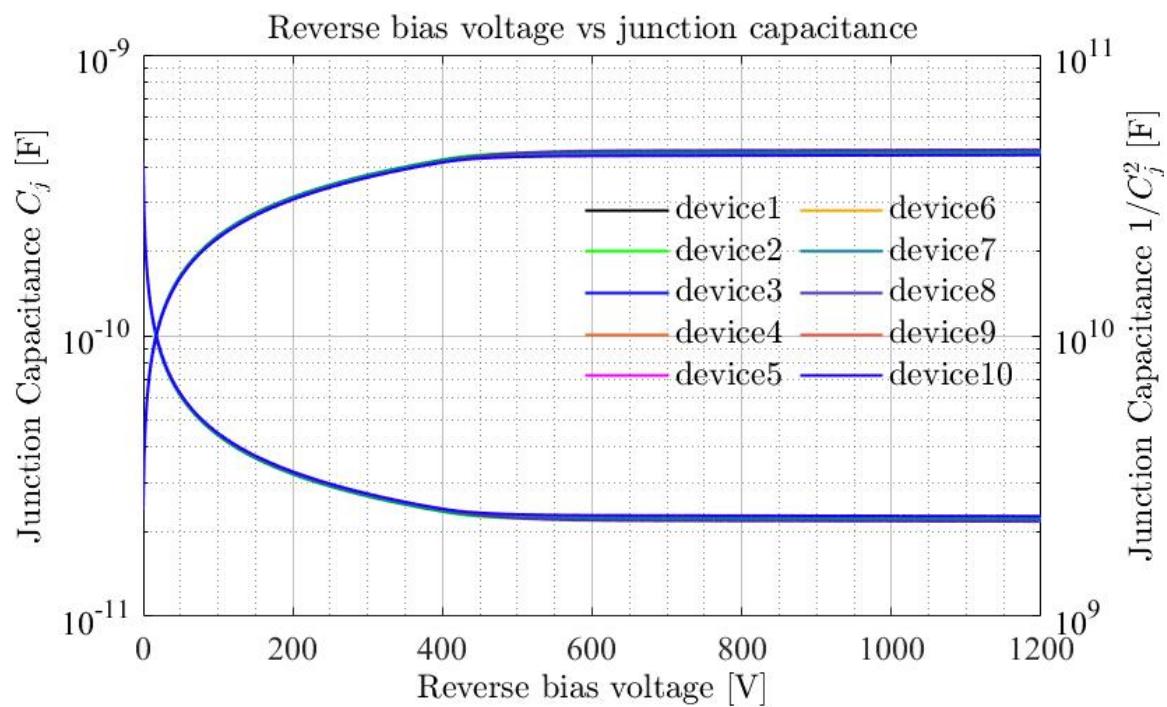

ダイオードモジュールの接合容量  $C_j$  はターンオフにおける空乏層電荷量に影響する。接合容量  $C_j$  は電圧依存性を持つため、高電圧印加時の接合容量を定量的に評価し、素子のスイッチング特性に与える影響を検討する。カーブトレーサ B1505A と高電圧バイアステー N1260A を用いて開発した SiC SBD モジュールに 3kV まで電圧印加し、モジュールの接合容量を測定した。図 2.15 に SiC SBD モジュールと SiC SBD 単体の CV 特性を示す。素子の直列化により、本モジュールは接合容量が約 1/10 倍となっている。これにより、ターンオフにおける接合容量の充電電荷量が減少し、高速スイッチングが期待できる。

以上の結果より、素子を直列に接合した本モジュールは耐圧とオン抵抗の両方がペアチップの直列数倍となることが確認できた。すなわち、直列化によって耐圧と順方向特性のトレードオフを素子単体の 2 乗から比例に改良することができる。

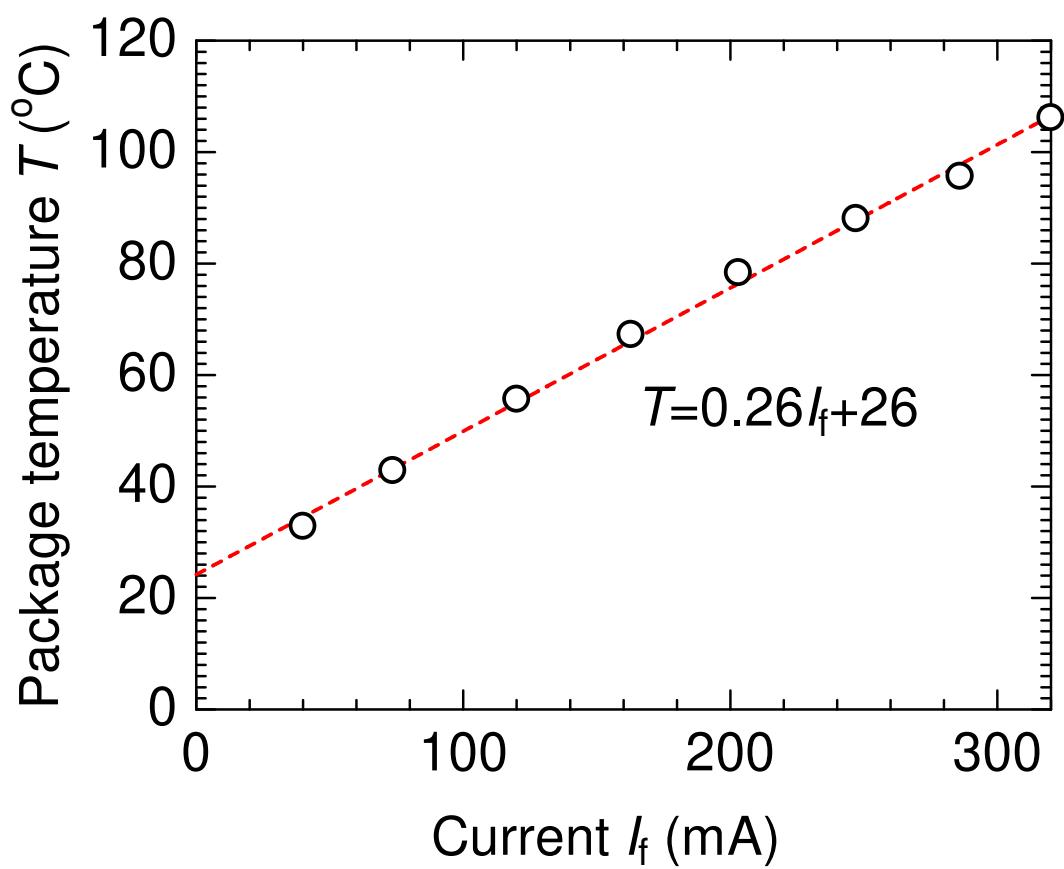

開発した SiC SBD モジュールは高電圧が印加されるため、ヒートシンクやファンによる強制空冷を

図 2.15 開発した SiC SBD モジュールと SBD 単体の CV 特性

行なうことは難しい。そこでモジュールパッケージ表面温度が  $100^{\circ}\text{C}$  となるモジュールの消費電力から、本モジュールの電流定格を求める。図 2.16 に順方向電圧・電流を本モジュールに印加した時の定常状態の順方向損失とパッケージ表面温度を示す。パッケージ表面温度が  $100^{\circ}\text{C}$  となる電圧  $V_f$  及び電流  $I_f$  はそれぞれ  $8.5\text{V}$ ,  $0.30\text{A}$  であり、順方向損失は  $2.5\text{W}$  となった。モジュールの電流定格を  $0.30\text{A}$  とすると、SBD 単体の 7%程度まで電流定格が低下しており、開発した SiC SBD モジュールは順方向電圧降下と逆方向漏れ抵抗が直列数に対して比例し、接合容量は反比例する。すなわち、開発した SiC SBD モジュールは順方向特性と耐圧のトレードオフを直列数によって調整することができる。

図 2.16 順方向印加電流に対するパッケージ表面温度

図 2.17 開発した SiC SBD モジュールと従来品の Si PiND モジュール

本節ではさらに従来品の Si PiND モジュールと開発した SiC SBD モジュールを静特性の観点で比較するため、両モジュールに対して順方向 IV 特性、漏れ電流特性および逆方向 CV 特性をそれぞれ測定した。開発した SiC SBD モジュールと同定格の Si PiND モジュール ESJC16-12X(Fuji Electric) を図 2.17 に示す。両モジュールの公称耐圧は 12kV であり、パッケージ構造やサイズもほぼ同じである。

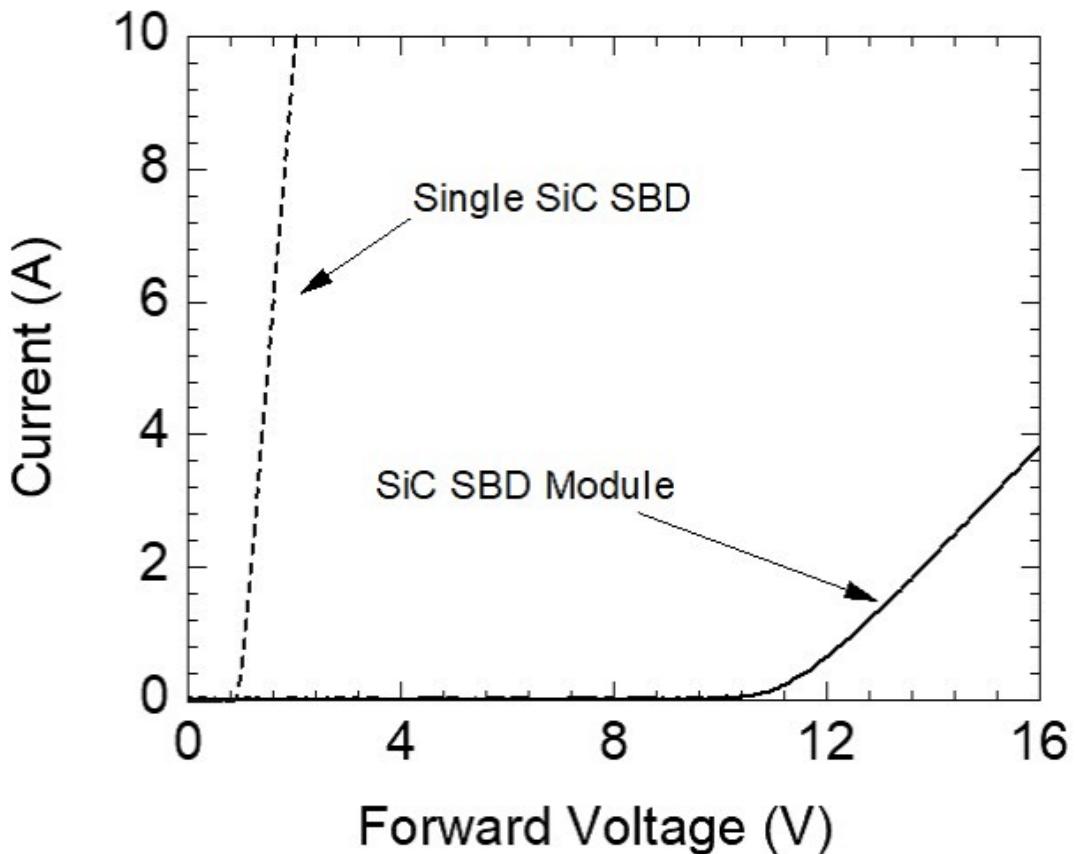

開発した SiC SBD モジュール及び Si PiND モジュールの順方向 IV 特性はこれまでと同様に半導体カーブトレーサ B1505A(Agilent) を用いた 4 端子測定により得る。図 2.18 に開発した SiC SBD モジュール及び Si PiND の順方向 IV 特性を示す。ただし、試験温度は 25°C の室温とした。1A 以上の大電流領域において、一次近似した直線の傾きと  $x$  切片から等価直列抵抗  $R_s$  及び立ち上がり電圧  $V_f$  をそれぞれ求める。表 2.2 に同定した  $R_s$ ,  $V_f$  を示す。室温での SiC SBD モジュールの等価直列抵抗  $R_s$  及び立ち上がり電圧  $V_f$  は共に Si PiND モジュールよりも大きく、順方向損失は SiC SBD モジュールの方が大きくなる。モジュール遮断時の損失はダイオードの AK 間に存在する漏れ抵抗  $R_{leak}$  により生じる。開発した SiC SBD モジュールと Si PiND モジュールは共に同耐圧であるため、直流高電圧を印加した時のデバイス印加電流より漏れ抵抗  $R_{leak}$  を決定する。絶縁抵抗計を用いてデバイスに直流 10kV を印加し、この時の絶縁抵抗を漏れ抵抗  $R_{leak}$  として測定した。表 2.2 に室温 25°C での漏れ抵抗  $R_{leak}$  を示す。SiC SBD モジュールの漏れ抵抗は Si PiND モジュールよりも低いため、遮断時の SiC SBD モジュールの損失は Si PiND に比べて大きい。

図 2.18 開発した SiC SBD モジュールと従来品の Si PiND モジュールの順方向 IV 特性

ダイオードモジュールの接合容量  $C_j$  はターンオフにおける空乏層電荷量に影響する。接合容量  $C_j$  は電圧依存性を持つため、高電圧印加時の接合容量を定量的に評価し、デバイスのスイッチング特性に与える影響を検討する。カーブトレーサ B1505A と高電圧バイアスティー N1260A を用いてモジュールに 3kV まで電圧印加し、両モジュールの接合容量を測定した。図 2.19 は SiC SBD モジュール及び Si PiND モジュールの CV 特性である。0V-3kV までの全域で SiC SBD モジュールの接合容量は Si PiND モジュールに比べて 4 倍以上大きく、ターンオフ時の接合容量の充電電荷量は多くなる。このため多数キャリアの空乏化に要するスイッチング損失の観点では SiC SBD モジュールが Si PiND モジュールよりも劣る。

表 2.2 開発した SiC SBD モジュールと従来品の Si PiND モジュールのオン抵抗  $R_s$ , 立ち上がり電圧  $V_f$  及び漏れ抵抗  $R_{\text{leak}}$  ( $T = 25^\circ\text{C}$ )

| Extracted Parameter                    | SiC SBD | Si PiND |

|----------------------------------------|---------|---------|

| $V_f$ (V)                              | 11      | 9.2     |

| $R_s$ ( $\Omega$ )                     | 1.2     | 0.46    |

| $R_{\text{leak}}$ ( $\text{G}\Omega$ ) | 3.2     | 4.1     |

図 2.19 開発した SiC SBD モジュールと従来品の Si PiND モジュールの CV 特性

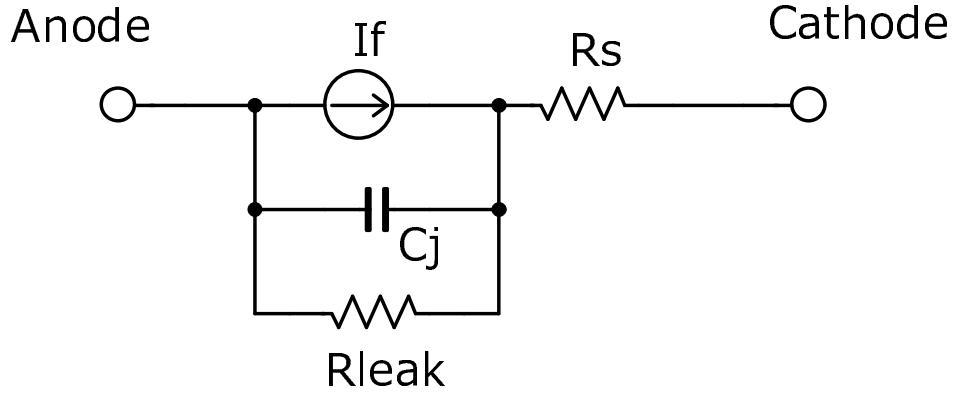

図 2.20 SBD 単体の等価回路モデル

### 2.3 SiC SBD モジュールの分担電圧の評価

本モジュールは小型化及び低損失化を図るため分圧抵抗を使用していない。そのため定常状態及び過渡状態において、直列接続された個々の素子の特性の違いが電圧分担の不均衡を引き起こし、特定の素子に電圧が集中した場合には過電圧による破壊に至る可能性がある。高周波 Cockcroft-Walton 回路への適用を考える上でも、モジュール内の各素子の電圧分担を定量的に評価する必要がある。ただし、モールドされたモジュール内における個々の素子の電圧を直接測定することは難しい。また各素子の遮断時のインピーダンスに対して電圧プローブの入力インピーダンスが無視できず、プロービングによって分担電圧が変化するため、実験における正確な測定が難しい。

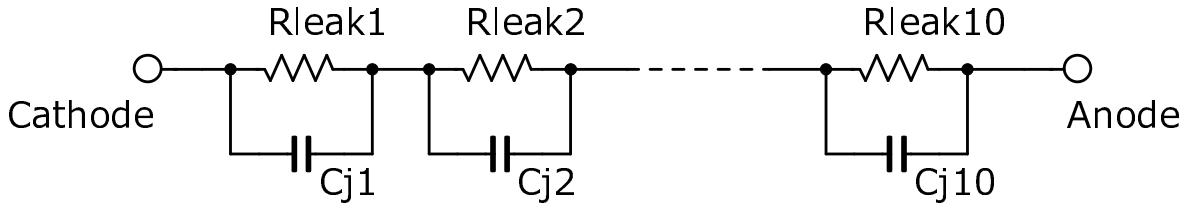

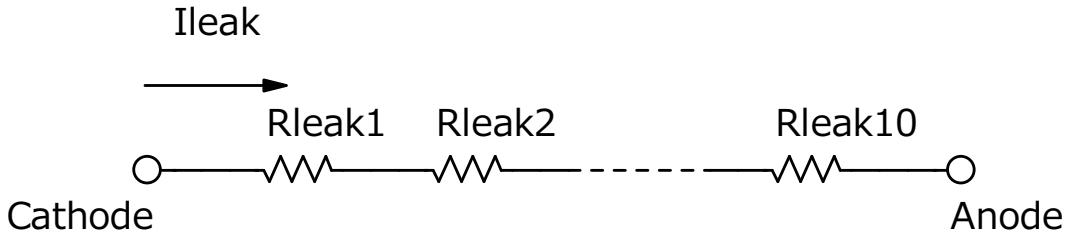

そのため本研究では 10 直列のダイオードモジュールの等価回路モデルを用いて定常状態及びスイッチング過渡状態における各素子の電圧分担を評価した。直列接続する個々のダイオード計 10 個の静特徴をそれぞれモデル化し、直列接続することで超高耐圧の SiC SBD モジュールモデルとする。高耐圧 SiC SBD 単体の等価回路モデルは図 2.20 に示すように電圧制御型の電流源  $I_f$  に対して直列に入るオン抵抗  $R_s$  と並列に入る接合容量  $C_j$  および漏れ抵抗  $R_{leak}$  で構成される [21]。このうち、電流源  $I_f$  と直列に入るオン抵抗  $R_s$  は順方向導通時の特性を示す。また接合容量  $C_j$  および漏れ抵抗  $R_{leak}$  は逆方向に電圧を印加したときの遮断特性を示す。本研究では逆方向特性に着目し、構築した各素子ごとの等価回路モデルを直列に接続した図 2.21 の超高耐圧 SiC SBD モジュールモデルを新たに開発した。

SBD の遮断状態の等価回路は接合容量  $C_j$  と漏れ抵抗  $R_{leak}$  の並列回路で表される。本 SBD モジュールの等価回路は SBD を直列接続しているため、図 2.21 に示す RC 並列回路が複数直列に接続された構成であると考えられる。同様に半導体カーブトレーサで測定した 10 素子分の逆方向 IV 特性と逆方向 CV 特性のをそれぞれモデル化し、遮断状態における SBD モジュールの等価回路モデルを開発した。

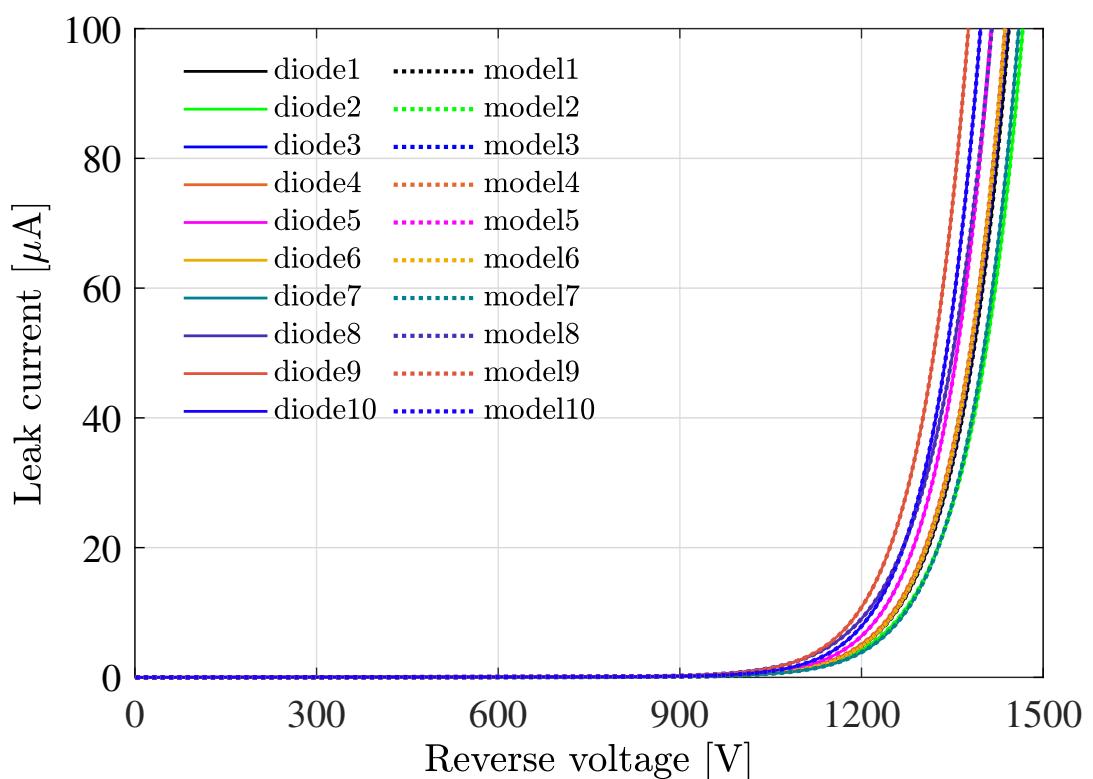

図 2.22 にカーブトレーサで測定した逆方向 IV 特性を示す。本 SiC SBD の逆方向 IV 特性は  $1\mu\text{A}$  以上のアバランシェ領域部分で物理式 (2.19) との乖離が大きい。アバランシェ領域で精度の良い IV 特性

図 2.21 遮断状態の SBD 単体の等価回路モデル

をモデル化するため、式(2.45)に示す多項式による近似を行う。ただし漏れ電流は  $I_{leak}$ 、逆方向電圧は  $V$  である。

$$I_{leak} = \sum_{i=0}^m a_i V^i \quad (2.45)$$

ここで、多項式の係数  $a_i (i = 0, 1, 2, \dots, m)$  は最小二乗法により求める。多項式の次数  $m$  は漏れ電流の2乗平均誤差 RMS が  $1\mu\text{A}$  ( $1.0 \times 10^{-6}$ ) 以下となり、かつ次数に対する RMS の変化分が小さくなる点で打ち切る。これにより、次数  $m$  を8次と決定し、この時の10素子の漏れ電流の2乗平均誤差 RMS は  $0.14\mu\text{A}$  ( $1.4 \times 10^{-7}$ ) となった。

図2.23に測定したCV特性を示す。接合容量の微分容量は空乏層電荷と電界の関係を示すPoisson方程式により表すことが可能である。本SiC SBDは図2.23の $1/C^2-V$ 特性に示すように、450V付近で空乏層が基板層に達し、微分容量が変化しなくなるパンチスルーエレメント構造であるが、ドリフト層の不純物濃度が一様でないためCV特性を式(2.46)でモデル化した[22]。ただし、 $C_{j0}$ はゼロバイアス時の接合容量、 $\phi_0$ はビルトインポテンシャル、 $m$ はグレーディング係数、 $x$ は数値定数である。この時の10素子の接合容量の誤差平均は  $6.7 \times 10^{-13}$  となり、十分に小さい。

$$C_j = C_{j0} \left( 1 - \frac{x \tanh(-\frac{V}{x})}{\phi_0} \right)^{-m} \quad (2.46)$$

図 2.22 逆方向IV特性

図 2.23 CV 特性と  $1/C^2$ -V 特性

図 2.24 定常遮断状態における SiC SBD の等価回路

### 2.3.1 定常遮断状態における直列接続された SiC SBD の電圧分担

本章では、開発した超高耐圧 SBD モジュールに逆バイアス電圧が印加された定常遮断状態において、直列接続された各 SBD の電圧分担について検討する。本モジュールは SBD のペアチップを直接直列に接続しており、定常遮断状態では  $R_{\text{leak}}$  のインピーダンスが支配的となる。すなわち、遮断状態における SBD モジュールの等価回路は図 2.24 に示す漏れ抵抗  $R_{\text{leak}}$  の直列回路となる。

定常状態におけるモジュール内の各ダイオードの電圧分担は与えられた漏れ電流  $I_{\text{leak}}$  に対して一意に決まる。漏れ電流  $I_{\text{leak}}$  から各ダイオード電圧を求めるため、式 (2.45) を式 (2.47) の陰関数に変換し、 $F_j(I_{\text{leak}}, v_j) = 0$  ( $j = 1, 2, \dots, 10$ ) を満たす素子の印加電圧を Newton 法を用いて求めた。

$$F_j(I_{\text{leak}}, v_j) = \sum_{i=1}^{m+1} a_{i-1} v_j^{i-1} - I_{\text{leak}} \quad (2.47)$$

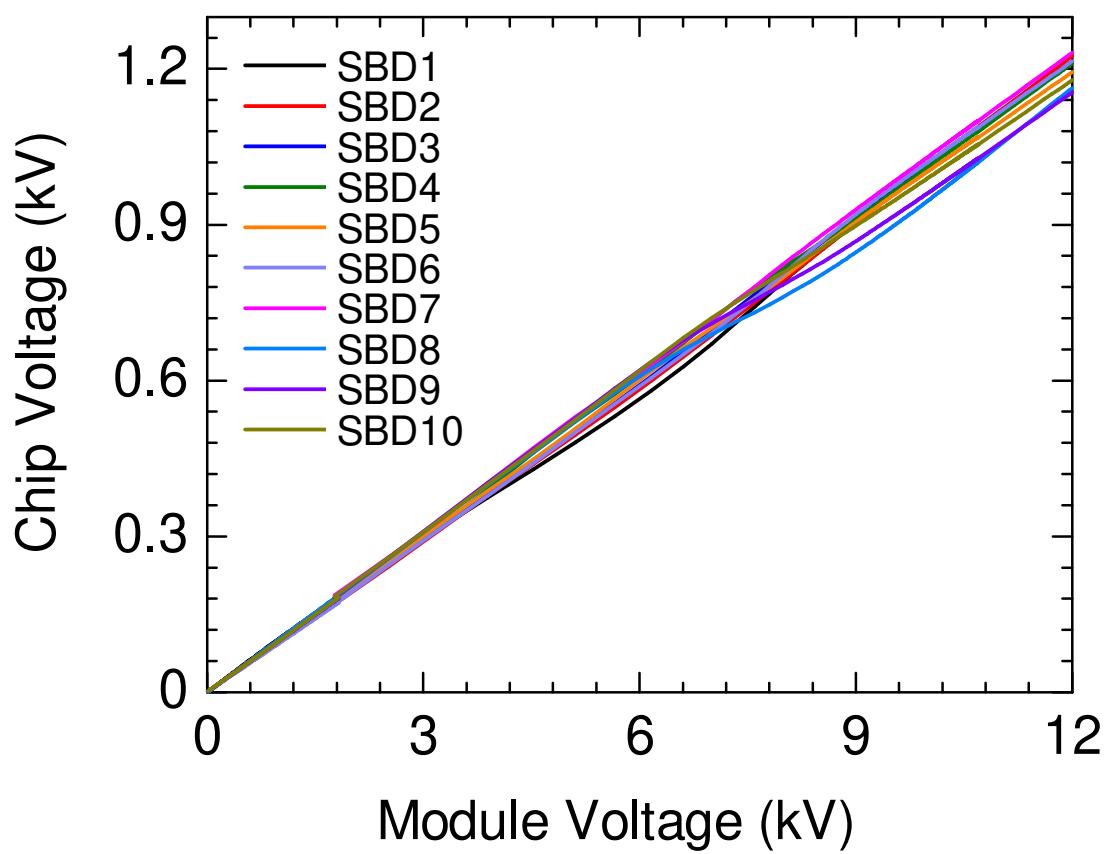

漏れ電流に対するモジュール内素子の印加電圧  $v_1, v_2, \dots, v_{10}$  の総和がモジュール印加電圧に相当する。モジュール印加電圧に対する各ダイオードの分担電圧を図 2.25 に示す。平均素子電圧 1.20kV に対し、SBD7 の 1.23kV が最も大きな印加電圧となり、SBD9 の 1.16kV が最も低い電圧となる。定常状態における分担電圧のばらつきは印加電圧に対して十分小さい。

図 2.25 定常状態における SiC SBD モジュールの電圧分担

### 2.3.2 スイッチング過渡状態における直列接続された SiC SBD の電圧分担

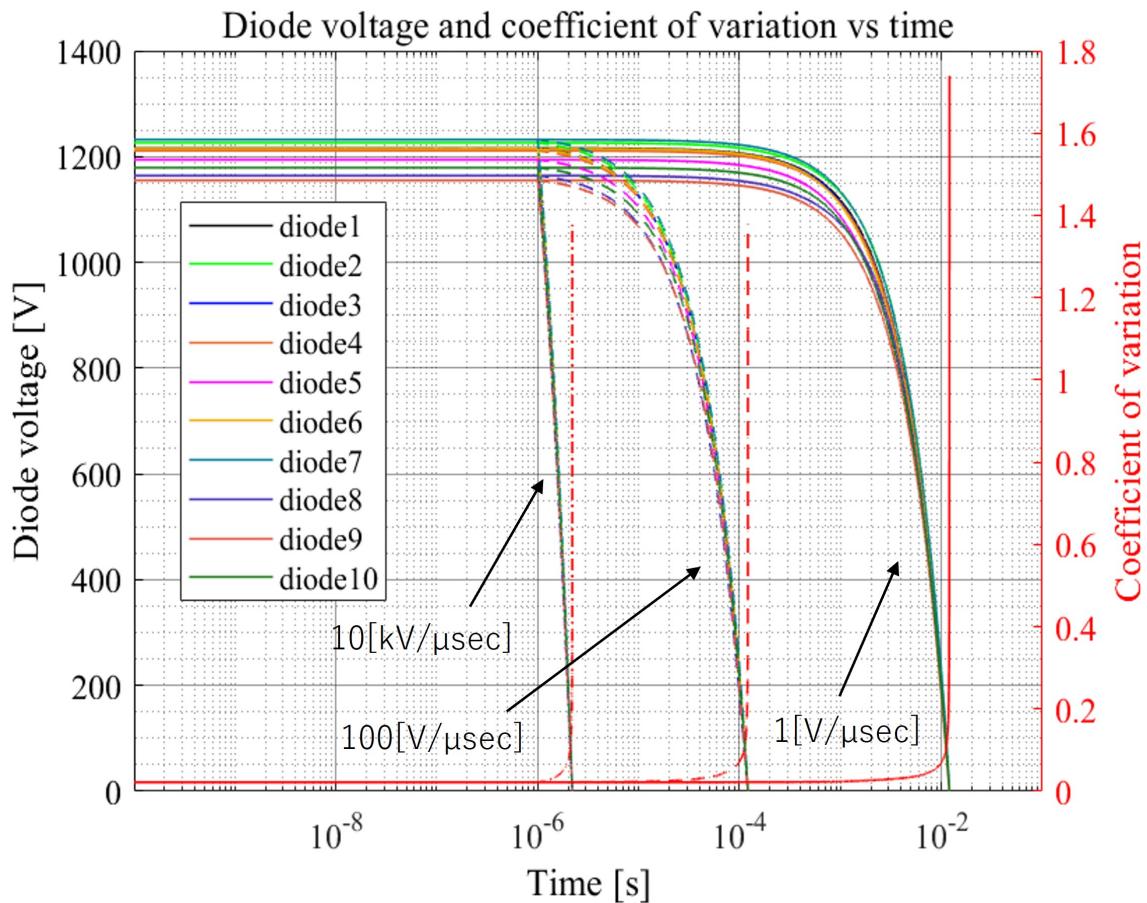

本節では、ターンオフの過渡状態におけるモジュール内のダイオードの電圧分担について議論する。図 2.21 に示す本モジュールのモデルに対し、ダイオードモジュールをターンオフさせる外部電源としてランプ状に電圧が変化する電圧源  $e(t)$  を考える。ただし電圧源は式 (2.48) に示すように、12kV を超えるまではランプ出力し、その後は一定出力とする。また、式 (2.48) 中の  $k$  はスイッチング速度  $dv/dt$  を示すパラメータである。

$$e(t) = \begin{cases} kt & (0 \leq t \leq \frac{12\text{kV}}{k}) \\ 12\text{kV} & (\frac{12\text{kV}}{k} \leq t) \end{cases} \quad (2.48)$$

式 (2.46) で表される接合容量  $C_{j(i)}$  ( $i = 1, 2, \dots, 10$ ) は電圧依存性を持ち、充放電電流  $I_{C_j}$  は式 (2.49) で与えられる。

$$I_{C_j} = C_j(v_i) \frac{dv_i}{dt} \quad (2.49)$$

図 2.21 の回路における回路方程式を式 (2.50) に示す。

$$\left\{ \begin{array}{l} i(t) = C_1(v_1) \frac{dv_1}{dt} + I_{\text{leak}1}(v_1) \\ i(t) = C_2(v_2) \frac{dv_2}{dt} + I_{\text{leak}2}(v_2) \\ \vdots \\ i(t) = C_{10}(v_{10}) \frac{dv_{10}}{dt} + I_{\text{leak}10}(v_{10}) \\ e(t) = L \frac{di}{dt} + R_s i(t) + v_1 + v_2 + \dots + v_{10} \end{array} \right. \quad (2.50)$$

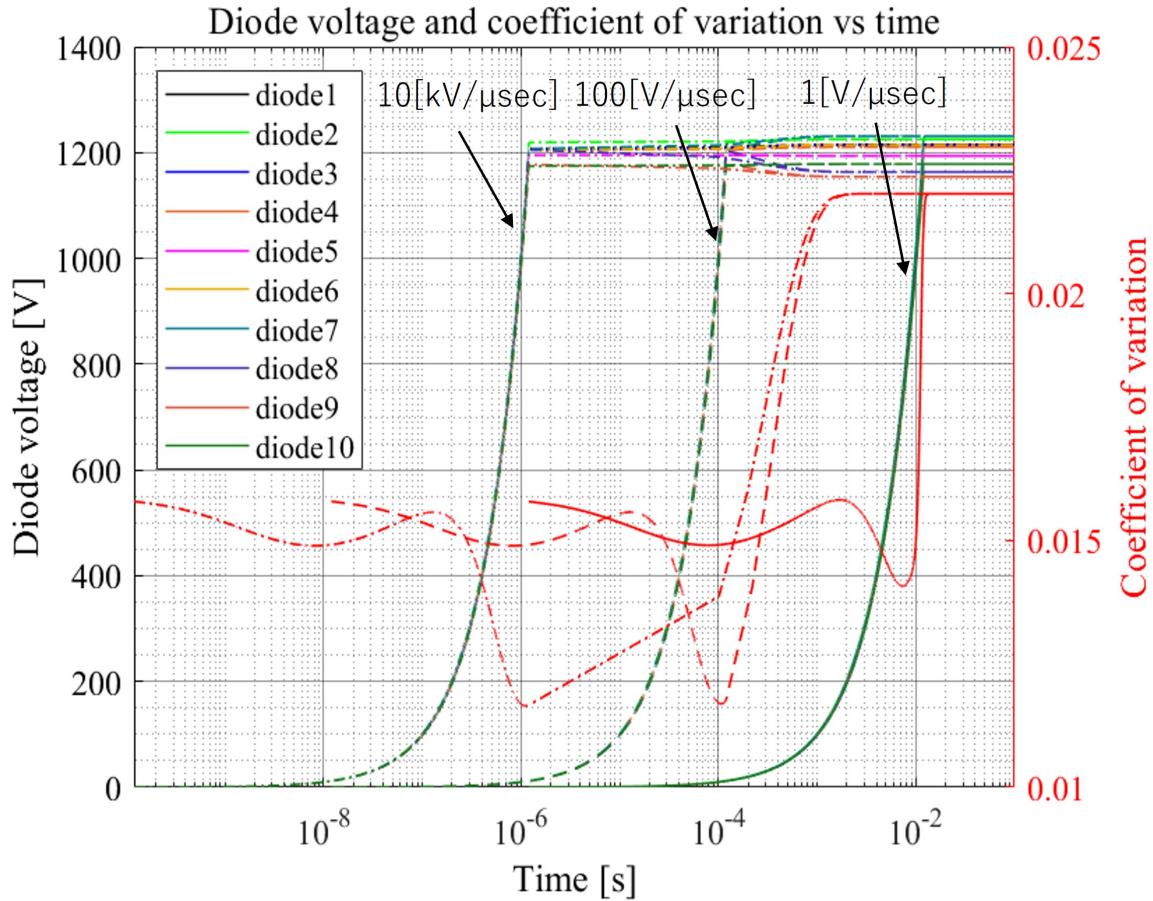

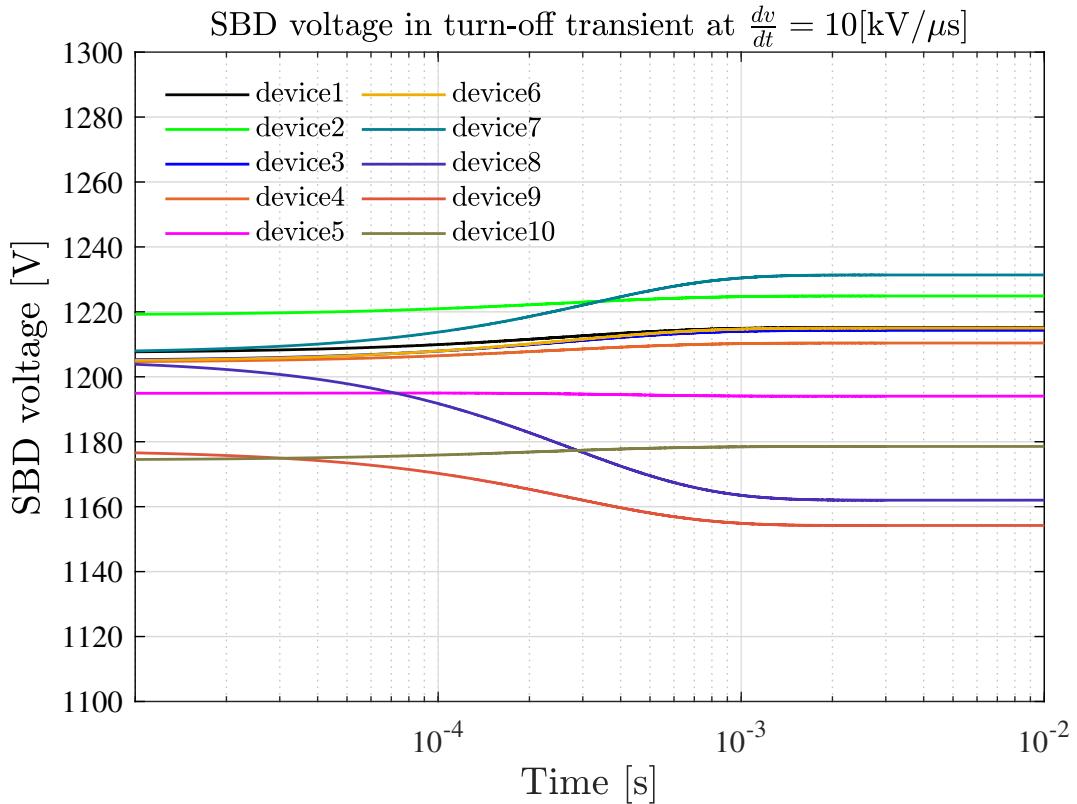

Runge-Kutta 法によって、式 (2.50) の連立方程式を時間区間 [0, 30msec] 及び初期条件  $v_1, v_2, \dots, v_{10} = 0$  として数値的に解き、時間応答を求める。ただし、スイッチング速度  $dv/dt$  は  $1\text{V}/\mu\text{s}, 100\text{V}/\mu\text{s}, 10\text{kV}/\mu\text{s}$  の 3 つの場合を考慮する。

図 2.26 に各ダイオード電圧の時間応答と変動係数 (標準偏差/平均) を示す。印加電圧が定格電圧 12kV に達した時間はスイッチング速度  $dv/dt = 1\text{V}/\mu\text{s}, 100\text{V}/\mu\text{s}, 10\text{kV}/\mu\text{s}$  のそれぞれに対して 12ms, 120μs, 1.2μs である。時間に対する電圧の変動係数から、印加電圧の電圧立ち上がり過程における分担電圧の相対的なばらつきは小さく、定常状態では分担電圧のばらつきが大きくなる。従って本モジュールでは、ターンオフ過程よりも定常状態での分担電圧のばらつきに注意する必要がある。

モジュール内の各 SBD に印加された電圧の緩和時間について議論するため、図 2.26 中のスイッチング速度  $dv/dt = 10\text{kV}/\mu\text{s}$  における SBD 印加電圧の時間応答の拡大図を図 2.27 に示す。図 2.27 に示すように、印加電圧が定格電圧に達した後の  $t = 100\mu\text{s}$  程度から各ダイオード電圧は定常状態での分担電圧に収束していく。モジュールに印加される電圧が定格電圧となってから定常状態に至るまでの緩和時間は定常状態における印加電圧に対する空乏層電荷量  $Q_{\text{static}}$  を基準とし、 $Q_{\text{static}} \pm 10\%$  の電荷量に達するまでの時間  $\tau_{\text{off}}$  と定義する。印加電圧に対する空乏層電荷量  $Q_{\text{static}}$  は式 (2.49) で表される充放電電

図 2.26 ターンオフでの電圧分担

流の時間応答を時間区間  $[0, \tau_{\text{off}}]$  で時間積分することで求められる。 $dv/dt = 100 \text{ V}/\mu\text{s}$  におけるモジュール内 10 素子のターンオフの緩和時間の平均は  $104 \mu\text{s}$  となり、標準偏差は  $1.7 \mu\text{s}$  であるため、ほとんどばらつきはない。従って  $100 \mu\text{s}$  以降は定常状態に達しているとみなしてもよい。

モジュール印加電圧が  $12 \text{ kV}$  に達した時刻における各ダイオードの分担電圧とスイッチング速度  $dv/dt$  の関係を図 2.27 に示す。 $dv/dt$  が大きい場合は、 $12 \text{ kV}$  に達した時点で接合容量で決まる分担電圧となるが、緩和時間を経て漏れ抵抗で電圧分担が決まる定常状態に移行する。 $dv/dt = 1.0 \text{ V}/\mu\text{s}$  以下のスイッチング速度が遅い領域では、立ち上がり時間に  $12[\text{ms}]$  以上を要するため、各ダイオードの電圧分担はほぼ漏れ抵抗により決まる。このため本モジュールを  $1.0 \text{ V}/\mu\text{s}$  以下のスイッチング速度で駆動する場合は定常状態の電圧分担を考慮すればよい。 $dv/dt$  が  $1.0 \text{ V}/\mu\text{s}$  以上になると、各ダイオードの分担電圧のばらつきは接合容量の影響を受けるようになり、 $dv/dt$  が  $100 \text{ V}/\mu\text{s}$  以上のスイッチング速度で駆動する場合は、印加電圧の上昇中における各ダイオードの電圧分担に対して接合容量の影響が支配的となる。表 2.3 に  $dv/dt = 100 \text{ V}/\mu\text{s}$  における定格電圧到達時の各ダイオード電圧と各ダイオード電圧における接合容量を示す。表 2.3 より、接合容量の小さなダイオード 2 では平均以上の電圧が印加され、逆

に接合容量の大きなダイオード9や10では平均電圧以下となっており、接合容量の影響が支配的であることが確認できる。

次に、ターンオンにおけるモジュール内素子の電圧分担について議論する。ターンオン時の回路方程

図 2.27 SBD の緩和時間

表 2.3 Diode voltage and junction capacitance more than  $dv/dt = 100[V/s]$

| SiC SBD      | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     | 10    |

|--------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Voltage[V]   | 1207  | 1219  | 1205  | 1205  | 1195  | 1205  | 1207  | 1205  | 1177  | 1174  |

| $C_j[\mu F]$ | 21.75 | 21.44 | 21.72 | 21.72 | 21.84 | 21.73 | 21.73 | 21.19 | 22.21 | 22.25 |

式は式(2.50)と同様であるが、印加電圧に対する漏れ電流と各SBDの接合容量の充電電圧に初期値を与える。ただし、各SBDの充電電圧の初期値はSiC SBDモジュールに12kV印加した時の定常状態での各SBDの分担電圧とする。この総和を外部電源の初期値  $V_{initial} = 12kV$  とし、電圧源を  $e(t) = -kt + V_{initial}$  として解析する。ターンオフと同様、スイッチング速度  $dv/dt$  は  $1V/\mu s$ ,  $100V/\mu s$ ,  $10kV/\mu s$  の3つの場合を想定して解析を行う。図2.28に各SBD電圧の時間応答と変動係数を示す。ターンオフ時に比較し

て、全体的に分担電圧のばらつきは大きく、印加電圧の減少に伴って分担電圧のばらつきは増加する。これは低電圧側で SBD の接合容量のばらつきが大きいことに起因しているが、低電圧であるため電圧分担のばらつきが問題となることはない。

図 2.28 ターンオン時の電圧分担

### 2.3.3 分担電圧に対するスイッチング速度の影響

本研究では、高周波 Cockcroft-Walton 回路に用いる超高耐圧 SBD モジュールを開発した。開発したモジュールは耐圧と損失のトレードオフを改善するため、SiC SBD のペアチップを直接直列にスタックしており、分圧抵抗がない構造であるため、定常状態及び過渡状態における電圧分担に関して議論した。

定常状態では漏れ電流に対する電圧降下の違いによって、分担電圧の差異がみられるが、ばらつきは素子単体の定格電圧 1.2kV に対して小さく、またこの時の損失も非常に小さい。

スイッチング過渡状態では本モジュールの接合容量と漏れ抵抗で決まる緩和時間が  $100\mu s$  程度であることから、スイッチング速度  $dv/dt$  を  $1.0V/\mu s$  以下で駆動する場合はモジュールの緩和時間よりも十分長い立ち上がり時間となるため、漏れ抵抗による電圧分担が支配的となる。スイッチング速度  $dv/dt$  を

100V/ $\mu$ s 以上で駆動する場合はモジュールの緩和時間よりも短い期間で電圧が立ち上がるため、接合容量による電圧分担が支配的となる。本モジュールでは漏れ抵抗のばらつきに比べ、接合容量のばらつきが小さいため、スイッチング過渡状態の分担電圧のばらつきは小さく、高周波化が可能である。

### 3 高周波高電圧電源の昇圧方式に関する検討

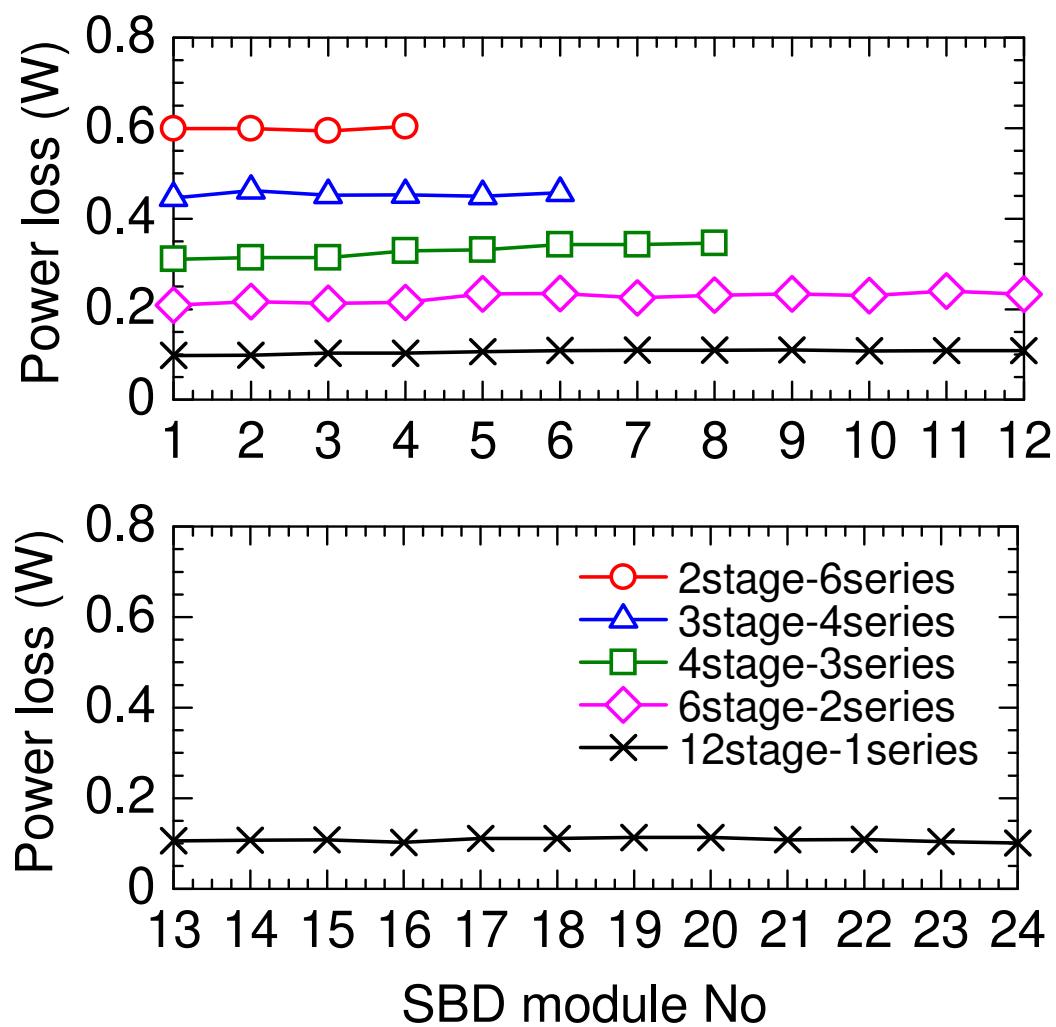

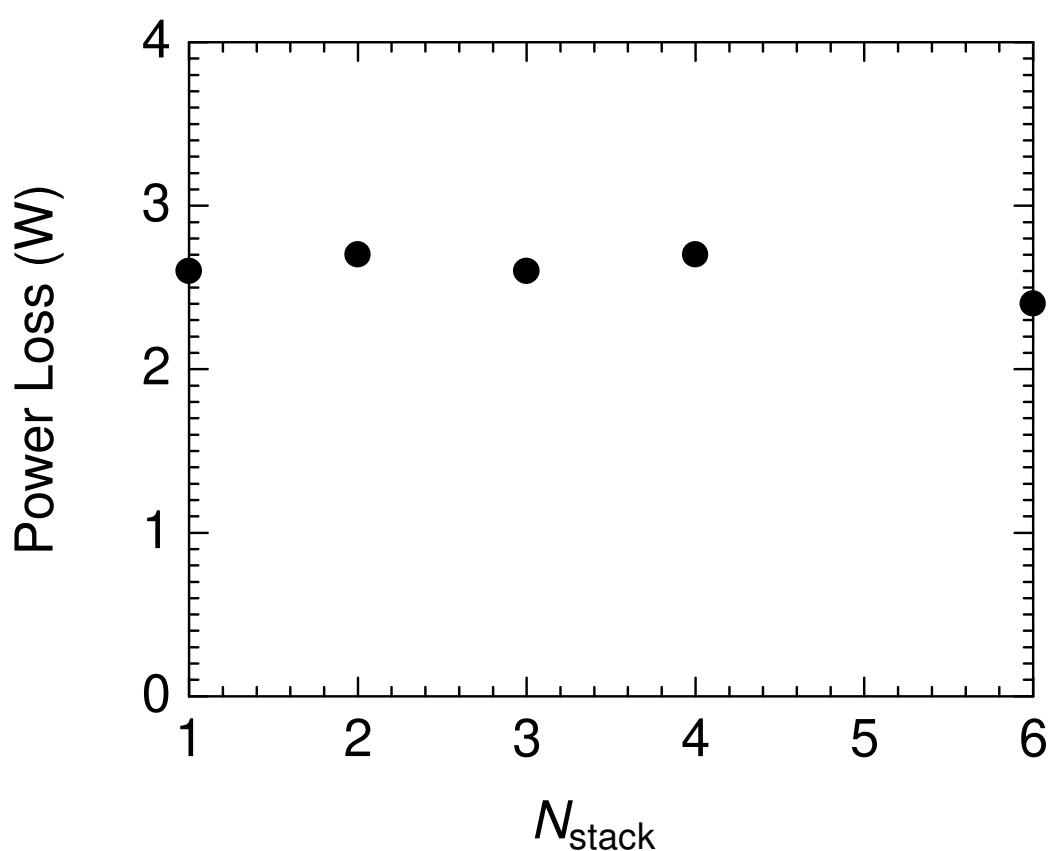

本研究では高周波 Cockcroft-Walton 回路で要求されるような超高耐圧の整流ダイオードとして、SiC SBD を 10 直列に接合した超高耐圧 SiC SBD モジュールの開発を行ってきた [23]。開発した SiC SBD モジュールは素子の直列数により任意の耐圧を設計することができ、更なる高耐圧化も可能である。ただし、モジュール化した場合、導通損失によるモジュールの発熱密度も直列数に応じて大きくなることから、熱的制約による高耐圧化の限界もある。そこで本章では多段式高電圧電源に用いる高周波 Cockcroft-Walton 回路の性能向上に有効な SBD の直列数について、Cockcroft-Walton 回路の段数と合わせて検討する。絶縁試験器やプラズマ発生装置の用途として必要な 10kV 級の高電圧電源を想定して、損失低減の方法に有効な回路構成を提案する。表 3.1 に示す電源仕様を満たすような Cockcroft-Walton 回路の段数と SiC SBD モジュールの組み合わせを設計し、損失をシミュレーションで評価した。Cockcroft-Walton 回路の段数と SBD の直列数は後述するように 2 段 6 直、3 段 4 直、4 段 3 直、6 段 2 直、12 段 1 直の 5 つの組み合わせを検証し、損失低減に有効な回路構成を導いた。また更なる高出力化に向けて、超高耐圧ダイオードモジュールを用いた高周波高電圧電源の効率的な設計方法についても議論を行った。

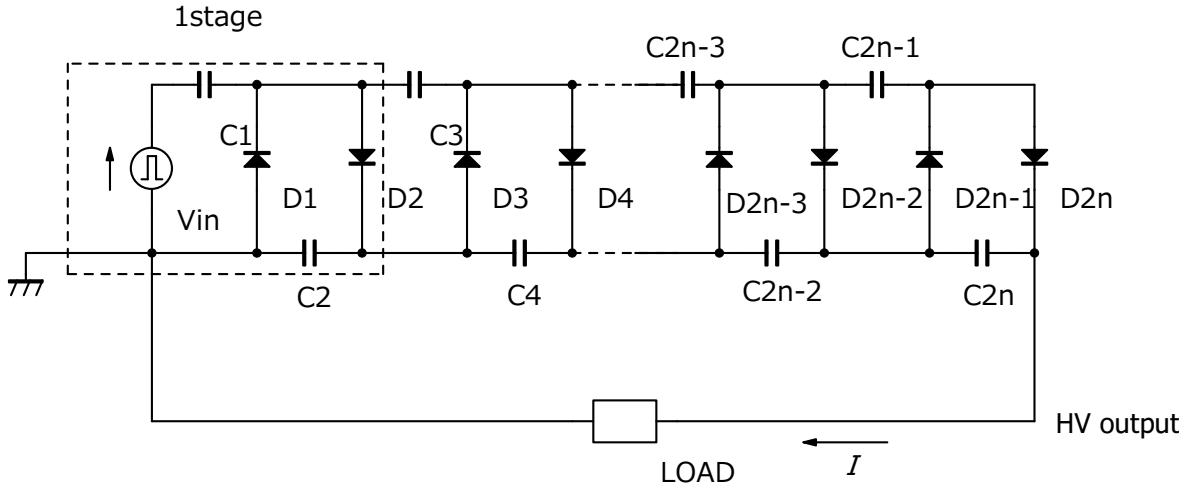

#### 3.1 Cockcroft-Walton 回路の段数と SBD の直列数の関係

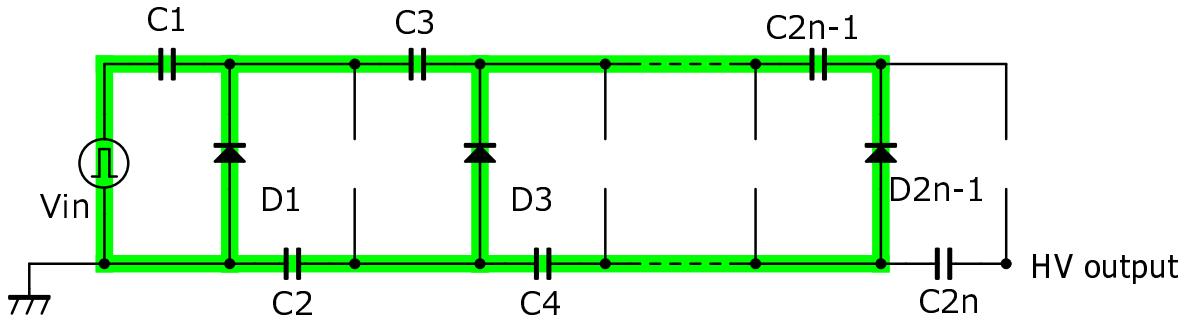

本節では Cockcroft-Walton 回路の動作原理を詳述し、回路の段数とダイオードの印加電圧の対応関係を明らかにした上で、段数と直列数の組み合わせの議論へつなげる。Cockcroft-Walton 回路は図 3.1 に示すように、ダイオードとコンデンサで構成された交流入力型の直流高電圧発生回路である。図 3.1 の破線部で示す部分を 1 段とし、段数を変えることで出力電圧を変えることができる。またダイオードとコンデンサの印加電圧は入力電圧  $V_{in}$  の 2 倍程度で済むため、低耐圧素子で高電圧回路を構成できるという長所があり、高電圧応用分野で広く使われている [24]。

入力電圧  $V_{in}$  の極性が図 3.1 の矢印の向きと逆の場合、奇数番目のダイオード  $D_1, D_3, \dots, D_{2n-1}$  が導通するため、図 3.2 に示す電流パスが形成され、奇数番目のコンデンサが充電される。極性が変わって入力電圧  $V_{in}$  の向きが反転すると、奇数番目のダイオードは遮断モードとなり、逆に偶数番目のダイオード  $D_2, D_4, \dots, D_{2n}$  が導通する。このため、図 3.3 に示すように偶数番目のコンデンサ  $C_2, C_4, \dots, C_{2n}$  への充電が始まる。1 周期で偶数番目のダイオードも奇数番目のダイオードも 1 回ずつ導通し、これを周期毎に繰り返すことで各コンデンサは電源側から電荷を供給され、出力に高電圧が発生する。

表 3.1 評価を行う電源の仕様

|                       |             |

|-----------------------|-------------|

| Frequency             | 100kHz      |

| Output power          | 300W        |

| Output voltage        | 10kV        |

| Output voltage ripple | $\leq 100V$ |

図 3.1 Cockcroft-Walton 回路

図 3.2 入力電圧が負の時の電流パス

$D_1$  が導通すると  $C_1$  の電圧は入力電圧  $V_{in}$  まで充電される。極性が変わり、 $D_1$  が遮断され、 $D_2$  を介して  $C_2$  への充電が始まると  $C_2$  の電圧は入力電圧  $V_{in}$  に  $C_1$  の電圧が加算され、入力電圧の 2 倍まで充電される。2 段目はコンデンサ  $C_2$  を基準として  $C_3$  を  $2V_{in}$  だけ、 $C_4$  を  $2V_{in}$  だけそれぞれ充電する。したがって  $C_4$  の対地電位はコンデンサ  $C_2$  の電圧に  $C_4$  の電圧を加算して  $4V_{in}$  となる。同様の手順で、 $n$  段目の出力ノードの電位は  $2nV_{in}$  となるため、 $n$  段 Cockcroft-Walton 回路の無負荷状態の出力電圧  $V_n$  は式 (3.1) で与えられる。

$$V_n = 2nV_{in} \quad (3.1)$$

負荷が接続されると出力端から負荷電流  $I$  が流れる。このため、各コンデンサは負荷電流に伴う放電と流出した電荷を補うための電源側からの充電を繰り返し、これによるリップル電圧  $V_{ripple}$  が発生する [25]。1 周期で負荷へ流出する電荷  $q$  は駆動周波数を  $f$  とすると、 $q = I/f$  である。コンデンサ  $C_2, C_4, C_6, \dots, C_{2n}$  は直列接続されているためにすべてのコンデンサで電荷  $q$  が放電する。次の周期までに、 $C_{2n-2}$  は負荷と  $C_{2n-1}$  に電荷  $q$  ずつ供給する必要がある。 $C_{2n-4}$  は負荷、 $C_{2n-3}$  および  $C_{2n-2}$  に電荷  $q$  ずつ放電するため、合計で  $3q$  だけ電荷を放出する。同様の手順を踏まえると、 $n$  段 Cockcroft-Walton

図 3.3 入力電圧が正の時の電流パス

回路のリップル電圧  $V_{\text{ripple}}$  は Cockcroft-Walton 回路のコンデンサがすべて同じ容量  $C$  であるとき、式 (3.2) で表現できる [25]。

$$\begin{aligned} V_{\text{ripple}} &= \frac{I}{fC} \left( \frac{1}{C_{2n}} + \frac{2}{C_{2n-2}} + \frac{3}{C_{2n-3}} + \dots + \frac{n}{C_2} \right) \\ &= \frac{I}{fC} \frac{n(n+1)}{2} \end{aligned} \quad (3.2)$$

式で (3.1) で与えられる無負荷電圧に対して負荷状態では電圧降下  $V_{\text{drop}}$  が発生する。コンデンサ  $C_2$  は各サイクル中に  $nq$  だけ電荷を失うので、コンデンサ  $C_1$  と  $C_2$  はそれぞれ  $V_{\text{in}} - nq/C_1$  と  $V_{\text{in}} - nq/C_2$  までしか充電することができない。同様に  $C_3$  で  $2V_{\text{in}} - 2nq/C_3$  までの充電となるため、高電圧側のコンデンサほど電圧降下量が大きくなる。Cockcroft-Walton 回路のコンデンサがすべて同じ容量  $C$  であるとき、電圧降下  $V_{\text{drop}}$  は一般化すると式 (3.3) で与えられる [25]。

$$V_{\text{drop}} = \frac{I}{fC} \left( \frac{2}{3}n^3 + \frac{n^2}{2} - \frac{n}{6} \right) \quad (3.3)$$

したがって負荷状態の出力電圧  $V_{\text{out}}$  は無負荷出力電圧  $V_n$  から電圧降下  $V_{\text{drop}}$  及びリップル電圧  $V_{\text{ripple}}$  を引いた式 (3.4) で与えられる [25]。

$$V_{\text{out}} = V_n - V_{\text{drop}} - \frac{1}{2}V_{\text{ripple}} \quad (3.4)$$

Cockcroft-Walton 回路において所望の出力電圧は段数  $n$ 、コンデンサ容量  $C$  及び入力電圧  $V_{\text{in}}$  で設計できる。Cockcroft-Walton 回路のコンデンサ容量  $C$  は負荷電流  $I$  に対して表 3.1 に示す要求されるリップル電圧  $V_{\text{ripple}}$  及び出力電圧  $V_{\text{out}}$  を満たすように設計式 (3.4) で決定する。ただし、Cockcroft-Walton 回路のコンデンサはすべて同じ容量  $C$  を用いるものとする。本研究では電源仕様より、出力電圧 10kV を満たすように Cockcroft-Walton 回路の段数  $n$  と SiC SBD の直列数を対応させることで、昇圧倍数の異なる Cockcroft-Walton 回路を設計する。ただし、段数が 12 段以上の場合は式 (3.1)～(3.4) より図 1.1 中の高電圧トランジスタの昇圧比が 1 以下となり、直流高電圧電源の構成として不適である。また段数が 1 段の場合は倍電圧整流回路であるため、考慮する段数は  $2 \leq n \leq 12$  と制約条件を設けた。前章までで示したように最大で 10 直列までの高耐圧モジュールを開発しており、素子の直列数を可変するこ

表 3.2 各回路構成で必要なコンデンサ容量と入力電圧

|                 | capacitance | Input voltage |

|-----------------|-------------|---------------|

| 2stage-6series  | 6.2nF       | 2.5kV         |

| 3stage-4series  | 20nF        | 1.7kV         |

| 4stage-3series  | 33nF        | 1.3kV         |

| 6stage-2series  | 72nF        | 0.92kV        |

| 12stage-1series | 260nF       | 0.51kV        |

とより、任意の耐圧が設計できる。しかし2段以上の段数において、必要な耐圧を満たすためには最大で6直列のダイオードモジュールで十分である。必要以上の直列化は導通損失が増加するため、6直列以上の構成は不要である。よって本章では実際に必要な耐圧を満たすために、最大で6直列までのダイオードモジュールを考える。SiC SBD の耐圧 1.2kV に対して、印加電圧を裕度 20% として 1kV と設定すると、段数と直列数の組み合わせとして 2 段 6 直、3 段 4 直、4 段 3 直、6 段 2 直、12 段 1 直がある。本モジュールは導通損失が支配的であるため Cockcroft-Walton 回路で発生する損失はモジュール印加電流と直列数によって決まるが、許容損失に対して直列数と印加電流の大きさはトレードオフの関係にある。すなわち、段数が多いほど低圧段での印加電流が大きくなり、その損失は電流の 2 乗に比例する。段数が少ないほどモジュールの耐圧は高くなり、オン抵抗が耐圧に比例して増加する。本研究では上述の Cockcroft-Walton 回路の段数と素子の直列数の組合せにおける損失をシミュレーションで評価した。仕様の出力電圧に対して Cockcroft-Walton 回路に用いる SiC SBD の総数は段数によらず 24 個となる。すなわち本検討は Cockcroft-Walton 回路での損失を目的関数とし、SiC SBD の総数を等式制約とした組合せ最適化に相当する。

式 (3.2), (3.3) より、降下電圧  $V_{\text{drop}}$  とリップル電圧  $V_{\text{ripple}}$  はコンデンサ容量  $C$  を増加させることで低減できるが、必要以上の大容量のコンデンサは電源の過渡応答を低下させると共に回路の体積が大きくなる。そこで各段数においてコンデンサ容量を最適化した。Cockcroft-Walton 回路では素子の印加電圧は入力電圧  $V_{\text{in}}$  の 2 倍程度である [25]。そのため、素子単体に直列数を掛けた素子耐圧が  $2V_{\text{in}}$  を超えるように制約条件の一つとして設定する。また電源仕様であるリップル電圧 100V 以下、出力電圧 10kV、出力電力 300W となる制約条件の下、入力電圧とコンデンサ容量を決定した。表 3.2 に各回路構成での必要なコンデンサ容量と入力電圧を示す。コンデンサ容量と入力電圧は段数  $n$  に対して互いにトレードオフの関係にある。高耐圧のコンデンサになるほど体積が大きくなる傾向にあるが、Cockcroft-Walton 回路の段数低減はコンデンサ容量の低減に有効である事がわかる。

表 3.3 シミュレーション条件

|                                |                                                                                                                                                                                                  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input voltage ( $V_{in}$ )     | 100Vac, 100kHz                                                                                                                                                                                   |

| Output impedance ( $Z_{out}$ ) | $1.5\Omega + 0.50\mu H$                                                                                                                                                                          |

| Capacitor ( $C_1 - C_{2n}$ )   | 2stage-6series 615R150GAD (10nF[10parallel], ESR=0.11Ω, ESL=40nH)<br>6stage-2series MKP1839410134HQ (100nF, ESR=250mΩ, ESL=70nH)<br>12stage-1series MKP1839439134HQ (390nF, ESR=7.0mΩ, ESL=68nH) |

| Line inductance ( $L_{line}$ ) | 24nH                                                                                                                                                                                             |

| Load resistance ( $R_{load}$ ) | 100kΩ                                                                                                                                                                                            |

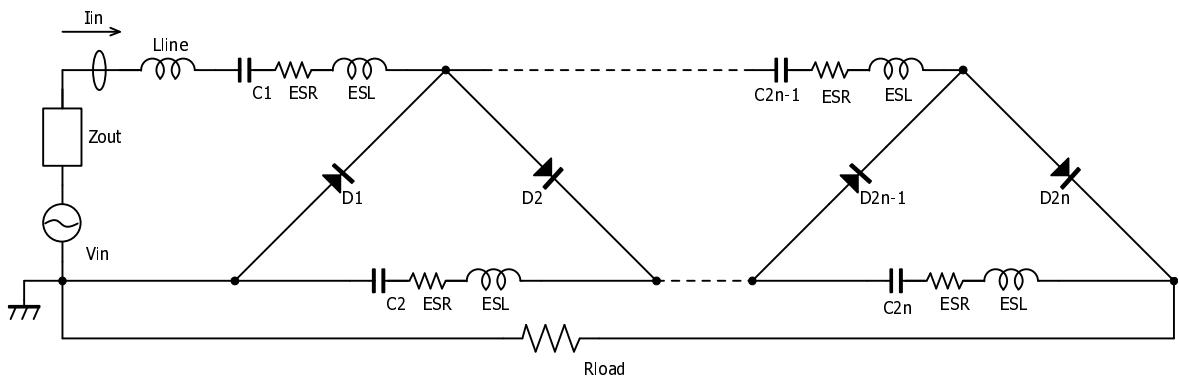

図 3.4 シミュレーションで考慮した回路

### 3.2 シミュレーションの妥当性の確認

シミュレーションを用いた損失評価を行う前段階として、実験とシミュレーション結果を比較し、シミュレーションモデルの妥当性を検証する。検証実験では2段6直、6段2直、12段1直のCockcroft-Walton回路に対して振幅100V、周波数100kHzの正弦波電圧を印加し、入力電流 $I_{in}$ を測定する。シミュレーションでは実験に用いた部品を等価回路モデルとして模擬する。表3.3に実験条件を図3.4に実験回路を示す。ダイオードモジュールは素子単体のIV特性、CV特性をモデル化し、分担電圧がすべて同一として直列数を1直、2直、6直と変えたダイオードモジュールのモデルを用いてシミュレーションを行った。実装するコンデンサは各場合で異なるため、静電容量、等価直列抵抗(ESR)及び等価直列インダクタンス(ESL)をインピーダンスアナライザ4294A(Agilent)で部品ごとに測定した。その他、配線のインダクタンス成分 $L_{line}$ についても同様にインピーダンスアナライザで測定を行った。またパワーアンプHSA4101(NF Corporation)の出力インピーダンス $Z_{out}$ はデータシート記載の値を用いて、電圧源に対して直列に接続するテブナン型等価回路として扱った。

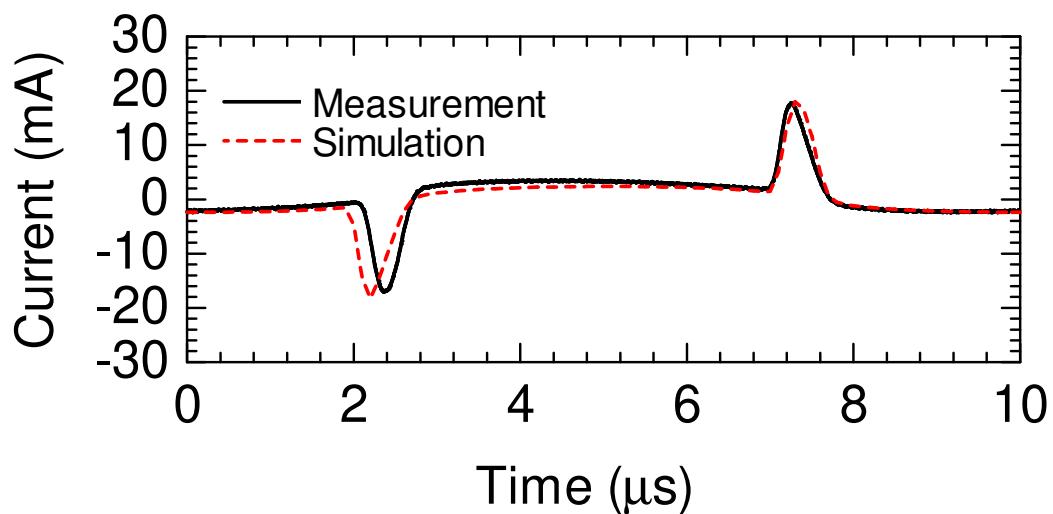

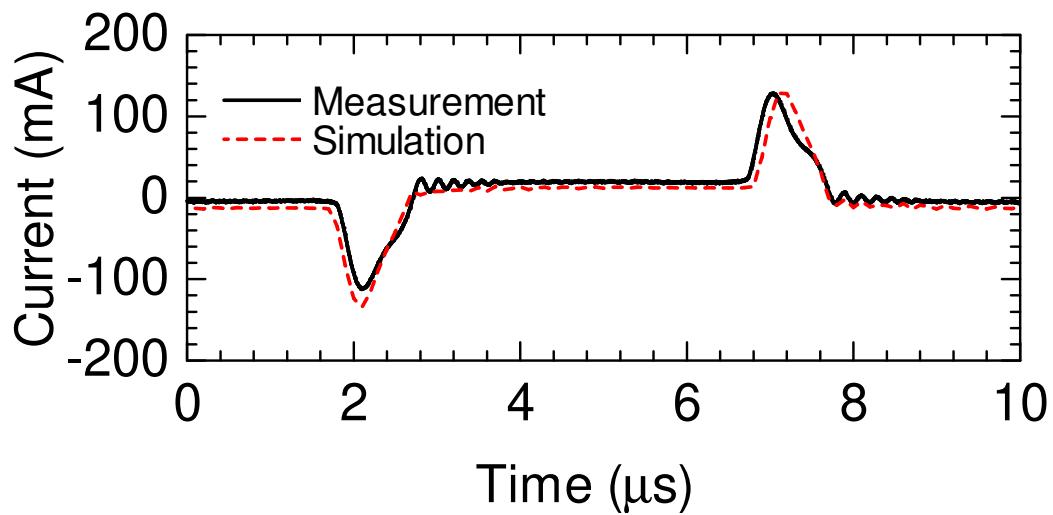

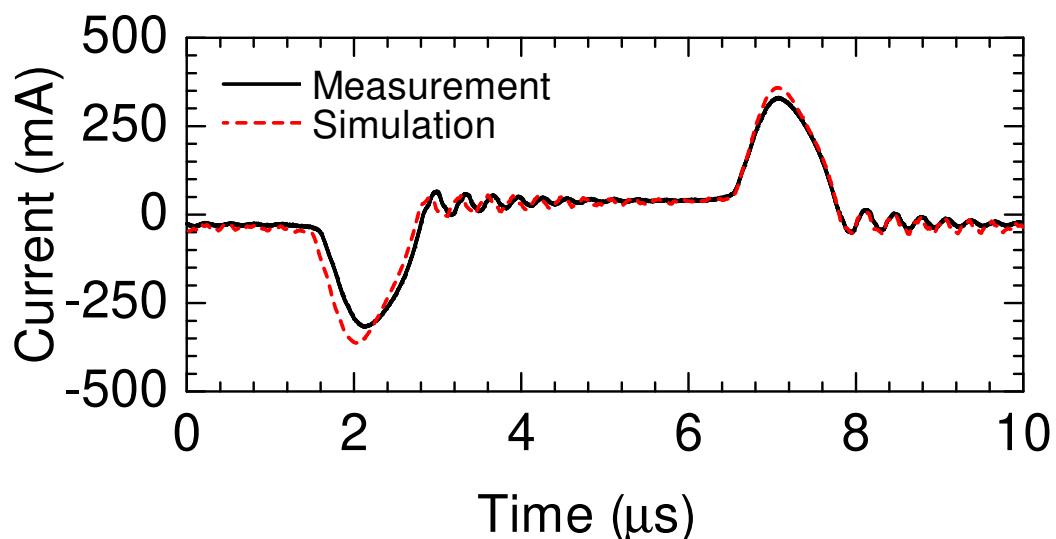

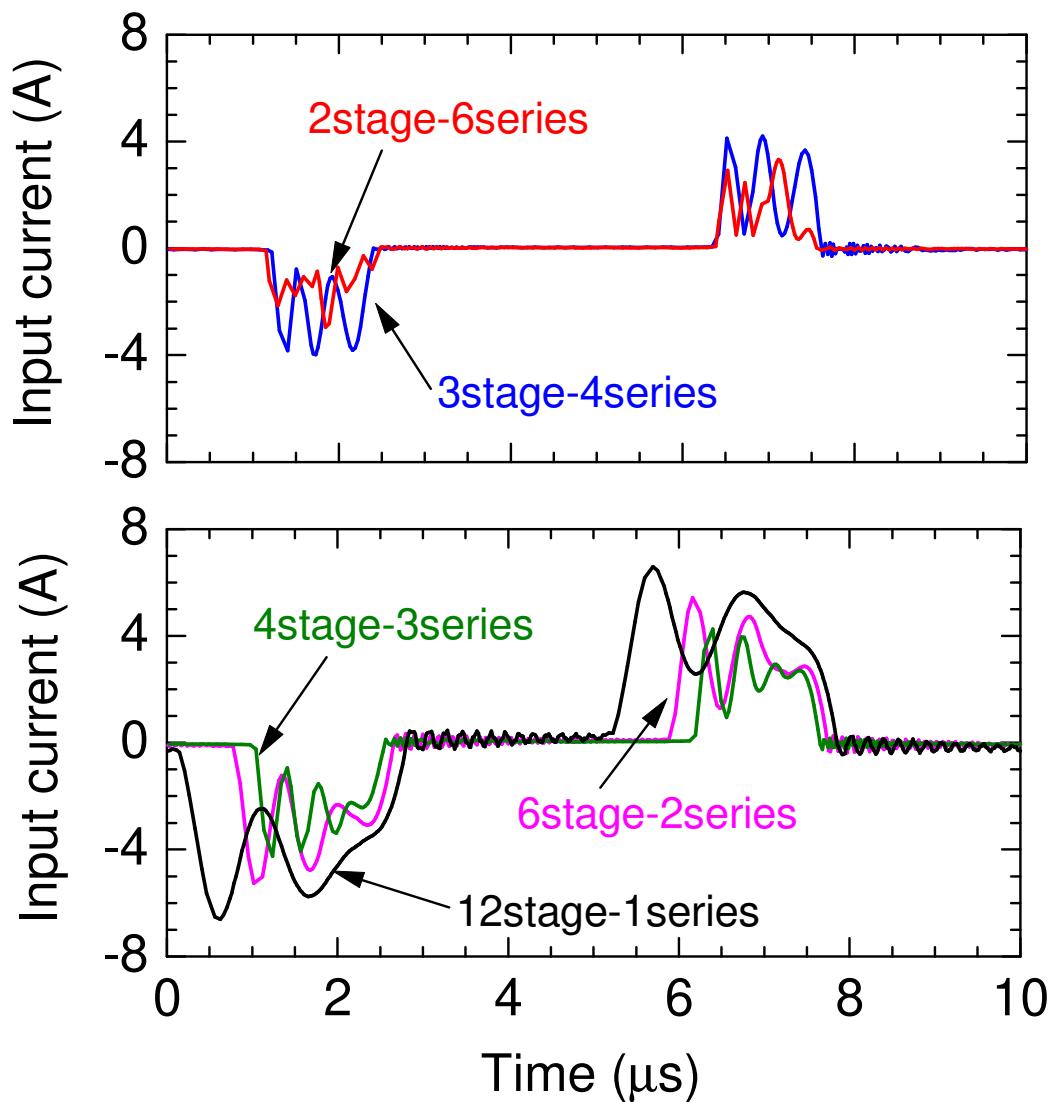

図3.5、3.6、3.7は各構成における入力電流 $I_{in}$ の時間応答である。実測と計算結果は良好に一致している。またダイオードモジュールの消弧時に発生するリングング振動の周波数も一致しており、シミュレーション上でCockcroft-Walton回路の動作を正確に模擬できている。次節では本ダイオードモジュ

図 3.5 2段 6直構成における入力電流の時間応答

ルモデルを使って、段数構成の異なる Cockcroft-Walton 回路の損失を解析し、損失低減に有効な SBD の直列数と Cockcroft-Walton 回路の段数構成について提案する。

図 3.6 6段2直構成における入力電流の時間応答

図 3.7 12段1直構成における入力電流の時間応答

### 3.3 モジュール直列数と電力損失の関係

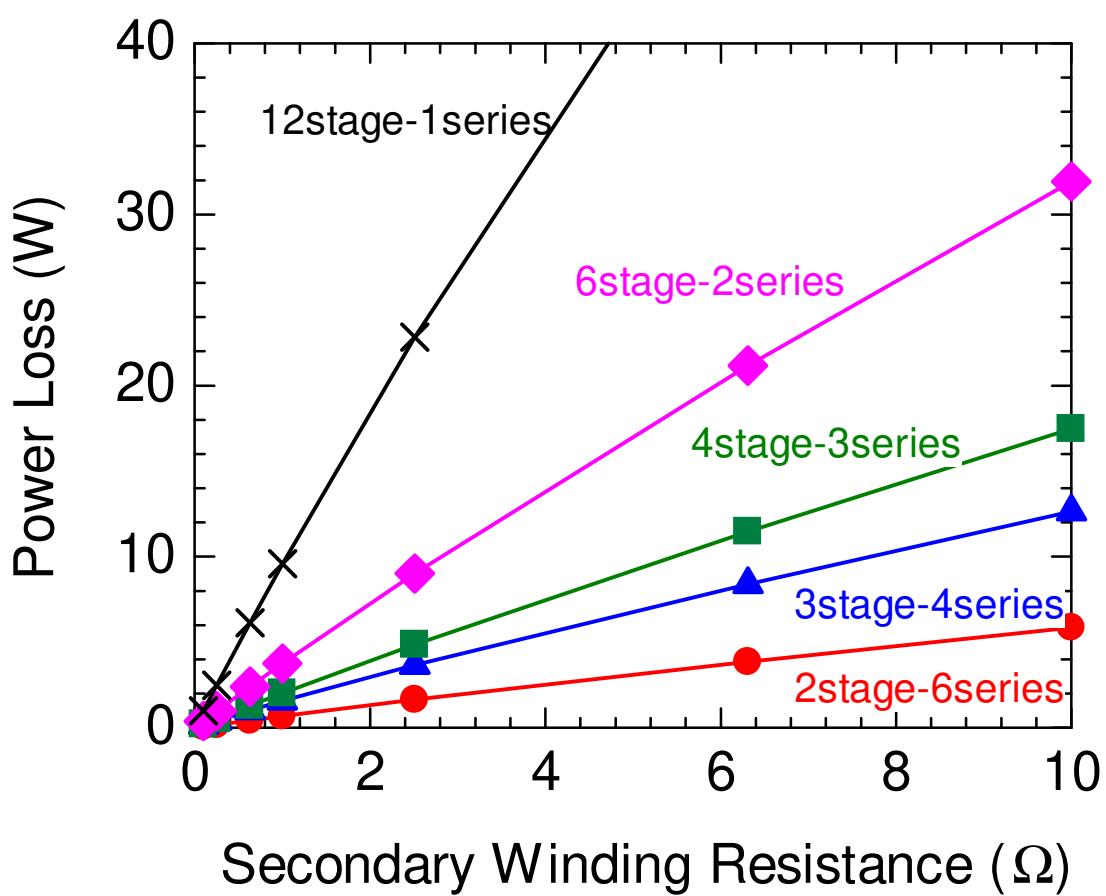

Cockcroft-Walton 回路のコンデンサには ESR が、トランスの 2 次巻線には巻線抵抗があり、これらにより導通損が生じる。本節では各構成において、回路に含まれる寄生抵抗による導通損を評価する。ただし、シミュレーション回路は図 3.4 とする。また各構成における部品やその寄生成分はそれぞれ表 3.3 に従うものとする。

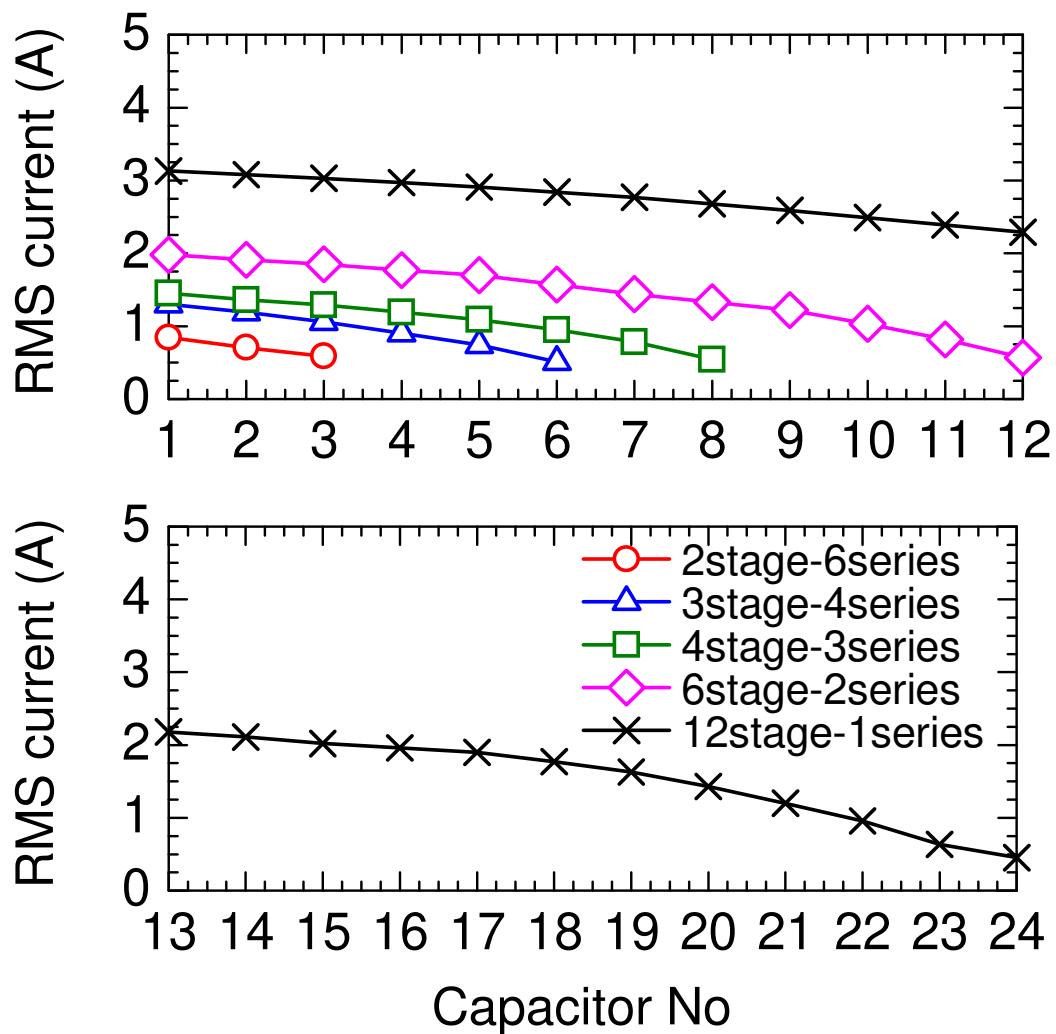

図 3.8 は各段数構成における Cockcroft-Walton 回路の入力電流の時間応答である。Cockcroft-Walton 回路の入力電流の通流幅とピーク値は多段化に伴って増加し、電流実効値が増大する。シミュレーション上でトランスの 2 次巻線抵抗をパラメータとして、巻線抵抗に対する導通損を評価した。図 3.9 に結果を示す。導通損失は巻線抵抗に比例し、巻線抵抗は巻数に比例するが、一方で銅損は電流の 2 乗にも比例する。そのため、段数が少ない構成ほど電流実効値が小さく、巻線抵抗における導通損失を効果的に減らすことができる。Cockcroft-Walton 回路の段数の低減は高電圧トランスにおける 2 次側巻線の銅損を抑制する効果があり、回路損失の低減に有効である。

Cockcroft-Walton 回路には段数の 2 倍の数のコンデンサが必要となる。各構成でコンデンサの ESR による導通損失を評価するため、各コンデンサの充電電流の時間応答から実効値を計算した。結果を図 3.10 に示す。ただし、横軸はコンデンサの番号を示し、図 3.4 に示すように低圧段から 1, 2, 3... と連番を振った。低電圧側のコンデンサほど充電電流は大きいことから、コンデンサの充放電損失は低圧側で支配的である。また多段化すると充電電流が増加し、段数分のコンデンサを充電する必要があるためコンデンサの充放電損失は増加する。

図 3.11 に各 SBD モジュールで生じる損失を、図 3.12 にすべての SBD モジュールで生じる損失の合計を各場合でそれぞれ示す。本モジュールは SiC SBD のチップ単体を直接直列に接続しており、オン抵抗と立ち上がり電圧が直列数  $N_{\text{stack}}$  に比例するため、モジュールの導通損失は直列数  $N_{\text{stack}}$  に応じて増加する。直列数  $N_{\text{stack}}$  の多いモジュールほど素子当たりの損失は増えるが、最も直列数の多い 2 段 6 直の場合でも高々 0.60W 程度であり、十分に低損失といえる。一方で直列数の少ない SiC SBD モジュールはオン抵抗と立ち上がり電圧が小さいため、モジュール当たりの損失は小さく設計できるが、モジュールの数が多いことや Cockcroft-Walton 回路の多段化に伴う印加電流の増加により、全体で生じる損失はほとんど変わらない。多直列化した SiC SBD モジュールと Cockcroft-Walton 回路の段数低減の効果により、寄生抵抗による導通損失の抑制が期待できる。

図 3.8 各構成における入力電流の時間応答

図 3.9 各構成における巻線抵抗に対する導通損

図 3.10 各構成におけるコンデンサの充放電電流の実効値

図 3.11 各構成における SBD での損失

図 3.12 直列数に対する全モジュールの損失

SiC SBD を多直列したダイオードモジュールモデルを高周波 Cockcroft-Walton 回路へ適用し、損失低減に有効な回路構成について検討した。SiC SBD の直列数を増加することにより、Cockcroft-Walton 回路の1段の電圧を高くすることができ、Cockcroft-Walton 回路の段数を低減することができる。段数を減らした Cockcroft-Walton 回路は入力電流が低減できるため、高電圧トランスの銅損及びコンデンサの ESR 損失の低減につながる。SiC SBD モジュールの素子の直列数の増加に伴って、オン抵抗と立ち上がり電圧は増加するが、段数低減によって電流実効値が減るためにモジュールでの導通損失は直列数にほとんど依存せず、高効率に電力変換が実現できる。

本研究では素子単体あたりの印加電圧を固定し、Cockcroft-Walton 回路の段数を変えることによる電力変換に与える影響を評価した。さらに高電圧化を図る場合にも本評価結果が援用できる。すなわち、高電圧化に伴って Cockcroft-Walton 回路の多段化と入力電圧の増加が求められるが、ダイオードモジュールの直列数を可能な限り増やし、Cockcroft-Walton 回路の段数を減らすことでトランスの2次巻線の銅損や Cockcroft-Walton 回路におけるコンデンサの ESR 損を効果的に減らすことができる。また、より電流定格の大きな素子への代替や素子の並列化によって、さらなる大電力化にも対応ができる。

## 4 高耐圧 SiC SBD モジュールを用いた高電圧直流電源の高周波動作

本章では、高耐圧 SiC SBD モジュールを用いた高電圧直流電源の高周波動作について検討する。高周波動作における課題である回路基板の寄生成分の影響を解析する。PCB 配線やデバイス構造由来の寄生成分はベクトルネットワークアナライザ (VNA) を用いて測定した。測定結果を基に、基板およびパッケージ内での寄生インダクタンスや容量の影響をモデル化し、回路動作への妥当性を確認する。これにより高電圧インバータ回路や Cockcroft-Walton 回路における電圧サージの評価が可能となり、寄生成分の影響を定量的に評価できることを示した。

また開発した SiC SBD モジュールを高周波 Cockcroft-Walton 回路に適用した。従来の Si PiND モジュールと比較し、開発した SiC SBD モジュールは逆回復電流がほとんど流れないとため、高速スイッチング時のリング振動が抑制される。これによりスイッチング損失が大幅に低減され、パッケージ温度の上昇も抑制されることを確認した。高周波動作時でも優れた熱特性を示すことが明らかとなった。

さらに開発したモジュールの大電力・高周波動作下における動作温度を検証した。300kHz 動作条件下で、出力電力が 452W の場合でもパッケージ表面温度の上昇がほとんど見られない。高周波高電圧直流電源の構成要素に開発した SiC SBD モジュールを用いることで、高効率化が可能である。

### 4.1 ベクトルネットワークアナライザ (VNA) を用いた回路寄生成分の同定

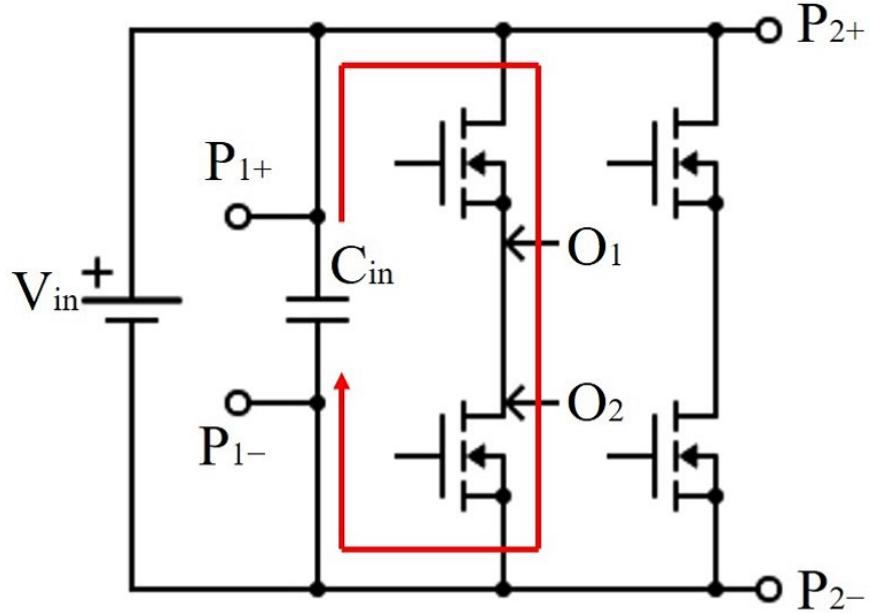

電源の小型化には駆動周波数の高周波化が必要であり、SiC パワーデバイスを用いることで実現可能である。高周波動作を実現するための高速スイッチングにおいてプリント基板 (PCB) の配線で構成するパワーループが持つ寄生成分がサージ電圧に与える影響が顕著となるため、パワーループの寄生成分を正確に同定する必要がある。本節では高電圧直流電源を構成するフルブリッジインバータについて、寄生成分の抽出を行い、その妥当性を検証した。

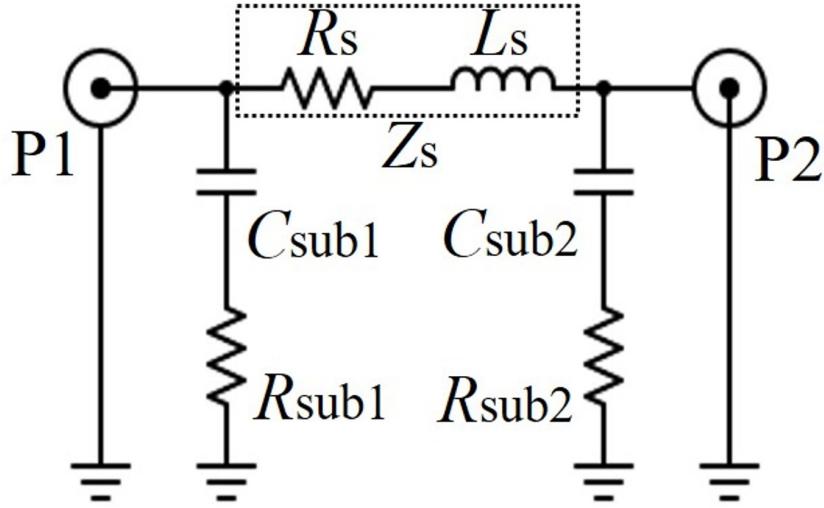

PCB 配線の寄生インダクタンス測定は、ネットワークアナライザ (VNA) を用いたシャントスルーフ法が適用可能である [26]。文献 [26] では図 4.1 に示すフルブリッジ回路の  $P_{1+}$ ,  $P_{2+}$  及び  $P_{1-}$ ,  $P_{2-}$  をそれぞれポートとして測定し、図 4.2 に示す基板配線の等価回路から寄生成分  $R_s$ ,  $L_s$  を抽出している。しかし本方式では図 4.1 の O1-O2 間の寄生成分については検討できていない。またシャントスルーフ法は 2 ポート測定であるものの、得られる結果は 1 ポート成分のみに相当する。すなわち基板の寄生容量  $C_{\text{sub}1}, C_{\text{sub}2}$  を通る電流パスに対してその影響を除去できるフル 2 ポート測定が望ましい。また文献 [26] ではプローブ先端を測定部に押し付ける測定方式であり、測定の再現性がプロービング圧に左右されることが言及されている。再現性を確保するためには測定ポートの位置を治具等で固定することが重要である。

本研究では新たに基準 GND 面を配置し、 $P_{1+}$ ,  $P_{1-}$  を測定ポートとしたフルブリッジ回路のパワーループに対してフル 2 ポート測定を検討する。MOSFET が実装される  $P_{2+}$ -O1 間及び O2-P<sub>2-</sub> 間

図 4.1 フルブリッジインバータのパワーループ

はショートバーで短絡し、固定した測定ポートの位置に対してVNAのポート拡張機能を適用することでパワーループの寄生成分のみ評価する。P端子およびN端子に電源が接続される。高電圧インバータでは配線間の絶縁距離を大きくとる必要があり、測定位置やプローブ圧によってSパラメータが変化する。そこで、パワーループ一巡の始点と終点であるP端子およびN端子からストリップ線路を基板外側に拡張し、接続用のSMAエッジターミナルを外側に張り出すように配置することで測定ケーブルとの固定を確実にする。ストリップ線路はケーブルやVNAの特性インピーダンスと整合するように、線路インピーダンスが $50\Omega$ となるように設定する。また拡張部のインピーダンスは校正用基板とVNAのポート延長機能を用いることで除去する。外側方向に測定ポートを伸ばすことで、VNAとの接続を端子で固定することができ、パワーループのみの寄生成分が測定できる。

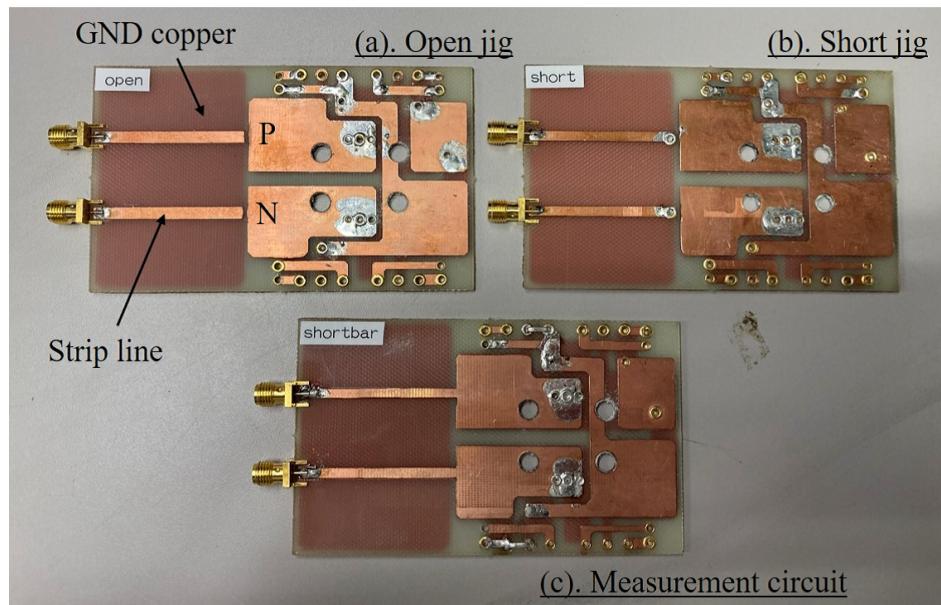

図4.3(a)はオープン校正用基板、(b)はショート用基板である。測定前にオープン基板とショート基板で構成に示すようにP,N端子にストリップ線路を接続し、先端にSMAエッジターミナルを配置することでVNAの測定ケーブルと接続する。ストリップ線路の特性インピーダンスが $50\Omega$ となるように線路幅:2.8mmとした。ただし、用いた基板の材質はガラスエポキシであり、誘電率:4.6、基板厚:1.7mm、銅箔厚さ:35μmである。また裏面の銅箔は2ポート測定における基準GND面とする。測定ケーブルとSMA端子は締め付けトルク0.90N·mで接続した。

VNAで測定されるSパラメータから、ストリップ線路の影響を除去する必要がある。測定ケーブルの端面で校正後、VNAのポート延長機能を用いることで、測定面をストリップ線路先端に移動させる。ストリップ線路先端でopenとshort校正を行うため、図4.3に示すopen校正用基板(a)とshort校正

図 4.2  $\pi$  型等価回路による PCB 配線の模擬

用基板 (b) を用いる。

open 基板は線路先端で開放し, short 基板は線路先端で背面の GND プレーンとビアを介して短絡している。測定面の移動後, 図 4.3(c) 中の FET 部分をショートバーで短絡した measurement 基板を用いてパワーループ寄生成分を測定する。上述した測定方法に従ってポート延長を施し, measurement 基板のフル 2 ポート測定を行う。VNA の測定値の最大誤差  $\Delta S_{11}^{\max}$  は式 (4.1) 及び (4.2) で与えられ, 測定対象のインピーダンスに依存する。

$$\Delta S_{11}^{\max} = |D| + |R - 1| \cdot S_{11} + |R| \cdot |M| \cdot S_{11}^2 \quad (4.1)$$

$$\begin{aligned} \Delta S_{21}^{\max} = & (|T - 1| + |M| \cdot S_{11} + |L| \cdot S_{22} \\ & + |M| \cdot |L| \cdot S_{21} \cdot S_{12}) S_{21} + |X| \end{aligned} \quad (4.2)$$

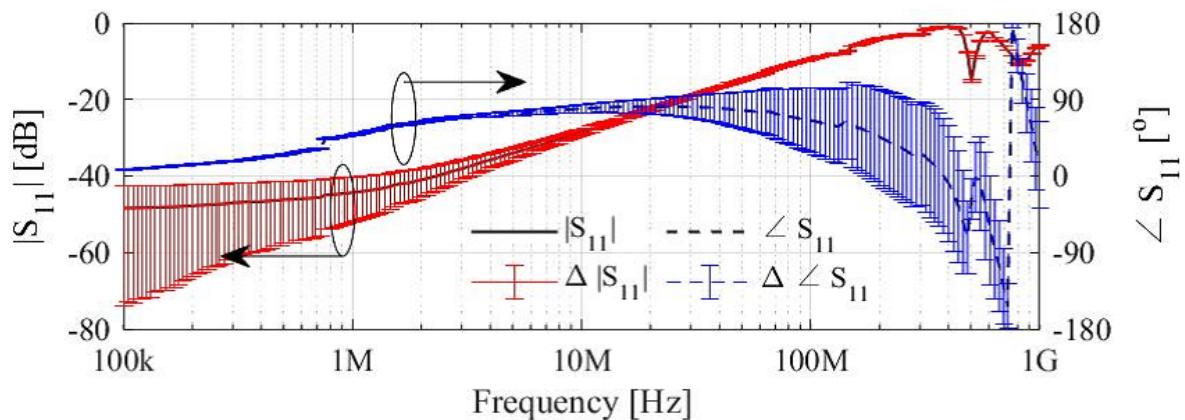

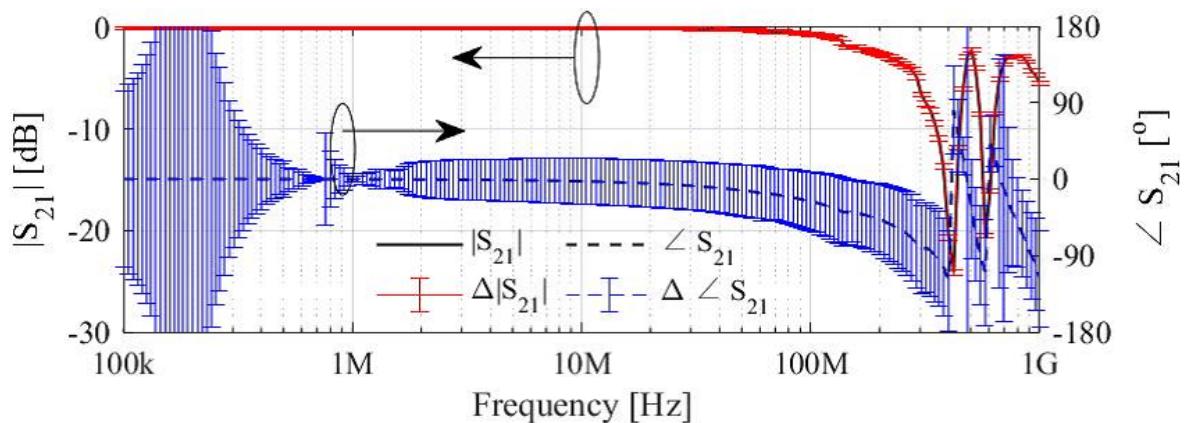

表 4.1 に示す IFBW = 10Hz, 入射信号の振幅  $P_m = 0\text{dB}$  における VNA(E5061B, Keysight) の仕様より, 測定した S パラメータ及びその誤差範囲を図 4.4 及び図 4.5 に示す。ただし,  $D$  は測定ポートの指向性,  $R$  は反射トラッキング,  $T$  は透過トラッキング,  $L$  はロードマッチ,  $M$  はソースマッチ,  $X$  はアイソレーションである。 $S_{11}$  は 100kHz – 1MHz で振幅の 100MHz – 1GHz で位相の測定の不確かさが増加するため, 基板配線の寄生成分を抽出する際は  $f = 10\text{MHz}$  での S パラメータを使用する。 $S_{21}$  についてはこの周波数における不確かさは小さい。

基板の等価回路モデルは図 4.2 に示す  $\pi$  型等価回路として定義し, S パラメータから Y パラメータへ

図4.3 測定ポートを拡張したフルブリッジインバータ基板

表4.1 ネットワークアナライザE5061Bの仕様

| D (dB) | M (dB) | L (dB) | R     | T     | X (dB) |

|--------|--------|--------|-------|-------|--------|

| 49     | 41     | 49     | 0.011 | 0.019 | 120    |

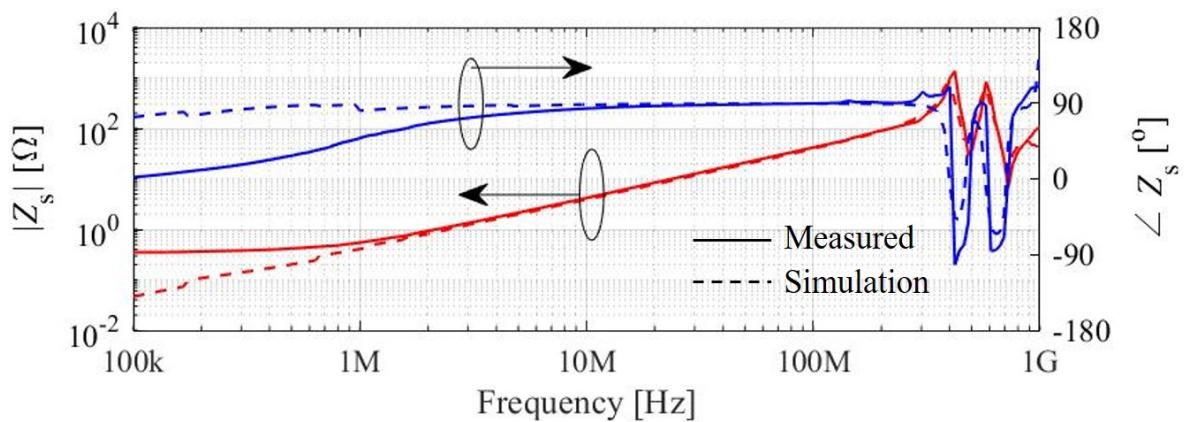

変換することで寄生成分を抽出する。また測定の妥当性を検証するために電磁界解析を用いて基板配線のインダクタンス成分を算出した。電磁界解析にはADS(Advanced Design System, Keysight)を使用し、モーメント法を用いたSパラメータ解析を行う。測定と同様に求まったSパラメータをYパラメータに変換し、 $\pi$ 型等価回路の寄生成分を算出する。図4.2中の $Z_s$ に関して、実測結果及びシミュレーション結果を図4.6に示す。1MHz – 500MHzの領域において測定結果と解析結果は良好に一致している。実測結果及び電磁界解析の $f = 10\text{MHz}$ で抽出した寄生インダクタンスはそれぞれ62nH, 64nHであり、誤差率は2%以下である。抽出したインダクタンスは配線自体が持つ自己インダクタンスだけでなく、パワーループを構成する配線間の相互インダクタンスも含まれている。本手法はフル2ポート測定のため基板の寄生容量に流れる電流パスを除去でき、VNAの測定精度からパラメータ抽出する周波数範囲を決定することで、PCB配線が持つ寄生インダクタンスを高精度に抽出することができる。

図 4.4  $S_{11}$  の測定の正確度図 4.5  $S_{21}$  の測定の正確度図 4.6 基板の  $Z-f$  特性

#### 4.2 Cockcroft-Walton 回路への SiC SBD モジュールの適用

10kV 以上の高電圧発生回路に単体の SiC SBD を適用する場合、式 (2.16) に示す耐圧とオン抵抗の関係により導通損失が耐圧の 2 乗に比例して大きくなる。開発した超高耐圧 SiC SBD モジュールは素子を複数個、直列接続することで耐圧と順方向特性のトレードオフを改良している。このため、本来耐圧の 2 乗に比例して大きくなる導通損失を耐圧に対して線形に抑えることができ、低損失化に寄与する。本節では開発した SiC-SBD モジュールにおける高周波動作の優位性を示すために、従来の Si PiND の諸特性を比較検討する。

開発した SiC SBD モジュールと同定格の Si PiND モジュール ESJC16-12X(Fuji Electric) を図 2.17 に示す。両モジュールの公称耐圧は 12kV であり、パッケージ構造やサイズもほぼ同じである。本節では Cockcroft-Walton 回路に用いる高耐圧ダイオードとして、図 2.17 に示す SiC SBD モジュール及び Si PiND モジュールの静特性及び動特性をそれぞれ比較し、モジュールの導通時と遮断時における諸特性について議論し、開発した SiCSBD モジュールの高周波特性が従来の Si PiND モジュールに比べて優位であることを示す。

表 4.2 実験条件

|                 |                                                                                                                    |

|-----------------|--------------------------------------------------------------------------------------------------------------------|

| Output voltage  | 10kV                                                                                                               |

| Inverter        | frequency:100kHz<br>duty:0.46                                                                                      |

| CW circuit      | capacitor:3200pF<br>SiC SBD or Si PiND Module                                                                      |

| HV transformer  | turn ratio 1:10<br>primary Inductance : 306 $\mu$ H<br>coupling factor 0.996<br>self resonant frequency : 363.4kHz |

| Load resistance | 20M $\Omega$ (5W)                                                                                                  |

#### 4.2.1 SiC SBD モジュールを用いた Cockcroft-Walton 回路の高周波動作

本節では 2 段 Cockcroft-Walton 回路の高耐圧ダイオードに図 2.17 に示す開発した SiC SBD モジュール及び従来品の Si PiND モジュールを適用し、回路で発生する損失及び電力変換効率を実験的に評価する。負荷電力に対するモジュールの印加電圧、電流およびパッケージ表面温度に着目するため、本動作試験では抵抗負荷を考え、出力電圧が 10kV となるようにインバータ入力電圧を調整した。表 4.2 に測定条件を示す。インバータには SiC MOSFET(Rohm, SCT3080KL) を用いており、高電圧トランスは Mn-Zn 系フェライトコア PC95 材 (TDK) に巻数比 1:10 の割合で巻いた。

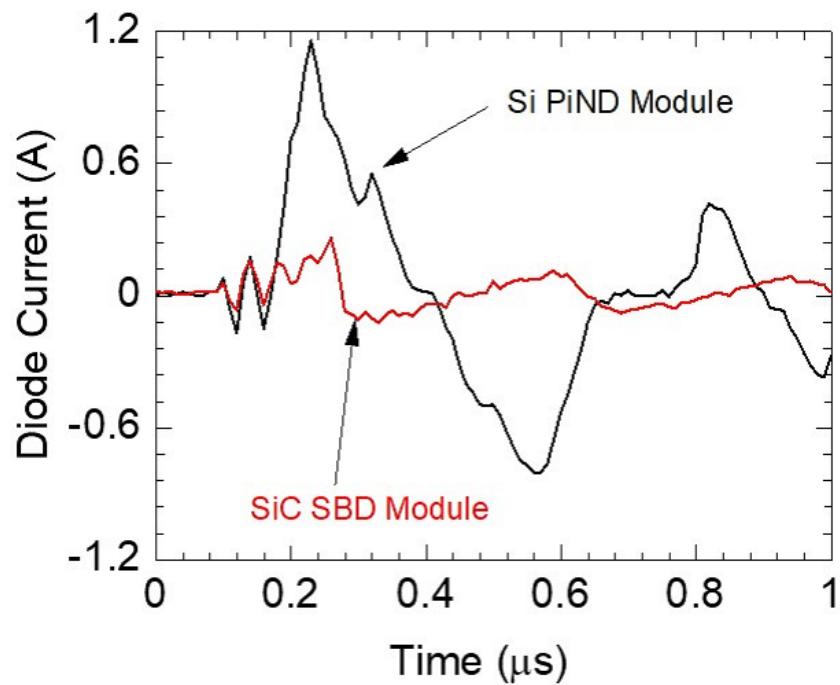

ダイオード D1 の電流と電圧を測定し、両モジュールのスイッチング特性を評価した。図 4.7 及び 4.8 に 2 段 Cockcroft-Walton 回路の 1 段目のダイオード (D1) の印加電流及び印加電圧の時間応答を示す。図 4.7 より、Si PiND モジュールではターンオン・ターンオフ共に少数キャリアの注入・掃き出しに時間を要するため、電流の導通期間が長く、スイッチングが遅い。特にターンオフ時に生じる逆回復現象によって、遮断状態に至るまでの時間が 0.29 $\mu$ sec と長く、スイッチング損失の増大を招く。また逆回復動作に伴うリングング振動によって 1 周期中に複数回ダイオードが点弧するため、導通損失及び逆回復損失がさらに増加する。これに対し SiC SBD モジュールでは逆回復現象が生じず、高速ターンオフが実現できている。また両モジュールは 0.6-0.7 $\mu$ sec でターンオンに伴う印加電圧の変化によって接合容量に変位電流が流れる。2 章で示した接合容量の大小関係より、SiC SBD モジュール端子間に生じる電圧のスルーレートは Si PiND モジュールに比べて 40% 程度低い。

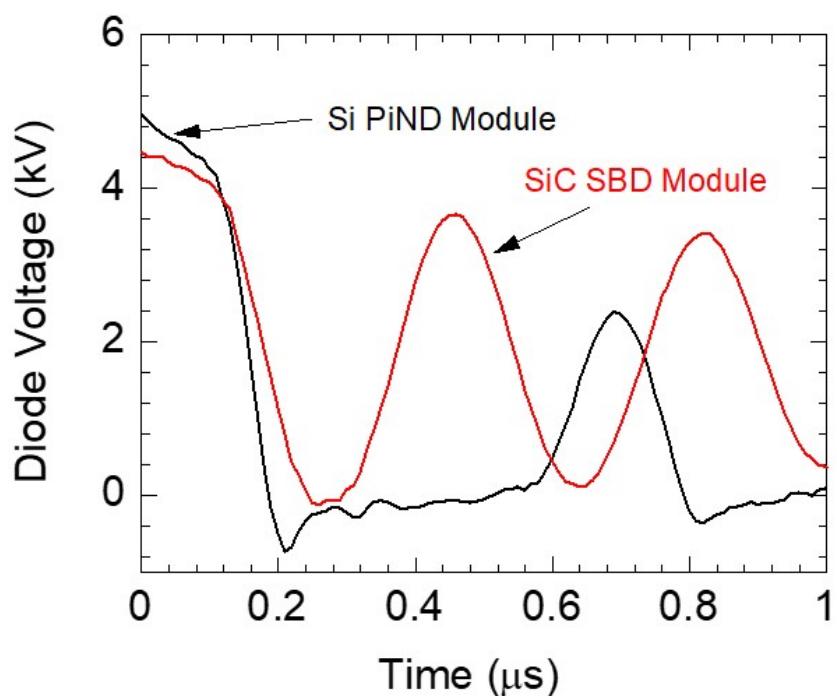

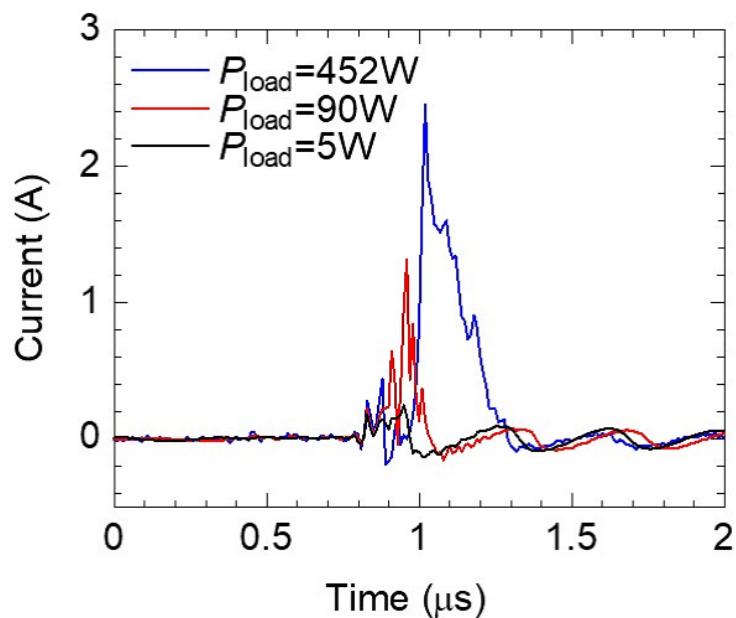

図 4.9, 4.10 は測定時の各モジュールのパッケージ表面温度である。SiC SBD モジュールでは素子の発熱は見られないが、Si PiND モジュールではスイッチング損失によって、パッケージ表面温度が 100°C を超える。このため、Si PiND モジュールを 100kHz 以上で動作させることは難しい。2 章で示したように開発した SiC SBD モジュールの静特性は Si PiND モジュールよりも劣っているが、高周波 Cockcroft-Walton 回路ではスイッチング損失が支配的であるため、素子で生じる損失は Si PiND モジュールが大きくなる。開発した SiC SBD モジュールを高周波 Cockcroft-Walton 回路に適用すること

図 4.7 モジュール印加電流の時間応答

で、モジュールで発生する損失が大幅に低減され、高周波駆動時の低損失化が可能になる。

図 4.8 モジュール印加電圧の時間応答

図 4.9 開発した SiC SBD モジュールのパッケージ表面温度

図 4.10 従来品 SiPiND モジュールのパッケージ表面温度

表 4.3 高周波 Cockcroft-Walton 回路の大電力出力実験

| Frequency       | 100kHz, 300kHz |

|-----------------|----------------|

|                 | 20MΩ(5W)       |

| Load resistance | 1MΩ(90W)       |

|                 | 200kΩ(452W)    |

#### 4.2.2 高周波 Cockcroft-Walton 回路の大電力化

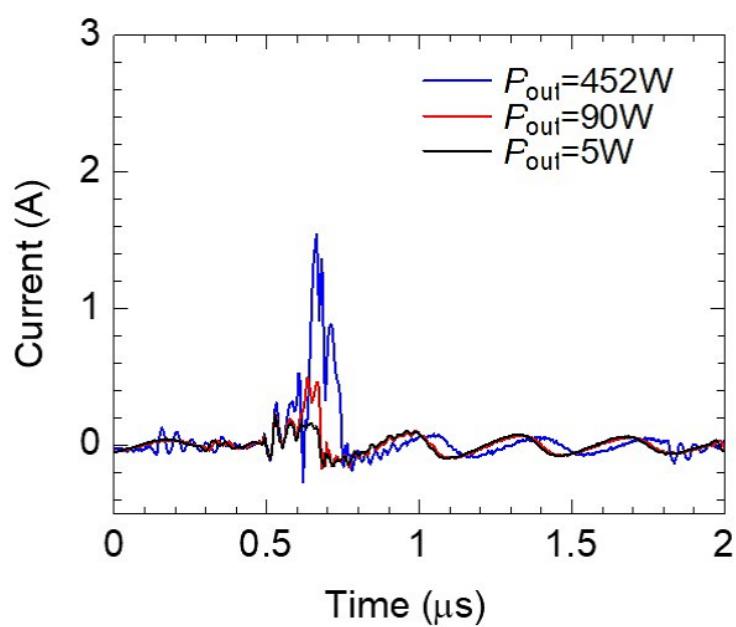

開発した SiC SBD モジュールは従来品の Si PiND モジュールに比べて導通損失では劣るが、高周波動作時はスイッチング損失が支配的であり、逆回復現象が原理的に発生しないため高速ターンオフが可能である。このため、開発した SiC SBD モジュールを高周波 Cockcroft-Walton 回路へ適用することで、回路の低損失化が期待できる。本節では、SiC SBD モジュールを用いた高周波 Cockcroft-Walton 回路の大電力出力動作を実験的に検討した。実験に用いるインバータと高電圧トランスは前節同様に表 4.2 とした。表 4.3 に示すように異なる負荷抵抗に対して、出力電圧 10kV を保つように入力電圧を制御し、Cockcroft-Walton 回路で発生する損失および電力変換効率について議論する。

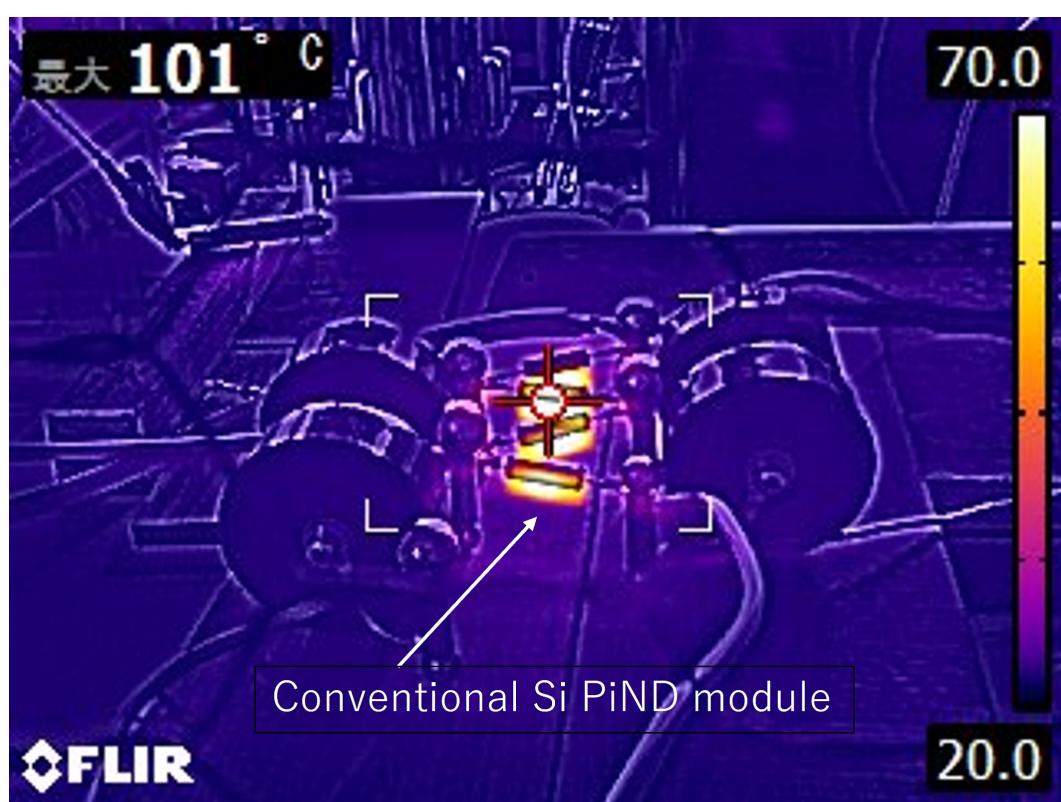

図 4.11 及び 4.12 は駆動周波数  $f = 100\text{kHz}$  及び  $300\text{kHz}$  での Cockcroft-Walton 回路のダイオード D1 の電流時間応答である。Cockcroft-Walton 回路はコンデンサインプット型整流回路であるため、モジュール印加電圧がコンデンサの電圧と立ち上がり電圧  $V_f$  の和を超える位相で SiC SBD モジュールは一時的に点弧し、接続されるコンデンサを充電した後、電流がゼロとなる位相で消弧する。このため、モジュール電流は図 4.11 及び 4.12 のようなスパイク上の電流となり、通流期間は負荷によって変動する。負荷の大出力化に伴って、負荷から流出するコンデンサの放電電荷量が増加する。モジュール電流の通流期間とピーク値は増加する。また  $300\text{kHz}$  での動作時は 1 周期あたりのコンデンサ充電電荷量が低減できるため、ピーク電流と導通期間が  $100\text{kHz}$  に比べて小さい。このように Cockcroft-Walton 回路では高周波化に伴ってモジュールの通過電流が減少するため、導通損失が減る。一般的に高周波駆動によってスイッチング損失は増加するが、本モジュールは優れたスイッチング特性をもち、導通損失が周波数に対して減少傾向にあるため、高周波化対応しやすい。

図 4.11 100kHz 動作時の SiC SBD モジュールの印加電流の時間応答

図 4.12 300kHz 動作時の SiC SBD モジュールの印加電流の時間応答

## 5 結言

### 5.1 結論

本研究では、SiC SBD を用いた高耐圧直流電源の設計と高周波応用に関する一連の研究を通じて以下の結論を得た。

1. SiC SBD の直列接続により耐圧向上とオン抵抗低減を両立する新しいモジュール設計を提案し、その有効性を実験的に確認した。

2. 開発した SiC SBD モジュールは分圧抵抗を省略することで小型化と低損失化を実現し、分担電圧の不均衡を定量的に評価した。これにより、高速スイッチング条件下でも安全に動作可能であることを示した。

3. 高周波高電圧電源への適用において、損失低減に有効な SBD の直列数を明らかにした。

4. SiC SBD モジュールの適用性を高周波 Cockcroft-Walton 回路で検証し、従来技術を大幅に上回る動作限界を達成した。

本研究成果は高周波高電圧直流電源のさらなる高効率化および小型化を実現する基盤技術となり、産業界における応用展開が期待される。今後は、実際の産業環境における長期信頼性の評価や、さらなる高周波化への対応が求められる。

### 5.2 産業への影響

本研究で開発された SiC SBD は、逆回復現象がないことから高周波 Cockcroft-Walton 回路に適用することで低損失・高周波駆動が可能である。特に本研究で提案された 12kV 耐圧の SiC SBD モジュールは、スイッチング損失と導通損失の両方を大幅に低減し、300kHz 以上の高周波駆動を実現できる。本技術により、プラズマ用の高電圧電源だけでなく、より高い電圧帯である X 線発生装置や粒子加速器、絶縁試験装置などに用いられる高電圧電源の高周波化も期待でき、産業機器の小型化と効率化に直接的な貢献をもたらすことになる。

寄生成分を精密に測定する手法として、VNA（ベクトルネットワークアナライザ）のポート延長機能を用いた新たな測定技術を提案した。この技術により、高周波回路設計時に問題となる基板の寄生成分を数値モデル化し、回路性能の向上を実現することが可能となった。

また SiC SBD モジュールの直列数の設計を通じて、最適な Cockcroft-Walton 回路の段数やモジュールの直列数を求め、効率的な高電圧電源の設計指針を示した。本研究で開発された技術は SiC デバイスを用いた次世代電力変換回路の基盤技術として、産業界での広範な応用が期待される。これにより、エネルギー効率の向上や運用コストの削減が実現し、低炭素社会への移行を支える基盤技術となる。

### 5.3 将来の展望

今後、SiC SBD を用いた高電圧電源はさらなる高周波化と高効率化が求められる。本研究で提案された技術を基に Cockcroft-Walton 回路や高周波インバータにおける最適化が進むことで、これまで高コストであった高周波高電圧電源の商業化が現実のものとなる。特に、SiC デバイスは高周波動作に適したユニポーラデバイスであるため、電力変換回路の小型化と効率向上を同時に達成するための鍵となる。加えて、寄生成分の測定と解析技術を活用することで、基板設計における電気特性の最適化が進み、信頼性の向上が期待される。

さらに、産業界での応用において Cockcroft-Walton 回路を用いた医療機器や産業機器への導入も進むと考えられる。高電圧発生回路の小型化は医療施設や研究機関での設置や運用コストを低減させ、これらの機器の普及を促進する。また、次世代電力デバイスとして、SiC SBD はエネルギー効率が重視される再生可能エネルギー分野でも広く応用される可能性がある。

一方で、今後の課題として、高電圧動作における熱抵抗の低減やさらなる電流容量の向上が挙げられる。これに対しては、モジュール構造の改良や接合技術の進展が必要とされる。これらの課題を解決することで、SiC デバイスを基盤とした電力変換技術のさらなる商業化が加速し、広範な産業分野での活用が期待される。

## 謝辞

本論文をまとめるにあたり、ご指導いただきました舟木剛教授、井渕貴章講師、福永崇平助教に心より感謝申し上げます。また、副査を務めていただいた高井重昌教授、牛尾知雄教授、ならびに徳島大学の北條昌秀教授に深く感謝いたします。

さらに、惜しみないご指導を賜りましたSiC応用技術共同研究講座の中村孝氏、奥田貴文特任准教授、杵村弘志特任研究員、花田俊雄特任研究員に厚く御礼申し上げます。

最後に、何かとお世話になりました舟木研究室の皆様に感謝するとともに、本研究に関わってくださったすべての方々に心より謝意を表します。

## 参考文献

- [1] John Kuffel and Peter Kuffel. *High voltage engineering fundamentals*. Elsevier, 2000.

- [2] Rolf Behling. *Modern diagnostic x-ray sources: technology, manufacturing, reliability*. CRC Press, 2021.

- [3] Shanglong Li, Zijian Wang, Xibo Yuan, Yonglei Zhang, Lijing Sun, Kai Wang, and Xiaojie Wu. A 10 kv/400 v sic based dc-dc converter with input-series-output-parallel configuration and three-loop control. *IEEE Transactions on Industry Applications*, Vol. 60, No. 5, pp. 7013–7029, 2024.

- [4] 鈴木良一. 乾電池駆動可搬型高エネルギー x 線発生装置の開発. *Synthesiology English edition*, Vol. 2, No. 3, pp. 221–228, 2009.

- [5] M. T. Tsai and C. W. Ke. Design and implementation of a high-voltage high-frequency pulse power generation system for plasma applications. In *2009 International Conference on Power Electronics and Drive Systems (PEDS)*, pp. 1556–1560, 2009.

- [6] Mengqi Li, Kang Luo, and Zilan Xiong. Design of adjustable high voltage pulse power supply driven by photovoltaic cells for cold plasma generation. In *2021 IEEE 4th International Electrical and Energy Conference (CIEEC)*, pp. 1–6, 2021.

- [7] John Douglas Cockcroft and Ernest TS Walton. Experiments with high velocity positive ions. *Proceedings of the royal society of London. Series A, containing papers of a mathematical and physical character*, Vol. 129, No. 811, pp. 477–489, 1930.

- [8] Shahid Iqbal. A hybrid symmetrical voltage multiplier. *IEEE Transactions on Power Electronics*, Vol. 29, No. 1, pp. 6–12, 2014.

- [9] H. Hino, T. Hatakeyama, and M. Nakaoka. Resonant pwm inverter linked dc-dc convertor using parasitic impedances of high-voltage transformer and its applications to x-ray generator. In *PESC '88 Record., 19th Annual IEEE Power Electronics Specialists Conference*, pp. 1212–1219 vol.2, 1988.

- [10] Yoshio Matsubara, Kazuhiko Onishi, Takashi Muraoka, Michinobu Sugita, Hideaki Kurisawa, Keizo Akita, Masaru Hamano, and Hiroshi Nakazato. Development of cockcroft-walton-type high-voltage dc generator with rf air-core transformer. *Electrical Engineering in Japan*, Vol. 160, No. 1, pp. 18–26, 2007.

- [11] Ioannis C. Kobougias and Emmanuel C. Tatakis. Optimal design of a half-wave cockcroft–walton voltage multiplier with minimum total capacitance. *IEEE Transactions on Power Electronics*, Vol. 25, No. 9, pp. 2460–2468, 2010.

- [12] Jayant Baliga. Modern power devices. 1987.

- [13] S. Kaplan, T. Griffin, and S. Bayne. Silicon vs silicon carbide device characterization. In *Digest of Technical Papers. PPC-2003. 14th IEEE International Pulsed Power Conference (IEEE Cat. No.03CH37472)*, Vol. 2, pp. 1217–1220 Vol.2, 2003.

- [14] Saijun Mao, Pengcheng Zhang, Jelena Popovic, and Jan Abraham Ferreira. Diode reverse recovery analysis of cockcroft-walton voltage multiplier for high voltage generation. In *2017 IEEE 3rd International Future Energy Electronics Conference and ECCE Asia (IFEEC 2017 - ECCE Asia)*, pp. 1765–1770, 2017.

- [15] B.J. Baliga. Power semiconductor device figure of merit for high-frequency applications. *IEEE Electron Device Letters*, Vol. 10, No. 10, pp. 455–457, 1989.

- [16] Saijun Mao, Jelena Popović, and Jan Abraham Ferreira. Diode reverse recovery process and reduction of a half-wave series cockcroft–walton voltage multiplier for high-frequency high-voltage generator applications. *IEEE Transactions on Power Electronics*, Vol. 34, No. 2, pp. 1492–1499, 2019.

- [17] Takumi Yasuda, Masataka Minami, Shin-ichi Motegi, and Masakazu Michihira. Suppression of ripple current in high step-up dc-dc converter utilizing cockcroft-walton circuit with inductor. In *2018 International Power Electronics Conference (IPEC-Niigata 2018 -ECCE Asia)*, pp. 992–997, 2018.

- [18] F. V. Robinson and V. Hamidi. Series connecting devices for high-voltage power conversion. In *2007 42nd International Universities Power Engineering Conference*, pp. 1205–1210, 2007.

- [19] Shiqi Ji, Zheyu Zhang, and Fred Wang. Overview of high voltage sic power semiconductor devices: development and application. *CES Transactions on Electrical Machines and Systems*, Vol. 1, No. 3, pp. 254–264, 2017.

- [20] Simon M Sze, Yiming Li, and Kwok K Ng. *Physics of semiconductor devices*. John wiley & sons, 2021.

- [21] Tsuyoshi Funaki, Tsunenobu Kimoto, and Takashi Hikihara. Evaluation of high frequency switching capability of sic schottky barrier diode, based on junction capacitance model. *IEEE transactions on power electronics*, Vol. 23, No. 5, pp. 2602–2611, 2008.

- [22] Hao Ding, Juin J. Liou, Claude R. Cirba, and Keith Green. An improved junction capacitance model for junction field-effect transistors. *Solid-State Electronics*, Vol. 50, No. 7, pp. 1395–1399, 2006.

- [23] Yuki Nomura, Tsuyoshi Funaki, Toshio Hanada, and Takashi Nakamura. Power conversion efficiency improvement of high voltage power supply with sic sbd module. In *2022 IEEE Workshop on Wide Bandgap Power Devices and Applications in Europe (WiPDA Europe)*, pp. 1–6, 2022.

- [24] Chung-Ming Young, Ming-Hui Chen, Tsun-An Chang, Chun-Cho Ko, and Kuo-Kuang Jen. Cascade cockcroft-walton voltage multiplier applied to transformerless high step-up dc–dc converter. *IEEE transactions on industrial electronics*, Vol. 60, No. 2, pp. 523–537, 2012.

- [25] Liran Katzir and Doron Shmilovitz. Effect of the capacitance distribution on the output impedance of the half-wave cockcroft-walton voltage multiplier. In *2016 IEEE Applied Power Electronics Conference and Exposition (APEC)*, pp. 3655–3658. IEEE, 2016.

- [26] 山口正通, 日下佳祐, 伊東淳一. 短絡治具を用いたシャントスルー法によるpcbパターン上の寄生インピーダンス測定法. 電気学会論文誌 D (産業応用部門誌), Vol. 141, No. 7, pp. 589–590, 2021.

## 研究業績

### 1. 査読付き論文

1. 野村 優貴, 舟木 剛, 花田 俊雄, 中村 孝, "SiC SBD を多直列接続した超耐圧ダイオードモジュールの電圧分担に関する一考察", 電気学会論文誌D (産業応用部門誌), 141巻, 8号, pp. 646-653, 2021.

2. 野村 優貴, 舟木 剛, "VNA のポート延長機能を用いたパワーループ寄生成分の抽出方法", 電気学会論文誌D (産業応用部門誌), 142巻, 6号, pp. 488-489, 2022.

3. 野村 優貴, 舟木 剛, "高耐圧 SiC ショットキーバリアダイオードモジュールを適用した高周波高電圧電源", エレクトロニクス実装学会誌, 28巻, 1号, pp. 123-131, 2025.

### 2. 國際会議

1. Y. Nomura, T. Funaki, T. Hanada and T. Nakamura, "Power Conversion Efficiency Improvement of High Voltage Power Supply With SiC SBD Module," 2022 IEEE Workshop on Wide Bandgap Power Devices and Applications in Europe (WiPDA Europe), Coventry, United Kingdom, 2022, pp. 1-6.

### 3. 口頭発表

1. 野村優貴, 中村孝, 舟木剛, “ダイオード接合容量の電圧依存性が Cockcroft-Walton 回路の電圧効率に与える影響に関する一考察”, 電気学会全国大会, 北海道科学大学, 2019.

2. 野村優貴, 舟木剛, 花田俊雄, 中村孝, "SiC ショットキーバリアダイオードを多直列した超耐圧モジュールにおける電圧分担に関する一考察", 電子デバイス研究会, 2020.