| Title        | Technical Note—Slowdown in the Energy<br>Efficiency of Analog-to-Digital Converters and a<br>Compressed-Sensing-Based Solution |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|

| Author(s)    | Kanemoto, Daisuke                                                                                                              |

| Citation     |                                                                                                                                |

| Version Type | VoR                                                                                                                            |

| URL          | https://doi.org/10.18910/101986                                                                                                |

| rights       |                                                                                                                                |

| Note         |                                                                                                                                |

### The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

# Technical Note—Slowdown in the Energy Efficiency of Analog-to-Digital Converters and a Compressed-Sensing-Based Solution

#### Daisuke Kanemoto

The University of Osaka

Email: dkanemoto@ieee.org; dkanemoto@eei.eng.osaka-u.ac.jp

Abstract—Power consumption remains a critical bottleneck in the design of sensor systems. To investigate power consumption problems in sensor circuits, we surveyed the latest developments in analog-to-digital converter (ADC) integrated circuits, which are indispensable components of sensor front ends. An evaluation based on the Walden figure-of-merit, using data from ADCs presented at the International Solid-State Circuits Conference, revealed a slowdown in the energy-efficiency improvement of state-of-the-art ADCs. To overcome this limitation, we are developing a compressed-sensing (CS)-based solution: a low-power sensing approach that combines random undersampling with CS reconstruction. A prototype wireless electroencephalogram system implemented on a general-purpose microcontroller reduces both sampling activity and radio duty cycle, achieving continuous operation at 72  $\mu W$  while maintaining signal fidelity. These efforts are expected to pave the way for next-generation ultralow-power and energy-harvesting sensor networks.

Index Terms—Analog-to-digital converter (ADC), compressed sensing (CS), energy efficiency, figure-of-merit (FoM)

#### I. INTRODUCTION

The rapid expansion of the Internet of Things and digital transformation is driving the widespread deployment of wireless sensor systems that collect and transmit data to clouds or edge computers. Such sensor systems are now being applied to a wide range of fields. Examples include healthcare [1] and BrainTech [2], structural health monitoring [3] of roads, bridges, and buildings, fault detection [4] in industrial equipment, and early warning of natural disasters [5], all of which will be critical for sustaining modern society. However, every sensor requires a power source, and many rely on batteries or, ideally, energy harvesters that scavenge the ambient energy. In battery-powered sensor networks, increasing the number of sensors leads to higher costs for battery replacement and maintenance. Although energy harvesters offer a potential solution to these challenges, the energy they can provide is fundamentally constrained.

A fundamental solution is to reduce the power consumption of the sensor circuitry. Ultralow-power operation contributes not only to battery life and maintenance cost reduction, but also to the development of fully battery-free systems that operate solely with harvested energy. Achieving such an efficiency requires fundamental technological innovation across the entire sensing chain, from the analog front-end to the wireless transceiver.

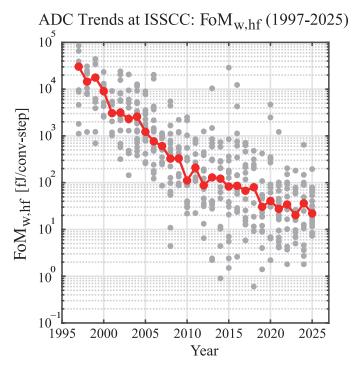

Fig. 1. Recent  ${\rm FoM_{w,hf}}$  trend of state-of-the-art ADCs reported in ISSCC (1997–2025). The red circles indicate the yearly medians. The plot shows a steady year-on-year improvement up to roughly 2010. Between 2010 and 2020 the rate of improvement slows noticeably, and from 2020 onward the median  ${\rm FoM_{w,hf}}$  appears to exhibit a pronounced slowdown.

This technical note briefly reviews the evolution of energy-efficiency improvements in analog-to-digital converters (ADCs), which are key circuits in analog front ends and represent one of the major bottlenecks in many sensing applications. It then introduces a novel sampling strategy, developed by the authors, that enables low-power sensing under severe energy constraints.

#### II. FOM TREND ANALYSIS

An ADC is a core building block of any sensing system that translates analog sensor outputs into digital data for subsequent processing. Since an ADC handles both the analog and digital domains and often integrates circuitry from both, it serves as a useful proxy for analyzing broader trends in sensor-oriented integrated circuit designs.

Multiple ADC architectures are available, including the flash, successive-approximation register, and delta–sigma types. Their performance is typically analyzed in terms of power consumption P, effective number of bits (ENOB), and signal bandwidth BW. These parameters are interdependent and present inherent trade-offs for power efficiency.

Figure-of-merit (FoM) metrics are widely used to compare the energy efficiency across designs. Two well-known examples are the FoM proposed by Richard Schreier, denoted  $\rm FoM_{\rm s},$  and that proposed by Richard H. Walden, denoted  $\rm FoM_{\rm w}.$  Because either metric leads to a similar conclusion in this technical note, we adopt  $\rm FoM_{\rm w}$  for our analysis, which is defined as

$$FoM_{w} = \frac{P}{2^{ENOB} \cdot 2BW}.$$

(1)

Because the ENOB depends on the input signal frequency, we adopt  $\mathrm{FoM}_{\mathrm{w,hf}}$ , calculated based on the ENOB measured with a high-frequency sinusoidal input, for our analysis.

Figure 1 shows a graph based on a comprehensive table compiled by Prof. Boris Murmann [6], which summarizes  ${\rm FoM_{w,hf}}$  data for ADCs presented at the International Solid-State Circuits Conference (ISSCC). Each gray dot represents the  ${\rm FoM_{w,hf}}$  of an ADC reported in a given year, whereas the red circles denote the yearly medians, which are connected by a solid line to clarify the overall trend. The plot presents a steady year-on-year improvement up to approximately 2010. Between 2010 and 2020, the rate of improvement slowed down noticeably, and from 2020 onward, the improvement in the median  ${\rm FoM_{w,hf}}$  showed signs of saturation. A possible reason for this slowdown is that further progress in analog circuitry is constrained by physical factors, such as thermal noise, jitter, and low supply voltages (for example, [7], [8]).

Uniform sampling, grounded in the sampling theorem, enables perfect signal reconstruction; therefore, it is regarded as a fundamental and universal approach. For applications requiring exact signal reconstruction, sampling based on the Nyquist criterion [9] is essential. However, in cases where a slight performance degradation is acceptable, alternative sampling strategies may be explored to achieve significant reductions in power consumption.

Given the pronounced slowdown in conventional circuitlevel improvements, architecture-level innovation is required to continue enhancing energy efficiency. To address this, we are developing a compressed-sensing (CS)-based solution: a low-power sensing system that enables data acquisition with inherent compression and represents one of the promising approaches for next-generation energy-efficient sensing.

## III. ENERGY-EFFICIENT SENSING SYSTEMS BASED ON A CS APPROACH

Figure 2(a) depicts the sampling behavior and power consumption of a conventional uniform-sampling sensing system. In this system, data are sampled periodically at intervals of  $T_s$ , and each sampling action consumes a specific amount of energy. When a predetermined amount of data has been

Fig. 2. Relationship between signal sampling (top) and power consumption (bottom). (a) shows conventional uniform sampling, and (b) shows random undersampling. "TX" denotes wireless transmission. Random undersampling reduces the number of activations of sampling circuits and decreases the frequency of wireless transmissions, thereby lowering overall power consumption

collected, it is transmitted through a wireless transceiver that consumes a significant amount of power. As described in the previous section, low-power circuit design is an effective approach to decrease the power consumption in such systems. However, because significant progress has already been made in energy-efficient integrated circuit designs, achieving further substantial reductions in circuit-level power consumption has become increasingly difficult.

To address this limitation, we propose a different approach: by employing random undersampling, the number of sampling operations can be reduced, thereby decreasing the volume of the acquired data (Fig. 2(b)). Consequently, the frequency of wireless transmission can also be significantly reduced. Although this method generates compressed signal representations, the original waveform can be reconstructed by leveraging the inherent sparsity of the signal in an appropriate transform basis and solving a suitable optimization problem on edge devices, personal computers, and cloud servers, where power constraints are less critical.

First, we developed a proof-of-concept wireless electroencephalogram (EEG) transmitter that applied random undersampling on a general-purpose microcontroller (Nordic Semiconductor nRF52840), which includes the path from the ADC to the Bluetooth Low Energy transceiver, and consumed 97  $\mu$ W [10]. The use of a generic frequency-domain basis limited both the compression ratio and reconstruction accuracy; however, it reduced the power by 72% relative to uniform sampling. A miniature thermoelectric generator driven by a  $2\,^{\circ}\text{C}$ -gradient powered the system continuously, demonstrating battery-free operation.

Next, to increase sparsity and enable higher compression, we previously demonstrated that basis learning on archived EEG signals significantly improves reconstruction accuracy [11]. More recently, we proposed a novel approach that constructs a basis by aligning similar waveforms obtained in the past, leveraging signal similarity rather than relying on traditional learning algorithms. This method achieves higher-fidelity reconstruction, even under high compression ratios [12]. Finally, we integrated this latter method into a second prototype with high compression based on the nRF52840, which operates at 72  $\mu$ W with a normalized mean-squared error (NMSE) of 0.116 [13]. Despite achieving higher fidelity, it consumes less power than a custom ASIC-based wireless EEG transmitter [14], which operates at 90  $\mu$ W.

We have also addressed artifacts that reduce sparsity and degrade CS accuracy. In particular, we have published several papers on exploiting the properties of random undersampling for mitigation schemes based on independent component analysis and outlier detection (for example, [15]–[17]). Our technique has also been applied to integrated circuit designs (for example, [18]–[21]). Furthermore, we have investigated the feasibility of leveraging the intrinsic randomness of random undersampling in lightweight cryptography [22].

Collectively, these efforts are part of an ongoing program to redefine sensing using CS. When perfect reconstruction is essential, uniform Nyquist rate sampling is required. In contrast, if a certain level of signal degradation is acceptable, the deliberate undersampling enabled by our proposed CS-based approach can yield significant power savings and enable new directions in signal-processing-driven sensing systems.

#### IV. CONCLUSION

This study quantified the recent slowdown in ADC power efficiency by analyzing  ${\rm FoM_{w,hf}}$  data reported at ISSCC. To address this challenge, we are currently investigating a CS-based solution, which combines random undersampling with CS reconstruction. Experimental prototypes built using a general-purpose microcontroller have demonstrated that this approach reduces both the sampling activity and further lowers the wireless transmission duty cycle of an EEG transmitter, thereby enabling operation at 72  $\mu{\rm W}$  while maintaining signal fidelity (NMSE = 0.116). Future work will focus on developing dedicated CS-based sensing chips and extending this approach to lightweight cryptographic sensor nodes. These efforts show a viable path toward the advancement of next-generation ultralow-power and energy-harvesting sensor networks.

#### ACKNOWLEDGMENT

This work was supported by JSPS KAKENHI Grant Number JP24K02914.

#### REFERENCES

- [1] S. Javaid, S. Zeadally, H. Fahim, and B. He, "Medical sensors and their integration in wireless body area networks for pervasive healthcare delivery: A review," *IEEE Sensors J.*, vol. 22, no. 5, pp. 3860–3877, Mar. 2022.

- [2] C.-T. Lin, C.-Y. Chiu, A. K. Singh, J.-T. King, L.-W. Ko, Y.-C. Lu, and Y.-K. Wang, "A wireless multifunctional SSVEP-based brain-computer interface assistive system," *IEEE Trans. Cogn. Devel. Syst.*, vol. 11, no. 3, pp. 375–383, Sep. 2019.

- [3] M. Z. Sarwar, M. R. Saleem, J.-W. Park, D.-S. Moon, and D. J. Kim, "Multimetric event-driven system for long-term wireless sensor operation for SHM applications," *IEEE Sensors J.*, vol. 20, no. 10, pp. 5350–5359, May 2020.

- [4] H. Darvishi, D. Ciuonzo, and P. S. Rossi, "A machine-learning architecture for sensor fault detection, isolation, and accommodation in digital twins," *IEEE Sensors J.*, vol. 23, no. 3, pp. 2522–2538, Feb. 2023.

- [5] H. Thirugnanam, S. Uhlemann, R. Reghunadh, M. V. Ramesh, and V. P. Rangan, "Review of landslide monitoring techniques with IoT integration opportunities," *IEEE J. Sel. Topics Appl. Earth Observ. Remote Sens.*, vol. 15, pp. 5317–5338, Jun. 2022.

- [6] B. Murmann, "ADC performance survey (ISSCC & VLSI circuit symposium)," 2025, [Online]. Available: https://github.com/bmurmann/ ADC-survey (accessed Jun. 26, 2025).

- [7] X. Tang, J. Liu, Y. Shen, S. Li, L. Shen, A. Sanyal, K. Ragab, and N. Sun, "Low-power SAR ADC design: Overview and survey of stateof-the-art techniques," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 69, no. 6, pp. 2249–2262, Jun. 2022.

- [8] B. Murmann, "Energy limits in A/D converters," in Proc. IEEE Faible Tension Faible Consommation (FTFC), Jun. 2013, pp. 1–4.

- [9] H. Nyquist, "Certain topics in telegraph transmission theory," Trans. Amer. Inst. Elect. Eng., vol. 47, pp. 617–644, Apr. 1928.

- [10] T. Miyata, D. Kanemoto, and T. Hirose, "Random undersampling wireless EEG measurement device using a small TEG," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2023, pp. 1–5.

- [11] K. Nagai, D. Kanemoto, and M. Ohki, "Applying K-SVD dictionary learning for EEG compressed sensing framework with outlier detection and independent component analysis," *IEICE Trans. Fundamentals*, vol. E104-A, no. 9, pp. 1375–1378, Sep. 2021.

- [12] D. Kanemoto and T. Hirose, "EEG measurements with compressed sensing utilizing EEG signals as the basis matrix," in *Proc. IEEE Int.* Symp. Circuits Syst. (ISCAS), May 2023, pp. 1–5.

- [13] D. Kanemoto, E. Takimoto, and T. Hirose, "Development of low-power and high-accuracy wireless EEG transmission system using compressed sensing with an EEG basis," in *Proc. IEEE Int. Symp. Circuits Syst.* (ISCAS), May 2025, pp. 1–5.

- [14] C. Chen, J. Yang, H. Wang, Z. Cao, S. Kananian, K. Chen, and A. S. Y. Poon, "A 90-μw penny-sized 1.2-gram wireless EEG recorder with 12-channel FDMA transmitter for month-long continuous mental health monitoring," in *Proc. IEEE Symp. VLSI Technol. Circuits*, Jun. 2022, pp. 248–249.

- [15] D. Kanemoto, S. Katsumata, M. Aihara, and M. Ohki, "Framework of applying independent component analysis after compressed sensing for electroencephalogram signals," in *Proc. IEEE Biomed. Circuits Syst. Conf. (BioCAS)*, Oct. 2018, pp. 145–148.

- [16] S. Katsumata, D. Kanemoto, and M. Ohki, "Applying outlier detection and independent component analysis for compressed sensing EEG measurement framework," in *Proc. IEEE Biomed. Circuits Syst. Conf.* (BioCAS), Oct. 2019, pp. 1–4.

- [17] D. Kanemoto, S. Katsumata, M. Aihara, and M. Ohki, "Compressed sensing framework applying independent component analysis after undersampling for reconstructing electroencephalogram signals," *IEICE Trans. Fundamentals*, vol. E103-A, no. 12, pp. 1647–1654, Dec. 2020.

- [18] R. Matsubara, D. Kanemoto, and T. Hirose, "Reducing power consumption in LNA by utilizing EEG signals as basis matrix in compressed sensing," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2024, pp. 1–5.

- [19] Y. Okabe, D. Kanemoto, O. Maida, and T. Hirose, "Compressed sensing EEG measurement technique with normally distributed sampling series," *IEICE Trans. Fundamentals*, vol. E105-A, no. 10, pp. 1429–1433, Oct. 2022.

- [20] K. Mii, D. Kanemoto, and T. Hirose, "0.36 μW/channel capacitively-coupled chopper instrumentation amplifier in EEG recording wearable devices for compressed sensing framework," *Jpn. J. Appl. Phys.*, vol. 63, 03SP54, 2024.

- [21] R. Matsubara, D. Kanemoto, and T. Hirose, "Design guidelines for noise in a low-noise amplifier using EEG signals as a basis matrix in compressed sensing system," in *Proc. IEEE Int. Conf. Consum. Electron.* (ICCE), Jan. 2025, pp. 1–5.

- [22] R. Tsunaga, D. Kanemoto, and T. Hirose, "Noise-masking cryptosystem using watermark and chain generation for EEG measurement with compressed sensing," in *Proc. IEEE Int. Conf. Consum. Electron. (ICCE)*, Jan. 2024, pp. 1–6.

Secretary for the IEEE Solid-State Circuits Society (SSCS) Kansai Chapter since 2023. He received the IEICE Young Researcher's Award in 2013.

Daisuke Kanemoto (Member, IEEE) received the B.S. degree in Electronics and Information Science from Kyoto Institute of Technology, Kyoto, Japan in 2004 and the M.S. and Ph.D. degrees in Electronic Engineering from The University of Osaka, Osaka, Japan in 2006 and 2011, respectively. From 2010 to 2013, he was an Assistant Professor in the Department of Electronics, Graduate School of Information Science and Electrical Engineering, Kyushu University, Fukuoka, Japan. From 2013 to 2019, he was an Assistant Professor in the Department of Research, Interdisciplinary Graduate School of Medicine and Engineering, University of Yamanashi, Yamanashi, Japan. From 2015 to 2017, he was a Visiting Assistant Professor in the Department of Electrical Engineering, Stanford University, Stanford, CA, USA. Since 2019, he has been an Associate Professor in the Division of Electrical, Electronic and Information Engineering, Graduate School of Engineering, The University of Osaka, Osaka, Japan. His research interests include analog circuits, mixed-signal integrated circuits, signal processing (including compressed sensing and machine learning), and next-generation sensing systems through hardware/software co-design.

Dr. Kanemoto is also a member of the Institute of Electronics, Information and Communication Engineers (IEICE). He served as the Technical Program Committee Chair and Vice-Chair of the International Conference on Solid-State Devices and Materials from 2020 to 2022; an Associate Editor for the IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences from 2013 to 2017; and an Associate Editor for the IEICE Transactions on Fundamentals of Electronics from 2019 to 2022. He has been a Chapter