| Title        | Reduction of hole traps in GaN MOS structures by high-pressure oxygen annealing                                                                                                                                                                                                                                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)    | Hara, Masahiro; Tomigahara, Kazuki; Nozaki,<br>Mikito et al.                                                                                                                                                                                                                                                                                                                     |

| Citation     | Applied Physics Letters. 2025, 127(16), p. 074011                                                                                                                                                                                                                                                                                                                                |

| Version Type | АМ                                                                                                                                                                                                                                                                                                                                                                               |

| URL          | https://hdl.handle.net/11094/102884                                                                                                                                                                                                                                                                                                                                              |

| rights       | This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. This article appeared in Hara Masahiro, Tomigahara Kazuki, Nozaki Mikito, et al. Reduction of hole traps in GaN MOS structures by high-pressure oxygen annealing. Applied Physics Letters 127, 074011 (2025); https://doi.org/10.1063/5.0292841. |

| Note         |                                                                                                                                                                                                                                                                                                                                                                                  |

# The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0292841

### Reduction of hole traps in GaN MOS structures by high-pressure oxygen annealing

Masahiro Hara, a) Kazuki Tomigahara, Mikito Nozaki, Takuma Kobayashi, and Heiji Watanabe

Graduate School of Engineering, The University of Osaka, Suita, Osaka 565-0871,

(Dated: 8 October 2025)

The impact of annealing pressure on hole traps in SiO<sub>2</sub>/p-type GaN MOS structures was investigated. The density of fast-response interface hole traps  $(N_{\text{hump}})$  was characterized from a hump in capacitance-voltage (C-V) characteristics of the MOS capacitors.  $N_{\text{hump}}$ was below  $2 \times 10^{12}$  cm<sup>-2</sup> and was almost unchanged at 200–800°C when annealed under 100 MPa, while atmospheric-pressure annealing at a higher temperature led to a higher  $N_{\text{hump}}$ , exceeding  $1 \times 10^{13} \text{ cm}^{-2}$  at  $800^{\circ}\text{C}$ . When samples first annealed at  $800^{\circ}\text{C}$  under atmospheric pressure were additionally annealed under 100 MPa, N<sub>hump</sub> was reduced to about  $2 \times 10^{12} \text{ cm}^{-2}$  regardless of the temperature of high-pressure annealing. Consequently, high-pressure oxygen annealing turned out to not only suppress the generation of interface hole traps but also reduce the traps once generated in GaN MOS structures.

a) Electronic mail: hara@prec.eng.osaka-u.ac.jp

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0292841

The wide bandgap, high critical electric field, and high saturation drift velocity make gallium nitride (GaN) uniquely suitable for high-power and high-frequency electronic devices<sup>1–3</sup>. By utilizing a high-density two-dimensional electron gas (2DEG) induced by piezoelectric and spontaneous polarization<sup>4,5</sup>, GaN-based heterojunction field-effect transistors (HFETs) have been important building blocks for high-frequency switching devices<sup>6</sup>. Recently, high-performance GaN metal-oxide-semiconductor field-effect transistor (MOSFETs) with a vertical structure have been demonstrated that have a high channel mobility and a low on-state resistance<sup>7–11</sup>.

The most fundamental components in these switching devices are MOS gate structures. The major requirement in fabricating MOS structures to improve the performance and reliability of devices is to reduce defects near a dielectric/semiconductor interface. In GaN MOS structures, low-density interface electron traps near the conduction band minimum ( $E_{\rm C}$ ) can be obtained<sup>12–18</sup>. On the other hand, the hole trap density near the valence band maximum ( $E_{\rm V}$ ) is very high<sup>19–21</sup>, causing a serious reliability issue of threshold voltage instability during switching operation of GaN MOS devices<sup>22,23</sup>. Thus, a gate dielectric formation process that can achieve sufficiently low hole trap density is desirable based on a physical understanding of hole traps.

A unique hump and a large hysteresis were observed in capacitance–voltage (C-V) curves of silicon dioxide  $(SiO_2)$ /p-type GaN MOS capacitors<sup>24–26</sup>, which results from hole trapping by fast-response interface defects and slow-response oxide traps, respectively<sup>24,27</sup>. The voltage range of the hump increased when post-deposition annealing (PDA) was performed at a higher temperature and/or the MOS structure had a thicker gallium oxide  $(GaO_x)$  interlayer<sup>24–26</sup> that is induced during the dielectric formation process<sup>13,14</sup>. This result indicates that defects thermally generated in the  $GaO_x$  interlayer in  $SiO_2/GaN$  structures are one of the major origins of the interface hole trap. Although these hole traps were challenging to sufficiently reduce only by controlling the conditions of gate dielectric formation process (deposition, annealing, etc.), no hump and a small hysteresis were obtained in GaN MOS structures fabricated on heavily magnesium (Mg)-doped epitaxial layers, achieving an exceptionally low hole trap density<sup>28,29</sup>.

Recent theoretical studies have discussed the origin of hole traps in GaN MOS structures<sup>30,31</sup>. Among various types of defects, oxygen vacancy ( $V_O$ ) in a GaO<sub>x</sub> layer is regarded as a possible candidate because  $V_O$  acts as a deep donor in bulk gallium oxides<sup>32–35</sup>. A first-principles calculation showed that heavily doped Mg atoms can form a complex with  $V_O$  in GaO<sub>x</sub> and passivate a hole trap<sup>31</sup>, supporting the experimental result of reduced hole trap density in heavily Mg doped GaN MOS structures<sup>28,29</sup>.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0292841

Although high-density Mg doping is a way for reducing hole traps, the flexibility of the device design and fabrication process is severely limited, and mobility degradation by enhanced impurity scattering is a serious concern. Thus, another process should be developed for passivating  $V_{\rm O}$ -related hole traps in a GaO<sub>x</sub> interlayer, and the authors focused on high-pressure treatment for GaN MOS structures, motivated by the ultra-high-pressure annealing (UHPA) process adopted for Mg ion-implanted p-type GaN<sup>36,37</sup>. High-temperature annealing is usually required for activation of implanted dopant atoms. In Mg-implanted GaN, however, thermal decomposition of GaN due to nitrogen desorption (i.e., generation of nitrogen vacancies) easily occurs at a high temperature (> 1000°C) under atmospheric pressure. It turned out that UHPA under 400–1000 MPa realized sufficient acceptor activation in Mg-implanted p-type GaN with effectively suppressing thermal decomposition of GaN. Therefore, high-pressure oxygen annealing is expected to be able to suppress generation of  $V_0$  in the  $GaO_x$  interlayer in MOS structures. Regarding the impact of high-pressure annealing (HPA) on electrical properties of GaN MOS structures, few studies have performed 400 MPa-annealing on n-type GaN MOS capacitors<sup>38</sup>. However, there exist no reports on p-type GaN MOS structures annealed under high pressure, and effects of HPA on hole traps are unclear. In this study, SiO<sub>2</sub>/GaN MOS structures were fabricated by performing oxygen annealing under 100 MPa, and the impact of annealing pressure on hole traps was systematically investigated.

Figure 1 depicts a process flow for fabricating SiO<sub>2</sub>/p-type GaN MOS structures. SiO<sub>2</sub>/GaN MOS capacitors were fabricated using GaN substrates, having a stacking structure with p<sup>-</sup>/p<sup>+</sup>/n<sup>+</sup>-GaN epitaxial layers (doping density:  $1 \times 10^{17}$ ,  $3 \times 10^{18}$ , and  $2 \times 10^{18}$  cm<sup>-3</sup>, respectively) grown on n-type GaN(0001) substrates. Although p-type GaN free-standing substrates are unavailable, backside contacts can be formed with a reduced parasitic capacitance at p-n junctions by introducing the heavily doped buffer layers ( $\sim 10^{18}~{\rm cm}^{-3}$ ). The samples were cleaned with acetone and 50% hydrogen fluoride (HF), followed by nitrogen (N2) annealing at 800°C for 20 min to activate Mg acceptors. After cleaning the samples with 50% HF again, SiO<sub>2</sub> was deposited by plasmaenhanced chemical vapor deposition (PECVD) under the following process conditions: substrate temperature of 400°C, pressure of 79 Pa, radio frequency (RF) power of 30 W, and tetraethyl orthosilicate (TEOS) and oxygen (O2) gas flows of 1 and 250 sccm, respectively. The SiO2 film was determined to be 26-28 nm thick by spectroscopic ellipsometry. Then, PDA was conducted in various conditions. HPA was performed with Hot Isostatic Pressing (HIP) Equipment (O<sub>2</sub>-Dr.HIP, Kobe Steel, Ltd.) under 100 MPa in O<sub>2</sub> diluted by argon (Ar) (O<sub>2</sub>/Ar: 20%) by varying the temper-

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0292841

ature from 200-800°C. Note that the O<sub>2</sub> partial pressure of 20% was the maximum value allowed for the equipment, while in principle higher  $O_2$  content is desired for  $V_0$  compensation. For comparison, PDA in a diluted O<sub>2</sub> ambient (O<sub>2</sub>/N<sub>2</sub>: 20%) was performed under atmospheric pressure of 0.1 MPa (atmospheric-pressure annealing, APA). Additionally, to investigate whether HPA is also effective for reducing hole traps, some samples were annealed in a pure O2 ambient at 800°C under atmospheric pressure, which generates a large amount of fast-response hole traps<sup>24,25</sup>, before performing HPA (APA+HPA). Finally, nickel (Ni) gate electrodes and aluminum (Al) backside contacts were formed by vacuum evaporation.

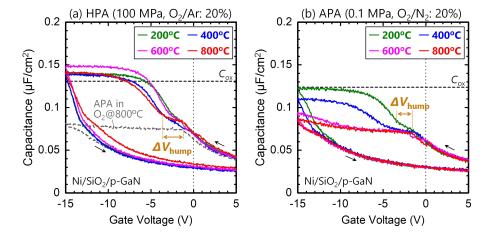

Figure 2 shows bidirectional C-V characteristics of the SiO<sub>2</sub>/p-type GaN MOS capacitors subjected to (a) HPA and (b) APA in a diluted O<sub>2</sub> ambient. The probe frequency of the measurement was 1 kHz, and the gate voltage was swept from depletion (positive bias) to accumulation (negative bias), and back to depletion again. We previously reported that the voltage range of the hump  $(\Delta V_{\text{hump}})$  resulting from hole capturing by interface hole traps gradually increased in 400°C-deposited SiO<sub>2</sub>/p-type GaN MOS capacitors when O<sub>2</sub> or N<sub>2</sub> annealing under atmospheric pressure was performed at a higher temperature (200-800°C)<sup>24,25</sup>, as an example of the O<sub>2</sub> annealing at 800°C shown in Fig. 2(a) (gray dashed line). In the case of 100 MPa-annealing, on the other hand,  $\Delta V_{\text{hump}}$  (observed at  $C \simeq 0.07-0.08 \,\mu\text{F/cm}^2$ ) was not much changed even at a higher annealing temperature, indicating that HPA suppressed thermal generation of interface hole traps. All the HPA-treated samples exhibited hole accumulation where the maximum capacitance  $(C_{\text{max}})$ of 0.14–0.15  $\mu$ Fcm<sup>2</sup> was close to the oxide capacitance ( $C_{\rm ox} \simeq 0.13 \ \mu$ Fcm<sup>2</sup>) estimated from the SiO<sub>2</sub> thickness determined by ellipsometry. To distinguish the impact of high pressure and low oxygen content on  $\Delta V_{\text{hump}}$ , APA was performed with the same  $O_2$  partial pressure of 20%. As shown in Fig. 2(b), an increase in  $\Delta V_{\text{hump}}$  and a decrease in  $C_{\text{max}}$  were clearly observed when annealed at a higher temperature under atmospheric pressure. This result is consistent with our previous report in which an annealing temperature-dependent increase in  $\Delta V_{\text{hump}}$  was observed regardless of the annealing ambient (pure  $O_2$  or  $N_2$ )<sup>24</sup>. As a result, it was revealed that the critical factor suppressing hole trap generation was not low oxygen content but high pressure.

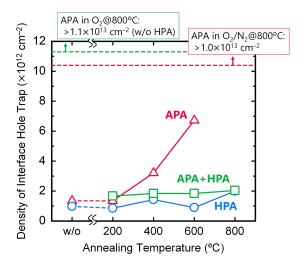

Then,  $\Delta V_{\text{hump}}$  was extracted from the experimental C-V curves by a differential analysis described elsewhere<sup>24</sup>, and the density of interface hole traps (N<sub>hump</sub>) was characterized based on  $N_{\text{hump}} = C_{\text{ox}} \Delta V_{\text{hump}}/e$ , where e is the elementary charge. Figure 3 shows the annealing temperature dependence of N<sub>hump</sub> in the SiO<sub>2</sub>/p-type GaN MOS capacitors. In the samples subjected to APA,  $N_{\text{hump}}$  significantly increased from  $1.4 \times 10^{12} \text{ cm}^{-2}$  for the annealing temperature be-

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0292841

low 200°C to over  $1.0 \times 10^{13}~\text{cm}^{-2}$  ( $\Delta V_{hump} > 13.5~\text{V}$ ) for  $800^{\circ}\text{C}$ -annealing (indicated by the red dashed line in Fig. 3). When HPA was performed, on the other hand,  $\Delta V_{\text{hump}}$  was in the range of 1.1–2.5 V for each sample, and  $N_{\text{hump}}$  stayed lower than  $2.0 \times 10^{12}$  cm<sup>-2</sup> regardless of the annealing temperature. As a result, it turned out that HPA did not cause thermal generation of interface hole traps in p-type GaN MOS structures.

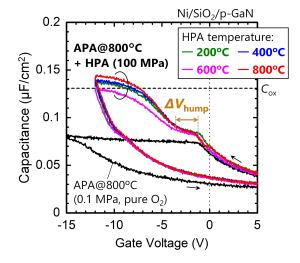

To further investigate the impact of HPA on interface hole traps, some samples were first annealed at 800°C in pure O2 ambient under atmospheric pressure, and then HPA under 100 MPa was additionally performed. Figure 4 shows the C-V characteristics of the SiO<sub>2</sub>/p-type GaN MOS capacitors subjected to combined annealing (APA+HPA). As reported in previous literature<sup>24,25</sup>, APA in O<sub>2</sub> at 800°C generated a large amount of interface hole traps, resulting in a large hump of the C-V curves ( $\Delta V_{hump} > 13.9$  V). When subsequent HPA was performed at 200-800°C,  $\Delta V_{\text{hump}}$  reduced to 2.1–2.5 V, and hole accumulation with  $C_{\text{max}} \simeq C_{\text{ox}}$  was observed regardless of the HPA temperature. The density of interface hole traps for the APA+HPA samples was 1.7- $2.0 \times 10^{12} \text{ cm}^{-2}$  almost independent of the HPA temperature (green square symbols in Fig. 3), while the density was above  $1.1 \times 10^{13}$  cm<sup>-2</sup> without HPA (green dashed line in Fig. 3). Therefore, HPA was revealed to not only suppress the generation of interface hole traps but also passivate the traps once generated in GaN MOS structures. Besides, since hole traps were reduced by HPA at the lowest temperature of 200°C, the critical factor is considered to be not additional oxidation during HPA but a high-pressure treatment in an O<sub>2</sub> ambient.

The mechanism of the hole trap reduction by HPA is hypothesized to be related to the generation and reduction of  $V_{\rm O}$  in the interfacial GaO<sub>x</sub> layer. It is presumed that, under atmospheric pressure, oxygen removal from a  $GaO_x$  interlayer easily occurs and is enhanced at a higher temperature in SiO<sub>2</sub>/GaN systems, even in an oxidant gas ambient, leading to a significant increase in the hole trap density. Based on the comparison between HPA and APA, on the other hand,  $V_0$ formation hardly occurs under 100 MPa, and V<sub>O</sub> once generated by high-temperature APA is compensated for by high-pressure oxygen annealing. This suggests that the decomposition kinetics of a thin GaO<sub>x</sub> interlayer in SiO<sub>2</sub>/GaN structures would be dominated by annealing pressure: it is more energetically stable for oxygen atoms to be desorbed from the  $GaO_x$  layer under atmospheric pressure, while the GaOx interlayer is stable under high pressure. Scanning transmission electron microscope (STEM) and energy dispersive X-ray spectroscopy (EDX) analysis of the SiO<sub>2</sub>/p-GaN MOS structures were performed, mainly focusing on the  $GaO_x$  interfacial layer. Figure 5 shows the cross-sectional high-angle annular dark field (HAADF)-STEM images and atomic percentage

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0292841

mapping of Ga and O elements analyzed by EDX near the SiO<sub>2</sub>/GaN interfaces subjected to (a) APA (pure O<sub>2</sub>, 800°C) and (b) APA and subsequent HPA. Unfortunately, changes in the interface structures (e.g., increases in the thickness and/or atomic density of the GaO<sub>x</sub> layer) were not clearly observed because an amorphous  $GaO_x$  interlayer was too thin to be identified. Despite this, it was found that oxygen annealing under 100 MPa did not cause the SiO2 film, GaN bulk, and their interface to degrade. Since we found that  $N_{\text{hump}}$  could be reduced by about an order of magnitude by HPA, physical and chemical analyses that can monitor such a minor change in the  $V_{\rm O}$  density, such as positron annihilation spectroscopy (PAS) technique<sup>39</sup>, are needed to fully clarify the mechanism behind the hole trap reduction.

It should be emphasized that the advantage of HPA can be obtained with lower pressure ( $\sim$ 100 MPa) than that of the UHPA process (400-1000 MPa) for acceptor activation in Mg-implanted p-type GaN. Thus, the proposed high-pressure treatment could more easily be applicable in the actual device fabrication process. From a technological point of view, investigating how low pressure can be accepted in terms of reducing the hole traps will be a future direction. Adopting the proposed process for actual MOSFET fabrication is also an important future work. Lastly, it should also be mentioned that large hysteresis due to slow-response oxide hole traps remained even after HPA was performed. Since the hysteresis was confirmed to monotonically increase with expanding the sweeping voltage range (maximum negative voltage: up to -15 V), it is challenging to quantitatively discuss the impact of HPA on oxide traps. Despite that, the presence of large hysteresis even after HPA suggests that the origin of oxide hole traps is different from interface traps that are passivated by HPA. For fully understanding the origins of different kinds of hole traps, further studies are necessary by controlling the annealing conditions (temperature and pressure) and depositing various dielectric materials (e.g., SiO<sub>2</sub>, aluminum oxide, etc.) with various methods (PECVD, atomic layer deposition, etc.). This approach would help to establish the fabrication process of highly reliable GaN MOS-gate transistors.

In summary, the impact of high-pressure oxygen annealing on fast-response interface hole traps in SiO<sub>2</sub>/p-type GaN MOS structures was systematically investigated. The density of the interface hole traps was kept lower than  $2 \times 10^{12}$  cm<sup>-2</sup> and was negligibly dependent on the annealing temperature (200-800°C) for 100 MPa-annealing (O2 partial pressure: 20%), while the density exceeded  $1 \times 10^{13}$  cm<sup>-2</sup> at  $800^{\circ}$ C when annealed under atmospheric pressure with the same O<sub>2</sub> partial pressure. When HPA was subsequently performed on the MOS capacitors that first annealed at 800°C in a pure O2 ambient under atmospheric pressure, the hole trap density was reduced by

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0292841

about an order of magnitude. Consequently, high-pressure oxygen annealing turned out to be effective for not only suppressing thermal generation of interface hole traps but also reducing the hole traps, which would be ascribed to the passivation of oxygen vacancy in the  $GaO_x$  interlayer. The present results are useful for the physical understanding of the origin of hole traps in GaN MOS structures and for developing gate dielectric formation processes for highly reliable GaN devices.

#### ACKNOWLEDGMENTS

This work was partly supported by the MEXT "Program for Creation of Innovative Core Technology for Power Electronics" (No. JPJ009777) and JSPS KAKENHI (Nos. 25K17640 and 25K22096).

#### DATA AVAILABILITY STATEMENT

The data that support the findings of this study are available from the corresponding author upon reasonable request.

# CONFLICT OF INTEREST

The authors have no conflicts to disclose.

## REFERENCES

<sup>1</sup>B. J. Baliga, Semicond. Sci. Technol. **28**, 074011 (2013).

<sup>2</sup>T. Kachi, Jpn. J. Appl. Phys. **53**, 100210 (2014).

<sup>3</sup>H. Amano, Y. Baines, E. Beam, M. Borga, T. Bouchet, P. R. Chalker, M. Charles, K. J. Chen, N. Chowdhury, R. Chu, C. De Santi, M. M. De Souza, S. Decoutere, L. Di Cioccio, B. Eckardt, T. Egawa, P. Fay, J. J. Freedsman, L. Guido, O. Häberlen, G. Haynes, T. Heckel, D. Hemakumara, P. Houston, J. Hu, M. Hua, Q. Huang, A. Huang, S. Jiang, H. Kawai, D. Kinzer, M. Kuball, A. Kumar, K. B. Lee, X. Li, D. Marcon, M. März, R. McCarthy, G. Meneghesso, M. Meneghini, E. Morvan, A. Nakajima, E. M. S. Narayanan, S. Oliver, T. Palacios, D. Piedra, M. Plissonnier, R. Reddy, M. Sun, I. Thayne, A. Torres, N. Trivellin, V. Unni, M. J. Uren, M. Van Hove, D. J.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0292841

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

- Wallis, J. Wang, J. Xie, S. Yagi, S. Yang, C. Youtsey, R. Yu, E. Zanoni, S. Zeltner, and Y. Zhang, J. Phys. D Appl. Phys. 51, 163001 (2018).

- <sup>4</sup>M. A. Khan, A. Bhattarai, J. N. Kuznia, and D. T. Olson, Appl. Phys. Lett. **63**, 1214 (1993).

- <sup>5</sup>F. Bernardini, V. Fiorentini, and D. Vanderbilt, Phys. Rev. B. **56**, R10024 (1997).

- <sup>6</sup>K. J. Chen, O. Haberlen, A. Lidow, C. L. Tsai, T. Ueda, Y. Uemoto, and Y. Wu, IEEE Trans. Electron Devices 64, 779 (2017).

- <sup>7</sup>T. Oka, Jpn. J. Appl. Phys. **58**, SB0805 (2019).

- <sup>8</sup>T. Oka, T. Ina, Y. Ueno, and J. Nishii, in 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD). (2019) pp. 303-306.

- <sup>9</sup>R. Tanaka, S. Takashima, K. Ueno, H. Matsuyama, and M. Edo, Jpn. J. Appl. Phys. **59**, SGGD02

- <sup>10</sup>K. Ito, S. Iwasaki, K. Tomita, E. Kano, N. Ikarashi, K. Kataoka, D. Kikuta, and T. Narita, Appl. Phys. Express 16, 074002 (2023).

- <sup>11</sup>K. Ikeyama, H. Tomita, S. Harada, T. Okawa, L. Liu, T. Kawaharamura, H. Miyake, and Y. Nagasato, Appl. Phys. Express 17, 064002 (2024).

- <sup>12</sup>H. C. Casey, Jr, G. G. Fountain, R. G. Alley, B. P. Keller, and S. P. DenBaars, Appl. Phys. Lett. **68**, 1850 (1996).

- <sup>13</sup>T. Yamada, J. Ito, R. Asahara, K. Watanabe, M. Nozaki, T. Hosoi, T. Shimura, and H. Watanabe, Appl. Phys. Lett. 110, 261603 (2017).

- <sup>14</sup>T. Yamada, K. Watanabe, M. Nozaki, H. Yamada, T. Takahashi, M. Shimizu, A. Yoshigoe, T. Hosoi, T. Shimura, and H. Watanabe, Appl. Phys. Express 11, 015701 (2017).

- <sup>15</sup>T. Hashizume, S. Kaneki, T. Oyobiki, Y. Ando, S. Sasaki, and K. Nishiguchi, Appl. Phys. Express 11, 124102 (2018).

- <sup>16</sup>Y. Ando, K. Nagamatsu, M. Deki, N. Taoka, A. Tanaka, S. Nitta, Y. Honda, T. Nakamura, and H. Amano, Appl. Phys. Lett. 117, 102102 (2020).

- <sup>17</sup>S. Kaneki and T. Hashizume, AIP Adv. **11**, 015301 (2021).

- <sup>18</sup>K. Aoshima, N. Taoka, M. Horita, and J. Suda, Jpn. J. Appl. Phys. **61**, SC1073 (2022).

- <sup>19</sup>W. Huang, T. Khan, and T. Paul Chow, J. Electron. Mater. **35**, 726 (2006).

- <sup>20</sup>K. Zhang, M. Liao, M. Imura, T. Nabatame, A. Ohi, M. Sumiya, Y. Koide, and L. Sang, Appl. Phys. Express 9, 121002 (2016).

- <sup>21</sup>M. Akazawa, Y. Tamamura, T. Nukariya, K. Kubo, T. Sato, T. Narita, and T. Kachi, J. Appl. Phys. 132, 195302 (2022).

- <sup>22</sup>A. Teramoto, M. Saito, T. Suwa, T. Narita, R. Kuroda, and S. Sugawa, IEEE Electron Device Lett. **38**, 1309 (2017).

- <sup>23</sup>Z. Zheng, L. Zhang, W. Song, T. Chen, S. Feng, Y. H. Ng, J. Sun, H. Xu, S. Yang, J. Wei, and K. J. Chen, IEEE Electron Device Lett. 42, 1584 (2021).

- <sup>24</sup>K. Tomigahara, M. Hara, M. Nozaki, T. Kobayashi, and H. Watanabe, Appl. Phys. Express **17**, 081002 (2024).

- <sup>25</sup>M. Hara, T. Kobayashi, M. Nozaki, and H. Watanabe, Appl. Phys. Lett. **126**, 022113 (2025).

- <sup>26</sup>M. Hara, K. Hirahara, K. Tomigahara, M. Nozaki, T. Kobayashi, and H. Watanabe, J. Appl. Phys. **138**, 055705 (2025).

- <sup>27</sup>T. Kobayashi, K. Tomigahara, M. Nozaki, T. Shimura, and H. Watanabe, Appl. Phys. Express **17**, 011003 (2024).

- <sup>28</sup>Y. Wada, H. Mizobata, M. Nozaki, T. Kobayashi, T. Hosoi, T. Kachi, T. Shimura, and H. Watan-abe, Appl. Phys. Lett. **120**, 082103 (2022).

- <sup>29</sup>H. Mizobata, M. Nozaki, T. Kobayashi, T. Shimura, and H. Watanabe, Appl. Phys. Express **16**, 105501 (2023).

- <sup>30</sup>S. Hattori, A. Oshiyama, and K. Shiraishi, J. Appl. Phys. **135**, 175303 (2024).

- <sup>31</sup>S. Hattori, A. Oshiyama, and K. Shiraishi, Appl. Phys. Lett. **125**, 161601 (2024).

- <sup>32</sup>J. B. Varley, J. R. Weber, A. Janotti, and C. G. Van de Walle, Appl. Phys. Lett. **97**, 142106 (2010).

- <sup>33</sup>T. Kobayashi, T. Gake, Y. Kumagai, F. Oba, and Y.-I. Matsushita, Appl. Phys. Express **12**, 091001 (2019).

- <sup>34</sup>M. D. McCluskey, J. Appl. Phys. **127**, 101101 (2020).

- <sup>35</sup>C. Kaewmeechai, J. Strand, and A. Shluger, Phys. Rev. B. **111**, 035203 (2025).

- <sup>36</sup>H. Sakurai, M. Omori, S. Yamada, Y. Furukawa, H. Suzuki, T. Narita, K. Kataoka, M. Horita, M. Bockowski, J. Suda, and T. Kachi, Appl. Phys. Lett. 115, 142104 (2019).

- <sup>37</sup>T. Kachi, T. Narita, H. Sakurai, M. Matys, K. Kataoka, K. Hirukawa, K. Sumida, M. Horita, N. Ikarashi, K. Sierakowski, M. Bockowski, and J. Suda, J. Appl. Phys. **132**, 130901 (2022).

- <sup>38</sup>M. Kanechika, T. Hirata, T. Tokozumi, T. Kachi, and J. Suda, Appl. Phys. Express **17**, 016502 (2023).

- <sup>39</sup>A. Uedono, S. F. Chichibu, Z. Q. Chen, M. Sumiya, R. Suzuki, T. Ohdaira, T. Mikado, T. Mukai, and S. Nakamura, J. Appl. Phys. 90, 181 (2001).

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0292841

• lightly doped p-GaN epilayer (~1×10<sup>17</sup> cm<sup>-3</sup>)

♦ wet cleaning (acetone & 50% HF)

♦ activation annealing (N<sub>2</sub>, 800°C, 20 min)

♦ wet cleaning (50% HF)

**♦ SiO₂ deposition by PECVD** (26–28 nm)

post-deposition annealing (PDA)

(1) 100 MPa, O<sub>2</sub>/Ar: 20%, 200-800°C [HPA]

(2) 0.1 MPa, O<sub>2</sub>/N<sub>2</sub>: 20%, 200-800°C [APA]

(3) 0.1 MPa, pure O<sub>2</sub>, 800°C

→ 100 MPa, O<sub>2</sub>/Ar: 20%, 200–800°C [APA+HPA]

**♦** Ni gate electrode & Al back contacts

FIG. 1. Process flow for the fabrication of SiO<sub>2</sub>/p-type GaN MOS capacitors.

FIG. 2. C-V characteristics of the SiO<sub>2</sub>/p-type GaN MOS structures annealed at various temperatures (200-800°C) under (a) a high pressure (HPA) or (b) atmospheric pressure (APA). Data obtained in an MOS capacitor underwent APA in O<sub>2</sub> ambient at 800°C are also shown by gray dashed line in (a). Oxide capacitance  $(C_{ox})$  obtained from spectroscopic measurement of the SiO<sub>2</sub> thickness is indicated by horizontal dashed lines.

FIG. 3. Density of interface hole traps obtained using the voltage range of the hump ( $\Delta V_{\text{hump}}$ ) in C-V characteristics of the SiO<sub>2</sub>/p-type GaN MOS structures subjected to high-pressure annealing (HPA), atmospheric-pressure annealing (APA), and combined annealing with APA (pure O<sub>2</sub>, 800°C) and subsequent HPA (APA+HPA).

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

FIG. 4. C-V characteristics of the SiO<sub>2</sub>/p-type GaN MOS structures subjected to annealing combined with APA in pure O<sub>2</sub> ambient at 800°C and subsequent HPA at 200–800°C (APA+HPA).

FIG. 5. Cross-sectional high-angle annular dark field scanning transmission electron microscope (HAADF-STEM) image and atomic percentage of Ga and O elements obtained by energy dispersive X-ray spectroscopy (EDX) near the  $SiO_2/p$ -type GaN interfaces subjected to (a) APA in pure  $O_2$  at  $800^{\circ}$ C and (b) APA combined with subsequent HPA.