| Title        | Implementation of Service Specifications on Distributed Computing Systems |  |

|--------------|---------------------------------------------------------------------------|--|

| Author(s)    | 山口,弘純                                                                     |  |

| Citation     | 大阪大学, 1998, 博士論文                                                          |  |

| Version Type | VoR                                                                       |  |

| URL          | https://doi.org/10.11501/3144071                                          |  |

| rights       |                                                                           |  |

| Note         |                                                                           |  |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

# Implementation of Service Specifications on Distributed Computing Systems

Hirozumi Yamaguchi

## Implementation of Service Specifications on Distributed Computing Systems

by

Hirozumi Yamaguchi

January 1998

Dissertation submitted to the Faculty of the Engineering Science of Osaka University in partial fulfillment of the requirements for the degree of a Doctor of Philosophy in Engineering

## Abstract

This thesis summarizes the work of the author as a master/doctor student of Osaka University on the implementation of service specifications on distributed computing systems.

In a distributed computing system, multiple computers, called protocol entities, communicate with each other, exchanging messages for synchronization and data transfer. On the implementation phase of such a distributed system, the behavior of all the protocol entities must be specified. The specification of each protocol entity is called a protocol entity specification and the set of all the protocol entity specifications is called a protocol specification. In general, the control flow of each protocol entity specification may become complicated, since it contains communications among other protocol entities for cooperative computing. Therefore, it is hard for designers to describe a protocol specification directly without mistake.

In the recent years, for designing reliable distributed computing systems, many approaches based on a design method, called protocol synthesis, have been studied. In the studies of protocol synthesis, from a service specification of a distributed system and a resource allocation, a protocol specification of the distributed system is automatically derived. At the level of service specifications, protocol entities and communication channels among them are hidden, and only the actions of the system and their temporal ordering are specified. The resource allocation specifies an allocation of I/O ports and internal resources to protocol entities. On the other hand, at the level of protocol specifications, for each protocol entity, its own actions, communications with other protocol entities and their temporal ordering are specified. Both service and protocol specifications provide the same behavior for the service users of distributed system.

In general, tradeoff exists between the class of service specifications and the complexity of derivation algorithms. Therefore, it is one of the goals for the researches of protocol synthesis to provide an efficient derivation algorithm for service specifications written in a powerful model. From such a point of view, this thesis provides the following two issues of protocol synthesis.

As the first issue, an algorithm to derive a protocol specification from a service specification written in an extended model of Petri nets and a resource allocation is proposed. In general, almost all distributed systems perform inputs/outputs with parameters and the internal calculation of their new values. Also they may be performed concurrently on single/multiple protocol entities. Therefore, an extended Petri net model, called a Petri net model with Registers (PNR model in short) is used so that parallel and choice can be naturally specified and I/O's with parameters and internal calculation of their new values can be formally modeled. In the proposed method, a resource allocation, which specifies an allocation of I/O gates and registers to protocol entities can be given. Therefore the method is flexible for the change of distributed environments, such as the increase/decrease of the number of computers and the alternation of database servers.

In the derivation algorithm, first, for each transition in a service specification, how each protocol entity simulates the behavior of the transition is decided based on a fixed simulation policy. The behavior of each transition is simulated independently of other transitions, therefore, the correctness of the simulation can be proved easily. Note that in the simulation policy, the way of exchanging messages may not be uniquely decided. In such a case, the way which needs the least number of messages can be decided using a technique to solve 0-1 integer linear programming problems. Then each protocol entity performs the simulation of the transitions in the same execution order as that in the service specification. As a result, the behavior of all the transition sequences in the service specification is simulated. For such a purpose, each protocol entity needs to extract the execution order of the related transitions by removing other transitions from the service specification. However, in Petri net based models, transitions may represent synchronous points, therefore, they cannot be removed easily. In the algorithm, using a property of Petri nets, they are removed without inconsistency.

Based on the proposed method, a derivation system, which derives a protocol specification from a service specification and a resource allocation has been developed. Also an execution system, which interprets a protocol entity spec-

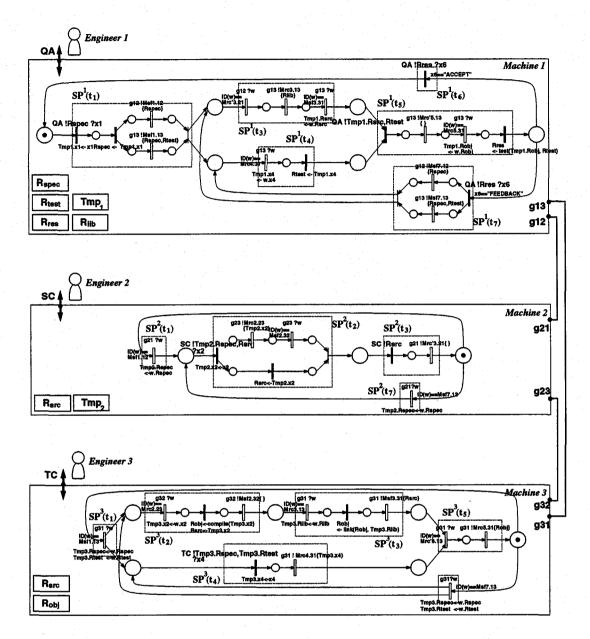

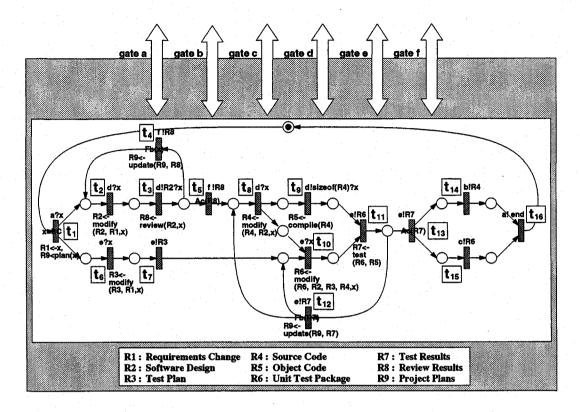

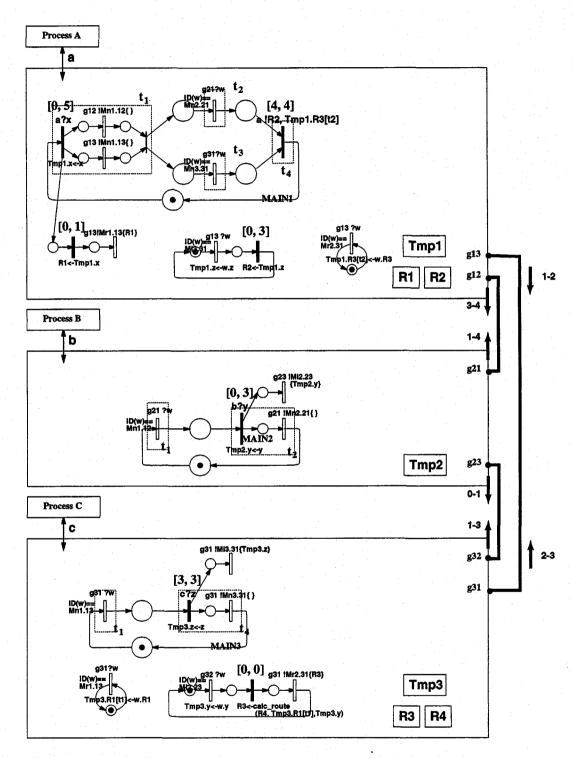

ification on one machine, communicating with others on a network, has been developed. Using these systems, the proposed method can be applied to Computer Supported Cooperative Work (CSCW). Suppose that all the activities of every worker are regarded as I/O events using computer tools, on a specific I/O gate for the worker. Also suppose that resources for a cooperative work, such as files, are represented as registers, and the modification of resources is regarded as the calculation of register values. At an abstract level, all of such I/O gates and registers are placed on one machine. Then the process of the cooperative work is described in PNR model. This process description is treated as a service specification. On the other hand, at an implementation level, suppose that each worker uses his own machine on a network. The machine is regarded as a protocol entity. Also suppose that the execution system is running on each protocol entity and I/O gates and registers are allocated to the protocol entities. The derivation system automatically derives a set of protocol entity specifications (a protocol specification) and each of them is interpreted by each execution system. As a result, the working process of each worker is automatically managed in a distributed environment. Using the above scheme, a protocol specification of ISPW-6 example process which specifies the modification of a software code and its examination is derived.

For distributed systems where time constraints between actions are specified, communication delays among protocol entities must be considered in their protocol specifications. As the second issue, an algorithm to derive a protocol specification from a service specification written in an extended model of time Petri nets, a resource allocation and maximum/minimum communication delays between each pair of protocol entities is proposed. In the proposed method, no synchronous clocks among protocol entities are assumed.

Protocol entities simulate the behavior of service specifications as follows. First, for each transition in a service specification, each protocol entity which has executed its I/O event sends notification to the protocol entities which will execute the I/O events of next transitions. Also each protocol entity which has calculated the new value of a register sends the value as early as possible, to the protocol entities which may need it in future. In this policy, it is necessary

to check whether there exist the time constraints of transitions in the protocol specification satisfying those in the service specification or not. It is also necessary to decide the time constraints if they exist. In the proposed method, time constraint of each transition to be decided is represented as a pair of variables and the restrictions among them are represented as linear inequalities. Using a technique to solve linear programming problems, they are decided automatically if they exist.

## List of Major Publications

- (1) Yamaguchi, H., Okano, K., Higashino, T. and Taniguchi, K.: Synthesis of Protocol Specifications from Service Specifications of Distributed Systems in a Marked Graph Model, IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, Vol.E77-A, No.10, pp.1623-1633, Oct. 1994.

- (2) Yamaguchi, H., Okano, K., Higashino, T. and Taniguchi, K.: "Synthesis of Protocol Entities' Specifications from Service Specifications in a Petri Net Model with Registers, Proceedings of the 15th IEEE International Conference on Distributed Computing Systems (ICDCS-15), pp.510-517, May 1995.

- (3) Yamaguchi, H., Okano, K., Higashino, T. and Taniguchi, K.: Protocol Synthesis in a Petri Net Model with Registers and Its Application, The Transactions of the Institute of Electronics, Information and Communication Engineers, Vol.J80-A, No.7, pp.1064-1072, Jul. 1997. (in Japanese)

- (4) Yamaguchi, H., Okano, K., Higashino, T. and Taniguchi, K.: Protocol Synthesis from Time Petri Net Based Service Specifications, Proceedings of the IEEE 1997 International Conference on Parallel and Distributed Systems (ICPADS'97), pp.236–243, Dec. 1997.

- (5) Yamaguchi, H., Okano, K., Higashino, T. and Taniguchi, K.: Protocol Synthesis in a Time Petri Net Model with Registers, Transactions of Information Processing Society of Japan, Vol. 39, No. 3, Mar. 1998 (to appear). (in Japanese)

## Acknowledgments

This work could be achieved owing to a great deal of helps of many individuals.

First, I would like to thank my supervisor Professor Kenichi Taniguchi of Osaka University, for his continuous support, encouragement and guidance of the work.

I'm very grateful to Professor Mamoru Fujii, Professor Toru Kikuno and Professor Hideo Miyahara for their invaluable comments and helpful suggestions concerning this thesis. I'm also very grateful to Professor Nobuki Tokura, Professor Masaru Sudo, Professor Toshinobu Kashiwabara, Professor Akihiro Hashimoto, Professor Kenichi Hagiwara, Professor Masaharu Imai, Professor Katsuro Inoue and Professor Toru Fujiwara for their valuable comments on this thesis.

I grieved to hear that Professor Seishi Nishikawa passed away in August, 1997. I will remember him with great affection and pray for the repose of his soul.

I would like to express my sincere gratitude to Associate Professor Teruo Higashino of Osaka University for his adequate guidance, valuable suggestions and discussions throughout this work. This work could not be achieved without his continuous support, encouragement and guidance.

I wish to express my special gratitude to research associate Dr. Kozo Okano of Osaka University for his continuous support, helpful suggestions, encouragement and adequate guidance.

I also wish to express my special gratitude to Assistant Professor Keiichi Yasumoto of Shiga University for his helpful suggestions and encouragement.

I wish to thank Professor Tadao Murata of University of Illinois for his helpful comments for starting this work.

Finally, I would like to thank all the members of Taniguchi Laboratory of Osaka University for their helpful advice.

# Contents

| 1 | Introduction |         |                                          | 1     |            |       |    |

|---|--------------|---------|------------------------------------------|-------|------------|-------|----|

| 2 | Definition   |         |                                          |       | 8          |       |    |

|   | 2.1          | Petri I | Net and Its Properties                   |       |            |       | 8  |

|   |              | 2.1.1   | Petri Net                                |       |            |       | 8  |

|   |              | 2.1.2   | Properties                               |       |            |       | 9  |

|   | 2.2          |         | Petri Net                                |       |            |       | 10 |

|   | 2.3          | Extens  | sion of Petri Net and Time Petri Net     |       |            |       | 10 |

|   |              | 2.3.1   | Petri Net Model with Registers           |       |            |       | 10 |

|   |              | 2.3.2   | Time Petri Net Model with Registers      | • • • |            | • •   | 12 |

| 3 | Pro          | tocol S | Synthesis from Petri Net Based Service S | Speci | ificat     | ions  | 14 |

|   | 3.1          | Service | e Specification and Resource Allocation  |       |            |       | 14 |

|   |              | 3.1.1   | Service Specification                    |       | <i>.</i> , | • •   | 14 |

|   |              | 3.1.2   | Resource Allocation                      |       |            |       | 16 |

|   | 3.2          | Protoc  | col Specification                        |       |            |       | 17 |

|   | 3.3          | Deriva  | ation Problem                            | • • • |            |       | 19 |

|   | 3.4          | Deriva  | ation Algorithm                          |       |            |       | 20 |

|   |              | 3.4.1   | Simulation of Each Transition            |       |            |       | 20 |

|   |              | 3.4.2   | Simulation of Transition Sequences       |       |            |       | 26 |

|   |              | 3.4.3   | Register Conflict                        |       |            | • **• | 29 |

|   | 3.5          | Sketch  | of Correctness Proof                     |       | • • •      |       | 32 |

|   | 3.6          | Evalua  | ation                                    |       |            | • •   | 36 |

|   | 3.7          | Concl   | usion                                    |       | · .        |       | 37 |

| 4                                                            | App  | olication of Protocol Synthesis: Cooperative Work Support | <b>38</b> |  |

|--------------------------------------------------------------|------|-----------------------------------------------------------|-----------|--|

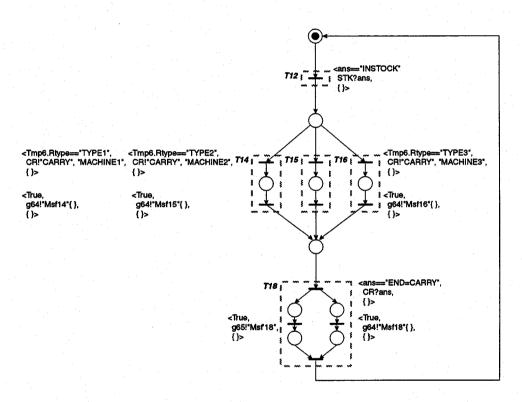

|                                                              | 4.1  | Why Is Protocol Synthesis Useful?                         | 38        |  |

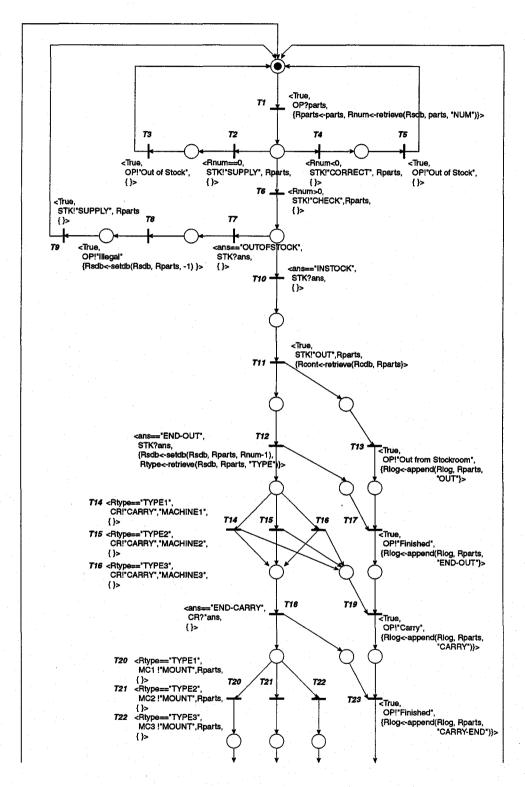

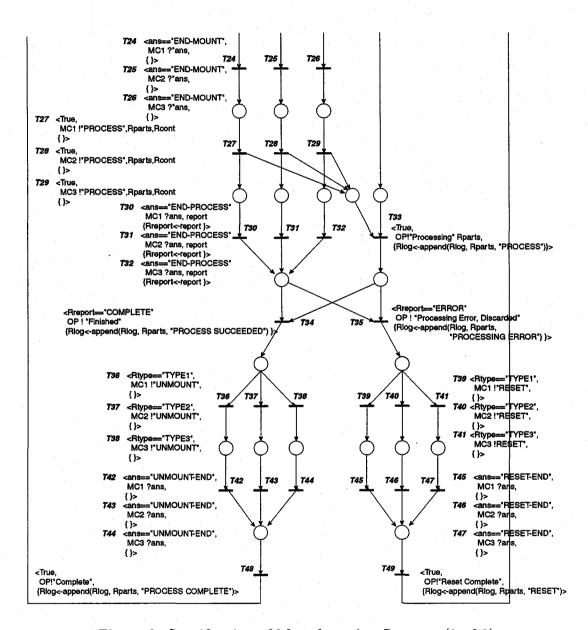

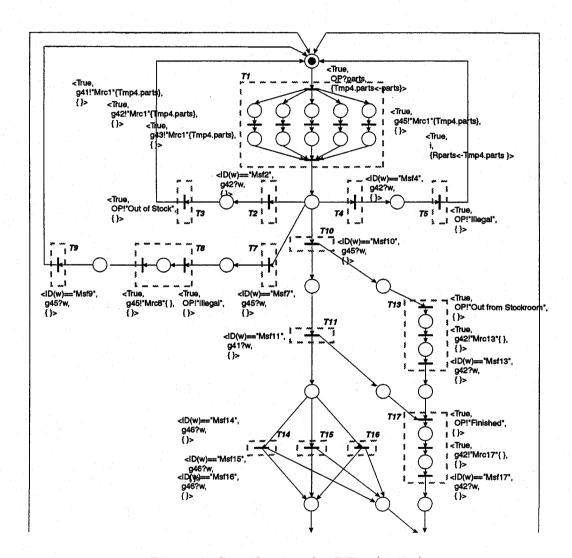

|                                                              | 4.2  | Process Modeling in PNR Model                             | 41        |  |

|                                                              |      | 4.2.1 Whole Description                                   | 41        |  |

|                                                              |      | 4.2.2 Task/Resource Allocation                            | 43        |  |

|                                                              | 4.3  | Derivation of Individual Descriptions                     | 44        |  |

|                                                              |      | 4.3.1 Individual Descriptions                             | 44        |  |

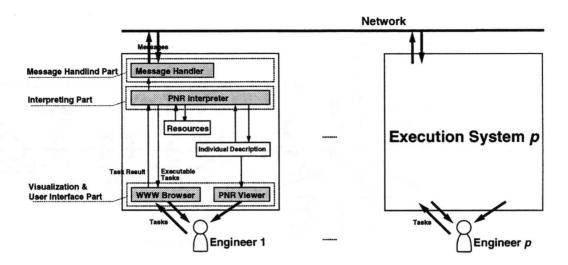

|                                                              | 4.4  | Computer Support for Cooperative Work                     | 46        |  |

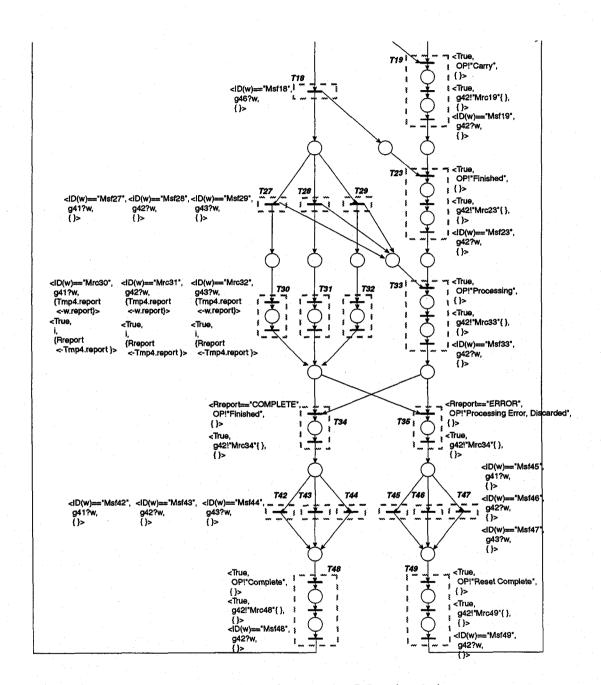

|                                                              |      | 4.4.1 Derivation System                                   | 46        |  |

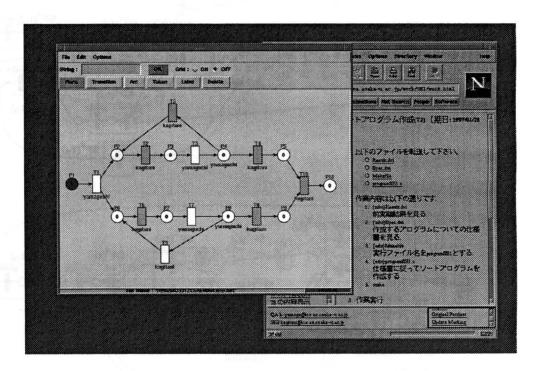

|                                                              |      | 4.4.2 Execution System                                    | 49        |  |

|                                                              |      | 4.4.3 Supporting Facilities                               | 50        |  |

|                                                              | 4.5  | Conclusion                                                | 55        |  |

| _                                                            | _    |                                                           |           |  |

| 5 Protocol Synthesis from Time Petri Net Based Service Speci |      |                                                           |           |  |

|                                                              | cati |                                                           | 56        |  |

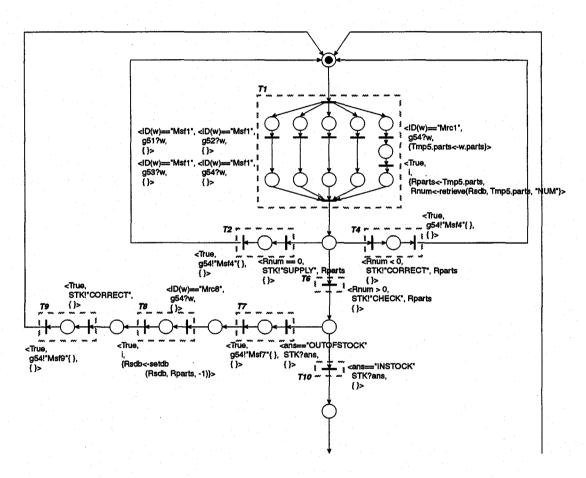

|                                                              | 5.1  |                                                           | 57        |  |

|                                                              | 5.2  | Resource Allocation and Communication Delays              | 58        |  |

|                                                              |      | 5.2.1 Resource Allocation                                 | 58        |  |

|                                                              |      | 5.2.2 Communication Delays                                | 59        |  |

|                                                              | 5.3  | Protocol Specification                                    | 59        |  |

|                                                              | 5.4  | Derivation Problem                                        | 60        |  |

|                                                              | 5.5  | Derivation Algorithm                                      | 63        |  |

|                                                              |      | 5.5.1 Deriving Nets                                       | 64        |  |

|                                                              |      | 5.5.2 Deciding Time Constraints                           | 65        |  |

|                                                              | 5.6  | Sketch of Correctness Proof                               | 73        |  |

|                                                              | 5.7  | Discussion                                                | 75        |  |

|                                                              | 5.8  | Conclusion                                                | 76        |  |

| ,                                                            | ~    |                                                           |           |  |

| б                                                            | Cor  | nclusion                                                  | 78        |  |

# Chapter 1

# Introduction

Due to the recent progress of high-speed networks and high-performance computers, many systems are implemented as distributed computing systems on networks, where computers communicate with each other for cooperation. On the implementation phase of such a distributed computing system, the behavior of all the computers must be specified. However, their control flows may become complicated, since they contain communications among the computers. Therefore, it is hard for designers to describe their behavior directly without mistake.

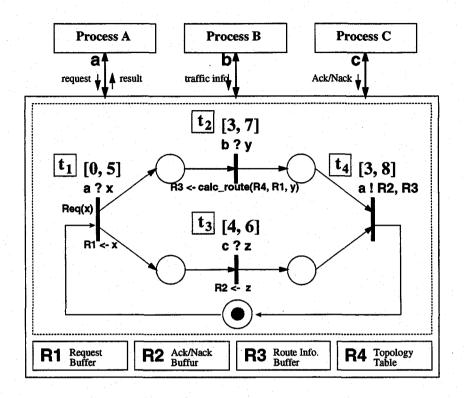

In the recent years, in order to design and implement reliable distributed computing systems, many studies of protocol synthesis [10, 11] have been studied. In protocol synthesis methods, the specification of a distributed system is described at two different abstract levels. At an abstract level, computers (protocol entities) and communication channels among them are hidden. The specification at this level is described as the I/O events on Service Access Points (SAP's), the modification of internal resources and their ordering. SAP's represent interfaces between the system and users. On the other hand, at an implementation level, each protocol entity has some of SAP's and internal resources. The specification at this level consists of a set of all the protocol entities' specifications, each of which is called a protocol entity specification. Each protocol entity specification is described as the I/O events on its SAP's, the modification of its internal resources, communications and their ordering. The specifications at the former and latter levels are called service and protocol

specifications, respectively. In protocol synthesis methods, a derivation algorithm automatically derives a protocol specification from a service specification and a resource allocation, which specifies an allocation of SAP's and internal resources to protocol entities. Therefore, it can prevent the mistake and reduce the complexity for describing protocol specifications.

Several approaches of protocol synthesis based on some computational models such as FSM/EFSM [23, 24, 25, 26], LOTOS [17, 18, 19, 20, 21, 22] and Petri nets [51, 53] have been proposed. In FSM/EFSM based approaches, parallel synchronization cannot be specified in service specifications essentially. It is a serious disadvantage point. In LOTOS based approaches, complex control flows can be specified in service specifications using several LOTOS operators such as parallel, choice, disenabling and process invocation. However, these approaches except [19] only focus on the efficient implementation of the control flows, therefore they do not consider to treat the calculation of state variables, which represent internal resources. Although variables are treated in [19], it only describes a way to delivery input values to protocol entities. Also the same problem can be found in Petri net based approaches, even though they have an advantage for the graphical representation of service and protocol specifications. It is desirable that both parallelism and choice can be specified and that the calculation of state variables can be modeled explicitly in service specifications.

Also those approaches are not sufficient for real-time distributed systems since they do not consider the urgency of services (time constraints). It is more complex and troublesome to decide suitable time constraints of protocol specifications under the presence of communication delays, satisfying the time constraints of service specifications. For service specifications with time constraints, a timed automaton based approach in [47] and a timed LOTOS based approach in [48] have been proposed. The former one is the first approach for this issue and the latter one is an extension so that they can treat service specifications with more complex structures, using a timed LOTOS model. Although these approaches can handle service specifications with time constraints between non-successive actions, they assume the existence of synchronous clocks among protocol entities. In addition, the state variables are not considered although

the transmission of their values among protocol entities may need additional communication delays.

In this thesis, the following three issues are described.

- 1. A protocol synthesis method from service specifications written in an extended Petri net model is proposed. The method provides how to simulate a service specification including parallelism and the calculation of state variables in a distributed environment, without inconsistency. In order to make the correctness of protocol specifications easy to prove, a simulation policy, which simulates the behavior of each transition independently, is adopted. The number of messages exchanged for simulating the behavior of each transition based on the simulation policy is minimized.

- 2. An application of the proposed protocol synthesis method is shown. From a whole process description of cooperative work in PNR model and an allocation of tasks to workers, a set of process descriptions of workers is automatically derived. A derivation system which derives a set of process descriptions of workers and an execution system which interprets a process description of a worker have been developed. Using the system, the efficiency of the synthesis method for cooperative work support is shown.

- 3. A protocol synthesis method from service specifications written in an extended time Petri net model is proposed. The method provides how to simulate a service specification with time constraints in a distributed environment under the presence of communication delays. Therefore the different cost measure, urgency of time, is introduced and an adequate simulation policy suitable for the cost measure should be adopted. In this method, a simulation policy, where each protocol entity holding the latest data sends it as soon as possible to the protocol entities which may need it in future is adopted, even though it may lead unnecessary messages. The total sum of possible time range intervals of actions in the protocol specification is maximized.

As the first issue of this thesis, a method for deriving a protocol specification from a service specification and a resource allocation is proposed. Both service

and protocol specifications are written in an extended Petri net model, called Petri Net model with Registers (PNR model in short). In general, almost all distributed systems perform inputs/outputs with parameters and the internal calculation of their new values. Also they may be performed concurrently on single/multiple protocol entities. In this thesis, a Petri net, where concurrency can be naturally treated, is extended so that such I/O's with parameters and the internal calculation of their new values can be treated. In PNR model, an I/O event executed on an I/O gate (SAP) and the calculation of new values of registers (state variables) are specified as an action of a transition. Also a predicate on input and register values can be also specified as one of the firing conditions of a transition. In the proposed method, a resource allocation, that is an allocation of I/O gates and registers to protocol entities, can be specified. It means that the method can cope with the change of distributed environments, such as increase/decrease of computers and alternation of database servers, by deriving a protocol specification again from the same service specification and a new resource allocation.

In the derivation algorithm, first, for each transition in a service specification, the behavior of each protocol entity for simulating the behavior of the transition is decided based on a fixed simulation policy. Note that not all the protocol entities are related to the simulation of the transition. Here, the behavior of each transition is simulated independently of other transitions. Therefore, the correctness of the simulation can be proved for each transition. It makes the correctness proof of the derivation algorithm easy. In the simulation policy, the ways of exchanging messages may not be uniquely decided. In such a case, it is desirable that the best one, which needs the least number of messages, can be found. In the proposed method, a 0-1 integer variable is introduced for each message to be exchanged. Its value is 1 if and only if the corresponding message is sent. Then the conditions to be satisfied based on the simulation policy are represented as 0-1 linear inequalities on those variables. Using a technique to solve 0-1 integer linear programming problems, a best solution to provide the least number of messages can be found. Then each protocol entity performs the simulation of the related transitions in the same execution order as that in the service specification. As a result, the behavior of all the transitions in the service specification is simulated in the protocol specification. For such a purpose, each protocol entity extracts the execution order of the related transitions from the service specification. In general, such an extraction is simple if the service specification is written in an FSM based model, since every transition can be removed by merging its unique input state with its unique output state. However, in Petri net based models, such a technique cannot be easily applied to all the transitions, since some transitions may represent synchronous points, that is, they may have several input/output states. In the algorithm, the Petri net of a service specification is restricted to be live and safe. Such a Petri net can be divided into a tuple of FSM's. Then the transitions which are not related to the protocol entity can be removed easily, and each protocol entity obtains the execution order of the related transitions.

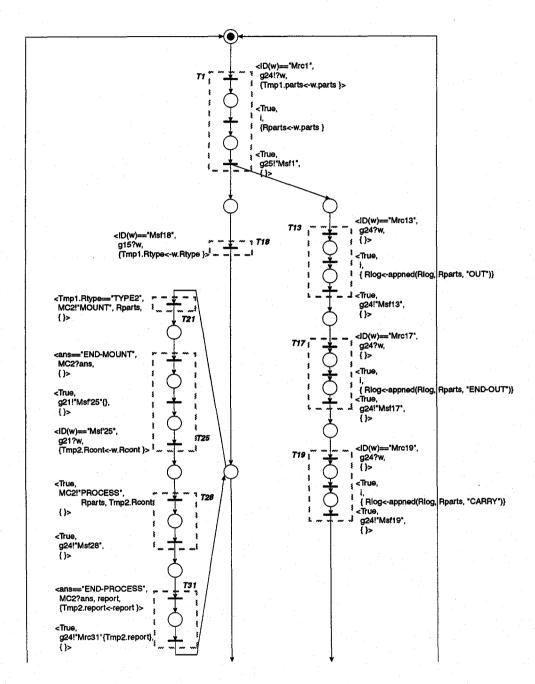

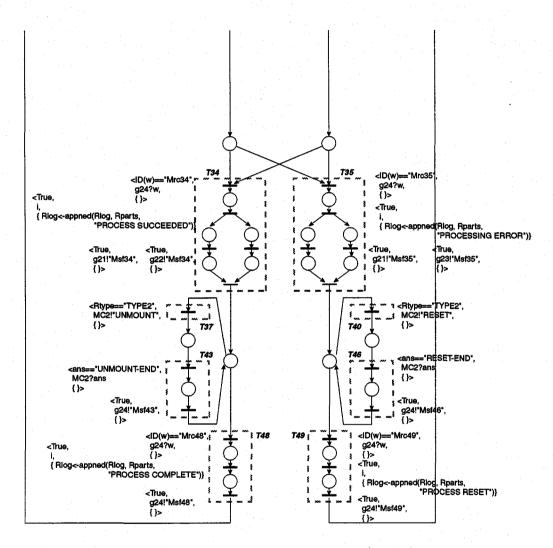

As the second issue of this thesis, a derivation system, which derives a protocol specification from a service specification and a resource allocation has been developed. Also an execution system, which interprets a protocol entity specification on one machine, communicating with others on a network has been developed. Using these systems, the proposed method can be applied to Computer Supported Cooperative Work (CSCW). Suppose that all the activities of each worker are regarded as I/O events using some tools, on a specific I/O gate for the worker. Also suppose that resources for cooperative work, such as files, are represented as registers, and the modification of resources is regarded as the calculation of the new values of the registers. At an abstract level, all of such I/O gates and registers are placed on one machine. Then the process of the cooperative work is described in PNR model. This working process description is treated as a service specification. On the other hand, at an implementation level, suppose that each worker uses his own machine on a network. The machine is regarded as a protocol entity. Also suppose that the execution system is running on each protocol entity and I/O gates and registers are allocated to protocol entities. The derivation system automatically derives a set of protocol entity specifications (a protocol specification) and each of them is interpreted by each execution system. As a result, the working process of each worker is automatically managed on a network. In this thesis, using the above scheme, a protocol specification of ISPW-6 example process [43] which specifies the modification of a software code and its examination is derived.

As the third issue of this thesis, a method for deriving a protocol specification from a service specification written in an extended model of time Petri nets [4], a resource allocation and maximum/minimum communication delays among protocol entities is proposed. The extended model is called a Time Petri Net model with Registers (TPNR model in short). The derived protocol specification satisfies the time constraints of the service specification.

In general, synchronous clocks which provide a precise global time are not always available in distributed systems, even though almost existing methods assume such a global time. Therefore, in distributed systems where a global time is not available, the way of simulating the behavior of service specifications with time constraints should be considered. In the derivation algorithm, the TPNR model is used, where each transition's time constraint is specified by the upper and lower bounds of the elapsed time from the time when all the previous transitions have been executed. Then for each transition in a service specification, the protocol entities which have executed the I/O events of its previous transitions send notification messages to the protocol entity which executes the I/O event of the transition. By receiving those messages, it can estimate the time when all of the I/O events of its previous transitions have executed in other protocol entities. Therefore, the time constraint of the I/O event can be decided. Also, messages for transmitting register values may need additional delays. Therefore, each protocol entity which has calculated the new value of a register sends the value as soon as possible to the protocol entities which may need it in future. Note that such a policy may lead unnecessary messages. Here, if the delays of notification and value transmission messages are considered, there may not exist the time constraints of transitions in protocol specifications which satisfy those in service specifications. Therefore, it is necessary to check whether such time constraints exist or not. It is also necessary to decide time constraints when needed. In the proposed method, the time constraint of each transition to be decided is represented as a pair of variables.

Then the relations among such variables are represented as linear inequalities. Using a technique to solve linear programming problems, they are decided automatically if they exist. Otherwise it is decided that the service specification cannot be implemented on the resource allocation and the minimum/maximum communication delays.

In this thesis, two methods for deriving protocol specifications from service specifications and resource allocations are presented. These methods are based on different concepts, therefore, the simulation policy and cost measure of one method are quite different from those of the another. The results of these researches can spread the applicable class of service specifications in protocol synthesis methods. They may be helpful for the design phase of reliable distributed computing systems.

# Chapter 2

# Definition

#### 2.1. Petri Net and Its Properties

#### 2.1.1 Petri Net

The formal definition of Petri nets [4] is given below.

**Definition 2.1** Petri Net: A Petri net is a kind of weighted, directed, bipartite graph, with an initial state called the initial marking, and is denoted by a 5-tuple  $PN = (P, T, F, W, M_0)$  (or simply  $(N, M_0)$  where N denotes (P, T, F, W)).

- P is a finite set of places,

- T is a finite set of transitions,  $P \cap T = \emptyset$  and  $P \cup T \neq \emptyset$ ,

- F is a set of arcs,  $F \subseteq P \times T \cup T \times P$ ,

- W is a weight function,  $W: F \to \{1, 2, 3, \ldots\}$  and

- $M_0$  is the initial marking,  $M_0: P \to \{0, 1, 2, 3, \ldots\}$ .

If a marking assigns a nonnegative integer k to a place p, we say that p is marked with k tokens.

For  $u, v \in P \cup T$ , we denote the arc from u to v by (u, v) and the weight of the arc (u, v) by w(u, v). A Petri net is said to be *ordinary* if the weights of all arcs are 1's. We also denote the preset  $\{v|(v, u) \in F\}$  of u by  $\bullet u$ , the postset  $\{v|(u, v) \in F\}$  of u by  $u \bullet$  and the set of all the elements in the postsets for the elements in  $u \bullet$  by  $u \bullet \bullet$ .

A transition t is said to be *enabled* if each input place p of t is marked with at least w(p,t) tokens. A firing of an enabled transition t removes w(p,t) tokens from each input place p and adds w(t,p) tokens to each output place p of t.

#### 2.1.2 Properties

**Definition 2.2** Liveness: A Petri net  $PN = (N, M_0)$  is said to be live if, for any pair of a marking M reachable from the initial marking  $M_0$  and a transition t, there exists a finite length of firing sequence (enabled transition sequence) from M which let fire the transition t.

**Definition 2.3** Safeness: A Petri net  $PN = (N, M_0)$  is said to be safe if, for any marking M reachable from  $M_0$ , the number of tokens for each place is at most one.

Liveness and safeness guarantee that a net is deadlock-free and that the number of its reachable states from the initial marking is finite, respectively.

Now we define a class of subgraphs of Petri nets.

**Definition 2.4** SM-Component on PN: A subgraph PN' of a Petri net PN is said to be an SM-component on PN if each transition in PN' has exactly one input place and one output place.

Here, we introduce the following theorem for live and safe Petri nets.

**Theorem 2.1** Decomposition of Live and Safe PN: For a live and safe Petri net PN, there exists a set of strongly connected SM-components which covers PN.

Proof: Live and safe Petri nets are strongly connected [4]. The procedure "Find" (it is described in 3.4.2) finds all the transitions and places which do not belong to any SM-component and appends them to one of SM-components. Also "Find" finds a loop and all the place-to-place paths belonging to the loop, and regards them as an SM-component. Therefore, each SM-component is strongly connected.

#### 2.2. Time Petri Net

Merlin's time Petri net (TPN) [1] is defined as follows.

**Definition 2.5** Time Petri Net: A time Petri net is an extended model of Petri nets and it is denoted by a 6-tuple  $(P, T, F, W, C, M_0)$  where

- $PN = (P, T, F, W, M_0)$  is a Petri net and

- $C: T \to 0 \cup Z^+ \times 0 \cup Z^+$  is a time constraint labelling function where  $Z^+$  denotes nonnegative rational numbers.

Each transition t in TPN is said to be enabled if, it is enabled in PN. Now suppose that t becomes enabled at time T and has a time constraint [Eft(t), Lft(t)]  $(Eft(t) \leq Lft(t))$ . t must not fire before T + Eft(t) and must not stay enabled beyond T + Lft(t).

In time Petri nets, only upper and lower bounds between the time when t becomes enabled and the time when t fires can be specified as constant values. Therefore, if we would like to specify the time constraints between two transitions from  $t_i$  to  $t_j$ , they must be successive transitions, that is,  $t_j \in t_i \bullet \bullet$  must hold.

#### 2.3. Extension of Petri Net and Time Petri Net

#### 2.3.1 Petri Net Model with Registers

In this chapter, we introduce a *Petri Net model with Registers* (*PNR model* in short) to formalize I/O's with values and the calculation of the new values of the state variables using input values. Suppose that a system has a finite number of registers which represent state variables (internal resources of a system) and I/O gates which represents SAP's (interfaces between the system and its users). In PNR model, a pair of an I/O event which occurs on an I/O gate and the calculation of new register values can be specified as the action of each transition.

**Definition 2.6** Petri Net Model with Registers: A Petri Net Model with Registers (PNR model) is denoted by a pair  $PNR = (PN, \Sigma)$ , where  $\Sigma$  is defined as a 8-tuple  $\Sigma = (G_s, R, V, E, G, C, \delta, Init)$ .

- PN is a Petri net,

- $G_s$  is a finite set of I/O gate symbols,

- R is a finite set of register variables,

- V is a finite set of input variables,

- E is a finite set of I/O event expressions, whose I/O gates are the elements in  $G_s$ ,

- G is a finite set of guard expressions,

- C is a finite set of register value substitution statements,

- $\delta: T \to G \times E \times C^*$  is a labelling function where  $C^* = \{s \mid s \subseteq C\}$  and

- $Init: R \to D$  is a function specifying the initial values of registers where D is a domain of register values.

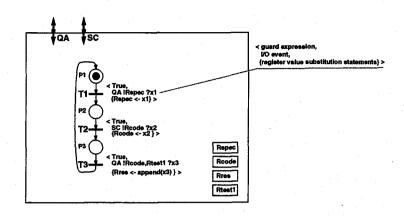

Each transition t has a label of 3-tuples  $\langle G(t), E(t), C^*(t) \rangle$ . An I/O event E(t) has the either form " $a!Exp_1(...), Exp_2(...), ... ?x, y, ...$ " or an internal event "i". "a" is an I/O gate symbol, " $!Exp_1(...), Exp_2(...), ...$ " is an output action emitting the values of " $Exp_1(...), Exp_2(...), ...$ ". "?x, y, ..." is an input action getting input values and assigning them to input variables "x, y, ...". The scope of those input variables is on the transition t. Register variables are global variables whose scope is on all the transitions. An internal event "i" means that no I/O event occurs on any I/O gate. A guard expression G(t) is a predicate whose arguments may be input variables on t and/or register variables. Each register value substitution statement in  $C^*(t)$  has a form like " $R_q \leftarrow f(..)$ ". f is a function whose arguments may be input variables on t and/or register variables, and returns the new value of  $R_q$ .  $C^*(t)$  is allowed to be an empty set  $\emptyset$ .

**Definition 2.7** Firing Rule of Transitions in PNR Model: A transition t is said to be enabled in PNR model  $PNR = (PN, \Sigma)$  iff t is enabled in PN and the value of guard expression G(t) is true. If an enabled transition t fires, the I/O

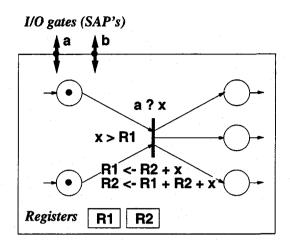

Figure 2.1: A Transition in PNR Model.

event E(t) is executed. If E(t) includes an input action and no input values are given from the I/O gate, t cannot fire until input values are given. Then all of the register value substitution statements in  $C^*(t)$  are executed in parallel. Note that each transition t is regarded as an atomic action.

An example of a transition in PNR model is shown in Fig. 2.1. Suppose that an input value given from I/O gate "a" is 3, and the values of registers  $R_1$  and  $R_2$  are 1 and 2, respectively. Now the value of the guard expression " $x > R_1$ " is true and each input place has a token. Therefore, the transition is enabled. If it fires, the I/O event "a?x" is executed (that is, the input value is actually read from I/O gate "a"). Then the register value substitution statements " $R_1 \leftarrow R_2 + x$ " and " $R_2 \leftarrow R_1 + R_2 + x$ " are executed in parallel. In this case, the values of registers  $R_1$  and  $R_2$  are substituted to 5 (= 2 + 3) and 6 (= 1 + 2 + 3), respectively.

#### 2.3.2 Time Petri Net Model with Registers

A Time Petri Net Model with Registers (TPNR model in short) is an extended model of time Petri nets. The definition is given below.

**Definition 2.8** Time Petri Net Model with Registers: A Time Petri Net Model with Registers (TPNR model) is denoted by a pair  $TPNR = (TPN, \Sigma)$  where

- TPN is a time Petri net and

- $\Sigma$  is a 8-tuple  $\Sigma = (G_s, R, V, E, G, C, \delta, Init)$ .

The definition of  $\Sigma$  is the same as that in Definition 2.6.

A transition t in TPNR model  $TPNR = (TPN, \Sigma)$  is said to be enabled if, it is enabled in TPN and the value of its guard expression is true. Now suppose that t becomes enabled at time T and has a time constraint [Eft(t), Lft(t)]  $(Eft(t) \leq Lft(t))$ . t must not fire before T + Eft(t) and must not stay enabled beyond T + Lft(t).

For example, assume that the transition in Fig. 2.1 has a time constraint [3, 5]. The transition must fire between times T+3 and T+5 unless it becomes disabled by time T+5. If it fires, its behavior is the same as that of the transition explained in Section 2.3.1.

Finally, in PNR and TPNR models, there can be a pair of transitions which substitutes/refers the value of the same registers concurrently.

**Definition 2.9** Register Conflict Transition Pair: In PNR or TPNR model, for a pair of  $t_i$  and  $t_j$  each of which is firable in parallel with the other, if (a) both  $t_i$  and  $t_j$  have the same register R's value substitution statements or (b)  $t_i$  has a register R's value substitution statement and  $t_j$  refers the value of R, the pair is called a register conflict transition pair.

# Chapter 3

# Protocol Synthesis from Petri Net Based Service Specifications

In this chapter, we propose an algorithm to derive a protocol specification in PNR model from a service specification in the same model and a resource allocation. In Section 3.1, we will show examples of a service specification and a resource allocation. The behavior of the service specification is also explained. In Section 3.2, we will show the derived protocol specification from the service specification and a resource allocation in Section 3.1. The behavior of the protocol specification is also explained. Then we formally define the derivation problem treated in this chapter, in Section 3.3. The derivation algorithm is described in Section 3.4. In Section 3.5, we will give a sketch of correctness proof. The experimental results of derivation time are shown in Section 3.6. Finally, we conclude this chapter in Section 3.7.

## 3.1. Service Specification and Resource Allocation

#### 3.1.1 Service Specification

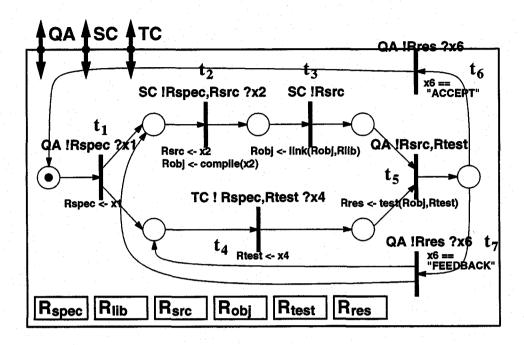

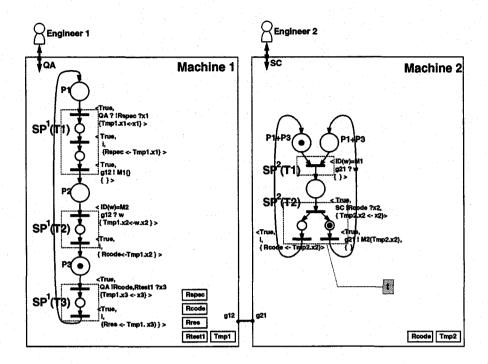

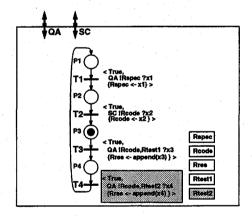

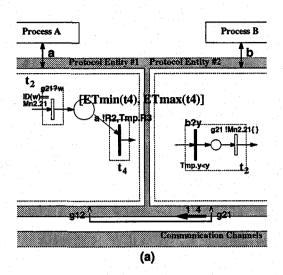

Let Sspec denote a service specification of a distributed system. Sspec is described in PNR model. Figure 3.1 shows an example Sspec. At the level of service specifications, protocol entities (computers) and communication channels among them are hidden. I/O gates "a", "b" and "c" are used as interfaces between the system and its users. Registers  $R_{db}$ ,  $R_{idx}$ ,  $R_{log}$  and  $R_{num}$  represent a database, a database index, a log-file and an access number, respectively.  $R_{usr}$

Figure 3.1: Service Specification in PNR Model.

and  $R_{res}$  are used for holding an input value and a calculation result, respectively.

On the transition  $t_1$ , a user ID given from I/O gate "a" (the value of usr), is stored to  $R_{usr}$  and an access number (the value of  $R_{num}$ ) is incremented. Then, which transition  $t_2$  or  $t_3$  fires is decided according to a keyword given from I/O gate "b" (the value of key). If the keyword is not found in the index (the value of  $R_{idx}$ ), then  $t_2$  fires and the value of  $R_{res}$  is set to null. Otherwise  $t_3$  fires and the value of  $R_{res}$  is set to the result of the retrieval of the database  $R_{db}$ . In parallel with  $t_2$  or  $t_3$ , the user ID and access number are appended to the log-file (the value of  $R_{res}$ ) on the transition  $t_4$ . Finally, the result of the retrieval (the value of  $R_{res}$ ) is emitted to I/O gate "a". Here, functions such as "retrieve" and "append" are user-defined. Their semantics are not necessary in the algorithm. Hereafter, the guard expressions whose values are identically true and the empty sets of register value substitution statements are omitted in

figures.

In this chapter, for simplifying the algorithm, we assume that Sspec satisfies the following restrictions.

- [Restriction 1] The Petri net of Sspec must be live and safe.

- [Restriction 2] Sspec must not include any register conflict transition pairs.

- [Restriction 3] Sspec must not include internal events "i".

The liveness and safeness are defined in Definitions 2.2 and 2.3, respectively. Restriction 1 is necessary for the derivation algorithm. It will be discussed in Section 3.4.2. The reason to assume Restriction 2 is shown in Section 3.4.3. Restriction 3 is not essential.

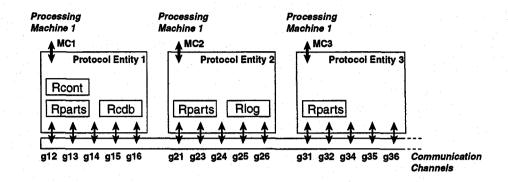

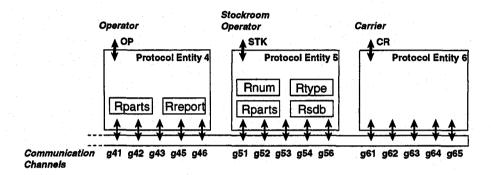

#### 3.1.2 Resource Allocation

At the level of protocol specifications, a distributed system consists of p protocol entities (PE's) 1, ..., p. Here, a protocol entity k is denoted by PE<sub>k</sub>. The I/O gates and registers used in Sspec are allocated to p protocol entities. Such an allocation is called a resource allocation and denoted by Alloc(p, Sspec). In Alloc(p, Sspec), each I/O gate is allocated to exactly one protocol entity, while each register can be allocated to more than one protocol entity.

Table 3.1 shows an example resource allocation Alloc(3, Sspec). In this resource allocation, one register  $R_{usr}$  is allocated to two protocol entities  $PE_1$  and  $PE_3$ . Similarly, the register  $R_{db}$  is allocated to two protocol entities  $PE_2$  and  $PE_3$ . Such a multiple allocation of one register means that there are some copies of the register and they are maintained by multiple protocol entities independently. It does not mean that there is a shared variable.

Here, we assume a restriction for Alloc(p, Sspec).

• [Restriction 4] For any pair of transitions  $t_i$  and  $t_j$  which share an input place p in Sspec, if  $G(t_i) \cap G(t_j) \neq$  false for some values of registers/inputs, I/O gates of their I/O events must be allocated to one protocol entity in Alloc(p, Sspec), that is,  $RPE(t_i) = RPE(t_j)$  must hold.

Table 3.1: Resource Allocation.

|          | $PE_1$    | $PE_2$                              | $PE_3$                     |

|----------|-----------|-------------------------------------|----------------------------|

| I/O gate | a, c      | b                                   |                            |

| Register | $R_{usr}$ | $R_{idx}, R_{log}, R_{res}, R_{db}$ | $R_{usr}, R_{db}, R_{num}$ |

RPE(t) is defined as follows.

**Definition 3.1** Responsible Protocol Entity: For each transition t in Sspec, suppose that the I/O event of t is executed on an I/O gate a. The protocol entity which has the I/O gate a is called a responsible protocol entity of t and denoted by RPE(t).

Restriction 4 prohibits a distributed choice, where more than one protocol entity has the initiative of the choice. In our derivation algorithm, we assume that the responsible protocol entity of  $t_i$  has the initiative of  $t_i$ . If Restriction 4 holds, for each choice, a protocol entity which has the initiative of all the transitions in the choice is uniquely decided. Note that there are several methods to decide such a protocol entity that has the initiative of a choice. However, we assume this for the simplicity of discussion.

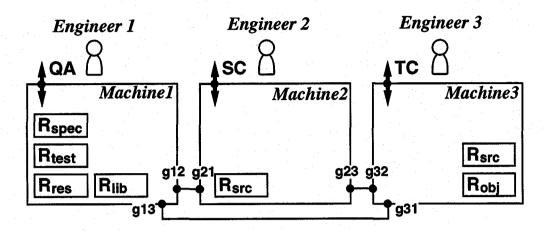

## 3.2. Protocol Specification

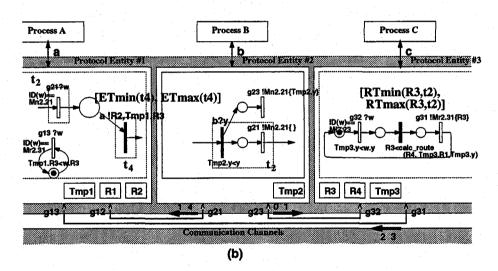

A service specification Sspec is implemented on p protocol entities. Here, the specification of each PE is called a protocol entity specification, and protocol entity specification of PE<sub>k</sub> is denoted by  $Pspec_k$ . Also a set of p protocol entity specifications  $\langle Pspec_1, ..., Pspec_p \rangle$  is called a protocol specification, and denoted by  $Pspec^{\langle 1,p \rangle}$ .

For each pair of  $PE_i$  and  $PE_j$ , there is a reliable duplex communication channel and the  $PE_i$ 's  $(PE_j$ 's) side of its ending point is modeled as an I/O gate  $g_{ij}$   $(g_{ji})$ . If  $PE_i$  executes an output event  $g_{ij}!d$ , the data d (a message) is transmitted to  $PE_j$  (message sending). If  $PE_j$  executes an input event  $g_{ji}?w$ , the transmitted message is assigned to the input variable w, and removed from

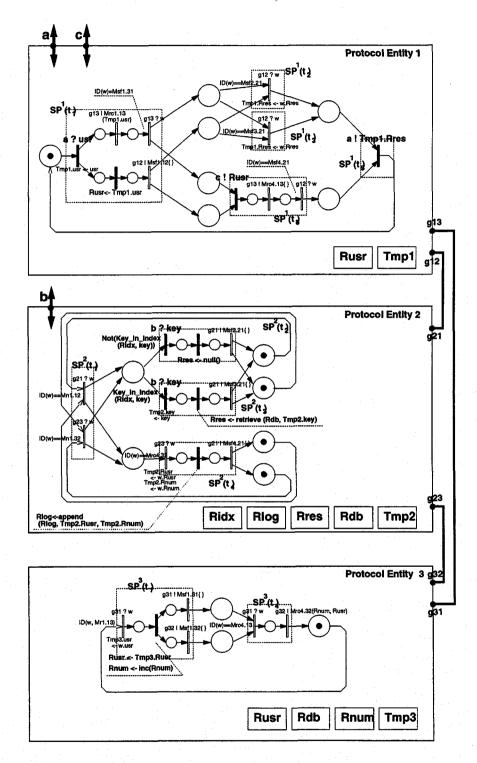

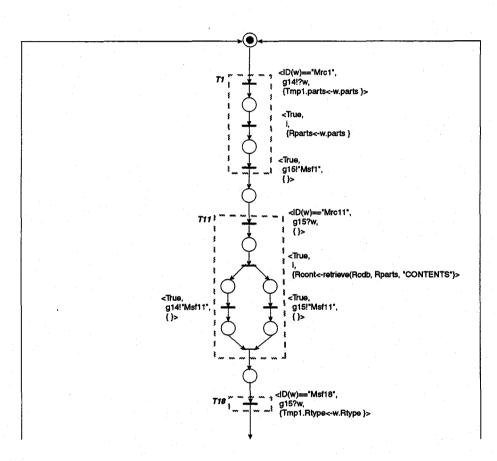

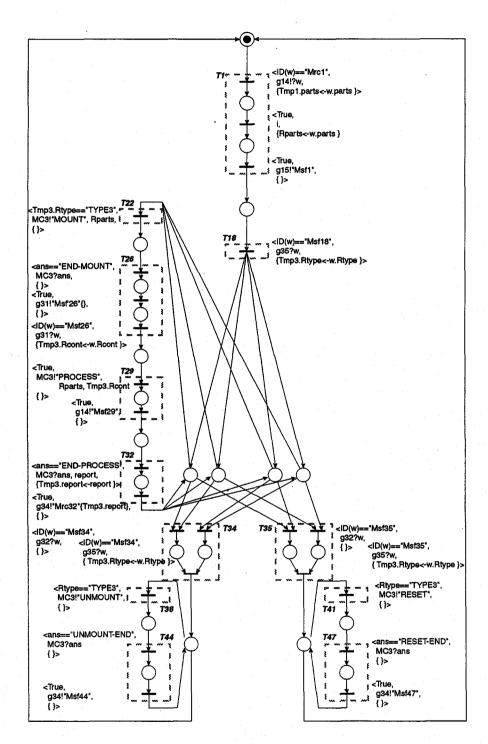

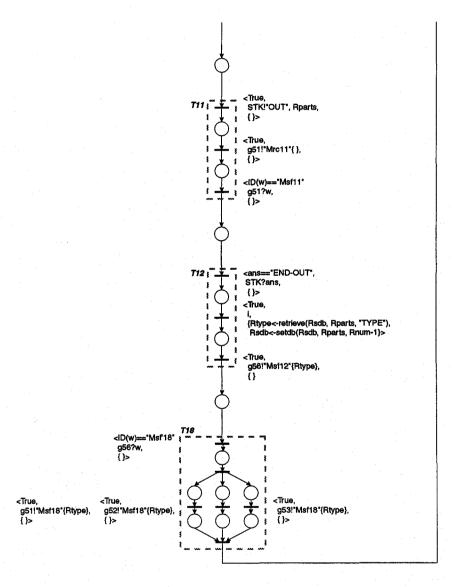

Figure 3.2: Protocol Specification in PNR Model.

the communication channel (message receiving). If there is no message in the channel,  $PE_j$  cannot execute any input action via  $g_{ji}$ . We assume that each message has its identifier (ID).  $PE_j$  gets the message ID from received data using a function ID. ID(w) returns the message ID included in an input variable w. We also assume that each  $PE_k$  has a local register  $Tmp_k$ .  $Tmp_k$  can hold multiple values. It can hold the values of input variables and registers received from the other protocol entities.  $Tmp_k.R_q$   $(Tmp_k.x)$  denotes the value of the register  $R_q$  (the input variable x) stored in  $Tmp_k$ .

For Sspec in Fig. 3.1 and Alloc(3, Sspec) in Table 3.1,  $Pspec^{\langle 1,3\rangle}$  in Fig. 3.2 is derived in our derivation algorithm. In  $Pspec^{\langle 1,3\rangle}$ , I/O event sequences executed on I/O gates "a", "b" and "c" are the same as those in Sspec. Note that in Fig. 3.2. for better readability, transitions for sending/receiving messages are represented as white rectangles.

#### 3.3. Derivation Problem

We formally define a derivation problem treated in this chapter as follows. From a given pair of a service specification Sspec described in PNR model and a resource allocation to p protocol entities Alloc(p, Sspec), which satisfy Restrictions 1, 2 and 3 in Section 3.1.1 and Restriction 4 in Section 3.1.2, the problem is to derive a correct protocol specification  $Pspec^{(1,p)}$ .

**Definition 3.2** Correctness: We say that  $Pspec^{\langle 1,p\rangle}$  is correct with respect to Sspec iff it is equivalent to Sspec.

The equivalence is defined below.

**Definition 3.3** Equivalence: Suppose that all the I/O events in  $Pspec^{\langle 1,p\rangle}$  via each I/O gate  $g_{ij}$  and internal events "i" are unobservable, and the other I/O events are observable. We say that Sspec and  $Pspec^{\langle 1,p\rangle}$  are equivalent if, both specifications are observational congruent [16].

**Definition 3.4** Observational Congruence: Sspec and  $Pspec^{(1,p)}$  are said to be observational congruent if the following conditions hold. (a) All the observable

I/O sequences in Sspec can be also observable in  $Pspec^{\langle 1,p\rangle}$  and vice versa. (b) After the execution of every observable I/O event sequences, the set of all the executable and observable I/O event sequences in Sspec and  $Pspec^{\langle 1,p\rangle}$  are the same.

For example, if a sequence of four I/O events by transitions  $t_1$ ,  $t_3$ ,  $t_4$  and  $t_5$ ,

a? "ID(352)"; b? "query=book"; c! "ID(352)"; a! "13 records were found"

is executable from the initial marking in Sspec in Fig 3.1, it is also executable in  $Pspec^{\langle 1,p\rangle}$  in Fig 3.2 and vice versa.

#### 3.4. Derivation Algorithm

Basically, our algorithm takes the following two steps to derive  $Pspec^{\langle 1,p\rangle}$ .

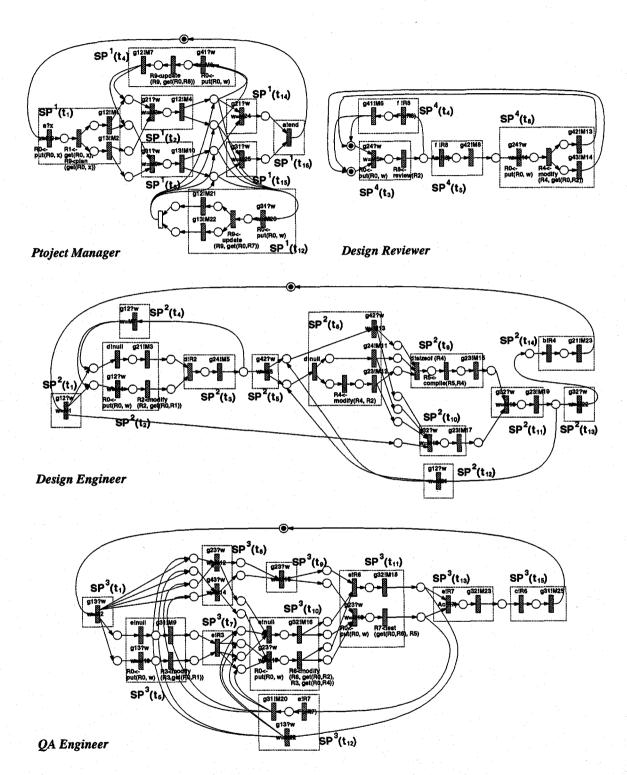

- [Step 1] For each  $t_i$  in Sspec, a set of p PNR-subnets  $SP^1(t_i),...,SP^p(t_i)$  is constructed. Each  $SP^k(t_i)$  is a part of  $Pspec_k$  and  $SP^1(t_i),...,SP^p(t_i)$  simulate the behavior of  $t_i$ . How to simulate  $t_i$  is decided based on a fixed policy (simulation policy of  $t_i$ ).

- [Step 2] Each  $Pspec_k$  is derived using the control flow of Sspec. For each  $k \ (1 \le k \le p)$ ,  $Pspec_k$  is derived by replacing  $t_i$  in Sspec with  $SP^k(t_i)$ . As a result,  $SP^k(t_1)$ , ...,  $SP^k(t_n)$  are executed in the same order as that of  $t_1, ..., t_n$ .

#### 3.4.1 Simulation of Each Transition

The components of each  $SP^k(t_i)$  are some of following transitions: (a) a transition with the I/O event and guard expression of  $t_i$ , (b) transitions with some of the register value substitution statements of  $t_i$ , (c) transitions with an output event for sending messages and (d) transitions with an input event for receiving messages, a guard expression for checking message ID's and register value substitution statements for storing received values of registers and/or input variables to a local temporary register  $Tmp_k$ .

Each  $SP^k(t_i)$  is constructed by composing these transitions based on the simulation policy of  $t_i$  described below.

#### [Simulation Policy of $t_i$ ]

- Suppose that  $RPE(t_i) = PE_u$ .  $PE_u$  executes  $t_i$ 's I/O event if (a) the value of the guard expression of  $t_i$  is true and (b) the simulation of all the previous transitions of  $t_i$  has been completed ( $PE_u$  can know it by receiving SF messages explained later). Note that  $PE_u$  may not know the values of some arguments (value of registers) of the I/O event and/or the guard expression. We assume that  $PE_u$  has already know those values by the above SF messages (this is also explained later). At the initial marking, we also assume that each protocol entity knows the initial values of all the registers.

- Each register  $R_q$ 's value substitution statement is executed by each protocol entity which has  $R_q$  (denoted by  $PE_v$ ).  $PE_u$  sends some of the following messages after the execution of the I/O event of  $t_i$ .

- Suppose that  $PE_v$  needs the values of some arguments (input variables and/or registers) of register  $R_q$ 's value substitution statement. If  $PE_u$  has some of those values, it sends them as a message (called a RC message) to  $PE_v$ .

- If an another protocol entity  $PE_{v'}$  ( $v' \neq u$ ) has some of such values,  $PE_u$  sends a message which requests  $PE_{v'}$  to send a RC messages (called a RC' message) to  $PE_v$ . If  $PE_{v'}$  receives the RC' message, it sends a RC message including those values to  $PE_v$ .

- If  $PE_v$  does not need any values of the arguments of the statement,  $PE_u$  sends a RC message including no value to  $PE_v$ .

As a result, each  $PE_v$  receives at least one RC message.

• Each PE<sub>v</sub> receives all of RC messages sent to PE<sub>v</sub> and executes some of the register value substitution statements of  $t_i$ . If u = v, PE<sub>u</sub> executes them after the execution of the I/O event of  $t_i$ .

- After the execution of the statements, each PE<sub>v</sub> sends a message (called a SF message) to each RPE(t<sub>j</sub>) (denoted by PE<sub>z</sub>) where t<sub>j</sub> is one of the next transitions of t<sub>i</sub>. If PE<sub>v</sub> holds the values of some arguments of t<sub>j</sub>'s I/O event and/or guard expression and PE<sub>z</sub> does not know those values, PE<sub>v</sub> includes those values in the SF message.

- If a protocol entity  $PE_{z'}$  ( $z' \neq z$  and  $z' \neq v$ ) holds the values of some arguments of  $t_j$ 's I/O event and guard expression and  $PE_z$  does not know those values,  $PE_u$  sends a message which requests  $PE_{z'}$  to send a SF message (called a SF' message) to  $PE_z$ .

- If  $PE_u$  does not send any of the above messages,  $PE_u$  sends a SF message to each  $PE_z$ .

For example, for the transition  $t_2$  in Sspec,  $SP^2(t_2)$  has three transitions of types (a), (b) and (c) (see Fig. 3.2). Also,  $SP^3(t_2)$  is not appeared, since PE<sub>3</sub> does not concern the simulation of  $t_2$ . Note that a message ID "Mrc<sub>i.xy</sub>" ("Msf<sub>i.xy</sub>") represents that it is a RC (SF) message sent from PE<sub>x</sub> to PE<sub>y</sub> for simulating the transition  $t_i$ .

#### Minimizing Number of Messages

Here, we consider to optimize  $Pspec^{\langle 1,p\rangle}$  based on an appropriate cost measure. In general, both communication and processing costs can be considered as the cost measures of distributed systems. The communication costs are, for example, the number or size of messages, the number of hops, average link utilization, and so on. Also the processing costs are load distribution, average CPU utilization and so on.

In our approach, it is uniquely decided which protocol entities execute  $t_i$ 's I/O event and register value substitution statements, based on the simulation policy of  $t_i$  and Alloc(p, Sspec). However, there are several ways of exchanging messages to simulate the behavior of  $t_i$ . For example, suppose that a register  $R_q$  is allocated to both RPE $(t_i)$  (say PE $_u$ ) and PE $_v$ . Also suppose that PE $_v$  ( $\neq u, v'$ ) needs to refer the value of  $R_q$  for executing a register value substitution statement of  $t_i$ . In this case, there are two ways to sends the value of  $R_q$  to

$PE_v$ . If  $PE_{v'}$  sends it, a RC' message is necessary from  $PE_u$  to  $PE'_v$ , therefore, the number of message is one more than that in the case  $PE_u$  directly sends the value to  $PE_v$ . However, suppose another case that  $PE_v$  needs not only the value of  $R_q$  but also the value of  $R_{q'}$  which is allocated only to  $PE_{v'}$ . If  $PE_{v'}$  sends them as a RC message, the number of message is one lesser than that in the case  $PE_u$  and  $PE_{v'}$  send the values of  $R_q$  and  $R_{q'}$ , respectively.

As mentioned above, processing costs are fixed in our method, however, communication costs are not. Therefore, we adopt the communication costs, especially the number of messages exchanged in simulating each  $t_i$ , as the cost measure and optimize it.

In this algorithm, we formalize such a problem as a 0-1 integer linear programming problem (a 0-1 ILP problem) and get an optimal solution. The following is the technique to get such a solution.

First, for each transition  $t_i$ , we introduce boolean variables. We assume that the values of these variables are 1 (true) or 0 (false).

#### [Variables]

- $RC'_{xy}$ : its value is 1 iff a RC' message is sent from  $PE_x$  to  $PE_y$ , otherwise 0.

- $RC_{xy}$ : its value is 1 iff a RC message is sent from  $PE_x$  to  $PE_y$ , otherwise 0.

- $RC_{xy}R_h$  ( $RC_{xy}x_k$ ): its value is 1 iff the RC message sent from  $PE_x$  to  $PE_y$  contains the value of a register  $R_h$  (an input variable  $x_k$ ), otherwise 0.

- $SF'_{xy}$ : its value is 1 iff a SF' message is sent from  $PE_x$  to  $PE_y$ , otherwise 0.

- $SF_{xy}$ : its value is 1 iff a SF message is sent from  $PE_x$  to  $PE_y$ , otherwise 0.

- $SF_{xy}R_h$ : its value is 1 iff the SF message sent from  $PE_x$  to  $PE_y$  contains the value of a register  $R_h$ , otherwise 0.

Then we represent the conditions to be satisfied if we follow the simulation policy of  $t_i$ , as 0-1 integer linear inequalities on these variables.

#### [0-1 Integer Linear Inequalities]

• For each tuple of protocol entities  $PE_x$ ,  $PE_y$  and a register  $R_h$ , the following inequalities must hold, due to the definitions of the variables  $RC_{xy}$ ,  $RC_{xy}$ - $R_h$ ,  $SF_{xy}$  and  $SF_{xy}$ - $R_h$ .

$$RC_{xy} \ge RC_{xy} R_h \tag{3.1}$$

$$SF_{xy} \ge SF_{xy} R_h$$

(3.2)

Also for each tuple of  $PE_x$ ,  $PE_y$  and an input variable  $x_k$ , the following inequality must hold, due to the definitions of the variables  $RC_{xy}$  and  $RC_{xy}$ .

$$RC_{xy} \ge RC_{xy} - x_k \tag{3.3}$$

• Hereafter, we denote the responsible protocol entity of  $t_i$  (RPE $(t_i)$ ) by PE<sub>u</sub>. For each pair of a protocol entity PE<sub>v</sub>  $(v \neq u)$  which executes at least one of the register value substitution statements of  $t_i$  and an input variable  $x_k$ , if PE<sub>v</sub> needs the value of  $x_k$  to execute substitution statements, the following must hold.

$$RC_{uv} x_k = 1 \tag{3.4}$$

The equation means that the value of the input variable is sent from  $PE_u$  to  $PE_v$ .

• For each pair of a protocol entity  $PE_v$  which executes at least one of the register value substitution statements and a register  $R_h$ , if  $PE_v$  does not hold  $R_h$  and  $PE_v$  needs the value of  $R_h$  to execute the substitution statements, the following inequality must hold.

$$\sum_{1 \le x \le p, x \ne v} RC_{xv} R_h \ge 1 \tag{3.5}$$

It means that at least one RC message which contains the value of  $R_h$  is sent to  $PE_v$ .

• For each pair of a protocol entity  $PE_{v'}$  ( $v' \neq u$ ) and a protocol entity  $PE_v$  ( $v \neq v'$ ) which executes at least one of the register value substitution statements of  $t_i$ , the following inequality must hold.

$$RC'_{uv'} \ge RC_{v'v} \tag{3.6}$$

It means that an RC' message is sent from  $PE_u$  (RPE $(t_i)$ ) to  $PE_{v'}$  if  $PE_{v'}$  sends at least one RC message.

• For each protocol entity  $PE_y$  which executes at least one of the register value substitution statements of  $t_i$ , the following inequality must hold.

$$\sum_{x \neq v} RC_{xv} \ge 1 \tag{3.7}$$

It means that at least one RC message must be sent to  $PE_v$ .

• For each pair of a protocol entity  $PE_v$  which executes at least one of the register value substitution statements of  $t_i$  and the responsible protocol entity of a transition  $t_j$  ( $t_j \in t_i \bullet \bullet$ ) (denoted by  $PE_z$  and  $z \neq v$ ), the following equation must hold.

$$SF_{vz} = 1 \tag{3.8}$$

It means that a SF message is sent from  $PE_v$  to  $PE_z$ .

• For each pair of a protocol entity  $PE_w$  ( $w \neq u$ ) which does not execute any of the register value substitution statements of  $t_i$  and the responsible protocol entity of a transition  $t_j$  ( $t_j \in t_i \bullet \bullet$ ) (denoted by  $PE_z$  and  $z \neq w$ ), the following inequality must hold.

$$SF'_{uw} \ge SF_{wz}$$

(3.9)

It means that a SF' message is sent to  $PE_w$  which sends a SF message and does not execute any of the register value substitution statements of  $t_i$ .

• For each pair of a register  $R_h$  and the responsible protocol entity of each  $t_j$  ( $t_j \in t_i \bullet \bullet$ ) (denoted by  $PE_z$ ), if  $PE_z$  needs the value of  $R_h$  to execute

the I/O event of  $t_j$ , the following inequality must hold.

$$\sum_{x \neq z, \text{PE}_x \text{holds} R_h} \text{SF}_{xz} R_h \ge 1 \tag{3.10}$$

It means that at least one SF message which contains the value of  $R_h$  is sent to  $PE_z$ .

• For the responsible protocol entity of each  $t_j$   $(t_j \in t_i \bullet \bullet)$  (denoted by  $PE_z$ ), the following inequality must hold.

$$\sum_{x \neq z} SF_{xz} \ge 1 \tag{3.11}$$

It means that a SF message is sent to PEz.

There may be some solutions which satisfy all of the above inequalities (3.1) - (3.11). In order to find the best solution which minimize the number of the messages for simulating the behavior of  $t_i$ , the following formula N is introduced.

$$N = \sum_{v'} \mathrm{RC}'_{uv'} + \sum_{v'} \sum_{v} \mathrm{RC}_{v'v} + \sum_{z} \mathrm{SF}'_{uz} + \sum_{w} \sum_{z} \mathrm{SF}_{wz}$$

N represents the total number of messages exchanged. A solution which minimizes N can be found using a technique to solve 0-1 ILP problems, where N is regarded as an objective function. Therefore, the way to exchange messages whose total number is minimized can be uniquely decided.

#### 3.4.2 Simulation of Transition Sequences

Each  $Pspec_k$  is derived using the control flow of Sspec.

It is derived by replacing  $t_i$  in Sspec by the corresponding PNR-subnet  $SP^k(t_i)$  if  $SP^k(t_i)$  is not empty. Otherwise  $t_i$  is replaced by a  $\varepsilon$ -transition (a transition with no label). Note that if  $SP^k(t_i)$  has only one input transition (a transition which has no input arcs) and only one output transition (a transition which has no output arcs), such replacement is only to reconnect the input (output) arc of  $t_i$  to the input (output) transition of  $SP^k(t_i)$ . Otherwise we add a  $\varepsilon$ -transition as a unique input (output) transition of  $SP^k(t_i)$ .

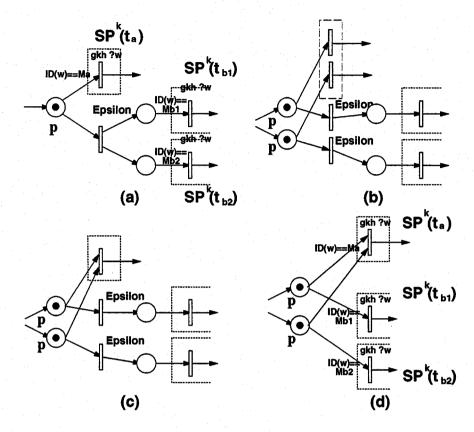

Figure 3.3: Removal of an  $\varepsilon$ -transition.

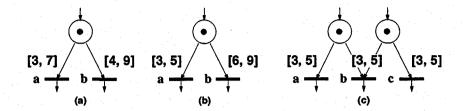

Figure 3.3(a) shows an example protocol entity specification  $Pspec_k$  with a  $\varepsilon$ -transition. In this marking,  $Pspec_k$  may receive one of three messages which force to start executing PNR-subnets  $SP^k(t_a)$ ,  $SP^k(t_{b_1})$  and  $SP^k(t_{b_2})$ . PE<sub>k</sub> must check the message ID and decide which subnets to execute. Here,  $\varepsilon$ -transitions can fire according to the firing rule of original Petri nets. However, after the free firing of the  $\varepsilon$ -transition,  $SP^k(t_{a_1})$  may not be executed even though the message "M<sub>a</sub>" arrives. To do so, we want to get such a structure that makes it possible to select  $SP^k(t_a)$  or both of  $SP^k(t_{b_1})$  and  $SP^k(t_{b_2})$ , as shown in Fig. 3.3(d).

We remove all  $\varepsilon$ -transitions in  $Pspec_k$ . The idea of removing  $\varepsilon$ -transitions is as follows. In Petri nets,  $\varepsilon$ -transitions represent synchronous points (that is, each of them has more than one input/output place). Therefore, it is difficult to use a well-known technique, which removes a  $\varepsilon$ -transition in a finite state

automaton, by merging the input and output states of the  $\varepsilon$ -transition. So we decompose the Petri net of  $Sspec_k$  into a set of finite state automata, and apply such technique to each decomposed  $\varepsilon$ -transitions.

In Section 3.1.1, we assume Restriction 1, where the Petri net of Sspec must be live and safe. Therefore, we can say that  $Pspec_k$  is also live and safe. From the live and safe Petri net  $PN_k$  of  $Pspec_k$ , the following procedure "Find" finds strongly connected SM-components  $SM_1$ , ...,  $SM_m$  which cover  $PN_k$  (see Theorem 2.1). Note that a SM-component is a subnet of  $PN_k$ , where each transition  $t_i$  has exactly one input place and one output place (see Definition 2.4).

The following procedure finds such a set of SM-components  $SM_1, ..., SM_m$ .

## [ Procedure Find ]

Initially, suppose i = 1.

- 1. Suppose that there are i-1 SM-components  $SM_1$ , ...,  $SM_{i-1}$  found on a given live and safe Petri net  $PN_k$ . If there exists an arc e which does not belong to any of  $SM_1$ , ...,  $SM_{i-1}$ , a directed loop which contains e exists on  $PN_k$  since  $PN_k$  is live and safe. Denote the loop by  $SM_i$  and go to the next step. If there is no such e, exit this procedure with m = i 1.

- 2. For each pair of places  $p_x$  and  $p_y$  on  $SM_i$ , if there exists a directed path from  $p_x$  to  $p_y$  on  $PN_k$  any of whose components except  $p_x$  and  $p_y$  does not belong to  $SM_i$ , append the path to  $SM_i$ . Continue this step until such a path does not exist. Go to the next step.

- 3. i = i + 1 and go to the first step.

Secondly, using  $SM_1,..., SM_m$  obtained by the above procedure, a procedure "Remove" removes all  $\varepsilon$ -transitions from  $Pspec_k$ .

#### [ Procedure Remove ]

1. Decompose  $PN_k$  into a set of SM-components  $SM_1, ..., SM_m$  using "Find".

- 2. Merge the decomposed transitions  $t_i$  which are not  $\varepsilon$ -transitions into one transition  $t_i$ .

- 3. For each  $\varepsilon$ -transition t, merge its input place with its output place (it is possible since it has only one input place and one output place).

4. Remove t by deleting t and its input and output arcs.

Finally,  $Pspec_k$  without  $\varepsilon$ -transitions is obtained.

An example to remove a  $\varepsilon$ -transition is shown in Fig. 3.3. A Petri net which contains a  $\varepsilon$ -transition t (Fig. 3.3(a)) is decomposed into two SM-components (Fig. 3.3(b)). Then decomposed transitions except t, which were the same transition are merged into one transition (Fig. 3.3(c)). Then each t is removed (Fig. 3.3(d)).

#### 3.4.3 Register Conflict

We assume that there is no register conflict transition pair in service specifications (see Restriction 2 in Section 3.1.1). If such a pair exists in service specifications, we may have to consider an additional control to prevent inconsistency in protocol specifications.

Suppose that there are two transitions  $t_1$  and  $t_2$  which are a register conflict pair in a service specification. Also suppose that their register value substitution statements are " $R \leftarrow 1$ " and " $R \leftarrow 2$ ", respectively. Here, the action of each transition is regarded as an atomic action in PNR model (see Definition 2.7). Therefore, in the service specification, if the transition  $t_1$  fires after  $t_2$ , the values of R is 1, otherwise 2. On the other hand, in a protocol specification, suppose that R is allocated to both  $PE_a$  and  $PE_b$ . In this case, both  $PE_a$  and  $PE_b$  execute both statements " $R \leftarrow 1$ " and " $R \leftarrow 2$ ". Here, in each PE, these two statements are parallel actions, since  $t_1$  and  $t_2$  in the service specification can fire in parallel. Here, for example,  $PE_a$  may execute " $R \leftarrow 1$ " after " $R \leftarrow 2$ " (the value of R becomes 1 in  $PE_a$ ) and  $PE_b$  may execute " $R \leftarrow 1$ " before " $R \leftarrow 2$ " (the value of R becomes 2 in  $PE_b$ ). In a correct protocol specification, all the values of R must be substituted to the same value. Therefore, the values of R's must be all 1's or all 2's in this case.

In our experiences, the service specifications of many practical distributed systems do not contain register conflict transition pairs. However, some service specifications may contain a few (not so often) register conflict pairs. For such a class, we use mutual exclusion control methods. Several methods have been investigated [12, 13] for such a purpose (for survey, see [14]). Here, we give following two solutions.

#### **Decentralized Solution**

We use Lamport's algorithm [12]. To make the discussion simple, we assume that each PE has its own clock and all the clocks show the same time. Note that Ref. [12] also shows that logical clocks which only need counter registers and time stamps and so on can be substituted for these clocks. Here, for each register conflict pair  $t_1$  and  $t_2$  in a service specification, we regard the section from the starting point of the simulation of  $t_1$  ( $t_2$ ) to its ending point as a critical section in a protocol specification, and use Lamport's algorithm.

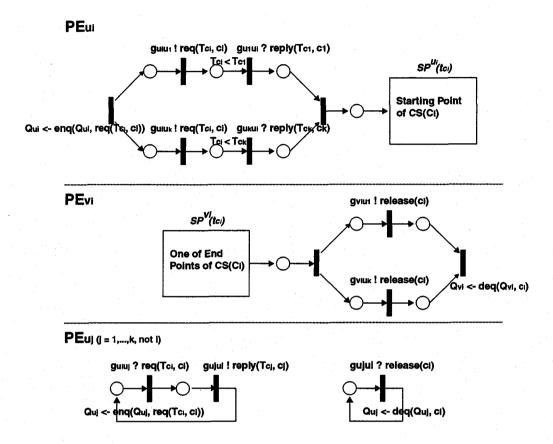

Suppose that there are a set of transitions  $t_{c_1}$ , ...,  $t_{c_k}$  in a service specification, each of them conflicts a register R with others. The algorithm uses three kinds of messages "req", "reply" and "release". Each message includes a pair  $(T_{c_i}, c_i)$ .  $c_i$  means that the message is related to a transition  $t_{c_i}$ .  $T_{c_i}$  is the time when the message generated (a time stamp). The responsible protocol entity of  $t_{c_i}$  (denoted by  $PE_{u_i}$ ) has a message queue  $Q_{u_i}$  which can sort entries by ordering of their time stamps. Now, we regard the section from the start of the simulation of each  $t_{c_i}$  (the head of  $SP^{u_i}(t_{c_i})$ ) to its end (the tail of  $SP^{v_i}(t_{c_i})$ , where  $PE_{v_i}$  is the responsible protocol entity of a transition in  $t_{c_i} \bullet \bullet$ ) as a critical section, and denote it by  $CS(c_i)$ . The algorithm is described below.

## [Decentralized Algorithm]

- 1. If  $PE_{u_i}$  tries to start the simulation of  $t_{c_i}$  (tries to enter the critical section  $CS(c_i)$ ), it sends a request message  $req(T_{c_i}, c_i)$  to each  $PE_{u_j}$   $(1 \leq j \leq k)$  and enqueues  $req(T_{c_i}, c_i)$  to  $Q_{u_i}$ .

- 2. Each  $PE_{u_j}$  which has received the message  $req(T_{c_i}, c_i)$  enqueues it to the queue  $Q_{u_j}$  and sends a reply message  $reply(T_{c_j}, c_j)$  to  $PE_{u_i}$ .

- 3. For each received message reply $(T_{c_j}, c_j)$   $(1 \leq j \leq k)$ ,  $PE_{u_i}$  checks (a)  $T_{c_i} > T_{c_j}$  and (b) the top entry of the queue  $Q_{u_i}$  has an identifier  $c_i$ . If so,  $PE_{u_i}$  starts the simulation of  $t_i$  (starts the execution of the critical section  $CS(c_i)$ ).

- 4. In our simulation policy, each of the responsible protocol entities of transitions in  $t_{c_i} \bullet \bullet$  can know the end of the simulation of  $t_{c_i}$  by receiving SF messages. Therefore any of such protocol entities (denoted by  $PE_{v_i}$ ) sends a release message release( $c_i$ ) to each  $PE_{u_j}$  if it knows that the execution of critical section  $CS(c_i)$  has been finished.

- 5. Each  $PE_{u_i}$  receives the release message release  $(c_i)$  and dequeues the entry with an identifier  $c_i$  from the queue  $Q_{u_i}$ .

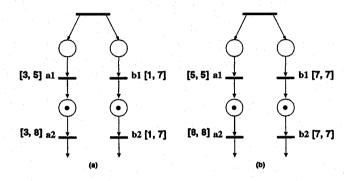

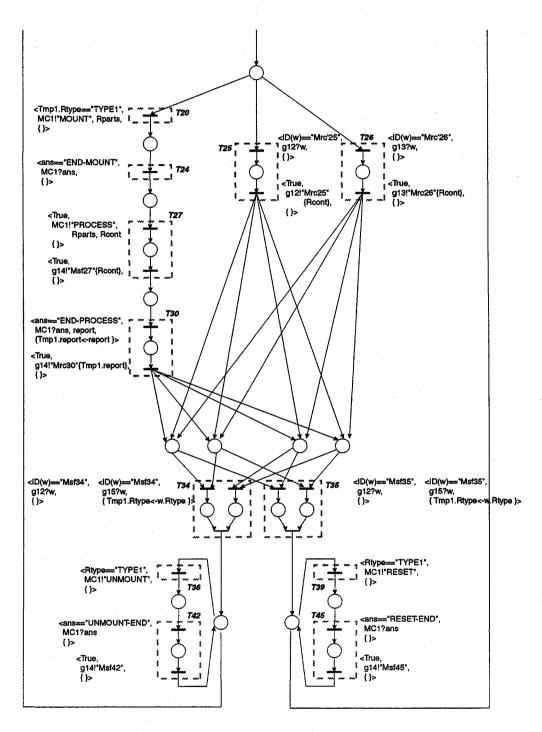

An implementation of the algorithm in PNR model is shown in Fig.3.4.

Note that the end of the critical section is informed by  $PE_{v_i}$  (the responsible protocol entity of a next transition of  $t_{c_i}$ ), not  $PE_{u_i}$  (the responsible protocol entity of  $t_{c_i}$ ). This is different from the original algorithm. Therefore  $PE_{v_i}$  must know the identifier  $c_i$ . To do so, we assume that all messages for simulating the behavior of  $t_{c_i}$  include the identifier  $c_i$ .

The algorithm can guarantee load fairness, on the other hand, it needs additional number of messages. Let k be the number of transitions which conflict the same register, and the algorithm needs 3(k-1) additional messages.

#### Centralized Solution

If we adopt a centralized control technique, the solution is simple. If  $PE_{u_i}$  tries to execute the critical section  $CS(c_i)$ , it sends a request message to a specific protocol entity  $PE_x$ . On  $t_{c_i}$ , the request message includes the names of all the registers whose values are substituted. If  $PE_{u_i}$  received a reply message from  $PE_x$ ,  $PE_{u_i}$  can start the execution of  $CS(c_i)$ . If  $PE_{v_i}$  finishes the execution of  $CS(c_i)$ , it sends a release message to  $PE_x$ .

$PE_x$  has a table which keeps the states of all the registers. Each register has two states "locked" and "unlocked". Also  $PE_x$  has a message FIFO queue. If  $PE_x$  receives a request message, it enqueues the message. For the top entry

Figure 3.4: Algorithm by Lamport.

of the queue,  $PE_x$  checks whether the states of all the registers specified in the entry are "unlocked" or not. If so,  $PE_x$  changes their states to "locked" and sends a reply message. If  $PE_x$  receives a release message, it dequeues the entry.

This technique needs the lesser number of messages than that of the previous one, however, the load of a specific protocol entity may become high.

## 3.5. Sketch of Correctness Proof

Here, we give a sketch of correctness proof for our derivation algorithm.

According to the algorithm, we can divide the proof into two independent phases. The first phase guarantees the correctness of the simulation of each transition. The second phase guarantees that the transitions are simulated in the same order as the execution order of the transitions in service specifications. In the first phase, for each  $t_i$ , we should show that the followings hold.

- (A1) (a) the evaluation of the guard expression's value, (b) the execution of the I/O event and (c) the execution of register value substitution statements are done in this order.

- (A2) (a), (b) and (c) are done with correct values.

In the simulation policy,  $RPE(t_i)$  first evaluates the value of  $t_i$ 's guard expression and executes  $t_i$ 's I/O event. Each protocol entity which executes some of  $t_i$ 's register value substitution statements cannot execute them without receiving RC messages. Here, all the RC messages are sent after the execution of the I/O event, since every protocol entity which sends RC messages sends them after receiving a RC' message from  $RPE(t_i)$  and  $RPE(t_i)$  sends RC' messages after the execution of the I/O event. Therefore, we can show that (A1) holds.

In order to show that (A2) holds, it is sufficient to show that both (A2.1) and (A2.2) hold.

- (A2.1) RPE $(t_i)$  knows all the values of the arguments of the guard expression and I/O event.

- (A2.2) Each protocol entity which executes some of register value substitution statements knows all the values of the arguments of the statements.

Now we assume that (A2.1) holds and show that (A2.2) holds.