| Title        | Low Power Design Method for Embedded Systems using VLIW Processor |  |

|--------------|-------------------------------------------------------------------|--|

| Author(s)    | 小林,悠記                                                             |  |

| Citation     | 大阪大学, 2007, 博士論文                                                  |  |

| Version Type | VoR                                                               |  |

| URL          | URL https://hdl.handle.net/11094/1631                             |  |

| rights       |                                                                   |  |

| Note         |                                                                   |  |

# Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

# Low Power Design Method for Embedded Systems using VLIW Processor

July 2007

Yuki KOBAYASHI

# Low Power Design Method for Embedded Systems using VLIW Processor

# Submitted to Graduate School of Information Science and Technology Osaka University

July 2007

Yuki KOBAYASHI

# **Publications**

### **Journal Articles (Refereed)**

- [J1] Yuki Kobayashi, Shinsuke Kobayashi, Keishi Sakanushi, Yoshinori Takeuchi, and Masaharu Imai: "HDL Generation Method for Configurable VLIW processor," IPSJ Journal, vol. 45, no. 5, pp. 1311–1321, May, 2004 (in Japanese).

- [J2] Yuki Kobayashi, Murali Jayapala, Praveen Raghavan, Francky Catthoor, and Masaharu Imai: "Methodology for Operation Shuffling and L0 Cluster Generation for Low Energy Heterogeneous VLIW Processors," ACM Trans. on Design Automation of Electronic Systems (to appear).

### **International Conference Papers (Refereed)**

- [I1] Yuki Kobayashi, Shinsuke Kobayashi, Koji Okuda, Keishi Sakanushi, Yoshinori Takeuchi, and Masaharu Imai: "Synthesizable HDL Generation Method for Configurable VLIW Processors," in Proc. Asia and South Pacific Design Automation Conference (ASP-DAC), pp. 843–846, Jan., 2004.

- [I2] Yuki Kobayashi, Murali Jayapala, Praveen Raghavan, Francky Catthoor, and Masaharu Imai: "Operation Shuffling for Low Energy L0 Cluster Generation on Heterogeneous VLIW Processors," in Proc. Embedded Systems for Real-Time Multimedia (ESTIMedia), pp. 81–86, Sep., 2005.

### **Domestic Conference Paper**

[D1] Yuki Kobayashi, Shinsuke Kobayashi, Toshiyuki Sasaki, Koji Okuda, Keishi Sakanushi, Yoshinori Takeuchi, and Masaharu Imai: "Synthesizable HDL Generation Method for Configurable VLIW Processors," IPSJ Symposium Series, vol. 2003, no. 11, pp. 259–264, Jul., 2003 (in Japanese).

# **Summary**

Nowadays, embedded systems require severe design constraints, such as high performance and low energy or low power consumption. Design productivity is also a major factor for designing embedded systems since life time of industrial products is becoming shorter and shorter, while designing complex microprocessors needs design space exploration, where designers have to try designing and evaluating a lot of architecture candidates.

Superscalar processors are well known as high performance processor architecture that issue multiple operations. However, superscalar processors need a special hardware to extract the parallelism from the instruction stream, and the additional hardware increases power consumption. To achieve high performance in embedded systems where low power is also a key factor, VLIW processors is assumed as a reasonable solution since they can issue multiple operations at a time and a compiler extracts the parallelism; without a special hardware, the power consumption of VLIW processors is smaller than that of superscalar processors.

Although VLIW processors are effective solution for embedded systems which require both of high performance and low power, there are a lot of architectural parameters to be decided by designers. Since these parameters significantly affect the performance and area, it is required to perform the design space exploration where designers evaluate many architectures to determine the optimal parameter set. However, designing a VLIW processor is very complex, and consequently time consuming and error-prone. Hence, design space exploration on VLIW processors could not have been performed sufficiently so far.

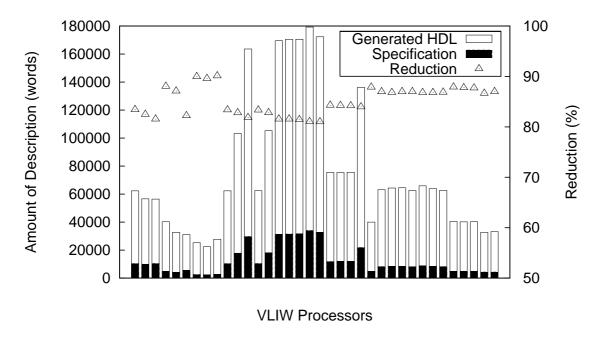

Chapter 3 describes a synthesizable HDL generation method for configurable VLIW processors, which supports a flexible architecture model, especially in dispatching rules. Experimental results shows that the proposed method can generate a VLIW processor from a high level specification description, which is 80% to 90% smaller than HDL description. And also, the generation time of HDL description is sufficiently short, that is from 2 to 15 seconds. Since the specification description supports a wide range of dispatching rules and the amount of description is sufficiently small, it is possible to generate a wide range of fine-quality VLIW processors in a short time. Therefore, the proposed method can significantly improve the design productivity of VLIW processors. (*Related publications:* [1] and [2])

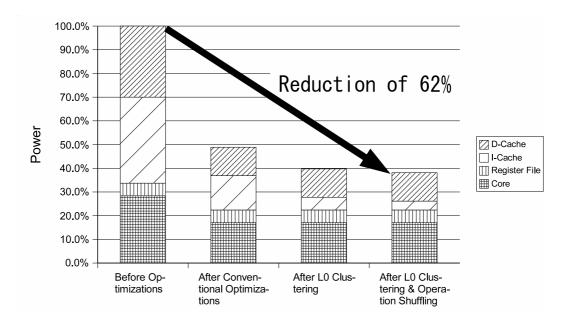

Then this thesis comes to the challenge for low power design. The power breakdown of VLIW processors indicates that the power bottleneck of VLIW processors is in the instruction memory hierarchy (e.g. instruction fetch). A loop buffer or L0 buffer architecture has been proposed to reduce the energy in the instruction memory hierarchy. The buffer locates between the instruction cache and the processor core and stores frequently-executed code to reduce the buffer access to the more power-consuming instruction cache. For further energy efficiency of L0 buffer in VLIW processors, L0 cluster architecture has also been proposed. Since the

architecture controls the buffer access more efficiently, the energy consumption is reduced furthermore. The result of L0 cluster generation is, however, sensitive to the schedule of target application.

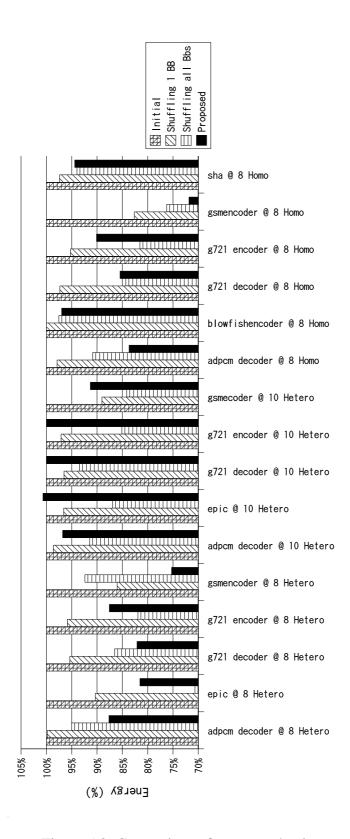

An operation shuffling algorithm is described in Chapter 4. This algorithm improves energy efficiency of L0 cluster by changing operation scheduling. Since an L0 cluster configuration is very sensitive to operation scheduling, various schedules are generated and evaluated in order to obtain an optimal schedule. By shuffling all basic blocks iteratively, energy consumption can be reduced significantly. To reduce the size of the exploration space, some heuristics are also described in Chapter 4. The experimental results show that the proposed operation shuffling algorithm successfully reduces the energy consumption in various VLIW processors including heterogeneous VLIW processors as well as homogeneous VLIW processors. (*Related publications:* [3] and [4])

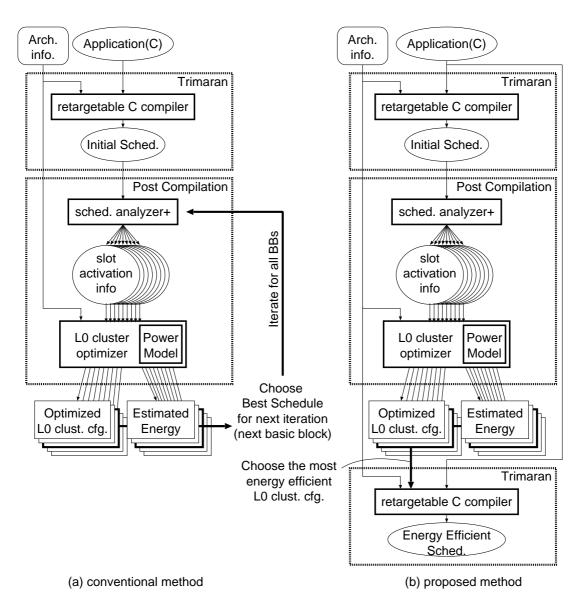

Since the simple operation shuffling takes huge amount of time even if the above heuristics are applied, a more efficient method to find a low energy operation schedule is then described in Chapter 5. Based on the analysis of characteristics of energy efficient L0 cluster configuration obtained from the operation shuffling, it is found that the optimal L0 cluster configuration is fixed after the first iteration of operation shuffling. Therefore, in the proposed method, the operation shuffling is performed only once for the most significant basic block and a compiler schedules again for the obtained cluster configuration. Some algorithms to schedule for a given cluster configuration are described in Chapter 5. By exploiting the scheduling algorithms, a compiler can generate a low energy schedule in a straightforward way. The experimental result shows that the proposed method can generate energy efficient schedules with 50 times shorter exploration time.

# **Preface**

Embedded systems are widely used in our daily life. People use the embedded systems unawarely, but most of processors in the world are embedded into such a system. Therefore, working on the field of embedded systems is very exciting for me.

Nowadays, the life cycle of industrial products is going to be shorter and shorter. One of this reasons is globalization which is typically led by growth of the internet. Merits and demerits of globalization aside, people wants to have a new product sooner and people involved in the development has to design a new product sooner.

Design automation, or electronic design automation (EDA), is a representative technology in this era. We cannot ignore the technology growth and have to keep up with the technology.

Low power or low energy is becoming a keyword in recently years. Global warming cannot be ignored and it will be a main bottleneck of human activity in near future.

Here it is very important for us to pursue a method which manages these challenges of embedded systems, that are design productivity and energy consumption.

This thesis first describes a generation method for configurable VLIW processors. This method enables high design productivity and make the design space exploration easier.

An operation shuffling algorithm is then described in this thesis. This algorithm improves energy efficiency by changing operation scheduling. Since an L0 cluster configuration is very sensitive to operation scheduling, various schedules should be evaluated in order to obtain an optimal schedule. By shuffling all basic blocks iteratively, energy consumption can be reduced significantly. To reduce the size of exploration space, some heuristics are also described.

Since a simple operation shuffling takes huge amount of time even if the above heuristics are applied, a more efficient method to find a low energy operation schedule is then described. By exploiting some scheduling algorithms, a compiler can generate a low energy schedule in a straightforward way.

I hope this thesis will make a significant direction in this field for our future.

# Acknowledgements

I would like to deeply thank Prof. Masaharu Imai, Osaka University, my supervisor. He has continuously supported me and my research and I always appreciate his technical insight which is always on target. Without his graciousness, I would not have enjoyed this fruitful period in my PhD days.

I would also like to thank Prof. Francky Catthoor, IMEC vzw and Katholieke Universiteit Leuven. He kindly welcomed me to IMEC and gave me a lot of thoughtful and valuable comments on my research work including journal and conference papers, as well as this thesis.

I am thankful to Prof. Takao Onoye, Osaka University, for reviewing this thesis.

I would like to thank associate professor Yoshinori Takeuchi and assistant professor Keishi Sakanushi for their daily advice. They have always taken care of our research and other worries.

I am thankful to Dr. Murali Jayapala, IMEC vzw. Without him, I would not have finished my work. He had made a basis of the work described in the latter half of this thesis. His comments always made me encouraged.

I thank Hiroaki Tanaka, Ittetsu Taniguchi, Takashi Hamabe, Hirofumi Iwato, Takuji Hieda, and other all members of Integrated System Design Laboratory in Osaka University for their helpful comments and suggestions in many aspects, especially in weekly seminars, and so on. I also thank Dr. Kyoko Ueda and Dr. Mohamed AbdElSalam Hassan. Special thanks to my contemporaries, Noboru Yoneoka, Hiroaki Tanaka, and Tatsuhiro Yoshimura. Conversation, lunch, and business trips with them were very pleasant, and have influenced my research as well. Chatting with friends makes me relaxed. I also thank secretary Yukako Nishikawa for her help especially on administrative papers.

I wish to thank Dr. Makiko Itoh, who made a basis of the work described in the former half of this thesis, and I would like to thank Dr. Shinsuke Kobayashi, who also helped the work a lot especially for the first few years in my research.

I wish to thank Andy Lambrechts, Praveen Raghavan. They helped me a lot in the beautiful country, Belgium. I also thank Daniele Scarpazza, Estela Rey Ramos, Javed Absar, David Novo Bruna, Theo Marescaux, Tom Vander Aa, Will Moffat, and other friends in IMEC. The stay in IMEC definitely has a significant influence not only for the period but also on whole of my life.

Finally, I owe a great deal of thanks to Yukiko who gave of her tenderness and sympathy during my PhD days and I would like to thank my parents and brother for supporting me through the years.

# **Contents**

| 1 | Intro | oduction 1                                                      |

|---|-------|-----------------------------------------------------------------|

|   | 1.1   | VLIW processor                                                  |

|   | 1.2   | Design Challenges                                               |

|   |       | 1.2.1 VLIW processor design challenges                          |

|   |       | 1.2.2 Low power embedded systems challenges                     |

|   | 1.3   | Related work                                                    |

|   | 1.4   | Approach for low power embedded systems using VLIW processors 6 |

|   | 1.5   | Main contributions                                              |

|   | 1.6   | Thesis organization                                             |

| 2 | Rela  | ated work                                                       |

|   | 2.1   | Approaches for hardware generation                              |

|   |       | 2.1.1 Approaches using a base processor                         |

|   |       | 2.1.2 Approaches using an architecture description language     |

|   | 2.2   | Overview of low power optimizations for embedded processors     |

|   | 2.3   | Low power optimization on instruction memory hierarchy          |

| 3 | Har   | dware generation for VLIW processors 13                         |

|   | 3.1   | Problem and motivation                                          |

|   | 3.2   | VLIW processor model                                            |

|   |       | 3.2.1 Dispatching model                                         |

|   |       | 3.2.2 Interrupt model                                           |

|   | 3.3   | Hardware architecture of targeted VLIW processor                |

|   |       | 3.3.1 Hardware overview of VLIW processor                       |

|   |       | 3.3.2 VLIW Processor Execution Model                            |

|   | 3.4   | Synthesizable HDL generation method for scalar processors       |

|   | 3.5   | Synthesizable HDL generation method for VLIW processors         |

|   |       | 3.5.1 Input of VLIW processor generation method                 |

|   |       | 3.5.2 Instruction dispatch pattern                              |

|   |       | 3.5.3 Control signals for dispatching                           |

|   |       | 3.5.4 Control signals for interrupt                             |

|   | 3.6   | Generation method for efficient VLIW processors                 |

|   |       | 3.6.1 Relation between FU allocation and design quality         |

|   |       | 3.6.2 Efficient resource group assignment method                |

|   | 3.7   | Experimental Results and Discussion                             |

|   |       | 3.7.2 Evaluation of efficient VLIW processor generation method               | 40       |

|---|-------|------------------------------------------------------------------------------|----------|

|   |       |                                                                              | 39<br>45 |

|   | 2.0   | 3.7.3 Evaluation of VLIW processor generation method with interrupt model    | 45       |

|   | 3.8   | Conclusion                                                                   | 46       |

| 4 | Оре   | eration shuffling algorithm for low energy L0 cluster                        | 49       |

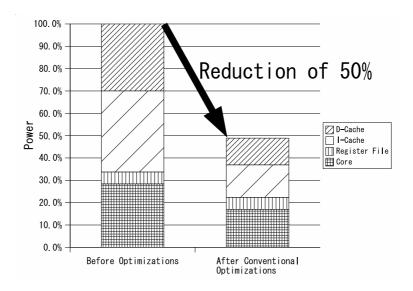

|   | 4.1   | Power breakdown of VLIW processors                                           | 49       |

|   | 4.2   | L0 buffer in VLIW processors and L0 cluster                                  | 50       |

|   | 4.3   | Motivation for impact of compiler                                            | 51       |

|   | 4.4   | Proposed operation shuffling algorithm on heterogeneous architectures        | 54       |

|   | 4.5   | Heuristics to limit the exploration space                                    | 56       |

|   |       | 4.5.1 Heuristic to shuffle one basic block at a time                         | 59       |

|   |       | 4.5.2 Heuristic to limit the number of basic blocks                          | 59       |

|   |       | 4.5.3 Heuristics to select the combination of assignment candidates          | 60       |

|   | 4.6   | Operation shuffling for multiple data clusters                               | 63       |

|   | 4.7   | Experimental results                                                         | 64       |

|   |       | 4.7.1 Potential gain of operation shuffling                                  | 65       |

|   |       | 4.7.2 Quality of pruning heuristics                                          | 66       |

|   |       | 4.7.3 Evaluation on multimedia benchmarks and different architecture flavors | 69       |

|   |       | 4.7.4 Discussion on operation shuffling over cycle boundaries                | 74       |

|   |       | 4.7.5 Relation between ILP and energy reduction                              | 74       |

|   | 4.8   | Conclusion                                                                   | 76       |

| 5 | Effic | cient energy reduction method                                                | 79       |

|   | 5.1   | Problem and motivation                                                       | 79       |

|   |       | 5.1.1 Analysis of existing operation shuffling approach                      | 81       |

|   | 5.2   | Overview of the proposed method                                              | 81       |

|   | 5.3   | Scheduling for a given L0 cluster configuration                              | 82       |

|   |       | 5.3.1 Algorithm to try to fill an inefficient cluster                        | 83       |

|   |       | 5.3.2 Algorithm to try to move operations to a shallower cluster             | 85       |

|   |       | 5.3.3 Algorithm to try to move operations to a wider cluster                 | 85       |

|   | 5.4   | Experimental Results                                                         | 86       |

|   | 5.5   | Conclusion                                                                   | 89       |

| 6 | Con   | clusion and future work                                                      | 91       |

|   | 6.1   | Conclusion                                                                   | 91       |

|   | 6.2   | Future work                                                                  | 92       |

|   |       | 6.2.1 Future work on VLIW synthesis                                          | 92       |

|   |       | 6.2.2 Future work on operation shuffling                                     | 93       |

| Α | BNF   | of processor specification description                                       | 101      |

|   |       |                                                                              |          |

# **List of Figures**

| 1.1  | Advantage of ASIPs                                                        | 2  |

|------|---------------------------------------------------------------------------|----|

| 1.2  | Overview of processor architectures                                       | 3  |

| 1.3  | System model using a VLIW processor                                       | 7  |

| 3.1  | VLIW processor model                                                      | 14 |

| 3.2  | Example of the dispatching model                                          | 15 |

| 3.3  | Control paths of scalar processor and VLIW processor                      | 17 |

| 3.4  | Execution model of VLIW processor                                         | 18 |

| 3.5  | An example of micro operation description and DFG generated from the de-  |    |

|      | scription.                                                                | 19 |

| 3.6  | An example of merging DFGs                                                | 20 |

| 3.7  | Example of table of instruction dispatch pattern $T_{IDP}$                | 21 |

| 3.8  | Enumeration of resource group for each slot                               | 22 |

| 3.9  | Example of FU conflict                                                    | 23 |

| 3.10 | Example of decode signal for resource group and operation                 | 24 |

|      | Merge of DFGs and selector insertion in the VLIW processor generation     | 26 |

| 3.12 | Hardware model of interrupt pipeline to handle a nonmaskable interrupt    | 27 |

| 3.13 | A dispatch table of the VLIW processor in the preliminary experiment      | 30 |

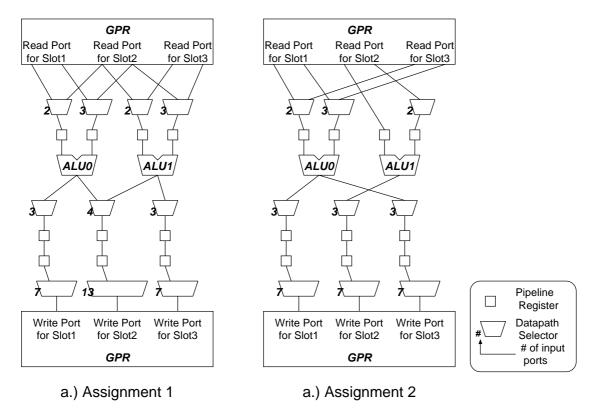

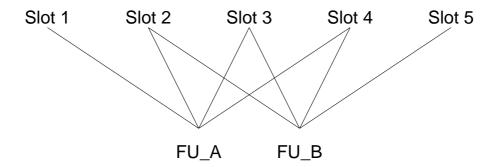

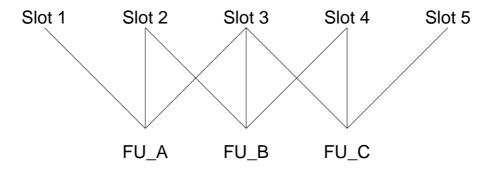

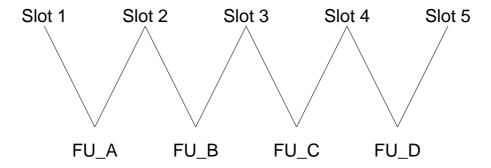

|      | Architecture of VLIW processors with different resource group assignment  | 32 |

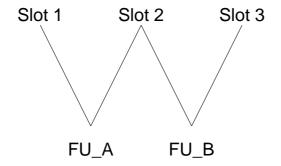

|      | Allocation of two FUs to three slots                                      | 33 |

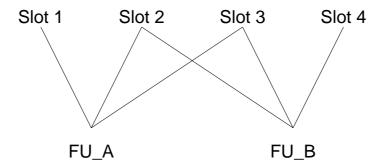

| 3.16 | Allocation of two FUs to four slots                                       | 33 |

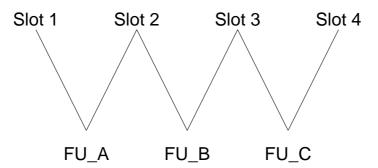

| 3.17 | Allocation of three FUs to four slots                                     | 34 |

|      | Allocation of two FUs to five slots                                       | 34 |

|      | Allocation of three FUs to five slots                                     | 35 |

|      | Allocation of four FUs to five slots                                      | 35 |

| 3.21 | Reduction of the amount of description                                    | 38 |

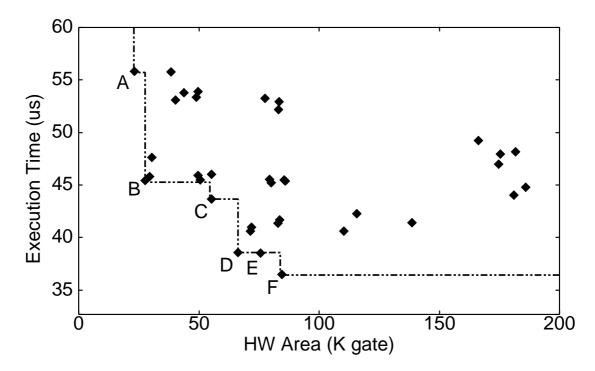

|      | Trade-off between HW area and execution time of FIR filter application    | 39 |

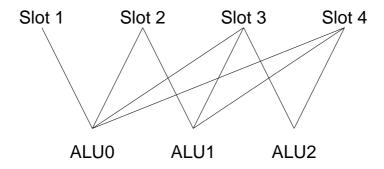

| 3.23 | FU allocation for ALUs in assignment 1                                    | 42 |

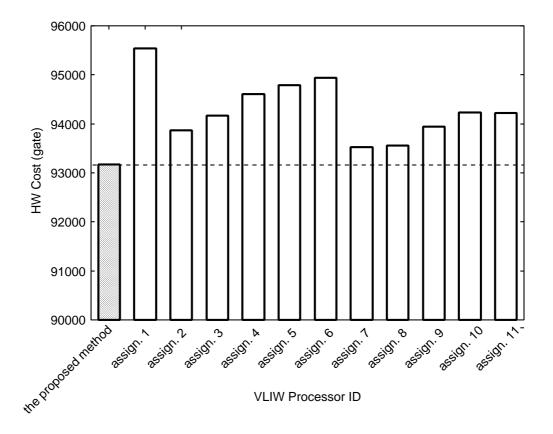

| 3.24 | Comparison of hardware area                                               | 43 |

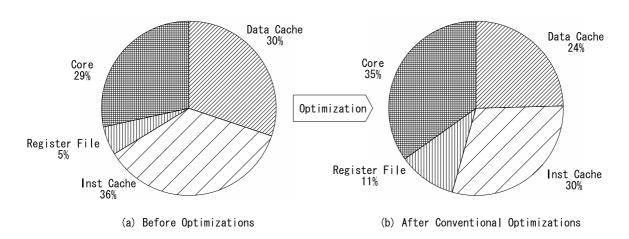

| 4.1  | Power breakdown of VLIW processor (a) before optimizations (b) after con- |    |

|      | ventional power optimizations                                             | 50 |

| 4.2  | Power reduction by the conventional power optimizations                   | 51 |

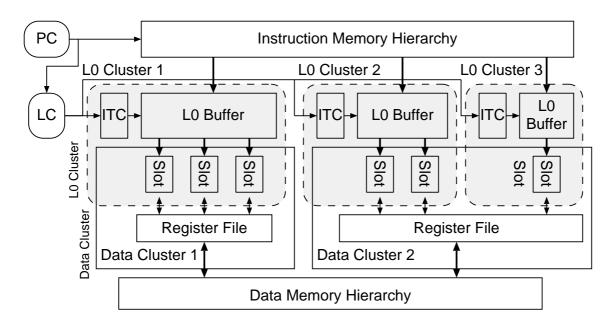

| 4.3  | A clustered VLIW processor                                                | 52 |

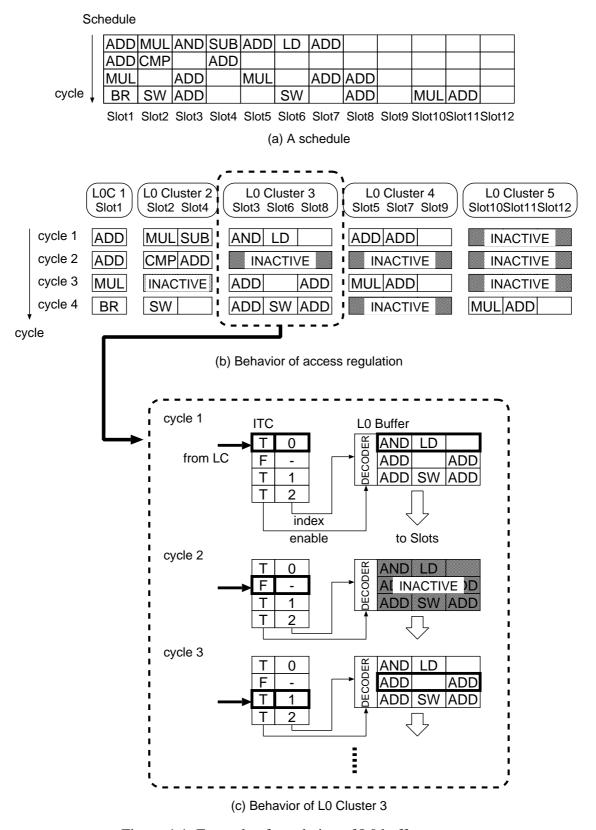

| 4.4  | Example of regulation of L0 buffer access                                 | 53 |

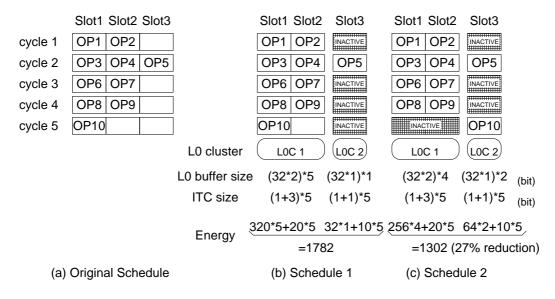

| Example illustrating energy reduction by schedule change. (operation length is |         |

|--------------------------------------------------------------------------------|---------|

| 32 bit)                                                                        | 54      |

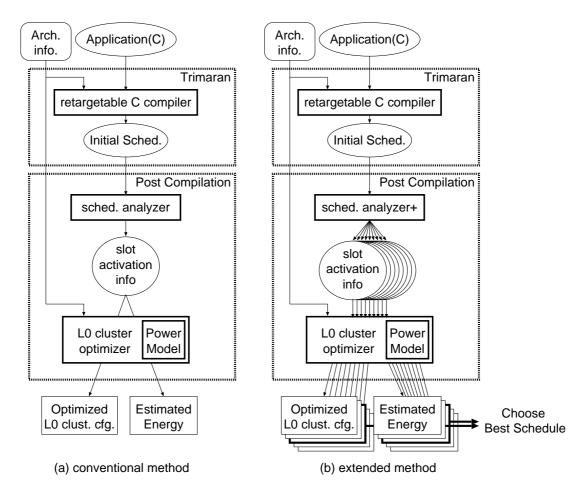

| Overview of an L0 cluster configuration improvement phase (a) in the conven-   |         |

| tional way, (b) with operation shuffling (proposed method)                     | 55      |

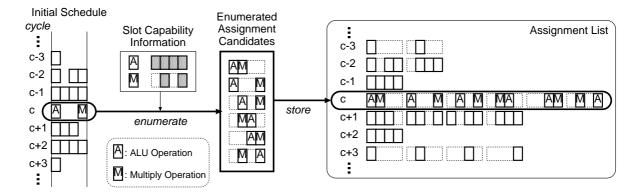

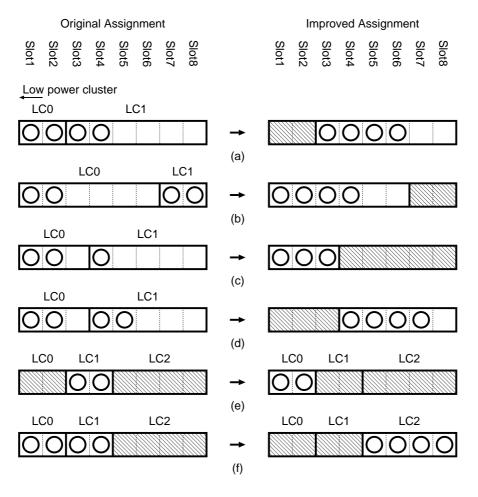

| Operation shuffling in each cycle                                              | 55      |

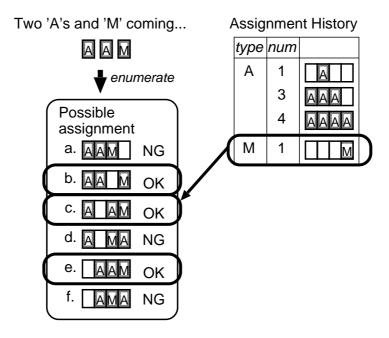

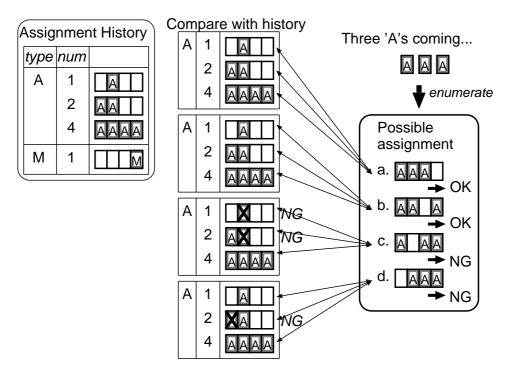

| Generation of operation shuffled schedules                                     | 57      |

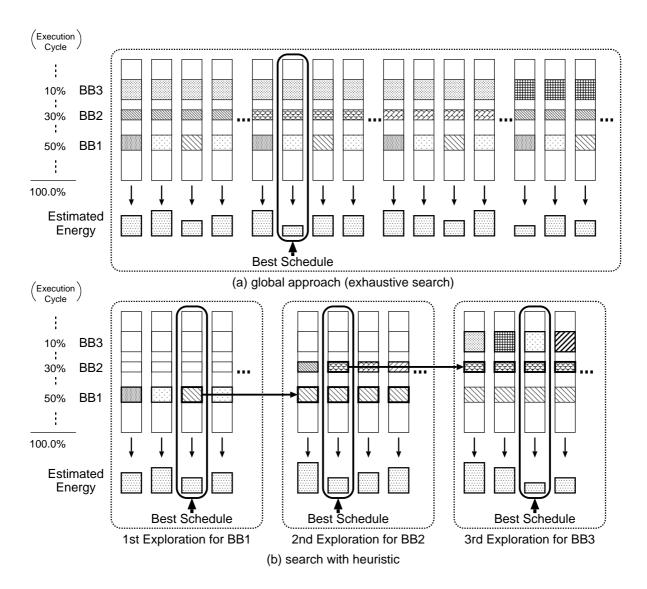

| A heuristic for multiple basic blocks                                          | 58      |

|                                                                                | 60      |

|                                                                                | 61      |

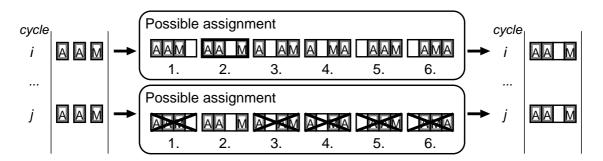

| Advanced dominance checking heuristic                                          | 62      |

| Dominance and advanced dominance checking                                      | 62      |

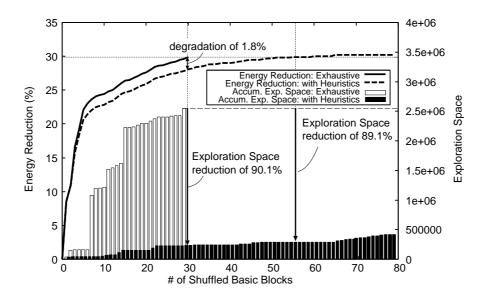

| Efficiency of the heuristics (epic@8 slot Homo)                                | 68      |

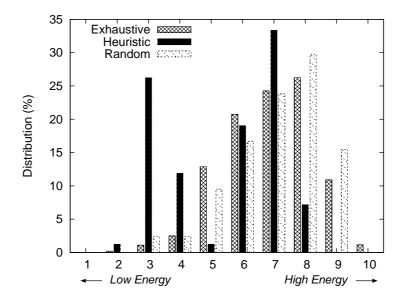

| Frequency distribution of energy of generated schedules (adpcm decoder@8       |         |

| slot Hetero)                                                                   | 69      |

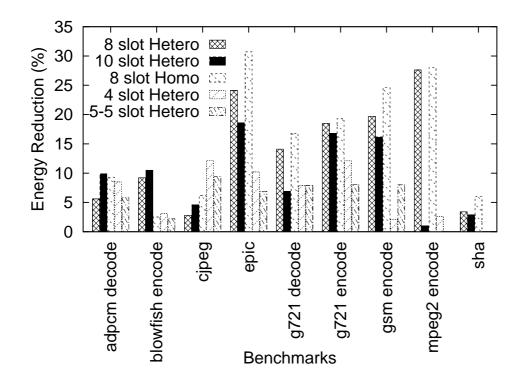

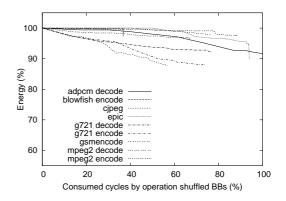

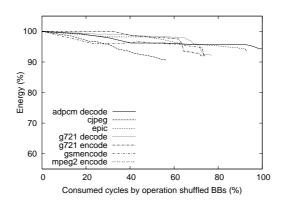

| Energy reduction of all benchmarks                                             | 70      |

| Energy reduction by shuffling operations in multiple BBs (8 slot Hetero)       | 70      |

| Energy reduction by shuffling operations in multiple BBs (10 slot Hetero)      | 70      |

| Energy reduction by shuffling operations in multiple BBs (8 slot Homo)         | 71      |

| Energy reduction by shuffling operations in multiple BBs (4 slot Hetero)       | 71      |

| Energy reduction by shuffling operations in multiple BBs (5-5 slot Hetero)     | 71      |

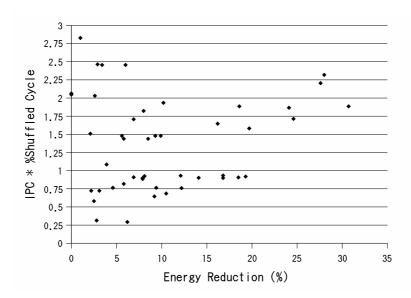

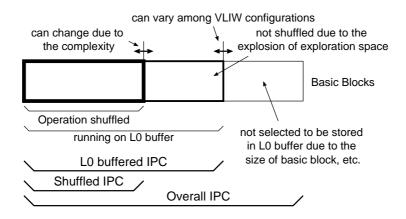

| Relation between overall IPC and energy reduction due to shuffling             | 75      |

| Various versions of IPC.                                                       | 76      |

|                                                                                |         |

|                                                                                | 0.0     |

|                                                                                | 80      |

| · ·                                                                            | 84      |

| Comparison of energy reduction                                                 | 90      |

| Power reduction by the proposed method.                                        | 93      |

|                                                                                | 32 bit) |

# **List of Tables**

| 3.1  | A VLIW pattern table of the VLIW processor in the preliminary experiment      | 29       |

|------|-------------------------------------------------------------------------------|----------|

| 3.2  | Resource group assignment 1                                                   | 30       |

| 3.3  | Resource group assignment 2                                                   | 30       |

| 3.4  | Synthesis results of the preliminary experiment                               | 31       |

| 3.5  | Parameters of designed VLIW processors                                        | 37       |

| 3.6  | Instruction set of designed VLIW processors                                   | 41       |

| 3.7  | FU allocation of designed VLIW processors                                     | 41       |

| 3.8  | Comparison of area and delay between designed VLIW processors                 | 42       |

| 3.9  | Allocation of two FUs to four slots for each VLIW pattern                     | 44       |

| 3.10 | Allocation of three FUs to four slots for each VLIW pattern                   | 44       |

| 3.11 | Occurrence conditions of added interrupts                                     | 45       |

| 3.12 | Behavior of added interrupts                                                  | 46       |

| 3.13 | Comparison of area and delay between VLIW processors with and without         |          |

|      | interrupts                                                                    | 46       |

| 4.1  | Slot capability of 8 slot heterogeneous VLIW processor                        | 65       |

| 4.2  | Slot capability of 10 slot heterogeneous VLIW processor                       | 65       |

| 4.3  | Slot capability of 4 slot heterogeneous VLIW processor                        | 65       |

| 4.4  | Slot capability of 2 data cluster 5-5 slot heterogeneous VLIW processor       | 65       |

| 4.5  | Energy reduction for MPEG2 encoder on 8-slot Hetero VLIW                      | 66       |

| 4.6  | Operation shuffling on multiple BBs (MPEG2 Encoder@8 slot Hetero)             | 66       |

| 4.7  | Minimum energy comparison between exhaustive exploration and with heuris-     |          |

|      | tics (Single BB)                                                              | 67       |

| 4.8  | Relation between energy reduction and shuffled cycles                         | 73       |

| 4.9  | Energy reduction for sha on 8-slot Hetero VLIW                                | 76       |

| 5.1  | Optimal cluster configuration and the number of required basic blocks to find |          |

|      |                                                                               |          |

|      | the configuration                                                             | 82       |

| 5.2  |                                                                               | 82<br>88 |

# **Chapter 1**

# Introduction

Embedded systems are widely used in our daily life and almost all of them have a programmable microprocessor inside. People might think most of microprocessors in the world are in personal computers; we call such kind of processor a general purpose processor (GPP). The number of GPPs inside personal computers is, however, less than 2% of the number of total processors in the world and most of processors locate in embedded systems [5]. An embedded system is usually dedicated to a few specific tasks, while a personal computer is intended to a wide range of applications. A portable audio player, mobile phone, and automobile are typical examples of embedded systems. We often see automated teller machines or electronic billboards in the city, most of which are controlled by microprocessors embedded. Thus, these kinds of embedded system have become an essential part of human activities in these days. Therefore, managing problems concerning microprocessors in embedded systems is very significant and profitable study.

Embedded systems often require severe constraints on performance and energy consumption. For instance, a modern audio player or mobile phone has a functionality of video player, as well as audio processing. Since video encoding or decoding needs huger computational effort than audio processing, such a system requires much more performance than ten years ago when the main task of such a system is only a simple audio processing. At the same time, such portable devices are typically battery-powered and they usually have limited space for a battery. Hence, they require extremely low energy consumption.

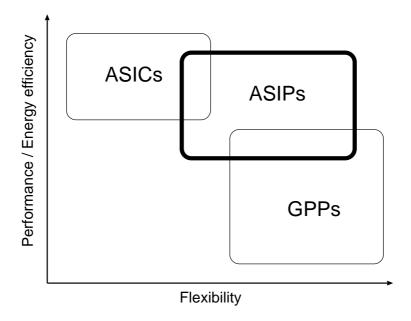

An embedded system can be typically implemented by using ASICs (Application Specific Integrated Circuits), GPPs, or ASIPs (Application Specific Instruction-set Processors). The advantage of ASICs is in the higher performance per area and lower power consumption than GPPs, but the limitation of ASICs is in the flexibility and extensibility in terms of a change of specification after the design completion. On the other hand, GPPs have the flexibility as a functionality of system is implemented by software which is programmable. GPPs are, however, usually not optimal for a target application. Hence, sometimes GPPs do not meet a performance requirement or they often exceed a power limitation of embedded systems. ASIPs can fulfill the requirements for flexibility as they are programmable using software, and for performance as they have an application specific instruction set. Therefore, ASIPs are appropriate for embedded systems due to flexibility and performance, as shown in Fig. 1.1.

Configurable processors are often used for designing ASIPs. Configurable processors have

Figure 1.1: Advantage of ASIPs.

some parameters to tune up their instruction set, such as the bit width of data path, the number of general purpose registers, and additional instructions. By using configurable processors, the design time can be shorter than the manual design since the basic architecture is almost fixed. While configurable processors can be more general purpose oriented, it can be more energy efficient or higher performance when their instruction set is tuned. Therefore, configurable processors are reasonable solution for the design of ASIPs.

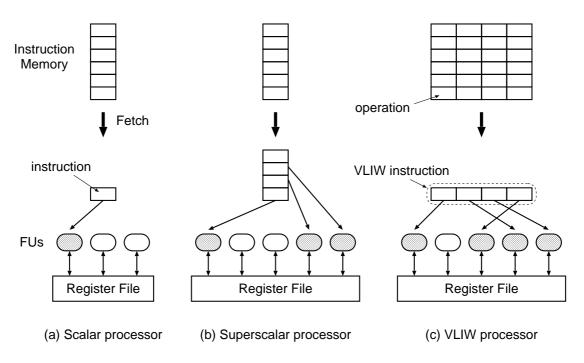

## 1.1 VLIW processor

In order to realize a higher-performance instruction set processor, superscalar architecture [6] and VLIW (Very Long Instruction Word) architecture [7] are proposed, which exploit instruction-level parallelism (ILP). Figure 1.2 depicts an overview of superscalar processor and VLIW processor as well as scalar processor. In a scalar processor, an operation (or instruction) is fetched from the instruction memory every cycle and assigned to a functional unit (FU or hardware resource) to execute it. In a superscalar processor, multiple operations are fetched from the instruction memory at a time and then a special hardware unit analyzes a parallelism among the operations. Then operations which can be executed in parallel are issued and executed. On the other hand, a VLIW processor fetches a VLIW instruction which contains multiple operations that can be executed in parallel. Since a compiler has extracted parallelism and scheduled operations, operations in a VLIW instruction can be issued with a simple hardware, while a superscalar processor dynamically analyzes parallelism and schedules operations using a special hardware.

Since a set of operations that can be executed in parallel varies in different VLIW architectures, object code of VLIW processor has no compatibility among different architectures. Binary compatibility of object code is, however, not necessarily important in embedded sys-

Figure 1.2: Overview of processor architectures.

tems, since software is typically provided together with a target system (hardware) in embedded systems and it can be compiled again in case that the target system is changed, while software and hardware are provided independently in personal computers. And also, a VLIW processor does not need the special hardware for operation scheduling, hence it has simpler hardware than a superscalar processor and it leads to less power consumption. Therefore, a VLIW ASIP is a perfect solution for embedded systems that require low energy consumption as well as high performance.

## 1.2 Design Challenges

Designing a low energy system using VLIW processor is, however, a challenging problem.

### 1.2.1 VLIW processor design challenges

Designing a VLIW processor is usually more complex than designing a scalar processor. A complex system makes a design time longer and error-prone. Therefore, a technique for improving the design productivity of VLIW processors is required.

VLIW architecture has many architecture parameters, such as the number of issue slots, the number of functional units. A dispatching rule, which represents which slot issues a certain operation and which combination of operations is allow to be executed at a time, is also an important parameter in VLIW architecture; an unprofitable dispatching rule, where the combination is not so much used, simply makes the hardware logic complex. Since it is difficult to properly define these parameters for the target application in a straightforward way, design

space exploration is commonly used, where designing and evaluating are iterated for a lot of architectures to determine an optimal parameter set. Thus, the technique for improving the design productivity is very important in terms of design space exploration as well.

### 1.2.2 Low power embedded systems challenges

Low energy is also a significant factor in design of modern VLIW processors. Traditionally, VLIW processors are beset by structural problems; a large size of object code, and complexity of logic compared with scalar processors. Power analysis of VLIW processor reveals that the significant amount of energy is consumed in the instruction memory hierarchy. For example in Lx processor, a VLIW processor designed by Hewlett-Packard and STMicroelectronics, up to 40% of the total processor energy is consumed in the instruction caches alone [8].

An L0 buffer (a.k.a. loop buffer) is an efficient technique to reduce energy consumption in the instruction memory hierarchy [9, 10, 11]. In most embedded applications, significant amount of execution time is spent in small program segments (which consist of loops). An L0 buffer stores these small program segments in a small buffer (SRAM or register file based) instead of a big instruction cache. Then the processor core only accesses to the buffer during the loop execution. This reduces the number of accesses to the higher level of the instruction memory hierarchy and therefore giving large energy reduction, for instance up to 60% as shown in [10].

In spite of such loop buffering techniques, the instruction memory remains a major power bottleneck in most VLIW processors because the conventional centralized loop buffer architecture is not so efficient. Despite adding it, an L0 buffer in VLIW processor consumes significant energy: about 20% in an 8 slot VLIW processor [12].

Since a VLIW processor does not issue operations from all slots in every cycle due to the limitation of ILP (instruction level parallelism) of application, some access to the instruction memory hierarchy is not necessary in some cycles. In order to reduce this unnecessary access, L0 cluster technique is proposed [13, 14].

The approach of L0 cluster can reduce energy consumption of embedded systems using VLIW processor, however, the optimal configuration of L0 cluster is very sensitive to a target application. Hence, an approach to efficiently obtain an optimal configuration is important in a low energy design of VLIW processors.

### 1.3 Related work

Some methods are proposed so far for low energy and the design productivity of processors.

In these years, designing processors using HDL (hardware description language) is a common way, since a target design has become larger and more complex. The design using HDL (e.g. VHDL, Verilog HDL) in register transfer level (RTL or RT level) is widely accepted and it promises much better design productivity than designing in gate level or transistor level that are used few decades ago. However, the size of design that can be implemented on a single silicon chip increases along with the advance of deep submicron technology. Therefore, it requires a further aggressive approach to design circuitry in higher level.

A processor design method that uses a base processor is one of the promising approaches that enable higher productivity in processor design. This method assumes a certain processor architecture as a base architecture and generates a derivative according to some additional specifications given as input. Since only extension to the base processor is needed to be specified, designers can obtain the target processor design in relatively shorter time. The flexibility of architecture is, however, limited because basic architecture parameters such as pipeline architecture are bounded to the base processor.

Another category of processor generation methods that help the design productivity of processor is known as architecture description language (ADL). The method takes higher level of description than RTL as input, which is usually a smaller amount of description than HDL. Then the method generates an HDL description which represents a structure that a designer intended to design. Since ADL supports a wide variety of architectures that should be evaluated in a phase of design space exploration, an approach using ADL is attractive for processor designers who seek the next generation of design methods.

A lot of researches are done on low energy processor design. One of the well-known techniques for the low energy requirement is clock gating. Since most of energy consumption is due to switching activity of wire or register, by gating a clock supply to a functional unit that is unused, unnecessary switching activity can be suppressed. Dynamic voltage and frequency scaling [15], substrate biasing, and power shut-off are also known as a technique to reduce energy consumption.

Besides the hardware approaches, some researches target software approaches for the low energy problem. One idea is to control voltage and frequency from software. Modern operating systems have such capability which decreases the clock frequency of processor when a processor is idle. Some researches target data locality in the data cache and tries to make data access more efficient [16].

As an approach to reduce power consumption in the instruction memory hierarchy, which consumes significant power in embedded systems, an L0 buffer or loop buffer [9, 10, 11] is a well known architecture. The buffer locates between the instruction cache and the processor core. By storing frequently executed code, that is loops, into a small buffer, it benefits energy reduction as well as performance improvement. Decode filter cache [17] is an architecture to reduce the power consumption of instruction decode as well as instruction fetch. Since decoding instructions also consumes significant power as well as fetching them, the approach tries to store decoded information into the buffer.

Some compiler techniques are also proposed to increase the utilization of loop buffer for further improvement of energy efficiency. A method proposed in [18] transforms code that cannot be executed on a loop buffer as it is. By applying some code transformation technique such as conditional instructions, the utilization of loop buffer can be improved. Another approach [19] optimizes software to efficiently use a loop buffer. The approach optimizes software using if-conversion and increases the utilization of loop buffer, and consequently reduces the instruction fetch power by 72%.

# 1.4 Approach for low power embedded systems using VLIW processors

This thesis proposes methods for each challenge discussed in Section 1.2. For the first challenge about VLIW processor design productivity, this thesis proposes a synthesizable HDL generation method for configurable VLIW processors, which takes a processor specification description as input and generates a synthesizable HDL description of a target VLIW processor. The proposed approach allows a designer to change the number of slots and pipeline stages, dispatching rules, and so on. Control and decode logic, and the data-path of a target VLIW processor are automatically generated from the processor specification description.

As the second method for low power design, an algorithm of operation shuffling is proposed. The algorithm generates and evaluates a lot of schedules for a target application, and it finds an energy efficient schedule. To reduce the exploration space, some heuristics are also proposed.

In order to minimize the iteration of operation shuffling, this thesis then proposes an efficient scheduling method that generates a low energy schedule for a given cluster configuration.

### 1.5 Main contributions

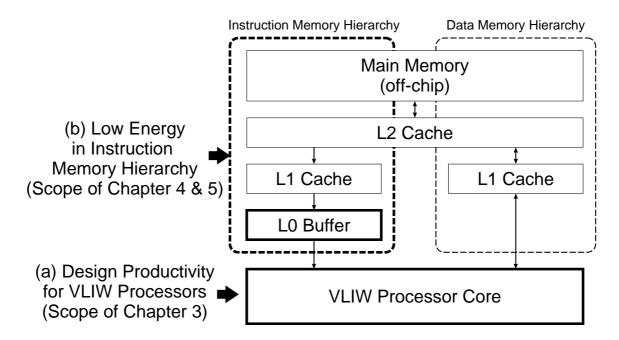

This thesis first describes a generation method for configurable VLIW processors in Chapter 3. Though VLIW processors are effective solution for embedded systems which require both of high performance and low energy, there are a lot of architectural parameters to be decided by designers. Since these parameters significantly affect the performance and area, it is required to perform the design space exploration where designers evaluate many architectures to determine the optimal parameter set. However, designing a VLIW processor is very complex, and consequently time consuming and error-prone. Hence, design space exploration on VLIW processors could not have been performed efficiently so far. The VLIW processor generation method described in Chapter 3 supports a flexible architecture model, especially in dispatching rules. Therefore, this method enables the design space exploration on a wide variety of VLIW architectures with high design productivity. Figure 1.3 depicts a system model using a VLIW processor. Chapter 3 focuses on the design productivity for VLIW processors as shown in Fig. 1.3 (a).

An operation shuffling algorithm is then described in Chapter 4. This algorithm improves energy efficiency by changing operation scheduling. Since an L0 cluster configuration is very sensitive to operation scheduling, various schedules should be evaluated in order to obtain an optimal schedule. By shuffling all basic blocks iteratively, energy consumption can be reduced significantly. To reduce the size of the exploration space, some heuristics are also described in Chapter 4.

Since a simple operation shuffling takes huge amount of time even if the above heuristics are applied, a more efficient method that finds a low energy operation schedule is then described in Chapter 5. By exploiting some scheduling algorithms described in the chapter, a compiler can generate a low energy schedule in a straightforward way. Chapter 4 and 5 focus on a low energy methods for the instruction memory hierarchy as shown in Fig. 1.3 (b).

Figure 1.3: System model using a VLIW processor.

## 1.6 Thesis organization

The rest of this thesis is organized as follows. Chapter 2 discusses related work. Chapter 3 describes a synthesizable HDL generation method for configurable VLIW processors. In Chapter 4 an operation shuffling algorithm for low energy embedded systems using VLIW processor is proposed. Chapter 5 describes an efficient method for low energy operation scheduling. Finally, Chapter 6 concludes this thesis.

# **Chapter 2**

# Related work

This chapter describes the previous studies on hardware generation and low energy technique for embedded systems.

## 2.1 Approaches for hardware generation

An embedded system can be typically implemented by using ASICs (Application Specific Integrated Circuits), GPPs (General Purpose Processors), or ASIPs (Application Specific Instruction-set Processors). ASICs have advantages in the performance per area and power consumption compared with general purpose processors. However, the flexibility of ASICs is very low since the circuits are almost fixed for a specific application. On the other hand, GPPs have the flexibility as they are fully programmable. GPPs are, however, usually not optimal for a target application in terms of performance and power consumption. Hence, GPPs sometimes do not meet a performance requirement and often exceed a power limitation of embedded systems. ASIPs can fulfill both the requirements for flexibility as they are programmable, and for performance as they have an application specific instruction set. Therefore, ASIPs are an appropriate solution for embedded systems.

Configurable processors are often used for designing ASIPs. Configurable processors have some parameters to tune up their instruction set, such as the bit width of data path, the number of general purpose registers, and additional instructions. By using configurable processors, the design time can be shorter than the manual design since the basic architecture is almost fixed. While configurable processors can be more general purpose oriented, it can be more energy efficient or higher performance when their instruction set is tuned. Therefore, configurable processors are reasonable solution for the design of ASIPs.

Various attempts for configurable processors to efficiently design ASIPs and make retargetable compiler and other software tools have been made [20]. Approaches for generation of configurable processors are classified into two categories as follows.

- 1. Approaches using a base processor (PEAS-I [21], MetaCore [22, 23], Xtensa [24])

- 2. Approaches using a processor specification description (ISDL [25, 26, 27], nML or Target [28, 29], LISA [30, 31, 32], EXPRESSION [33, 34, 35])

In this section, a brief overview of these approaches is presented.

### 2.1.1 Approaches using a base processor

PEAS-I [21] uses a basic CPU called PEAS-I CPU. PEAS-I CPU includes an ALU, a shifter, a multiplier, and a divider. Based on the results of application profiling, hardware algorithm of multiplier and divider is selected and unused instructions are omitted automatically. However, designers cannot change architecture of pipeline stage.

MetaCore [22, 23] is an environment to develop an ASIP for digital signal processing. Although MetaCore allows using basic instructions, optional instructions, and user-defined instructions, the number of pipeline stages are fixed. Moreover, MetaCore does not support VLIW architectures.

Xtensa [24] utilizes a customizable RISC processor core, and designers can add a new instruction using special language to improve performance. It is, however, impossible to freely change a pipeline structure.

An approach using a base processor is a method to design an ASIP based on a base processor core by changing the number of registers and adding custom instructions. This approach has an advantage in reduction of design labor, however, has a disadvantage in lack of flexibility to change the instruction bit width or the number of pipeline stages.

### 2.1.2 Approaches using an architecture description language

ISDL [25, 26, 27] is an instruction set description language for VLIW processors, which can generate software tools. However, the pipeline structure is not so flexible, since an architecture is generated from a highly abstracted description based on the supposed pipeline structure.

nML [28, 29] focuses on the instruction set. The abstraction level of the nML language is in a programmer's model of target processor. It is easy to modify the instruction set, however, the detailed architecture model is hard to specify due to the high abstraction level. And also, a generation method for VLIW architecture is not reported.

EXPRESSION [36, 33] allows designers to describe detailed specification that can represent VLIW processors as well. EXPRESSION can generate simulators and compilers for rapid design space exploration, however, a synthesizable HDL generation method for VLIW processors, especially the support for FU sharing, is not reported.

The approach of LISA [30, 31, 32] can describe architectures considering pipeline structure, and can design VLIW architectures or superscalar architectures. However, a pipeline controller supporting a pipeline stall is not generated unless operations for pipeline registers are explicitly described. Furthermore, though LISA can generate synthesizable HDL description for control logic, it is not reported to generate entire data-path of processor.

Although an approach using an ADL description has disadvantages in increase of description, it can describe a detailed processor specification and generate various architectures.

In design of ASIPs, a method that allows various pipeline structures and that can generate a control logic, that is usually error-prone in manual design, is desirable. Unfortunately, there has not been any method that can generate VLIW processors effectively and flexibly. Therefore, this thesis proposes a VLIW processor generation method from a processor specification description to specify a detail of processor and to explore large design space of VLIW processors.

# 2.2 Overview of low power optimizations for embedded processors

There are a lot of researches on low energy processor design. One of the well-known techniques for the low energy requirement is clock gating. Since most of energy is consumed due to switching activity of wire or register, by gating a clock supply to a functional unit that is unused, unnecessary switching activity can be suppressed. Dynamic voltage and frequency scaling, substrate biasing, and power shut-off are also known as a technique to reduce energy consumption.

Besides the hardware approaches, some researches target software approaches for the low energy problem. One idea is to control voltage and frequency from software. Modern operating systems have such capability which decreases the clock frequency of processor when a processor is idle. Some researches target data locality or layout in the data cache and tries to make data access more efficient [16]. A compiler-guided low power method for scratch pad memories [37] optimizes memory-data layout to maximize bank idleness of scratch pad memories.

As an approach to reduce power consumption in the instruction memory hierarchy, which consumes significant power in a processor, an L0 buffer or loop buffer [9, 10, 11] is well known. The buffer locates between the instruction cache and the processor core. By storing frequently executed code, e.g. inner most loops, into a small buffer, it benefits energy reduction as well as performance improvement. Decode filter cache [17] is an architecture to reduce the power consumption of instruction decode as well as instruction fetch. Since decoding instructions also consumes significant power as well as fetching them, the approach tries to store decoded information into the buffer.

For further improvement of energy efficiency in loop buffers, some compiler techniques are also proposed, which try to increase the utilization of loop buffer. A method proposed in [18] transforms code that cannot be executed on a loop buffer as it is. A loop that has a transfer of control (e.g. branch operation) inside or a loop where the number of iterations is unknown cannot be executed on a loop buffer. By applying some code transformation technique such as a conditional instruction or an explicit manipulation of the loop counter, the utilization of loop buffer can be improved. Another approach [19] optimizes software to efficiently use a loop buffer. The compiler technique optimizes software using if-conversion and increases the utilization of loop buffer, and consequently reduces the power of instruction fetch by 72%.

# 2.3 Low power optimization on instruction memory hierarchy

An L0 buffer (a.k.a. loop buffer) is an efficient technique to reduce energy consumption in the instruction memory hierarchy [9, 10]. In most embedded applications, significant amount of execution time is spent in small program segments (which consist of loops). The technique stores these small program segments in a small L0 buffer (SRAM or register file based) instead of the big instruction cache. Then the processor core only accesses to the buffer during the loop execution. This reduces the number of accesses to the higher level of the instruction memory

hierarchy and therefore giving large energy reduction, for instance up to 60% as shown in [10].

In a simple application of the monolithic L0 buffer to a VLIW processor, at each cycle the operations would be fetched for all the slots of the VLIW from the monolithic L0 buffer. However, such a monolithic L0 buffer is not effective as not all slots are always active. This implies that some slots would require unnecessary buffer access for NOP operation [13]. Hence, L0 cluster generation was proposed to obtain a low energy system [13, 14].

In a clustered VLIW processor, 'clustered' usually refers to data-path clusters. For example, the TI C6X processor has clustered data-path [38], which can issue up to eight operations at a time, and has two separated register files. If many FUs are connected to a monolithic register file, it leads to significant increase of delay time, area, and power consumption. Therefore, many researchers have tried to cluster FUs and divide a register file in order to decrease the number of FUs connected to each register file. The clustered register file reduces the number of ports of register file, which reduces the delay, area, and energy of the register file. Clustered register file is almost always used in VLIWs with a larger number of issue slots [39, 40]. Note that data clustering may cause increase of execution cycles since sometimes a copy operation is needed to move data between register files, while instruction clustering does not cause such a problem.

Some VLIW architectures like Lx processor have a notion of instruction clustered instruction fetch [41]. However, the instruction clusters correspond directly to the data clusters, while this thesis makes an instruction cluster explicitly separated from a data cluster to increase the exploration freedom; an L0 cluster can be applied independently for data clusters. This results in larger gains of up to energy reduction of 75% as demonstrated in [14].

A loop buffer or loop cache has been studied for years, which aims for energy reduction on instruction memory hierarchy as well as performance improvement. By exploiting such a loop buffering mechanism, L1 or higher cache access rate is reduced by up to 38% [9], and it leads energy reduction of overall instruction memory of up to 67% [10]. A loop buffer is implemented as a register file or SRAM based architecture and access to buffer is fully controlled by a control unit (e.g. LC and ITC, described in Section 4.2), while a loop cache has possibility of cache miss whose performance penalty cannot be accepted in certain embedded applications.

Operation shuffling for instruction clusters has been studied only in the recent past [42, 43]. Similar to the work presented in this article, their objective is an overall hardware/software energy reduction for embedded VLIW processors. However, their target is on the instruction cache, while this thesis focuses on L0 buffers and generation of L0 clusters.

# **Chapter 3**

# Hardware generation for VLIW processors

This chapter describes the proposed VLIW processor generation method. First, a target VLIW processor model is explained. Secondly, a scalar processor generation method that the proposed VLIW processor generation method is based on is introduced. Finally, the proposed VLIW processor generation method is described.

### 3.1 Problem and motivation

Designing a VLIW processor is usually more complex than a scalar processor which issues only one operation at a time. A complex system makes a design time longer; describing complex control logic of such a system is tedious and error-prone. Therefore, a technique for improving the design productivity of VLIW processors is required.

VLIW architecture has many architecture parameters, such as the number of issue slots, the number of functional units. A dispatching rule, which represents which slot issues a certain operation and which combination of operations is allowed to be executed at a time, is also an important parameter in VLIW architecture; an unprofitable dispatching rule, where the combination is not so much used, simply makes the hardware logic complex. Since it is difficult to define these parameters appropriately for the target application in a straightforward way, design space exploration is commonly used, where designing and evaluating a lot of architectures to determine an optimal parameter set. Thus, the technique for improving the design productivity is very important in terms of design space exploration as well.

### 3.2 VLIW processor model

This section introduces a VLIW processor model [44] that the proposed VLIW processor generation method uses. This model can represent various architecture of VLIW processors.

A VLIW instruction consists of multiple operations that are executed simultaneously. Dispatching is a managing process to assign issued operations to appropriate FUs A Slot is a unit to issue an operation. A VLIW processor has one or more slots and issues multiple operations

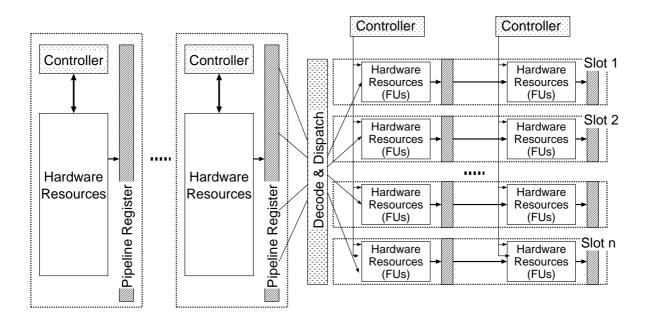

Figure 3.1: VLIW processor model.

from the slots in parallel. Note that a VLIW processor with one slot is equivalent to a scalar processor in this model.

Figure 3.1 illustrates a hardware model of VLIW processor. In first few pipeline stages, a VLIW instruction is fetched, and then it is decoded and operations are dispatched into FUs. A data-path in each pipeline stage consists of *hardware resources*, that are mainly combinational circuits, and pipeline registers to send data into the next pipeline stage. An FU is a kind of a hardware resource. In normal operation mode without any pipeline interlock, hardware resources receive input data from the previous pipeline registers, and send output data into the next pipeline registers.

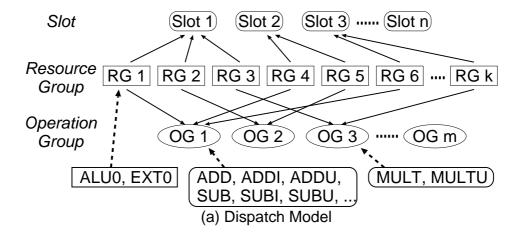

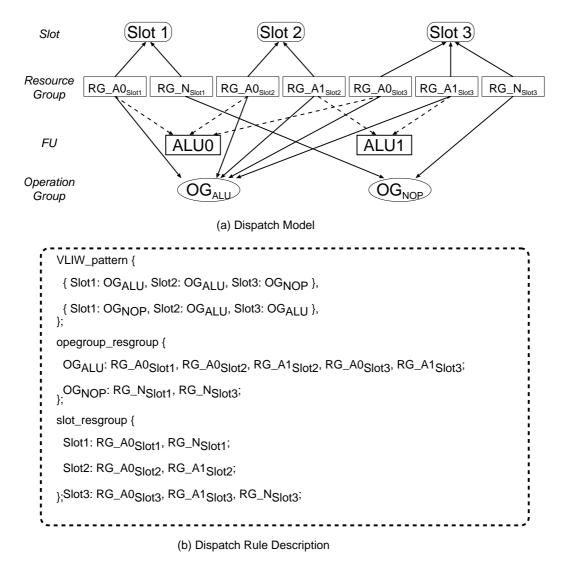

### 3.2.1 Dispatching model

Figure 3.2 (a) shows the dispatching model of [44]. To represent complex dispatching rules in a simple description, two concepts, *operation group* and *resource group*, are introduced. An *operation group* is a set of operations that have the same characteristic on dispatching, for instance, a member of operation group can be executed on the same kind of FUs. A *resource group* is a set of FUs that are used when a certain operation is executed in a certain slot. Note that a resource group belongs to one slot and one operation group. In Fig. 3.2 (a), operations ADD, ADDI, and so on are members of operation group OG1. Resource group RG1 consists of FUs ALU0 and EXT0. RG1 belongs to OG1 and Slot1. An FU can belong to one or more resource groups, which means that a shared FU is represented by belonging to multiple resource groups. In this way, dispatching rules are described using three relations; between slots and operation groups, between slots and resource groups, and between operation groups and resource groups. Figure 3.2 (b) shows a dispatching rule description of the above model.

```

slot_opegroup {

{ Slot1: OG1, Slot2: OG1, Slot3: OG3, ... },

{ Slot1: OG1, Slot2: OG2, Slot3: OG1, ... },

...

};

opegroup_resgroup {

OG1: RG1, RG4, RG6;

OG2: RG2, RG5;

};

slot_resgroup {

Slot1: RG1, RG2, RG3;

Slot2: RG4, RG5;

};

(b) Dispatch Rule Description

```

Figure 3.2: Example of the dispatching model.

Micro-operation description to be explained later is described for a pair of a resource group and an operation. This method allows to represent a wide range of dispatching rules as a designer intends to make.

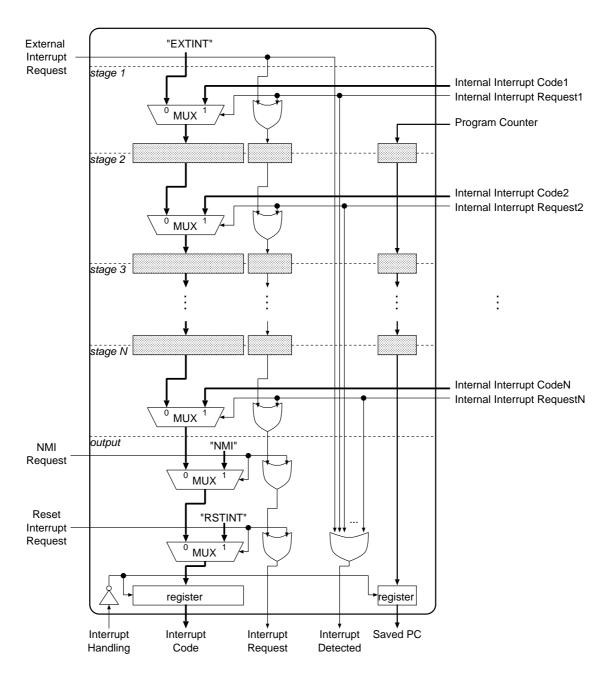

### 3.2.2 Interrupt model

The proposed interrupt model of VLIW processor is shown below.

- Supported interrupt type and instruction canceling policy (in descending order of priority)

- Reset interrupt (the highest priority): cancel all instructions policy

- Nonmaskable interrupt: cancel all instructions policy

- Internal interrupt: cancel descending instructions policy

- External interrupt (the lowest priority): wait all instruction completion policy

- Precise interrupt

- Select the highest-priority interrupt among multiple interrupts occurred at a time

The proposed interrupt model is based on the interrupt model of a scalar processor [45]. Cancel all instructions policy annuls all operating instructions and starts interrupt processing immediately after an interrupt request signal is asserted. Cancel descending instructions policy annuls only descending instructions when an interrupt occurs, and starts interrupt processing after completion of ascending instructions. Wait all instruction completion policy annuls no instructions but suppresses fetching a new instruction, and interrupt processing is started after completion of all instructions that were being executed when an interrupt request signal was asserted.

## 3.3 Hardware architecture of targeted VLIW processor

This section describes an overview of target VLIW processor and execution model of the processor.

### 3.3.1 Hardware overview of VLIW processor

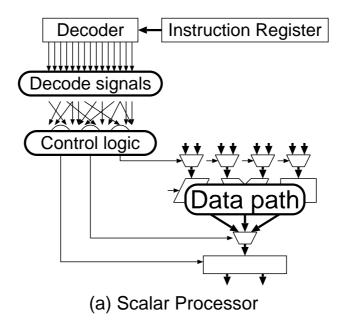

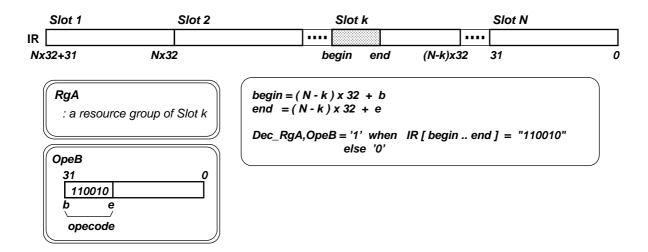

Figure 3.3 illustrates control paths of scalar processor and VLIW processor. As shown in Fig. 3.3 (a), a data-path of scalar processor is controlled by decode signals that are generated from the value of the instruction register. On the other hand, in a VLIW processor,  $Dec_{rg,ope}$ , decode signal for resource group and operation, is generated from the value of the instruction register,  $Dec_{slot,opeg}$ , decode signal for slot and operation group, is generated from combinations of  $Dec_{rg,ope}$ ,  $Det_{ptrn}$ , detection signal for VLIW pattern, is generated from combinations of  $Dec_{slot,opeg}$ ,  $Actv_{rg}$ , resource group activation signal, is generated from combinations of  $Det_{ptrn}$ . Then, a VLIW processor controls a data-path by  $Actv_{rg}$  and  $Dec_{rg,ope}$ , as shown in Fig. 3.3 (b).

A decode signal for resource group and operation ( $Dec_{rg,ope}$ ) is a signal to identify an operation in the instruction register. As was mentioned earlier, since micro-operation description is described for a pair of a resource group and an operation, this signal and a micro-operation description have one-to-one mapping. For instance, if operation ADD executing on resource group RG1 exists, a signal corresponding to its micro-operation is  $Dec_{RG1,ADD}$ . A decode signal for slot and operation group ( $Dec_{slot,opeg}$ ) is a signal to identify an operation group to be issued from the slot.  $Dec_{Slot1,ALU}$  is a signal representing that an operation in operation group ALU is issued from Slot1. A detection signal for VLIW pattern ( $Det_{ptrn}$ ) is a signal to identify a VLIW pattern in the instruction register, for instance, a signal representing the third pattern is  $Det_3$ . A resource group activation signal ( $Actv_{rg}$ ) is a signal representing that the resource group is assigned to a detected VLIW pattern, for instance, an activation signal of RG1 is  $Actv_{RG1}$ . In case that multiple candidates of resource group exist for an operation

Figure 3.3: Control paths of scalar processor and VLIW processor.

Figure 3.4: Execution model of VLIW processor.

in a certain slot, all corresponding signals  $Dec_{rg,ope}$  become active, however, only one signal  $Actv_{rg}$  is active. Then an operation can be successfully executed without any conflict of FU.

#### 3.3.2 VLIW Processor Execution Model

Figure 3.4 illustrates the execution model of VLIW processor. In the proposed model, a VLIW processor runs with repetition of steps as follows. First, a VLIW instruction is fetched from an instruction memory, and stored to the instruction register. Secondly, operations in the VLIW instruction are decoded. Operation groups for each operation are obtained, and a VLIW pattern is detected according to a combination of the operation groups. Thirdly, a data-path is controlled by switching data-path selectors according to prepared information corresponding to the detected VLIW pattern. Finally, operations are executed in the data-path controlled in the previous step.

In the proposed method, FUs assigned to a VLIW pattern are determined first, and then control signals of a data-path are generated using the information of assignment.

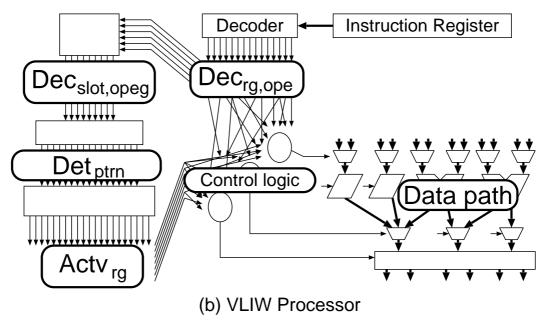

Figure 3.5: An example of micro operation description and DFG generated from the description.

# 3.4 Synthesizable HDL generation method for scalar processors

This section introduces a scalar processor generation method [46]. The proposed VLIW processor generation method is based on this method.

In the method of [46], a data flow graph (DFG) corresponding to an instruction is derived from a micro-operation description representing behavior in each pipeline stage of instruction, and then DFGs corresponding to all instructions are merged into one data path that represents an entire processor. Figure 3.5 (a) shows an example of micro-operation description. In Fig. 3.5 (a), behavior in pipeline stage 2, 3, and 5 are described. First, keyword *wire* declares three 32 bit variables, src0, src1, and res. In stage 2, values of operands, src0 and src1, are read from general purpose register GPR. In stage 3, src0 and src0 are added by ALU, and the result is stored into res. In stage 5, the result is written back into GPR.

Information of connections between FUs is extracted from the micro-operation description in Fig. 3.5 (a). A DFG in Fig. 3.5 (b) is corresponding to a micro-operation description in Fig. 3.5 (a).

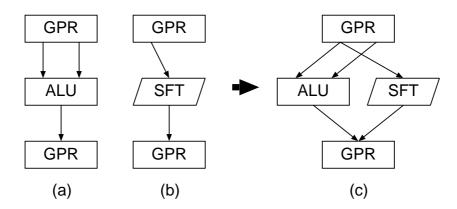

Figure 3.6 shows an example of merging DFGs. Figure 3.6 (a) and (b) are DFGs of an addition operation and a shift operation, respectively. These DFGs are merged into a DFG shown in 3.6 (c). Moreover, since the proposed method is based on [47], the method can control pipeline hazards such as structural hazards.

Figure 3.6: An example of merging DFGs.

# 3.5 Synthesizable HDL generation method for VLIW processors

This section describes the details of the proposed VLIW processor generation method. First, input of the algorithm is explained. Then a generation method of VLIW processor based on the model shown in section 3.2 is proposed.

Let a *VLIW pattern* denote a categorized VLIW instruction that has the same property in dispatching. In the proposed method, FUs dispatched to a VLIW pattern are decided before HDL generation.

## 3.5.1 Input of VLIW processor generation method

This section defines input of the proposed generation method. First, dispatching rules are defined, secondly, an entire processor specification description is defined.

Let Slot be a set of slots, RG be a set of resource groups, OG be a set of operation groups. OpegResg, a relation between an operation group and resource groups, and SlotResg, a relation between a slot and resource groups, are represented as follows:

$$og \in OG, OpegResg(og) \subseteq RG, OpegResg(og) \neq \emptyset,$$

(3.1)

$$s \in Slot, SlotResg(s) \subseteq RG, SlotResg(s) \neq \emptyset,$$

(3.2)

A VLIW pattern, VLIW\_ptrn, is represented as follows:

$$s \in Slot, VLIW\_ptrn(s) \in OG.$$

(3.3)

SlotOpeg means a set of VLIW pattern as follows:

$$SlotOpeg = VLIW\_ptrn.$$

(3.4)

Therefore, a dispatching rule DispatchRule is represented as follows:

$$DispatchRule = \{SlotOpeg, OpegResg, SlotResg\}$$

(3.5)

Figure 3.7: Example of table of instruction dispatch pattern  $T_{IDP}$ .

Let Res be a set of hardware resources, Operation be a set of definitions of operation that include opecode and operand for each operation, IO be a set of input/output ports of processor, Mod be a set of micro-operation descriptions. Then Spec, the input of the proposed VLIW processor generation method, is represented as follows:

$$Spec = \{Slot, Res, RG, Operation, \\ OG, IO, DispatchRule, Mod\}$$

(3.6)

# 3.5.2 Instruction dispatch pattern

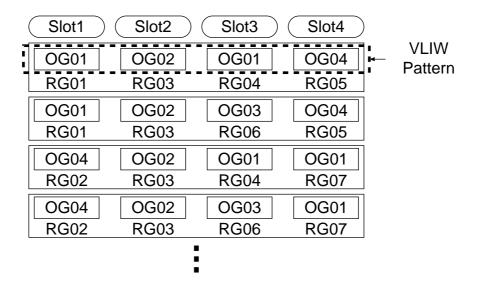

In the proposed method, assignment of resource groups to a VLIW pattern is determined before HDL generation. We call this assignment an *instruction dispatch pattern*. All of instruction dispatch patterns are gathered into a table of instruction dispatch pattern,  $T_{IDP}$ . Figure 3.7 shows an example of  $T_{IDP}$ . The first entry of the  $T_{IDP}$  represents that resource groups RG01, RG03, RG04, RG05 are used for VLIW pattern {OG01, OG02, OG01, OG04}.

In this section, an assignment method of resource group to VLIW patterns is described. The method consists of two steps as follows.

- 1. Enumeration of resource groups that can execute an operation in an operation group assigned to a slot.

- 2. Determination of resource group assignment to VLIW pattern.

The input of this algorithm is the following items; relations between slots and operation groups that are equivalent to VLIW patterns, relations between slots and resource groups, and relations between operation groups and resource groups. The output is  $T_{IDP}$ .

Figure 3.8: Enumeration of resource group for each slot.

**(1) Enumeration of resource groups** In this step, resource groups, that can execute an operation group in each slot of VLIW pattern, are enumerated.

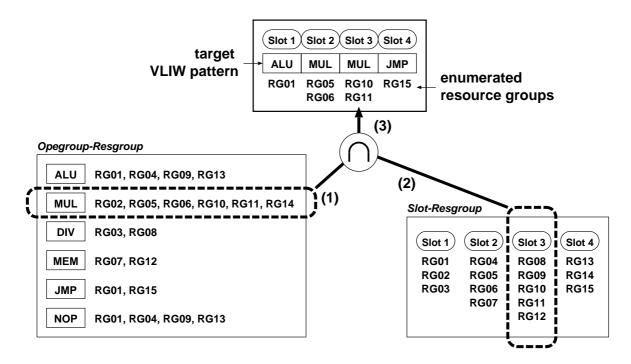

First, according to relations between operation groups and resource groups, resource groups that can perform the operation groups in each slot of VLIW pattern are calculated. Figure 3.8 shows an example that tries to enumerate resource groups for slot 3 of target VLIW instruction. In Fig. 3.8 (1), a set of resource groups that can execute MUL operation group is fetched.

Then, according to relations between slots and resource groups, resource groups that really belongs to the slot are selected from them. In Fig. 3.8 (2), a set of resource groups that belong to slot 3 fetched, and then intersection of these two sets are calculated in order to determine resource groups available for this VLIW instruction.

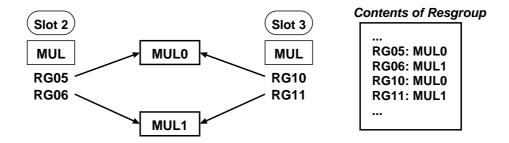

**(2) Determination of Resource Group Assignment** In the resource groups calculated in the previous step, multiple resource groups are sometimes enumerated for a slot. Therefore, it is necessary to determine one resource group for a slot without any conflict of FU among resource groups determined for other slots. In an example of Fig. 3.9, RG05 and RG10 both use the same FU, MUL0. Then, in case that Slot2 uses RG05 or RG06, Slot3 has to use RG11 or RG10, respectively.

Algorithm 1 shows an algorithm that determines one resource group for a slot. FU and Rg are a set of FUs and resource groups, respectively, that are empty at the beginning of this algorithm.  $RG_s$  is the resource groups belonging to slot s calculated in the previous step. If FUs(rg), FUs included in rg, do not overlap with FU, FUs(rg) are added to FU and rg is added to Rg. If a combination of resource groups that have no FU conflict is found,

Figure 3.9: Example of FU conflict.

#### **Algorithm 1** Resource group Decision Algorithm.

```

boolean function SelectResgroup(s, FU, Rg) {

foreach rg in RG_s {

if (FUs(rg) \notin FU) // no conflict. {

if (s.next = null) {

Rg = Rg \cup rg;

adopt(Rg); // done.

return true;

} else if (true = SelectResgroup(s.next, FU \cup FUs(rg), Rg \cup rg)) {

return true;

}

}

}

}

return false;

```

this algorithm outputs Rg and finishes. The computational complexity of this algorithm is  $O(nf^2g^s)$ , where s, f, g, n are the number of slots, FUs, resource groups, and VLIW patterns, respectively.

# 3.5.3 Control signals for dispatching

This section describes a generation method of control signals for dispatching in a VLIW processor.

#### 3.5.3.1 Decode signals for resource group and operation

A decode signal for a pair of a resource group and an operation,  $Dec_{rg,ope}$ , comprises a logical product of comparisons of opecode and corresponding field in the instruction register.

$$Dec_{rg,ope} = \bigwedge_{opecode \in Opecode_{ope,Slot(rg)}} (IR[Begin(opecode)..End(opecode)] = Value(opecode)),$$

(3.7)

Figure 3.10: Example of decode signal for resource group and operation.

where Slot(rg) returns slot corresponding to rg.  $Opecode_{ope,slot}$  includes a set of opecode for ope in slot; an opecode consists of value and range of bit field in the instruction register. Figure 3.10 shows an example of  $Dec_{rg,ope}$  where the length of operation is 32 bit. In this example, by checking a bit field from begin to end in the instruction register (IR), we can know whether operation OpeB that can be executed on RgA is coming to the instruction register. Note that the decode signal is active if and only if the instruction register contains an operation ope that can be executed on rg.

#### 3.5.3.2 Decode signals for slot and operation group

Let  $RG_{slot}$  be a set of resource groups that belong to slot. Then  $Dec_{slot,og}$ , a decode signal for a pair of a slot and an operation group, is represented as a logical sum of  $Dec_{rg,ope}$  as follows:

$$Dec_{slot,og} = \bigvee_{\substack{ope \in og \\ rg \in RG_{slot}}} Dec_{rg,ope} \wedge Exist(rg, ope), \tag{3.8}$$

where Exist(rg, ope) is the function that returns true if operation ope executing on rg is defined in input, otherwise returns false.

#### 3.5.3.3 VLIW pattern detection signals

Let Slot be a set of all slots, and  $Opegroup(ptrn_{slot})$  be an operation group that corresponds to slot in VLIW pattern ptrn.

A detection logic of VLIW pattern ptrn,  $Det_{ptrn}$ , is represented as a logical product of  $Dec_{slot.opeg}$  as follows:

$$Det_{ptrn} = \bigwedge_{\substack{slot \in Slot \\ opeg = Opegroup(ptrn_{slot})}} Dec_{slot, opeg}.$$

$$(3.9)$$

#### 3.5.3.4 Resource group activation signals

Let Slot(rg) be a slot that resource group rg belongs to,  $Det_{ptrn}$  be a detection signal of VLIW pattern in instruction dispatch pattern ptrn, and  $Resgroup(ptrn_{slot})$  be a resource group that corresponds to slot in ptrn.

$Actv_{rg}$ , an activation signal of rg, is represented as a logical sum of  $Det_{ptrn}$  as follows:

$$Actv_{rg} = \bigvee_{ptrn \in T_{IDP}} Det_{ptrn} \wedge (rg = Resgroup(ptrn_{Slot(rg)})).$$

(3.10)

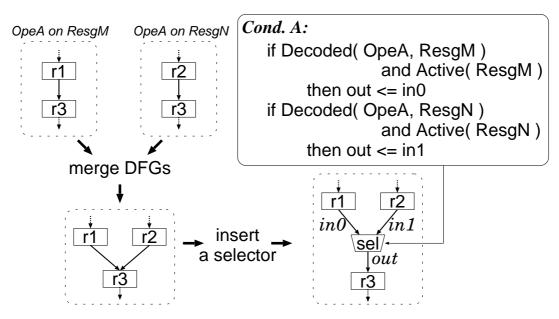

#### 3.5.3.5 Control signals of data-path selectors

In the proposed method, a micro-operation description is specified for each pair of an operation and a resource group. Then a data-path of an entire processor is generated by merging DFGs derived from micro-operation descriptions. Since merging often causes signal conflicts at input port of FU, data-path selectors are inserted, so that the conflicts are resolved.

This section describes control logic of the data-path selector, which represents a condition of selection.

A DFG that is derived from a micro-operation description of operation ope executed on resource group rg is valid when the instruction register holds a value that represents ope and rg is activated, as described in Section 3.3. Hence, the logic can be represented by a logical product of an activation signal for rg and an decode signal for a pair of rg and ope. Assume that a DFG that is derived from a micro-operation description of ope executed on rg is  $DFG_{ope,rg}$ . Then, logic for a selector to form  $DFG_{ope,rg}$  is represented as follows:

$$Cond_{DFG_{ope,rg}} = Dec_{rg,ope} \wedge Actv_{rg}$$

(3.11)

Figure 3.11 shows merging DFGs and inserting a data-path selector. When operation OpeA executed on resource group ResgM is decoded (identified) and ResgM is activated, the DFG that represents operation OpeA executed on ResgM becomes valid. In other words, the inserted selector is controlled to select the edge derived from the DFG.

By using the activation signal, it is possible to form an appropriate DFG in case that multiple candidates of FU exist for an operation to be executed on the same slot. For example of Fig. 3.11, a certain slot can issue OpeA, however, depending on a combination of operations in other slots, the slot uses either r1 or r2. It is hard to decide only with decode signals which FU is to be used for OpeA; if another slot uses r1, this slot has to use r2, and vice versa.

## 3.5.4 Control signals for interrupt

Since a reset and an external interrupt are independent from a concept of VLIW processor, such as slot, the same model of [45] can be applied to a VLIW processor. Therefore, this section discusses a model for a nonmaskable interrupt and an internal interrupt.

#### 3.5.4.1 Nonmaskable interrupt