| Title        | 全可観測な環境での論理回路のテスト容易化設計に関<br>する研究 |

|--------------|----------------------------------|

| Author(s)    | 温, 暁青                            |

| Citation     | 大阪大学, 1993, 博士論文                 |

| Version Type | VoR                              |

| URL          | https://doi.org/10.11501/3065910 |

| rights       |                                  |

| Note         |                                  |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

# 全可観測な環境での 論理回路のテスト容易化設計に関する研究

1993年1月

温晓青

# 全可観測な環境での 論理回路のテスト容易化設計に関する研究

1993 年 1 月

温晓青

# 内容梗概

正しく設計された集積回路であっても、製造段階で何らかの欠陥が生じる可能性がある. また開発段階では、正しい設計を得るために試作回路について故障原因を究明することが必要である.集積回路のテスト、つまり、製造された回路が設計通りに動作するか否かを調べる故障検査、および設計通りに動作しない回路の不良箇所を指摘する故障診断は、集積回路の開発にとって重要な役割を果たしている.

近年、集積回路の大規模化と高機能化につれて、故障検査はますます困難になってきている。まず、故障検査に必要なテストベクトルの生成においては、回路規模の増大により生成時間が大きな問題となる。テスト生成ができたとしても、通常その数が膨大であるため、多量生産される集積回路のテストにとって、テストの実施時間も大きな問題となる。また、CMOS 回路技術が主流になりつつあるため、CMOS 回路に特有の新しい故障に対する検査方法の開発も重要な課題となる。

故障診断は一般的に故障検出よりはるかに困難である。最近では、特定用途向け集積回路 (Application Specific IC: ASIC) の多用により、故障診断が以前より頻繁に行なわれるので、迅速かつ効率的な故障診断手法の開発も急務となっている。

集積回路のテストの問題を根本的に解決するために、従来からテスト容易化設計というアプローチが用いられている。その基本的な考え方は、回路設計後にテストを考えるのではなく、テスト容易な回路を設計することである。その代表的な例は順序回路のスキャン設計であり、順序回路の故障検査をそれより簡単な組合せ回路の故障検査におきかえるものである。

故障診断では、従来から回路の内部状態を観測するプロービング技術が用いられて来ている。最近では、電子ビームプロービング技術とCADシステムの統合による高度な故障診断システムである電子ビームテスタが開発されている。電子ビームプロービング技術を用いることにより回路内の大部分の信号線が観測できるため、故障診断は容易になる。しかし、電子ビームプロービング技術は、短いテスト系列を用いるときにのみ有効である。任意の論理回路が短いテスト系列をもつ保証がないため、テスト容易化設計を施して回路が短いテスト系列をもつようにすることが、電子ビームプロービング技術を実現するために必要である。

電子ビームプロービング技術に基づいて、回路内のすべてのゲートの出力線が観測できる と仮定するテスト環境を全可観測な環境と呼ぶ、本論文は、全可観測な環境におけるテスト 容易な論理回路の特徴、性質および構成法についての研究成果をまとめたものである。

第1章では、本研究の背景や目的について述べている。

第2章では、研究の対象回路とする論理回路の基本概念、および論理回路のテストとテ

スト容易化設計について紹介している.

第3章では、全可観測な環境を実現する電子ビームプロービング技術と、全可観測な環境におけるテスト容易化設計の必要性について述べている。

第4章では、全可観測な環境でのテスト容易な組合せ回路である k - UCP 回路の概念と 故障検査について述べている。 k - UCP 回路は NOT ゲートと k 入力の基本論理ゲートで構成される。 k - UCP 回路において、長さ k+1 のテスト系列ですべての縮退故障を検出する ことができ、長さ k(k+1)+1 のテスト系列ですべてのスタック・オープン故障を検出する ことができる。 さらに、k - UCP 回路の拡張として、k - R 回路を提案している。

第5章では、組合せ回路をk- UCP 回路に変換する手法について述べている。この変換での付加ゲート数を最小にする方法を見つけることはNP完全問題なので、ヒュリスティックな手法を用いてその解決を試みた。実験結果は、k入力 NAND または NOR ゲートからなる回路をk- UCP 回路に変換するためのオーバーヘッドが少ないことを示している。

第6章では、全可観測な環境での順序回路のテスト容易化設計として、k-UCP順序回路およびk-UCPスキャン回路を提案している。いずれの順序回路の組合せ部分もk-UCP回路である。しかし、普通の順序回路の場合、k-UCP回路に変換された組合せ部分に所要のテストベクトルを繰り返し印加することは困難かまたは不可能である。k-UCP順序回路においては回路内のフリップ・フロップの入力側にゲートを挿入することにより、またk-UCPスキャン回路においてはスキャンパスの組み方を工夫することにより、組合せ部分へのテストベクトルの繰り返し印加を容易にしている。それぞれの回路においては、長さ3(k+1)とk+1のテスト系列ですべての縮退故障をテストすることができることを示している。

第7章では、テスト容易な順序回路への変換方法について述べている。実験結果は、スキャンパスをもち、かつ組合せ部分が k入力 NAND または NOR ゲートのみを含む順序回路をk-UCP スキャン回路に変換するためのオーバーヘッドが少ないことを示している。

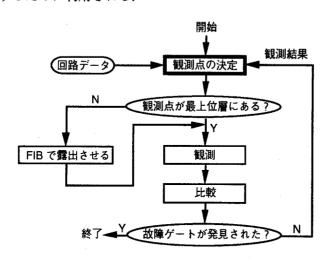

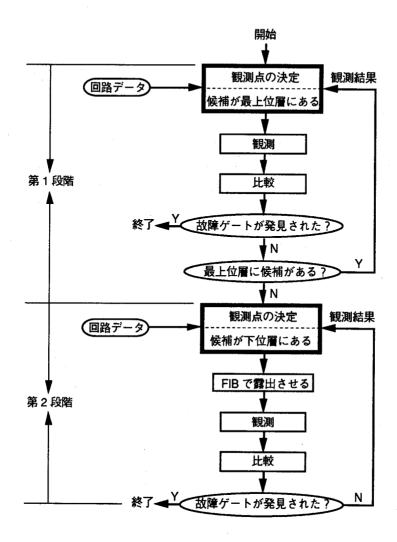

第8章ではまず、CMOSのk-UCP 回路のスタック・オープン故障の診断手法について述べている。k-UCP 回路にテスト集合を印加したとき、故障ゲートの出力線および他のいくつかの信号線に異常系列が現われる。これらの異常系列の位置と異常系列が基本系列と異なるビットの位置を用いて故障診断を行なう手法を示している。また、一般の論理回路の故障診断にも適用できる電子ビームテスタに基づくガイディド・プローブ法による 2 段階の故障診断過程を提案している。第1 段階では、最上位層にある信号線のみを観測点の候補とし、高速な観測点決定手法を用いて被疑部分回路を効率よく絞り込む。第2 段階では、下位層にある信号線をコストの高い FIB で露出させる必要があるので、最小の平均観測回数が得られる観測点決定手法を用いる。その結果、回路全体の故障診断を効率よく行なうことができる。

第9章では、本研究のまとめと今後の課題について述べている.

# 目 次

| 第1章             | 章 序論        | Ä                          | 1  |

|-----------------|-------------|----------------------------|----|

| 1.1             | 研究の         | 书景                         | 1  |

| 1.2             | 研究の         | 目的                         | 3  |

| 1.3             | 論文の         | 構成                         | 4  |

| 第2章             | <b>新</b> 論理 | <b>望回路のテストとテスト容易化設計</b>    | 7  |

|                 |             | 路の概念                       |    |

|                 |             | 本論理素子による記述                 |    |

| _               |             | ランジスタによる記述                 |    |

| 2.2             |             | 路の設計と製造                    |    |

|                 |             | 路のテスト                      |    |

|                 |             | 章モデル                       |    |

| -               | 2.3.1.1     | <b>故障モデルの概念</b>            | 13 |

|                 |             | 縮退故障                       |    |

|                 |             | スタック・オープン故障                |    |

|                 |             | 単一故障と多重故障                  |    |

| 2.              |             | 章検出と故障診断                   |    |

| _,              | 2.3.2.1     | 基本用語                       |    |

|                 | 2.3.2.2     | 故障検出                       | 16 |

|                 | 2.3.2.3     | 故障診断                       | 18 |

| 2.4             |             | 路のテスト容易化設計                 | 20 |

|                 |             | スト容易化設計の必要性                |    |

|                 |             | スト容易化設計手法                  |    |

|                 | 2.4.2.1     | 概説                         |    |

|                 |             | テスト容易化設計例 - スキャン設計         |    |

|                 |             | 組込み自己テスト (BIST) の概念        |    |

| 2.5             |             |                            |    |

| 笋っき             | · 夕司        | 観測なテスト環境                   | 25 |

|                 |             |                            | -  |

| 3.1             |             | ームフローとング技術                 | 25 |

|                 |             | 側な環境<br>測な環境でのテストとテスト容易化設計 | 27 |

|                 |             | 側な現境 (の) 人下とす人下谷勿1(故計      | 27 |

| J. <del>4</del> | ょこめ         |                            | 29 |

| 第 4 章           |             | 観測な環境での組合せ回路のテスト           | 31 |

| 4.1             | k-UCP       | ・回路の定義                     | 31 |

| 4.2 基本系列3                        | 33 |

|----------------------------------|----|

| 4.2.1 基本系列の定義 3                  | 33 |

| 4.2.2 基本系列の生成                    | 35 |

| 4.2.2.1 スタック・オープン故障用の基本系列の生成     | 35 |

| 4.2.2.2 縮退故障用の基本系列の生成 3          | 38 |

| 4.3 k - UCP 回路の故障検出              | 38 |

| 4.4 通常のテスト環境における k-UCP 回路の故障検出 3 | 39 |

|                                  | 40 |

| 4.4.1.1 故障影響の伝搬                  | 40 |

|                                  | 41 |

|                                  | 13 |

| 4.4.2 テスト生成法 4                   | 14 |

|                                  | 15 |

| 4.5 k - UCP 回路概念の拡張 4            | 15 |

| 4.5.1 k-R 回路の定義 4                | 16 |

|                                  | 17 |

|                                  | 19 |

| 4.6 まとめ                          | 50 |

|                                  |    |

| 第5章 全可観測な環境での組合せ回路のテスト容易化設計 5    | 1  |

| 5.1 概説 5                         | 51 |

| 5.2 k-U回路への変換 5                  | 52 |

| 5.3 k-UP回路への変換 5                 | 53 |

| 5.4 k-UC 回路への変換 5                | 53 |

| 5.4.1 k+1彩色解問題 5                 | 54 |

| 5.4.2 回路の対象部分の抽出 5               | 56 |

| 5.4.3 回路変換手法 5                   | 57 |

| 5.5 実験結果と考察 5                    | 59 |

|                                  | 50 |

|                                  |    |

| 第6章 全可観測な環境での順序回路のテスト 6          | 1  |

| 6.1 概説 6                         | 51 |

| 6.2 問題点                          | 52 |

| 6.3 k-UCP 順序回路 6                 | 53 |

| 6.3.1 基本概念 6                     | 53 |

| 6.3.2 テスト方法                      | 54 |

| 6.4 k-UCPスキャン回路                  | 55 |

| 6.4.1 基本系列の性質 6                  |    |

| 6.4.2 基本概念                       |    |

|                                  |    |

| 6.4.3 テスト方法 6                    | 58 |

| 第 7 章 全可観測な環境での順序回路のテスト容易化設計    | 71  |

|---------------------------------|-----|

| 7.1 k-UCP 順序回路への変換              | 71  |

| 7.1.1 回路変換手法                    | 71  |

| 7.1.2 実験結果                      | 72  |

| 7.2 k-UCP スキャン回路への変換            | 73  |

| 7.2.1 回路変換手法                    |     |

| 7.2.2 実験結果                      |     |

| 7.3 まとめ                         |     |

|                                 |     |

| 第8章 全可観測な環境での論理回路の故障診断          | 79  |

| 8.1 k-UCP 回路の故障診断               | 79  |

| 8.1.1 基本原理                      | 79  |

| 8.1.2 故障診断表の生成                  | 82  |

| 8.1.3 故障診断手法                    | 85  |

| 8.2 ガイディド・プローブ法による故障診断の効率化      | 88  |

| 8.2.1 基本概念                      | 88  |

| 8.2.1.1 ガイディド・プローブ法の原理          | 88  |

| 8.2.1.2 被疑部分回路                  | 89  |

| 8.2.1.3 電子ビームテスタに基づくガイディド・プローブ法 | 91  |

| 8.2.2 観測点の効率的な決定方法              | 92  |

| 8.2.2.1 基本条件                    | 92  |

| 8.2.2.2 観測木と故障確率                | 93  |

| 8.2.2.3 平衡決定法                   | 95  |

| 8.2.2.4 最適決定法                   | 98  |

| 8.2.3 実験結果と考察                   | 100 |

| 8.3 まとめ                         | 101 |

| 第 9 章 総括 1                      | 03  |

|                                 |     |

| 謝辞 1                            | 07  |

| 参考文献 1                          | 09  |

| 研究発表一覧表 1                       | 13  |

# 序論

# 1.1 研究の背景

集積回路(Integrated Circuit: IC)は、シリコン基板内にダイオード、トランジスタ、抵抗および容量を作り込み、これらを総合配線して電子回路を構成したものである。その特徴は、小型、高速、省電力および高信頼性である。高性能マイクロプロセッサや大容量メモリなどに代表されるように、集積回路は近代の産業と社会に計り知れないほど大きな影響を与えており、将来にもなくてはならない存在として発展していくものと思われる[1].

集積回路は60年代の初期に発明されて以来,集積度と機能面において急速な発展を遂げてきた.初期は集積回路内のトランジスタがわずか2個であったが,現在は回路の最小線幅がコンマ数ミクロンになっており,数百万ものトランジスタを搭載する集積回路が製造されている.機能面においては,簡単な論理演算しかできない集積回路から複雑なシステムを搭載する集積回路へと進歩してきた.

集積回路の急速な進歩を支えてきているのは設計技術,製造技術およびテスト技術である.設計技術と製造技術は、与えられた回路仕様に対して自動的に設計を行なう自動合成システムやコンマ数ミクロン線幅の回路パターンを正確に扱うサブミクロン級微細加工技術に代表されるように、この数十年で大きな進歩を遂げてきた。ところが、設計技術と製造技術の目覚ましい進歩に比べて、テスト技術は必ずしも大幅な進展をしてこなかった。その結果、テストは集積回路の発展にとって主要な問題点になっている[2-4]。

集積回路のテストとはその故障検査と故障診断の両方を意味する. 故障検査とは, 回路が設計通りに動作するか否かを調べることである. 故障診断とは, 設計通りに動作しない回路に対し, その原因を突き止めることであり, その中心は不良箇所を指摘することである.

### 故障検査

故障検査ではまず、すべての対象故障に対して、正常時と故障時の回路の出力値が異なるような入力ベクトルを生成する。これをテスト生成といっている。生成したテストベクトルを回路に印加し回路の応答値を観測する。応答値が期待値と異なれば、回路に故障があるものと判断される。すべてのテストベクトルに対する応答値が期待値と一致すれば、回路が正

常であると認められる[5-7]。これをテストの実施といっている。

テスト生成では、対象故障に対して故障箇所でその影響を顕在化させ、観測のためにさらにその故障の影響を外部出力線まで伝搬させる必要がある。大規模または複雑な回路の場合、テスト生成時間は長すぎる場合がある。テスト生成ができても、テストベクトル数が膨大になった場合、それらを保存するために多くのメモリ容量が必要であるし、テストの実施時間も長くなり、多量生産にとって深刻な問題となる[2-4]。

故障検査における諸問題を解決するアプローチとして,テスト生成アルゴリズムの効率 化およびテスト容易化設計などが知られている.

Dアルゴリズム [8] が提案されて以来,組合せ回路に対して多くのテスト生成アルゴリズムが提案されている。現在,PODEM [9], FAN [10], CONT [11], SOCRATES [12] などが知られている。しかし、順序回路に対しては、一般的に有効なものは提案されていない [13].

テスト生成アルゴリズムを改良するだけでは、故障検査における諸問題を根本的に解決することができない。そこで、回路設計後にテストを考えるのではなく、設計段階においてもテストへの考慮を取り入れてテスト容易な回路を設計する、いわゆるテスト容易化設計(Design For Testability)が研究されている [14-20]。その代表的な例は順序回路の故障検査を組合せ回路の故障検査におきかえるスキャン設計である。テスト容易化設計の導入により、回路仕様の実現にとって余分なハードウェアや動作速度の低下などのオーバーヘッドが生じることがある。以前はハードウェアがテスト時間より高価であったため、なるべく少ないハードウェアで設計を行なう傾向があった。しかし最近では、集積技術の発達により、ハードウェアのコストが著しく安くなってきており、回路仕様の実現にとって余分なハードウェアの付加を伴うテスト容易化設計の導入が現実的なアプローチとなっている。また、大規模な回路の故障検査に必要な時間が増加する一方で、ハードウェアを導入してもテストを容易にすることが必要になってきている。

#### 故障診断

故障診断は、集積回路の開発にとって重要な意味をもつ。その主な理由として三つが挙げられる。第1は、開発段階での故障原因の究明である。集積回路の開発では、機能の異常、特性の不良、マージン不良など、数多くの問題が生じる。量産へ移行できる設計・プロセスを確立するためには、故障原因を究明するための診断・設計の修正・試作というサイクルを繰り返すことが余儀なくされている。特に、集積回路の主流となりつつある特定用途向け集積回路の場合、開発期間の短縮と開発コストの低減が必須なので、設計・開発を効率化するため、迅速かつ的確な故障診断が不可欠となる。第2は、量産段階において発生する不良の原因究明である。歩留りなどが低下した場合、原因を明らかにし、設計やプロセス上の対策を立てる必要がある。第3は、市場で発生した故障の原因究明である。システムが大規模化し、1個の集積回路の故障が重大な影響を及ぼすため、早急な対策が必要である。

故障診断は故障検査と異なって、回路が正常か異常かのチェックのみではなく、異常の原因を突き止めることを目的とするため、故障検査よりも困難であることは明らかである。特に、外部出力線しか観測できない場合、故障診断ができるのは極めて小さい回路に限られてしまう。そこで、従来から回路の内部状態をプロービングにより観測する技術は故障診断にとって不可欠なものとなっている。

プロービング技術は接触系と非接触系に分けられる。最初に使用されていたのは金属の針によるプロービングであった。この方法では、回路の電気的な特性および回路構造そのものを破壊する恐れがあるので、集積度の高い集積回路には適用できない。非接触系のプロービング技術では電子ビームなどによるプローブを利用するため、回路の電気的な特性や構造を壊す恐れがなく、集積度の高い集積回路にも適用できる[23-26]。電子ビームプロービング技術を利用するため、集積回路の封装を壊す必要があるので、その使用は故障診断に限られている。

以上,集積回路の故障検査と故障診断の問題点とこれまでの解決の試みについて述べた. 基本的には,これまでの解決法を三つのグループに大別することができる. 第 1 は外部出入力線しか観測・制御できないという通常のテスト環境で効率化を図る方法である. 第 2 は回路構造を変更するテスト容易化設計である. 第 3 はテスト環境を変える方法であり,その代表は電子ビームプロービング技術に基づくテスト方法である.

#### 1.2 研究の目的

本論文では、外部出力線しか観測できないようなテスト環境を通常のテスト環境と呼び、 すべてのゲートの出力線が観測できるようなテスト環境を全可観測なテスト環境, あるいは 単に全可観測な環境と呼ぶ。

これまでは、テスト容易化設計と全可観測な環境でのテストに関する研究が独立的に進められてきた。つまり、テスト容易化設計は通常のテスト環境で行なわれ、全可観測な環境ではテスト容易化設計が施されていない。これは、通常のテスト環境でのテスト生成に比べ、全可観測な環境でのテスト生成は簡単であるからである。しかし以下の理由で、全可観測な環境においてもテスト容易化設計を行なう必要がある。

全可観測な環境の基礎となる電子ビームプロービング技術では、高速動作中の回路の内部 状態を観測するために、ストロボ法が用いられる[27]. そのため、テスト系列を回路に繰り 返し印加することが必要である。また、高速かつ正確な観測を行なうために、回路を短い問 期の周期動作状態にする必要がある[28,29]. つまり、電子ビームプロービング技術で用い られるテスト系列は二つの条件を満たさなければならない。第1はテスト系列が短いこと であり、第2はそのテスト系列を回路に繰り返し印加することができることである。全可 観測な環境で生成されたテスト系列は、電子ビームプロービング技術を用いたテスト環境で 使用できるほど短くない場合もある。また、順序回路においては、テスト系列が短くても、それを回路に繰り返し印加することができない場合が多い。したがって、全可観測な環境においても、回路が短くてかつ繰り返し印加することができるテスト系列をもつように回路設計を工夫する必要がある。つまり、全可観測な環境においてもテスト容易化設計が必要である。

さらに、電子ビームプロービング技術では、1本の内部信号線の状態を測定するために相当長い時間がかかる。多くの信号線を観測しなければならない場合に、故障診断の所要時間が長くなる。すなわち、なるべく少ない観測回数で故障診断を行なう必要がある。これも、全可観測な環境においてもテスト容易化設計が必要な理由である。

このように、全可観測な環境においてもテスト容易化設計が必要である。しかしこれまでは、この方面の研究は少ない。短いテスト系列でテストできるように論理回路を変換する方法として、組合せ回路を適当に変換することにより、5個[34]または3個[35]のテストベクトルでテストできることが示されている。しかし、これらの方法では、信号線の縮退故障のみを対象故障としている他、回路を構成する素子の種類や入力数についての制限が厳しい。また、回路変換は主に局所的な置換で行なわれ、オーバーヘッドが大きいと思われる。そこで、より広範的、系統的なアプローチを取るべく、本研究では以下のことを具体的な目標とする。

- (1) 全可観測な環境において、短いテスト系列を有する組合せ回路と順序回路の概念を 提案する. 信号線の縮退故障の他に、スタック・オープン故障をも対象故障とす る. また、生成したテスト系列を回路に繰り返し印加することができるようにす る.

- (2) 提案したテスト容易な論理回路の故障検査と故障診断の手法を示す.

- (3) 任意の論理回路から提案したテスト容易な論理回路への効率的な変換手法を提案する。また、ベンチマーク回路を用いて実験を行ない、その有効性を確かめる。

- (4) 全可観測な環境において、一般の論理回路の故障診断に対しても効率的な手法を提案する.

#### 1.3 論文の構成

本論文は次のように構成されている。第 1 章では、本研究の背景、目的および構成について述べる。第 2 章では、論理回路のテストとテスト容易化設計の基本概念について簡単に述べる。第 3 章では、回路の内部状態を観測する電子ビームプロービング技術について述べ、それに基づく全可観測な環境においてもテスト容易化設計が必要である理由を明らかにする。第 4 章では、全可観測な環境での組合せ回路のテスト容易設計である k - UCP 回路と k - R 回路の概念およびテスト手法について述べる。第 5 章では、任意の組合せ回路をk - UCP 回路に変換する手法について述べる。第 6 章では、全可観測な環境での順序回路の

テスト容易設計である k-UCP 順序回路および k-UCP スキャン回路の概念およびテスト手法について述べる。第7章では,任意の順序回路をテスト容易な順序回路に変換する手法について述べる。第8章では,k-UCP 回路のスタック・オープン故障の効率的な故障診断手法,および一般の論理回路の故障診断にも使用できるガイディド・プローブ法の効率化について述べる。第9章では,本論文のまとめと今後の課題について述べる。

# 論理回路のテストとテスト容易化設計

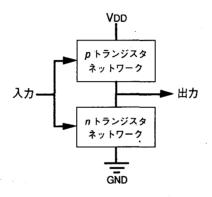

本章では、本論文で対象回路とする論理回路, 論理回路のテストおよび論理回路のテスト 容易化設計に関する基本概念について説明する。

# 2.1 論理回路の概念

集積回路は使用するトランジスタの種類により、バイポーラ回路と MOS 回路に分類される。前者は一般に高速であるが消費電力が大きく、製造工程が複雑でかつ大きなチップ面積を必要とするのに対して、後者はほぼその反対であり、大規模な集積回路に MOS が多用されている。特に、 MOS 集積回路の中で CMOS 集積回路が低消費電力用として一般に用いられている [1].

集積回路はその内部信号の取り扱い方により、アナログ集積回路とディジタル集積回路に 大別される。前者はA/D、D/Aの相互変換を含み、後者は論理演算を行なう論理回路と論理 値を記憶するメモリに分かれる。アナログ集積回路よりディジタル集積回路の方が圧倒的に 多いが、これは集積回路のデジタル適性に基づく[1]。

論理回路とは,入力値,出力値および内部状態の値が論理値 0 または 1 の組合せとして表現できる回路である.論理回路はさらに組合せ回路と順序回路に分類される [5-7,51]. 組合せ回路は,出力値がそのときの入力値により一意的に決まる回路である.すなわち,その出力は入力変数のブール関数で表すことができる.一方,順序回路は,現在の入力値のみならず,過去にどのような入力値がどのような順序で加えられたかも現在の出力値に影響を与える.

一般に、論理回路を記述する方法としては、自然言語による記述、VHDL などのハードウェア記述言語による記述、真理値表による記述、論理式による記述、基本論理素子による記述、トランジスタ、抵抗、容量などによる記述、レイアウト情報による記述などがある. 以下では、基本論理素子による記述とトランジスタによる記述について説明する.

#### 2.1.1 基本論理素子による記述

基本論理素子は論理ゲートと記憶素子を含む. 論理ゲートとは, AND, OR, NAND, NOR, NOT, XOR, XNOR などの基本的な論理演算を行なう回路のことである. 主な論理ゲートの機能と記号を表 2.1 に示す.

| ゲート名 | 記号          | <br>論理式                       |

|------|-------------|-------------------------------|

| AND  | × Z         | Z = x <sub>A</sub> y          |

| OR   | xz          | $Z = x_V y$                   |

| NAND | хz          | $Z = \overline{x_A y}$        |

| NOR  | х<br>у z    | $Z = \overline{xvy}$          |

| NOT  | x——Z        | $Z \approx \overline{X}$      |

| XOR  | х <b></b> z | $Z = x \sqrt{y} \sqrt{x} x y$ |

| XNOR | хz          | Z = XAYVXAŸ                   |

表 2.1 主な論理ゲートの機能と記号

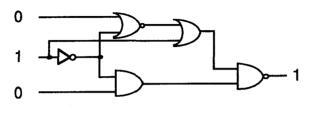

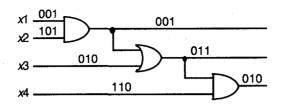

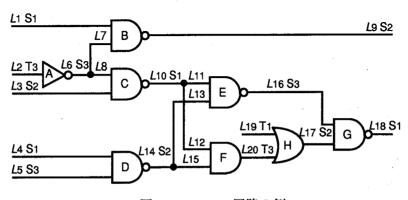

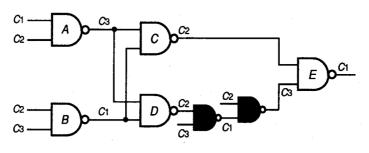

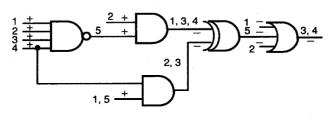

組合せ回路は AND, OR, NAND, NOR, NOT, XOR, XNOR などの論理ゲートを用いて実現できる。実際には、NANDゲートまたは NOR ゲートを用いるだけでも、任意の組合せ回路を実現することができる [51]. 組合せ回路の例を図 2.1 に示す。この回路の入力値は 0,1,0 である。回路の出力値はその入力値により一意的に決まって 1 である。

図 2.1 組合せ回路の例

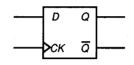

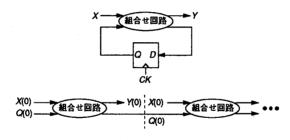

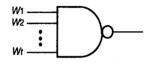

順序回路を表現するため、論理ゲートの他に、内部状態を記憶する素子も必要である。図 2.2 はもっとも基本的な記憶素子である D- フリップ・フロップの記号を示す。

図 2.2 D-フリップ・フロップの記号

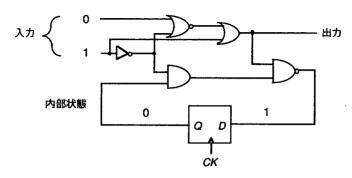

図2.2では、CKより同期用のクロック・パルスが印加される。クロック・パルスがないとき、Qの値が保持される。クロック・パルスが印加されると、QがDの値となる。回路全体の動作がクロック・パルスで同期される順序回路が同期式順序回路と呼ばれている。図2.3 に同期式順序回路の例を示す。この回路の現在の出力値は、現在の外部入力値の0と1だけではなく、フリップ・フロップの出力値である内部状態にも依存する。

図 2.3 同期式順序同路の例

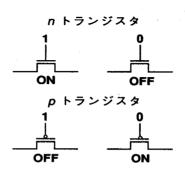

#### 2.1.2 トランジスタによる記述

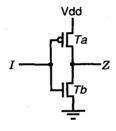

ここでは、CMOS 回路の場合について説明する。CMOS 回路では、2種類の MOS トランジスタ、nトランジスタとpトランジスタ、が使用される [1]。nトランジスタとpトランジスタをスイッチと見なすことができる。これを図 2.4 に示す。

図 2.4 MOS トランジスタ

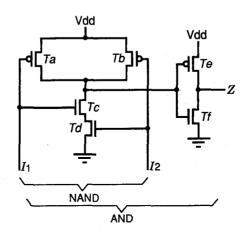

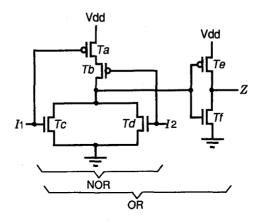

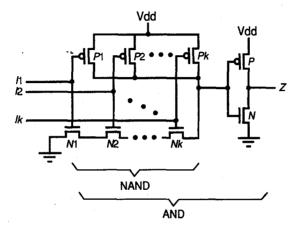

図 2.5 から図 2.7 に CMOS の 2 入力 AND, OR, NAND, NOR および NOT ゲートのトランジ

スタによる記述を示す。図 2.8 に CMOS ゲートの一般構成を示す。CMOS ゲートの特徴は、正常時には、pトランジスタ側とnトランジスタ側の両方とも導通状態または非導通状態にならないことである。

図 2.5 CMOS の 2 入力 NAND と AND ゲート

図 2.6 CMOS の 2 入力 NOR と OR ゲート

図 2.7 CMOS の NOT ゲート

図 2.8 CMOS ゲートの一般構造

本論文では、組合せ回路とD-フリップ・フロップを記憶素子とする同期式順序回路を対象回路とする。また、低消費電力で大規模集積回路に適したCMOS技術が論理回路の主な製造技術となってきているため、本論文ではトランジスタによる記述の論理回路とはCMOS論理回路を指すものとする。

#### 2.2 論理回路の設計と製造

通常、論理回路の設計は複数の段階に分けて行なわれる、図2.9に主な設計段階を示す。

図 2.9 論理回路の設計の流れ

このような階層化設計の流れは回路データの変換の流れと見なすことができる. すなわち, ある段階での設計というのは, 与えられた上位の設計データを下位のより詳細な設計データに変換することである. この設計段階の最上位の設計データはユーザからの要求であり. 最下位の設計データは直接に製造に使用されるレイアウト・データである.

各設計段階では、回路を表現する方法が異なる。下位に下がるにつれて、回路表現が詳細になってくる。仕様設計では、自然言語に近いもので回路記述を行なう。機能設計では、ALU、レジスタやメモリを用いて回路を表現する。論理設計では、論理ゲートやフリップ・

フロップなどで回路を表現する.回路設計では、トランジスタ、抵抗や容量などを用いて回路記述を行なう.最後にレイアウト設計では、金属、ポリシリコン、コンタクトなどを表す長方形で回路を表現する.このレイアウト・データを用いて製造が行なわれる.

# 2.3 論理回路のテスト

正しく設計された回路であっても、製造段階で様々な故障が導入され、出来上がった回路が設計通りに動作しない場合がある。故障の原因は、シリコン基板の汚れ、マスクのずれ、アルミ配線の腐食などと様々である。その結果として、回路に断線やショットなどの物理故障が起こり、その影響が外部出力線での誤動作として現われる。集積回路の量産段階や納品検査のときなどは、正常に動作しない回路は破棄されるが、開発段階において正しい設計を得るためまたは量産段階において歩留まりを高めるために、正常に動作しない回路に対しその原因を突き止めることが必要である。つまり、回路が設計通りに動作する否かを調べる故障検出および設計通りに動作しない回路の故障原因を突き止める故障診断が必要である。論理回路のテストとはその故障検出および故障診断の両方を意味する。

故障検査ではまず、すべての対象故障に対して、正常時と故障時の回路の出力が異なるような入力ベクトルを生成する。これをテスト生成といっている。生成したテストベクトルを回路に印加し回路の応答値を観測する。応答値が期待値と異なれば、回路に故障があるものと判断される。すべてのテストベクトルに対する応答値が期待値と一致すれば、回路が正常であると認められる [5-7]。故障診断においては、テスト生成の他に、故障位置を特定する手法も必要となる。

以下では、テスト生成における故障モデルの概念、故障検査用テスト生成アルゴリズム、 および故障診断の主な手法について説明する.

#### 2.3.1 故障モデル

テスト生成では、故障をどのように取り扱うかが重要である。まず、故障を意識しない生成法がある。例えば、n入力の組合せ回路は  $2^n$  個の可能な入力ベクトルをもち、それらをすべて印加することにより、その回路の論理機能が設計通りであるか否かを調べることができる。しかし、nが少しでも大きくなると、 $2^n$  は膨大な数になり、実際には使えなくなる。したがって、より現実的なテスト生成方法では、回路に対して対象故障を仮定してから、すべての対象故障が回路に存在するかどうかを調べることにより故障検出を行ない、どの対象故障が存在するかを調べることにより故障診断を行なう。

対象故障の決め方として、二つの方法が考えられる。第1の方法では、物理的に起こりうるすべての故障を対象故障とする。しかし、現実的には、物理的に起こりうるすべての故障をあらかじめ調べることが不可能であったり、対象故障の数が莫大であったりするために、物理的に起こりうる故障を直接に取り扱うことが不可能に近い。第2の方法では、多

種多様な物理的故障の抽象化である故障モデルが用いられている.

# 2.3.1.1 故障モデルの概念

故障モデルは故障の影響,つまり故障が信号値にもたらす変化を表すものである。故障モデルの使用により以下の利点が得られる[5-7]。

- (1) 起こりやすい物理故障に対するテストベクトルを生成することができる.

- (2) テスト生成の効率化をはかることができる.

- (3) 故障診断が簡単になる.

各設計レベルでは異なる故障モデルを考えるのが普通である。各設計レベルとそれに対応 する故障モデルを表 2.2 に示す。

| 回路記述      | 故障モデル                    |

|-----------|--------------------------|

| レジスタ転送レベル | 機能故障                     |

| ゲートレベル    | 縮退故障<br>遅延故障<br>ブリッジ故障   |

| トランジスタレベル | スタック・オン故障<br>スタック・オープン故障 |

| レイアウトレベル  | 断線 短絡<br>クロストーク          |

表 2.2 設計レベルと故障モデル

現在よく使用されている故障モデルは、ゲートレベルの縮退故障モデルとブリッジ故障モデル、およびトランジスタレベルのスタック・オープン故障モデルとスタック・オン故障モデルである。本論文では、故障モデルで仮定される故障を単に故障と呼ぶことにする。以下では、本論文で対象故障とする縮退故障とスタック・オープン故障について説明する。

### 2.3.1.2 縮退故障

縮退故障は従来から用いられてきたゲートレベル回路における故障モデルである [5-7]. これは信号線が論理値 1 または 0 に固定される故障を表す故障モデルである. 論理 1 に固定される縮退故障を 1 縮退故障と呼び, 論理値 0 に固定される縮退故障を 0 縮退故障と呼ぶ. 例えば, 信号線が電源にショートされた故障は 1 縮退故障でモデル化できる.

図 2.10 に示す 2 入力 NAND ゲートにおいては、6 個の縮退故障が考えられる。つまり、入力線 a と b の 1 縮退故障と 0 縮退故障,および出力線 Z の 1 縮退故障と 0 縮退故障である。しかし、a と b の 0 縮退故障は任意の入力ベクトルに対して Z の 1 縮退故障と同じ値

を出力するので、この3個の故障は等価故障である。その中の1個の故障、例えば、Zの1縮退故障を対象故障とすればよい。このときのZの1縮退故障が代表故障と呼ばれている。したがって、2入力 NAND ゲートの場合、入力線aとbの1縮退故障、および出力線Zの1縮退故障と0縮退故障を対象故障とすれば十分である。

図 2.10 2 入力 NAND ゲート

1個の縮退故障を検出するために、1個のテストベクトルが必要である。例えば、2入力 NAND ゲートの入力線 a の 1 縮退故障故障を検出するには、 $\langle a=0,b=1\rangle$  を印加すればよい。これは、正常時のゲートの出力は 1 であるが、故障時のゲートの出力は 0 であるからである。また、1個のテストベクトルで複数の縮退故障を検出することも可能である。例えば、 $\langle a=0,b=1\rangle$  で、a の 1 縮退故障故障と出力線 Z の 0 縮退故障を検出することができる。2入力 NAND ゲートのすべての縮退故障を検出するために、 $\langle a=1,b=0\rangle,\langle a=0,b=1\rangle$  および  $\langle a=1,b=1\rangle$  という 3 個のテストベクトルを印加すればよい。

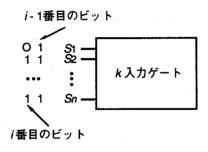

一般に、k入力 AND ゲートと NAND ゲートのすべての縮退故障を検出するために、k+1 個のテストベクトル V1, V2, ..., Vk+1 が必要である.ここで、Vi=<a1, a2, ..., ai-1, ai, ai+1, ..., ak+1>, ai=0, aj=1, j=1, 2, ..., k+1,  $i\neq j$  である.また,k入力 OR ゲートと NOR ゲートのすべての縮退故障を検出するために,k+1 個のテストベクトル NOT(V1), NOT(V2), ..., NOT(V2), が必要である.NOT の縮退故障を検出するには,V10 と V21 を印加すればよい.

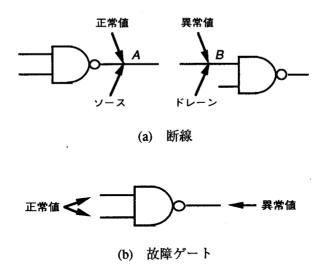

#### 2.3.1.3 スタック・オープン故障

CMOS ゲートは、正常動作時にはp側とn側のどちらかが必ず導通状態にあるが、故障時にはどちらも非導通状態または導通状態になる可能性がある。つまり、CMOS 論理回路ではゲートレベル回路の縮退故障モデルではモデル化できない故障が起こりうる [26,44,45].

例えば、図 2.5 に示した CMOS の 2 入力 NAND ゲートのトランジスタ Ta が永久開放状態になったとする. < In = 0, In = 1> を印加したとき、p 側とn 側のどちらも非導通状態になるので、出力は高抵抗状態になる。このとき、< In = 0, In = 1> を印加する直前の入力値により決まる出力値が保たれ、このときの出力値となる。つまり、このような故障により組合せ回路は順序回路のような動作をしてしまう。

このようにトランジスタの開放故障はゲートレベル回路の信号線の縮退故障モデルで表せないので、新しい故障モデルを設ける必要がある。この新しい故障モデルをスタック・オープン故障モデルといっている[26,44].

縮退故障がゲートレベル回路の故障モデルであるのに対して、スタック・オープン故障モ

デルはトランジスタレベル回路の故障モデルである.1個の縮退故障を検出するためには,1個のテストベクトルで十分なのに対して,1個のスタック・オープン故障を検出するためには,連続する2個のテストベクトルが必要である[52].例えば,図2.5の2入力NANDゲートのトランジスタ Taのスタック・オープン故障を検出するには,まず初期化ベクトルと呼ばれる < n = 1,n = 1 を印加して,ゲートの出力値を0に設定する.続いてテストベクトルと呼ばれる < n = 0, n = 10 を印加する.正常時には,出力値は1であるが,故障時には,n = 10 個のどちらも非導通状態になるので,出力値はその直前の出力値0となる.

テストベクトル対で複数のスタック・オープン故障を検出することができる場合もある. 図 2.5 の 2 入力 NAND ゲートのトランジスタ Tc と Td のスタック・オープン故障を < I = X1, I2 = X2> と < I1 = I1, I2 = I2 というテストベクトルの対で検出することができる. ここで、X1 または X2 のいずれかが論理値 I2 となる. I3 NAND ゲートのすべてのスタック・オープン故障を検出するベクトルの対は (< I1 = I1, I2 = I2>, (< I1 = I3, (< I3 = I4 = I5), (< I3 = I5 である. ここで、(1 または (2 のいずれかが論理値 (1 となる.

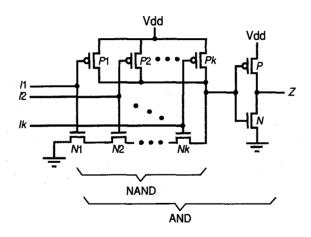

図 2.11 および図 2.12 に CMOS の k 入力 AND, OR, NAND, NOR ゲートの構成図を示す. k 入力 AND ゲートと NAND ゲートのすべてのスタック・オープン故障を検出するために, k+1 個のテストベクトル対 (P, V1), (P, V2), ..., (P, Vk), (Q, P) が必要である.ここで,P=<1,  $1,\ldots,1>$ ,  $Q=<x1,x2,\ldots,xk+1>$ ,  $x1x2\ldots xk+1=0$ ,  $Vi=<a1,a2,\ldots,ai-1,ai,ai+1,\ldots,ak+1>$ ,  $ai=0,aj=1,j=1,2,\ldots,k+1$ ,  $i\neq j$  である.また,k 入力 OR ゲートと NOR ゲートのすべてのスタック・オープン故障を検出するために,k+1 個のテストベクトル対 (NOT(P), NOT(V1)), (NOT(P), NOT(V2)), ..., (NOT(P), NOT(Vk)), (NOT(P), NOT(P)) が必要である.NOT のスタック・オープン故障を検出するために,O1 と O1 を印加すればよい.

#### 2.3.1.4 単一故障と多重故障

一般に、単一故障とは回路に 1 個の故障しか起こらないと仮定する故障モデルであり、 多重故障とは回路内に複数の故障が起こると仮定する故障モデルである。開発 段階または製造の初期段階では、多重故障の可能性が高いが、使用段階では、単一故障を仮 定しても十分である。また、上に述べたように、単一故障の検出を目標に生成されたテスト ベクトルにより多重故障が検出される場合もある。本論文では、主に単一縮退故障と単一ス タック・オープン故障を対象故障とする。

#### 2.3.2 故障検出と故障診断

#### 2.3.2.1 基本用語

論理回路のテストを考察するとき,故障と誤りという概念を区別する必要がある.故障

図 2.11 CMOS の k 入力 NAND と AND ゲート

図 2.12 CMOS の k 入力 NOR と OR ゲート

(Fault)とは回路の内外に存在する回路動作を異常にさせる物理的な要素である.配線の断線や短絡,素子の物理的な欠陥は故障であるし,また,外部からの電磁波や $\alpha$ -線などによる影響も故障と見なされる.一方,誤り(Error)とは故障による回路動作に現れる異常である.ある信号波形が期待していたものと異なった波形を示したり, $\alpha$ -線の入射によりメモリの内容が変化することは誤りである.

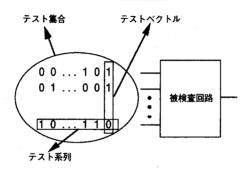

テストベクトル,テスト系列およびテスト集合といった用語は頻繁に使用されている。テストベクトルとは同じ時刻にすべての入力線に印加される入力値であり、テスト系列とは1本の入力線に印加されるすべての入力値であり、テスト集合とはすべての入力線に印加されるすべての入力値である。これらの用語の区別を図 2.13 に示す。

# 2.3.2.2 故障検出

テスト生成を行なうにあたってまず、故障モデルを決めて対象故障リストを作る、それか

図 2.13 用語説明

ら、そのリストにあるすべての故障に対してテストベクトルを求める.

テスト生成を行なうとき、故障の影響が故障したゲートの出力線に現れるようにする故障 設定および故障の影響が観測できる信号線に現れるようにする故障伝搬の両方を考慮する必 要がある.外部出力端子しか観測できないテスト環境では、テスト生成は一般に困難である が、全可観測な環境では、故障の影響を伝搬させる必要がなく、故障設定のみを行なえば充 分ので、テスト生成は容易になる.その一方、全可観測な環境を実現するには、次章で述べ るような特別な技術が必要なので、通常のテスト環境でテスト生成を行ない回路に故障があ るかどうかを調べることが望まれる.

組合せ回路のテスト生成に関する研究は、従来から盛んに行なわれてきた. D[8], PODEM [9], FAN [10], CONT [11], そして SOCRATES [12] などのテスト生成のための優れたアルゴリズムが提案されている. これらの方法はいずれも縮退故障を故障モデルとしているが、最近、これらの方法に基づく、スタック・オープン故障検出用のテスト生成アルゴリズムも提案されている [26, 45, 52].

組合せ回路の場合に比べ,順序回路のテスト生成ははるかに困難である.順序回路のテスト生成手法は主に2種類ある.状態遷移表を用いる手法[6,16,19]では,順序回路をブラックボックスと見なして,適当なテスト系列を印加し,状態遷移表で規定された回路の機能を確かめる.順序回路テスト問題を組合せ回路のテスト問題におきかえる手法[3,6,16,19]では,図2.14のように同期式順序回路を時間展開することにより,既存の組合せ回路のテスト生成アルゴリズムの利用を可能にする.

図 2.14 同期式順序回路の時間展開

#### 2.3.2.3 故障診断

論理回路の故障診断とは故障箇所を見い出すことである。一般に故障診断を行なう前に、汎用テスタを用いて種々のテストベクトルによるテストや回路のブロック構成などを利用して、被疑範囲を可能な限り限定してから、信号線の観測により故障診断を行なう。現状では、被疑範囲を1Kゲート程度に絞ってから故障診断を行なうとの報告がある[31]。論理回路の故障診断には、以下の三つの手法がよく用いられている。

# 手法1 (対話法)

この手法 [32] では、観測したい信号線を決め、そこに適当な論理値を設定して観測する、観測結果が期待値と一致するか否かにより故障の位置特定を行なう。

この手法では、故障の状況、観測の結果から判断して、制御すべき信号線、論理値を決定する必要がある。したがってこの手法では、テスト実行者とのインタラクティブな対話を想定している。手法1では、人間の代わりにAI的な手法を駆使することも可能である[46]。しかし現状では、人間が観測の結果から判断を下し、故障を仮定し、故障診断を行なう方が効果的である。手法1の欠点は自動的に故障診断が行なえないことである。

# 手法2 (ガイディド・プローブ法)

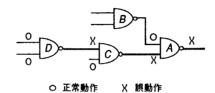

この手法[19,31]ではまず、故障モデルを仮定し、故障の影響が回路に現れるようにするテストベクトルを生成する。生成したテストベクトルを印加して回路に故障があるかどうかを調べる。回路の観測できる信号線で誤動作を観測したとき、故障は誤動作信号線の入力側にあるとして入力側の信号線を1本ずつプローブする。プローブとは、信号線の観測とそのシミュレーション値との比較照合である。入力側の信号線で分岐がある場合は、誤動作の存在する側にのみ遡る。以上の操作を故障ゲートが見つかるまで繰り返す。なお、故障ゲートとは入力線に誤動作がないのに出力線が誤動作しているゲートである。

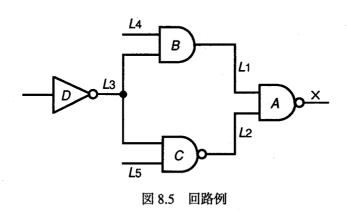

例えば、図 2.15 に示す回路の外部出力線で誤動作を観測したとする.このとき、ゲート A の入力線をプローブする.もしゲート C の出力線で誤動作を観測したら、次にゲート C の入力線をプローブする.もしゲート D の出力線で誤動作を観測したら、次にゲート D の入力線をプローブする.ゲート D の入力線に正常値を観測したら、ゲート D が故障していることが分かる.

この手法の長所はプローブすべき信号線のシミュレーションによる期待値さえあれば確実 に故障ゲートを絞り込める点にある。したがって、この手法は自動的な故障診断システムに 適用できる。その問題点は、段数の多い回路に対して、ゲート 1 段ずつ誤動作信号を追跡 していたのでは、故障絞り込みの効率が悪いことである。またこの手法では、原則的にはす

図2.15 故障追跡の例

べての信号線に対する期待値が必要である.しかし、大規模な回路のすべての期待値を記憶していたのでは、その記憶容量が膨大になってしまう.

# 手法 3 (故障辞書法)

これは内部信号線を含む観測できる信号線に現れる信号値の状況から故障箇所を推定する機能をもつテストベクトルを利用する方法である[19.33].

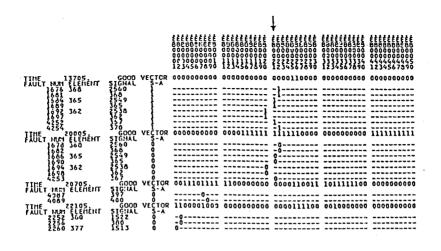

故障辞書の例を図 2.16 に示す. ここで EB0001~EB0050 は内部信号線を含む観測できる信号線である. "TIME13705" などはテストベクトルを表す. "GOOD VECTOR" は正常時の出力値を示す. "一" は正常値であることを意味する. ここでは, 縮退故障を対象にしている. 例えば, テストベクトル "TIME 13705" を印加したときの観測結果により, 故障番号 (FAULT NUM) が 1676, 1681, 1684, 1689, 1692, 1697, 4252, 4254 である故障を診断することができる. なお. "ELEMENT" と "SIGNAL" はそれぞれゲートと信号線を意味する.

この手法は手法2の問題点を解決できる. 故障辞書を利用すれば、故障の候補箇所を数 箇所まで絞り込むことが可能なので、プローブすべき信号線数は少なくて済み、それらの期 待値をすべて用意することも可能である.

図 2.16 故障辞書の例

この手法には次の欠点がある。第1は、テスト生成が依然として困難で、テストベクトルと信号線の期待値の記憶容量が手法2のそれより少ないものの、大規模な回路の場合となると問題が残る。第2は、1個のテストベクトルを印加したあと、内部信号線を含むすべての観測点の論理値を測定する必要があって、時間がかかることである。

### 2.4 論理回路のテスト容易化設計

# 2.4.1 テスト容易化設計の必要性

組合せ回路のテスト生成問題は NP 完全問題である [50,51]. すなわち,その問題を入力数の多項式時間で解決するアルゴリズムを見つけることは極めて困難である。実際に使用される論理回路に対して効率的な生成手法はあるが、大規模な回路になると、生成時間が非常に長くなる場合がある。

順序回路のテスト生成問題は組合せ回路のそれよりはるかに困難である。状態遷移表を用いて順序回路のテスト生成を行なうとき,入力数がn,状態数がrの場合,テスト系列の長さは $O(n^*r^*r!)$ である [6]。このため,nとrが少しでも大きければ,この手法は現実的でなくなる。図 2.14 のように同期式順序回路を時間展開することにより,順序回路のテスト問題を組合せ回路のテスト問題におきかえる手法では,初期状態の設定,多重故障の取り扱い,入力数と素子数の増加などの問題がある。

論理回路のテストの本質的な困難さを原因に、高集積化と高機能化に伴い、論理回路のテスト生成時間が増大している。また、テストベクトル数も増大し、それを記憶するメモリ容量や印加時間も増大している。その結果、テストコストが全コストで占める割合いは年々増加する傾向にある[2-4].

組合せ回路と順序回路のテスト生成問題を根本的に解決するために、設計段階においても、テストを考慮に入れる必要がある。すなわち、テスト容易な回路を設計することが必要である。テスト容易化設計の利点は、テスト生成が容易になり、テストの実施時間が短くなることである。その欠点は、素子数や外部入出力ピン数の増加、および動作速度の遅れなどである。そこで、総合的なコストの観点から、テスト容易化設計手法を使用するか、またどのテスト容易化設計手法をどの程度まで使用するかを判断する必要がある。

# 2.4.2 テスト容易化設計手法

#### 2.4.2.1 概説

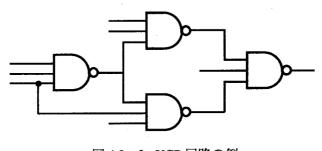

組合せ回路のテスト容易化設計手法は、三つのグループに分類することができる。まず、 テスト生成を必要としない方法がある。その代表として、回路分割による全数テスト [15、 53] やシンドロームテスト容易化設計 [54] などがある。また、回路構造を限定することによ りそのテストを簡単にする方法もある. このような方法では,半加算器アレー [55,56], PLA [57-59], あるいはカットポイントセルラアレー [60] などの基本単位を用いて,規則性のある回路を構成する. さらに,回路変更による方法がある. その代表として,XOR ゲートを挿入する方法 [6] や回路を 2 入力ゲートで構成されるように変更する方法 [34,35] などがある.

順序回路のテスト容易化設計手法は、状態図レベルのテスト容易化設計 [6] およびスキャン設計 [5-7, 18] に分類することができる。

次に、テスト容易化設計の代表例であるスキャン設計について説明する。

# 2.4.2.2 テスト容易化設計例-スキャン設計

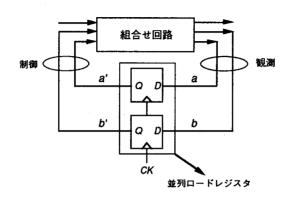

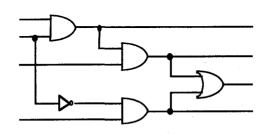

図 2.17 に同期式順序回路の一例である.この回路の D-フリップ・フロップが並列ロードレジスタを構成していると見なすことができる.つまり,クロック・パルスにより,信号線 a, b の値が同時にフリップ・フロップにセットされる.順序回路のテストが困難である主な原因は,信号線 a, b'から組合せ部分に所要のテストベクトルを印加すること,および信号線 a, b の値を観測することが難しいためである.この考察をもとに提案されたのがスキャン設計である.スキャン設計にも様々な種類がある.以下では,スキャンパス設計について説明する.

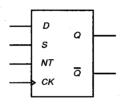

スキャンパス設計では、D-フリップ・フロップをシフトレジスタラッチに改造する。図 2.18 にシフトレジスタラッチの記号を示す。NT=0 のとき、クロック・パルスにより Dの 値が Qにセットされる。NT=1 のとき、クロック・パルスにより Sの値が Qにセットされる。クロック・パルスがないとき、Qの値が保持される。

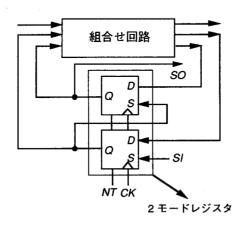

このようなシフトレジスタラッチを図 2.19 に示すように接続する. このようにすれば、シフトレジスタラッチは2モードレジスタを構成することになる. このレジスタの動作モードは NT により選択される. 正常動作 (NT=0) のとき、従来の並列ロードレジスタとして動作し、テスト (NT=1) のとき、シフトレジスタとして動作する.

図 2.17 同期式順序回路の例

図 2.18 シフトレジスタラッチの記号

図 2.19 スキャンパス順序回路

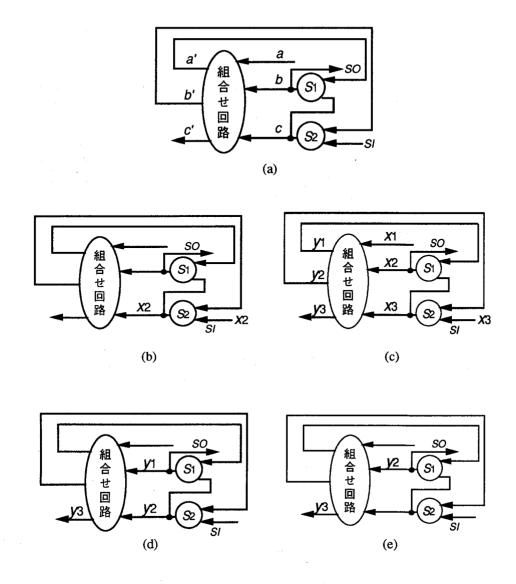

スキャンパスが存在することにより,順序回路のテストの問題はその組合せ部分回路のテストの問題におきかえられる.例えば,図 2.20 (a) の回路の組合せ部分をテストするために,a,b,cから x1,x2,x3 を印加する必要がある.また,a',b',c'に現われる応答 y1,y2,y3 を観測する必要がある.スキャンパスがあれば,これらの操作は簡単にできる.

図 2.20 (b) に示すようにまずレジスタをテストモードにする. SIに x2 を与えて,クロック・パルスを印加すると, x2 を c にセットすることができる.次に図 2.20 (c) に示すように,SIに x3 を与えて,クロック・パルスを印加すると, x2 を b, x3 を c にセットすることができる.このとき, x1 を a に与えると,組合せ部分に所要のテストベクトルを印加することになる.

図 2.20 (c) に示したように、テストベクトル x1, x2, x3 に対する組合せ部分の応答を y1, y2, y3 とする. y3 は外部信号線 c' に現われているので簡単に観測できる. y1, y2 を観測するために、まずレジスタを正常モード、すなわち並列ロードモードにする. このとき、クロック・パルスを印加すると、図 2.20 (d) に示すように, y1, y2 は a, bにセットされる. これで、SOから y1 を観測することができる. 次に、レジスタをテストモードにしてクロック・パルスを印加すると、図 2.20 (e) に示すように, y2 は b にシフトされる. つまり、SO から y1 を観測することができる.

図 2.20 スキャンパス順序回路のテスト例

この例から明らかなように、順序回路のテストの問題は、スキャンパスを利用することにより、その組合せ部分回路のテストの問題におきかえられ、現実的に解決できる問題となる.

# 2.4.2.3 組込み自己テスト (BIST) の概念

実際のテストは通常テスタと呼ばれる高価な設備でを行なわれる。テスタでは、テストベクトルの生成、記憶、印加およびテスト結果の判定などが行なわれる。テストベクトル数が多くなると、高価なテスタを専用する時間が長くなり、テストコストも当然高くなる。テス

ト生成のコストのみではなく,テスト実施のコストをも低減させるために,組込み自己テスト (BIST) の概念が提案されている [5-7,17,19].

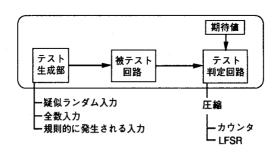

図 2.21 に示すように、組込み自己テストでは、テストベクトルの生成と印加、テスト結果の判定などのテスタ機能を回路内部で実現することにより、テスト実施のコストを安くする。組込み自己テストでは、テスト生成部を内蔵するので、ハード的に簡単に実現できるものでなければならない。そこで、疑似ランダム入力、全数入力や規則的に発生される入力などを用いるテストが多用されている。また、被テスト回路の応答をそのまま期待値と比較するのではなく、一旦圧縮されてから比較を行なう。この圧縮によく用いられるのは、カウンタや LFSR などである。

図 2.21 BIST の概念

#### 2.5 まとめ

本章ではまず、本研究で対象回路とする組合せ回路と順序回路の概念について説明した. 特に論理回路の基本論理ゲートおよび D-フリップ・フロップによる表現法について説明した. 順序回路は構造的に組合せ回路より複雑で、そのテストもはるかに困難である.

次に、論理回路のテストの基本概念、特に縮退故障やスタック・オープン故障などの重要な故障モデルについて説明し、またk入力 AND、OR、NAND、NOR ゲートおよび NOT ゲートのすべての縮退故障やスタック・オープン故障を検出するテストベクトルを示した。

さらに、論理回路のテスト容易化設計の基本概念および主な手法について紹介した. 特に順序回路のスキャンパス設計について詳しく説明した. スキャンパス設計では、回路内のすべてのフリップ・フロップはテスト時にシフトレジスタを形成するため、回路へのテストベクトルの印加および回路内部状態の観測は大幅に簡単化される.

# 全可観測な環境

全可観測な環境は、電子ビームプロービング技術の使用を背景としている。本章では、電子ビームプロービング技術について述べ、全可観測な環境でのテストの特徴と全可観測な環境におけるテスト容易化設計の必要性について説明する。

# 3.1 電子ビームプロービング技術

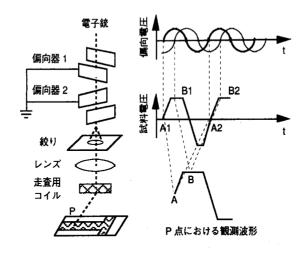

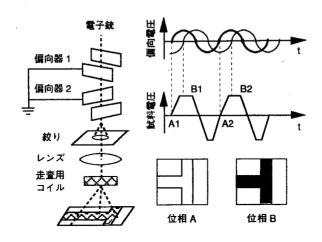

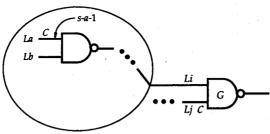

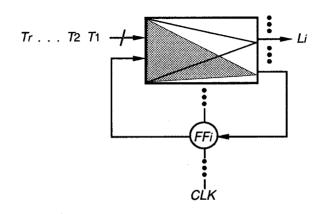

電子ビームプロービング技術の母体は走査形電子顕微鏡である[47].動作状態の集積回路チップ表面を電子ビーム走査したとき検出される 2 次電子の量は表面に形成される電界分布により影響を受ける。一般に、電圧の低い部分は検出された 2 次電子が多いため明るく、電圧の高い部分は検出された 2 次電子が少ないため暗いという電圧コントラスト像が得られる [23]. また 2 次電子のエネルギー分布は信号線の電圧だけ移動するので、エネルギー分析器により信号線の電圧を定量的に測定することができる [23]. 一方、波形を測定する場合には、検出系の応答速度に限界があるため、ストロボ法を用いる [27]. すなわち、図 3.1 に示すように、電子ビームを短いパルスにし、その周期を被観察回路の動作周期と一致させて信号線を照射する。電子ビームと回路動作の位相を少しずつ動かして、2 次電子を検出することにより波形の観測が可能となる。また図 3.2 に示すように、位相を固定したまま電子ビームを 2 次元走査することにより、特定の位相状態での電圧像が得られる。

この原理に基づき,集積回路の故障診断を行なう装置は,一般に電子ビームテスタと呼ばれている. 従来の CAD 環境との統合により,観測したい信号線を論理図で指定するだけで,その信号線へのビームの位置決め,プロービング,結果の処理と表示が自動的に行なわれる高性能な電子ビームテスタが開発されている [30].

電子ビームテスタの構成や機能は、その目的とする診断内容や適用デバイスによりそれぞれ若干異なる。一般の電子ビームテスタは、電子銃から発生した電子ビームを細く絞って集積回路チップ表面の測定点に照射する電子ビーム鏡筒、電子ビームを短いパルスにするパルスゲート、電子レンズ、偏向器、被観察回路を挿入する真空の試料室などを含む。真空の試料室にはモータ駆動のステージ、エネルギー分析器、2次電子検知器などが含まれている。

さらに 2 次電子信号の処理回路,制御装置,ストロボ回路,被観察回路のトライバ,像と 波形の表示部,計算機などから構成されている.被観察回路の損傷を避けるため電子ビーム の加速電圧は 1 Kv 前後と低い.

図3.1 ストロボ法による電圧波形測定

図 3.2 ストロボ法による電圧像測定

電子ビームテスタを用いる場合,集積回路チップの最上位層の信号線を直接に観測できる。報告によると,2層 Al 配線の回路なら95% の信号線を観測できる電子ビームテスタが既に開発されている。特に、ゲートアレイの場合、ゲート間の信号線が最後に形成されるので、大部分のゲートの出力線が最上位層の信号線として現われる。表3.1 はいくつかの実際の回路の最上位層への配線率を示す。

| 回路 | ゲート数   | 配線数  | 最上位層配線率 |

|----|--------|------|---------|

| ·  |        | 000  | 00.70   |

| Α  | 2.3 K  | 303  | 96.7 %  |

| В  | 3.5 K  | 2643 | 99.1 %  |

| C  | 15.0 K | 6331 | 98.4 %  |

| D  | 15.5 K | 5851 | 99.4 %  |

表 31 最上位層への配線率

電子ビームプロービング技術の特徴は以下の通りである.

- (1) 機械的に非接触、非破壊である.

- (2) スポットが微小である.

- (3) 配線との間に容量がなく高速の波形観測が可能である.

- (4) ビームの位置決めが容易である.

# 3.2 全可観測な環境

電子ビームテスタを用いて回路内部の多くの信号線の論理値を観測することができるので、テストを行なうとき、故障の影響を外部出力線まで観測のために伝搬させる必要がない。したがって、ゲートレベルの回路を対象にするとき、回路内の各ゲートの出力線が観測できると仮定することは非現実ではない。このようなテスト環境を全可観測なテスト環境、あるいは単に全可観測な環境と呼ぶ。これに対し、外部出力線しか観測できないテスト環境を通常のテスト環境と呼ぶ。

# 3.3 全可観測な環境でのテストとテスト容易化設計

全可観測な環境でテストを行なうとき、故障の影響を観測できる信号線まで伝搬させる必要がない。したがって、全可観測な環境において、テスト生成は簡単にできる。

しかし、全可観測な環境で使用できるテスト系列はいくつかの要求を満たさなければならない。これについて第1章でも触れたが、基本的にはテスト系列が短くなければならない。また、電子ビームテスタなどを用いるとき、その短いテスト系列を回路に繰り返し印加しなければならない。全可観測な環境で生成されたテスト系列はどの回路の場合でも十分短いという保証がない。また、順序回路でよくあるように、その組合せ部分が短いテスト系列を有しても、それを連続的に回路に繰り返し印加することができない。

全可観測な環境での中心問題は、如何にして短いテスト系列を作るか、および如何にして それを連続的に回路に繰り返し印加するかである。これまでは、人手によりなるべく短いテ スト系列を作ることが考えられていた。これは技術者の経験によるところが大きく、費用も 時間もかかる場合が多い. 自動的に生成を行なう試みもあったが[29,32], どのような回路に対しても有効であるという保証はない. このように回路構造を変えずにアルゴリズムを改良するだけでは自ら限界がある. この問題を根本的に解決するためにテスト容易化設計を考える必要がある.

全可観測な環境の概念やそれを実現する技術の確立は近年のことであるが、かつて、最小長のテスト系列でテスト可能な回路をどのように構成すればよいかなどを調べる研究が行われていた[34,35]。それは、テスト系列の長さの下限を知っていれば、それより短いテスト系列で回路をテストしようとする無駄な努力が省かれるからであった。また、テスト系列の長さの下限は実際に生成したテスト系列の長さの評価の尺度にもなるからであった。次に、その代表的な研究例[35]を紹介する。

図 3.3 3入力でテスト可能な回路例

簡単な例として図 3.3 の回路について説明する。2 入力 AND ゲートの縮退故障は  $SA = \{011, 101, 110\}$  に属する 2 個の系列でテスト可能であり,2 入力 OR 素子の縮退故障は  $SO = \{100, 010, 001\}$  に属する 2 個の系列でテスト可能である。したがって,図 3.3 のように入力割当を行なえば,長さ 3 の系列ですべての縮退故障がテスト可能となる。

図 3.4 3 入力でテスト可能でない回路例

しかし、図 3.4 の回路の場合には 3 入力でテスト可能ではない。このとき、次のような方法で 3 入力でテスト可能なように変換することができる。

(1) 与えられた組合せ回路を 2 入力の AND ゲートと OR ゲートと NOT ゲートを用いて樹枝状回路として実現する.

- (2) 外部入力線に SA または SO の系列を割り当てる。各ゲートについて割り当てられた入力系列がテスト可能ならばその系列を外部出力線に伝搬させる。テスト可能でなければ、AND または OR ゲートを用いて展開し、テスト可能なようにする。

- (3) すべてのゲートに系列が割り当てられるまで(2)を繰り返す.

例えば、図3.4の回路は図3.5の回路のように3入力テスト可能とすることができる。このとき、2個のゲートと2本の外部入力線、2本の外部出力線が付加されている。テスト系列は、その長さを3より短くすることができないので、これは最小長のテスト系列となる。

図 3.5 3 入力でテスト可能な回路への変換

しかし、このテスト容易化設計には以下のような欠点がある.

- (1) 対象故障は信号線の縮退故障のみである. 現在 CMOS 技術が多用されているため, CMOS に特有のスタック・オープン故障をも対象にする必要がある.

- (2) 回路を構成する素子の種類や入力数についての制限が厳しい。

- (3) 回路変換は主に置換で行なわれ、オーバーヘッドが大きいと思われる.

- (4) 故障診断手法が示されていない。

そこで、これからの章では、より広範的、系統的なアプローチを取り、テスト容易な論理 回路の概念、テスト方法、および構成方法について提案する。

#### 3.4 まとめ

電子ビームプロービング技術の基本原理について述べた。電子ビームプロービング技術を用いることにより、回路内の最上位層にある信号線を観測することができる。この技術を背景に、回路のすべてのゲートの出力線が観測できるテスト環境、いわゆる全可観測な環境を定義した。電子ビームプロービング技術を使用する前提条件として、被観測回路が短いテスト系列をもち、かつその系列が回路に繰り返し印加することができることである。このため、全可観測な環境においてもテスト容易化設計が必要である。

# 全可観測な環境での組合せ回路のテスト

本章では、全可観測な環境でのテスト容易な組合せ回路について述べる [36-40]. 基本的な考え方は回路構造を限定することである。本章ではまず、k-UCP 回路の定義、テスト生成法、および故障検査法について述べる。次に、k-UCP 回路の拡張である k-R 回路の概念について述べる。

#### 4.1 k-UCP 回路の定義

定義 4.1 k入力 AND, OR, NAND, NOR ゲートおよび NOT ゲートで構成される組合せ回路を、k- U 回路と呼ぶ。

定義 4.2 k-U 回路において、k 入力のゲートの入出力線に異なる色を、NOT ゲートの入出力線とファンアウトの信号線に同じ色を塗るように、k+1 種の色ですべての信号線を塗ることができるとき、この k-U 回路は k+1 色解をもつという。k+1 色解をもつ k-U 回路を k-U 回路と呼ぶ。

定義 4.3 k-U 回路において,表 4.1 に示すルールにしたがって,正極性(+)と負極性(-)をすべての信号線に割り当てることができるとき,このk-U 回路は正しい極性をもつ k-U 回路を k-U 回路と呼ぶ.

定義 4.4 k+1 色解と正しい極性をもつ k-U 回路を k-U 回路と呼ぶ。

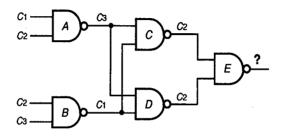

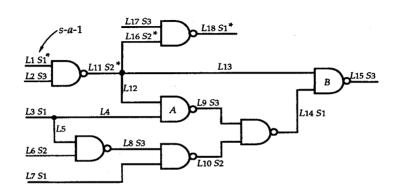

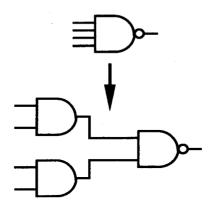

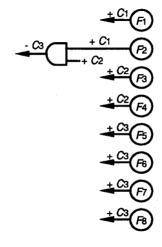

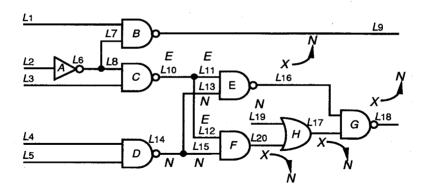

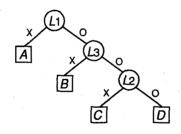

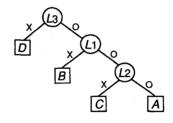

図 4.1 と図 4.2 にそれぞれ 2 - UCP 回路と 3 - UCP 回路の例を示す。一般に、任意の組合 せ回路は付加ゲートにより k - UCP 回路に変換できる。図 4.3 にその一例を示す。図 4.3 (a) の回路の外部入力線にどのような 3 色の色塗りをしてもゲート E の入力線の色が必ず同じ になるので、図 4.3 (a) の回路は k - UCP 回路ではない。この回路は 2 個の NAND ゲートを

|      | 入力  | 出力  |

|------|-----|-----|

| NAND | +   | +   |

| AND  | +   | ı   |

| NOR  | ı   | -   |

| OR   | •   | +   |

| NOT  | -/+ | +/- |

表 4.1 k-UCP 回路の極性割当ルール

付加することにより図 4.3 (b) の 2 - UCP 回路に変換できる。回路変換手法については、次章で詳しく述べる。

図 4.1 2-UCP 回路の例

図 4.2 3 - UCP 回路の例

k - UCP 回路を構成するゲートの種類をさらに限定することにより、k - UC - NAND 回路 と k - UC - NOR 回路が得られる.

定義 4.5 k入力 NAND ゲートからなる k-UCP 回路を k-UC - NAND 回路と呼ぶ.

定義 4.6 k入力 NOR ゲートからなる k- UCP 回路を k- UC - NOR 回路と呼ぶ.

(a) k-UCP でない回路例

(b) 2-UCP 回路への変換

図 4.3 回路変換の例

明らかに、NAND ゲートまたは NOR ゲートからなる組合せ回路は必ず正しい極性をもつ.

# 4.2 基本系列

k- UCP 回路のテスト集合は、あらかじめ生成されている 2(k+1) 個の系列から、与えられた k- UCP 回路に応じて作られる。この 2(k+1) 個の系列を k- 基本系列と呼ぶ。k- UCP 回路の k- 基本系列は回路構造に関係なく、故障モデルと kの値により決まる。以下では、スタック・オープン故障用と縮退故障用の k- 基本系列の定義と生成法について述べる。

#### 4.2.1 基本系列の定義

定義 4.7 スタック・オープン故障用の k-基本系列は、次の条件を満たす 2(k+1) 個の論理値  $0 \ge 1$  からなる系列  $S1, S2, \ldots, Sk+1, T1, T2, \ldots, Tk+1$  である.

- (1) NAND( $S_1, S_2, ..., S_{i-1}, S_{i+1}, ..., S_{k+1}$ ) =  $S_i$ NOT( $S_i$ ) =  $T_i$

- (2) S1, S2, ..., Si-1, Si+1, ..., Sk+1 は k入力 NAND ゲートのすべてのスタック・オープン故障を検出することができ、Si は NOT ゲートのすべてのスタック・オープン

故障を検出することができる.

補題 4.1 スタック・オープン故障用の k- 基本系列  $S_1, S_2, ..., S_{k+1}, T_1, T_2, ..., T_{k+1}$  は 次の性質をもつ.

- (1) AND(S1, S2, ..., Si-1, Si+1, ..., Sk+1) = TiOR(T1, T2, ..., Ti-1, Ti+1, ..., Tk+1) = SiNAND(S1, S2, ..., Si-1, Si+1, ..., Sk+1) = SiNOR(T1, T2, ..., Ti-1, Ti+1, ..., Tk+1) = TiNOT(Si) = Ti, NOT(Ti) = Si

- (2) S1, S2, ..., Sk+1 (T1, T2, ..., Tk+1) は k入力 AND と NAND (OR と NOR) ゲートの すべてのスタック・オープン故障を検出することができ、Si と Ti は NOT ゲート のすべてのスタック・オープン故障を検出することができる。

次に示す系列はスタック・オープン故障用の2-基本系列である.

$$S_1 = 1 \ 0 \ 1 \ 0 \ 1 \ 1 \ 1$$

$T_1 = 0 \ 1 \ 0 \ 1 \ 0 \ 0$  (4.1.a)

$S_2 = 1 \ 1 \ 0 \ 1 \ 1 \ 0 \ 1$   $T_2 = 0 \ 0 \ 1 \ 0 \ 0 \ 1 \ 0$  (4.1.b)

$S_3 = 0 \ 1 \ 1 \ 1 \ 0 \ 1 \ 0$   $T_3 = 1 \ 0 \ 0 \ 0 \ 1 \ 0 \ 1$  (4.1.c)

定義 4.8 縮退故障用の k-基本系列は、次の条件を満たす 2(k+1) 個の論理値  $0 \ge 1$  からなる系列  $S1, S2, \ldots, Sk+1, T1, T2, \ldots, Tk+1$  である.

- (1) NAND(S1, S2, ..., Si-1, Si+1, ..., Sk+1) = SiNOT(Si) = Ti

- (2) S1, S2, ..., Si-1, Si+1, ..., Sk+1 は k 入力 NAND ゲートのすべての縮退故障を検出することができ、Si は NOT ゲートのすべての縮退故障を検出することができる.

補題 4.2 縮退故障用の k - 基本系列 S1, S2, ..., Sk + 1, T1, T2, ..., Tk + 1 は次の性質をもつ.

- (1) AND $(S_1, S_2, ..., S_{i-1}, S_{i+1}, ..., S_{k+1}) = T_i$ OR $(T_1, T_2, ..., T_{i-1}, T_{i+1}, ..., T_{k+1}) = S_i$ NAND $(S_1, S_2, ..., S_{i-1}, S_{i+1}, ..., S_{k+1}) = S_i$ NOR $(T_1, T_2, ..., T_{i-1}, T_{i+1}, ..., T_{k+1}) = T_i$ NOT $(S_i) = T_i$ , NOT $(T_i) = S_i$

- (2) S1, S2,..., Sk+1 (T1, T2,..., Tk+1) は k 入力 AND と NAND (OR と NOR) ゲートの すべての縮退故障を検出することができ、Si と Ti は NOT ゲートのすべての縮退

故障を検出することができる.

次に示す系列は縮退故障用の2-基本系列である.

$$S1 = 0 \ 1 \ 1$$

$T1 = 1 \ 0 \ 0$  (4.2.a)

$S2 = 1 \ 0 \ 1$   $T2 = 0 \ 1 \ 0$  (4.2.b)

$S3 = 1 \ 1 \ 0$   $T3 = 0 \ 0 \ 1$  (4.3.c)

明らかに、ある故障モデルに対する k-基本系列は唯一ではない。例えば、4.1 式に示したスタック・オープン故障用の2-基本系列は、縮退故障用の2-基本系列でもある。

#### 4.2.2 基本系列の生成

# 4.2.2.1 スタック・オープン故障用の基本系列の生成

スタック・オープン故障用の k-基本系列は次の手続きにより生成される.

# 手続き BG1 (スタック・オープン故障用の k-基本系列を生成する)

- (1) k(k+1) 個の対  $\langle i,j \rangle$   $(i,j=1,2,...,k+1;i\neq j)$  に番号 1,2,...,k(k+1) を次のように 割り当てる.

- (1-a) 対 < k+1, 1 >に番号 1 を割り当てる。m=1 とする。

- (1-b) これまで割り当てられた番号の最大値を m とし、 m をもつ対を < h. ト とする.

- (1-c) 番号が割り当てられておらずかつ 1 番目の要素が i である対の集合  $SP = \{ \langle i, D \rangle \}$  を求める.

- (1-d) SPが空であれば、(2)へ移る. そうでなければ、SPの中で一番小さい t をもつ対に番号 m+1 を割り当て、(1-b) に戻る.

- (2) (1) で番号が割り当てられた k(k+1) 個の対  $\langle i,j \rangle$   $(i,j=1,2,...,k+1;i\neq j)$  を番号順に並べて、系列  $R: \langle k+1,1 \rangle, \langle 1,2 \rangle,...,a,b,c,...$  を形成する.

- (3) 系列 R を構成する対の2番目の要素を取り出し、一番前に k+1 を加えて、系列 S:  $k+1,1,2,\ldots,a,b,c,\ldots$  を形成する。

- (4) Pt = (x1, x2, ..., xt-1, xt, xt+1, ..., xk+1) とする.ここで, $xt = 0, xi = 1, i = 1, 2, ..., k+1, i \neq t$  とする.P1, P2, ..., Pk+1 を系列 S の示す順番に並べると,系列 P: Pk+1, P1, P2, ..., Pa, Pb, Pc, .... が得られる.

- (5) 系列 P を論理値 0 と 1 からなる行列と見なす.この行列の i 行目を Si と定義する.また,Ti を Si の否定と定義する.なお,i=1,2,...,k+1 とする.

補題 4.3 手続き BG1 の (1) では、すべての対に番号が割り当てられる。また、番号 g をもつ対の 2 番目の要素と番号 g+1 をもつ対の 1 番目の要素は等しい(g=1,2,...,k(k+1) - 1).

(証明) k=2 と k=3 のとき,この補題の前半が明らかに成立する。k=t のとき,この補題の前半が成立すると仮定する。k=t+1 のときの対を図 4.4 に示す.対 < t+2, 2 > に番号が割り当てられるまで,対 < t+2, 1 > を含む行と対 < 1, 2 > を含む列にあるすべての対に番号が割り当てられている。番号が割り当てられていない対 < i, j > を < i-1, j-1 > に書き換えると,k=t のときの対となる.よって,この補題の前半が成立する.この補題の後半が成立することは手続き BG1 の (1) より明かである.

図 4.4 k=t+1 のときの対の番号付け

補題 4.4 系列 Pには、Piに Pjが続く対が 1 個しかない( $i, j = 1, 2, ..., k+1; i \neq j$ ).

(証明) 任意のi,j  $(i,j=1,2,...,k+1;i\neq j)$  に対して,系列S にはi にj が続く対が1 個しかないことを証明すればよい.系列R に対 < i, j> があるので,i にj が続く対は必ず系列S に存在する.また,もし系列S にはi にj が続く対が存在すれば,系列R には対 < i, j> が必ず存在する.系列R に対 < i, j> が1 個しかないので,系列S にもi にj が続く対が1 個しかないことが分かる.よって,この補題が成り立つ.

定理 4.1 手続き BG1 で求められた 2(k+1) 個の系列 S1, S2, ..., Sk+1, T1, T2, ..., Tk+1 は スタック・オープン故障用の <math>k- 基本系列である.

(証明) Tiの定義より、NOT(Si) = Tiである、次に、NAND(S1, S2, ..., Si-1, Si+1, ..., Sk+1) = <math>Ti が成立することを証明する、なお、i=1,2,...,k+1 とする.

Siの t ビット目の値を Si(t) とする。Piの定義より,S1, S2, ..., Sk+1 には 0 が 1 個しかない。それで,任意の t について,NAND(S1(t), ..., Si-1(t), Si+1(t), ..., Sk+1(t)) = Si(t) である。よって、NAND(S1, S2, ..., Si-1, Si+1, ..., Sk+1) = Si が成り立つ。

系列 PにPiPi, ..., PiPi-1, PiPi+1, ..., PiPkおよびPjPi( $i \neq j$ )があるので、CMOS の k入力 NAND ゲートのすべての単一スタック・オープン故障を検出することができるテストベクトルが S1, S2, ..., Si-1, Si+1, ..., Sk+1 に含まれていることが分かる.

明らかに、手続き BG1 で求められたスタック・オープン故障用の k - 基本系列の長さは k(k+1)+1 である.

Siには 0 と 1 が含まれているので,それで NOT ゲートのすべての縮退故障を検出することができる.また,S1, S2, ..., Si- 1, Si+ 1, ..., Sk+ 1 には,<0, 1, ..., 1>, <1, 0, ..., <1, 1, ..., 1> が含まれている.2.3.1.2 で述べたように,これらの系列は k 入力 NAND ゲートのすべての縮退故障を検出することができる.よって,手続き BG1 で求められた 2(k+1) 個の系列 S1, S2, ..., Sk+ 1, T1, T2, ..., Tk+ 1 は縮退故障用の k- 基本系列でもある.

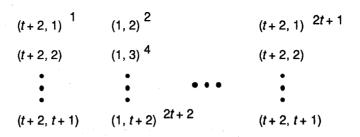

- 例 4.1 手続き BG1 を用いて 3 UCP 回路のスタック・オープン故障用の基本系列を生成する場合、各段階での実行結果は次の通りである。

- (1) では、12 個の対  $\langle i,j \rangle$   $(i,j=1,2,3;i\neq j)$  に番号  $1,2,\ldots,12$  を割り当てる.その結果は次に示す.

- (2)で得られた系列 R は <4, 1>, <1, 2>, <2, 1>, <1, 3>, <3, 1>, <1, 4>, <4, 2>, <2, 3>, <3, 2>, <2, 4>, <4, 3>, <3, 4> である.

- (3) で得られた系列 S は 4, 1, 2, 1, 3, 1, 4, 2, 3, 2, 4, 3, 4 である.

- (4) P1 = (0, 1, 1, 1)', P2 = (1, 0, 1, 1)', P3 = (1, 1, 0, 1)', P4 = (1, 1, 1, 0)' とする.得られた系列 P は P4, P1, P2, P1, P3, P1, P4, P2, P3, P2, P4, P3, P4 である.

- (5) 系列 Pを次のような論理値 0 と 1 からなる行列と見なす.

よって、得られた基本系列は次の通りである.

| S1 = 10101011111111              | $T1 = 0 \ 1 \ 0 \ 1 \ 0 \ 1 \ 0 \ 0 \ 0 \ 0 \$ |

|----------------------------------|------------------------------------------------|

| S2 = 1 1 0 1 1 1 1 0 1 0 1 1 1 1 | $T2 = 0 \ 0 \ 0 \ 0 \ 1 \ 0 \ 0 \ 1 \ 0 \ 0 \$ |

| S3 = 1 1 1 1 0 1 1 1 0 1 1 0 1   | <i>T</i> 3 = 0 0 1 0 0 0 0 1 0 1 0 0 0         |

| S4 = 0 1 1 1 1 1 1 0 1 1 1 0 1 0 | T4 = 1 0 0 0 0 0 1 0 0 0 1 0 1                 |

#### 4.2.2.2 縮退故障用の基本系列の生成

縮退故障用の k-基本系列は次の手続きにより生成される.

手続き BG2 (縮退故障用の k-基本系列を生成する)

- (2) Si = a1 a2 ... ak+1 とする. なお, ai = 0, aj = 1,  $j \neq i$ , j = 1, 2, ..., k+1. Ti = NOT(Si) と する.

- (3) i=i+1 とする.  $i \le k+1$  であれば、(2) に戻る.

手続き BG2 より、次の定理は明らかである。

定理 4.2 手続き BG2 で求められた 2(k+1) 個の系列 S1, S2, ..., Sk+1, T1, T2, ..., Tk+1 は縮退故障用の <math>k-基本系列である.

手続き BG2 で求められた縮退故障用の k-基本系列の長さは k+1 である。手続き BG1 で求められた基本系列と異なって、手続き BG2 で求められた基本系列は縮退故障にのみ有効である。

#### 4.3 k-UCP 回路の故障検出

k-UCP 回路のテスト集合は次の手続きにより簡単に生成できる.

**手続き TG** (k-UCP 回路のテスト集合を生成する)

- (1) 故障モデルとkの値に応じて、手続きBG1 または手続きBG2 でk-UCP回路の2(k+1) 個のk-基本系列を求める、

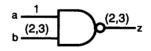

- (2) 与えられた k UCP 回路の信号線に塗られた k+1 種の色を C1, C2, ..., Ck+1 とする. 色 Ci と正極性をもつ外部入力線に k 基本系列の Si を,色 Ci と負極性をもつ外部入力線に k 基本系列の Si を対応させる.

手続き TG で外部入力線に対応させられた基本系列はその回路のテスト集合となる。

定理 4.3 全可観測な環境で、k- UCP 回路のすべての単一縮退故障は長さ k+1 のテスト系列で検出でき、単一縮退故障と単一スタック・オープン故障は長さ k(k+1)+1 のテスト系列で検出できる。

(証明) k-UCP 回路の定義と基本系列の性質(補題 4.1 と補題 4.2) より分かるように、手続き TG で求められたテスト集合を k-UCP 回路に印加したとき、回路内の任意のゲー

トの入力線に、その信号線が色 Ci と正極性をもつ場合に Si、その信号線が色 Ci と負極性をもつ場合に Ti が印加されることになる。補題 4.1 と補題 4.2 より、全可観測な環境では、k-UCP 回路のすべての単一縮退故障と単一スタック・オープン故障が検出できる。

例 4.2 図 4.1 の 2 - UCP 回路のテスト集合を求める. まず, 図 4.1 の回路のすべての信号線に色を塗り,極性を割り当てる. C1, C2, C3 は 3 種類の色を表す. 手続き TG で求められたテスト集合は次の通りである.

$$S1 \rightarrow L1, L4; S2 \rightarrow L2; S3 \rightarrow L5; T3 \rightarrow L2.$$

k- UCP 回路のテスト集合の生成は極めて簡単で、所要時間も少ない。また、実用的なkの値が2または3であるので、テスト系列の長さは7または13と短い。このため、テスト集合を記憶するためのメモリ容量は少ない。さらに、シミュレーションを行なわなくても、各信号線の色と極性よりその信号線のテスト集合に対する期待値を得ることができ、これらの期待値を保存する必要がない。したがって、k- UCP 回路の使用は、集積回路の大規模化によるテスト集合の生成時間、シミュレーションの時間、およびテスト系列と期待値の記憶容量の増加問題の解決策となる。

# 4.4 通常のテスト環境における k-UCP 回路の故障検出

このように、全可観測な環境において k - UCP 回路の故障検出は少ないテストベクトルで行なえることを明らかにした。本節では、それらのテストベクトルの、通常のテスト環境における故障検出率を求める。これは、k - UCP 回路に適した故障シミュレーション手法により行なわれる。

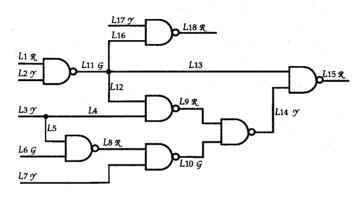

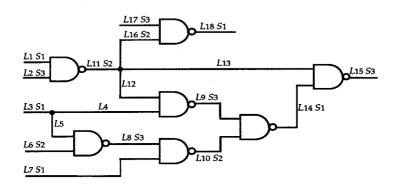

以下では、説明を簡単にするため、2 - UC - NAND 回路の場合のみについて述べる。図 4.5 に 2 - UC - NAND 回路の例を示す。R, G, Y は 3 種類の色を示す。得られる結論は一般のk - UCP 回路の場合にも簡単に拡張できる。

図 4.5 2 - UC - NAND 回路の例

#### 4.4.1 故障シミュレーションの方法

### 4.4.1.1 故障影響の伝搬

手続き TG で生成されたテスト集合を正常回路に印加したとき,各信号線に基本系列が現われる。その例を図 4.6 に示す。

図 4.6 2 - UC - NAND 回路へのテスト系列の印加

あるゲートの入力線または出力線に縮退故障があれば、そのゲートの出力系列が基本系列でなくなる。そのゲートの出力線が他のゲートの入力線でもあるとき、その故障影響が回路内の他の信号線に伝わる可能性もある。その例を図 4.7 に示す。L1 に 1 縮退故障があるとき、L1 にある系列は S1 と異なる系列となり、S1\* で表す。この故障の影響は L11, L16, L18 に伝わる。

故障影響は回路内の他の信号線に伝わることがあるが、必ずしも外部出力線まで伝わると は限らない、すなわち、故障影響の伝搬が阻止される可能性はある。

図 4.7 故障 2 - UC - NAND 回路の例

定義 4.9 回路に故障が存在するとき、入力線が異常系列をもち出力線が基本系列をもつようなゲートを、その故障の伝搬阻止ゲートと呼ぶ、

例えば、図 4.7 に示した回路において、ゲート A と B は伝搬阻止ゲートである。伝搬阻止ゲートの存在により、故障影響の伝搬は回路内で阻止される。故障が 1 縮退故障であるとき、あるゲートが伝搬阻止ゲートである必要十分条件は次の定理で与えられる。

定理 4.4 2-UC-NAND 回路において、1縮退故障をもつ信号線の色が C であるとする。あるゲートがその1縮退故障の伝搬阻止ゲートであるための必要十分条件は、そのゲートの1本の入力線の色が C であり、もう1本の入力線に異常系列があることである。

#### 4.4.1.2 対象故障数の削減

NAND ゲートのみからなる回路において、すべての 1 縮退故障と分岐の幹上にある 0 縮退故障を考えれば十分である。 0 縮退故障を処理するため、フロンティア・ゲートの概念を導入する。

図 4.8 伝搬阻止ゲートの効果

定義 4.10 Lを分岐の幹とする。あるゲートの入力線がLからの分岐であるとき,そのゲートをLのフロンティア・ゲートと呼ぶ。

明らかに、ある幹の0縮退故障はその幹のフロンティア・ゲートの出力線の1縮退故障

の等価故障である。したがって、その幹の0縮退故障の影響が外部出力線に伝わる必要条件は、その幹の少なくとも1個のフロンティア・ゲートの出力線の1縮退故障の影響が外部出力線に伝わることである。

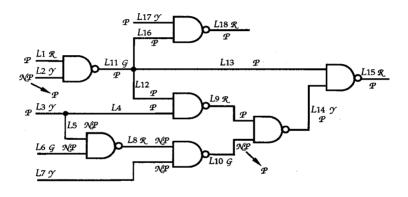

以上に述べたことに基づき、対象故障数を削減する手続きを提案する. ここで、回路内の信号線に割当られた3種類の色をC1, C2 およびC3 とする. また、P は伝搬(Propagation)を、NP は非伝搬(Non-Propagation)を表す.

### 手続き FNR (対象故障数を削減する)

- (1) *i*を1とする. 故障リスト FL を空にする.

- (2) Pを各外部出力線に割り当てる.

- (3) 次の規則にしたがって、PまたはNPを残りの信号線に割り当てる、

- 規則 1: あるゲートの出力線が Pをもち、かつ入力線にどの記号も割当られていないとする. 入力線に色 Ci がなければ、Pを入力線に割り当てる. 1本の入力線に色 Ci があれば、Pをその入力線に割り当て、NPをもう 1本の入力線に割り当てる. あるゲートの出力線が NPをもち、かつ入力線にどの記号も割当られていないとする。この場合、NPを入力線に割り当てる.

- 規則 2: 分岐のすべての枝が NP をもち,かつその分岐の幹にどの記号も割当られていない場合, NPを分岐の幹に割り当てる.分岐の少なくとも1本の枝がPをもち,しかもその分岐の幹にどの記号も割当られていない場合,Pをその幹に割り当てる.

- (4) ゲートGの入力線をL1 とL2 とする.L1 がNPを,L2 が色C1 とD8 そのゲート の出力線がD8 もつならば、L1 のD8 のD8 の以力線がD8 もつならば、D9 の以内をD1 の以内をD1 の以内をD2 に変える.

- (5) Pをもつ信号線の1縮退故障を故障リストFLに入れる.

- (6) Lを分岐の幹とする. その幹の少なくとも 1 個のフロンティア・ゲートの出力線が Pをもつなら、Lの 0 縮退故障を故障リスト FL に入れる.

| (7) | i=i+1とする. | i≤3のとき. | (1) に戻る. |  |

|-----|-----------|---------|----------|--|

例 4.3 図 4.9 に示す回路内の信号線の色 R に対して Pと NPを割り当てる。明らかに,色 Pに対して,L5, L6, L7, L8 の 1 縮退故障の影響は外部出力線に伝わらない。

手続き FNR を用いることにより、その影響が必ず外部出力線に伝わらない故障を発見することができ、これらの故障は対象故障集合から取り除かれる。

図 4.9 対象故障数の削減

#### 4.4.1.3 故障シミュレーション手続き

以下では、ある信号線 L の 1 縮退故障 f の影響が外部出力線に伝わるか否かを調べる手続きについて述べる。 f は手続き FNR により求められた対象故障リスト中にあるとする。このシミュレーションでは、基本系列を意味する N と異常系列を意味する Eが用いられる。なお、信号線 L の色を C とする。

### 手続き FS (故障シミュレーションを行なう)

- (1) L から外部出力線まですべてのパスを求める、パスを L L1(L1) L2(L2) . . . Lh(L1h) Lpo で表す、ここで、Lpo は外部出力線である。Li が分岐の幹のとき、Li を空とする、Li が 2 入力 NAND ゲートの入力線のとき、Li がそのゲートへのもう 1 本の入力線とする(i = 1, 2, . . . , h)、Li をパス線、Li をペア線と呼ぶ。

- (2) Lに Eを割り当てる、Lから外部出力線までのすべてのパス上のパス線でないペア線に Nを割り当てる、

- (3) Nと Eを次のように残りの信号線に割り当てる. パス線 Li に Nまたは Eが割り当てられており、パス線 Li-1 に Nまたは Eが割り当てられているとする. Li-1 にペア線がないとき、Li に Li-1 と同じシンボルを割り当てる. Li-1 にペア線があり、しかも Li-1 とLi-1 が Nをもつとき、Li に Nを割り当てる. Li-1 または Li-1 が Eをもち、しかも Li-1 も Li-1 も色 C をもたない場合、Li に E を割り当てる. Li-1 (Li-1) が E をもち、しかも Li-1 (Li-1) が色 C をもつ場合、Li に Nを割り当てる.

- (4) 少なくとも 1本の外部出力線が Eをもつなら、信号線 L の 1 縮退故障 f の影響は 外部出力線に伝わる.

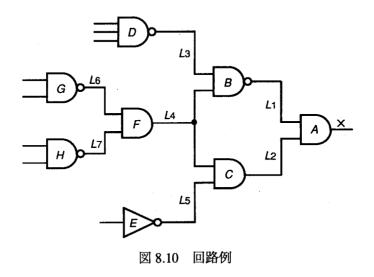

例 4.4 図 4.10 に示す回路の信号線 L1 の 1 縮退故障の影響が外部出力線に伝わるか否か を調べる. L1 から外部出力線までのパスは次に示す.

L1 - L3() - L4(L6) - L7() - L8(L10) - L11 L1 - L3() - L4(L6) - L7() - L9(L5) - L12 L1 - L3() - L5(L9) - L12

手続き FSの(2)を実行した結果を次に示す.

L1E - L3() - L4(L6N) - L7() - L8(L10N) - L11 L1E - L3() - L4(L6N) - L7() - L9(L5) - L12 L1E - L3() - L5(L9) - L12

手続き FS内の(3)を実行した結果を次に示す.

L1E - L3E() - L4E(L6N) - L7E() - L8E(L10N) - L11E L1E - L3E() - L4E(L6N) - L7E() - L9E(L5) - L12N L1E - L3E() - L5E(L9) - L12N

これにより、信号線 $L_1$ の1縮退故障の影響は外部出力線に伝わることが分かる.

図 4.10 故障シミュレーションの例

分岐の幹の 0 縮退故障はその幹のフロンティア・ゲートの出力線の 1 縮退故障と等価である。その幹のフロンティア・ゲートが複数ある場合、少なくとも 1 個のフロンティア・ゲートの出力線の 1 縮退故障の影響が外部出力線に伝わるなら、分岐の幹の 0 縮退故障の影響も外部出力線に伝わる。

手続き FS を用いることにより、通常のテスト環境における、全可観測な環境で生成されたテスト集合の故障検出率を調べることができる.

#### 4.4.2 テスト生成法

前節では、全可観測な環境で生成されたテスト集合を用いても通常のテスト環境で一部の 故障を検出することができることを示した。そのテスト集合で検出できない故障について、 さらにテスト生成を行なう必要がある.このために、D, PODEM, FAN, CONT, SOCRATES などのテスト生成アルゴリズムを用いることができる.被検査回路は一般の回路ではなく、2 - UC - NAND 回路であるため、回路特徴を利用したアルゴリズムを用いることが考えられる

2-UC-NAND 回路において、一つの彩色解は一つのテスト集合に対応する。つまり、ある故障が検出されるように彩色解を求めればよい。このため、伝搬阻止ゲートの概念を用い故障影響の伝搬が阻止されないように彩色解を求める必要がある。この方法は従来のテスト生成アルゴリズム手法に似ている。

もう一つの方法では、2 - UC - NAND 回路のすべての彩色解を求めて、各彩色解に対応するテスト集合の和集合はその回路の通常のテスト環境でのテスト集合とする。

### 4.4.3 実験結果と考察

提案した故障シミュレーション手続きFS を C 言語によりプログラム化し、実験を行なった. 使用したコンピュータは富士通の S-4/LC(12.5 MIPS)である。実験用の回路は ISCAS 1985 のベンチマーク組合せ回路である [71].

表 4.2 は全可観測な環境で生成されたテスト集合の,通常のテスト環境における故障検出率を示す.

| 回路        | 故障検出率(%) | 観測率(%) |

|-----------|----------|--------|

| 2UC-17    | 94.1     | 33.3   |

| 2UC-ADDER | 61.3     | 83.3   |

| 2UC-432   | 16.5     | 87.4   |

| 2UC-499   | 66.4     | 63.2   |

| 2UC-1908  | 19.8     | 87.7   |

| 2UC-2670  | 13.2     | 88.4   |

| 2UC-3540  | 9.8      | 93.4   |

| 2UC-5315  | 19.9     | 91.3   |

| 2UC7552   | 14.7     | 83.7   |

表 4.2 実験結果

表 4.2 の結果は、全可観測な環境においても、100%の故障検出率を得るためにすべてのゲートの出力線が観測できるとしなくてもよいことを示している。必要な観測点数と全ゲート数の比率は表 4.2 に示されている。この情報は、クロスチエック法 [21,22] などを用いて回路内に観測点を設けるときに有用である。

#### 4.5 k-UCP 回路概念の拡張

全可観測な環境では、k-UCP 回路の故障検出と故障診断は短いテスト系列で行なうことができる。しかし、k-UCP 回路を構成するゲートとしては、k入力 AND, OR, AND, NAND ゲートおよび NOT ゲートしか使用できない。つまり、任意の組合せ回路をk-UCP 回路に

変換するとき、まずk入力でないゲートをk入力のゲートによる等価な部分回路に変換する必要がある。このため、ゲートの入力数に関する制限をなくすことが望ましい。以下では、k-R 回路を提案し、この問題を解決する。

# 4.5.1 k-R回路の定義

定義 4.11 NOT ゲート, XOR ゲート, XNOR ゲート, および入力数が k 以下の OR, AND, NAND, NOR ゲートで構成される組合せ回路を拡張 k-U 回路と呼ぶ.

定義  $4.1\ 2$  拡張 k-U 回路において,表 4.3 に示すルールにしたがって,正極性(+)と負極性(-)をすべての信号線に割り当てることができるとき,この拡張 k-U 回路が正しい極性をもつという.

|      | 入力  | 出力   |

|------|-----|------|

| NAND | +   | +    |

| AND  | +   |      |

| NOR  | 1   |      |

| OR   | •   | +    |

| NOT  | -/+ | +/-  |

| XOR  | -/+ | - /+ |

| XNOR | -/+ | - /+ |

表 43 k-R 回路の極性割当ルール

定義 4.12 は定義 4.3 の拡張である. 例えば, 負極性を OR ゲートの入力線に, 正極性を OR ゲートの出力線に割り当てなければならない. また, XOR ゲートまたは XNOR ゲート の入力線と出力線に同じ極性を割り当てる必要がある.

定義 4.13  $U=\{1,2,\ldots,k+1\}$  とする. 拡張 k-U 回路の各信号線に U の空でない部分集合を割り当てる. 信号線 L に割当られた部分集合を L の重みと呼ぶ。回路内の各信号線の重みが次の条件を満たすとき、その回路が k-均衡性をもつという.

- 回路内の任意の t入力の AND, OR, AND, NOR ゲートの入力線の重みを  $W_1, W_2, ..., W_t$ , 出力線の重みを Wとすると,  $W=U-(W_1+W_2+...+W_t)$ と  $W_i-(W_1+...W_{i-1}+W_{i+1}+...+W_t)$   $\neq \emptyset$  が成り立つ.なお, $i=1,2,...,t \leq k$ とする.

- (2) 回路内の任意の XOR または XNOR ゲートの入力線の重みを W1, W2 とすると,

$W_1 - W_2 \neq \emptyset$ と $W_2 - W_1 \neq \emptyset$ が成り立つ。

(3) 回路内の任意の NOT ゲートの入力線の重みと出力線の重みが等しい.

定義 4.14 正しい極性と k-均衡性をもつ拡張 k-U 回路を k-R 回路と呼ぶ.

例えば、図 4.11 に示す回路は 4-R 回路である.

図 4.11 4-R 回路の例

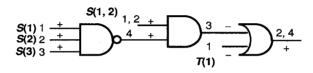

### 4.5.2 k-基本系列の定義

k - UCP 回路と同様に、k - R 回路のテスト集合もあらかじめ生成されている基本系列から構成される。

3-基本系列の例を次に示す。

$$S(1) = 0 \ 1 \ 1 \ 1$$

$T(1) = 1 \ 0 \ 0 \ 0$

$S(1, 2) = 0 \ 0 \ 1 \ 1$   $T(1, 2) = 1 \ 1 \ 0 \ 0$

$S(2, 3, 4) = 1 \ 0 \ 0 \ 0$   $T(2, 3, 4) = 0 \ 1 \ 1 \ 1$

基本系列は次の性質をもつ.

# 補題 4.5 k-R 回路において、次の結論が成り立つ。

回路内の任意のt入力 AND, NOR, NAND, NOR ゲートの入力線の重みを $W_1, W_2, ...$ ,  $W_t$ , 出力線の重みをWとすると、次の式が成り立つ。 AND  $(Pk(W1), Pk(W2), \ldots, Pk(Wt)) = Nk(W)$

OR  $(N_k(W_1), N_k(W_2), ..., N_k(W_k)) = P_k(W)$

NAND  $(Pk(W1), Pk(W2), \dots, Pk(Wt)) = Pk(W)$

NOR  $(Nk(W1), Nk(W2), \ldots, Nk(Wt)) = Pk(W)$

(2) 回路内の任意の XOR または XNOR ゲートの入力線の重みをW1, W2, 出力線の重みをW とすると、次の式が成り立つ。

XOR (Pk(W1), Pk(W2)) = Pk(W)

XOR(Nk(W1), Nk(W2)) = Nk(W)

XNOR (Pk(W1), Pk(W2)) = Nk(W)

XNOR (Nk(W1), Nk(W2)) = Pk(W)

(3) 回路内の任意の NOT ゲートの入力線または出力線の重みを Wとすると, 次の式が成り立つ。

NOT (Pk(W)) = Nk(W), NOT (Nk(W)) = Pk(W)

(証明) 定義 4.13 より、結論 (3) が明らかである。次に、NAND (Pk(W1), Pk(W2), ..., Pk(Wi)) = Pk(W) が成立することを証明する。他の式については、ほぼ同様に証明できる。

Pk(Wi), Pk(W2), ..., Pk(Wi) は論理値  $0 \ge 1$  からなる系列である。Pk(W1) などの i ビット目をPk(W1, i) などで表す。一般性を失うことなく,Pk(W1, i) = 0 と仮定する。 $W = U - W = U - (W1 + ... Wi + 1 + Wi + 1 + ... + Wi) \neq 0 \ge i \in W$  であるため, $i \in W1$  である。つまり,Pk(W1, i) = 0 である。NAND (Pk(W1, i), Pk(W2, i), ..., Pk(Wt, i)) = 1 であるため,NAND (Pk(W1, i), Pk(W2, i), ..., Pk(Wt, i)) = Pk(W, i) である。なお,i = 1, 2, ..., k + 1 とする。よって,NAND (Pk(W1), Pk(W2), ..., Pk(Wt)) = Pk(W) である。

#### 補題 4.6 k-R 回路において、次の結論が成り立つ、

- 回路内の任意の t入力 AND, NAND(OR, NOR)ゲートの入力線の重みを  $W_1, W_2, ...$  、 $W_t$  とすると、 $P_k(W_1), P_k(W_2), ..., P_k(W_t)$ ( $N_k(W_1), N_k(W_2), ..., N_k(W_t)$ )を印加することにより、そのゲートのすべての縮退故障を検出することができる。

- 回路内の任意の XOR または XNOR ゲートの入力線の重みを  $W_1$ ,  $W_2$  とすると,  $P_k(W_1)$  と  $P_k(W_2)$  または  $N_k(W_1)$  と  $N_k(W_2)$  を印加することにより、そのゲートのすべての縮退故障を検出することができる.

- 回路内の任意の NOT ゲートの入力線または出力線の重みを Wとすると、Pk(W)または Nk(W) を印加することにより、そのゲートのすべての縮退故障を検出することができる。

(証明) 図 4.12 に示すように、t入力 NAND ゲートの入力線の重みを W1, W2, ..., Wtと すると、Pk(W1)、Pk(W2), ..., Pk(Wt) を印加することにより、そのゲートのすべての縮退故 障を検出することができることを証明する。他の結論はほぼ同様に証明できる。

図 4.12 t入力 NAND ゲート

$W = U - (W_1 + ... W_{t-1} + W_{t+1} + ... + W_t) \neq \emptyset$  であるため,次の式を満たすような  $w_1, w_2, ..., w_t, w$  が必ず存在する.

$w1 \in W1, w1 \notin W2, \ldots, w1 \notin Wt$  $w2 \notin W1, w2 \in W2, \ldots, w2 \notin Wt$

$wt \notin W1, wt \notin W2, ..., wt \in Wt$  $w \notin W1, w \notin W2, ..., w \notin Wt$

これで、図 4.13 に示すように、t入力 NAND ゲートのすべての縮退故障を検出するようなベクトルが Pk(W1), Pk(W2), ..., Pk(Wt) に含まれることが分かる。図 4.13 では、w1, w2, ..., wt, w がビットの位置を意味する。つまり、S(W1), S(W2), ..., S(Wt) にはそのゲートのすべての縮退故障を検出するようなベクトルが含まれている。よって、t入力 NAND ゲートのすべての縮退故障は Pk(W1), Pk(W2), ..., Pk(Wt) を印加することにより検出できる。

|       | W1 | <b>w</b> 2 |       | wt | W |

|-------|----|------------|-------|----|---|

| S(W1) | 0  | 1          | • • • | 1  | 1 |

| S(W2) | 1  | 0          | • • • | 1  | 1 |

| :     | :  | :          | •••   | :  | : |

| S(Wt) | 1  | 1          | •••   | 0  | 1 |

図 4.13 補題 4.6 の証明

#### 4.5.3 縮退故障の検出

補題 4.6 より、k-R 回路において、重み Wと正極性(負極性)をもつ外部入力線に基本系列 S(W)(T(W))を印加することにより、すべての縮退故障が検出できる。基本系列の長さが k+1 であるので、次の定理が成立する。

定理 4.5 全可観測な環境において、k-R 回路のすべての縮退故障は長さ k+1 のテスト系列で検出できる。

図 4.14 に 3-R 回路の例とそのテスト集合を示す.

図 4.14 テスト集合の例

#### 4.6 まとめ

本章では、全可観測な環境でのテスト容易な組合せ回路として、k - UCP 回路および k - R 回路を提案した。

k- UCP 回路は NOT ゲートと k入力のゲートで構成され、いくつかの構造上の制約も受ける。そのため、k- UCP 回のすべての縮退故障とスタック・オープン故障は、全可観測な環境においてそれぞれ長さ k+1 と k(k+1)+1 のテスト系列で検出できる。実際の k の値が 2 または 3 なので、テスト系列は非常に短い。

k-UCP 回路のテスト集合はあらかじめ生成されている基本系列より構成される.基本系列の長さが回路のテスト系列の長さなので、なるべく短い基本系列を生成しなければならない。本章では、縮退故障用とスタック・オープン故障用の短い基本系列の生成手法についても述べた。

次に、k-UCP 回路のすべての縮退故障を検出するには、一部のゲートの出力線を観測するだけでよいことを明らかにした。それは、k-UCP 回路にテスト集合を印加したとき、一部の縮退故障の影響は外部出力線に伝わるからである。実験結果では、最多 93.4%、最少 33.3% のゲートの出力線を観測すれば十分である。このような情報は、クロスチエック法などで回路内に観測点を設けるとき有用である。

さらに、k-UCP 回路におけるゲートの入力線数がkであるという制約をなくすため、k-R 回路を提案した。k-R 回路は NOT ゲート、および入力線数がk以下の基本ゲートで構成される。k-R 回路のすべての縮退故障は、全可観測な環境において長さk+1のテスト系列で検出できる。k-R 回路は一般的な回路で、k-UCP 回路、k-UC-NOR 回路などをそれの特例と見なすことができる。

# 全可観測な環境での 組合せ回路のテスト容易化設計

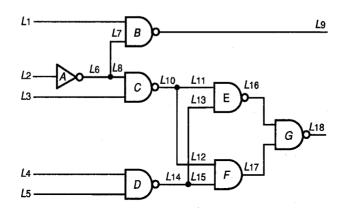

#### 5.1 概説

任意の組合せ回路は必ずしも k - UCP 回路ではない。例えば,図 5.1 の 2 - U 回路は 3 色解をもたない。なぜなら,外部入力線にどの色を塗っても L16 と L17 が同じ色になるからである。また,この回路は 2 - UP 回路でもない。なぜなら,ゲート G の入力線に正極性が必要なのにゲート F が負極性を提供しているからである。OR ゲート H をゲート G と F の間に挿入することにより、図 5.1 の回路は図 4.1 に示した 2 - UCP 回路に変換できる。

図 5.1 3 色解と正しい極性をもたない回路

このように、任意の組合せ回路は k - UCP 回路に変換できるが、オーバーヘッドの問題および k - U 回路が k+1 色解をもつか否かを決定する問題がある。本章では、これらの問題を考慮して回路変換法を提案する [38, 40].

回路変換の目標は、なるべく少ないオーバーヘッドで与えられた組合せ回路を k-UCP 回路に変換することである。一般に、回路変換のオーバーヘッドはゲート数で評価されるが、これは CMOS 回路の場合に必ずしも適当ではない。例えば、4 入力 NAND ゲートは図 5.2 に示すように 2 入力のゲートで構成されるように変換できる。ゲート数は 1 から 3 に増え

るが、トランジスタ数は8から16に増える。増加率はゲート数では200%であるが、トランジスタ数では100%である。一般に、トランジスタ数はチップ面積をゲート数より正確に反映するので、本論文では、トランジスタ数で回路変換のオーバーヘッドを評価する。

図 5.2 4 入力 NAND ゲートの分解

k-UCP 回路への変換は3段階に分けて行なわれる。

- (1) 与えられた組合せ回路から k-U 回路への変換

- (2) k-U 回路から k-UP 回路への変換

- (3) k-U 回路から k-UC 回路への変換

明らかに, これらの変換を  $(1) \rightarrow (2) \rightarrow (3)$  の順に実行した結果は k - UCP 回路であり,  $(1) \rightarrow (3) \rightarrow (2)$  の順に実行した結果も k - UCP 回路である.

#### 5.2 k-U回路への変換

この変換では、与えられた組合せ回路をk-U回路に変換する。ここではまず、kの値を決める必要がある。k の値を決める方法は 2 通りある。第 1 は設計者が指定する方法であり、第 2 は k-U回路に変換するための付加トランジスタ数が最小になるように決める方法である。2番目の方法ではまず、与えられた回路のすべてのゲートのファンイン数を調べ、その最大値を  $f_{MAX}$  とする。合理的な k の値は 2 と  $f_{MAX}$  の間にあるので、各 k に対してファンイン数を調整するのに必要な付加トランジスタの数を計算し、付加トランジスタの数が一番少ない k の値を最終の k の値とする。

kの値が決まれば、次は NOT ゲート以外の各ゲートのファンイン数がすべて kになるように変換を行なう。例えば、4 入力 NAND ゲートについては、図 5.2 に示したように 2 入力のゲートによる構成におきかえる。さらに、XOR、XNOR ゲートなどの AND、OR、NAND、NOR および NOT ゲート以外のゲートを AND、OR、NAND、NOR および NOT ゲートで構成

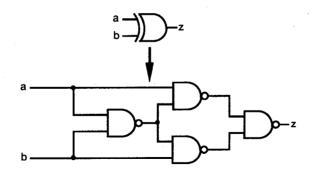

されるように変換する。例えば、XOR ゲートは、図 5.3 に示すように 2 入力 NAND ゲートからなる部分回路におきかえることができる。

図 5.3 XOR ゲートの 2 入力 NAND ゲートによる表現

k-U 回路への変換は難しい問題ではないが、変換のオーバヘッドを少なくするための工夫が必要である [48]. 明らかに、n を回路のゲート数とすると、この変換の計算量は O(n) である.

#### 5.3 k-UP 回路への変換

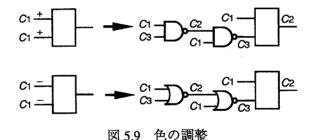

この変換では、極性の調整を行なうことにより、k-U回路をk-UP回路に変換する.具体的にはまず、k-U 回路の各信号線に表 4.1 に示したルールにしたがって極性を割り当てる.同じ信号線に異なる極性が割り当てられたとき、図 5.4 に示すようにその信号線に AND または OR ゲートを挿入して極性の調整を行なう.n を回路のゲート数とすると,この変換の計算量は O(n) である.

図 5.4 極性の調整

# 5.4 k-UC 回路への変換

この変換を行なうとき、まず与えられた k- U 回路が k+1 彩色解をもつか否かを決定する必要がある.

色  $C1,C2,\ldots,Ck$  が k 入力のゲートの入力線に割り当てられたとき,そのゲートの出力線に割り当てるべき色は明らかに Ck+1 である.このように,これまでの外部入力線への色の割り当てにより色が一意的に決まる信号線を探し出す操作を色の含意操作と呼ぶ.回路のすべての外部入力線に色が割り当てられたとする.色の含意操作により他のすべての信号線にも色が割り当てられるようになれば,この回路は k+1 彩色解をもつことが分かる.すべての外部入力線に対する任意の色の割り当てのもとで色の含意操作を行なっても,少なくとも 1本の信号線には色を割り当てることができなければ,この回路は k+1 彩色解をもたないことが分かる.

このことより、k-U回路がk+1彩色解をもつか否かを決定する問題は、n次元空間での探索問題として形式化できることが分かる。k-U回路がk+1彩色解をもつか否かを決定する問題を単にk+1彩色解問題と呼ぶ。以下では、k+1彩色解問題がNP完全であることを証明する。k+1彩色解問題がNP完全であることは、それを解く多項式時間のアルゴリズムを発見すれば、すべてのNP完全問題を解く多項式時間のアルゴリズムを発見したことを意味する。つまり、k+1彩色解問題を解く多項式時間のアルゴリズムを発見することは極めて困難である。現実的には、NP完全問題をヒュリスティックな方法で解決せざるを得ない。

# 5.4.1 k+1 彩色解問題

本節では、k+1 彩色解問題が NP 完全であることを証明する.一般に,ある問題が NP 完全であることの証明は 2 段階に分けて行なわれる [49,50].まず,その問題が NP 問題である,つまり多項式時間の非決定性アルゴリズムで解けることを証明する.次に,ある既知の NP 完全問題が多項式時間のアルゴリズムでその問題に帰着できることを示せばよい.

# 補題 5.1 k+1 彩色解問題は NP 問題である.

(証明) 与えられた k-U 回路の外部入力線へのすべての色の割り当ての集合を S とする. k+1 彩色解問題を次の非決定性アルゴリズム AL1 により解くことができる.

# アルゴリズム AL1 (k+1彩色解問題を解く)

- (1) 集合Sから非決定的に一つの色の割り当てSを選ぶ。

- (2) sのもとで色の含意操作によりすべての信号線に矛盾なく色が割り当てられれば、その回路が k+1 彩色解をもつ、そうでなければ、その回路が k+1 彩色解をもたない。

アルゴリズム AL1 が明らかに多項式時間のアルゴリズムなので、彩色解問題は NP 問題であることが分かる。

定義 5.1 グラフG=(V,E) と整数の集合  $\{1,2,...,m\}$  が与えられたとする.  $(u,v) \subset E$  だ 対して  $f(u) \neq f(v)$  となるような関数  $f:V \to \{1,2,...,m\}$  が存在するとき,グラフGは m彩色可能であるという。任意のグラフGと  $\{1,2,...,m\}$  に対して,Gが m彩色可能か否かを決定する問題を m彩色可能性問題と呼ぶ [49,50].

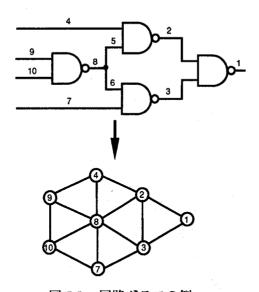

グラフのm彩色可能性問題はNP完全であることがすでに証明されている [49,50]. 以下では,グラフのk+1彩色可能性問題が多項式時間のアルゴリズムでk+1彩色解問題に帰着できることを証明することにより,k+1彩色解問題もNP完全であることを示す.そのため,まず,次のアルゴリズムでk-U回路をグラフに変換する.

アルゴリズム AL2 (k-U回路をグラフに変換する)

- (1) 回路内のゲートの出力線を頂点とする.

- (2) ゲートの入力線を表す頂点を辺で結ぶ、

- (3) ゲートの出力線を表す頂点とそのゲートの入力線を表す頂点を辺で結ぶ。 □

AL2 の実行例を図 5.5 に示す. AL2 で得られるグラフを回路グラフと呼ぶ.

図 5.5 回路グラフの例

補題 5.2 グラフの k+1 彩色可能性問題が多項式時間のアルゴリズムで k+1 彩色解問題に帰着できる.

(証明) ここで、グラフの3彩色可能性問題は2-U回路が3彩色解をもつか否かを決定する問題に帰着できることを証明する。 $k \ge 3$  の場合についてほぼ同様に証明できる.

明らかに、アルゴリズム AL2 は多項式時間で実行できる。また、回路グラフから 2-U

回路を求める多項式時間のアルゴリズムも存在する. さらに、アルゴリズム AL2 から分かるように、回路グラフが3彩色可能である必要十分条件はその2-U回路が3彩色解をもつことである. よって、グラフの3彩色可能性問題が多項式時間のアルゴリズムで3彩色解問題に帰着できる. □

補題5.1と補題5.2から明らかなように、次の定理が成り立つ。

# 定理 5.1 k+1 彩色解問題は NP 完全である.

k- UC 回路への変換ではまず,k- U 回路が k+1 色解をもつか否かを決定する必要がある。しかし,この k+1 彩色解問題は NP 完全問題であるため,多項式時間で解決するアルゴリズムを発見するのは極めて困難である。つまり,ヒューリスティックな手法を用いてこの問題の解決を試みざるを得ない。以下ではまず,k+1 彩色解問題の規模を小さくする手法について述べる。次に,k+1 彩色解問題のヒューリスティックな手法を用いた解決法を提案する。

#### 5.4.2 回路の対象部分の抽出

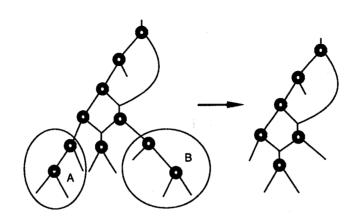

k+1彩色解問題を考える場合,回路全体を対象とする必要はない.樹枝状の回路は明らかに彩色解をもつので,図 5.6 に示す A と B のような樹枝状の部分回路を取り除いてから k+1 彩色解問題を考えれば十分である.

定義 5.2 入力線がすべて外部入力線である樹枝状の部分回路を取り除いたあとの部分回路をもとの回路の対象部分と呼ぶ。

図 5.6 回路の対象部分の例

このように、回路の対象部分を抽出することにより、回路の規模が小さくなり、問題解決の所要時間も少なくなる。

### 5.4.3 回路変換手法

彩色解問題は n 次元空間での探索問題として形式化できる。そこで,この問題を解く基本的な考え方は,外部入力線へのすべての色の割り当てを試してみて,彩色解をもたらすような色の割り当てが存在するかどうかを調べることである。k-U 回路において,1 本の外部入力線に対して k+1 個の可能な色の割り当てがある。すべての信号線に対する色の割り当ての数は, $(k+1)^n$  である。つまり,この探索操作を工夫しなければ,回路規模が少しでも大きくなると時間がかかり過ぎて実用的でなくなる。

提案する手法の基本的な考え方は次の通りである.一度に 1 本の外部入力線を選び,それにある色を割り当て,色の含意操作を行なう.色の矛盾があれば,その外部入力線に残りの可能な色の中から一つ選んで割り当てる.色の矛盾とは,同じゲートの少なくとも 2 本の入力線に同じ色が割り当てられていることである.もしその外部入力線のすべての可能な色が試されたら,その直前に色が割り当てられた外部入力線に残りの可能な色の中から一つ選んで割り当てる.もし最初に色を割り当てられた外部入力線のすべての可能な色が試されたら,その回路はk+1彩色解をもたないことが分かる.もし矛盾がなければ,次の外部入力線を選んで.同様の操作をしていく.

この過程において、色の含意操作は大きな役割をもつ、まず、それにより速く色の矛盾を発見することができる、次に、色の含意操作により外部入力線の色が自動的に決まるかまたは割り当て可能な色が限定されることになる。これより、外部入力線の色は速く決まることになる。

図 5.7 不確定含意操作の例

図 5.8 確定含意操作の例

k+1 彩色解問題を解決する方法では、色の矛盾を発見したら、バックトラックを起こして探索を続ける。実行時間を短縮するため、バックトラックの回数を少なくする必要がある。このため、外部入力線を選択していく順番が重要である。以下では、回路の信号線にレベルを付け、それを利用して外部入力線の選択を行なう。

### 手続き LA (各信号線にレベルを割り当てる)

- (1) 外部出力線にレベル1を付ける.

- (2) NOT ゲートの入出力線のレベルを等しくする.

- (3) k入力ゲートの入力線のレベルをそれの出力線のレベルより一つ大きくする.

- (4) 分岐の幹のレベルはその枝のレベルの中で一番大きいものと等しくする.

外部入力線のヒューリスティックな選択方法を次に示す.

#### 手続き ES (外部入力線を選択する)

- (1) まだ色が決っていない外部入力線の中から、一番大きいレベルをもつ信号線を選択し、それに色を割り当てる。

- (2) 一番大きいレベルをもつ外部入力線が2本以上ある場合,残りの割り当て可能な色の種類の少ない信号線を選択し、それに色を割り当てる.

次のアルゴリズムでは、k-U 回路がk+1 彩色解をもつか否かを調べ、彩色解をもたない場合、25.9 に示すようにゲートを挿入して回路変換を行なう.

# 手続き CM (彩色解の決定と回路変換を行なう)

- (1) まだ色が決まっていない外部出力線から手続き ES により 1本の信号線を選んで一つの色を割り当て、この信号線と色をスタック Lに入れる。残りの割り当て可能な色とこの信号線をスタック Sに入れ、(2)へ移る。すべての外部出力線に色が割り当てられたら、回路が彩色解をもつとして終了する。

- (2) 色の含意操作を行なう. 色の矛盾がなければ(1)に戻る. 色の矛盾があれば, (3)へ 移る.

- (3) 今回の色の割り当てを無効にする. Sのトップにある要素を取り出し、それが示す信号線にそれが示す色を割り当て、(2)に戻る. Sが空であれば、彩色解が存在しないことが分かり、(4)へ移る.

- (4) Lのトップにある要素が示す信号線と色で信号線に色を割り当て、色の含意操作を行なう。色の矛盾については、ゲートを挿入することによりそれを解消する。(1)に戻る。

### 5.5 実験結果と考察

提案した回路変換手法を C 言語によりプログラム化し、回路変換の実験を行なった。使用したコンピュータは富士通の S-4/LC (12.5 MIPS) である。実験用の回路は ISCAS 1985のベンチマーク組合せ回路である [71].

実験結果は表 5.1 に示す。実験 1 と 2 において,k の値は 2 である。これはベンチマーク 回路を構成するゲートの大部分が 2 入力のゲートであるからである。実験 1 では,まずも との回路を 2 - U 回路に変換し,さらに 2 - UP 回路に変換し,最後に 2 - UC 回路に変換した。その結果は AND, OR, NAND, NOR, NOT などの各種のゲートを含む k - UCP 回路である。実験 2 では,まずもとの回路を 2 入力 NAND ゲートからなる回路に変換し,さらに 2 - UC 回路に変換した。その結果は 2 - UC - NAND 回路である。表 5.1 の 2 - UC 2 は,実験 2 での 2 入力 NAND ゲートで構成される回路から 2 - UC 回路への変換のオーバーヘッドを示している。

|        |         | オーバーヘッド(%) |      |      |

|--------|---------|------------|------|------|

| 回路     | トランジスタ数 | 実験 1       | 実験 2 | 2-UC |

| mc432  | 896     | 154.9      | 84.4 | 7.3  |

| mc499  | . 2180  | 41.1       | 26.2 | 4.6  |

| mc880  | 1802    | 116.0      | 56.0 | 6.3  |

| mc1355 | 2308    | 32.6       | 17.2 | 2.8  |

| mc1908 | 3430    | 85.4       | 39.0 | 3.8  |

| mc2670 | 5364    | 84.5       | 33.4 | 3.6  |

| mc3540 | 7504    | 92.2       | 54.9 | 3.4  |

| mc5315 | 11262   | 85.9       | 52.2 | 4.2  |

| mc7552 | 15396   | 69.0       | 36.7 | 7.5  |

表 5.1 実験結果

実験結果から明らかなように、実験 2 のオーバーヘッドは実験 1 のそれより小さい。また、表 5.1 の "2-UC" のオーバーヘッドは非常に小さい。つまり、与えられた回路は k 入力 NAND ゲートのみを含むとき、それを k - UCP 回路に変換するためのオーバーヘッドが非常に小さい。

#### 5.6 まとめ

任意の組合せ回路を k- UCP 回路に変換する手法について述べた。この変換は 3 段階に分けて行なわれる。まず最初の段階で,与えられた回路を k- U 回路に変換する。次の 2 段階で,k- U 回路を k- UP 回路と k- UC 回路に変換する。この中でもっとも困難な変換は k- U 回路から k- UC 回路への変換である。この変換ではまず,k- U 回路が k+ 1 色解をもつか否かについて決定する必要がある。この決定問題は NP 完全問題であることを証明した。本章では,ヒューリスティックな手法でこの問題の解決を図った。基本的な考え方は,外部入力線へのすべての色の割り当ての中から彩色解をもたらすようなものを探索することである。この探索を速くするために,外部入力線のヒューリスティックな選び方,および色の含意操作などを提案した。

実験結果より次のことが分かった.

- (1) 与えられた回路を k UC NAND または k UC NOR 回路に変換するためのオーバーヘッドは様々なゲートからなる一般の k UCP 回路に変換するためのオーバーヘッドより少ない.

- (2) 与えられた回路が k 入力 NAND または NOR ゲートで構成される場合,それを k-UC NAND 回路または k UC NOR 回路に変換するためのオーバーヘッドが非常に小さく,実用範囲内である.実際の論理回路の設計では,ゲートアレイ形式の設計をはじめ,2 入力 NAND または NOR ゲートが多用される場合が多いため,k UCP 回路の概念は論理回路の実際のテストに役立つと思われる.

# 全可観測な環境での 順序回路のテスト

#### 6.1 概説

実際に使用される論理回路の大部分は組合せ回路ではなく、順序回路である. 2.4.1 で述べたように、順序回路のテストは組合せ回路のそれよりはるかに困難である.

第 4 章では、全可観測な環境でのテスト容易な組合せ回路について述べた。与えられた組合せ回路は k - UCP 回路であれば、短いテスト系列で故障検出できることを明らかにした。本章では、第 4 章で得られた結果をもとに、全可観測な環境でのテスト容易な順序回路について述べる [42, 43].

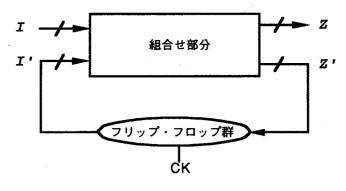

ここでは、クロック線を除く各信号線の縮退故障を対象故障とする。また、D-フリップ・フロップ を記憶素子とする。以下では、D-フリップ・フロップ のことを単にフリップ・フロップ と呼ぶ。一般の同期式順序回路を図 6.1 に示す。

図 6.1 一般の順序回路

図6.1より明らかなように、フリップ・フロップの入出力線は組合せ部分の出入力信号線でもある。つまり、組合せ部分に注目し、その入力線より組合せ部分に所要のテストベクトルを印加すれば、回路全体の縮退故障が検出されることになる。また、組合せ部分を短いテスト系列でテストするため、それを k-UCP 回路に変換することが考えられる。

しかし、この方法には大きな問題点がある。それは、フリップ・フロップの出力線を通じて順序回路の k - UCP 組合せ部分に所要のテストベクトルを印加することは必ずしも簡単であるとは限らない。このような印加が簡単にできるように、さらに回路構造を制限する必要がある。本章では、このような印加が簡単にできる順序回路として、k - UCP 順序回路と k - UCP スキャン回路を提案する。全可観測な環境では、いずれの回路においても、少ないテストベクトルで故障検出と故障診断を行なうことができる。また、所要のテストベクトルは連続的に繰り返し印加することができる。

本章ではまず、順序回路の組合せ部分を k - UCP 回路に変換してテストを行なうときの問題点を明らかにする。次に、k - UCP 順序回路と k - UCP スキャン回路の概念およびテスト方法について述べる。以下では、縮退故障の基本系列のことを単に基本系列と呼ぶ。

#### 6.2 問題点

すでに述べたように、順序回路の組合せ部分への入力線を通じて組合せ部分に所要のテストベクトルを印加すれば、回路全体の縮退故障がテストされることになる。組合せ部分への入力線は外部入力線の他にフリップ・フロップの出力線である場合もあるため、順序回路の k-UCP 組合せ部分に所要のテストベクトルを印加することは必ずしも簡単であるとは限らない、これを次の例で具体的に説明する。

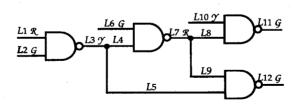

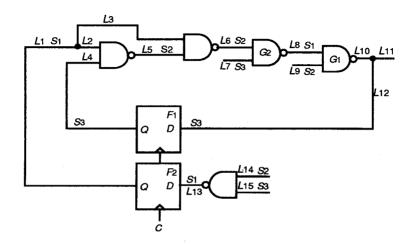

例 6.1 図 6.2 の順序回路の組合せ部分は 2-UCP 回路に変換されている。この回路の組合せ部分をテストするために、F1 の出力線を通じて基本系列 S2 を、F2 の出力線を通じて基本系列 F3 を印加する必要がある。図 6.2 に示したように、F3 と F4 の出力線の値が F3 と F4 の出力線の値が F4 の出力線を通じて基本系列 F4 の出力線の値が F4 の出力線を通じて基本系列 F4 の出力線を通じて

図 6.2 基本系列が印加不能な例

順序回路がスキャンパスをもつ場合,そのスキャンパスを通じて組合せ部分に所要のテストベクトルを印加することができるが,必要でないベクトルも印加しなければならない可能性がある。スキャンパスの長さをnとすれば,k+1個のテストベクトルを組合せ部分に印加するため,最悪の場合,k(n-1) 個の必要でないベクトルが印加されてしまう。nが大きければ,テストベクトルの印加時間が長くなってしまう。また,電子ビームテスタを使用するときに必要な短い周期の周期動作を確立できない問題点もある。

つまり、順序回路の場合における主な問題点は、フリップ・フロップの出力線を通じて、 所要の基本系列を組合せ部分に印加することが困難かまたは不可能なことである。以下で は、この問題を解決するためのテスト容易な順序回路を提案する。

#### 6.3 k-UCP順序回路

# 6.3.1 基本概念

k- UCP 順序回路の基本的な考え方は,順序回路の組合せ部分を k- UCP 回路に変換し, さらにフリップ・フロップ周りの構造を限定することにより,k- UCP 組合せ部分へのテストベクトルの印加を簡単にすることである.

# 定義 6.1 以下の条件を満たす順序回路を k-UCP 順序回路と呼ぶ.

- (1) 組合せ部分が k-UCP 回路である

- (2) 各フリップ・フロップの入力線は以下のいずれかの種類に属する.

- (2-a) フリップ・フロップの入力線はある部分回路の出力線である。その部分回路は *k* UCP 組合せ回路でかつすべての入力線が外部入力線である。このようなフリップ・フロップを I 型フリップ・フロップと呼ぶ。

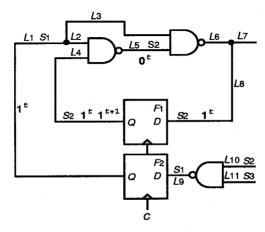

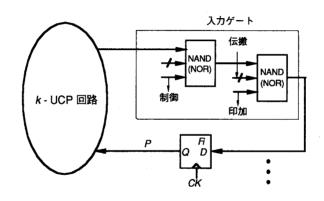

- (2-b) フリップ・フロップの入力線はある部分回路の出力線である。その部分回路は図 6.3 に示すように直列につながる 2 個のk入力 NAND(NOR)ゲートで構成され, 2(k-1) 本の外部入力線をもつ。それらの外部入力線を図 6.3 に示すようにそれぞれ制御線,伝搬線,および印加線と呼ぶ。このようなフリップ・フロップを NAND (NOR) II 型フリップ・フロップと呼ぶ。その 2 個のゲートを入力ゲートと呼ぶ。

例えば、図 6.4 に示す回路は明らかに 2-UCP 順序回路である.

明らかに、k - UCP 順序回路の組合せ部分への入力線は 3 種類に分けられる。つまり、I型フリップ・フロップの出力線、II型フリップ・フロップの出力線、および外部入力線である。

図 6.3 k-UCP 順序回路の定義

図 6.4 2 - UCP 順序回路

# 6.3.2 テスト方法

全可観測な環境において、k - UCP 順序回路は簡単にテストできる。すなわち、k - UCP 順序回路の組合せ部分への基本系列の印加は簡単にできる。以下ではまず、その一例を示す。次に、k - UCP 順序回路の一般のテスト方法を示す。以下では、Si(r) と Ti(r) はそれぞれ基本系列 Si と Ti の r ビット目の値を表す。

# 例 6.2 全可観測な環境で、図 6.4 に示した順序回路は次のようにテストできる.

- (1) L7 に 0 を D に D を D た D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D を D に D に D を D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D

- (2) L7に0を, L9に T2(1)を, L14に S2(1)を, L15に S3(1)を印加し, クロック・パルスを与える. このとき, S2(1)は L4に, S1(1)は L1に現われる. これにより, S2(1)は L6に現われる. つまり, S1(1)が L8に印加される. よって, S1と S3の1

ビット目の値が L7 と L8 に印加される。同様にして、残りのビットを印加することができる。このようにして、L7 と L8 の縮退故障もテストできる。

一般の順序回路は次の手続きによりテストされる.

# 手続き TSF (k-UCP 順序回路をテストする)

- (1) 任意のフリップ・フロップ Fに対して、次の操作を行なう。F: が I 型フリップ・フロップであれば、その k UCP 組合せ部分回路の外部入力線に対応する基本系列を印加する。F: の入力線が NAND (NOR) II 型フリップ・フロップであれば、(1) を制御線に、(1) を伝搬線に、(1) を伝搬線に、(1) を日加線に印加し、(1) を一方を通じて印加すべき基本系列とする。また、残りの外部入力線に対応する基本系列を印加する。

- (2-b) NAND (NOR) II 型フリップ・フロップに対して、0 (1) を制御線に、1 (0) を伝搬線に、P(r) を印加線に印加し、クロック・パルスを与える。ここで、Pを Fi を通じて印加すべき基本系列とする。また、残りの外部入力線に対応する基本系列のr ビット目の値を印加する。

- (2-c) r=r+1 とする.  $r \le k+1$  であれば、(2-a) へ戻る.

手続き TSE に示したように、一般の k- UCP 順序回路のテストは 2 段階に分けて行なわれる。 第 1 段階では、k+1 個のテストベクトルが印加される。第 2 段階では、2(k+1) 個のテストベクトルが印加される。第 8 章で述べるように、それらのテストベクトルで縮退故障の故障診断を行なうこともできる。したがって、次の定理が成り立つ。

定理 6.1 全可観測な環境において、3(k+1) 個のテストベクトルで k- UCP 順序回路のすべての縮退故障の検出と診断を行なうことができる。また、それらのテストベクトルを連続的に繰り返し印加することができる。

kは通常2または3なので、全可観測な環境においては、k-UCP順序回路の故障検出と故障診断は、少ないテストベクトルで行なうことができる。さらに、3(k+1)個のテストベクトルを連続的に繰り返し印加することができるので、これらのテストベクトルは電子ビームテスタを用いるテスト環境に適用できる。

#### 6.4 k-UCP スキャン回路

スキャンパスをもつ順序回路の場合、そのスキャンパスを再構成することにより、組合せ

部分への基本系列の印加を簡単にすることができる。以下ではまず、基本系列の性質について述べる。次に、k-UCPスキャン回路の概念とテスト方法について述べる。

#### 6.4.1 基本系列の性質

定義 6.2 A = a1 a2 ... an と <math>B = b1 b2 ... bn を論理値  $0 \ge 1$  からなる系列とする. a1 = bn と ai = bi 1 (i = 2, ..., n) であれば、 $A \in B$  の循環シフトと呼び、A = r(B) で表す.

例えば、A=10010はB=01001の循環シフトである。縮退故障の基本系列の間にも循環シフトの関係が存在する。縮退故障の2-基本系列では、S1=r(S3)、S3=r(S2)、T2=r(T1)などが簡単に確かめられる。一般に、1個の基本系列が他の基本系列の循環シフトであるための必要十分条件を次に示す。

補題 6.1 k-基本系列 Si(Ti) が Sj(Tj) の循環シフトである必要十分条件は  $i=j+1 \mod k$  +1  $(i,j=1,2,\ldots,k+1)$  である.

(証明) T基本系列はS基本系列の否定なので、ここでは、S基本系列の場合のみについて証明する。

まず十分性を証明する.  $i \ge j$ が  $i = j + 1 \mod k + 1$  (i, j = 1, 2, ..., k + 1) を満たすとする. i > 1のとき, j = i - 1となる. Siのiビット目の値が0で, 他は全部1なので, Si = r(Sj - 1)である. i = 1のとき, j = k + 1なので, S1 = r(Sk + 1)である.

次に必要性を証明する. Si = r(Sj) とする. i > 1 のとき、Si の定義から明らかなように、j は必ず i-1 である. また、i=1 のとき、j は必ず k+1 である.

定義 6.3  $h_1 - h_2 - \dots - h_n$  を  $1, 2, \dots, k+1$  からなる系列とし、Si と Ti ( $i=1, 2, \dots, k+1$ )を k - 基本系列とする。Shi = r(Shi+1)( $i=1, 2, \dots, n-1$ )であれば、 $h_1 - h_2 - \dots - h_n$  を k - 有効系列と呼ぶ。

例えば、1-3-2、3-2-1、2-1-3は2-有効系列である. しかし、1-2-3は2-有効系列ではない. k-有効系列の定義から、次の補題は明らかである.

補題 6.2  $h_1 - h_2 - \dots - h_m - c$ ,  $c - f_1 - f_2 - \dots - f_n$  が k - 有効系列であれば、  $h_1 - h_2 - \dots - h_m - c - f_1 - f_2 - \dots - f_n$  も k - 有効系列である( $m \ge 2$ 、 $n \ge 2$ ).

補題 6.3  $h_1 - h_2 - \ldots - h_i - h_{i+1} - \ldots - h_m$  が k - 有効系列であれば、 $h_1 - h_2 - \ldots - h_i$  も k - 有効系列である( $2 \le i \le m$ ).

例えば、2-1-3、3-2-1、1-3-2が2-有効系列なので、補題6.2より、2-1-3-2-1-3-2-1-3-2も2-有効系列である。また、補題6.3より、2-1-3-2も2-有効系列である。

$i-(i-1)-\ldots-2-1-\ldots-(k+1)-k-\ldots-(i+2)-(i+1)$  を任意回繰り返して得られる系列を Ek(i) で表す( $i=1,2,\ldots,k+1$ )、例えば、 $E2(1)=1-3-2-1-3-2-\ldots$  である。k-有効系列の定義と補題 6.2 より、Ek(i) が k- 有効系列であることが分かる。

Ek(i) の 1 番目の要素から m 番目の要素までの部分系列を Ek(i, m) で表す。 例えば、 E2(1, 5) = 1 - 3 - 2 - 1 - 3 である。 k - 有効系列の定義と任意の <math>k - 有効系列が i (i = 1, 2, ..., k + 1) で始まることより、次の補題が成り立つ。

補題 6.4 i で始まる長さ m の k - 有効系列は Ek(i, m) で表すことができる.

例えば、 $2-1-3=E_2(2,3)$ 、 $3-2-1-3-2-1-3=E_2(3,7)$ である。

k- 有効系列に関するもう一つの問題は、 $h1, h2, \ldots, hm$ ( $hi=1,2,\ldots, k+1; i=1,2,\ldots, m$ )が長さ m の基本系列を構成するか否かである。 $h1, h2,\ldots, hm$  の中の t ( $t=1,2,\ldots, k+1$ ) の数を  $Qt(h1, h2,\ldots, hm)$ で表す。例えば、Q1(1,2,1,1,3)=3、Q2(1,2,1,1,3)=1、Q3(1,2,1,1,3)=1 である。明らかに、次の補題が成り立つ。

補題 6.5  $h_1, h_2, ..., h_m$   $(h_i = 1, 2, ..., k + 1; i = 1, 2, ..., m)$  が長さ  $m \circ k$  - 有効系列を構成するための必要十分条件は i (i = 1, 2, ..., k + 1) が存在し, $Q_t(Ek(i, m)) = Q_t(h_1, h_2, ..., h_m)$  (i = 1, 2, ..., k + 1) を満たすことである。また、その k - 有効系列は Ek(i, m)である。

例えば、1,1,2,2,3 を考える。Q1(E2(2,5))=2=Q1(1,1,2,2,3)、Q2(E2(2,5))=2=Q2(1,1,2,2,3)、Q3(E2(2,5))=1=Q3(1,1,2,2,3) であるので、1,1,2,2,3 は 2 - 有効系列を構成する。その系列は 2 - 1 - 3 - 2 - 1 = E2(2,5) である。

#### 6.4.2 基本概念

まず、k-UCPスキャン回路の一例を示す。

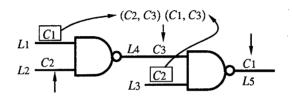

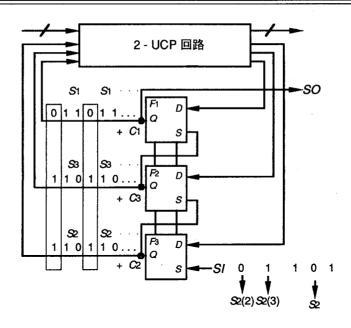

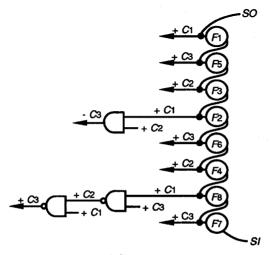

例 6.3 図 6.5 に示す順序回路を考える。その組合せ部分がすでに 2- UCP 回路に変換されている。また,各フリップ・フロップの出力線に割り当てられた極性はすべて正極性である。SI- P3- P2- P1- SO のようにスキャンパスが構成されている。P1, P3 の出力線に割り当てられた色は C1, C2, C3 である。また,1-3-2 は 2-4 効系列である。

図 6.5 基本系列の印加例

まず、 $P_1, P_2, P_3$  に 0, 1, 1 を設定する。次に、 $0 = S2(2), 1 = S2(3), S2 \dots$  を SI より順次に印加する。ここで、S2(2) は基本系列 S2 の 2 ビット目の値を表す。明らかに、 $P_1, P_2, P_3$  の出力はそれぞれ S1, S3, S2 の繰り返しである。すなわち、この順序回路の 2 - UCP 組合せ部分に所要の基本系列を連続的に繰り返し印加することができる。これにより組合せ部分を短い周期の周期動作にすることができる。

図6.5 に示した順序回路の組合せ部分には、基本系列を連続的に繰り返し印加することができる。一般に、このような性質をもつ回路を次のように定義することができる。

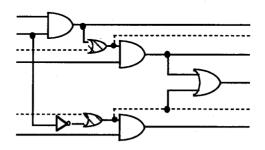

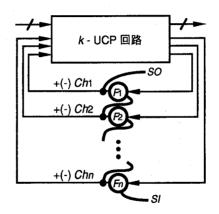

定義 6.4 図 6.6 の F1, F2, ..., Fn をフリップ・フロップとする。 スキャンパス  $SI \rightarrow Fn \rightarrow Fn-1 \rightarrow ... \rightarrow F1 \rightarrow SO$  をもつ順序回路が次の条件を満たせば,この順序回路を k - UCP スキャン回路と呼ぶ。

- (1) 組合せ部分が k-UCP 回路である.

- (2) F1, F2,..., Fn の出力線が同じ極性をもつ.

- (3) F1, F2,..., Fn の出力線の色を Ch1, Ch2,..., Chn とすると, h1 h2 ... hn が k 有 効系列である.

明らかに、図 6.5 に示した回路は 2-UCP スキャン回路である.

## 6.4.3 テスト方法

図 6.6 k-UCP スキャン回路の定義

一般に、k-UCPスキャン回路は次の手続きによりテストできる.

#### 手続き TSC (k-UCPスキャン回路をテストする)

- (1) すべてのフリップ・フロップの出力線が正極性をもつとき、スキャンパスを通じて $F_1, F_2, \ldots, F_n$  に $Sh_1(1), Sh_2(1), \ldots, Sh_n(1)$  を印加する。すべてのフリップ・フロップの出力線が負極性をもつとき、スキャンパスを通じて $F_1, F_2, \ldots, F_n$  に $Th_1(1), Th_2(1), \ldots, Th_n(1)$  を印加する。

- (2) すべてのフリップ・フロップが正極性をもつとき、SI にSh2(2), Sh2(3), ..., Sh2(k+1) を印加する. すべてのフリップ・フロップ が負極性をもつとき、SI に Th2(2), Th2(3), ..., Th2(k+1) を印加する.

定理 6.2 全可観測な環境において、k+1 個のテストベクトルで k-1 UCP スキャン回路 のすべての縮退故障の故障検査と故障診断を行なうことができる。また、それらのテストベクトルを連続的に繰り返し印加することができる。

(証明) ここでは、すべてのフリップ・フロップが正極性をもつ場合について証明する. すべてのフリップ・フロップが負極性をもつ場合については、同様に証明できる.

k - UCP スキャン回路においてまず,スキャンパスを通じて,F1, F2, ...,Fn にSh1(1),Sh2(1), ...,Shn(1) を印加する.次に,SI にSh2(2),Sh2(3),...,Sh2(k+1) を印加する.ここで,Si(t) は基本系列のSi のt ビット目の値を表す.これにより,Fn の出力はShn となる.Ft の出力をSht ( $t \le n$ ) とすると,Ft-1 の出力はSht-1(1),Sht(1),Sht(2),...,Sht(k) となる.h1 - h2 - ... - hn がk - 有効系列なので,Sht-1 = Sht である.つまり,Ft-1 の出力はSht-1 である.したがって,Fi の出力は必ずShi である.

SI にさらに Shn(1) を印加したとき、 $F1, F2, \ldots, Fn$  にそれぞれ  $Sh2(k+1), Sh3(k+1), \ldots$ , Shn-1(k+1), Shn(1) が現れる。 $h1 - h2 - \ldots - hn$  が k - 有効系列なので、Sh1(k+1) = Sh1(1),

Sh3(k+1) = Sh2(1), ..., Shn-1(k+1) = Shn-1(1) となる。つまり、SI にさらにShn(2), Shn(3), ... ., Shn(k+1)を順次印加すると、Fi の出力は必ずShi の繰り返しとなる。また、SI にShn を繰り返し印加すると、Fi の出力は必ずShi の繰り返しとなる。

#### 6.5 まとめ

全可観測な環境においては、順序回路を少ないテストベクトルでテストするため、その組合せ部分を k - UCP 回路に変換することが考えられる、組合せ部分が k - UCP 回路である順序回路のすべての縮退故障のテストは、本来 k+1 個のテストベクトルで十分である。しかし、その k+1 個のテストベクトルを印加することは、フリップ・フロップの出力線を経由しなければならない場合、困難かまたは不可能である。この問題を解決するため、全可観測な環境でのテスト容易な順序回路を提案した。

まず、フリップ・フロップの入力側の構造を限定することによりテストベクトルの印加を容易にする k - UCP 順序回路を提案し、k - UCP 順序回路内のすべての縮退故障は 3(k+1) 個のテストベクトルでテストできることを示した。 3(k+1) 個のテストベクトルの内の 2(k+1) 個は本来必要な k+1 個のテストベクトルを印加するためのものである。順序回路がスキャンパスをもつ場合、そのスキャンパスの組み方を工夫することにより、k+1 個のテストベクトルを余分な入力ベクトルを伴わずに印加することができる。そのような順序回路は提案した k - UCP スキャン回路である。つまり、k - UCP スキャン回路内のすべての縮退故障は k+1 個のテストベクトルでテストできる。

組合せ回路と異なり、順序回路の場合は、回路の短いテスト系列を繰り返し印加することができない可能性がある。そのとき、回路の短い周期の周期動作を確立することができないので、電子ビームテスタを利用した故障診断はできない。提案したテスト容易な順序回路においては、短いテスト系列を回路に連続的に繰り返し印加することができる。このため、提案した回路は電子ビームテスタを用いた故障診断に適していることが分かる。

# 全可観測な環境での順序回路のテスト容易化設計

第6章で述べたように、k- UCP 順序回路または k- UCP スキャン回路の縮退故障については、全可観測な環境において、少ないテストベクトルで検出と診断を行なうことができる。しかし、任意の順序回路は、必ずしも k- UCP 順序回路または k- UCP スキャン回路であるとは限らない。本章では、任意の順序回路を k- UCP 順序回路または k- UCP スキャン回路に変換する方法を提案する [52,53]。

#### 7.1 k-UCP順序回路への変換

#### 7.1.1 回路変換手法

ここで、変換前の順序回路はn個のフリップ・フロップ $P_1, P_2, \ldots, F_n$ をもつとする.

#### 手続き SM1 (k-UCP 順序回路への変換を行なう)

- (1) 組合せ部分を k-UCP 回路に変換する.

- (3) Fが I型フリップ・フロップであれば、(6)へ移る。

- (4)  $F_t$ の入力線があるゲートの出力線であれば、その入力線をLとする、そうでなければ、 $F_t$ の入力線が必ず分岐の枝である、このとき、分岐の幹をLとする、

- (5) L が正(負)極性をもつなら、図 6.3 に示したように直列につなぐ 2 個の k 入力 NAND (NOR) ゲートを L へ挿入する.

- (6) t=t+1とする.  $t \le n$ であれば、(3) へ戻る.

例えば、図 6.2 に示した順序回路は手続き SM1 により、図 6.4 に示した 2 - UCP 順序回路 に変換されている.

#### 7 1 2 実験結果

手続き SM1 に示したように、任意の順序回路は 2 段階を経て k- UCP 順序回路に変換される。第 1 段階では、順序回路の組合せ部分が k- UCP 回路に変換される。第 2 段階では、フリップ・フロップの入力側に必要に応じて入力ゲートを挿入する。第 2 段階では、最良の場合には、付加ゲート数は 0 であるが、最悪の場合には、付加ゲート数は 2n である。なお、n は順序回路内のフリップ・フロップの数である。また、第 1 段階と第 2 段階での付加外部入力線数はそれぞれ k+1 と 2(k-1) である。

C言語で手続き SM1 をプログラム化し、実験を行なった、使用したコンピュータは富士通の S-4/LC(12.5 MIPS)である、実験用の回路は ISCAS 1989 のベンチマーク順序回路である [72].

実験結果を表 7.1 に示す。"original Tr.s" は変換前の回路のトランジスタの数を、"2-U" は組合せ部分が 2 入力 NAND(NOR)ゲートで構成されるように変換するために付加したトランジスタの数を、"color" は組合せ部分が彩色解をもつように変換するために付加したトランジスタの数を、"IG" は入力ゲートを挿入するために付加したトランジスタの数を表す。

| original Tr.s |         | ado  | ded Tr. s  |       | overhe |       |         |             |

|---------------|---------|------|------------|-------|--------|-------|---------|-------------|

| circuit       | (): F/F |      | 2-U        | color | IG     | whole | partial | time (sec.) |

| s27 (c)       | 96      | (3)  | 10 (NOR)   | 0     | 16     | 27.1  | 15.1    | 0.6         |

| s208 (c)      | 518     | (8)  | 168 (NOR)  | 24    | 36     | 44.0  | 8.7     | 9.4         |

| s298 (c)      | 834     | (14) | 336 (NOR)  | 80    | 112    | 63.3  | 16.4    | 16.4        |

| s344 (c)      | 914     | (15) | 98 (NOR)   | 128   | 84     | 33.9  | 20.9    | 19.4        |

| s349 (c)      | 924     | (15) | 216 (NAND) | 40    | 72     | 35.5  | 9.8     | 20.4        |

| s382 (c)      | 1060    | (21) | 436 (NAND) | 64    | 92     | 55.8  | 10.4    | 26.6        |

| s420 (c)      | 1034    | (16) | 402 (NAND) | 24    | - 88   | 49.7  | 7.8     | 39.4        |

| s444 (c)      | 1136    | (21) | 460 (NAND) | 48    | 92     | 52.8  | 8.8     | 26.1        |

| s510 (c)      | 1082    | `(6) | 564 (NAND) | 160   | 44     | 71.0  | 12.4    | 79.7        |

表 7.1 k-UCP 順序回路への変換の実験結果

"2-U" と "color" の結果は 2 - UCP 回路である. 結果として, s27, s208, s298, s344 の組合せ部分は 2 入力 NOR ゲートで構成されるように変換された. s349, s382, s420, s444, s510 の組合せ部分は 2 入力 NAND ゲートで構成されるように変換された.

"whole" はベンチマーク順序回路を 2 - UCP 順序回路に変換したときのオーバーヘッドを表す。また、"partial" はもとの回路の組合せ部分が 2入力 NAND または NOR ゲートで構成されると仮定して 2 - UCP 順序回路に変換したときのオーバーヘッドを表す。それぞれは次のように計算した。

whole =

$$(2-U) + \text{color} + \text{IG}$$

) / (original Tr.s)

partial =  $(\text{color} + \text{IG})$  / (original Tr.s +  $(2-U)$ )

#### 7.2 k-UCP スキャン回路への変換

# 7.2.1 回路変換手法

k-UCPスキャン回路への回路変換は2段階に分けて行なう。まず、与えられた順序回路の組合せ部分をk-UCP回路に変換する。次に、回路全体がk-UCPスキャン回路の定義の2番目と3番目の条件を満たすようにさらに変換を行なう。

任意の組合せ回路をk-UCP回路に変換する手法については、第5章で述べた。

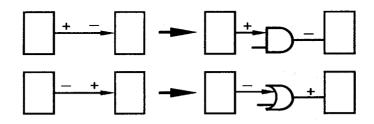

k-UCP 回路に対して,極性の割り当ての結果は1通りしかないので,もし各フリップ・フロップの出力線の極性が異なるならば,付加ゲートで極性を調整する必要がある.図 5.4 に調整の方法を示した.この調整では,1個のフリップ・フロップに対して,高々1個のk入力 AND または OR が必要である.

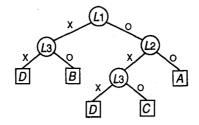

各フリップ・フロップに割り当てられた色を Ch1, Ch2, ..., Chn とする。h1, h2, ..., hn が  $t1 \rightarrow t2 \rightarrow \ldots \rightarrow tn$  という k-有効系列を構成すれば, $SI \rightarrow Ftn \rightarrow Ftn$ -1  $\rightarrow \ldots \rightarrow Ft1 \rightarrow SO$  というスキャンパスを構成することにより k- UCP スキャン回路が得られる。h1, h2, ..., hn が k-有効系列を構成しなければ、次に述べる変換が必要である。