|              |                                                                                   |

|--------------|-----------------------------------------------------------------------------------|

| Title        | 高画質液晶ディスプレイ向け駆動回路の小規模化に関する研究                                                      |

| Author(s)    | 工藤, 泰幸                                                                            |

| Citation     | 大阪大学, 2009, 博士論文                                                                  |

| Version Type | VoR                                                                               |

| URL          | <a href="https://hdl.handle.net/11094/1956">https://hdl.handle.net/11094/1956</a> |

| rights       |                                                                                   |

| Note         |                                                                                   |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

高画質液晶ディスプレイ向け

駆動回路の小規模化に関する研究

2009年1月

工 藤 泰 幸

高画質液晶ディスプレイ向け駆動回路の小規模化に関する研究

2009年1月

工藤 泰幸

高画質液晶ディスプレイ向け

駆動回路の小規模化に関する研究

提出先 大阪大学大学院情報科学研究科

提出年月 2009 年 1 月

工 藤 泰 幸

# 研究業績

## A. 学術論文誌論文

- [1] Y.Kudo, S.Nishitani, T.Furuhashi, H.Man, and S.Uchida : “Development of a 15.5-in.STN-LCD Monitor with CRT Interface,” *Journal of the Society for Information Display*, Vol.5, No.4, pp.359-361 (1997).

- [2] 工藤泰幸, 赤井亮仁, 江里口卓也, 大門一夫, 薦田憲久：“モバイル機器向け TFT-LCD の階調時分割駆動方式,” 電子情報通信学会論文誌 C, Vol.J92-C, No.4 (採録決定).

## B. 国際会議

- [1] S.Nishitani, H.Man, Y.Kudou, T.Futami, and T.Inuzuka : “New Drive Method to Eliminate Crosstalk in STN-LCDs,” in *Proc. of Society for Information Display 1993 (SID '93)*, pp.97-100 (1993).

- [2] Y.Kudo, S.Nishitani, T.Furuhashi, H.Man, and T.Futami : “A Two-Line Simultaneous Selection Method for Fast-Response STN-LCDs,” in *Proc. of Asia Display 1995*, pp.245-248 (1995).

- [3] Y.Kudo, S.Nishitani, T.Furuhashi, H.Man, and T.Futami : “Evaluation of Grayscale for 2 Line Simultaneous Selection,” in *Proc. of Society for Information Display 1996 (SID '96)*, pp.857-860 (1996).

- [4] H.Man, S.Nishitani, T.Furuhashi, Y.Kudo, and S.Endo : “Enhanced Hi-Addressing Technology for Fast Response Color STN-LCDs,” in *Proc. of 1997 International Display Research Conference (IDRC '97)*, pp.M75-M80 (1997).

- [5] Y.Kudo, S.Nishitani, T.Furuhashi, H.Man, and S.Uchida : “Development of 15.5 inches STN-LCD Monitor with CRT Interface,” in *Proc. of Society for Information Display 1997 (SID '97)*, pp.891-894 (1997).

- [6] Y.Kudo, H.Man, S.Endo, and T.Inuzuka : “Enhanced Hi-Addressing Drive for High Performance STN-LCDs,” in *Proc. of International Display Workshops 1997 (IDW '97)*, pp.257-260 (1997).

- [7] Y.Kudo, A.Akai, T.Furuhashi, T.Matsudo, and Y.Yokota : “Low-power & High-integration Driver IC for Small-sized TFT-LCDs,” in *Proc. of Society for Information Display 2003 (SID '03)*, pp.1244-1247 (2003).

- [8] Y.Kudo, T.Eriguchi, A.Akai, T.Matsudo, and Y.Yokota : “Advanced Driver IC Techniques for Mobile AM-LCDs,” in *Proc. of International Display Workshops 2003 (IDW '03)*, pp.347-350 (2003).

- [9] Y.Kudo, T.Eriguchi, A.Akai, and Y.Yokota : “Low Power, Small Chip-size Mobile AM-LCD Drivers Using Time-sharing Output Architecture,” in *Proc. of International Meeting on Information Display 2005 (IMID '05)*, pp.854-857 (2005).

- [10] Y.Kudo, A.Akai, T.Eriguchi, N.Takada, T.Furuhashi, and Y.Yokota : “New Developments in Mobile AM-LCD Drivers,” in *Proc. of Society for Information Display 2006 (SID 2006)*, pp.1402-1405 (2006).

- [11] Y.Kudo, A.Akai, N.Takada, Y.Kurokawa, and Y.Yokota : “Advanced Driver IC Technologies for Mobile Display Applications,” in *Proc. of SID Mobile Displays 2006*, in CD-ROM (2006).

- [12] Y.Kudo, A.Akai, N.Takada, Y.Kurokawa, and Y.Yokota : “New Developments in Mobile LCD Drivers,” in *Proc. of SID Mobile Displays 2007*, in CD-ROM (2007).

## C. 国内講演

- [1] 工藤泰幸, 西谷茂之, 古橋勉, 真野宏之, 二見利男：“高速応答 STN-LCD の駆動方法に関する考察,” 電子情報通信学会技術研究報告, Vol.94, No.503, pp.13-18 (1995).

- [2] 工藤泰幸：“IMID'05／IDRC'05 報告－有機 TFT&フレキシブル－,” 映像情報メディア学会技術報告, Vol.29, No.68, pp.3-6 (2005).

- [3] 工藤泰幸：“SID'06 報告－ディスプレイエレクトロニクス－,” 電子情報通信学会技術研究報告, Vol.107, No.179, pp.15-18 (2006).

- [4] 赤井亮仁, 工藤泰幸, 江里口卓也, 大門一夫：“モバイル機器向け TFT 液晶ドライバ IC の低電力回路技術,” 電子情報通信学会技術研究報告, Vol.106, No.499, pp.141-144 (2007).

- [5] 高田直樹, 工藤泰幸, 赤井亮仁, 大門一夫：“モバイル機器向け TFT 液晶ドライバ IC の高性能ガンマ調整技術,” 電子情報通信学会技術研究報告, Vol.106, No.499, pp.145-148 (2007).

## D. 解説

- [1] 遠藤秀介, 工藤泰幸, 岩壁靖：“31cm(12.1 型) 高速応答・高精細のカラーSTN 液晶表示モジュール,” 日立評論, Vol.78, No.12, pp.57-62 (1996).

- [2] 遠藤秀介, 工藤泰幸, 岩壁靖：“スーパークリアカラー液晶～高画質・高速応答・低消費電力の実,” 電子技術, Vol.39, No. 7, pp.28-31 (1997).

- [3] 遠藤秀介, 岩壁靖, 工藤泰幸：“12.1 形高速応答スーパークリアカラー液晶,” 電子ディスプレイ技術 1997 年, pp.11-16 (1997).

- [4] 古橋勉, 新田博幸, 工藤泰幸, 真野宏之：“液晶駆動の回路と構成,” 応用物理, Vol.68, No.7, pp.821-826 (1999).

- [5] 新田博幸, 工藤泰幸：“カラー液晶ディスプレイ・システム詳解 • フィールド・シーケンシャル方式,” トランジスタ技術, Vol.37, No.432, pp.255-268 (2000).

- [6] 工藤泰幸：“液晶ディスプレイ入門 第6回：LCDの駆動技術,” 「液晶」, Vol.4, No. 4, pp.56-63 (2000).

- [7] 渡辺昌行, 工藤泰幸：“携帯電話向け液晶表示システム用 LSI の最新動向 —カラー STN 液晶コントローラと TFT 液晶コントローラの開発—,” 月刊ディスプレイ, Vol. 9, No. 2, pp.19-24 (2003).

- [8] 星野剛史, 工藤泰幸, 望月有人, 丸山幸伸：“ネットワーク時代に向けた統合ユーザインターフェース,” 日立評論, Vol.89, No.10, pp.56-59 (2007).

# 内容梗概

本論文は、筆者が 1991 年から現在まで（株）日立製作所マイクロエレクトロニクス機器開発研究所、システム開発研究所ならびに中央研究所において、2007 年から現在までに大阪大学大学院情報科学研究科マルチメディア工学専攻在学中に行ってきた、高画質液晶ディスプレイ（Liquid Crystal Display 以下、LCD）向け駆動回路の小規模化に関する研究成果をまとめたものである。

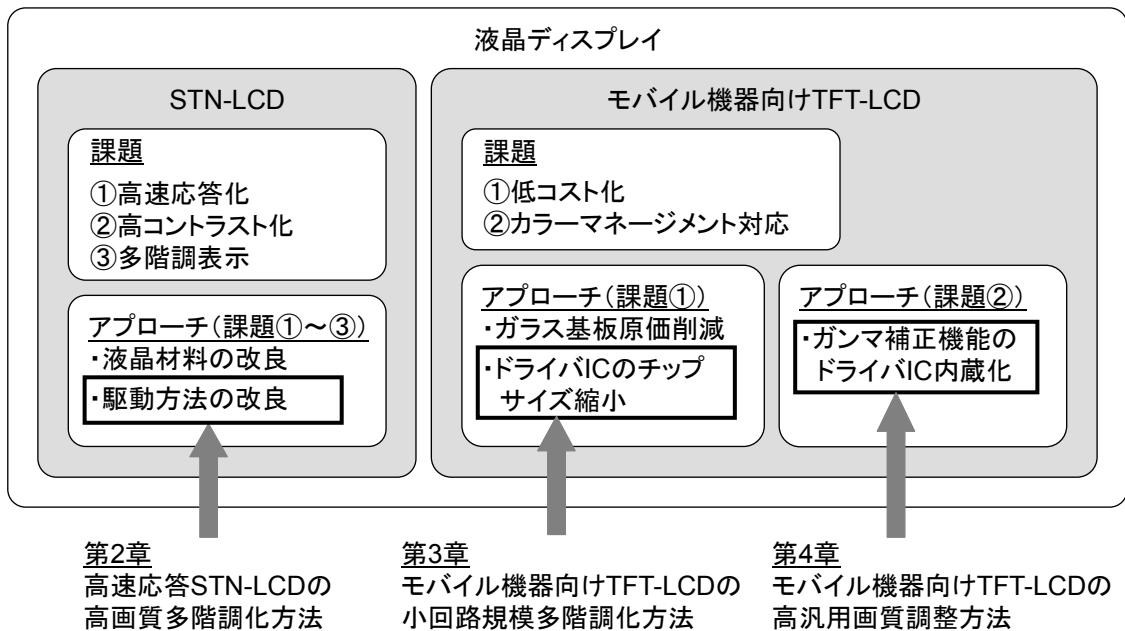

LCD は、薄型・軽量の特徴を有する表示デバイスとして、携帯電話やデジタルスチールカメラ等のモバイル機器から薄型テレビ等の大型機器に到るまで、幅広い製品分野への普及が図られている。現在実用化されている主な LCD の種類として、低成本で製造可能な STN（Super Twisted Nematic）-LCD と、高画質表示が可能な TFT（Thin Film Transistor）-LCD がある。これらの LCD においては、近年の多様なマルチメディアサービスの普及に伴い、色の再現性や臨場感を向上させるための多階調表示に対する要求が高まっている。しかし、STN-LCD において多階調表示を実現するためには、表示がちらついて見えるフリッカと呼ばれる現象を抑制する必要がある。一方、TFT-LCD における多階調表示の実現については、液晶に印加する電圧レベル数の増加により駆動回路であるドライバ LSI の回路規模が増大するため、低成本化が課題となる。

このような背景のもと、本研究では、LCD の駆動方法およびドライバ IC の回路構成を最適化することで、上記課題を解決する方法を提案する。まず、STN-LCD の多階調表示については、倍速表示によるフリッカの抑制を図り、これを少ないバッファメモリ容量で実現可能な高速応答 STN-LCD の高画質多階調化方法を提案する。次に、TFT-LCD の多階調表示については、ドライバ IC の回路規模を削減可能な、モバイル機器向け TFT-LCD の小回路規模多階調化方法を提案する。さらに、多種多様な TFT-LCD に対するガンマ調整を可能にすることでドライバ IC の汎用性を高め、製造コストの削減を図るモバイル機器向け TFT-LCD の高汎用画質調整方法を提案する。本論文は全 5 章から構成される。

第 1 章の序論では、高画質 LCD 向け駆動回路の小規模化の必要性および実現課題について述べ、関連する従来研究を概観すると共に、本論文の目的と位置付けを明らかにする。

第 2 章では、高速応答 STN-LCD を対象とし、FRC（Frame Rate Control）法による多階調表示方法をベースに、フレーム周波数を高周波数化する方法の有用性を示す。また、

FRC 处理をメモリの前段と後段に分離することでフレームメモリの増加を最小化する 2 周波合成 FRC 法を提案する。さらに、提案方法を PC モニタ向け STN-LCD に適用し、有用性に対する評価を行う。

第 3 章では、モバイル機器向け TFT-LCD を対象とし、DAC (Digital Analog Converter) 处理を表示データの上位ビットの階調表現のみに適用し、下位ビットの階調表現はドライバ IC の出力タイミング制御で実現してドライバ IC の回路規模を削減する階調時分割駆動法を提案する。次に、階調時分割駆動の課題となるデータ電圧のレベル変動に対し、出力タイミングの最適化と電圧レベルの補正機能を提案し、上記課題を解決する。さらに、提案方法をモバイル機器向け TFT-LCD に適用し、有用性に対する評価を行う。

第 4 章では、TFT-LCD の低コスト化を目的に、1 個のドライバ IC が output するデータ電圧レベルをプログラム化することで、多種多様な TFT-LCD に適用可能なガンマ補正を可能とし、製造コストの削減を図る画質調整方法を提案する。ガンマ補正の実現においては、3 つの調整機能（振幅調整、傾き調整、微調整）を組み合わせる 3 ステップガンマ補正法を提案し、回路構成の簡略化とガンマ補正精度とのバランスを最適化する。最後に、提案方法をモバイル機器向け TFT-LCD に適用し、有用性に対する評価を行う。

第 5 章では、結論として本研究で得られた成果を要約した後、今後に残された課題について述べる。

# 目次

|                                           |    |

|-------------------------------------------|----|

| 第 1 章 序論 .....                            | 1  |

| 1.1 研究の背景 .....                           | 1  |

| 1.2 従来研究 .....                            | 4  |

| 1.2.1 STN-LCD の多階調表示方法 .....              | 4  |

| 1.2.2 TFT-LCD の多階調表示方法 .....              | 6  |

| 1.2.3 TFT-LCD の画質調整方法 .....               | 6  |

| 1.3 研究の方針 .....                           | 7  |

| 1.4 本論文の構成 .....                          | 10 |

| 第 2 章 高速応答 STN-LCD の高画質多階調化方法 .....       | 13 |

| 2.1 緒言 .....                              | 13 |

| 2.2 従来の多階調表示方法と問題点 .....                  | 14 |

| 2.2.1 画質劣化問題 .....                        | 14 |

| 2.2.2 従来の画質劣化対策の問題点と課題 .....              | 23 |

| 2.3 2 周波合成 FRC 法 .....                    | 26 |

| 2.3.1 2 周波合成 FRC 法の考え方 .....              | 26 |

| 2.3.2 FRC パターンの最適化によるシャドーイング低減 .....      | 29 |

| 2.4 適用結果と考察 .....                         | 33 |

| 2.4.1 適用対象 .....                          | 33 |

| 2.4.2 提案方法の性能評価と考察 .....                  | 34 |

| 2.5 結言 .....                              | 37 |

| 第 3 章 モバイル機器向け TFT-LCD の小回路規模多階調化方法 ..... | 39 |

| 3.1 緒言 .....                              | 39 |

| 3.2 従来の多階調表示方法と問題点 .....                  | 41 |

| 3.2.1 小回路規模化問題 .....                      | 41 |

| 3.2.2 従来の小回路規模化方法の問題と課題 .....             | 45 |

| 3.3 階調時分割駆動法 .....                        | 48 |

|                                              |           |

|----------------------------------------------|-----------|

| 3.3.1 階調時分割駆動法の考え方 .....                     | 48        |

| 3.3.2 カップリング性電圧変動の抑制 .....                   | 51        |

| 3.3.3 リーク性電圧変動の抑制 .....                      | 53        |

| 3.4 適用結果と考察 .....                            | 55        |

| 3.4.1 適用対象 .....                             | 55        |

| 3.4.2 提案方法の性能評価と考察 .....                     | 56        |

| 3.5 結言 .....                                 | 58        |

| <b>第4章 モバイル機器向け TFT-LCD の高汎用画質調整方法 .....</b> | <b>61</b> |

| 4.1 緒言 .....                                 | 61        |

| 4.2 従来のガンマ補正法と問題点 .....                      | 63        |

| 4.2.1 小回路規模化問題 .....                         | 63        |

| 4.2.2 従来の小回路規模化方法の問題と課題 .....                | 66        |

| 4.3 3ステップガンマ補正法 .....                        | 67        |

| 4.3.1 3ステップガンマ補正法の考え方 .....                  | 67        |

| 4.3.2 実現回路構成 .....                           | 69        |

| 4.4 適用結果と考察 .....                            | 75        |

| 4.4.1 適用対象 .....                             | 75        |

| 4.4.2 提案方法の性能評価と考察 .....                     | 76        |

| 4.5 結言 .....                                 | 80        |

| <b>第5章 結論 .....</b>                          | <b>83</b> |

| 5.1 本研究のまとめ .....                            | 83        |

| 5.2 今後の課題 .....                              | 84        |

| 謝辞 .....                                     | 87        |

| 参考文献 .....                                   | 89        |

# 第 1 章

## 序論

### 1.1 研究の背景

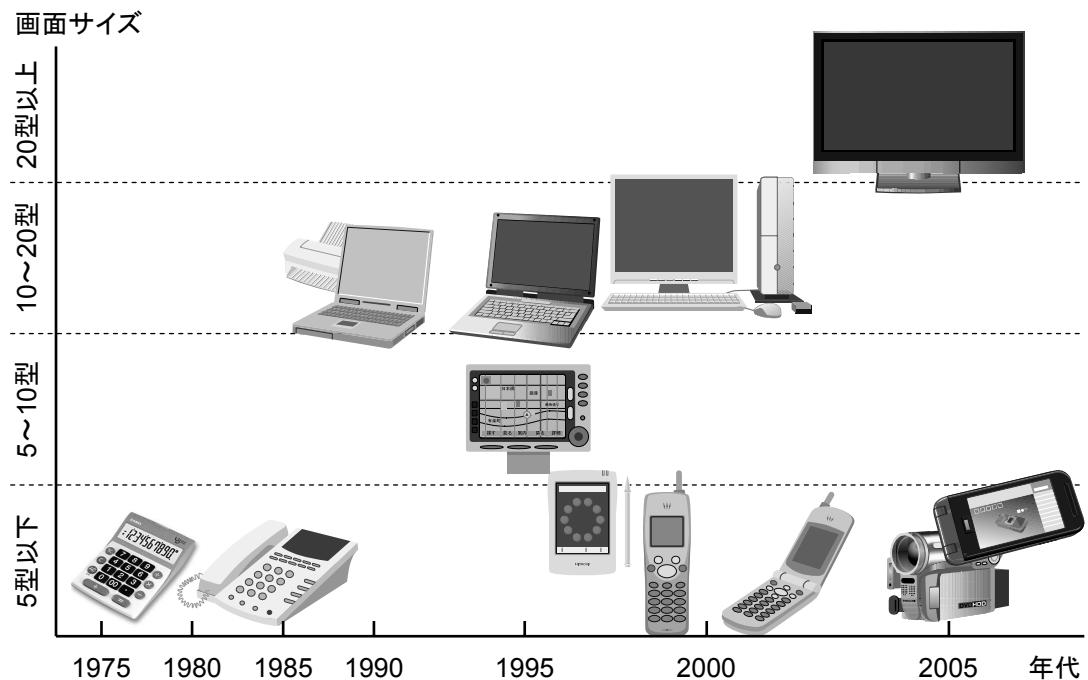

薄型と軽量を特徴に持つ液晶ディスプレイ（Liquid Crystal Display, 以下 LCD）は、図 1.1 に示すように卓上電卓の表示デバイスとして商品化されて以来、大型化やバックライトの適用による視認性向上によりワードプロセッサや PC (Personal Computer) 等のモニタに採用され、近年では、携帯電話から薄型テレビまで、多種多様な情報装置に採用されている。

図 1.1 LCD の適用用途

現在、主に使用されている LCD には、光の反射率を制御することで表示輝度を調整する反射型 LCD と、バックライトからの光の透過率を制御することで表示輝度を調整する

透過型 LCD がある。この中で、透過型 LCD は反射型に比べて高画質であり、現在の情報機器で採用される LCD の主流であることから、本研究では透過型 LCD を研究の対象とする。さらに、透過型 LCD には STN (Super Twisted Nematic) -LCD に代表される単純マトリクス型と、TFT (Thin Film Transistor) -LCD に代表されるアクティブマトリクス型があり、これらは、アプリケーションに応じて適宜使い分けられる。

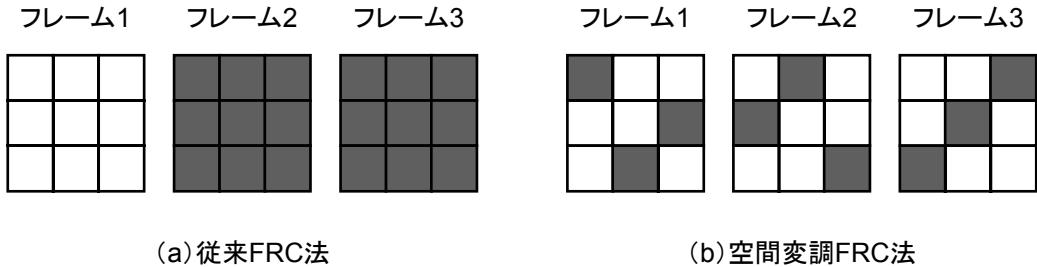

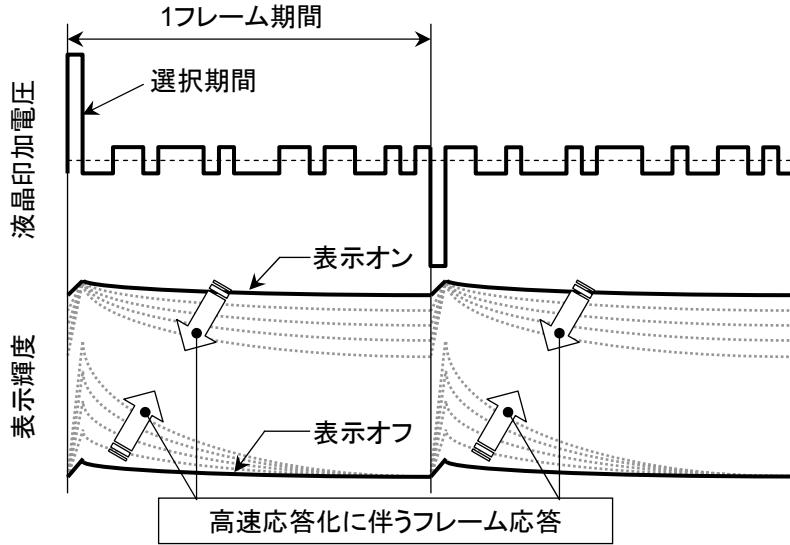

まず、単純マトリクス型の STN-LCD は、直交する透明電極の交点で画素を形成し、その交点を駆動する構造であることから製造コストが低い反面、後に述べる TFT-LCD に比べて画質が劣る。このことから、現在 STN-LCD は、低価格帯の携帯電話を中心に、比較的解像度が低く、かつ最高画質を必要としない中小型の情報機器に採用されている。STN-LCD の画質向上に関する主な課題として、多階調表示化、高速応答化、高コントラスト化が挙げられる。この中で、多階調表示化については表示オンと表示オフの 2 値をベースに、複数フレームで見た場合の表示オン／表示オフの点灯率を制御する FRC (Frame Rate Control) 法[1]が一般に採用され、自然画や GUI (Graphical User Interface) を違和感なく表現可能な 64 階調表示が実用化されている[2]。また、高速応答化については液晶材料の改良が進められ、現在では応答時間 : 150ms (立上り + 立下り) 程度を達成し[3]、マウス動作や簡易動画に対して十分な視認性を得ることが可能である。しかしながら、STN-LCD の高速応答化に伴い、FRC 法における表示オン／表示オフの切り替えが顕在化し、階調表示部にフリッカと呼ばれるちらつきが見えやすくなることが知られている[4]。さらに、ある走査から次の走査までの期間に表示輝度が低下するフレーム応答現象が発生してコントラスト低下する副作用も確認されている[5]。これらの画質劣化に対する解法としては幾つかの駆動方法が提案されており、一定の効果を挙げている[6][7][8][9][10]。しかしながら、いずれの方法も追加となる回路規模が大きく、STN-LCD の最大の特徴である低コスト性の犠牲を余儀なくされている。したがって、高速応答 STN-LCD において多階調表示を実現するためには、問題となるフリッカの発生とコントラスト低下を、最小限の製造コストで抑制することが課題となる。

一方、アクティブマトリクス型の TFT-LCD は、ガラス基板上に TFT によるアクティブ素子と保持容量を画素毎に形成し、液晶印加電圧を記憶する構造をとる。このため、高速応答の液晶材料を用いてもフレーム応答現象が発生せずに高コントラスト表示が得られる。しかし、その製造には大規模集積回路に匹敵する環境と技術が必要であるため、STN-LCD に比べると製造コストが高い。このため TFT-LCD は、写真や動画を楽しむアプリケーションを中心に、高機能な携帯電話や薄型テレビへの採用が図られている。今後さらに TFT-LCD を普及させるためには、製造技術の向上によるガラス基板の原価低減と同時に、

周辺部品であるカラーフィルタやドライバ IC の原価低減も必要である。特に、携帯電話を中心としたモバイル機器向け TFT-LCD では、ドライバ IC (Integrated Circuit) の価格が LCD 全体の総原価の 2 割以上と大きな割合を占めるため、ドライバ IC のコストダウンは大きな課題である。ここで、ドライバ IC においては、表示色数の増加や高解像度化といったディスプレイ性能の向上が、チップサイズの増大、すなわちコストアップに直接影響する。例えば TFT-LCD では、データ線に印加するデータ電圧のレベルによって階調を制御する方法[11]が主流であるため、ドライバ IC には入力される表示データをデータ電圧に変換する DAC (Digital Analog Converter) を搭載する[12][13]。この DAC は駆動するデータ線の本数分必要であり、1 個のドライバ IC につき、通常は数百個の DAC が搭載される。したがって、表示色数の増大は DAC の回路規模（入力ビット数）の増加、解像度の増加は DAC 搭載数の増加を伴う。現在、携帯電話を中心としたモバイル機器においても、表示色数は大型表示装置並の 26 万色表示（18 ビットカラー）が主流であり、これを実現するためには、R (Red), G (Green), B (Blue) 各 64 階調（6 ビット）が必要となる。以上のことから、TFT-LCD 低コスト化をドライバ IC のコストダウンによって実現するためには、如何に少ない回路規模で多階調表示を実現できるかが重要な課題となる。

さらに近年では、インターネットショッピングの利用や、DSC (Digital Still Camera) や DVC (Digital Video Camera) を用いて撮影したコンテンツをプリントアウトしたり、インターネットに投稿したりする機会が増えている。これに伴い、画像を扱う入出力デバイスの間で色調を統一化する、カラーマネージメント技術[14][15]の重要性が増している。カラーマネージメント技術では、入力または出力画像の明るさと信号の強さ（表示データ）との関係であるガンマ特性を、機器間で統一することが必要である。ここで、CRT (Cathode Ray Tube) ディスプレイのガンマ特性は、一般的には表示輝度が入力信号の指数関数である。また、指数関数の指数はガンマ値と呼ばれ、2.2 であることが通常である[16]。このことから、カメラ等の他の入力機器は、CRT ディスプレイで見たときに画像が自然に見えるように、画像信号のレベルを補正することでカラーマネージメントを実現しており、この表示システムが一般化している。このため、従来の表示システムを変更せず LCD を用いて自然な影像を表示するためには、LCD のガンマ値を CRT と同じに揃える必要がある。ところが、LCD のガンマ特性（データ電圧に対する表示輝度の関係）は、上記した指数関数的な特性ではなく、逆 S 字型のカーブを有する[17]。したがって、所望するガンマ値を実現するためには、表示データとデータ電圧の関係を適切に対応させるガンマ補正が必要となる。この際、モバイル機器向け TFT-LCD においては、TFT-LCD に必要な駆動回路を 1 個のドライバ IC に全て内蔵する構成が一般的であるため[18][19]、上記ガンマ補正も

ドライバ IC に内蔵できる程度の回路規模に抑える必要がある。

以上の STN-LCD および TFT-LCD の階調表示方法、および画質調整方法における課題を解決するため、本論文では、LCD の駆動方法およびドライバ IC の回路構成の最適化に基づく以下の方法を提案する。

- (1) 高速応答 STN-LCD の多階調表示において発生するフリッカとコントラスト低下の問題を、最小限のコストアップで同時に抑制する方法。

- (2) モバイル機器向け TFT-LCD の課題である低コスト化を、多階調表示に必要な回路規模の削減により実現し、ドライバ IC の製造コストの削減を図る方法。

- (3) 多種多様なモバイル機器向け TFT-LCD のガンマ補正を 1 個のドライバ IC で可能とし、製造コストの削減を図る方法。

## 1.2 従来研究

本節では、本研究で取り扱う前節の課題と関連する従来研究について述べる。

### 1.2.1 STN-LCD の多階調表示方法

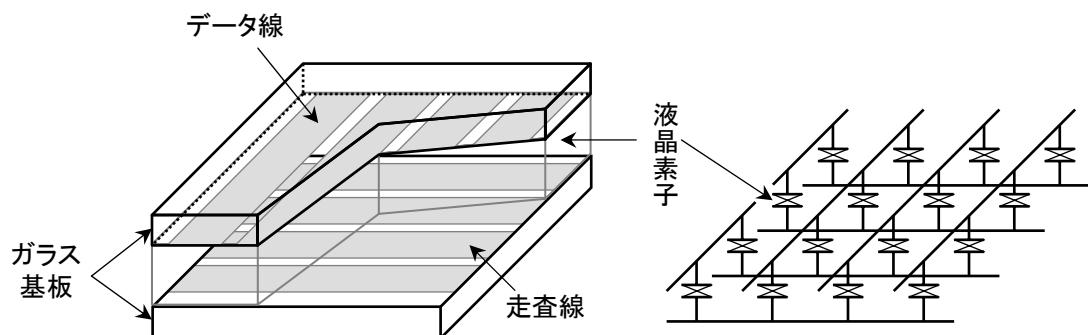

STN-LCD の多階調方法を述べるに先立ち、その前提となる STN-LCD の駆動方法について述べる。マトリクス表示を行う STN-LCD では、直交する走査線とデータ線の各透明電極の間に液晶素子を封入し、それぞれの電極の交点で画素を構成する[20][21]。

図 1.2 STN-LCD の構造と等価回路

代表的な駆動方法としては、APT (Alt-Pleshko Technique) 法[22]や、IAPT (Improved Alt-Pleshko Technique) 法[23]があり、これらの方法は、STN-LCD の表示輝度が印加電

圧の実効値に応答することを利用し、走査線には選択期間を示す選択電圧を 1 走査期間ずつ線順次に印加すると共に、データ線には選択された走査線上の各画素の表示オン／表示オフのデータに応じたデータ電圧を印加する。それ以外の非選択期間では、表示データによらず一定の電圧実効値が印加されるように、2 値のデータ電圧の中間レベルに相当する非選択電圧を走査線に印加する。この動作により、選択電圧が印加される期間のデータ電圧のみで各画素の表示オン／表示オフを制御することができる。

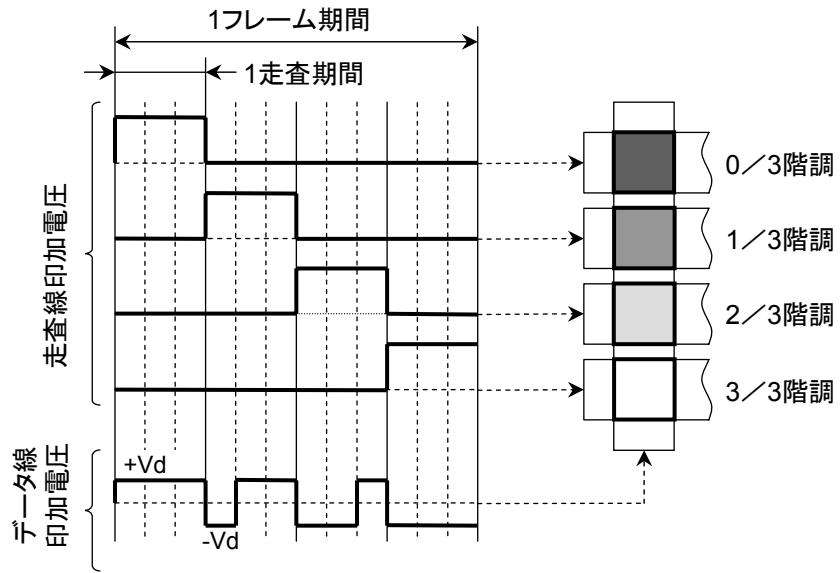

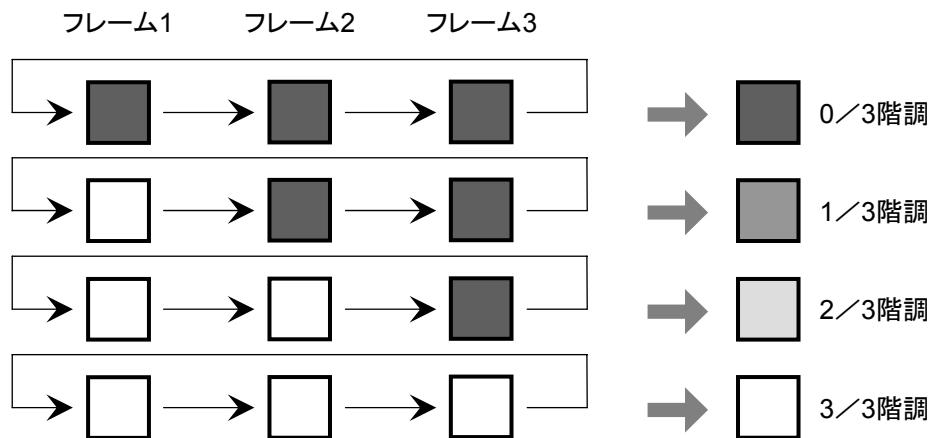

一方、上記した駆動方法は表示オン／表示オフの 2 値表現を前提とするため、STN-LCDにおいて多階調表示を実現する方法として、1 走査期間におけるデータ電圧の表示オン／表示オフの印加時間比率を制御する PWM (Pulse Width Modulation) 法[24]や、複数フレームを 1 周期としてこの中で表示オン／表示オフの表示回数を制御する FRC 法[1]が提案されている。この中で、PWM 法はデータ電圧波形の変化点数が増大するため、シャドーイングと呼ぶ表示むらによる画質劣化が増加しやすい[25]。このため、PWM 法は携帯電話向け等の小型で低解像度のパネルへ一部採用されているが、それ以外の STN-LCD では FRC 法が広く採用されている。FRC 法の課題はフリッカが見えやすいことであり、この原因は、表示オン／表示オフがフレーム毎に切り替わるため、その輝度変動が知覚されやすいことによる。この改善にあたっては、表示オン／表示オフの切り替えタイミングを画素毎に異ならせることにより、輝度変動を分散させる空間変調 FRC 法[26]が提案され、大きな改善効果が得られている。しかしながら、空間変調 FRC 法を適用しても、液晶の応答時間が速くなるにしたがい輝度変動が急激になるため、フリッカが知覚されやすくなる。

さらに、液晶の高速応答化に伴い、上記した表示輝度の電圧実効値応答性が薄れ、選択電圧と非選択電圧の電位差に対して輝度が応答するフレーム応答と呼ばれる現象が顕在化し、コントラストが低下する[5]。この課題の解決にあたっては、選択電圧を印加するインターバルを短くするアプローチが有効であり、フレーム周波数を高く設定する Hi-FAS (High Frequency Amplitude Selection) 法[6]や、複数のラインを同時に選択して 1 フレーム期間中に選択電圧を複数回印加する MLA (Multi Line Addressing) 法[7][8]、さらには全て走査線を同時に選択する AA (Active Addressing) 法[9][10]が提案されている。

以上のことから、STN-LCD の課題である多階調表示化、高速応答化、高コントラスト化を同時に実現するためには、液晶の高速応答化の副作用であるフリッカの発生とコントラスト低下を抑制することが重要な課題となる。さらに、上記課題に取り組むにあたっては、STN-LCD の最大の特徴である低コスト性を失わないことが必要である。

### 1.2.2 TFT-LCD の多階調表示方法

TFT-LCD は STN-LCD とは異なり、TFT によるアクティブ素子と保持容量をガラス基板上に画素毎に形成する[20][27]。したがって、選択電圧が印加される期間のデータ電圧のみが TFT 素子を通じて液晶素子に印加され、次の選択電圧が印加されるまで保持される。また、非選択期間において印加されるデータ電圧は液晶素子には伝達されず、液晶印加電圧への影響はない。このことから、TFT-LCD ではデータ電圧のレベルによって階調を表現する方法が一般的に採用されている。しかしながら、前節で述べたとおり、TFT-LCD では表示する階調数を多くすればするほど、DAC の回路規模が増加するため、ドライバ IC のチップサイズが増大して製造コストが上昇する。この課題を解決するアプローチとして、DAC の前段に FRC 法やディザリング法[28]による表示データの処理を行い、DAC の入力ビット数を削減する方法が提案されている。しかしながら、これらの方法はフリッカの発生や解像度感の低下といった画質劣化が発生することから、その適用は一部の階調表現のみに限定されている。さらに、別のアプローチとして、パネル製造時に駆動回路の一部を画素部周辺エリアに一体形成することで、ドライバ IC のチップサイズを削減する技術が提案されている[29][30][31][32][33]。しかしながら、現在 TFT-LCD の画素部に広く採用されているアモルファスシリコン TFT[34][35]を用いて駆動回路の一部を形成することは性能的に困難であるため、この方法の適用は高速スイッチングが可能な低温ポリシリコン TFT-LCD[36][37][38]に限定される。

以上のことから、TFT-LCD の課題である多階調表示を低成本で実現するためには、ドライバ IC の主要回路である DAC の回路規模をフリッカ等の画質劣化なく削減することと同時に、アモルファスシリコン TFT-LCD にも適用できるように、パネルに搭載する回路を不要にする必要がある。

### 1.2.3 TFT-LCD の画質調整方法

TFT-LCD の画質調整の重要な項目であるガンマ補正を実施するには、表示データとデータ電圧の関係を適正化すれば良い。ガンマ補正を実現するアプローチの 1 つとして、表示データが有する階調数よりも多いデータ電圧を用意し、その中から所望のガンマ特性となる組み合わせを選択する方法がある[39][40]。この方法はデジタル処理で容易にガンマ補正が実現できる利点がある一方、表示データの有する階調数よりも分解能の高い DAC が必要となる。さらに、選択したデータ電圧の組み合わせを記憶するための制御レジスタが必要となる。これらの回路規模の増大は、低成本化が激しいモバイル機器向けドライバ

ICにおいては無視できないほど大きく、適用が困難である。

ガンマ補正を実現するその他のアプローチとして、DACに入力するデータ電圧自体を、予め所望するレベルに設定する方法がある。この実現方法として、データ電圧の各レベルをドライバ IC の製造時に用いるフォトマスクの変更により切り換える方法が報告されている[41]。この方法は、ドライバ IC に追加回路を必要としない利点がある一方、ドライバ IC の製造後にガンマ値を変更する場合、あるいは異なるガンマ特性を持つ TFT-LCD を駆動する場合には、再度フォトマスクを作成してドライバ IC を製造する必要が生じる。一般に TFT-LCD のガンマ特性は、使用する液晶材料によって多様に変化することから、上記の方法は、製造効率および開発コストの面において課題がある。この課題を解決するため、データ電圧のレベル設定をプログラム化し、多種多様な TFT-LCD に適用させるための回路を追加することで製造コストの削減を図る方法が報告されている[42]。しかし、報告されている提案方法はいずれも回路規模が大きく、専用の電源 IC を必要とする。このため、1チップのドライバ IC が一般的なモバイル機器向け TFT-LCD においては、これらの方法を適用することは困難である。

以上のことから、モバイル機器向け TFT-LCD のガンマ補正を低コストで実現するためには、1つのドライバ IC で多種多様な TFT-LCD に適用できると同時に、ドライバ IC のチップサイズに大きなインパクトを与えない回路規模である必要がある。

### 1.3 研究の方針

本研究の目的は、LCD の駆動方法およびドライバ IC の回路構成の最適化方法を 1.1 節で示した各々の課題に対して提案し、STN-LCD および TFT-LCD の高画質化と低コスト化を目指すものである。本研究で提案する 3 つの方法は、(1) 高速応答 STN-LCD の高画質多階調化方法と、(2) モバイル機器向け TFT-LCD の小回路規模多階調化方法と、(3) モバイル機器向け TFT-LCD の高汎用画質調整方法である。(1) の高速応答 STN-LCD の高画質多階調化方法は、自然画を含む動画コンテンツの表示を違和感なく実現するものであり、STN-LCD を搭載した情報機器の性能向上、および TFT-LCD を搭載した情報機器の STN-LCD への置き換えによる低コスト化に貢献することが目標である。(2) のモバイル機器向け TFT-LCD の小回路多階調化方法は、自然画を含む動画コンテンツの表示を低成本で実現するものであり、TFT-LCD を搭載したモバイル機器の低価格化、およびその普及に貢献することが目標である。(3) のモバイル機器向け TFT-LCD の高汎用画質調

整方法は、多種多様な TFT-LCD のガンマ補正を 1 個のドライバ IC で可能とし、LCD 製造コストの削減を実現するものであり、全ての画像の入出力機器間で色調を統一化するカラーマネージメント技術の普及に貢献することが目標である。

本研究で提案する 3 つの方法と、本研究により性能向上を図る LCD 分野にとっての観点の関係を図 1.3 に示す。

図 1.3 各種 LCD の課題と各章の位置付け

以下に各々の課題に対する解決方針を示す。

#### (1) 高速応答 STN-LCD の高画質多階調化方法

従来の FRC 法を高速応答 STN-LCD に適用した際に発生するフリッカは、フレーム毎の表示輝度の変動が知覚されることが原因である。そこで、フレーム周波数を高くすることで輝度変動のインターバルを短縮し、フリッカを抑制する方法を提案する。この際、フレーム周波数の高速化は装置におけるグラフィック処理のパフォーマンス低下を招く副作用が懸念される。そこで、高フレーム周波数駆動法を実現するためのフレームメモリを LCD モジュール側に内蔵し、ホスト側の処理負荷は増加させないアプローチをとる。しかしながら、上記アプローチはフレームメモリの追加によるコストアップを伴うため、STN-LCD の特徴である低コスト性を損なう恐れがある。そこで、フレームメモリに入力する表示データの一部に対し、予め FRC 法による表示オン／表示オフデータへの変換処

理を行うと共に、周波数変換されてフレームメモリから出力される表示データに対しても FRC 处理を行う 2 周波合成 FRC 法を提案する。これにより、課題である必要フレームメモリ容量の削減とフリッカの抑制を同時に実現する。

一方、高フレーム周波数駆動法の適用により 1 走査期間が短縮されるため、印加電圧実効値に対する電圧波形歪みの影響が相対的に高まる。この影響により、シャドーイングと呼ぶ表示むら[43]が増大する副作用が生じる。この改善に向けては、前節で述べた空間変調 FRC 法における表示オン／表示オフの切り替えタイミングの良否により、印加電圧波形の歪み量が異なることが分かっている[44]。そこで、表示オン／表示オフの切り替えタイミングを最適化するアプローチにより、シャドーイングの発生を抑制する。

### (2) モバイル機器向け TFT-LCD の小回路規模多階調化方法

ドライバ IC の主要回路である DAC の回路規模を削減するアプローチとして、DAC の搭載個数を削減する、あるいは DAC の 1 個あたりの回路規模を削減することが考えられる。前者のアプローチは、パネル側に駆動回路の一部を搭載することで実現可能であるが、先に述べたとおりアモルファスシリコン TFT-LCD への適用は困難である。そこで、DAC の 1 個あたりの回路規模削減を目的に、表示データの上位ビットの階調表現を DAC で実現し、下位ビットの階調表現を出力タイミングの制御で実現する階調時分割駆動法を提案する。これにより、DAC が必要とする回路規模は表示データの上位ビット分のみとなり、パネル側の搭載する回路も不要となる。ここで、階調時分割方法は、1 走査期間を複数の期間に分割し、下位ビットの表示データと分割の順番が一致した期間のみ、データ電圧をデータ線に出力する。したがって、1 走査期間の前半に印加されたデータ電圧は、後半の期間ではデータ線の寄生容量によって保持されることとなる。このため、データ線からのリード電流が多い場合や、隣接するデータ線から誘導されるカップリング歪みが大きい場合、保持されたデータ電圧が変動して所望の表示輝度とならない場合がある。そこで、データ電圧の出力タイミングの最適化とデータ電圧の補正機能を追加するアプローチにより、データ電圧のレベル変動を抑制する。

### (3) モバイル機器向け TFT-LCD の高汎用画質調整方法

従来のデータ電圧のプログラム化によるガンマ補正是、データ電圧を生成するための基準電圧を離散的に複数用意し、個々の基準電圧レベルを調整する。このため、各基準電圧の設定情報を記憶するための制御レジスタの数が多く、これが回路規模の増大原因となる。そこで、TFT-LCD のガンマ補正カーブが逆 S 字型であることに着目し、下記 2 つの項目を優先的に設定し、その後にカーブの細かな調整を加えることで効率の良い補正を行う。

- (a) 最低階調と最高階調の電圧レベル

- (b) ほぼ直線形状となる中央階調付近の傾き

制御レジスタの設定項目については、上記 2 つに対応した「振幅」「傾き」、その後の細かな調整を「微調整」とし、この順番でガンマ補正を実施する。これにより、複数のデータ電圧レベルをまとめて調整することで回路構成を簡略化し、ドライバ IC のチップサイズに大きなインパクトを与えないことを狙う。さらに、ガンマ補正の精度と回路規模のバランスを両立するため、基準電圧のレベル数および各基準電圧の調整刻み幅については、複数の TFT-LCD パネルのガンマ特性に基づき最適値を決定するアプローチをとる。

## 1.4 本論文の構成

本論文では、第 2 章以降を以下のように構成する。

第 2 章では、文献[45][46]に基づき、高速応答 STN-LCD の高画質多階調化方法として、フレーム周波数を高くする駆動方法により従来の空間変調 FRC 法で発生するフリッカを抑制する。さらに、高フレーム周波数駆動法を適用する際の課題となるフレームメモリの増加を、FRC 処理をフレームメモリの前段と後段に分離する 2 周波合成 FRC 法により最小化する。さらに、高フレーム周波数駆動法の適用に伴うシャドーイングの増大を、空間変調 FRC 法における表示オン／表示オフの切り替えタイミングの最適化により抑制する。最後に、上記提案方法を PC モニタ向け STN-LCD に適用し、有用性に対する評価を行う。

第 3 章では、[47][48]に基づき、モバイル機器向け TFT-LCD の小回路規模多階調化方法として、DAC 処理を表示データの上位ビットの階調表現のみに適用し、下位ビットの階調表現はドライバ IC の出力タイミング制御で実現する階調時分割駆動法を提案し、多階調表示化に伴うドライバ IC の回路規模増大を抑制する。次に、階調時分割駆動の課題となるデータ電圧のレベル変動については、出力タイミングの最適化と電圧レベルの補正機能の提案により抑制する。さらに、本提案方法をモバイル機器向け TFT-LCD に適用し、有用性に対する評価を行う。

第 4 章では、文献[49][50]に基づき、モバイル機器向け TFT-LCD の高汎用画質調整方法として、1 個のドライバ IC の出力電圧レベルをプログラム化することにより、多種多様な TFT-LCD に適用可能なガンマ補正方法を提案し、製造コストの削減を図る。さらに、ガンマ補正の実現手段として、3 つの調整機能（振幅調整、傾き調整、微調整）の組み合

わせ方法を提案し、回路構成の簡略化とガンマ補正精度とのバランスを最適化する。最後に、本提案方法をモバイル機器向け TFT-LCD に適用し、有用性に対する評価を行う。

第 5 章では、結論として本研究で得られた成果を要約した後、今後に残された課題について述べる。

## 第 2 章

# 高速応答 STN-LCD の高画質多階調化方法

### 2.1 緒言

本章では、高速応答 STN-LCD の多階調表示におけるちらつき抑制方法およびその実現回路方法を提案し、高画質で低コストな STN-LCD の提供を実現する。

STN-LCD は、直交する透明電極の交点で画素を形成し、その交点を駆動する構造であることから、画素毎にスイッチング素子を設ける TFT-LCD に比べて製造コストが低い。このため STN-LCD は、比較的解像度が低く、かつ最高画質を必要としない中小型の情報機器に主に採用されている。しかしながら、このような情報機器においても簡易的な動画表示や自然画表示を扱うアプリケーションが増大しており、STN-LCD においても画質の向上が求められている。画質に関する具体的な改善項目としては、多階調表示化、高速応答化、高コントラスト化が挙げられる。現在、液晶材料や駆動方法の改善により、応答時間についてはマウス動作や毎秒 15 コマ程度の簡易動画を残像感なく視認可能な 150ms (立上り + 立下り)、コントラストについては画像を表現する上で充分実用的な 50 : 1 を実現している[51][52][53]。一方、多階調表示化については、応答時間が 350ms 程度の遅い液晶に対しては、自然画や GUI をより滑らかに表現可能な 64 階調表示を実現できるものの、上記した 150ms ではフリッカの発生により画質が劣化する問題が顕在化する。したがって、STN-LCD の高画質化を図るためにには、高速応答化に伴う多階調表示の画質劣化を抑制することが必要である。

従来、高速 STN-LCD の多階調表示時に発生するフリッカの抑制手段として、データ電圧レベルを表示データに応じて変調する PHM (Pulse Height Modulation) 法[54]や、AM (Amplitude Modulation) 法[55]等が提案されている。これらの方法は、複数フレーム周期における表示オン／表示オフの点灯率によって液晶印加電圧の実効値を制御する FRC 法とは異なり、1 フレームで液晶印加電圧実効値を制御することができる。つまり、フリッカの原因となるフレーム毎の輝度変動が原理的に発生しないため、フリッカを抑制することができる。しかしながら、上記の方法は、データ電圧のレベル数の増大および電圧レ

ベルを決定するための論理規模が大きいため、追加となる回路規模が増大し、STN-LCD の最大の特長である低コスト性を損なう問題がある。したがって、より安価にフリッカを抑制可能な多階調表示方法が必要である。

本章では、高速応答 STN-LCD における高コントラスト表示技術の一つである高フレーム周波数駆動法に着目し、この駆動方法と FRC 法を組み合わせることにより、輝度変動が発生するインターバルを短縮してフリッカを抑制する方法を提案する。高フレーム周波数駆動法は考え方自体が単純である反面、表示システムの処理負荷増大によるグラフィック処理のパフォーマンス低下が懸念される。さらには、液晶印加電圧実効値に対する電圧波形歪みの影響が相対的に高まり、シャドーイングと呼ぶ表示むらが増大する要因となる。そこで、前者の課題については、高フレーム周波数化を実現するために必要なフレームメモリを LCD モジュール側に内蔵することで、処理負荷の増加を抑制する方法を提案する。この際、フレームメモリの前段と後段の両方で FRC 処理を実行する 2 周波合成 FRC 法を提案し、フレームメモリ容量の最小化を図る。また、後者の課題については、空間変調 FRC 法を実行する際の画素毎の表示オン／表示オフの切り替えタイミングを最適化することで印加電圧波形の歪み発生量を最小化し、シャドーイングの発生を抑制する。

以下、2.2 節では、従来の多階調表示方法について説明し、問題点と課題を明らかにする。2.3 節では、提案方法である、高フレーム周波数駆動法によるフリッカ抑制方法、および高フレーム周波数駆動法を低コストで実現するための 2 周波合成 FRC 法について説明する。2.4 節では、提案方法を用いることによる画質評価の結果および考察について述べ、本方法の有用性を示す。

## 2.2 従来の多階調表示方法と問題点

本節では、従来の多階調表示方法について説明し、高速応答 STN-LCD に適用する際の問題を明らかにする。

### 2.2.1 画質劣化問題

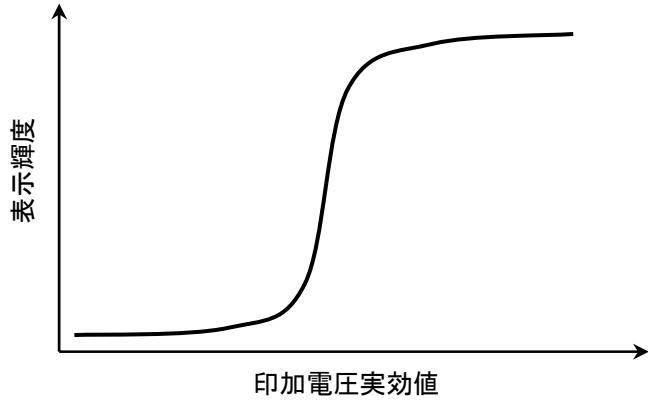

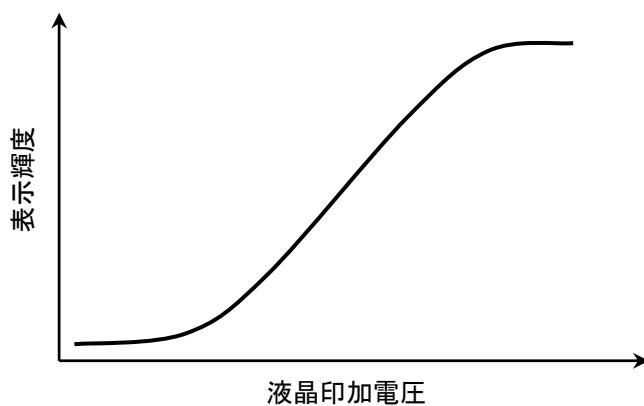

STN-LCD では、前章の図 1.2 で示したように、2 枚のガラス基板の各内面に走査線とデータ線がマトリクス状に配置され、その間に液晶が封入される。そして、走査線とデータ線の交点が画素となり、それぞれの電極に所定の電圧を印加して駆動を行う。STN-LCD のガンマ特性は、図 2.1 に示すように印加電圧実効値に応じて表示輝度が変化する[21][56]。

この特性を利用し、印加電圧実効値を画素毎に制御することにより、任意の画像表示を実現する。

図 2.1 STN-LCD のガンマ特性

図 2.2 は、代表的な駆動法である APT 法を例にとり、走査線とデータ線の駆動波形を示したものである。まず走査線には、先頭から順に選択電圧： $+Vs$  を 1 走査期間ずつ印加すると共に、それ以外の非選択期間では非選択電圧（0 電圧）を印加する。一方データ線には、選択電圧の印加タイミングに同期して、 $-Vd$  または $+Vd$  のデータ電圧を印加する。データ電圧の決め方は、選択された走査線上の表示データがオンの場合は $-Vd$ 、オフの場合は $+Vd$  とする。この一連の動作で 1 フレームが完結し、次の 1 フレームでは、再び先頭から選択電圧を印加する。ただし、今度は全ての印加電圧の極性を反転する。これは、液晶に直流電圧を長時間印加すると残像現象や劣化が発生するためであり、これを防止するためには液晶印加電圧の極性を一定周期で反転させる交流化を行う。ここで、各画素への印加電圧は、走査線印加電圧とデータ電圧の差電圧となる。したがって、走査線に選択電圧が印加される期間では表示データに応じ  $|Vs + Vd|$  または  $|Vs - Vd|$  が、その他の非選択期間では表示データによらず  $|Vd|$  が印加される。このことから、 $i$  行  $j$  列目の画素に印加される表示オン時の電圧実効値を  $\langle U_{ij} \rangle_{on}$ 、表示オフ時の電圧実効値を  $\langle U_{ij} \rangle_{off}$  とすると、これらは以下の計算式から求めることができる。

$$\langle U_{ij} \rangle_{on} = \sqrt{\frac{(Vs + Vd)^2 + (N-1) \cdot Vd^2}{N}} \quad (2.1)$$

$$\langle U_{ij} \rangle_{off} = \sqrt{\frac{(Vs - Vd)^2 + (N-1) \cdot Vd^2}{N}} \quad (2.2)$$

ここで、 $N$  は駆動する走査線の数である。式 (2.1), 式 (2.2) から分かるように、ある画素に印加される電圧実効値は、その画素に与えられる表示データにより決定するため、画素毎に表示輝度を制御することが可能となる。

図 2.2 APT 法の駆動波形

さらに、 $(Vs/Vd) = a$  を式 (2.1), 式 (2.2) へそれぞれ代入し、 $\langle U_{ij} \rangle_{on}$  と  $\langle U_{ij} \rangle_{off}$  の比であるオン／オフ比を求めると、式 (2.3) に示す結果となる。

$$\frac{\langle U_{ij} \rangle_{on}}{\langle U_{ij} \rangle_{off}} = \sqrt{\frac{a^2 + 2a + N}{a^2 - 2a + N}} \quad (2.3)$$

式 (2.3) から、オン／オフ比が最大になるのは  $a = \sqrt{N}$  の時であり、この条件においてコントラストが最大になる。なお、 $a = \sqrt{N}$  を最適バイアス比と呼び、これを式 (2.3) に代入すると、式 (2.4) に変形することができる。

$$\frac{\langle U_{ij} \rangle_{on}}{\langle U_{ij} \rangle_{off}} = \sqrt{\frac{\sqrt{N} + 1}{\sqrt{N} - 1}} \quad (2.4)$$

式 (2.4) から分かるように、オン／オフ比は、走査線の数 :  $N$  のみによって決まり、 $N$  の値が大きい程、オン／オフ比が小さくなる。また、式 (2.1) と式 (2.2) に  $(Vs/Vd)$

$=a=\sqrt{N}$  を代入し、選択電圧の振幅： $V_{spp}$  とデータ電圧の振幅： $V_{dpp}$  を求めると、それぞれ、式 (2.5), 式 (2.6) に示す結果となる。

$$V_{spp} = \sqrt{\frac{2\sqrt{N}}{\sqrt{N}-1}} \cdot \langle U_{ij} \rangle_{off} \quad (2.5)$$

$$V_{dpp} = \sqrt{\frac{2N\sqrt{N}}{\sqrt{N}-1}} \cdot \langle U_{ij} \rangle_{off} \quad (2.6)$$

具体的な例として、式 (2.5), 式 (2.6) にそれぞれ  $N=300$  本、 $\langle U_{ij} \rangle_{off} = 2.00V$  を代入すると、 $V_{spp}=50.47V$ ,  $V_{dpp}=2.91V$  となる。また、これらの結果を式 (2.1) に代入すると、 $\langle U_{ij} \rangle_{on} = 2.119V$  となり、 $\langle U_{ij} \rangle_{off}$  との電圧実効値差が非常に小さいことが分かる。このため STN-LCD では、図 2.1 に示したように僅かな電位差でも表示輝度が大きく変化するようにガンマ特性を急峻化し、 $N$  の値が大きい場合にも充分なコントラストが得られるようにしている。なお、選択電圧の振幅： $V_{spp}$  は約 50V と高電圧であることから、振幅を低電圧化してドライバ IC の低コスト化を図る方法として、図 2.3 に示すように非選択電圧の基準電位をフレーム毎にレベルシフトする IAPT 法[23]が提案されている。この方法により、液晶印加電圧波形は、図 2.2 で示した基本波形と同一のまま、選択電圧の振幅を約  $1/2$  にすることができる。

図 2.3 IAPT 法の駆動波形

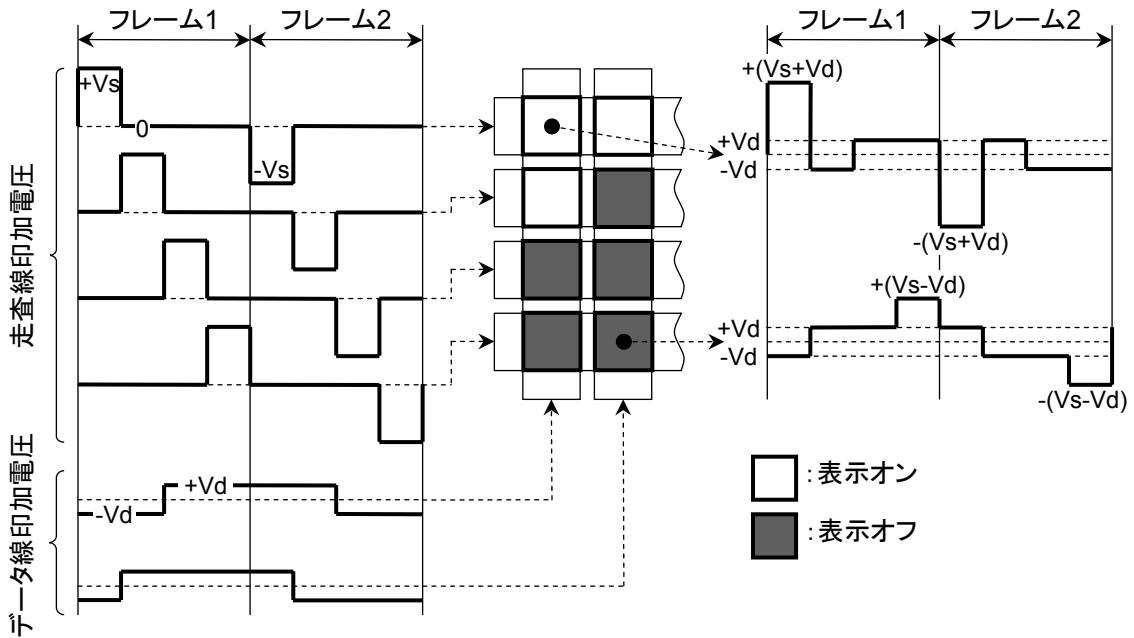

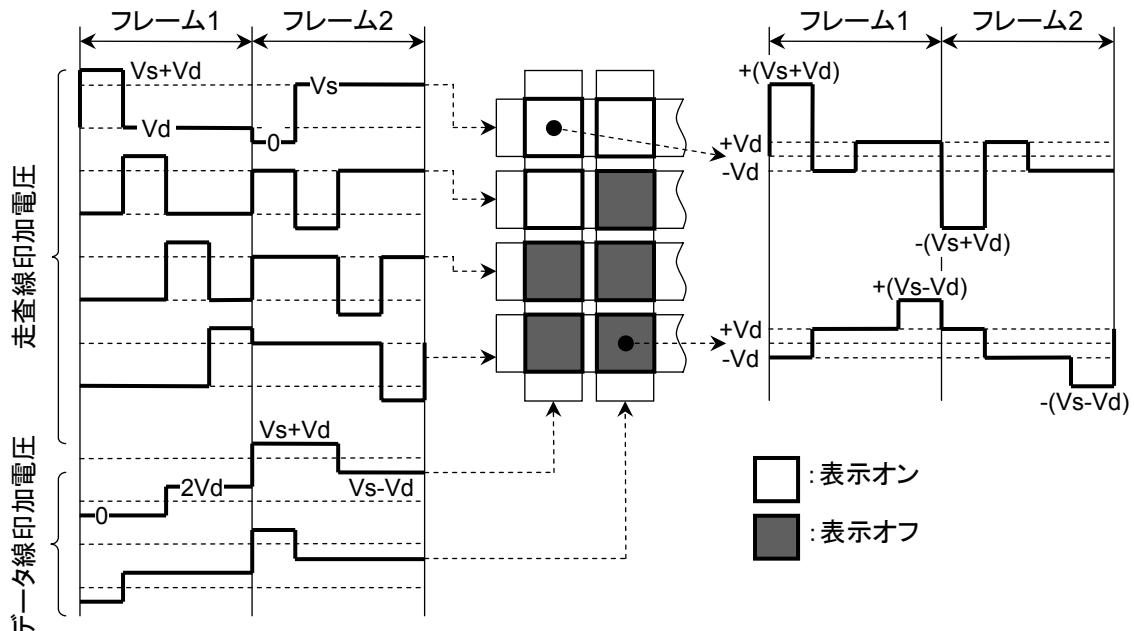

選択電圧の振幅を低減する別の解法として、IHAT（Improved Hybrid Addressing Technique）法[57]やMLA法[7][8]がある。これらの駆動方法は、複数の走査線に同時に選択電圧を与える駆動方法であるが、先に述べたAPT法やIAPT法と同様、非選択期間の電圧実効値を表示データによらず一定にする必要がある。これを実現するため、直交関数を用いた演算によりデータ電圧のレベルを決定する。図2.4はIHAT法の一例として、2本の走査線を同時選択する場合の駆動波形を示したものである。まず走査線に印加する電圧は、 $2 \times 2$ の直交関数の値にしたがい、 $+Vs$ ,  $-Vs$ の選択電圧を1走査期間ずつ2回印加する。ここで選択電圧の極性は、直交関数が+1ならば $+Vs$ , -1ならば $-Vs$ となる。一方、データ線に与えるデータ電圧は、選択された2本の走査線上における表示データの値と直交関数との一致数にしたがい、 $+Vd$ 電圧、0電圧、 $-Vd$ 電圧の中から1レベルを選択して印加する。ここで、表示データは、表示オンを-1、表示オフを+1とし、直交関数との一致数が2, 1, 0の場合、データ電圧はそれぞれ $+Vd$ , 0,  $-Vd$ とする。この結果、ある画素に印加される電圧波形を見ると、2回の選択期間における液晶印加電圧の実効値は、その画素に与えられた表示データに依存して異なることが分かる。また、非選択期間の印加電圧は、表示データによらず、2水平期間中1回は0、残りの1回は $+Vd$ または $-Vd$ となり、電圧実効値としては一定となる。したがって、APT法やIAPT法と同様、個々の画素に所望の電圧実効値を与えることが可能である。

図2.4 IHAT法の駆動波形

ここで、同時に選択する走査線の数を  $m$  とした場合、 $i$  行目の走査線に印加する電圧： $V_{si}(t)$  は、式 (2.7) から求めることができる。ここで、 $Si(t)$  は  $\pm 1, 0$  の値をとる直交関数である。一方、 $j$  行目のデータ線に印加するデータ電圧： $V_{dj}(t)$  は、式 (2.8) から求めることができる。式 (2.8) において、 $I_{ij}$  は  $i$  行  $j$  列番目の表示データで、表示オンの時は  $-1$ 、表示オフの時は  $+1$  の値をとる。

$$V_{si}(t) = \sqrt{\frac{N\sqrt{N}}{2m(\sqrt{N}-1)}} \cdot Si(t) \cdot \langle U_{ij} \rangle_{off} \quad (2.7)$$

$$V_{di}(t) = \sqrt{\frac{N\sqrt{N}}{2m(\sqrt{N}-1)}} \cdot \sum_{i=1}^N Si(t) \cdot I_{ij} \cdot \langle U_{ij} \rangle_{off} \quad (2.8)$$

ここで、 $i$  行  $j$  列目の画素に印加される電圧実効値： $\langle U_{ij} \rangle$  は、式 (2.9) から求めることができ、式 (2.7)、式 (2.8) を代入してこれを変形すると、式 (2.10) に示す結果となる。なお  $V_{srms}$  は選択電圧： $V_{si}(t)$  の電圧実効値である。この式から、 $\langle U_{ij} \rangle$  は表示データ  $I_{ij}$  のみで制御可能であることが分かる。

$$\langle U_{ij} \rangle = \sqrt{\frac{1}{T} \int_0^T [V_{si}(t) - V_{dj}(t)]^2 dt} \quad (2.9)$$

$$\langle U_{ij} \rangle = \sqrt{\frac{2(\sqrt{N} - I_{ij})}{\sqrt{N}}} \cdot V_{srms} \quad (2.10)$$

また、式 (2.10) に基づき、 $\langle U_{ij} \rangle_{on}$ 、 $\langle U_{ij} \rangle_{off}$  の比であるオン／オフ比を求めると、式 (2.11) となる。これは、式 (2.3) で示した APT 法のオン／オフ比と等しい。

$$\frac{\langle U_{ij} \rangle_{on}}{\langle U_{ij} \rangle_{off}} = \frac{\sqrt{\frac{2(\sqrt{N} - (-1))}{\sqrt{N}}} \cdot V_{srms}}{\sqrt{\frac{2(\sqrt{N} - (+1))}{\sqrt{N}}} \cdot V_{srms}} = \sqrt{\frac{\sqrt{N} + 1}{\sqrt{N} - 1}} \quad (2.11)$$

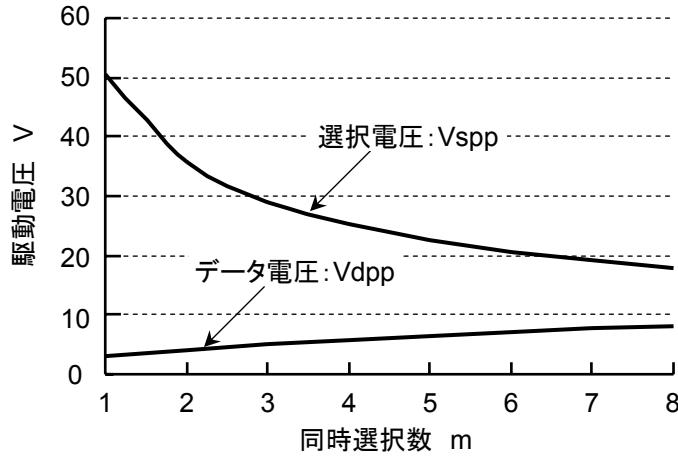

次に、式 (2.7)、式 (2.8) に基づき、選択電圧の振幅： $V_{spp}$  とデータ電圧の振幅： $V_{dpp}$  を求めると、式 (2.12)、式 (2.13) に示す結果となり、同時選択線数： $m$ 、走査線数： $N$ 、および  $\langle U_{ij} \rangle_{off}$  の関数となる。具体的な例として、式 (2.13) に  $m=1 \sim 8$ 、 $N=300$  本、 $\langle U_{ij} \rangle_{off}=2.00V$  を代入すると、図 2.5 に示す特性となる。図 2.5 から分かるように、同時選択線数： $m$  が大きくなるほど、データ電圧の振幅は大きくなり選択電圧の振幅は小さ

くなる。一方、 $m$  が大きくなるほど、直交関数との積和演算に必要な回路規模が増大するため、 $m$  の値は 2~4 が最適値であるとされている[58][59]。

$$V_{spp} = \sqrt{\frac{2N\sqrt{N}}{m(\sqrt{N}-1)}} \cdot \langle U_{ij} \rangle_{off} \quad (2.12)$$

$$V_{dpp} = \sqrt{\frac{2m\sqrt{N}}{(\sqrt{N}-1)}} \cdot \langle U_{ij} \rangle_{off} \quad (2.13)$$

図 2.5 同時選択線数と駆動電圧の関係

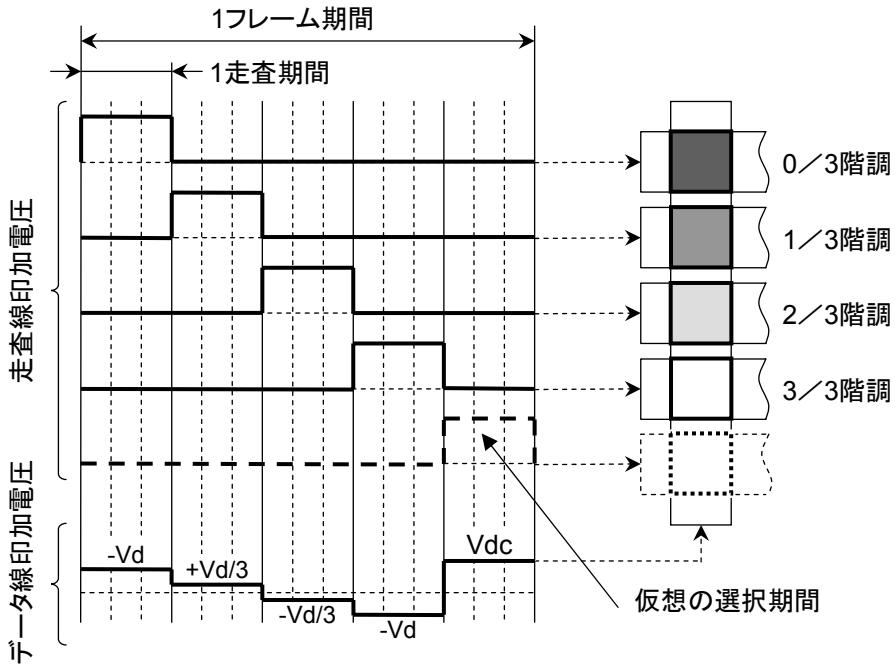

上記した各種駆動方法は、全て表示オンと表示オフの 2 値を対象としているため、中間調を表示するためには、基本的に表示オン／表示オフの 2 値を用いて表現する必要がある。これを実現する方法の一つである PWM 法[24]は、1 走査期間を複数の期間に分割し、それぞれの分割期間に対するデータ電圧の印加時間を制御することで、中間階調を得る方法である。例えば APT 法にて 4 階調を表現する場合、図 2.6 に示すように 1 走査期間を 3 分割し、この中で  $-V_d$  (表示オンのデータ電圧) の割合を 0~3 とすれば、 $0/3$  (階調率 : 0%),  $1/3$  (階調率 : 33%),  $2/3$  (階調率 : 67%),  $3/3$  (階調率 : 100%) の 4 階調を得ることができる。しかしながら、PWM 法では 1 走査期間毎に必ずデータ電圧が変化するため、これに伴い液晶素子を通して走査線印加電圧へ誘導されるクロストーク歪みの発生頻度が高まり、液晶印加電圧実効値の変動が大きくなる。前述したように STN-LCD では僅かな電圧変動でも表示輝度が大きく変化することから、PWM 法を適用するとシャドーイングと呼ぶ表示むらが増大する。このため、現在 PWM 法は、走査線の数が少ない（ガシマ特性を急峻にする必要がない）、一部の小型パネルのみに適用されている。

図 2.6 PWM 法の原理

STN-LCD の多階調表示を実現する別の方針として, FRC[1]法が提案されている。FRC 法は, 複数フレームを 1 周期とし, フレーム毎に表示オン／表示オフの点灯回数を制御する方法である。例えば 4 階調の塗りつぶし表示を行う場合, 図 2.7 に示すように 3 フレームを 1 周期とし, 表示オンの点灯回数を 0~3 回とすれば, PWM 法と同様に, 0/3 (階調率 : 0%), 1/3 (階調率 : 33%), 2/3 (階調率 : 67%), 3/3 (階調率 : 100%) の 4 階調を得ることができる。

図 2.7 FRC 法の原理

しかしながら、FRC 法はフレーム毎の表示オン／表示オフの切換りが表示輝度の変動となるため、フリッカとして知覚されやすい。そこで、図 2.8 に示すように表示オン／表示オフの表示タイミングを画素間で異ならせる、空間変調 FRC 法が提案されている[26]。空間変調 FRC 法では、あるフレームで見た場合、中間階調の表示部に表示オン／表示オフが混在する。以下、この表示オン／表示オフの混在パターンを FRC パターンと呼ぶ。ここで、図 2.8 で示す FRC パターンは  $3 \times 3$  画素のマトリクスが 1 単位となっており、この単位で表示輝度の平均（表示オンの点灯数）を見ると各フレーム等しくなっていることが分かる。このことから、表示輝度の変動が抑制され、フリッカを大幅に抑制することが可能となる。空間変調 FRC 法は、従来の応答時間である 350ms（立上り + 立下り）に対しては有効な手段であり、自然画や GUI を違和感なく表現可能な 64 階調表示が実用化されている[2]。しかしながら、150ms 以下の高速応答 STN-LCD に同じ方法を適用すると FRC パターンの切り替わり自体が知覚され、表示流れや細かいちらつきといった新たな種類のフリッカが顕在化する。

図 2.8 空間変調 FRC 法の原理（1／3 階調表示）

一方、STN-LCD の高速応答化は、上記した多階調表示時のフリッカ問題のみならず、コントラストの低下も誘発する。これは、液晶の応答時間が高速化すると、図 2.9 に示すように表示輝度が印加電圧の実効値だけでなく瞬間値にも応答し始めるためである。この現象はフレーム応答と呼ばれ、選択期間では表示オフ（黒）の表示輝度が上昇し、非選択期間中では表示オン（白）の表示輝度が低下するため、その結果としてコントラストが低下する[5]。

以上のことから、高速応答 STN-LCD において、自然画や GUI を違和感なく表現可能な 64 階調以上を実現するためには、上記したフリッカとコントラスト低下の 2 つの画質劣化を同時に抑制することが必要である。

図 2.9 フレーム応答現象のイメージ

### 2.2.2 従来の画質劣化対策の問題点と課題

高速応答 STN-LCD における第 1 の課題であるフリッカ抑制については、PHM 法がその解法として提案されている[54]。PHM 法では、選択電圧を印加する期間において、表示データに応じたレベルのデータ電圧を印加する。この際、非選択期間の印加電圧も表示データに依存して変化するため、印加電圧実効値が  $|Vd|$  とならない。そこで PHM 法では、図 2.10 に示すように、1 フレーム期間の最後において、どの走査線にも選択電圧を印加しない仮想の選択期間を設け、この期間で印加電圧実効値を補正するためのデータ電圧を印加する。ここで、補正用のデータ電圧  $Vdc$  については、以下の式により算出することが可能である。

$$Vdc = \sqrt{N - \sum_{m=1}^{N, m \neq i} a_m^2} \cdot Vd \quad (2.14)$$

PHM 法においては、液晶印加電圧実効値を 1 フレーム期間で制御できることから、フリッカの原因となるフレーム毎の輝度変動を抑制することが可能である。しかしながら、式 (2.14) から分かるように、例えば 64 階調を実現する場合、データ電圧を 64 レベル以上用意する必要があるため、ドライバ IC のチップサイズが大幅に増加し、製造コストが上昇する可能性が高い。

図 2.10 PHM 法の液晶印加電圧波形

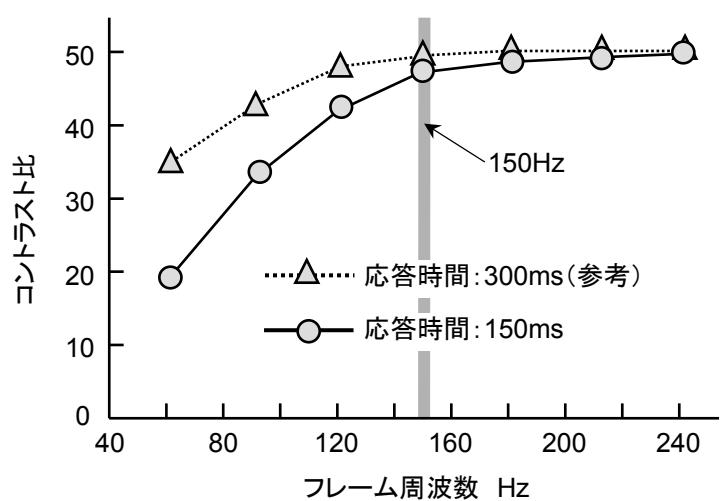

フリッカを抑制する別のアプローチとして、輝度変動が発生する時間間隔を短縮する高フレーム周波数駆動法が提案されている[4][60][61][62]. この方法は、従来の空間変調 FRC 法の延長で実現できることから、新たな演算回路を必要とせずコストアップが少なく、応答時間 : 150ms の液晶に対してはフレーム周波数 : 150Hz 以上でフリッカを抑制できることが知られている[4]. しかしながら、フレーム周波数の高速化は、ホスト側に搭載されるグラフィックメモリへのアクセス頻度が高まるため、他のグラフィック処理に必要なメモリアクセス頻度が低下する. このため、グラフィック処理のパフォーマンス低下につながる可能性が高い. これを解消する手段として、ホスト側から転送するフレーム周波数は従来のままとし、LCD モジュール側で高フレーム周波数化することが考えられる. しかし、このアプローチを実現するためにはフレームメモリの追加が必要となる. さらに、高フレーム周波数駆動は 1 走査期間が短縮するため、印加電圧の波形歪みの影響が相対的に大きくなり、PWM 法と同様にシャドーイングの増大が懸念される.

一方、高速応答化の第 2 の課題であるコントラスト低下問題については、選択電圧を印加するインターバルを短くするアプローチが有効であり、Hi-FAS 法、MLA 法、AA 法の各駆動方法が提案されている. Hi-FAS 法[6]は、前述の高フレーム周波数駆動と同じ考え方であり、その課題も共通である. なお、フレーム応答を抑制可能なフレーム周波数は、

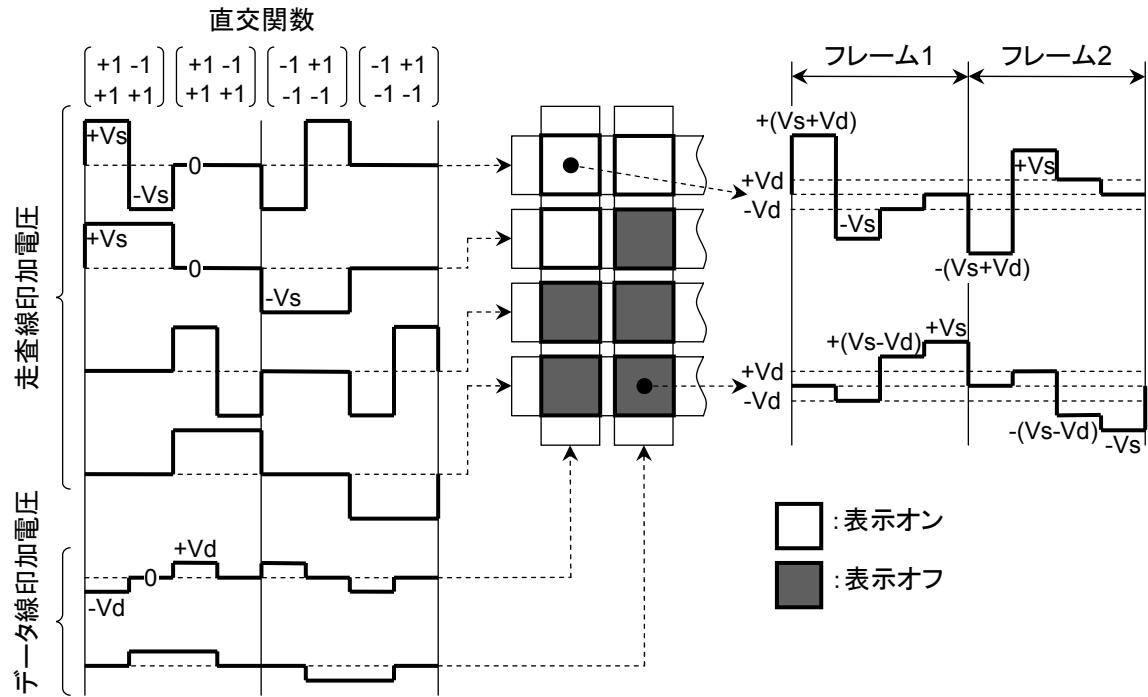

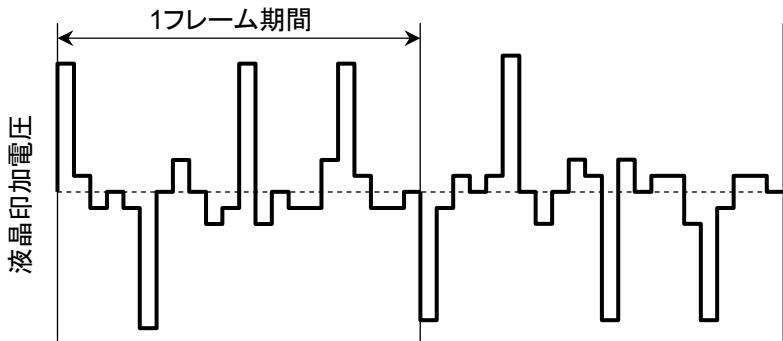

FRC 法と同じく 150Hz 以上であることが知られている[51][53]. MLA 法[7][8]は、先に述べた IHAT 法をベースとして、図 2.11 に示すように、 $m$  回の選択期間をフレームに分散し、非選択期間の長さを短くすることで、フレーム応答を抑制する。ここで、 $m$  回の選択期間をどの位に設定すれば良いかについては、フレーム応答の抑制効果と回路規模とのトレードオフがあり、 $m=4\sim 8$  が、最もコストパフォーマンスが良いとされている。AA 法[9][10]は、MLA 法を発展させ、全ての走査線を同時に選択する方法である。AA 法では、1 フレーム全てが選択期間であると考えることができ、図 2.12 に示すように液晶印加電圧波形のレベル変動量が少ない。これにより、フレーム応答が抑制され表示輝度も本来の実効値応答を示すようになる。しかしながら、MLA 法や AA 法は、直交関数との積和演算でデータ電圧を決定する際、同じ表示データを 1 フレーム期間に渡って何度も使用するため、フレームメモリが必要となる。さらに、上述した  $m=4\sim 8$  の場合、データ電圧が 7 ～15 レベル必要となるため、ドライバ IC の製造コストが上昇する可能性が高い。

図 2.11 MLA 法の液晶印加電圧波形

図 2.12 AA 法の液晶印加電圧波形

以上述べた、高速応答 STN-LCD 向けの各駆動法における製造コストの上昇要因を表 2.1 にまとめる。表 2.1 から分かるように、いずれの組み合わせにおいてもフレームメモリが

必要であるものの、ドライバ IC については空間変調 FRC 法の高フレーム周波数化と Hi-FAS 駆動の組み合わせが、最も出力レベル数が少ないため低コストであるといえる。そこで、この組み合わせを本章で提案する駆動法のベースとし、課題であるフレームメモリ追加およびシャドーイング増大の最小化を図る。

表 2.1 各種画質劣化対策法の課題

| # | 課題解決手段                  |            | 回路規模増加の要因 |             |

|---|-------------------------|------------|-----------|-------------|

|   | フリッカ抑制                  | 高コントラスト化   | フレームメモリ   | データ電圧レベル    |

| 1 | PHM 法                   | MLA 法／AA 法 | 必要        | 表示階調数以上     |

| 2 |                         | Hi-FAS 法   | 必要        |             |

| 3 | 空間変調 FRC +<br>高フレーム周波数化 | MLA 法／AA 法 | 必要        | 7 レベル以上     |

| 4 |                         | Hi-FAS 法   | 必要        | 2 または 3 レベル |

## 2.3 2 周波合成 FRC 法

本節では、前節で述べた低コスト化と画質劣化の課題を解決するため、2 周波合成 FRC 法の提案による必要フレームメモリ容量の削減と、2 周波合成 FRC 法で発生するシャドーイングの最小化方法を示す。

### 2.3.1 2 周波合成 FRC 法の考え方

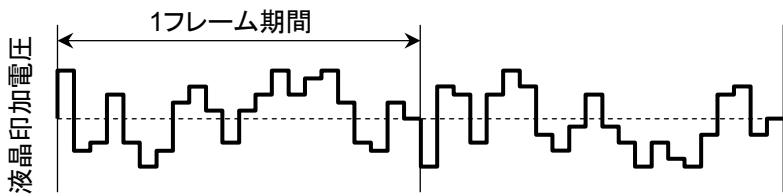

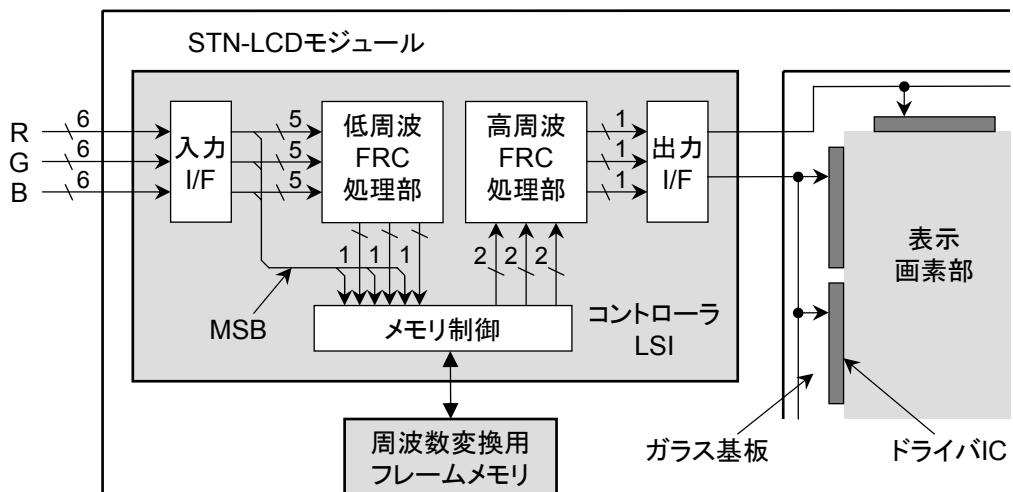

前節で述べたように、従来の空間変調 FRC 法を高フレーム周波数化する方法では、グラフィック処理のパフォーマンスを維持するためにフレームメモリを STN-LCD モジュール側に内蔵する必要があるため、コストアップを伴う。具体的な回路のブロック図は、図 2.13 に示す構成となる。ここで、空間変調 FRC 法を実現する処理ブロックに着目すると、入力の表示データは、RGB 各 6 ビットであるのに対し、出力は RGB 各 1 ビットである。つまり、空間変調 FRC 法におけるデータ処理は、表示データのビット削減処理と考えることもできる。したがって、例えば図 2.13 に示した空間変調 FRC 法のデータ処理をフレームメモリの前段に移動させれば、フレームメモリの容量を  $1/6$  まで削減することが可能である。しかし、この方法は、フレーム周波数は変化するものの表示オン／表示オフの切り替わり周波数自体が変化しないことが容易に考えられ、目的である高フレーム周波数化を実現することにはならない。

図 2.13 従来の高フレーム周波数駆動のブロック図

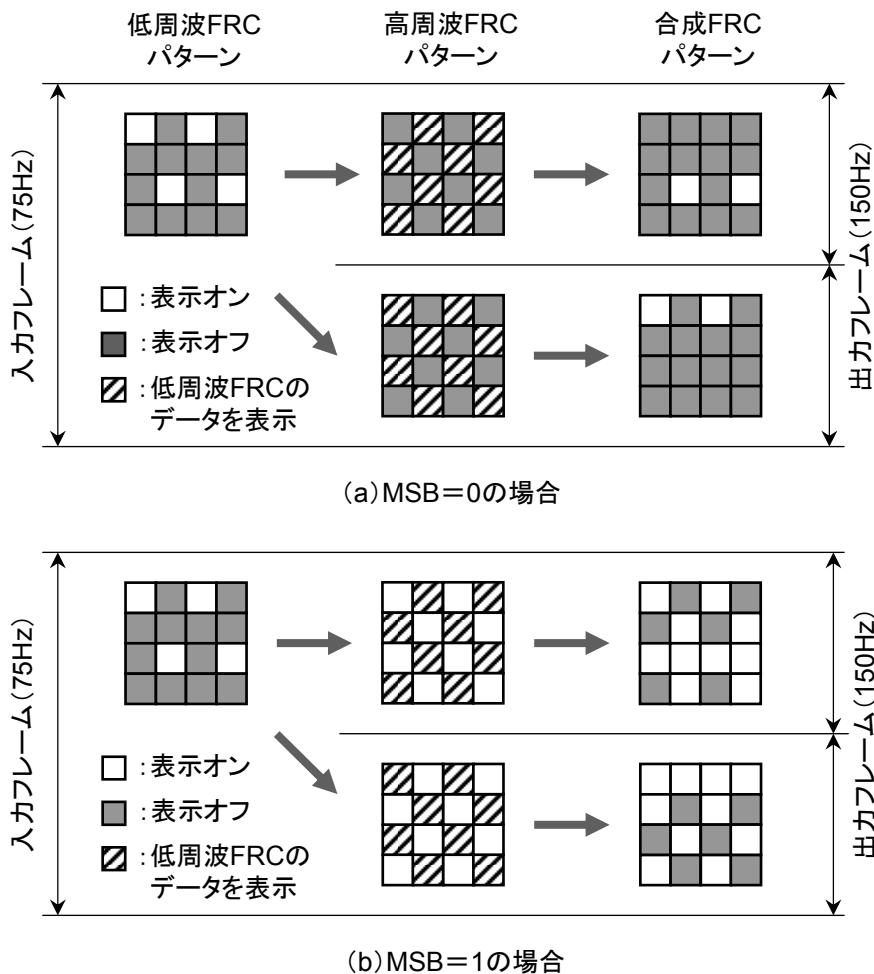

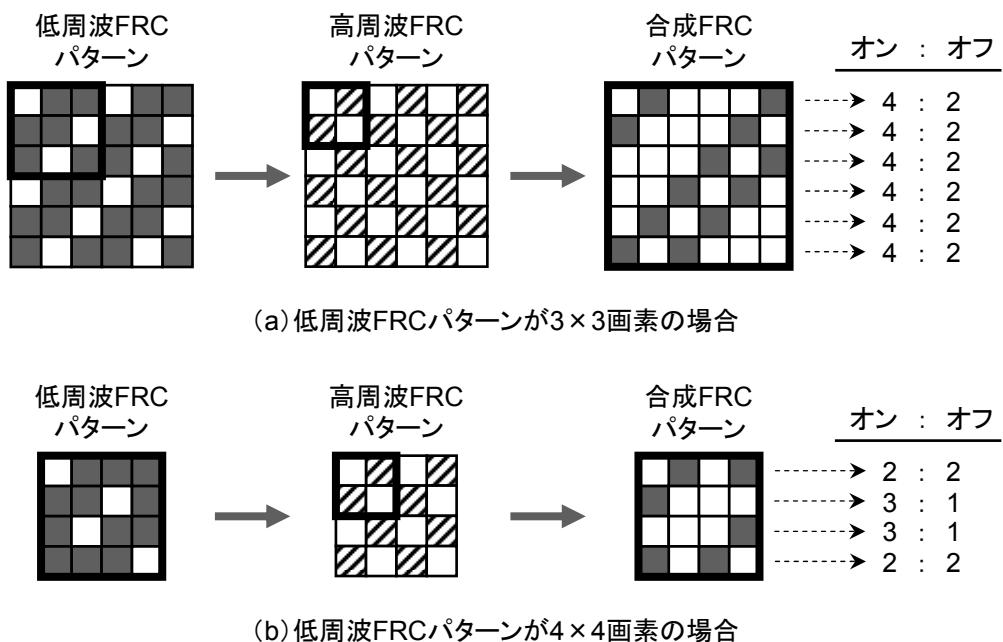

そこで、空間変調 FRC 法の処理を、フレーム周波数変換前に実施する低周波 FRC 处理部と、フレーム周波数変換後に実施する高周波 FRC 处理部に分離し、これらを組み合わせる 2 周波合成 FRC 法を提案する。2 周波合成 FRC 法では、図 2.14 に示すように低周波 FRC 处理部で表示データのビット数を削減と共に、高周波 FRC 处理部で FRC パターンの切り替わり周波数を高速化する。これにより、課題である空間変調 FRC 法のフリッカ抑制とフレームメモリ容量削減の両立を図る。

図 2.14 2 周波合成 FRC 法のブロック図

次に、2 周波合成 FRC 法の具体的な実現方法を以下に示す。まず、前述したように、フレーム応答と空間変調 FRC 法のフリッカを抑制可能なフレーム周波数は、双方共に 150Hz

以上と言わわれている。一方、現在の表示データのフレーム周波数は 60Hz～75Hz が一般的である。したがって、ホスト側の出力する表示データのフレーム周波数を 75Hz に設定し、これを STN-LCD モジュール側で 2 倍速に変換することで 150Hz を実現する。次に、高周波 FRC 処理部と低周波 FRC 処理部で処理を行う表示データのビットの割り当てについて述べる。まず、フレームメモリ容量削減の観点からは、低周波 FRC 処理部でできるだけ多くのビット数を割り当てることが望ましい。一方、フリッカ抑制の観点からは、高周波 FRC 処理部から出力される表示データには FRC 処理が施され、FRC パターンが毎フレーム変化していることが必要である。したがって、高周波 FRC 処理部には 1 ビット分を、低周波 FRC 処理部には残りのビットを割り当てるることにする。例えば、RGB 各 6 ビットの表示データの場合、下位 5 ビットを低周波 FRC 処理部で 1 ビットの低周波 FRC パターンに変換し、最上位ビット（Most Significant Bit, 以下 MSB）と共にフレームメモリへ書き込む。その後、フレームメモリから読み出される MSB を高周波 FRC パターンに変換し、同じくフレームメモリから読み出される低周波 FRC パターンとの合成を行う。高周波 FRC パターンは図 2.15 に示すように千鳥パターンをベースとし、低周波 FRC パターンと MSB データを 50%ずつ表示するためのフィルタ機能を実現する。例えば、MSB が“0”ならば、合成後の FRC パターンの 50%は表示オフ、残りの 50%は低周波 FRC パターンとなる。一方、MSB が“1”ならば、合成後の FRC パターンの 50%は表示オン、残りの 50%は低周波 FRC パターンとなる。この動作を実現する高周波 FRC 処理部は、1 画素毎に MSB と低周波 FRC パターンを交互に選択するセレクタ回路により容易に実現可能である。したがって、従来の FRC 処理と比較して回路規模が増大する問題は発生しない。なお、高周波 FRC パターンを千鳥パターンにする理由は、合成後の FRC パターンの空間周波数を高くすることがフリッカの抑制に有効なためである[63]。ここで、図 2.15 に示したように、高周波 FRC パターンは 150Hz で切り替わることから、合成後の FRC パターンも同様に 150Hz で切り替わる。したがって、2 周波合成 FRC 法を適用することにより、高速応答 STN-LCD の多階調表示において課題となるフリッカの発生を抑制することが可能である。

一方、合成後の FRC パターンによって表現される階調率：CPR は以下の式で算出することが可能である。ここで、LPR は低周波 FRC パターンの階調率である。ここで、LPR がとりうる値は 32 種類（5 ビット）であり、一方 MSB については 2 種類である。したがって、CRP がとりうる階調率の種類は、 $32 \times 2 = 64$  種類となる。つまり 6 ビット分の階調を表現することが可能である。

$$CPR = \frac{LPR + MSB}{2} \quad (2.15)$$

以上述べたように、2周波合成FRC法では、高速応答STN-LCDの多階調表示において課題となるフリッカの発生を抑制すると同時に、FRC処理部の回路規模を増大させることなく、高フレーム周波数変換に必要なフレームメモリの容量を従来の1/3(6ビット→2ビット)に削減することが可能である。

図 2.15 2周波合成FRC法におけるFRCパターンの合成イメージ

### 2.3.2 FRCパターンの最適化によるシャドーイング低減

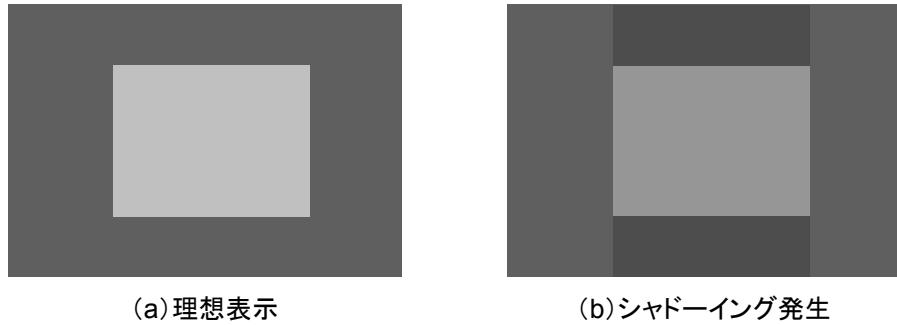

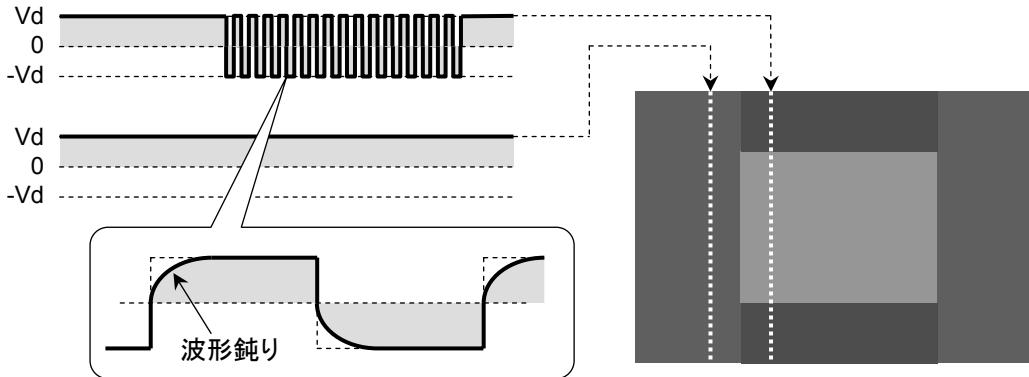

本節では、2周波合成FRC法における残りの課題であるシャドーイング低減について述べる。2.2.2節で示したとおり、高フレーム周波数駆動では1走査期間が短縮されること

から印加電圧波形の歪みの影響が相対的に大きくなり、その結果、液晶印加電圧実効値の変動量が増加する。この結果、図 2.16 に示すように、中間階調表示部の上下において、本来同じ表示輝度である背景部にシャドーイングと呼ぶ表示むらが発生する[43]。シャドーイングの主な発生要因の一つとして、中間階調表示部と背景部におけるデータ電圧の周波数の相違が挙げられる[44]。例えば、図 2.17 に示すように中間階調表示のデータ電圧の周波数が背景部よりも高い場合、電圧変化時の波形鈍りがより多く発生し、特に非選択期間の液晶印加電圧実効値を低下させる。この結果、中間階調表示部に関わるデータ線上の全画素の印加電圧実効値が、背景部に関わるデータ線上の画素に対して低くなるため、表示輝度の差となって現れる。

図 2.16 シャドーイング発生のイメージ

図 2.17 データ電圧波形鈍りに起因したシャドーイングのメカニズム

データ電圧の周波数の違いに起因するシャドーイングの解決にあたっては、中間階調表示部と背景部におけるデータ電圧の周波数差を縮小することが有効である。これを実現化可能な駆動方法として、IHAT 法における 2 ライン同時選択の変形である Hi-Addressing 法を適用する[51][52][53][61][64]。これにより一般的に使用されている APT 法に比べ、デ

ータ電圧の周波数の差を、約 40% 削減することが可能である。

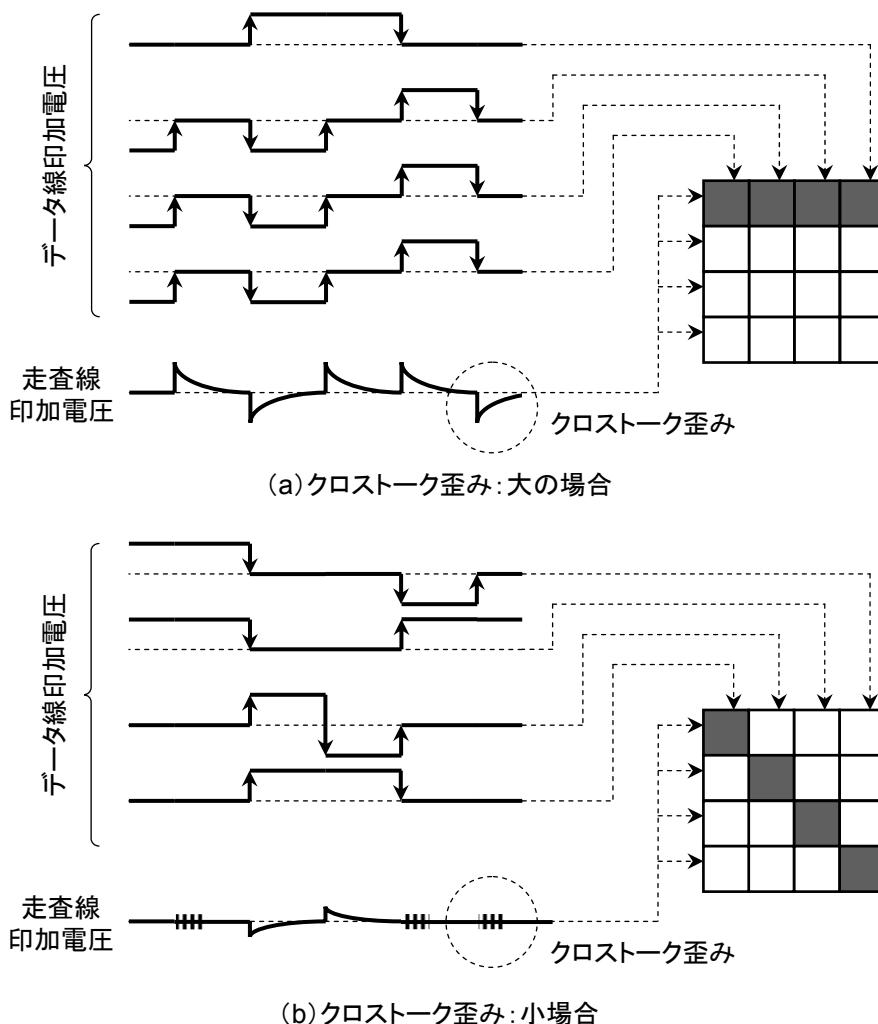

一方、シャドーイングの他の発生要因として、データ電圧の変動が液晶素子を介して走査線印加電圧へ誘導される、クロストーク歪みの発生がある。このクロストーク歪みの発生量は、FRC パターンに依存する。図 2.18 は、前述の Hi-Addressing 法を用いて、同じ階調率の 2 種類の FRC パターンを表示した際の液晶印加電圧波形を示したものである。図 2.18 (a) の FRC パターンの場合、全てのデータ電圧が同じ方向へ一斉に変化し、これによりクロストーク歪みが増大してシャドーイングが発生しやすい。これに対し、図 2.18 (b) の FRC パターンの場合は、データ電圧の変化方向が反対向きになる確率が高まり、クロストーク歪みが互いに相殺される。この効果により、シャドーイングの発生を大きく低減することが可能である。

図 2.18 FRC パターンとクロストーク歪みの関係

上記した点に着目すると、ある走査期間から次の走査期間への移行時、言い換えればデータ線方向に連続する画素において、表示オンから表示オフへ変化する数と表示オフから表示オンへ変化する数が等しい FRC パターンを生成すれば、クロストーク歪みを抑制することができる。このことは、FRC パターンを形成するマトリクス内において、表示オン／表示オフの割合が、どの行でも一定（図 2.18 (b) の場合、 $2 : 2$ ）という条件と等価である。以上のことから、2 周波合成 FRC 法においてクロストーク歪みを抑制するためには、合成後の FRC パターンがこの条件を満たす必要がある。ここで、高周波 FRC パターンについては、図 2.15 に示したように  $2 \times 2$  画素の千鳥パターンとし、このパターンについては固定とする。一方、低周波 FRC パターンについては、図 2.19 に示す  $3 \times 3$  画素のマトリクスと  $4 \times 4$  画素のマトリクスについて比較する。なお、これらの低周波 FRC パターンは共に、表示オンと表示オフの割合がどの行でも一定である。まず、 $3 \times 3$  画素の低周波 FRC パターンの場合、合成後の FRC パターンのマトリクスサイズは、低周波 FRC パターンと高周波 FRC パターンのマトリクスサイズの最小公倍数であることから  $6 \times 6$  画素となる。このとき、合成後の FRC パターンは、マトリクス内における表示オン／表示オフの割合が全ての行で  $4 : 2$  となり、先に述べたクロストーク歪み抑制の条件を満たす。一方、 $4 \times 4$  画素の低周波 FRC パターンとの合成では、合成後の FRC パターンのマトリクスサイズは  $4 \times 4$  画素となり、マトリクス中における表示オン／表示オフの比が行毎に異なる。

図 2.19 各種低周波 FRC パターンに対する合成 FRC パターン

上記の違いについて考察すると、 $3 \times 3$  画素マトリクスの場合、例えば偶数列に位置する表示オンは、左右に隣接する  $3 \times 3$  画素マトリクスにおいては奇数列に位置する。このため、高周波 FRC パターンと合成しても、表示オンがそのまま表示される確率は全ての行で 50% となる。これに対し、 $4 \times 4$  画素マトリクスの場合は、偶数列に位置する表示オンは、左右に隣接する  $4 \times 4$  画素マトリクスにおいても偶数列に位置する。このため、高周波 FRC パターンと合成しても、表示オンがそのまま表示される確率が 50% とならない。逆に、この確率を全ての行で 50% にするためには、マトリクス内の全ての行において、表示オンの数が偶数列と奇数列とで等しくする必要がある。以上をまとめると、2 周波合成 FRC 法においてクロストーク歪みを抑制するためには、低周波 FRC パターンに対して以下の 2 つの条件を同時に満たせば良い。

- (1) マトリクス内の全ての行において、表示オン／表示オフの割合が等しい

- (2) 行方向のマトリクスサイズが奇数である。または、マトリクス内の全ての行において、表示オンの数が偶数列と奇数列とで等しい。

## 2.4 適用結果と考察

本節では、提案した多階調表示方法を実際の STN-LCD に適用し、表示特性を評価することにより、提案方法の有用性について検証を行う。

### 2.4.1 適用対象

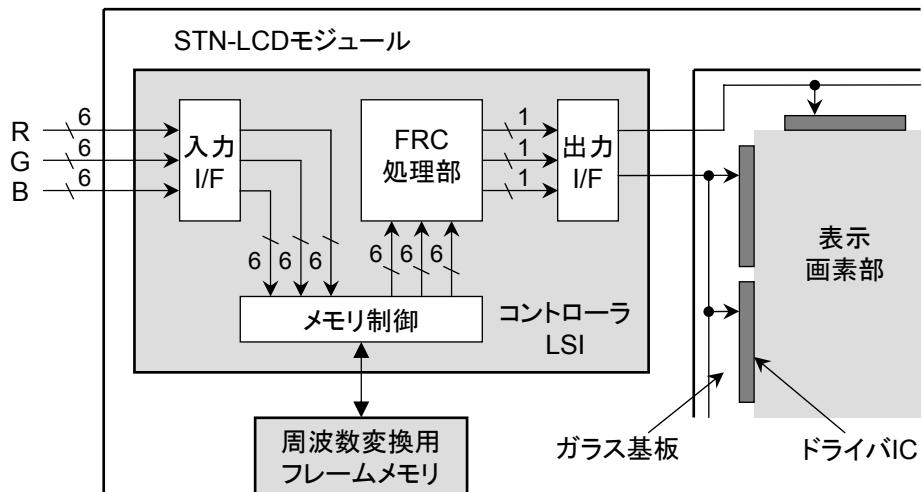

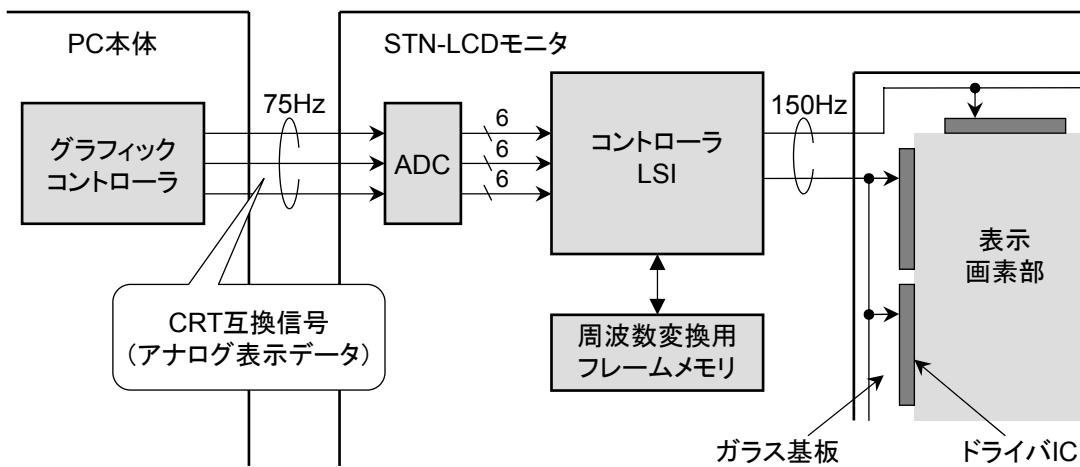

提案方法を適用した STN-LCD の主な仕様を表 2.2 に示す。この STN-LCD は、デスクトップ型 PC 用のモニタが主な用途である。このため、CRT モニタとの互換性確保を目的に、PC 本体のグラフィックコントローラからはフレーム周波数 75Hz の CRT 用アナログ表示データを受け取る。そして、図 2.20 のブロック構成に示すように、モニタ内部にある ADC (Analog Digital Convertor) により入力データを RGB 各 6 ビットのデジタル表示データに変換し、コントローラ LSI へ出力する。コントローラ LSI では、図 2.13 で示した各種の信号処理を行い STN-LCD 用の 1 ビットの表示データに変換し、ドライバ IC に転送する。

表 2.2 評価に用いた STN-LCD の主な仕様

| # | 項目    | 仕様                |

|---|-------|-------------------|

| 1 | 解像度   | 1024×768 画素       |

| 2 | 画面サイズ | 15.5 インチ          |

| 3 | 表示色数  | 26 万色             |

| 4 | 応答時間  | 150ms (立上り + 立下り) |

図 2.20 STN-LCD の表示系のブロック構成

#### 2.4.2 提案方法の性能評価と考察

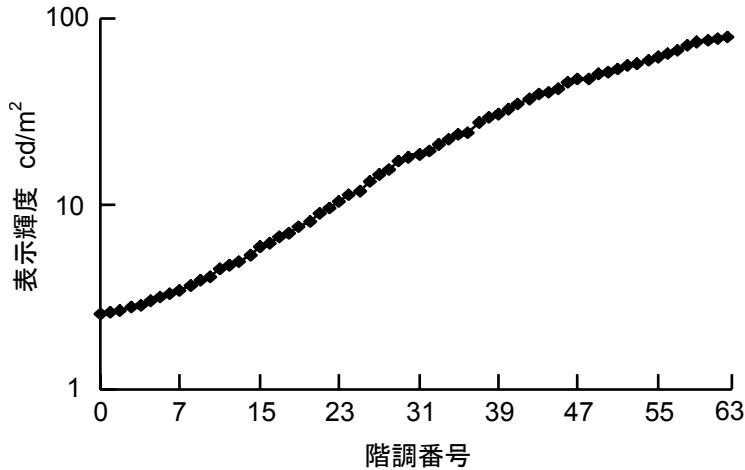

上記の STN-LCD に対し、画質評価用のテストパターンを実際に表示させて表示特性の評価を行った。図 2.21 は、全画面をグレー階調でべた塗り表示させた場合の、階調番号と表示輝度の関係を示したものである。グラフの横軸である階調番号は表示データと一致しており、表示データは RGB 各 6 ビット (64 階調表示) であることから 0~63 の値をとる。グラフの縦軸は表示輝度の測定値であり、測定ポイントは画面中央、測定装置はコニカミノルタホールディングス（株）製の色彩輝度計 CS-100A である。なお、表示画面をグレー階調の全面べた塗りにした理由は、シャドーイングによる輝度変動の影響を最大にするためである。仮にシャドーイングの影響を受ける階調が存在すると、階調番号に対する表示輝度のカーブが不連続となり、場合によっては隣接階調間で表示輝度が逆転することが予想される。したがって、カーブが滑らかに遷移するほど、シャドーイングの発生が抑制されていると評価することができる。図 2.21 から分かるように、提案方法は若干の不連続

性はあるものの表示輝度の逆転はなく、階調番号（表示データ）に応じて異なる表示輝度の階調表示を実現できていることが分かる。

図 2.21 階調番号－表示輝度特性

次に、フリッカに対する評価結果について示す。前節で述べたように、応答時間：150ms の液晶において、空間変調 FRC 法で発生するフリッカを抑制可能なフレーム周波数は 150Hz 以上である。そこで、各階調を実際に表示させてフリッカの有無を目視にて観測した。その結果、表 2.3 に示すように、フリッカが識別可能な階調（評価：△）が散見されたものの、同じ程度のフリッカは従来の 350ms 応答の製品においても発生していることから、実用上問題ないレベルである。以上のことから、2 周波合成 FRC 法におけるフリッカの抑制効果は妥当であるといえる。なお、評価：△の階調が離散的に発生している理由は、FRC パターンの完結周期が階調毎に異なるためであり、特に完結周期が長い階調に△が多い。

次に、提案の多階調表示方法におけるフレーム応答の抑制効果について述べる。図 2.9 で示したように、フレーム応答が発生している場合、選択期間では黒の輝度が上昇し、非選択期間では白の輝度が低下するため、結果としてコントラストが低下する。したがって、コントラストを測定することでフレーム応答の発生を間接的に評価できる。図 2.22 はフレーム周波数とコントラスト比の関係を示したものである。コントラスト比は、全画面白表示時と全画面黒表示時の表示輝度の比であり、測定ポイントは画面中央、測定装置はニカミノルタホールディングス（株）製の色彩輝度計 CS-100A である。図 2.22 からフレーム周波数が高くなるにしたがってコントラストは上昇し、提案のフレーム周波数である 150Hz 以上においてほぼ飽和していることが分かる。以上の結果から、本提案の 2 周波合成 FRC 法に適用により、フレーム応答を抑制できていることが分かる。

表 2.3 フリッカ発生の目視評価結果

| 階調 | 評価結果 | 階調 | 評価結果 | 階調 | 評価結果 | 階調 | 評価結果 |

|----|------|----|------|----|------|----|------|

| 0  | ○    | 16 | ○    | 32 | ○    | 48 | ○    |

| 1  | △    | 17 | ○    | 33 | ○    | 49 | ○    |

| 2  | △    | 18 | ○    | 34 | △    | 50 | ○    |

| 3  | △    | 19 | ○    | 35 | ○    | 51 | ○△   |

| 4  | ○    | 20 | ○    | 36 | ○    | 52 | ○    |

| 5  | ○    | 21 | ○    | 37 | ○    | 53 | ○    |

| 6  | ○    | 22 | ○    | 38 | ○    | 54 | ○    |

| 7  | ○    | 23 | ○    | 39 | ○    | 55 | △    |

| 8  | ○    | 24 | ○    | 40 | ○    | 56 | ○    |

| 9  | ○    | 25 | ○    | 41 | ○    | 57 | ○    |

| 10 | ○    | 26 | ○    | 42 | ○    | 58 | ○    |

| 11 | ○    | 27 | ○    | 43 | ○    | 59 | ○    |

| 12 | △    | 28 | ○    | 44 | ○    | 60 | △    |

| 13 | ○    | 29 | ○△   | 45 | ○    | 61 | △    |

| 14 | ○    | 30 | ○    | 46 | ○    | 62 | △    |

| 15 | ○    | 31 | ○    | 47 | ○    | 63 | ○    |

○：見えない、△：識別可能（実用レベル）、×：気になる

図 2.22 フレーム周波数とコントラスト比の関係

## 2.5 結言

本章では、従来の多階調表示方法を高速 STN-LCD に適用した際に課題となるフリッカの発生、およびフレーム応答によるコントラスト低下に対し、これらを同時に抑制する高フレーム周波数駆動法を提案した。また、高フレーム周波数駆動法を実現する上でのフレームメモリの増加問題に対し、必要メモリ数を従来の  $1/3$  に削減可能な 2 周波合成 FRC 法を提案した。さらに、高フレーム周波数駆動法におけるシャドーイングの増大の問題を、Hi-Addressing 法の適用および FRC パターンの最適化により抑制する方法を提案した。最後に、これらの提案方法を応答時間 : 150ms の PC モニタ向け STN-LCD に適用し、以下の評価結果を得た。

- (1) 64 階調全てにおいて、隣接階調間で輝度が逆転する等の不具合は確認されなかった。

- (2) フレーム周波数 150Hz にて、全ての階調のフリッカレベルが実用域であった。

- (3) フレーム周波数 150Hz にて、フレーム応答によるコントラスト低下を抑制した。

以上の結果から、モニタ用途に適用可能な表示性能と製造コストを両立できることを確認し、提案方法の有効性を実証した。提案の多階調表示方法は、(株)日立製作所製 FLORA Prius 330 に適用されている。図 2.23 に製品の写真を示す。

図 2.23 提案方法を搭載した製品の写真

今後の課題として、TFT-LCDにおいて適用が進んでいるガンマ補正への対応が挙げられる。今後、低価格帯の情報機器においても、画像をより忠実に再現する要求が強くなると考えられ、この実現にあたってはガンマ補正を中心とした色調整が必要である。STN-LCDにおけるガンマ調整は、FRC法における表示オン／表示オフの点灯比率を、階調番号（表示データ）に応じて適正に最適化することが考えられる。しかしながら、この実現にあたっては、FRCパターンの完結周期を長くし、より細かい表示オン／表示オフの点灯比率を設定できるようにする必要がある。例えば64階調の場合、最低でも完結周期を256フレームとして256階調を用意し、その中から適切な64階調を選ぶ必要がある。この際、FRCパターンの完結周期の長期化に伴う回路規模の増大、およびフリッカの増加が予想されるため、これらの解決が今後の課題である。

## 第 3 章

# モバイル機器向け TFT-LCD の小回路規模多階 調化方法

### 3.1 緒言

本章では、モバイル機器向け TFT-LCD の多階調表示において、これを実現するドライバ IC の回路規模を削減する方法を提案し、低コストな TFT-LCD の提供を実現する。

TFT-LCD は、STN-LCD と同様に直交するデータ線と走査線の交点で画素を形成し、その交点を駆動する。STN-LCD と異なる点は、画素毎に TFT によるアクティブ素子および保持容量を形成していることであり、選択電圧が印加される期間のデータ電圧のみが TFT を通じて液晶素子に印加され、次の選択期間までデータ電圧は保持容量により保持される。この特徴により、TFT-LCD は高コントラスト化や高速応答化といった高画質化が可能となる。しかしながら、今後 TFT-LCD をさらに普及させるためには低コスト化が必須課題であり、製造技術の向上によるガラス基板の原価低減と同時に、周辺部品の原価低減も必要である。その中でも、ドライバ IC の価格は総原価の 2 割以上を占めると言われており、低コスト化が大きな課題となっている。

一方、近年のモバイル機器においては、DSC の撮影画像やワンセグ放送の画像等を視聴する機会が増え、これらの画像を違和感なく表現するための多色表示がディスプレイに求められている。これを受け、現在市販されている携帯電話の色数は、従来の 256 色表示（8 ビットカラー）から 26 万色表示（18 ビットカラー）へと主流が移行している。しかしながら、表示色数の増加はドライバ IC のチップサイズの増大、すなわちコストアップに直接反映する。この理由は、TFT-LCD ではデータ電圧のレベルによって多階調を表現するためであり、具体的には表示データをデータ電圧に変換する DAC の回路規模（入力ビット数）が増大する。以上のことから、TFT-LCD の多階調表示を実現するためには、ドライバ IC のチップサイズ、特に DAC の回路規模増大を如何に抑制するかが課題となる。

従来、ドライバ IC のチップサイズを削減する手段として、データ線毎に搭載される DAC

の 1 個あたりの回路規模を削減するアプローチと, DAC の搭載個数を削減するアプローチが提案されている。前者のアプローチの実現方法として, FRC 法による表示データのビット数削減を DAC の前段で実施し, DAC の入力ビット数を削減する方法が提案されている[65]。しかしながら、この方法は TFT-LCD の応答時間が STN-LCD よりも 1 衍速いことからフリッカが発生しやすい。このため, FRC 法の適用は, 表示輝度差の極力少ない 2 階調間, 例えば RGB 各 6 ビット階調であれば最下位ビットの表現のみに限定されている。

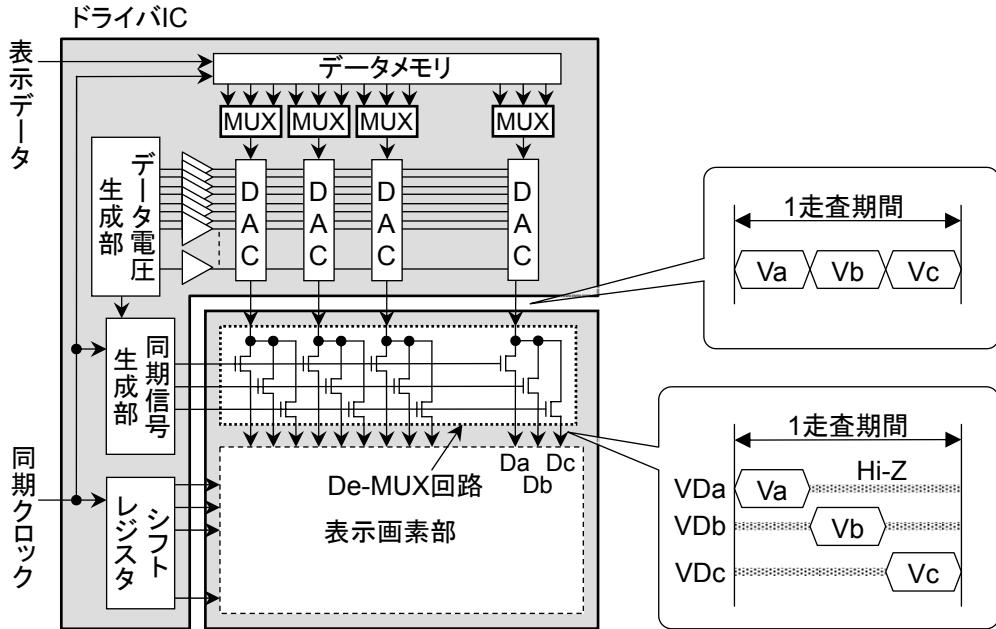

一方, 後者のアプローチである DAC 搭載個数の削減については, 複数のデータ線に対応するデータ電圧をドライバ IC からマルチプレックスして出力し, ガラス基板上に形成されたデ・マルチプレクサ回路で各データ線に分配する, データ線時分割駆動法が提案されている[29][66][67]。しかしながら、この方法はガラス基板に形成するデ・マルチプレクサ回路に高速のスイッチ動作を必要とするため, 高速スイッチングが可能な低温ポリシリコン TFT-LCD にその適用が限定されている。以上のことから, 本研究の課題を解決するためには, ドライバ IC の主要回路である DAC の回路規模を画質劣化なく削減すると同時に, アモルファスシリコン TFT-LCD にも適用できるように, ガラス基板に搭載する回路を不要にする新たな駆動方法が必要である。

本章では, データ電圧をマルチプレックスして DAC に与えることで, DAC の入力ビット数を削減できる点に着目し, 表示データの下位ビットに相当するデータ電圧を 1 走査期間でマルチプレックスして DAC に入力し, マルチプレックスの順番と表示データの下位ビットとが一致するタイミングでドライバ IC からデータ電圧を出力する, 階調時分割駆動法を提案する。提案方法の適用により, DAC の入力ビット数は表示データの上位ビット分のみとなり, ドライバ IC のチップサイズ削減効果が図れると同時に, パネル側に搭載する回路も不要となる。一方, 階調時分割駆動法においては, 1 走査期間の特定期間のみデータ電圧を出力することから, 例えば 1 走査期間の前半で出力されたデータ電圧は, 後半の期間ではデータ線の寄生容量により保持されることになる。ここで, データ線からのリーク電流や, 隣接するデータ線からの外乱がある場合, 保持されたデータ電圧が変動する可能性が高い。そこで, データ電圧の出力タイミングの最適化, およびデータ電圧の補正機能を追加するアプローチによりデータ電圧変動の影響を最小化する。

以下, 3.2 節では, 従来の多階調表示方法について説明し, 問題点と課題を明らかにする。3.3 節では, 提案方法である時分割駆動法によるドライバ IC のチップサイズ削減, およびこの方法における課題点の解決方法について説明する。3.4 節では, 提案方法を適用したドライバ IC の性能評価, TFT-LCD の画質評価の結果および考察について述べ, 本方法の有用性を示す。

## 3.2 従来の多階調表示方法と問題点

本節では、TFT-LCD における従来の多階調表示方法について説明し、モバイル機器用途に適用する際の問題を明らかにする。

### 3.2.1 小回路規模化問題

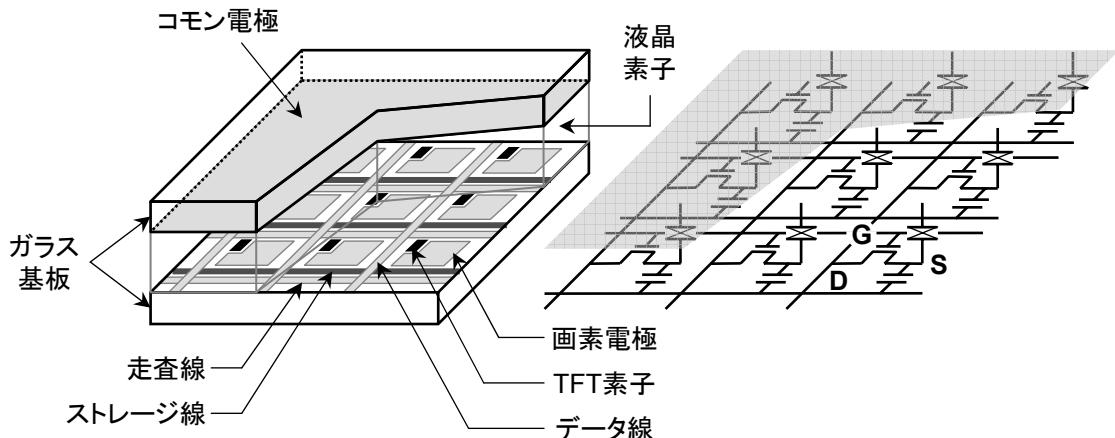

TFT-LCD の構造は、図 3.1 に示すように、複数のデータ線と走査線がマトリクス状に形成され、それぞれの交点に画素が形成される。各画素部にはアクティブ素子である TFT が配置され、ゲート端子 (G) に走査線が、ドレイン端子 (D) にはデータ線が接続される。さらにソース端子 (S) は保持容量と液晶素子に接続され、保持容量の対向側はストレージ線、液晶素子の対向側はコモン電極に接続される。

図 3.1 TFT-LCD の構造と等価回路

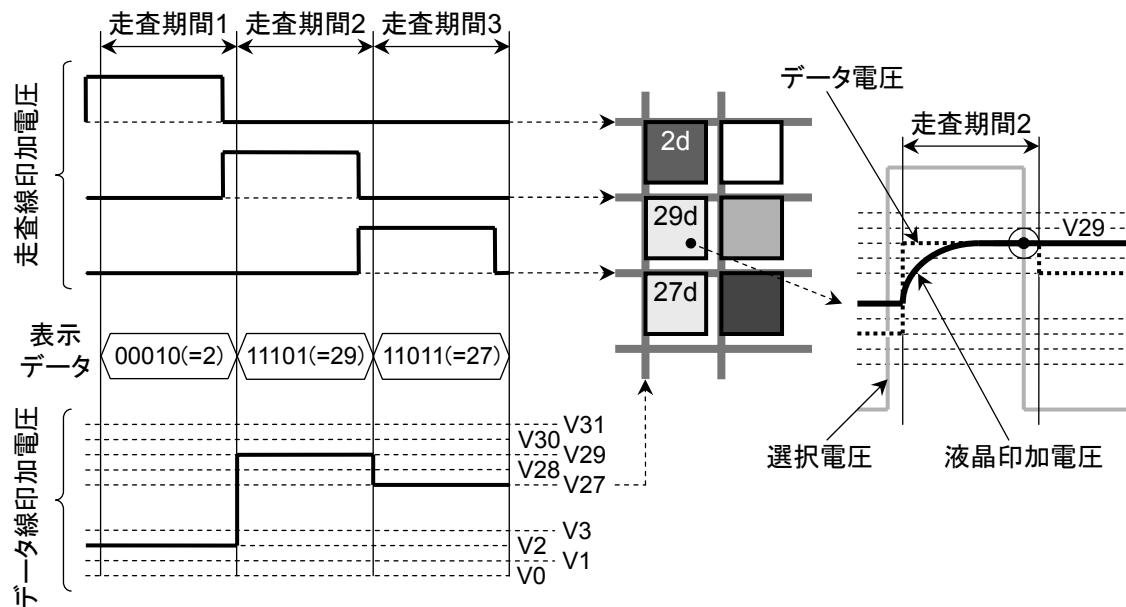

一方、TFT-LCD のガンマ特性は、図 3.2 に示すように液晶印加電圧に応じて表示輝度が変化する。TFT-LCD の駆動法としては、図 3.3 に示す線順次走査法が一般に用いられる[68]。線順次走査法では、TFT をオン状態にして画素を書き込み状態するための選択電圧を、先頭の走査線から 1 走査期間ずつ順次印加する。データ線には、書き込み状態にある画素に対し、表示データに応じたデータ電圧を印加する。例えば図 3.3 に示すように、5 ビット (32 階調) の表示データが”00010”の場合は V2 を印加し、表示データが”11101”的場合は V29 を印加する。次に、印加されたデータ電圧は、TFT を介して保持容量に供給される。電圧供給後は、TFT が次の走査線選択のためにオフ状態になっても、データ電圧

が保持される。ここで、ストレージ線とコモン電極には共通のコモン電圧が印加される。したがって、液晶素子にはデータ電圧とコモン電圧の差電圧が印加され続け、次のフレームまで表示輝度を維持することができる。なお、TFT-LCD では表示オン／表示オフ間のデータ電圧を自由に設定できるため、ガンマ特性を STN-LCD と比べて緩やにすることが可能である。これにより、液晶印加電圧の目標値からのずれに対する表示輝度の変動マージンが拡大する共に、データ電圧のダイナミックレンジを 5V 程度と大きく設定し、充分なコントラスト比を確保することができる。

図 3.2 TFT-LCD のガンマ特性

図 3.3 線順次走査法の駆動波形

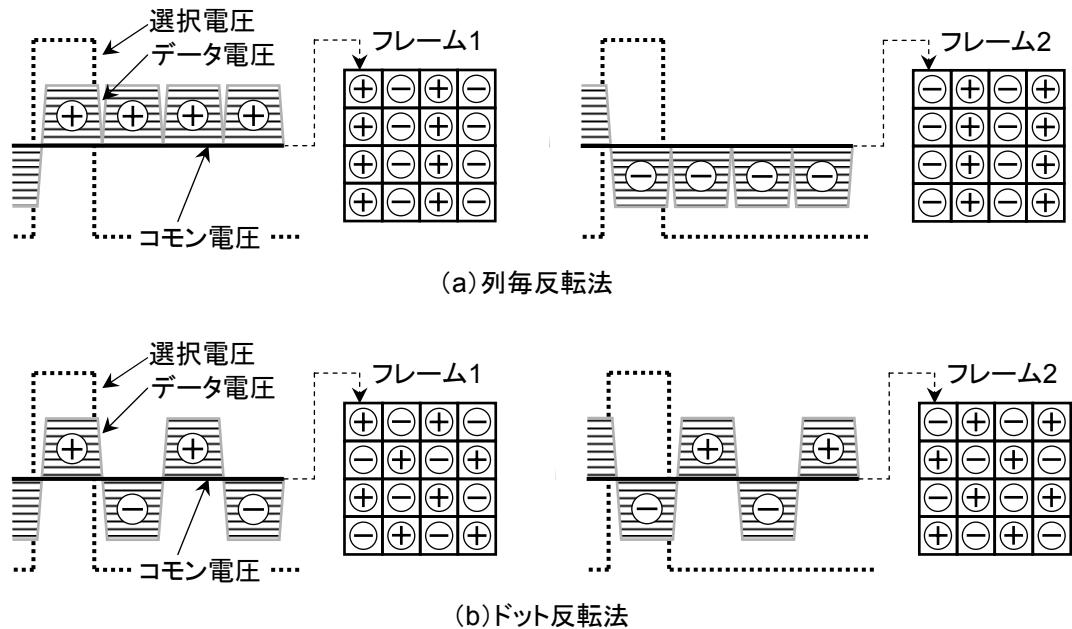

ここで、TFT-LCD では STN-LCD と同様に、液晶に直流電圧を長時間印加すると残像現象や劣化が発生するため[69][70]、液晶印加電圧の極性を一定周期で反転させる交流化を行う。交流化を実現する駆動方法としては、図 3.4 に示すようにコモン電圧を固定とし、これを基準に正極側と負極側のデータ電圧をフレーム毎に交互に印加する方法が提案されている。しかし、あるフレームで全ての画素に同じ極性を印加すると、正極性と負極性における僅かな液晶印加電圧の差が画面全体の輝度変動となるため、上記の方法はフリッカとして知覚されやすい。そこで、画面内に正極性と負極性の画素を混在させることでフリッカを抑制することを目的に、データ線毎に異なる極性を与える列毎反転法や、画素毎に異なる極性を与えるドット反転法が提案され、実用化されている[71][72][73]。

図 3.4 コモン電圧固定法

列毎反転法やドット反転法においてはコモン電圧が固定レベルであることから、データ電圧のダイナミックレンジは 10V 前後必要となる。このため、これらの駆動方法を実現するためのドライバ IC は高耐圧プロセスが必要となり製造コストが上昇する。この課題を解決する方法として、コモン電圧のレベルを 1 走査期間毎に振幅させることで、相対的な電位差を確保するコモン電圧反転法が提案されている[74][75]。コモン電圧反転法では、図 3.5 に示すように、例えば表示オン時のデータ電圧が 5V の場合、コモン電圧を 0V と 5V に設定することで、データ電圧のダイナミックレンジを 5V にすることが可能となる。

このため、標準的ロジックプロセスを用いてドライバ IC を製造することが可能となり、製図コストの削減に大きく貢献することができる。しかしながら、コモン電圧反転法では、表示パターンに依存してデータ電圧が一斉に同じ方向へ変化する場合があり、前章の図 2.18 で示した STN-LCD の場合と同様のメカニズムでコモン電圧へのクロストーク歪みが発生しやすい。この結果、走査線数が多い（1 走査期間が短い）高解像度パネルやコモン線の寄生容量の大きい大画面パネルを駆動する際は、コモン電圧のクロストーク歪みが 1 走査期間内に収束しきれず、所望の液晶印加電圧を書き込めない場合がある。その結果、横スメアと呼ぶ前章のシャドーイングと同様の表示むらが発生する[76]。

図 3.5 コモン電圧反転法

以上、説明した各種駆動方法の特徴を表 3.1 にまとめる。表 3.1 から分かるように、各駆動方法には製造コストや画質等で一長一短があるため、高画質が優先される大型テレビ用途にはドット反転法が、低コストが優先されるモバイル機器用途にはコモン電圧反転法が現在では主に適用されている[77][78]。

表 3.1 各種駆動方法の特徴比較

| # | 項目      | 列毎反転法                     | ドット反転法 | コモン電圧反転法 |

|---|---------|---------------------------|--------|----------|

| 1 | データ電圧振幅 | 10V 前後                    | 10V 前後 | 5V 前後    |

| 2 | 画質      | 縦スメア懸念                    | 良好     | 横スメア懸念   |

| 3 | パネル消費電力 | 列毎反転法 < コモン電圧反転法 < ドット反転法 |        |          |

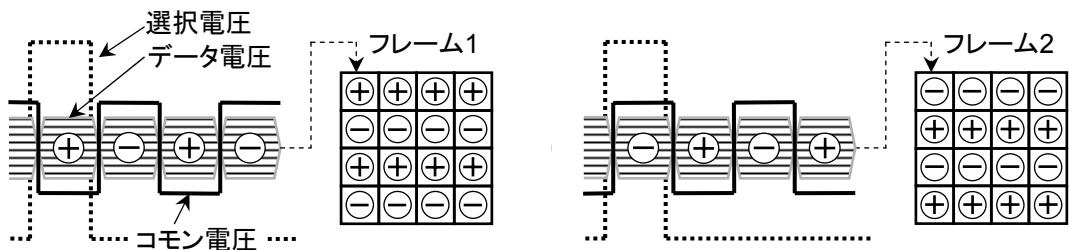

図 3.6 は、上記したコモン電圧反転法を実現するためのドライバ IC の構成図である。図 3.6 に示すように、走査側には選択電圧を出力するためのシフトレジスタ、データ側には 1 ライン分の表示データを格納するデータメモリと、データメモリから出力される表示データをデータ電圧に変換するための DAC を搭載する。なお、コモン電圧の生成回路に

については、単純な矩形波の生成回路であるためここでは省略する。次に、データ電圧の出力回路について述べる。まず負荷容量が大きい大型 TFT-LCD を駆動する場合、図 3.6 (a) に示すように DAC の出力毎に OP (Operational) アンプによるボルテージフォロア回路を設け、低インピーダンス化して駆動能力を高くする分散アンプ型構成が実用化されている[79]。一方、モバイル機器向け TFT-LCD のような負荷容量の小さいパネルを駆動する場合、比較的低い駆動能力でも 1 走査期間内でデータ電圧を収束させることが可能である。そこで、図 3.6 (b) に示すように DAC の前段にボルテージフォロア回路を設け、OP アンプの搭載個数を削減する集中アンプ型構成が提案され、実用化されている[77][80]。

図 3.6 ドライバ IC の出力回路構成

集中型アンプ構成においては、表示する色数を増加すると OP アンプの搭載個数が増加する課題がある。例えば、4096 色表示 (RGB 各 4 ビットの 12 ビットカラー) の場合、データ電圧は RGB 各 16 レベルであるから、OP アンプの必要搭載数は 16 個で良い。一方、26 万色表示 (RGB 各 6 ビットの 18 ビットカラー) の場合は、OP アンプの必要搭載数は 64 個と 4 倍必要となる。したがって、集中アンプ構成のドライバ IC を低コストで実現するためには、多階調表示を如何に少ない回路規模で実現するかが重要な課題となる。

### 3.2.2 従来の小回路規模化方法の問題と課題

集中アンプ型構成を前提とした回路規模削減の解決アプローチとして、DAC の 1 個あたりの回路規模を削減する手段と、DAC の搭載個数を削減する手段が提案されている。前

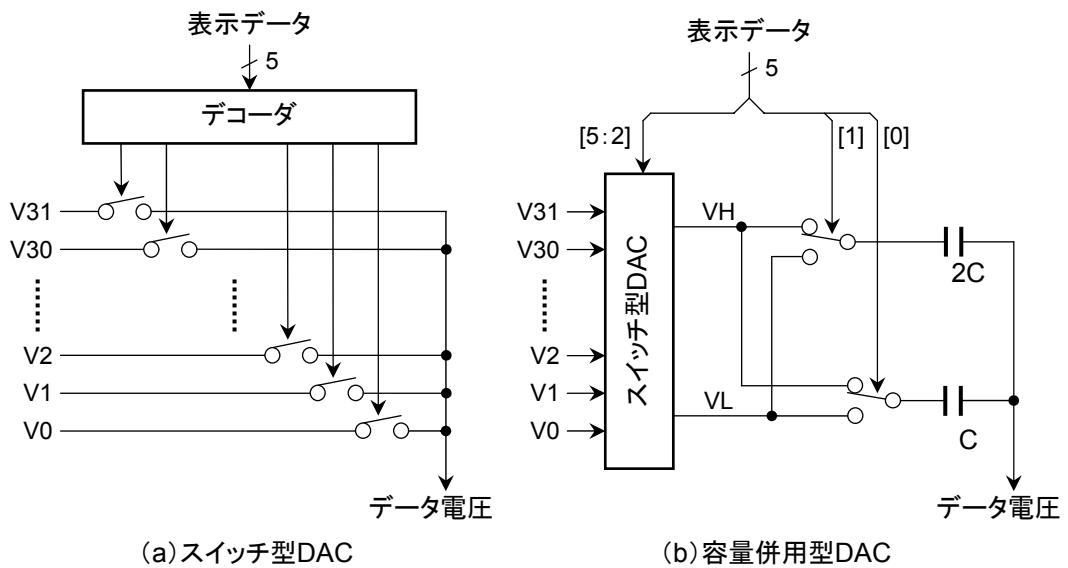

者のアプローチの一つは、DAC の入力ビットを削減して分解能を下げる事であり、この実現方法として FRC 法による表示データのビット数の削減処理を、DAC の前段に設ける方法が提案されている[65]。FRC 法は前章の STN-LCD 用の多階調表示法と同じく、複数フレームを 1 周期とし、フレーム毎に表示オン／表示オフの点灯回数を制御する方法である。しかし、TFT-LCD では応答時間が STN-LCD よりも 1 行速いことから、FRC 法を表示輝度差の大きい 2 階調間に適用するとフリッカが顕著となる。このため、FRC 法の適用は、表示輝度差の極力少ない 2 階調間、例えば RGB 各 6 ビット階調であれば最下位ビットの表現のみに限定されている。一方、同様のアプローチとして、ディザリング法による表示データのビット数削減も提案されている[29]。この方法は、フリッカを抑制できるものの、解像度の低下感が知覚されるため、現在ではほとんど採用されていない。また、DAC の 1 個あたりの回路規模を削減する別のアプローチとして、DAC の回路構成を簡素化する容量併用型 DAC が提案されている[81][82]。この方法は、図 3.7 に示すように、従来型の DAC はスイッチ素子で構成するのに対し、下位ビット分についてはリニア変換しても実用上問題ないことに着目し、この部分の DAC を容量分割によって実現して回路規模を削減するものである。しかしながら、この方法は、DAC の出力をそのままデータ線に接続すると電圧レベルが変動するため、これを防止するためには DAC の出力毎にボルテージフォロア回路を設ける分散アンプ型構成が前提となる。したがって、対象とする集中アンプ構成には適用が困難である。

図 3.7 DAC の各種実現回路

次に、回路規模削減の後者のアプローチである DAC の搭載個数を削減する方法としては、データ線時分割駆動法が提案され、実用化されている[29][66][67]。データ線時分割駆動法は、例えば図 3.8 に示すように、隣接する 3 本のデータ線を 1 つのグループとして扱う。ドライバ IC は、1 走査期間を 3 分割し、上記した 3 本分のデータ電圧をマルチプレックスして出力する。一方、TFT-LCD のパネル側はデ・マルチプレクサ回路を搭載し、データ電圧を分配して各データ線に出力する。図 3.3 で示した動作との違いは、データ線にデータ電圧を印加するタイミングが、データ線によって異なる点である。しかし、1 走査期間の終了時には全てのデータ線にデータ電圧が印加されるため、線順次駆動法としての目的を果たすことが可能である。なお、1 走査期間の最初の分割期間でデータ電圧が印加されるデータ線は、その後の分割期間ではフローティング状態となるが、データ線自身に寄生容量を有するため、印加されたデータ電圧の電位を保持することが可能である。以上の動作原理により、データ線をグループ化して時分割で駆動しても正しい表示が可能であり、グループ化するデータ線の本数が 3 本の場合、ドライバ IC の DAC 搭載数と出力ビン数を、それぞれ 1/3 に削減することができる。

図 3.8 データ線時分割駆動法

一方、前述のデ・マルチプレクサ回路を実現するためのスイッチング素子は、1 走査期間に複数のデータ電圧を分配するだけの動作速度が要求される。ここで、モバイル向け TFT-LCD の画素部に広く採用されているアモルファスシリコン TFT の電子移動度は

$0.5\text{cm}^2/\text{Vs}$  程度[34][35]であり、ガラス基板に形成する上での標準的な設計ルール、および一般的なドライバICの出力電圧範囲に基づき動作周波数を算出すると約 20~40kHz となる。これに対し、データ線時分割駆動法を実現するために必要な動作周波数は下記の式 (3.1) から算出することができる。ここで、 $F_s$  は必要となるスイッチング周波数、 $F_f$  はフレーム周波数、 $N$  は走査線数、 $D$  は分割数である。例えば、図 3.8 で示した 1 走査期間を 3 分割する駆動法において、フレーム周波数: 60Hz、走査ライン数: 320 本とした場合、式 (3.1) から  $F_s$  は約 60kHz となる。このため、アモルファスシリコン TFT をデ・マルチプレクサとして適用することは、動作周波数が不足しているため困難である。

$$F_s = F_f \cdot N \cdot D \quad (3.1)$$

以上のことから、データ線時分割出力法を実現するにあたっては、アモルファスシリコン TFT よりも 1~2 衍移動度が大きく[36][37][38]、高速スイッチングが可能な低温ポリシリコン TFT-LCD のみにその適用が限定されている。

### 3.3 階調時分割駆動法

本節では、前節で述べた課題を解決するため、DAC の回路規模を削減しつつ、アモルファスシリコン TFT-LCD にも適用できるように、パネルに搭載する回路を不要にする階調時分割駆動法を提案する。

#### 3.3.1 階調時分割駆動法の考え方

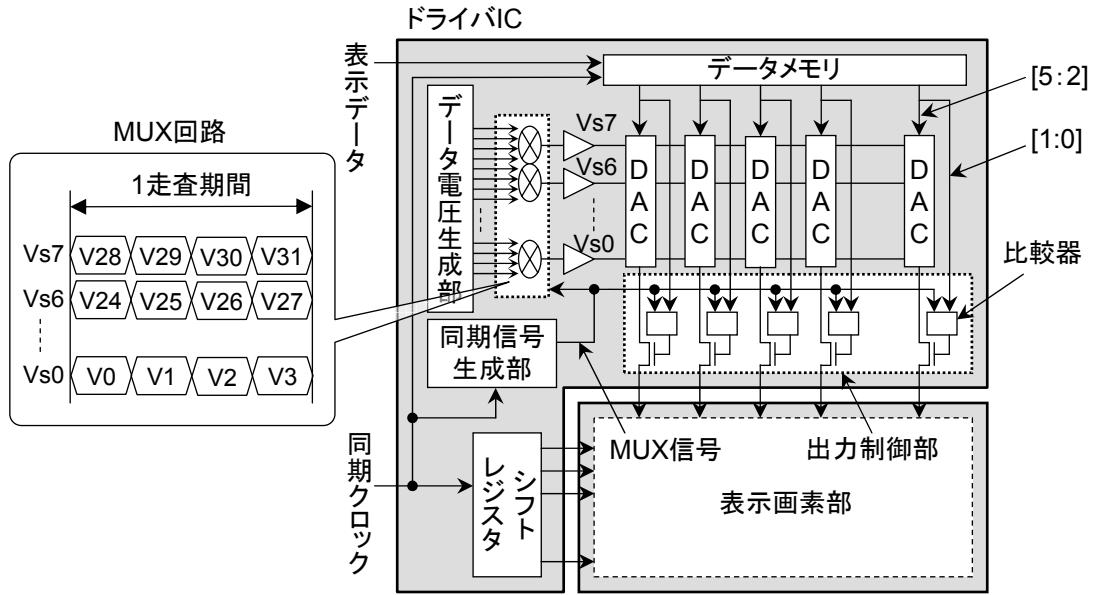

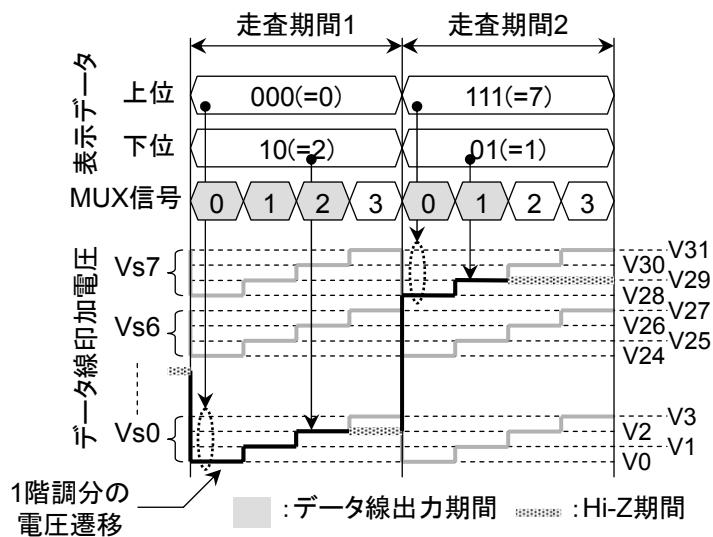

階調時分割駆動法では、DAC の回路規模を削減するため、DAC の 1 個当たりの回路規模を削減するアプローチをとる。この実現にあたり、上位ビットの階調表現を DAC 回路で実現し、下位ビットの階調表現を出力タイミングの制御によって実現する。例えば 5 ビットの表示データにおいて、上位を 3 ビット、下位を 2 ビットとする場合、図 3.9 に示すようにドライバ IC の内部に、8 個のマルチプレクサ回路を設ける。マルチプレクサ回路は、1 走査期間を 4 分割し、隣接する 4 レベルのデータ電圧を順番に DAC に供給する。DAC は、8 個のマルチプレクサから与えられたデータ電圧の中から、表示データの上位 3 ビットにしたがって 1 レベルを選択する。選択されたデータ電圧はさらに出力制御部によって制御され、表示データの下位 2 ビットと分割の順番が一致した期間のみ、データ電圧をデータ線に出力する。この動作により、32 種類の階調表現を可能とする。

図 3.9 階調時分割駆動法の回路構成

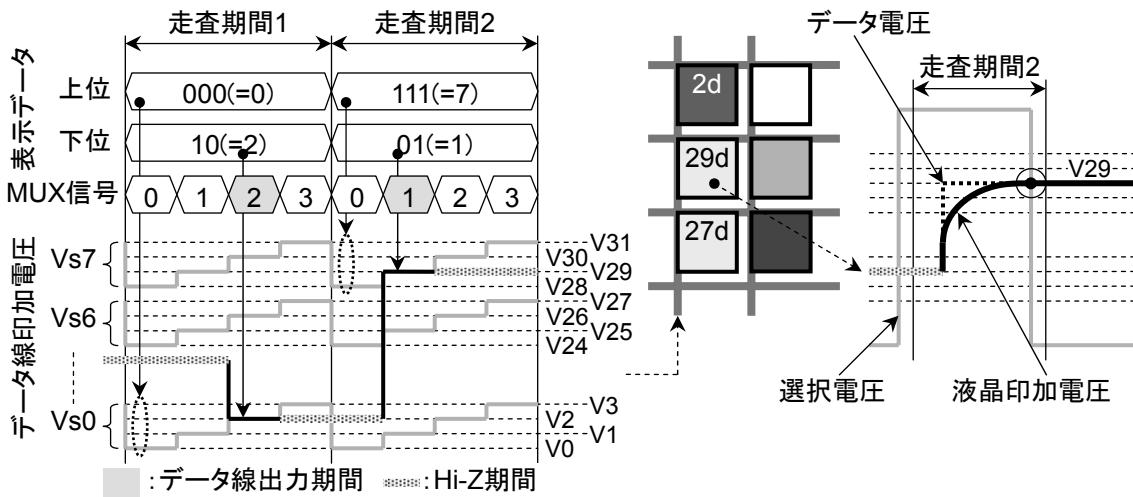

図 3.10 は、階調時分割駆動法の具体的な動作例として、先の図 3.3 と同じ表示データを駆動する例を示したものである。図 3.10において、始めの 1 走査期間における表示データの上位ビットは 000 (=0) である。これに応じ、DAC はデータ電圧 Vs0 を選択する。一方、表示データの下位 2 ビットは 10 (=2) である。これに応じ、出力スイッチは時分割順番を示す MUX 信号が “2” の期間のみ Vs0 電圧をデータ線に出力する。以上の結果、4 レベルある Vs0 電圧の中で低電圧側から 3 番目のデータ電圧である V2 が、データ線に印加される。同様に、次の 1 走査期間では、表示データの上位 3 ビットの値が 111 (=7) であることから、Vs7 のグループが選択される。そして表示データの下位 2 ビットが 01 (=1) であることから、MUX 信号が “1” の期間のみ Vs7 電圧をデータ線に出力する。その結果、4 レベルの Vs7 電圧の中で、低電位側から 2 番目の V29 がデータ線に印加される。なお、前述したように、データ線はそれ自身に寄生容量を有するため、印加されたデータ電圧の電位は保持される。ここで、図 3.3 で示した動作との違いは、データ線にデータ電圧を出力するタイミングが表示データに依存して異なる点である。しかし、先に述べたデータ線時分割駆動法と同様、1 走査期間の終了時には全てのデータ線にデータ電圧が印加されるため、線順次駆動としての目的を果たすことが可能である。

図 3.10 階調時分割駆動法の動作波形

なお、図 3.10 を用いた説明では上位ビットと下位ビットの割合を 3 : 2 としたが、これに限られる訳ではなく、上位ビットの割合が少ないほど小回路規模化が可能である。しかし、その分下位ビットに対応した 1 走査期間の分割数が増えるため、1 回の分割期間の短縮により、印加するデータ電圧が収束しない可能性がある。したがって、データ電圧の収束時間を考慮した上で、時分割数を決定する必要がある。そこで、代表的なパネル解像度に対して適用可能な時分割数を、フレーム周波数 :  $F_f$ , パネルの走査線数 :  $N$ , データ線の寄生容量 :  $C_d$ , 抵抗成分 :  $R_d$  をパラメータに算出した。その結果を表 3.2 にまとめる。

なお、計算時分割数 :  $D_m$  は以下の式 (3.2) ~ (3.4) から算出し、適用時分割数 :  $D_a$  は、 $D_m$  を超えない範囲で最大の 2 の累乗数とした。

表 3.2 パネル解像度と最適時分割数

| 解像度             | $132 \times 176$ | $176 \times 40$ | $240 \times 320$ |

|-----------------|------------------|-----------------|------------------|

| フレーム周波数 : $F_f$ | 90Hz             |                 |                  |

| 垂直ライン数 : $N$    | 176              | 240             | 320              |

| 想定寄生容量 : $C_d$  | 20pF             | 30pF            | 60pF             |

| 想定抵抗成分 : $R_d$  | $100k\Omega$     |                 |                  |

| 1 走査期間 : $H$    | 63μs             | 46μs            | 35μs             |

| 収束時間 : $T$      | 10μs             | 15μs            | 30μs             |

| 計算時分割数 : $D_m$  | 6.3              | 3.1             | 1.2              |

| 適用時分割数 : $D_a$  | 4                | 2               | 1                |

$$1\text{走査期間} : H = \frac{1}{Ff \cdot N} \quad (3.2)$$

$$\text{収束時間} : T = 5 \cdot Cd \cdot Rd \quad (3.3)$$

$$\text{計算時分割数} : Dm = \frac{H}{T} \quad (3.4)$$

表 3.2 から分かるように、階調時分割駆動法は、解像度の低いパネルに対して時分割数を多く設定できるため、回路規模の削減効果が高い。なお、本章では表示データを 5 ビット（32 階調）として駆動法を説明しているが、実際には RGB 各 6 ビットの 18 ビットカラーが現在の主流である。そこで、先に述べた FRC 法を最下位ビットの表現に適用することで、RGB 各 6 ビットに対応する。

ここで、先に述べたように階調時分割駆動法では、ドライバ IC から出力されるデータ電圧を、データ線自身の寄生容量で保持することを前提とする。このため、データ電圧の保持期間において、以下の 2 種類の電圧変動が予想され、画質への影響が懸念される。

- (1) カップリング性電圧変動

- (2) リーク性電圧変動

そこで、それぞれの電圧変動に対し、データ電圧の出力タイミングの最適化と、データ電圧の補正機能を新たに付け加え、保持期間におけるデータ電圧の変動を抑制する。

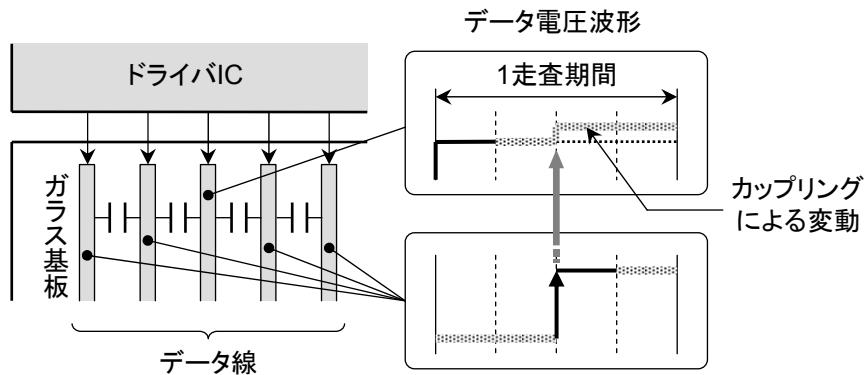

### 3.3.2 カップリング性電圧変動の抑制

まず始めに、第 1 の課題であるカップリング性電圧変動の発生メカニズム、およびその抑制方法について述べる。階調時分割法では、図 3.11 に示すように、あるデータ線に対しては 1 走査期間中の第 1 期間にデータ電圧が印加され、隣接のデータ線には第 3 期間にデータ電圧が印加される場合がある。この場合、データ線間の容量結合により、先に印加されたデータ電圧の保持電位が変動する。この現象をカップリング性電圧変動と呼ぶ。カップリング性の電圧変動量は、データ電圧の遷移量、言い換えれば表示データに依存する。そこで、H-SPICE[83]を用いた回路シミュレーションを実施し、ワースト条件（V0 印加の後に V31 を印加する）におけるカップリング性電圧変動量を求めた。その結果、カップリング性の電圧変動量はワーストの条件において 20mV 以上であることが分かった。電圧変動量は、

概ね 15mV を超えると画質劣化が顕在化し始める可能性がある。したがって、カップリング性電圧変動に対する対策が必要である。

図 3.11 カップリング性電圧変動

そこで、図 3.12 に示すように、データ線の出力期間を、当初の表示データと分割順番との一致期間のみから、1 走査期間の開始から表示データに一致するまでの期間に変更する。この変更により、1 走査期間中の第 2 分割期間以降においては、データ電圧の遷移量は必ず 1 階調分の電圧差となる。これにより、カップリング性変動の影響を最小化することができ、HSPICE によるシミュレーションにおいても電圧変動量を 10mV 以下に抑制可能になることを確認した。

図 3.12 カップリング性電圧変動の改善方法

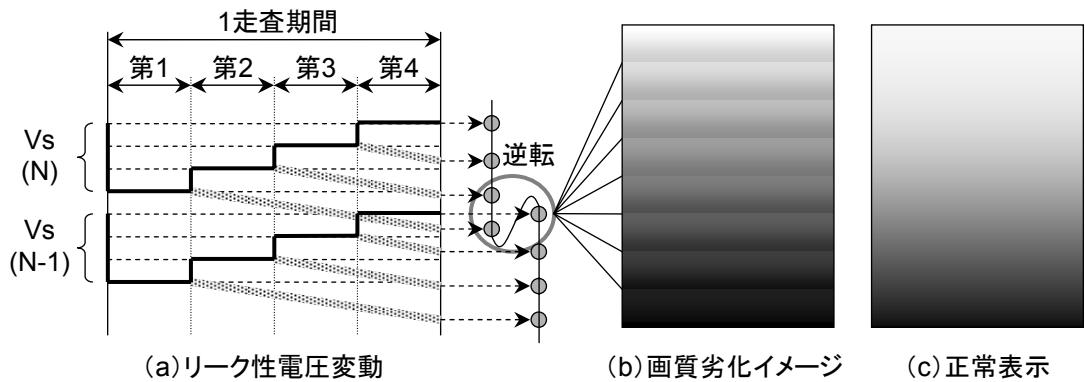

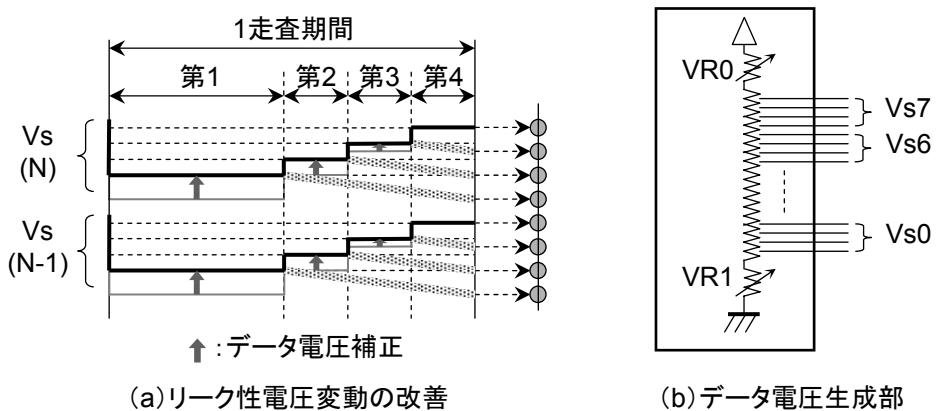

### 3.3.3 リーク性電圧変動の抑制

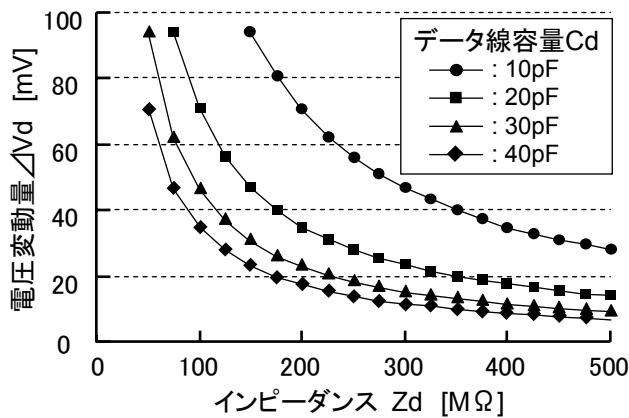

次に、第2の課題であるリーク性電圧変動の発生メカニズム、およびその抑制方法について述べる。階調時分割駆動法では、データ線から他の回路に流れるリーク電流が存在すると、データ線の保持電位が変動するため、その程度によっては正常な表示が困難になる。この現象をリーク性電圧変動と呼ぶ。リーク性電圧変動の量： $\Delta V_d$  は、データ線の寄生容量： $C_d$  と電流リークパスのインピーダンス： $Z_d$  に依存し、以下の式により算出することができる。

$$\Delta V_d = V_0 - V_0 \cdot e^{-\frac{t}{C_d \cdot Z_d}} \quad (3.5)$$

ここで、 $V_0$  は初期電圧、 $t$  はデータ電圧の保持時間である。例えば、 $V_0=4V$ 、 $C_d=20pF$ 、 $Z_d=200M\Omega$ 、 $t=35\mu s$  (1分割期間に相当) の場合、図 3.13 に示すように  $V_d$  は  $35mV$  となり、これは 64 階調表示における 1 階調分の電位差に相当する。この結果、図 3.14 に示すように隣接階調の電圧レベルが逆転し、グラデーション表示において段差状の画質劣化が生じる。

図 3.13 インピーダンスと電圧変動量の関係 ( $V_0=4V$ ,  $t=35\mu s$ )

リーク性電圧変動を抑制するため、まずリーク性電圧変動の原因となる保持期間の短縮を図る。具体的には、図 3.15 (a) に示すように第 2~4 分割期間を短くし、残りの時間を第 1 分割期間に割り当てる。これに加え、電圧変動分を予めデータ電圧に加算しておくことで補正する機能を設ける。これにより、電圧変動が発生した場合にも、1 走査期間の最後には、データ電圧を正しいレベルに整定可能である。なおこの機能は、図 3.15 (b) に

示すように、可変抵抗 VR0, VR1 をデータ電圧生成部内に設け、これらの可変抵抗値を分割期間毎に変更するという簡単な回路で実現可能である。

図 3.14 リーク性電圧変動による画質劣化

図 3.15 リーク性電圧変動の改善（電圧補正）

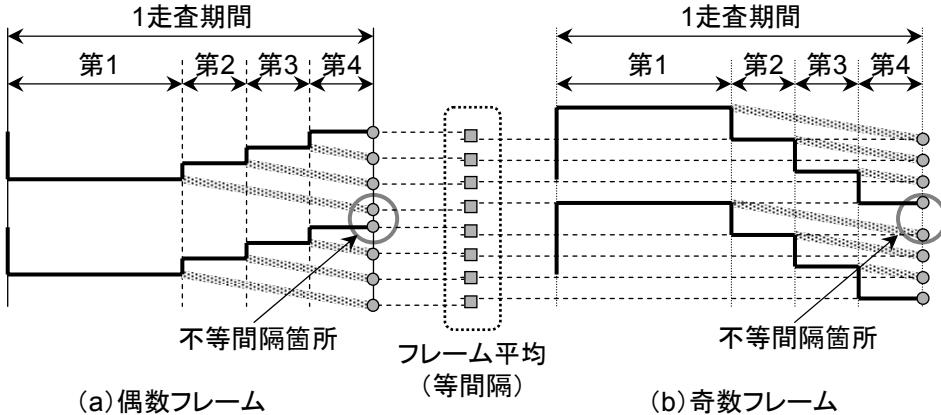

さらに、上記したデータ電圧の補正に対するマージン向上を目的に、データ電圧をマルチプレックスして DAC に与える順序をフレーム毎に切り換える機能を併用し、電圧変動の影響を分散させる。例えば、図 3.16 に示すように偶数フレームではマルチプレックスの順番を高電圧から低電圧とし、奇数フレームにおいては反対に低電圧から高電圧へ遷移させる。これにより、偶数・奇数の 2 フレームで見た場合、電圧変動量が最大の第 1 期間と最小の第 4 期間、それ以外の第 2 期間と第 3 期間がペアになる。その結果、図 3.16 に示すように、仮に偶数フレームと奇数フレームのデータ電圧レベルに多少の不等間隔が生じっていても、これらの平均レベルが実効的にデータ線に印加される。したがって、隣接階調の電位差のずれをさらに精度良く補正して、等間隔化することが可能である。

図 3.16 リーク性電圧変動の改善（フレーム切り替え）

## 3.4 適用結果と考察

本節では、提案した階調時分割駆動法を実際の TFT-LCD 向けドライバ IC に適用し、ドライバ IC のチップサイズ、消費電力、表示特性を評価することで提案方法の有用性について検証を行う。

### 3.4.1 適用対象

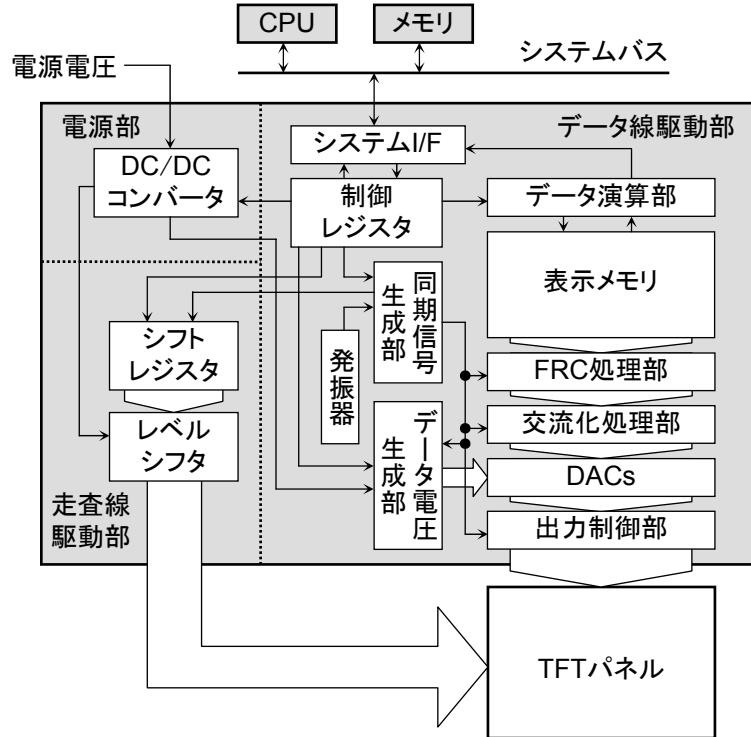

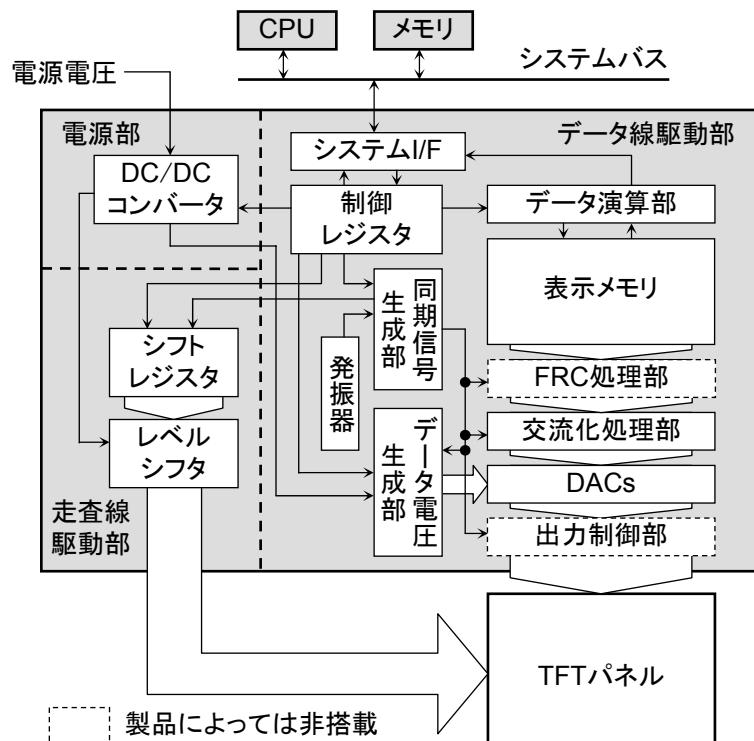

階調時分割駆動法の有用性を検証するにあたり、解像度の異なる 2 種類のドライバ IC を製造した。これらのドライバ IC は、図 3.17 に示す回路構成をベースにしており、図 3.9 で示した構成との違いは、表示メモリ、同期信号生成部、電源部、走査駆動部等の表示に必要な要素を全て 1 チップに統合していることである。この回路構成は、モバイル機器向けドライバ IC においては一般的であり、特に表示メモリの搭載はホスト側からの表示データの転送を画面の更新箇所のみにすることができる。したがって、静止画表示が多いモバイル機器においては、表示データの転送に伴う消費電力を大幅に削減することができる [77][84][85]。また、26 万色表示 (RGB 各 6 ビット) に対応させるため、表示データの最下位ビットを FRC 法で表現するための FRC 処理部を表示メモリの後段に搭載する。なお、ホスト側の装置は（株）マキシマ画像研究所製の信号発生器 MG15150 を使用し、インストラクション信号および表示データをドライバ IC に転送することで任意画像の表示を実現する。

図 3.17 提案したドライバ IC の回路構成

### 3.4.2 提案方法の性能評価と考察

表 3.3 に提案のドライバ IC と従来のドライバ IC における主要特性の比較を示す。同じ解像度で比較した場合、従来の駆動法を採用したドライバ IC に対し、本章で提案の階調時分割駆動法を適用したドライバ IC は、 $132 \times 176$  画素対応において 30%， $176 \times 220$  画素対応において 25%，チップサイズを削減することができた。さらに、ドライバ IC 単体の消費電力に関しては、各解像度において 40% 以上削減することができた。消費電力が削減した理由は、図 3.6 (b) と図 3.9 との比較から分かるように、データ電圧を DAC に出力する OP アンプの数が削減したこと、OP アンプに供給するバイアス電流の総和を削減できたためである。以上のことから、階調時分割駆動法を適用することにより、本研究の目的であるドライバ IC のチップサイズ削減への有用性を確認すると共に、消費電力削減に対する有用性についても確認することができた。図 3.18 に提案方法を搭載したドライバ IC (解像度 :  $132 \times 176$  画素) のチップ写真を示す。

表 3.3 ドライバ IC の主要特性

| 解像度   | 132×176 画素 |       | 176×220 画素 |       |

|-------|------------|-------|------------|-------|

| 駆動方法  | 従来方法       | 提案方法  | 従来方法       | 提案方法  |

| 時分割数  | 無し         | 4     | 無し         | 2     |

| チップ面積 | 100%       | 70%   | 100%       | 75%   |

| 消費電力  | 3.1mW      | 1.7mW | 5.0mW      | 3.0mW |

| プロセス  | 0.35μm ルール |       |            |       |

図 3.18 ドライバ IC のチップ写真 (132×176 画素)

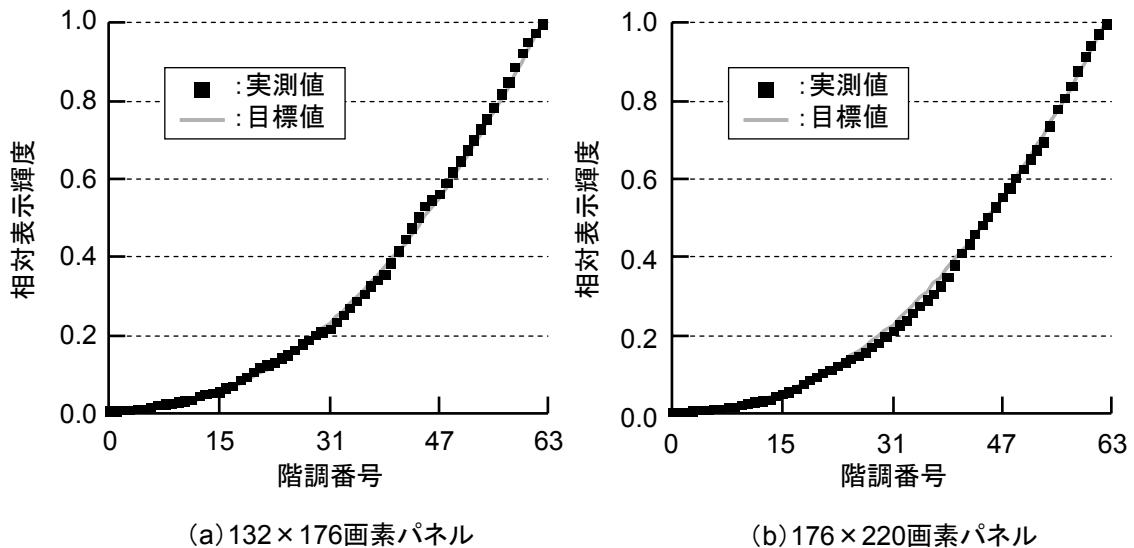

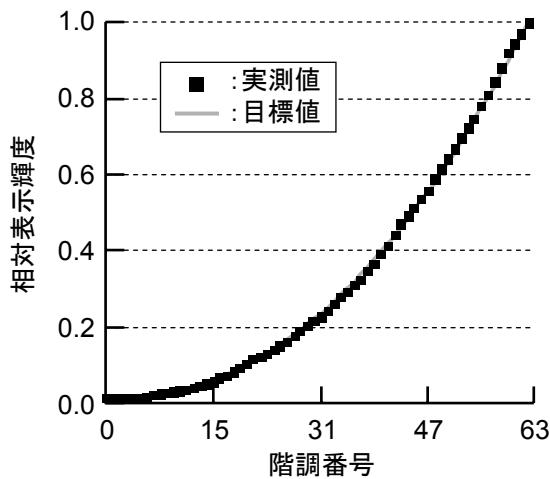

次に、提案のドライバ IC を TFT-LCD に実装し、全画面をグレー階調でべた塗り表示させた場合の、階調番号と表示輝度の関係を測定した。図 3.19 がその結果である。グラフの横軸である階調番号は表示データと一致しており、表示データは RGB 各 6 ビット (64 階調表示) であることから 0~63 の値をとる。グラフの縦軸は表示輝度の測定値であり、測定ポイントは画面中央、測定装置はコニカミノルタホールディングス（株）製の色彩輝度計 CS-100A である。図中のプロット点が提案方法の測定結果であり、グレーの線は目標とする表示輝度（相対値）である。目標の特性は、現在の表示ディスプレイにおいて一般的に適用されているガンマ値=2.2 の特性であり、下記の式から算出することができる。なお、TFT-LCD のガンマ特性（データ電圧-表示輝度特性）は、図 3.2 に示したように目標のカーブとは異なる。そこで、提案のドライバ IC では、DAC に入力するデータ電圧のレベルを調整することで、目標のカーブにフィッティングさせるガンマ補正を実施している。この機能については、次章にて詳細を述べる。

$$(目標の表示輝度) = \frac{(階調番号)^{2.2}}{64^{2.2}} \quad (3.6)$$

仮にカップリング性電圧変動やリーク性電圧変動の影響を大きく受ける階調が存在すると、細線で示した目標のガンマ特性から大きく外れ、隣接階調間での表示輝度の逆転等が発生することが予想される。したがって、理想特性に近いほど、電圧変動の発生が抑制さ

れていると評価することができる。図 3.19 から、カーブに若干の凹凸はあるものの、提案方法の懸念事項であった輝度の逆転現象もなく、実用上充分なレベルで目標の特性にフィッティングできていることが分かる。

図 3.19 階調番号ー表示輝度特性

### 3.5 結言

本章では、モバイル機器向け TFT-LCD の小回路規模多階調表示を実施するにあたり、ドライバ IC のチップサイズ縮小に効果的なコモン電圧反転法と集中アンプ型構成の組み合わせを採用すると共に、集中アンプ形構成の課題である階調数に依存して OP アンプの搭載個数が増大する問題を、階調時分割駆動法の提案により抑制した。同時に、ガラス基板上に搭載するデ・マルチプレクサの回路を不要とし、アモルファスシリコン TFT-LCD への適用を可能とした。さらに、階調時分割駆動法において発生が予想されたカップリング性とリーク性の電圧変動に対し、データ電圧の出力タイミングの最適化と、データ電圧の補正機能を新たに付け加えることで抑制した。これらの提案方法を、解像度 132×176 画素および 176×220 画素の TFT-LCD に適用し、以下の評価結果を得た。

- (1) 従来の駆動法を適用したドライバ IC に比べ、チップサイズを 25%以上削減した。

- (2) 従来の駆動法を適用したドライバ IC に比べ、消費電力を 40%以上削減した。

(3) 64 階調全てにおいて隣接階調間の輝度の逆転等は確認されず、目標のガンマ値：2.2 にはほぼフィッティングした。

以上の結果から、モバイル機器向け TFT-LCD 用途に適用可能な製造コストと表示性能を両立できることを確認し、提案方法の有効性を実証した。なお、本章で提案の階調時分割駆動法を適用したドライバ IC は、(株)ルネサステクノロジ社から HD66782, HD66791, R61500 他の製品として実用化され、コストパフォーマンスの優れた製品としての評価を得ている。

今後の課題としては、大画面／高精細パネルへの対応、および 256 階調化への対応が挙げられる。携帯電話を中心としたモバイル機器は継続して高機能化が進んでおり、ディスプレイに対する要求も予想以上に強まっている。本章で提案した階調時分割駆動法の対応解像度は  $176 \times 220$  画素が上限であり、ワールドワイドにおいてはボリュームゾーンであるものの、日本では既に  $240 \times 320$  画素以上が主流となっている[86]。さらに表示色数においても今後は 1667 万色表示（RGB 各 256 階調の 24 ビットカラー）が標準になることが予想される。したがって、これらの解像度と表示色数に対応する低コストなドライバ IC の実現が今後の課題である。

## 第 4 章

# モバイル機器向け TFT-LCD の高汎用画質調整 方法

### 4.1 緒言

本章では、モバイル機器向け TFT-LCD の画質調整方法として、1 個のドライバ IC の出力電圧レベルをプログラム化することにより、多種多様な TFT-LCD に適用可能なガンマ補正方法を提案し、製造コストの削減を図る。

モバイル機器の中心である携帯電話に搭載される機能は、従来の E メールの送受信から DSC による写真撮影が一般的化し、現在ではワンセグに代表されるテレビ放送の受信機能が高級機種に搭載されている。さらに近年では、インターネットショッピングの利用や、DSC や DVC を用いて撮影したコンテンツをプリントアウトしたり、インターネットに投稿したりする機会が増えている[87]。これらの進化に伴い、画像を扱う入出力デバイスの間で色調を統一化する、カラーマネージメント技術の重要性が増している。カラーマネジメント技術は、プロファイルによる実現方法[88][89]と標準色空間による実現方法[90][91][92]に大別される。例えば DSC の撮影画像をディスプレイに表示する場合、プロファイルによる方法では DSC の撮影データをデバイスに依存しない色空間に変換し、その色空間を介してディスプレイ用の表示データに再度変換することで色調の統一を図る。一方、標準色空間による方法では、画像データと色調の関係を全てのデバイスで標準化すること色調の統一を図る。後者の方法は画像データの取り扱いが単純であり、規格の一つである sRGB (Standard RGB) は、現在 Windows OS (Operation System) の標準色空間として採用されている[93]。したがって、今後モバイル機器においても、sRGB に準拠したデバイスが製品化されることが予想される。sRGB は元来、CRT ディスプレイの色表現特性に基づいて制定された規格であり、ガンマ値は 2.2 である[90]。したがって、sRGB に準拠するためには、TFT-LCD のガンマ値も 2.2 であることが条件となる。しかし、TFT-LCD のガンマ特性は CRT のように指数関数的な特性ではなく、前章の図 3.2 で示し

たカーブを有する。したがって、所望するガンマ特性を得るために、表示データとデータ電圧との関係を適正化するガンマ補正が必要となる。

一方、モバイル機器向け TFT-LCD 市場は当初日本メーカーが独占していたが、大型 TFT-LCD 向けの旧世代の製造ラインを改造することで対応が図れることもあり、2004 年頃から韓国メーカーが本格参入を開始し、現在では中国メーカーも加わり競争が激化している [94]。このため、モバイル機器向け TFT-LCD の価格は急激に下落しており、今後も更なる価格競争が続くことが予想される。このため、TFT-LCD を構成する全ての部品に対し、コストダウンは必須の課題となっている。

従来、TFT-LCD のガンマ補正を実施する方法として、入力される表示データが持つ階調数よりも多いデータ電圧を用意し、その中から所望のガンマ特性となる組み合わせを選択する方法が提案されている[39][40]。他の方法としては、DAC に入力するデータ電圧自体を予め所望するレベルに設定するアプローチがあり、ドライバ IC の製造時に用いるフォトマスクの変更によりこれを実現する方法が報告されている[41][95]。さらには、制御レジスタを用いてデータ電圧のレベル設定をプログラム化し、多種多様な TFT-LCD に適用可能にする方法が報告されている[42]。しかしながら、データ電圧の組み合わせを選択する方法やデータ電圧をプログラム化する方法は追加となる回路規模が大きく、フォトマスクを変更する方法は、回路規模は小さいものの異なるガンマ特性への対応が困難であるため開発コストが上昇する。以上のことから、モバイル機器向け TFT-LCD のガンマ補正を低コストで実現するためには、1 つのドライバ IC で多種多様な TFT-LCD に適用できると同時に、ドライバ IC のチップサイズに大きなインパクトを与えない回路規模である必要がある。

本章では、制御レジスタを用いてデータ電圧のレベル設定をプログラム化することにより、多種多様な TFT-LCD への適用を図る。この際、従来の提案方法はデータ電圧のベースとなる基準電圧を離散的に複数用意し、個々の基準電圧レベルを広範囲に調整していることが回路規模の増大要因となっている。そこで、TFT-LCD におけるガンマ補正のカーブが逆 S 字型であることに着目し、下記 2 つの項目を優先的に設定し、その後にカーブの細かな調整を加えることで、効率の良い補正を行う。

- (a) 最低階調と最高階調の電圧レベル

- (b) ほぼ直線形状となる中央階調付近の傾き

制御レジスタの設定項目については、上記 2 つに対応した「振幅」「傾き」、その後の細かな調整を「微調整」とし、この順番でガンマ補正を実施する。これにより、基準電圧の

調整範囲を狭くして回路構成を簡略化し、ドライバ IC のチップサイズ増大に大きなインパクトを与えないことを狙う。

以下、4.2 節では、従来のガンマ補正方法について説明し、問題点と課題を明らかにする。4.3 節では、提案のガンマ補正方法による回路規模削減、およびこの方法における課題点の解決方法について説明する。4.4 節では、提案方法を用いることによる画質評価の結果および考察について述べ、本方法の有用性を示す。

## 4.2 従来のガンマ補正法と問題点

本節では、従来のガンマ補正法について説明し、モバイル機器向け TFT-LCD に適用する際の問題を明らかにする。

### 4.2.1 小回路規模化問題

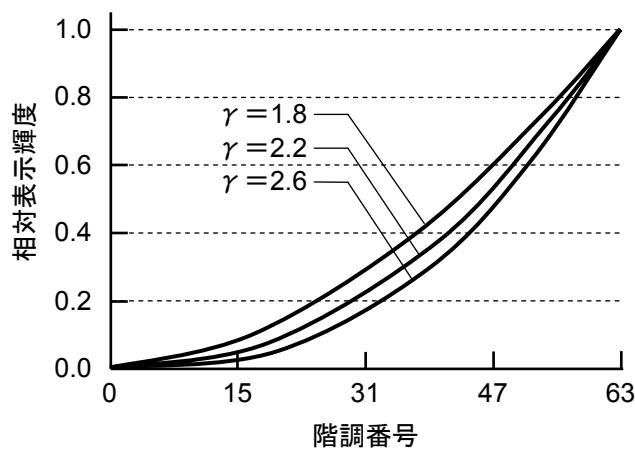

一般に人間の視覚特性は、輝度が指数関数的に変化した場合に直線性を感じる[96]。このため、ディスプレイにおいても、下記の関係式に示すように表示データの示す階調番号に対し、表示輝度が指数関数的に変化することが望ましい。ここで、指数  $\gamma$  の値はガンマ値と呼ばれ、図 4.1 にガンマ値を 1.8~2.6 に設定した場合の特性を示す。

$$\text{表示輝度} = a \cdot (\text{階調番号})^\gamma + b \quad (4.1)$$

図 4.1 階調番号－表示輝度特性

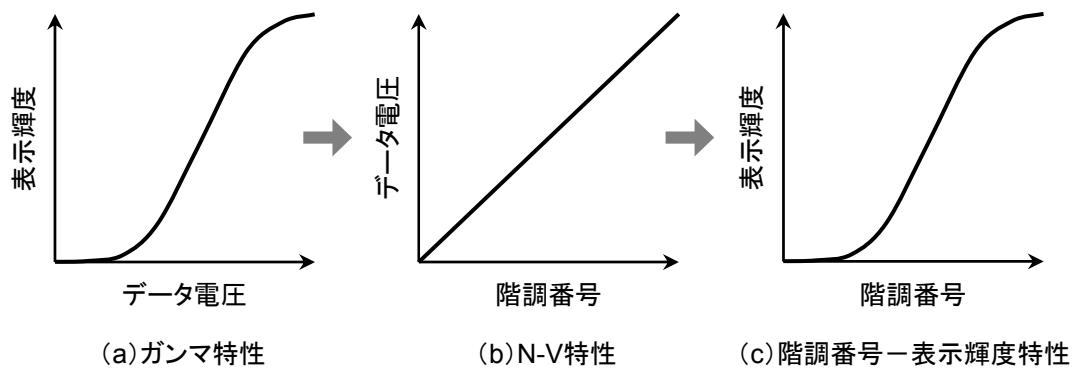

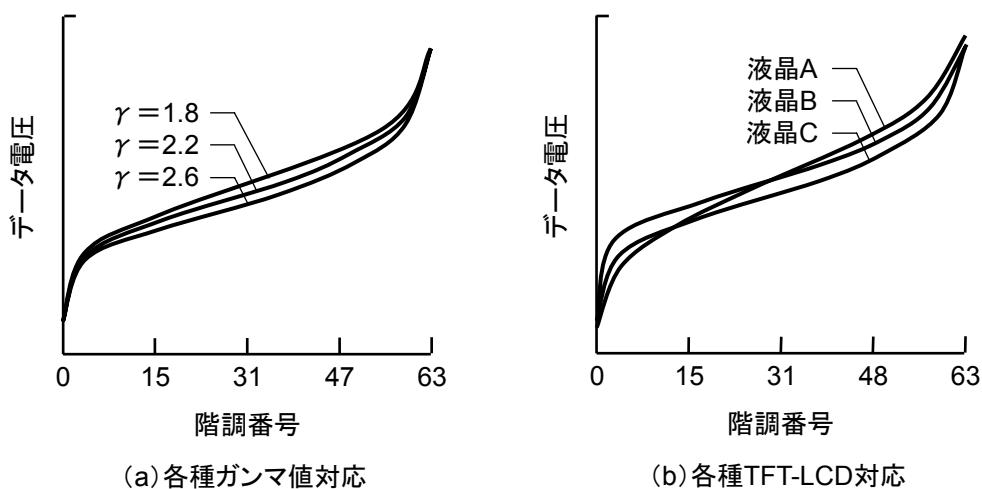

一方、TFT-LCD ではデータ電圧に応じて表示輝度が変化し、この特性は一般にガンマ特性と呼ばれる。TFT-LCD のガンマ特性は、図 4.2 (a) に示すカーブを有する。このため、例えば階調番号とデータ電圧の関係（以下、N-V 特性と呼ぶ）を、図 4.2 (b) に示す単純な線形にすると図 4.2 (c) に示すカーブとなり、図 4.1 に示したカーブとフィッティングしない。このことから、TFT-LCD における階調番号ー表示輝度特性を所望のカーブにするためには、N-V 特性を補正する必要がある。図 4.3 (a) は、ある 1 種類の TFT-LCD において、ガンマ値 : 1.8, 2.2, 2.6 を実現する N-V 特性、図 4.3 (b) は 3 種類の TFT-LCD においてガンマ値 : 2.2 を実現するための N-V 特性を示したものである。このように、N-V 特性を適切に補正することで、所望のガンマ値を得ることができる。以下、この補正をガンマ補正と呼ぶ。

図 4.2 ガンマ補正の必要性

図 4.3 ガンマ補正後の N-V 特性

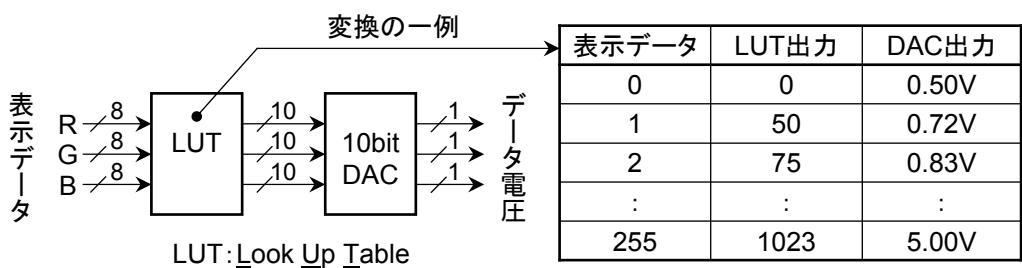

従来、TFT-LCD におけるガンマ補正のアプローチの一つとして、図 4.4 に示すように入力される表示データが持つ階調数よりも多い階調を用意し、その中から所望のガンマ特性となる組み合わせを選択する方法がある。例えば、256 階調 (8bit) 表示を行う場合、1024 階調 (10bit) 分のデータ電圧とリニア DAC を用意し、この中から 256 階調分の組み合わせをルックアップテーブル等のデコーダを用いて選択することでガンマ補正を実現する[39]。さらに多階調となる 1024 階調 (10bit) の場合には、8192 階調 (13bit) 分のデータ電圧から選択する方法も報告されている[40]。これらの方法はデジタル処理で容易にガンマ補正が実現できる利点がある一方、入力される表示データが持つ階調数よりも分解能の高い DAC を用意する必要がある。前章でも述べたように、DAC はデータ線の本数分用意する必要があるため、仮に 1 つの DAC における回路規模増大は僅かでも、それが何百倍にもなって反映される。このため、上記の方法はドライバ IC のチップサイズが増大する問題がある。さらに、ガンマ値を任意に調整するためには、上記ルックアップテーブルの値を制御レジスタに記憶する必要があり、例えば 64 階調表示の場合、制御レジスタのビット数は、最低でも 448bit (=64 階調 × 7bit) と膨大となる。これらの理由から、低コスト化が激しいモバイル機器向けドライバ IC への適用は、回路規模増大の点から困難である。

図 4.4 ルックアップテーブルによるガンマ補正法

ガンマ補正の別のアプローチとして、ドライバ IC の製造時において、DAC に入力するデータ電圧自体を予め所望するレベルに設定する方法がある。これを実現する方法として、データ電圧の各レベルをラダー抵抗で生成し、ラダーを構成する個々の抵抗値を製造時に用いるフォトマスクを利用して変更する方法が報告されている[41]。この方法は、精度の高いガンマ補正が期待できる一方、ドライバ IC 製造後にガンマ値を変更する必要がある場合、あるいは異なるガンマ特性を持つ TFT-LCD を駆動する場合には、適合させることができ難である。この場合、再度フォトマスクを作成し、ドライバ IC を製造する必要が生じる。特にモバイル機器においては、製品のライフサイクルが短く、新モデルの開発のた

びに TFT-LCD の特性が変更となる場合が多いため、上記の方法は開発コストが上昇する問題がある。

#### 4.2.2 従来の小回路規模化方法の問題と課題

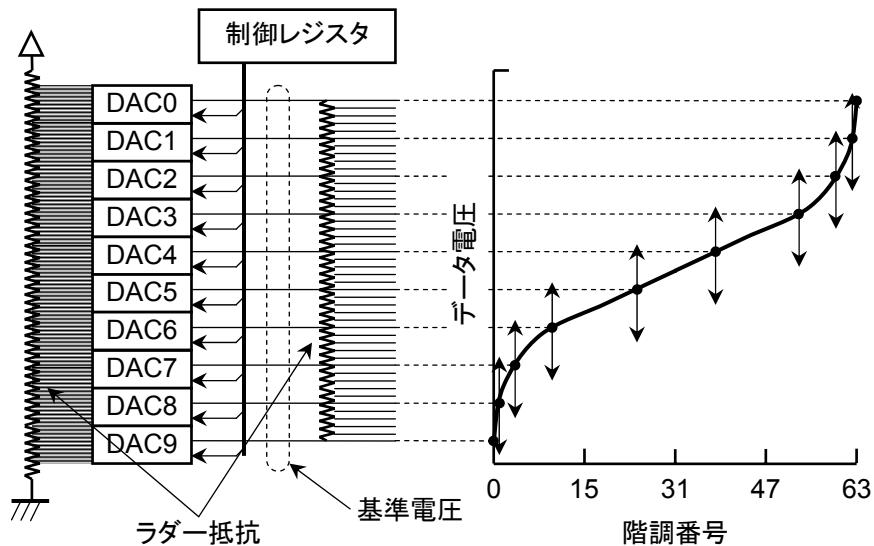

上記課題を解決する方法として、データ電圧のベースとなる基準電圧を離散的に複数用意すると共に、個々の基準電圧レベルを調整するための制御レジスタを設けることで、ドライバ IC の製造後においてもガンマ補正を実現可能にする方法が報告されている[42]。この方法によれば、例えば図 4.5 に示すように 10 レベルの基準電圧を設け、隣接の基準電圧間をラダー抵抗により分圧することでデータ電圧を生成する。ガンマ特性を変更する場合は、ホスト側から制御レジスタのデータを書き換え、これに連動して各 DAC が候補となる基準電圧の中から 1 レベルを選択する。この動作により、データ電圧の各レベルが調整され、ガンマ補正を実現する。基準電圧を設けた理由は、データ電圧のレベルを全て独立に調整すると回路規模が膨大になるためであり、10 レベルの基準電圧を離散的に設けることで電源電圧 : 5V 時における 39mV ステップの電圧調整を実現し、実用的な調整精度を得ている[42]。

図 4.5 基準電圧調整によるガンマ補正法

ここで、基準電圧の調整機能を実現するための回路規模について考えると、まず各基準電圧の候補となる電圧レベルの数は、電源電圧を調整刻み幅で除算することで算出可能である。そこで、先に示した電源電圧 : 5V、調整刻み幅 : 39mV を代入すると、候補の電圧レベル数は 128 と推定することができる。つまり、1 個の基準電圧を調整するために 128 to

1 の DAC が必要となり、基準電圧数の総数は 20 個（正極性／負極性、各 10 個）であることから、上記ガンマ補正法を実現するためは、128 to 1 の DAC が 20 個必要となる。128 to 1 の DAC の回路規模は、例えば 64 階調表示における表示データをデータ電圧に変換する DAC (64 to 1) の 2 個分に相当する。したがって、128 to 1 の DAC の 20 個は、64 to 1 の DAC の 40 個分となる。これに対し、ドライバ IC に搭載される DAC の数は、 $132 \times 176$  画素の場合 396 個である。したがって、上記ガンマ補正法をドライバ IC に適用する場合、DAC 搭載数が約 10% 増加すると推定することができる。

一方、基準電圧の設定値を記憶するための制御レジスタのビット数は、以下の式から算出可能であり、先に述べた候補の電圧レベル数：128、基準電圧数：20 個を代入することで 140bit と推定することができる。

$$\text{制御レジスタ数} = \log_2(\text{候補の電圧レベル数}) \cdot \text{基準電圧数} \quad (4.2)$$

ここで、現在市販されているモバイル向けドライバ IC では、表示状態や駆動条件をホスト側からのインストラクションで変更するための制御レジスタを内蔵しているが、ビット数の合計は 250bit 程度である。したがって、上記した 140bit を追加すると、制御レジスタの必要ビット数が 50% 以上増加することになる。先に述べたように、現在モバイル機器向け TFT-LCD の価格は急激に下落しており、ドライバ IC に対してもコストダウンの要求が非常に強い。この状況の中、従来のガンマ補正法を適用することは、回路規模の増加分が大きいことから困難である。したがって、モバイル機器向け TFT-LCD のガンマ補正を低コストで実現するためには、1 つのドライバ IC で多種多様な TFT-LCD に適用可能である同時に、ドライバ IC のチップサイズに大きなインパクトを与えない回路規模で実現することが課題となる。

## 4.3 3 ステップガンマ補正法

本節では、前節で述べたガンマ補正機能の実現における小回路規模化の課題を解決するため、3 ステップガンマ補正法とこれを実現するための回路構成を提案する。

### 4.3.1 3 ステップガンマ補正法の考え方

前節で述べたとおり、モバイル機器向け TFT-LCD のドライバ IC では、表示状態や駆動条件をホスト側からインストラクションで変更するための制御レジスタを内蔵する。そ

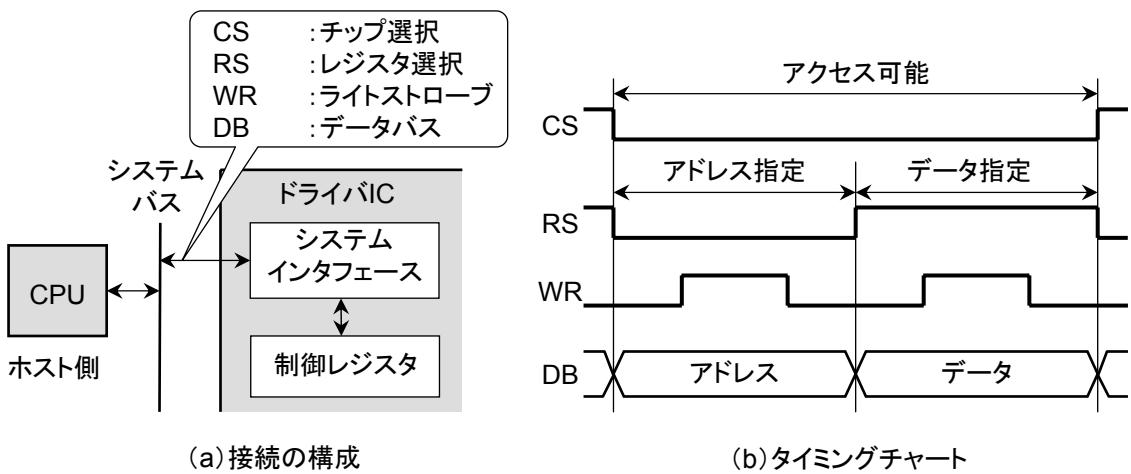

こで、ガンマ補正のための設定項目を制御レジスタに追加することで、ドライバ IC 製造後のガンマ補正を実現する。ドライバ IC とホスト側は、例えば図 4.6 (a) に示すように汎用の 80 系 CPU に準拠したバスインターフェースにより接続する[97][98]。そして、図 4.6 (b) に示すタイミングチャートにしたがい、ホスト側からドライバ IC への制御レジスタへの書き込み動作を実施する。なお、制御レジスタの設定値は予めホスト側に記憶しておき、電源立ち上げ動作のたびに上記した動作を実施する。したがって、制御レジスタの設定値を変更したい場合は、ホスト側のプログラムを変更することで対応可能である。

図 4.6 ドライバ IC とホスト側のインターフェース

次に、データ電圧の調整については、図 4.3 で示した N-V カーブに着目する。図 4.3 から分かるように、それぞれの N-V において逆 S 字型の基本カーブは変わらず、主な相違点は下記の 2 項目である。このことから、これら 2 つの項目を優先的に調整し、その後にカーブの曲率等の細かな調整を加えることで、効率の良いガンマ補正を行う。

- (a) 0 階調と 63 階調の電圧レベル

- (b) ほぼ直線形状となる中央階調付近の傾き

制御レジスタの設定項目については、N-V 特性の「振幅」「傾き」「微調整」の 3 項目とし、この順番でデータ電圧の調整を実現する 3 ステップガンマ補正法を提案する。ここで、「微調整」は従来の基準電圧の調整と同じ作用を狙うための機能であるが、「振幅」と「傾き」の調整を完了した後に実施するため、電圧レベルの調整範囲を狭くすることが可能である。これにより、1 個の基準電圧を調整するための DAC の回路規模、および制御レジスタのビット数を削減する。

### 4.3.2 実現回路構成

以下、3ステップガンマ補正法を実現する回路構成を示す。

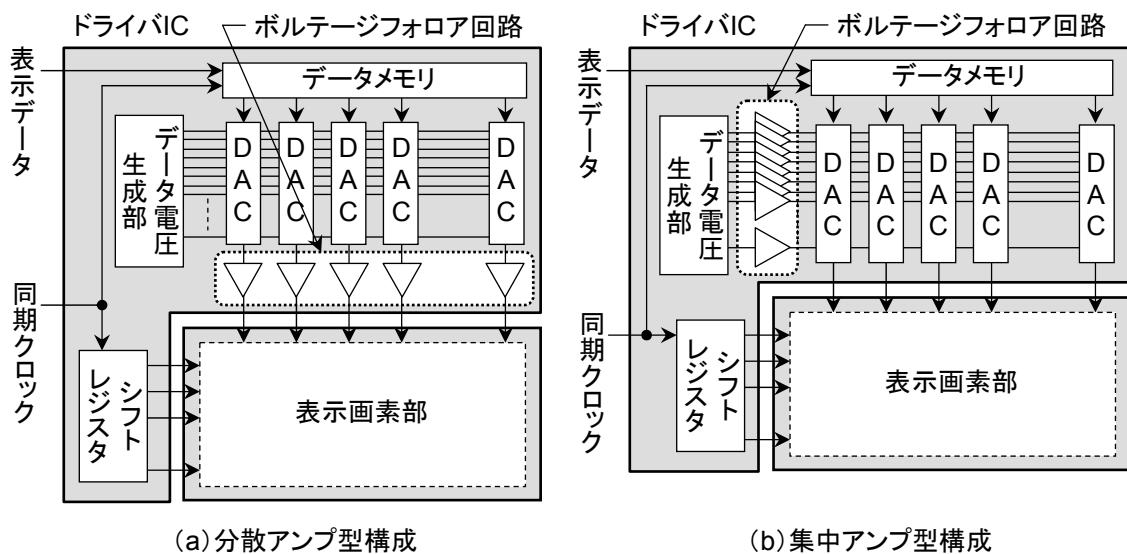

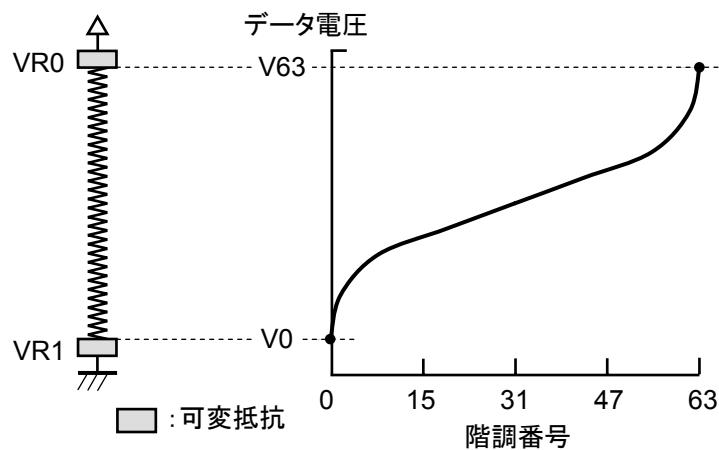

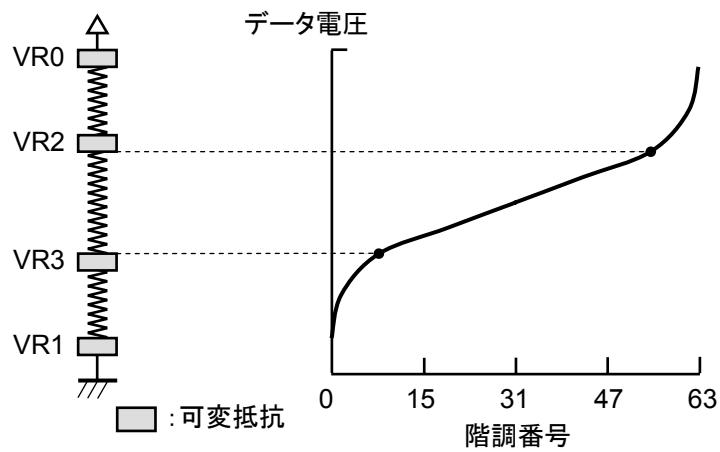

#### (1) 振幅調整

まず、最初のステップである振幅調整は、図4.7に示すようにデータ電圧の最大レベルであるV63と電源電圧間、および最小レベルであるV0とグランド間に、可変抵抗VR0、VR1を付加することで実現する。これらの可変抵抗の設定に対するガンマ特性の補正作用を、図4.8のN-V特性を用いて説明する。まず、図4.8(a)では、V63を変化させずにV0の電圧レベルを調整する。この動作を実現するには可変抵抗VR1の抵抗値を調整すれば良い。例えば、V0を低くする（振幅を大きくする）場合は可変抵抗VR0の抵抗値が小さくなるように、V0を高くする（振幅を小さくする）場合は可変抵抗VR1の抵抗値が大きくなるように調整する。次に、図4.8(b)では、図4.8(a)とは逆にV0を変化させずにV63の電圧レベルを調整する。この動作を実現するには可変抵抗VR0の抵抗値を調整すれば良い。例えば、V63を低くする（振幅を小さくする）場合は可変抵抗VR0の抵抗値が大きくなるように、V63を高くする（振幅を大きくする）場合は可変抵抗VR0の抵抗値が小さくなるように調整する。最後に、図4.8(c)では、V0とV63間の振幅は変えずに電圧レベルのオフセットを調整する。この動作を実現するには、先に示したVR1とVR0の設定方法を用いて、V0とV63の電圧レベルを同時に調整すれば良い。

図4.7 振幅調整機能の実現回路

図 4.8 振幅調整の実現方法

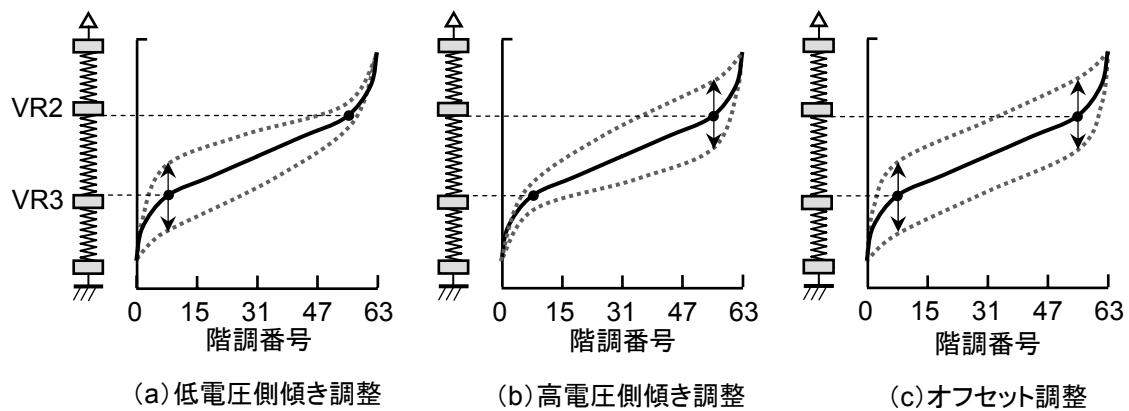

## (2) 傾き調整

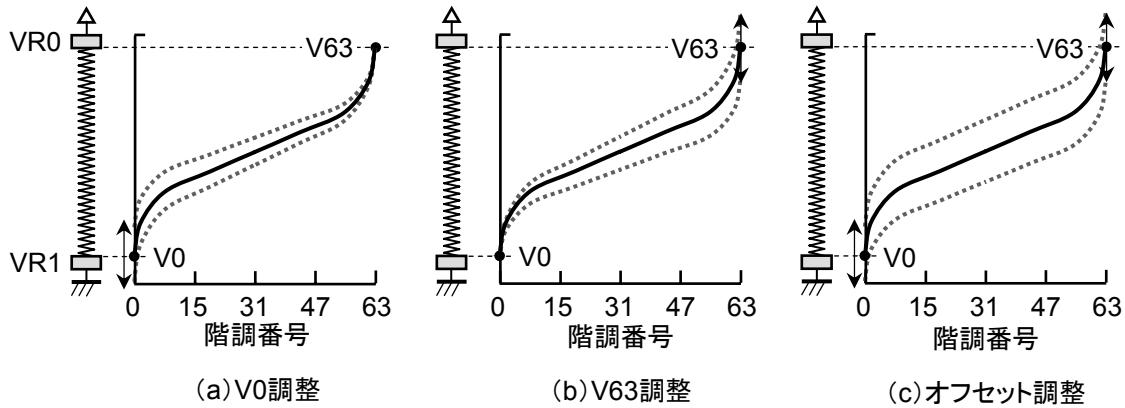

2番目のステップである傾き調整については、図4.9に示すように逆S字カーブにおける曲率がほぼゼロになる付近に可変抵抗VR2とVR3を挿入することで実現する。これらの点は、V0とV63間の電位差をほぼ3等分した位置となる。これらの可変抵抗の設定に対するガンマ特性の補正作用を、図4.10のN-V特性を用いて説明する。まず、図4.10(a)では、高電圧側の傾きは大きく変化させずに低電圧側の傾きを調整する。この動作を実現するには可変抵抗VR3の抵抗値を調整すれば良い。例えば、傾きを大きくする場合は可変抵抗VR3の抵抗値が小さくなるように、傾きを小さくする場合は可変抵抗VR3の抵抗値が大きくなるように調整する。次に、図4.10(b)では、図4.10(a)とは逆に低電圧側の傾きを変化させずに高電圧側の傾きを調整する。この動作を実現するには可変抵抗VR2の抵抗値を調整すれば良い。例えば、傾きを大きくする場合は可変抵抗VR2の抵抗値が小さくなるように、傾きを小さくするには可変抵抗VR2の抵抗値が大きくなるように調整する。最後に、図4.10(c)では、高電圧側と低電圧側の傾きは変えずに、可変抵抗を挿入した箇所の電圧レベルのオフセットを調整する。この動作を実現するには、先に示したVR2とVR3の設定方法を用いて、可変抵抗を挿入した箇所の電圧レベルを同時に調整すれば良い。なお、先の振幅調整で設定するV0、V63の電圧レベルは、傾き調整によって変動することはない。したがって、振幅調整と傾き調整をそれぞれ独立に設定することが可能である。

図 4.9 傾き調整機能の実現回路

図 4.10 傾き調整の実現方法

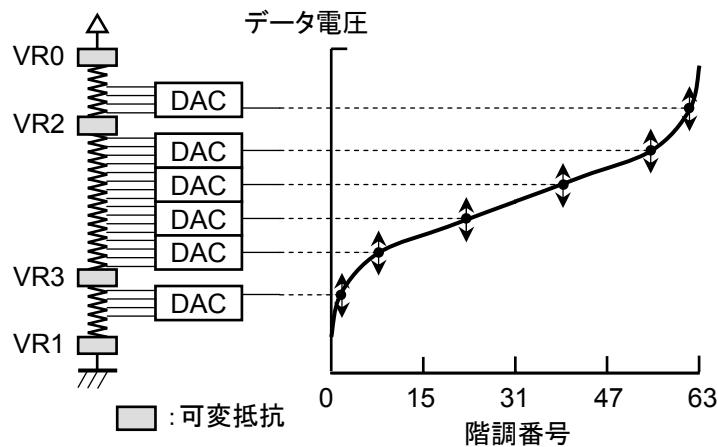

### (3) 微調整

最後のステップである微調整は、図 4.11 に示すように基準電圧を離散的に複数用意し、個々の基準電圧の調整は、候補としてラダー抵抗から出力される電圧レベルを、DAC を用いて選択することにより実現する。図 4.11 から分かるように、DAC が選択する電圧レベルはラダー抵抗から生成されているため、前のステップである振幅および傾き調整によって設定される電圧関係に影響を及ぼさない。したがって、局所的なデータ電圧範囲でのオフセット調整等、細かな調整が可能となる。

図 4.11 微調整機能の実現回路

ここで、用意する基準電圧のレベル数と、それぞれの基準電圧の調整刻み幅は、調整精度を決定する上で重要な設定項目である。そこで、これらの項目をパラメータに、図 4.3 に示した N-V 特性にフィッティングさせた場合の調整誤差の最大値を求めた。その結果を表 4.1 および表 4.2 に示す。なお、各基準電圧レベルの組み合わせについては、基準電圧間を直線で結んだ場合に N-V 特性との誤差が極力小さくなるように、下記の組み合わせとした。

- [4 レベル] : V1, V16, V47, V62

- [6 レベル] : V1, V8, V20, V43, V55, V62

- [8 レベル] : V1, V4, V8, V20, V43, V55, V59, V62

また、表 4.1 および表 4.2 に記載の調整刻み幅は、隣接階調間の電位差： $\Delta V_d$  との相対比を示しており、例えば刻み幅 = 1.0 は 1 階調相当分の電位差に相当する。さらに、調整最大誤差については下記の計算式にて算出し、例えば 100% のずれは 1 階調分の誤差を意味する。

$$\text{調整最大誤差} = \frac{|\text{目標電圧} - \text{設定電圧}|}{\Delta V_d} \quad (4.3)$$

最大誤差が 50% 程度であれば実用上問題はなく、この条件を満たし、最も回路規模が少ない（調整刻み幅が大きい）組み合わせは、基準レベル数：6、調整刻み幅：1.0 の場合である。したがって、この組み合わせを微調整の実現方法とする。なお、上記の組み合わせ

において、電源電圧：5V 時における調整刻み幅の絶対値は 30mV 前後（設定値に依存）となり、従来方法[42]で報告された 39mV よりも 20%以上小さい。このことから、提案方法は従来方法よりも高い精度でガンマ補正を実施することが可能である。

表 4.1 各種ガンマ特性に対する調整誤差

| 基準電圧<br>レベル数 | 調整刻み幅 | 調整最大誤差 %       |                |                |

|--------------|-------|----------------|----------------|----------------|

|              |       | $\gamma = 1.8$ | $\gamma = 2.2$ | $\gamma = 2.6$ |

| 4            | 1.0   | 110%           | 111%           | 94%            |

|              | 0.5   | 79%            | 92%            | 94%            |

| 6            | 1.0   | 55%            | 50%            | 55%            |

|              | 0.5   | 46%            | 50%            | 43%            |

| 8            | 1.0   | 110%           | 111%           | 94%            |

|              | 0.5   | 79%            | 92%            | 94%            |

表 4.2 各種 B-V 特性に対する調整誤差

| 基準電圧<br>レベル数 | 調整刻み幅 | 調整最大誤差 % |      |      |

|--------------|-------|----------|------|------|

|              |       | 液晶 A     | 液晶 B | 液晶 C |

| 4            | 1.0   | 96%      | 111% | 139% |

|              | 0.5   | 89%      | 92%  | 112% |

| 6            | 1.0   | 56%      | 50%  | 56%  |

|              | 0.5   | 56%      | 50%  | 52%  |

| 8            | 1.0   | 54%      | 47%  | 50%  |

|              | 0.5   | 44%      | 45%  | 44%  |

各基準電圧の調整範囲については、既に前のステップで N-V 特性の大半のカーブを設定できていることから広範囲に設ける必要はない。そこで、先の基準レベル数：6、調整刻み幅：1.0 において、調整範囲をそれぞれ 8 段階にすることで N-V 特性に充分フィッティングできていることから、この値を微調整の調整範囲とする。

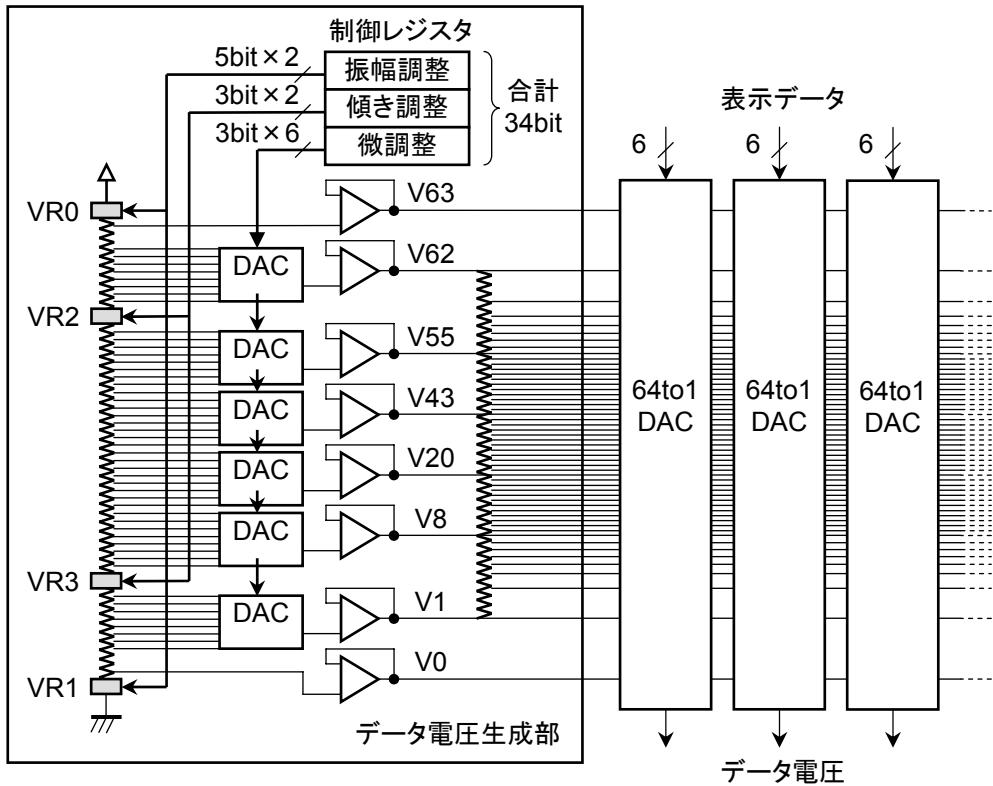

#### (4) 全体構成

データ電圧生成部の全体構成を図 4.12 に示す。基準電圧は、先の検討結果に基づいて 6 レベルとし、振幅調整で設定される V0 および V63 と合わせ、ボルテージフォロア回路に

よってインピーダンス変換して次段のラダー抵抗に接続する。そしてダラー抵抗により 64 階調全てのデータ電圧レベルを分圧して生成する。なお、本回路構成において 256 階調を実現する場合、基準電圧のレベル数は変えずにラダー抵抗の分割数を増加させて対応する。

図 4.12 データ電圧生成部の構成

次に 3 ステップガンマ補正法の回路規模について考察する。まず、図 4.12 に示した回路構成に基づき、必要となる DAC の種類と個数を求める。表 4.3 はその結果である。前節で述べえた従来技術と同様に、表示データをデータ電圧に変換する DAC (64 to 1) を基準に考えると、32 to 1 は  $1/2$  個分、8 to 1 は  $1/8$  個分に相当する。したがって、3 ステップガンマ補正法に必要な DAC の総数は、64 to 1 に換算すると 4 個分になる。この値は、前節で推定を行った従来方法の DAC 換算数 : 40 個に対し、 $1/10$  の回路規模であることが分かる。一方、制御レジスタのビット数については、図 4.12 に示したようにビット数の合計は 34bit である。ただし実際には、データ電圧の極性を一定周期毎に反転する交流化の必要があるため、正極・負極性用の 2 種類、すなわち 2 倍の 68bit 必要となる。これに対し、従来方法[42]における制御レジスタのビット数の合計は、先に述べたとおり 140bit と

推定される。したがって、提案方法における制御レジスタのビット数は、従来方法の半分以下であることが分かる。

以上のことから、提案の 3 ステップガンマ補正法は従来方法と比べて回路規模を大幅に削減することができるため、コスト競争の厳しいモバイル機器向け TFT-LCD のドライバ IC に適用可能である。

表 4.3 3 ステップガンマ補正法に必要な DAC の種類と個数

| DAC の種類 | 個数                | 64to1 換算 |

|---------|-------------------|----------|

| 32to1   | $2 \times 2$ (正負) | 2 個      |

| 8to1    | $8 \times 2$ (正負) | 2 個      |

| 合計      |                   | 4 個      |

## 4.4 適用結果と考察

本節では、提案した 3 ステップガンマ補正法を実際の TFT-LCD に適用し、表示特性を評価することで提案方法の有用性について検証を行う。

### 4.4.1 適用対象

階調時分割駆動法の有用性を検証するにあたり、解像度の異なる 3 種類のドライバ IC を製造した。表 4.4 に評価に用いた TFT-LCD の主要仕様を示す。各 TFT-LCD はそれぞれ製造メーカの異なるパネルを用いており、ガンマ特性はそれぞれ異なる。ガンマ補正機能については、いずれも図 4.12 に示した回路構成を実装している。

表 4.4 評価に用いた TFT-LCD の主要仕様

| 項目      | 液晶 A             | 液晶 B             | 液晶 C             |

|---------|------------------|------------------|------------------|

| 画面サイズ   | 1.8 インチ          | 2.0 インチ          | 2.8 インチ          |

| 解像度     | $132 \times 176$ | $240 \times 320$ | $480 \times 640$ |

| 表示階調数   | 64 階調            | 64 階調            | 256 階調           |

| TFT モード | アモルファス<br>シリコン   | アモルファス<br>シリコン   | 低温ポリ<br>シリコン     |

液晶 A と液晶 B に用いたドライバ IC は、図 4.13 に示す回路構成をベースにしており、表示メモリ、同期信号生成部、電源部、走査駆動部等の表示に必要な要素を全て 1 チップに統合している。液晶 C は、低温ポリシリコン TFT を用いて走査駆動部をガラス基板に内蔵する構成のため、上記構成から走査駆動部を除いた回路構成となる。なお、ホスト側の装置には（株）マキシマ画像研究所製の信号発生器 MG15150 を使用し、インストラクション信号および表示データをドライバ IC に転送することで任意画像の表示を実現する。図 4.14 に提案方法を搭載したドライバ IC（液晶 B に実装）のチップ写真を示す。

図 4.13 ドライバ IC の全体回路構成

図 4.14 ドライバ IC のチップ写真（液晶 B に実装）

#### 4.4.2 提案方法の性能評価と考察

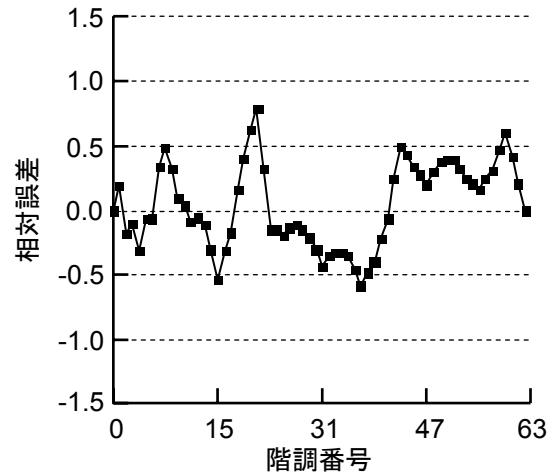

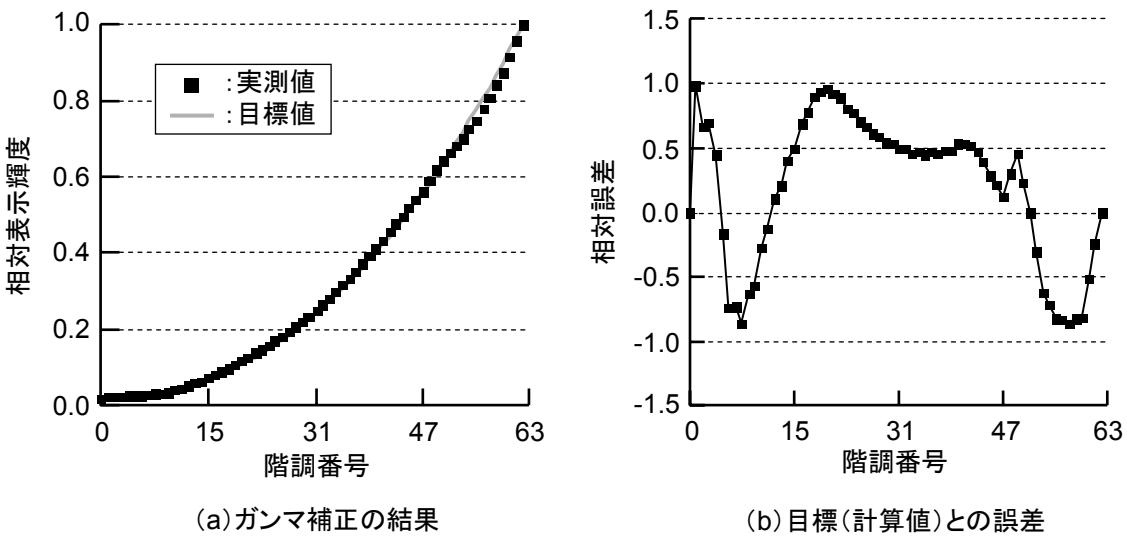

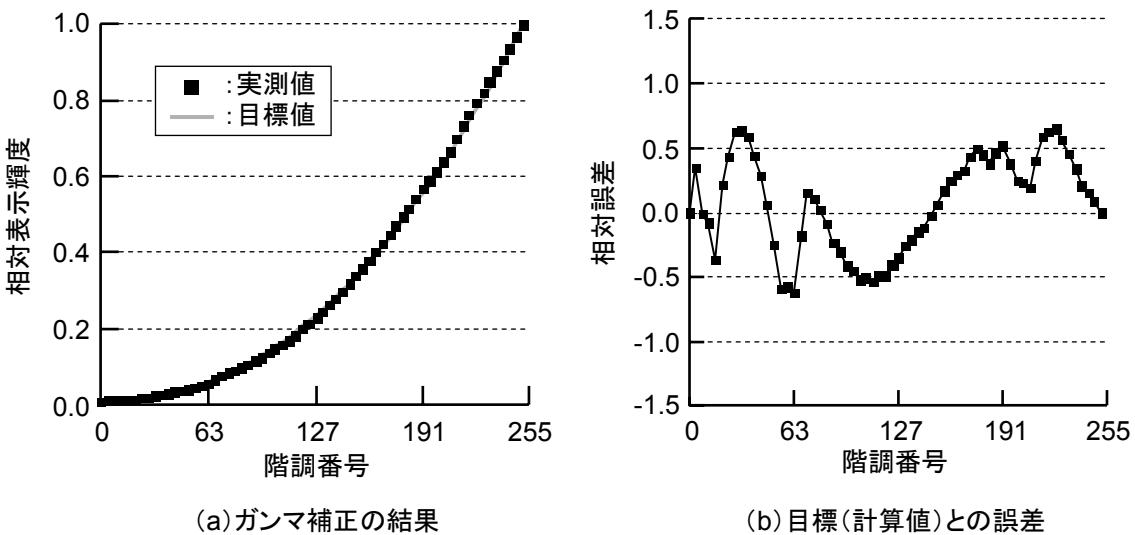

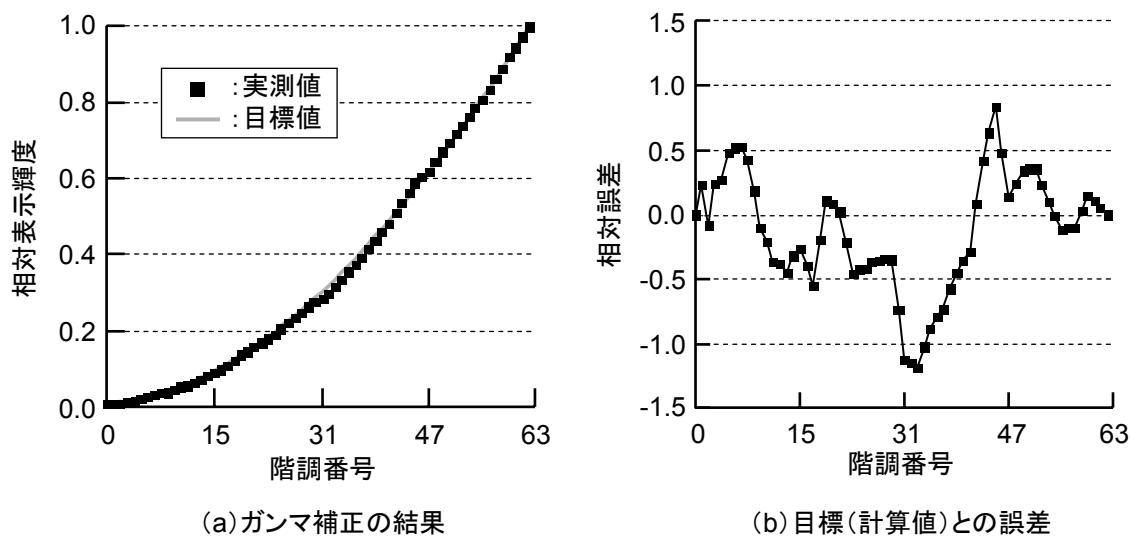

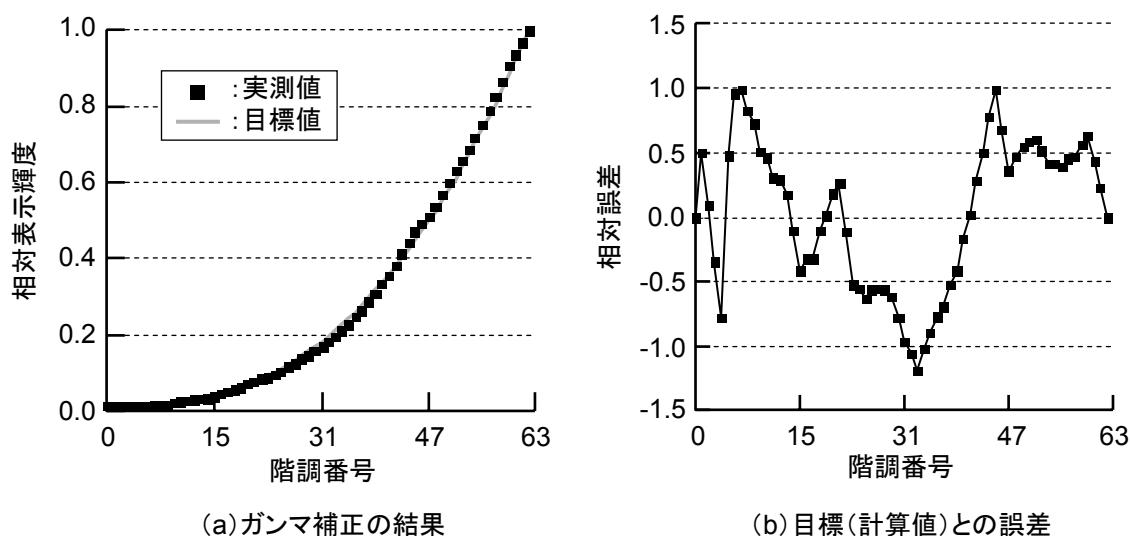

上記 3 種類の TFT-LCD に対し、ガンマ値 : 2.2 を目標に制御レジスタの値を最適化し

た。図4.15～図4.17は、レジスタ最適化後における各TFT-LCDの階調番号一表示輝度特性の測定結果、および測定結果から算出した相対誤差である。まず、各図の(a)は測定結果を示すグラフである。グラフの横軸である階調番号は表示データと一致しており、表示データは64階調表示の場合はRGB各6ビットであることから0～63の値をとり、256階調表示の場合はRGB各8ビットであることから0～255の値をとる。グラフの縦軸は表示輝度の測定値であり、測定ポイントは画面中央、測定装置はコニカミノルタホールディングス(株)製の色彩輝度計CS-100Aである。図中のプロット点が提案方法の測定結果であり、グレーの線は目標とする表示輝度(相対値)である。したがって、測定結果が目標のカーブに近づいている程、精度良くガンマ補正が実現できていると評価することができる。一方、各図の(b)は測定結果に対する目標輝度(ガンマ値:2.2)との誤差を、目標輝度に対する相対値として、下記の計算式により算出したものである。この指標において、例えば相対誤差が1.0である場合、目標輝度との誤差が1階調分であること意味する。なお、256階調表示に対応するドライバICは、64階調分のデータ電圧をベースに、隣接するデータ電圧を単純に分圧することで256階調化する。したがって、分圧により生成した階調の表示輝度は、分圧比に応じた値になることが明らかである。したがって、これらの表示輝度測定については省略し、ベースの64階調を輝度測定の対象とした。

$$\text{相対誤差} = \frac{(\text{実測輝度} - \text{目標輝度})}{1 \text{ 階調分の輝度差}} \quad (4.4)$$

(a) ガンマ補正の結果

(b) 目標(計算値)との誤差

図4.15 ガンマ補正後の表示輝度特性(液晶A)

図 4.16 ガンマ補正後の表示輝度特性（液晶 B）

図 4.17 ガンマ補正後の表示輝度特性（液晶 C）

図 4.15～図 4.17 の結果から、測定した TFT-LCD の特性はいずれも目標とするカーブ上にほぼプロットされており、相対誤差の最大値は 1.0 階調分以下であった。したがって、各種 TFT-LCD に対するフィッティング効果は充分実用的である。

次に、評価した TFT-LCD の中の 1 種類（液晶 A）を用いて、ガンマ値 = 1.8 および 2.6 にフィッティングさせた場合の評価を行った。評価の手法は先と同じく、階調番号 - 表示輝度特性の測定、および測定結果に対する目標輝度との誤差の算出である。これらの結果

を図 4.18 および図 4.19 に示す。図 4.18 および図 4.19 の結果から、同一のパネルにおいてガンマ値を変更した場合にも誤差の最大値は 1.2 階調分以内であり、こちらも実用上充分な精度である。

以上の結果から、本提案の 3 ステップガンマ補正法を搭載したドライバ IC は、多種多様な TFF-LCD の特性に合わせてガンマ特性を高い精度で調整可能である。このことから、目的とするドライバ IC の汎用性向上による低コスト化、および少ない回路規模による高精度なガンマ補正の実現に対し、その有効性を確認することができた。

図 4.18 ガンマ補正後の表示輝度特性（ガンマ値=1.8）

図 4.19 ガンマ補正後の表示輝度特性（ガンマ値=2.6）

## 4.5 結言

本章では、モバイル機器向け TFT-LCD でガンマ補正を実施するにあたり、ドライバ IC 内にガンマ補正用の制御レジスタを内蔵することで、ドライバ IC 製造後においてもホスト側からガンマ特性を変更可能とし、ドライバ IC の汎用性向上を実現した。また、ガンマ補正機能の追加に伴う回路規模増大の課題に対し、N-V 特性を「振幅」「傾き」「微調整」の順番で調整する 3 ステップガンマ補正法を提案し、基準電圧の調整範囲を狭くできる小回路規模化効果により上記課題を解決した。さらに、提案方法を実現する具体的な回路構成を提示し、調整精度と回路規模に関して以下の算出結果を得ると共に、提案方法を解像度  $132 \times 176$  画素、 $240 \times 320$  画素、 $480 \times 640$  画素のメーカの異なる 3 種類の TFT-LCD に適用し、以下の評価結果を得た。

- (1) 従来方法よりも 20%以上高い精度でガンマ調整機能を実現することができた。

- (2) 従来方法に比べてガンマ補正に必要な回路規模を約  $1/10$ 、制御レジスタの必要ビット数を約  $1/4$  に削減することができた。

- (3) 上記 3 種類の TFT-LCD に対し、ガンマ値:2.2 へのフィッティングを実施した結果、目標特性との誤差は 1.0 階調分以下であった。

- (4)  $132 \times 176$  画素の TFT-LCD を用いてガンマ値:1.8, 2.2, 2.6 へのフィッティングを実施した結果、目標特性との誤差は 1.2 階調分以下であった。

以上の結果から、モバイル機器向け TFT-LCD 用途に適用可能な製造コストと調整性能を両立できることを確認し、提案方法の有効性を実証した。なお、本章で提案の 3 ステップガンマ補正法を適用したドライバ IC は（株）ルネサステクノロジ社から HD66773, HD781, R63400 他の製品として実用化され、現在までに累計 10 億個近くを出荷している。また、3 ステップガンマ補正法は、モバイル機器向けドライバ IC におけるデファクトスタンダードとして、多くのメーカのドライバ IC に搭載されている。

今後の課題として、TFT-LCD の固体ばらつきによってガンマ特性が変動することから、この問題の解決が挙げられる。固体ばらつきの補正方法としては、例えばドライバ IC に不揮発性のメモリ回路を内蔵し、パネル毎にガンマ補正の設定値を記憶させることで対応する方法が考えられる[98][99]。この場合、工場出荷時の検査方法を含め、如何に効率の良い補正システムを提案するかが課題となる。一方、先に述べた sRGB に代表される標準色空間では、ガンマ値の他に原色表示 (RGB) および白色表示の色座標が規定される。こ

これらへの対応は、基本的にはバックライトとカラーフィルタの最適設計により実施されるが、先に述べた固体ばらつきの問題は残る。そこで、ドライバ IC に色調整機能を搭載することで、パネル毎に色バランスを調整する解決方法を考えることができる。この場合、如何に少ない回路規模で色調整をドライバ IC に実装できるかが今後の課題である。

# 第 5 章

## 結論

### 5.1 本研究のまとめ

本論文では、情報機器の表示デバイスとして広く採用されている LCD の多階調表示法における画質向上、低コスト化、および画質調整に関する機能向上を目的として、LCD の駆動方法およびドライバ IC の回路構成を最適化する方法について提案し、その効果についての研究成果を以下の 4 章に分けて述べた。

第 1 章では、STN-LCD およびモバイル向け TFT-LCD における共通課題が高画質化と低コスト化の両立であることを論じ、LCD の駆動方法およびドライバ IC の回路構成に関する研究動向と課題を整理した。この結果に基づき、高速応答 STN-LCD の高画質多階調化方法、モバイル機器向け TFT-LCD の小回路規模多階調化方法、モバイル機器向け TFT-LCD の高汎用画質調整方法を 3 つの課題として取り上げ、それぞれの解決方針を示した。

第 2 章では、従来の多階調表示方法を高速 STN-LCD に適用した際に課題となるフリッカの発生、およびフレーム応答によるコントラスト低下に対し、これらを同時に抑制する高フレーム周波数駆動法を提案した。また、高フレーム周波数駆動法を実現する上でのフレームメモリの増加問題に対し、必要メモリ数を従来の  $1/3$  に削減可能な 2 周波合成 FRC 法を提案した。さらに、高フレーム周波数駆動法におけるシャドーイングの増大の問題を、Hi-Addressing 法の適用および FRC パターンの最適化により抑制する方法を提案した。これらの提案方法を応答時間 : 150ms の PC モニタ向け STN-LCD に適用し、モニタ用途に適用可能な表示性能と製造コストを両立できることを確認して提案方法の有効性を実証した。

第 3 章では、モバイル機器向け TFT-LCD の小回路規模多階調表示を実施するにあたり、ドライバ IC のチップサイズ縮小に効果的なコモン電圧反転法と集中アンプ型構成の組み合わせを採用すると共に、集中アンプ形構成の課題である階調数に依存して OP アンプの搭載個数が増大する問題を、階調時分割駆動法の提案により抑制した。同時に、ガラス基

板上に搭載するデ・マルチプレクサ回路を不要とし、アモルファスシリコン TFT-LCD への適用を可能とした。さらに、階調時分割駆動法において発生が予想されたカップリング性とリーク性の電圧変動に対し、データ電圧の出力タイミングの最適化と、データ電圧の補正機能を新たに付け加えることで抑制した。これらの提案方法を、解像度  $132 \times 176$  画素および  $176 \times 220$  画素の TFT-LCD に適用し、モバイル機器向け TFT-LCD 用途に適用可能な製造コストと表示性能を両立できることを確認して提案方法の有効性を実証した。

第 4 章では、モバイル機器向け TFT-LCD でガンマ補正を実施するにあたり、ドライバ IC 内にガンマ補正用の制御レジスタを内蔵することで、ドライバ IC 製造後においてもホスト側からガンマ特性を変更可能とし、ドライバ IC の汎用性向上を実現した。また、ガンマ補正機能の追加に伴う回路規模増大の課題に対し、N-V 特性を「振幅」「傾き」「微調整」の順番で調整する 3 ステップガンマ補正法を提案し、基準電圧の調整範囲を狭くできる小回路規模化効果により上記課題を解決した。これらの提案方法を解像度  $132 \times 176$  画素、 $240 \times 320$  画素、 $480 \times 640$  画素のメーカーの異なる 3 種類の TFT-LCD に適用し、モバイル機器向け TFT-LCD 用途に適用可能な製造コストと調整性能を両立できることを確認して提案方法の有効性を実証した。

## 5.2 今後の課題

最後に、本研究の今後の課題について述べる。

### (1) 動画表示の高画質化

現在、携帯電話を中心としたモバイル機器においても、ゲーム機能やテレビ放送の受信等、動画を扱うアプリケーションが増加している。このため、動画に対する高画質化、特に動画ぼやけに対する改善要求が従来よりも強まっている。TFT-LCD の動画ぼやけを改善するアプローチとしては、液晶の高速応答化と網膜残像対策が挙げられる。前者の高速応答化については、液晶材料や駆動方法の改良が図られ、これらの技術は薄型テレビ用途で実用化されている[100][101][102]。しかしながら、モバイル機器においては野外での使用も想定されるものの、液晶の応答速度は低温環境下において極端に低下する特性を有する。したがって、低温時における液晶の応答速度を如何に改善して視認性を向上させるかが、今後の課題である。一方、後者の網膜残像は、TFT-LCD のように表示輝度をホールドするディスプレイの場合、人間は画像切り替え時の 2 つの画像を重ねて認識し、画像の輪郭をぼやけたと判断する現象である[103]。この改善にあたっては、輝度のホールド期間

を短縮する黒挿入駆動や倍速駆動が提案され、薄型テレビ用途に実用化されている [104][105][106]. しかし、倍速駆動をモバイル向けに適用する場合、消費電力や必要フレームメモリ容量の増加が問題となるため、この問題の解決が今後の課題である.

## (2) 低消費電力化