| Title        | 高周波通信用バイポーラ/BiCMOS LSIの高集積化・高機能化に関する研究 |  |

|--------------|----------------------------------------|--|

| Author(s)    | 佐藤, 久恭                                 |  |

| Citation     | 大阪大学, 2011, 博士論文                       |  |

| Version Type | VoR                                    |  |

| URL          | https://hdl.handle.net/11094/2054      |  |

| rights       |                                        |  |

| Note         |                                        |  |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

# 高周波通信用バイポーラ/BiCMOS LSI の高集積化・ 高機能化に関する研究

佐藤 久恭 2011年8月

## 内容梗概

本論文は、筆者が大阪大学大学院工学研究科電気電子情報工学専攻量子電子デバイス工学部門集積エレクトロニクス講座集積機能デバイス領域(谷口研究室)にて行った「高周波通信用バイポーラ/BiCMOS LSI の高集積化・高機能化に関する研究」の研究成果をまとめたものであり、以下の7章で構成されている。

#### 第1章

本章では、本研究の背景、高周波通信用 LSI における課題と本研究の目的について述べた後、本論文の構成の概略を述べた.

#### 第2章

光通信などの高速有線通信向け LSI は,数 100M~数 10 Gbps (bit per second) で動作する.バイポーラ論理回路は高速動作という利点を有しているが,面積が大きいという欠点がある.また,論理回路を効率よく構成するために,マスタスライス方式と呼ばれるセミカスタム LSI を使用するが,従来のセル構成方式であるシンプルゲートセル方式やマクロセル方式は,それぞれ得意とする論理回路があり,それ以外では不使用な素子があったり,セル面積が増大したりと,集積効率が悪いという問題があった.

本章では、論理回路の集積密度を改善することを課題として面積可変論理セル VSC(Variable Size Cell)方式を提案した。本方式ではユニットとよぶ4つのトランジスタから構成される小さな単位に分割し、複数のユニットを使用することで論理セルを構成した。また、1ユニットで1つのメモリセルを構成できるように工夫を加えた。0.6 μm バイポーラプロセスにて、12k ゲートと 36k ビットのメモリを内蔵したマスタスライス LSI を試作した。本方式を用いることで、通信用 LSI の論理回路集積密度を 20~30%向上させることができた。

#### 第3章

通信用 LSI ではシリーズゲートと呼ばれる縦積み 2 段の論理回路を使用する. この回路の最低動作電圧は約  $2.5 \, V$  であり、論理回路の外部インターフェース電圧や電池の終端電圧である  $2 \, V$  以下で動作させることができず、2 電源が必要であったり、消費電力が大きいという問題があった.

本章では、2 V 以下で動作するシリーズゲート回路を提案した。縦積み 2 段のうち、下段の差動対を定電流回路と併用することで低電圧化を可能とし、このために下段の差動対に入力される信号の電源電圧依存性を取り入れた。  $f_T=12$  GHz の  $0.6~\mu m$  バイポーラプロセスを用い、提案回路を用

いて 1/4 分周器 (4 進カウンタ) を試作した. 実測により、1.4 V の電圧で動作することを確認し、フリップフロップ 1 段あたり 0.35 mW と極めて小さい消費電力にて 600 MHz の動作周波数が得られた.

#### 第4章

回路をより高速,高周波動作させるためには、シリーズゲート回路の出力段にエミッタフォロワ 回路を付加して負荷駆動能力を上げるが、このエミッタフォロワ回路の電流が多いために消費電力 が大きくなるという欠点がある.

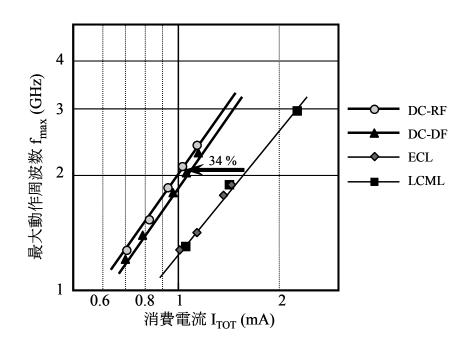

本章では、エミッタフォロワによる高速、高周波動作という利点を生かしつつ、エミッタフォロワの低電流化を図ったエミッタフォロワ直接制御型回路を提案した。入力信号に応じて2つのエミッタフォロワ電流を切り替えるようにすることで、エミッタフォロワ電流を半分にすることができる。この構成により、エミッタフォロワ電流をすべて負荷容量の充電に充てることができ、立ち上がり時間の短縮も可能となった。出力インピーダンスが高くなり、出力が不安定になるという問題に対しては、抵抗フィードバックもしくはダイオードフィードバックによる安定回路を付加することで解決した。  $f_T=25~{\rm GHz}~0~0.35~{\rm \mu m}$  バイポーラプロセスを用いて、従来回路(エミッタフォロワ有/無)と提案回路(抵抗フィードバック/ダイオードフィードバック)、合わせて4種の回路構成の1/4、1/5分周デュアルモジュラスプリスケーラを試作、評価した。同一の動作周波数(2 GHz)で比較すると、提案回路は従来回路よりも34%の低消費電力化が図れた。

#### 第5章

無線通信用トランシーバは、個別部品、IC、LSI へとその集積度を向上させ、小型、低コスト、低消費電力化を図ってきた. LSI 化するに当たって、高周波動作、不要波抑圧、システム全体での性能補償といった課題がある.

本章では、中間周波数処理 LSI 実現に向けて、小型な直交変調器、HPA (High Power Amplifier) の温度特性に合わせたアッテネータ、PLL の高速ロックアップ、信号アイソレーション向上について提案した。  $f_7$ =20 GHz の  $0.8~\mu m$  BiCMOS プロセスを用い、中間周波数処理 LSI を試作、検証し、要求される性能を満足することが確かめられた。本研究の成果は、1.9~GHz 帯として世界初の中間周波数処理 LSI として製品化されている。

#### 第6章

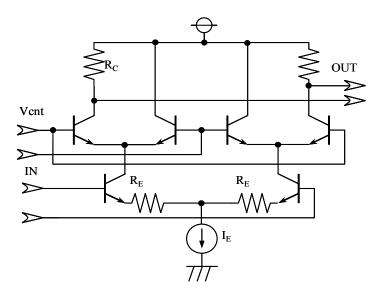

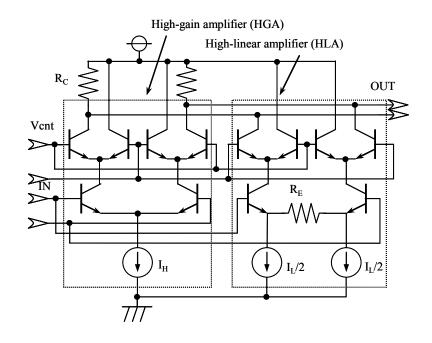

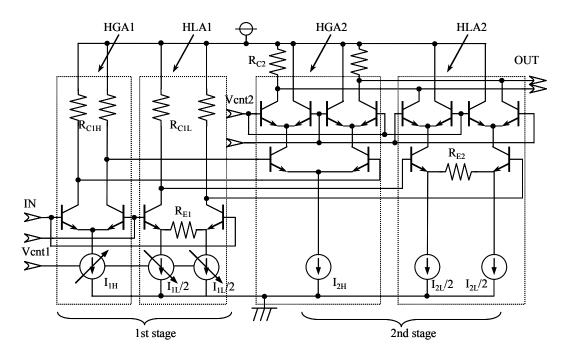

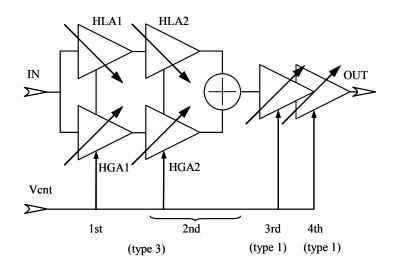

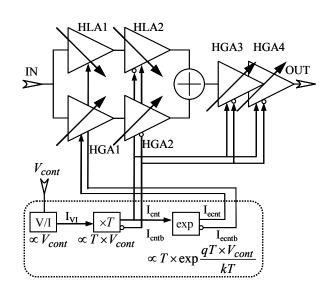

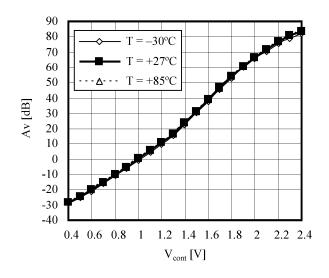

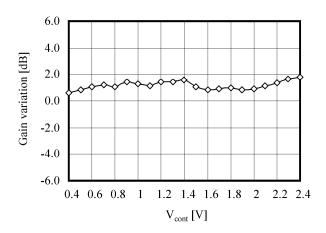

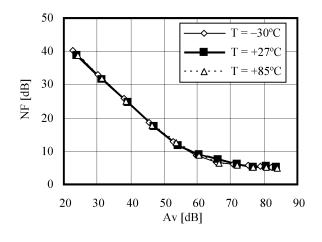

WCDMA (Wideband Code Division Multiple Access) のような無線システムにおいては、入力信号振幅のレンジが 90 dB と極めて広い. このため、無線トランシーバには可変利得アンプを設け、後段にある A/D コンバータの入力レンジをオーバフローしないようにしている. この可変利得アンプは、信号振幅が小さい場合には利得を大きくするとともに、かつ雑音特性がよくなければならず、

逆に信号振幅が大きい場合には、利得を下げるとともに線形性がよくなければならない.可変利得アンプの可変レンジそのものは、回路を多段化することで実現可能であるが、従来の可変利得アンプでは、低雑音と高線形の両立が困難であった.

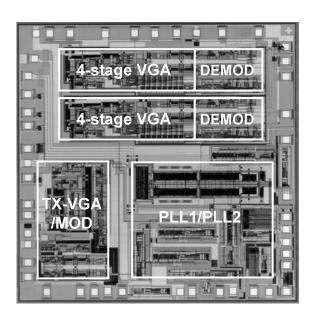

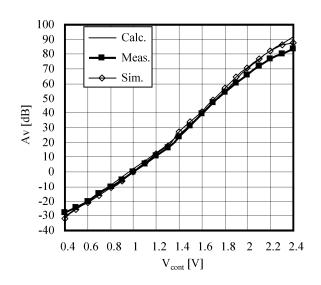

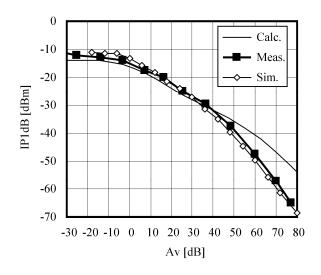

本章では、WCDMA への適用を目的として、入力信号振幅のレンジが 90 dB と極めて広い可変利得アンプについて提案した。高利得、低雑音のアンプと低利得、高線形のアンプを並列に配置する方式を採用した。また、並列アンプの利得配分、線形性配分を最適化するため、利得と線形性に関する解析式を新規に導出した。 $f_T=26~{\rm GHz}$  の  $0.5~{\rm \mu m}$  BiCMOS プロセスを用いて検証を行い、雑音、線形性特性が要求性能を満足する良好な特性であることを確認した。また、導出した可変利得アンプの解析式が、実測、シミュレーションとよく一致することを確認した。提案する可変利得アンプを含む中間周波数処理 LSI は WCDMA 用として製品化されている。

## 第7章

本論文で取り上げた各研究課題に関する成果についてまとめた.

# 目次

| 第1章  | 序論                                | 1  |

|------|-----------------------------------|----|

| 1.1  | 研究の背景                             | 1  |

| 1.2  | 研究対象,研究分野                         | 2  |

| 1.3  | 研究目的および論文構成                       | 3  |

| 第2章  | バイポーラマスタスライス LSI 用面積可変論理セル        | 7  |

| 2. 1 | 緒言                                | 7  |

| 2.2  | 従来のセル構成                           | 8  |

| 2.3  | VSC マスタスライス                       | 10 |

| 2.4  | コンフィギュラブル RAM                     | 13 |

|      | 2.4.1 メモリセル                       | 13 |

|      | 2.4.2 ユニット構成                      | 14 |

|      | 2.4.3 VSC 方式の効果                   | 15 |

| 2.5  | VSC 方式の実装例                        | 16 |

|      | 2.5.1 チップフロアプラン                   | 16 |

|      | 2.5.2 論理回路                        | 17 |

|      | 2.5.3 コンフィギュラブル RAM の構成           | 18 |

|      | 2.5.4 プロセス技術                      | 19 |

|      | 2.5.5 評価結果                        | 20 |

| 2.6  | 結言                                | 22 |

| 第3章  | 低電圧動作バイポーラシリーズゲート回路               | 25 |

| 3. 1 | 緒言                                | 25 |

| 3. 2 | 回路設計                              | 25 |

|      | 3.2.1 低電圧シリーズゲート                  | 25 |

|      | 3.2.2 V <sub>EE</sub> 追従バッファ(VTB) | 27 |

|      | 3.2.3 基準電圧発生回路                    | 30 |

|      | 3.2.4 フリップフロップ                    | 31 |

| 3.3  | LSG および VTB の検証                   | 31 |

|      | 3.3.1 プロセス技術                      | 31 |

|      | 3.3.2 DC 特性                       | 33 |

|      | 3. 3. 3 AC 特性                     | 35 |

| 3. 4 | 結言                              | 37 |

|------|---------------------------------|----|

| 第4章  | エミッタフォロワ直接制御型フリップフロップ回路         | 41 |

| 4. 1 | 緒言                              | 41 |

| 4.2  | 直接制御エミッタフォロワ                    | 42 |

|      | 4.2.1 基本回路構成                    | 42 |

|      | 4.2.2 レベル安定化回路付き直接制御エミッタフォロワ    | 43 |

|      | 4.2.3 回路シミュレーション結果              | 44 |

| 4.3  | フリップフロップ回路                      | 47 |

|      | 4.3.1 従来回路                      | 47 |

|      | 4.3.2 ダイオードフィードバック型直接制御エミッタフォロワ | 49 |

|      | 4.3.3 抵抗フィードバック型直接制御エミッタフォロワ    | 50 |

|      | 4.3.4 従来回路との比較                  | 51 |

|      | 4.3.5 抵抗レベルシフト回路                | 53 |

| 4.4  | 評価結果                            | 54 |

| 4. 5 | 結言                              | 58 |

| 第5章  | 1.9 GHz PHS 用中間周波数処理 LSI        | 61 |

| 5. 1 | 緒言                              | 61 |

| 5. 2 | 1 チップ化へ向けた課題と対応                 | 62 |

| 5. 3 | チップ構成                           | 63 |

| 5. 4 | 回路設計                            | 64 |

|      | 5.4.1 直交変調器                     | 64 |

|      | 5.4.2 アッテネータ                    | 65 |

|      | 5.4.3 送受信ミキサ                    | 66 |

|      | 5.4.4 PLL シンセサイザ                | 67 |

|      | 5.4.5 基準電圧発生回路                  | 70 |

| 5.5  | プロセス技術                          | 70 |

| 5.6  | レイアウト                           | 72 |

| 5. 7 | 評価結果                            | 73 |

| 5.8  | 結言                              | 77 |

| 第6章  | 可変利得アンプの高線形化                    | 81 |

| 6. 1 | 緒言                              | 81 |

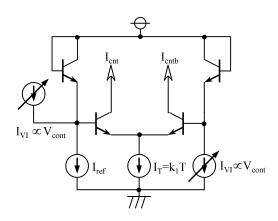

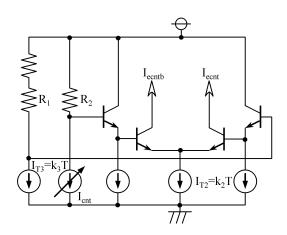

| 6.2  | 可変利得アンプの設計                      | 82 |

|      | 6.2.1 可変利得アンプの回路構成              | 82 |

| 研: | 究業績 | 績                          | )9             |

|----|-----|----------------------------|----------------|

| 謝  | 辞.  |                            | )7             |

| 第  | 7章  | 結論10                       | )3             |

|    | 6.4 | 結言                         | <del>9</del> 9 |

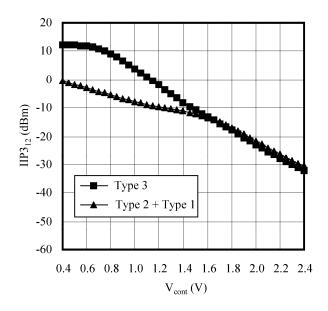

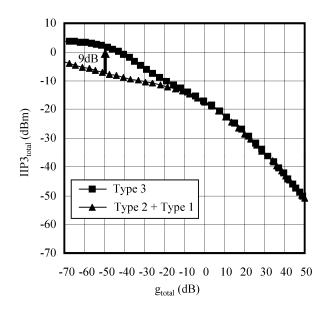

|    | 6.3 | 評価結果および解析式との比較             | <del>9</del> 5 |

|    |     | 6.2.5 回路パラメータの決定と設計手順      | 94             |

|    |     | 6.2.4 温度補償                 | 91             |

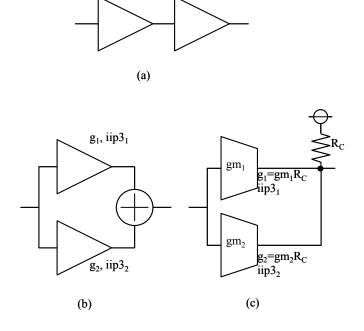

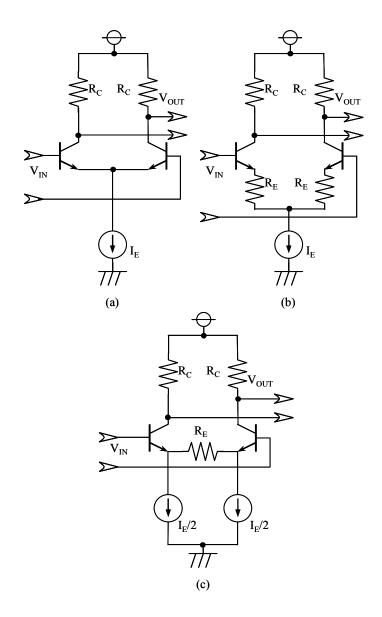

|    |     | 6.2.3 可変利得アンプの利得と IIP3 の解析 | 37             |

|    |     | 6.2.2 パラレルアンプの利得と IIP3     | 35             |

## 第1章 序論

## 1.1 研究の背景

1947年にAT&Tベル研究所のBardeen, Brattain, Shockley らによって点接触トランジスタが発明されてから 60年以上が経つ。この間、プレーナ型トランジスタ、自己整合トランジスタ、2層ポリシリコントランジスタへとデバイス技術が進展し、SiGe バイポーラトランジスタで遮断周波数が 300 GHz を超えるものや[1]、SiGe BiCMOS プロセスで 0.38 THz の無線トランシーバを実現したものが発表されている [2]。一方、1970年代後半から本格的に開発されてきた CMOS (Complementary Metal Oxide Semiconductor)は、回路構成が簡単であるとともに、デバイスを微細化するとトランジスタの高集積化、低消費電力化が達成されるスケーリング則を生かし、急速に発展してきた。最近発表された 32 nmの CMOS プロセスを用いた 64 ビットマイクロプロセッサは実に 31 億個のトランジスタが集積されている [3]。複数の無線通信機能を有した高性能なコンピュータがタブレットコンピュータやスマートフォンとして持ち運べるようになり、低燃費を謳うハイブリット車には 1 台当たり 50~100個のマイコンが搭載される時代となってきている。このように半導体デバイスの進歩が現代のエレクトロニクス社会にはなくてはならないものとなっている。

近年の携帯機器をはじめとする無線通信機器の発展はめざましく,最新の携帯電話においては,通常の携帯電話機能の他, GPS(Global Positioning System),携帯電話・移動体端末向け地上波デジタルテレビ放送,Bluetooth,無線LANといった,さまざまな無線システムが内蔵されている. 20 数年前では,携帯電話がショルダーバッグサイズであったことを考えると隔世の感がある.携帯電話が現在のように小型多機能化された一つの大きな要因は,RFトランシーバの小型高集積化技術が進んだことによる.

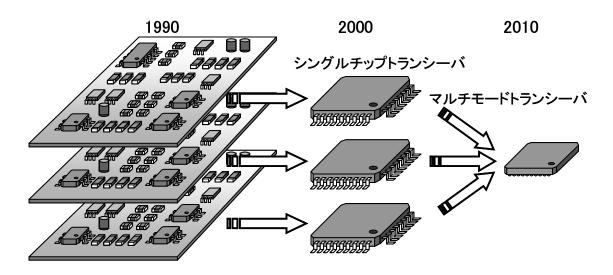

90 年代半ばごろまで、受信 IC、送信 IC、PLL シンセサイザといった複数の IC や個別部品で構成されていた RF トランシーバ部は、その後、徐々に 1 チップ化されていく(図 1.1). 携帯電話用と

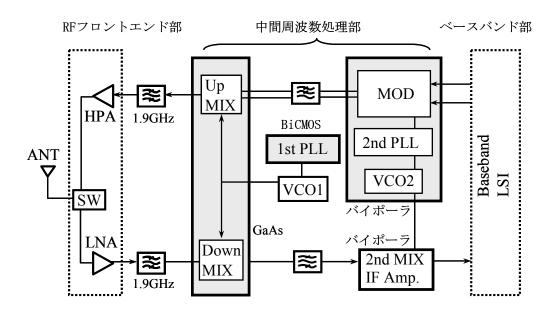

図 1.1: 無線トランシーバの高集積化

して初めて IC 化されたものは、95 年に発表された 1.5 µm バイポーラプロセスを用いた 900 MHz 帯の GSM(Global System for Mobile Communications)用トランシーバであった[4]. その後、2000 年ごろから Bluetooth や無線 LAN 用の 1 チップトランシーバが発表され、最近では複数の無線システムを搭載したマルチモードトランシーバが出現している[5][6]. アナログ回路や高周波回路は、トランジスタの微細化がそのまま高集積化につながるわけではない. 一つには容量素子、インダクタといった微細化の恩恵を受けにくい受動素子の存在、もう一つは外付けされる SAW フィルタ (surface acoustic wave filter)のような高い Q を持ち、低雑音なフィルタを単純にはオンチップ化することが困難であることなどが挙げられる。このため、無線通信用 LSI の高集積化、高機能化のためには、システムを構成するさまざまな機能ブロックをオンチップ化する絶え間ない技術革新が必要となる.

バイポーラトランジスタは、高速な応答速度、高い負荷駆動能力、すぐれた雑音特性を活かし、シリアル/パラレル変換回路といった高速有線通信用 LSI や、無線通信用高周波アナログ回路など、高速、高周波分野に用いられてきた。一方で、CMOS トランジスタは、スケーリング則が生かせ、プロセス技術の進展とともに高集積化が図れるため、大規模デジタル回路に用いられてきた。プロセス技術の進展とともに動作周波数は年々向上しているが、高速なバイポーラ、高集積な CMOS という関係は 30 年以上続いている。

近年では CMOS トランジスタの性能が向上し、GHz 帯で動作する RF トランシーバが数多く発表されている. 性能よりも SoC (System on Chip) 化による小型化が強く要求される無線通信システムにおいては CMOS プロセスが用いられ、雑音特性や消費電流がより重視される分野においては Bi CMOS プロセスが用いられるといった両者の棲み分けがなされている. バイポーラ/Bi CMOS が高周波動作、低消費電流で CMOS に対して優位性を維持していくためには、性能や消費電流を更に改善するとともに、高集積化や高機能化といった課題に取り組んでいく必要がある. 具体的には下記のような課題が挙げられる.

- 1) 素子利用効率の高いレイアウト手法

- 2) 低電源電圧化回路技術

- 3) 低電流/高周波回路アーキテクチャ

- 4) オンチップ化に適した回路構成

## 1.2 研究対象,研究分野

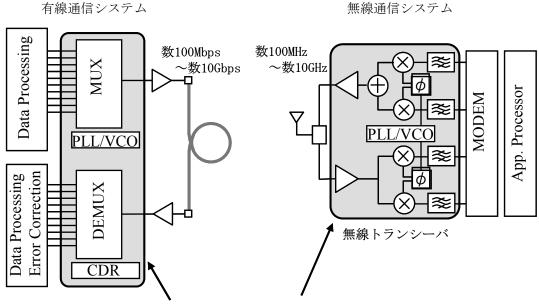

図1.2に本研究の研究分野,研究対象を示す.

光通信などの有線通信では、ケーブルと直接接続されるドライバ/レシーバアンプとデジタルデータ処理部との間に高周波で動作する送受信トランシーバ部がある。この LSI には、送受信データを多重もしくは拡散するマルチプレクサ (MUX: Multiplexer)、デマルチプレクサ (DEMUX: Demultiplexer)、クロック・データリカバリ回路 (CDR: Clock Data Recovery)、これらの回路に基準クロックを供給する PLL シンセサイザ (Phase Locked Loop synthesizer) などから構成される。また、携帯電話のような無線通信システムでは、アンテナから入力される無線信号をベースバンド信号に変換する無線トランシーバ部がある。これらのトランシーバ部には高周波で動作する論理回路や、アンプ、ミキサといった高周波アナログ回路を含み、これらの回路を研究対象とする。

有線/無線システムの高速論理回路, 高周波アナログ回路

図 1.2: 研究分野, 研究対象

## 1.3 研究目的および論文構成

本研究の目的は、第1にバイポーラトランジスタが持つ高い周波数応答、高い負荷駆動能力をさらに改善しつつ、高集積化、高機能化、低消費電力化を図る要素技術を確立すること。第2に、そこで得られた技術を高周波通信用LSIとして実用化することにある。

図 1.3 に第  $2\sim6$  章の研究項目と論文構成を示す。第 2 章はバイポーラマスタスライスで使用される論理回路の小面積化と高機能化に関するものであり,第 3, 4 章はバイポーラ回路の低電圧化,低消費電力化に関するものである。第 5 章はこれらの要素技術を取り入れた無線通信用 LSI の高集積化技術,実用化技術に関するものであり,第 6 章では回路の高線形化に対する設計技術について述べる。

以下に各章の研究目的を述べる.

第2章では、マスタスライスにおけるバイポーラ論理回路の高集積化、およびビット・ワード構成が柔軟なコンフィギュラブルメモリの搭載を目的として、素子の利用効率が高い面積可変論理セル VSC (Variable Size Cell) 方式の提案を行う。0.6 μm バイポーラプロセスにて 12k ゲートと 36k ビットのメモリを内蔵したマスタスライス LSI を試作し、その効果を検証する.

第3章では、低電圧バイポーラ回路の提案を行う。通信用 LSI ではシリーズゲートと呼ばれる縦積み2段の論理回路を多用するが、この回路の最低動作電圧は約2.5 V であり、消費電力を削減することが困難であるという問題がある。本章では、2 V 以下で動作するシリーズゲート回路を提案し、0.6  $\mu$ m バイポーラプロセスを用いた 1/4 分周器 (4 進カウンタ) を試作し、その動作を検証する。

#### 有線通信 無線通信 第5章 第3章 PHS用中間周波数処理LSI バイポーラ回路の 高集積化 第2章 低雷圧化 実用化技術 論理回路の 小面積化 第6章 第4章 高機能化 広ダイナミックレンジ可変利 高速, 低消費電力化 得アンプの高線形化 要素技術 要素技術/実用化技術 要素技術

図 1.3: 第 2~6 章の研究項目と論文構成

第4章では、高周波動作を改善しつつ、エミッタフォロワの低電流化を図るために、新規のエミッタフォロワ回路を提案する。0.35 µm バイポーラプロセスを用いて 1/4、1/5 分周プリスケーラの試作を行い、消費電力および最高動作周波数について従来回路と比較を行う。

第5章では、無線通信用LSIの高集積化、高機能化を目的として、小型な直交変調器、HPA(High Power Amplifier)の温度特性に合わせたアッテネータ、PLLの高速ロックアップ、信号アイソレーション向上について提案する。 0.8 μm BiCMOS プロセスを用い、PHS(Personal Handy-phone System) 用中間周波数処理LSIを試作、検証し、これらの技術の実用化について議論する.

第6章では、通信用 LSI のキーコンポーネントとなる可変利得アンプの高線形化回路技術を提案する. また、可変利得アンプの利得、および線形性について新たに回路解析を行い、実測結果と比較することでその解析式の妥当性を議論する.  $0.5~\mu m$  BiCMOS プロセスを用いて提案する可変利得アンプを含む WCDMA (Wide-band Code-Division Multiple Access) 中間周波数処理 LSI を試作、評価した結果を示す.

最後に、第7章において、本論文を通して得られた結果を述べる.

## 参考文献

- [1] M. Khater, J. S. Rieh, T. Adam, A. Chinthakindi, J. Johnson, R. Krishnasamy, M.Meghelli, F. Pagette, D. Sanderson, C. Schnabel, K. T. Schonenberg, P. Smith, K. Stein, A. Stricker, S.-J. Jeng, D. Ahlgren, and G. Freeman, "SiGe HBT Technology with fmax/f<sub>T</sub> = 350/300 GHz and gate delay below 3.3 ps," Proc. IEEE Int. Electron Device Meeting, pp. 247-250, Dec. 2004.

- [2] J. D. Park, S. Kang, and A. M. Niknejad, "A 0.38THz Fully Integrated Transceiver Utilizing Quadrature Push-Push Circuitry," Symp. VLSI Circuits Dig. Tech. Papers, pp. 22-23, June. 2011.

- [3] R.J. Riedlinger, R. Bhatia, L. Biro, B. Bowhill, E. Fetzer, P. Gronowski, T. Grutkowski, "A 32nm 3.1 billion transistor 12-wide-issue Itanium® processor for mission-critical servers," ISSCC Dig. Tech. Papers, pp. 84-86, Feb. 2011.

- [4] T. D. Stetzler, I. G. Post, J. H. Havens, and M. Koyama, "A 2.7V 4.5V Single-Chip GSM Transceiver RF Integrated Circuit," IEEE J. Solid-State Circuits, vol. 30, no. 12, pp. 1421-1429, Dec., 1995.

- [5] 佐藤久恭, "招待講演 無線通信用 LSI の技術動向と課題,"電子情報通信学会,システム LSI ワークショップ,第8回,pp. 75-82, 2004-11-30

- [6] 佐藤久恭, "招待講演 RF トランシーバのマルチモード,マルチバンド化," 電子情報通信 学会技術研究報告. ICD, 集積回路 110(140), pp. 43-48, 2010-07-17-22

# 第2章 バイポーラマスタスライス LSI 用面積可変論 理セル

## 2.1 緒言

マスタスライス方式とは、マスタと呼ばれる下地(トランジスタや抵抗などの素子)を形成する工程と、スライスと呼ばれる配線工程からなり、マスタ部分を共通化し、スライス部分のみを変えることによってさまざまな論理を実現する方式である。このため、フルカスタムで一から LSI を開発する方式よりも、開発の TAT (Turn Around Time) を短縮できるとともに、開発コスト、製造コストを大幅に削減することができる。特にバイポーラマスタスライス LSI は、その高速性を生かして、汎用コンピュータのメインフレームや光通信などの高速データ処理システムの核となる LSI として古くから使われている。システムの高性能化のために、常に高速化と高集積化が要求され、これらの要求に応えるべく数々のバイポーラマスタスライスが開発されており、新しいプロセス技術に加え新しい回路およびセル方式の採用によって高性能化を実現してきた[1]-[7].

CMOS マスタスライスの場合, pMOS トランジスタと nMOS トランジスタのみで回路が構成されるため,トランジスタをアレイ状に並べ,必要なトランジスタ数のみ使用して論理回路を構成することができる. pMOS と nMOS の使用比率はほぼ等しいため,素子の利用効率は比較的高い.一方,バイポーラ回路は,npnトランジスタ以外に種々の抵抗を使用するため,素子をアレイ状に並べることが困難で,バイポーラマスタスライスでは一定数のトランジスタと抵抗をひとまとまりにしたセルをアレイ状に並べる. 使用するトランジスタ数や抵抗の数は論理回路毎に異なるため,未使用の素子が多数存在し,集積度は CMOS マスタスライスと比べてあまり向上しなかった.このため,バイポーラマスタスライスの高集積化のためには,構成する論理回路に依らず素子の利用効率が高い新たなセル方式が必要となる.

一方で、高速通信システムにおいては、データイコライザ用ルックアップテーブルやバッファメモリなど多くのメモリを使用する。RAM(Random Access Memory)と論理回路のオンチップ化は、RAMと論理 LSI 間の入出力バッファの遅延や消費電力を削減するとともに実装面積の小型化に貢献する。これまでにもバイポーラマスタスライスに専用 RAM を内蔵した例はあるが[8]-[9]、論理規模が小さく、専用 RAM の制御回路を実現する程度であったり、専用 RAM であるがゆえにメモリサイズの柔軟性に欠けるという問題があった。このため、システムの性能向上のためには、論理回路の集積度向上や、フレキシブルなメモリ構成が必要となってくる。

本章では、素子の利用効率が高いバイポーラマスタスライス LSI 用面積可変論理セル VSC(Variable Size Cell)について述べるとともに、VSC 方式を用いたメモリセル構成を提案する. また、VSC 方式の実装例として、32k ビットの専用 RAM を内蔵したバイポーラマスタスライスの設計について述べ、試作評価結果を示す. 結言にて本章の結論を示す.

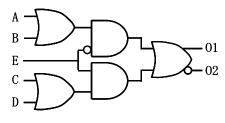

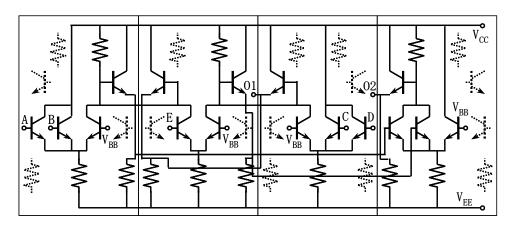

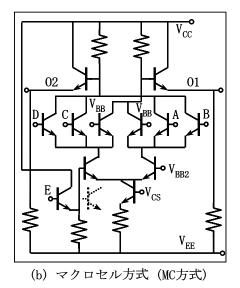

(a) シンプルゲートセル方式 (SC方式) (b) マクロセル方式 (MC方式)

図 2.1: 従来のバイポーラ論理回路のセル構成(3 入力 OR/NOR)

## 2.2 従来のセル構成

一般にバイポーラマスタスライスに採用されているセル方式には2種類ある.一つはシンプルゲートセル方式(SC 方式)であり、他の一つはマクロセル方式(MC 方式)と呼ばれているものである.シンプルゲートセル方式は、ECL(Emitter Coupled Logic)の基本ゲートである3入力0R/NORを実現できるだけの素子が用意されたセル構成になっており、以下の特徴を有する.

- (1) OR/NOR などの基本ゲートを構成する場合にセル内の未使用素子が少ない.

- (2)セレクタ,フリップフロップなど,複数の基本論理からなる複合ゲートを実現する場合に、多くのセルを必要とする.

一方,マクロセル方式とは、差動対を縦積み2段にしたシリーズゲート回路を採用し、セレクタやフリップフロップなどの複合ゲートを実現できる比較的多くの素子で構成されているセル方式であり、次のように特徴をまとめることができる.

- (1)複合ゲートを効率よく実現できる.

- (2) OR/NOR など基本ゲートを構成する場合, セル内に未使用素子が残る.

図 2.1 に 3 入力 0R/NOR e, 従来のセル構成であるシンプルゲートセル方式 (SC 方式) とマクロセル方式 (MC 方式) で実現した例を示す.ここで,SC 方式は,1 つのセル内にトランジスタ 6 個,抵抗 6 個を含む構成で,MC 方式は,1 つのセル内にトランジスタ 13 個,抵抗 6 個を含む構成として

いる. 図 2.1(a) に示すように、SC 方式では未使用素子は 0 であるが、(b) の MC 方式では 6 個のトランジスタと 1 個の抵抗が未使用となる (図中の点線で示された素子).

複合ゲートの例 (セレクタ)

(a) シンプルゲートセル方式 (SC方式: 4セル使用)

図 2.2: 従来のバイポーラ論理回路のセル構成(セレクタ)

|       | SC方式      | MC方式      |

|-------|-----------|-----------|

| 単純ゲート | 0         | × 未使用素子多い |

| 複合ゲート | × セルが複数必要 | 0         |

表 2.1: セル構成の比較

図 2.2 に複合ゲートであるセレクタを, SC 方式と MC 方式で実現した例を示す. SC 方式では 4 つのセルを組み合わせる必要があり, かつ, 8 つのトランジスタと 9 個の抵抗が未使用になっている. 一方, MC 方式ではシリーズゲートの特徴を生かし, 1 つのセルで複合ゲートを構成することができる. トランジスタ 1 個だけが未使用となる.

以上のように、双方の方式には一長一短がある.表 2.1 にセル構成の比較をまとめる.マスタスライス上に実現される実際のシステムでは、基本ゲートと複合ゲートが組み合わさって構成されているので、上記のいずれの方式を採用しても、あらかじめ用意されたセル内の素子数が実際必要となる素子数と常に適合するわけではなく、未使用素子が存在して高集積化の妨げとなっていた.

## 2.3 VSC マスタスライス

この問題を解決するために、より少ない数のトランジスタと抵抗で構成される基本単位を組み合わせることによって、単純な論理でも比較的複雑な論理にでも対応できる面積可変論理セル Variable Size Cell(VSC)を考案した[10][11].素子の使用効率向上のために、従来のバイポーラマスタスライスのセルを細分化し、基本単位として CMOS ゲートアレイのベーシックセルのように小さいまとまり(ユニット)を導入した.論理回路の規模に応じて使用するユニットの数を変えて1つのセルを構成するため、論理セルの面積は論理回路毎に異なる.この際、ユニット当たりの素子数の決定と抵抗値の設定方法が課題となる.

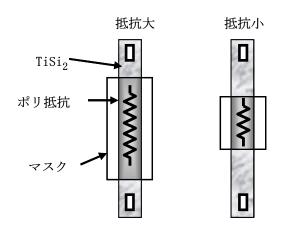

図 2.3: TiSi2 による抵抗可変

ECL 回路には、差動増幅回路の負荷抵抗、定電流回路用抵抗、エミッタフォロワ回路用抵抗に加え、シリーズゲート構成のためのインプットフォロワ抵抗といったさまざまな抵抗が必要となる、従来のセルはこれらを含んで1つのセルとしていたため、構成要素が多くなっている.したがって、従来のセルを細分化するには、少数の抵抗パターンで複数種類の抵抗値を実現する手法が必須となる. 拡散抵抗の場合、その抵抗値は素子を形成するマスタ工程で決定されてしまうため、スライス工程で抵抗を可変にするのは困難である.

このため、マスタ工程であらかじめ作りつけたポリシリコンパターンの表面を合金化(シリサイド化)して抵抗値を決める方法を採用した。図 2.3 は  ${\rm TiSi}_2$ (チタンシリサイド)による抵抗可変を示すパターン図である。シリサイド化されない部分をマスクすることにより、選択的に  ${\rm TiSi}_2$ 部とポリシリコン抵抗部を作り分けることができる。このマスクはスライス工程に入っているため、後から自由に抵抗値を決定することができる。

通常、ポリシリコン抵抗のシート抵抗値は数 100~数  $k\Omega$ であるのに対して、 $TiSi_2$ のシート抵抗値は数  $\Omega$ 程度と非常に小さいため、この部分の抵抗は十分無視することができる。また、全面的にシリサイド化することで、メタル配線の下のクロスアンダ配線として使用できるという利点がある。このため、ユニット内の配線領域を小さくすることができ、ユニットの面積も小さくすることができる。

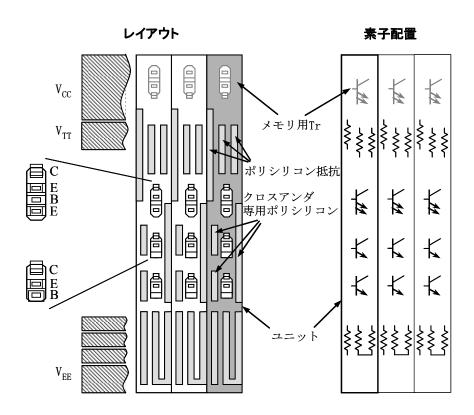

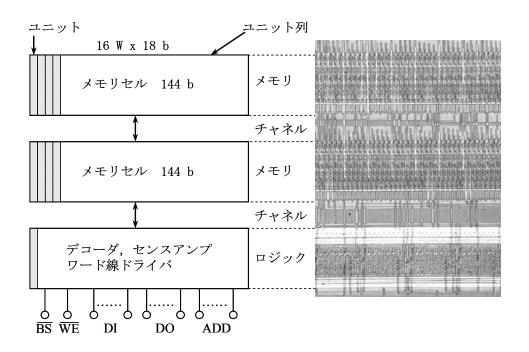

図 2.4 に VSC 方式のレイアウトと素子配置を示す. 1 ユニット当たり, 4 つのトランジスタと 5 本のポリシリコン抵抗で構成される. トランジスタの脇にある 3 本のポリシリコンはクロスアンダ

図 2.4: VSC 方式のレイアウトと素子配置

配線専用である。4つのトランジスタの内、3つを論理ゲートに使用し、残る1つは、後で述べるようにメモリセル専用である。論理ゲートを構成する場合は、太い電源ラインが必要であるが、メモリセルの場合は不要であるため、このメモリ専用トランジスタは $V_{CC}$ 電源ラインの下に埋め込むことにより、ユニットの面積増加を防いでいる。

論理ゲートに使用する1ユニット当たりのトランジスタ数は、少ない方がトランジスタの利用効率はよいが、一方で、ポリシリコン抵抗の面積が占める割合が大きくなり、使用するユニット数が増えると未使用のポリシリコン抵抗が増えて素子の利用効率が下がってしまう。このため、1ユニットで1ビットのメモリセルが構成でき、使用頻度の高い2入力 OR/NOR、3入力 OR、3入力 NORを2ユニットで構成できる1ユニット4トランジスタ(論理ゲートとしては3トランジスタ)を選択した。セレクタやフリップフロップなどの複合論理は、必要なユニット数だけ用いて構成する。

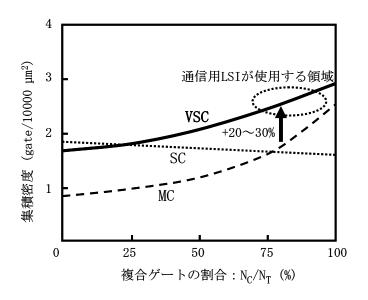

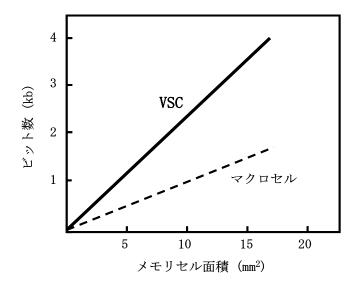

ここで VSC 方式の有効性を定量的に評価するためにシンプルゲートセル (SC) 方式およびマクロセル (MC) 方式とのゲート密度の比較を行った。シンプルゲートセル方式の例として,1 セル内にトランジスタ 6 個,抵抗 5 個程度を用意し,3 入力 0R/NOR までの機能を実現できる構成を想定し,マクロセル方式として,1 セル内にトランジスタ 13 個,抵抗 6 個程度を用意し,0 ラッチやセレクタ機能を実現できる構成を想定した。図 0 に、0 に 0 に 0 に 0 に 0 に、0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に 0 に

$N_C$ :複合ゲートのゲート数, $N_T$ : 総ゲート数

図 2.5: 集積密度比較

わらず, 通信用 LSI においてはフリップフロップやセレクタといった複合ゲートの比率が高く, 多くの場合,  $N_{\rm C}/N_{\rm T}$  は 75 %以上となっている. このような領域では, VSC は従来セル方式より 20~30 % ゲート集積密度が高い.

## 2.4 コンフィギュラブル RAM

#### 2.4.1 メモリセル

VSC のユニットを用いたビット構成がフレキシブルなメモリ構成をコンフィギュラブル RAM と呼び、作りつけの固定メモリ構成を専用 RAM と呼ぶ。専用 RAM は、メモリ専用の回路、レイアウトを用いて非常に効率よくメモリを構成することができるが、他の用途には転用できず、使用しなければこの領域は無駄な部分となってしまう。一方、コンフィギュラブル RAM は専用 RAM のように高集積化はできないが、VSC のユニットを用いているため、ビット構成が柔軟で、かつ不要な場合は論理ゲートとして使用することができる。通信用 LSI では、データキャッシュ、バッファメモリ、信号波形イコライザ用のルックアップテーブルなど、サイズが固定で大規模なメモリが必要で、このような用途には専用 RAM が適している。一方、論理回路の中で一時的にデータや制御信号を格納するレジスタの場合には、大規模なメモリ容量は不要で、むしろビット構成の柔軟性が要求されるため、コンフィギュラブル RAM を使うのが効率的である。本マスタスライスでは、専用 RAM とコンフィギュラブル RAM の双方を搭載している。この節ではコンフィギュラブル RAM について述べる。

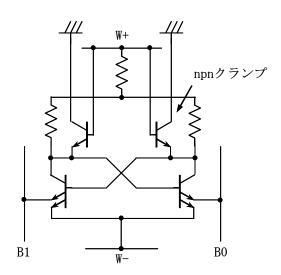

バイポーラのメモリセルは、ベースとコレクタが互いにクロスカップル接続された 2 つの npn トランジスタと、データ読み出し時の電流でコレクタが飽和しないようにするクランプ素子から構成される. このクランプ素子として、ショットキーバリアダイオード(SBD)や、pnp トランジスタが使用されるが、特に集積度が求められる場合には、メモリセル面積が小さくなる pnp トランジスタによるクランプ回路が用いられる. クロスカップル接続された npn トランジスタのベース (p型)、コレクタ (n型)がそれぞれ、クランプ用 pnp トランジスタのコレクタ (p型)、ベース (n型)と構造

図 2.6: コンフィギュラブル RAM のメモリセル回路

的にマージできるため、メモリセルが小さくなるためである。一方、このようなメモリセルでは、バイポーラマスタスライスにおける論理構成には不要であるSBDやpnpトランジスタをユニット内に組み込まなければならず、かえってゲート密度の低下や、面積増大による速度劣化をもたらす。

このため、論理セルと構造的に親和性がある npnトランジスタクランプ型メモリセルを新たに考案した[12]. 図 2.6 にコンフィギュラブル RAM のメモリセル回路を示す。メモリセルは、4 つの npnトランジスタと 3 つの抵抗から構成される。論理ゲートの構成には不要な SBD や pnpトランジスタを使用しないため、素子の利用効率低下を防げる。上 2 つの npnトランジスタは、ビット線 BO、BI がアクティブになったとき、抵抗による電圧降下により下側のクロスカップルされたトランジスタが飽和領域に入るのを防ぐように電圧クランプする働きを持つ。読み込み電流は直接  $V_{CC}$  ライン(グランド)から供給されるため、通常巨大なワード線ドライバのトランジスタサイズを小さくでき、またこれにより、論理セルを用いてワード線ドライバを構成することができるようになる。

#### 2.4.2 ユニット構成

2.3 節で述べたように、VSC のコンセプトは、4 つのトランジスタと 5 本の抵抗からなるユニッ

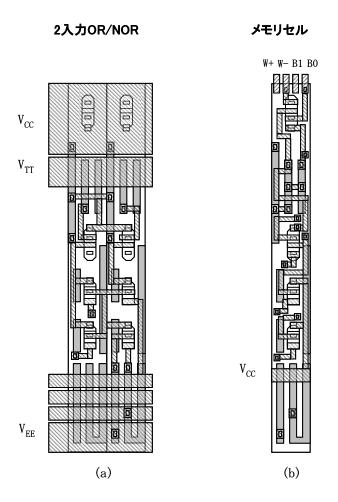

図 2.7: 論理回路とメモリセルの構成例

図 2.8: ビット密度比較

トをアレイ状に並べておき、単純ゲート、複合ゲートなど、さまざまな種類の論理ゲートを必要数だけユニットを使用して構成することにある。最小単位が小さいため、単純ゲートに対しても、複合ゲートに対しても、不要素子を最小限に留めることができる。4 つのトランジスタの内、3 つを論理ゲートに使用し、残る1 つは、メモリセル専用である。論理ゲートを構成するときには電源ラインに埋め込まれている4つ目の埋め込みトランジスタを使用することにより、図2.6のメモリセルを1ユニットで構成できる。4 つのトランジスタのうち、2 つはダブルエミッタ構造のトランジスタであり、メモリセルで使用するとともに、2 出力のエミッタフォロワやラッチを構成するときのクロスカップルトランジスタとして使用する。

図 2.7 に論理回路とコンフィギュラブル RAM のメモリセルの構成例を示す。図 2.7 (a) は 2 入力 0R/NOR をレイアウトパターンで,2 ユニットで構成される。トランジスタはすべて使用している。3 つの電源配線  $(V_{CC}, V_{EE}, V_{TT})$  と 3 つの基準電圧  $(V_{BBI}, V_{BB2}, V_{CS})$  が 1 層配線でユニットを横切っている。信号ピンの引き出しは,縦方向に走る 2 層配線で行う。通常 GND (グランド) に設定される  $V_{CC}$  ラインの下にトランジスタが埋め込まれている。図 2.7 (b) はメモリセルのレイアウトパターンである。論理回路の場合と異なり,電流が少ないため,太い電源ラインは不要で,細い  $V_{CC}$  ラインのみが横切っている。このため,4 つトランジスタすべてが使用可能となる。

#### 2.4.3 VSC 方式の効果

VSC 方式の効果を見積もるために VSC 方式と従来のマクロセル方式を使ったメモリのビット密度を比較した.マクロセル方式は 14 のトランジスタ,9 本の抵抗から構成され,1 つのマクロセルで2 ビットのメモリセルが構成できると仮定した.

図 2.8 に VSC 方式とマクロセル方式それぞれのメモリセル面積とビット数の関係を示す。 VSC 方式のメモリビット密度は 250 ビット/ $mm^2$ であり,従来のマクロセル方式と比べ,2 倍以上の集積度である.

## 2.5 VSC 方式の実装例

VSC 方式を採用したユニットアレイと 32k ビットの専用 RAM を内蔵したマスタスライス LSI を設計した. 以下,  $0.6~\mu m$  バイポーラプロセスを用いて試作したマスタスライス LSI の仕様, および評価結果について述べる.

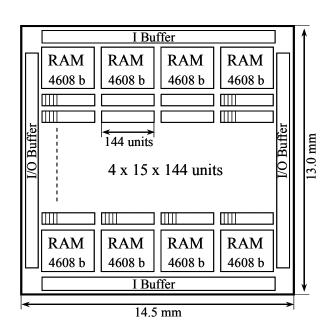

#### 2.5.1 チップフロアプラン

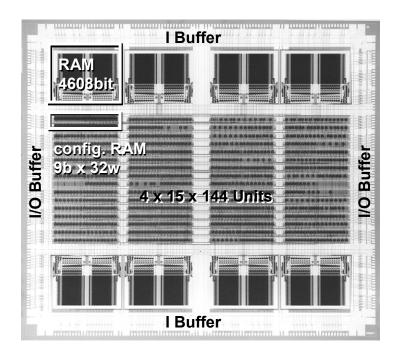

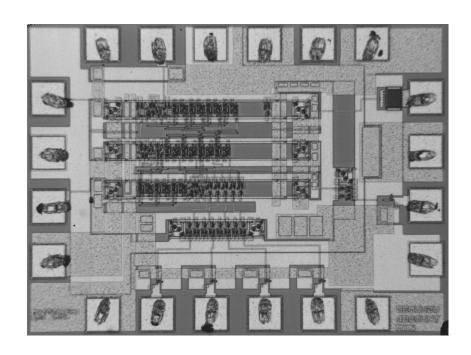

マスタスライス LSI のチップフロアプランを図 2.9 に示す. 上下に 8 個の専用 RAM が配置され、中央に論理回路用ユニットが配置されている. トータル 8640 ユニットが 15 行に並べられている. 電源ラインを確保するため、1 行は 4 列に分割され、1 ブロック当たり 144 ユニットとなっている. ユニットサイズは 18 x 225  $\mu$ m² である. 複合ゲート換算で 12.1k ゲート相当となる. ブロック間 は配線のためのチャネルとなっており、1 チャネル 35 トラックの配線本数である. もし、すべてのユニットをコンフィギュラブル RAM として使用した場合、制御回路も含め 5.8k ビットとなる. 基準電圧発生回路は、それぞれのブロックの両端に置かれている.

図 2.9: マスタスライスのチップフロアプラン

ユニットセルと専用 RAM はそれぞれ、34.6k および 174.6k トランジスタが集積されており、トータルのトランジスタ数は 209k である.チップサイズは 14.5 x 13  $\rm mm^2$  である.チップの周辺には、144 個の入力パッドと 128 個の入出力パッドが配置されている.5 個の入力パッドと 1 つの出力パッドは専用 RAM テスト専用である.

#### 2.5.2 論理回路

ユニットセルで構成する論理回路部は 2 段のシリーズゲート構成である. 論理振幅は 460 mV, スイッチング電流は速度性能と消費電力のバランスを取って 0.2 mA としている. エミッタフォロワ電流は, 駆動能力に応じて, 0.15, 0.45, 0.68 mA の 3 種類の電流値を選べるようにしている. このうち, 0.15 mA は D-ラッチのクロスカップルといった論理ゲート内でのみ, 使用できる.

電源  $V_{EE}$  および  $V_{TT}$  の電圧はそれぞれ,-4.5 V,-2.0 V である. $V_{EE}$  はスイッチング段および,入力フォロワのための電源で, $V_{TT}$  はエミッタフォロワの終端電圧である. $V_{EE}$  はまた,コンフィギュラブル RAM の制御回路にも使用される.

出力バッファは内部論理回路の信号振幅を ECL 100K と呼ばれる標準 I/0 インターフェースに変換する. 出力バッファの出力レベルは温度補償回路によって安定化されている. 基準電圧発生回路は、2 つの参照電圧  $V_{BB1}$  と  $V_{BB2}$ , および定電流源回路用バイアス電圧  $V_{CS}$  を生成する. これらの電圧は、温度、電源電圧に対して安定となるように、バンドギャップレファレンス回路[13]を用いて生成されている. マスタスライスの諸元を表 2.2 に纏める.

なお、標準 I/O インターフェースである ECL 100K は負電源で規定されている.これは ECL の出力レベルが、 $V_{CC}$  に接続された負荷抵抗の電圧降下とベースエミッタ間電圧  $V_{be}$  で決定されるためで、 $V_{CC}$  をグランドに、 $V_{EE}$ 、 $V_{TT}$  を負電源とすることで出力レベルが  $V_{EE}$  や  $V_{TT}$  の変動によらなくなるためである.この ECL 100K インターフェースを考慮した本章、および第 3 章では負電源を使用している.一方、ニッケル水素やリチウムイオンといったバッテリは正電源であるため、バッテリ駆動を考慮した回路では正電源を使用している.第 4 章から第 6 章までは正電源である.

表 2.2: マスタスライス諸元

| トランジスタ数     | ロジック 34.6 k<br>RAM 174.6 k |

|-------------|----------------------------|

| メモリセル       | 36864                      |

| トラック数       | 2924                       |

| スイッチング電流    | 0.2 mA                     |

| エミッタフォロワ電流  | 0.45 mA / 0.68 mA          |

| I/0ピン数      | 144 / 128                  |

| 電源電圧        | -4.5 V / -2.0 V            |

| I/0インターフェース | ECL100K                    |

### 2.5.3 コンフィギュラブル RAM の構成

図 2.10 にコンフィグラブル RAM のブロック図とチップ拡大写真を示す。RAM の構成は 16 ワード x 18 ビットである。メモリセルは 288 ユニットを使用し,2 列に配置されている。一番下の列はメモリの制御回路であり,デコーダ,ワード線ドライバ,センスアンプなどが論理ゲートを用いて構成されている。RAM のブロックサイズは制御回路を含めて,990 x 2600  $\mu$ m<sup>2</sup> である。

メモリセルだけなく、制御回路までも VSC のユニットセルを用いて実現できるため、いろいろなビット・ワード構成が可能である。 16 ワード x 18 ビットだけでなく、 32 ワード x 9 ビット、 32 ワード x 18 ビットといった構成ができる。 RAM のサイズは、ユニット 1 列分(144 ユニット/144 ビット)毎に増減することができる。

図 2.10: コンフィギュラブル RAM のレイアウト

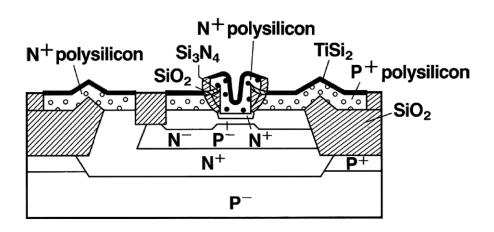

#### 2.5.4 プロセス技術

マスタスライス LSI を  $0.6 \mu m$  2 層ポリシリコン自己整合技術のバイポーラプロセスで試作した.トランジスタの断面図を図 2.11 に示す.この構成の特長は,ポリシリコンエミッタ電極とシリサイド化されたベース電極が自己整合技術によって形成される点である.すなわち,1 つのマスクで,エミッタ電極の穴開け,ベース電極との分離,エミッタ注入,エミッタポリシリコン形成まで行うことができ,エミッタ部を精度良く,かつ,寄生成分を小さくすることができる.ベース電極は,寄生抵抗を小さくするためにチタンシリサイド化されている.エミッタサイズは  $0.6 \times 2.0 \ \mu m^2$  であり,分離エリアを除く実行トランジスタサイズは  $15 \ \mu m^2$  である.最小サイズトランジスタの遮断周波数は  $8 \ GHz$  である.

配線は 4 層であり、1 層目はユニット内の未使用ポリシリコン抵抗をチタンシリサイド化したセル内配線である。2 層目、3 層目はそれぞれ、 $3.0~\mu m$  ピッチの AlSi,  $4.5~\mu m$  ピッチの AlSiCu である。これらの配線は、セル内配線、セル間配線に使用される。4 層目は電源ライン専用となる.

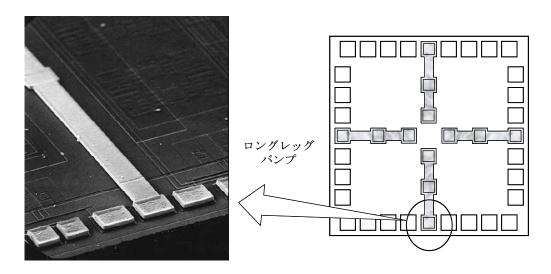

多ピン化に対応するため、TAB(Tape automated bonding)を採用した. TAB は、ワイヤによるボンディングではなく、テープ状に形成されたリードとパッドを接続する方法である. パッド上にはTABに対応するためバンプが形成される. このバンプは、パッド上にクロム銅がスパッタ形成されたのち、25 μm 厚の金メッキが施されて形成される. 今回、このバンプメタルをパッシベーション膜上の再配線層として使用した. バンプメタルを電源パッドからチップ中央部まで延長し、直接電源を供給する. その形状からロングレッグバンプ(足長バンプ)と呼ばれる再配線層により、電源ラインの配線抵抗を低減することが可能となる. このロングレッグバンプは5番目の配線層に対応する. ロングレッグバンプの SEM 写真(Scanning Electron Microscope)を図2.12に示す. ロングレッグバンプを採用することにより、電源ラインの電圧降下が、チップ中央で40 mV から20 mV 以下に低減できた. パッシベーション膜上に形成されるため、下層にある配線との寄生容量は、通常のメタル配線よりも小さくなっている.

図 2.11: トランジスタ断面図

図 2.12: ロングレッグバンプ

#### 2.5.5 評価結果

速度性能を評価するため、テストチップを用いてさまざまな負荷条件でのゲート遅延時間を測定した。表 2.3 にゲート遅延特性をまとめる。無負荷でのインバータのゲート遅延は、消費電力 1.8 mW のとき、110 ps であった。ファンイン 1 つ当たりの遅延増は 26 ps、ファンアウト 1 つ当たりの遅延増は 14 ps であった。1 層目と 2 層目の配線遅延は、エミッタフォロワ電流が 0.45 mA のとき、それぞれ、45 および 33 ps/mm である。エミッタフォロワ電流を 0.68 mA に増加させると、配線遅延はそれぞれ、33 および 23 ps/mm となる。

専用 RAM とコンフィギュラブル RAM の特性を表 2.4 に纏める. 専用 RAM のアドレスアクセスタイムは 3.0 ns,書き込みパルス幅は 5.5 ns,消費電力は 1.3 W である. コンフィギュラブル RAM のアドレスアクセスタイムは,32 ワード x 9 ビット構成で 1.8 ns,消費電力は 0.41 W である. スタンバイ時と読み出し時の電流は,それぞれ 120  $\mu$ A,800  $\mu$ A である.

表 2.3: ゲート遅延特性

| 基本遅延時間   | 110 ]         | ps/1.8 mW                            |

|----------|---------------|--------------------------------------|

| ファンイン遅延  | 26 ps/fan-in  |                                      |

| ファンアウト遅延 | 14 ps/fan-out |                                      |

| 配線遅延     | 1st           | 45 ps/mm $@I_{ef} = 0.45 \text{ mA}$ |

|          | 2nd           | 33 ps/mm                             |

|          | 1st           | 33 ps/mm $@I_{ef} = 0.68 \text{ mA}$ |

|          | 2nd           | 23 ps/mm                             |

|          |               |                                      |

表 2.4: RAM の特性

専用RAM (256 w x 18 b)アドレスアクセスタイム3.0 ns書き込みパルス幅5.5 ns消費電力1.3 Wブロックサイズ2.8 mm x 2.15 mmコンフィギュラブル RAM (32 w x 9 b)アドレスアクセスタイム1.8 ns消費電力0.41 W

図 2.13: マスタスライス LSI チップ写真

図 2.13 にマスタスライス LSI のチップ写真を示す. 256 ワード x 69 ビットの専用 RAM が 2 個, 16 ワード x 18 ビットのコンフィグラブル RAM, 9k ゲートの論理回路が集積されている. ユニットセルの左上隅にあるのがコンフィグラブル RAM である.

## 2.6 結言

Variable Size Cell (VSC) 方式によって、単純な OR/NOR ゲートでもフリップフロップのような複合ゲートでも未使用素子を減らすことが出来、使用効率を上げることができた。従来のシンプルゲート方式やマクロセルセル方式と比較してゲート集積密度は 20~30 %向上した。また、電源ラインの下にトランジスタを埋め込むことで、セル面積を増加させることなく、1 ユニットで1 ビットのメモリセルを実現できるようにした。これにより論理ゲート用のユニットを使用してビット、ワード構成に柔軟性のあるコンフィグラブル RAM を効率よく構成できる。従来方式と比較してビット密度は2倍以上向上する。この技術を用いて36k ビットの専用 RAMと12k ゲートの論理ゲートを持つマスタスライス LSI を試作した。基本ゲート遅延は110 ps、消費電力は1.8 mW/ゲートであった。RAM のアドレスアクセスタイムは、専用 RAMで3.0 ns、32 ワード x 9 ビット構成のコンフィギュラブル RAMで1.8 ns が得られた。また、TAB 用のバンププロセスを配線として使用するロングレッグバンプを採用することにより、電源ラインの電圧降下が、チップ中央で40 mV から20 mV 以下に低減できた。

文献[12]の発表以降もバイポーラマスタスライスの高集積化,大規模 RAM の搭載が進み,また,VSC 方式のコンセプトをベースにした製品も数社から発表された.1990 年代の後半からは大規模マスタスライスの分野は徐々に CMOS のゲートアレイ,セルベース,エンベデッドセルアレイに置き換わっているが,高周波で動作するアナログ回路を含むビルディングブロック方式のマスタスライス LSI は現在でもバイポーラが主流である.VSC 方式を可能とするシリサイドによる抵抗値可変の手法はこれらのマスタスライスには必須の技術である.また,発表当時は特異な技術と捉えられていたバンププロセスによる配線は,現在ではフリップチップ実装の際にごく普通に使用されている.この再配線技術を用いて,高Qなインダクタを形成し,無線通信用トランシーバを高性能化する試みも行われている.

## 参考文献

- [1] M. Suzuki, S. Horiguchi, and T. Sudo, "A 5K-gate bipolar masterslice LSI with a 500 ps loaded gate delay," IEEE J. Solid-State Circuits, vol. 18, no. 5, pp. 585-592, Oct. 1983.

- [2] E. Gonauser, B. Unger, R. Rauschert, A. Glasl, and K. Schon, "A bipolar 230 ps masterslice cell array with 2600 gates," IEEE J. Solid-State Circuits, vol. 19, no. 3, pp. 299-305, Jun. 1984.

- [3] M. Suzuki and S. Horiguchi, "A 333 ps/800 MHz 7 K-gate bipolar macrocell array employing 4 level metallization," IEEE J. Solid-State Circuits, vol. 19, no. 4, pp. 474-479, Aug. 1984.

- [4] W. Brackelmann, H. Fritzsche, H. Ullrich, and A. Wieder, "A 150-ps 9000-gate ECL masterslice," IEEE J. Solid-State Circuits, vol. 20, no. 5, pp. 1032-1035, Oct. 1985.

- [5] M. Suzuki, M. Hirata, and Y. Ito, "An 86 K component bipolar VLSI masterslice with a 290-ps loaded gate delay," IEEE J. Solid-State Circuits, vol. 22, no. 1, pp. 41-46, Feb. 1987.

- [6] B. Coy, A. Mai, and R. Yuen, "A 13000 gate 3 layer metal bipolar gate array," Proc. CICC, pp. 20.1/1-3, May 1988.

- [7] M. Tamamura, S. Shiotsu, M. Hojo, K. Nomura, S. Emori, H. Ichikawa, and T. Akai, " A 9.5-Gb/s Si-bipolar ECL array," IEEE J. Solid-State Circuits, vol. 27, no. 11, pp. 1575-1578, Nov. 1992.

- [8] R. T. Masumoto, "Configurable on-chip RAM incorporated into high speed logic array," Proc. CICC, pp. 240-243, May 1985.

- [9] Y. Sugo, M. Tanaka, Y. Mafune, T. Takeshima, S. Aihara, and K. Tanaka, "An ECL 2.8ns 16K RAM with 1.2K logic gate array," ISSCC Dig. Tech. Papers, pp. 256-257, Feb. 1986.

- [10] T. Nishimura, H. Sato, M. Tatsuki, T. Hirao, and Y. Kuramitsu, "A bipolar 18K-gate variable size cell masterslice," IEEE J. Solid-State Circuits, vol. 21, no. 5, pp. 727-732, Oct. 1986.

- [11] 西村尚, 蔵満洋一, 平尾正, "17.8K ゲート ECL マスタスライス," 電子材料, pp. 110-115, July 1986.

- [12] H. Satoh, T. Nishimura, M. Tatsuki, A. Ohba, S. Hine, and Y. Kuramitsu, "A 209 K-transistor ECL gate array with RAM," IEEE J. Solid-State Circuits, vol. 24, no. 5, pp. 1275-1279, Oct. 1989.

- [13] R. J. Widlar, "New developments in IC voltage regulators," IEEE J. Solid-State Circuits, vol. 6, pp. 2 7, Feb. 1971.

## 第3章 低電圧動作バイポーラシリーズゲート回路

## 3.1 緒言

前章で述べたように、バイポーラ論理回路では差動対を縦積み2段にしたシリーズゲート回路構成にすることによって、複合ゲートを効率よく構成することができる。しかしながら、縦積み2段であるがゆえに、必要とされる電源電圧が大きく、低電源電圧動作化を困難にしていた。この回路の最低動作電圧は2.5Vであり、論理回路の外部インターフェース電圧や電池の終端電圧である2V以下で動作させることができず、2電源が必要であったり、消費電力が大きいという問題がある。

携帯電話,無線 LAN (Wireless Local Area Network)等の携帯無線通信機器では連続動作時間の点から素子の低消費電力化が重要な課題の一つである.この要求に応えるためにいくつかの低電圧技術が発表されている[1]-[3].これらの回路はそれぞれ2.2 V,2.5 V,1.5 V という低電圧で動作するが,バイポーラ回路の最も有利な点であるシリーズゲート回路を構成しにくく,電源電圧変動に対する考慮も十分されていないなど,実用的ではなかった.電源電圧変動によるスイッチング電流の変化はトランジスタの飽和やノイズマージンの低下を招いたりする.低電圧動作では電圧マージンが少ないだけに特に重要な問題となる.

本章では、2 V 以下で動作し、かつ電源電圧補償されたバイポーラシリーズゲート回路[4]について述べる。まず、はじめに低電圧シリーズゲート LSG(Low-voltage Series Gate)と、電源電圧  $V_{EE}$  に追従するバッファ VTB( $V_{EE}$ -Traced Buffer)の概念について述べ、次にこの回路を 1/4 分周器 (4 進カウンタ)に適用した例を示し、最後に試作、評価結果を紹介する。

## 3.2 回路設計

### 3.2.1 低電圧シリーズゲート

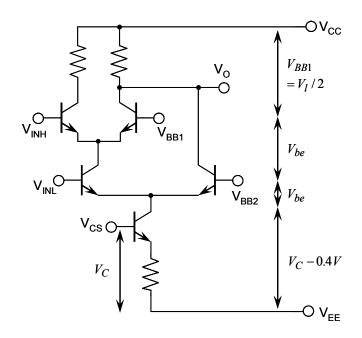

前章で述べた ECL 回路からエミッタフォロワを取り除いたものを LCML (Low-level Current Mode Logic) と呼ぶ。エミッタフォロワのベースーエミッタ間電圧分だけ低電圧で動作する。また,エミッタフォロワ電流がないため,負荷駆動能力を要求しない回路では低消費電力化が図れる。図 3.1 に LCML 回路を示す。 $V_{CC}$  は通常グランド GND に, $V_{EE}$  は負電源に接続される。この回路図は 2 段のシリーズゲート構成である。バイポーラ回路においては電源電圧の範囲はトランジスタのベースーコレクタの飽和によって制限される。図 3.1 の回路において, $V_{BB1}$  は上位入力用の基準電圧で,論理振幅  $V_I$  の半分に設定される。下位入力用の基準電圧  $V_{BB2}$  は, $V_{BB1}$  の  $1V_{be}$  分低下した電圧に設定される。LCML では上位入力トランジスタが論理振幅分必ず飽和し,また 0.4 V 程度の軽い飽和状態ならばほとんど速度遅延に影響を及ぼさないことから,すべてのトランジスタはベースーコレクタが 0.4 V までは順バイアスされてもよいと仮定した。定電流回路のトランジスタのコレクタノードと  $V_{EE}$  間の電圧は  $V_{C}$  - 0.4 V となる。ここで  $V_{C}$  は 1.1 V であり,バンドギャップレファレンス回路の出力電圧である。従って,最小電源電圧  $V_{EE}$  min はこれらの総和であり,以下のように表される。

$$V_{EE_{\min}} = -V_l/2 - 2V_{be} - V_C + 0.4~V$$

(3. 1) ここで $V_l = 0.4~$  V,  $V_{be} = 0.8~$  V,  $V_C = 1.1~$  V とすると,  $V_{EE_{\min}}$  は-2.5 V となる. 電源電圧, 温

$V_{EE\,\mathrm{min}} = -V_l/2 - 2V_{be} - V_C + 0.4 = -2.5V$

図 3.1: LCML 回路

図 3.2: 低電圧シリーズゲート Low-voltage Series-Gate(LSG)

度、プロセス等の各種マージンを考慮すると、現実的な電源電圧は-3.0 V程度である[5].

最も簡単な電源電圧の低減方法は、定電流回路の代わりに抵抗、MOS FET 等を用いて電流源を構成することである。しかし、これらの方法は電流源の制御が難しく、プロセス、温度、電源電圧変動に対して定電流特性を維持することが困難である。

必要となる最低電源電圧を下げるために、シリーズゲートの下位入力トランジスタと定電流トランジスタをマージした。図 3.2 に提案する低電圧シリーズゲート (LSG: Low-voltage Series-Gate) の回路を示す。基本的には、電流源が抵抗タイプの 2 段シリーズゲートと同じである。最小電源電圧 $V_{EE\,min}$  は次のように表される。

$$V_{EE_{\min}} = -V_l / 2 - V_{be} - V_C + 0.4V \tag{3. 2}$$

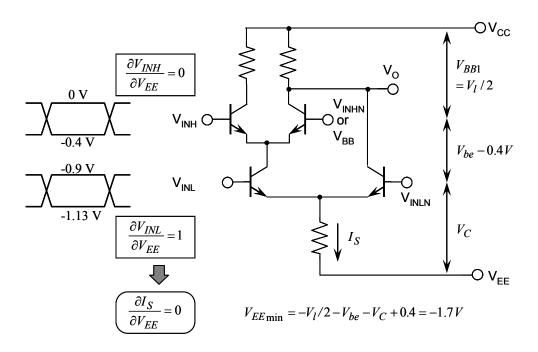

上記と同じ値を代入すると、 $V_{EE\,min}$  は-1.7Vとなる。従来のLCMLでは、下位入力電圧 $V_{INL}$ 、 $V_{INLN}$  は通常上位入力電圧 $V_{INH}$ , $V_{INHN}$  より 1  $V_{be}$  分低い電圧に設定される。これらの電圧は電源電圧  $V_{EE}$  に依存しない。スイッチング電流  $I_S$  は、下位差動対に入力される $V_{INL}$ , $V_{INLN}$  のうち、どちらか高い方の電圧で決定される。従ってこのままでは、下位入力トランジスタのベースと $V_{EE}$  間の電圧が $V_{EE}$  に応じて変化することになり、差動対のスイッチング電流の変動を招く。

そこで,下位入力は,出力特性が定電流回路用基準電圧 $V_{CS}$ と対応した下位入力用のバッファ回路によって駆動されるようにした。 $V_{EE}$  追従バッファ (VTB:  $V_{EE}$ -Traced Buffer) と呼ぶバッファの出力は $V_{EE}$  の変動に追従して変化する ( $\partial V_{INL}/\partial V_{EE}=1$ ). これにより,下位入力の"H"レベルと $V_{EE}$  間の電圧は一定となり,スイッチング電流も $V_{EE}$  に依らず一定となる。標準状態で, $V_{INL}$  の"H"レベルは-0.9 V,"L"レベルは-1.13 V に設定している。

VTB はそれ自身、OR/NOR などの論理を組むことができる。シリーズゲートの下位入力は、セレクタのセレクト信号やフリップフロップのクロック入力であるため、これらの入力に接続される論理回路を VTB(あるいは  $V_{EE}$  追従論理ゲート)に置き換えればよく、VTB を下位入力毎に挿入するわけではない。また、シリーズゲートの入力ピンに、上位入力、下位入力の属性を持たせることにより、論理検証の際には、下位入力と  $V_{EE}$  追従論理ゲートの出力が接続されていることを検証することが可能である。

## 3.2.2 V<sub>FF</sub> 追従バッファ (VTB)

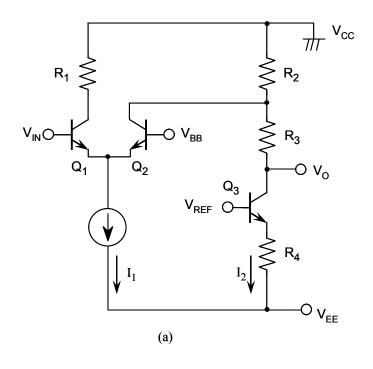

図 3.3(a)は  $V_{EE}$  追従バッファの基本回路である。出力電圧 $V_O$  の特性は、基準電圧 $V_{CS}$  と同じであり、電源電圧 $V_{EE}$  に追従しなければならない。

今,入力電圧 $V_{IN}$  が"H"レベルの時,トランジスタ  $\mathbb{Q}_2$  はオフするので,"H"レベルの出力電圧 $V_{OH}$  は次式で表される.

$$V_{OH} = V_{CC} - (R_2 + R_3)I_2 \tag{3. 3}$$

ここで

$$I_2 = (V_{REF} - V_{be} - V_{EE})/R_4 \tag{3.4}$$

である. 式(3. 4)の両辺を $V_{EE}$ で偏微分すると $V_{OH}$ の $V_{EE}$ 依存性を表す式が求まる.

$$\frac{\partial V_{OH}}{\partial V_{EE}} = -\frac{\left(R_2 + R_3\right)}{R_4} \left(\frac{\partial V_{REF}}{\partial V_{EE}} - 1\right) \tag{3. 5}$$

$\partial V_{REF}/\partial V_{EE}=0$  かつ,  $R_2+R_3=R_4$  の場合には式(3.5)は 1 になる. $V_{OH}$  の特性は定電流回路用基準電圧 $V_{CS}$  と同じ特性となり,次段のゲートのスイッチング電流は電源電圧に依らず一定となる.

図 3.3: VEE 追従バッファ(VTB): (a)基本回路, (b)詳細回路

入力電圧が"L"レベルの時,トランジスタ  $\mathbb{Q}_2$  は導通する."L"レベルの出力電圧 $V_{OL}$  は次のように表される.

$$V_{OL} = V_{CC} - R_2(I_1 + I_2) - R_3 I_2$$

(3. 6)

スイッチング電流 $I_1$ は $V_{EE}$ に依存しないので、上記と同じ条件の時には、

$$\frac{\partial V_{OL}}{\partial V_{EE}} = 1 \tag{3. 7}$$

が得られる. (3. 5)および(3. 7)より,出力電圧 $V_O$ は"H"レベル,"L"レベルともに $V_{EE}$ に完全に追従することがわかる.

$V_{EE}$  追従バッファの全回路図を図 3.3(b)に示す.  $V_{CS}$  は $V_{EE}$  に追従し、 $I_3$  は $V_{EE}$  に依らず一定なので、トランジスタ  $Q_3$  のベース電圧( $V_{REF}=V_{CC}-R_5I_3$ )の $V_{EE}$  依存性は 0 である.

また、 $R_3$ の設計自由度を上げるために、トランジスタ $Q_6$ と抵抗 $R_8$ を挿入している。本回路は、 $R_3$ の両端にかかる電圧を $V_{EE}$ に追従して増減することによって、出力レベルの電源電圧依存性を相殺している。したがって、動作電源電圧範囲を広く取るには、 $R_3$ の両端にかかる電圧を大きく確保することが望ましい。一方、低電圧で動作するには、 $R_4$ の両端にかかる電圧は可能な限り小さく設定することが望ましい。これらのことから求められる仕様によっては、 $R_3 > R_4$ となり、 $R_2 + R_3 = R_4$ という条件を満たさなくなる恐れがある。また、 $R_3$ は出力インピーダンスを直接増加させるため、負荷容量が大きいときに周波数応答の劣化を招く。 $R_3$ の両端にかかる電圧を大きくとることと、 $R_3$ の値を小さく設定することを両立させるために、トランジスタ $Q_6$ と抵抗 $R_8$ で構成される電流源が必要となる。後で述べるように、 $Q_6$ と $R_8$ は $V_{EE}$ 依存性に影響せず、 $V_{EE}$ 追従のために必要な回路ではないため、不要な場合は削除可能である。

"H"レベルでの出力電圧 $V_{OH}$ は,

$$V_{OH} = V_{CC} - (R_2 + R_3)(I_2 + I_4)$$

(3. 8)

で表される. ここで,

$$I_{2} = (V_{REF} - V_{EE} - V_{be}) / R_{4}$$

$$= -(V_{CS} - V_{EE} - V_{be}) R_{5} / (R_{4} \cdot R_{7}) - (V_{EE} + V_{be}) / R_{4}$$

(3. 9)

$$I_4 = (V_{CS} - V_{EE} - V_{be}) / R_8 \tag{3. 10}$$

である. 従って、 $V_{OH}$  と $V_{EE}$  の関係は次式で表される.

$$\frac{\partial V_{OH}}{\partial V_{EE}} = \left(\frac{R_5 \left(R_2 + R_3\right)}{R_4 \cdot R_7} - \frac{R_2 + R_3}{R_8}\right) \left(\frac{\partial V_{CS}}{\partial V_{EE}} - 1\right) + \frac{R_2 + R_3}{R_4} \tag{3.} \quad 11)$$

ここで $V_{CC}=0V$ ,  $\partial V_{be}/\partial V_{EE}\cong 0$  とした. 式(3. 11)の右辺第1項は、 $\partial V_{CS}/\partial V_{EE}=1$ であるから0になる. 従って、式(3. 11)は簡単に

$$\frac{\partial V_{OH}}{\partial V_{EE}} = \frac{R_2 + R_3}{R_4} \tag{3. 12}$$

で表される. ここで  $R_8$  が含まれていないことに注目する. トランジスタ  $Q_6$  および抵抗  $R_8$  を用いて,  $R_2+R_3=R_4$  となるように  $V_{EE}$  依存性に影響することなく自由に  $R_3$  を調整することができる. これにより  $\partial V_{OH}$  / $\partial V_{EE}$  =1 となる. したがって,次段に接続される回路のスイッチング電流は電源電圧の変動に対して安定な特性となる.

入力電圧が"L"レベルの時には、トランジスタ  $Q_2$  は導通状態になり、出力電圧は  $I_1 \cdot R_2$  だけ降下する.  $V_{OH}$  のときと同様の議論により、 $\partial V_{OL}/\partial V_{EE}$  もまた 1 となる.  $V_{OUT}$  から出力される信号振幅 (=  $V_{OH}$  - $V_{OL}$ )は、230 mV である.

出力電圧 $V_O$ に対する温度の影響は以下のとおりである。まず、式(3.8)の両辺を温度Tで偏微分する。 $V_{OH}$  と温度との関係は次式で表される。

$$\frac{\partial V_{OH}}{\partial T} = \frac{\partial}{\partial T} \left[ -\frac{R_2 + R_3}{R_4} \left\{ \left( \frac{R_4}{R_8} - \frac{R_5}{R_7} \right) (V_{CS} - V_{be}) - V_{be} \right\} \right]$$

(3. 13)

抵抗値の温度係数は抵抗値に依らずほとんど一定であるので、式(3.13)は、

$$\frac{\partial V_{OH}}{\partial T} = -\frac{R_2 + R_3}{R_4} \left\{ \left( \frac{R_4}{R_8} - \frac{R_5}{R_7} \right) \left( \frac{\partial V_{CS}}{\partial T} - \frac{\partial V_{be}}{\partial T} \right) - \frac{\partial V_{be}}{\partial T} \right\}$$

(3. 14)

と変形できる.  $R_2+R_3=R_4$ であり、また、スイッチング電流が一定になるように $\partial V_{CS}/\partial T$ は  $\partial V_{be}/\partial T$ と等しくなるように設定するため、式(3. 14)は簡単に

$$\frac{\partial V_{OH}}{\partial T} = \frac{\partial V_{be}}{\partial T} = \frac{\partial V_{CS}}{\partial T} \tag{3. 15}$$

と表される. これは $V_{OH}$  が温度特性に関しても $V_{CS}$  と同じ特性を持っていることを示している. 以上により、 $V_{EE}$  追従バッファ VTB の出力電圧は電源電圧 $V_{EE}$  , 温度 T ともに基準電圧 $V_{CS}$  と同じ特性を示すことがわかる. VTB は LCML レベルの入力( $V_{IH}=0$  V, $V_{IL}=-0.4$  V)を次段のシリーズゲートの下位入力用レベル( $V_{OH}=-0.9$  V, $V_{OL}=-1.13$  V)に変換する.

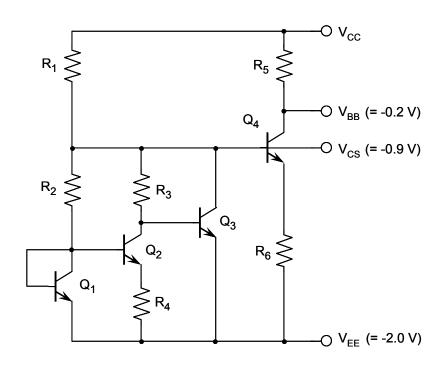

## 3.2.3 基準電圧発生回路

バンドギャップを利用した回路[6] を基に基準電圧発生回路を設計した。回路は 2 V で動作するように最適化を行った。図 3.4 に示す基準電圧発生回路は上位入力の論理閾値である  $V_{BB}$  と定電流回路用基準電圧  $V_{CS}$  を発生する。標準状態で  $V_{BB}$  = -0.2 V,  $V_{CS}$  = -0.9 V である。通常  $V_{CS}$  -  $V_{EE}$  の電圧は温度によらず一定となるよう,1.2~1.25 V 程度の値が選ばれるが,ここでは 1.1 V(=

図 3.4: 基準電圧発生回路

図 3.5: フリップフロップ回路

-0.9+2.0) としている.これにより, $V_{CS}$  は負の温度依存性を持ち, $\partial V_{CS}/\partial T \cong \partial V_{be}/\partial T$  となっている.このため, $R_6$  に流れる電流,すなわち  $R_5$  に流れる電流が温度に依らず,ほぼ一定の特性となり, $V_{BB}$  の特性や, $V_{CS}$  に接続される電流源の電流特性が温度補償される.

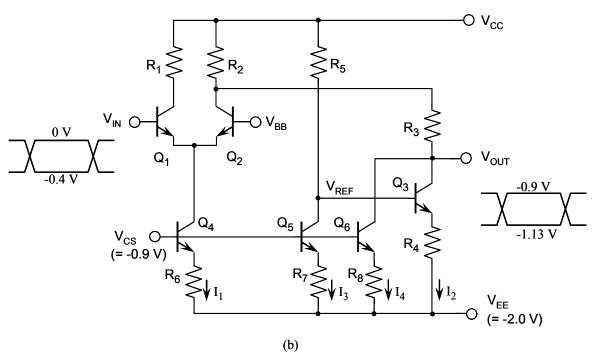

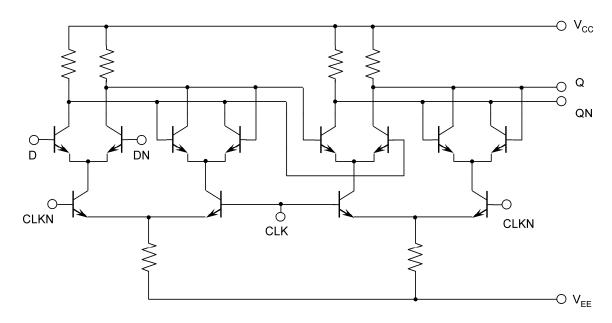

## 3.2.4 フリップフロップ

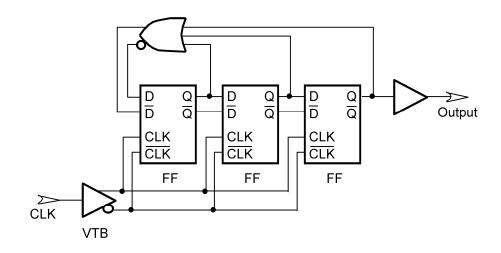

図 3.5 に低電圧シリーズゲートの例として、マスタースレーブフリップフロップ回路を示す.2 段のシリーズゲートと抵抗による電流源から構成されている.データ入力 D,DN とデータ出力 Q,QN は LCML レベル ( $V_H$  = 0 V, $V_L$  = -0.4 V)であり,クロック入力 CLK,CLKN は  $V_{EE}$  追従バッファによって駆動される.これにより,抵抗タイプの電流源であってもスイッチング電流が電源電圧,温度の影響を受けないようになる.

# 3.3 LSG および VTB の検証

低電圧シリーズゲート回路および  $V_{\rm EE}$  追従バッファを検証するために、 $0.8~\mu m$  バイポーラプロセスを用いてテストチップを試作した。図  $3.6~\rm K$  にチップ写真を示す。チップサイズは  $1.25~\rm x$   $0.95~\rm mm^2$  である。チップには、DC 特性を評価するブロックと、AC 性能(周波数特性)を評価するブロックが含まれている。以下、使用したプロセスおよび評価結果について述べる。

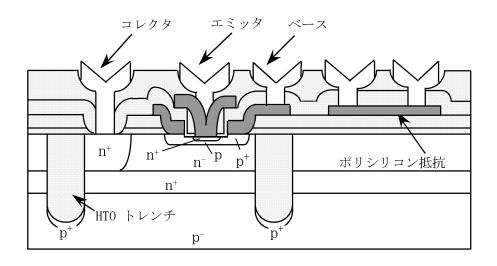

## 3.3.1 プロセス技術

回路の試作に使用したプロセスは、 $0.8 \mu m 2$  層ポリシリコン自己整合プロセス (DPSA: Double-Polysilicon Self-Aligned technology)である。トランジスタの断面図を図3.7に示す。素子分離は高温酸化膜 (HTO) 埋め込みのトレンチ分離である。トレンチの幅と深さは、それぞれ、 $0.8 \mu m$ ,  $5 \mu m$  である。抵抗はP型ポリシリコン抵抗を使用し、ベース電極と同時に形成される。

図 3.6: 試作チップ写真

図 3.7: トランジスタ断面図

ポリシリコン抵抗のシート抵抗値は、低抵抗、高抵抗それぞれが 300  $\Omega/\Box$ , 800  $\Omega/\Box$ である. また、温度係数は、それぞれ 0 ppm/ $\mathbb C$ 、-400 ppm/ $\mathbb C$ である.

表 3.1 にプロセス技術についてまとめる。最小エミッタサイズは  $0.4 \times 0.9 \ \mu m^2$  である。エミッタ・コレクタ間のブレークダウン電圧  $BV_{ceo}$  は 7 V 以上,DC 電流利得  $h_{FE}$  は 100,遮断周波数は 12 GHz である.

表 3.1: トランジスタパラメータ

#### 0.8 µm 2層ポリシリコン、自己整合、トレンチ分離

| 最小エミッタサイズ  | $0.4 \times 0.9 \ \mu\text{m}^2$ |

|------------|----------------------------------|

| ブレークダウン電圧  | BVceo > 7 V                      |

| 直流電流利得     | $h_{FE} = 100$                   |

| ベース・コレクタ容量 | $C_{TC} = 4.0 \text{ fF}$        |

| ベース・エミッタ容量 | $C_{TE} = 3.8 \text{ fF}$        |

| コレクタ・基板容量  | $C_{TS} = 5.0 \text{ fF}$        |

| 遮断周波数      | $f_T = 12 \text{ GHz}$           |

ECL ゲートの遅延時間は,FI(ファンイン) = FO(ファンアウト) = 1 のとき 59  $ps(I_S=0.24 mA)$  である.消費電力は, $V_{EE} = -4.0 V$  で 1.4 mW である.LCML のゲート遅延時間は 69 ps であり,このときの消費電力は  $V_{EE} = -3.0 V$  で 0.72 mW である.LCML のフリップフロップのトグル周波数は,消費電力 3.04 mW のとき,5 GHz である.

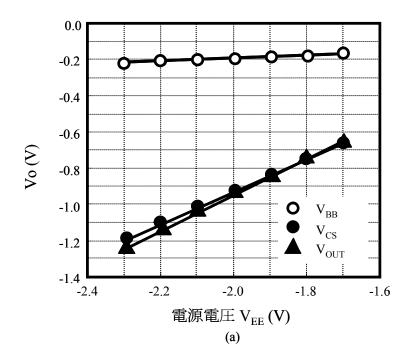

#### 3.3.2 DC 特性

図3.8(a)に、 $V_{EE}$ 追従バッファ VTBの出力電圧  $V_{OUT}$  ("H"レベル)と基準電圧発生回路の出力電圧  $(V_{BB}, V_{CS})$ の特性を示す。横軸は電源電圧  $V_{EE}$  である。白丸は論理しきい値  $V_{BB}$ ,黒丸は定電流回路用基準電圧  $V_{CS}$ ,三角は VTB の出力電圧を示す。

$V_{BB}$ の  $V_{EE}$  依存性は 0.074 V/V である. これは,電源電圧が-2.0 V  $\pm 15$ %のとき, $V_{BB}$  の変動が 22 mV であることに相当する.  $V_{CS}$  と  $V_{OUT}$  の  $V_{EE}$  依存性は,それぞれ 0.892 V/V,0.999 V/V である. これらはほぼ 1 に等しく, $V_{EE}$  の変動にほぼ完全に追従することを示している.

図 3.8(b)に、 $V_{BB}$ 、 $V_{CS}$ 、 $V_{OUT}$  の温度依存性を示す。 $V_{CS}$ 、 $V_{OUT}$  はスイッチング電流が一定になるように負の温度特性を持つように設計されている。

以上のことから、VTB の出力は、電源電圧、温度ともに  $V_{CS}$  の特性とよく一致しており、下位入力トランジスタが定電流源として働くことが確認できた。

図 3.8:  $V_{BB}$ ,  $V_{CS}$  と VTB の DC 特性: (a) 電源電圧依存性, (b) 温度依存性

図 3.9: 1/4 分周器(4 進カウンタ)のブロック図

#### 3.3.3 AC 特性

フリップフロップのスイッチング電流は 87  $\mu$ A である. 電源電圧が 2V の時のフリップフロップ の消費電力は 348  $\mu$ W である.

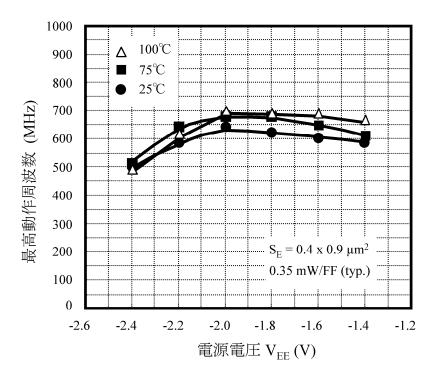

図 3.10 に 1/4 分周器の最高動作周波数の実測結果を示す。3 本の曲線は 25,75,100℃のときの実測値である。 $V_{EE} = -2.0$  V, 25 ℃のときの最高動作周波数は 640 MHz である。1/4 分周器の消費電力は、 $V_{EE} = -2.0$  V で 3.3 mW である(評価のための出力バッファ、基準電圧発生回路含まず)。電源電圧-2.4 V から-1.4 V の広範囲の電圧において 500 MHz 以上で動作するが、-1.4 V では下位入力トランジスタの飽和により論理振幅が小さくなり、-1.3 V では動作しなかった。現実的な電圧下限は-1.6 V である。実測データは、電源電圧、温度に対する依存性が比較的小さく、安定して回路が動作することを示している。

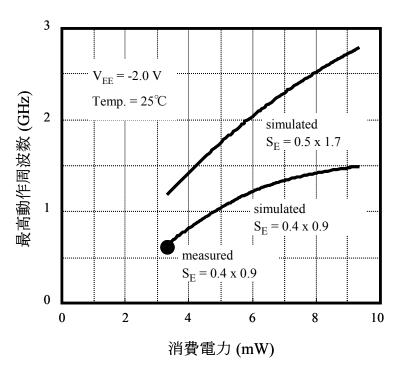

図 3.11 に 1/4 分周器のシミュレーション結果を示す.下側の曲線はエミッタサイズが  $0.4 \times 0.9 \ \mu m^2$  のもの,上側の曲線はエミッタサイズが  $0.5 \times 1.7 \ \mu m^2$  のものである.黒丸は実測値である(640 MHz, $3.3 \ m$ W).実測とシミュレーション結果はよく一致している.本試作では,低消費電力化を狙った設計を行ったが,シミュレーション結果は,回路パラメータを変更することにより,1/4 分周器は  $2.9 \ GHz$  で動作することを示している.

図 3.10: 1/4 分周器の最高動作周波数の  $V_{EE}$  依存性

図 3.11: 1/4 分周器の最高動作周波数(シミュレーション結果)

図 3.12: 1/4 分周器のシミュレーション波形

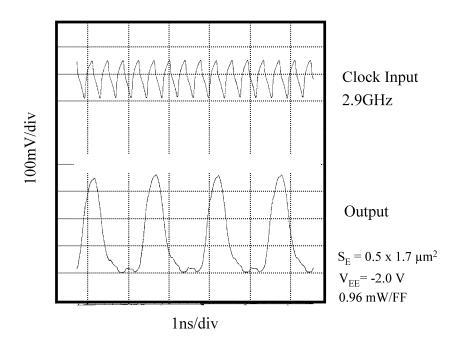

図 3.12 に、1/4 分周器のシミュレーション波形を示す。上側の波形は、フリップフロップのクロック入力、すなわち、 $V_{EE}$  追従バッファ VTB の出力波形、下側の波形は 1/4 分周器の出力波形である。クロック入力は 2.9 GHz、エミッタサイズが  $0.5 \times 1.7 \ \mu m^2$ 、電源電圧 $-2.0 \ V$ 、フリップフロップ 1 個当たりの消費電力が  $0.96 \ mV$  である。回路シミュレーション結果は、 $2.9 \ GHz$  で 1/4 分周器が正常動作することを示している。このときの 1/4 分周器の消費電力は  $9.3 \ mV$  である。

# 3.4 結言

2 V 以下で動作する低電圧シリーズゲート Low-voltage Series-Gate (LSG) と  $V_{EE}$  追従バッファ  $V_{EE}$ -Traced Buffer (VTB) について述べた。  $0.8~\mu m$  2 層ポリシリコン自己整合プロセスを用いて回路を試作した。実測した  $V_{EE}$  追従バッファの出力電圧は,電源電圧,温度ともに安定した特性を示し,基準電圧  $V_{CS}$  の特性とよく一致している。 1/4 分周器  $(4~\ell u)$  カウンタ) の実測では, 3.3~m W, 640~m Hz で動作し,-1.6~V でも正常動作した。 広範囲な  $V_{EE}$  範囲をカバーするとともに,回路は電源電圧,温度の変動に対して安定に動作する事を確認した。 また,トランジスタサイズを変更した回路シミュレーションでは, 1/4 分周器は, 9.3~m W, 2.9~m W の 1/4~m W

バイポーラトランジスタはプロセスが変わっても、ベース・エミッタ間電圧  $V_{be}$ やトランジスタが飽和するベース・コレクタ間電圧はほとんど変化しないため、本章で述べた低電圧化技術はプロセスに依らず展開可能であり、最新のプロセスにおいてもなお、優位性を示す技術である.

十数年前のプロセスであるが、得られた 1/4 分周器の電流と周波数特性は、現在の 65 nm CMOS

に匹敵する性能である。また、近年の低電力無線においては、アルカリ乾電池2本で動作し、かつ、その終端電圧である2V以下での動作が求められている。このようなアプリケーションにおいても十分対応可能な技術である。

# 参考文献

- [1] M. Nakaya, S. Kato, K. Tsukamoto, H. Sakurai, T. Kondo, and Y. Horiba, "A Bipolar 2500-gate Subnanosecond Masterslice LSI," IEEE J. Solid-State Circuits, vol. 16, no. 5, pp. 558-562, Oct. 1981.

- [2] C. L. Chen, "2.5V Bipolar/CMOS Circuits for 0.25 μm BiCMOS Technology," Symp. VLSI Circuits Dig. Tech. Papers, pp. 121-122, May. 1991.

- [3] B. Razavi, Y. Ota, and R. G. Swarts, "Low Voltage Techniques for High Speed Digital Bipolar Circuits," Symp. VLSI Circuits Dig. Tech. Papers, pp. 31-32, May. 1993.

- [4] H. Sato, K. Ueda, N. Sasaki, T. Ikeda, and K. Mashiko, "A Voltage Compensated Series-Gate Bipolar Circuit Operating at Sub-2 V," IEEE J. Solid-State Circuits, vol. 29, no. 10, pp. 1200-1205, Oct. 1994.

- [5] M. Suzuki, M. Hirata, and S. Konaka, "43-ps 5.2-GHz Macrocell Array LSI's," IEEE J. Solid-State Circuits, vol. 23, no. 5, pp. 1182-1188, Oct. 1988.

- [6] R. J. Widlar, "New Developments in IC Voltage Regulators," IEEE J. Solid-State Circuits, vol. 6, no. 1, pp. 2-7, Feb. 1971.

# 第4章 エミッタフォロワ直接制御型フリップフロップ 回路

## 4.1 緒言

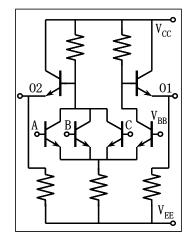

PLL シンセサイザ (Phase-Locked Loop synthesizer) は、有線通信、無線通信用 LSI だけでなく、 デジタル回路においても、その基準周波数発生回路として広く用いられている.携帯電話、コード レス電話、無線 LAN といった無線通信用 PLL シンセサイザは、数 GHz から数 10 GHz で発振する VCO(Voltage Controlled Oscillator)の発振周波数を所望の周波数に分周するプリスケーラや、分 周後の比較的低周波で動作するロジックやチャージポンプなどから構成される.このうち, GHz オ ーダで動作する PLL シンセサイザで最も動作電流が多いのはプリスケーラである. 無線機器のよう に通信時間や待機時間を少しでも長くしたいアプリケーションにおいては,プリスケーラの低電流 化は極めて重要な課題の1つである. バッテリ駆動される移動体通信においては、プリスケーラ用 として Low-level Current Mode Logic (LCML)がよく用いられる. しかしながら、電流を絞ってい ったときに高くなる出力インピーダンスが高周波動作の妨げとなることがある.このような場合, 出力インピーダンスが低いエミッタフォロワを出力バッファとして持つ Emitter Coupled Logic (ECL)が高周波動作に優位となる. 図 4.1 に定電流タイプのエミッタフォロワを持った従来の ECL 回路を示す。エミッタフォロワは、次段の入力容量や配線容量など、寄生容量を駆動するのに 有利な一方で、必要とされないときでも定常的に DC 電流が流れ、消費電力が大きいという欠点が ある.この不必要な電流を削減し、電力・遅延積を改善するために、いくつかのアクティブフルダ ウン電流型エミッタフォロワが提案されている[1]-[6]. しかし,これらの回路には以下のような 問題がある:(1)容量のような付加素子が必要[1]-[3],(2)相補出力を取るのが困難[1],[3],[4],

図 4.1: ECL 回路(定電流エミッタフォロワ)

[6], (3)制御素子の動作を調整するために特別な電圧が必要[5], [6]. このため、これらの回路の適用は限定されてしまう.

本章では、まず、余分な DC 電流を削減する直接制御エミッタフォロワと出力レベル安定化回路 [7]の基本回路構成と、回路シミュレーションによる従来の定電流エミッタフォロワとの比較を行う.次に、本回路を元に、高速、低消費電力化したフリップフロップ[8]について述べる.合わせて2種類の出力レベル安定化回路を紹介する.最後に、提案するフリップフロップを用いて試作したデュアルモジュラスプリスケーラの評価結果について述べ、本フリップフロップの優位性を検証する.

## 4.2 直接制御エミッタフォロワ

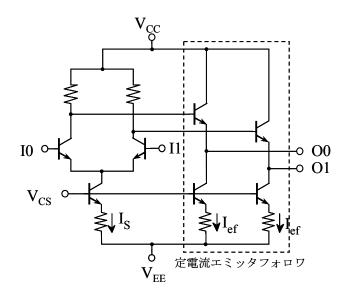

#### 4.2.1 基本回路構成

前節で述べたようにエミッタフォロワの欠点は、不要な時も含め、常時、定電流が流れていることである。大電流が必要なのは、出力信号の立ち上がり、もしくは立ち下がりの期間であり、負荷容量を駆動するために、ダイナミックに変化する電流特性が求められる。すなわち、プッシュプル構成が望ましいが、高速動作を維持するために、トランジスタが飽和しない領域で使用する必要がある。そこで、差動出力が相補的に立ち上がり、立ち下がり動作することを利用し、エミッタフォロワの電流源がスイッチ動作させることを提案する。図 4.2 にこのアイデアを具体化した直接制御エミッタフォロワ (DC-EF: Directly Controlled Emitter-Follower) の基本回路構成を示す。エミッタフォロワの電流源は1つにし、トランジスタ  $Q_5$  と  $Q_6$  からなる差動対により切り替えるようにした。差動対は入力信号から直接制御される。図 4.1 の従来の ECL と比較すると、トランジスタ  $Q_8$  が増え、エミッタフォロワの抵抗が1つ減った構成である。多くの場合、抵抗よりもトランジスタの方が面積が小さいため、トータルの面積は小さくなっている。基本的な動作は以下のとおりで

図 4.2: 直接制御エミッタフォロワ(DC-EF)

ある.

"H"から"L"(立ち下がり期間):入力 I0 が立ち上がり,I1 が立ち下がると,トランジスタ  $Q_1$  のコレクタ(ノード A)は負荷抵抗  $R_1$  により電圧が低下する.そうすると,エミッタフォロワのトランジスタ  $Q_3$  がオフし,出力 00 のレベルが低下し始める.このとき,トランジスタ  $Q_5$  は入力 I0 から直接制御されてオンとなる.エミッタフォロワ電流  $I_{\rm ef}$  は,トランジスタ  $Q_5$  を介して流れるが,トランジスタ  $Q_3$  がオフであるため,出力 I00 から引き抜くことになる.このため,出力につながっている負荷容量を急速に放電する.

"H"から"L"(立ち下がり期間): 入力 I0 が立ち下がると、ノード A の電圧が上がる。トランジスタ  $Q_3$  はオンし、出力 00 の電位が立ち上がる。このとき、トランジスタ  $Q_5$  はオフするため、不要なエミッタフォロワ電流を流すことなく、トランジスタ  $Q_3$  の電流の大半は負荷容量を急速に充電することに使われる。

従来の ECL 回路において、エミッタフォロワ電流は、出力が"H"、"L"に関わらず定常電流を流しているのに対し、直接制御エミッタフォロワでは、出力"H"の時のプルダウン電流はほぼ 0 であり、出力"L"の時に多くなる。入力 I0 と I1 が直接、エミッタフォロワのプルダウントランジスタを制御するため、これまでのアクティブプルダウン回路よりも高速にプルダウン動作を始める。また、容量結合に必要な容量素子や、バイアス電流も必要とならない。この回路では、エミッタフォロワ電流を半分にすることができ、電流ペナルティもない。しかしながら、次節で述べるように、出力"H"の時、エミッタフォロワ電流がほぼ 0 となるため、"H"レベルが不安定となる問題がある。このため、レベル安定化回路が必要となる。

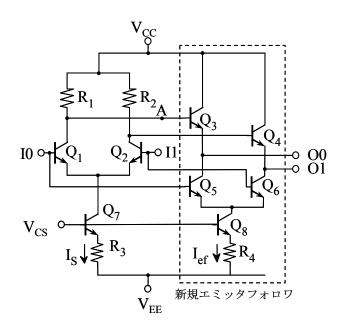

#### 4.2.2 レベル安定化回路付き直接制御エミッタフォロワ

図 4.2 の基本回路構成のままでは、"H"レベルが不安定となる問題があるため、レベル安定化回路を新たに考案した. 図 4.3 にフィードバック型レベル安定化回路付き直接制御エミッタフォロワ

図 4.3: フィードバック型レベル安定回路付き直接制御エミッタフォロワ (FB-DC-FE)

図 4.4: フィードバック型レベル安定回路の有無による出力波形の比較

(FB-DC-FE: Directly Controlled Emitter-Follower with a FeedBack type level stabilizer) を示す。トランジスタ  $Q_9 \sim Q_{11}$  および  $R_5$  からなるレベル安定化回路が付加されている。トランジスタ  $Q_9$  および  $Q_{10}$  は、ベース、コレクタ間がショートされたダイオード接続となっており、出力レベルに応じて、その高い方のトランジスタのみがオンする。この電流は、トランジスタ  $Q_3$  もしくは  $Q_4$  を流れ、 $Q_3$  もしくは  $Q_4$  が完全にオフすることを防ぐ役割を持つ。00 の出力レベルが"H"の時、トランジスタ  $Q_3$  がオン、 $Q_5$  がオフとなるが、トランジスタ  $Q_9$  を介してフィードバック電流  $I_{fb}$  が  $Q_3$  に流れる。一方、00 の出力レベルが"L"の時、 $Q_9$  はオフし、代わりに  $Q_{10}$  の電流が  $Q_4$  に流れる。"H"レベルの時にトランジスタ  $Q_3$  もしくは  $Q_4$  が完全にオフしない程度の微少電流を流すだけで良く、フィードバック電流  $I_{fb}$  はエミッタフォロワ電流よりも小さく設定される。

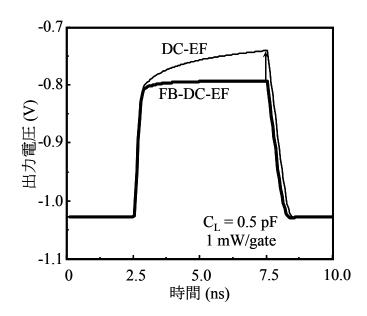

図 4.4 に、直接制御エミッタフォロワについて回路シミュレーションした結果を示す。フィードバック型レベル安定化回路の有無による出力波形の比較を行っている。回路当たりの消費電力はどちらも 1 mW に設定している。電源電圧-3.0 V、信号振幅 250 mV、負荷容量として 0.5 pF を付けている。出力波形を見て明らかなように、安定化回路がある FB-DC-EF は、出力"H"レベルが安定しているのに対し、安定化回路がない DC-EF では、出力レベルが徐々に高くなり、5 ns 後には、安定化回路がある FB-DC-EF と比較して約 60 mV 高くなる。また、出力レベルが高くなっている分、立ち下がり時間も長くなっている。

#### 4.2.3 回路シミュレーション結果

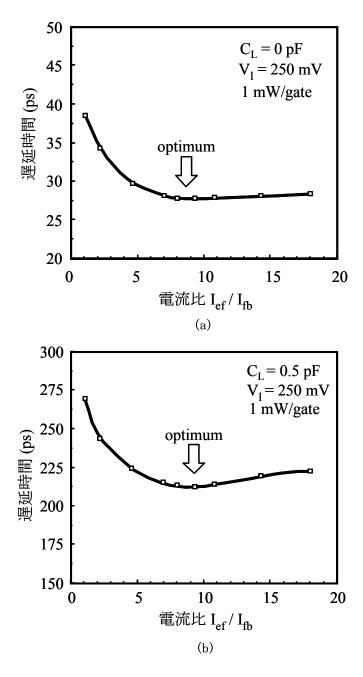

高速動作と低消費電力化を両立させるために、エミッタフォロワ電流  $I_{\rm ef}$  とフィードバック電流  $I_{\rm fb}$  の比を最適化する必要がある。ここでは、 $I_{\rm ef}$  >  $I_{\rm fb}$  、および  $I_{\rm ef}$  +  $I_{\rm fb}$  が一定の条件で、 $I_{\rm ef}$  /  $I_{\rm fb}$  の値を変化させて、回路の遅延時間がどう変化するか調べた。検討に用いたプロセスは、 $0.8~\mu m$  2 層ポリシリコン、自己整合型バイポーラプロセスで、実効的な最小エミッタサイズは、0.5~x 1.  $7~\mu m^2$

図 4.5:  $I_{\rm ef}/I_{\rm fb}$  とゲート遅延時間: (a)負荷容量なし, (b)負荷容量 0.5 pF

である.

図 4.5 に電流比  $I_{\rm ef}/I_{\rm fb}$  とゲート遅延時間の関係を示す。図 4.5 (a) は,負荷容量として同じ回路を接続し,それ以外の寄生容量は 0 ( $C_{\rm L}$  =0 pF) とした場合,図 4.5 (b) は,負荷容量として同じ回路を接続するとともに 0.5 pF の容量を付加 ( $C_{\rm L}$  = 0.5 pF) した場合である。どちらも 1 回路当たりの消費電力は 1 mW とし,信号振幅は 250 mV とした.

消費電力一定の条件で比較しているため、 $I_{\rm ef}/I_{\rm fb}$ が大きくなるほど、エミッタフォロワ電流に割

り当てられる電流が多くなり,遅延時間も短くなるが,あまり  $I_{\rm ef}/I_{\rm fb}$  の比を大きく取りすぎると, ''H''が不安定になる影響が出てきて, かえって遅延時間が長くなる. このため,  $I_{\rm ef}/I_{\rm fb}$  の比に最適 点があることになる.

図 4.5(a) より,負荷が軽いときは, $I_{\rm ef}/I_{\rm fb}$ の比が 8~9 の時に遅延時間が最小となり,図 4.5(b) より,負荷が重いときには, $I_{\rm ef}/I_{\rm fb}$ の比が 9~10 の時に最適点となる.出力レベル安定化に必要な電流  $I_{\rm fb}$ は  $I_{\rm ef}$ の約 10 分の 1 であるため,フィードバック型安定化回路の電流ペナルティはごく僅かであることがわかる.

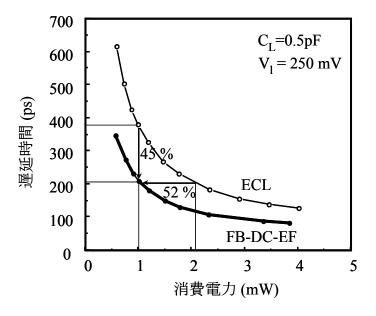

次に、 $I_{\rm ef}/I_{\rm fb}$ の比を 10 に固定した状態で、消費電力を振ったときの遅延時間を調べた。消費電力の変更は、トランジスタサイズはそのままで、抵抗値を一律変化させることで行った。図 4.6 にフィードバック型レベル安定回路付き直接制御エミッタフォロワ FB-DC-FE と従来の ECL の比較を示す。電源電圧は $-3.0~\rm V$ 、信号振幅は 250  $\rm mV_{pps}$  (peak-to-peak single-end: 差動の片側入力)、負荷容量として同一の回路を出力に接続するとともに  $0.5~\rm pF$  の容量を付加している。消費電力  $1~\rm mW$  の条件では、ECL が 379 ps であるのに対し、FB-DC-FE は 207 ps であった。同一の消費電力の条件で、FB-DC-FE は従来の ECL よりも 45 %の高速化が図れている。同一の遅延時間の条件では、FB-DC-FE は ECL よりも 52 %低消費電力である。

図 4.6: 消費電力とゲート遅延時間

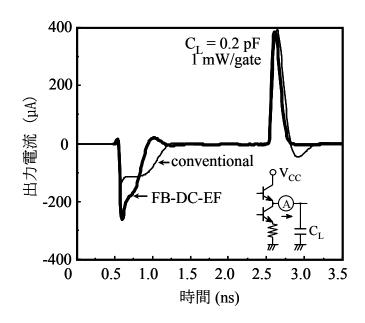

図 4.7: 出力電流波形

図 4.7 に FB-DC-FE と ECL のスイッチング遷移期間における充放電電流のシミュレーション波形を示す. 評価条件は,信号振幅 250  $\mathrm{mV}_{\mathrm{pps}}$ ,電源電圧-3.0 V,消費電力 1  $\mathrm{mW}$ ,負荷容量 0.2 pF である. 出力電圧が立ち下がるときのプルダウン電流は,FB-DC-FE の方が瞬間的により多く流れ,ピーク電流は-260  $\mathrm{\mu A}$  であった.この値は ECL よりも 1.9 倍大きい.このため,急速に負荷容量を放電させることができる.プルアップ電流はプルダウン電流ほど,明確な差はないが,FB-DC-FE の方が ECL よりも僅かに早く立ち上がり,充電時間も早く完了する.FB-DC-FE を使用することにより,立ち上がり時間,立ち下がり時間ともに改善され,より高速な応答が可能であることがわかる.

# 4.3 フリップフロップ回路

#### 4.3.1 従来回路

図 4.8(a)に従来の ECL の,(b)に LCML のフリップフロップ回路を示す. どちらも逆位相のクロックが入力される 2 つの D-ラッチから構成される. ECL と LCML の差は,エミッタフォロワがあるかないかの差である. LCML は,エミッタフォロワによる電流増加がないこと,ベース・エミッタレベルシフトがないため 3 V 以下で動作することが可能であることから,バッテリ駆動が要求される移動体通信では LCML のフリップフロップが使われることが多い [9], [10]. 消費電力を削減するために,電流を減らすと,信号振幅を確保するために負荷抵抗  $R_c$  が大きくなる. 出力インピーダンスが大きくなることは以下のような問題が生じる. まず,第一に負荷抵抗と寄生容量による時定数が大きくなり,最高動作周波数に制限がかかってしまう. 特にフリップフロップでは,負荷抵抗に接続されるトランジスタ数が多いために,元々自分自身の寄生容量が大きい. 第二に,立ち上がりは抵抗でプルアップし,立ち下がりはトランジスタでプルダウンするため,負荷抵抗が大きくな

図 4.8: フリップフロップ回路: (a) ECL, (b) LCML

ると両者のインピーダンスに差が生じ、立ち上がりと立ち下がりがアンバランスとなる. 出力信号のデューティが問題となる場合には注意が必要となる. 第三に、次段のベース電流が負荷抵抗に流れるため、クロック信号が変化したときに瞬間的に電流が流れ、負荷抵抗が大きい場合には出力信号にスパイクノイズや信号の揺れが発生する場合がある.

ECL と LCML を比較すると、スイッチング電流が同一のとき、ECL フリップフロップの動作周波数は LCML の約 2 倍、消費電流も約 2 倍となる. 負荷が軽いときの最高動作周波数と電流の逆数の積で表される FOM(Figure of merit) はほぼ同等であるが、負荷が重たくなるに従って、LCML は動作周波数の劣化が大きい. また、LCML は負荷抵抗と寄生容量で動作周波数が決定されてしまうため、FOM の改善が困難である. このため、ECL のエミッタフォロワ電流の削減が、FOM の改善に有効な

手段となる. 以降では、2種類のフィードバック型安定化回路付き直接制御エミッタフォロワについて議論し、また、電源電圧の低減についても紹介する.

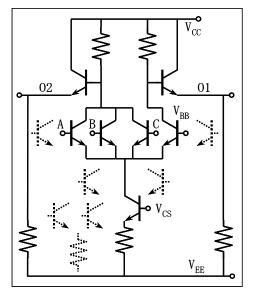

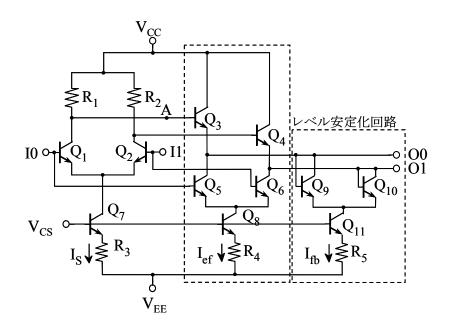

#### 4.3.2 ダイオードフィードバック型直接制御エミッタフォロワ

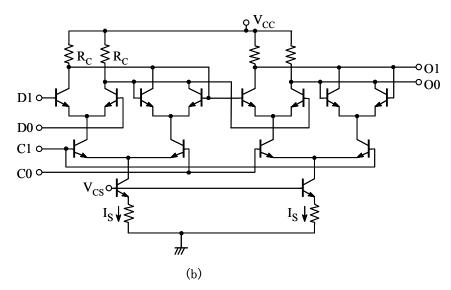

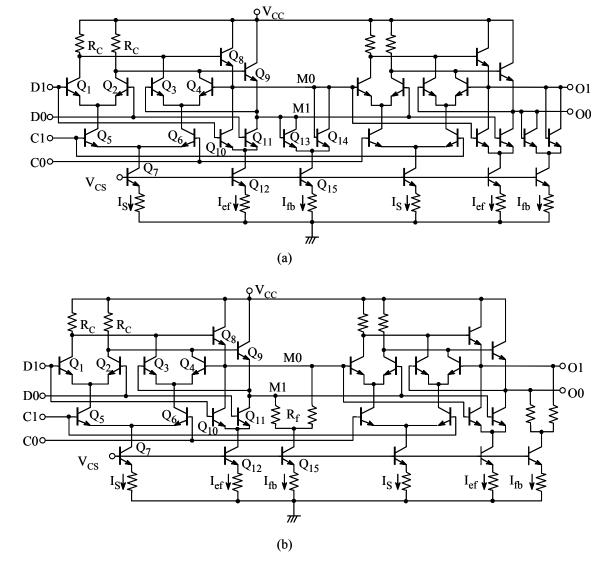

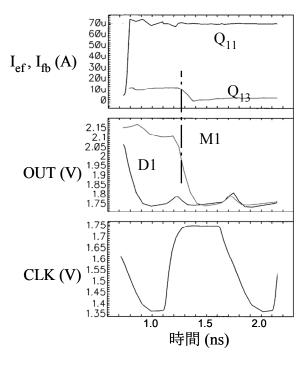

図 4.9(a) にダイオードフィードバック型直接制御エミッタフォロワ (DC-DF: Directly Controlled emitter-follower with a Diode Feedback)を用いたフリップフロップの回路を示す。マスターラッチ,スレーブラッチともにエミッタフォロワを持っている。エミッタフォロワ電流  $I_{\rm ef}$  は直接データ入力 D1 および D0 によって制御される。 $Q_{13} \sim Q_{15}$  がダイオードフィードバック型安定化回路を構成する。以下,マスターラッチの基本動作を説明する。

初期条件は、マスターラッチの出力 M1 が"H"、データ入力 D1 が"L"とする. クロック入力 C1 が

図 4.9: フリップフロップ回路: (a) ダイオードフィードバック (DC-DF), (b) 抵抗フィード バック (DC-RF)

"L"から"H"に変化すると、マスターラッチはデータ読み込みモードになる。 $Q_{11}$  と  $Q_{13}$  がオンするので、プルダウン電流  $(I_{ef}+I_{fb})$  が出力 M1 の容量を急速に放電する。出力 M1 が "L"になると、 $Q_{13}$  はオフする。回路シミュレーションによるタイミングチャートを図 4.10 に示す。

一方,マスターラッチの出力 MO が立ち上がろうとするとき, $Q_{10}$  と  $Q_{14}$  はオフしている.プルダウン電流はほぼ遮断されているので,エミッタフォロワトランジスタ  $Q_8$  の電流はすべて充電に使われるため,出力 MO の電圧は急速に立ち上がる.出力 MO が"H"になると, $Q_{14}$  はオンする. $Q_{10}$  はカットオフしているが,微少なフィートバック電流  $I_{fb}$  が  $Q_8$  を流れるため,出力 MO の"H"レベルは安定し,出力インピーダンスも高くなることはない.スレーブラッチの動作もマスターラッチと同様である.

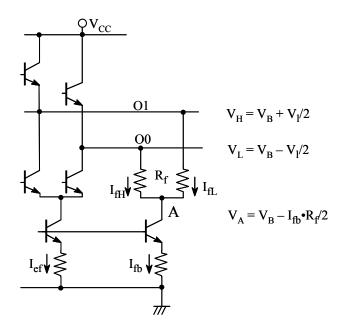

## 4.3.3 抵抗フィードバック型直接制御エミッタフォロワ

図 4.9(b) に抵抗フィードバック型直接制御エミッタフォロワ (DC-RF: Directly controlled emitter-follower with a Resistor Feedback)を用いたフリップフロップの回路を示す。 DC-RF に あったプルダウンダイオード  $Q_{13}$  と  $Q_{14}$  はフィードバック抵抗  $R_f$  に置き換えられている.

出力レベルをフィードバックすることにより,出力"H"のエミッタフォロワトランジスタに電流を流して,出力"H"のレベルを安定化するという回路の基本的なコンセプトは DC-DF と同じである. 図 4.11 に抵抗フィードバック型レベル安定化回路の動作を示す.初期状態として,出力 01 が"H",出力 00 が"L"とする. "H"レベル  $V_H$  と "L"レベル  $V_L$  はそれぞれ  $V_B$  +  $V_1/2$ ,  $V_B$  -  $V_1/2$  で表される.  $V_B$  はスレッショルド電圧,すなわち  $V_H$  と  $V_L$  の中点, $V_L$  は信号振幅である.フィードバック電流  $I_{fH}$  と  $I_{fL}$  は次式で表される.

図 4.10: タイミングチャート

図 4.11:抵抗フィードバック型レベル安定回路

$I_{fH} = (I_{fb} + V_1/R_f)/2$  $I_{fL} = (I_{fb} - V_1/R_f)/2$

出力 01 の電圧はプルダウン電流  $I_{ff}$ によって安定な $^{\prime\prime}$  $H^{\prime\prime}$ レベルを保持する.

ノード A の電圧は、 $V_B$  –  $I_{fb}$ - $R_f/2$  となる.これは  $V_H$ 、 $V_L$  を含まず、一定の値である.これは、フィードバック電流源を含むノード A の寄生容量が出力 O1 や O0 に影響を及ぼさないことを意味している.さらに、フィードバック抵抗  $R_f$  は、DC-DF におけるフィードバックダイオードよりも寄生容量が小さい.このため、DC-RF を用いたフリップフロップの最大動作周波数は、DC-DF よりも高くなる.

#### 4.3.4 従来回路との比較

従来の ECL 回路では、2つのエミッタフォロワ(フリップフロップとしては4つ)が定常電流を消費しているのに対し、DC-DFや DC-RFでは1つのエミッタフォロワ電流が交互に流れる構成である。安定化回路に必要な電流は、エミッタフォロワ電流よりも十分小さいために、DC-DFや DC-RFのエミッタフォロワ電流は ECL と較べ、約半分となる.

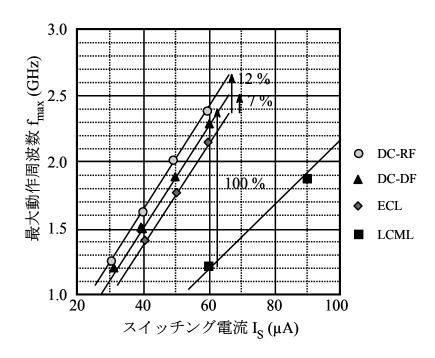

図 4.12 に、LCML、ECL、DC-DF、DC-RF のフリップフロップを用いた 1/4、1/5 分周デュアルモジュラスプリスケーラの最高動作周波数についての回路シミュレーション結果を示す。比較のために、条件は以下のように統一した。信号振幅 400 mV,電源電圧 3 V,入力信号 400 mV $_{pp}$ , $I_{ef}=I_{S}$ 、 $I_{fb}=I_{S}/7$  としている。スイッチング電流 60  $\mu$ A のとき,DC-DF の最高動作周波数  $f_{max}$  は,ECL よりも 7 %高く,DC-RF の  $f_{max}$  は ECL よりも 12 %高いという結果が得られた。また,DC-RF は LCML よりも 約 2 倍の周波数で動作する。同一の周波数で比較すると,DC-DF や DC-RF は LCML よりも約半分の電流となる。

図 4.12: スイッチング電流  $I_S$  と最大動作周波数  $f_{max}$

図 4.13: 出力波形

文献[1]に示されるアクティブプルダウンの効果は、基本回路の遅延時間を改善するものの、フリップフロップに関する改善効果は比較的小さい.これは、クロック入力が変化する前にデータ入力が先に変化しているためで、エミッタフォロワ電流はすでに切り替わりが始まっており、出力信号の変化とアクティブフルダウン電流が同期していないからである.

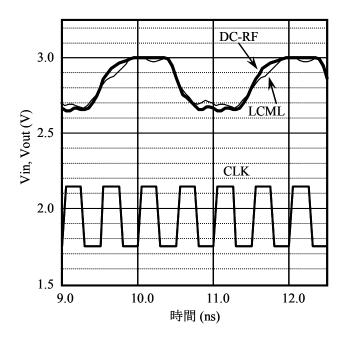

図 4.13 に LCML と DC-RF を用いた 1/4 分周プリスケーラの出力波形を示す. 図の上がフリップフロップの出力ノードの電圧であり、下が入力したクロックの波形である. 入力周波数は 2 GHz, 信号振幅 400 mV, 電源電圧は 3.0 V である. LCML には、4.3.1 節で触れたように次段の過渡的なベース電流による出力波形の揺れが発生していることがわかる. これらのディンプルは誤動作の要因となったり、位相雑音の劣化を引き起こしたりする. また、立ち上がりの時間も遅くなっている.

#### 4.3.5 抵抗レベルシフト回路

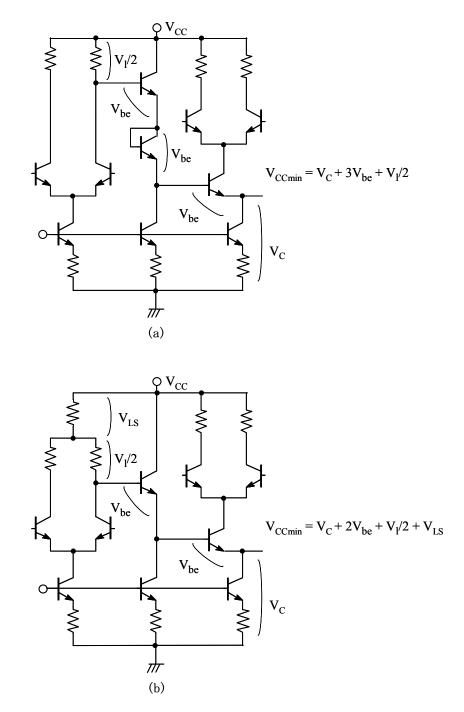

図 4.14(a)に示すように、従来の ECL フリップフロップでは、シリーズゲートの下位入力であるクロック入力は上位入力であるデータ入力よりもダイオード 1 つ分(1  $V_{be}$ )だけレベルシフトされている。このような場合、最低電源電圧  $V_{Cmin}$  は、 $V_C$  + 3  $V_{be}$  +  $V_I$ /2 で表される。ここで  $V_C$  は電流源のオーバーヘッド、 $V_{be}$  はベース・エミッタ間電圧、 $V_I$  は信号振幅である。 $V_C$  、 $V_{be}$  、 $V_I$  をそれぞれ 0.4  $V_I$  0.8  $V_I$  0.4  $V_I$  と仮定すると最低電源電圧は 3.0  $V_I$  となる。これは終端電圧が 2.7  $V_I$  のバッテリ駆動には適さない。図 4.14(b)に抵抗レベルシフト回路を示す。ダイオード 1 つ分をレベルシフトするのではなく、負荷抵抗と  $V_{CC}$  の間にレベルシフト抵抗を入れることにより、レベルシフト量を 0.8  $V_I$  よりも小さくすることができる。この場合の最低電源は、 $V_C$  + 2  $V_{be}$  +  $V_I$ /2 +  $V_{LS}$ で与えられる。ここで  $V_{LS}$  はレベルシフト電圧であり、トランジスタの飽和を防ぎ、かつダイオード1 つ分の電圧よりも小さい値でなければならない。 $V_{LS}$  を 0.4  $V_I$  としたときの最小電源電圧は 2.6  $V_I$  となる。すなわち、従来の ECL よりも 0.4  $V_I$  電源電圧を下げることができる。

プリスケーラのクロック入力(下位入力)は、クロックドライバによって与えられているため、クロックドライバは抵抗によるレベルシフタを持っていなければならない.クロックドライバが抵抗レベルシフト回路を採用し、同時に DC-DF もしくは DC-RF の回路を採用することは可能である.

図 4.14: 最低電源電圧: (a) ダイオードレベルシフト, (b) 抵抗レベルシフト

# 4.4 評価結果

提案する回路を検証するために、同一の Si ウエハ上に複数個の 1/4, 1/5 分周デュアルモジュラスプリスケーラを搭載して実測評価を行った.

図 4.15: 1/4, 1/5 分周デュアルモジュラスプリスケーラ

| S <sub>E</sub> (effective) | 0.3 x 0.5 |

|----------------------------|-----------|

| $\mathbf{f}_{T}$           | 25 GHz    |

| Cje                        | 1.4 fF    |

| Cjc                        | 2.0 fF    |

| Cjs                        | 1.7 fF    |

| rb                         | 560 ohm   |

|                            |           |

表 4.1: デバイスパラメータ

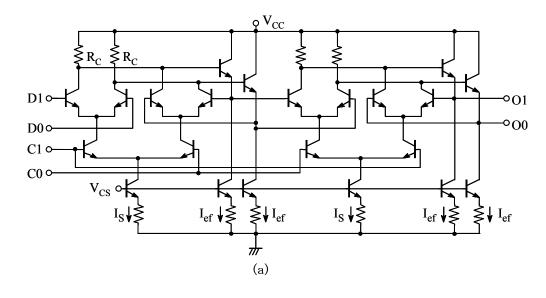

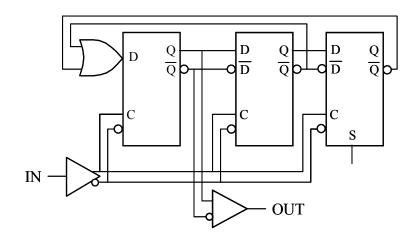

図 4.15 にプリスケーラのブロック図を示す. プリスケーラは 3 つのフリップフロップ, クロックドライバ, 測定のための出力バッファから構成されている. LCML, ECL, DC-DF, DC-RF の 4 つのフリップフロップを試作, 評価した. クロックドライバと出力バッファは, フリップフロップと同じエミッタフォロワを用いている.

$0.35~\mu m~BiCMOS~プロセス[11]$ を用いて種々のエミッタフォロワを用いたデュアルモジュラスプリスケーラを試作した. 回路に用いたバイポーラトランジスタの代表的なデバイスパラメータを表4.1 に示す. 実効的なエミッタサイズは  $0.3~x~0.5~\mu m^2$ , 遮断周波数  $f_{\tau}$  は 25~GHz である.

デュアルモジュラスプリスケーラのチップ写真を図 4.16 に示す。チップサイズは  $1.0 \times 1.0 \text{ mm}^2$  である。このチップに 2 種類のプリスケーラが搭載されている。LCML と比較して,DC-RF のフリップフロップではトランジスタ数が約 2 倍になっているが,面積増は約 20%である。これは同一の周波数で動作させるために,DC-RF フリップフロップは LCML のおよそ半分のスイッチング電流でよく,DC-RF のトランジスタサイズは LCML の半分となるためである。プリスケーラは評価のために,50  $\Omega$  駆動の出力バッファが出力に付加されている。出力バッファの電源パッドはプリスケーラの電源パッドと分離されており,プリスケーラのみの電流を測定することができる。

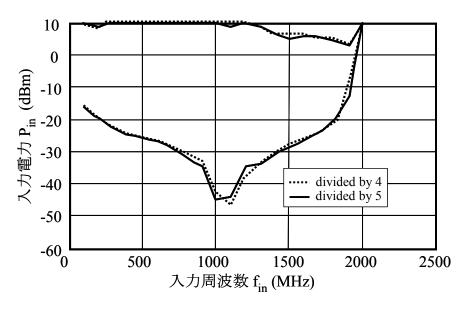

図 4.17 に DC-RF を用いたプリスケーラの入力周波数と入力感度の関係を示す。周波数毎の入力電力の上限と下限を表している。電源電圧は 3.0 V,出力バッファを除くプリスケーラ全体の消費電流は 935  $\mu$ A である。実測結果では,入力電力-15 dBm(約 112 mV $_{pp}$ )のとき,動作周波数レンジは

図 4.16: プリスケーラチップ写真

図 4.17: DC-RF の入力感度: $V_{CC}$  = 3.0 V,  $I_{TOT}$  = 935  $\mu A$ ,  $V_1$  = 400 m V

100 MHz から 1.8 GHz であった. 1/4 分周モードと 1/5 分周モードで特性にほとんど差がなかった. 入力電力-4 dBm(約 400 mV $_{\rm pp}$ )のときの最大動作周波数は,1.85 GHz であった.

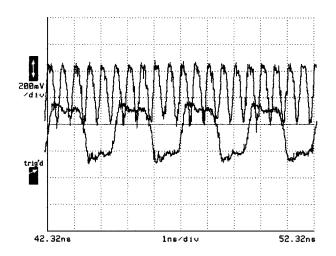

図 4.18: DC-RF プリスケーラの出力波形:1/5 分周モード, $f_{\rm in}$  = 2 GHz,  $V_{\rm in}$  = 400 mV, $I_{\rm TOT}$  = 1.03 mA, $V_{\rm CC}$  = 3.0 V

図 4.19: 電源電圧と最大動作周波数 fmax

図 4.18 に 1/5 分周モードでの DC-RF プリスケーラの出力波形を示す。入力周波数  $f_{\rm in}$  は 2 GHz,入力振幅 400 mV $_{\rm pp}$ ,プリスケーラの出力振幅 400 mV $_{\rm pp}$ ,電源電圧 3.0 V である。プリスケーラの電流が 1.03 mA のとき,最大動作周波数は 2.11 GHz であった。1/4 分周モードでは 2.09 GHz であった。

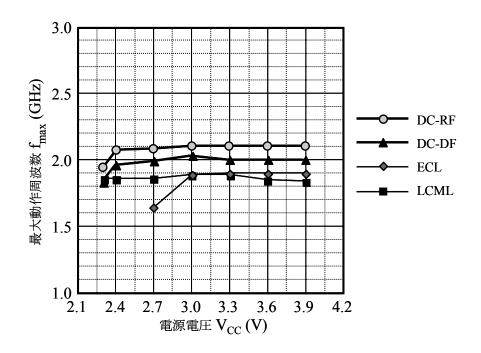

3 V 以下の動作を確認するために、4 種類のプリスケーラの動作を比較した. 図 4.19 に、DC-RF、DC-DF、ECL、LCML に対する最大動作周波数と電源電圧の関係を示す. 抵抗値を変えた、すなわち

図 4.20: 最大動作周波数  $f_{max}$ :  $V_{in}$  = 400 mV,  $V_{l}$  = 400 mV,  $V_{CC}$  = 3.0 V

スイッチング電流を変えた試作チップの中から,それぞれの回路形式で概ね  $2\,GHz$  動作するプリスケーラを選んで比較を行った。DC-EF,DC-DF,ECL の消費電流はそれぞれ, $1.03\,mA$ , $1.05\,mA$ , $1.43\,mA$  である。抵抗レベルシフト回路をつかったクロックバッファを採用することにより,DC-RF と DC-DF の回路動作は, $2.4\sim3.9\,V$  の電源電圧範囲をカバーしていることがわかる。一方,従来の ECL では,トランジスタの飽和により,電源電圧  $2.7\,V$  で最大動作周波数が劣化している。

種々のプリスケーラに対する消費電流と最大動作周波数の関係を図 4.20 に示す.すべての実測データは,入力振幅  $400~\text{mV}_{pp}$ ,電源電圧 3.0~V のときのものである.従来回路の ECL と LCML の性能はほぼ同等であった.4.3.1 節で触れたように,ECL の最大動作周波数  $f_{max}$  は LCML の約 2 倍であるが,消費電流もほぼ 2 倍となるからである.これに対し,DC-RF,DC-DF の場合,エミッタフォロワ電流がほぼ半分になる上に,ECL よりも動作周波数が高くなるために,消費電流と最大動作周波数の関係では従来回路より大幅に向上している.同一の動作周波数で比較した場合,DC-DF のトータル消費電流は LCML より 32~Which の消費電流は LCML より 34~Which 得られた.

# 4.5 結言

ダイオードフィードバック型レベル安定化回路付き直接制御エミッタフォロワ(DC-DF)と抵抗フィードバック型レベル安定化回路付き直接制御エミッタフォロワ(DC-RF)について述べた. エミッタフォロワで消費される不要な DC 電流を削減することにより, 高周波動作と低消費電流化が可能となる. 試作した 1/4, 1/5 分周デュアルモジュラスプリスケーラの電流は, DC-DF を使用した場合, 従来の LCML よりも 32 %少なく, DC-RF の消費電流は LCML より 34 %小さいという結果が得ら

れた. DC-RF を用いたプリスケーラは 2.1 GHz で動作し、このときのトータル電流は 1.03 mA であった.

また、抵抗レベルシフト回路を使ったクロックバッファを採用することにより、DC-RF と DC-DF のプリスケーラが、 $2.4 \sim 3.9~V$  の広い電源電圧範囲で動作することを確認した. バッテリ駆動で必要な 3.0~V 以下で動作が可能であり、高周波動作を維持しつつ、低消費電力化が図れる. 実測結果により、提案する DC-RF と DC-DF が、低消費電力が要求される移動体通信に適していることが確認できた.

本章では、主にフリップフロップ回路、およびプリスケーラについて述べたが、エミッタフォロワは様々な回路に使用されており、本提案の適用範囲も限定されるものではない。エミッタ電流とフィードバック電流の比に最適点が存在するが、ある程度の比を確保していれば、性能に対する電流比の感度は高くないため、設計上、最適化の負荷は重くないと考える。実際、本プリスケーラは、次章で述べるプロセスが異なる PHS (Personal Handy-phone System)用中間周波数処理 LSI の他、WCDMA (Wideband Code Division Multiple Access)用中間周波数処理 LSI、Bluetooth 用トランシーバなどで実用化されている。さらに、エミッタフォロワ電流が半分になるという基本的なコンセプトは CMOS ソースフォロワにも適用可能である。

# 参考文献

- [1] K. Y. Toh, C. T. Chuang, T. C. Chen J. D. Warnock, G. P. Li, K. Chin, and T. H. Ning, "A 23 ps/3.2 mW ECL gate," ISSCC Dig. Tech. Papers, pp. 224-225, Feb. 1989.

- [2] H. Itoh, T. Saitoh, T. Yamada, M. Yamamoto, and A. Masaki, "Advanced ECL with new active pull-down emitter-followers," Proc. 1988 BCTM, pp. 23-35, Oct. 1988.

- [3] C. T. Chuang and K. Chin, "High-speed low-power charge-buffered active-pull-down ECL circuit," Proc. 1990 BCTM, pp. 132-135, Oct. 1990.

- [4] C. T. Chuang, K. Chin, P. F. Lu, and H. J. Shin, "High-speed low-power darlington ECL circuit," IEEE J. Solid-State Circuits, vol. 28, no. 12, pp. 1374-1376, Dec. 1993.

- [5] H. J. Shin, "A self-biased feedback-controlled pull-down emitter follower for high-speed low-power bipolar logic circuits," IEEE J. Solid-State Circuits, vol. 29, no. 4, pp. 523-528, Apr. 1994.

- [6] T. Kuroda, T. Fujita, M. Noda, P. Thai, L. Yang, and D. Gray, "Capacitor-free level-sensitive active pull-down ECL circuit with self-adjusting driving capability," Symp. VLSI Circuits Dig. Tech. Papers, pp. 29-30, June 1993.

- [7] N. Sasaki, H. Sato, K. Ueda, K. Mashiko, and H. Shibata, "A New Emitter-Follower Circuit for High-Speed and Low-Power ECL," IEICE Transactions on Electronics, vol. E78-C, no. 4, pp. 374 380, Apr. 1995.

- [8] H. Sato, N. Nagisa, and T. Miki, "A Flip-Flop Circuit with a Directly Controlled Emitter-Follower and a Level Stabilizer for Low-Power Prescalers," IEICE Transactions on Electronics, vol. E82-C, no. 3, pp. 504 - 510, Mar. 1999.

- [9] M. Mizuno, H. Suzuki, M. Ogawa, K. Sato, and H. Ichikawa, "A 3-mW 1.0-GHz silicon-ECL dual-modulus prescaler IC," IEEE J. Solid-State Circuits, vol. 27, no. 12, pp. 1794-1798, Dec. 1992.

- [10] T. Seneff, L. McKay, K. Sakamoto, and N. Tracht, "A sub-1mA 1.5-GHz silicon bipolar dual modulus prescaler," IEEE J. Solid-State Circuits, vol. 29, no. 10, pp. 1206-1211, Oct. 1994.

- [11] T. Igarashi, S. Kubo, K. Suda, T. Nakashima, Y. Ohtsu, M. Yamawaki, and S. Asai, "A manufacturable 0.35 μm BiCMOS using self-aligned cobalt silicide technology," Proc. 27th European Solid-State Device Research Conf., pp. 420-423, Sep. 1997.

# 第5章 1.9 GHz PHS 用中間周波数処理 LSI

# 5.1 緒言

近年,携帯電話,無線 LAN, Bluetooth 等の無線通信機器市場は急速に拡大している。この分野は、携帯性、通話時間の点から、小型軽量、低消費電力が最も強く要求される分野である。また、端末の低価格化が今日の急激な加入者増の一因であることを考えると、半導体部品の低価格化も重要である。このため、できるだけ多くの部分をシリコン化し、1チップに集積することが有効な手段である。携帯電話用1チップトランシーバとして、1995年に初めてUHF(Ultra High Frequency)帯もしくは900 MHz帯の中間周波数処理部分を1チップ化したものが報告された[1]。ほぼ同時期に、2GHz帯においても変調器あるいは復調器を集積したものが報告されているが[2]-[3]、高周波ゆえに集積度が低かった。そのころの市販の端末では高価な化合物半導体や、個別半導体を用いて構成している状態であった。この理由として、高周波回路を1チップに集積できるだけの十分な性能を持ったシリコンプロセスがなかったこと、LSI内部ブロック間の高周波クロストークやデジタル回路のノイズを抑圧する技術が確立されていなかったことなどが挙げられる。

PHS (Personal Handy-phone System) は L 帯のデジタルコードレスフォンである. ハンドセットは屋内のコードレスフォンとしてだけでなく,屋外では,公衆網に接続されるマイクロセル方式移動体電話としても使用できる. PHS のサービスは 1995 年に開始した. マイクロセル方式を採用することで,一般的な携帯電話よりも出力電力が小さく(携帯電話が 200 mW~2 W であるのに対し, PHSは 20 mW),長時間の通話が可能であることが特長である. バッテリ消費が少ないことから,近年では,USB (Universal Serial Bus)ドングルに無線システムを納め,パーソナルコンピュータと接続することで,高速なデータ通信としても使用されている.

図 5.1: 第1世代 PHS の IC 構成例

図 5.1 に PHS のサービスが開始されたときの第 1 世代 PHS の IC 構成例を示す. HPA (High power amplifier),LNA (Low noise amplifier),送受切り替えスイッチ (SW) といった RF フロントエンドは GaAs のディスクリート部品もしくはモジュールで構成されている. 中間周波数処理部は複数の IC やディスクリート部品で構成されており,1.9 GHz で動作する送信ミキサ (Up MIX) や受信ミキサ (Down MIX) は GaAs のモジュール,ファースト PLL (1st PLL) は BiCMOS プロセスによる汎用 IC,直交変調器 (MOD),セカンド PLL (2nd PLL),セカンド VCO (VCO2) はバイポーラプロセスによる専用 IC,セカンドミキサ (2nd MIX) や IF アンプ (IF Amp.) は汎用 IC を使用している. このように第 1 世代の PHS では複数の IC やディスクリート部品で構成されているため,部品コストが高く,消費電流や実装面積が大きいという問題があった.

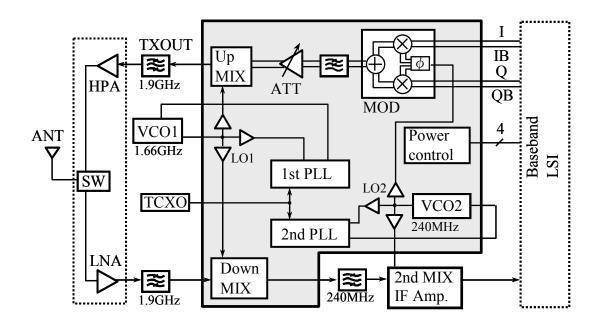

本章では、 $0.8 \mu m$  高周波 BiCMOS プロセスを用いて、 $1.9 \, GHz$  動作の送受信ミキサ、デュアル PLL、直交変調器等、PHS の中間周波数処理部をほぼ  $1 \, f$  チップに納めた LSI について述べる。  $1.9 \, GHz$  帯 として、世界初の $1 \, f$  チップトランシーバである。中間周波数処理部を $1 \, f$  チップに集積するとともに、 $3 \, V$  のバッテリ電流を削減することを目的としている。まず、はじめに取り組むべき課題について述べ、次にブロック構成や、個々の回路について課題解決方法を説明する。使用したプロセスおよびレイアウトについて述べた後、最後に試作、評価結果を紹介する。

# 5.2 1 チップ化へ向けた課題と対応

1.9 GHz 動作の回路を1チップ化した前例がなく、参考となる文献もなかったため、想定しうる課題を挙げ、一つ一つ対応していくこととした.以下に1チップ化へ向けた課題と対応を挙げる.

#### 1) 低消費電流化 1(動作電流)

従来の中間周波数処理部は、上述のように複数の IC やディスクリート部品で構成されているため、入出力毎にインピーダンスマッチングが必要な上に、エミッタフォロワなどの出力バッファが必要であった。送信系においては、外付け部品を排除し、すべての信号パスをオンチップ化することでバッファを不要とし、低消費電流化を図った。

HPA の利得は負の温特を持ち、温度が上がるとともに出力電力が小さくなる.このため、従来では出力電力が小さくなっても仕様を満足するように、HPA や送信ミキサの出力をあらかじめ大きくするという方法が取られていた.このため、HPA や送信ミキサの消費電流が大きいという問題があった.今回、正の温特を持つアッテネータを送信ミキサ前に挿入することで、HPA の温特を打ち消し、送信ミキサの余分な電流を削減した.アッテネータは中間周波数で動作するため、消費電流は小さい.

#### 2) 低消費電流化 2(待機時電流)

従来の IC では、非動作時においても完全に電流が遮断されず、数 10~数 100μA 程度のバイアス電流が流れるものが多かった。このため、中間周波数処理部全体としての待機時電流が多く、待ち受け時間が短いという問題があった。このため、すべての回路ブロック毎に電流遮断のスイッチを設けるとともに、基準電圧発生回路を含むバイアス回路も完全にオフできるようにした。動作モードに応じて必要なブロックのみを動作させるパワー制御回路を内蔵した。動作モードはベースバンド LSI から送られる信号により設定される。

#### 3) 外付け部品削減

低コスト化と小実装面積化のためには、主要回路のオンチップ化だけでなく、外付け部品

の削減を図る必要がある. 送信部には、ローカル信号の2次および3次の高調波を抑圧するフィルタを内蔵し、外付けSAWフィルタ(surface acoustic wave filter)を削除した. フィルタを削除することで、フィルタ駆動用のバッファが不要となり、低消費電流化を図ることが可能となる.

4) PLL シンセサイザの高速ロックアップ化

TDMA(Time Division Multiple Access)では、送信、受信が間欠的に動作する. PLL シンセサイザのロックアップ時間を短縮することで、PLL シンセサイザを立ち上げる時間を遅らせることができ、その分だけ低消費電力化が図れる.

5)1.9 GHz 動作回路のオンチップ化

受信ミキサや送信ミキサは、1.9 GHz の高い周波数で動作するため、従来では、GaAs のモジュールが用いられてきた。これを置き換えるため、高周波で動作するバイポーラトランジスタと CMOS トランジスタが両立する Bi CMOS プロセスを新たに開発した。

6) 高周波クロストークやデジタルノイズ抑圧

1.9 GHz 動作の高周波回路, VCO や他のアナログ回路, デジタル回路を 1 チップ化するため, 高周波クロストークやデジタルノイズによる性能劣化を抑える必要がある. ブロック間の信号アイソレーションを向上させるために, 各回路ブロックを電源/グランドのシールドラインで囲むようにした. また, 基板ノイズを吸収する p+シールドライン専用のパッドを新たに用意した.

5.3以降で、採用したブロック構成や、個々の回路について課題解決へのアプローチについて詳細に述べる.

# 5.3 チップ構成

図 5.2 に中間周波数処理 LSI のブロック図を示す. 2 つの PLL シンセサイザ(1st PLL, 2nd PLL), 送信ミキサ(Up MIX), 受信ミキサ(Down MIX), 可変利得アッテネータ(ATT), 直交変調器(MOD), セカンド VCO(VCO2)を内蔵した. ファースト VCO(VCO1), セカンドミキサ(2nd MIX), IF アンプが中間周波数処理部でのオフチップ部である. RF フロントエンドは GaAs MMIC で構成されており, HPA, LNA, 送受切り替えスイッチ等が 1 チップ化されている [4]. コストやサイズの観点では, フロントエンド部もシリコン化し, 送受信部を 1 チップ化するのが理想的であるが, 当時のシリコンプロセスでは, 2GHz 帯で効率の良い HPA や NF(Noise figure)の小さい LNA をオンチップするのは困難であるため, 本 LSI では別チップとした. 近年では, 要求性能が比較的緩い Bluetooth や ZigBee 向け RF トランシーバは CMOS での 1 チップ化が可能となっているものの[5]-[6], 要求性能が厳しい携帯電話や無線 LAN といった用途では, 高効率 HPA や低雑音 LNA を 1 チップ化するのは困難であるため, 現在でも GaAs や SiGe HBT (Heterojunction Bipolar Transistor)を用いた外付け部品で対応している. 特に非常に出力電力が大きい HPA のオンチップ化はまだ研究段階である.

本 LSI ではダブルコンバージョン方式を採用しており、1.9 GHz の信号を受けて、受信ミキサは 240 MHz の中間周波数に変換する. セカンドミキサや IF アンプが必要であるが、低価格で低消費 電力の IC がすでに入手可能であるため、ここでは外付けにしている. セカンドミキサ以降を外付けにすることにより、DECT (European cordless telephone)の様な他のシステムに容易に適用可能である.

図 5.2: 中間周波数処理 LSI ブロック図

同様に送信部もダブルコンバージョン方式を採用している. 直交変調器の後段に, セカンドローカル信号の2次および3次高調波を抑圧するローパスフィルタを内蔵したので, I/Q入力からTXOUTまで信号がチップ外に出ることなく, すべてチップ内で処理できるようにしている. このローパスフィルタは単純なRCフィルタで構成した.

TXOUT の出力電力を調整し、また、接続される GaAs HPA の利得の温度依存性を打ち消すために可変利得アッテネータを送信ミキサの前段に挿入している.

ダブルコンバージョン方式に対応するため、2個のPLLを内蔵している。それぞれのローカル信号は、アイソレーションを取るためにバッファを経由して各ブロックに分配される。ファーストPLL/ファーストVCOが生成するファーストローカル信号LO1は送信ミキサ、受信ミキサ双方に供給される。セカンドローカル信号LO2は直交変調器とセカンドミキサに分配される。ベースバンドLSIからの4ビットの制御信号は、送信モード、受信モード、PLL動作モード等に応じて各ブロックのパワー制御するための信号である。

# 5.4 回路設計

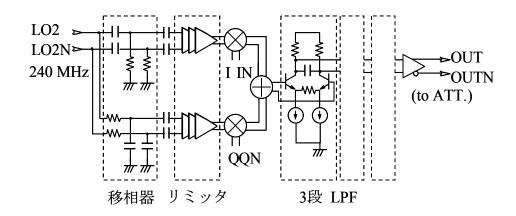

#### 5.4.1 直交変調器

図 5.3 に直交変調器 (MOD) の回路図を示す. 90 度移相器にはローカルバッファを介して 240 MHz のセカンドローカル信号が入力される. 90 度移相器には、周波数分周器タイプやポリフェーズフィルタタイプのものがあるが、周波数分周器タイプは分周器が必要な上に VCO を 2 倍もしくは 4 倍の周波数で発振させるため消費電流が大きく、ポリフェーズフィルタタイプは精度を上げるには面積が大きいという欠点がある. このため、より消費電力の点で有利な RC/CR タイプ[7]を使用した. RC/CR タイプの移相器は、プロセスの変動によって HPF と LPF の遮断周波数が変動し、I 側と

図 5.3: 直交変調器

Q側の振幅がアンバランスになるという欠点がある. 遮断周波数の変動による I 側と Q 側の振幅誤差に対応するため,後段に 3 段のリミッタアンプを挿入した. リミッタアンプのベース電流による特性変化, DC オフセットによる特性劣化を低減するため,移相器とリミッタアンプは AC 結合とした.

ベースバンド LSI から来た I/Q 信号はダブルバランスミキサでローカル信号と混合,加算され,出力段に接続される. ローカル信号の 2 次および 3 次の高調波は,-30 dBc 以下に抑圧する必要がある. ミキサ出力段での 2 次および 3 次歪みは,それぞれ-25 dBc,-20 dBc であるため,システム要求により,さらにそれぞれ 5 dB,10 dB 抑圧しなければならない.このため,出力段にローパスフィルタ機能を付加した.プロセスばらつきを考慮して,3 段のフィルタとした.これにより I/Q 入力から TXOUT まで信号がチップ外に出ることなく,すべてチップ内で処理できるようになり,外付け部品を削除できるとともに外部駆動用のバッファも不要となる.

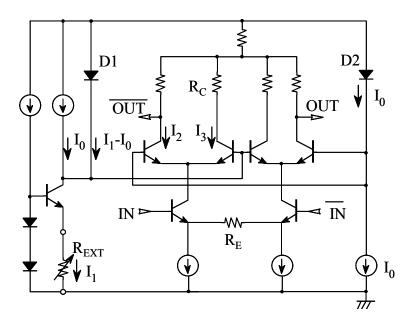

## 5.4.2 アッテネータ

図 5.4 に示すアッテネータ回路は、送信ミキサの出力電力を調整すると共に、GaAs HPA の負の温度依存性を持つ利得を補償する. 外付け抵抗  $R_{\rm EXT}$  はアッテネータの利得調整用である. 可変範囲は約 10 dB である. この回路の利得は 2 つのダイオード、D1、D2 の電流比で決まるため、利得は以下の式で表される.

$$Gain = \frac{2R_C}{R_E} \frac{I_2}{I_2 + I_3}$$

$$= \frac{2R_C}{R_E} \frac{I_0}{I_1}$$

ここで、 $I_2:I_3=I_0:(I_1-I_0)$ 、 $I_1=V_{be}/R_{EXT}$ である。 $V_{be}$  は負の温度依存性を持つため、利得は正の温度依存性を持つ。回路パラメータは HPA の温度依存性を打ち消すように設定した。これにより、高温での HPA の利得低下を補うための余分な電流を流す必要がなくなり、低消費電力化が図れる。また、システム全体での利得の温度変化が小さくなるため、HPA が持つ可変利得範囲を小さくできるという利点もある。

図 5.4: アッテネータ

図 5.5: 受信ミキサ

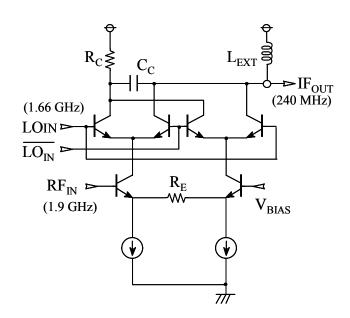

## 5.4.3 送受信ミキサ

受信ミキサや送信ミキサは、1.9 GHz の高い周波数で動作するため、高周波での利得や雑音に優れたバイポーラトランジスタと CMOS トランジスタを集積した BiCMOS プロセスを新たに開発した. プロセスの概要については後で説明する.

送信ミキサ, 受信ミキサは, ローカル信号リークを押さえるために, いずれもダブルバランスミキサで構成されている. 送信ミキサは 240 MHz の IF 信号から, 1.9 GHz の RF 信号に変換する. 出

力段に差動アンプとエミッタフォロワを設け、出力インピーダンスが 50  $\Omega$ に近くなるように設計されている。このため、送信ミキサの出力端 TXOUT には、外部の 50  $\Omega$ マッチング回路が不要となり、外付け部品を削減できる。

受信ミキサ(図 5.5)は、1.9 GHz の RF 信号を 240 MHz の IF 周波数 (中間周波数)に変換する. 通常は送信ミキサ同様、エミッタフォロワを使用するが、受信ミキサは大きな電力出力が不要であること、線形性を向上させるにはエミッタフォロワに多くの電流を流さなければならないことから、消費電流を考慮してオープンコレクタとした. 外付けのインダクタ負荷が受信ミキサの出力に接続される.  $R_{\rm c}$  と  $C_{\rm c}$  でローパスフィルタが構成されており、不要な高調波を抑え、線形性を改善する.

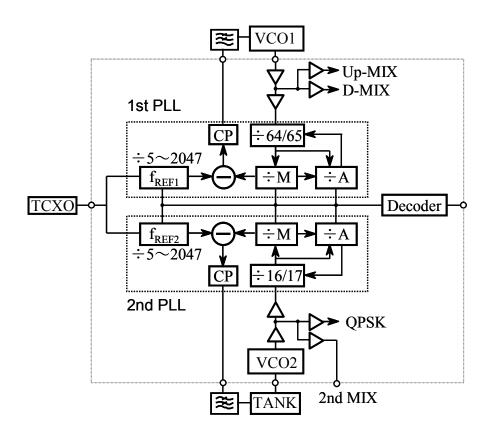

### 5.4.4 PLL シンセサイザ

ダブルコンバージョンに対応して、2つの PLL シンセサイザを内蔵した。図 5.6 にデュアル PLL シンセサイザ (1st PLL、2nd PLL)のブロック図を示す。ファースト VCO (VCO1) は外付けのモジュール、セカンド VCO (VCO2) は内蔵である。動作周波数は、ファーストローカル信号が  $1\sim2$  GHz、セカンドローカル信号が  $100\sim400$  MHz である。PLL は 22 ビットのシリアルデータによりプログラミングされ、最初の 2 ビットが各ブロックのパワー制御、3 ビットがシフトレジスタ選択に使用される。4つのシフトレジスタが、ファーストとセカンドのローカル信号の周波数設定とレファレンス周波数  $f_{REF1}$ 、 $f_{REF2}$ の設定に用いられる。残りの 17 ビットで分周比を指定する。PHS として使用する際には、レファレンス周波数は、ファーストローカル信号で 300 kHz (PHS のチャネル間隔)、セカン

図 5.6: デュアル PLL シンセサイザ

図 5.7: L0 バッファ回路

ドローカル信号で 50 kHz に設定される.

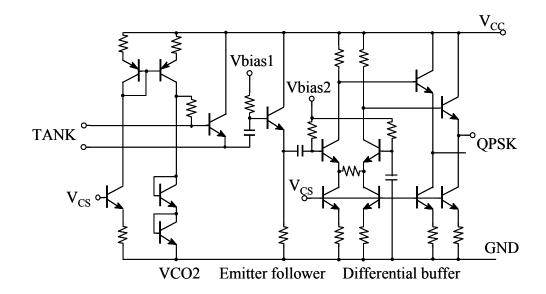

生成されたファーストとセカンドのローカル信号はバッファ回路を通して、それぞれ送受信ミキサ、セカンドミキサ/直交変調器に供給される。ローカル信号の減衰を防ぐためと、接続される負荷が変動したときに VCO の発振周波数が変化するのを抑制するためである。図 5.7 にセカンド VCO とバッファ回路を示す。バッファ回路は、エミッタフォロワと差動アンプからなる 2 段のバッファから構成される。セカンド VCO (VCO2) はコルピッツ型発信器で、アクティブ素子やバイアス回路を内蔵している。比較的大きな L と C からなる共振回路 (TANK) は内蔵化が困難であるため外付けとした。

時分割多重アクセス TDMA (Time division multiple access)においては、PLL シンセサイザは間欠的に動作するため、パワー制御信号が PLL に起動をかけたとき、短い時間でロックアップすることが求められる。5.2 で述べたように、ロックアップ時間の短縮により、PLL シンセサイザを立ち上げる時間を遅らせることができ、その分だけ低消費電力化が図れる。以下、提案する PLL シンセサイザ構成について説明する。

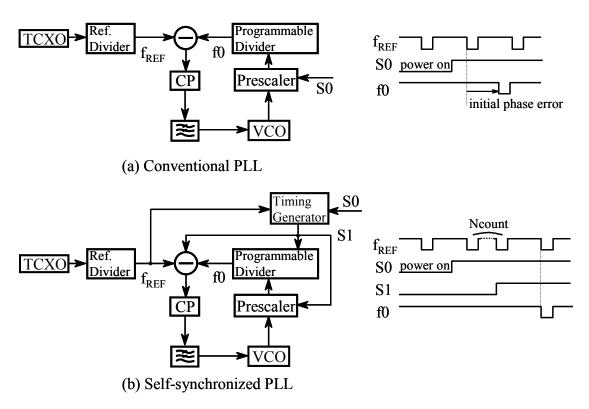

図 5.8(a) に示す従来の PLL においては,レファレンス周波数  $f_{REF}$  と分周された VCO 周波数  $f_{REF}$  と分周された VCO 周波数  $f_{REF}$  と 非同期信号となっている.パワー制御信号  $f_{REF}$  と がこれらの信号とは独立に立ち上がるからである.このため,位相比較器は,たとえ  $f_{REF}$  と  $f_{REF}$  の半分であるとみなす場合がある.このような初期の位相誤差はロックアップタイムの長時間化やばらつきを引き起こす可能性がある.

図 5.8(b) に新規に考案した自己同期型 PLL の構成図を示す。新たに追加したタイミング発生器が,S0 と  $f_{REF}$  から制御信号 S1 を生成する。S1 は位相比較器,プログラマブル分周器,プリスケーラに分配される。S1 は  $f_{REF}$  と同期しているために, $f_{REF}$  と f0 の間の初期位相誤差が最小限に抑えられる。もし,初期の段階で  $f_{REF}$  = f0 であった場合,初期の位相誤差は 0 となる。

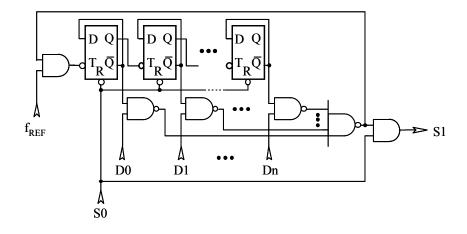

図 5.9 に示すタイミング発生器は N ビットのカウンタから構成されている. D0 から Dn によってビット数 N を設定する. N ビットカウンタは,プリスケーラの起動に対して正確な遅延時間を生成

する. N 個のカウント後、 $f_{REF}$ の立ち下がりエッジで S1 が立ち上がる. このため、位相比較器、プログラマブル分周器、プリスケーラは  $f_{REF}$  と同期して動作する. N カウントの遅延時間は約 10  $\mu s$  であり、ロックアップ時間と比較して無視できるほどの時間である.

図 5.8: 自己同期型 PLL

図 5.9: タイミング発生器

図 5.10: 基準電圧発生回路

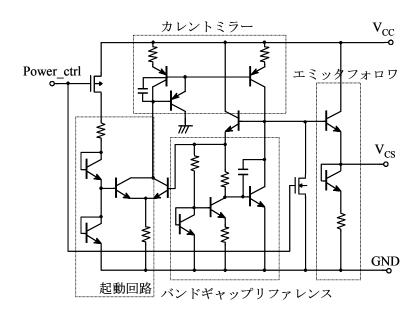

### 5.4.5 基準電圧発生回路

基準電圧発生回路は各回路ブロックの動作電流を決定する基準電圧  $V_{CS}$  を供給する.  $V_{CS}$  を 0 V にすることにより各回路ブロックはパワーオフされる. 受信モード,送信モード,PLL シンセサイザオンモード,スリープモードなどの動作モードに応じて必要なブロックのみを動作させるため,基準電圧発生回路は個々の回路ブロックに配置した. 基準電圧発生回路およびそれに接続されるアナログブロックはパワー制御ピンによって動作モード(送信,受信,PLL オン,スリープ)に応じて電流が遮断される.

スリープモード時の待機時電流削減という課題に対しては、すべての回路ブロック毎に電流遮断のスイッチを設けるとともに、基準電圧発生回路を含むバイアス回路も完全にオフできるようにした. 基準電圧発生回路を図 5.10 に示す. スリープモードでは、パワー制御回路からの信号 Power\_ctrl によってバンドギャップリファレンス回路および起動回路がオフされ、基準電圧発生回路の消費電流もほぼ 0 にカットされる.

携帯機器はバッテリ駆動であるため電源電圧が大きく変動する. 電源電圧の変動によって特性が変化すると、その変動マージンを含めた設計が必要であるため、余分な電流を必要とする. 電源電圧の変動によって特性が変化しないようにするには、 $V_{CS}$  の電源電圧依存性を極力小さくする必要がある. このため、本回路では自己バイアス型バンドギャップレファレンス回路を基本に、起動回路、カレントミラー、エミッタフォロワ回路から構成される方式を採用した. この結果、 $V_{CS}$  の電源電圧依存性は  $1.6\,$  mV/V と極めて小さい値が得られている.

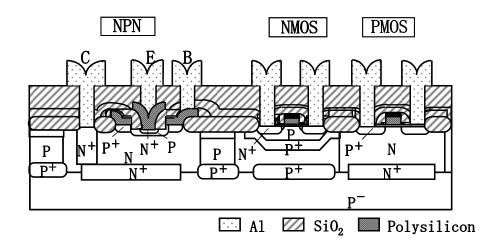

# 5.5 プロセス技術

LSI の試作に使用したプロセスは、 $0.8~\mu m$  高周波 BiCMOS であり、これは CBiCMOS プロセス[8] を元に、 $f_T=20~GHz$  の npn トランジスタ、ラテラル pnp トランジスタ、2 層ポリ容量を追加した

図 5.11: トランジスタ断面図

表 5.1: プロセス諸元

| NPN       | $S_E = 0.5 \text{ x } 5.7  \mu\text{m}^2$<br>$f_T = 20 \text{ GHz}, f_{\text{max}} = 24 \text{ GHz}$<br>$C_{\text{TC}} = 9 \text{ fF}, \text{Rb=155 Ohm}$ |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMOS      | $Ln = 0.8 \mu m$ $T_{OX} = 18 nm$ $Vth = 0.76 V$                                                                                                          |

| PMOS      | Vth = -0.78 V                                                                                                                                             |

| Resistor  | n-polysilicon 150 Ohm/squre                                                                                                                               |

| Capacitor | 2 poly, $2.7 \text{ fF/}\mu\text{m}^2$                                                                                                                    |

ものである. 1.9 GHz 動作に対応するため、高周波に対応したバイポーラトランジスタが必要であるが、CMOS とバイポーラを同時形成しようとすると CMOS の熱処理温度が高いために、バイポーラの浅い接合ができないという問題が発生する. このため、CMOS を形成後、バイポーラを形成するプロセスを新たに開発した. CMOS とバイポーラを個別に形成することによるマスク枚数増加という課題に関しては、バイポーラトランジスタは 2 層ポリシリコン自己整合プロセスを用いることで対応した. ベース拡散は専用のマスクが必要となるが、エミッタは自己整合によりマスクが不要となる. エミッタはエミッタポリシリコン形成後にポリシリコンからの拡散によって形成される.

図 5.11 にトランジスタ断面図を示す. npn トランジスタは上述のように 2 層ポリシリコン自己整合プロセスで,ベースポリシリコン形成後に側壁酸化によってエミッタ開口部が決定されるため,実効エミッタ幅は設計ルールよりも小さい 0.5 μm である. これにより,より微細で寄生容量が小さいトランジスタが実現している. CMOS トランジスタは 0.8 μm 標準 CMOS プロセスで,デジタル回路のセルライブラリとの共有化を図っている.

抵抗は n+ポリシリコンを用いてエミッタ電極と同時に形成される. 高容量素子は窒化膜をポリ

シリコンで挟んだ構造で、下部電極はベース電極と同時に形成される.表 5.1 に諸元をまとめる.

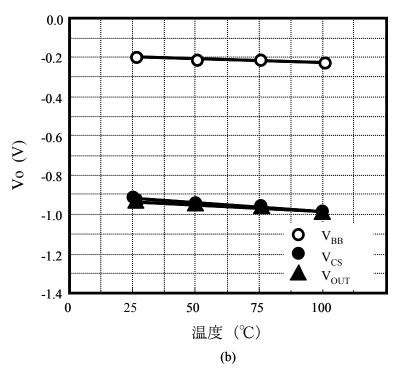

# 5.6 レイアウト

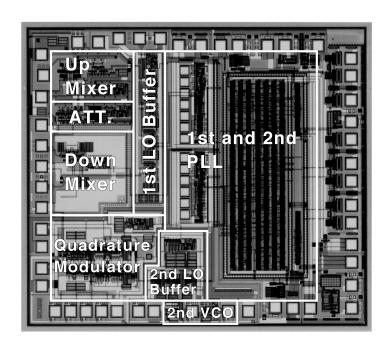

図 5.12 に中間周波数処理 LSI のチップ写真を示す. チップサイズは  $3.4 \times 3.0 \text{ mm}^2$  である. 高周波回路では信号のアイソレーションが重要であり,特に PLL シンセサイザの干渉に気を付けなければならない. 5.2 で述べたデジタルノイズの抑圧という課題に対しては,高周波ブロック/アナログブロックと PLL シンセサイザのデジタルブロックを極力分離することで対応した. チップの右半分はデュアル PLL のロジック部で,左半分はアナログブロックである. さらに,両者の間にファーストローカルとセカンドローカルのバッファを配置した.

信号のアイソレーションの方法の一つとして、電源パッドの近くで電源ラインを分離し、別々のブロックに分配するという方法がある。電源パッドが1つでよいため、ピン数が少なくて済むという利点がある。しかしながら、高周波においては電源パッドは理想的なACグランドではないため、この手法では十分なアイソレーションが取れない。そこで、高周波クロストークの低減という課題に対して以下のように対応した。

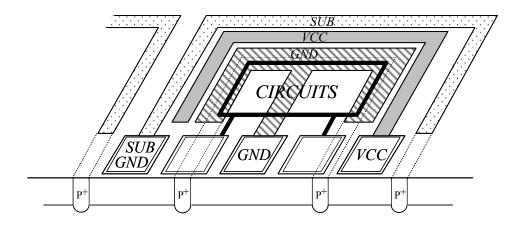

各アナログブロックにはそれぞれ独立の電源,グランドパッドを設け,各ブロックはグランドライン,電源ラインで囲むと共に,最外周は p+シールドで囲んだ(図 5.13). p+シールドラインは他のどこにも接続されない専用のサブグランドパッドに接続され,チップ外のグランドに接続される.グランドとサブグランドに分けた理由は,p+シールドラインが他のブロックからの干渉により揺れたときの影響が回路グランドに及ばないようにするためである.グランドライン上の p+コンタクトはラッチアップ対策である.

図 5.12: チップ写真

図 5.13: 電源ラインのレイアウト

グランドシールドラインによって,数  $100 \, \mu m$  離れたパッドとの信号アイソレーションは, $1.9 \, GHz$  で約  $40 \, dB$  である.  $p+シールドラインによりさらに <math>5 \, dB$  アイソレーションを向上することができる.  $2 \, \text{つのパッドの距離が互いに } 1 \, \text{mm}$  以上離れているとき,たとえば,受信ミキサの出力と VCO2 の出力では,  $1.9 \, GHz$  での信号アイソレーションは  $55 \, dB$  であり,  $240 \, MHz$  では  $82 \, dB$  である.

# 5.7 評価結果

これまで述べた課題に対するアプローチが有効に働き、要求性能を満足するか確認するために、 試作した中間周波数処理 LSI を評価した.

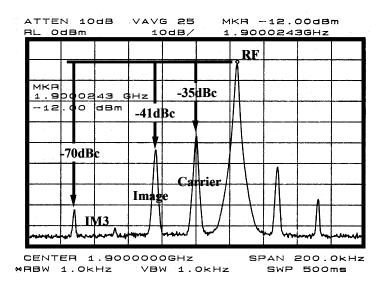

図 5.14 に,電源電圧 3 V, $I/Q = 380 \text{ mV}_{pp}$ , $\pi/4 \text{ QPSK}$  変調(all-0 パターン)の時の送信ミキサ

図 5.14: TXOUT 出力スペクトラム ( $f_{RF}$  = 1.9 GHz,  $f_{L0}$  = 1.66 GHz,  $f_{IF}$  = 240 MHz, I/Q = 380 mV<sub>pp</sub>,  $\pi/4$  QPSK all-0 パターン)

の出力スペクトラムを示す. 中心周波数は  $1.9\,\mathrm{GHz}$  であり, 所望波は  $24\,\mathrm{kHz}$  ずれたところにある. ファーストローカル信号は  $1.66\,\mathrm{GHz}$ , 送信ミキサに入力される IF 周波数は  $240\,\mathrm{MHz}$  である. キャリア抑圧 $-35\,\mathrm{dBc}$ , イメージ抑圧 $-41\,\mathrm{dBc}$  が得られた. また, 3 次相互変調歪みは $-70\,\mathrm{dBc}$  である.

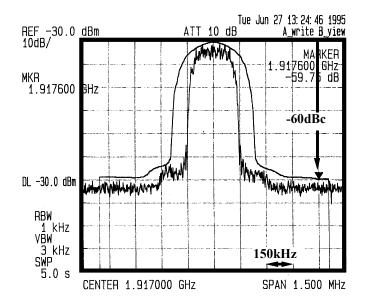

図 5.15 に $\pi/4$  QPSK 変調 (PN9 ランダムパターン) 入力時の出力スペクトルを示す. 周波数設定は図 5.14 と同様である. 600 kHz 離調の隣接チャネル漏洩電力は-60 dBc であった. デジタルノイズによるスプリアスもなく, 所望の特性が得られている.

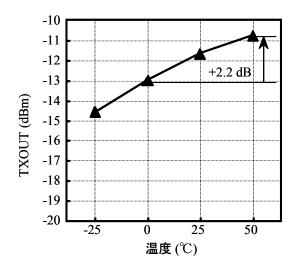

図 5.16 に送信ミキサ出力 TXOUT の出力電力と温度の関係を示す。 アッテネータに持たせた正の

図 5.15: TXOUT 出力スペクトラム( $f_{RF} = 1.9 GHz$ ,  $I/Q = 380 \text{ mV}_{pp}$ ,  $\pi/4$  QPSK PN9 ランダムパターン)

図 5.16: TXOUT の温度依存性

温度特性により、0 から 50  $\mathbb{C}$  の温度変化で出力電力は 2.2 dB 増加する. GaAs HPA のゲインの温度依存性は約-2.5 dB であるので、ほぼ温度補償されることが確認できた.

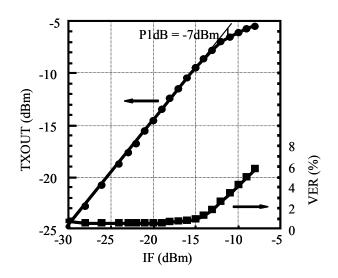

図 5.17 に IF 入力信号の振幅を変化させたときの TXOUT の出力電力と直交変調器単体のベクトルエラーを示す。 PN9 ランダムパターン入力時のベクトルエラーは,出力-9.5 dBm のとき直交変調器単体で約 1 %であった。 PLL 込みのトータルベクトルエラーは 4.4 %である.このときの振幅誤差は 0.1 dB,位相誤差は 2.3° である.また,バーストモード(送受が時分割で切り替わる)時のベクトルエラーは 4.5 %であった.

変調精度を考慮した送信ミキサの最大出力電力は-9.5 dBm である. 後段のパワーアンプのゲイ

図 5.17: TXOUT の IF 入力依存 ( $f_{RF}=1.9$  GHz,  $f_{IF}=240$  MHz,  $f_{L0}=1.66$  GHz,  $\pi/4$  QPSK PN9 ランダムパターン)

図 5.18: ダウンミキサの変換利得( $f_{RF}$  = 1.9 GHz,  $P_{\rm in}$  = -40 dBm,  $f_{L0}$  = 1.66 GHz,  $f_{\rm IF}$  = 240 MHz)

ン特性から要求される-12 dBm のスペックを満たしている. 出力電力が 1 dB 劣化するポイント 0P1dB は-7 dBm である. 直交変調器の変調精度は要求仕様を満足しており,90 度移相器が精度よく動作していることが確認できた.

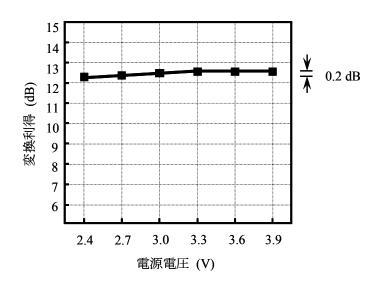

図 5.18 は受信ミキサの変換利得と電源電圧の関係を示すグラフである. 電源電圧が 2.7 V から 3.6 V まで変化したときの利得変動は、0.2dB に抑えることができた。2.4 V から 3.9 V の範囲でも破綻をきたすことなく動作することが確認できた. 電圧補償された基準電圧発生回路により、電源電圧マージンを確保できるとともに、動作マージン確保のための余分な電流も不要となった。

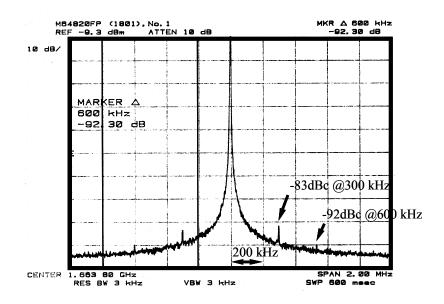

ファースト PLL の評価は外付け VCO モジュールとループフィルタを用いて行った. 図 5.19 にファーストローカル信号の出力スペクトラムを示す. レファレンス周波数は 300 kHz, 発振周波数は 1.6638 GHz である. 600 kHz 離調のスプリアスレベルは-92 dBc, 位相雑音は 2 kHz オフセットで-77 dBc/Hz である. 1.6848 GHz から 1.6512 GHz へのチャネル選択ロックアップタイムは 0.91 ms, スリープモードから動作モードへの遷移であるパワーオンロックアップタイムは 1.1 ms であった. この値は,毎回安定に得られる. 一方,従来の PLL 方式では,このパワーオンロックアップタイムは、 $1.1\sim2.4$  ms のばらつきを生じた.考案した自己同期型 PLL が有効に動作することを確認することができた.

図 5.19: 1st PLL の L0 出力スペクトラム ( $f_{L0}$  = 1.6638 GHz,  $f_{REF1}$  = 300 kHz)

表 5.2: 評価結果

| 送信      | ベクトルエラー率        | 4.4 %   |

|---------|-----------------|---------|

| (PLL含む) | 振幅誤差            | 0.1 dB  |

|         | 位相誤差            | 2.3°    |

|         | イメージリジェクション     | -41 dBc |

|         | 隣接チャネル漏洩電力      | -60 dBc |

|         | 占有帯域幅           | 247 KHz |

| 送信ミキサ   | 1dBコンプレッションポイント | −7 dBm  |

| 受信ミキサ   | 変換利得            | 12 dB   |

|         | 雑音指数 (DSB)      | 12 dB   |

|         | IIP3            | -7 dBm  |

| 消費電流    | 送信時消費電流         | 44 mA   |

|         | 受信時消費電流         | 24 mA   |

|         | 待機時消費電流         | < 1 μΑ  |

LSI 全体の消費電流は、電源電圧 3.0~V のとき、送信時 44~mA、受信時 24~mA である。スリープ時は LSI すべてのブロックがオフし、このときの電流は  $1~\mu A$  以下である。図 5.1 に示した第 1 世代の中間周波数処理部では、3~Fップのトータル消費電流が、送信時 195~mA、受信時 159~mA であり、それぞれ、4~9の 1 以下、6~90 1 以下に低減できた。

中間周波数処理 LSI のその他の主な特性を表 5.2 に示す. これらの値はすべて所望の要求仕様を満たしている. 評価データはすべて 48 ピン QFP にパッケージして測定したものである.

# 5.8 結言

0.8 µm 高周波 BiCMOS プロセスを用いた PHS の中間周波数処理 LSI について述べた. 低消費電力に適した回路構成, プロセス変動に強い回路構成を採用するとともに, 各ブロック間の信号干渉を低減する電源レイアウトを採用することにより, 中間周波数処理機能をほぼ1チップに集積した. 試作評価した結果, 1.9 GHz で正常に動作し, 要求仕様を満たすことを確認した. また, 自己同期型 PLL を提案し, 従来の PLL のパワーオンロックアップタイムが 1.1~2.4 ms であるのに対し, 自己同期型 PLL は 1.1 ms と, 高速化, 安定化を図ることができた. 送信時 44 mA, 受信時 24 mA と, 従来の個別半導体部品を用いた場合に較べ消費電流を 4分の 1 以下に低減した. バッテリ動作に必要な 2.7~3.6 V での正常動作も確認できた. 本研究の成果は, 1.9 GHz 帯として世界初の中間周波数処理 LSI として実用化されている.

本中間周波数 LSI の発表後,無線トランシーバはますます高周波化,高集積化,低消費電力化が進んでいる. 2011 年現在では、さらに高性能な SiGe BiCMOS プロセスを用いた携帯電話用 1 チップ無線トランシーバや、より高周波な UWB トランシーバが製品化されている. また、CMOS プロセスの微細化にともなって、MOS トランジスタの性能や集積度が上がり、ベースバンド処理部と無線トランシーバを一体化したものも実用化されている. アンプやミキサ、PLL シンセサイザといった無線トランシーバのサブブロックは、それぞれがまったく異なる回路で構成されており、また、異

なる特性が要求される.このため、これ1つを実現すればすべての回路を1チップ化できるという 技術は存在せず、1チップ化しやすいアーキテクチャや回路構成を今後も研究していかなければな らない.本章で述べた信号のアイソレーション技術、PLLシンセサイザの高速ロックアップ技術な どは、現在でも使用されている貴重な技術である.

# 参考文献

- [1] T. D. Stetzler, I. G. Post, J. H. Havens, and M. Koyama, "A 2.7V 4.5V Single-Chip GSM Transceiver RF Integrated Circuit," IEEE J. Solid-State Circuits, vol. 30, no. 12, pp. 1421-1429, Dec., 1995.

- [2] T. Tsukahara, M. Ishikawa, and M. Muraguchi, "A 2-V 2-GHz Si-Bipolar Direct-Conversion Quadrature Modulator," IEEE J. Solid-State Circuits, vol. 31, no. 2, pp. 263-267, Feb., 1996.

- [3] C. Takahashi, R. Fujimoto, S. Arai, T. Itakura, T. Ueno, H. Tsurumi, H. Tanimoto, S. Watanabe, and K. Hirakawa, "A 1.9 GHz Si Direct Conversion Receiver IC for QPSK Modulation Systems," ISSCC Dig. Tech. Papers, pp. 138-139, Feb., 1995.