|              |                                                                                                           |

|--------------|-----------------------------------------------------------------------------------------------------------|

| Title        | Low-Voltage and Small-Area Design and Implementation of Narrowband and Wideband CMOS Low-Noise Amplifiers |

| Author(s)    | 木原, 崇雄                                                                                                    |

| Citation     | 大阪大学, 2009, 博士論文                                                                                          |

| Version Type | VoR                                                                                                       |

| URL          | <a href="https://hdl.handle.net/11094/2408">https://hdl.handle.net/11094/2408</a>                         |

| rights       |                                                                                                           |

| Note         |                                                                                                           |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

**Low-Voltage and Small-Area Design and

Implementation of Narrowband and

Wideband CMOS Low-Noise Amplifiers**

( 狹帯域・広帯域CMOS低雑音増幅器の

低電圧化および小面積化に関する研究 )

**Takao Kihara**

木原 崇雄

**Division of Electrical, Electronic and Information

Engineering, Graduate School of Engineering,

Osaka University**

**February 2009**

# Abstract

This dissertation addressed low-voltage and small-area design and implementation of narrow-band and wideband CMOS low-noise amplifiers (LNAs). It was organized into five chapters and two appendixes. The summaries of each chapter were as follows:

## Chapter 1

A background for this work and fundamentals of LNAs were described.

## Chapter 2

A 1.0 V, 5 GHz two-stage CMOS LNA with inductive source degeneration was demonstrated. Its design methodology based on analytical expressions was also presented. The two-stage topology consisting of common-source and common-gate stages was more suitable for low-voltage operation than a conventional cascode topology. The complete analytical expressions of the LNA performance were first derived from the small-signal equivalent circuits. The LNA fabricated in a 0.15  $\mu$ m fully-depleted silicon-on-insulator (FD-SOI) CMOS process occupied 0.25 mm<sup>2</sup> and achieved an  $S_{11}$  of less than  $-10$  dB,  $NF$  of 1.7 dB, voltage gain of 23 dB, and  $IIP_3$  of  $-6.1$  dBm at 5.4 GHz with a power consumption of 8.3 mW. These measurements were consistent with calculations obtained from the derived analytical expressions.

## Chapter 3

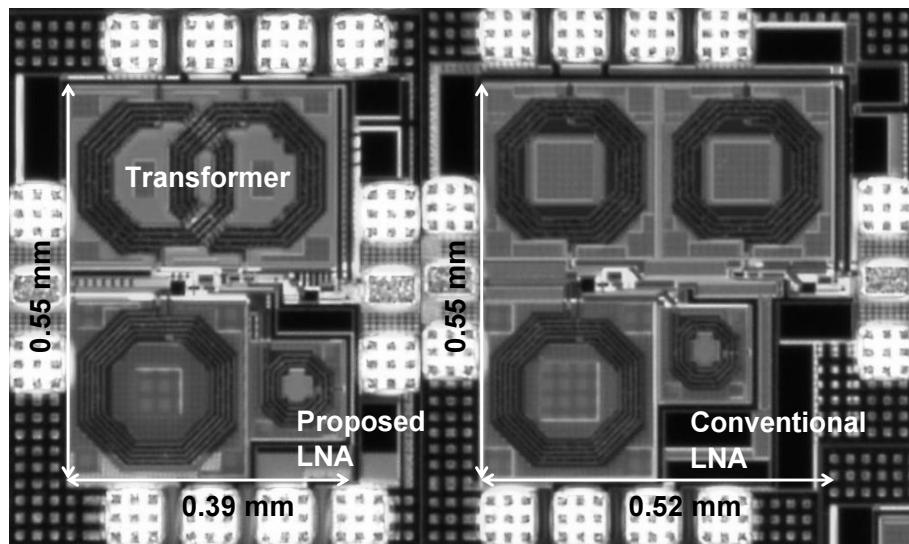

A 0.5 V, 5 GHz transformer folded-cascode CMOS LNA was demonstrated. The chip area of a conventional folded-cascode LNA was reduced by partially coupling the internal inductor with the load inductor. The effects of the magnetic coupling between these inductors on the LNA performance were also analyzed. The LNA fabricated in a 90 nm digital CMOS process achieved an  $S_{11}$  of  $-14$  dB,  $NF$  of 3.9 dB, and voltage gain of 16.8 dB at 4.7 GHz with a power consumption of 1.0 mW. The chip area of the presented LNA was 25% (0.21 mm<sup>2</sup>) smaller than that of the conventional folded-cascode LNA (0.29 mm<sup>2</sup>).

## Chapter 4

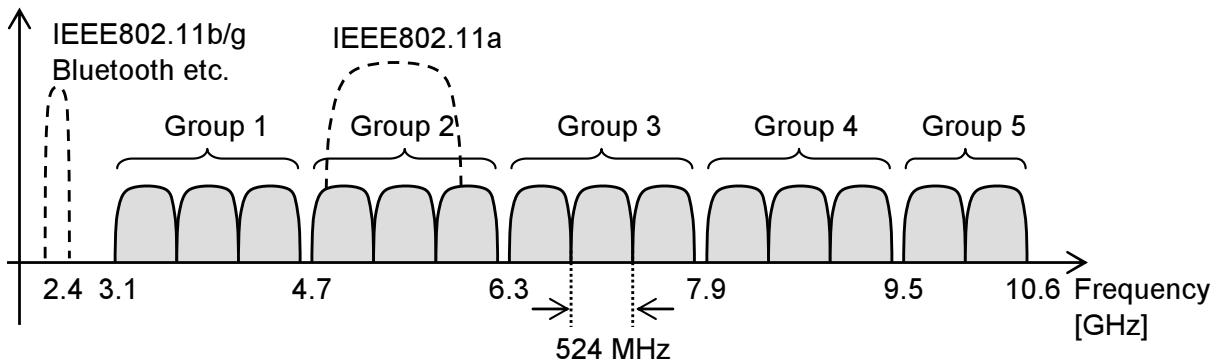

A 1.0 V, 3.1–10.6 GHz transformer noise-canceling CMOS LNA based on a common-gate topology was demonstrated. The transformer consisting of the input and shunt-peaking inductors partly canceled the noise originating from the common-gate transistor and load resistor. The combination of the transformer with the output series inductor provided wideband input impedance matching. The LNA designed for ultra-wideband (UWB) applications was fabricated in a 90 nm digital CMOS process. It achieved an  $S_{11}$  of less than  $-10$  dB,  $NF$  of less than 4.4 dB, and  $S_{21}$  of more than 9.3 dB with a power consumption of 2.5 mW and occupied the smallest chip area ( $0.12\text{ mm}^2$ ) among previously reported 3.1–10.6 GHz CMOS LNAs.

## Chapter 5

The achievements obtained in this work were summarized and this dissertation was concluded.

# Acknowledgments

First of all, I would like to express my gratitude to my supervisor, Professor Kenji Taniguchi (Division of Electrical, Electronic and Information Engineering, Graduate School of Engineering, Osaka University). His appropriate and critical advices always lead me to many successful research.

I am very grateful to Professor Tetsuya Yagi (Division of Electrical, Electronic and Information Engineering, Graduate School of Engineering, Osaka University) and Associate Professor Masanori Hashimoto (Department of Information Systems Engineering, Graduate School of Information Science and Technology, Osaka University) for their advices and suggestions on writing this dissertation.

I would like to thank Professor Toshimichi Ito, Professor Masanori Ozaki, Professor Mitsuhiro Katayama, Professor Masahiko Kondo, Professor Takashi Sugino, Professor Toshiaki Su-hara, Professor Yusuke Mori, and Professor Seizo Morita (Division of Electrical, Electronic and Information Engineering, Graduate School of Engineering, Osaka University) for their helpful suggestions on the dissertation.

I am highly grateful to Associate Professor Toshimasa Matsuoka (Division of Electrical, Electronic and Information Engineering, Graduate School of Engineering, Osaka University) for his leading my research and valuable advices.

I would like to thank Dr. Guechol Kim (Mokpo National University) for his teaching measurement facilities and discussions on LNA measurements. I would like to express my appreciation to Mr. Hisayasu Sato (Renesas Technology and Osaka University) for his technical suggestions and helpful advices on my research. I would like to thank Dr. Yoshiyuki Shimizu (Texas Instruments Japan Limited), Dr. Sungwoo Cha, Mr. Keisuke Ueda (Renesas Technology), Mr. Yoshihiro Utsurogi (The Chugoku Electric Power Co., Inc.), Mr. Bunsei Murakami, Mr. Masaru Goto (Denso Corporation), Mr. Keiji Nakamura (Toyota Motor Corporation), Mr. Lee Tuck Yang (Singapore), Mr. Hae-Ju Park, Mr. Isao Takobe, and Mr. Fumiaki Yamashita (Osaka University) for their supports and discussions on radio-frequency integrated circuits. I also would like to thank Dr. Yoshinari Kamakura, Dr. Tsukasa Ida (Osaka University), Mr. Tomoyuki Tanaka (Renesas Technology), and Mr. Daisuke Kanemoto (Osaka University) for their valuable comments and help. I would like to thank Ms. Noriko Furuta and Ms. Yuko Nomura (Osaka University) for their various supports.

I appreciate various educational programs and financial supports from the Osaka University Global COE Program, “Center for Electronic Devices Innovation”, granted from the Ministry of

Education, Culture, Sports, Science and Technology of Japan.

Finally, I would like to thank my family for their constant supports and caring.

# Contents

|          |                                                            |           |

|----------|------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                        | <b>1</b>  |

| 1.1      | Background . . . . .                                       | 1         |

| 1.2      | Fundamentals of Low-Noise Amplifiers . . . . .             | 2         |

| 1.2.1    | Low-Noise Amplifier . . . . .                              | 2         |

| 1.2.2    | Performance Metrics . . . . .                              | 3         |

| 1.3      | Outline of This Dissertation . . . . .                     | 8         |

|          | Bibliography . . . . .                                     | 8         |

| <b>2</b> | <b>Two-Stage CMOS LNA</b>                                  | <b>11</b> |

| 2.1      | Introduction . . . . .                                     | 11        |

| 2.2      | Cascode LNA with Inductive Source Degeneration . . . . .   | 12        |

| 2.2.1    | Analytical Expressions . . . . .                           | 12        |

| 2.2.2    | Limitations . . . . .                                      | 16        |

| 2.3      | Two-Stage LNA with Inductive Source Degeneration . . . . . | 16        |

| 2.3.1    | Circuit Topology . . . . .                                 | 16        |

| 2.3.2    | Small-Signal Equivalent Circuit . . . . .                  | 17        |

| 2.3.3    | Analytical Expressions . . . . .                           | 20        |

| 2.4      | Design Methodology . . . . .                               | 21        |

| 2.5      | Experimental Results and Discussion . . . . .              | 25        |

| 2.5.1    | Inductor . . . . .                                         | 25        |

| 2.5.2    | S-parameters . . . . .                                     | 27        |

| 2.5.3    | NF . . . . .                                               | 27        |

| 2.5.4    | Linearity . . . . .                                        | 27        |

| 2.5.5    | Comparison . . . . .                                       | 31        |

| 2.6      | Conclusion . . . . .                                       | 32        |

|          | Bibliography . . . . .                                     | 34        |

| <b>3</b> | <b>Transformer Folded-Cascode CMOS LNA</b>                 | <b>37</b> |

| 3.1      | Introduction . . . . .                                     | 37        |

| 3.2      | Circuit Topology . . . . .                                 | 37        |

| 3.3      | Effect of Magnetic Coupling . . . . .                      | 38        |

| 3.3.1    | Input Impedance . . . . .                                  | 39        |

|          |                                                 |           |

|----------|-------------------------------------------------|-----------|

| 3.3.2    | Gain . . . . .                                  | 42        |

| 3.3.3    | Noise . . . . .                                 | 43        |

| 3.3.4    | Stability . . . . .                             | 47        |

| 3.4      | Design . . . . .                                | 47        |

| 3.4.1    | Transistors . . . . .                           | 47        |

| 3.4.2    | Transformer and Inductor . . . . .              | 48        |

| 3.5      | Experimental Results and Discussion . . . . .   | 48        |

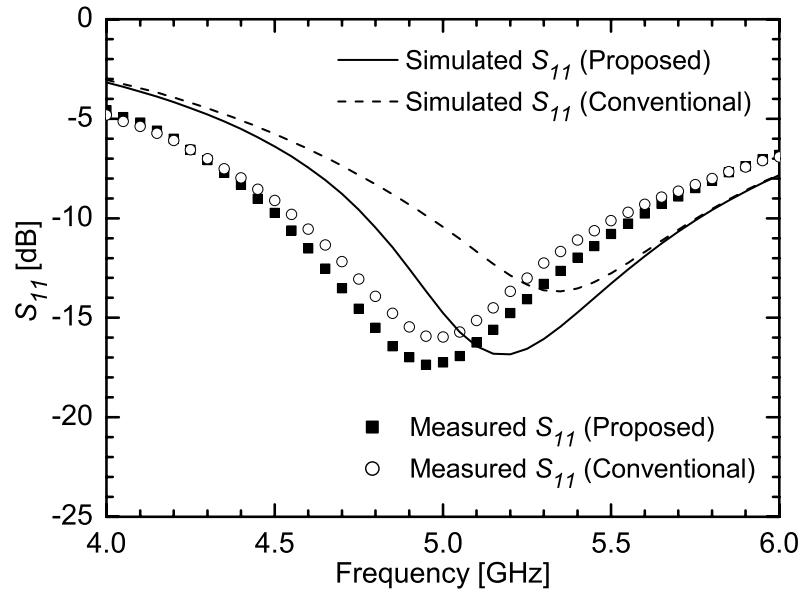

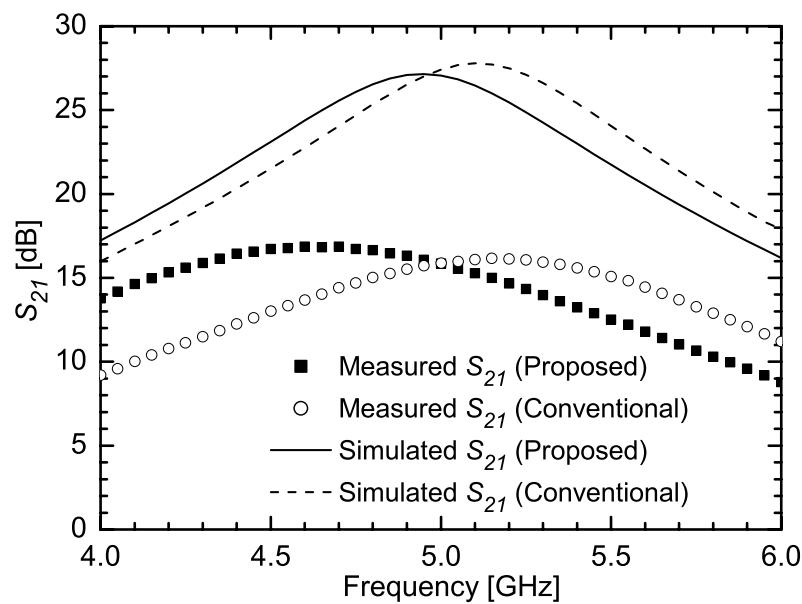

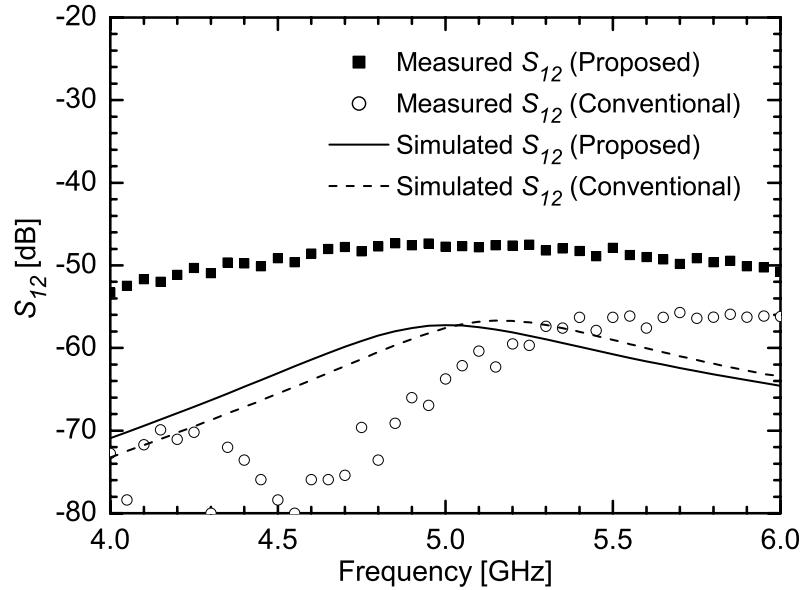

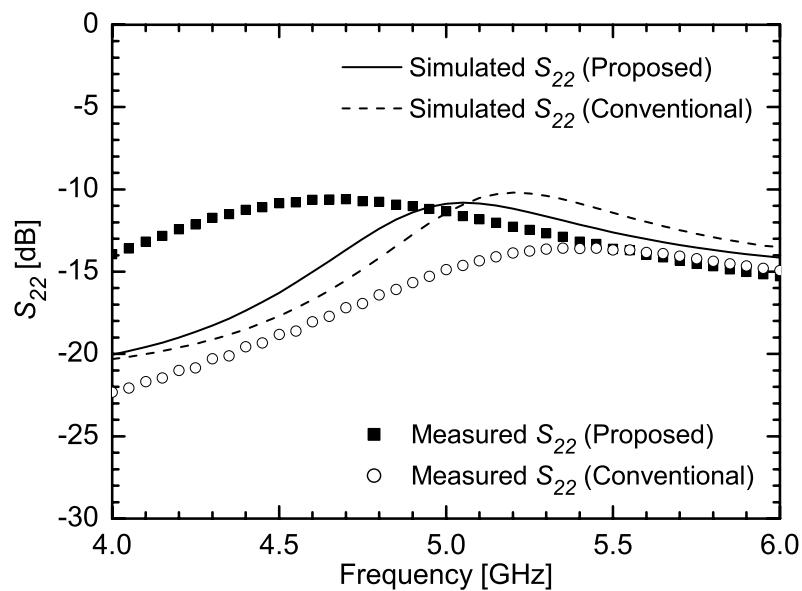

| 3.5.1    | S-parameters . . . . .                          | 51        |

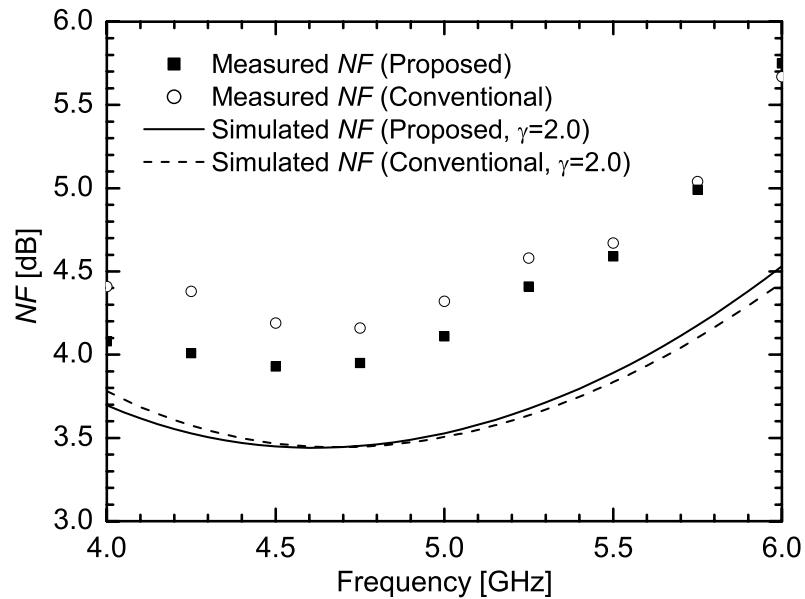

| 3.5.2    | NF . . . . .                                    | 51        |

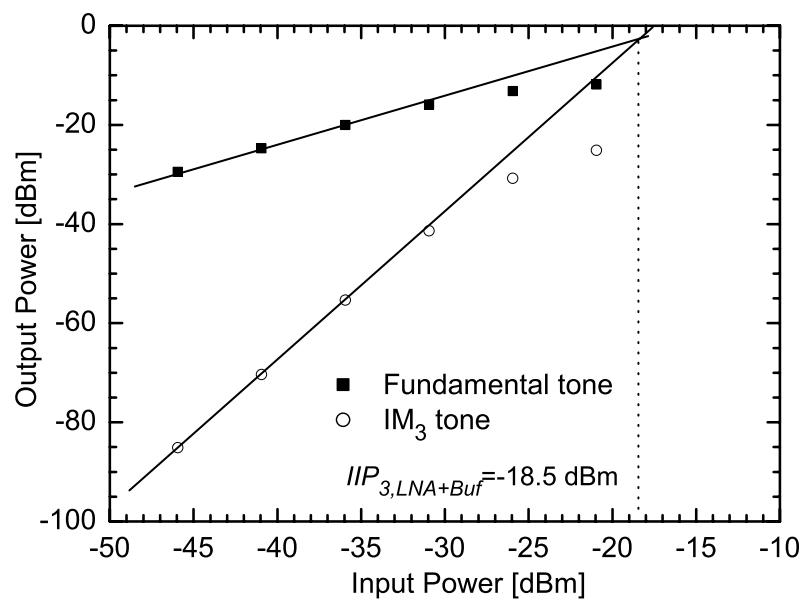

| 3.5.3    | Linearity . . . . .                             | 51        |

| 3.5.4    | Comparison . . . . .                            | 55        |

| 3.6      | Conclusion . . . . .                            | 55        |

|          | Bibliography . . . . .                          | 57        |

| <b>4</b> | <b>Transformer Noise-Canceling UWB CMOS LNA</b> | <b>59</b> |

| 4.1      | Introduction . . . . .                          | 59        |

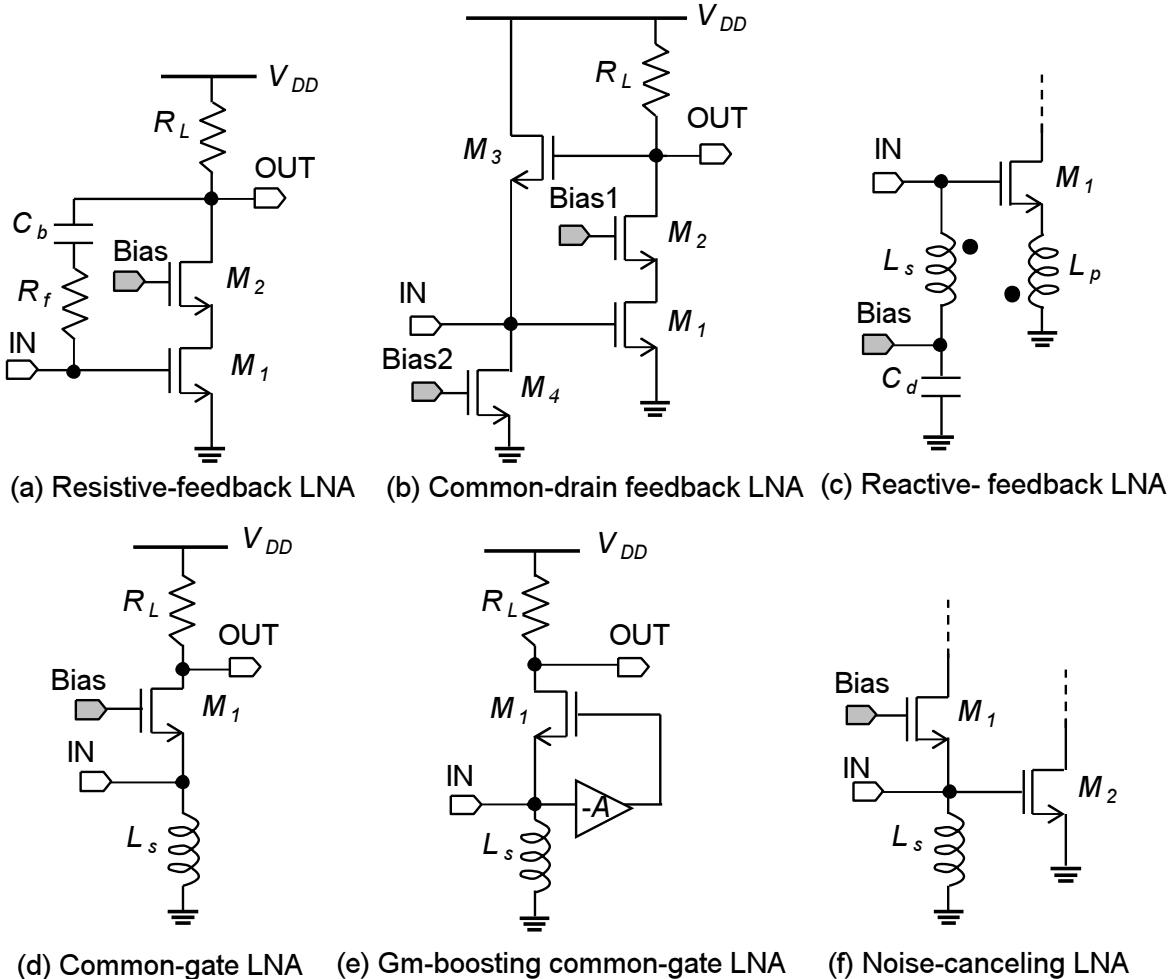

| 4.2      | Wideband CMOS LNAs . . . . .                    | 60        |

| 4.2.1    | Common-Source LNAs . . . . .                    | 60        |

| 4.2.2    | Common-Gate LNAs . . . . .                      | 62        |

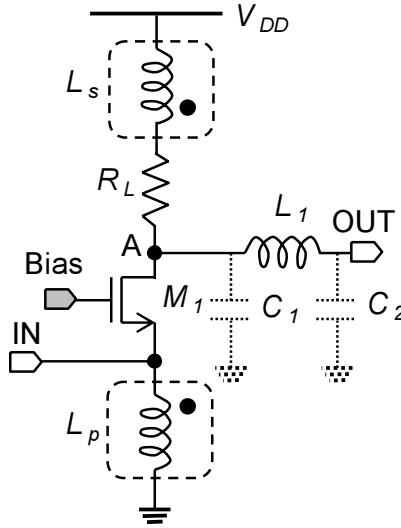

| 4.3      | Transformer Noise-Canceling LNA . . . . .       | 63        |

| 4.3.1    | Circuit Topology . . . . .                      | 63        |

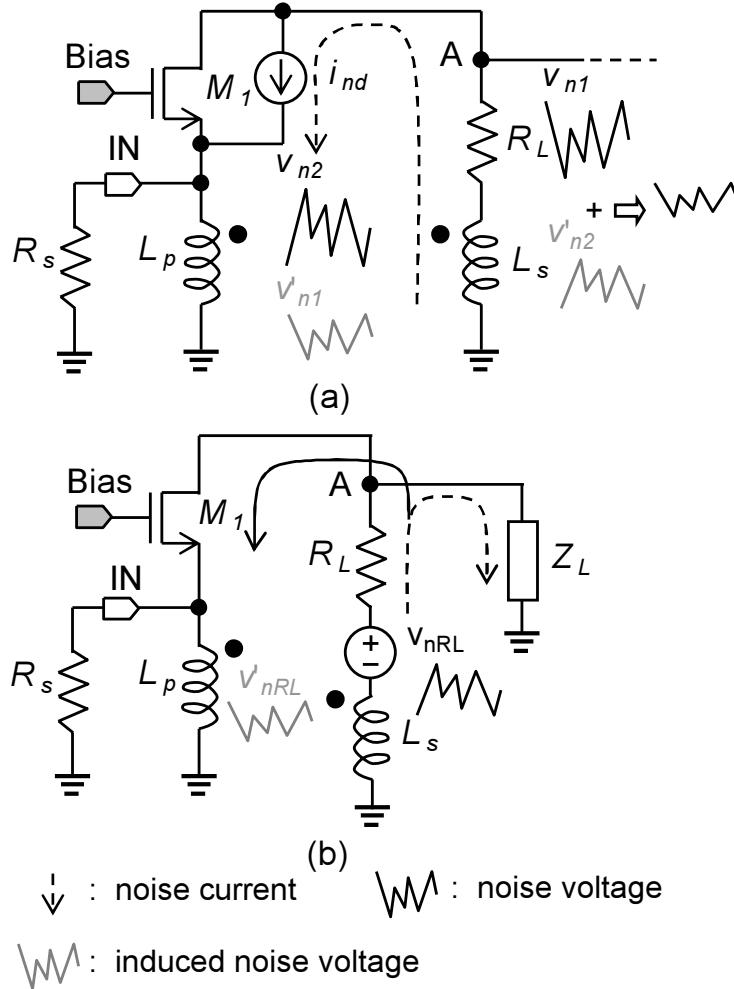

| 4.3.2    | Noise Cancellation . . . . .                    | 64        |

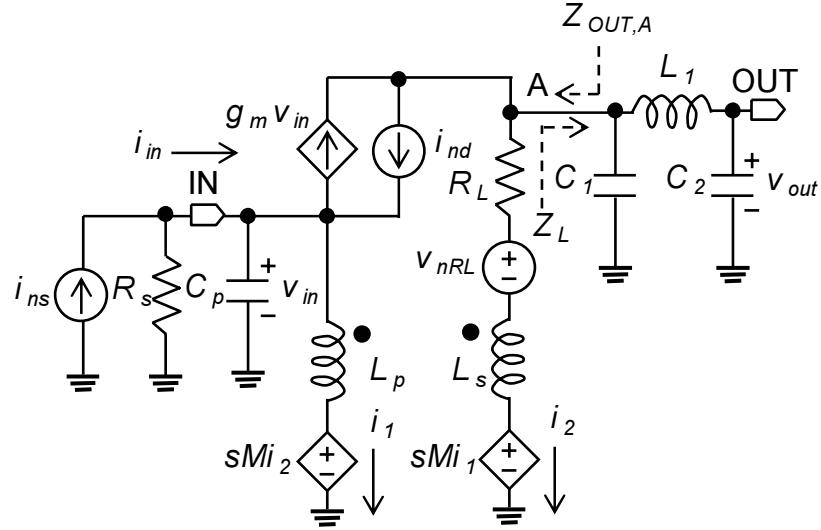

| 4.4      | Circuit Analysis . . . . .                      | 67        |

| 4.4.1    | Noise . . . . .                                 | 67        |

| 4.4.2    | Input Impedance Matching . . . . .              | 69        |

| 4.4.3    | Gain . . . . .                                  | 74        |

| 4.4.4    | Stability . . . . .                             | 75        |

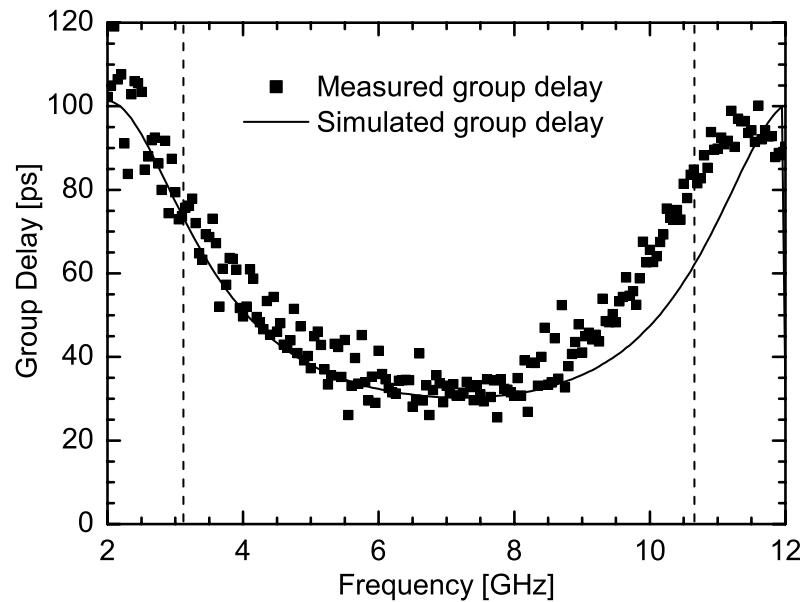

| 4.4.5    | Group Delay . . . . .                           | 78        |

| 4.5      | Design . . . . .                                | 78        |

| 4.5.1    | Input Transistor and Load Resistor . . . . .    | 78        |

| 4.5.2    | Transformer . . . . .                           | 78        |

| 4.5.3    | Output Series Inductor . . . . .                | 80        |

| 4.6      | Experimental Results and Discussion . . . . .   | 81        |

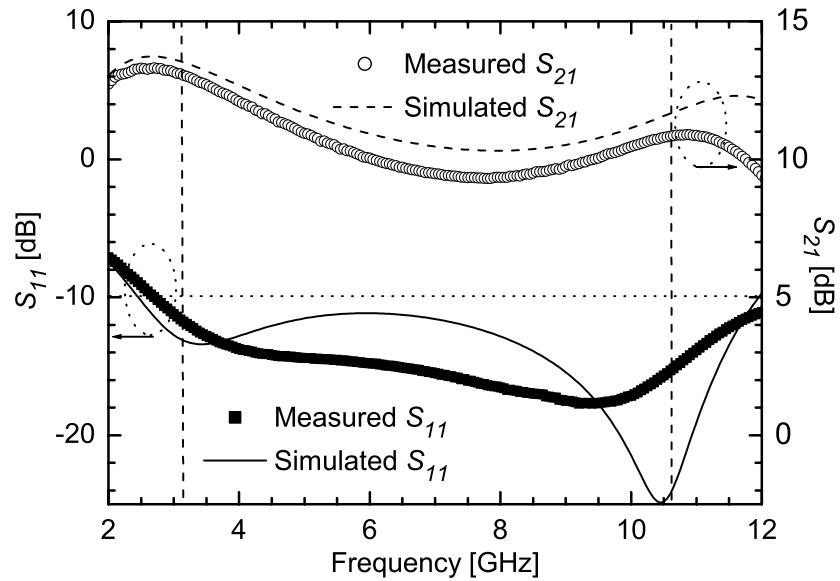

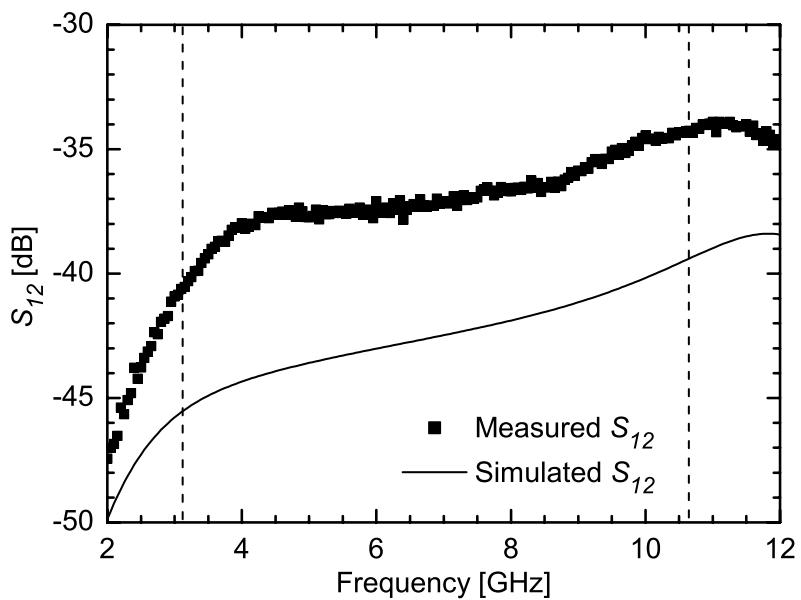

| 4.6.1    | S-parameters . . . . .                          | 83        |

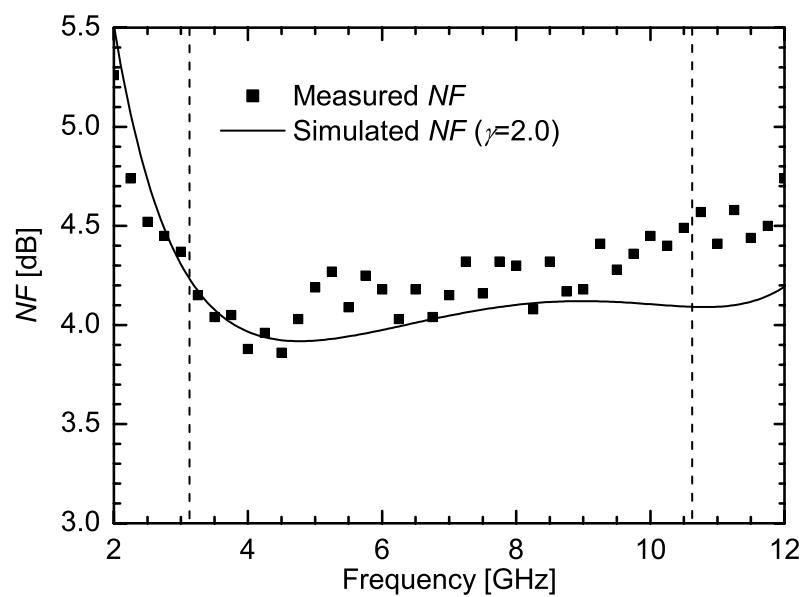

| 4.6.2    | NF . . . . .                                    | 83        |

| 4.6.3    | Linearity . . . . .                             | 83        |

| 4.6.4    | Comparison . . . . .                            | 87        |

| 4.7      | Conclusion . . . . .                            | 87        |

|          | Bibliography . . . . .                          | 90        |

| <b>5</b> | <b>Conclusion</b>                               | <b>93</b> |

---

|          |                                                                       |            |

|----------|-----------------------------------------------------------------------|------------|

| <b>A</b> | <b>NF Derivations</b>                                                 | <b>95</b>  |

| A.1      | Two-Stage LNA . . . . .                                               | 95         |

| A.1.1    | $F_{M_1}$ . . . . .                                                   | 96         |

| A.1.2    | $F_{M_2}$ . . . . .                                                   | 97         |

| A.1.3    | $F_{R_I}$ and $F_{R_L}$ . . . . .                                     | 98         |

| A.2      | Transformer Folded-Cascode LNA . . . . .                              | 99         |

| A.2.1    | $F_{M_1}$ . . . . .                                                   | 100        |

| A.2.2    | $F_{M_2}$ . . . . .                                                   | 101        |

| A.2.3    | $F_{L_I}$ and $F_{L_L}$ . . . . .                                     | 102        |

|          | Bibliography . . . . .                                                | 103        |

| <b>B</b> | <b>Frequency Responses of <math>Y_I</math> and <math>1/Y_I</math></b> | <b>105</b> |

| B.1      | $Y_I$ . . . . .                                                       | 105        |

| B.2      | $1/Y_I$ . . . . .                                                     | 105        |

|          | <b>Achievements</b>                                                   | <b>107</b> |

# List of Figures

|      |                                                                                                      |    |

|------|------------------------------------------------------------------------------------------------------|----|

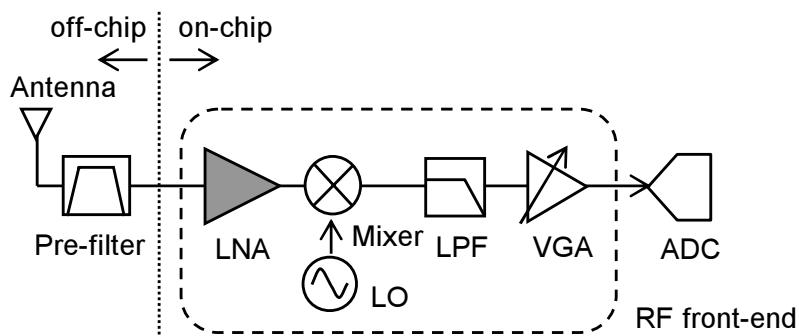

| 1.1  | Block diagram of a typical wireless receiver. . . . .                                                | 2  |

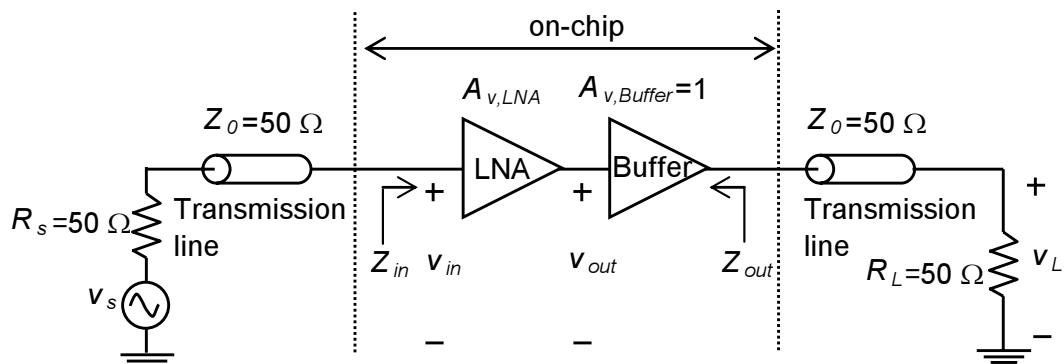

| 1.2  | LNA cascaded with a buffer for measurement. . . . .                                                  | 3  |

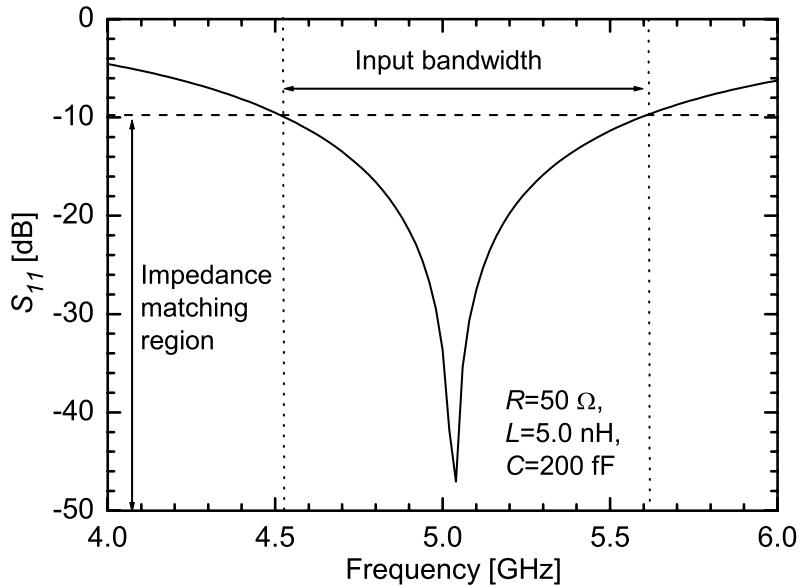

| 1.3  | Calculated $S_{11}$ for $Z_{in} = R + sL + 1/sC$ . . . . .                                           | 4  |

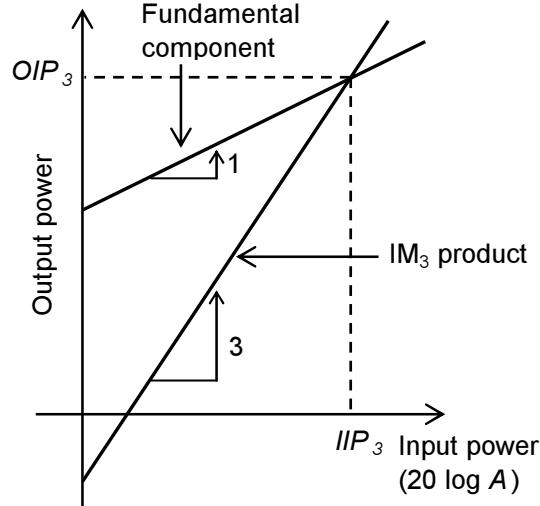

| 1.4  | Third-order intercept point. . . . .                                                                 | 7  |

| 1.5  | Stability of a two-port network. . . . .                                                             | 8  |

| 2.1  | Schematic of the cascode LNA with inductive source degeneration. . . . .                             | 12 |

| 2.2  | Small-signal equivalent circuit of the cascode LNA. . . . .                                          | 13 |

| 2.3  | Calculated $NF$ versus $W_1$ with $I_d$ as a parameter. . . . .                                      | 14 |

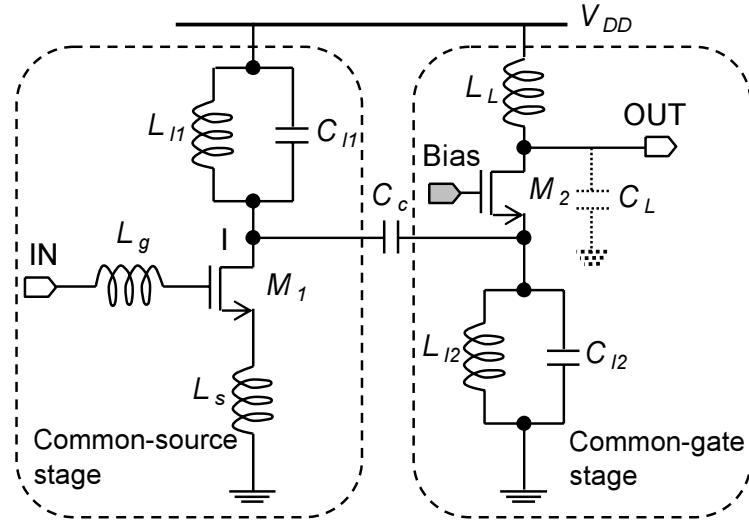

| 2.4  | Schematic of the two-stage LNA with inductive source degeneration. . . . .                           | 17 |

| 2.5  | (a) Input section of the LNA and (b) the Thevenin's equivalent circuit of the input section. . . . . | 18 |

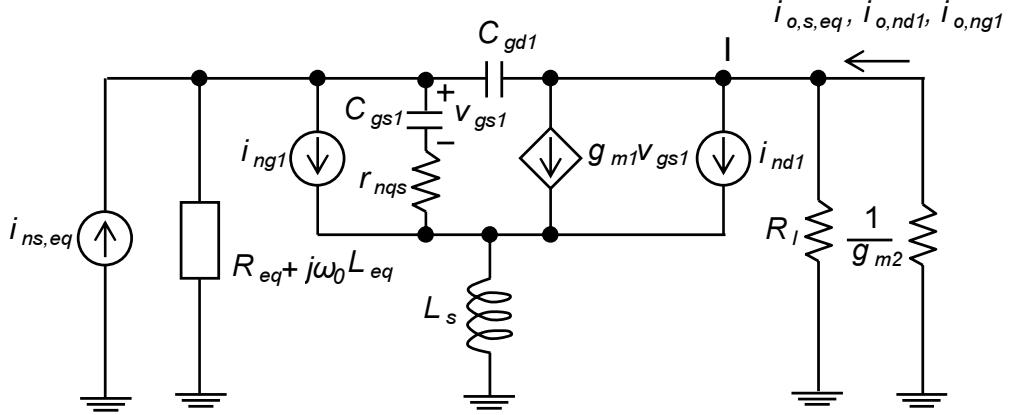

| 2.6  | Small-signal equivalent circuit of the common-source stage. . . . .                                  | 19 |

| 2.7  | Small-signal equivalent circuit of the common-gate stage. . . . .                                    | 19 |

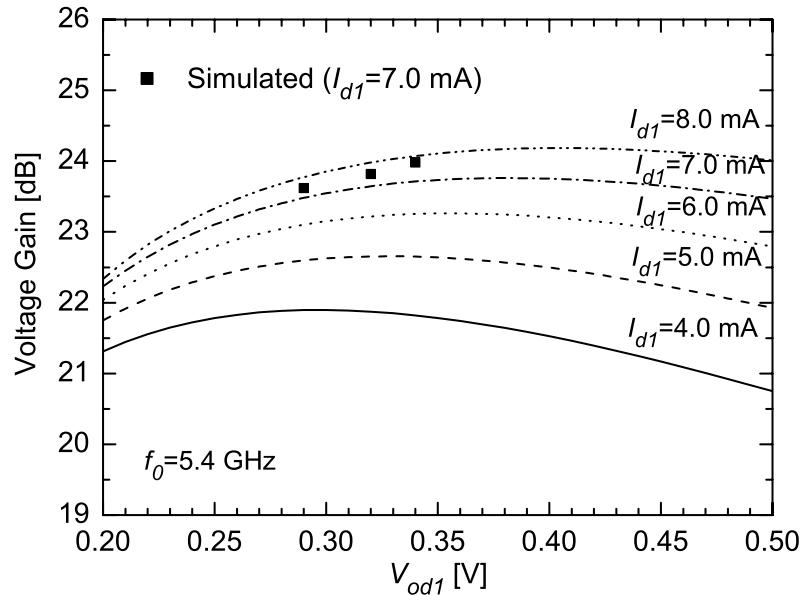

| 2.8  | Calculated and simulated voltage gain versus $V_{od1}$ with $I_{d1}$ as a parameter. . . . .         | 23 |

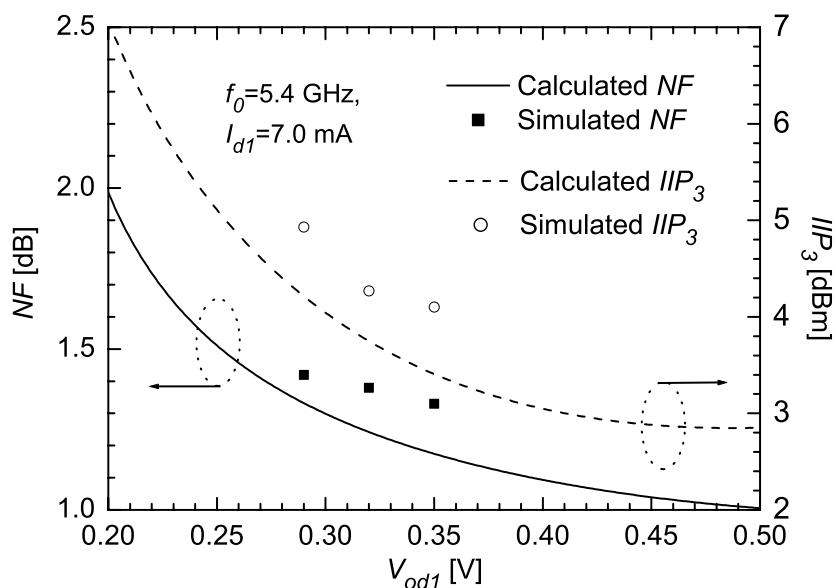

| 2.9  | Calculated and simulated $NF$ and $IIP_3$ versus $V_{od1}$ . . . . .                                 | 23 |

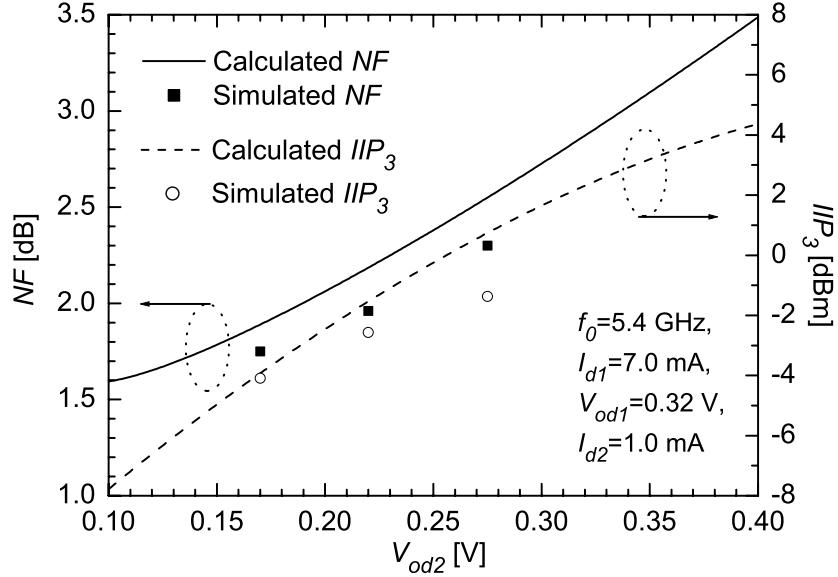

| 2.10 | Calculated and simulated $NF$ and $IIP_3$ versus $V_{od2}$ . . . . .                                 | 24 |

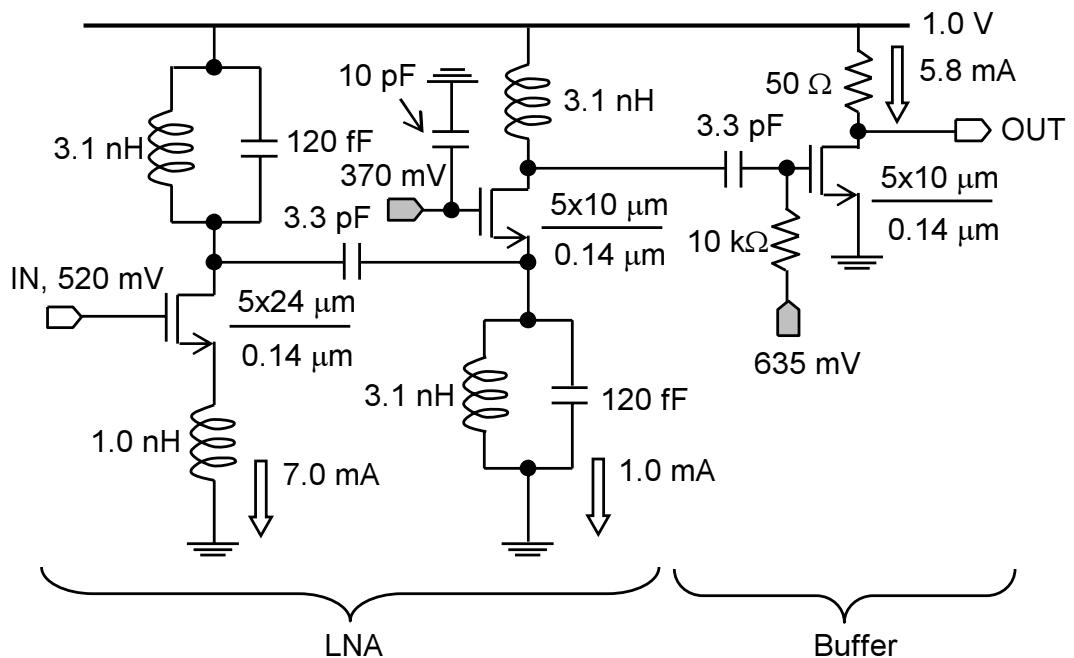

| 2.11 | Complete schematic of the designed two-stage LNA. . . . .                                            | 26 |

| 2.12 | Micrograph of the fabricated LNA. . . . .                                                            | 26 |

| 2.13 | Measured and simulated $L$ of the fabricated 3.1 nH inductor. . . . .                                | 28 |

| 2.14 | Measured and simulated $Q$ of the fabricated 3.1 nH inductor. . . . .                                | 28 |

| 2.15 | Measured and simulated $S_{11}$ and $S_{21}$ of the LNA. . . . .                                     | 29 |

| 2.16 | Measured and simulated $S_{12}$ and $S_{22}$ of the LNA. . . . .                                     | 29 |

| 2.17 | Measured and simulated $NF$ of the LNA. . . . .                                                      | 30 |

| 2.18 | Measured $IIP_3$ of the LNA with the buffer. . . . .                                                 | 30 |

| 2.19 | Measured $IIP_3$ of the stand-alone buffer. . . . .                                                  | 31 |

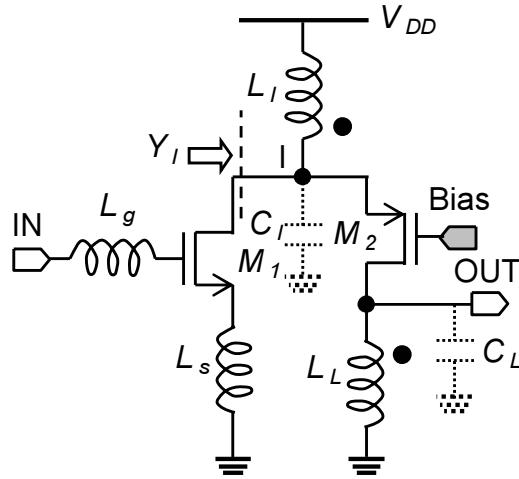

| 3.1  | Schematic of the proposed LNA. . . . .                                                               | 38 |

| 3.2  | Small-signal equivalent circuit of the input stage. . . . .                                          | 40 |

| 3.3  | Small-signal equivalent circuit of the common-gate stage. . . . .                                    | 40 |

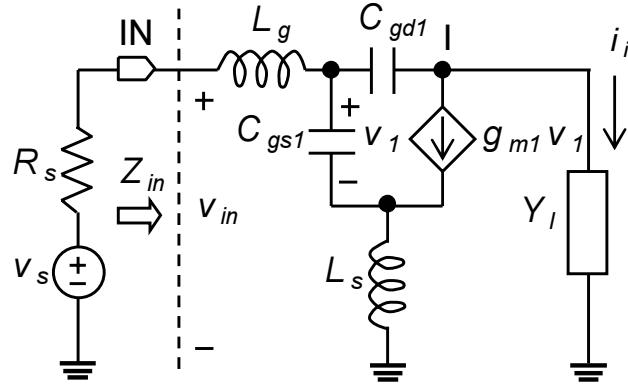

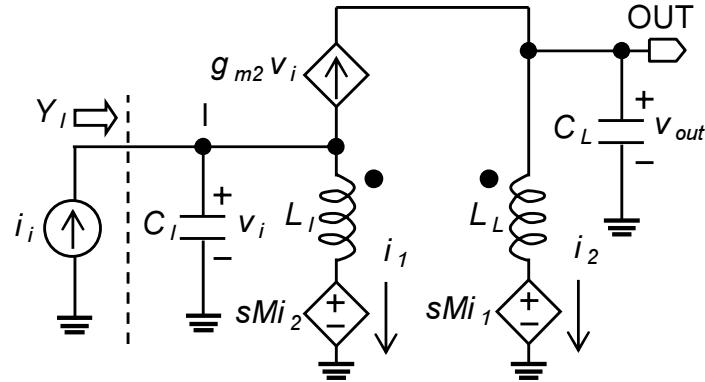

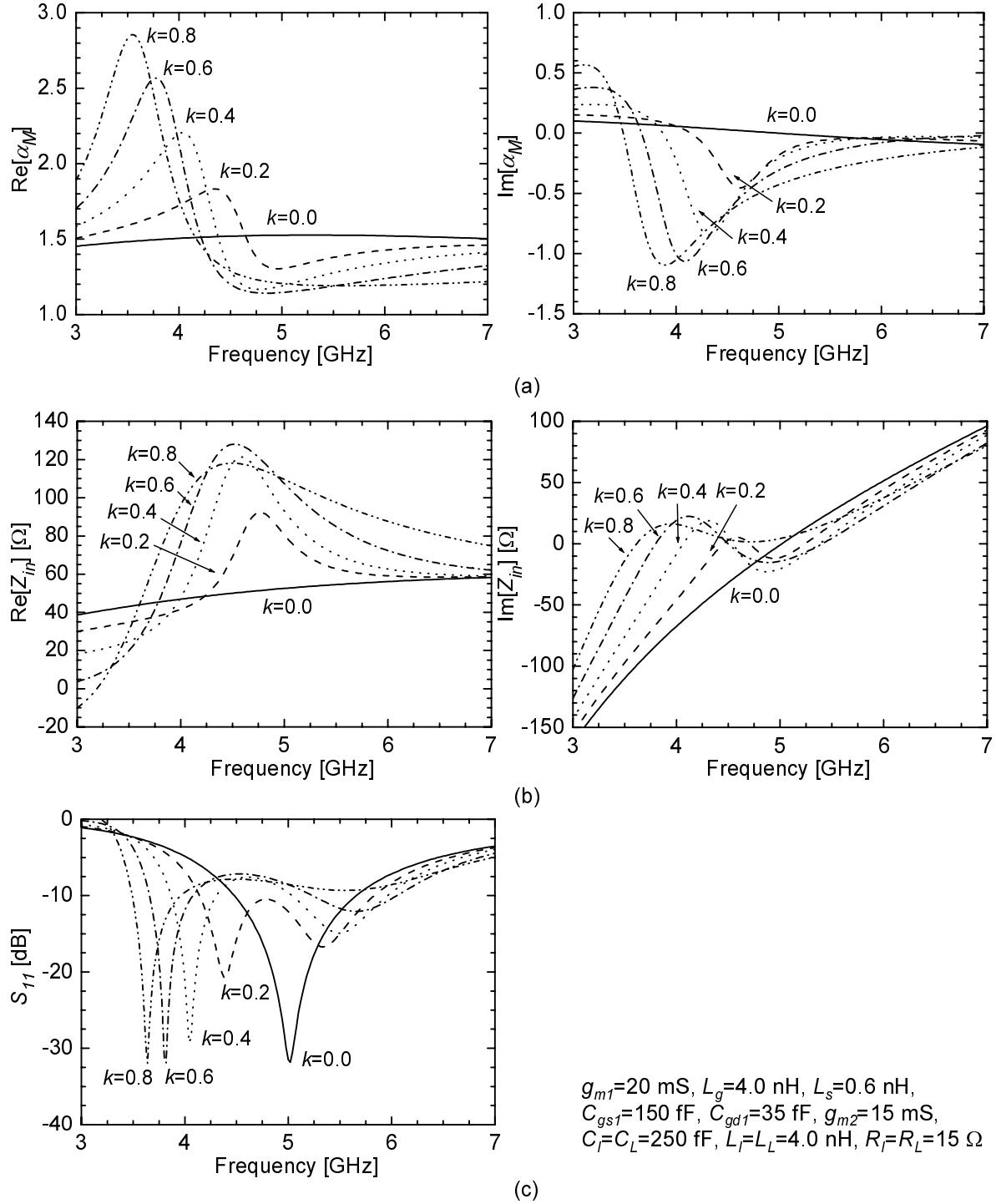

| 3.4  | Calculated (a) $\alpha_M$ , (b) $Z_{in}$ , and (c) $S_{11}$ with $k$ as a parameter. . . . .         | 41 |

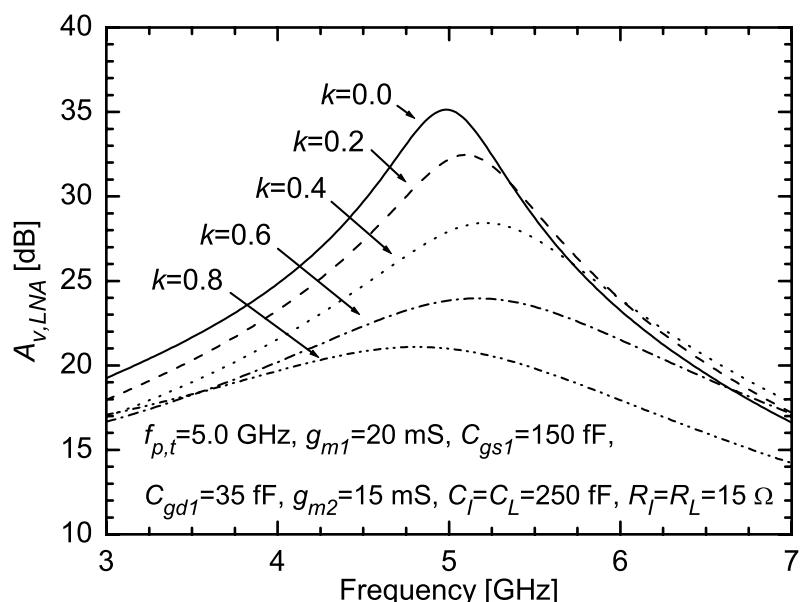

| 3.5  | Calculated voltage gain with $k$ as a parameter. . . . .                                             | 44 |

---

|      |                                                                                                                                                 |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.6  | Calculated voltage gain with $k$ as a parameter for $L_L = L_I = 1/\omega_{p,t}^2(1+k)C_L$ . . . . .                                            | 44 |

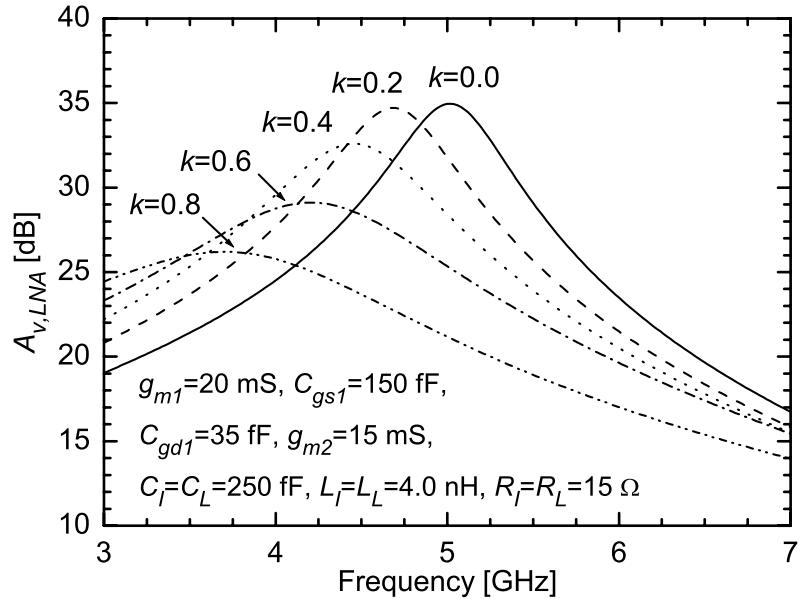

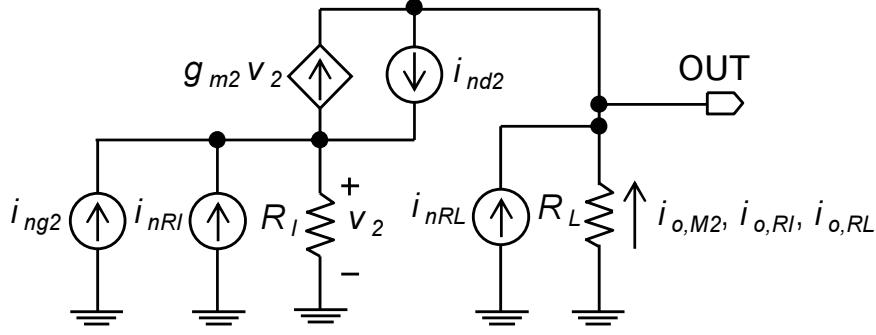

| 3.7  | Mechanisms for noise reduction of $i_{nd2}$ . . . . .                                                                                           | 45 |

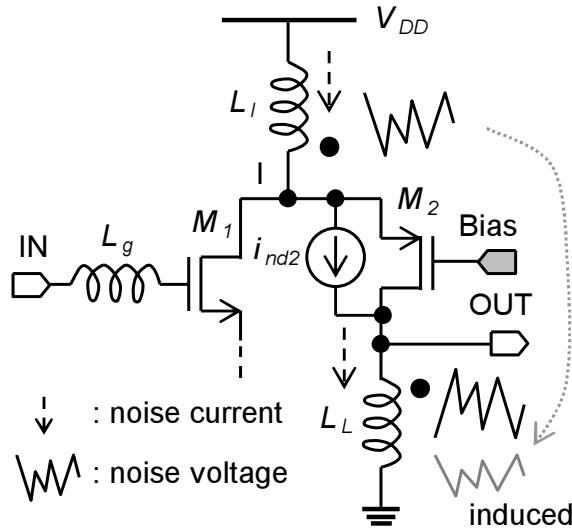

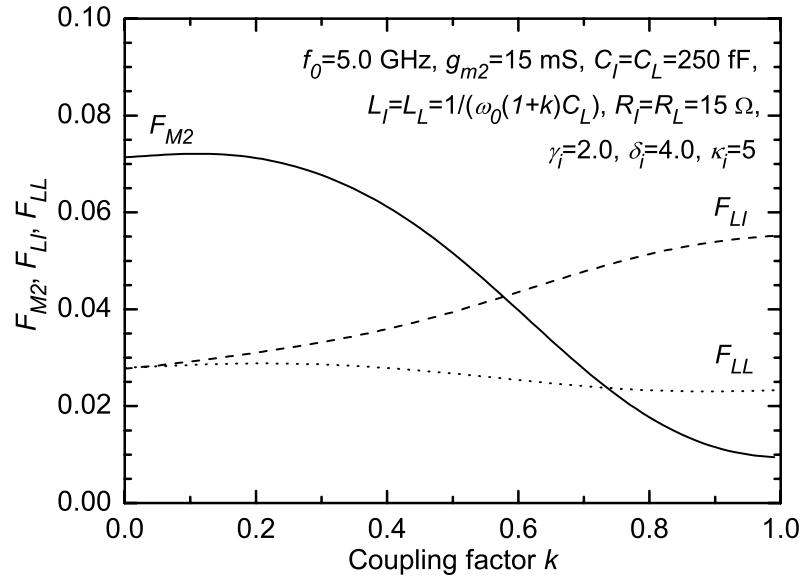

| 3.8  | Calculated $F_{M_2}$ , $F_{R_I}$ , and $F_{R_L}$ versus $k$ . . . . .                                                                           | 46 |

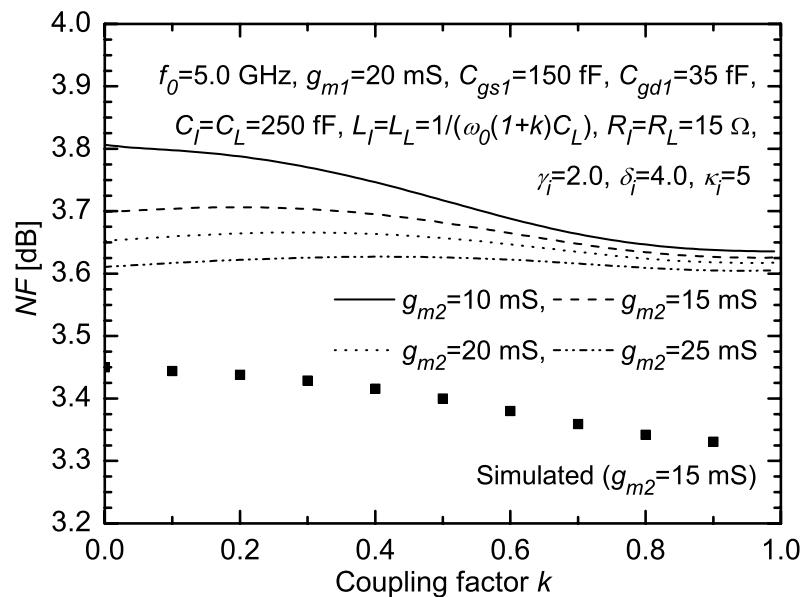

| 3.9  | Calculated and simulated $NF$ versus $k$ . . . . .                                                                                              | 46 |

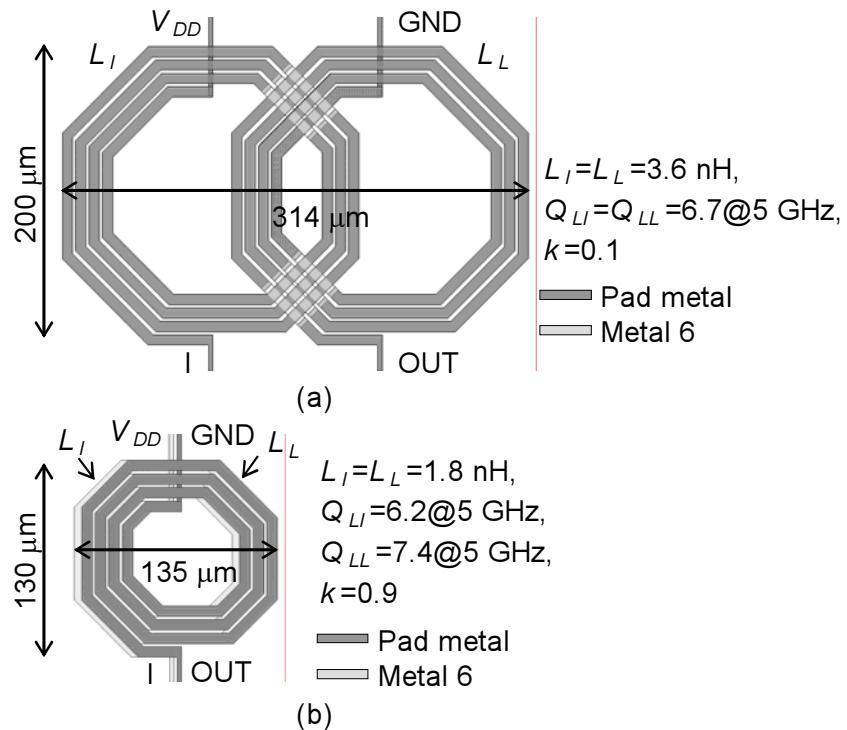

| 3.10 | Layout of (a) a partially-coupled transformer and (b) a stacked transformer. . . . .                                                            | 49 |

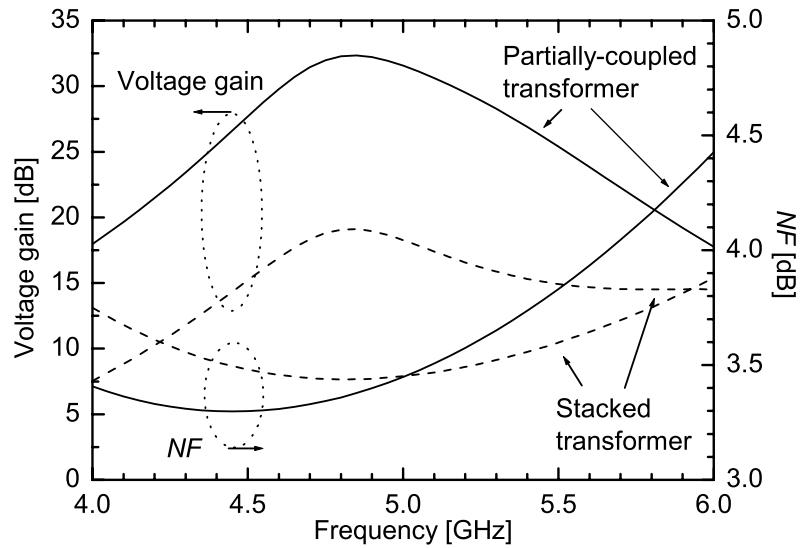

| 3.11 | Simulated voltage gain and $NF$ of LNAs employing the partially-coupled transformer (solid line) and stacked transformer (dashed line). . . . . | 49 |

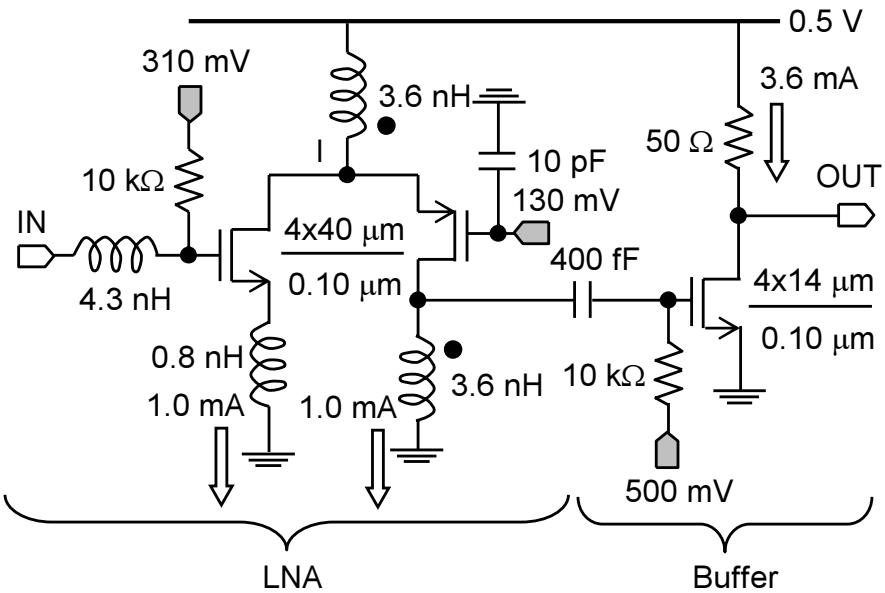

| 3.12 | Complete schematic of the designed transformer folded-cascode LNA. . . . .                                                                      | 50 |

| 3.13 | Micrograph of the proposed LNA (left) and conventional folded-cascode LNA (right). . . . .                                                      | 50 |

| 3.14 | Measured and simulated $S_{11}$ of the LNAs. . . . .                                                                                            | 52 |

| 3.15 | Measured and simulated $S_{21}$ of the LNAs. . . . .                                                                                            | 52 |

| 3.16 | Measured and simulated $S_{12}$ of the LNAs. . . . .                                                                                            | 53 |

| 3.17 | Measured and simulated $S_{22}$ of the LNAs. . . . .                                                                                            | 53 |

| 3.18 | Measured and simulated $NF$ of the LNAs. . . . .                                                                                                | 54 |

| 3.19 | Measured $IIP_3$ of the proposed LNA with the buffer. . . . .                                                                                   | 54 |

| 4.1  | UWB frequency bands . . . . .                                                                                                                   | 59 |

| 4.2  | Wideband CMOS LNAs. . . . .                                                                                                                     | 62 |

| 4.3  | Schematic of the proposed LNA. . . . .                                                                                                          | 64 |

| 4.4  | Small-signal equivalent circuit with noise sources. . . . .                                                                                     | 65 |

| 4.5  | Mechanisms for noise cancellation of (a) $i_{nd}$ and (b) $v_{nR_L}$ . . . . .                                                                  | 66 |

| 4.6  | Simulated $NF$ and $NF_{min}$ of the LNAs with and without noise cancellation ( $k = 0, 1.0$ ) . . . . .                                        | 68 |

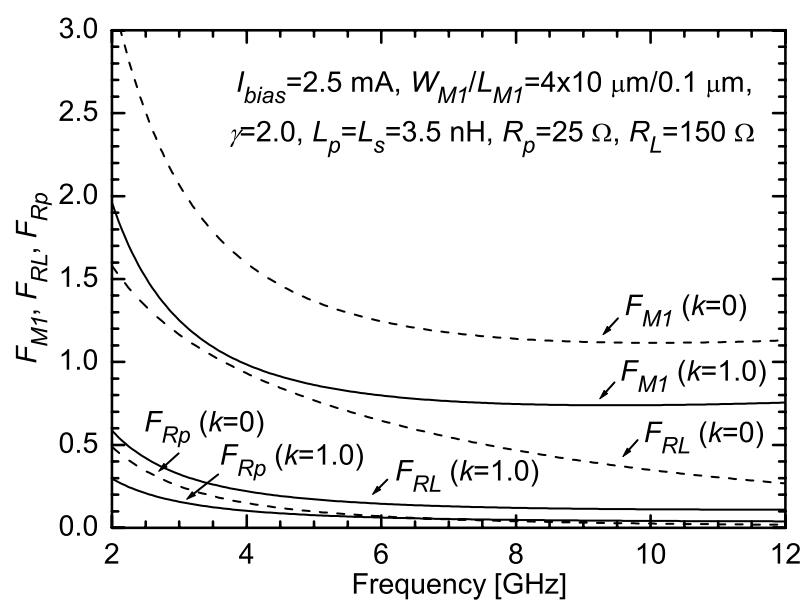

| 4.7  | Simulated noise contributions from $M_1$ , $R_L$ , and $R_p$ to the LNAs with and without noise cancellation ( $k = 0, 1.0$ ). . . . .          | 68 |

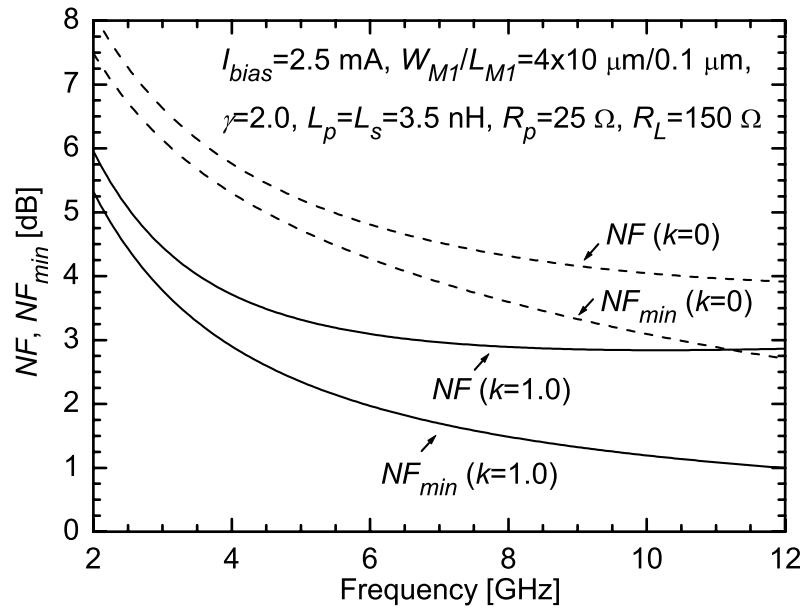

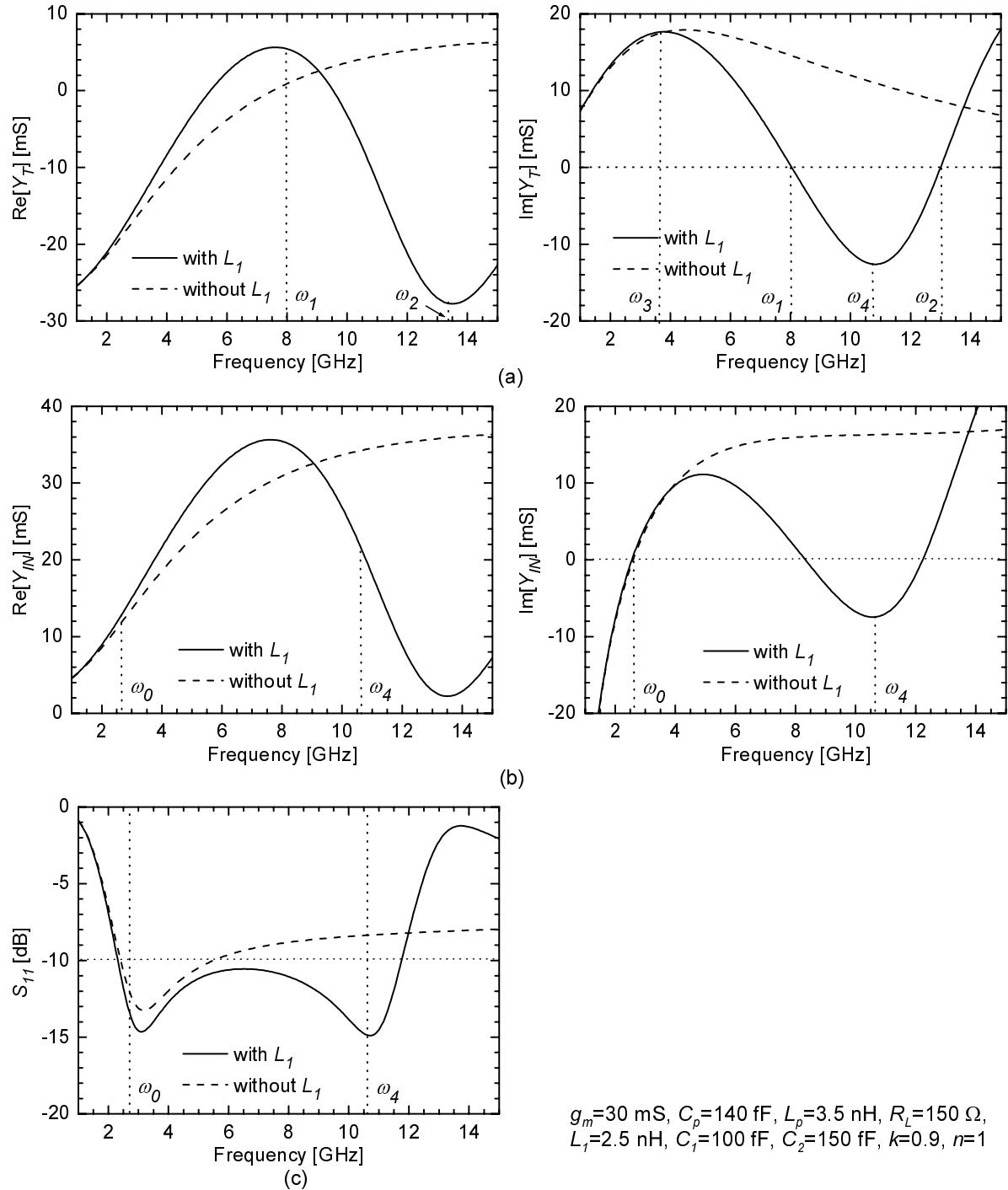

| 4.8  | Calculated (a) $F$ , $F_{M_1}$ , and $F_{R_L}$ ( $R_L = 50 \Omega$ ) versus $n$ and (b) $NF$ with $R_L$ as a parameter. . . . .                 | 70 |

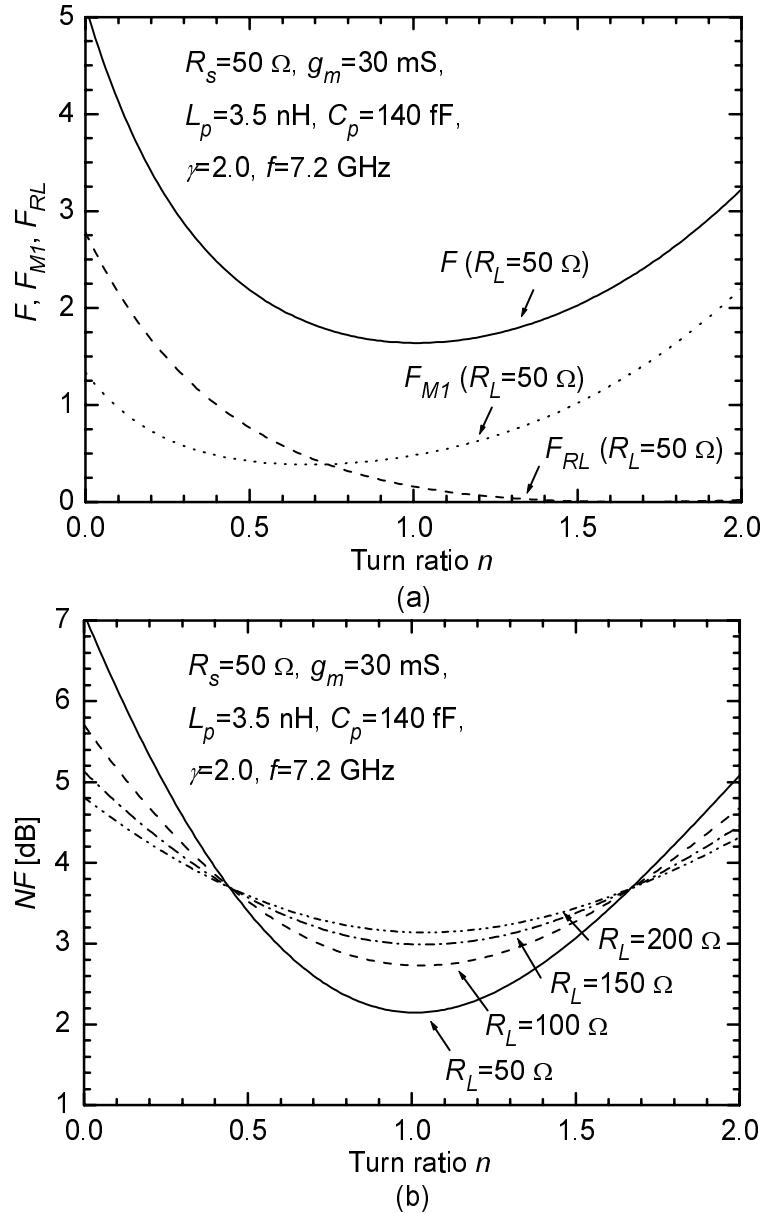

| 4.9  | Calculated real and imaginary parts of (a) $Y_T$ and (b) $Y_{IN}$ , and (c) $S_{11}$ of the LNAs with and without $L_1$ . . . . .               | 72 |

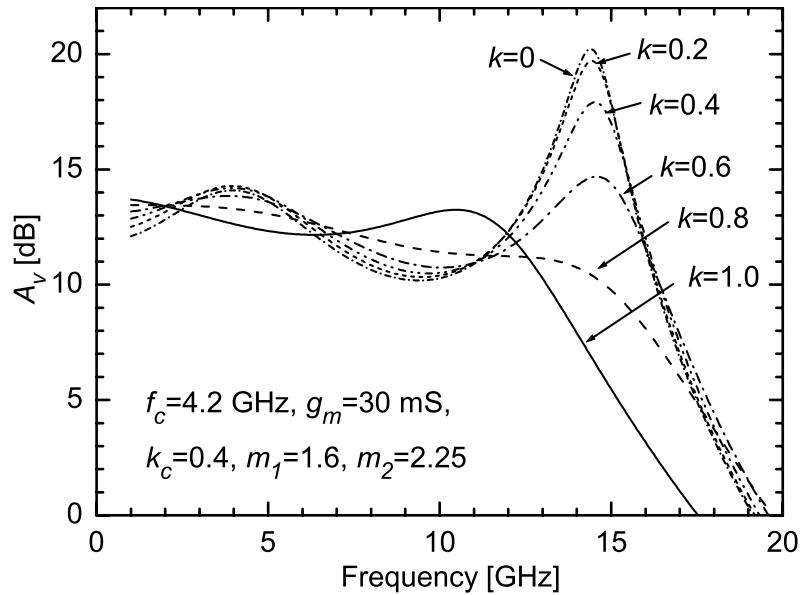

| 4.10 | Calculated $A_v$ of the proposed LNA with $k$ as a parameter. . . . .                                                                           | 76 |

| 4.11 | Calculated $A_v$ and $S_{21}$ of the proposed LNA with $k = 0.9$ . . . . .                                                                      | 76 |

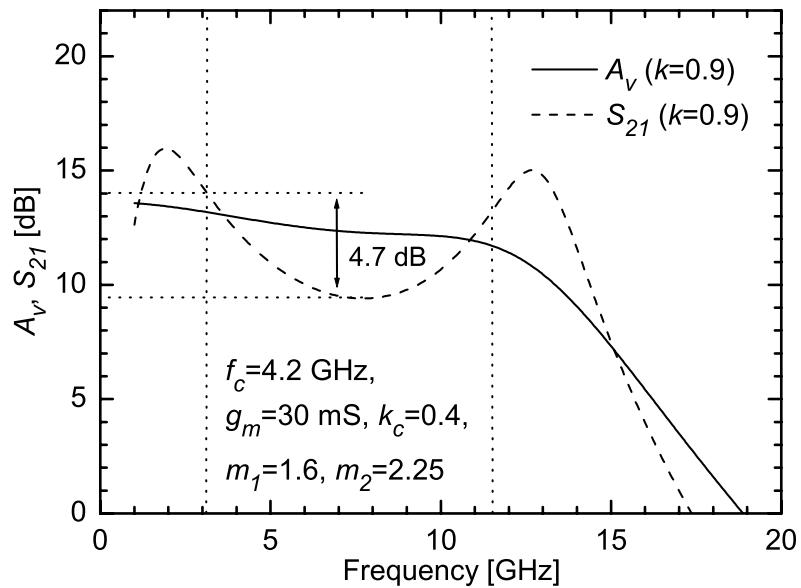

| 4.12 | Simulated $K$ and $B_1$ of the proposed LNA. . . . .                                                                                            | 77 |

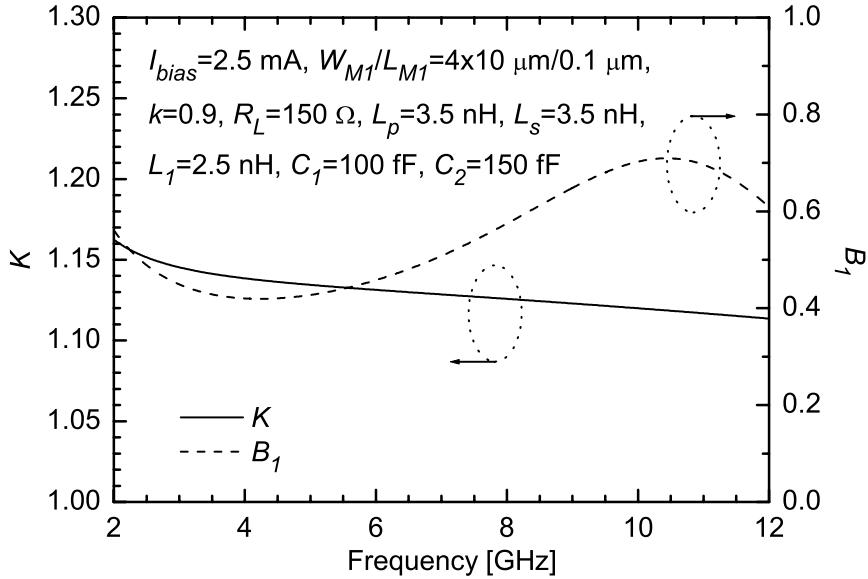

| 4.13 | Simulated group delays with (a) $L_p$ and (b) $L_1$ as a parameter. . . . .                                                                     | 79 |

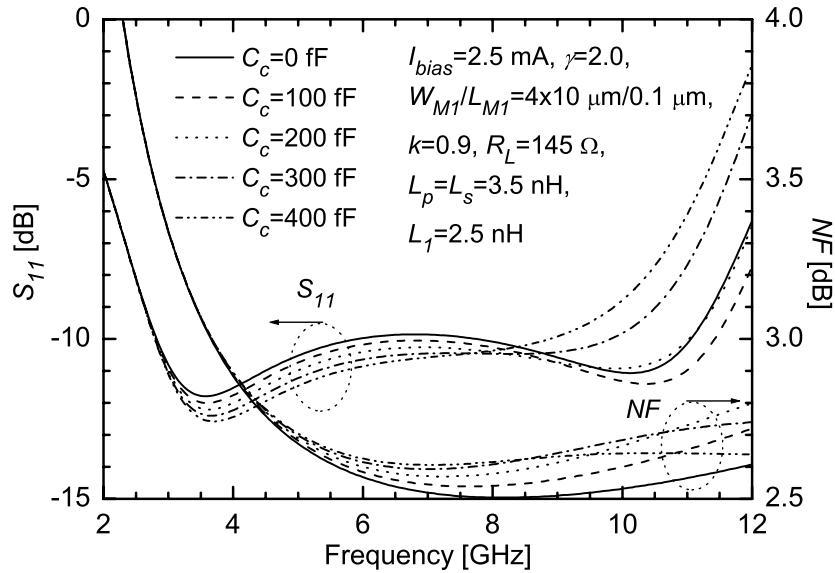

| 4.14 | Simulated $S_{11}$ and $NF$ of the LNA with $C_c$ as a parameter. . . . .                                                                       | 80 |

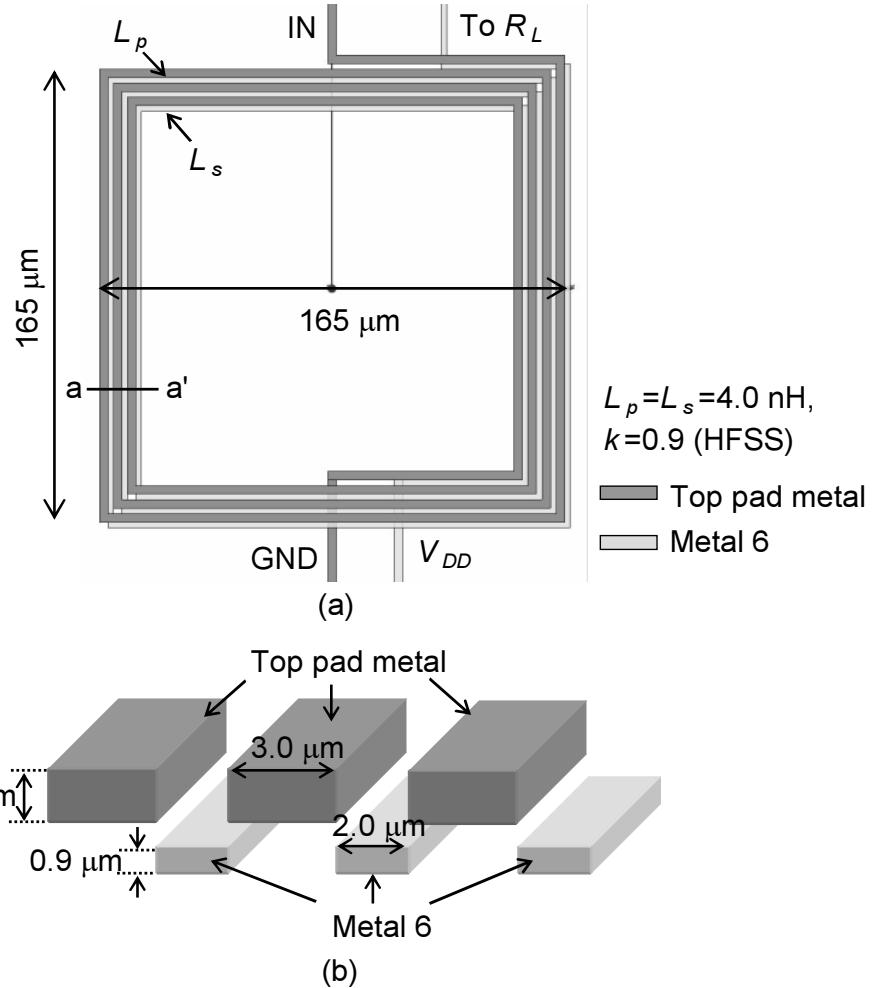

| 4.15 | (a) Top view and (b) cross section a-a' of the designed transformer. . . . .                                                                    | 81 |

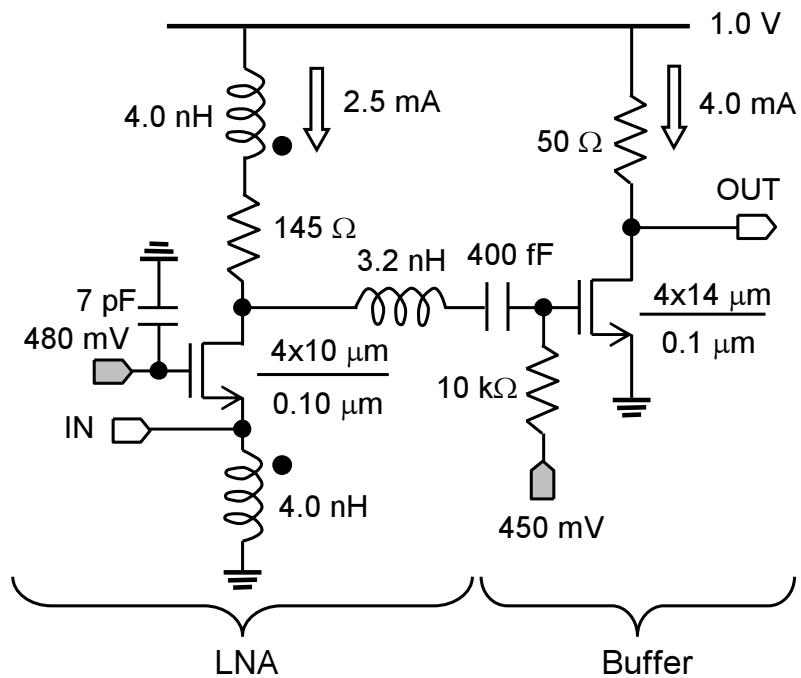

| 4.16 | Complete schematic of the designed transformer noise-canceling LNA . . . . .                                                                    | 82 |

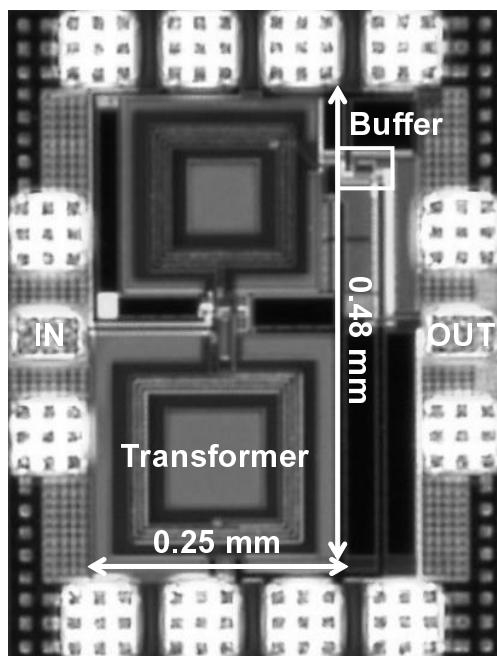

| 4.17 | Micrograph of the fabricated LNA. . . . .                                                                                                       | 82 |

| 4.18 | Measured and simulated $S_{11}$ and $S_{21}$ of the LNA. . . . .                                                                                | 84 |

| 4.19 | Measured and simulated $S_{12}$ of the LNA. . . . .                                                                                             | 84 |

| 4.20 | Measured and simulated group delays of the LNA. . . . .                                                                                         | 85 |

| 4.21 | Measured and simulated $NF$ of the LNA. . . . .                                                                                                 | 85 |

|      |                                                                                               |     |

|------|-----------------------------------------------------------------------------------------------|-----|

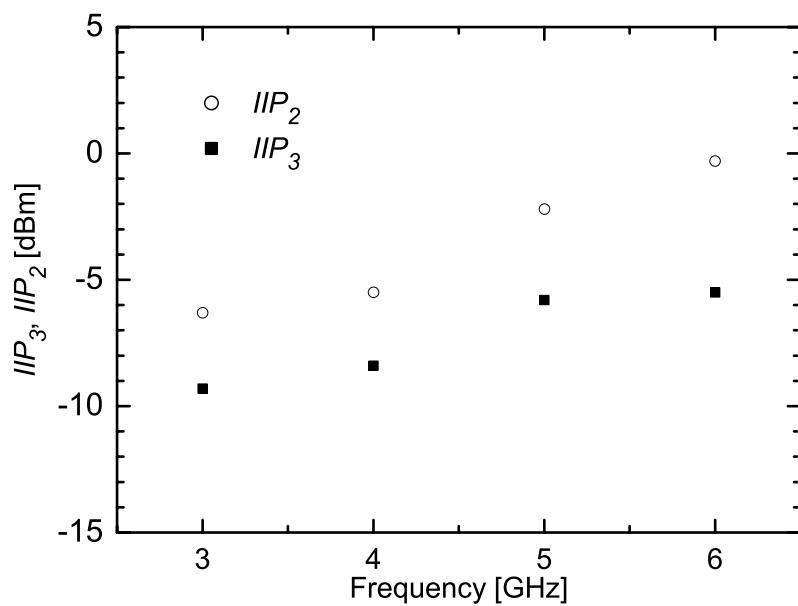

| 4.22 | Measured $IIP_3$ of the LNA at 3 GHz. . . . .                                                 | 86  |

| 4.23 | Measured $IIP_3$ and $IIP_2$ of the LNA. . . . .                                              | 86  |

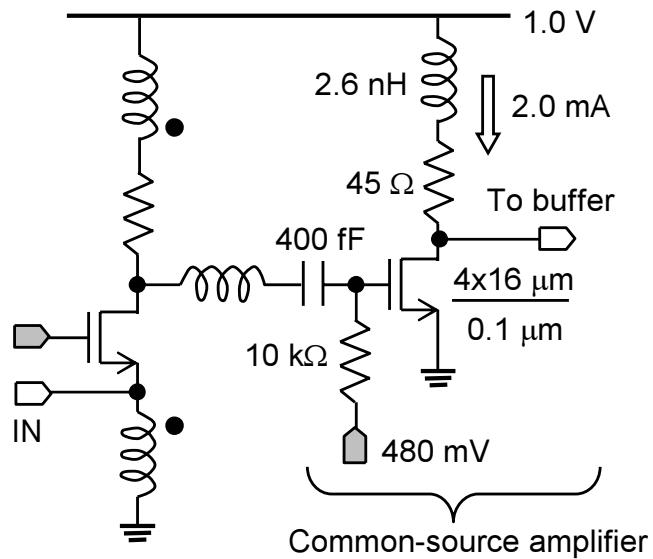

| 4.24 | Common-source amplifier with a load inductor. . . . .                                         | 89  |

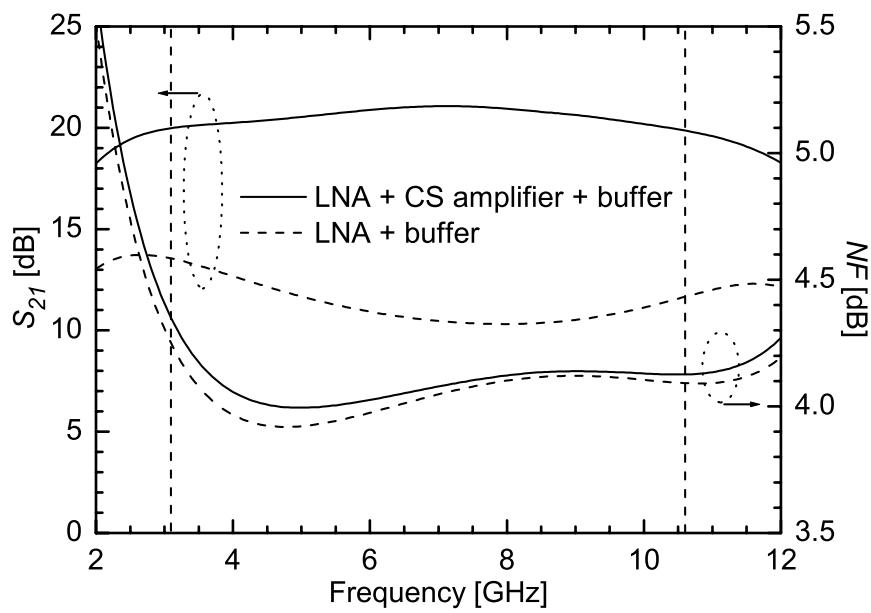

| 4.25 | Simulated $S_{21}$ and $NF$ of the LNAs with and without the common-source amplifier. . . . . | 89  |

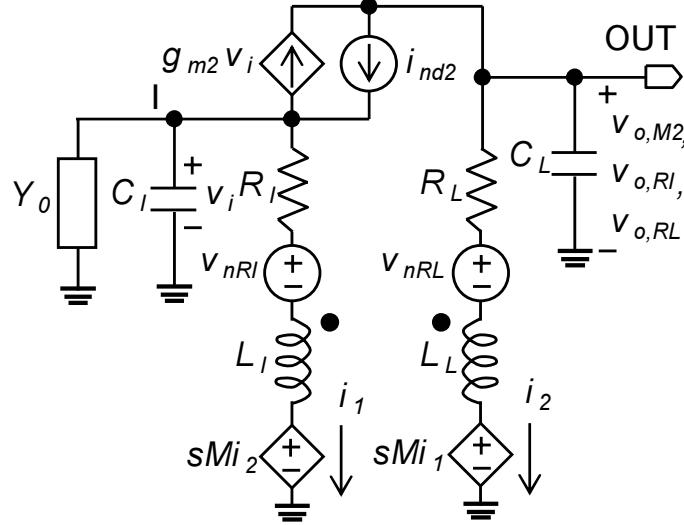

| A.1  | Noise equivalent circuit of the input stage . . . . .                                         | 96  |

| A.2  | Noise equivalent circuit of the common-gate stage . . . . .                                   | 98  |

| A.3  | Noise equivalent circuit of the input stage. . . . .                                          | 100 |

| A.4  | Noise equivalent circuit of the common-gate stage. . . . .                                    | 102 |

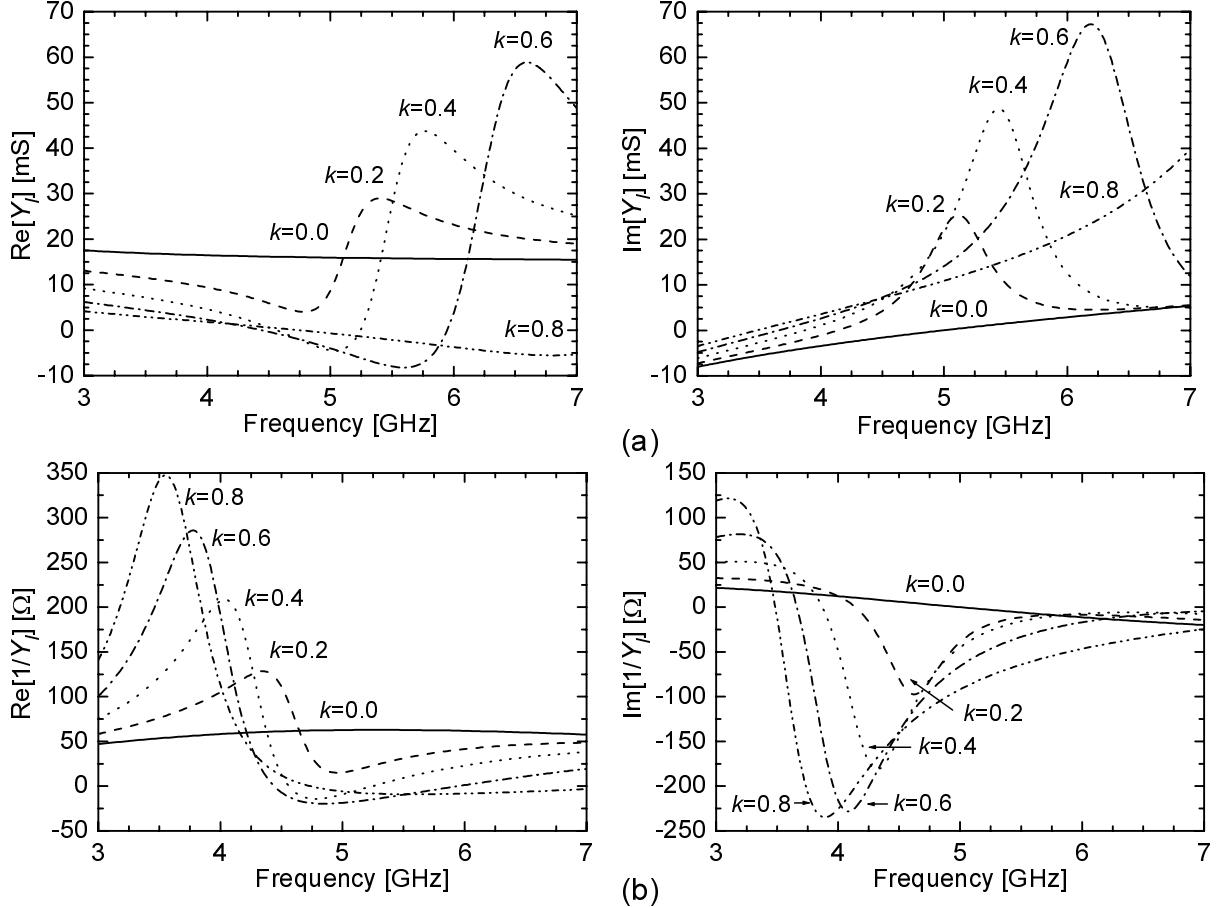

| B.1  | Calculated (a) $Y_I$ and (b) $1/Y_I$ with $k$ as a parameter. . . . .                         | 106 |

# List of Tables

|     |                                                                        |    |

|-----|------------------------------------------------------------------------|----|

| 2.1 | Specifications of LNAs for WLAN receivers. . . . .                     | 22 |

| 2.2 | Comparison of the LNA performance at 5.4 GHz. . . . .                  | 31 |

| 2.3 | Measured performance and comparison of 1.0 V, 5 GHz CMOS LNAs. . . . . | 33 |

| 3.1 | Measured performance and comparison of low-voltage CMOS LNAs. . . . .  | 56 |

| 4.1 | Measured performance and comparison of wideband CMOS LNAs. . . . .     | 88 |

# Chapter 1

## Introduction

### 1.1 Background

The high-frequency performance of metal-oxide semiconductor field-effect transistors (MOSFETs) has improved rapidly, due to advances in complementary metal-oxide-semiconductor (CMOS) process technologies [1]. This allows us to implement radio-frequency integrated circuits (RFICs) for the front-ends of wireless transceivers by using Si CMOS technologies. The Si CMOS technology has two advantages over SiGe or III-V compound semiconductor technologies, conventionally used for RFICs. First, the CMOS technology costs lower than the others, due to fewer masks layers and processing steps. For example, a  $0.13\text{ }\mu\text{m}$  CMOS process costs approximately 20% lower than a  $0.13\text{ }\mu\text{m}$  SiGe BiCMOS process [1, 2]. Second, the CMOS technology allows high integration of RF circuits with digital circuits on one chip, called system-on-a-chip (SoC), which can achieve higher performance and lower chip cost [3, 4]. Thus, CMOS implementation of RFICs is indispensable for creating low-cost and high performance wireless communication devices.

However, the scaling of MOSFETs has imposed two stringent requirements on CMOS RFICs.

One is low-voltage operation. As MOSFETs scale down, the allowable supply voltages of ICs decrease to maintain the device reliability. Reference [5] predicts that the supply voltage of low-power digital ICs will decrease to 0.5 V in 2016. Considering the integration with digital circuits, we need to design RF circuits that can operate at the same supply voltage. Most existing RF circuits, which require more than 1.0 V supplies, can not operate under such a low supply voltage. Low-voltage circuit topologies are becoming more important.

The other is small chip area or low cost. The CMOS fabrication cost has been increasing dramatically with the scaling of MOSFETs. Reference [6] shows that a 45 nm (state-of-the-art) CMOS process costs approximately 10 times as much as a  $0.13\text{ }\mu\text{m}$  (most widely used) CMOS process. The chip cost of ICs mainly depends on the chip area. The chip area of digital circuits, which mostly consist of transistors, decreases as CMOS processes scale down, and consequently the chip cost does not increase dramatically. On the other hand, the chip area of RFICs remains almost constant even with the scaling of CMOS processes, because RF circuits require many pas-

sive components such as inductors, capacitors, and transmission lines. They shrink very slowly compared to transistors. Thus, the small-area implementation of RF circuits is another important consideration when using state-of-the-art CMOS technologies.

The goal of this research is to propose and demonstrate low-voltage (1.0 V or less) and small-area (0.25 mm<sup>2</sup> or less) CMOS low-noise amplifiers (LNAs) for narrowband (5 GHz) and wideband (3.1–10.6 GHz) wireless receivers. Narrowband receivers, which have input bandwidths of less than 1 GHz, are employed in cellular phones, global positioning systems (GPS), Bluetooth systems, and wireless local area network (WLAN) systems, etc. On the other hand, wideband receivers are mainly used in ultra-wideband (UWB) systems and can be applied to multiband/multistandard systems. LNAs are essential building blocks for all wireless receivers, while they require relatively high supply voltages and large chip area (i.e., many inductors). This causes the difficulties for creating low-voltage and small-area receiver chips. In addition, the circuit topologies of narrowband LNAs are quite different from those of wideband ones, which means that different topologies suitable for each receiver are required. Low-voltage, small-area and narrowband/wideband CMOS LNAs can therefore contribute to low-voltage and low-cost wireless receivers.

## 1.2 Fundamentals of Low-Noise Amplifiers

### 1.2.1 Low-Noise Amplifier

The LNA is the first building block of RF front-ends for wireless receivers. Figure 1.1 shows a block diagram of a typical wireless receiver. The RF front-end, which consists of an LNA, mixer, local oscillator (LO), low-pass filter (LPF), and variable gain amplifier (VGA), amplifies and converts high-frequency signals into low-frequency ones with the desired signal-to-noise ratio (SNR). First, the LNA amplifies signals received by an antenna. Second, the mixer downconverts the high-frequency signals to low-frequency ones by using the LO and then the LPF filters out unwanted high-frequency components in the signals. Finally, the VGA adjusts the signal levels

Figure 1.1: Block diagram of a typical wireless receiver.

for an analog-to-digital converter (ADC). The RF front-end is usually integrated on one chip.

The LNA determines the input bandwidth and noise performance of the wireless receiver and must meet the following requirements:

- Input impedance matching — The input impedance of the LNA is set to the characteristic impedance of the transmission line (i.e.,  $Z_0 = 50 \Omega$ ) for a small input reflection coefficient and maximum power transfer.

- Sufficient gain — The LNA gain must be large enough to reduce the noise contributions from the following building blocks (mixer, LPF, and VGA) to the receiver.

- Low noise performance — The noise performance of the receiver is mainly determined by that of the LNA.

- High linearity — The maximum achievable linearity of the receiver is limited by the linearity of the LNA.

- Stability — The LNA oscillates when it has a negative input or output resistance.

## 1.2.2 Performance Metrics

LNA performance metrics for input impedance matching, noise, gain, and linearity are described in terms of an LNA with a buffer with a  $50 \Omega$  output impedance, as shown in Fig. 1.2. RF devices are generally terminated with a resistance  $R_L$  of  $50 \Omega$ , and then measured using a signal source with a resistance  $R_s$  of  $50 \Omega$ . However, the output impedances of LNAs are not designed to  $50 \Omega$  but to be high, because the LNAs need to drive capacitive inputs of on-chip mixers or additional amplifiers. This means that, in the measurement of stand-alone LNAs, the  $50 \Omega$  termination causes inaccurate measurements, in particular, lower gain measurements. For accurate measurements of LNA performance, the LNAs are usually integrated together with buffers, whose input impedances are capacitive, emulating the practical termination. In addition, the buffers have  $50 \Omega$

Figure 1.2: LNA cascaded with a buffer for measurement.

output impedances, providing output impedance matching. The effects of the buffers on the LNA performance can be ignored or de-embedded, as will be shown below.

### Input Impedance Matching

The quality of input impedance matching is evaluated by the input reflection coefficient  $S_{11}$ , given by [7]

$$S_{11} = \frac{Z_{in} - R_s}{Z_{in} + R_s}, \quad (1.1)$$

where  $Z_{in}$  is the input impedance of the LNA. Equation (1.1) indicates that the buffer has little impact on  $S_{11}$ . Figure 1.3 shows the frequency characteristic of  $S_{11}$  for  $Z_{in} = R + sL + 1/sC$ , which represents the input impedance of a typical narrowband LNA. An  $S_{11}$  of less than  $-10$  dB is generally required for input impedance matching and the frequency range is called the input bandwidth.

Figure 1.3: Calculated  $S_{11}$  for  $Z_{in} = R + sL + 1/sC$ .

### Gain

The LNA gain is measured as the forward transmission coefficient  $S_{21}$  [7]. The voltage gain of the LNA is defined as the ratio of the output voltage  $v_{out}$  to the input one  $v_{in}$ :

$$A_v \equiv \frac{v_{out}}{v_{in}}. \quad (1.2)$$

When the LNA is followed by a unity-gain buffer with  $Z_{out} = R_L$  as shown in Fig. 1.2,  $S_{21}$  can be expressed as

$$S_{21} = \frac{v_L}{v_s/2} = 2 \frac{v_{out}}{v_s}, \quad (1.3)$$

where  $v_s$  represents the signal voltage and  $v_L$  the output voltage at  $R_L$ . The input voltage of the LNA is given by

$$v_{in} = \frac{Z_{in}}{R_s + Z_{in}} v_s. \quad (1.4)$$

Substituting Eq. (1.4) into Eq. (1.3), we obtain

$$S_{21} = \frac{2Z_{in}}{R_s + Z_{in}} \frac{v_{out}}{v_{in}} = \frac{2Z_{in}}{R_s + Z_{in}} A_v, \quad (1.5)$$

which corresponds to  $A_v$  for  $Z_{in} = R_s$ . This means that, under input impedance matching condition, the  $S_{21}$  of the LNA with the unity-gain buffer equals the voltage gain of the stand-alone LNA.

### Noise Figure

The noise performance of the LNA is evaluated by the noise figure (NF), defined as  $10 \log_{10} F$ , where  $F$  is the ratio of the input  $SNR_{IN}$  to the output  $SNR_{OUT}$  [8]:

$$F \equiv \frac{SNR_{IN}}{SNR_{OUT}}. \quad (1.6)$$

Equation (1.6) indicates that NF is a measure of the degradation of the SNR. By introducing the total output noise power  $P_{n,OUT}$  and the output noise power due to the source,  $P_{n,OUT,R_s}$ , we can express Eq. (1.6) as

$$F = \frac{P_{n,OUT}}{P_{n,OUT,R_s}}, \quad (1.7)$$

which allows the NF calculations of the LNA.

The overall  $F$  of a cascaded system (i.e., receiver or LNA with a buffer) is given by the Friis formula [9]:

$$F_{all} = 1 + (F_1 - 1) + \frac{F_2 - 1}{G_p}, \quad (1.8)$$

where  $F_1$  and  $F_2$  represent the noise factor of the first and second stages, respectively, and  $G_p$  the power gain of the first stage. Equation (1.8) indicates that the noise performance of the first stage is critical to the overall noise performance of the cascaded system and the gain of the first stage reduces the noise contribution from the second stage. In the case of wireless receivers, the first stage represents an LNA, and the second stage the other building block consisting of a mixer, filter, and VGA. In the measurement of the LNA with the buffer, the LNA usually has so large gain that the influence of the buffer on NF measurements is small.

### Third-Order Intercept Point

The LNA linearity is evaluated by the third-order intercept point ( $IP_3$ ), measured from a two tone test [10]. The input-output relationship of the LNA can be approximated by

$$v_{out}(t) \approx \alpha_1 v_{in}(t) + \alpha_2 v_{in}^2(t) + \alpha_3 v_{in}^3(t). \quad (1.9)$$

Applying two tones with the same amplitude  $A$  ( $v_{in}(t) = A \cos \omega_1 t + A \cos \omega_2 t$ ) to the LNA, we obtain the output voltage as

$$\begin{aligned} v_{out}(t) = & \left( \alpha_1 + \frac{9}{4} \alpha_3 A^2 \right) A \cos \omega_1 t + \left( \alpha_1 + \frac{9}{4} \alpha_3 A^2 \right) A \cos \omega_2 t \\ & + \frac{3}{4} \alpha_3 A^3 \cos(2\omega_1 - \omega_2) t + \frac{3}{4} \alpha_3 A^3 \cos(2\omega_2 - \omega_1) t + \dots \end{aligned} \quad (1.10)$$

The components at  $2\omega_1 - \omega_2$  and  $2\omega_2 - \omega_1$  are called third-order intermodulation ( $IM_3$ ) products and appear in the vicinity of  $\omega_1$  and  $\omega_2$  for  $\omega_1 \simeq \omega_2$ . The fundamental component and  $IM_3$  product are plotted versus the input on a logarithmic scale as shown in Fig. 1.4. The  $IM_3$  products increase with the slope of three, whereas the fundamental components increase with the slope of one. The intersection of the two lines is  $IP_3$ , and the horizontal and vertical coordinates of  $IP_3$  are called the input  $IP_3$  ( $IIP_3$ ) and output  $IP_3$  ( $OIP_3$ ), respectively. At the  $IP_3$ , the fundamental components have the same amplitude as the  $IM_3$  products:

$$|\alpha_1| A_{IIP_3} = \frac{3}{4} |\alpha_3| A_{IIP_3}^3, \quad (1.11)$$

where  $9\alpha_3 A^2/4$  is ignored against  $\alpha_1$ . The  $IIP_3$  is thus given by

$$A_{IIP_3} = \sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|}, \quad (1.12)$$

and the  $OIP_3$  is equal to  $\alpha_1 A_{IIP_3}$ . The  $IIP_3$  expressed in power is as follows:

$$P_{IIP_3} = \frac{A_{IIP_3}^2}{2R_s}, \quad (1.13)$$

which we will simply express as  $IIP_3$ .

The  $A_{IIP_3}$  of a cascaded system is approximated as [10]

$$\frac{1}{A_{IIP_3}^2} \approx \frac{1}{A_{1,IIP_3}^2} + \frac{A_{v1}^2}{A_{2,IIP_3}^2}, \quad (1.14)$$

where  $A_{1,IIP_3}$  and  $A_{2,IIP_3}$  represent the  $A_{IIP_3}$  of the first and second stages, respectively, and  $A_{v1}$  the voltage gain of the first stage. Equation (1.14) indicates that the achievable maximum linearity of the cascaded system is limited by the first stage and the nonlinearity of the second stage become significant when the gain of the first stage is large. In the measurement of the LNA with the buffer, the  $IIP_3$  without the effect of the buffer can be calculated from Eq. (1.14).

Figure 1.4: Third-order intercept point.

## Stability

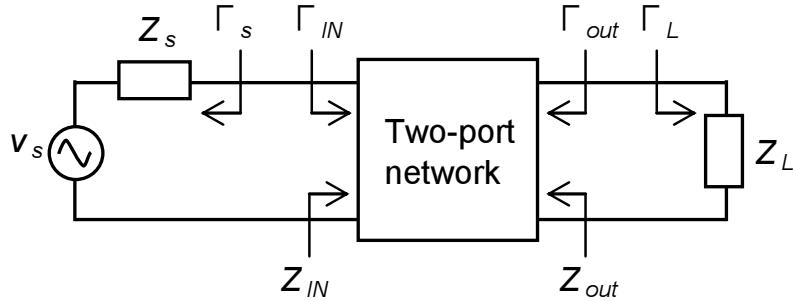

A two-port network like an LNA oscillates when either the input or output port presents a negative resistance. The two-port is unconditionally stable when it meets the following conditions [7]:

$$|\Gamma_s| < 1, \quad (1.15)$$

$$|\Gamma_L| < 1, \quad (1.16)$$

$$|\Gamma_{IN}| = \left| S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L} \right| < 1, \quad (1.17)$$

$$|\Gamma_{OUT}| = \left| S_{22} + \frac{S_{12}S_{21}\Gamma_s}{1 - S_{11}\Gamma_s} \right| < 1, \quad (1.18)$$

where  $\Gamma_s$ ,  $\Gamma_{IN}$ ,  $\Gamma_L$ , and  $\Gamma_{OUT}$  represent the source, input, load, and output reflection coefficients, respectively, as shown in Fig. 1.5. Equations (1.15)–(1.18) state that the real parts of the input and output impedances must be positive [7]:

$$\operatorname{Re}[Z_{IN}] > 0, \quad (1.19)$$

$$\operatorname{Re}[Z_{OUT}] > 0. \quad (1.20)$$

The unconditional stability of the two-port can be evaluated by other parameters:  $K$  and  $B_1$ , given by [7]

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}S_{21}|}, \quad (1.21)$$

$$B_1 = 1 + |S_{11}|^2 - |S_{22}|^2 - |\Delta|^2, \quad (1.22)$$

Figure 1.5: Stability of a two-port network.

respectively, where  $\Delta = S_{11}S_{22} - S_{12}S_{21}$ . The necessary and sufficient conditions for unconditional stability are  $K > 1$  and  $B_1 > 0$ .

### 1.3 Outline of This Dissertation

This dissertation proposes and demonstrates low-voltage and small-area CMOS LNAs for narrowband and wideband wireless receivers. The dissertation is organized as follows.

Chapter 2 presents a 1.0 V two-stage CMOS LNA with inductive source degeneration for 5 GHz applications. Complete analytical expressions of the LNA performance are derived, and then the design methodology based on the derived expressions are presented.

Chapter 3 presents a 0.5 V, 5 GHz area-efficient transformer folded-cascode CMOS LNA, which consumes much smaller chip area than the two-stage CMOS LNA presented in Chapter 2. The transformer reduces the chip area of a conventional folded-cascode CMOS LNA, but affects the LNA performance. The effects of the transformer are analyzed, and a transformer structure that has a small impact on the LNA performance are presented.

Chapter 4 presents a 1.0 V transformer noise-cancelling CMOS LNA for fullband UWB (3.1–10.6 GHz) applications. The transformer partly cancels the noise originating from the transistor and load resistor, thereby improving the LNA noise performance without increased chip area and power consumption. The noise cancellation mechanisms are described and a wideband impedance matching technique is also presented.

Chapter 5 concludes the dissertation.

### Bibliography

- [1] H. S. Bennett, R. Brederlow, J. C. Costa, P. E. Cottrell, W. M. Huang, J. Anthony A. Immorlica, J.-E. Mueller, M. Racanelli, H. Shichijo, C. E. Weitzel, and B. Zhao, “Device and technology evolution for Si-based RF integrated circuits,” *IEEE Trans. Electron Devices*, vol. 52, no. 7, pp. 1235–1258, Jul. 2005.

- [2] J. Pekarik, D. Geenberg, B. Jagannathan, R. Groves, J. R. Jones, R. Singh, A. Chinthakindi, X. Wang, M. Breitwisch, D. Coolbaugh, P. Coorell, J. Florky, G. Freeman, and R. Krishnasamy, "RFCMOS technology from  $0.25\mu\text{m}$  to 65nm: The state of the art," in *Proc. IEEE Custom Integrated Circuits Conf.*, San Francisco, CA, Sep. 2004, pp. 217–224.

- [3] M. Hammes, C. Kranz, D. Seippel, J. Kissing, and A. Leyk, "Evolution on SoC integration: GSM baseband-radio in  $0.13\mu\text{m}$  CMOS extended by fully integrated power management unit," *IEEE J. Solid-State Circuits*, vol. 43, no. 1, pp. 236–245, Jan. 2008.

- [4] A. Afsahi, J. J. Rael, A. Behzad, H.-M. Chien, M. Pan, S. Au, A. Ojo, C. P. Lee, S. B. Anand, K. Chien, S. Wu, R. Roufoogaran, A. Zolfaghari, J. C. Leete, T. Long, K. A. Carter, M. Nariman, K.-K. Yeung, W. Morton, M. Gonikberg, M. Seth, M. Forbes, J. Pattin, L. Gutierrez, S. Ranganathan, L. Ning, E. Blecker, J. Lin, T. Kwan, R. Zhu, M. Chambers, M. Rofougaran, A. Rofougaran, J. Trachewsky, and P. V. Rooyen, "A low-power single-weight-combiner 802.11abg SoC in  $0.13\mu\text{m}$  CMOS for embedded applications utilizing an area and power efficient Cartesian phase shifter and mixer circuit," *IEEE J. Solid-State Circuits*, vol. 43, no. 5, pp. 1101–1118, May 2008.

- [5] International Roadmap Committee. (2008) International technology roadmap for semiconductors 2007 edition. [Online]. Available: <http://www.itrs.net>

- [6] H. Tsuchikawa, M. Takakuwa, and S. Sugatani, "Electron beam direct writing technology combined with silicon shuttle service," in *4th ISMI Symp. on Manufacturing Effectiveness*, Austin, TX, Oct. 2007.

- [7] G. Gonzalez, *Microwave Transistor Amplifiers*, 2nd ed. Upper Saddle River, NJ: Prentice Hall, 1997.

- [8] T. H. Lee, *The Design of CMOS Radio-Frequency Integrated Circuits*, 2nd ed. Cambridge: Cambridge University Press, 2004.

- [9] H. T. Friis, "Noise figures of radio receivers," *Proc. IRE*, vol. 32, no. 7, pp. 419–422, Jul. 1944.

- [10] B. Razavi, *RF Microelectronics*. Upper Saddle River, NJ: Prentice Hall PTR, 1998.

# Chapter 2

## Two-Stage CMOS LNA

### 2.1 Introduction

Cascode CMOS LNAs with inductive source degeneration [1–3] are widely used for narrowband wireless receivers, such as GPS [4, 5], cellular phone [6–8], and WLAN receivers [9–11]. The cascode LNAs have achieved both good input impedance matching ( $|S_{11}| < -10$  dB) and low noise performance ( $NF \simeq 2.0$  dB) with reasonable power consumption ( $\sim 10$  mW), due to many design methodologies [1, 12–17] and advances in CMOS processes. However, the LNAs require relatively high supply voltages ( $> 1.0$  V) to achieve both good noise and linearity performance.

In addition, the previous design methodologies pay much attention on noise optimization, but little on its linearity. Modern wireless systems, in particular, cellular and WLAN systems impose high linearity requirements on LNAs [18, 19]. Low-voltage circuit topologies and design methodologies considering both noise and linearity are required.

This chapter proposes a two-stage CMOS LNA suitable for low-voltage operation and its design methodology based on the analytical expressions of the gain, noise, and linearity. These expressions are derived from the small-signal equivalent circuits of the LNA. The proposed design methodology is expanded from the previous my work [20], which is applied to the cascode CMOS LNA. The 1.0 V two-stage LNA designed for 5 GHz WLAN applications is implemented in a 0.15  $\mu$ m fully-depleted silicon-on-insulator (FD-SOI) CMOS technology [21, 22], and both its performance and design methodology are verified.

This chapter is organized as follows. Section 2.2 overviews the conventional cascode CMOS LNA with inductive source degeneration and describes its simple analytical expressions and limitations. Section 2.3 presents the two-stage CMOS LNA and its small-signal equivalent circuit, and then derives the analytical equations of the gain, noise, and linearity. Section 2.4 presents the design methodology based on these equations. Section 2.5 shows the measurement results of the fabricated LNA, and Section 2.6 concludes the chapter.

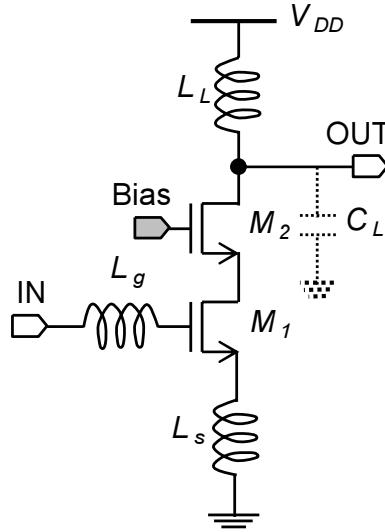

## 2.2 Cascode LNA with Inductive Source Degeneration

Figure 2.1 shows the conventional cascode LNA with inductive source degeneration [1–3]. The inductors  $L_g$  and  $L_s$  are connected to the gate and source terminals of the common-source transistor  $M_1$ , providing input impedance matching at an operating frequency. The cascode transistor  $M_2$  reduces the Miller effect due to the gate-drain capacitance of  $M_1$ , improving the reverse isolation performance of the LNA. The load inductor  $L_L$  resonates with the load parasitic capacitance  $C_L$ , providing a high impedance.

Figure 2.1: Schematic of the cascode LNA with inductive source degeneration.

### 2.2.1 Analytical Expressions

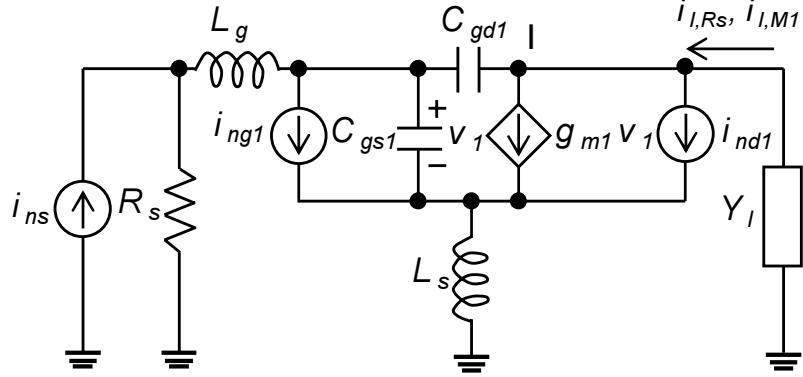

Analytical expressions of the input impedance, gain, noise, and linearity of the cascode LNA are derived from the small-signal equivalent circuit shown in Fig. 2.2, where the resistors,  $1/g_{m2}$  and  $R_s$ , represent  $M_2$  and the signal source resistance, respectively.

#### Input Impedance

The source inductor  $L_s$  provides a resistive component for the LNA input impedance  $Z_{in}$ , and the gate inductor  $L_g$  adjusts the resonance frequency of  $Z_{in}$  to the desired operating frequency. The small-signal equivalent circuit shown in Fig. 2.2 gives the input impedance:

$$Z_{in} = \omega_{T1} L_s + j\omega(L_g + L_s) + \frac{1}{j\omega C_{gs1}}, \quad (2.1)$$

Figure 2.2: Small-signal equivalent circuit of the cascode LNA.

where  $\omega_{T_1} = g_{m1}/C_{gs1}$  is the unity current gain frequency of  $M_1$  and  $g_{m1}$  and  $C_{gs1}$  are the transconductance and gate-source capacitance of  $M_1$ , respectively. Selecting  $L_s$  such that  $L_s = R_s/\omega_{T_1}$  allows input impedance matching around the resonance frequency:

$$\omega_0 = \frac{1}{\sqrt{(L_g + L_s)C_{gs1}}}. \quad (2.2)$$

### Gain

The voltage gain of the LNA is determined by the equivalent resistance of the load LC tank and  $\omega_{T_1}$ . The output current  $i_{out}$ , given by  $g_{m1}v_{gs1}$  where  $v_{gs1} = v_{in}/sC_{gs1}Z_{in}$ , flows into the load LC tank, and the voltage gain at  $\omega_0$  is therefore given by

$$A_v = \left| \frac{v_{out}}{v_{in}} \right| = \left| \frac{i_{out}R_{L_L}}{v_{in}} \right| = \left| \frac{g_{m1}R_{L_L}}{j\omega_0 C_{gs1}Z_{in}} \right| = \frac{g_{m1}R_{L_L}}{\omega_0 C_{gs1}\omega_{T_1}L_s} = \frac{R_{L_L}}{R_s} \left( \frac{\omega_{T_1}}{\omega_0} \right), \quad (2.3)$$

where  $R_{L_L}$  is the equivalent resistance of the load LC tank at the resonance frequency of  $\omega_L$  ( $= 1/\sqrt{L_L C_L}$ ) and is approximated by [23]

$$R_{L_L} \approx \frac{\omega_L^2 L_L^2}{R_{L_L,s}} = Q_{L_L}^2 R_{L_L,s}, \quad (2.4)$$

where  $Q_{L_L}$  and  $R_{L_L,s}$  are the quality factor and parasitic series resistance of  $L_L$ , respectively. The resonance frequency of the load LC tank,  $\omega_L$ , is generally set to  $\omega_0$ .

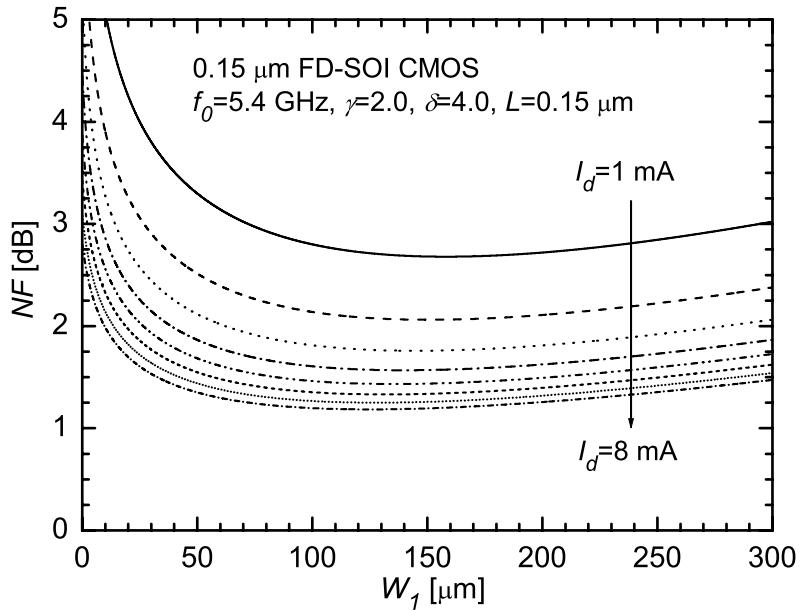

Figure 2.3: Calculated  $NF$  versus  $W_1$  with  $I_d$  as a parameter.

## Noise

The LNA noise performance depends on the gate width of  $M_1$ ,  $W_1$ , for a fixed current consumption. The noise factor of the LNA is given by [1, 15]

$$F = 1 + \frac{\gamma\chi}{\alpha_1} g_{m1} R_s \left( \frac{\omega_0}{\omega_{T_1}} \right)^2 + \frac{\alpha_1 \delta}{\kappa g_{m1} R_s}, \quad (2.5)$$

$$\chi = 1 - 2|c|\alpha_1 \sqrt{\frac{\delta}{\kappa\gamma}} + \frac{\delta\alpha_1^2}{\kappa\gamma}, \quad (2.6)$$

where  $\alpha_1 = g_{m1}/g_{d01}$  and  $g_{d01}$  is the zero-bias drain conductance of  $M_1$ ;  $\gamma$  and  $\delta$  are the drain noise current factor ( $\gamma = 2/3$  in long-channel MOSFETs [24, 25], but  $\gamma > 2/3$  in short-channel MOSFETs [26]) and the induced gate noise current factor ( $\delta = 2\gamma$  [27]), respectively, and  $c$  is the correlation coefficient between these noise currents ( $c \simeq j0.395$  [24]);  $\kappa$  is the Elmore constant ( $\kappa = 5$  [27]). Equations (2.5) and (2.6) provide an optimum  $g_{m1}$  or  $W_1$  for noise performance. The calculated  $NF$  versus  $W_1$  with the drain current  $I_d$  as a parameter is shown in Fig. 2.3, where  $0.15 \mu\text{m}$  FD-SOI CMOS process parameters are used. Increasing  $I_d$  leads to a lower  $NF$ , and the optimum gate width  $W_{1,opt}$  is found for each  $I_d$ . The gate width  $W_1$  is generally set to  $W_{1,opt}$ .

## Linearity

The cascode LNA consists of the common-source and cascode transistors, and hence the overall  $IIP_3$  of the LNA can be approximated as that of a cascade system, as shown in Section 1.2.2:

$$\frac{1}{A_{LNA,IIP_3}^2} \approx \frac{1}{A_{1,IIP_3}^2} + \frac{A_{v1}^2}{A_{2,IIP_3}^2}, \quad (2.7)$$

where  $A_{1,IIP_3}$  and  $A_{2,IIP_3}$  represent the  $IIP_3$  of the common-source and cascode transistors in the expression of the voltage amplitude, respectively;  $A_{v1}$  represents the voltage gain of the common-source transistor and is given by

$$A_{v1} = \frac{1}{g_{m2}R_s} \left( \frac{\omega_{T1}}{\omega_0} \right). \quad (2.8)$$

The  $IIP_3$  of each transistor  $M_i$  ( $i = 1, 2$ ) can be derived from the drain current equation, given by [28]:

$$I_{di} = \frac{1}{2} \mu_0 C_{ox} \frac{W_i}{L_i} \frac{V_{odi}^2}{1 + \Theta V_{odi}} \frac{1}{1 - \lambda V_{dsi}}, \quad (2.9)$$

where  $V_{odi}$ , defined by  $V_{odi} = V_{gsi} - V_{thi}$ , is the overdrive voltage of  $M_i$  and  $V_{thi}$  is the threshold voltage of  $M_i$ ;  $W_i$  and  $L_i$  are the gate width and length of  $M_i$ , respectively;  $\lambda$  is the channel-length modulation coefficient;  $\Theta = \mu_0/(2v_{sat}L) + \theta$  and  $v_{sat}$  is the saturation velocity of the carrier,  $\mu_0$  the carrier mobility under low electric field, and  $\theta$  the mobility reduction parameter. For a signal small  $v_{in}(t)$  applied to the LNA, the output current of each transistor is expressed as [19]

$$I_{di}(t) = \frac{c_0(c_1 + c'_i v_i(t))^2}{c_2 + c_3 v_i(t) + c'^2_i c_4 v_i^2(t)} \quad (i = 1, 2), \quad (2.10)$$

$$c'_i = \frac{1}{j\omega_0 C_{gs1} Z_{in}} \quad (i = 1), \quad -1 \quad (i = 2), \quad (2.11)$$

$$c_0 = \frac{1}{2} \mu_0 C_{ox} \frac{W_i}{L_i}, \quad (2.12)$$

$$c_1 = V_{odi}, \quad (2.13)$$

$$c_2 = (1 + \Theta V_{odi})(1 - \lambda V_{dsi}), \quad (2.14)$$

$$c_3 = (1 + \Theta V_{odi})\lambda A_{vi} + c'_i(1 - \lambda V_{dsi})\Theta, \quad (2.15)$$

$$c_4 = \Theta \lambda A_{vi}, \quad (2.16)$$

where  $v_1(t) = v_{in}(t)$  and  $v_2(t) = -A_{v1}v_{in}(t)$ . Substituting the Taylor expansion coefficients of Eq. (2.10) such as  $\alpha_1$  and  $\alpha_3$  into Eq. (1.12), we obtain

$$A_{i,IIP_3}^2 = \frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right| = \frac{4}{3} \left| \frac{c_1 c_2^2 (c_1 c_3 - 2c'_i c_2)}{(-c'_i c_2 + c_1 c_3)[(-c'_i c_2 + c_1 c_3)c_3 - 2c'_i c_1 c_2 c_4]} \right|. \quad (2.17)$$

Substituting Eqs. (2.8) and (2.17) into Eq. (2.7) gives the overall  $IIP_3$  of the cascode LNA.

## 2.2.2 Limitations

### Circuit Topology

The cascode LNA is not suitable for low-voltage operation, because it requires a supply voltage of more than two drain-source saturation voltages ( $V_{DD} > 2V_{DS,sat}$ ) to operate the cascode transistor. No cascode transistor allows the LNA to operate at lower supply voltages, but causes poor performance (i.e., a lower gain and higher  $NF$ ) due to the Miller effect. An alternative circuit to reduce the effect is required.

### Small-Signal Equivalent Circuit

The small-signal equivalent circuit shown in Fig. 2.2 ignores the gate-drain capacitance of  $M_1$ ,  $C_{gd1}$  and input parasitic capacitance  $C_p$  originating from a gate inductor, input pad, and electrostatic-discharge (ESD) devices. These capacitances cause the following effects on the LNA performance:

- $C_{gd1}$  increases effective  $C_{gs1}$  and  $L_s$  (i.e., the Miller effect), having an impact on the input impedance matching as well as the noise and gain performance [19].

- $C_p$  reduces  $Z_{in}$ , changing the input impedance matching condition [15, 29].

The next section will present a low-voltage circuit topology with a small Miller effect and its complete small-signal equivalent circuit including the above parasitic capacitances.

## 2.3 Two-Stage LNA with Inductive Source Degeneration

This section presents a two-stage LNA with inductive source degeneration and describes its small-signal equivalent circuit and analytical expressions.

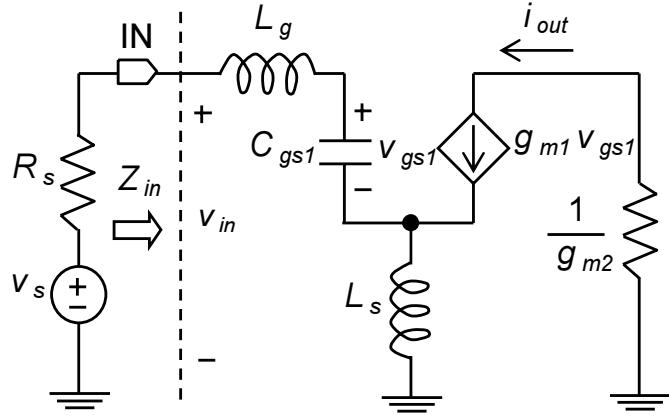

### 2.3.1 Circuit Topology

Figure 2.4 shows the two-stage LNA that consists of the common-source stage with inductive source degeneration and the common-gate stage. The two internal LC tanks,  $L_{I1}C_{I1}$  and  $L_{I2}C_{I2}$ , provide high impedances at the resonance frequencies, and thereby the signal current amplified by the common-source transistor  $M_1$  flows into the common-gate transistor  $M_2$ , which alleviates the Miller effect of  $M_1$ . The common-gate stage converts the current to the output voltage using the load LC tank  $L_LC_L$ . The DC-blocking capacitor  $C_c$  separates the DC voltages of two stages. The required supply voltage of the two-stage LNA is only more than  $V_{DS,sat}$ , so that the LNA can operate at lower supply voltages than the cascode LNA.

Figure 2.4: Schematic of the two-stage LNA with inductive source degeneration.

### 2.3.2 Small-Signal Equivalent Circuit

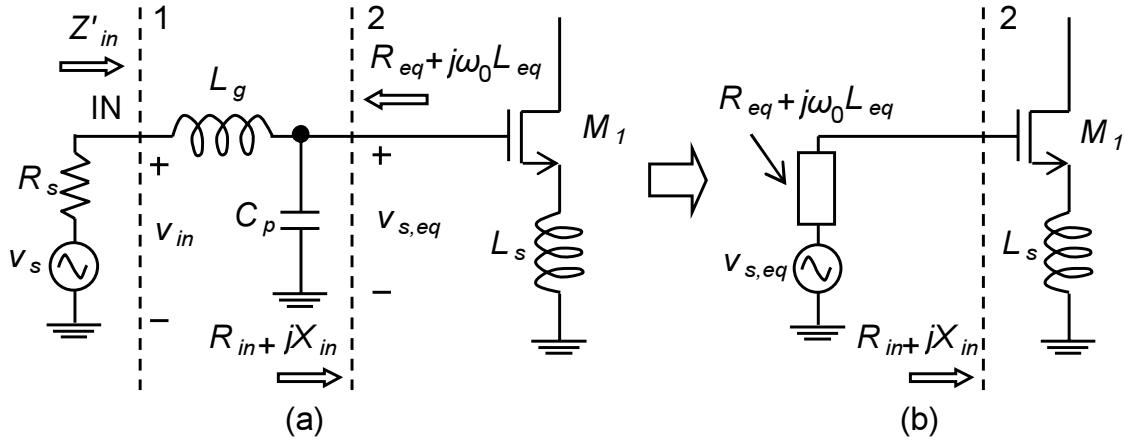

The input parasitic capacitance  $C_p$  varies the LNA input impedance. The input section of the two-stage LNA is shown in Fig. 2.5(a). The input impedance looking into the right hand side of reference plane 1 is given by

$$Z'_{in} = \frac{R_{in}(1 - \omega_0^2 L_g C_p) + j(\omega_0 L_g + X_{in} - \omega_0^2 L_g C_p X_{in})}{1 - \omega_0 C_p X_{in} + j\omega_0 C_p R_{in}}, \quad (2.18)$$

where  $R_{in}$  and  $X_{in}$  are the resistance and reactance of the input impedance looking into the right hand side of reference plane 2, respectively. On the other hand, the equivalent source impedance looking into the left hand side of reference plane 2,  $R_{eq} + j\omega_0 L_{eq}$ , is given by

$$R_{eq} = \frac{R_s}{\omega_0^2 C_p^2 R_s^2 + (1 - \omega_0^2 C_p L_g)^2}, \quad (2.19)$$

$$L_{eq} = \frac{L_g - C_p(\omega_0^2 L_g^2 + R_s^2)}{\omega_0^2 C_p^2 R_s^2 + (1 - \omega_0^2 C_p L_g)^2}. \quad (2.20)$$

Using the above impedances, we can derive the input impedance matching condition as

$$Z'_{in} = R_s \quad (2.21)$$

or

$$R_{eq} = R_{in}, \quad (2.22)$$

$$\omega_0 L_{eq} = -X_{in}. \quad (2.23)$$

Figure 2.5: (a) Input section of the LNA and (b) the Thevenin's equivalent circuit of the input section.

The equivalent signal source voltage  $v_{s,eq}$  applied to reference plane 2 is also given by

$$v_{s,eq} = \frac{v_s}{1 - \omega_0^2 C_p L_g + j\omega_0 C_p R_s}. \quad (2.24)$$

From Thevenin's theorem, the input section can be expressed as Fig. 2.5(b).

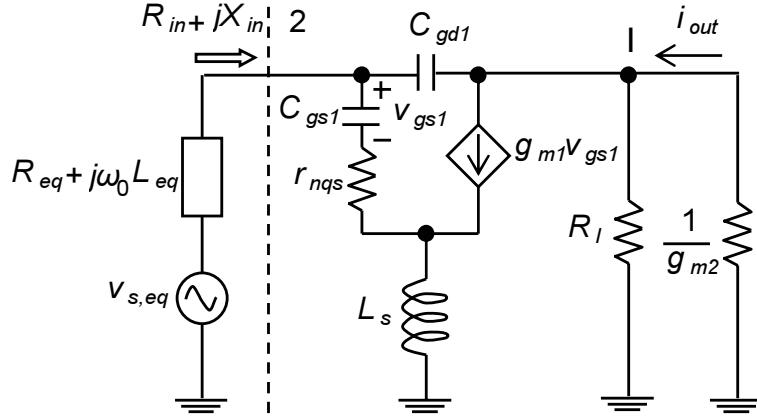

The gate-drain capacitance of  $M_1$ ,  $C_{gd1}$ , causes the Miller effect, varying the LNA input impedance. Figure 2.6 shows the small-signal equivalent circuit of the common-source stage including  $C_{gd1}$ . For more accurate analysis, the non-quasi-static (NQS) resistance  $r_{nqs} = 1/\kappa g_{m1}$  [19] is also included. Using Figure 2.6, we can derive the input impedance  $Z_{in} = R_{in} + jX_{in}$  at reference plane 2 as

$$R_{in} = \frac{r_{nqs} + \omega_{T1} L_s}{\alpha_M}, \quad (2.25)$$

$$X_{in} = \frac{\omega_0 L_s - \frac{1}{\omega_0 C_{gs1}}}{\alpha_M}, \quad (2.26)$$

$$\begin{aligned} \alpha_M &= 1 + \frac{g_{m1}}{Y_I/\alpha_{gd1} + j\omega C_{gs1}} + \frac{Y_I (1 - \omega^2 L_s C_{gs1} + j\omega L_s g_{m1})}{Y_I/\alpha_{gd1} + j\omega C_{gs1}} \\ &\approx 1 + \alpha_{gd1} \left( \frac{g_{m1}}{Y_I} + 1 - \omega^2 L_s C_{gs1} + j\omega L_s g_{m1} \right), \end{aligned} \quad (2.27)$$

$$\alpha_{gd1} = \frac{C_{gd1}}{C_{gs1}}, \quad (2.28)$$

$$Y_I = \frac{1}{R_I} + g_{m2}, \quad (2.29)$$

where  $Y_I$  represents the input admittance of the common-gate stage at node I. In Eq. (2.27),  $j\omega C_{gs1}$  is ignored against  $Y_I/\alpha_{gd1}$ . The resistance  $R_I$  represents the parallel resistance of  $R_{L_{I1}}$

Figure 2.6: Small-signal equivalent circuit of the common-source stage.

Figure 2.7: Small-signal equivalent circuit of the common-gate stage.

and  $R_{L_{I2}}$  (i.e.,  $R_{L_{I1}}/\!/R_{L_{I2}}$ ), where  $R_{L_{Ii}}$  ( $i = 1, 2$ ) is the equivalent resistance of the internal LC tank,  $L_{Ii}C_{Ii}$ , at the resonance frequency of  $\omega_{L_{Ii}} = 1/\sqrt{L_{Ii}C_{Ii}}$  and is approximated by Eq. (2.4). The transconductance  $g_{mi}$  of  $M_i$  is given by a derivative of Eq. (2.9):

$$g_{mi} = \frac{\partial I_{di}}{\partial V_{odi}} = \frac{1}{2}\mu_0 C_{ox} \frac{W_i}{L_i} \frac{V_{odi}(2 + \Theta V_{odi})}{(1 + \Theta V_{odi})^2} \frac{1}{1 - \lambda V_{dsi}}. \quad (2.30)$$

Equations (2.27) and (2.29) show that decreasing  $g_{m2}$  leads to a larger  $\alpha_M$ , resulting in a lower  $Z_{in}$ .

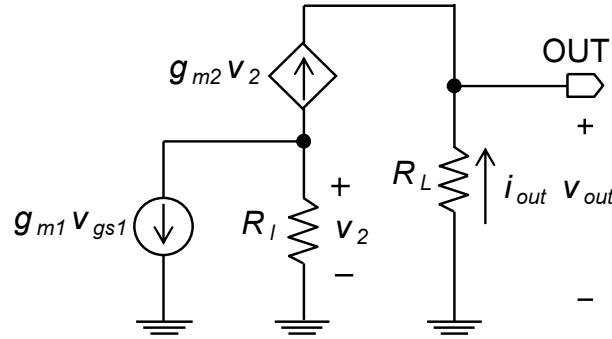

Figure 2.7 shows the small-signal equivalent circuit of the common-gate stage. The Miller effect due to  $C_{gd2}$  is negligible, because the gate terminal of  $M_2$  is connected to the AC ground. The NQS resistance of  $M_2$  is also negligible. The resistance  $R_L$  represents the equivalent resistance of the load LC tank  $L_L C_L$ , and is given by Eq. (2.4).

### 2.3.3 Analytical Expressions

The equivalent circuit presented in the previous subsection provides more precise analytical expressions of the LNA performance than the simple equivalent circuit shown in Section 2.2. The analytical equations of the gain, noise, and linearity are derived in this subsection.

#### Gain

The output current  $i_{out}$  flows into the output load  $R_L$ , generating the output voltage:

$$v_{out} = -i_{out}R_L. \quad (2.31)$$

From Figs. 2.6 and 2.7,  $i_{out}$  is given by

$$i_{out} = \frac{g_{m1}v_{s,eq}}{2R_{in} \cdot j\omega_0\alpha_M C_{gs1}} \left( \frac{R_I}{R_I + 1/g_{m2}} \right), \quad (2.32)$$

where input impedance matching is assumed (i.e.,  $R_{eq} = R_{in}$  and  $\omega_0 L_{eq} = -X_{in}$ ). The voltage gain of the LNA is defined as the ratio of the output voltage to the input voltage at reference plane 1 (see Fig. 2.5(a)):

$$A_{v,LNA} \equiv \left| \frac{v_{out}}{v_{in}} \right| = 2 \left| \frac{v_{out}}{v_s} \right| = 2 \left| \frac{v_{out}}{v_{s,eq}(1 - \omega_0^2 C_p L_g + j\omega_0 C_p R_s)} \right|, \quad (2.33)$$

where  $Z'_{in} = R_s$  is assumed. Substituting Eqs. (2.31) and (2.32) into (2.33) gives

$$A_{v,LNA} = \frac{R_L}{R_{in}\alpha_M} \left( \frac{\omega_{T_1}}{\omega_0} \right) \left| \frac{1}{1 - \omega_0^2 C_p L_g + j\omega_0 C_p R_s} \right| \left( \frac{R_I}{R_I + 1/g_{m2}} \right), \quad (2.34)$$

which indicates that a large  $C_p$  and small  $g_{m2}$  lead to a decrease in  $A_{v,LNA}$ .

#### Noise

The noise of  $M_1$ ,  $M_2$ ,  $R_I$ , and  $R_L$  contribute to the overall LNA noise. The LNA noise factor can be derived from the small-signal equivalent circuits shown in Figs. 2.6 and 2.7:

$$F_{LNA} = 1 + F_{M_1} + F_{M_2} + F_{R_I} + F_{R_L}, \quad (2.35)$$

$$F_{M_1} = \frac{\gamma_1\chi_1}{\alpha_1} g_{m1} R_{eq} \left( \frac{\omega_0}{\omega_{T_1}} \right)^2 + \frac{\alpha_1\delta_1}{\kappa_1 g_{m1} R_{eq}}, \quad (2.36)$$

$$F_{M_2} = 4R_{eq}\alpha_M^2 \left( \frac{\omega_0}{\omega_{T_1}} \right)^2 \frac{\gamma_2\chi_2 g_{m2}}{\alpha_2}, \quad (2.37)$$

$$F_{R_I} = 4R_{eq}\alpha_M^2 \left( \frac{\omega_0}{\omega_{T_1}} \right)^2 \frac{1}{R_I}, \quad (2.38)$$

$$F_{R_L} = 4R_{eq}\alpha_M^2 \left( \frac{\omega_0}{\omega_{T_1}} \right)^2 \frac{(1 + 1/g_{m2}R_I)^2}{R_{L_{3,p}}}, \quad (2.39)$$

where  $F_{M_1}$ ,  $F_{M_2}$ ,  $F_{R_I}$ , and  $F_{R_L}$  represent the noise contributions from  $M_1$ ,  $M_2$ ,  $R_I$ , and  $R_L$ , respectively, and  $\chi_1$  and  $\chi_2$  are given by

$$\chi_1 = (1 + \alpha_{gd1})^2 - 2|c|\alpha_1 \sqrt{\frac{\delta_1}{\kappa_1\gamma_1}}(1 + \alpha_{gd1}) + \frac{\alpha_1^2\delta_1}{\kappa_1\gamma_1}, \quad (2.40)$$

$$\chi_2 = \left( \frac{1 + 1/g_{m2}R_I}{1 + g_{m2}R_I} \right)^2 + \left( \frac{\omega_0}{\omega_{T_2}} \right)^2 \frac{\alpha_2^2\delta_2}{\kappa_2\gamma_2}, \quad (2.41)$$

respectively. The detailed derivations are summarized in Appendix A.1. Equations (2.36)–(2.39) indicate that increasing  $\omega_{T_1}$  leads to a lower  $NF$  and a lower  $g_{m2}$  (higher  $\alpha_M$ ) results in the increase of  $F_{M_2}$ ,  $F_{R_I}$ , and  $F_{R_L}$ .

### Linearity

The two-stage LNA consists of the common-source and common-gate stages, and hence the overall  $IIP_3$  of the LNA can be derived in the same way as that of the cascode LNA:

$$\frac{1}{A_{LNA,IIP_3}^2} \approx \frac{1}{A_{1,IIP_3}^2} + \frac{A_{v1}^2}{A_{2,IIP_3}^2}, \quad (2.42)$$

$$A_{v1} = \left| \frac{v_i}{v_{in}} \right| = \frac{\frac{1}{g_{m2}}/R_I}{R_{in}\alpha_M} \left( \frac{\omega_{T_1}}{\omega_0} \right) \left| \frac{1}{1 - \omega_0^2 C_p L_g + j\omega_0 C_p R_s} \right|, \quad (2.43)$$

$$A_{i,IIP_3}^2 = \frac{4}{3} \left| \frac{c_1 c_2^2 (c_1 c_3 - 2c'_i c_2)}{(-c'_i c_2 + c_1 c_3)[(-c'_i c_2 + c_1 c_3)c_3 - 2c'_i c_1 c_2 c_4]} \right|, \quad (2.44)$$

$$c'_i = \frac{1}{j\omega_0 \alpha_M C_{gs1} R_{in} (1 - \omega_0^2 L_g C_p + j\omega_0 C_p R_s)} \quad (i = 1), -1 \quad (i = 2), \quad (2.45)$$

where  $A_{1,IIP_3}$  and  $A_{2,IIP_3}$  represent the  $IIP_3$  of the common-source and common-gate stages in the expression of the voltage amplitude, respectively;  $A_{v1}$  represents the voltage gain of the common-source stage and  $v_i$  the voltage at node I as shown in Fig. 2.6;  $c_0 - c_4$  in Eq. (2.44) are given by Eqs. (2.12)–(2.16).

## 2.4 Design Methodology

This section describes a design methodology of the two-stage LNA that meets the typical specifications of LNAs for WLAN receivers [18], shown in Table 2.1. In this design,  $0.15\ \mu\text{m}$  FD-SOI CMOS process and device parameters are used, and the current consumption and supply voltage are set to  $8.0\ \text{mA}$  and  $1.0\ \text{V}$ , respectively. There are thirteen design variables: the bias currents of the two transistors ( $I_{d1}$  and  $I_{d2}$ ), the overdrive voltages ( $V_{od1}$  and  $V_{od2}$ ), the gate widths and lengths ( $W_1/L_1$  and  $W_2/L_2$ ), gate and source inductances ( $L_g$  and  $L_s$ ), internal inductances ( $L_{I1}$  and  $L_{I2}$ ), and load inductance ( $L_L$ ). The gate lengths,  $L_1$  and  $L_2$ , are set to the minimum gate length in order to increase  $\omega_{T_i}$ , resulting in a lower  $NF$  [1]. Once  $I_{di}$  and  $V_{odi}$  are determined,

Table 2.1: Specifications of LNAs for WLAN receivers.

|                   |       |

|-------------------|-------|

| Frequency [GHz]   | 5.4   |

| $S_{11}$ [dB]     | < -10 |

| Voltage Gain [dB] | >20   |

| $NF$ [dB]         | <2.0  |

| $IIP_3$ [dBm]     | > -5  |

$W_i$  can be calculated from Eq. (2.9). Consequently, we can reduce thirteen design variables to nine ones such as  $I_{d1}$ ,  $I_{d2}$ ,  $V_{od1}$ ,  $V_{od2}$ ,  $L_g$ ,  $L_s$ ,  $L_{I1}$ ,  $L_{I2}$ , and  $L_L$ . In what follows, these nine design variables are determined from the derived equations.

### Bias Currents of $M_1$ and $M_2$

The gain specification determines the distribution of bias currents of  $M_1$  and  $M_2$ ,  $I_{d1}$  and  $I_{d2}$ . Equation (2.34) indicates that the voltage gain of the LNA mainly depends on  $\omega_{T_1}$  ( $\propto I_{di}$ ) and  $R_L$  (i.e.,  $Q_L$ ). The quality factors of on-chip inductors are determined by process technologies and inductor structures ( $Q_L \simeq 8$  at 5 GHz in this design). Therefore,  $I_{d1}$  is selected to satisfy the gain specification, and then  $I_{d2}$  to the rest of the given bias current:  $I_{d2} = I_{spec} - I_{d1}$ . Figure 2.8 shows the calculated voltage gain versus  $V_{od1}$  with  $I_{d1}$  as a parameter. Note that  $g_{m2}$  is set to infinity in Eq. (2.34). For comparison, simulations for  $I_{d1} = 7.0$  mA are also plotted in Fig. 2.8. This and the following simulations of the LNA were carried out using the small-signal and noise FD-SOI MOSFET models shown in [30] and Agilent Advanced Design System (ADS). Figure 2.8 shows that the calculations are comparable to the simulations, and the given specification is satisfied in the range of 4.0–8.0 mA. Taking account of process and temperature variations and the effect of  $M_2$ , we select  $I_{d1}$  to 7.0 mA for a voltage gain of 23 dB including a 3 dB margin, and then  $I_{d2}$  to 1.0 mA.

### Overdrive Voltage of $M_1$

Increasing overdrive voltage of  $M_1$ ,  $V_{od1}$ , leads to a lower  $NF$  and  $IIP_3$ . Figure 2.9 shows the calculated and simulated  $NF$  and  $IIP_3$  versus  $V_{od1}$  for  $I_{d1} = 7.0$  mA. In the calculations and simulations,  $M_2$  was set to be noiseless, and  $g_{m2}$  and  $A_{2,IIP_3}^2$  to infinity in Eqs. (2.37)–(2.39) and (2.42), respectively. Besides, the noise parameters such as  $\gamma_i$ ,  $\delta_i$ , and  $\alpha_i$  based on the experimental results [30] were used. Figure 2.9 shows that the calculations are comparable to the simulations and the noise performance improves with increasing  $V_{od1}$ , while the linearity deteriorates. The degradation of the linearity can be explained as follows: For input impedance matching ( $Z'_{in} = R_s$ ), the constant current  $i_{in} = v_{in}/R_s$  injects into the LNA. In this case, the

Figure 2.8: Calculated and simulated voltage gain versus  $V_{od1}$  with  $I_{d1}$  as a parameter.

Figure 2.9: Calculated and simulated  $NF$  and  $IIP_3$  versus  $V_{od1}$ .

Figure 2.10: Calculated and simulated  $NF$  and  $IIP_3$  versus  $V_{od2}$ .

gate-source voltage of  $M_1$  is approximated by

$$v_{gs1} \approx \frac{i_{in}}{j\omega_0 C_{gs1}} = \frac{v_{in}}{j\omega_0 C_{gs1} R_s}. \quad (2.46)$$

For a fixed  $I_{d1}$ , the gate width, i.e., the gate-source capacitance of  $M_1$ ,  $C_{gs1}$ , decreases with increasing  $V_{od1}$ , which results in an increase of  $v_{gs1}$ , as shown in Eq. (2.46). Although the MOSFET generally has higher linearity with increasing  $V_{od}$  (because  $I_{di}$  is proportional to  $V_{odi}$  when  $V_{odi}$  is large), the degradation of linearity due to the increase in  $v_{gs1}$  becomes significant in the range of 0.20–0.50 V, causing poor linearity. Taking account of additional noise of the common-gate stage, we set  $V_{od1}$  to 0.32 V, which results in  $W_1 = 5 \times 24 \mu\text{m}$  (24 gate fingers, each with a unit of 5  $\mu\text{m}$  width) and provides calculated  $NF = 1.25 \text{ dB}$  and  $IIP_3 = 3.8 \text{ dBm}$ .

### Overdrive Voltage of $M_2$

Increasing the overdrive voltage of  $M_2$ ,  $V_{od2}$ , allows high linearity, but causing a higher  $NF$ . Figure 2.10 shows the calculated and simulated  $NF$  and  $IIP_3$  versus  $V_{od2}$  for  $I_{d1} = 7.0 \text{ mA}$ ,  $V_{od1} = 0.32 \text{ V}$ , and  $I_{d2} = 1.0 \text{ mA}$ . Increasing  $V_{od2}$  results in better linearity but poor noise performance. The reason for a higher  $NF$  is that increasing  $V_{od2}$  leads to a decrease in  $g_{m2}$  and increase in  $\alpha_M$  for a fixed  $I_{d2}$ , which results in a larger  $F_{M2}$ ,  $F_{R_I}$ , and  $F_{R_L}$ , as shown in Eqs. (2.37)–(2.39). Figure 2.10 also shows that the difference between the  $IIP_3$  calculations and simulations increases at higher  $V_{od2}$ : the calculated  $IIP_3$  becomes higher than the simulated  $IIP_3$  as  $V_{od2}$  increases. This difference originates from the simplification of  $I_{di}$  (Eq. (2.9)) and

the  $IIP_3$  approximation of two nonlinear stages in cascade (Eq. (2.42)). With a few simulations, we can avoid to overestimate the achievable  $IIP_3$ . From Fig. 2.10, we can find  $V_{od2} = 0.17$  V, at which the noise and linearity specifications are satisfied on both calculation and simulation. This results in  $W_2 = 50$   $\mu$ m and calculated  $NF = 1.85$  dB and  $IIP_3 = -4.1$  dBm.

## Inductors

The gate and source inductances,  $L_g$  and  $L_s$ , are determined from the impedance matching conditions. Substituting the determined design variables into Eqs. (2.22) and (2.23) gives  $L_g \simeq 3.3$  nH and  $L_s \simeq 1.0$  nH. The source inductor  $L_s$  is implemented by a 2.5-turn square spiral inductor with a diameter of 115  $\mu$ m, a metal width of 8  $\mu$ m, and a metal spacing of 2  $\mu$ m, while the gate inductor  $L_g$  by a bonding wire [29], which has a higher  $Q$  than on-chip inductors [19, 31], resulting in a smaller  $NF$ .

The inductances in the LC tanks,  $L_{I1}$ ,  $L_{I2}$ , and  $L_L$ , are determined from the resonance frequency, given by  $\omega = 1/\sqrt{LC}$ . Substituting  $f = 5.4$  GHz and  $C = 300$  fF into  $L = 1/\omega^2C$ , we obtain an  $L$  of 3.1 nH. For these inductors, 3.5-turn square spiral inductors with a diameter of 170  $\mu$ m, a metal width of 8  $\mu$ m, and a metal spacing of 2  $\mu$ m are used.

Figure 2.11 shows the complete schematic of the designed two-stage LNA. For measurements, a unity-gain common-source amplifier with a 50  $\Omega$  output resistor is used as a buffer. The 10 pF capacitor provides the AC ground for the gate terminal of  $M_2$ . The bias voltages are generated by current mirror circuits (not shown).

## 2.5 Experimental Results and Discussion

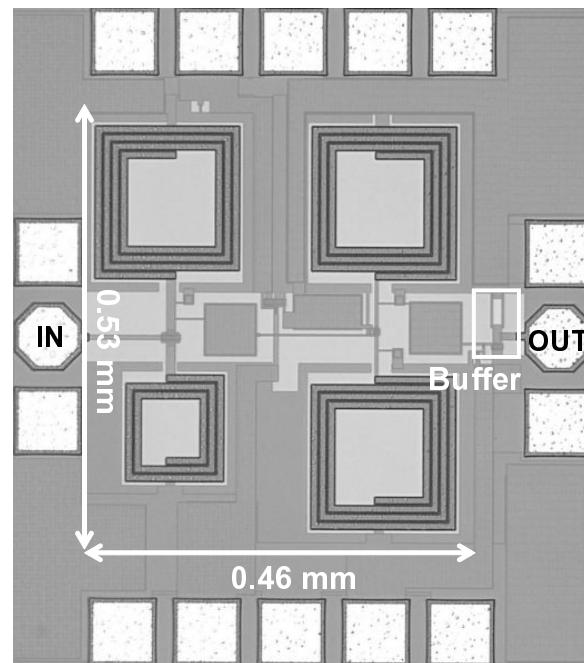

The designed two-stage LNA was fabricated in a 0.15  $\mu$ m FD-SOI CMOS process with a high resistivity substrate ( $\sim 1$  k $\Omega$ ·cm), metal-insulator-metal (MIM) capacitors, and five metal layers including a 1.95- $\mu$ m thick metal layer. The cut-off frequency of a 0.15  $\mu$ m NMOS consisting of 48 gate fingers with a unit of 5  $\mu$ m width was approximately 54 GHz for  $V_{ds} = 1$  V and  $I_d = 7$  mA [21]. A micrograph of the fabricated LNA is shown in Fig. 2.12. The active chip area excluding pads was 0.46 mm  $\times$  0.53 mm. The input and output pads were not ESD protected. The stand-alone buffer and inductor for  $L_{I1}$ ,  $L_{I2}$ , and  $L_L$  were also fabricated on the same chip. The current consumption of the LNA and buffer were 8.3 mA and 5.8 mA from a 1.0 V supply voltage, respectively. The S-parameters,  $NF$  and  $IIP_3$  of the LNA without  $L_g$  were measured using on-wafer RF probes. The above characteristics of the LNA with  $L_g$  were calculated based on the measurements [30]. This avoids instrumental error originating from a bonding wire  $L_g$ .

### 2.5.1 Inductor

The S-parameters of the fabricated 3.1 nH inductor were measured using an Agilent Technologies HP8722ES network analyzer and then converted into Y-parameters. The inductance and quality

Figure 2.11: Complete schematic of the designed two-stage LNA.

Figure 2.12: Micrograph of the fabricated LNA.

factor,  $L$  and  $Q$ , can be calculated from the Y-parameters and following equations [32]:

$$L = \text{Im} \left[ \frac{1/Y_{11}}{\omega} \right], \quad (2.47)$$

$$Q = \frac{\text{Im} [1/Y_{11}]}{\text{Re} [1/Y_{11}]} . \quad (2.48)$$

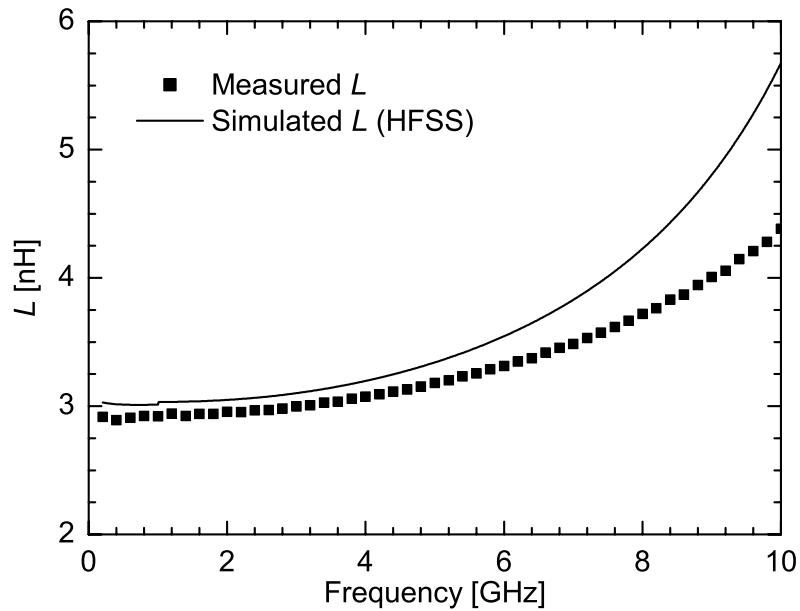

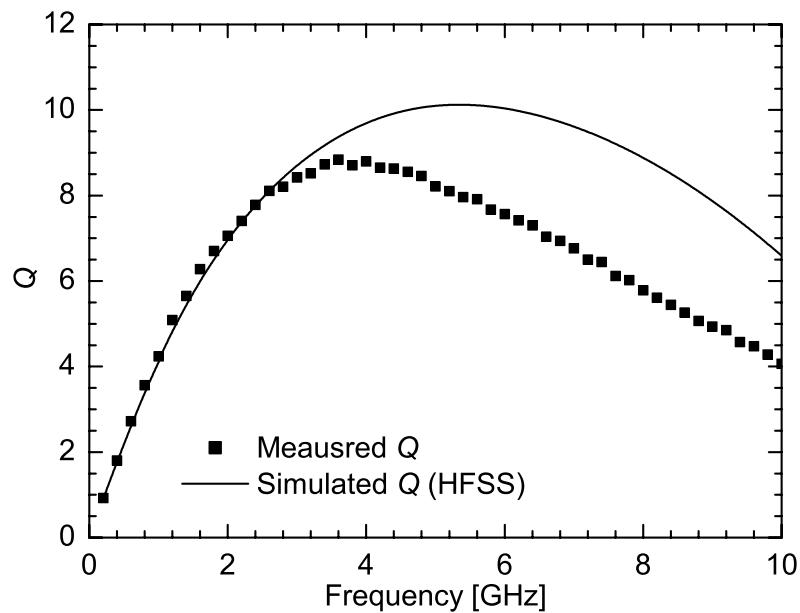

Figures 2.13 and 2.14 show the measured  $L$  and  $Q$  of the inductor, respectively. For comparison, the  $L$  and  $Q$  achieved using a three-dimensional (3-D) electromagnetic simulator (Ansoft HFSS) are also shown in Figs. 2.13 and 2.14, respectively. The measured  $L$  was 3.2 nH and  $Q$  was 8.0 at 5.4 GHz.

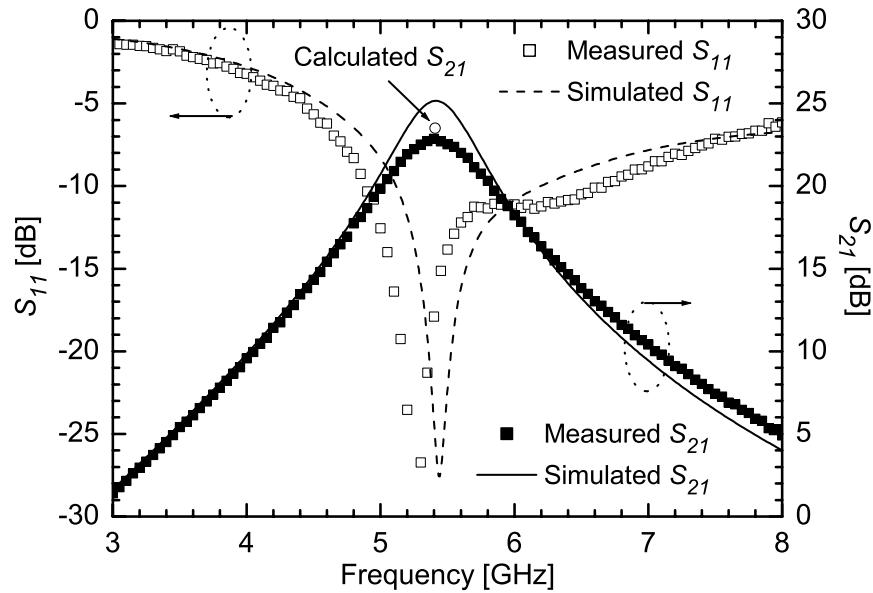

## 2.5.2 S-parameters

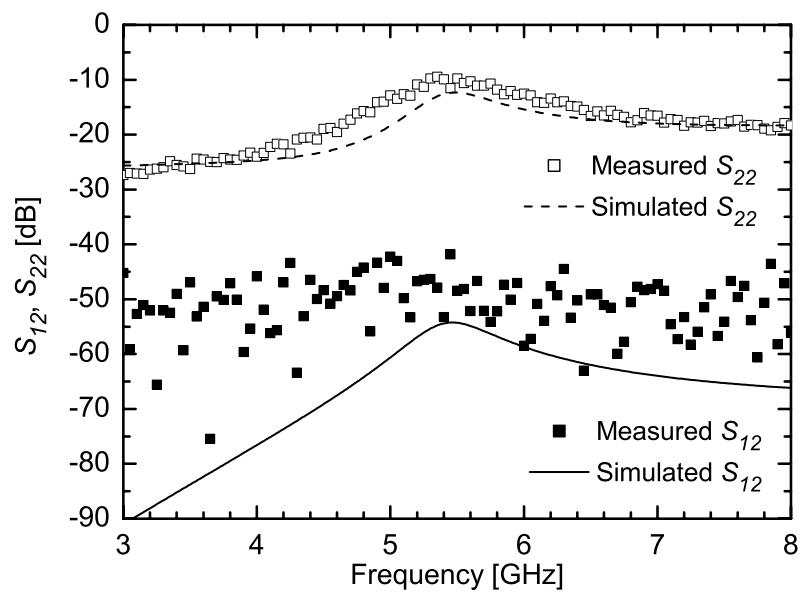

Figures 2.15 and 2.16 show the measured and simulated S-parameters of the LNA with an ideal gate inductor of 3.3 nH. The S-parameters were measured using the same network analyzer as in the inductor measurements. An  $S_{11}$  of less than  $-10$  dB was achieved around 5.4 GHz, where a maximum  $S_{21}$  was 23 dB, which met the WLAN specification shown in Tab. 2.1. The agreements between the measurements and simulations are due to the small-signal FD-SOI MOSFET models proposed in [30]. Figure 2.16 shows that  $S_{12}$  and  $S_{22}$  are  $-46$  dB and  $-9.9$  dB at 5.4 GHz, respectively. The discrepancy between the measured and simulated  $S_{12}$  is attributed to measurement limits. The measured  $S_{12}$  of the stand-alone buffer (not shown) was  $-29$  dB. The  $S_{12}$  of the stand-alone LNA was thus approximately  $-17$  dB.

## 2.5.3 NF

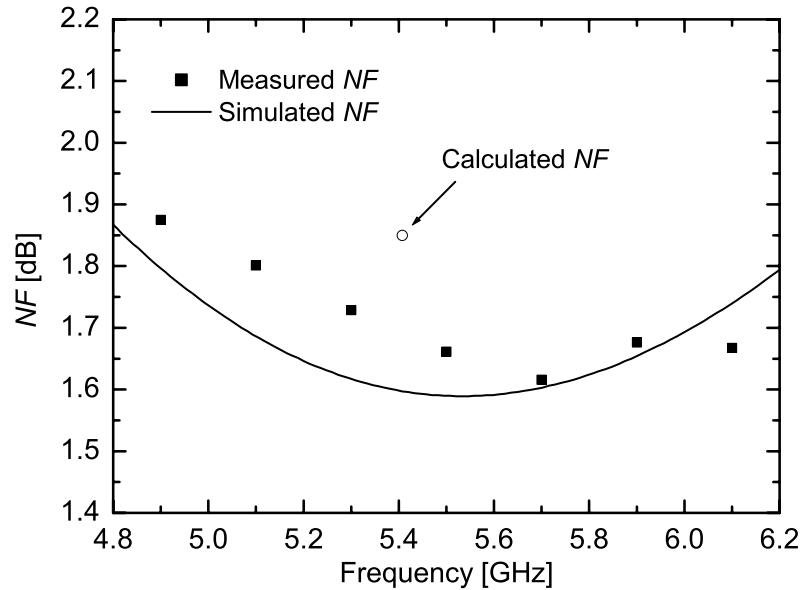

Figure 2.17 shows the measured and simulated  $NF$ . The  $NF$  was measured using an Agilent Technologies HP8970B noise figure meter and Maury automated tuner system. The LNA achieved an  $NF$  of 1.7 dB at 5.4 GHz, satisfying the noise specification. The measurements agree well with the simulations, due to the noise models proposed in [30].

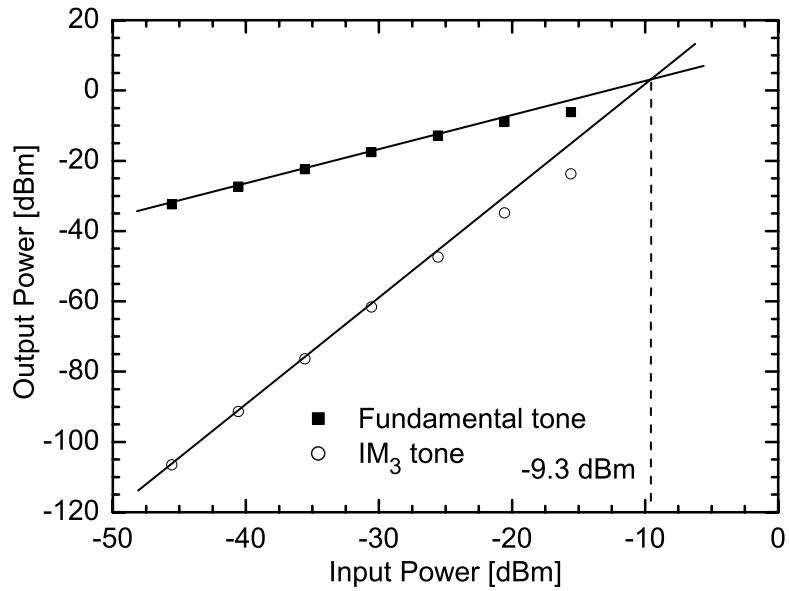

## 2.5.4 Linearity

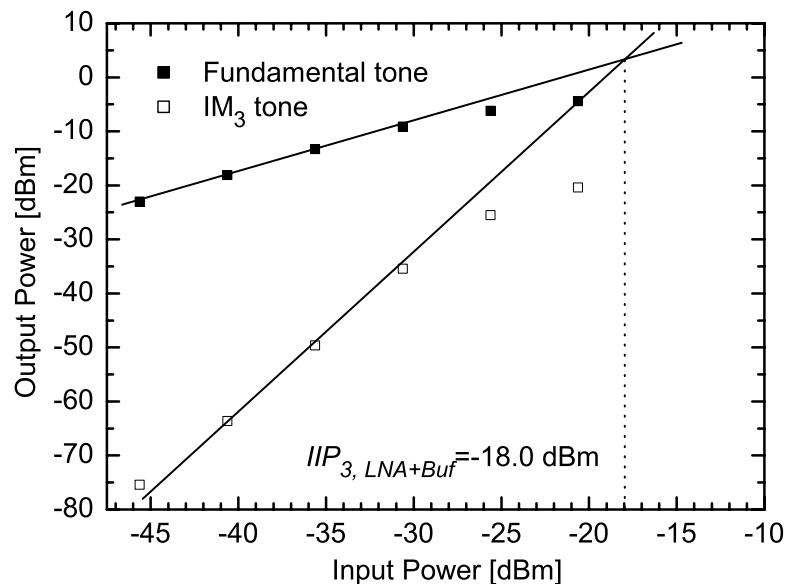

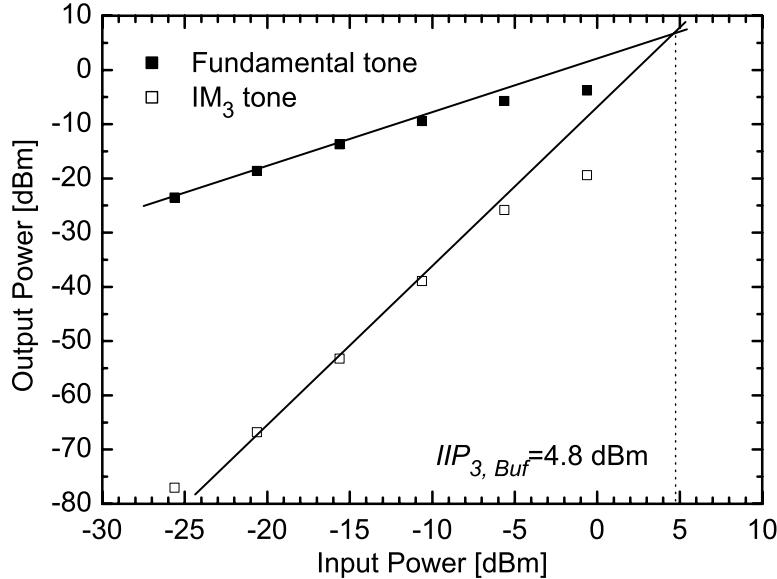

Figures 2.18 and 2.19 show the measured output power of the fundamental tones and third-order intermodulation ( $IM_3$ ) products for two tones (5.4 and 5.41 GHz), applied to the LNA and stand-alone buffer. The two tones were generated by Agilent Technologies HP8671B and E4438C signal generators, and the fundamental and  $IM_3$  tones were measured using an Agilent Technologies E4448A spectrum analyzer. The measured  $IIP_3$  of the LNA with the buffer was  $-18.0$  dBm, while that of the stand-alone buffer was 4.8 dBm. The  $IIP_3$  of the LNA without the buffer can be calculated from the following equation:

$$\frac{1}{A_{LNA,IIP_3}^2} \approx \frac{1}{A_{LNA+Buf,IIP_3}^2} - \frac{A_{v,LNA}^2}{A_{Buf,IIP_3}^2}, \quad (2.49)$$

Figure 2.13: Measured and simulated  $L$  of the fabricated 3.1 nH inductor.

Figure 2.14: Measured and simulated  $Q$  of the fabricated 3.1 nH inductor.

Figure 2.15: Measured and simulated  $S_{11}$  and  $S_{21}$  of the LNA.

Figure 2.16: Measured and simulated  $S_{12}$  and  $S_{22}$  of the LNA.

Figure 2.17: Measured and simulated  $NF$  of the LNA.

Figure 2.18: Measured  $IIP_3$  of the LNA with the buffer.

Figure 2.19: Measured  $IIP_3$  of the stand-alone buffer.

where  $A_{v,LNA}$  is the voltage gain of the LNA and  $A_{LNA,IIP_3}$ ,  $A_{Buf,IIP_3}$ , and  $A_{LNA+Buf,IIP_3}$  represent the  $IIP_3$  of the LNA, buffer, and LNA cascaded with the buffer in the expression of voltage amplitude, respectively. Substituting  $IIP_{3,LNA+Buf} = -18.0$  dBm,  $IIP_{3,Buf} = 4.8$  dBm and  $A_{v,LNA} = 22.5$  dB into Eq. (2.49) gives  $IIP_{3,LNA} = -6.1$  dBm.

## 2.5.5 Comparison

Table 2.2 shows a comparison of the LNA performance obtained from the measurements, simulations, and calculations. The simulated and calculated voltage gain and  $NF$  were consistent with the measured results, which satisfied the specifications. The calculated  $IIP_3$  agreed well with the simulated one, but these results were slightly different from the measured  $IIP_3$ . The difference can be attributed to inaccurate FD-SOI MOS device parameters used in the simulations

Table 2.2: Comparison of the LNA performance at 5.4 GHz.

|               | Gain [dB] | $NF$ [dB] | $IIP_3$ [dBm] |

|---------------|-----------|-----------|---------------|

| Specification | 20        | 2.0       | -5.0          |

| Measurement   | 23        | 1.70      | -6.1          |

| Simulation    | 25        | 1.60      | -3.0          |

| Calculation   | 23        | 1.85      | -4.1          |

and calculations. Although the fabricated LNA did not meet the  $IIP_3$  specification, its linearity can be improved by increasing  $I_{d2}$  as shown in Section 2.4.

Table 2.3 shows a summary of the LNA and a comparison with previously reported 1.0 V, 5 GHz CMOS LNAs. The figure of merits for LNAs,  $FoM_1$  and  $FoM_2$  included in Table 2.3, are defined as [36]:

$$FoM_1[\text{mW}^{-1}] = \frac{\text{Gain}[\text{lin}]}{\text{Power}[\text{mW}] \cdot (NF[\text{lin}] - 1)}, \quad (2.50)$$