| Title                     | 低電圧システムオンチップの高速・低電力回路技術に<br>関する研究 |  |  |

|---------------------------|-----------------------------------|--|--|

| Author(s)                 | 水野, 弘之                            |  |  |

| Citation 大阪大学, 2001, 博士論文 |                                   |  |  |

| Version Type              | VoR                               |  |  |

| URL                       | https://doi.org/10.11501/3184380  |  |  |

| rights                    |                                   |  |  |

| Note                      |                                   |  |  |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

I 28/75

# 低電圧システムオンチップの 高速・低電力回路技術に関する研究

2000年

水野 弘之

# 低電圧システムオンチップの 高速・低電力回路技術に関する研究

2000年

水野 弘之

# 内容梗概

システムオンチップ (SOC) は、数種の回路が複合した構造を持つ LSI であり、日本では、「システム LSI」と呼んで注目されている。今日、SOC は、システムの要求する「機能」、「性能」、「価格」を同時に満たすシステムソリューションを、ネットワーク市場や携帯電話市場等の競争が激化する市場において短時間に提示するために必要不可欠なデバイスとなっている。本論文は、低電圧システムオンチップの高速・低電力回路技術に関して、筆者が 1993 年から (株) 日立製作所中央研究所において実施した研究をまとめたもので、全体は7章から構成されている。以下、各章ごとにその内容の概要を述べる。

#### 第1章序論

本章では本研究の背景として、LSIの電源電圧の推移について述べる。その中で、低電圧化の目的は、「高集積化のための低電圧化」、「低電力化のための低電圧化」、「高速化のための低電圧化」の三つに分類され、SOCの高性能化に極めて大きな効果があることを述べる。また、低電圧化の推移とその目的の推移について述べ、その中で低電圧化の目的は時代とともに変化していることと、今日ではそれは全てのLSIの必須項目であることを述べる。

さらに、低電圧化には大きく分けて、「低電圧化に伴う動作速度低下」、「低電圧化に伴う電力増加」の二つの課題があり、前者の課題から派生した課題として、「低電圧化に伴う回路特性不整合」、「低電圧化に伴う特性ばらつき増加」の二つの課題があることを述べる。

本論文では、第2章から第4章の検討を通して、「低電圧化に伴う動作速度低下」と「低電圧化に伴う電力増加」の課題について解決策を検討する。また、第5章の検討を通じて「低電圧化に伴う回路特性不整合」の課題について、第6章の検討を通じて「低電圧化に伴う特性ばらつき増加」の課題について、それぞれ解決策を検討する。

#### 第2章 低電圧ロジック回路の高速・低電力化

本章では、低電圧ロジック回路の高速・低電力化について述べる。ロジック回路はSOCの中で最も重要な回路要素の一つであり、ロジック回路の性能はSOC全体の性能に大きく影響を与える。本章では、「低電圧化に伴う電力増加」と「低電圧化に伴う動作速度劣化」をいかにして同時に解決するかという命題は、サブスレッショルドリーク電流をいかにして削減するかという命題に等しいとし、微細化に伴って指数関数的に増加するサブスレッショルドリーク電流の低減技術を中心に述べる。

本章では基板バイアス制御によるリーク電流削減技術を、大規模高速 LSI(SH4 マイコン:3.3 M Trs, 200 MHz) に搭載した開発事例を述べる。従来の基板バイアス制御方式では基板インピーダンスが高くなる等の弊害により、アクティブ時の高速動作を維持することが困難であった。この課題を解決するために、基板インピーダンス切り替え型基板バイアス制御方式を開発した。チップ上に約1万個のスイッチセルと呼ぶ低基板インピーダンス化回路を分散配置する方式で、アクティブ時の高速動作と、スタンバイ時の低リーク消費電流特性の両立を、世界で初めて製品レベルのLSIで実用化した技術である。

さらに、上記 SH4 マイコンでの基板バイアス制御において新たに明らかとなった、GIDL (Gate Induced Drain Leakage) 電流による消費電流増加という課題についても述べる。 GIDL 電流を抑制するための方式について検討し、新しい基板バイアス制御方式 (低電圧基板バイアス制御方式) を提案する。

#### 第3章 低電圧 SRAM 回路の高速・低電力化

本章では、低電圧 SRAM 回路の高速・低電力化について述べる。SRAM 回路を使用しない LSI は存在しないといえるほど、LSI において SRAM 回路は重要な構成要素である。 当然、SOC においても SRAM 回路は必須回路要素である。

低電圧 SRAM 回路においては、「低電圧化に伴う動作速度劣化」から派生した課題として、サブスレッショルドリーク電流によるビット線ノイズ増加と、スタティック・ノイズ・マージン (SNM) 劣化の課題が新たに発生することを示す。本章では、従来のメモリセルでは接地電位に接続されていたソース線を積極的に駆動するソース線駆動型メモリセルを提案する。MOSトランジスタの耐圧の課題があるが、完全 CMOS メモリセルの構造をほとんど変更せずに上記ビット線ノイズ増加と SNM の課題を同時に解決できる。

#### 第4章 低電圧キャッシュの高速・低電力化、

キャッシュは、今日のマイクロプロセッサ性能に大きく影響を与える重要な回路要素である。高速 SRAM の多くがキャッシュとして用いられることから、本章では低電圧キャッシュの高速・低電力化について述べる。一般的にはキャッシュには SRAM 回路を使用するが、第3章で主に述べたメモリセルの制御方式の工夫による高速・低電力化のほかに、さまざまな方式的アプローチを適用できるという特徴がある。

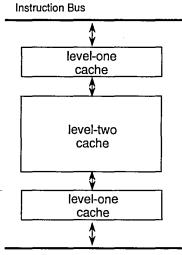

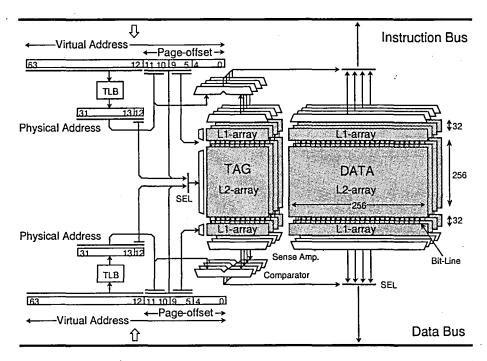

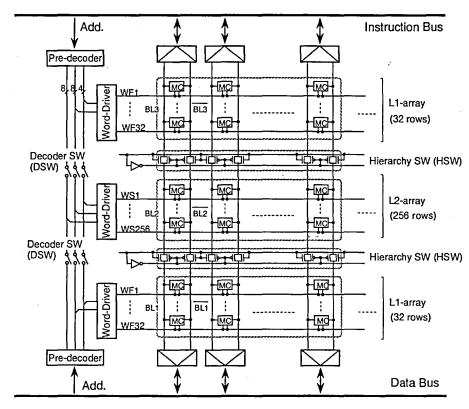

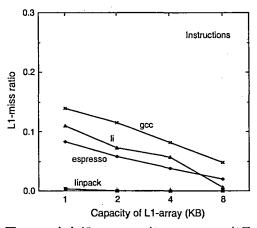

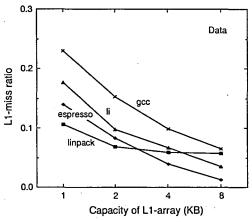

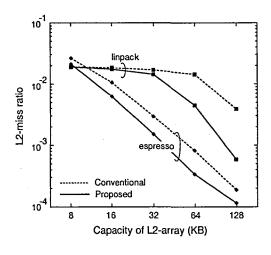

本章では、方式的アプローチにより、低電圧キャッシュを高速・低電力化できるビット線分離型メモリ階層方式を提案する。この方式は、低電圧でも低容量の SRAM は高速に動作するという特徴を利用し、一つのメモリセルアレイを階層化することにより実効的に高速なキャッシュ動作を達成している。

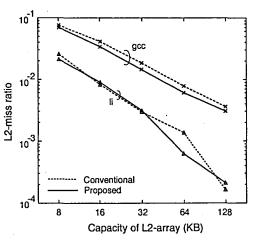

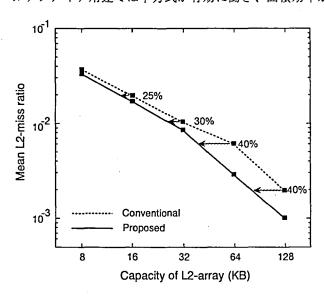

キャッシュは電力を大量に消費するチップ外アクセスを低減することが可能であり、マイクロプロセッサ等の LSI の低電力化に有効である。本章では、低電圧キャッシュによる低電力技術についても合わせて検討する。キャッシュの低電力化には、キャッシュのヒット率を向上させることが効果的である。一般に、高いヒット率を得るためには大容量のキャッシュを用いることが一般的である。しかし、大容量のキャッシュはチップ面積を増加させ、また高速動作を阻害する。この二つの相反する要求に応じることが可能な、小面積で高ヒット率が得られるキャッシュ構造について検討し、上記ビット線分離型メモリ階層方式を使用してユニファイドキャッシュを2ポート化したビット線分離型ユニファイドキャッシュを提案する。

#### 第 5 章 低電圧 DRAM 回路の高速化

多種多様の回路要素が集積化される SOC では、「低電圧化に伴う回路特性不整合」の課題は深刻である。SOC の代表的な例として、ロジック LSI に DRAM を混載した DRAM 混載ロジック LSI が挙げられる。DRAM のセンス系回路は、CMOS ロジック回路とは異なってアナログ回路的な要素を多く含む。そのため、「低電圧化による回路特性不整合」が生じやすい。本章では低電圧 DRAM 回路の高速化について述べ、「低電圧化に伴う回路特性不整合」の課題について論ずる。

SOC上の回路要素は個別チップ上で実現されてきたものとは異なる仕様になることが多い。たとえば、DRAM 混載ロジック LSI においては、混載 DRAM 回路は汎用 DRAM 回路よりも低電圧で動作させる必要がある。また、単体の汎用 DRAM と比較して生産数が限られており、量産効果が少ない。そのため、低コスト化のために DRAM 回路を混載することにより生ずる製造プロセス複雑化の低減が強く望まれている。例えば、DRAM 回路

で使用するトランジスタ仕様を、ロジック LSI で使用するトランジスタ仕様に合わせる。本章ではさらに、これらの事柄を SOC の基本設計事項として、混載用 DRAM センス系回路について論ずる。

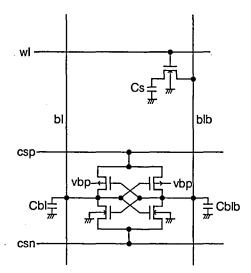

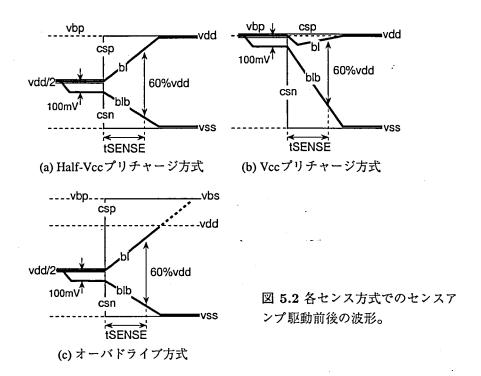

ここでは、「低電圧化に伴う回路特性不一致」の課題に対する解決策として、それぞれの回路を構成する MOS トランジスタの動作領域を一致させる手法を検討した。この手法の適用例として本章では、(a) メモリセルが接続されたビット線は Half-Vcc プリチャージし、センスアンプが接続されたビット線は Vcc プリチャージして、両ビット線間を NMOS 容量で容量結合するデュアルプリチャージレベルセンス方式と、(b) 再書込み時に、センスアンプに接続された一対のビット線のうち、メモリセルが接続されたビット線のみを駆動するシングルビット線再書き込み方式と、(c)Vcc プリチャージされたビット線対電位を PMOS のゲート端子に入力してグローバルビット線をタイミングレスで増幅する PMOS ダイレクトセンス方式を用いた DRAM センス系回路を提案する。

#### 第6章 低電圧クロック系の高速化

「低電圧化に伴う特性ばらつき増加」の解決策として、自立分散的手法を論ずる。これは特性ばらつきを相互調停によって相補することにより、特性ばらつきに強いシステムを構成する手法である。この手法の適用例として、本章では低電圧クロック系の高速化について述べる。

今日のほとんど全てのLSIは、同期式回路で構成されている。このような同期式回路における重要な回路要素として、クロック系がある。近年のLSIでは1GHzを超える周波数で動作するものもあり、このような高速LSIの実現には高精度なクロックが必須である。特にSOCではチップ面積が大きくなることが多く、クロック系の性能はSOCの性能に多大な影響を与える。

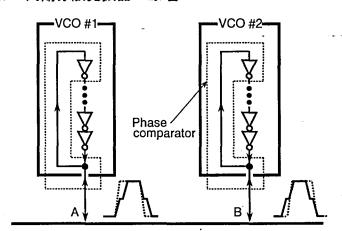

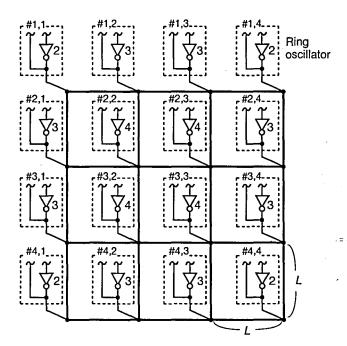

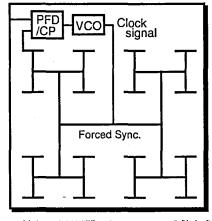

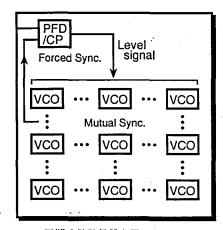

マイクロプロセッサ等の LSI で一般に用いられているクロック系は、PLL 等からなるクロック発生系と、そのクロック発生系で発生したクロックをフリップフロップやラッチまで分配するクロック分配系に分けられる。今日の LSI では、クロック発生系で発生したクロックを一方的にクロック分配系によって LSI 内で分配し、内部のフリップフロップやラッチを同期している。いわゆる中央集権的な"強制同期 (Forced Synchronization)"方法である。しかし、この方法では、クロック分配系を構成するバッファの低電圧化に伴う特性ばらつきの増加によって、クロックを低ジッタや低スキューに分配することが困難になる。

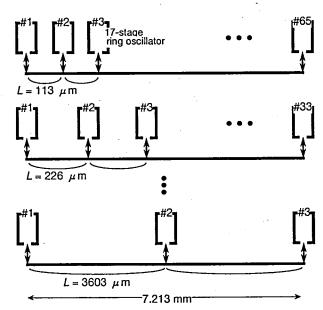

本章では、上記の"強制同期"とは対極的な同期手法として、"相互同期 (Mutual Synchronization)"による自立分散的なクロック系を提案する。これは複数の分散した発振器同士を同一位相・同一周波数で相互発振させることを可能にする同期分散発振器 (Synchronous Distributed Oscillator; SDO) を用いて、低電圧でも高い周波数のクロックを、低ジッタ・低スキューで大規模 LSI 上に分配することを可能にする。

#### 第7章結論

本章では、第2章から第6章の各章で得られた結果をもとに、第1章で述べた低電圧 化の四つの課題に対する解決策を整理し、今後に残された課題について述べる。 .

· ,

# 目次

| 1 | 序論  |                                                 | 1  |

|---|-----|-------------------------------------------------|----|

|   | 1.1 | 低電圧化の三つの目的                                      | 2  |

|   | 1.2 | 低電圧化の推移                                         | 2  |

|   | 1.3 | 低電圧化に伴う四つの課題                                    | 4  |

|   | 1.4 | 本論文の構成                                          | 5  |

|   | 参考  | 文献                                              | 8  |

| 2 | 任雷  | 圧ロジック回路の高速・低電力化                                 | 9  |

| - | 2.1 | 緒言                                              | 9  |

|   | 2.2 | ロジック回路の低電圧化の推移と課題                               | 10 |

|   | 2.3 | 従来のサブスレッショルドリーク電流削減技術                           | 12 |

|   | 2.0 | 2.3.1 スタンバイ時サブスレッショルドリーク電流削減技術                  | 12 |

|   |     | 2.3.2 アクティブ時サブスレッショルドリーク電流削減技術                  | 16 |

|   | 2.4 | 基板インピーダンス切り替え型基板バイアス制御方式によるサブスレッショ              | 10 |

|   |     | ルドリーク電流削減技術・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 19 |

|   |     | 2.4.1 全体構成                                      | 20 |

|   |     | 2.4.2 電源ネットおよび基板バイアスネット構成                       | 23 |

|   |     | 2.4.3 スタンダードセルレイアウトおよびウェル構造                     | 25 |

|   |     | 2.4.4 詳細回路                                      | 28 |

|   | 2.5 | 基板インピーダンス切り替え型基板バイアス制御方式の測定結果                   | 31 |

|   |     | 2.5.1 状態遷移時の過渡特性                                | 31 |

|   |     | 2.5.2 リーク電流特性                                   | 33 |

|   |     | 2.5.3 負電圧発生回路 (vbcg) 特性                         | 34 |

|   | 2.6 | 基板バイアス制御の限界 (GIDL 電流によるリーク電流増加)                 | 36 |

|   | 2.7 | 低電圧基板バイアス制御方式による GIDL 電流削減技術                    | 37 |

|   |     | 2.7.1 基本概念                                      | 37 |

|   |     | 2.7.2 測定結果                                      | 37 |

|   | 2.8 | 結言                                              | 39 |

|   | 参考  | 文献                                              | 40 |

| 3 | 低電  | 圧 SRAM 回路の高速・低電力化                               | 43 |

|   | 3.1 | 緒言                                              | 43 |

|   | 3.2 | SRAM 回路の低電圧化の推移と課題                              | 44 |

|   | 3.3 | 完全 CMOS メモリセルの低電圧高速動作                             | 45  |

|---|-----|---------------------------------------------------|-----|

|   |     | 3.3.1 低電圧高速動作のための主な駆動方式                           | 45  |

|   |     | 3.3.2 完全 CMOS メモリセルのスタティックノイズマージン                 | 46  |

|   | 3.4 | ソース線駆動型 (DSL) メモリセル                               | 48  |

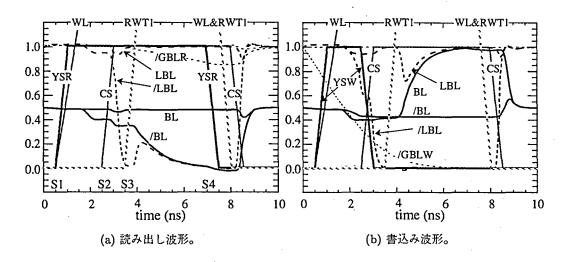

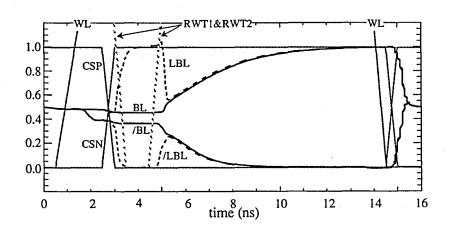

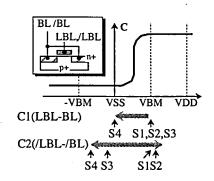

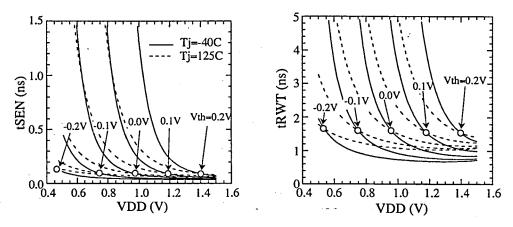

|   |     | 3.4.1 読み出し動作                                      | 49  |

|   |     | 3.4.2 書き込み動作                                      | 51  |

|   | 3.5 | ソース線駆動型 (DSL) メモリセルの駆動回路                          | 53  |

|   | 3.6 | その他の低電圧メモリセル                                      | 54  |

|   | 3.7 | 結言                                                | 57  |

|   | 参考  | 文献                                                | 58  |

|   | /丘帝 | 圧キャッシュの高速・低電力化                                    | 0.1 |

| 4 |     |                                                   | 61  |

|   | 4.1 | 緒言                                                |     |

|   | 4.2 | キャッシュの低電圧化の推移と課題                                  |     |

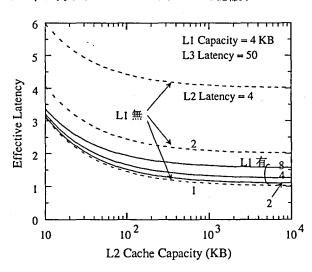

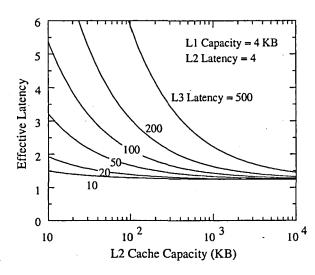

|   | 4.3 | メモリの階層化による高速化・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |     |

|   |     | 4.3.1 実効レイテンシの解析式化                                | -   |

|   |     | 4.3.2 メモリの階層化による実効レイテンシの評価                        |     |

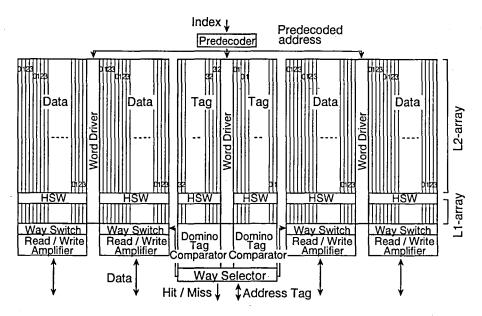

|   | 4.4 | ビット線分離型メモリ階層方式を用いたキャッシュ                           |     |

|   |     | 4.4.1 全体構成                                        |     |

|   |     | 4.4.2 ビット線分離型メモリ階層方式を用いたデータ部                      |     |

|   |     | 4.4.3 ドミノタグ比較器を用いたタグ部                             |     |

|   |     | 4.4.4 エイリアシング問題                                   |     |

|   | 4.5 | ビット線分離型メモリ階層方式を用いたキャッシュの試作結果                      |     |

|   | 4.6 | キャッシュによる LSI の低電力化                                | 81  |

|   |     | 4.6.1 キャッシュの小面積化                                  |     |

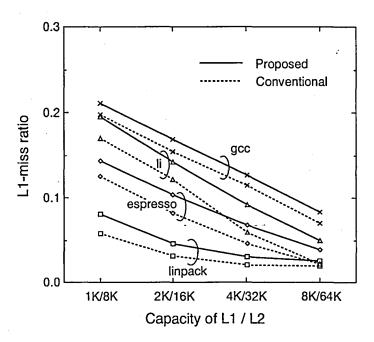

|   |     | 4.6.2 キャッシュの 2 ポート化                               | 82  |

|   | 4.7 | ビット線分離型ユニファイドキャッシュ                                | 83  |

|   |     | 4.7.1 全体構成                                        | 83  |

|   |     | 4.7.2 競合問題                                        | 85  |

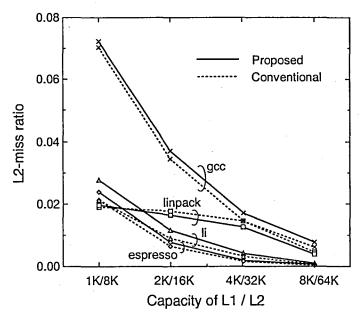

|   |     | 4.7.3 方式性能評価                                      | 86  |

|   | 4.8 | 結言                                                | 88  |

|   | 参考  | 文献                                                | 89  |

| 5 | 低電  | 圧 DRAM 回路の高速化                                     | 93  |

|   | 5.1 | 緒言                                                | 93  |

|   | 5.2 | 低電圧混載 DRAM 回路の基本設計方針                              |     |

|   | 5.3 | DRAM センス系回路の低電圧化の課題                               |     |

|   | 0.0 | 5.3.1 従来センス系回路の概要                                 |     |

|   |     | 5.3.2 従来センス系回路におけるセンス時間の低電圧特性                     |     |

|   | 5.4 | 低電圧 DRAM センス系回路の提案                                |     |

|   | 0.4 | 5.4.1 回路の概要                                       |     |

|   |     | 5.4.2 動作方法                                        |     |

|   |     | 5.4.2 <b>到作力伝</b>                                 | 102 |

|   |     |                                                   |     |

|   | ٠.  |

|---|-----|

| _ | 2 X |

| vii |  |

|-----|--|

|     |  |

|            | 5.5 | 結言                                               | 108 |

|------------|-----|--------------------------------------------------|-----|

|            | 参考  | 文献                                               | 109 |

|            |     |                                                  |     |

| 6          | 低電  | 圧クロック系の高速化                                       | 111 |

|            | 6.1 | 緒言                                               | 111 |

|            | 6.2 | クロック系の低電圧化の課題                                    | 112 |

|            | 6.3 | 同期分散発振器を用いたクロック系の提案                              | 113 |

|            |     | 6.3.1 同期分散発振器の原理                                 | 114 |

|            |     | 6.3.2 同期分散発振器のクロック系への応用                          |     |

|            | 6.4 | 同期分散発振器の基本特性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |     |

|            | 0.1 | 6.4.1 引き込み特性                                     |     |

|            |     |                                                  |     |

|            |     |                                                  |     |

|            | 6.5 | 同期分散発振器の試作結果・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |     |

|            | 6.6 | 結言                                               | 125 |

|            | 参考  | 文献                                               | 126 |

|            |     |                                                  |     |

| 7          | 結論  |                                                  | 129 |

|            | 7.1 | 本研究により明らかにされた事項                                  | 129 |

|            | 7.2 | 今後に残された課題                                        | 132 |

|            | 参考  | 文献                                               | 134 |

|            |     |                                                  |     |

| 謝          | 辞   |                                                  | 135 |

| <b>₩</b> ; | 究業績 | <b>*</b>                                         | 137 |

|            |     |                                                  |     |

# 第1章

# 序論

今日、大規模集積回路 (Large Scale Integration; LSI) はありとあらゆるものに搭載され、その中には指輪に搭載された例もある。<sup>1</sup> それらの LSI が使用されている代表的な例として、携帯電話やパーソナルコンピュータ (PC) を挙げることができる。日本において、2000年には携帯電話の加入者数が据え置き型電話の加入者数を超えると予測されており、さらに 2001年においては、PC の所有率が TV のそれを超えると予想されている。両方の例において、LSI はその構成要素の中心的役割を果たしている。

このように今日では極めて身近な存在となった LSI であるが、さらに近年、LSI の集積化が進むにつれて異なる種類の回路要素を同一チップ上に集積できるようになり、これによってシステムを構成するのに必要な回路の多くが一つのチップ上に集積できるようになった。これらの数種の回路が複合した構造を持つ LSI を特にシステムオンチップ (Systemon-a-chip; SOC) と呼び、日本では、「システム LSI」と呼んで注目されている。既に国際会議等ではワンチップ TV [1] やワンチップ PC [2] などが発表されており、ワンチップ携帯電話が実現されるのもそれほど遠い将来ではないように思われる。今日、SOC は、システムの要求する「機能」、「性能」、「価格」を同時に満たすシステムソリューションを、ネットワーク市場や携帯電話市場等の競争が激化する市場において短時間に提示するために必要不可欠なデバイスとなっている。

本論文では、このような SOC を低い電源電圧で、高速かつ低電力に動作させる回路技術について述べる。 SOC の開発には、プロセス技術、デバイス技術、回路技術、CAD(Computer Aided Design) 技術、マイクロアーキテクチャ技術、アーキテクチャ技術、ソフトウェア技術に加えて、パッケージ技術などの数え切れないほど多くの技術が必要である。本論文では、その中でも特に回路技術を中心に述べる。回路技術は、物理限界という枠の中で物理現象をうまく利用して開発されるデバイス技術と、完全に人間の知識の中で理論的に開発されるアーキテクチャ技術という、一見全く異なる二つの技術を結びつける重要な仲介技術であり、LSI の性能に大きな影響を与える技術である。また、電源電圧の低電圧化は次節で述べるような極めて大きな影響を与える技術である。また、電源電圧の低電圧化は次節で述べるような極めて大きな効果があり、低電圧 SOC の実現は新しい市場を開拓するほどの可能性を秘めている。産業的も経済的にも極めて大きな影響を与える研究分野であるといえる。

<sup>1998</sup>年の Java 開発者会議「JavaOne'98」では、参加者全員に Java Ring という指輪が配られた。その指輪には Java が動作する LSI と電池が組み込まれており、コンピュータと通信することができる。この Java Ring をコンピュータに接続し、コンピュータから Java Ring に自分のプロフィールを書き込むことができた。さらに、その参加者の Java Ring であるプログラムを実行させ、参加者全員の結果を集めて 1 つの複雑な計算を行うデモンストレーションが行われた。

## 1.1 低電圧化の三つの目的

LSI において、電源電圧は特に重要なパラメータであり、電源電圧の値によって回路構成は大きく変化する。回路技術は電源電圧の変化に応じて開発が進められてきたともいえる。LSI を低電圧で動作させることの目的は大きく分けて以下の3通りに分類できる。

#### 高集積化のための低電圧化

低電圧化しないで MOSトランジスタを微細化した場合、MOSトランジスタ内の電界強度が増加し、多くのホットキャリアが発生する。これによって、デバイスの信頼性が低下すると同時に大きなドレイン電流を得ることが困難になる [3]。また、MOSトランジスタの酸化膜にも大きな電界が印加され、酸化膜の信頼性が低下する [4]。低電圧化することで、ホットキャリアの発生を抑制ながら微細化することが可能になり、LSIを構成する MOSトランジスタの信頼性を維持できる。さらに、MOSトランジスタの動作に必要な耐圧を低くできる。例えば電界強度を増加させずに MOSトランジスタを微細化する定電界スケーリング則を適用でき [5]、多くの回路をチップ上に集積できる。

#### 高速化のための低電圧化

上記のように、低電圧で動作させることによって MOS トランジスタを微細化できる。微細化によって信号振幅に対する負荷を小さくでき、回路を高速に動作できる。微細化に伴う MOS トランジスタのパラメータの設計方法には種々の方法があるが、例えば定電界スケーリング則に沿って、電源電圧  $V_{\rm DD}$  を  $1/\alpha$  にし、ゲート長  $L_{\rm g}$ 、ゲート幅  $W_{\rm g}$ 、ゲート酸化膜  $t_{\rm ox}$  を  $1/\alpha$  倍に微細化した場合、ゲート負荷容量  $C_{\rm g}$ 、ドレイン電流  $I_{\rm ds}$  はそれぞれ  $1/\alpha$  となり、回路の遅延 (=CV/I) は  $1/\alpha$  になる。

#### 低電力化のための低電圧化

CMOS 回路の消費電力は、主として負荷の充放電によって生じる。負荷の充放電による消費電力  $P_{\mathrm{load}}$  は、負荷容量を  $C_{\mathrm{load}}$ 、負荷の駆動頻度を f、負荷の駆動振幅を  $V_{\mathrm{swing}}$ 、電源電圧を  $V_{\mathrm{DD}}$  とすれば、

$$P_{\text{load}} = f \cdot C_{\text{load}} \cdot V_{\text{swing}} \cdot V_{\text{DD}} \tag{1.1}$$

で与えられる。CMOS 回路では負荷の駆動振幅は電源電圧と同じ値になるため、電源電圧の2乗に比例して低電力化できる。

### 1.2 低電圧化の推移

LSIの電源電圧は年々低下しているが、前節で述べたように低電圧化の目的は大きく分けて3種類あり、時代とともにその目的は異なっている。本節では低電圧化の推移とその目的の推移について述べる。

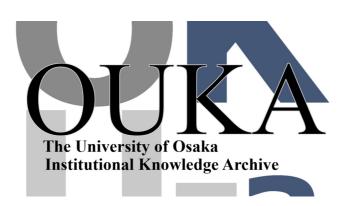

図 1.1にロジック LSI と DRAM の電源電圧推移を示す [6]。1990 年頃は、LSI の低電圧化の目的は「高集積化のための低電圧化」が主であった。この低電圧化が顕著に行われた例として、DRAM を挙げることができる。DRAM は大容量化のために高集積化の要求がもっとも高い LSI の一つであり、テクノロジドライバとして DRAM のメモリセルおよびその周辺回路の微細化は急速に進められた。そのため、DRAM は他の LSI よりも急速に低電圧化がなされてきた。 1Mb DRAM 以降では他の LSI との入出力インターフェースの

図 1.1 ロジック LSI (コア電圧と I/O 電圧) と DRAM の電源電圧推移。 ロジック LSI には SIA ロードマップの電源電圧推移を示した。 DRAM はアレイ電圧推移を示した。

ための標準化電圧の低電圧化が、DRAM 内部回路の低電圧化に追いつかないという事態になり、DRAM はチップ外部から入力される標準規格電圧をチップ内部で降圧して使用している [7,8]。

ところが 1990 年代前半からは、文献 [9] に代表されるような、「低電力化のための低電圧化」が脚光を浴びることになる。スケーリング則で算出される電圧値よりも低電圧で MOSトランジスタを用い、消費電力を削減する方法が注目された。第2章で述べる多くのサブスレッショルドリーク電流低減技術が、CMOS デジタル回路設計における最重要研究課題の一つに挙げられるようになったのもこの頃である。主な国際会議等でローパワーのセッションが設けられるなど、低電圧回路に関する多くの研究が進められた。低電力化が目的であることから、アーキテクチャ・設計・回路・デバイス・プロセス・実装といったあらゆる技術が低電力化のために開発されはじめた。つまり、この頃の低電圧回路はあくまで低電力化を目的とした、いわば特殊用途のLSI向けに開発されていたといえる。

しかし、1995年からは再びその様子が変わることになる。図 1.1で示されたように、1995年頃までは LSI の入出力インターフェースの標準化された電圧に沿って LSI の電源電圧は決定されてきた。これがチップの低電圧化の妨げの要因の一つに数えられてきた。ところが、1995年以降では、多くの LSI でいわゆる "I/O 電圧"と"コア電圧"という 2 電源を供給するチップ電源形態を持つようになってきた。このような電源形態が普及すると、コア電圧をある程度自由に設定できるようになる。これにより、LSI はスケーリング則に沿った微細化が比較的容易に進められることになり、「高速化のための低電圧化」が急激な勢いで進められることになった。さらにこの頃から、LSI の発熱の問題からの低電圧化の要求も強まった。ハイエンドプロセッサの中には、数十 W の消費電力を持つチップも少なくはなく、そのようなチップでは高速化のために低電力化することが必須であり、「高速化と低電力化のための低電圧化」がなされてきたといえる。

さらに近年注目されつつある電源電圧の推移としては、幅広い電源電圧範囲 (従来の MOS トランジスタや熱設計で決まる電源電圧から、低速であるが LSI が正常に動作する低電圧まで)をサポートする LSI が多く登場するようになったことが挙げられる。これらの LSI の中には、電源電圧と動作周波数を LSI の動作モードによって切り替えて使用されるものもある。すなわち、低速動作で十分な場合には低い電源電圧で動作させ、高速動作が必要な場合には高い電源電圧で動作させる。電源電圧  $V_{\rm DD}$  と動作周波数 f を変化させれば、消費電力  $P_{\rm load}$  は式 (1.1)で示されるように 3 乗に比例して低減できるために、低電力化の効果が大きい [10-12]。

# 1.3 低電圧化に伴う四つの課題

前節で述べたように低電圧化の目的は時代と共に変化しているが、今日では低電圧化は全てのLSIに必須の条件である。しかし、低電圧化には以下の課題がある。

#### 低電圧化に伴う動作速度低下

1.1 節では低電圧化によって回路を高速に動作できると述べた。しかし、これは低電圧化と同時にスケーリング則に沿って全ての MOS トランジスタのパラメータを変えることができる場合である。実際には後で述べるように、しきい値電圧のスケーリングは困難であり、理想的なスケーリングは実現できない。さらに、スケーリング則は MOS トランジスタに関するものであり、LSI の動作速度は MOS トランジスタだけで決定されるものではないという事実もある。例えば、微細化によって配線負荷容量が増加すると、高速化が阻まれる。

#### 低電圧化に伴う電力増加

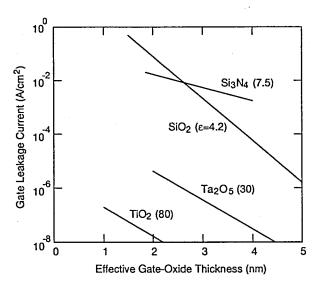

1.1 節では低電圧化によって低電力化できると述べた。しかし、これも理想的なスケーリング則が実現できる場合である。実際には、スケーリング則どおりにしきい値電圧を低くすると、サブスレッショルドリーク電流が著しく増加する。これは、スケーリング則は MOSトランジスタのオン時の飽和電流値に関するものであり、オフ時のサブスレッショルド電流に関するものではないという事実に起因している。さらに、近年では CMOS 回路の貫通電流による電力消費やゲート酸化膜リーク電流に伴う電力消費 [13] などが無視できない電力増加要因として顕れている。

また、上記の「低電圧化に伴う動作速度低下」の課題から派生した課題として、以下の課題がある。

#### 低電圧化に伴う回路特性不整合

回路の駆動電流である MOSトランジスタのドレイン電流は、二つの成分からなっている。一つは電界によって電子が動くことから生じるドリフト電流であり、もう一つは熱拡散によって電子が動くことによって生じる拡散電流である。電流発生要因が異なるために、両者の電流のドレイン電圧依存性および温度依存性は大きく異なっている。2 電源電圧が高い場合、電源電圧に対してしきい値電圧が低いため、回路特性はドレイン電流のドリフト電流成分によって主に決定される。しかし、低電圧では上記拡散電流の成分が相対的に大きくなり、さらに回路構成によってその成分割合が大きく異なる。これによって、低電圧では回路構成によって電源電圧特性や温度特性が異なり、回路間での特性不整合が生じる。

#### 低電圧化に伴う特性ばらつき増加

スケーリング則に従って MOSトランジスタを微細化する際に、MOSトランジスタの製造精度も同様にスケーリングして高精度化する必要があるが、実際にはこれは困難である。このため、低電圧化に伴って製造ばらつきによる MOSトランジスタの特性ばらつきの影響は増加する。また、MOSトランジスタが原子の数で数えられるような寸法まで微細化されるようになれば、量子化ノイズが発生する。これも MOSトランジスタのばらつき要因となる [14]。

<sup>&</sup>lt;sup>2</sup>例えば温度特性については、高温ではドリフト電流は電子の動きが格子振動によって抑制されるために小さくなるのに対して、拡散電流は高温で逆に大きくなる。

# 1.4 本論文の構成

SOC を構成する要素としては、スタンダートセルの集合からなるセルライブラリとマクロに大きく分けられるが、機能で分類すれば、ロジック回路、メモリ回路、アナログ回路、クロック系、I/O 回路、電源回路に大きく分類できる。本論文は、前節で述べた低電圧化に伴う4つの課題に対する解決策を検討するために、上記した SOC 構成要素の中で、ロジック回路、SRAM 回路、キャッシュ、DRAM 回路、クロック系の5種類の要素回路に関して、低電圧動作時の高速・低電力回路技術を研究したものである。以下、本論文の構成を詳しく述べる。

## 「低電圧化に伴う動作速度劣化」と「低電圧化に伴う電力増加」の課題について

SOCには多種多様の回路が集積されるが、本論文ではSOCを構成する回路要素のうち、ロジック回路、SRAM回路、キャッシュの各回路要素に関して、「低電圧化に伴う動作速度低下」と「低電圧化に伴う電力増加」の課題について論じる。

第2章では、低電圧ロジック回路の高速・低電力化について述べる。ロジック回路は SOC の中で最も重要な回路要素の一つであり、ロジック回路の性能は SOC 全体の性能に 大きく影響を与える。低電圧ロジック回路における高速・低電力化のキーとなるのは、微細 化に伴って指数関数的に増加するサブスレッショルドリーク電流の低減技術である。1990 年代前半から 1998 年にかけて研究されてきた低電力化のためのサブスレッショルドリーク削減技術は、今日、実用化の時代へと進みつつあるといえる。

そこで第2章では、基板バイアス制御によるリーク電流削減技術を、大規模高速 LSI(SH4 マイコン:3.3 M Trs, 200 MHz) に搭載した開発事例を述べる。従来の基板バイアス制御方式では基板インピーダンスが高くなる等の弊害により、アクティブ時の高速動作を維持することが困難であった。この課題を解決するために、基板インピーダンス切り替え型基板バイアス制御方式を開発した。チップ上に約1万個のスイッチセルと呼ぶ低基板インピーダンス化回路を分散配置する方式で、アクティブ時の高速動作と、スタンバイ時の低リーク消費電流特性の両立を、世界で初めて製品レベルの LSI で実用化した技術である。

さらに、第2章では上記 SH4 マイコンでの基板バイアス制御において新たに明らかとなった、GIDL(Gate Induced Drain Leakage) 電流による消費電流増加という課題についても述べる。GIDL 電流を抑制するための方式について検討し、新しい基板バイアス制御方式 (低電圧基板バイアス制御方式) を提案する。

第3章では、低電圧 SRAM 回路の高速・低電力化について述べる。SRAM 回路を使用しない LSI は存在しないといえるほど、LSI において SRAM 回路は重要な構成要素である。当然、SOC においても SRAM 回路は必須回路要素である。例えばマイクロプロセッサでは、キャッシュや TLB(Translation Look-aside Buffer) として用いられている。また、小容量のメモリとしてはレジスタファイルや各種バッファ等も SRAM 回路で構成されている。特にキャッシュは、今日のマイクロプロセッサにとって性能に大きく影響を与える重要な回路要素である。

そこで第3章では、従来の低電圧 SRAM 回路の高速・低電力化技術を述べた後、完全 CMOS メモリセルの構造をほとんど変更せずに、低電圧動作時の読み出し速度向上と書き込み時の低消費電力化を実現するソース線駆動方式のメモリセル構造を提案する。このソース線駆動型メモリセルは、従来のメモリセルでは接地電位に接続されていたソース線

を積極的に駆動することにより、低電圧時での高速動作と高ノイズマージンを両立するメモリセル制御方式である。

1995年6月に京都にて開催された学会においてソース線駆動メモリセルを発表後、低電圧回路関連の書籍に低電圧 SRAM メモリの代表な例として記載されるなど大きな反響を呼び、その後、各種の類似した低電圧メモリセルも発表される流れを作った。 第3章では、その中でも代表的な低電圧メモリセルについて、その特徴を述べる。

キャッシュは、今日のマイクロプロセッサ性能に大きく影響を与える重要な回路要素である。高速 SRAM の多くがキャッシュとして用いられることから、第4章では低電圧キャッシュの高速・低電力化について述べる。一般的にはキャッシュには SRAM 回路を使用するが、第3章で主に述べたメモリセルの制御方式の工夫による高速・低電力化のほかに、さまざまな方式的アプローチを適用できるという特徴がある。

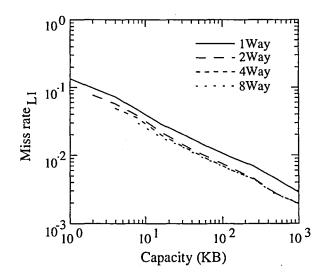

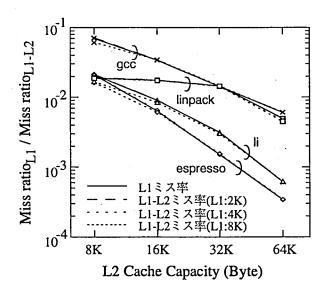

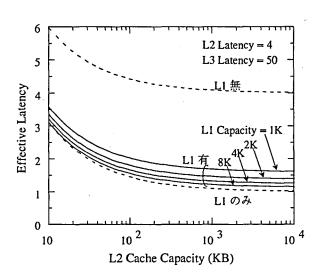

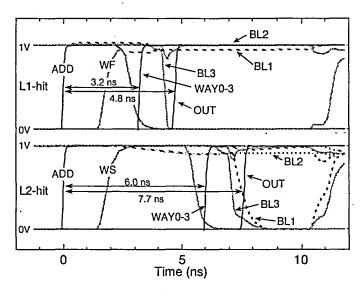

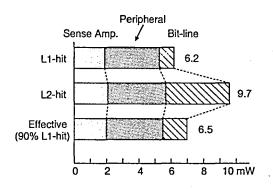

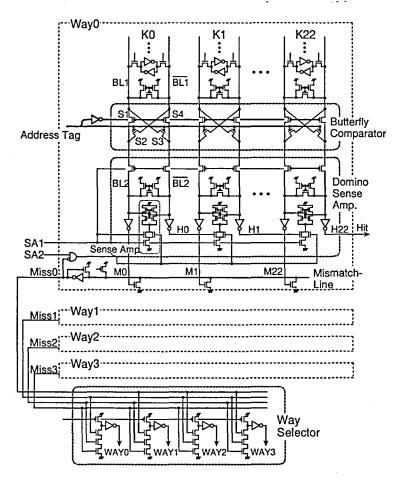

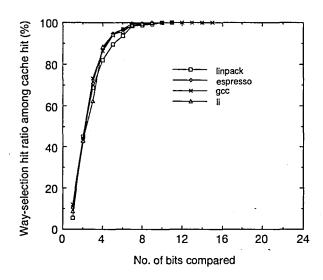

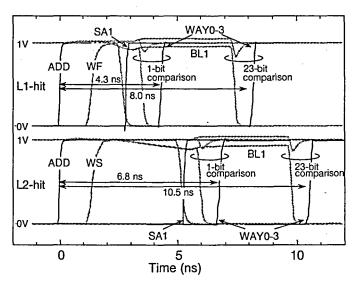

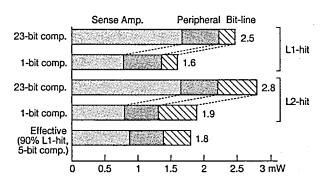

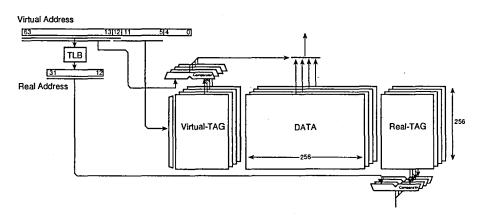

そこで第4章では、方式的に低電圧キャッシュを高速・低電力化できるビット線分離型メモリ階層方式を提案する。この方式は、低電圧でも低容量の SRAM は高速に動作するという特徴を利用し、一つのメモリセルアレイを階層化することにより実効的に高速なキャッシュ動作を達成している。この方式を用いて試作した、16KB+2KB・4ウェイ・セット・アソシアティブ構造のキャッシュの開発結果を述べる。

キャッシュは電力を大量に消費するチップ外アクセスを低減することが可能であり、マイクロプロセッサ等の LSI の低電力化に有効である。第4章では、低電圧キャッシュによる低電力技術についても合わせて検討する。キャッシュの低電力化には、キャッシュのヒット率を向上させることが効果的である。一般に、高いヒット率を得るためには大容量のキャッシュを用いることが一般的である。しかし、大容量のキャッシュはチップ面積を増加させ、また高速動作を阻害する。第4章では、この二つの相反する要求に応じることが可能な、小面積で高ヒット率が得られるキャッシュ構造について検討し、上記ビット線分離型メモリ階層方式を使用してユニファイドキャッシュを2ポート化したビット線分離型ユニファイドキャッシュを提案する。

#### 「低電圧化に伴う回路特性不整合」の課題について

多種多様の回路要素が集積化される SOC では、「低電圧化に伴う回路特性不整合」の課題は深刻である。SOC の代表的な例として、ロジック LSI に DRAM を混載した DRAM 混載ロジック LSI が挙げられる。DRAM のセンス系回路は、CMOS ロジック回路とは異なってアナログ回路的な要素を多く含む。そのため、「低電圧化による回路特性不整合」が生じやすい。本論文では第5章において低電圧 DRAM 回路の高速化について述べ、「低電圧化に伴う回路特性不整合」の課題について論ずる。

SOC上の回路要素は個別チップ上で実現されてきたものとは異なる仕様になることが多い。たとえば、DRAM 混載ロジック LSI においては、混載 DRAM 回路は汎用 DRAM 回路よりも低電圧で動作させる必要がある。また、単体の汎用 DRAM と比較して生産数が限られており、量産効果が少ない。そのため、低コスト化のために DRAM 回路を混載することにより生ずる製造プロセス複雑化の低減が強く望まれいる。例えば、DRAM 回路で使用するトランジスタ仕様を、ロジック LSI で使用するトランジスタ仕様に合わせる。第5章ではさらに、これらの事柄を SOC の基本設計事項として、混載用 DRAM センス系回路について論ずる。

ここでは、「低電圧化に伴う回路特性不一致」の課題に対する解決策として、それぞれ

の回路を構成する MOSトランジスタの動作領域を一致させるという手法を検討した。この手法の適用例として第5章では、(a) メモリセルが接続されたビット線は Half-Vcc プリチャージし、センスアンプが接続されたビット線は Vcc プリチャージして、両ビット線間を NMOS 容量で容量結合するデュアルプリチャージレベルセンス方式と、(b) 再書込み時に、センスアンプに接続された一対のビット線のうち、メモリセルが接続されたビット線のみを駆動するシングルビット線再書き込み方式と、(c) Vcc プリチャージされたビット線対電位を PMOS のゲート端子に入力してグローバルビット線をタイミングレスで増幅する PMOS ダイレクトセンス方式を用いた DRAM センス系回路を提案する。

### 「低電圧化に伴う特性ばらつき増加」の課題について

「低電圧化に伴う特性ばらつき増加」の解決策として、自立分散的手法を論ずる。これは特性ばらつきを相互調停によって相補することにより、特性ばらつきに強いシステムを構成する手法である。この手法の適用例として、第6章において低電圧クロック系の高速化について述べる。

今日のほとんど全てのLSIは、同期式回路で構成されている。このような同期式回路における重要な回路要素として、クロック系がある。近年のLSIでは1GHzを超える周波数で動作するものもあり、このような高速LSIの実現には高精度なクロックが必須である。特にSOCではチップ面積が大きくなることが多く、クロック系の性能はSOCの性能に多大な影響を与える。

マイクロプロセッサ等の LSI で一般に用いられているクロック系は、PLL 等からなるクロック発生系と、そのクロック発生系で発生したクロックをフリップフロップやラッチまで分配するクロック分配系に分けられる。今日の LSI では、クロック発生系で発生したクロックを一方的にクロック分配系によって LSI 内で分配し、内部のフリップフロップやラッチを同期している。いわゆる中央集権的な"強制同期 (Forced Synchronization)"方法である。しかし、この方法では、クロック分配系を構成するバッファの低電圧化に伴う特性ばらつきの増加によって、クロックを低ジッタや低スキューに分配することが困難になる。

数 GHz 動作の論理回路を実現する技術として、チップ全体を単一のクロック信号に同期して動作させるのではなく、チップを複数のブロックに分割しそれぞれのブロック間を非同期で動かす手法も近年提案されている [15]。これも自立分散的な手法の一つであるが、第6章では、上記の"強制同期"とは対極的な同期手法として、"相互同期 (Mutual Synchronization)"による自立分散的なクロック系を提案する。これは複数の分散した発振器同士を同一位相・同一周波数で相互発振させることを可能にする同期分散発振器 (Synchronous Distributed Oscillator; SDO) を用いて、低電圧でも高い周波数のクロックを、低ジッタ・低スキューで大規模 LSI 上に分配することを可能にする。

#### 低電圧化の今後の課題について

第7章では、第2章から第6章の各章で得られた結果をもとに上記した四つの課題の 解決策について整理し、今後に残された課題について述べる。

# 参考文献

- [1] L. Nederlof, "One-Chip TV", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 26-27, Feb. 1996.

- [2] F. Norrod and R. Wawrzynek, "A Multimedia-Enhanced x86 Processor", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 220-221, Feb. 1996.

- [3] T. Kunikiyo, M. Takenaka, Y. Kamakura, M. Yamaji, H. Mizuno, M. Morifuji, K. Taniguchi and C. Hamaguchi, "A Monte Carlo Simulation of Anisotropic Electron Transport in Silicon Including Full Band Structure and Anisotropic Impact-Ionization Model", J. of Appl. Phys., vol. 75, no. 1, pp. 297-312, Jan. 1994.

- [4] H. Mizuno, M. Morifuji, K. Taniguchi and C. Hamaguchi, "Theoretical calculation of impact ionization rate in SiO<sub>2</sub>", J. of Appl. Phys., vol. 74, pp. 1100-1105, July 1993.

- [5] R.H. Donnard, "Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions", *IEEE J. of Solid-State Circuits*, vol. 9, no. 5, Oct. 1974.

- [6] "The National Technology Roadmap for Semiconductors", tech. report, Semiconductor Industry Assn., San Jose, Calif., 1999.

- [7] T. Mano, J. Yamada, J. Inoue and S. Nakajima, "Submicron VLSI Memory Circuits", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 234-235, Feb. 1983.

- [8] K. Itoh, "Trends in Megabit DRAM Circuit Design", *IEEE J. of Solid-State Circuits*, vol. 25, no. 3, pp. 778-789, June 1990.

- [9] A.P. Chandrakasan, S. Sheng and R.W. Brodersen, "Low-Power CMOS Digital Design", IEEE J. of Solid-State Circuits, vol. 27, no. 4, pp. 473-484, Apr. 1992.

- [10] L. Nielsen, C. Niessen, J. Sparso and K. van Berkel, "Low-Power Operation using Self-Timed Circuits and Adaptive Scaling of Supply Voltage", *IEEE Trans. Very Large-Scale Integration (VLSI) Systems*, pp. 391-397, Dec. 1994.

- [11] V. Gutnik and A. Chandrakasan, "An Efficient Controller for Variable Supply-Voltage Low Power Processing", Symp. on VLSI Circuits Dig. of Tech. Papers, pp. 158-159, June 1996.

- [12] T. Pering, T. Burd and R. Brodersen, "The Simulation and Evaluation of Dynamic Voltage Scaling Algorithms", Int'l Symp. on Low Power Electronics and Design (ISLPED), pp. 76-81, Aug. 1998.

- [13] T. Inukai and T. Hiramoto, "Suppression of Stand-by Tunnel Current in Ultra-Thin Gate Oxide MOSFETs by Dual Oxide Thickness MTCMOS (DOT-MTCMOS)", Extended Abstract of the 1999 Int'l Conf. on Solid State Devices and Materials (SSDM), pp. 264-265, Sept. 1999.

- [14] H-S. Wong and Y. Taur, "Three-Dimensional "Atomistic" Simulation of Discrete Randum Dopant Distribution Effects in Sub-0.1μm MOSFET's", Int'l Electron Devices Meeting (IEDM) Tech. Dig., pp. 705-708, Dec. 1996.

- [15] S. Schuster, W. Reohr, P. Cook, D. Heidel, M. Immediato and K. Jenknis, "Asynchronous Interlocked Pipelined CMOS Circuits Operating at 3.3-4.5GHz", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 292-293, Feb. 2000.

# 第2章

# 低電圧ロジック回路の 高速・低電力化

## 2.1 緒言

本章では低電圧ロジック回路の高速・低電力化について論ずる。ロジック回路は今日の LSIの中で最も重要な回路要素の一つであり、ロジック回路の性能は SOC の性能に大きな 影響を与える。

本章ではまず始めにロジック回路の低電圧化の推移について述べる。その後、低電圧ロジック回路の高速・低電力化の妨げとなっているサブスレッショルドリーク電流について、 従来のサブスレッショルドリーク電流削減技術を詳しく述べる。

代表的な上記リーク削減技術としては、電源スイッチによる方法と基板バイアス制御による方法が挙げられるが、本章では、基板バイアス制御による上記リーク電流削減技術を、大規模高速 LSI(SH4 マイコン:3.3 M Trs, 200 MHz) に搭載した開発事例を述べる [1,2]。従来の基板バイアス制御方式では基板インピーダンスが高くなる等の弊害により、アクティブ時の高速動作を維持することが困難であった。この課題を解決するために、基板インピーダンス切り替え型基板バイアス制御方式を提案する。この方式では、チップ上に約1万個のスイッチセルと呼ばれる低基板インピーダンス化回路を分散配置することにより、アクティブ時の高速動作と、スタンバイ時の低リーク消費電流特性を両立できる。

また、本章では SH4 マイコンでの基板バイアス制御において新たに明らかとなった GIDL(Gate Induced Drain Leakage) 電流による消費電流増加についても述べる。GIDL 電流を抑制する新しい基板バイアス制御方式 (低電圧基板バイアス制御方式) を提案する。

最後に、基板バイアス制御を行った SH4 マイコンに、低電圧基板バイアス制御方式を適用した結果を述べる。

## 2.2 ロジック回路の低電圧化の推移と課題

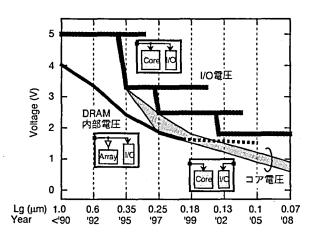

図 2.1にロジック LSI のコア電源電圧とサブスレッショルドリーク電流のトレンドを示す。各世代で予測される電源電圧のトレンドについては 1999 年発表の SIA ロードマップ [3] の値を元に計算した。本ロードマップでは、高速 LSI(high-speed) と低電力 LSI(low-power) に分けてトレンドが示されているが、それぞれのしきい値電圧については電源電圧の 1/3 の値に設定した。

図 2.1 電源電圧 (実線) とサブスレッショルドリーク電流 (破線) のトレンド。0.25 μm 世代でのチップ上の MOS トランジスタのトータルゲート幅が 10 m と仮定した。トランジスタ数は世代の二乗に比例して増加するが、ゲート幅は世代に反比例して減少する。そのため、リーク電流の値は世代に比例して増加すると仮定した。また、温度 Tj は 75℃ を仮定した。

微細化が進むに従い、急激にサブスレッショルドリーク電流が増加している。特に低電力 LSI では LSI の充放電電流を削減するために低い電源電圧に設定されており、そのためにサブスレッショルドリーク電流が大きくなっている。このサブスレッショルドリーク電流の増加は、スケーリング則ではサブスレッショルド特性はスケーリングされないという事実に起因している。1

第1章で述べた「低電圧化に伴う電力増加」の課題の主たる要因はこのサブスレッショルドリーク電流である。この電力増加を抑えるためにしきい値電圧を高くすると、「低電圧化に伴う動作速度低下」を招く。「低電圧化に伴う電力増加」と「低電圧化に伴う動作速度劣化」をいかにして同時に解決するかという命題は、上記サブスレッショルドリーク電流をいかにして削減するかという命題に等しいといっても過言ではない。

また、サブスレッショルドリーク電流は他にも影響を及ぼす。例えば、サブスレッショルドリーク電流は回路動作にはあまり依存しないために、回路が動作しないスタンバイ時でも流れてしまうという特徴がある。本来、10年以上前に実用化されていたバイポーラトランジスタによる ECL 回路等とは異なり、CMOS 回路は動作しないときの消費電力が零であるというのが一つの特徴であった。それゆえ CMOS 回路は、今日の 1000 万トランジスタを超える規模の大規模集積化を可能とし、今日の高性能高速 LSI の実現を可能にしたといえる。上記サブスレッショルドリーク電流によって、この前提が崩れることになる。

さらにまた、サブスレッショルドリーク電流の別の弊害として、LSIのリーク電流テス

<sup>1</sup>スケーリング則は MOS トランジスタのオン時の飽和電流値に関するものであり、オフ時のサブスレッショルド電流に関するものではない。

ト  $(I_{DDQ}$  テスト) ができなくなることが挙げられる [4,5]。  $I_{DDQ}$  テストとは、トランジスタがスイッチングしていない静止時に LSI の電源電流を測って、故障の有無を検出する方法である。故障がなければ静止時にはわずかな電流が流れるだけであるが、故障があると大きな電流が流れることを利用する。LSI のテスト手法として主流の機能テスト (ファンクションテスト) と比較すると、少ないテストパターンで多くの故障を検出できるという特徴がある。 $^2$  上記サブスレッショルドリーク電流は故障による微小電流をスクリーニングし、 $I_{DDO}$  テストを困難にする。

上記したように、低電圧ロジック回路における高速・低電力化のキーとなるのは、微細化にともなって指数関数的に増加するサブスレッショルドリーク電流の低減技術である。この技術は1990年代前半から1998年にかけて多く研究されてきた。次節では、現在までに提案された主なサブスレッショルドリーク電流削減技術について述べる。

$<sup>^2</sup>$ LSI の集積度の向上にともない、テスト工程の負荷が急激に増加している。一般に、ゲート数が n 培になれば、ファンクションテストに必要なテストパターンの数は  $n^2$  培になるといわれている。現在では、スキャンパス手法や BIST(Built-in Self Test) 手法といったテスト 容易化設計の手法を用いて、テストパターン数の削減する方向に向かっている。 $I_{\rm DDQ}$  テスト手法もテストパターン削減手法の一種である。さらにまた、現在主流のファンクションテストでは発見しにくいタイプの故障が増加する傾向にある。たとえば、開放故障、短絡故障、絶縁不良、スイッチング動作時の過渡状態の異常などである。

# 2.3 従来のサブスレッショルドリーク電流削減技術

従来のサブスレッショルドリーク電流の低減技術は大きく分けて次の2種類に分類できる。 $^3$

- (1) スタンバイ時のサブスレッショルドリーク電流削減技術

- (2) アクティブ時のサブスレッショルドリーク電流削減技術

サブスレッショルドリーク電流はCMOS 回路が動作していないときにも流れるため、LSI のスタンバイ状態とアクティブ状態の両方の消費電力を増加させることになる。しかしながら、スタンバイ時には負荷の充放電による消費電力が少なくなるため、LSI の消費電力の中でサブスレッショルドリーク電流による電力消費の比率が大きくなる。そのため、特にスタンバイ時のサブスレッショルドリーク電流の低減技術が盛んに研究されている。

以下、スタンバイ時のサブスレッショルドリーク電流削減技術を中心として、主なサブスレッショルドリーク電流技術を紹介する。

#### 2.3.1 スタンバイ時サブスレッショルドリーク電流削減技術

スタンバイ時のサブスレッショルドリーク電流低減技術に関してはさまざまな方式が提 案されているが、以下の二つの方式に大分できる。

- (1) 電源と回路の間にスイッチ MOS を設けて、スタンバイ時にはこのスイッチ MOS を オフする方式。(電源スイッチ方式)

- (2) MOSトランジスタの基板バイアスを制御し、スタンバイ時にはそのしきい値が高くなるように制御する方式。(基板バイアス制御方式)

#### 電源スイッチ方式

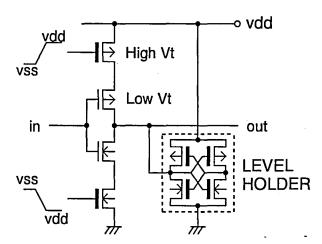

第1章で記述したように、DRAM は大容量化のために微細化の要求がもっとも高いLSI の一つであり、テクノロジドライバとして DRAM のメモリセルおよびその周辺回路の微細化は急速に進められた。そのため、DRAM 回路は他のLSI 回路よりも急速に低電圧化がなされ、DRAM 回路におけるサブスレッショルドリーク電流の低減技術は早くから検討されている。図 2.2は主として DRAM 回路に用いることを前提にしたサブスレッショルドリーク電流削減技術である [6-8]。電源ラインと回路との間に電源スイッチを挿入し、回路が待機中にその電源スイッチをオフ状態にして回路に流れるサブスレッショルドリーク電流を削減するというのが基本的な考え方である。

しかし、スタンバイ時に電源スイッチをオフにすると電源遮断と同様の状態になり、回路中に蓄えられた情報や状態が消えてしまう問題が生じる。このため、回路中に LEVEL HOLDER 等のデータ保持回路を付加し、これには常時電源を給電して情報を記憶する方法が多く検討されている [9]。

³現在のLSI は、アクティブ状態やスタンバイ状態といった多くの動作状態を持っていることが多い。これらの動作状態は LSI を使用したシステムの電力消費を最小限にとどめるために用いられる。すなわち、LSI を用いて情報処理を行いたいときには LSI をアクティブ状態にし、LSI を使用しない場合にはスタンバイ状態にして LSI の電力消費を削減する。本来、CMOS 回路を用いた LSI では何も情報処理しない場合の消費電力は零になるため、このような動作状態は必要ではない。しかし、現在のほとんど全ての LSI は同期型であり、LSI の消費電流のうちの無視できない部分がその同期のためのクロック系によって消費されている。このために、何も情報処理を行わないときにクロック系を停止させるスタンバイ状態が必要となる。

図 2.2 電源スイッチを用いたリーク低減方式。LEVEL HOLDER は高しきい値の MOS トランジスタがオフしたときのデータ保持に用いる。

さらに、電源スイッチをオフにしても回路中の各ノードに充電されている電位はすぐには放電されないという特徴を用いた記憶保持方式も提案されている [10]。 $T_a$  秒で消去されてしまうのであれば、 $T_a$  秒間隔に電源スイッチをオンにして各ノードの電位が完全に消去されないように制御する。DRAM のリフレッシュの考え方をロジック LSI の回路中の各ノード電荷の保持に用いた方式だといえる。

また、近年では上記したような電源スイッチによって完全に回路の電源を遮断するのではなく、ダイオード等を利用してある程度電源間に電位差を残し、回路内部情報・状態保持と低リーク電流状態を両立させる方式も提案されている [11,12]。

#### 電源スイッチ方式の課題

電源スイッチ方式によるサブスレッショルドリーク電流削減技術は、大きなリーク電流 削減能力があり効果が大きいが、以下に挙げるような欠点がある。

- (1-a) 従来の電源ネットとは別に、その電源ネットからスイッチ MOS を介してできる仮想電源ネットが必要となる。

- (1-b) スイッチ MOS があるために仮想電源ネットのインピーダンスが高くなる。仮想電源ネットは回路の電源ラインに相当するため、回路の動作速度が低下したり、回路特性ばらつきの要因となる。

- (1-c) 一般にスタンバイ時にラッチ等の情報保持回路の情報を保持できない。

- (1-d) スタンバイ時には電源ラインと回路とがスイッチ MOS によって切り放されるため、 $I_{\text{DDO}}$  テストを使用できなくなる。

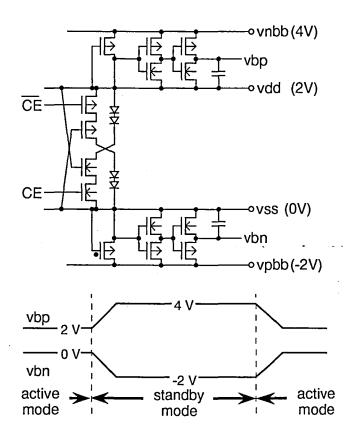

それらの欠点を補うためには、CAD ツールへの対応が必須である。図 2.3は電源スイッチのゲート幅と、回路中  $(1.0\,\mathrm{V}\,0.25\,\mu\mathrm{m}\,32\,\mathrm{b}\,\mathrm{m}\,\mathrm{f}$ 器) の全 MOS トランジスタのゲート幅の合計との比率に対する、回路の動作速度の関係を示したものである。電源スイッチのゲート幅を変えることによって、回路の動作速度が大きく変化することが分かる。また、電源スイッチを挿入して電源インピーダンスが高くなれば、動作しない回路はデカップリング容量のように働く。したがって、周りの回路の動作状態も回路の動作速度に影響を与えるようになる。このような動作状態の挙動をどのように CAD で取り扱うかが大きな課題である。

この電源スイッチ方式の製品への適用例としては、Intel 社の StrongARM がある [13]。 電源パッドと回路の間に PMOS スイッチがあり、sleep モードではそのスイッチをオフす

る。これによって、 $50\,\mu\text{A}$  の待機時電流を実現できている。この例では、トータルで  $27\,\text{nF}$  という大きなオンチップデカップリング容量を内蔵することにより、仮想電源線のインピーダンス上昇を防いでいる。

#### 基板バイアス制御方式

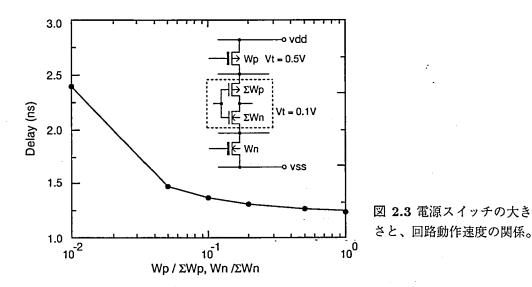

図 2.4 しきい値電圧の基板バイアス依存性。

MOSトランジスタは図 2.4のようにその基板電位 Vbb を変化させれば、しきい値電圧 Vth が変化する。この現象を利用し、従来の CMOS 回路では電源電位に固定していた MOSトランジスタの基板電位を、電源電圧とは独立して制御する方法が基板バイアス制御によるサブスレッショルドリーク電流削減技術である。すなわち、アクティブ時には基板電位を浅くして MOSトランジスタのしきい値電圧を低くし、スタンバイ時には基板電位を深くして MOSトランジスタのしきい値電圧を高く制御する。スタンバイ時のサブスレッショルドリーク電流を小さく抑えることができる。

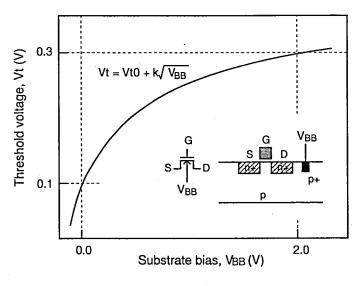

基板バイアス制御によるリーク電流削減技術についても多くの研究開発が進められている。図 2.5は一つの例である。外部から入力される基板バイアス用の電源 (vnbb および

図 2.5 基板バイアス制御に よるスタンバイ時リーク電 ・流削減技術。

vpbb) を用いて、基板バイアス値の電位を図 2.5内の波形図のように、動作時と待機時で 切り替えている [14]。 vbp が PMOS の基板バイアス、vbn が NMOS の基板バイアスで ある。

上述したように、基板バイアス制御方式は、従来は電源ラインに固定して接続されていた MOSトランジスタの基板端子を、電源ラインから分離して制御する方式である。しかし、従来のように基板端子を電源ラインに接続した状態のままで、実効的に基板端子の電位を制御する方法も提案されている [15]。この方法では、例えば2入力 NAND であれば待機時にその二つの入力が共にL'になるようにする。一般に、入力が2本以上ある NAND や NOR等の論理ゲートやそれらを組み合わせた複合ゲートに流れるリーク電流は、その入力パターンによって変化する。たとえば、2入力 NAND では二つの入力に全て'L'を入力したときが最もリーク電流が小さくなる。これは縦積みになった MOSトランジスタの電源ラインに接続されていない MOSトランジスタのソース電位が電源ラインの電位から分離することによる基板バイアス効果と、Drain Induced Barrier Lowering (DIBL) 効果によって、その MOSトランジスタのしきい値電圧が高くなるためである。参考文献 [15] はこの効果を利用し、回路が動作していないときになるべく各論理ゲートのリーク電流が小さくなる入力条件に設定する方式を提案している。このような論理の組み方は難しいが、論理の組み方だけでリーク電流が削減できることは魅力的である。

#### 基板バイアス制御方式の課題

従来は使用していなかった MOS トランジスタの基板端子を制御する方式であるため、 CMOS の回路構成を従来構成から変えずに適用可能であり、電源ラインに回路が接続され たままであるため、チップ選別のための  $I_{DDQ}$  テストが可能という利点がある。基板バイアス制御技術の主な欠点としては、以下のものを挙げることができる。

- (2-a) 従来電源に接続されている基板バイアス電位を独立して制御するために、電源ネットとは別に基板バイアスネットが必要になる。

- (2-b) 基板バイアスネットのインピーダンスが高くなり、ノイズによって基板バイアス電 位が変化しやすくなる。これは回路特性ばらつきの要因となり、最悪ラッチアップ等 の現象を引き起こす。

- (2-c) しきい値電圧を基板バイアス効果で変化させているが、一般にしきい値電圧の基板 バイアス依存性は MOS トランジスタのゲート長 (Lg) が微細化されるにともない小 さくなってしまう。

- (2-d) 基板バイアス効果が大きい方がしきい値電圧の制御性が向上するが、一般に CMOS 回路は基板バイアス効果が小さい方が高速で動作する。基板バイアス効果を大きくなるように MOS トランジスタを設計するというのは相反する要求になる。

- (2-e) スタンバイ時とアクティブ時でしきい値電圧をより大きく変化させるためには、より深い基板バイアスを印加すればよい。しかし、このような深い基板バイアスの印加は MOSトランジスタのドレイン・ウェルあるいはウェル・ウェル間等に大きな電位差を生じさせることになり、pn 接合リーク電流を増大させる。

この中でも (2-b) はもっとも重要な課題の一つである。基板電位の変動に対する回路特性の解析についても多くの研究がなされているが [16,17]、基板バイアス制御によって基板インピーダンスの上昇は避けられない。これにより、SOI のヒストリー効果 [18,19] のような効果が一般のバルクの CMOS 回路においても生じる危険性がある。このため、アクティブ時にも基板バイアス電位を浅く印加して、基板バイアス電位の変動の影響を小さくして、大規模回路での基板バイアス制御を行った研究結果もある [20]。この例では DCTコアプロセッサを 0.9 V 150 MHz 10 mW で動作させることに成功している。4

#### 2.3.2 アクティブ時サブスレッショルドリーク電流削減技術

スタンバイ時のサブスレッショルドリーク電力削減技術については、2.3.1 節で記述したような様々な技術がすでに実用化段階にあるといえる。今後問題となるのが、アクティブ時のサブスレッショルドリーク電流である。図 2.1で示したように、近い将来にはアクティブ時の消費電流の50%を超える割合がサブスレッショルドリーク電流によるものになると予想され、アクティブ時サブスレッショルドリーク電流の低減は、今後の低電圧回路における必須技術の一つである。

現在まで様々なアクティブ時サブスレッショルドリーク電流削減技術が提案されているが、基本的な考え方は

「回路に要求された性能を満たすのに必要な、最低限のしきい値電圧によって 回路を動作させる。」

である。ここでは代表的な例として、「動的基板バイアス制御方式」と「デュアルしきい値 方式」を紹介する。

<sup>42.4</sup> 節では、この欠点を解決する基板バイアス制御方式を提案する。

#### 動的基板バイアス制御方式

通常のLSIでは、設計マージン等により、しきい値電圧を回路に要求された性能を満たすために必要な値よりも低い値に設定している。したがって、設計マージンが小さくできれば、それだけしきい値電圧を高く設定でき、アクティブ時およびスタンバイ時の両方のサブスレッショルドリーク電流が低減できる。

設計マージンを最小化する技術として、回路の製造ばらつきによる特性ばらつきを補正する動的基板バイアス制御技術がある。MOSトランジスタのしきい値を、要求される性能を満たす最適値になるように MOSトランジスタに印加する基板バイアスの値を制御する。ここで、回路に要求される性能の検出方法には、MOSトランジスタのリーク電流を検出する方式や、インバータの遅延特性を検出する方式等が提案されている。

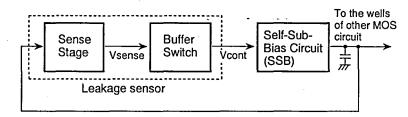

図 2.6 動的基板バイアス制御を用いたばらつき補償回路。

基板バイアス制御を用いて MOS トランジスタのしきい値電圧を調整するという考え方 自体は古くから提案されている手法である [21,22]。図 2.6は MOS トランジスタに流れる サブスレッショルドリーク電流をモニタして、しきい値電圧の調整を自動的に行う動的基板バイアス制御方式である [23]。 この例では、しきい値電圧ばらつきを  $\pm 0.025$  V まで低減することに成功している。

また、基板バイアス制御と電源電圧制御を組み合わせて制御し、さらに回路の遅延特性を外部クロックに同期する方式も提案されている [24]。その他、多くの動的基板バイアス制御技術が提案されている [17,25]。大規模な回路に適用した例としては、図 2.6の方式と電源電圧制御を組み合わせた方式を用いて、44万トランジスタ規模の  $0.4\,\mu\mathrm{m}$  40 MHz 32bマイクロプロセッサの動作に成功した例がある [26]。

このような動的基板バイアス制御技術において課題となるのが、基板インピーダンスの上昇である。基板インピーダンスが高いと基板にノイズが乗るために回路特性が変動する。もともと動的基板バイアス制御技術は、製造ばらつき等による回路特性ばらつきの補正が目的である。したがって、新たな回路特性変動要因の増加はしきい値制御の効果を小さくしてしまう。また、深い基板バイアスの印加によって、製造ばらつきがしきい値ばらつきに大きく影響するという事実もある [27]。基板バイアスを順方向にも印加させることによって深い基板バイアス印加を避ける方式や [28]、2.4 節で記述する方法と同様の考え方を用いて基板を低インピーダンスに保つ試みもされているが [17]、基板バイアスの安定供給はこれからの研究課題といえよう。

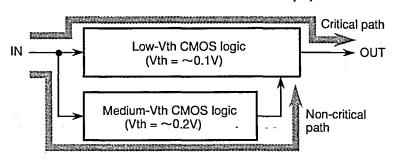

#### デュアルしきい値方式

回路のインプリメンテーション技術として、設計時に MOS トランジスタしきい値設定を最適化してリーク電流を削減する技術も多く提案されている。具体的な方法の一例としては、2 種類のしきい値電圧の MOS トランジスタを使い分け、低しきい値 MOS トランジスタの使用個数をなるべく少なくする手法が提案されている [29]。

図 2.72種しきい値 MOS の使い分けによるリーク電流削減技術。

図 2.7は 3 種類のしきい値電圧の MOS トランジスタを用いて、回路のクリティカルパスは低しきい値の MOS トランジスタで構成し、それ以外はそれよりも高いしきい値電圧の MOS トランジスタで構成する方式である [30]。チップ全体での低しきい値 MOS トランジスタの数を減らすことができ、リーク電流を小さくすることがきる。多くの大規模回路への適用例があり、たとえば、 $0.12\mu\text{m-}L_{\text{eff}}$  480MHz のマイクロプロセッサで使用された例も報告されている [31]。

# 2.4 基板インピーダンス切り替え型基板バイアス制御方式による サブスレッショルドリーク電流削減技術

2.3 節では、従来のサブスレッショルドリーク電流低減技術を紹介したが、本節では、サブスレッショルドリーク電流低減技術を用いた大規模高速 LSI の開発事例について記述する [1,2]。サブスレッショルドリーク電流削減方法としては、 $I_{DDQ}$  テストの重要性を考慮して基板バイアス制御による方法をベースにした。しかし、従来の基板バイアス制御では 2.3.1 節で述べたように多数の欠点がある。特に、基板バイアス制御方式では基板インピーダンスの上昇は避けられない。インピーダンスが高いと基板にノイズが乗り、デバイスのばらつき要因となり、高速動作との両立は困難である。本研究ではこれらの課題を解決し、動作時の高速動作とスタンバイ時の低消費電力を両立する基板インピーダンス切り替え型 基板バイアス制御方式 (Switched Substrate-Impedance Substrate-Bias Control Scheme) を開発した。以下、その方式について詳しく述べる。

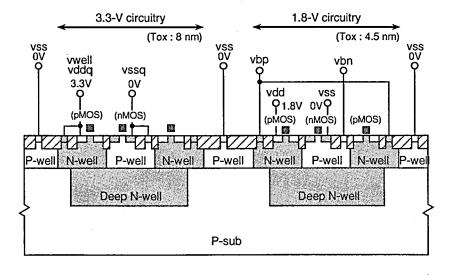

大規模高速 LSI としては、日立のオリジナルアーキテクチャである SuperH アーキテクチャを用いた SH4 マイコンを使用することにした [32,33]。 SH4 マイコンはハンドヘルドコンピュータやゲーム機等に組み込み用途向けに開発されたマイクロプロセッサである。消費電力あたりの性能が高いことが特徴である。電源電圧はコア用の 1.8 V と、I/O とリアルタイムクロック用の 3.3 V の 2 電源で動作し、5 段パイプライン、2 ウェイスーパスカラ方式を採用することにより、200 MHz で 360 MIPS の整数演算処理能力を持つ。また、3D グラフィック用に 4 次元行列演算回路等を設け、1.4 GFLOPS の浮動小数点演算性能を有している。一方、使用しているデバイス・プロセスは、5 層アルミ配線による 0.2  $\mu$ m CMOS テクノロジをベースに、3.3 V 信号を入出力する I/O 回路用に酸化膜厚が厚くてしきい値電圧が高い MOS トランジスタと、1.8 V で動作するコア回路用に酸化膜厚が薄くてしきい値電圧の低い MOS トランジスタが用意されている。消費電力については、ドライストーンベンチマーク動作時の評価で 1 W である。開発した SH4 マイコンの主要諸元を表 2.1に、そのテクノロジおよびデバイス諸元を表 2.2に示す。

表 2.1 SH4 の主要諸元

| Superscalar           | Two-issue                                                                 |  |

|-----------------------|---------------------------------------------------------------------------|--|

| Cache                 | 8KB (instruction), 16KB (data)                                            |  |

| Graphic               | Special instruction for 3D CG                                             |  |

| Integrated peripheral | MMU, DMAC, Serial I/F, Timer                                              |  |

|                       | Real-time clock, SDRAM I/F                                                |  |

| Clock frequency       | $200\mathrm{MHz}\ (1.6\mathrm{V}\ T_{\mathrm{a}} = 75\mathrm{^{\circ}C})$ |  |

| Performance           | 360 MIPS VAX, 1.4 GFLOPS                                                  |  |

| Power supply          | 1.8 V (vdd), 3.3 V (vwell, vddq)                                          |  |

| Power consumption     | 1.0 W (Dhrystone, typical, active mode)                                   |  |

| Standby current       | 1.3 mA (clk off quiet, active mode)                                       |  |

|                       | $46.5\mu\mathrm{A}$ (standby mode)                                        |  |

|                       | $17.8 \mu\text{A}$ (data retention mode, vdd= $1.0 \text{V}$ )            |  |

| Technology       | $0.2\mu\mathrm{m}$ , $p$ -sub, triple-well CMOS                                      |

|------------------|--------------------------------------------------------------------------------------|

| $L_{g}$          | $0.2\mu\mathrm{m}$ (1.8-V device), $0.35\mu\mathrm{m}$ (3.3-V device)                |

| $t_{ m ox}$      | 4.5 nm (1.8-V device), 8 nm (3.3-V device)                                           |

| $V_{ m th}^*$    | 0.15 V (1.8-V device), 0.45 V (3.3-V device)                                         |

| Metal            | Metal 1-3 (0.88- $\mu$ m pitch), Metal 4-5 (1.76- $\mu$ m pitch)                     |

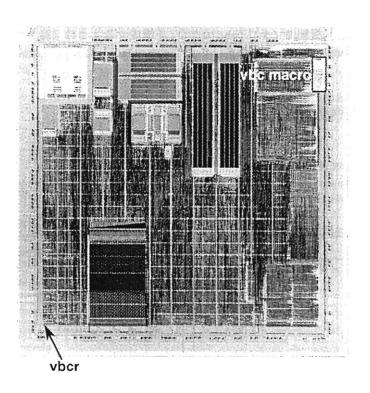

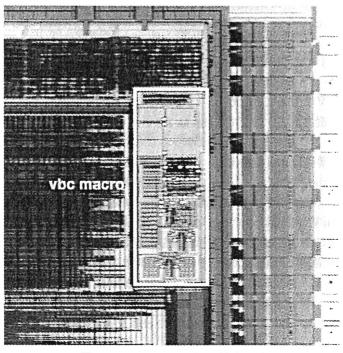

| Area             | $6.84 \times 6.84 \mathrm{mm^2}$ , (vbc macro: $209.44 \times 645.9 \mathrm{mm^2}$ ) |

| Transistor count | 3.3 M                                                                                |

表 2.2 SH4 のプロセスおよびデバイスの主要諸元

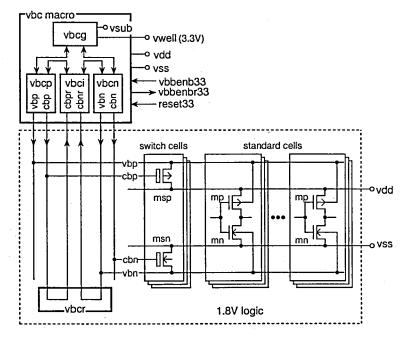

#### 2.4.1 全体構成

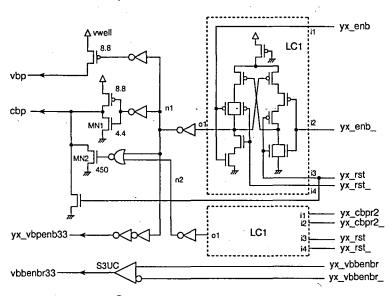

図 2.8 基板インピーダンス切り替え型基板バイアス制御方式の全体構成。

図 2.8に基板インピーダンス切り替え型基板バイアス制御方式の全体構成を示す。 $1.8\,\mathrm{V}$  系ロジックのスタンダードセル内の基板は全て電源と分離したセル構造を取り (ここでは PMOS および NMOS の基板電位をそれぞれ vbp および vbn と記す)、それらの基板電位を vbc マクロと呼ばれる基板制御マクロ (vbc macro) と  $1.8\,\mathrm{V}$  系ロジック内に配置されて いるスイッチセル (switch cell) によって制御する。一つのスイッチセル内には二つの厚酸 化膜 MOS トランジスタ<sup>5</sup> が格納されており、それぞれ、vbp と vdd および vbn と vss 間 に接続されている。二つの MOS のそれぞれのゲートは cbp および cbn ネットに接続されており、cbp および cbn の電位は vbc マクロによって制御される。スイッチセルは SH4 マイコン全体で約  $1\,\mathrm{T}$  固分散配置される。

<sup>\*</sup>  $V_{\rm th}=V_{\rm gs}$  at  $I_{\rm ds}=10\,{\rm nA},\,W=10\,\mu{\rm m}$

$<sup>^5</sup>$ この二つの MOS トランジスタには基板パイアスは印加されない。スタンパイ時にこの二つの MOS に流れるサブスレッショルドリーク電流を低減するためには、二つの MOS のしきい値電圧を高くする必要がある。そのために厚酸化膜 MOS を使用した。なお、厚酸化膜 MOS はしきい値が  $1.8\,\mathrm{V}\,$  系ロジックに使用されている薄酸化膜 MOS よりも約  $0.3\,\mathrm{V}\,$ 高い。

cbpr、cbnr は cbp および cbn 電位をモニタするためのそれぞれのリターン信号である。 vbc マクロから出力された cbp および cbn 信号は 1.8 V 系ロジック内を通過した後、vbc マクロから最遠端に配置されている vbcr と呼ばれるリターンセルで cbpr および cbnr というネット名に変更されて vbc マクロに戻る。

vbc マクロは図 2.8に示されるように、4 つの回路ブロックから構成されている。vbcp、vbcn はそれぞれ PMOS、NMOS の基板電位を制御する回路ブロックであり、vbp、vbn、cbp、cbn 信号はこれらの回路ブロックから生成される。vbci は vbc マクロを制御する外部回路とのインターフェース回路と、cbp および cbn のリターン信号 (cbpr および cbnr)を受ける回路と、パワーオンリセット回路が格納された回路ブロックである。vbcg はスタンバイ時に NMOS の基板バイアスに印加する電位 (vsub 電位)を作るための負電圧発生回路である。

各回路ブロックの電源電圧については、vbcp は vwell と vss が、vbcn は vdd と vsub が、vbci は vdd と vss が、vbcg は vwell と vss がそれぞれ供給されている。したがって、vbcp、vbcn、vbcg の内部回路にかかる電源電圧は高々vwell 電圧である。vwell=vddq (vddq は I/O 電圧) とすることにより、I/O 回路に使用している厚酸化膜の MOS トランジスタと同一の MOS トランジスタを vbc マクロに使用できる。

表 2.3 動作状態と基板電位 (vbp,vbn) およびスイッチセル制御線 (cbp,cbn) 電位の関係

| vbbenb33 | State   | vbp          | vbn          | cbp          | cbn          |

|----------|---------|--------------|--------------|--------------|--------------|

| 0.0V     | Active  | 1.8V (vdd)   | 0.0V (vss)   | 0.0V (vss)   | 1.8V (vdd)   |

| 3.3V     | Standby | 3.3V (vwell) | -1.5V (vsub) | 3.3V (vwell) | -1.5V (vsub) |

vsub = vdd - vwell

図 2.9 動作波形例

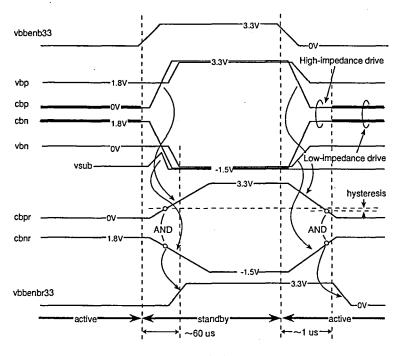

各動作モード時の vbp、vbn、cbp、cbn の電位を表 2.3に、波形を図 2.9に示す。基板電位は vbc マクロに入力される vbbenb33 信号によって、以下のように制御される。

$1.8\,\mathrm{V}\,$  系ロジックをスタンバイ状態に遷移するには、vbbenb33 をアサートする。これにより、cbp および cbn にはスイッチセル内の MOS をオフするような電位が印加され、さらに、vbc マクロから vbp および vbn にそれぞれ  $3.3\,\mathrm{V}$  (vwell 電位) および  $-1.5\,\mathrm{V}$  (vsub=vdd-vwell 電位) が供給される。各信号の時間的変化は図  $2.9\,\mathrm{cm}$  したようになる。vbbenb33 のアサート  $(3.3\,\mathrm{V})$  により、vbp=cbp= $3.3\,\mathrm{V}$ 、vbn=cbn= $-1.5\,\mathrm{V}$  に遷移し、ある時間が経過した後に、リターン信号 cbpr、cbnr が cbpr=cbp= $3.3\,\mathrm{V}$ 、cbnr=cbn= $-1.5\,\mathrm{V}$  に遷移する。これを検出して vbbenbr33 は  $3.3\,\mathrm{V}$  になる。

一方、アクティブ状態に遷移するには、vbbenb33 をネゲートする。これにより、cbp および cbn にはスイッチセル内の MOS がオンするような電位が印加され、スイッチセルによって基板電位 vbp および vbn には電源電位と同じ電位が供給される。各信号の時間的変化は 図 2.9で示したように、vbbenb33 が  $3.3\,\mathrm{V}$  から  $0\,\mathrm{V}$  に遷移すると、vbp= $1.8\,\mathrm{V}$ 、cbp= $0\,\mathrm{V}$ 、vbn= $0\,\mathrm{V}$ 、cbn= $1.8\,\mathrm{V}$  に遷移する。その後ある時間が経過した後に、リターン信号 cbpr、cbnr が cbpr=cbp= $0\,\mathrm{V}$ 、cbnr=cbn= $1.8\,\mathrm{V}$ 、vbbenbr= $0\,\mathrm{V}$  に遷移する。

ここで特徴的なのは、cbp、cbn の出力インピーダンスが2段階に変化することである。 スタンバイ状態からアクティブ状態に遷移する場合、リターン信号 cbpr、cbnr に cbp、cbn の電位が現れるまでの時間は cbp および cbn は高インピーダンスで駆動される。その後、 cbpr および cbnr の電位を検出することで cbp、cbn は低インピーダンスに駆動される。こ のように2段階に分けて cbp、cbn を駆動することにより、

- (1) アクティブ状態では cbp、cbn は低インピーダンスに駆動され、1.8 V 系ロジックの動作によるノイズの影響を低減できる。

- (2) cbp が 0 V、cbn が 1.8 V に駆動されると、多数のスイッチセル内の MOS が同時に オンする。cbp、cbn の駆動を高インピーダンスでゆっくりと駆動することで多数あるスイッチセル内の MOS の同時スイッチングノイズを低減できる。

以上でわかるように、アクティブ時には多数のスイッチセル内の MOSトランジスタがオンして、電源と基板 (vbp,vbn) が短絡され、基板インピーダンスが低く保たれる。ところが、スタンバイ時に基板 (vbp,vbn) を駆動する MOSトランジスタは、vbcマクロ内の一つの MOSトランジスタのみである。したがって、基板 (vbp,vbn) は高インピーダンスになる。基板ノイズによる誤作動が懸念されるが、ここではスタンバイ時には 1.8 V 系ロジックは動作しない (スイッチングしない) という制御を行うことにより誤作動を防いでいる。この制御のために、スタンバイ状態からアクティブ状態に遷移した時には、基板電位がアクティブ状態の電位になったことを検出してから 1.8 V 系回路の動作を始めている。基板電位検出には vbbenbr33 信号を使用している。前記のように、vbbenbr33 は vbbenb33の戻り信号として働き、基板電位は cbp、cbn 電位によって決定されるため、cbp、cbn 電位から得られる vbbenbr33 をモニタすることで基板の電位状態を検出できる。

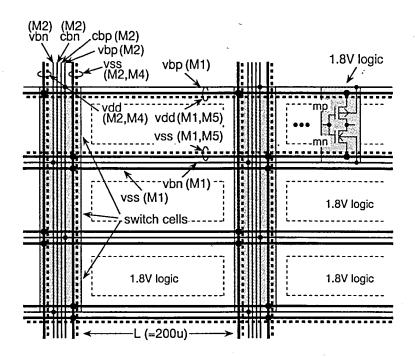

#### 2.4.2 電源ネットおよび基板バイアスネット構成

図 2.10に電源 (vdd,vss)、基板バイアス (vbp,vbn)、基板バイアス制御線 (cbp,cbn) のネット構成を示す。スイッチセルは縦方向に連続して配置されている。また、スイッチセルと隣合うスイッチセルの横方向の間隔 L はある値以内で可変にしている。SH4 では最大  $L=200\,\mu\mathrm{m}$  とした。 $^6$  アクティブ時にはスイッチセルによって基板電位が駆動されるため、スイッチセルを後述するように多数設けることにより、基板を低インピーダンスにできる。ネット配線については、セル列と平行して横方向には  $M1(\mathsf{X}\mathsf{y})$  ル配線第 1 層目) で配線された vdd,vss,vbp,vbn が平行に配線されている。vbp は上下二つのセルによって共有され、その上下に vdd が平行して配線されている。また、vbn も上下二つのセルによって共有され、その上下に vss が平行して配線されている。vdd、vss は 2.5 ピッチ 幅で、vbp、vbn は 0.5 ピッチ幅である。また、縦方向には 8.5 ピッチ幅の  $M2(\mathsf{X}\mathsf{y})$  ル配線第 2 層目) で配線された vdd、vss、0.5 ピッチ幅の M2 で配線された vbp、vbn、cbp、cbn がスイッチセル上を配線されており、M1 と M2 の交点で、それぞれ vdd、vss、vbp、vbn がメッシュ状に接続されている。

電源配線については、上記 M1 と M2 による細かいピッチの電源メッシュ構造に加えて、 膜厚が M1-M3 の 2 倍ある M4-M5 を用いた荒いピッチの電源メッシュによる電源補強が なされている (破線)。縦方向に配線されている M2 の vdd、vss の上部に M4 で配線された vdd、vss を配線しているが、この両者を接続するためには M3 の配線層を介する必要である。この接続をすべてのスイッチセル上で行うと M3 が縦方向に配線されることになり、M3 の横方向のパスが無くなるという問題がある。SH4 では M2 と M4 の電源線の接続を、4つごとのスイッチセル上でのみ行っている。このようにすることによって、M3 の 横方向の配線パスを確保することができる。M5 の電源線は先の4つごとのスイッチセル上でのみに配置している。

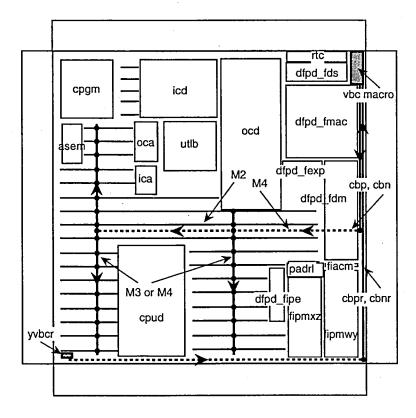

図 2.11に SH4 のフロアプランと、cbp、cbn、cbpr、cbnr のネット構成とリターンセル vbcr の配置関係を示す。図 2.10で示したように vbp および vbn はスイッチセルを並べることによってメッシュ状に配線されるが、cbp、cbn はメッシュ状には配線されず、ストライプ状に配線される。このストライプ状の配線を M3 および M4 を用いてシャントし、フィッシュボーン状に配線している。cbp および cbn の配線抵抗は、vbc マクロから最遠端のスイッチセルまでが vbc マクロ内の cbp および cbn の駆動 MOS のオン抵抗 (約  $20\Omega$ ) の 10 倍以下になるように、M3 および M4 のシャント線幅を決定した。8 また、リターンセルは各スイッチセル内で cbp、cbn の伝搬時間の一番遅いスイッチセルの cbp、cbn 到達タイミングよりも遅いタイミングで cbpr、cbnr が戻せるように配置する。SH4 では図 2.11のように vbc マクロから一番遠い場所に vbc マクロと対角する位置に配置している。

$<sup>^6</sup>$ 間隔 L は電源線のインピーダンス、電源配線のマイグレーション、MOS トランジスタが動作することで vbp や vbn に生じるドレイン-基板カップリングによる基板ノイズを考慮して決定した。

<sup>7</sup>最小配線ピッチを1ピッチとしている。

$<sup>^8</sup>$ SH4 では  $4.8\mu m$  幅とした。その時の cbp/cbn 配線抵抗は  $0.045\Omega/\square \times 14mm/4.8\mu m=130\Omega$ 。

図 2.10 電源 (vdd,vss)、基板バイアス (vbp,vbn)、基板バイアス制御線 (cbp,cbn) のネット構成

図 2.11 基板バイアス制御線 (cbp,cbn)、リターン信号 (cbpr,cbnr) のネット構成

#### 2.4.3 スタンダードセルレイアウトおよびウェル構造

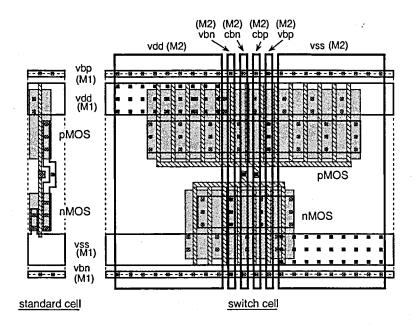

図 2.12にスタンダードセルとスイッチセルのレイアウトを示す。スタンダードセルはインバータを例にした。vbp、vbn、vdd、vss は 4 本の平行した M1 配線によって給電されている。vbp、vbn はそれぞれシリサイド化された基板給電拡散層によっても給電されている。スタンダードセルは縦方向に鏡面対称に配置される。これによって vbp および vbn が上下の隣接するスタンダードセルと共有することができ、面積を削減している。

一方、スイッチセルについては、スタンダードセルと同じセル高さで、M1 による vbp、vbn、vdd、vss の給電線はスタンダードセルと同じ位置にある。縦方向に平行して配線されている M2 配線は、電源強化線 2 本と、この 2 本の電源強化線の間に、vbp、vbn 強化線 2 本と、cbp、cbn が 2 本が平行して配置されている。両端の電源強化線 vdd、vss によって、比較的インピーダンスの高い 4 本の基板バイアス制御線を外来ノイズから守ることができる。

図 2.13にウェル構造を示す。N-well は PMOS を形成するための N 型ウェル、P-well は NMOS を形成するための P 型ウェルである。NISO は N-well、P-well よりも深いところ にある N 型ウェルであり、いわゆる 3 重ウェル構造になっている。

3.3 V 系回路は基本的に厚酸化膜 MOSトランジスタで構成されており、その部分については厚酸化膜 MOSトランジスタのしきい値は高いために基板バイアス制御は行っていない。一方、1.8 V 系回路は薄酸化膜 MOSトランジスタで構成されており、図 2.12で示したように基板バイアス制御が可能な構造になっている。

なお、1.8V 系回路と 3.3V 系回路とは NISO によって電気的に分離されている。したがって、NISO によって分離した回路は別々の基板電位を与えることができる。また、PLLを内蔵する CPG マクロや CPU マクロ等の各マクロは独立した NISO の島上に形成されている。また、P 基板 (P-sub) は VSS 電位に固定されており、各 NISO の間にはその固定のためのガードバンドが配置されている。各 NISO の島で発生した基板ノイズは、容量結合により P-sub に伝搬しようとするが、上記のように P-sub はガードバンドで低インピーダンスに接地電位に固定されている。P-sub に現れるノイズは小さくでき、各回路ブロックで発生したノイズが他のブロックに影響するのを低減できる。例えば外部ピンとのインターフェースを行う PAD マクロは、外部ピンを内部の信号振幅よりも大きな振幅で駆動することから大きなノイズを発生する。このノイズが CPG 等のアナログ回路に影響するのを防げる。

図 2.14に SH4 のチップ写真、図 2.15に vbc マクロの拡大写真を示す。

図 2.12 スタンダードセルとスイッチセルのレイアウト

図 2.13 ウェル構造

図 2.14 SH4 のチップ写真

図 2.15 vbc マクロ部の拡大写真

#### 2.4.4 詳細回路

ここでは、基板制御マクロ (vbc マクロ) を構成する 4 つの回路ブロックについて詳細回路構成を述べる。なお、vbcn(NMOS 基板制御回路ブロック) については、vbcp(PMOS 基板制御回路ブロック) を相補な回路構成にしたものであるため、ここでは説明を省略する。

#### vbcp(PMOS 基板制御回路ブロック)

図 2.16 vbcp 回路図

図 2.16に vbcp (PMOS 基板制御回路ブロック) の回路図を示す。LC1 はレベル変換回路であり、vbci からの  $1.8 \, V$  振幅デュアルレール信号を、vwell から vss までの  $3.3 \, V$  振幅信号に変換している。回路動作としては、ノード n1 およびノード n2 を用いて、前記した cbp の出力インピーダンスの 2 段階切り替えを行っている。yx\_enb がネゲートすることによりノード n1 が  $0 \, V$  になるが、これによって、vbp はハイインピーダンス状態になり、cbp は  $0 \, V$  になる。cbp が  $0 \, V$  になることでスイッチセル内の PMOS がオンし、vbp は  $1.8 \, V$  に駆動される。ここで、cbp は  $1.8 \, V$  系ロジック全体に配線されており、その負荷容量は大きい。したがって、cbp はゆっくりと  $0 \, V$  に駆動される。その遷移を cbp の戻り信号 cbpr の遷移によって検出し、vbci が yx\_cbpr2 をアサートする。これによりを n2 が  $0 \, V$  になる。cbp は先に n1 によって制御される  $0 \, V$  に駆動されるが、 n1 が  $0 \, V$  でかつ n2 が  $0 \, V$  の時は  $0 \, V$  になることで cbp は低インピーダンスに  $0 \, V$  に駆動される。以上のようにして  $0 \, V$  に下した cbp の  $0 \, V$  段階駆動を実現している。

基板電位を電源と分離した場合、電源投入時の電源電圧上昇により基板と MOS のソースあるいはドレイン間が順方向バイアスされ、電源間貫通電流が増加したりラッチアップが発生する等の問題が懸念される [34]。vbcp ではパワーオンリセット期間中の yx\_rst のアサートによって vdd 電源系とは無条件に cbp を  $0\,V$  に駆動することでこの問題を回避している。 $9\,V$

$<sup>^9</sup>$ 仮に電源投入が  $1\,\mathrm{V}/\mu\mathrm{s}$  で行われたとすると、この電源投入で基板に流れる電流は基板容量を  $10\,\mathrm{nF}$  とすると約  $10\,\mathrm{mA}$  になる。一方、スイッチセル数を  $8000\,\mathrm{mB}$  とすると、 $\mathrm{cbp=0}\,\mathrm{V}$  でスイッチセル内のトランジスタによって電

vbci (インターフェース回路ブロック)

図 2.17 vbci 回路図

図 2.17に vbci の回路図を示す。vbci は vbc マクロを制御する外部回路とのインターフェース回路と、cbp および cbn のリターン信号 (cbpr および cbnr) を受ける回路と、パワーオンリセット回路が格納された回路ブロックである。

外部からの vbbenb33 や kx\_vreser33 等の  $3.3\,\mathrm{V}$  振幅の信号は vbci 内部ですぐに  $1.8\,\mathrm{V}$  振幅のデュアルレール信号に変換され、vbcp および vbcn に入力される。vbci から vbcp、vbcp への各信号線はデュアルレール信号を用い、vbcp、vbcn 内部でレベル変換  $(1.8\,\mathrm{V}$  振幅信号を  $3.3\,\mathrm{V}$  振幅信号に変換) している。

cbp および cbn のリターン信号 (cbpr および cbnr) を受ける回路としては、初段にシュミット入力バッファを用いている。これは cbpr および cbnr はそこに接続されている負荷が大きいことから非常に緩やかに遷移する信号であるためである。

パワーオンリセット回路は RC の充放電時間を利用した簡単なものを使用した。その出力は電源 vdd が投入されてから徐々に 0V から 1.8V に充電される。したがって、yx\_rst は一定時間アサートされ、一定時間後 (数十  $\mu$ s 後) にネゲートされる。

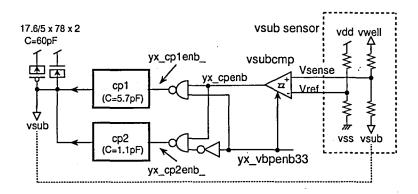

#### vbcg (負電圧発生回路ブロック)

図 2.18に vbcg のブロック図を示す。vbcg は電源回路であり、vsub 電位を発生する回路である。大きく分けて3つの回路ブロックからなり、チャージボンプ回路 cp1 と cp2 およびその制御回路から構成される。制御回路では図中の vsub sensor 部で vwell、vdd、vss、vsub 電位をモニタし、Vsense 電位と Vref 電位が同じ電位になるように cp1 あるいは cp2を ON/OFF する。したがって、安定状態では Vsense=Vref となることから、

$$\frac{\text{vwell} + \text{vsub}}{2} = \frac{\text{vdd} + \text{vss}}{2} \tag{2.1}$$

$$vsub = vdd + vss - vwell (2.2)$$

源と基板間に流せられる電流は Vth=0.45 V at  $10\,\mathrm{nA}/15\,\mu\mathrm{m}$   $\Rightarrow$  Vth=0.72 V at  $1\,\mu\mathrm{A}/15\,\mu\mathrm{m}$  (S=90 mV/dec) より、vdd=0.72 V で約  $8000\times30\,\mu\mathrm{m}/15\,\mu\mathrm{m}\times1\,\mu\mathrm{A}=16\,\mathrm{mA}$  となる。vdd=0.7 V 程度で十分に基板電位を電源電位に駆動できる。

図 2.18 vbcg 回路図

となる。

チャージポンプ回路 cp1 と cp2 の違いはポンピング容量の違いである。cp1 のポンピング容量は cp2 のポンピング容量の 5 倍の容量に設定されている。アクティブ状態では yx\_vbpenb33 がネゲートされるため cp2 が使用される。アクティブ状態では vsub 電位は vbc マクロ内でのみ使用されるのため、それほど電流が流れない。このため、ポンピング能力の小さい cp2 を使用する。逆にスタンバイ状態では yx\_vbpenb33 がアサートされるため cp1 が使用される。スタンバイ状態では vsub 電位は 1.8 V 系ロジック全体に供給されるため、vsub には pn 接合リーク等の電流が流れる。このため、ポンピング能力の大きな cp1 を使用する。このように動作状態でポンピング容量を変えることで vsub 電位のリップルを小さくできる。

また、状態によって、Vsense と Vref の電圧を比較するコンパレータ vsubcmp の動作電流も変えている。yx\_vbpenb33 がアサートされるスタンバイ時には vsub には主回路の vbn が接続されるため大きな基板容量が接続されることになる。したがって、vsub はゆっくりと変化する。vsubcmp は高速に動作する必要がないため、動作電流を制限して低電力化している。一方、yx\_vbpenb33 がネゲートされるアクティブ時には、vsub には vbc マクロ内の回路だけが接続されるため、比較的小さな容量が vsub に接続されることになる。vsub は高速に変化することになるため、vsubcmp を高速に動作するように動作電流値を大きくしている。

## 2.5 基板インピーダンス切り替え型基板バイアス制御方式の測定 結果

ここでは基板インピーダンス切り替え型基板バイアス制御技術を用いた SH4 の測定結果を示す。vbc マクロの特性評価はプローブボードによって、SH4 のリーク測定は BGA パッケージ版を評価プリント基板上で行った。測定温度はいずれも室温である。

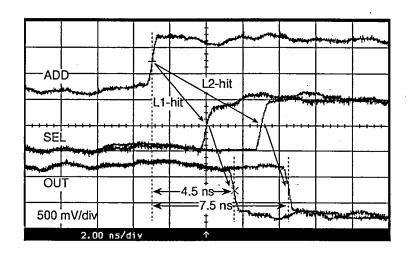

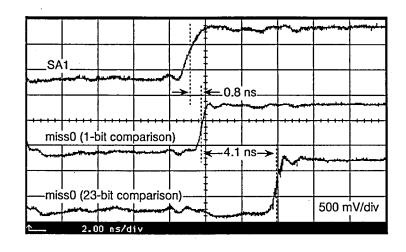

#### 2.5.1 状態遷移時の過渡特性

アクティブ状態からスタンバイ状態への遷移

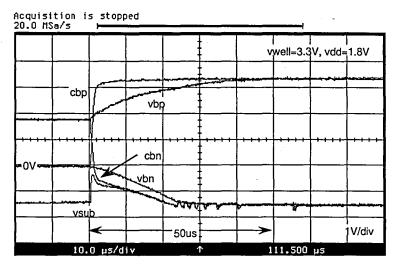

図 2.19 スタンバイ状態遷移時の vbp,vbn,cbp,cbn,vsub 波形

図 2.19にアクティブ状態からスタンバイ状態へ遷移したときの基板電位 (vbp,vbn)、基板バイアス制御線 (cbp,cbn) および、チップ内部で発生した NMOS 基板バイアス用負電圧 (vsub) の測定波形を示す。 vwell=3.3 V、vdd=1.8 V の時の波形である。遷移には約  $50\,\mu s$  かかっていることがわかる。 $^{10}$

#### スタンバイ状態からアクティブ状態への遷移

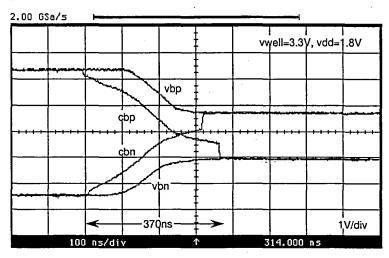

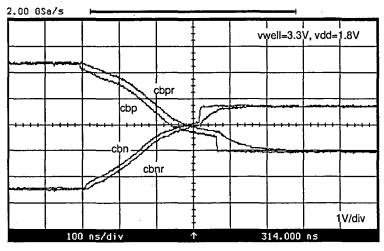

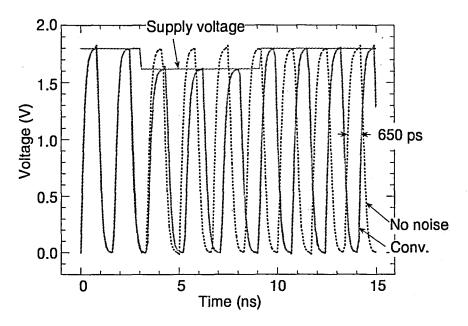

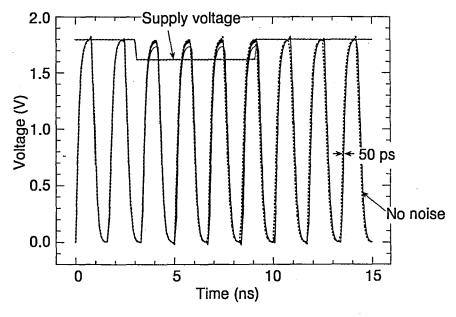

スタンバイ状態からアクティブ状態へ遷移したときの基板電位 (vbp,vbn)、基板バイアス制御線 (cbp,cbn) の測定波形を図 2.20に、基板バイアス制御線 (cbp,cbn)、リターン信号 (cbpr,cbnr) の測定波形を図 2.21にそれぞれ示す。vwell= $3.3\,\mathrm{V}$ 、vdd= $1.8\,\mathrm{V}$  の時の波形である。vbp、vbn 電位の復帰には約 300 ns かかっている。また、約 370 ns 付近で cbp および cbn の 2 段階駆動が正しく行われていることがわかる。vbbenbr33 信号は測定波形には無いが、cbpr および cbnr の遷移を検出して約 370 ns のところでネゲートされている。

$<sup>^{10}</sup>$ 遷移直後に vsub 電位が -1.5 V から約 -0.4 V まで上昇している。vsub 電位は NMOS の基板バイアスとして用いられているため、vsub 電位が正電位になると pn 接合がいたるところで順方向にバイアスされる。この vsub 電位の上昇電圧は cbp ネット上の 1.8 V の電荷と、vbn ネット上の 0 V の電荷と、vsub ネット上の -1.5 V の電荷の容量分割に加えて、チャージポンプの駆動力等によって決まる。vsub 電位を正電位にならないようにするためには、cbn ネットを駆動する MOS の駆動能力をチャージポンプの駆動能力以下にすればよい。本設計では vbn ネットの寄生容量は cbn の寄生容量の 10 倍以上であることを考慮して、ほぼ同じ駆動能力になるように設計している。

図 2.20 アクティブ遷移時の vbp,vbn,cbp,cbn 波形

図 2.21 アクティブ遷移時の cbp,cbn,cbpr,cbnr 波形

### 2.5.2 リーク電流特性

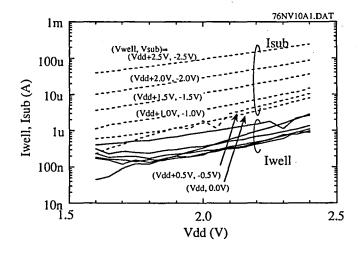

図 **2.22** idd の電源電圧 vdd . 依存性

図 **2.23** isub および iwell の 電源電圧 vdd 依存性

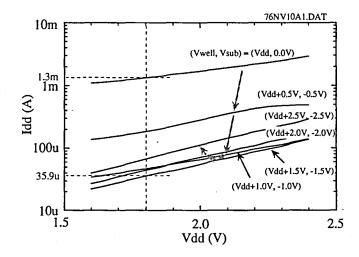

次にリーク電流の測定結果を示す。NMOS の基板に流れる基板電流 isub も測定できるように、負電圧発生回路 (vbcg) をオフにして、負電圧 (vsub) はチップ外部から印加できるようにして測定を行った。 $^{11}$  スタンバイ時の SH4 の電源リーク電流 idd の電源電圧 vdd 依存性を図 2.22に、isub および iwell 電流依存性を図 2.23に示す。印加している基板バイアス値 (vbp,vbn)=(vwell,vsub) をパラメータとしている。電源電圧 vdd= $1.8\,\mathrm{V}$ 、vwell= $3.3\,\mathrm{V}$ 、vsub= $-1.5\,\mathrm{V}$  という設計値ではリーク電流は以下のようになる。

$$idd = 1.3 \, mA$$

(基板バイアス制御無) (2.3)

基板バイアス制御により、約 1/36 にリーク電流が削減できている。また、その時の iwell および isub 電流は図 2.23より以下のようになる。

$$iwell = 0.17 \,\mu A \tag{2.5}$$

$$isub = 6.1 \,\mu A \tag{2.6}$$

$<sup>^{11}</sup>$ PMOS の基板電流は、vwell 電源に流れる電流 iwell によって測定できる。負電圧発生回路 (vbcg) の諸特性については、2.5.3 節で記述する。

特に isub 電流が多いのは、pn 接合リークによるものと考えられる。図 2.22においても基板バイアスを深く印加することにより、スタンバイリーク電流 idd が減少しているが、基板を過剰に引くことで逆に増加している。この現象については、2.6 節で詳しく述べる。

## 2.5.3 負電圧発生回路 (vbcg) 特性

次に、スタンバイ時の NMOS の基板バイアス電位である負電圧 (vsub) を発生する負電 圧発生回路 (vbcg) の諸特性を示す。スタンバイ時に動作する回路であるため、十分な負荷 駆動能力と低電力を実現するための高効率電圧変換特性が求められる。

図 **2.24** vbcg の Isub-Vsub 特性 (スタンバイ時)

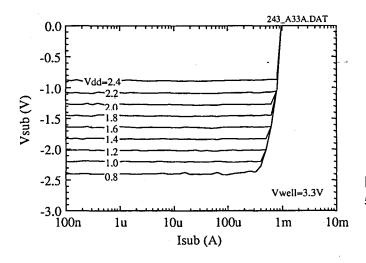

図 2.24にスタンバイ時の、vsub 電位の負荷電流 isub 依存性を示す。vdd をパラメータとして  $0.8\,\mathrm{V}$  から  $2.4\,\mathrm{V}$  まで  $0.2\,\mathrm{V}$  ステップで変化させている。これより、vdd= $1.8\,\mathrm{V}$  の時で vbcg 内のチャージポンプの最大許容負荷電流 isub max =  $600\,\mu\mathrm{A}$  であることがわかる。一般に vsub に流れる電流は pn 接合リーク電流だけであるため、SH4 のチップサイズを考えると十分な電流供給能力があることがわかる。また、得られた負電圧 (vsub) と vdd には式 (2.2) の関係が得られていることがわかる。

図 **2.25** vbcg の Isub-Idd, Iwell 特性 (スタンバイ時)

図 2.25にスタンバイ時の、iwell および idd の負荷電流 isub 依存性を示す。vdd をパラメータとして  $0.8\,\mathrm{V}$  から  $2.4\,\mathrm{V}$  まで  $0.2\,\mathrm{V}$  ステップで変化させている。なお、スタンバイ時

図 2.26 vbcg の電流効率

の無負荷の時には、vdd=1.8V で、 $iwell=2\mu A$ ,  $idd=0.6\mu A$  であった。

図 2.26に vwell=3.3 V、スタンバイ時の vbcg の電流変換効率 (isub/iwell) を示す。vdd をパラメータとして 0.8 V から 2.4 V まで 0.2 V ステップで変化させた。vdd=1.8 V の時の電流効率は以下のようになる。

電流効率 =

$$32\%$$

(isub= $1\mu$ A) (2.7)

$$66\%$$

(isub= $10 \,\mu\text{A}$ ) (2.8)

$$74\%$$

(isub= $100 \mu A$ ) (2.9)

本試作では、若干大きめの負荷駆動能力を持つようにチャージポンプ回路のポンピング容量およびポンピング周波数を設計したため、低負荷領域での電流効率が若干悪くなっている。

## 2.6 基板バイアス制御の限界 (GIDL 電流によるリーク電流増加)

2.5 節で述べたように、基板インピーダンス切り替え型基板バイアス制御方法によって高速動作を維持しながらの基板バイアス制御に成功し、数十  $\mu$ A のスタンバイ状態 (Standby mode) を実現できた。しかし、この高温で LSI をテストする場合、サプスレッショルドリーク電流は  $50^{\circ}$ C で約 1 桁上昇する。したがって、このスタンバイ状態時に  $I_{DDQ}$  テストを実行する場合、数百  $\mu$ A のリーク電流はまだ大きすぎる。 $^{12}$  ここでは更なる低リーク電流化を検討する。

基板バイアス制御によるサブスレッショルドリーク電流削減効率を高くするには、基板バイアスを深く印加する方法がある。しかし、図 2.22からわかるように、あまり深く印加しすぎると逆に増加する。これは基板を深く印加すると MOSトランジスタのドレイン・ウェルあるいはウェル・ウェル間等に大きな電位差が生じ、pn 接合リークが増加するからであると考えられる。 $^{13}$  また、もう一つの大きな原因は GIDL(Gate-Induced Drain Leakage)電流である。特に近年の薄い酸化膜を用いた MOSトランジスタでは、深い基板印加によって GIDL 電流が著しく増加する [35]。

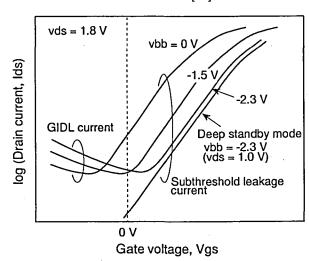

図 2.27 基板電位の印加によるドレイン電流特性の変化。

図 2.27はその様子を示したものである。上側の三本の曲線を見て分かるように、深い基板電位 vbb を印加するに従い、オフ時のサブスレッショルドリーク電流は減少して再び増加する。

一方、一番下側の曲線は、基板を深く印加すると同時にドレイン電圧 vds を低くした場合の特性である。次にこの性質を利用した新しいリーク電流削減方式 (低電圧基板バイアス制御方式) を用いたデータリテンション状態 (Data retention mode) の実現方法についてを述べる。

$<sup>^{12}1</sup>$  個の MOS の不良によるリーク増加は、1 個の MOS のオン電流の数分の 1 として  $100~\mu A$  程度になる可能性がある。したがって、正常時のリーク電流は  $100~\mu A$  以下にする必要性がある。

<sup>13</sup>また、図 2.23から、N+-P ウェル接合リークの方が P+-N ウェル接合リークよりも大きいことがわかる。

## 2.7 低電圧基板バイアス制御方式による GIDL 電流削減技術

#### 2.7.1 基本概念

ここでは、基板バイアス制御と電源電圧制御を組み合わせた新しいリーク電流削減方式 (低電圧基板バイアス制御方式) によるデータリテンション状態 (Data retention mode) を 提案する。この方式では、基板バイアスを印加した状態で、さらに内部回路の情報が消去 されない程度に電源電圧 vdd を下げる。

基板バイアスを印加した状態からさらに電源電圧 vdd を下げることにより、

- (1) ドレイン電圧が低下するため、DIBL(Drain Induced Barrier Lowering) 現象により MOSトランジスタのしきい値電圧が高くなる。

- (2) 基板バイアス電位が一定の条件のもとで電源電圧が低下することにより、各 MOSトランジスタのソース電位と基板電位の電位差が大きくなる。すなわち、ドレインあるいはソースとウェル pn 接合間の電位差を変化させないで実効的に基板バイアスが深く印加される。

- (3) 基板バイアスが深くなることにより、DIBL 現象がより顕著になる。

という効果により、基板バイアス制御だけの時よりもサブスレッショルドリーク電流による消費電力を大幅に抑えることができる。さらに、DIBL 現象はゲート長 Lg が短くなるほど大きくなるため、微細化が進めばそれだけ効果が増すという特徴がある。

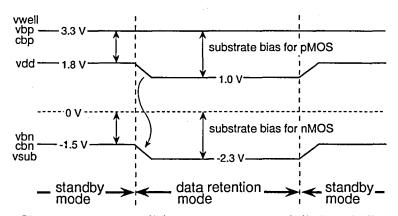

2.4 節で示した基板インピーダンス切り替え型性基板バイアス制御方式では、式 (2.2) の関係にしたがって NMOS 基板バイアス電位が発生されるため、上記条件をスタンバイ時の電源電圧を  $1.8\,\mathrm{V}$  から  $1\,\mathrm{V}$  に減少させるだけで容易に実現できる (図 2.28)。

図 2.28 スタンバイ状態とデータリテンション状態間での遷移

#### 2.7.2 測定結果

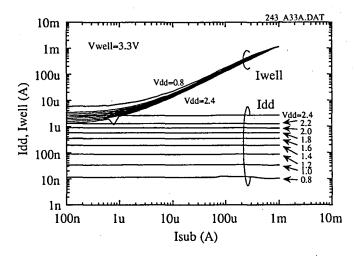

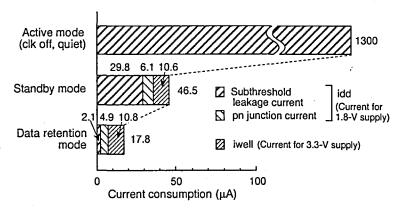

図 2.29に SH4 マイコンのスタンバイ状態とデータリテンション状態でのリーク電流測定結果を示す。測定温度は室温である。データリテンション状態は前節で示したように、スタンバイ状態において電源電圧を  $1.8\,\mathrm{V}$  から  $1\,\mathrm{V}$  まで減少させた状態である。なお、iwell には負電源発生回路 (vbcg) の消費電流と基板電流が含まれている。

何も動作しないアクティブ状態でのリーク電流は、基板バイアス制御を行わない場合の スタンバイ電流に相当する。この場合消費電流は1.3mAであった。それに対して、基板バ

図 2.29 スタンバイ状態とデータリテンション状態でのリーク電流測定結果

イアス制御を行ったスタンバイ状態では、ぞれが  $46.5\,\mu\mathrm{A}$  まで減少している。負電圧発生 回路 vbcg の電流効率を考慮すると、基板電流とサブスレッショルドリーク電流はそれぞれ、 $6.1\,\mu\mathrm{A}$ 、 $29.8\,\mu\mathrm{A}$  であることがわかる。さらに、低電圧基板バイアス制御を行ったデータリテンション状態では、 $17.8\,\mu\mathrm{A}$  まで消費電流が削減している。このとき、基板電流とサブスレッショルドリーク電流はそれぞれ、 $4.9\,\mu\mathrm{A}$ 、 $2.1\,\mu\mathrm{A}$  である。データリテンション状態によって、サブスレッショルドリーク電流を  $2\,\mathrm{fr}$ 以上削減できている。

## 2.8 結言

本章では低電圧ロジック回路の高速・低電力化について論じた。まず始めに、ロジック回路の低電圧化の推移とそれに伴う課題について述べた。特に重要な課題であるサブスレッショルドリーク電流については、従来から提案されている主な方式を述べた。

スタンバイ時のサブスレッショルドリーク電流低減方式としては、スタンバイ時に回路への電源供給を遮断する電源スイッチ方式と、スタンバイ時に MOSトランジスタの基板端子に深いバイアスを印加する基板バイアス制御方式がある。電源スイッチ制御方式は CADによるサポートが必要な一方、基板バイアス制御方式は複雑な CAD によるサポートが不要であるという特徴がある。また、基板バイアス制御方式では、 $I_{DDQ}$  テストも可能である。しかし、基板バイアス制御方式には大きな課題として、動作時の基板インピーダンスの上昇が挙げられ、これによって LSI の動作時の高速性が失われることがわかった。

低電圧・低しきい値 MOS トランジスタを用いた大規模高速 LSI において、スタンバイ 時の消費電力の削減と、アクティブ時の高速動作を両立させるために、基板インピーダン ス切り替え型基板バイアス制御方式を提案した。

本提案方式を、 $0.2\mu m$  CMOS・5 層アルミ配線・デュアル酸化膜厚プロセスを用いた、1.8 V SH4 マイコン (3.3 M Trs, 200 MHz) に適用し、200 MHz という高速動作を維持しながらの基板バイアス制御を実証した。リーク電流を約1.7 桁削減でき、スタンバイ時の消費電流は1.3 mA から $46.5 \mu A$ (室温における実測)まで低下させることができた。

また、上記 SH4 マイコンにおいて、更なる低電力スタンバイ状態の実現のために基板バイアスをより深く印加すると、GIDL 電流等によってスタンバイ時電流が逆に増加してしまうことがわかった。基板バイアス印加時の GIDL 電流削減方法についても検討し、上記基板バイアス制御方式に電源電圧制御を組み合わせた新しい基板バイアス制御方式 (低電圧基板バイアス制御方式)を提案した。

この低電圧基板バイアス制御方式では、電源電圧を  $1.8\,\mathrm{V}$  から  $1\,\mathrm{V}$  に低減し、DIBL 効果と基板バイアス効果によって大幅なリーク電流削減を可能とする。本技術を基板バイアス制御した  $\mathrm{SH4}$  マイコンに適用し、リーク電流を更に約  $1\,\mathrm{桁削減}$ でき、スタンバイ時の消費電流を  $46.5\,\mu\mathrm{A}$  から  $17.8\,\mu\mathrm{A}$  にまで低減できた。

## 参考文献

- [1] H. Mizuno, K. Ishibashi, T. Shimura, T. Hattori, S. Narita, K. Shiozawa, S. Ikeda and K. Uchiyama, "A 18-μA-Standby-Current 1.8-V 200-MHz Microprocessor with Self Substrate-Biased Data Retention Mode", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 280-281, Feb. 1999.

- [2] H. Mizuno, K. Ishibashi, T. Shimura, T. Hattori, S. Narita, K. Shiozawa, S. Ikeda and K. Uchiyama, "A 18-μA-Standby-Current 1.8-V 200-MHz Microprocessor with Self Substrate-Biased Data Retention Mode", *IEEE J. of Solid-State Circuits*, vol. 34, no. 11, pp. 1492-1500, Nov. 1999.

- [3] "The National Technology Roadmap for Semiconductors", tech. report, Semiconductor Industry Assn., San Jose, Calif., 1999.

- [4] J.M. Soden, C.F. Hawkins and A.C. Miller, "Identifying defects in deep-submicron CMOS ICs", *IEEE Spectrum*, pp. 66-71, Sep. 1996.

- [5] D. Josephson, M. Storey and D. Dixon, "Microprocessor I<sub>DDQ</sub> Testing: A Case Study", IEEE Design & Test of Computers, vol. 12, no. 2, pp. 42-52, Summer 1995.

- [6] T. Sakata, M. Horiguchi, and K. Itoh, "Subthreshold-Current Reduction Circuits for Multi-Gigabit DRAM's", Symp. on VLSI Circuits Dig. of Tech. Papers, pp. 45-46, May 1993.

- [7] M. Horiguchi, T. Sakata and K. Itoh, "Switched-Source-Impedance CMOS Circuit for Low Standby Subthreshold Current Giga-scale LSI's", Symp. on VLSI Circuits Dig. of Tech. Papers, pp. 47-48, May 1993.

- [8] S. Mutoh, T. Douseki, Y. Matsuya, T. Aoki, and J. Yamada, "1V High-Speed Digital Circuit Technology with 0.5μm Multi-Threshold CMOS", Proc. 6th Annu. IEEE Int. ASIC Conf. Exhibit, pp. 186-189, 1993.

- [9] S. Shigematsu, S. Mutoh, Y. Matsuya, Y. Tanabe and J. Yamada, "A 1-V High-Speed MTCMOS Circuit Scheme for Power-Down Application Circuits", *IEEE J. of Solid-State Circuits*, vol. 32, no. 6, pp. 861-869, June 1997.

- [10] H. Akamatsu, T. Iwata, H. Yamamoto, T. Hirata, H. Yamaguchi, H. Kotani and A. Matsuzawa, "A Low Power Data Holding Circuit with an Intermittent Power Supply Scheme", Symp. on VLSI Circuits Dig. of Tech. Papers, pp. 14-15, May 1996.

- [11] H. Makino, Y. Tsujihashi, K. Nii, C. Morishima, Y. Hayakawa, T. Shimizu and T. Arakawa, "An Auto-Backgate-Controlled MT-CMOS Circuit", Symp. on VLSI Circuits Dig. of Tech. Papers, pp. 42-43, June 1998.

- [12] K. Kumagai, H. Iwaki, H. Yoshida, H. Suzuki, T. Yamada and S. Kurosawa, "A Novel Powering-down Scheme for Low Vt CMOS Circuits", Symp. on VLSI Circuits Dig. of Tech. Papers, pp. 44-45, June 1998.

- [13] R. Stephany, K. Anne, J. Bell, G. Cheney, J. Eno, G. Hoeppner, G. Joe, R. Kaye, J. Lear, T. Litch, J. Meyer, J. Montanaro, K. Patton, T. Pham, R. Reis, M. Silla, J. Slaton, K. Snyder and R. Witek, "A 200MHz 32b 0.5W CMOS RISC Micropro-

- cessor", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 238-239, Feb. 1998.

- [14] K. Seta, H. Hara, T. Kuroda, M. Kakumu and T. Sakurai, "50% Active-Power Saving without Speed Degradation using Standby Power Reduction (SPR) Circuit", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 318-319, Feb. 1995.

- [15] Y. Ye, S. Borker and V. De, "A New Technique for Standby Leakage Reduction in High-Performance Circuits", Symp. on VLSI Circuits Dig. of Tech. Papers, pp. 40-41, June 1998.

- [16] T. Kuroda, T. Fujita, S. Mita, T. Mori, K. Matsuo, M. Kakumu and T. Sakurai, "Substrate Noise Influence on Circuit Performance in Variable Threshold-Voltage Scheme", Int'l Symp. on Low Power Electronics and Design (ISLPED), pp. 309-312, Aug. 1996.

- [17] H. Mizuno, M. Miyazaki, K. Ishibashi, Y. Nakagome and T. Nagano, "A Lean-Power Gigascale LSI using Hierarchical V<sub>BB</sub> Routing Scheme with Frequency Adaptive V<sub>T</sub> CMOS", Symp. on VLSI Circuits Dig. of Tech. Papers, pp. 95-96, June 1997.

- [18] F. Assaderaghi, G.G. Shahidi, M. Hargrove, K. Hathorn, H. Hovel, S. Kulkarni, W. Rausch, D. Sadana, D. Schepis, R. Schulz, D. Yee, J. Sun, R. Dennard and B. Davari, "History-Dependence of Non-Fully Depleted (NFD) Digital SOI Circuits", Symp. on VLSI Technology Dig. of Tech. Papers, pp. 122-123, June 1996.

- [19] G.G. Shahidi, A. Ajmera, F. Assaderaghi, R.J. Bolam, E. Leobandung, W. Rausch, D. Sankus, D. Schepis, L.F. Wagner, K. Wu and B. Davari, "Partially-Depleted SOI Technology for Digital Logic", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 426-427, Feb. 1999.

- [20] T. Kuroda, T. Fujita, S. Mita, T. Nagamatsu, S. Yoshioka, K. Suzuki, F. Sano, M. Norishima, M. Murota, M. Kako, M. Kinugawa, M. Kakumu and T. Sakurai, "A 0.9V 150MHz 10mW 4mm<sup>2</sup> 2-D Discrete Cosine Transform Core Processor with Variable-Threshold-Voltage Scheme", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 166-167, Feb. 1996.

- [21] M. Kubo, R. Hori, O. Minato and K. Sato, "A Threshold Voltage Controlling Circuit for Short Channel MOS Integrated Circuits", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 54-55, Feb. 1976.

- [22] J.B. Burr and J. Shott, "A 200mV Self-Testing Encoder/Decoder using Standford Ultra-Low-Power CMOS", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 84-85, Feb. 1995.

- [23] T. Kobayashi and T. Sakurai, "Self-Adjusting Threshold-Voltage Scheme (SATS) for Low-Voltage High-Speed Operation", *Proc. Custom Integrated Circuits Conf.* (CICC), pp. 271-274, May 1994.

- [24] M. Mizuno, K. Furuta, S. Narita, H. Abiko, I. Sakai and M. Yamashina, "Elastic-Vt CMOS Circuits for Multipule On-Chip Power Control", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 300-301, Feb. 1996.

参考文献

- [25] M. Miyazaki, M. Mizuno and K. Ishibashi, "A Delay Distribution Squeezing Scheme with Speed-Adaptive Threshod-Voltage CMOS (SA-CMOS) for Low Voltage LSIs", Int'l Symp. on Low Power Electronics and Design (ISLPED), pp. 49-53, Aug. 1998.

- [26] K. Suzuki, S. Mita, T. Fujita, F. Yamane, F. Sano, T. Sakurai, A. Chiba, Y. Watanabe, K. Matsuda, T. Maeda and T. Kuroda, "A 300MIPS/W RISC core processor with variable supply-voltage scheme in variable threshold-voltage CMOS", Proc. Custom Integrated Circuits Conf. (CICC), pp. 587-590, May 1997.

- [27] S. Narendra, D. Antoniadis and V. De, "Impact of Using Adaptive Body Bias to Compensate Die-to-die Vt Variation on Within-die Vt Variation", Int'l Symp. on Low Power Electronics and Design (ISLPED), pp. 229-232, Aug. 1999.

- [28] M. Miyazaki, G. Ono, T. Hattori, K. Shiozawa, K. Uchiyama and K. Ishibashi, "A 1000-MIPS/W Microprocessor using Speed-Adaptive Threshold-Voltage CMOS with Forward Bias", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 420-421, Feb. 2000.

- [29] Z. Chen, C. Diaz, J.D. Plummer, M. Cao and W. Greene, "0.18μm Dual Vt MOSFET Process and Energy-Delay Measurement", Int'l Electron Devices Meeting (IEDM) Tech. Dig., pp. 851-854, Dec. 1996.

- [30] K. Fujii, T. Douseki and M. Harada, "A Sub-1V Triple-Threshold CMOS/SIMOX Circuit for Active Power Reduction", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 190-191, Feb. 1998.

- [31] N. Rohrer, C. Akrout, M. Canada, D. Cawthron, B. Davari, R. Floyd, S. Geissler, R. Goldblatt, R. Houle, P. Kartschoke, D. Kramer, P. McCormick, G. Salem, R. Schulz, L. Su and L. Whitney, "A 480MHz RISC Microprocessor in a 0.12μm L<sub>eff</sub> CMOS Technology with Copper Interconnections", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 240-241, Feb. 1998.

- [32] O. Nishii, F. Arakawa, K. Ishibashi, S. Nakano, T. Shimura, K. Suzuki, M. Tachibana, Y. Totsuka, T. Tsunoda, K. Uchiyama, T. Yamada, T. Harrori, H. Maejima, N. Nakagawa, S. Narita, M. Seki, Y. Shimazaki, R. Satomura, T. Takasuga and A. Hasegawa, "A 200MHz 1.2W 1.4GFLOPS Microprocessor with Graphic Operation Unit", Int'l Solid-State Circuit Conf. (ISSCC) Dig. of Tech. Papers, pp. 288-289, Feb. 1998.

- [33] F. Arakawa, "SH4 RISC Microprocessor for Multimedia", HOT CHIPS IX, pp. 165-176, Aug. 1997.

- [34] 伊藤 清男, "超 LSI メモリ"、1994 年、倍風館、pp. 245-251.

- [35] T.Y. Chan, J. Chen, P.K. Ko and C. Hu, "The Impact of Gate-Induced Drain Leakage Current on MOSFET Scaling", Int'l Electron Devices Meeting (IEDM) Tech. Dig., pp. 718-721, Dec. 1987.

## 第3章

# 低電圧 SRAM 回路の 高速・低電力化

## 3.1 緒言

SRAM 回路を使用しない LSI は存在しないといえるほど、LSI において SRAM 回路は重要な構成要素の一つである。例えばマイクロプロセッサでは、キャッシュや TLB(Translation Look-aside Buffer) として SRAM は必須の回路要素である。また、小容量のメモリとしてはレジスタファイルや各種バッファ等も SRAM 回路で構成されている。特にキャッシュは、今日のマイクロプロセッサにとって性能に大きく影響を与える重要な回路構成要素である。本章では低電圧 SRAM 回路の高速・低電力化について述べる。

まず始めに、SRAM 回路の低電圧化の推移と課題について述べる。SRAM 回路の低電圧動作特性にはメモリセル構造が大きく関係している。ここでは特にメモリセル構造の推移について詳しく述べる。

次に、比較的良好な低電圧動作特性を持つ完全 CMOS メモリセルについて、従来から 提案されている低電圧で高速に動作させるための駆動方法について述べる。ここでは、完 全 CMOS メモリセルを低電圧で高速に動作させるために重要なスタティックノイズマージ ンについて、電源電圧とメモリセルを構成するトランジスタのしきい値電圧の関係につい ても詳しく述べる。

以上の結果をもとにして本章では、完全 CMOS メモリセルの構造をほとんど変更せずに、低電圧動作時の読み出し速度向上と書き込み時の低消費電力化を実現するソース線駆動方式の新しいメモリセル構造を提案する [1-3]。このソース線駆動型メモリセルは、従来のメモリセルでは接地電位に接続されていたソース線を積極的に駆動することにより、低電圧時での高速動作と高ノイズマージンを実現するメモリセル制御方式である。ここではその低電圧動作特性について詳しく述べる。

1995年にソース線駆動メモリセルを発表後、各種の類似した低電圧メモリセルが発表された。ここではその中でも代表的な低電圧メモリセルについて、その特徴を述べる。

## 3.2 SRAM 回路の低電圧化の推移と課題

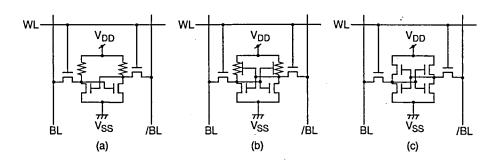

図 **3.1** 代表的な SRAM メモリセル (a) 高抵抗メモリセル、(b)TFT 負荷メモリセル、(c) 完全 CMOS メモリセル。

SRAM 回路の低電圧動作特性にはメモリセル構造が大きく関係している。代表的な SRAM のメモリセルを図 3.1に示す。SRAM 用のメモリセルとしては、(a) 高抵抗負荷を用いた高抵抗メモリセル、(b) 高抵抗負荷をメモリセルの上に積層したポリシリコン TFT(Thin Film Transistor) で形成する TFT 負荷メモリセル、(c) 高抵抗負荷を Si 基板上の PMOSトランジスタで形成する完全 CMOSメモリセルの 3 つに大きくわけることができる。いずれのメモリセルにおいても、N型の駆動 MOSトランジスタと負荷抵抗あるいはトランジスタからなるインバータで正帰還ループを形成することにより、二つの記憶ノードにデータ保持し、ワード線 WL に接続された N型の転送 MOSトランジスタを介してデータの読み書きを行う。

高抵抗メモリセルは、動作電圧マージンが小さいために、一般的に 2V 程度が動作下限である。しかし、メモリセル面積が小さくて済むため大容量 SRAM に広く用いられている。また、メモリセルの待機時に高抵抗負荷に貫通電流が流れつづけるために、SRAM の待機時電流が大きくなる欠点がある。

一方、TFT 負荷メモリセルは、製造プロセスは複雑になるが、高抵抗負荷メモリセルと同等の集積度が達成できるという特徴がある。読み出し時にワード線を電源電圧よりも高い電圧まで昇圧するワード線ブースト方式を用いて、1V での動作に成功した例が報告されている [4] が、一般に1V以下の低電圧化には限界があるといえる。待機時電流については、高抵抗メモリセルよりも小さく抑えることができる。

完全 CMOS メモリセルはメモリセル面積が大きいため、集積度が小さいという欠点がある。 $0.13\,\mu\mathrm{m}$  CMOS テクノロジを用いて、 $2.49\,\mu\mathrm{m}^2$  のメモリセル面積を実現した例も報告されているが [5]、一般には約  $49\mathrm{F}^2$  (F は配線ピッチの半分) 程度の大きさである。低電圧特性としては、上記 3 種類の中ではもっとも良好で、古くから  $1\mathrm{V}$  の動作例が報告されている [6]。待機時電流についても、上記 3 種類の中でもっとも小さく抑えることができる。

上記したように、特に 1.5 V 以下の低電圧で高速動作させるためには、メモリセルとしては完全 CMOS メモリセルが適している。また、完全 CMOS メモリセルはロジックプロセスで構成できるために、大規模なロジック回路が集積される LSI に混載する場合にも好適である。以下、完全 CMOS メモリセルを低電圧で動作させるための方法について検討する。

## 3.3 完全 CMOS メモリセルの低電圧高速動作

### 3.3.1 低電圧高速動作のための主な駆動方式

文献 [6] は完全 CMOS メモリセルを用いることにより 1V での読み出し動作を実現している。しかし、動作速度が若干遅いという課題がある。低電圧化によってメモリの読み出し速度が低下する理由はメモリセルがビット線をドライブする能力が低下するためである。低電圧時のドライブ能力を向上させ、高速動作を実現するための方法としては、以下が提案されている。

- (1) メモリセルには周辺回路の電源電圧よりも高い電圧を与える方法 [7,8]。メモリセル自体の容量は比較的小さいので、その部分に高い電圧を与えても消費電力の増加にはつながり難いという性質を使用している。

- (2) 読み出し時にワード線に電源電圧以上の電圧を与え、転送 MOSトランジスタの駆動能力を上げる方法 (Boosted Word Voltage Scheme) [4]。この方法は DRAM のワード線プーストに似た方式であり、もともと TFT 負荷メモリセルを低電圧で動作させるために提案されたものであるが、完全 CMOS メモリセルでも効果がある。転送 MOSトランジスタのしきい値低下と同様の効果が得られるため、高速なメモリアクセスが可能である。

- (3) メモリセルの転送 MOS トランジスタのしきい値電圧 ( $V_{th}$ ) だけを下げる方法 [9]。

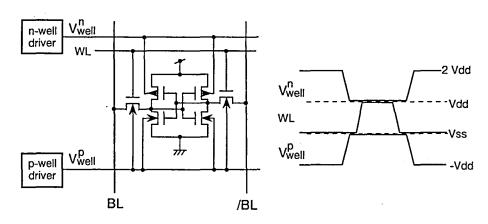

- (4) メモリセルの基板バイアスを制御する方法 (図 3.2) [10]。

方法 (1) については、メモリセルに高電位を印加するために安定した動作が期待でき、同時に高速な読み出し速度を得ることができるが、消費電力に対する低電圧化の効果が少ないという欠点がある。

方法 (2),(3) については、転送 MOSトランジスタの駆動能力が向上するために低電圧での高速動作が期待できるが、後に述べるスタティックノイズマージン (SNM) が劣化する欠点があり 1V 以下の低電圧で使用することは困難である。さらにまた、方法 (3) については、低  $V_{th}$  化がトランジスタのサブスレッショルドリーク電流の増加によるビット線対間ノーマルモードノイズを生じ、このノイズによって読み出しマージンが小さくなるという課題がある [12]。また当然この現象は、非動作時の消費電流の増加を招くことになり、1.5V 以下の低電圧動作には適さない。

図 3.2 ダイナミックリークカットオフ SRAM のメモリセル駆動方法

方法(4)は、2.3.1節で述べたロジック回路で用いられている基板バイアス制御方式を、 メモリセルに応用した、ダイナミックリークカットオフ SRAM と呼ばれるメモリセル制御 方式である (図 3.2) [10]。待機時には基板バイアスを印加し、メモリセルを構成するトラ ンジスタのしきい値を高くし、サブスレッショルドリーク電流を低減している。また、読 み出し時には基板バイアスを浅くし、トランジスタのしきい値電圧を低くして高速読み出 し動作を実現している。読み出し時にメモリセルを構成するトランジスタのしきい値が低 くなるために、ワード線ブースト方式と同様に SNM の劣化が課題である。

### 完全 CMOS メモリセルのスタティックノイズマージン

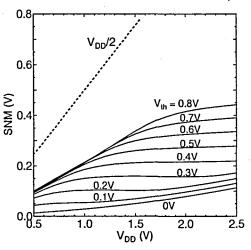

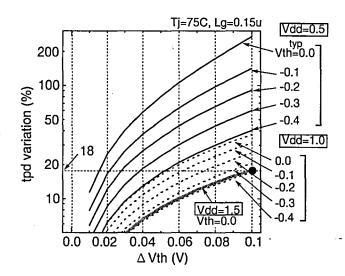

図 3.3 スタティックノイズマージン (SNM) 図 3.4 スタティックノイズマージン (SNM) バータの最大ノイズマージン ( $V_{

m DD}/2$ )を示のみ変化させた。 している。

のしきい値電圧 ( $V_{

m th}$ ) 依存性。しきい値電圧 のしきい値電圧 ( $V_{

m th}$ ) 依存性。メモリセルの はメモリセルを構成する全てのトランジス ラッチを構成する4つのトランジスタのしき タに適用した。破線は理想的な CMOS イン い値は 0.8 V で、転送 MOS のしきい値電圧

上記したように、スタティックノイズマージン (SNM) [11] はメモリセルの低電圧高速動 作において、重要なパラメータである。所定の電圧にプリチャージされている相補なビッ ト線対に、メモリセル内の記憶ノードを接続して読み出し動作を行う SRAM セルにおい ては、読み出し時にワード線をアサートすると、ビット線対から'0'を記憶しているメモ リセル内の記憶ノードへ電流が流れ込む。これによってその記憶ノードの電位が上昇する。 プロセスばらつき等でメモリセルが対称にできていない場合には、この電位上昇によって メモリセル内のデータが反転してしまう。この読み出し時のメモリセル内の記憶ノード対 間の電圧マージンをスタティックノイズマージンと呼ぶ。

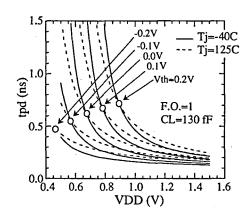

図 3.3に完全 CMOS メモリセルの SNM の計算結果を示す。0.15 μm の CMOS テクノロ ジを仮定した。また、駆動 MOSトランジスタと転送 MOSトランジスタのゲート幅比 (β 比) は 1.7 に設定している。メモリセルを低電圧で駆動するほど、また、メモリセルを構成 するトランジスタのしきい値電圧が低くなるほど SNM が小さくなることがわかる。

図 3.4は、メモリセルのラッチを構成する 4 つの MOS トランジスタ (2 つの負荷 PMOS トランジスタと 2 つの駆動 NMOS トランジスタ) のしきい値電圧は高しきい値 (0.8 V) に 固定して、転送 MOS トランジスタのしきい値電圧だけを変化させた場合の計算結果である。転送 MOS トランジスタのしきい値は SNM に大きく影響することがわかる。上記した読み出し時にワード線に電源電圧以上の電圧を与える方法 [4] では、実効的に転送 MOS トランジスタのしきい値電圧を低く設定したことと同様になるため、低電圧では SNM が著しく劣化してしまうことがわかる。

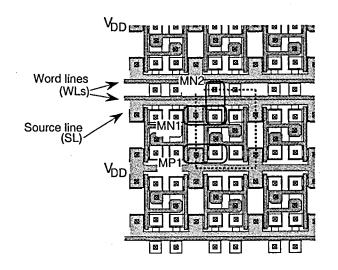

## 3.4 ソース線駆動型 (DSL) メモリセル

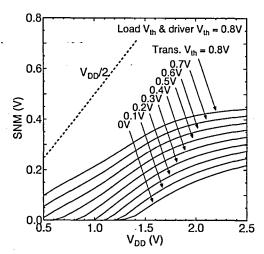

図 3.5 (a) ソース線駆動型 (DSL) メモリセルと (b) 従来の完全 CMOS メモリセル。

本節では、低電圧で高速に動作する新しいメモリセル構造 (ソース線駆動型メモリセル; Driving source line (DSL) cell) を提案する [1-3]。図 3.5は提案したメモリセルと従来の完全 CMOS メモリセルの回路図を示している。従来の完全 CMOS メモリセルとは、駆動 MOS トランジスタのソース電極の処理の仕方が異なっている。従来メモリセルでは駆動 MOS トランジスタのソース電極は接地して使用しているが、本提案メモリセルではソース線 SL として独立して駆動する。

ソース線 SL の詳しい駆動方法については以下の節で述べるが、読み出し時にはソース線 SL に負電位を与えて駆動 MOSトランジスタと転送 MOSトランジスタのビット線駆動能力を向上させ、書き込み時にはソース線 SL をフローティング状態にして、小量のビット線電位差による書き込みを可能にしている。すなわち、ワード線 WL やメモリセルに高電位を印加する代わりに、メモリセルのソース線 SL に負電位を印加する方式である。読み出し時にはメモリセルに大きな電源電圧が印加されたように振舞うため、低電圧でも大きなスタティックノイズマージンが確保できる。

図 3.6にソース線駆動型メモリセルのレイアウト例を示す。従来の完全 CMOS メモリセ

図 3.6 DSL メモリセルのレイアウト図面。

ルと同様に、電源線  $(V_{DD})$  は上下のセルで共有されており、接地線は上下のセルで分離されている。この接地線をソース線 SL として上下のセルで独立して制御する。したがって、従来のメモリセルのレイアウトと同一で面積増加がない。

#### 3.4.1 読み出し動作

#### 基本動作

図 3.7 ソース線駆動型 (DSL) メモリセルの読み出し方法。

図 3.7に従来の完全 CMOS メモリセルと DSL メモリセルとの読み出し方法の違いを示す。従来メモリセルではメモリセルからのデータの読み出しは、ワード線 WL を 'H' にし、駆動 MOSFET により、プリチャージしてあるビット線 BL,/BL の電位を負方向に駆動させ、この変化をセンスアンプによって増幅して読み出している。それに対し、DSL メモリセルでは、読み出し時にワード線を 'H' にすると同時にソース線 SL を 0V から負電位に駆動する。負電位  $(V_{SL})$  に駆動することにより、

- (1) 駆動 MOS(図 3.5の MN1) のソース・ゲート 間電圧差が大きくなる。

- (2) 駆動 MOS のソース・基板電位が順方向バイアスされ、基板バイアス効果によって駆動 MOS のしきい値が低くなる。

- (3) 転送 MOS(図 3.5の MN2) のソース電位 (メモリセルのノード電位) が低くなること により、転送 MOS のソース・ドレイン間電圧差が大きくなると同時に、転送 MOS のソース・ゲート 間電圧差が大きくなるワード線ブースト効果が生じる。

- (4) 同じく転送 MOS のソース電位が低くなることで、転送 MOS のソース・基板間電位 差が小さくなり、転送 MOS の基板バイアス効果が小さくなる。

これらの効果により、メモリセルのビット線駆動電流が著しく大きくなる。

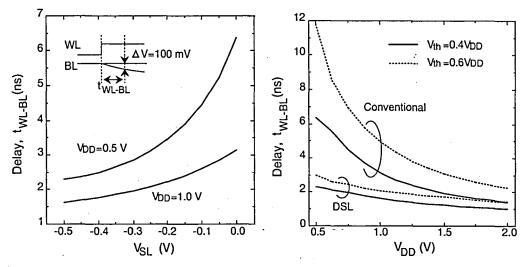

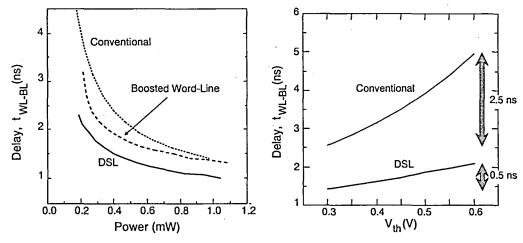

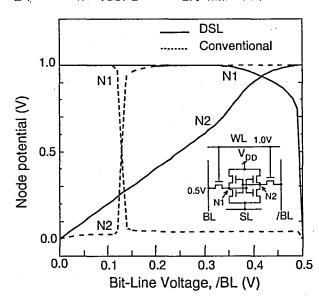

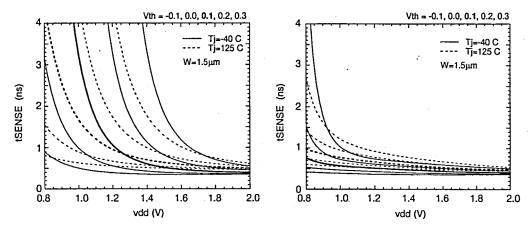

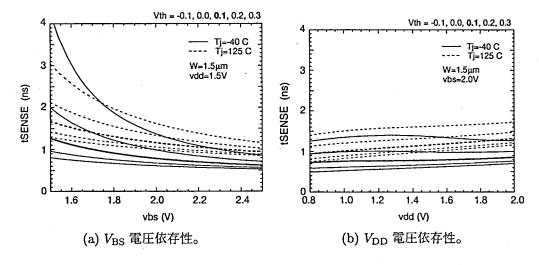

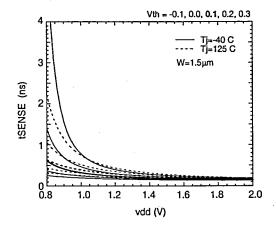

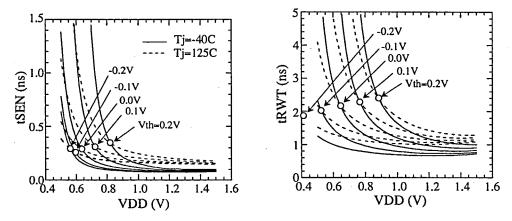

図 3.8に DSL メモリセルの読み出し時間のソース線駆動電圧  $(V_{SL})$  依存性を、図 3.9に電源電圧  $(V_{DD})$  依存性を示す。評価には  $0.25\,\mu\mathrm{m}$  テクノロジのメモリセル  $(2.5\times3\mu\mathrm{m})$  を仮定し、ビット線に接続されているメモリセルの数は列方向に 256 個、行方向に 32 ビットであると仮定した。読み出し時間  $t_{WL-BL}$  は、ワード線が立ち上がってからビット線対が  $100\,\mathrm{mV}$  まで開くまでの時間と定義した。図 3.8においては、しきい値電圧は電源電圧  $V_{DD}$  の 40%に設定した。同図において、ソース線駆動電圧  $(V_{SL})$  が 0V の場合が、従来の完全 CMOS メモリセルでの読み出し速度に相当する。

特に高しきい値メモリセルを低電圧で使用した場合に大きな読み出し時間短縮効果があることがわかる。DSL メモリセルでは、電源電圧が $0.5\,\mathrm{V}$  の時でも従来メモリセルの電源電圧が $1.3\,\mathrm{V}$  の時と同じ読み出し速度が得られ、電源電圧 $0.5\,\mathrm{V}$  で約 $0.5\,\mathrm{V}$  で約 $0.5\,\mathrm{V}$  で約 $0.5\,\mathrm{V}$  で約 $0.5\,\mathrm{V}$  で

$(V_{SL})$  依存性。

図 3.8 読み出し時間のソース線駆動電圧 図 3.9 読み出し時間の電源電圧 (VDD) 依存 性。 $V_{\rm SL}=-0.5\,{

m V}$ 。

図 3.10 読み出し速度と消費電力の比較。

図 3.11 読み出し速度としきい値電圧 (V<sub>th</sub>) の関係。

で約50%高速化できている。また、図3.8よりソース線駆動電圧 $V_{SL}$ としては、-0.5V程 度で十分効果があることがわかる。以下ではソース線の駆動電圧は基本的に -0.5 V とし て評価する。

図 3.10にメモリセルの読み出し速度の消費電力の関係を示す。同図には従来メモリセ ル (点線) とワード線をメモリセルに印加されているアレイ電圧よりも高い電圧で駆動す るワード線ブースト方式 [4] のメモリセル (破線) の特性も示している。ブースト電圧は  $V_{\mathrm{DD}} + 0.5\,\mathrm{V}$  とした。いずれのメモリセルでも、しきい値電圧は電源電圧の60%に設定し た。従来の方式と比較して、DSLメモリセルは優れた速度・電力特性を持つことがわかる。

低電圧動作において、しきい値ばらつきに対する耐性は重要な要素である。図 3.11は読 み出し速度のしきい値電圧依存性を示している。電源電圧は 1.0 V に、しきい値電圧のば らつきは ±0.15 V に設定した。しきい値電圧の変動に対する読み出し速度の変化は、従来 メモリセルと比較して DSL メモリセルでは約1/5に抑えられていることがわかる。

#### 寄生バイポーラ効果の影響

図 3.12 ウェル構造と寄生バイトーラトランジスタ。

図 3.13 ソース線リーク電流  $(I_{SL})$  のソース線駆動電圧  $(V_{SL})$  依存性 (実測)。

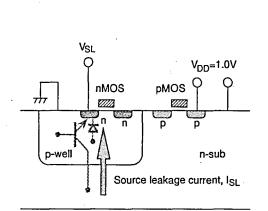

ソース線駆動型メモリセルでは、ソース線を負電位に駆動するためにメモリセルの駆動 MOS のソース・基板間の pn 接合が順方向バイアスされる。図 3.12に示した DSL メモリセルのウェル構造からわかるように、ソース線を負電位に駆動することで p-well と駆動 MOS n 拡散層が順方向バイアスされる。これにより、駆動 MOS n 拡散層と p-well と n-sub からなる n pn 寄生バイボーラトランジスタがオンし、n-sub から駆動 MOS n 拡散層に大きなソース線リーク電流 ( $I_{SL}$ ) が流れることが懸念される。

図 3.13にソース線リーク電流  $(I_{SL})$  のソース線駆動電圧  $(V_{SL})$  依存性の測定結果を示す。 32b のメモリセルでのリーク電流を室温で測定した。ソース線電位  $(V_{SL})$  が -0.5 V の時のソース線リーク電流  $(I_{SL})$  は約 100 nA である。この測定結果から、懸念されたソース線リーク電流  $(I_{SL})$  は無視できる程度に小さいことがわかる。

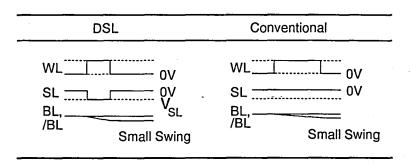

#### 3.4.2 書き込み動作

| DSL                                | Conventional              |  |  |  |

|------------------------------------|---------------------------|--|--|--|

| SL (Hi-Z) 0.0V BL, /BL Small Swing | SL0.0V BL, /BL Full Swing |  |  |  |

図 3.14 ソース線駆動型 (DSL) メモリセルの書き込み方法。

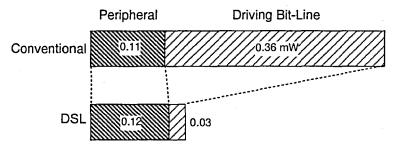

図 3.14に従来の完全 CMOS メモリセルと DSL メモリセルとの書き込み方法の違いを示す。従来メモリセルでは、ビット線 BL,/BL の電位差を電源電圧  $V_{DD}$  まで広げ、ワード線 WL を 'H' にすることによって書き込みを実行している。負荷の大きなビット線 BL,/BL を大きな振幅で駆動する必要があることから消費電力が大きいという課題がある。それに

対して、DSL メモリセルでは、ソース線 SL を 'L' からフローティング状態にして ('L' から 'H' にしても同様な効果がある)、ビット線を小振幅に駆動することで書き込みを実行する。以下、電源電圧を 1.0V、MOSFET のしきい値電圧を 0.4V に設定して書き込み動作特性を詳しく説明する。

ソース線 SL をフローティング状態にした場合は、メモリセルの駆動 MOS トランジスタ (図 3.5の MN1) の駆動能力がなくなり、ビット線 BL,/BL に与えた小量の電位差により、メモリセル内の記憶ノード電位が容易に変化する。たとえば、BL,/BL に 0.4V,0.5V の電位をそれぞれ与えると、メモリセル内の記憶ノード電位はそれぞれ 0.4V,0.5V に近くなる。ソース線 SL を 'H' にした場合は、メモリセル内の記憶ノード電位のうち、'L' であった方の電位は  $V_{\rm DD}-V_{\rm th}(0.6V)$  に上昇し、ワード線を 'H' にしビット線の一方に  $V_{\rm DD}-V_{\rm th}(0.6V)$  よりも低い電位 (例えば 0.4V) が与えられると、二つあるメモリセル内の記憶ノード電位のうち一方はその電位になる。

ソース線 SL をフローティング状態にするか 'H' に駆動するかのいずれかの方法で、メモリセル内の記憶ノードにビット線 BL,/BL の電位差を反映させ、最後にワード線を 'L'、ソース線 SL を 'L' にすることにより反映されたデータを、メモリセルをラッチ型のセンスアンプのように用いることによって電源電圧差まで増幅させる。

書き込み動作で必要なビット線 BL,/BL 振幅が小さいことから、負荷の大きなビット線 BL,/BL の充放電に伴う電力を小さくできる。たとえば、MOS トランジスタのしきい値電 圧は電源電圧  $V_{\rm DD}$  の 40%に設定した場合、 $V_{\rm DD}-V_{\rm th}(0.6V)$  は電源電圧  $V_{\rm DD}$  の 60%程度 になる。従って、ビット線に高々電源電圧  $V_{\rm DD}$  の 10%の電位変化を与えればよい。この場合、ビット線の充放電による電力増加は従来のメモリセルの場合のわずか 1%で済む。

図 3.15 書き込み時のメモリセルの ノード 電圧 (N1,N2) の、ビット線 電位依存性。

図 3.15に書き込み時のメモリセルのノード電圧の、ビット線電位依存性を示す。電源電圧は 1.0V、ビット線のプリチャージ電圧は 0.5 V に設定した。従来メモリセルでは、ビット線のプリチャージ電圧から 0.4 V 程度低電圧の 0.1 V 程度までビット線を駆動する必要があることがわかる。これは、メモリセル内のラッチ回路が動作しているために、ラッチされているデータを反転させるためには多くの電流が必要で、この電流はビット線をかなり低電圧まで駆動しないと得られないためである。

それに対して、DSL メモリセルではメモリセル内のラッチ回路には電源は供給されていないために、ラッチされていたデータを反転させるための電流がほとんど必要ない。そのため、ビット線のプリチャージ電圧から 0.1 V 程度低電圧の 0.4 V までビット線を駆動すれば、メモリセル内のノード電圧が書き込みデータに対応した値に反転している。

書き込み動作の最後には、フローティング状態にしたソース線を'L'レベルに駆動する。 これによってメモリセル自体がラッチとして動作し、メモリセル内のノードに書きこまれ た微小電位差が増幅される。

なお、擬似リード状態のセル<sup>1</sup> に対しては、書き込み時には DRAM セルのように動作する。すなわち、ワード線が 'H' に駆動されてソース線がフローティング状態になると、メモリセル内のラッチへの給電がなくなるために、データはノードの寄生容量だけで保持される。ワード線が 'H' となっている時間が長い場合にはデータ保持が難しくなるが、一般にワード線のアサート期間はノードに溜まった電荷が放電されるよりも十分に短いために問題とならない。

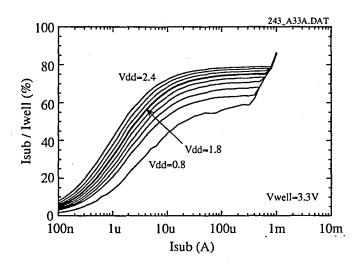

図 3.16 ソース線駆動型メモリセルの書き込み動作消費電力。

図 3.16に書き込み動作の消費電力の、従来のメモリセルとの比較を示す。書き込み周期は 50 MHz、電源電圧は 1.0V、ビット線プリチャージ電圧は 0.5 V に設定した。DSL メモリセルにおける周辺回路の消費電力の増加はソース線駆動回路の消費電力である。従来のメモリセルの場合と比較して、ビット線の充放電による電力消費を約 90%削減し、全体では約 70%の低電力化が達成されていることがわかる。

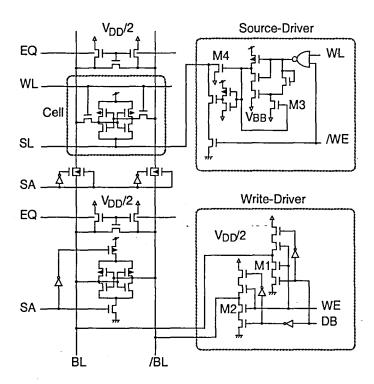

## 3.5 ソース線駆動型 (DSL) メモリセルの駆動回路

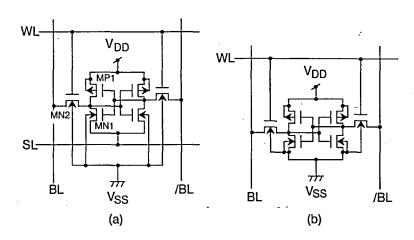

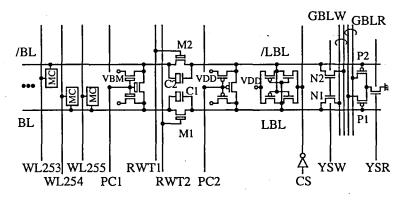

DSL メモリセルをメモリ回路として動作させるために必要な周辺駆動回路を図 3.17に示す。図 3.17では簡単のため MOSFET の基板電極の接続は省略しているが、図 3.5と同様に P 型 MOSFET の基板電極は  $V_{\rm DD}$  に N 型 MOSFET の基板電極は接地点電位  $V_{\rm SS}$  に接続する。イコライザには N 型 MOSFET を用い、 $V_{\rm DD}/2$  の電位にプリチャージし、ラッチ型のセンスアンプを用いている。

ソース線駆動回路は、メモリセルと同じ高しきい値 MOS トランジスタで構成されている。ワード線 WL が 'H' に駆動されると、ソース線 SL は  $V_{SL}$  電位に駆動される。その時、フォードバック MOS トランジスタ M3 によって貫通電流が流れることを防いでいる。

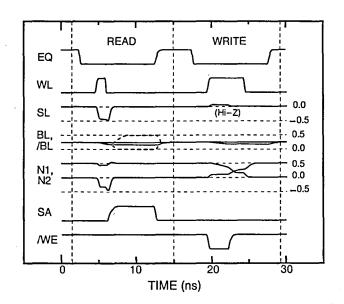

図 3.18がシミュレーション結果である。電源電圧は 0.5V に、しきい値電圧は電源電圧 の 40%に設定した。読み出し時は、イコライザ線 EQ を 'L'、ワード線 WL を 'H' にし、

<sup>1-</sup>本のワード線上には多くのメモリセルが接続されており、書き込みはそのうちの一部のメモリセルにしか実行されない。このように書き込み動作が行われないメモリセルに対しては、ワード線が'H'に駆動されるだけである。

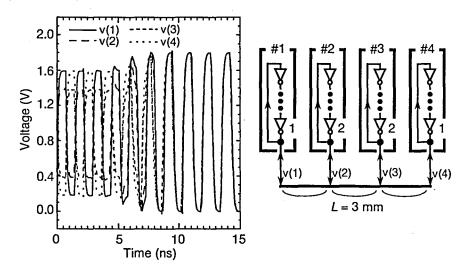

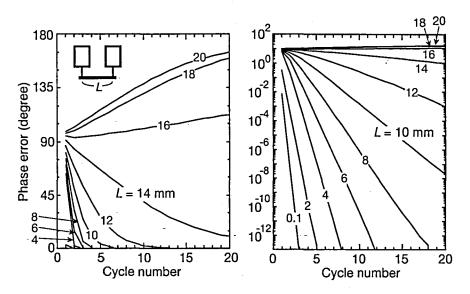

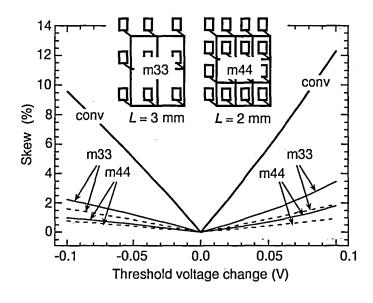

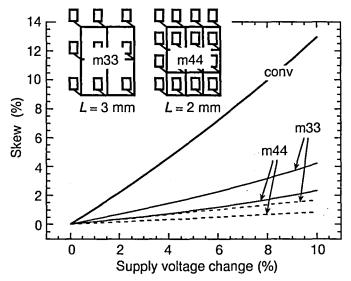

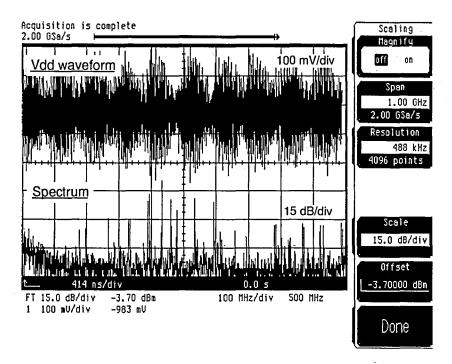

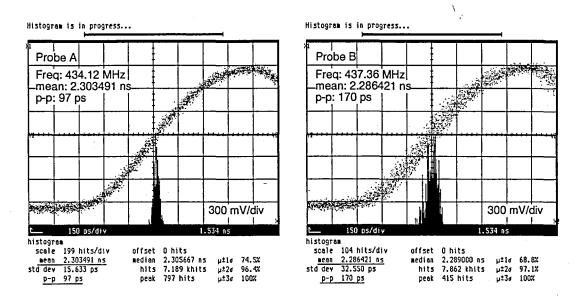

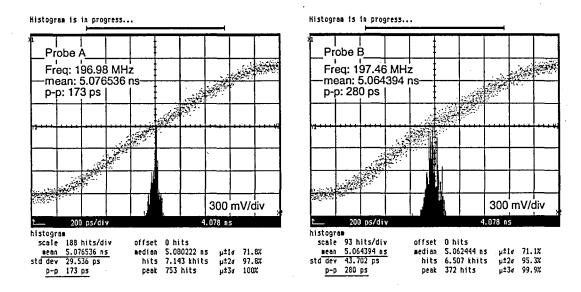

ソース線ドライバを用いてソース線 SL を -0.5 V に駆動する。このシミュレーションでは ノード電圧は -0.3 V まで減少している。次に、ビット線 BL,/BL が約 100 mV 程度開いた ところで、センスアンプ線 SA を 'H' にしてセンスアンプを起動し、ビット線 BL,/BL の 電位差を電源電圧差まで増幅する。このシミュレーションでは図 3.17では同時に Y スイッチをオフにして、負荷の大きなビット線 BL,/BL が電源電圧まで開くのを防いでいる。