| Title        | Accelerating GPU Programs by Reducing Irregular<br>Control Flow and Memory Access |

|--------------|-----------------------------------------------------------------------------------|

| Author(s)    | Okuyama, Tomohiro                                                                 |

| Citation     | 大阪大学, 2013, 博士論文                                                                  |

| Version Type | VoR                                                                               |

| URL          | https://hdl.handle.net/11094/24957                                                |

| rights       |                                                                                   |

| Note         |                                                                                   |

### Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

# Accelerating GPU Programs by Reducing Irregular Control Flow and Memory Access

January 2013

Tomohiro OKUYAMA

# Accelerating GPU Programs by Reducing Irregular Control Flow and Memory Access

Submitted to Graduate School of Information Science and Technology Osaka University

January 2013

Tomohiro OKUYAMA

### **Published Papers**

### **Journal Papers**

- Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "A Task Parallel Algorithm for Finding All-Pairs Shortest Paths Using the GPU," *International Journal of High Performance Computing and Networking*, vol.7, no.2, pp.87– 98, April 2012.

- Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "Fast Blocked Floyd-Warshall Algorithm on the GPU," *IPSJ Transactions on Advanced Computing Systems*, vol.3, no.2, pp.57–66, June 2010 (In Japanese).

### **International Conference Papers**

Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "A Task Parallel Algorithm for Computing the Costs of All-Pairs Shortest Paths on the CUDAcompatible GPU," *Proceedings of the 6th International Symposium on Parallel* and Distributed Processing with Applications (ISPA 2008), pp.284–291, Sydney, Australia, December 2008.

#### **Domestic Conference Papers**

1. Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "Fast Blocked Floyd-Warshall Algorithm on the GPU," *Proceedings of High Performance Computing Symposium 2010 (HPCS 2010)*, pp.9–16, January 2010 (In Japanese).

### **Oral Presentations**

Kentaro Shigeoka, Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "A Parallel Method for Accelerating Parameter Sweep on the GPU," *IPSJ* SIG Notes, 2012-HPC-136, 8 pages, September 2012 (In Japanese).

- Yoshiyuki Asai, Takeshi Abe, Masao Okita, Tomohiro Okuyama, Nobukazu Yoshioka, Shigetoshi Yokoyama, Masaru Nagaku, Kenichi Hagihara, and Hiroaki Kitano, "Multilevel modeling of Physiological Systems and Simulation Platform: PhysioDesigner, Flint and Flint K3 service," *Proceedings of the* 12th IEEE/IPSJ International Symposium on Applications and the Internet (SAINT 2012), pp.215–219, Izmir, Turkey, July 2012.

- 3. Tadashi Yoshikawa, Tomohiro Okuyama, Masao Okita, Yoshiyuki Asai, Takeshi Abe, Taishin Nomura, Tetsuya Yagi, and Kenichi Hagihara, "Preliminary Evaluation of OpenMP-based Parallel Simulation by Focusing on Similarity of Formulas in Biophysical Models," Proceedings of the 10th Symposium on Advanced Computing Systems and Infrastructures (SACSIS 2012), 2 pages, May 2012 (In Japanese).

- 4. Nobuya Fukui, Tomohiro Okuyama, Masao Okita, Takeshi Abe, Yoshiyuki Asai, Taishin Nomura, and Kenichi Hagihara, "An Agent Allocation for a parallel biophysical simulator *insilicoSim*," *Proceedings of the IEICE General Conference*, 2 pages, March 2012 (In Japanese).

- Hiroto Kanda, Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "An Instrumentation Method for Analyzing Efficiency of Memory Access in CUDA Programs," *IPSJ SIG Notes*, 2012-HPC-133, 8 pages, March 2012 (In Japanese).

- 6. Masao Okita, Tomohiro Okuyama, Nobuya Fukui, Ryu Matsui, Takeshi Abe, Heien Eric, Yoshiyuki Asai, Taishin Nomura, and Kenichi Hagihara, "Automatic Parallelization of Heterogeneous Biological Simulator insilicoSim," Proceedings of the 24th Bioengineering Conference, 2012 Annual Meeting of BED/JSME, 2 pages, January 2012 (In Japanese).

- Kentaro Shigeoka, Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "Evaluation of A Parallelization Technique for Parameter Sweep Applications using CUDA," *Proceedings of High Performance Computing Symposium 2012* (HPCS 2012), p.74, January 2012 (In Japanese).

- Tomohiro Okuyama, Masao Okita, Takeshi Abe, Yoshiyuki Asai, Taishin Nomura, and Kenichi Hagihara, "Accelerating General and Heterogeneous Biophysical Simulation Using the GPU Interpreter for Solving ODEs," Proceedings of the 4th Global COE International Symposium on Physiome and Systems Biology for Integrated Life Sciences and Predictive Medicine, 1 pages, November 2011.

- 9. Ryu Matsui, Tomohiro Okuyama, Masao Okita, Takeshi Abe, Yoshiyuki Asai, Taishin Nomura, and Kenichi Hagihara, "Focusing on dependencies in biophysical models to improve scheduling in *insilicoSim*," *Proceedings of the Annual Meeting of IPSJ Kansai Branch 2011*, 7 pages, September 2011 (In Japanese).

- Hiroto Kanda, Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "A Low Overhead Method for Timestamp Logging in CUDA Programs," *Proceedings of the Annual Meeting of IPSJ Kansai Branch 2011*, 3 pages, September 2011 (In Japanese).

- Tomohiro Okuyama, Masao Okita, Takeshi Abe, Yoshiyuki Asai, Taishin Nomura, and Kenichi Hagihara, "Accelerating Interpreter of General Biophysical Simulatior '*insilicoSim*' on the GPU," *IPSJ SIG Notes*, 2011-HPC-130, 8 pages, July 2011 (In Japanese).

- 12. Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "Auto Tuned Floyd-Warshall Algorithm on the GPU," Proceedings of the Work in Progress Session held in connection with the 19th Euromicro International Conference on Parallel, Distributed and Network-Based Computing (PDP 2011), 2 pages, Ayia Napa, Cyprus, February 2011.

- Hiroto Kanda, Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "A Log Generation Tool for Analyzing the Performance of CUDA Kernels," *IPSJ* SIG Notes, 2010-HPC-126, 7 pages, July 2010 (In Japanese).

- Hiroto Kanda, Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "Preliminary Evaluation of A Trace Generation Tool for Time Series Analysis of CUDA kernels," *Proceedings of High Performance Computing Symposium* 2010 (HPCS 2010), p.62, January 2010 (In Japanese).

- Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "Accelerating Floyd Warshall Algorithm Using CUDA," *Proceedings of the Annual Meeting of IPSJ* Kansai Branch 2008, pp.35–38, October 2008 (In Japanese).

- Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "Accelerating All-Pairs Shortest Path Problem Using CUDA," *IPSJ SIG Notes*, 2008-HPC-114, pp.145–150, March 2008 (In Japanese).

- Tomohiro Okuyama, Fumihiko Ino, and Kenichi Hagihara, "Comparing Implementations of All-Pairs Shortest Path Problem on the GPU using CUDA," *Proceedings of High Performance Computing Symposium 2008 (HPCS 2008)*, p.58, January 2008 (In Japanese).

### Abstract

The graphics processing unit (GPU) is recently used as a massively parallel processor to speed up general computation. However, the GPU can decrease the performance of irregular computation, because the GPU is based on the single instruction, multiple data (SIMD) architecture. The irregular computations here are conditional branches and memory accesses, which vary the behavior of threads depending on the input data. In particular, different control flow between threads causes redundant computations to follow each control flow. Moreover, uncoalesced memory accesses waste the memory bandwidth of the GPU. Therefore, there are many challenges to accelerate applications that depend on irregular computation.

This thesis presents GPU-based acceleration methods for three applications, aiming at developing techniques to efficiently process irregular computation on the GPU. We focus on irregular GPU programs that have similar threads in the entire program, although naive parallelization methods fail to exploit the similarity of threads. Our main approach is to gather similar threads for the SIMD operations before executing threads on the GPU. We achieve this preprocessing by observing the similarity of memory access pattern for the first application. For the third application, we use the similarity of operations that are executed by threads. For the second application, we evaluate another approach, which employs an algorithm that eliminates the irregularity by using a regular data structure instead of a pointer-based data structure. The details are described below.

First, we describe an acceleration method for finding the all-pairs shortest paths (APSPs) using the GPU. The APSP problem is a graph operation that finds shortest paths between all two vertices in a graph. This computation requires many uncoalesced memory accesses to refer to the graph data, while the memory bandwidth bounds the performance. Our method is based on an iterative algorithm that repeatedly solves the single-source shortest path (SSSP) problem in parallel on the GPU. We exploit the coarse-grained parallelism by using a task parallelization scheme that associates a task with an SSSP problem, in addition to the fine-grained parallelism in an SSSP problem. This scheme solves multiple SSSP problems at a time, allowing us to share the graph data on a fast on-chip memory, as well as reducing irregular memory accesses. As a result, the speedup over the existing SSSP-based implementation ranges from a factor of 2.8 to that of 13, depending on the graph topology.

We next present acceleration methods for the Floyd-Warshall (FW) algorithm using the GPU, which is another algorithm to solve the APSP problem. This algorithm uses a matrix representation of a graph, which eliminates irregular control flow and memory accesses. The proposed method contains two variations, both designed to reduce data access to off-chip memory based on an iterative blocked FW (BFW) algorithm. The first method also reduces the number of instructions using registers rather than the shared memory. The other method increases the block size because it is inversely proportional to the amount of off-chip memory access. For graphs with 256–1024 vertices, both methods are 4% faster than an existing recursive BFW method. The first method achieves approximately 70% of peak computational performance.

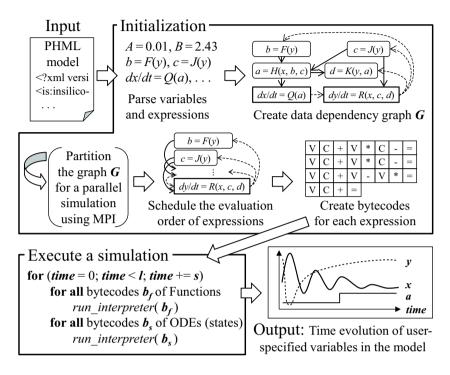

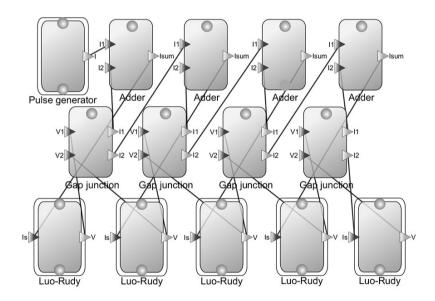

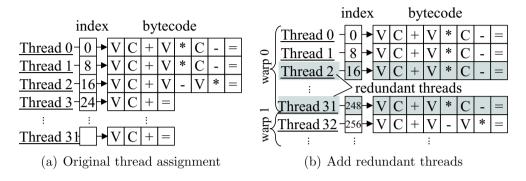

Finally, we demonstrate a GPU-based general biophysical simulator, called Flint. With this application, the program for threads depends on the input data, as well as the data values. Therefore, it is required to reduce the difference of control flow between threads. Flint handles heterogeneous biophysical models described by a large set of ordinary differential equations (ODEs). It uses an internal bytecode representation of simulation-related expressions to handle various biophysical models built for general purposes. The interpretation of bytecodes causes a heavy use of conditional branches. To reduce the irregular branches, we preprocess the bytecodes, which groups the similar bytecodes to assign a bytecode group to a SIMD core of the GPU. In addition, each group is unified to a unified bytecode to reduce memory accesses. We then implement two acceleration methods for Flint using a GPU. The first method interprets multiple bytecodes in parallel on the GPU. The second method translates a model into a source code through the internal bytecode, which speeds up the compilation of the generated source codes, because the code size is diminished by the bytecode unification. The first method simulates a model containing approximately 40,000 expressions 24 times faster than that on a CPU core. The second method achieves a performance of 2.4 times higher than that of the former method.

These results show that the GPU can be used for accelerating applications that include irregular computation. In particular, the task parallel scheme used for the APSP problem can improve the throughput of computation that includes the same type of independent subproblems. The technique used for our biophysical simulator will be applied to other ODE-based simulations. Moreover, it can be applied to an application that assigns different operations to threads. These findings will contribute to the realization of a general technique for efficient processing of irregular computation on the GPU and other accelerators.

### Acknowledgements

I would first like to express gratitude to my advisor, Professor Kenichi Hagihara, for his guidance and support during my years at Hagihara laboratory, and for advices and suggestions throughout this work. I would also like to sincerely thank the member of the thesis committee, Professor Toshimitsu Masuzawa, for taking the time to read this thesis and provide helpful questions and comments. I also offer my sincere thanks to Associate Professor Fumihiko Ino, who has guided my undergraduate study and this work and has gave me helpful advice and suggestions. I am deeply grateful to Assistant Professor Masao Okita, who has helped me in research skills.

I would also like to offer thanks to Professor Taishin Nomura of Graduate School of Engineering Science at Osaka University and Dr. Yoshiyuki Asai of the Open Biology Unit at Okinawa Institute of Science and Technology, for giving me the opportunity to join the collaborative project on biophysical simulations. I am deeply grateful to Mr. Takeshi Abe of the Open Biology Unit at Okinawa Institute of Science and Technology, for his support in developing the biophysical simulator Flint. I would like to thank Dr. Eric Heien, who has firstly developed the simulator that became a basis for Flint.

Finally, I am indebted to members of Hagihara laboratory, for their daily support and creative discussions.

## Contents

| 1        | Intr | roduction                                                                                                                                               | 1 |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|          | 1.1  | Background                                                                                                                                              | 1 |

|          | 1.2  | Objectives                                                                                                                                              | 3 |

|          | 1.3  | Contributions of Thesis                                                                                                                                 | 4 |

|          | 1.4  | Outline of Thesis                                                                                                                                       | 5 |

| <b>2</b> | Con  | npute Unified Device Architecture                                                                                                                       | 7 |

| 3        | Tasl | k Parallel Algorithm for Finding APSPs 11                                                                                                               | L |

|          | 3.1  | Introduction                                                                                                                                            | 1 |

|          | 3.2  | Related Work                                                                                                                                            | 2 |

|          | 3.3  | All-Pairs Shortest Path Problem                                                                                                                         | 4 |

|          |      | 3.3.1 Definition $\ldots \ldots \ldots$ | 4 |

|          |      | 3.3.2 SSSP-based Iterative Algorithm                                                                                                                    | õ |

|          | 3.4  | Task Parallel Algorithm                                                                                                                                 | ĉ |

|          |      | 3.4.1 Cost Computation                                                                                                                                  | ) |

|          |      | 3.4.2 Task Size Determination                                                                                                                           | 3 |

|          |      | 3.4.3 Path Recording                                                                                                                                    | õ |

|          | 3.5  | Experimental Results                                                                                                                                    | ĉ |

|          |      | 3.5.1 Performance Scalability on Graph Size                                                                                                             | 7 |

|          |      | 3.5.2 Performance Stability on Graph Attributes                                                                                                         | 9 |

|          |      | 3.5.3 Overhead of Path Recording                                                                                                                        | 3 |

|          | 3.6  | Conclusion                                                                                                                                              | 3 |

| <b>4</b> | Acc  | celerating Floyd–Warshall Algorithm using the GPU 38                                                                                                    | 5 |

|          | 4.1  | Introduction                                                                                                                                            | 5 |

|          | 4.2  | Floyd-Warshall Algorithm                                                                                                                                | ĉ |

|          |      | 4.2.1 Iterative Blocked Floyd–Warshall Algorithm                                                                                                        | 7 |

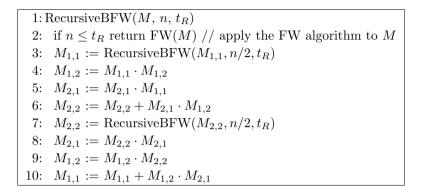

|          |      | 4.2.2 Recursive Blocked Floyd-Warshall Algorithm                                                                                                        | 9 |

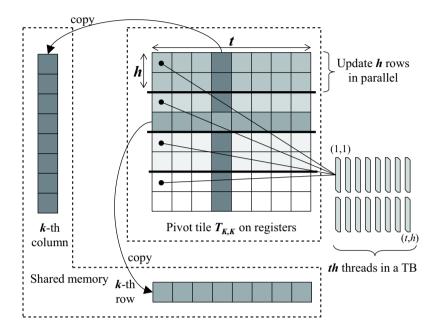

|          | 4.3  | Iterative Blocked Floyd-Warshall Algorithm on the GPU 40                                                                                                | ) |

|          |      | 4.3.1 Common Design                                                                                                                                     | ) |

|          |      | 4.3.2 Matrix Multiplication based Iterative BFW                     | 44 |

|----------|------|---------------------------------------------------------------------|----|

|          |      | 4.3.3 Two-level Blocking Iterative BFW                              | 47 |

|          | 4.4  | Auto-Tuning Technique for Matrix Multiplication based Iterative BFW | 47 |

|          |      | 4.4.1 GPU Performance Model for Computation Time Estimation .       | 49 |

|          |      | 4.4.2 Automatic Parameter Selection                                 | 50 |

|          | 4.5  | Experiments                                                         | 51 |

|          |      | 4.5.1 Environment                                                   | 51 |

|          |      | 4.5.2 Performance Analysis                                          | 55 |

|          |      | 4.5.3 Evaluation of Auto-tuning Technique                           | 59 |

|          | 4.6  |                                                                     | 61 |

|          |      |                                                                     |    |

| <b>5</b> |      |                                                                     | 69 |

|          | 5.1  |                                                                     | 69 |

|          | 5.2  |                                                                     | 70 |

|          | 5.3  | 1 5                                                                 | 71 |

|          | 5.4  | Example Physiological Models                                        | 73 |

|          | 5.5  | 0 0                                                                 | 74 |

|          |      | 5.5.1 Interpreter-based Simulation Using the GPU                    | 74 |

|          |      | 5.5.2 Translator-based Simulation Using the GPU                     | 80 |

|          | 5.6  | Experimental Results                                                | 81 |

|          |      | 5.6.1 Performance Evaluation                                        | 82 |

|          |      | 5.6.2 Performance Analysis of Interpreter-based Simulation          | 86 |

|          |      | 5.6.3 Performance Analysis of Translator-based Simulation           | 88 |

|          |      | 5.6.4 Precision Analysis of Simulation Results                      | 90 |

|          | 5.7  | Conclusion                                                          | 92 |

| c        | Corr | clusion                                                             | 95 |

| 6        |      |                                                                     |    |

|          | 6.1  |                                                                     | 95 |

|          | 6.2  | Future Work                                                         | 97 |

# List of Figures

| 2.1  | CUDA hardware model                                                                                                                                                                                                                                                                          | 10 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | CUDA programing model                                                                                                                                                                                                                                                                        | 10 |

| 3.1  | Algorithm for reconstructing the sequence of vertices that compose<br>the shortest path between $s$ and $t$                                                                                                                                                                                  | 17 |

| 3.2  | Cost minimization. (a) For each vertex $v$ in the graph, (b) the costs of its neighbors $n_0$ , $n_1$ , and $n_2$ are updated in the scattering phase.                                                                                                                                       | 17 |

| 3.3  | Iterative algorithm for finding an SSSP from the source vertex $s \in V$ .                                                                                                                                                                                                                   | 18 |

| 3.4  | Adjacency list representation. Array $Va$ stores the indices to the head<br>of each adjacency list in $Ea$ . Array $Ea$ and $Wa$ store adjacency lists<br>of every vertex and edge weight, respectively                                                                                      | 18 |

| 3.5  | Pseudo code of scattering kernel [1]. This kernel is responsible for a single vertex $v$ and updates the costs of its adjacent vertices                                                                                                                                                      | 19 |

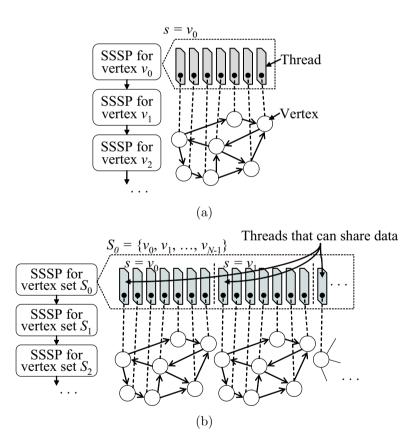

| 3.6  | Comparison of parallelization scheme between (a) previous method<br>[1] and (b) proposed method. Our kernel solves N SSSP problems at<br>a time. The graph data is shared between threads that are responsible<br>for the same vertex but in different SSSP problems                         | 19 |

| 3.7  | Algorithm for finding SSSPs from each s of source vertices $S_k$                                                                                                                                                                                                                             | 21 |

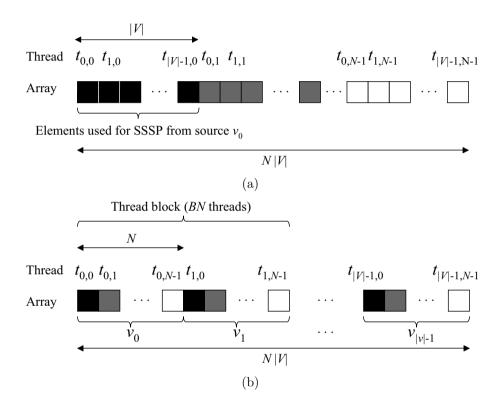

| 3.8  | Array interleaving for coalesced memory accesses. (a) A straight-<br>forward layout for $Ma$ , $Ca$ , and $Ua$ stores all data for every SSSP<br>problems into contiguous sequences. (b) The same vertices but for<br>different problems are stored in a contiguous address space. $B = 2$ , | 22 |

| 2.0  |                                                                                                                                                                                                                                                                                              |    |

| 3.9  | Pseudo code of proposed scattering kernel. This kernel solves $N$ SSSP problems in parallel                                                                                                                                                                                                  | 24 |

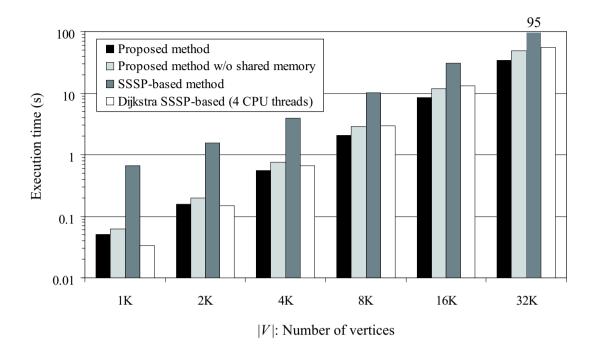

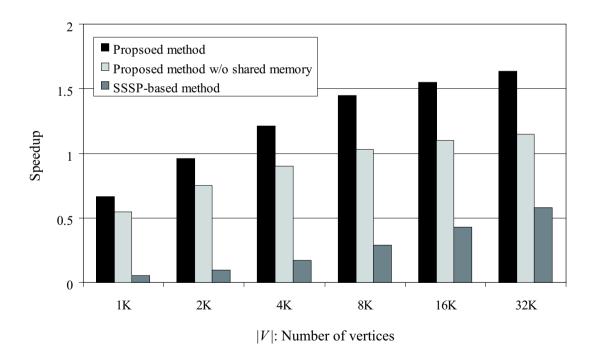

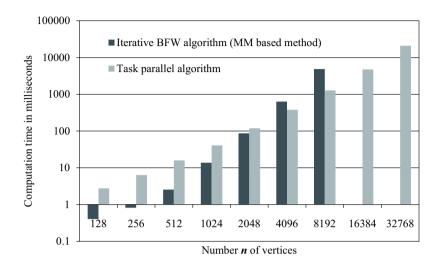

| 3.10 | Computation time for random graphs with different number $ V $ of vertices. Results are presented in seconds.                                                                                                                                                                                | 28 |

| 3.11 | Speedup over the SSSP-based implementation running on the CPU.                                                                                                                                                                                                                               | 28 |

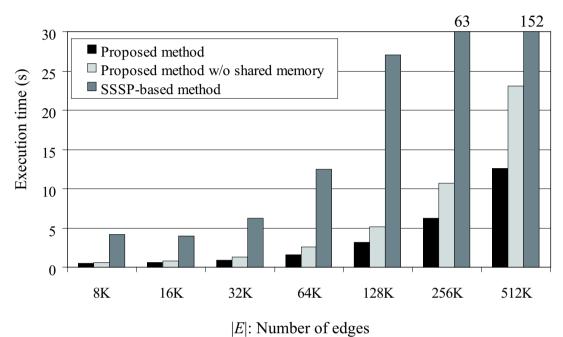

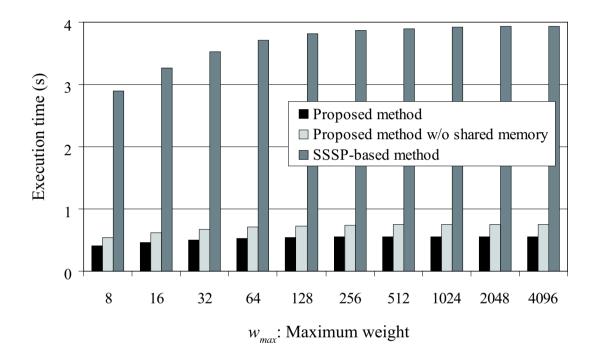

|      | Computation time for random graphs with different number $ E $ of edges. The number $ V $ of vertices is fixed to $ V  = 4K$                                                                                                                                                                 | 30 |

|      |                                                                                                                                                                                                                                                                                              |    |

| 3.13 | Computation time for random graphs with different maximum weight $w_{max}$ . The number $ V $ of vertices and the number $ E $ of edges are |          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.14 | fixed to $ V  = 4K$ and $ E  = 16K$                                                                                                         | 31       |

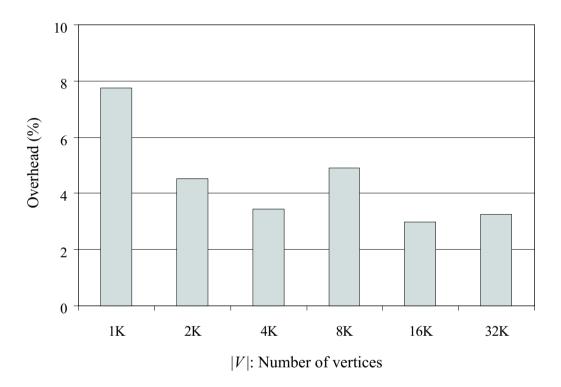

|      | ber $ V $ of vertices. Overhead explains the increased time due to the recording kernel called after cost computation                       | 34       |

| 4.1  | FW algorithm.                                                                                                                               | 38       |

| 4.2  | Iterative blocked FW algorithm.                                                                                                             | 38       |

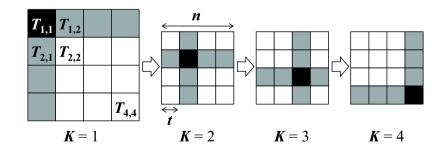

| 4.3  | Tile updating process of the iterative BFW algorithm $(n/t = 4)$ . A black tile represents the pivot tile. Gray tiles are the pivot row and |          |

|      | pivot column tiles, while white tiles are the non-pivot tiles                                                                               | 38       |

| 4.4  | Recursive blocked FW algorithm.                                                                                                             | 41       |

| 4.5  | Recursive blocking of the matrix $M$ in the recursive BFW algorithm.                                                                        | 41       |

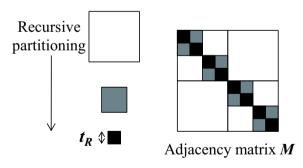

| 4.6  | Byte/operation ratio $N_b/N_c$ of memory access to computation de-<br>manded by the iterative BFW algorithm and that of global memory       |          |

|      | bandwidth to computational performance of the GPU ( $n = 8192$ )                                                                            | 43       |

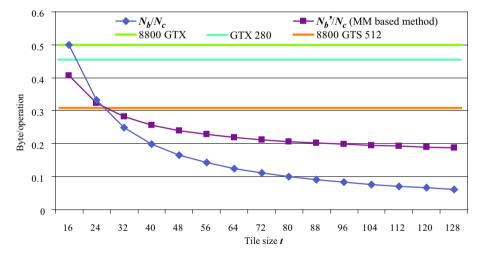

| 4.7  | Using on-chip memory for updating the pivot tile                                                                                            | 46       |

| 4.8  | Partitioning of the computational region in the matrix multiplication based method                                                          | 46       |

| 4.9  | On-chip memory usage of the non-pivot kernel with the MM based method.                                                                      | 48       |

| 1 10 | method                                                                                                                                      | 40<br>48 |

|      | On-chip memory usage of the non-pivot kernel with the two-level                                                                             |          |

|      | blocking method.                                                                                                                            | 52       |

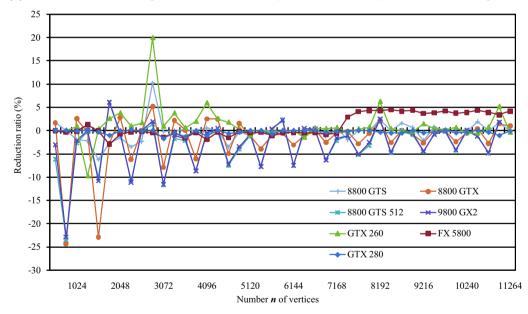

|      | Flow of the auto-tuning mechanism for the MM based method Reduction ratio (%) of computation time with $t = 32$ compared to                 | 52       |

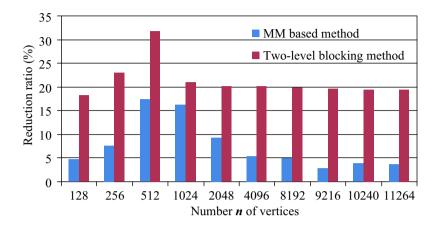

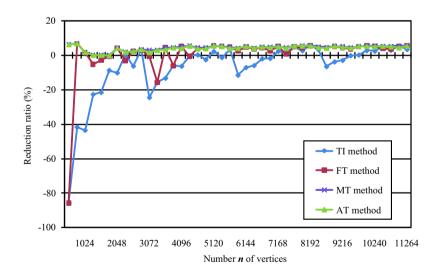

| 4.10 | that of with $t = 16. \dots \dots$    | 58       |

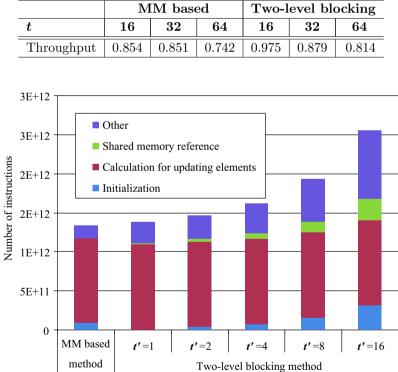

| 4.14 | Breakdown analysis of the number of instructions in the non-pivot kernel. The number $n$ of vertices is $n = 8192$ .                        | 58       |

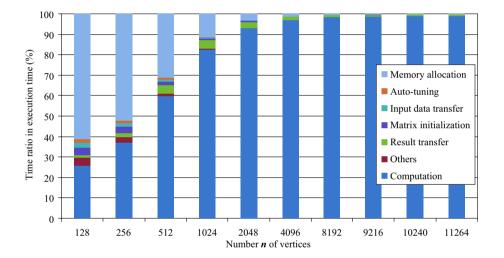

| 4.15 | Breakdown analysis of the execution time with $t = 32$ using GeForce GTX 280.                                                               | 63       |

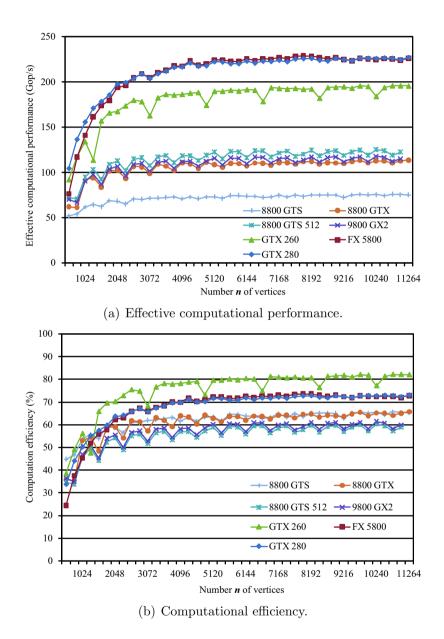

| 4.16 | Effective computational performance and computational efficiency of                                                                         |          |

|      | the MM based method on 7 different GPUs with $t = 32$                                                                                       | 64       |

| 4.17 | Computation time of the MM based method and an task parallel algorithm for random graphs using GeForce GTX 280                              | 65       |

| 4 18 | Reduction ratio of the computation time of the non-pivot kernel ( $t =$                                                                     | 00       |

| 1.10 | 32) using GeForce GTX 280                                                                                                                   | 65       |

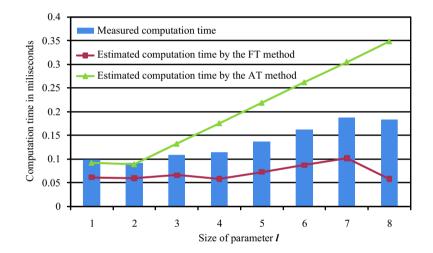

| 4.19 | Computation time with varying the size of parameter $l$ of the MM                                                                           |          |

|      | based method $(n = 512)$ .                                                                                                                  | 66       |

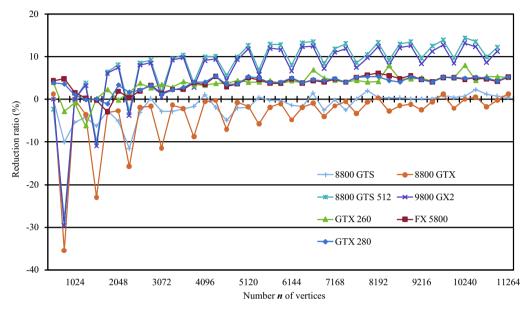

| 4.20 | Reduction ratio of the computation time of iterative BFW method<br>with $t = 32$ on different GPUs                             | 67 |

|------|--------------------------------------------------------------------------------------------------------------------------------|----|

| 5.1  | Flow chart of Flint                                                                                                            | 75 |

| 5.2  | Structure of an example of a PHML model. The five rounded rect-                                                                |    |

| 5.0  | angles at the bottom represent Luo-Rudy cells                                                                                  | 75 |

| 5.3  | Scheduling the evaluation order of expressions. Dependencies on states (shown as dash lines) are ignored during the scheduling | 78 |

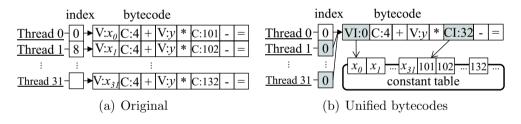

| 5.4  | Reordering bytecodes based on their similarity. "V" and "C" rep-                                                               | 10 |

| 0.4  | resent instruction for pushing a variable and constant, respectively;                                                          |    |

|      | "index" is an array of indices pointing to the head of each bytecode.                                                          | 78 |

| 5.5  | Adding redundant threads to avoid divergent branches                                                                           | 83 |

| 5.6  | Unifying bytecodes to reduce memory accesses. "VI" and "CI" are                                                                |    |

|      | opcodes for the indirect reference of a variable and constant, respec-                                                         |    |

|      | tively                                                                                                                         | 83 |

| 5.7  | Pseudo code for the kernels of the interpreter                                                                                 | 84 |

| 5.8  | Pseudo code for a GPU-enabled simulation generated by the TS method.                                                           | 85 |

| 5.9  | Pseudo code for an OpenMP-enabled simulation generated by the TS                                                               |    |

|      | method                                                                                                                         | 85 |

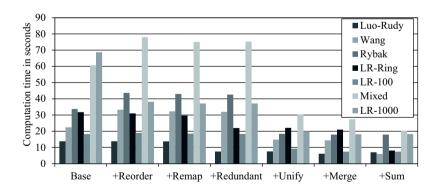

| 5.10 | Computation time of the IS method with each optimization. Results                                                              |    |

|      | are presented in seconds                                                                                                       | 89 |

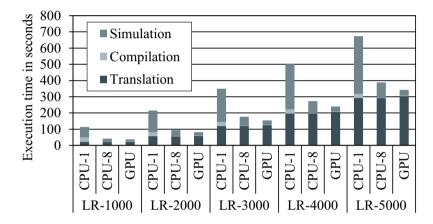

| 5.11 | Computation time of the TS method using coupled Luo-Rudy models                                                                |    |

|      | with varying numbers of cells                                                                                                  | 91 |

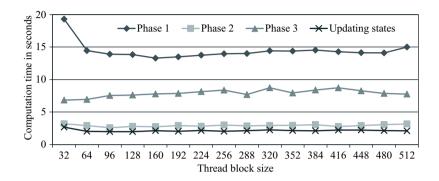

| 5.12 | Execution time of each kernel in the simulation program for LR-5000                                                            |    |

|      | generated by the TS method                                                                                                     | 93 |

## List of Tables

| 3.1 | Computation time for some graph topologies. Results are presented<br>in seconds | 30 |

|-----|---------------------------------------------------------------------------------|----|

| 4.1 | Symbols for representing GPU specifications                                     | 43 |

| 4.2 | Experimental environment for the GT200 GPUs                                     | 54 |

| 4.3 | Experimental environment for the G90 and G80 GPUs                               | 54 |

| 4.4 | Parameters and resource usage of the non-pivot kernel                           | 54 |

| 4.5 | Parameter $l$ for the non-pivot kernel using GTX 280                            | 57 |

| 4.6 | Computation time for random graphs $[2]$ with a different number $n$ of         |    |

|     | vertices. Results are presented in milliseconds                                 | 57 |

| 4.7 | Kernel execution time of the iterative BFW methods with $n = 8192$ .            |    |

|     | Results are shown in milliseconds                                               | 57 |

| 4.8 | Instruction throughput of the non-pivot kernel using GeForce GTX                |    |

|     | 280. The number $n$ of vertices is $n = 8192. \ldots \ldots \ldots$             | 58 |

| 5.1 | Number of functions and ODEs in the tested models.                              | 83 |

| 5.2 | Total execution time with output of the results. Results are presented          |    |

|     | in seconds                                                                      | 87 |

| 5.3 | Global memory footprint for the IS method (KB)                                  | 87 |

| 5.4 | Computation time without output of the results. Results are pre-                |    |

|     | sented in seconds.                                                              | 87 |

| 5.5 | Effective memory bandwidth (GB/s)                                               | 89 |

| 5.6 | Number of bytecodes before unifying them. Each item shows the                   |    |

|     | series of the number of bytecodes in each phase separated by right              |    |

|     | arrows                                                                          | 89 |

| 5.7 | Number of different opcode sequences in each phase. Each item shows             |    |

|     | the series of numbers separated by right arrows                                 | 91 |

| 5.8 | Compilation time for the source codes generated using the TS method.            |    |

|     | Results are presented in seconds                                                | 91 |

| 5.9 | Relative root mean square errors                                                | 93 |

## Chapter 1

## Introduction

#### 1.1 Background

The graphics processing unit is a dedicated hardware component to accelerate graphics tasks, which is used with specialized application programming interfaces (APIs) such as OpenGL [3] and DirectX [4]. In recent years, the general-purpose computation on the GPU (GPGPU) [5] employs this hardware to speed up general scientific computation using the high computational performance of the GPU. For this purpose, NVIDIA provides a software development environment called the compute unified device architecture (CUDA) instead of graphics APIs. This environment allows us to use the GPU as a massively parallel processor that runs thousands of threads on hundreds of cores.

The parallel computing model of the CUDA-compatible GPU is called single instruction, multiple threads (SIMT) [6] model. With this model, the GPU runs multiple threads that process the same program, namely kernel. The GPU assigns a batch of threads called warp to a group of cores. Although, these cores process threads in the single instruction, multiple data (SIMD) fashion, programmers do not have to mind the SIMD width and the number of cores in the GPU. They can write a kernel as a sequential program. Each thread has a thread index to control its behavior, for instance, accessing different data by threads.

This characteristic facilitates the development of GPU programs. However, to achieve higher performance, developers should consider the underlying SIMD architecture. For example, if threads in a warp branch in a different way, the warp decreases the computational efficiency because it follows each control flow of threads. These branches are called divergent branches. In addition, the memory coalescing is important to utilize the wide memory bandwidth of the GPU. The coalesced memory access is a localized memory access from a warp.

Therefore, the GPU has been applied to applications that have data parallelism,

because these applications have a regular memory access pattern and all threads follow the same control flow. The regular memory access facilitates the coalescing of memory access on the GPU. Many researches show that GPUs achieve substantial performance for these applications, which reaches ten times or more speedups compared to that on the CPU.

Meanwhile, there are many challenges to accelerate irregular programs using SIMD processors. Irregular programs typically use pointer-based data structures or more complex data structures. These programs cause many irregular computation including irregular control flow and memory accesses, because the behavior of programs deeply depends on the data. There have been many researches to process these irregular programs on SIMD machines. A general approach is to emulate a multiple instruction, multiple data (MIMD) machine on a SIMD machine [7]. For the SIMD machines, a typical register-based programming model provides less flexibility, which requires programmers to explicitly operate on vector registers. To provide more flexibility, Shu and Wu [8] developed a runtime system to emulate MIMD threads on a SIMD machine. There is also another approach that statically translates a thread-based program to the program that runs on a SIMD machine [9].

For the GPU, CUDA provides a more flexible thread-based programming model compared to that for SIMD machines described above. However, the irregular computation decreases the computational efficiency of the GPU. For the GPU program, irregular control flow can cause divergent branches because threads can follow different flow each other. Irregular memory access can prevent memory coalescing. In addition, irregular computation can prevent the utilization of the fast on-chip shared memory. This memory enables us to reduce off-chip memory accesses by sharing data between threads. However, threads tend to refer to different data each other in irregular programs, resulting in no data that can be shared between threads.

In this thesis, we describe GPU-based acceleration methods for three applications that have irregular computation. The first two applications are programs to find all-pairs shortest paths (APSPs) using different algorithms. The third application is a general biophysical simulator. These applications have threads that operate in the similar way on the GPU, although naive parallelization methods run threads that execute different operations on SIMD cores of the GPU. Our basic approach is to statically rearrange the threads and data assignment to reduce irregular computation before executing the program on the GPU. Therefore, we also assume that the operations of threads are reproducible for the same input data. In other words, the thread having the same thread index executes the same operation, if we give the same input data. In particular, the control flow of thread is independent of random numbers and data that are written by concurrent memory writes without exclusive control.

The details of these applications are described below.

All-Pairs Shortest Path Problem Graph operations are typical irregular computation. These operations cause many irregular memory accesses to chase the pointers, because graphs are commonly represented by pointer-based data structures. In addition, the control flow depends on the given graph, which may cause many divergent branches on the GPU.

The APSP problem is a graph operation that finds shortest paths between all two vertices in a given graph. This problem has been applied to a wide variety of fields such as bioinformatics [10] and computer aided design (CAD) [11].

However, the APSP problem requires a large amount of computation. For instance, the Floyd-Warshall (FW) [12, 13] algorithm solves this problem in  $O(|V|^3)$ time, where |V| represents the number of vertices in a graph. A straightforward method for solving the APSP problem is to iteratively compute single-source shortest path (SSSP) for every source vertex. Dijkstra's algorithm [14] accelerated with a Fibonacci heap is known as a fast method to find an SSSP for a sparse graph. Using this algorithm, we can find APSPs in  $O(|V||E| + |V|^2 \log |V|)$  time, where |E|represents the number of edges in a graph. In contrast to algorithmic studies mentioned above, many researchers are trying to accelerate the algorithms using various accelerators, including GPUs [1, 15, 16], field-programmable gate arrays (FPGAs) [17], and clusters [18].

General Biophysical Simulator Numerical integration, referred to here as a simulation, of biophysical and physiological models enables researchers to analyze and understand various physiological functions. With the advance of measurement technology in physiology, the degrees of freedom used for mathematical modeling have rapidly increased. Large models now contain thousands of dynamic variables and mathematical expressions. Generally, the development of such models requires a number of model modifications, each of which is followed by a simulation that runs for millions of time steps. These time-consuming processes motivated us to accelerate lengthy simulations.

A biophysical simulator, called Flint, is designed to process general and heterogeneous biophysical models. This simulator numerically integrates a model described by a large set of ordinary differential equations. Flint uses an internal interpreter to simulate a variety of models built for general purpose. The interpreter causes many branches depending on the bytecodes that represent simulation related expressions.

#### 1.2 Objectives

We focus on accelerating three applications, aiming at discussing techniques to implement irregular programs that run efficiently on the GPU. Fast Computation of APSPs by SSSP-based Algorithm Using CUDA, Harish and Narayanan [1] present a fast SSSP-based method for large graphs, which iteratively computes SSSPs on the GPU. However, with this algorithm, threads perform in different ways because a thread is corresponding to a vertex in a graph. In particular, it can be further accelerated by memory access optimization. For example, the algorithm may be modified such that it fully uses the entire memory hierarchy, including fast but small on-chip shared memory. Therefore, the goal is to accelerate the computation of APSPs on the GPU by reducing irregularity in the memory accesses. For this purpose, we use a coarse-grained parallelism that exists between different SSSP problems.

**Computation of APSPs Using Floyd-Warshall Algorithm** For sparse graphs, our task parallel algorithm achieves reasonable speedup using the GPU. However, this method increases the execution time for dense graphs because its complexity depends on the number of edges, in addition to the number of vertices. On the other hand, the complexity of the FW algorithm depends only on the number of vertices. Therefore, we evaluate the performance of the FW algorithm on the GPU.

General Biophysical Simulator Using the GPU This application is an example of more complex and advanced application compared to the APSP problem. The computation, as well as the data, of this application depends on the given biophysical model. Therefore, the simulator is required to automatically parallelize the simulation for the GPU. In addition, the input model includes a variety of mathematical expressions. Consequently, a naive parallelization causes numerous divergent branches and degrades the performance of the GPU. This simulator must coordinate thread assignment to reduce divergent branches for efficiently utilizing the GPU.

#### **1.3** Contributions of Thesis

The main results of this thesis are summarized as follows.

Task Parallel Algorithm for Finding APSPs Using the GPU We have developed a task parallel algorithm that computes multiple SSSPs in parallel on the GPU. Our method uses the coarse-grained parallelism between SSSP problems, in addition to the fine-grained parallelism in each SSSP problem. A task parallelization scheme is used to exploit the coarse-grained parallelism, which associates a task with an SSSP problem. This scheme enables us to efficiently access graph data by sharing the data between threads on the GPU. Moreover, the use of two-level parallelism increases the number of threads on the GPU, which is beneficial to an efficient computation.

The experimental result shows that our method is 2.8 to 13 times faster than the iterative SSSP-based method, although the speedup depends on the graph topology.

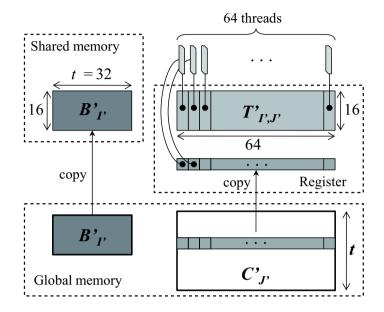

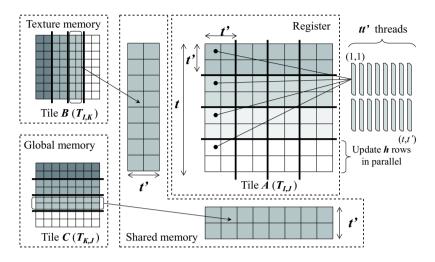

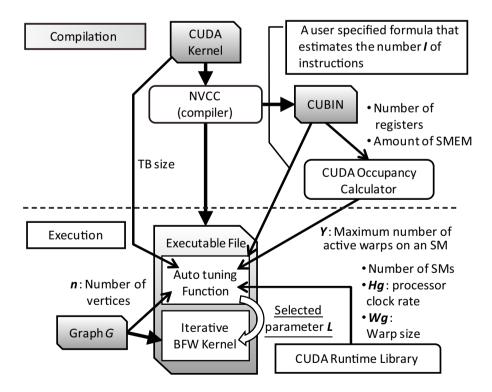

**Iterative Blocked FW Algorithm Using the GPU** We have implemented a fast iterative blocked Floyd-Warshall (BFW) algorithm on the GPU. The proposed method contains two variations, both designed to reduce data access to off-chip memory because the bandwidth limits the performance of the FW algorithm. The first method applies a fast matrix multiplication routine to the computation, aiming at reducing the number of instructions. The other method uses a two-level blocking technique to reduce the on-chip memory usage.

As a result, both methods show 4% faster performance than an existing fast recursive BFW algorithm for 256–1024 vertices. For larger graphs, our matrix multiplication based method shows similar performance as that of the recursive method. The effective performance of this method is approximately 70% of peak computational performance, which indicates that our implementation successfully derives the performance of the GPU.

**GPU-based Fast Simulation of General Biophysical Models** We have developed two acceleration methods for Flint using the GPU. The first one simultaneously interprets multiple bytecodes on the GPU. It automatically parallelizes the simulation using a level scheduling algorithm. The bytecodes are reordered by their similarity to assign similar bytecodes to a warp, which reduces divergent branches. In addition, this method also unifies the similar bytecodes to a unified bytecode to reduce data amount of memory accesses. The second method translates a model into a CUDA code. This method generates the code from the unified bytecodes to a migractical range.

The interpreter-based method achieves 24 times speedup over the CPU based simulation for a model with approximately 40,000 expressions. The translator-based method is up to 2.4 times faster than the interpreter-based method.

#### **1.4** Outline of Thesis

The rest of this thesis is organized as follows. Chapter 2 summarizes an overview of GPU and CUDA. Chapter 3 and Chapter 4 present the acceleration methods for the APSP algorithm using the GPU and evaluate their performance. We describe an SSSP based method that explores the task parallelism in Chapter 3. The acceleration

of FW algorithm is described in Chapter 4. Chapter 5 presents a fast general biophysical simulator using the GPU and shows experimental results. Chapter 6 concludes this thesis and discusses the future work.

### Chapter 2

## Compute Unified Device Architecture

The GPU is a hardware component to accelerate graphics processing. The CUDA [6] framework provides a general-purpose parallel computing environment for the GPU, which enables the execution of thousands or more threads in parallel on the GPU.

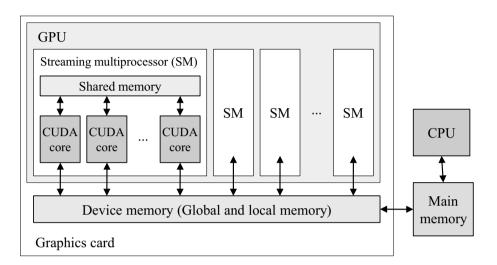

Figure 2.1 shows an overview of the architecture of CUDA-compatible GPU. The GPU employs a hierarchical architecture that consists of several streaming multiprocessors (SMs), each having CUDA cores for processing threads. In an SM, these cores simultaneously execute the same instruction as single instruction, multiple data (SIMD) processors. The number of CUDA cores in an SM depends on the GPU architecture, while the number of SMs in a GPU varies by the GPU. The CUDA cores within the same SM are allowed to share on-chip memory called shared memory, which is as fast as registers. This memory hierarchy is useful to save the memory bandwidth between CUDA cores and off-chip memory, because it can be used as a software cache shared by multiple CUDA cores belonging to the same SM.

On the other hand, the off-chip memory, called device memory, has larger latency that is 400–600 clock cycles per memory transaction [6]. CUDA logically partitions this memory in some memory areas having different functions. The most general area is called global memory. All CUDA cores can read and write data to this memory. The CPU also can transfer data between the main memory and the global memory. CUDA also uses a part of device memory as the local memory of each thread, which is a thread local storage for temporal variables if the thread lacks registers.

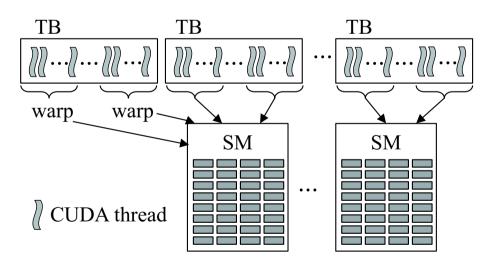

Corresponding to its hierarchical processor architecture, CUDA has a hierarchical thread programming model (Figure 2.2). That is, threads are structured into equalsized groups, each called a thread block (TB), while all threads execute the same program, namely a kernel. Programmers write the kernel as a C-like function. All threads simultaneously execute the same kernel with different thread indices to perform SIMD computation. Threads in the same TB run on a single SM and have synchronization capability within them. These threads can also share data using the shared memory.

Meanwhile, a kernel cannot synchronize different TBs on the GPU, because each TB will be independently assigned to an SM. Therefore, developers have to write their kernel such that there is no data dependence among different TBs. Due to the same reason, the GPU does not have a mechanism that synchronizes all threads. Such global synchronization involves splitting the kernel into two pieces, which are then launched sequentially from the CPU. The synchronization is accomplished by terminating the first piece of kernel.

An SM processes a TB in the following way. Supposing that a TB is assigned to an SM, the SM splits the TB into groups of threads called warps. The number of threads in a warp, which is defined as 32 threads in current hardware, is called as the warp size. Each of warps is then processed by the SM in a SIMD fashion. Therefore, branching threads in the same warp will divergent the warp. Such divergent warps [6] significantly degrade the computational efficiency, because instructions must be serialized due to different control flows.

Generally, each SM executes multiple TBs in parallel, because the GPU architecture is designed to hide the memory access latency with independent computation of different warps. This also explains why TBs must be independent. Such independent TBs are useful to allow SMs to continue computation by switching the TBs that have to wait data from device memory. Therefore, it is better to assign multiple TBs to every SM. However, memory resources such as the shared memory and registers usually limit the number of TBs per SM.

To achieve higher performance, it is necessary to utilize the device memory bandwidth, which reaches more than 100 GB/s. For the global memory access, localized memory access from a warp is important to achieve the full utilization of this wide memory bus. This technique is called memory coalescing [6]. Using this technique, the global memory accesses issued from threads in a (half-) warp can be coalesced into a single memory transactions if the source/destination address satisfies an alignment requirement. Otherwise, the GPU issues multiple memory transactions if a warp accesses a wide address range. The requirements for memory coalescing differ according to the generation of GPU architecture, summarized in the following.

**G80 and G90 GPUs (Tesla architecture)** The G80 architecture is the first CUDAcompatible GPU architecture. The G90 GPUs add the support for atomic functions on the global memory, which provides atomic read-modify-write capabilities. These architectures have the most restricted coalescing rule; a thread with ID N within the half-warp should access address base + N, where base is a multiple of 16 bytes. They also have no cache for the device memory. GPUs of these architectures have 8 CUDA cores per SM. The shared memory size is 16 KB per SM.

We use these architectures for evaluations in Chapter 3 and Chapter 4. It should be noted that the proposed algorithm in Chapter 3 assumes the strict requirement to be executable on these older GPUs.

GT200 GPUs (Tesla architecture) The requirements of coalesced memory accesses are relaxed, such that threads in a half-warp can access to data in any order by a memory transaction if the data is in the same memory segment of size 32, 64, or 128 bytes. GT200 GPUs also have 8 CUDA cores and 16 KB of shared memory per SM.

We use this architecture in Chapter 4.

GF100 GPUs (Fermi architecture) These GPUs have 2-level cache for the device memory. Consequently, a global memory transaction is issued for a cache line (128 bytes). GPUs of this architecture have 32 or 48 CUDA cores per SM. The L1 cache and the shared memory share 64 KB of on-chip memory. The shared memory size is configurable: 16 KB or 48 KB per SM.

We evaluate our biophysical simulator described in Chapter 5 using a Fermi GPU having 32 CUDA cores per SM.

Figure 2.1: CUDA hardware model.

Figure 2.2: CUDA programing model.

### Chapter 3

## Task Parallel Algorithm for Finding APSPs

#### 3.1 Introduction

In this chapter, we propose an SSSP-based algorithm to accelerate the cost computation of APSPs. The cost of a path here is given by the sum of the weights of edges composing the path. Our method enhances Harish's method [1] by exploiting not only off-chip memory but also on-chip memory. However, we use a different parallelization scheme for computing APSPs in order to save the bandwidth between offchip memory and CUDA cores. In addition to the fine-grained parallelism exploited by the previous method, we exploit the coarse-grained parallelism existing between different SSSP problems. That is, the proposed scheme exploits task parallelism so that it solves in parallel multiple SSSP problems with different sources. This allows CUDA cores to simultaneously access the same data because each CUDA core takes the responsibility for solving one of the task-parallel problems. Such common access leads to an efficient use of on-chip shared memory, which is useful to reduce data accesses to off-chip memory. Furthermore, the proposed scheme contributes to achieve higher speedup with more parallel tasks and less synchronization on the GPU. We also describe how the paths can be recorded with their costs.

The rest of the chapter is organized as follows. Section 3.2 gives an introduction of related work. Section 3.3 describes the APSP problem and summarizes the iterative SSSP-based method. Section 3.4 presents our algorithm and Section 3.5 shows experimental results. Finally, Section 3.6 concludes the chapter.

#### 3.2 Related Work

There are two widely known algorithms to find APSPs: an SSSP-based iterative algorithm and the FW algorithm. The former algorithm repeatedly solves SSSP problems with varying the source vertex  $s \in V$  on a graph G = (V, E, w), where Vand E are the sets of vertices and edges in G, respectively. The function  $w : E \to W$ assigns a weight to each edge, where W is a set of edge weights. The SSSP problem finds the shortest paths from s to all other vertices  $v \in V$ . A fast solution of SSSP problems is required to speed up the SSSP-based iterative algorithm. The Dijkstra's algorithm [14] and the Bellman-Ford algorithm [19, 20] are widely known algorithms to find SSSPs.

The Dijkstra's algorithm finds SSSPs for a directed graph having non-negative edge weights. This algorithm can reduce its computational amount using a priority queue. Using Fibonacci heap [21] to implement the priority queue, the complexity of this algorithm is reduced to  $O(|V| \log |V| + |E|)$ . However, the binomial heap is commonly used as the priority queue rather than the Fibonacci heap, because the Fibonacci heap uses a complex data structure. Using the binomial heap, the complexity of the Dijkstra's algorithm is  $O((|V| + |E|) \log |V|)$ . On the other hand, these improvements might not be suitable for the parallel computing, because it is not easy to efficiently operate on these heaps in parallel.

The Bellman-Ford algorithm requires O(|E||V|) computations, which is larger than that of the Dijkstra's algorithm. However, this algorithm can handle graphs having negative edge weights. This algorithm has doubly-nested loops. The inner loop can be easily parallelized because there is no data dependency. However, the SSSP-based iterative algorithm using the Bellman-Ford algorithm tends to have larger complexity of  $O(|E||V|^2)$  than that of the FW algorithm, because the number |E| of edges is greater than the number |V| of vertices in general.

Harish and Narayanan [1] present two APSP algorithms, namely the FW algorithm and the SSSP-based iterative algorithm, both implemented using CUDA. They demonstrate that the SSSP-based implementation takes approximately 10 seconds to obtain APSP costs for a graph of |V| = 3072 vertices. The speedup over the CPU-based FW implementation reaches a factor of 17. With respect to memory consumption, their SSSP-based algorithm requires O(|V|) space while the FW algorithm requires  $O(|V|^2)$  space, because the FW algorithm represents a graph in a matrix of size |V|, called adjacency matrix. This advantage allows us to deal with larger graphs, up to |V| = 30,720 vertices processed within two minutes. However, only off-chip memory is used because (1) there is no data that can be shared between CUDA cores and (2) the entire graph data is too large for 16 KB of on-chip memory.

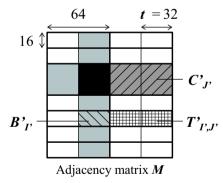

Katz and Kinder [15] propose an optimized version of the FW implementation running on the CUDA-compatible GPU. Their method is based on an iterative blocked FW (BFW) algorithm proposed by [22], which partitions the adjacency matrix into two dimensional tiles and iteratively updates these tiles. It takes 13.7 seconds to compute APSPs for a graph of |V| = 4096. A multi-GPU version is also presented to demonstrate the scalability of their method. It takes 354 seconds to process a graph of |V| = 11,264 vertices on two NVIDIA GeForce 8800 GT cards.

The recursive BFW method proposed by Buluç et al. [23], which recursively divides the adjacency matrix into tiles. This method uses a fast matrix multiplication method [24] to achieve higher performance. In particular, this method allows the GPU to efficiently run the matrix multiplication routine at a low depth of its recursion, because the routine processes large submatricies on the GPU. For |V| = 4096, their method computes APSPs in 1.01 seconds using GeForce 8800 Ultra, which reaches 126.7 Gflop/s.

Bleiweiss [25] implements Dijkstra's algorithm and A\* search algorithm [26] with a priority queue using CUDA. Their implementations are designed for agent navigation in crowded game scenes, where multiple point-to-point shortest paths are simultaneously computed for smaller graphs. Thus, their problem is slightly different from our target problem.

Micikevicius [16] presents an OpenGL-based method that implements the FW algorithm on the GPU by mapping it to the graphics pipeline. The implementation runs on an NVIDIA GeForce 5900 Ultra, which demonstrates three times faster results compared with a 2.4 GHz Pentium 4 CPU. It takes approximately 203 seconds to compute APSPs for |V| = 2048.

Harish et al. [27] presented another matrix calculation based method for finding APSPs on the GPU. This algorithm requires  $O(|V|^3 \log |V|)$  computations, which is larger than that of the FW algorithm. They adopt a lazy evaluation technique to accelerate their method for sparse graphs. This technique speeds up their method by 2–3 times. Their method finds APSPs in 0.3 seconds for a graph with |V| = 2048 using GeForce GTX 280, and in 2.2 seconds for |V| = 4096. This method can also handle a large graph that is too large to be stored in the off-chip memory of the GPU by dividing the matrix representation of the graph. For instance, this method processes a graph with |V| = 30K in 3072 seconds. In addition, they show that the lazy evaluation technique can be applied to the recursive BFW method by Buluç et al. and achieves a same range of 2–3 times speedup as that of their matrix calculation base method.

An FPGA-based method is proposed by [17]. They implement a tiled version of the FW algorithm and develop an analytical model to predict the performance for larger FPGAs. As compared with a CPU-based method running on a 2.2 GHz Opteron, their method reduces execution time for |V| = 16,384 from approximately four hours to 15 minutes, achieving a speedup of 15.2.

An auto-tuning approach is proposed by [28] to accelerate the iterative BFW algorithm on the CPU. Their method is optimized by cache blocking and single instruction, multiple data (SIMD) parallelization [29, 30]. It employs a two-level

blocking algorithm and selects the appropriate tile size for each level of cache. Using a 3.6 GHz Pentium 4 CPU, it takes 30 seconds to solve an APSP problem for |V| = 4096.

Finally, Srinivasan et al. [18] show a cluster approach to parallelize the FW algorithm on a distributed memory machine. However, the performance does not scale well with the number of computing nodes, because the data size |V| seems to be small for the deployed cluster. A speedup of 1.2 is observed on a 32-node system when using a graph with |V| = 4096.

With respect to the FW implementation, the computation time mentioned above is limited by the memory bandwidth rather than the arithmetic performance: 76.8, 36.8, and 80.1 GB/s (9.6, 4.6, and 10 GFLOPS) on the FPGA [17], the CPU [28], and the GPU [15], respectively. Similarly, the SSSP-based method can be regarded as a memory-intensive application rather than a compute-intensive application. Actually, it requires two operations and at least two memory accesses to update the cost of a vertex. Thus, considering the ratio of the memory bandwidth to the arithmetic performance, the SSSP-based method requires at least 1 B/FLOP while the GPU employed by [1] provides 0.25 B/FLOP. Therefore, the performance will be increased if we save the memory bandwidth between off-chip memory and CUDA cores.

#### **3.3** All-Pairs Shortest Path Problem

#### 3.3.1 Definition

The APSP problem is to find the shortest paths between all pair (u, v) of vertices on a given graph G = (V, E, w), where V is the set of vertices in G, E is the set of edges in  $G, w : E \to W$  is a function that assigns a weight to each edge, and  $u \in V$ and  $v \in V$  are vertices in G. The edge  $(u, v) \in E$  is a directed edge from the vertex  $u \in V$  to the vertex  $v \in V$ . The edge weight  $w(u, v) \in W$  represents the weight of the edge (u, v), where W is the set of edge weights. In this thesis, we assumes that  $W = \mathbb{N}$  for simplicity. In other words, the edge weight is a non-negative integer. In this chapter, |V| represents the number of vertices in G and |E| is the number of edges in G.

This problem outputs the length of shortest paths between all pairs of vertices and the sequences of vertices that compose each shortest path. The path from the vertex  $v_1 \in V$  to the vertex  $v_k \in V$  is a sequence  $v_1, v_2, \cdots, v_k$  of vertices that satisfy  $(v_i, v_{i+1}) \in E$  for  $1 \leq i < k$ .

The length of path  $v_1, v_2, \dots, v_k$  is the sum of edge weights on the path, namely,  $\sum_{i=1}^{k-1} w(v_i, v_{i+1})$ . The shortest path from  $u \in V$  to  $v \in V$  is the path that has most shortest length of path among all paths between u and v.

shortest length of path among all paths between u and v.

Note that the sequence of vertices that compose the shortest path between any two vertices can be easily reconstructed from the cost of APSPs and the graph G. Figure 3.1 shows the reconstruction algorithm for the shortest path between vertex s and t. In this figure, D is the distance matrix, the element D[u, v] of which represents the cost of the shortest path from vertex u to v.

Moreover, there is a demand to calculate the costs of paths in a short time. Therefore, the proposed methods focus on accelerating the computation of the cost of APSPs. However, to facilitate the reconstruction, we also show a method to record parent vertices with our task parallel algorithm in this chapter.

#### 3.3.2 SSSP-based Iterative Algorithm

Harish and Narayanan [1] compute the costs of APSPs in a directed graph G = (V, E, w) with positive weights. In the following, let |V| and |E| be the number of vertices and that of edges, respectively. Given a graph G, the method computes an SSSP |V| times with varying the source vertex  $s \in V$ . This iteration is sequentially processed by the CPU, but each SSSP problem is solved in parallel on the GPU.

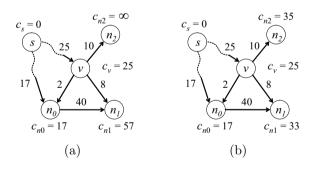

To solve an SSSP problem, an iterative algorithm [1] is implemented using CUDA. This algorithm associates every vertex  $v \in V$  with cost  $c_v$ , which represents the cost of the current shortest path from the source s to the destination v. The algorithm then minimizes every cost until converging to the optimal state. This cost minimization is done by processing two phases alternatively: the scattering phase and the checking phase. In the scattering phase, all vertices try to minimization works for a single vertex v. After this, the checking phase confirms whether the previous scattering phase has changed the costs of vertices.

Figure 3.3 shows this algorithm. Firstly, the cost of every vertex  $v \in V$  except the source s is initialized to infinity, which means that v is not reachable from s at the initial state. On the other hand, the cost is set to zero for the source s. The cost minimization then begins at line 4 for a set M of vertices, where M is the modification set, which contains vertices whose neighbor(s) have not yet reached to the optimal state. Given such a vertex  $v \in M$ , the algorithm updates the cost  $c_n$ at line 9, for every neighbor  $n \in V$  such that  $(v, n) \in E$ . The updated cost here is temporally stored to a variable  $u_n$  in order to check convergence later at line 13. Vertices that have changed their costs are added to set M for further minimization (line 14). The iteration stops when M becomes empty.

This algorithm requires synchronization between the scattering phase and the checking phase (line 12). Otherwise, some processing elements might overwrite the updated cost  $u_v$  after  $u_v$  has been confirmed to be minimal. It also should be noted that the algorithm requires atomic instructions to correctly process the scattering phase. Since multiple processing elements can update the same cost  $u_n$  at the same

time, we have to deal with the consistency of concurrent write accesses. Atomic instructions solve this issue but they are supported only on GPUs with compute capability 1.1 and higher [6]. If we lack this capability, the minimum cost  $u_n$  will be overwritten by a larger cost at line 9, resulting in a wrong result.

We now explain how Harish and Narayanan implement the algorithm on the GPU. As we mentioned earlier, there is no global synchronization mechanism in CUDA. Therefore, they develop two kernels, each for the scattering phase and for the checking phase. In both kernels, a thread is responsible for a vertex  $v \in V$  in the graph. Thus, the cost minimization is parallelized using |V| threads.

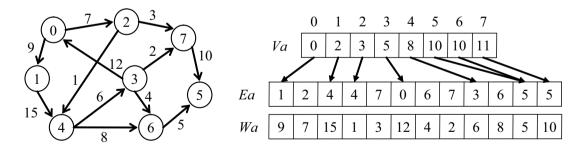

Figure 3.4 illustrates how a graph is represented in their kernels. They employ an adjacency list representation to store a graph in device memory. In this representation, each vertex data has a pointer to its adjacency list of edges. The adjacency list of vertex v here contains every neighboring vertex  $n \in V$  such that  $(v, n) \in E$ . Harish and Narayanan convert these lists into arrays Va, Ea, and Wa, which store vertex set V, edge set E, and edge weights assigned by w, respectively. As shown in Figure 3.4, element Va[v] has an index to array Ea, where the head of the adjacency list of v exists. Since all adjacency lists are concatenated into array Ea of size |E|, the adjacency list of vertex v is stored from element Va[v] to Va[v+1] - 1 in Ea. Similarly, the weight of edge Ea[i] is stored in Wa[i], where  $0 \leq i \leq |E| - 1$ . In addition to the arrays mentioned above, they use additional arrays Ma, Ca, and Ua to store modification set M, current cost  $c_v$ , and updated cost  $u_v$ , respectively. Each of these arrays has |V| elements and its index v corresponds to vertex v. They store these three arrays in device memory.

Figure 3.5 shows a pseudo code of the scattering kernel, which implements lines 6–11 in Figure 3.3. This kernel is invoked for every thread  $t_v$ , which is responsible for vertex  $v \in V$ . After this kernel execution, the CPU launches the second kernel to process the checking phase. This checking kernel updates array Ma and also sets a flag to true if any updated cost is found. The CPU then checks this flag to determine if the iteration should be stopped or not. Thus, the flag prevents the CPU from scanning the entire array Ma.

#### **3.4** Task Parallel Algorithm

We now describe the proposed algorithm for accelerating the computation of APSPs on a directed, positively weighted graph G. Firstly, we present how our algorithm accelerates the cost computation of Harish's SSSP-based method. We then describe how the algorithm records the paths after the cost computation.

| Input                                       | D: distance matrix                                   |  |  |

|---------------------------------------------|------------------------------------------------------|--|--|

|                                             | w: weight function                                   |  |  |

|                                             | s: source vertex                                     |  |  |

|                                             | t: destination vertex                                |  |  |

| Output                                      | $path\_array:$ shortest path from $s$ to $t$         |  |  |

| 1: Recor                                    | $\operatorname{nstructPath}(D, w, s, t)$             |  |  |

| 2: <b>if</b> $(s = t)$                      |                                                      |  |  |

| 3: pu                                       | 3: $push(path\_array, s)$                            |  |  |

| 4: return success                           |                                                      |  |  |

| 5: <b>if</b> $(D[s,t] \mathrel{!=} \infty)$ |                                                      |  |  |

| 6: pu                                       | $sh(path\_array, s)$                                 |  |  |

| 7: for $n$ in Successor $(s)$               |                                                      |  |  |

| 8: i                                        | $\mathbf{f} \left( w(s,n) + D[n,t] = D[s,t] \right)$ |  |  |

| 9:                                          | <b>return</b> SearchPath $(D, n, t)$                 |  |  |

| 10: <b>ret</b> u                            | <b>irn</b> error /* The path does not exist.*/       |  |  |

Figure 3.1: Algorithm for reconstructing the sequence of vertices that compose the shortest path between s and t.

Figure 3.2: Cost minimization. (a) For each vertex v in the graph, (b) the costs of its neighbors  $n_0$ ,  $n_1$ , and  $n_2$  are updated in the scattering phase.

```

SSSP_Algorithm(s, V, E, w)

/* s: source vertex */

1: initialize c_v := \infty and u_v := \infty for all v \in V /* u_v: updated cost of vertex v */

/* c_v: current cost of vertex v */

2: c_s := 0

3: M := \{s\}

4: while M is not empty do

5:

for each vertex v \in V in parallel do

/* Scattering phase */

if v \in M then

6:

7:

remove v from M

for each neighboring vertex n \in V such that (v, n) \in E do

8:

9:

u_n := \min(c_n, c_v + w(v, n))

/* w(v, n): weight of edge (v, n) */

10:

end for

11:

end if

synchronization

12:

if c_v > u_v then

/* Checking phase */

13:

14:

add v to M

15:

c_v := u_v

end if

16:

17:

end for

18: end while

```

Figure 3.3: Iterative algorithm for finding an SSSP from the source vertex  $s \in V$ .

Figure 3.4: Adjacency list representation. Array Va stores the indices to the head of each adjacency list in Ea. Array Ea and Wa store adjacency lists of every vertex and edge weight, respectively.

```

SSSP_Scattering_Kernel(Va, Ea, Wa, Ma, Ca, Ua)

1: v := \text{threadID}

2: if Ma[v] = \text{true then}

3: Ma[v] := \text{false}

4: for i := Va[v] to Va[v + 1] - 1 do

5: n := Ea[i]

6: Ua[n] := \min(Ua[n], Ca[v] + Wa[n])

7: end for

8: end if

```

Figure 3.5: Pseudo code of scattering kernel [1]. This kernel is responsible for a single vertex v and updates the costs of its adjacent vertices.

Figure 3.6: Comparison of parallelization scheme between (a) previous method [1] and (b) proposed method. Our kernel solves N SSSP problems at a time. The graph data is shared between threads that are responsible for the same vertex but in different SSSP problems.

#### **3.4.1** Cost Computation

As shown in Figure 3.6(b), our algorithm computes N tasks in parallel, where a task deals with an SSSP problem. This task parallel scheme allows us to share graph data between different tasks. Another important benefit is that it allows the kernel to generate more threads at a launch. This leads to an efficient execution on the GPU, which employs a massively multithreaded architecture. Since the algorithm we use for a single SSSP problem is the same one developed by [1], we explain here how tasks are grouped to share the graph data.