|              |                                                                                     |

|--------------|-------------------------------------------------------------------------------------|

| Title        | Power Reduction Method and Design of ASIPs for Embedded Systems                     |

| Author(s)    | Iwato, Hiroyumi                                                                     |

| Citation     | 大阪大学, 2013, 博士論文                                                                    |

| Version Type | VoR                                                                                 |

| URL          | <a href="https://hdl.handle.net/11094/25159">https://hdl.handle.net/11094/25159</a> |

| rights       |                                                                                     |

| Note         |                                                                                     |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

# Power Reduction Method and Design of ASIPs for Embedded Systems

January 2013

Hirofumi IWATO

# Power Reduction Method and Design of ASIPs for Embedded Systems

Submitted to

Graduate School of Information Science and Technology

Osaka University

January 2013

Hirofumi IWATO

# **Publications**

## **Journal Articles (Refereed)**

[J1] Hirofumi Iwato, Keishi Sakanushi, Yoshinori Takeuchi, and Masaharu Imai, "A Small-area and Low-power SoC for Less-invasive Pressure Sensing Capsules in Ambulatory Urodynamic Monitoring," IEICE TRANSACTIONS on Electronics, Vol.E95-C, No.4, pp.487-494, 2012.

[J2] Hirofumi Iwato, Keishi Sakanushi, Yoshinori Takeuchi, and Masaharu Imai, "Low-power ASIP Generation Method by Extracting Minimum Execution Conditions," IPSJ Transactions on System LSI Design Methodology, Vol.3, pp. 222-233, 2010.

## **International Conference Papers (Refereed)**

[I1] Hirofumi Iwato, Keishi Sakanushi, Yoshinori Takeuchi, and Masaharu Imai, "Low Power SoC for Pressure Measurement Capsules in Ambulatory Urodynamic Monitoring," COOL Chips XIII, April, 2010.

[I2] Hirofumi Iwato, Keishi Sakanushi, Yoshinori Takeuchi, and Masaharu Imai, "Low Power ASIP Generation Method by Means of Extracting Non-redundant Activation Conditions," Student Forum of the 13th Asia and South Pacific Design Automation Conference (ASP-DAC), January, 2008.

[I3] Hirofumi Iwato, Keishi Sakanushi, Yoshinori Takeuchi, and Masaharu Imai, "Low Power VLIW Processor Generation Method by Means of Extracting Non-redundant Activa-

tion Conditions,” in Proceedings the 5th IEEE/ACM International Conference on Hardware/Software Codesign and System Synthesis (CODES/ISSS), pp. 227-232, 2007.

[I4] Hirofumi Iwato, Keishi Sakanushi, Yoshinori Takeuchi, and Masaharu Imai, ”Low Power Configurable Processor Generation Method with Fine Clock Gating to Pipeline Registers and Register Files,” in Proceedings the 13th Workshop on Synthesis and System Integration of Mixed Technologies (SASIMI), pp.241-245, 2006.

## **International Conference Papers (Invited)**

[I5] Hirofumi Iwato, Keishi Sakanushi, Yoshinori Takeuchi, and Masaharu Imai, ”Architecture Level Power Reduction Method for Configurable Processor Generation,” in Proceedings 8th International Forum on Application-Specific Multi-Processor SoC (MPSoC), June, 2008.

## **Domestic Conference Papers**

[D1] Hirofumi Iwato, Keishi Sakanushi, Yoshinori Takeuchi, Masaharu Imai, Akira Matuzawa, and Yoshihiko Hirao, ”The Architecture of an SoC for Miniature Size Capsule to Measure Pressure Inside Body,” Medical Information and Communications Technology, no. 9, pp. 99-112, July, 2009 (in Japanese).

[D2] Hirofumi Iwato, Takuji Hieda, Hiroaki Tanaka, Jun Sato, Keishi Sakanushi, Yoshinori Takeuchi, and Masaharu Imai, ”Highly Extensible Base Processors for Short-term ASIP Design,” IEICE Technical Report, VLD2007-92, vol. 107, no. 336, pp. 19-24, November, 2007 (in Japanese).

[D3] Hirofumi Iwato, Keishi Sakanushi, Yoshinori Takeuchi, and Masaharu Imai, ”Generation Method for Low Power Configurable Processor,” IPSJ Symposium Series, vol. 2005, no. 9, pp. 219-224, August, 2005 (in Japanese).

# Summary

In recent years, embedded systems are widely used in our daily life. To implement a lot of requirements in a small embedded system, tight constraints must be met at the same time. Power consumption is the most important constraint for modern embedded systems. For high performance systems, power consumption increases heat of embedded systems, and for small systems, power consumption requires bigger battery capacity and increases system size.

Application Specific Instruction-set Processors (ASIPs) are appropriate to implement embedded systems because ASIPs can offer high performance per energy and high programmability. To design high performance embedded systems, Very Long Instruction Word (VLIW) type ASIPs (VLIW ASIPs) are suitable, and Design Space Exploration (DSE) must be performed to determine the optimal architecture parameters. On the other hand, to implement small embedded systems, small scalar ASIPs with specific instructions must be designed by taking into account the characteristics of the target systems.

This thesis discusses two topics to challenge low power embedded system designs for high performance systems and small systems. First, this thesis proposes a low power VLIW ASIP generation method. The proposed method generates VLIW ASIPs with clock gating technique, which is a well known low power technique to reduce power consumption of flip flops. Power reduction by clock gating depends on gating signals of registers, and the gating signals are derived from execution conditions of the registers. In order to minimize power consumption of pipeline registers in a large-scale data path of a VLIW ASIP, the proposed method automatically extracts the minimum execution conditions from ASIP generation procedures. The experimental results show that the proposed method drastically reduce power consumption of VLIW ASIPs, and overheads to implement clock gating are small.

The second topic is to design the pressure sensing system for Ambulatory Urodynamic Mon-

itoring (AUM). In AUM, the sensors measure pressure data of the bladder and the rectum, and the size of the sensor must be small for less-invasive tests. Therefore, designing the small capsular sensor is beneficial to less-invasive urodynamic tests. To design small pressure capsule, the System-on-a-Chip (SoC) which integrates almost functions of the capsule is strongly required. This thesis describes the requirements and constraints of the SoC, the designs of the capsule, the SoC, and the ASIP which is designed for this application. The experimental results show that the designed SoC and ASIP are low power consumption and small area implementation, the implemented capsule satisfies constraints for AUM, and correct operations of the sensing system are confirmed.

# Acknowledgments

I would like to deeply thank Prof. Masaharu Imai for guiding me throughout my PhD days. I appreciate his advices, technical suggestions, and insights for my researches. Through discussions with him, I have acquired expertise in my research area.

I would like to thank Prof. Takao Onoe and Prof. Tetsuya Yagi for reviewing this thesis and comment on my study.

I would like to thank Prof. Yoshinori Takeuchi for his guidance. His sound advices motivate me to improve my research and papers, and he takes a great care of me at all times.

I am thankful to Dr. Keishi Sakanushi. His beneficial comments on my work help me to progress my research. He teaches me a lot of things about researching, writing paper, and academic mentality.

I would like to thank Dr. Kyoko Ueda, Dr. Mohamed AbdElSalam Hassan, Dr. Yuki Kobayashi, and Dr. Hiroaki Tanaka. They friendly discuss with me on my research and give many useful comments and advices.

I thank to Dr. Takuji Hieda. He is co-worker and helps me at various situations. Wit talking with him makes my PhD days enjoyable.

I would like to thank Dr. Makiko Itoh, Dr. Shinsuke Kobayashi. They made the basis of my research.

I would like to thank Prof. Masaya Miyahara, Dr. Takashi Kurashina, and Mr. Kennichi Matsunaga. They help development of the SoC that is described in this thesis, and their modules are implemented in the SoC.

I am thankful to Ittetsu Taniguchi, Takashi Hamabe, Takahiro Notsu, Hyun Kim Long, Takeshi Shiro, Takahiro Itoh, Akira Kobashi, Yu Okuno, Hitoshi Nakamura, Ayataka Kobayashi, Aiko Takabe, Kazuhiro Kobashi, Masahiro Kondo, Hiroki Ohsawa, and the rest of all members

of Integrated System Design Laboratory in Osaka University. They helped me and made my student life joyful and vivid.

I wish to thank my parents Yuji and Michiko, and my sister Mina and her husband Hideyuki Nishizawa, and also nephew Ryo and niece Yuki.

And Finally, for my dear Yuki, thank you for supporting me with your precious smile.

# Contents

|          |                                                          |           |

|----------|----------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                      | <b>3</b>  |

| 1.1      | Embedded System Design with ASIPs . . . . .              | 4         |

| 1.2      | Design Challenges . . . . .                              | 5         |

| 1.2.1    | ASIP Generations with Low Power Technique . . . . .      | 5         |

| 1.2.2    | An SoC for Pressure Measurement Capsule in AUM . . . . . | 6         |

| 1.3      | Contributions . . . . .                                  | 7         |

| 1.4      | Organization . . . . .                                   | 8         |

| <b>2</b> | <b>Related Work</b>                                      | <b>9</b>  |

| 2.1      | Low Power Techniques for Digital Circuits . . . . .      | 9         |

| 2.2      | ASIP Generation Methods . . . . .                        | 10        |

| 2.2.1    | ASIP Generation Methods . . . . .                        | 10        |

| 2.2.2    | Minimum Execution Conditions . . . . .                   | 11        |

| 2.3      | Automatic Clock Gating Methods . . . . .                 | 12        |

| 2.4      | Urodynamic Monitoring Systems . . . . .                  | 13        |

| <b>3</b> | <b>Low Power VLIW ASIP Generation Method</b>             | <b>15</b> |

| 3.1      | Basic of VLIW ASIP Generation . . . . .                  | 15        |

| 3.1.1    | Micro-Operation Description . . . . .                    | 15        |

| 3.1.2    | VLIW ASIP Dispatching Model . . . . .                    | 17        |

| 3.1.3    | VLIW ASIP Controller Model . . . . .                     | 19        |

| 3.1.4    | VLIW ASIP Generation Flow . . . . .                      | 21        |

| 3.2      | Low-power VLIW ASIP Generation . . . . .                 | 22        |

|          |                                                                       |           |

|----------|-----------------------------------------------------------------------|-----------|

| 3.2.1    | Insertion of Gating Circuits . . . . .                                | 22        |

| 3.2.2    | Extraction of Minimum Execution Conditions . . . . .                  | 22        |

| 3.2.3    | Generating Gating Signals with Minimum Execution Conditions . . . . . | 29        |

| 3.2.4    | Generation of Scalar ASIPs . . . . .                                  | 31        |

| 3.3      | Experiments . . . . .                                                 | 31        |

| 3.3.1    | Evaluation of Hardware Variation . . . . .                            | 32        |

| 3.3.2    | Evaluation of Software Variation . . . . .                            | 37        |

| 3.4      | Conclusion . . . . .                                                  | 37        |

| <b>4</b> | <b>Design of an SoC for Pressure Sensing Capsules in AUM</b>          | <b>39</b> |

| 4.1      | Requirements for Pressure Sensing Capsules . . . . .                  | 39        |

| 4.2      | System Overview . . . . .                                             | 40        |

| 4.3      | MeSOC Overview . . . . .                                              | 43        |

| 4.3.1    | Design Constraints . . . . .                                          | 43        |

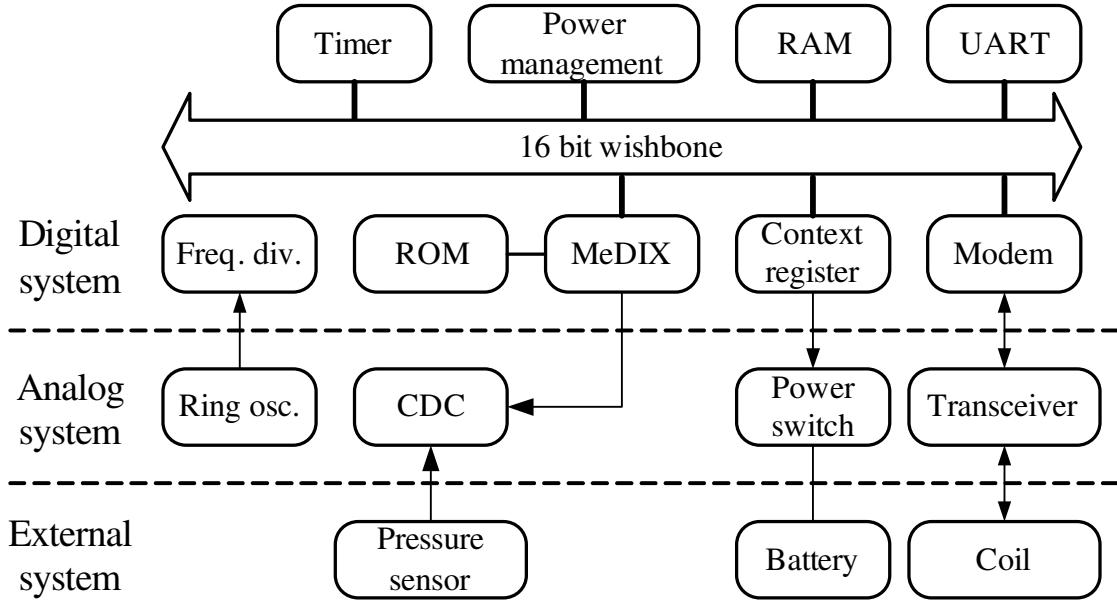

| 4.3.2    | MeSOC Task and Architecture . . . . .                                 | 43        |

| 4.3.3    | Power Management . . . . .                                            | 46        |

| 4.4      | Analog System . . . . .                                               | 46        |

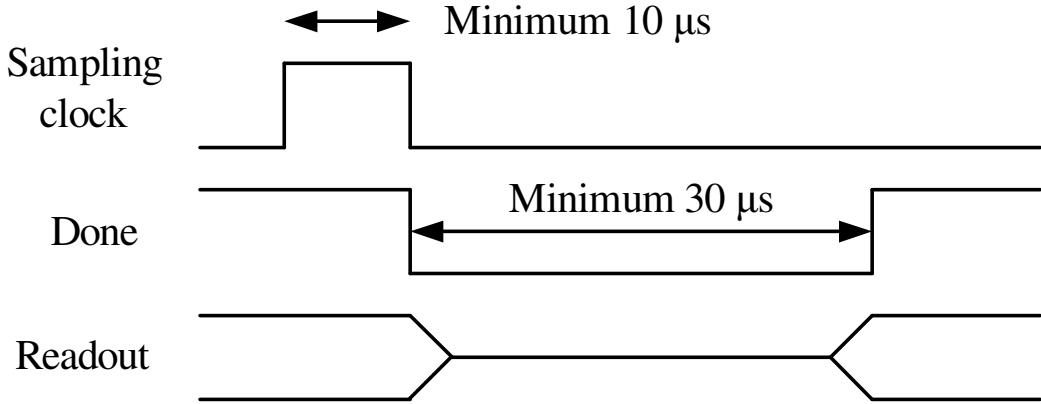

| 4.4.1    | CDC . . . . .                                                         | 47        |

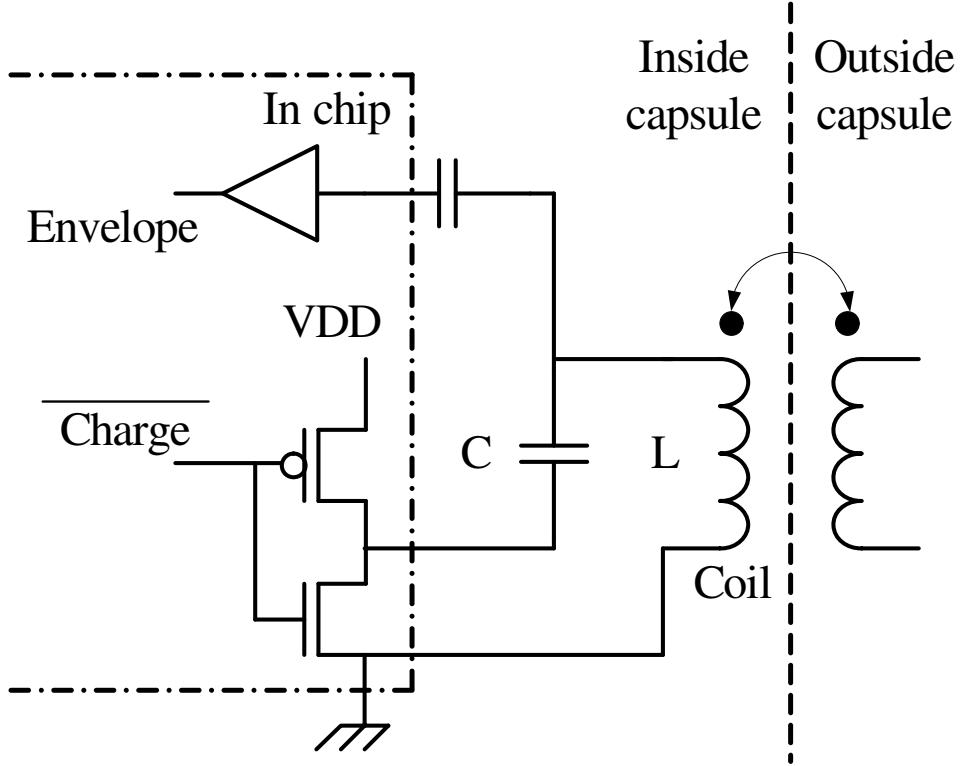

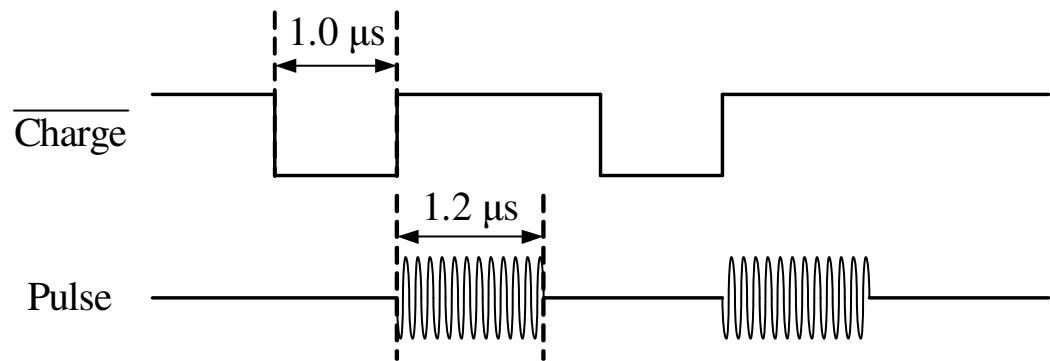

| 4.4.2    | Wireless Transceiver . . . . .                                        | 48        |

| 4.5      | Digital Architecture . . . . .                                        | 50        |

| 4.5.1    | MeDIX-I . . . . .                                                     | 50        |

| 4.5.2    | CDC Control . . . . .                                                 | 52        |

| 4.5.3    | Wireless Modem . . . . .                                              | 52        |

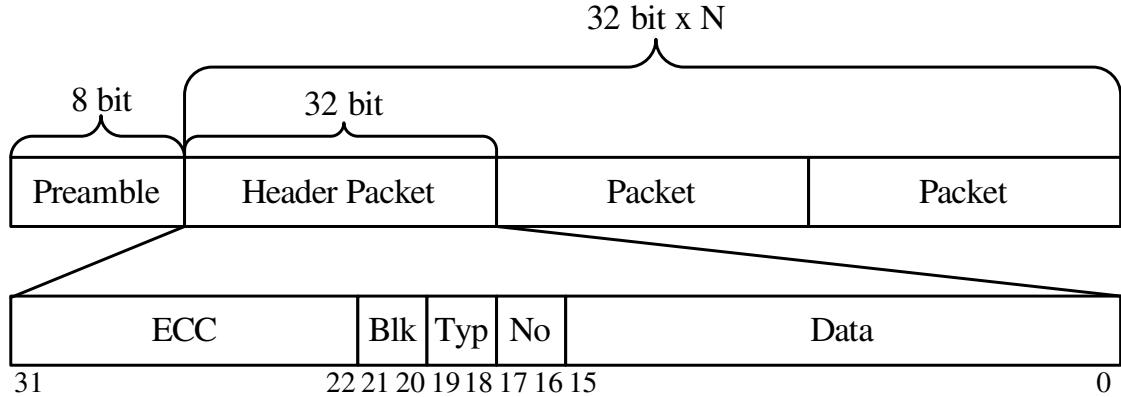

| 4.5.4    | Packet Format . . . . .                                               | 58        |

| 4.5.5    | Error Correcting Code . . . . .                                       | 58        |

| 4.5.6    | Communication Protocol . . . . .                                      | 62        |

| 4.6      | Experimental Results . . . . .                                        | 64        |

| 4.6.1    | Simulation Results . . . . .                                          | 64        |

| 4.6.2    | Implementation Results . . . . .                                      | 65        |

| 4.7      | Conclusion . . . . .                                                  | 71        |

|                                                                         |           |

|-------------------------------------------------------------------------|-----------|

| <b>5 Conclusion and Future Work</b>                                     | <b>73</b> |

| 5.1 Conclusion                                                          | 73        |

| 5.2 Future Work                                                         | 74        |

| 5.2.1 Future Work on the Low Power VLIW ASIP Generation                 | 74        |

| 5.2.2 Future Work on the Design of an SoC for Pressure Sensing Capsules | 75        |

# List of Figures

|     |                                                                     |    |

|-----|---------------------------------------------------------------------|----|

| 1.1 | A trade-off between flexibility and performance per energy. . . . . | 4  |

| 2.1 | Clock gating. . . . .                                               | 10 |

| 2.2 | Operand Isolation. . . . .                                          | 10 |

| 3.1 | MOD of ADD on RG1 (ADD, RG1). . . . .                               | 16 |

| 3.2 | VLIW ASIP model. . . . .                                            | 18 |

| 3.3 | Decoder model of VLIW ASIPs. . . . .                                | 19 |

| 3.4 | Clock gating schemes. . . . .                                       | 23 |

| 3.5 | Converted RCGs. . . . .                                             | 24 |

| 3.6 | Unified RCG. . . . .                                                | 25 |

| 3.7 | Constructed data path. . . . .                                      | 27 |

| 3.8 | Modified decoder model. . . . .                                     | 29 |

| 3.9 | Area reduction by applying clock gating. . . . .                    | 35 |

| 4.1 | Pressure measurement system and capsules. . . . .                   | 40 |

| 4.2 | The work flow of pressure sensing. . . . .                          | 41 |

| 4.3 | The work flow of wireless transmission. . . . .                     | 42 |

| 4.4 | Flow chart of a typical MeSOC task. . . . .                         | 44 |

| 4.5 | Block diagram of the MeSOC architecture. . . . .                    | 45 |

| 4.6 | Asynchronous protocol of CDC. . . . .                               | 47 |

| 4.7 | Wireless circuit for the capsule sensor. . . . .                    | 48 |

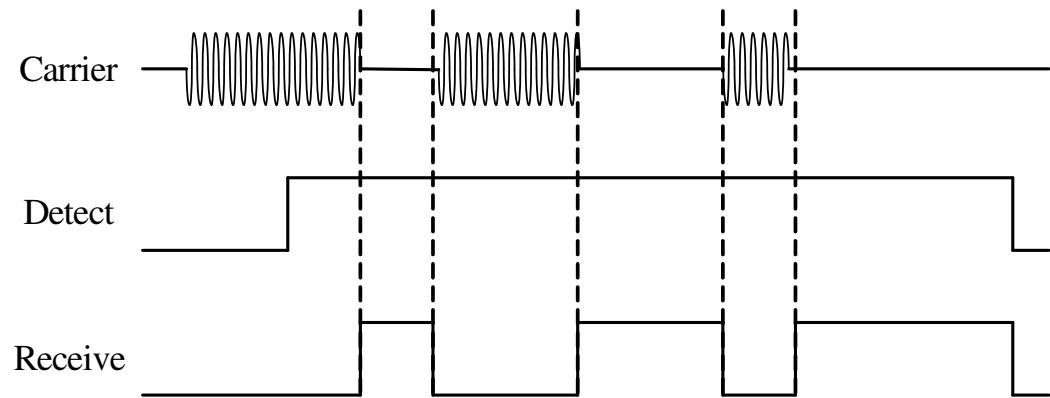

| 4.8 | RF signal transmission. . . . .                                     | 49 |

| 4.9 | RF signal receiving. . . . .                                        | 49 |

|      |                                                           |    |

|------|-----------------------------------------------------------|----|

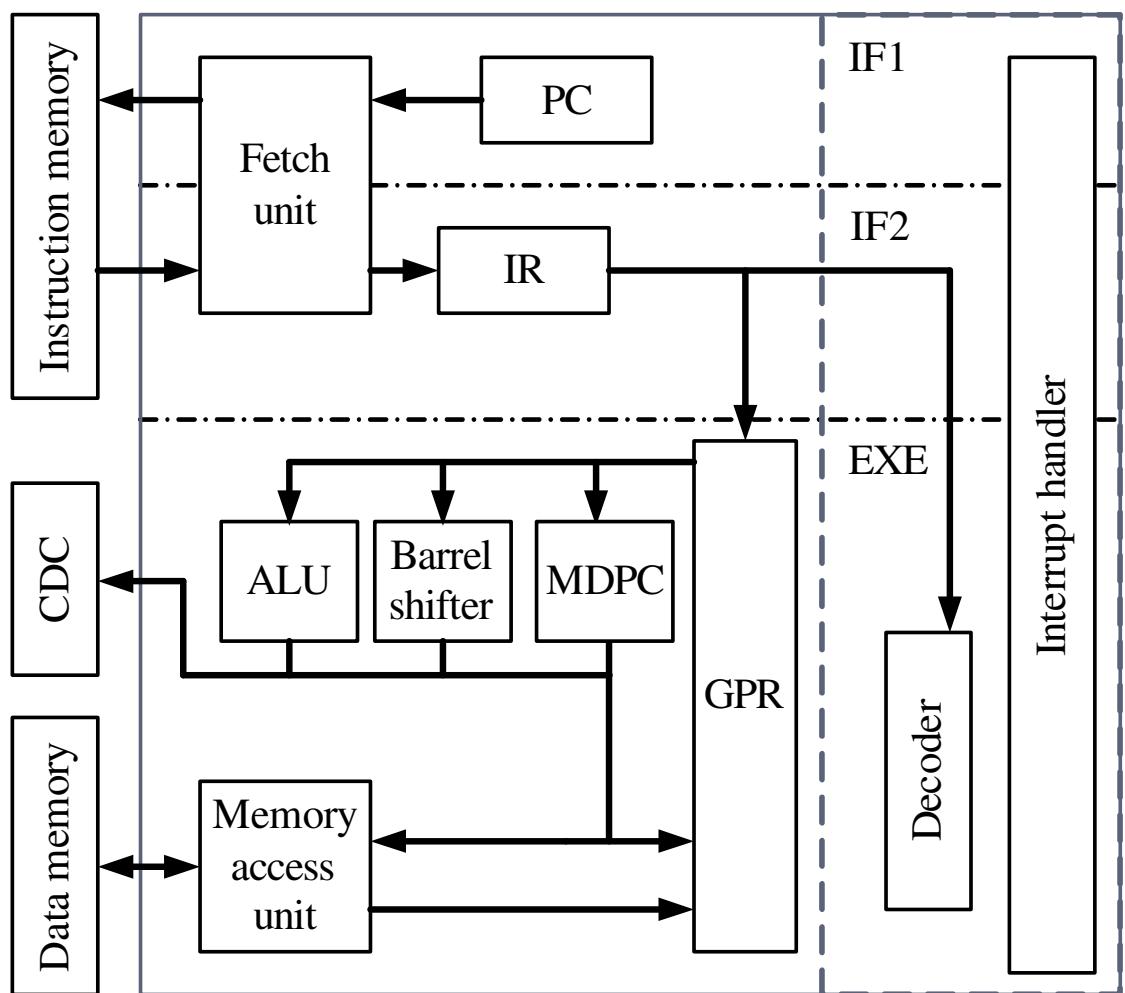

| 4.10 | Block diagram of MeDIX-I.                                 | 51 |

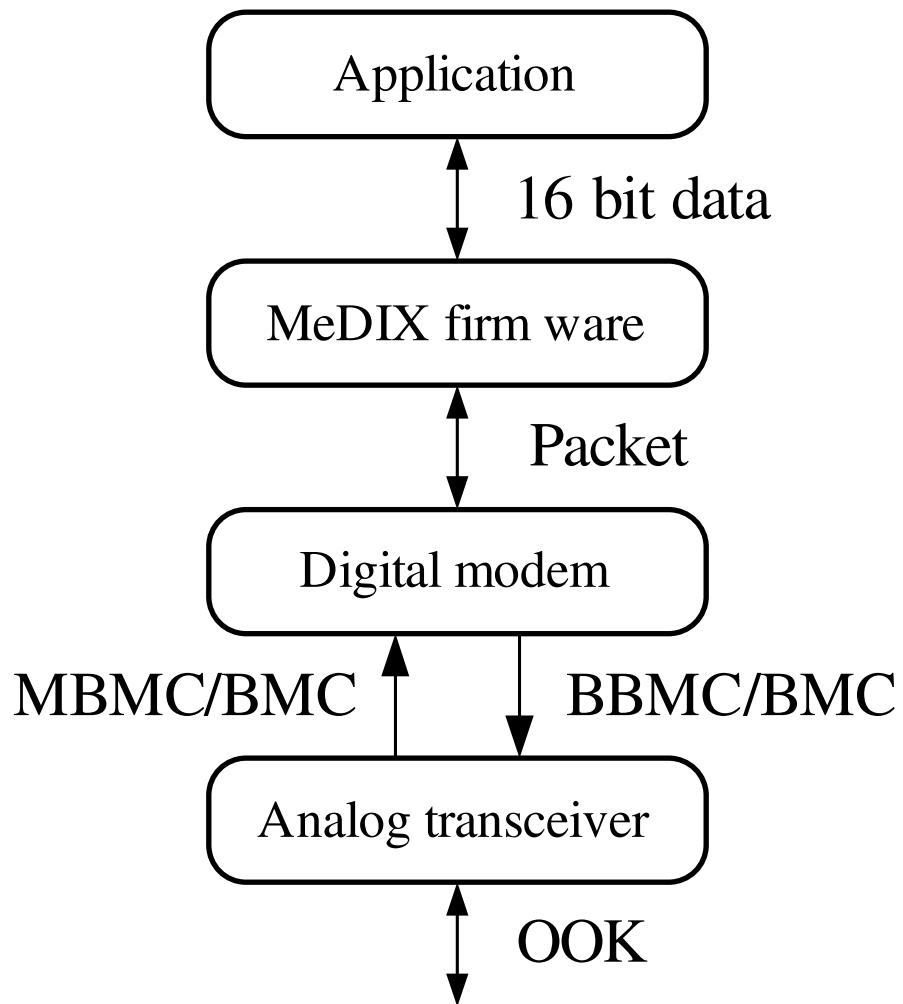

| 4.11 | Protocol stack on this SoC.                               | 53 |

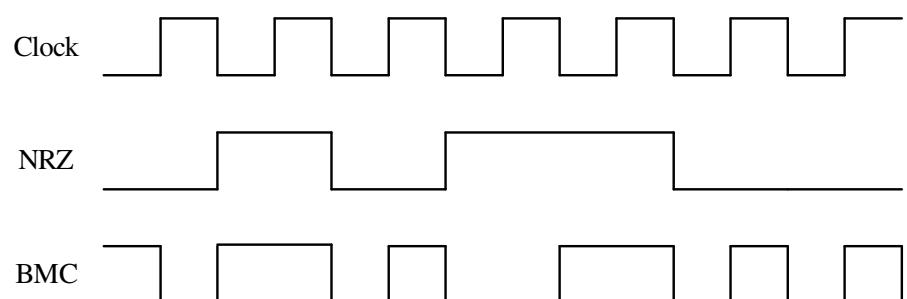

| 4.12 | Line codes for the SoC.                                   | 53 |

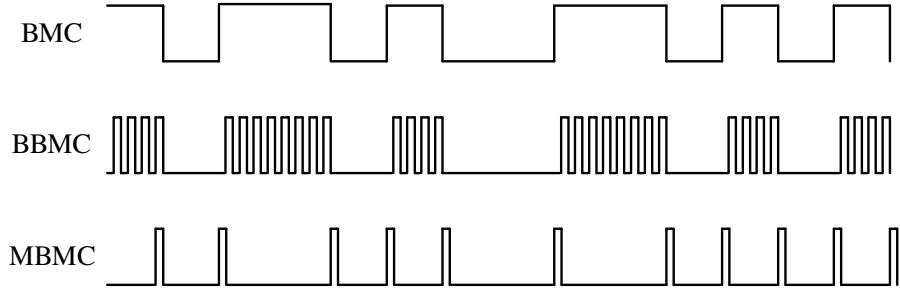

| 4.13 | Relationship with BMC, BBMC, and MBMC.                    | 54 |

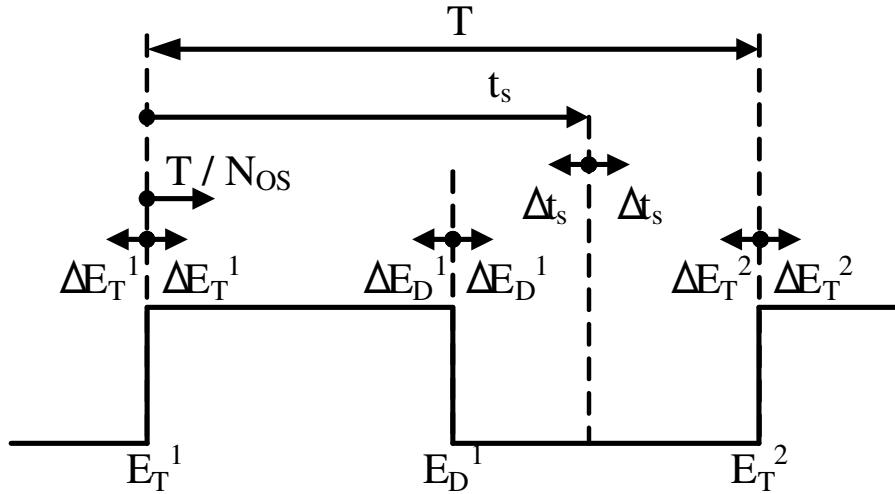

| 4.14 | Timing degradation of received signal.                    | 55 |

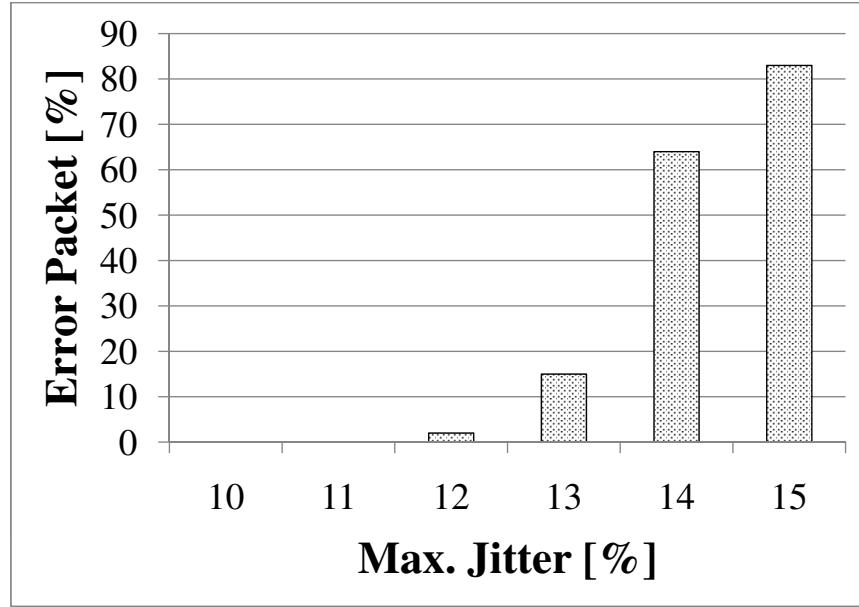

| 4.15 | Packet error rate on jitter rate.                         | 57 |

| 4.16 | Packet format.                                            | 58 |

| 4.17 | MDPC( $2^M$ ) calculation algorithm.                      | 60 |

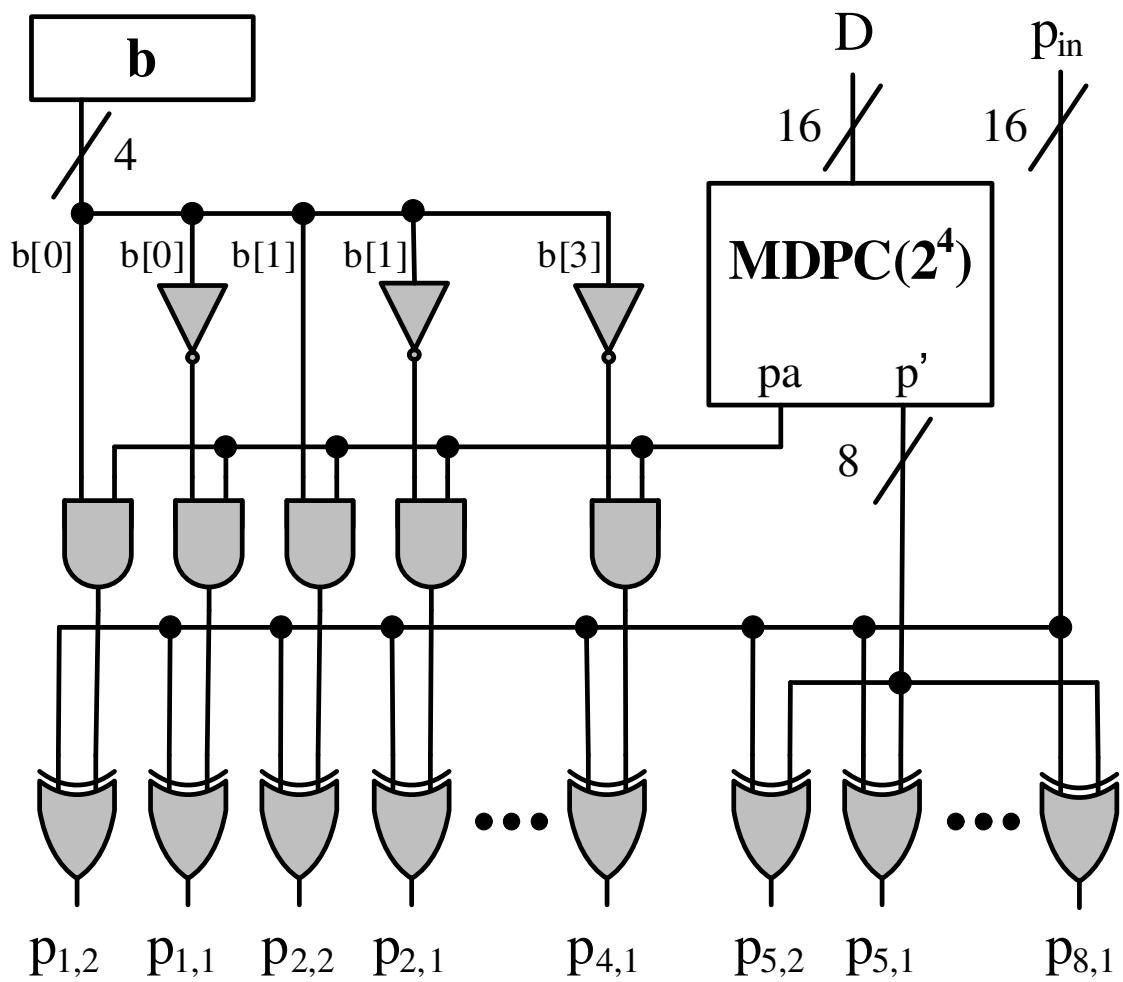

| 4.18 | MDPC( $2^8$ ) calculation circuit by using MDPC( $2^4$ ). | 61 |

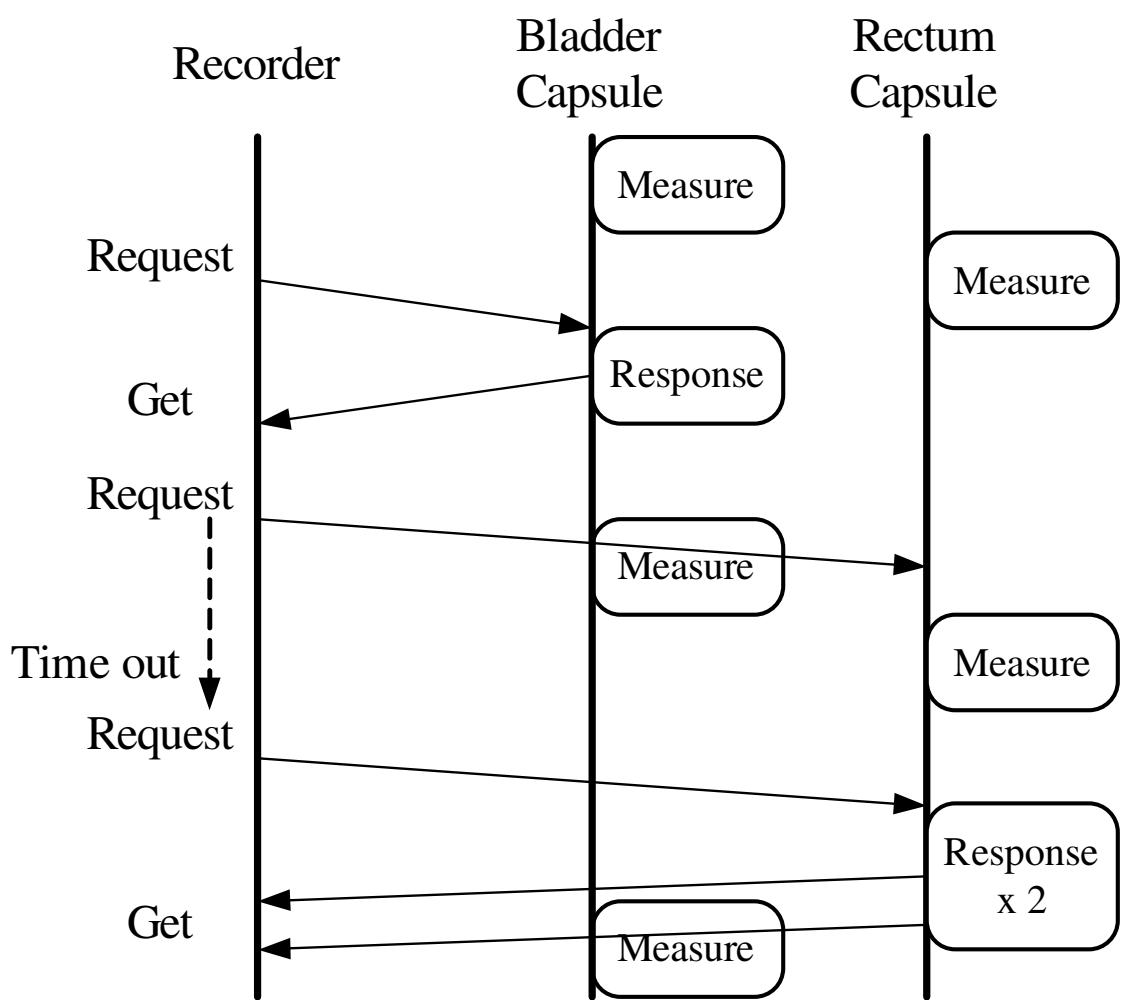

| 4.19 | Communication timeline.                                   | 63 |

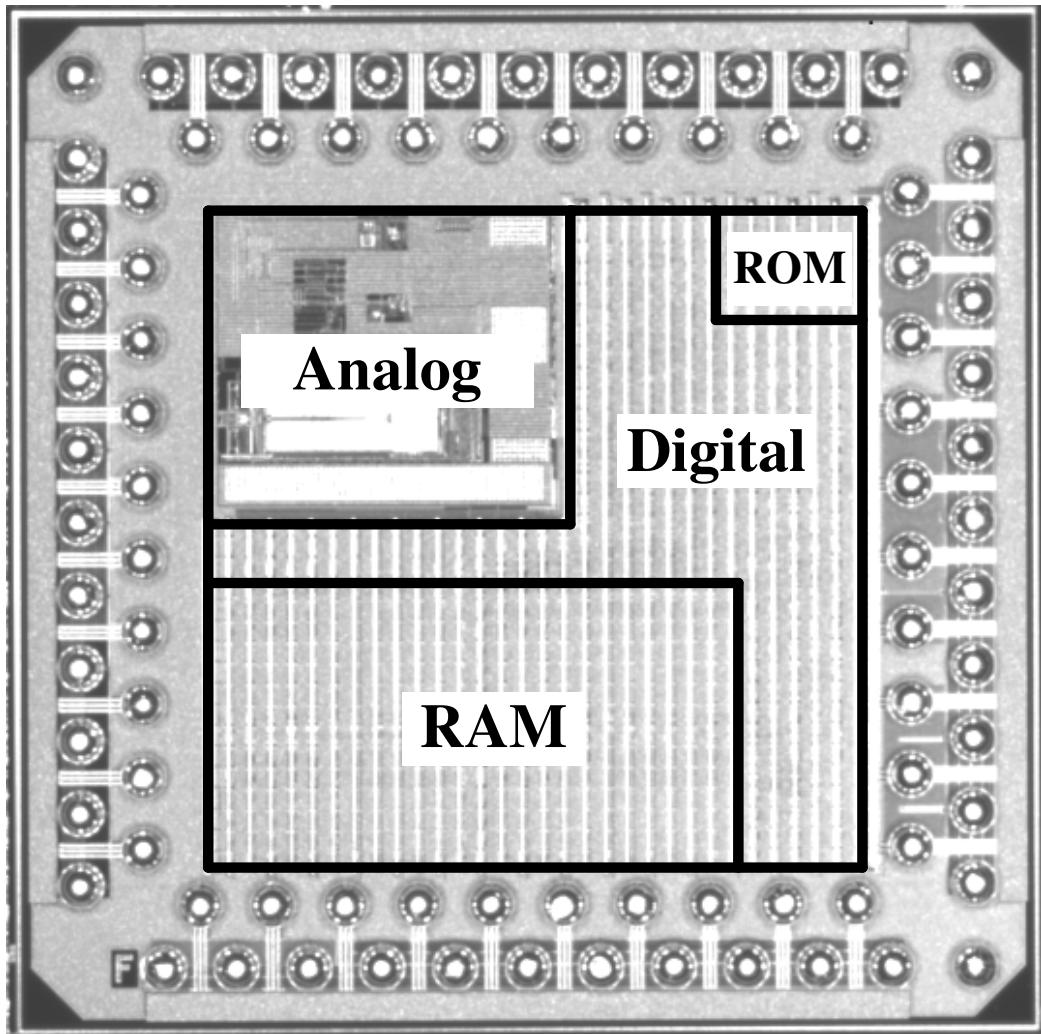

| 4.20 | Chip micrograph.                                          | 66 |

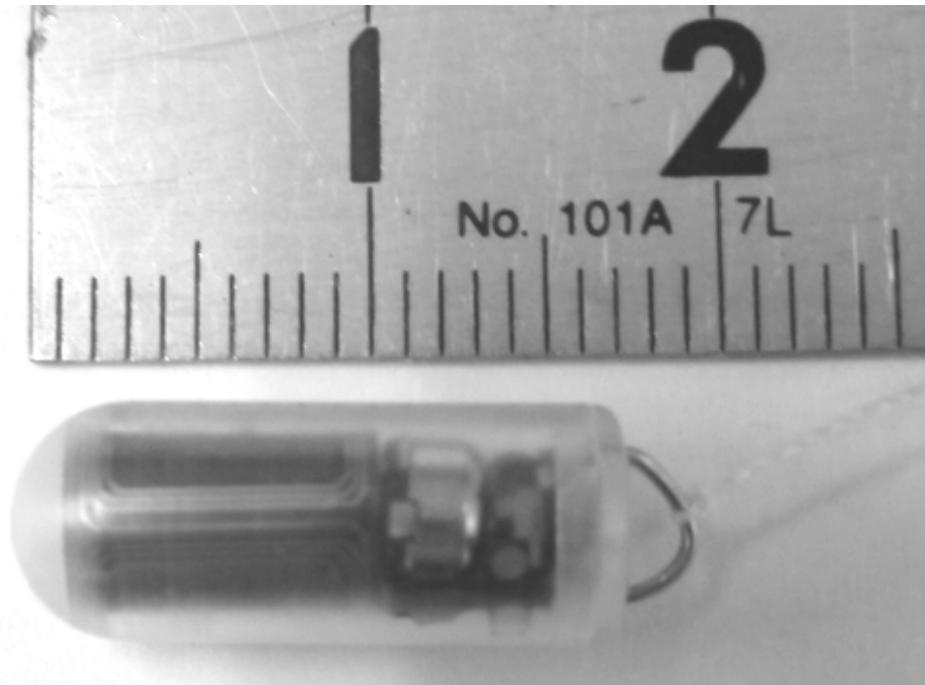

| 4.21 | Photo of an assembled capsule prototype.                  | 67 |

| 4.22 | Test environment of CDC pressure sensing.                 | 68 |

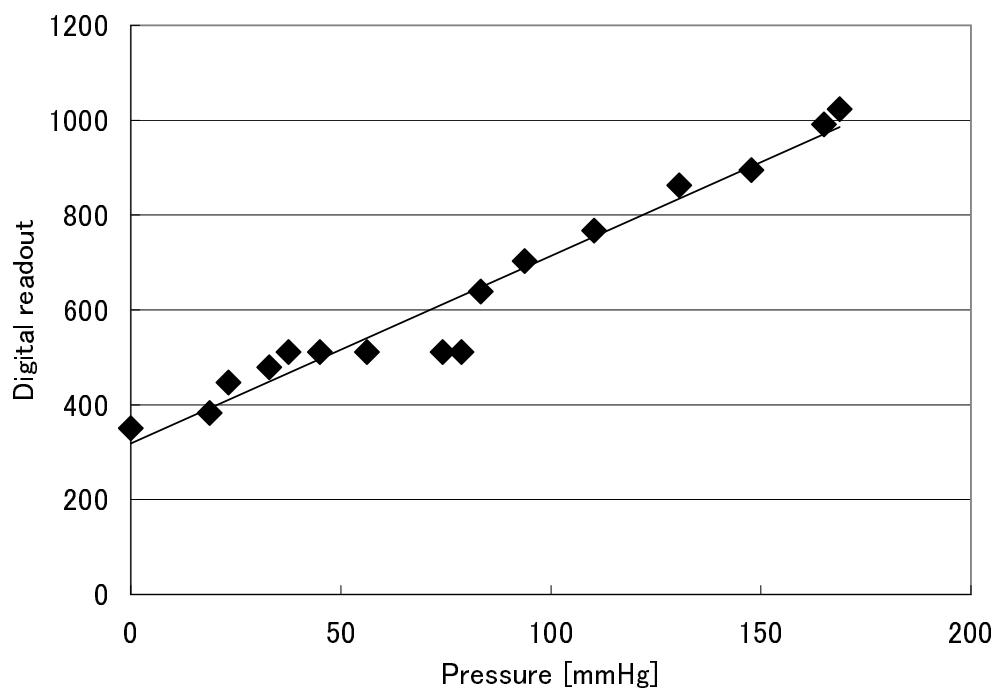

| 4.23 | Pressure readout of CDC.                                  | 68 |

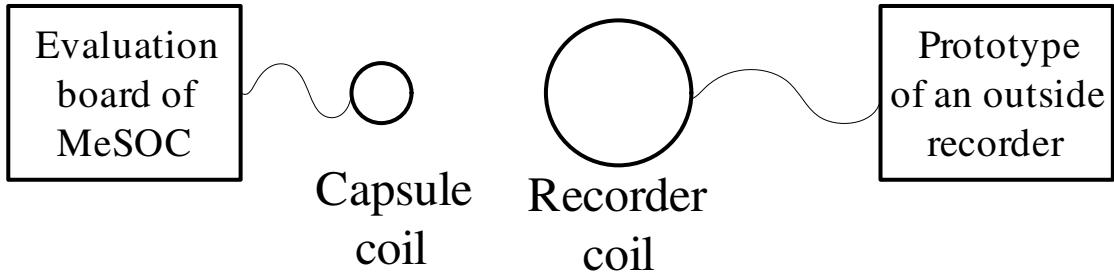

| 4.24 | Test environment of wireless communication.               | 69 |

# List of Tables

|     |                                                                                                   |    |

|-----|---------------------------------------------------------------------------------------------------|----|

| 3.1 | Example of $T_{IDP}$ . . . . .                                                                    | 21 |

| 3.2 | Power comparison on single-scalar DLX, varying number of pipeline stages. . . . .                 | 33 |

| 3.3 | Power comparison on VLIW DLX, varying number of parallel issues. . . . .                          | 34 |

| 3.4 | Power consumption of pipeline registers in 4-slot VLIW ASIP according to appearance rate. . . . . | 36 |

| 4.1 | Use of baseband coding . . . . .                                                                  | 54 |

| 4.2 | MDPC calculation of $2^2$ . . . . .                                                               | 59 |

| 4.3 | MDPC calculation of $2^3$ . . . . .                                                               | 60 |

| 4.4 | Power consumption of the digital block . . . . .                                                  | 64 |

| 4.5 | Chip summary . . . . .                                                                            | 65 |

| 4.6 | Comparison of the pressure sensing systems . . . . .                                              | 70 |

# Chapter 1

## Introduction

Nowadays embedded systems are used to make our daily life useful and safe. Ubiquitous information systems such as cellular phones, tablet computers, sensor networks, and medical systems are widely adopted in modern society. Since each application requires a lot of functions in small size implementation, the design constraints of embedded systems are very tight. Especially in modern embedded systems, power consumption is the critical problem. For the systems which require high performance computing, power consumption increases heat of the systems and makes the design difficult. On the other hand, for the systems which require portable and small implementation, not requiring high performance, power consumption increases battery capacity, and makes the system size bigger. There are a various types of requirements for embedded systems and power reduction is the common design challenge for designers.

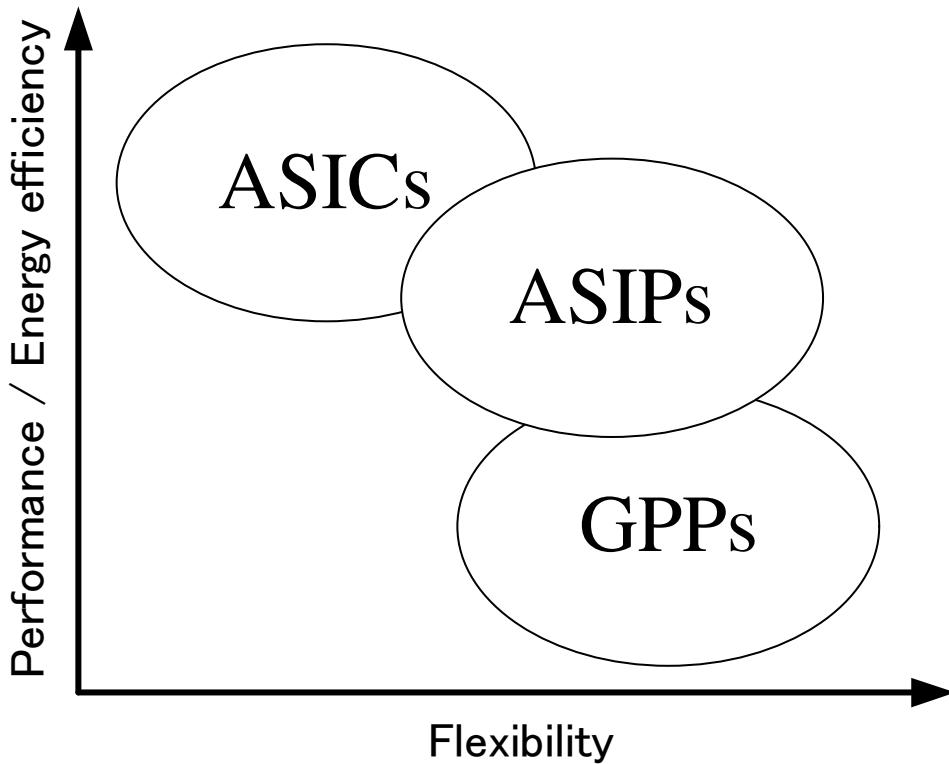

Embedded systems are implemented by Application Specific Integrated Circuits (ASICs), General Purpose Processors (GPPs), or Application Specific Instruction-set Processors (ASIPs). ASICs can achieve high computation performance with low power consumption, but they have disadvantage of flexibility: they are cannot reprogrammed after design completion. In contrast, GPPs can offer flexibility to designers, however, they are not efficient implementation in terms of performance per energy. On the other hand, as shown in Figure 1.1, ASIPs can meet the conflicting requirements by means of using application specific instructions. ASIPs offer high flexibility and high performance per energy at the same time. Therefore ASIP is appropriate

Figure 1.1: A trade-off between flexibility and performance per energy.

architecture to implement embedded systems.

## 1.1 Embedded System Design with ASIPs

For high performance processor architecture, superscalar processor [1] and Very Long Instruction Word (VLIW) processor [2] are proposed. Both types exploit Instruction-Level Parallelism (ILP) to increase Instructions Per Cycle (IPC) performance; however, they have difference in instruction scheduling mechanism. Superscalar processors fetch multiple instructions at the same cycle, detect ILP by hardware, and schedule the instructions at execution time. Therefore, superscalar processors need extra hardware to implement parallel execution. Such extra hardware increase implementation size and power consumption. On the other hand, VLIW processors do not need extra hardware to detect ILP and schedule instructions because instructions are analyzed by software, and the scheduled instructions are placed on instruction memories in

advance. Since VLIW processors can perform parallel execution by simple hardware, VLIW is the suitable architecture for high performance embedded systems.

For small and low power embedded systems, VLIW and superscalar architecture are not suitable; small scalar ASIPs with a limited instruction set are appropriate. In such systems, designing small and low power ASIPs is not sufficient to meet the design constraints. By taking into account the rest of the functional blocks in the system, appropriate implementation of special instructions is required for low power design. Therefore, the low power ASIP design for small systems depends on each particular application.

## 1.2 Design Challenges

To design low power embedded systems with ASIPs is still challenging task for designers.

### 1.2.1 ASIP Generations with Low Power Technique

When designing VLIW type ASIPs (VLIW ASIPs), or scalar ASIPs, simultaneously satisfying the tight constraints is required: computation performance, area, and power consumption. For this purpose, Design Space Exploration (DSE) should be performed to determine the optimal architecture parameters of ASIPs [3]. One of the main concerns is that DSE is time consuming task; manually performed DSE decreases design productivity.

For rapid DSE, the automatic ASIP generation methods that achieves significant short design time have been proposed [4–8]. The generation methods automatically generate ASIPs based on the specifications described with Architecture Description Language (ADL) [9]. Designers can flexibly describe architecture with ADL and reduce design time by using architecture generation. However, the conventional ASIP generation methods place a priority on minimizing area and delay. For reducing power consumption, it is required to generate ASIPs with low power techniques.

There are many low power techniques through all design levels. In Register Transfer Level (RTL), clock gating [10] and operand isolation [11] are familiar. Based on the gating conditions, clock gating cuts off the clock supplies causing unnecessary switching inside the registers. Operand isolation stops unnecessary switching to temporarily unused blocks in a data path.

Since an enormous amount of energy is consumed by registers in synchronous circuits [12], the clock gating appears to be a promising technique for power reduction. Generally, there are many pipeline registers in the large-scale data path of a VLIW ASIP. Furthermore, the number of pipeline registers rapidly increases when widening the parallel issue or deepening the pipeline; thus a large amount of energy is dissipated in the pipeline registers [13]. For this reason, clock gating on pipeline registers is expected to be effective for VLIW ASIP generation.

### **1.2.2 An SoC for Pressure Measurement Capsule in AUM**

Biomedical information sensing has become an essential part of health care systems. Measuring accurate biomedical information throughout the day is indispensable for diagnosing symptoms. This thesis deals with pressure measurement capsules for urodynamics as a beneficial specific application of a small embedded system.

Detrusor pressure measurement is indispensable for diagnosing Lower Urinary Tract Symptoms (LUTS) attributed to underlying causes such as neurogenic bladder, prostatic hyperplasia, and malignancy. Since the detrusor pressure can be calculated by subtracting the abdominal pressure from the intravesical pressure [14], the pressures in the urinary bladder and rectum are simultaneously evaluated by using cystometry [15], which is a major method to measure the detrusor pressure [16]. However, the results of cystometry tend to fail to reproduce and explain symptoms because cystometry involves artifacts by means of non-physiological procedures, e.g., confining patients to a stressful examination room for hours, inserting catheters through the urethra, and filling the bladder with saline. For better urodynamic study, any artifacts should be removed.

Ambulatory Urodynamic Monitoring (AUM) has become an established diagnosing method for LUTS [17]. AUM is expected to reduce artifacts for pressure measurement because AUM releases patients from the stressful environment and investigates the natural activity of the urinary system in daily life. To conduct pressure measurement in AUM, several pressure sensing systems have been proposed by using catheters or implanting sensing devices. Although these systems can be used in home, the results are still supposed to contain artifacts. To improve plausibility of the recorded data, inserting catheters and invasive incision should be removed

for less-invasive pressure measurement in AUM.

In order to perform AUM, sensing devices must be small capsule form because big sensors make patients feel uncomfortable, or even pain, resulting undesirable artifacts. A small capsule can be inserted in the bladder and directly measure pressure data. Since insertion is less-invasive and the inserted capsule does not disturb daily activities, the capsule sensor contributes less-invasive pressure sensing in AUM. Several pressure sensing devices have been proposed to tackle realizing AUM. However, the proposed sensing devices are too big to implement in a miniature size capsule. The main reason of the big size is due to the multiple chips on a Printed Circuit Board (PCB). To implement small size pressure measurement sensor for AUM, a System on a Chip (SoC), which integrates multiple components in a single chip, is an appropriate solution to the capsule form pressure sensing devices.

## 1.3 Contributions

This thesis discusses low power embedded system design with ASIP generation for both high-performance and small applications.

As a low power design for high-performance systems, a low power VLIW ASIP generation method is described. To apply clock gating to VLIW ASIP generation method is necessary for low power ASIP design because VLIW ASIPs contain a lot of pipeline registers. Power reduction by clock gating depends on gating conditions. Extracting the minimum execution conditions is important for reducing power consumption. However, the extraction in a complex data path is time consuming and error-prone task. The low power VLIW ASIP generation method automatically extracts the minimum execution conditions in ASIP generation procedures. By using the minimum execution conditions, the proposed method generates clock gating control signals and minimizes pipeline register activities.

As a low power design for small systems, the design of an SoC with an ASIP for pressure sensing capsules for AUM is tackled. By using the ASIP, the SoC is designed as small enough to implement the pressure sensing capsules which are inserted in the bladder and rectum. The main tasks of the SoC are: sensing pressure data in the bladder and rectum, receiving commands and transmitting the data to an outside recorder via wireless link. Designs of sensing system

framework, capsule implementation, SoC architecture, wireless protocols, digital circuits for wireless modem, and an ASIP are studied in this thesis. The ASIP design is the main concern of the SoC. The ASIP in the SoC is very small and pipeline registers are not used in it. Therefore, although the low power VLIW ASIP generation method described in this thesis is applicable, it is not effective. Effective implementation of specific instructions is required to contribute power reduction and small area implementation.

## 1.4 Organization

The remainder of this thesis is organized as follows. Chapter 2 discusses related work. Chapter 3 describes low power VLIW ASIP generation method by means of extracting minimum execution conditions. The designs of the pressure sensing capsule and the SoC for AUM are studied in Chapter 4. Conclusion and future work are described in Chapter 5.

# Chapter 2

## Related Work

This chapter describes related work of ASIP generation methods, low power techniques and methods, and pressure sensing systems for AUM.

### 2.1 Low Power Techniques for Digital Circuits

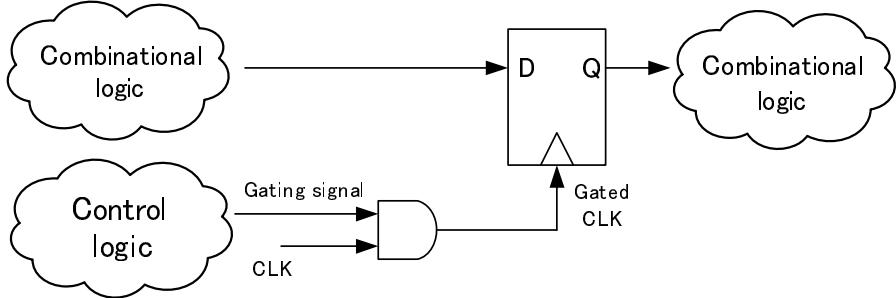

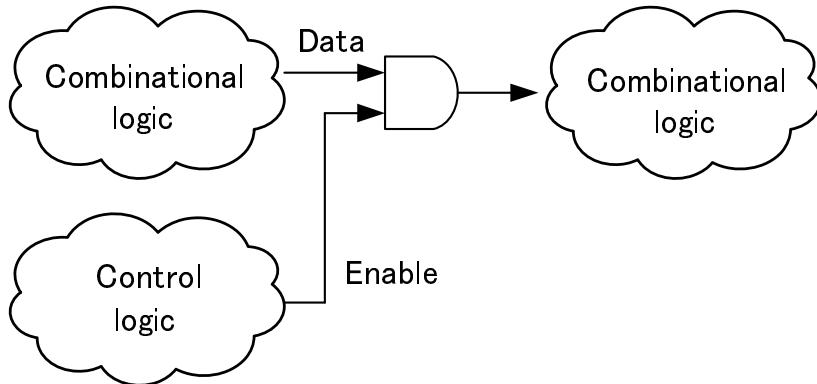

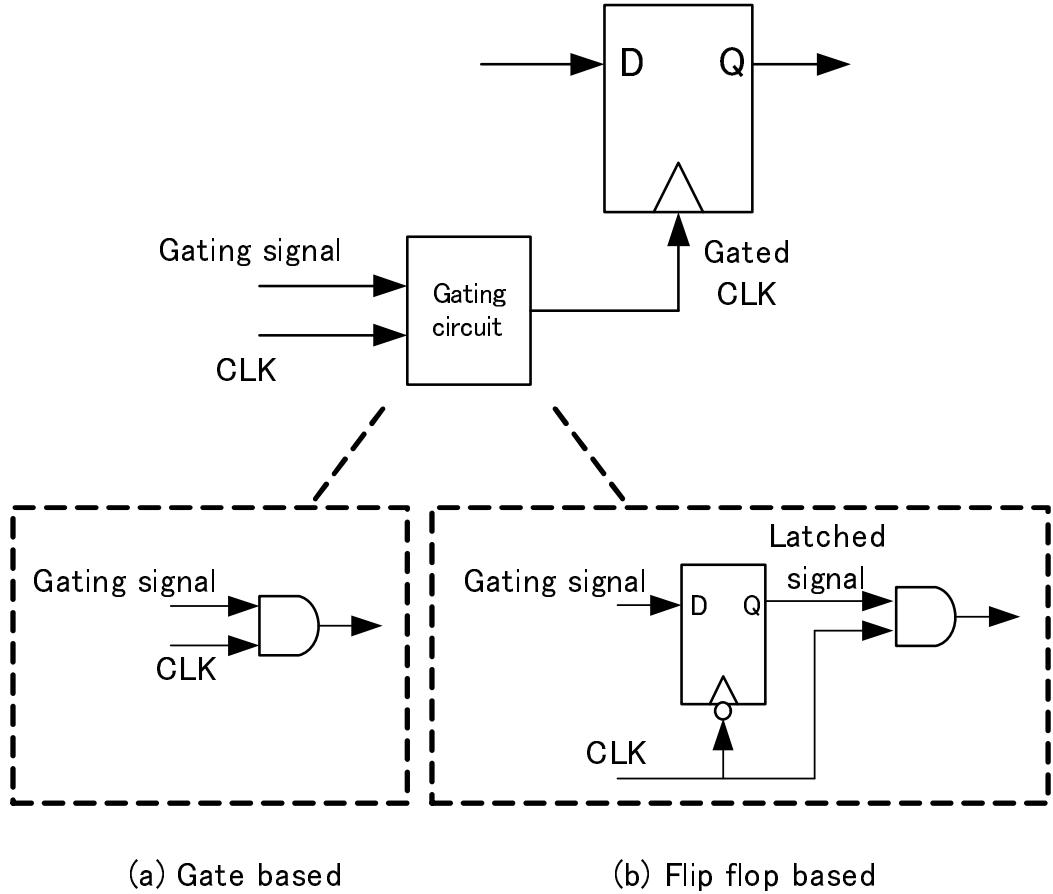

There are mainly two low power techniques for digital circuit design: clock gating and operand isolation. Figure 2.1 and 2.2 show clock gating circuit and operand isolation circuits.

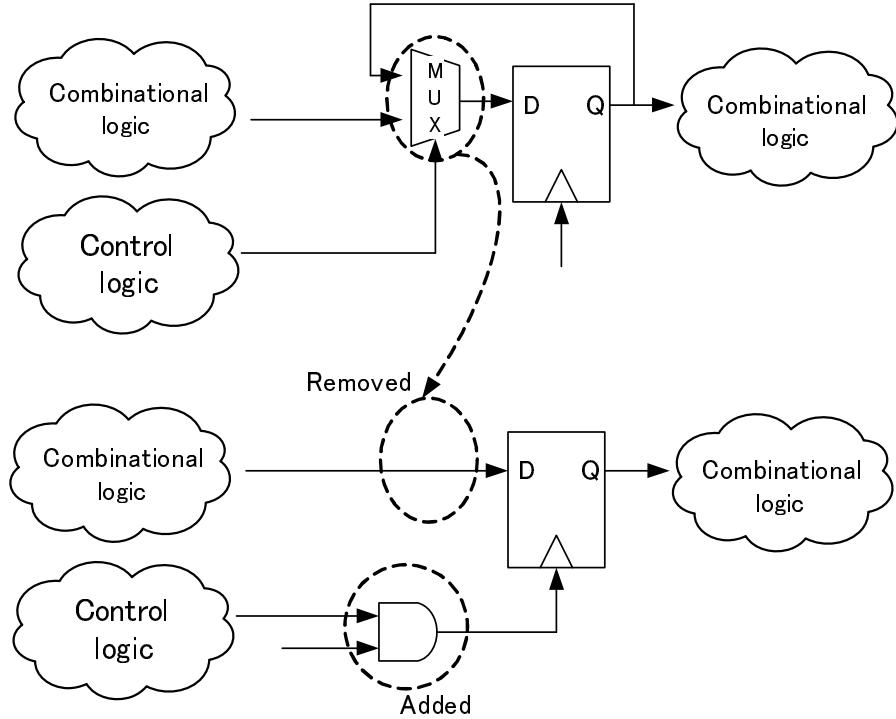

Clock gating shuts off redundant clock supplies to flip flops when the output of the flip flops are not necessary in the following calculation stages. Additionally, clock gating can reduce power consumption in clock trees if the clock gate can be placed on higher level of the tree. Although clock gating is the effective low power technique, clock gating has a disadvantage in layout design; the placed gates make clock tree synthesis difficult because clock skew increases.

On the other hand, operand isolation stops unnecessary signal switchings to combinational logics. Operand isolation can reduce power consumption if the target combinational logic consumes large energy. However, Operand isolation involves many circuit overheads. The inserted gates increases size, power consumption, and critical path delay. To use operand isolation, designers have to care the overheads and determine isolation targets to gain net power reduction.

Figure 2.1: Clock gating.

Figure 2.2: Operand Isolation.

## 2.2 ASIP Generation Methods

In this section, the overview of ASIP generation method is described, and the issue for applying clock gating to the ASIPs generated by those method is discussed.

### 2.2.1 ASIP Generation Methods

In order to automatically generate ASIPs, scalar ASIP and VLIW ASIP generation methods are proposed [7] [18]. Those methods generate ASIPs with an ADL called Micro Operation Description (MOD). The MOD describes architecture parameters, port information, using resources, the data flows of instructions. By using MODs, ASIP generation methods automatically construct a data path and a controller. In the generation methods, pipeline registers are

automatically inserted, and control logic for the pipeline registers are created as follow:

$$en_p = \overline{stall_{stage_p}}, \quad (2.1)$$

where  $p$  is a pipeline register and  $stage_p$  represents the pipeline stage number to which  $p$  belongs.  $stall_n$  stands for a condition of a pipeline interlock caused by several situations, e.g., structural hazard or multi-cycle operation. When  $en_p$  is true, data are stored and calculation advances to the next pipeline stage, and when  $en_p$  is false, pipeline stage  $stage_p$  is stalled. Since the aim of conventional VLIW ASIP generation is to design high-speed and small-area ASIPs; the form of signal (2.1) is simplified as much as possible.

### 2.2.2 Minimum Execution Conditions

To apply clock gating to pipeline registers in an ASIP, using control signal (2.1) is a trivial method. By using control signal (2.1) for clock gating, clocks are supplied to all pipeline registers when the pipeline is not stalled. However, applying control signal (2.1) has less effect on power reduction because the pipeline rarely stalls in well-optimized VLIW programs. To reduce power consumption in such cases, it is necessary to consider the fact that a large portion of the data path is idle during instruction execution even if the pipeline is not stalled. Clocks must be supplied to only necessary pipeline registers for power reduction.

In order to supply clocks to the only necessary pipeline registers, *minimum execution conditions* are introduced in this thesis. The minimum execution conditions of a resource are conditions for clock supply and represented by a set of the instructions which use the resource for their execution, i.e., the resource is used only when the instructions in the condition are executed. By using the minimum execution conditions for the control signals of clock gating, clock supplies are limited to only necessary pipeline registers; therefore, power consumption is reduced.

Manual extraction of the minimum execution conditions is not practical because it requires a long-term design period and is error-prone. An automated extraction method of the minimum execution conditions is strongly required. To automatically obtain gating signals, two major approaches are known: forward [19] [20] and backward [21]. The forward approach extracts the gating signals through high-level synthesis processes using high-level architecture infor-

mation. On the other hand, the backward approach extracts the signals by analyzing low-level designs. A merit of the backward approach is that it can be widely applied to arbitrary circuits. However, they need long calculation time and involve large area overhead due to the analysis of their complex design. Therefore, the forward approach is suitable for VLIW ASIP generation. Obviously, a forward approach must be designed for each high-level synthesis method. With respect to the VLIW ASIP generation method, an automated extraction method of minimum execution conditions is not known yet.

## 2.3 Automatic Clock Gating Methods

Several automatic clock gating insertion methods and tools are currently available.

Power Compiler [22], which is the most widely known commercial tool, automatically inserts gates into the clock lines of registers. However, it does not extract the gating signals of the registers; that is, the efficiency of clock gating by Power Compiler rests on the shoulders of designers. Power Compiler forces designers to manually derive the gating signals from complex RTL designs for additional power reduction. Manual extraction of the signals is very time consuming, because VLIW ASIP contains several hundred pipeline registers; it is not suitable for design space exploration. Automated extraction of the gating signals is strongly required.

A clock gating method based on finite state machines [19] [23] extracts the gating signals of registers by analyzing the finite state machines. To use this method, the circuit must obviously contain the finite state machines and be feedback-free pipelines. Since the finite state machines are not suitable for pipeline processors, it cannot be applied to VLIW ASIP generation.

A clock gating method based on the Observability Don't Care (ODC) [21] can derive the gating signals of registers by ODC calculation. At present, this approach appears to be the most powerful clock gating method because of its high scalability and applicability. Unfortunately, ODC calculation takes too long time to completely apply such large-scale circuitry as VLIW ASIPs. To complete the calculation in practical time, a calculation time limit is introduced in the method. In addition, ODC-based clock gating extraction causes an enormous area overhead due to duplicating the circuits to create gating signals. A more suitable extraction method is still required to calculate the minimum execution conditions for VLIW ASIPs.

## 2.4 Urodynamic Monitoring Systems

The pressure monitoring systems for AUM must be small for less-invasive measurement, and the system must not make patients feel pain, or even discomfort.

To conduct pressure measurement in AUM, several pressure sensing systems using transurethral catheters have been proposed [24–27]. Although these systems can be used in home, the results are still supposed to contain artifacts because the catheters adversely affect the test results [28] and limit patient's mobility. To improve plausibility of the recorded data, catheters should be removed for less-invasive pressure measurement in AUM.

Several pressure sensing systems which do not use catheters have been proposed [29–31].

The system in [29, 30] implants a capsule in the bladder and transmits data. Although the system requires incision, it could be used in the less invasive tests because the capsule is sufficiently small to be inserted in the bladder through the urethra. However, the system cannot simultaneously measure multiple pressure in the body because the system does not support multiple wireless communication. To correctly perform AUM, pressure data at multiple locations must be measured at the same time. Therefore, these systems are not enough to use pressure sensing for AUM.

The balloon-type remote bladder pressure sensor reported in [31] can measure and transmit the bladder pressure every five minutes. However, the balloon is difficult to employ in AUM because of its size, power consumption, time resolution, and wireless functionality:

- Since diameter of the balloon is 25 mm, invasive incision is supposed to be necessary to implant the balloon.

- Collecting data every five minutes is too coarse to capture the rapid transition of pressure.

- Unidirectional wireless communication is inconvenience for the quality control, communication control for the multiple capsules, and research and development of the capsules.

Especially, the size of the balloon becomes an big obstacle for the less-invasive system. The large size of the balloon is due to multiple chips on a PCB. The multiple chips needs large implementation area as well as many batteries for high power consumption. Accordingly, the most important technical issue to downsize the capsule is to integrate almost system in one

chip. A small-area and low-power SoC is strongly required to design such miniature capsules for AUM.

# Chapter 3

## Low Power VLIW ASIP Generation Method

This chapter describes a VLIW ASIP generation method to generate low-power VLIW ASIPs by automatically extracting minimum execution conditions for clock gating. The proposed method extracts the conditions of pipeline registers based on the forward approach using MOD [7], which specifies the high-level architecture of a VLIW ASIP. By employing the MODs, the proposed method can extract the minimum execution conditions of the pipeline registers through the VLIW ASIP generation processes, analyzing neither RTL descriptions nor netlists.

### 3.1 Basic of VLIW ASIP Generation

A VLIW ASIP is generated based on MODs and a VLIW ASIP model [18] [8]. In this section, MODs, the VLIW ASIP model, and the VLIW ASIP generation flow are described.

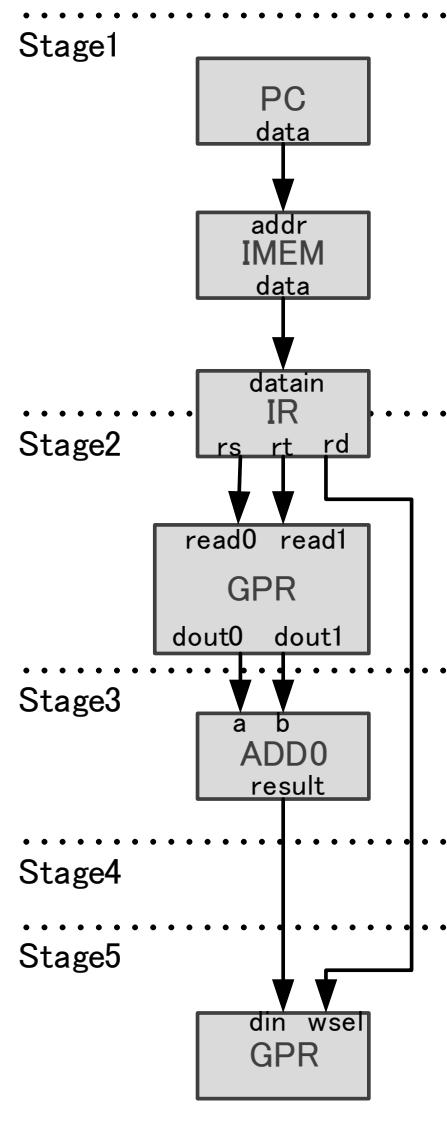

#### 3.1.1 Micro-Operation Description

The architecture of a VLIW ASIP is specified with MODs. An MOD is identified as a pair of an operation  $ope$  and a resource group  $rg$ :  $m = (ope, rg)$ . A set of all MODs specified by designers are represented by  $M$ . The MOD specifies the architecture of operation  $ope$  that is executed on resource group  $rg$ . An operation is a minimum executable unit such as an

```

wire [31:0] reg1;

wire [31:0] reg2;

wire [31:0] sum;

stage 1: {

wire [31:0] cur_pc;

wire [31:0] inst_word;

cur_pc  = PC.read();

inst_word = IMEM.read(cur_pc);

IR.write(inst_word);

};

stage 2: {

reg1 = GPR.read0(rs);

reg2 = GPR.read1(rt);

};

stage 3: {

sum = ADD0.add(reg1, reg2);

};

stage 4: {

};

stage 5: {

GPR.write(rd, sum);

};

```

Figure 3.1: MOD of ADD on RG1 (ADD, RG1).

arithmetic operation, and a resource group is a set of hardware resources necessary for the operation. The architecture specified by an MOD can be converted to a Resource Connection Graph (RCG), which represents the data path of the corresponding operation in the form of the connections of resource ports.

Figure 3.1 is the example of an arithmetic addition described as the MOD of operation ADD on resource group  $RG1 = \{PC, IMEM, IR, GPR, ADD0\}$ , where PC, IMEM, IR, GPR, and ADD0 are hardware resources. In Fig.3.1, the left side description is the MOD of ADD on RG1, and the right side diagram is the corresponding RCG. In Fig.3.1, the two pieces of data,  $reg1$  and  $reg2$ , from register file GPR at stage 2 are sent to adder ADD0 at stage 3, and then the output is stored in the GPR at stage 5. Signals  $rs$ ,  $rt$ , and  $rd$  stand for register indexes from instruction register IR. IMEM is a memory accessing unit that fetches VLIW instructions indicated by the address data from the program counter PC. In this way, the MOD contains not only connection information, but also such high-level architecture information as resource function and purpose.

### 3.1.2 VLIW ASIP Dispatching Model

Describing the dispatching behavior is the main concern of the VLIW ASIP specification. To handle this issue, the dispatching pattern of the VLIW ASIP is modeled as following three concepts: a slot, an operation group, and a resource group. Designers can specify the dispatching rule of the VLIW ASIP by slots, operation groups, resource groups, and their relations.

Slots are parallel dispatching units of the VLIW ASIP. One operation can be dispatched from a slot in one clock cycle.

Let  $slot\_num$  be the number of slots,  $O$  be a set of all operations, and  $ope_n \in O$  be an operation dispatched from  $n$ -th slot, a VLIW instruction  $inst$  is composed of multiple operations:

$$inst = (ope_1, ope_2, ope_3, \dots, ope_{slot\_num}). \quad (3.1)$$

Note that single-scalar ASIP corresponds to a one slot VLIW ASIP; our method can also deal with both single-scalar and VLIW ASIPs.

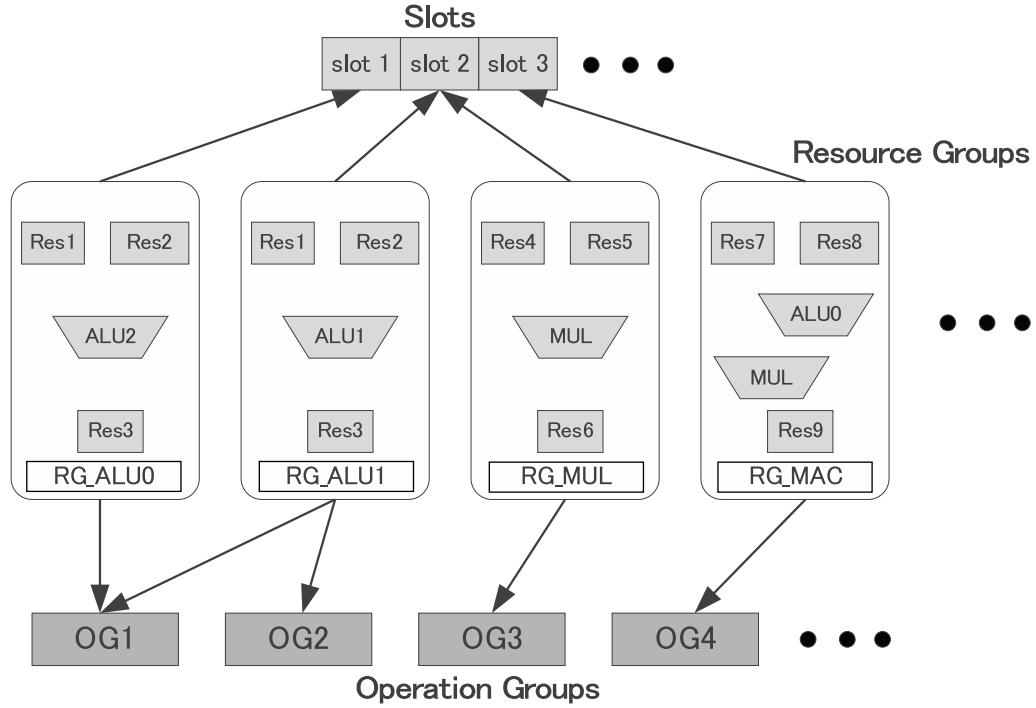

Figure 3.2: VLIW ASIP model.

Let  $RG$  be a set of all resource groups and  $R$  is a set of all resources, resource group  $rg \in RG$  is a set of hardware resources:  $rg \subseteq R$ .

The relation between slots and resource groups:  $RSR$  is

$$RSR = \{(s, rg) \mid 1 \leq s \leq slot\_num, rg \in RG\}. \quad (3.2)$$

Pair  $(s, rg)$  represents that the operations dispatched from  $s$ -th slot are executed on  $rg$ .

Let  $OG$  be a set of all operation groups, an operation group  $og \in OG$  is a set of operations:  $og \subseteq O$ .

The relation between a resource group and an operation group:  $RRO$  is

$$RRO = \{(rg, og) \mid rg \in RG, og \in OG\}. \quad (3.3)$$

Pair  $(rg, og) \in RRO$  indicates that the operations categorized in  $og$  can be performed on  $rg$ .

As specification, the number of slot  $slot\_num$ , operations  $O$ , resources  $R$ , resource groups

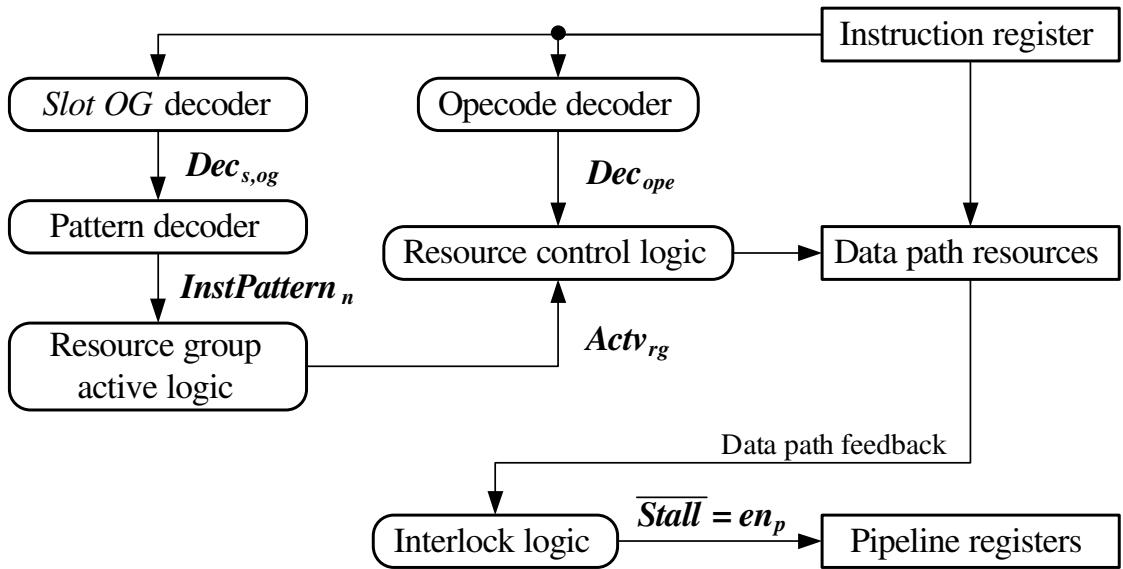

Figure 3.3: Decoder model of VLIW ASIPs.

$RG$ , operation groups  $OG$ , the relation between slots and resource groups  $RSR$ , and the relation between a resource group and an operation group  $RRO$  are given by designers.

Figure 3.2 illustrates a model of a VLIW ASIP. In Fig.3.2, the operations categorized in operation group OG1, which can be performed on resource groups RG\_ALU0 and RG\_ALU1, can be simultaneously issued from slots 1 and 2.

### 3.1.3 VLIW ASIP Controller Model

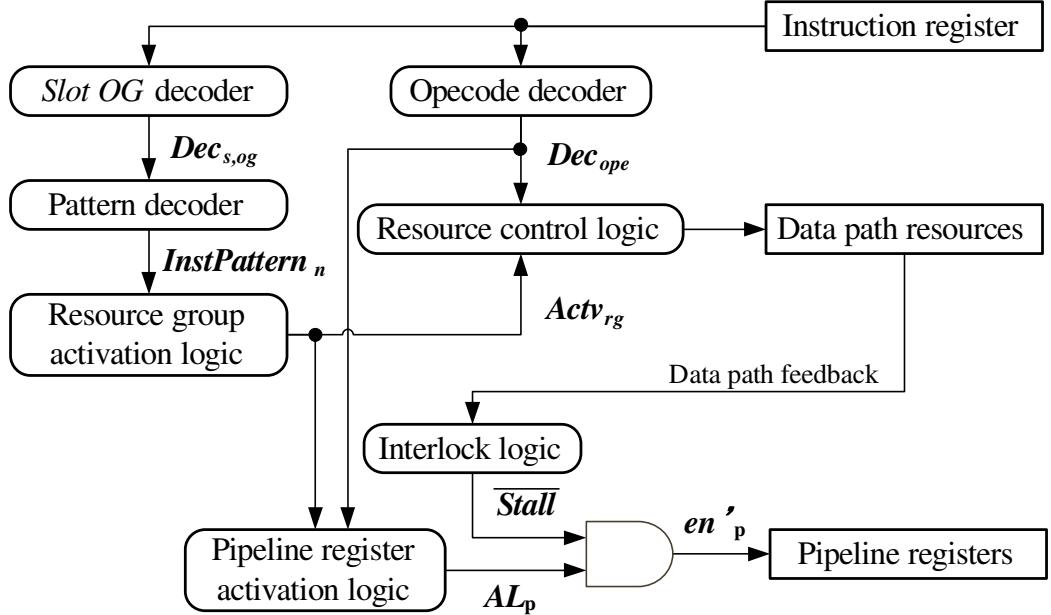

The decoder model of VLIW ASIPs is shown in Fig.3.3. To calculate the control logic for data path resources,  $Dec_{ope}$  and  $Actv_{rg}$  are needed.

$Dec_{ope}$  of operation  $ope$  is decode logic on opcode.  $Dec_{ope}$  is calculated as

$$Dec_{ope}(inst) = \begin{cases} \text{true} & \text{if } \exists ope_n \in inst, \text{ code}_{ope} = \text{code}_{ope_n} \\ \text{false} & \text{otherwise,} \end{cases} \quad (3.4)$$

where  $\text{code}_{ope}$  is the function that returns the opecode of  $ope$  and VLIW instruction  $inst$  is stored in the instruction register.

To dispatch operations to appropriate resource groups, the controller calculates  $Dec_{s,og}$ ,  $InstPattern_n$ , and  $Actv_{rg}$ .  $Dec_{s,og}$  is the decode logic indicating that the operation dispatched from  $s$ -th slot belongs to  $og \in OG$ :

$$Dec_{s,og}(inst) = \bigvee_{\substack{(s, rg) \in RSR \\ ope \in og}} Dec_{ope}(inst) \wedge Exist(rg, ope), \quad (3.5)$$

$$Exist(rg, ope) = \begin{cases} true & \text{if } \exists (rg, og) \in RRO, ope \in og \\ false & \text{otherwise.} \end{cases} \quad (3.6)$$

In order to activate the appropriate resource groups for the dispatched instruction, pattern detecting logic  $InstPattern_n(inst)$  is calculated:

$$InstPattern_n(inst) = \bigwedge_{\substack{T_{IDP_n} \in T_{IDP} \\ (s, rg, og) \in T_{IDP_n}}} Dec_{s,og}(inst), \quad (3.7)$$

where  $T_{IDP}$  is the table of instruction dispatching patterns calculated by the algorithm proposed by Kobayashi, et al. [8] [18], and  $T_{IDP_n}$  is the  $n$ -th entry in  $T_{IDP}$ . Dispatching pattern  $T_{IDP_n}$  can be described as a set of  $(s, rg, og)$  which indicates that the operations in  $og$  can be dispatched from  $s$ -th slot and executed on  $rg$ .

An example of  $T_{IDP}$  is shown in Table 3.1.  $InstPattern_n(inst)$  indicates that the pattern of dispatched instruction  $inst$ . For instance, following Table 3.1, when  $InstPattern_2(inst)$  is true, the pattern of  $inst$  is  $(OG2, OG2, OG2, OG2)$  and the corresponding resource groups which execute  $inst$  are  $(RG5, RG2, RG3, RG6)$ .

$Actv_{rg}$  is an activation logic of resource group  $rg$ :

$$Actv_{rg}(inst) = \bigvee_{\substack{T_{IDP_n} \in T_{IDP} \\ (s, rg, og) \in T_{IDP_n}}} InstPattern_n(inst). \quad (3.8)$$

Table 3.1: Example of  $T_{IDP}$

| n | 1st slot | 2nd slot | 3rd slot | 4th slot |

|---|----------|----------|----------|----------|

| 1 | OG1      | OG2      | OG3      | OG4      |

|   | RG1      | RG2      | RG3      | RG4      |

| 2 | OG2      | OG2      | OG2      | OG2      |

|   | RG5      | RG2      | RG3      | RG6      |

| 3 | OG1      | OG1      | OG3      | OG4      |

|   | RG1      | RG7      | RG8      | RG4      |

According to the pattern of VLIW instructions, the assignments of operations to appropriate resource group are controlled by  $Actv_{rg}$ .

Resource control logic is calculated by using  $Dec_{ope}$  and  $Actv_{rg}$ . On the other hand, the control logic for pipeline registers is calculated only with feed back signals from data path. However, such control incurs unnecessary activation of pipeline registers. As a result, the pipeline registers dissipate unnecessary power.

### 3.1.4 VLIW ASIP Generation Flow

VLIW ASIP generation consists of two parts. The first part is data path construction that consists of four procedures: RCG conversion, RCG merging, signal conflict resolution, and pipelining. First, RCGs are converted from MODs. Second, all RCGs are combined by RCG merging to construct a prototype of the data path. Third, multiplexers are inserted, and finally, pipeline registers are inserted into appropriate locations. At each procedure, the generation method retrieves execution conditions that are used to generate steering signals and resource control signals in the second part. The second part is controller construction. The control signals for the resources in the VLIW ASIP are generated using the execution conditions obtained in the previous data path construction part.

## 3.2 Low-power VLIW ASIP Generation

In this section, the low-power VLIW ASIP generation method is proposed. First, the insertion of gating circuits is discussed, then, the extraction of minimum execution conditions is proposed.

### 3.2.1 Insertion of Gating Circuits

Due to the power overhead of the gating circuit, inserting one gating circuit before a few flip flops is ineffective; to increase the clock gating impact, one gating circuit must be shared by as many flip flops as possible. Such shared gating circuits reduce not only the power overhead of the gating circuits but also the power consumption of the clock trees at the same time. In clock tree synthesis, the shared gating circuit can be placed on the upper level of the clock tree. The proposed method also follows this basic insertion strategy.

Additionally, as mentioned in [10] and [32], selecting gating circuit schemes is crucial to increase circuit stability and to decrease implementation overhead. As shown in Fig. 3.4, the gate based (a) and flip flop based (b) schemes are mainly used. Gate based scheme is low overhead, but cannot stop glitches from gating signals, and the flip flop based scheme has overhead of gating signal latch, but can stop glitches. Despite its area and power overhead, the proposed method adopts the flip flop based gating scheme because it can block glitch noises that cause incorrect register activation.

### 3.2.2 Extraction of Minimum Execution Conditions

In this section, a formal extraction method of minimum execution conditions of the pipeline registers is proposed in the following four data path construction procedures.

#### 3.2.2.1 RCG conversion

Resource Connection Graphs (RCGs) are generated from MODs. An RCG is represented by directed graph  $G_m = (R_m, E_m)$  where  $m = (ope, rg)$  is an identifier of an MOD,  $R_m$  is a

Figure 3.4: Clock gating schemes.

resources used by  $m$ ,  $E_m = \{(o, i) | o, i \in P\}$  is a set of data transfers used by  $m$ , pair  $(o, i)$  represents a data transfer from output port  $o$  to input port  $i$ , and  $P$  is a set of all resource ports.

A set of execution conditions  $Cond_e$  for each data transfer  $e \in E_m$  is retrieved in the RCG extraction.  $Cond_e$  is described as

$$Cond_{e \in E_m} = \{(ope, rg) | m = (ope, rg)\}. \quad (3.9)$$

$Cond_e$  denotes that data transfer  $e$  is executed when operation  $ope$  on resource group  $rg$  is dispatched.

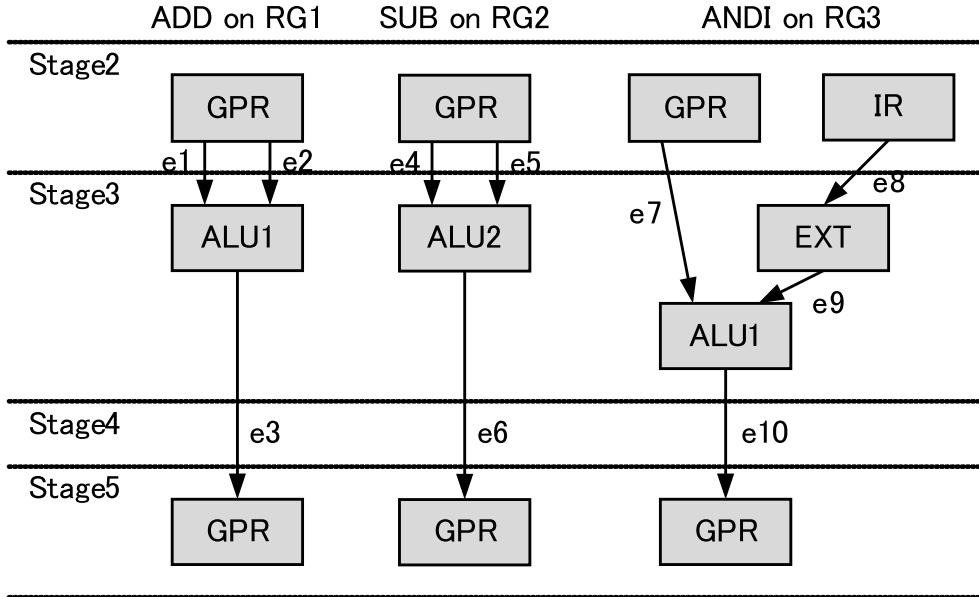

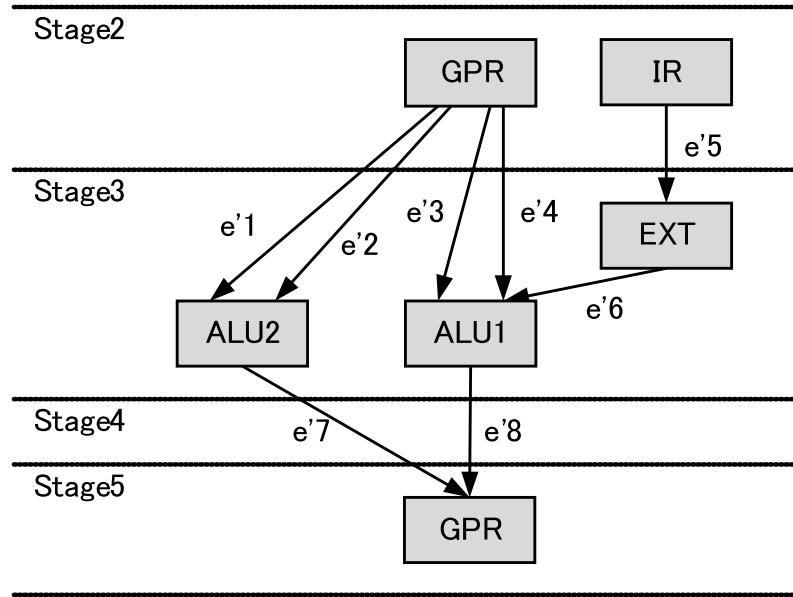

Figure 3.5 shows an example of extracted RCGs. For clarity, the ports of the RCGs and Stage1 are omitted. In the example, the three RCGs correspond to *ADD* on  $RG_1$ , *SUB* on  $RG_2$ , and *ANDI* on  $RG_3$ , respectively. *GPR*, *IR*, *EXT*, *ALU1*, and *ALU2* are the resources,

Figure 3.5: Converted RCGs.

and the edges labeled  $e_1$  to  $e_{10}$  are the data transfers. Here, sets of the conditions for the data transfers in Fig.3.5 are retrieved in the form of Eq.(3.9) as follows:

$$\begin{aligned}

Cond_{e_1} &= \{(ADD, RG_1)\}, & Cond_{e_2} &= \{(ADD, RG_1)\}, \\

Cond_{e_3} &= \{(ADD, RG_1)\}, & Cond_{e_4} &= \{(SUB, RG_2)\}, \\

Cond_{e_5} &= \{(SUB, RG_2)\}, & Cond_{e_6} &= \{(SUB, RG_2)\}, \\

Cond_{e_7} &= \{(ANDI, RG_3)\}, & Cond_{e_8} &= \{(ANDI, RG_3)\}, \\

Cond_{e_9} &= \{(ANDI, RG_3)\}, & Cond_{e_{10}} &= \{(ANDI, RG_3)\}.

\end{aligned}$$

Figure 3.6: Unified RCG.

### 3.2.2.2 RCG Merging

After all MODs are converted, they are merged into a unified RCG  $G' = (R', E')$ .  $R'$  and  $E'$  are calculated as follows:

$$R' = \bigcup_{\forall m \in M} R_m$$

$$E' = \bigcup_{\forall m \in M} E_m,$$

where  $M$  is a set of all identifiers of MODs consisting of the VLIW ASIP. Since data transfers  $E_m$  are merged into  $E'$ , conditions  $Cond_e$  of all extracted RCGs are also merged. The new conditions of data transfers  $Cond'_e$  are calculated as

$$Cond'_{e' \in E'} = \bigcup_{\forall m \in M, \forall e \in E_m, e' = e} Cond_e. \quad (3.10)$$

The three operations in the example in Fig.3.5 are merged into the unified RCG illustrated as Fig.3.6. The conditions of data transfers  $e'1$  to  $e'8$  are newly calculated as follows:

$$\begin{aligned}

Cond'_{e'1} &= \{(SUB, RG_2)\}, & Cond'_{e'2} &= \{(SUB, RG_2)\}, \\

Cond'_{e'3} &= \{(ADD, RG_1), (ANDI, RG_3)\}, & Cond'_{e'4} &= \{(ADD, RG_1)\}, \\

Cond'_{e'5} &= \{(ANDI, RG_3)\}, & Cond'_{e'6} &= \{(ANDI, RG_3)\}, \\

Cond'_{e'7} &= \{(SUB, RG_2)\}, \\

Cond'_{e'8} &= \{(ADD, RG_1), (ANDI, RG_3)\}.

\end{aligned}$$

The unified RCG is the prototype of the data path. Then multiplexers and pipeline registers are inserted in the following procedures.

### 3.2.2.3 Signal Conflict Resolution

Multiplexers are inserted in order to resolve signal conflicts occurring in unified RCG  $G'$  such as  $e'7$  and  $e'8$  in Fig.3.6. The RCG in which the multiplexers are inserted is described as  $G'' = (R'', E'')$ .

A multiplexer is inserted before an input port, which is the multiple destination of some data transfers. Here, a set of edges conflicting at identical input port  $i$ :  $ECI_i$  is described as

$$ECI_i = \{(o', i') \mid o' \in P, i' \in P, (o', i') \in E', i' = i\}. \quad (3.11)$$

Since the multiplexers are inserted, the signal connections change. The conditions of data transfers  $E''$  should be calculated, too. A set of the conditions of data transfer  $e'' \in E''$  is described as follows:

$$Cond''_{e''} = \begin{cases} \bigcup_{\forall e' \in ECI_{dest_{e''}}} Cond'_{e' \in E'} & \text{if } e'' \in E_{MR}, \\ Cond'_{e' \in E'} \\ \text{such that } dest_{e'} = dest_{e''} & \text{if } e'' \in E_{RM}, \\ Cond'_{e' \in E'} \text{ such that } e' = e'' & \text{otherwise,} \end{cases} \quad (3.12)$$

where  $dest_e$  is a destination port of data transfer  $e$ ,  $E_{MR}$  is a set of data transfers that connect a multiplexer to a resource, and  $E_{RM}$  is a set of data transfers selected by a multiplexer.

Figure 3.7: Constructed data path.

### 3.2.2.4 Pipelining

For pipelining  $G''$ , pipeline registers are required for data transfers that cross pipeline stage boundaries. The RCG in which the pipeline registers are inserted is described as  $G'''$ . The location of a pipeline register  $p = (o, n)$  can be described as a pair of output port  $o$  and stage number  $n$  where the pipeline register is placed because one pipeline register is shared by several data transfers from  $o$ . A set of edges connected to identical output port  $o$ :  $ECO_o$  is

$$ECO_o = \{(o'', i'') \mid o'', i'' \in P, (o'', i'') \in E'', o'' = o\}. \quad (3.13)$$

In  $ECO_o$ , a set of data transfers crossing stage boundaries  $ECOX_o$  is

$$ECOX_o = \{(o', i') \mid \text{stage}_{o'} < \text{stage}_{i'}, \text{for all } (o', i') \in ECO_o\}, \quad (3.14)$$

where  $stage_x$  represents the pipeline stage number to which port  $x$  belongs.

In  $G''$ , a set of data transfers crossing stage boundaries is

$$E''_{CROSS} = \bigcup_{o \in P_{out}} ECOX_o. \quad (3.15)$$

Finally, a set of pipeline registers  $PREG$  is obtained as

$$PREG = \bigcup_{(o,i) \in E''_{CROSS}} \{p \mid p = (o, n), stage_o \leq n < stage_i\}. \quad (3.16)$$

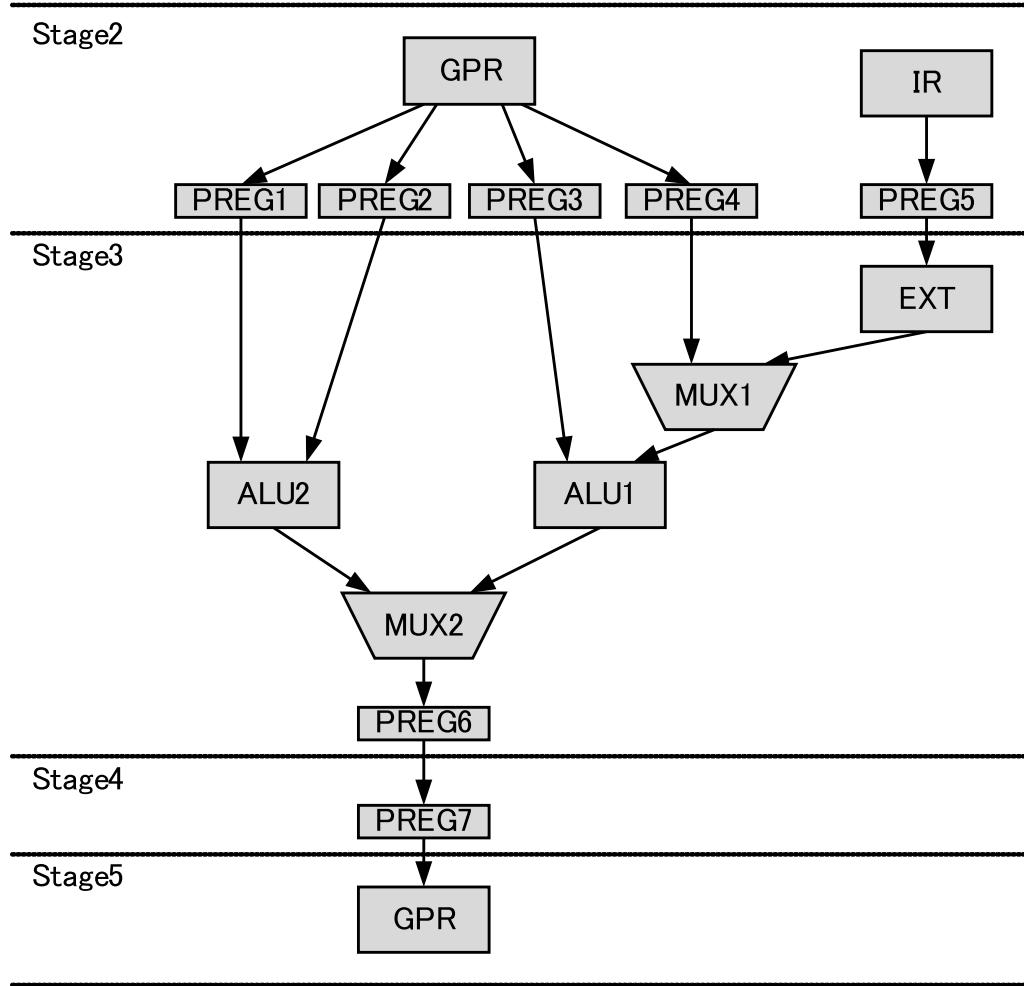

Figure 3.7 depicts the data path after inserting multiplexers MUX and pipeline registers PREG in the unified RCG in Fig.3.6. Pipeline registers  $PREG1$  to  $PREG7$  are inserted in the appropriate points.

Here, the execution conditions of the inserted pipeline registers are calculated. The execution conditions for the pipeline registers are derived from the conditions of the data transfers calculated by Eq.(3.12). Since the pipeline registers are shared by some data transfers, a set of execution conditions  $EC_p$  of pipeline register  $p = (o, n)$  is calculated as

$$EC_p = \bigcup_{p=(o,n), (o,i) \in ECOX_o} Cond''_{(o,i)}. \quad (3.17)$$

$EC_p$  is a set of  $m = (ope, rg)$  such that  $ope$  dispatched to  $rg$  requires  $p$  for execution. Let  $G'''_m \subseteq G'''$  be a necessary data path for executing  $m$  and  $PREG_m \in G'''_m$  be a set of the pipeline registers that is required for execution by  $ope$  dispatched to  $rg$ , extracted  $EC_p$  can be also described as:

$$EC_p = \{m \mid m \in M, p \in PREG_m\}. \quad (3.18)$$

For the pipeline registers in Fig.3.7, execution conditions  $EC_p$  are calculated as follows:

$$EC_{PREG1} = \{(SUB, RG_2)\},$$

$$EC_{PREG2} = \{(SUB, RG_2)\},$$

$$EC_{PREG3} = \{(ADD, RG_1), (ANDI, RG_3)\},$$

$$EC_{PREG4} = \{(ADD, RG_1)\},$$

$$EC_{PREG5} = \{(ANDI, RG_3)\},$$

$$EC_{PREG6} = \{(ADD, RG_1), (SUB, RG_2), (ANDI, RG_3)\},$$

$$EC_{PREG7} = \{(ADD, RG_1), (SUB, RG_2), (ANDI, RG_3)\}.$$

Figure 3.8: Modified decoder model.

Thus the execution conditions for pipeline registers are calculated. In the next section, creating gating signals for pipeline registers is discussed.

### 3.2.3 Generating Gating Signals with Minimum Execution Conditions

To suppress the unnecessary activations of pipeline register  $p$ , a new control signal  $en'_p$  with additional logic  $AL_p$  is introduced:

$$en'_p(inst) = \overline{stall_{stage_p}} \wedge AL_p(inst), \quad (3.19)$$

$$AL_p(inst) = \bigvee_{\substack{m \in EC_p \\ (ope, rg) = m}} Dec_{ope}(inst) \wedge Activ_{rg}(inst), \quad (3.20)$$

where  $EC_p$  is the derived execution condition in Eq.(3.18). The modified decoder model of VLIW ASIP with  $AL_p$  is shown in Fig.3.8.

Here, correct execution is defined as that the execution result of an operation on the VLIW ASIP generated by the proposed method is same as that by the traditional method.

**Theorem 1.** *VLIW ASIPs clock-gated with  $en'_p$  guarantee correct execution.*

*Proof.* The new logic  $en'_p$  does not prevent the data flow in  $G'''_m$  because every pipeline register  $p \in \text{PREG}_m$  is activated when  $m$  is dispatched. Therefore, the execution result of the VLIW ASIP by the proposed method is same as that by the traditional method, i.e., correct execution is guaranteed.  $\square$

**Theorem 2.** *Let a minimum execution condition be an execution condition such that removing one element from the execution condition causes incorrect execution of the generated VLIW ASIP, execution condition Eq.(3.18) is minimum.*

*Proof.* Consider that any  $m \in EC_p$  is removed,  $p$  is not activated when  $m$  is dispatched. However, this removing causes incorrect execution because  $p \in \text{PREG}_m$ . Hence,  $EC_p$  in Eq.(3.18) is the minimum execution condition.  $\square$

Using execution condition  $EC'_p \supseteq EC_p$  for Eq.(3.20) can correctly execute operations. Therefore, the traditional VLIW ASIP generation method constantly deals with  $EC'_p$  as  $EC'_p = M$  for all  $p$ . This generation strategy results in reducing area and delay because  $AL_p$  can be constantly treated as *true*.

Using Eq.(3.19), the gating signals of the pipeline registers in the VLIW data path illustrated in Fig.3.7 can be calculated as follows:

$$\begin{aligned}

en'_{PREG1}(inst) &= \overline{stall_2} \wedge \{Dec_{SUB}(inst) \wedge Actv_{RG_2}(inst)\}, \\

en'_{PREG2}(inst) &= \overline{stall_2} \wedge \{Dec_{SUB}(inst) \wedge Actv_{RG_2}(inst)\}, \\

en'_{PREG3}(inst) &= \overline{stall_2} \wedge \{Dec_{ADD}(inst) \wedge Actv_{RG_1}(inst) \\

&\quad \vee Dec_{ANDI}(inst) \wedge Actv_{RG_3}(inst)\}, \\

en'_{PREG4}(inst) &= \overline{stall_2} \wedge \{Dec_{ADD}(inst) \wedge Actv_{RG_1}(inst)\}, \\

en'_{PREG5}(inst) &= \overline{stall_2} \wedge \{Dec_{ANDI}(inst) \wedge Actv_{RG_3}(inst)\}, \\

en'_{PREG6}(inst) &= \overline{stall_3} \wedge \{Dec_{ADD}(inst) \wedge Actv_{RG_1}(inst) \\

&\quad \vee Dec_{SUB}(inst) \wedge Actv_{RG_2}(inst) \\

&\quad \vee Dec_{ANDI}(inst) \wedge Actv_{RG_3}(inst)\}. \\

en'_{PREG7}(inst) &= \overline{stall_4} \wedge \{Dec_{ADD}(inst) \wedge Actv_{RG_1}(inst) \\

&\quad \vee Dec_{SUB}(inst) \wedge Actv_{RG_2}(inst) \\

&\quad \vee Dec_{ANDI}(inst) \wedge Actv_{RG_3}(inst)\}.

\end{aligned}$$

### 3.2.4 Generation of Scalar ASIPs

Scalar ASIPs correspond to the special case of VLIW ASIP: single slot, single resource group, and single operation group. Therefore, the proposed method can be easily applied to generation of scalar ASIPs.

## 3.3 Experiments

Two experiments were carried out using the integer subset of DLX [33] [34] to confirm the effectiveness of the proposed method.

For each experiment, the following three types of ASIPs were generated:

**NCG:** Not clock gated VLIW ASIPs by the traditional generation method

**PC:** VLIW ASIPs clock gated by Power Compiler

**PM:** VLIW ASIPs generated by our proposed method.

Note that clock gating was only applied to the pipeline registers in the data path of the generated VLIW ASIPs. The generated ASIPs were synthesized using Design Compiler under a minimizing area constraint and physically synthesized by IC Compiler using a  $0.18\mu\text{m}$  CMOS technology library operating on 1.8 V.

Programs were randomly generated based on the appearance rate of each instruction. The appearance rates of the instructions in a compiled program are a much more dominant factor than the instruction sequence in the case of using clock gating. Therefore, the characteristics of the programs were modeled as appearance rate in this experiment. For instance, a low IPC program can be modeled as a high NOP appearance rate.

### 3.3.1 Evaluation of Hardware Variation

In the first experiment, both single-scalar and VLIW type ASIPs were generated. The single-scalar type ASIPs were extended with Multiply ACCumulate (MAC) instruction by varying the pipeline depth from two to seven stages. The VLIW type ASIPs were designed on a single-scalar ASIP of five stages and homogeneously expanded to two, four, and six slots. Note that the 2-slot processor contains 65 pipeline registers, the 4-slot processor 124, and the 6-slot processor 183; they are large-scale designs. In this experiments, the appearance ratios of the program are as follows: load/store are 30%, multiplication is 3.5%, division is 1%, branch/jump are 5%, and integer instruction is 60.5%. These rates were determined by reference to the analysis report of the compiled SPEC benchmarks for MIPS processors [35]. All cache access were assumed to hit in this experiment.

Note that applying Power Compiler to PM did not affect the circuits because Power Compiler does not insert clock gating into the already gated registers. All pipeline registers of PM are already clock gated by the proposed method.

The experimental results are shown in Table 3.2 and Table 3.3. The results show the area, delay, and power comparison of the generated ASIPs. Slot # and the pipeline depth are the number of parallel issues and the pipeline depth, respectively. Total power is the power con-

Table 3.2: Power comparison on single-scalar DLX, varying number of pipeline stages.

| Pipeline depth | Type |                         |            | Total power | Pipeline registers |           | Clock    |      |

|----------------|------|-------------------------|------------|-------------|--------------------|-----------|----------|------|

|                |      | Area [μm <sup>2</sup> ] | Delay [ns] | [μW/MHz]    | [μW/MHz]           | Delta [%] | [μW/MHz] | [ps] |

| 3              | NCG  | 445255                  | 20.09      | 169.1       | 17.4               |           | 32.8     | 46   |

|                | PC   | 440625                  | 20.09      | 147.3       | 8.5                | -51.3     | 30.7     | 88   |

|                | PM   | 441330                  | 20.43      | 146.5       | 3.1                | -78.2     | 27.8     | 137  |

| 4              | NCG  | 446785                  | 17.34      | 179.0       | 25.3               |           | 33.3     | 62   |

|                | PC   | 440632                  | 17.50      | 163.7       | 16.1               | -36.6     | 30.6     | 105  |

|                | PM   | 442388                  | 15.57      | 153.3       | 6.6                | -73.9     | 30.4     | 106  |

| 5              | NCG  | 451319                  | 17.33      | 185.8       | 31.5               |           | 34.9     | 67   |

|                | PC   | 443782                  | 15.57      | 169.1       | 22.8               | -27.6     | 32.2     | 84   |

|                | PM   | 447188                  | 15.57      | 155.3       | 8.2                | -73.9     | 29.8     | 109  |

| 6              | NCG  | 512422                  | 12.10      | 239.3       | 63.2               |           | 44.0     | 74   |

|                | PC   | 496831                  | 12.06      | 209.7       | 48.4               | -23.3     | 38.6     | 107  |

|                | PM   | 503537                  | 12.06      | 174.4       | 12.1               | -80.9     | 32.4     | 113  |

| 7              | NCG  | 526083                  | 12.10      | 250.1       | 68.0               |           | 44.9     | 68   |

|                | PC   | 510137                  | 12.06      | 218.7       | 49.2               | -27.6     | 41.4     | 96   |

|                | PM   | 517711                  | 12.06      | 183.5       | 12.4               | -81.7     | 34.6     | 104  |

Table 3.3: Power comparison on VLIW DLX, varying number of parallel issues.

| Slot # | Type | Area<br>[ $\mu\text{m}^2$ ] | Delay<br>[ns] | Total<br>power<br>[ $\mu\text{W}/\text{MHz}$ ] | Pipeline  |              | Clock                                |              |

|--------|------|-----------------------------|---------------|------------------------------------------------|-----------|--------------|--------------------------------------|--------------|

|        |      |                             |               |                                                | registers | Delta<br>[%] | tree<br>[ $\mu\text{W}/\text{MHz}$ ] | Skew<br>[ps] |

| 1      | NCG  | 451319                      | 17.33         | 185.8                                          | 31.5      |              | 34.9                                 | 67           |

|        | PC   | 443782                      | 15.57         | 169.1                                          | 22.8      | -27.6        | 32.2                                 | 84           |

|        | PM   | 447188                      | 15.57         | 155.3                                          | 8.2       | -74.0        | 29.8                                 | 109          |

| 2      | NCG  | 651106                      | 12.06         | 300.7                                          | 97.9      |              | 54.1                                 | 100          |

|        | PC   | 625762                      | 12.06         | 262.1                                          | 80.3      | -18.0        | 66.9                                 | 112          |

|        | PM   | 631341                      | 12.06         | 193.5                                          | 11.2      | -88.6        | 38.3                                 | 123          |

| 4      | NCG  | 1074753                     | 12.02         | 462.1                                          | 179.4     |              | 87.0                                 | 117          |

|        | PC   | 1029118                     | 12.07         | 395.5                                          | 152.4     | -15.1        | 81.4                                 | 140          |

|        | PM   | 1038249                     | 12.07         | 265.8                                          | 20.8      | -88.4        | 52.3                                 | 116          |

| 6      | NCG  | 1596043                     | 12.08         | 659.3                                          | 263.6     |              | 118.9                                | 78           |

|        | PC   | 1530117                     | 12.12         | 553.0                                          | 233.4     | -11.5        | 110.5                                | 114          |

|        | PM   | 1544843                     | 12.14         | 350.9                                          | 35.1      | -86.7        | 63.9                                 | 133          |

Figure 3.9: Area reduction by applying clock gating.

sumption of all circuits, and Pipeline registers stands for the power breakdown by the pipeline registers. Delta is the ratio of the power reduction compared to NCG. Clock tree is the power breakdown of the clock trees, and Skew is the global clock skew of the ASIPs.

As observed in Table 3.2, the power consumption of the pipeline registers of PM is reduced approximately 80% compared to NCG in every case, and PC is reduced approximately 35 %. In addition, the power consumption of every clock tree also decreased. The same trend is observed in Table 3.3. These results show that the proposed method shuts off more redundant clock supplies than the clock gated VLIW ASIPs by Power Compiler.

Area reduction (from NCG to the others) is confirmed because the multiplexers inside the registers are removed. As shown in Fig 3.9, multiplexers are removed and a clock gate is inserted. In general, an  $N$ -bit register needs  $N$  multiplexers, and once clock gating is applied, multiple multiplexers are replaced by one clock gate because the flip flops in a register share one clock source. Therefore, implementation area is reduced when clock gating is applied.

Table 3.4: Power consumption of pipeline registers in 4-slot VLIW ASIP according to appearance rate.

| Case | Int. | Multi | Load/ | NOP   | Ctrl. | Power          |       |       |

|------|------|-------|-------|-------|-------|----------------|-------|-------|

|      |      |       | Cycle | store |       | [ $\mu$ W/MHz] |       |       |

|      | [%]  | [%]   | [%]   | [%]   | [%]   | NCG            | PC    | PM    |

| 1    | 60.5 | 4.5   | 30    | 0     | 5     | 201.2          | 197.0 | 49.8  |

| 2    | 90   | 0     | 5     | 0     | 5     | 264.8          | 278.1 | 126.7 |

| 3    | 70   | 0     | 5     | 20    | 5     | 246.9          | 265.9 | 103.4 |

| 4    | 50   | 0     | 5     | 40    | 5     | 241.3          | 262.1 | 85.9  |

| 5    | 84   | 6     | 5     | 0     | 5     | 190.4          | 165.9 | 38.3  |

Area reduction is an innate advantage of clock gating. On the other hand, negligible area overheads occur owing to the implementation of the minimum execution conditions (from PC to PM). The area overhead reflects the increase of operators in Eq.(3.19). Compared to Eq.(2.1), Eq.(3.19) has more operators and terms to implement minimum execution conditions. Nevertheless, the overheads are small. This is because the extra terms in Eq.(3.19) also exist in the VLIW ASIPs generated by the traditional VLIW generation method; therefore they do not affect the overheads. The extra operators only result in small area overhead.

Critical delay overheads are confirmed to be negligible. Besides being an innate disadvantage of clock gating, clock skew increases in almost cases. Though the skew increases, the difference of skew between PC and PM is small. The skew results suggest that the proposed method has less extra effect on the clock skew.

For all the ASIPs, the overheads of the calculation time by the proposed method are within several seconds on a workstation operating on 3 GHz using 4 GB memory. This shows that the proposed method has little extra computational overhead compared to the traditional VLIW ASIP generation.

### 3.3.2 Evaluation of Software Variation

In the second experiment, to confirm the impact of various programs on the power consumption of the pipeline registers, the appearance rates of the integer, multi-cycle, load/store, No OPeration (NOP), and control operations were varied on the 4-slot VLIW ASIP. The multi-cycle operations include multiplication and division, which take 32 cycles to finish operation.

Table 3.4 shows the results of the five cases. The differences of power reduction are due to the differences of data path utilization in each program.

With respect to PC, the power consumption is increased from case 1 to 2 because no multi-cycle operations were issued. This is because PC cannot reduce power consumption when no multi-cycle operations are issued. In case 2, 3, and 4, the power overhead by the gating circuit is just accumulated from NCG to PC. The combination of the traditional VLIW generation method and Power Compiler worsens power consumption in such cases. By increasing multi-cycle operation in case 5, power consumption of both PC and PM are reduced because pipelines are stalled.

PM achieves substantial power reduction, as shown in Table 3.4. In cases 2, 3, and 4, power consumption decreased, although no multi-cycle operations were issued, showing that gating condition generated by the proposed method stopped unnecessary clock supplies while the pipeline was not stalled. Power consumption decreased while the NOP rate increased because NOP did not activate any data path modules.

The proposed method can reduce the power consumption of any programs because even a well optimized program contains the unused registers.

## 3.4 Conclusion

In this chapter, a low-power VLIW ASIP generation method is proposed. The proposed method automatically extracts the minimum execution conditions of the pipeline registers in the generated VLIW ASIPs and shuts off the excess clock supplies to the pipeline registers by clock gating. The experimental results showed that the power consumption of the pipeline registers in the VLIW ASIPs generated with the proposed method was reduced about 80% compared to the VLIW ASIPs that were not clock gated, and about 60% compared to the VLIW ASIPs that

were clock gated by Power Compiler with negligible delay and area overhead.

# Chapter 4

## Design of an SoC for Pressure Sensing Capsules in AUM

In this chapter, the design of pressure sensing capsules for AUM is described. The almost functions of the capsules are integrated in an SoC: Medical SOC (MeSOC). The MeSOC is designed with an ASIP: MeDical Instruction-set eXtension type I (MeDIX-I).

First, technical requirements for pressure sensing capsule are clarified, and the pressure sensing system and the capsule are described. Secondly, the design of the MeSOC is described. Then, the designs of the digital systems, including MeDIX-I, are described.

### 4.1 Requirements for Pressure Sensing Capsules

Many reports in urodynamics suggest the requirements for pressure sensing devices. The technical requirements for the instruments in AUM are summarized as follows:

- To record the detrusor pressure, the pressure data of the bladder and rectum must be measured simultaneously.

- For less invasive tests, the instruments must be sufficiently small to pass through the urethra, the outer diameter of which is about 6.5 mm.

- The capsule should continuously operate for at least 72 hours to enable the investigation of irregularly occurring symptoms [36] .

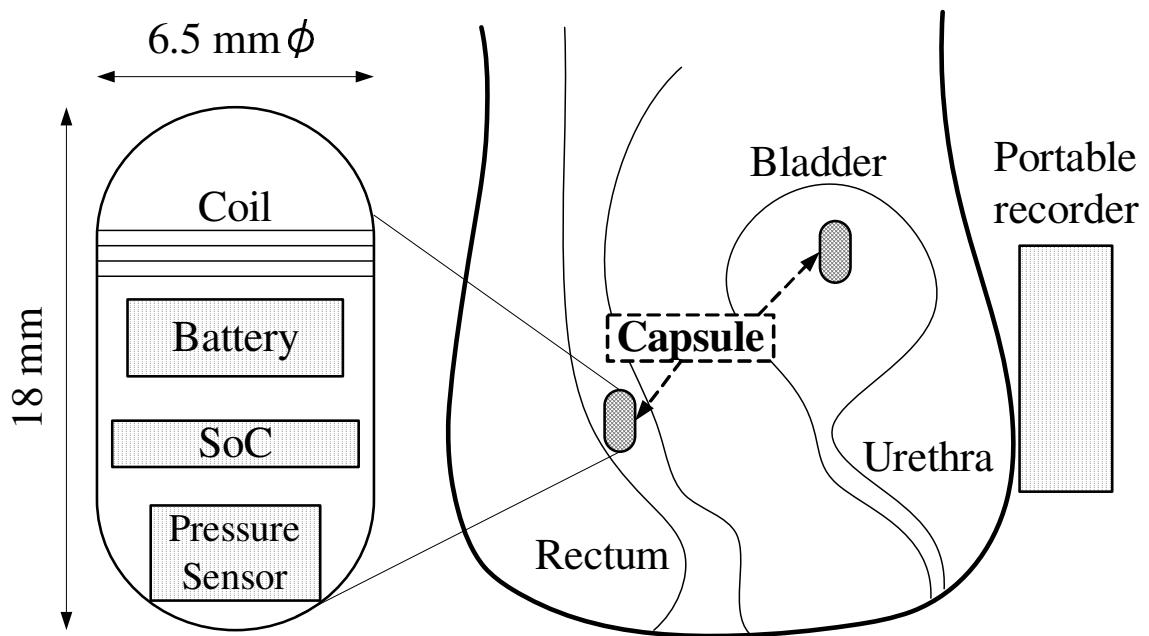

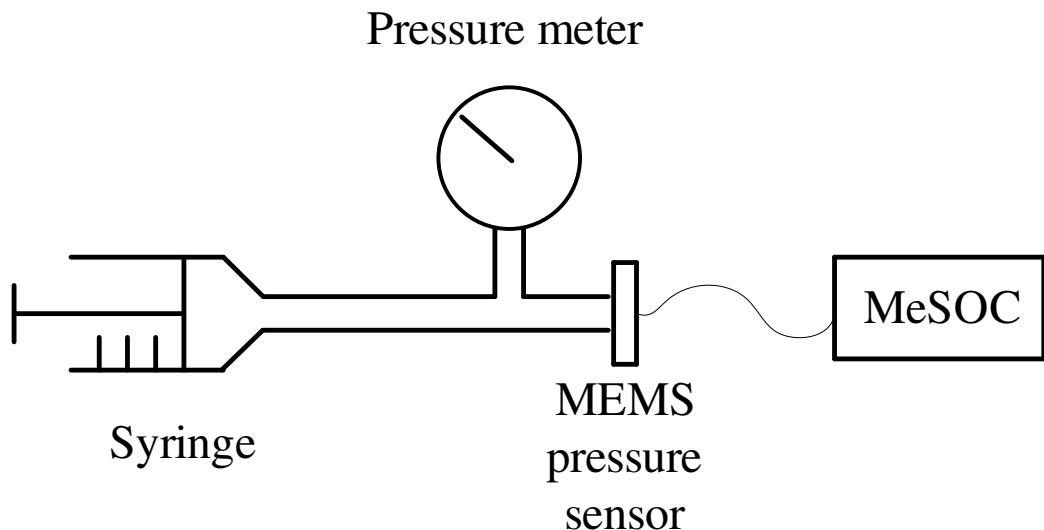

Figure 4.1: Pressure measurement system and capsules.

- To create urinary diary, the pressure data can be self-monitored or automatically recorded [37].

- According to the International Continence Society (ICS), a pressure range of 0-225 mmHg is necessary for correct measurement [38].

- For quality control, the instruments require calibration in the body before measurement starts [16].

- For the same reason, the minimum time resolution required for recording is 15 Hz to carry out cough tests [38]. Coughs should be recorded to ensure that abdominal and intravesical pressures respond equally [16].

## 4.2 System Overview

In order to satisfy the strict requirements shown in Section 4.1, the less-invasive pressure sensing system with tiny capsules is presented in this section. Figure 4.1 shows the biotelemetry

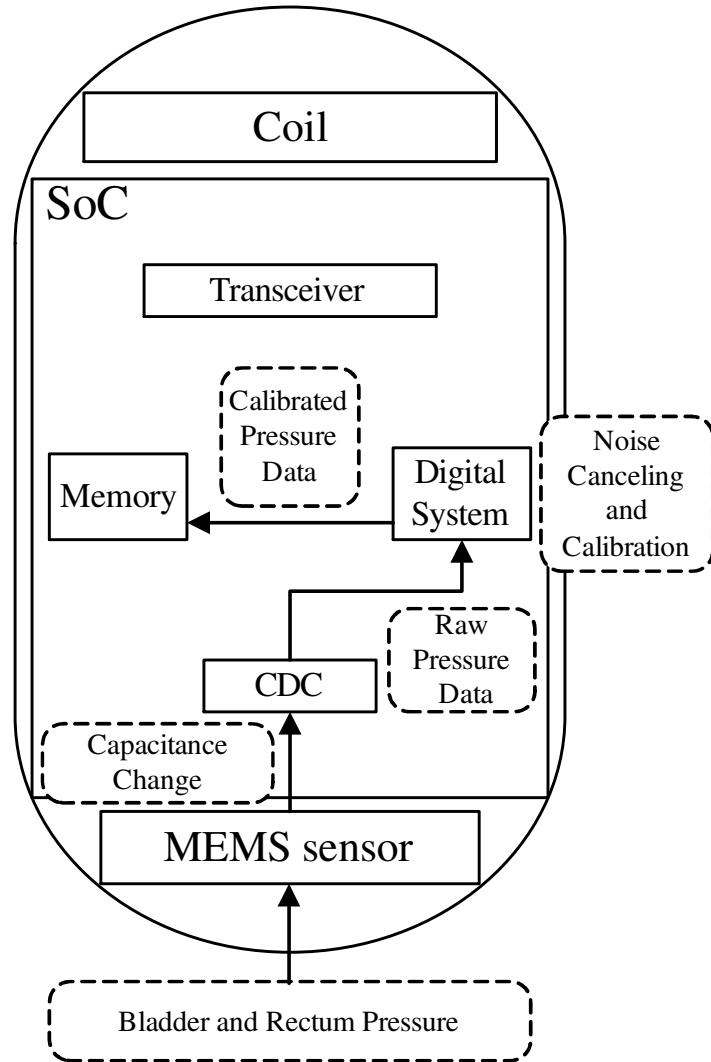

Figure 4.2: The work flow of pressure sensing.

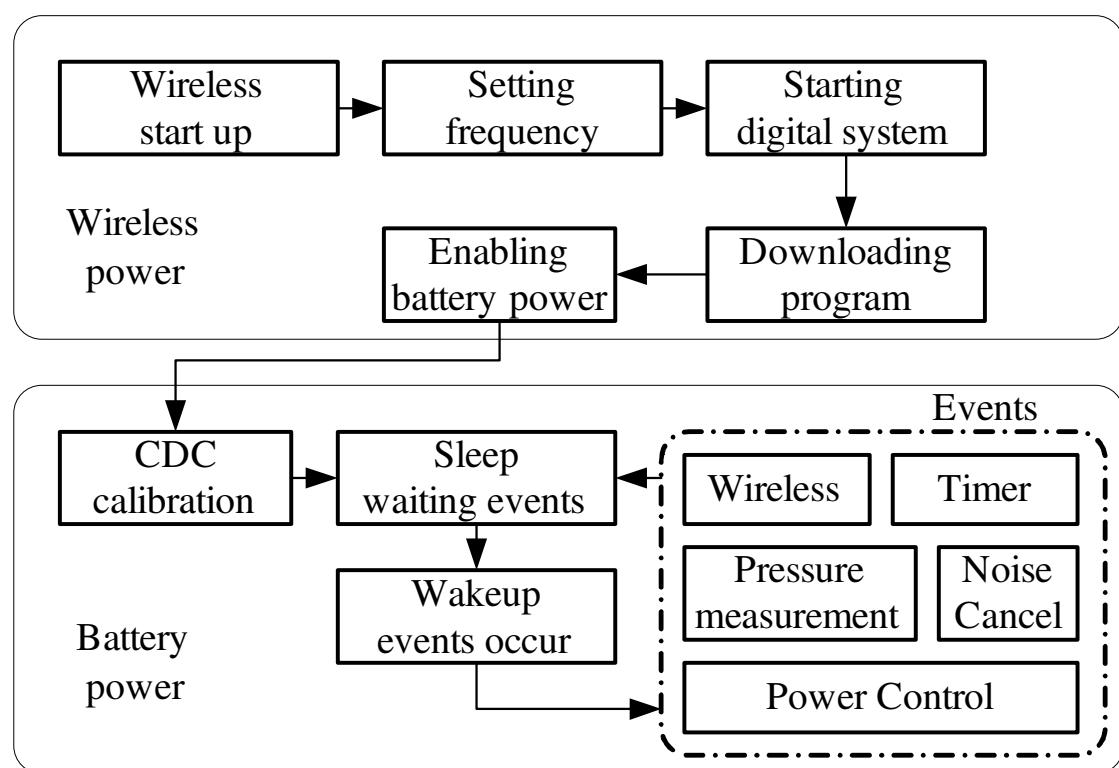

system with two capsules. To record pressure data, the tiny airtight capsules are inserted into the bladder and rectum. The capsules communicate with a portable recorder attached on the body and transmit data as the patient goes about his/her daily life. The capsule consists of four components as shown in Fig. 4.1: a communication coil, a battery, a MEMS capacitive pressure sensor [39], and the MeSOC. The MeSOC integrates the digital converter for the MEMS sensor [40], which is called Capacitance-to-Digital Converter (CDC), a wireless transceiver [41], and a digital system based on the MeDIX-I.

Work flows of the capsule are shown in Fig. 4.2 and 4.3. As shown in Fig. 4.2, to perform

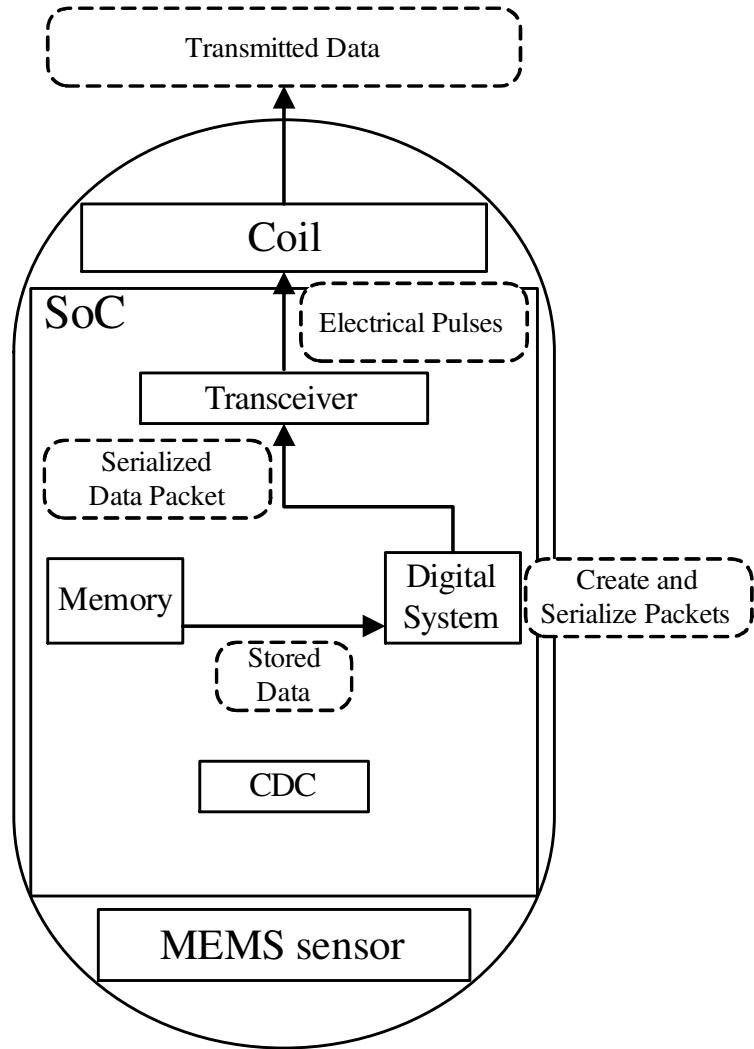

Figure 4.3: The work flow of wireless transmission.

pressure sensing, the MEMS sensor in the capsule measures the bladder and rectum pressure. The CDC in the SoC reads the MEMS capacitance and outputs the digital value of raw pressure data. Then the digital system calibrates the raw data and stores them in the memory.