| Title        | Control Methods for Quality of Service on ATM<br>Networks |

|--------------|-----------------------------------------------------------|

| Author(s)    | Kamiyama, Noriaki                                         |

| Citation     | 大阪大学, 1996, 博士論文                                          |

| Version Type | VoR                                                       |

| URL          | https://doi.org/10.11501/3110092                          |

| rights       |                                                           |

| Note         |                                                           |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

Control Methods for Quality of Service on ATM Networks

Osaka University December 1995

Noriaki Kamiyama

Doctoral Dissertation

1

Control Methods for Quality of Service on ATM Networks (ATM 網における通信品質保証のための制御技術に関する研究)

Noriaki Kamiyama

Department of Communication Engineering Graduate School of Engineering Osaka University

December 1995

This thesis investigates control methods guaranteeing QOS on the ATM network. The ATM network accommodates many kinds of services. These services are categorized into two groups, isochronous and error-free. For isochronous services, the QOS guarantee is important. We investigate former studied methods and propose a new scheme which satisfies all requirements of isochronous services. On the other hand, the decrease of the block (a unit of error control) loss probability is significant for error-free services. The FEC-SSCS technique is efficient to respond this demand, so we evaluate the message level performance of FEC-SSCS combined with Go-Back-N on the ATM network. This thesis consists of the following 5 chapters.

Chapter 1 provides a review of the ATM technology and its problems. The necessities of the control satisfying QOS for each connection and the significance of this research are clarified.

Chapter 2 proposes a new control method which guarantees QOS for isochronous services, e.g. voice or video. These services are very sensitive to a transmission delay, and it is difficult to introduce a retransmission mechanism because of its long delay. STM satisfies these requirements by allocating time slots for each connection. This allocation excludes an interference among connections in the network. On the other hand, because ATM is based on asynchronous multiplexing, the variation of a transmission delay and the loss of information occur in the ATM network.

It is efficient to allocate cell transmitted positions for each connection on the ATM network. This means a virtual STM transmission. We propose a new method based on this concept and call it Quasi-STM(Q-STM). This method achieves a cell loss free and delay jitter free transmission on the ATM network. Moreover, the Q-STM method suppresses the increase in a time switching delay by introducing a new concept, subframe. The statistical multiplexing gain is also obtained even in the Q-STM allocated slots, since a normal ATM service class is accommodated in addition to the Q-STM service class. The frame structure, the concept of the ATM service class, the switch architecture, and the call setup procedure are described respectively.

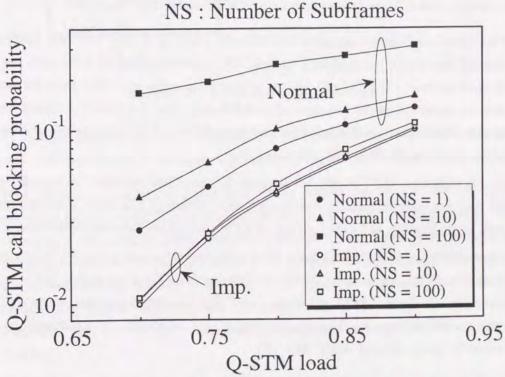

Chapter 3 investigates the performance of the Q-STM method, treating the design issues and the evaluation of availability. It is necessary to determine the algorithms of the call setup and the number of subframes. For the sake of obtaining the general indices for these design problems, (i)the availability of call setup algorithms considered in chapter 2 are evaluated and (ii) the influence of the number of subframes are investigated. Through these evaluation, the efficient algorithms and number of subframes are clarified.

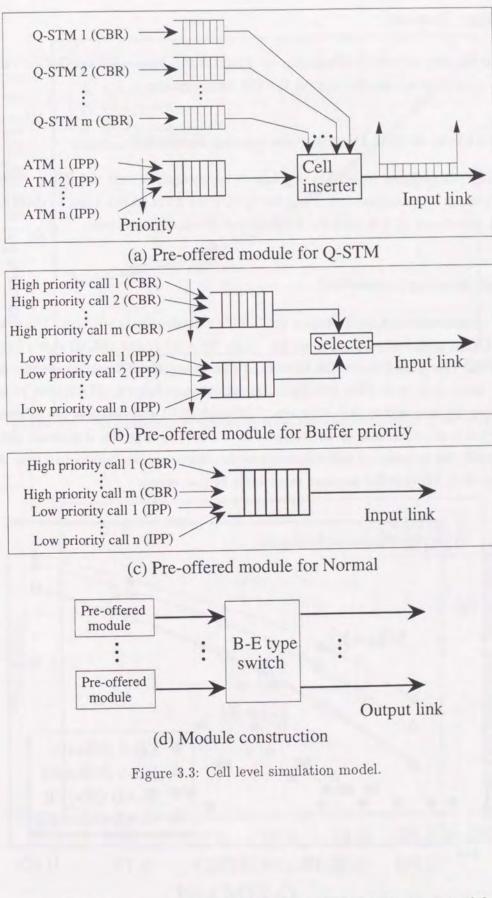

In order to clarify the availability of the Q-STM method, (iii) the QOS of the ATM service class and (iv)the call setup time caused by introducing the Q-STM method are evaluated. Although the QOS of the Q-STM service class is guaranteed, that of the ATM service class seems to be degraded because this class has a lower priority than the Q-STM class. Besides, the treated bandwidth spreads widely in the B-ISDN environment. This brings the allocation of a large number of slots for one broadband Q-STM call. These demerits of the Q-STM method are evaluated quantitatively. For the first three evaluations, computer simulations are used.

Chapter 4 presents the performance analysis of the QOS control method for error-free services, e.g. data communication or high density picture. For error-free services, it is important to decrease

### Preface

the block loss probability in the ATM network. The FEC-SSCS technique is efficient to satisfy this requirement. In this chapter, we analyze the message level performance of FEC-SSCS. The message level performance is significant, since it is what users actually feel. In order to evaluate the message level performance on the ATM network, three layers (a message, a block, and a cell) must be considered. However, the analysis considering these three layers has not been done yet. We re-evaluate the performance of the combination of FEC-SSCS and Go-Back-N when the three layers are considered.

Chapter 5 summarizes the overall conclusions reached in this thesis.

The work summarized in this thesis is conducted by the author during his Ph.D. course at the Department of Communication Engineering, Graduate School of Engineering, Osaka University.

#### Osaka, Japan December 1995

Noriaki Kamiyama

## Acknowledgements

This research described here has been carried out during the author's doctoral course at the Graduate School of Engineering, Osaka University, under the guidance of Professor Hiromasa Ikeda at the Department of Communication Engineering, Faculty of Engineering, Osaka University, Japan.

The author would like to express his appreciation to Professor Hiromasa Ikeda for his guidance, continuing encouragement, and valuable discussions throughout this research.

The author would also like to thank Professor Norihiko Morinaga, Professor Sadao Kurazono, Professor Akira Hasegawa, Professor Hajime Maeda of the Faculty of Engineering, Osaka University, and Professor Tadahiro Kitahashi of the I.S.I.R. for their kind encouragement and guidance.

The author is much indebted to Associate Professor Hiromi Okada for his helpful support and directions during the course of this research.

The author wishes to acknowledge the help offered by Lecturer Miki Yamamoto and Assistant Professor Hideki Tode. Their untiring efforts made it possible for the author to bring this thesis into being. The author would like to express his greatest appreciation to Assistant Professor Chikara Ohta of the Faculty of Engineering, Gunma University, Japan, for his helpful discussions and invaluable suggestions in guidance.

The author expresses his appreciation to Associate Professor Noboru Babaguchi of the I.S.I.R., Associate Professor Fumitaka Uchio of the Faculty of Engineering, Wakayama University, and Mrs. Kayoko Gotoh for their encouragement and support.

Gratitude is also owed to past and present members of Ikeda Laboratory. Special thanks go to Mr. Young Bok Choi, Mr. Yasuharu Sakai, Mr. Toshihito Hirata, Mr. Yoshiaki Ueno, Mr. Ken Ojiri, Mr. Kazuto Nishimura, Miss Yukiko Yamashita, and Mr. Hirohito Miki for their valuable advice, continuing encouragement, and deep friendship. They have all been very supportive of this endeavor. The author wishes to express his appreciation to the SCAT for their grants and financial supports. The author also shows gratitude to Mr. Roger Goble for his English advice. Finally, the author thanks his entire family for their patience and support during the whole period of his education.

ii

# Contents

|   | Pre  | face                                                 | i   |

|---|------|------------------------------------------------------|-----|

|   | Ack  | cnowledgements                                       | iii |

| 1 | Intr | roduction                                            | 1   |

| 2 | Syn  | chronous Transmission in ATM Networks                | 7   |

|   | 2.1  | Introduction                                         | 7   |

|   | 2.2  | Problems for Isochronous Services in ATM Networks    | 9   |

|   | 2.3  | Transmission of Isochronous Traffic                  | 12  |

|   |      | 2.3.1 Delay Jitter Compensation on AAL 1             | 12  |

|   |      | 2.3.2 Buffer Priority Control                        | 15  |

|   |      | 2.3.3 Stop-and-Go Queueing                           | 17  |

|   | 2.4  | Quasi-STM Transmission Method                        |     |

|   |      | 2.4.1 Frame Structure                                | 20  |

|   |      | 2.4.2 ATM Service Class                              | 23  |

|   |      | 2.4.3 Switch Architecture                            | 23  |

|   |      | 2.4.4 Call Setup                                     | 31  |

|   | 2.5  | Conclusion                                           | 39  |

| 3 | Per  | formance Evaluation of Q-STM Method                  | 41  |

|   | 3.1  | Introduction                                         | 41  |

|   | 3.2  | Simulation Model Formulation                         | 42  |

|   | 0.2  | 3.2.1 Source Model                                   | 42  |

|   |      | 3.2.2 Simulation Model                               | 43  |

|   | 3.3  | Design Issues                                        | 46  |

|   | 0.0  | 3.3.1 Algorithms of Slot Distribution among Subframe |     |

|   |      | 3.3.2 Algorithms of Slot Arrangement in Subframe     | 49  |

|   |      | 3.3.3 Number of Subframes                            | 49  |

|   | 3.4  | Evaluation of Availability                           | 51  |

|   | 0.1  | 3.4.1 Influence on ATM Class QOS                     | 52  |

|   |      |                                                      | 53  |

|   | 3.5  | 3.4.2 Call Setup Time                                | 62  |

|   | 0.0  | Conclusion                                           | 02  |

| 4 | Per | ormance Analysis of FEC-SSCS for ABR Class              | 5  |

|---|-----|---------------------------------------------------------|----|

|   | 4.1 |                                                         | 55 |

|   | 4.2 | Improvement of Block Loss Rate                          | 59 |

|   |     | 4.2.1 Selective Cell Discarding                         | 71 |

|   |     | 4.2.2 Forward Error Correction in SSCS                  | 72 |

|   | 4.3 | Analysis Model Formulation                              | 72 |

|   | 4.4 | Analysis                                                | 75 |

|   |     | 4.4.1 Block Acceptance Probability                      | 75 |

|   |     | 4.4.2 Block Forwarding Delay                            | 78 |

|   |     | 4.4.3 Message Forwarding Delay                          | 81 |

|   |     | 4.4.4 Reflection of Network Load                        | 82 |

|   | 4.5 | Performance Evaluation                                  | 83 |

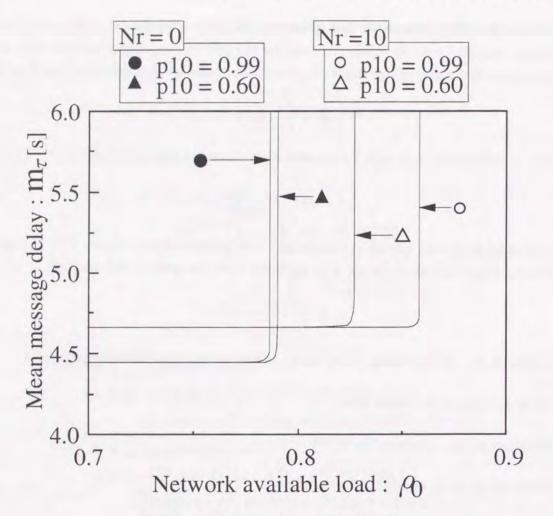

|   |     | 4.5.1 Impact for Available Load                         | 84 |

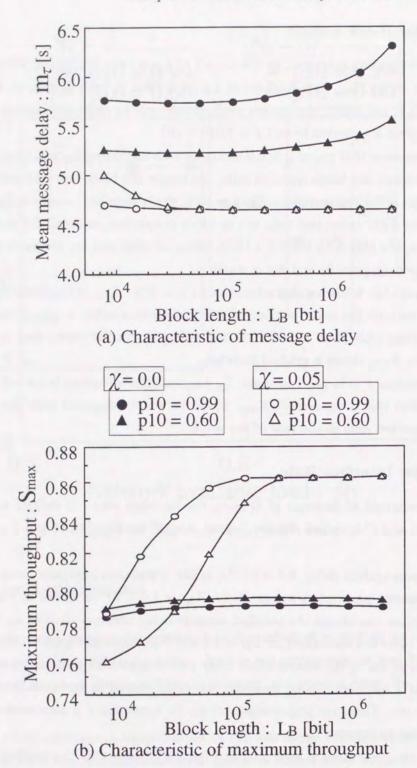

|   |     | 4.5.2 Impact for Block Length                           | 85 |

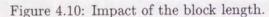

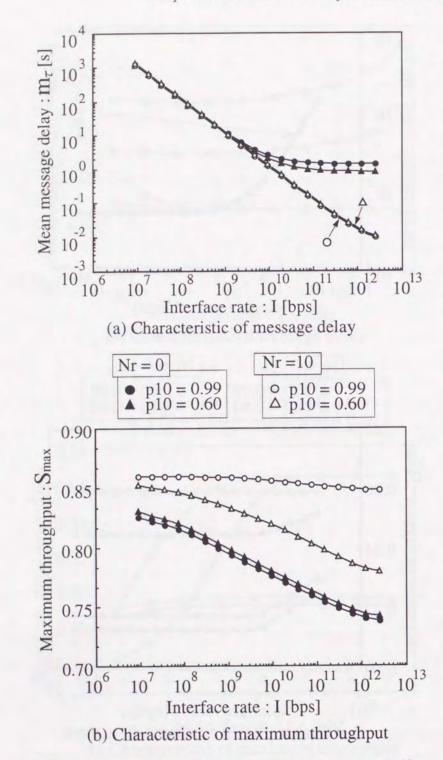

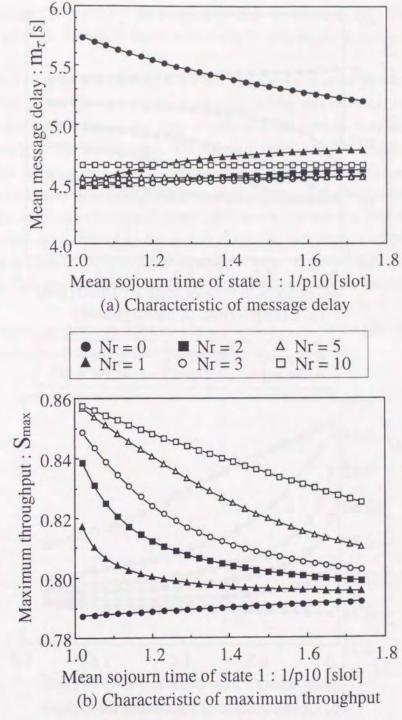

|   |     | 4.5.3 Impact for Interface Rate                         | 85 |

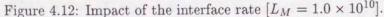

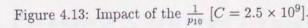

|   |     | 4.5.4 Impact for Mean Number of Consecutive Cell Losses | 87 |

|   | 4.6 | Conclusion                                              | 90 |

| 5 | Con | clusions                                                | 93 |

#### 5

# Bibliography

95

v

# Chapter 1 Introduction

The establishment of a digital switching technology realizes an Integrated Services Digital Network(ISDN). Different kinds of services, e.g. voice, video, or computer communication, are accommodated in ISDN in the forms of a digital signal. This network can provide a unified interface to each terminal [1].

Recently, data communication between several kinds of computers has been increasing because of the appearance of distributed computing. A demand for services requiring broad bandwidth, e.g. a long distance simulation using a super computer or a high density picture for medical treatment is growing more and more [2]. Now, a Broadband-ISDN(B-ISDN) is expected to be the next-generation network satisfying these high demands [3]. B-ISDN is to accommodate many kinds of broadband services, whose rate exceeds 10*Mbps*, in addition to ordinary services, e.g. voice communication. These services can be grouped into two categories, an *isochronous* service and an *error-free* service. Examples of an isochronous service are voice and video. These services are very sensitive to a delay variance quality. On the other hand, example of an error-free service is data communication. Although an error-free service does not require a timing synchronization, it demands error free transmission.

B-ISDN requires the following two abilities. The first is a high speed switching capability(the throughput of a switching node in B-ISDN will be in *Gbps* range [3]). The second is the flexible accommodation of various kinds of services, including bursty services whose rate changes widely with time. A Synchronous Transfer Mode(STM), which has provided isochronous services, satisfies the first requirement. On the other hand, a storing and forwarding type network which has accommodated error-free services, e.g. a packet switching or a frame relay network, meets the second one. However, none of these ordinary networks can satisfy both demands simultaneously.

A new technology called Asynchronous Transfer Mode(ATM) has been recommended as the transmission and switching system of B-ISDN in International Telecommunication Union Telecommunication Standardization Sector(ITU-TS) [4]. ATM has two main concepts [3]: (1)synchronous time switching using a time slot of fixed length and (2)asynchronous transmission based on a label multiplexing. Using a transmission unit of the fixed 53bytes length, called "cell", enables it to switch information bits quickly as in STM. ATM is superior to packet based networks from the viewpoint of this high speed capability. In a packet based network using a variable length transmission unit, a switching delay can not be decreased enough to satisfy the B-ISDN requirements because of its software based processing.

#### Chapter 1. Introduction

Senders on the ATM network can insert cells into any slots, and each cell is distinguished by the 5bytes label attached for 48bytes ATM payload. The label multiplexing enables it to accommodate services flexibly whose rate changes widely. On the other hand, there is no label concept in the STM network. Because each connection is distinguished by its position within a time frame, information bits are sent within the preassigned positions. ATM is superior to STM from the viewpoint of this flexible capability. ATM is considered to be the most attractive transmission method which incorporates merits from both STM and packet based networks.

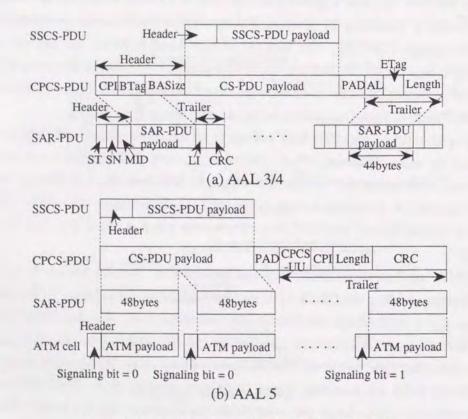

The functions of the ATM network are provided by three layers, a physical layer, an ATM layer, and an ATM Adaptation Layer(AAL) [3]. The protocols for packaging data into cells are collectively referred to as AAL. The purpose of this layer is to efficiently fragment various kinds of higher layer data, such as Internet Protocol(IP) packets, voice samples, and video frames, into cells and to reconstruct cells into a higher layer frame. AAL consists of two sublayers, a Segmentation And Reassembly(SAR) sublayer and a Convergence Sublayer(CS). The SAR sublayer is responsible for breaking data into cells and reassembling cells into upper layer data units. CS is responsible for managing the flow of data to and from the SAR sublayer.

Four types of AALs are considered [5, 7, 8]. AAL 1 and 2 is for an isochronous, continuous bit-rate transmission, e.g. voice and movie. On the other hand, AAL 3/4 and AAL 5 are for an error-free, bursty transmission, such as data communication. The description of AAL 3/4 and AAL 5 is shown in section 4.2.

In the ATM network, three methods are considered for service accommodation: a Constant Bit Rate(CBR), a Variable Bit Rate(VBR), and an Available Bit Rate(ABR) [5]. CBR is supported by AAL 1, and cells generated by one sender terminal are accommodated in the network at a constant rate. VBR is supported by AAL 2, and cells generated by the sender terminal are transmitted at a variable rate. However, a time frame concept exists in VBR, and the time frame synchronization is necessary for both sender and receiver terminals. Hence, these two classes are considered for isochronous services. On the other hand, ABR supports error-free services. Calls of this class are not allocated bandwidth, and their transmission rates are changed dynamically according to the network load.

Next, we describe how to accommodate an isochronous service and an error-free service respectively, as well as some problems caused in ATM for each service category.

Isochronous services, including voice and video, are almost treated as CBR [12]. The rate of video sources is variable because of an encoding which reduces required bandwidth. However, it is possible to treat a video source as CBR by means of providing a buffer at the sender terminal. If a video source is treated as CBR, an estimation of required bandwidth and a Usage Parameter Control(UPC) become simpler. However, accommodating video sources as VBR has some attractive merits. Through a statistical multiplexing, the network can carry more VBR video calls than CBR ones. Alternatively, users can obtain better quality with VBR than CBR video if both sources are accommodated with the same bandwidth [13]. In this case, video sources will use AAL 2(a complex UPC is necessary for this protocol, so the standardization is under way).

Next, we consider some problems in the ATM network for isochronous services. Each CBR(VBR) service should be allocated required bandwidth in order to guarantee QOS. The reason is as follows. The sensitiveness to a delay quality makes it difficult to introduce a retransmission mechanism. Without a bandwidth reservation, CBR(VBR) services are faced with a serious QOS degradation when congestion happens in the network.

Besides, it must be noted that the bandwidth allocation in the ATM network does not mean the assurance of QOS directly as the case of the STM network. The reason for this is as follows. We must pay attention to the propagation of the congestion caused among ABR services to CBR(VBR) services, because the CBR(VBR) traffic shares the same resources in the network with the ABR traffic. In addition to this factor, the "label multiplexing" of cells causes a variance in a cell transmission delay for CBR(VBR). Therefore, some controls which guarantee the QOS of CBR(VBR) must be introduced on the ATM network.

Senders of *error-free* services, such as data communication, tend to send cells with a high rate during a short period and remain idle for a long time. If bandwidth is allocated to these services, a peak rate will be assigned and the network efficiency will be degraded. A Fast Reservation Protocol(FRP) allocating bandwidth for each burst was proposed [14, 15]. The consumption of bandwidth is limited to the period when information is actually sent. However, the failure of a bandwidth reservation increases the data forwarding delay in FRP.

Now, the definition of ABR is in progress at the ATM Forum [16, 17]. The rate is controlled based on the load information generated by ATM nodes. Therefore, a congestion can occur because of the control delay between congested nodes and terminals. However, ABR can satisfy a required Quality Of Service(QOS), i.e. a cell loss rate, a cell forwarding delay, and a delay jitter, since error-free services are not sensitive to a delay quality(retransmission is possible). ABR is attractive because of the flexible accommodation of error-free services.

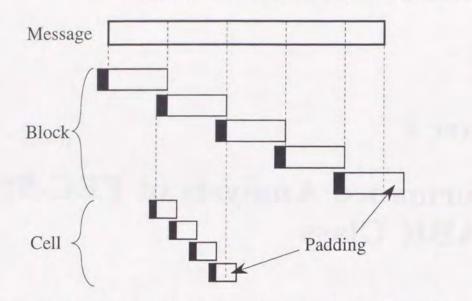

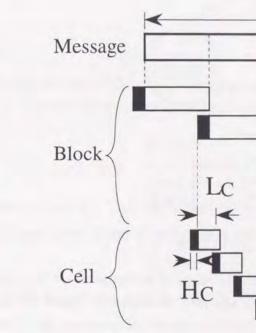

Next, we consider some problems in the ATM network for error-free services. The perfect prevention of bit errors and information loss caused by a congestion is impossible in the ATM network. However, the forwarding of the whole information bits without any error is necessary for error-free services, e.g. data communication, so an error control is indispensable for these services. The error control will be introduced in AAL or a transport layer in the ATM network. The unit of this error control is described as a "block" in this thesis. Both sender and receiver terminals must perform per-block processing for each block during the block period. Some examples of this per-block processing are a header and trailer generation, an error control, and a timer control. In general, it is better to use a few large blocks instead of many small blocks to carry a given amount of data, because the protocol processing time required for each block can be a bottleneck of throughput [18]. As a result, the block length tends to be longer as the interface rate increases: the size of a Transmission Control Protocol(TCP) block is 512bytes, 1500bytes for ethernet networks, 4352bytes for a Fiber Distributed Data Interface(FDDI) networks, and 9180bytes is the default for IP over ATM [19, 20].

The small size of a cell is desirable for isochronous services because of the following two reasons [5]. First, the longer cell causes a longer waiting time at switches. Second, it takes more time to get enough data to fill one ATM cell payload from a low rate voice source if the cell size becomes

#### Chapter 1. Introduction

longer<sup>1</sup>. Because the bandwidth of the ATM network will continue to grow, the first problem can be negligible, however the second problem will continue to remain. Therefore, the size of 53bytes has been recommended from ITU-TS. However, this size is too small compared to the block length.

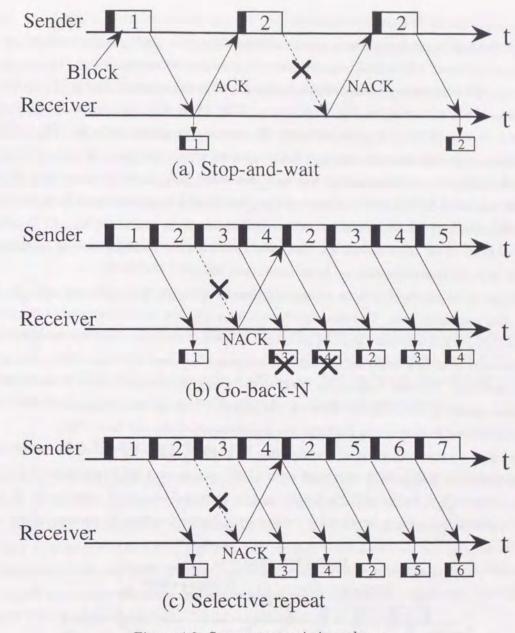

As a result, each block is fragmented into many cells(in the case of the 9180bytes block size, one block consists of 192 cells using AAL 5). It has been known that the fragmentation of a block into small pieces can cause disastrously low performance if any of the pieces are lost in transit [18]. The loss of any cells constituting one block causes the retransmission of whole part of the block and a throughput degradation. When only the lost cells are retransmitted, this degradation can be relieved. However, cell-based retransmission requires an 8 byte sequence number field for each cell [22], then it becomes a high overhead of 15%. The superiority of a frame-based retransmission to a cell-based one has been also clarified numerically [23]. As a result, the throughput degradation of the ATM network caused by the fragmentation of a data block will be a serious problem [18, 24].

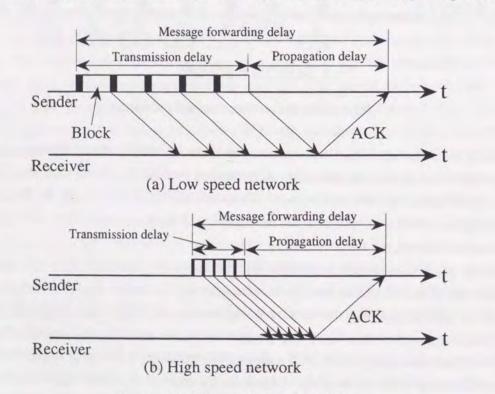

The interface rate in the ATM network will be much faster than ordinary data networks: it will be faster than 150*Mbps* in the ATM network and, on the other hand, it is less than 64*kbps* in packet exchange networks and, less than 1.5*Mbps* in frame relay networks. Moreover, it will continue to grow in the ATM network. A message(a unit of information expected to be transmitted, e.g. one data file) forwarding delay consists of two portions, a message transmission delay and a propagation delay. The improvement of the interface rate decreases only the transmission delay. The propagation delay will be large compared with the transmission one, then become a dominant factor of the forwarding delay in gigabit networks or ATM networks [25, 26]. Once retransmission occurs, one round trip propagation delay is added to the message forwarding delay. Hence, the delay caused by retransmission may be a dominant factor of the forwarding delay of a large volume message, so it is important to reduce the number of retransmission in the ATM network.

The control method diminishing the block loss probability is indispensable for ABR services. This is derived from the two reasons mentioned above: the throughput degradation caused by a block fragmentation and the relative increment of a propagation delay caused by a growth in the bandwidth.

Some control methods must be introduced to guarantee the QOS of isochronous services and improve the QOS of error-free services. The main purpose of this thesis is to investigate control methods which aim to satisfy above requirements.

In chapter 2, control methods guaranteeing some of QOS for isochronous services are discussed. Among the proposed methods so far, three representative control methods are considered in this thesis: a delay jitter compensation method introduced in AAL 1 [27, 28, 29, 30, 31], a buffer priority control [26, 32, 34, 35, 36, 37], and stop-and-go queueing [38, 39, 40, 41, 42]. We summarize the purposes and limits of these schemes.

The STM network has satisfied the QOS of isochronous services in addition to realizing a high speed transmission by means of hardware based switching. The allocation of time slots for each connection enables it to achieve high performance because this reservation excludes the interference among connections. However, error-free services are not suited for a STM type network. Therefore, a number of literatures have argued for a technology which combines a packet-based transmission with a Time Division Multiplexing(TDM) system(such as STM) [43, 44, 45, 46]. Here, it is efficient to consider allocating cell transmitted positions for each call on the ATM network. This means a virtual STM transmission on ATM. We propose a new method based on this concept and call it Quasi-STM(Q-STM) [47, 48, 49].

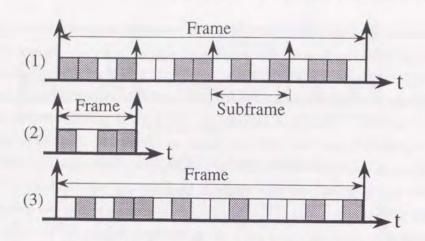

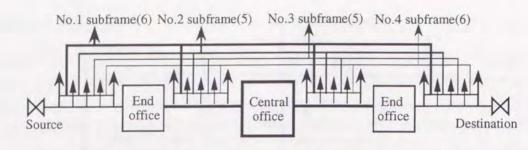

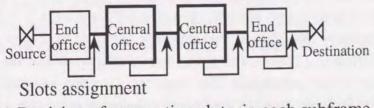

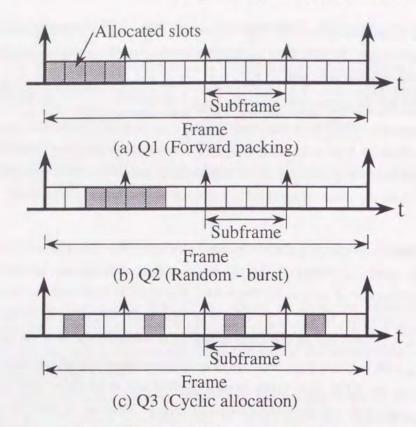

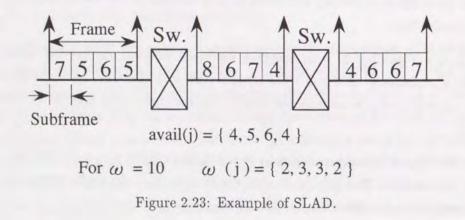

This method realizes a cell loss free and delay jitter free transmission on the ATM network. In order to allocate a cell transmitted position for each call, frame and slot concepts are introduced on a time axis. The frame is a period of bandwidth allocation, and the slot is a unit of it. Because this method is based on the ATM network, the time slot corresponds to the ATM cell slot. This slot length is too long compared with the STM network, so the frame length becomes large(if 64kbps voice source is accommodated, the frame size is 6ms). Thus, the time switching delay becomes large, so we newly introduce a new concept, subframe, which is composed by splitting one frame into multiple equivalent time intervals. The subframe concept can decrease the time switching delay. As a result, this method constructs three layers on a time axis, the frame, the subframe, and the slot. By the way, the statistical multiplexing gain is also obtained even in the allocated slots, since a normal ATM service class is accommodated in addition to the Q-STM service class. A frame structure, a concept of ATM service class, a switch architecture, and a call setup procedure are described respectively.

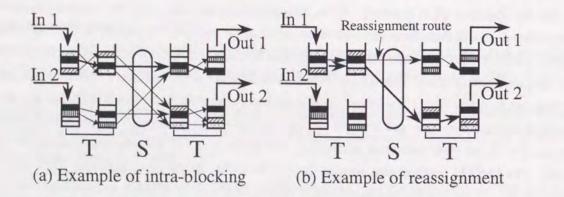

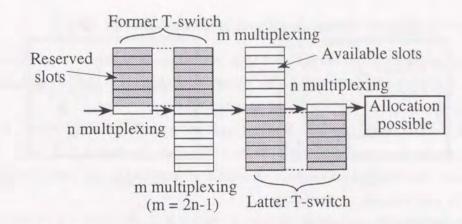

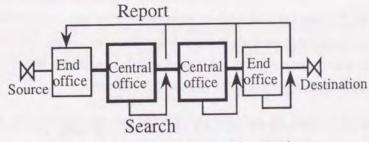

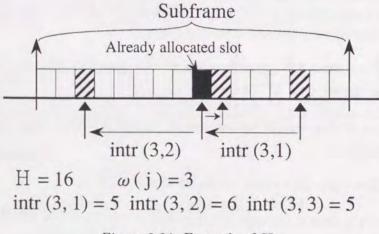

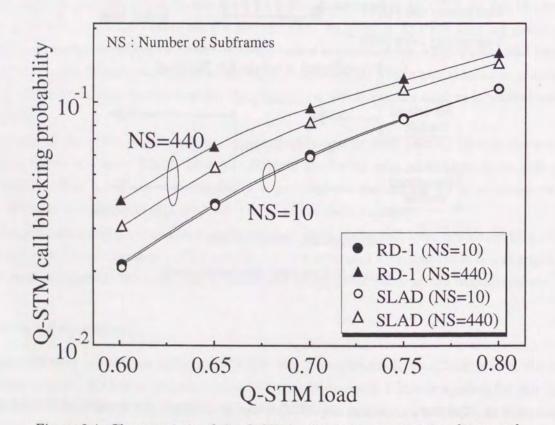

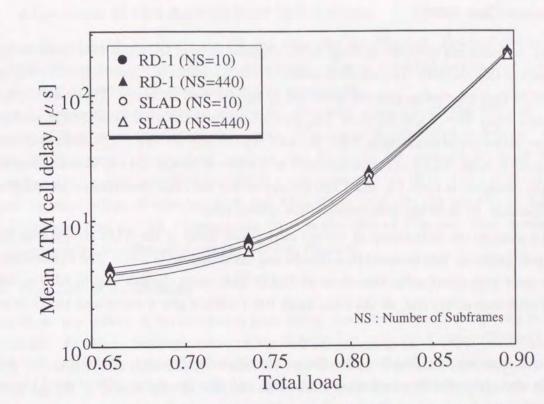

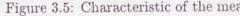

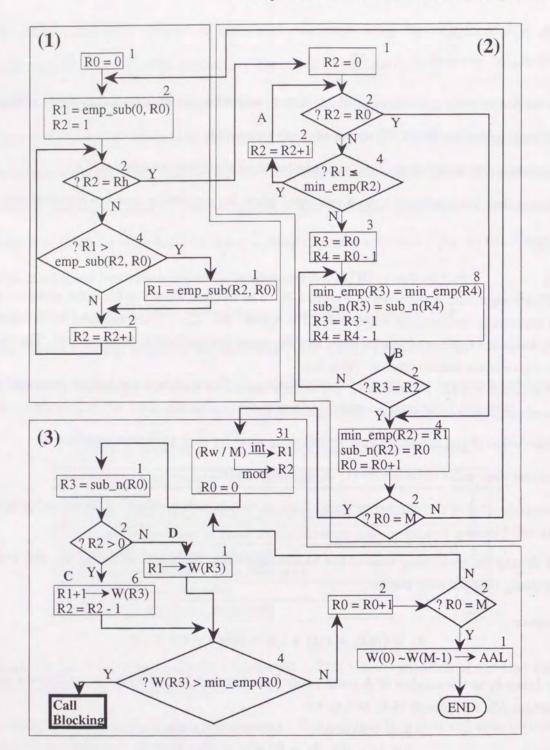

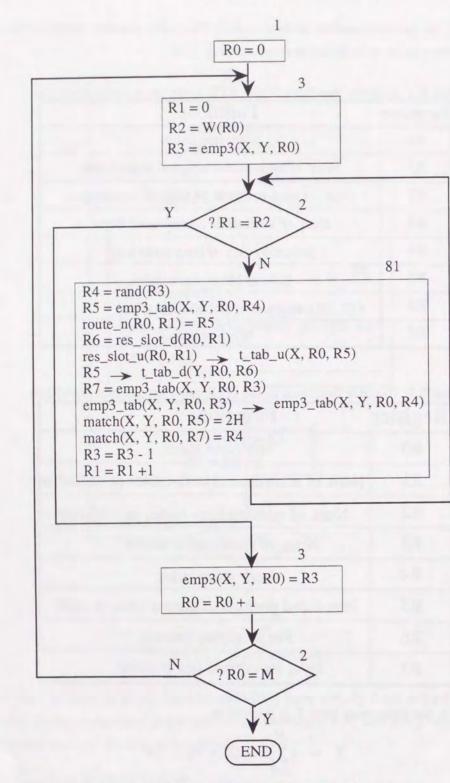

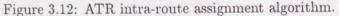

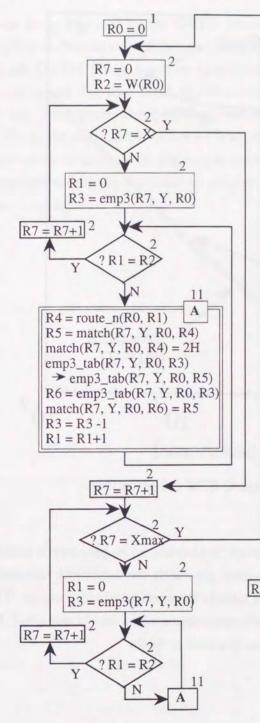

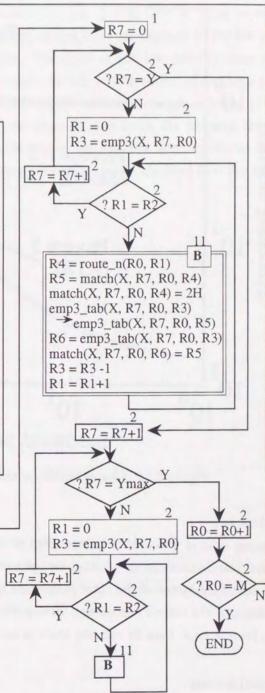

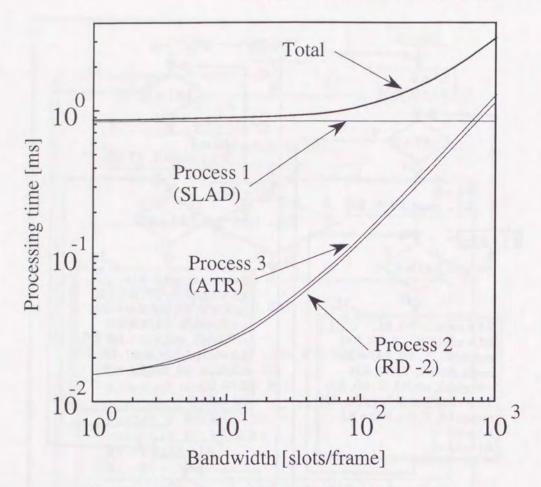

In chapter 3, we investigate performance of the Q-STM method, treating design issues and evaluating the availability [50, 51]. Because the Q-STM method regards the subframe as a period of time switching and uses Time switch-Space switch-Time switch(TST) structure to exchange Q-STM cells, the call setup procedure of the Q-STM method consists of three processes: the calculation of the number of slots allocated within each subframe, the slots allocation on each link, and the reservation of intra-switch routes. Except for the third process, algorithms of each process affect some properties of Q-STM and ATM cells. Through the performance evaluation of these call setup algorithms, the efficient algorithms for each process are clarified.

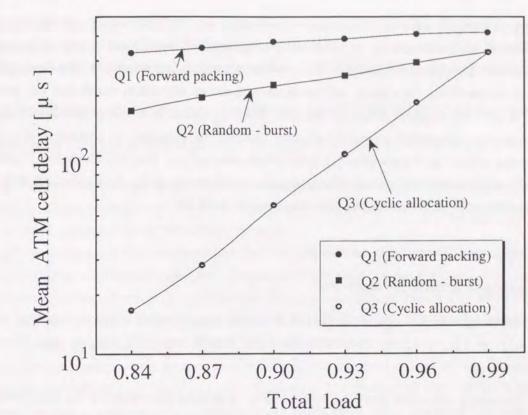

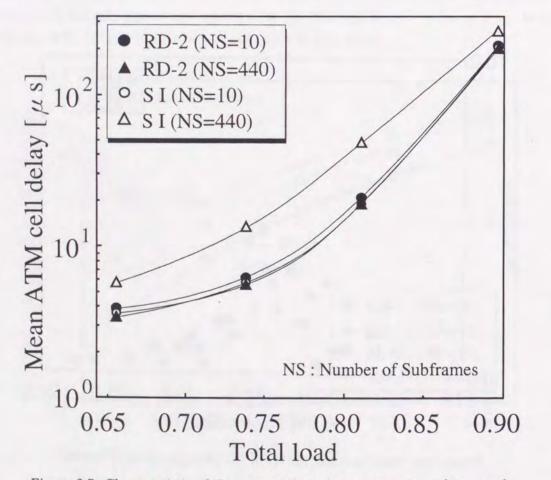

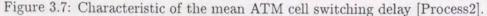

The subframe length can not be obtained easily, because this size affects three qualities: the Q-STM cell end-to-end delay, the Q-STM call blocking probability, and the QOS of the ATM service class. We evaluate the influence of the number of subframes for these three qualities, then roughly obtain the most efficient value.

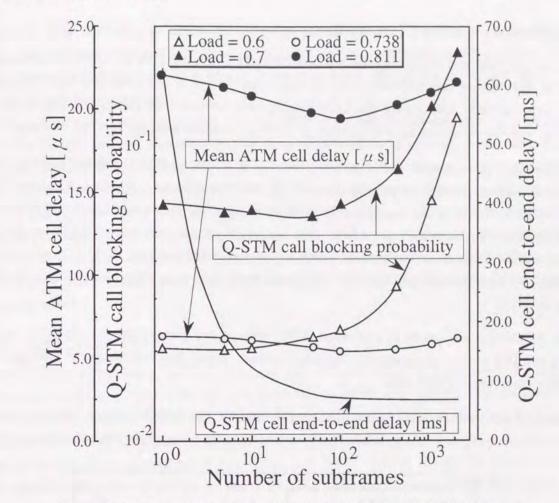

In order to clarify the availability of the Q-STM method, we evaluate the QOS of the ATM service class and the call setup time caused by introducing the Q-STM method. Though the QOS of the Q-STM service class is guaranteed, the QOS of the ATM service class seems to be degraded. This is because that the ATM class corresponds to a low priority class compared with the Q-STM class. To understand the degree of the degradation numerically, the mean intra-switch cell delay of the ATM service class is compared to a buffer priority control and a normal ATM.

Because treated bandwidth spreads widely in the B-ISDN environment, the frame length must be long in order to accommodate a narrowband service. Therefore, a large number of slots must be allocated for a broadband service. This leads the apprehension of an unpardonable growth of the Q-STM call setup time. We construct the algorithms and sum up the all required steps, then clarify the additional call setup time.

In chapter 4, we consider some methods decreasing the block loss probability of error-free services.

<sup>&</sup>lt;sup>1</sup>There is a concept of a partially filled cell [21] in which each cell is transmitted when a part of ATM payload(e.g. 8bytes) is filled. In this case, the delay caused by making up one cell is small even when the cell size is large. However, partially filled cells waste bandwidth and costly.

There are three factors that cause a block loss: a random bit error, a burst bit error, and congestion [52]. Although errors in fiber transmission are extremely rare, it is known to take the long burst mode if they do occur [5]. AAL introduces a Cyclic Redundancy Check(CRC) to detect or correct a few bit errors. However, CRC can not correct a burst bit error. Therefore, a burst bit error as well as a congestion result in a cell loss, so the techniques which consider cell loss are important in decreasing the block loss rate.

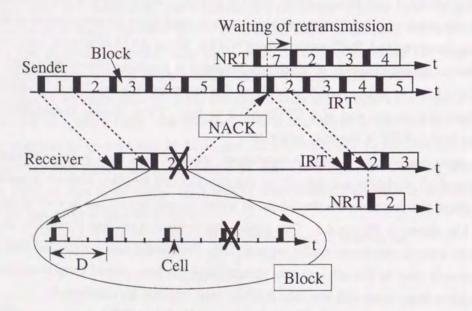

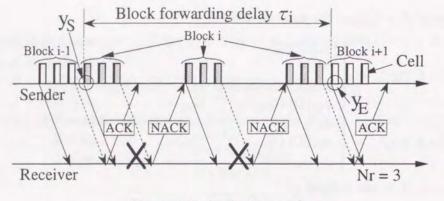

Two kinds of methods have been proposed: one is the selective cell discarding method [6, 19, 53], and the other is a cell based Forward Error Correction(FEC) introduced in a Service Specific Convergence Sublayer(SSCS) [54, 55, 56, 57, 58]. SSCS is an upper sublayer of CS and treats the process depending on the service. The former method needs a software-based complex processing at ATM switching nodes. On the other hand, the additional process is necessary only to both sender and receiver terminals for the latter method. The B-ISDN environment requires a high speed switching capability, so we consider that FEC-SSCS is superior to the selective cell discarding method. By adding some FEC redundant cells to each block, FEC-SSCS makes it possible to recover the block containing some lost cells without retransmission if the number of lost cells is less than or equal to the number of redundant cells within the block. We analyze the performance of FEC-SSCS to clarify the efficiency for several parameters [59].

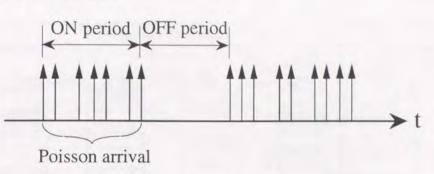

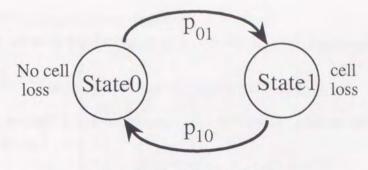

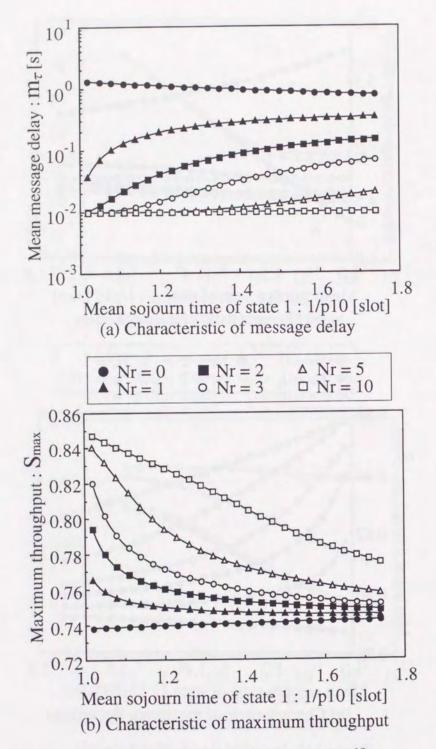

The message level performance is significant, since it is what users actually feel. In order to evaluate the message level performance on the ATM network, three layers (a message, a block, and a cell) must be considered. However, the performance of FEC-SSCS considering the three layers has not been analyzed yet. We respect these three layers. When the number of lost cells among a block exceeds the number of redundant cells, FEC-SSCS can not recover the block. In this case, it is assumed that the corrupted block is retransmitted based on a Go-Back-N(GBN) in this thesis. The two state Markov chain is applied to the cell loss process in order to consider the burst cell loss tendency at ATM nodes. The mean message forwarding delay is evaluated for the case of fixing cell loss rate. On the other hand, in the case of reflecting the network load to the cell loss rate, the maximum throughput is investigated. We evaluate these qualities against the network load, the block length, the interface rate, and the mean number of consecutive cell losses.

In chapter 5, we summarize the overall conclusions obtained in this thesis.

# Chapter 2 Synchronous Transmission in ATM Networks

### 2.1 Introduction

One important category of services accommodated in B-ISDN is an isochronous service. The examples of this kind of service are an ordinary telephone supported by a circuit switching network(i.e. STM) or Narrowband-ISDN(N-ISDN). A video distribution, e.g. video on demand [60, 61, 62], television conference, or remote education are new applications and also good representatives of isochronous services. These new services will become one of the main applications of B-ISDN in future.

Isochronous services have a strict requirement for a forwarding delay quality: both a mean value and a variance(jitter). If the forwarding delay becomes large, receivers experience an unnatural pause of a conversation in voice or a distortion of a picture in video. The large delay variance causes an information loss because information bits which do not arrive in time for their playing back are dropped at the receiver. Therefore, the delay jitter also degrades these qualities.

In addition to this requirement, a video service needs to be assured a low cell loss rate(for example, The ATM network permits each sender to transmit a cell in an arbitrary time slot and cells are

broadcast quality video requires less than  $1.2 \times 10^{-9}$  end-to-end cell loss rate [12]) because users are very sensitive to a degradation of a picture quality. As a result, high requirements for these QOSs(the mean delay, the delay jitter, and the cell loss rate) exist in the ATM network for isochronous services. multiplexed by a label attached in the cell header. Hence, there is a possibility that plural number of cells arrive at a certain output port of an ATM switching fabric at the same time, and some amount of a memory facility are necessary to store cells. This principle makes the following four problems for isochronous services: (1)a delay jitter, (2)a buffer overflow caused by VBR, (3)a cell collision in the ATM switching fabric, and (4)propagation of congestion caused by ABR. The explanation of these four problems is shown in section 2.2.

Some control methods must be introduced to guarantee the QOS of isochronous services. In section 2.3, we consider some methods which aim for the assurance of the isochronous service QOS. Among proposed methods so far, three representative control methods are considered: a delay jitter compensation method introduced in AAL 1, a buffer priority control, and a stop-and-go queueing.

The simplest method to answer the first problem, i.e. recovering a timing of CBR services, may be the attachment of some memories to receivers. AAL 1 absorbs the delay jitter caused in the ATM

network by means of adding some amount of delay [27, 28, 29, 30, 31]. The amount of the required memory will become extremely large because the number of connections communicating with the same receiver simultaneously continues to increase. The another problem is that the establishment of the volume of the additional delay to recover a delay jitter is difficult.

To resolve the second and fourth problem, buffer priority controls have been proposed [26, 32, 33, 34. 35, 36, 37]. Introducing a concept of priorities among isochronous services can avoid the second problem, and establishing them between CBR(VBR) and ABR enables it to prevent the fourth one. Although these methods can guarantee the cell loss rate and the worst-case queueing delay(statistically), the maximum delay jitter and the deterministic guarantee of the worst-case delay can not be assured.

The stop-and-go queueing method [38, 39, 40, 41, 42] responds to the second and the fourth problems and partially the first one by introducing a time frame concept. It provides guaranteed services per connection with no cell loss and end-to-end delay of a constant plus a small bounded jitter term. However, the cell queuing delay is much larger than any other methods if the flexibility of bandwidth allocation is kept. Furthermore, the fluctuation of cell delay within a frame can occur because of interaction among cells of other connections.

The STM network has satisfied the QOS of isochronous services in addition that a high speed transmission has been realized by a hardware based switching. The allocation of time slots for each connection enables it because this reservation excludes the interference among connections. However, error-free services are not suited for a STM type network. Therefore, a number of literatures have argued the technology which combines a packet-based transmission with a TDM system(such as a STM) [43, 44, 45, 46]. Here, it is efficient to consider the allocation of cell transmitted positions for each call on the ATM network. This means a virtual STM transmission on ATM. We propose this new method named as Q-STM [47, 48, 49].

In this scheme, a time *frame* concept is introduced. The frame is divided into some numbers of subframes, all of which are the same length. The subframe is again divided into slots, which is a unit of bandwidth allocation. Because the time positions of each call are fixedly allocated with respect to all links on the route, the time switching of slots at each switch is necessary for the flexibility of slot reservation. In the Q-STM method, the basic period of this time switching is not a frame but a subframe, which remarkably reduces storing delay at each intermediate node. Furthermore, this scheme also provides general ATM service class<sup>1</sup>, which is free from a restriction of time frames, in addition to the Q-STM service class. So two kinds of cells(Q-STM and ATM cell) are mixed on one link. Because of the allocation of time positions, Q-STM calls are able to be not only realized the transmission of cell loss free and no intranetwork delay jitter, but also performed UPC structurally. And vacant position in a frame, which may occur due to the rate fluctuation of Q-STM calls or which is not reserved by Q-STM calls, can be utilized by ATM calls. In other words, ATM class cells can use not only non-allocated slots for Q-STM, but also the cell position without a Q-STM cell even if it is in the slot allocated for Q-STM. By the effects of statistical multiplexing of ATM cells, slots not used by Q-STM cells are utilized efficiently.

<sup>1</sup>In this thesis, we simply call this class of cells as "ATM cell".

2.2. Problems for Isochronous Services in ATM Networks

## 2.2 Problems for Isochronous Services in ATM Networks

In the ATM network, the following four problems exist for isochronous services: (1)a delay jitter, (2)a buffer overflow caused by VBR, (3)a cell collision in ATM switching fabric, and (4)propagation of congestion caused by ABR. In this section, we explain these four problems briefly.

#### [1. Delay jitter]

The information of a voice source is encoded at a constant period. For instance, an analog voice source is quantized 8bits digital information in the  $125\mu s$  interval [21]. Therefore, digital information bits are sent at the constant rate<sup>1</sup> On the other hand, the rate of video sources is variable because of an encoding scheme which reduces required bandwidth. By a technique of a high efficient encoding, e.g. H.261, MPEG1, and MPEG2 [63, 64], required bandwidth is decreased dramatically. In the case of a High Density TeleVision(HDTV), the original analog bandwidth, e.g. several Gbps, is reduced to around 20Mbps by MPEG2 [5]. If a video source is treated as CBR, an estimation of required bandwidth and UPC become simpler. Therefore, some video sources are sent as CBR. As a result, many isochronous services will be accommodated in the ATM network as a CBR service.

The sender of a CBR service transmits cells at a constant interval T, and the receiver must read arrived cells at the same interval T. However, a cell experiences a forwarding delay variance(jitter) because of a queueing at an ATM switch. This delay jitter caused one queue is accumulated because each connection passes plural number of ATM nodes. Besides, the estimation of the upper limit of a jitter is difficult. As a result, the recovery of a CBR source timing is one of the important issues in the ATM network.

#### [2. Buffer overflow caused by VBR]

If all isochronous services are supported as CBR and the sum of the rate of all CBR services accommodated to a certain link is less than the link capacity, the queue length of cells waiting to be transmitted in the ATM switch does not become long. Although the size of a memory attached to the ATM switch is finite, the amount of memories which are necessary to avoid the buffer overflow completely can be understood. However, accommodating a video source as VBR has some attractive merits. Through a statistical multiplexing, the network can carry more VBR video calls than the case of CBR. Alternatively, users can obtain better delay quality with VBR than CBR video when both sources are accommodated as the same average rate [13]. Therefore, it is reasonable to consider that some VBR calls will be supported in addition to CBR for isochronous services in future.

Provided that all VBR services are allocated bandwidth in a peak rate, buffer overflow at the ATM switch will not occur in this case, too. However, the peak rate allocation degrades the network efficiency and increases a cost. Therefore, it is important to accommodate these VBR sources with the rate which is less than their peak. In this case, it is necessary to introduce a Call Acceptance Control(CAC) at a call setup in order to guarantee the worst cell loss rate caused at passing ATM

<sup>&</sup>lt;sup>1</sup>In addition to this constant rate encoding, a variable rate encoding has been considered. It stops cell transmission while a silent period and tries to save the network resource. In this case, the cell transmission rate during a talking period is constant. Therefore, we can apply the following discussion to this variable encoding case, too.

nodes. However, CRC must satisfy the most strict requirement for the worst cell loss rate. In other words, the most strict quality level is applied for all isochronous services. As a result, the efficiency of isochronous service accommodation degrades because of the buffer overflow caused by VBR.

#### [3. Cell collision in ATM switching fabric]

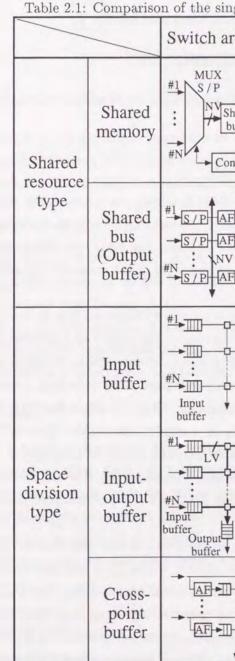

Many kinds of ATM switch architectures have been studied [94, 95, 96, 97]. The ATM switch falls into one of two broad categories: (i)a multistage, self routing array and (ii)a single stage fabric.

The multistage switch consists of many small switch elements, and each cell passes some elements [65]. In general, the larger the size of a switching fabric becomes, the higher the required switching speed becomes. Therefore, the multistage switch is considered to be an attractive ATM switching architecture for a central office class switch which connects 1000 - 10000 lines [94]. However, there is a possibility that a cell collides another cell at passing switch elements. The cell loss caused by this internal blocking can not be ignored, so some routing techniques avoiding an internal blocking have been considered [66, 67]. These non-blocking self routing arrays can evade a cell collision at passing switch elements, however, they require a complex control which are against the fundamental principle of ATM: removing a software-based complicated processing from a switching node in order to realize a high speed capability.

The other category of an ATM switch is the single stage fabric. There is no internal blocking and each cell can be exchanged with a simple processing. This category is again classified into two subcategories: a space division switch and a shared resource switch.

The examples of the space division switch are an input buffer switch [68] and a crossbar switch [69]. Though a high speed memory access is not necessary for the input buffer switch, a Head Of Line(HOL) phenomenon<sup>1</sup> degrades throughput much. Providing a memory for each cross point of input lines and output ones, the crossbar switch realizes a high performance. However, the amount of memories is proportional to the square of the switch size and the efficiency of memories is worse than other architectures.

The final category of ATM switches, i.e. the shared resource switch, can achieve the best performance from the viewpoint of a memory efficiency, a throughput, and a simplicity. A shared memory switch and an output buffer switch [70, 71, 72] exemplify this category. The problem of these switches is a required high speed memory access capability. This difficulty limits a switch scale. Hence, it is efficient to make an upper limit to the number of cells which can be accepted simultaneously at the same output port because the probability that many cells go to the same output link at the same time is little. A knockout switch [73] is one example of this shared resource switch. This switch provides the upper limit on the number of cells simultaneously accepted at an output port of a switching fabric, so it decreases a memory access speed. The knockout switch causes a cell loss at an output port of a switching fabric when cells exceeding the capacity try to go to the same output port simultaneously. An input and output buffer switch [74] is an alternative method to decrease a memory access speed. Though the output port contention can be avoided, an additional scheduling is necessary for each input port. Table 2.1 summarizes the single stage ATM switch architectures.

#### 2.2. Problems for Isochronous Services in ATM Networks

For multistage switches, a complex control requires in order to avoid a cell internal blocking at the ATM switch. Therefore, we consider that the shared resource switch is preferable. However, the cell collision at output ports of the ATM switching fabric occurs if we construct a large scale switch. This cell loss also leads the efficiency degradation of isochronous service accommodation.

N: Number of input links V: Link capacity S/P : Serial - parallel converter AF: Address filter L : Speed up ratio inside switching fabric P/S : Parallel - serial converter

| igle stage AI                                                                                                                         | M switch arch         | itecture.    |

|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|

| rchitecture                                                                                                                           | Memory<br>access rate | Control rate |

| DMUX<br>P/S<br>whared<br>buffer                                                                                                       | 2NV                   | 2NV          |

| Output<br>buffer<br>$F \longrightarrow P/S \rightarrow$<br>$F \longrightarrow P/S \rightarrow$<br>$F \longrightarrow P/S \rightarrow$ | (N+1)V                | v            |

|                                                                                                                                       | 2V                    | 2NV          |

|                                                                                                                                       | (L+1)V                | v            |

|                                                                                                                                       | 2V                    | v            |

### Table 2.1: Comparison of the single stage ATM switch architecture.

<sup>&</sup>lt;sup>1</sup>When a head cell of a queue is waiting, behind cells must wait even if the aimed output ports are available.

#### [4. Propagation of congestion caused by ABR]

An ABR sender starts to transmit cells without a bandwidth allocation and changes a transmission rate depending on the network load [75, 76, 77]. When the network falls a congestion state because of e.g. the increment of number of ABR connections, a rate control method informs senders to decrease the rate. However, the estimations of the control delay and the best threshold value(a trigger of the control) are difficult, so cell loss caused by ABR congestion can not be avoided perfectly. Because isochronous services accommodated as CBR or VBR are multiplexed with ABR services on the same link, the congestion will propagate to CBR(VBR) services. In other words, the bandwidth allocation of isochronous services in the ATM network does not mean the assurance of QOS as the case of the STM network.

#### 2.3 Transmission of Isochronous Traffic

In this section, three former methods, which aim to satisfy some requirements among four problems mentioned previous section, are introduced.

#### 2.3.1 Delay Jitter Compensation on AAL 1

In the ATM network, each cell experiences a variable delay in addition to a fixed delay. The fixed delay is caused by a propagation delay and, on the other hand, the variable delay is produced by a queueing at passing ATM nodes. The upper layer of CBR receivers requires AAL 1 to deliver information at a constant interval. The transport of a CBR signal through the ATM network is usually referred as circuit emulation [30, 34].

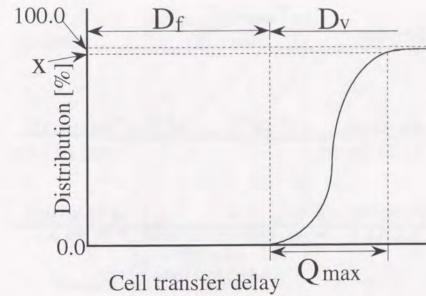

The one solution to compensate delay jitter caused in the ATM network is an introduction of a buffer which absorbs the delay variance at AAL 1 of receivers. The AAL 1 of a CBR sender transmits cells at the same interval, T, and the AAL 1 of a CBR receiver delivers cells to the upper layer every Tcycle. As mentioned above, total delay consists of two parts, fixed delay including propagation delay and variable delay. Fixed one can be defined as the minimum delay. To adjust the total delay to fixed value, adequate amount delay which is less than  $D_T$  is wasted in the buffer. This additional delay absorbs the variance of delay. As a result, the variable delay(which is less than  $D_T$ ) is controlled to the same value,  $D_T$ . If a cell experiences the variable delay exceeding  $D_T$ , it is dropped at the receiver AAL 1. This is because that the amount of the delay jitter can not be controlled to  $D_T$  by adding delay in this case.

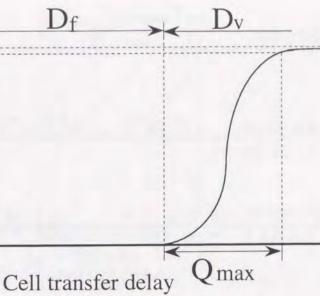

Figure 2.1 shows the example of a delay distribution between a sender and receiver. Let define  $D_f$ as a fixed delay and  $D_v$  as a variable delay. The ratio of cells whose  $D_v$  is less than  $Q_{max}$  is x%. The adjustment of  $D_v$  to  $Q_{max}$  guarantees that x% cells experience the same delay  $D_f + Q_{max}$ . These x%cells are sure to arrive at the receiver buffer before the instance they should be delivered to the upper layer. Other (1-x)% cells will delay exceeding  $D_f + Q_{max}$ , so the adjustment is impossible and they are lost by receivers. Therefore, the cell loss rate (1 - x)% can be guaranteed if the additional delay is controlled to satisfy

(2.1)

2.3. Transmission of Isochronous Traffic

The calculation of  $D_T$  is important issue because  $D_T$  gives the tradeoff between a cell loss quality and a cell delay quality, memory cost. Some ways of  $D_T$  determination have been considered [27, 28, 29]: blind delay, absolute timing, and accumulated variable delay. Next, we explain these methods briefly.

#### Blind Delay

of  $D_T$  gives a growth of a cell delay and required memory.

#### Absolute Timing

simplicity of the control, this method is ideal. However, the synchronization of both terminals seems to cost much.

#### Added Variable Delay

This technique is to actually measure the variable delay of the first cell. The variable delay is caused in queueing facilities, so ATM switches or ATM cross connect nodes calculate the queueing delay of the

$$D_T \ge Q_{max}.$$

Figure 2.1: Example of the cell delay distribution.

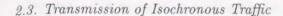

The AAL of a receiver starts to read the first cell at the arrival time of it plus  $Q_{max}$  as shown in Figure 2.2<sup>1</sup>. Let  $d_1$  denote  $D_v$  of the first cell. The following cells are read at the T interval. For all cells, it is assured that  $D_T = d_1 + Q_{max} \ge Q_{max}$ . Therefore, the condition (2.1) is satisfied. The calculation of  $D_T$  of this method is very simple and any complex facilities are not necessary. However, the obtained  $D_T$  will be longer than the ideal value  $Q_{max}$  because of  $d_1$ . The unnecessary increment

This method is based on the assumption that both a sender and a receiver use the same global clock and a synchronization of two terminals is established. A sender sets the first cell emission time into the AAL header, then a receiver reads the cell at the tagged time plus  $Q_{max}$  and  $D_f$  as shown in Figure 2.3. Then, all other cells are read at the same interval T. In this method,  $D_T = Q_{max}$  is guaranteed for all cells and the condition (2.1) is satisfied. From the viewpoint of a delay, a memory cost, and a

<sup>&</sup>lt;sup>1</sup>The fixed delay  $D_f$  is omitted in Figure 2.2-2.4.

# T Sender Receiver (ATM layer) Receiver (AAL) Qmax T (Additional fixed value) Figure 2.2: Blind delay mechanism. T Sender 2 Receiver 1 7 2 (ATM layer) Receiver 2 13 (AAL) A Qmax

Figure 2.3: Absolute timing mechanism.

(Absolute delay measured by grobal clock)

first cell and adds the value to a time stamp in the AAL header. As a result, a receiver can understand  $d_1$  correctly and determines the additional delay for the first cell as  $Q_{max} - d_1$  as shown in Figure 2.4. The following cells are read at the T interval. Like the absolute timing method,  $D_T = Q_{max}$  is assured for all cells. Though this also shows the ideal performance, the complex additional function is necessary for each ATM switch and cross connect.

In order to guarantee the cell loss rate caused at receiver buffers, all of three methods described above require the information for the cell delay distribution exemplified in Figure 2.1 for each connection. However, it is usually difficult to obtain the distribution at any instance. Moreover, the required memory at a receiver will continue to increase rapidly because the number of connections which are simultaneously connected to the same terminal will grow. If the cell delay jitter is bounded like Distributed Queueing Dual Bus(DQDB) [92], these two problems are improved and the delay jitter

compensation on AAL 1 will become reasonable [93].

#### 2.3.2 Buffer Priority Control

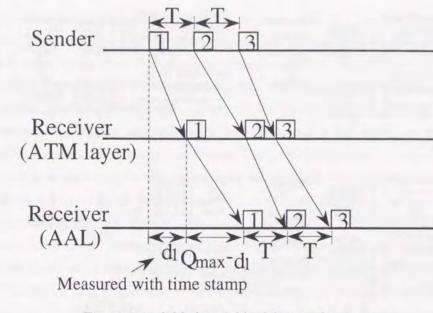

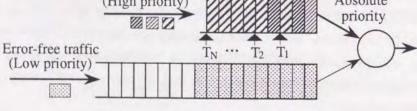

Isochronous services have various QOS requirements, e.g. an admissible end-to-end cell loss probability is  $10^{-8}$  for video communication and  $10^{-3}$  for telephony [36]. If the cells from all services are handled in the same manner, the resource management of the ATM network must be carried out according to the QOS requirements of the most demanding services (the second problem described in section 2.2). Moreover, congestion caused among ABR services will affect CBR(VBR) services (the fourth problem described in section 2.2). To solve these two problems, a buffer priority control [26, 32, 33, 34, 35, 36, 37] has been considered to be efficient. Buffer priority controls are classified into two categories: a delay priority and a loss priority(space priority). The former mainly gives preferential delay treatment, while the latter provides preferential loss treatment to high priority calls [35]. Next, we describe some buffer priority control schemes.

The delay priority schemes perform a priority control by means of a server scheduling as shown in Figure 2.5(a)-(d). Some delay priority schemes have been proposed, e.g. an absolute priority [78, 79], a Minimum Laxity Threshold(MLT), a Queue Length Threshold(QLT) [32], and a Periodical Bandwidth Allocation(PBA) [34]. The absolute priority gives an absolute priority to the isochronous traffic(corresponding to the high priority class in general). In other words, the errorfree traffic (corresponding to the low priority class in general) are served only when there is no cell in the high priority class queue as shown in Figure 2.5(a). Although this scheme is simple, the QOS of the low class cells seem to be more degraded than other schemes.

MLT gives priority to the isochronous traffic when the Minimum Laxity(ML) of the isochronous cells<sup>1</sup> is less than or equal to a threshold, L; otherwise priority is given to the error-free traffic as depicted in Figure 2.5(b). QLT gives priority to the error-free traffic when the number of queued

Figure 2.4: Added variable delay mechanism.

<sup>14</sup>

<sup>&</sup>lt;sup>1</sup>It is defined as the amount of time until the first deadline of all queued isochronous cells expires.

Chapter 2. Synchronous Transmission in ATM Networks

Figure 2.6: Structure of NTCD-MB.

error-free cells is above a threshold, T; otherwise isochronous cells are given priority as shown in Figure 2.5(c). Both MLT and QLT achieve essentially the same performance tradeoff which is better than the absolute priority [32]. MLT requires a complex calculation to obtain ML, so QLT seems to be the best method among these three schemes. The upper limit of the delay jitter for an isochronous service can not be guaranteed by the absolute priority, MLT, or QLT.

In order to realize this assurance and decrease the influence on the error-free traffic, PBA selects isochronous cells periodically as depicted in Figure 2.5(d). The transmission period of the isochronous traffic,  $T_p$  is determined dynamically to guarantee all isochronous cells to be transmitted in T. In other words,  $T_p$  is derived from  $T_p = T/N(T)$ , where N(T) is the number of isochronous cells arrived during T period. The difficulty of the scheduling algorithm weakens the attraction of this method.

#### 2.3. Transmission of Isochronous Traffic

In the loss priority (space priority), e.g. a threshold scheme [35, 37, 80] and an overwriting scheme [35, 37], an error-free cell is dropped (dropped information can be recovered by retransmission) and its buffer space is given to an isochronous cell to avoid congestion. All cells are queued into the same buffer provided some thresholds in the threshold scheme. When the queue length exceeds the threshold  $T_i$ , all arrived cells of class i to N(N) is the number of priority classes) are dropped as shown in Figure 2.5(e). In the overwriting scheme, an isochronous cell arriving at a full buffer can be replaced with an error-free cell arriving earlier as depicted in Figure 2.5(f). Although the threshold scheme is simple, a complex processing is necessary for the overwriting scheme. On the other hand, the performance of the latter scheme is better than the former one.

The loss priority control can not reduce a cell delay jitter of isochronous traffic. If only the delay priority mechanism is introduced, however, the efficiency of isochronous service accommodation becomes worse because the most strict required cell loss rate is applied to all isochronous services. Therefore, a Nested Threshold Cell Discarding with Multiple Buffers(NTCD-MB) has been proposed [33]. NTCD-MB combines the delay priority (absolute priority) and the loss priority (threshold scheme); all isochronous cells which consist of plural priority classes are inserted to the high priority buffer and all error-free cells are queued in the low priority buffer as shown in Figure 2.6. The high priority buffer is always given the priority to the low priority buffer as the absolute priority, and each priority class made in isochronous services are treated as the threshold scheme within the high priority buffer. This scheme satisfies both two purposes of the buffer priority control: the prevention of the congestion propagation from ABR to CBR(VBR) and the increment of the acceptable number of isochronous services.

Though the buffer priority control can solve the second and the fourth problems described in section 2.2, introducing this control is not enough to satisfy the all requirements of isochronous services. The problems are listed as follows.

- The delay jitter is not bounded except for the PBA method.

- cell loss rate for isochronous services, this contention must be considered.

- memory is necessary, and the queueing delay increases in this case.

#### 2.3.3 Stop-and-Go Queueing

In this section, we explain the stop-and-go queueing [38, 39, 40, 41, 42] which aims at the perfect avoidance of cell loss caused by a buffer overflow and the restriction in an intranetwork delay jitter.

• The third problem explained in section 2.2, i.e. single stage and large scale ATM switch architectures cause a cell collision at output ports, is out of this control. In order to guarantee the

• A buffer priority control applies the QOS guarantee to whole cells constituting one priority class. For example, when  $10^{-9}$  cell loss rate is guaranteed for one isochronous priority class, one connection of this class may experience  $10^{-8}$  cell loss rate while another connection of the same class experiences  $10^{-10}$  cell loss rate. In order to guarantee QOS for each connection on the buffer priority control, a buffer has to be provided for each connection and connection based priority control is necessary. A fair queueing approach [81] is one example to guarantee QOS for each connection based on the buffer priority control. However, a complex control and large

Chapter 2. Synchronous Transmission in ATM Networks

Figure 2.7: Stop-and-Go queueing strategy.

This method resolves the second and the fourth problem mentioned in section 2.2. Moreover, the assurance of the upper limit of a delay variance responds the first problem partially: makes it simple to recover CBR timing at the AAL 1 of receivers(see section 2.3.1).

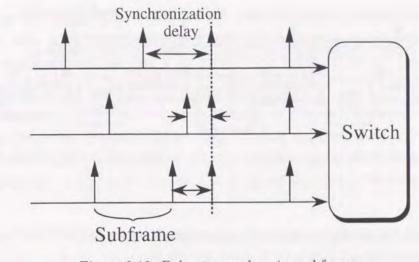

This scheme consists of two strategies, an admission policy and a stop-and-go queueing. It assumes a frame, whose length is T, in a time axis. In the admission policy, each call is accepted based on the maximum number of cells which can be transmitted during a frame T with respect to all links on the route. By only this strategy, it is impossible to guarantee no cell loss at each intermediate node because each source tends to make a burst on random position. To prevent a buffer overflow, the stop-and-go queueing is introduced. In this control, all cells arriving during one frame time are stored at an intermediate node, and then transmitted to the next node. The stop-and-go queueing keeps the number of cells transmitted during the frame less than or equal to the maximum number determined by the admission policy. In order to simplify the frame-based queueing, a switch architecture has been proposed [42]: two buffers are provided for each output link as shown in Figure 2.7. This is the same structure of a double buffer method on a digital switch. Arrived cells are stored into one buffer and cells are transmitted to the output link from the other buffer simultaneously. The roles, i.e. reading and writing, are exchanged at each frame boundary. The stop-and-go queueing assumes a frame-based synchronization, so a buffer is attached in front of a switching fabric to realize this synchronization. The amount of this synchronization buffer is the proper value for each input link and less than the frame length.

By both strategies, cell losses caused by the buffer overflow at each intermediate node are prevented, and all cells are transmitted with bounded intra-network delay jitter within one frame. This scheme, however, can not remove cell loss caused by the output port contention at a switching fabric (the third problem described in section 2.2).

The end-to-end (from the source to the destination) delay, D is

$$D = Q + \tau + d, \tag{2.2}$$

where Q is a constant delay caused by a buffering,  $\tau$  is a propagation delay, and d is a fluctuation of the delay caused by the statistical multiplexing. At all intermediate nodes, additional buffering delay for synchronization of frames from different links is necessary, which is bounded by T. Thus, we have

$$nT \le Q \le 2nT,\tag{2.3}$$

#### 2.4. Quasi-STM Transmission Method

where n is the number of intermediate nodes on the route of the corresponding call. Since  $Q \gg \tau$  and 0 < d < T, the end-to-end delay and the width of intra-network delay jitter are proportional to T. So, the longer T leads to the greater network delay. However, the shorter T is, the worse the flexibility of bandwidth allocation becomes, because each call is allocated the bandwidth by means of the number of cells within one frame. Here, we summarize the demerits of this scheme.

- allocation.

- CBR timing is necessary.

- introduced if it tries to guarantee a cell loss free transmission.

#### Quasi-STM Transmission Method 2.4

Here, it is efficient to consider the allocation of cell transmitted positions for each isochronous call on the ATM network because a time slot reservation resolves all four problems mentioned in section 2.2 without any complex processing during cell transmission. In other words, the ATM time slot allocation for each call has three merits. First, even if any type of the ATM switching fabric is used, the collision of cells at the output ports have never occurred by means of time scheduling. Second, a cell delay jitter is prevented in a network because the cell transmitted positions are determined exactly whole the network. Thus, a CBR receiver becomes simpler. Third, the distribution of a cell arrival interval is controlled by means of the slot allocation algorithm, so we can moderate burstness of isochronous traffic by using some sophisticated slot allocation algorithms.

We propose the new method named as Q-STM [47, 48, 49]. The main features of the proposal method are summarized as next three items.

- the routes. Thus the switching of time slots at each intermediate switch is needed.

- the subframe which is composed by splitting a frame into the same time interval.

- are suitable in this service class. Hence, there are two different types of cells, Q-STM cells and ATM cells, on a link.

In the following four subsections, the frame structure, the ATM service class, the switch architecture, and the call setup procedure are explained respectively. After explaining the fundamental frame concept of the Q-STM method, we describe the aim and meaning of the subframe introduction by

• The queueing delay is much longer than other methods if it preserves the flexibility of bandwidth

• It is impossible to avoid a delay jitter perfectly in this scheme, so other method which recover

• The cell collision within the ATM switching fabric can not be avoided, thus non-blocking fabric(e.g. the input-output switch, the output switch, and the shared memory switch) should be

(1) All Q-STM calls are allocated fixed time positions in a frame to transmit cells over all links on

(2) The period of time switching is not the frame which is the period of bandwidth allocation, but

(3) In addition to the Q-STM service class, a normal ATM service class without frame concept is composed in order to accommodate high bursty calls efficiently and improve link utilization. Calls with high burst or relative tolerance of a cell loss, i.e. error-free services(data communication),

Chapter 2. Synchronous Transmission in ATM Networks

Figure 2.9: Example of the slots allocation.

means of comparing some alternatives in the frame structure subsection. In the ATM service class subsection, the meaning of this service class is explained. We summarize the requirements to realize the Q-STM switch, then compare some switch architectures in the switch architecture subsection. Finally in the call setup subsection, some algorithms are proposed and investigated qualitatively.

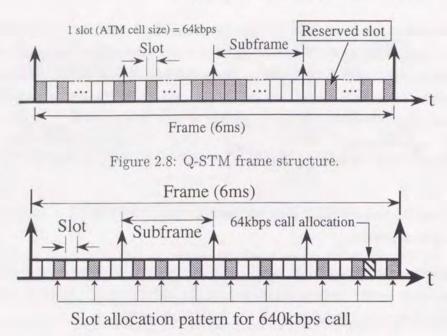

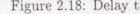

#### 2.4.1 Frame Structure

#### **Fundamental Concept**

In order to allocate transmitted cell position on the ATM network, it is necessary to introduce a frame and a slot concept on a time axis: a frame is a period of bandwidth allocation and a slot is a unit of bandwidth allocation. For example, the frame length is  $125\mu s$ , which corresponds to a sampling period of a voice source, and the slot length is 8bits in the conventional STM network. It is convenient to set the slot length equal to the amount of information transmitted from the lowest rate service during a frame period. In this case, reserving one slot per one frame just corresponds to the allocation of the lowest rate service. In the ATM network, the time slot synchronization has already established; one time slot is equal to the ATM cell length. Because the Q-STM method is based on the ATM network and cell-based switching, it is efficient to set the slot length as the ATM cell size. Moreover, we assume that the lowest rate isochronous service accommodated into the Q-STM service class is 64kbps voice service. It takes 6ms to make one cell from 64kbps source because the ATM cell payload is  $48bytes^1$ . As mentioned later, the queueing which is three times of the frame length is necessary at the maximum for each node. When the call passes several nodes, the queueing delay will be longer than the limit permitted for isochronous services. For example, a per switch cell transfer delay should be below  $500 \mu s$  for services such as DS-1/DS-3 circuit emulation [12].

#### 2.4. Quasi-STM Transmission Method

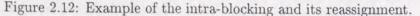

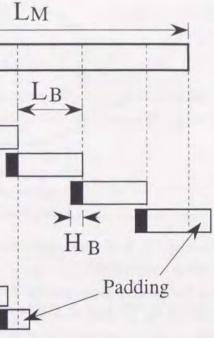

The longer a frame is, the better the flexibility of bandwidth allocation becomes because bandwidth of each call is assigned in the form of the number of cells in a frame. From viewpoints of delay performance, the shorter frame size is preferable because a frame is stored for time switching at each node. To satisfy above two conflicting requirements, the Q-STM method introduces a new time frame concept named as "subframe". Therefore, this scheme uses a frame structure consisting of three layers, "the frame", the "subframe", and the "slot", as shown in Figure 2.8. Time switching is executed on the subframe basis, that is composed by splitting one frame into multiple equivalent time intervals. A time table whose period is the subframe length is prepared for each subframe. The referred table is switched at each subframe boundary. The number of subframes within one frame(or the subframe length) is an interesting parameter because it affects many qualities in the Q-STM network. We roughly obtain the most efficient number through some quantitative evaluations in section 3.3.3.

6ms as mentioned before. For the call of 640kbps, 10 slots should be allocated. These allocated slots can be placed anywhere in a frame.

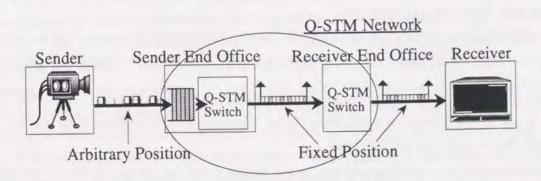

Next, we mention how to insert Q-STM cells transmitted from each source. At the entrance point of the Q-STM network, arriving Q-STM cells are queued for each connection, then inserted to the allocated slots. The Q-STM network is defined between the sender end office and the receiver end office. Thus, this entrance point is located at the sender end office. As a result, the Q-STM frame structure is not introduced on the upstream subscriber line(from the sender terminal to the sender end office). On the other hand, the Q-STM frame concept is provided on the downstream subscriber line(from the receiver end office to the receiver terminal) as shown in Figure 2.10. Each Q-STM call can transmit cells in any slots if they are reserved for the call. There is no delay variance within the Q-STM network after the transmitted slot is determined at the sender end office. The Q-STM source terminal can not send cells exceeding its bandwidth. Consequently UPC is realized constructively for Q-STM calls.

The bandwidth allocation is performed by reserving required number of time slots within the frame. It should be noted that one call can be allocated slots over plural subframes. In Figure 2.9, we show the example of the Q-STM slot allocation where the bandwidth are 64kbps and 640kbps. When the link speed is 156Mbps and one slot is equivalent to 64kbps, the number of slots in a frame is about 2200  $\left(\frac{48\times8}{6.4\times10^4}\times\frac{1.56\times10^8}{53\times8}\simeq 2200\right)$ . In this example, the number of subframe is 4, so the number of slots in a subframe is about 550. It is too difficult to show 2200 slots in the figure, so the number of slots in the figure is less than actual frame. 64kbps is assumed to be the slowest call, so the frame length is

Figure 2.10: Bounds of the Q-STM network.

<sup>&</sup>lt;sup>1</sup>Actually, one byte of the ATM cell payload is reserved for AAL 1. For the sake of a calculation convenience, 48bytes cell payload is assumed to be used for user information in this thesis.

Chapter 2. Synchronous Transmission in ATM Networks

Figure 2.11: Comparison of the frame concept.

#### Meaning of Subframe Introduction

We describe the significance of the subframe concept by comparing with two cases without subframes. Here, n indicates the number of subframes within one frame. As shown in Figure 2.11, the following three models are considered.

- (1) Introducing the subframe concept, and making the subframe a time switching period(proposed Q-STM method corresponds to this case)

- (2) Without the subframe concept, matching the frame length with the subframe length of the first case

- (3) Without the subframe concept, matching the frame length with the frame length of the first case

The three cases are compared from the three viewpoints: (A)a flexibility of bandwidth allocation<sup>1</sup>, (B)a buffering delay caused in a time switch(it is proportional to the amount of required memory), and (C) a required call setup time.

### [Comparison between (1) and (2)]

The flexibility of bandwidth allocation of (1) is n times as large as that of (2). The buffering delay and the required time switch size of (1) are same as those of (2). When the same amount of bandwidth is allocated, the number of reserved slots of (1) is n times as large as that of (2).

### [Comparison between (1) and (3)]

The flexibility of bandwidth allocation and the required number of allocating slots are same for (1) and (3). The time switching delay and its memory size of (3) is n times as large as those of (1).

Judging from above comparison, the availability of the subframe introduction is evident. However, there is a fear of the growth of a call setup time. The quantitative evaluation for the Q-STM call setup time will be shown in section 3.4.2.

#### 2.4. Quasi-STM Transmission Method

#### 2.4.2 ATM Service Class

The Q-STM method introduces a normal ATM service class which has no frame concept in addition to the Q-STM service class. Thus, both Q-STM and ATM cells are transmitted on a link in mixed state. By introducing this service class, we obtain following effects.

- kept by Q-STM and we can obtain a statistical multiplexing gain from them.

In general, isochronous traffic is accommodated in the Q-STM service class and error-free traffic is supported in the ATM service class. When VBR call is supported as the Q-STM class, the vacant cell position inside the allocated slot may occur because of the rate fluctuation of the source. ATM cells are allowed to be inserted in these spaces in addition to the slots which are not allocated for Q-STM calls. By this strategy, even though time slots are reserved for each Q-STM call, we can obtain the statistical multiplexing gain and improve the utilization of the link. This is not derived from the conventional STM network.

Now, Q-STM cells has a complete priority in assigned slots, so ATM class cells can be regarded as low priority cells. Thus, the QOS of the ATM service class are greatly affected by the distribution of allocated slots and the characteristics of the Q-STM traffic. In the Q-STM method, the distribution of Q-STM cells within a frame can be controlled by means of the slot allocation pattern. The degradation of the ATM service class QOS is moderated by scattering reserved slots position within the frame. Therefore, the Q-STM call setup algorithm is important. We discuss this matter in section 2.4.4.

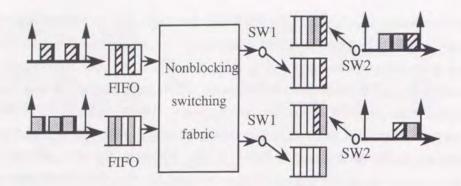

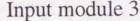

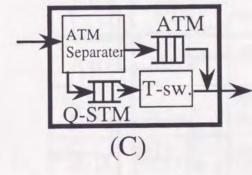

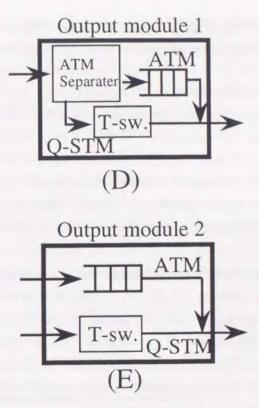

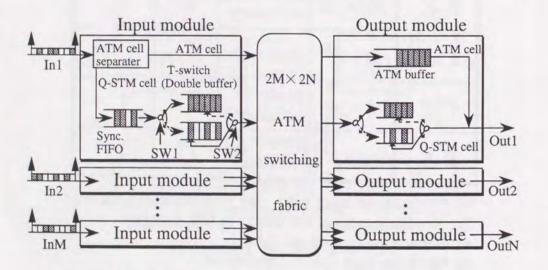

#### 2.4.3 Switch Architecture

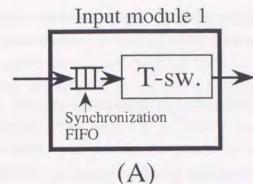

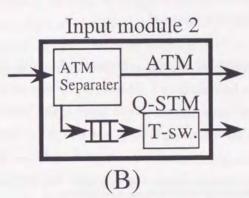

A Time switch (T-switch) which executes time switching of slots is necessary in the switch for the Q-STM scheme. In this subsection, we investigate and compare some switch architectures for the Q-STM scheme. Then, the cell switching motion inside the switch is explained briefly.

#### **Basic Assumption**

In order to realize the virtual STM transmission on the ATM network, it is necessary to introduce the concept of the frame, which is a period of bandwidth allocation, and the slot, which is a unit of it, like the ordinary STM network. When heterogeneous services requiring various bandwidth are accommodated, plural number of slots must be assigned for one call. Therefore, a Time Slot Sequence Integrity(TSSI) [82, 83, 84] becomes a problem like N-ISDN. TSSI is to maintain a cell sequence for a call allocated plural slots. The double buffer structure is useful to resolve this problem, so it has been adapted to many digital switches. In the double buffer structure, two T-switches are provided: information is read from one and written to the other at the same time. The function is switched at the boundary of the time switching period(i.e. the frame in STM and the subframe in the Q-STM method). The Q-STM method also adopts the double buffer structure to maintain TSSI easily.

Although only T-switch can construct the switching facility, it is efficient to combine T-switch with a Space switch (S-switch) to built a large scale switch. Among some combination of both switches,

22

(1) The services with very high burstiness or tolerance for cell loss can be accommodated efficiently.

(2) The slots which are not used by Q-STM calls can be used by ATM class cells, so they are not

<sup>&</sup>lt;sup>1</sup>Bandwidth is allocated by reserving some time slots within one frame. The minimum interval of bandwidth which can be accommodated is one slot/ one frame. Therefore, the longer the frame length is, the more the flexibility of bandwidth allocation becomes.

#### 2.4. Quasi-STM Transmission Method

a TST structure, providing two T-switches at the both sides of S-switch, has been considered to be the best one from the viewpoint of a scalability [85, 86]. The Q-STM method also adopts the TST structure like many digital switches.