| Title        | Process development of ultra-fine pitch assembly for system-in-package devices |

|--------------|--------------------------------------------------------------------------------|

| Author(s)    | Lee, Yong-Won                                                                  |

| Citation     | 大阪大学, 2013, 博士論文                                                               |

| Version Type | VoR                                                                            |

| URL          | https://doi.org/10.18910/26189                                                 |

| rights       |                                                                                |

| Note         |                                                                                |

#### The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

#### **Doctoral Dissertation**

Process development of ultra-fine pitch assembly for system-in-package devices

Yong-Won Lee

**July 2013**

Graduate School of Engineering Osaka University

# Process development of ultra-fine pitch assembly for system-in-package devices

A DISSERTATION PRESENTED

by

#### Yong-Won Lee

to

# THE GRADUATE SCHOOL OF ENGINEERING IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### **Doctor of Philosophy**

IN THE SUBJECT OF

ADAPTIVE MACHINE SYSTEMS

OSAKA UNIVERSITY

OSAKA, JAPAN July 2013

© 2013 – Yong-Won Lee All Rights Reserved.

#### **OSAKA UNIVERSITY**

# Process development of ultra-fine pitch assembly for system-in-package devices

by

#### Yong-Won Lee

THE PRESENT DISSERTATION HAS BEEN APPROVED BY THE DISSERTATION COMMITEE AS A DOCTORAL DISSERTATION

Professor Katsuaki Suganuma, Chair Professor Katsuhiro Hirata Associate Professor Koji Hagihara Associate Professor Masaya Nogi Associate Professor Shijo Nagao

> OSAKA, JAPAN July 2013

Dissertation Advisor Katsuaki Suganuma

Yong-Won Lee

Author

## Process development of ultra-fine pitch assembly for system-in-package devices

#### **Abstract**

This dissertation describes the development of robust assembly processes for a high-density system-in-package (SiP) with lead-free solder interconnected devices, including various elemental selection criteria, design strategies, and experimental techniques. A comprehensive study was undertaken to evaluate various assembly parameters of 01005s as they relate to highly reliable products. The study evaluated solder printing-related parameters, such as types of solder paste, stencil, and stencil design, and pick-and-place machine-related parameters, such as types of vision camera, and vacuum pick-up nozzle. This study identifies and evaluates the key parameters affecting solder paste printing. These include stencil-related parameters, such as laser machine type, laser-cutting time, electrolyte type and electro-polishing time, and metallic stencil material type, and printing process-related parameters, such as solder paste type, print speed, and print pressure. In addition, three types of stencils (laser-cut stainless steel with coarse-grained SUS304 microstructure, laser-cut stainless steel with fine-grained SUS301 microstructure, and electroformed nickel) were investigated by measuring transfer efficiency as a function of the area ratio of the stencil apertures. This study proposes a solution to assembly problem by minimizing or eliminating soldering defects, such as tombstoning, voiding, and spattering in the assembly of 0201 chip components using micro via-in-pads of 95 wt.%Sn-5 wt.%Sb solder alloy. Four different micro via-in-pad designs were compared: 1) ultra-small via-in-pads; 2) small via-in-pads; 3) large via-in-pads; 4) capped via-in-pads, and no via-in-pads. Furthermore, this study designed experiments to evaluate multiple alternatives for several steps in the reworking process. Two commonly used techniques for cleaning pads were evaluated: the manual soldering iron and the semi-automatic system. Boards with and without retrofit fixtures were evaluated. Because the reliability of the reworked solder joint was also a concern, a reliability study consisting of crosssectional analysis, scanning electron microscopy (SEM), thermal cycling, drop shock, and shear

test was conducted to determine the reliability of the reworked solder joints. In summary, based on the results of this study, recommendations are made for mass production and implementation of emerging packages, such as 01005s, flip-chips, CSPs, and BGAs. In addition, the findings provide process guidelines for a high-density SiP module with ultra-fine pitch solder interconnected devices and lead-free solder alloys.

#### **Preface**

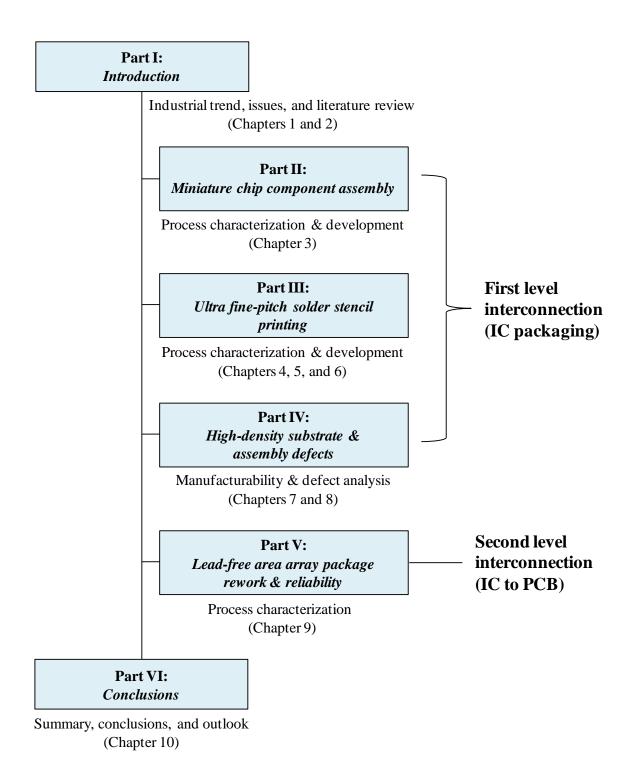

This dissertation is submitted for the degree of Doctor of Philosophy at Osaka University. The doctoral dissertation work was carried out under the supervision of Professor Dr. Katsuaki Suganuma in the Department of Adaptive Machine Systems at Osaka University between the years of 2007 and 2013. This dissertation is written based on author's over twelve years experience in advanced microelectronics packaging and in the development of interconnection technology, especially soldering and surface mount technology for various applications. Except where acknowledgement and reference to previous work is made, this work is, to the best of my knowledge, original, and has been carried out without collaboration. Neither this, nor any substantially similar dissertation has been, or is being, submitted for any other degree, diploma or qualification at any other university. This dissertation contains fewer than 60,000 words, and is identical to that which was examined, except for corrections as required by the examiners. The dissertation consists of ten chapters, which are grouped into six parts for convenience. Chapter 3 through 9 is the core parts of this study which cover the objective and overview, experimental procedures, results and discussions, and summary. These chapters were written for publication as research articles.

## **Table of Contents**

| Ab  | ostract | t                                                         | i     |

|-----|---------|-----------------------------------------------------------|-------|

| Pro | eface   |                                                           | 111   |

| Та  | ble of  | f Contents                                                | iv    |

| Lis | st of F | Figures                                                   | V111  |

|     |         | Гables                                                    |       |

| Ab  | brevi   | ation                                                     | XX1   |

| Ac  | know    | rledgement                                                | XX111 |

|     |         |                                                           |       |

| PA  |         | I   AN INTRODUCTION AND OVERVIEW                          |       |

| 1   | Intr    | oduction                                                  | 3     |

|     | 1.1     | Motivations                                               |       |

|     |         | 1.1.1 Implementing lead-free electronics                  |       |

|     |         | 1.1.2 Miniaturized electronics assembly                   |       |

|     |         | 1.1.3 System-in-package technologies                      |       |

|     | 1.2     | Historical background                                     |       |

|     |         | 1.2.1 Technological driving force                         |       |

|     |         | 1.2.2 Problem description                                 |       |

|     | 1.3     | The goal and outline of this dissertation                 | 24    |

| 2   | Rec     | ent progresses                                            | 29    |

|     | 2.1     | Passive chips in modern system-in-packages                | 30    |

|     |         | 2.1.1 Impact of 01005 chips in electronics manufacturing  |       |

|     |         | 2.1.2 Assembly processes for 01005 chip components        |       |

|     |         | 2.1.3 Assembly critical parameters for high process yield | 33    |

|     | 2.2     | Printing fine-pitch solder paste                          | 37    |

|     |         | 2.2.1 Process characterization of the stencil printing    | 37    |

|     |         | 2.2.2 Stencil fabrication technology                      |       |

|     |         | 2.2.3 Post surface finish of stencil aperture walls       | 44    |

|     |         | 2.2.4 Characteristics of solder powder                    | 45    |

|     | 2.3     | High-density substrate and assembly defects               |       |

|     |         | 2.3.1 Micro via-in-pads                                   | 49    |

|     |         | 2.3.2 Voiding and spattering defects                      | 49    |

|     |         | 2.3.3 Tombstoning defect                                  | 54    |

|     | 2.4     | Lead-free assembly and rework                             | 56    |

|            | 2.5  | 2.4.1 Lead-free rework assembly for BGA and CSP packages                                                                                            | 57  |

|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| PA         | ART  | II   MINIATURE-SIZED CHIP COMPONENT ASSEMBLY                                                                                                        | 7   |

| 3          |      | effect of selected process parameters on defects in the assembly of 01005                                                                           | -   |

|            | 3.1  | Objective and overview                                                                                                                              |     |

|            | 3.2  | Experimental                                                                                                                                        |     |

|            | 3.3  | Results and discussion                                                                                                                              |     |

|            |      | 3.3.1 Assembly process analysis                                                                                                                     |     |

|            | 3.4  | 3.3.2 Reliability results                                                                                                                           |     |

| <b>P</b> A | The  | III   ULTRA-FINE PITCH SOLDER STENCIL PRINTING  effects of acid electrolytes and electropolishing conditions on the permance of the small apertures |     |

|            | 4.1  | Objective and overview                                                                                                                              |     |

|            | 4.2  | Experimental                                                                                                                                        |     |

|            | 4.3  | Results and discussion                                                                                                                              |     |

|            |      | 4.3.1 The effect of the acid solution as electrolyte                                                                                                |     |

|            |      | 4.3.2 The effect of EP time                                                                                                                         |     |

|            | 4.4  | Summary                                                                                                                                             | 124 |

| 5          |      | effects of electropolishing on the printing performance of the small apertu                                                                         |     |

|            |      |                                                                                                                                                     | 125 |

|            | 5.1  | Objective and overview                                                                                                                              | 126 |

|            | 5.2  | EP process analysis                                                                                                                                 |     |

|            |      | 5.2.1 Materials and methods                                                                                                                         |     |

|            |      | 5.2.2 Design of the experiments                                                                                                                     |     |

|            | га   | 5.2.3 Results and discussion                                                                                                                        |     |

|            | 5.3  | Solder printing behavior                                                                                                                            |     |

|            |      | <ul><li>5.3.1 Materials and methods</li><li>5.3.2 Design of the experiments</li></ul>                                                               |     |

|            |      | 5.3.3 Results and discussion                                                                                                                        |     |

|            |      | 5.3.3.1 Electropolished laser-cut stencil vs. electroformed stencil                                                                                 |     |

|            |      | 5.3.3.2 SMD pads vs. NSMD pads                                                                                                                      |     |

|            | 5.4  | Summary                                                                                                                                             |     |

| 6          | The  | effect of stencil materials on stencil printing performance                                                                                         | 15/ |

| U          | 1116 | enect of stellen materials on stellen printing performance                                                                                          | 134 |

|            | 6.1  | Objective and overview                                                                                                                              | 155 |

|            | 6.2  | Noble stencil technology development                                                                                                                | 156 |

|   |     | 6.2.1 Experimental                                                  | 156   |

|---|-----|---------------------------------------------------------------------|-------|

|   |     | 6.2.2 Results and discussion                                        | 163   |

|   |     | 6.2.2.1 Stencil material characterizations                          | 163   |

|   |     | 6.2.2.2 Stencil fabrication process analysis                        | 170   |

|   | 6.3 | Flip-chip assembly and SMT process                                  | 179   |

|   |     | 6.3.1 Experimental                                                  | 179   |

|   |     | 6.3.1.1 Test vehicle                                                |       |

|   |     | 6.3.1.2 Materials and methods                                       |       |

|   |     | 6.3.1.3 Design of the experiments                                   |       |

|   |     | 6.3.2 Results and discussion                                        |       |

|   | 6.4 | Summary                                                             | 195   |

| P | ART | IV   HIGH-DENSITY SUBSTRATE AND ASSEMBLY DEI                        | FECTS |

| 7 | The | effect of micro via-in-pad designs on tombstoning defect            | 199   |

|   | 7.1 | Objective and overview                                              | 200   |

|   | 7.2 | Experimental                                                        |       |

|   |     | 7.2.1 Materials and methods                                         | 200   |

|   |     | 7.2.2 Design of the experiments                                     |       |

|   |     | 7.2.3 FEM thermal simulation                                        |       |

|   | 7.3 | Results and discussion                                              |       |

|   |     | 7.3.1 The effect of micro via-in-pad designs on tombstoning         |       |

|   |     | 7.3.2 The effect of stencil aperture size on tombstoning            |       |

|   |     | 7.3.3 The effect of reflow profile on tombstoning                   |       |

|   |     | 7.3.4 FEM simulation results                                        |       |

|   | 7.4 | Summary                                                             | 219   |

| 8 | The | effect of micro via-in-pad designs on voiding and spattering defect | 220   |

|   | 8.1 | Objective and overview                                              |       |

|   | 8.2 | Experimental                                                        |       |

|   |     | 8.2.1 Materials and methods                                         |       |

|   |     | 8.2.2 Design of the experiments                                     |       |

|   | 8.3 | Results and discussion                                              |       |

|   |     | 8.3.1 The effect of micro via-hole size on voiding                  |       |

|   |     | 8.3.2 The effect of micro via-in-pad designs on spattering          |       |

|   |     | 8.3.3 The effect of stencil opening size on spattering              |       |

|   | 0.4 | 8.3.4 The effect of reflow profile on spattering                    |       |

|   | 8.4 | Summary                                                             | 244   |

| P | ART | V   LEAD-FREE REWORK AND RELIABILITY                                |       |

| 9 | The | effects of reworked board assemblies with lead-free BGA packages    | 247   |

|   | 9.1 | Objective and overview                                              | 248   |

|   | 9.2 | Experimental                                                        |       |

|    | 9.3                  | Results                            | s and discussion                        |                   |

|----|----------------------|------------------------------------|-----------------------------------------|-------------------|

|    |                      | 9.3.1                              | Pads clean-up process results           | 256               |

|    |                      | 9.3.2                              | Thermal profile development             | 261               |

|    |                      | 9.3.3                              | DIC measurement                         |                   |

|    |                      | 9.3.4                              | Reliability study                       | 265               |

|    |                      | 9.3.5                              | Microstructure analysis                 |                   |

|    |                      | 9.3.6                              | Rework placement gap                    | 276               |

|    | 9.4                  | Summ                               | ary                                     |                   |

| PA | RT                   | VI                                 | CONCLUSIONS                             |                   |

|    |                      |                                    |                                         | 004               |

| 10 | Cone                 | clusion                            | s and outlook                           |                   |

| 10 | <b>Con</b> o         | clusion<br>Summ                    | s and outlookary and concluding remarks | 282               |

| 10 | <b>Con</b> o         | clusion Summ Outloo                | s and outlookary and concluding remarks | 282               |

| 10 | <b>Con</b> o         | Summ Outloo 10.2.1                 | s and outlookary and concluding remarks | 282<br>286<br>286 |

| 10 | <b>Con</b> o         | Summ Outloo 10.2.1                 | s and outlookary and concluding remarks | 282<br>286<br>286 |

| 10 | Conc<br>10.1<br>10.2 | Summ<br>Outloo<br>10.2.1<br>10.2.2 | s and outlookary and concluding remarks |                   |

## List of Figures

#### **CHAPTER 1**

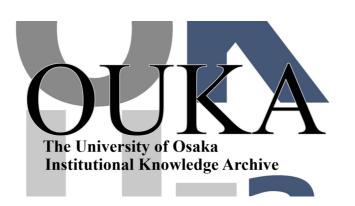

| Figure 1.1: | Principal methods for joining engineering materials. Notes: (a) mechanical fastening; (b) adhesive bonding; (c) welding; (d) diffusion bonding; (e) soldering and brazing                                                                                                                                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

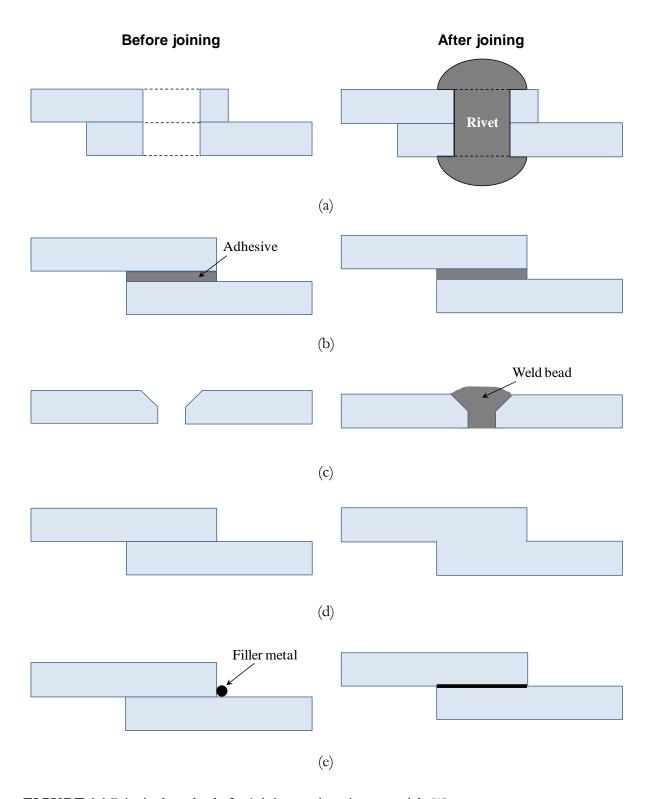

| Figure 1.2: | Some common solder joint configurations. Shaded area is solder and $a$ , $\beta$ are different materials. Notes: (a) die or substrate bonding; (b) solder bump; (c) leadless chip carrier; (d) leaded chip carrier                                                                                                                                                                                                                                |

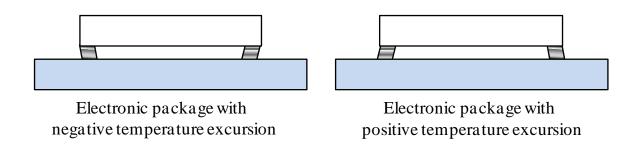

| Figure 1.3: | Development of strains in an electronic device                                                                                                                                                                                                                                                                                                                                                                                                    |

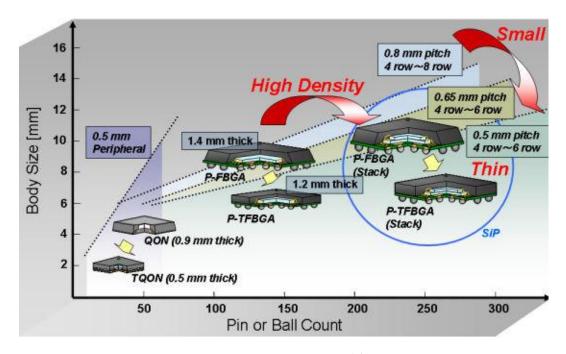

| Figure 1.4: | Package technology trends                                                                                                                                                                                                                                                                                                                                                                                                                         |

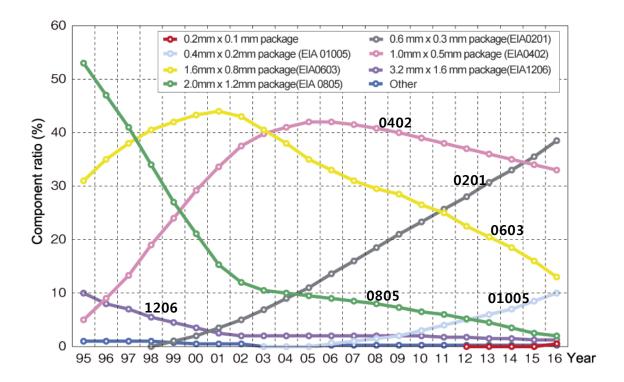

| Figure 1.5: | Trends in the shares of various component sizes. The $1.0 \times 0.5$ mm chip (0402) type has the highest component ratio as of 2009, but it has passed its shipment peak. The $0.6 \times 0.3$ mm chip (0201) type is rapidly increasing in place of the $1.0 \times 0.5$ mm chip (0402). In 2015, the ratio of the $0.6 \times 0.3$ mm chip (0201) type is expected to exceed that of the 0402 chip. The graph is based on Murata's projections |

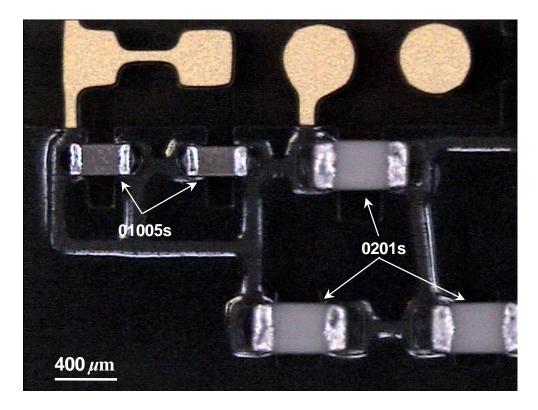

| Figure 1.6: | Size comparisons of tiny 01005 chip components with 0201 size chip components 14                                                                                                                                                                                                                                                                                                                                                                  |

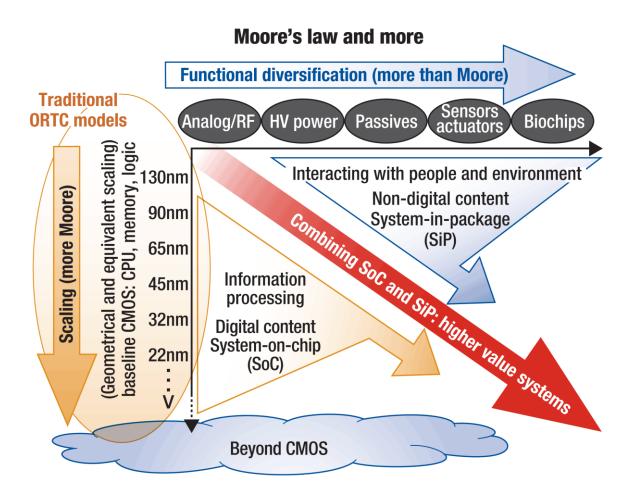

| Figure 1.7: | System-in-package integration leapfrogs traditional scaling approaches, providing "More than Moore" functionality                                                                                                                                                                                                                                                                                                                                 |

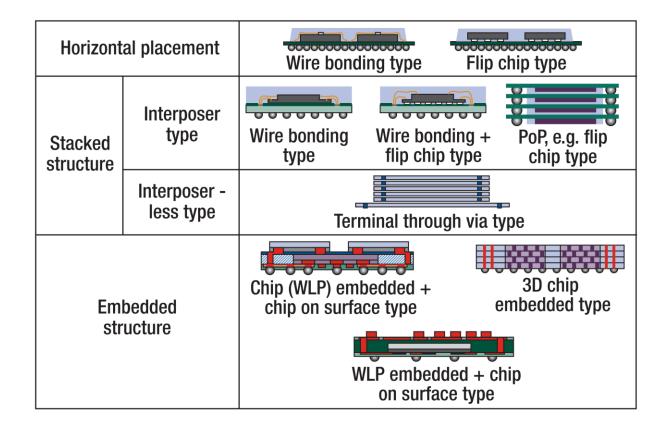

| Figure 1.8: | Variations of current system-in-package methodologies                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 1.9: | Organization of the present dissertation                                                                                                                                                                                                                                                                                                                                                                                                          |

|             | CHAPTER 2                                                                                                                                                                                                                                                                                                                                                                                                                                         |

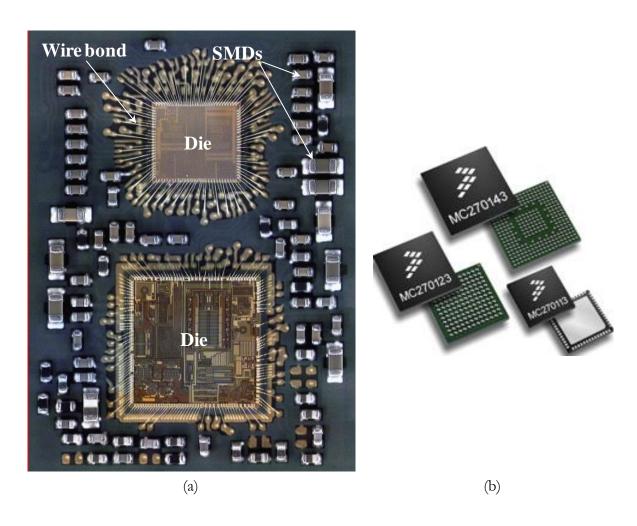

| Figure 2.1: | Typical RF SiP platform                                                                                                                                                                                                                                                                                                                                                                                                                           |

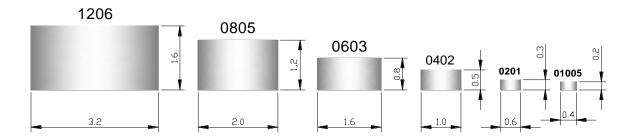

| Figure 2.2: | Dominant passive component dimensions (mm)                                                                                                                                                                                                                                                                                                                                                                                                        |

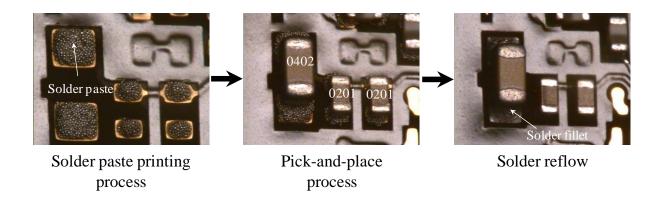

| Figure 2.3: | Cell phone RF section utilizing surface-mount passives by (a) assembled RF module; (b) over-molded RF module package                                                                                                                                                                                                                                                                                                                              |

| Figure 2.4: | Process mapping for SMT line                                                                                                                                                                                                                                                                                                                                                                                                                      |

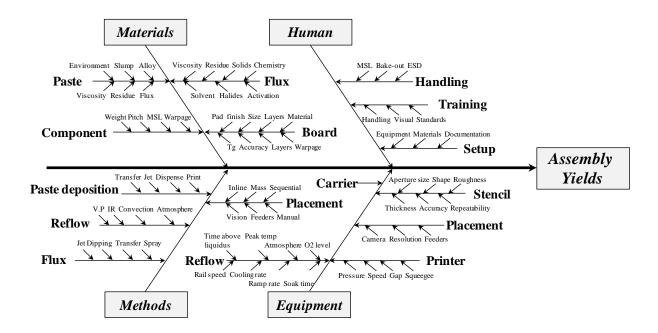

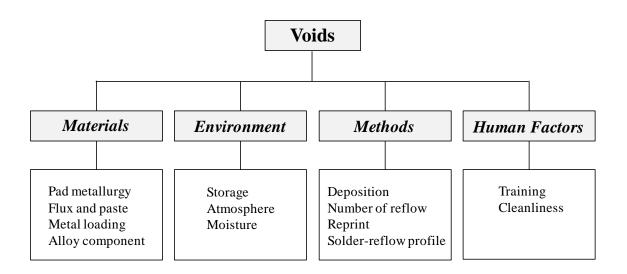

| Figure 2.5: | Cause and effect diagram of factors that influence lead-free assembly                                                                                                                                                                                                                                                                                                                                                                             |

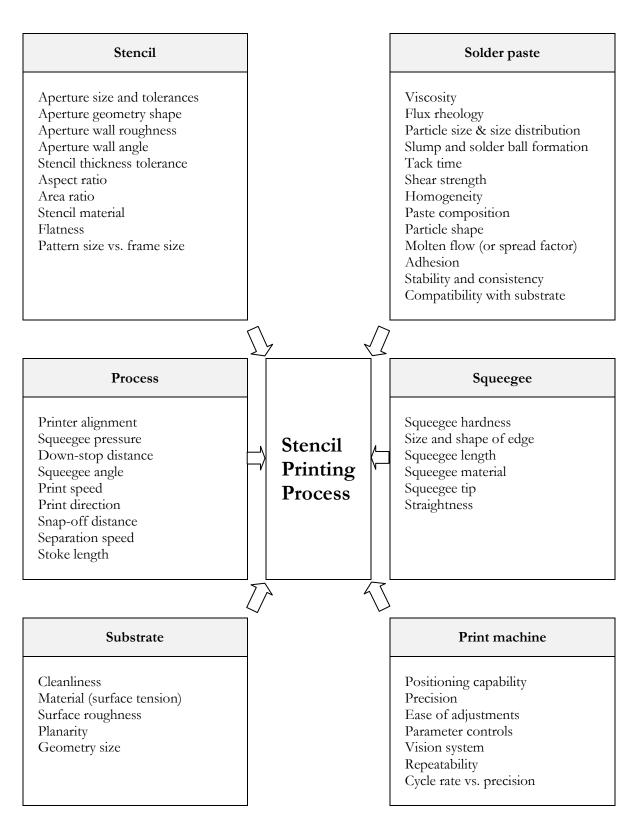

| Figure 2.6: | Factors that influence the stencil printing process                                                                                                                                                                                                                                                                                                                                                                                               |

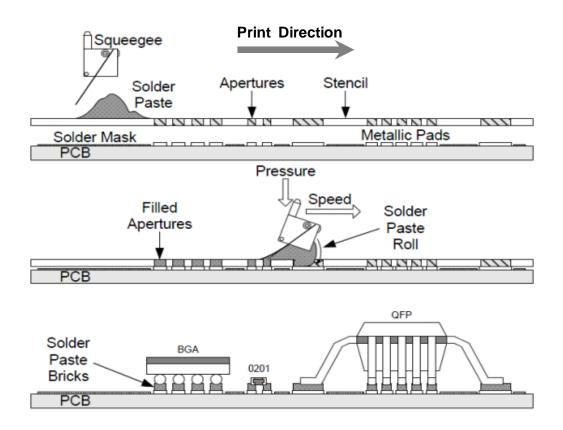

| Figure 2.7: | Stencil printing operation illustrations                                                                                                                                                                                        |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

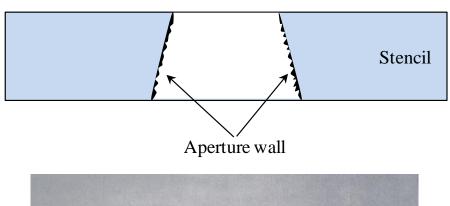

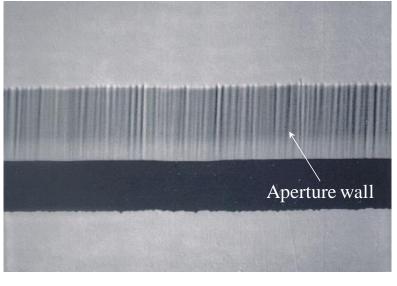

| Figure 2.8: | Stencil apertures made by (a) electroforming; (b) laser-cut                                                                                                                                                                     |

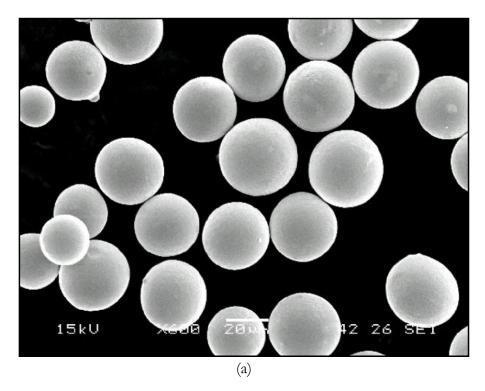

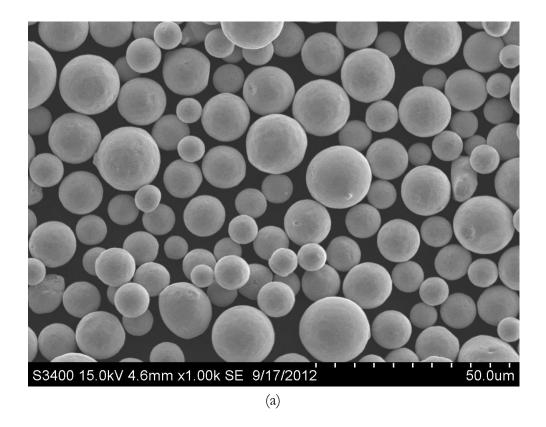

| Figure 2.9: | SEM pictures of type 3 95wt.%Sn–5wt.%Sb solder powder. Notes: (a) X600; (b) X1,00047                                                                                                                                            |

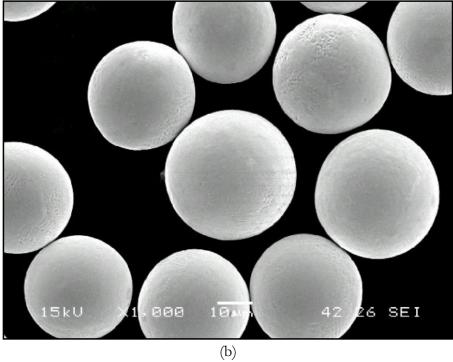

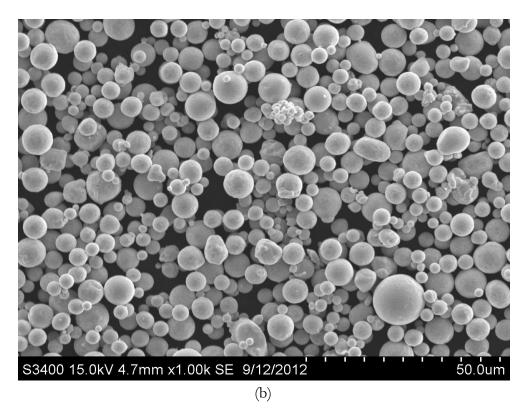

| Figure 2.10 | 0: SEM pictures of type 4 95wt.%Sn–5wt.%Sb solder powder. Notes: (a) X600; (b) X1,00048                                                                                                                                         |

| Figure 2.1  | : Factors contributing to void formation50                                                                                                                                                                                      |

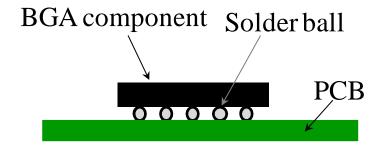

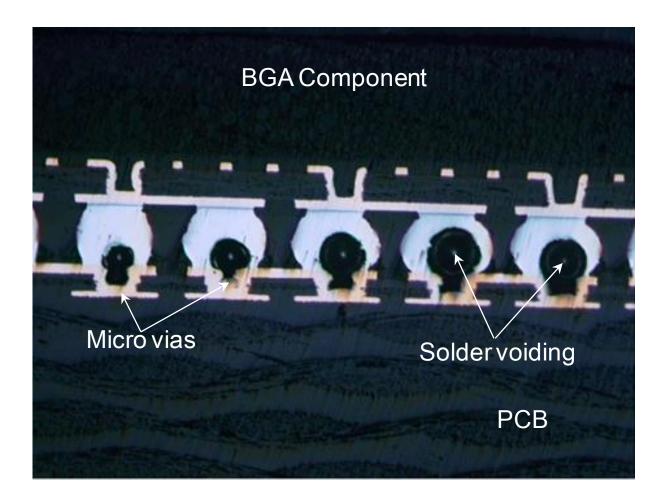

| Figure 2.12 | 2: Cross-section of BGA solder joints formed on micro via. Voids tend to form at the opening of micro via                                                                                                                       |

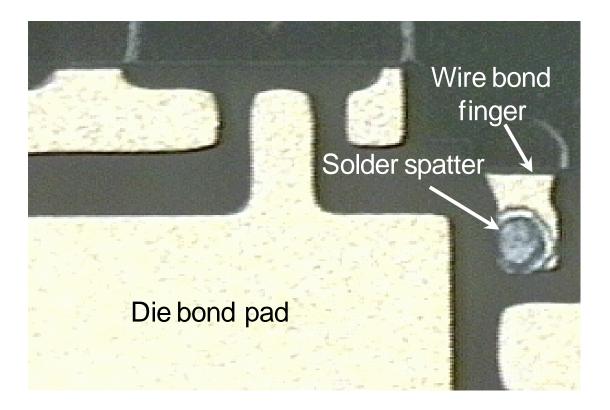

| Figure 2.13 | 3: Picture of solder spattered at reflow. Note the tiny solder droplets on the wire bond finger                                                                                                                                 |

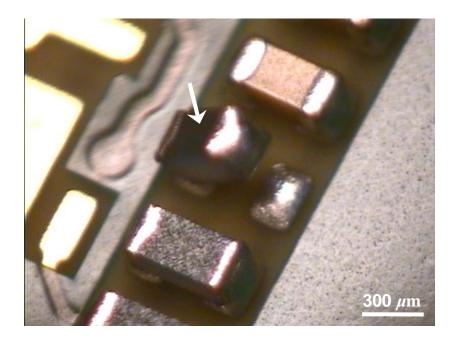

| Figure 2.14 | 4: Example of tombstone, indicated by the arrow: 0201 chip resistor stands on one of its ends55                                                                                                                                 |

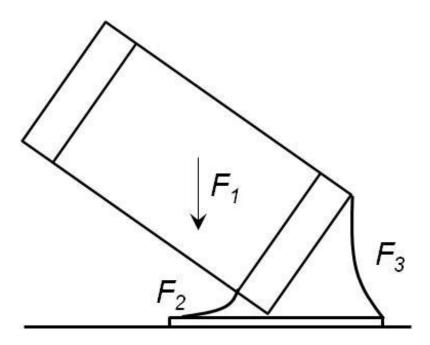

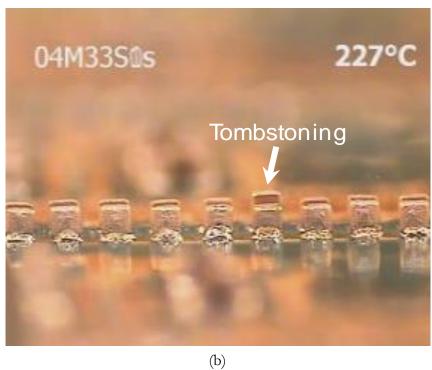

| Figure 2.1  | 5: Schematic representation of the forces acting on a chip as it tombstones55                                                                                                                                                   |

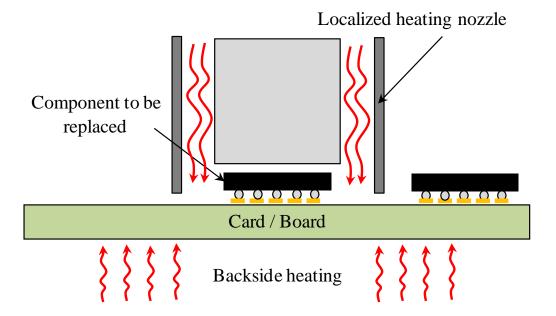

| Figure 2.10 | 5: Illustration depicting the replacement of a component attached to a printed circuit board (PCB) utilizing a localized heating technique                                                                                      |

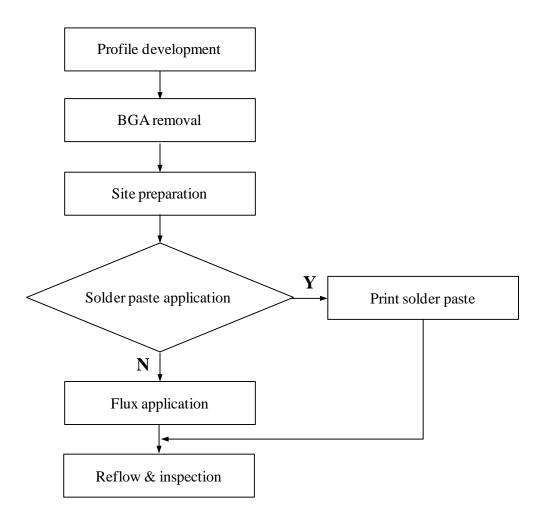

| Figure 2.1  | 7: Area array package rework process59                                                                                                                                                                                          |

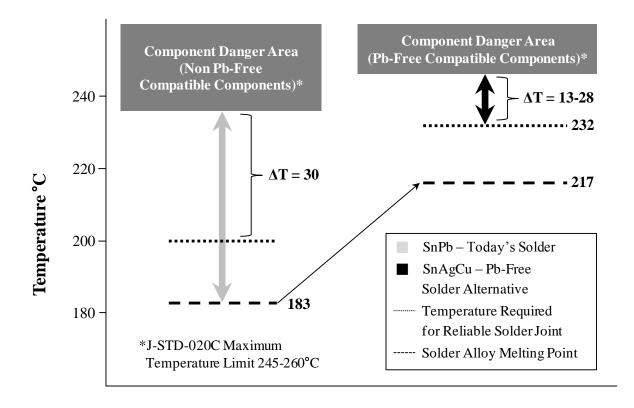

| Figure 2.18 | 3: Lead-free tighter process window. The diagrams show a significant reduction in the Pb-free process window compared to SnPb assembly; this is caused by the difference in melting temperatures and component survival ability |

|             | CHAPTER 3                                                                                                                                                                                                                       |

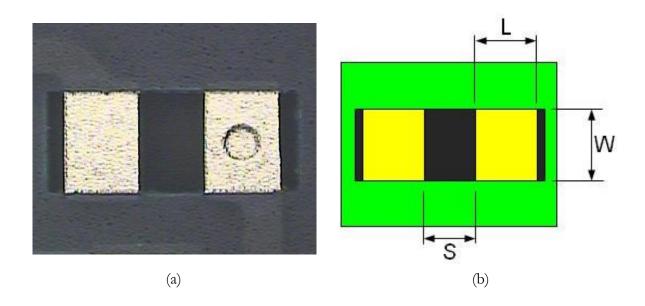

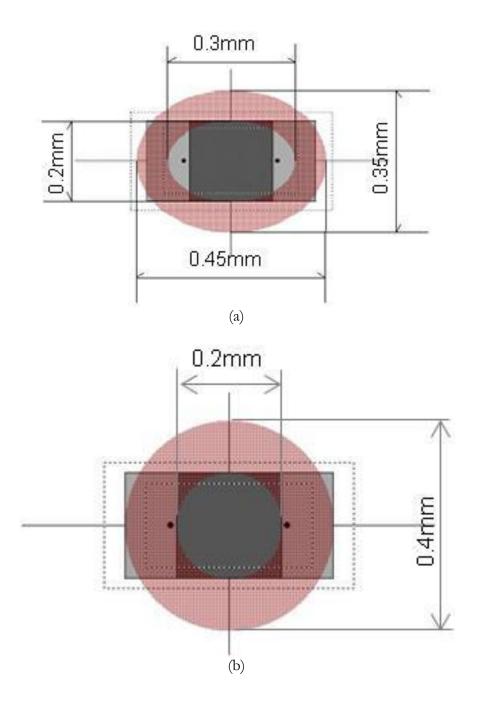

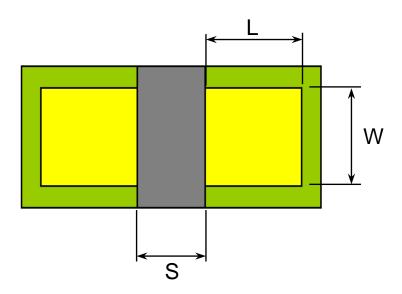

| Figure 3.1: | Schematic of component pad design for 01005 chip components. Notes: (a) Photograph of pad and solder mask; (b) pad geometry                                                                                                     |

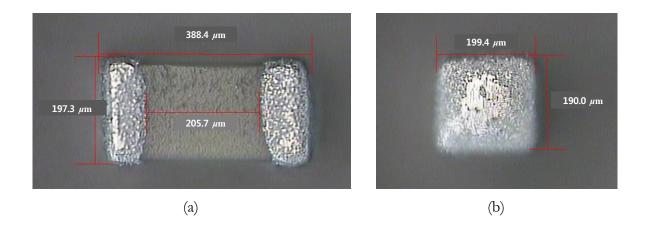

| Figure 3.2: | 01005 chip capacitor components, metrics (mm). Notes: (a) Top view; (b) side view                                                                                                                                               |

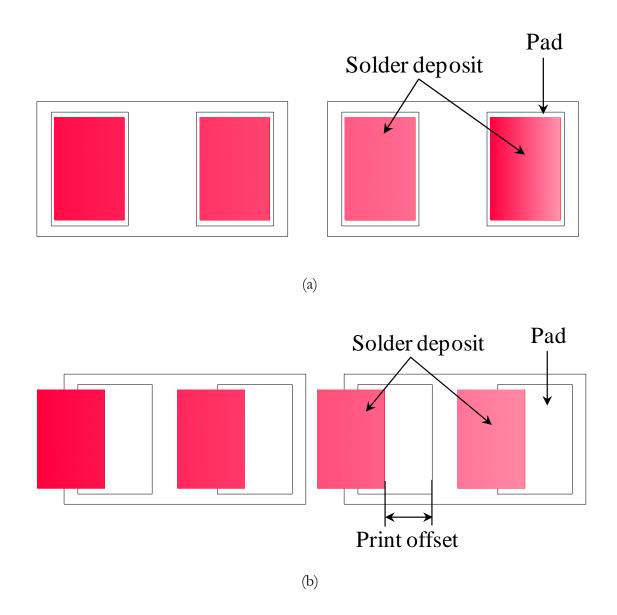

| Figure 3.3: | Print offset scenario for 01005 chip components. Notes: (a) $0 \mu m$ ; (b) $100 \mu m$ 72                                                                                                                                      |

| Figure 3.4: | Nozzle types used in this experiment. Notes: (a) 906 nozzle; (b) 926 nozzle74                                                                                                                                                   |

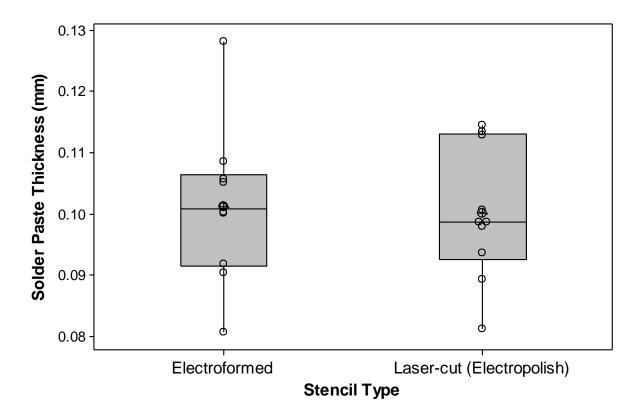

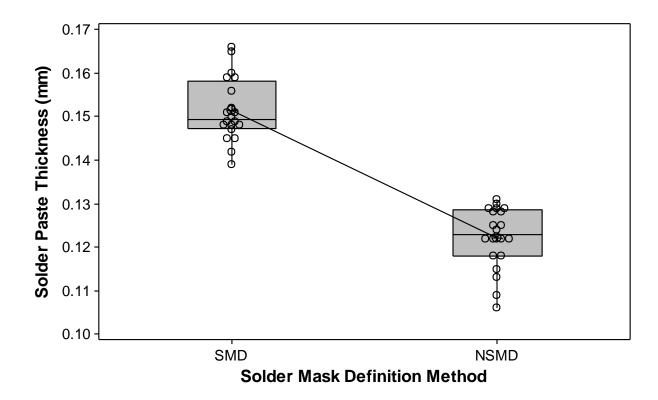

| Figure 3.5: | Solder paste thickness comparisons for 01005 chip components. Note: The box plot shows the smallest value, the first quartile, the median, the third quartile, and the largest value                                            |

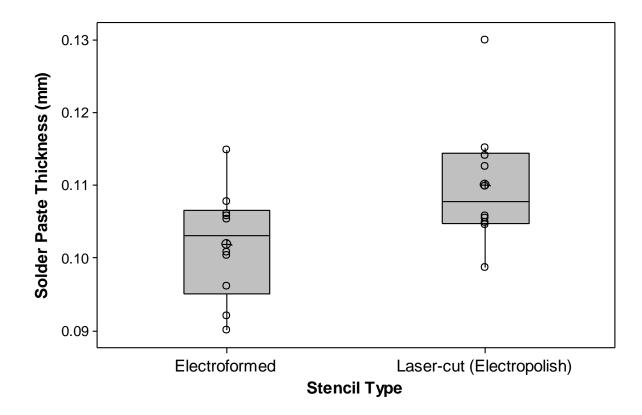

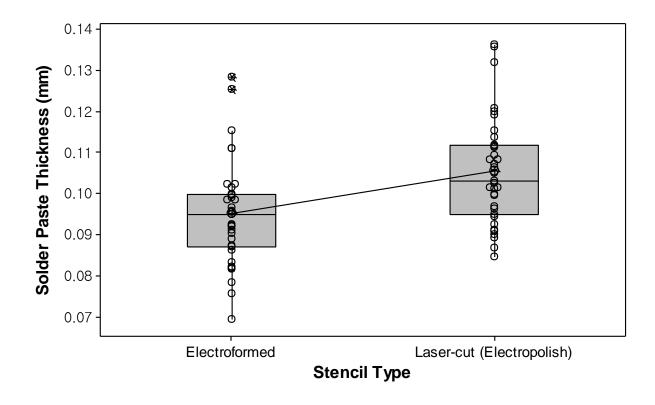

| Figure 3.6:  | Solder paste thickness comparisons for 0201 chip components. Note: The box plot shows the smallest value, the first quartile, the median, the third quartile, the largest value, and the outlier    |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

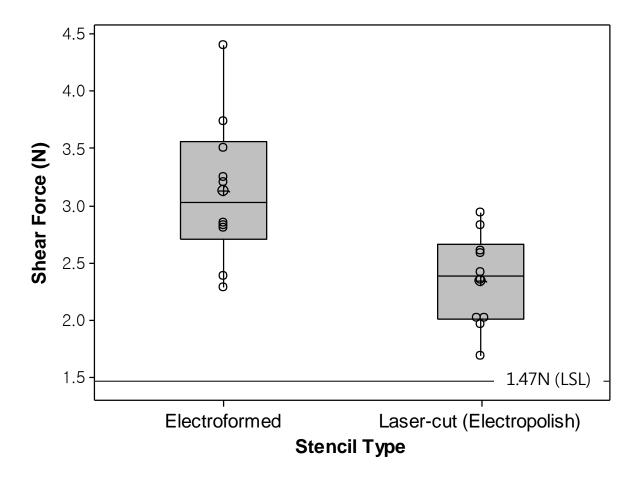

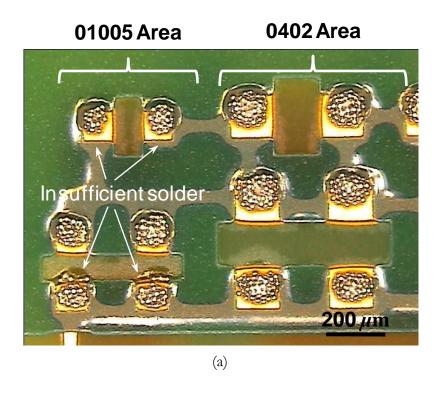

| Figure 3.7:  | Shear force comparisons on 01005 chip components for each stencil type. Note: The box plot shows the smallest value, the first quartile, the median, the third quartile, and the largest value      |

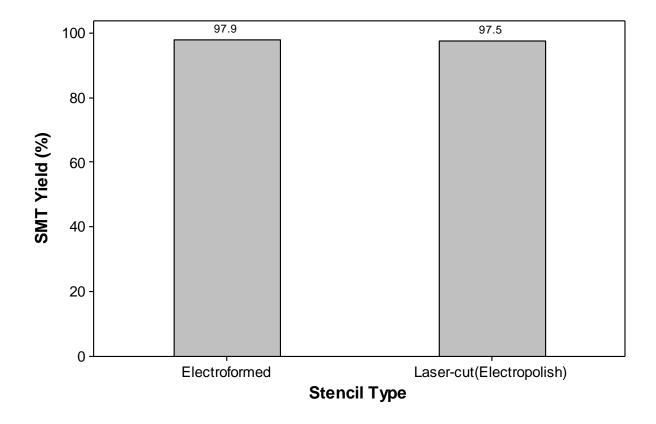

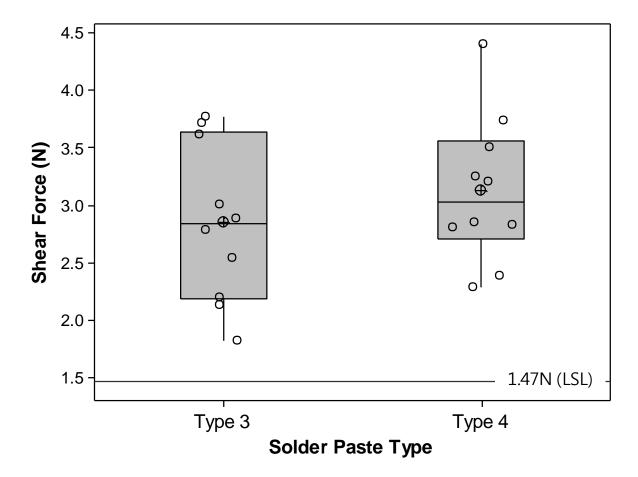

| Figure 3.8:  | Yield comparisons on 01005 chip components for each stencil type81                                                                                                                                  |

| Figure 3.9:  | Solder deposition on 01005 pads for each solder paste type. Notes: (a) Type 3; (b) type 4                                                                                                           |

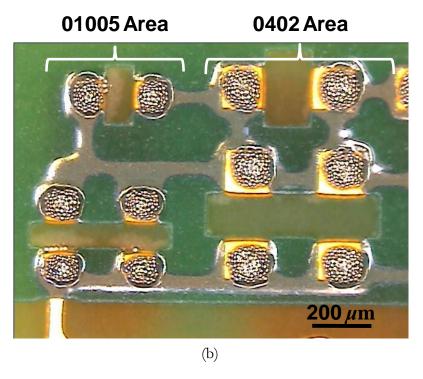

| Figure 3.10: | Shear force comparisons on 01005 chip components for each solder paste type. Note: The box plot shows the smallest value, the first quartile, the median, the third quartile, and the largest value |

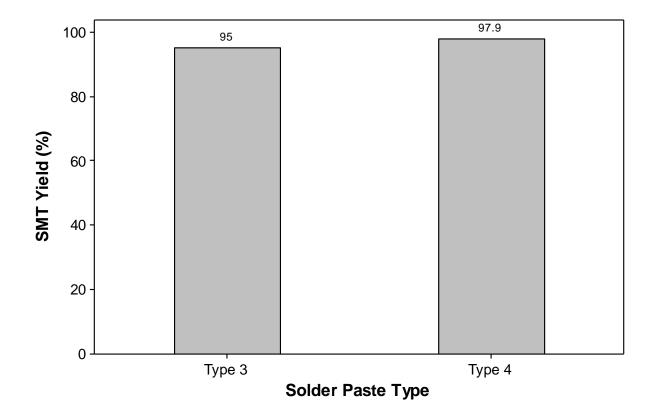

| Figure 3.11: | Yield comparisons on 01005 chip components for each solder paste type84                                                                                                                             |

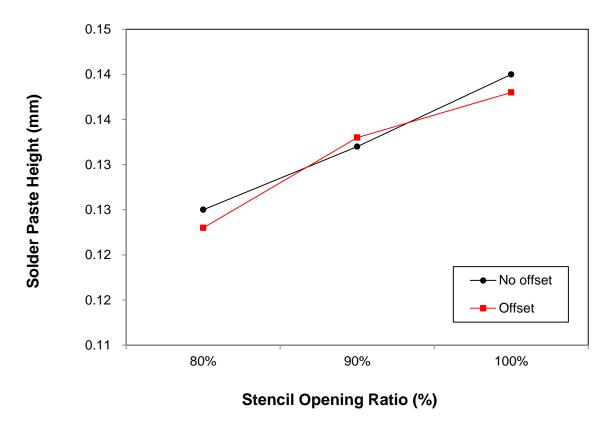

| Figure 3.12: | Solder paste height comparison on 01005 chip components for each stencil opening ratio                                                                                                              |

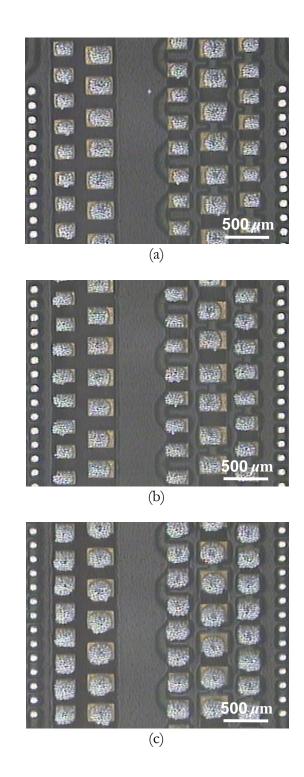

| Figure 3.13: | Solder deposition on 01005 pads with each stencil opening ratio. Notes: (a) 80 percent; (b) 90 percent; (c) 100 percent                                                                             |

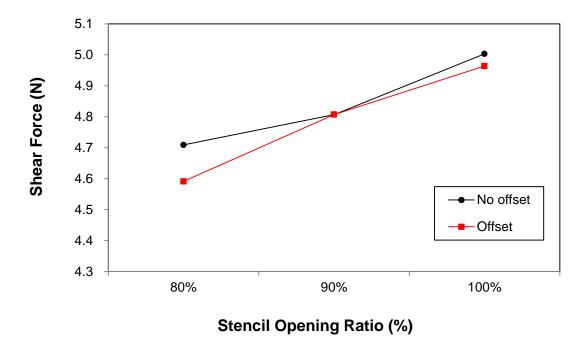

| Figure 3.14: | Shear force comparison on 01005 chip components for each stencil opening ratio                                                                                                                      |

|              | 87                                                                                                                                                                                                  |

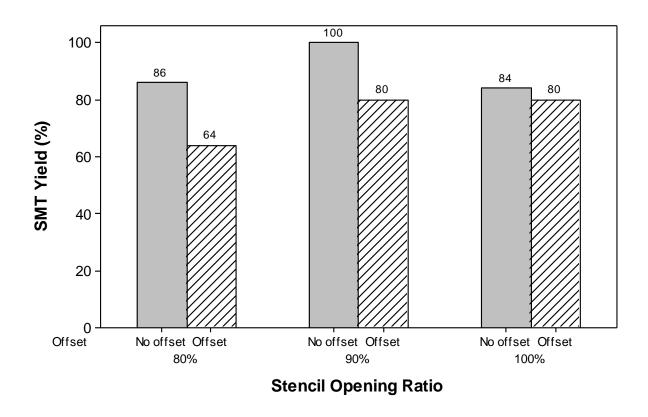

| Figure 3.15: | Yield comparisons on 01005 chip components for each stencil opening ratio90                                                                                                                         |

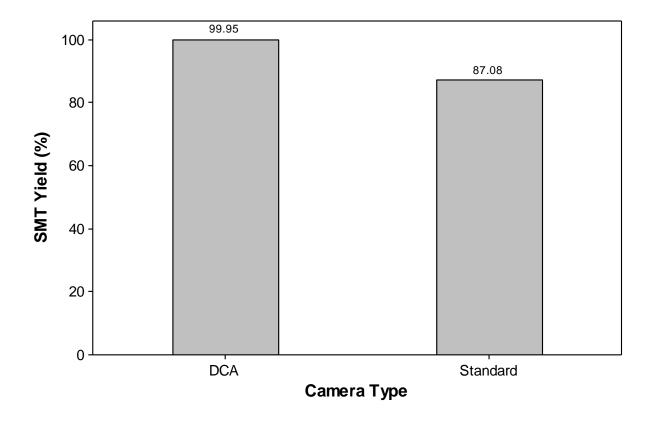

| Figure 3.16: | Pickup rate comparisons on 01005 chip components for each camera type91                                                                                                                             |

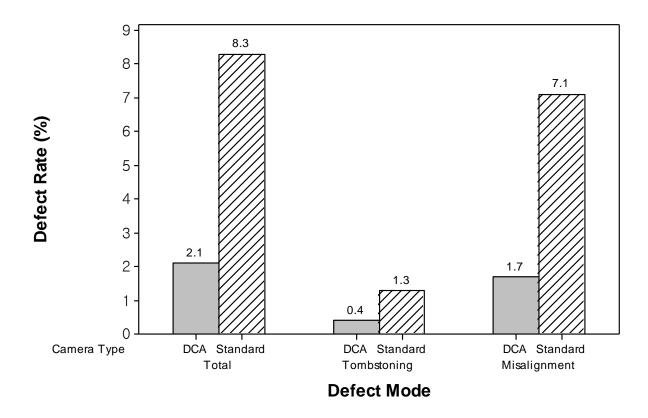

| Figure 3.17: | Defect rate comparisons on 01005 chip components for each camera type92                                                                                                                             |

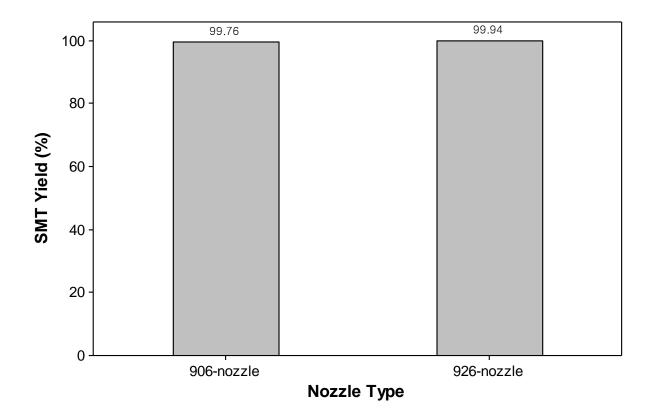

| Figure 3.18: | Pickup rate comparisons on 01005 chip components for each nozzle type93                                                                                                                             |

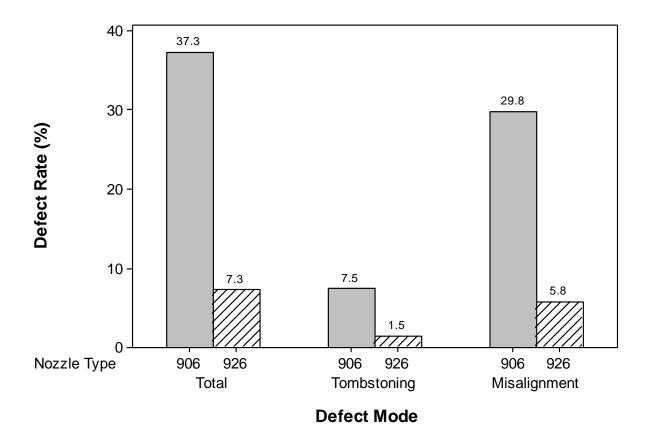

| Figure 3.19: | Defect rate comparisons on 01005 chip components for each nozzle type94                                                                                                                             |

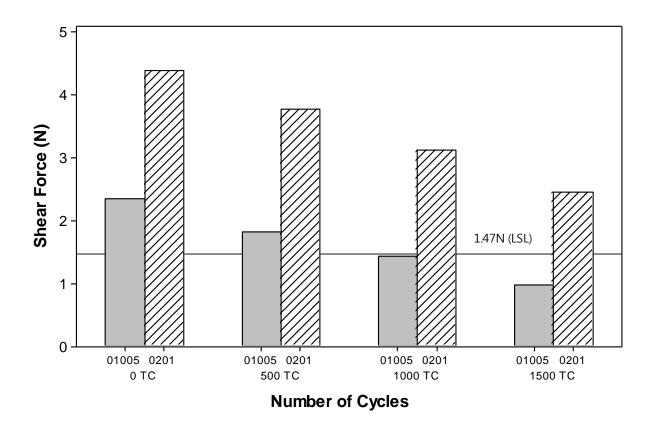

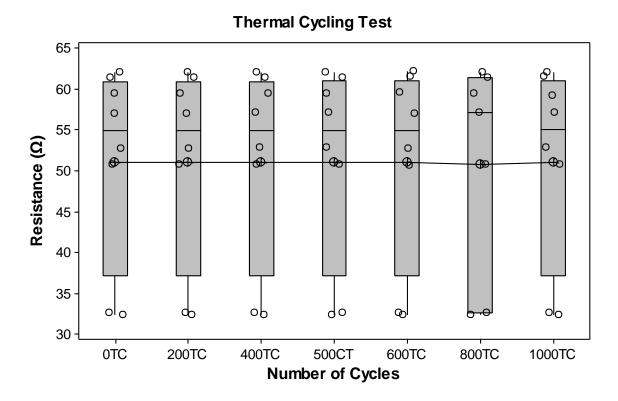

| Figure 3.20: | Shear strength after temperature cycling test96                                                                                                                                                     |

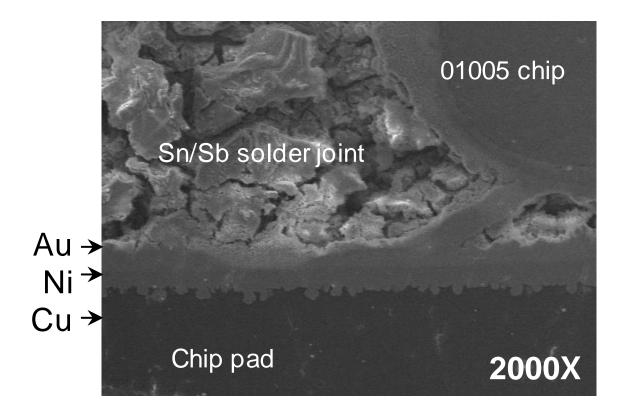

| Figure 3.21: | Cross-sections of the 01005 chip components for each temperature cycle97                                                                                                                            |

| Figure 3.22: | Cross-section of the 01005 chip components after 1,500 temperature cycles98                                                                                                                         |

|              | CHAPTER 4                                                                                                                                                                                           |

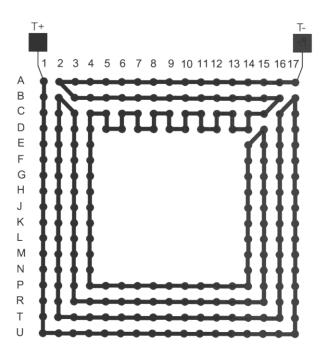

| Figure 4.1:  | Schematic diagram of the topside of board on the test vehicle106                                                                                                                                    |

| Figure 4.2:  | Schematic of component pad design                                                                                                                                                                   |

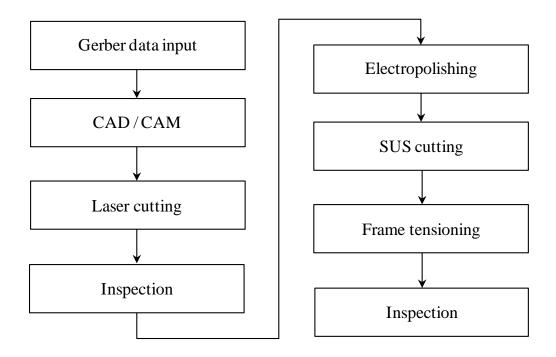

| Figure 4.3:  | Manufacturing steps of the laser-cut stencil                                                                                                                                                                                |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

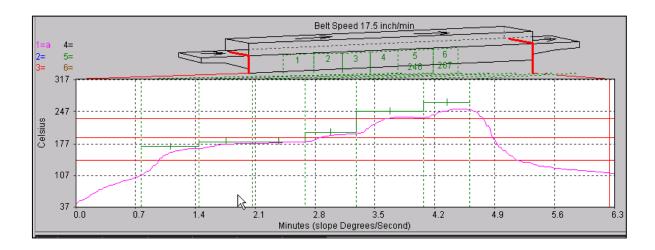

| Figure 4.4:  | Reflow actual profile for experiment run                                                                                                                                                                                    |  |  |  |  |

| Figure 4.5:  | SEM pictures taken from electropolished laser-cut stencils. Notes: (a) 85 wt.% phosphoric acid solution; (b) 95 wt.% of phosphoric acid solutions                                                                           |  |  |  |  |

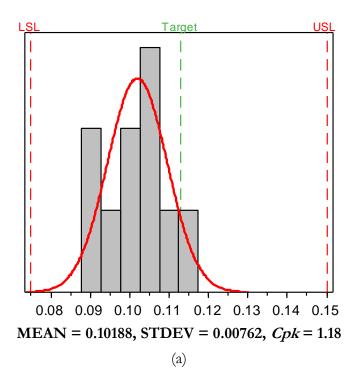

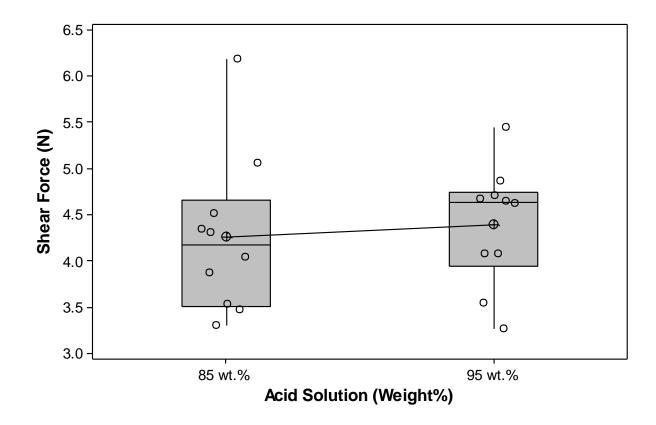

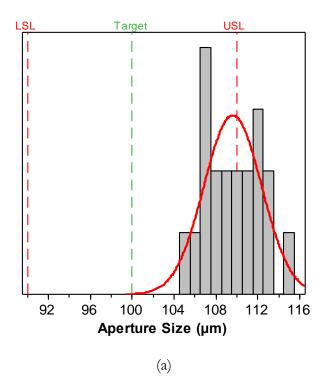

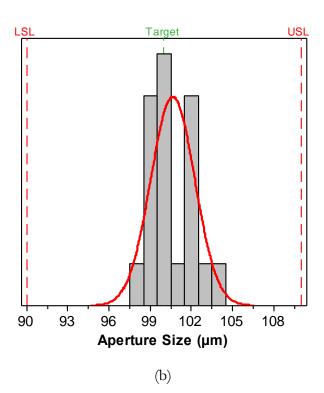

| Figure 4.6:  | Process capability plot of (a) 85 wt.% of phosphoric acid solution and (b) 95 wt.% of phosphoric acid solution                                                                                                              |  |  |  |  |

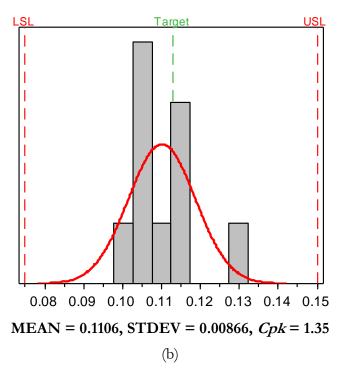

| Figure 4.7:  | Solder paste thickness measurement results for two phosphoric acid solutions. Note: The box plot showing the smallest value, the first quartile, the median, the third quartile, the largest value, and the outlier         |  |  |  |  |

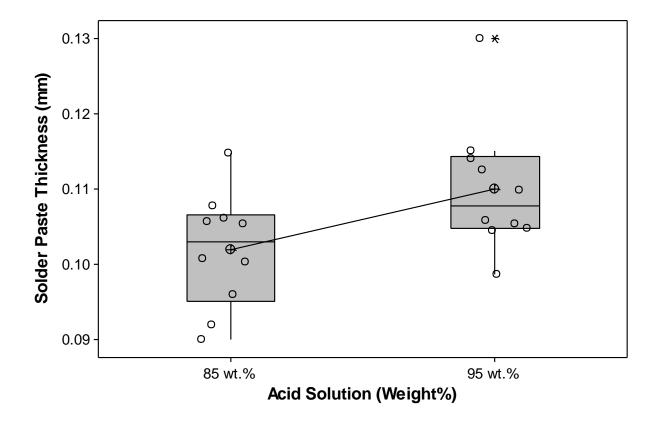

| Figure 4.8:  | Component shear test results for each acid solution. Note: The box plot showing the smallest value, the first quartile, the median, the third quartile, and the largest value                                               |  |  |  |  |

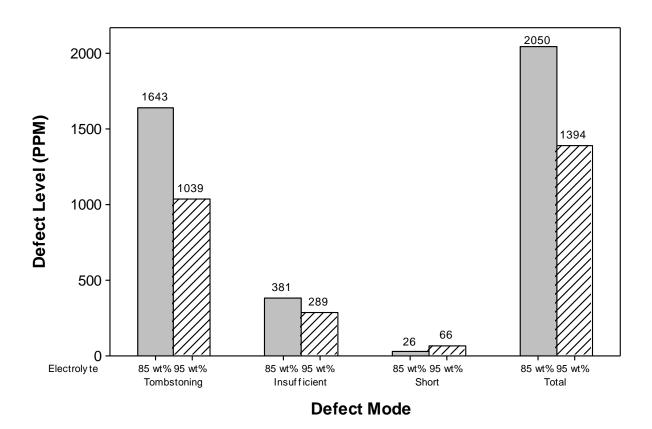

| Figure 4.9:  | Total number of SMT defects by two phosphoric acid solutions                                                                                                                                                                |  |  |  |  |

| Figure 4.10: | SEM pictures taken from laser-cut stencil apertures by different EP time. Notes: (a) 0.05-mm-thick; (b) 0.08-mm-thick; (c) 0.10-mm-thick                                                                                    |  |  |  |  |

|              | CHAPTER 5                                                                                                                                                                                                                   |  |  |  |  |

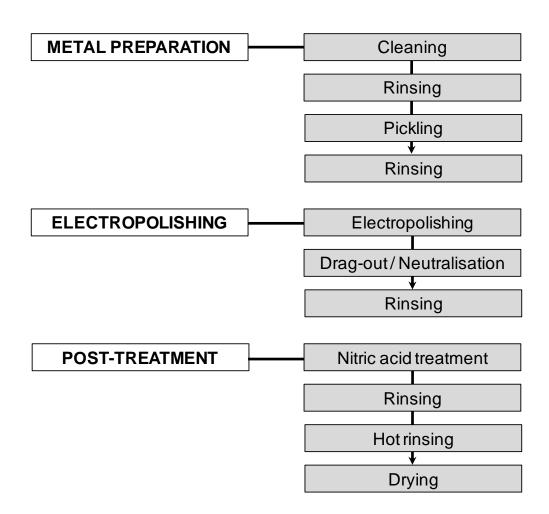

| Figure 5.1:  | Schematic diagram of the typical process flow chart                                                                                                                                                                         |  |  |  |  |

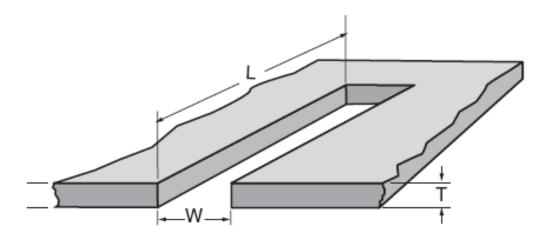

| Figure 5.2:  | Dimensions of the stencil aperture                                                                                                                                                                                          |  |  |  |  |

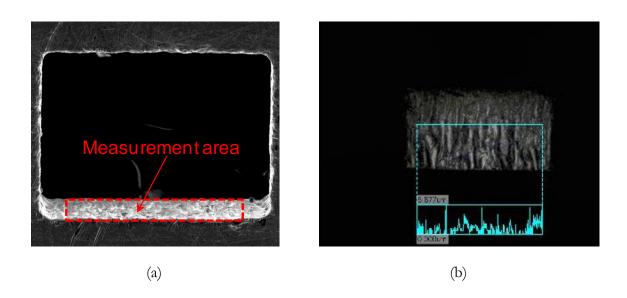

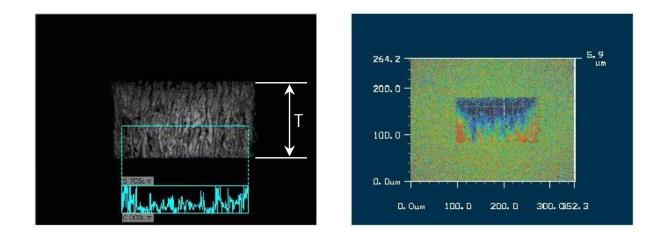

| Figure 5.3:  | Measurement of surface roughness: (a) measurement area of aperture wall; (b) surface roughness profile. Note: Surface roughness ( <i>Ra</i> ) was measured through the center of the material; original magnification: 500X |  |  |  |  |

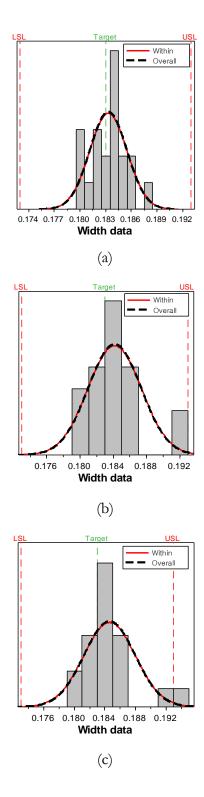

| Figure 5.4:  | Histograms of aperture width distribution for the laser-cut stencil for each EP time. Notes: (a) No EP; (b) low EP; (c) high EP                                                                                             |  |  |  |  |

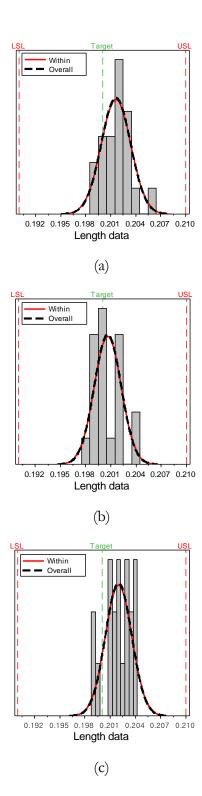

| Figure 5.5:  | Histograms of aperture length distribution for the laser-cut stencil for each EP time. Notes: (a) No EP; (b) low EP; (c) high EP                                                                                            |  |  |  |  |

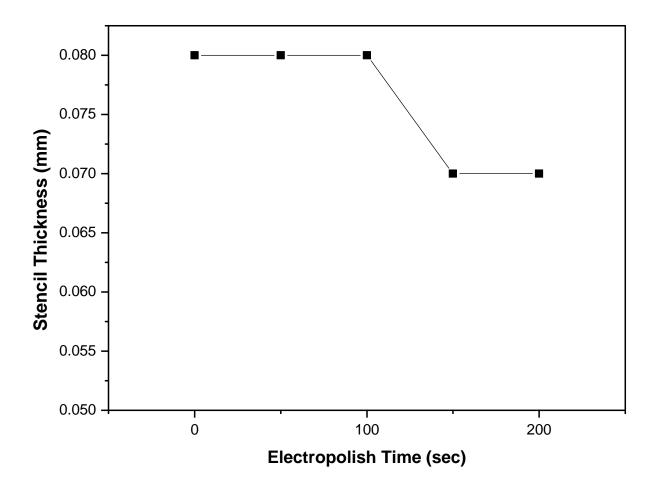

| Figure 5.6:  | Relationship between EP time and stencil thickness                                                                                                                                                                          |  |  |  |  |

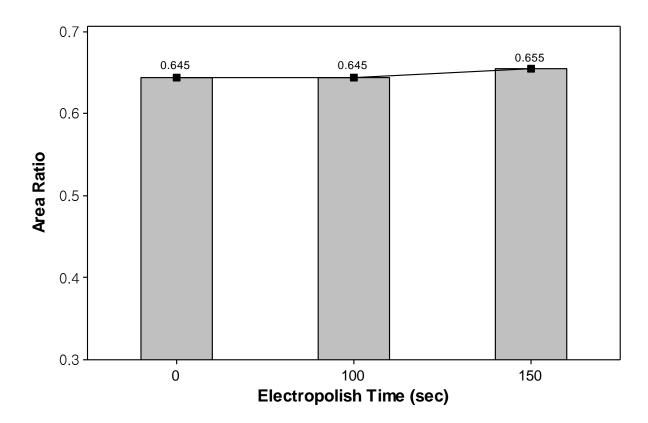

| Figure 5.7:  | Relationship between EP time and area ratio                                                                                                                                                                                 |  |  |  |  |

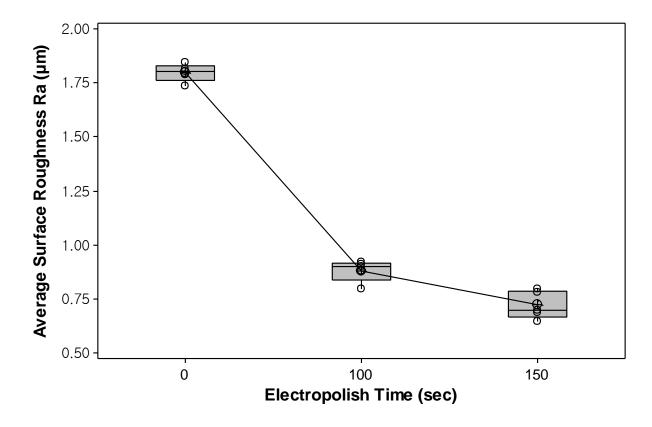

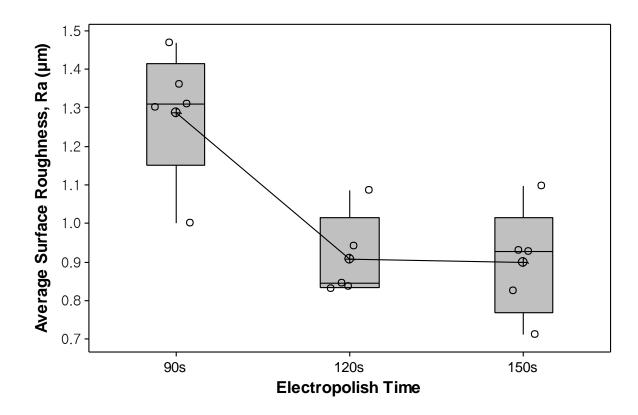

| Figure 5.8:  | Relationship between EP time and aperture surface roughness (Ra). Note: The box plot showing the smallest value, the first quartile, the median, the third quartile, and the largest value                                  |  |  |  |  |

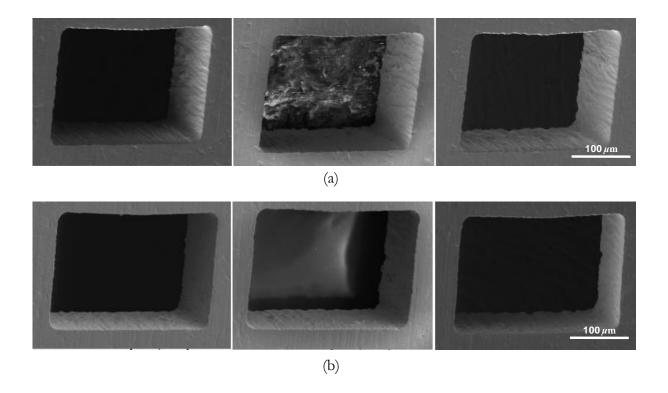

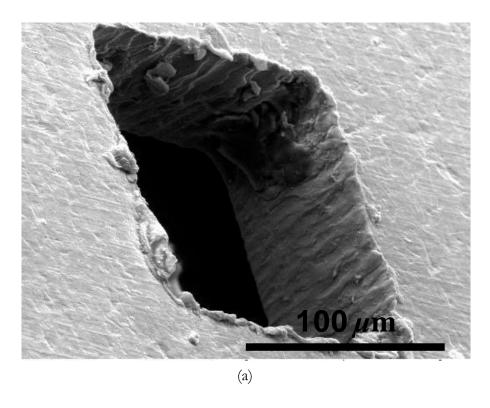

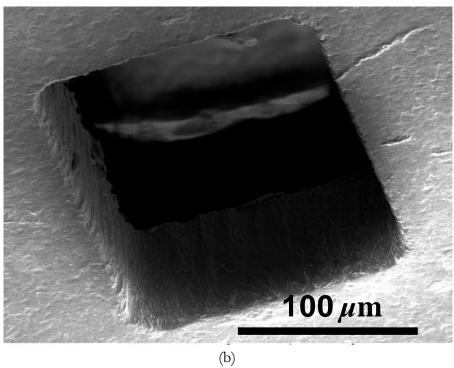

| Figure 5.9:  | (a) SEM images of square aperture wall geometry after laser-cutting; (b) after EP. Notes: A microscopic view of the same surface before and after EP shows that the                                                         |  |  |  |  |

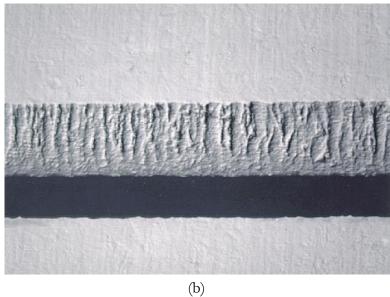

|              | cutting speed: 4 mm/s; EP time: 100 s (Low EP); original magnification: 600X                                                                                                                                                 |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

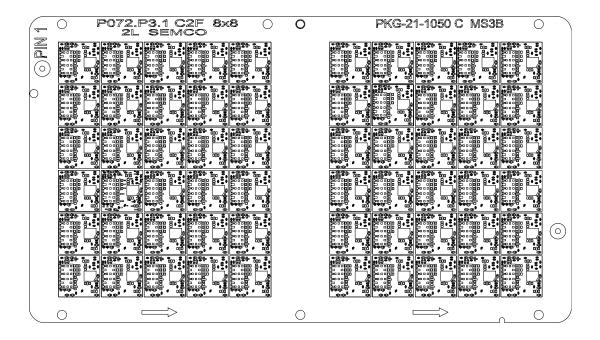

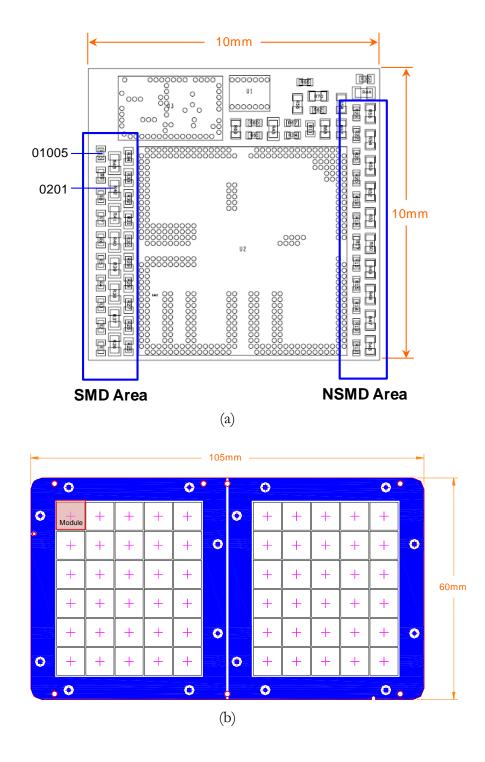

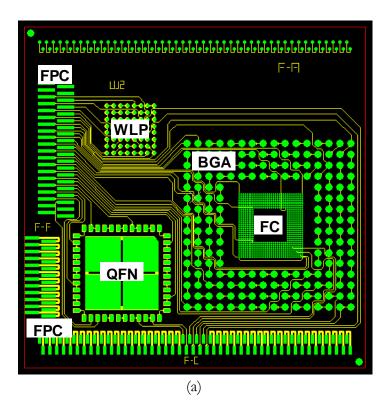

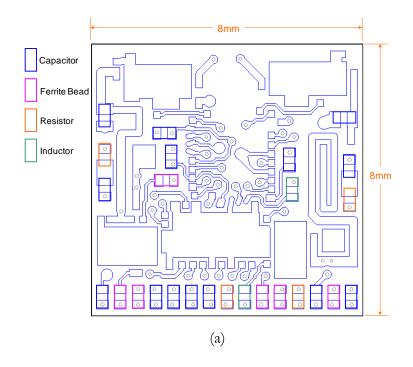

| Figure 5.10: | Test vehicle design for printing experiments: (a) module design; (b) top-side view that shows entire PCB substrate strip outline. Note: SMD refers to solder-mask-defined pad and NSMD refers to non-solder-mask-defined pad |  |  |  |  |

| Figure 5.11: | Solder paste thickness comparisons for each stencil type                                                                                                                                                                     |  |  |  |  |

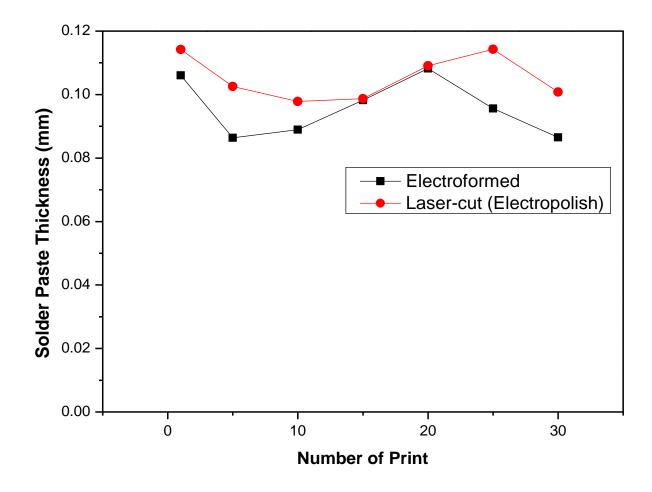

| Figure 5.12: | Effect of repeat paste printing without wiping for each of the stencils146                                                                                                                                                   |  |  |  |  |

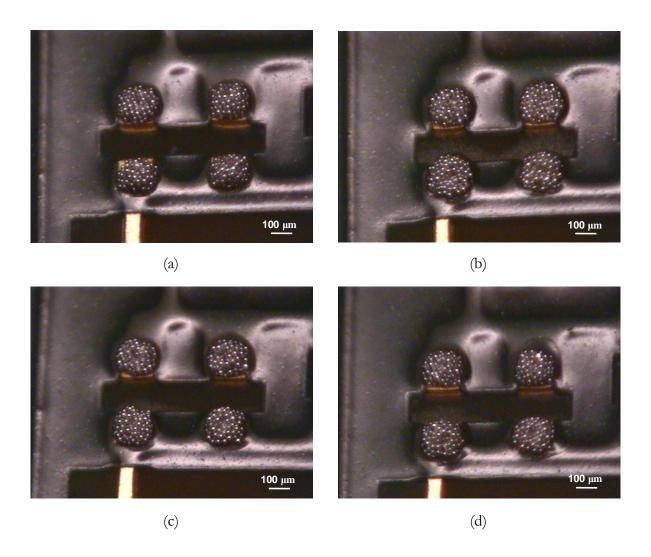

| Figure 5.13: | 3: OM images showing the solder deposition results of repeat printing for the electroformed stencils. Notes: (a) First print; (b) tenth print; (c) 20th print; (d) 30th print                                                |  |  |  |  |

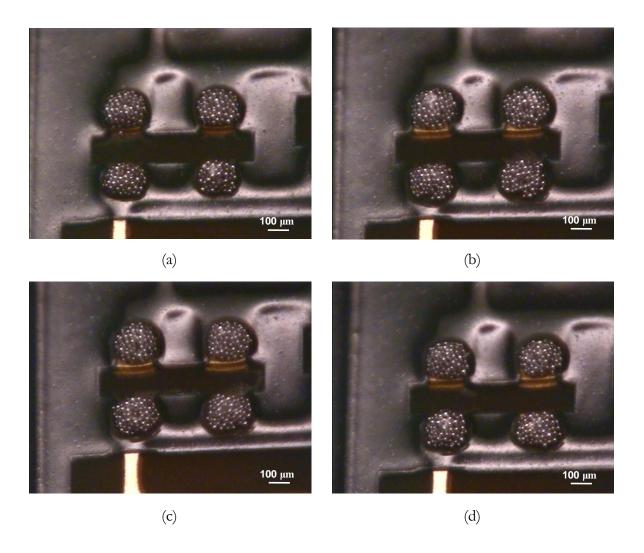

| Figure 5.14: | OM images showing the solder deposition results of repeat printing for the electropolished laser-cut stencils. Notes: (a) First print; (b) tenth print; (c) 20th print; (d) 30th print.                                      |  |  |  |  |

| Figure 5.15: | Solder paste thickness comparisons for each solder-mask-definition method. Note: The box plot shows the smallest value, the first quartile, the median, the third quartile, and the largest value                            |  |  |  |  |

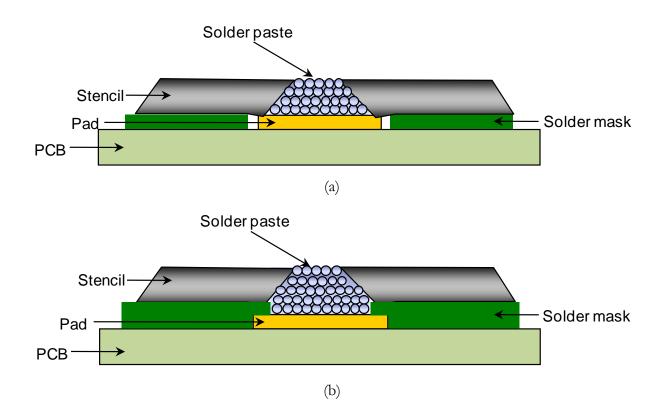

| Figure 5.16: | Structure of the solder pads using different solder-mask definition methods. Notes: (a) non-solder-mask-defined pad; (b) solder-mask-defined pad151                                                                          |  |  |  |  |

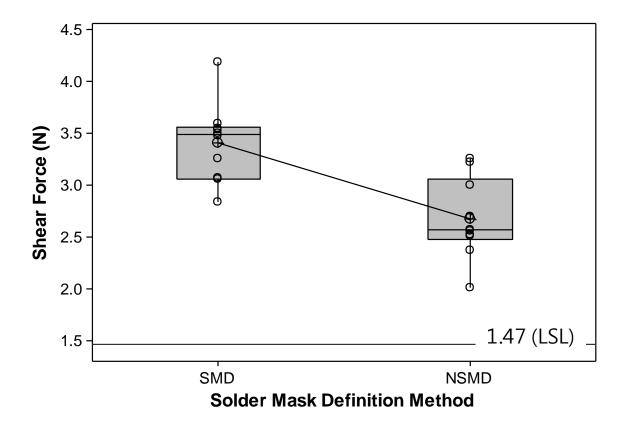

| Figure 5.17: | Shear force comparisons for each solder-mask definition method                                                                                                                                                               |  |  |  |  |

|              | CHAPTER 6                                                                                                                                                                                                                    |  |  |  |  |

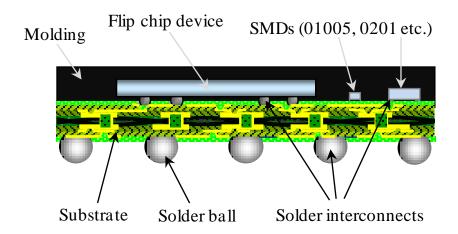

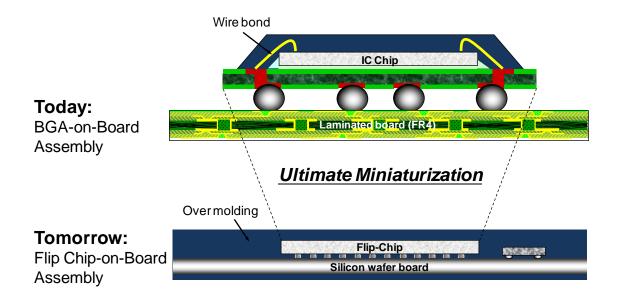

| Figure 6.1:  | Schematic diagram of the flip chip-on board assembly with silicon wafer substrate                                                                                                                                            |  |  |  |  |

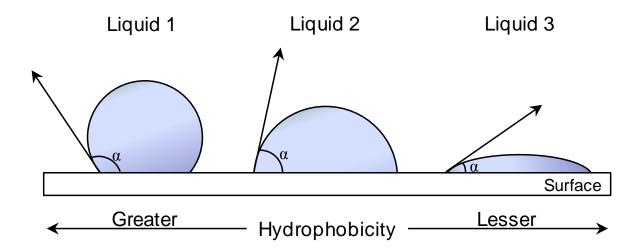

| Figure 6.2:  | A schematic illustration of a various contact angles                                                                                                                                                                         |  |  |  |  |

| Figure 6.3:  | Measurement of surface roughness. Note that surface roughness (Ra) is measured through center of material                                                                                                                    |  |  |  |  |

| Figure 6.4:  | Photographs of laser-cut system used                                                                                                                                                                                         |  |  |  |  |

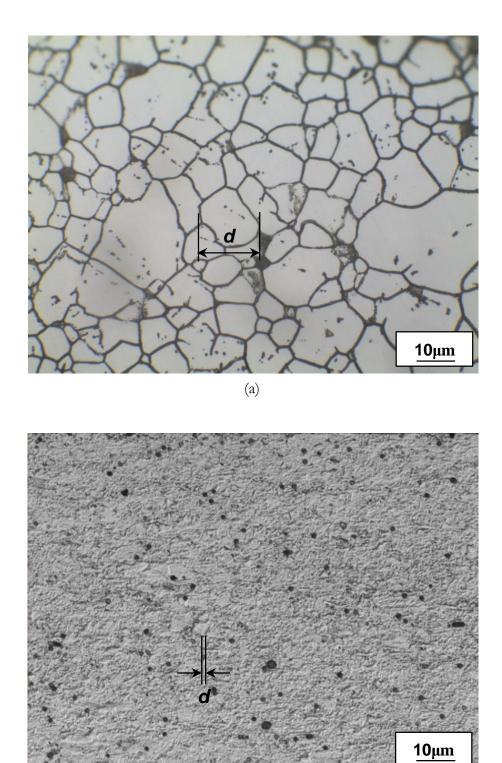

| Figure 6.5:  | Microstructure of stainless steel used. Notes: (a) Coarse-grained SUS304 stainless steel; (b) fine-grained SUS301 stainless steel                                                                                            |  |  |  |  |

| Figure 6.6:  | Process capability plot. Notes: (a) Coarse-grained SUS304 stainless steel ( $Cpk = 0.05$ ); (b) fine-grained SUS301 stainless steel ( $Cpk = 1.95$ )                                                                         |  |  |  |  |

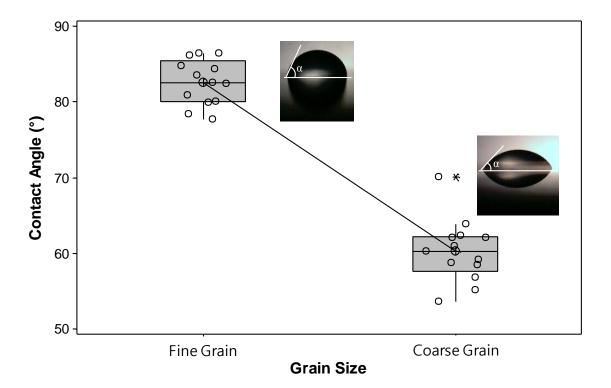

| Figure 6.7:  | Relationship between grain size of stainless steel and contact angle168                                                                                                                                                      |  |  |  |  |

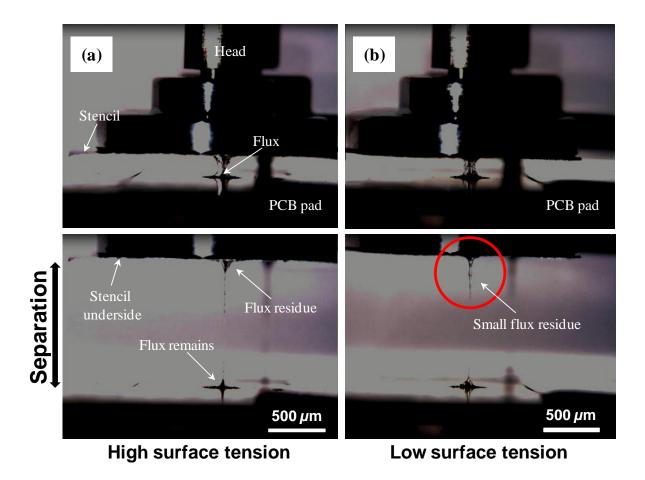

| Figure 6.8:  | High-speed microscope images of substrate/stencil separation process. Notes: (a) Coarse-grained SUS304 stainless steel; (b) fine-grained SUS301 stainless steel169                                              |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

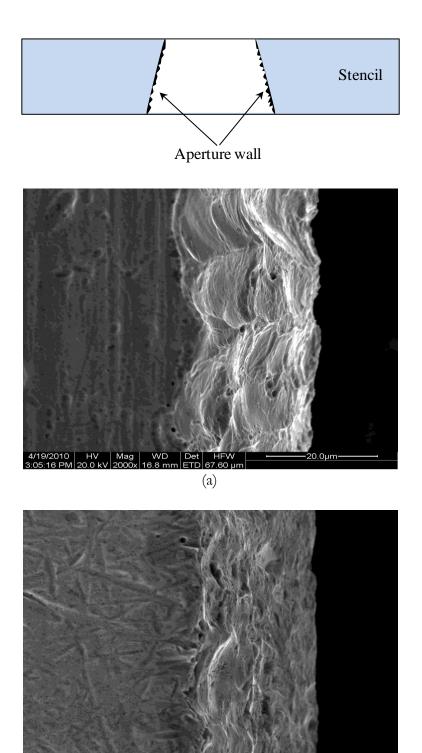

| Figure 6.9:  | SEM images of stencil aperture wall for each material type. Notes: (a) Coarse-grained SUS304 stainless steel; (b) fine grained SUS301 stainless steel                                                           |

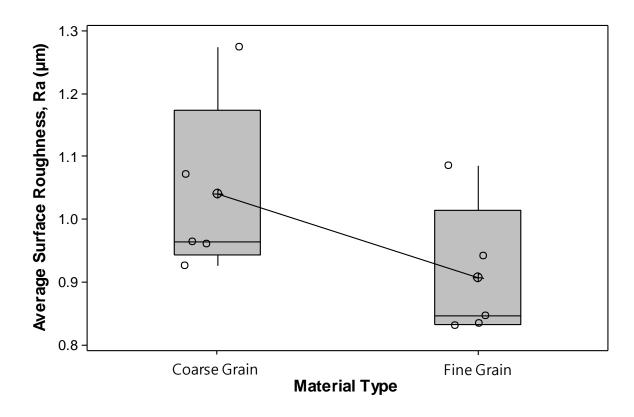

| Figure 6.10: | Relationship between grain size of steel and surface roughness (Ra). Note: The box plot shows the smallest value, the first quartile, the median, the third quartile, and the largest value                     |

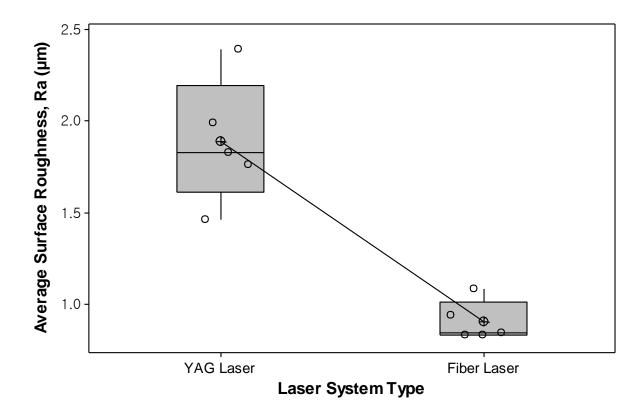

| Figure 6.11: | Relationship between laser system type and surface roughness (Ra). Note: The box plot shows the smallest value, the first quartile, the median, the third quartile, and the largest value                       |

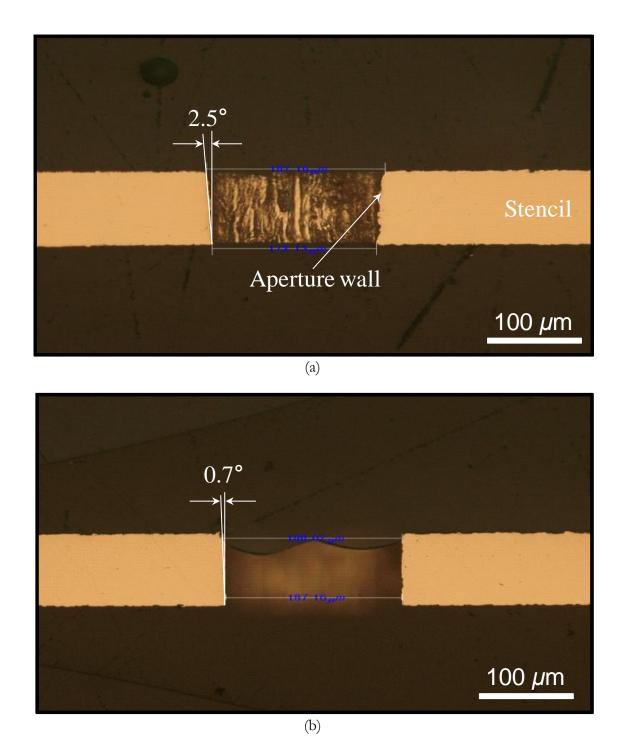

| Figure 6.12: | Comparison of tapered stencil wall apertures. Notes: (a) The standard YAG laser; (b) the diode-pumped new fiber laser                                                                                           |

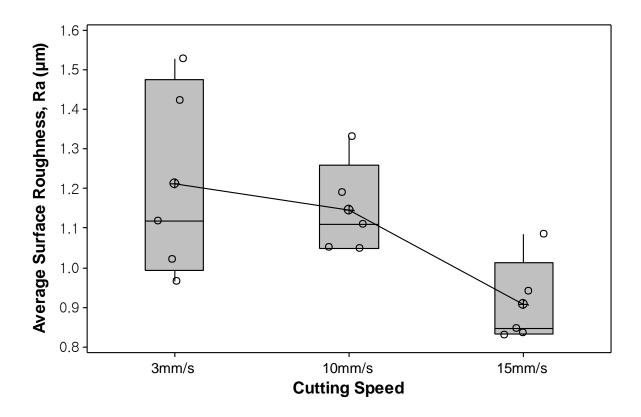

| Figure 6.13: | Relationship between laser cutting speed and surface roughness ( <i>Ra</i> ). Note: The box plot shows the smallest value, the first quartile, the median, the third quartile, and the largest value            |

| Figure 6.14: | Relationship between EP time and surface roughness (Ra). Note: The box plot shows the smallest value, the first quartile, the median, the third quartile, and the largest value                                 |

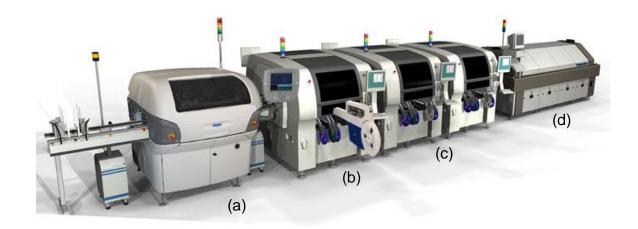

| Figure 6.15: | Investigation of flip-chip assembly in the SMT process. The tools depicted in the photograph are : (a) screen printer, (b) pick & place machine #1, (c) fine-pitch pick & place machine #2, and (d) reflow oven |

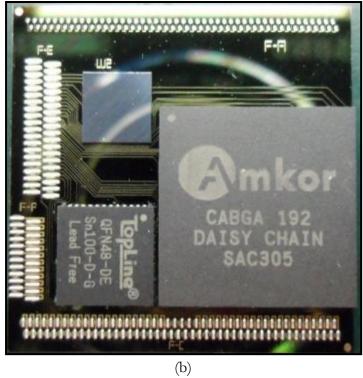

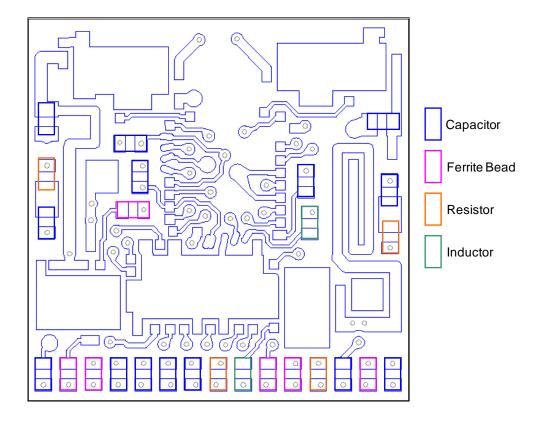

| Figure 6.16: | Test board layout showing schematic with mounted components. Notes: (a) Test vehicle design; (b) assembled silicon substrate                                                                                    |

| Figure 6.17: | SEM image of flip-chip pads on silicon substrate                                                                                                                                                                |

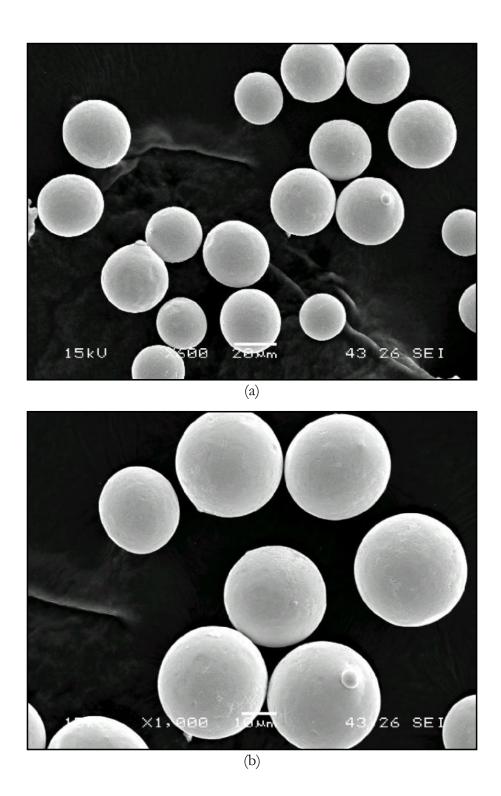

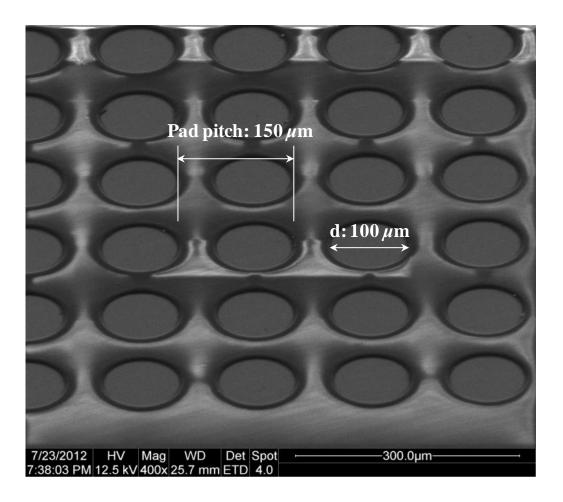

| Figure 6.18: | SEM photograph of solder powder. Notes: (a) Type 6; (b) type 7184                                                                                                                                               |

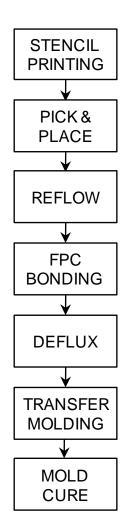

| Figure 6.19: | Process flow for the assembly of silicon substrate                                                                                                                                                              |

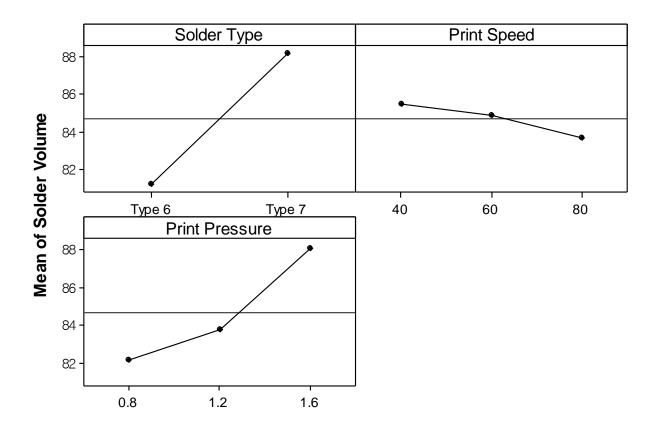

| Figure 6.20: | Main effects plot for solder volume                                                                                                                                                                             |

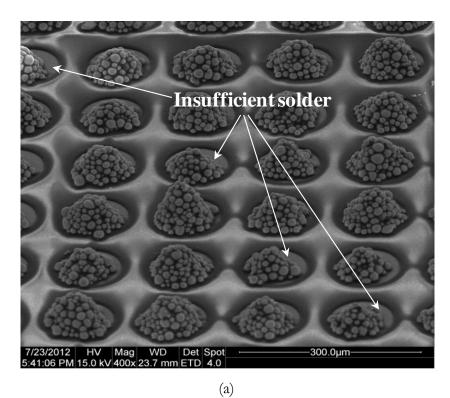

| Figure 6.21: | SEM images of solder deposition on 150 $\mu$ m pitch flip-chip pads for each solder paste type. Insufficient solder paste deposit, indicated by the arrows. Notes: (a) Type 6; (b) type 7                       |

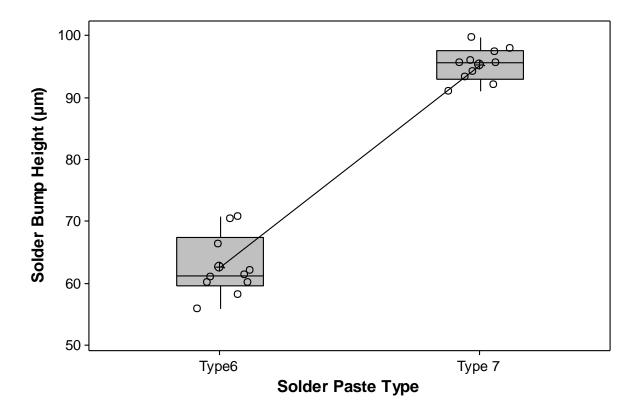

| Figure 6.22: | Solder bump height comparison for each solder type. Note: The box plot shows the smallest value, the first quartile, the median, the third quartile, and the largest value                                      |

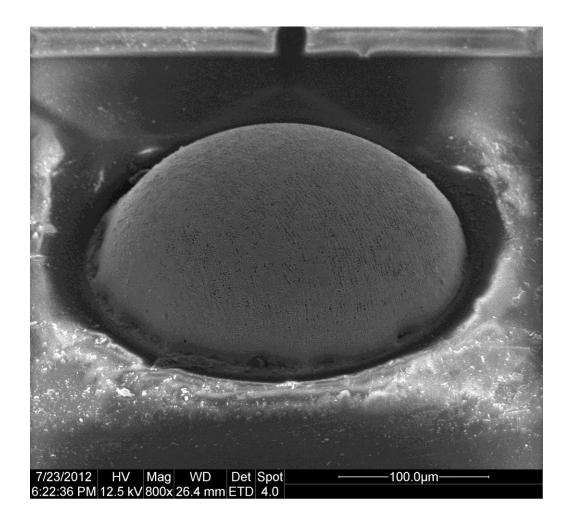

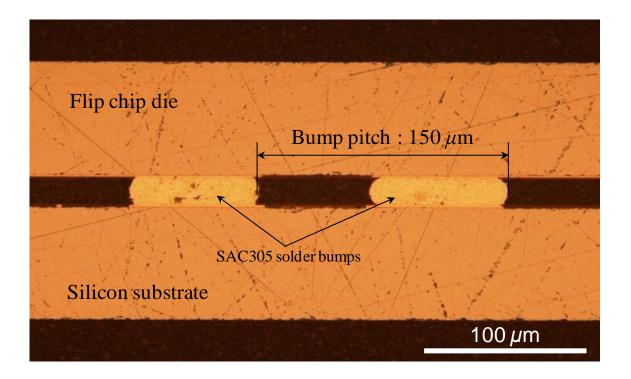

| Figure 6.23: | SEM image of solder bump on silicon substrate pad, average bump height 95 $\mu$ m, pitch 150 $\nu$ m. Note: Print of type 7 paste on pads. Original magnification X800 192                                      |

| Figure 6.24: | Resistance changes throughout the thermal cycling test. Note: Flip-chip device with type 7 paste                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.25: | Cross-section of MUF and over molded FCOB assembly. Note that cross-sectioning picture showing good solder joint formation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|              | CHAPTER 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 7.1:  | Test vehicle design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

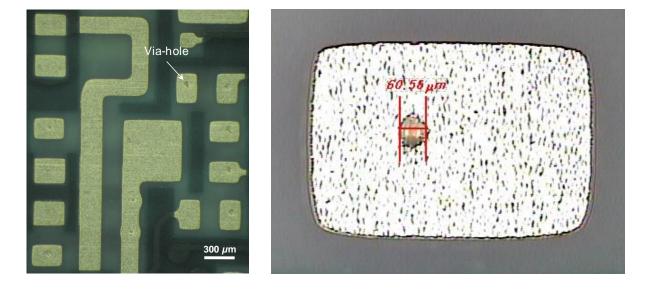

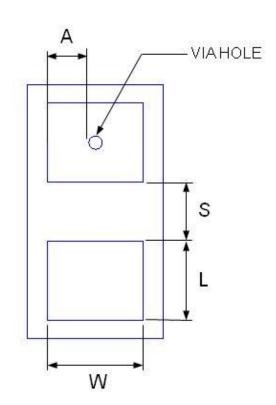

| Figure 7.2:  | Example of micro via-in-pads: the via-hole is 60 µm in diameter202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

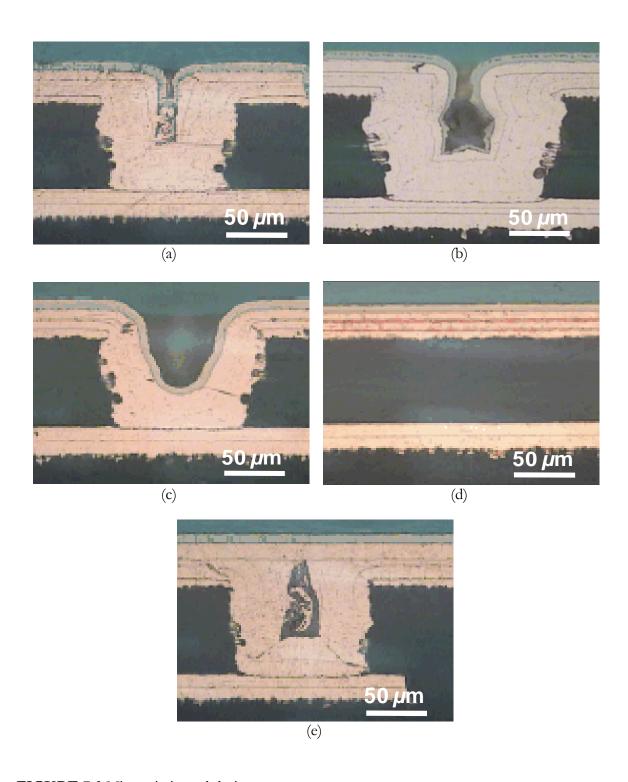

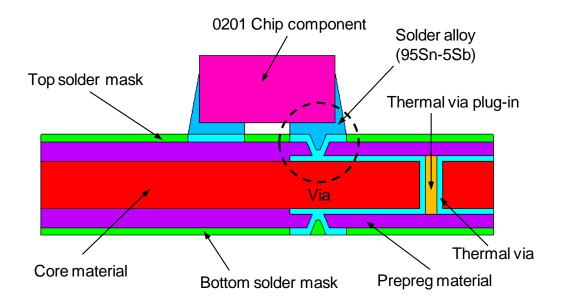

| Figure 7.3:  | Micro via-in-pad design. Notes: (a) Ultra-small via-in-pads; (b) small via-in-pads; (c) large via-in-pads; (d) no via-in-pads; (e) capped via-in-pads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

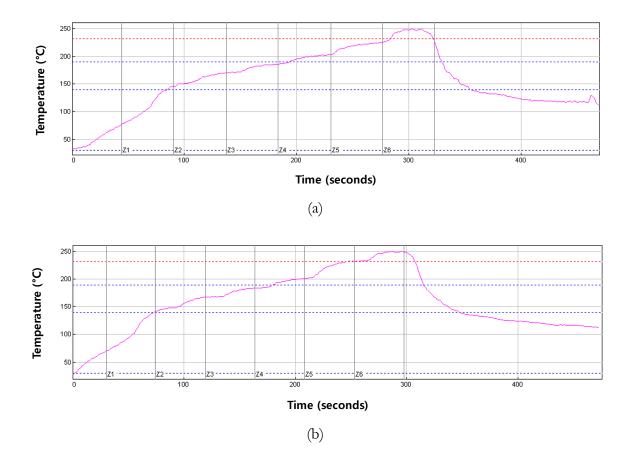

| Figure 7.4:  | Actual reflow profile. Notes: (a) Long-preheat condition; (b) short-preheat condition 205                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

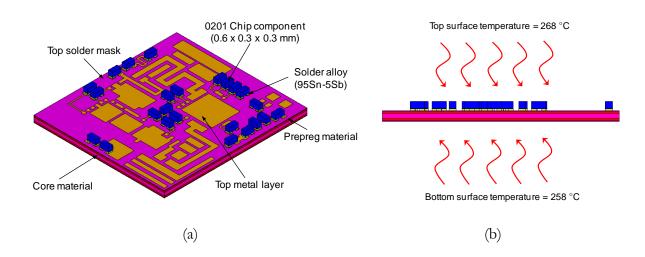

| Figure 7.5:  | Schematic of micro via-in-pad structure for thermal simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 7.6:  | 3D thermal simulation models. Notes: (a) Assembled package; (b) board temperature setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

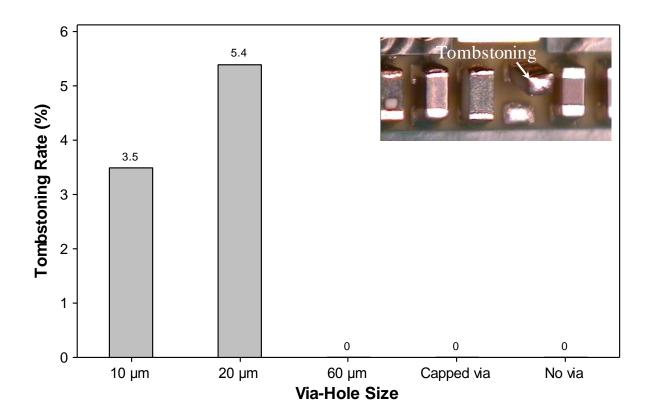

| Figure 7.7:  | Relationship between micro via-in-pad design and tombstoning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

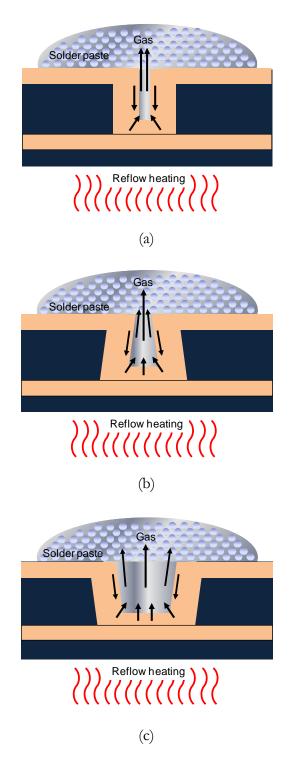

| Figure 7.8:  | Schematic diagrams of (a) cup-like via-hole, (b) funnel-like via-hole, and (c) bowl-like via-hole                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

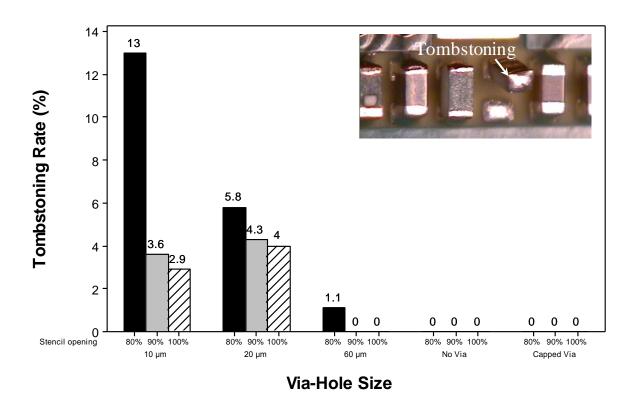

| Figure 7.9:  | Relationship between stencil opening ratio and tombstoning rate at micro via-in-pads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

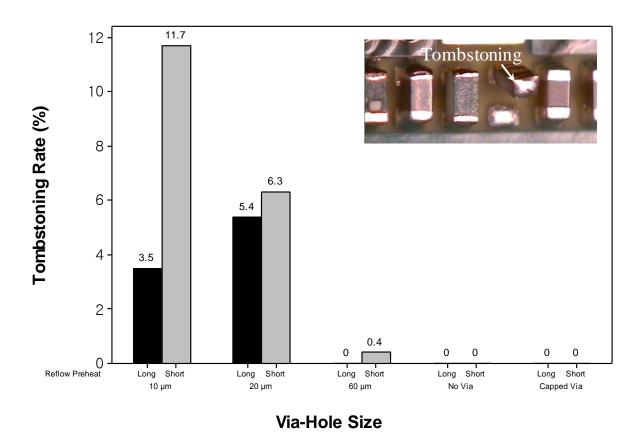

| _            | Relationship between reflow preheat condition and tombstoning rate in micro via-<br>in-pads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

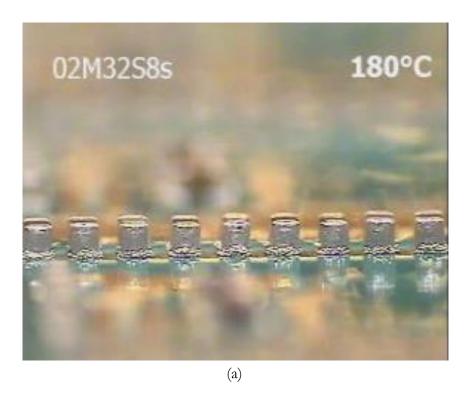

| Figure 7.11: | SMT scope images of (a) reflow soak zone (180°C) and (b) reflow zone (227°C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 7.12: | Schematic representations of the forces acting on a chip as it is tombstoning. Notes: (a) solder paste conditions before melting during the reflow process; (b) conditions of melting solder at only one side of the electrode when the temperatures are different at both sides of the electrode with a chip component; tombstoning will occur if: $F4+F6 > F2+F3+F5$ ; $F1$ , $F2$ : moment of tack force power with solder paste; $F3$ : moment of weight of self weight with chip component; $F4$ : moment of melting solder surface tension at chip electrode area; $F5$ : moment of melting solder surface tension under the chip component and $F6$ : moment of flux spurting force at the via-hole |

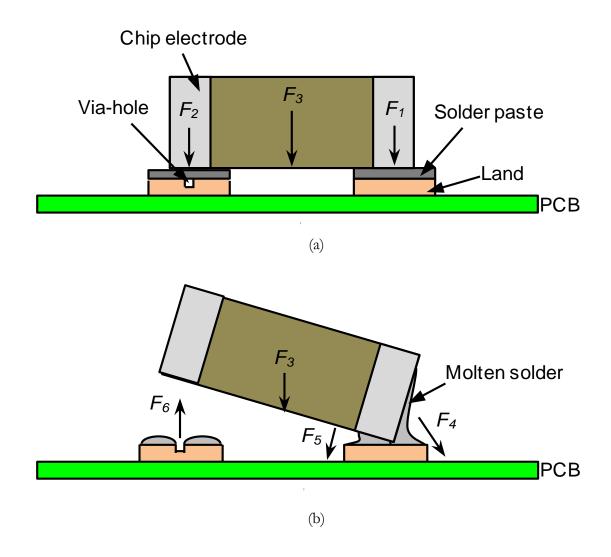

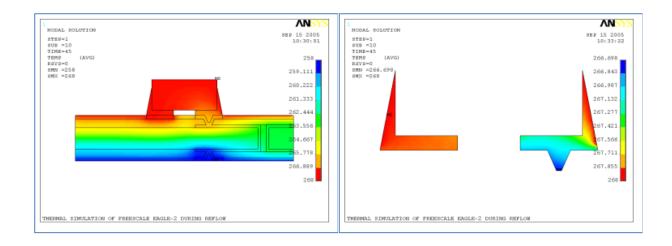

| Figure 7.13: | FEM simulation results for solder joint with a small via-in-pad. Note: The via-hole is 20 $\nu$ m in diameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 7.14: | FEM simulation results for solder joint with a small via-in-pad. Note: The via-hole is 60 μm in diameter                                                                                                |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | CHAPTED 0                                                                                                                                                                                               |

|              | CHAPTER 8                                                                                                                                                                                               |

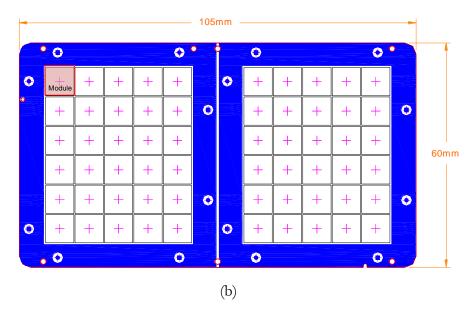

| Figure 8.1:  | Test vehicle design. Notes: (a) Module design; (b) top side view that shows whole PCB substrate strip outline                                                                                           |

| Figure 8.2:  | Schematic of passive chip component pad design and via-hole location224                                                                                                                                 |

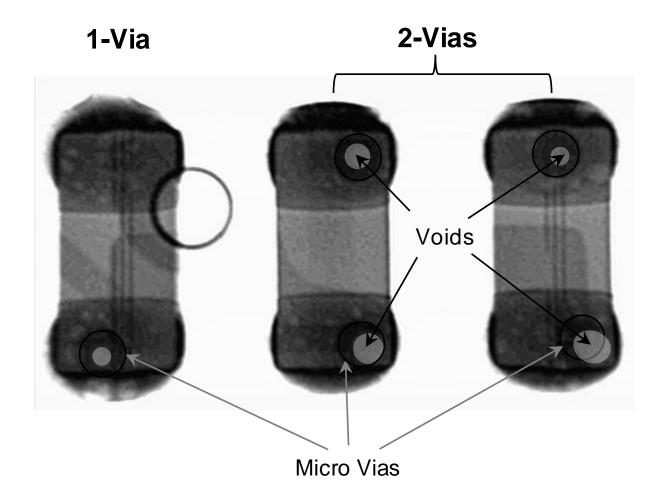

| Figure 8.3:  | Example of X-ray image of test vehicles with voids and voiding area evaluation using computer software                                                                                                  |

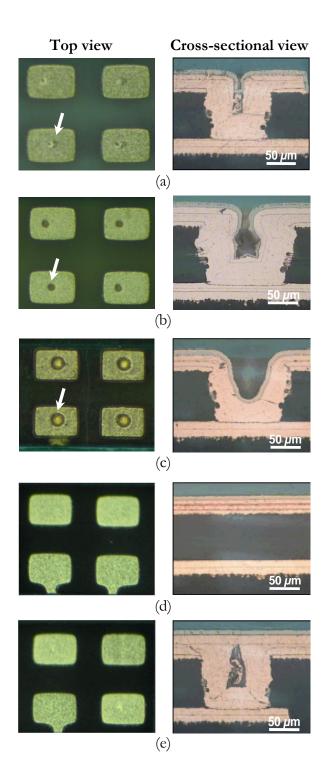

| Figure 8.4:  | Optical images of each micro via-in-pad, with the via-hole indicated by arrows. Notes: (a) ultra-small via-in-pad; (b) small via-in-pad; (c) large via-in-pad; (d) no via-in-pad; (e) capped via-in-pad |

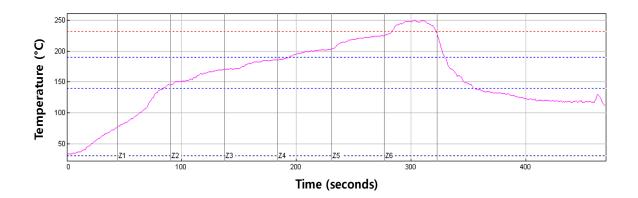

| Figure 8.5:  | A representative of reflow profile: long-preheat condition (84 s)                                                                                                                                       |

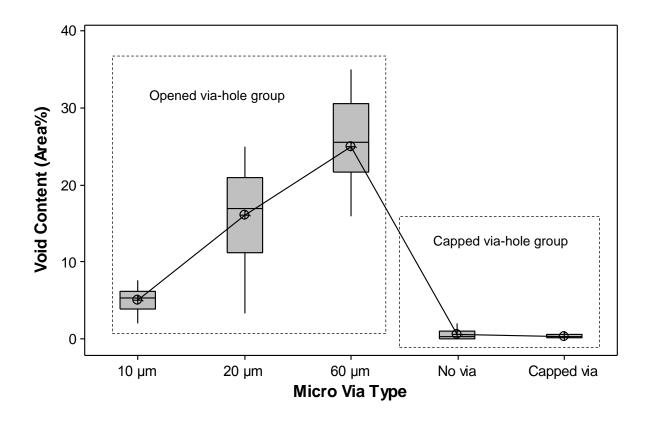

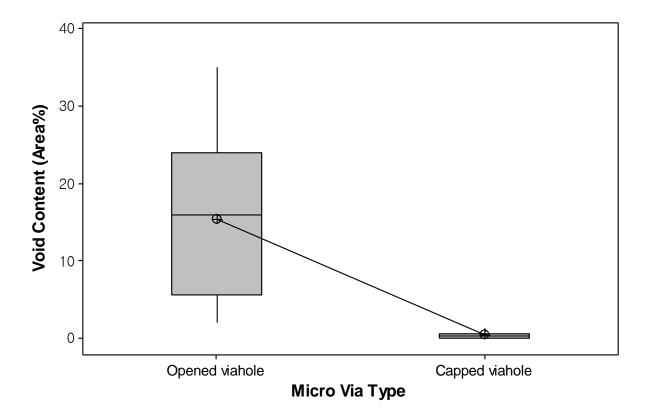

| Figure 8.6:  | Relationship between micro via-hole size and voiding. Note: The box plot shows the smallest value, the first quartile (Q1), the median, the third quartile (Q3), and the largest value                  |

| Figure 8.7:  | Void content comparisons for each via-hole group. Note: The box plot shows the smallest value, the first quartile (Q1), the median, the third quartile (Q3), and the largest value                      |

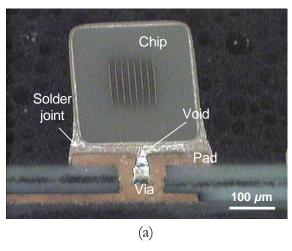

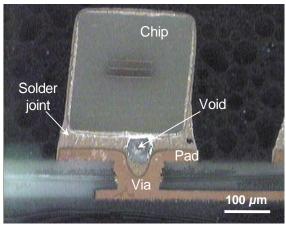

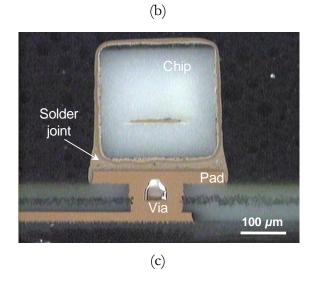

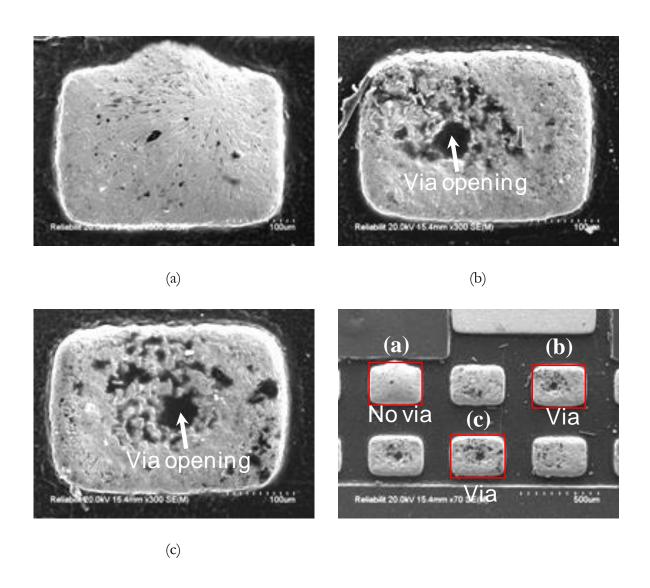

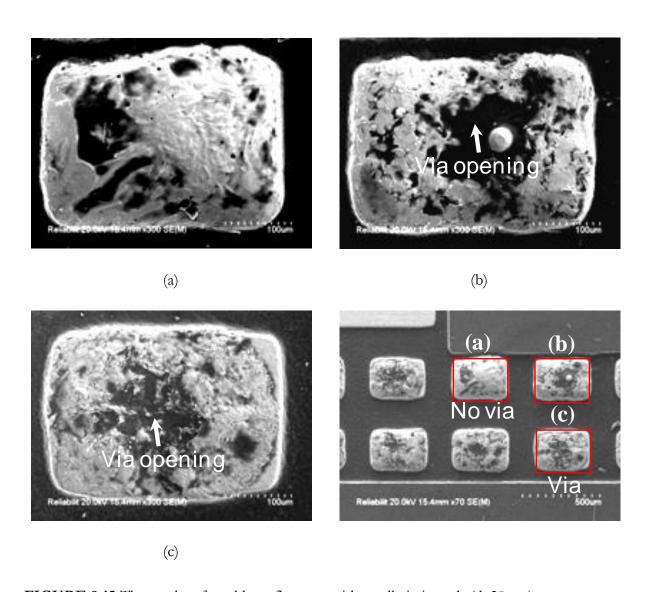

| Figure 8.8:  | Representative cross-sectional view of voiding in the solder joint at micro via-in pads. Notes: (a) Small via-in-pad; (b) large via-in-pad; (c) capped via-in-pad233                                    |

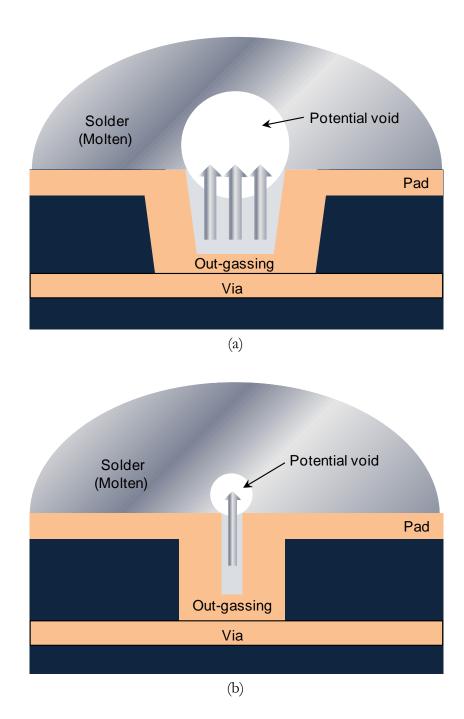

| Figure 8.9:  | Schematic diagram of voiding formation in the solder joints with different micro vias. Notes: (a) Large via-in-pad; (b) small via-in-pad                                                                |

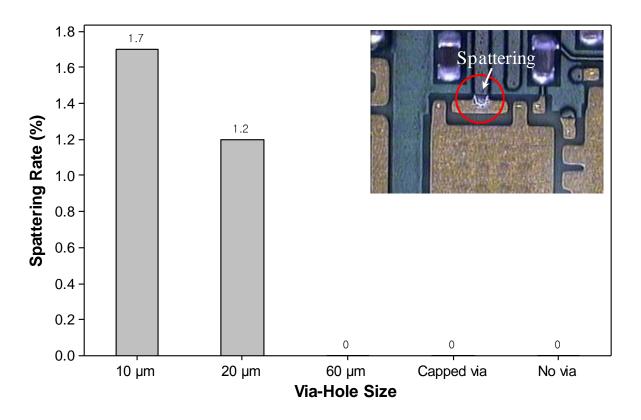

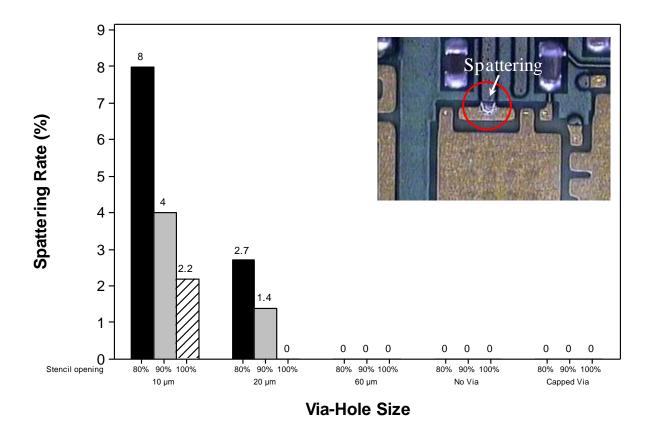

| Figure 8.10: | Relationship between micro via-hole size and spattering rate                                                                                                                                            |

| Figure 8.11: | The results of a solder reflow test with large via-in pads (d: 60 $\mu$ m). Notes: (a) No via-in-pad; (b), (c) via-in-pads                                                                              |

| Figure 8.12: | The results of a solder reflow test with small via-in pads (d: 20 $\mu$ m). Notes: (a) No via-in-pad; (b), (c) via-in-pads                                                                              |

| Figure 8.13: | Relationship between stencil opening ratio and spattering rate in micro via-in-pads                                                                                                                     |

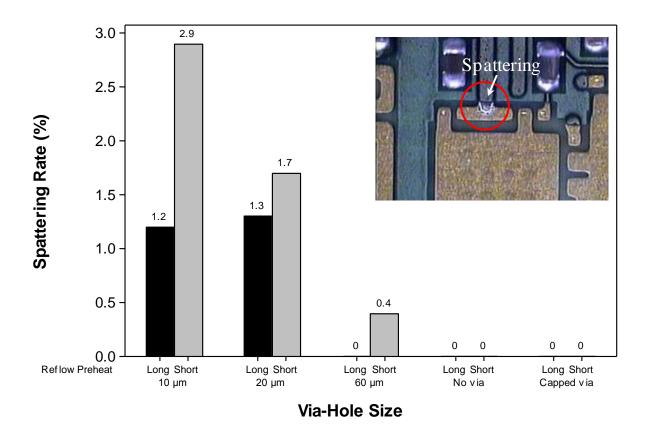

| Figure 8.14: | Relationship between reflow preheat condition and spattering rate in micro via-in-pads                                                                                                                  |

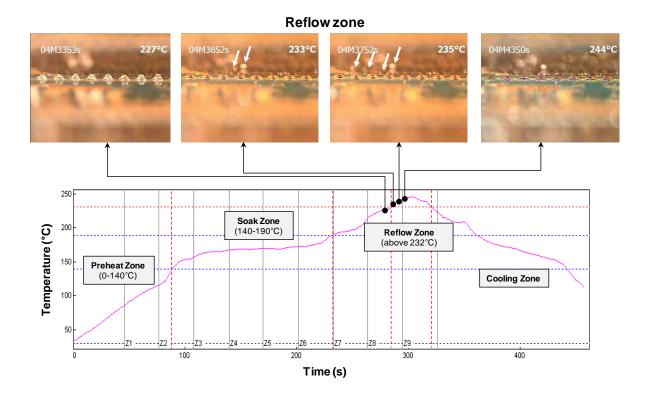

| Figure 8.15: | SMT scope images of reflow process for spattering phenomenon. Note: The solder droplet on the pad, indicated by the arrow                                                                               |

#### **CHAPTER 9**

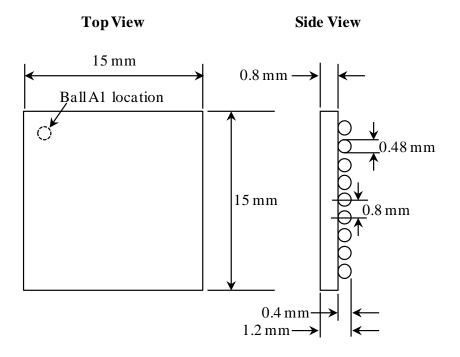

| Figure 9.1:  | BGA mechanical outline                                                                                                                                                            |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 9.2:  | BGA 208 test vehicle substrate daisy chains                                                                                                                                       |

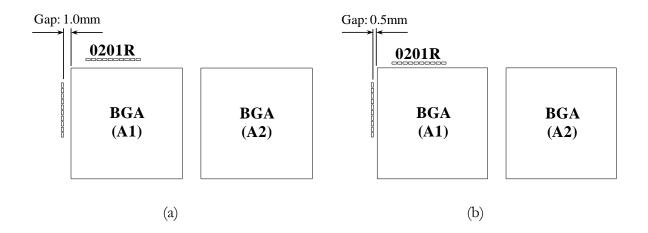

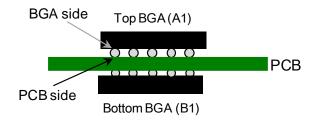

| Figure 9.3:  | BGA-to-0201R chip placement gap scenario: (a) 1.0 mm; (b) 0.5 mm. Note that A1 is BGA site to be rework and A2 is adjacent BGA site251                                            |

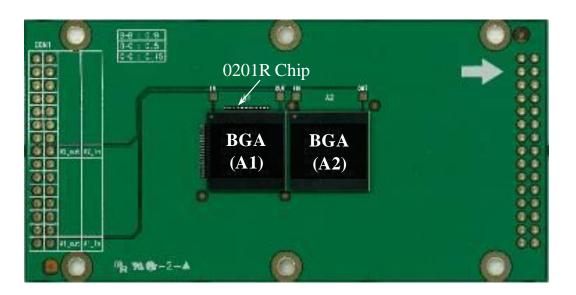

| Figure 9.4:  | Photograph of the rework assembled test board                                                                                                                                     |

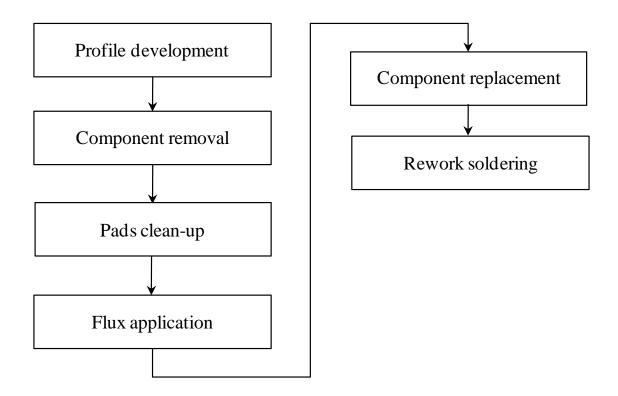

| Figure 9.5:  | General BGA rework process flow                                                                                                                                                   |

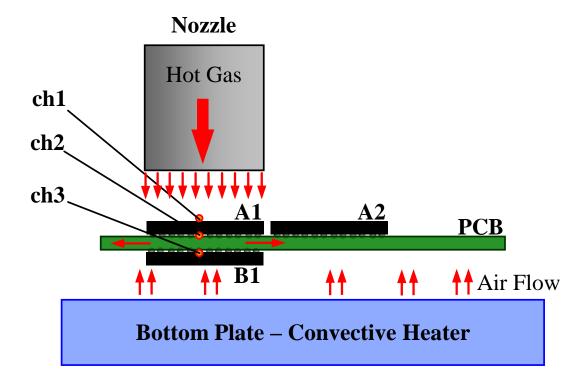

| Figure 9.6:  | Illustration of thermocouple locations and heating system for BGA rework. Note that ch1, ch2 and ch3 are thermocouple locations                                                   |

| Figure 9.7:  | A close-up view of the pads cleaned for each pads clean-up method. Notes: (a) Manual soldering iron and solder wick; (b) semi-automatic system using a vacuum desoldering machine |

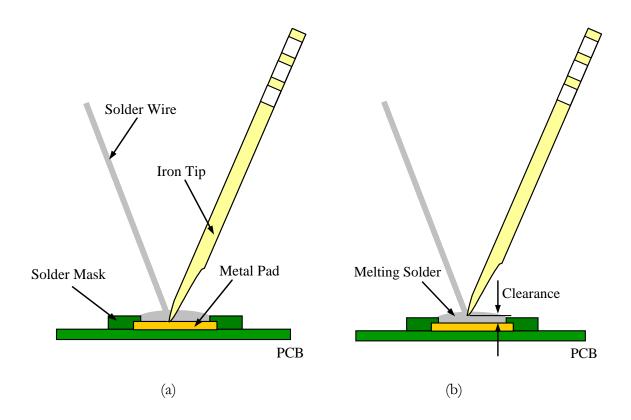

| Figure 9.8:  | Schematic diagram of pads clean-up methods by manual soldering iron technique. Notes: (a) On-contact; (b) off-contact                                                             |

| Figure 9.9:  | Schematic diagram of solder deposited pads displaying surface shapes identified. Notes: (a) Flat; (b) convex; (c) concave; (d) inclined                                           |

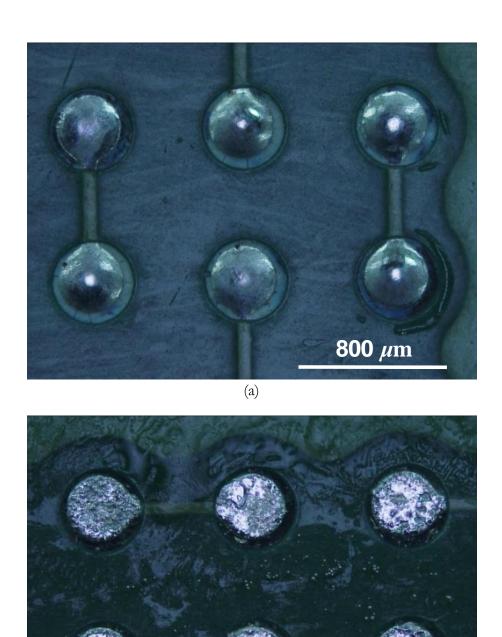

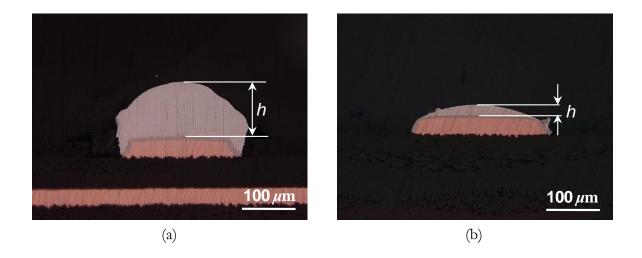

| Figure 9.10: | Cross-section of soldered on pads. Notes: (a) As-reflowed soldered pad; (b) as-reworked soldered pad                                                                              |

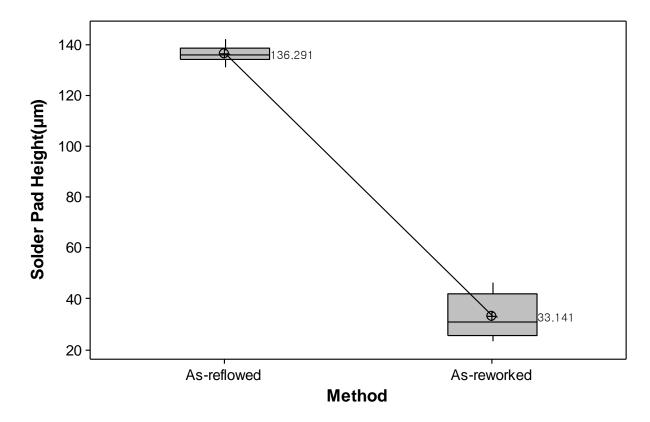

| Figure 9.11: | Resultant averages solder pad height. Note that the box plot shows the smallest value, the first quartile (Q1), the median, the third quartile (Q3) and the largest value260      |

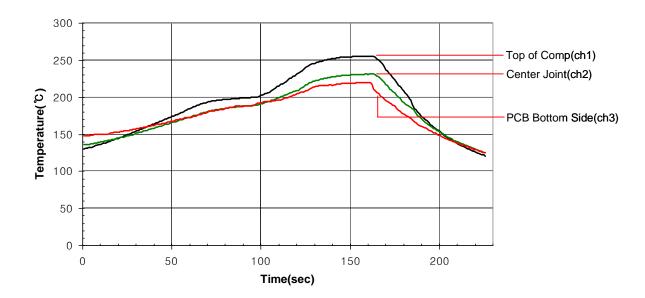

| Figure 9.12: | Thermal profile for lead-free BGA rework. Notes: (ch1) Top of the BGA component; (ch2) solder joint of the BGA component; (ch3) bottom side of the PCB                            |

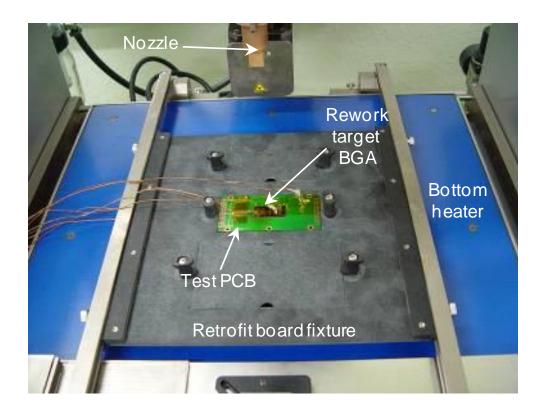

| Figure 9.13: | Photograph of retrofit board fixture applied                                                                                                                                      |

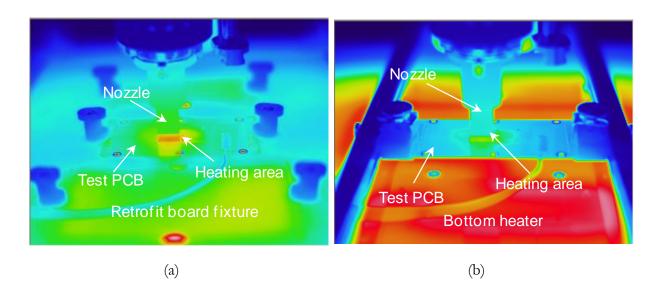

| Figure 9.14: | Result of IR imaging analysis. Notes: (a) With retrofit board fixture; (b) without retrofit board fixture                                                                         |

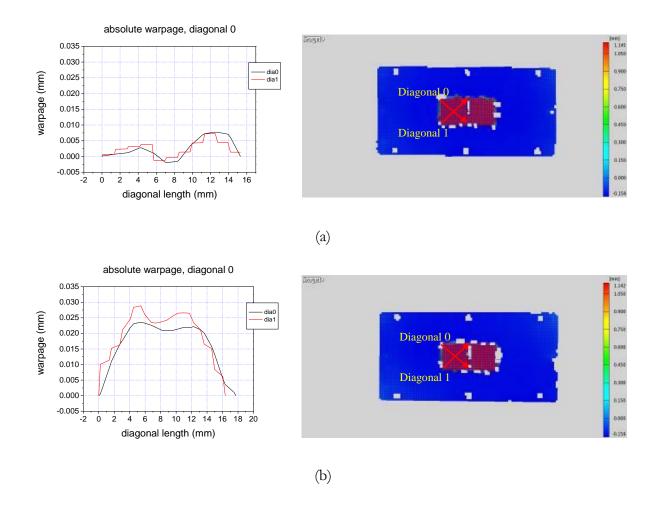

| Figure 9.15: | Result of warpage measurement for component side. Notes: (a) As-reflowed BGA component; (b) as-reworked BGA component                                                             |

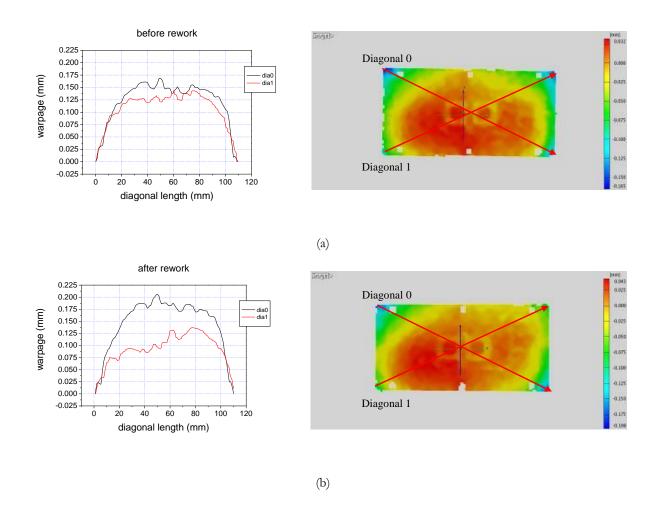

| Figure 9.16: | Result of warpage measurement for PBA side. Notes: (a) As-reflowed PBA; (b) as-reworked PBA                                                                                       |

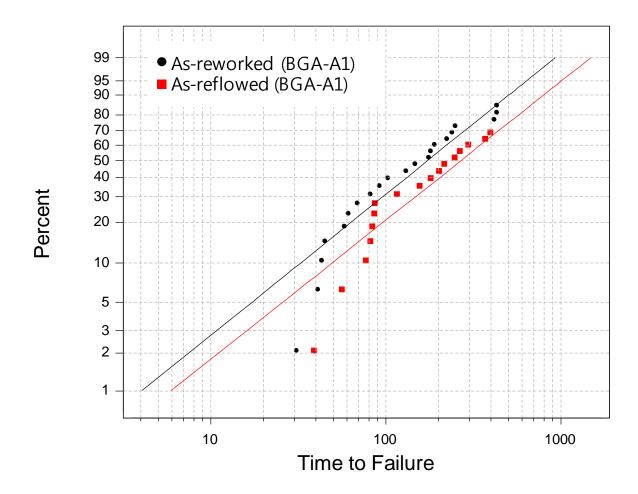

| Figure 9.17: | Weibull distributions for as-reworked samples and as-reflowed samples270                                                                                                          |

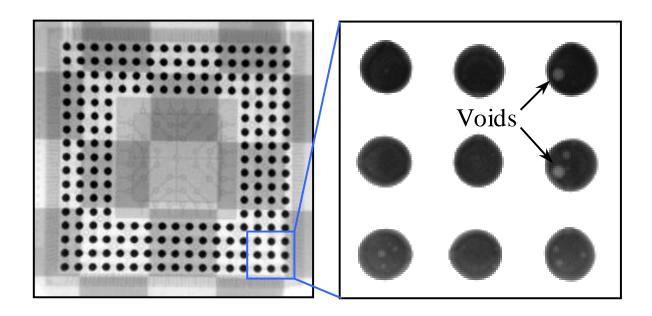

| Figure 9.18: | X-ray image of as-reworked BGA component271                                                                                                                                       |

| Figure 9.19: | Interfacial IMCs at the interface between the copper pad with ENIG finish on the board and 95.5wt.%Sn-4.0wt.%Ag-0.5wt.%Cu (SAC405) solder ball attached: (a) A solder joint of a SAC405 BGA on a board pad with ENIG finish showing (Cu, Ni) <sub>6</sub> Sn <sub>5</sub> IMCs and (b) a solder joint of a SAC405 BGA on a board pad with ENIG finish showing Ag <sub>3</sub> Sn IMC layer. Needle-like features in the microstructure of solder joints |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

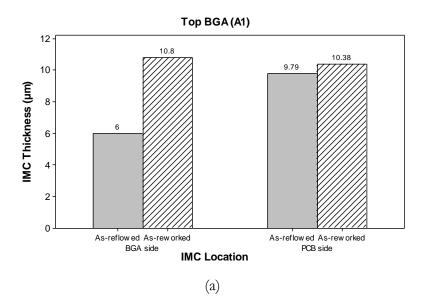

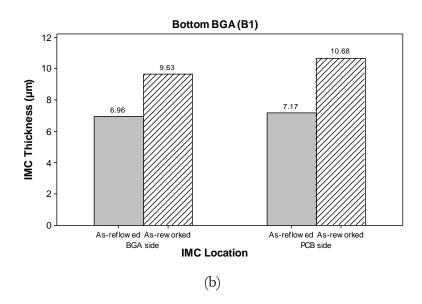

| Figure 9.20: | Result of IMC layer thickness measurement. Notes: (a) Top side; (b) bottom side 274                                                                                                                                                                                                                                                                                                                                                                     |  |

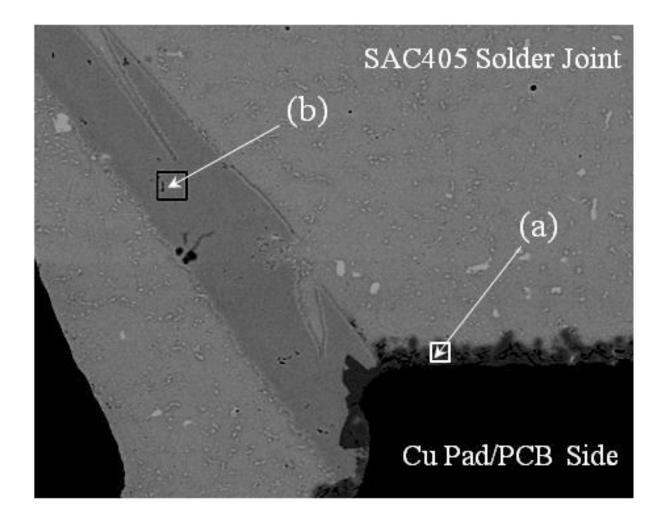

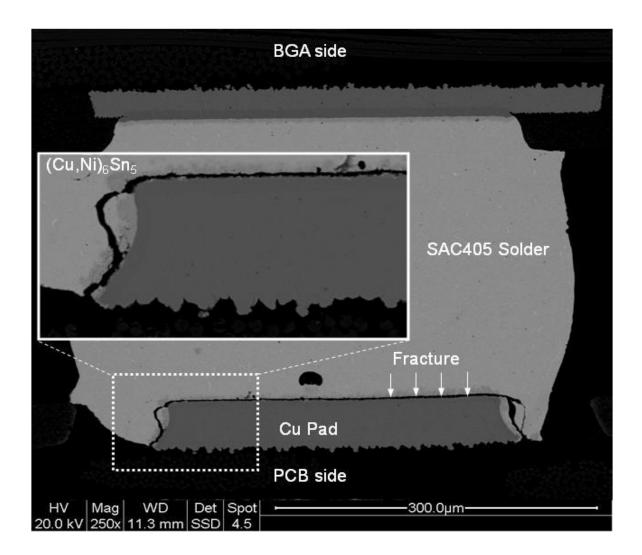

| _            | Crack propagates through the (Cu, Ni) <sub>6</sub> Sn <sub>5</sub> IMC after the drop test according to the JESD22-B111 standard                                                                                                                                                                                                                                                                                                                        |  |

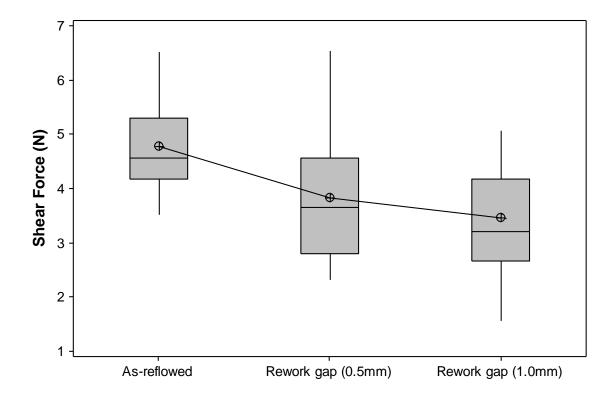

| Figure 9.22: | Average shear forces at the different BGA-to-passive components placement gaps for as-reflowed and as-reworked samples                                                                                                                                                                                                                                                                                                                                  |  |

| CHAPTER 10   |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

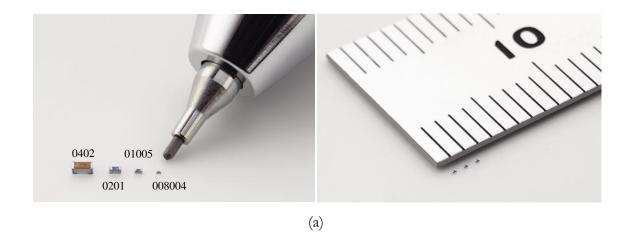

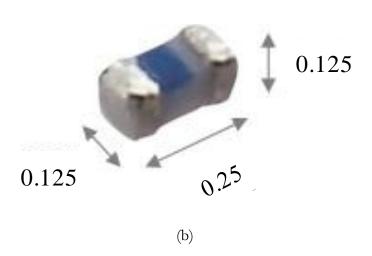

| 0            | 008004 (0201 metric) chip components. Notes: (a) Comparison of 008004 chip size with larger size chip components and a 0.5mm tip; (b) 008004 chip components (0.25 mm $\times$ 0.125 mm)                                                                                                                                                                                                                                                                |  |

Table 4.5:

### List of Tables

|            | CHAPTER 1                                                                                      |  |  |  |

|------------|------------------------------------------------------------------------------------------------|--|--|--|

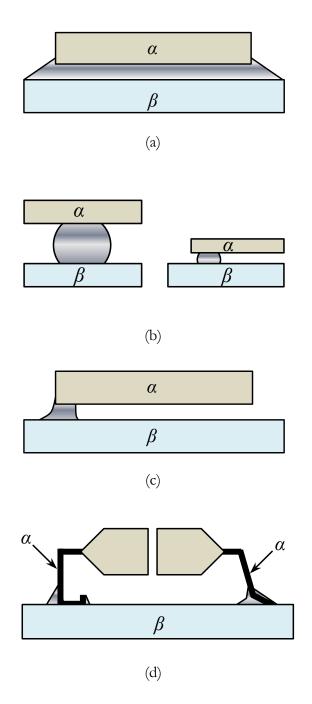

| Table 1.1: | Coefficient of thermal expansion for materials used in electronic assemblies                   |  |  |  |

| Table 1.2: | Lead consumption by product                                                                    |  |  |  |

| Table 1.3: | Chip-to-package pitches                                                                        |  |  |  |

| Table 1.4: | Effect of higher process temperatures on various microelectronic board assemblies              |  |  |  |

|            | CHAPTER 2                                                                                      |  |  |  |

| Table 2.1: | Comparison of stencil materials in key performance areas                                       |  |  |  |

| Table 2.2: | Classification of solder powder size, expressed as percent of sample by weight – nominal sizes |  |  |  |

|            | CHAPTER 3                                                                                      |  |  |  |

| Table 3.1: | Pad dimension in the test vehicle                                                              |  |  |  |

| Table 3.2: | Dimensional tolerances for chip capacitors                                                     |  |  |  |

| Table 3.3: | Design of the experiment matrix                                                                |  |  |  |

| Table 3.4: | Types of vision camera used                                                                    |  |  |  |

| Table 3.5: | Two-sample <i>t</i> -test results for solder paste thickness comparison                        |  |  |  |

|            | CHAPTER 4                                                                                      |  |  |  |

| Table 4.1: | Pad dimension in the test vehicle                                                              |  |  |  |

| Table 4.2: | Parameters of EP                                                                               |  |  |  |

| Table 4.3: | Laser-cut stencil fabrication parameters                                                       |  |  |  |

| Table 4.4: | Reflow process parameters111                                                                   |  |  |  |

| Table 4.7: | Two-sample <i>t</i> -test results for shear force                                           | 118 |  |  |

|------------|---------------------------------------------------------------------------------------------|-----|--|--|

|            |                                                                                             |     |  |  |

|            | CHAPTER 5                                                                                   |     |  |  |

| Table 5.1: | Chemical composition of the SUS304 stainless steel (Weight %)                               | 128 |  |  |

| Table 5.2: | Laser-cutting system used                                                                   | 128 |  |  |

| Table 5.3: | Parameters of EP                                                                            | 130 |  |  |

| Table 5.4: | EP variable factors                                                                         | 130 |  |  |

| Table 5.5: | Measured aperture sizes for each EP time (PCB side)                                         | 135 |  |  |

| Table 5.6: | Stencil geometry                                                                            |     |  |  |

| Table 5.7: | Two-sample <i>t</i> -test results for each stencil type                                     |     |  |  |