| Title        | Research on area-efficient, low power reference circuit |

|--------------|---------------------------------------------------------|

| Author(s)    | Bogoda, Appuhamylage Indika Udaya Kumara                |

| Citation     | 大阪大学, 2012, 博士論文                                        |

| Version Type | VoR                                                     |

| URL          | https://hdl.handle.net/11094/26865                      |

| rights       |                                                         |

| Note         |                                                         |

# Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

工事 15796

# Research on area-efficient, low power reference circuit

# Bogoda Appuhamylage Indika Udaya Kumara

2011

# Research on area-efficient, low power reference circuit

Bogoda Appuhamylage Indika Udaya Kumara

2011

# Abstract

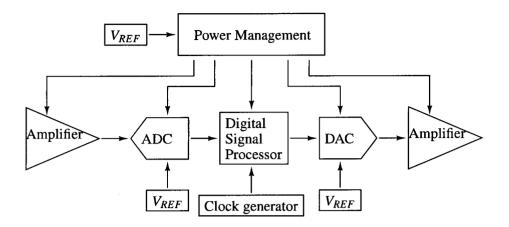

The main part of this research was dedicated to propose a new area-efficient and low power bandgap reference (BGR) circuit. Two new BGR circuit architectures utilizing current switched and current memory techniques are presented. Both circuits are designed using manufacturer-provided device models and operations are verified by using SPICE (Simulation Program with Integrated Circuit Emphasis) simulations. Moreover, to study the design area occupation, layout designing is also carried out.

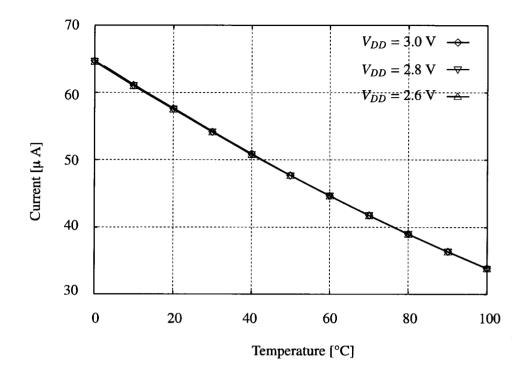

The final part of the research was carried out to propose a novel ultra-low-power temperature independent current reference, which is designed by using subthreshold CMOS devices. In this work also, SPICE simulations were performed to verify the circuit operations, and the results are presented. Therefore, this dissertation consists of six chapters.

In Chapter 1, a brief introduction of this research is given, including research background, objectives and dissertation structure.

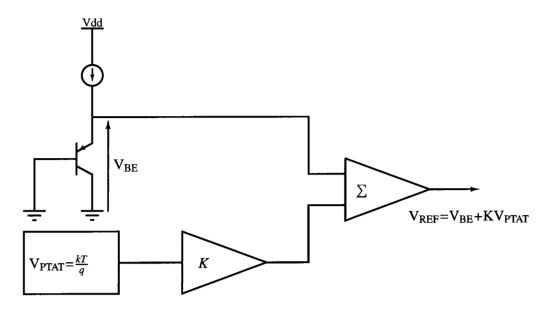

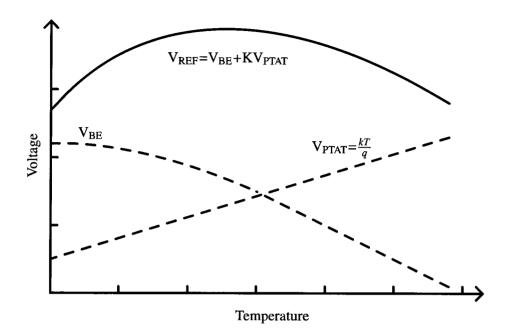

In Chapter 2, the conventional BGRs are reviewed and the major problems of available CMOS BGRs are discussed.

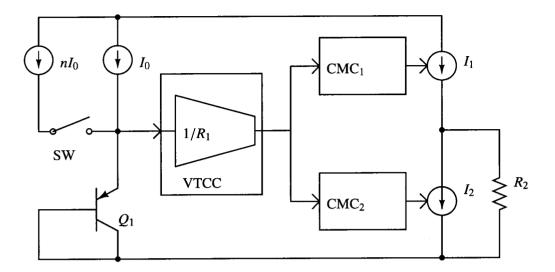

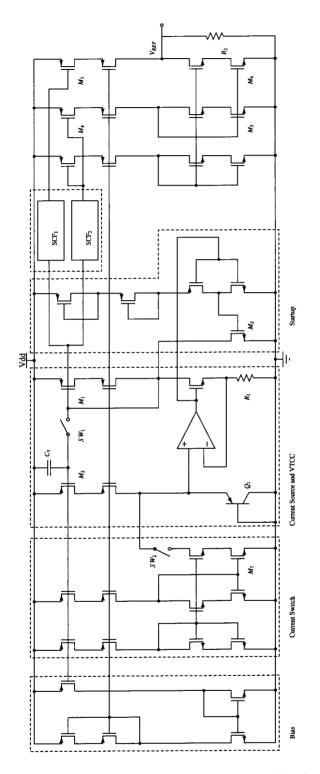

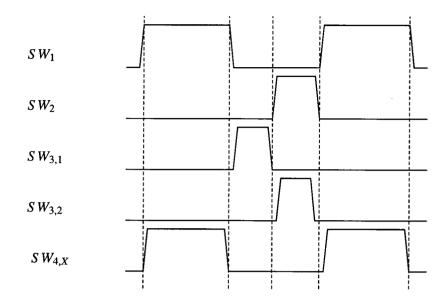

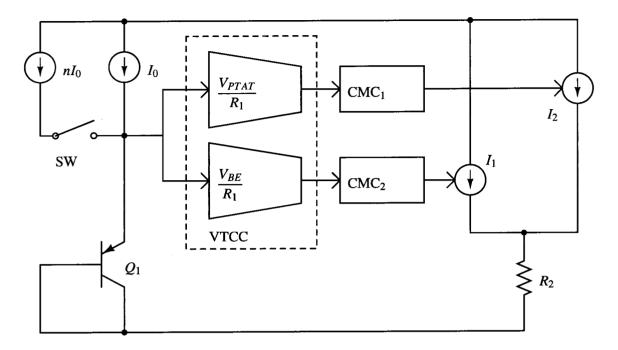

In Chapter 3, an area efficient CMOS bandgap reference with switched-current and currentmemory technique is presented.

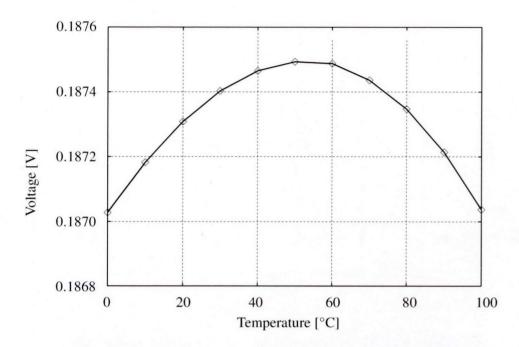

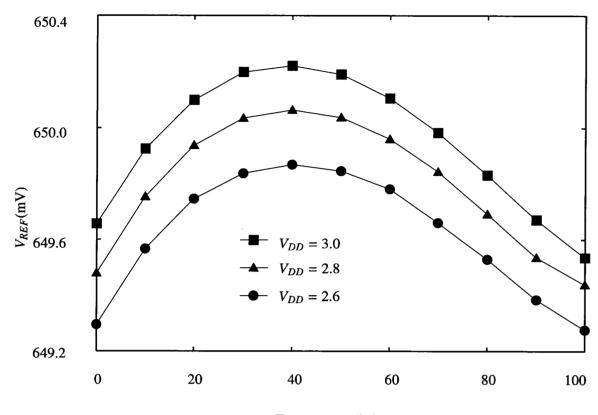

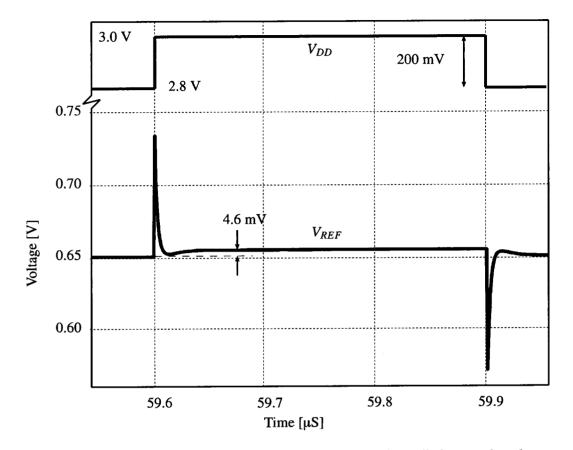

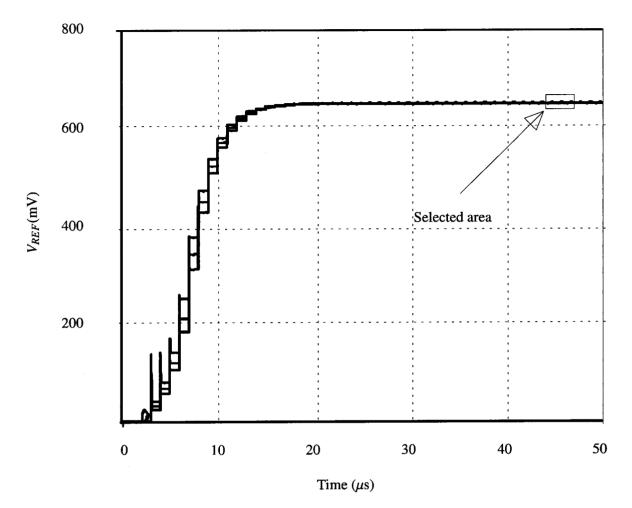

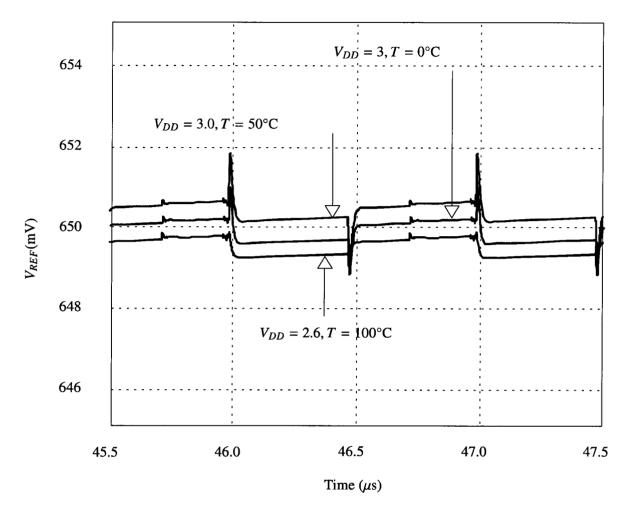

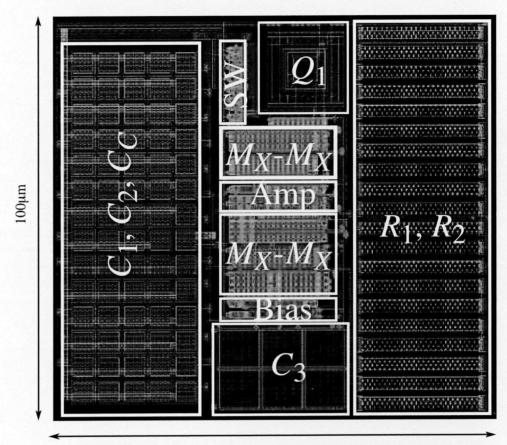

The proposed circuit uses only one parasitic bipolar transistor to generate reference voltage so that significant area reduction is achieved. The circuit produces an output of about 650 mV, and simulated results show that the temperature coefficient of output is less than 10.7 ppm/°Cin the temperature range from 0 °C to 100 °C. The average current consumption is about 49.5  $\mu$ A in the above temperature range. Furthermore, output can be set to almost any value. The circuit was designed and simulated in 0.25  $\mu$ m CMOS technology. The layout occupies less than 0.011 mm<sup>2</sup> (100  $\mu$ m × 110  $\mu$ m).

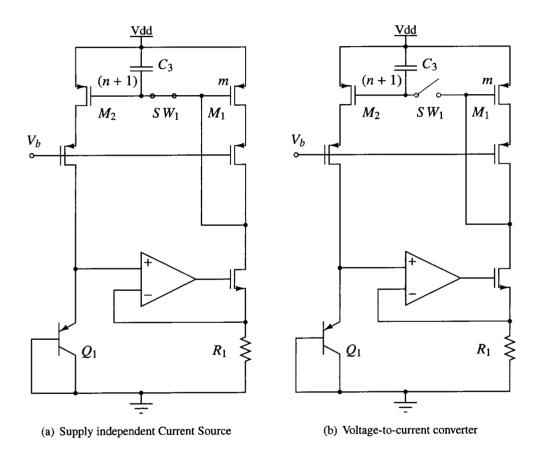

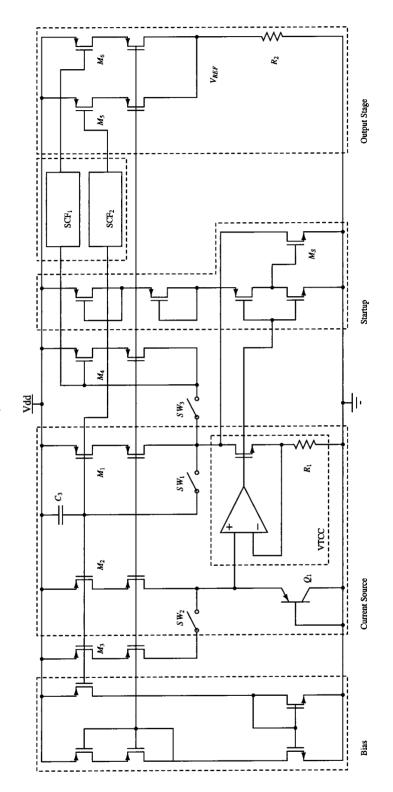

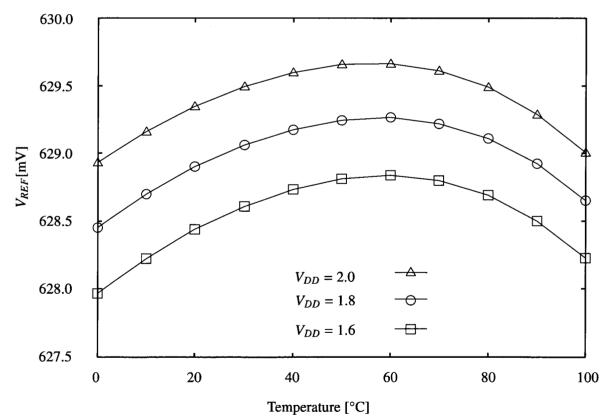

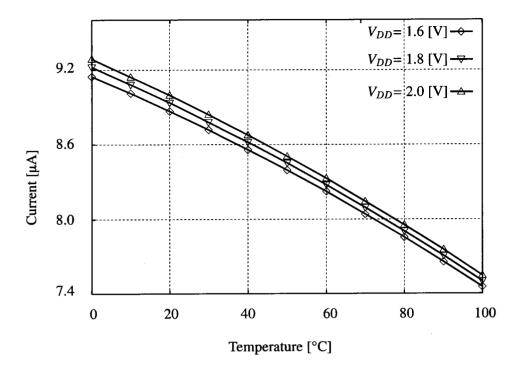

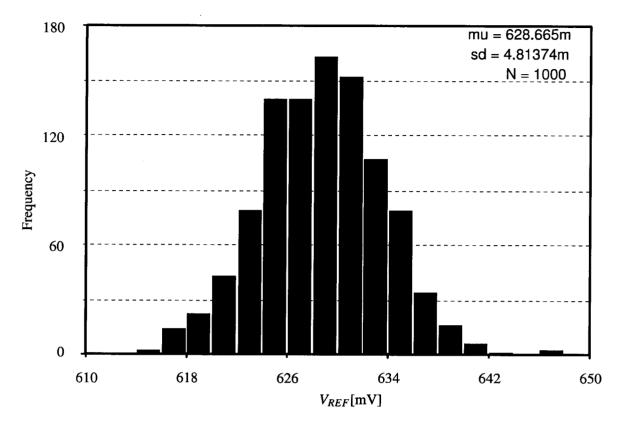

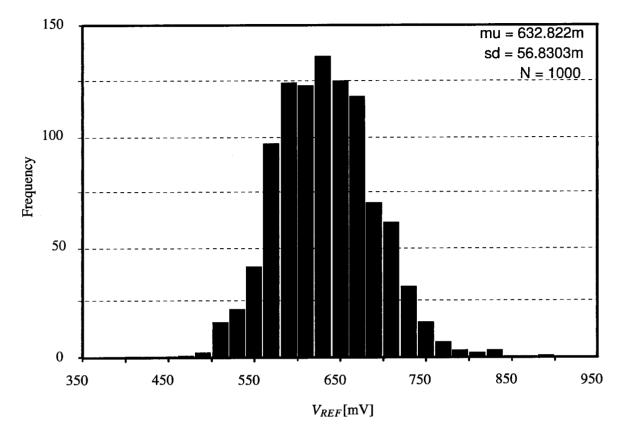

In Chapter 4, an area efficient, low power, fractional CMOS bandgap reference utilizing switchedcurrent and current-memory techniques is presented. The proposed circuit uses only one parasitic bipolar transistor and built-in current source to generate reference voltage. Therefore significant area and power reduction is achieved, and bipolar transistor device mismatch is eliminated. In addition, output reference voltage can be set to almost any value. The proposed circuit is designed and simulated in 0.18  $\mu$ m CMOS process, and simulation results are presented. With a 1.6 V supply, the reference produces an output of about 628.5 mV, and simulated results show that the temperature coefficient of output is less than 13.5 ppm/°C in the temperature range from 0 °C to 100 °C. The average current consumption is about 8.5  $\mu$ A in the above temperature range. The core circuit, including current source, operational amplifier, current mirrors and switched capacitor filters, occupies less than 0.0064 mm<sup>2</sup> (80  $\mu$ m × 80  $\mu$ m).

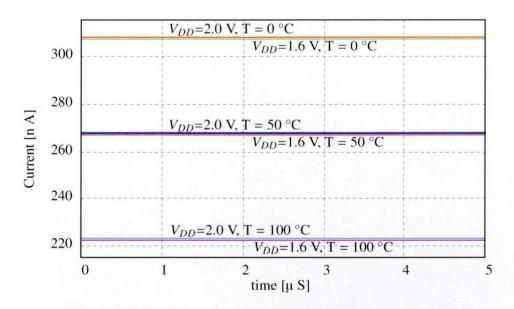

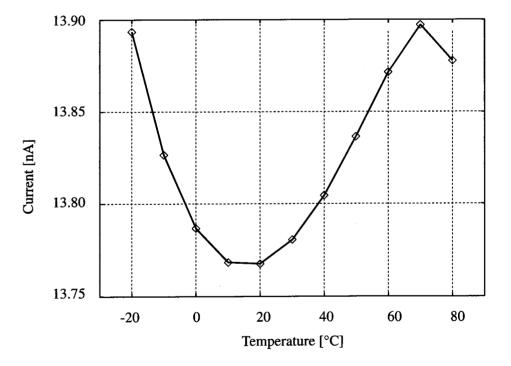

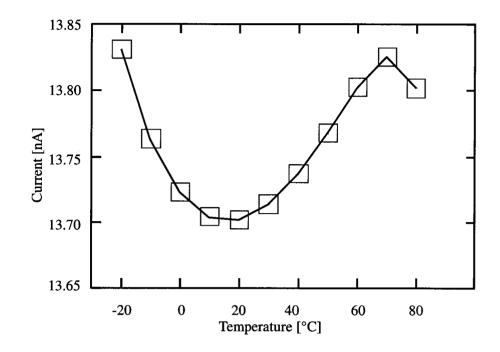

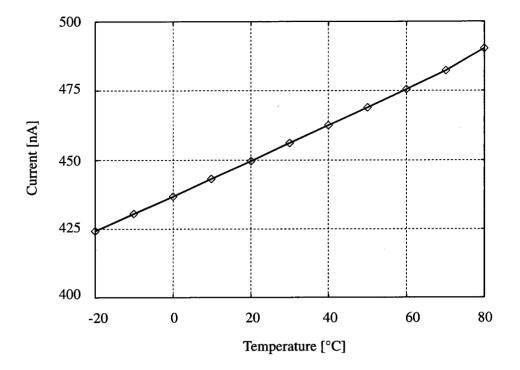

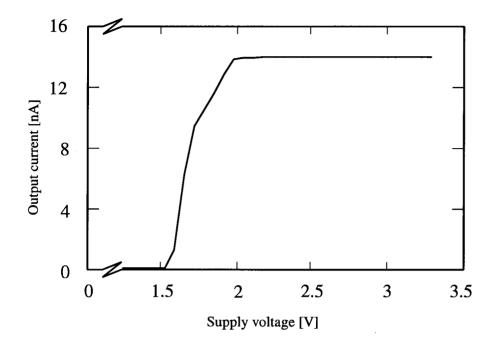

In Chapter 5, a novel temperature-compensated, ultra-low-power current reference based on two  $\beta$ -multipliers whose resistors are replaced by nMOS devices operated in the deep triode region is

presented. The circuit, designed by a 0.25  $\mu$ m CMOS process, produces an output reference current of 13.7 nA at room temperature. Simulated results show that the temperature coefficient of the output is less than 100 ppm/°C in the range from -20 °C to 80 °C and the average power dissipation is 0.9 W.

In Chapter 6, conclusions of this study and recommendations for further research are given.

# Acknowledgement

It is a pleasure to thank the many people who made this thesis possible.

I would like to express my deep and sincere gratitude to my supervisor, Professor Emeritus Kenji Taniguchi (currently at Nara national college of technology), for his warm encouragement and thoughtful guidance. His wide knowledge and his great efforts to explain things clearly and simply have been of great value for me.

I also thank the members of my thesis committee: Professor Tetsuya Yagi, Associate Professor Toshimasa Matsuoka, and Associate Professor Masanori Hahsimoto, whose helpful suggestions increased readability and reduced ambiguity.

I would like to thank Professor Toshimichi Ito, Professor Yusuke Mori, Professor Mitsuhiro Katayama, Professor Masanori Ozaki, Professor Toshiaki Suhara, Professor Masahiko Kondow, Professor Yutaka Ohmori, and Professor Seizo Morita for their detailed and constructive comments, and for their important support throughout this work.

Also, special thanks go to Associate Professor Yoshinari Kamakura, for his professional advice and guidance in assisting and supporting this research.

This thesis would not have been possible without the help and support of my second supervisor, Associate Professor Toru Ido (currently at Wolfson Microelectronics Corporation), not to mention his advice and unsurpassed knowledge of analog circuit designing.

I especially want to thank Dr. Shunsuke Okura (currently at Renesas Electronics Corporation), for his guidance during my research and study at Osaka University. His perpetual energy and enthusiasm in research had motivated me. In addition, he was always accessible and willing to help me with any thing I needed.

Special thanks are due to my parents Edmon S. Bogoda and Sheela Bogoda, and all dear friends, who enriched my life with their time, love, and friendship, who helped me to accept the sad things that happen in life, and who never stopped reminding me of the wonderful world outside of my research.

I dedicate this thesis to my father and my late mother, who will always be in my heart.

# Contents

| 1 | Intr | oduction 1                                          |  |  |  |  |  |  |

|---|------|-----------------------------------------------------|--|--|--|--|--|--|

|   | 1.1  | Introduction                                        |  |  |  |  |  |  |

|   | 1.2  | Research objectives                                 |  |  |  |  |  |  |

|   | 1.3  | Dissertation framework                              |  |  |  |  |  |  |

| 2 | Volt | age Reference 5                                     |  |  |  |  |  |  |

|   | 2.1  | Introduction                                        |  |  |  |  |  |  |

|   | 2.2  | Forward-biased diode reference                      |  |  |  |  |  |  |

|   |      | 2.2.1 Temperature behavior of $V_{BE}$              |  |  |  |  |  |  |

|   |      | 2.2.2 PTAT voltage                                  |  |  |  |  |  |  |

|   |      | 2.2.3 Bandgap reference                             |  |  |  |  |  |  |

|   | 2.3  | Zener references                                    |  |  |  |  |  |  |

|   | 2.4  | Subthreshold references                             |  |  |  |  |  |  |

|   | 2.5  | Comparison                                          |  |  |  |  |  |  |

|   | 2.6  | Summary                                             |  |  |  |  |  |  |

| 3 | Area | Area-efficient bandgap reference                    |  |  |  |  |  |  |

|   | 3.1  | Introduction                                        |  |  |  |  |  |  |

|   | 3.2  | Architecture of the proposed circuit                |  |  |  |  |  |  |

|   | 3.3  | I I I I I I I I I I I I I I I I I I I               |  |  |  |  |  |  |

|   |      | 3.3.1 Circuit operation                             |  |  |  |  |  |  |

|   |      | 3.3.2 Switched-capacitor filter (SCF) 25            |  |  |  |  |  |  |

|   |      | 3.3.3 Differential amplifier                        |  |  |  |  |  |  |

|   | 3.4  | Design issues and accuracy analysis                 |  |  |  |  |  |  |

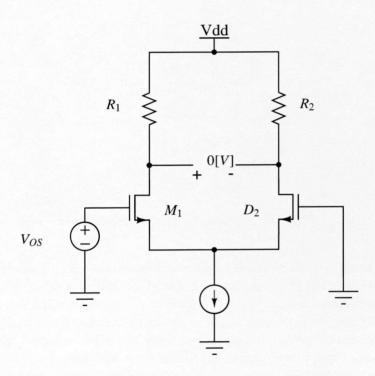

|   |      | 3.4.1         Input offset voltage         26       |  |  |  |  |  |  |

|   |      | 3.4.2       Current mirror ratios       28          |  |  |  |  |  |  |

|   |      | 3.4.3 Switched feedthrough                          |  |  |  |  |  |  |

|   | 3.5  | Simulation results                                  |  |  |  |  |  |  |

|   | 0.0  | 3.5.1 Temperature sweep                             |  |  |  |  |  |  |

|   |      | 3.5.2 Stability verification                        |  |  |  |  |  |  |

|   |      | 3.5.3 Power Supply variation and transient response |  |  |  |  |  |  |

|   | 3.6  | Layout                                              |  |  |  |  |  |  |

|   | 3.7  |                                                     |  |  |  |  |  |  |

|   | 3.8  | Comparison         47           Summary         48  |  |  |  |  |  |  |

|   | 5.0  | Summary                                             |  |  |  |  |  |  |

| 4 | Low                               | -power bandgap reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53  |  |  |  |  |

|---|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

|   | 4.1                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53  |  |  |  |  |

|   | 4.2                               | Proposed low-power bandgap reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54  |  |  |  |  |

|   |                                   | 4.2.1 Conception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54  |  |  |  |  |

|   |                                   | 4.2.2 Circuit operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55  |  |  |  |  |

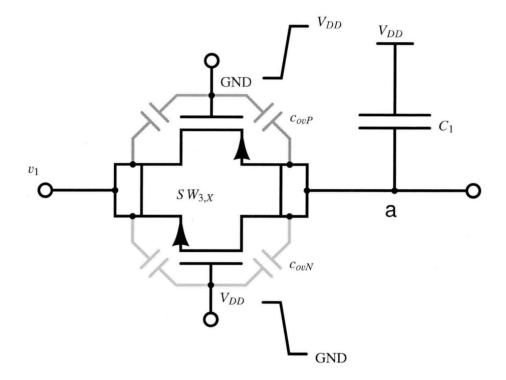

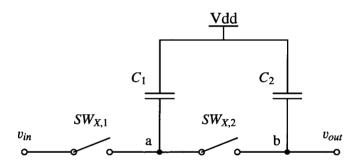

|   |                                   | 4.2.3 Switched capacitor filter (SCF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60  |  |  |  |  |

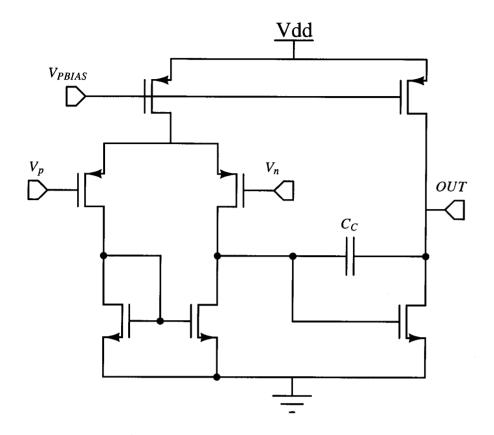

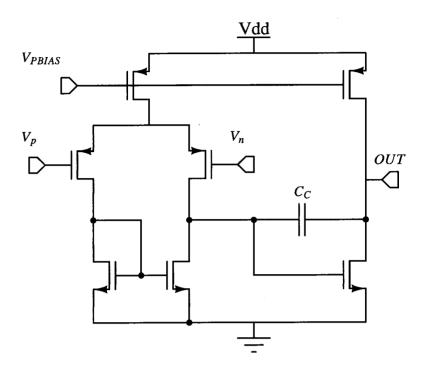

|   |                                   | 4.2.4 Differential amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 61  |  |  |  |  |

|   | 4.3                               | Design issues and accuracy analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62  |  |  |  |  |

|   |                                   | 4.3.1 Input offset voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62  |  |  |  |  |

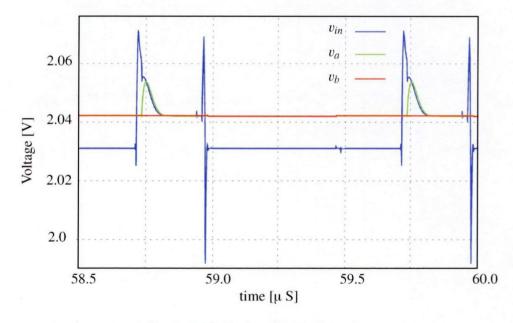

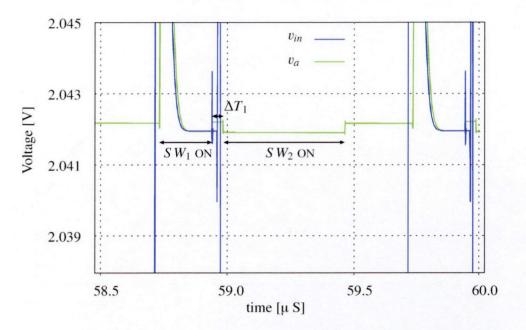

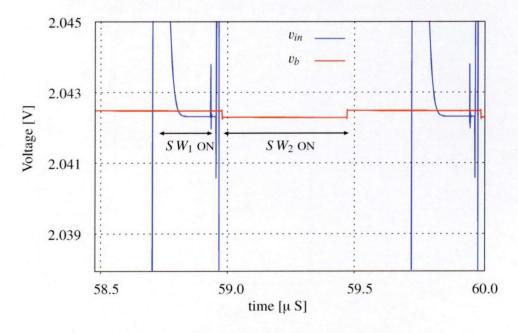

|   |                                   | 4.3.2 Switched feedthrough                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63  |  |  |  |  |

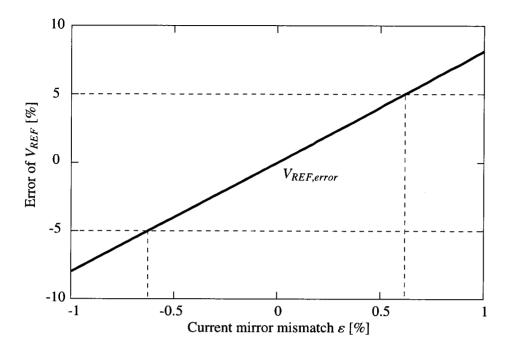

|   |                                   | 4.3.3 Current mirror ratios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64  |  |  |  |  |

|   | 4.4                               | Simulation results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65  |  |  |  |  |

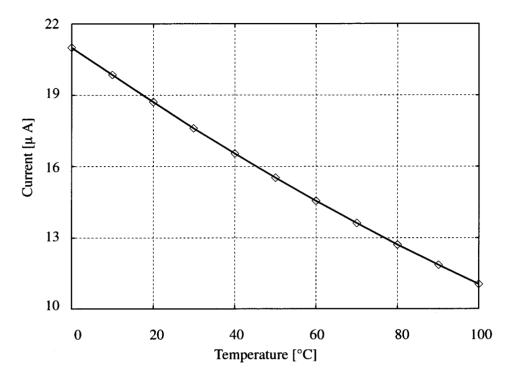

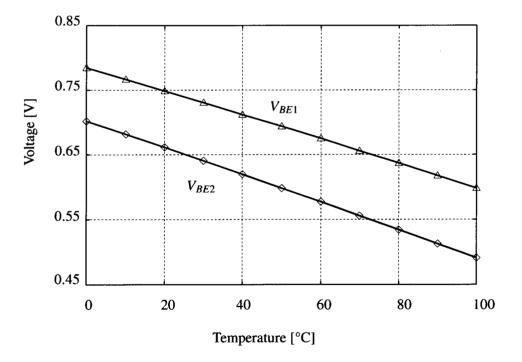

|   |                                   | 4.4.1 Temperature sweep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65  |  |  |  |  |

|   |                                   | 4.4.2 Monte Carlo verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 70  |  |  |  |  |

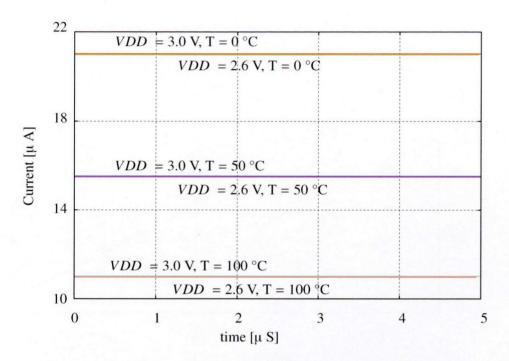

|   |                                   | 4.4.3 Power supply variation and transient response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 71  |  |  |  |  |

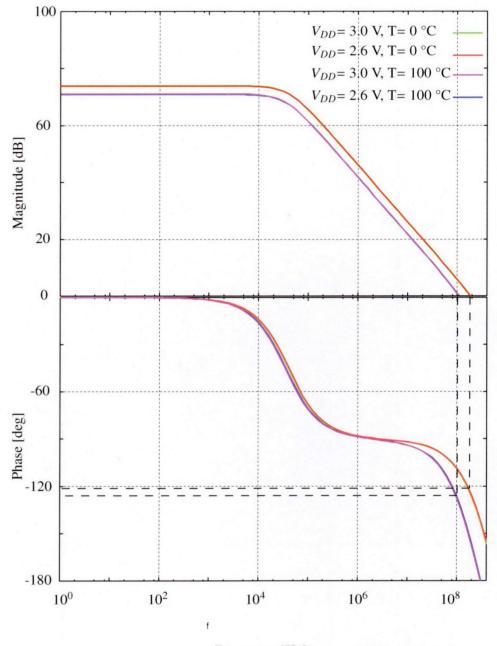

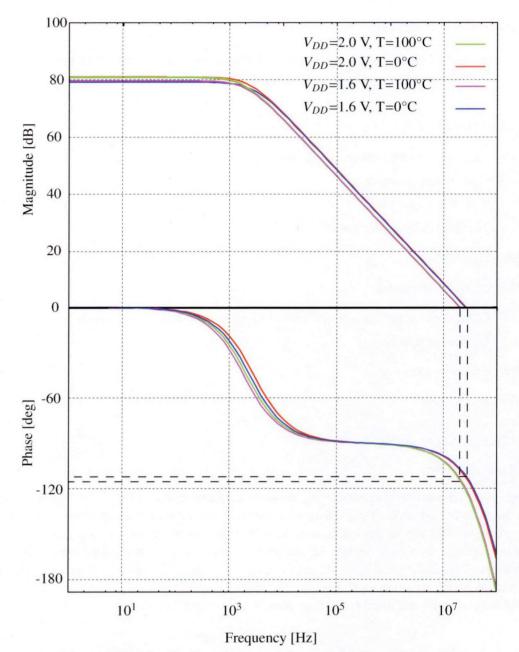

|   |                                   | 4.4.4 Stability verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73  |  |  |  |  |

|   | 4.5                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74  |  |  |  |  |

|   | 4.6                               | Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75  |  |  |  |  |

|   | 4.7                               | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 75  |  |  |  |  |

|   |                                   | Summary Trees to the trees to t |     |  |  |  |  |

| 5 | Ultra-low power current reference |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |  |  |

|   | 5.1                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79  |  |  |  |  |

|   | 5.2                               | Structure of the proposed current reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 80  |  |  |  |  |

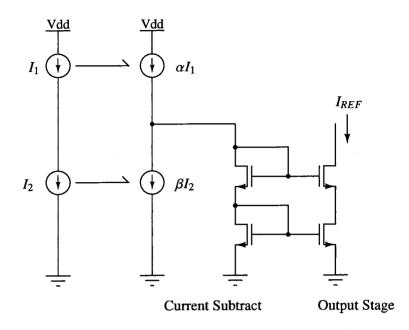

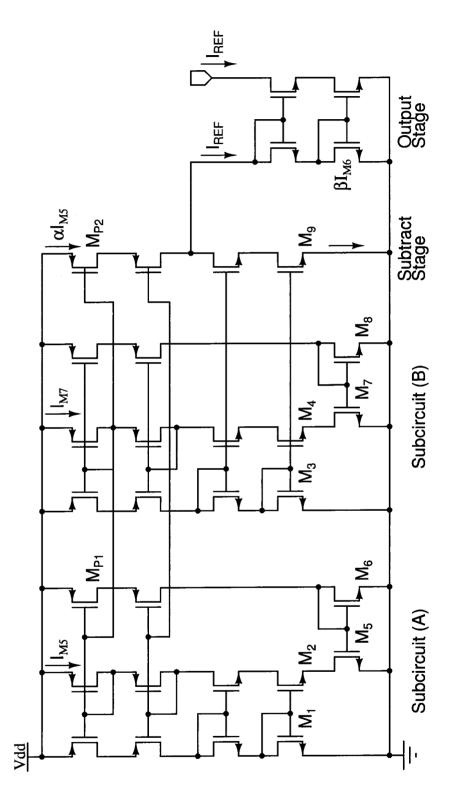

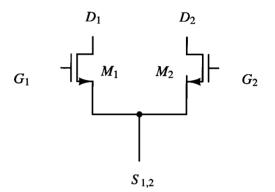

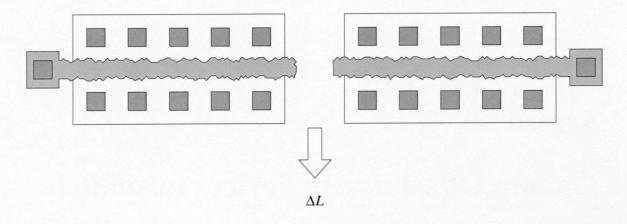

|   |                                   | 5.2.1 Operation principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 80  |  |  |  |  |

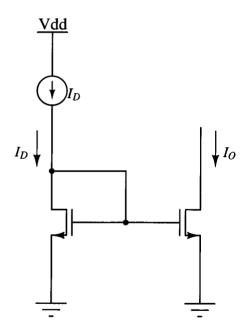

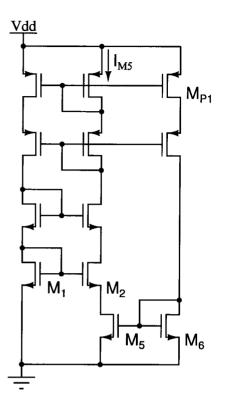

|   |                                   | 5.2.2 Current source subcircuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80  |  |  |  |  |

|   |                                   | 5.2.3 Temperature independent current source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 83  |  |  |  |  |

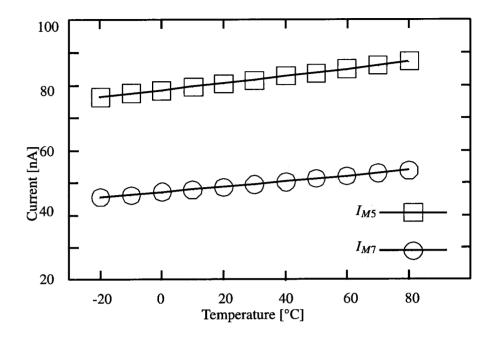

|   | 5.3                               | Simulation results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 85  |  |  |  |  |

|   |                                   | 5.3.1 Temperature sweep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85  |  |  |  |  |

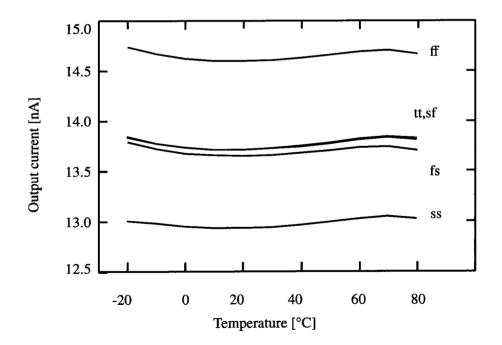

|   |                                   | 5.3.2 Corner simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87  |  |  |  |  |

|   |                                   | 5.3.3 Power supply dependence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87  |  |  |  |  |

|   | 5.4                               | Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 89  |  |  |  |  |

|   | 5.5                               | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89  |  |  |  |  |

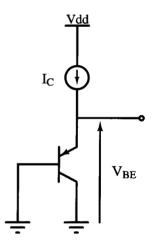

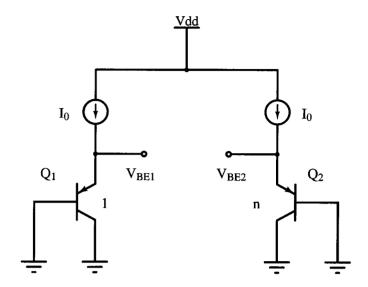

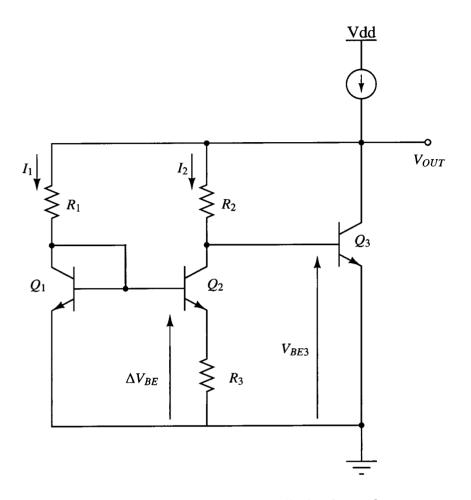

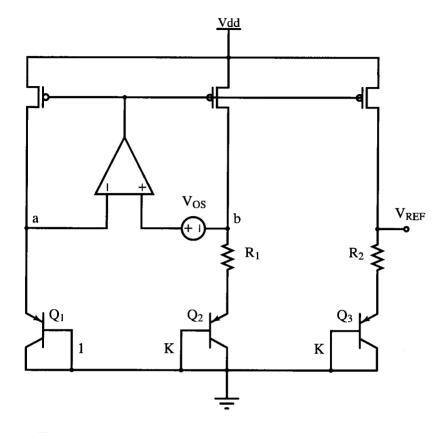

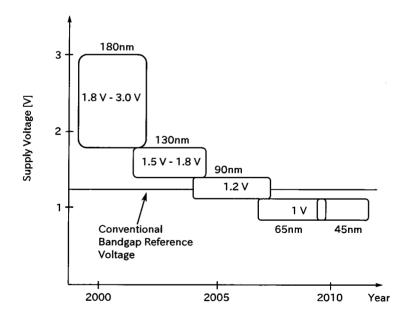

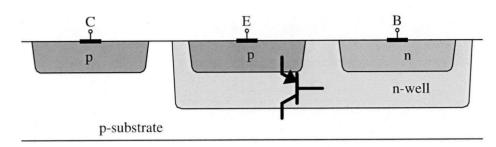

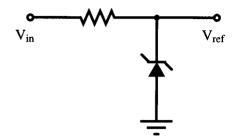

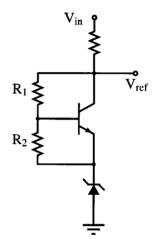

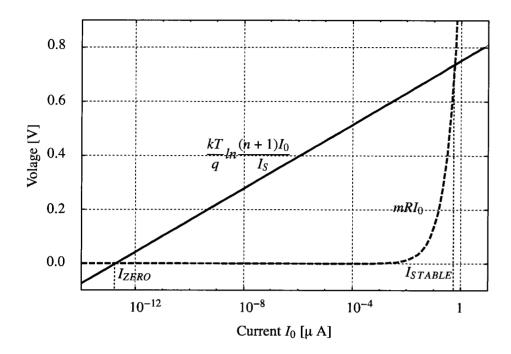

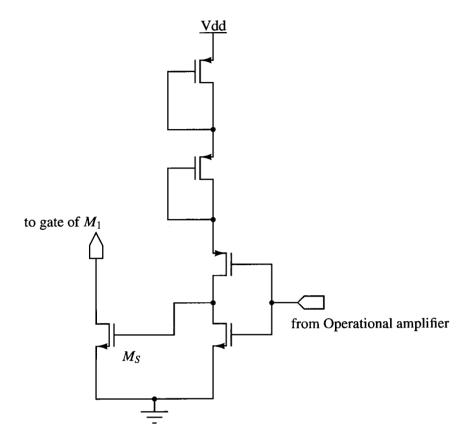

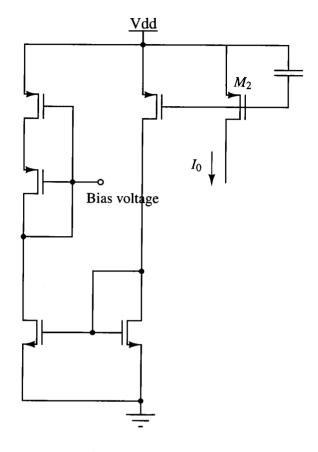

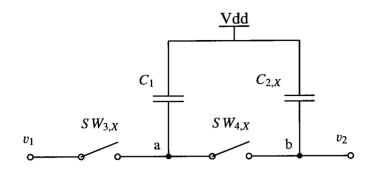

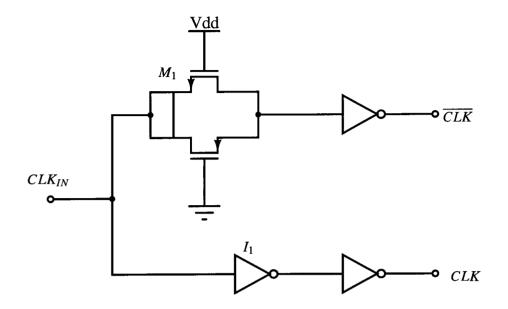

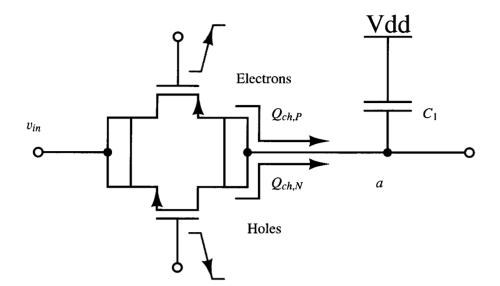

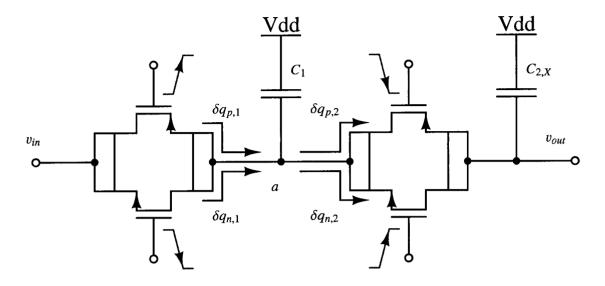

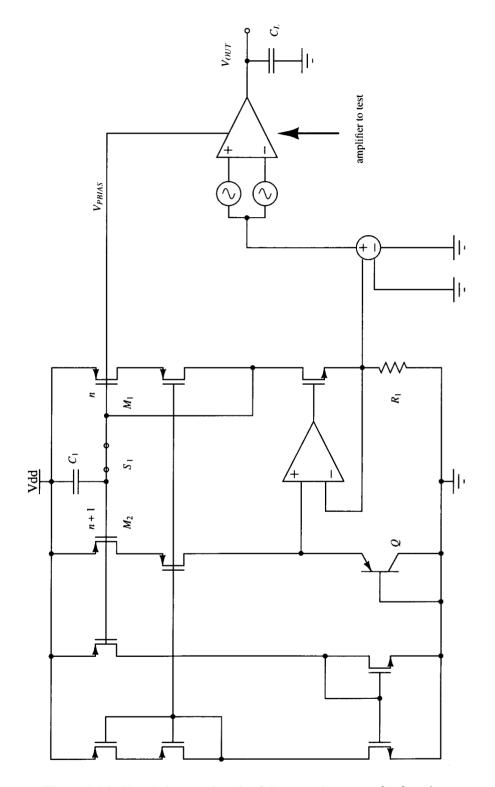

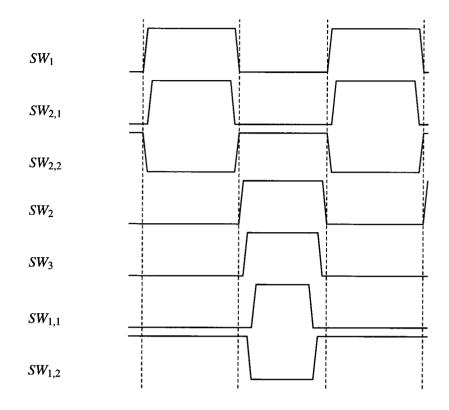

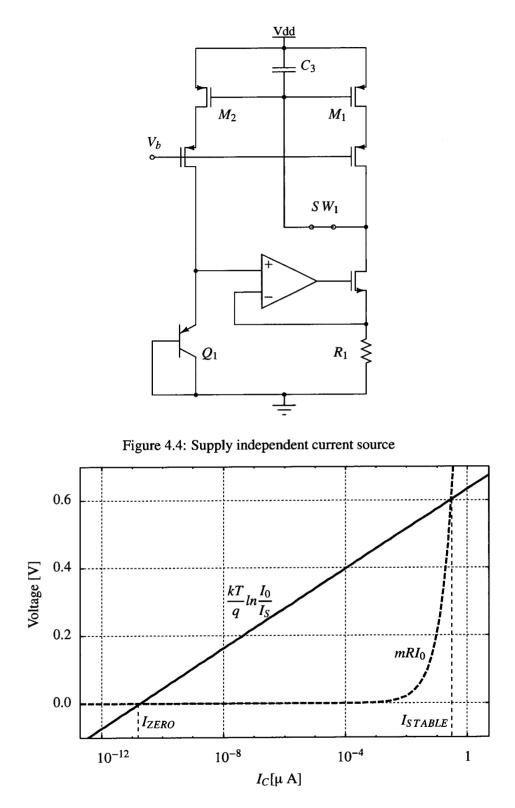

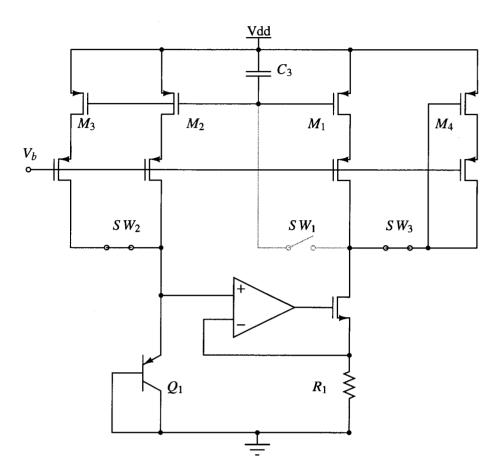

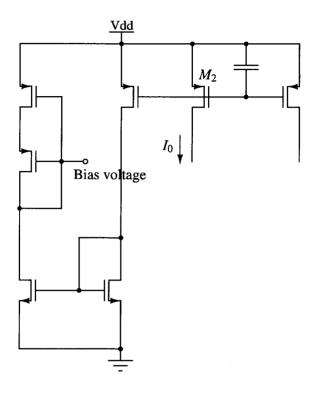

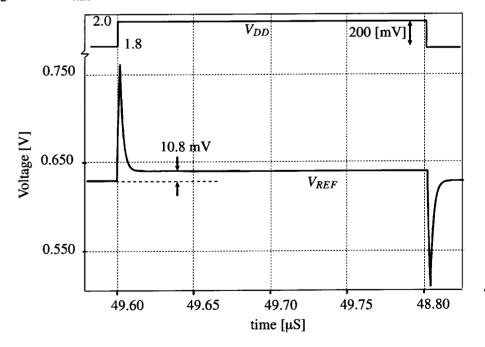

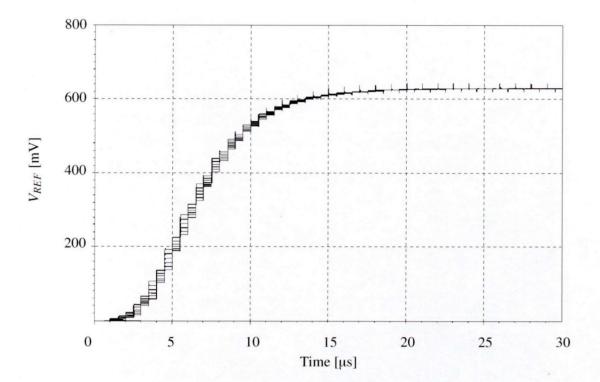

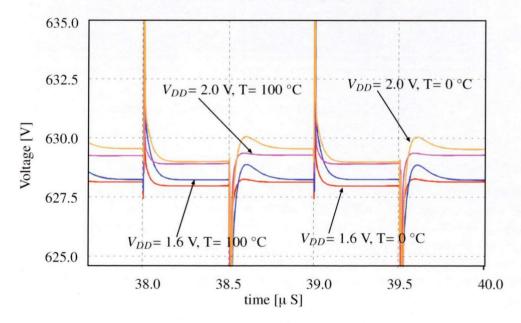

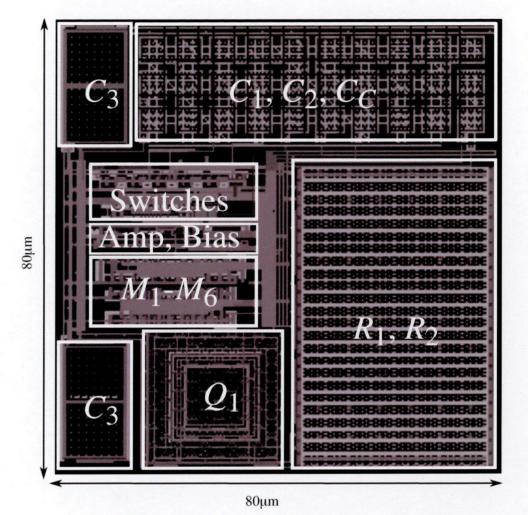

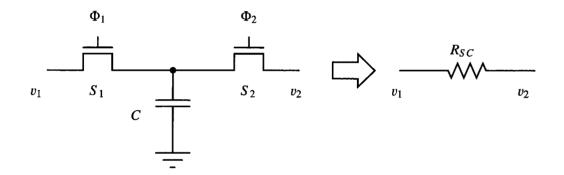

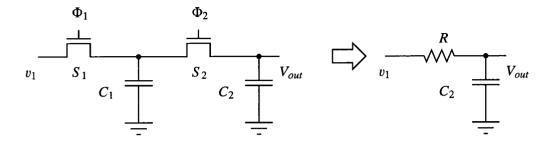

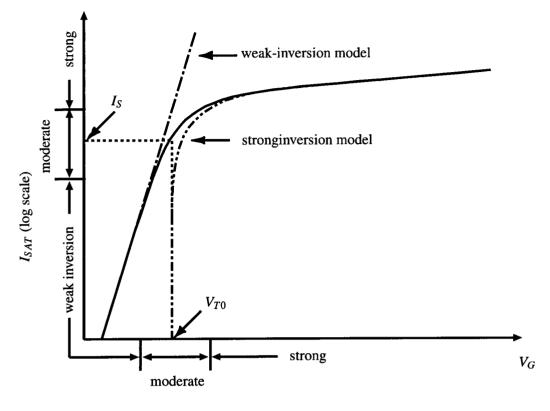

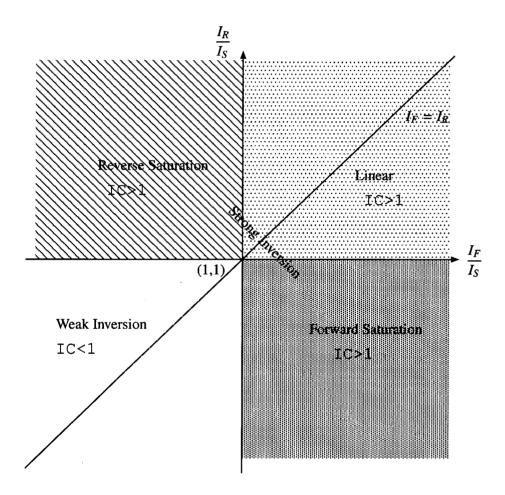

| _ | _                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 93  |  |  |  |  |