|              |                                                                                   |

|--------------|-----------------------------------------------------------------------------------|

| Title        | 3次元構造によるMMICの高集積化・高機能化に関する研究                                                      |

| Author(s)    | 西川, 健二郎                                                                           |

| Citation     | 大阪大学, 2004, 博士論文                                                                  |

| Version Type | VoR                                                                               |

| URL          | <a href="https://hdl.handle.net/11094/2706">https://hdl.handle.net/11094/2706</a> |

| rights       |                                                                                   |

| Note         |                                                                                   |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

2004年1月23日

# 3次元構造による MMIC の高集積化・ 高機能化に関する研究

西川 健二郎

## 内容梗概

本論文は、3次元構造を用いた超小型、高集積ミリ波帯 MMIC 及び SiMMIC の高周波化、高機能化に関する研究で得られた成果をまとめたものである。

本研究では、MMIC の小型・高集積化、高機能化、低コスト化の実現を目的として、新たに3次元構造を活用した小型低損失の受動回路に対し、各種回路構成の検討、理論的検討を加えた。さらに、能動回路との組合せにより各種の機能回路小型化を実現する設計法を確立している。本論文はこれらの研究成果をまとめたものであり、以下に示す8章から構成される。

第1章は序論であり、本研究の背景と目的について述べる。

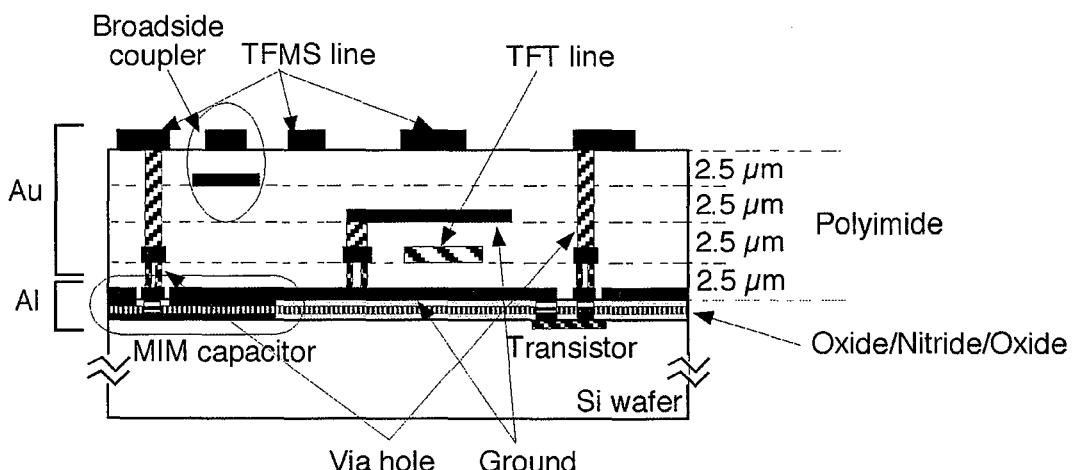

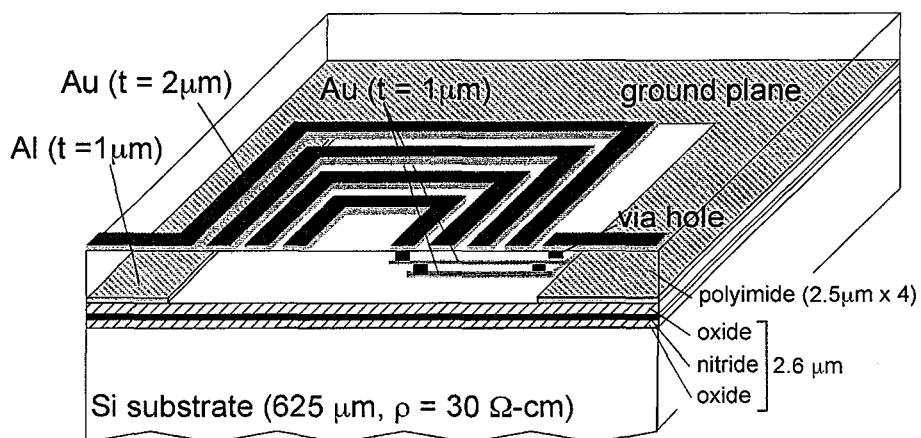

第2章では、半導体基板上に誘電体薄膜を多層に積層し、その上にマイクロ波回路を形成する3次元 MMIC を提案する。3次元 MMIC の基本構造を示すとともに、従来のマイクロストリップ型 MMIC との比較により、その特徴を明確にし、3次元 MMIC が小型、高集積化に極めて有効であることを示す。次に、3次元 MMIC を実現するプロセス技術として、誘電体膜としてポリイミドを用いた3次元 MMIC 製造プロセスについて述べ、開発したプロセスの均一性、信頼性が従来のプロセスと比較しても十分な性能を有することを示す。さらに、製造プロセス時間の短縮化と信頼性の向上を目的とした感光性 BCB を用いた3次元 MMIC 製造プロセスについても述べ、感光性 BCB 膜を用いた3次元 MMIC ではプロセス時間の短縮だけでなく、その低吸湿性から導体配線のレイアウト自由度がポリイミドと比較して大幅に向上することを試作結果とともに示す。

第3章では、3次元構造を活かした超小型基本受動回路を提案し、その設計法、性能を示している。まず、3次元 MMIC のキーコンポーネントである薄膜マイクロストリップ線路（TFMS 線路）の特徴を明らかにし、MMIC 上で TFMS 線路を用いて高密度レイアウトを実現するための手法を明らかにしている。多層構造を用いて実現したブロードサイドカプラの特徴を示し、その設計手法を提案している。180 度信号分配回路の小型化広帯域化を同時に実現するために、上記ブロードサイドカプラを適用した新たなマーチャンドバランならび、カプラの不平衡性を補償する新たな補正法を提案し、バランの広帯域化を実現している。また、同相成分分配回路の小型化を実現するために積層型ウイルキンソンディバイダを提案し、半導体基板上及び積層誘電体膜最上層に信号配線を形成し、誘電体膜中間層に信号配線と平行にスリットを入れた接地導体を形成した構成とすることにより、高インピーダンス線路の積層化を MMIC レベルで初めて実現すると同時に小型化を実現している。本章で提案している受動回路は試作によりその性能、提案構成の効果を確認している。

第4章では、3次元構造を適用した化合物系デバイスをから構成される基本能動回路について、それらの小型化設計法を提案するとともに、RF 回路を 1チップに集積化した高集積 20GHz

帯 3 次元 MMIC 1 チップ受信機の設計、試作により 3 次元 MMIC の小型化、高集積化の有効性を明らかにしている。まず、小型化に適し、かつ高利得を実現できるカスコード型増幅器の構成と設計法について述べる。カスコード接続されるソース接地 FET とゲート接地 FET 間の伝送線路とゲート接地 FET のゲートと接地導体間の伝送線路を最適化することにより、増幅器特性を制御できることを示している。また、負帰還回路部にドレイン接地 FET を配置し、FET の相互コンダクタンスを変えることにより、帰還量を変化させるアクティブ帰還型可変利得増幅器を提案し、その構成と設計法について述べ、歪み特性を大幅に改善できることを理論解析及び試作により明らかにしている。さらに、整合回路を積層する小型化回路構成法を周波数変換器に適用することを提案し、その設計法について述べるとともに、第 3 章で示した受動回路との組合せにより、超小型なバランス型またはイメージ抑圧型周波数変換器を実現している。小型化、高集積化を実現するための発振器構成及び設計法についても提案している。最後に、機能回路を 1 チップに集積化した 3 次元 MMIC 受信機について、その構成及び設計法を示すとともに試作により MMIC の性能を確認した。

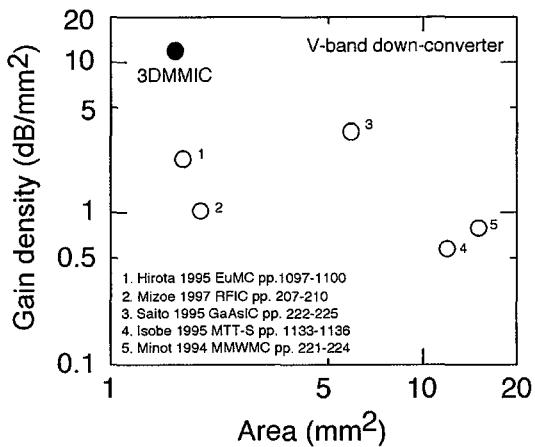

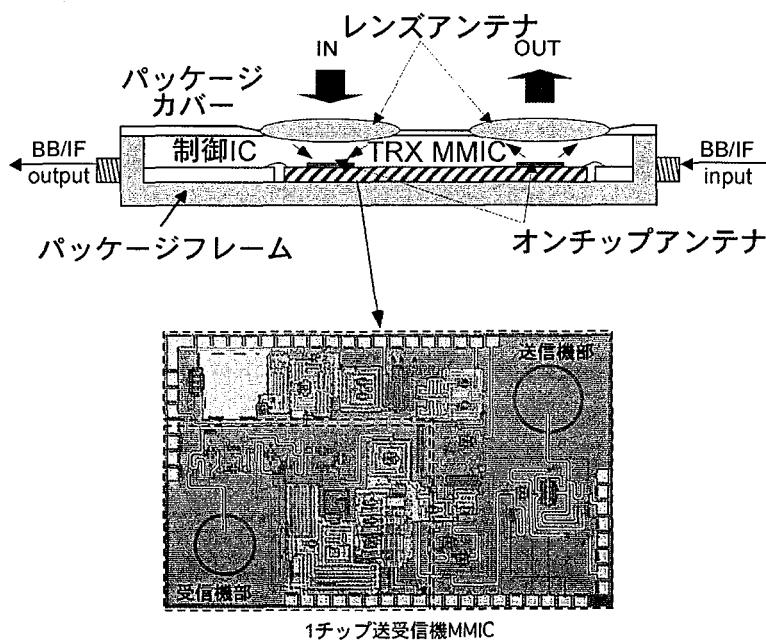

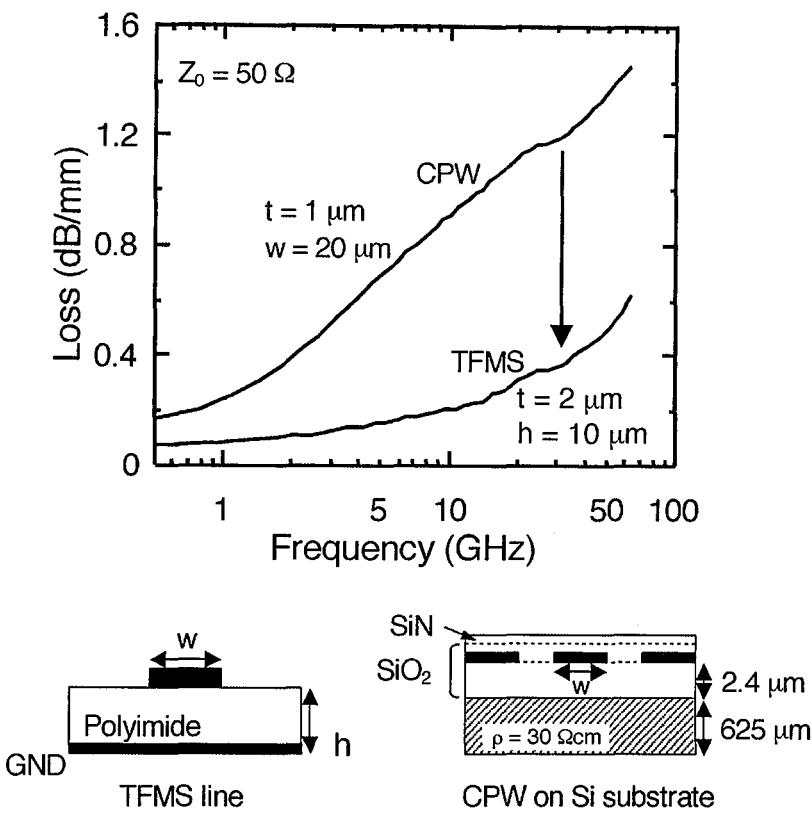

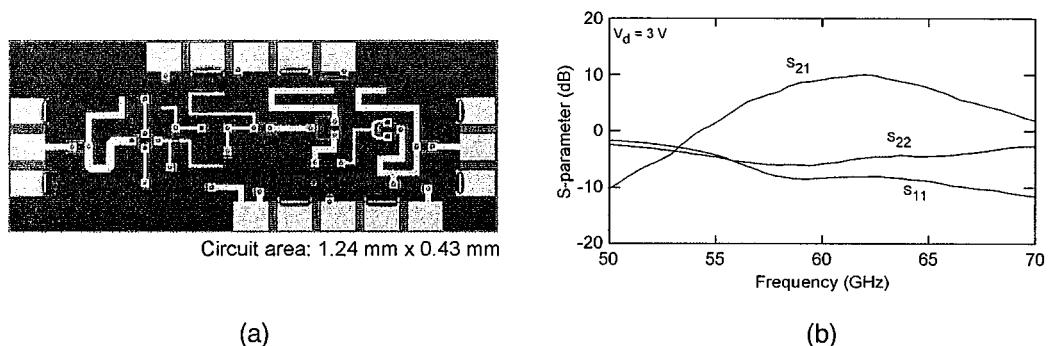

第 5 章では、ミリ波帯、特に 60GHz 帯への 3 次元 MMIC の適用に焦点を当て、3 次元 MMIC 技術がミリ波帯 MMIC の小型化高集積化に極めて有効であることを TFMS 線路の特性及び高集積 MMIC の試作によって明らかにしている。設計性、小型化、高集積化の観点から従来のマイクロストリップ線路、コプレーナ線路との比較により、TFMS 線路のミリ波帯での優位性を明らかにしている。ミリ波帯 MMIC の高集積化を実現する構成及び設計法について示すとともに、60GHz 帯 1 チップダウンコンバータ 3 次元 MMIC を実現し、3 次元 MMIC のミリ波帯での効果を明らかにしている。

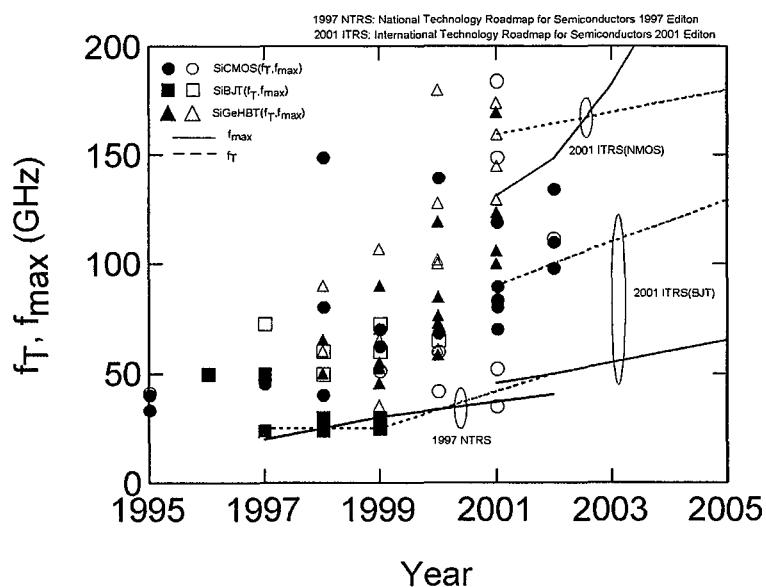

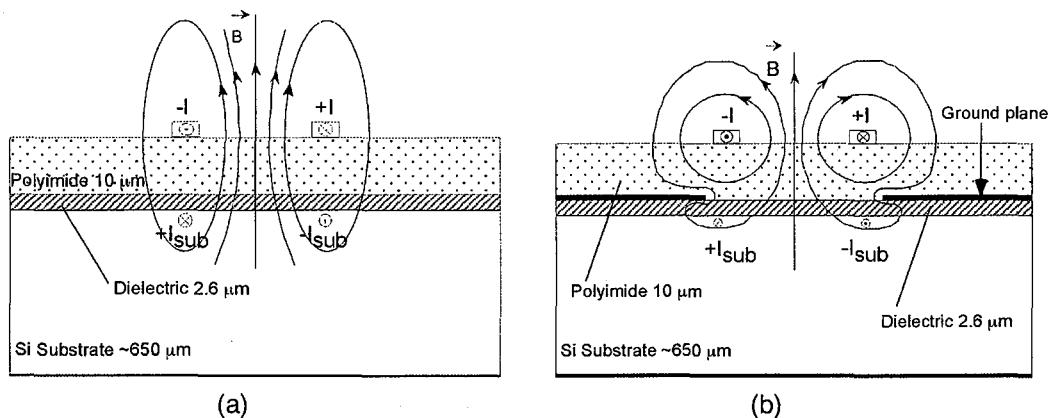

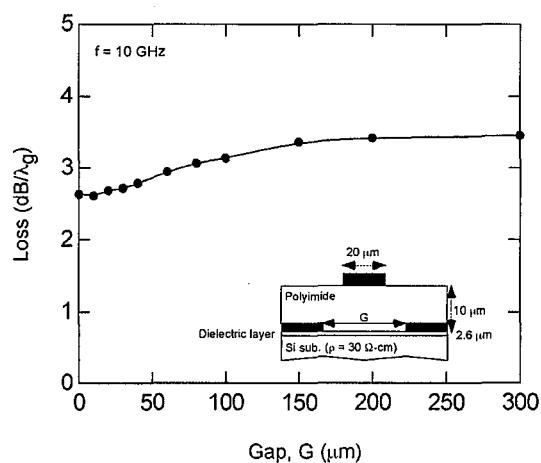

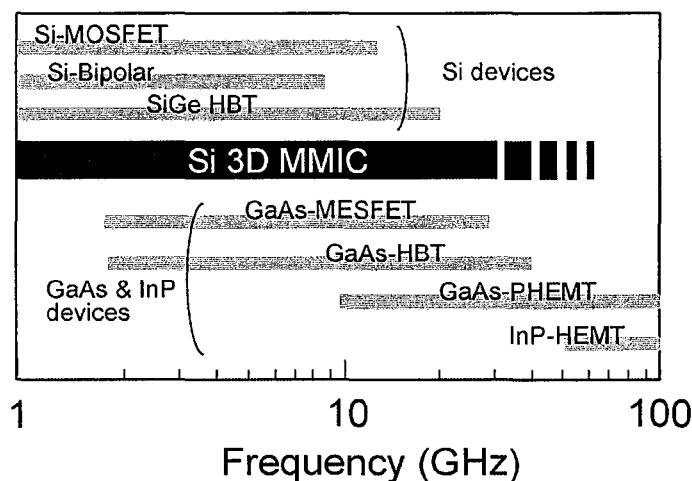

第 6 章では、3 次元 MMIC 技術を SiMMIC に適用した Si 3 次元 MMIC を提案し、SiMMIC の高周波化と低電圧化を実現できることを明らかにしている。3 次元構造により低抵抗 Si 基板とマイクロ波線路を Si 基板上に形成する接地導体により分離できることを提案し、Si 基板上のマイクロ波線路の損失を大幅に低減できることを明らかにする。3 次元構造を適用した Si 3 次元 MMIC インダクタを提案し、その特徴、性能をシミュレーション、試作により明らかにしている。低損失マイクロ波線路を用いたリアクティブ整合回路構成を提案し、SiMMIC の高周波動作と低電圧動作の両方を実現できることを明らかにしている。試作により実現した Si 3 次元 MMIC は広帯域設計により、高周波動作、低電圧動作と同時に広帯域化を達成している。最後に機能回路を集積化した C 帯 1 チップ受信機 MMIC について述べている。

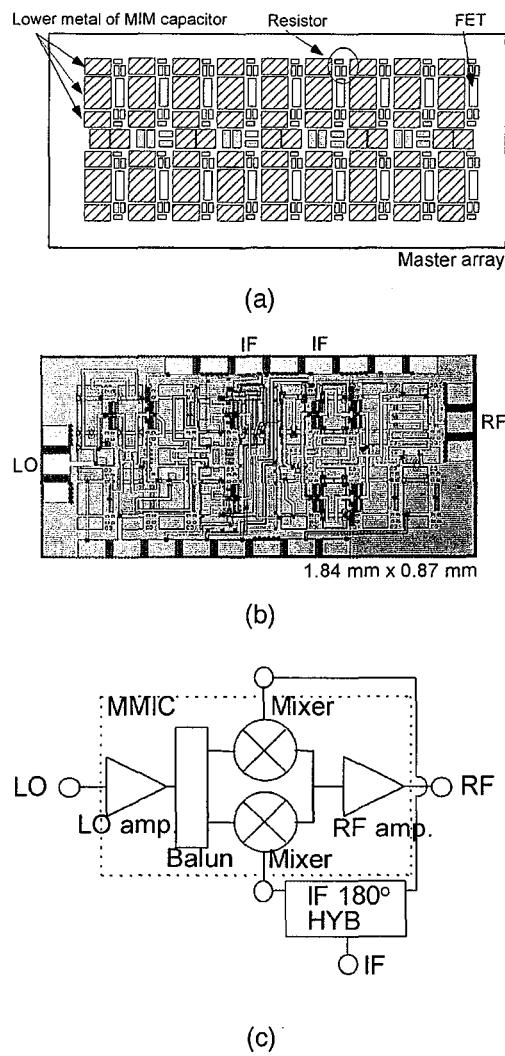

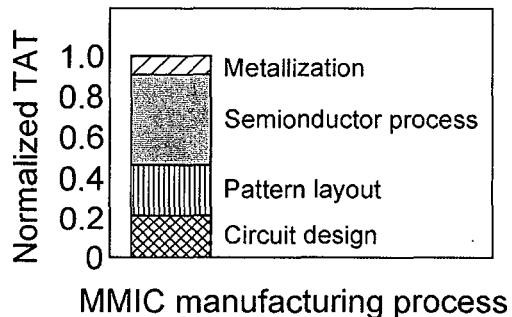

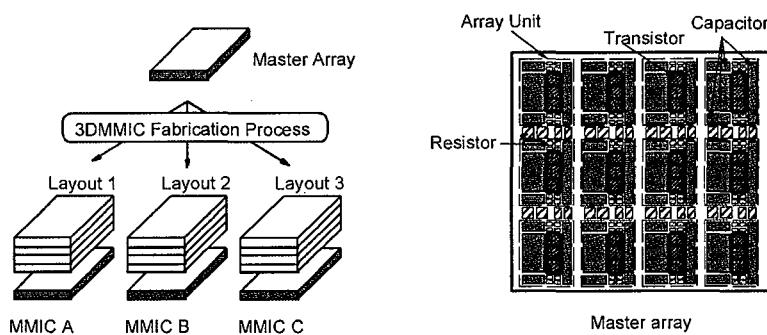

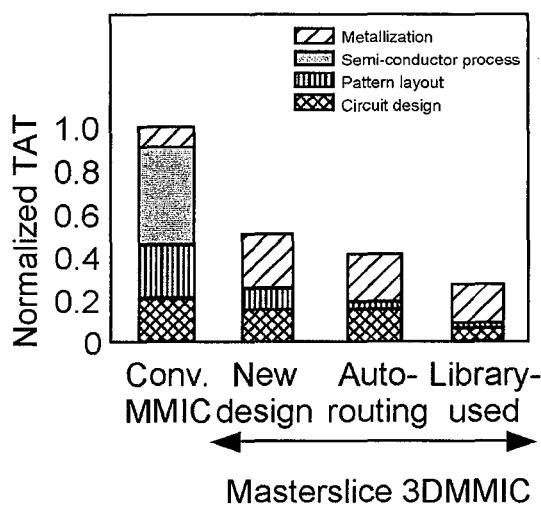

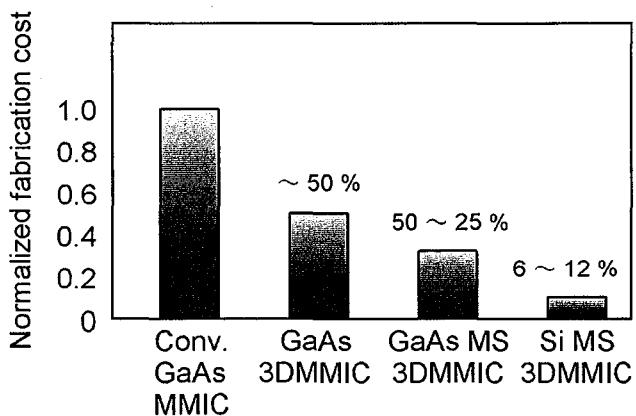

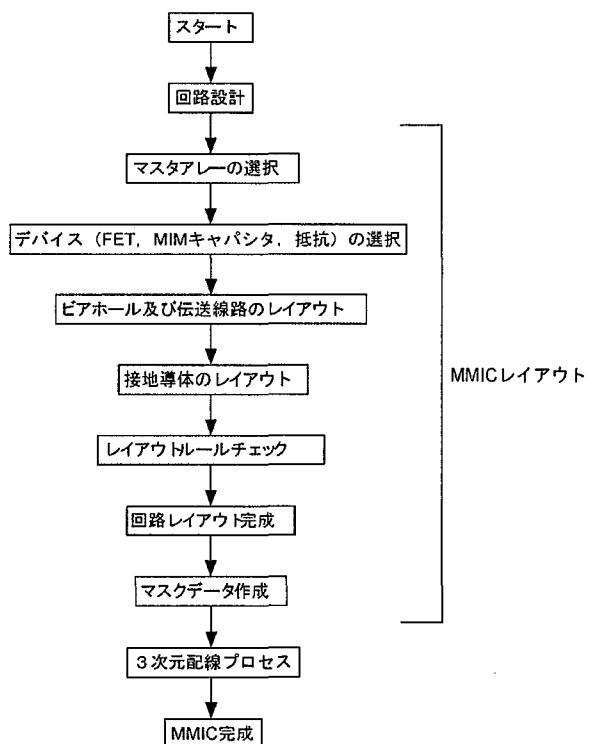

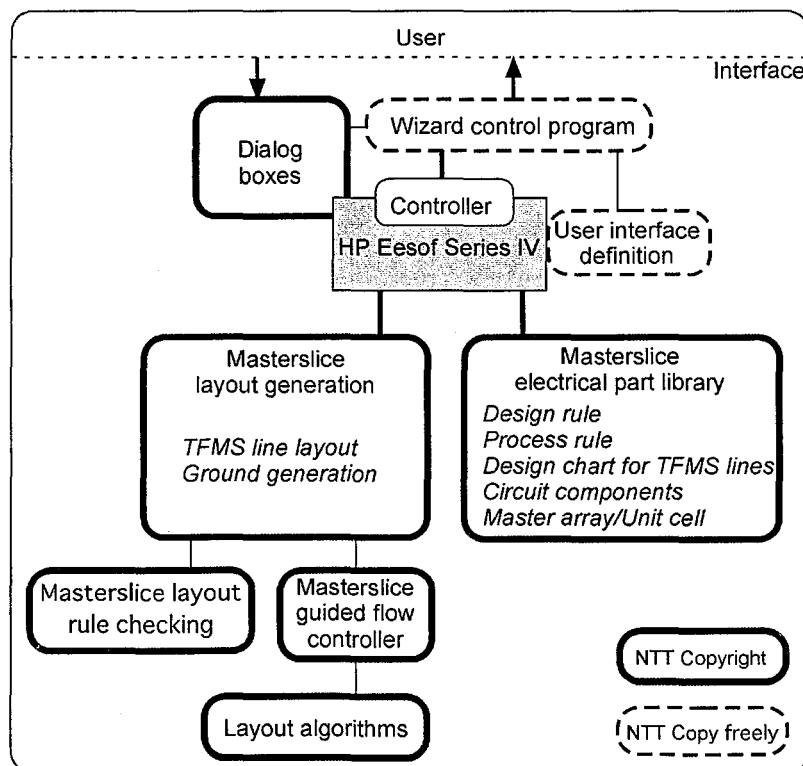

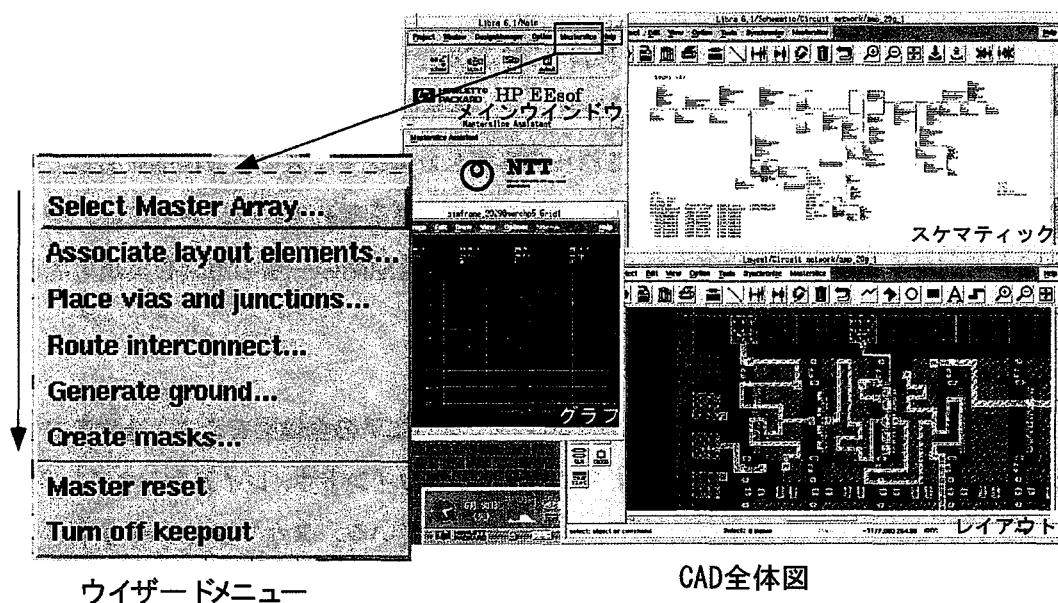

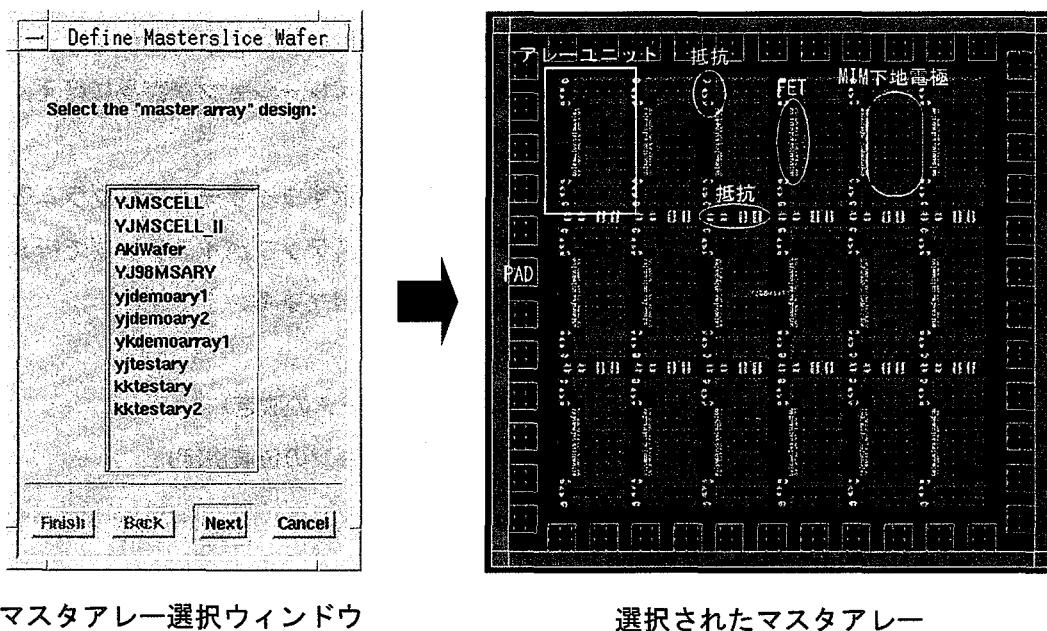

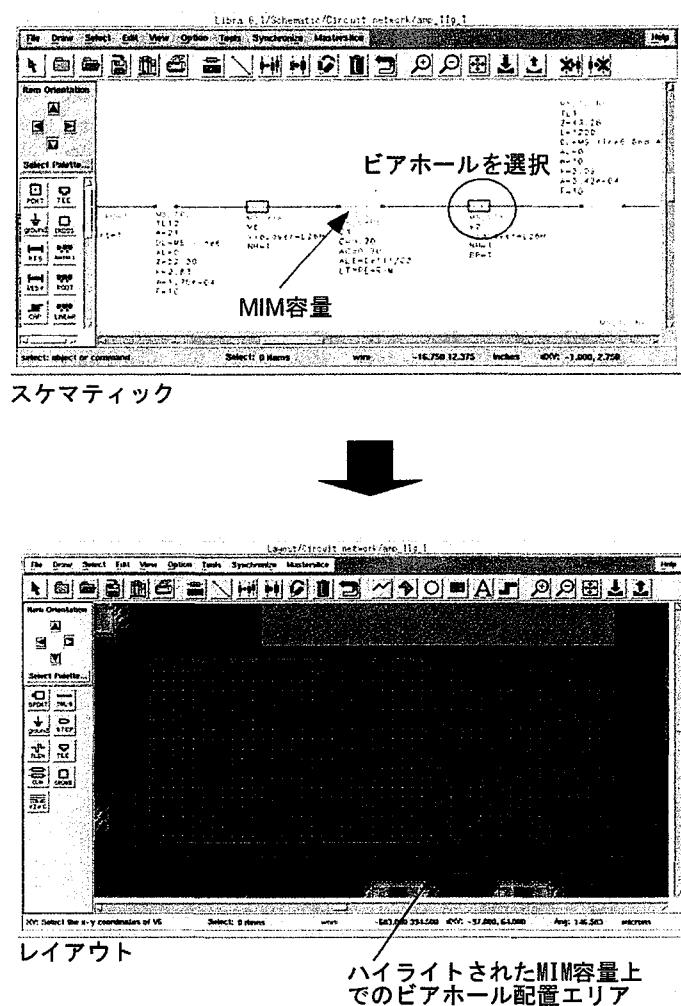

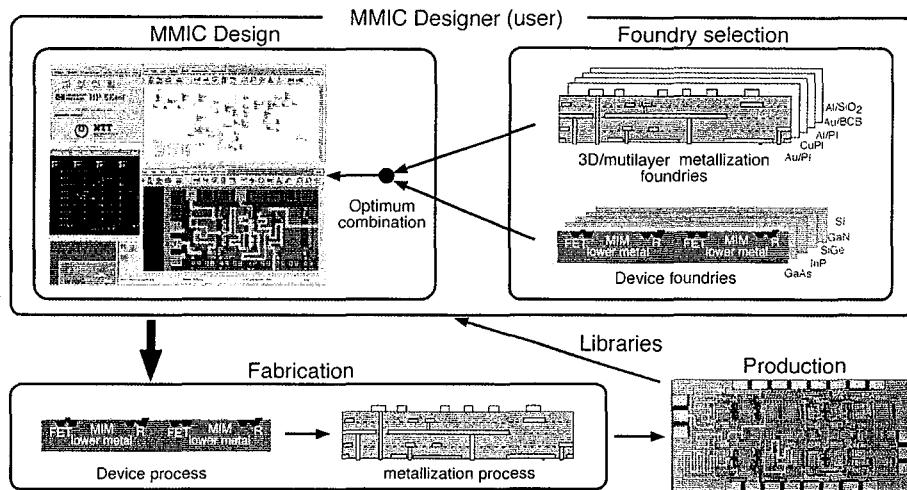

第 7 章は、新たに提案するマスタスライス型 3 次元 MMIC 設計法について述べている。マスタスライス型 3 次元 MMIC 設計法は 3 次元 MMIC 技術をベースとしてゲートアレー的設計法を取り入れたマイクロ波回路のセミカスタム設計法である。始めにマスタスライス型 3 次元 MMIC 設計法の概念と利点を述べるとともに、この技術が MMIC 開発の大幅な短縮化、低コスト化を

実現できることを示している。また、マスタスライス型3次元MMIC設計フローに基づくCADソフトウェアを開発し、これによりマイクロ波回路の開発が大幅に簡易化できることを明らかにするとともに、提案する設計法を用いて実現した高集積1チップ受信機MMICの構成及び特性について述べ、開発手法が妥当であることを確認する。

第8章は本論文全体の総括である。

## 謝辞

本論文をまとめるにあたり、終始、懇切かつ御熱心な御指導及び御助言を賜りました大阪大学大学院工学研究科通信工学専攻・小牧省三教授に謹んで深謝の意を表します。

本論文をまとめるに際して、有益な御討論、御助言を賜りました大阪大学大学院通信工学専攻・塩澤俊之教授に謹んで深謝の意を表します。

また、本論文に対して有益なる御助言を頂きました大阪大学大学院通信工学専攻・森永規彦教授（現広島国際大学教授）、河崎善一郎教授、馬場口登教授、産業科学研究所・元田浩教授、ならびに電子情報エネルギー専攻・北山研一教授に深く感謝致します。

本論文は筆者が日本電信電話株式会社において 1992 年以来行った研究をまとめたものであり、この間、NTT 無線システム研究所超高周波回路研究グループ及び NTT ワイヤレスシステム研究所第 2 プロジェクトにおいて、終始変わらぬご指導を頂きました元ワイヤレスシステム研究所第 2 プロジェクトリーダ・相川正義博士（現佐賀大学教授）、徳満恒雄博士（現富士通カントムデバイス（株）），豊田一彦博士に深く感謝いたします。また、本研究の回路技術について多くのご議論を頂きました鴨川健司博士（現 NTT ドコモ（株））に感謝いたします。

本研究を遂行するにあたり常に御指導、御鞭撻頂きました元 NTT 無線システム研究所・山本平一博士（現奈良先端科学技術大学院大学教授）、元 NTT ワイヤレスシステム研究所所長・小桧山賢二博士（現慶應義塾大学教授）、元同所長・故鮫島秀一博士、元 NTT 未来ねっと研究所所長・河内正夫博士（現同社先端技術総合研究所所長）に感謝いたします。御指導いただきました元無線システム研究所無線方式研究部部長・森田浩三博士（現コトペール（株）），同研究部部長栗田修博士（現ルーセントテクノロジー），元ワイヤレスシステム研究所研究企画部長／第 2 プロジェクトリーダ・田中将義博士（現日本大学教授），元未来ねっと研究所ワイヤレスシステムイノベーション研究部部長・水野秀樹博士（現東海大学教授）に感謝いたします。

日本電信電話（株）において本研究を進めるに際し、3 次元 MMIC プロセス技術を開発いただきました元 NTTLISI 研究所・平田一雄博士（現新日本無線（株）），山崎王義博士（現 NTT 第 3 部門），平野真博士（現 NTT フォトニクス研究所），杉谷末広氏（現 NTT フォトニクス研究所），山口力氏（現 NTT マイクロシステムインテグレーション研究所），井上考氏（現東日本電信電話（株））他の方々に感謝いたします。

本研究について御指導、御議論いただきました元未来ねっと研究所ワイヤレス装置研究グループグループリーダ・村口正弘博士（現 NTT フォトニクス研究所テラビットデバイス研究部部長），元同グループリーダ・荒木克彦氏（現適応信号処理研究グループリーダ），廣田哲夫博士（現金沢工業大学教授），中津川征士氏（現 NTT 第 3 部門），NTT アドバンステクノロジ

一 (株)・菅田孝之博士他に感謝いたします。

Hewlett Packard 社・Gary Hawisher 氏(現 Agilent Technology)はじめ多数の Hewlett Packard 社 CAD 開発グループの皆様にはマスタスライス CAD ソフトウェアの開発に多大な尽力を頂きました。また、測定に関して御協力頂きました NTT アドバンステクノロジー(株)・望月秀之氏、横山新一氏に感謝いたします。

## 論文目次

|                                     |    |

|-------------------------------------|----|

| 第1章 序論                              | 1  |

| 1.1 研究の背景                           | 1  |

| 1.2 本研究の目的と論文の構成                    | 2  |

|                                     |    |

| 第2章 3次元 MMIC の構造とその特徴               | 6  |

| 2.1 まえがき                            | 6  |

| 2.2 3次元 MMIC の基本構造とその特徴             | 6  |

| 2.3 ポリイミドを用いた3次元 MMIC 製造プロセス        | 8  |

| 2.4 感光性 BCB を用いた3次元 MMIC 製造プロセス     | 12 |

| 2.4.1 製造プロセス                        | 12 |

| 2.4.2 BCB 3次元 MMIC の配線構造            | 13 |

| 2.5 まとめ                             | 14 |

| 参考文献                                | 16 |

|                                     |    |

| 第3章 3次元 MMIC 受動回路                   | 17 |

| 3.1 まえがき                            | 17 |

| 3.2 薄膜マイクロストリップ (TFMS) 線路           | 17 |

| 3.2.1 TFMS 線路の特性                    | 17 |

| 3.2.2 高密度レイアウトのためのTFMS 線路の最小配置間隔    | 22 |

| 3.3 ブロードサイドカプラ                      | 25 |

| 3.4 3次元 MMIC マーチャンドバラン              | 28 |

| 3.5 積層型ウイルキンソンディバイダ                 | 34 |

| 3.6 まとめ                             | 37 |

| 参考文献                                | 39 |

|                                     |    |

| 第4章 3次元 MMIC 基本能動回路と1チップ受信機への適用     | 41 |

| 4.1 まえがき                            | 41 |

| 4.2 カスコード型増幅器                       | 41 |

| 4.2.1 カスコード型 FET の特徴                | 41 |

| 4.2.2 20GHz 帯カスコード型増幅器 3次元 MMIC の性能 | 44 |

| 4.3 アクティブ帰還型可変利得増幅器                 | 46 |

|                                    |    |

|------------------------------------|----|

| 4.3.1 アクティブ帰還型可変利得増幅器の構成及びその特徴     | 46 |

| 4.3.2 アクティブ帰還型可変利得増幅器 MMIC の性能     | 51 |

| 4.4 周波数変換器                         | 55 |

| 4.4.1 バランス型アップコンバータ                | 55 |

| 4.4.2 イメージリジェクションミキサ               | 57 |

| 4.5 電圧制御発振器                        | 59 |

| 4.6 20GHz 帯 1 チップ受信機               | 60 |

| 4.7 まとめ                            | 62 |

| 参考文献                               | 63 |

| 付録 4.1 GaAs MESFET 等価回路パラメータ       | 65 |

| <br>第 5 章 3 次元構造によるミリ波帯 MMIC の高集積化 | 67 |

| 5.1 まえがき                           | 67 |

| 5.2 ミリ波帯における 3 次元 MMIC の伝送線路特性     | 67 |

| 5.2.1 TFMS 線路の基本特性                 | 67 |

| 5.2.2 最小隣接線路間隔                     | 70 |

| 5.3 ミリ波帯受動回路の特性                    | 71 |

| 5.3.1 V 帯ウイルキンソンディバイダ              | 71 |

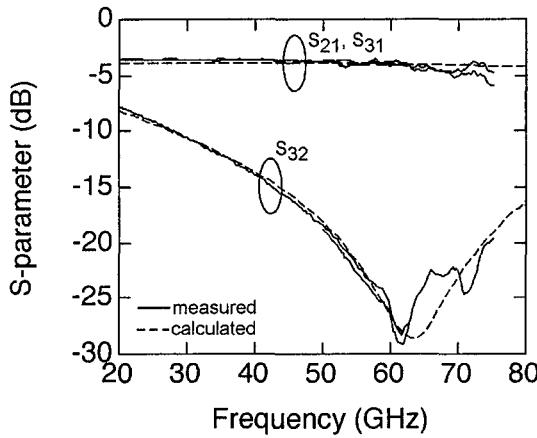

| 5.3.2 V 帯ブロードサイドカプラ                | 72 |

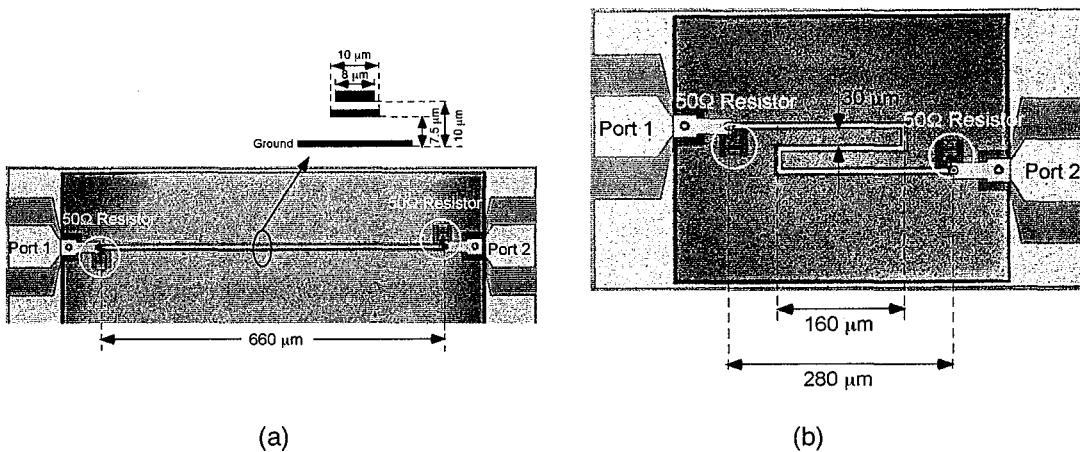

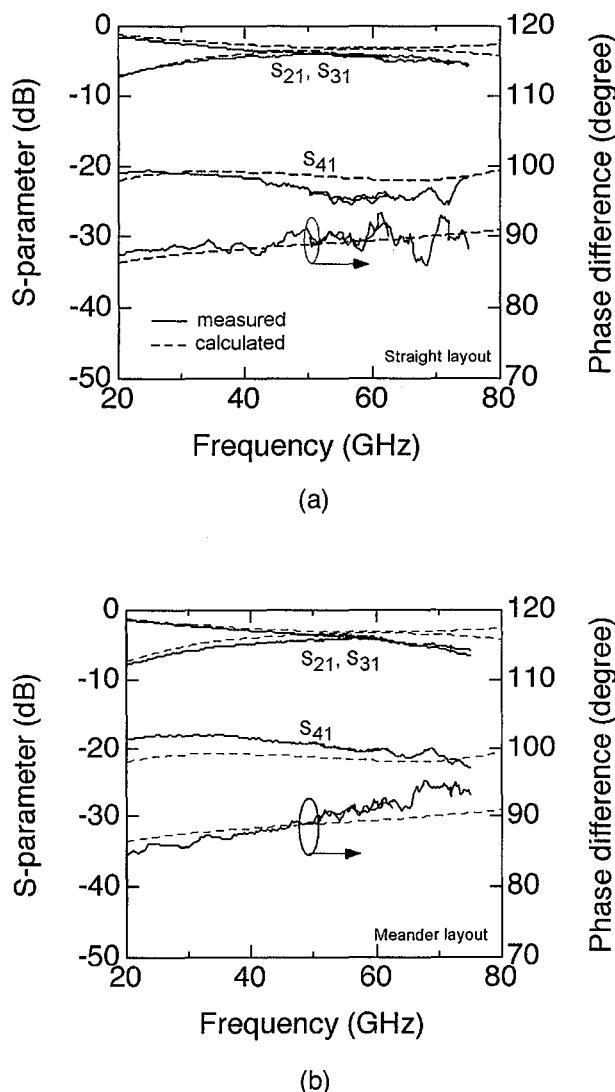

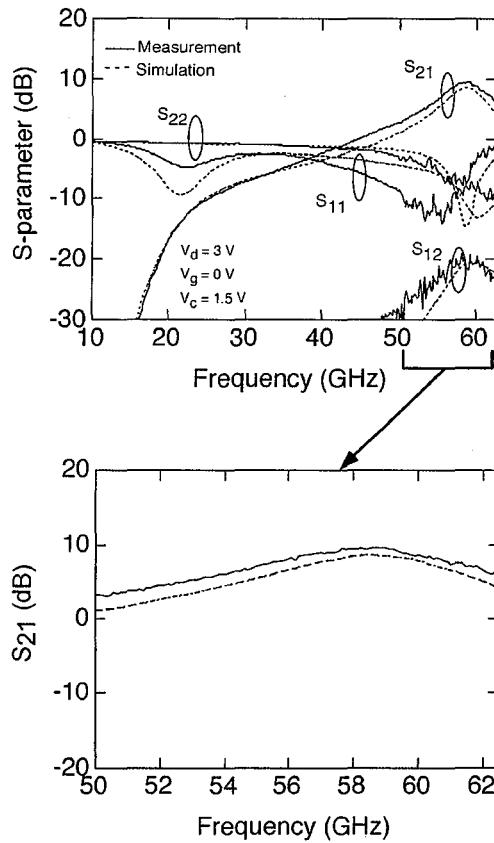

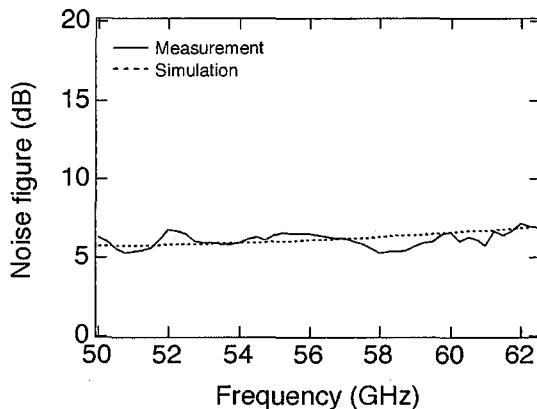

| 5.4 V 帯超小型増幅器 3 次元 MMIC            | 74 |

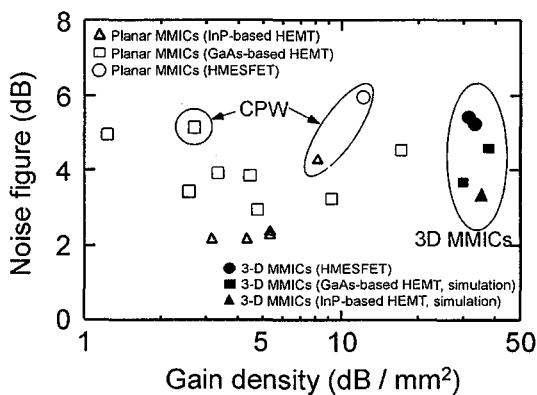

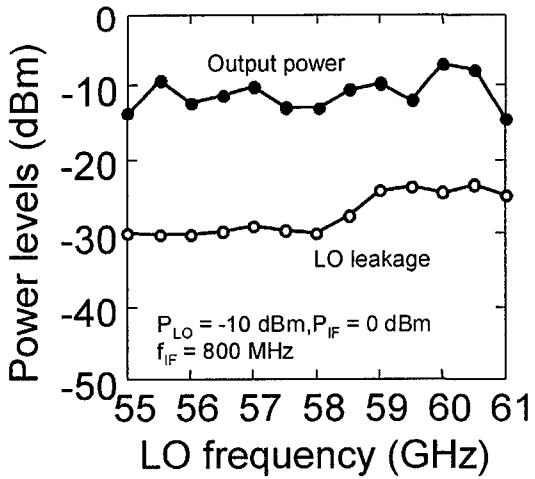

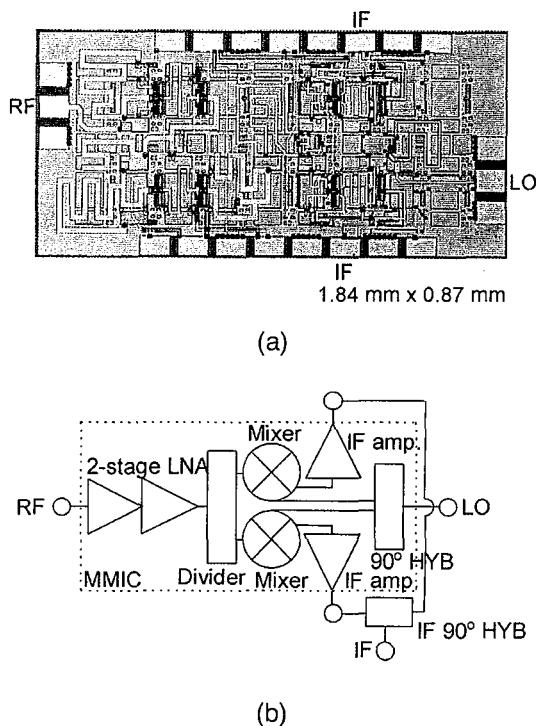

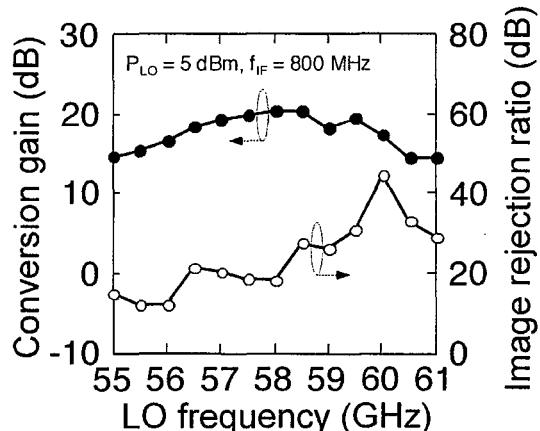

| 5.5 V 帯高集積 3 次元 MMIC               | 77 |

| 5.5.1 アップコンバータ MMIC                | 77 |

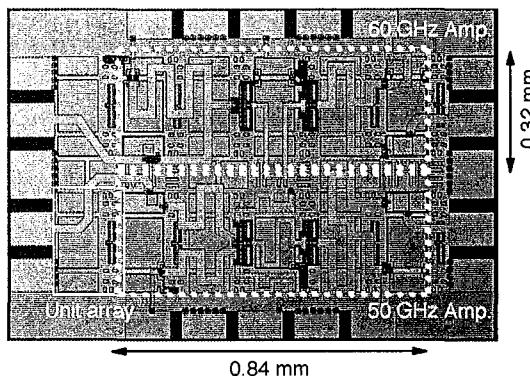

| 5.5.2 ダウンコンバータ MMIC                | 78 |

| 5.6 ミリ波 3 次元 MMIC の今後の展開           | 80 |

| 5.7 まとめ                            | 82 |

| 参考文献                               | 83 |

| <br>第 6 章 3 次元構造による SiMMIC の高性能化   | 85 |

| 6.1 まえがき                           | 85 |

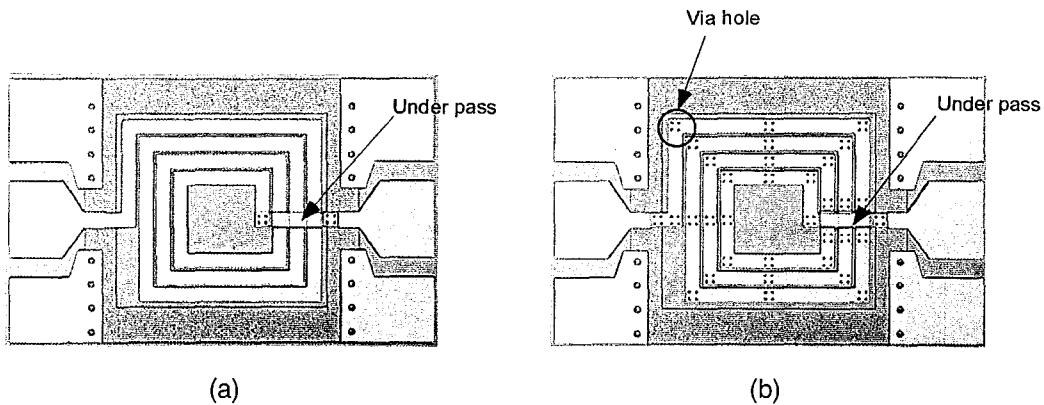

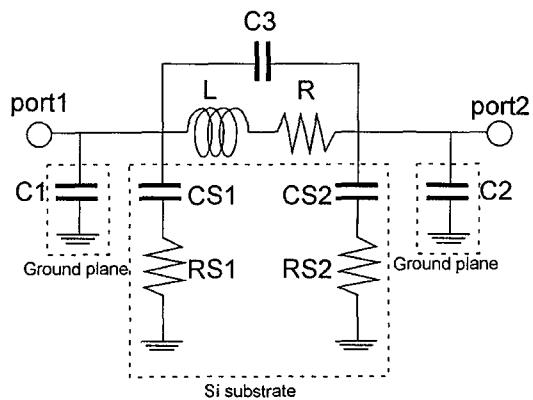

| 6.2 Si 3 次元 MMIC の構造               | 86 |

| 6.2.1 基本構造と Si 3 次元 MMIC の特徴       | 86 |

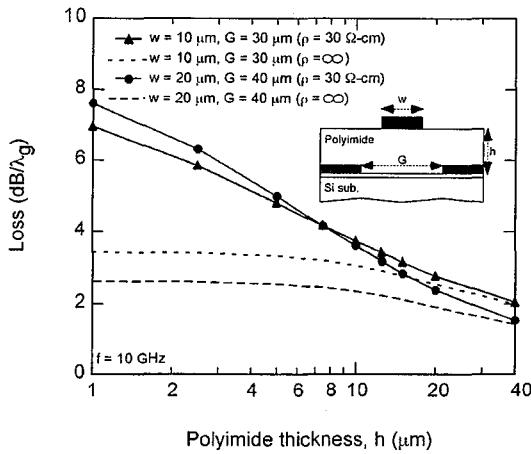

| 6.2.2 Si 基板上の TFMS 線路特性            | 87 |

| 6.3 Si 3 次元 MMIC インダクタ             | 88 |

|                                        |     |

|----------------------------------------|-----|

| 6.3.1 基本構造とその特徴                        | 88  |

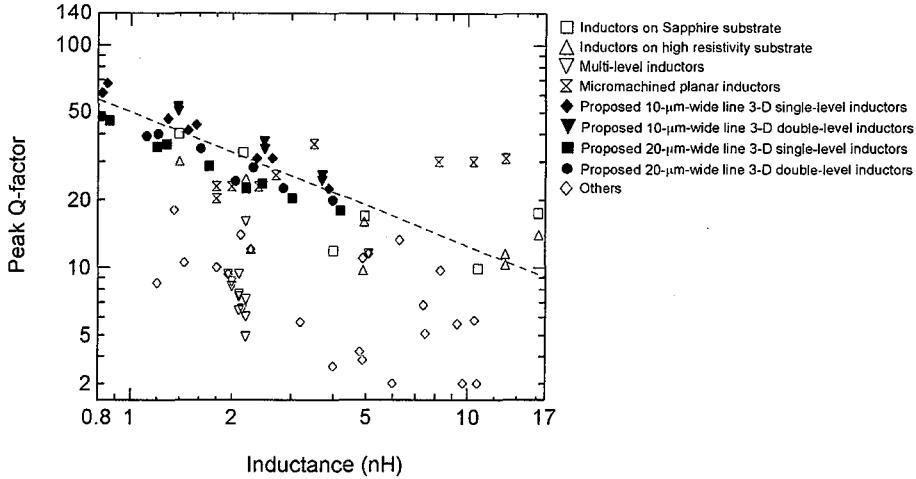

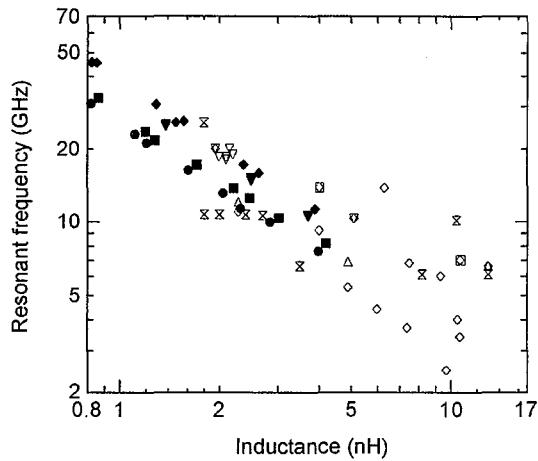

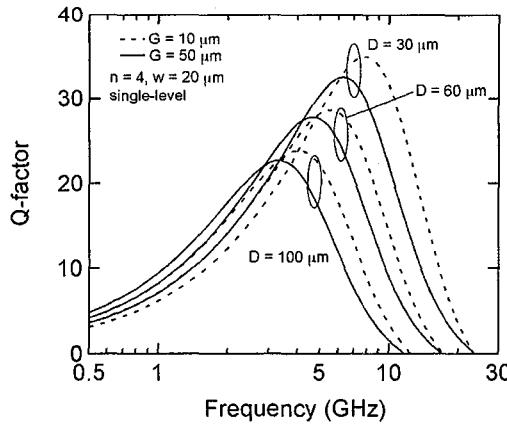

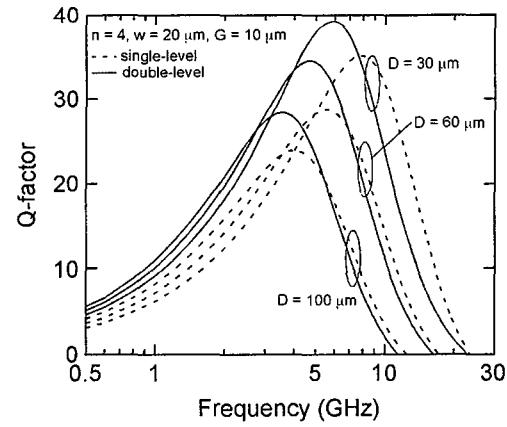

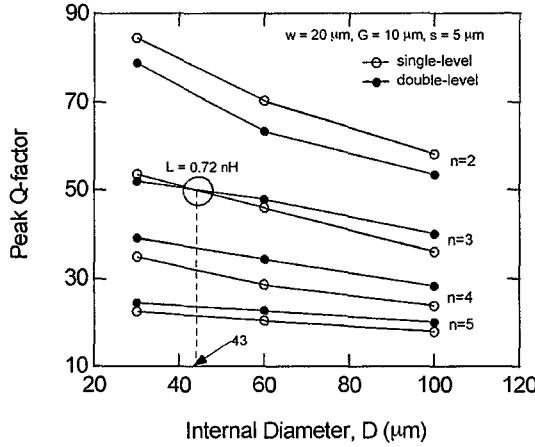

| 6.3.2 マルチレベル化によるインダクタの高 Q 化            | 90  |

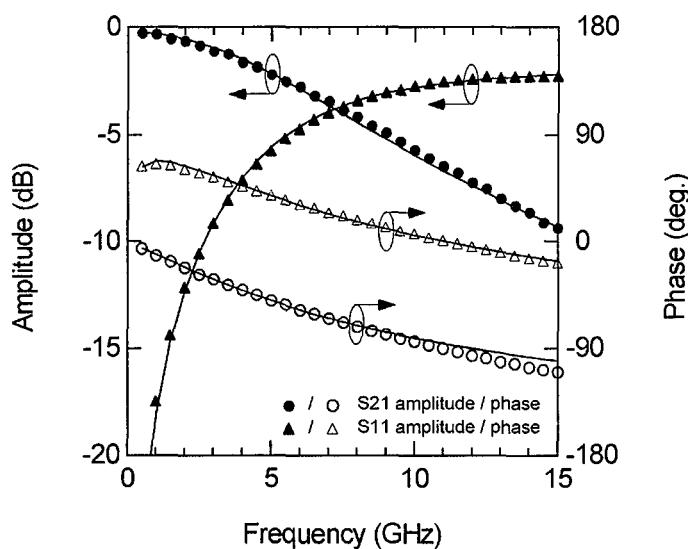

| 6.3.3 Si 3 次元 MMIC インダクタの性能評価          | 91  |

| 6.3.4 Si 3 次元 MMIC インダクタの最適デザインへの指針    | 93  |

| 6.3.5 LNA への適用                         | 95  |

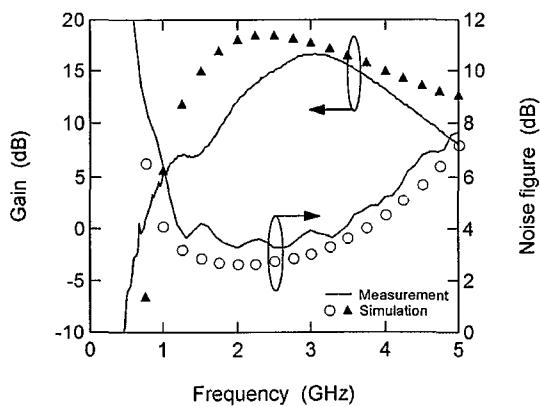

| 6.4 Si 3 次元 MMIC 増幅器                   | 97  |

| 6.4.1 Ka 帯 Si 3 次元 MMIC 増幅器            | 97  |

| 6.4.2 1V 動作 X 帯 Si 3 次元 MMIC 増幅器       | 99  |

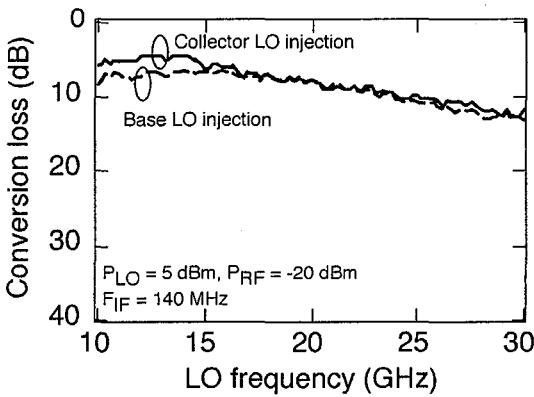

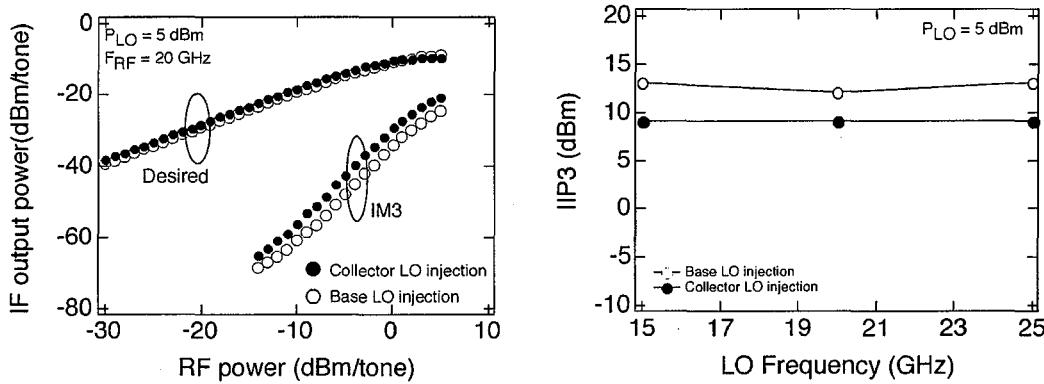

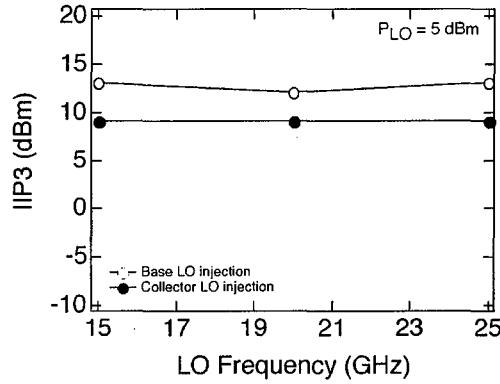

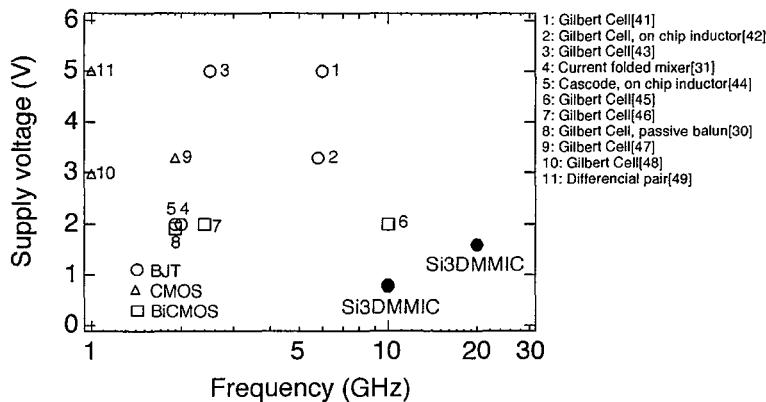

| 6.5 Si 3 次元 MMIC ベース／コレクタ局発注入広帯域ミキサ    | 102 |

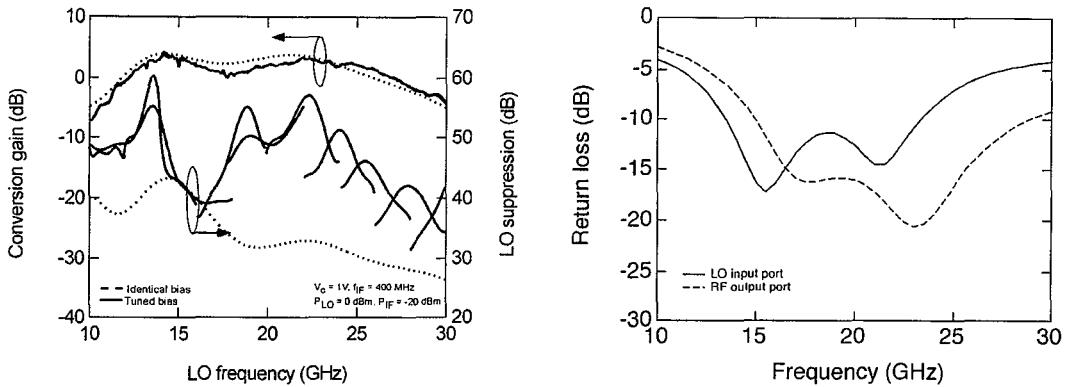

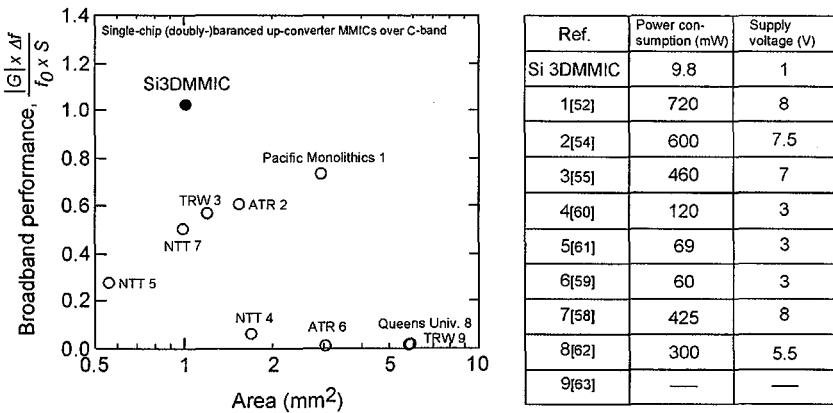

| 6.6 Si 3 次元 MMIC 広帯域バランス型アップコンバータ      | 108 |

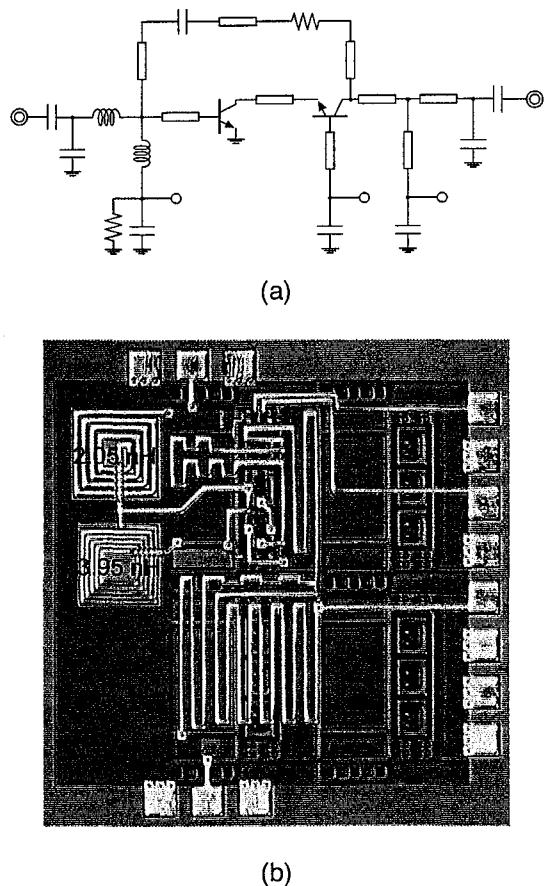

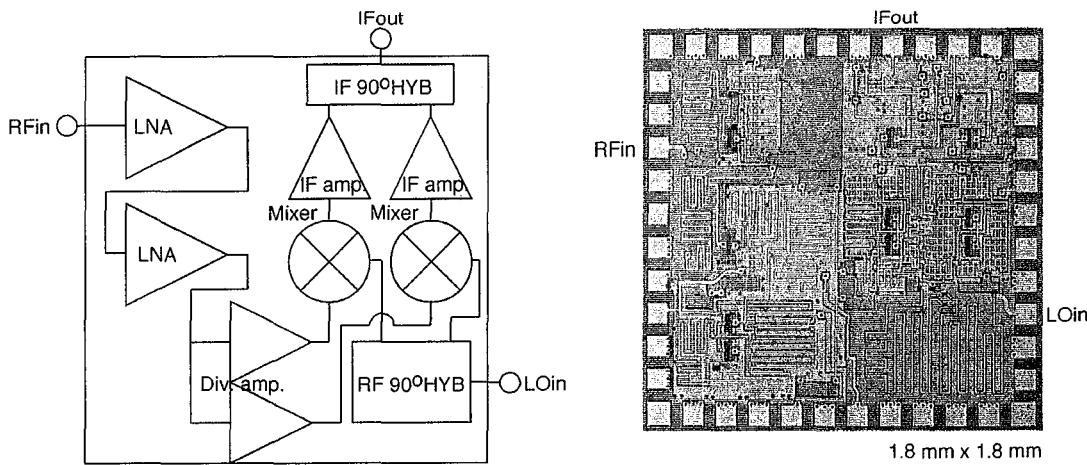

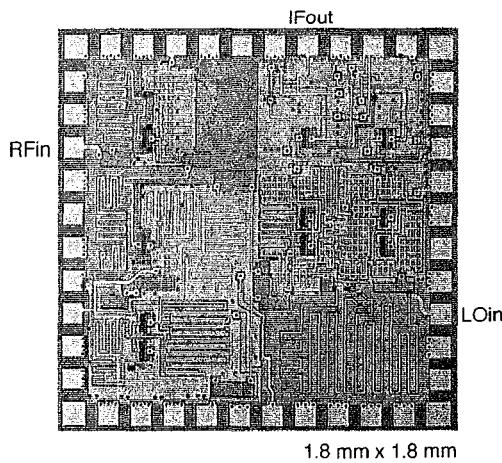

| 6.7 高集積 C 帯 1 チップ Si 3 次元 MMIC 受信機     | 111 |

| 6.8 Si 3 次元 MMIC の今後の展開                | 113 |

| 6.9 まとめ                                | 115 |

| 参考文献                                   | 116 |

| <br>第 7 章 3 次元構造によるマスタスライス型 MMIC 設計法   | 123 |

| 7.1 まえがき                               | 123 |

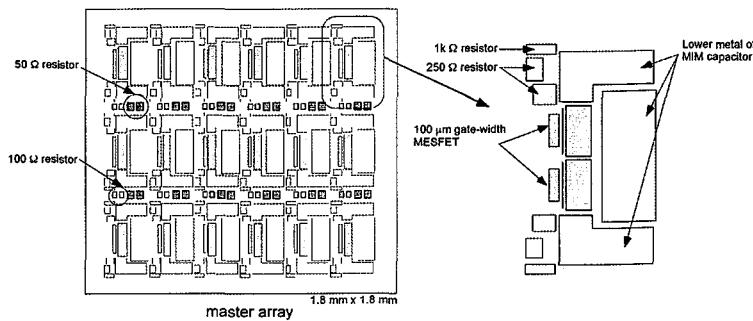

| 7.2 マスタスライス型 3 次元 MMIC の概念と特徴          | 124 |

| 7.2.1 マスタスライス型 3 次元 MMIC               | 124 |

| 7.2.2 マスタスライス型 3 次元 MMIC の特徴           | 125 |

| 7.2.3 マスタスライス型 3 次元 MMIC の経済化効果        | 126 |

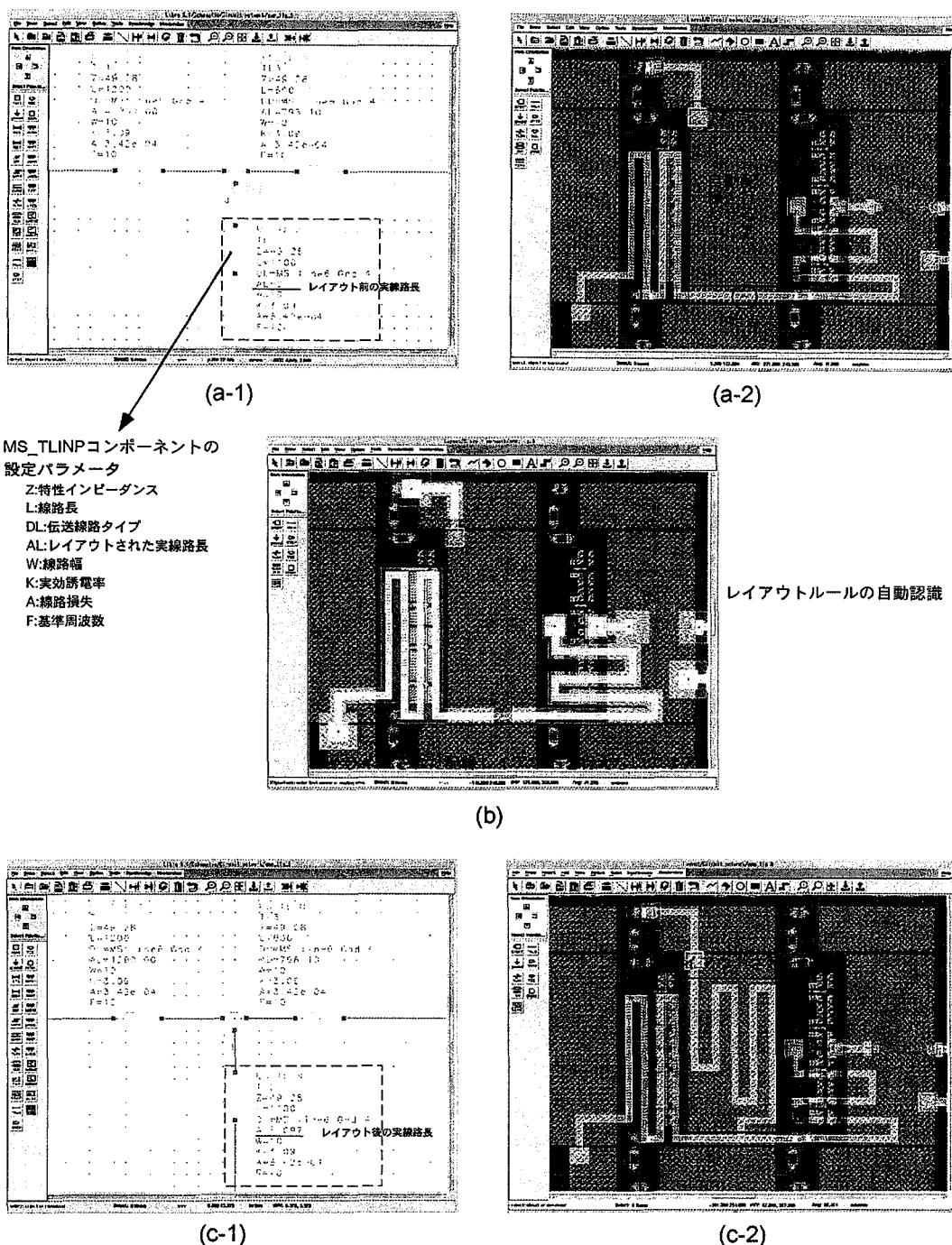

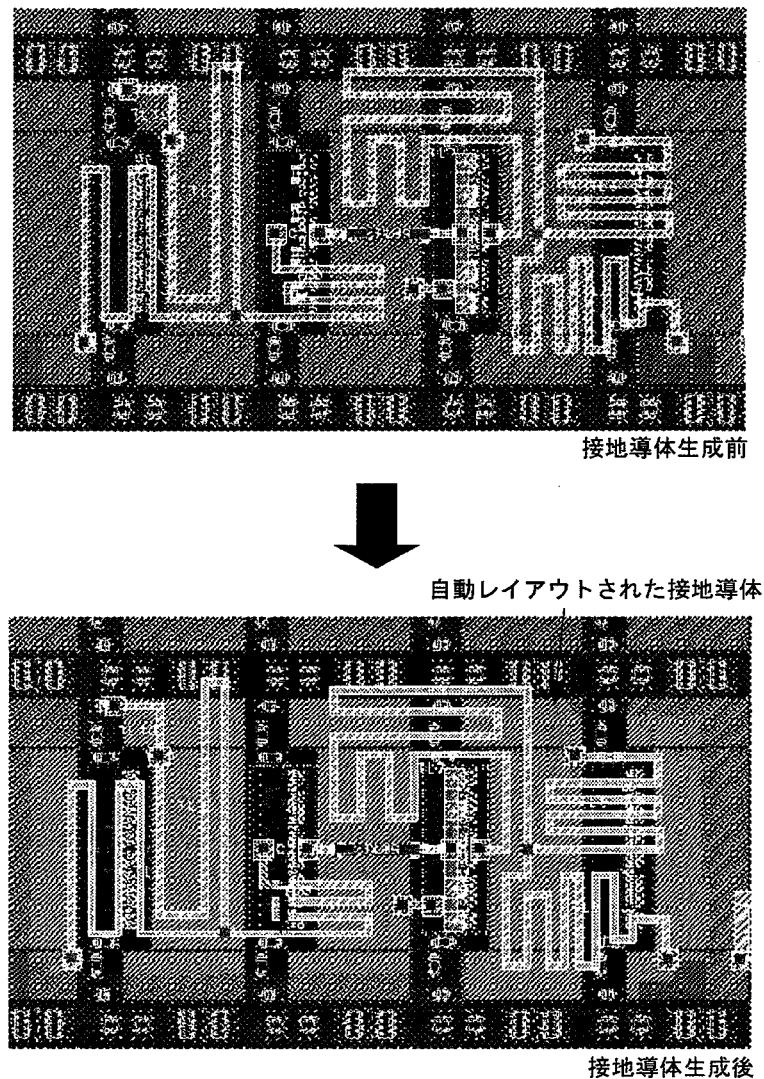

| 7.3 マスタスライス型 3 次元 MMIC に基づく CAD ソフトウェア | 127 |

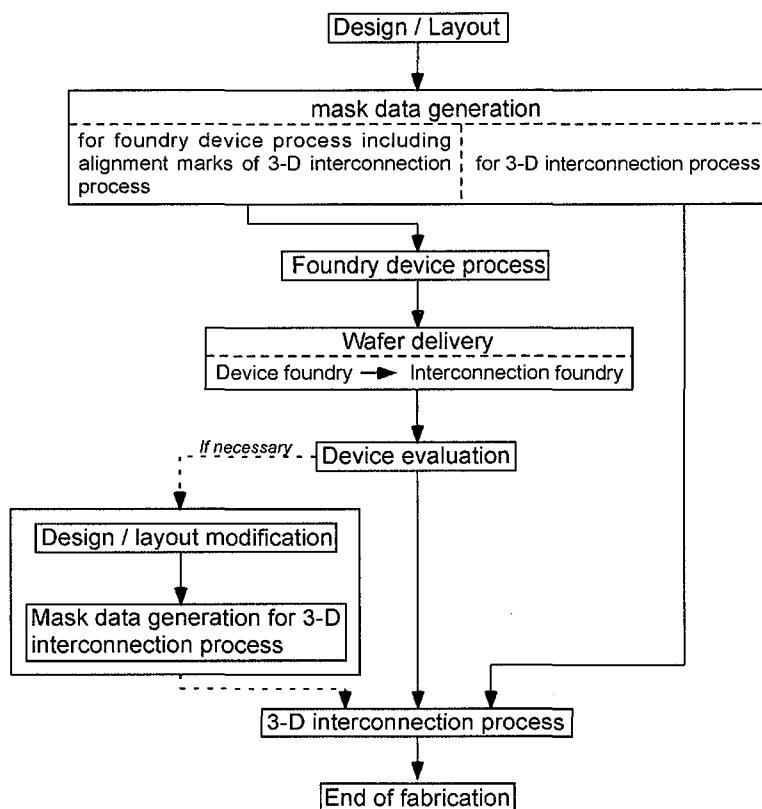

| 7.3.1 マスタスライス型 3 次元 MMIC 設計フロー         | 127 |

| 7.3.2 マスタスライス型 3 次元 MMICCAD ソフトウェア     | 128 |

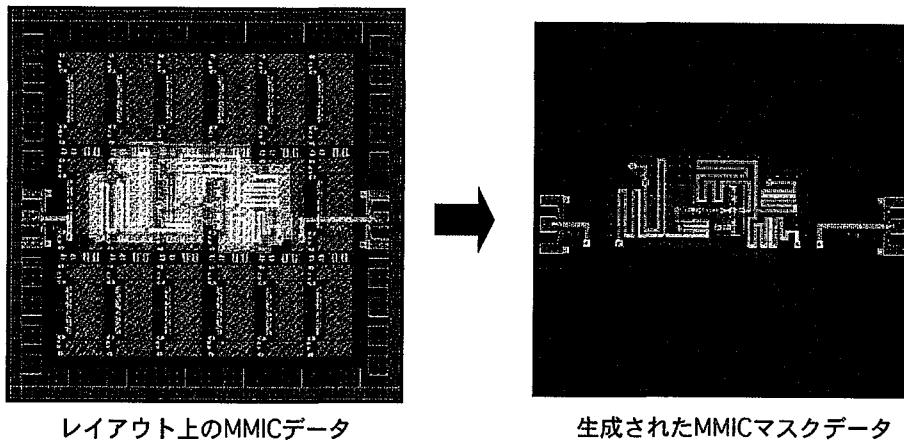

| 7.4 高集積マスタスライス型 3 次元 MMIC の実現例         | 135 |

| 7.5 マスタスライス型 3 次元 MMIC の今後の展開          | 138 |

| 7.6 まとめ                                | 142 |

| 参考文献                                   | 143 |

| <br>第 8 章 結論                           | 145 |

| 本研究に関わる研究業績                            | 147 |

| その他の研究業績                               | 152 |

# 第1章 序論

## 1.1 研究の背景

携帯電話に代表されるように、1990年代前半からのワイヤレス通信サービスの急速な拡大により、通信装置の小型化、高性能化、低コスト化、低消費電力化、開発期間短縮（短TAT）化が求められてきた。また、90年代後半からはワイヤレスLANのような高速データ通信サービスの開始や自動車レーダに代表されるセンサの実現により、通信装置への上記の要求がますます強くなってきた。さらには、高速通信を実現するため、使用周波数帯の高周波化も行われている。一方、このようなワイヤレス通信装置に使用されるモノリシックマイクロ波集積回路（Monolithic Microwave Integrated Circuit; MMIC）は、1980年代に米国で軍事用として本格的に開発されたのを端緒として、その後、90年代に入って、一般のワイヤレス通信用として応用されるようになってきた。さらに、応用範囲の拡大に伴い、1チップ上に複数の機能を搭載した高機能MMICの開発が多くなってきており、MMICには一層の小型、高集積化と低コスト化が求められている。

現在主流となっているMMICは、化合物半導体ウエハの裏面に接地導体、表面に信号線導体を形成するマイクロストリップ型MMICと半導体ウエハ表面に接地導体と信号線導体を形成するコプレーナ型MMICである。マイクロストリップ型MMICでは信号線幅はウエハ厚に依存するため、信号線幅を小さくすることが難しく、波長に依存したハイブリッド回路などの受動回路の面積が大きくなり、チップ全体に占める受動回路の面積は能動回路部の数倍に達している。

コプレーナ型MMICはウエハ厚に依存せずに信号線幅を決めることができるが、コプレーナ線路を実現するために信号線の両側に一定幅の接地導体を形成する必要があり、伝送線路全体として見た場合の線路幅はマイクロストリップ型とあまり変わりなく、依然として受動回路の占める面積は大きくなる。また、両形式と関係なくインダクタやキャパシタ、抵抗といった集中定数素子を用いる集中定数型MMICは低い周波数帯においては小型化に有利であるが、集中定数素子の周波数限界のために高周波数帯には適用できない。低コスト化に有利なSi系デバイスは、近年の高性能化によって数GHz帯のSiMMICの開発も活発となっているが、Siウエハの低抵抗性によりSiMMICの一層の高周波化は困難であった。これらのMMIC設計においては伝送線路の曲がり部、ピアホール、隣接素子間結合等の寄生成分を考慮して設計する必要がある。つまり、電磁界解析を適用して等価回路と実際のパターンレイアウトの間を往復するバックアノーテニションを行う必要があり、この設計プロセスがMMICの開発時間を長期化させる要因の一つとなっており、低コスト化の妨げとなっている。

このような既存のMMIC技術の持つ問題点を解決し、MMICの飛躍的小型化、高集積化を実現する新たな3次元構造のMMICを提案し、基本受動回路／能動回路設計技術を確立し、高

集積 1 チップ MMIC の実現を目指す。提案する 3 次元構造の MMIC によりミリ波帯 MMIC 高集積化, SiMMIC の高周波化, 高性能化を実現する。さらには MMIC 設計ノウハウが不要となり, MMIC 開発期間の短縮を実現するマスタスライス型 MMIC を提案する。

## 1.2 本研究の目的と論文の構成

本論文は MMIC の小型・高集積化, 高機能化, 低コスト化の実現を目的として, 3 次元構造を用いた超小型, 高集積ミリ波帯 MMIC 及び SiMMIC の高周波化, 高機能化について検討したものである。さらに, MMIC 設計の一層の簡易化を実現するために開発したマスタスライス設計手法をベースとした CAD ソフトウェアについても述べる。

まず, MMIC に要求されている特性, 克服すべき問題点等を述べるとともに, 本研究の目的である小型・高集積化, 高機能化, 低コスト化を実現する手法について示す。本論文では, 特に, 高集積化, 低コスト化が困難であるミリ波帯 MMIC に対して 3 次元 MMIC を適用することにより, 3 次元配線のミリ波帯での特性を明らかにし, RF 回路～IF 回路までの 1 チップ集積化を初めて実現した。これにより, チップ面積の小型化のみならず, MMIC と外部の接続端子数の低減を実現できるため, ミリ波 MMIC の実装コストを大きく下げることが可能となる。次に, 低コスト化の観点から, 低抵抗基板を用いた SiMMIC の高周波化について検討し, Si 3 次元 MMIC を提案するとともに, 基板による損失を克服する低損失受動回路を実現し, かつリアクティブ整合回路を適用した K 帯～Ka 帯で動作する SiMMIC を世界で初めて実現した。これにより, MMIC コストの大幅な低減を実現するとともに, ベースバンド～RF までの 1 チップ化が可能となる。最後に, 3 次元 MMIC 技術とマスタスライス設計法を組合せたマスタスライス型 3 次元 MMIC 設計法について述べ, この設計法をベースとした CAD ソフトウェアを開発した。これは, MMIC のソフトウェアとして初めての自動レイアウト機能を持つとともに, MMIC 設計の大幅な簡易化ならびに, 開発期間の短縮とコストの一層の低減をもたらすものである。

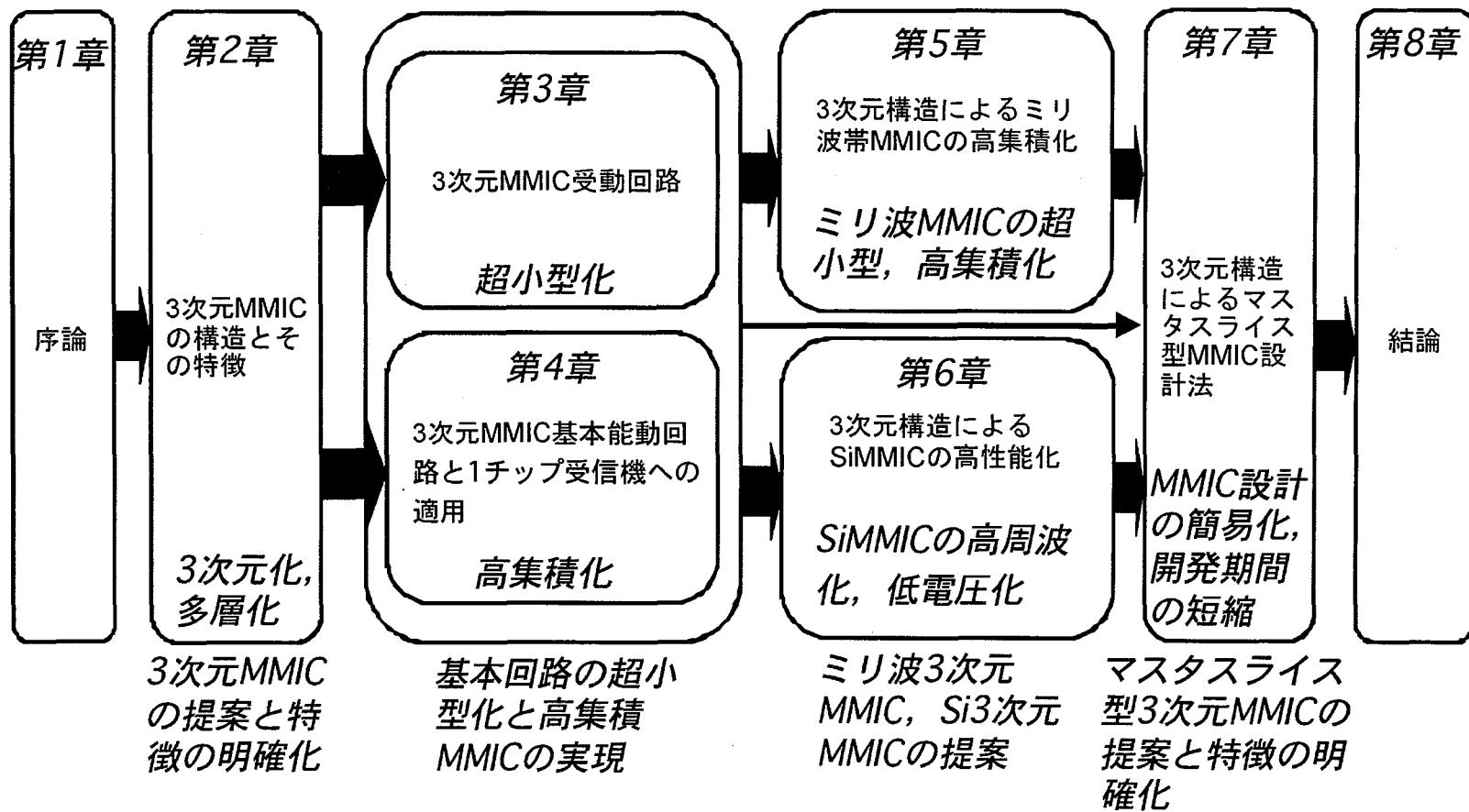

図 1.1 に本論文の構成を示す。

第 1 章は序論であり, 本研究の背景, 目的, 論文構成について述べている。

第 2 章では, 半導体基板上に誘電体薄膜を多層に積層し, その上にマイクロ波回路を形成する 3 次元 MMIC を提案する。3 次元 MMIC の基本構造を示すと同時に, 従来の平面構成型 MMIC との比較により, その特徴を明確にし, 3 次元 MMIC が小型, 高集積化に極めて有効であることを構造的観点から示す。次に, 3 次元 MMIC を実現するために新たに開発した 2 つのプロセス技術について述べる。まず, 誘電体膜としてポリイミドを用いた 3 次元 MMIC 製造プロセスについて述べ, 開発したプロセスの均一性, 信頼性が, 平面構成型 MMIC 製造プロセスと比較して, 同等であることを示す。次に, 製造プロセス時間の短縮化と一層の信頼性の向上実現を目的として開発した感光性 BCB を用いた 3 次元 MMIC 製造プロセスについて述べる。BCB 3

次元 MMIC ではその製造プロセスの特徴を活かして新たにトレンチ構造の配線を提案, 実現している。ここで提案するトレンチ構造の配線はピアホールプロセスを用いて実現され, 伝送線路損失が小さいという特徴を持っている。

第3章では, 3次元構造によって実現した超小型基本受動回路について提案し, それらの構成, 特徴について述べる。まず, 3次元 MMIC のキーコンポーネントである薄膜マイクロストリップ線路 (TFMS 線路) の特徴を述べるとともに, 高密度レイアウトを実現するための伝送線路レイアウト手法を明確にする。次に, 多層構造を用いて実現したブロードサイドカプラ及びブロードサイドカプラを応用したマーチャンドバランについてその構成, 設計法, 特性について示す。ブロードサイドカプラは近接層間膜に 2 本の信号配線を平行に配置し, その積層された 2 本の伝送線路の結合により実現している。ここでは 2 本の伝送線寸法とカプラの結合度の関係を明確にし, カプラの強結合と小型化 (従来の平面構成と比較して 1/20 の小型化) の両立を実現している。マーチャンドバランは 180 度信号分配合成回路であり, 2 つの小型なブロードサイドカプラとそれらを接続する伝送線路により構成している。この構成により, カプラ部で生じる不平衡性を補償し, バランの広帯域動作を実現している。積層型ウイルキンソンパワーディバイダは半導体基板上及び積層誘電体膜最上層に信号配線を形成し, 誘電体膜中間層に信号配線と平行にスリットを入れた接地導体を形成した構成である。この構成により, ディバイダを構成する  $70\Omega$  という高インピーダンス線路の積層化を MMIC レベルで初めて実現すると同時に小型化を実現している。

第4章では, 3次元構造の化合物系デバイスを用いた基本能動回路について述べるとともに, それらを 1 チップに集積化した 20GHz 帯 1 チップ受信機 MMIC について述べる。まず, 小型化に適し, かつ高利得を実現できるカスコード型増幅器の構成と設計法について述べる。カスコード接続されるソース接地 FET とゲート接地 FET 間の伝送線路と, ゲート接地 FET のゲートと接地導体間に伝送線路を導入することを提案し, それらの線路長を最適化することにより, 増幅器特性が向上することを明らかにする。次に, 負帰還回路部にドレイン接地 FET を配置し, FET の相互コンダクタンスを変えることにより, 帰還量を変化させるアクティブ帰還型可変利得増幅器を提案し, その構成と設計法について述べ, 減衰動作時の歪み特性が大幅に改善することを示す。周波数変換器についてはアップコンバータ／ダウンコンバータ両構成について述べる。整合回路を積層する小型化回路構成とその設計法について述べるとともに, 第3章で示した受動回路との組合せにより, 超小型なバランス型またはイメージ抑圧型周波数変換器が実現できることを示す。小型化と高性能化を実現する発振器構成を提案し, その設計法について述べる。最後に, 機能回路を 1 チップに集積化した高集積 3 次元 MMIC 受信機について, その構成, 設計法, 及び特性を示す。

第5章では, ミリ波帯での 3 次元 MMIC の実現に焦点を当て, 3 次元 MMIC 技術がミリ波帯

MMIC の小型化高集積化に極めて有効であることを示す。TFMS 線路のミリ波帯での特性について、従来のマイクロストリップ線路、コプレーナ線路との比較により、その優位性を示す。さらに、曲がり部等の不連続部の特性について明らかにし、その特性が従来の最適化されたマイクロストリップ線路の不連続部と同等であることを示す。次に、ミリ波帯 MMIC の高集積化を実現する構成及び設計法を示すとともに、実現した V 帯 1 チップダウンコンバータ／アップコンバータについて述べ、ミリ波 3 次元 MMIC がミリ波帯においても極めて高い集積度を実現できることを示す。最後に、3 次元 MMIC 技術を応用したミリ波 MMIC／モジュールの一体化構成（アンテナ一体化ミリ波システムオンパッケージ）を提案し、その特徴、利点、今後の課題を明らかにする。

第 6 章では、基板とマイクロ波線路を分離できるという 3 次元 MMIC 技術の特徴を用いた SiMMIC の高周波化、低電圧化について述べる。低抵抗 Si 基板とマイクロ波線路を Si 基板上に形成する接地導体により分離することにより、Si 基板上のマイクロ波線路の損失を大幅に低減できることを示すとともに、その構造を適用した高 Q インダクタの設計法について述べる。これらの低損失受動素子を用いることにより、従来にない SiMMIC の高周波動作（K 帯増幅器）を実現している。さらに、低損失マイクロ波線路を用いたリアクティブ整合回路を適用した回路構成により、1V 動作という低電圧動作を X 帯増幅器で実現している。さらに、Si トランジスタの低入力インピーダンスの特徴と低インピーダンス線路を用いた超小型、広帯域周波数変換器の設計法を提案、実現している。次に、機能回路を集積化した低電圧、広帯域動作 C 帯 1 チップトランシーバ Si 3 次元 MMIC の構成と設計法について述べている。最後に、Si 3 次元 MMIC 技術の今後の適用領域について述べている。

第 7 章では、新たに提案するマスタスライス型 3 次元 MMIC 設計法について述べる。提案する設計法は 3 次元 MMIC 技術をベースとしてゲートアレー的設計法を取り入れたマイクロ波回路のセミカスタム設計法である。初めに、マスタスライス型 3 次元 MMIC 設計法の概念と利点を述べるとともに、この技術により MMIC 開発の大幅な短縮化、低コスト化が実現できることを示す。次に、新たに開発したマスタスライス型 3 次元 MMIC 設計フローに基づく CAD ソフトウェアについてその特徴を述べる。開発した CAD ソフトウェアのウイザード機能、自動配線レイアウト機能を用いることにより、マイクロ波回路の開発が大幅に簡易化されることを示すとともに、提案する設計法を用いて実現した高集積 1 チップマスタスライス型 3 次元 MMIC 受信機について述べる。最後に、3 次元 MMIC の設計自由度を拡大し、かつ MMIC 開発コストの低減を期待できる開発手法を提案し、その開発手法の特徴を述べるとともに今後の課題を示す。

第 8 章では本論文全体を総括する。

図 1.1 本論文の構成

3次元MMIC

の提案と特

徴の明確化基本回路の超小

型化と高集積

MMICの実現ミリ波3次元

MMIC, Si3次元

MMICの提案マスタスライス

型3次元MMICの

提案と特徴の明

確化

## 第2章 3次元 MMIC の構造とその特徴

### 2.1 まえがき

ワイヤレス通信の発展に伴って、MMIC の小型化、高集積化の要求が高まってきている。これまでの MMIC はマイクロストリップ線路を主体としたマイクロストリップ型 MMIC、コプレーナ線路を主体としたコプレーナ型 MMIC（ユニプレーナ型 MMIC）が開発されてきた。マイクロストリップ型 MMIC は基板裏面に接地導体を形成し、基板表面に半導体や伝送線路が形成された MMIC である。コプレーナ型 MMIC は基板表面に信号線、接地導体、半導体が形成される MMIC である。これらの平面型 MMIC では基板厚の影響や接地導体面積の確保のため、MMIC の飛躍的な小型化、高集積化が困難であった。

本章では MMIC の飛躍的な小型化、高集積化を実現するために、基板上に誘電体膜と金属導体を多層に積層し、多層誘電体膜内でマイクロ波回路を形成する 3 次元 MMIC を提案する。まず、3 次元 MMIC の基本構造とその特徴を明確にする。次に誘電体膜としてポリイミドを用いた 3 次元 MMIC 製造プロセスの概要について述べる。最後に、InPHEMT 等の高性能デバイスとの集積化や 3 次元 MMIC 製造プロセスの短 TAT 化を目的とした感光性 BCB (BenzoCycroButene) を用いた製造プロセスの概要について述べる。

### 2.2 3次元 MMIC の基本構造とその特徴

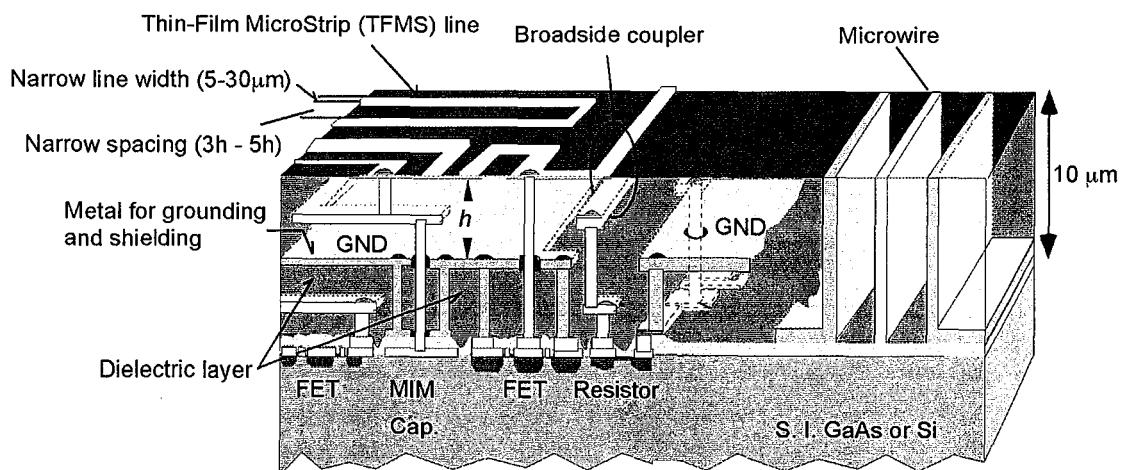

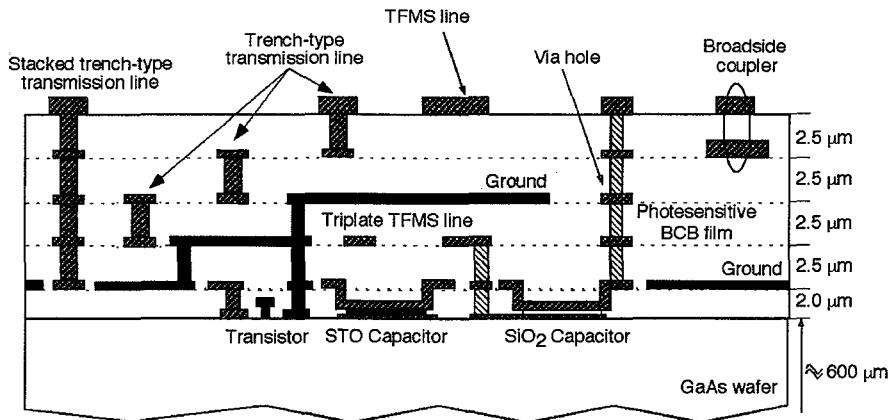

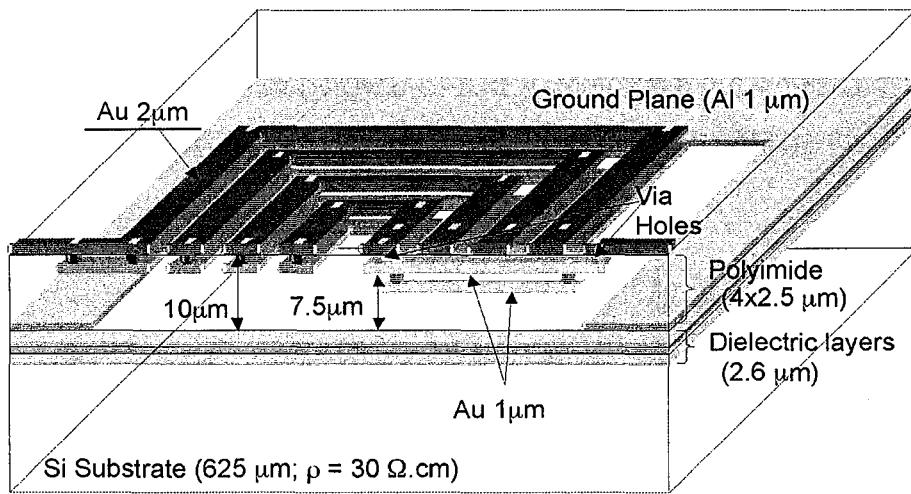

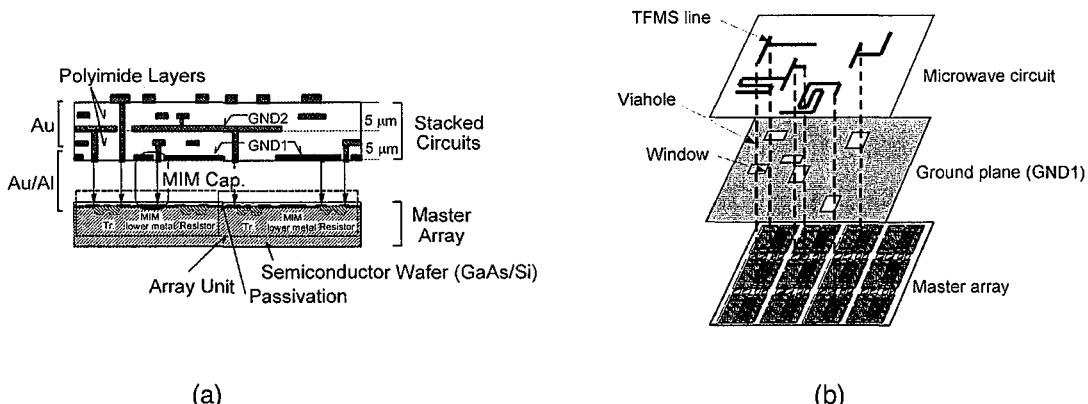

図 2.1 3次元 MMIC の基本構造

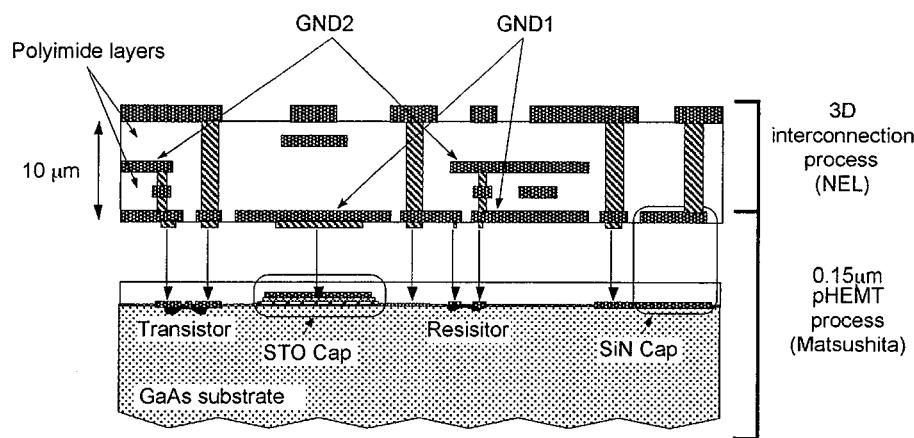

図 2.1 は 3 次元 MMIC の基本構造を示している。トランジスタ、抵抗等が形成される半導体基板上に誘電体膜と金属導体を多層に積層する多層化構造の MMIC である。誘電体膜は 1 層当たり  $2.5\mu\text{m}$  厚でありトータル 4 層構造とし、 $10\mu\text{m}$  厚となる。ここに示す例においては従来の

平面型 MMIC プロセスの 2 層配線と 4 層誘電体膜上の 4 層金属配線を合わせて 6 層配線構造となっている。MIM キャパシタは第 1 層と第 2 層金属配線で形成される。誘電体膜として、ポリイミドと感光性 BCB を用いている。配線厚さは第 1 層配線が  $0.7\mu\text{m}$ 、第 2 層から第 5 層配線までが  $1\mu\text{m}$ 、最上層配線を  $2\mu\text{m}$  としている。各層間はピアホールで接続される。接地導体はいずれの層においても形成することができる。さらに 3 次元 MMIC では図に示すような Microwire [1] と呼ぶ誘電体膜を貫いて形成される厚膜配線 ( $10\mu\text{m}$  厚) も同時に形成できる。

3 次元 MMIC は信号線、接地導体を基板の表面に形成するコプレーナ型 MMIC と多層誘電体膜上に信号線を形成するマイクロストリップ型 MMIC の両構造を合わせ持つ MMIC といえる。

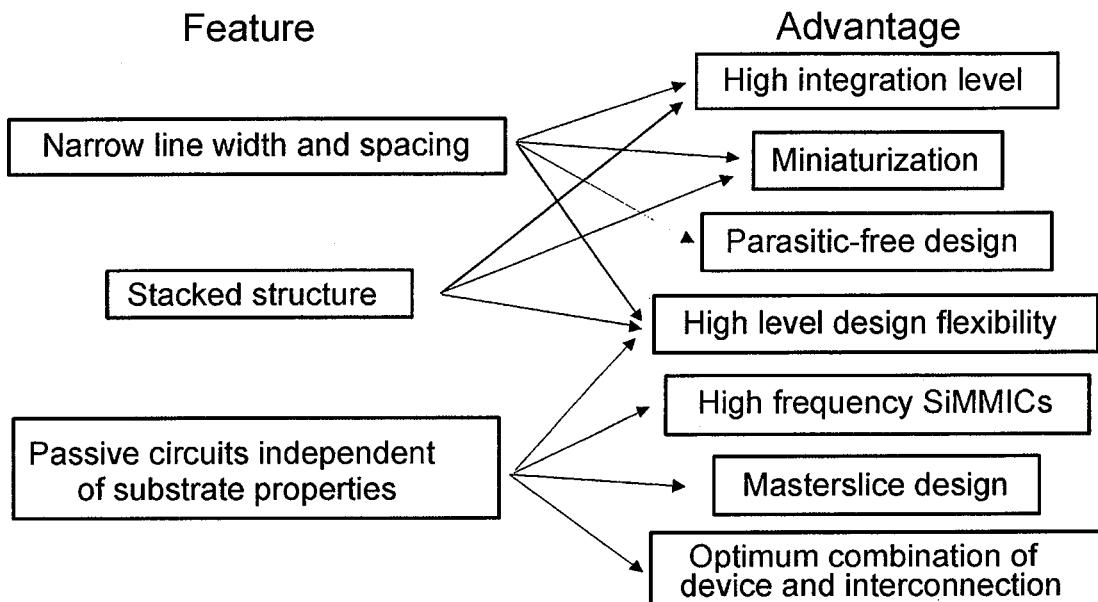

3 次元 MMIC は伝送線路として薄膜マイクロストリップ (Thin Film MicroStrip:TFMS) 線路 [2] と呼ぶマイクロストリップ線路を主に用いる。これは基板上の導体を接地導体、誘電体膜最上層導体を信号線としても基板厚は  $10\mu\text{m}$  と薄いことから名付けられている。この TFMS 線路構造により、信号線幅  $5\mu\text{m}$  から  $30\mu\text{m}$  の範囲において特性インピーダンス  $10\Omega$  から  $100\Omega$  の伝送線路を実現することができる（第 3 章で詳細を述べる）。また、そのときの線路間隔も狭くすることができる。接地導体の配置自由度により、例えば誘電体膜中間層に接地導体を配置することにより、その上層部、下層部に分けてマイクロ波回路を形成することができる（積層マイクロ波回路）。また、半導体基板上に接地導体を配置し、その上部にマイクロ波回路を形成できることから、基板上の接地導体のアイソレーション特性により半導体基板の特性に関わらず、同一性能を持つマイクロ波回路を実現できる。Microwire はその金属厚さから導体損の小さいマイクロ波線路として動作するだけでなく、壁面間の結合を利用した結合線路を実現できる。さらに、これらを接地導体とすることにより、その左右に形成される回路の遮蔽壁として利用することができ、高アイソレーションな高密度構造を実現できる。このような 3 次元 MMIC の構造的特徴により、図 2.2 に示すように以下の効果が得られる。

- 1 ) TFMS 線路は最大でも  $10\mu\text{m}$  の基板厚であるため、線路幅及び隣接線路間隔を微少に形成できる（不連続部を小さくできる）ので小型・高密度な配線を実現できる。さらに線路をメアンダ状等に折り曲げてレイアウトできるため、設計自由度が大きくなり、一層の高密度化が可能となる。

- 2 ) 接地導体を挟んで上下に回路を形成できるため、回路面積の小型・高密度化を実現できる。

- 3 ) 接地導体を半導体基板上に形成できるため、基板の導電性等の特性に関係なくマイクロ波線路を形成できる。特に Si 基板との組合せにおいては、たとえ Si 基板が導電性であっても、低損失なマイクロ波線路を実現できる（第 6 章において詳述する）。

- 4 ) 接地導体を半導体基板上に形成する構造はさらに、基板上のデバイスを選択することにも使用できるため、効果的にマスタスライス設計法を実現可能とする（第 7 章において詳述する）。これらの構造的特徴を組合せることにより、極めて高い設計自由度を得ることができ、かつ

図 2.2 3 次元 MMIC の特徴

超小型・高密度な 3 次元 MMIC を実現することができる。

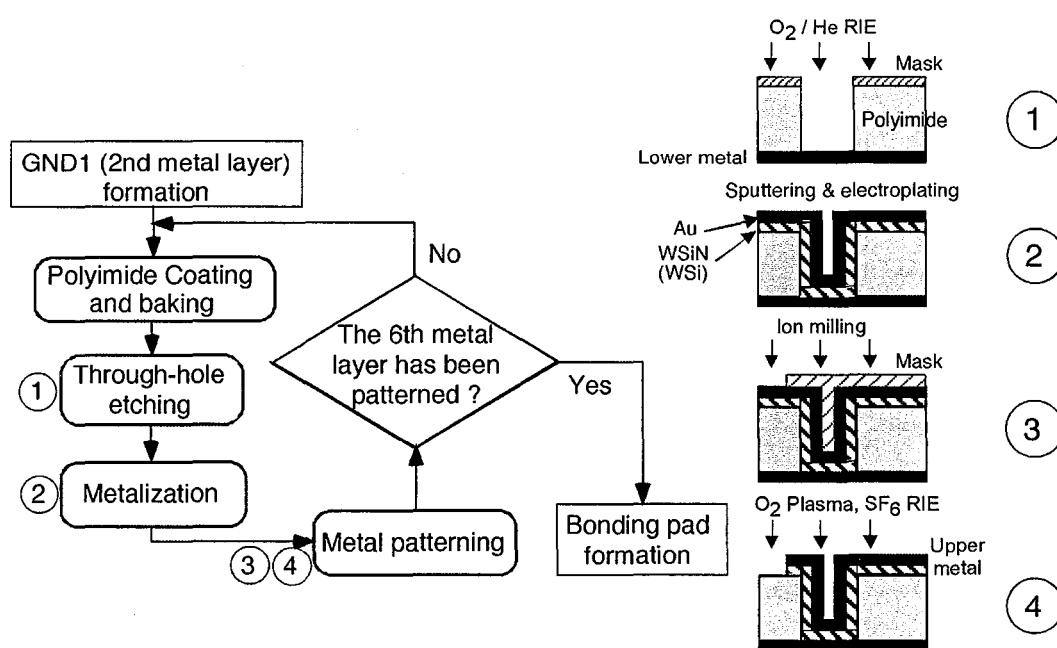

### 2.3 ポリイミドを用いた 3 次元 MMIC 製造プロセス [1]

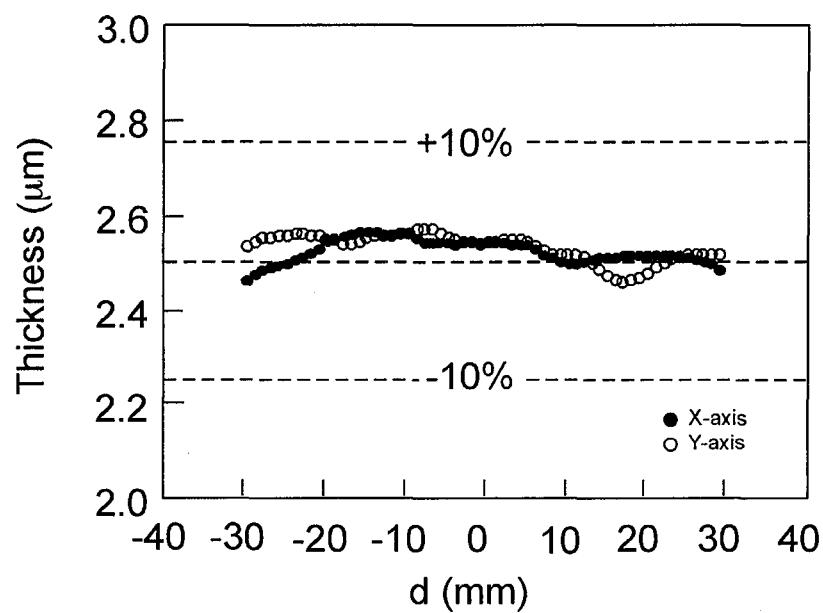

3 次元 MMIC を実現するために、FMIT (Folded Metal Interconnect Technology) と呼ぶ新しい誘電体膜を用いた多層配線プロセスを開発した。図 2.3 に製造プロセスフローを示す。1) 下層金属配線形成後、ポリイミドをスピンドルコートにより塗布、加熱し、ポリイミド膜を形成する。2) O<sub>2</sub>/He RIE (Reactive Ion Etching) によりポリイミドを加工し、ビアホールを形成する。3) ストップペタルとして WSiN をスパッタリングでポリイミド上に形成した後、電解めっきにより金をその上に形成する。4) イオンミリングにより、金属配線のパターンニングを行う。5) O<sub>2</sub> プラズマ及び SF<sub>6</sub> RIE によりパターンニングのためのマスクを取り除く。このプロセスを最上層金属配線が形成されるまで繰り返し行う。なお、最上層金属配線形成時には、同時に Microwire の形成を行う。このポリイミドを用いた 3 次元 MMIC 製造プロセスの特徴は、O<sub>2</sub>/He RIE を用いることによりビアホールの側壁エッチングを防ぐことを可能としている。低電流電解めっき法により、アスペクト比の極めて高い Microwire を形成可能としている。3 つの特徴はストップペタルを用いることによりイオンミリングがポリイミドを加工するのを防いでいる。図 2.4 は 3 インチ GaAs ウエハ上に形成したポリイミド膜のウエハ面内の厚さを測定したものである。黒丸が X 軸方向、白丸が Y 軸方向の結果である。製造ターゲットは 2.5 μm 厚である。測定結果から両方向とも 2.5 μm ± 3% 以内にポリイミド膜厚を制御できていることが

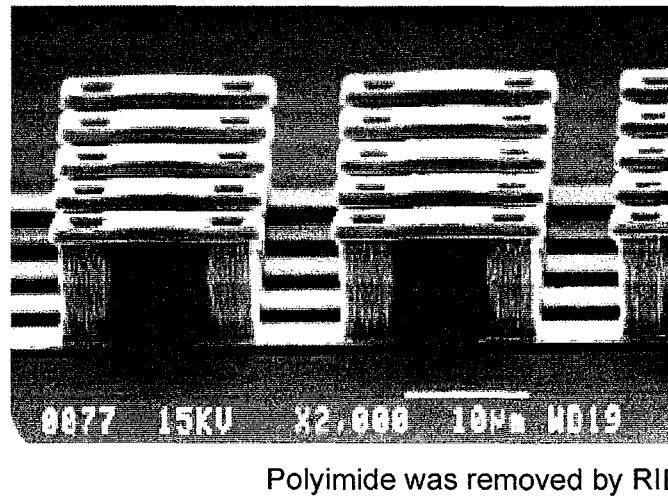

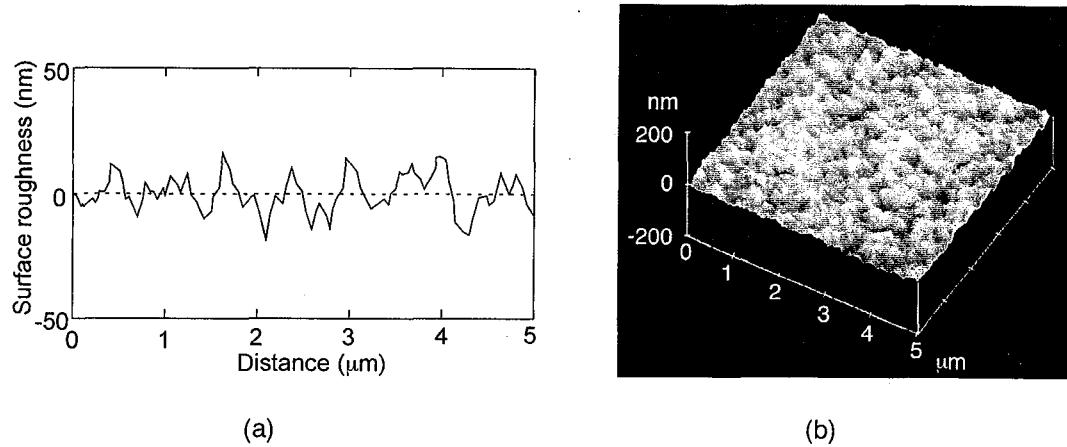

わかる。3次元 MMIC 製造プロセスにおいて、ウエハ面内でほぼ均一な膜厚制御を実現しており、良好な MMIC の製造歩留まりが期待できる。図 2.5 は Microwire 技術により実現したポリイミド膜最上層から最下層までをつらぬくビアホールチェーンの SEM 写真を示している。なお、ポリイミド膜は SEM 観察のために RIE により取り除いている。図に示されるように  $10\mu\text{m}$  のビアホールをほぼ垂直に実現できていることがわかる。また、図 2.6 はポリイミド膜上に形成した金属導体の表面粗さを測定した結果である。表面粗さは  $\pm 15\text{nm}$  以下である。この値は信号線厚が  $1\mu\text{m}$  または  $2\mu\text{m}$  に対して 2 衍小さい値であり、 $100\text{GHz}$  を越える周波数帯域においても金属導体の表面粗さを考慮する必要が無いことを示している。最後に、表 2.1 にポリイミドを用いた 3次元 MMIC 製造プロセスの特性をまとめると、3次元 MMIC 配線部は歩留まり、信頼性とも良好な特性を実現している。

図 2.3 ポリイミドを用いた 3 次元 MMIC 製造プロセス

図 2.4 ポリイミド膜のウエハ面内膜厚

図 2.5 3次元 MMIC プロセスで形成した Microwire の SEM 写真

図 2.6 ポリイミド上に形成される導体の表面粗さ

(a)表面粗さ, (b) 3次元イメージ図

表 2.1 ポリイミドを用いた 3 次元 MMIC 製造プロセスの特性

|                                                                                |                                        |                                                        |

|--------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------|

| Material constant of polyimide                                                 |                                        | $\epsilon_r = 3.3, \tan\delta = 0.0001 @ 1\text{MHz}$  |

| Breakdown voltage of polyimide film                                            |                                        | $3 \times 10^6 \text{ V/cm}$                           |

| Metal structure                                                                |                                        | Au (1 $\mu\text{m}$ or 2 $\mu\text{m}$ ) / WSiN or WSi |

| Via hole size                                                                  | 10 $\mu\text{m}$ height                | 5 $\mu\text{m} \times$ 5 $\mu\text{m}$ mask size       |

|                                                                                | 2.5 $\mu\text{m}$ height               | 3 $\mu\text{m} \times$ 3 $\mu\text{m}$ mask size       |

| Film thickness control                                                         |                                        | 2.5 $\mu\text{m} \pm 3\%$                              |

| Roughness of metal surface                                                     |                                        | < 15 nm                                                |

| Yield                                                                          |                                        | 100 %                                                  |

| Reliability (with passivation)                                                 | JEDEC standard:<br>No.22-A101-B @ 10 V | Pass                                                   |

|                                                                                | JEDEC standard:<br>No.22-A110-B        | Pass                                                   |

| Characteristic impedance of TFMS line:<br>$w = 5 \mu\text{m} - 30 \mu\text{m}$ |                                        | 10 $\Omega$ – 100 $\Omega$                             |

## 2.4 感光性 BCB を用いた 3 次元 MMIC 製造プロセス [3] - [5]

### 2.4.1 製造プロセス

感光性 BCB を誘電体膜として用いた 3 次元 MMIC の開発目的は、次の 3 つである。ミリ波帯への 3 次元 MMIC の応用のためにも InP 系デバイス等の高性能デバイスの 3 次元 MMIC 化、製造プロセス時間の短縮、ペアチップ実装への適用である。ポリイミドを用いた 3 次元 MMIC ではプロセス温度が 300°C となり、InP 系デバイス等のプロセス温度を越えてしまい、集積化が困難である。従って、プロセス温度がデバイスのプロセス温度以下であることが必要である。

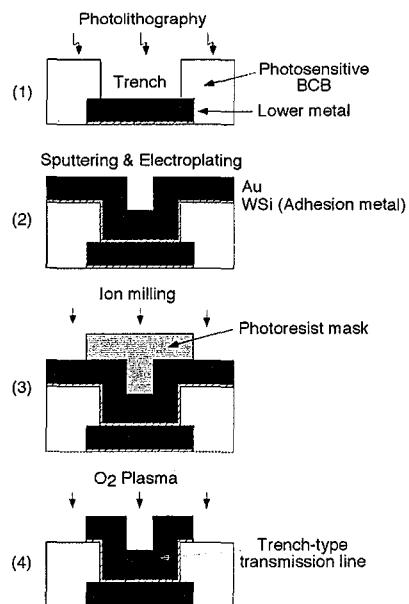

ポリイミドは吸湿性が高く（約 2%），ペアチップ実装を考慮した場合信頼性確保の点からより低い吸湿性材料であることが必要である。さらにポリイミドと比較して製造プロセス工程が少ないことを考慮して、感光性 BCB の使用を決定した。感光性 BCB は誘電率 2.7、吸湿性 0.2% 以下、プロセス温度 250°C である。図 2.7 は感光性 BCB を用いた製造プロセスを示している。

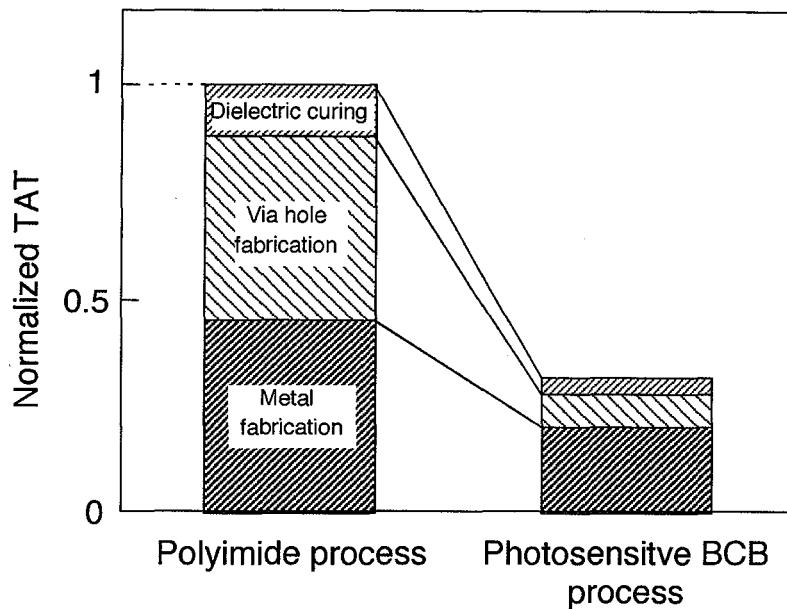

(1) 下層金属配線パターン形成後、感光性 BCB をスピンドルコートにより塗布、加熱する。その後、フォトリソグラフィにより、BCB 膜上にビアホール、トレンチ配線（2.4.2 で詳細を述べる）用の加工を行う。(2) 密着用金属（WSi）及びシード金属としての金をスパッタリングにより BCB 膜上に形成する。その上に、めっきにより金配線を形成する。(3) 金配線はフォトレジストマスクを用いて、イオンミリングによりパターンニングされる。(4) フォトレジストマスクを O<sub>2</sub> プラズマにより除去する。このプロセスを最上層配線形成まで繰り返す。図 2.8 はポリイミドを用いた場合の製造プロセス時間と感光性 BCB を用いた場合の製造プロセス時

図 2.7 感光性 BCB を用いた 3 次元 MMIC 製造プロセス

図 2.8 ポリイミド版 3 次元 MMIC と感光性 BCB 版 3 次元 MMIC 製造プロセス時間の比較

間を比較した図である。感光性 BCB は低プロセス温度、低吸湿性のため、キュア時間がポリイミドのほぼ 1/3 となる。フォトレジストマスクのエッティングレートは非常に低い値であるため、下層誘電体膜を保護するストップメタルを使用しなくてもよい。ビアホール、トレンチの加工をフォトリソグラフィで行うため、ビアホール加工時間の大幅な短縮を実現している。従って、トータルで製造プロセス時間をポリイミドプロセスと比較して約 1/3 にすることができる。さらに感光性 BCB の低吸湿性は金属配線パターンニングの大幅な自由度向上をもたらす。つまり、誘電体膜内に水分がほとんどないため、加熱時等の水分の放出を考慮する必要がないため、ビアホール、配線の配置に関する制限を取り除くことができる。

#### 2.4.2 BCB 3 次元 MMIC の配線構造

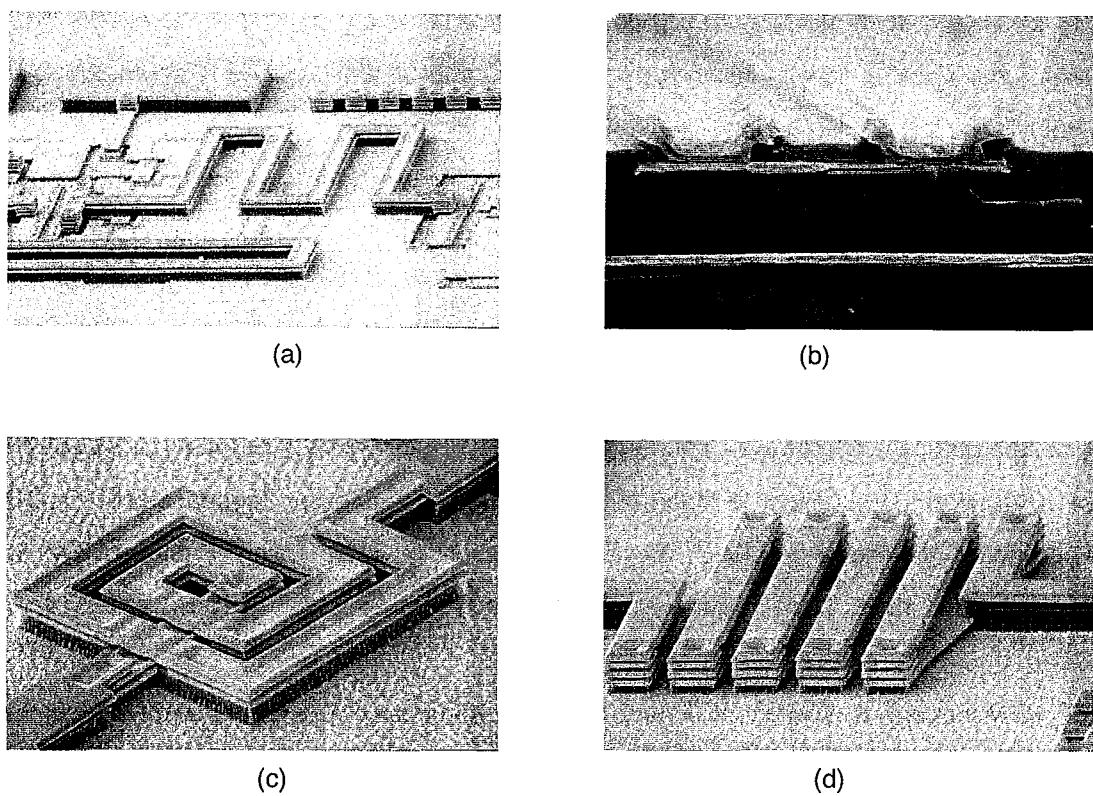

図 2.9 は InGaP/InGaAs/GaAs heterostructure MESFET (HMESFET) [6], [7] を用いた BCB 3 次元 MMIC の構造を示している。最下層に  $2\mu\text{m}$  厚の BCB 膜、その上に  $2.5\mu\text{m} \times 4$  層の BCB が形成される。最下層の BCB 膜はトランジスタの T 型ゲートを支える役目を担っている。従来の  $\text{SiO}_2$  を用いた容量だけでなく、容量の小型化、大容量化に有利な高誘電体材料である STO ( $\text{SrTiO}_3$ ) を用いた容量を集積している [3]。ビアホールは層間ごとに形成する構成である。層間ビアホールを層間を接続する本来のビアホール機能だけでなく、それらを溝のようにのはすことにより伝送線路として動作させることができる（トレンチ線路）。さらに層間ビアはスタッカドビア構造をとるため、トレンチ線路の厚さを変えることも可能である。このように金

図 2.9 HMESFET を用いた感光性 BCB 3 次元 MMIC の構造

層厚の厚い伝送線路は導体損失を低減することができるので、特に低い周波数帯で伝送線路の低損失化に有効である。トレンチ線路を伝送線路やスパイラルインダクタへ適用することにより、C 帯において TFMS 線路を用いた場合と比較して 30%以上の低損失化を実現している [5]。図 2.10 はトレンチ線路を試作したチップ写真である。BCB 膜は SEM 写真撮影のために取り除いている。(a) は増幅器の整合回路をトレンチ線路で形成した例である。(b) は幅広の伝送線路に 2 つのトレンチ線路を積層した例である。(c) はスパイラルインダクタ、(d) はソレノイドインダクタの例であり、これらの写真からもわかるように、配線自由度が大きく、かつ良好な伝送線路を実現できていることが確認できる。

## 2.5 まとめ

3 次元 MMIC を提案し、その特徴を明確に示すと同時に 3 次元 MMIC が小型、高集積化に極めて有効であることを示した。3 次元構造を実現するプロセス技術として、ポリイミドを用いたプロセス、感光性 BCB を用いたプロセスを開発し、それぞれの特徴を示した。

図 2.10 トレンチ線路を用いた種々の受動回路チップ写真

(a)整合回路, (b)伝送線路, (c)スパイラルインダクタ, (d)ソレノイドインダクタ

## 参考文献

- [1] M. Hirano, K. Nishikawa, I. Toyoda, S. Aoyama, S. Sugitani, and K. Yamasaki, "Three-dimensional Passive Circuit Technology for Ultra-Compact MMIC's," *IEEE Trans. Microwave Theory Tech.*, Vol. 43, No. 12, pp. 2845-2850, Dec. 1995.

- [2] T. Tokumitsu, T. Hiraoka, H. Nakamoto, and M. Aikawa, "Multilayer MMIC using a 3 $\mu$ m x 3-layer Dielectric Film Structure," *IEICE Trans. Electron.*, Vol. E75-C, No. 6, pp. 698-706, June 1992.

- [3] K. Inoue, K. Kamogawa, K. Nishikawa, K. Ikuta, K. Onodera, and M. Hirano, "Three-dimensional MMIC Interconnect Process Using Photosensitive BCB and STO Capacitors," in *Proc. 28th European Microwave Conf.*, Amsterdam, The Netherlands, Oct. 1998, pp. 642-647.

- [4] K. Nishikawa, S. Sugitani, K. Inoue, K. Kamogawa, T. Tokumitsu, I. Toyoda, and M. Tanaka, "A Compact V-Band 3-D MMIC Single-Chip Down-Converter Using Photosensitive BCB Dielectric Film," *IEEE Trans. Microwave Theory Tech.*, Vol. 47, No. 12, pp. 2512-2518, Dec. 1999.

- [5] K. Nishikawa, S. Sugitani, K. Inoue, T. Ishii, K. Kamogawa, B. Piernas, and K. Araki, "Low-loss, Passive Components on BCB-based 3-D MMIC Technology," in *IEEE MTT-S Int. Microwave Symp., Dig.*, Phoenix, AZ, May, 2001, pp. 1881-1884.

- [6] Y. Yamane, K. Onodera, T. Nittono, K. Nishimura, K. Yamasaki, and A. Kanda, "A D-DLL (double lightly doped drain) structure H-MESFET for MMIC applications," *IEEE Trans. Microwave Theory Tech.*, Vol. 45, pp. 2229-2233, Dec. 1997.

- [7] K. Onodera, K. Nishimura, T. Nittono, Y. Yamane, and K. Yamasaki, "Symmetric and asymmetric InGaP/InGaAs/GaAs heterostructure MESFET and their application to V-band amplifiers," *IEICE Trans. Electron.*, Vol. E81-C, pp. 868-875, June 1998.

## 第3章 3次元 MMIC 受動回路

### 3.1 まえがき

第3章では3次元構造を適用した伝送線路と超小型基本受動回路の設計法及びその特性について述べ、3次元MMIC受動回路が小型でかつ良好な特性、設計性を得ることを示す。まず、3次元MMICで使用する薄膜マイクロストリップ(Thin Film MicroStrip, TFMS)線路の構成とそれらの特性について示す。次に多層構造を用いて実現したブロードサイドカプラ及び上記カプラを適用したマーチャンドバランについて述べる。カプラは隣接層間膜に2本の信号配線を平行に配置し、強結合と小型化(従来の平面構成と比較して1/20の小型化)の両立を実現している。バランについてはカプラの不平衡性を補償する新たな補正法を提案し、バランの広帯域化法について述べる。最後に、積層型ウイルキンソンパワーディバイダの設計法、特性について述べる。このディバイダは半導体基板上及び積層誘電体膜最上層に信号配線を形成し、誘電体膜中間層に信号配線と平行にスリットを入れた接地導体を形成した構成としている。この構成により、高インピーダンス線路の積層化をMMICレベルで初めて実現すると同時に小型化を実現している。

### 3.2 薄膜マイクロストリップ(TFMS)線路

#### 3.2.1 TFMS線路の特性

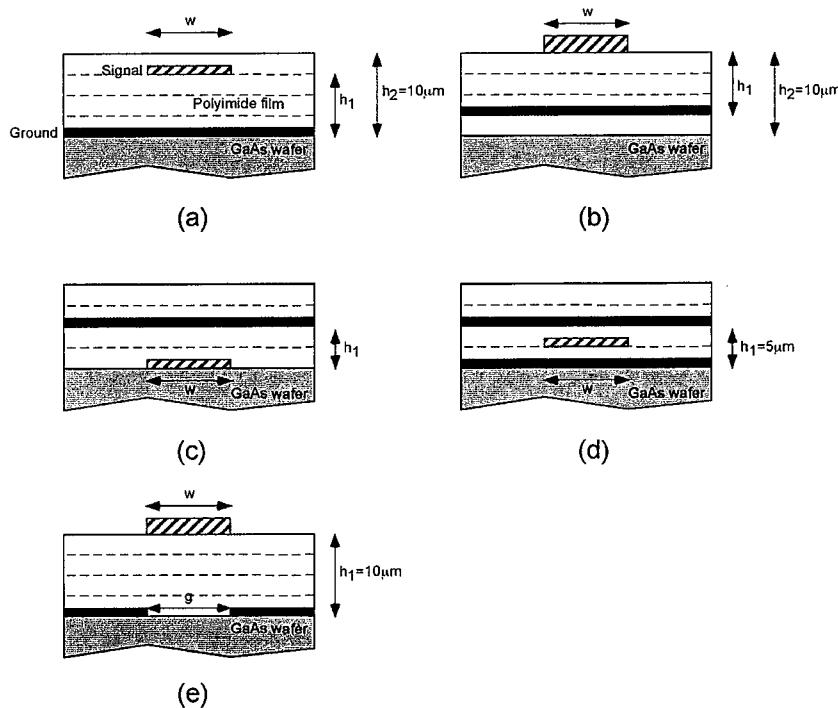

第2章で提案した3次元MMICはポリイミド層4層、配線層6層の多層構造であり、さらにMicrowireによる厚膜配線も実現することができる。この配線構造により様々な形態の伝送線路を実現できる[1] - [6]。図3.1は3次元MMICで頻繁に用いられる伝送線路の構成を示している。図(a)は接地導体を半導体ウエハ上に配置し、信号線をポリイミド多層膜中に形成する。図(b)は信号線をポリイミド層の最上層に配置し、接地導体をポリイミド多層膜中に形成する。この2つはTFMS線路の基本となるものである。図(c)は信号線を半導体ウエハ上に配置し、接地導体をポリイミド多層膜中に形成しており、逆TFMSと呼ぶ。この線路は図(a), (b)のTFMS線路と比較して、信号線を誘電率の高い半導体ウエハ上に配置しているため、一波長当たりの実線路長を短くすることができる。さらに、ポリイミド多層膜中の接地導体をはさんで図(b)のTFMS線路と組み合わせて使用することにより伝送線路の積層構造を実現することができ、MMICの小型化、高集積化を実現できる。積層された伝送線路は接地導体が間にあるため、線路間のアイソレーションを十分にとることができる。図(d)は接地導体を半導体ウエハ上及びポリイミド膜中間層に配置し、その間に信号線を形成している。トリプレートTFMS線路と呼ぶ。この構造の伝送線路も図(b)のTFMS線路と組み合わせることにより、伝送線路の積層化を実現できる。図(e)は信号線をポリイミド膜最上層、接地導体を半導体ウエハ上に配置し、信号線直

図 3.1 3 次元 MMIC 上の伝送線路

(a)TFMS 線路, (b)TFMS 線路, (c)逆 TFMS 線路, (d)トリプレート TFMS 線路,

(e)スリット付 TFMS 線路

下の接地導体にスリットを入れた構成であり、スリット付 TFMS 線路である。この構成では信号線下に接地導体がないため、信号線の容量成分を従来の TFMS 線路と比較して小さくすることができる。つまり、同じ信号線幅ではより高い特性インピーダンスを持つ伝送線路を実現できる。また同じ特性インピーダンスを実現する場合には信号線幅を大きくすることができるの低損失化を実現できる。

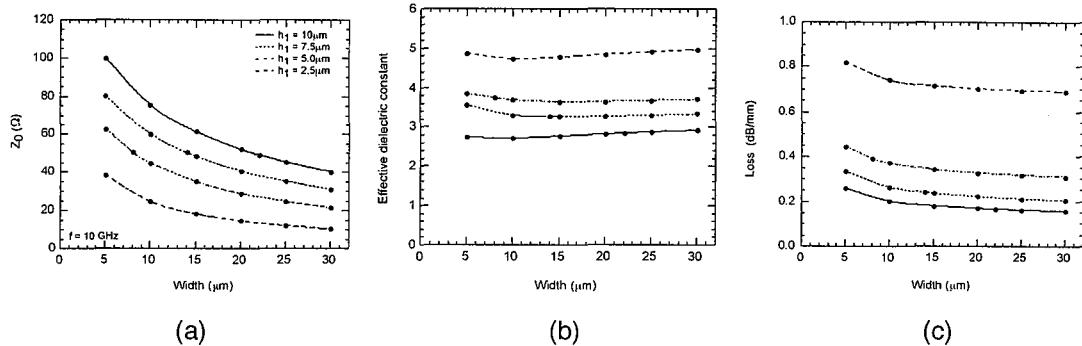

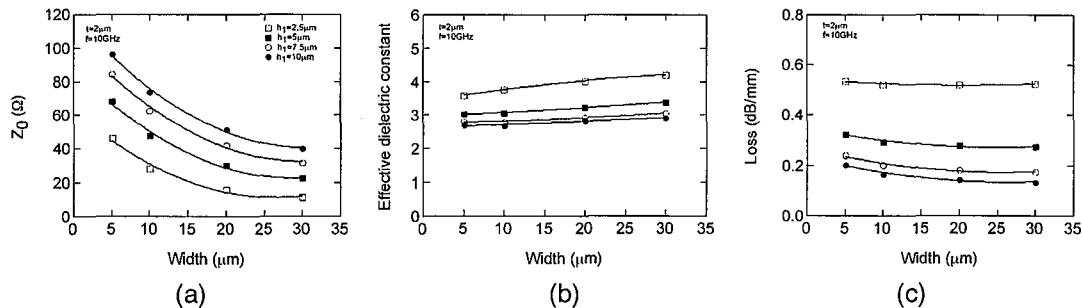

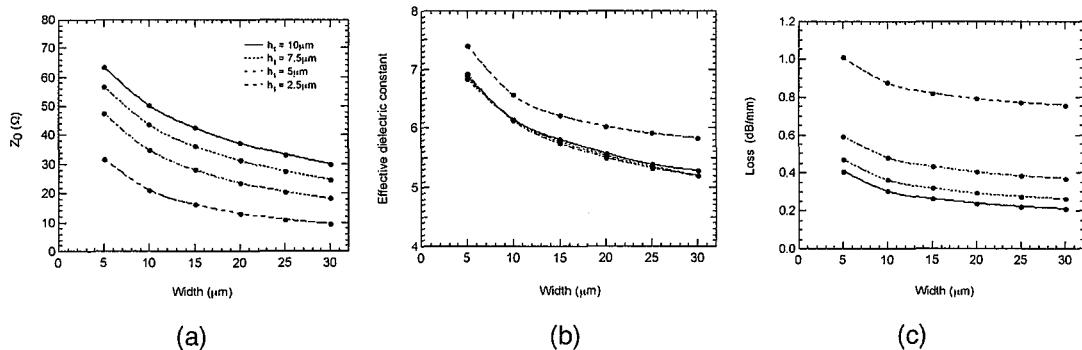

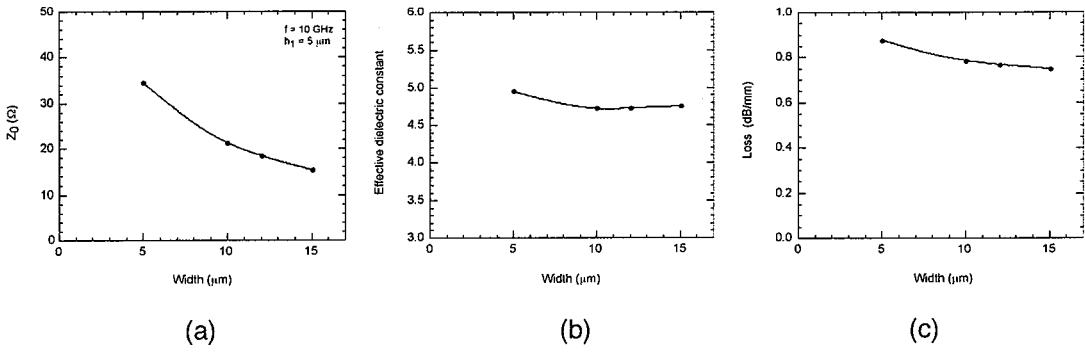

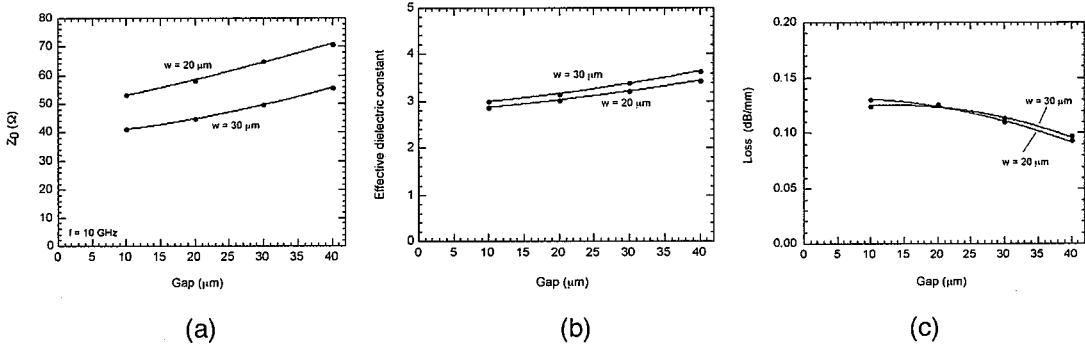

図 3.2 から図 3.6 にこれらの伝送線路の特性インピーダンス、実効誘電率、伝送損失の計算値を示す。これらの値は有限要素法による電磁界解析プログラム [7] や市販の電磁界シミュレータを用いて計算したものである。なお、計算した信号線幅の下限はプロセス限界からくる  $5\mu\text{m}$ 、上限は実際に使用する特性インピーダンスの範囲を考慮して  $30\mu\text{m}$  とした。計算に用いたパラメータは、周波数  $10\text{GHz}$ 、導体（金）の導電率  $4.1 \times 10^7$ 、ポリイミドの誘電率 3.3、ポリイミドの誘電正接 0.0004 (1MHz)、GaAs の誘電率 12.6 である。これらの図に示す伝送線路特性パラメータは設計チャートとして第 7 章で述べるマスタスライス CAD ソフトウェアに組み込み 3 次元 MMIC の良好な設計性を実現している。図 3.1(a), (b) に示す TFMS 線路においては信号線幅、基板厚を変えることにより特性インピーダンスを  $100\Omega$  から  $10\Omega$  まで変化さ

せることができる（図 3.2, 3.3）。逆 TFMS 線路においては特性インピーダンスの実現範囲は  $65\Omega$  から  $10\Omega$  であり、実効誘電率は 5 以上である（図 3.4）。スリット付 TFMS 線路においては特性インピーダンス  $50\Omega$ （信号線幅  $30\mu\text{m}$ ）の伝送損失は  $0.11\text{dB/mm}$  と低い値を実現している。このタイプの伝送線路は低損失が必要である LNA や発振器の共振器等に用いる。

図 3.2 TFMS 線路（図 3.1(a)）の特性

(a) 特性インピーダンス, (b) 実効誘電率, (c) 損失

図 3.3 TFMS 線路（図 3.1(b)）の特性

(a) 特性インピーダンス, (b) 実効誘電率, (c) 損失

図 3.4 逆 TFMS 線路（図 3.1(c)）の特性

(a) 特性インピーダンス, (b) 実効誘電率, (c) 損失

図 3.5 トリプレート TFMS 線路 (図 3.1(d)) の特性

(a) 特性インピーダンス, (b)実効誘電率, (c)損失

図 3.6 スリット付 TFMS 線路 (図 3.1(e)) の特性

(a) 特性インピーダンス, (b)実効誘電率, (c)損失

ポリイミドを基板としたマイクロストリップ線路の損失の周波数依存性はある基準周波数での損失を基にして以下の式で示される [8] .

$$\alpha(f) = \alpha_c(F) \cdot \sqrt{\frac{f}{F}} + \alpha_d(F) \cdot \frac{f^2}{F^2}$$

$\alpha_c(F)$  : 基準周波数での導体損失,  $\alpha_d(F)$  : 基準周波数での誘電体損失

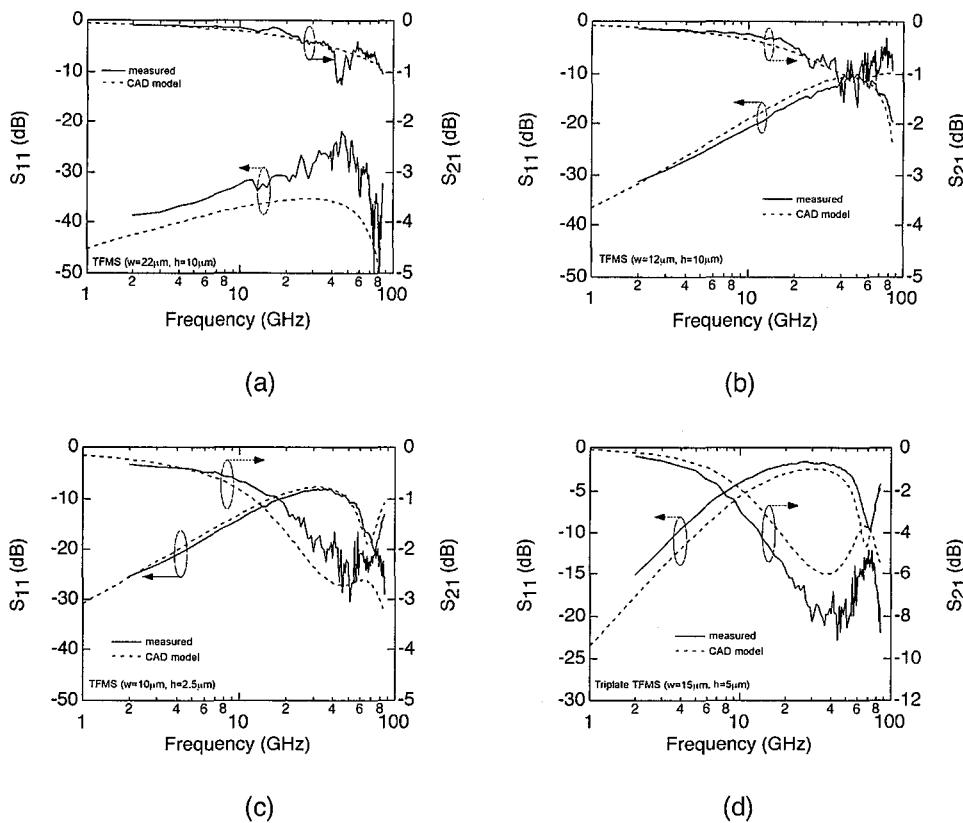

回路設計においては上記の式を用いて任意周波数での損失を計算した. 図 3.7 に TFMS 線路 (線路長 1mm) の測定した S パラメータと CAD ソフトウェア上の伝送線路モデルに上記式を適用し, 計算した S パラメータを示す. 図(a)は  $w=22\mu m$ ,  $h=10\mu m$  の TFMS 線路 ( $50\Omega$ ) , 図(b)は  $w=12\mu m$ ,  $h=10\mu m$  の TFMS 線路 ( $70\Omega$ ) , 図(c)は  $w=10\mu m$ ,  $h=2.5\mu m$  の TFMS 線路 ( $30\Omega$ ) , 図(d)は  $w=15\mu m$ ,  $h=5\mu m$  のトリプレート TFMS 線路 ( $15\Omega$ ) である. 実線が測定値, 破線が計算値である. 両者はいずれのタイプの伝送線路においてもよく一致している. これらの結果は上記に示した 10GHz で計算した伝送線路設計チャートと損失の周波数依存性を示す式を組み合わせることにより設計性の良い TFMS 線路モデルを実現していることを示しており, 3 次

図 3.7 CAD 上の伝送線路モデルと測定値の S パラメータの比較

- (a) TFMS 線路( $50\Omega$ ), (b)TFMS 線路( $70\Omega$ ), (c)TFMS 線路( $30\Omega$ ),

(d) トリプレート TFMS 線路( $15\Omega$ )

元 MMIC の良好な設計性を実現するものである。

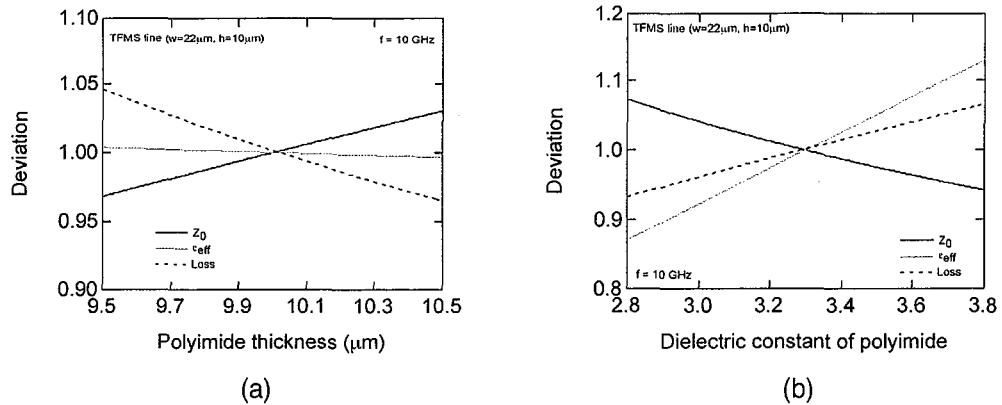

ポリイミド膜厚及びポリイミドの誘電率は製造プロセス上ばらつきを考慮する必要があるパラメータである。図 3.8 は TFMS 線路の特性パラメータのポリイミド膜厚及び誘電率依存性を示した計算値である。信号線幅  $22\mu\text{m}$  の TFMS 線路 ( $50\Omega$ ) を用いて計算した値である。図(a)は膜厚依存性、図(b)は誘電率依存性である。図中の黒実線が特性インピーダンス、灰色実線が実効誘電率、破線が損失を示している。ポリイミド膜厚が設計データである  $10\mu\text{m}$  から  $\pm 5\%$  変化しても、特性インピーダンスで  $3.5\%$  以下、実効誘電率で  $0.5\%$  以下、損失で  $5\%$  以下の変動率に収まっている。一方、ポリイミドの誘電率はポリイミドが水を吸うことにより変動することが知られている。図では設計データの  $3.3$  に対して  $\pm 15\%$  まで変化したときの値を示している。実効誘電率が一番大きく変動し、最大で  $12\%$  変化する。しかしながら、これらの変動率は MMIC 設計上無視できる値である。

図 3.8 ポリイミド膜厚及びポリイミドの誘電率変動が伝送線路特性に与える影響

(a) ポリイミド膜厚の影響, (b) ポリイミドの誘電率の影響

図 3.9 隣接線路間結合と増幅器特性

(a) 20GHz 帯増幅器, (b) 増幅器の特性

### 3.2.2 高密度レイアウトのための TFMS 線路の最小配置間隔

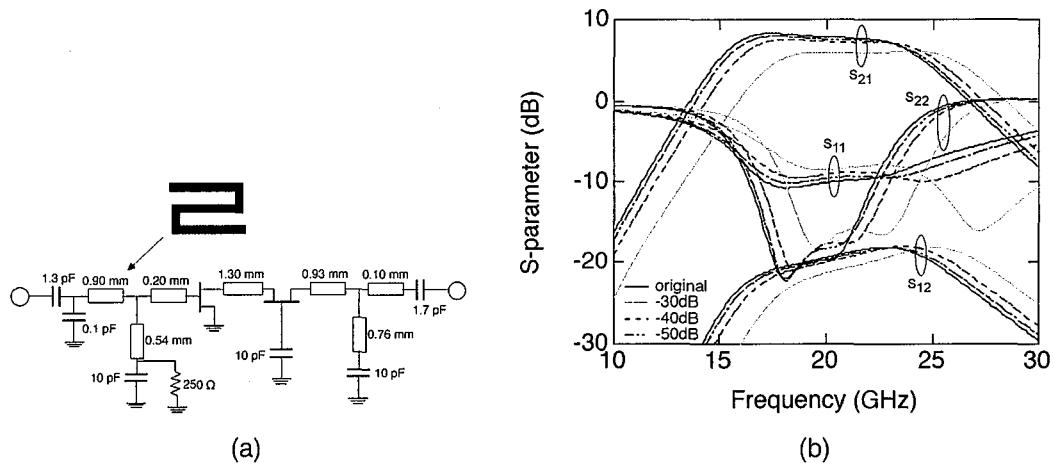

TFMS 線路の間隔を小さくし密に配置するほど回路の高集積化を実現できるが、隣接線路間の結合が増加し伝送特性が劣化するという問題がある。ここでは回路設計上、隣接線路間の結合を無視出来得る隣接する線路の最小間隔を明らかにする。図 3.9 は隣接線路間の結合が実際の増幅器特性に及ぼす影響についてシミュレーションにより検討した結果を示している。図(a)は 20GHz 帯の等価回路図であり、線路幅  $12\mu\text{m}$  の TFMS 線路 ( $70\Omega$ ) で整合回路を構成している。各 TFMS 線路はメアンダ状に配置され、その線路間隔を変えることにより隣接線路間の結合を変化させている。使用しているデバイスは GaAs MESFET であり、カスコード接続している。図(b)はシミュレーション結果である。図には隣接線路間の結合が無い場合、 $-30\text{dB}$ ,  $-40\text{dB}$ ,

図 3.10 TFMS 線路の隣接線路間結合と線路間隔の関係

(a) TFMS 線路モデル, (b)結合度

図 3.11 逆TFMS 線路の隣接線路間結合と線路間隔の関係

(a)逆TFMS 線路モデル, (b)結合度

-50dB のときの特性を示している。結合が大きくなるに従って、中心周波数が高い方へずれていくのがわかる。これは隣接線路間結合が大きくなると、その伝送線路の電気長が短くなるためである。この図では結合が-30dB のとき、増幅器特性が大きく劣化している。従って、結合が-40dB 以下であれば隣接線路間結合を無視してもよいといえる。つまり、-40dB 以下となるように隣接線路間隔を取ることによって、設計の簡易化を実現できる。

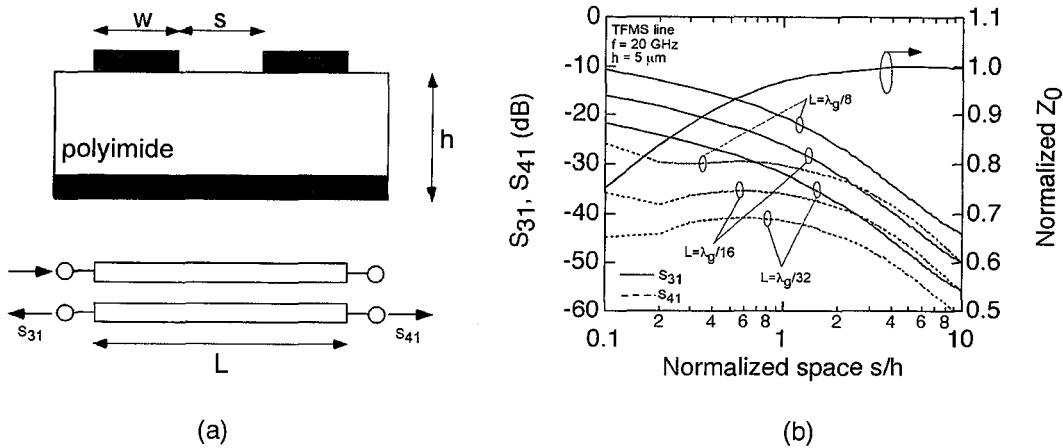

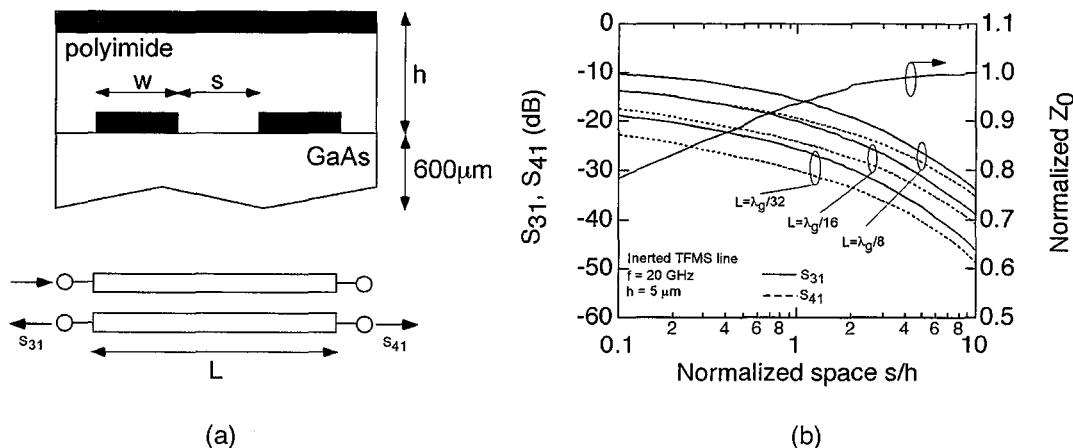

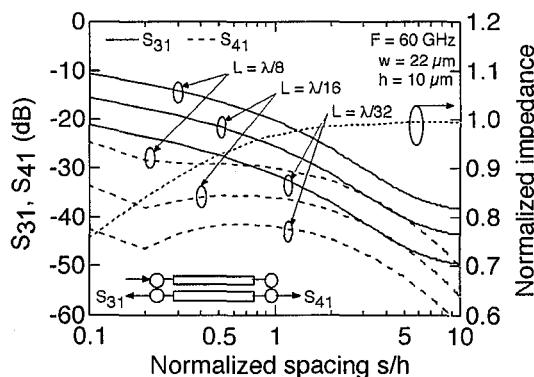

図 3.10, 図 3.11 に隣接線路間隔と結合度の関係を示す。図 3.10 は TFMS 線路に関するものであり、図(a)にシミュレーションモデルを示している。シミュレーションは市販の電磁界シミュレーションにより行った。図(b)は 20GHz のときのシミュレーション結果であり、合わせて 1/4 波長時の線路の特性インピーダンスのずれを規格化して示している。結合度としてパック

図 3.12 隣接線路間結合度と線路間隔の関係を示す測定値

(a) $S_{31}$ , (b) $S_{41}$

ワード結合 ( $S_{31}$ ) , フォワード結合 ( $S_{41}$ ) を示している。実線が  $S_{31}$ 、破線が  $S_{41}$  である。隣接する線路の長さが  $1/32$  波長のとき,  $s/h=2.3$  以上で  $S_{31}<-40\text{dB}$ , 線路長が  $1/16$  波長のとき,  $s/h=4$  以上で  $S_{31}<-40\text{dB}$  を実現する。 $S_{41}$  はそれ以下の値である。一方、図 3.11 は逆 TFMS 線路に関するものであり、TFMS 線路と同様のシミュレーション結果を示している。隣接する線路の長さが  $1/32$  波長のとき,  $s/h=6$  以上で  $S_{31}<-40\text{dB}$  を実現する。隣接する線路長がこれより短い場合には、より小さい  $s/h$  で  $S_{31}<-40\text{dB}$  を実現できる。また、このときの特性インピーダンスは隣接線路間の結合の影響をほとんど受けていない。

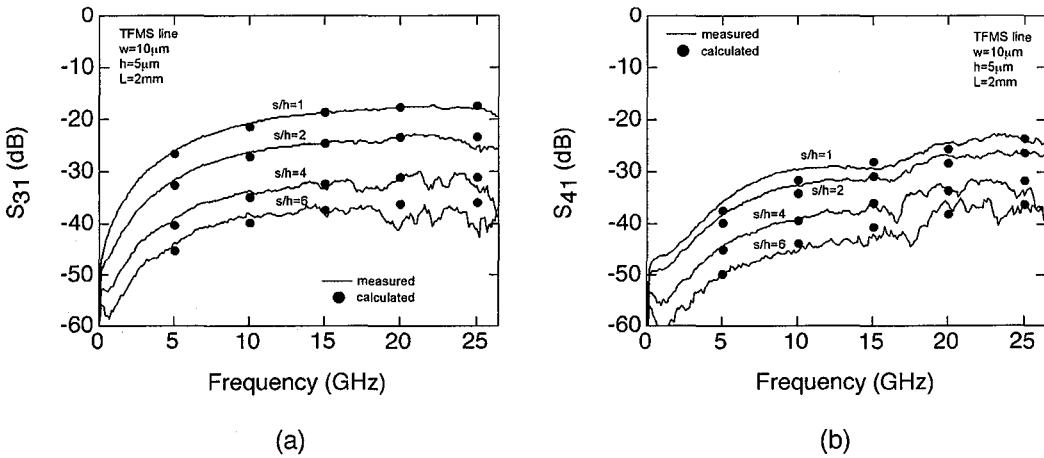

図 3.12 は 2 本の TFMS 線路 ( $w=10\mu\text{m}$ ,  $h=5\mu\text{m}$ ,  $L=2\text{mm}$ ) を平行に配置し、その 2 本の TFMS 線路間の結合 ( $S_{31}$ ,  $S_{41}$ ) を測定した結果である。実線が測定値、黒丸が電磁界シミュレーションによる計算値である。線路長  $2\text{mm}$  は  $21.4\text{GHz}$  で  $1/4$  波長となる長さである。線路間隔として  $s/h=1, 2, 4, 6$  のときの値を示している。測定値及び計算値はよく一致しており、このシミュレーション結果が有効であることがわかる。 $S_{31}$  は  $21.4\text{GHz}$  のとき  $s/h=6$  で  $-40\text{dB}$  である。線路長が約  $1/16$  波長となる  $5\text{GHz}$  では  $s/h=4$  で  $-40\text{dB}$  を実現できることを示している。実際にはメアンダ形状に TFMS 線路をレイアウトするときには隣接線路の線路長を  $1/32$  波長以下とすることが多く線路間隔はより小さい値とすることができます。従って、このような線路間隔の基準に基づいてレイアウトすることにより、回路面積を大幅に小型化できると同時にメアンダ形状に有るにも関わらず設計上 1 本の TFMS 線路として扱うことができる。3 次元 MMIC はこのような微細配置可能な TFMS 線路を用いて回路を構成できるため、小型で高密度な回路レイアウトを実現できる。

### 3.3 ブロードサイドカプラ

マイクロ波回路において、方向性結合器は不可欠な基本素子であり、バランス型回路等、さまざまな回路に用いられる。平面型 MMIC ではランゲカプラやブランチライン型ハイブリットが実現されているが、 $1/4$  波長線路を複数使用するため大きな回路面積を必要としていた。3 次元 MMIC では多層構造を利用して  $1/4$  波長線路を上下に重ねるブロードサイドカプラ [10] が提案されている。ここでは、ブロードサイドカプラの結合度を決める重要なパラメータである線路幅及び線路間の膜厚について詳細に検討した結果を示す。

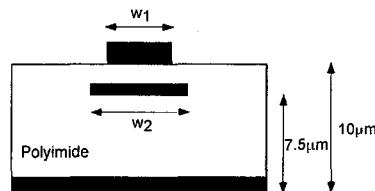

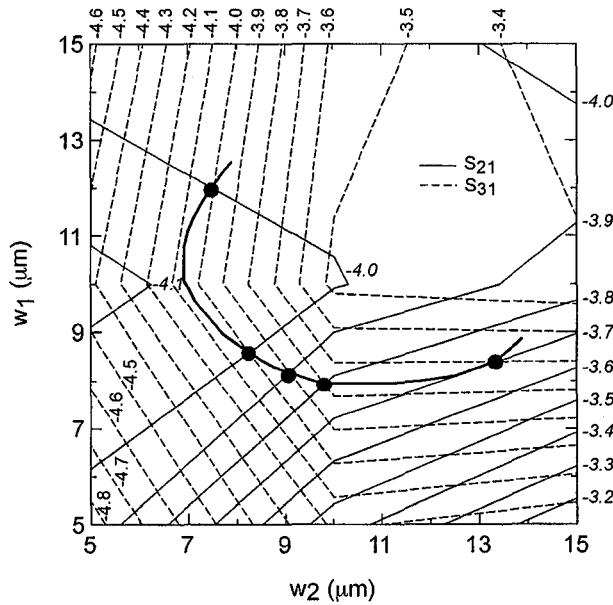

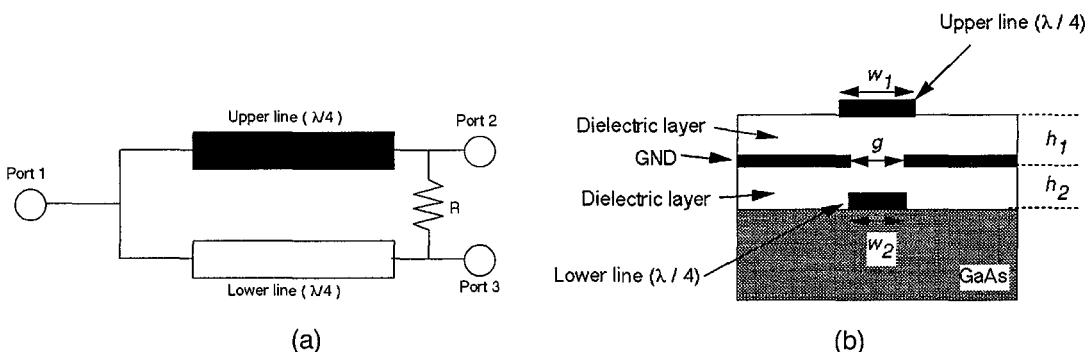

図 3.13 は 3 次元 MMIC で実現されるブロードサイドカプラの断面図である。接地導体を半導体基板上に形成し、ポリイミド膜最上層及びその直下の層に導体を重ねた構成である。 $w_1$ ,  $w_2$  はカプラを形成する導体の幅であり接地導体からの距離はそれぞれ  $7.5\mu\text{m}$ ,  $10\mu\text{m}$  である。上層導体の厚みは  $2\mu\text{m}$ , 下層導体の厚みは  $1\mu\text{m}$  である。導体間のポリイミド膜厚は  $1.5\mu\text{m}$  (1 層当たりのポリイミド膜厚は  $2.5\mu\text{m}$  (導体厚  $1\mu\text{m}$  含む) としている) である。図 3.14 は導体幅  $w_1$  及び  $w_2$  の値を変化させたときの  $S_{21}$  及び  $S_{31}$  の等高線表示した図である。実線が  $S_{21}$ , 破

図 3.13 ブロードサイドカプラの断面図

図 3.14 ブロードサイドカプラの設計チャート

図 3.15 導体間の誘電体膜厚がカプラの結合特性に与える影響

(a)結合特性, (b)位相特性

線が  $S_{31}$  の等高線を示し、図中のイタリック数字が  $S_{21}$  の等高線の値、90 度回転させた数字が  $S_{31}$  の値を示している。太い実線は  $S_{21}=S_{31}$  となるようにトレースした線であり、カプラの分配振幅が等しくなる  $w_1$ ,  $w_2$  を示している。この結果から、低損失かつ等分配な特性を得るために  $w_2>w_1$  とする必要があることがわかる。 $W_2=13.4\mu\text{m}$ ,  $w_1=8.4\mu\text{m}$  で結合度-3.7dB,  $w_2=10\mu\text{m}$ ,  $w_1=8\mu\text{m}$  で結合度-3.8dB を得る。さらにこの図から、導体幅がプロセスばらつき等で数 $\mu\text{m}$  設計値よりずれたとしてもカプラ特性にはほとんど影響しないことがわかる。

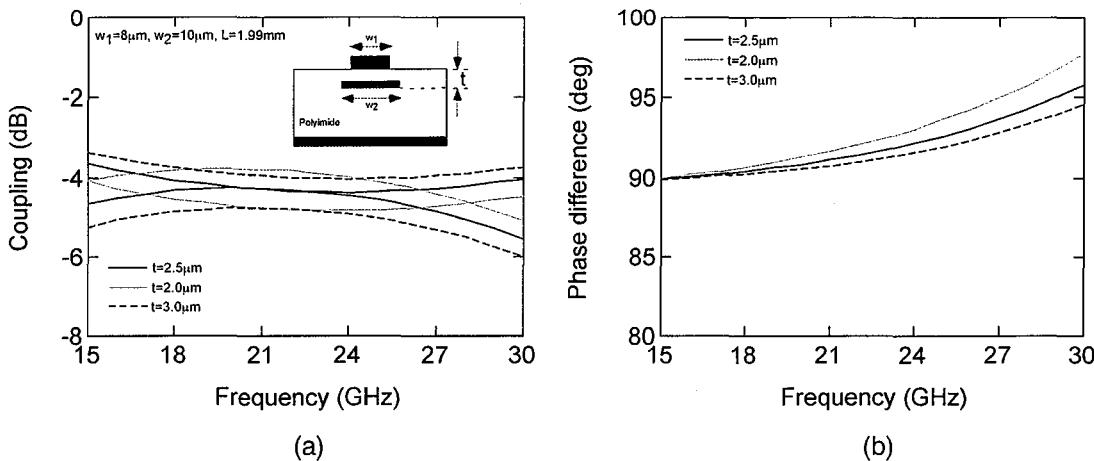

図 3.15 は積層される導体間の誘電体膜厚が結合特性に与える影響について検討した図である。導体幅  $w_1=8\mu\text{m}$ ,  $w_2=10\mu\text{m}$ , 線路長  $L=1.99\text{mm}$  として電磁界シミュレータを用いて計算した値である。図(a)は結合特性、図(b)は位相差を示している。図中の黒実線が設計値の膜厚  $2.5\mu\text{m}$ 、灰色実線が膜厚  $2\mu\text{m}$ 、破線が膜厚  $3\mu\text{m}$  のときの特性を示している。カプラの結合特性は導体間の膜厚に依存し、膜厚変動 $\pm 0.5\mu\text{m}$  で分配特性は最大 0.8dB, 0.6 度ずれることがわかる。

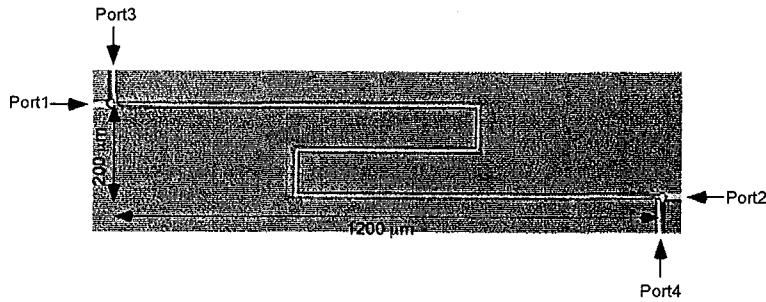

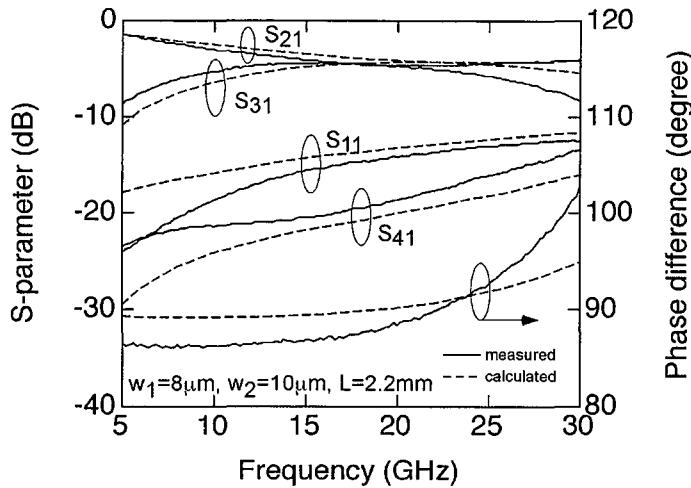

実際に試作した 18GHz 帯ブロードサイドカプラのチップ写真を図 3.16 に示す。メアンダ状に折り曲げたレイアウトを行い、 $0.2\text{mm}\times 1.2\text{mm}$  という小型なサイズで実現している。設計サイズは  $w_1=8\mu\text{m}$ ,  $w_2=10\mu\text{m}$ ,  $L=2.2\text{mm}$  である。図 3.17 は試作したブロードサイドカプラの測定結果を示している。実線は測定値、破線は計算値である。計算値は市販の回路シミュレータ Hpeesof Libra (Agilent ADS) に搭載される結合線路モデルに以下のパラメータを入れて計算した値である。

$$\text{偶モード特性インピーダンス } Z_{\text{even}}=121\Omega$$

$$\text{奇モード特性インピーダンス } Z_{\text{odd}}=21\Omega$$

$$\text{偶モード実効誘電率 } \epsilon_{\text{even}}=3.04$$

図 3.16 試作したブロードサイドカプラのチップ写真

図 3.17 試作したブロードサイドカプラの特性

奇モード実効誘電率  $\epsilon_{\text{odd}}=4.22$

偶モード伝送損失  $\alpha_{\text{even}}=0.15 \text{dB/mm}$  (10GHz)

奇モード伝送損失  $\alpha_{\text{odd}}=0.60 \text{dB/mm}$  (10GHz)

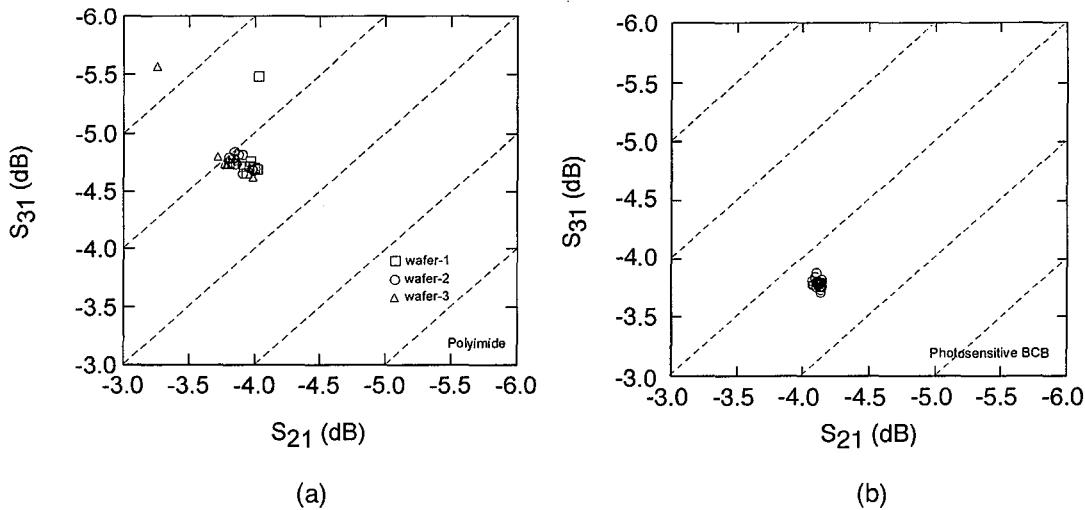

これらの値はブロードサイドカプラが電気的に対称となっていると仮定して電磁界シミュレーションより求めた値である。図に示すように測定値と計算値はほぼ等しい特性を示している。ブロードサイドカプラは 12.4GHz から 24.2GHz において出力振幅誤差 1dB 以内、位相差 89° ±3°,  $S_{11}<-13.1 \text{dB}$ ,  $S_{41}<-16.3 \text{dB}$  を実現しており、小型で良好な特性を達成した。この結果は、ブロードサイドカプラは上記パラメータを用いることにより市販回路シミュレータにより良好に設計できることを示している。図 3.18 はポリイミド膜(図(a))及びBCB 膜(図(b))を用いた 3 次元 MMIC 上に試作したブロードサイドカプラの特性ばらつきを示したものである。両方の場合とも、出力振幅にわずかな差が生じているが良好な再現性を実現している。

本節ではブロードサイドカプラの特性と導体幅及び導体間膜厚の関係を明らかにした。試作したブロードサイドカプラを評価し、良好な設計性、再現性を実現できることを示した。

図 3.18 ブロードサイドカプラの特性ばらつき

(a)ポリイミド版3次元MMIC, (b)BCB版3次元MMIC

### 3.4 3次元 MMIC マーチャンドバラン

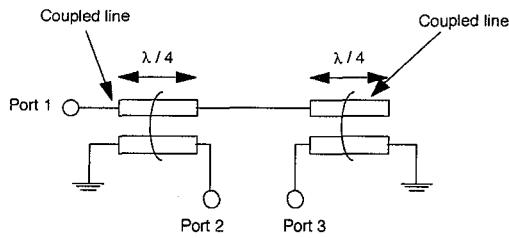

マーチャンドバラン [11] は 180 度信号分配回路であり、カプラ 2 つを組み合わせて実現できるため MMIC においてもバランス回路等によく用いられており、平面型 MMIC ではランゲカプラやインタディジタルカプラを用いて構成される [12] - [16]。図 3.19 は、マーチャンドバランの等価回路図であり、2 本の 1/4 波長のカプラを用いて図に示すように接続する。カプラの散乱行列  $[S]$  を

$$[S] = \begin{bmatrix} 0 & \alpha & \beta & 0 \\ \alpha & 0 & 0 & \beta \\ \beta & 0 & 0 & \alpha \\ 0 & \beta & \alpha & 0 \end{bmatrix}$$

とするとポート 2 及び 3 に出力される信号は以下のように示すことができる。

$$S_{21} = -\frac{\alpha \cdot \beta \cdot (1 + \beta^2 - \alpha^2)}{1 + \beta^2}$$

$$S_{31} = \frac{\alpha \cdot \beta \cdot (1 + \beta^2 - \alpha^2)}{1 + \beta^2}$$

従って、ポート 1 から入力した信号はポート 2 とポート 3 に等振幅で互いに逆相で出力する。

図 3.20 はマーチャンドバランの特性とカプラの位相速度差及び偶モードの特性インピーダンスの関係を示した図である。図(a)はカプラの偶モードの特性インピーダンス  $Z_{\text{even}}=121\Omega$  のとき、

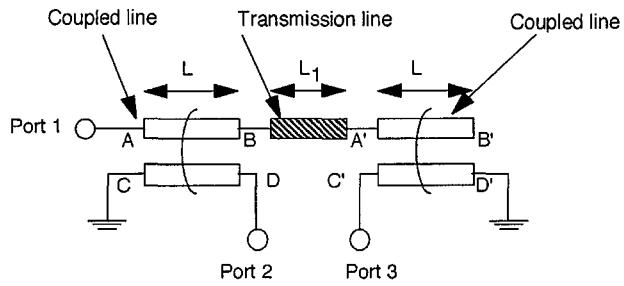

図 3.19 マーチャンドバランの等価回路図

図 3.20 マーチャンドバランの特性

(a)  $Z_{\text{even}} = 121\Omega$ , (b)  $Z_{\text{even}} = 500\Omega$

マーチャンドバランの出力特性（振幅誤差及び位相差）の位相速度差依存性を示したものであり、図(b)は  $Z_{\text{even}}=500\Omega$  のときのバランの出力特性を示している。実線が位相差、破線が振幅誤差を示している。これらの結果からカプラの偶モードの特性インピーダンスが大きいほど位相速度差の影響を小さくすることができるといえる。さらに位相速度差がない場合 ( $\epsilon_{\text{odd}}/\epsilon_{\text{even}}=1$ ) には周波数に関わらず等振幅で逆相出力となることがわかる。MMICにおいてはカプラ部の偶モードと奇モードの位相速度を一致させることは極めて困難でありかつ、偶モードの特性インピーダンスを数  $100\Omega$  という高インピーダンス化することも極めて難しいため、マーチャンドバランの広帯域化を実現することは困難であった。

一方 Pavia ら [17] は多層構造を用いて偶モードの高インピーダンス化を実現し、バランの広帯域化を実現している。彼等が提案する構造は GaAs 基板裏面に接地導体を配置し、基板表面及びその上に形成された誘電体膜上に信号導体を配置する多層構造である。しかしながらこの構造では GaAs 基板上の信号線幅が  $100\mu\text{m}$  以上となり、極めて大きい回路面積を必要とし、他の回路との集積化は難しい。この節では 3.3 節で述べた 3 次元 MMIC ブロードサイドカプラと短い TFMS 線路を用いて小型でかつ広帯域なマーチャンドバランを提案する。

図 3.21 広帯域マーチャンドバランの構成

図 3.22 広帯域マーチャンドバランの等価回路図

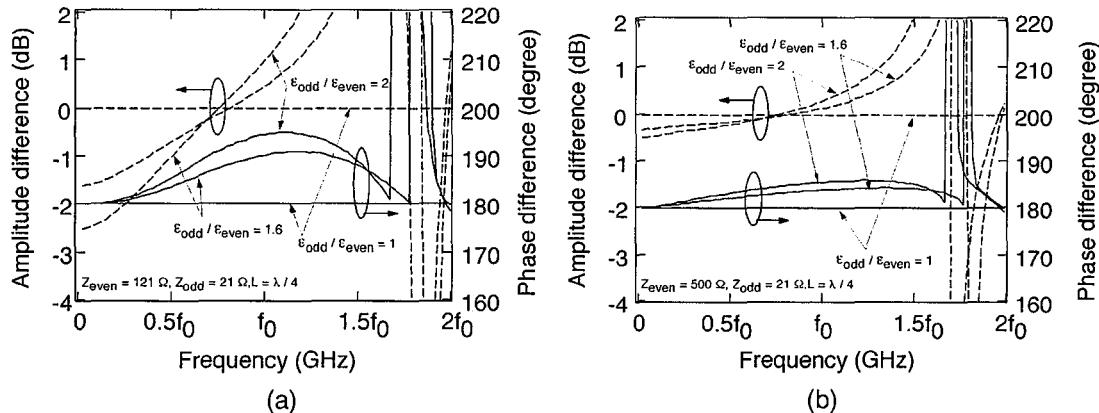

図 3.21 は提案する広帯域マーチャンドバランの構造 [18] を示した図である。一方、図 3.22 はその等価回路を示している。提案するマーチャンドバランはブロードサイドカプラとそれを接続する TFMS 線路のみから成る簡易な構成である。カプラの接続に使う TFMS 線路はカプラのアンバランス性を効果的に改善し、バラン全体の特性として広帯域化を実現する。図 3.23 は提案するマーチャンドバランの動作原理を示す図である。図(a)は振幅誤差、図(b)は位相差の変化を示している。計算に用いたブロードサイドカプラ、TFMS 線路のパラメータを図中に示している。破線はカプラの直交モードの位相速度が同じでカプラを直接接続した場合である。灰色実線は位相速度に差があるカプラを直接接続した場合である。黒実線は位相速度が同じで TFMS 線路を用いてカプラを接続した場合である。この計算結果が示すように、カプラの直交モードの位相速度差が原因となるバランの振幅誤差、位相差のずれる方向と TFMS 線路を挿入したことにより生じるバランの振幅誤差、位相差のずれる方向が 0dB, 180 度に対して互いに逆になっていることがわかる。つまり、直交モードの位相速度に差があるカプラを用いてマーチャンドバランを構成する場合にカプラ間を適当な長さの TFMS 線路を用いて接続することにより、位相速度に差があることより生じるバランのバランス特性のずれを補正することができ

図 3.23 TFMS 線路によるバランのバランス特性の補償

(a) 振幅, (b)位相

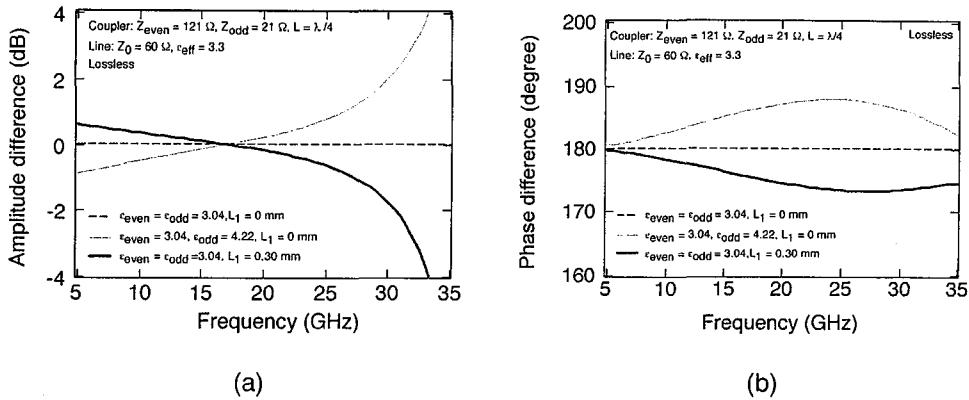

図 3.24 TFMS 線路長とバランの動作帯域の関係

る。カプラを接続する TFMS 線路をインダクタ及びキャパシタより構成される  $\pi$  型の等価回路と見ると、TFMS 線路はカプラのオープンポート側の線路に接続されていることから等価回路からインダクタを取り除くことができるので、キャパシタが並列に接続されているとすることができる。従って、等価的に偶モードの位相速度を遅くすることにより、奇モードとの位相速度差を小さくすることを意味している。

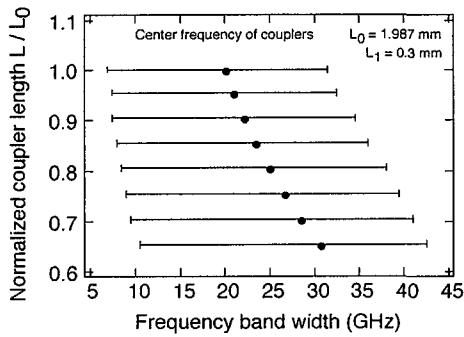

図 3.24 は 20GHz 帯 3 次元 MMIC マーチャンドバランのカプラを接続する TFMS 線路の線路長とバランの動作帯域の関係を示している。横軸は TFMS 線路の線路長、縦軸は中心周波数 (20GHz) で規格化した動作帯域を示している。バランの動作帯域としてバランがバランス型回路等に使われることを想定して位相差  $180^\circ \pm 10^\circ$  以内、振幅誤差 1dB 以内 [19] でかつ出力信号の 3dB 帯域を満たす周波数領域と規定している。計算に用いたブロードサイドカプラのパラメータは以下の通りである。

$$Z_{\text{even}}=121\Omega, \epsilon_{\text{even}}=3.02, \alpha_{\text{even}}=0.15\text{dB/mm}(10\text{GHz})$$

$$Z_{\text{odd}}=21\Omega, \epsilon_{\text{odd}}=4.22, \alpha_{\text{odd}}=0.60\text{dB/mm}(10\text{GHz})$$

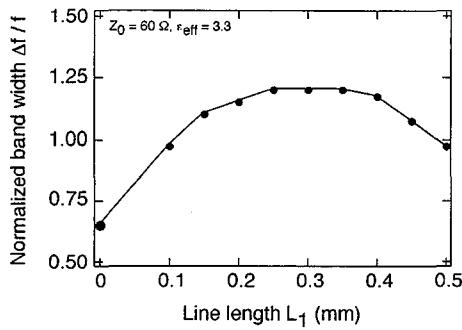

図 3.25 マーチャンドバランの振幅、位相特性 ( $L_1=0.3\text{mm}$ )

図 3.26 ブロードサイドカプラの線路長とバランの動作帯域の関係

$L=1.99\text{mm}$

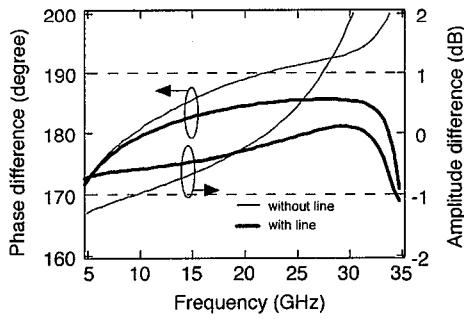

また、TFMS 線路の特性インピーダンスは  $60\Omega$ 、実効誘電率は 3.3 である。この計算結果から、挿入する TFMS 線路の線路長を 0.25mm から 0.35mm (約  $0.04\lambda$ ) とすることによりバランの動作帯域を TFMS 線路を挿入しない場合と比較して 80%以上拡大することができる。つまり、TFMS 線路を用いてカプラを接続するという簡易な方法でバランの広帯域化を容易に実現することができる。図 3.25 は挿入した TFMS 線路の線路長  $L_1=0.3\text{mm}$  のときのマーチャンドバランの位相差と振幅誤差の特性を示している (太い実線)。図には比較のため、従来のカプラを直接接続する構成の計算結果も合わせて示している (細い実線)。また、破線はバランの動作帯域を示す境界線である。この計算結果では 5GHz から 35GHz において、バランの出力振幅誤差 1dB 以内、位相差  $180^\circ \pm 10^\circ$  以内を実現している。20GHz では振幅誤差 1dB、位相差 176° であり、バランの広帯域特性を実現している。

図 3.26 はマーチャンドバランを構成するブロードサイドカプラの線路長を変えたときのバランの動作帯域を計算した結果を示している。縦軸は  $1/4$  波長で規格化したカプラの線路長であり、横軸は周波数を示している。横軸のバーはバランの動作帯域を示しており、黒丸はバランの中心周波数 (カプラの線路長が  $1/4$  波長となる周波数) を示している。挿入している TFMS

図 3.27 試作した広帯域マーチャンドバランのチップ写真

図 3.28 広帯域マーチャンドバランの測定結果

線路の線路長は 0.3mm である。動作周波数の上限はカプラの中心周波数の上昇と同様に高くなるが、動作周波数の下限は微増するのみである。カプラの長さを 30%短くすることにより、バランの動作帯域を 28%広くすることができる。従って、カプラの中心周波数を高く（線路長を短く）してもバランの動作周波数の上限のみを高くすることができるので、回路の小型化、広帯域化を容易に実現することが可能である。

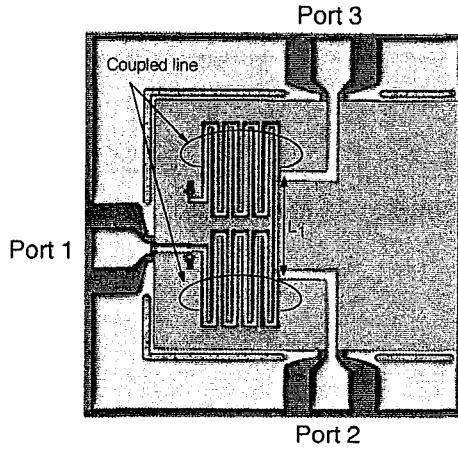

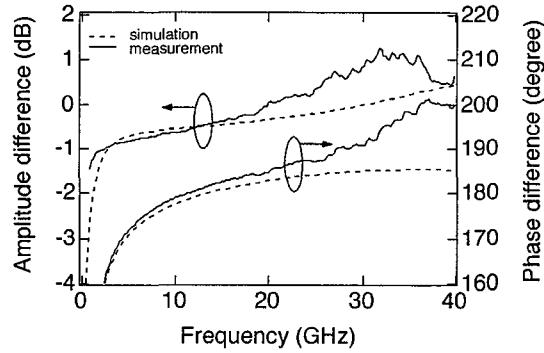

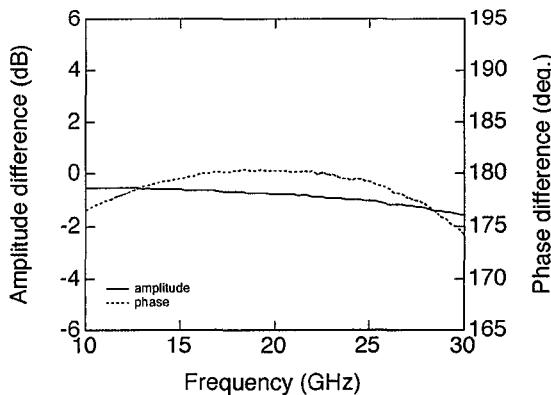

次に実際に試作した 20GHz 帯 3 次元 MMIC マーチャンドバランの特性について述べる。図 3.27 は試作したマーチャンドバランのチップ写真である。試作したバランはカプラの線路長  $L=1.5\text{mm}$ , TFMS 線路の線路長  $L_1=0.2\text{mm}$  ( $Z=64\Omega$ ,  $\epsilon_{\text{eff}}=3.3$ ) である。一層の小型化を実現するためにカプラはメアンダ状に形成しており、バランのサイズは  $0.2\text{mm} \times 0.4\text{mm}$  である。ポート 1 はカプラの下層配線に接続し、ポート 2 及びポート 3 は上層配線に接続する構成としている。図 3.28 は測定値を示している。実線が測定値、破線が計算値である。測定値から試作したマーチャンドバランの動作帯域は 8.2GHz から 30GHz を実現している。これは図 3.24 で示した規格化した動作帯域で 1.09 である。特に高周波側で測定値と計算値がずれる原因是カプラの

オーブンポート部の見積もりが実際のフリンジング容量より小さかったためであると推察される。しかしながら、従来のカプラを直接接続して実現されるマーチャンドバランと比較して約1.7倍の広帯域化を実現した。

本節では新たな3次元MMICマーチャンドバランを提案し、TFMS線路でカプラを接続するという簡易な方法でバランの広帯域化、小型化を実現した。この結果は今後のMMICの小型化、高集積化に有益である。

### 3.5 積層型ウイルキンソンディバイダ

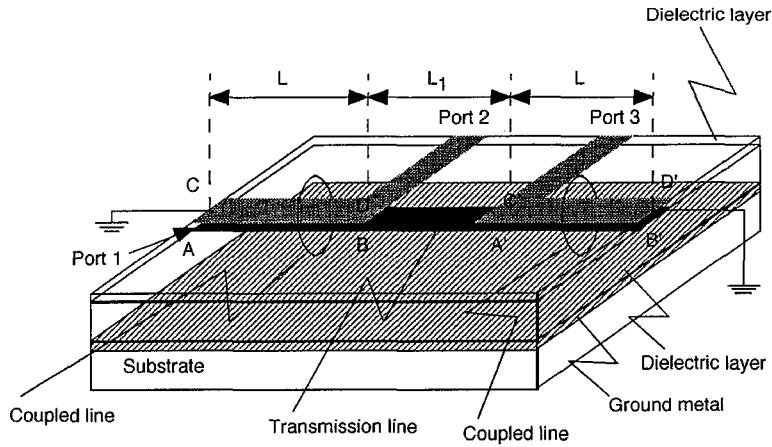

ウイルキンソンディバイダはバランス型回路等に頻繁に用いられる受動回路であり、3次元MMICではTFMS線路の使用によりこのような $1/4$ 波長線路により構成される受動回路を平面型MMICと比較して十分小さい面積で実現できる。今後さらなる小型化、高集積化を実現するために積極的に積層構造を利用する必要がある。しかしながら、現在の3次元MMICは $2.5\mu\text{m} \times 4$ 層ポリイミド層の構造においてはウイルキンソンディバイダを構成する $70.7\Omega$ という比較的高い特性インピーダンスのTFMS線路を積層構成することはプロセスルール、線路損失の問題により困難であった。本節ではこのような高インピーダンス線路の積層構成を実現する3次元構造を提案し、提案構造を用いたウイルキンソンディバイダについて述べる。

図3.29は提案する積層型ウイルキンソンディバイダの構成[20]を示している。図(a)は等価回路図、図(b)は断面図である。誘電体膜中間層に接地導体を形成し、その上部(誘電体膜最上層)及びGaAs基板上にTFMS線路、逆TFMS線路を形成する積層構造である。高い特性インピーダンスを実現するために上下TFMS線路の中心線上の接地導体にスリットを形成している。TFMS線路直下及び直上の接地導体にスリットを設けることによりTFMS線路のもつ接地容量値を低減させることができるので、高い特性インピーダンスを実現できる。この構造によ

図3.29 積層型ウイルキンソンディバイダの構成

(a)等価回路図、(b)断面図

図 3.30 1/4 波長線路の結合度と ウイルキンソンディバイダのアイソレーション特性の関係

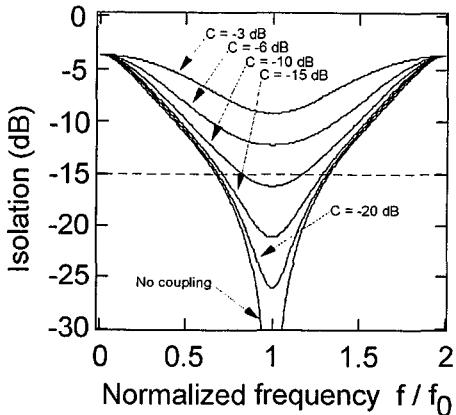

り、特性インピーダンス  $70.7\Omega$  という高い値を持つ TFMS 線路の積層化を実現し、ウイルキンソンディバイダの占める面積を従来の  $1/2$  に小型化できる。提案構成においては上下の TFMS 線路間で結合が生じるため、ウイルキンソンディバイダの特性に影響を与えない程度の結合度となるように伝送線路幅、スリット幅等を決める必要がある。

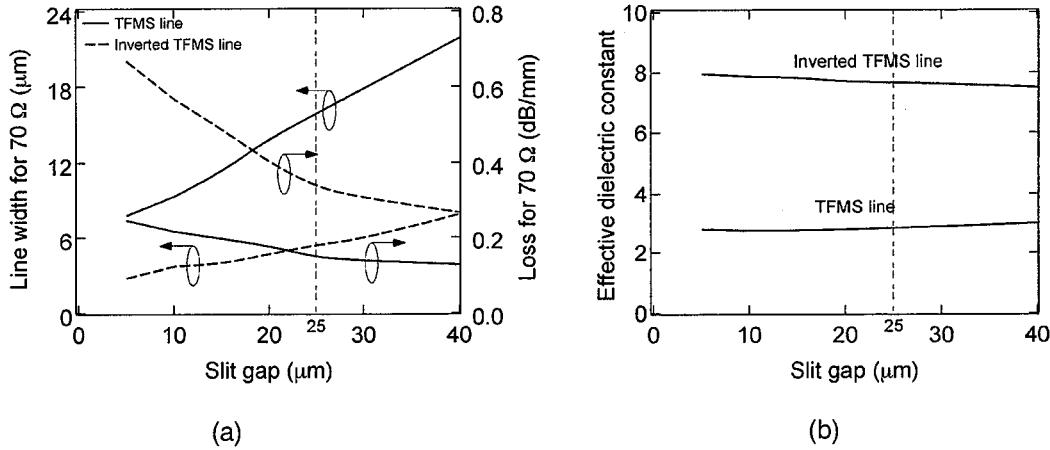

図 3.30 はウイルキンソンディバイダを構成する 1/4 波長線路に結合がある場合にその結合度とディバイダの分配端子間のアイソレーション特性を示した図である。結合度が大きくなるほどアイソレーション特性が悪くなっているのがわかる。アイソレーション特性-15dB 以下を実現する場合、結合度-15dB 以下であれば結合がない場合とほぼ等しい動作帯域を実現できる。従って、積層 TFMS 線路の結合度が-15dB 以下でかつ各線路の特性インピーダンスが  $70.7\Omega$  なるように TFMS 線路幅、スリット幅を決定する。実際には図 3.29 に示す積層構造においては疎結合が予測されるので、まずスリット幅、線路幅を決定し、その寸法での結合度を確認する方法で構造を決定する。

図 3.31 は接地導体のスリット幅を変えたときその上下に形成される TFMS 線路、逆 TFMS 線路が  $70\Omega$  となる導体幅及び損失(図(a))、実効誘電率(図(b))を示している。周波数 20GHz のときの値である。シミュレーションは HP-eesof HFSS を用いて行った。TFMS 線路及び逆 TFMS 線路の実効誘電率に大きな差あることから、1/4 波長線路の損失が等しくなるようにスリット幅を決定した。以下に構造パラメータを示す。

スリット幅 :  $25\mu\text{m}$

TFMS 線路 :  $w_1=16\mu\text{m}$ ,  $\alpha_1=0.15\text{dB/mm}(10\text{GHz})$ ,  $\epsilon_{\text{eff}1}=2.85$ ,  $\lambda/4=2.22\text{mm}$

逆 TFMS 線路 :  $w_2=5.5\mu\text{m}$ ,  $\alpha_2=0.34\text{dB/mm}(10\text{GHz})$ ,  $\epsilon_{\text{eff}2}=7.71$ ,  $\lambda/4=1.35\text{mm}$

これらの値より、1/4 波長線路での損失差は  $0.126\text{dB}$ 、位相差は  $0.17^\circ/\text{mm}$  であり無視できる値である。図 3.32 は上記構造の TFMS 線路を用いた場合の線路間の結合度を計算した結果で

図 3.31 積層される TFMS 線路の特性と中間層接地導体のスリット幅の関係

(a) 特性インピーダンスが  $70\Omega$  となる線路幅と損失, (b) 実効誘電率

図 3.32 積層された TFMS 線路の結合度

ある。TFMS 線路、逆 TFMS 線路で実長さが異なり、実際に結合する線路長は 1.35mm となる。この計算結果から、結合度は-15dB 以下であることがわかりこの構成をウイルキンソンディバイダに適用しても従来のウイルキンソンディバイダと同等の特性が得られることが予測できる。

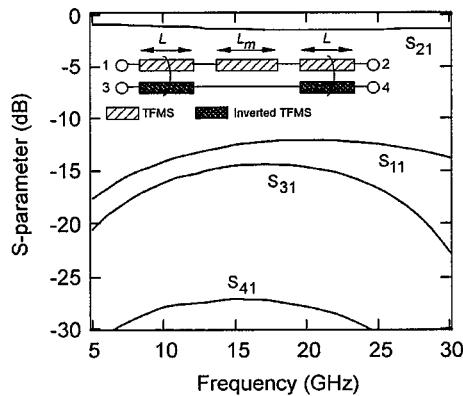

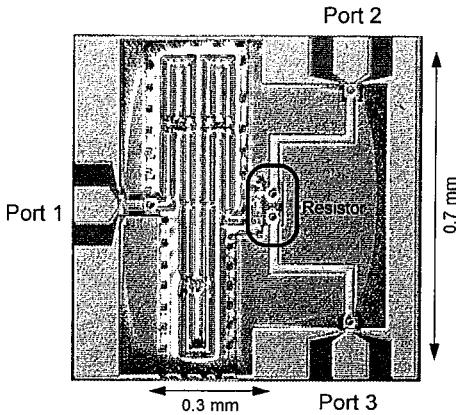

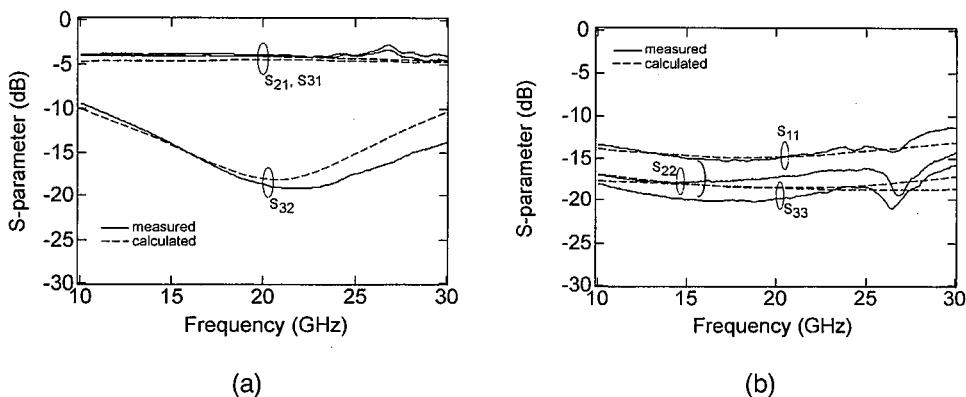

図 3.33 は試作した積層構成ウイルキンソンディバイダのチップ写真である。TFMS 線路は一層の小型化のためにメアンダ状に形成している。アイソレーション抵抗は導体損失を考慮して最大のアイソレーション特性を実現するように最適化 ( $110\Omega$  を用いている) している。ディバイダ部は  $0.3\text{mm} \times 0.7\text{mm}$  と超小型である。図 3.34 は試作したウイルキンソンディバイダの測定結果である。実線が測定結果、破線はシミュレーション結果であり、両者はよく一致している。挿入損失は 10GHz から 30GHz において  $0.5\text{dB} \pm 0.5\text{dB}$  であり、ポート間の誤差もほとんどない。アイソレーション-15dB を得る周波数帯域は 15.8GHz から 28GHz であり、従来構成と

図 3.33 試作した積層型ウイルキンソンディバイダのチップ写真

図 3.34 積層型ウイルキンソンディバイダの測定値

(a)通過特性／アイソレーション, (b)反射特性

比較して同等の帯域幅である。21.4GHz でアイソレーション-19.2dB を実現している。反射特性は帯域内において-11dB 以下である。

70Ωという比較的高い値の特性インピーダンスを持つTFMS 線路の積層構成を新たに提案し、それを用いた積層型ウイルキンソンディバイダを提案、実現した。この結果ディバイダの面積を従来と比較して 1/2 以下とすることが可能となった。さらに試作した 20GHz 帯ディバイダの特性は従来とほぼ同等の性能である。

### 3.6 まとめ

本章では 3 次元 MMIC の受動基本素子であるブロードサイドカプラ、マーチャンドバラン、ウイルキンソンディバイダについて提案し、その特性を明らかにした。これらは 3 次元構造を有効に活用し、TFMS 線路を積層して実現している。その結果平面構造の回路と比較して 1/2

以下の面積で実現している。この結果は3次元MMICの小型化、高集積化の実現に大きく貢献する。

## 参考文献

- [1] T. Tokumitsu, T. Hiraoka, H. Nakamoto, and M. Aikawa, "Multilayer MMIC Using a  $3 \mu\text{m} \times N$ -layer Dielectric Film Structure," IEICE Trans. Electron, Vol. E75-C, No. 6, pp. 698-706, June 1992.

- [2] T. Tokumitsu, M. Hirano, K. Yamasaki, C. Yamaguchi, and M. Aikawa, "Highly Integrated 3-D MMIC Technology Being Applied to Novel Masterslice GaAs- and SiMMIC's," in 18th IEEE GaAs IC Symp. Dig., Nov. 1996, pp. 151-154.

- [3] I. Toyoda, T. Tokumitsu, and M. Aikawa, "Highly Integrated Three-dimensional MMIC Single-chip Receiver and Transmitter," IEEE Trans. Microwave Theory Tech., Vol. 44, No. 12, pp. 2340-2346, Dec., 1996.

- [4] I. Toyoda, M. Hirano, and T. Tokumitsu, "Three-dimensional MMIC and Its Application: An Ultra-wideband Miniature Balun," IEICE Trans. Electron, Vol. E78-C, No. 8, pp. 919-924, Aug. 1995.

- [5] M. Hirano, K. Nishikawa, I. Toyoda, S. Aoyama, S. Sugitani, and K. Yamasaki, "Three-dimensional Passive Circuit technology For Ultra-compact MMIC's," IEEE Trans. Microwave Theory Tech., Vol. 43, No. 12, pp. 2845-2850, Dec. 1995.

- [6] K. Onodera, M. Hirano, M. Tokumitsu, I. Toyoda, K. Nishikawa, and T. Tokumitsu, "Folded U-shape Microwire Technology For Ultra-compact Three-dimensional MMIC's," IEEE Trans. Microwave Theory Tech., Vol. 44, No. 12, pp. 2347-2353, Dec. 1996.

- [7] M. Matsubara and T. Angkaew, "Analysis of Waveguide with Loss or Gain by the Finite-element-method," IEICE Trans. Vol. J71-C, No. 10, pp. 1398-1403, Oct. 1988.

- [8] S. Banba and H. Ogawa, "Small-sized MMIC Amplifiers Using Thin Dielectric Layers," IEEE Trans. Microwave Theory Tech., Vol. 43, No. 3, pp. 485-492, March 1995.

- [9] K. Nishikawa, I. Toyoda, K. Kamogawa, T. Tokumitsu, and M. Tanaka, "Three-dimensional Monolithic Microwave Integrated Circuit Technology For Fully Computer-aided Design-compatible Monolithic Microwave Integrated Circuit Development," International Journal of RF and Microwave CAE, Vol. 8, No. 6, pp. 498-506, Nov. 1998.

- [10] I. Toyoda, T. Hirota, T. Hiraoka, and T. Tokumitsu, "Multilayer MMIC Branch-line Coupler and Broad-side Coupler," 1992 IEEE Microwave and Millimeter-wave Monolithic Circuits Symp. Dig., June 1992, pp. 79-82.

- [11] N. Marchand, "Transmission-line Conversion Transformers," Electronics, Vol. 17, No. 12, pp. 142-145, 1944.

- [12] D. Neilson, B. Allen, M. Kintis, and M. Hoppe, "A Broad-band Up-converter IC," 1992 IEEE

- Microwave and Millimeter-wave Monolithic Circuits Symp. Dig., June 1992, pp. 163-166.

- [13] M. Tsai, "A New Compact Wide-band Balun," 1993 IEEE Microwave and Millimeter-wave Monolithic Circuits Symp. Dig., June 1993, pp. 123-125.

- [14] S. Maas and K. Chen, "A Broad-band, Planar, Doubly Balanced Monolithic Ka-band Diode Mixer," IEEE Trans. Microwave Theory Tech., Vol. 41, No. 12, pp. 2330-2335, Dec. 1993.

- [15] Y. Ryu, K. Kobayashi, and A. Oki, "A Monolithic Broad-band Doubly Balanced EHF HBT Star Mixer With Novel Microstrip Balun," 1995 IEEE Microwave and Millimeter-wave Monolithic Circuits Symp. Dig., May 1995, pp. 155-158.

- [16] S. Maas, "A Broad-band Planar Monolithic Ring Mixer," 1996 IEEE Microwave and Millimeter-wave Monolithic Circuits Symp. Dig., June 1996, pp. 51-54.

- [17] A. Pavio and A. Kikel, "A Monolithic Or Hybrid Broad-band Compensated Balun," 1990 IEEE MTT-S Int. Microwave Symp. Dig., June 1990, pp. 483-486.

- [18] K. Nishikawa, I. Toyoda, and T. Tokumitsu, "Compact and Broad-band Three-dimensional MMIC Balun," IEEE Trans. Microwave Theory Tech., Vol. 47, No. 1, pp. 96-98, Jan. 1999.

- [19] S. Maas, *Microwave Mixers Second Edition*, Artech House Inc., 1993.

- [20] K. Nishikawa, T. Tokumitsu, and I. Toyoda, "Miniaturized Wilkinson Power Divider Using Three-dimensional MMIC Technology," IEEE Microwave And Guided Wave Letters, Vol. 6, No. 10, pp. 372-374, Oct. 1996.

## 第4章 3次元 MMIC 基本能動回路と1チップ受信機への適用

### 4.1 まえがき

第4章では GaAsMESFET を用いた3次元 MMIC 基本能動回路について述べるとともにそれらを1チップに集積化した20GHz 装1チップ受信機について述べる。基本能動回路は小型化、高集積化、高性能化を同時に実現するために、整合回路の積層化と高利得を実現する構成法を組合せて設計している。基本増幅器回路として、小型化に適し、かつ高利得を実現できるカスコード型増幅器の構成を採用している。カスコード接続されるソース接地 FET とゲート接地 FET 間の伝送線路とゲート接地 FET のゲートと接地導体間の伝送線路を最適化することにより、増幅器特性の向上と入出力整合を取りやすくすることができる。さらに、増幅器特性の上記伝送線路長依存性について明らかにする。可変利得増幅器については、負帰還回路部にドレイン接地 FET を配置し、ドレイン接地 FET の相互コンダクタンスを変えることにより、帰還量を変化させるアクティブ帰還型可変利得増幅器を提案し、その構成と設計法について述べ、減衰動作時の歪み特性が大幅に改善することを示す。周波数変換器についてはバランス型アップコンバータ／イメージリジェクション型ダウンコンバータ両構成について述べる。整合回路を積層する小型化回路構成とその設計法について述べるとともに、第3章で示した受動回路との組合せにより、超小型な周波数変換器が実現できることを示す。発振器については小型化を実現する構成及び設計法について述べる。最後に、機能回路を1チップに集積化した1チップ受信機について、その構成及び設計法、試作回路の特性について示す。

### 4.2 カスコード型増幅器

#### 4.2.1 カスコード型 FET の特徴

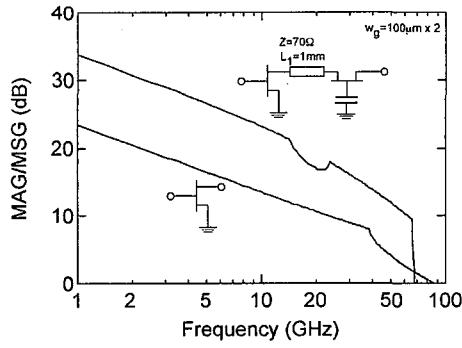

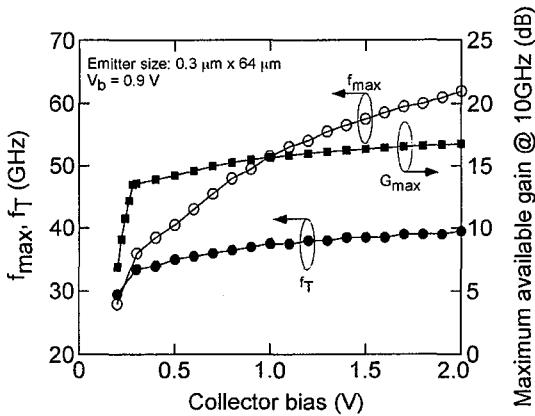

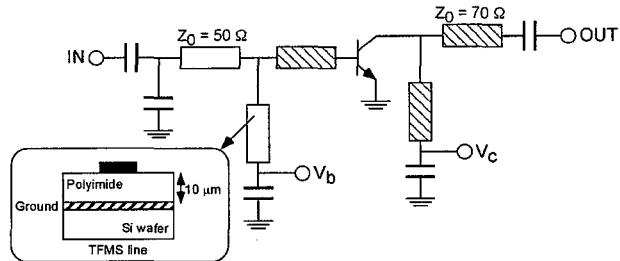

増幅器において高利得を得るためにには通常ソース接地 FET を用いた1段増幅器を継続接続して多段増幅器構成とする。このとき FET 間に整合回路、バイアス回路が必要であり増幅器の面積は大きくなる。一方、カスコード接続された FET はソース接地 FET と比較して、高利得、高出力インピーダンス、高アイソレーションである [1] - [4]。ソース接地 FET とゲート接地 FET を直接または伝送線路を介して接続することにより、段間整合回路を省略できるとともに、バイアス回路も両 FET で共用できるため増幅器の小型化を実現できる。3次元 MMIC ではソース接地 FET とゲート接地 FET を TFMS 線路を用いて接続し、TFMS 線路長を変えることにより、高利得化と広帯域化を実現している [2] - [4]。図 4.1 はカスコード接続 FET の最大有能利得 (MAG) / 最大安定利得 (MSG) の計算結果を示している。図中には合わせてソース接地 FET の MAG / MSG の計算結果も示す。カスコード接続 FET はソース接地 FET とゲート接地 FET を特性インピーダンス  $70\Omega$ 、線路長 1mm の伝送線路で接続した構成である。

図 4.1 カスコード FET の最大利得 (MSG/MAG)

図 4.2 TFMS 線路の線路長とカスコード FET の  $S_{11}$ ,  $S_{22}$  の関係

計算に用いたデバイスは GaAsMESFET ( $w_g=200\mu m$ ) (等価回路パラメータを付録 4.1 に示す) である。図に示すように、カスコード FET の最大利得はソース接地 FET と比較して FET の  $f_{max}$  の 80% の周波数帯まで 7dB から 10dB 高い値を実現することができる。これはソース接地 FET を用いた 1 段増幅器を継続接続した 2 段増幅器の利得とほぼ等しい値である。また、カスコード FET の 20GHz 付近のリップルは MAG の領域 ( $K>1$ ) であり、利得が MSG の外挿ラインより低下している。しかし、ソース接地 FET の MSG と比較しても十分大きい値となっている。従って、カスコード接続 FET を用いて増幅器を構成することにより、小型でかつ高利得な増幅器 MMIC を実現できる。

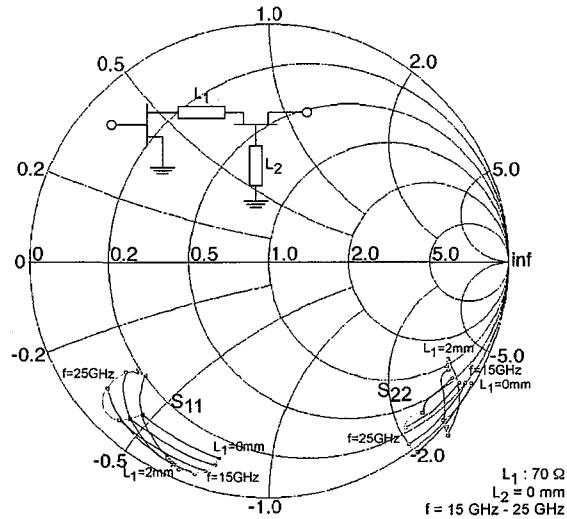

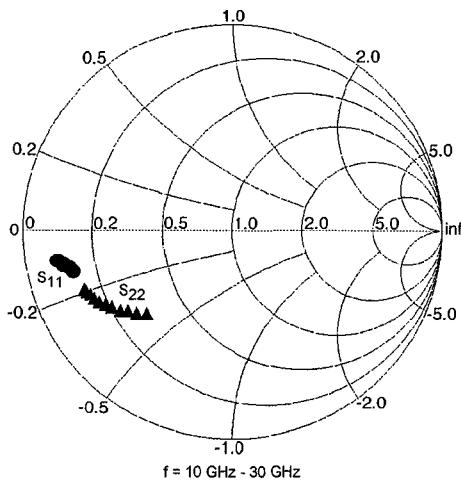

図 4.2 はソース接地 FET とゲート接地 FET の間の TFMS 線路 (特性インピーダンス  $70\Omega$ ) の線路長を 0mm から 2mm ( $0.22\lambda_g$ ) まで変えたときのカスコード FET の  $S_{11}$ ,  $S_{22}$  の軌跡を示したものである (周波数は 15GHz から 25GHz)。図中に計算に用いたカスコード FET モデルを示す。FET 間の接続及びゲート接地 FET のゲート側に TFMS 線路を用いた構成である。FET

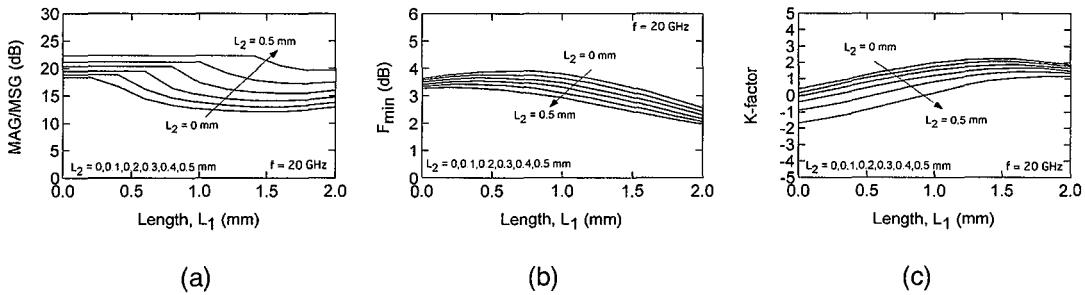

図 4.3 カスコード FET の特性と TFMS 線路  $L_1$  の特性インピーダンスの関係(a) MSG/MAG, (b)  $F_{\min}$ , (c) K-factor図 4.4 カスコード FET の特性と TFMS 線路  $L_2$  の線路長の関係(a) MSG/MAG, (b)  $F_{\min}$ , (c) K-factor

は  $w_g=200\mu m$  のものを用いている。 $S_{11}$  は低周波側ではスミスチャートの内から外へ向かって移動し、高周波側では内、外、内と円を描くような軌跡をとる。 $S_{22}$  は低周波側ではスミスチャートの外から内へ向かって移動し、高周波側では外、内、外と円を描く軌跡となる。このようにソース接地 FET とゲート接地 FET を接続する TFMS 線路の線路長を変えることにより、カスコード FET の入出力インピーダンスを自由に変えることができる。高利得化とともに広帯域化も同時に実現できることがわかる。ここで注意すべき点は、 $S_{22}$  はある線路長、周波数帯でスミスチャートの外周で出てしまうため不安定となる。従って実際の MMIC 設計時には安定化対策が必要である。

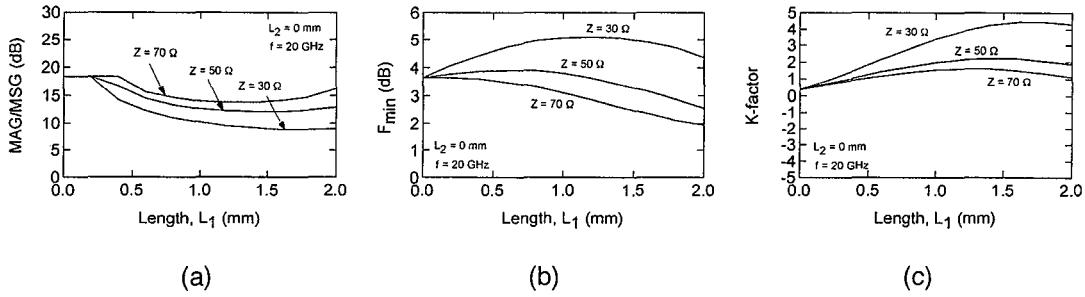

次に 20GHz 帯でのカスコード FET の特性と  $L_1$  及び  $L_2$  の TFMS 線路の線路長の関係を詳細に示す。ここではゲート幅  $100\mu m$  の FET を用いて計算している。図 4.3 は TFMS 線路  $L_1$  の特性インピーダンスを変えたときのカスコード FET の MAG/MSG (最大利得),  $F_{\min}$  (最小雑音指数), K-factor (安定係数) の値を示している。図 4.3 より、最大利得、最小雑音指数とも  $70\Omega$  のものが最も良い値であり、安定係数も特性インピーダンス  $70\Omega$  のとき線路長 0.8mm 以上で 1 を越える。つまり、 $L_1$  の特性インピーダンス値は高いほどカスコード FET の高性能化

(高利得, 低雑音, 安定化) を実現できるといえる。図 4.4 は TFMS 線路  $L_2$  の線路長を変えたときの特性変化を示している。 $L_2$  の線路長を長くすることにより, 最大利得は高い値及び最小雑音指数は小さい値になっていくのがわかる。しかしながら安定係数は線路長が長くなるにしたがって低くなり,  $L_2$  の線路長が 0.5mm のときには  $L_1$  の長さに関係なく 1 以下となる。この場合には  $L_1$  の長さに関係なく不安定となっていることを示している。つまり,  $L_2$  の線路長を長くすることにより, 負性抵抗が発生し利得を増加, 雑音指数を低下させることができるが, カスコード FET の不安定性が増加することになる。 $L_2$  の線路長を長くしすぎると, 増幅器設計において強固な安定化対策 (整合回路内に損失を持たせる等) をとる必要があるため, カスコード FET の高利得, 低雑音化の効果を整合回路の損失で相殺する可能性がある。従って,  $L_2$  の線路長は利得, 雑音性能と回路の安定度の両方を考慮して決定する必要がある。

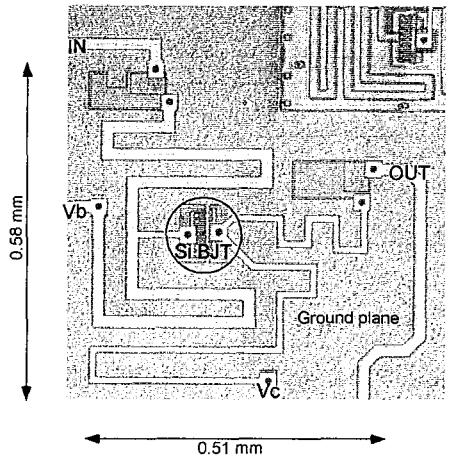

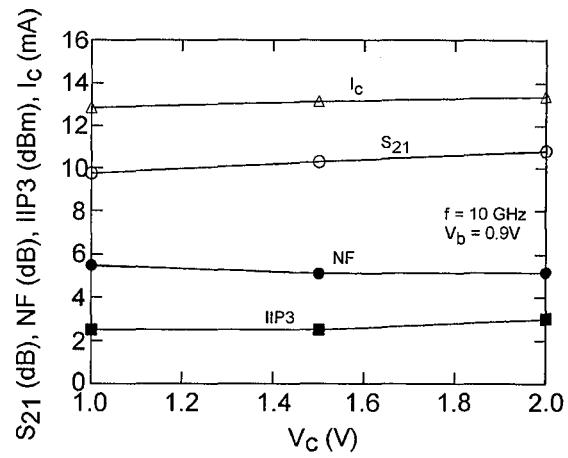

#### 4.2.2 20GHz 帯カスコード型増幅器 3 次元 MMIC の性能

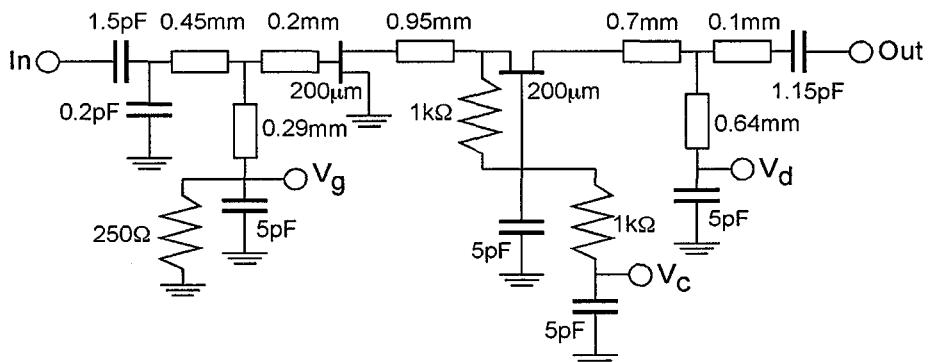

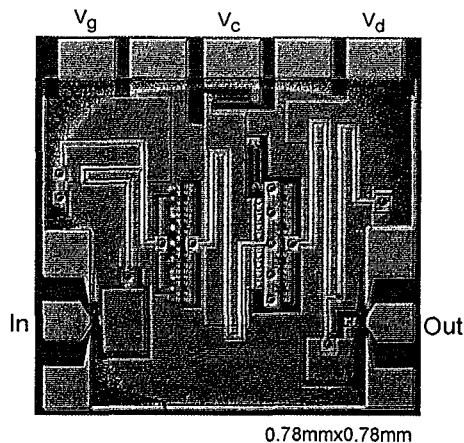

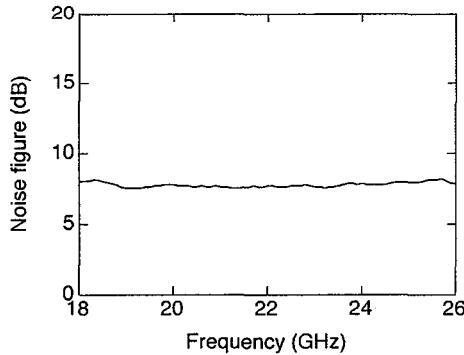

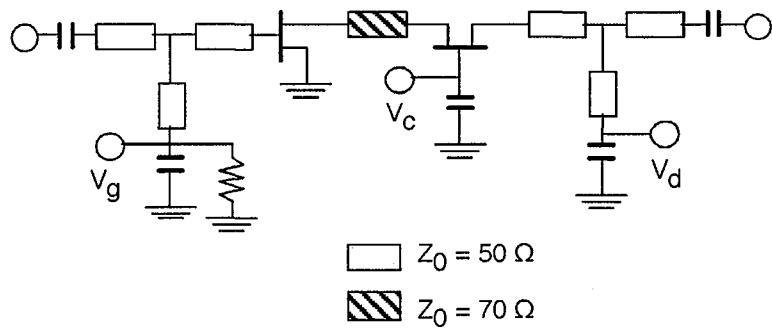

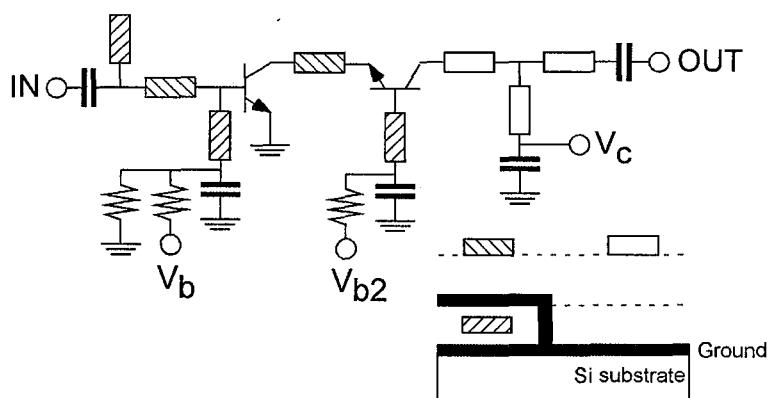

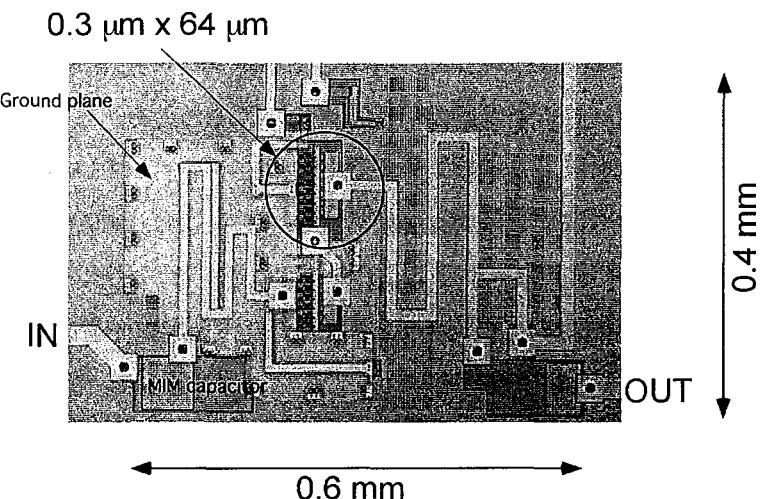

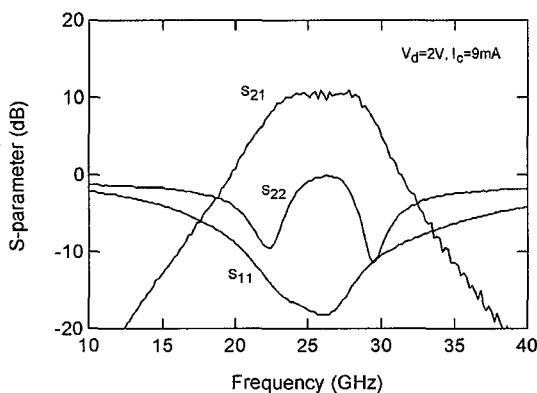

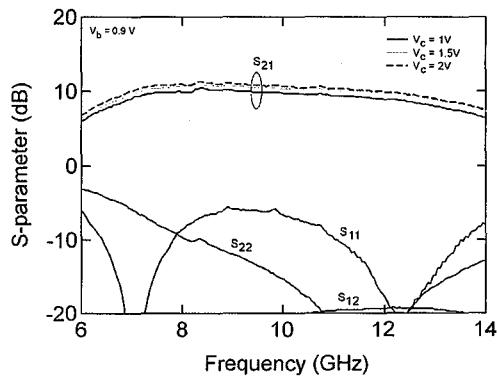

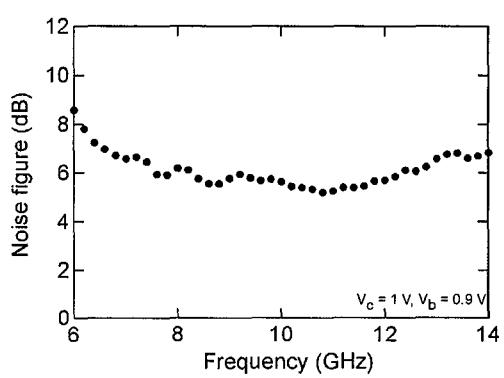

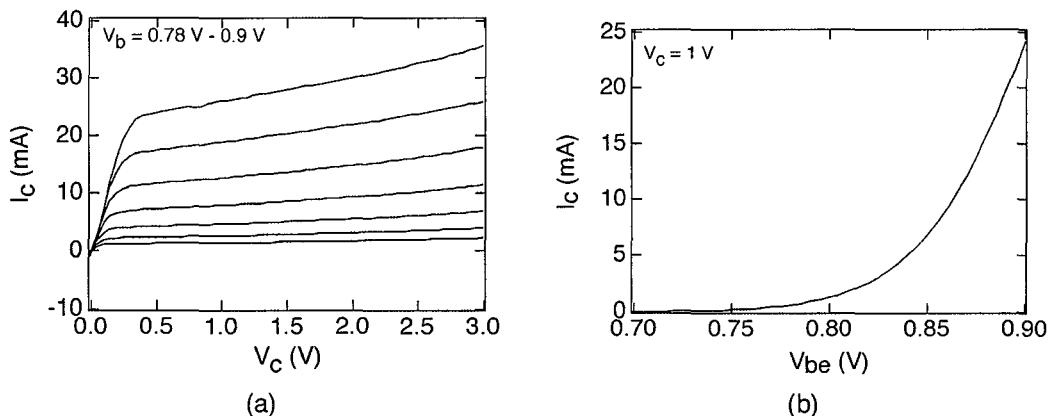

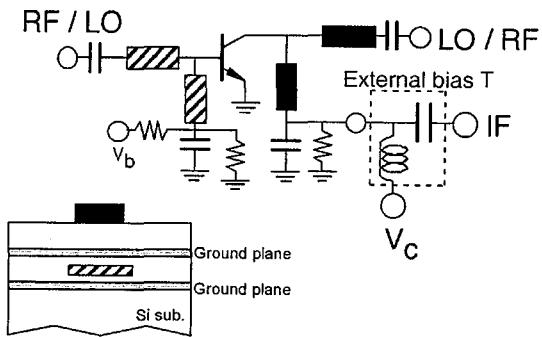

図 4.5 は試作した 20GHz 帯カスコード型増幅器の等価回路図である。整合回路を構成する TFMS 線路は使用する MESFET の性能, TFMS 線路の損失, 増幅器の面積を考慮して特性インピーダンス  $70\Omega$  (ポリイミド基板厚  $10\mu\text{m}$ ) である。 $70\Omega$  の TFMS 線路は線路幅が  $12\mu\text{m}$  であり (第 2 章参照), メアンダ状にレイアウトすることによりコンパクトに整合回路を実現することができる。カスコード接続される FET を接続する TFMS 線路は線路長  $0.95\text{mm}$  である。各 TFMS 線路は所望帯域幅, 利得を実現する最短線路長となるよう最適化している。低周波領域で安定化を行うために入力整合回路に  $250\Omega$  の抵抗を並列接続している。使用している FET のサイズはゲート幅  $200\mu\text{m}$  である。図 4.6 は試作した 20GHz 帯カスコード増幅器のチップ写真である。チップサイズは  $0.78\text{mm} \times 0.78\text{mm}$  (実質的な回路面積は  $0.7\text{mm} \times 0.6\text{mm}$ ) であり, 極めて小さい面積で実現している。図 4.7 は増幅器の周波数特性を示している。図 (a) は S-

図 4.5 20GHz 帯カスコード型増幅器の等価回路図

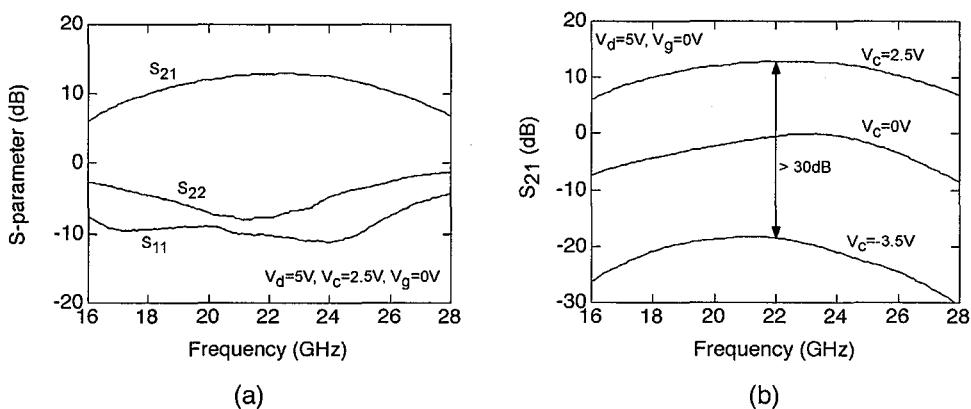

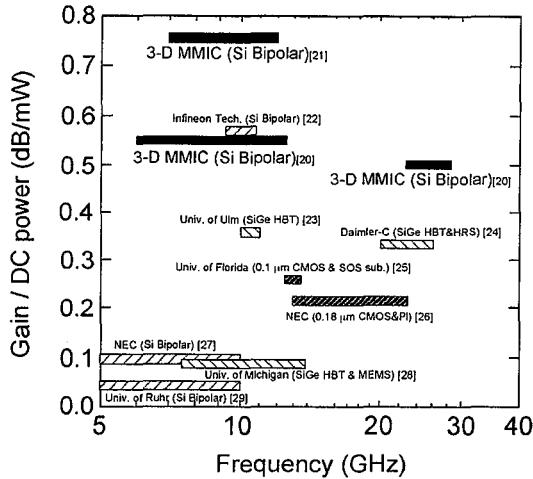

パラメータ、図 (b) はコントロールバイアス  $V_c$  を変えたときの利得可変特性を示している。18GHz から 26GHz 帯において、 $S_{21}=11\text{dB}\pm1\text{dB}$ ,  $S_{11}<-9\text{dB}$ ,  $S_{22}<-4\text{dB}$ ,  $S_{12}<-25\text{dB}$  を実現している。また、利得可変幅は帯域内において 30dB 以上である。図 4.8 は NF 特性を示しており、8dB 以下である。これらの特性はマイクロストリップ型 MMIC で実現される増幅器と比較して 1.5 倍以上の利得／面積比を実現している。ここで実現したカスコード型増幅器は小型でかつ高利得、広帯域な特性、大きな利得可変特性を有しているため、高集積 MMIC 実現において段間のレベル調整、受信利得制御等には広い用途に適用できる。

図 4.6 試作したカスコード型増幅器のチップ写真

図 4.7 試作したカスコード型増幅器の特性

(a)S パラメータ、(b)利得可変特性

図 4.8 試作したカスコード型増幅器の NF 特性

### 4.3 アクティブ帰還型可変利得増幅器

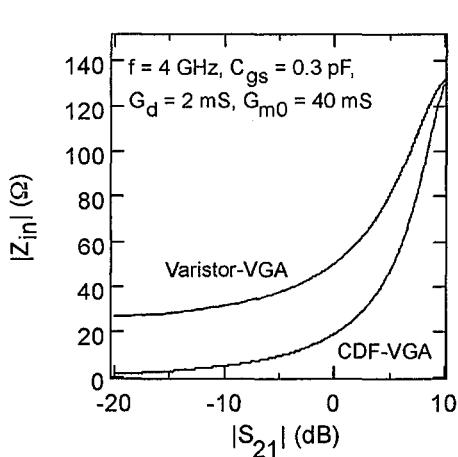

可変利得増幅器は受信利得制御、送信電力制御、段間レベル調整等いろいろな用途に使用される。従来の可変利得増幅器としては 4.2 節で述べたようなカスコード接続 FET [5] またはデュアルゲート FET [6] を用いてゲート接地 FET (第 2 ゲート) のゲートバイアスを制御することにより増幅器の利得を制御する方法がある。また、フィードバック型増幅器のフィードバック回路部にバリスタを用い、バリスタの抵抗値を変えることによりフィードバック量を可変に増幅器の利得を制御する方法がある [7]。カスコード FET やデュアルゲート FET を用いる方法では利得減衰時の線形性が低いという問題がある。これは FET の相互トランスクタンス ( $g_m$ ) の値が小さいために生じる。一方バリスタ帰還型可変利得増幅器ではバリスタの最小抵抗値が最大帰還量を決定するため、利得減衰値の最大値に制限があり、利得可変幅を大きくするには多段化を余儀なくされる。本節では上記問題点を解決する新たなアクティブ帰還型可変利得増幅器を提案、実現する。

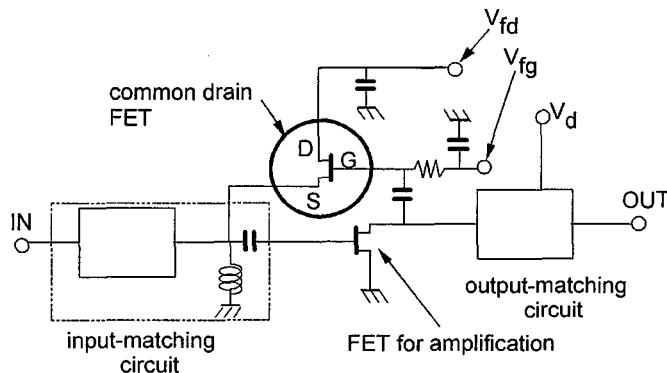

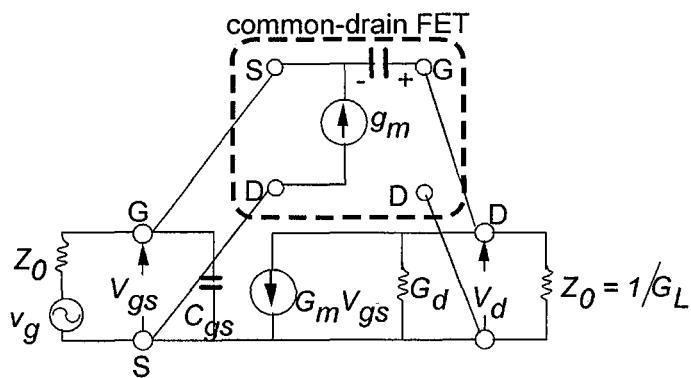

#### 4.3.1 アクティブ帰還型可変利得増幅器の構成及びその特徴

図 4.9 は新たに提案するアクティブ帰還型可変利得増幅器の基本構成を示している [8]。帰還回路部にドレイン接地 FET (CDF) を形成し、ドレイン接地 FET の  $g_m$  を変えることにより帰還量を制御し、増幅器の利得を可変にする構成である。図 4.10 は主増幅部 (ここではソース接地 FET (CSF) としている) と CDF で構成される帰還回路を FET の等価回路パラメータで示した図である。等価回路を簡易化するため CDF は  $g_m$  のみで示している。CSF, CDF の Y 行列を

$$[Y_{CSF}] = \begin{bmatrix} j\omega C_{gs} & 0 \\ G_{m0} & G_d \end{bmatrix}$$

$$[Y_{CDF}] = \begin{bmatrix} g_m & -g_m \\ 0 & 0 \end{bmatrix}$$

ただし、 $G_{m0}$ は $G_m$ の線形パラメータである。

とすると、図4.10に示す等価回路のY行列は

$$[Y] = \begin{bmatrix} j\omega C_{gs} + g_m & -g_m \\ G_{m0} & G_d \end{bmatrix}$$

と表せる。従って上式より等価回路の $S_{21}$ 及び入力インピーダンス $Z_{in}$ は以下のようになる。

$$\begin{aligned} S_{21} &= \frac{-2G_{m0}Z_0}{1 + Z_0G_d + (1 + Z_0G_d + Z_0G_{m0})Z_0g_m + j\omega Z_0C_{gs}(1 + Z_0G_d)} \\ &\approx \frac{-2G_{m0}Z_0}{1 + (1 + Z_0G_{m0})Z_0g_m} \end{aligned}$$

$$Z_{in} = \frac{1 + Z_0G_d}{(1 + Z_0G_d + Z_0G_{m0})g_m + j\omega C_{gs}(1 + Z_0G_d)} \approx \frac{1}{(1 + Z_0G_{m0})g_m}$$

図4.9 アクティブ帰還型可変利得増幅器の構成

図4.10 アクティブ帰還型可変利得増幅器の主要部の等価回路図

これらの式は  $S_{21}$ ,  $Z_{in}$  とも帰還回路部のドレイン接地 FET の  $g_m$  により制御できることを示しており、次の3つのことを行うことができる。

- 1) 幅器の利得は CDF の  $g_m$  が 0 (ゲート電圧がピンチオフのとき) のとき最大利得を取り、 $g_m$  が最大のとき、増幅器の利得は最小となる。

- 2) 増幅器の入力インピーダンスは CDF の  $g_m$  が最大のとき、最小となる。この入力インピーダンスを如何に小さくするかによって、増幅器の最大入力電力が決定する。図 4.11 は CDF 帰還型可変利得増幅器とバリスタ帰還可変利得増幅器の入力インピーダンスを比較したものである。主増幅部の FET パラメータは両者とも同じである。また、バリスタとして CDF と同じ FET を用いそのドレインソース間抵抗により構成している。入力インピーダンスは利得の減少とともに小さくなり、その値は CDF 帰還型可変利得増幅器の入力インピーダンスの方が小さいことがわかる。

- 3) 利得減衰動作時においては温度変化に対する増幅器の利得変動を小さく抑えることができる。これは主増幅部の FET の相互コンダクタンス及び、CDF の相互コンダクタンスが温度変化により同じ方向に変化するが、帰還量の観点から見た場合主増幅部の利得増減方向と帰還量の増減方向が反対となるためである。この温度補償効果は以下の式で示すことができる。

$$\frac{\partial S_{21}}{\partial g_m} \approx \frac{-2Z_0\alpha(1-Z_0^2\alpha g_m^2)}{(1+Z_0g_m+Z_0^2\alpha g_m^2)^2} = \frac{-2Z_0\alpha(1-Z_0^2G_{m0}g_m)}{(1+Z_0g_m+Z_0^2G_{m0}g_m)^2}$$

ただし  $G_{m0}=\alpha g_m$  と仮定している。

増幅器の利得変動は  $G_{m0}g_m = \frac{1}{Z_0^2}$  のとき 0 とすることができる。さらに  $g_m$  の値が大きい場合

(減衰動作時) には分母の  $(G_{m0}g_m Z_0^2)^2$  項の値が大きくなり  $\frac{\partial S_{21}}{\partial g_m} \approx 0$  となるので利得変動を抑えることができる。

次にアクティブ帰還型可変利得増幅器の歪み特性について述べる。ここでは文献 [9], [10] で述べられている FET の相互コンダクタンスの非線形性のべき級数展開を用いてその特性を示す。主増幅部 FET の相互コンダクタンス  $G_m$  はゲートソース間電圧  $V_{gs}$  とすると

$$G_m = G_{m0} + G_{m1}V_{gs} + G_{m2}V_{gs}^2$$

と示すことができる。図 4.10 より

$$V_d = -\frac{G_m}{G_L + G_d} V_{gs} = -\frac{G_{m0}V_{gs} + G_{m1}V_{gs}^2 + G_{m2}V_{gs}^3}{G_L + G_d}$$

となる。等振幅の入力信号を  $\omega_1$ ,  $\omega_2$  とし、CDF の  $g_m$  の変化による可変利得増幅器の入力インピーダンス、 $Z_{in}$  の低下を考慮して、 $V_{gs}$  は以下のように示すことができる。

$$V_{gs} = A v_g (\cos(\omega_1 t) + \cos(\omega_2 t))$$

$$A = \frac{Z_{in}}{Z_{in} + Z_0} = \frac{\frac{1}{g_m}}{\frac{1}{g_m} + (1 + G_m Z_0) Z_0}$$

上式より基本波成分 ( $\omega_1$  または  $\omega_2$ ) の出力は

$$V_{d\ fundamental} = -\frac{G_{m0} A v_g + \frac{9}{4} G_{m2} (A v_g)^3}{G_L + G_d} \cos(\omega_n t)$$

$$n = 1 \text{ or } 2,$$

一方 3 次混変調歪み成分 ( $2\omega_1 - \omega_2$ ) の出力は

$$V_{d 2\omega_1 - \omega_2} = -\frac{\frac{3}{4} G_{m2} (A v_g)^3}{G_L + G_d} \cos((2\omega_1 - \omega_2)t)$$

と示すことができる。従って、基本波と 3 次歪みとの D/U 比は以下のように示すことができる。

$$\begin{aligned} [D/U]_{CDF} &= 20 \log \left| \frac{V_{d\ fundamental}}{V_{d 2\omega_1 - \omega_2}} \right| = 20 \log \left| \frac{G_{m0} A v_g + \frac{9}{4} G_{m2} (A v_g)^3}{\frac{3}{4} G_{m2} (A v_g)^3} \right| \\ &\approx 20 \log \left| \frac{4 G_{m0}}{3 G_{m2} (A v_g)^2} \right| \end{aligned}$$

同様にして、パリスタ帰還型可変利得増幅器における基本波と 3 次歪みとの D/U 比は以下のように示すことができる。

$$[D/U]_{Varistor} = 20 \log \left| \frac{\left( G_{m0} - \frac{1}{R_{fb}} \right) B v_g + \frac{9}{4} G_{m2} (B v_g)^3}{\frac{3}{4} G_{m2} (B v_g)^3} \right| \approx 20 \log \left| \frac{4 \left( G_{m0} - \frac{1}{R_{fb}} \right)}{3 G_{m2} (B v_g)^2} \right|$$

$$\text{ただし, } B = \frac{R_{fb} + Z_0}{R_{fb} + (2 + G_m Z_0) Z_0}$$

ここで、パリスタ部は抵抗  $R_{fb}$  のみとしている。CDF 帰還型可変利得増幅器の D/U 比のパリスタ帰還型可変利得増幅器の D/U 比を比較すると、図 4.11 より  $A v_g < B v_g$  となるので CDF 帰還型可変利得増幅器の D/U 比の方が大きくなる。さらに、CDF 帰還型では分子の項は  $G_{m0}$  で一定である。これは CDF のユニラテラル性に起因している。これに対してパリスタ帰還型では  $G_{m0} - 1/R_{fb}$  ( $R_{fb}$  は入力電力  $v_g$  の増加とともに小さくする必要がある) となっているので分子の項は  $v_g$  の増加とともに減少する。この違いは特に高い入力電力（減衰動作）時に両者の D/U

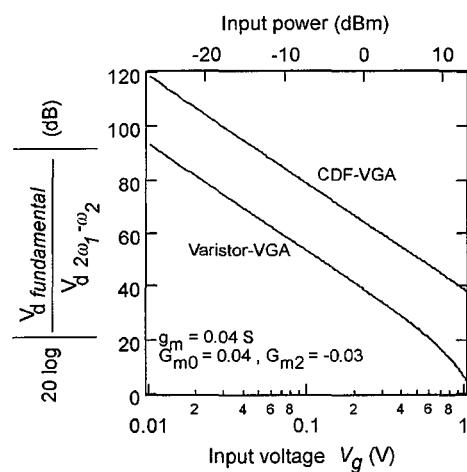

比の差が大きくなることを示している。図 4.12 は D/U 比の入力電力依存性を計算した図である。いずれの入力電力においても CDF 帰還型可変利得増幅器の D/U 比が大きな値を示しており、その差は 10dB 以上である。図 4.13 は可変利得増幅器の利得を可変させたときの D/U 比を計算した図である。この計算値においても CDF 帰還型の方が大きい D/U 比を実現しており、特に減衰動作時の差が大きくなるのがわかる。従って、CDF 帰還型可変利得増幅器はバリスタ型と比較してより高い線形性を実現できることがわかる。

図 4.11 入力インピーダンスと

増幅器利得の関係

図 4.12 D/U 比の入力電力依存性

図 4.13 D/U 比の増幅器利得依存性

### 4.3.2 アクティブ帰還型可変利得増幅器 MMIC の性能

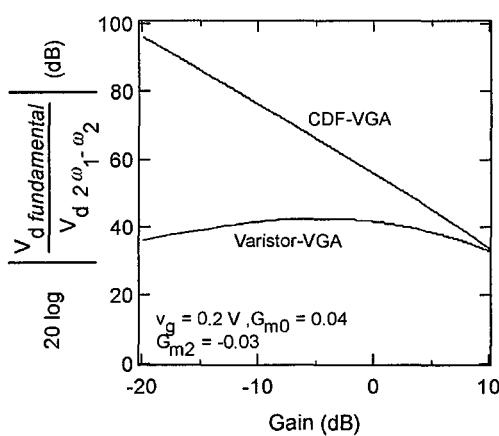

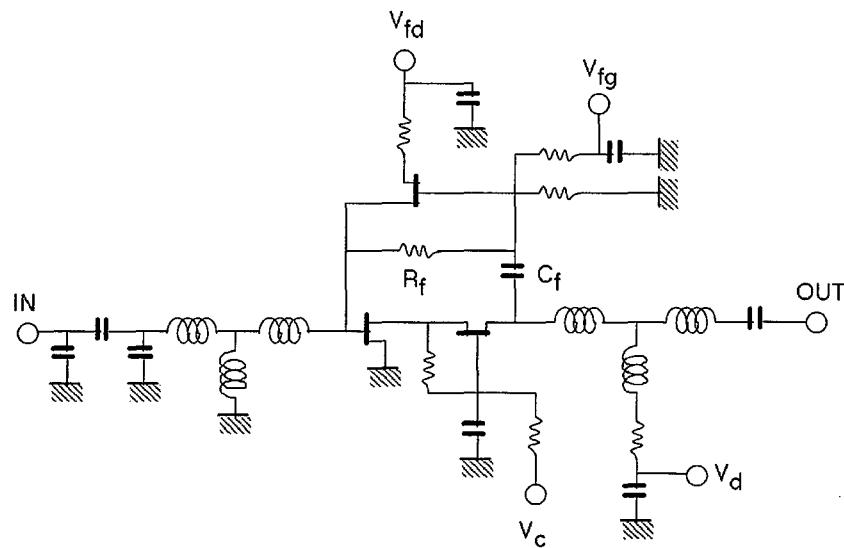

図 4.14 は試作した 4GHz 帯 CDF 帰還型可変利得増幅器の等価回路図である。主増幅部は高利得化のためカスコード FET を用いている。帰還回路部は CDF, DC ブロック容量  $C_f$ , 増幅器の高利得動作時の安定性を実現するための帰還抵抗  $R_f$  より構成している。使用しているデバイスは付録 4.1 に示す  $0.3\mu\text{m}$  GaAs MESFET であり、FET のゲート幅は  $200\mu\text{m}$  である。FET サイズは所望の最小利得、可変利得幅、温度安定性を実現するために決定した。図 4.15 は試作した MMIC のチップ写真であり、 $1.41\text{mm} \times 1.43\text{mm}$  の小型なチップサイズで実現している。

図 4.14 試作した CDF 帰還型可変利得増幅器の等価回路図

図 4.15 試作した MMIC のチップ写真

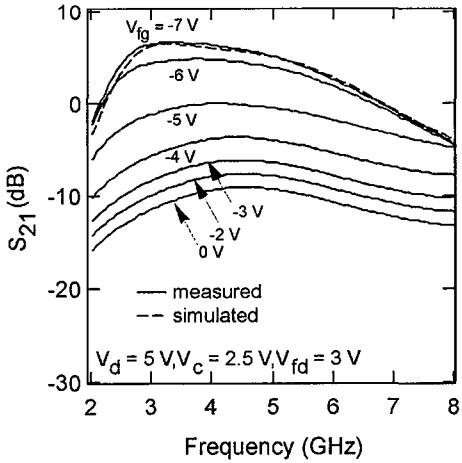

図 4.16 試作した増幅器の利得可変特性

図 4.17 試作した増幅器の NF 特性

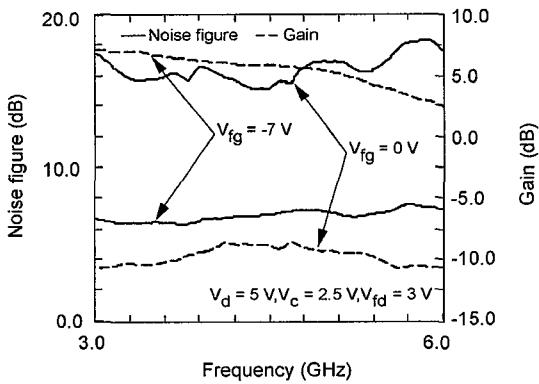

図 4.16 は可変利得特性の測定値である。実線が測定値、破線が最大利得時の計算値であり、測定値とよく一致している。増幅器利得は図 4.14 に示す等価回路上の CDF のゲートバイアス  $V_{fg}$  を制御して可変している。 $V_d$ ,  $V_c$ ,  $V_{fd}$  はそれぞれ 5V, 2.5V, 3V である。利得可変幅は 3GHz から 4.5GHz において 15dB 以上を実現している。このとき  $V_{fg}$  は-7V から 0V の間で制御している。出力リターンロスの変動幅は利得可変範囲において、3.5dB 以下である。一方入力リターンロスは利得減衰に伴って劣化する。これは実際のシステムにおいては前段に LNA を配置することによりマスキングされるため許容できる。図 4.17 は NF 特性を示した図である。実線が NF 特性、破線が対応する利得を示している。NF は最大利得時に 7dB、最小利得時に 17dB である。NF 特性の可変幅は 10dB であり、利得可変幅と比較して低く抑えられている。

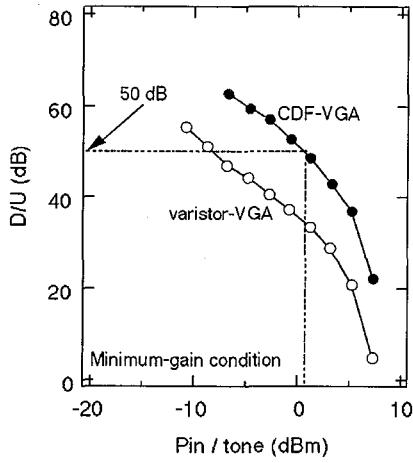

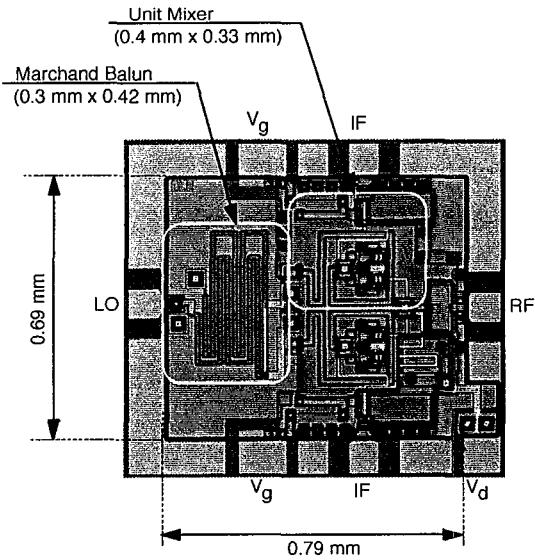

図 4.18 は増幅器への入力電力と D/U 比（基本波と 3 次混変調歪みの比）の関係を示した測定値である。可変利得増幅器は減衰動作を行っている。図には同時に試作したバリスタ帰還型

図 4.18 減衰動作時の D/U 比と入力電力の関係

図 4.19 CDF 帰還型可変利得増幅器の線形性と CDF のゲートバイアスの関係

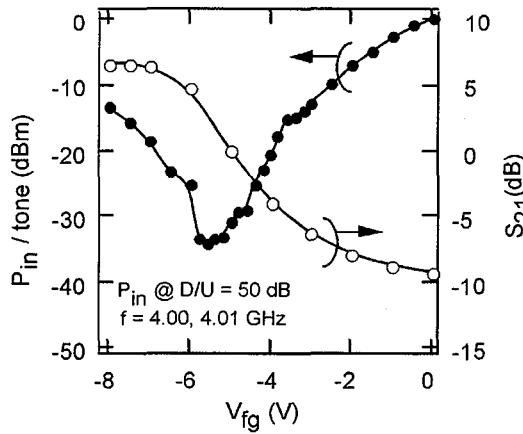

可変利得増幅器 MMIC (CDF 部をゲート接地 FET を用いたバリスタに変更) の測定値も合わせて示している。CDF 帰還型の D/U 比はバリスタ帰還型と比較して 15dB 以上高い値を示している。また、D/U 比 50dB を実現する最大入力電力では 8dB の改善を実現しており、その値は 0dBm である。図 4.19 は CDF 帰還型可変利得増幅器の線形性と CDF のゲートバイアスの関係を示している。そのバイアス時の増幅器利得も合わせて示している。黒丸は D/U 比 50dB を実現するための最大入力電力、白丸は増幅器利得を示している。この図は黒丸の折れ線以下の入力電力では D/U 比 50dB 以上であることを示している。最大入力電力は最大利得時から利得を下げてくると一旦減少し、その後（図では  $V_{fb}=-5.8V$  のとき）増加し、 $V_{fb}=0V$  のとき 0dBm を実現する。これら結果は CDF 帰還型可変利得増幅器が極めて高い線形性を実現していることを示している。

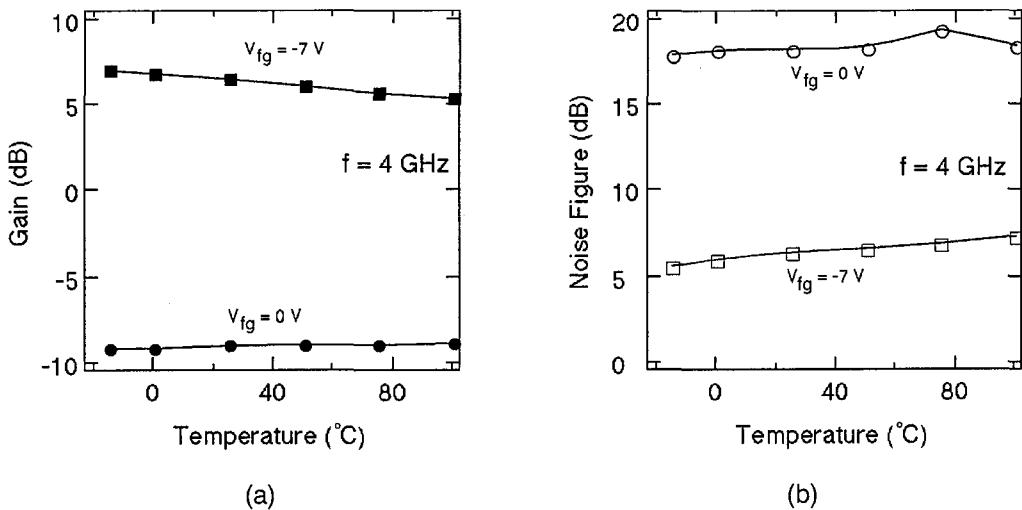

図 4.20 は可変利得増幅器の利得及び NF の温度依存性を示している。図(a)が利得、図(b)が

図 4.20 増幅器の利得及び NF の温度依存性

(a)利得特性, (b)NF 特性

図 4.21 D/U 比の温度依存性

NF である。-15°Cから 100°Cまで温度を変えた時、最大利得時の利得変動は 2dB、最小利得時の利得は温度変化に依存せずほぼ一定である。一方 NF は最大利得時および最小利得時とも 2dB の変動がある。図 4.21 は D/U 比の温度依存性を示した図である。測定した温度は-15°C, 25°C, 100°Cである。いずれの温度においても D/U 比 50dB を実現する入力電力は 0dBm で一定であることがわかる。これらの温度依存性の測定結果から、CDF 帰還型可変利得増幅器の持つ温度補償効果が作用していることが示された。

帰還回路にドレイン接地 FET を用いた CDF 帰還型可変利得増幅器を提案、試作し、その動作原理、測定結果を示した。提案する増幅器は線形性が高く、かつ温度補償機能により温度安定性が高い回路構成である。

#### 4.4 周波数変換器

周波数変換器は送信機、受信機において必要不可欠な機能回路であり、特にバランス型構成の周波数変換器は LO 成分やイメージ成分を抑圧する機能を有しているため重要である。しかしながらバランス型周波数変換器は同相信号分配合成回路や 90 度／180 度ハイブリッドと複数の単位ミキサで構成されているため、MMIC 上で大きな面積を占めていた [11] - [14]。特にハイブリッド等の受動回路の占める面積が大きい。送受信機の 1 チップ化、高集積化を実現するためにはこれら周波数変換器の小型化、高集積化が不可欠である。本節では 3 次元 MMIC 技術を用いてハイブリッド等の受動回路の小型化だけでなく、周波数変換器全体を積層構造により小型化、高集積化する構成、設計法について述べる。

##### 4.4.1 バランス型アップコンバータ

バランス型アップコンバータは RF 出力部での LO 信号の漏れを位相的にキャンセルする構成であり、LO 信号の入力側に逆相信号を実現するハイブリッドを配置するもの、ミキサからの RF 出力側で逆相合成するもの、LO 信号入力側及び RF 出力側の両方に 90 度ハイブリッドを配置する構成がある。いずれの場合にも IF 信号は逆相で入力する。ここでは、ハイブリッド回路の損失の影響を軽減するとともに LO 信号をリアクティブに終端することにより変換損失の低減が図れる LO 信号を逆相入力する構成法を採用した。さらに単位ミキサは変換損失の小さいゲート局発注入型ミキサを用いた。

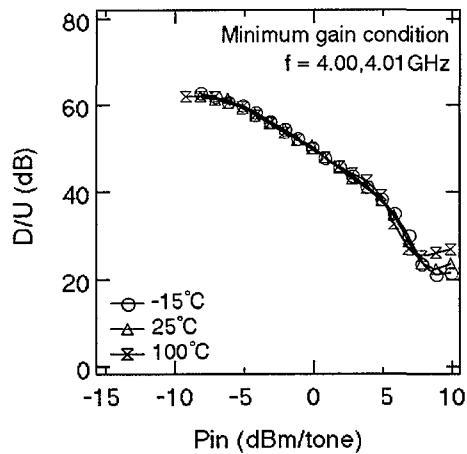

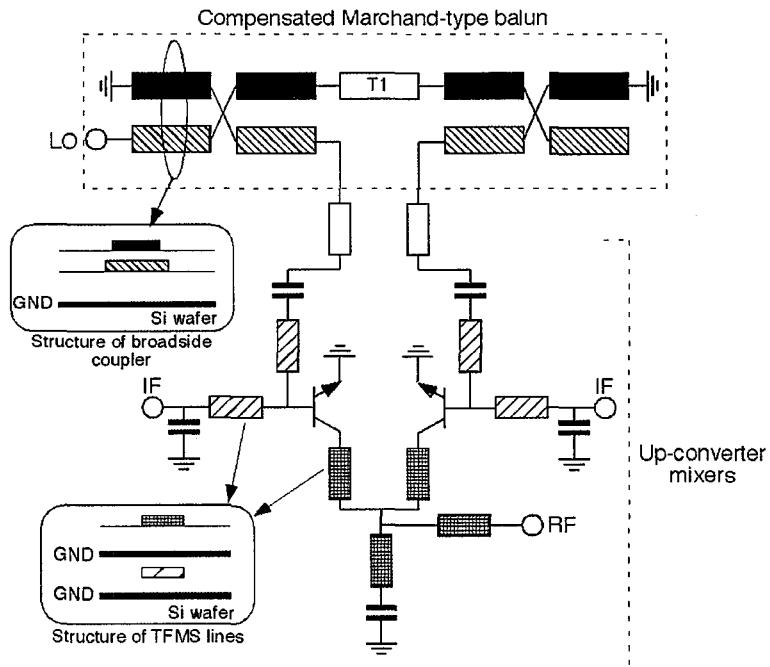

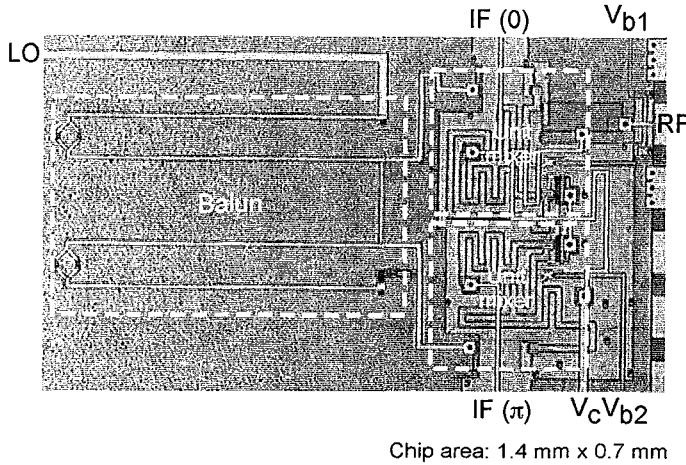

図 4.22 はバランス型アップコンバータの構成を示している [15]。LO 信号を逆相分配する

図 4.22 バランス型アップコンバータの構成

図 4.23 試作したバランス型アップコンバータ MMIC のチップ写真

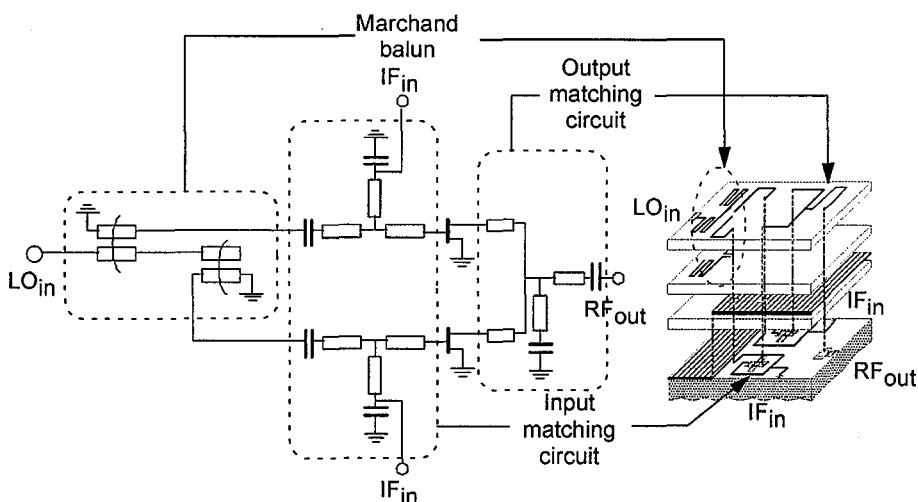

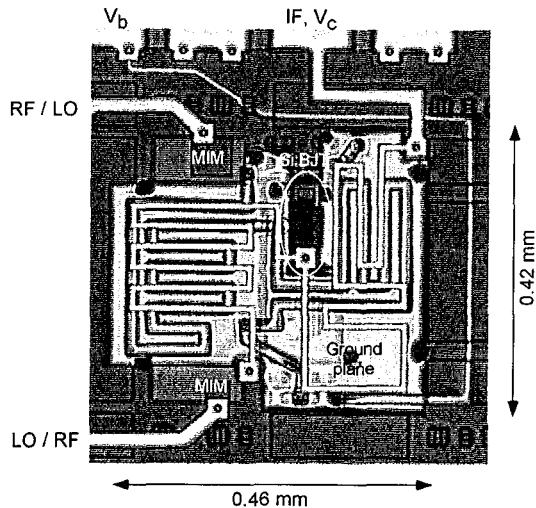

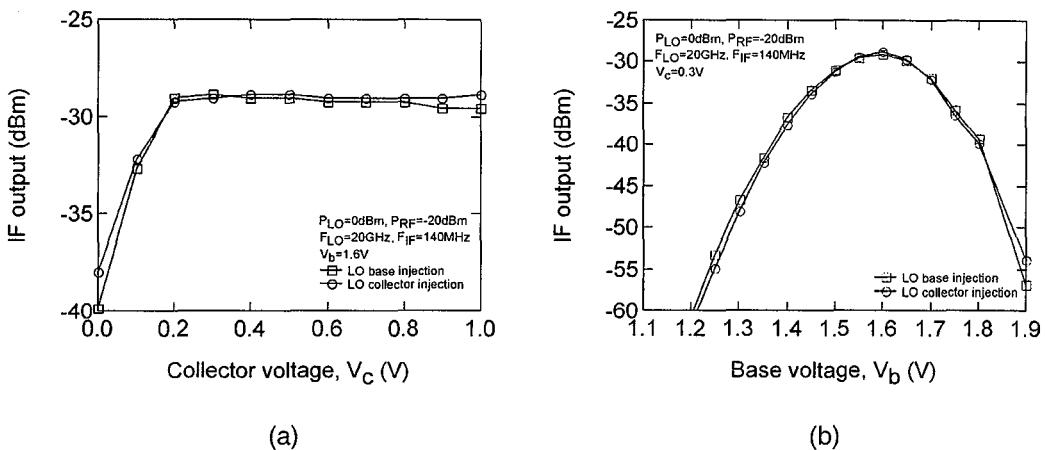

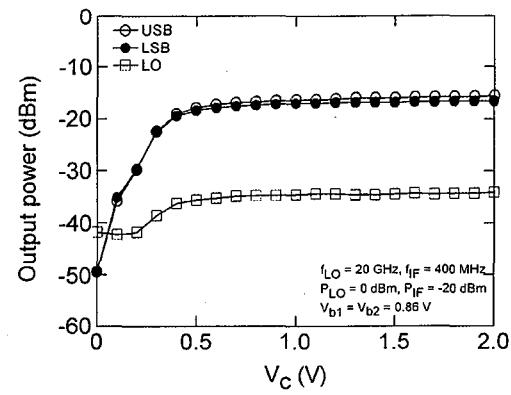

回路として第 3 章で提案しているマーチャンド型バラン [16] を用いている。単位ミキサの入出力整合回路はポリイミド層中間層に接地導体を配置し、その上下に配置する積層構成としている。入力整合回路はバランの出力インピーダンスに整合するように構成している。出力整合回路は単位ミキサからの RF 信号の合成回路を兼ねており、合成点では逆相で出てくる LO 信号漏洩分を反射して FET へ戻す構成とし、変換利得が最大となるように FET と合成点までの距離を最適化している [11]。図 4.23 は試作したバランス型アップコンバータ MMIC のチップ写真である。単位ミキサの整合回路は FET の回りに積層して配置することにより小型化を実現している。バランはメアンダ状に配置している。単位ミキサは 0.4mmx0.33mm、バランは 0.3mmx0.42mm でありトータル回路面積は 0.79mmx0.69mm と超小型である。FET はゲート幅 200 $\mu$ m の 0.3 $\mu$ m GaAs MESFET (付録 4.1 参照) を用いている。

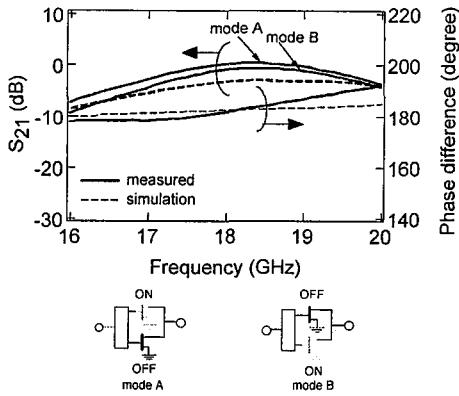

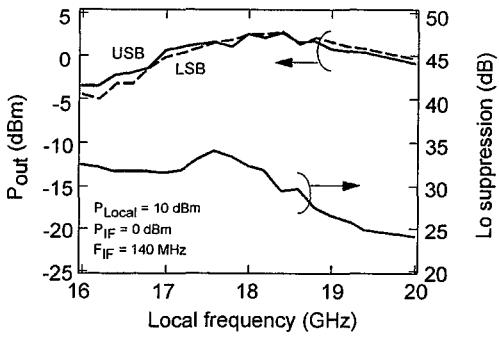

図 4.24 はバランス型アップコンバータのバランス特性を示す測定値である。実線が測定値、破線が計算値である。測定は単位ミキサの FET の片方を OFF とし、ON 状態の FET を増幅器として動作させ、LO 入力端子 RF 出力端子への通過特性を測り、FET の ON/OFF 状態を切り替えたときの通過特性の差を評価している。16GHz から 20GHz において、振幅差 2dB 以内、位相差  $185^\circ \pm 7^\circ$  であり、良好なバランス性を実現している。また、計算値ともよく一致している。図 4.25 は RF 端子での RF 出力、LO 抑圧比の LO 周波数依存性を示している。LO 入力電力 10dBm、IF 入力電力 0dBm、IF 周波数は 140MHz である。測定帯域内において、RF 出力は LSB、USB とも -5dBm 以上である。一方、LO 抑圧比は 24dB 以上を実現している。また、出力 IP3 は 12dBm である。ドレイン電圧は 3V、ゲート電圧は -0.75V、ドレイン電流は 23mA

図 4.24 バランス型アップコンバータの

バランス特性

図 4.25 RF 出力, LO 抑圧比の周波数特性

である。この結果は試作した 3 次元 MMIC バランス型アップコンバータが良好なバランス特性を実現できるとともに小型化、広帯域化も実現している。

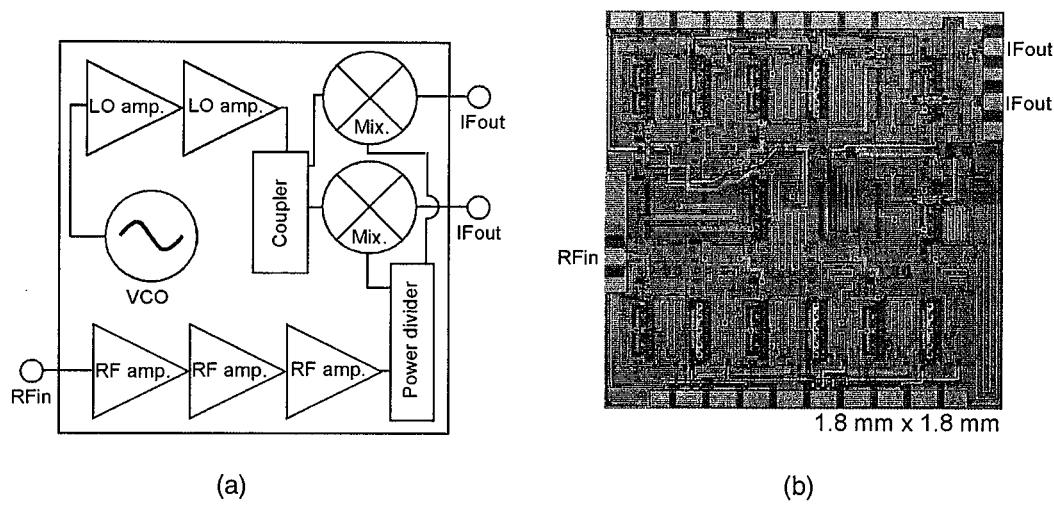

#### 4.4.2 イメージリジェクションミキサ

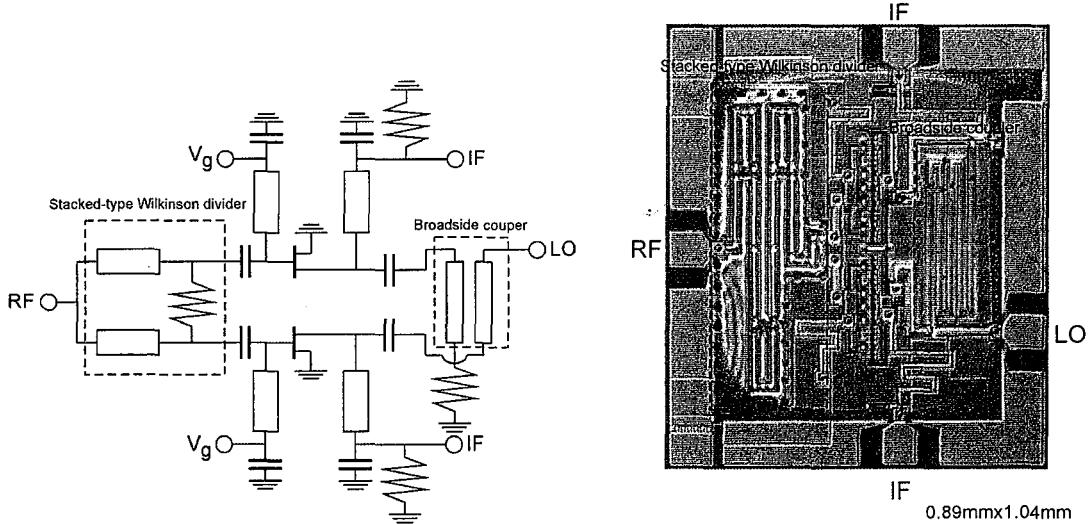

イメージリジェクションミキサは IF 出力のイメージ成分を位相的にキャンセルさせるものであり、受信機に必要不可欠である。イメージリジェクションミキサは 2 つの単位ミキサと同相信号分配回路、90 度ハイブリッドで構成される。図 4.26 は実現した 3 次元 MMIC イメージリジェクションミキサの構成 [17] である。同相信号分配回路として第 3 章で提案した積層型ウイルキンソンディバイダ [18]、90 度ハイブリッドとしてブロードサイドカプラ [19] を用いている。FET はゲート幅 200 $\mu\text{m}$  の 0.3 $\mu\text{m}$  GaAs MESFET である。単位ミキサはドレイン局発注入ミキサ [14] であり、RF 信号を FET のゲートから、LO 信号をドレイン側から入力し、IF 信号をドレイン側から取り出す構成である。このミキサ構成はドレイン側より比較的レベルの高い LO 信号を入力し、ドレイン電圧を変化させ、これに伴う FET の相互コンダクタンスの変化を利用して周波数変換を行うものである。このミキサの特徴はドレイン電圧を LO 信号で変化させるため、FET へのドレイン電圧の印加を必要とせず、消費電力が 0 となることである。単位ミキサは小型化を実現するため、RF 信号入力側、LO 信号入力側とも TFMS 線路と容量のみの簡単な構成で整合回路を実現している。RF 信号入力側に損失の小さいウイルキンディバイダ、LO 信号入力側にブロードサイドカプラを配置している。IF 信号は LO 信号に対しては十分大きく、IF 信号に対しては無視し得るシャントキャパシタを介して出力する。損失の小さいウイルキンソンディバイダは RF 信号入力側、比較的損失の大きいブロードサイドカプラは LO 信号入力側に配置している。これはミキサの飽和領域レベルの LO 入力信号を使用するため、

図 4.26 イメージリジェクションミキサの等価回路図

図 4.27 試作したイメージリジェクションミキサ MMIC のチップ写真

図 4.28 イメージリジェクションミキサの周波数特性

プロードサイドカプラの損失を無視でき得るためである。

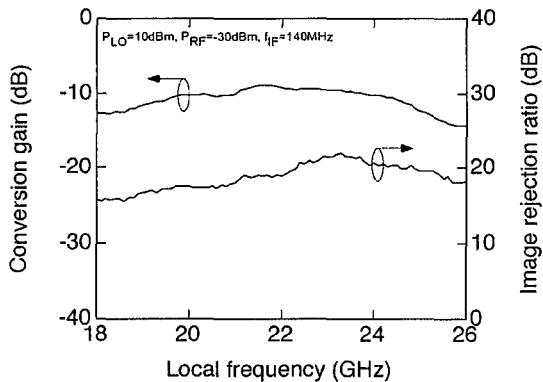

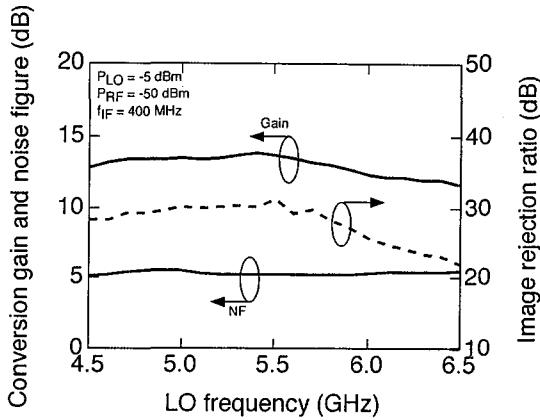

図 4.27 は試作したイメージリジェクションミキサ MMIC のチップ写真である。チップサイズは 0.89mmx1.04mm と超小型であり、従来のコプレーナ線路で構成される MMIC と比較して 1/2 以下のサイズである。図 4.28 はイメージリジェクションミキサの周波数特性を示している。LO 入力 10dBm, RF 入力-30dBm, IF 周波数 140MHz, ゲート電圧は-0.95V である。19.4GHz から 24.6GHz において、変換利得-10dB±1dB, イメージ抑圧比 17.3dB 以上を実現している。この結果は 3 次元 MMIC 技術により、超小型でかつ広帯域なイメージリジェクションミキサを実現でき、受信機の高集積化を実現可能にさせるものである。

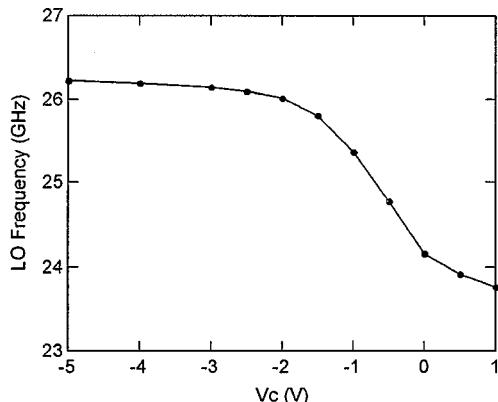

#### 4.5 電圧制御発振器

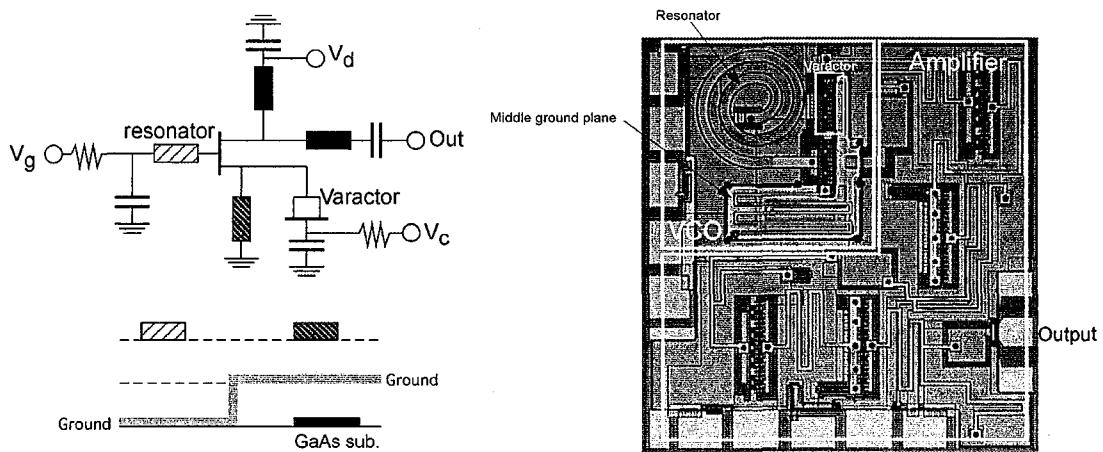

電圧制御発振器（VCO）は送受信機においてキーとなる機能回路の1つである。1チップ送受信機を実現するためにはVCOの小型化、特に共振器部の小型化が重要である。図4.29は20GHz帯3次元MMICVCOの回路構成である。能動素子としてソース接地FETを用いている。ソース側にショートスタブと可変リアクタンス素子としてFETを用いたバラクタ（ソース・ドレイン間を短絡させ、ゲート・ドレイン間及びゲート・ソース間容量を使用する）を配置したシリーズフィードバック型発振器である。共振器はゲート側に配置し、線路幅30μmの低損失TFMS線路（40Ω, 0.16dB/mm）を使用している。出力整合回路は2本の逆TFMS線路より構成され、ポリイミド層中間層接地導体を用いて前述のショートスタブと積層構成となっている。使用しているFETは主FET、バラクタともゲート幅100μmの0.3μm GaAs MESFETである。

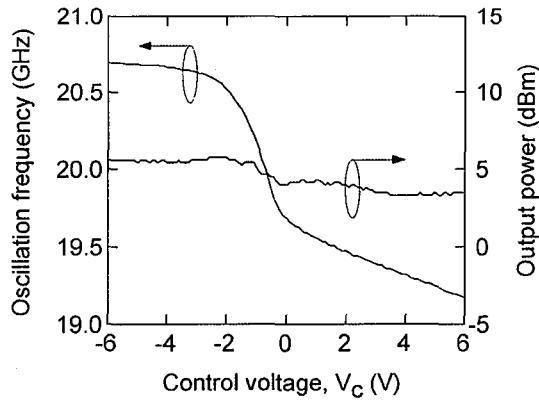

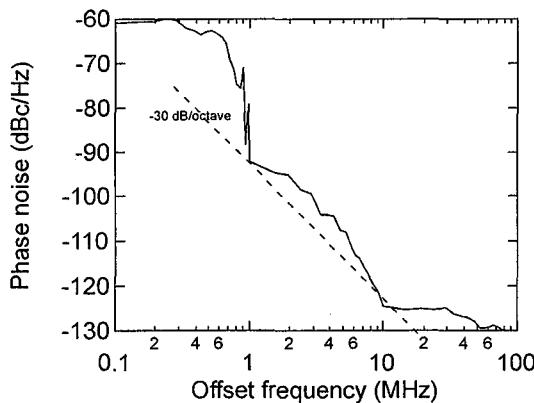

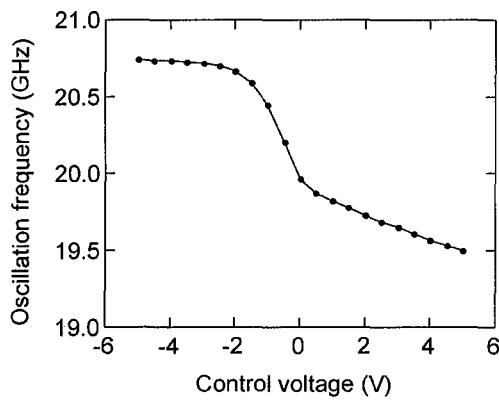

図4.30はVCOと出力用2段増幅器を一体にした3次元MMIC発振器のチップ写真である。VCOの共振器部は小型化するためにスパイラル状に配置している。また、主FETとバラクタ用FETも真横にレイアウトすることにより、一層小型化を実現している。増幅器はゲート幅200μmのFETを用いたカスコード型増幅器である。VCO部は0.6mmx0.6mmと超小型であり、トータルサイズは1mmx1mmである。このサイズは従来のコプレーナ線路を用いたVCOと比較して約1/3の小型化を実現している。図4.31は発振周波数及び出力の測定値である。発振周波数はバラクタの制御電圧を-6Vから6Vまで変えることにより20.7GHzから19.2GHzまで可変にすることができる。このときの発振出力は4.5dBm±1dBmである。図4.32は20GHzでの位相雑音である。測定はスペクトルアナライザを用いて直接読み取った値である。1MHz offsetにおいて-92dBc/Hzを実現しており、GaAs MESFETを用いて実現されるVCOの位相雑音と

図4.29 VCOの等価回路図

図4.30 試作したVCOMMICのチップ写真

図 4.31 試作した VCOMMIC の発振周波数及び発振出力

図 4.32 試作した VCOMMIC の位相雑音

しては妥当な値である。ドレン電圧は 3V、ゲート電圧は 0V である。3 次元 MMICVCO は平面構成の MMICVCO と比較して 1/3 の小型化を実現できるとともに良好な特性を実現できることを明らかにした。

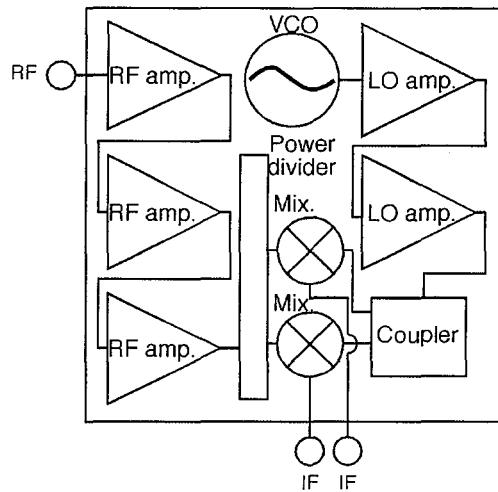

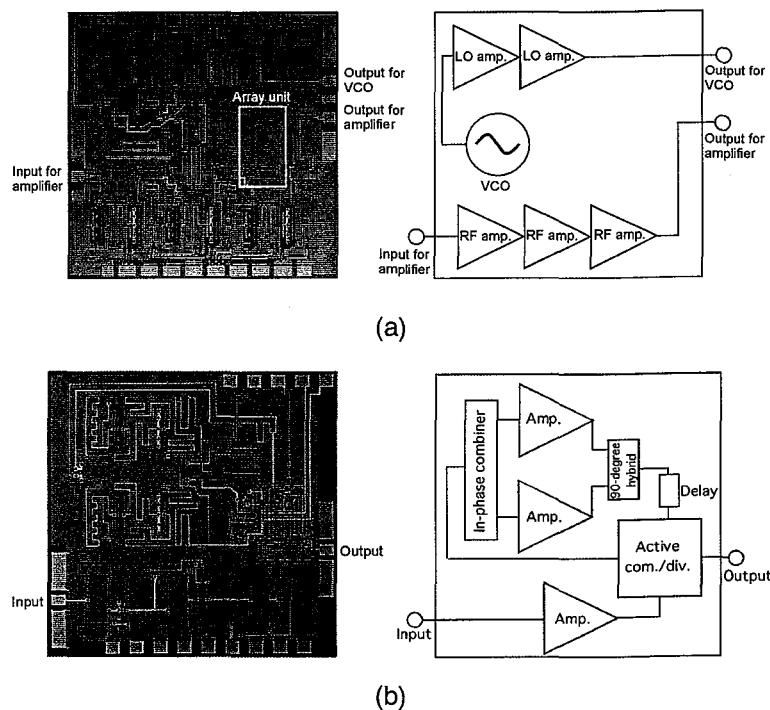

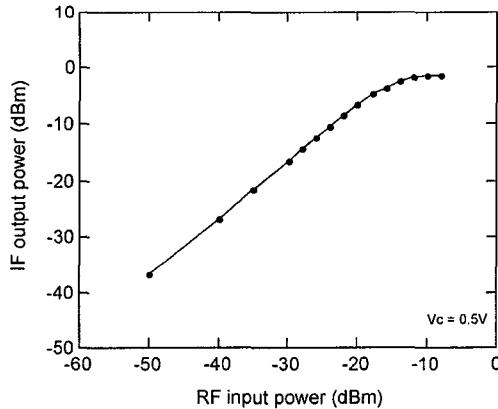

#### 4.6 20GHz 帯 1 チップ受信機

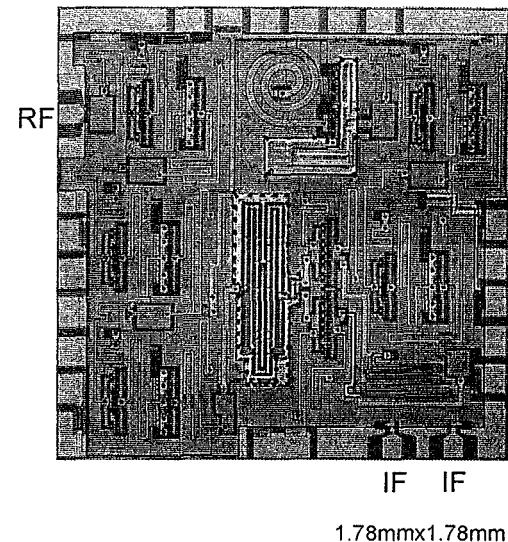

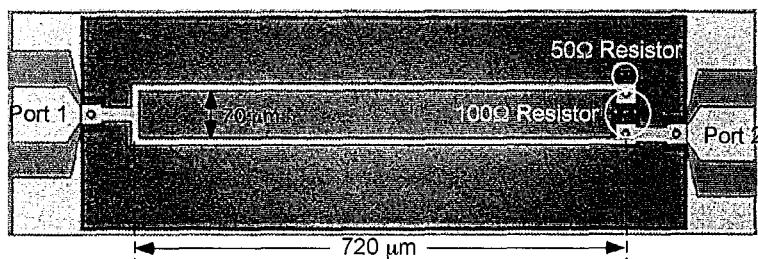

本節ではこれまで述べてきた 3 次元 MMIC 機能回路を基にして実現した 20GHz 帯高集積 1 チップ受信機 3 次元 MMIC [17], [20] について述べる。図 4.33 は 1 チップ受信機 MMIC の構成図であり、3 段フロントエンド RF 増幅器、VCO、2 段 LO 用増幅器、ウイルキンソンディバイダ、ブロードサイドカプラ、2 つの単位ミキサから成るイメージリジェクションミキサが集積化されている。受信機に必要な RF 機能回路全てを 1 チップ MMIC 上に実現している。図 4.34 は 3 次元 MMIC のチップ写真であり、チップサイズは 1.78mmx1.78mm と超小型であり、各機能回路の平均面積も 0.3mm<sup>2</sup> である。これは従来の平面構成の 1 チップ受信機 MMIC と比較して 2 倍以上の集積化、小型化を実現している。

図 4.33 1 チップ受信機 MMIC の構成

図 4.34 試作した 1 チップ受信機

MMIC のチップ写真

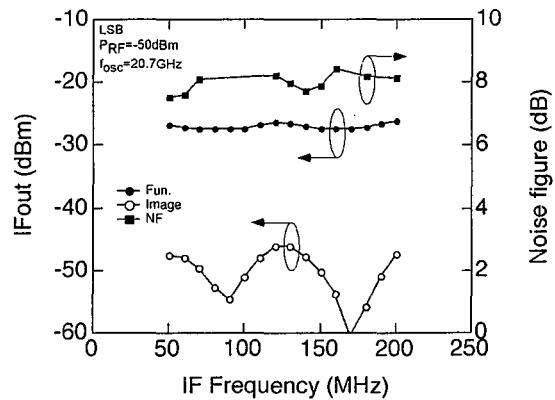

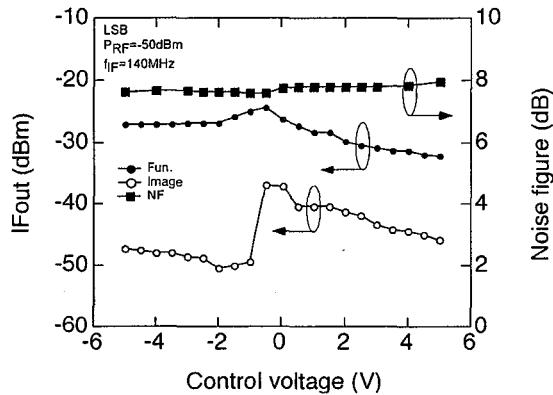

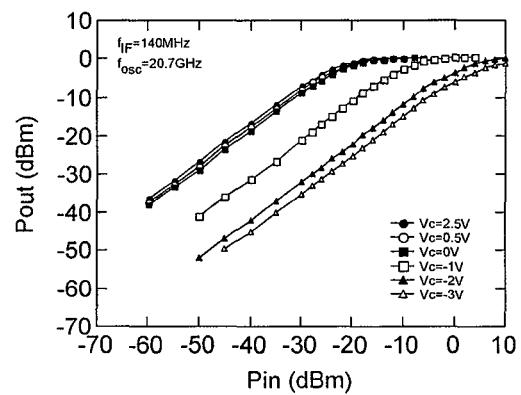

図 4.35 はオンチップ VCO の発振周波数と VCO のコントロール電圧の関係を示したものであり、1.2GHz の周波数可変範囲を実現している。図 4.36 は受信機特性の IF 周波数依存性を示している。LO 周波数は 20.7GHz である。RF 入力-50dBm, IF 周波数 50MHz から 200MHz のとき、IF 出力は-27dBm 以上（変換利得 23dB 以上）、イメージ抑圧比 19dB 以上である。NF は約 8dB である。図 4.37 は IF 周波数 140MHz としたときの VCO のコントロール電圧（LO 周波数）依存性を示している。VCO の可変周波数帯域内において、IF 出力-32dBm 以上（RF 入力-50dBm 時）、イメージ抑圧比 15dB 以上、NF 8dB 以下を実現している。図 4.38 は LO 周波数 20.7GHz, IF 周波数 140MHz のときの受信機の入出力特性を示している。RF フロントエンド増幅器の利得可変量は 20dB 以上であり、IF 出力は飽和領域まで良好な線形性を保っている。飽和出力は 0dBm 以上である。これらの結果は 3 次元 MMIC 技術により、小型、高集積な 1 チップ受信機 MMIC を実現できることを示した。その集積度 [21] は平面構成の高集積 MMIC と比較して 2 倍以上である。またその特性も良好である。

図 4.35 1 チップ受信機 MMIC に集積化された VCO の発振周波数

図 4.36 1 チップ受信機 MMIC 特性の IF 周波数依存性

図 4.37 1 チップ受信機 MMIC 特性の VCO 制御電圧依存性

図 4.38 1 チップ受信機 MMIC の入出力特性

#### 4.7 まとめ

3 次元 MMIC 技術を用いて小型化を実現した増幅器、周波数変換器、電圧制御発振器について、その小型化手法について述べた。さらにこれら 3 次元 MMIC 機能回路を用いて 20GHz 帯 1 チップ高集積化受信機 MMIC を実現した。受信機 MMIC はチップサイズが 1.78mmx1.78mm と超小型であり、平面回路構成の高集積 MMIC と比較しても 2 倍以上の集積度を実現した。これらの結果は 3 次元 MMIC 技術が MMIC の小型化高集積化に極めて有効であることを示すとともに、MMIC の高集積化により RF 部の低コスト化を実現でき得る可能性を持っているといえる。

## 参考文献

- [1] E. Niehenke, R. Hess, J. Rosen, L. Dickens, and J. Faulkner, "A Compact Broad-band Multifunction ECM MIC Module," *IEEE Trans. Microwave Theory Tech.*, Vol. 30, No. 12, pp. 2194-2200, Dec. 1982.

- [2] I. Toyoda, T. T. Tokumitsu, and M. Aikawa, "Highly Integrated Three-dimensional MMIC Single-chip Receiver And Transmitter," *IEEE Trans. Microwave Theory Tech.*, Vol. 44, No. 12, pp. 2340-2346, Dec. 1996.

- [3] T. Tokumitsu, M. Hirano, K. Yamasaki, C. Yamaguchi, K. Nishikawa, and M. Aikawa, "Highly Integrated Three-dimensional MMIC Technology Applied To Novel Masterslice GaAs- And Si-MMIC's," *IEEE Journal of Solid-State Circuits*, Vol. 32, No. 9, pp. 1334-1341, Sept. 1997.

- [4] K. Nishikawa, S. Sugitani, K. Inoue, K. Kamogawa, T. Tokumitsu, I. Toyoda, and M. Tanaka, "A Compact V-band 3-D MMIC Single-chip Down-converter Using Photosensitive BCB Dielectric Film," *IEEE Trans. Microwave Theory Tech.*, Vol. 47, No. 12, pp. 2512-2518, Dec. 1998.

- [5] R. Larue, S. Bandy, and G. Zdasiuk, "A High Gain, Monolithic Distributed Amplifier Using Cascode Active Elements," *1991 IEEE Microwave and Millimeter-wave Monolithic Circuits Symp. Dig.*, pp. 23-26, 1991.

- [6] C. Liechi, "Performance of Dual-gate GaAs MESFET's as Gain Controlled Low-noise Amplifiers and High-speed Modulators," *IEEE Trans. Microwave Theory Tech.*, Vol. 23, No. 6, pp. 461-469, June 1975.

- [7] M. Muraguchi and M. Aikawa, "A Linear Limiter: A 11 GHz Monolithic Low Distortion Variable Gain Amplifier," in *1991 IEEE MTT-S International Microwave Symp. Dig.*, pp. 525-528, 1991.

- [8] K. Nishikawa and T. Tokumitsu, "An MMIC Low-distortion Variable-gain Amplifier Using Active Feedback," *IEEE Trans. Microwave Theory Tech.*, Vol. 43, No. 12, pp. 2812-2816, Dec. 1995.

- [9] T. Tan, K. Kotzebue, D. Braun, J. Centanni, and D. Mcquate, "A Low-distortion K-band GaAs Power FET," *IEEE Trans. Microwave Theory Tech.*, Vol. 36, No. 6, pp. 1023-1031, June 1988.

- [10] R. Turckey and C. Rauscher, "Modeling The 3rd-order Intermodulation-distortion Properties of a GaAs F.E.T.," *Electron Lett.*, Vol. 13, No. 17, pp. 508-509, Aug. 1977.

- [11] T. Hirota and M. Muraguchi, "K-band Frequency Up-converter Using Reduced-size Couplers and Dividers," in *1991 IEEE GaAs IC Symp. Dig.*, pp.53-56, Nov. 1991.

- [12] T. Takenaka and H. Ogawa, "Miniaturized MMIC mixers; Image Rejection and Balanced

- Mixers Using Multilayer Microstrip Lines and Line-unified HEMT Modules," IEICE Trans. Electron., Vol. E75-C, No. 6, pp. 689-697, June 1992.

- [13] A. Minakawa and T. Tokumitsu, "A 3-7 GHz Wide-band Monolithic Image-rejection Mixer on a Single-chip," IEICE Trans. Electron., Vol. E76-C, No. 6, pp. 955-960, June 1993.

- [14] A. Minakawa and T. Hirota, "An Extremely Small 26 GHz Monolithic Image-rejection Mixer Without DC Power Consumption," IEEE Trans. Microwave Theory Tech., Vol. 44, No. 9, pp. 1634-1637, Nov. 1993.

- [15] K. Nishikawa, I. Toyoda, and T. Tokumitsu, "Miniaturized Three-dimensional MMIC K-band Upconverter," IEEE Microwave and Guided Wave Lett., Vol. 7, No. 8, pp. 230-232, Aug. 1997.

- [16] K. Nishikawa, I. Toyoda, and T. Tokumitsu, "Compact and Broad-band Three-dimensional MMIC Balun," IEEE Trans. Microwave Theory Tech., Vol. 47, No. 1, pp. 96-98, Jan. 1999.

- [17] K. Nishikawa, K. Kamogawa, T. Tokumitsu, M. Aikawa, M. Hirano, and S. Sugitani, "Highly-integrated Three-dimensional MMIC 20-GHz Single-chip Receiver," in 26th European Microwave Conference Dig., pp. 199-203, Sept. 1996.

- [18] K. Nishikawa, T. Tokumitsu, and I. Toyoda, "Miniaturized Wilkinson Power Divider Using Three-dimensional MMIC Technology," IEEE Microwave And Guided Wave Letters, Vol. 6, No. 10, pp. 372-374, Oct. 1996.

- [19] I. Toyoda, T. Hirota, T. Hiraoka, and T. Tokumitsu, "Multilayer MMIC Branch-line Coupler and Broad-side Coupler," 1992 IEEE Microwave and Millimeter-wave Monolithic Circuits Symp. Dig., pp. 79-82, June 1992.

- [20] K. Nishikawa, I. Toyoda, K. Kamogawa, T. Tokumitsu, and M. Tanaka, "Three-Dimensional Monolithic Microwave Integrated Circuit Technology for Fully Computer-Aided Design-Compatible Monolithic Microwave Integrated Circuit Development," International Journal of RF and Microwave CAE, Vol. 8, No. 6, pp.498-506, Nov. 1998.

- [21] 西川健二郎,豊田一彦,鴨川健司,徳満恒雄, "高集積3次元MMIC," NTT R&D, Vol. 45, No. 12, pp. 1285-1292, Dec. 1996.

## 付録 4.1 GaAs MESFET 等価回路パラメータ

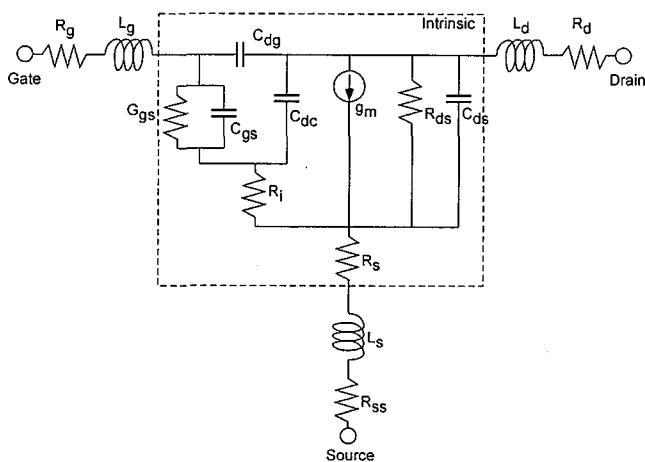

第4章で使用した  $0.3\mu\text{m}$  プロセスの GaAs MESFET (SAINT300A) の等価回路パラメータを示す。

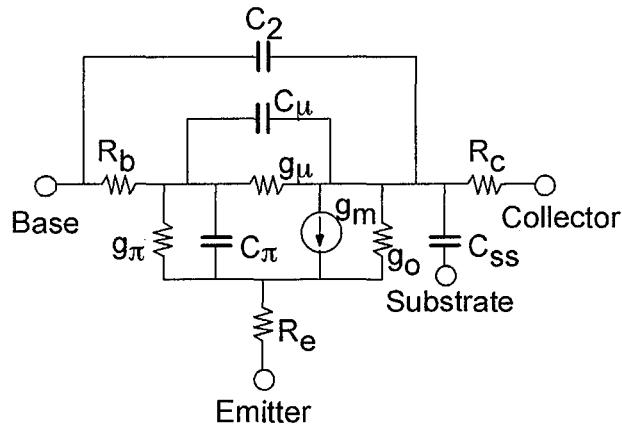

図付 4.1 は MESFET の等価回路図である。

図付 4.1 GaAs MESFET の等価回路図

表付 4.1 は各ゲートバイアス ( $V_g=3V$ ) での MESFET の等価回路モデルパラメータである。

表付 4.1 GaAs MESFET の等価回路モデルパラメータ

| $V_d$ (V)             | 3        | ←      | ←      | ←      | ←      | ←      |

|-----------------------|----------|--------|--------|--------|--------|--------|

| $V_g$ (V)             | 0        | -0.2   | -0.4   | -0.6   | -0.8   | -1     |

| $I_{ds}$ (mA)         | 14       | 10     | 6      | 4      | 1      | 0      |

| $g_m$ (mS)            | 21.8     | 20.3   | 17.5   | 13.7   | 8.72   | 3.44   |

| $t$ (psec)            | 1.31     | 1.35   | 1.46   | 1.66   | 2.06   | 2.78   |

| $C_{gs}$ (pF)         | 0.123    | 0.116  | 0.108  | 0.0975 | 0.0833 | 0.0668 |

| $G_{gs}$ (mS)         | 0        | 0      | 0      | 0      | 0      | 0      |

| $R_i$ ( $\Omega$ )    | 3.60     | 4.16   | 4.69   | 5.16   | 4.99   | 4.94   |

| $C_{dg}$ (pF)         | 0.0141   | 0.0145 | 0.0149 | 0.0157 | 0.0169 | 0.0183 |

| $C_{dc}$ (pF)         | 0        | 0      | 0      | 0      | 0      | 0      |

| $C_{ds}$ (pF)         | 0.0192   | 0.0191 | 0.0192 | 0.0189 | 0.0185 | 0.0184 |

| $R_{ds}$ ( $\Omega$ ) | 482.4    | 487.2  | 507    | 577.1  | 785.9  | 1691   |

| $R_s$ ( $\Omega$ )    | 0.2      | 0.553  | 1.11   | 1.49   | 1.52   | 0.633  |

| $R_g$ ( $\Omega$ )    | 2.41     | ←      | ←      | ←      | ←      | ←      |

| $L_g$ (nH)            | $3.8e-3$ | ←      | ←      | ←      | ←      | ←      |

| $R_d$ ( $\Omega$ )    | 2.47     | ←      | ←      | ←      | ←      | ←      |

| $L_d$ (nH)            | 0.01     | ←      | ←      | ←      | ←      | ←      |

| $L_s$ (nH)            | $2e-4$   | ←      | ←      | ←      | ←      | ←      |

| $R_{ss}$ ( $\Omega$ ) | 2.67     | ←      | ←      | ←      | ←      | ←      |

$0.3\mu\text{m}$  GaAs MESFET  $w_g=100\mu\text{m}$

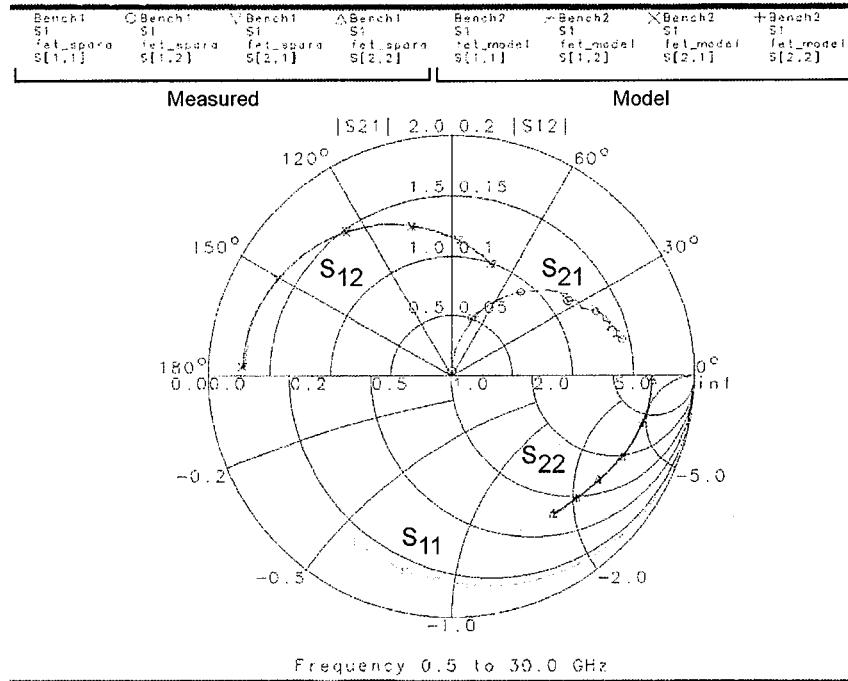

図付 4.2 は  $V_d=3V$ ,  $V_g=-0.2V$  のときの測定値と等価回路パラメータの比較した図であり、測定値と FET モデルはよく一致している。

図付 4.2 FET の測定値と等価回路モデルの比較

## 第5章 3次元構造によるミリ波帯 MMIC の高集積化

### 5.1 まえがき

近年、ミリ波帯を用いたワイヤレスアプリケーションや自動車レーダ、センサー等の開発が活発に行われている。特に、RF部のコアとなるMMICの開発は盛んであり、MMICの高集積化に注目が集まっている。上記のアプリケーションにおいては、ミリ波帯を使用しているといえども携帯電話に代表される低周波数帯のMMICと同様に、低コスト、高集積、高性能が求められている。しかし、現在開発されているミリ波帯MMIC [1] - [5] はチップサイズが大きく、機能回路ごとのチップとなっている。一部受信機能を1チップ化したものも開発されている [6] がチップサイズが極めて大きいものとなっている。これはミリ波帯においては回路間の結合や伝送線路の不連続部がMMICの特性を劣化させるために、直線的な設計をせざるを得ず、集積度を上げることが困難であるためである。さらに設計時に不連続部等を電磁界シミュレーション等で詳細に検討する必要があり、設計、レイアウトが複雑かつ時間がかかるものとなっている。

本章ではミリ波帯での小型、高集積MMICを実現するため、ミリ波帯、特にV帯への3次元MMICの適用に焦点を当て、3次元MMIC技術がミリ波帯MMICの小型化高集積化に極めて有効であることを示す。TFMS線路のミリ波帯での特性について、従来のマイクロストリップ線路、コプレーナ線路との比較により、その優位性を示す。さらに、曲がり部等の不連続部の特性について明らかにし、その特性が従来の最適化されたマイクロストリップ線路の不連続部と同等であることを示す。さらに、ミリ波帯MMICの高集積化を実現する構成及び設計法について示すとともに、実現したV帯1チップアップコンバータ／ダウンコンバータMMICについて述べる。

### 5.2 ミリ波帯における3次元MMICの伝送線路特性 [7]

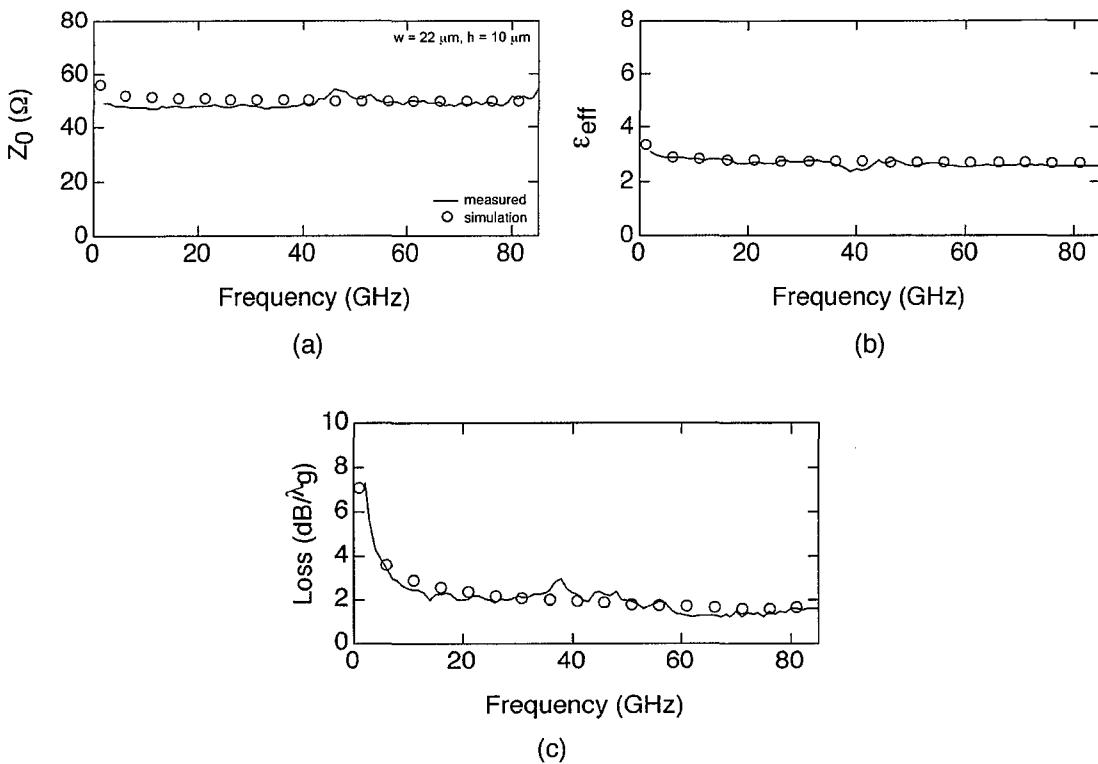

#### 5.2.1 TFMS線路の基本特性

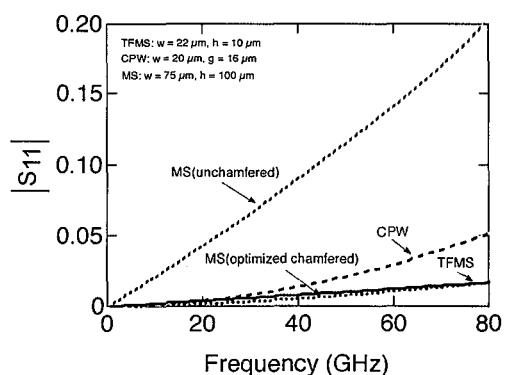

図5.1は線路幅22μm(誘電体基板厚10μm)のTFMS線路の特性を示した測定値である。ネットワークアナライザによりS-parameterを測定し、そのデータより特性インピーダンス、実効誘電率、損失を求めている。また、同図には市販の電磁界シミュレータ(Sonnet Inc.社em)で計算した値も合わせて示している(○で示す)。特性インピーダンス、実効誘電率とも測定した85GHzまではほぼ一定の値を示しており、周波数分散の小さい特性を持っている。また損失は20GHz以上において2dB/λ<sub>g</sub>以下であり60GHzでは1.7dB/λ<sub>g</sub>である。測定値と計算値はよく一致しており、シミュレーションによる特性把握が十分可能であり、設計精度が良いことを示している。

図 5.1 TFMS 線路の周波数特性

(a) 特性インピーダンス, (b)実効誘電率, (c)損失

表 5.1 60GHz での各種伝送線路の特性比較

| $f = 60 \text{ GHz}$                                | TFMS<br>$h = 10 \mu\text{m}$<br>$w = 22 \mu\text{m}$ | Microstrip<br>$h = 100 \mu\text{m}$<br>$w = 75 \mu\text{m}$ | CPW<br>$g = 16 \mu\text{m}$<br>$w = 20 \mu\text{m}$ |

|-----------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------|

| Guided wavelength $\lambda_g$ (mm)                  | 2.96                                                 | 1.72                                                        | 2.03                                                |

| Electrical length of 90-degree bend (degree)        | 2.3                                                  | 14.7                                                        | 9.4                                                 |

| Reflection coefficient $ S_{11} $ of 90-degree bend | 0.0122                                               | 0.141                                                       | 0.0294                                              |

| Electrical length of via pad size (degree)          | 2.4 - 3.6                                            | 31.4 - 41.9                                                 | —                                                   |

| Inductance of via-hole (pH)                         | 1.8                                                  | 14                                                          | —                                                   |

| Loss per wavelength (dB / $\lambda_g$ )             | 1.7                                                  | 0.46                                                        | 1.68                                                |

表 5.1 は TFMS 線路, マイクロストリップ線路, コプレーナ線路のそれぞれの 50Ω線路の 60GHz での特性を比較したものである。それぞれの物理寸法は TFMS 線路が線路幅 22μm, ポリイミド基板厚 10μm, マイクロストリップ線路が線路幅 75μm, GaAs 基板厚 100μm (この値はマイクロストリップ線路を用いて実現する MMIC の一般的な GaAs ウエハの厚みである),

コプレーナ線路は線路幅 20 $\mu\text{m}$ , 信号線と接地導体のギャップ 16 $\mu\text{m}$  (GaAs 基板厚 600 $\mu\text{m}$ ) である。表に示すように、TFMS 線路の 90 度ペンド, ピアホールパッド, ピアホールのインダクタンスの値は他の線路と比較して 1/4 から 1/10 の値であり、極めて小さい値であるといえる。この TFMS 線路の特性はペンドやピアパッド等の不連続部は従来の伝送線路と比較して極めて小さく、回路設計を簡略化するだけでなく伝送線路をコンパクトに配置することができることを示している。また、波長あたりの損失もコプレーナ線路とほぼ同等である。マイクロストリップ線路の損失と比較すると約 4 倍の値となっているが、後に 60GHz 帯の低雑音増幅器の特性で示すようにこの損失の差は機能回路実現には問題とならない値である。

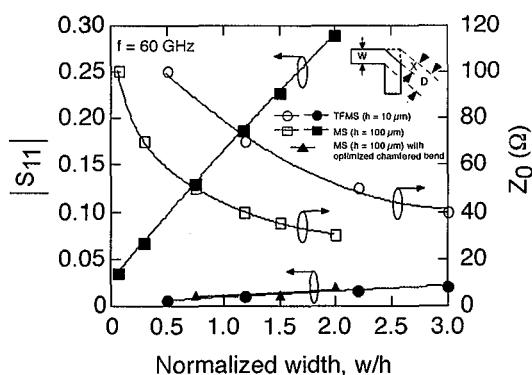

図 5.2 は 60GHz での TFMS 線路とマイクロストリップ線路の 90 度ペンドの反射特性の線路幅依存性を比較したものである。合わせて対応する線路幅の特性インピーダンスも同時に示している。TFMS 線路は単純に 90° に曲げた場合のデータ（黒丸で示す）、マイクロストリップ線路 (GaAs 基板厚 100 $\mu\text{m}$ ) は単純に 90° に曲げた場合と（黒四角で示す）、コーナーで発生する不連続を極力抑えるように次式で示される条件のもとに曲がり部の角にきざみを入れて最適化された場合（黒三角で示す） [8] を示している。

$$\frac{X}{D} = 0.52 + 0.65 \times e^{(-1.35 \times (W/H))}$$

W : 線路幅, H : 基板厚

この図が示すように TFMS 線路の単純な曲がり部の反射係数はマイクロストリップ線路の単純な曲がり部に比較して極めて小さく、マイクロストリップ線路の最適化された曲がり部の値とほぼ同等である。さらにその小さい反射特性はその特性インピーダンスが 100 $\Omega$ から 40 $\Omega$ という広いインピーダンス範囲で実現している。図 5.3 は表 5.1 に示した 50 $\Omega$ 伝送線路の 90 度ペ

図 5.2 90 度ペンドの反射特性の線路

幅依存性

図 5.3 90 度ペンドの反射特性の

周波数依存性

ント部の反射特性の周波数依存性を示している。TFMS 線路のペンド部の反射特性はすべての周波数において他の伝送線路のものに比較して極めて小さい値であり、0.02 以下である。これは理想的に最適化されたマイクロストリップ線路のペンド部とほぼ同等の値である。これらの結果は TFMS を用いることにより、曲がり部等の寄生成分を考慮せずに回路設計が可能であることを示しており、回路設計の簡易化（回路設計からレイアウトへのストレートフォワード設計）を実現できる可能性が高いことを示している。さらに、曲がり部を多数使用することが可能となり、メアンダ線路等により回路の小型化を実現できることを示している。

### 5.2.2 最小隣接線路間隔

隣接伝送線路間の結合特性は線路間隔と電気長に依存している。1/4 波長線路の結合係数は一般的に以下の式で示される。

$$k = \frac{Z_{even} - Z_{odd}}{Z_{even} + Z_{odd}}$$

$$Z_m = \frac{1}{\sqrt{C_m^a \cdot C_m}} \quad (\text{m is even or odd})$$

$Z_{even}$ ,  $Z_{odd}$  は even モード, odd モードの特性インピーダンスであり,  $C$  は真空中の光の速度である。 $C_m^a$  は空気中での even モード, odd モードの結合容量,  $C_m$  は誘電体中での結合容量を示している。 $Z_m$ ,  $C_m^a$ ,  $C_m$  は規格化線路間隔 ( $s/h$ ,  $s$ : 線路間隔,  $h$ : 基板厚) に依存している。さらに  $Z_0$  は以下の式で示される。

$$Z_0 = \sqrt{Z_{even} \cdot Z_{odd}}$$

図 5.4 は 50ΩTFMS 線路が並走してレイアウトされた場合の隣接線路間結合と線路間隔の関係を示したものである。結合量として  $S_{31}$  (バックワードカップリング),  $S_{41}$  (フォワードカップリング) を示す。

図 5.4 60GHz での TFMS 線路の隣接線路間結合と線路間隔の関係