|              |                                                                                 |

|--------------|---------------------------------------------------------------------------------|

| Title        | GaAs/Siの電子デバイス応用に関する研究                                                          |

| Author(s)    | 藍郷, 崇                                                                           |

| Citation     | 大阪大学, 1997, 博士論文                                                                |

| Version Type | VoR                                                                             |

| URL          | <a href="https://doi.org/10.11501/3129245">https://doi.org/10.11501/3129245</a> |

| rights       |                                                                                 |

| Note         |                                                                                 |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

GaAs/Si の電子デバイス応用に

関する研究

1996年11月

藍郷 崇

**GaAs/Si の電子デバイス応用に

関する研究**

**1996年11月**

**藍郷 崇**

# GaAs/Siの電子デバイス応用に関する研究

## 内容概略

本研究は有機金属気相成長法（MOCVD法）によりSi基板上に成長させたGaAsエピタキシャル層（以下GaAs/Si）の電子デバイスへの応用に関するものであり、成長方法、エピ層の評価、電子デバイスへの応用、デバイスの信頼性について述べたものである。

論文は7章で構成されている。

第1章では、GaAs/Siの特長およびそれを電子デバイスへ応用することの意義、結晶成長技術とデバイス応用に関する開発概要について述べる。さらにはその開発過程で明らかになったGaAs/Siの問題点を述べ、本研究の位置づけと目的を明らかにする。

第2章では、MOCVD装置の概要とこの装置を用い二段階成長法で行った電子デバイス用GaAs/Siの成長条件について述べる。また本研究で用いた縦型高速回転タイプのMOCVD装置が、その構造上Si基板からのSiのオートドーピングが防止できることも示す。

第3章では、成長したGaAs/Siが電子デバイス用ウェーハとしての仕様を満足しているかを評価するために、キャリア密度、膜厚の面内均一性、バッファ層のリーク電流、キャリア移動度および表面モホロジーを調べた結果について述べる。面内均一性については、4インチウェーハにおいて膜厚で平均値±1.5%、キャリア密度で平均値±5%のばらつきに押さえられており、良好であることが示された。バッファ層のリーク電流に関してはGaAs-Si界面層の影響が考えられたため、その界面層のキャリア密度をC-V測定とRaman散乱で評価し、少なくともキャリア密度 $1 \times 10^{18} \text{ cm}^{-3}$ で厚さ $0.1 \mu\text{m}$ 程度の導電層が形成されていることがわかった。リーク電流の値は若干GaAs/GaAsよりも大きかったが、その絶対値からは電流は絶縁層内を流れていると考えられ、界面導電層のリークパスとしての影響はほとんど見られなかった。キャリア移動度はnon-dopeでp型のGaAs/GaAsについて77Kで約 $6000 \text{ cm}^2/\text{V} \cdot \text{sec}$ であり、かなり高品質の膜であることがわかった。表面モホロジーはAFMで観察し、as-grownの状態で表面荒さの平均二乗根（RMS）が $2 \times 2 \mu\text{m}^2$ の範囲で $2.3 \text{ nm}$ と良好な値を示した。

さらにGaAs/Siの放熱性を評価するため、デバイスのゲートショットキー接合

を利用して測定した熱抵抗の結果についても述べる。結果として、用いたサンプルにおいては、GaAs/Siの熱抵抗はGaAs/GaAsの約2/3とGaAs/Siの熱的優位性が実証され、また計算とも比較的良好く一致した。

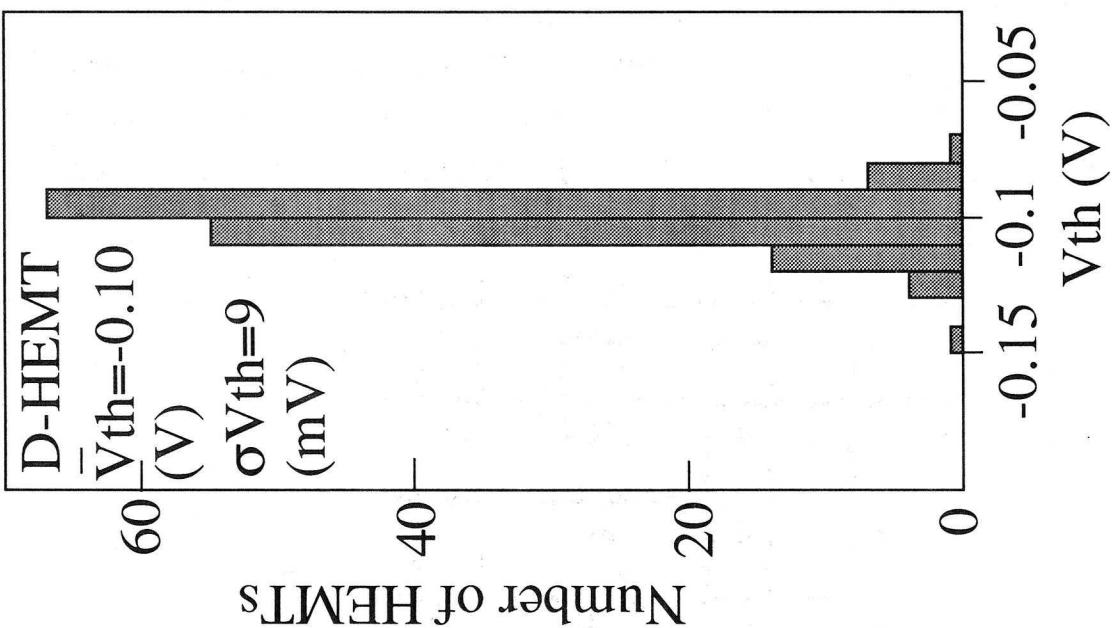

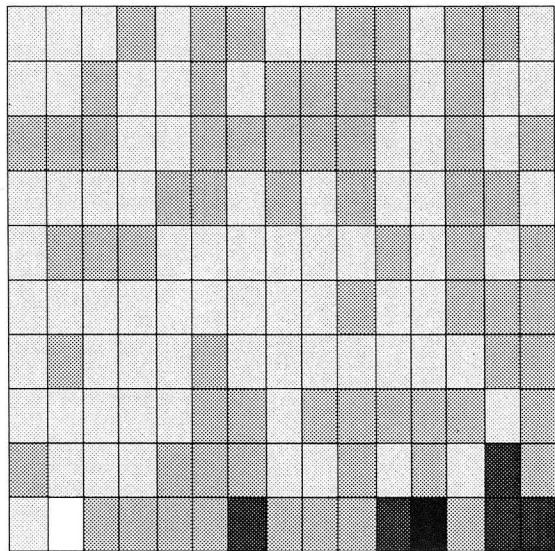

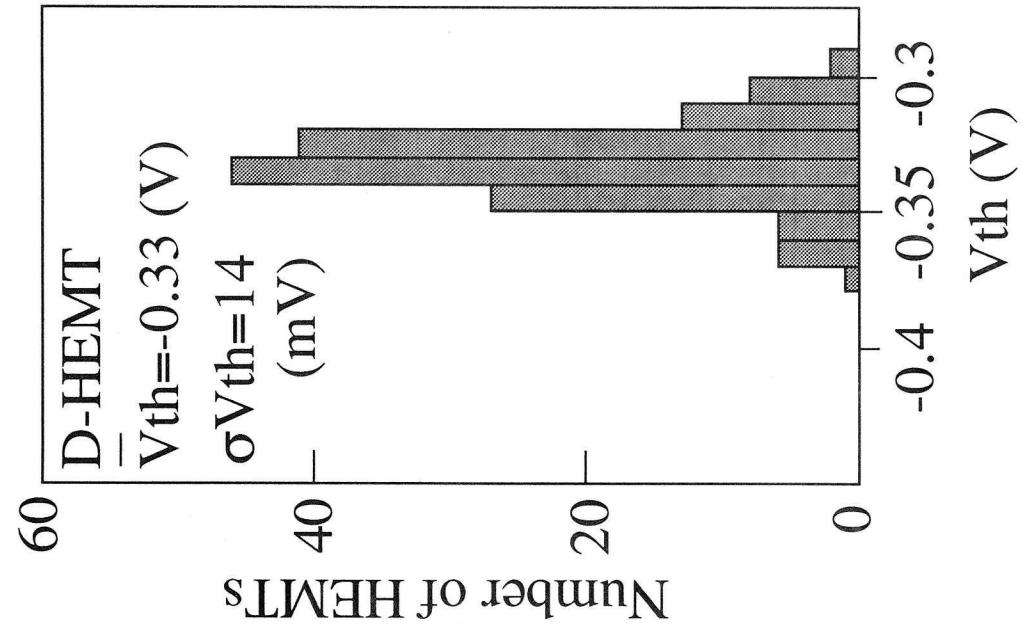

第4章では、高電子移動度トランジスタ（HEMT）構造を持つGaAs/Siを試作し、そのしきい値電圧分布と高周波特性を評価した結果について述べる。しきい値電圧のマクロ（ウェーハ面内）評価においては、結晶成長装置の特性を反映したと思われる、膜厚あるいはキャリア密度のゆるやかな面内分布に基いた分布が観察されたが、ミクロ（ $1.95 \times 1.9 \text{ mm}^2$ 内）評価においては  $V_{th}$  の平均値  $-0.10 \text{ V}$  に対し標準偏差  $\sigma V_{th} = 9 \text{ mV}$  という HEMT/GaAs に匹敵する極めて優れた均一性が得られた。しかもこの高い均一性は結晶内部に存在する転位数の多少にかかわらず得られており、転位は HEMT のようなエピタキシャル層を用いるデバイスのしきい値電圧分布には影響を与えていないことが明らかになった。

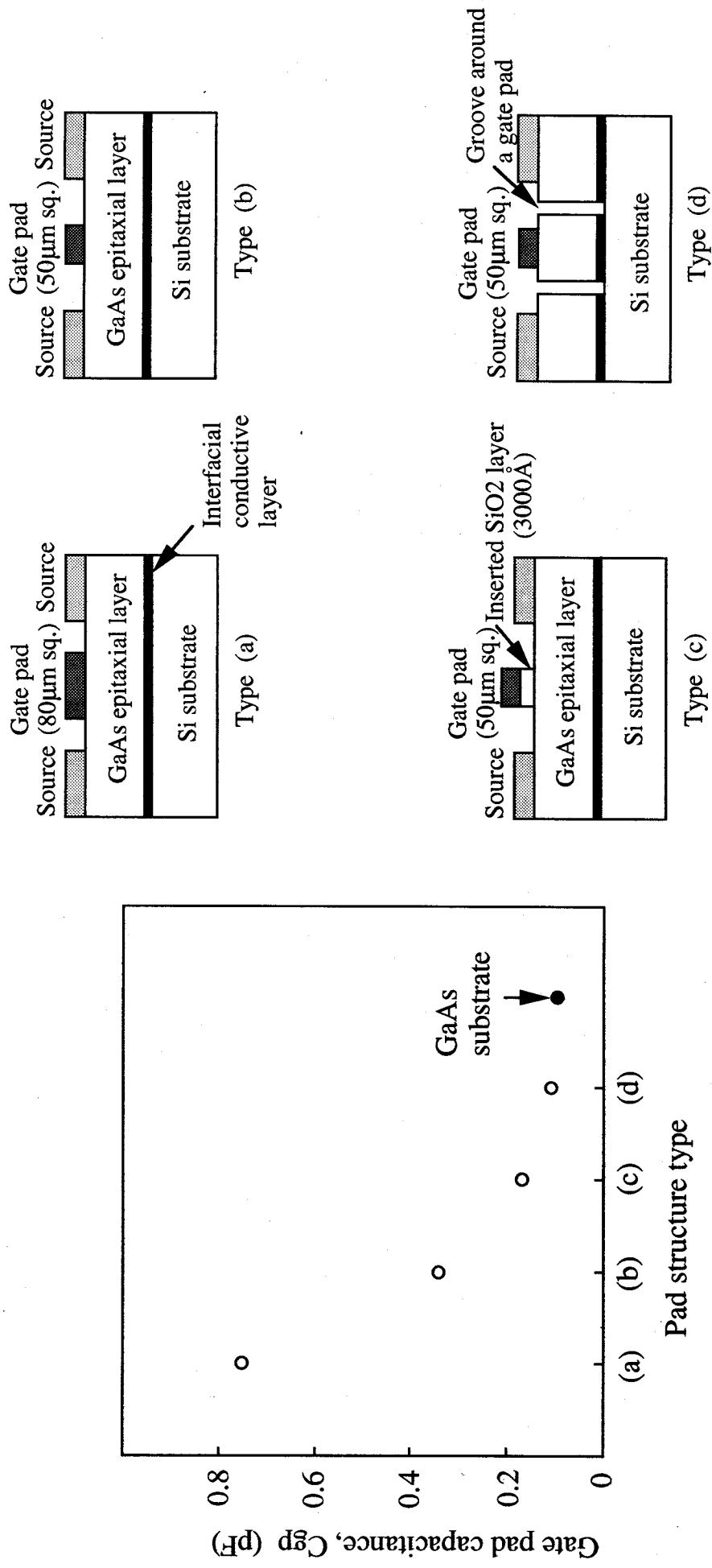

高周波評価によって HEMT/Si は HEMT/GaAs に比べて寄生成分、とくに寄生容量の影響を大きく受けていることが明らかになった。この寄生容量は、主として Si 基板 - GaAs 界面の導電層によって誘起されたゲートパッド容量によるものであり、パッド面積の縮小やパッド下絶縁層の挿入等の比較的容易なプロセスにより GaAs 基板上のパッド容量並に減少できることがわかった。実際にそのような対策を施した HEMT/Si はゲート長  $0.8 \mu \text{m}$  で  $24 \text{ GHz}$  の  $f_T$  と  $f_{max}$  を示し、HEMT/GaAs に遜色のない特性を示した。

第5章では、GaAs/Si を用いてパワー MESFET を試作した結果について述べる。ゲート幅の大きいデバイスは入力真性容量が大きいため、必然的にゲートパッドによる入力寄生容量の影響が小さくできるという観点より、まず GaAs 基板上のデバイスとほぼ同じ方法で設計し、必要となる全ゲート幅から入力真性容量を求め、その 10% を許容できる入力寄生容量としてゲートパッドとゲートバスラインに割り振るという方法でデバイス設計を行った。その結果、ゲートバスライン下に絶縁膜を挿入せざるを得なかつたが、小信号等価回路パラメータの評価より、ほぼ設計通りの寄生容量の値になっていることが確かめられた。

このパワー MESFET を携帯電話での応用を想定した条件 ( $f = 0.85 \text{ GHz}$ ,  $V_{ds} = 3.6 \text{ V}$ ) で評価した結果は、線形領域での利得が約  $20 \text{ dB}$ 、また  $1 \text{ dB}$  コンプレッション時の出力が  $25.7 \text{ dBm}$  ( $370 \text{ mW}$ )、その時の電力付加効率が 57% であった。これは GaAs/GaAs デバイスと同等であり、パワー MESFET 構造であれば、上記の設計指針で GaAs/Si 特有の寄生容量をほとんど影響のないレベルまで低減でき、GaAs 基板上のものと遜色ないデバイスが得られることが実証された。

第6章では第5章で試作した MESFET/Si と MESFET/GaAs を用いて直流による通

電高温放置試験を行い、両者の信頼性を評価した結果について述べる。両者とも故障のモードは同じであり、ゲートの一部が動作しなくなったことによるノンピングチオフ現象とドレイン電流の増加が見られた。故障部位の分析により、ゲートのAl電極の一部がソースあるいはドレイン電極方向に拡散してゲート部分から消失していることがわかり、さらにAlとチャネルのGaAsとの界面では相互反応の結果絶縁物が形成されている可能性の高いことが示された。この加速試験からチャネル温度130℃の時のMESFET/Siの平均故障時間（MTTF）として $1.28 \times 10^6$ hrと通常の市販レベルのMESFET/GaAsと同等の値が得られ、デバイスの経時劣化をもたらす可能性があるとして懸念されていたGaAs/Si中に存在する転位や残留応力は、デバイスの信頼度に影響を与えないことが証明された。

第7章は本研究の結果をまとめたものである。

# 目次

|                                     |    |

|-------------------------------------|----|

| 第1章 序論 .....                        | 1  |

| 1.1 はじめに .....                      | 1  |

| 1.2 Si基板上のGaAs .....                | 1  |

| 1.2.1 結晶成長 .....                    | 1  |

| 1.2.2 デバイス応用 .....                  | 2  |

| 1.2.3 GaAs/Siの問題点 .....             | 3  |

| 1.3 本研究の目的 .....                    | 3  |

| 第2章 MOCVDによる電子デバイス用GaAs/Siの成長 ..... | 8  |

| 2.1 はじめに .....                      | 8  |

| 2.2 結晶成長 .....                      | 8  |

| 2.2.1 成長系 .....                     | 8  |

| 2.2.2 基板処理 .....                    | 10 |

| 2.2.3 成長手順 .....                    | 10 |

| 2.3 成長条件 .....                      | 10 |

| 2.4 Siのオートドーピングについて .....           | 11 |

| 2.5 まとめ .....                       | 12 |

| 第3章 電子デバイス用GaAs/Siウェーハの評価 .....     | 14 |

| 3.1 はじめに .....                      | 14 |

| 3.2 面内均一性 .....                     | 14 |

| 3.2.1 膜厚 .....                      | 14 |

| 3.2.2 キャリア密度 .....                  | 14 |

| 3.3 リーク電流 .....                     | 14 |

| 3.3.1 GaAs-Siの界面評価 .....            | 14 |

| 3.3.2 リーク電流評価 .....                 | 21 |

| 3.4 キャリア移動度 .....                   | 23 |

| 3.5 表面モホロジー .....                   | 23 |

| 3.6 GaAs/Siの熱抵抗 .....               | 26 |

| 3.6.1 測定方法および結果 .....               | 26 |

| 3.6.2 計算による検証 .....                 | 26 |

| 3.7 まとめ .....                       | 32 |

|                               |    |

|-------------------------------|----|

| 第4章 HEMT/Siのしきい値電圧分布と高周波特性評価  | 34 |

| 4.1 はじめに                      | 34 |

| 4.2 実験方法                      | 34 |

| 4.2.1 結晶成長およびデバイスプロセス         | 34 |

| 4.2.2 GaAs/AlGaAsの選択ドライエッチング  | 35 |

| 4.3 試作したHEMT/Siの直流特性          | 37 |

| 4.4 HEMT/Siのしきい値電圧分布          | 37 |

| 4.4.1 しきい値電圧マクロ分布             | 37 |

| 4.4.2 しきい値電圧ミクロ分布             | 41 |

| 4.5 HEMT/Siの高周波特性             | 45 |

| 4.5.1 Sパラメータ測定                | 45 |

| 4.5.2 HEMT/Siの小信号等価回路         | 48 |

| 4.5.3 等価回路パラメータ               | 51 |

| 4.5.4 寄生成分の起因源                | 51 |

| 4.6 寄生成分の影響を低減したHEMT/Siの高周波特性 | 57 |

| 4.6.1 パッド容量の低減                | 57 |

| 4.6.2 パッド容量を低減したHEMT/Siの高周波特性 | 58 |

| 4.7 まとめ                       | 60 |

| <br>第5章 パワーMESFET/Siの試作       | 64 |

| 5.1 はじめに                      | 64 |

| 5.2 デバイス設計                    | 64 |

| 5.2.1 全ゲート幅                   | 64 |

| 5.2.2 活性層厚                    | 66 |

| 5.2.3 単位ゲート幅                  | 66 |

| 5.2.4 ゲートボンディングパッド数           | 66 |

| 5.2.5 パワーMESFET構造における寄生容量の影響  | 67 |

| 5.3 デバイスプロセス                  | 68 |

| 5.4 直流特性                      | 68 |

| 5.5 高周波特性                     | 72 |

| 5.5.1 等価回路パラメータ               | 72 |

| 5.5.2 入出力特性                   | 73 |

| 5.5.3 電源電圧依存性                 | 73 |

| 5.6 まとめ                       | 75 |

|                       |    |

|-----------------------|----|

| 第6章 GaAs/Si電子デバイスの信頼性 | 76 |

| 6.1 はじめに              | 76 |

| 6.2 実験方法              | 76 |

| 6.3 実験結果              | 77 |

| 6.3.1 故障モード           | 77 |

| 6.3.2 故障部位の同定と解析      | 80 |

| 6.3.3 デバイスの寿命解析       | 86 |

| 6.4 まとめ               | 89 |

| 第7章 結論                | 90 |

| 謝辞                    | 93 |

| 本研究に関する発表論文           | 94 |

| 本研究に関する学会報告           | 96 |

# 1. 序論

## 1.1 はじめに

GaAsおよびGaAs系混晶は、MESFET（Metal Semiconductor Field Effect Transistor）やHEMT（High Electron Mobility Transistor）あるいはHBT（Hetero Bipolar Transistor）を代表とする超高速デバイス、また発光ダイオード、レーザダイオード等の光デバイス用材料として現在広範囲に用いられている。特に近年の移動体通信機器市場の飛躍的な拡大により、GaAs系電子デバイスさらにはGaAs基板の需要が急激に増加している。一方Si基板は現在の半導体産業を支える基本材料であることはもとより、機械的堅牢さ、良好な熱伝導性、大口径な基板等GaAs基板では得られない魅力を備えている。Si基板上にGaAsをエピタキシャル成長させた、いわゆるGaAs/Si基板は、この両者の特長を合わせ持つことで上記デバイスの特性向上かつコストダウンが期待できるのみならず、オプトエレクトロニクスデバイス等の新デバイスへの応用も可能になる。

本研究の目的は、このGaAs/Si基板の電子デバイスへの適用可能性を調べることである。GaAs/Si技術は1980年代前半に開発され<sup>(1)</sup>、多くの研究機関でエピ成長および電子デバイスや光デバイスへの応用という両面から研究が進められてきた。しかし高密度の転位、残留応力、Si基板あるいはSi-GaAs界面の導電性等ハテロエピタキシャル基板であるが故の問題点が明らかになってきたため<sup>(2-7)</sup>、まだ現在までは実デバイス用基板としての積極的な使用の動きは見られていない。しかし本研究により、応用デバイスによってはGaAs/Si基板でもGaAs/GaAs基板と同等な特性の得られることが初めて示され、GaAs/Si基板が実用性のある材料として再び見直され始めている。

## 1.2 Si基板上のGaAs

### 1.2.1 結晶成長

Si基板上のGaAs成長はGeをバッファ層として用いる方法がまず1980年代初めに行われた<sup>(8-10)</sup>。その後MBEを用いたSi基板上へのGaAs直接成長が、IBM<sup>(11)</sup>、MIT<sup>(12)</sup>、Illinois大学<sup>(13, 14)</sup>で行われ、日本でも沖電気<sup>(1, 15)</sup>がMOCVDを用いて、低温で成長させたGaAs薄膜をバッファ層とするいわゆる二段階成長法を報告した。これらの方法によりSi基板上に直接single domainで鏡面のGaAsを成長させることができた。

1990年代に入ると、GaAs層の結晶性向上のため、成長の初期条件あるいは前処理に関する報告<sup>(16, 17)</sup>やALEによるAlAs層をバッファ層に用いた報告<sup>(18)</sup>がなされるようになり、また富士通からは、表面モロジー改良のため研磨したGaAs/Si基板への再成長<sup>(19)</sup>や四段階成長法<sup>(20)</sup>が提案されるようになった。さら

に筆者等の研究グループからはあらかじめ水素中でSi基板を高温前処理しておくことにより、成長時のpre-heating温度が低減できること<sup>(21)</sup>が示されている。一方オプトエレクトロニクスデバイスへの応用の際には重要になると予想される、マスクレスでの選択成長も試みられている<sup>(22)</sup>。

### 1.2.2 デバイス応用

GaAs/Siの電子デバイスへの応用は、MESFETやHEMTに対するものが多く、1980年代の中頃までにはIllinois大学でHEMT<sup>(23)</sup>が、MITでMESFET<sup>(24-26)</sup>が試作された。また沖電気ではゲート長 $1\mu\text{m}$ で17段のMESFETリングオシレータを試作し、ゲート当たり $1.1\text{mW}$ のpower dissipationでdelay time 51psを報告している<sup>(27)</sup>。高周波における評価は最初にIllinois大学によってなされ、ゲート長 $0.25\mu\text{m}$ のMESFETを試作し55GHzのカットオフ周波数と18GHzでの雑音指数2.8dBを達成した<sup>(28)</sup>。さらに同大学では、ゲート長 $1\mu\text{m}$ のHEMT/SiとHEMT/GaAsの高周波評価も行い、両者ともカットオフ周波数が15GHzで差が見られないことを示している<sup>(29)</sup>。一方GaAs/SiをデジタルIC用基板として用いる試みはTIによってなされ<sup>(30)</sup>、1kbitのSRAMを試作し、access timeが6~14nsとGaAs基板に匹敵する値を報告した<sup>(31)</sup>。またATTでもGaAs/Si基板を用いたMESFETのリングオシレータで一段当たりのdelay time 52ps<sup>(32)</sup>や、さらにはHEMTのリングオシレータでdelay time 28ps<sup>(33)</sup>を報告している。1980年代後半からは電子移動度の大きいInGaAs層をGaAs/Siデバイスに取り入れる試みが始まり、ドープされたInGaAsをチャネルとしたゲート長 $0.5\mu\text{m}$ のMESFETで52GHzのカットオフ周波数が報告された<sup>(2)</sup>。さらに1990年代に入ると富士通を中心にInGaAsを電子走行層としたHEMTのDCFL<sup>(34)</sup>やプリスケーラIC<sup>(35)</sup>が試作されるようになり、リングオシレータで一段当たりのdelay time 31.3ps、128/129分周のプリスケーラで電源電圧1.5V、入力周波数3.6GHz、消費電力9.8mWが確認されている。

光デバイスに関しては、Ge中間層を持ったGaAs/Siを用いてLEDが試作されたのが最初である<sup>(9, 10)</sup>。LDに関しては、1984年にMITで77Kでのパルス発振が最初の報告であり<sup>(36)</sup>、その後名古屋工業大学では歪み超格子を用いる方法<sup>(37)</sup>で、Illinois大学ではオフ基板を用いる方法<sup>(38)</sup>で転位密度を低減してしきい値電流密度を下げ、室温でのパルス発振が得られるようになった。更に1987年には室温での連続発振がGaAs基板を用いたものに匹敵するしきい値電流密度で達成されている<sup>(39)</sup>。また近年ではオプトエレクトロニクスデバイスへのGaAs/Siの応用も試みられるようになっている<sup>(40)</sup>。

### 1.2.3 GaAs/Siの問題点

前記のように種々のデバイス応用が試みられてきたGaAs/Si基板であるが、基本的な問題点としてSiとGaAsの約4%の格子不整合および約2.5倍の熱膨張係数の差に基づく転位と熱歪みの発生がある。転位はas-grownの状態で約 $10^8\text{cm}^{-2}$ 存在しており、再結合中心になるため特に発光素子において大きな問題となる。さらにGaAs/Si基板を用いたイオン注入MESFETにおいても転位の存在によるしきい値電圧の変化が観察されている<sup>(41, 42)</sup>。

転位低減に関しては、高温アニールを行う方法<sup>(43, 44)</sup>、歪み超格子を用いる方法<sup>(45-47)</sup>等があり、1980年代末までには $10^6\text{cm}^{-2}$ 台までに転位を減らすことが可能になった。さらに1990年前後からはMEEを用いるNTTの方法<sup>(48)</sup>、歪み超格子と高温アニールを併用する筆者等の研究グループ<sup>(49)</sup>や名古屋工業大学<sup>(50)</sup>の方法が報告され、転位密度は $10^5\text{cm}^{-2}$ 台以下までになった。一方熱歪みに関しては、GaAs層の残留応力は約 $10^9\text{dyn/cm}^2$ であることが示されている<sup>(51)</sup>。長寿命の半導体レーザを得ようとした場合には、これを $10^8\text{dyn/cm}^2$ 以下にしなければならないことが報告されており<sup>(52, 53)</sup>、またこの応力はウェーハに反りを発生させるため、より大口径のGaAs/Siではプロセスが困難になってくる。レーザに関しては、InGaAs中間層と活性層を用いることにより転位密度と応力を同時に低減させ寿命改善がなされており<sup>(40)</sup>、ウェーハの反りについても、InAlGaAs/AlGaAsの歪み超格子をバッファ層にし、かつエピ層厚を減らす等<sup>(54)</sup>の方法により従来の1/3程度にまで反りを押さえることが可能になっている。

GaAs/Siのもう一つの基本的問題として、結晶成長中にoutdiffusionした基板のSi原子によりSi-GaAs界面に形成される導電層、あるいはSi基板自身の導電性による影響があげられる。デバイス試作の初期では高周波評価が不十分であったこともあり、この問題はあまり指摘されていなかったが、Sパラメータ測定による等価回路評価が進展するにつれ、特にディスクリート素子においてそれが特性に悪影響を与えるものとして認識されてきた<sup>(2, 3)</sup>。さらに筆者等の研究<sup>(55-57)</sup>や他機関からの報告<sup>(4, 5)</sup>により、Si-GaAsの界面導電層の存在が、コンダクタンスおよび寄生容量の増加としてGaAs/Si電子デバイスの特性を劣化させていることが明らかになった。

## 1.3 本研究の目的

本研究の目的は、前記のような長短所を合わせ持つこのGaAs/Si基板が適用できる電子デバイス分野を調べることであるが、電子デバイスの中でも転位等の影響を受けにくいであろうとの予想より多数キャリアデバイスに絞り、またGaAs/Si成長自体がエピタキシャル成長であることから、活性層がエピタキシャル層であるデバイス（エピタキシャルデバイス）を用いて研究を行った。具体的には

HEMT構造を持つGaAs/Si（HEMT/Si）およびMESFET構造を持つGaAs/Si（MESFET/Si）に対してデバイスを試作し、アナログ、デジタル両方への応用を想定した評価を行った。その内容は以下の通りである。

- (1) MOCVD法を用いて高品質で安定にHEMT/SiやMESFET/Siを得るための成長前処理および成長に関する条件を確立する。

- (2) 成長したGaAs/Si基板に対し膜厚、キャリア密度の均一性、バッファ層のリーコ電流、キャリア移動度、表面モホロジー、の評価を行い、電子デバイス用ウェーハとしての仕様を満たしているかを検討する。また熱抵抗の測定により熱放散の優位性に関する知見を得る。

- (3) 転位密度の異なるHEMT/Siのしきい値電圧分布評価により、転位がデバイス特性に及ぼす影響の有無を調べる。また高周波評価から得られる等価回路パラメータ解析に基づき、GaAs/Si電子デバイス固有の問題点を調べその解決法を検討する。

- (4) (3)で得られた解決法を取り入れて試作したパワーMESFET/Siの入出力特性評価から、GaAs/Si基板のパワー素子への適用可能性を探る。

- (5) MESFET/Siの通電高温放置試験を行い、GaAs/Si電子デバイスの信頼性をGaAs/GaAsデバイスと比較評価する。

#### （参考文献）

- (1) Masahiro Akiyama, Yoshihiro Kawarada, and Katsuzo Kaminishi : Jpn. J. Appl. Phys. **23** (1984) L843.

- (2) G. W. Wang, C. Ito, M. Feng, R. Kaliski, D. McIntyre, C. Lau, and V. Eu : Appl. Phys. Lett. **55** (1989) 1552.

- (3) M. N. Charasse, B. Bartenlian, B. Gerard, J. Hirtz, M. Laviron, A. M. de Parscau, M. Derevonko, and D. Delagebeaudeuf : Jpn. J. Appl. Phys. **28** (1989) L1896.

- (4) S. Sriram, R. L. Messham, T. J. Smith, H. M. Hobgood, and M. C. Driver : Proc. 1990 IEEE Gallium Arsenide Integrated Circuit Symposium (1990) 229.

- (5) Alexandros Georgakilas, George Halkias, Aris Christou, Christos Papavassiliou, George Perantinos, George Konstantinidis, and Paul N. Panayotatos : IEEE Trans. Electron Devices **40** (1993) 507.

- (6) H. K. Choi, and C. A. Wang

N. H. Karam : Appl. Phys. Lett. **59** (1991) 2634.

- (7) Takashi Egawa, Yoshiaki Hasegawa, Takashi Jimbo, and Masayoshi Umeno : Jpn. J. Appl. Phys. **31** (1992) 791.

- (8) B.Y. Tsaur, M. W. Geis, John C. C. Fan, and R.P. Gale: *Appl. Phys. Lett.* **38** (1981) 779.

- (9) Yukinobu Shinoda, Takashi Nishioka, and Yoshiro Ohmachi: *Jpn. J. Appl. Phys.* **22** (1983) L450.

- (10) Robert M. Fletcher, D. Ken Wagner, and Joseph M. Ballantyne : *Appl. Phys. Lett.* **44** (1984) 967.

- (11) W. I. Wang : *Appl. Phys. Lett.* **44** (1984) 1149.

- (12) B-Y. Tsaur, and G. M. Metze : *Appl. Phys. Lett.* **45** (1984) 535.

- (13) W. T. Masselink, T. Henderson, J. Klem, R. Fischer, P. Pearah, and H. Morkoç M. Hafich, P. D. Wang, and G. Y. Robinson : *Appl. Phys. Lett.* **45** (1984) 1309.

- (14) R. Fischer, W. T. Masselink, J. Klem, T. C. McGinn, M. V. Llein, and H. Morkoç J. H. Mazur, and J. Washburn : *J. Appl. Phys.* **58** (1985) 374.

- (15) Masahiro Akiyama, Yoshihiro Kawarada, Takashi Ueda, Seiji Nishi and Katsuzo Kaminishi : *J. Cryst. Growth* **77** (1986) 490.

- (16) K. Fujita, Y. Shiba, and T. Yamamoto : *J. Cryst. Growth* **99** (1990) 341.

- (17) N. Takagi, T. Eshita, S. Miyagaki, M. Kimura, and K. Takasaki : *Mat. Res. Soc. Symp. Proc.* (1992) 305.

- (18) N. Ohtsuka, K. Kitahara, M. Ozeki, and K. Kodama : *J. Cryst. Growth* **99** (1990) 346.

- (19) Tatsuya Ohori, Haruyoshi Suehiro, Kazumi Kasai, and Junji Komeno : *Proc. Int. Symp. GaAs and Related Compounds* (1992) 175.

- (20) S. Ohkubo, K. Takai, N. Takagi, S. Miyagaki, T. Eshita, and K. Takasaki : *Proc. Int. Symp. GaAs and Related Compounds* (1992) 187.

- (21) A. Jono, A. Tachikawa, T. Aigo, and A. Moritani : *J. Cryst. Growth* **145** (1994) 353.

- (22) A. Hashimoto, T. Fukunaga, and N. Watanabe : *J. Cryst. Growth* **99** (1990) 352.

- (23) R. Fischer, T. Henderson, J. Klem, W. T. Masselink, W. Kopp, and H. Morkoç C. W. Litton : *Electron. Lett.* **20** (1984) 945.

- (24) John C. C. Fan : Extended Abs. the 16th Conf. on Solid State Devices and Materials (1984) 115.

- (25) G. M. Metze, H. K. Choi, and B-Y. Tsaur : *Appl. Phys. Lett.* **45** (1984) 1107.

- (26) H. K. Choi, B-Y. Tsaur, G. M. Metze, G. W. Turner, and J. C. C. Fan : *IEEE Electron Device Lett.* **5** (1984) 207.

- (27) Toshio Nonaka, Masahiro Akiyama, Yoshihiro Kawarada, and Katsuzo Kaminishi : *Jpn. J. Appl. Phys.* **23** (1984) L919.

- (28) M. I. Askun, and H. Morkoç

L. F. Lester, K. H. G. Duh, P. M. Smith, and P. C. Chao

M. Longerbone, and L. P. Erickson : Appl. Phys. Lett. **49** (1986) 1654.

- (29) Russel J. Fischer, William F. Kopp, Jon S. Gedymin, and Hadis Morkoç : IEEE Trans. Electron Devices **33** (1986) 1407.

- (30) Hisashi Shichijo, and Jhang Woo Lee : Mat. Res. Soc. Symp. Proc. (1986) 173.

- (31) Hisashi Shichijo, J. W. Lee, Will V. McLevige, and A. H. Taddiken : IEEE Electron Device Lett. **8** (1987) 121.

- (32) F. Ren, N. Chand, P. Garbinski, S. J. Pearton, C. S. Wu, L. D. Urbanek, T. Fullowan, N. Shah, and M. D. Feuer : Electron. Lett. **24** (1988) 1039.

- (33) F. Ren, Naresh Chand, Young-Kai Chen, S. Pearton, D. M. Tennant, and D. J. Resnick : IEEE Electron Device Lett. **10** (1989) 559.

- (34) Haruyoshi Suehiro, Shigeru Kuroda, Tadayuki Miyata, Tatsuya Ohori, and Masahiko Takikawa : Extended Abs. the Int. Conf. on Solid State Devices and Materials (1992) 115.

- (35) 志村忠幸、末廣晴彦、大堀達也、中舎安弘、渡邊祐、黒田滋、滝川正彦：信学技報 ED94-131 (1994) 19.

- (36) T. H. Windhorn, G. M. Metze, B-Y. Tsaur, and John C. C. Fan : Appl. Phys. Lett. **45** (1984) 309.

- (37) Shiro Sakai, Tetsuo Soga, Masanari Takeyasu, and Masayoshi Umeno : Jpn. J. Appl. Phys. **24** (1985) L666.

- (38) R. Fischer, W. Kopp, and H. Morkoç

M. Pion, A. Specht, G. Burkhardt, H. Appelman, D. McGougan, and R. Rice : Appl. Phys. Lett. **48** (1986) 1360.

- (39) H. Z. Chen, A. Ghaffari, H. Wang, H. Morkoç, and A. Yariv : Optics Lett. **12** (1987) 812.

- (40) 江川孝志、長谷川義晃、山本圭、神保孝志、梅野正義：信学技報 ED92-51 (1992) 43.

- (41) 山岸長保、木村有、上田孝、小野沢幸子、秋山正博：第 51 回応用物理学会学術講演会予稿集 (1990) 29p - T - 7.

- (42) Akihiro Moritani, Akiyoshi Tachikawa, Aiji Jono, Takashi Aigo, Yoichi Ikematsu, Yoshiaki Sano, Chouho Yamagishi, and Masahiro Akiyama : to be published in Jpn. J. Appl. Phys.

- (43) C. Choi, and N. Otsuka

G. Munns, R. Houdre, and H. Morkoç

S. L. Zhang, D. Levi, and M. V. Klein : Appl. Phys. Lett. **50** (1987) 992.

- (44) H. L. Tsai, and J. W. Lee : Appl. Phys. Lett. **51** (1987) 130.

- (45) T. Soga, and S. Hattori

S. Sakai, M. Takeyasu, and M. Umeno : Electron. Lett. **20** (1984) 917.

- (46) R. Fischer, D. Neuman, H. Zabel, and H. Morkoç

C. Choi, and N. Otsuka : Appl. Phys. Lett. **48** (1986) 1223.

- (47) Masafumi Yamaguchi, Mitsuru Sugo, and Yoshio Itoh : Appl. Phys. Lett. **54** (1989) 2568.

- (48) Kazuhiko Nozawa, and Yoshiji Horikoshi : Jpn. J. Appl. Phys. **30** (1991) L668.

- (49) Akiyoshi Tachikawa, Aiji Jono, Takashi Aigo, and Akihiro Moritani : Extended Abs. of the Int. Conf. on Solid State Devices and Materials (1992) 635.

- (50) Tetsuo Soga, Takashi Jimbo, and Masayoshi Umeno : Appl. Phys. Lett. **56** (1990) 1433.

- (51) 秋山正博 : 京都大学学位論文 (1991)

- (52) Taibun Kamejima, Koichi Ishida, and Junji Matsui : Jpn. J. Appl. Phys. **16** (1977) 233.

- (53) A. R. Goodwin, P. A. Kirkby, I. G. A. Davies, and R. S. Baulcomb : Appl. Phys. Lett. **34** (1979) 647.

- (54) Tatsuya Ohori, Haruyoshi Suehiro, Kazumi Kasai, and Junji Komeno : Jpn. J. Appl. Phys. **33** (1994) 4499.

- (55) Takashi Aigo, Hirokatsu Yashiro, Mitsuhiro Goto, Aiji Jono, Akiyoshi Tachikawa, and Akihiro Moritani : Jpn. J. Appl. Phys. **32** (1993) 5508.

- (56) Takashi Aigo, Mitsuhiro Goto, Aiji Jono, Akiyoshi Tachikawa, and Akihiro Moritani : Proc. Int. Symp. GaAs and Related Compounds (1993) 87.

- (57) Takashi Aigo, Mitsuhiro Goto, Yasumitsu Ota, Aiji Jono, Akiyoshi Tachikawa, and Akihiro Moritani : IEEE Trans. Electron Devices **43** (1996) 527.

## 2. MOCVDによる電子デバイス用GaAs/Siの成長

### 2.1 はじめに

本章では、MOCVDによる二段階成長法<sup>(1)</sup>を用いてHEMT/SiやMESFET/Siを成長させる際の基本的成長条件について述べる。ここで示される条件は、次章以降で述べられるウェーハあるいはデバイス評価からのフィードバックを受け、高品質でかつ安定に電子デバイス用GaAs/Si基板を得るために改良されてきたものである。

### 2.2 結晶成長

#### 2.2.1 成長系

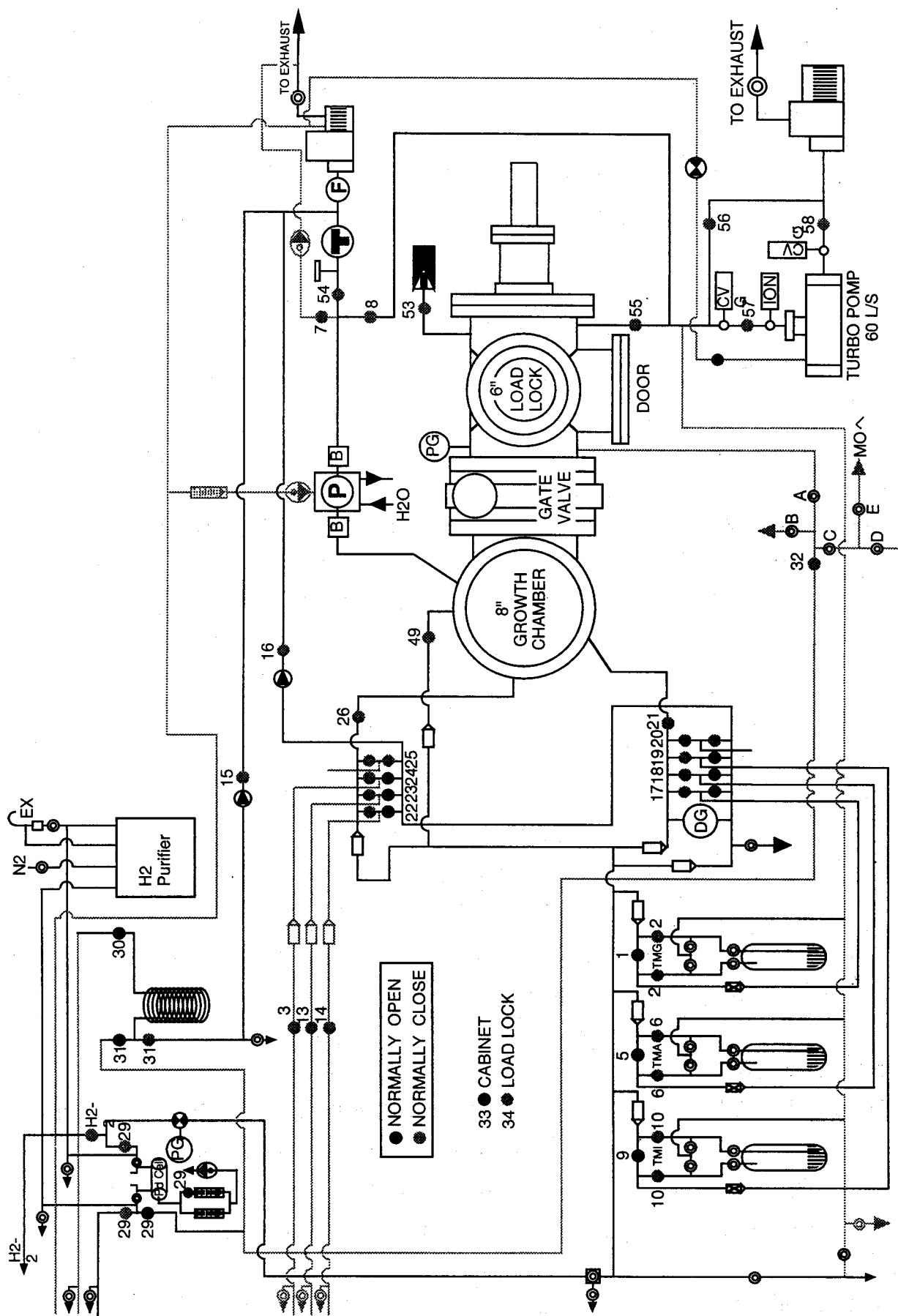

結晶成長は縦型高速回転MOCVD装置を用いて行った。装置の系統図を図2.1に示す。ガス配管は1/4インチのステンレス管であり、ガス流量制御はマスフローコントローラによって行われている。バルブおよびマスフローコントローラはコンピュータによりプログラム制御されている。装置は準備室と成長室に分けられ、それぞれステンレス製であり、ゲートバルブによって仕切られている。基板サセプターはモリブデン製であり、2インチ3枚、3インチ、4インチならば各1枚のウェーハがセットでき、準備室にはそのサセプターが最高3枚まで入れられるようになっている。サセプター回転に関しては、回転軸のシール材として二重の磁気シールを用いることにより、真空保持と約1500rpmまでの回転を可能にしている。また加熱には抵抗加熱を用いている。

キャリアガスとしては水素をパラジウム透過型の純化装置を通した後用いた。成長は約60Torrの減圧下で行い、排気は準備室に対してはロータリポンプとターボ分子ポンプを用い、プロセス用としてはロータリポンプを用いた。排ガスは乾式の除害装置を通して処理した後大気中に放出した。

サセプターに付着したGaAsは20回の成長に1回の割合でエッティングした。エッティングにはアンモニア：過酸化水素水=1:50の混合液を使用し、脱イオン水での洗浄を行った後、装置内で800°C、10分間の空焼きを行った。

成長に用いた原料は、トリメチルガリウム (TMG)、トリメチルアルミニウム (TMA) およびアルシン ( $\text{AsH}_3$ ) とドーピングのためのジシラン ( $\text{Si}_2\text{H}_6$ ) である。TMGとTMAはステンレス製のバブラーに封入されており、バブラーの温度によって蒸気圧を調整し、水素によるバブリングで必要量を得るようになっている。成長系のリークチェックは、原料に毒性の高いアルシンを使用していることから、また高品質な成長膜を得るためにも必要不可欠である。これは装置メンテナンス時のベーキング後にHeリークディテクタを用いて行っており、気密性が十分にあることを確認している。

図2.1 MOCVD装置系統図

### 2.2.2 基板処理

用いたSi基板は(100)面で<011>方向に3°オフセットを有するものである。この基板を以下の手順によって処理し使用した。

- (1)  $\text{H}_2\text{SO}_4 : \text{H}_2\text{O}_2 = 1 : 1$ により10分間エッチングを行い、表面の重金属を除去する。

- (2) 脱イオン水により10分間流水洗浄を行う。

- (3)  $\text{HF} : \text{H}_2\text{O} = 1 : 10$ で30秒間エッチングを行い、表面の酸化膜を除去する。

- (4) 脱イオン水により3分間流水洗浄を行う。この時Si基板の表面が完全に疎水性になっていることを確認する。

以上の処理を行った後、基板を装置の準備室内にセットした。

### 2.2.3 成長手順

成長手順は以下の通りである。

- (1) 準備室内をロータリーポンプとターボ分子ポンプで排気する。

- (2) 真空度が $4 \times 10^{-5}$ Torrになった段階でゲートバルブを開放し、基板の乗ったサセプターを成長室に搬送した後ゲートバルブを閉める。

- (3) 使用する材料ガス( $\text{TMG}$ 、 $\text{TMA}$ 、 $\text{AsH}_3$ 、 $\text{Si}_2\text{H}_6$ )の各バルブを開ける。

- (4) サセプターを約800rpmで回転させ、回転が安定した後成長室内を60Torrに圧力調整する。

- (5)  $\text{AsH}_3$ を流し始めると同時にウェーハの昇温を開始する。

- (6) 設定されたプログラムにより自動で成長が行われる。このプログラムの内容および成長条件については次節で説明する。

- (7) 成長終了後、 $\text{AsH}_3$ はサセプターが約300°Cになるまで流し、その後止める。サセプターの回転は温度が約200°Cになるまで続ける。

- (8) サセプターを準備室内に戻しゲートバルブを閉めた後、準備室内を $\text{N}_2$ ガスで大気圧にして基板を取り出す。

## 2.3 成長条件

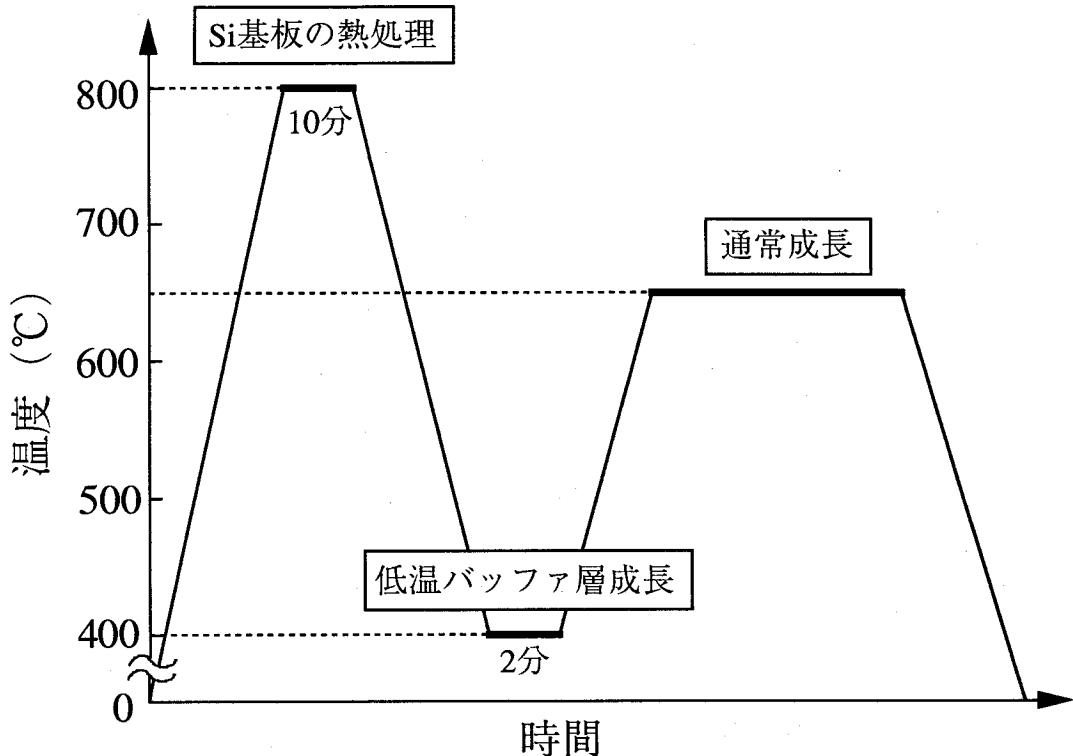

図2.2に典型的な二段階成長の成長プログラムの例を示す。まずウェーハを800°Cまで昇温し、10分間保持する。これはSi基板表面の酸化膜を除去するためである。その後400°Cまで降温し、2分間GaAsを成長する。ここで成長される膜厚は200~300Åである。再び650°Cまで昇温し、GaAsおよびAlGaAsを所定の厚さ成長する。

MOCVDを用いた成長においては、成長速度は原料の供給律速であるが、通常V属元素とIII属元素の比(V/III比)の大きい条件で成長を行うためIII属元素の供

図2.2 典型的なGaAs/Siの成長プログラム

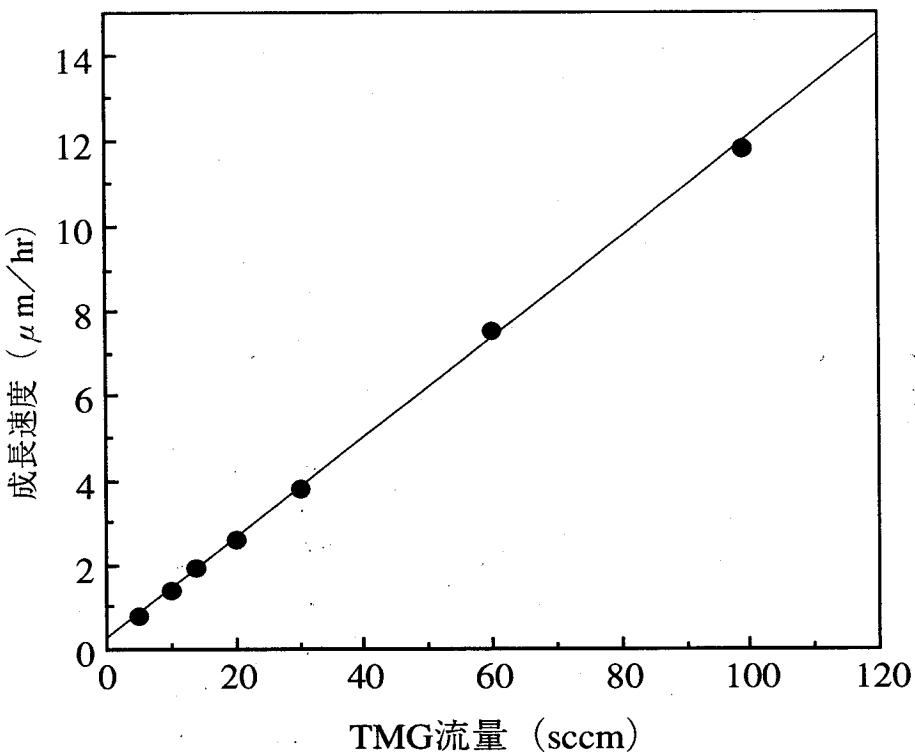

給量で成長速度が決定される。図2.3に本研究で用いた成長装置でのTMG流量とGaAsの成長速度との関係を示す。この図より約 $1\text{ }\mu\text{m}/\text{hr}$ ～約 $12\text{ }\mu\text{m}/\text{hr}$ までかなり広範囲に成長速度のリニアリティが得られていることがわかる。

MESFETやHEMT構造を成長させる場合、バッファ層は $1\sim 2\text{ }\mu\text{m}$ であり、一方活性層は数百Å～数千Åである。そのためバッファ層と活性層を同一の成長速度で成長させることは、スループットと膜厚の制御性からみて好ましくない。本研究においてはGaAsのバッファ層は $7\text{ }\mu\text{m}/\text{h}$ 、活性層は $3.5\text{ }\mu\text{m}/\text{h}$ で成長させ、成長時のV/III比はそれぞれ30と60であった。またAlGaAs層に関しては、成長速度はバッファ層が $2.5\text{ }\mu\text{m}/\text{h}$ 、活性層が $1.2\text{ }\mu\text{m}/\text{h}$ で、V/III比はそれぞれ100と200であった。

#### 2.4 Siのオートドーピングについて

GaAs/Si成長の問題点の一つとして、Si基板からのオートドーピングがあげられる。これによるドーピング量は $10^{16}\sim 10^{17}\text{cm}^{-3}$ オーダにもなるため<sup>(2)</sup>、オートドーピングを回避しないとデバイス用高抵抗バッファ層が得られないばかりでなく、活性層のキャリア密度の均一性にも悪影響を与える。しかし本研究で用いたGaAs/Siにはオートドーピングは見られなかった。これは用いたMOCVD装置が縦型高速回転のタイプであり、高速で回転しているため上方から供給されているガスが強く引きつけられて横方向へ広がり、その結果ウェーハ表面でのガス流速

図 2.3 TMG 流量と GaAs の成長速度との関係

が速くなったためと思われる。例としてSi基板上に成長したGaAsバッファ層の残留不純物は室温で $10^{15}\text{cm}^{-3}$ 以下（n型）、AlGaAsは $10^{16}\text{cm}^{-3}$ 以下（p型）であった。これはオートドーピング防止のためSi裏面に絶縁膜のコーティングが必要な横型タイプ<sup>(3)</sup>のものに比べ、縦型高速回転タイプの大きな利点と考えられる。

## 2.5 まとめ

MOCVDによる二段階成長法を用いてHEMTやMESFET構造を成長させる際の基本的成长手順および成長条件について述べた。この条件によりデバイス用高品質のエピタキシャル膜を安定して得ることができる。また本研究で用いたタイプのMOCVD装置は、その構造上Siのオートドーピングが防止できることも新たな知見として示すことができた。

### （参考文献）

- (1) Masahiro Akiyama, Yoshihiro Kawarada, and Katsuzo Kaminishi : Jpn. J. Appl. Phys. **23** (1984) L843.

- (2) S. Nozaki, A. T. Wu, and J. J. Murray

T. George

T. Egawa, and M. Umeno : Appl. Phys. Lett. **57** (1990) 2669.

- (3) 山本圭、江川孝志、曾我哲夫、神保孝志、梅野正義：信学技報 ED91-30

(1991) 53.

### 3. 電子デバイス用GaAs/Siウェーハの評価

#### 3.1 はじめに

本章では、GaAs/Siを電子デバイス用ウェーハとして用いる際に必要な、キャリア密度、膜厚の面内均一性、バッファ層のリーク電流、キャリア移動度、表面モホロジー、について行った評価結果について述べる。またGaAs/Siの熱放散性の良さを実証するために、ショットキー接合の順方向電圧の温度依存性から熱抵抗を求め、計算との比較を行ったのでその結果についても述べる。

#### 3.2 面内均一性

##### 3.2.1 膜厚

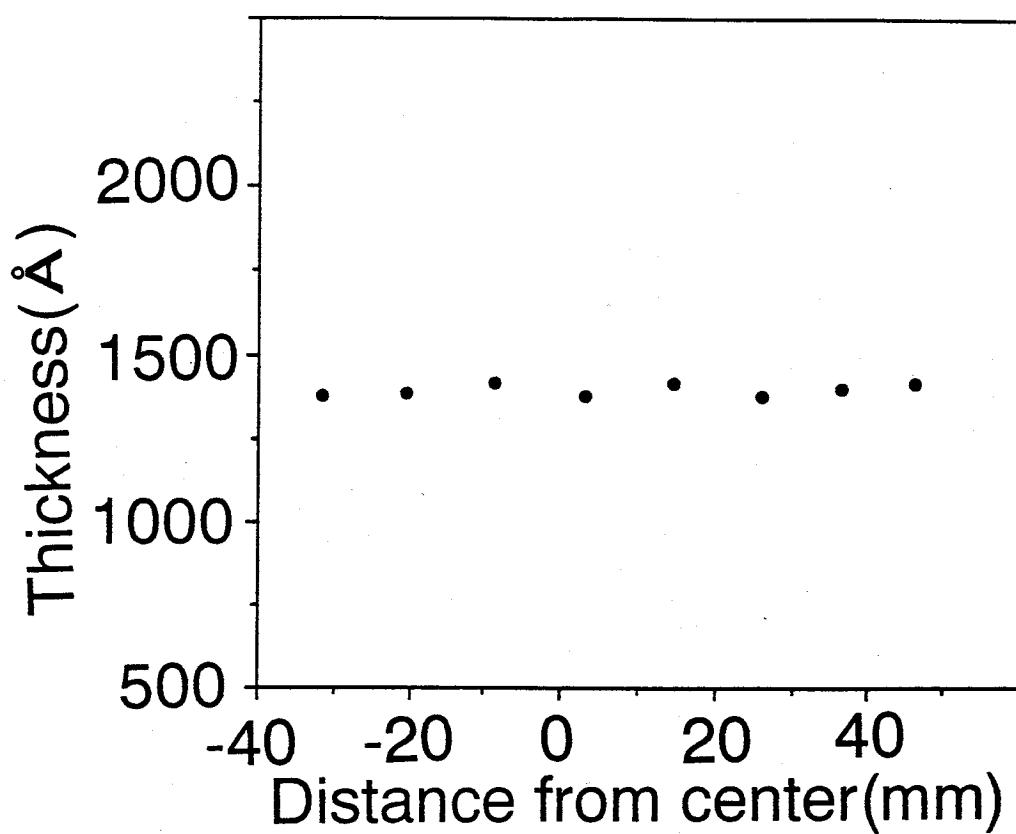

図3.1、図3.2に4インチウェーハにおける膜厚の面内均一性を示す（ウェーハ端より5mm以内は除く）。膜厚の測定方法は成長したGaAs/SiのGaAs側の一部をマスクし、残りのGaAsのみを弗酸系エッチング液で選択エッチングした後、マスクを除去して触針型段差計（装置名DEKTAK）を用いて行った。図3.1は膜厚が約 $3\mu\text{m}$ と比較的厚く成長させた時のもので、図3.2は膜厚が約 $0.15\mu\text{m}$ と薄く成長させた時のものである。どちらの場合においても均一性は平均値に対し±1.5%以内に入っており良好である。

##### 3.2.2 キャリア密度

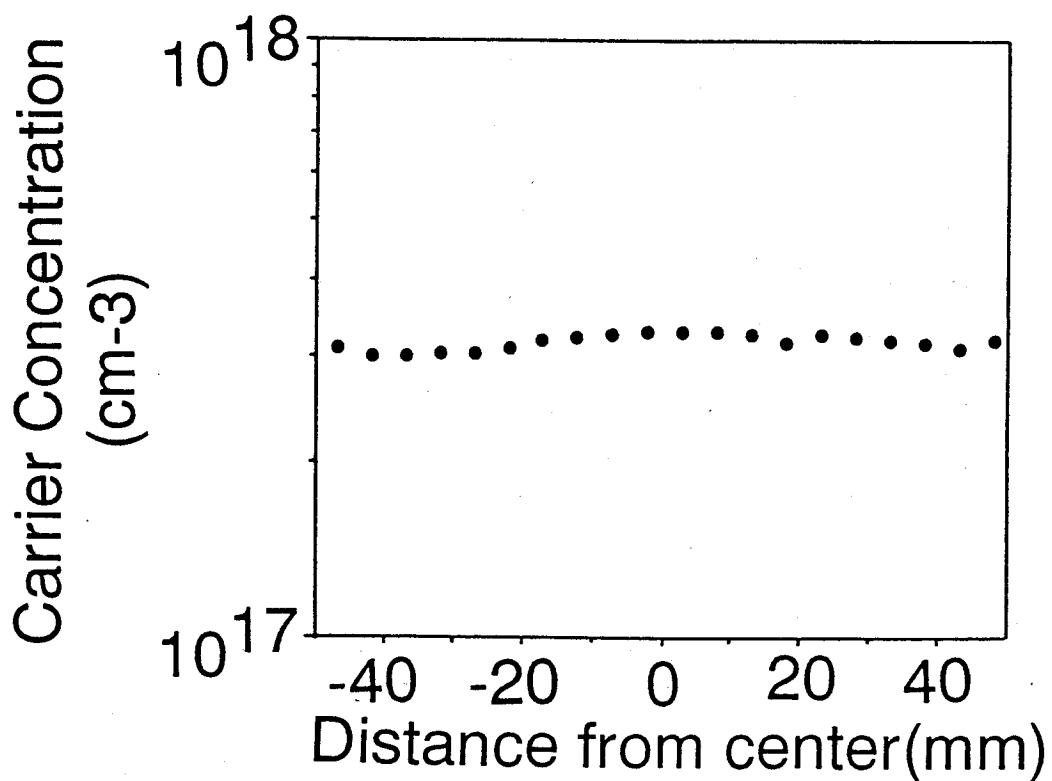

図3.3に $3.2 \times 10^{17}\text{cm}^{-3}$ ドーピングした時の、4インチウェーハにおけるキャリア密度の面内均一性を示す。測定はC-V法を用いており、ほぼウェーハ全面を評価している。均一性は良好で、平均値に対し±5%以内に入っている。

膜厚とキャリア密度において得られたこれらの高い均一性は、本研究で用いたGaAs/SiウェーハがHEMT IC等の試作も可能なレベルにあることを示している。

#### 3.3 リーク電流

##### 3.3.1 GaAs-Siの界面評価

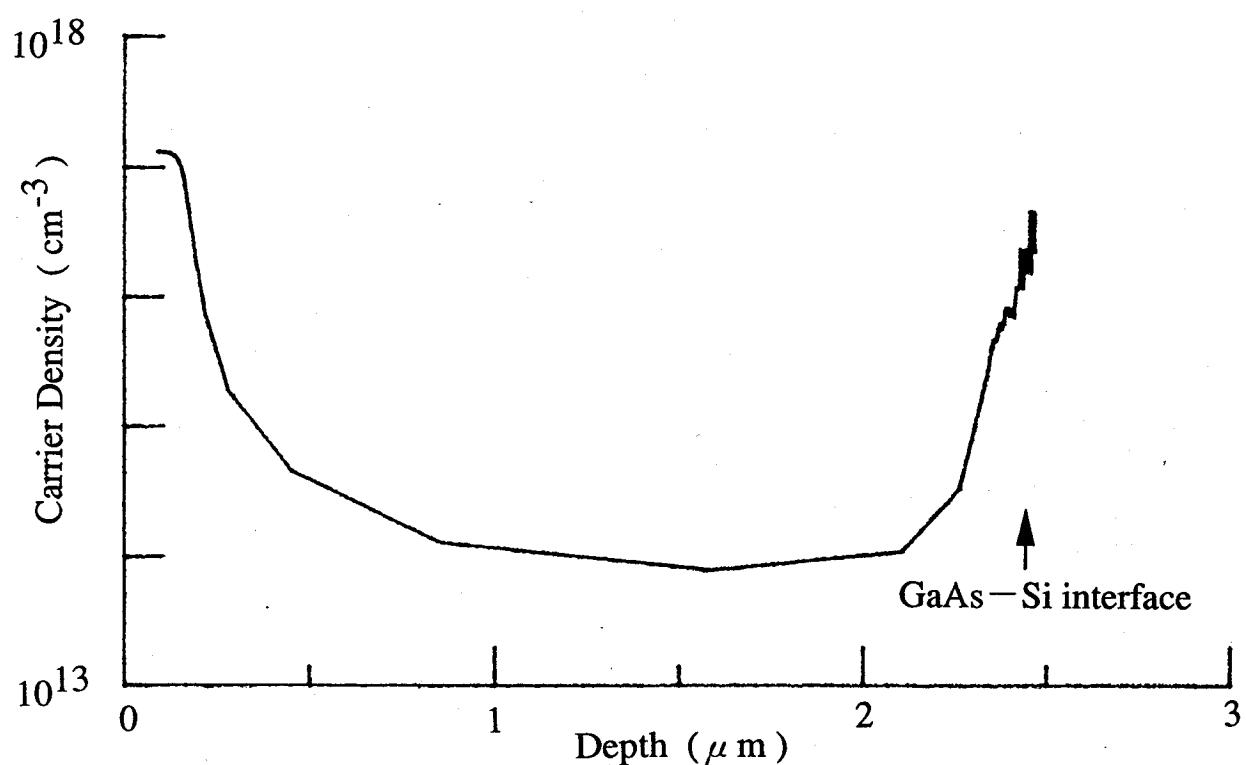

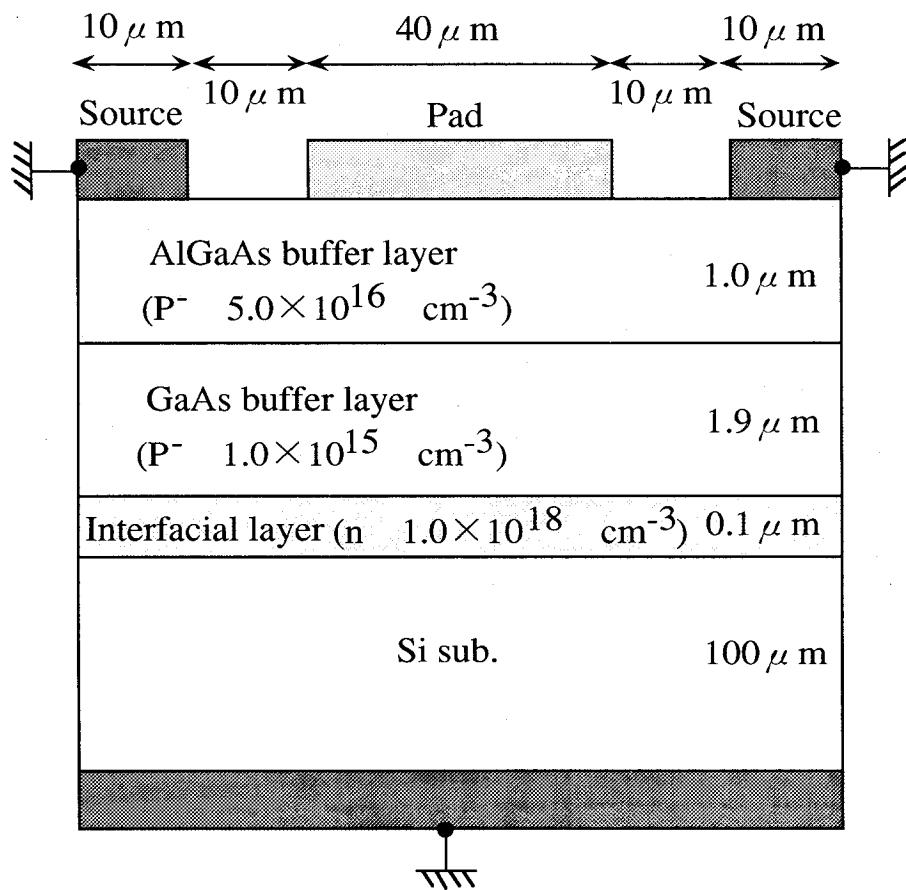

転位は不純物の拡散パスとして働くことが知られているが、GaAs/Siの場合GaAsとSiの界面には $10^{11}\text{cm}^{-3}$ 以上の転位が存在するため、成長中に基板のSi原子が転位を通ってGaAsエピ層に拡散することが考えられる<sup>(1, 2)</sup>。図3.4はバッファ層を約 $2.3\mu\text{m}$ 、活性層を約 $0.2\mu\text{m}$ 成長させたGaAs/SiのキャリアプロファイルをC-V法により測定したものであるが、GaAsとSiの界面と思われる所でキャリア密度が急増し、実際に基板のSi原子が拡散していることがわかる。この界面導電層のキャリア密度とその厚さをより詳しく評価するためにRaman散乱を用いた測定を行った<sup>(3, 4)</sup>。

図3.1 4インチウェーハにおける膜厚均一性 (I)

図3.2 4インチウェーハにおける膜厚均一性 (II)

図 3.3 4 インチウェーハにおけるキャリア密度均一性

図 3.4 GaAs/Si のキャリアプロファイル

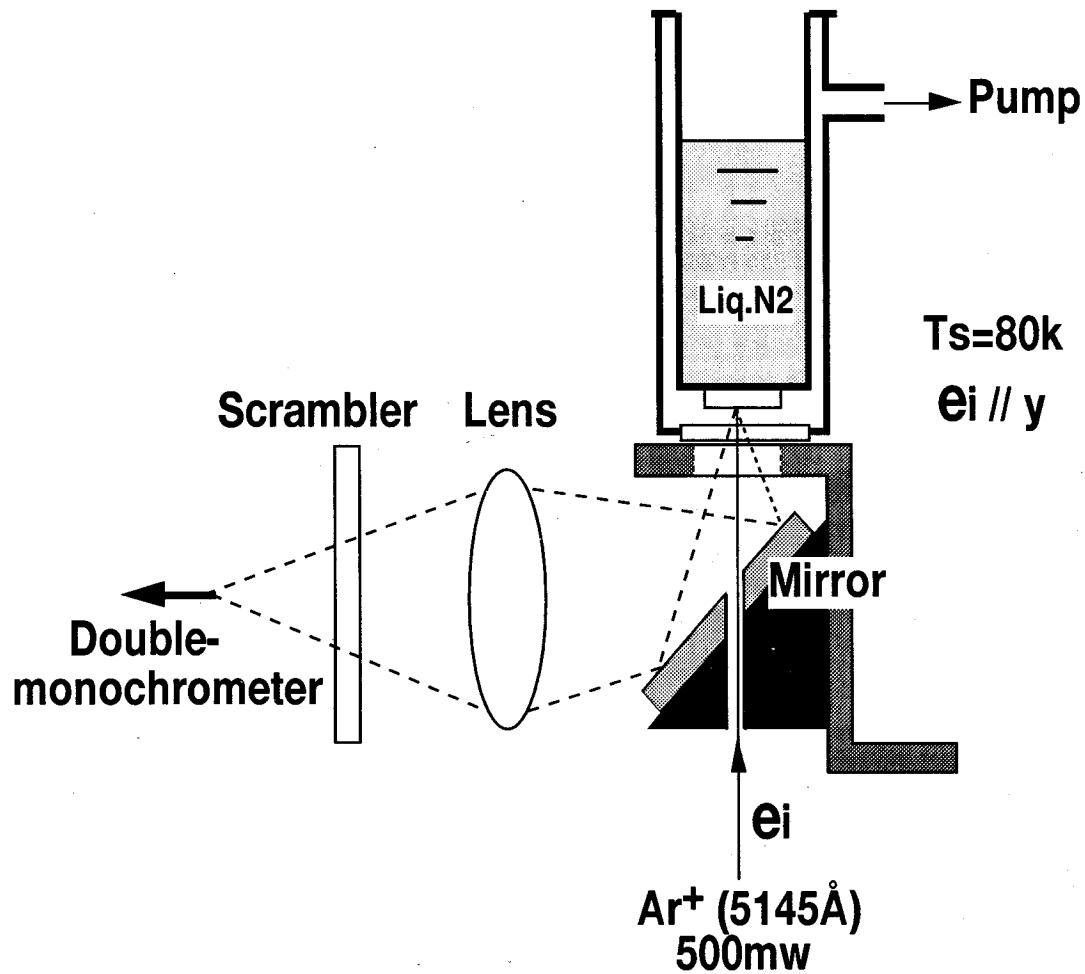

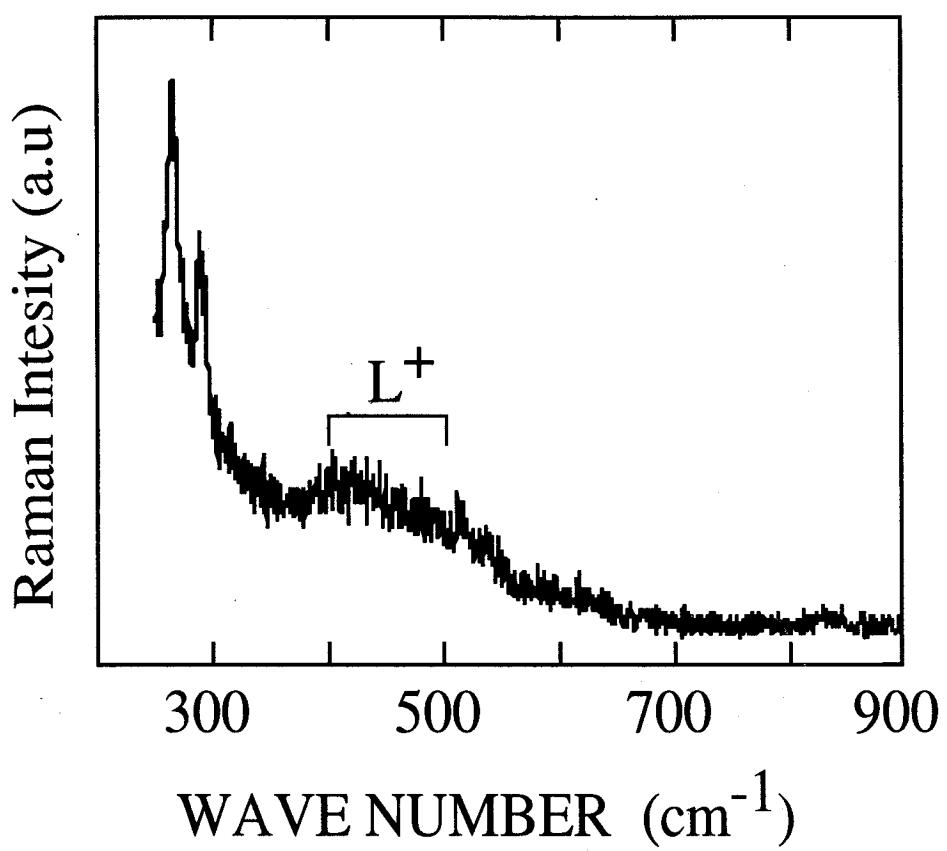

図3.5に測定系を示す。サンプルは $3\mu\text{m}$ GaAsを成長させたGaAs/SiのGaAs側をGaAs基板に貼り付け、基板のSiを90°Cの50%KOH水溶液で約3hrエッチングして作成した。Raman散乱は、励起光としてAr<sup>+</sup>レーザ（5145Å）を用い、後方散乱で低温（～80K）で行った。LO-phonon-plasmonモード（L<sup>+</sup>）によるピーク位置の波数からサンプルのキャリア密度は次式によって求められる。

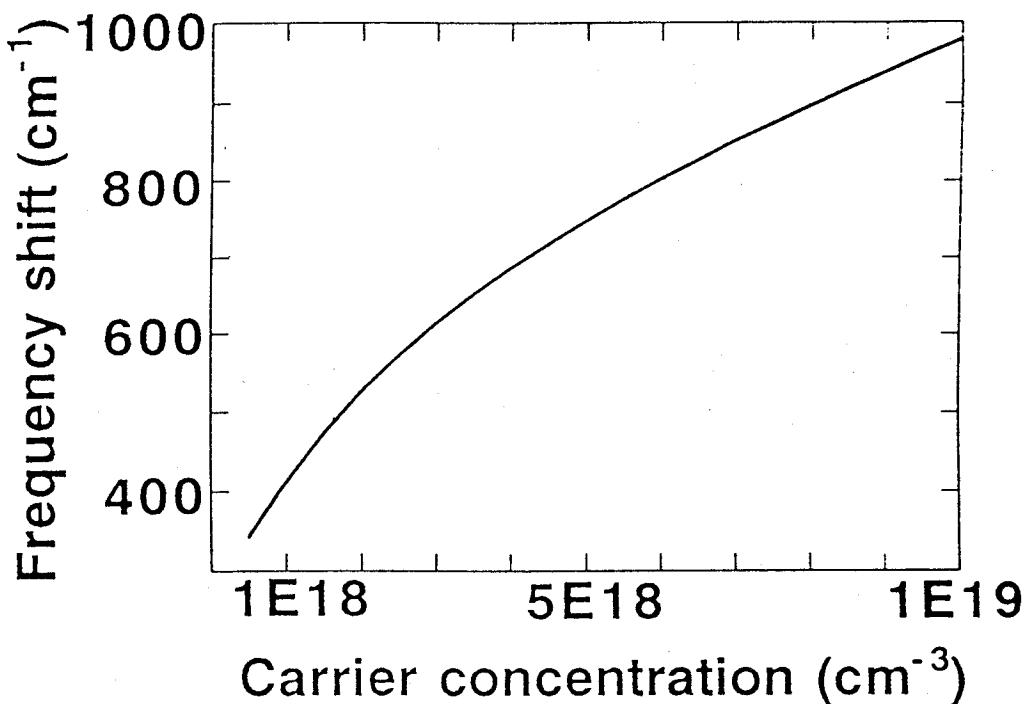

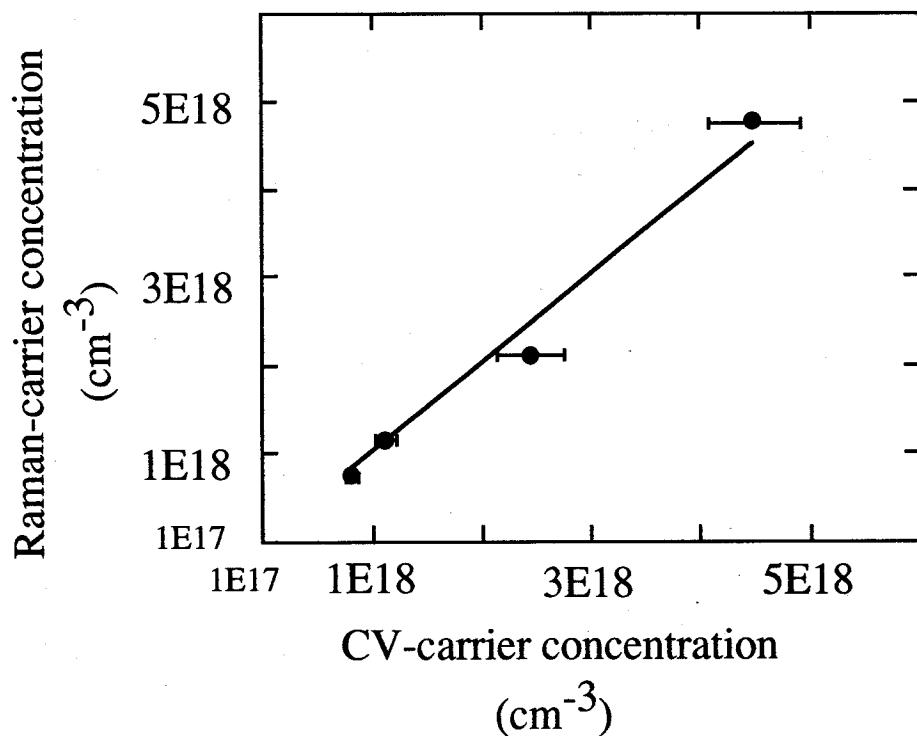

$$\omega^2 = \frac{1}{2} \{ (\omega_L^2 + \omega_p^2) + [(\omega_L^2 + \omega_p^2)^2 - 4\omega_p^2\omega_T^2]^{1/2} \} \quad (3.1)$$

ここで $\omega$ はL<sup>+</sup>の波数、 $\omega_L$ 、 $\omega_T$ はGaAs中のLOフォノン、TOフォノンの波数でそれぞれ293cm<sup>-1</sup>、268cm<sup>-1</sup>である。また $\omega_p$ はプラズモンの波数で、nを電子密度、eを電子電荷、 $\epsilon_{\infty}$ を光学的誘電率、m\*を電子の有効質量とすると、 $\omega_p = 4\pi ne^2 / (\epsilon_{\infty} m^*)$ と表される。（3.1）式から求められるnと $\omega$ の計算結果を図3.6に示す。本研究で用いた測定系においてはキャリア密度が $5 \times 10^{17}\text{cm}^{-3}$ 以下では対応する信号が観測できなかったため、 $10^{18}\text{cm}^{-3}$ 台のキャリア密度に対して計算している。またRaman散乱と通常のC-V法によって得られるキャリア密度の相関を図3.7に示すが、この図よりほぼ同一の値を示すと見てよいことがわかる。実際に得られた散乱データを図3.8に示す。400～500cm<sup>-1</sup>付近に見られるなだらかなピークがL<sup>+</sup>であり、このピークの上限値520cm<sup>-1</sup>からキャリア密度の最大値は $2 \times 10^{18}\text{cm}^{-3}$ 程度であることがわかる。またAr<sup>+</sup>レーザの侵入長が～0.1μmであることから、GaAsとSiの界面からGaAs内に少なくとも0.1μmは $10^{18}\text{cm}^{-3}$ 台のキャリア密度を持った層が存在していることがわかる。今回の評価からはこの導電層の厚さを決めるることは難しいが、図3.4のプロファイルでは界面より0.1～0.15μm離れると $10^{15}\text{cm}^{-3}$ 台にまで残留不純物密度が下がっており、またプロファイルプロットを用いた他研究機関からの評価結果<sup>(5)</sup>も考慮すると、界面導電層の厚さは0.1μm程度と考えられる。

図 3.5 Raman 散乱測定系

図 3.6 Raman シフト量より得られるキャリア密度の計算

図 3.7 Raman シフト量から得られるキャリア密度と C-V 測定から得られるキャリア密度の相関

図 3.8 GaAs – Si 界面層から得られた散乱データ

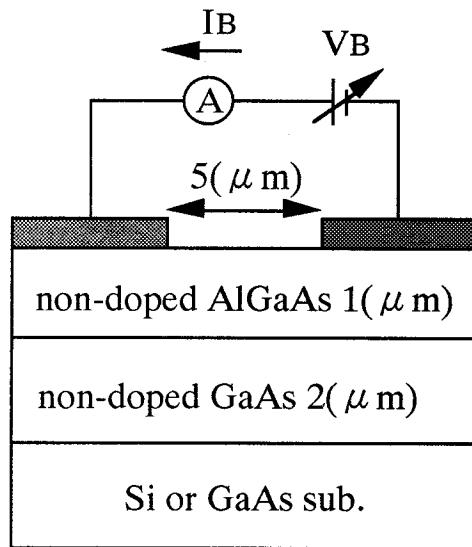

### 3.3.2 リーク電流評価

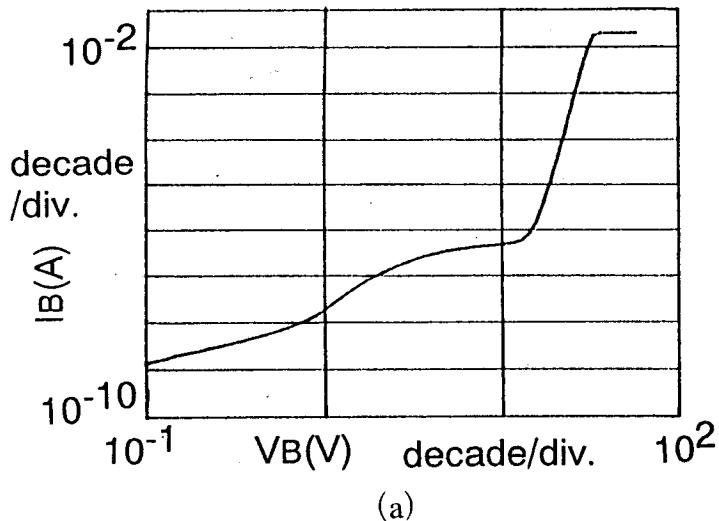

前節で示したようにGaAsとSiの界面にはキャリア密度が $10^{18}\text{cm}^{-3}$ で厚さ $0.1\mu\text{m}$ 程度の導電層が存在し、かつGaAsエピ層の厚さは $\sim 4\mu\text{m}$ が限度であるため、表面にデバイスを形成した時、この界面導電層によって電極間リークが増大する可能性がある。リーク電流の評価は図3.9に示すように、SiあるいはGaAs基板上に成長したnon-dope GaAs ( $2\mu\text{m}$ ) / non-dope AlGaAs ( $1\mu\text{m}$ ) の表面に幅 $100\mu\text{m}$ で $5\mu\text{m}$ 離れた対向電極を形成し測定した。図3.10 (a) にはSi基板の場合、(b) にはGaAs基板の場合の測定結果を示す。本研究で用いた成長条件ではnon-dopeのAlGaAs層はp-になるが、電極としてAuGe/Auを用いているために電極－サンプル－電極間ではn<sup>+</sup>-p<sup>-</sup>-n<sup>+</sup>接合が形成されていると思われる。そのため印加電圧が低い場合には再結合電流あるいは拡散電流が流れていると考えられる。印加電圧が高くなるとドリフトによると思われる電流が増加し、最終的には急増に至るが、その様子がSi基板の場合とGaAs基板の場合とで異なっていることがわかる。GaAs基板の場合には測定サンプルが破損していたが、これは電流が急増する時点で約 $10^5\text{V}/\text{cm}$ の電界が印加されていることから絶縁破壊によるものと考えられる。従って成長したnon-dope層の純度としてはかなり高いものが得られていると思われる。一方Si基板上non-dope層の場合には、GaAs基板よりも低い電圧で電流が増え始め、かつ電圧依存性を持っており、上述したn<sup>+</sup>-p<sup>-</sup>-n<sup>+</sup>接合でのブレークダウンの可能性が考えられる。以上の結果は、Si基板上のnon-dope層の方が残留不純物密度が高いあるいは転位に付随した欠陥等が多く存在するためにブレークダウンが生じやすい、すなわちバッファ層としては耐圧が小さいことを示している。しかし通常のデバイス動作時に印加されるバイアス範囲 (10~20V以下程度) でのリーク電流はGaAs/GaAsとほぼ同等であることから、実際のデバイスに与える影響は少ないと思われる。さらにリーク電流の絶対値からは電流は絶縁層内を流れていると考えられるため、界面導電層がリークパスになっていることも少ないと思われる。これらのこととは本節で評価したnon-dope層を電子デバイスのバッファ層として用いた場合にGaAs/GaAsとGaAs/Siのデバイス直流特性、特にドレインコンダクタンス、に差は見られなかったという結果（第4章参照）からもわかる。

図 3.9 バッファ層のリーク電流測定系

図 3.10 Si 基板上 (a) と GaAs 基板上 (b) の AlGaAs/GaAs

バッファ層のリーク電流の比較

### 3.4 キャリア移動度

成長した膜の移動度評価において、non-dope層の評価は膜の基本特性を把握する上で重要である。そこでnon-dopeのGaAs層とAlGaAs層に関してホール測定を行ったが、GaAs/Siでは前述のように界面導電層が存在し正確な値が測定できなかったためGaAs/GaAs系で評価した。その結果を表3.1に示す。GaAs、AlGaAsとともにp型であり室温では移動度が小さく測定精度が落ちるため、移動度は77Kでの、残留キャリア密度は室温での値を示してある。表3.1よりp型GaAsで77Kでの移動度が約 $6000\text{cm}^2/\text{V}\cdot\text{sec}$ とかなり高品質の膜が得られていることがわかる。

GaAs/GaAs系でGaAs層の品質の高さが確認されても、GaAs/Siにおいては内部に存在する転位が品質、電子デバイスの場合は特に移動度に悪影響を及ぼすものとして懸念される。しかしGaAs/Siに形成したn<sup>+</sup>AlGaAs/GaAsによる二次元電子ガスを用いた移動度の評価によると、77Kならば転位密度が $10^7\text{cm}^{-2}$ 以下で、室温ならば $10^8\text{cm}^{-2}$ 以下で転位の移動度への影響がほとんど見られなくなることが報告されている<sup>(6)</sup>。as-grownのGaAs/Siの転位密度は $\sim 10^8\text{cm}^{-2}$ であるため、室温あるいはそれ以上で動作させるデバイスへの応用に関しては、転位による移動度の低下はないと考えて良い。従ってGaAs/GaAs系でエピ膜の高い品質（高移動度）が確認されていれば、as-grownのGaAs/Si系でも室温あるいはそれ以上では同様の移動度が得られていると考えられる。

### 3.5 表面モロジー

電子デバイス用のエピウェーハが備えるべき条件の一つとして良好な表面モロジーがある。ウェーハ表面の荒れやピットによる微視的な凸凹は、その上に形成されたデバイスにおいて局所的な電界集中を誘起し、特性を劣化させる可能性がある。またエッチング等のデバイスプロセスによってその凸凹が増大され、最終的にデバイス不良を引き起こす場合があることも報告されている<sup>(7)</sup>。

表3.1 GaAs 基板上 non-dope GaAs と AlGaAs の残留キャリア密度と移動度

|                                | タイプ | V/III比 | 残留キャリア密度<br>(室温)<br>( $\text{cm}^{-3}$ ) | 移動度 (77K)<br>( $\text{cm}^2/\text{V}\cdot\text{sec}$ ) |

|--------------------------------|-----|--------|------------------------------------------|--------------------------------------------------------|

| non-dope GaAs                  | p   | 39.6   | $1.2 \times 10^{15}$                     | 5930                                                   |

| non-dope AlGaAs<br>(Al混晶比0.25) | p   | 105.1  | $3.9 \times 10^{15}$                     | 870                                                    |

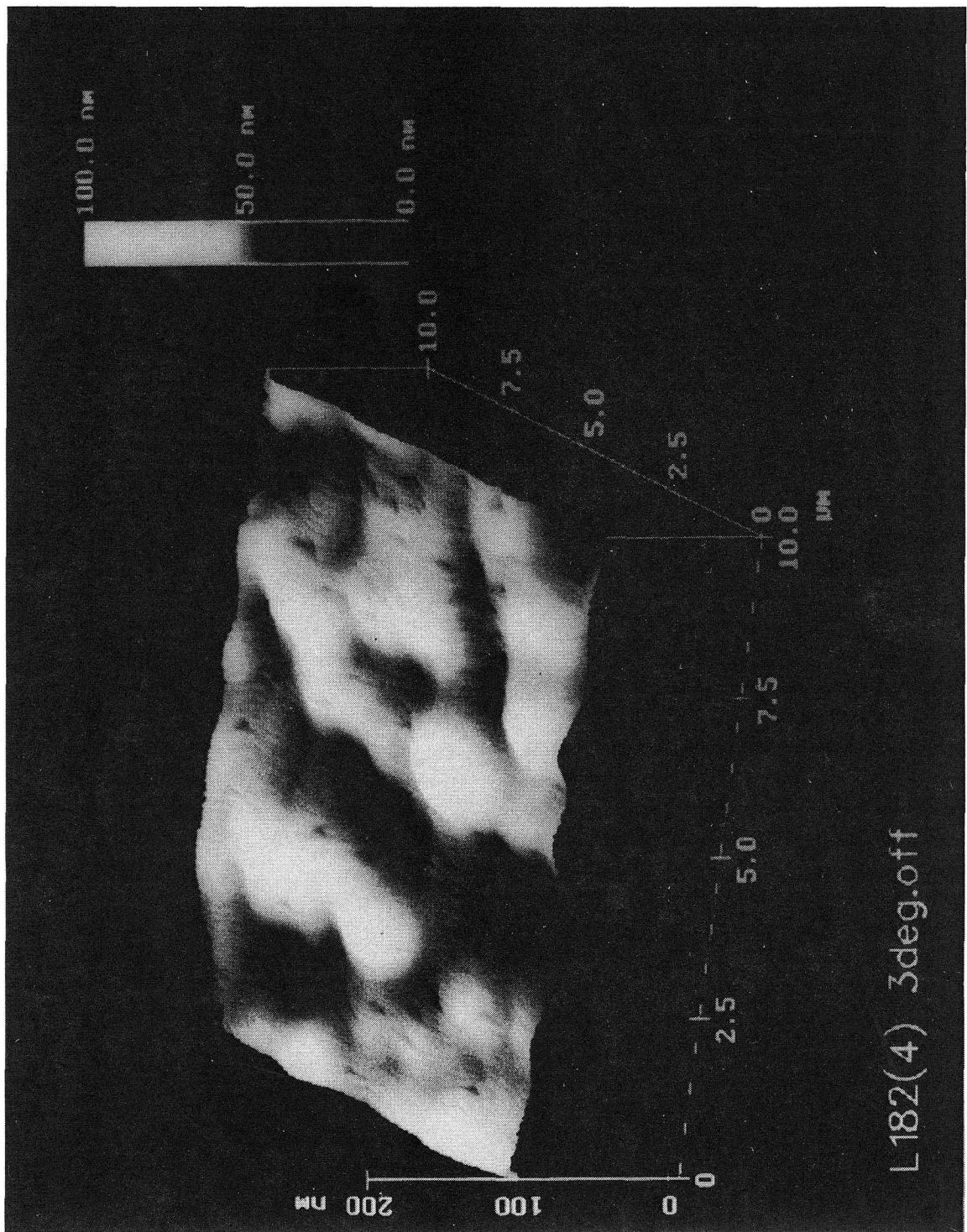

図3.11に $3\mu\text{m}$ GaAsを成長したGaAs/SiのAFM (Atomic Force Microscope) による観察像を示す。サンプルはas-grownの状態であり、 $10\times10\mu\text{m}^2$ の範囲を測定している。この像よりきわめて平坦度の高い表面が得られていることがわかる。GaAs/Siはヘテロ成長であるため基本的に表面モホロジーは荒れやすく、ピットやヒロックが発生しやすいが、表面荒さの平均二乗根 (RMS) の値として $2\times2\mu\text{m}^2$ の範囲で $2.3\text{nm}$ 、表面の凸凹の高低差として約 $15\text{nm}$ と、四段階成長法<sup>(8)</sup>や研磨再成長法<sup>(9)</sup>に匹敵する値が得られている。またGaAs層の成長前にSi基板の高温での表面クリーニングが必要なため、成長炉内残留物の付着によるゴミ(パーティクル)の増加も問題となるが、本研究で用いたGaAs/Siウェーハにおいてはパーティクル数は $50\sim100\text{個}/\text{cm}^2$ と実用上ほとんど問題のないレベルであった。

図3.11 as-grown GaAs/Siの表面AFM像 (GaAs厚3  $\mu$ m)

### 3.6 GaAs/Siの熱抵抗

#### 3.6.1 測定方法および結果

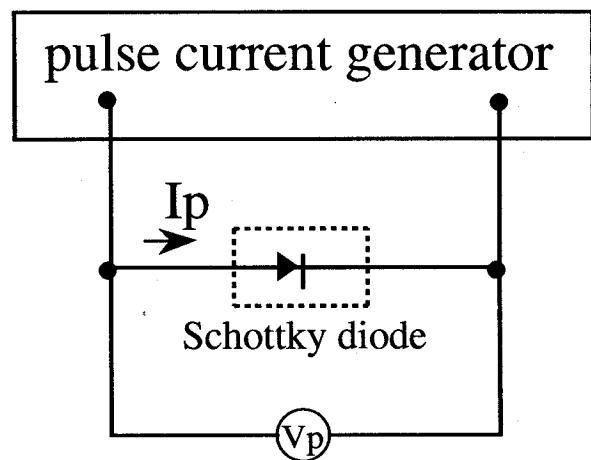

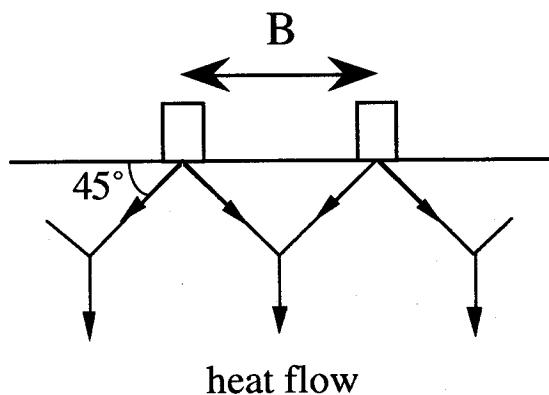

GaAs/Siを電子デバイスに適用する際のメリットの一つとして放熱性の改善による特性の向上がある。Akiyamaらは、GaAs/SiとGaAs/GaAsを用いてパワーMESFETを試作し、それらを動作させた時のデバイス表面温度を測定してGaAs/Siの放熱性の良さを示しているが<sup>(5, 10)</sup>、本研究においてはデバイスのゲートショットキー接合の順方向電圧の温度依存性より熱抵抗を求めた。

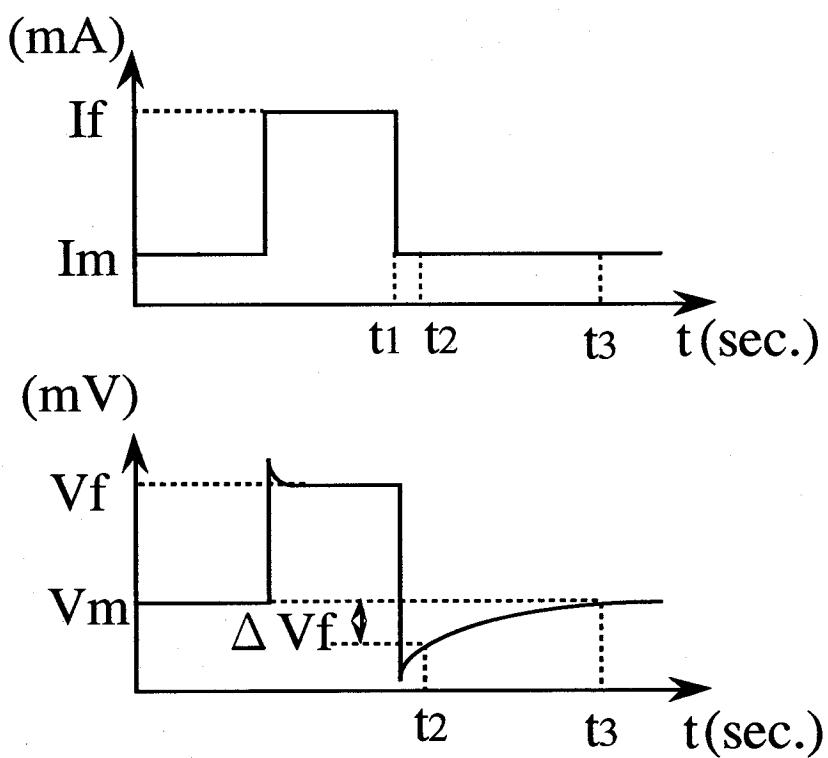

測定原理を図3.12に示す。まず発熱を無視できる程度の電流 $I_m$ で順方向電圧 $V_m$ を測定し、この $V_m$ の温度係数 $a$  (V/°C) をあらかじめ求めておく。次に加熱電流 $I_f$ をパルスとして流し（この時の順方向電圧を $V_f$ とする）、時刻 $t_1$ の時再び $I_m$ に落とす。サンプルは加熱されているため電圧は $V_m$ より小さい値となり、時刻 $t_3$ で定常状態に戻る。ここで本来は、 $t_3$ での電圧と $t_1$ での電圧の差が加熱されたことによる変化分 ( $\Delta V_f$ ) であるが、パルスを切った直後は波形が不安定であるため、delay timeをとり $t_3$ と $t_2$ での差を $\Delta V_f$ とした。熱抵抗 $R_{th}$ の値は次式より求められる。

$$R_{th} = \frac{\Delta V_f / a}{I_f \times V_f} \quad (3.2)$$

測定条件として、 $I_m = 0.5\text{mA}$ 、 $I_f = 50\text{mA}$ 、パルス幅 $1\mu\text{s}$ 、delay time ( $t_2 - t_1$ ) =  $1\mu\text{s}$ 、 $t_3 - t_1 = 10\mu\text{s}$ とした。

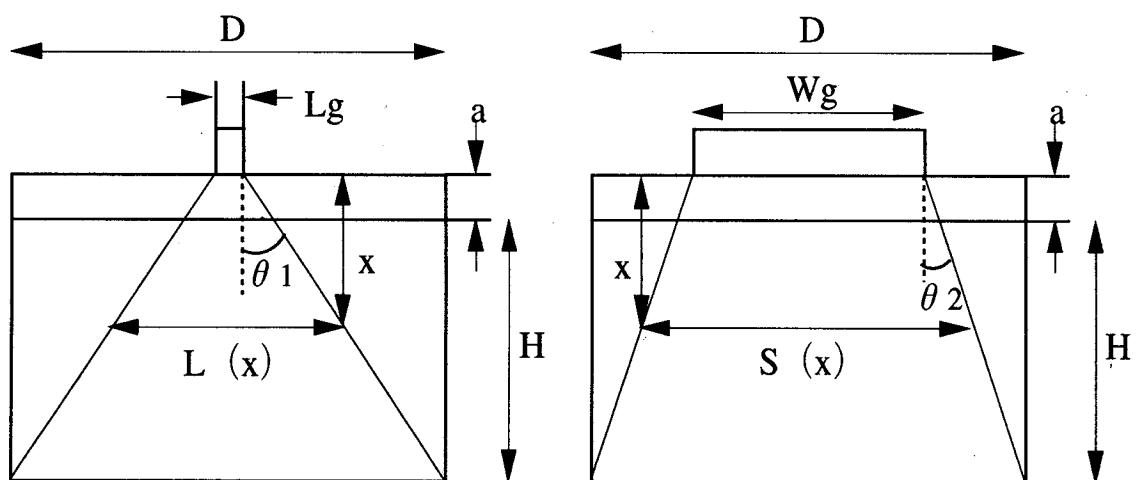

サンプルは次章で述べるHEMTを用い、図3.13にその形状を示す。基板は正方形でその一辺の長さ (D) は $10\text{mm}$ 、また基板のほぼ中央にゲート長 ( $L_g$ )  $1\mu\text{m}$ 、ゲート幅 ( $W_g$ )  $100\mu\text{m}$ のショットキー接合が形成されており、基板厚 (H) は $400\mu\text{m}$ 、エピ厚 (a) は $3.6\mu\text{m}$ である。さらにこの基板はInハンダでシステムに貼り付けられている。測定結果としてGaAs/Siで $36 \pm 5\text{°C/W}$ 、GaAs/GaAsで $57 \pm 5\text{°C/W}$ が得られ、GaAs/Siの放熱性の良さが熱抵抗の形でも実証された<sup>(11)</sup>。

#### 3.6.2 計算による検証

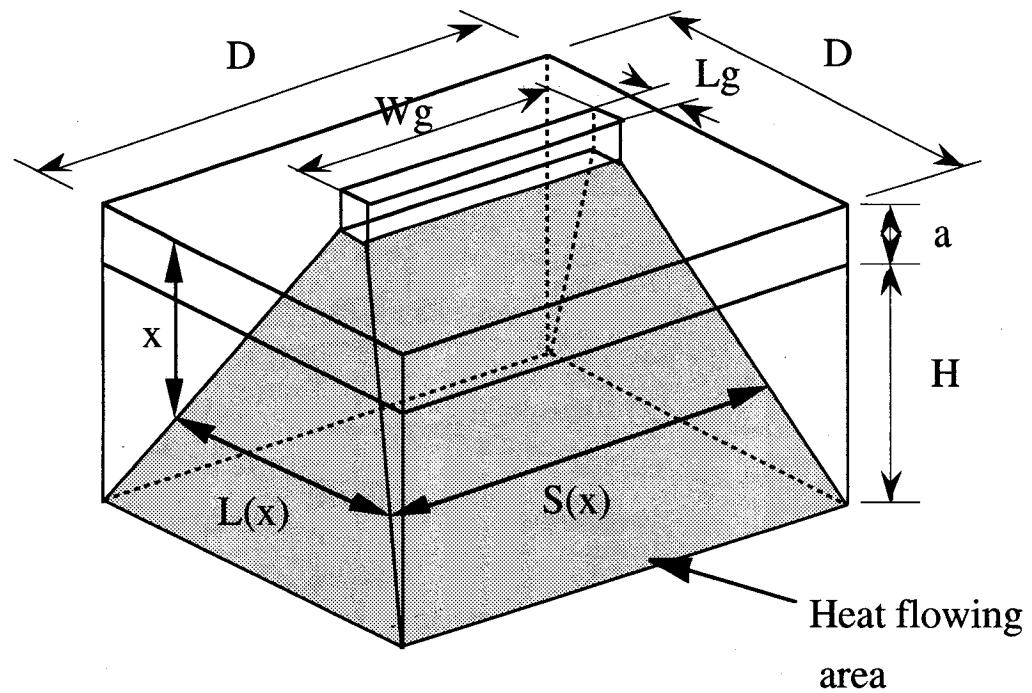

実験によって得られた熱抵抗の値が妥当であるかを確かめるため、計算による検証を行った。図3.14を用いて計算方法を説明する。計算にあたって以下の仮定を用いた。

- (1) ショットキー接合から発生した熱は基板の底面をめがけて流れる。

- (2) HEMT構造であるためGaAsとAlGaAsが形成されているが、全てGaAsの熱伝導率を用いる。

図 3.12 热抵抗の测定原理

図 3.13 热抵抗測定に用いたサンプルの形状

図 3.14 热抵抗計算のための説明図

(3) ステムおよびInハンダの熱抵抗は小さいものとして無視する。

図3.14からわかるように

$$L(x) = L_g + 2x \tan \theta_1 = L_g + 2x \frac{\frac{D - L_g}{2}}{H+a} \sim L_g + 2x \frac{D}{2H}$$

$$= L_g + x \frac{D}{H} \quad (3.3)$$

$$S(x) = W_g + 2x \tan \theta_2 = W_g + 2x \frac{\frac{D - W_g}{2}}{H+a} \sim W_g + 2x \frac{D}{2H}$$

$$= W_g + x \frac{D}{H} \quad (3.4)$$

となる。微小体積  $L(x) \times S(x) \times \delta x$  における熱抵抗  $\delta R$  は、通常の電気抵抗の場合と同様に、 $\kappa$  を熱伝導率として

$$\delta R = \frac{1}{\kappa} \times \frac{\delta x}{L(x) \times S(x)} \quad (3.5)$$

で求められる。

したがって GaAs/Si の場合の熱抵抗  $R_{GaAs/Si}$  は、GaAs と Si の熱伝導率をそれぞれ  $\kappa_{GaAs}$ 、 $\kappa_{Si}$  とすると

$$R_{GaAs/Si} = \frac{1}{\kappa_{GaAs}} \int_0^a \frac{dx}{(L_g + x \frac{D}{H}) (W_g + x \frac{D}{H})} + \frac{1}{\kappa_{Si}} \int_a^{a+H} \frac{dx}{(L_g + x \frac{D}{H}) (W_g + x \frac{D}{H})} \quad (3.6)$$

となる。(3.6)式の第一項がエピ層の熱抵抗、第二項がSi基板の熱抵抗である。

GaAs/GaAsの場合には熱抵抗 $R_{\text{GaAs/GaAs}}$ は、

$$R_{\text{GaAs/GaAs}} = \frac{1}{\kappa_{\text{GaAs}}} \int_0^{a+H} \frac{dx}{(L_g + x \frac{D}{H}) (W_g + x \frac{D}{H})} \quad (3.7)$$

となる。(3.6)、(3.7)式を用い、 $\kappa_{\text{GaAs}} = 1.50 \text{ W}/\text{°C} \cdot \text{cm}$ 、 $\kappa_{\text{Si}} = 0.47 \text{ W}/\text{°C} \cdot \text{cm}$ として基板厚に対する熱抵抗の計算結果を図3.15に示す。図3.15から、荒い仮定を立てたにもかかわらず比較的実験結果との一致は良いことがわかる。

図3.15 热抵抗の計算結果

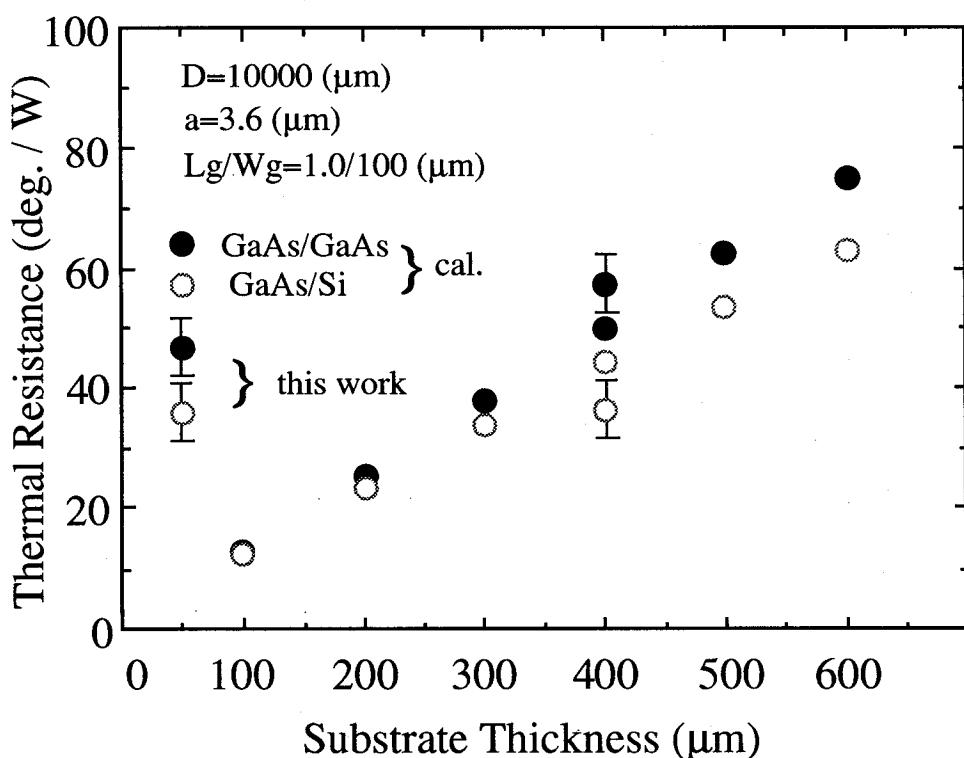

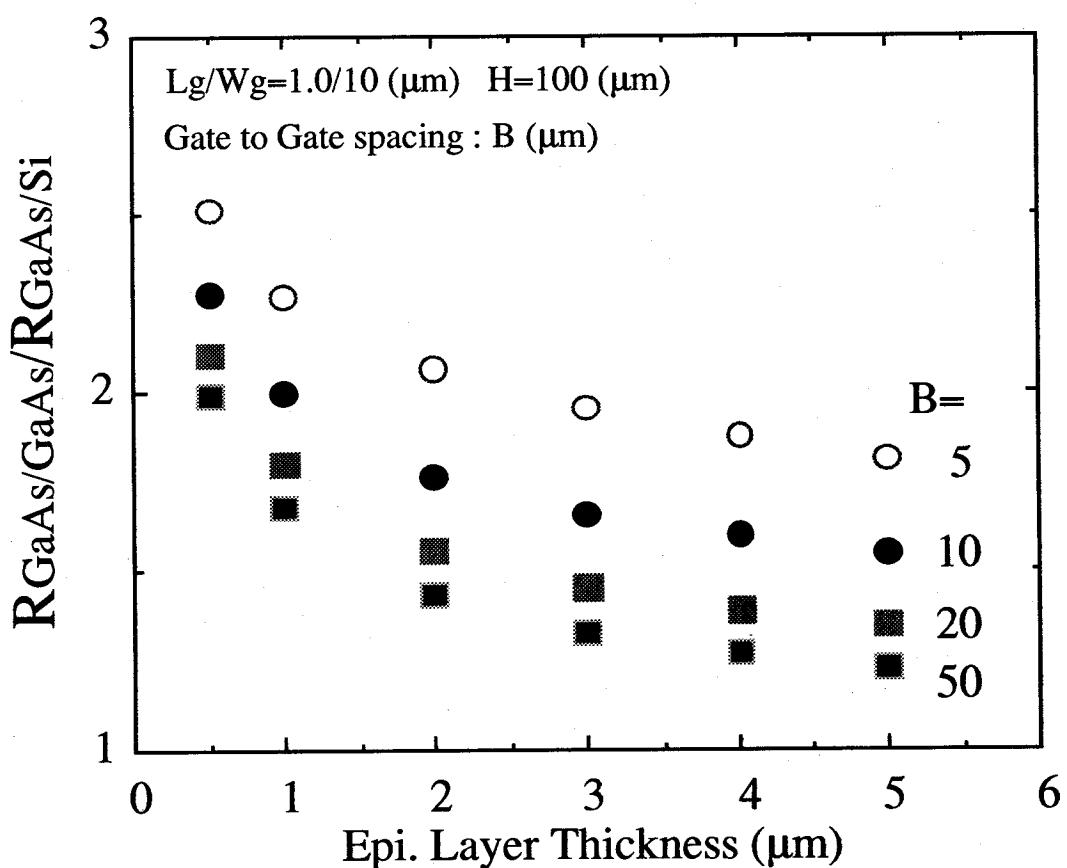

この計算方法がある程度有効であることがわかったため、次にデバイス密度が上がった場合の熱抵抗を計算した。この場合は図3.16に示すように、B ( $\mu\text{m}$ ) 離れて隣接しているデバイスのゲート電極から発生した熱がゲートの下方45度以内を流れると仮定し、さらに熱流がぶつかった点以降は基板と垂直に流れるとした<sup>(12)</sup>。この仮定のもと、ゲート電極が一本の場合と同様の方法で熱抵抗を計算し、GaAs/GaAsとGaAs/Siの熱抵抗の比 $R_{\text{GaAs/GaAs}}/R_{\text{GaAs/Si}}$ を求めた。デバイスの $L_g/W_g = 1.0/10 \mu\text{m}$ 、基板厚H=100  $\mu\text{m}$ とした時の結果を図3.17に示す<sup>(13)</sup>。ゲート

図 3.16 デバイスが集積された場合の熱抵抗計算に仮定した熱流の模式図

図 3.17 デバイスが集積された場合の熱抵抗計算結果

ゲート間隔 (B) をパラメータにとり、エピ層の厚さに対する  $R_{\text{GaAs/GaAs}} / R_{\text{GaAs/Si}}$  を求めてある。エピ層が薄く、またゲート-ゲート間隔が小さくなる程 GaAs/Si の放熱性の良さが活きてくることがわかるが、転位や界面導電層の影響を低減するためにはエピ厚は臨界膜厚（約  $4 \mu\text{m}$ ）以下で厚い程良い。従って両者のトレードオフによってエピ厚は決められるべきであるが、図3.17よりたとえ臨界膜厚付近であっても GaAs/GaAs の 2/3 程度の熱抵抗に押さえられている。これは GaAs/Si を IC や第5章で述べるような櫛形ゲート電極を持つパワーFET に応用する時の大いな利点であると考えられる。

### 3.7 まとめ

GaAs/Si を電子デバイス用ウェーハとして用いる際の基本評価として、キャリア密度、膜厚の面内均一性、バッファ層のリーク電流、キャリア移動度および表面モロジー、を調べた。面内均一性については、4インチウェーハにおいて膜厚で平均値 ± 1.5%、キャリア密度で平均値 ± 5% のばらつきに押さえられており、良好であることが示された。バッファ層のリーク電流に関しては GaAs-Si 界面層の影響が考えられたため、その界面層のキャリア密度を C-V 測定と Raman 散乱で評価し、少なくともキャリア密度  $1 \times 10^{18} \text{ cm}^{-3}$  で厚さ  $0.1 \mu\text{m}$  程度の導電層が形成されていることがわかった。バッファ層のリーク電流の値は若干 GaAs/GaAs よりも大きかったが、その絶対値からは電流は絶縁層内を流れていると考えられ、界面導電層のリークパスとしての影響はほとんど見られなかった。キャリア移動度は non-dope で p 型の GaAs/GaAs について 77K で約  $6000 \text{ cm}^2/\text{V} \cdot \text{sec}$  が得られ、高品質の膜であることがわかった。表面モロジーは AFM で観察し、as-grown の状態で表面荒さの RMS が  $2 \times 2 \mu\text{m}^2$  の範囲で  $2.3 \text{ nm}$  と良好な値を示した。さらに表面パーティクル数も  $50 \sim 100 \text{ 個}/\text{cm}^2$  とデバイス作成に問題のないレベルにあることがわかった。

GaAs/Si の放熱性の良さを実証するために、デバイスのゲートショットキー接合を利用して熱抵抗を測定した。その結果、用いたサンプルにおいては GaAs/Si の熱抵抗は GaAs/GaAs の約 2/3 であることがわかり、また計算とも比較的良く一致した。さらにデバイスが集積された場合を想定した計算より、集積度が上がるほど GaAs/Si の放熱性の良さが発揮されることが示された。

以上より本研究で用いた GaAs/Si は電子デバイス用ウェーハとしての基本特性は十分備わっていると考えられ、さらに放熱性の良さも実証されていることより、特に IC やパワーデバイス応用に有効であると期待できる。

(参考文献)

- (1) A. Freundlich, A. Leycuras, and J. C. Grenet

C. Grattepain : Appl. Phys. Lett. **53** (1988) 2635.

- (2) Yong Kim, Moo Sung Kim, and Suk-Ki Min

Choochon Lee : J. Appl. Phys. **69** (1991) 1355.

- (3) 二木登史郎、立川昭義、城生愛次、藍郷崇、森谷明弘：第42回応用物理学関係連合講演会予稿集28p-TB-2.

- (4) Toshiro Futagi, Akiyoshi Tachikawa, Aiji Jono, Yoji Morikawa, Takashi Aigo and Akihiro Moritani : to be published in Jpn. J. Appl. Phys.

- (5) 秋山正博：京都大学学位論文 (1991)

- (6) 大堀達也：応用物理 第64巻 第2号 (1995) 119.

- (7) T. Ohori, H. Suehiro, S. Mitagaki, T. Miyagaki, and K. Kasai : Proc. Symp. on Alloy Semiconductor Physics and Electronics (1994) 57.

- (8) S. Ohkubo, K. Takai, N. Takagi, S. Miyagaki, T. Eshita, and K. Takasaki : Proc. Int. Symp. GaAs and Related Compounds (1992) 187.

- (9) Tatsuya Ohori, Haruyoshi Suehiro, Kazumi Kasai, and Junji Komeno : Proc. Int. Symp. GaAs and Related Compounds (1992) 175.

- (10) H. Inomata, S. Nishi, M. Akiyama, M. Itoh, S. Takahashi, and K. Kaminishi : Proc. Int. Symp. GaAs and Related Compounds (1985) 481.

- (11) Takashi Aigo, Hirokatsu Yashiro, Aiji Jono, Akiyoshi Tachikawa, and Akihiro Moritani : Electron. Lett. **28** (1992) 1737.

- (12) Yoichi Aono, Asamitsu Higashisaka, Tadayuki Ogawa, and Fumio Hasegawa : Jpn. J. Appl. Phys. **17** (1978) 147.

- (13) Takashi Aigo, Hirokatsu Yashiro, Mitsuhiro Goto, Aiji Jono, Akiyoshi Tachikawa, and Akihiro Moritani : Jpn. J. Appl. Phys. **32** (1993) 5508.

## 4. HEMT/Siのしきい値電圧分布と高周波特性評価

### 4.1 はじめに

HEMTは化合物半導体の大きな特長である高速性を最も活かしており、デジタル、アナログどちらの応用においてもキーとなるデバイスである。さらにエピタキシャル成長を必要とすることから、GaAs/Si応用の一つとして適していると考えられる。HEMT/Siをデジタルデバイスへ適用する際には、GaAs/Si内部に存在する多数の転位のHEMTのしきい値電圧分布に対する影響の有無を評価する必要があり、アナログデバイスの際には、前章で述べたGaAs-Si界面の導電層あるいはSi基板の導電性によって誘起される寄生容量、寄生抵抗の影響を考慮する必要がある。

本章では、転位のHEMT/Siしきい値電圧分布に対する影響を、マクロ的（ウェーハ全面）およびミクロ的（ $1.95 \times 1.9\text{mm}^2$ 内）な範囲で評価した結果について述べる。また高周波測定をもとにした等価回路パラメータ解析より得られた寄生成分の影響、その起因について考察する。さらにこの寄生成分の低減方法と実際の試作によるその有効性について述べる。

### 4.2 実験方法

#### 4.2.1 結晶成長およびデバイスプロセス

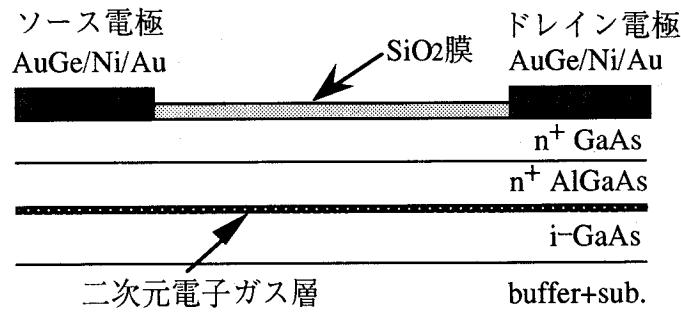

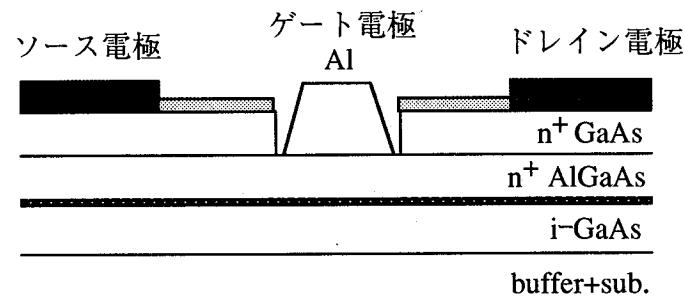

成長方法は第二章で述べたように二段階成長法を用い、Si基板はチョクラルスキー法で成長させた抵抗率が $10\sim50\Omega\cdot\text{cm}$ のもの（以下中抵抗Si基板と呼ぶ）とフローティングゾーン法で成長させた $2000\sim6000\Omega\cdot\text{cm}$ のもの（以下高抵抗Si基板と呼ぶ）を用いた。この理由はSi基板の導電性が寄生成分の大小に影響するかを確かめるためである。またSi基板の厚さは $600\mu\text{m}$ である。エピ層の構造は図4.1に示すようにSi基板上にバッファ層としてノンドープのGaAsとAlGaAsを $1.5\mu\text{m}$ ずつ成長させ、その上にチャンネル層のノンドープGaAsを $0.05\mu\text{m}$ 、電子供給層の $n^+AlGaAs$ をキャリア密度 $7\sim12\times10^{17}\text{cm}^{-3}$ で $0.05\mu\text{m}$ 成長させている。更に最上部にコンタクト層として $n^+GaAs$ をキャリア密度 $1.5\times10^{18}\text{cm}^{-3}$ で $0.1\mu\text{m}$ 成長させている。

|                       |         |                                        |

|-----------------------|---------|----------------------------------------|

| n <sup>+</sup> GaAs   | 0.1 μm  | 1.5x10 <sup>18</sup> cm <sup>-3</sup>  |

| n <sup>+</sup> AlGaAs | 0.05 μm | 7~12x10 <sup>17</sup> cm <sup>-3</sup> |

| undoped GaAs          | 0.05 μm |                                        |

| undoped AlGaAs        | 1.5 μm  |                                        |

| undoped GaAs          | 1.5 μm  |                                        |

| Si sub.               |         |                                        |

図 4.1 試作した HEMT/Si の層構造

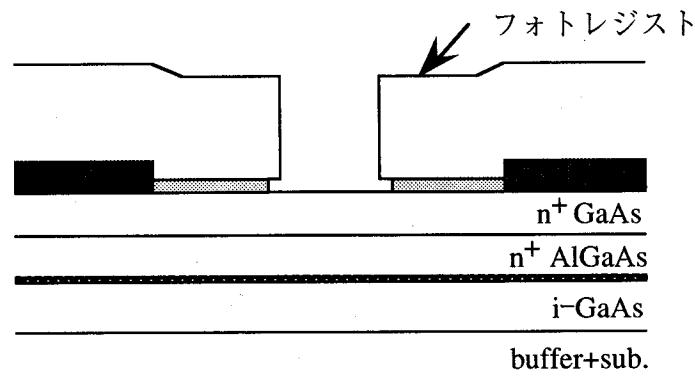

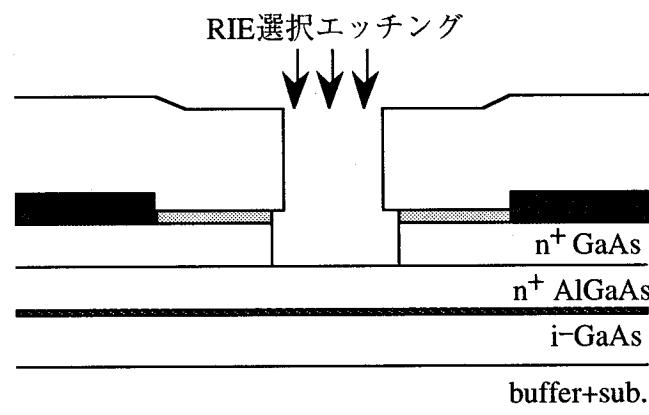

試作したHEMTのプロセスフローを図4.2に示す。メサエッチングによる素子分離の後、ウェーハの表面に保護膜としてSiO<sub>2</sub>をプラズマCVD法で約2000 Å堆積する。リフトオフ法でAuGe/Ni/Auを形成し、オーミック電極とするため420℃で合金化処理を行う(a)。通常のフォトリソグラフィでゲート窓を形成した後ゲート部分のSiO<sub>2</sub>膜をウェットエッチングによって除去する(b)。最上層のn<sup>+</sup>GaAsを、CCl<sub>2</sub>F<sub>2</sub>/Heの混合ガスを用いたドライエッチングにより選択的に除去した後(c)、ゲート電極としてAlを約2000 Å蒸着する(d)。なお表面パッシベーション膜は用いていない。

#### 4.2.2 GaAs/AlGaAsの選択ドライエッチング

前述のプロセスで重要なのがGaAs/AlGaAsの選択ドライエッチングである。HEMTのしきい値電圧は電子供給層であるn<sup>+</sup>AlGaAsの厚さとキャリア密度の積で決められるため最上層のn<sup>+</sup>GaAsは完全にエッチングされている必要があるが、それによるn<sup>+</sup>AlGaAs層へのダメージは避けなければならない。従ってこのドライエッティングには高い選択比と低いダメージの両者が同時に要求される。

本研究で用いたドライエッティング装置は平行平板型であり、エッティング条件としてCCl<sub>2</sub>F<sub>2</sub>とHeの圧力比が1、エッティング時圧力が0.045Torr、入力パワーが0.05W/cm<sup>2</sup>を用いた。この条件でのGaAsのエッティングレートは~2000 Å/min.、AlGaAsでは~10 Å/min.であり、GaAs/AlGaAsの選択比として~200が得られた。この値は、デバイス試作に十分適用できるものと思われる<sup>(1)</sup>。また、このドライエッティングを用いて試作したゲートショットキー接合のφ<sub>Bn</sub>およびn値は、ウェットエッティングを用いたものと有意差は見られないため、低ダメージのドライエッティングが実現しているものと考えられる。

(a) ソース、ドレイン電極形成

(b) ゲートトリソグラフィ

(c) GaAs/AlGaAs選択ドライエッティング

(d) ゲート電極蒸着、リフトオフ

図 4.2 HEMT プロセスフロー図

### 4.3 試作したHEMT/Siの直流特性

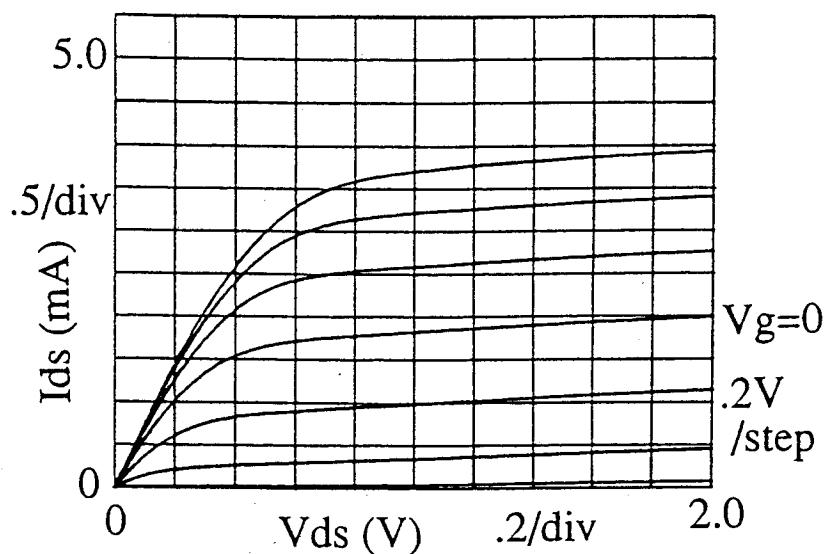

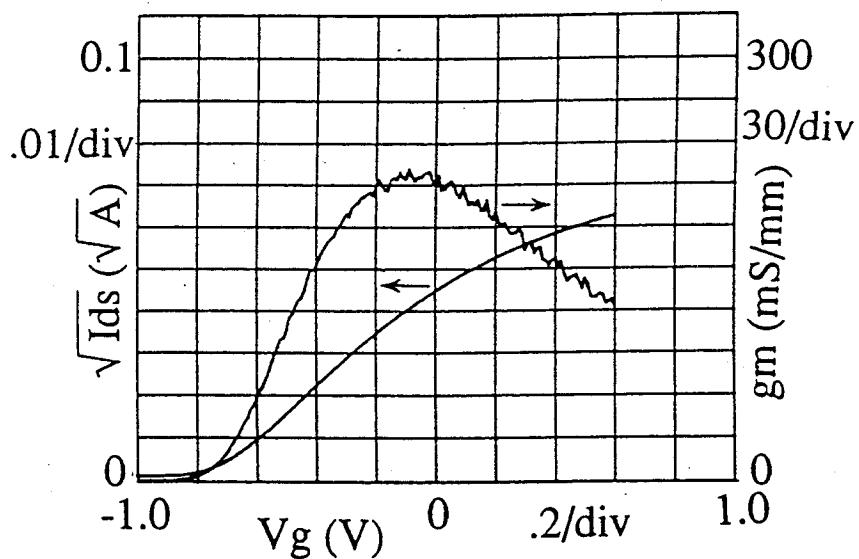

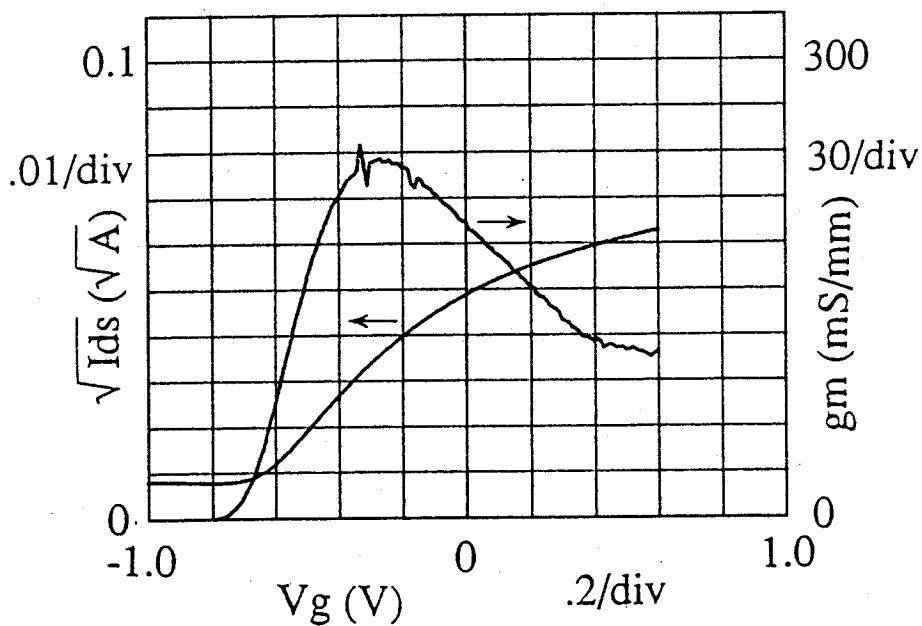

図4.3に試作したHEMT/Siのドレイン電圧 ( $V_{ds}$ ) - ドレイン電流 ( $I_{ds}$ ) 特性を、図4.4にドレイン電圧が2Vの時のゲート電圧 ( $V_{gs}$ ) に対する伝達コンダクタンス ( $g_m$ ) および $\sqrt{I_{ds}}$ の変化の様子を示す<sup>(2)</sup>。ゲート長 $L_g$ 、ゲート幅 $W_g$ はそれぞれ $0.8 \mu m$ 、 $20 \mu m$ であり、電子供給層 $n^+AlGaAs$ のドーピング密度は $9.5 \times 10^{17} cm^{-3}$ である。図4.3よりドレインコンダクタンスが小さく、良好なピンチオフ特性を示していることがわかる。また $g_m$ の最大値として $220 mS/mm$ が得られている。HEMT/GaAsについて行った同様の評価を図4.5、図4.6に示すが、HEMT/SiとHEMT/GaAsとでほとんど差は見られていない。従って前章で示した基板の違いによるその上に成長したバッファ層のリーク電流の差は、実際の静特性においては問題にならないレベルであると考えられる。

### 4.4 HEMT/Siのしきい値電圧分布

#### 4.4.1 しきい値電圧マクロ分布

as-grownHEMT/Siのしきい値電圧を3インチウェーハ全面にわたって測定した（周辺部5mmを除く）。測定数は200～250素子であり、各HEMTのゲート長は $1.2 \mu m$ 、ゲート幅は $20 \mu m$ 、ゲート方位は<011>である。しきい値電圧 ( $V_{th}$ ) の値は、 $V_{ds}$ が2Vの時の $V_{gs}$ 対 $\sqrt{I_{ds}}$ のグラフより直線を外挿して求めた。またここで用いたSi基板は全て中抵抗のものである。

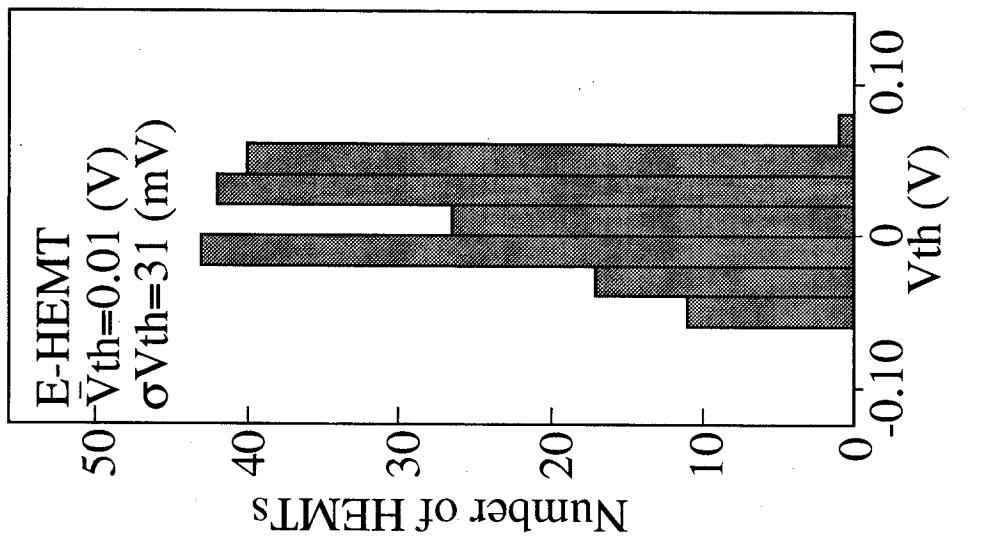

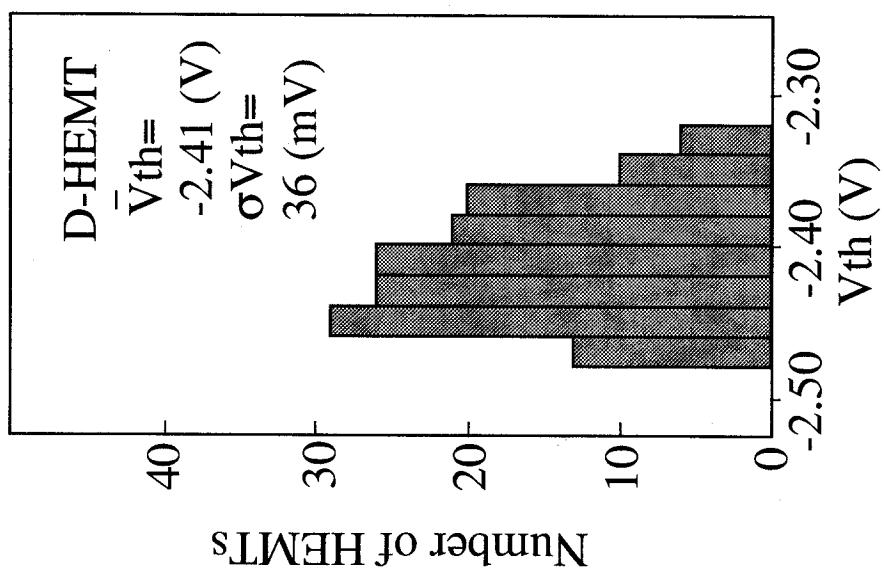

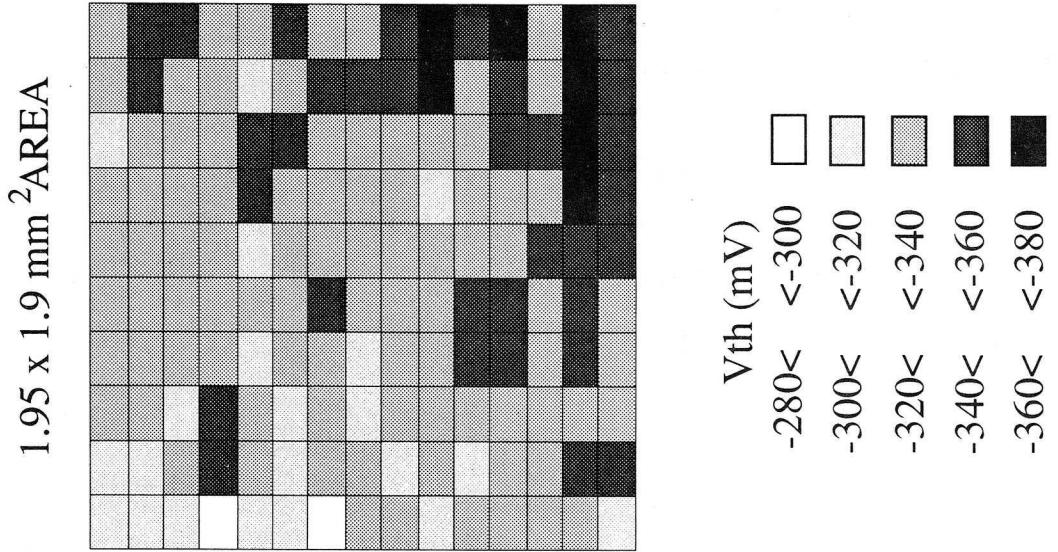

図4.7にディプリジョン型HEMT（D-HEMT）、図4.8にエンハンスマント型HEMT（E-HEMT）についての $V_{th}$ 分布ヒストグラムを示す<sup>(2)</sup>。 $n^+AlGaAs$ 層の膜厚とキャリア密度で決定される $V_{th}$ の設計値に対し、 $\pm 60 mV$ 以内の $V_{th}$ を持つ素子を良とすると、D、E-HEMTとも歩留まりは70%以上であった。この歩留まりのもと、D-HEMTについては $V_{th}$ の平均値 $-2.41 V$ に対し標準偏差 $\sigma V_{th}=36 mV$ 、E-HEMTについては、平均値 $0.01 V$ に対し標準偏差 $31 mV$ と比較的良好な値が得られた。また他のウェーハにおいて、 $V_{th}$ の平均値 $-0.09 V$ に対し標準偏差 $\sigma V_{th}=27 mV$ という値も得られている。これらの $V_{th}$ 分布の特徴として、成長装置に依存すると思われる膜厚あるいはキャリア密度の面内分布を反映した、ウェーハ内一方向へのゆるやかな $V_{th}$ シフトが観察されたが、 $\sigma V_{th}$ の値から中規模ICの作製には十分な均一性を示しているといえる<sup>(3)</sup>。

図 4.3 試作した HEMT/Si の  $V_{ds}$  -  $I_{ds}$  特性 ( $L_g \diagup W_g = 0.8 \diagup 20 \mu m$ )

図 4.4 試作した HEMT/Si の  $g_m$ 、 $\sqrt{I_{ds}}$  のゲート電圧依存性 (@  $V_{ds} = 2V$ )

図 4.5 試作した HEMT/GaAs の  $V_{ds} - I_{ds}$  特性 ( $L_g \times W_g = 0.8 \times 20 \mu m$ )

図 4.6 試作した HEMT/GaAs の  $g_m$ 、 $\sqrt{I_{ds}}$  のゲート電圧依存性 (@  $V_{ds} = 2V$ )

図4.8 E-HEMTのしきい値電圧面内分布

$(L_g \diagup W_g = 1.2 \diagup 20 \mu \text{m})$

図4.7 D-HEMTのしきい値電圧面内分布

$(L_g \diagup W_g = 1.2 \diagup 20 \mu \text{m})$

#### 4.4.2 しきい値電圧ミクロ分布

前述のように、HEMT/Siの $V_{th}$ のマクロ分布はD、E-HEMTとともにかなり均一であることがわかった。しかし転位の $V_{th}$ に対する影響を評価するためには、膜厚やキャリア密度のばらつき、さらにデバイスプロセス上のはらつきを無視できる狭い領域での $V_{th}$ 分布を測定する必要がある。

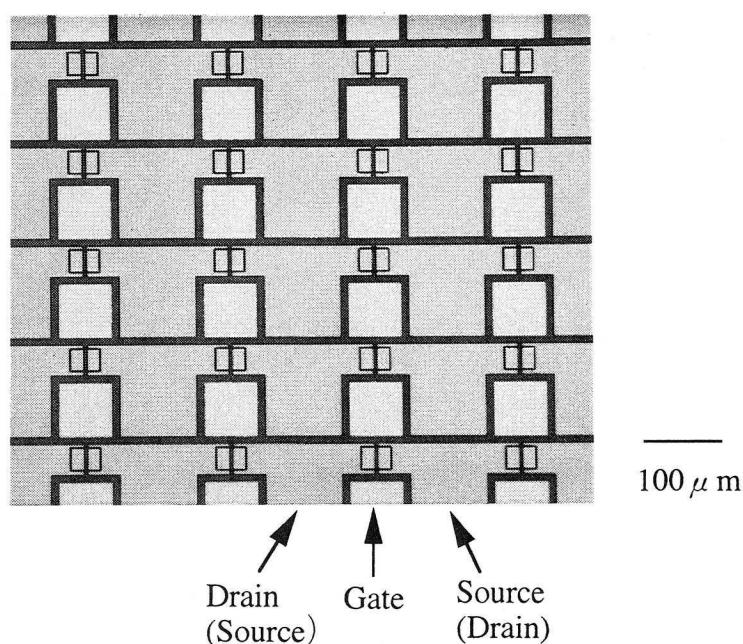

図4.9に本研究で用いた $V_{th}$ ミクロ分布測定用パターンを示す<sup>(4)</sup>。 $1.95 \times 1.9\text{mm}^2$ 内に150ヶのHEMT（ピッチは $130\text{ }\mu\text{m} \times 190\text{ }\mu\text{m}$ ）が形成されており、各HEMTの $L_g$ は $1.2\text{ }\mu\text{m}$ 、 $W_g$ は $30\text{ }\mu\text{m}$ である。このパターンを用い、as-grownのHEMT/Siについて行った $V_{th}$ ミクロ分布のヒストグラムと分布パターンを図4.10に示す<sup>(4)</sup>。図4.10からわかるように、 $V_{th}$ の平均値 $-0.10\text{V}$ に対し標準偏差 $\sigma V_{th}=9\text{mV}$ ときわめて優れた均一性を示している。 $V_{th}$ の分布パターンも一様で、隣り合った素子間で $40\text{mV}$ 以上の $V_{th}$ シフトはなく、故障素子も見られない。これは転位の分布に対応して $V_{th}$ が $50\text{mV}$ 以上変化するために、転位のネットワーク分布が $V_{th}$ 分布に対応して観察される通常のGaAs基板を用いたイオン注入MESFETの結果<sup>(5, 6)</sup>や、 $V_{th}$ が $50 \sim 100\text{mV}$ のシフト量で急激に変化するas-grownのGaAs/Siを用いたイオン注入MESFETの結果<sup>(7)</sup>と対照的である。イオン注入にはその後のアニールが必須であり、このアニールプロセスが転位あるいはそれに付随した欠陥等と注入イオンとの相互作用を引き起こすため、その相互作用が生じた部分で注入イオンの活性化率が影響を受け、 $V_{th}$ のばらつきとなって観察される<sup>(8, 9)</sup>。一方HEMTプロセスはそのアニールを必要としないことがHEMT/Siの $V_{th}$ 分布の転位に対する鈍感さの最も大きな理由だと思われる。しかしながらas-grownのHEMT/Siであり、転位が高密度で存在しすぎるために、かえってその影響が平均化され、見かけ上均一性が優れているように観察されている可能性も否定できない。

図4.9  $V_{th}$ ミクロ分布測定用パターン

1.95 x 1.9 mm<sup>2</sup> AREA

図4.10 as-grownHEMT/Siにおける $V_{\text{th}}$ ミクロ分布のヒストグラムと

分布パラメータ ( $L_g/W_g = 1.2/30 \mu\text{m}$ )

図4.11に3回アニールを行って転位を低減したHEMT/Siについての図4.10と同様の評価結果を示す<sup>(10)</sup>。アニールを行った位置は $1.5\mu\text{m}$ のノンドープのGaAs層成長後である。この場合も $V_{\text{th}}$ の平均値 $-0.33\text{V}$ に対し標準偏差 $\sigma V_{\text{th}}=14\text{mV}$ と優れた均一性を示し、分布パターンもas-grownの場合と同様である。as-grownでは $10^8\text{cm}^{-2}$ オーダーの、3回アニールでは $10^6\text{cm}^{-2}$ オーダーの転位が存在していることから、測定したHEMTのゲート電極下の転位数の平均は、as-grownの場合には $\sim 30$ 個となり、3回アニールの場合には $\sim 0.3$ 個（ゲート電極3本中どれか1本の下に転位がある）となる。このような転位数の差があるにもかかわらず、 $\sigma V_{\text{th}}$ にも分布パターンにも差がみられないことから、転位はHEMT/Siの $V_{\text{th}}$ には影響していないと結論でき、HEMT/SiでもHEMT/GaAsと同様、膜厚やキャリア密度のウェーハ面内均一性を上げることが $V_{\text{th}}$ の高い均一性を得るための最も重要な条件であるといえる。

表面モホロジーと $V_{\text{th}}$ 均一性に関しては、GaAs/Siの表面モホロジーがGaAs/GaAsに比べ劣っているため、その表面の凸凹やピットがデバイスプロセスを経ることで大きくなり、最終的にデバイス不良をもたらすことが報告されている<sup>(11)</sup>。しかし本研究のHEMT/Siにおいては、as-grownの場合でもそのような故障素子は観察されていないことから、前章で示したAFMの結果に加え、デバイス試作を通じても表面モホロジーの良好さが証明されている。

図4.11 3回アニールを行ったHEMT/SiにおけるV<sub>th</sub>ミクロ分布のヒストグラムと分布パラメータ ( $L_g/W_g = 1.2/\sqrt{30 \mu \text{m}}$ )

## 4.5 HEMT/Siの高周波特性

### 4.5.1 Sパラメータ測定

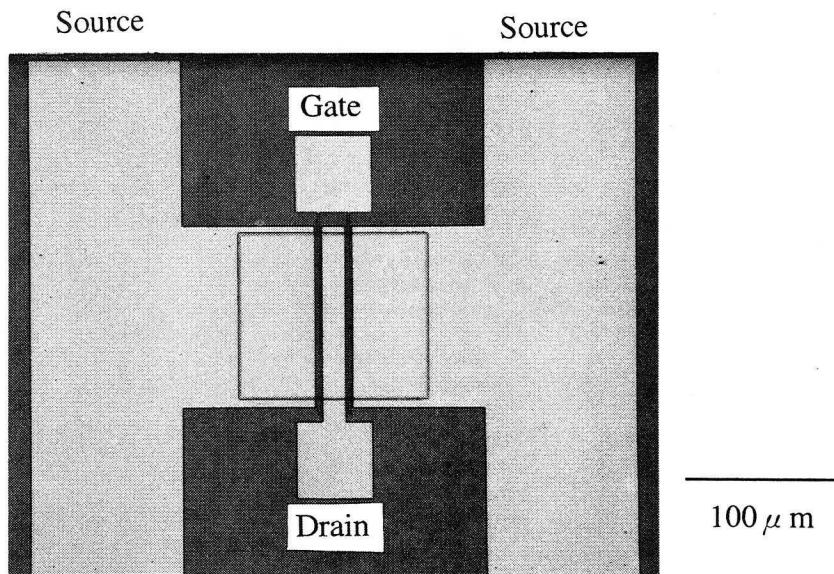

高周波特性の評価はウェーハプローバを用い、1~20GHzの範囲でSパラメータを測定することで行った。測定に用いたHEMTパターンを図4.12に示す。 $L_g=0.8\ \mu m$ 、 $W_g=105\times 2\ \mu m$ であり、測定条件は $V_{ds}=2V$ 、 $V_{gs}$ は直流評価において $g_m$ の最大値が得られる値に設定した。

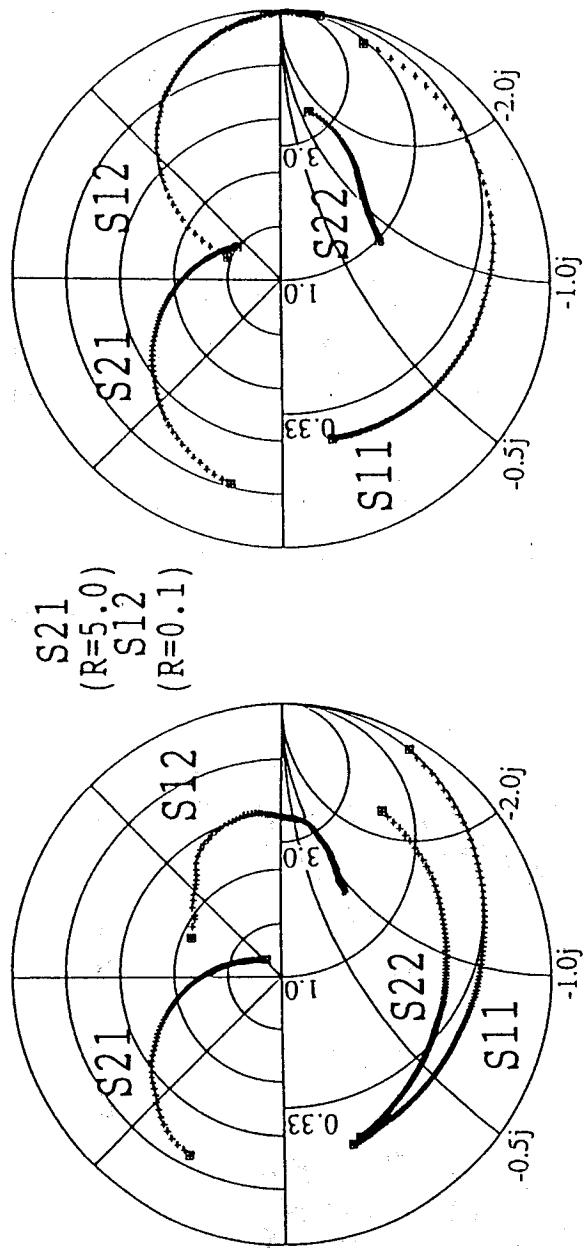

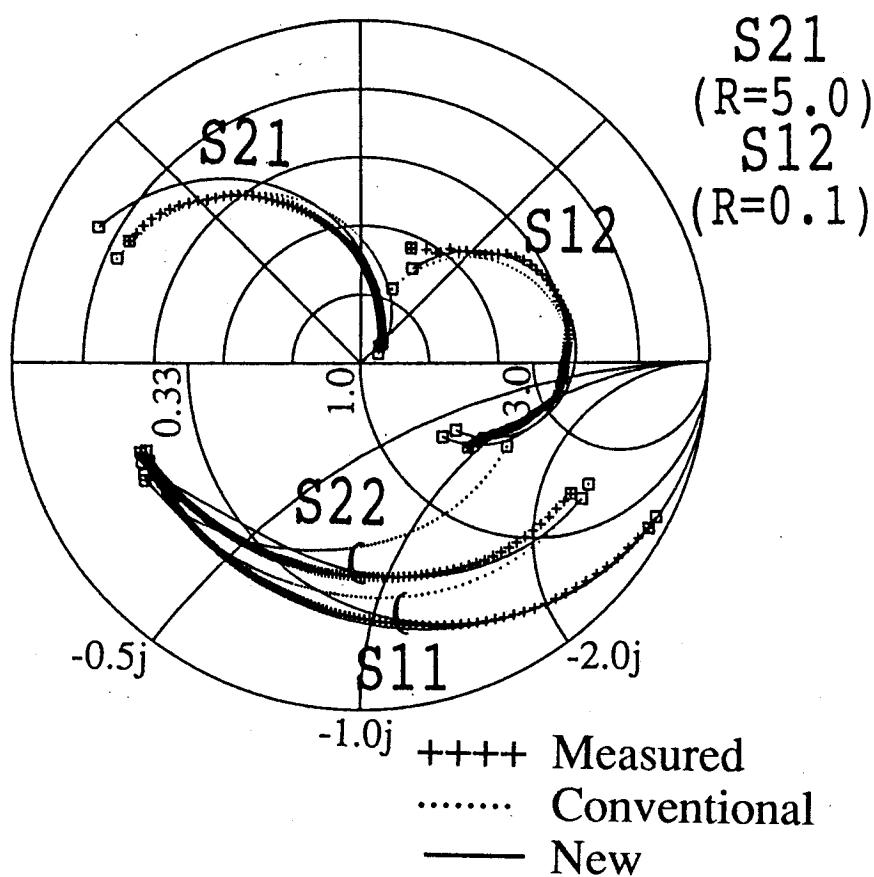

測定したSパラメータの典型例をHEMT/Siについて図4.13に、HEMT/GaAsについて図4.14に示す<sup>(2)</sup>。両者の比較から

- (a) HEMT/GaAsの方が $S_{21}$ の絶対値が大きい。

- (b) HEMT/GaAsの方が $S_{12}$ の絶対値が大きい。

- (c) HEMT/Siの方が $S_{22}$ の位相シフトが大きい。

がわかる。このうち (a) については電子供給層の $n^+AlGaAs$ の厚さとキャリア密度がHEMT/SiとHEMT/GaAsとで若干異なっていたことによる $g_m$ の差を反映したものと思われ、(b) については上述の電子供給層の違いあるいはゲート形成プロセスのばらつきによる $C_{gd}$ （ゲート・ドレイン間容量）の差によるものと思われる。一方 (c) はバッファ層や基板を介して電極間に寄生容量や寄生抵抗が発生している時に観察されるものであり、Si基板の導電性あるいはSi基板-GaAs界面の導電層の影響が現れている。

図 4.12 高周波測定に用いたHEMTパターン ( $L_g / W_g = 0.8 / 210\ \mu m$ )

図4.14 HEMT/GaAsの実測Sパラメータ

図4.13 HEMT/Siの実測Sパラメータ

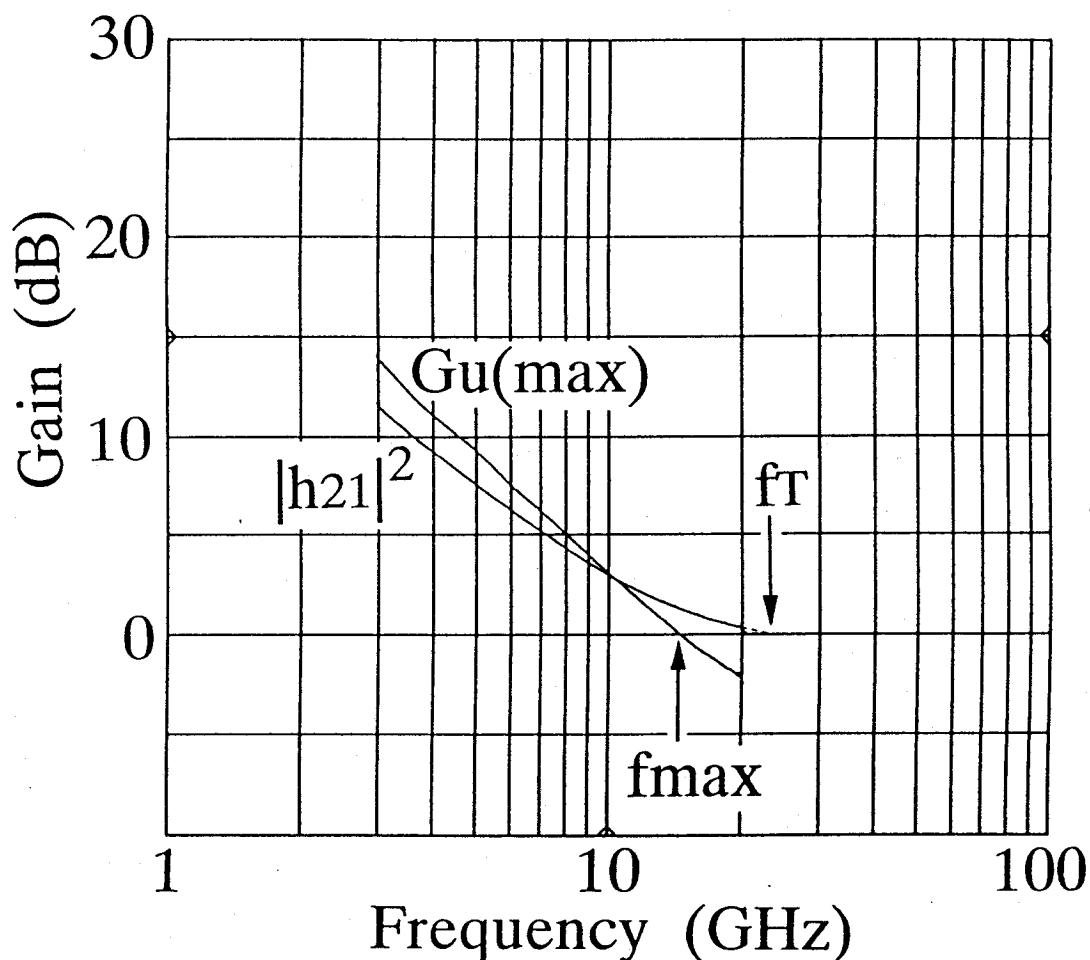

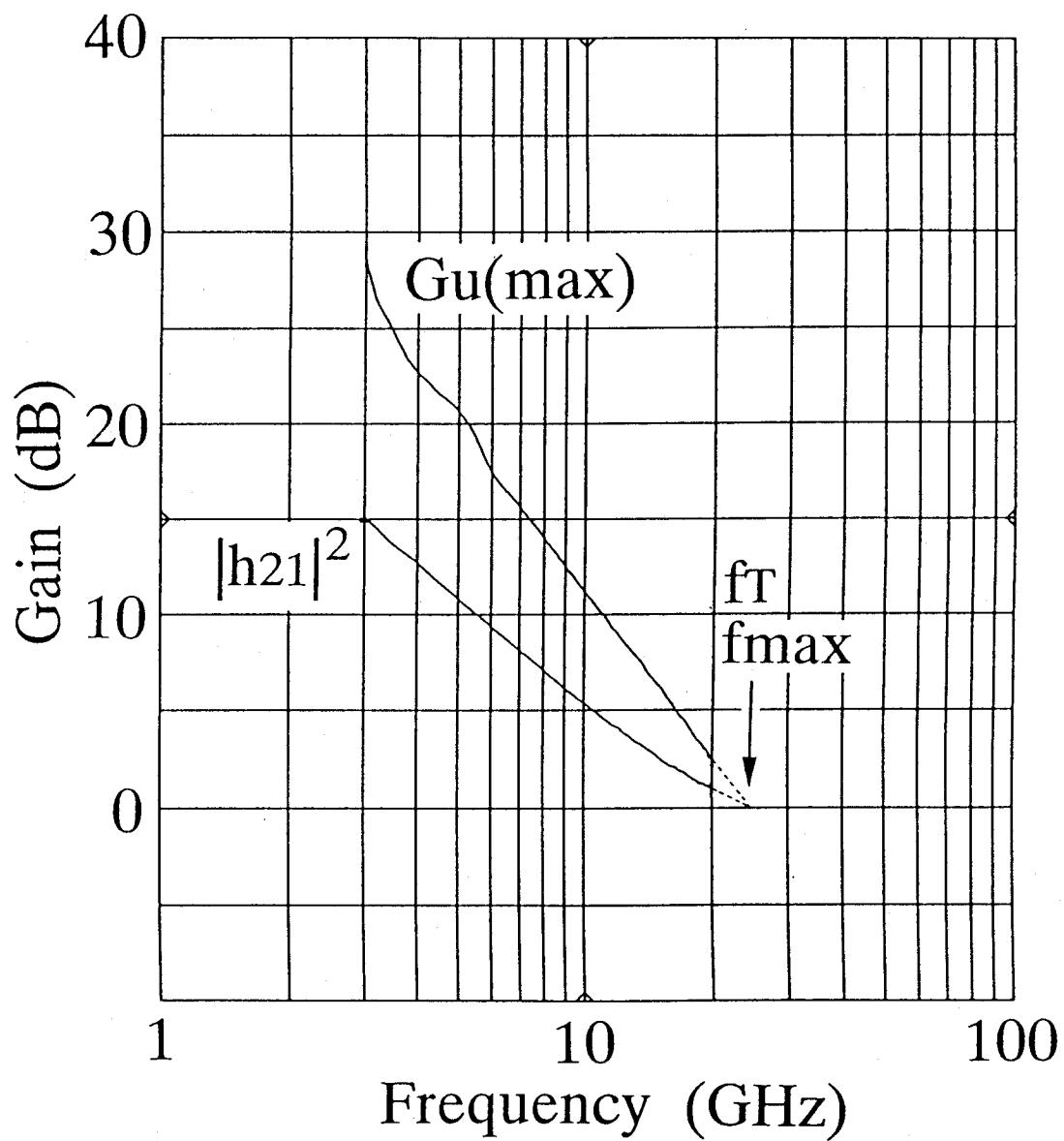

HEMT/Siについて、実測したSパラメータから求めた電流増幅率 ( $|h_{21}|^2$ ) および最大単方向電力利得 ( $G_{u(\max)}$ ) の周波数特性を図4.15に示す。またHEMT/GaAsについての同様の評価を図4.16に示す。 $|h_{21}|^2=0\text{dB}$ となる周波数が遮断周波数 ( $f_T$ ) であり、 $G_{u(\max)}=0\text{dB}$ となる周波数が最高発振周波数 ( $f_{\max}$ ) であるという定義に従うと、HEMT/Siの $f_T$ と $f_{\max}$ はそれぞれ23GHzと15.3GHzと求められ、HEMT/GaAsについては20.6GHzと27.0GHzとなる。HEMT/Siの $f_T$ がHEMT/GaAsより大きくなっているのは、通常 $-6\text{dB/oct.}$ で減衰する $|h_{21}|^2$ が、HEMT/Siに関しては特に高周波側でその減衰率から大きくずれていることによる見かけ上のものである。さらにHEMT/Siでは $f_{\max}$ が $f_T$ より小さいという通常のHEMT/GaAsでは見られない現象も観察されており、これらのHEMT/GaAsより劣った特性は前述した寄生成分の存在によるものと考えられる。

図4.15 試作したHEMT/Siの電流増幅率、最大単方向電力利得の周波数依存性 ( $L_g / W_g = 0.8 / 210 \mu\text{m}$ )

図 4.16 試作したHEMT/GaAsの電流増幅率、最大単方向

電力利得の周波数依存性 ( $L_g / W_g = 0.8 / 210 \mu m$ )

#### 4.5.2 HEMT/Siの小信号等価回路

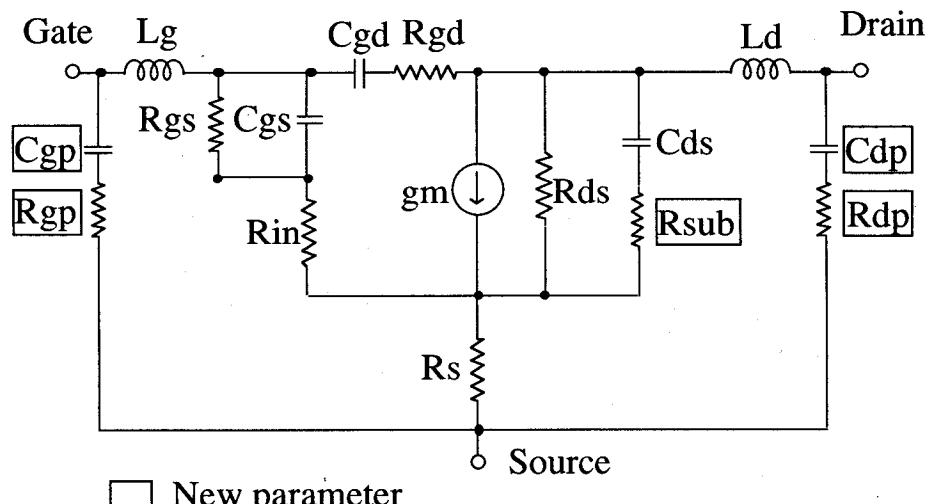

前節で述べたようにHEMT/SiはHEMT/GaAsに比べ寄生容量や寄生抵抗の影響を大きく受けていると考えられるが、それを定量的に調べるため等価回路シミュレーションを行った。図4.17にシミュレーションに用いた回路を示す<sup>(2)</sup>。通常用いられる等価回路に比べ、 $C_{gp}$ 、 $R_{gp}$ が入力側に、 $C_{dp}$ 、 $R_{dp}$ 、 $R_{sub}$ が出力側に加えられている。

図4.17 HEMT/Siの解析に用いた小信号等価回路

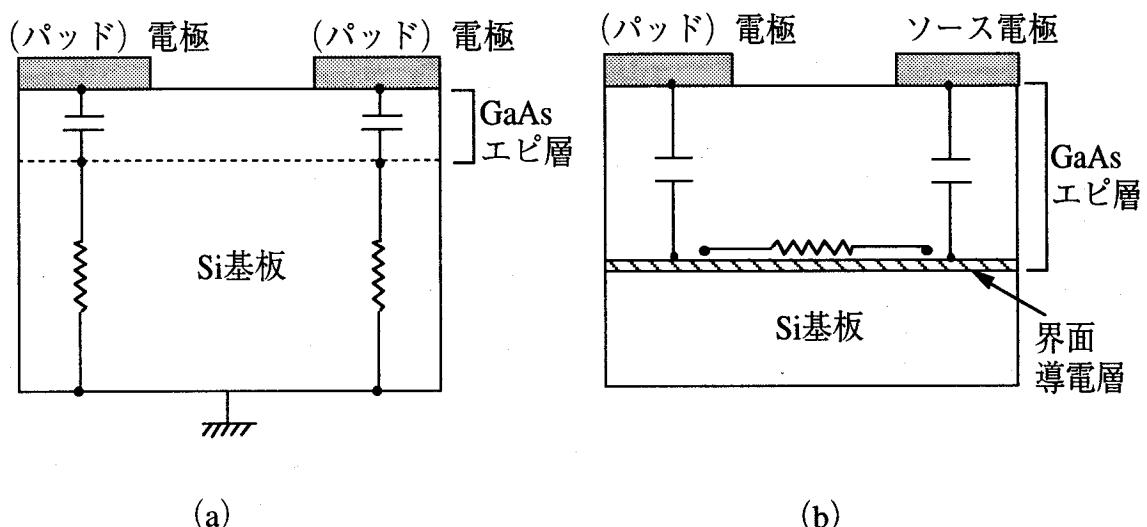

$C_{gp}$ 、 $R_{gp}$ あるいは $C_{dp}$ 、 $R_{dp}$ は図4.18 (a)、(b) に示すように、

- (1) ゲートやドレイン電極に繋がっているパッド電極は比較的大きな面積を有する（この場合は $80 \times 80 \mu\text{m}^2$ ）が、Si基板の導電性のためこの電極と裏面のアース電位との間で誘起された寄生容量と寄生抵抗（図4.18 (a) 参照）

- (2) Si基板-GaAs界面の導電層のため上記パッド電極とソース電極（アース電位）との間で発生した寄生容量と寄生抵抗（図4.18 (b) 参照）

図4.18 GaAs/Siデバイスに特有な寄生容量と寄生抵抗の原因がSi基板にある場合(a)と界面導電層にある場合(b)の説明図

のどちらか、あるいは両者の影響を表している。また $R_{\text{sub}}$ はソース・ドレイン間でのSi基板あるいは界面の抵抗成分を考慮したものである。

この等価回路を用いたシミュレーションの結果を、通常の回路を用いた場合と比較して図4.19に示す。この図から明らかのように、新しい等価回路の方が実測Sパラメータとのフィッティングが良く、その誤差も通常回路の場合の16%に比べ2.1%にまで改善されていることから、新等価回路によってHEMT/Si特有の寄生成分が定量的に取り扱えることがわかる。

図 4.19 新しい等価回路を用いたシミュレーション結果

#### 4.5.3 等価回路パラメータ

シミュレーションによって得られた等価回路パラメータの一例をHEMT/SiとHEMT/GaAsについて表4.1に示す。この表からわかるように、 $C_{ds}$ 、 $C_{gp}$ 、 $C_{dp}$ はHEMT/Siの方が数倍～一桁以上大きな値を示している。GaAs基板の場合 $f_T \propto g_m / (C_{gs} + C_{ds})$ であるが、Si基板の場合は $C_{gs}$ が $C_{gs} + C_{gp}$ となり、かつ $C_{ds}$ もGaAs基板の場合より大きくなるため $f_T$ が大きく劣化することになる。また $C_{ds}$ 、 $C_{dp}$ の増大は出力インピーダンスを小さくするため電力利得が大きくならず、その結果 $G_u^{(max)}$ が増えない。この入出力両方に付加された寄生容量が図4.15で示したHEMT/Siに固有な周波数特性の原因である。

一方新たに加えた抵抗性パラメータ $R_{gp}$ 、 $R_{dp}$ 、 $R_{sub}$ のうち、一般的に $R_{gp}$ 、 $R_{dp}$ はHEMT/GaAsの方が大きいが、 $R_{sub}$ はむしろHEMT/Siの方が大きくなっている。これはHEMT/GaAsについては、 $R_{ds}$ がバッファ層のみならず基板の抵抗をも含んだ形で出力抵抗とみなせることから $R_{sub}$ は必要ないことを示していると思われる。しかしHEMT/Siにおける $R_{sub}$ は、Si基板あるいはSi基板-GaAs界面の導電性で決められる抵抗と考えることができ、バッファ層の抵抗で決められるソース・ドレイン間抵抗 $R_{ds}$ と区別できるものと思われる。HEMT/Siにおいて出力抵抗をこのように2種類に分けると、得られた $R_{ds}$ はHEMT/GaAsとほとんど同じ値になるが、これは両者のドレインコンダクタンスに差がないという4.3節のDC評価とも矛盾しないことから、HEMT/Siにおけるこのような出力抵抗の取り扱いは妥当であると考えられる。

#### 4.5.4 寄生成分の起因源

HEMT/Siの特性に影響を与える寄生成分の起因源として、Si基板あるいはSi基板-GaAs界面の導電性のどちらがより支配的であるかを調べることは、特性向上させる対策を得るために重要である。

同じ構造のHEMT/Siについて、Si基板を中抵抗と高抵抗にした場合の等価回路パラメータを、基板の抵抗の変化に敏感だと思われるパラメータに絞って表4.2に示す。この表からわかるように、 $C_{ds}$ 、 $C_{gp}$ 、 $C_{dp}$ はむしろ高抵抗基板の方が大きな値を示し、また $R_{gp}$ 、 $R_{dp}$ 、 $R_{sub}$ はほとんど変わっていない。これらの結果は、HEMT/Siの寄生成分が図4.18 (a) のようにSi基板の導電性によって発生するものではないことを示している。一方図4.18 (b) のようにSi基板-GaAs界面の導電層を寄生成分の起因源とみなすと、その導電層の厚さとキャリア密度およびSi基板上に成長させたバッファ層の厚さで上記寄生容量と寄生抵抗の値がほとんど決まると考えられるため、実験結果を矛盾なく説明できる。

界面導電層を寄生成分の起因源とみなすことの妥当性に関し、パッド容量を例にとってシミュレーションを行った<sup>(12)</sup>。シミュレーションに用いたパッド断面

表 4.1 HEMT/Si と HEMT/GaAs の等価回路パラメータ

$(L_g / W_g = 0.8 / 210 \mu m)$

|                        | on Si | on GaAs |

|------------------------|-------|---------|

| gm (mS)                | 77.3  | 64.9    |

| Cgs (pF)               | 0.31  | 0.41    |

| Cgd (pF)               | 0.06  | 0.04    |

| Cds (pF)               | 0.27  | 0.06    |

| Rin ( $\Omega$ )       | 5.4   | 12.9    |

| Rgd ( $\Omega$ )       | 391   | 152     |

| Rs ( $\Omega$ )        | 7.5   | 1.9     |

| Rgs (k $\Omega$ )      | 60.1  | 28.6    |

| Rds ( $\Omega$ )       | 184   | 202     |

| Lg (pH)                | 115   | 103     |

| Ld (pH)                | 145   | 20      |

| Cgp (pF)               | 0.44  | 0.07    |

| Cdp (pF)               | 0.49  | 0.02    |

| Rsub ( $\Omega$ )      | 67.7  | 14.3    |

| Rdp ( $\Omega$ )       | 9.6   | 42.8    |

| Rgp ( $\Omega$ )       | 23.2  | 76.7    |

| f <sub>r</sub> (GHz)   | 23.0  | 20.6    |

| f <sub>max</sub> (GHz) | 15.3  | 27.0    |

New parameters

表 4.2 基板の導電率による等価回路パラメータの変化

|                   | on Si<br>(Middle-resistivity) | on Si<br>(High-resistivity) | on GaAs |

|-------------------|-------------------------------|-----------------------------|---------|

| Cds (pF)          | 0.27                          | 0.29                        | 0.06    |

| Cgp (pF)          | 0.44                          | 0.75                        | 0.07    |

| Cdp (pF)          | 0.49                          | 0.60                        | 0.02    |

| Rsub ( $\Omega$ ) | 67.7                          | 83.1                        | 14.3    |

| Rdp ( $\Omega$ )  | 9.6                           | 9.2                         | 42.8    |

| Rgp ( $\Omega$ )  | 23.2                          | 23.5                        | 76.7    |

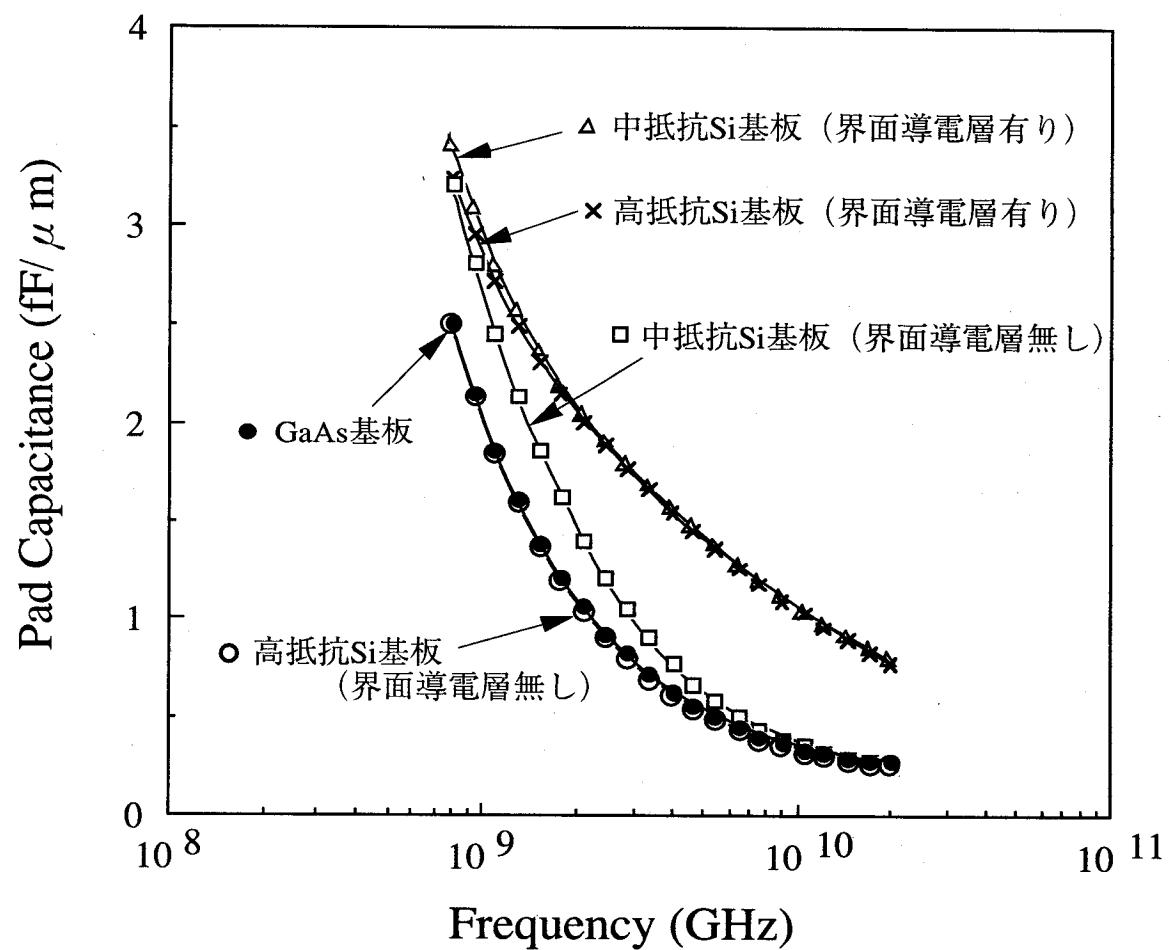

構造を図4.20に示す。Si基板上にGaAsおよびAlGaAsバッファ層が形成され、その上にパッドが形成された構造になっている。パッドは幅 $40\mu\text{m}$ であり、その両側から $10\mu\text{m}$ 離れてソース電極（アース電位）がある。また裏面もアース電位になっている。パッドをショットキー性電極とした時の周波数に対するパッド容量変化の計算結果を図4.21に示す。パッド容量はパッドの奥行き $1\mu\text{m}$ 当たりの値を示しており、パラメータとしては、Si基板の抵抗率および界面導電層の有無をとっている。界面導電層のキャリア密度及び厚さは第三章で述べた評価結果の値（ $1 \times 10^{18}\text{cm}^{-3}$ 、 $0.1\mu\text{m}$ ）を用い、また比較のためon GaAsの場合も示してある。この図から、界面導電層が存在すればSi基板の抵抗率にかかわらずパッド容量がほぼ同じになり、かつon GaAsより大きくなることがわかり、実験結果と同様の結果が得られた。また逆に界面導電層が存在しなければ、高抵抗Si基板程度の抵抗率でもon GaAs並の値になることがわかる。なおパッド容量に周波数分散があるのでキャリアの動きが周波数の増加に追随しなくなるためである。

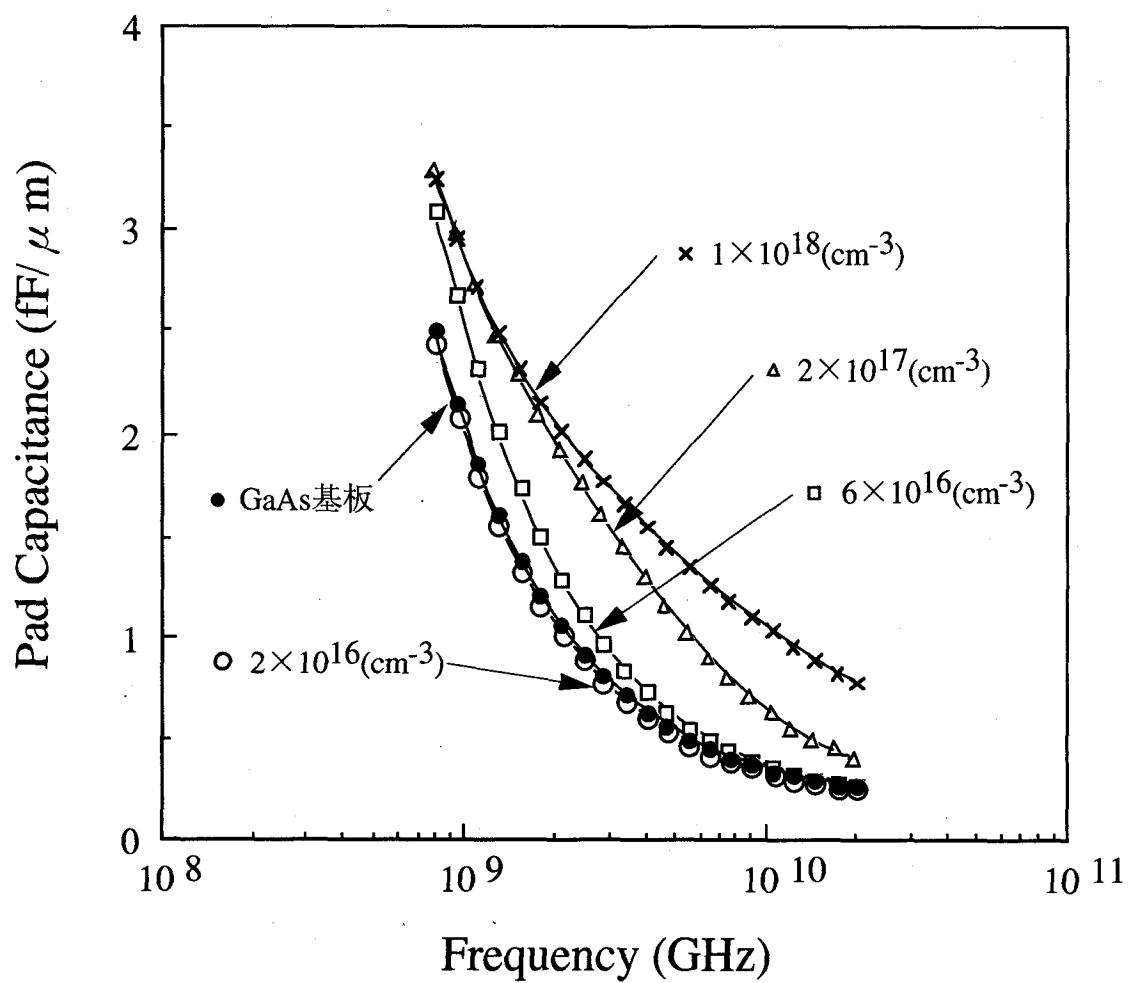

次に界面導電層のキャリア密度を変えた時の図4.21と同様のシミュレーション結果を図4.22に示す<sup>(12)</sup>。図4.22よりキャリア密度が $2 \times 10^{16}\text{cm}^{-3}$ 以下でないとパッド容量がon GaAs並にはならないことがわかり、GaAs-Si界面でのp型ドーパントの導入や成長温度を下げるによる基板のSi原子の拡散抑制等の方法で界面導電層のキャリア密度を低減させデバイス特性の向上を図ることは、二桁の低減を各成長毎に確実に行わなければならないことになり結晶成長技術的にかなり難しいと考えられる。そこでデバイス設計あるいはプロセスからの対処による寄生

図 4.20 シミュレーションに用いたパッド断面構造

図4.21 Si基板の導電率および界面導電層の有無によるパッド容量変化

のシミュレーション結果

図 4.22 界面導電層のキャリア密度とパッド容量変化

のシミュレーション結果

成分の低減が必要になるが、その方法と結果については次節で述べる。

#### 4.6 寄生成分の影響を低減したHEMT/Siの高周波特性

##### 4.6.1 パッド容量の低減

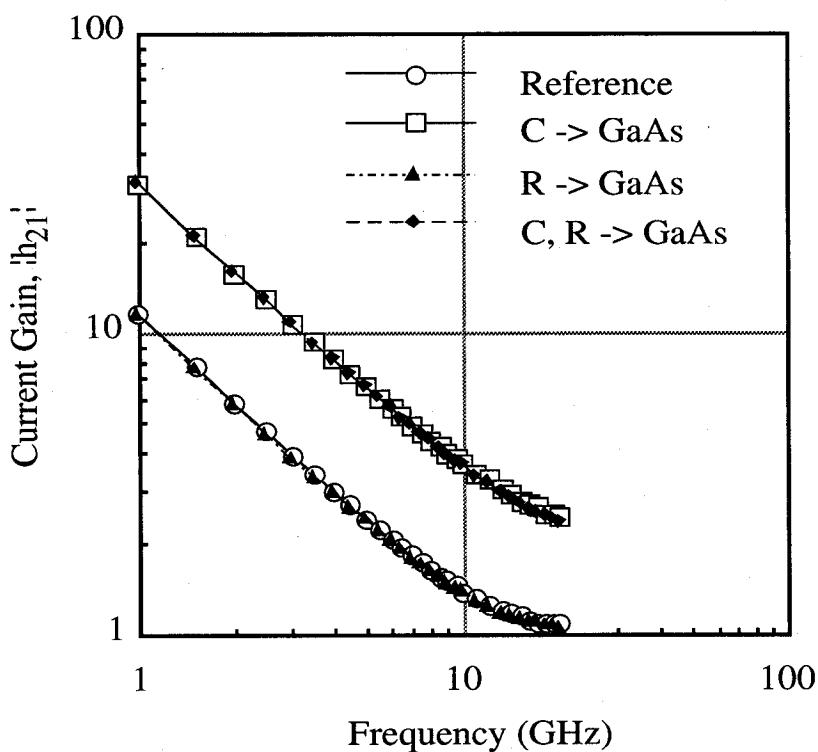

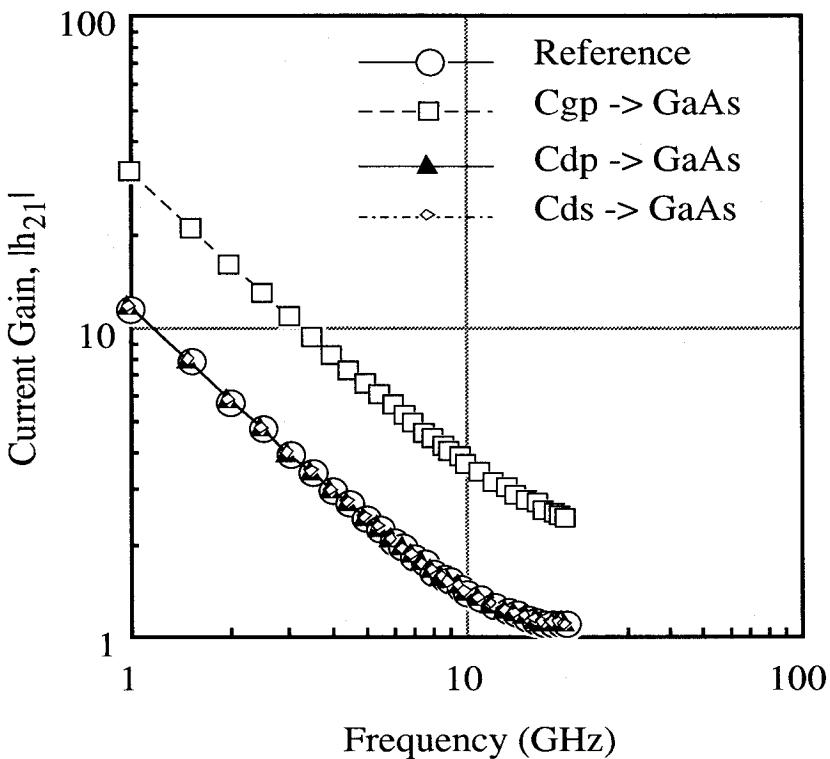

HEMT/Si特有の寄生成分のうち、最も高周波特性を劣化させるパラメータを見い出すためシミュレーションを行った。図4.23は各寄生容量および寄生抵抗がHEMT/GaAsと同じ値になった場合の $|h_{21}|$ の計算結果を示してある<sup>(13)</sup>。この図においてRef.として示してあるのがHEMT/Siの実測値、C $\rightarrow$ GaAsというのはHEMT/Siの $C_{gp}$ 、 $C_{dp}$ 、 $C_{ds}$ のみがHEMT/GaAsの値に等しくなったと仮定した場合、R $\rightarrow$ GaAsというのはHEMT/Siの $R_{gp}$ 、 $R_{dp}$ のみがHEMT/GaAsの値に等しくなったと仮定した場合、の計算値で、C、R $\rightarrow$ GaAsというのは両者がHEMT/GaAsの値に等しくなったと仮定した場合である。図4.23より寄生容量低減の方が $|h_{21}|$ の向上に大きく寄与することがわかる。次に各寄生容量の内どれが最も $|h_{21}|$ に影響を与えるかを計算したのが図4.24である<sup>(13)</sup>。この図も図4.23と同様に、Ref.がHEMT/Siの実測値で、たとえばC $\rightarrow$ GaAsというのはHEMT/Siの $C_{gp}$ のみがHEMT/GaAsの値に等しくなったと仮定した場合の計算値である。4.5.3節でも述べたように、パッド容量とくに $C_{gp}$ の低減が $f_T$ の向上に最も有効であることがわかる。またG<sub>u(max)</sub>についても同様のシミュレーションを行いC<sub>gp</sub>、C<sub>dp</sub>、C<sub>ds</sub>の

図 4.23 HEMT/Si における各寄生成分の低減効果

図 4.24 HEMT/Si における各寄生容量の低減効果

低減がそれぞれほぼ等しい寄与率で  $f_{\max}$  の向上に有効であることがわかった<sup>(13), (14)</sup>。

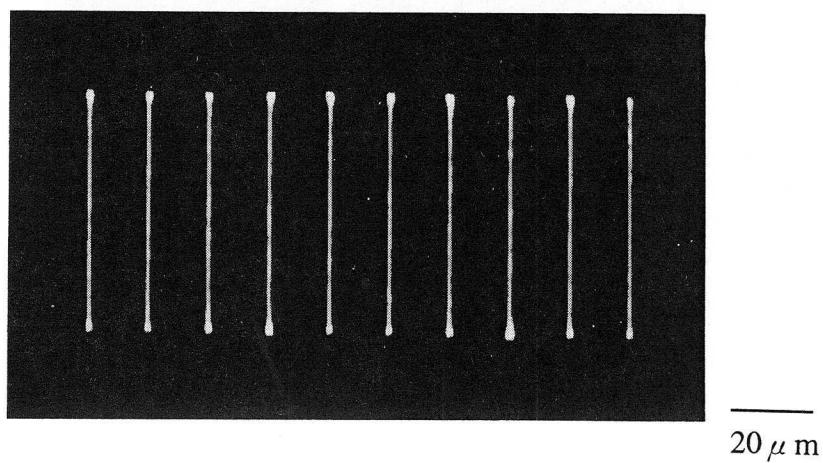

以上よりパッドがもたらす寄生容量を低減することが高周波特性の向上に不可欠であることがわかったため、パッドの面積あるいは構造による容量の違いを図 4.25 (a) ~ (d) のようなパッドで評価した。図 4.25 (a) は通常構造でパッド面積が  $80 \times 80 \mu m^2$ 、(b) は通常構造でパッド面積が  $50 \times 50 \mu m^2$ 、(c) は  $3000 \text{ \AA}$  の  $\text{SiO}_2$  を介した構造でパッド面積が  $50 \times 50 \mu m^2$ 、(d) はパッド周囲の GaAs 層を界面の導電層も含めて除去した構造でパッド面積が  $50 \times 50 \mu m^2$  である。パッド容量値としては、このようなパッドを持ったデバイスを実際に試作評価し、その  $C_{gp}$  の値を用いた。この図からほぼ面積比に応じてパッド容量が変化しており、絶縁層の挿入やパッドを独立構造にすることも有効であることがわかる。また (d) の構造ではほとんど GaAs 基板上の値（図中 GaAs substrate と示してある）と等しい値が得られていることから、Si 基板 - GaAs 界面の導電層が寄生容量の原因であることが再確認できる。

#### 4.6.2 パッド容量を低減したHEMT/Siの高周波特性

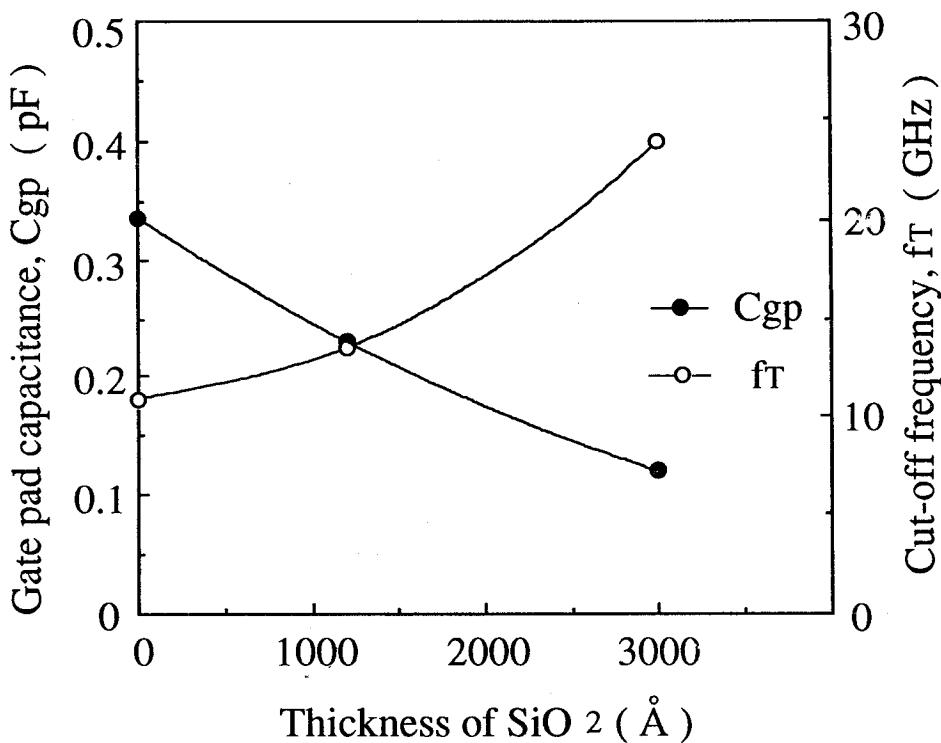

ゲートパッド下に  $\text{SiO}_2$  を挿入した HEMT/Si について、その  $C_{gp}$  と  $f_T$  の関係を図 4.26 に示す<sup>(10)</sup>。HEMT の  $L_g$  は  $0.8 \mu m$ 、 $W_g$  は  $210 \mu m$ 、パッド面積は  $50 \times 50 \mu m^2$

図4.25 パッド構造と容量の関係

図 4.26 ゲートパッド下に挿入した  $\text{SiO}_2$  膜の厚さとゲートパッド容量およびカットオフ周波数の関係

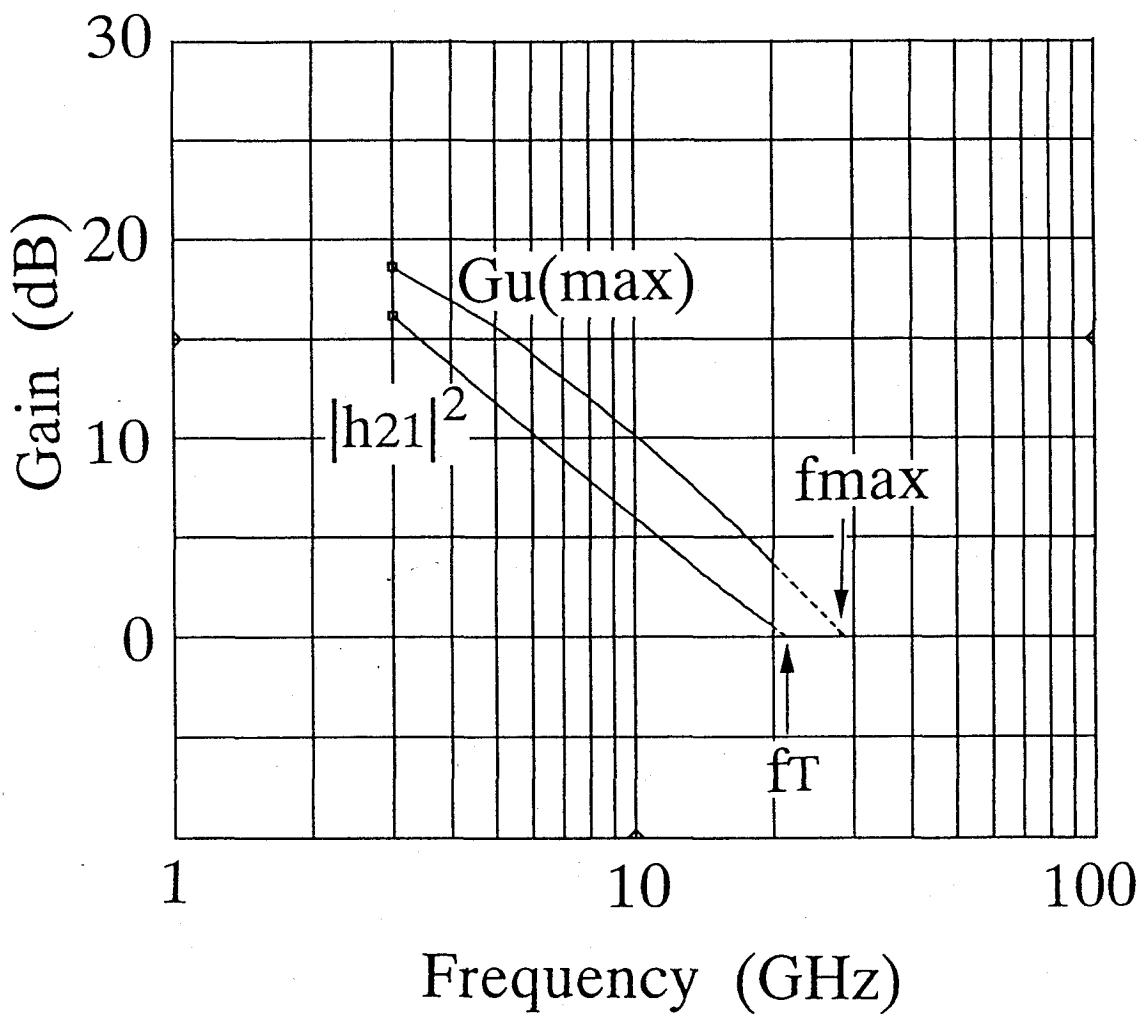

である。この図からわかるように、挿入した  $\text{SiO}_2$  の厚さが増えるとともに  $C_{\text{gp}}$  が減少していき、 $f_T$  が大幅に向上している。 $\text{SiO}_2$  の挿入厚が  $3000 \text{ \AA}$  の時の HEMT/Si の周波数特性を図 4.27 に示す<sup>(10)</sup>。図 4.15 と比べれば明らかかなように、 $|h_{21}|^2$ 、 $G_u$  とも絶対値が大きくなり、 $-6 \text{ dB/oct.}$  の減衰率からのズレもほとんどなくなっている。その結果  $f_T$  と  $f_{\text{max}}$  は  $24 \text{ GHz}$  とこのゲート長での HEMT/GaAs に匹敵する値が得られている。

以上の結果より、HEMT/Si の高周波特性を劣化させるパッド容量特にゲートパッド容量の影響は、パッド面積の縮小とパッド下の絶縁膜挿入によってほとんど GaAs 基板上のパッド並に小さくできることが明らかになった。パッド形成に関するこのような変更はプロセス上の困難さをそれほど伴わないとため、HEMT/Si を実用化していく上での障害にはならないと思われる。

#### 4.7 まとめ

HEMT/Si を試作し、そのしきい値電圧分布と高周波特性を評価した。しきい値電圧のマクロ評価においては、結晶成長装置の特性を反映したと思われる膜厚あるいはキャリア密度のゆるやかな面内分布に基いた分布が観察されたが、ミクロ評価においては HEMT/GaAs に匹敵する極めて優れた均一性が得られた。しかも

図4.27 パッド容量を低減したHEMT/Siの電流増幅率、最大単方向電力利得の周波数依存性 ( $L_g/W_g=0.8/210\mu m$ )

この均一性は結晶内部に存在する転位数の多少にかかわらず得られており、転位はHEMTのようなエピタキシャル層を用いるデバイスのしきい値電圧分布には影響を与えていないことが明らかになった。さらに表面の凸凹やピットに起因すると思われる故障素子も見られないことから、表面モホロジーもデバイス制作に十分耐えうるレベルにあることが示された。

高周波評価を通じてHEMT/SiはHEMT/GaAsに比べて寄生成分、とくに寄生容量の影響を大きく受けていることが明らかになった。この寄生容量は主として、Si基板-GaAs界面の導電層によって誘起されたゲートパッド容量によるものであり、パッド面積の縮小やパッド下絶縁層の挿入等の比較的容易なプロセスによりGaAs基板上のパッド容量並に減少できることがわかった。実際にそのような対策を施したHEMT/SiはHEMT/GaAsに遜色のない特性を示した。

GaAs/Siの電子デバイスへの応用の一つとして有望と思われるHEMTに関し、デジタル、アナログそれぞれの応用に対する基礎評価を行い、デバイス形成プロセスにおいて一部考慮すべき点はあるもののGaAs基板上の素子と同等の特性を得た。これはGaAs/GaAsを代替するものとしてGaAs/Siが非常に有望な技術であることを示すものである。

#### (参考文献)

- (1) Kohki Hikosaka, Takashi Mimura, and Kazukiyo Joshin : Jpn. J. Appl. Phys. **20** (1981) L847.

- (2) Takashi Aigo, Mitsuhiro Goto, Aiji Jono, Akiyoshi Tachikawa, and Akihiro Moritani : Proc. Int. Symp. GaAs and Related Compounds (1993) 87.

- (3) 菅野卓雄監修：超高速化合物半導体デバイス（培風館）

- (4) Takashi Aigo, Aiji Jono, Akiyoshi Tachikawa, Ryuichi Hiratsuka, and Akihiro Moritani : Appl. Phys. Lett. **64** (1994) 3127.

- (5) Hiroshi Nakamura, Hajime Matsuura, Takashi Egawa, Yoshiaki Sano, Toshimasa Ishida, and Katsuzo Kaminishi : Extended Abs. of the Int. Conf. on Solid State Devices and Materials (1985) 429.

- (6) H. Matsuura, H. Nakamura, Y. Sano, T. Egawa, T. Ishida, and K. Kaminishi : Proc. IEEE GaAs Integrated Circuit Symp. (1985) 67.

- (7) 山岸長保、木村有、上田孝、小野沢幸子、秋山正博：第51回応用物理学会学術講演会予稿集（1990）29p-T-7.

- (8) 宮澤信太郎：応用物理 第56巻（1987）19.

- (9) Shintaro Miyazawa, and Yasunobu Ishii : IEEE Trans. Electron Devices **31** (1984) 1057.

- (10) Takashi Aigo, Mitsuhiro Goto, Yasumitsu Ota, Aiji Jono, Akiyoshi Tachikawa, and Akihiro Moritani : IEEE Trans. Electron Devices **43** (1996) 527.

- (11) T. Ohori, H. Suehiro, S. Mitagaki, T. Miyagaki, and K. Kasai : Proc. Symp. on Alloy Semiconductor Physics and Electronics (1994) 57.

- (12) Yoji Morikawa, Takashi Aigo, Yasumitsu Ota, Mitsuhiro Goto and Akihiro Moritani : 15th Electronic Materials Symp. (1996) 131.

- (13) Mitsuhiro Goto ; Private communication.

- (14) Mitsuhiro Goto, Yasumitsu Ota, Takashi Aigo, and Akihiro Moritani : IEEE Trans. Microwave Theory and Techniques **44** (1996) 668.

## 5. パワーMESFET/Siの試作

### 5.1 はじめに

近年の移動体通信技術の発達とともに、電子の移動度が高く低消費電力という特長を持つGaAs系デバイスは、送信部および受信部のキーコンポーネントとしてますます重要になり、その需要は飛躍的に増大している。大口径化が可能で熱伝導性に優れたGaAs/Siをこの分野のデバイス、特にパワーデバイスに応用することは、デバイスのコストを下げ、かつ特性の向上が期待できるため、その意義は大きい。

本章ではGaAs/Siを用いたパワーMESFETを試作し、その直流特性および携帯電話での使用を想定した周波数0.85GHz、電源電圧3.6Vでの入出力特性について述べる。またパワーMESFETが、デバイス構造上GaAs/Si特有のパッド容量の影響を低減させるのに有効であることも示す。

### 5.2 デバイス設計

#### 5.2.1 全ゲート幅

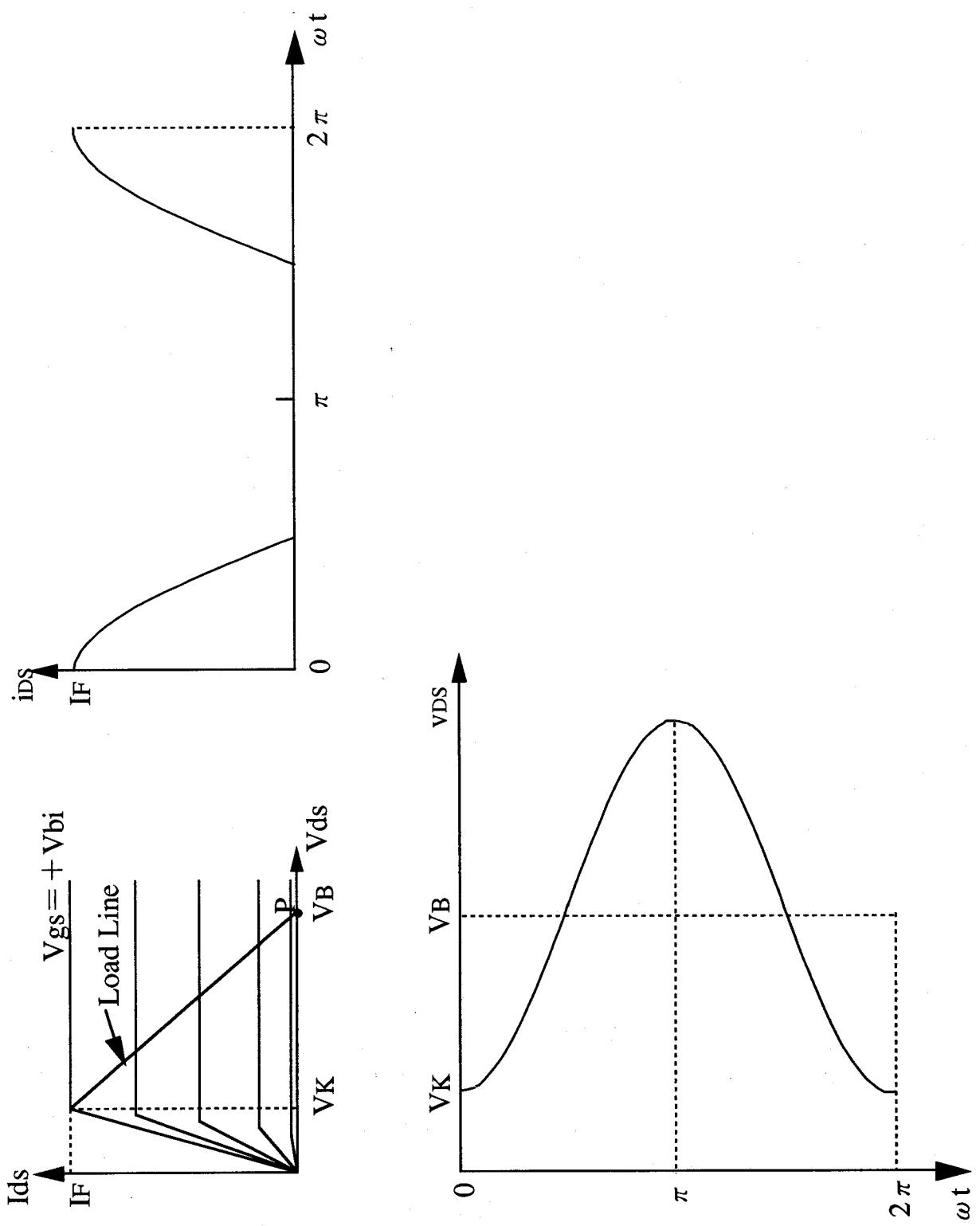

携帯電話等での使用を想定した場合、その出力は0.5～1Wクラスであることが多い。本研究では素子の作り易さを考え、最大出力 $P_{o(sat)}$ が0.5Wとなるように設計した。また実際の動作はAB級で行わせるのが普通であるが、ここでは計算のためB級動作とした。

図5.1を参照して説明する。この図において点Pを動作点とし、そこでドレンバイアスを $V_B$  (V) とする。またニード電圧を $V_K$  (V) 、ゲートバイアスを正方向へ拡散電位 $V_{bi}$ まで振り込んだ時のドレン電流を $I_{F(max)}$  (A/mm) としてドレン電流 $i_{DS}$ を表すと、B級動作の場合の流通角は $\pi$ であることを考慮し、

$$i_{DS} = I_{F(max)} \times \cos \omega t \quad (0 \leq \omega t \leq \pi/2) \\ (3\pi/2 \leq \omega t \leq 2\pi) \quad (5.1)$$

$$i_{DS} = 0 \quad (\pi/2 \leq \omega t \leq 3\pi/2)$$

となり、またドレン電圧 $v_{DS}$ は

$$v_{DS} = V_B - (V_B - V_K) \times \cos \omega t \quad (0 \leq \omega t \leq 2\pi) \quad (5.2)$$

となる。

図5.1 B級動作時ににおけるドレイン電流とドレイン電圧の波形

$i_{DS}$  をフーリエ展開すると、

$$i_{DS} = I_{F(max)} / \pi \times (1 + (\pi / 2) \cos \omega t + (2\text{次以上の項})) \quad (5.3)$$

となる。第1項がドレイン電流の直流成分、第2項が基本波成分である。これより直流入力電力  $P_{DC}$  と基本波出力電力  $P_o$  は、

$$P_{DC} = I_{F(max)} \times (V_B - V_K) / \pi \quad (5.4)$$

$$P_o = I_{F(max)} \times (V_B - V_K) / 4 \quad (5.5)$$

と求められる<sup>(1)</sup>。

(5.5) 式をもとに  $P_o = 0.5W$  を得るための全ゲート幅  $W_g$  を計算すると、 $I_{F(max)} = 250\text{mA/mm}$ 、 $V_B = 3.6V$ 、 $V_K = 1.5V$  として、 $W_g = 3.8\text{mm}$  となる。しかし表面空乏層等の影響があるため、実際のFETでは (5.5) 式で得られる値の1.5倍程度の  $W_g$  で作製する必要がある<sup>(2)</sup>。

### 5.2.2 活性層厚

$I_{F(max)} = 250\text{mA/mm}$ 、活性層のキャリア密度を  $2 \times 10^{17}\text{cm}^{-3}$ 、ゲート長  $L_g \sim 1\mu\text{m}$  として、Fukuiの結果<sup>(3)</sup> よりチャネル厚は  $\sim 0.1\mu\text{m}$  と求められる。ゲートはリセス構造にするため、この厚さにリセス深さ  $\sim 0.2\mu\text{m}$  を加え、活性層厚は  $0.3\mu\text{m}$  とした。

### 5.2.3 単位ゲート幅

ゲートの一端に入力した信号が他端へ伝搬していく際、その減衰量が大きいとゲート全面にわたって均一電位で動作しているとみなせなくなる。分布定数回路モデルによるFETの動作解析<sup>(2)</sup> をもとにして、動作周波数（約1GHz）で均一電位にあるとみなせる一本のゲート幅（単位ゲート幅）  $W_u$  を求めると、 $\sim 250\mu\text{m}$  となる。しかしこの値はGaAs基板上のデバイスに対してであり、GaAs/Siの場合には基板の容量性を考えるとさらに小さくする必要があると思われる。そこで、試作デバイスにおいては  $W_u = 200\mu\text{m}$  とし、また全ゲート幅は5.2.1節での計算を考慮しつつ  $W_u \times 28\text{本} = 5.6\text{mm}$  とした。

### 5.2.4 ゲートボンディングパッド数

パワーFETは数多くの単位ゲートに同相で信号を入力しなければならないが、その際単位ゲート1本毎に入力パッドを設けることは不可能である。そこで入力

パッド1個当たり単位ゲート何本までならば均一動作（同相動作）条件が保てるかを求める必要がある。

この解析はD'Asaroらによって行われており<sup>(4)</sup>、必要なボンディングパッド数をN<sub>pad</sub>、全ゲート幅をW<sub>g</sub>、単位ゲート幅をW<sub>u</sub>、ゲート-ゲート間隔をL<sub>gg</sub>とするとき、

$$N_{\text{pad}} > W_g \times L_{\text{gg}} / (2 \times W_u^2) \quad (5.6)$$

と求められる。W<sub>g</sub>=5.6mm、L<sub>gg</sub>=15μm、W<sub>u</sub>=200μmで計算すると、N<sub>pad</sub>>1.05となるためこれを満たす最小の整数をとってN<sub>pad</sub>=2とした。これはゲートボンディングパッド数であるが、ドレインに関しても同じパッド数とした。

### 5.2.5 パワーMESFET構造における寄生容量の影響

前章で述べたように、GaAs/Si電子デバイスはパッドの容量とくにゲートパッドの寄生容量が入力容量の増加をもたらし、高周波特性を劣化させている。従ってパワーFETにおいても、この寄生容量の影響を考慮した設計をする必要がある。FETの性能指数の一つとしてカットオフ周波数(f<sub>T</sub>)をとって考えると、f<sub>T</sub>は

$$\begin{aligned} f_T &= g_m / (2\pi (C_{in} + C_{ds})) \\ &\sim g_m / (2\pi (C_{gs} + C_{gp})) = g_m / (2\pi C_{gs} (1 + \frac{C_{gp}}{C_{gs}})) \end{aligned} \quad (5.7)$$

と表せる。ここでC<sub>in</sub>は入力容量、C<sub>gs</sub>、C<sub>gp</sub>はそれぞれ入力真性容量、入力寄生容量（ゲートパッド容量）であり、またC<sub>ds</sub>は前章のシミュレーション結果よりその影響は小さいとして除いてある。パワーFETの場合は、構造上全ゲート幅が大きい、すなわちC<sub>gs</sub>がもともと大きいデバイスであるため、多少C<sub>gp</sub>が存在してもC<sub>gp</sub>/C<sub>gs</sub>は小さくできる。これが、Si基板の高い熱伝導率と相まってパワーMESFETがGaAs/Siの応用デバイスとして最適であると考えられる理由である。

一般的にC<sub>gp</sub>はC<sub>gs</sub>の10%以内で設計することが望ましく<sup>(2)</sup>、また各ゲートフィンガーを繋ぐバスラインもパッドと同様に寄生容量を発生させると考える必要がある。活性層上にあるゲート電極によって発生するV<sub>g</sub>=0Vの時の容量を便宜上C<sub>gs</sub>とみなし、試作デバイスのサイズ(L<sub>g</sub>/W<sub>g</sub>=0.8/5600μm)と活性層のキャリア密度からC<sub>gs</sub>を計算すると、C<sub>gs</sub>~10pFとなる。従ってC<sub>gp</sub>は1pF以下となり、パッドを50×50μm<sup>2</sup>で2個とすると、その容量は図4.25より0.35×2pFなのでゲートバスラインは0.3pF以下でなければならない。バスラインの面積(5×400μm<sup>2</sup>)を考えると、これを直接バッファ層の上に形成しては寄生容量が大きくなりすぎる可

能性がある。従ってバスラインは絶縁層を介して形成した。

### 5.3 デバイスプロセス

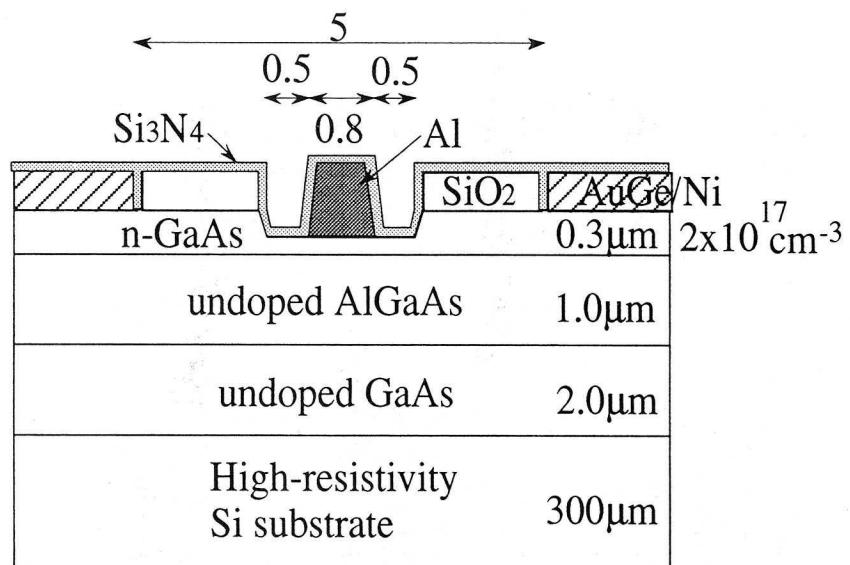

試作したパワーMESFETの断面模式図を図5.2<sup>(5)</sup>に示す。使用したSi基板は高抵抗(2~6kΩ·cm)で<011>方向に3°オフしたものである。成長方法は通常の二段階成長法であり、ノンドープGaAsを2μmとノンドープAlGaAsを1μm成長させた後、活性層として2×10<sup>17</sup>cm<sup>-3</sup>のn-GaAsを0.3μm成長させた。またGaAs基板上にも同じ構造を成長させた。

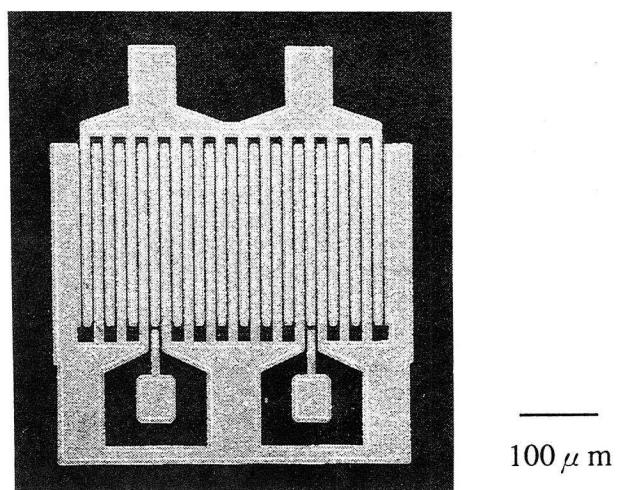

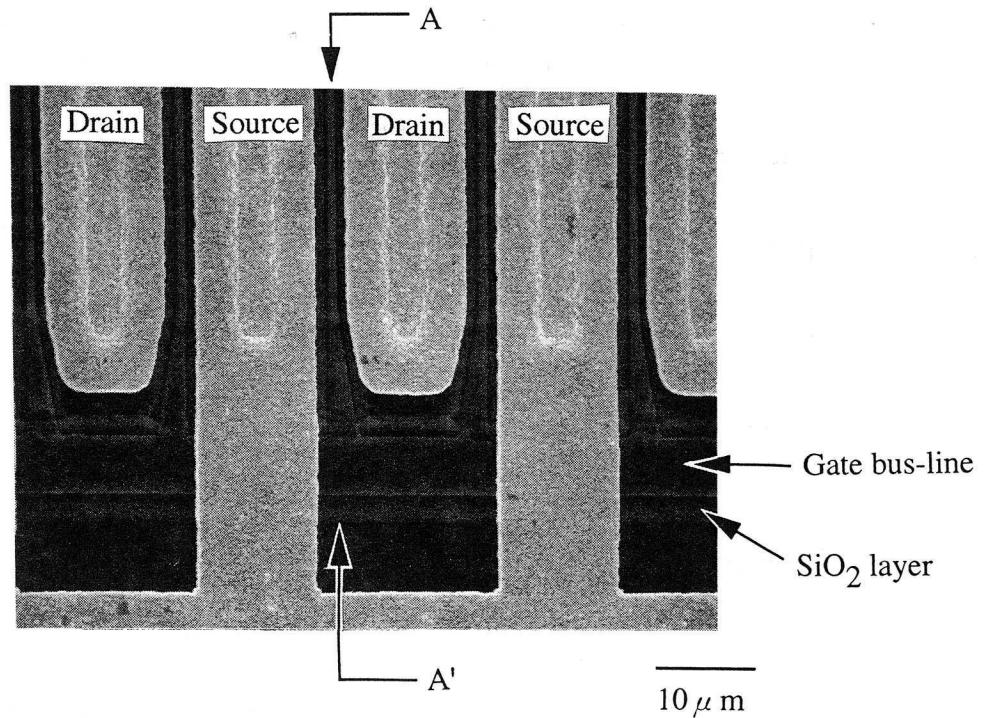

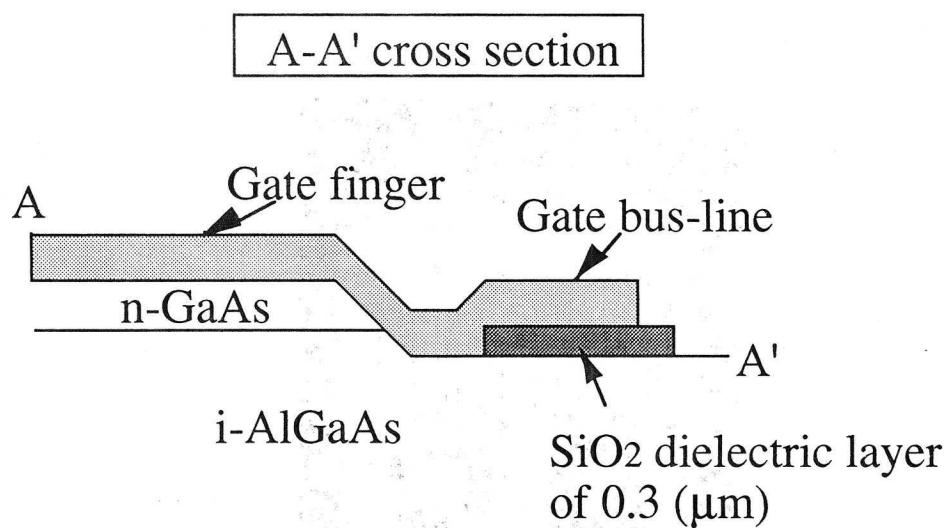

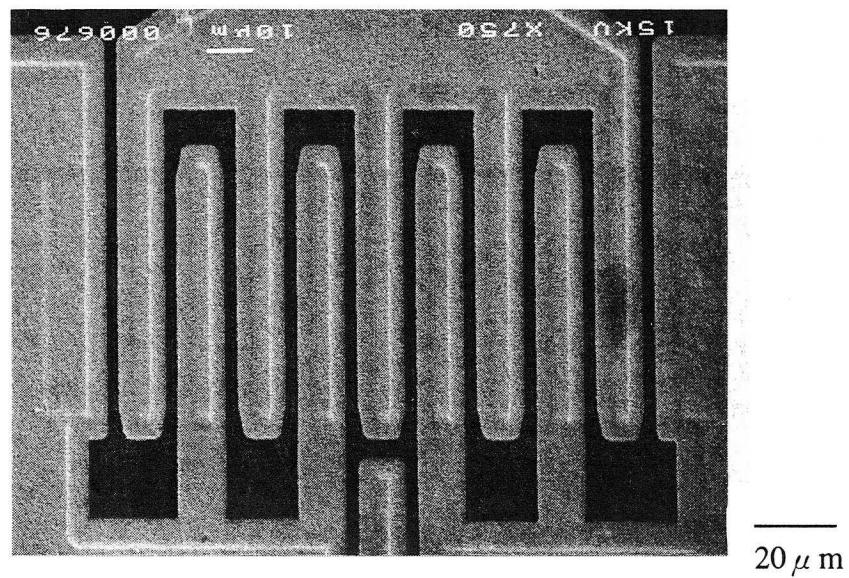

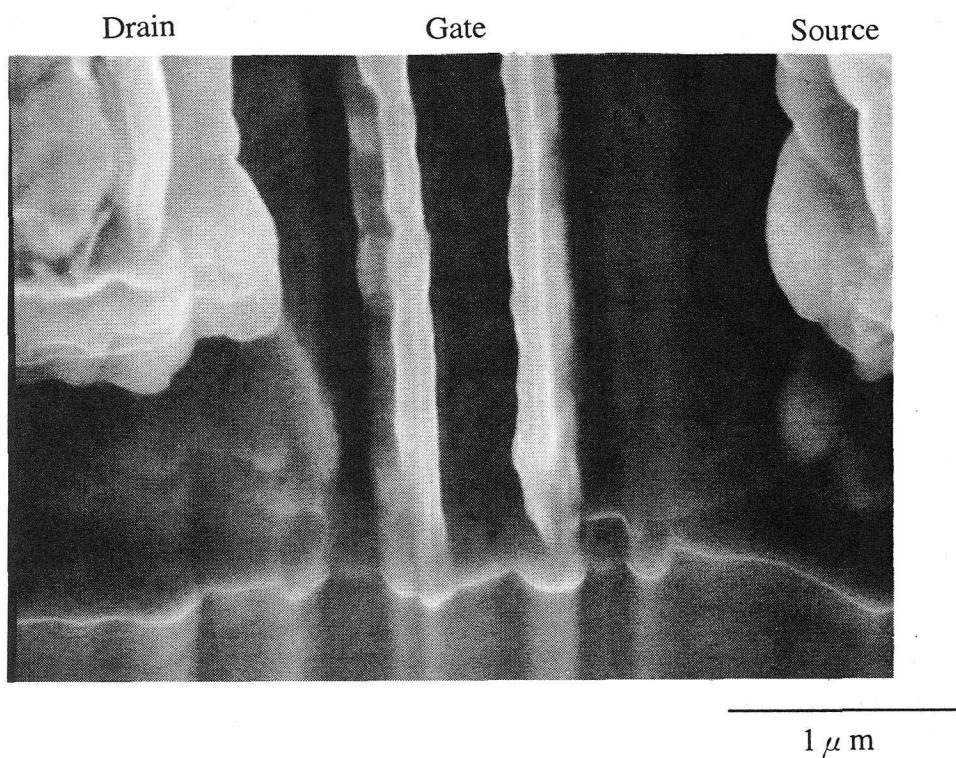

デバイス構造は、メサエッチングによる素子アイソレーション後オーミック電極としてAuGe/Ni/Auを蒸着し、ウェットエッチングでリセスを形成してAlによりゲート電極を形成した。ゲート長は0.8μm、リセス長は約0.5μmである。表面保護膜としてプラズマCVDによりSi<sub>3</sub>N<sub>4</sub>を堆積し、ソース電極とゲートバスラインのクロスオーバー部にはAuメッキを用いたエアーブリッジを形成した。裏面はSi基板を300μmまでラッピングし、Ti/Auを蒸着した後チップ化した。完成了チップの平面SEM写真を図5.3に示す。またゲートバスラインは約0.3μmのSiO<sub>2</sub>層を介して形成したが、そのゲートバスラインとバスライン周辺構造のSEM写真を図5.4に、図5.4のA-A'における断面模式図を図5.5に示す。なおGaAs基板を用いたパワーMESFETにはこの構造は用いていない。

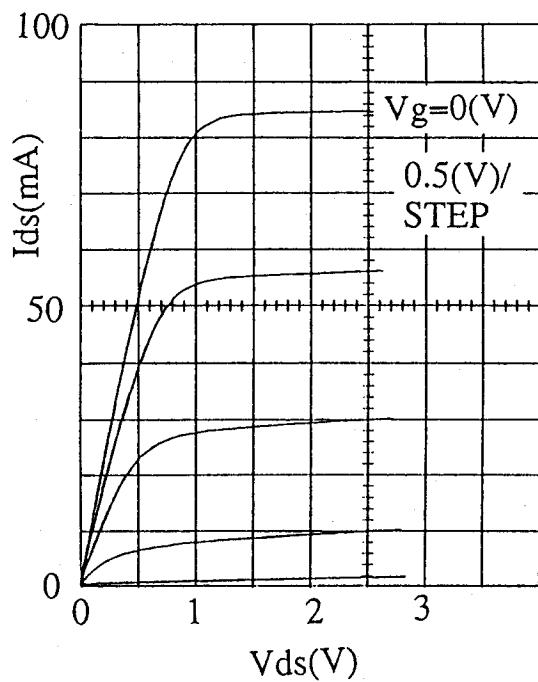

### 5.4 直流特性

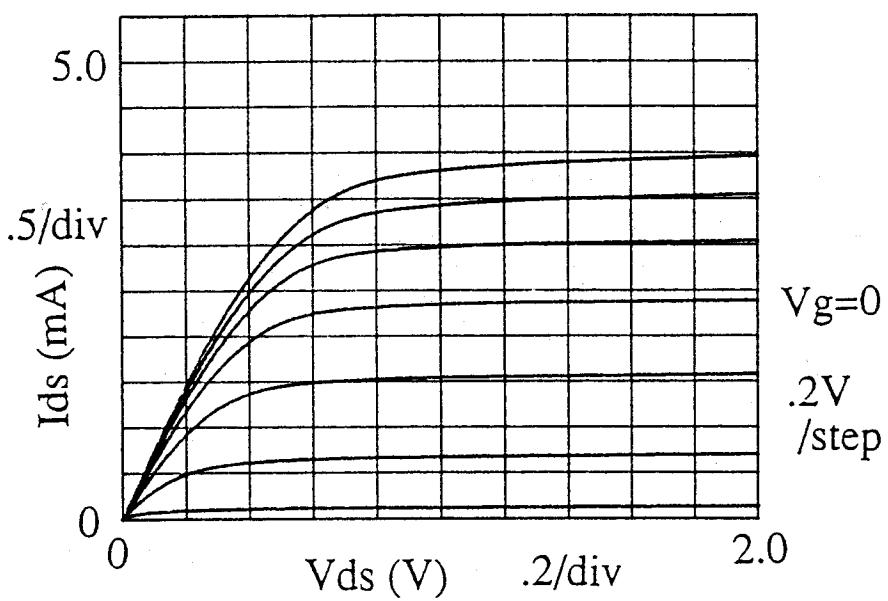

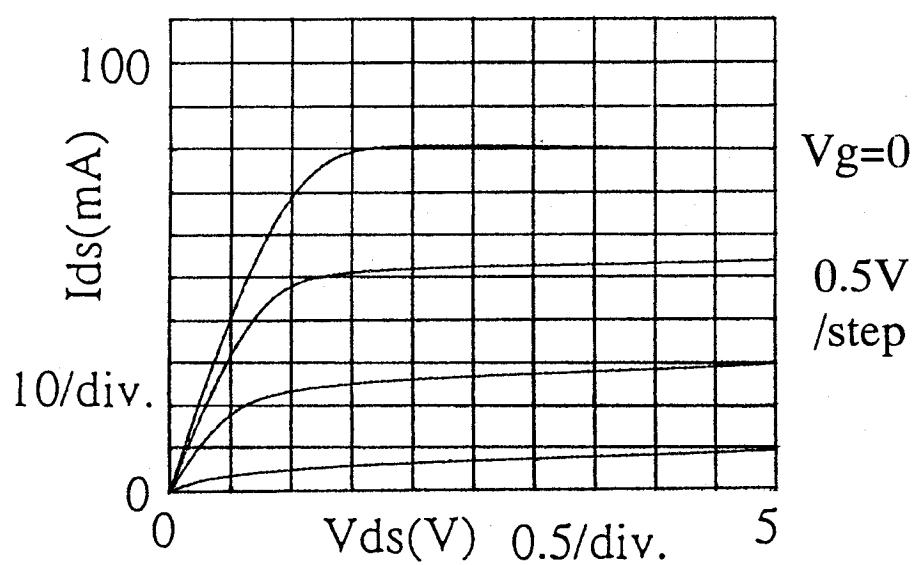

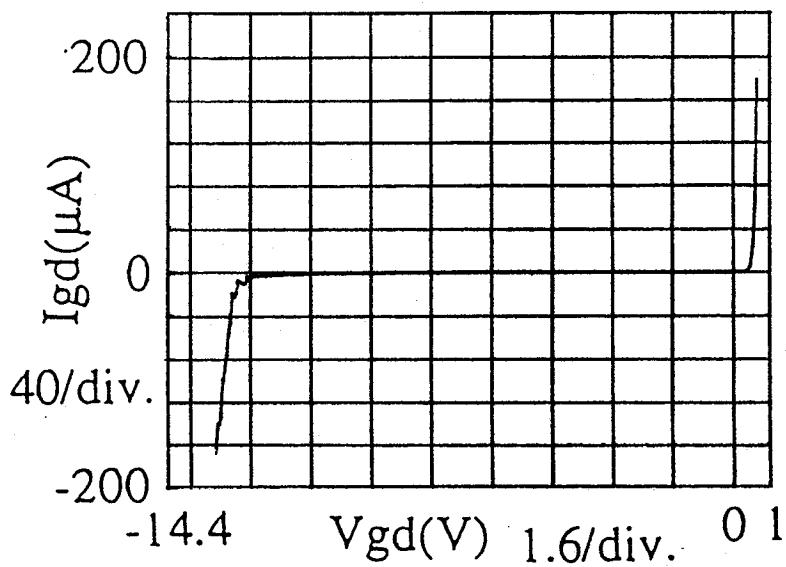

図5.6に試作したMESFET/SiのV<sub>ds</sub>-I<sub>ds</sub>特性を<sup>(5)</sup>、また図5.7にV<sub>gd</sub>-I<sub>gd</sub>特性を示す<sup>(5)</sup>。全ゲート幅は500μmである。ピンチオフ特性は良好で、GaAs基板と差はなく、I<sub>dss</sub>=170~180mA/mm、g<sub>m(max)</sub>=120~130mS/mmであった。またピンチオフ電圧は-2~-2.5Vであった。ゲートのショットキー特性もGaAs基板と差はなく、V<sub>gdo</sub>はゲート電流が500μA/mmの時で規定すると-12~-14Vであった。

図 5.2 試作したパワー MESFET の断面模式図

図 5.3 完成したチップの SEM 写真 ( $L_g = 0.8 \mu m$ 、 $W_g = 5600 \mu m$ )

図 5.4 ゲートバスラインとバスライン周辺構造の SEM 写真

図 5.5 図 5.4 の A-A' における断面模式図

図 5.6 試作した MESFET/Si の  $V_{ds}$  -  $I_{ds}$  特性 ( $L_g = 0.8 \mu m$ 、 $W_g = 500 \mu m$ )

図 5.7 試作した MESFET/Si の  $V_{gd}$  -  $I_{gd}$  特性 ( $L_g = 0.8 \mu m$ 、 $W_g = 500 \mu m$ )

## 5.5 高周波特性

### 5.5.1 等価回路パラメータ

$L_g/W_g = 0.8/500 \mu m$ 、ゲートパッド1個 ( $50 \times 50 \mu m^2$ ) のMESFET/SiについてSパラメータを測定した。測定条件はHEMT/Siの場合と同様に、 $V_{ds}$ は2Vで $V_{gs}$ は直流評価において $g_m$ の最大値が得られた値である。

HEMT/Siの場合と同じ小信号等価回路を用いて抽出した等価回路パラメータのうち入出力容量に関するものを、数個のMESFET/SiとMESFET/GaAsについて平均し、表5.1に示す。このデバイスディメンジョンでは $C_{gp}/C_{gs}$ の値はMESFET/Siで0.70、MESFET/GaAsで0.31になっており、 $f_T$ 、 $f_{max}$ ともMESFET/GaAsのほうが良好な値を示している。しかし実際のパワーMESFETのディメンジョン ( $L_g/W_g = 0.8/5600 \mu m$ ) に表5.1の値をあてはめて計算すると、 $C_{gs}$ は $5600/500 = 11.2$ 倍になり $C_{gp}$ は約2倍（実際のパワーMESFETはパッドが2個でバスラインの面積はほぼ2倍であるため）になる。従って $C_{gp}/C_{gs}$ はGaAs/Siで0.12、GaAs/GaAsで0.06になる。この結果はほぼ設計通りであり、GaAs/Siを用いてもパワーMESFET構造ならば寄生容量の影響を問題のないレベルにまで低減できることを示している。

表 5.1 MESFET/Si と MESFET/GaAs の入出力容量に関する等価回路パラメータ ( $L_g = 0.8 \mu m$ 、 $W_g = 500 \mu m$ )

|                 | MESFET/Si | MESFET/GaAs |

|-----------------|-----------|-------------|

| $C_{gp}$ (pF)   | 0.44      | 0.18        |

| $C_{gs}$ (pF)   | 0.63      | 0.56        |

| $C_{dp}$ (pF)   | 0.36      | 0.21        |

| $C_{ds}$ (pF)   | 0.14      | 0.54        |

| $f_T$ (GHz)     | 15        | 16          |

| $f_{max}$ (GHz) | 26        | 30          |

### 5.5.2 入出力特性

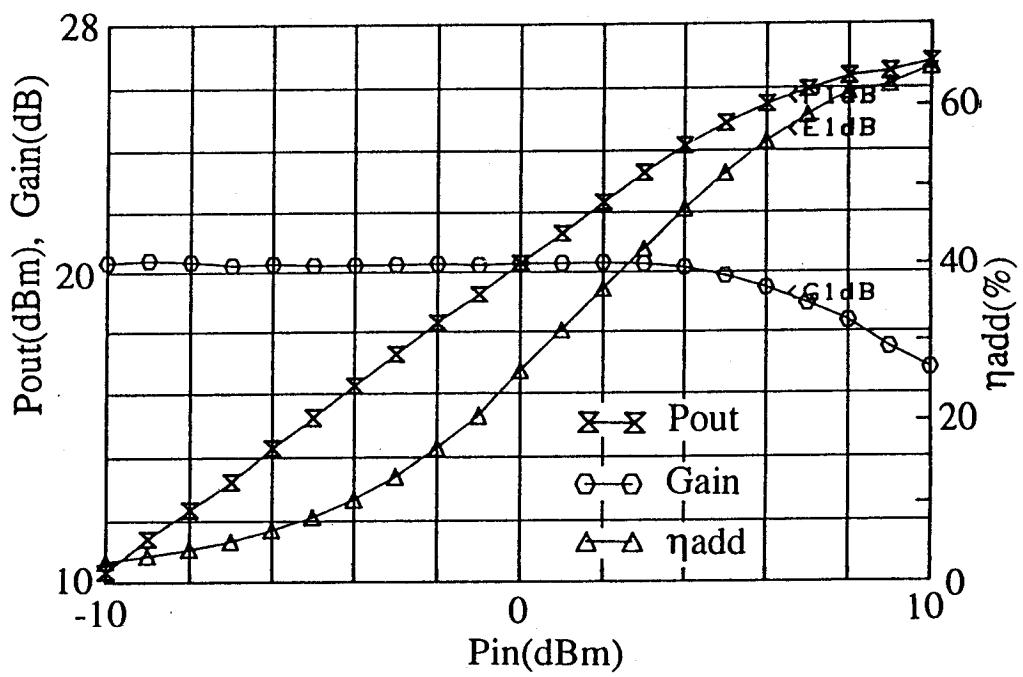

試作したパワーMESFET/Siの入出力特性を図5.8に示す<sup>(5)</sup>。測定周波数は0.85GHz、電源電圧は3.6V、AB級動作( $I_{ds} \sim 0.1I_{dss}$ )である。測定はロードプル法を用いて行ない、小信号Sパラメータの値で入出力の整合をとった後、 $P_{in}=10\text{dBm}$ の時出力が最大となるように整合を取り直している。図より線形領域での利得( $G_L$ )が約20dBと良好な値の得られていることがわかり、また1dBコンプレッション時の出力( $P_{1\text{dB}}$ )と利得( $G_{1\text{dB}}$ )は、 $P_{1\text{dB}}=25.7\text{dBm}$ (370mW)および $G_{1\text{dB}}=19.2\text{dB}$ であった。また電力付加効率( $\eta_{add}$ )は1dBコンプレッション時で、 $\eta_{add}=57\%$ であった。飽和出力 $P_{o(sat)}$ は27dBmすなわち約500mWであり、ほぼ設計通りの値が得られた。さらに電源電圧を5Vにした時、入力10dBmに対して出力30dBm(1W)が得られた。これらの値、とくに線形利得は市販されているGaAs基板を用いたデバイスと同等あるいはそれ以上と考えられ、GaAs/Siを用いて実用に十分耐えうるデバイスが作製できることが示された。ゲート幅とパッド数の関係については、(5.6)式から分かるようにゲート幅がある程度大きくなるまでパッド数は増やす必要がない。従って許容される $C_{gp}$ の絶対値が大きくなるように必要な出力(ゲート幅)を考慮すれば、本試作で行ったような小さいパッドの形成やゲートバスライン下の絶縁膜挿入等をする必要がなくなりGaAs/Siの応用においてさらに有利になると思われる。

### 5.5.3 電源電圧依存性

携帯電話の小型、軽量化のためには電池数を減らすことが必須であるが、それに伴い、より低電源電圧で動作するデバイスが必要になってくる。そこで今回試作したパワーMESFET/Si特性の電源電圧依存性を評価した。

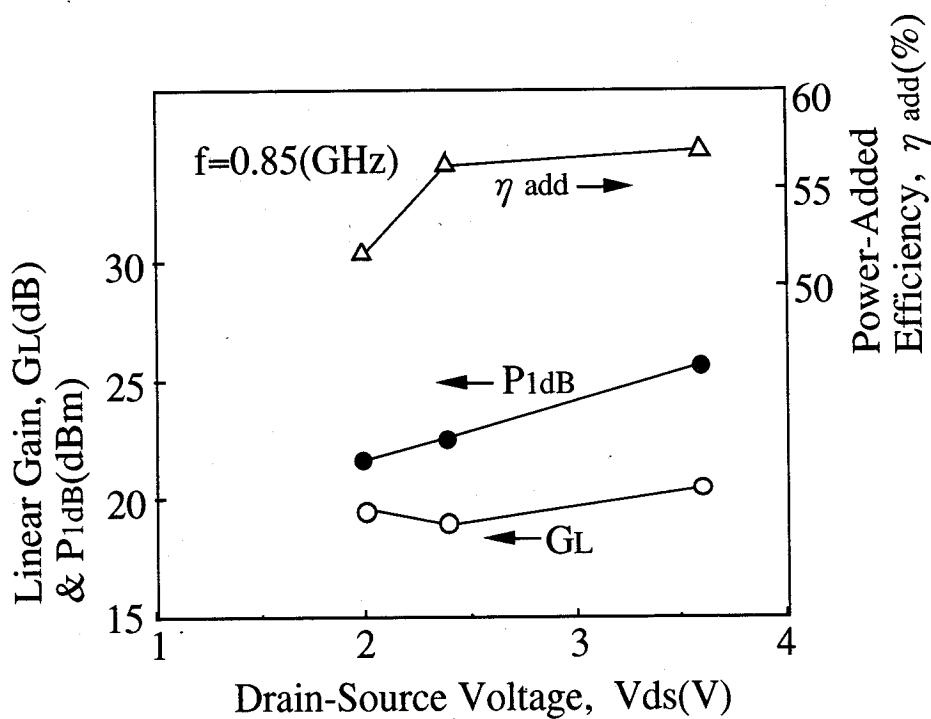

図5.9に電源電圧に対する $G_L$ 、 $P_{1\text{dB}}$ 、 $\eta_{add}$ の依存性を示す<sup>(5)</sup>。 $V_{ds}=2.4\text{V}$ までは $G_L$ 、 $\eta_{add}$ とともにほとんど劣化せず、通常のGaAs基板上デバイスと同様の結果が得られた。これはGaAs/Siデバイスであってもキャリア移動度(あるいは $g_m$ )の電界依存性がGaAs/GaAsと同等であるためと考えられ、GaAs/Siの転位やモホロジー等が移動度に影響を与えていないことが再確認できる。

低電源電圧化のために最も単純でかつ有効な方法は、ソース・ドレイン電極間隔を狭くし実効的な電界強度を高めることである。GaAs/Si基板の場合は放熱性が良いため加えてゲート・ゲート間隔も狭くでき、低電源電圧動作とチップサイズの縮小を同時に達成できる。この点でもMESFET/GaAsに比べ有利であると考えられる。

図 5.8 試作したパワー MESFET/Si の入出力特性

( $L_g = 0.8 \mu m$ 、 $W_g = 5.6mm$ 、 $f = 0.85GHz$ 、 $V_{ds} = 3.6V$ 、 $I_{ds} \sim 0.1I_{dss}$ )

図 5.9  $G_L$ 、 $P_{1dB}$ 、 $\eta_{add}$  の電源電圧に対する依存性

## 5.6 まとめ

GaAs/Siを用いてパワーMESFETを試作した。ゲート幅の大きいデバイスは必然的に $C_{gp}/C_{gs}$ を小さくできるという観点より、まずGaAs基板上のデバイスとほぼ同じ方法で設計し、必要となる全ゲート幅から入力真性容量を求め、その10%を許容できる入力寄生容量としてゲートパッドとゲートバスラインに割り振るという方法をとった。その結果、ゲートバスライン下に絶縁膜を挿入せざるを得なかつたが、小信号等価回路パラメータの評価より、ほぼ設計通りに寄生容量の値が低減されたことが示された。このパワーMESFETを携帯電話での応用を想定した条件 ( $f=0.85\text{GHz}$ 、 $V_{ds}=3.6\text{V}$ ) で評価し、GaAs基板を用いたデバイスと同等の入出力特性が得られた。さらに $V_{ds}=2.4\text{V}$ という、より厳しい条件でも特性はほとんど劣化しなかった。

以上の結果より、パワーMESFET構造であれば、4章で示したようなパッド構造の変更をすることなくGaAs/Si特有の寄生容量をほとんど影響のないレベルまで低減でき、GaAs基板上のものと遜色ないデバイスが得られることがわかつた。さらに熱放散性が良いこと、および大口径化が可能であることを加えると、GaAs/Siは現在需要が急増しているGaAsパワーFET用基板として十分実用に値すると考えられる。

### (参考文献)

- (1) 阿部浩之、三村高志、茅根直樹（編集）：光、マイクロ波半導体応用技術（サイエンスフォーラム）

- (2) 福田益美、平地康剛：GaAs電界効果トランジスタの基礎（電子情報通信学会編）

- (3) H. Fukui : Int. Electron Devices Meet. Tech. Dig. (1978) 140.

- (4) D' Asaro, L. A., J. V. Dilorenzo, and H. Fukui : Int. Electron Devices Meet. Tech. Dig. (1977) 371.

- (5) Takashi Aigo, Seiji Takayama, Mitsuhiro Goto, Yasumitsu Ota, Aiji Jono, Akiyoshi Tachikawa, and Akihiro Moritani

Toshihiko Ichioka and Masahiro Akiyama : Proc. Int. Symp. Compound Semiconductors (1995) 747.

## 6. GaAs/Si電子デバイスの信頼性

### 6.1 はじめに

前章までの結果より、GaAs/Siを用いた電子デバイスは、パワーFET構造のようなゲート幅の大きいデバイスであればパターン変更することなく、また低雑音FETのようなゲート幅の小さいデバイスであっても、ゲートパッド構造の変更のみでGaAs/GaAsデバイスに匹敵する特性が得られることがわかった。

GaAs/Si電子デバイスの実用化のためには、次に信頼性を評価することが必要である。GaAs/Siの場合、信頼性に悪影響を与えるものとして高密度で存在する転位が考えられる。レーザダイオードや発光ダイオードをGaAs/Siで作成すると、この転位のため劣化がGaAs/GaAsに比べ著しく早いことが報告されている<sup>(1, 2)</sup>。しかし電子デバイスの場合は通常チャネル温度100~150°Cで動作させ、一方転位の増殖、運動は350~400°C以上でないと生じない<sup>(3)</sup>ことからその影響は小さいと考えられる。実際KorniliosらはGaAs/SiとGaAs/GaAsのMESFETの高温放置試験を行い、両者の信頼性には差がみられないとしている<sup>(4)</sup>。しかし電界による転位の動きあるいは劣化モードの存在を考慮すると、バイアスをかけて試験することが必要である。

本章では前章で試作したGaAs/SiとGaAs/GaAsのMESFETを用いて行った高温通電放置試験の結果について述べる。またあわせて劣化部位の観察結果についても述べる。

### 6.2 実験方法

使用したデバイスは前章で試作したパワーMESFETで、ゲート長は0.8 μm、全ゲート幅は500 μm（単位ゲート幅は50 μm）である。このMESFETをAu-Snはんだを用いてトランジスタ用ヘッダに貼り付け、Auワイヤーボンディングによって端子ピンと接続した。デバイスの数はMESFET/Si、MESFET/GaAs各々10個ずつを1セットとし、それをN<sub>2</sub>ガス雰囲気で180°C、210°C、240°Cの恒温槽の中に入れ、直流で通電した。

デバイスの物理、化学的劣化反応をアレニウスモデルを用いて評価する場合、温度はチャネルの温度とする必要がある。従って通電時に消費される電力とサンプルの熱抵抗によって決まるチャネルの温度上昇分を、周囲温度に加えなければならない。実際には熱抵抗の温度依存性を考えなければならない<sup>(5)</sup>が、本研究においては室温で測定した熱抵抗R<sub>th</sub>を用い、次式によってチャネル温度T<sub>ch</sub> (°C) を決定した。

$$T_{ch} = T_{amb} + R_{th} \times (V_{ds} \times I_{ds}) \quad (6.1)$$

ここで $T_{amb}$ は周囲温度、 $V_{ds}$ 、 $I_{ds}$ はそれぞれドレイン電圧とドレイン電流である。 $R_{th}$ についてはヘッダに取り付けた後のMESFET/SiとMESFET/GaAsについて、それぞれ数個ずつ第3章に述べた方法で測定し、平均値としてMESFET/Siで102°C/W、MESFET/GaAsで225°C/Wを得た。また $V_{ds}$ 、 $I_{ds}$ は $V_{ds} = 3V$ 、 $I_{ds} = I_{dss}$ に設定した。この理由は電流を流したことによる転位の状態変化がもし存在するならば、チャネルを広げておくことによりそれを促進するためである。個々のデバイスとしては特性の揃ったものを用い、 $I_{dss}$ としては試験時に測定系全体を流れた電流の平均値を使用した。その結果 $T_{ch}$ として、

$$T_{amb} = 180^{\circ}\text{C} \text{ の時 } T_{ch} = 199^{\circ}\text{C} \text{ (GaAs/Si)} , 223^{\circ}\text{C} \text{ (GaAs/GaAs)}$$

$$T_{amb} = 210^{\circ}\text{C} \text{ の時 } T_{ch} = 231^{\circ}\text{C} \text{ (GaAs/Si)} , 257^{\circ}\text{C} \text{ (GaAs/GaAs)}$$

$$T_{amb} = 240^{\circ}\text{C} \text{ の時 } T_{ch} = 260^{\circ}\text{C} \text{ (GaAs/Si)} , 284^{\circ}\text{C} \text{ (GaAs/GaAs) を得た。}$$

測定パラメータとしては飽和ドレイン電流 $I_{dss}$ 、逆方向ゲート電圧 $V_b$ 、順方向ゲート電圧 $V_f$ 、ソース+ドレイン抵抗 $R_s + R_d$ 、チャネル抵抗 $R_o$ を選び、 $I_{dss}$ はドレイン電圧が2.5Vの時を、 $V_b$ 、 $V_f$ はゲート電流がそれぞれ $500\mu\text{A/mm}$ 、 $50\mu\text{A/mm}$ の時を測定した。また $R_s + R_d$ 、 $R_o$ は $I_{ds} \sim 0$ の時のソース、ドレイン間抵抗より求めた<sup>(4)</sup>。

測定は、予定の放置時間が経過し電源を切り温度を下げた後一晩おいて行った。サンプルが故障したか否かの判断は次節に述べる基準に基づいたが、ある時間経過後（試験開始後n回目の測定）で故障とみなされたサンプルは、n-1回目の測定時における経過時間を寿命とした<sup>(6)</sup>。

### 6.3 実験結果

#### 6.3.1 故障モード

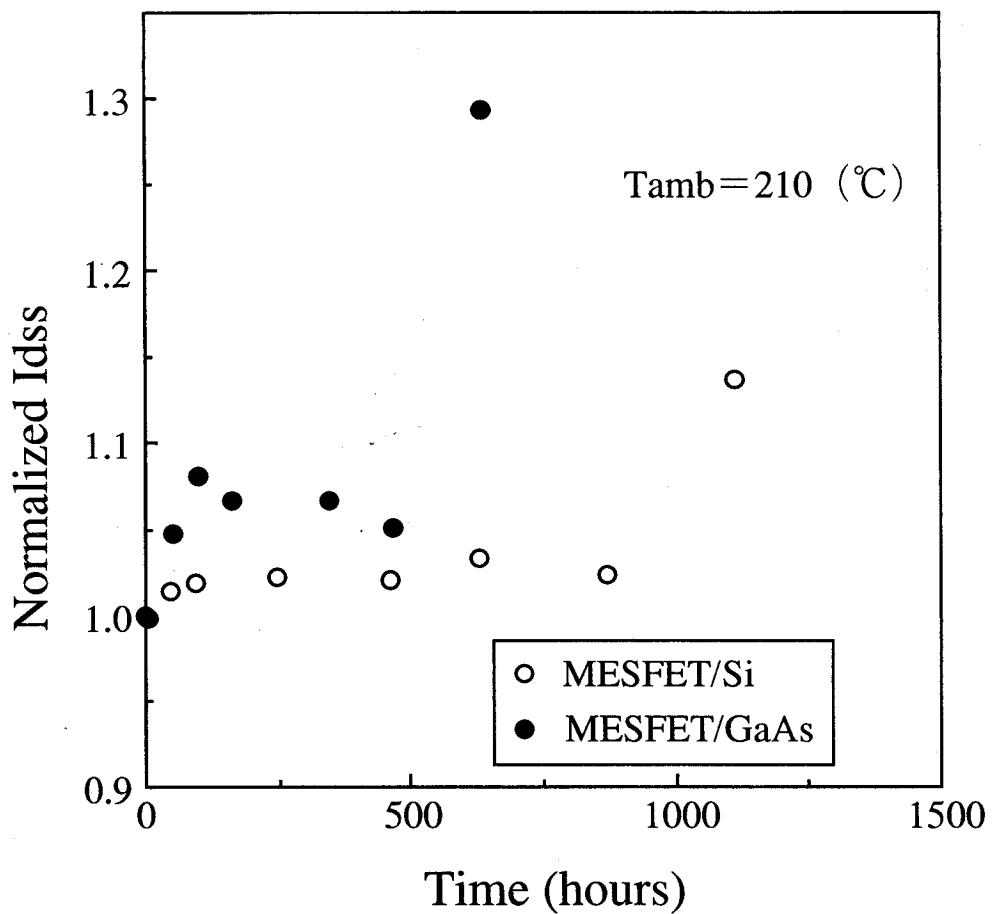

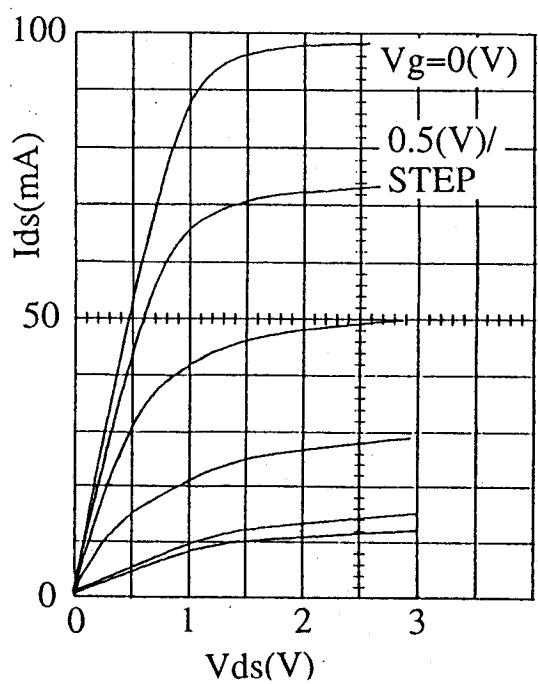

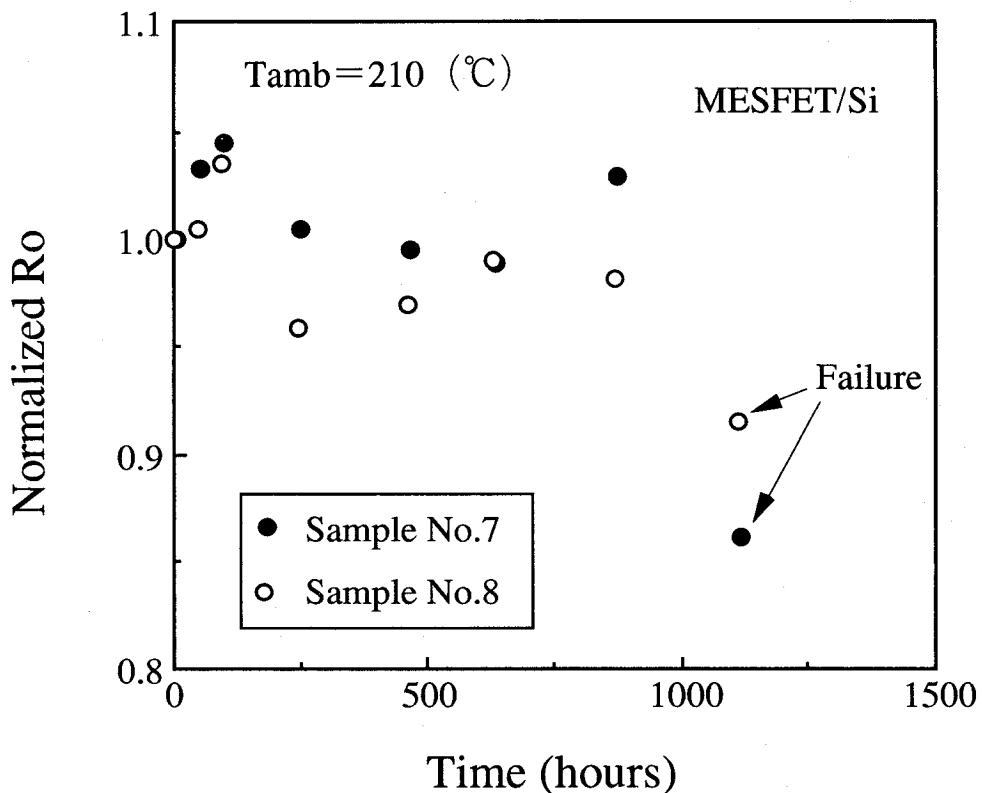

図6.1に $T_{amb} = 210^{\circ}\text{C}$ で通電放置試験を行ったMESFET/SiとMESFET/GaAsの $I_{dss}$ の変化を示す。 $I_{dss}$ は初期値で規格化してあるが、両方ともある時間が経過すると10%以上増加していることがわかる。この時のMESFET/Siの $I_{ds} - V_{ds}$ 特性を初期状態と比較して図6.2 (a)、(b) に示すが、図6.2 (a) の初期状態において通常のピンチオフ特性を示していたものが、(b) の約1100hr経過後にはピンチオフしなくなっていることがわかる。またこの現象はMESFET/GaAsにおいても同様に観察されているため、 $I_{dss}$ が10%以上増加しノンピンチオフ状態が生じたサンプルを故障とみなした。

図 6.1 高温通電放置試験を行った MESFET/Si と MESFET/GaAs の

I<sub>dss</sub> の変化 (T<sub>amb</sub> = 210°C)

(a)

(b)

図 6.2 初期状態の MESFET/Si の静特性 (a) と 1100 時間経過後の静特性 (b)

$(T_{amb} = 210^{\circ}\text{C})$

### 6.3.2 故障部位の同定と解析

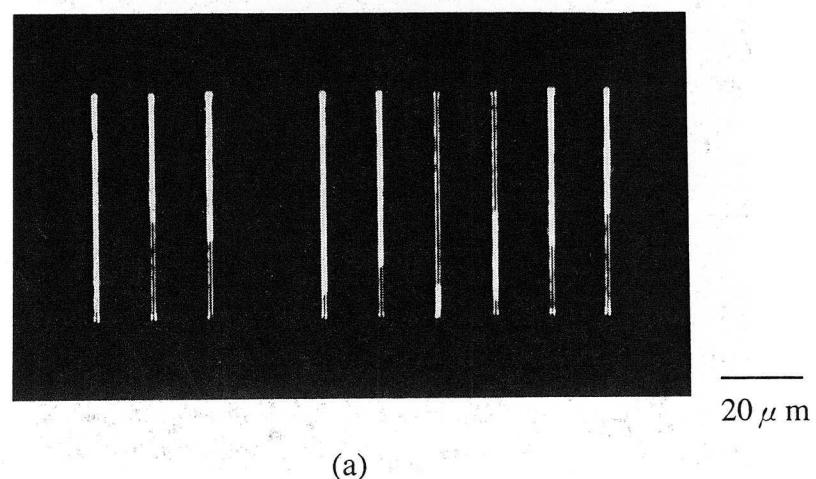

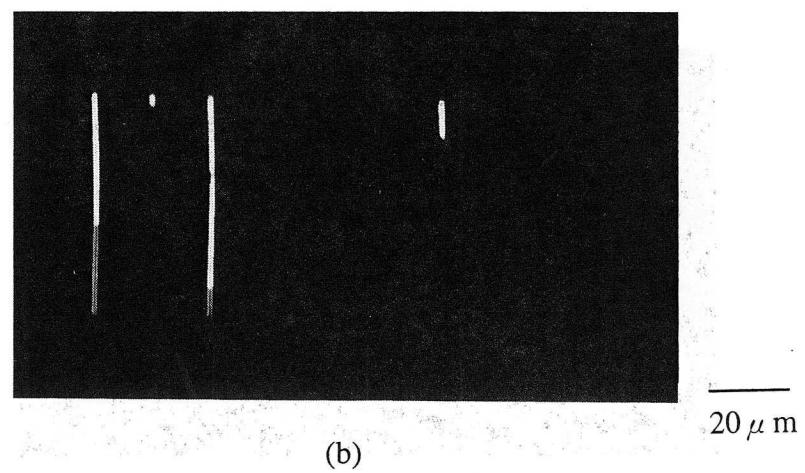

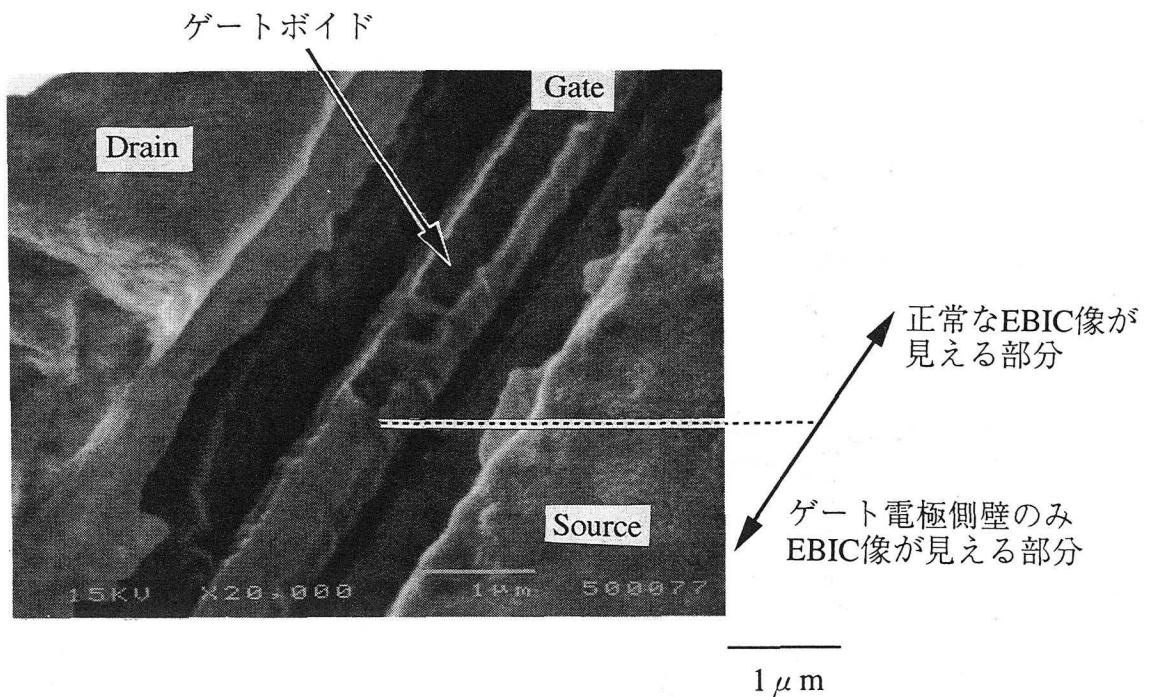

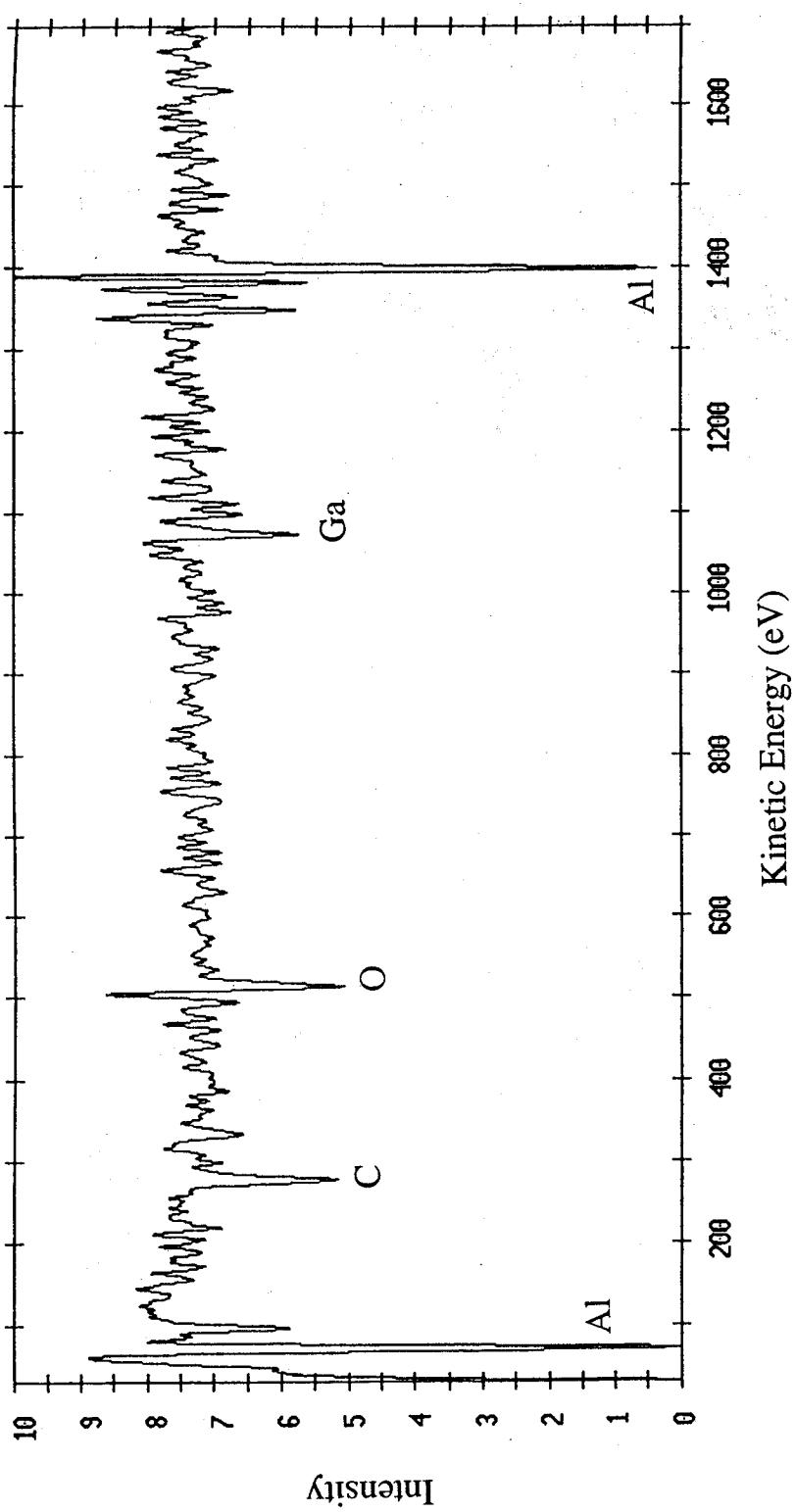

故障したMESFET/SiとMESFET/GaAsについてEBIC像を観察した。図6.3 (a)、(b)にサンプルのSEM像と初期状態のEBIC像をMESFET/Siに関して示す。また図6.4 (a)、(b)には故障したMESFET/SiとMESFET/GaAsのEBIC像を示す。この図から、故障サンプルにおいてはEBIC像が一部見えなくなっている中でも全く見えない部分とゲート電極の側壁のみ見えている部分のあることがわかる。またゲート電極表面の $\text{Si}_3\text{N}_4$ パッシバーション膜をRIEで除去した後のサンプルについて、EBIC像が正常に観察されている部分とゲート電極の側壁のみ観察されている部分の境界のSEM写真を図6.5に示す。図6.5よりEBIC像が正常に観察されているにもかかわらず、ゲート電極にボイドが発生していることがわかる。このボイド部分の断面SEM写真を図6.6に示す。ゲート電極のAlが中央部で消失しU字型の電極になっているのがわかるが、全て消失してはいないためまだショットキー特性を保っているものと考えられる。これは電極のドレン側にボイドが発生して故障になることが報告されている通常のAlゲート電極の場合<sup>(7, 8)</sup>とは異なっている。また図6.5から、ゲート電極の側壁のみEBIC像が観察されている部分ではAl電極が薄くなっているのがわかる。さらにEBIC像が全く観察されない部分でもAl電極は薄くなっていたが、その部分のオージェ分析結果を図6.7に示す。Alの信号の他にC、O、Ga等の信号が観察されており、ゲートのAlとGaAsの相互拡散が生じていることが推定される。この高温通電放置試験の前に250°Cで約600時間の放置のみの試験を行ったが、サンプルは全く劣化しなかったことを考え合わせてゲート電極劣化のモデルを示すと、

①電界のエネルギー等によって最初にゲート電極の中央部からAlが動きゲートから消失していくが、その量があまり多くない時にはまだショットキー電極として動作する。

②消失したAlの量が多くなりかつGaAsとの相互反応も進行していくことにより、界面に高抵抗の反応生成物が形成されるようになってくる。この反応はゲート電極の中央部から進行するため側壁部ではまだ多少ショットキー的なふるまいを示している。

③最終的に電極全体が高抵抗になり、ゲートとして動作しなくなる。

と考えられる。図6.8には初期値で規格化したチャネル抵抗 $R_o$ の経時変化を示す。故障した時点で $R_o$ が小さくなっているのは、ゲートの一部が動作しなくなったことにより測定された電流値が増え、見かけ上抵抗が下がったと見なされたためであるが、初期～故障直前までの経過時間においては $R_o$ はほとんど変化していない。これより、上述したゲートとGaAsとの相互反応は両者の界面近くで生じており、通常のgate sinkingのように内部へ進行する<sup>(4)</sup>ものではないことがわかる。

(a)

(b)

図 6.3 試験に使用したサンプルの SEM 像 (a) と初期状態の EBIC 像 (b)

(a)

(b)

図 6.4 故障した MESFET/Si (a) と MESFET/GaAs (b) の EBIC 像

図 6.5 ゲート電極故障部分の SEM 像（電極表面の  $\text{Si}_3\text{N}_4$  パッシベーション膜除去後）

図 6.6 ゲートボイド部の断面 SEM 像

図6.7 故障したゲート電極部のオージェ分析結果

図6.8 初期値で規格化したチャネル抵抗  $R_o$  の経時変化

次に消失したAlの動きに関しては、故障したゲート電極の周辺にAlの蓄積部が観察されないことから、Alのエレクトロマイグレーションの可能性は少ないと考えられる。そこでゲート電極を中心に基板方向及びソース、ドレイン方向でオージェ分析を行った。その結果ゲート電極端からソース電極側へ0.2~0.3  $\mu$ m離れた点でもAlが存在していることがわかり、消失したゲートのAlは表面のごく近傍を通ってソースあるいはドレイン電極方向へ拡散したと考えられる。

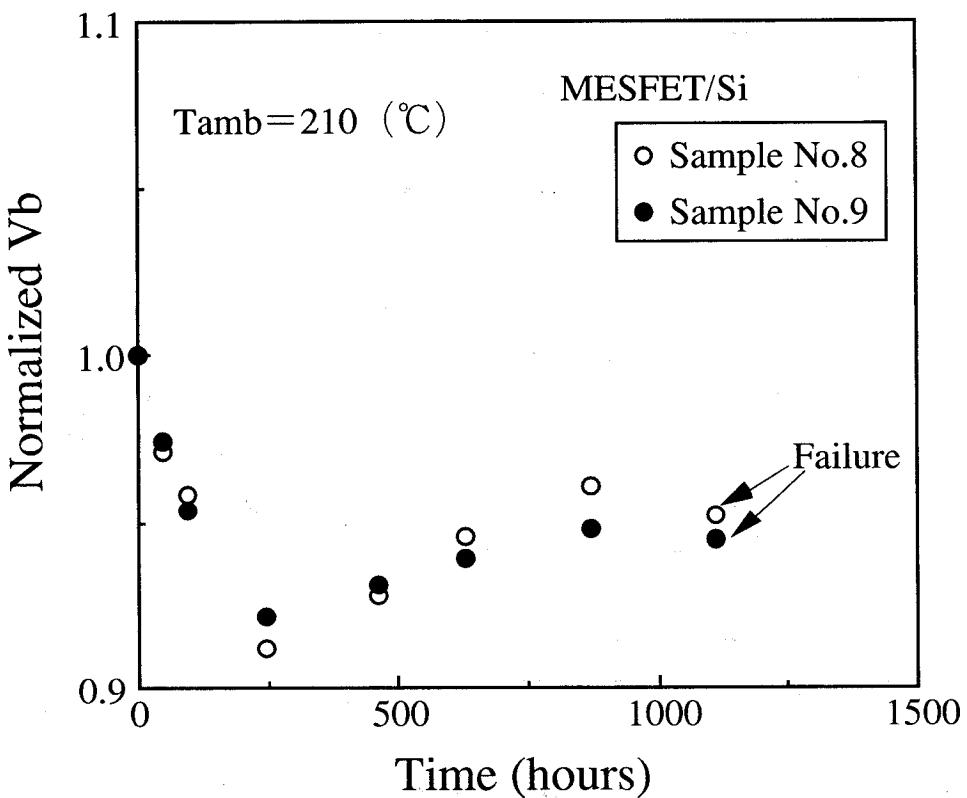

図6.9に初期値で規格化した逆方向ゲート耐圧  $V_b$  の経時変化を示す。250時間程度経過するまで  $V_b$  の絶対値は減少し、その後増加していくのがわかる。前述したゲート電極劣化のモデルを考慮すると、

①初期~250時間経過：Al電極とGaAsとの間に存在する自然酸化膜等の影響により、初期にはMIS likeな接合が形成され、そのため見かけ上のゲート耐圧は高かったが、熱によるアニールの効果でその影響が除去されて耐圧が下がった。（本来のAl-GaAsショットキー接合によって決まる耐圧になった）

②250時間以降：ゲートとGaAsの反応で形成された界面生成物のため正常動作できるゲート面積が狭くなり、逆方向ゲート電流が流れにくくなつた結果として再び耐圧が上がつたように観察された。

図6.9 初期値で規格化した逆方向ゲート耐圧  $V_b$  の経時変化

ということが  $V_b$  の経時変化の説明の一つとして考えられる。またここで示したゲート電極形状の変化や  $V_b$  のふるまいは GaAs/Si、GaAs/GaAs に関係なく観察されているため、GaAs/Si 中に存在する転位がデバイス故障の原因になっていることはないと思われる。

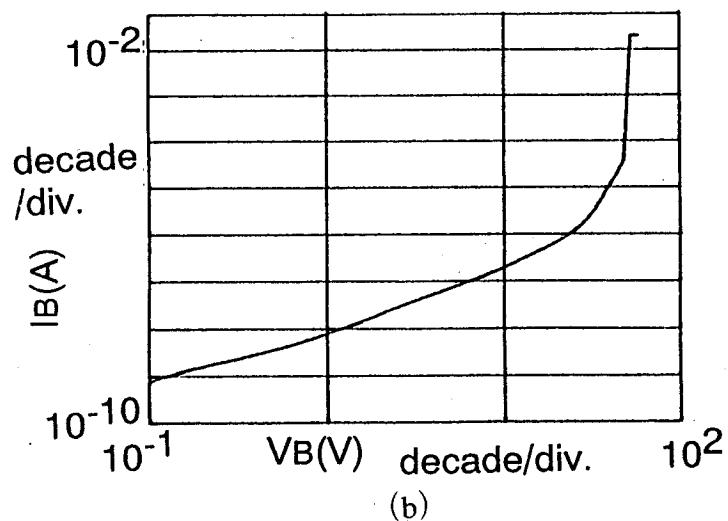

### 6.3.3 デバイスの寿命解析

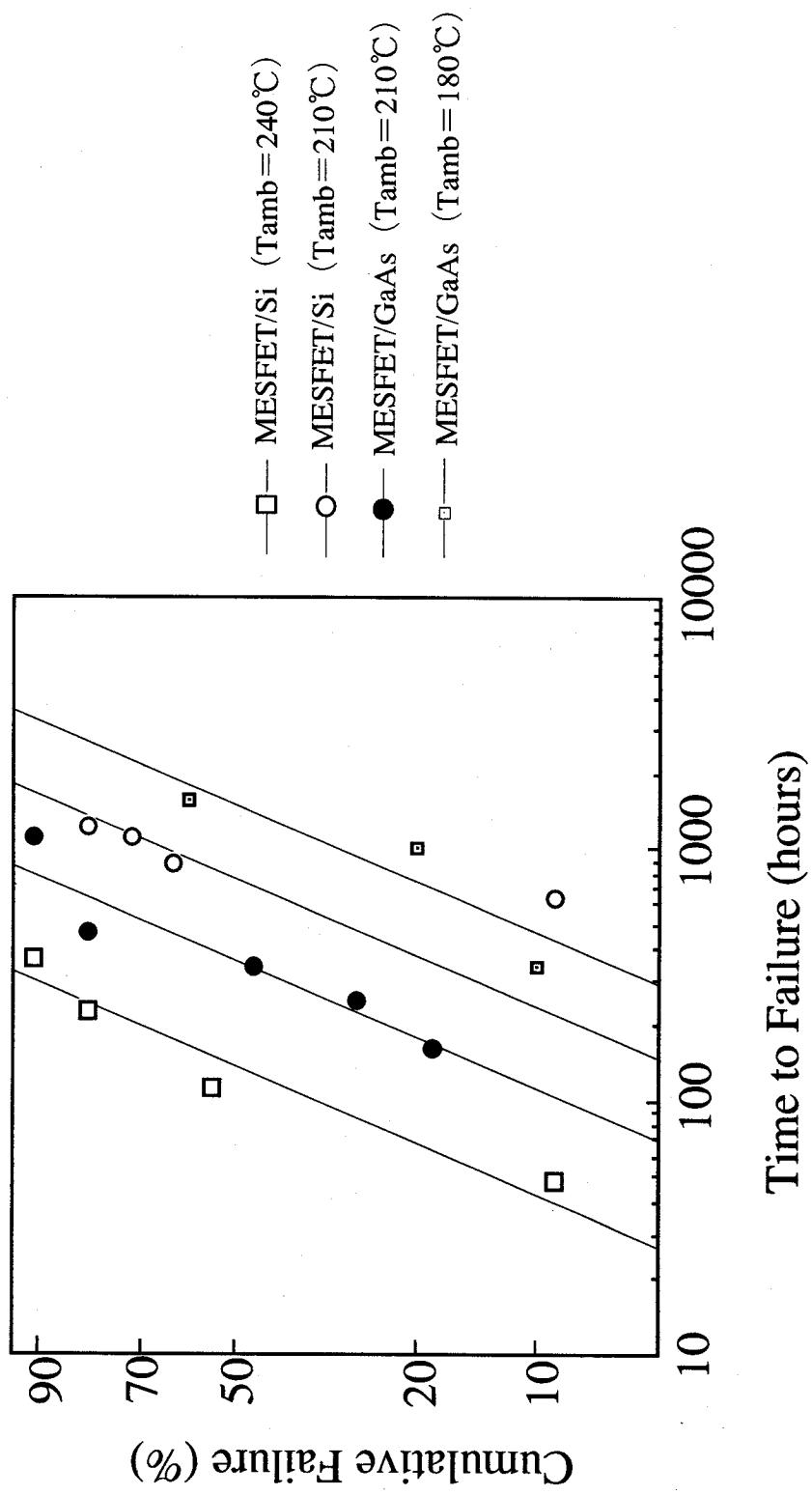

図6.10に  $T_{amb} = 240^{\circ}\text{C}$  の時の MESFET/Si と  $T_{amb} = 210^{\circ}\text{C}$  の時の MESFET/Si、MESFET/GaAs、および  $T_{amb} = 180^{\circ}\text{C}$  の時の MESFET/GaAsについて求めた Weibull プロットを示す。 $T_{amb} = 240^{\circ}\text{C}$  と  $210^{\circ}\text{C}$  の MESFET/Si の結果が同じ傾きであることから、本試験で用いた加速ストレスのかけ方が妥当であり、加速の程度による故障モードの変化はないことがわかる。また MESFET/Si と MESFET/GaAs が同じ傾きであることは、6.3.1節で述べたように故障のモードが同じであることを示している。図6.10より平均故障時間 MTTF (Mean Time to Failure) を求めると、

$T_{amb} = 240^{\circ}\text{C}$  の時の MESFET/Si : MTTF = 163hr

$T_{amb} = 210^{\circ}\text{C}$  の時の MESFET/GaAs : MTTF = 421hr

$T_{amb} = 210^{\circ}\text{C}$  の時の MESFET/Si : MTTF = 895hr

図 6.10 MESFET/Si、MESFET/GaAs の Weibull プロット

$T_{amb} = 180^{\circ}\text{C}$  の時のMESFET/GaAs : MTTF = 1791hr

が得られる。

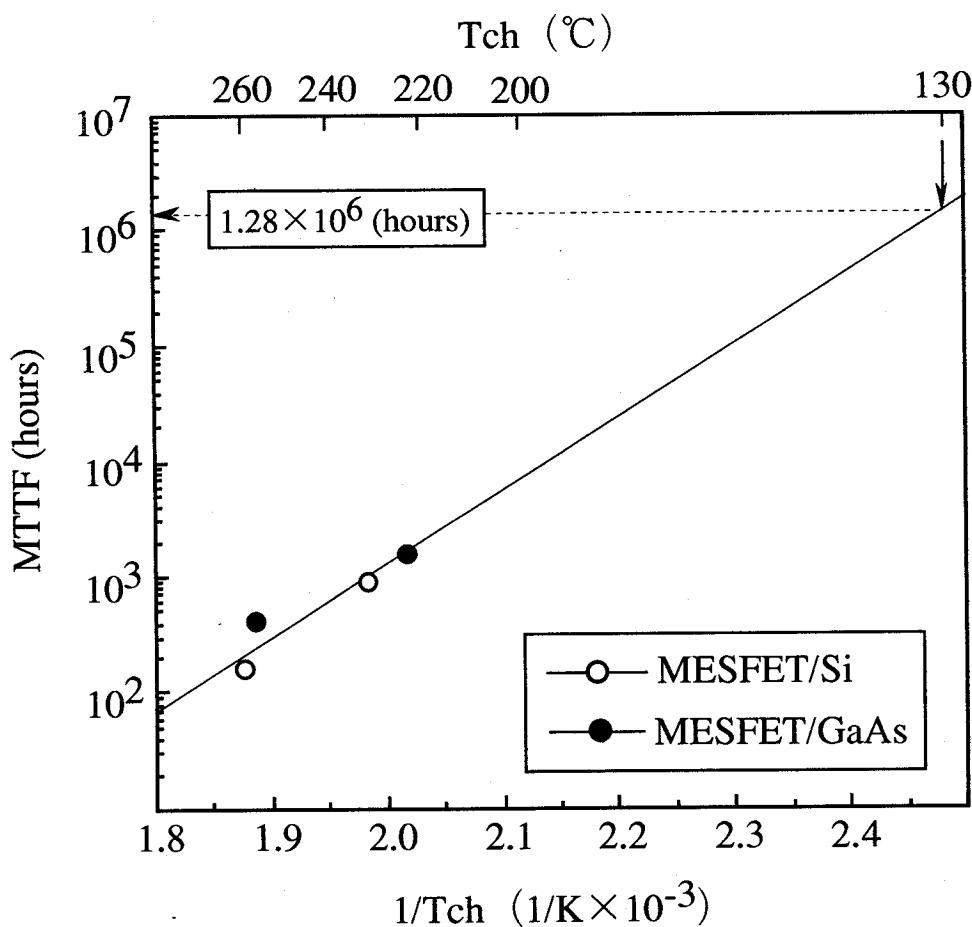

得られたMTTFとデバイスのチャネル温度から求めたArrheniusプロットを図6.11に示す。MESFET/SiとMESFET/GaAsがほぼ同じ直線にのっていることより両者の寿命もほぼ等しいと考えられ、従ってGaAs/Siの転位がデバイスの信頼度に影響を与えていることはないと思われる。またこのプロットの傾きより活性化エネルギー $E_a$ を求めるとき、 $E_a = 1.26\text{eV}$ となるが、この値もAlのエレクトロマイグレーションというよりはゲートのAlの拡散による劣化の場合の値<sup>(8)</sup>に近い。図6.11のグラフを外挿することによりチャネル温度130°Cの時のMTTFは $1.28 \times 10^6$ hrと求められるが、これは一般のMESFET/GaAsに匹敵する値であり<sup>(9)</sup>、第5章で示した入出力特性の結果と合わせて、GaAs/Si電子デバイスはその特性および信頼性の点において十分実用に値するものと結論できる。

図6.11 アレニウスプロット

## 6.4 まとめ

MESFET/SiとMESFET/GaAsを用いて直流による通電高温放置試験を行い、信頼性を評価した。両者とも故障のモードは同じであり、ゲートの一部が動作しなくなったことによるノンピンチオフ現象とドレイン電流の増加が観察された。EBIC、SEMおよびオージェ分析により、ゲートのAl電極の一部がソースあるいはドレイン電極方向に拡散してゲート部分から消失していることがわかり、さらにAlとチャネルのGaAsとの界面では相互反応の結果絶縁物が形成されている可能性の高いことが示された。この加速試験より、MESFET/SiもMESFET/GaAsもその寿命はほとんど同じであることがわかり、さらにその絶対値もチャネル温度130℃の時のMESFET/SiのMTTFとして $1.28 \times 10^6$ hrと通常の市販レベルのMESFET/GaAsと同等の値が得られていることから、GaAs/Si中に存在する転位はデバイスの信頼度に影響を与えないことが証明された。

以上の結果および前章で示されたパワーMESFET/Siの入出力特性より、GaAs/Siはその特長が最も活かせると思われる高出力デバイスへの応用において、信頼性まで含めた総合特性でGaAs/GaAsデバイスに遜色なく、同デバイスを十分代替する能力を持っていると考えられる。

### (参考文献)

- (1) H. K. Choi, and C. A. Wang

N. H. Karam : Appl. Phys. Lett. **59** (1991) 2634.

- (2) Takashi Egawa, Yoshiaki Hasegawa, Takashi Jimbo, and Masayoshi Umeno :

Jpn. J. Appl. Phys. **31** (1992) 791.

- (3) 秋山正博：京都大学学位論文（1991）

- (4) N. Kornilios and K. Tsagaraki

J. Stoemenos

A. Christou : Quality and Reliability Engineering International **7** (1991) 323.

- (5) K. J. Russell and J. K. Dhiman : 24th Proc. 1986 Internat. Reliability Physics Symp. (1986) 150.

- (6) JIS 規格 : JIS C5003

- (7) K. Katsukawa, Y. Kose, M. Kanamori, and S. Sando : 22nd Proc. 1984 Internat. Reliability Physics Symp. (1984) 59.

- (8) S. Kashiwagi, S. Takase, T. Usui, and T. Ohono : 25th Proc. 1987 Internat. Reliability Physics Symp. (1987) 97.

- (9) W. T. Anderson and A. Christou : "Semiconductor Device Reliability" ( Kluwer Academic Publishers) 423.

## 第7章 結論

本論文においてはMOCVD法を用いて成長したGaAs/Siの電子デバイスへの応用に関して、高品質で安定にデバイス用基板を得るための成長前処理および成長条件、成長した基板の評価（均一性、リーク電流、キャリア移動度、モホロジー）、GaAs/Si電子デバイス固有の問題点抽出とその解決法、その解決法を取り入れて試作したパワーMESFET/Siの評価、さらにはそのMESFET/Siの通電高温放置試験による信頼性評価について述べた。得られた結果の要約は以下の通りである。

(1) 通常の二段階成長法を用いてHEMTやMESFET構造を持つGaAs/Si基板を成長させる際の基本的成長条件を確立できた。また本研究で用いたタイプのMOCVD装置は、その構造上Siのオートドーピングが防止できることも新たな知見として示すことができた。

(2) 成長した電子デバイス用GaAs/Siについて、キャリア密度、膜厚の面内均一性、バッファ層のリーク電流、キャリア移動度および表面モホロジーを評価した。面内均一性については、4インチウェーハにおいて膜厚で平均値±1.5%、キャリア密度で平均値±5%のばらつきに押さえられており、良好であることが示された。GaAs-Si界面の評価より、界面には少なくとも $1 \times 10^{18} \text{ cm}^{-3}$ で $0.1 \mu \text{m}$ 程度の導電層の存在が認められたが、バッファ層のリーク電流に関してはその絶対値から電流は絶縁層内を流れていると考えられ、この界面導電層の影響はほとんど見られなかった。キャリア移動度はp型のGaAs/GaAsについて77Kで約 $6000 \text{ cm}^2/\text{V} \cdot \text{sec}$ であり、高品質の膜が得られていることがわかった。表面モホロジーはAFMで観察し、as-grownの状態で表面荒さのRMSが $2 \times 2 \mu \text{m}^2$ の範囲で $2.3 \text{ nm}$ 、表面の凸凹の高低差として約 $15 \text{ nm}$ と良好な値を示した。さらに表面パーティクル数も $50 \sim 100 \text{ 個}/\text{cm}^2$ とデバイス作成に問題のないレベルにあることがわかった。

GaAs/Siの放熱性の良さを実証するために、デバイスのゲートショットキー接合を利用して熱抵抗を測定した。その結果用いたサンプルにおいてはGaAs/Siの熱抵抗はGaAs/GaAsの約 $2/3$ であることがわかり、また計算とも比較的良好一致した。さらにデバイスが集積された場合を想定した計算より、集積度が上がるほどGaAs/Siの放熱性の良さが発揮されることが示された。

(3) HEMT/Siを試作し、そのしきい値電圧分布と高周波特性を評価した。しきい値電圧のマクロ評価においては、結晶成長装置の特性を反映したと思われる膜厚あるいはキャリア密度のゆるやかな面内分布に基いた分布が観察されたが、ミクロ評価においてはas-grownのHEMT/Siにおいて、 $V_{th}$ の平均値 $-0.10 \text{ V}$ に対し標準

準偏差  $\sigma V_{th} = 9\text{mV}$  と HEMT/GaAs に匹敵する極めて優れた均一性が得られた。しかもこの均一性は結晶内部に存在する転位数の大小にかかわらず得られており、転位はHEMTのようなエピタキシャル層を用いるデバイスのしきい値電圧分布には影響を与えていないことが明らかになった。さらに表面の凸凹に起因すると思われる故障素子も見られないことから、表面モホロジーもデバイス制作に充分耐えうるレベルにあることが示された。

高周波評価からはHEMT/SiはHEMT/GaAsに比べて寄生成分、とくに寄生容量の影響を大きく受けていることが明らかになった。この寄生容量は主として、Si基板-GaAs界面の導電層によって誘起されたゲートパッド容量によるものであり、パッド面積の縮小やパッド下絶縁層の挿入等の比較的容易なプロセスによりGaAs基板上のパッド容量並に減少できることがわかった。実際にそのような対策を施したHEMT/SiはHEMT/GaAsに遜色のない特性を示した。

(4) GaAs/Siを用いた電子デバイスの欠点である寄生容量（パッド容量）の影響を低減させるため、パワーMESFETを試作した。これはゲート幅の大きいデバイスは入力真性容量が大きいため、必然的に入力寄生容量の影響が小さくできるという観点からである。方法としては、まずGaAs基板上のデバイスとほぼ同じ方法で設計し、必要となる全ゲート幅から入力真性容量を求め、その10%を許容できる入力寄生容量としてゲートパッドとゲートバスラインに割り振るという方法をとった。その結果、ゲートバスライン下に絶縁膜を挿入せざるを得なかつたが、小信号等価回路パラメータの評価より、ほぼ設計通りに寄生容量の影響が押さえられたことが示された。このパワーMESFET ( $L_g/W_g = 0.8/5600 \mu\text{m}$ ) を携帯電話での応用を想定した条件 ( $f = 0.85\text{GHz}$ 、 $V_{ds} = 3.6\text{V}$ ) で評価し、線形領域での利得が約20dB、1dBコンプレッション時の出力が25.7dBm (370mW)、またその時の電力付加効率が57%とGaAs基板を用いたデバイスと同等の入出力特性が得られた。さらに $V_{ds} = 2.4\text{V}$ という、より厳しい条件でも特性はほとんど劣化しなかつた。

(5) MESFET/SiとMESFET/GaAsを用いて直流による通電高温放置試験を行い、両者の信頼性を評価した。両者とも故障のモードは同じであり、ゲートの一部が動作しなくなつたことによるノンピンチオフ現象とドレイン電流の増加が観察された。EBIC、SEMおよびオージェ分析により、ゲートのAl電極がソースあるいはドレイン電極方向に拡散してゲート部分から消失していることがわかり、さらにAlとチャネルのGaAsとの界面では相互反応の結果絶縁物が形成されている可能性の高いことが示された。この加速試験より、MESFET/SiもMESFET/GaAsもその寿命はほとんど同じであることがわかり、さらにその絶対値もチャネル温度130°Cの時のMESFET/SiのMTTFとして $1.28 \times 10^6\text{hr}$ と通常の市販レベルのMESFET/GaAsと同等の値が得られていることから、GaAs/Si中に存在する転位

はデバイスの信頼度に影響を与えないことが証明された。

以上よりGaAs/Siの電子デバイスへの応用に関して、従来より欠点として指摘されてきた高密度転位およびSi—GaAs界面の導電層の影響については、エピタキシャルデバイスであれば転位はその電気的特性にも信頼性にも影響を及ぼさないことが明らかになった。また界面の導電層も寄生容量を誘起するものの、パワーMESFETのような大きなゲート幅のデバイスであればパターンを変更することなくその問題を回避でき、実用に値するデバイスが得られることがわかった。さらに熱放散の良さも確認されていることより、GaAs/Siは特にパワーデバイス分野においてGaAs/GaAsを十分代替できることが実証された。

(謝辞)

本論文をまとめるにあたって、大阪大学工学部 濱口智尋教授には多大なる御指導、御鞭撻を賜り心より感謝致します。また、御指導、御助言をいただいた大阪大学工学部 吉野勝美教授、尾浦憲治郎教授、西原浩教授、森田清三教授、谷口研二教授に深謝致します。

本研究は新日本製鐵株式会社技術開発本部先端技術研究所半導体基盤研究部において行われたものであり、同研究部主幹研究員 森谷明弘博士には終始一貫して御指導を賜り心より感謝の意を表します。また研究の機会を与えられ、研究の遂行に対して御指導、御鞭撻いただいた、新日本製鐵株式会社顧問 岩崎裕博士、先端技術研究所長 奥村直樹博士、半導体基盤研究部長 車田克彦氏に心から感謝致します。

本研究を遂行するにあたっては、半導体基盤研究部の方々から多くの御協力をいただいた。成長、評価に関しては、二木登史郎氏、矢部愛次氏、藤田恭久氏、立川昭義氏、デバイス試作、評価に関しては、高山誠治氏、鈴木哲哉氏、シミュレーションに関しては、太田泰光博士、後藤光彦氏、森川陽二氏の多大な御協力をいただいた。これらの方々を初めとして、研究を支えていただいた多くの方々に感謝致します。

(本研究に関する発表論文)

- (1) Takashi Aigo, Hirokatsu Yashiro, Aiji Jono, Akiyoshi Tachikawa, and Akihiro Moritani "Comparison of electronic characteristics and thermal resistance for HEMTs grown on GaAs and Si substrates" : Electron. Lett. **28** (1992) 1737.

- (2) Takashi Aigo, Hirokatsu Yashiro, Mitsuhiro Goto, Aiji Jono, Akiyoshi Tachikawa, and Akihiro Moritani "Thermal resistance and electronic characteristics for high electron mobility transistors grown on Si and GaAs substrates by metal-organic chemical vapor deposition" : Jpn. J. Appl. Phys. **32** (1993) 5508.

- (3) Takashi Aigo, Mitsuhiro Goto, Aiji Jono, Akiyoshi Tachikawa, and Akihiro Moritani "Evaluations of V<sub>th</sub> uniformities and f<sub>T</sub> for HEMT/Si fabricated using GaAs/AlGaAs selective dry etching" : Proc. Int. Symp. GaAs and Related Compounds (1993) 87.

- (4) Takashi Aigo, Aiji Jono, Akiyoshi Tachikawa, Ryuichi Hiratsuka, and Akihiro Moritani "High uniformity of threshold voltage for GaAs/AlGaAs high electron mobility transistors grown on a Si substrate" : Appl. Phys. Lett. **64** (1994) 3127.