|              |                                                                                 |

|--------------|---------------------------------------------------------------------------------|

| Title        | MOSスタティックRAMの高速化に関する研究                                                          |

| Author(s)    | 和田, 知久                                                                          |

| Citation     | 大阪大学, 1994, 博士論文                                                                |

| Version Type | VoR                                                                             |

| URL          | <a href="https://doi.org/10.11501/3098875">https://doi.org/10.11501/3098875</a> |

| rights       |                                                                                 |

| Note         |                                                                                 |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

# MOSスタティックRAMの高速化 に関する研究

1994年

和 田 知 久

# 内容梗概

本論文は、筆者が昭和58年三菱電機株式会社に入社以来、同社ULSI開発研究所において行なってきたスタティック型ランダムアクセスメモリ(SRAM)の研究開発における、「MOSスタティックRAMの高速化に関する研究」の成果をまとめたもので、特に設計面からの高速化の手法に重点を置いており、本文は序論の章、結論の章を含め、7章より構成されている。

## 第1章 序論

本章では本研究に関連する分野における歴史的背景と、高速SRAMに関する開発の沿革と現状について概説し、本研究を行なうに至った動機と目的を明らかにする。

SRAMの高速化のアプローチとして、1) アレイアーキテクチャ、2) 回路技術、そして3) コンピュータシステムにキャッシュメモリとして使用された場合の論理構成の最適化の3つの方法を用い、それぞれの検討結果を2章、3章、4章で述べる。また、5章では高速化時に信頼性的問題となるノイズとソフトエラーの問題の解決策について述べる。そして、6章にて工学的応用としての高速高集積1MSRAMの実用化について述べ、7章で内容をまとめることとする。

## 第2章 アーキテクチャによるSRAMの高速化

本章では、SRAMの高速化のアプローチとしてメモリアレイを構成するワード線ならびにビット線の構成方法(メモリアレイアーキテクチャ)による高速化の手法を示す。

まず最初に、吉本らにより提案された分割ワード線構成(Divided Word Line)を進化させた変形分割ワード線構成(Modified Divided Word Line)を提案し、変形分割ワード線構成がSRAMのワード線選択の高速化を実現できるアーキテクチャであることを示す。

次に、新しいビット線構成であるT字型ビット線構成(T-shaped Bit Line)を提案し、T字型ビット線構成が高速化および多ビット構成に適するビット線アーキテクチャであることを示す。

## 第3章 回路技術によるSRAMの高速化

本章では、SRAMの高速化のアプローチとして回路技術による高速化の手法を示す。

まず最初に、アドレス入力信号の変化を感知して同期パルスを発生し、そのパルスを用いて内部回路を同期させて動作させるATD方式(Address Transition Detection)を用いた高速化の概要を説明する。

次に、ATDを利用したデータバスプリチャージとデュアルレベルデータバスプリチャージ方式を提案し、チップ内部のデータバスの高速化の方法を示す。

さらに、ATDを用いたデータ出力プリセット方式を提案し、高速化の問題のひとつであるノイズを低減しながら高速化を実現する方法を示す。

## 第4章 キャッシュメモリとしてのSRAMの高速化

高速SRAMが最も必要とされるアプリケーションは高性能のコンピュータシステムであり、主にSRAMはキャッシュメモリとして使用されている。キャッシュメモリはある大きさの固まったデータをアクセスするので完全なランダムアクセスを必要としない。

本章ではキャッシュメモリをCPUと同じチップ内に集積するときに有効なOn-Chipキャッシュメモリ用の解析的なアクセスタイムモデルを示す。

また、そのアクセスタイムモデルを用いてキャッシュメモリの論理構成と物理構成によるスピードのトレードオフを示し、キャッシュメモリとしてSRAMを高速化する方法を示す。

## 第5章 SRAMの高速化に対する信頼性上の問題と解決策

本章では、SRAMを高速化するときの信頼性上の問題であるノイズとソフトエラーの問題について述べる。

まず最初に、高速なオフチップドライバによる電源線のバウンスノイズ発生をモデル化してモデル式を提案し、低ノイズ化するための解決策を示す。

次に、高速化すなわちサイクルタイムを短くするとソフトエラー率が上昇するメカニズムを明らかにし、これを解決する方法を示す。

## 第6章 工学的応用（高速高集積1MSRAMの実用化による検証）

第2章～第5章までの結果を踏まえ、具体的な高集積1MSRAMを実用化するに当たり応用面での検討、評価結果について述べる。

高性能ショートチャネルトランジスタと変形分割ワード線構成、ATDによるデュアルレベルデータバスプリチャージ、高感度センスアンプ、ゲートコントロール型データバスドライバなる技術により高速アクセスタイム14nsを実現した。

また同時に、高速1MSRAMでテスト時間短縮のために新しく採用したビット構成可変方式とその評価結果を述べる。

## 第7章 結論

第2章から第6章までの研究成果を総括して、本研究の結論を述べる。

# 目次

## 第1章 序論

|                |   |

|----------------|---|

| 1.1 関連分野の歴史的背景 | 1 |

| 1.2 本研究の目的     | 4 |

| 1.3 本研究の内容     | 4 |

| 1.4 参考文献       | 7 |

## 第2章 アーキテクチャからの高速化

|                           |    |

|---------------------------|----|

| 2.1 はじめに                  | 15 |

| 2.2 変形分割ワード線構成            | 16 |

| 2.2.1 分割ワード線構成と変形分割ワード線構成 | 16 |

| 2.2.2 適用例および結果            | 17 |

| 2.3 T字型ビット線構成             | 20 |

| 2.3.1 通常ビット線構成とT字型ビット線構成  | 20 |

| 2.3.2 適用例および結果            | 22 |

| 2.4 結論                    | 25 |

| 2.5 参考文献                  | 27 |

## 第3章 回路技術面からの高速化

|                            |    |

|----------------------------|----|

| 3.1 はじめに                   | 29 |

| 3.2 ATD方式の概要               | 29 |

| 3.3 データバスプリチャージによる高速化      | 30 |

| 3.3.1 データバスプリチャージ          | 30 |

| 3.3.2 デュアレベルデータバスプリチャージ    | 34 |

| 3.4 出力プリセットによる高速化と低ノイズ化の両立 | 36 |

| 3.5 結論                     | 40 |

| 3.6 参考文献                   | 41 |

## 第4章 キャッシュメモリとしての高速化

|                                 |    |

|---------------------------------|----|

| 4.1 はじめに                        | 43 |

| 4.2 On-Chipキャッシュメモリ用のアクセスタイムモデル | 43 |

| 4.2.1 背景                        | 43 |

| 4.2.2 キャッシュメモリの構成               | 44 |

| 4.2.3 解析的アクセスタイムモデル             | 46 |

| A デコード遅延                        | 47 |

| B ワード線遅延                        | 50 |

|                 |    |

|-----------------|----|

| C ビット線／センスアンプ遅延 | 51 |

| D データバス／出力遅延    | 55 |

| E アクセスタイム       | 56 |

| 4.2.4 モデルの検証    | 57 |

| 4.3 結論          | 63 |

| 4.4 参考文献        | 64 |

## 第5章 SRAMの高速化に対する信頼性上の問題と解決策

|                                    |    |

|------------------------------------|----|

| 5.1 はじめに                           | 65 |

| 5.2 出力バッファの解析的モデル                  | 65 |

| 5.2.1 CMOS出力バッファの電源ノイズ             | 65 |

| 5.2.2 データ出力バッファの解析的近似              | 67 |

| 5.2.3 モデルと回路シミュレーションSPICEとの比較      | 69 |

| 5.2.4 電圧降圧回路を組み合わせた低ノイズ出力バッファ      | 70 |

| 5.3 SRAMソフトエラー率の逆サイクルタイム依存性        | 72 |

| 5.3.1 メモリセルの構成                     | 73 |

| 5.3.2 ソフトエラー率の測定結果                 | 73 |

| 5.3.3 解析                           | 74 |

| 5.3.3.1 SRAMのソフトエラー率の通常のサイクルタイム依存性 | 74 |

| 5.3.3.2 ソフトエラー率の逆サイクルタイム依存性        | 76 |

| 5.3.4 ソフトエラー率のサイクルタイム依存性に対する考察     | 78 |

| 5.3.4.1 他の実験結果                     | 78 |

| 5.3.4.2 ドライバトランジスタのしきい値電圧を上げる効果    | 79 |

| 5.3.4.3 高抵抗負荷の抵抗値を下げる効果            | 80 |

| 5.3.5 ソフトエラー率のサイクルタイム依存性のまとめ       | 80 |

| 5.4 結論                             | 82 |

| 5.5 参考文献                           | 84 |

## 第6章 工学的応用 (高速高集積1MSRAMの実用化による検証)

|                         |    |

|-------------------------|----|

| 6.1 はじめに                | 85 |

| 6.2 ビット構成可変14nsの1MSRAM  | 85 |

| 6.2.1 回路設計              | 85 |

| A チップアーキテクチャ            | 85 |

| B 変形分割ワード線構成            | 87 |

| C センスアンプ回路              | 87 |

| D ゲート制御型データバスドライバ       | 88 |

| E デュアレレベルデータバスプリチャージ    | 89 |

| F ビット構成可変機能             | 89 |

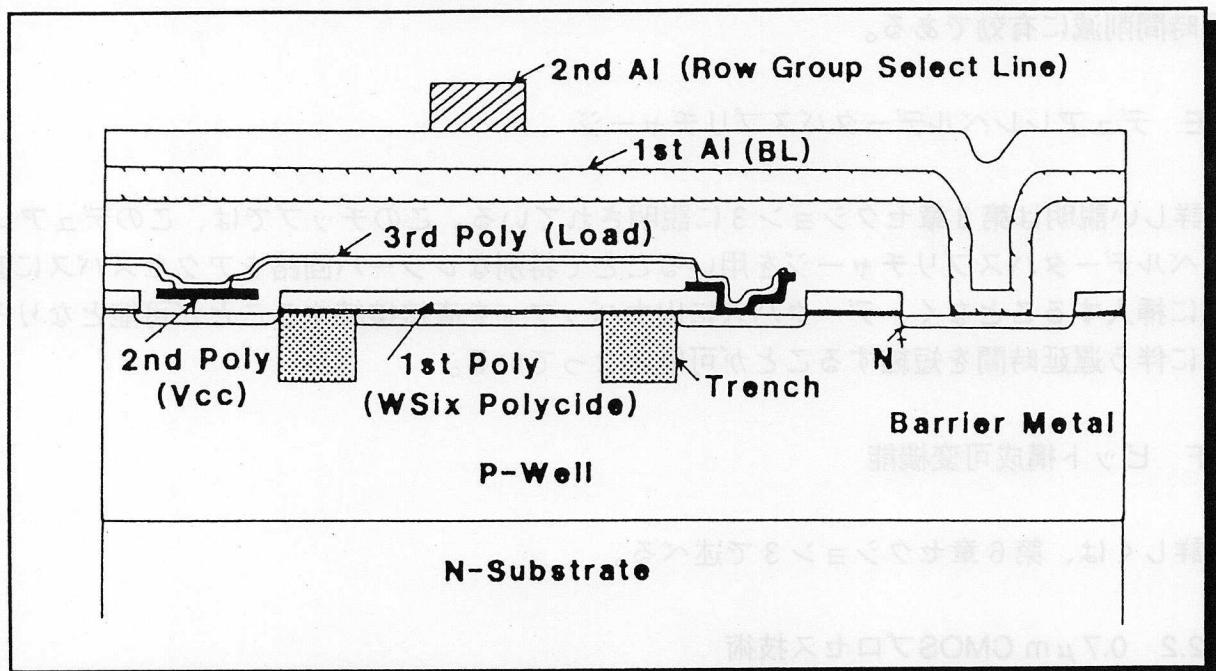

| 6.2.2 0.7 μm CMOSプロセス技術 | 89 |

|                             |     |

|-----------------------------|-----|

| 6.3 メモリの新テスト機能としてのビット構成可変機能 | 93  |

| 6.3.1 SRAMのテスト              | 94  |

| 6.3.2 回路技術                  | 94  |

| 6.3.3 評価結果                  | 97  |

| 6.4 結論                      | 100 |

| 6.5 参考文献                    | 101 |

| <br>第7章 結論                  |     |

| 7.1 本研究の結論                  | 105 |

| 7.2 謝辞                      | 109 |

| 研究業績目録                      | 110 |

# 第1章

## 序論

## 1.1 関連分野の歴史的背景

スタティックランダムアクセスメモリ（以後SRAM）の開発は、1969年のIntel社のPチャンネル型シリコンゲートの256ビットランダムアクセスメモリ（Intel 1101）に始まった。SRAMは1ビット情報を保持するメモリセルを構成するために4～6個のトランジスタが必要であり、ダイナミックRAM（DRAM）の1トランジスタ／1キャパシタ構成に比べて同一製造技術水準（同一のチップサイズと同一の最小サイズ）では集積度が1/4で、ビットコストが高いという本質的な欠点を有している。しかしながら、1)リフレッシュ動作が不要、2)動作タイミングが簡単で使いやすい、3)読み出し／書き込み速度が高速、4)スタンバイ電流が小さいなどのメリットを発揮してDRAMがコンピュータの主記憶におもに使われているのに対して、SRAMは多種多用な用途に使用されその需要は増大している。SRAMの究極の性能は高集積性、高速性、低消費電力性を兼ね備えることであるが、用途によって要求性能は異なっている。

SRAMの用途でリフレッシュ動作不要、使い易さおよび低ビットコストを必要とするのは端末機器、計測器用の小容量メモリシステムや、ハードディスク装置の小容量のバッファメモリを対象としたもの[1-1]～[1-6]で、アクセス時間は55nsから100ns以上と高速ではないが、動作時の消費電力を200mW～300mWに抑えている。

また、SRAMの用途で特に低消費電力を必要とするものはハンディーターミナル、ラップトップ／ノート型コンピュータ、電子手帳、ペン入力パソコンなどの携帯機器の主記憶であり、バッテリーバックアップによる不揮発性メモリ[1-7]～[1-10]として使用され、スタンバイ時の消費電力は10μW以下に低減されている。このような低スタンバイ電力と低動作電力は1970年代後半に現われた高抵抗ポリシリコンを負荷抵抗素子として用いたメモリセルの採用[1-11]～[1-14]と、コンプリメンタリMOS（以後CMOS）プロセスの微細化の促進によって達成され、以後低消費電力性と高速性を両立するSRAMが開発されている[1-15]～[1-48]。その後、4M以上の大容量のSRAMではさらなる低スタンバイ電力達成のために高抵抗ポリシリコン負荷に変わって、薄膜トランジスタが採用[1-49]～[1-51]され一層の低スタンバイ電力が実現された。

また、SRAMの用途で特に高速性を必要とするものはスーパーコンピュータの主記憶、ワークステーションおよびパーソナルコンピュータのキャッシュ／バッファメモリなど[1-15]～[1-48]で、マイクロプロセッサの著しい速度向上に対応する高速なSRAMが必要とされた。特に、数量の多いパーソナルコンピュータにキャッシュメモリが使用された以降キャッシュメモリとしての高速SRAMの需要は大きく成長している。

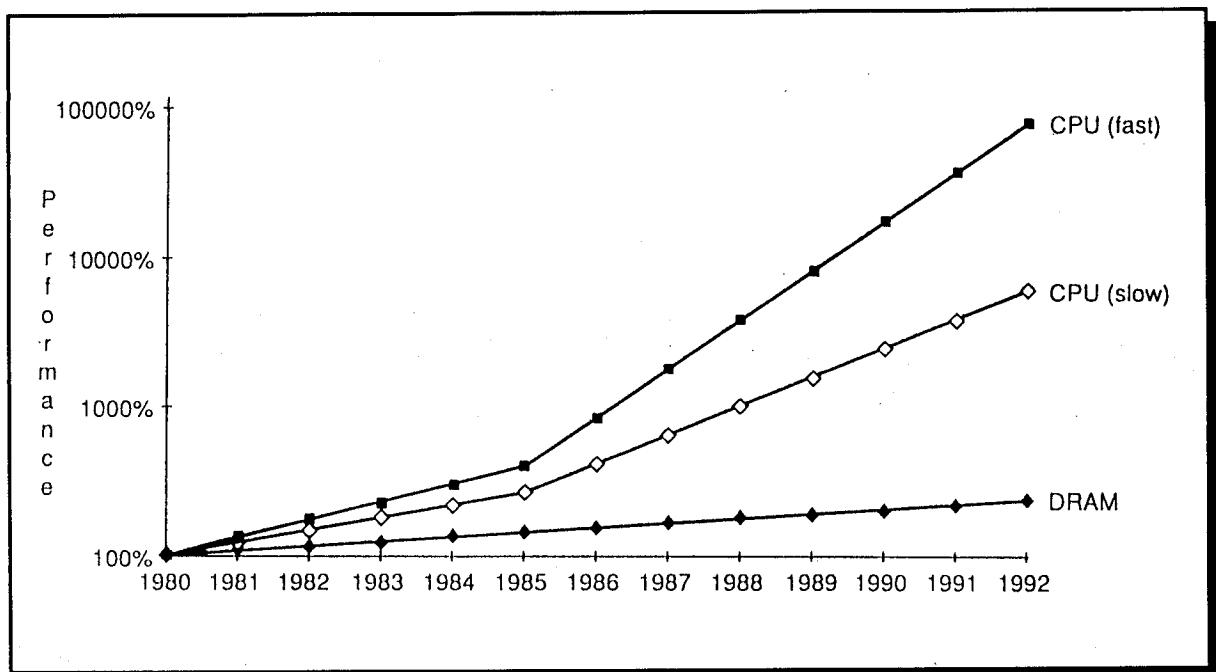

図1-1-1にマイクロプロセッサの動作スピードと主記憶を構成するDRAMのスピードの推移を示す[1-52]。比例縮小則[1-53]に従った微細化の促進、回路面の工夫、縮小命令セットコンピュータ(RISC)に代表されるアーキテクチャの改善によってマイクロプロセッサの動作周波数は1985年以降年率2倍のスピードで性能向上を実現したが、主記憶として使用されるDRAMのスピードの向上は、微細化と同時に集積度が向上していることもありプロセッサに比べて緩やかで、両者の間に大きなスピードギャップが生じた。こ

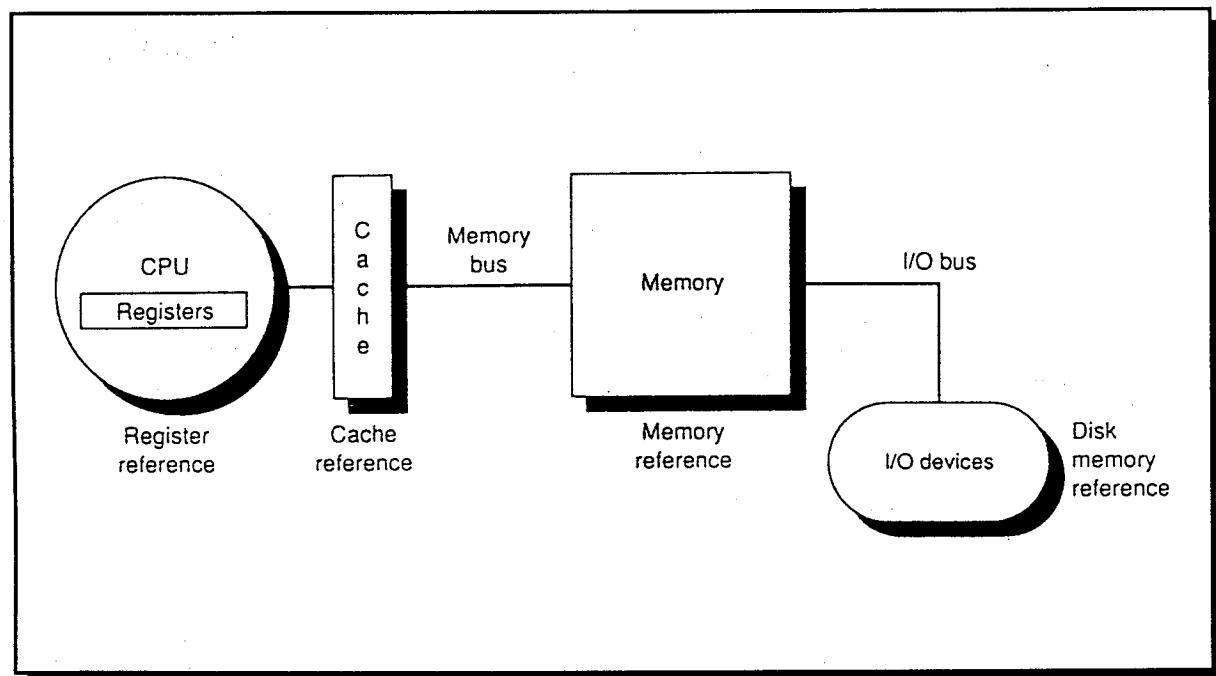

のスピードギャップを埋めるコンピュータアーキテクチャからの解決策が高速なSRAMを使用するキャッシュメモリであり、図1-1-2に示すようなメモリの階層構成が主流になってきた。

図1-1-1：マイクロプロセッサとDRAMのスピードの推移

図1-1-2：メモリの階層構成

キャッシュメモリとは主記憶よりもプロセッサに近いレベルに置かれた高速かつ低容量のメモリである。プロセッサが主記憶内のデータをアクセスする場合、場所的局所性

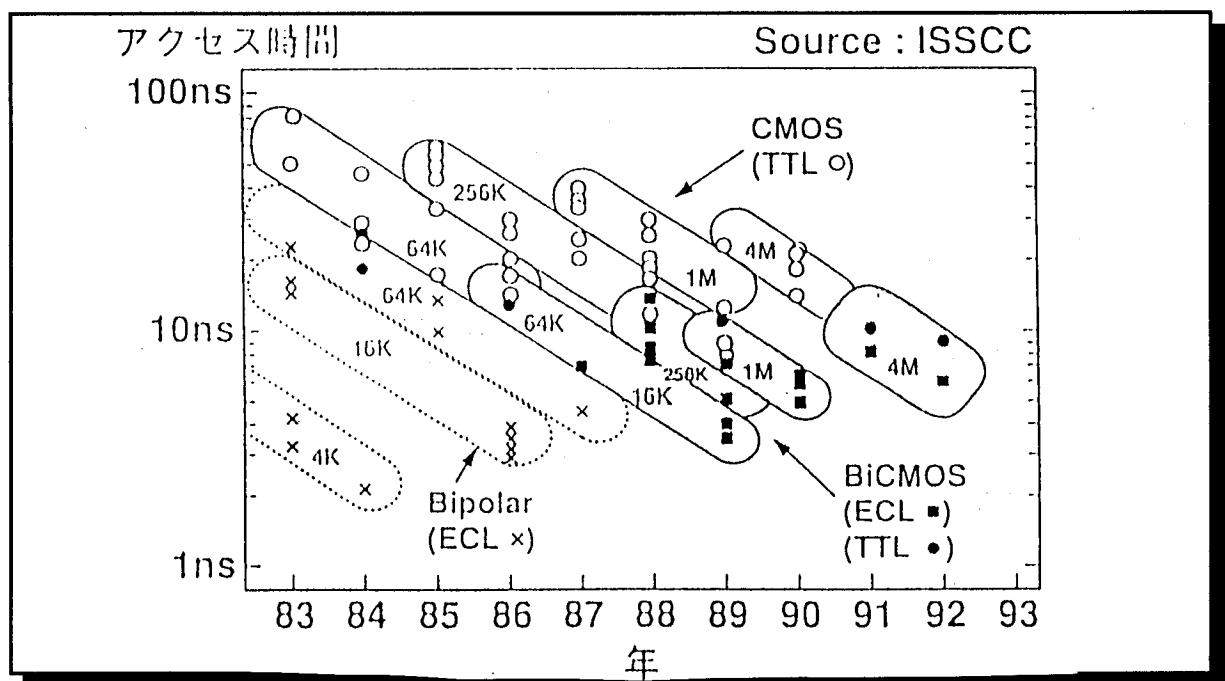

と時間的局所性の2つの局所性がある。前者は1度アクセスされたデータの近傍のアドレスにあるデータがアクセスされる確率が高い性質であり、後者は1度アクセスされたデータは近い将来再びアクセスされる可能性が高い性質である。キャッシュメモリは、主記憶内のデータをある単位（ブロック）ごとにキャッシュメモリにコピーし、以上述べた2つの局所性を利用してメモリの平均のアクセス時間を下げるものである。したがって、キャッシュメモリは主記憶に対して十分な高速性が必要であり高速なSRAMが使用されている。しかし、小容量のキャッシュメモリと言えども主記憶容量の増大に伴ってSRAMの集積度を上げる必要があり、微細化の促進だけでプロセッサと同一の性能向上を実現するのは困難であり、設計面での工夫やプロセスの改良が行なわれてきた。図1-1-3に国際固体素子回路会議（International Solid State Circuit Conference）に登場した高速SRAMのアクセス時間の推移を示す。プロセス技術としてCMOSプロセス技術、バイポーラトランジスタとCMOSを組み合わせたBiCMOSプロセス技術、バイポーラプロセス技術の3種類の技術が使われてきている。バイポーラ技術では10ns以下の非常に高速なアクセス時間を実現できるが、メモリセルがバイポーラトランジスタで構成されセルサイズが大きく、またメモリセルの各ビットの消費電力が大きいので高集積に向かず64Kビットが開発された最大容量である。一方、CMOSでは高集積が可能であるが高速性ではバイポーラに劣りアクセス時間10ns程度以上のものが開発されている。そして、高集積でかつ10ns以下のSRAMは主にBiCMOS技術で製造されている[1-54]～[1-65]。

図1-1-3：高速SRAMのアクセス時間の推移

## 1.2 本研究の目的

本研究の目的は高性能なコンピュータシステムに必要なキャッシュメモリに使用されるSRAMの高速化であり、特に設計面からSRAMの高速化を実現することを目的としている。

具体的には、1) SRAMの高速化を実現するためにSRAMのメモリアレイ構成（アーキテクチャ）の最適化による高速化の方法[1-66]～[1-68]を明らかにしつつ、2) 回路技術による高速化の方法[1-69]～[1-71]を明らかにすることを目的としている。また、3) キャッシュメモリとして使用されたときのアクセス時間をモデル化し、高速なキャッシュメモリの構成方法[1-72]を明らかにすることを目的としている。さらに、4) 高速化により発生する信頼性上の問題点とその解決方法[1-73]、[1-74]を明らかにすることを目的としている。

## 1.3 本研究の内容

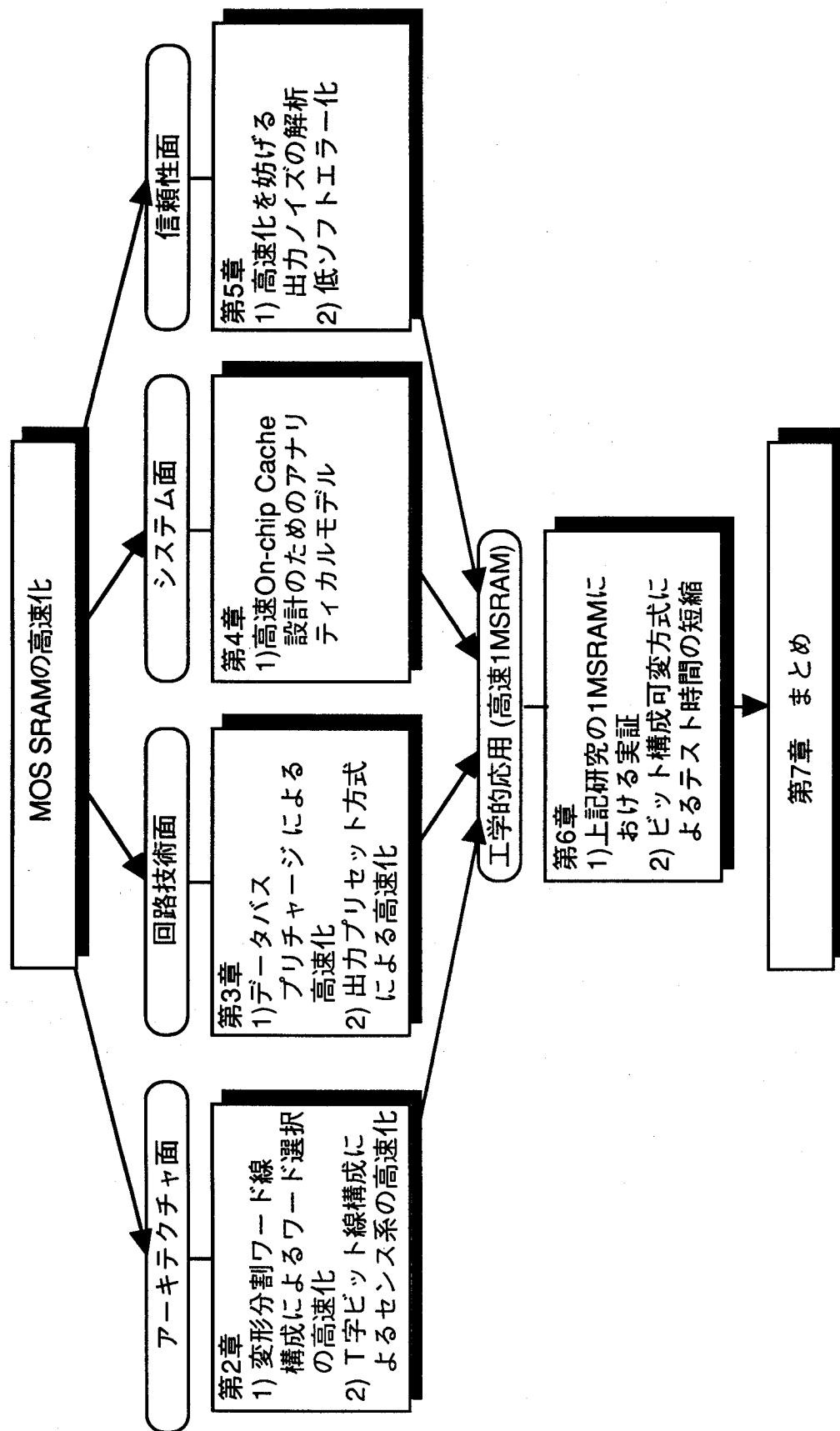

本論文は上述の目的を達成するために著者が行なった研究の成果を述べるものであり、本論文の構成は次の通りである。本論文の構成を図1-3-1に示す。

### 第1章 序論

本章では本研究に関連する分野における歴史的背景と、本SRAMの高速化に関する研究について概説する。

### 第2章 アーキテクチャによるSRAMの高速化

吉本らにより提案された分割ワード線構成(Divided Word Line)を進化させた変形分割ワード線構成(Modified Divided Word Line)を提案し、変形分割ワード線構成がSRAMのワード線選択の高速化を実現できるアーキテクチャであることを示す。

次に、新しいビット線構成であるT字型ビット線構成(T-shaped Bit Line)を提案し、T字型ビット線構成が高速化および多ビット構成に適するビット線アーキテクチャであることを示す。

### 第3章 回路技術によるSRAMの高速化

まず最初にアドレス入力信号の変化を感じて同期パルスを発生し、そのパルスを用いて内部回路を同期させて動作させるATD方式(Address Transition Detection)を用いた高速化の概要を説明する。

次に、ATDを利用したデータバスプリチャージとデュアルレベルデータバスプリチャージ方式を提案し、チップ内部のデータバスの高速化の方法を示す。

さらに、ATDを用いたデータ出力プリセット方式を提案し、高速化の問題のひとつであるノイズを低減しながら高速化を実現する方法を示す。

#### 第4章 キャッシュメモリとしてのSRAMの高速化

高速SRAMが最も必要とされるアプリケーションは高性能のコンピュータシステムであり、主にSRAMはキャッシュメモリとして使用されている。キャッシュメモリはある大きさの固まったデータをアクセスするので完全なランダムアクセスを必要としない。

本章ではキャッシュメモリをCPUと同じチップ内に集積するときに有効なOn-Chipキャッシュメモリ用の解析的なアクセスタイムモデルを示す。

また、そのアクセスタイムモデルを用いてキャッシュメモリの論理構成と物理構成によるスピードのトレードオフを示し、キャッシュメモリとしてSRAMを高速化する方法を示す。

#### 第5章 SRAMの高速化に対する信頼性上の問題と解決策

SRAMを高速化するときの信頼性上の問題であるノイズとソフトエラーの問題について述べる。まず高速なオフチップドライバによる電源線のバウンスノイズ発生をモデル化してモデル式を提案し、低ノイズ化するための解決策を示す。

次に、高速化すなわちサイクルタイムを短くするとソフトエラー率が上昇するメカニズムを明らかにし、これを解決する方法を示す。

#### 第6章 工学的応用 (高速高集積1MSRAMの実用化による検証)

第2章～第5章までの結果を踏まえ、具体的な高集積1MSRAMを実用化するに当たり応用面での検討、評価結果について述べる。

高性能ショートチャネルトランジスタと変形分割ワード線構成、ATDによるデュアルレベルデータバスプリチャージ、高感度センスアンプ、ゲートコントロール型データバスドライバなる技術により高速アクセスタイム14nsを実現した。

また同時に、高速1MSRAMでテスト時間短縮のために新しく採用したビット構成可変方式とその評価結果を述べる。

#### 第7章 結論

第2章から第6章までの研究成果を総括して、本研究の結論を述べる。

図1-3-1：本論文の構成

## 1.4 参考文献

- [1-1] 富沢、穴見、田中. "16KビットNMOSスタティックRAM," 工業調査会 電子材料, pp.50-54.

- [1-2] O. Minato, T. Masuhara, T. Sasaki, Y. Sakai, T. Hayashida, K. Nagasawa, K. Nishimura, T. Yasui, and T. Miyauchim " A HICMOSII 8K x 8 Static RAM," ISSCC Dig. Tech. Papers, Feb. 1982, pp.256-257.

- [1-3] S. Konishi, J. Matsunaga, T. Ohtani, M. Sekine, M. Isobe, T. Iizuka, Y. Uchida, and S. Kohyama, "A 64Kb CMOS RAM," ISSCC Dig. Tech. Papers, Feb. 1982, pp.258-259.

- [1-4] H. Shinohara, K. Anami, T. Yoshihara, K. Kihara, Y. Kohno, Y. Akasaka, and S. Kayano, "A fast 8K x8 Mixed CMOS Static RAM," IEEE Trans. Electron Devices, ED-32, 9, pp.1792-1796 (Sept. 1985).

- [1-5] H. Shinohara, K. Anami, K. Ichinose, T. Wada, Y. Kohno, Y. Kawai, Y. Akasaka, and S. Kayano, "A 45ns 256K CMOS SRAM with Tri-Level Word Line," ISSCC Dig. Tech. Papers, Feb. 1985, pp.62-63.

- [1-6] H. Shinohara, K. Anami, K. Ichinose, T. Wada, Y. Kohno, Y. Kawai, Y. Akasaka, and S. Kayano, "A 45ns 256K CMOS SRAM with Tri-Level Word Line," IEEE J. Solid-State Circuits, SC-20, 5, pp.929-934 (Oct. 1985).

- [1-7] T. Iizuka, K. Ochiai, T. Ohtani, K. Kondo, S. Kohyama, "A Static 16Kb Bulk CMOS RAM," ISSCC Dig. Tech. Papers, Feb. 1980, pp.226-227.

- [1-8] K. Ochiai, Y. Kawakami, S. Kohyama, H. Igarashi, K. Fushikida, "A 15nW Standby Power 64Kb CMOS RAM," ISSCC Dig. Tech. Papers, Feb. 1982, pp.260-261.

- [1-9] M. Yoshimoto, K. Anami, H. Shinohara, T. Yoshihara, H. Takagi, S. Nagao, S. Kayano, and T. Nakano, "A 64Kb full CMOS RAM with divided word line structure," ISSCC Dig. Tech. Papers, Feb. 1983, pp.58-59.

- [1-10] T. Watanabe, H. Hayashi, I. Sakaki, Y. Akatsuka, T. Yujide, H. Yamamoto, O. Kudoh, S. Takahashi, and T. Hara, "A Battery Backup 64K CMOS RAM with Double Level Aluminum Technology," ISSCC Dig. Tech. Papers, Feb. 1983, pp.60-61.

[1-11] T. R. O'Connell, J. M. Hartman, E. D. Errett, G. S. Larch, and W. C. Dunn, "A 4K static clocked and nonclocked RAM design," ISSCC Dig. Tech. Papers, Feb. 1977, pp.14-15.

[1-12] G. S. Leach, J. M. Hartman, R. L. Clark, and T. R. O'Connell, "A 1K x 8 bit 5V Only Static RAM," ISSCC Dig. Tech. Papers, Feb. 1978, pp.104-105.

[1-13] T. Masuhara, O. Minato, T. Sakaki, H. Nakamura, Y. Sakai, T. Yasui, and K. Uchibori, "2K x 8b HMOS Static RAMs," ISSCC Dig. Tech. Papers, Feb. 1980, pp.224-225.

[1-14] T. Ohzone, S. Kondo, K. Tujii, T. Shiragasawa, T. Ishihara, and S. Horiuchi, "A 64Kb Static RAM," ISSCC Dig. Tech. Papers, Feb. 1980, pp.236-237.

[1-15] O. Minato, T. Masuhara, T. Sakai, Y. Sakai, K. Yoshizaki, "HI-CMOSII 4K Static RAM," ISSCC Dig. Tech. Papers, Feb. 1981, pp.14-15.

[1-16] M. Isobe, J. Matsunaga, T. Sakurai, T. Ohtani, K. Sawada, H. Nozawa, T. Iizuka, and S. Hohyama, "A 46ns 256K CMOS RAM," ISSCC Dig. Tech. Papers, Feb. 1984, pp.214-215.

[1-17] K. Hardee, M. Griffus, R. Glavas, "A 30ns 64K CMOS RAM," ISSCC Dig. Tech. Papers, Feb. 1984, pp. 216-217.

[1-18] T. Ozawa, S. Koshimaru, O. Kudo, H. Ito, T. Yamanaka, N. Yasuoka, H. Asai, N. Harashima, and S. Kikuchi, "A 25ns 64K CMOS RAM," ISSCC Dig. Tech. Papers, Feb. 1984, pp.218-219.

[1-19] O. Minato, T. Masuhara, T. Sakaki, Y. Sakai, and T. Hayashida, "A 20ns 64K CMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1984, pp.222-223.

[1-20] J. Miyamoto, S. Saito, H. Momose, H. Shibata, K. Kanzaki, and T. Iizuka, "A 28ns CMOS SRAM with Bipolar Sense Amplifiers," ISSCC Dig. Tech. Papers, Feb. 1984, pp.224-225.

[1-21] S. Yamamoto, K. Ushibori, K. Nagasawa, S. Meguro, T. Yasui, O. Minato, and T. Masuhara, "A 256K CMOS SRAM with Variable-Impedance Loads," ISSCC Dig. Tech. Papers, Feb. 1985, pp.58-59.

[1-22] Y. Kobayashi, H. Eguchi, O. KUdoh, T. Hara, H. Ooka, I. Sakaki, M. Andoh, and M. Tameda, :A 10  $\mu$  W Standby Power 256K CMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1985, pp.60-61.

[1-23] K. Ochiai, H. Yasuda, K. Kobayashi, T. Kondoh, and F. Masuoka, "A 17ns 64K CMOS SRAM with a Schnitt trigger Sense amplifier," ISSCC Dig. Tech. Papers, Feb. 1985, pp.64-65,

[1-24] N. Okazaki, F. Miyaji, K. Kobayashi, Y. Harada, J. Aoyama, and T. Shimada, "A 30ns 256K Full CMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1986, pp.204-205.

[1-25] S. E. Shuster, B. A. Chappel, R. L. Franch, P. F. Grier, S. P. Klepner, J. F. S. Lai, R. A. Lipa, R. J. Perry, W. E. Pokorny, and M. A. Roberge, "A 15ns CMOS 64K RAM," ISSCC Dig. Tech. Papers, Feb. 1986, pp.206-207.

[1-26] S. T. Flannagan, P. A. Reed, P. Voss, S. Nogle, B. Simon, D. Sheng, R. Kung, and J. J. Barnes, "Two 64K CMOS SRAM with 13ns Access Time," ISSCC Dig. Tech. Papers, Feb. 1986, pp.208-209.

[1-27] S. Kayano, K. Ichinose, Y. Kohno, H. Shinohara, K. Anami, S. Murakami, T. Wada, Y. Kawai, and Y. Akasaka, "25-ns 256Kx1/64Kx4 CMOS SRAM's," IEEE J. Solid-State Circuits, vol. SC-21, pp. 686-691, Oct. 1986.

[1-28] S. Hanamura, O. Minato, T. Masuhara, Y. Sakai, T. Yamanaka, N. Moriwaki, and F. Kojima, "A 256K CMOS SRAM with Internal Refresh," ISSCC Dig. Tech. Papers, Feb. 1987, pp.250-251.

[1-29] A. Roberts, J. Dreibelbis, G. Braceras, J. Gabric, L. Gilbert, R. Goodwin, E. Hedberg, T. MAffirr, L. Meunier, D. Moran, P. Nguyen, D. Reed, R. Reismiller, and R. Sasaki, "A 256K SRAM with On-chip Power Supply Conversion," ISSCC Dig. Tech. Papers, Feb. 1987, pp.252-253.

[1-30] K. Wang, M. Bader, P. Voss, V. Soorholtz, R. Mauntel, H. Mendez, and R. Kung, "A 21ns 32K x 8 CMOS SRAM with a Selectively Pumped P-well Array," ISSCC Dig. Tech. Papers, Feb. 1987, pp.254-255.

[1-31] T. Komatsu, N. Okazaki, T. Nishihara, S. Kayama, N. Hoshi, J. Aoyama, and T. Shimada, "A 35ns 1Mb CMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1987, pp.258-259.

- [1-32] O. Minato, T. Sasaki, S. Honjo, K. Ishibashi, Y. Sasaki, N. Moriwaki, K. Nishimura, Y. Sakai, S. Meguro, M. Tsunematsu, and T. Masuhara, "A 42ns 1mb CMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1987, pp.260-261.

- [1-33] T. Wada, T. Hirose, H. Shinohara, Y. Kawai, K. Yuzuriha, Y. Kohno, and S. Kayano, "A 34ns 1Mb CMOS SRAM using Triple Poly," ISSCC Dig. Tech. Papers, Feb. 1987, pp.262-263.

- [1-34] T. Ohtani, K. Hashimoto, M. Matsui, J. Tsujimoto, H. Iwai, M. Saitoh, H. Shibata, H. Sasaki, M. Isobe, J. Matsunaga, and T. Iizuka, "A 25ns 1Mb CMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1987, pp.264-265.

- [1-35] K. Sasaki, S. Hanamura, K. Ueda, T. Oono, O. Minato, K. Nishimura, Y. Sakai, S. Megro, M. Tsunematsu, T. Masuhara, M. Kubotera, H. Toyoshima, "A 15ns 1Mb CMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1988, pp.174-175.

- [1-36] H. Shimada, Y. Tange, K. Tanimoto, M. Shiraishi, N. Suzuki, and T. Nomura, "An 18ns 1Mb CMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1988, pp.176-177.

- [1-37] F. List, S. Bell, S. Chu, J. Dikken, C. Hartgring, J. Raemaekers, B. Walsh, and R. Salters, "A 25ns Low-Power Full CMOS 1M (128Kx8) SRAM," ISSCC Dig. Tech. Papers, Feb. 1988, pp.178-179.

- [1-38] H. Lee, B. El-Kareh, R. Glaker, G. Graventies, R. Lipa, J. Maslack, J. Pessetto, W. Pokorny, M. Roberge, . Williams, H. Zelelr, and K. Beilstein, "An Experimental 1Mb CMOS SRAM with Configurable Organization and Operation," ISSCC Dig. Tech. Papers, Feb. 1988, pp.180-181.

- [1-39] S. Flannagan, S. Nogle, A. Faber, N. Herr, R. Mauntel, B. Engles, and R. Kung, "A 16ns 256K x 1 CMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1988, pp.182-183.

- [1-40] T. Wada, K. Anami, Y. Kawai, K. Yuzuriha, Y. Kohno, T. Matsukawa, and S. Kayano, "A 14ns 1Mb CMOS SRAM with Variable Bit-Organization Features," ISSCC Dig. Tech. Papers, Feb. 1988, pp.252-253.

- [1-41] F. Towler, J. Chu, R. Houghton, P. Lane, B. A. Chappell, T. I. Chappell, and S. E. Schuster, "A 128K 6.5ns Access/5ns Cycle CMOS ECL Static RAM," ISSCC Dig. Tech. Papers, Feb. 1989, pp.30-31.

[1-42] K. Sasaki, S. Hanamura, K. Ishibashi, T. Yamanaka, N. Hashimoto, T. Nishida, K. Shimohigashi, and S. Honjo, "A 9ns 1Mb CMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1989, pp.34-35.

[1-43] T. Hirose, H. Kuriyama, S. Murakami, K. Yuzuriha, T. Mukai, K. Tsutsumi, Y. Nishimura, Y. Kohno, and K. Anami, "A 20ns 4Mb CMOS SRAM with Hierarchical Word Decoding Architecture," ISSCC Dig. Tech. Papers, Feb. 1990, pp.132-133.

[1-44] S. Flannagan, P. Pelley, N. Herr, B. Engles, T-S, Feng, S. Nogle, J. Eagen, R. Dunnigan, L. Day, and R. Kung, "An 8ns CMOS 64Kx4 and 256Kx1 SRAM," ISSCC Dig. Tech. Papers, Feb. 1990, pp.134-135.

[1-45] S. Murakami, K. Fujita, M. Ukita, K. Tsutsumi, Y. Inoue, O. Sakamoto, M. Ashida, Y. Nishimura, Y. Kohno, and K. Anami, "A 21mW 4Mb CMOS SRAM for Battery Operation," ISSCC Dig. Tech. Papers, Feb. 1991, pp.46-47.

[1-46] T. Chappell, B. Chappell, S. Shuster, J. Allan, S. Klepner, R. Joshi, and R. France, "A 2ns Cycle, 4ns-Access 512Kb CMOS ECL SRAM," ISSCC Dig. Tech. Papers, Feb. 1991, pp.48-49.

[1-47] K. Sasaki, K. Ishibashi, K. Ueda, K. Komiya, T. Yamanaka, N. Hashimoto, H. Toyoshima, F. Kojima, and A. Shimizu, "A 7ns 140mW 1Mb CMOS SRAM with Current Sense Amplifier," ISSCC Dig. Tech. Papers, Feb. 1992, pp.208-209.

[1-48] M. Matsumiya, S. Kawashima, M. Sakata, T. Miyabo, T. Koga, K. Itabashi, K. Mizutani, T. Ema, K. Toyoda, T. Yabu, H. Shimada, N. Suzuki, and M. Ookura, "A 15ns 16Mb CMOS SRAM with Reduced Voltage Amplitude Data Bus," ISSCC Dig. Tech. Papers, Feb. 1992, pp.214-215.

[1-49] S. Hayakawa, M. Kakumu, A. Aono, H. Takeuchi, K. Sato, K. Noguchi, T. Ohtani, T. Yoshida, T. Nakayama, T. Asami, S. Morita, M. Kinugawa, J. Matsunaga, K. Maeguchi, and K. Ochiai, "A  $1 \mu A$  Retention 4Mb SRAM with a Thin-Film Transistor Load Cell," ISSCC Dig. Tech. Papers, Feb. 1990, pp.128-129.

[1-50] K. Sasaki, K. Ishibashi, T. Yamanaka, K. Shimohigashi, N. Moriwaki, S. Honjo, S. Ikeda, A. Kioke, S. Meguro, and O. Minato, "A 23ns 4Mb CMOS SRAM with  $0.5 \mu A$  Standby Current," ISSCC Dig. Tech. Papers, Feb. 1990, pp.130-131.

- [1-51] K. Ishibashi, K. Takasugi, T. Yamanaka, T. Hashimoto, and K. Sasaki, "A 1V TFT-Load SRAM Using a Two-Step Word Voltage Method," ISSCC Dig. Tech. Papers, Feb. 1992, pp.206-207.

- [1-52] Hennessy, J., and D. Patterson [1990], *Computer Architecture: A Quantitative Approach*, Morgan Kaufmann Publishers, San Mateo, Calif.

- [1-53] R. H. Dennard, F.H. Gaanslen, H. N. Yu, V. L. Redeout, E. Bassous, and A. R. Leblanc, "Design of ion-implanted MOS FET's with very small physical dimensions," IEEE J. Solid-State Circuits, SC-9, pp.256-268 (1974).

- [1-54] N. Tamba, S. Miyaoka, M. Odaka, K. Ogiue, K. Yamada, T. Ikeda, M. Hirano, H. Higuchi, and H. Uchida, "An 8ns 256K BiCMOS RAM," ISSCC Dig. Tech. Papers, Feb. 1988, pp.184-185.

- [1-55] R. A. Kertis, D. D. Smith, and T. L. Bowman, "A 12ns 256K BiCMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1988, pp.186-187.

- [1-56] H. V. Tran, D. B. Scott, P. K. Fung, R. H. Havemann, R. E. Eklund, T. E. Ham, R. A. Haken, and A. Shah, "An 8ns Battery Back-Up Submicron BiCMOS 256K ECL SRAM," ISSCC Dig. Tech. Papers, Feb. 1988, pp.188-189.

- [1-57] M. Suzuki, S. Tachibana, A. Watanabe, S. Shukuri, H. Higuchi, T. Nagano, and K. Shimohigashi, "A 3.5ns, 500mW 16Kb BiCMOS ECL RAM," ISSCC Dig. Tech. Papers, Feb. 1989, pp.32-33.

- [1-58] H. Tran, K. fung, D. Bell, R. Chapman, M. Harward, T. Suzuki, R. Havemann, R. Eklund, R. Fleck, D. Le, C. Wei, N. Iyengar, M. Rodder, R. Haken, and D. Scott, "An 8ns BiCMOS 1Mb ECL SRAM with a Configurable Memory Array Size," ISSCC Dig. Tech. Papers, Feb. 1989, pp.36-37.

- [1-59] M. Matsui, H. Momose, N. Urakawa, Y. Urakawa, T. Maeda, A. Suzuki, K. Sato, K. Makita, J. Matsunaga, and K. Ochiai, "An 8ns 1Mb ECL BiCMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1989, pp.38-39.

- [1-60] Y. Maki, S. Kamata, , Y. Okajima, T. yamauchi, and H. Fukuma, "A 6.5ns 1Mb BiCMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1990, pp.136-137.

- [1-61] M. Takada, K. Nakamura, T. Takeshima, K. Furuta, T. Yamazaki, K. Imai, S.

Oh, Y. Fukuda, Y. Minato, and H. Kimoto, "A 5ns 1Mb ECL BiCMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1990, pp.138-139.

[1-62] H. Shimada, S. Kawashima, M. Matsumiya, N. Suzuki, K. Itabashi, K. Kazio, Y. Miyamoto, and M. Kagohashi, "A 10ns 4Mb BiCMOS TTL SRAM," ISSCC Dig. Tech. Papers, Feb. 1991, pp.52-53.

[1-63] Y. Okajima, Y. Sato, K. Kurosawa, and S. Yamada, "A 7ns 4Mb BiCMOS SRAM with A Parallel Testing Circuit," ISSCC Dig. Tech. Papers, Feb. 1991, pp.54-55.

[1-64] H. Kato, A. Suzuki, T. Hamano, T. Kobayahsi, K. Sato, T. Nakayama, H. Gojohbori, T. Maeda, K. Ochiai, "A 9ns 4Mb BiCMOS SRAM with 3.3V Operation," ISSCC Dig. Tech. Papers, Feb. 1992, pp.210-211.

[1-65] K. Nakamura, T. Oguri, T. Atsumo, M. Takada, A. Ikemoto, H. Suzuki, T. Nishigori, and T. Yamazaki, "A 6ns 4Mb ECL I/O BiCMOS SRAM with LV-TTL Mask Option," ISSCC Dig. Tech. Papers, Feb. 1992, pp.212-213.

[1-66] Y. Kohno, T. Wada, K. Anami, Y. Kawai, K. Yuzuriha, T. Matsukawa, and S. Kayano, "A 14-ns 1-Mbit CMOS SRAM with Variable Bit Organization," IEEE J. Solid-State Circuits, vol. SC-23, pp. 1060-1066, Oct. 1988.

[1-67] US patent, Tomohisa Wada, Kenji Anami, Shuji Murakami, "semiconductor memory device," No. 5280441, Jan. 18, 1994.

[1-68] Toru Shiomi, Tomohisa Wada et al., "A 5.8ns 256K BiCMOS TTL SRAM with T-Shaped Bit Line Architecture," IEEE J. Solid-State Circuits, vol. SC-28, pp. 1362-1369, Dec. 1993.

[1-69] S. Kayano, K. Ichinose, Y. Kohno, H. Shinohara, K. Anami, S. Murakami, T. Wada, Y. Kawai, and Y. Akasaka, "25-ns 256Kx1/64Kx4 CMOS SRAM's," IEEE J. Solid-State Circuits, vol. SC-21, pp. 686-691, Oct. 1986.

[1-70] Y. Kohno, T. Wada, K. Anami, Y. Kawai, K. Yuzuriha, T. Matsukawa, and S. Kayano, "A 14-ns 1-Mbit CMOS SRAM with Variable Bit Organization," IEEE J. Solid-State Circuits, vol. SC-23, pp. 1060-1066, Oct. 1988.

[1-71] T. Wada, T. Hirose, H. Shinohara, Y. Kawai, K. Yuzuriha, Y. Kohno, and S. Kayano, "A 34-ns 1-Mbit CMOS SRAM Using Triple Polysilicon," IEEE J. Solid-State

Circuits, vol. SC-22, pp.727-732, Oct 1987.

[1-72] T. Wada, S. Rajan, and S. A. Przybylski, " An Analytical Access Time Model for On-Chip Cache Memories," IEEE J. Solid-STATE Circuits, vol. SC-27, pp. 1147-1156, Aug. 1992.

[1-73] T. Wada, M. Eino, and K. Anami, "Simple Noise Model and Low-Noise Data-Output Buffer for Ultra High-Speed Memories," IEEE J. Solid-State Circuits, vol. SC-25, No. 6, pp.1586-1588, December 1990.

[1-74] S. Murakami, T. Wada, M. Eino, M. Ukita, Y. Nishimura, K. Suzuki, and K. Anami, "A New Soft-Error Phenomenon in ULSI SRAM's -Inverted Dependence of Soft-Error Rate on Cycle Time-," IEICE TRANSACTIONS, vol. E74, No. 4, April 1991.

## 第2章

### アーキテクチャによる高速化

## 2.1 はじめに

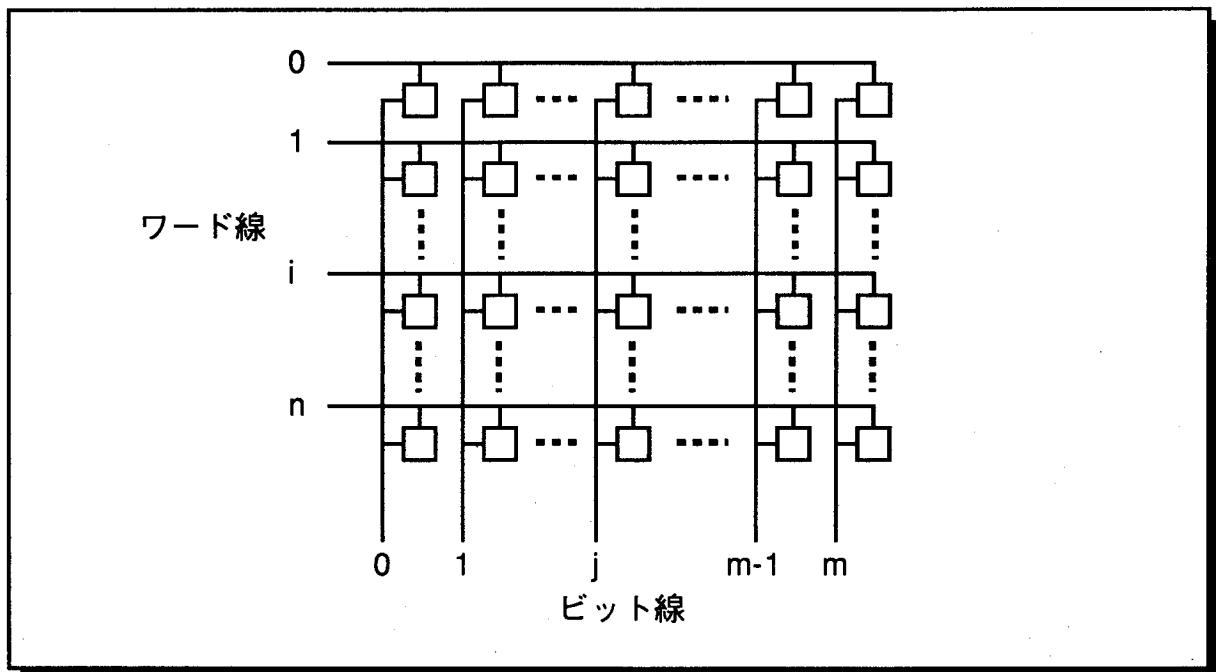

一般にSRAM、DRAMそしてRead Only メモリ（以後ROM）などの半導体メモリは図2-1-1に示されるように1ビットの情報を蓄えるメモリセルが2次元のアレイ状に配列され、行方向にはWord Line（ワード線）、列方向にはBit Line（ビット線）と呼ばれる複数の信号線がアレイ上で直交しており。i行目のワード線と、j列目のビット線を指定することで2次元アレイ中の $i$ 行 $j$ 列のメモリセルを指定することができる。

図2-1-1：半導体メモリの2次元のアレイ構成

データの読み出しのときには、この2次元のアレイ構成の中で1つのワード線を選択し、メモリセルのデータをビット線に伝達してそのビット線の信号をセンスアンプで増幅する。したがって、高速化のためにはワード線の高速な選択ならびにビット線におけるデータの高速なセンスが重要となる。

本章では上記ワード線、ビット線の構成すなわちアレイアーキテクチャによるSRAMの高速化について述べる。吉本らにより提案された分割ワード線構成(Divided Word Line)を進化させた変形分割ワード線構成(Modified Divided Word Line)を提案し、SRAMのワード線選択を高速化できることを示す。

次に、新しいビット線構成であるT字型ビット線構成(T-shaped Bit Line)を提案し、T字型ビット線構成が高速化および多ビット構成に適するアーキテクチャであることを示す。

## 2.2 変形分割ワード線構成

### 2.2.1 分割ワード線構成と変形分割ワード線構成

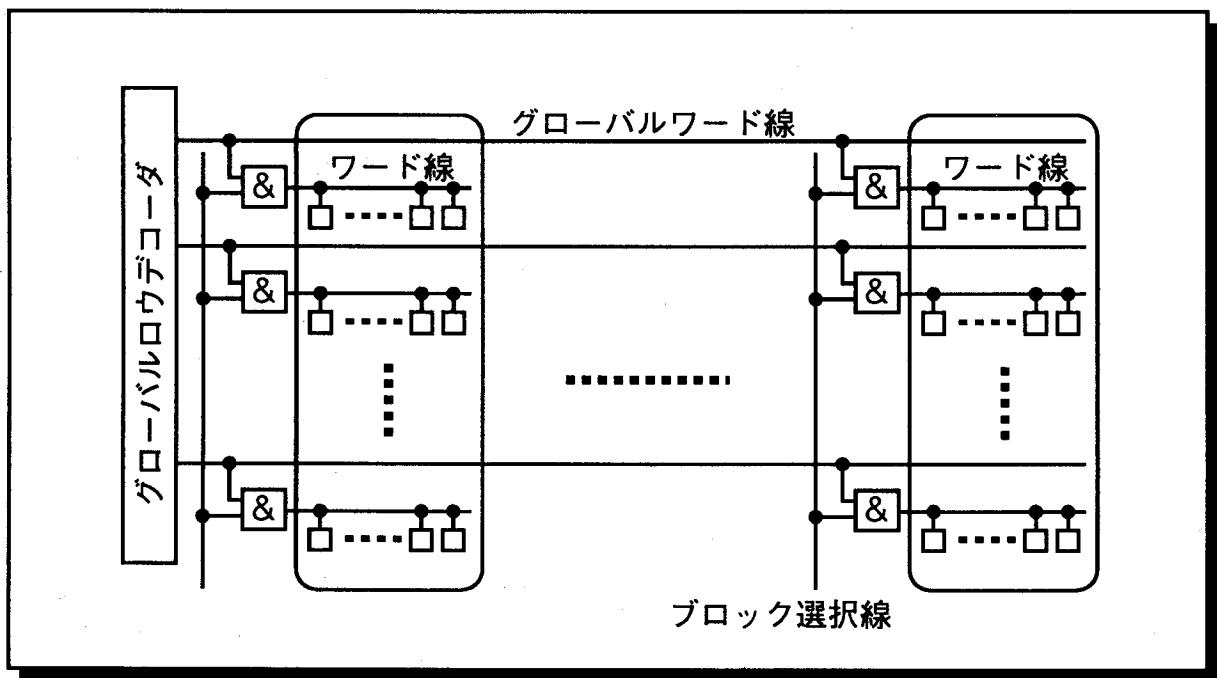

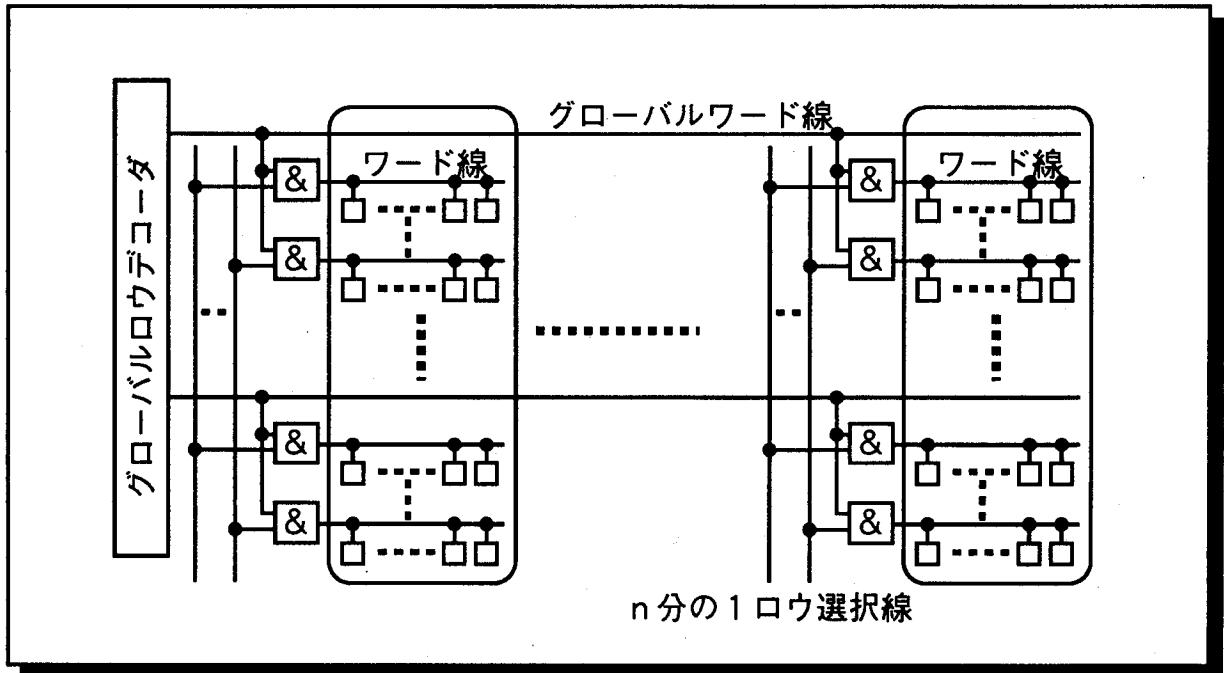

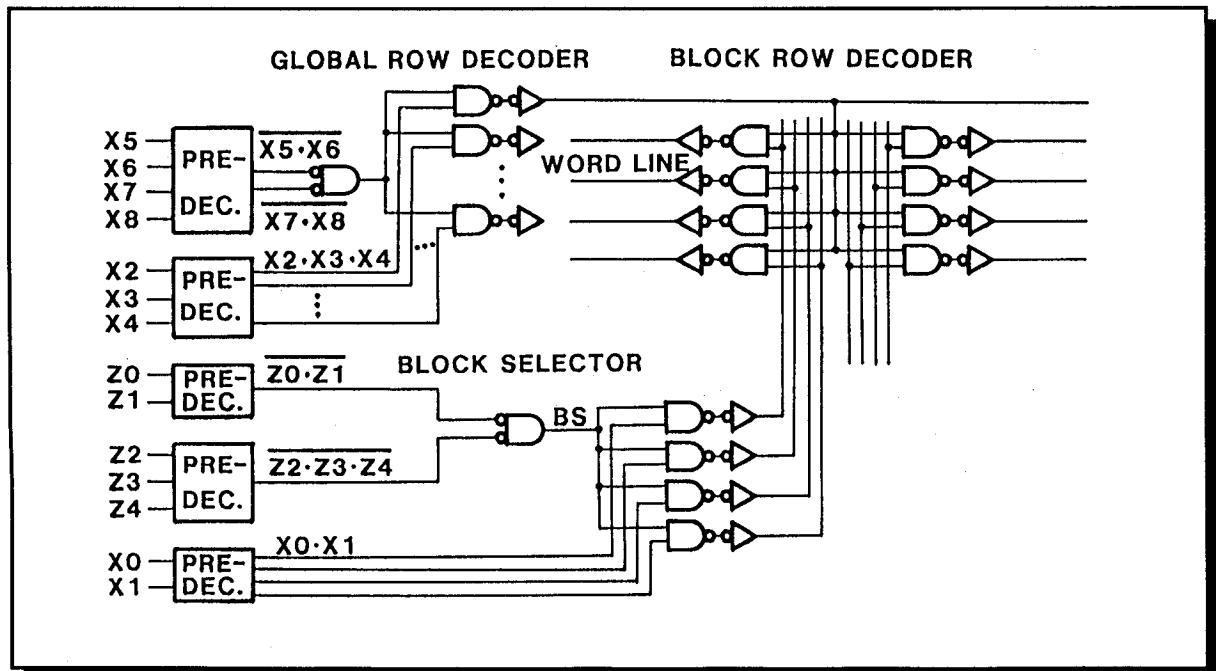

変形分割ワード線構成は吉本ら[2-1]による分割ワード線構成を改良したものである。図2-2-1は分割ワード線構成の概念図、図2-2-2は変形分割ワード線構成の概念図である。両者ともメモリアレイがブロック分割されているSRAMのワード線の選択方法であり、ワード線は水平方向に走るグローバルワード線と垂直方向に走るブロック選択線（分割ワード線構成の場合）、 $n$ 分の1口ウ選択線（変形分割ワード線構成の場合）により選択される。

図2-2-1：分割ワード線構成の概念図

分割ワード線構成の場合、グローバルワード線はブロック分割数と等しい数のゲートに入力される、またブロック選択線は1ブロック中のワード線数と等しい数のゲートに入力される。一般的に1ブロック中のワード線数はブロック分割数より数倍のオーダで大きいので、ブロック選択線の負荷容量は大きくなりブロック選択線の選択スピードが遅くなる。変形分割ワード線はこの問題を解決するものである。ブロック選択線を多重化し、ブロック選択線の負荷容量を分割する。このとき、グローバルワード線はこの多重度の大きさの行グループ( $n_R$ )を同時に選択することになり、グローバルワード線の負荷容量は $n_R$ と共に上昇する。ワード線の選択はグローバルワード線とブロック選択線もしくは $n$ 分の1口ウ選択線の論理積であるので、遅い方の選択信号により決定される。したがって、変形分割ワード線構成ではパラーメータ $n_R$ を最適化することでグローバルワード線と $n$ 分の1口ウ選択線のスピードを均等化し、ワード線選択を高速化すること

ができる。

図2-2-2：変形分割ワード線構成の概念図

## 2.2.2 適用例および結果

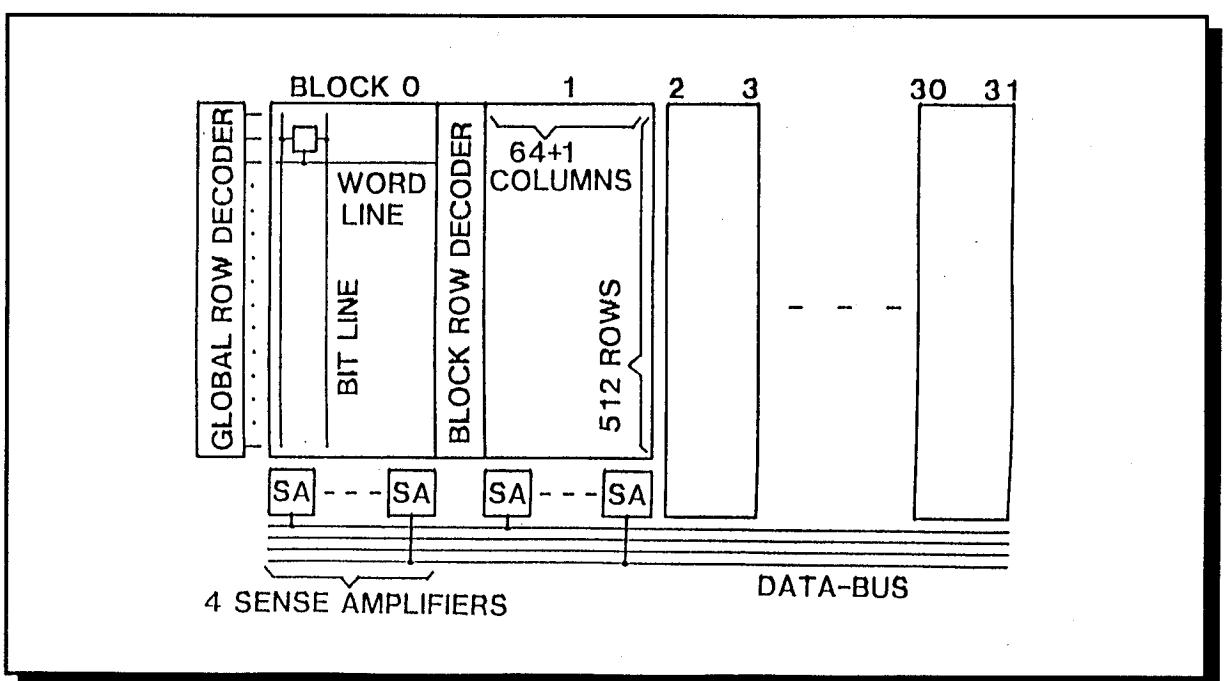

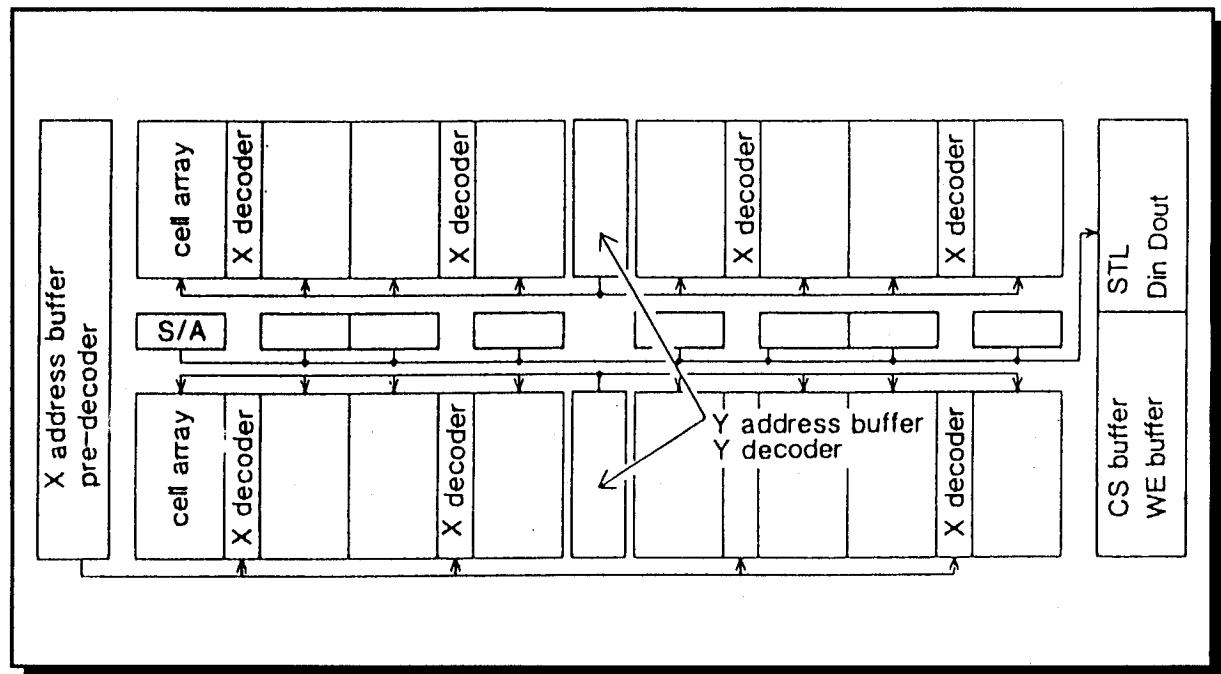

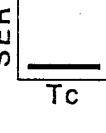

図2-2-3は変形分割ワード線構成が適用された1MSRAM[2-2]のメモリアレイのブロック分割を示した図である。

図2-2-3：変形分割ワード線構成が適用された1MSRAM[2-2]のメモリアレイ図

1Mビットのメモリセルアレイは512行×2048列からなり、32のブロックに分割されている。消費電力低減のために32の内1つのメモリブロックのみが活性化される。各メモリブロックは512行と1列の冗長メモリセル列を含む65列からなり65のメモリセルが1本のワード線に接続されている。ワード線はタンゲステンシリサイド化されたポリシリコンで形成されており、シート抵抗は約5オーム/□である。この低抵抗かつ低容量ワード線が高速化の一つの要因であり、ワード線のC R遅延を0.5nsに短縮している。各メモリブロックは256Kワード×4ビット構成に対応するために、さらに4つのサブブロックに分割されている。行選択信号は変形分割ワード線構成により階層的にデコードされており、各2ブロックごとに配置されたブロックロウデコーダとチップ左端に配置されたグローバルロウデコーダによりワード線デコードが行なわれる。

図2-2-4はワード線の選択方法を示すデコード回路である。X0-X8およびZ0-Z4はそれぞれ行選択とブロック選択のためのアドレス信号である。Xアドレスの上位X2-X8はグローバルロウデコーダにてプリデコードされ、複数のグローバルワード線の中の1本を選択する。この1MSRAMでは行グループ数 $n_R$ は4で最適化されており、グローバルワード線は各ブロックロウデコーダの8個のNANDゲートに入力される。1本のグローバルワード線に対応する行グループ数×ブロック分割数のワード線の内の1本は図2-2-4に示されるようにZアドレスによるブロック選択信号とXアドレスの残りの下位X0-X1のプリデコード信号により選択される。

図2-2-4：ワード線の選択方法を示すデコード回路

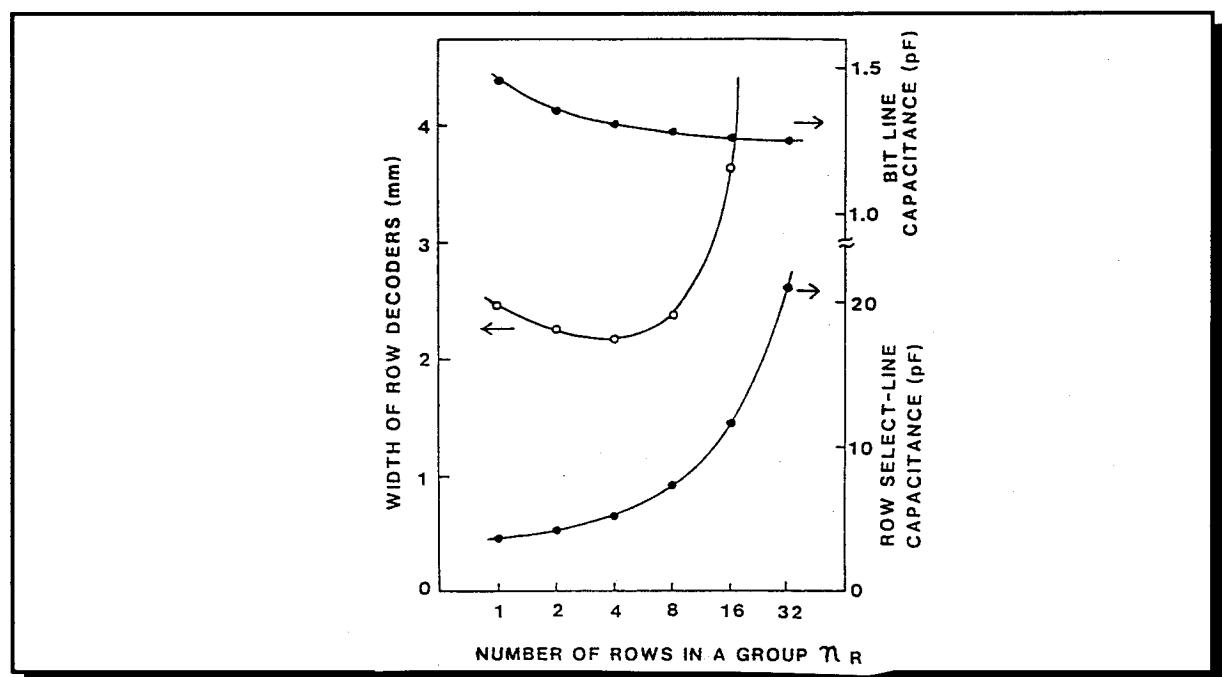

図2-2-5はビット線を1層目、グローバルワード線を2層目の金属配線で形成した場合の変形分割ワード線構成の効果を示した図である。X軸は行グループの大きさ $n_R$ で1が通常の分割ワード線構成に対応する。 $n_R$ が増加するごとに、グローバルワード線との

クロスオーバー容量が減るのでビット線容量が減少し、高速化に有利となる。同時に、グローバルロウデコーダの面積は減少し、ブロックロウデコーダの面積は増加しチップサイズを最小化する最適点が存在する。最適ポイントは設計ルールやメモリ容量で変化するが、この1MSRAMでは最適値が4となっている。水平方向に走るグローバルワード線の容量は増加するが、垂直方向の  $n$  分の1ロウ選択線の容量は減少し、 $n_R$  を変えることで信号線の容量配分を均衡化し速度性能を最適化することが可能となる。結果的にこの1MSRAMの標準アクセス時間14nsの50%即ち7nsの高速なワード線選択時間を実現した。

図2-2-5：変形分割ワード線構成の効果

## 2.3 T字型ビット線構成

### 2.3.1 通常ビット線構成とT字型ビット線構成

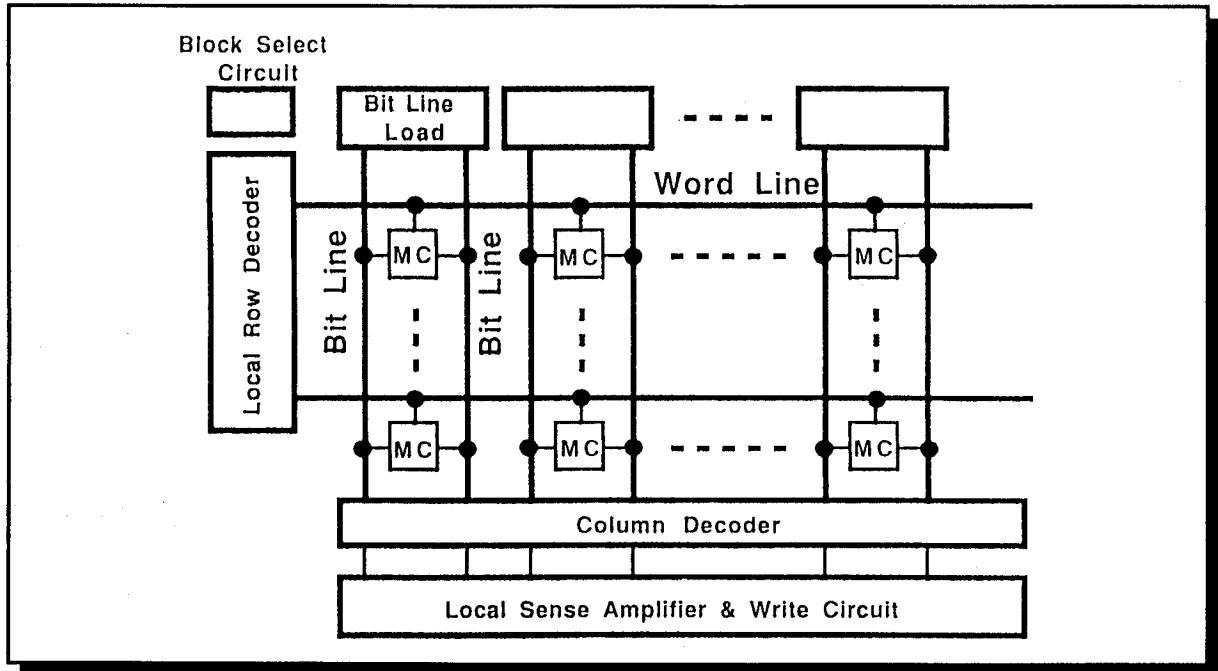

図2-3-1は通常のビット線構成を示す図である。図中、ローカルロウデコーダはメモリセルアレイの左端に配置され、ビット線負荷、カラムデコーダ、ローカルセンスアンプおよび書き込み回路はメモリセルアレイの上下に配置されている。通常、SRAMの標準パッケージは幅が狭いので、このようなメモリセルアレイの上下に多数の回路を配置する方法はチップの幅を増加させ、標準パッケージに適さない。

図2-3-1：通常のビット線構成図

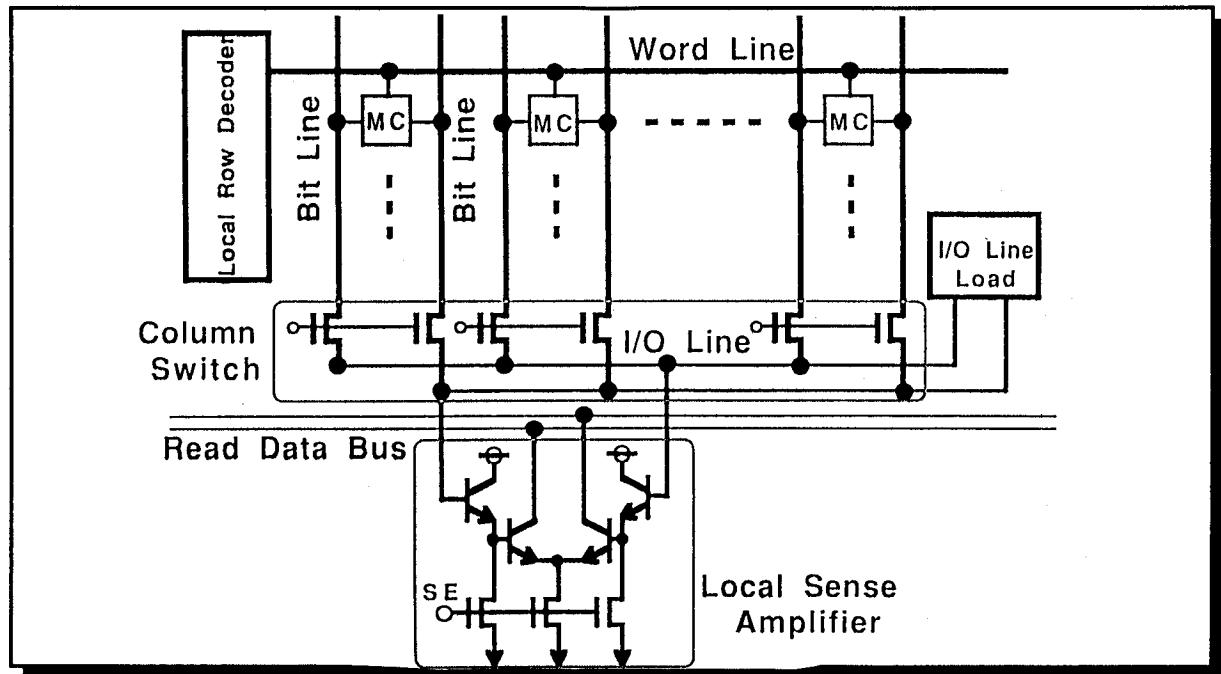

また、Tranら[2-3]や鈴木ら[2-4]によって報告されているように、高速のデータセンスのためには各カラム（ビット線対）ごとにバイポーラトランジスタを設けるダイレクトカラムセンシングが有効であるが、通常ビット線ピッチが小さいことによる面積的制限によりダイレクトカラムセンシングを実現するのは困難であり、通常図2-3-2に示されるようにカラムスイッチを用いて複数のカラムスペースを用いてバイポーラセンスアンプを配置する方法がとられている。この方法では、I/O線の容量の増加とカラムスイッチが直列に挿入されているので、センス時間が増加する問題があり、また複数のカラムごとにセンスアンプが1つしか配置されないので非常に大きな数のI/O、多数のセンスアンプが同時に動作するSRAMを構成するのには適さない。

新しく提案したT字型ビット線構成[2-5]は通常直線であるビット線をT字型にして、（1）幅の狭い標準パッケージに合うアレイ構成、（2）高速なデータセンスを実現するためのダイレクトカラムセンシングが実現可能なアレイ構成、を実現することを目的

としている。

図2-3-2：通常のバイポーラセンスアンプ配置方法

図2-3-3：T字型ビット線構成

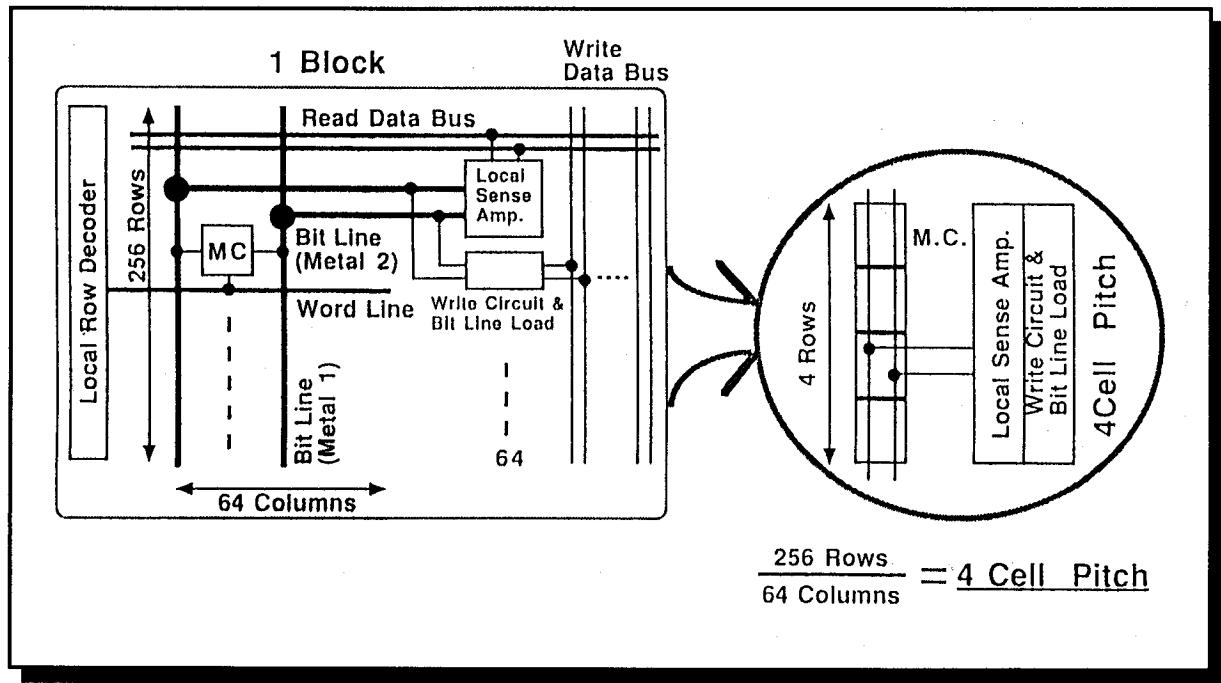

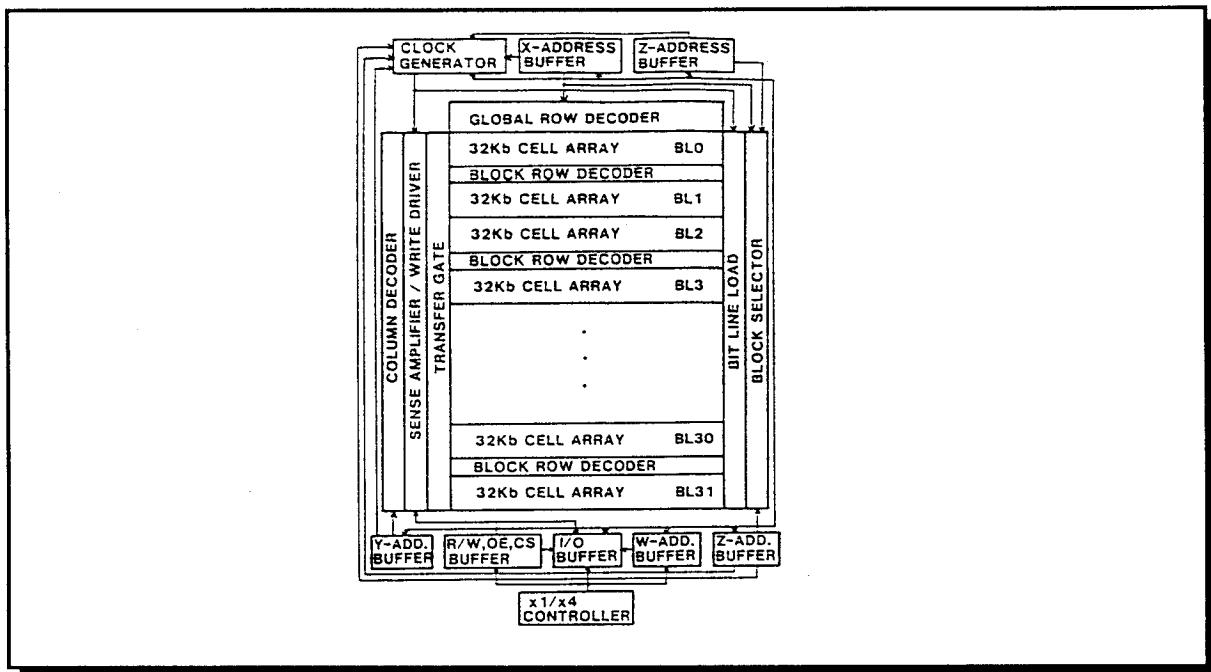

図2-3-3はT字型ビット線構成を示す図である。この方式では、ビット線は接続されたメタル1とメタル2からなっておりワード線とメタル2のビット線は並行に置かれている。カラムピッチはT字型ビット線構成によって1ブロックのカラム数とロウ数の比で緩和され、カラムピッチを広げることができる。この図はT字型ビット線構成が適用さ

れた256K BiCMOS TTL SRAM[2-6]の例であり、1ブロックは256口ウ／64カラムで構成されているので、メタル2のビット線は4口ウごとにメタル1のビット線に接続されている。このように、T字型ビット線構成はカラムピッチを緩和し各カラムごとにセンスアンプを配置するダイレクトセンシングを可能とする。

### 2.3.2 適用例および結果

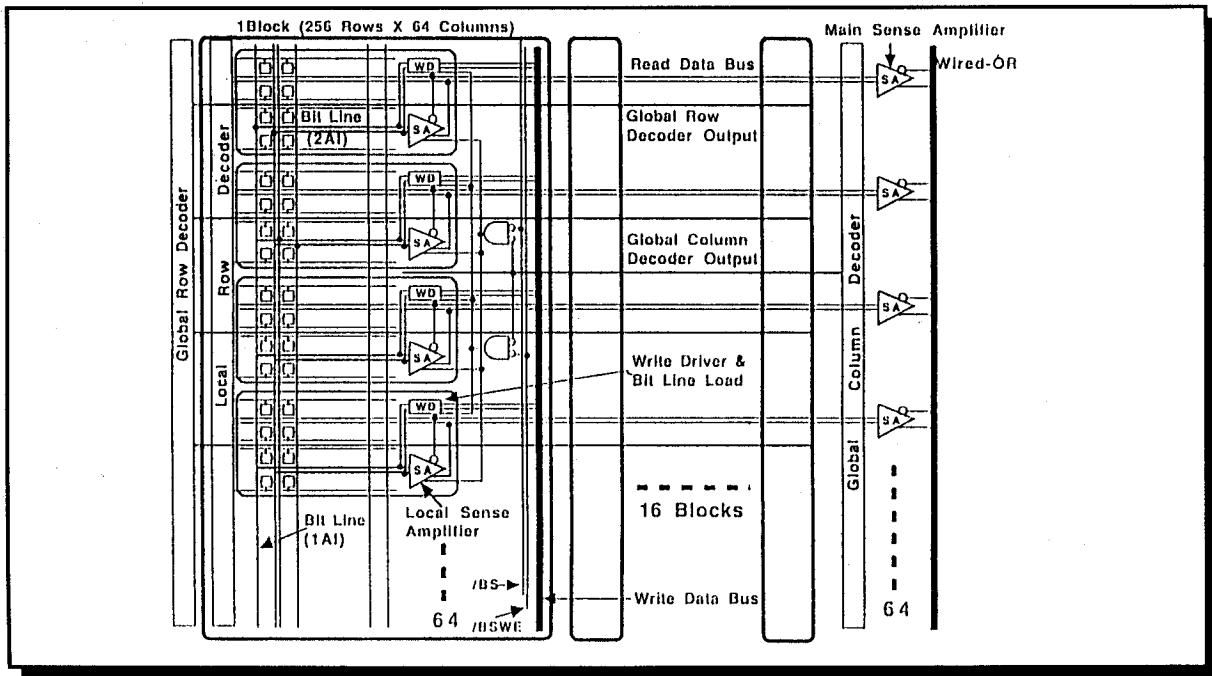

図2-3-4は256K BiCMOS TTL SRAMで使用された変形分割ワード線構成とT字型ビット線構成を組み合わせたメモリアレイの構成を示した図である。各ブロックに配置されたローカルセンスアンプの出力はワイヤードORでリードデータバスに接続されており、チップ端に配置されたメインセンスアンプに入力されている。トータル64組のリードデータバスがメモリアレイ上に配置されており、64ビットという大きい幅のデータをリードデータバス専用の面積を設けることなしに一度に取り出すことが可能である。したがって、T字型ビット線構成は高性能ワークステーション等に用いられるI/O数の大きなキャッシュメモリを実現するのに適している。

図2-3-4：256K BiCMOS TTL SRAMのメモリアレイの構成

この例では4ビットのI/O構成なので、64ビット中の4ビットをカラムデコーダ出力により選択する必要がある。したがって隣接した4つのローカルセンスアンプはひとつのカラムデコーダ出力でコントロールされており、カラムデコーダ出力は16行おきにメモリアレイ上に配線される。結果的に、メモリアレイの一端にグローバルロウデコーダを配置し、もう一端にグローバルカラムデコーダを配置する対称性のよいチップレイアウトが可能となる。また従来各メモリブロックごとに重複して配置する必要があったカラムデコーダが1箇所に配置されるのでチップサイズを低減することができる。グ

ローバルロウデコーダ出力線、グローバルカラムデコーダ出力線、リードデータバス線およびメタル2のビット線はすべてメタル2で形成することができ、すべてメモリアレイ上を並行して走るのでチップサイズを大きくすることではなく、高密度なメモリセルアレイを実現できる。

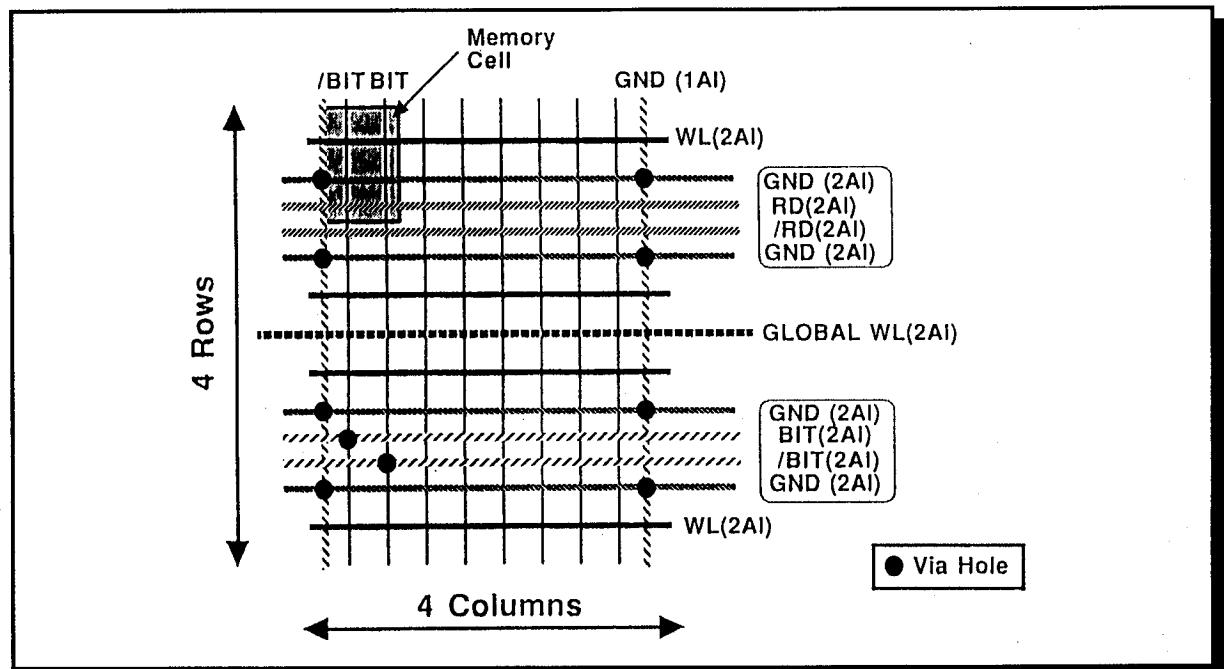

図2-3-5：4行4列分のメモリアレイ上の配線図

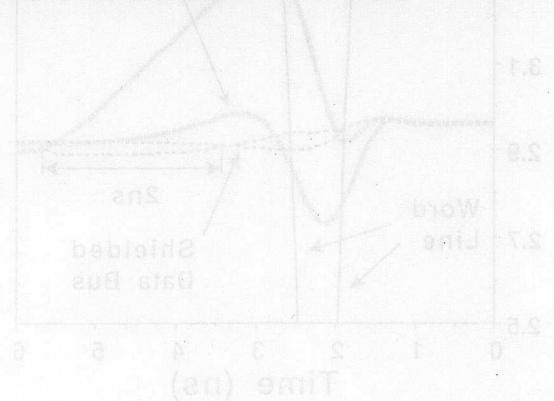

図2-3-6：シールド配線の有り／無しの回路シミュレーションでの比較

図2-3-5は4行4列分のメモリアレイ上の配線を示した図である。T字型ビット線構成

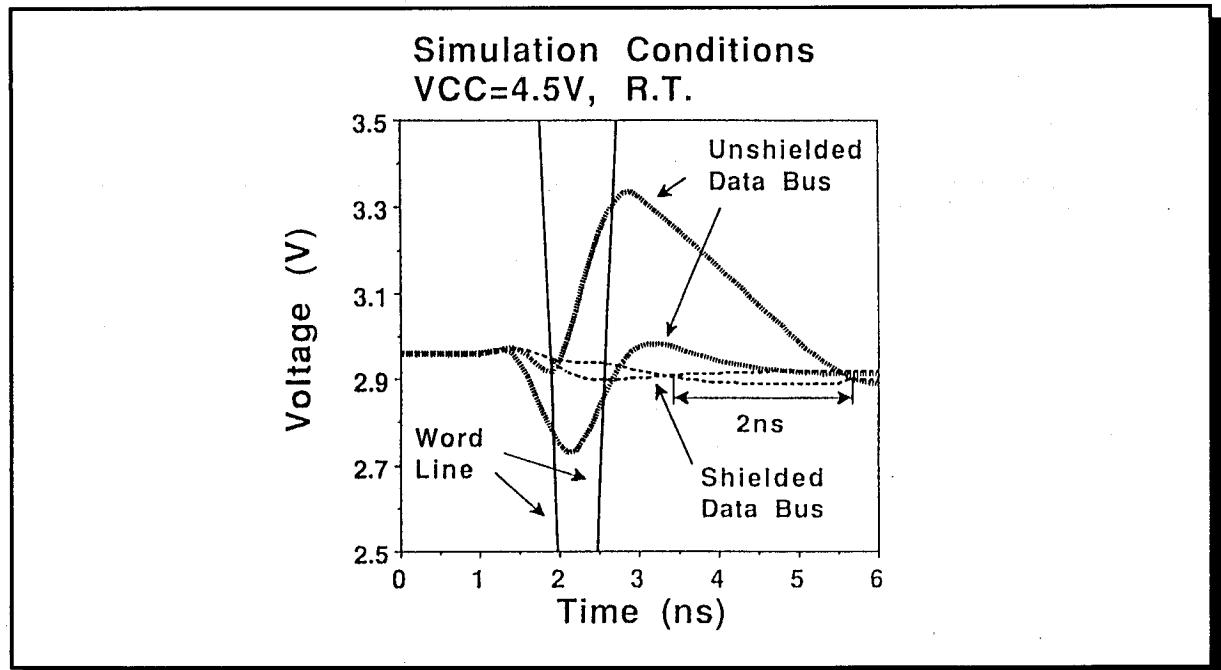

では、小振幅動作するビット線やリードデータバス線が大振幅で動作するグローバルワード線（グローバルロウデコーダ出力）、グローバルカラムデコーダ出力線と平行して走るので、小振幅信号が大振幅信号からのカップリングノイズを受けることによる誤動作に対策をする必要がある。そのカップリングの問題は図2-3-5に示すように小振幅信号線と大振幅信号線の間に低インピーダンスの固定レベルの線（シールド配線）を挿入することで解決することができる。図2-3-6はこのシールド配線の有り／無しを回路ミュレーションで比較した結果であり、2nsのアクセスタイムを短縮することができた。

図2-3-7はT字型ビット線構成を適用した256K BiCMOS TTL SRAMのチップ写真であり長辺側には入力バッファとブロック選択回路のみが配置されている。チップ短辺が短縮され、 $4.28 \times 11.05 = 47.3\text{mm}^2$ が実現された。

図2-3-7：256K BiCMOS TTL SRAMのチップ写真

図2-3-8：SRAMのシミュレーション結果。SRAMのアクセスタイム：2ns

図2-3-8はSRAMのシミュレーション結果である。図2-3-5で示した値の上にT字型構成を適用した結果である。図2-3-6で示したシールド配線の有り／無しによる比較結果である。

## 2.4 結論

本章ではワード線、ビット線の構成すなわちアレイアーキテクチャによるSRAMの高速化について述べた。

- (1) ワード線選択の高速化の手法として、吉本らにより提案された分割ワード線構成を発展させた変形分割ワード線構成を考案した。

- (2) 変形分割ワード線構成はチップサイズ、ビット線容量のトレードオフを最適化し、信号線容量配分を均衡化し速度性能を最適化することが可能であることを示した。

- (3) 変形分割ワード線構成はメモリセルアレイ上を走るグローバルワード線の本数を減らすので、ビット線容量を減らし、またデコーダ面積を最小化できることを示した。

- (4) 新しいビット線構成であるT字型ビット線構成を考案した。

- (5) T字型ビット線構成は通常メモリアレイの上下に配置されるセンスアンプ／ビット線負荷回路をメモリアレイの左右に配置することを可能とし、標準SRAMで通常用いられてる幅の狭いパッケージに適したチップ構成を実現することを示した。

- (6) T字型ビット線構成はカラムピッチを緩和し各カラムごとにセンスアンプを配置するダイレクトセンシングを可能とし、高速化に適したビット線アーキテクチャであることを示した。

- (7) T字型ビット線構成は64ビット程度の大きなデータ幅を1つのメモリブロックから取り出すことを可能とし、キャッシュメモリなどのI/O数の大きいメモリに適することを示した。

- (8) T字型ビット線構成は各メモリブロックごとに重複して配置する必要があったカラムデコーダの1箇所配置を可能とし、チップサイズを低減することができることを示した。

- (9) T字型ビット線構成は分割ワード線構成や変形分割ワード線構成との整合性が良く、グローバルロウデコーダ出力線、グローバルカラムデコーダ出力線、リードデータバス線およびメタル2のビット線はすべてメタル2で形成することができ、すべてメモリアレイ上を並行して走るのでチップサイズを大きくすることなく、高密度なメモリセルアレイを実現できることを示した。

(10) (9) で発生する小振幅信号の大振幅信号からのカップリングノイズによる誤動作は小振幅信号線と大振幅信号線の間に低インピーダンスの固定レベルの線（シルード配線）を挿入することで解決することができることを示した。

## 2.5 参考文献

[2-1] M. Yoshimoto et al., "A divided word-line structure in the static RAM and its application to a 64K full CMOS SRAM," IEEE J. Solid-State Circuits, vol. SC-18, pp. 479-485, Oct. 1983.

[2-2] Yoshio Kohno, Tomohisa Wada, Kenji Anami, Yuji Kawai, Kojiro Yuzuriha, Takayuki, Matsukawa, and Shimpei Kayano, "A 14-ns 1-Mbit CMOS SRAM with Variable Bit Organization," IEEE J. Solid-State Circuits, vol. SC-23, pp. 1060-1066, Oct. 1988.

[2-3] H. V. Tran et al., "An 8-ns 256K ECL SRAM with CMOS memory array and battery backup capability," IEEE J. Solid-State Circuits, vol. SC-23, pp. 1041-1047, Oct. 1988.

[2-4] M. Suzuki et al., "A 3.5-ns, 500-mW 16K-bit BiCMOS ECL SRAM," IEEE J. Solid-State Circuits, vol. SC-24, pp. 1233-1237, Oct., 1989.

[2-5] US patent, Tomohisa Wada, Kenji Anami, Shuji Murakami, "semiconductor memory device," No. 5280441, Jan. 18, 1994.

[2-6] Toru Shiomi, Tomohisa Wada et al., "A 5.8ns 256K BiCMOS TTL SRAM with T-Shaped Bit Line Architecture," IEEE J. Solid-State Circuits, vol. SC-28, pp. 1362-1369, Dec. 1993.

## 第3章

### 回路技術面からの高速化

### 3.1 はじめに

アクセスタイムは大きく分類して（1）ワード線の選択時間、（2）ビット線対がセンス可能な電位差になる時間、（3）ビット線対のデータを増幅しデータバスを介してデータを出力バッファに転送する時間、そして（4）出力バッファがチップ外部容量を駆動する時間に分れる。

本章ではまず最初にHardeeらのアドレス入力信号の変化を感知し同期パルスを発生し、そのパルスを用いて（2）ビット線対がセンス可能な電位差になる時間を短縮する、ATD方式(Address Transition Detection)を用いた高速化の概要を説明する。次にATDを用いた高速化の第2の方法として、（3）ビット線対のデータを増幅しデータバスを介してデータを出力バッファに転送する時間を短縮する、著者らが考案したATDを用いたデータバスプリチャージ方式、デュアルレベルデータバスプリチャージ方式を示し、本方式によるチップ内部のデータバスの高速化の方法を示す。そしてATDを用いた高速化の第3の方法として、（4）出力バッファがチップ外部容量を駆動する時間を短縮する、著者らが考案したATDを用いたデータ出力プリセット方式を説明し、高速化の問題のひとつであるノイズを低減しながらかつ高速化を実現する方法を示す。

### 3.2 ATD方式の概要

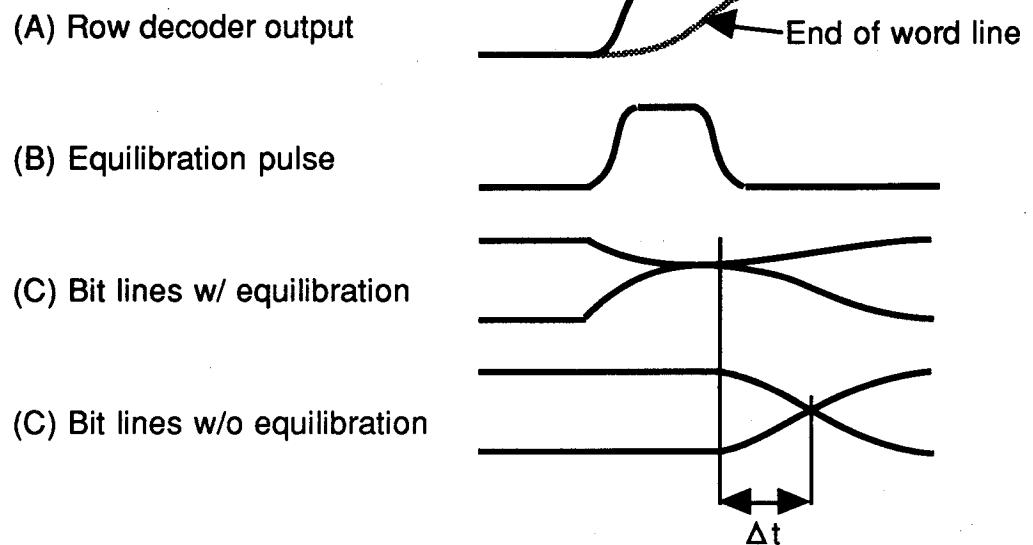

ATD方式はHardeeらの論文[3-1]により初めて紹介された方式であり、現在SRAMの高速化や低消費電力化のために広く使用されている技術である。HardeeらのSRAMは1層の金属配線と2層のポリシリコン配線を使用していた。当時まだポリシリコン層の低抵抗化は一般的ではなく、ポリシリコンの典型的な抵抗値は $15-30\Omega$ と高く、ポリシリコンで形成されたワード線の遅延時間は大きな問題で、SRAMのアクセスタイムを制限していた。図3-2-1はATDを用いてこの問題を解決する方法を示した図である。

ワード線の容量は非常に大きいのでRC時定数が図3-2-1(A)に示すように、ワード線の両端に大きな遅延時間が発生する。このワード線遅延時間の間に、ビット線対をショートし等電位とし、ビット線対を以前の状態から新しい状態に遷移させていく、イコライズ状態から新状態に遷移させる。図3-2-1(C)と(D)に示すように、ビット線対が新しい状態に遷移する時間を $\Delta t$ 分短縮することが可能である。この $\Delta t$ はこのSRAMではアクセスタイムの30%以上を占めていた。

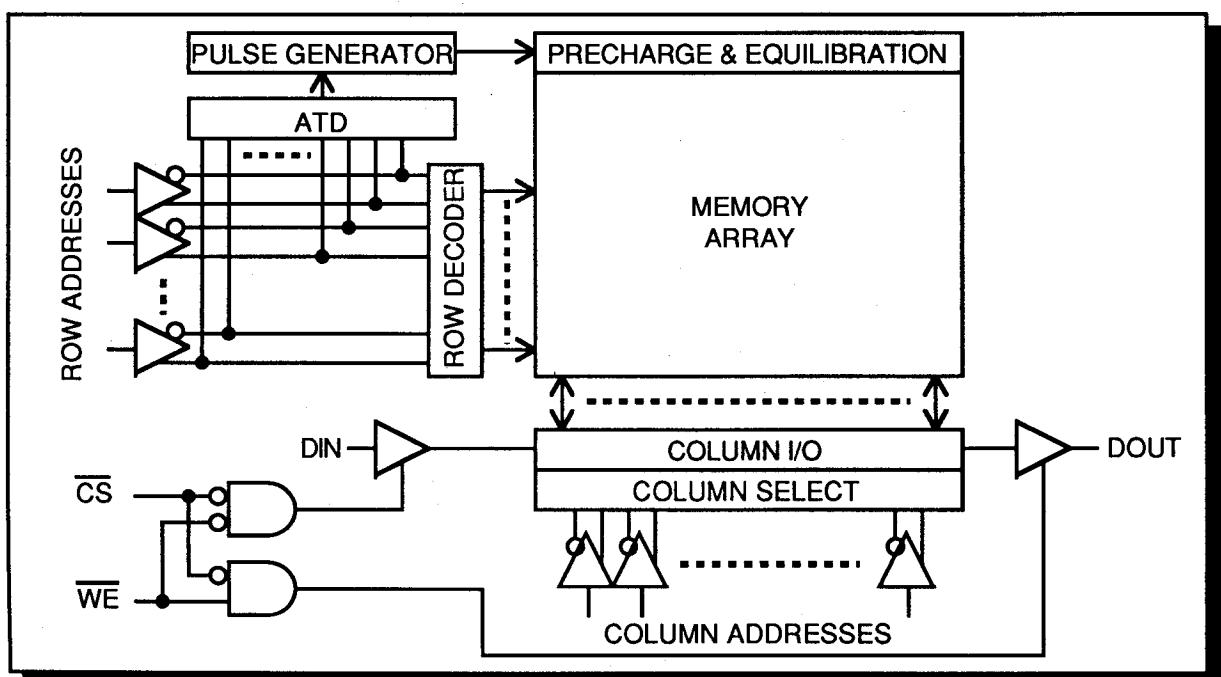

図3-2-2はこのATD方式を用いるSRAMのブロックダイアグラムである。すべてのロウアドレス入力線(A0-7)はロウデコーダを駆動するだけでなく、ATD回路に入力されている。任意のロウアドレス入力の遷移がATD回路で検出され、パルス発生回路にトリガを与える。パルス発生回路はセルフタイムのパルスを発生し、ビット線対をイコライズするイコライズ回路を駆動しその後ビット線対のイコライズをやめる。

図3-2-1：ATDによる高速化方法

図3-2-2：ATD方式を用いるSRAMのブロックダイアグラム

### 3.3 データバスプリチャージによる高速化

#### 3.3.1 データバスプリチャージ

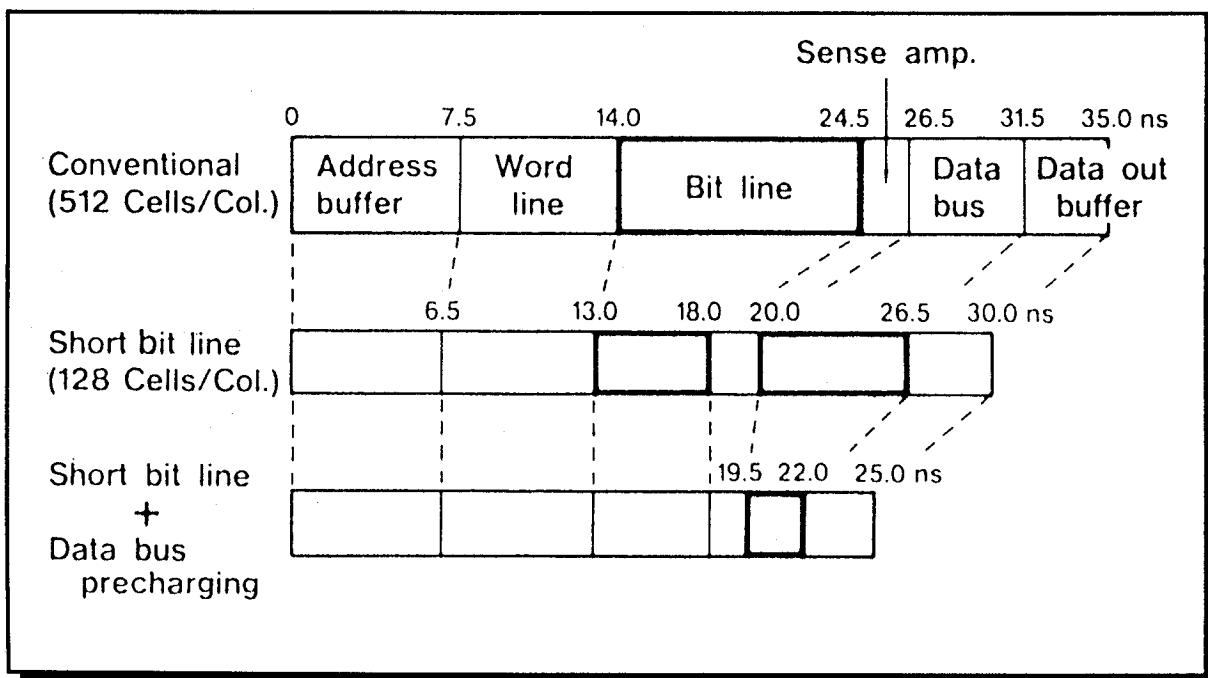

Hardeeらはワード線のRC遅延の間にビット線対をATDを用いて平衡状態にすることで高速化を実現したが、ワード線を構成するポリシリコンのポリサイド化による低抵抗化や多層の金属配線でのシャントによりワード線の遅延時間が短縮されたSRAMでは、Hardeeらの方法は高速化に大きなインパクトがなくなった。

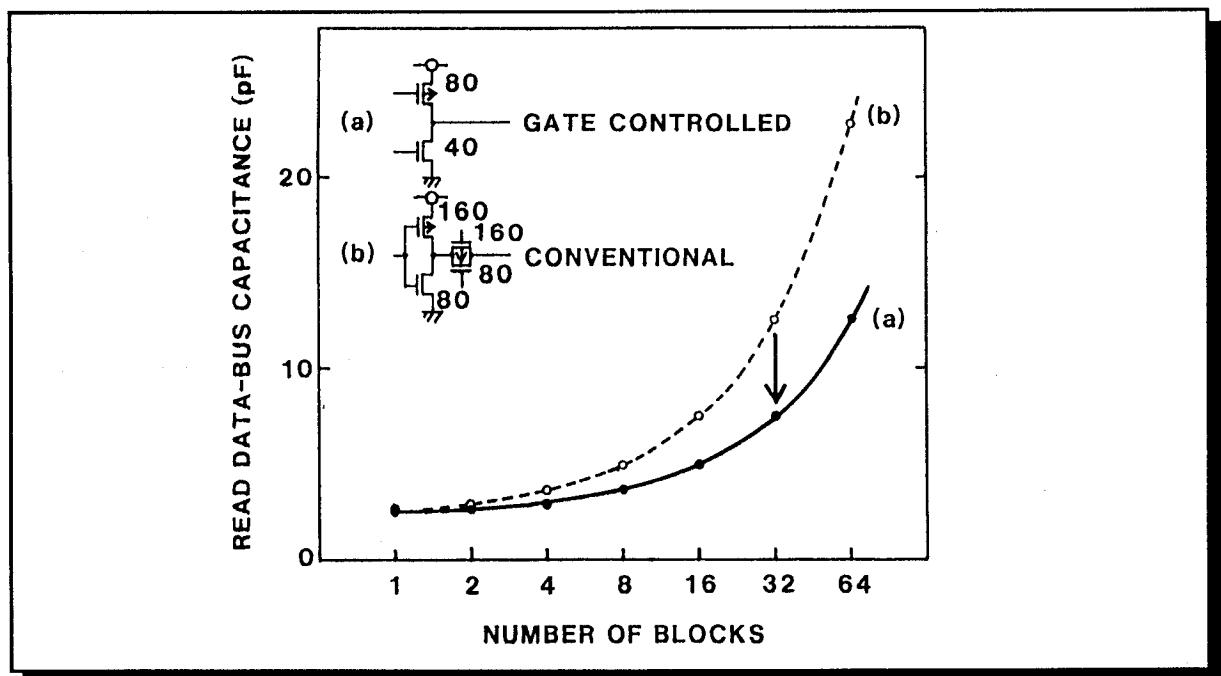

図3-3-1：256K SRAMのブロックダイアグラム

図3-3-1は著者らによる256K SRAMのブロックダイアグラムである[3-2]。このようにメモリセルアレイが多ブロック分割（この場合16ブロック）された場合、各ブロック間を結ぶデータバス線が長くなり同時に容量が大きくなる。著者らが考案したデータバスプリチャージ[3-2]、[3-4]はこのように多ブロック分割され遅延時間が増大したSRAMのデータバス遅延を低減する方法であり、Hardeeらの方法とは異なる高速化を目的とするATDパルスの使用方法である。

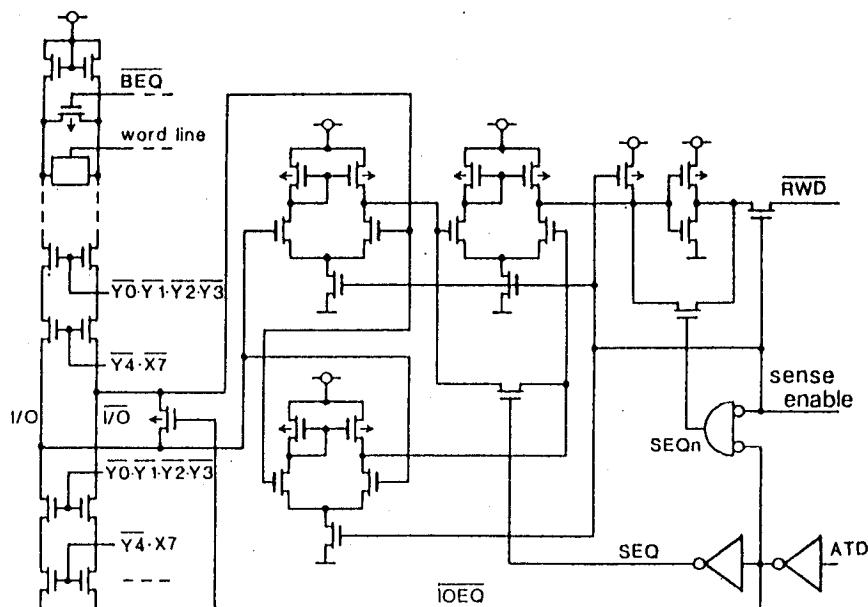

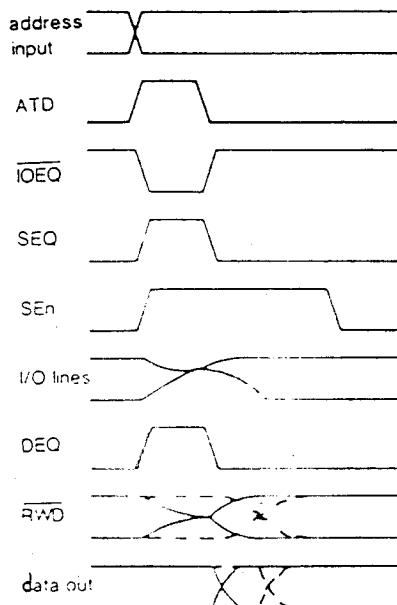

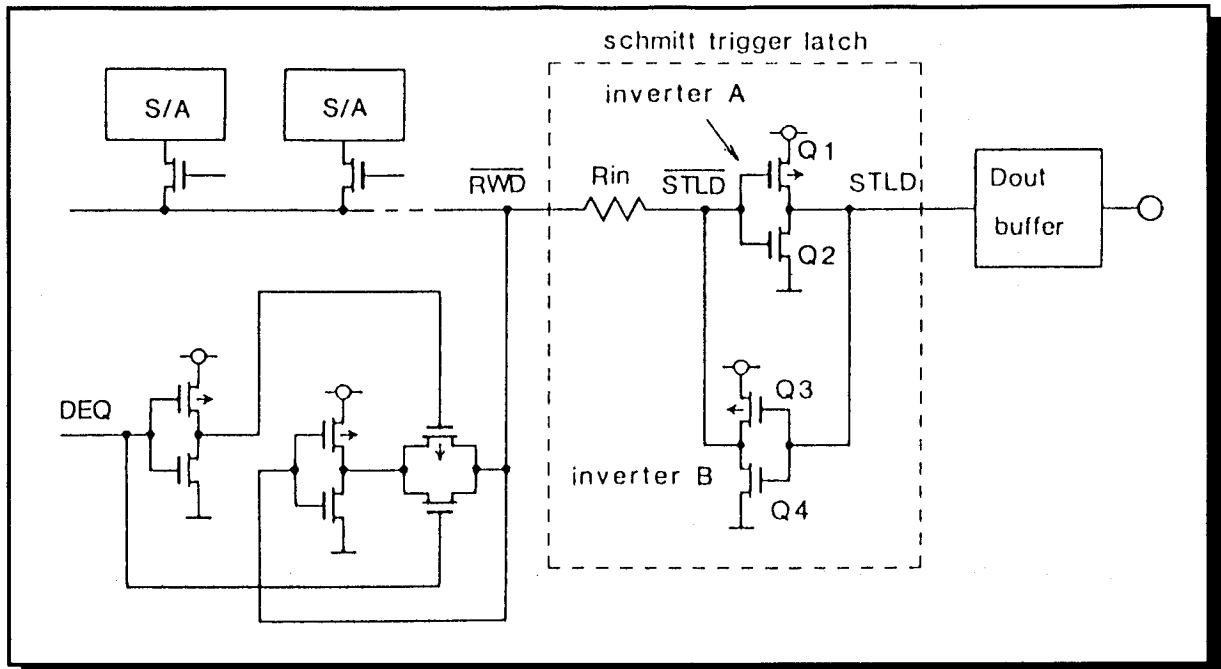

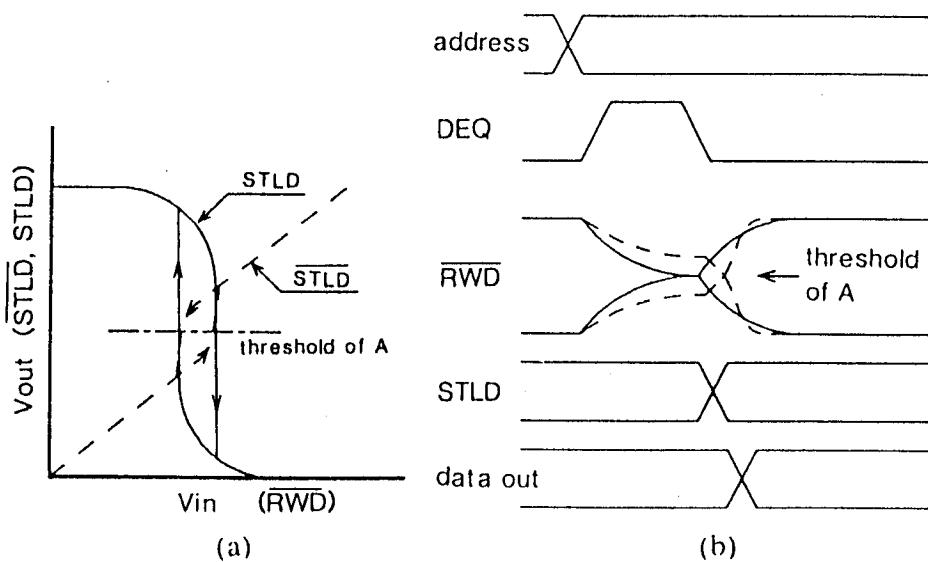

図3-3-2はこの256K SRAMのセンス系の回路図であり、図3-3-3はセンス系のタイミングダイアグラムであり、図3-3-4はデータバスプリチャージ回路とシュミットトリガラッチ回路である。アドレス入力の遷移を検出してATDパルスが発生する。図3-3-3に示すように、ATDパルスからIOEQ(I/O line equalize), SEQ(Sense amp equalize), SEn(nth-Sense amp enable)そしてDEQ(Data bus equalize)などのパルスが生成される。BEQ(Bit line equalize)はビット線対のイコライズをするものでHardeeらの方法と同じであるが、SEQnそしてDEQはデータバスを電源/GNDの中間電位にプリチャージするものである。データバスRWD(Read write data bus)の中間電位プリチャージはシュミットトリガラッチ(STL)回路と組み合わされデータバスの遅延時間を最小化している。図3-3-3でRWDとdata outの実線と破線がデータバスプリチャージあり／無しの場合の波形をそれぞれ示している。

図3-3-2: 256K SRAMのセンス系の回路図

図3-3-3: センス系のタイミングダイアグラム

DEQおよびSEQnがHigh状態のときCMOSインバータの入出力は短絡されデータバスRWDはそのCMOSインバータの論理しきい値電圧すなわち中間電位にプリチャージされている。そしてDEQおよびSEQnがLowになった後、データがデータバスを転送される。しかし、データバスが中間プリチャージ状態の時に以前の読み出しデータがoutput data outに保持される必要がある。これを満足するためにSTL回路が出力バッファ直前に設けられている。STLは以前のデータを保持するので、データバスが中間プリチャージ

ジ状態の時でもdata outに以前のデータを出力させる。

図3-3-4：データバスプリチャージ回路とシュミットトリガラッチ回路

STL回路はクロスカップルに接続されたインバータとポリサイドで形成された抵抗により構成されている。図3-3-5(a)と(b)はSTLの入出力特性とタイミングダイアグラムを示したものである。ノードSTLDは絶えずインバータBによってプルアップもしくはプロダウントされており、そのレベルは入力抵抗RinとトランジスタQ3とQ4の抵抗比で決定される。ここでは、データバスRWDが中間状態にプリチャージされてもSTLDがインバータAの論理しきい値（データバスの中間プリチャージレベルに等しい）に到達しないように設定されている。

DEQおよびSEQnがLowに遷移した後、STLDはRWDに追随して動き、インバータAの論理しきい値を横切り、その後STLDが変化する。入力抵抗の電位差は400mVと設定しているので、RWDの400mVの変化でSTLを反転させることができる。また、データバスのプリチャージレベルを決めているのは図3-3-2のセンスアンプの最終段のCMOSインバータと図3-3-4のDEQによりコントロールされるCMOSインバータであり、STLのしきい値もCMOSインバータで決定されており、同一のチャネル幅比Wp/Wnをこれら3ヶのCMOSインバータで使用することでプロセス変動などによるデバイスパラメータの変動に対して、データバスプリチャージレベルとSTLのしきい値の関係は常に保証される。図3-3-6はアクセス時間の比較をしたもので、この256KSRAMではデータバスプリチャージによりデータバスでの遅延時間を6.5nsから2.5nsに4.0ns短縮し、13%以上のアクセスタイムの短縮を実現した。

図3-3-5：STLの入出力特性とタイミングダイアグラム

図3-3-6：アクセス時間の比較

### 3.3.2 デュアレベルデータバスプリチャージ

上記データバスプリチャージはATDを用いて、データバス遅延を減少させる方法であるが、データバスを中間値にプリチャージするのでその中間値を受ける特別なレシーバ回路が必要になる。著者らによる256KSRAM[3-2]ではシュミットトリガラッチ回路が用いられ、Komatsuらによる1MSRAM[3-3]ではdual-threshold data transfer circuitが用

いられている。これらのレシーバ回路はアクセスパスに直列に挿入され、また少なくとも1段のステージを必要とする。一般的にこのようなデータバスプリチャージ方式はデータバス容量が非常に大きい場合に使用されるので、段数が少ないと入力容量の大きな出力バッファを接続することが可能であり、特殊なレシーバ回路を挿入することは適さない。

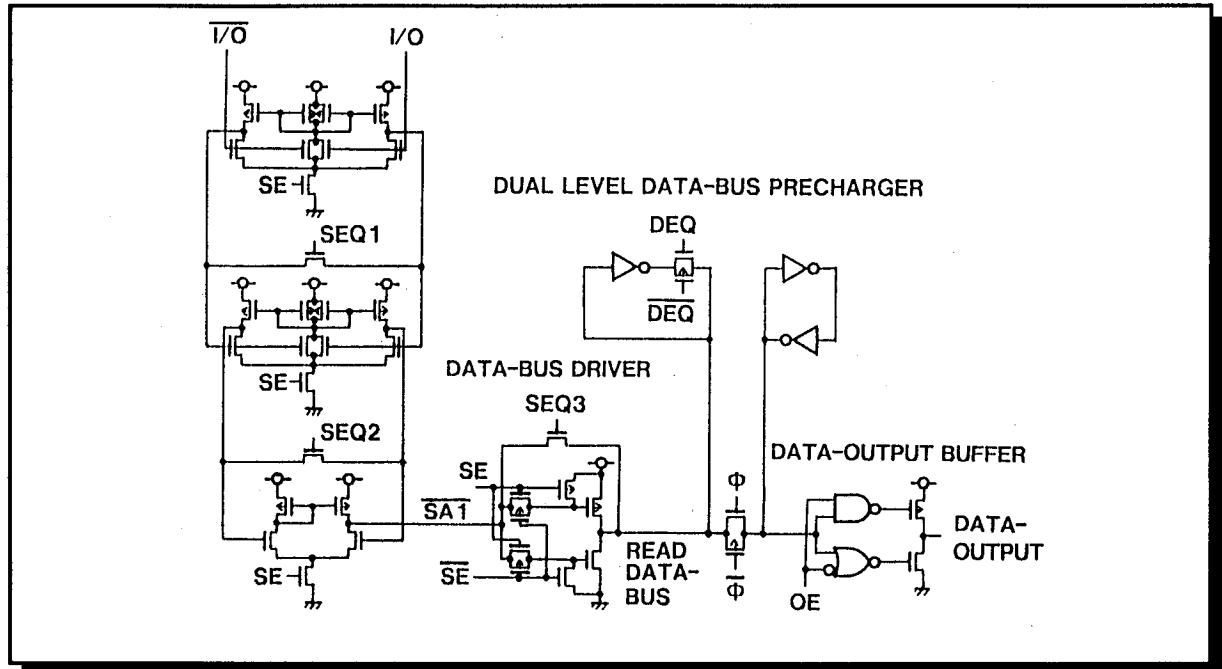

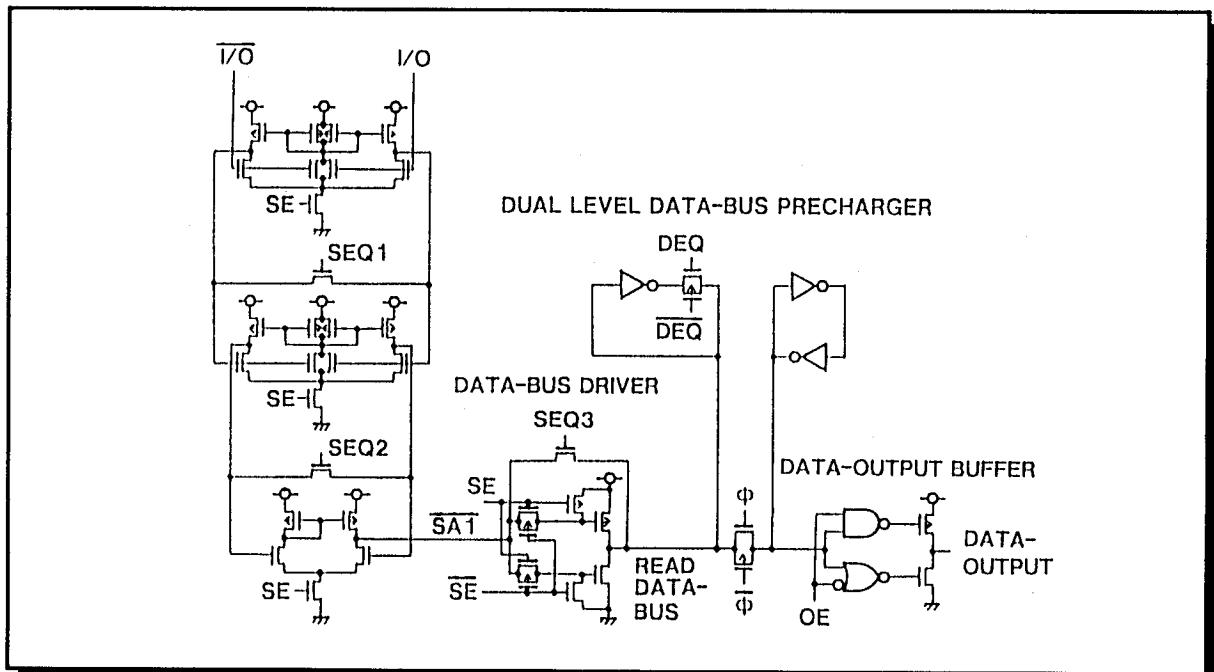

図3-3-7：1MSRAM[3-4]の読み出し系の回路図

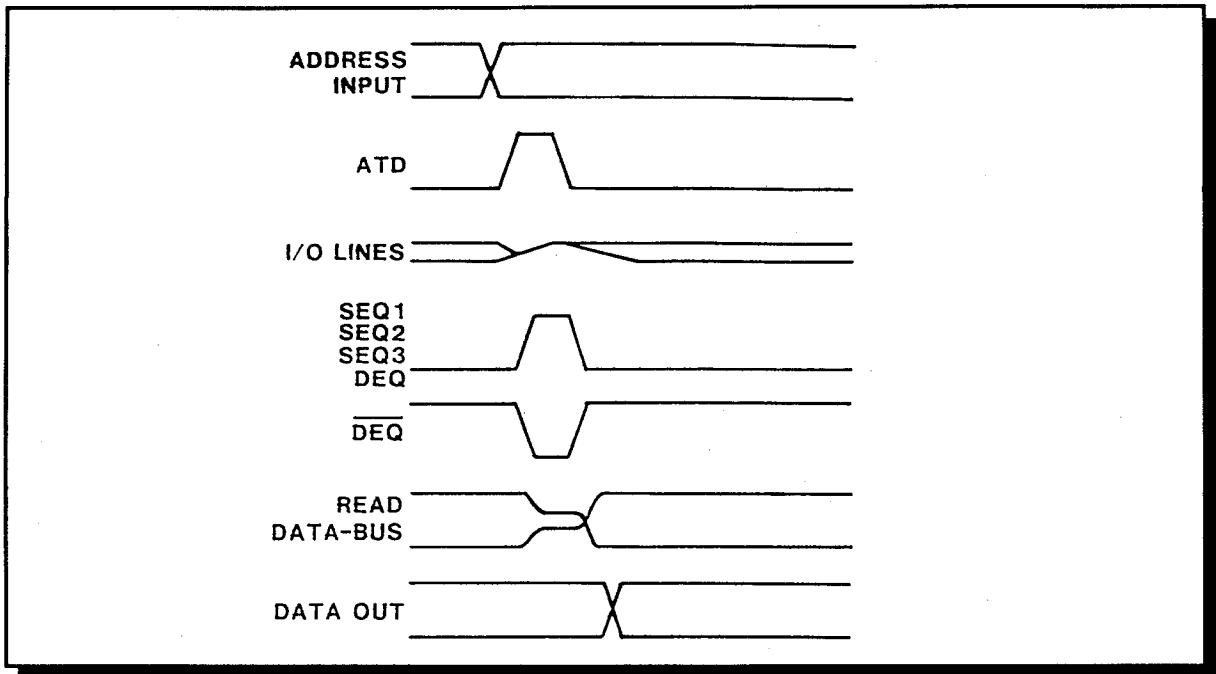

著者らが考案したデュアルレベルデータバスプリチャージ[3-4]はこの点を改良するもので、出力バッファの論理しきい値の少し上もしくは下のレベルに以前のデータにしたがってデータバスをプリチャージする方法である。図3-3-7は著者らの1MSRAM[3-4]で使用された読み出し系の回路図であり、図3-3-8は同タイミングダイアグラムである。SEQ3(Sense amp equalize3)、DEQ(Data bus equalize)およびDEQ(Data bus equalize)はATDパルスから生成されたデータバスプリチャージ用の制御パルスである。出力バッファの入力点に接続されたデバイスサイズの小さいラッチ回路に前サイクルのデータが保持されており、この前サイクルのデータにしたがってデータバスのプリチャージレベルは2種類の異なるレベルとなる。ここではそれらのレベルは2Vと3Vとなっており、出力バッファのしきい値を中間の2.5Vに設定している。

このデュアルレベルデータバスプリチャージを用いることで特別なレシーバ回路をアクセスパスに直列に挿入することなく、データバスに出力バッファを直接接続することが可能となりそれに伴う遅延時間を短縮することが可能となる。ここで設定ではデータバスのプリチャージレベルと出力バッファの論理しきい値の差は500mVであり、これは上記データバス中間値プリチャージの入力抵抗の電位差400mVとほぼ同じであり、どちらにしてもデータバスがプリチャージレベルから400mV～500mVの変動してデータが次段に転送されるのでプリチャージレベルをデュアルにすることによる速度に対する

るデメリットは少ない。

図3-3-8：読み出し系のタイミングダイアグラム

### 3.4 出力プリセットによる高速化と低ノイズ化の両立

このセクションでは第3の方法として著者らが考案した出力プリセット方式[3-5]による高速化と低出力ノイズ化を述べる。

アクセスタイムは大きく分類して（1）ワード線の選択時間、（2）ビット線対がセンス可能な電位差になる時間、（3）ビット線対のデータを増幅しデータバスを介してデータを出力バッファに転送する時間、そして（4）出力バッファがチップ外部容量を駆動する時間に分れる。Hardeeらの方法は（2）を短縮し、著者らが提案したデータバスプリチャージとその変形のデュアレレベルデータバスプリチャージは（3）を短縮するものである。そしてデータ出力プリセットは低ノイズ化を実現しながら（4）を短縮するものである。一般にSRAMの出力ピンには30pF～100pF程度の容量が接続される。この容量の充放電を高速化するのはドライブ能力の大きい回路を用いればよい、しかしながら低インピーダンスのドライバを用いるとチップ内部の電源線／接地線にバウンス（ノイズ）を発生しRAMの誤動作を誘発する可能性がある。特に、多数の出力バッファを持ちそれが同時にスイッチングするような場合、そのバウンスが増大する。データ出力プリセット方式はこの電源線／接地線にバウンスを増大させずにアクセス時間を短縮する方法である。

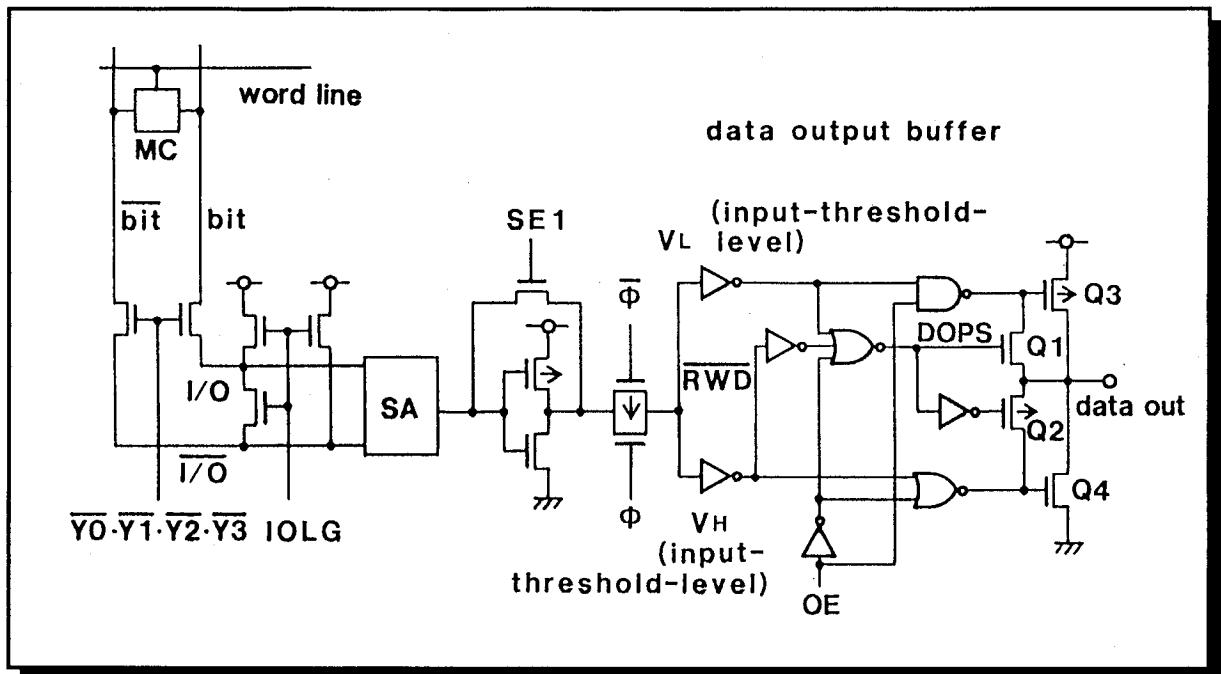

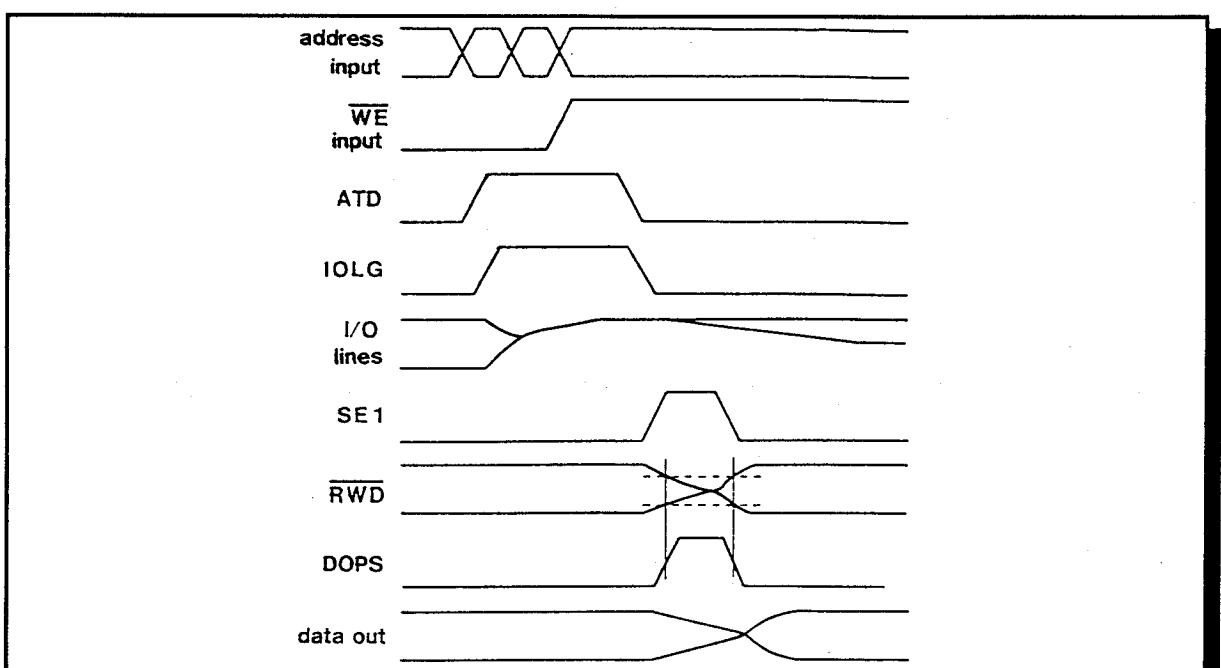

図3-4-1は著者らによる1MSRAM[3-5]の出力プリセット方式を用いた読み出し系の回路図である。それに対応するタイミングダイアグラムが図3-4-2に示されている。

図3-4-1：1MSRAM[3-5]の読み出し系の回路図

IOLG (I/O line equalize) と SE1 (Sense enable1) の 2 つのパルスが ATD パルスより発生される。IOLG は I/O 線対をイコライズする (Hardee らの方法) 、SE1 は High の時に CMOS インバータの入出力を短絡してデータバス RWD を中間値にプリチャージする (データバスプリチャージ)。したがって、データバス RWD は SE1 が Low に遷移した後、中間値からメモリセルから読み出されたデータに応じて High もしくは Low に遷移する。

図3-4-2：1MSRAM[3-5]のタイミングダイアグラム

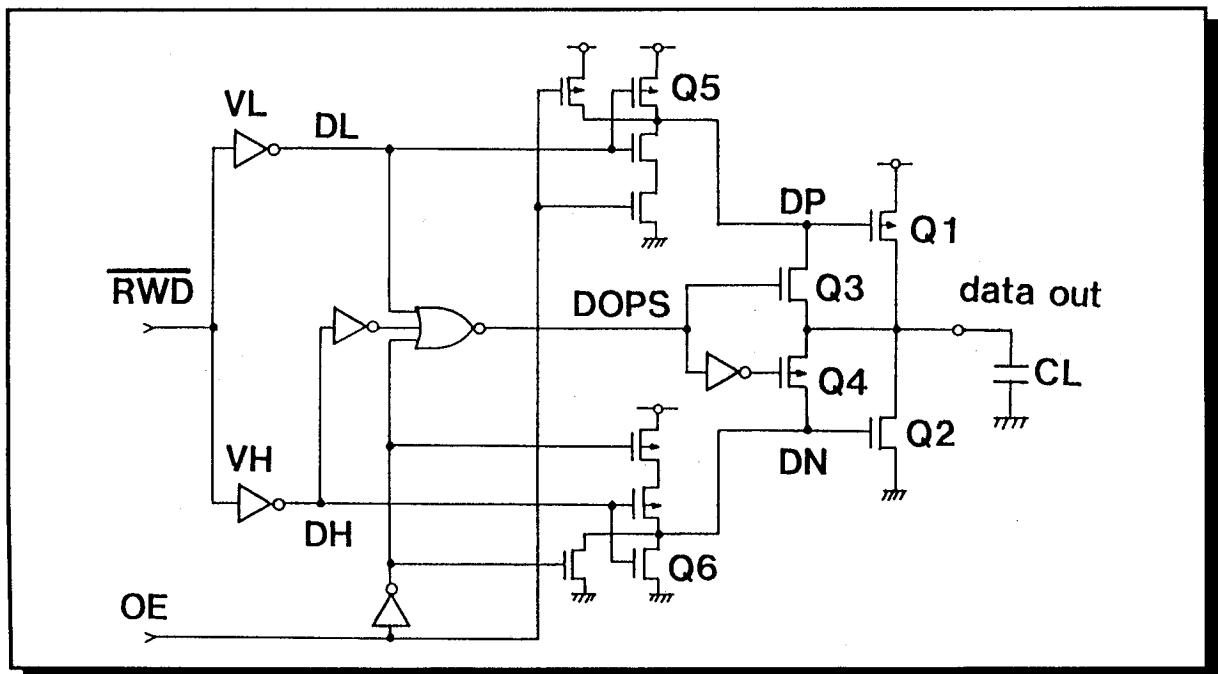

図3-4-3は出力バッファのみを詳細に示した図である。出力バッファの第1段目は2種類の異なる論理しきい値を持つCMOSインバータより構成されている。2つの論理しきい値VHとVLはそれぞれ $3/4V_{cc}$ と $1/4V_{cc}$ である。RWDはSE1にしたがって先にも述べたように中間電位( $1/2V_{cc}$ )にプリチャージされる。したがって、この時DOPS(Data output pre-set)がHighとなり、パルスが自動的に発生される。data outがLowであった場合P型MOSFET Q2のソース、ドレイン、ゲート端子はすべてLowであり、N型MOSFET Q1のノードはそれぞれLow、High、Highとなる。したがって、Q2はOFF状態となりQ1はON状態となっている。したがって、出力ノードを充電する電流がQ1を通り流れ。この時ノードDPはQ5とQ1の抵抗比と出力ノードの電位で決まる電位に落ち、Q3をONさせる。そして、Q3とQ1を流れる電流により、出力ノードはLowから中間値へ充電される。

一方、data outがHighであった場合同様なメカニズムでQ4とQ2を流れる放電電流により出力ノードはHighから中間値へ放電される。この設計ではQ1およびQ2のチャネル幅はQ3およびQ4のそれよりかなり小さく設定してあるので、おもな充放電電流はQ3とQ4を流れ、Q1とQ2による出力バッファの面積の上昇を5%以下に低減している。

図3-4-3：出力バッファ回路

data outが中間値になった時Q1とQ2の両者はONしている。この設計ではQ5とQ1のチャネル幅によりこの時のDPのレベルを $V_{cc}-0.5V$ となるようにしている。同様に、Q2とQ6によりDNは0.3Vとしている。したがってdata outが中間値になった時、出力トランジスタQ3とQ4の両者はOFF状態となっておりトランジスタQ3、Q4を通じて貫通電流は流れない。但し、Q1、Q2を通じて電流は流れ。この値は、出力バッファ1つに対して1.5mAとしている。しかし、出力レベルが中間状態となるのは1回の読み出し動

作にに対して10ns以下であり、影響は小さい。このようにして、出力バッファは真のデータが現われる前に中間電位にプリセットされ、出力端子は中間レベルからHighもしくはLowレベルに変化する。

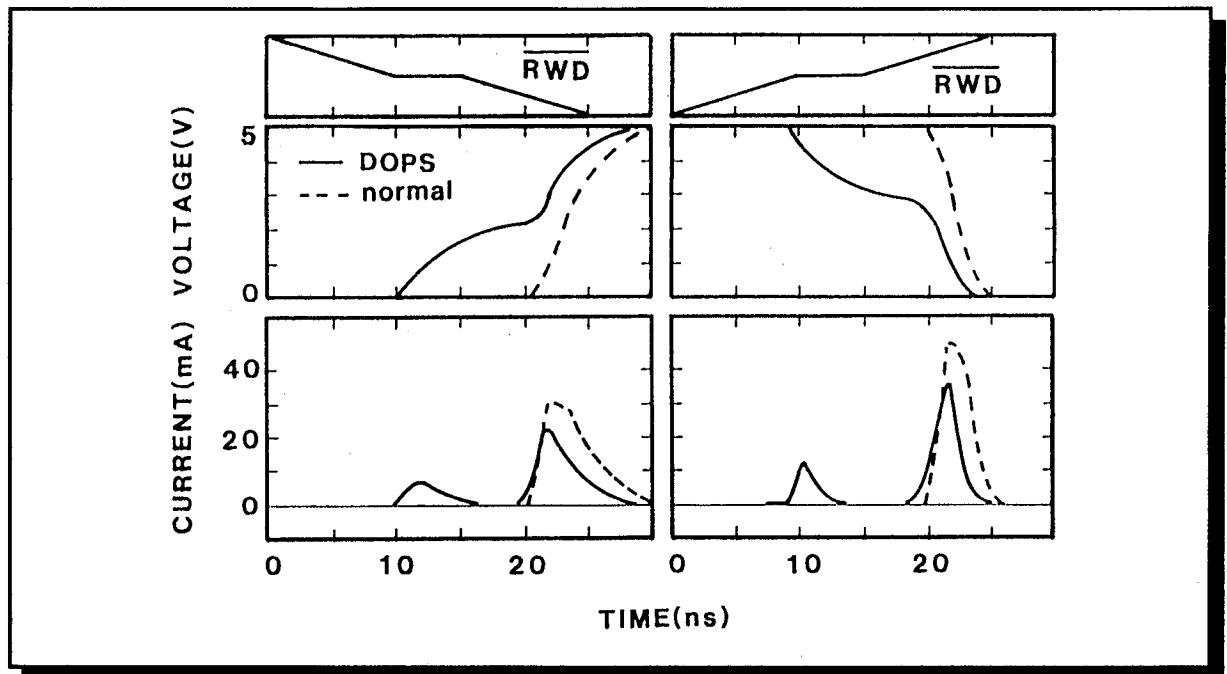

図3-4-4：出力バッファのシミュレーション波形

図3-4-4は回路シミュレータSPICE2による出力バッファのシミュレーション波形である。出力負荷容量は30pFである。左側はRWD (Read write data bus)のHighからLowへの変化に対応し、右側はRWDのLowからHighへの変化に対応する。最下段は出力バッファの電流波形を示し、中段は電圧波形である。点線は通常の場合であり、実線は出力プリセット方式を使用した例である。結果的に、1MSRAM[3-5]では出力端子の遷移時間が半減しアクセスタイムを10%短縮した。また同時に、チップ内部の電源線／接地線にバウンシングノイズを発生させる電流のピーク値ならびに最大傾斜値を30%削減した。

### 3.5 結論

本章では回路技術、とくにATDを利用するSRAMの高速化について述べた。

- (1) ATDを用いた高速化の別の手法としてデータバスプリチャージを考案した。

- (2) データバスと出力バッファの間にシュミットトリガラッチ(STL)回路を設けて、データバスプリチャージ中にデータ出力端子が前サイクルの状態を保持することを可能とした。

- (3) データバスプリチャージは著者らによる256KSRAM[3-2]で、データバスでの遅延時間を6.5nsから2.5nsに4.0ns短縮し、13%以上のアクセスタイムの短縮を実現した。

- (4) データバスプリチャージの特別なレシーバ回路を不要とする、データバスを2種類の異なるレベルにプリチャージするデュアルレベルデータバスプリチャージを考案した。

- (5) デュアルレベルデータバスプリチャージは特別なレシーバ回路のアクセスパスへの直列挿入する必要性をなくし、データバスに出力バッファを直接接続することを可能とし、それに伴う遅延時間の短縮が可能であることを示した。

- (6) ATDを用いた高速化の別の手法としてデータ出力プリセットを考案した。

- (7) データ出力プロセットはチップ内部の電源線／接地線にバウンスを増大させずに出力バッファがチップ外部容量を駆動する時間を短縮することを示した。

- (8) データ出力プリセットは著者らによる1MSRAM[3-5]のバウンシングノイズの原因の電流のピーク値ならびに最大傾斜値を30%削減ながら、アクセス時間を10%削減した。

### 3.6 参考文献

- [3-1] Kim C. Hardee and Rahul Sud, "A Fault-Tolerant 30ns/375mW 16K x 1 NMOS Static RAM," IEEE J. Solid-State Circuits, vol. SC-16, pp. 435-443, Oct. 1981.

- [3-2] S. Kayano, K. Ichinose, Y. Kohno, H. Shinohara, K. Anami, S. Murakami, T. Wada, Y. Kawai, and Y. Akasaka, "25-ns 256Kx1/64Kx4 CMOS SRAM's," IEEE J. Solid-State Circuits, vol. SC-21, pp. 686-691, Oct. 1986.

- [3-3] T. Komatsu, N. Okazaki, T. Nishihara, S. Kayama, N. Hoshi, J. Aoyama, and T. Shimada, "A 35ns 1Mb CMOS SRAM," ISSCC Dig. Tech. Papers, Feb. 1987, pp.258-259.

- [3-4] Y. Kohno, T. Wada, K. Anami, Y. Kawai, K. Yuzuriha, T. Matsukawa, and S. Kayano, "A 14-ns 1-Mbit CMOS SRAM with Variable Bit Organization," IEEE J. Solid-State Circuits, vol. SC-23, pp. 1060-1066, Oct. 1988.

- [3-5] T. Wada, T. Hirose, H. Shinohara, Y. Kawai, K. Yuzuriha, Y. Kohno, and S. Kayano, "A 34-ns 1-Mbit CMOS SRAM Using Triple Polysilicon," IEEE J. Solid-State Circuits, vol. SC-22, pp.727-732, Oct 1987.

## 第4章

### キャッシュメモリとしての高速化

## 4.1 はじめに

高速SRAMが最も必要とされるアプリケーションは高性能のコンピュータシステムであり、主にSRAMはキャッシュメモリとして使用されている。キャッシュメモリはある大きさの固まったデータをアクセスするので完全なランダムアクセスを必要としない。

また、キャッシュメモリにはブロックサイズ、アソシアティビティのようなキャッシュメモリのヒット率に関する論理的なパラメータ（以後、論理パラメータ）が加わり、この論理パラメータのLSI上での構成方法でSRAMのアクセスタイムも影響を受ける。

本章では、高速SRAMの最も大きい応用分野であるキャッシュメモリのアクセスタイムの最適化に対して有効なアクセスタイムモデルについて述べる[4-11]。このモデルは特に設計自由度の高いオンチップキャッシュの解析的モデルであり、通常のキャッシュサイズ、ブロックサイズ、アソシアティビティのような論理パラメータ以外にメモリアレイの物理構成に関するパラメータ（以後、物理パラメータ）を含んでいる。このモデルにより、詳細な回路設計なしにキャッシュメモリのスピードを見積ることができ、多種多様なキャッシュメモリ設計の最適化をすることができる。

そして、そのアクセスタイムモデルを用いてキャッシュメモリの論理構成と物理構成によるスピードのトレードオフを示し、キャッシュメモリとしてSRAMを高速化する方法を示す。

## 4.2 On-Chipキャッシュメモリ用のアクセスタイムモデル

### 4.2.1 背景

VLSI技術の急速な進歩に伴ってマイクロプロセッサのクロック周波数は飛躍的に向上してきている。この高速クロックの利点を性能に有効に発揮させるには、ペナルティなしにマイクロプロセッサにメモリシステムからインストラクションやデータを供給する必要があり、高いバンド幅でインストラクションやデータを転送する必要がある。しかし、論理ゲートのスピードはVLSI技術の向上で非常に高速になっている一方で、メモリのアクセススピードはそれほど向上していない。その1つの理由はVLSI技術の向上と同時に必要とされるメモリ容量も増大しているからである。したがって、キャッシュメモリは高速なコンピュータシステムを実現する場合重要な技術となってきた。

ほとんどのキャッシュメモリに関する研究はミス率、トラフィック率という典型的なキャッシュメモリの性能評価指標を最小化することを主にしている。しかし、本当の性能評価指標は与えられたワークロード（仕事）の実行時間である。多くの場合、オンチップキャッシュはシステムのサイクルタイムを決めるクリティカルな要因である。そのため、論理パラメータ（キャッシュサイズ、ブロックサイズ、アソシアティビティ）とキャッシュアクセスタイムの関係を定量化することは重要となる。この定量化により、キャッシュ

シメモリ設計者がキャッシュメモリを最適化し最良の設計を実現することが可能となる。オンチップキャッシュの場合、設計者が標準SRAMでオフチップキャッシュを構成するのに比べて構成に対してフレキシブルに設計することができるので、この定量式は特にオンチップキャッシュの場合にさらに有効となる。

オンチップキャッシュメモリを設計する場合、論理パラメータ（キャッシュサイズ、ブロックサイズ、アソシアティビティ）がキャッシュアクセスタイムに影響を与えるだけでなく、メモリアレイのアスペクトレシオのような物理的な構成を決める物理パラメータもアクセスタイムに影響を与える。DuncombeのSPURマイクロプロセッサのキャッシュシステムのレポート[4-1]では、キャッシュサイズとアスペクトレシオのアクセスタイムに対する影響を検討している。このレポートの中でキャッシュアクセスタイムはSPICE非線形回路シミュレータによって求められている。しかし、この方法では大きなキャッシュメモリ設計の自由度をカバーするには多数回のシミュレーションの実行が必要となる。その上、SPICEは論理パラメータや物理パラメータ以外に多数の回路的パラメータも必要となり、SPICEだけで有限時間内に多種多様なキャッシュメモリ設計すべてをカバーし、最適解を見つけることは困難である。仮に、シンプルでかつある程度の精度があり広いキャッシュメモリ設計の自由度をカバーするアクセスタイムのモデルが存在すれば、設計者はそのモデルにより最速のアクセスタイムを持つキャッシュや論理パラメータを選ぶことができる。これにより設計の最適解に近い構成を探し、最終的に集中的なSPICEシミュレーションで設計を最適化することができる。

#### 4.2.2 キャッシュメモリの構成

表4-2-1：アクセスタイムモデルパラメータ

| Symbols Meanings |                                    | Parameters & Equations              |

|------------------|------------------------------------|-------------------------------------|

| B                | Block Size                         | 4B, 8B, 16B, 32B                    |

| A                | Associativity                      | 1, 2, 4, 8                          |

| S                | Number of sets                     | 256, 512, 1K, 2K, 4K, 8K, 16K       |

| Ndwl             | # of segments per word line (Data) | 1, 2, 4...                          |

| Ndbl             | # of segments per bit line (Data)  | 1, 2, 4...                          |

| Ntwl             | # of segments per word line (Tag)  | 1, 2, 4...                          |

| Ntbl             | # of segments per bit line (Tag)   | 1, 2, 4...                          |

| Rows             | Number of rows in a sub-array      | S/Ndbl                              |

| Cols             | Number of columns in a sub-array   | 8·B·A/Ndwl                          |

| Subs             | Number of sub-arrays               | Ndwl·Ndbl                           |

| C                | Cache size                         | $B·A·S = S/Ndbl·B·A/Ndwl·Ndwl·Ndbl$ |

この解析モデルに用いられるパラメータを表4-2-1にまとめる。B、A、およびSは主

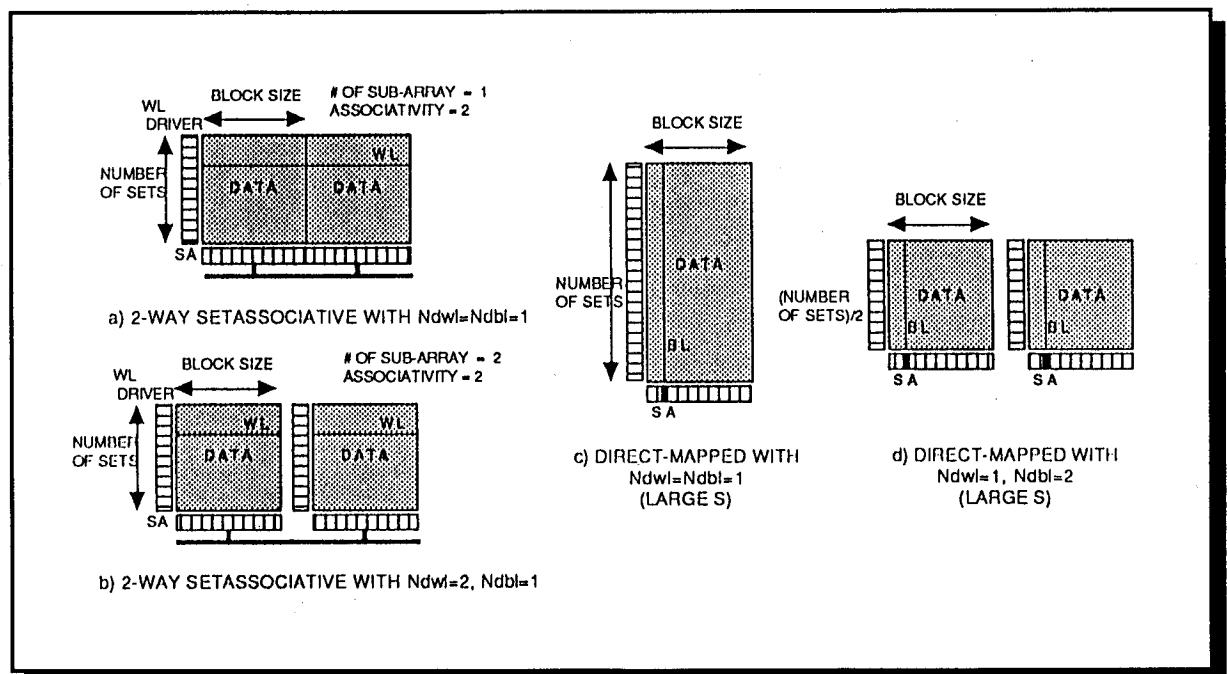

要論理パラメータであり、それぞれはブロックサイズ、アソシアティビティ、セット数に対応する。これらの他に物理的構成に関する4つの物理パラメータ ( $N_{dw1}$ 、 $N_{db1}$ 、 $N_{tw1}$ 、 $N_{tb1}$ ) を新たに導入した。 $N_{dw1}$ はデータアレイ中のワード線の分割数であり、 $N_{db1}$ はデータアレイ中のビット線の分割数である。分割されたワード線に対応するセグメントはそのセグメントごとにワード線ドライバをもっており、1つのワード線に対応する $N_{dw1}$ 個のセグメントはある特定のロウアドレスに対応し同時に選択される。分割されたビット線に対応するセグメントはそのセグメントごとにセンスアンプをもち、1つのビット線に対応する $N_{db1}$ 個のセグメントはある特定のカラムアドレスに対応する。しかし、特定のカラムアドレスに対して1つのセンスアンプ（セグメント）のみが活性化される。したがって、同時に選択されるメモリセル数および同時に活性化されるセンスアンプ数は $N_{dw1}$ や $N_{db1}$ によって変化しない。 $N_{tw1}$ および $N_{tb1}$ はタグアレイに関して同様に定義される。図4-2-1(a)は最も基本的な2ウェイセットアソシアティブのキャッシュメモリの構成であり、 $N_{dw1}=N_{db1}=1$ に対応する。ここで、セット数Sはアレイのロウの数 (Rows) と等しくなり、(8·B·A)はアレイのカラムの数 (Cols) と等しくなる。

図4-2-1：キャッシュメモリの構成

- (a)  $N_{dw1}=N_{db1}=1$  の 2 ウエイセットアソシアティブキャッシュ

- (b)  $N_{dw1}=2, N_{db1}=1$  の 2 ウエイセットアソシアティブキャッシュ

- (c)  $N_{dw1}=N_{db1}=1$  ならびにセットサイズSが大きいダイレクトマップキャッシュ

- (d)  $N_{dw1}=1, N_{db1}=2$  ならびにセットサイズSが大きいダイレクトマップキャッシュ

図4-2-1(a)の例では、ワード線の長さ(8·B·A)は長すぎてワード線の遅延がアクセスタイムの中の主要な成分になる場合がある。このような場合、ワード線をもっと短いセグメントに分割（すなわち、 $N_{dw1} > 1$ ）することでアクセスタイムを減らすことが可能になる場合がある。図4-2-1(b)は4-1-1(a)と同じキャッシュを異なる物理構成 ( $N_{dw1}=2$ )

で構成したものであり、より小さいワード線遅延を持つ（図中の2本のワード線は同時に選択される）。

他のアクセスタイムを決定する大きな要因としてビット線の遅延がある。図4-2-1(c)は大きなセット数を持つ場合のデータアレイの構成を示している。このアレイ構成はビット線容量が大きくなる構成に対応しておりビット線遅延を増大させる。そのビット線遅延時間を減らすために、ビット線は分割され複数のセグメントにすることができる（すなわち、 $Ndbl > 1$ ）。図4-2-1(d)は4-1-1(c)と同じキャッシュメモリアレイを $Ndbl=1$ で $Ndbl=2$ で構成した場合である。この場合、ある特定のビット線に対応するセンスアンプの1つが選択／活性化される。

$Ndbl=1$ 、 $Ndbl=2$ のアレイ構成（図4-2-1(b)）と $Ndbl=2$ 、 $Ndbl=1$ のアレイ構成（図4-2-1(d)）は図のように一見同じ構成のように見えるが、これらの2つの構成は異なる数の行／列のアドレス信号線に対応する。前者は後者の半分のセット数を持ち、後者は前者の半分の(B·A)を持つ。

#### 4.2.3 解析的アクセスタイムモデル

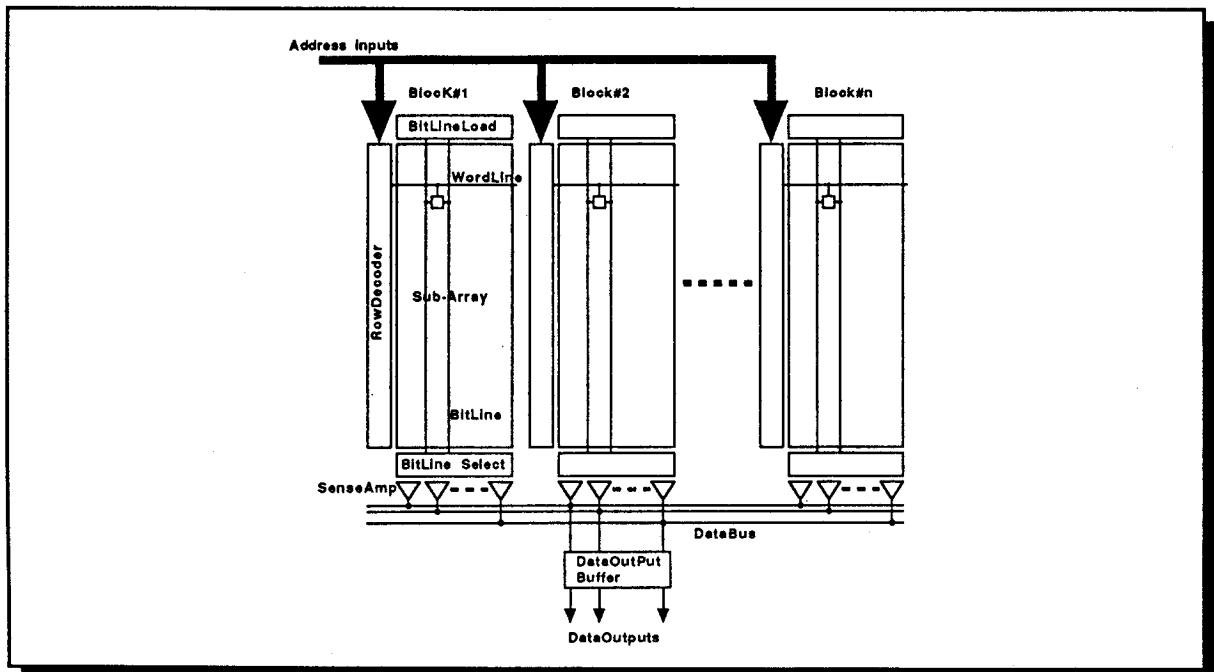

図4-2-2に標準的なRAMアレイを示す。

図4-2-2：標準的なRAMアレイ

メモリブロックは $n$ 個のサブブロックに分割されており、各々のサブブロックはロウデコーダ、ビット線負荷、カラムデコーダ、マルチプレクサ、センスアンプなどの周辺回路を含んでいる。読み出し動作は入力アドレスのデコード、対応するワード線のハイレベルへの駆動、メモリセルのデータのビット線への転送、ビット線電圧の感知増幅、チップ内部データバスのドライブ、そして出力バスの駆動からなる。このアクセスタイ

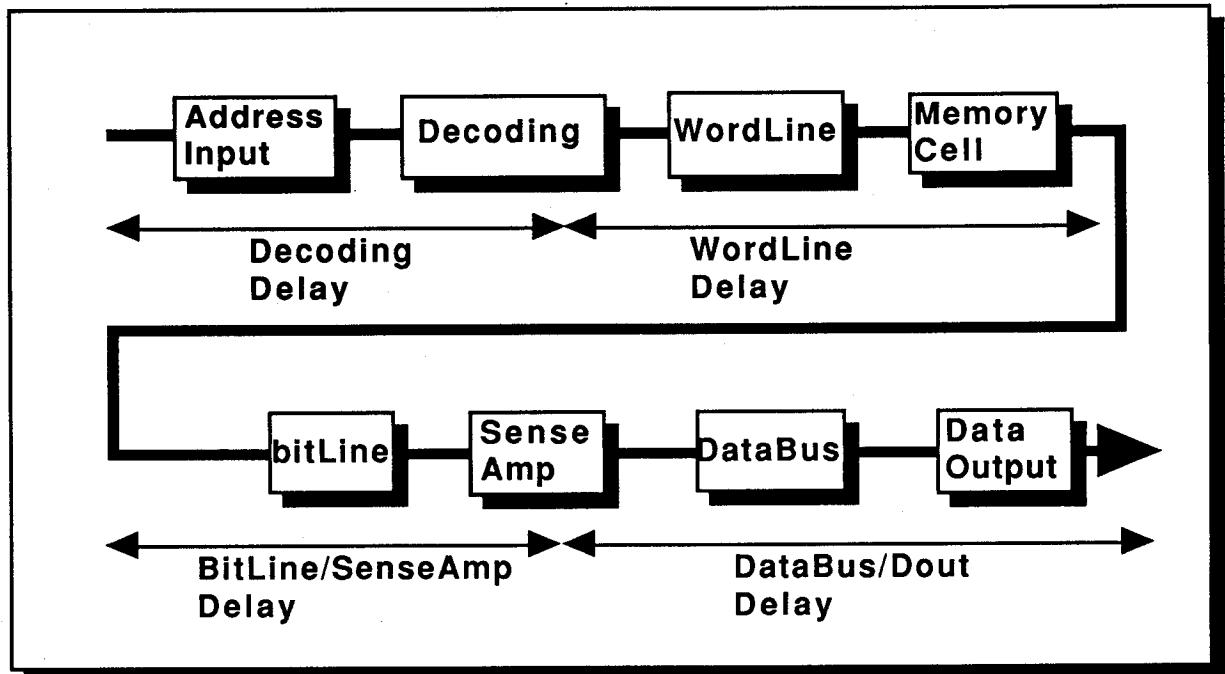

ムモデルでは図4-2-3に示すように、全体を大きく4つのコンポーネント（デコード遅延、ワード線遅延、ビット線／センスアンプ遅延、データバス／出力遅延）に分解している。

図4-2-3：クリティカルパス

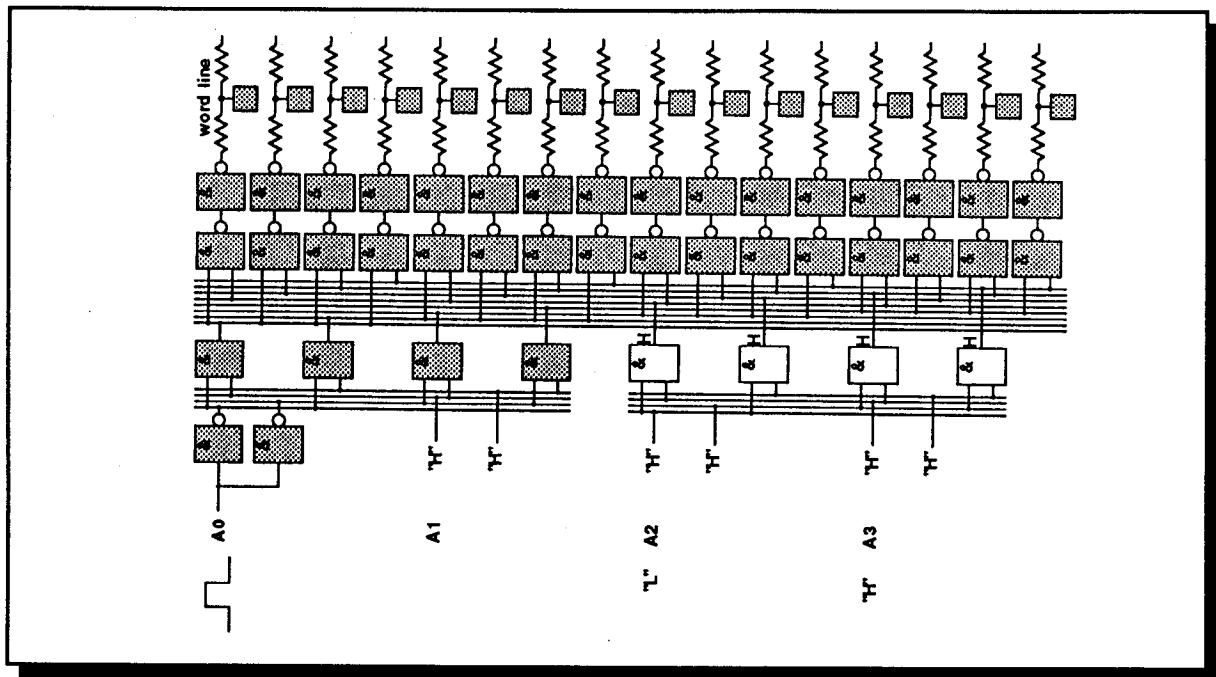

#### A デコード遅延

図4-2-4は典型的な4ビットのデコード回路である。ワード線ドライバとワード線も含まれている、しかしアドレス信号A0のフェイズスプリッタ（同相およびその反転を作るバッファ回路）がインバータ2ヶ（2つの反転信号）に変更され、他のアドレスのフェイズスプリッタ出力がすべてハイレベルに固定されている。以上の修正により、A0信号によりすべてのワード線ドライバ／ワード線がコントロールされるようになる。この変更は回路の動作を変えるのだが、入力段からワード線ドライバまでの遅延時間には影響を与えない。何故なら、遅延バスに添ったゲートは同一であり同一の駆動能力を持ち、同一の入出力の接続すなわち負荷容量が同じであるからである。したがって、図4-2-4のデコーダの遅延時間はファンアウトが大きい場合の回路の最適化問題[4-2]と考えることができる。

各ゲートの遅延時間はそのファンアウト数と入力数に比例すると仮定すると、トータルのデコード遅延( $T_{decode}$ )は以下の式で現すことができる[4-3]。

$$T_{decode} = t_0 \cdot f_{out} \cdot N_{in} \cdot N_{stage} \quad (4-2-1)$$

ここで、 $t_0$ はファンアウト1のインバータの遅延時間、 $f_{out}$ は各論理ゲートの平均ファンアウト数、 $N_{in}$ は各論理ゲートの平均入力数、そして $N_{stage}$ はトータルの論理ゲート

の段数である。各論理ゲートはインバータ、NANDゲート、NORゲートのいずれかである。Ninが2の場合は2入力NANDもしくは2入力NORゲートに対応する。TdecodeがNinに比例するという仮定はショートチャネルトランジスタの場合に直列接続のトランジスタの数に遅延時間が大きく依存しないので、それほど正確ではない場合もありうる。しかし、NinはTdecodeを最小化した場合1から2の間と小さい値になり誤差は10%以下となり、この仮定は大きくは違わない。

図4-2-4：4ビットデコーダ

トータルのファンアウト数FOUTtotalは以下の式で与えられる。

$$FOUT_{total} = f_{out}^{N_{stage}} = \frac{C_{N_{stage}+1}}{C_1} \cdot Total\ WL \quad (4-2-2a)$$

ここでC1は初段すなわちインバータ2ヶの入力容量であり、CNstage+1は各ワード線ドライバの入力容量である。Nstageはデコーダの初段からワード線ドライバの前段（ワード線ドライバは含まない）までの段数である。

すべてのワード線ドライバ数(Total WL)はデータアレイとタグアレイを含めるとS・(Ndwl+Ndwl)となるので、式(4-2-2a)は以下のようになる。

$$f_{out}^{N_{stage}} = \frac{C_{N_{stage}+1}}{C_1} \cdot S \cdot (N_{dw1} + N_{tw1}) \quad (4-2-2b)$$

初段は複雑な論理ゲートでなくインバータなので、アドレス入力数Naddは以下のよ

うになる。

$$N_{add} = \log_2 S = N_{in}^{N_{stage}-1} \quad (4-2-3)$$

式(4-2-2b)および(4-2-3)を(4-2-1)に代入すると、以下の式(4-2-4)がえられる。

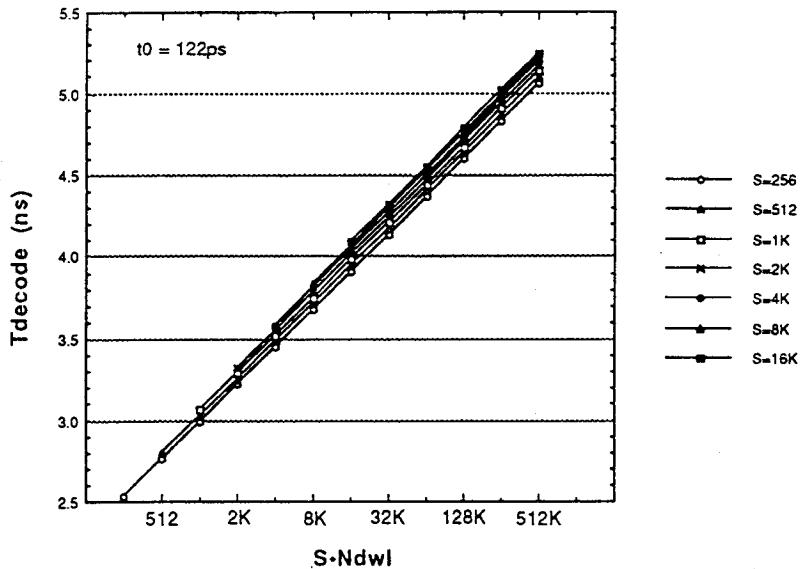

$$T_{decode} = t_0 \cdot \left( \frac{C_{N_{stage}+1}}{C_1} \cdot S \cdot (N_{dwI} + N_{twI}) \right)^{1/N_{stage}} \cdot (\log_2 S)^{1/(N_{stage}-1)} \cdot N_{stage} \quad (4-2-4)$$

この式(4-2-4)は  $T_{decode}$  は  $N_{stage}$  の関数であり与えられた  $S$ 、  $N_{dwI}$ 、  $N_{twI}$  に対して最小値を持つことを示している。  $N_{stage}$  は通常 10 以上なので、  $N_{stage} - 1$  は  $N_{stage}$  と近似することができる。したがって、  $T_{decode}$  の最小値(4-2-5a)が  $dT_{decode}/dN_{stage} = 0$  を解くことで以下のように得られる。

$$T_{decode} = t_0 \cdot D^{1/\ln D} \cdot \ln D \quad (4-2-5a)$$

ここで、

$$D = \left( \frac{C_{N_{stage}+1}}{C_1} \right) \times (S \cdot \log_2 S) \times (N_{dwI} + N_{twI}) \quad (4-2-5b)$$

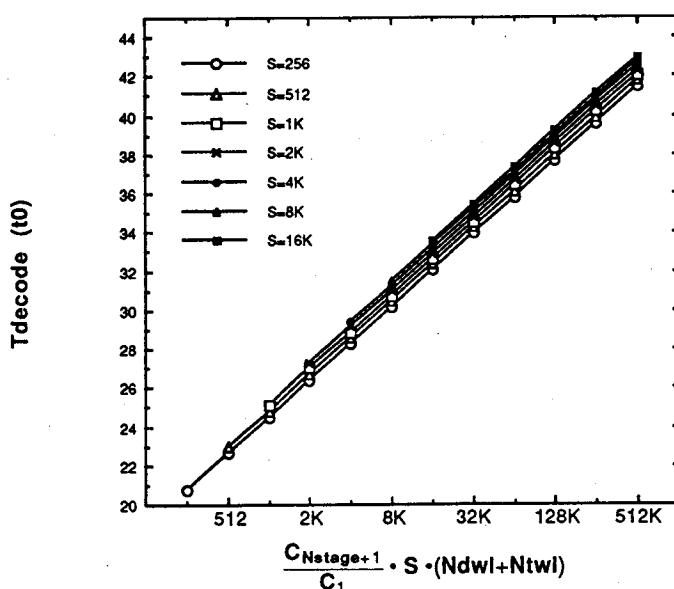

図4-2-5は最小のデコード遅延  $T_{decode}$  を示した図である。  $S \cdot (N_{dwI} + N_{twI})$  即ち、トータルのワード線ドライバの数に対して大きな依存性を持っている、しかし  $S \cdot (N_{dwI} + N_{twI})$  を固定し  $S$ だけを変えた場合はあまり変化しない。これは  $N_{in}$  パラメータがトータルのデコード遅延に大きな影響がないことを示している。

図4-2-5：デコード遅延

本デコード遅延モデルの限界は各ゲートの入力容量は考慮されているが、配線遅延のような寄生容量は無視されている点と実際のデコーダ回路はチップ上のレイアウトの制約などにより段数を減らし格段のファンアウトを大きく取る場合があり、このモデルのように最適化されない点である。結果的に、このデコード遅延モデルはデコード遅延の理論的小最小値を与えることになる。

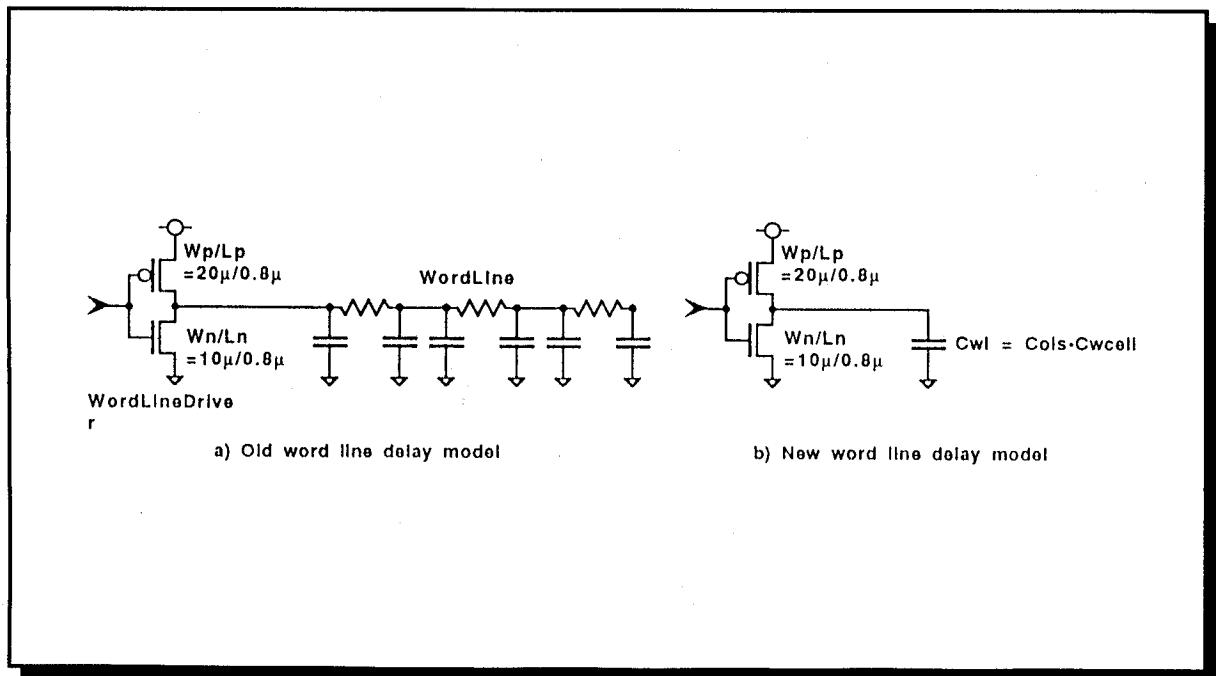

## B ワード線遅延

ワード線ドライバは立ち上がり時間と立ち下がり時間が同じになるようにプルアップとプルダウンのトランジスタサイズが適切に設定されたCMOSインバータと考える。2  $\mu\text{m}$ ルール時代の1層ポリシリコンのワード線は図4-2-6(a)のように、分散RCとしてモデル化することができる。しかし、最近の新しいプロセスではダブルワード線方式[4-5]、[4-6]と称し、メタルワード線がポリシリコンワード線と並行に配置され、ポリシリコンワード線はメタルでシャントされる。通常、それらの配線容量は駆動されるすべてのトランジスタのゲート容量より十分に小さい。0.8  $\mu\text{m}$  CMOSプロセス[4-9]では $W=L=1\text{ }\mu\text{m}$ のトランジスタのゲート容量は1.95fFであり、フィールド酸化膜上のポリシリコン配線の容量は $0.075\text{ fF}/\mu\text{m}^2$ と十分に小さい。したがって、ダブルワード線構造は図4-2-6(b)のようにランプ容量でモデル化することができる。

図4-2-6：ワード線モデル

(a) 旧ワード線モデル、(b) 新ワード線モデル

簡単なモデルで計算すると、ワード線遅延 $T_{wl}$ は以下のようになる。

$$T_{wl} = \frac{C_{total} \cdot \Delta V}{I} = \text{Cols} \cdot C_{wcell} \cdot \frac{V_{dd}}{2 \cdot I_{dn}} = \left( \frac{4 \cdot C_{wcell} \cdot V_{dd}}{I_{dn}} \right) \times (B \cdot A) \times \left( \frac{1}{N_{dw1}} \right) \quad (4-2-6)$$

ここで $C_{wcell}$ はメモリセル1ヶあたりのワード線容量であり、通常2つのパストランジスタのゲート容量に相当する。 $V_{dd}$ は電源電圧であり、通常は5V。 $I_{dn}$ はワード線トライバのNMOSトランジスタの平均飽和電流（ $V_{gs}=V_{ds}$ のとき）であり、PMOSトランジスタの平均飽和電流 $I_{dp}$ と等しいと仮定している。

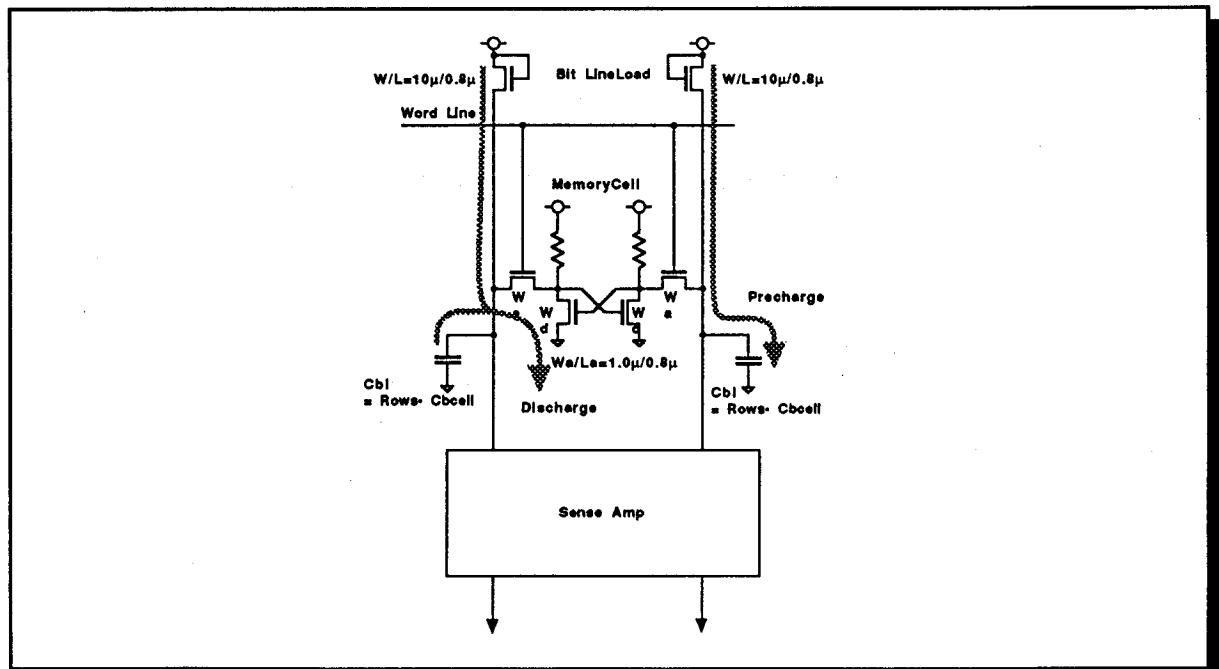

### C ビット線／センスアンプ遅延

図4-2-7はビット線とその周辺回路であり、メモリセル、ビット線負荷、センスアンプから構成されている。 $C_{bl}$ はビット線容量であり、サブアレイのビット長( $S/N_{dbl}$ )と1ビット当たりのビット線の単位容量 $C_{bcell}$ の積となる。 $C_{bcell}$ は主としてパストランジスタのドレイン部のジャンクション容量が占めている。クロックで制御されたビット線負荷を用いる設計も可能であるが、ここでは簡単のためにDC動作のビット線負荷を仮定する。DCビット線負荷は通常小さい振幅を持つので、ビット線負荷トランジスタは線形抵抗と考えることができ、メモリセルのパストランジスタは飽和領域で動作していると考えることができる。図4-2-8(a)は簡略化されたビット線遅延モデルであり、メモリセル電流 $I_c=0$ はビット線の充電動作に対応し、 $I_c$ が0でない場合はビット線の放電動作に対応する。

キルヒホッフの法則により、

$$C_{bl} \frac{\partial V_b}{\partial t} = \frac{V_{pre} - V_b}{R_l} - I_c \quad (4-2-7)$$

図4-2-7：メモリセル周辺回路

図4-2-8：簡略化されたビット線遅延モデル

ここで  $V_{pre}$  はビット線最大プリチャージレベルであり、この場合  $V_{dd} - V_{th}$  になる。式 (4-2-7) を解くと、

$$V_b = V_{pre} - R_l \cdot I_c \left( 1 - \exp \left( - \frac{t}{R_l \cdot C_{bl}} \right) \right) \quad \text{discharge} \quad (4-2-8a)$$

$$V_b = V_{pre} - R_l \cdot I_c \cdot \exp \left( - \frac{t}{R_l \cdot C_{bl}} \right) \quad \text{precharge} \quad (4-2-8b)$$

式(4-2-8a)は放電時に対応し、(4-2-8b)は充電時に対応する。

図4-2-8(b)はこれらの波形図を示したものである。差動センス電圧  $\Delta V$  はこれらの電圧の差であるので、 $\Delta V$  は以下のようになる。

$$\Delta V = R_l \cdot I_c \left( 1 - 2 \cdot \exp \left( - \frac{t}{R_l \cdot C_{bl}} \right) \right) \quad (4-2-9)$$

したがって、 $\Delta V = 0$  のとき、

$$t_1 = - R_l \cdot C_{bl} \cdot \ln 0.5 = 0.7 R_l \cdot C_{bl} \quad (4-2-10)$$

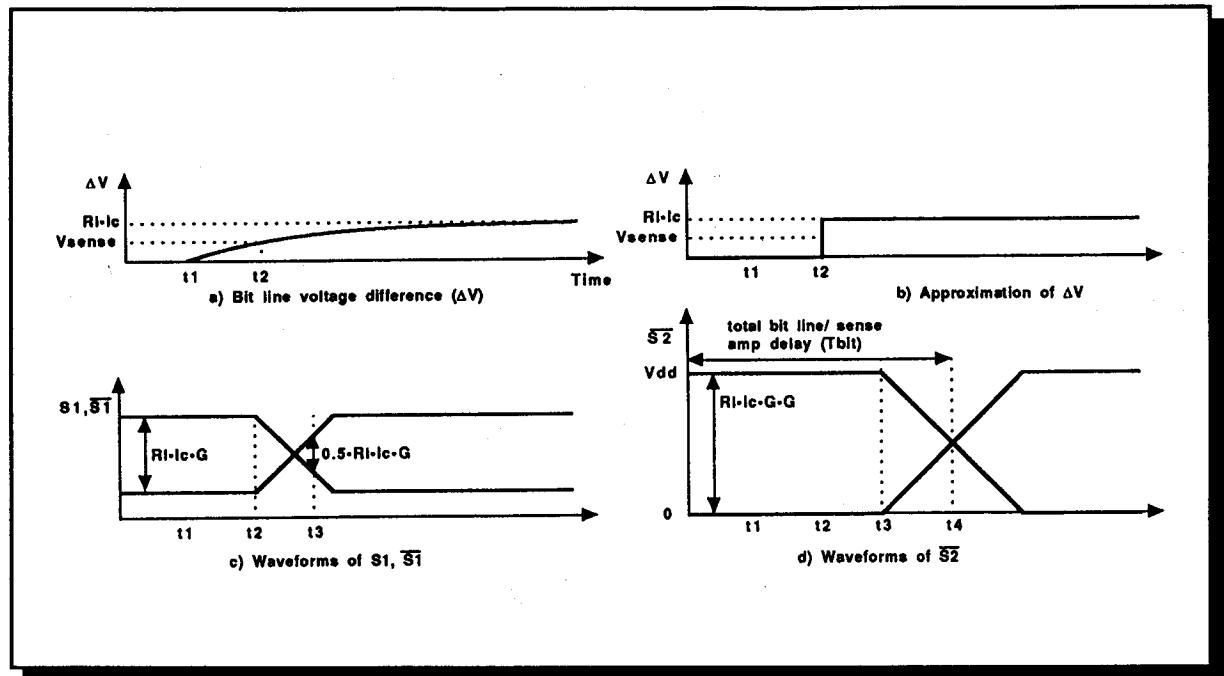

図4-2-9：センスアンプ周辺の信号波形

(a) ビット線電位差  $\Delta V$ 、(b)  $\Delta V$ の近似波形、(c)  $S_1$ 、 $\bar{S}_1$ 信号波形、(d)  $S_2$ 波形

図4-2-9(a)は  $\Delta V$ の時間依存性を示したものである。  $\Delta V = V_{sense}$  の時の時間  $t_2$  は以下のようになる。

$$t_2 = -R_1 \cdot C_{bl} \cdot \ln \left[ 0.5 \left( 1 - \frac{V_{sense}}{R_1 \cdot I_c} \right) \right] \quad (4-2-11)$$

ここで  $V_{sense}$  はセンスアンプによって正しくセンス動作が行なわれる最小差動電位である。センスアンプ遅延を解析するためにこの波形は図4-2-9(b)のように  $t_2$  でのステップ入力と近似する。

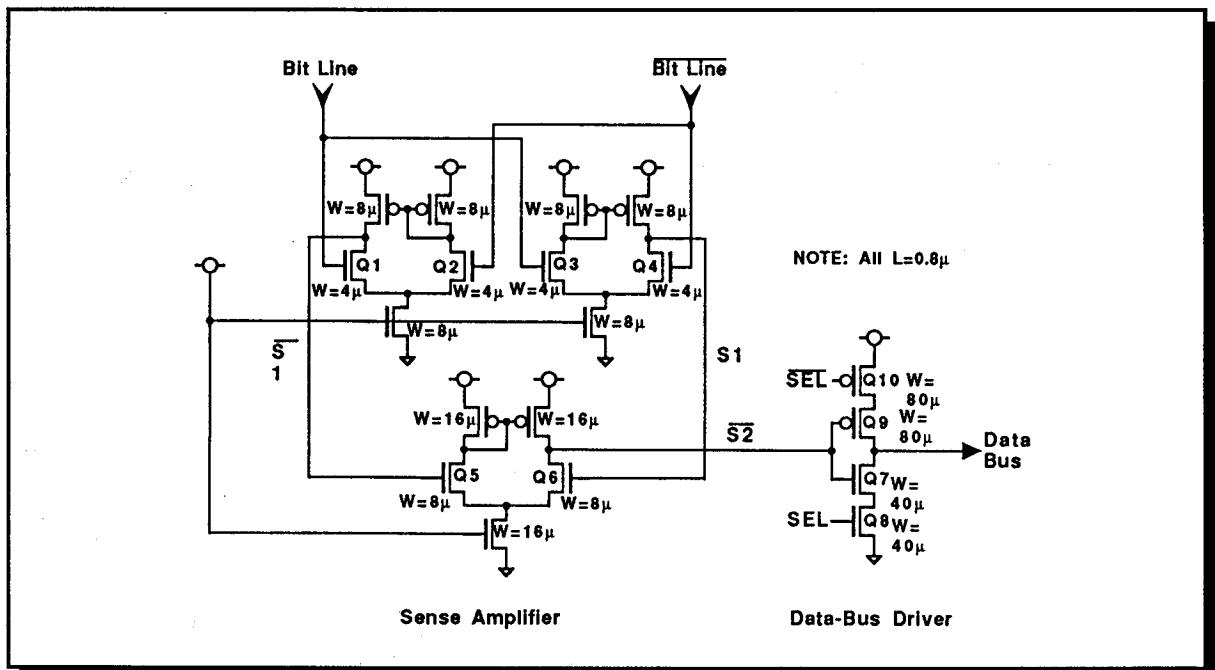

図4-2-10はセンスアンプとデータバスドライバである。このセンスアンプは3つのカレントミラー型差動ステージからなり、ビット線間の差動電圧を感知増幅し、 $V_{dd}$ の大きさ程度まで増幅する。したがって、各々のセンスアンプ段は式(4-2-12)で与えられるゲイン  $G$  を持つ。

$$R_1 \cdot I_c \cdot G^2 = V_{dd} \quad (4-2-12)$$

ここで  $R_1 \cdot I_c$  はビット線の最大振幅である。初段の2つのカレントミラー型差動ステージと2段目のカレントミラーセンスアンプが同じ消費電流を持つと仮定すると、NMOSトランジスタ  $Q_1-Q_4$  は  $G_m/2$  の相互コンダクタンスを持ち、 $Q_5-Q_6$  は  $G_m$  の相互コンダクタンスを持つことになる。センスアンプ1段目の遅延時間( $t_3 - t_2$ )は以下のようになる。

$$t_3 - t_2 = \frac{C_{\text{total}} \cdot \Delta V}{I} = \frac{\frac{3}{4}G \cdot (R_L \cdot I_C) \cdot C_{\text{cm}}}{\frac{G_m}{2} \cdot R_L \cdot I_C} = \frac{3 \cdot G \cdot C_{\text{cm}}}{2 \cdot G_m} \quad (4-2-13)$$

ここで $C_{\text{cm}}$ は2段目のセンスアンプの入力容量となる。 $(4-2-12)$ 式の $G$ を $(4-2-13)$ 式に代入すると、

$$t_3 - t_2 = \frac{3 \cdot C_{\text{cm}}}{2 \cdot G_m} \sqrt{\frac{V_{dd}}{R_L \cdot I_C}} \quad (4-2-14)$$

図4-2-10：センスアンプ

NMOSトランジスタQ1-Q4が飽和している場合、

$$G_m = \mu_n \cdot C_{\text{ox}} \cdot \left(\frac{W}{L}\right) \cdot (V_{gs} - V_{tn}) \quad (4-2-15)$$

したがって、

$$\frac{C_{\text{cm}}}{G_m} = \frac{C_{\text{ox}} \cdot W \cdot L}{\mu_n \cdot C_{\text{ox}} \cdot \left(\frac{W}{L}\right) \cdot (V_{gs} - V_{tn})} = k \cdot L^2 \quad (4-2-16)$$

式 $(4-2-16)$ は初段センスアンプの遅延時間( $t_3 - t_4$ )は $L^2$ に比例することを示しており、この遅延時間は微細トランジスタを用いることで改善できることを示している。

同様の方法で2段目のセンスアンプの遅延時間( $t_4 - t_3$ )を計算すると以下のようになる。

$$t_4 - t_3 = \frac{V_{dd} \cdot C_{dbd}}{2 \cdot G_m \cdot R_l \cdot I_c \cdot \sqrt{\frac{V_{dd}}{R_l \cdot I_c}}} = \frac{C_{dbd}}{2 \cdot G_m} \sqrt{\frac{V_{dd}}{R_l \cdot I_c}} \quad (4-2-17)$$

ここで、 $C_{dbd}$ はデータバスドライバの入力容量である。大きな $G_m$ はセンスアンプでの消費電力が大きいことに対応し、この遅延時間を減らすには消費電力を大きく取る必要がある。

したがって、トータルのビット線／センスアンプ遅延は以下のように示すことができる。

$$T_{bit} = \frac{1}{2 \cdot G_m} \sqrt{\frac{V_{dd}}{R_l \cdot I_c}} (3C_{cm} + C_{dbd}) - \ln \left( 0.5 \left( 1 - \frac{V_{sense}}{R_l \cdot I_c} \right) \right) \cdot R_l \cdot C_{bcell} \times (S) \times \left( \frac{1}{N_{dbl}} \right) \quad (4-2-17a)$$

ビット線負荷をクロック動作した場合の遅延時間は $T_{bit(clock)} = T_{bit} - t_1$ となるので、

$$T_{bit(clock)} = \frac{1}{2 \cdot G_m} \sqrt{\frac{V_{dd}}{R_l \cdot I_c}} (3C_{cm} + C_{dbd}) + \left( - \ln \left( 0.5 \left( 1 - \frac{V_{sense}}{R_l \cdot I_c} \right) \right) - 0.7 \right) \cdot R_l \cdot C_{bcell} \times (S) \times \left( \frac{1}{N_{dbl}} \right) \quad (4-2-17b)$$

図4-2-10で、データバスドライバは多数のドライバが同一のデータバスに接続される場合があるので、Clocked CMOSが使用されている。SEL信号および $\overline{SEL}$ 信号はアドレス信号もしくはタグ部でのヒット信号によりコントロールされる。タグ部のヒット信号の場合はSEL信号はセンスアンプ出力の $S_2$ 信号より遅い場合が考えられる、すなわちクリティカル時間がタグによって決定する場合である。しかし、sawadaらの32KBのキャッシュメモリ設計[4-7]にあるようにタグアレイのセンスアンプ電流を増加することでこのタグによるペナルティは消すことが可能である。Hillによって示されたデータ[4-8]によれば、カスタム設計のダイレクトマップのキャッシュと2ウェイセットアソシアティブのキャッシュのアクセス時間の差は2%である。したがって、式(4-2-17a)、(4-2-17b)はセットアソシアティブキャッシュの解析にも使用可能である。

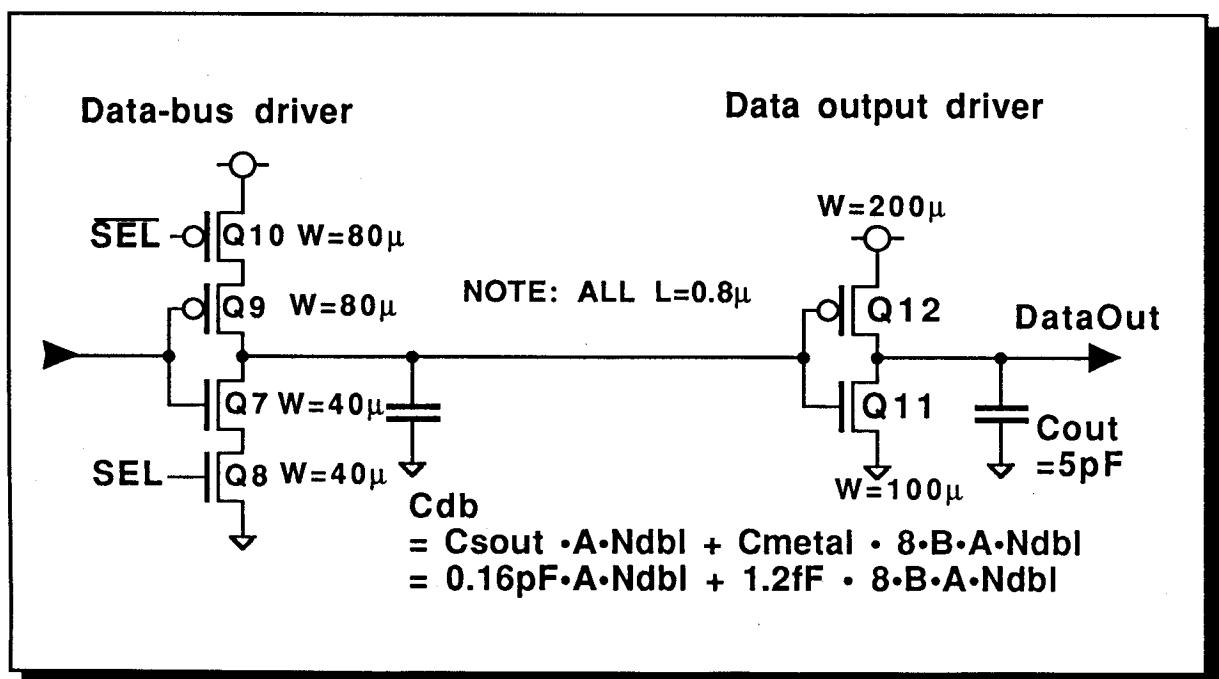

#### D データバス／出力遅延

図4-2-11はデータバスドライバから出力ドライバを示している。データバス／出力遅延 $T_{out}$ は以下のように示される。

$$T_{out} = \frac{C_{total} \cdot \Delta V}{I} = \frac{(C_{db} + C_{dod}) \cdot V_{dd}}{2 \cdot I_{dbd}} + \frac{C_{out} \cdot V_{dd}}{2 \cdot I_{dod}} \quad (4-2-18a)$$

$$C_{db} = C_{sout} \cdot A \cdot N_{dbl} + C_{metal} \cdot 8 \cdot B \cdot A \cdot N_{dbl} \quad (4-2-18b)$$

即ち、

$$T_{out} = \frac{V_{dd}}{2} \left( \frac{C_{dod}}{I_{dbd}} + \frac{C_{out}}{I_{dod}} \right) + \frac{V_{dd} \cdot C_{sout} \times (A \cdot N_{dbl})}{2 \cdot I_{dbd}} + \frac{4 \cdot V_{dd} \cdot C_{metal}}{I_{dbd}} \times (B \cdot A \cdot N_{dbl}) \quad (4-2-18c)$$

ここで  $C_{db}$  はデータバス容量でありデータバスドライバの出力容量( $C_{sout} \cdot A \cdot N_{dbl}$ )とメタル配線容量( $C_{metal} \cdot 8 \cdot B \cdot A \cdot N_{dbl}$ )の和となる。 $C_{sout}$  はデータバスドライバの出力容量、 $C_{metal}$  はメモリセル1ビットに対応するメタル配線の容量である。 $C_{dod}$  は出力ドライバの入力容量、 $C_{out}$  は出力ドライバの出力容量である。 $V_{dd}$  は電源電圧であり、ここでは5V、 $I_{dbd}$  および  $I_{dod}$  はデータバスドライバと出力ドライバの充放電電流であり、ここでは充電と放電の電流値が同じであるとしている。

図4-2-11：データバスドライバから出力ドライバまでの回路図

## E アクセスタイム

以上の結果をまとめると、トータルのアクセス時間  $T_{access}$  は以下のようになる。

$$\begin{aligned}

T_{\text{access}} = & t_0 \cdot D^{1/\ln D} \cdot \ln D \\

& + \left( \frac{4 \cdot C_{\text{wcell}} \cdot V_{\text{dd}}}{I_{\text{dn}}} \right) \times (B \cdot A) \times \left( \frac{1}{N_{\text{dw1}}} \right) \\

& + \frac{1}{2 \cdot G_m} \sqrt{\frac{V_{\text{dd}}}{R_l \cdot I_c}} (3C_{\text{cm}} + C_{\text{dbd}}) \\

& + \left( -\ln \left( 0.5 \left( 1 - \frac{V_{\text{sense}}}{R_l \cdot I_c} \right) \right) \right) \cdot R_l \cdot C_{\text{bcell}} \times (S) \times \left( \frac{1}{N_{\text{db1}}} \right) \\

& + \frac{V_{\text{dd}}}{2} \left( \frac{C_{\text{dod}}}{I_{\text{dbd}}} + \frac{C_{\text{out}}}{I_{\text{dod}}} \right) \\

& + \frac{V_{\text{dd}} \cdot C_{\text{sub}}}{2 \cdot I_{\text{dbd}}} \times (A \cdot N_{\text{db1}}) \\

& + \frac{4 \cdot V_{\text{dd}} \cdot C_{\text{metal}}}{I_{\text{dbd}}} \times (B \cdot A \cdot N_{\text{db1}})

\end{aligned} \tag{4-2-19}$$

$$D = \left( \frac{C_{N_{\text{stage}}+1}}{C_1} \right) \times (S \cdot \log_2 S) \times (N_{\text{dw1}} + N_{\text{tw1}}) \tag{4-2-5b}$$

式(4-2-19)において、第1項はデコード遅延、第2項はワード線遅延、第3項および第4項はビット線／センスアンプ遅延、第5から7項はデータバス／出力遅延に対応している。式(4-2-19)および(4-2-5b)はVdd、C、Idの様な最小限の回路的パラメータとB、A、Sなる論理パラメータおよびNdwl、Ntwlのようなアレイの物理的構成に関する物理パラメータからなっている。近似的に回路パラメータを決めた後で、アクセス時間Taccessは論理パラメータと物理パラメータを変えて最適化することができる。

#### 4.2.4 モデルの検証

以後のアクセスタイムモデルや回路シミュレータSPICEを用いた計算では、0.8 μmのCMOSプロセスを仮定して話を進める。用いられたSPICEトランジスタパラメータはStandord大学の講義で用いられたものを使用した[4-9]。

モデル中の回路パラメータはこのSPICEトランジスタモデルから計算されており、回路の定数は図4-2-6、4-1-7、4-8(a)、4-10および4-11に示されている。結果的に使用したパラメータは $t_0=122\text{ps}$ 、 $C_{\text{wcell}}=3.36\text{fF/cell}$ 、 $I_{\text{dn}}=3.3\text{mA}$ 、 $V_{\text{dd}}=5\text{V}$ 、 $I_c=0.2\text{mA}$ 、 $R_l=1.2\text{K}\Omega$ 、 $C_{\text{bcell}}=2.5\text{fF/cell}$ 、 $G_m=0.45\text{mA/V}$ 、 $C_{\text{cm}}=15.5\text{fF}$ 、 $C_{\text{dbd}}=0.266\text{pF}$ 、 $V_{\text{sense}}=100\text{mV}$ 、 $C_{\text{sub}}=0.16\text{pF}$ 、 $C_{\text{metal}}=1.2\text{fF/cell}$ 、 $C_{\text{dod}}=0.67\text{pF}$ 、 $I_{\text{dbd}}=6.6\text{mA}$ 、 $C_{\text{out}}=5\text{pF}$ 、そして $I_{\text{dod}}=33\text{mA}$ である。

図4-2-12は式(4-2-5)を用いて得られるデコード遅延Tdecodeを示した図である。ここで、 $C_1=2 \cdot C_{N_{\text{stage}}+1}$ 、すなわちワード線ドライバのサイズとフェイズスプリッタのサイズは等しいとし $N_{\text{dw1}}=N_{\text{db1}}$ としている。単位遅延時間 $t_0$ は7段のリングオシレーターのSPICEシミュレーションにより得られた値である。このデコード遅延モデルは先に述べたようにデコード遅延の理論的最小値を与え、またデコード回路の構成は様々な構成が考えられるので、SPICEシミュレーションとの比較は行なっていない。

図4-2-12：デコーダ遅延

図4-2-13：ワード線遅延

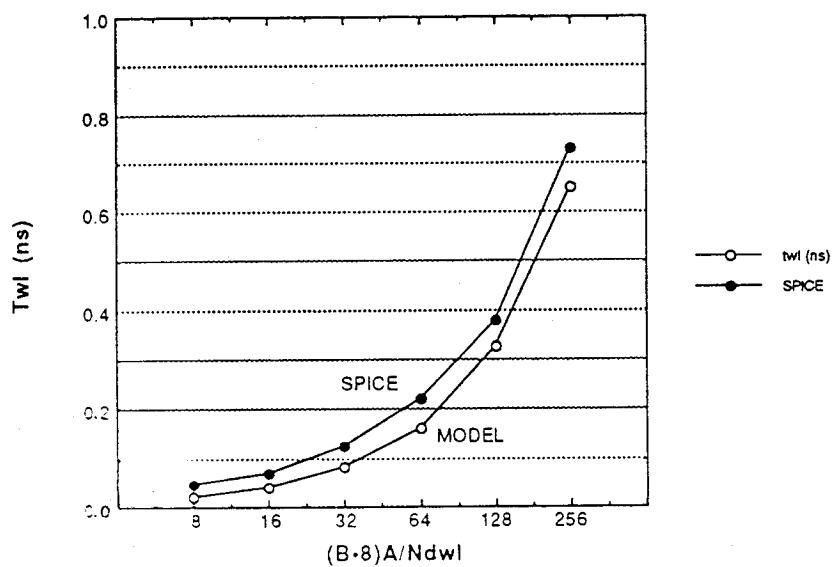

図4-2-13はモデル式(4-2-6)とSPICEシミュレーションによるワード線遅延TwIの論理パラメータに対する依存性を比べたものである。計算およびSPICEシミュレーションに使用されたデバイスのサイズは図4-2-6(b)および4-1-7に示されている。SPICEとモデルは非常に良い一致を示した。

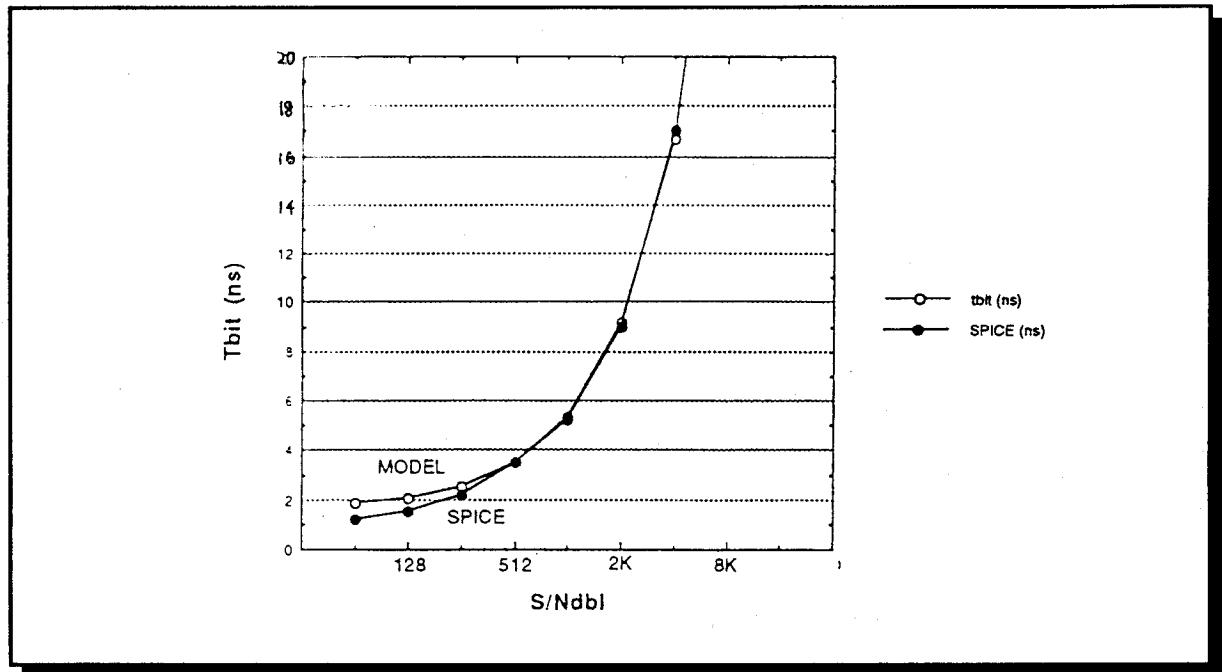

図4-2-14はビット線／センスアンプ遅延をデータアレイ中の行（ロウ）の数に対して

プロットしたものである。ここで、ビット線容量は $C_{bcell}=2.5\text{fF}/\text{cell}$ が用いられている[4-10]。タグアレイに対するビット線／センスアンプ遅延は同一のグラフの $N_{dbl}$ を単純に $N_{tbl}$ に置き換えることで得られる。256行以下のとき、アクセスタイムモデルとSPICEシミュレーションの間に少しの違いがあるがアレイの行（口ウ）数が大きい時は非常に良い一致を示している。

図4-2-14：ビット線／センスアンプ遅延

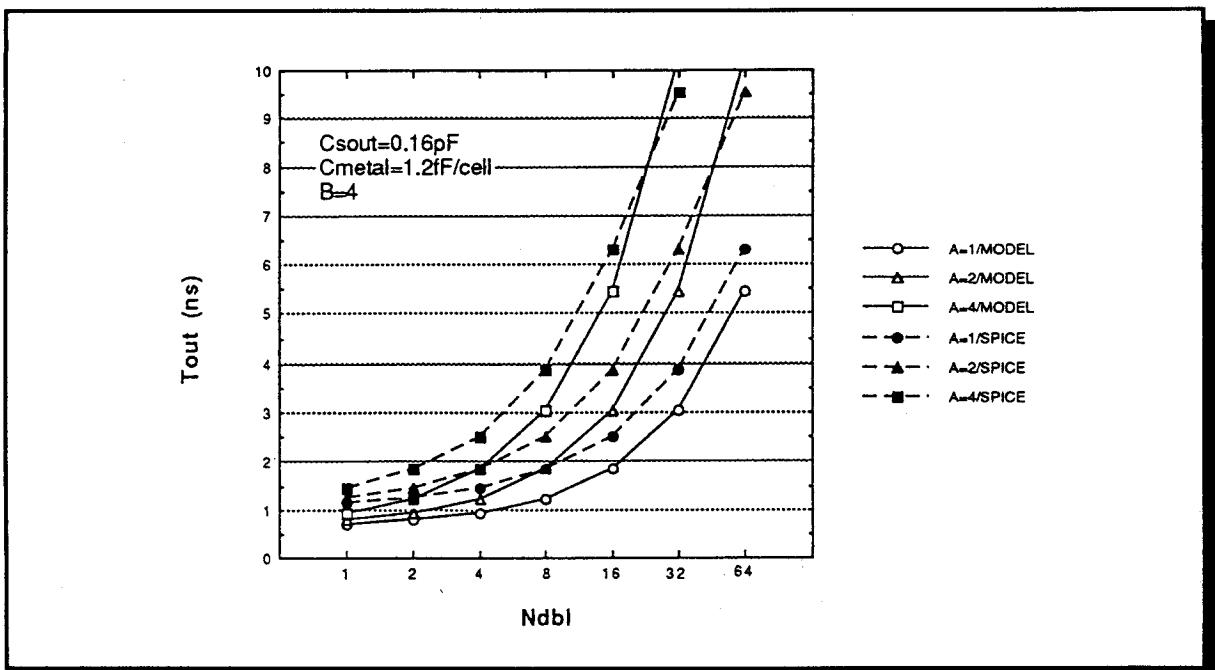

データバス／出力遅延とデータアレイ中のビット線の分割数 $N_{dbl}$ の関係を図4-2-15に示す。 $C_{sout}=0.16\text{pF}$ および $C_{metal}=1.2\text{fF}/\text{cell}$ は著者らの1MSRAMの論文[4-10]から計算した。SPICEの結果とアクセスタイムモデルの結果の間に少しの違いが見られる。この、誤差はモデルでは入力信号がステップ波形という仮定により生じていると考えられる。SPICEシミュレーションでは入力波形の立ち上がり時間／立ち下がり時間の効果が考慮されているが、モデルではこの効果は無視されている。しかしながら、絶対差は1ns以下であり、小さい。

したがってSPICEとアクセスタイムモデルの違いは1.5ns以下であり、8-nsのアクセス時間を持つキャッシュメモリでは20%程度の誤差となる。しかしながら、この解析的アクセスタイムモデルの目的は設計者にアクセス時間を最小とする論理パラメータやメモリアレイの物理構成を決める物理パラメータを選択させることであり、このアクセスタイムモデルはそのようなパラメータがアクセスタイムの各コンポーネントにどのように影響するかを示すので、その目的は十分に達成されている。

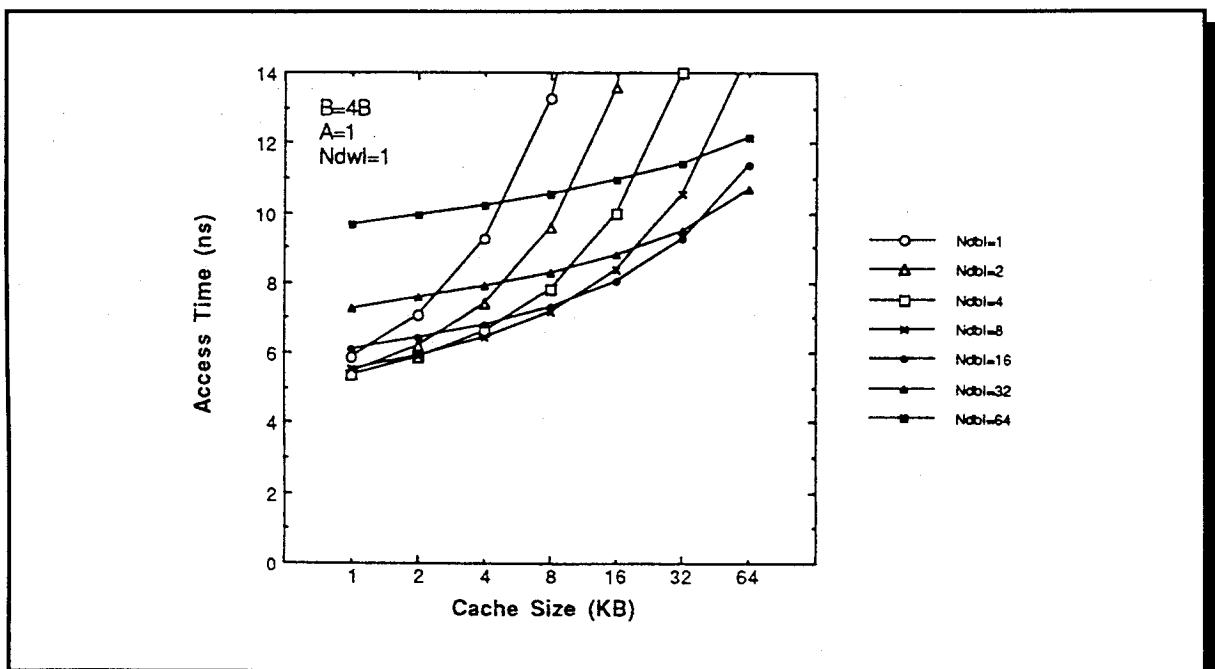

図4-2-16は $B=4$ バイト、 $A=1$ 、 $N_{dwl}=1$ の時のアクセスタイムとキャッシュサイズの関係を示したものである。1キロバイト程度の小容量のキャッシュメモリでは $N_{dbl}$ によらずアクセスタイムはほぼ同じであるが、大容量のキャッシュでは $N_{dbl}$ はアクセスタイムに大きな影響を与える。したがって、与えられたキャッシュサイズに対して $N_{dbl}$ や $N_{dwl}$

などの物理パラメータを変えることでアクセスタイムは最適化することができる。最適なNdblやNdwlが使用された場合、キャッシュ容量の増加に対するアクセスタイムの増加は最小に抑えることができる。図4-2-16の結果より最適化されたアクセスタイムはおよそキャッシュサイズの対数に比例した。

図4-2-15：データバス／出力遅延

図4-2-16：キャッシュサイズとアクセスタイムの関係

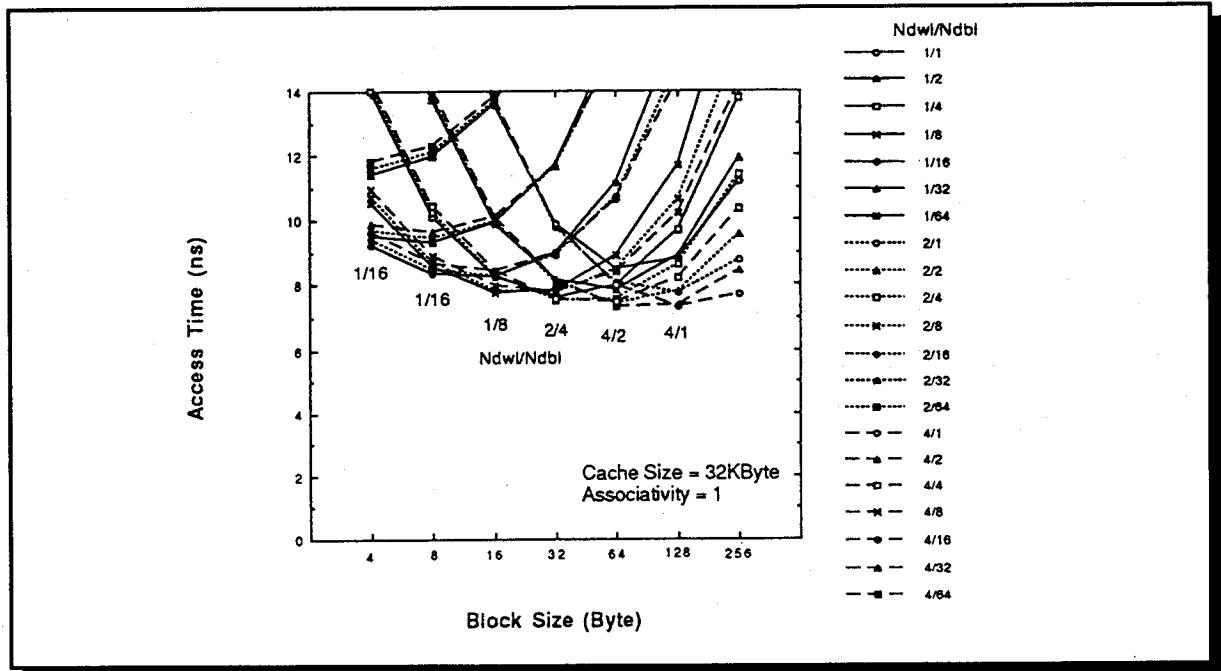

図4-2-17は32キロバイトのダイレクトマップ型キャッシュメモリでブロックサイズB

とNdblおよびNdwlを変化させた場合のアクセスタイムを示したものである。

図4-2-17：ブロックサイズとアクセスタイムの関係

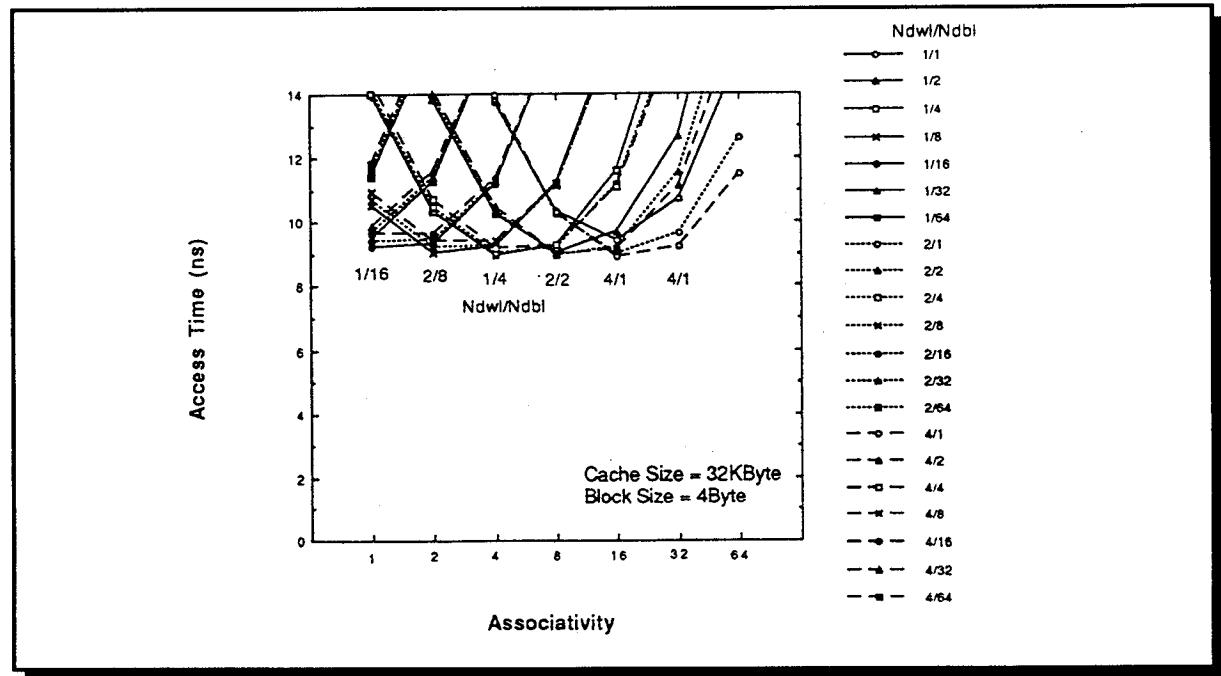

図4-2-18：アソシアティビティとアクセスタイムの関係

それぞれのブロックサイズBに対応する最小のアクセスタイムはそれぞれに異なる Ndwl/Ndblの値に対応している。図中、各Bの最小のアクセスタイムに対応するNdwl/Ndblが示されている。ブロックサイズBが小さい時（すなわち、縦に長く幅の狭いキャッシュ構成）、小さいNdwl/Ndblが最小のアクセスタイムに対応する。ブロックサイズ

が増加するにしたがって、最適のNdwl/Ndbl値は増加する。また図より最適なNdwl/Ndblが使用された場合、ブロックサイズが大きい方が小さいアクセスタイムに対応する。64バイトのブロックサイズは4バイトのブロックサイズに比べて20%高速である。

しかし図4-2-18に示すように、アソシアティビティが増加してもアクセスタイムは減少しない。ブロックサイズBやアソシアティビティAの増加はワード線の長さの増加に対応する。BおよびAはアクセスタイムモデル式(4-2-19)の第2項、6項、7項に現われる。しかし、第2項および6項ではBとAは積の形で現われる。したがって、図4-2-17と図4-2-18のアクセスタイムの差は第6項による。これはアソシアティビティが増加した時データバスドライバの数が増加しデータバス容量が増加することに対応する。このデータバスの容量の増加が図4-2-17で示されるワード線長が増加することによるアクセスタイムの増加をキャンセルしている。

## 4.3 結論

本章では高速SRAMの主な用途であるキャッシュメモリに応用した場合のアクセスタイムの最適化について述べた。

(1) オンチップキャッシュメモリに適した解析的アクセスタイムモデルを提案し、その妥当性を検証した。

(2) この解析的アクセスタイムモデルはキャッシュサイズC、ブロックサイズB、アソシアティビティAなどの一般的なキャッシュの論理パラメータのほかにサブアレイのアスペクトレシオやサブアレイ数を決める物理パラメータ ( $N_{dwl}$ 、 $N_{dbl}$ 、 $N_{twl}$  および  $N_{tbl}$ ) を含んでおり、これにより詳細な回路設計なしにキャッシュメモリのスピードを見積ることができ、多種多様なキャッシュメモリの設計自由度をカバーすることができる。

(3) この解析的アクセスタイムモデルにより、与えられたキャッシュサイズC、ブロックサイズB、アソシアティビティAに対して、最速のアクセスタイムに対応する最適なアレイ構成を決める物理パラメータが存在することが解かった。

(4) 最適なアレイ物理パラメータ ( $N_{dwl}$ 、 $N_{dbl}$ 、 $N_{twl}$  および  $N_{tbl}$ ) を使用したとき、アクセスタイムはキャッシュサイズの対数にほぼ比例して増加することが判明した。

(5) 最適なアレイ物理パラメータ ( $N_{dwl}$ 、 $N_{dbl}$ 、 $N_{twl}$  および  $N_{tbl}$ ) が使用された場合、大きいブロックサイズBは小さいアクセスタイムに対応する。しかし、アソシアティビティの増加によりデータバス容量が増加するため、大きいアソシアティビティは必ずしも小さいアクセスタイムに対応しないことが判明した。

## 4.4 参考文献

- [4-1] R.R. Duncombe, "The SPUR Instruction Unit: An On-Chip Instruction Cache Memory for a High Performance VLSI Multiprocessor," Technical Report UCB/CSD 87/307, Computer Science Division, University of California, Berkeley, August, 1986.

- [4-2] H.C. Lin and L.W. Linholm, "An Optimized Output Stage for MOS Integrated Circuits," IEEE J. Solid-State Circuits vol. SC-10, pp. 106-109, 1975.

- [4-3] Carver Mead and Lynn Conway, Introduction to VLSI Systems, Addison Wesley Publishing Company, 1980.

- [4-4] T. Sakurai and A.R. Newton, "Delay Analysis of Series-Connected MOSFET Circuits," IEEE J. Solid-State Circuits, vol. SC-26, NO.2, Feb. 1991.

- [4-5] Paul Chow, The MIPS-X RISC Microprocessor, Kluwer Academic Publishers, 1989.

- [4-6] T. Yamanaka, T. Ozawa, S. Koshimaru, O. Kudo, H. Ito, N. Yasuoka, H. Asai, N. Harashima, abd S. Kikuchi,"A 25-ns 64K Static RAM," IEEE J. Solid-State Circuits, vol. SC-19, No.5, Oct. 1984.

- [4-7] Kazuhiro Sawada, et al, " A 32-Kbyte Integrated Cache Memory," IEEE J. Solid-State Circuits, vol. SC-24, No.4, pp. 881-888, Aug. 1989.

- [4-8] Mark D.Hill, " A Case for Direct-Mapped Caches", IEEE COMPUTER, pp. 25-39, Dec. 1988.

- [4-9] M.G. Johnson and N.P.Jouppi, "Transistor Model for a Synthetic 0.8um CMOS Process," Submitted to the IEEE Circuits & Devices Magazine.

- [4-10] Y. Kohno et al., "A 14-ns 1-Mbit CMOS SRAM with Variable Bit Organization," IEEE J. Solid-State Circuits, vol. SC-23, pp. 1060-1066, Oct. 1988.

- [4-11] T. Wada, S. Rajan, and S. A. Przybylski, " An Analytical Access Time Model for On-Chip Cache Memories," IEEE J. Solid-State Circuits, vol. SC-27, pp. 1147-1156, Aug. 1992.

## 第5章

# SRAMの高速化に対する信頼性上の 問題と解決策

## 5.1 はじめに

VLSIプロセスおよびデバイス技術の進歩により、SRAMを構成する素子の高速スイッチングが実現されている。しかし、高速スイッチングにより発生するチップ内部の電源線やグランド線に発生するバウンスノイズはアクセスタイムが短くなるにつれて問題となってきた。特に、データ出力バッファは非常に大きなチップ外部の容量を駆動するので、大きなコンダクタンスを持ち主たるノイズ源になっている。

また、高抵抗負荷を用いたSRAMのメモリセルはそのメモリセルサイズの小面積の利点を活かして標準SRAMに使用されている。高集積化と同時にその高抵抗負荷の抵抗値も上昇を続けており前世代小容量品と同じスタンバイ電流スペックを実現している。通常高抵抗負荷を用いたSRAMではワード線がHighに上がった選択状態になったときメモリセルのHighを保持しているノード電位が電源Vccより低下し、非選択になった後その高抵抗を介して非常に大きなミリ秒のオーダの時定数で充電されるので、サイクルタイムが短くなるにつれてソフトエラー率が上昇する。

本章ではまず最初に出力バッファの出力波形を高速化する障害となる出力の同時スイッチングによるチップ内部の電源電位に発生するバウンスノイズのモデリングとその対策方法を述べ、それを実現する電圧降圧回路を組み合わせた低ノイズ出力バッファを提案する[5-1]。

次に、通常高速化すなわちサイクルタイムを短くするとソフトエラー率が上昇するメカニズムを明らかにし、これと逆のサイクルタイムを長くするとソフトエラー率が上昇する逆依存性の存在を示し、この逆依存性を利用してソフトエラー率を下げる方法を述べる[5-7]。

## 5.2 出力バッファの解析的モデル

VLSIプロセスおよびデバイス技術の進歩により、RAMの動作スピードは著しく向上しており、高速スイッチングにより発生するチップ内部の電源線やグランド線に発生するバウンスノイズはアクセスタイムが短くなるにつれて問題化している。データ出力バッファは大きなチップ外部の容量を駆動するので、大きなコンダクタンスを持ち主なノイズ源になっている。

本項では、データ出力バッファによる電源電位に発生するバウンスの解析的モデルを示す。具体的には解析モデルは出力バッファトランジスタのコンダクタンス、出力電位振幅、および電源の寄生インダクタンスとバウンス電位の関係を示す。また、電圧降圧回路を組み合わせた低ノイズ出力バッファを提案しその効果を示す。

### 5.2.1 CMOS出力バッファの電源ノイズ

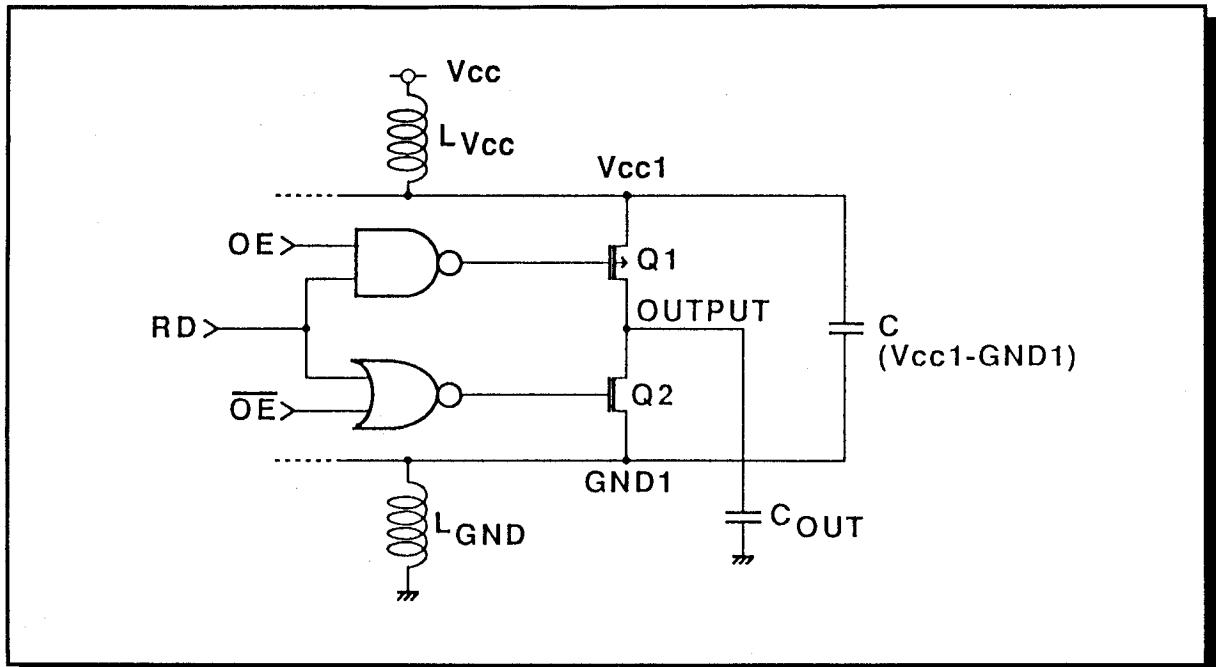

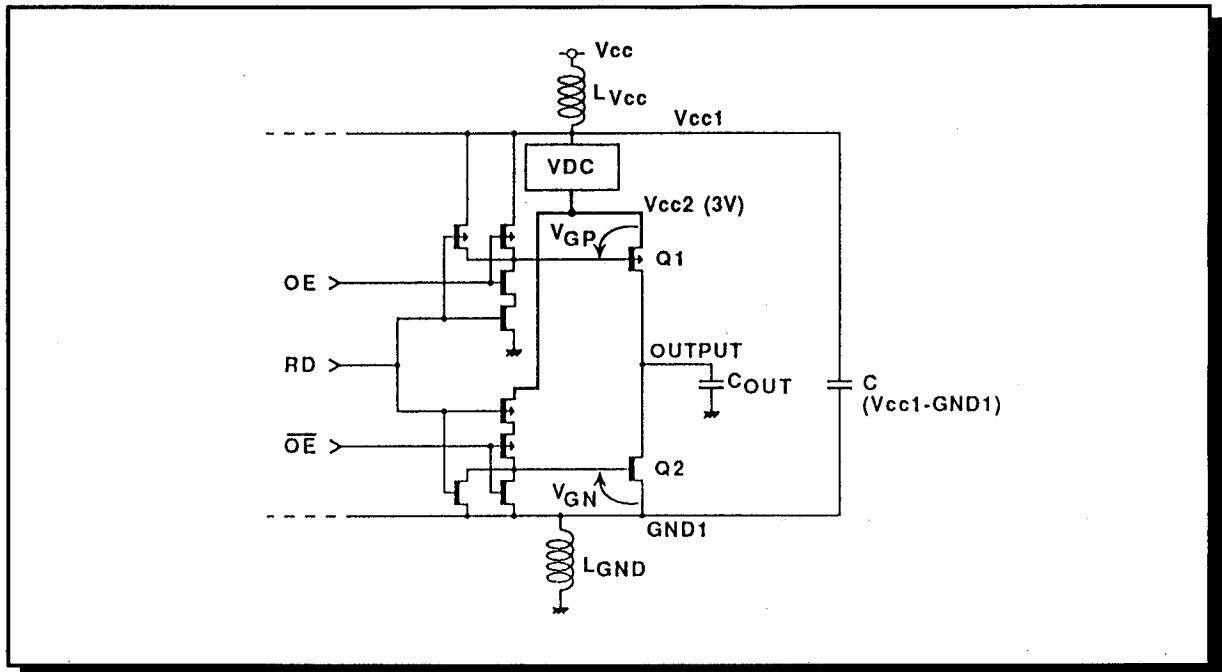

一般的なCMOS型出力バッファに電源線の寄生インダクタンスを含めた図を図5-2-1に示す。

図5-2-1：電源線の寄生インダクタンスを含めた一般的なCMOS型出力バッファ

リードデータ信号(RD)はNANDもしくはNORゲートにより出力トランジスタQ1、Q2に転送される。出力イネイブル信号OE(Output enable)はデータ出力バッファのモードを制御する。OEがHighレベルのとき出力バッファは活性化され、Lowレベルのとき出力バッファはハイインピーダンスを出力する。

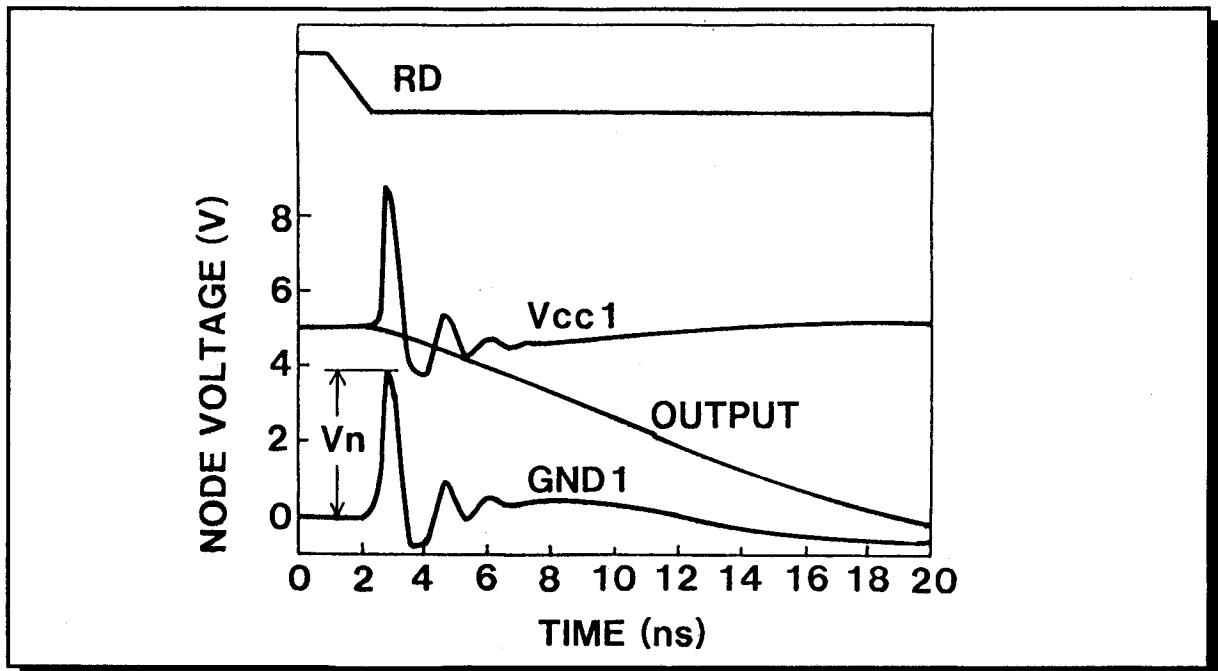

回路シミュレーションプログラムSPICEによるデータ出力バッファのHighからLowへの変化時のシミュレーション結果を図5-2-2に示す。使用したパラメータを以下に示す。Q1のL/W=1.0  $\mu\text{m}$ /220  $\mu\text{m}$  × 8、Q2のL/W=1.5  $\mu\text{m}$ /200  $\mu\text{m}$  × 8、Vcc=5V、LVcc=10nH、LGND=10nH、CVcc1-GND1=500pF、そしてCOUT=100pF × 8である。バイトワイド構成のRAMを仮定して、チャネル幅および出力容量は8倍されている。チップ内部の電源電位Vcc1/GND1にL × di/dtによりノイズが発生する。この場合GND1のノイズは直接COUTの放電により発生するがVcc1のノイズはGND1とVcc1のカップリング容量CVcc1-GND1により間接的に発生する。

図5-2-2：データ出力バッファのHighからLowへの変化時のシミュレーション結果

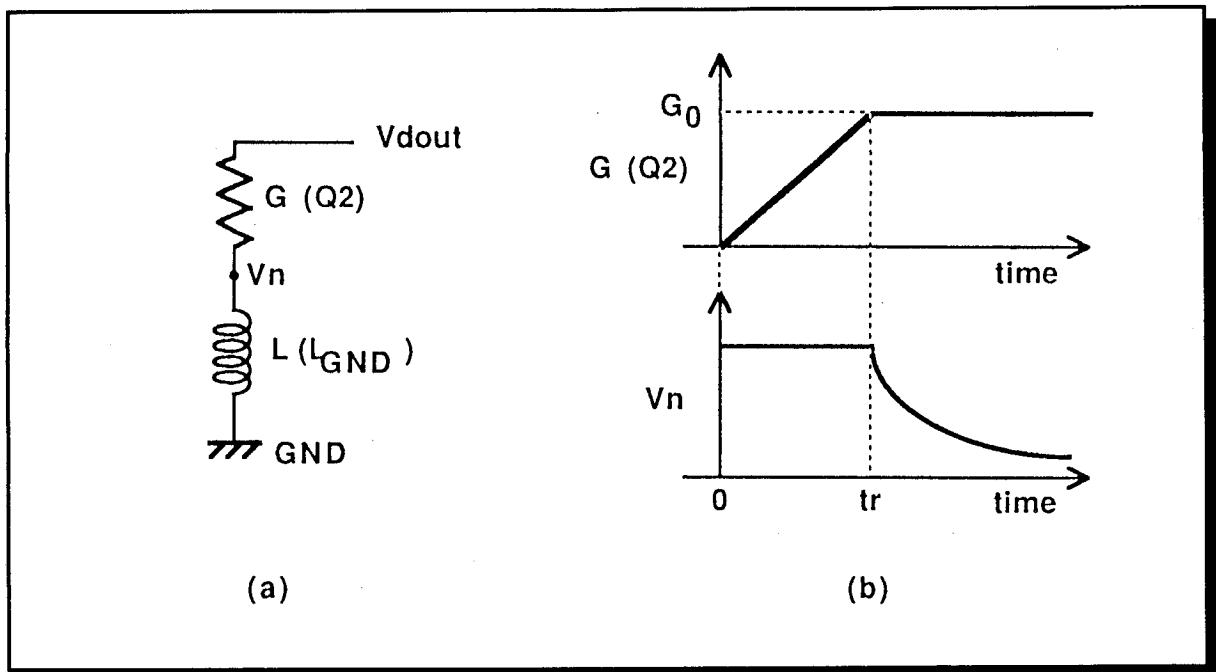

### 5.2.2 データ出力バッファの解析的近似

寄生インダクタンスLGNDによるGND1上に発生するノイズを解析するために、図5-2-3(a)のような簡単な時間可変抵抗とインダクタを考える。Q2の入力波形はLowからHighへ一定の傾きで変化すると仮定し、そのスイッチング時間を $t_r$ とする。Q2をショートチャネルトランジスタとすると、ゲート電位にはほぼ1次比例で飽和領域のトランジスタのコンダクタンスは変化するので、トランジスタQ2のコンダクタンスGは以下のようになる。

$$G = \frac{G_0}{t_r} t \quad (0 < t \leq t_r) \quad (5-2-1a)$$

$$G = G_0 \quad (t_r < t) \quad (5-2-1b)$$

ここで $G_0$ はQ2の最大コンダクタンスである。動作中のQ2のゲート入力はHighレベルとなり、これは $V_{cc1}$ の電位である。これはGND1のノイズのカッピングを受ける。したがって、Q2に印加されるゲート／ソース電圧はGND1の浮き上がりによって影響を受けないので、ノイズ電位 $V_n$ の出力トランジスタのコンダクタンスへの影響は無視することができる。このノイズ電位 $V_n$ は以下のように示される。

$$V_n = L \frac{di}{dt} \quad (5-2-2)$$

ここでLはGND線の寄生インダクタンス(LGND)である。

図5-2-2に示すように、COUTが比較的大きいときデータ出力ノードのスイッチング時間はtrよりかなり大きい。

図5-2-3：データ出力バッファモデル

(a) 時間可変抵抗とインダクタによる出力バッファモデル、(b) ノイズ波形

したがって、ノイズがピークを持つときの出力レベル  $V_{dout}$  は定数と考えることができます。

$$V_{dout} - V_n = \frac{i}{G} \quad (5-2-3)$$

式(5-2-1)および(5-2-2)を(5-2-3)に代入し解くと以下の式が得られる。

$$V_n = \frac{1}{1 + \frac{tr}{L \cdot G_0}} V_{dout} \quad (0 < t \leq tr) \quad (5-2-4a)$$

$$V_n = \frac{1}{1 + \frac{tr}{L \cdot G_0}} V_{dout} \cdot \exp\left(-\frac{t - tr}{L \cdot G_0}\right) \quad (tr < t) \quad (5-2-4b)$$

この結果は図5-2-3(b)に示されており、結果的にピークノイズ電圧  $V_{nmax}$  は以下のようになる。

$$V_{nmax} = \frac{1}{1 + \frac{tr}{L \cdot G_0}} V_{dout} \quad (5-2-5)$$

### 5.2.3 モデルと回路シミュレーションSPICEとの比較

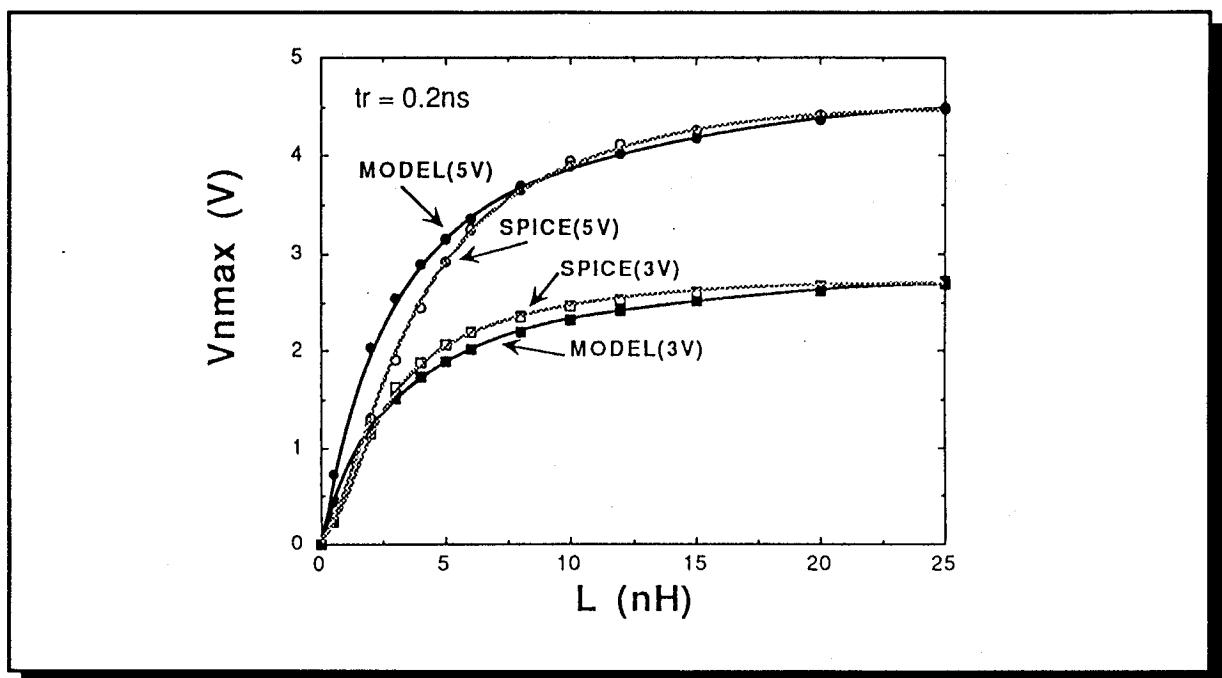

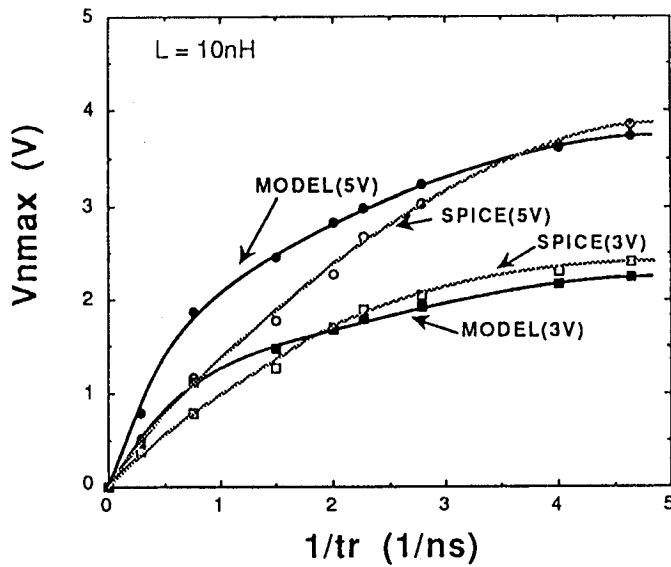

図5-2-4は $V_{dout}=3$ および $5V$ 、 $G_0=0.065(1/\Omega)$ 、 $tr=0.2ns$ のときのインダクタンス $L$ とピークノイズ電圧 $V_{nmax}$ の関係を示したグラフである。モデルはSPICEと非常に良く一致している。また $L$ の増加と共に $V_{nmax}$ は増加するがすぐに飽和し、その飽和値は $V_{dout}$ と等しくなる。

図5-2-4：インダクタンス $L$ とピークノイズ電圧 $V_{nmax}$ の関係

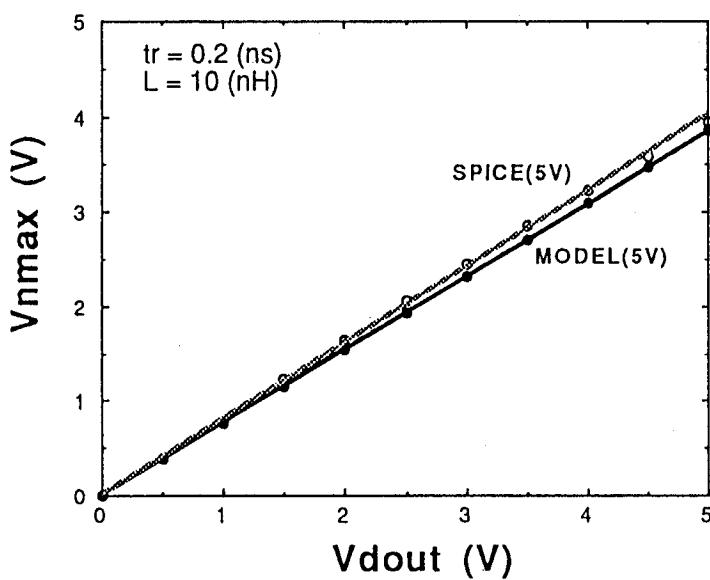

$L=10nH$ 、 $G_0=0.065(1/\Omega)$ のときのスイッチング時間の逆数( $1/tr$ )と $V_{nmax}$ の関係を図5-2-5に示す。 $V_{dout}=5V$ のときモデルは $1/tr$ が $2(1/ns)$ 以下の領域で大きくなっているが、ほぼモデルとSPICEの結果は一致している。その一致していない領域では、Q2の入力信号が一定の傾きで変化するという仮定が成り立っていないと考えられる。図5-2-6は $V_{nmax}$ と $V_{dout}$ の関係を示す。SPICEとモデルは良く一致しており、ノイズ電位 $V_n$ は $V_{dout}$ に正比例の関係がある。

結果的に、ピークノイズ電圧 $V_{nmax}$ を下げるためには $L \cdot G_0$ より $tr$ が大きくかつ $V_{dout}$ が小さいことがピークノイズ電圧 $V_{nmax}$ を下げるために必要となる。大きな $tr$ および小さな $G_0$ は出力バッファでの遅延時間を増加させることに対応し、また $V_{nmax}$ は $V_{dout}$ に一次比例の関係にあるので、超高速デバイスの低ノイズ化には電源ピンを増加させて寄生インダクタンスを減らす方法もしくは出力電圧振幅を最小化するのが有効となる。

図5-2-5：スイッチング時間の逆数( $1/tr$ )とピークノイズ電圧 $V_{nmax}$ の関係

図5-2-6：出力振幅 $V_{dout}$ とピークノイズ電圧 $V_{nmax}$ の関係

#### 5.2.4 電圧降圧回路を組み合わせた低ノイズ出力バッファ

今回新しく考案した電圧降圧回路を組み合わせた低ノイズ出力バッファを図5-2-7に示す。降圧回路VDCは最大の $V_{dout}$ を $V_{cc2}=3V$ に降圧する。Q2の最大ゲート／ソース

間電圧VGNおよびQ1のVGPは3V以下に制限される。したがって、G0の電源電圧Vcc依存性はなくなり、同時にスイッチング時間trのVcc依存性が減少する。

図5-2-7：電圧降圧回路を組み合わせた低ノイズ出力バッファ

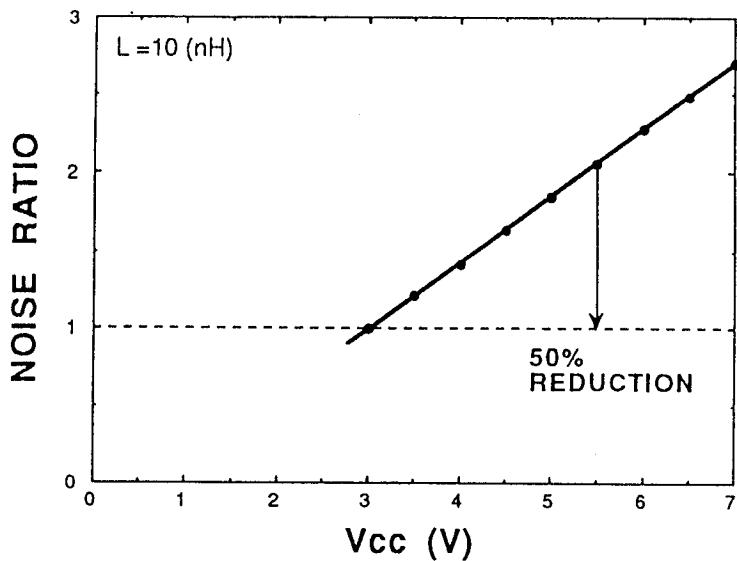

式(5-2-5)のノイズのピーク値の比 $V_{nmax}$  (VDC不使用時) /  $V_{nmax}$  (VDC使用時)を $tr$ 、 $G0$ 、 $Vdout$ の電源依存性を考慮して $Vcc=4.5V$ のときデータ出力バッファでの遅延時間が等しいという条件で求めると図5-2-8のようになる。通常のRAMは $5V \pm 10\%$ すなわち $4.5V$ から $5.5V$ で動作するので、最悪条件 $Vcc=5.5V$ のノイズと電位降圧回路を組み合わせた低ノイズ出力バッファを比べるとノイズのピーク値は約半分となる。このとき、スピードに対する最悪条件 $Vcc=4.5V$ の遅延時間は両者で等しい。したがって出力振幅 $Vdout$ を小振幅化し、ピークノイズに影響を与える $tr$ 、 $G0$ 、 $Vdout$ なるパラメータの電源電位依存性を減らすことで低ノイズ高速動作を実現できる。

図5-2-8：ノイズのピーク値の比  $V_{nmax}$  (VDC不使用時) /  $V_{nmax}$  (VDC使用時)

### 5.3 SRAMソフトエラー率の逆サイクルタイム依存性

本項では高抵抗負荷を用いたSRAMにおけるソフトエラー率の新現象「逆サイクルタイム依存性」について述べる。高抵抗負荷を用いたSRAMのメモリセルはそのメモリセルサイズの小面積の利点を生かして標準SRAMに使用されている。高集積化と同時にその高抵抗負荷の抵抗値も上昇を続けており前世代の小容量デバイスと同じスタンバイ電流スペックを実現している。通常高抵抗負荷を用いたSRAMではワード線がHighに上がった選択状態になったとき、メモリセルのHighを保持しているノード電位が電源Vccより低下し、非選択になった後その高抵抗を介してミリ秒のオーダの非常に大きな時定数で充電されるので、サイクルタイムが短くなるにつれてソフトエラー率が増加する[5-2]、[5-3]。

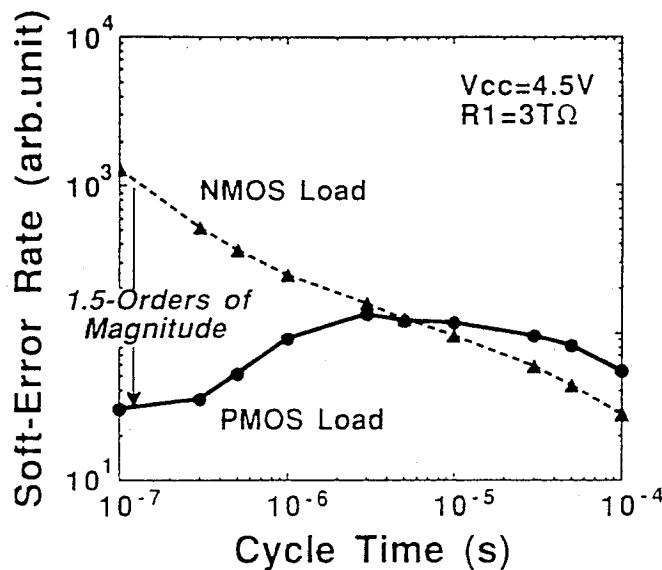

今まで種々の高抵抗負荷型SRAMのソフトエラー率の改善方法[5-4]、[5-5]が報告されているが、いずれも上記サイクル時間依存性に関係するものである。論文[5-4]では、ビット線負荷デバイスとしてNMOSを用いたSRAMでのソフトエラー率を議論しており、メモリセル中のアクセストランジスタおよびドライバトランジスタを流れる電流を高抵抗からの充電電流より小さくすることでソフトエラー率を改善している。

本項では新現象であるPMOS負荷を用いたSRAMにおけるサイクル時間を短くするとソフトエラー率が現象する「逆サイクルタイム依存性」を述べる。この新現象によりサイクルタイム100nsでのソフトエラー率は1.5桁改善された。さらに本新現象を説明する新モデルを提案し「通常サイクルタイム依存性」、「逆サイクルタイム依存性」、

「サイクルタイム依存性なし」なる3種の依存性がどのようなメモリセルパラメータにより発生するかを明らかにする。

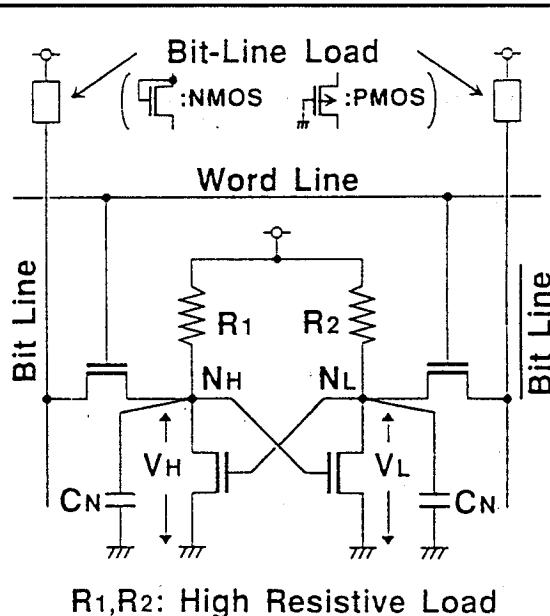

### 5.3.1 メモリセルの構成

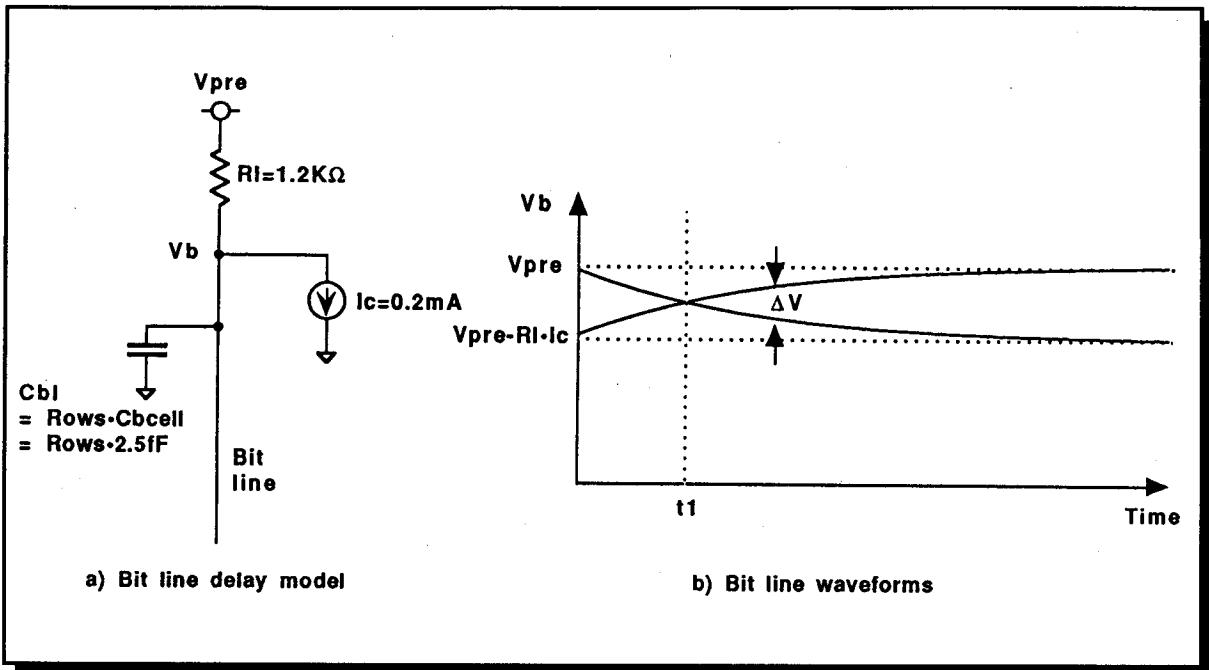

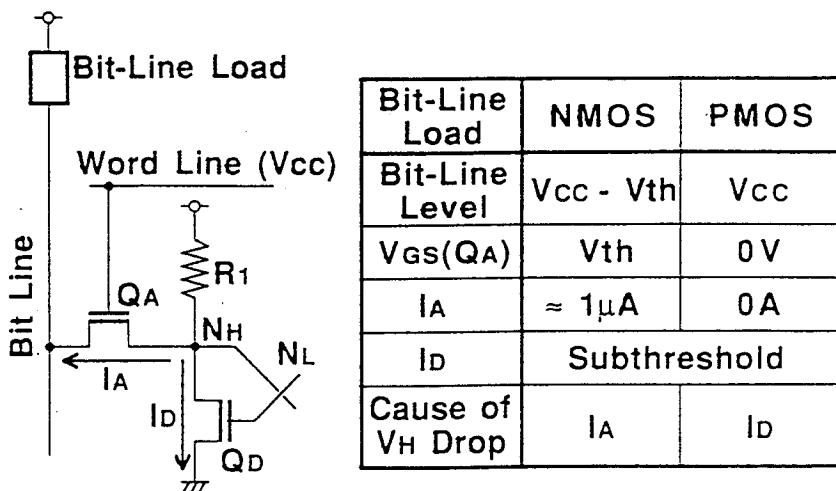

図5-3-1に高抵抗負荷型SRAMのメモリセルとその周辺回路構成を示す。メモリセルは4個のNMOSトランジスタと2個の高抵抗( $R_1$ 、 $R_2$ )から構成されるフリップフロップと2個のトランジスファーゲートからなる。ノード $N_H$ と $N_L$ はそれぞれ"High"と"Low"の電位 $V_H$ と $V_L$ を保持する。アルファ線が半導体中を通過したときに発生する電子がノード $N_H$ に収集されたときソフトエラーが発生する。生成された電子によりノード容量 $C_N$ の電位 $V_H$ のレベルを低下させる。この低下した $V_H$ のレベルが $V_L$ より低い場合メモリセルに保持されたデータは反転する。また、ビット線電位は電源 $V_{cc}$ との間に接続されたビット線負荷デバイス (NMOSまたはPMOS) を介して供給される。

図5-3-1：高抵抗負荷型SRAMのメモリセルとその周辺回路構成

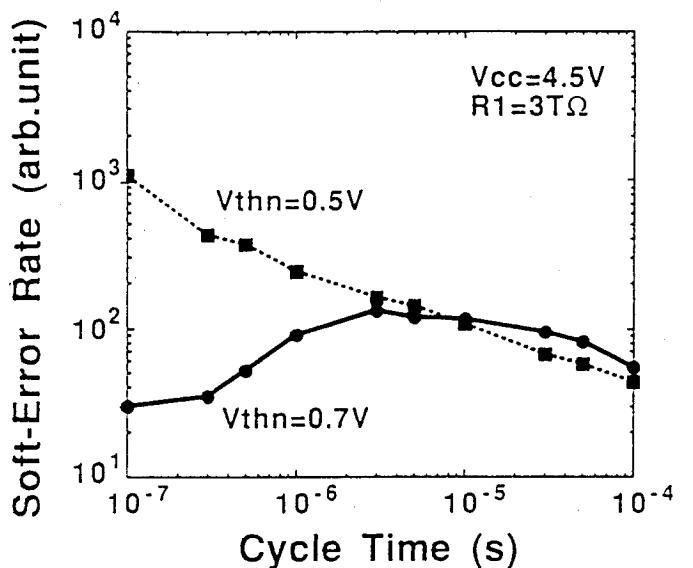

### 5.3.2 ソフトエラー率の測定結果

図5-3-2は3TΩ (テラオーム) の高抵抗負荷を用いた1MSRAM [5-6]の電源電位4.5Vにおけるソフトエラー率の測定結果である。アルファ線源はAm241で室温25°Cで測定した。実線と点線はそれぞれビット線負荷にPMOSもしくはNMOSを用いた場合に対応する。点線は通常のサイクルタイム依存性であり、実線はサイクルタムが10μs以下でサイクルタイムが短くなるにしたがってソフトエラー率が減少するソフトエラー率の逆サイクルタイム依存性である。この逆サイクルタイム依存性によりNMOSビット線負荷の通常SRAMよりサイクルタイムが短い領域でソフトエラー率が改善している。100ns

のサイクルタイムで約1.5桁改善されている。

図5-3-2：1MSRAM [5-6]のソフトエラー率の測定結果

### 5.3.3 解析

本節ではソフトエラー率の逆サイクルタイム依存性のメカニズムを解析する。まず最初にNMOSビット線負荷の通常SRAMの通常のサイクルタイム依存性を説明する。そしてその後この新現象である逆サイクルタイム依存性を解析する。

#### 5.3.3.1 SRAMのソフトエラー率の通常のサイクルタイム依存性

図5-3-3に"High"のデータを記憶するノード $N_H$ まわりの回路図とNMOS/PMOSビット線負荷の比較を示す。 $Q_A$ および $Q_D$ はそれぞれアクセストランジスタとドライバトランジスタである。NMOSビット線負荷を持つSRAMでは、ビット線電位は $V_{cc} - V_{th}$ であり、 $V_{th}$ はビット線負荷のNMOSトランジスタのしきい値電圧である。ワード線が選択され $V_{cc}$ となったときのアクセストランジスタ $Q_A$ のゲート/ソース電位 $V_{GS}$ は $V_{th}$ に等しい。したがって、ワード線が選択されたとき $Q_A$ のドレイン電流 $I_A$ はノード $N_H$ を急速にビット線電位である $V_{cc} - V_{th}$ にプルダウンする。またワード線が選択されたときメモリセルのビット線放電電流がノード $N_L$ の電位 $V_L$ を数百mV浮き上げて、 $Q_D$ のサブスレッシュホールド電流 $I_D$ も増加する。しかしNMOSビット線負荷の場合、 $I_A$ は $I_D$ 比べて十分大きく $I_D$ は無視できる。

図5-3-3：ノードNHまわりの回路図とNMOS/PMOSビット線負荷の比較

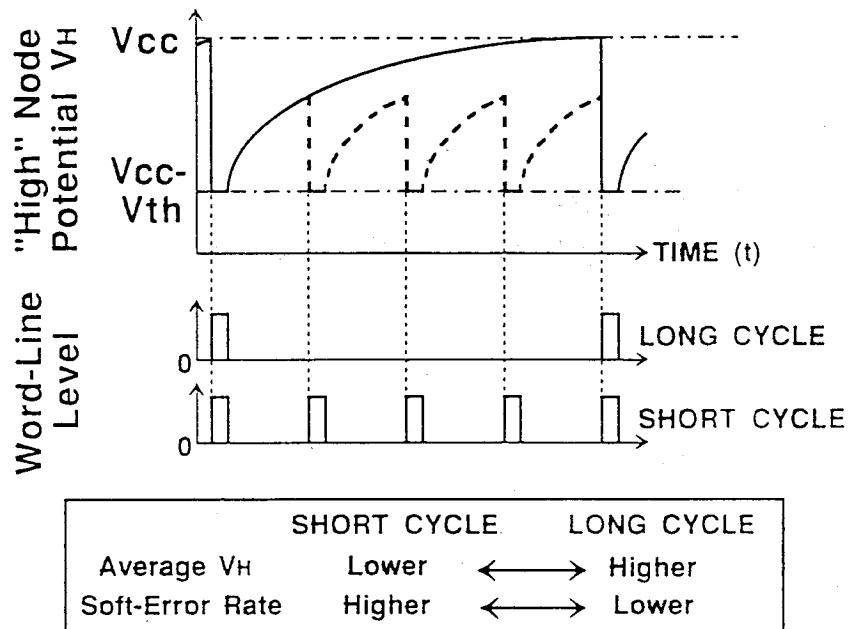

図5-3-4はノードNHの電位 $V_H$ の読み出し動作時の時間的変化を示した図である。実線はサイクルタイムが長い場合、点線はサイクルタイムが短い場合を示している。

図5-3-4：ノードNHの電位 $V_H$ の読み出し動作時の時間的変化

ワード線が選択されたとき $V_H$ は $V_{cc}-V_{th}$ に低下し、ワード線が非選択状態の間にしだいに充電され $V_{cc}$ に近づく。したがって、長いサイクルタイムは $V_H$ がより高い電位へ充電されることに対応する。ワード線が非選択のときメモリセルノードのプルアップは高

抵抗でのみ行なわれるので、ソフトエラーは主としてワード線が非選択状態で発生する。それゆえ、 $V_H$ の平均電位 $V_{HA}$ がソフトエラー率に関係する。結果的に、図5-3-4が示すようにサイクルタイムが短い場合、 $V_{HA}$ は低下しソフトエラー率は増大する。

### 5.3.3.2 ソフトエラー率の逆サイクルタイム依存性

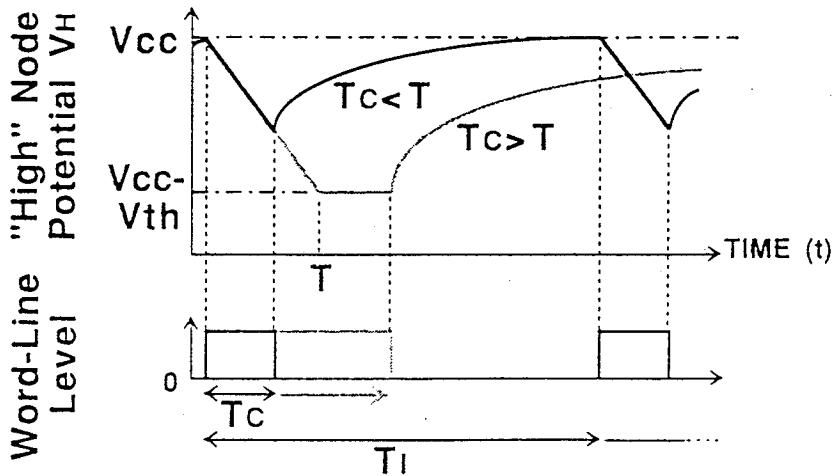

PMOSビット線負荷に対応するメモリセルの動作も図5-3-3に示されている。PMOSビット線負荷の場合ビット線電位は $V_{cc}$ となる。ワード線が選択され $V_{cc}$ になったとき、ゲート／ソース電圧は0Vであるので $Q_A$ はOFFしている。したがって、この場合 $I_A$ は流れず、 $I_D$ がノード $N_H$ をプルダウンする原因となる。 $I_D$ は $I_A$ に比べて非常に小さいので $V_H$ が低下するには比較的長い時間を必要とする。以下にノード $N_H$ の電位低下を解析する。 $V_H$ の電位は以下のように現される。

$$V_H(t) = V_{cc} - \frac{I_D}{C_N} \cdot t \quad (5-3-1)$$

ここで $t$ はワード線1本の選択時間である。式(5-3-1)より、ワード線の選択期間中に $V_H$ は単調に減少する。 $V_H$ が $V_{cc}-V_{th}$ に到達するとアクセストランジスタのゲート／ソース電位は $V_{th}$ となりアクセストランジスタがONするので、 $V_H$ の電位の低下は止る。 $V_H(t)=V_{cc}-V_{th}$ となる時間 $T$ を求める式(5-3-1)より以下のようになる。

$$T = V_{th} \cdot \frac{C_N}{I_D} \quad (5-3-2)$$

したがって、 $t > T$ では $V_H(t)=V_{cc}-V_{th}$ となる。

図5-3-5はPMOSビット線負荷に対応する $V_H$ の時間依存性を示した図である。ワード線の選択時間をサイクルタイム $T_C$ 、ワード線の選択インターバルを $T_I$ とすると、

$$T_I = T_C \cdot N_W \quad (5-3-3)$$

となり、 $N_W$ はワード線の数に対応する。 $T_C < T$ のとき、 $V_H$ は式(5-3-1)にしたがって減少し実線で示したようになる。そして、ワード線の非選択後 $V_H$ は高抵抗により充電され増加する。したがって、 $T_C$ が減少するに従って $V_H$ の低下は抑制され平均電位 $V_{HA}$ が高くなる。一方、 $T_C > T$ のとき $V_H$ は灰色線で示したように $V_{cc}-V_{th}$ でクランプされる。 $V_H$ の再充電時間は $T_I - T_C$ となり $T_C$ に比例するので、サイクル時間が短いほど平均電位 $V_{HA}$ は減少しこれはNMOSビット線負荷の場合と類似している。

高抵抗 $R_1$ がノード容量 $C_N$ を充電するので、充電期間の $V_H(t)$ は以下のようになる。

$$V_H(t) = V_{cc} - \Delta V \cdot \exp\left(-\frac{t}{C_N \cdot R_1}\right) \quad (0 \leq t \leq T_I - T_C) \quad (5-3-4)$$

図5-3-5：PMOSビット線負荷に対応するV<sub>H</sub>の時間依存性

ここで $\Delta V$ はワード線の選択中のノード電位の低下分である。ソフトエラー率を求めるためにV<sub>HA</sub>を求める。式(5-3-1)、(5-3-2)および(5-3-4)より、

$$V_H(T_C) = \frac{1}{T_I - T_C} \int_0^{T_I - T_C} \left[ V_{cc} - \frac{I_D}{C_N} \cdot T_C \cdot \exp\left(-\frac{t}{C_N \cdot R_1}\right) \right] dt \quad (0 \leq T_C \leq T) \quad (5-3-5)$$

$$V_H(T_C) = \frac{1}{T_I - T_C} \int_0^{T_I - T_C} \left[ V_{cc} - V_{th} \cdot \exp\left(-\frac{t}{C_N \cdot R_1}\right) \right] dt \quad (T_C > T) \quad (5-3-6)$$

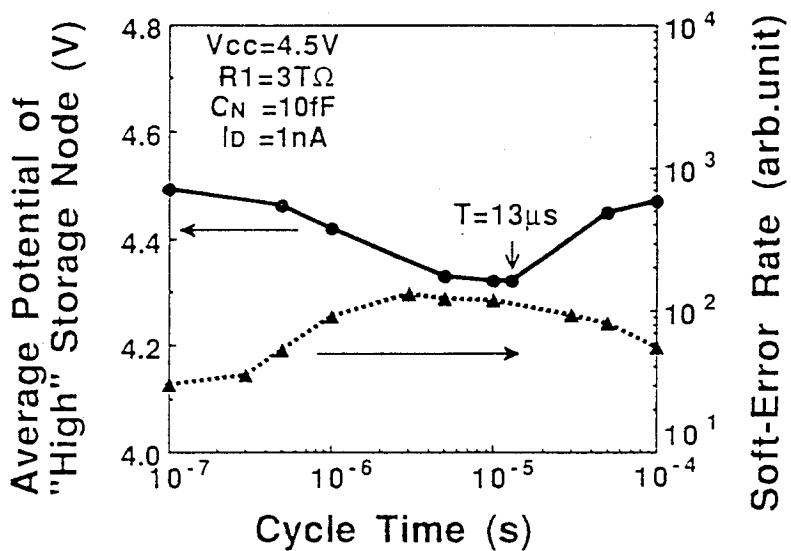

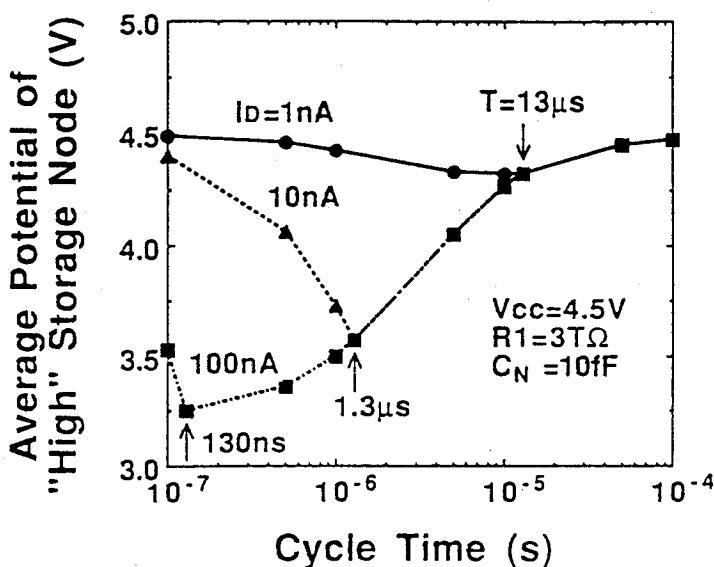

図5-3-6は式(5-3-5)、(5-3-6)より計算されたV<sub>HA</sub>を測定されたソフトエラー率と同時に示した図である。ここでデバイスは高抵抗負荷を用いた1MSRAM [5-6]であり、高抵抗値 $R_1=3T\Omega$ である。また、 $T_I=T_C \times 16K$ 、 $V_{cc}=4.5V$ 、 $I_D=1nA$ である。Nノード容量 $C_N$ はゲート酸化膜容量、PN接合容量からなりおよそ $10fF$ である。ビット線負荷の $V_{th}$ はバックゲート効果を含めて $1.3V$ である。先にも述べたように、サイクルタイムが短くなるとV<sub>HA</sub>は増加する。ここで臨界サイクルタイムTは $13\mu s$ であり、計算はソフトエラー測定結果と良い一致を示した。したがって、ノードN<sub>H</sub>の低下の時定数を考慮することで逆サイクルタイム依存性が説明される。

図5-3-6:  $V_{HA}$ を測定されたソフトエラー率

### 5.3.4 ソフトエラー率のサイクルタイム依存性に対する考察

本節では前節の解析結果をもとにソフトエラー率のサイクルタイム依存性をさらに議論し、ソフトエラー率のサイクルタイム依存性を減らす／無くす方法を述べる。

#### 5.3.4.1 他の実験結果

図5-3-7はPMOSビット線負荷を用いたSRAMの他のソフトエラー率のサイクルタイム依存性の測定結果である。メモリセル内のドライバトランジスタのしきい値電圧 $V_{thn}$ をパラメータとして変化してある。実線の $V_{thn}=0.7V$ は逆サイクルタイム依存性が現われており、図5-3-2および図5-3-6と同じである。一方、点線の $V_{thn}=0.5V$ では通常NMOSビット線負荷のサイクルタイム依存性が現われている。これは、セクション5.2.4で述べたようにドライバトランジスタQDのゲート／ソース電位が数百ミリボルト浮き上がることによる。すなわち、 $V_{thn}$ の減少で $ID$ が増大したのが原因である。

平均ノード電位 $V_{HA}$ を $ID$ を1nAから100nAまでパラメータとして変化させて計算したものを図5-3-8に示す。 $ID=1nA$ は $V_{thn}=0.7V$ に対応し、 $V_{thn}$ の減少は $ID$ の増加に対応する。実線の $ID=1nA$ は図5-3-6と同じであり同じ臨界サイクルタイム $T=13 \mu s$ となる。式(5-3-2)により、 $T$ と $ID$ は反比例の関係であるので、 $ID$ の増加と共に $T$ は減少する。それと同時にノード平均電位 $V_{HA}$ も図5-3-8のように減少する。したがって、 $V_{thn}$ が0.7Vから0.5Vに減少した時 $ID$ が2桁以上増加し、 $T$ は約100ns以下になる。したがって、サイクルタイムの減少にしたがって $V_{HA}$ は単調に減少し、通常のサイクルタイム依存性が現われている。

V<sub>thn</sub>: Threshold Voltage of Driver Transistors

図5-3-7：他のPMOSビット線負荷SRAMのソフトエラー率の測定結果

図5-3-8：平均ノード電位V<sub>HA</sub>の計算値

#### 5.3.4.2 ドライバトランジスタのしきい値電圧を上げる効果

前節の議論よりPMOSビット線負荷を持つSRAMではドライバトランジスタQ<sub>D</sub>のサブスレッシュホールドリーク電流IDがソフトエラー率のサイクルタイム依存性に関係する。図5-3-8よりサブスレッシュホールドリーク電流IDを1nA以下にすればV<sub>HA</sub>はほぼすべてのサイクルタイムにおいてV<sub>cc</sub>になる。したがって、ドライバトランジスタのV<sub>thn</sub>を必

必要な値に上げることでソフトエラー率のサイクルタイム依存性をなくし、それを長いサイクルタイムに対応する低い値に保つことができる。この場合 $V_{thn}$ は0.7Vである。

### 5.3.4.3 高抵抗負荷の抵抗値を下げる効果

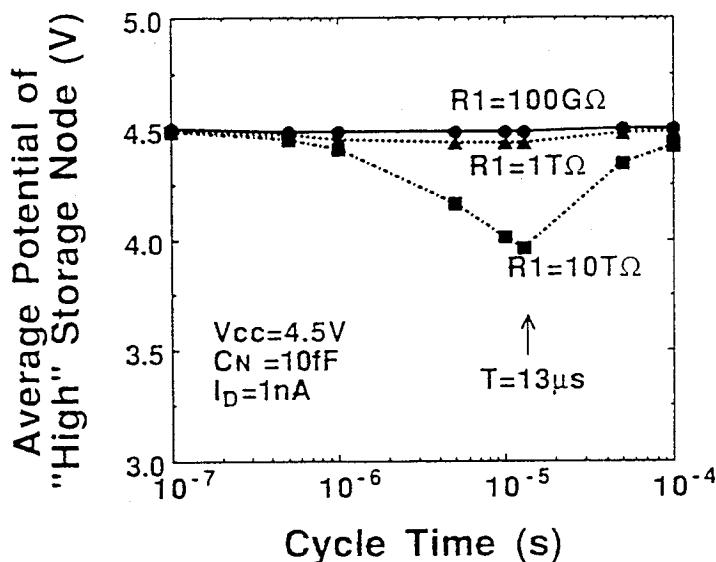

ソフトエラーのサイクルタイム依存性はハイノードの電位 $V_{HA}$ の低下を抑制すればよいので、高抵抗値を下げるることでも同じ効果を実現することができる。図5-3-9は高抵抗値 $R_1$ をパラメータとして $V_{HA}$ のサイクルタイム依存性を示したものである。

図5-3-9：高抵抗値 $R_1$ をパラメータとしての $V_{HA}$ のサイクルタイム依存性

サブスレッシュホールドリーク電流 $I_D$ は1nAである。式(5-3-2)で示されるように、臨界サイクルタイム $T$ は $R_1$ に依存しない。高抵抗値 $R_1$ を下げることで、電位 $V_{HA}$ をすべてのサイクルタイムでほぼ $V_{cc}$ に保つことができる。この場合、 $R_1=100G\Omega$ であり、ソフトエラー率のサイクルタイム依存性がほぼなくなる。

### 5.3.5 ソフトエラー率のサイクルタイム依存性のまとめ

PMOSビット線負荷SRAMのソフトエラー率のサイクルタイム依存性はメモリセルのドライバトランジスタのしきい値電圧 $V_{thn}$ と高抵抗負荷の抵抗値 $R_1$ に関係することが判明した。結果は図5-3-10にまとめられている。1MSRAM [5-6]では $V_{thn}=0.5V$ 、 $R_1=3T\Omega$ で通常のNMOSビット線負荷を使用したSRAMと同じソフトエラー率のサイクルタイム依存性が観測された。

$V_{thn}=0.7V$ にしきい値電圧を上げることで、新現象であるソフトエラー率の逆サイクルタイム依存性が観測された。また、さらにメモリセルのドライバトランジスタのしき

い値電圧を上げるかもしくは高抵抗値 $R_1$ を $100G\Omega$ 以下にすることでソフトエラー率のサイクルタイム依存性をなくすことが可能であることが予測された。

|                |                                                                                          | V <sub>thn</sub> | R <sub>1</sub>    |

|----------------|------------------------------------------------------------------------------------------|------------------|-------------------|

| Conventional   | SER<br> | 0.5V             | $3T\Omega$        |

| New Phenomenon | SER<br> | 0.7V             | $3T\Omega$        |

| Predicted      | SER<br> | $>0.7V$          | $3T\Omega$        |

|                |                                                                                          | 0.7V             | $\leq 100G\Omega$ |

V<sub>thn</sub>: Threshold Voltage of Driver Transistor

R<sub>1</sub> : Impedance of High Resistive Load

図5-3-10：ソフトエラー率とメモリセルパラメータとの関係

## 5.4 結論

本章ではSRAMを高速化するときの信頼性上の問題である出力バッファによる電源バウンスノイズとソフトエラーのサイクルタイム依存性の問題とその解決策について述べた。

- (1) 出力バッファのスイッチングのときにチップ内部の電源／GND電位に発生する電位バウンス（ノイズ）の解析的モデルを提案した。

- (2) このモデルは回路シミュレーションプログラムSPICEの結果と良い一致を示した。

- (3) このモデルは $L \cdot G_0$ （ $L$ は寄生インダクタンス、 $G_0$ は出力トランジスタの最大コンダクタンス）よりスイッチング時間 $t_r$ が大きくかつ出力電圧振幅 $V_{dout}$ が小さいことがピークノイズ電圧 $V_{nmax}$ を下げるために必要となることを示した。

- (4) 大きな $t_r$ および小さな $G_0$ は出力バッファでの遅延時間を増加させることに対応し、また $V_{nmax}$ は $V_{dout}$ に一次比例の関係にあるので、超高速デバイスの低ノイズ化には電源ピンを増加させて寄生インダクタンスを減らす方法もしくは出力電圧振幅を最小化するのが有効であることを示した。

- (5) (4) の方法を実現する電位降圧回路を組み合わせた低ノイズ出力バッファを提案し、5V±10%スペックのデバイスにおいて最悪値の遅延時間を同一にしたまま、ノイズの最悪値を約半分に低減できることを示した。

- (6) 新現象であるソフトエラー率の逆サイクルタイム依存性を発見しそのメカニズムを解析した。

- (7) ソフトエラー率の逆サイクルタイム依存性はPMOSビット線負荷を用いたSRAMで発生し、ドライバトランジスタQDのしきい値電圧 $V_{thn}$ 、高抵抗負荷の抵抗値 $R_1$ に関係することがわかった。

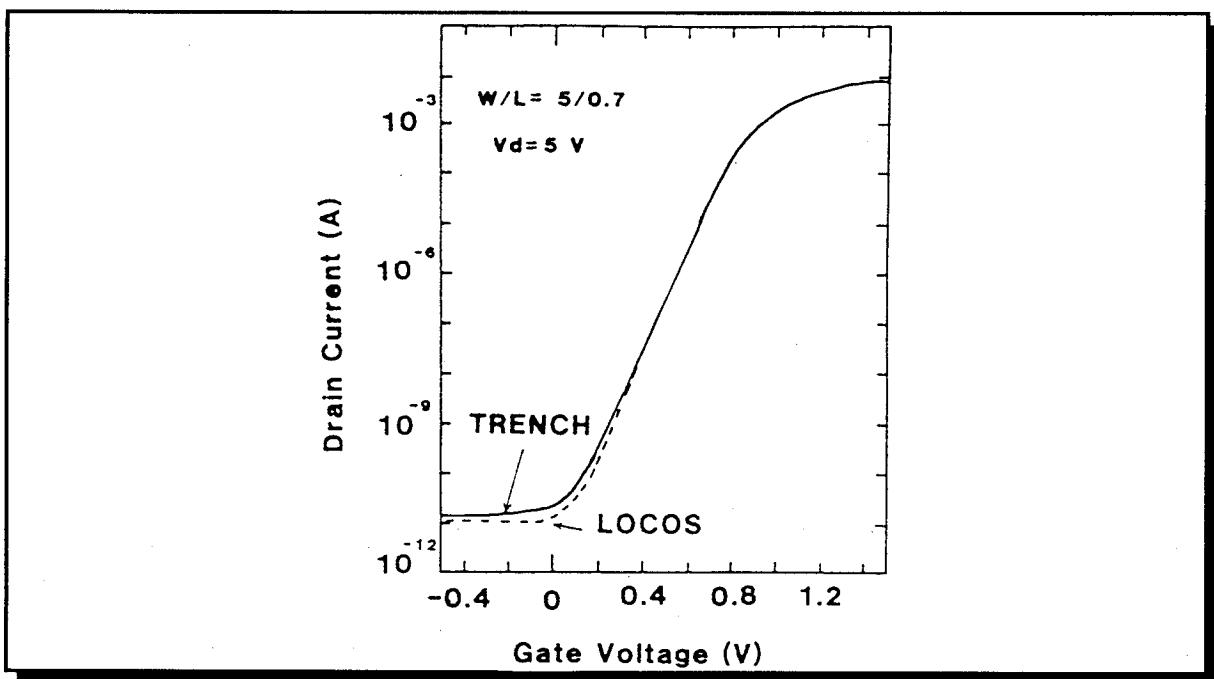

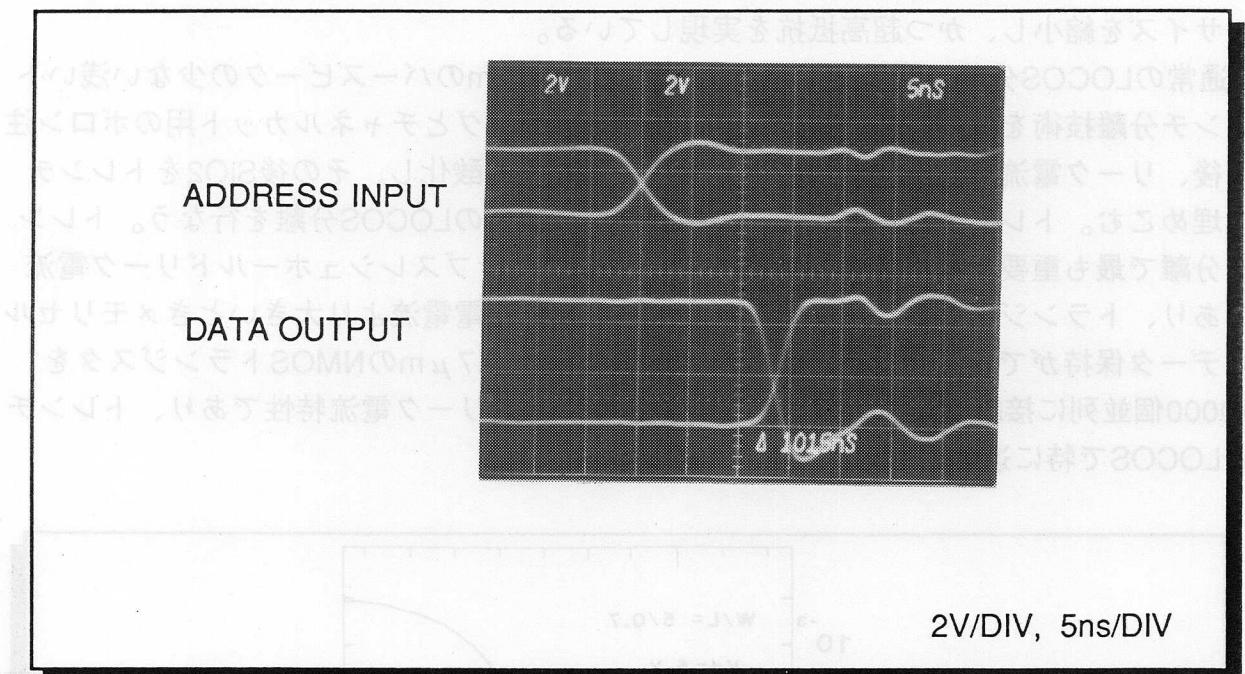

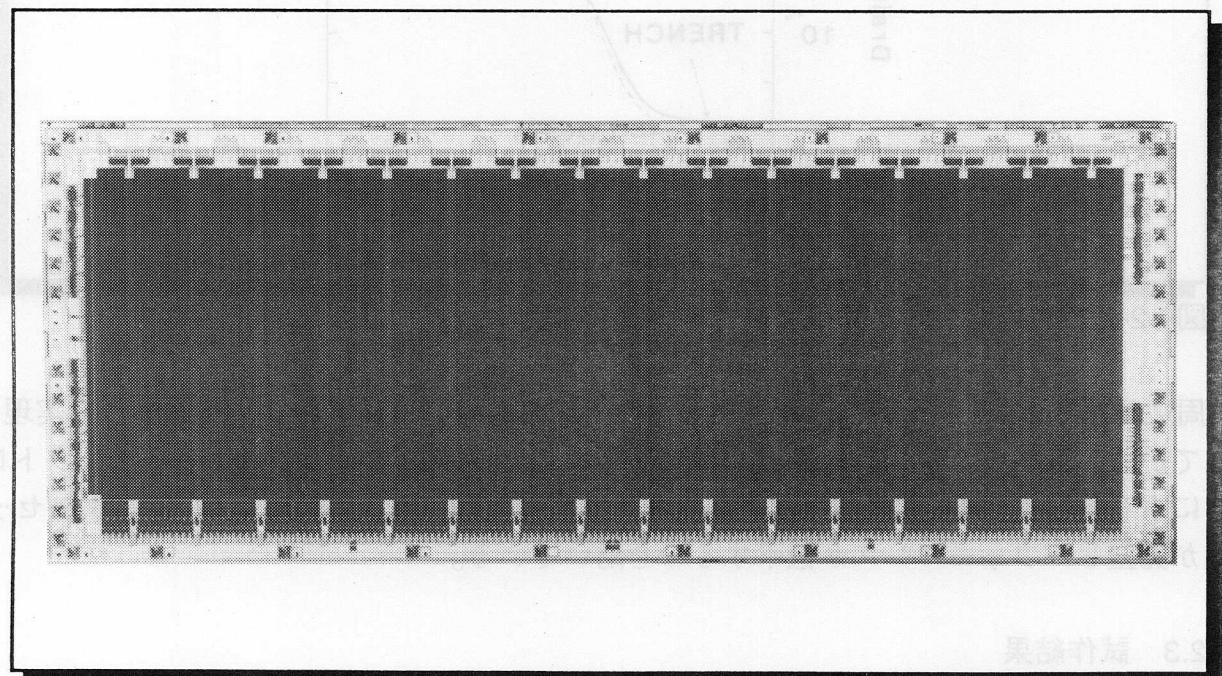

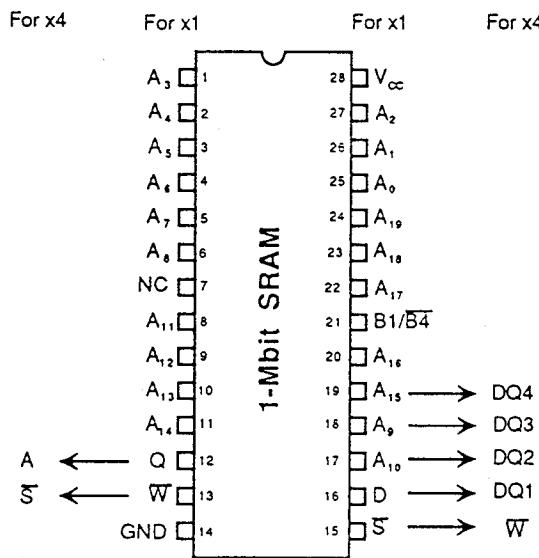

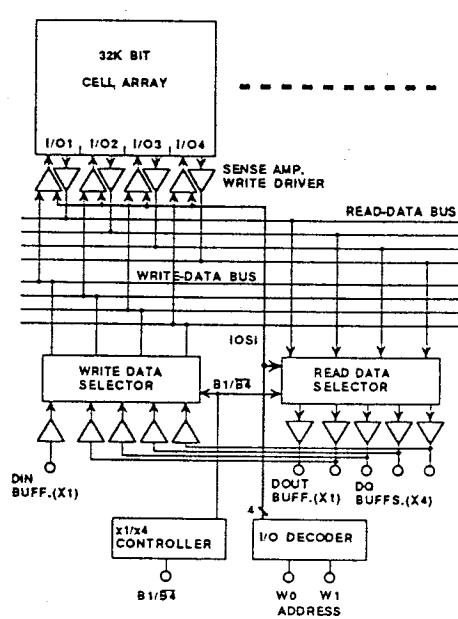

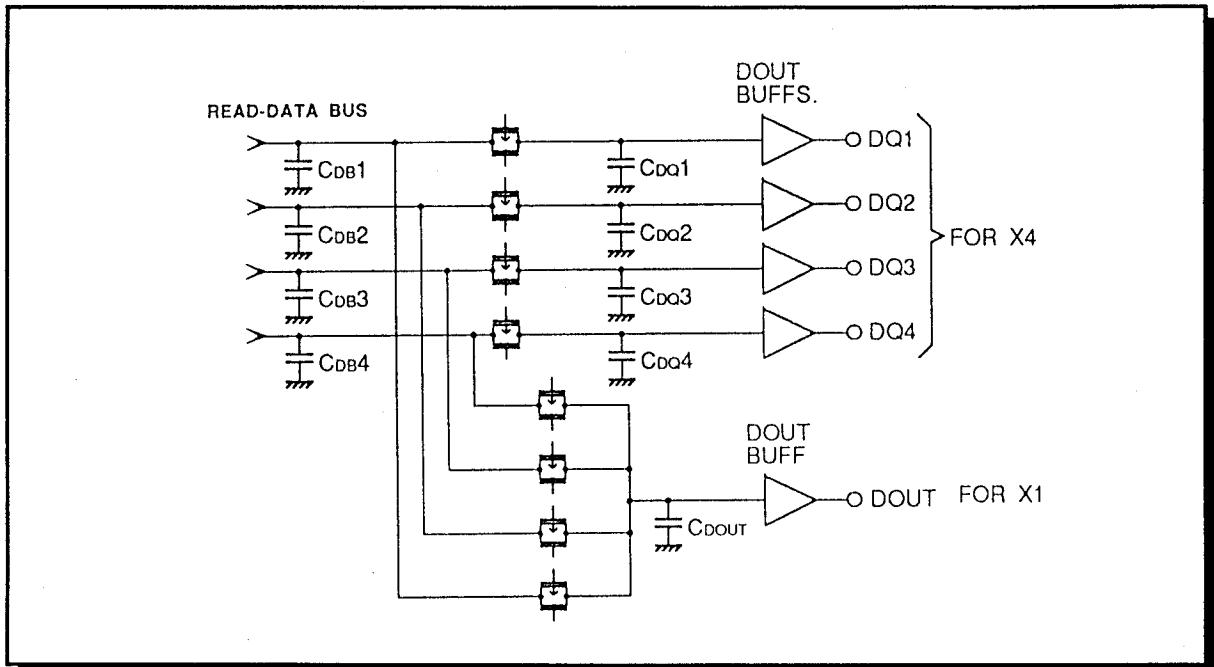

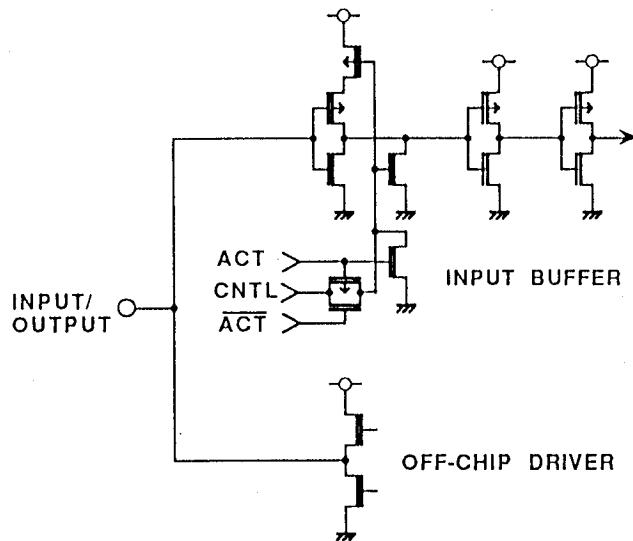

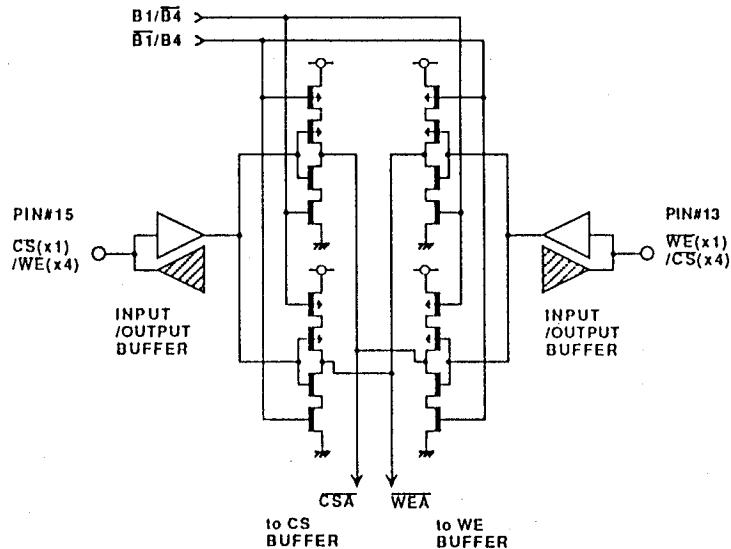

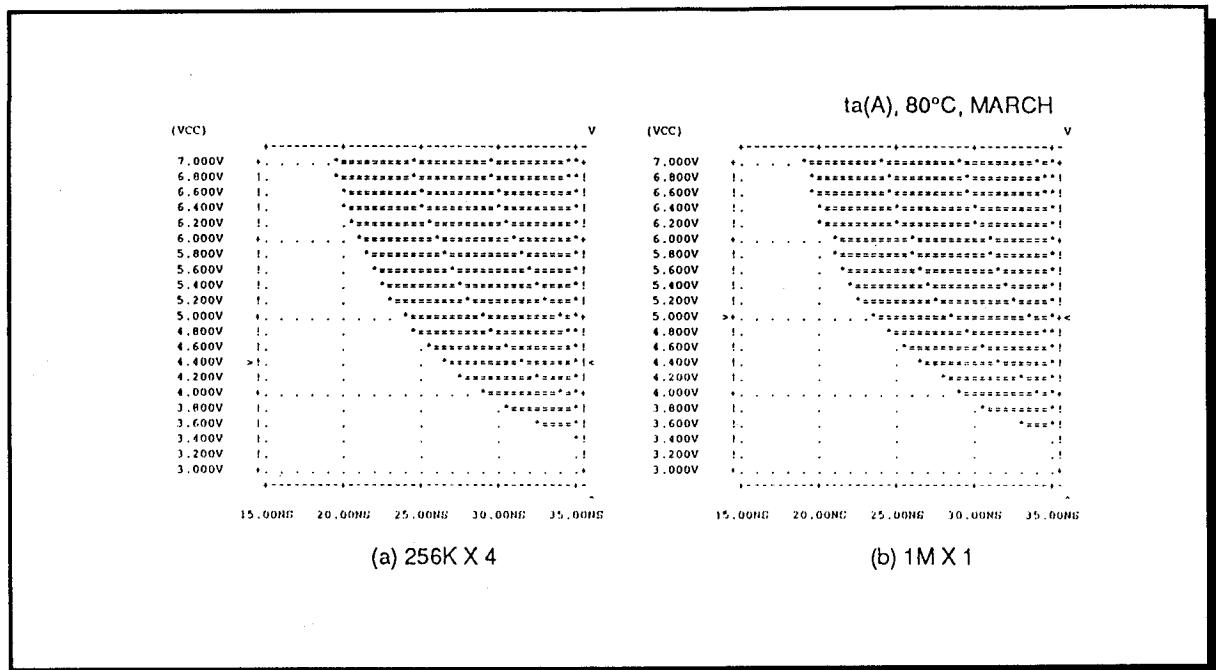

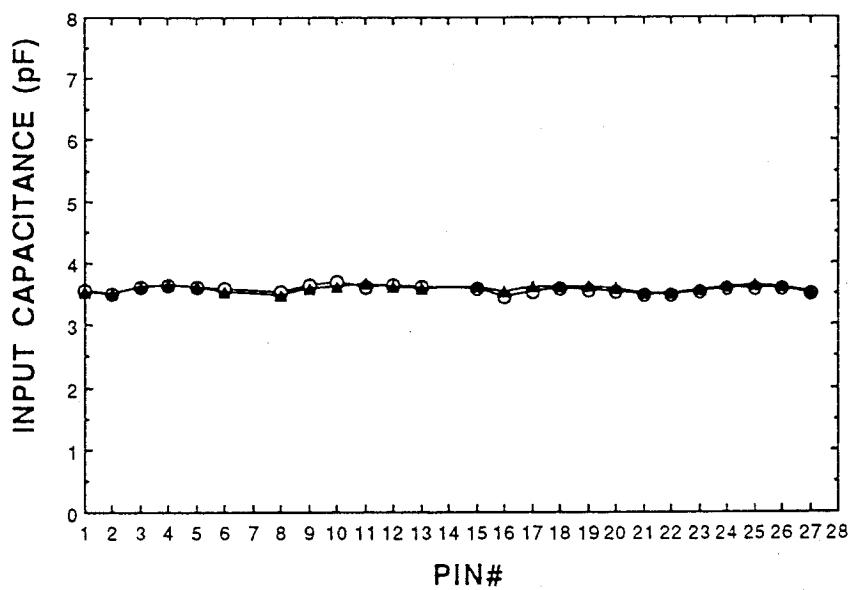

- (8) PMOSビット線負荷を用いたSRAMでもNMOSビット線負荷のSRAMが持つ通常のサイクルタイム依存性は発生し、1MSRAM [5-6]では $V_{thn}=0.5V$ かつ $R_1=3T\Omega$ で観測された。