|              |                                                                             |

|--------------|-----------------------------------------------------------------------------|

| Title        | 低誘電率絶縁膜デバイスの超微細ピッチ接合法における接合部および下部配線層の応力低減に関する研究                             |

| Author(s)    | 久田, 隆史                                                                      |

| Citation     | 大阪大学, 2014, 博士論文                                                            |

| Version Type | VoR                                                                         |

| URL          | <a href="https://doi.org/10.18910/34464">https://doi.org/10.18910/34464</a> |

| rights       |                                                                             |

| Note         |                                                                             |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

博士学位論文

低誘電率絶縁膜デバイスの超微細ピッチ接合法における

接合部および下部配線層の応力低減に関する研究

久田 隆史

2013年12月

大阪大学大学院工学研究科

## 目次

|                                                      |    |

|------------------------------------------------------|----|

| 第 1 章 序論                                             | 1  |

| 1.1 研究の背景                                            | 1  |

| 1.1.1 半導体素子の高集積化・高速化                                 | 1  |

| 1.1.2 半導体製品の多ピン化・高密度化                                | 2  |

| 1.2 半導体素子の高速化に伴う層間絶縁膜の変遷                             | 4  |

| 1.3 チップの外部端子接続技術の動向                                  | 6  |

| 1.3.1 ワイヤボンディング                                      | 6  |

| 1.3.2 フリップチップボンディング                                  | 7  |

| 1.4 配線層ダメージの課題と研究目的                                  | 9  |

| 1.4.1 ワイヤボンディングにおける外部端子接続時の接合荷重・超音波印加による層間絶縁膜の破壊     | 9  |

| 1.4.2 フリップチップボンディングにおける外部端子接続時のチップと基板の熱応力による層間絶縁膜の破壊 | 10 |

| (1) 低温はんだによる応力低減                                     | 10 |

| (2) 貫通電極を有するインターポーラ上に複数チップを搭載するパッケージにおける応力場の解析       | 12 |

| 1.5 研究の構成と流れ                                         | 14 |

| 第 2 章 ワイヤボンディングにおける下部配線層構造最適化による配線層ダメージの低減           | 16 |

| 2.1 緒言                                               | 16 |

| 2.2 パッド下部配線構造の複合弾性率の導出                               | 16 |

| 2.3 外部端子接続時の配線層に生じる応力場の解明                            | 20 |

| 2.3.1 FEM 解析モデル                                      | 20 |

| 2.3.2 外部端子接続時の荷重によって配線層に生じる応力の解析                     | 21 |

| 2.3.3 外部端子接続時の超音波印加によって配線層に生じる応力の解析                  | 25 |

| 2.4 ワイヤブル試験におけるパッドはがれ発生率と配線層の応力の相関の解明                | 37 |

| 2.4.1 ワイヤボンディング実験                                    | 37 |

| 2.4.2 パッド下部配線構造と配線層ダメージの関係                           | 38 |

| 2.4.3 パッド下部配線構造の複合弾性率と線層ダメージの関係                      | 39 |

| 2.5 結言                                               | 40 |

| 第 3 章 フリップチップ接合用材料の機械的特性がフリップチップのパッド下部配線層の熱応力に与える影響  | 41 |

| 3.1 緒言                                               | 41 |

|                                                                      |     |

|----------------------------------------------------------------------|-----|

| 3.2 はんだ微細試験片による引張試験                                                  | 41  |

| 3.2.1 試験方法                                                           | 41  |

| 3.2.2 組織観察                                                           | 42  |

| 3.2.3 引張試験結果                                                         | 42  |

| 3.2.4 クリープ特性                                                         | 47  |

| 3.3 フリップチップ接合の冷却時の応力場の解明                                             | 49  |

| 3.3.1 FEM 解析モデル                                                      | 49  |

| 3.3.2 解析結果                                                           | 52  |

| 3.4 結言                                                               | 54  |

| <br>第4章 貫通電極を有するインターポーラ上に複数チップを搭載するパッケージの<br>マイクロ接合部およびチップ下部配線層の応力低減 | 55  |

| 4.1 緒言                                                               | 55  |

| 4.2 インターポーラ上に複数チップを平面配置するパッケージと MCM FCPBGA の<br>熱機械的解析               | 56  |

| 4.2.1 インターポーラ上に複数チップを平面配置するパッケージと MCM FCPBGA の<br>設計検討               | 56  |

| 4.2.2 FEM 解析モデル                                                      | 62  |

| 4.2.3 インターポーラの機械特性による応力・反りへの影響                                       | 64  |

| 4.2.4 チップ・インターポーラの接合順序とインターポーラ厚みによる応力への影響                            | 70  |

| 4.3 インターポーラ上に複数チップを積層するパッケージの熱機械的解析                                  | 80  |

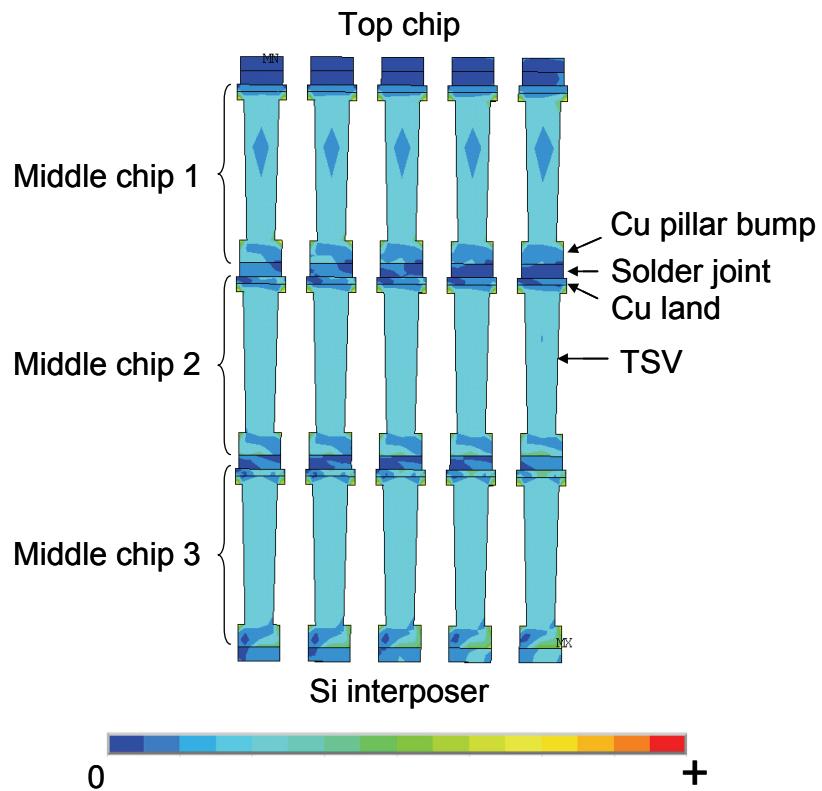

| 4.3.1 FEM 解析モデル                                                      | 80  |

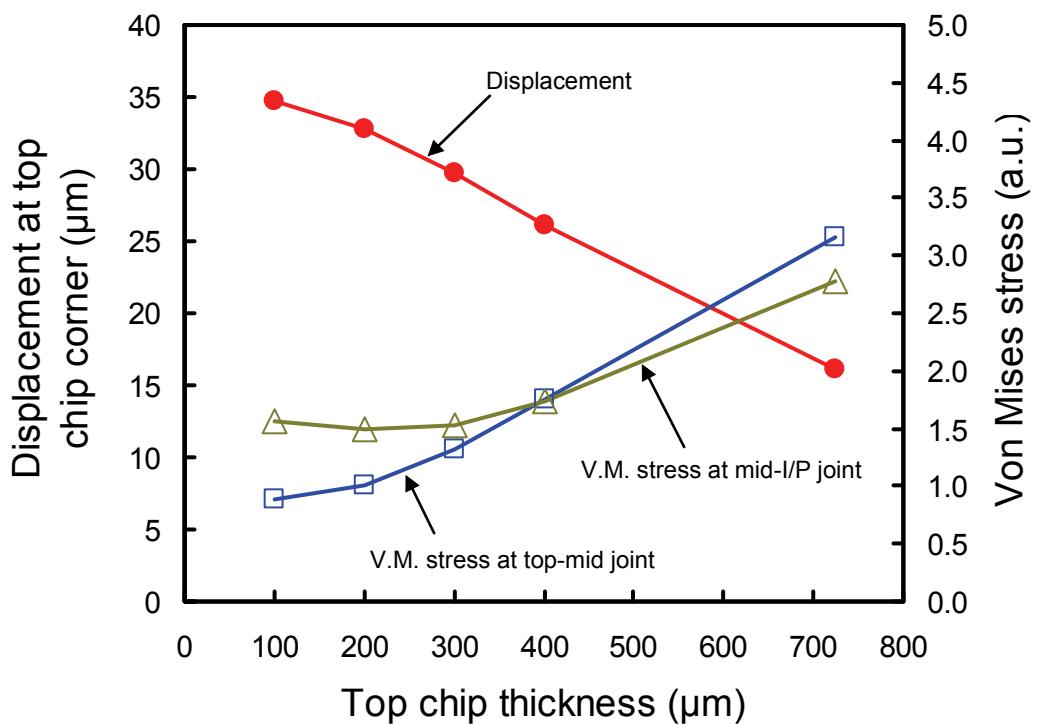

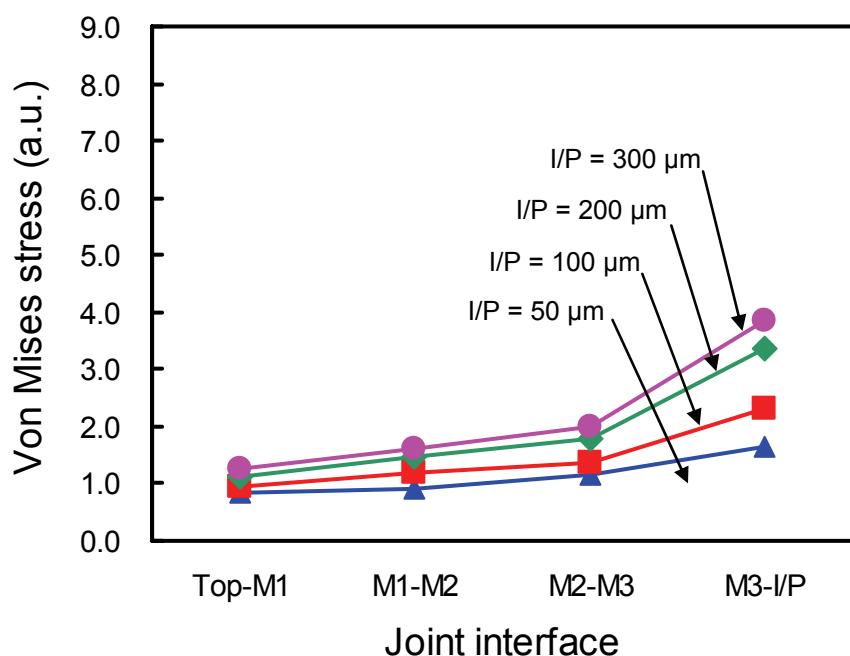

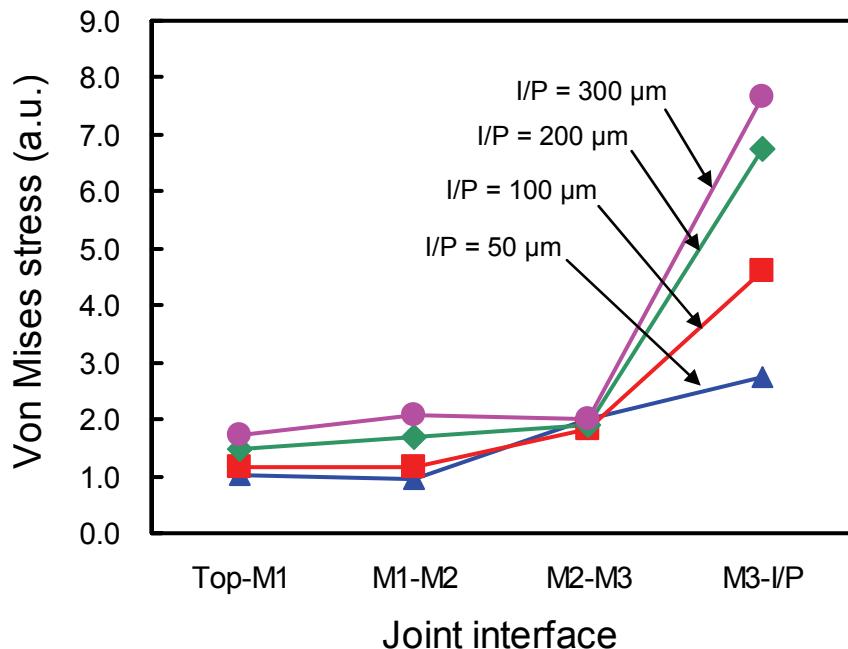

| 4.3.2 トップチップの厚みとインターポーラの厚みによる接合部応力・<br>チップ反りへの影響                     | 84  |

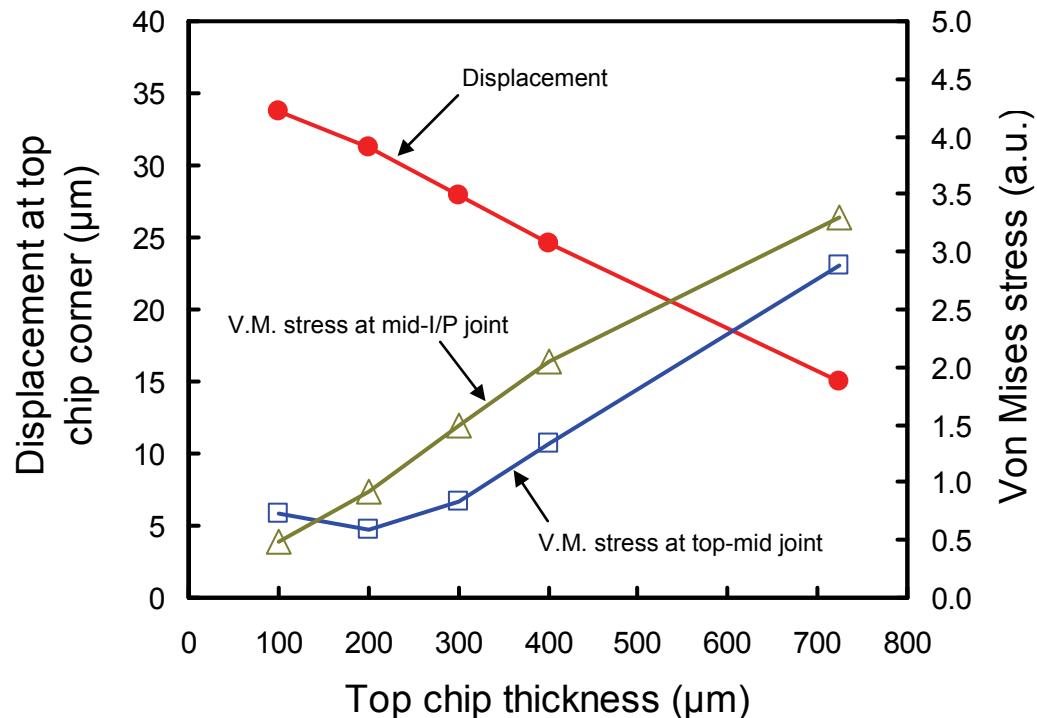

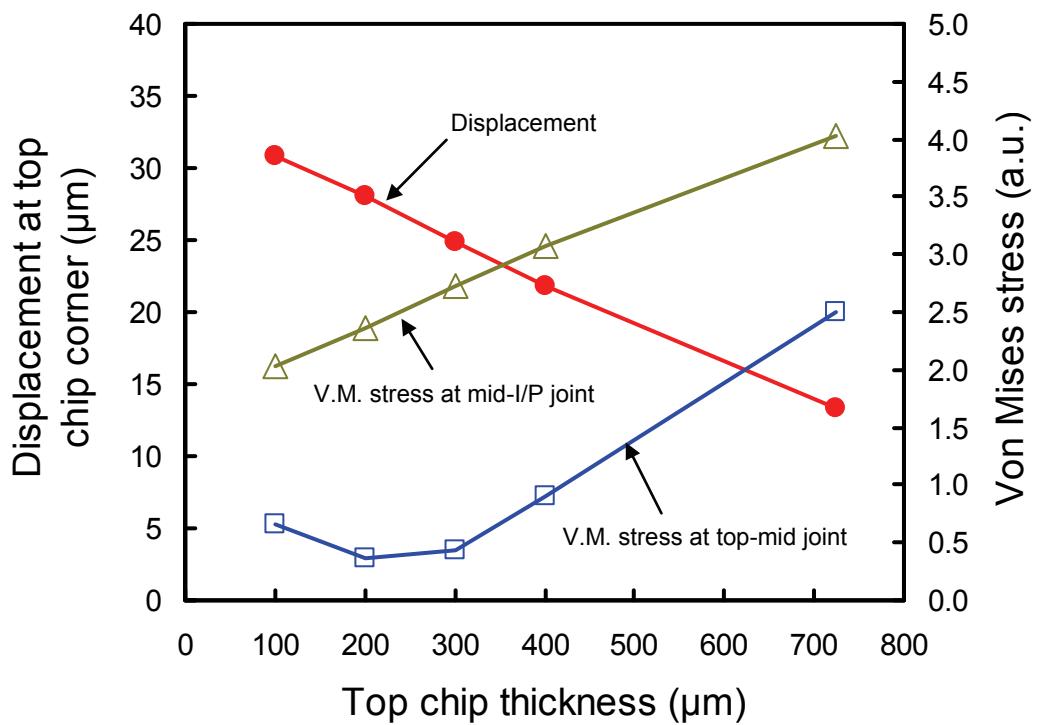

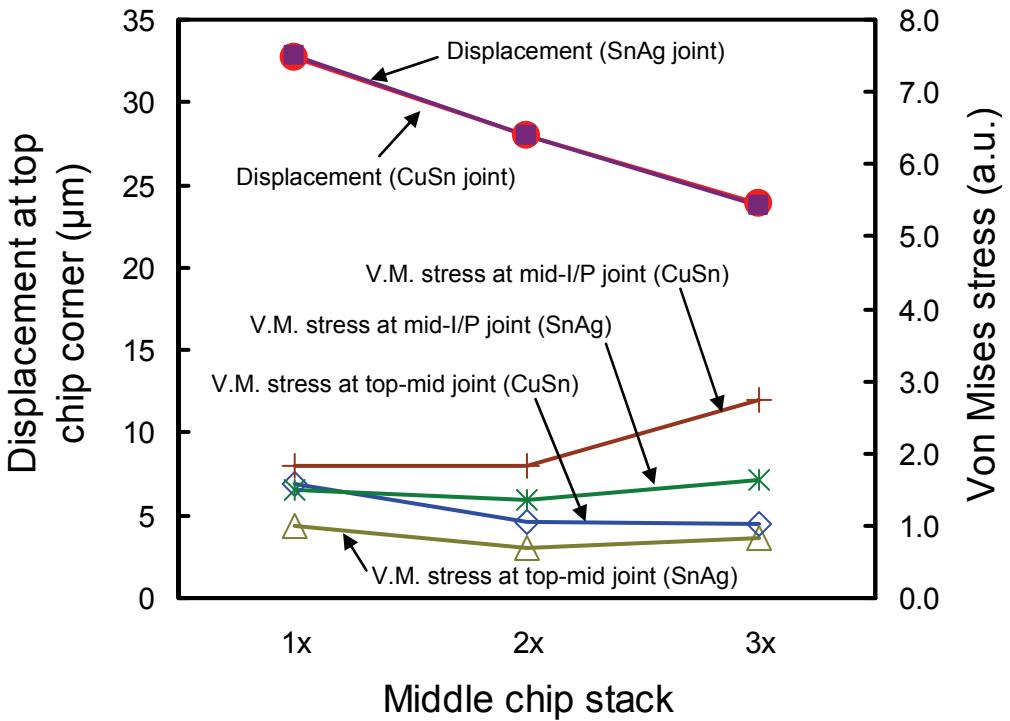

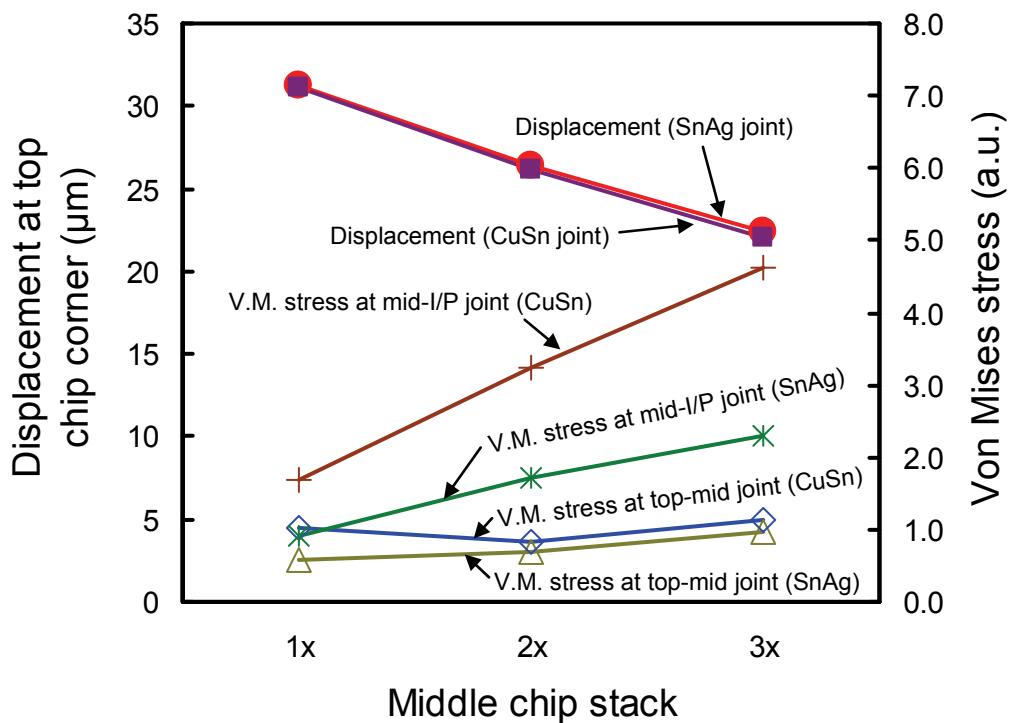

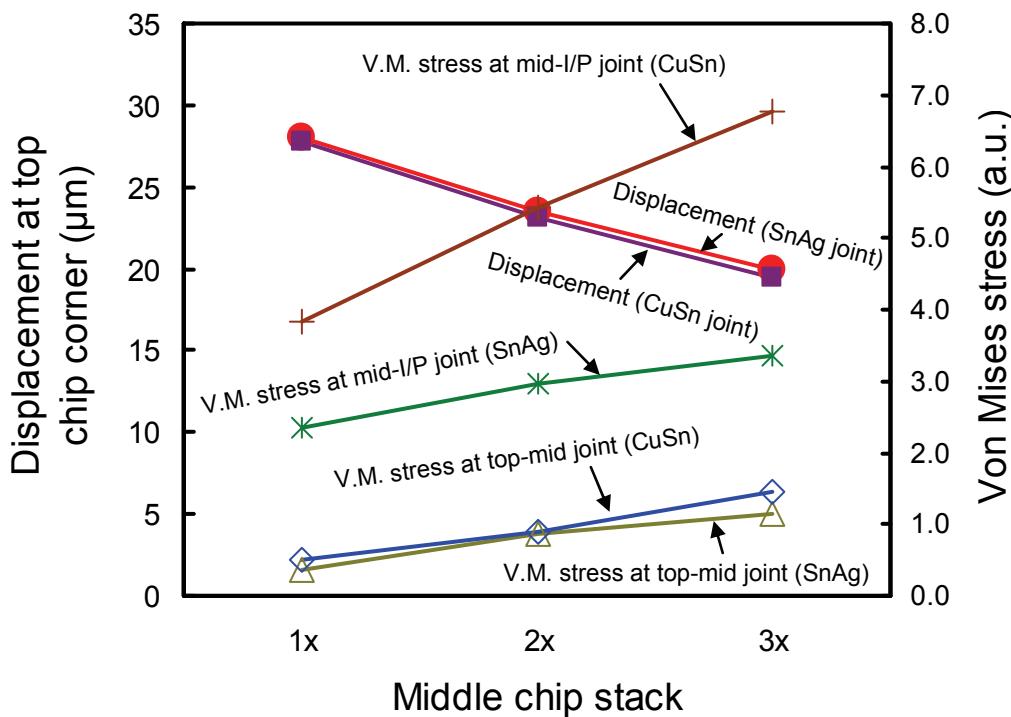

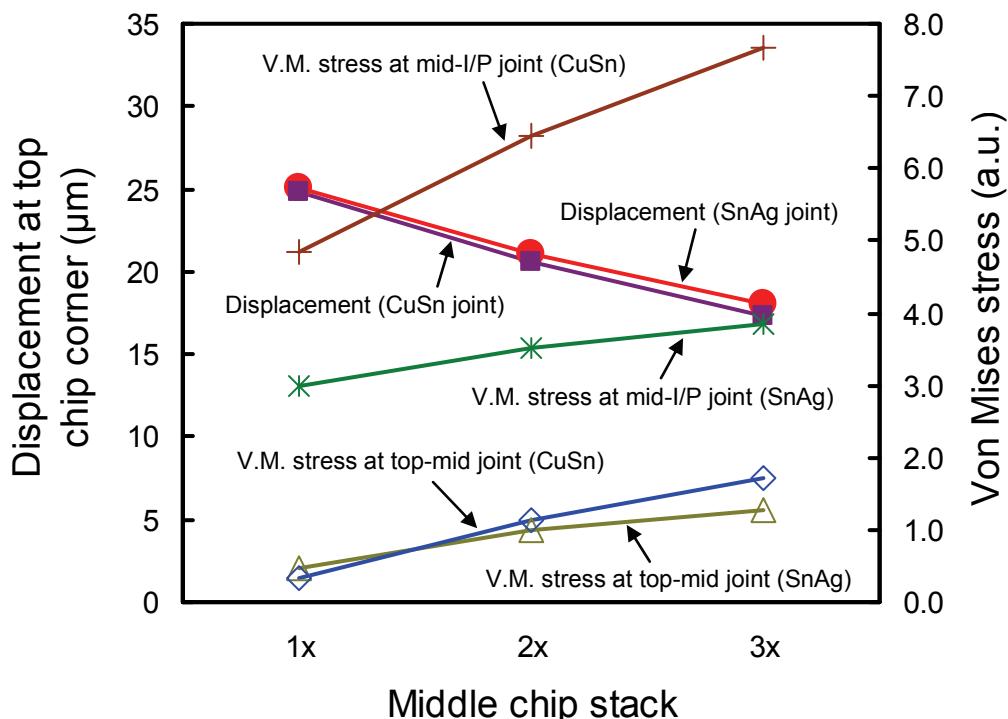

| 4.3.3 ミドルチップの積層数・インターポーラの厚みおよび接合部の機械特性による<br>接合部応力・チップ反りへの影響         | 87  |

| 4.4 結言                                                               | 91  |

| <br>第 5 章 結論                                                         | 94  |

| 謝辞                                                                   | 97  |

| <br>参考文献                                                             | 98  |

| I . 本研究に関する発表論文                                                      | 105 |

| II . 本研究に関する学会発表                                                     | 105 |

# 第1章 序論

## 1.1 研究の背景

### 1.1.1 半導体素子の高集積化・高速化

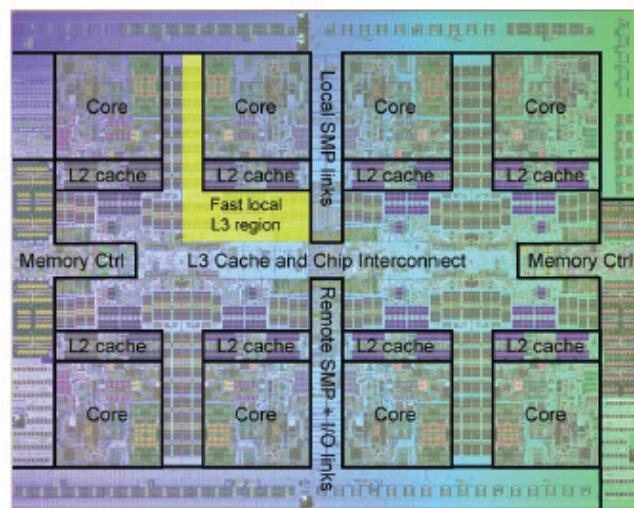

トランジスタの発明に始まる半導体素子は、素子プロセスの微細化を推し進めることで、集積回路 (IC: Integrated Circuit), 大規模集積回路 (LSI: Large-scale Integration), 超大規模集積回路 (VLSI: Very Large Scale Integration) と集積度を高め続けてきた。半導体素子の黎明期から現在に至るまで、バイポーラから CMOS への転換など大きな技術的革新を伴いながらも、主に素子サイズの微細化が高速化・高性能化を牽引してきた<sup>1-3)</sup>。このことは有名なムーアの法則<sup>4,5)</sup>として、その内容は多少の変遷があるものの現在では一般的に“集積回路上のトランジスタ数は 18 ヶ月ごとに倍になる”と要約される。ムーアの法則を実現すべく策定されてきた半導体技術のロードマップ<sup>6)</sup>は半導体技術の研究開発の指針として関連する材料技術、プロセス技術、解析技術、設計技術などの発展に大きな役割を果たしてきた。2000 年前後からは微細化による様々な物理制約が顕現するようになり、配線抵抗を低減するための Cu 配線<sup>7)</sup>, Si サブストレートとの浮遊容量を低減する SOI (Silicon on Insulator)<sup>8)</sup>, 電子移動度を高める歪 Si<sup>9)</sup>, 配線層の寄生容量を低減する低誘電率の Low-k/Ultra low-k (ULK) 絶縁膜<sup>10-12)</sup>, ゲート酸化膜からのリーク電流を低減する High-k メタルゲート<sup>13)</sup>などの新技術が微細化と共に導入されてきた。2010 年に IBM が発表した POWER7 プロセッサ<sup>14)</sup>では 45 nm のテクノロジ・ノードで SOI・Cu 配線・Low-k/ULK 絶縁膜を用いて 567 mm<sup>2</sup> のチップに 12 億個のトランジスタが集積されている。Fig. 1.1 は POWER7 のチップの写真であり、図中には各機能ブロックを示した。

本研究では、パッケージとの接続を行うチップ上の外部接続端子の下部構造で破断等の故障を起こしやすい Low-k/ULK を用いたデバイスを研究対象とする。配線層の層間絶縁膜については後で詳述する。

Fig. 1.1 The photograph of the IBM POWER7 chip<sup>14)</sup>.

### 1.1.2 半導体製品の多ピン化・高密度化

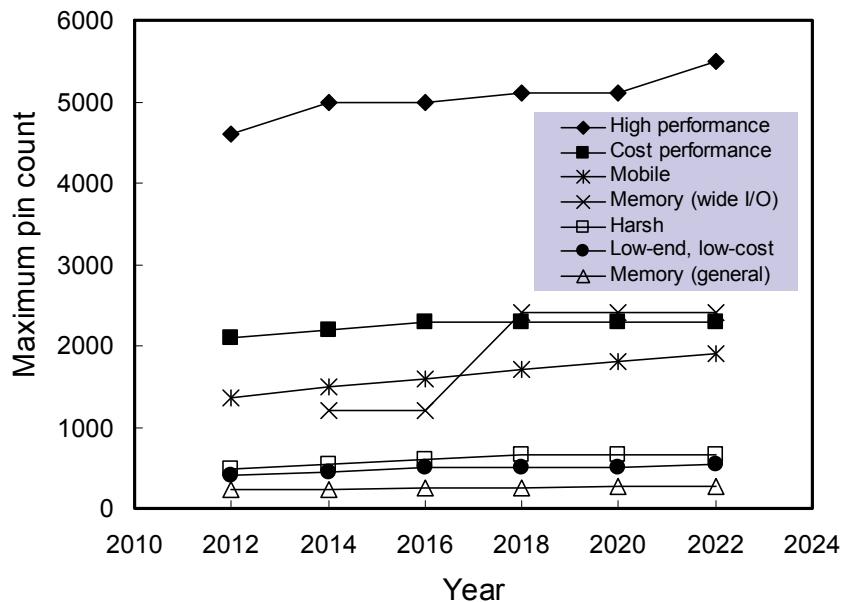

半導体素子の高集積化・高速化に伴い、メモリのバス幅の拡大や多様な外部インターフェイスの拡張が行われ、モバイル向け半導体からハイエンドサーバー向け半導体まであらゆる製品セグメントでパッケージの入出力端子の多ピン化が進められてきており、その傾向は今後も続くものと予想されている<sup>6, 15)</sup>。Fig. 1.2 は筆者が 2013 年度版日本実装技術ロードマップ<sup>15)</sup>の数値をもとに作成したグラフであり、各製品セグメントごとのパッケージの最大端子数のロードマップを示している。サーバー向けプロセッサなどの高性能製品は、最大端子数が 2012 年に 4600 であるのに対し 2022 年には 5500 まで増加すると予測されている。携帯電子機器製品においても 2012 年の 1360 ピンから 2022 年の 1900 ピンに大きく端子数の増加が見込まれている。Wide I/O メモリ<sup>16)</sup>は 2016 年から 2018 年の間でバス幅の拡大によって大きくピン数が増えると予想されている。また、他の製品セグメントでも上記の製品セグメントほどではないがピン数は増えるものと考えられている。一般的に端子数が 1000 ピン以上の製品ではチップ接合技術としてフリップチップボンディングが多く用いられ、低価格で 1000 ピン以下の半導体にはワイヤボンディングが多く用いられてきた。後述するように、ピン数の増加に伴ってチップ上の接続端子のピッチは微細化が進むことになる。

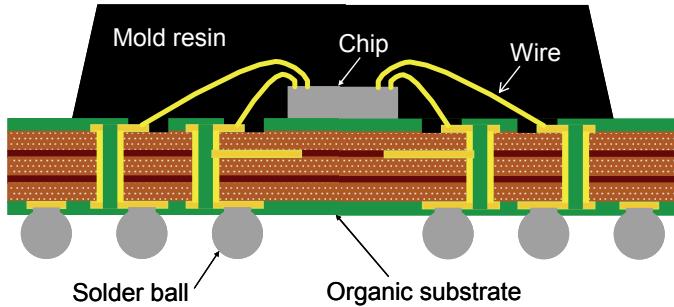

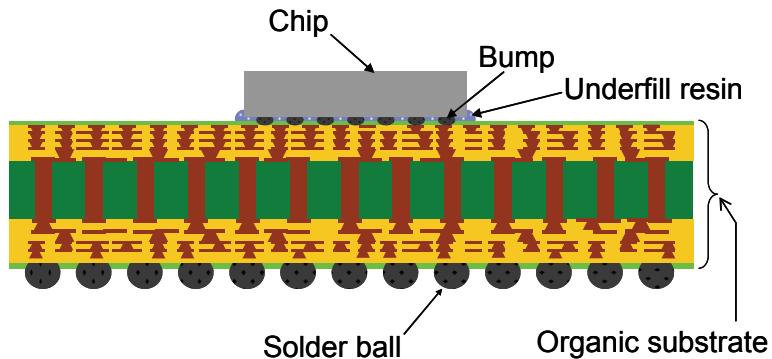

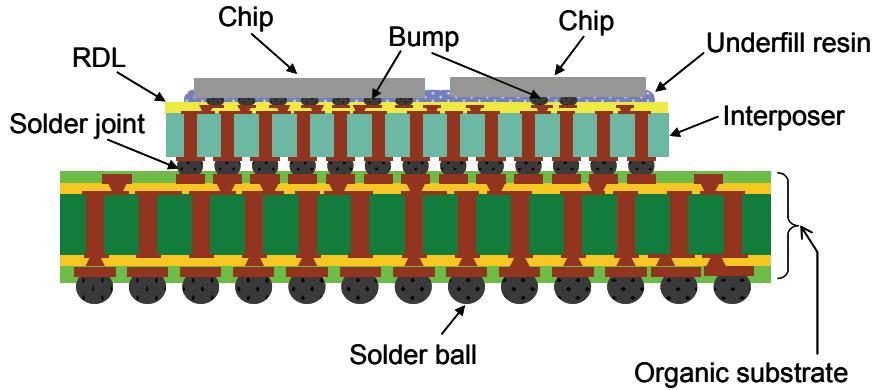

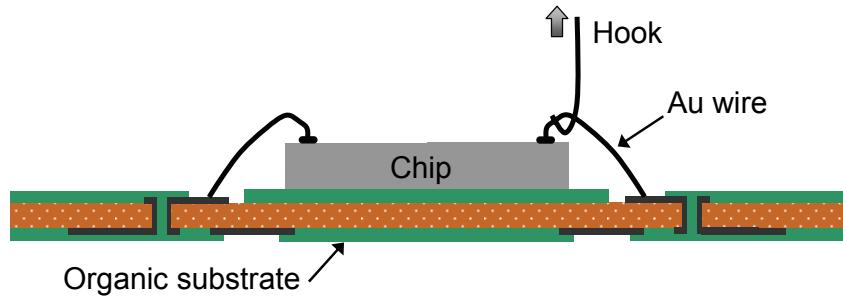

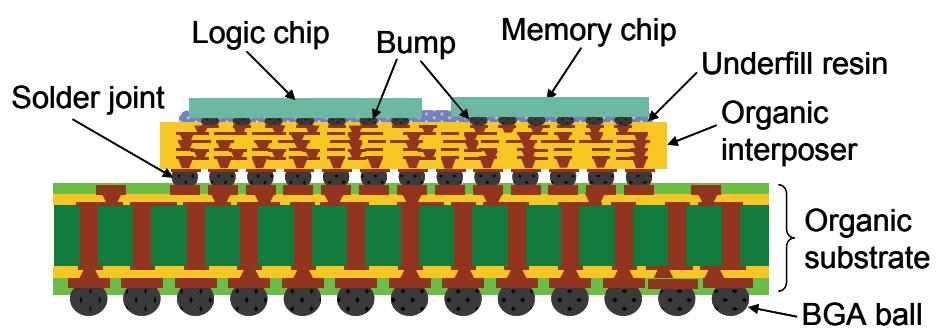

本研究では、ワイヤボンディング、フリップチップボンディングを用いたパッケージを研究対象とする。Fig. 1.3 は PBGA (Plastic Ball Grid Array) の断面図である。有機基板上にチップをダイアタッチ材で接着し、チップ上の外部接続端子と基板上の接続端子をワイヤボンディングで結線した後に、モールド封止、BGA ボール付けを行う。Fig. 1.4 は FCPBGA (Flip Chip Plastic Ball Grid Array) の断面図である。チップ回路面に形成されたバンプを有機基板上の接続端子に接続し、バンプ接続部を保護する

Fig. 1.2 Roadmap of maximum pin count by product segment<sup>15)</sup>.

Fig. 1.3 Schematic cross-section of PBGA.

Fig. 1.4 Schematic cross-section of FCPBGA.

ためのアンダーフィル材をチップと基板間に塗布する。Fig. 1.4 には封止材のない構成を示したが、チップ裏面に TIM (Thermal Interface Material) を介して金属製のふたを取り付けて封止するパッケージ形態が使われることも多い。

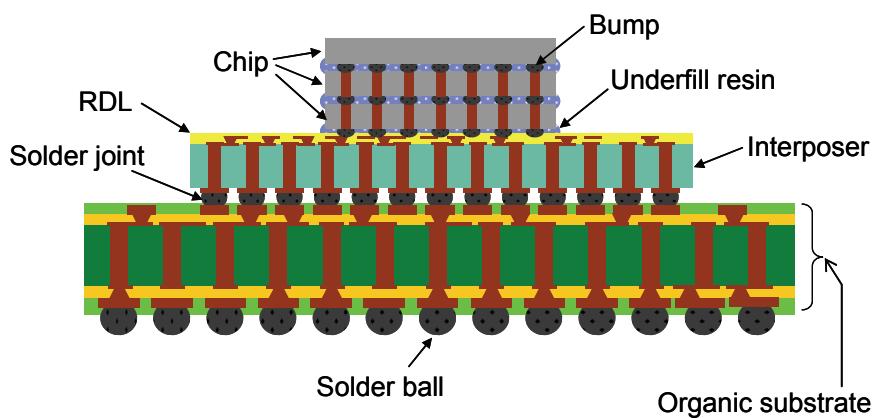

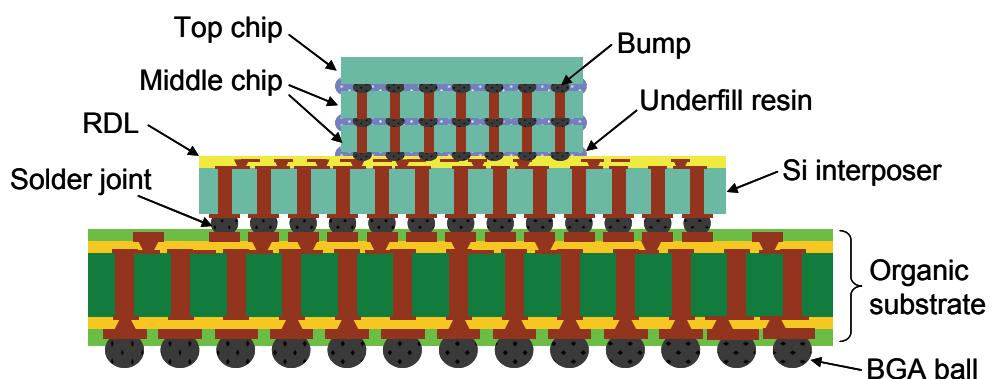

FCPBGA は高性能品に使用されてきたが、有機基板上の配線幅が 10  $\mu\text{m}$  以上であり今後も配線幅の微細化は見込まれているが<sup>6, 15)</sup>、高集積化の進む半導体素子の性能を十分に活用できなくなりつつある。このため、2~3  $\mu\text{m}$  以下の微細配線を形成でき、貫通電極を有するシリコン・インターポーヴやガラス・インターポーヴなどを有機基板上に搭載し、そのインターポーヴ上に複数チップを搭載することでチップ間の配線距離を短くし、高性能化と高密度化を図る 2.5D と呼ばれるパッケージ形態の研究開発が活発に行われてきた<sup>17-27)</sup>。2.5D パッケージは Xilinx により FPGA (Field Programmable Gate Array) への応用が 2011 年に発表された<sup>28)</sup>。また複数チップを積層し、TSV (Through Silicon Via) を介してチップ間の伝送経路を形成する 3D-IC パッケージも JEDEC (JEDEC Solid State Technology Association) による Wide I/O メモリの MPGA (Micropillar Grid Array Package) の標準策定<sup>29)</sup>、Micron による HMC (Hybrid Memory Cube) の発表<sup>30)</sup>、Altera と TSMC によるヘテロジニアス 3D-IC の試作品開発の発表<sup>31)</sup>などで本格的な普及への期待が高まっている。本研究では、有機基板とインターポーヴ、インターポーヴとチップ、チップとチップの各積層面で多くのマイクロ接合を有する 2.5D および 3D-IC パッケージも研究対象とする。Fig. 1.5 は 2.5D パッケージの断面図で、有機基板上にインターポーヴを搭載し、その

Fig. 1.5 Schematic cross-section of 2.5D package.

Fig. 1.6 Schematic cross-section of 3D-IC package.

上に複数チップを平置きで搭載する。インター pocer 上には図に示す RDL (Re-distribution Layer) と呼ばれるポリイミドを絶縁層とした再配線層を形成する場合と、Si インター pocer の場合には半導体の後工程と同じ配線プロセスを使って配線層を形成する場合がある。またインター pocer はチップ接続面と基板接続面をつなぐ貫通穴が形成されている。Fig. 1.6 に示す 3D-IC パッケージではチップは積層して接続される。最上部のチップとインター pocer の間に置かれる中間のチップには貫通穴を設け上下の伝送経路とし、他の構成は 2.5D パッケージと同様である。

## 1.2 半導体素子の高速化に伴う層間絶縁膜の変遷

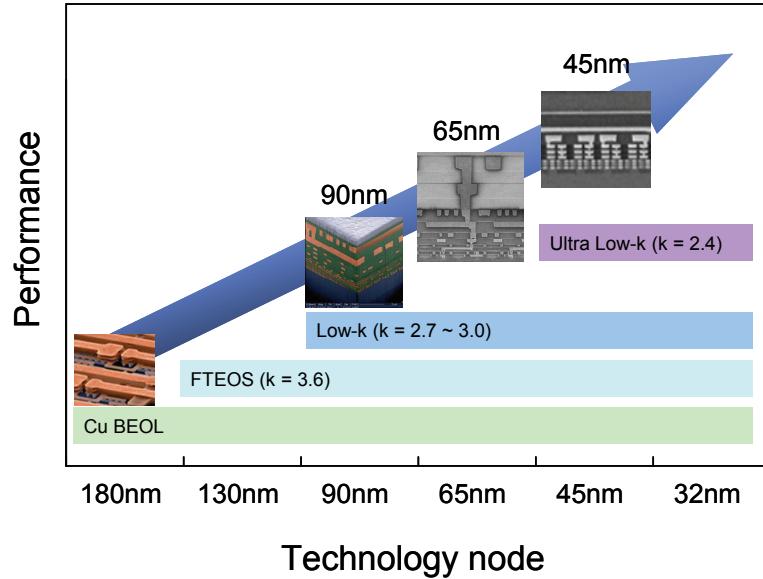

半導体集積回路の高性能化はトランジスタ素子の微細化により実現してきた。素子の微細化・高集積化に合わせてメタル配線の微細化も進められてきたが、配線層の微細化が進むとメタル配線層での RC (Resistive-Capacitive) 遅延が高速動作を実現する上で課題となってくる。これに対してメタル配線の材料を Al から Cu に変更して配線抵抗を低減する技術開発<sup>1-3, 7)</sup> と層間絶縁膜の誘電率を低減する技術開発<sup>1-3, 10-12)</sup> が行われてきた。Fig. 1.7 は半導体のテクノロジ・ノードと配線層における新技術導入の概念図である。横軸にテクノロジ・ノードを取り、縦軸は性能を目安として示す。180 nm の世代で Cu 配線の導入が始まり、130 nm の世代で SiO<sub>2</sub> に F を添加して比誘電率を 3.6 程度に下げた FTEOS (Fluorinated Tetraethyl Orthosilicate, SiOF)<sup>2, 32, 33)</sup> が配線層の絶縁膜として適用され、その後 Low-k 材、

Fig. 1.7 Conceptual chart for innovations in the back-end-of-line (BEOL) layers.

Table 1.1 Material properties of dielectric films.

|                                | $\text{SiO}_2$ | FTEOS | Low-k (SiCOH) | ULK (porous SiCOH) |

|--------------------------------|----------------|-------|---------------|--------------------|

| Dielectric constant            | 4.1            | 3.6   | 2.7~3.0       | 2.4                |

| Elastic modulus (GPa)          | 70             | 66    | 9.0           | 4.6                |

| Poisson's ratio                | 0.20           | 0.18  | 0.28          | 0.28               |

| CTE (ppm/ $^{\circ}\text{C}$ ) | 0.7            | 0.57  | 16.4          | 14                 |

ULK 材の導入が進んできた。Low-k 材は  $\text{SiO}_2$  に C を添加した  $\text{SiOC}$  や  $\text{SiCOH}$  などが使われ<sup>2, 32-34)</sup>、一般的に比誘電率が 3.0 以下のものを指す。ULK 材は  $\text{SiOC}$  や  $\text{SiCOH}$  を多孔質化したポーラス  $\text{SiOC}$  やポーラス  $\text{SiCOH}$  などが用いられ<sup>2, 12, 34-36)</sup>、一般的に比誘電率が 2.5 以下のものを指す。

Table 1.1 に本研究で解析に用いた層間絶縁膜の材料特性を示す。比誘電率の小さい層間絶縁膜は弾性率が小さくなる傾向があり、Low-k 材、ULK 材は  $\text{SiO}_2$  に比べて線膨張係数(CTE: Coefficient of Thermal Expansion) が一桁大きい。また層間絶縁膜の機械的強度に関しては標準化された測定手法が確立されておらず比較可能な数値が整理されていないが、低誘電率化は空孔率を高めることが主たる方法であり、空孔率を高めると弾性率と機械的強度が低下すると考えられている<sup>33, 36)</sup>。

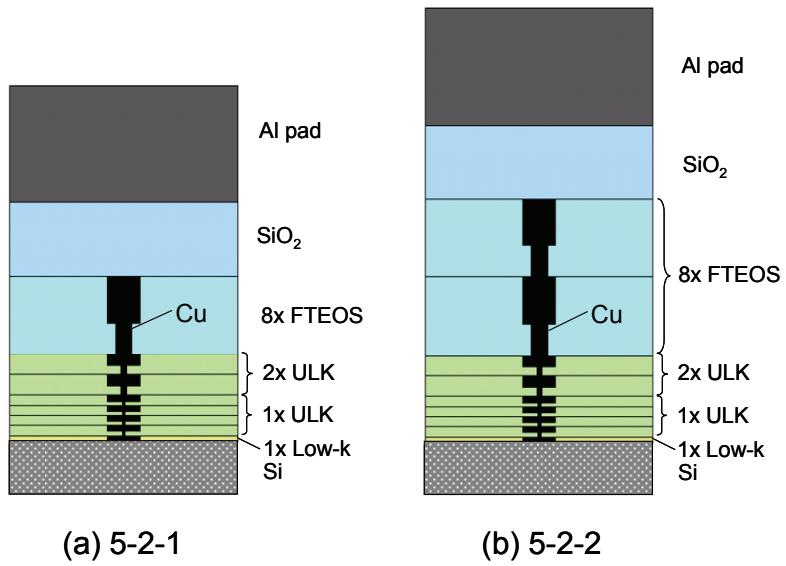

半導体デバイスの配線層の断面図の一例を Fig. 1.8 に示す。ここでは 1x, 2x, 8x 層の各層の積層数を使って(a) 5-2-1, (b) 5-2-2 と表記した 2 つの異なる構造を示している。層構成はシリコン基板の上に low-k, ULK, FTEOS,  $\text{SiO}_2$ , Al パッドの順で積層されたものである。1x と示した層は最も微細な配線ルールを適用する配線層で最下層に low-k 材、その上の 4 層に ULK 材を適用する。2x と 8x の層はそれぞれ 1x の 2 倍と 8 倍の配線ルールを適用すると仮定し、2x 層に ULK, 8x 層に FTEOS を用いる。本稿では 1x 層を 5 層・2x 層を 2 層・8x 層を 1 層積層した構成を 5-2-1 と表記し、1x 層を 5 層・2x 層

Fig. 1.8 Cross-sections of film stacks in the back-end-of-line layers (a) 5-2-1 and (b) 5-2-2.

を 2 層・8x 層を 2 層積層した構成を 5-2-2 と表記する。一般的にシリコンサブストレート直上はローカル配線のために微細な配線ルールを適用し、Al パッドに近い上部の配線層はグローバル配線のために緩い配線ルールを適用する。図中ではおおよその配線ルールの倍数を用いて最も微細な配線層を 1x とし、その約 2 倍のルールの配線層を 2x、約 8 倍のルールの配線層を 8x と記している。この例では 1x および 2x の層に RC 遅延を低減するため Low-k あるいは ULK の低誘電率絶縁膜を用いている。先端テクノロジのデバイスでは導電材料に Cu を用い、デュアルダマシンのメッキ工法で Cu 配線を形成する。ワイヤボンド部やフリップチップ接合部のパッド下部も有効な配線エリアとして配線パターンを形成するのが一般的である。配線層の積層数や配線パターンは多様な組み合わせが可能で、デバイスの性能仕様やコスト目標などに応じて選択する。ワイヤボンド部あるいはフリップチップ接合部のボンドパッド下部構造全体の機械的特性は、配線層の積層構造や配線パターンに影響される。外部端子接続時にパッド下部で破壊が発生しないようにすることは重要な設計要件である。

### 1.3 チップの外部端子接続技術の動向

#### 1.3.1 ワイヤボンディング

ワイヤボンディングはチップの外部端子接続技術として最も普及した技術であり様々なタイプのパッケージで用いられてきた。チップの高集積化によって多ピン化の進展してきたロジック半導体においてはボンドパッド(接続端子)ピッチの微細化が大きな技術トレンドであった。1990 年代には 100 μm ピッチの壁を越えるべく技術開発が進められていたが<sup>37)</sup>、2000 年代以降も 100 μm 以下の技術開発が進み<sup>38-40)</sup>、現在では 35 μm ピッチの技術確立がなされている<sup>15)</sup>。ワイヤボンディングの微細化には、ボンディング時の超音波の高周波化<sup>41, 42)</sup>、微小ボール形成時の形状安定化<sup>43, 44)</sup>、細線でのループ形状の安定化<sup>45)</sup>、パッド上のプローブマークの影響の最小化<sup>46-49)</sup>など様々な取り組みが行われてきた。低成本のフリップチップパッケージの普及に伴い、ワイヤボンドパッケージのピン数は大きな伸びは

見込まれておらず、今後のパッドピッチの微細化は 2022 年でも  $30\text{ }\mu\text{m}$  と考えられている<sup>15)</sup>。近年では先端テクノロジーの Low-k/ULK デバイス上でのワイヤボンディングの研究開発が活発に行われており、その課題については次節で述べる。

### 1.3.2 フリップチップボンディング

フリップチップボンディングによるチップ接続技術は 1960 年代に IBM によってメインフレームコンピュータ向けに商業生産されたのを初めとし、主に高性能コンピュータ向けの半導体で長年に渡って使用してきた。開発当初はチップ上に形成されるバンプには、はんだめつきされた銅コアが用いられていたが、1970 年代初頭には Pb が 95% 以上の高融点はんだが使われるようになった<sup>50-52)</sup>。はんだバンプを持つチップをリフローを用いてフリップチップボンディングで接続する技術は C4 (Controlled Collapse Chip Connection) とも呼ばれ、現在でもこの呼称は広く使われている。チップを接続する基板は長年セラミックが使われてきたが、感光性ポリイミドを用いてフォトビアを形成したビルドアップ基板にフリップチップボンディングを行う技術が 1992 年に開発された<sup>53, 54)</sup>。有機材料を使うビルドアップ基板は Cu 配線などとの複合材として線膨張係数が  $17\text{ ppm}/^\circ\text{C}$  程度であり  $8\text{ ppm}/^\circ\text{C}$  程度のアルミナセラミック基板と比べると、 $3\text{ ppm}/^\circ\text{C}$  の Si チップとの線膨張係数のミスマッチが大きくなる。このためビルドアップ基板上のフリップチップボンディングでは接合部を保護するためチップと基板間にアンダーフィル樹脂を用いる手法が採られた。現在ではフォトビアよりも信頼性に優れるレーザービアを用いたビルドアップ基板が主流になっている<sup>55)</sup>。山中らは、 $15\text{ mm}$  角で  $0.15\text{ mm}$  厚のチップと Sn-2.5Ag はんだを用いて  $0.30\text{ mm}$  厚の基板に  $100\text{ }\mu\text{m}$  ピッチのフリップチップボンディングを行うと、基板の線膨張係数が  $3\text{ ppm}/^\circ\text{C}$ ,  $8\text{ ppm}/^\circ\text{C}$ ,  $15\text{ ppm}/^\circ\text{C}$  の場合、接合部の歪がそれぞれ約 0.7%, 約 1.0%, 約 2.0% であり、微細ピッチのフリップチップボンディングには低線膨張係数基板が重要であることを示した<sup>56)</sup>。2013 年度版日本実装ロードマップでは、ビルドアップ基板のコア材、ビルドアップ材それぞれに低線膨張係数化の要求があることを示している<sup>15)</sup>。一例を挙げるとコストパフォーマンス電子機器向けビルドアップ基板では、コア材で 2012 年の  $8\text{ ppm}/^\circ\text{C}$  に対して 2022 年では  $6\text{ ppm}/^\circ\text{C}$  が、またビルドアップ材では 2012 年の  $45\text{ ppm}/^\circ\text{C}$  に対して 2022 年では  $20\text{ ppm}/^\circ\text{C}$  の線膨張係数 (X-Y) が求められている。

2006 年 7 月に施工された RoHS (特定有害物質使用規制) によって鉛の使用が規制されることになり、接合材であるはんだは鉛フリーはんだへの移行が進んできた<sup>57, 58)</sup>。フリップチップボンディングに関する鉛の使用は規制の適用除外が続いている<sup>59)</sup> が大型チップでも鉛フリーはんだでの技術確立が進んできている<sup>60, 61)</sup>。ビルドアップ基板でのフリップチップボンディングで鉛入りはんだを用いる場合には、バンプに鉛が 95wt% 以上の高融点はんだと基板上のプリソルダに Sn-37Pb 共晶はんだを使うのが代表的である。鉛フリーはんだを用いる場合は、Sn と数 wt%Ag の組成のバンプと SnAgCu (SAC) のプリソルダを使うのが代表的である。Table 1.2 に鉛入りおよび鉛フリーはんだの融点とヤング率を示す。鉛入りはんだでフリップチップボンディングを行う場合、プリソルダの SnPb 共晶はんだの融点である  $183^\circ\text{C}$  近辺が凝固点となるが、鉛フリーはんだの場合には凝固点が  $220^\circ\text{C}$  近辺と約  $40^\circ\text{C}$  高くなる。また鉛入りはんだでの接合部は高融点はんだの特性が支配的となり、鉛フリーはんだの接合部の

Table 1.2 Material properties of solders<sup>62)</sup>.

|              | Melting temperature (°C) | Young's modulus (GPa) |

|--------------|--------------------------|-----------------------|

| Sn-95Pb      | 300                      | 18.4                  |

| Sn-37Pb      | 183                      | 31.7                  |

| Sn-3Ag       | 221                      | 42.0                  |

| Sn-3Ag-0.5Cu | 217                      | 41.6                  |

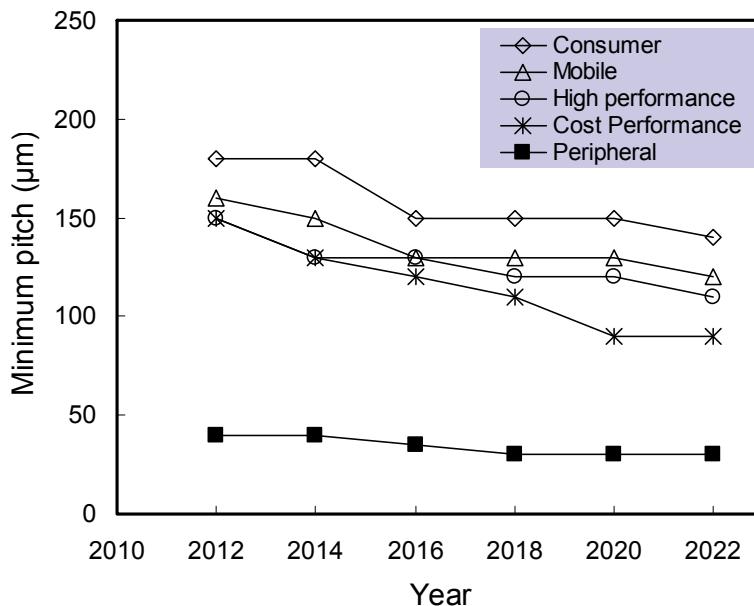

Fig. 1.9 Roadmap of maximum pin count by product segment<sup>15)</sup>.

ヤング率は鉛入りはんだの接合部に比べて約 2 倍高くなると考えられる。さらに高融点はんだは Pb の延性が高い。このため鉛フリーはんだでビルトアップ基板を用いてフリップチップボンディングを行うとチップと基板の線膨張係数のミスマッチにより接合部周辺の熱応力が、鉛入りはんだの場合に比べて高くなる。

Fig. 1.9 は筆者が 2013 年度版日本実装技術ロードマップ<sup>15)</sup>の数値をもとに作成したグラフであり、各製品セグメントごとのフリップチップボンディングの最小パッドピッチのロードマップを示している。低価格民生品、携帯電子機器、コストパフォーマンス、高性能の各カテゴリーはエリアアレイを想定している。2012 年では低価格民生品、携帯電子機器、コストパフォーマンス、高性能の各カテゴリーで、最小パッドピッチはそれぞれ 180 μm, 160 μm, 150 μm, 150 μm である。これらは今後も微細化が進み、2022 年にはコストパフォーマンスで 90 μm ピッチにまで縮小される見込みである。先に述べた山中らの解析では 100 μm ピッチのフリップチップボンディングで、基板の線膨張係数が 15 ppm/°C の場合、接合部の歪が約 2.0% であると報告されており、さらにピッチが 50 μm に微細化されると接合部の歪は約 3.5% まで大きくなることが示されている<sup>56)</sup>。フリップチップボンディングの微細化に伴い今後も接合部の歪・熱応力は増大するものと考えられる。Fig. 9 中のペリフェラルはパッドがチップ周

辺に配置されたものである。現在でも最小ピッチ  $40\text{ }\mu\text{m}$  が実現されており、2022年には  $30\text{ }\mu\text{m}$  まで微細化が進むと考えられている。ペリフェラルのフリップチップボンディングは、特に日本において携帯電話やデジタルカメラなどに搭載される薄型パッケージ向けで Au スタッドバンプによる Au-はんだ接合<sup>63, 64)</sup> などが使われてきた。近年では接合信頼性や耐エレクトロマイグレーション性に優れる Cu ピラーを用いたフリップチップボンディング技術が開発され<sup>65, 66)</sup>、モバイル製品のアプリケーションプロセッサーなどで量産されている。また Cu ピラーはシングルチップパッケージのみならず、2.5D パッケージや 3D-IC パッケージでチップとインターポーラーあるいはチップとチップを微細ピッチで接合する際の重要な技術と考えられている。

## 1.4 配線層ダメージの課題と研究目的

Low-k や ULK を用いたチップ配線層の層間絶縁膜の機械的強度が低く、パッケージング工程中、パッケージング後の 2 次実装中あるいは製品使用時にパッケージからかかる応力によってチップ内部のメタル配線層が破断する課題がある。Low-k/ULK デバイスは、デバイス単体では正常に機能するよう製造されてもパッケージに組み込むと、特に端子接続部において、パッケージからの機械的応力によってデバイス内部に破壊を起こし正常な機能を失うことがある。これはチップとパッケージの相互作用(CPI: Chip-package interaction)の問題として Low-k/ULK 世代のデバイスで顕在化している<sup>67-70)</sup>。本研究の目的は、ワイヤボンディングとフリップチップボンディングのそれぞれの接合技術において、接合後の初期製造品質で問題となるクラックやダメージの原因となるチップ配線層および接合部の応力に着目し、この応力に影響を与える因子を調べ、応力低減を実現する手法を求めることがある。

### 1.4.1 ワイヤボンディングにおける外部端子接続時の接合荷重・超音波印加による層間絶縁膜の破壊

チップ側の接合は最大 1%程度の Si あるいは Cu を添加した Al パッド上にボールボンドで行われる。Al パッド表面には不動態の酸化膜が形成されるため超音波併用の熱圧着方式が用いられている。ワイヤ先端に放電による溶融で形成されたボールはキャビラリによってパッドに圧着され、ボールの塑性変形と超音波印加によって酸化膜を破り Al の新生面と接合を形成する。ボールボンドにおけるボールの塑性変形挙動や接合の形成メカニズムはボールボンドのプロセス安定性、信頼性の確保に重要であり、詳細な研究報告がなされてきた<sup>71, 72)</sup>。

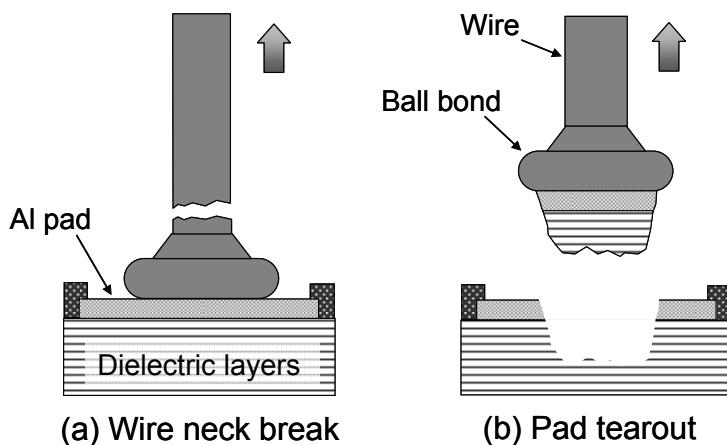

ワイヤボンディングによる Low-k/ULK チップのパッド下部配線層の破壊はボンディング時の荷重・超音波印加によって起こると考えられており、ボールボンド後のルーピング中にパッドが剥がれる、ワイヤブル試験でパッドが剥がれる破断モードで十分な強度が得られない、信頼性試験で配線が破断するといった問題となる<sup>73-76)</sup>。ワイヤボンド部の接合強度を測定する試験としては Fig. 1.10 に示すワイヤブル試験が広く用いられている。ワイヤブル試験は本来はルーピングされたワイヤの強度を測定する試験で、Fig. 1.11 (a) に示すワイヤのネック部での破断が正常モードとなる。Low-k/ULK 配線膜を用いたデバイスでボンディング時にパッド下部配線層にダメージがある場合、Fig. 1.11 (b) に示すようにボールボンドされたパッドの下の配線層から剥れるモードが発生する。

Fig. 1.10 Wire pull test.

Fig. 1.11 Breakage modes in wire pull testing (a) wire neck break and (b) pad tearout.

ワイヤボンディングによって Low-k/ULK 層で剥がれが発生する現象については、ワイヤの機械的特性の影響<sup>74)</sup>、ボンディング条件による影響<sup>77)</sup>を調べた実験的解析やパッド下部配線構造の影響を調べた数値解析<sup>78-80)</sup>など多数の報告がなされている。本研究においては、デバイスの配線層の構造パラメータ（絶縁膜積層数、絶縁膜厚み、配線パターン）を変動させた場合の複合特性を求め、ワイヤボンディングのプロセス条件下（ボンド荷重、超音波振動印加）で、Low-k/ULK 層内に発生する応力場がいかに変動するかを FEM (Finite Element Method) を用いて調べた。また、配線層の構造パラメータを変動させたときの応力とワイヤボンディング実験から求めたパッド剥がれ発生率の相関を求め、ワイヤボンディングにおいて配線層内の応力低減を実現する配線層構造の条件を求めた。

#### 1.4.2 フリップチップボンディングにおける外部端子接続時のチップと基板の熱応力による層間絶縁膜の破壊

##### (1) 低融点はんだによる応力低減

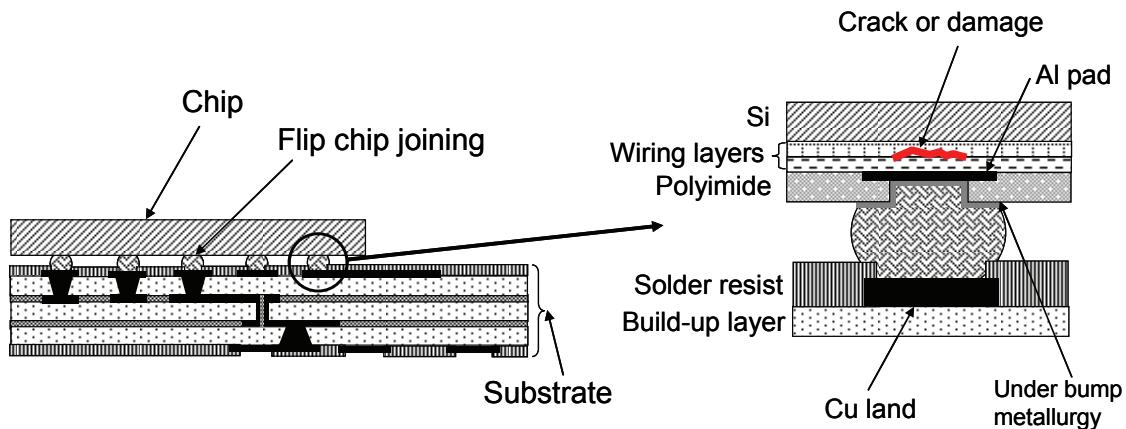

FCPBGA パッケージにおいて、チップ接合はチップキャリア基板上の電極にプリソルダおよびフラックスを塗布した後にチップを搭載しリフローではんだ接合を行う方式が主流となっている。デバイスの絶縁膜の Low-k/ULK 化と鉛フリーはんだによる接合温度の高温化により、Fig. 1.12 に示すようにシリコンチップと基板の線膨張係数の差に起因するパッド下部への熱機械的応力によって、特に、チ

Fig. 1.12 Schematic diagram of damage in ULK dielectric layer under the pad.

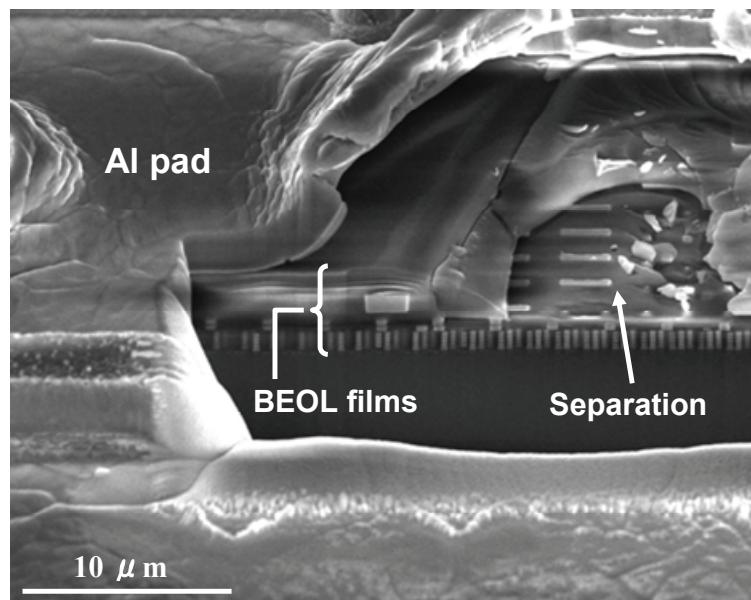

Fig. 1.13 Cross section photograph of flip chip joint and damage in ULK layer.

ツッコナー部のパッド下部配線層にクラック、ダメージが発生する問題が顕在化する。これは超音波顕微鏡でチップ裏面から観察すると白いスポットとなるため、ホワイトバンプと呼ばれており<sup>50)</sup>、パッド下部配線構造の影響<sup>81, 82)</sup>、チップサイズと冷却時のチップ温度の不均一性の影響<sup>83)</sup>、チップキャリア基板の機械特性の影響<sup>84)</sup>、基板上のパッドの組成と接合部のSnの過冷却の影響<sup>85)</sup>などの様々な解析が報告してきた。Fig. 1.13にフリップチップボンディング後のパッド下部Low-k/ULK層に発生したダメージの断面写真を示す。写真の上部はチップであり、下部が基板である。チップ側のボンドパッドの下（写真では上側）の配線層にダメージが見られる。

フリップチップボンディングにおけるチップとパッケージの相互作用の問題を低減するためには、従来のFCPBGAのプロセスでのフリップチップボンディングのパラメータ最適化などに加えて以下のような方式も検討してきた。

- 熱機械的応力の原因であるチップと基板の線膨張係数のミスマッチを小さくするために基板の線膨張係数を下げる<sup>56)</sup>。

- フリップチップボンディング後のフラックス洗浄の不要な無洗浄フラックスを用いて、フリップ

チップボンディング後に高温保持したままアンダーフィルを塗布・硬化し、室温まで冷却することなく接合部周りの保護を行う<sup>86)</sup>.

- チップあるいは基板上にアンダーフィルを先塗りして、フリップチップボンディングとアンダーフィル塗布を同時に行い、室温まで冷却することなく接合部周りの保護を行う<sup>87)</sup>.

- 低融点はんだを用いて接合温度を下げ、接合温度と室温の温度差を小さくすることで熱機械的応力の低減を図る<sup>88)</sup>.

上記の Low-k/ULK チップの配線層の応力低減手法の中から、本研究では低温はんだによる応力低減を取り上げた。低融点はんだは環境負荷低減の観点からも注目され Sn-Bi 系や In 系など各種組成で広範な研究が進められている<sup>89, 90)</sup>。現在多く使われている SnAg はんだバンプと SnAgCu プリソルダのチップ接合では、過冷却を考慮しなければ接合温度が 220°C 近辺であり、低融点はんだによって 140~150°C 程度に接合温度を下げるときチップと基板の線膨張係数のミスマッチによってパッド下部の配線層に生じる応力が低減されることは自明と考えられる。しかし、パッド下部配線層の応力は、はんだ接合部の弾性率やクリープ特性にも依存するため、一概に接合温度の低下で期待する応力低減が実現されないこともあり得る。低融点はんだの機械的特性は先行研究で報告されているものもある<sup>89, 91-95)</sup>が、チップ接合のようなマイクロ接合の大きさでは粒界の大きさや結晶方位の影響が顕著になる<sup>96)</sup>。本研究では苅谷らが開発した微細試験片の引張試験法<sup>97)</sup>を用いて融点 139°C の Sn-58Bi, 融点 143°C の In-3Ag および比較として融点 217°C の Sn-3Ag-0.5Cu (SAC305) の機械的特性を評価し、これを用いて FCPBGA におけるボンドパッド下部配線層に生じる応力場の解析を行った。

## (2) 貫通電極を有するインターポーラ上に複数チップを搭載するパッケージにおける応力場の解析

先に述べたように半導体デバイスの性能向上を維持し高密度実装を実現する技術として 2.5D/3D-IC パッケージの研究開発が活発に行われている。2.5D/3D-IC パッケージでは有機基板上では実現できない微細配線をシリコンインターポーラ上に形成し、さらに 3D-IC パッケージではチップ間を TSV を用いて接続することで、伝送経路の短縮と電源・グランド配置の均一性を高め、シグナルインテグリティとパワーインテグリティを向上し<sup>17)</sup>、バスのクロック周波数は抑えながらもバス幅を広げることでデータ転送レートを高める<sup>16, 30)</sup>。2.5D/3D-IC パッケージを実現する上で重要なチップおよびインターポーラの TSV 技術に関しては様々な研究開発が進められており<sup>17, 18, 98, 99)</sup>、2022 年にはシリコンインターポーラの TSV ピッチは 20 μm まで、TSV 径は 10 μm まで微細化することが求められている<sup>15)</sup>。高アスペクト比で微細な TSV を形成するには穴空け加工、導体金属の穴埋め加工それぞれで困難を伴うためシリコンインターポーラは 100 μm 程度まで薄化する必要がある。チップとチップあるいはチップとシリコンインターポーラの接合では、チップの配線層やインターポーラ上の配線層の影響を考慮しても線膨張係数のミスマッチによる接合部にかかる熱機械的応力は大きなものではない。しかしながら薄化されたインターポーラは有機基板上に接合されるため、インターポーラ上に搭載するチップとの接合部には基板の熱収縮による影響が出ることが報告されている<sup>100, 101)</sup>。また、近年ではシリコンに代わり安価なガラスをインターポーラに用いる研究開発も進展している<sup>22, 26, 27)</sup>。ガラスの線膨張係数

は Si に近いものもあるが、一般的には  $8\sim10 \text{ ppm}/\text{°C}$  程度であり、ガラスインター pocer を用いた場合には、シリコンインター pocer と異なる応力場が発生すると考えられる。チップ接合のピッチは TSV ピッチと等しく  $50 \mu\text{m}$  以下が必要とされ、従来のはんだバンプではなく Cu ピラーが用いられる。2.5D/3D-IC パッケージでは複数回の接合が行われるため複数回の加熱時にも安定性を保つために Cu ピラーと基板のパッド間のはんだ接合部を金属間化合物化する IMC (Intermetallic Compound) 接合が好ましいとの考えがある。この場合 Cu の弾性率( $E = 117 \text{ GPa}^{100, 101}$ ) と CuSn の金属間化合物の弾性率( $E = 110 \text{ GPa}^{100, 101}$ ) は SnAg はんだや SnAgCu はんだよりも高くなるため接合部周りの応力が大きくなる課題がある。

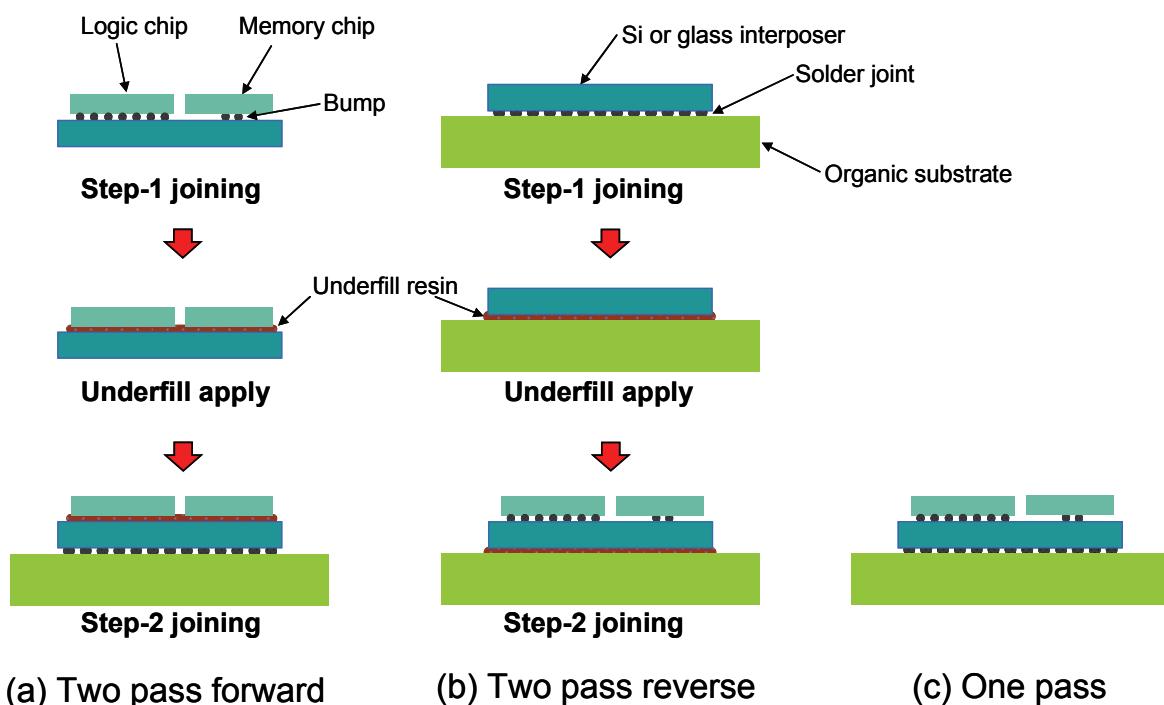

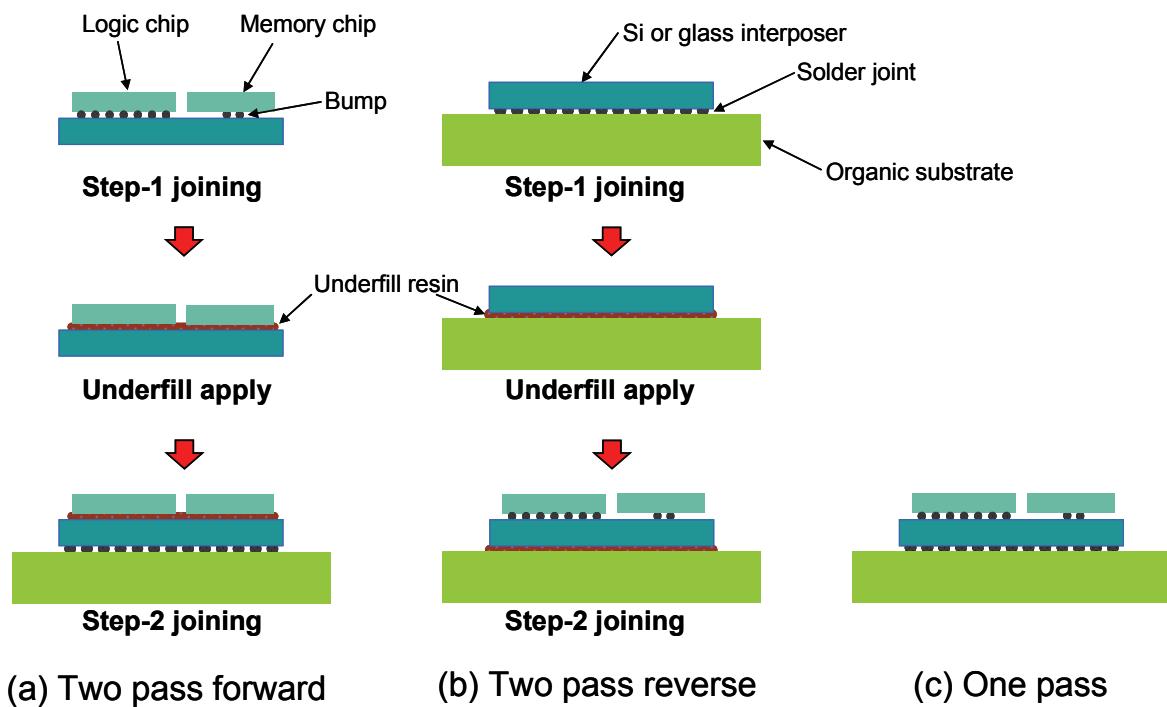

本研究ではチップとインター pocer の接合およびインター pocer と基板の接合によってマイクロ接合部と Low-k/ULK 層に生じる応力場を調べた。シリコンおよび 2 種類の異なるガラスのインター pocer の機械的特性、インター pocer の TSV 密度、チップとインター pocer それぞれの厚みを主要な因子として取り上げ、また Fig. 1.14 に示すチップ、インター pocer、有機基板の接合の 3 つの異なる組み立てプロセスフローをに着目して接合後に発生する応力との関係を解明した。Fig. 1.14 のプロセスフローは、インター pocer にチップを接合してアンダーフィルを封入した後、インター pocer を基板に接合する 2 段階接続(a)，基板にインター pocer を接合してアンダーフィルを封入した後、チップをインター pocer に接合する逆の順序の 2 段階接続(b)，チップをインター pocer 上に、インター pocer を基板上にマウントし、同時に接合を行う(c)，という 3 つのパターンを仮定した。

Fig. 1.14 Three different process flows of chip and interposer joining for 2.5D package.

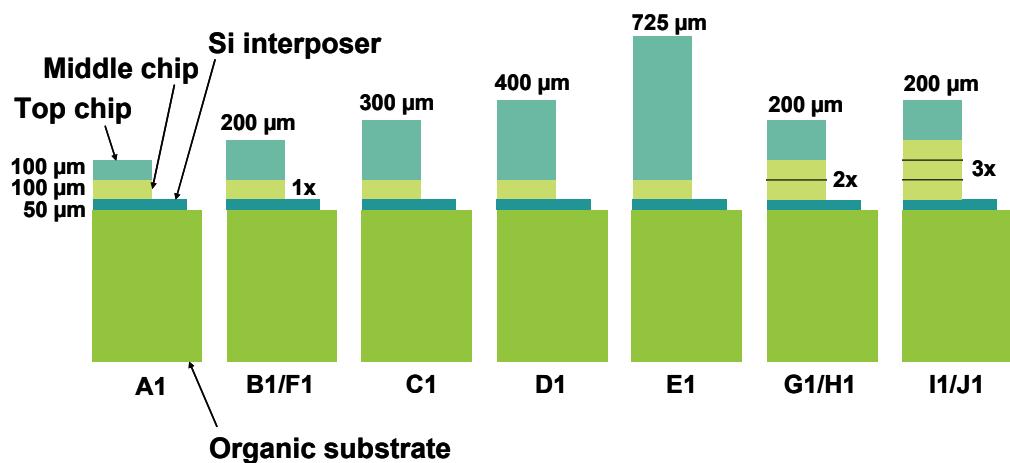

3D-IC パッケージではインターポーラ上に多数のチップを積層する場合に、チップおよびインターポーラの厚み、チップの積層数、接合部のはんだの機械的特性の各因子に着目し、マイクロ接合部とチップ配線層に生じる応力に与える影響を調べた。解析を行ったパッケージ構成の概略は次の通りである。有機基板上にインターポーラが積層されたその上にミドルチップとトップチップを積層した構成を基本として、トップチップの厚みを  $100 \mu\text{m}$  から  $725 \mu\text{m}$  に変化させたケース、ミドルチップは  $100 \mu\text{m}$  に固定してその積層数を 2 段、3 段と変化させたケース、さらにこれらの組み合わせでインターポーラの厚みを  $50 \mu\text{m}$  から  $300 \mu\text{m}$  まで変化させた。これらの因子が各チップ間およびチップとインターポーラ間の接合部とチップ配線層にかかる応力に与える影響の解明を行い、応力低減につながる各因子の設計指針を得た。

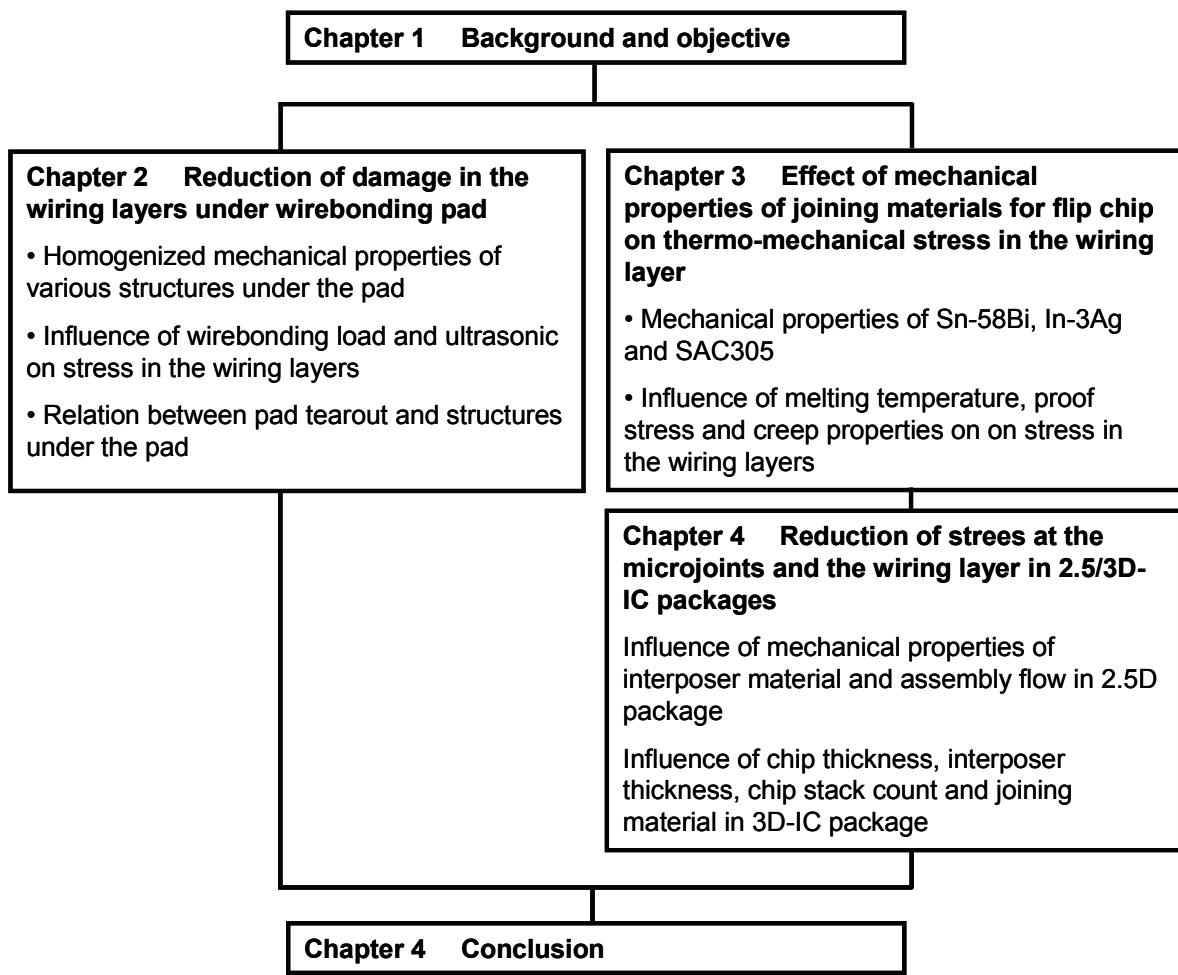

## 1.5 研究の構成と流れ

Fig. 1.15 に本研究の流れを示す。第 1 章では研究の背景となる半導体素子の微細化とそれに伴う配線層の層間絶縁膜の Low-k/ULK 化の動向と Low-k/ULK 材の特徴、ワイヤボンディングとフリップチップボンディングの 2 つのチップ接合技術の動向について述べた。次にこれら 2 つのチップ接合技術を Low-k/ULK チップに用いた時に課題となる Low-k/ULK 絶縁膜のダメージと、それぞれの接合技術で Low-k/ULK 絶縁膜を用いた配線層の応力を低減するための影響因子について詳述した。最後に全体の研究の流れを示した。

第 2 章では、ワイヤボンディングのパッド下部配線層の構造による応力場への影響を解析するため、均質化法によって異なるパッド下部構造ごとに複合機械特性を求めた。その特性を用いてワイヤボンディングの荷重と超音波印加によって発生する応力場と応力低減に有効な配線構造を解明した。さらにワイヤボンディングの実験からパッド剥がれの発生率とパッド下部配線層の複合弾性率との間の相関を求め、複合特性を用いた配線構造の最適化の有用性を検証した。

第 3 章では、フリップチップボンディングでのパッド下部配線層の応力を低減する手法として Sn-58Bi と In-3Ag の 2 種類の低融点はんだによる接合を取り上げた。2 種類の低融点はんだと SAC305 はんだの微細試験片を用いて引張試験を行い、これらのはんだのマイクロ接合の大きさでの機械的特性を求めた。ここで得られた応力歪み曲線とクリープ特性を用いて、バンプとプレソルダーの材料を変えた組み合わせで熱機械的応力の解析を行い、はんだの融点、弾性率、0.2%耐力、クリープ特性がパッド下部配線層に生じる応力に与える影響を論じた。

第 4 章では、微細配線の可能なインターポーラ上にフリップチップボンディングで複数チップを接合し、構造的にも複雑度の高い 2.5D パッケージと 3D-IC パッケージを取り上げた。2.5D パッケージと 3D-IC パッケージで接合部とパッド下部配線層の応力場に影響を与える特徴的な因子として、インターポーラの機械特性、チップ・インターポーラ・有機基板の接続順序、チップとインターポーラの厚みの組み合わせ、チップ積層数に着目した。これらの因子を変化させて FEM 解析により応力場と反り挙動を解明し、プロセスでの実装性を考慮して接合部・パッド下部配線層の応力を低減する指針を論じた。

Fig. 1.15 Research flowchart of this study.

## 第 2 章 ワイヤボンディングにおける下部配線層構造最適化による配線層ダメージの低減

### 2.1 緒言

低誘電率絶縁膜の Low-k 材や ULK 材を用いたチップでは、パッケージング工程中、パッケージング後の 2 次実装あるいは製品使用時にパッケージからかかる応力によってチップ内部のメタル配線層が破断する課題がある。ワイヤボンディングを用いる場合では、Fig. 1.11 に示したようにワイヤブル試験において正常モードであるワイヤネック切れ(a)ではなく、異常モードであるボンドパッドがメタル配線層から剥がれる不良モード(b)がよく知られている<sup>73-76</sup>。

筆者は、2D FEM (Finite Element Method) によりワイヤボンディング中の荷重と超音波の印加時に最大主応力の発生箇所が ULK 層の Cu 配線とビアの近傍であることを見出した。本研究では、3D FEM を用いてパッド下部の配線構造を因子として配線層内の応力場を求め、パッド下部配線層の最適化による接合時の応力低減手法を検討した。本来、パッド剥がれの原因となる絶縁層内の応力場は、絶縁層内の微細配線構造を再現したモデルによって解析を行うことが望ましい。しかし、ワイヤボンディングの接合のスケールでデバイスの微細配線を忠実に再現したモデルでは、解を得られるシミュレーション条件を設定するまでに多くの試行が必要であり、またひとつのモデルの解析時間も非常に長くなる。それに対して本研究では、繰返し性のある配線パターンで配線層の構造を均質化する方法に着目し、均質化により求めた複合特性を用いて応力解析を行うことで簡便に積層配線構造の比較評価を行う方法の確立を試みた。絶縁膜の厚みや配線密度を変化させた様々なパッド下部の配線構造を均質化によって求め、その特性を用いてワイヤボンディング荷重と超音波印加によりパッド下部の絶縁層にかかる応力の変化と、応力を低減できるパッド下部構造を解明した。ここでは Cu 配線やビアと相關絶縁膜の密着性は完全であると前提した。また、ここで求めた応力場は均質化した材料中のものであり、破断箇所と直接の相関を求めるにはマイクロモデルでの詳細解析が別途必要となる。

FEM の結果を検証するため、ULK 材を用いた 32 nm 世代のチップでワイヤボンディングの実験を行った。実験結果からパッド剥がれの発生率とパッド下部構造の関係を調べ、均質化特性を用いた FEM 解析結果とワイヤブル試験でのパッド剥がれの結果に高い整合性が見られることを実証した。

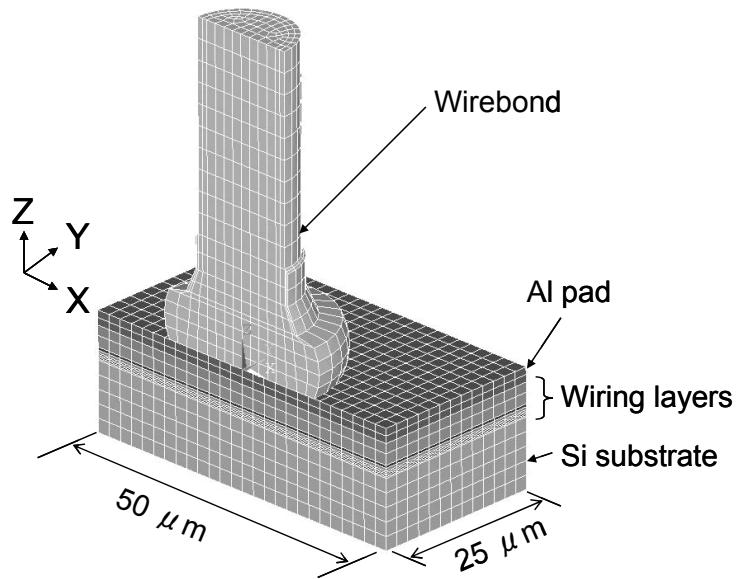

### 2.2 パッド下部配線構造の複合弾性率の導出

Fig. 2.1 にワイヤボンド・Al パッド・配線層およびシリコン基板のモデルを示す。解析空間としてワイヤボンドを中心 X 方向に 50 μm, Y 方向に 25 μm の領域を設定したハーフモデルを用いた。ボール径は 27 μm, ワイヤ径 15 μm, キャピラリのボールとの接触面の最大径 25 μm, ボール厚み 7 μm で、35 μm ピッチのワイヤボンディングを想定した。

パッド下部の配線層は、Fig. 1.8 に示す 2 種類の積層を解析対象とした。各構成材料のバルク特性を Table 2.1 に示す。ここではバルク材料を等方材料として扱う。Al パッド, Cu 配線は半導体工程でそれぞれ化学気相成長、めっきによって形成される。筆者らの過去の実験結果、解析結果との整合性を考慮し、表中の数値を採用した。また絶縁膜材料についても同様に表中の数値を用いた。1x, 2x, 8x の

Fig. 2.1 Half model of wirebond, Al pad, wiring layers and Si substrate.

Table 2.1 Material properties.

|                  | Elastic modulus (GPa) | Poisson's ratio |

|------------------|-----------------------|-----------------|

| Au ball          | 78                    | 0.33            |

| Al pad           | 48                    | 0.33            |

| Cu wiring        | 110                   | 0.33            |

| SiO <sub>2</sub> | 70                    | 0.20            |

| FTEOS            | 66                    | 0.18            |

| Low-k            | 9                     | 0.28            |

| ULK              | 4.6                   | 0.28            |

| Cap dielectric   | 104                   | 0.28            |

| Si               | 165                   | 0.22            |

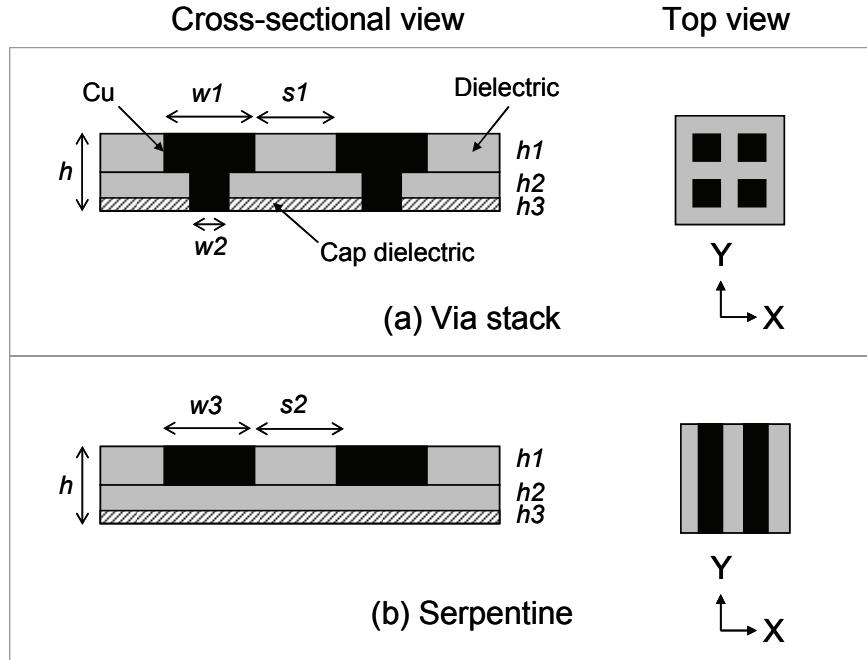

各配線層における配線構造として Fig. 2.2 に示すような 2 種類の構造を検討する。Cu 配線に用いるデュアル・ダマシン工法では配線とビアを一度のめっきで形成し、Cu の絶縁膜への拡散を防止するためビア層の底部に薄いキャップ絶縁膜を配するのが一般的である。配線とビアを合わせた 1 層の厚みを  $h$  とし、そのうち配線部分の厚みを  $h_1$ 、ビア部分の上層の絶縁膜の厚みを  $h_2$ 、ビア部分のキャップ絶縁膜の厚みを  $h_3$  と定義した。

Fig. 2.2 (a)はビア・スタックと呼ぶ構造で正方のメタル配線パターンの中央にビアを配置したもので、Fig. 2.2(b)はサーぺンタインと呼ぶビアを持たない配線のみのパターンである。Table 2.2 はこれらの寸法を示す。この中で、評価モデルのバリエーションとして配線間スペース( $s_1, s_2$ )をメタル配線の 1 倍、

2倍, 3倍とした条件を与え, ビア・スタック構造・サーペンタイン構造でそれぞれ VS-1, VS-2, VS-3, Serp-1, Serp-2, Serp-3 と呼ぶ。2x, 8x の各層の厚みは, 1x の厚みのそれぞれ 2倍, 8倍としているが, キャップ絶縁膜の厚みはこれよりも低い倍率を用いている点には注意を要する。

Fig. 2.2 Cu line and via structures for homogenization (a) Via stack and (b) Serpentine.

Table 2.2 Dimensions of Cu line and via (unit: nm).

|                   |           | 8x            | 2x   | 1x  |

|-------------------|-----------|---------------|------|-----|

| <b>h</b>          |           | 1600          | 800  | 200 |

| <b>h1</b>         |           | 960           | 240  | 120 |

| <b>h2</b>         |           | 520           | 100  | 40  |

| <b>h3</b>         |           | 120           | 60   | 40  |

| <b>Via stack</b>  | <b>w1</b> | 1760          | 440  | 220 |

|                   | <b>w2</b> | 400           | 100  | 50  |

|                   | <b>s1</b> | <b>VS-1</b>   | 440  | 220 |

|                   |           | <b>VS-2</b>   | 880  | 440 |

|                   |           | <b>VS-3</b>   | 1320 | 660 |

| <b>Serpentine</b> | <b>w3</b> | 1760          | 440  | 220 |

|                   | <b>s2</b> | <b>Serp-1</b> | 440  | 220 |

|                   |           | <b>Serp-2</b> | 880  | 440 |

|                   |           | <b>Serp-3</b> | 1320 | 660 |

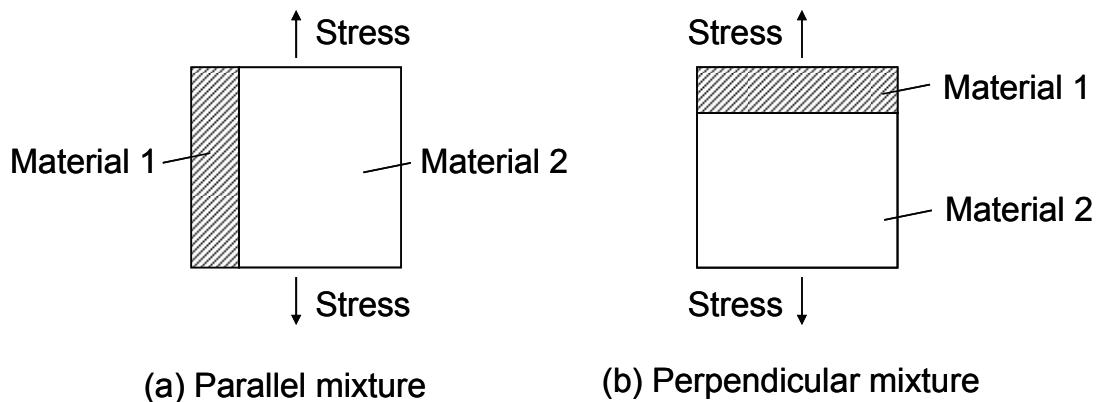

1x 層に Low-k と ULK, 2x 層に ULK, 8x 層に FTEOS の絶縁材料を用い, ビア・スタック, サーペンタインそれぞれに 3 種類ずつの構造の組み合わせで, ANSYS Multiscale.Sim<sup>®</sup>を用いて均質化モデルを作成し複合則によりこれらの構造それぞれで弾性率とポアソン比の複合特性を求めた. ここでは, 1x Low-k 層, 1x ULK 層, 2x ULK 層および 8x FTEOS 層それぞれで, Fig. 2.2 に示すような配線部絶縁膜, ビア部絶縁膜, キャップ絶縁膜, Cu 配線および Cu ビアで構成されるビアスタックおよびサーペンタインの構造を繰返しの基本単位として均質化を行なった. 弾性率の複合則は, Fig. 2.3(a)に示すような応力に平行に 2 つの材料が配置された構造では以下の(2.1)式に従い, Fig. 2.3(b)に示すような応力に垂直に 2 つの材料が配置された構造では(2.2)式に従う.

$$E_c = V_1 E_1 + V_2 E_2 \quad (2.1)$$

$$E_c = (V_1/E_1 + V_2/E_2)^{-1} \quad (2.2)$$

ここで  $E_c$  は複合特性,  $E_1$  は材料 1 の特性,  $E_2$  は材料 2 の特性,  $V_1$  は材料 1 の体積率,  $V_2$  は材料 2 の体積率であり,  $V_1$  と  $V_2$  は,

$$V_1 + V_2 = 1 \quad (2.3)$$

の関係を満たす. ANSYS Multiscale.Sim<sup>®</sup>では(2.1)式, (2.2)式を組み合わせて複合特性の計算を行う. ポアソン比も同様の計算となる.

Fig. 2.3 Schematic of mixture of two materials (a) parallel mixture, and (b) perpendicular mixture.

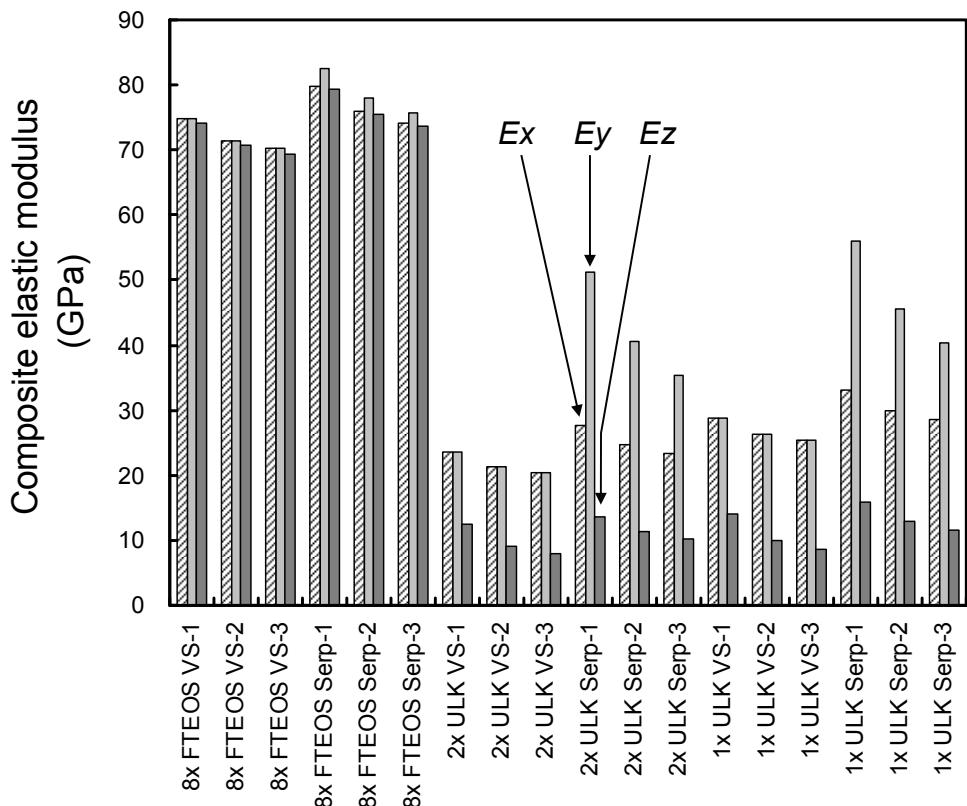

Fig. 2.4 に求められた複合弾性率を示す。この図では 1x 層の low-k 材での結果は省略した。バルク材料は等方であるが、配線構造の非対称性によって X, Y, Z 方向のそれぞれの弾性率  $E_x$ ,  $E_y$ ,  $E_z$  は異なる数値が得られる。ビア・スタックについては X, Y 方向が対称のため  $E_x$  と  $E_y$  は同じ数値となる。1x 層と 2x 層を比較すると 2x 層の弾性率のほうが低くなる。これは 2x 層のほうが弾性率の高いキャップ絶縁膜の体積比率が小さいためである。VS-1, VS-2, VS-3 の比較と Serp-1, Serp-2, Serp-3 の比較から、弾性率の高い Cu の配線密度を高くする（配線間隔を狭くする）ほど複合弾性率が高くなることが分かる。

## 2.3 外部端子接続時の配線層に生じる応力場の解明

### 2.3.1 FEM 解析モデル

Au ボール, Al パッド,  $\text{SiO}_2$  膜, Si 基板にはバルクの材料特性を適用し, 1x, 2x, 8x 層には均質化モデルで求めた複合特性を用いて、ワイヤボンディング荷重および超音波印加によって発生する応力を ANSYS Mechanical® Ver.14 で解析した。Au ボールは接合時の変形後の形状で解析を行っているため弾性体として扱い、Al パッドには硬化則を適用した。ここで用いた Al パッドの降伏応力は 70 MPa である。本研究で調べたモデルのマトリックスを Table 2.3 に示す。モデル 1, 2, 3 は、1x, 2x, 8x 各層をビア・スタックとし、その配線スペースを変化させた VS-1, VS-2, VS-3 を用いるものである。同様に

Fig. 2.4 Composite elastic modulus of various combination of different dielectric films and wiring structures.

Table 2.3 Model matrix of various structures.

| Model type | Structures in 1x, 2x and 8x | SiO <sub>2</sub> thickness (μm) | 8x layer stack count | Al thickness (μm) |

|------------|-----------------------------|---------------------------------|----------------------|-------------------|

| 1          | VS-1                        | 1.4                             | 1 L                  | 2.1               |

| 2          | VS-2                        | 1.4                             | 1 L                  | 2.1               |

| 3          | VS-3                        | 1.4                             | 1 L                  | 2.1               |

| 4          | Serp-1                      | 1.4                             | 1 L                  | 2.1               |

| 5          | Serp-2                      | 1.4                             | 1 L                  | 2.1               |

| 6          | Serp-3                      | 1.4                             | 1 L                  | 2.1               |

| 7          | VS-1                        | 0.7                             | 1 L                  | 2.1               |

| 8          | VS-1                        | 2.1                             | 1 L                  | 2.1               |

| 9          | VS-1                        | 1.4                             | 0 L                  | 2.1               |

| 10         | VS-1                        | 1.4                             | 2 L                  | 2.1               |

| 11         | VS-1                        | 1.4                             | 1 L                  | 1.2               |

| 12         | VS-1                        | 1.4                             | 1 L                  | 4.0               |

モデル 4, 5, 6 はサーペンタインの配線スペースを変化させた Serp-1, Serp-2, Serp-3 を用いるものである。モデル 7 と 8 は配線構造を VS-1 に固定し, Al パッド下の SiO<sub>2</sub> の厚みを変化させたものである。モデル 9 と 10 は同じく配線構造を VS-1 に固定し, 8x 層を用いないものと 2 層入れたものとなる。モデル 11 と 12 は VS-1 構造で Al パッドをそれぞれ 1.2 μm と 4.0 μm としたものである。

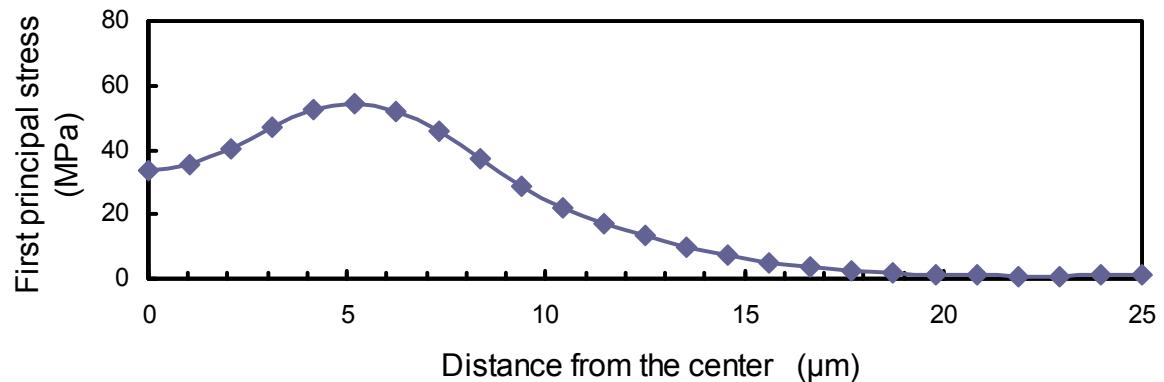

### 2.3.2 外部端子接続時の荷重によって配線層に生じる応力の解析

それぞれのモデルでボールボンドのキャピラリ接触面に対してボンディング中にかかる荷重を想定して 68.6 mN を与え, パッド下部の配線絶縁膜に発生する応力を調べた。Fig. 2.5 はモデル 1 の第一主応力のコンター図であり, Z 方向の変位は強調表示されている。Fig. 2.6 はモデル 1 の FTEOS 層(a),

Fig. 2.5 Contour diagram of first principal stress of model-1.

(a) FTEOS layer

(b) 2x ULK layer

(c) 1x ULK layer

Fig. 2.6 Stress distribution from the center of model-1.

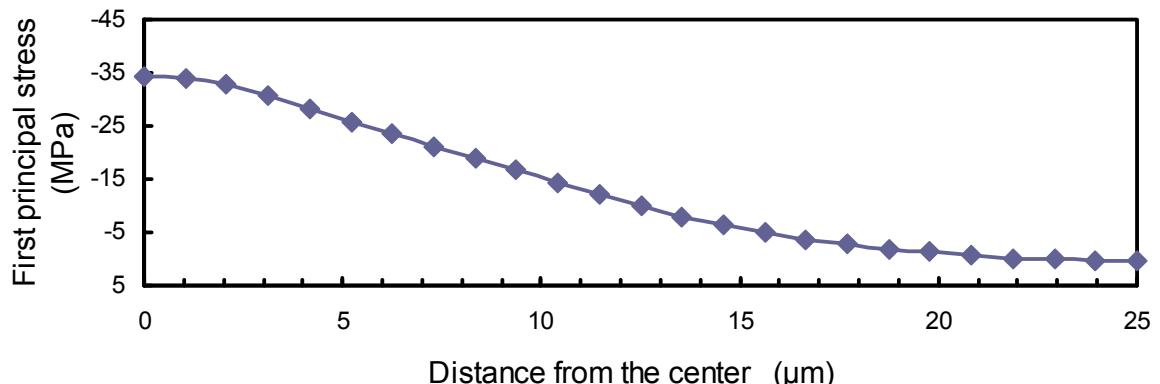

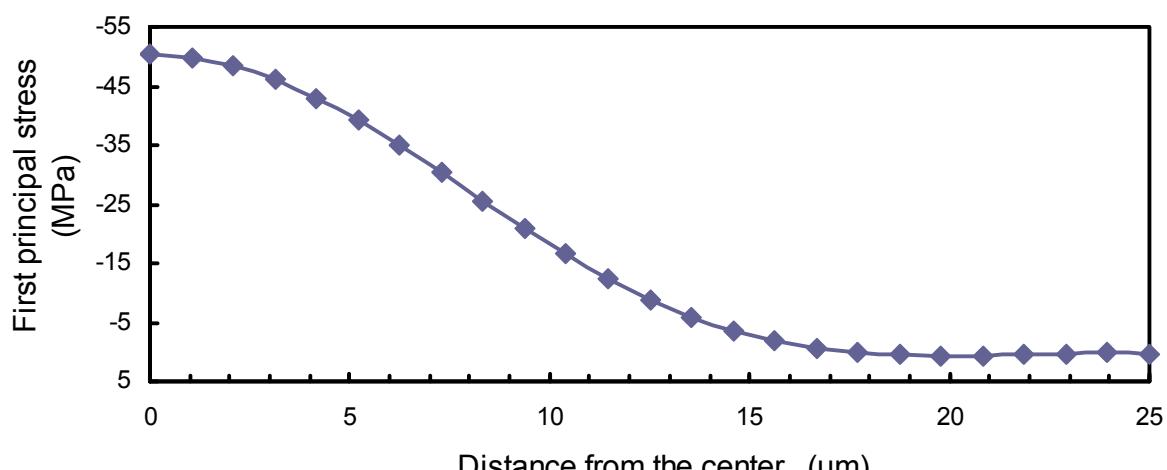

2x ULK 層(b), 1x ULK 層(c)の各層の厚みの中心を通る面でのボールボンドの中心からの応力分布を示す。センター図からの判別は難しいが、8x FTEOS 層内での第一主応力は、引張応力として働き、ボールボンド中心から 5 μm ほど外側で最大となっている。これに対し 2x ULK, 1x ULK の層内では最大の第一主応力はボールボンドの中心に位置し、圧縮応力となる。また 1x ULK 層の最大主応力は 2x ULK 層の最大主応力よりも高い。ここではモデル 1 の応力分布のみ示したが他のモデルでも同じ傾向が見られた。以下の配線構造、配線密度および積層構造の影響は ULK 層で最大主応力の発生している 1x ULK 層を対象に検討する。

### 配線構造と配線密度による応力低減の評価

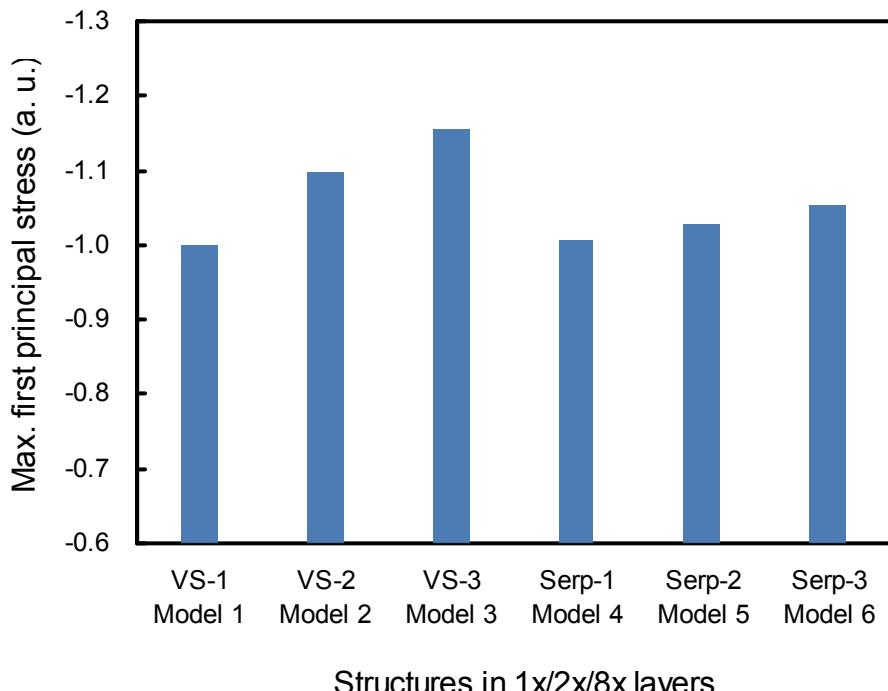

Fig. 2.7 はモデル 1 から 6 までのボールボンドの中心部の下部の 1x 層内での第一主応力を示したものであり、すべて圧縮応力である。ここでは相対比較のためモデル 1 の最大主応力を基準として任意単位でプロットした。モデル 1, 2, 3 のビアスタックの配線間隔を変化させた比較では、配線間隔が広がる、すなわち 1x, 2x, 8x の各層で複合弾性率が低くなるほど応力が大きくなりほぼ直線の関係が見られる。また同様の関係がモデル 4, 5, 6 のサーペンタインでも得られる。ビアスタックとサーペンタインでは配線間隔の変化に対する応力の変化の程度が異なっている。Fig. 2.4 でビアスタックとサーペンタインで  $E_z$  の変化に大きな差は見られないため、応力の変化の程度が異なるのは X, Y 方向での構造の対称性の違いに起因しているものと推察される。VS-1 と Serp-1 ではほぼ同じ最大主応力であるが、配線間隔の広い VS-3 と Serp-3 を比較すると VS-3 の方が 9.9%高い最大主応力となる。配線密度の低い配線ではビア接続を行なわないサーペンタイン構造が応力抑制に有利であることが分かる。

Fig. 2.7 First principal stress (compressive stress) in 1x ULK layer under the center of ball bond (model-1, 2, 3, 4, 5 and 6).

### 積層構造による応力低減の評価

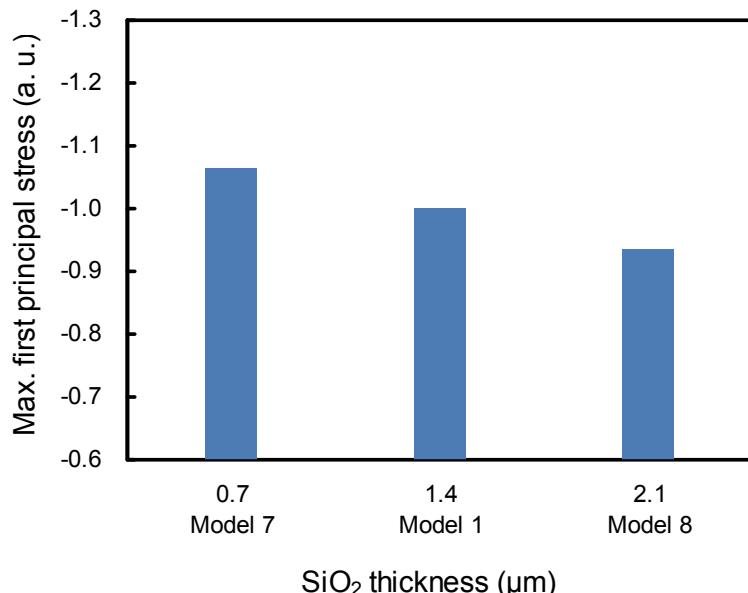

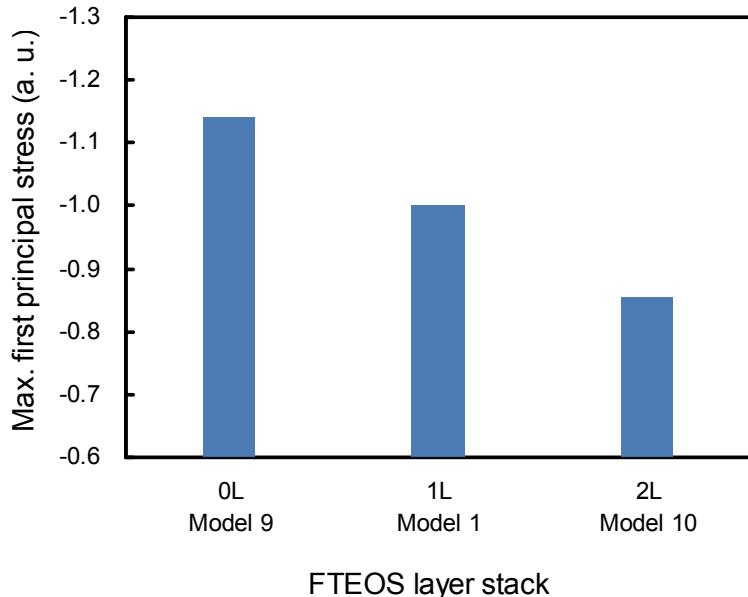

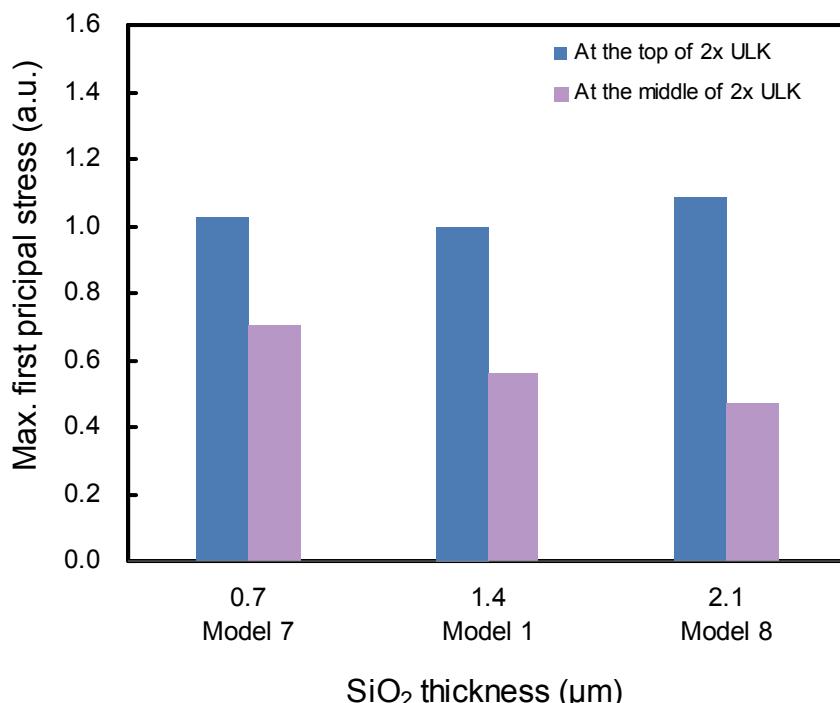

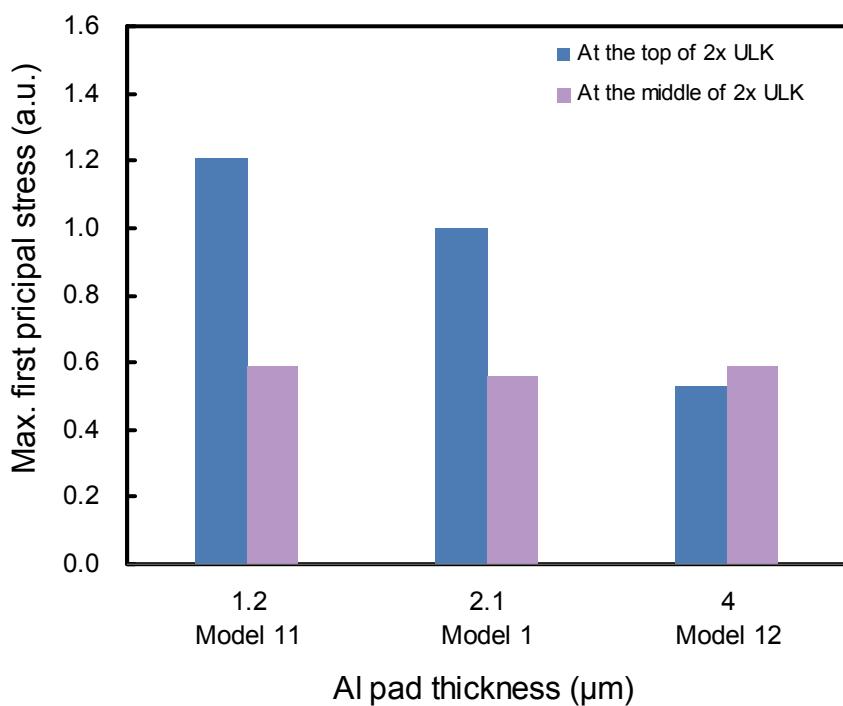

第一主応力に対する Al パッド直下の  $\text{SiO}_2$  の厚みの影響はモデル 1, 7 および 8 の比較となる (Fig. 2.8)。 $\text{SiO}_2$  厚みが  $1.4 \mu\text{m}$  から  $0.7 \mu\text{m}$  になると応力が 6.5% 高くなり、 $\text{SiO}_2$  厚みが  $1.4 \mu\text{m}$  から  $2.1 \mu\text{m}$  になると応力が 6.5% 低くなるため  $\text{SiO}_2$  の厚みが増すと 1x ULK 層内の最大主応力が減少する相関関係が見られる。同様に 8x FTEOS 層の比較をモデル 1, 9 および 10 で行う (Fig. 2.9) と FTEOS 層が厚いほど 1x ULK 層で応力が低下することが分かる。モデル 1 に比べるとモデル 10 は FTEOS の厚みが 2 倍になっており、1x ULK 層に発生する応力は 14% 低くなっている。また FTEOS 層のないモデル 9 はモデル 1 に比べて 14% 応力が高く、FTEOS の厚みと 1x ULK 層内の最大主応力の間に相関関係が見られる。ULK 層の上部に配する  $\text{SiO}_2$ 、FTEOS は 2x ULK に比べて  $E_z$  で 7 倍程度弾性率が高く、これらの層の厚みを大きくすることで 1x ULK 層内に発生する第一主応力を低減できることが分かる。

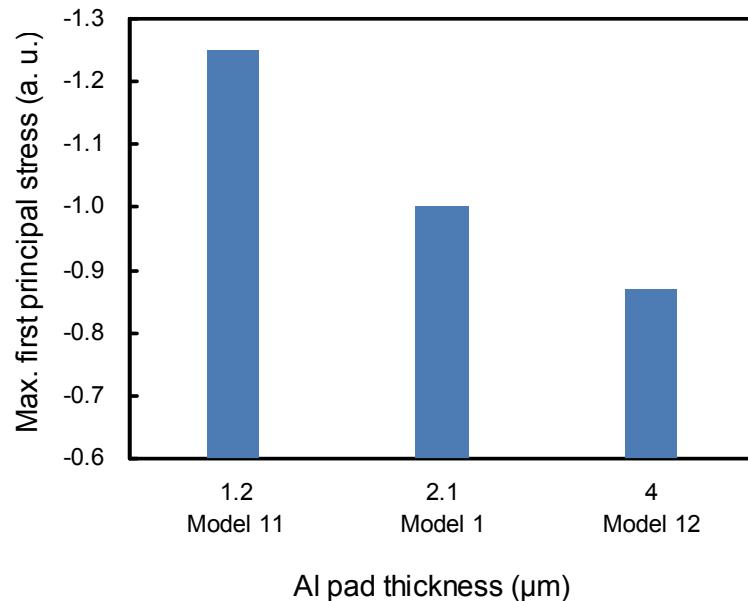

Fig. 2.10 は Al パッドの厚みと 1x ULK 層の最大主応力の関係を示したものである。モデル 1 の  $2.1 \mu\text{m}$  の Al パッドの場合に比べてモデル 11 の  $1.2 \mu\text{m}$  の場合では 25% 最大主応力が高くなるのに対して、モデル 12 の  $4.0 \mu\text{m}$  の場合では 13% 最大主応力が減少する。ここでも Al パッドの厚みが増すにつれて 1x ULK 層の最大主応力が減少する相関が認められる。

Fig. 2.8 First principal stress (compressive stress) in 1x ULK with variable  $\text{SiO}_2$  thickness (model-1, 7 and 8).

Fig. 2.9 First principal stress (compressive stress) in 1x ULK with variable 8x FTEOS thickness (model-1, 9 and 10).

Fig. 2.10 First principal stress (compressive stress) in 1x ULK with variable Al pad thickness (model-1, 11 and 12).

### 2.3.3 外部端子接続時の超音波印加によって配線層に生じる応力の解析

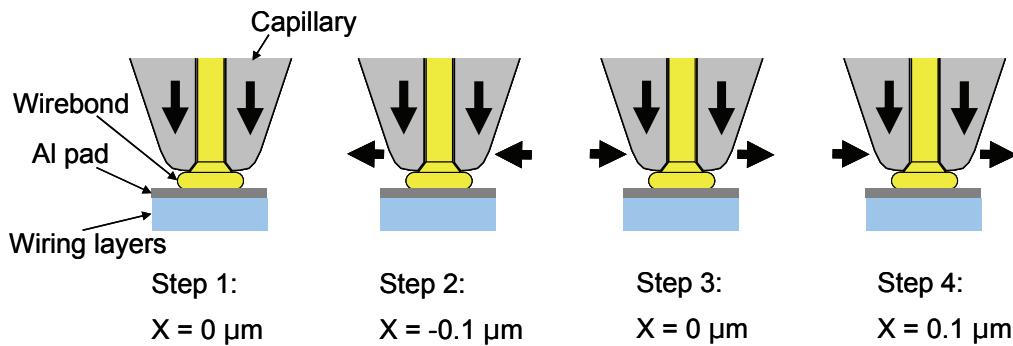

超音波印加の影響を調べるために、Fig. 2.11 に示す 4 ステップのモデルを作成した。ステップ 1 は前節と同じようにキャピラリ接触面に荷重を与えたモデルである。ここで与えた荷重は 49 mN である。ステップ 2 では同じ荷重を付与した状態で X 軸上で-0.1 μm の変位を与えた。この時、Au ボールと Al パッドの界面には固定モードの設定を用いた。次にステップ 3 では+0.1 μm の変位を与えて初期ボンディング位置に戻し、さらにステップ 4 でも+0.1 μm の変位を与えて 0.1 μm の振幅の振動の各過程で発生

する応力を解析した。モデルの組み合わせは前節と同じく Table 2.3 に示した 12 通りの組み合わせである。

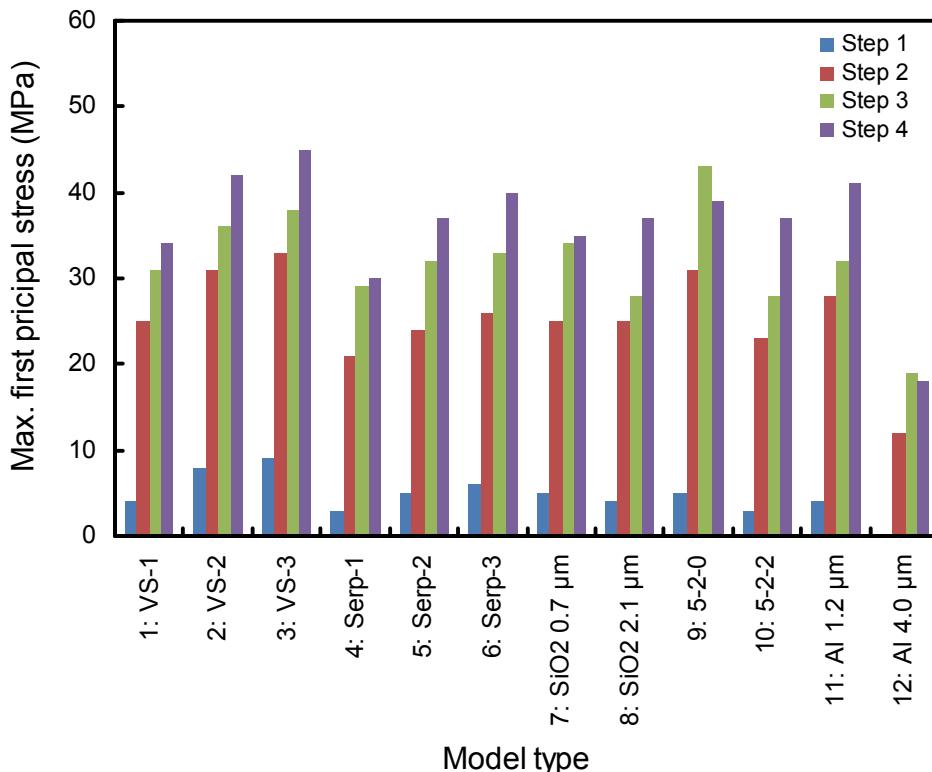

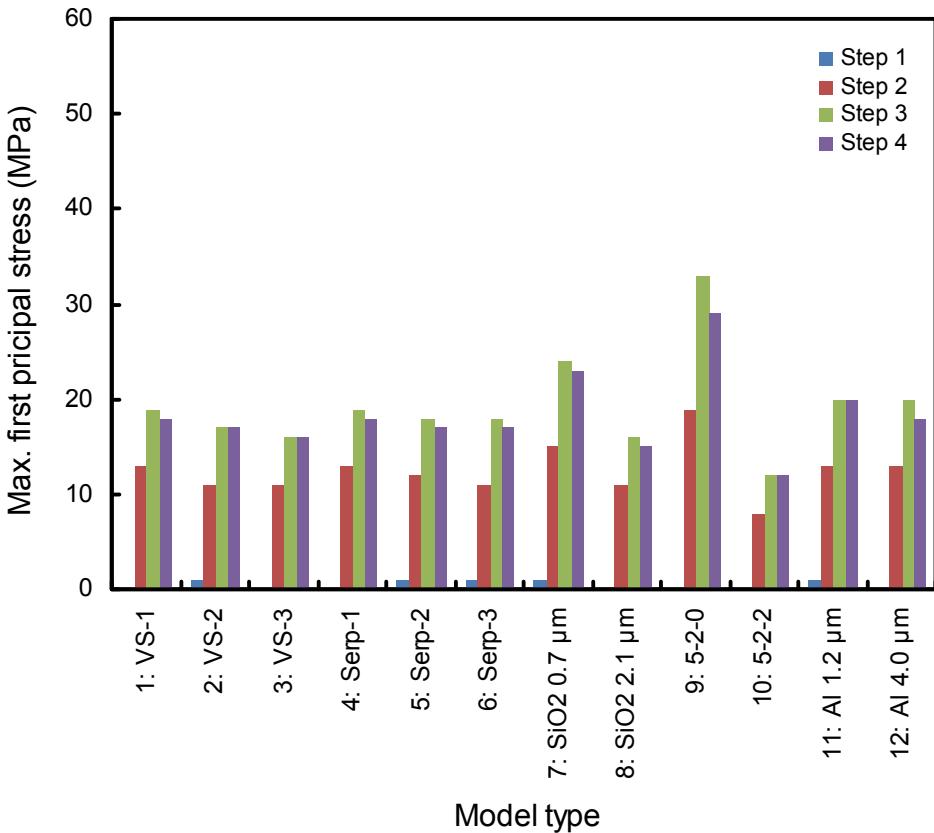

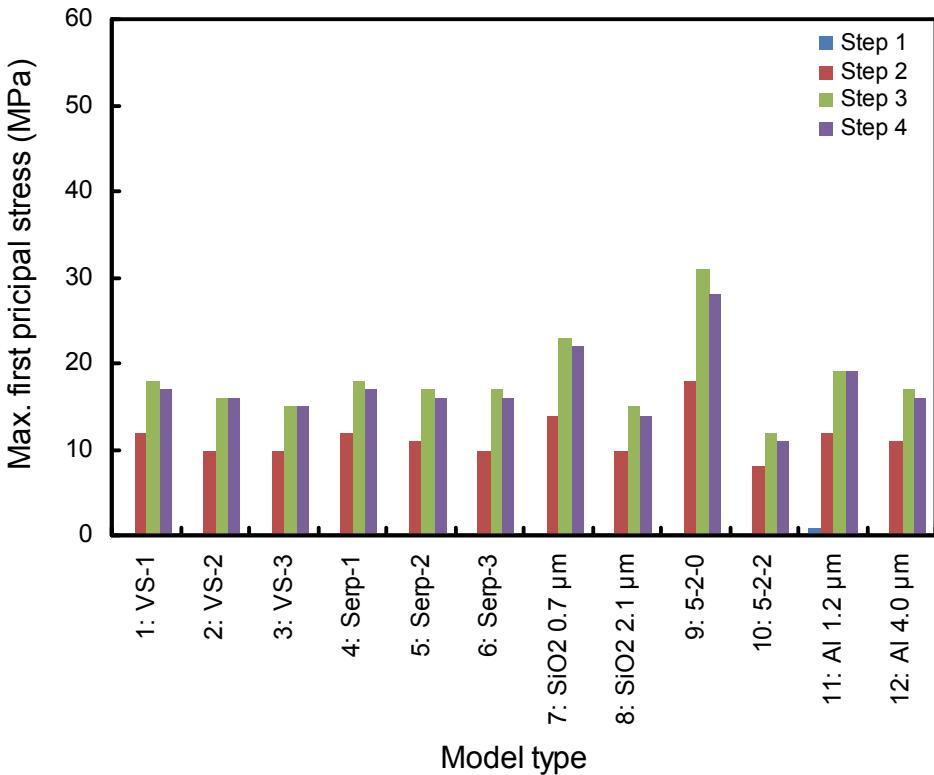

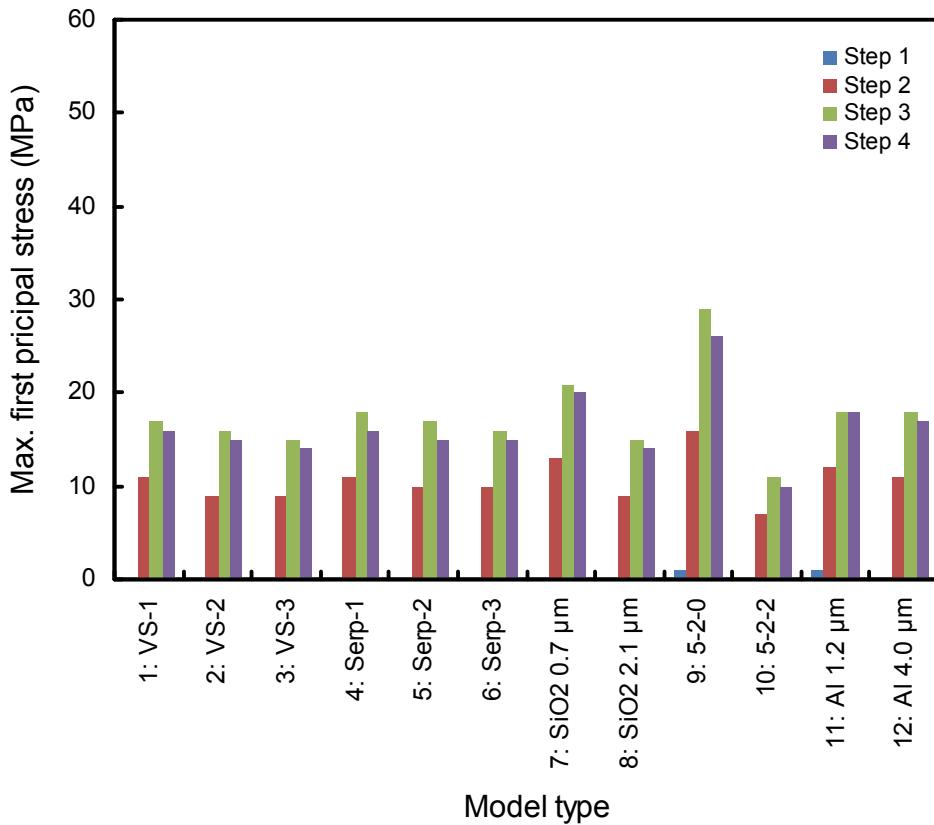

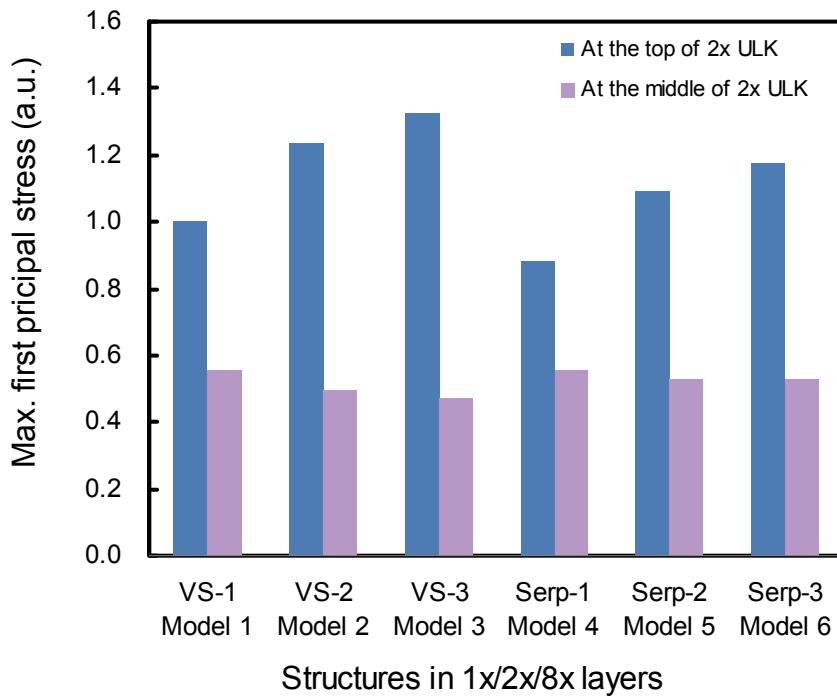

Fig. 2.12 は、ステップ 1 から 4 に 2x ULK 層の上面つまり FTEOS 層との界面で発生する最大の第 1 主応力を各モデルごとに示したグラフである。同様に Fig. 2.13 は 2x ULK 層の中央面で発生する最大の第 1 主応力、Fig. 2.14 は 1x ULK 層の上面つまり 2x ULK 層との界面で発生する最大の第 1 主応力、Fig. 2.15 は 2x ULK 層の中央面で発生する最大の第 1 主応力を示すものである。ここで示す応力はすべ

Fig. 2.11 Analysis steps to simulate ultrasonic vibration during wirebonding.

Fig. 2.12 Maximum first principal stress at the top of 2x ULK layer.

Fig. 2.13 Maximum first principal stress at the middle of 2x ULK layer.

Fig. 2.14 Maximum first principal stress at the top of 1x ULK layer.

Fig. 2.15 Maximum first principal stress at the middle of 1x ULK layer.

て引張応力である。これらのグラフを比較すると 2x ULK 上面の応力はモデル 12 の Al パッド厚み 4  $\mu\text{m}$  の場合を除いて、下部の 2x ULK 中央面、1x ULK 上面、1x ULK 中央面よりも概ね 1.5 倍以上大きい。また各モデルごとに発生している応力の傾向は 2x ULK 中央面、1x ULK 上面、1x ULK 中央面で非常に類似しているが、2x ULK における傾向のみが異なっている。ステップ 1 の荷重のみの場合の応力は、2x ULK 中央面、1x ULK 上面、1x ULK 中央面ではすべてのモデルで 1 MPa 以下と非常に小さい。一方で 2x ULK 上面ではモデル 12 を除いて 10 MPa 未満ではあるが明らかに他の面よりも大きな応力が生じている。2x ULK 上面では、モデル 9 と 12 を除いて最大応力はステップ 4 で発生しているが、2x ULK 中央面、1x ULK 上面、1x ULK 中央面ではすべてのモデルでステップ 3 で最大応力が発生している。ただしこれらのうちいくつかのモデルではステップ 3 と 4 でほぼ同じ応力値となるものがある。2x ULK 上面で見られる応力の発生の傾向はその下部の他の面と大きく異なっている。これは 2x ULK が弾性率の違いの大きな FTEOS 層との界面であるためであると考えられる。しかしながら硬化則を適用した Al パッドの厚みが 4  $\mu\text{m}$  の場合のみ 2x ULK 上面と他の面での顕著な違いは認められない。

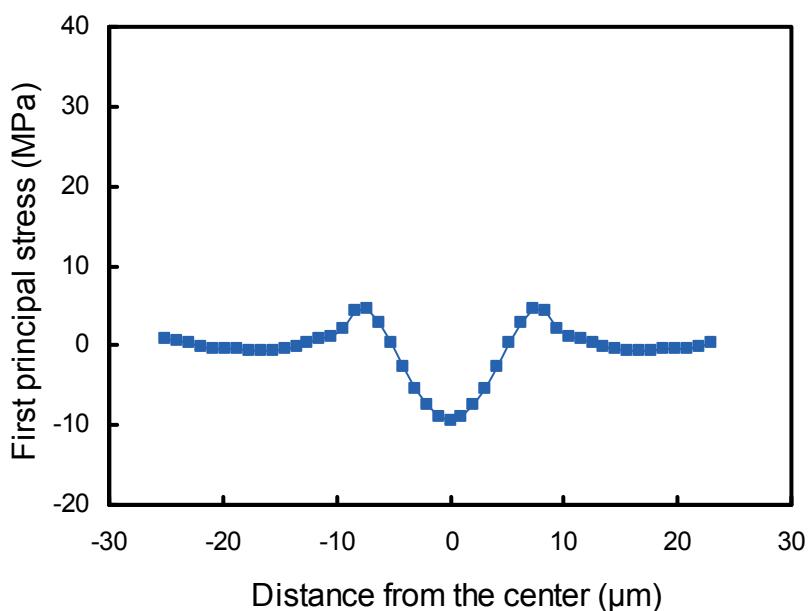

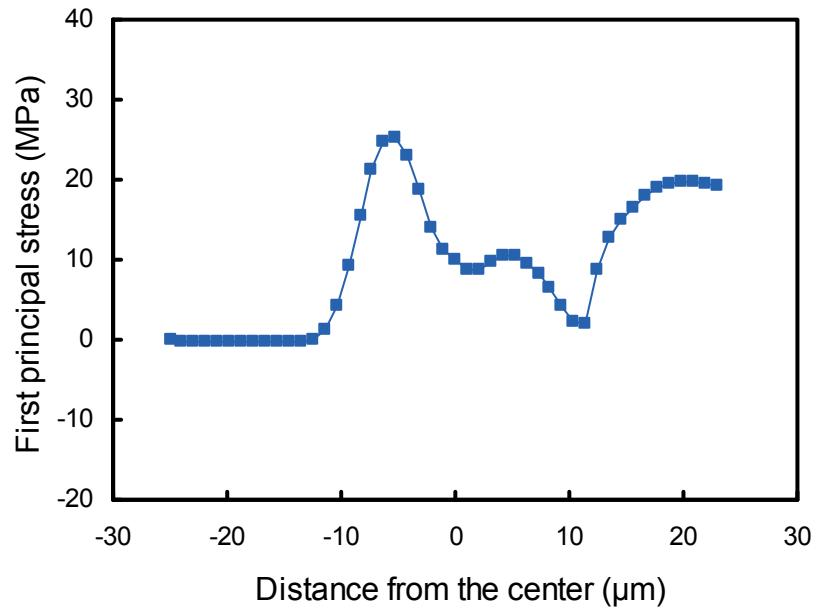

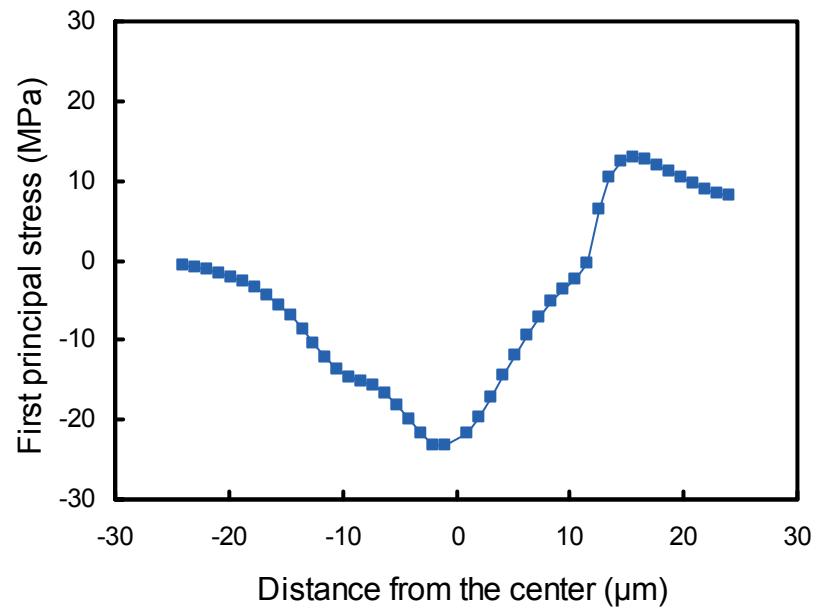

Fig. 2.16, Fig. 2.17, Fig. 2.18, Fig. 2.19 はそれぞれステップ 1, ステップ 2, ステップ 3, ステップ 4 でのモデル 1 の 2x ULK 上面におけるボンディング中心を通る X 軸上での応力分布を示すものである。ステップ 1 ではボールの中心部付近で圧縮応力となるが、キャピラリ接触部分のやや内側の中心から 7.3  $\mu\text{m}$  の位置で引張応力のピークがある。荷重のみの場合、応力分布は正負の方向で対称となる。ステップ 2 で -0.1  $\mu\text{m}$  の変位を与えると負の側のキャピラリ接触部分の内側近辺で 25 MPa の最大応力を

発生し、正の側ではキャピラリ接触部分の内側近辺で 10 MPa の低いピークとボールの外側で 20 MPa のピークを発生する。ステップ 3 で  $+0.1 \mu\text{m}$  の変位を与えてボンディング中心位置に戻すと正の側のキャピラリ接触部分の内側近辺のピークは 24 MPa まで上昇し、ボールの外側のピークは負の側に移動する。さらにステップ 3 で  $+0.1 \mu\text{m}$  の変位を与えると正の側のキャピラリ接触部分の内側近辺のピークは 34 MPa まで上昇し、これがステップ 1 から 4 での最大の応力値となる。ここで図示はしないが、各ステップでの応力のピークの傾向は配線密度を変化させたモデル 1 から 6 では非常によく類似している。また  $\text{SiO}_2$  層, FTEOS 層, Al パッドをそれぞれ厚くしたモデル 8, 10, 12 では中心付近の 2 つのピークの分離は消滅して 1 つのピークとなる。逆に  $\text{SiO}_2$  層, FTEOS 層, Al パッドをそれぞれ薄くしたモデル 7, 9, 11 では 3 つのピークの分離はより明確になる。

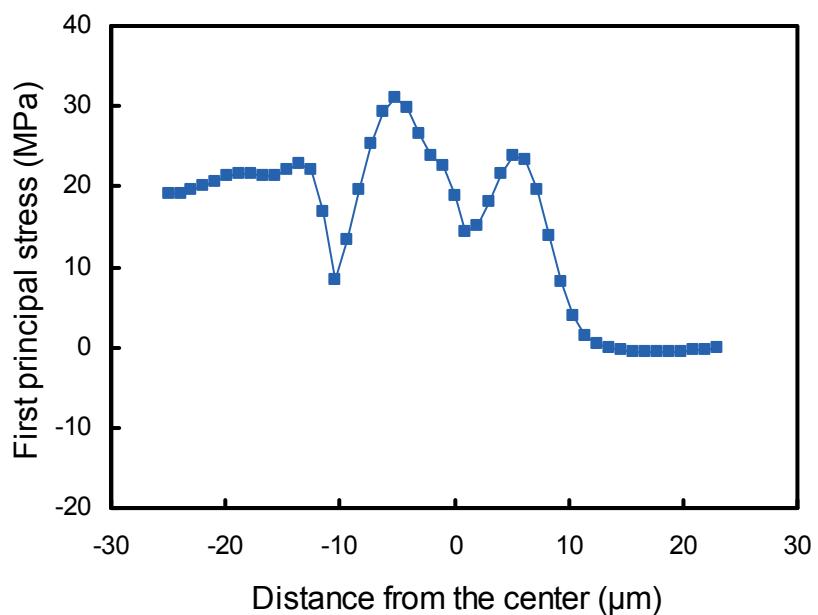

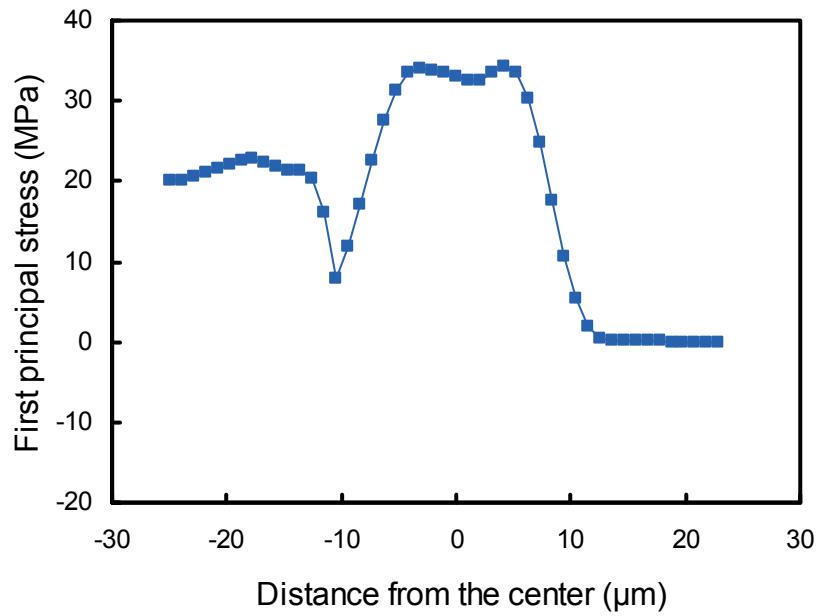

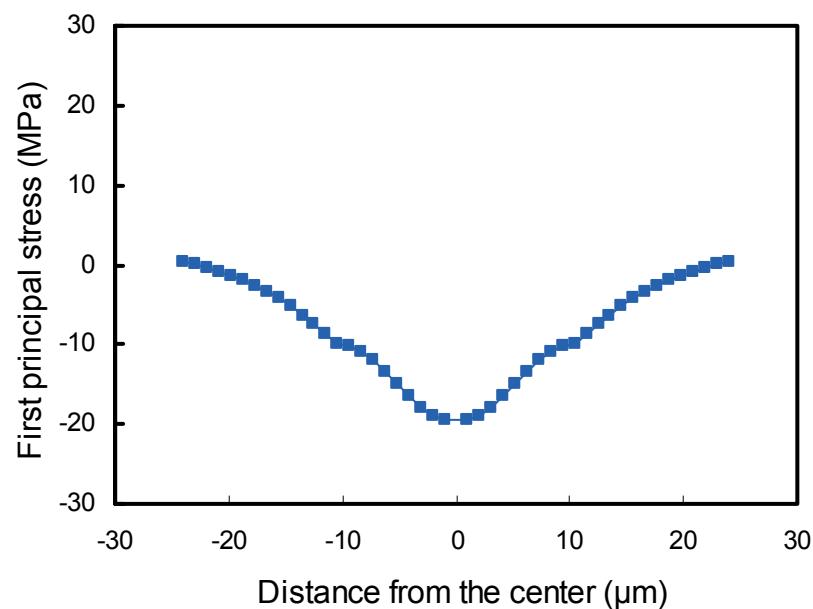

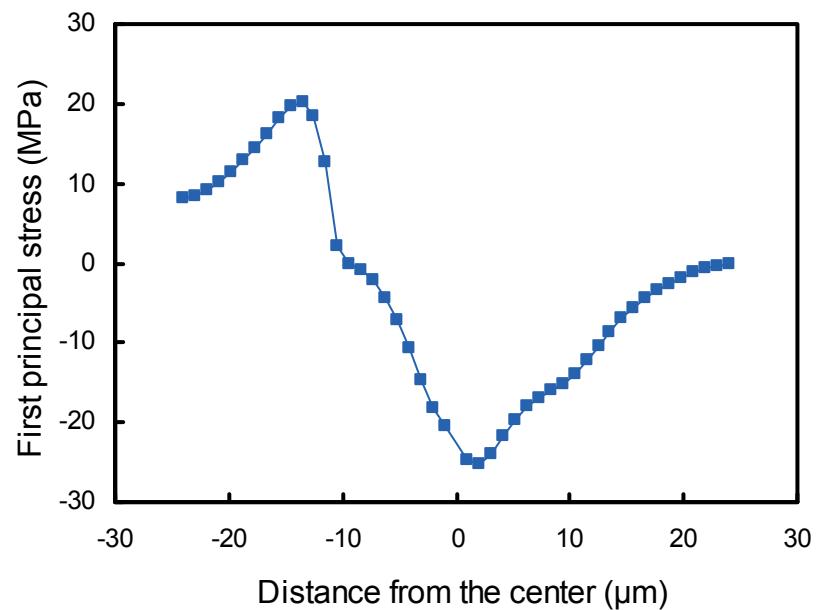

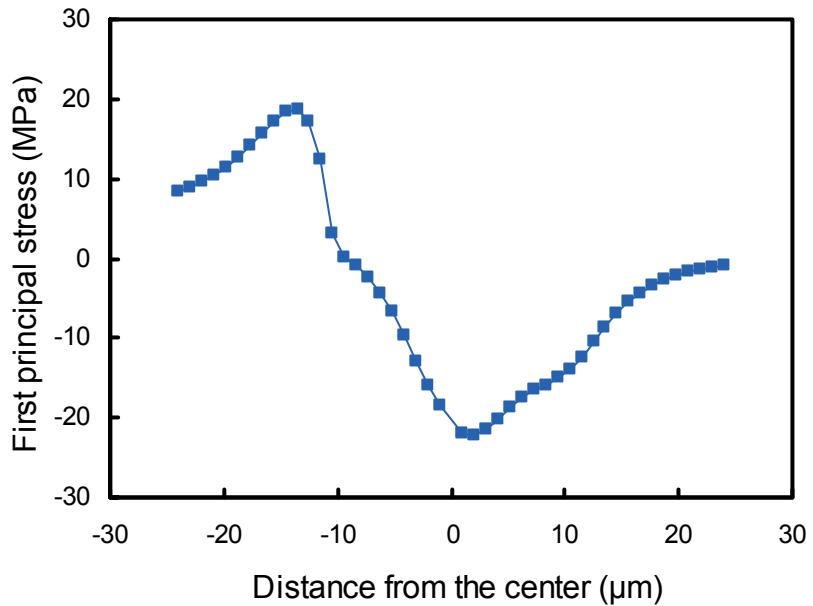

Fig. 2.20, Fig. 2.21, Fig. 2.22, Fig. 2.23 はそれぞれステップ 1, ステップ 2, ステップ 3, ステップ 4 でのモデル 1 の 2x ULK 中央面におけるボンディング中心を通る X 軸上での応力分布を示すものである。2x ULK 中央面ではステップ 1 の荷重のみの印加ではパッド両端部を除き圧縮応力が発生し、ボンディング中心部で最大の応力となる。ステップ 2 では 2x ULK 上面と異なり変位を与えた方向と反対の正の側のボール端部付近で急激に応力値が大きくなり最大の引張応力のピークが生じる。ステップ 3 と 4 の変位方向を正の向きに反転させた場合では、ステップ 2 の応力分布を正負に反転させた分布形状に近いものとなり、負の側のボール端部付近で最大の引張応力のピークが生じる。全ステップ中の最大の応力はステップ 3 で発生している。この応力分布の傾向は、 $\text{SiO}_2$  層, FTEOS 層, Al パッドの厚みを変化させたモデルも含めてすべてのモデルでほぼ同様のものとなる。

Fig. 2.16 Stress distribution at the top of 2x ULK layer of model-1 at step 1.

Fig. 2.17 Stress distribution at the top of 2x ULK layer of model-1 at step 2.

Fig. 2.18 Stress distribution at the top of 2x ULK layer of model-1 at step 3.

Fig. 2.19 Stress distribution at the top of 2x ULK layer of model-1 at step 4.

Fig. 2.20 Stress distribution at the middle of 2x ULK layer of model-1 at step 1.

Fig. 2.21 Stress distribution at the middle of 2x ULK layer of model-1 at step 2.

Fig. 2.22 Stress distribution at the middle of 2x ULK layer of model-1 at step 3.

Fig. 2.23 Stress distribution at the middle of 2x ULK layer of model-1 at step 4.

#### 配線構造と配線密度による応力低減の評価

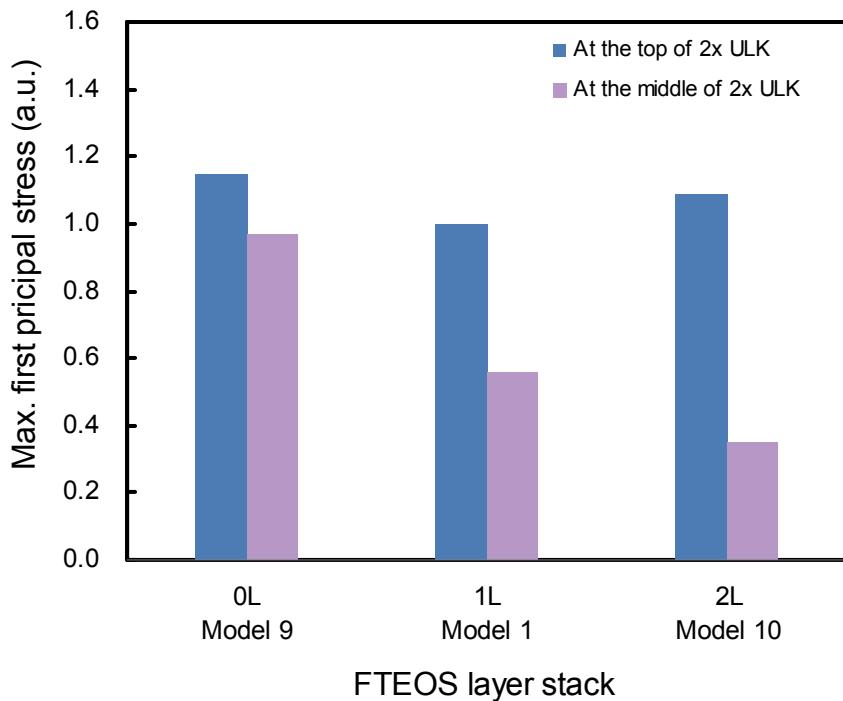

Fig. 2.24 に配線構造ビア・スタックとサーペンタインの 2 種類でそれぞれ配線密度変化させたモデル 1 から 6 の 2x ULK 上面および中央面すべてのステップの中で発生する最大の応力を示す。ここではモデル 1 の 2x ULK 上面で生じる最大応力を基準として任意単位で表示した。2x ULK 上面に生じる引張応力の傾向は、先述の荷重の影響を調べた結果と一致している。VS-3 は VS-1 に比べて 32%高い応力値となり、Serp-3 は Serp-1 に比べて 34%高い応力値となっており、ビア・スタック、サーペンタインそれぞれの構造で配線密度が低くなると応力は大きくなる。また Serp-1 は VS-1 に比べて 12%低い応力値であり、サーペンタイン構造のほうが応力低減に有利である。一方、2x ULK 中央面で発生する最大の応力は 2x ULK 上面とは異なる傾向を示している。VS-3 は VS-1 に比べて 16%低い応力値となり、Serp-3 は Serp-1 に比べて 5%低い応力値となっており、ビア・スタック、サーペンタインそれぞれの構造で配線密度が低くなると応力は小さくなる。また Serp-1 は VS-1 に比べて 1%未満の応力値の差であり、構造の違いによる影響はわずかである。2x ULK 上面に生じる応力が 2x ULK 中央面に生じる応力よりも大きいことから、応力低減には 2x ULK 上面での傾向を踏まえて、ビア・スタック構造よりもサーペンタイン構造を探り、配線密度を高めることが応力低減に有効であると考える。

Fig. 2.24 Maximum first principal stress (tensile stress) in the 2x ULK layer (model-1, 2, 3, 4, 5 and 6).

### 積層構造による応力低減の評価

積層構造による応力低減を評価するため  $\text{SiO}_2$  層, FTEOS 層, Al パッドそれぞれの厚みが応力に与える影響を調べた。Fig. 2.25 は  $\text{SiO}_2$  層の厚みを  $0.7 \mu\text{m}$ ,  $1.4 \mu\text{m}$ ,  $2.1 \mu\text{m}$  に変化させたモデル 7, 1, 8 の最大応力を Fig. 2.24 と同様にプロットしたグラフである。2x ULK 上面においては応力と  $\text{SiO}_2$  層の厚みに明確な関係は認められないが、2x ULK 中央面では  $\text{SiO}_2$  層の厚みが増加すると応力も単調に減少する関係が認められる。Fig. 2.26 は FTEOS 層の層数を 0 層, 1 層, 2 層に変化させたモデル 9, 1, 10 の最大応力を Fig. 2.24 と同様にプロットしたグラフである。ここでも Fig. 2.25 と同様に 2x ULK 上面においては応力と FTEOS の層数の間に明確な関係は認められないが、2x ULK 中央面では FTEOS の層数が増加すると応力も単調に減少する関係が認められる。一般的には ULK 上部に積層される弾性率や破断強度の高い  $\text{SiO}_2$  層や FTEOS 層の厚みを増すとパッド剥がれが発生しにくくなると考えられているが、2x ULK 上面で得られた最大応力の結果はこれと合致しない。一方で 2x ULK 中央面で得られた最大応力の結果は上記の考えに合致している。パッド剥がれの現象が発現するのはワイヤのルーピング中やワイヤブル試験でワイヤからの引張荷重がかかる時であり、この時には  $\text{SiO}_2$  層や FTEOS 層の厚みの 2x ULK 上面に生じる応力への影響は異なってくると考えられる。ワイヤからの引張荷重により生じる ULK 層での引張応力はここでは解析を行っていないため今後研究すべき課題となる。Fig. 2.27 は Al パッドの厚みを  $1.2 \mu\text{m}$ ,  $2.1 \mu\text{m}$ ,  $4.0 \mu\text{m}$  に変化させたモデル 11, 1, 12 の最大応力を Fig. 2.24 と同様にプロットしたグラフである。2x ULK 上面において Al パッド厚みが増加すると応力が単調に減少する関係が見られる。Al パッド厚み  $4.0 \mu\text{m}$  のモデルでは  $1.2 \mu\text{m}$  のモデルに比べて 56% 応力が減少して

おり、Al パッドを厚くすることによる応力低減の効果は大きい。一方で 2x ULK 中央面では応力と Al パッド厚みの間に明確な関係は認められない。SiO<sub>2</sub>層、FTEOS 層の厚みを変化させた結果と異なる傾向となっているのは、Al パッドの弾性率が低く硬化則を適用した塑性変形の影響と考えられる。

ここでは SiO<sub>2</sub> 層、FTEOS 層の厚みを増しても最大応力の生じる 2x ULK 上面では応力低減が見られない結果が得られた。ワイヤに引張荷重がかかる場合に SiO<sub>2</sub> 層、FTEOS 層の厚みが ULK 層の応力に与える影響は今後の研究課題である。Al パッド厚みを増すと ULK 層内での最大主応力を大きく低減できることが分かった。しかし厚い Al パッド上のワイヤボンディングでは Al スプラッシュが大きくなりやすく、特にファインピッチのボンディングで接合条件のプロセスウィンドウが小さくなる懸念があるため Al パッドを無制限に厚くはできない。このためデバイスの配線ルールやワイヤボンディングピッチの仕様を踏まえて ULK 層の応力低減を図る各層厚みと構造の最適化が必要となる。

Fig. 2.25 Maximum first principal stress (tensile stress) in the 2x ULK layer (model-1, 7 and 8).

Fig. 2.26 Maximum first principal stress (tensile stress) in the 2x ULK layer (model-1, 9 and 10).

Fig. 2.27 Maximum first principal stress (tensile stress) in the 2x ULK layer (model-1, 11 and 12).

## 2.4 ワイヤブル試験におけるパッドはがれ発生率と配線層の応力の相関の解明

### 2.4.1 ワイヤボンディング実験

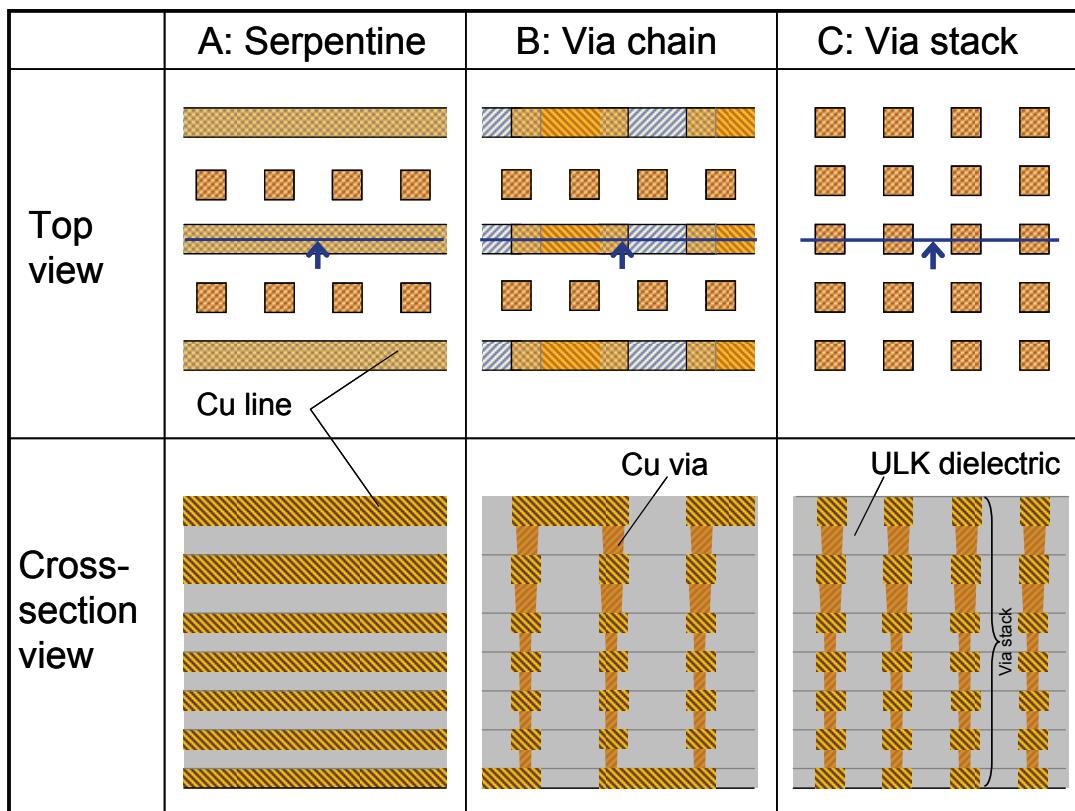

実験で用いた試料は 32 nm テクノロジーのチップで、パッドピッチ 35  $\mu\text{m}$ , パッド開口幅 29  $\mu\text{m}$  のワイヤボンディング・パッドが配置されている。パッドの組成は Al-0.5%Cu で 2.1  $\mu\text{m}$  の厚みである。Fig. 2.2 で示した 5-2-1 と 5-2-2 の 2 種類のメタル配線層の構成のチップを準備した。このチップはパッド下部に様々な種類の配線構造を持つが、ここでは Fig. 2.28 に示すサーペンタイン、ビア・チェイン、ビア・スタックの 3 種類の配線構造を持つパッド上にワイヤボンディングした結果を考察する。ビア・チェイン構造は各配線層をビア接続し、デイジー・チェインを形成したものである。図示したようにビア・チェイン配線間にビア・スタック構造を配置し、配線のピッチを変えることで配線密度を変化させたバリエーションがある。同様にサーペンタインでも配線密度を変化させたバリエーションがある。5-2-1 のチップではこれら全ての構造で実験を行い、5-2-2 のチップではビア・チェイン構造のみで実験を行った。

Fig. 2.28 Via chain structure under the bond pad of the test chip.

## 2.4.2 パッド下部配線構造と配線層ダメージの関係

試料のチップを PBGA (Plastic Ball Grid Array) 基板にチップ付けした後、 $15\text{ }\mu\text{m}$  径の 99.99% Au の金線を用いてワイヤボンディングし、ワイヤブル試験を行った。破断モードは、ワイヤネック切れを正常モードとし、パッド剥がれを不良モードとした。それぞれの破断モードは Fig. 1.11 (a), (b) に示したものである。Fig. 2.29 はワイヤブル後にパッド剥がれが発生したパッドを FIB (Focused Ion Beam) で加工した後に SEM (Scanning Electron Microscope) で観察した写真である。破断の最下部は ULK 層にあり、初期クラックがこの層で発生したと考えられる。

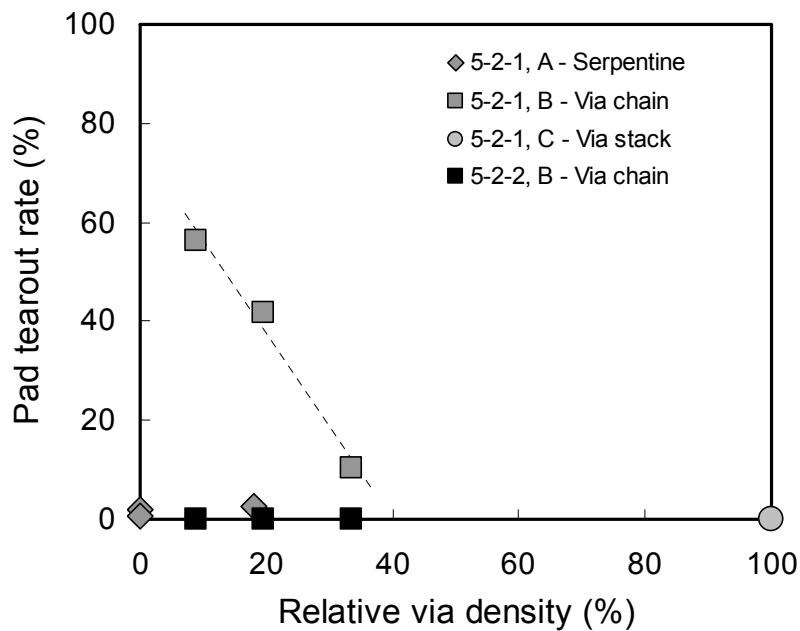

5-2-1, 5-2-2 それぞれの積層のチップで配線構造・配線密度の異なる下部構造を持つパッドにワイヤボンディングしワイヤブル試験でのパッド剥がれ発生率を調べた。パッド下部の配線密度の指標としてビアの密度を算出し、ビア・スタック構造のビア量を基準とした相対ビア密度とパッド剥がれ発生率の関係を求めたグラフを Fig. 2.30 に示す。図中の相対ビア密度が 0% は、サーペンタイン構造の配線パターンは存在するものの上下配線をつなぐビアがまったく使われていないものを指す。

5-2-1 の構成では、ビア・チェインの相対ビア密度が約 10% のところでパッド剥がれの発生率が一番高く、相対ビア密度が 35% 程度まで高くなるとパッド剥がれ発生率は著しく低下する。サーペンタインとビア・チェインで約 20% の相対ビア密度の場合においてパッド剥がれ発生率に顕著な差が見られる。ビア・スタックは相対ビア密度が 100% であり、パッド剥がれが発生していない。5-2-2 の積層のチップではビア・チェインのどのビア密度でもパッド剥がれは発生しておらず、5-2-1 の結果と顕著な差が現れている。

Fig. 2.29 SEM photograph of a pad tearout after FIB sectioning.

### 2.4.3 パッド下部配線構造の複合弾性率と線層ダメージの関係

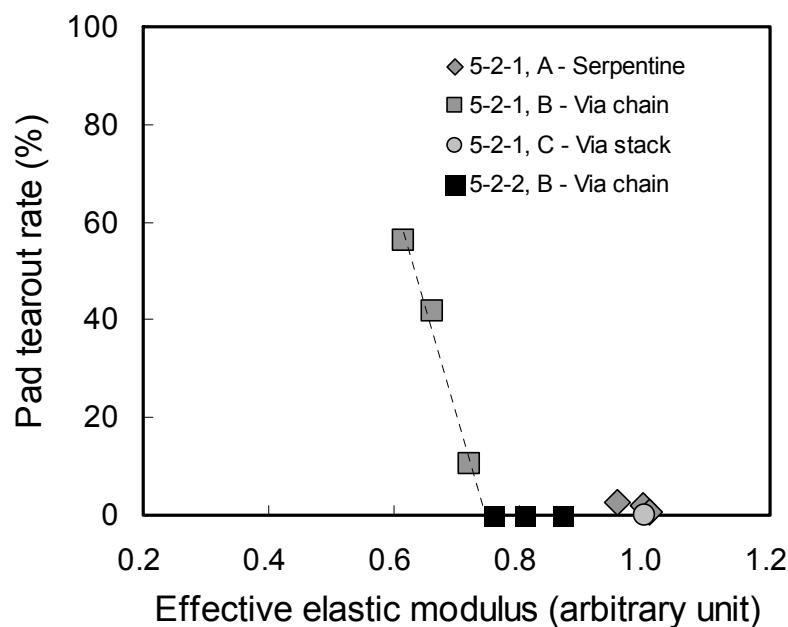

5-2-1 のビア・チェイン構造では相対ビア密度とパッド剥がれ発生率に明らかな相関が見られるが、5-2-1 のサーぺンタイン構造および 5-2-2 のビアチェイン構造ではパッド剥がれ発生率が低く相対ビア密度との相関は明確ではない。さらに各配線構造で 1x 層から SiO<sub>2</sub> 層まで積層された構造体としての Z 方向の実効弾性率を複合則を用いて算出し、パッド剥がれ発生率との相関を求めた (Fig. 2.31)。これより積層構成や配線構造によらず、実効弾性率がある閾値を下回ると急激にパッド剥がれ発生率が高くなることが確認できる。しかしながらここで得られたサーぺンタインとビア・スタックでのパッド剥

Fig. 2.30 Pad tearout rate as a function of relative via density.

Fig. 2.31 Pad tearout rate as a function of effective elastic modulus

がれ発生率は低いものであり、サーペンタインとビア・スタックそれぞれの構造で急激にパッド剥がれ発生率が増える実効弾性率の閾値はFig. 2.31で見られるビア・チェインのものとは異なることもあり得る。

## 2.5 結言

Low-k, ULK を層間絶縁膜に用いるチップのボンドパッド下部の層構成・配線構造を変化させたときの各層の複合特性を均質化モデルから算出し、3D FEM モデルでワイヤボンディング荷重および超音波印加によって ULK 層内に発生する応力を FEM 解析により求めた。ビアスタック構造、サーペンタイン構造ともに配線密度が高い方が応力を低減できる。配線構造を比べるとビア・スタック構造よりもサーペンタイン構造の方が応力が低くなる。Al パッドの厚みを増すと ULK 層内での最大主応力を低減できる。 $\text{SiO}_2$ , FTEOS の厚みを増すと 2x ULK 層の中央面では応力低減が期待できるが、最大応力の生じる 2x ULK 層の上面では超音波印加による引張応力の低減は見られない。 $\text{SiO}_2$ , FTEOS の厚みの影響はワイヤから引張荷重がかかる場合についても研究する必要があると考える。

ボンドパッド下部に異なる層構成・配線構造を持つチップを用いて行ったワイヤボンディングの実験から、積層された配線構造体としての実効弾性率を因子としてパッド剥がれとの関係を求めるパッド剥がれが急激に増える閾値となる実効弾性率が容易に推定できることが分かった。ただし配線構造のタイプが異なる場合に閾値は変動することが予想され、さらなる実験データでの検証が必要であるが、配線構造ごとの実効弾性率と応力の関係からパッド剥がれを低減する層構成や配線構造の比較検討を行うことは初期段階での設計パターンの絞込みに有用であると考える。

本研究で調べた繰返し性のある基本的な配線構造は均質化によって複合特性を求める方法に適しているが、特異性・局所性の高い配線パターンでは均質化で求める複合特性から応力を推定することができない場合もあり得る。そのようなケースでは詳細なマイクロモデルでの解析が必要となる。

## 第3章 フリップチップ接合用材料の機械的特性がフリップチップのパッド下部配線層の熱応力に与える影響

### 3.1 緒言

現在、鉛フリーはんだは電子機器の実装において広く普及しており、フリップチップ接合ではチップ上に Sn-Ag バンプと基板上の Sn-Ag-Cu のプレソルダーを用いるのが代表的である。鉛フリーはんだは、Sn-Pb 共晶はんだに比べて融点が高く、かつ弾性率も高いため、はんだ接合部やチップのパッド下部の配線層の応力が高くなる。Fig. 1.12 に示すように、フリップチップ接合の冷却時にチップと基板の線膨張係数のミスマッチにより発生する応力で、特にチップコーナー付近のパッド下部の配線層に用いられる Low-k / Ultra low-k (ULK) 絶縁膜においてクラックやダメージが起こりやすい。この現象は、チップ裏面から超音波顕微鏡で観察すると白いスポットに見えるためホワイトバンプと呼ばれている<sup>50)</sup>。この課題に対してフリップチップの接合温度を下げることで熱機械的応力を低減するために、様々な低融点はんだの検討が行われてきた<sup>88, 92)</sup>。

アレイ配置のフリップチップのピッチは 150 μm 程度まで微細化されてきており、接合部は 80 μm 程度となっている。チップ接合のような微小サイズにおいては粒界の大きさや結晶方位がその機械特性に影響を与えることが知られている<sup>96)</sup>。本研究では、低融点はんだでパッド下部配線層に生じる応力を低減することに着目し、低融点の 2 種類のはんだ、Sn-58 mass%Bi(以降 Sn-58Bi, 融点 139°C) と In-3 mass%Ag(以降 In-3Ag, 融点 143°C)，と従来から広く用いられている Sn-3 mass%Ag-0.5 mass%Cu(以降、SAC305) の計 3 種類のはんだを用意し、微細試験片（直径 0.5 mm, 標点距離 2.0 mm）を作製して引張試験を行い、機械的特性を求めた。ここで得られた 0.5%耐力とクリープ特性を用いて、はんだバンプと Cu ピラーの 2 種類のバンプ構造と各はんだのプレソルダーとの組み合わせで FCPBGA のフリップチップ接合後にパッド下部配線層にかかる熱応力を FEM (Finite element method) で解析し、接合温度とフリップチップ接合用材料の機械的特性がフリップチップ接合材料のフリップチップのパッド下部配線層の熱応力に与える影響を解明した。

### 3.2 はんだ微細試験片による引張試験

#### 3.2.1 試験方法

本研究では Sn-58Bi, In-3Ag, SAC305 の 3 種類のはんだを準備し、苅谷らが開発した溶融はんだを射出形成する方法<sup>97)</sup>で微細試験片を作製した。それぞれのはんだインゴットを各はんだの融点直下の温度で押し出し加工し、直径 1.2 mm の線材を作製した。その後、金型を用いてホットプレート上にて線材を融点 +30°C の温度で溶融させ、直径 0.5 mm, 標点距離 2.0 mm のダンベル形状の微細試験片を作製した。溶融はんだの凝固時の冷却速度は 4~5°C/s であった。この試験片には時効処理は施さなかった。引張試験には鷺宮製作所製微小加重試験機 LMH-207-10 を用い、4 条件の歪み速度 ( $5.0 \times 10^{-4} \text{ s}^{-1}$ ,  $1.0 \times 10^{-3} \text{ s}^{-1}$ ,  $5.0 \times 10^{-3} \text{ s}^{-1}$ ,  $1.0 \times 10^{-2} \text{ s}^{-1}$ ) と 3 条件の温度 (室温(25°C), 80°C, 120°C) で測定を行った。歪み速度はクロスヘッドの変位で制御し、試験片の破断が発生するまで初期歪み速度を維持した。3 種類のはんだの試験片それぞれで各条件の測定を行った。

初期試料を中央部付近でカッターで切断し、研磨紙およびアルミナ研磨材を用いて断面研磨を行った。さらに In-3Ag の試料はクロスセクションポリッシャーを用いてイオンビームによる研磨を施した。それぞれの試料の断面は SEM (Scanning electron microscope) と EDX (Energy dispersive X-ray spectrometry) により観察した。

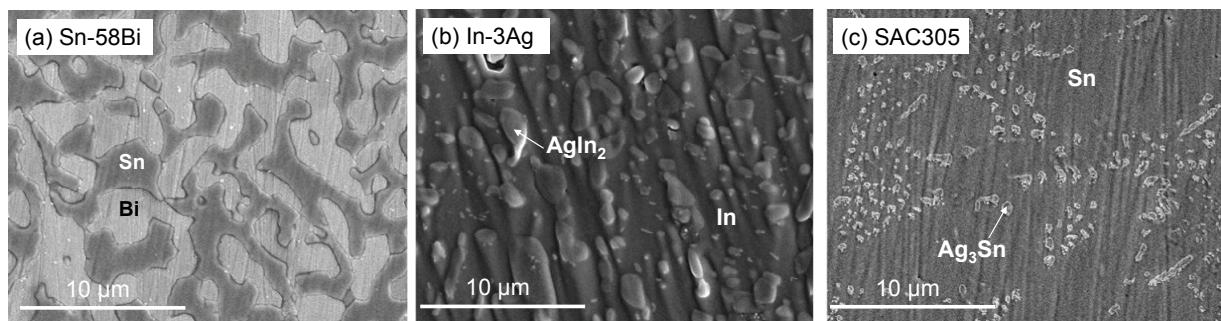

### 3.2.2 組織観察

Fig. 3.1(a)は Sn-58Bi の初期試料の SEM 写真である。EDX の結果から濃灰色の領域は Sn 相、淡灰色の領域は Bi 相である。Fig. 3.1(b)は In-3Ag の組織を示す。EDX の結果から淡灰色の粒状の組織は  $\text{AgIn}_2$  であり、その大きさは約 0.1  $\mu\text{m}$  から約 10  $\mu\text{m}$  である。また濃灰色の領域は In 相である。Fig. 3.1(c)は SAC305 の組織を示す。EDX の結果より淡灰色の微細粒は  $\text{Ag}_3\text{Sn}$  である。ほとんどの  $\text{Ag}_3\text{Sn}$  粒の大きさは 1  $\mu\text{m}$  以下である。また濃灰色の領域は Sn 相である。SnCu の金属間化合物はこの試料では特定することができなかった。

### 3.2.3 引張試験結果

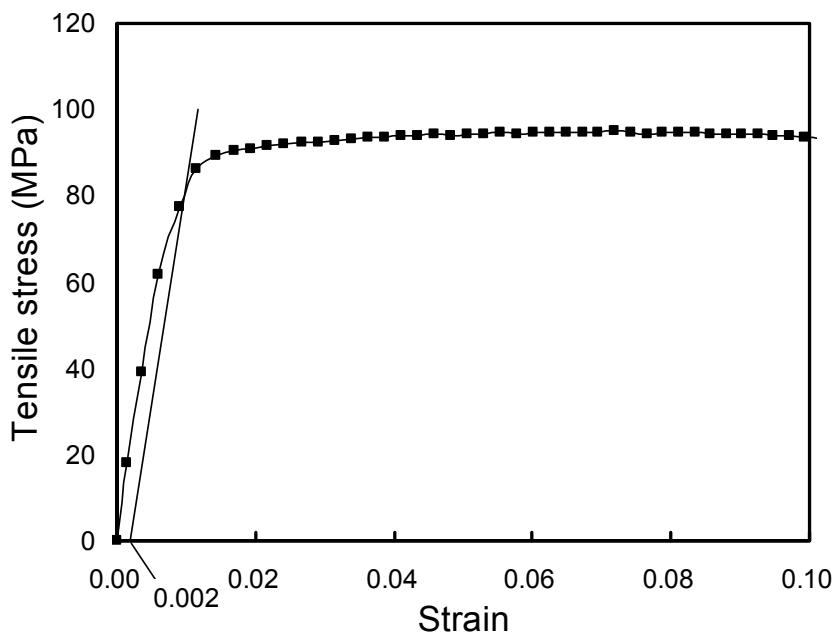

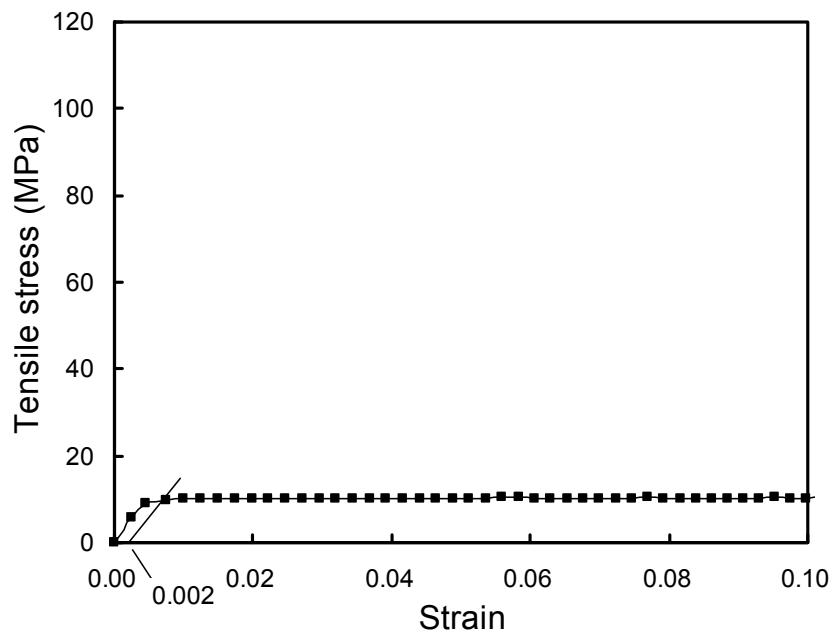

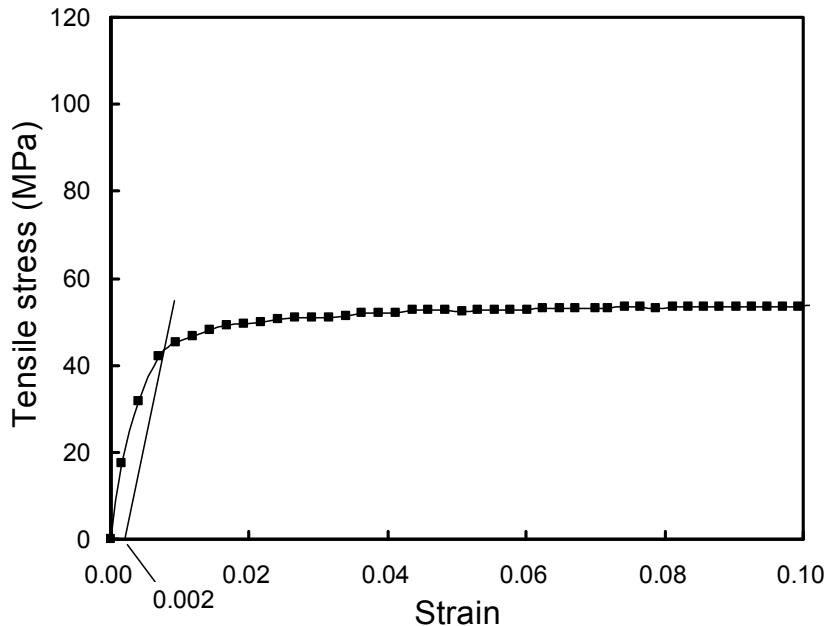

Fig. 3.2, Fig. 3.3, Fig. 3.4 は引張試験から求めた Sn-58Bi, In-3Ag, SAC305 の歪み速度  $5.0 \times 10^{-3} \text{ s}^{-1}$ , 室温(25°C)における応力-歪み曲線である。ここでは試料の標点部分は体積一定で変形すると考えて、測定ポイントごとの断面積を用いて応力値を求めた。同じく体積一定の変形として歪みは次式を用いて求めたものである。

$$\varepsilon = \ln[(L + \Delta l) / L] \quad (3.1)$$

ここで  $\varepsilon$  は歪み,  $L$  は初期標点距離,  $\Delta l$  は変位である。各図の直線は、弾性変形領域のデータから最小二乗法で求めた傾きを持ち、歪み 0.2%, 応力 0 の点を通るものである。この直線と応力-歪み曲線の交点から各はんだの 0.2%耐力を求めた。これらは Sn-58Bi で約 80 MPa, In-3Ag で約 10 MPa, SAC305 で約 42 MPa となる。融点の近い Sn-58Bi と In-3Ag であるが 0.2%耐力に大きな違いが現れている。また SAC305 は両者の中間に近い 0.2%耐力である。

Fig. 3.1 SEM photographs of sectioned initial specimens for (a) Sn-58Bi, (b) In-3Ag and (c) SAC305.

Fig. 3.2 Stress-strain curve for Sn-58Bi at the strain rate of  $5.0 \times 10^{-3} \text{ s}^{-1}$  at R. T.

Fig. 3.3 Stress-strain curve for In-3Ag at the strain rate of  $5.0 \times 10^{-3} \text{ s}^{-1}$  at R. T.

Fig. 3.4 Stress-strain curve for SAC305 at the strain rate of  $5.0 \times 10^{-3} \text{ s}^{-1}$  at R. T.

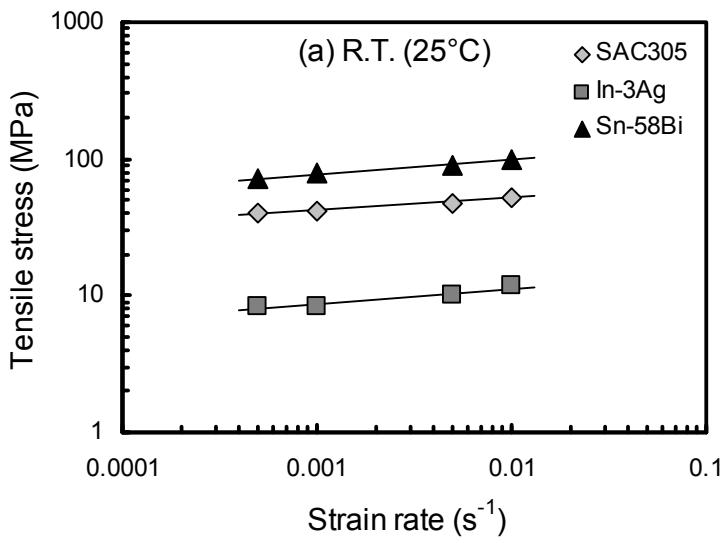

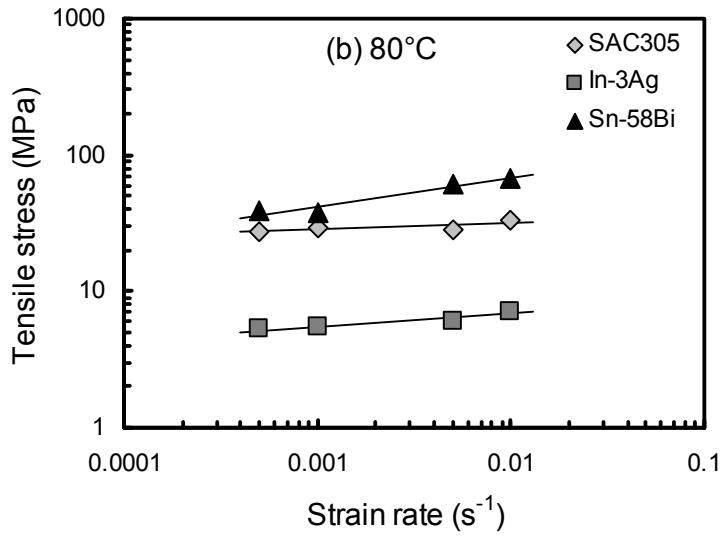

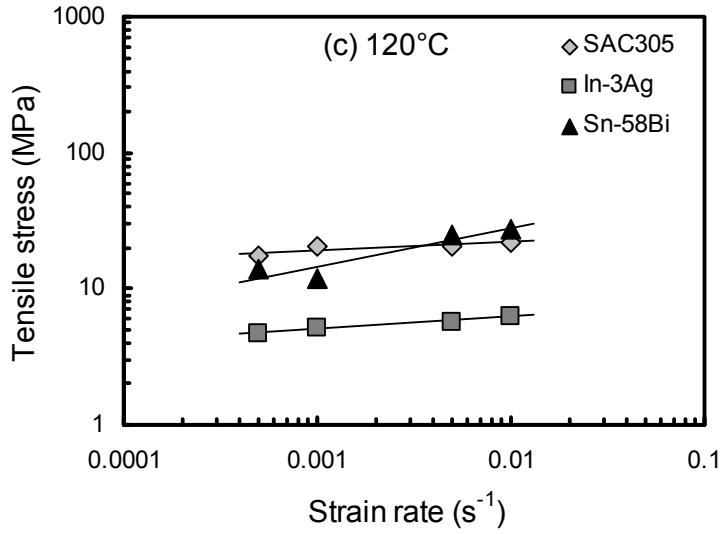

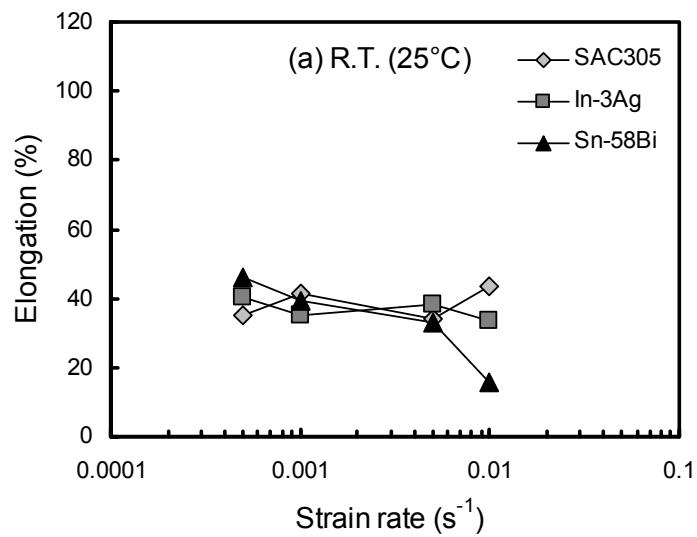

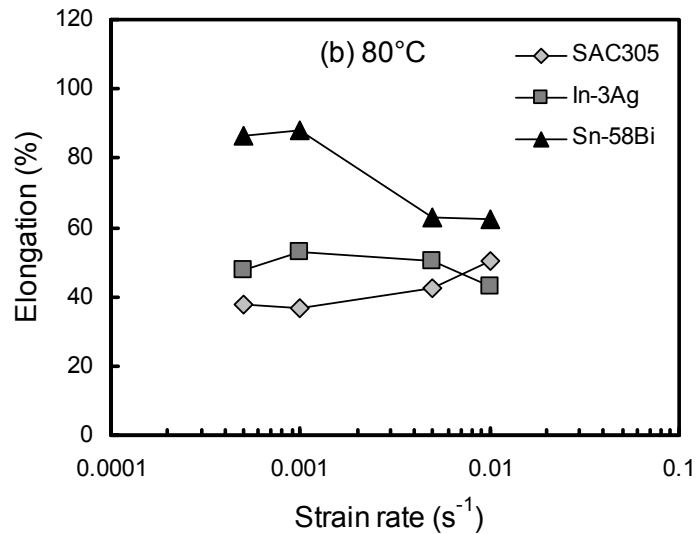

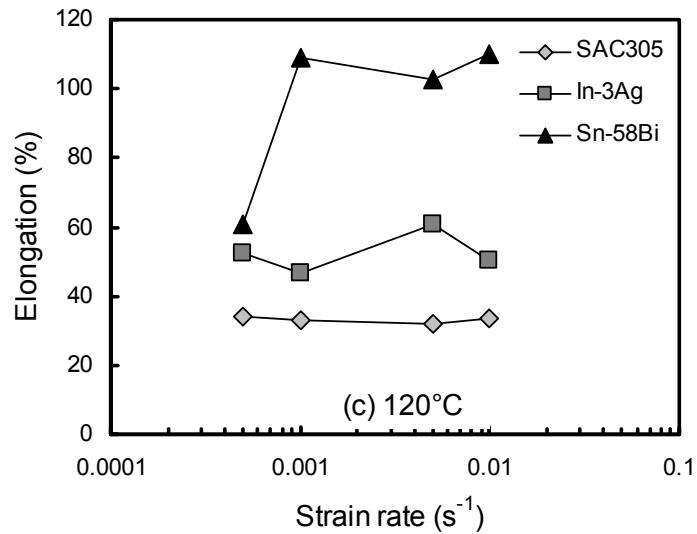

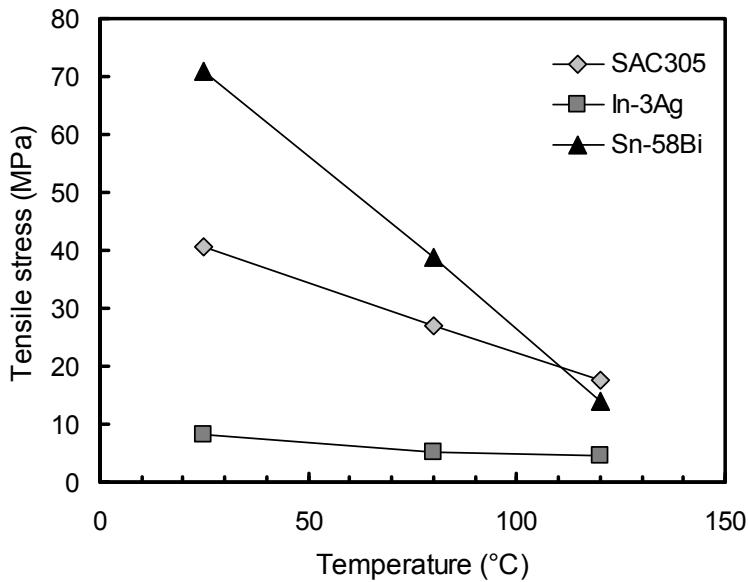

Fig. 3.5, 3.6, 3.7 はそれぞれ室温(25°C), 80°C および 120°C における引張応力と歪み速度の相関を示す。Fig. 3.8, 3.9, 3.10 はそれぞれ室温, 80°C および 120°C における伸びと歪み速度の相関を示す。また Fig. 3.11 は歪み速度  $5 \times 10^{-4} \text{ s}^{-1}$  における引張応力と温度の相関を示す。

Fig. 3.5 から室温では 3 種類のはんだで引張応力が大きく異なることが分かる。Sn-58Bi が最も引張応力が高く 71~100 MPa, 次いで SAC305 の引張応力が 41~53 MPa であり, In-3Ag が最も低く 8.3~12 MPa となり、それぞれ歪み速度が増加すると引張応力が増加する傾向が見られる。Fig. 3.6, Fig. 3.7 のそれぞれ 80°C および 120°C の場合でも Sn-58Bi と In-3Ag は歪み速度の増加にしたがって引張応力が増加しているが、SAC305 は歪み速度の増加による引張応力の増加は顕著ではない。Fig. 3.11 から温度上昇による引張応力の低下は Sn-58Bi で最も大きく、120°C では Sn-58Bi と SAC305 の引張応力が同等になることが分かる。また、In-3Ag の引張応力は室温から 120°C の間で大きな変化を示していない。

Fig. 3.8 で示すように室温での Sn-58Bi, In-3Ag, SAC305 の伸びは最も高歪み速度の場合を除いて大きな差異はない。Fig. 3.9, Fig. 3.10 で見られるよう Sn-58Bi は温度の上昇とともに伸びは大きくなり、歪み速度と伸びの相関も認められる。歪み速度  $5 \times 10^{-3} \text{ s}^{-1}$  の 120°C での伸びは 25°C の場合の約 3 倍である。これは Sn-58Bi の融点が 139°C であることによると考えられる。一方で In-3Ag と SAC305 では温度上昇による伸びの大きな増大は見られない。In-3Ag の融点(143°C)は Sn-58Bi に近いが顕著な違いが認められる。

Fig. 3.5 Relationship between tensile stress and strain rate at R. T.

Fig. 3.6 Relationship between tensile stress and strain rate at 80°C.

Fig. 3.7 Relationship between tensile stress and strain rate at 120°C.

Fig. 3.8 Relationship between elongation and strain rate at R. T.

Fig. 3.9 Relationship between elongation and strain rate at 80°C.

Fig. 3.10 Relationship between elongation and strain rate at 120°C.

Fig. 3.11 Relationship between tensile stress and temperature at strain rate of  $5.0 \times 10^{-4} \text{ s}^{-1}$ .

### 3.2.4 クリープ特性

一般的に定常クリープを表すのにノートン則が用いられる.

$$\dot{\varepsilon} = A\sigma^n \quad (3.2)$$

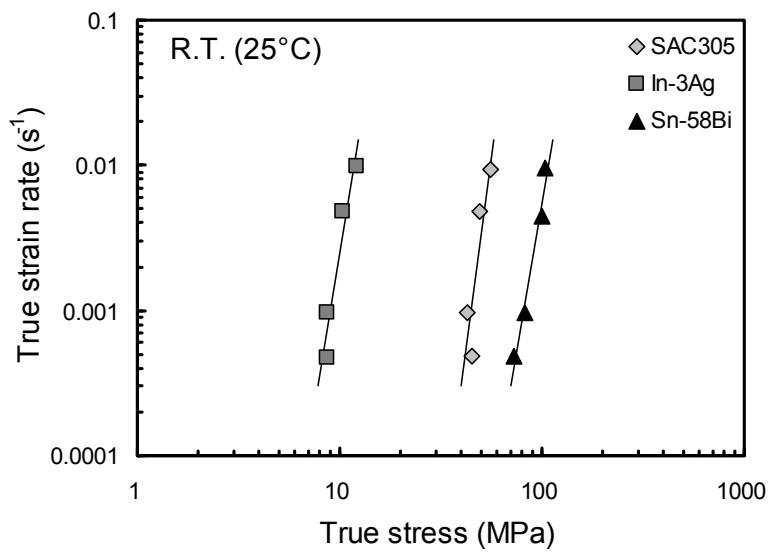

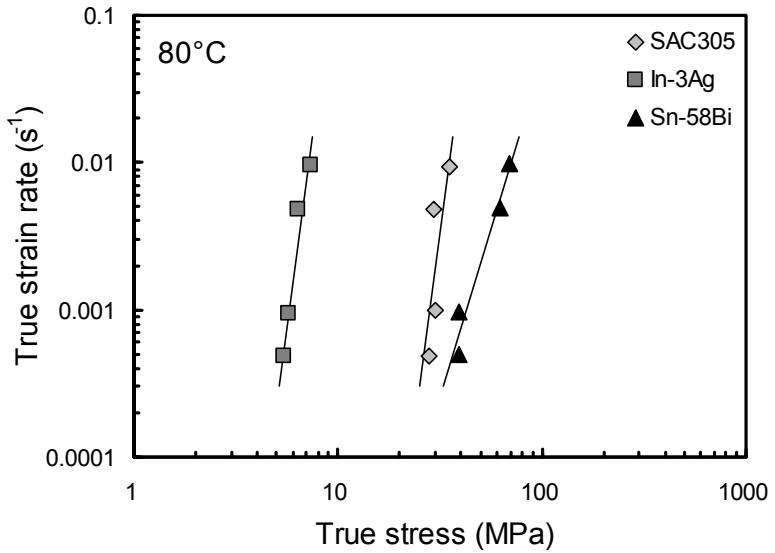

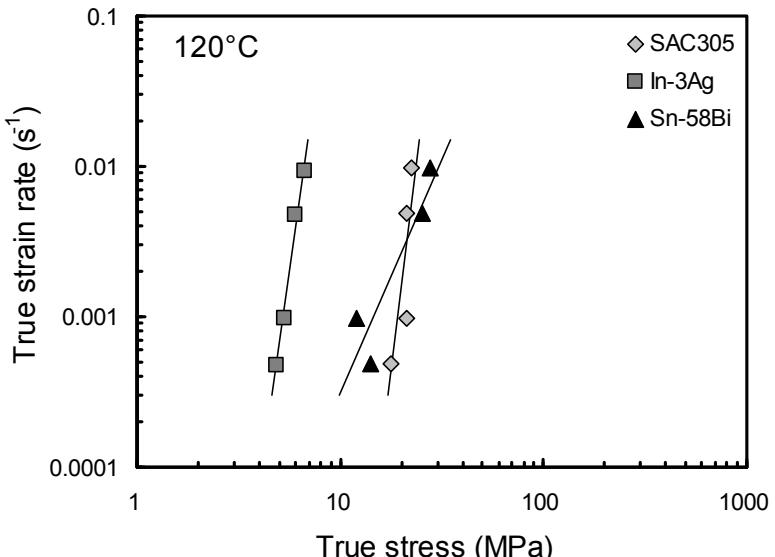

ここで  $\dot{\varepsilon}$  は歪み速度,  $A$  は係数,  $\sigma$  は引張応力,  $n$  は応力指数である. Fig. 3.12, Fig. 3.13, Fig. 3.14 はそれぞれ室温, 80°C および 120°C での真歪み速度と真応力の相関を両対数グラフで示したものである. 近似直線はデータより最小二乗法で求め, それぞれの近似直線から係数  $A$  と応力指数  $n$  を求めた.

Table 3.1 はそれぞれのはんだの係数  $A$  と応力指数  $n$  をまとめたものである. 係数  $A$  はすべてのはんだで温度の上昇とともに大きくなる. Sn-58Bi の係数は, ここで調べた温度範囲では  $10^{12}$  のオーダーで変化するが, In-3Ag の係数は  $10^1$  のオーダーでわずかにしか変化しない. また SAC305 の係数は  $10^2$  のオーダーの変化となる. Sn-58Bi の応力指数  $n$  は温度の上昇とともに減少する. ここで得られた Sn-58Bi の応力指数は直径 10 mm の試料を用いて測定された既報<sup>93)</sup>の数値と同様の傾向を示している. In-3Ag の応力指数は 80°C で最大値 10.4 となり, 調べた温度範囲で単調増加あるいは単調減少の傾向は示していない. この温度範囲での In-3Ag の応力指数の傾向を示すにはさらに多くの温度での測定が必要と考えられる. SAC305 の応力指数は温度の上昇とともに増加し, いずれの温度でも大きな値(> 10)となっている. この値は Sn-3.5Ag-0.75Cu のクリープ特性を求めた既報<sup>102)</sup>の値と近いものである.

Sn-58Bi と In-3Ag の融点は近いところにあるが, 80°C と 120°C の応力指数は大きく異なっている. また室温と 120°C における係数も大きく異なるものである. 本研究では試料に時効処理を行わなかった. 微細試験片における時効処理のクリープ特性に与える影響についてはさらに今後の研究が必要である.

Fig. 3.12 Relationship between true strain rate and true stress at R. T.

Fig. 3.13 Relationship between true strain rate and true stress at  $80^\circ\text{C}$ .

Fig. 3.14 Relationship between true strain rate and true stress at  $120^\circ\text{C}$ .

Table 3.1 Creep properties obtained with 0.5-mm-diameter specimens.

| Solder  | Temperature (°C) | Constant A (MPa/s)     | Stress exponent n |

|---------|------------------|------------------------|-------------------|

| Sn-58Bi | 25               | $1.48 \times 10^{-19}$ | 8.3               |

|         | 80               | $4.07 \times 10^{-11}$ | 4.5               |

|         | 120              | $2.51 \times 10^{-07}$ | 3.1               |

| In-3Ag  | 25               | $1.30 \times 10^{-11}$ | 8.3               |

|         | 80               | $1.30 \times 10^{-11}$ | 10.4              |

|         | 120              | $1.20 \times 10^{-10}$ | 9.6               |

| SAC305  | 25               | $1.08 \times 10^{-20}$ | 10.3              |

|         | 80               | $4.41 \times 10^{-19}$ | 10.6              |

|         | 120              | $4.63 \times 10^{-18}$ | 11.2              |

### 3.3 フリップチップ接合の冷却時の応力場の解明

#### 3.3.1 FEM 解析モデル

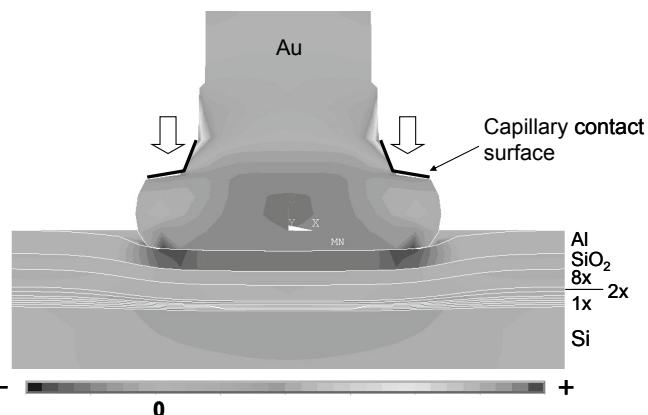

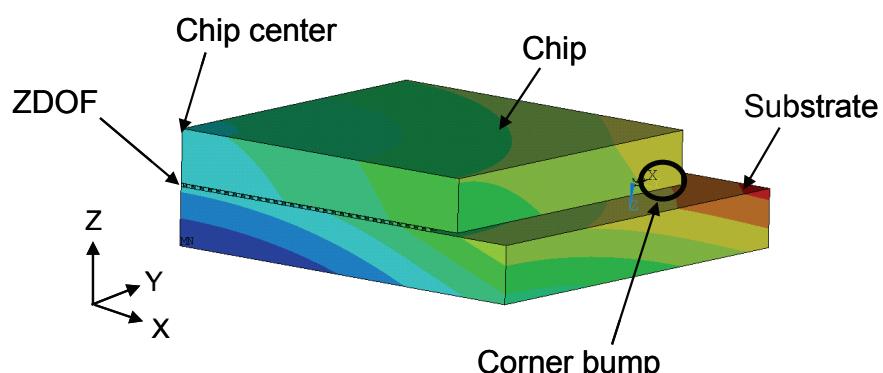

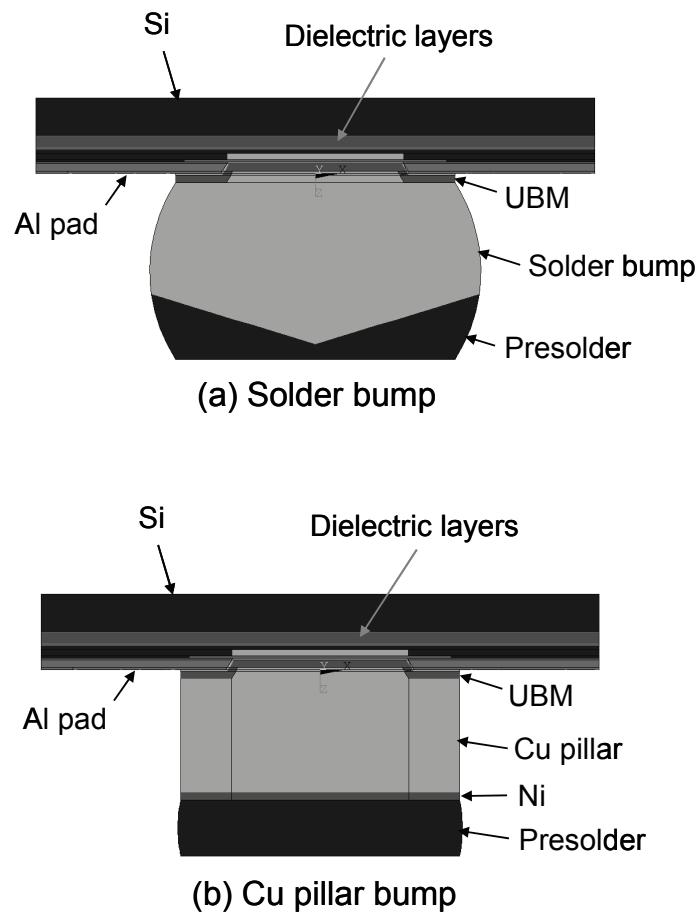

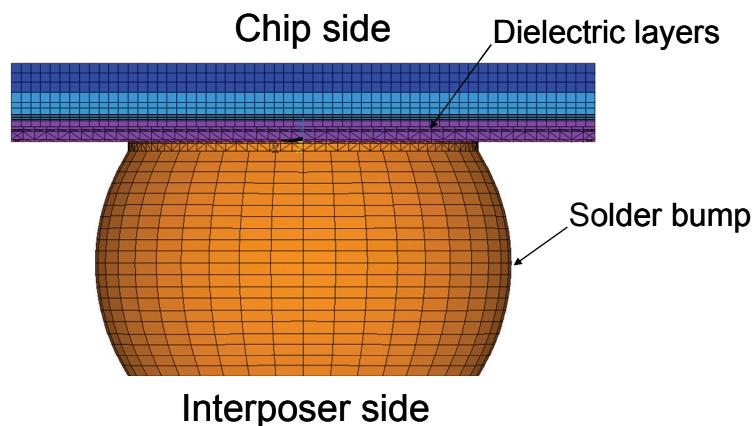

上で得られた各はんだの機械特性を用いてフリップチップ接合時のパッド下部配線層に発生する応力を ANSYS Mechanical® Ver.14 のマルチスケール解析により調べた。Fig. 3.15 はここで用いた FCPBGA の 1/4 のマクロモデルを示す。固定点(ZDOF: Zero degrees of freedom)はチップ・基板の中心で基板のチップ搭載面上に設定した。ミクロモデルはチップコーナーのプレソルダー、バンプ、UBM(Under bump metallurgy)とチップの Si、パッドおよびパッド下部配線層を含むモデルとした。バンプは Fig. 3.16(a) に示すはんだバンプと Fig. 3.16(b) に示す Cu ピラーバンプの 2 種類の構成を用いた。Table 2 に各部の寸法を示す。UBM は Al パッド上に Cu, Ni の順で形成し、その上にバンプを形成すると仮定している。基板のチップより大きな外周部分はフリップチップ接合部の応力にほとんど影響しないことが以前の解析で確認されており、本研究では基板の大きさはチップよりもわずかに大きい 11.85 mm 角とした。接合部の高さは UBM からプレソルダーまでを含めて 50  $\mu\text{m}$  とした。はんだバンプの先端部はモデルの

Fig. 3.15 Macro model of FCPBGA (1/4 model).

Fig. 3.16 Micro model of (a) solder bump and dielectric wiring layer, and (b) Cu pillar bump and dielectric wiring layer.

Table 3.2 Dimensions used in this analysis.

|                     |                                         |

|---------------------|-----------------------------------------|

| Chip size           | 10.05 mm x 10.05 mm                     |

| Chip thickness      | 0.785 mm                                |

| Bump pitch          | 0.15 mm                                 |

| Bump diameter       | Solder: 0.089 mm<br>Cu pillar: 0.075 mm |

| UBM diameter        | 0.075 mm                                |

| UBM thickness       | Cu: 0.45 $\mu$ m<br>Ni: 2.0 $\mu$ m     |

| Joint height        | 0.050 mm                                |

| Substrate size      | 11.85 mm x 11.85 mm                     |

| Substrate thickness | 0.856 mm                                |

簡素化のため円錐形状とし中央部は基板のパッド表面から 5  $\mu\text{m}$ , 外周部でパッド表面から 17.5  $\mu\text{m}$  の位置に設定した。はんだバンプの最大直径は約 89  $\mu\text{m}$  である。Cu ピラーは先端に 2  $\mu\text{m}$  の厚みの Ni を有し, プレソルダーは 15  $\mu\text{m}$  の厚みと設定とし, UBM からプレソルダーまで円柱形上とした。なおバンプは 150  $\mu\text{m}$  ピッチでフルアレイ配置とした。

フリップチップ接合から室温までの冷却をマクロモデルで解析し, 室温降下後の歪み条件を使ってマイクロモデルの解析を行った。レファレンス温度は各はんだの融点とし, 各はんだの融点から 70°C までの冷却が 64 s, 70°C から室温までの冷却が 113 s となるプロファイルを用いた。各はんだ部分には定常クリープ則と硬化則を適用した。定常クリープ則には先の測定で得られた数値を用いた。硬化則には歪み速度  $5 \times 10^{-3} \text{s}^{-1}$  で得られた応力-ひずみ曲線から代表的な数値を探り, 多直線近似のパラメータを設定した。Table 3.3 に本研究で用いた材料特性を示す。基板の各数値は, 一般的なビルドアップ基板の樹脂材, Cu 配線, ガラス繊維などを想定した複合特性である。各はんだの弾性率は硬化則の多直線近似で ANSYS Mechanical<sup>®</sup>により求めた数値である。一般的に公表されている数値<sup>62)</sup>よりもかなり低いものであるが, 弾性率のみ一般的な数値を用いると解析内で整合性が取れなくなるためここではこの数値をそのまま用いた。本解析では Al, Cu, Ni は弾性体として扱った。なお UBM とバンプ, バンプとプレソルダー, プレソルダーと基板上の Cu ランドの各界面付近では金属間化合物(IMC: Intemetalllic compound)が形成される。一般的に金属間化合物は弾性率が高く, 金属間化合物化による接合部の機械的特性の変化は無視できない場合があるが, この解析では金属間化合物の形成が無視できる程度であるとの仮定を置いている。

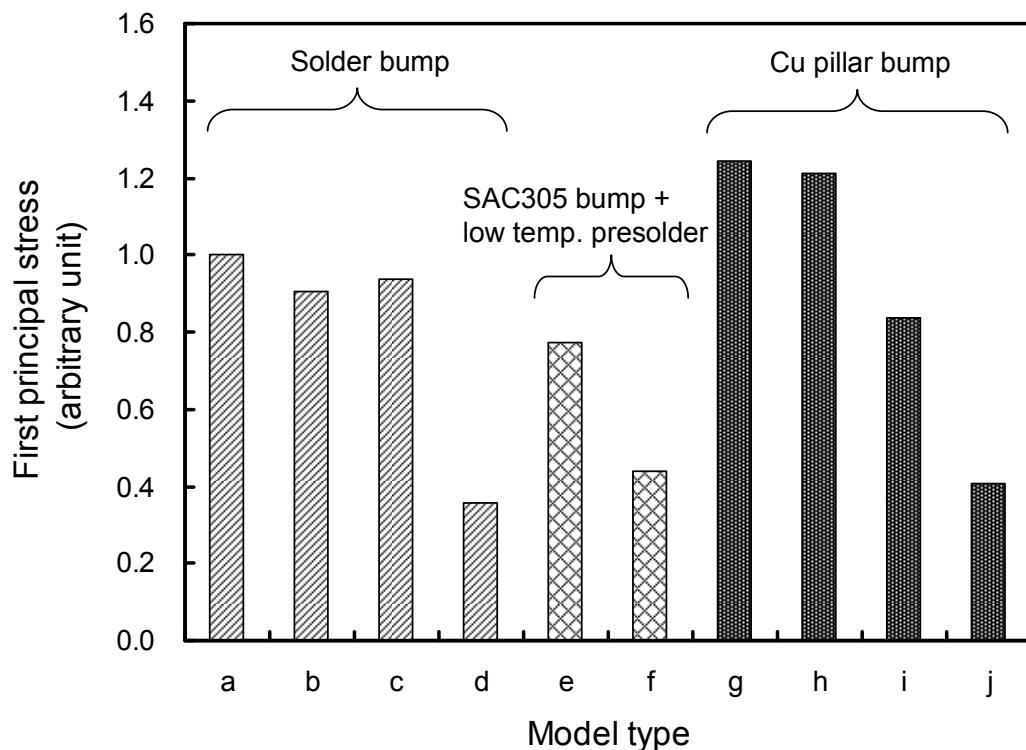

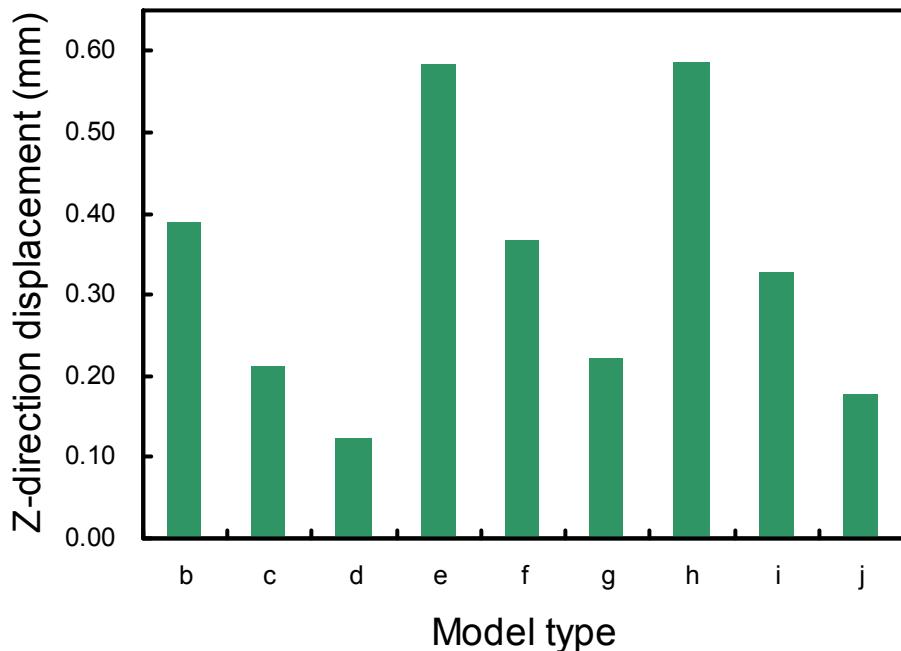

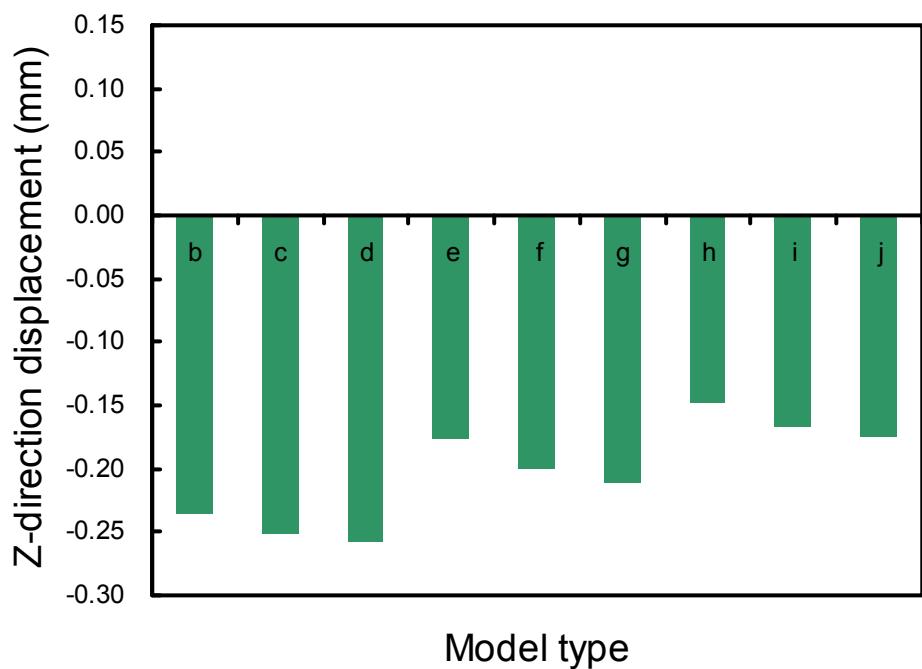

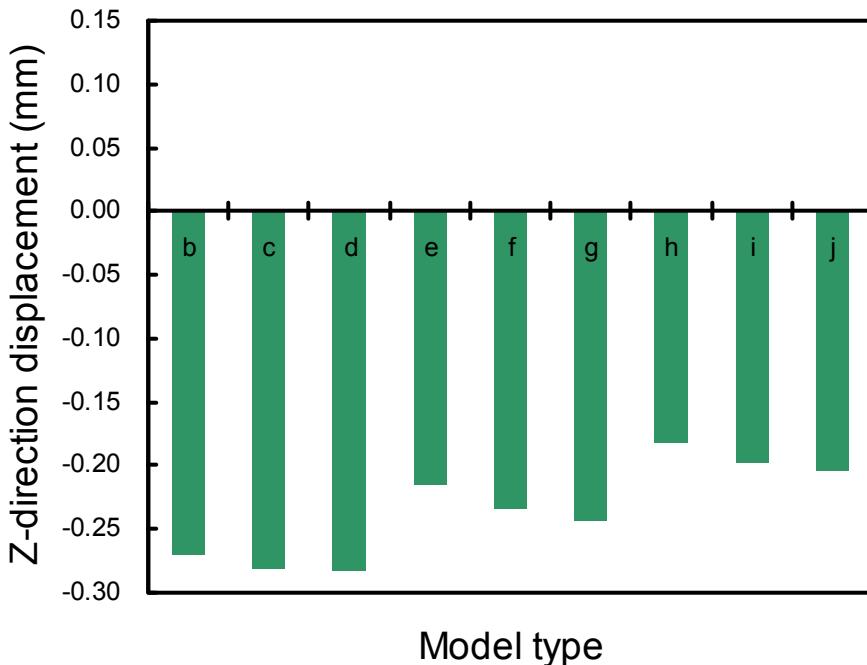

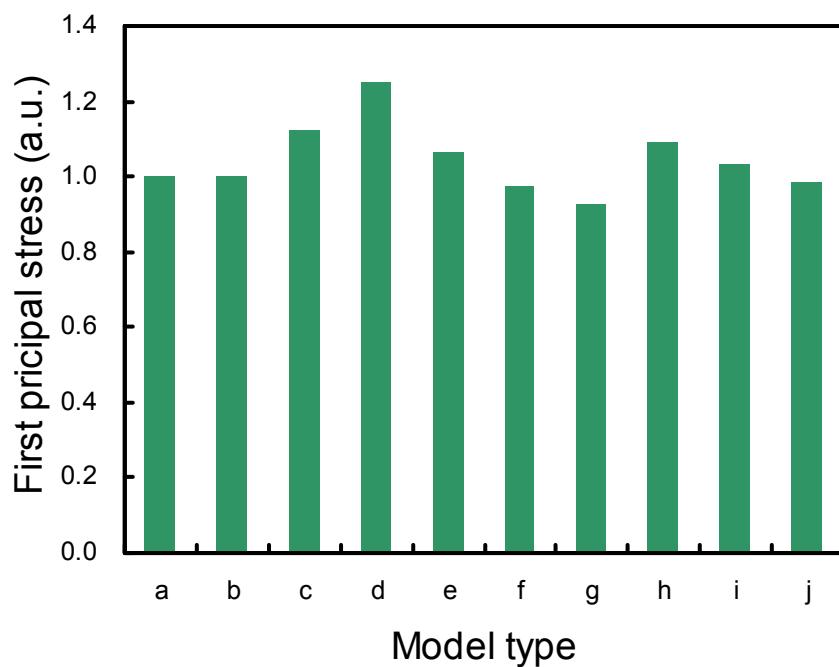

Table 3.4 には本解析で用いたバンプとプレソルダーの組み合わせを示す。モデル a, b, c, d はバンプとプレソルダーに同じはんだを用い, モデル d, e はバンプを SAC305 としプレソルダーのみ低融点はんだとした。接合はプレソルダーによって行われると仮定しレファレンス温度は低温はんだの融点とした。モデル g, h, i, j はバンプを Cu ピラーとし, プレソルダーで接合される前提である。モデル b と h は SAC305 で Sn の過冷却を仮定してレファレンス温度を 180°C にしたケースである。

Table 3.3 Material properties (at R. T.) used in this analysis.

|                  | E (GPa) | Poisson's ratio | CTE (ppm/ $^{\circ}\text{C}$ ) |

|------------------|---------|-----------------|--------------------------------|

| Si               | 165     | 0.22            | 3.2                            |

| Dielectric layer | 7.5     | 0.28            | 14                             |

| Substrate        | 22      | 0.30            | 17                             |

| Al               | 69      | 0.30            | 22                             |

| Cu               | 117     | 0.32            | 17                             |

| Ni               | 207     | 0.31            | 13                             |

| Sn-58Bi          | 12      | 0.40            | 15                             |

| In-3Ag           | 2.3     | 0.40            | 22                             |

| SAC305           | 12      | 0.41            | 22                             |

Table 3.4 Model matrix.

| Model type | Bump      | Presolder | Ref. temp. (°C) |

|------------|-----------|-----------|-----------------|

| a          | SAC305    | SAC305    | 220             |

| b          | SAC305    | SAC305    | 180             |

| c          | Sn-58Bi   | Sn-58Bi   | 139             |

| d          | In-3Ag    | In-3Ag    | 143             |

| e          | SAC305    | Sn-58Bi   | 139             |

| f          | SAC305    | In-3Ag    | 143             |

| g          | Cu pillar | SAC305    | 220             |

| h          | Cu pillar | SAC305    | 180             |

| i          | Cu pillar | Sn-58Bi   | 139             |

| j          | Cu pillar | In-3Ag    | 143             |

### 3.3.2 解析結果

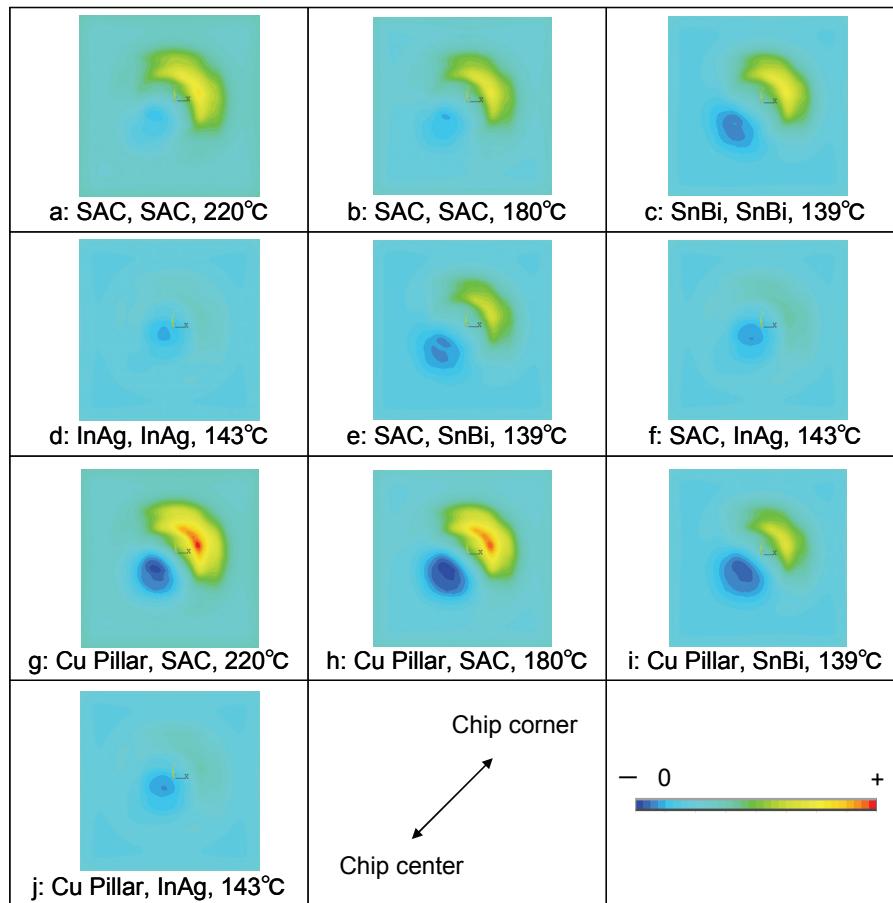

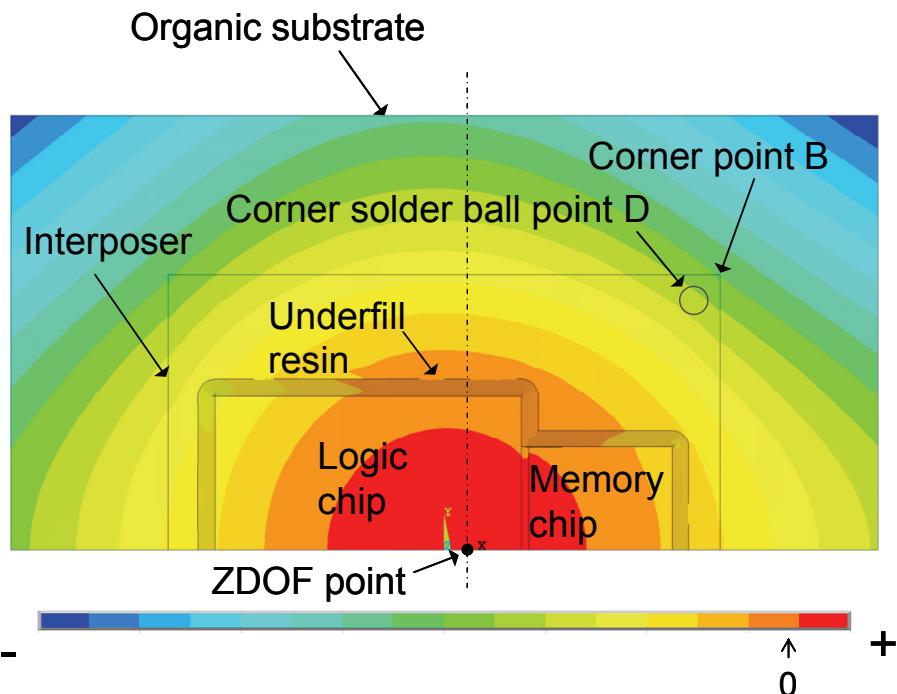

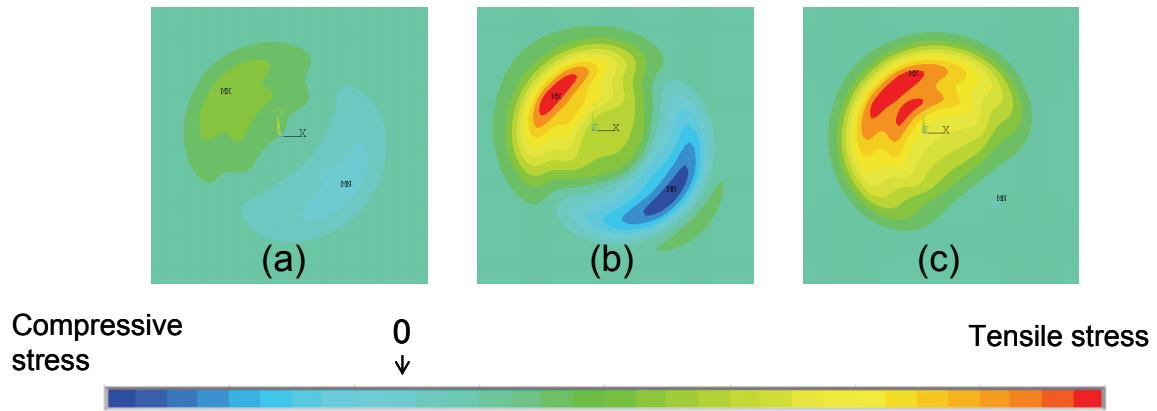

Fig. 3.17 はフリップチップ接合後に室温まで冷却された状態での、チップコーナーのパッド下部の絶縁層における各モデルの第一主応力のコンター図である。各図の右上がチップのコーナー方向で左下がチップの中央方向である。各コンター図の応力のスケールはすべて同一に設定した。SAC305 と Sn-58Bi を用いたモデルではチップ中央側に最大の圧縮応力が発生し、チップコーナー側に最大の引張応力が発生していることが分かる。また In-3Ag を用いたモデルではバンプ中央部付近に最大の圧縮応力が発生している。最大の引張応力はこのコンター図からは判別しにくいがチップコーナー側に発生している。

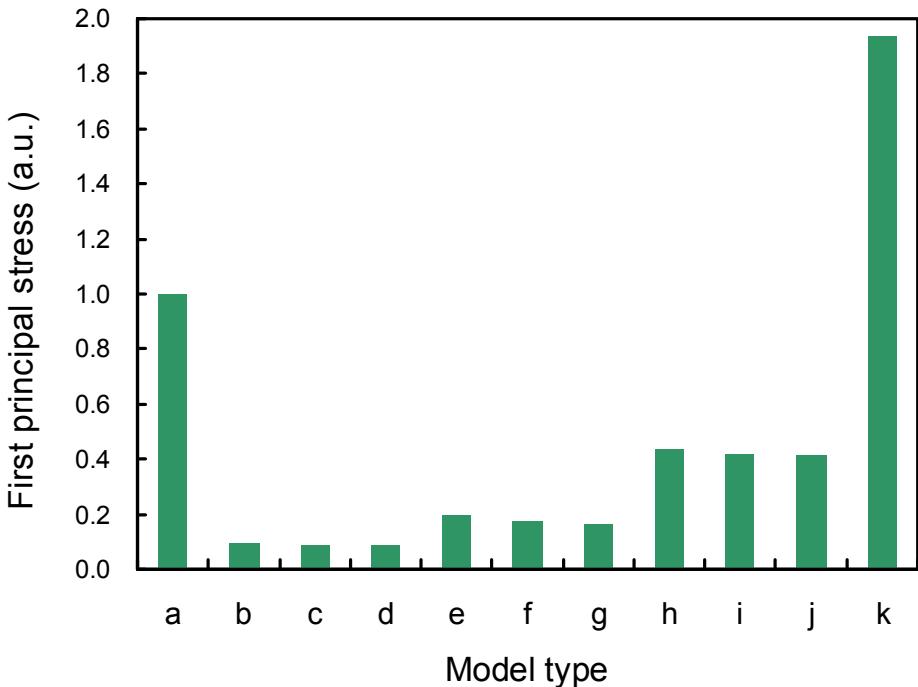

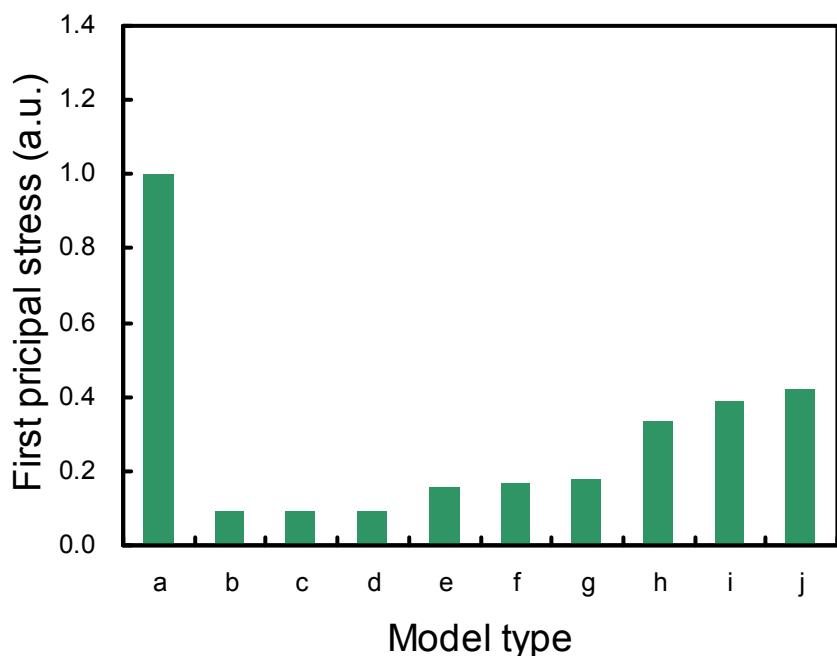

Fig. 3.18 は各モデルのチップコーナーのバンプ下部の絶縁層に発生する最大の第一主応力を示す。これはすべて引張応力であり、比較のためモデル a を基準として任意単位で表示した。モデル a と b はバンプ、プレソルダーとともに SAC305 でありレファレンス温度が 220°C から 180°C に下がると応力が約 10% 低減する。これに対しモデル c の Sn-58Bi の場合はレファレンス温度が 139°C にもかかわらずモデル a に対する応力は約 6% の減少にすぎない。これは接合部の主体となる SAC305 のクリープが Sn-58Bi に比べて大きいことと 0.2% 耐力が小さいことによると考えられる。ここで用いた室温での SAS305 の 0.2% 耐力は約 42 MPa であるのに対し、Sn-58Bi の 0.2% 耐力は約 80 MPa である。モデル d の In-3Ag の場合、モデル a に比べて応力は約 65% 減少する。これはレファレンス温度、クリープ特性、0.2% 耐力の違いが大きく影響していると考えられる。室温での In-3Ag の 0.2% 耐力は約 10 MPa である。モデル e と f はバンプを SAC305 とし、プレソルダーを低融点はんだとしたものである。モデル c に対してモデル e の応力は約 14% 減少している。モデル e では SAC305 の機械的特性が接合部の機械的特性で支配的となり、モデル c に比べてクリープが大きく、0.2% 耐力が小さいためと考えられる。またモデル d に対してモデル f の応力は約 24% 大きい。これは In-3Ag に比べてクリープが大きく、0.2% 耐力の大きい SAC305 の機械特性が支配的になったためと考えられる。モデル g～j の Cu ピラーバンプの場合、

Fig. 3.17 Contour diagrams of first pricipal stress in the dielectric layer under corner bump for model a to j.

Fig. 3.18 First pricipal stress in the dielectric layer under corner bump for model a to j.

SAC305 のプレソルダーのモデル g, h に対し Sn-58Bi のモデル i では 30%以上応力が減少し, In-3Ag のモデル j では 65%以上応力が減少する。またはんだバンプのモデル a~d と g~j をそれぞれ比較すると SAC305 の場合は Cu ピラーのほうが 20%以上応力が増加し, In-3Ag の場合は Cu ピラーのほうが約 14%応力が増加する。これは Cu の高い弾性率によるものと考えられる。一方で Sn-58Bi の場合は Cu ピラーのほうが約 10%応力が減少する。Sn-58Bi は 0.2%耐力が 80 MPa と高いため弾性変形域が大きく、バンプ形状の影響が大きいのではないかと推察する。

これらのモデルによる解析では, In-3Ag を用いた接合部のフォン・ミーゼス応力は 10 MPa 程度であり, SAC305 を用いた接合部のフォン・ミーゼス応力は 47 MPa 程度である。これら 2 つのはんだ接合部は塑性変形域に到達している。一方で Sn-58Bi の接合部のフォン・ミーゼス応力は 65~72 MPa 程度であり弾性変形域にとどまる。このことが低融点である Sn-58Bi はんだで大きな応力低減効果を得られない要因であると考える。また Cu ピラーバンプも同様に弾性変形域にとどまることから SAC305 バンプよりも応力が増加すると考えられる。

以上より In-3Ag を用いるとフリップチップのパッド下部絶縁層の応力を低減する効果が大きいことが分かった。Sn-58Bi の場合, バンプは SAC305 の場合が最も応力低減効果がある。Cu ピラーを用いると SAC305 プレソルダーとの組み合わせでは, はんだバンプの場合よりも 20%以上応力が増加することになる。

### 3.4 結言

Sn-58Bi と In-3Ag の 2 種類の低融点はんだと SAC305 の計 3 種類のはんだで直径 0.5 mm の微細試験片を作製し, 3 つの温度条件および 4 つの歪み速度条件で引張試験を行った。この試験から, 歪み速度  $5.0 \times 10^{-3} \text{ s}^{-1}$ , 室温(25°C)の条件で Sn-58Bi, In-3Ag, SAC305 の 0.2%耐力はそれぞれ約 80 MPa, 約 42 MPa, 約 10 MPa となった。また室温でのクリープは In-3Ag, SAC305, Sn-58Bi の順で大きいことが分かった。ここで得られた各はんだの機械的特性を用いて, FCPBGA のフリップチップ接合の冷却後にチップ上のパッド下部配線層の絶縁膜に発生する応力を FEM で解析した。Sn-58Bi と In-3Ag の融点はほぼ等しいが, 機械的特性の違いによりパッド下部にかかる応力は両者で顕著に異なっている。クリープが大きく, 0.2%耐力が約 10 MPa と非常に小さい機械的特性により, In-3Ag を用いた接合部は塑性変形域に達し, 応力低減の効果が大きいことが分かった。一方, Sn-58Bi を用いた接合部は 0.2%耐力が約 80 MPa と高いため弾性変形域にとどまり, 応力低減の効果は限定的である。また Cu ピラーバンプと SAC305 のプレソルダーを用いる場合, SAC305 のはんだバンプと SAC305 のプレソルダーの場合に比べて 20%以上応力が増加するとの結果を得た。これは Cu ピラーバンプが弾性変形域にとどまることによると考えられる。

本研究では, フリップチップ接合後の応力に着目し, その低減手法を解明した。In-3Ag の接合直後の応力低減効果は大きいが, 塑性変形は大きくなると考えられる。パッケージ設計時には, 熱サイクルでの繰り返し応力によるフリップチップ接合部の累積歪みが信頼性に与える影響を考慮して, 歪みを抑制する適正なアンダーフィル材を選択するなどの工夫が重要となると考えられる。

## 第4章 貫通電極を有するインターポーラ上に複数チップを搭載するパッケージのマイクロ接合部およびチップ下部配線層の応力低減

### 4.1 緒言

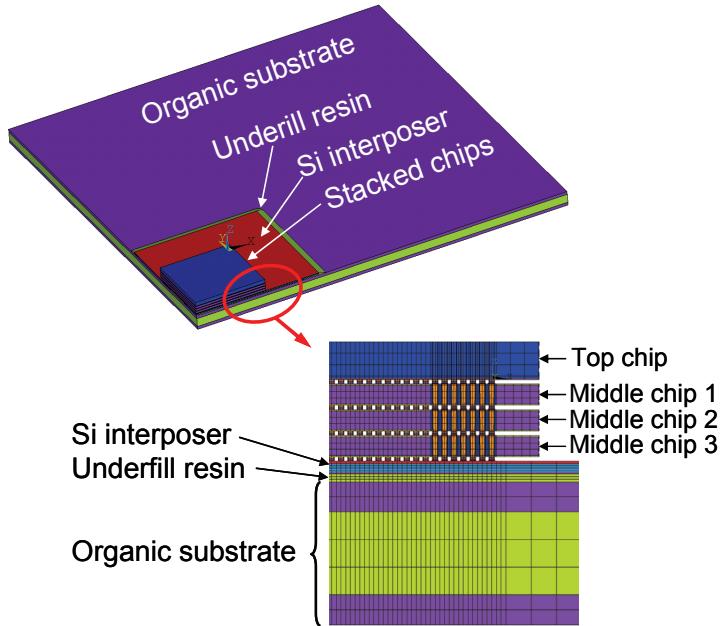

本章では、貫通電極を有するインターポーラ上にフリップチップボンディングで複数チップを搭載するパッケージのチップ接合後のマイクロ接合部およびチップ下部配線層の応力低減を研究対象とした。構造として、インターポーラ上に複数チップを平面配置する2.5Dパッケージとインターポーラ上に複数チップを積層する3D-ICパッケージの2つを取り上げた。2.5Dパッケージでは、応力に影響を与える因子としてチップとインターポーラの接続順序、インターポーラの機械的特性、インターポーラの厚みに着目した。3D-ICパッケージでは、応力に影響を与える因子としてチップの厚み、インターポーラの厚み、チップの積層数、接合部の機械的特性に着目した。ここではチップ接合後の応力低減を議論し、パッケージ使用時の信頼性に関わる接合部の歪みについての議論は行っていない。

2.5Dパッケージは、微細配線を形成できるインターポーラを有機基板上に搭載し、そのインターポーラ上に複数チップを平面配置して搭載する構造となる。2.5Dパッケージでは複数チップを搭載するためインターポーラが大型になり、チップとインターポーラ、インターポーラと有機基板でそれぞれのマイクロ接合面を持つ。またインターポーラの材料はシリコン、ガラスおよび有機基板などが提案されておりその機械的特性もそれぞれ異なるものである。このためパッケージ組み立てプロセスで考慮すべきマイクロ接合部にかかる応力や各部の反りに影響する要因は従来のFCPBGAに比べて複雑になる。2.5Dパッケージに搭載するチップは、FPGAのように同一設計のチップを複数搭載するホモジニアス構成を取る場合と、ロジックチップ、メモリチップ、アナログチップ、MEMS (Micro Electro Mechanical Systems)チップなどの異種チップを混在させるヘテロジニアス構成を取る場合がある。本研究ではロジックチップとWide I/Oメモリの2種類のチップを搭載する構成の2.5Dパッケージを想定し、従来から用いられている有機基板上に複数チップを搭載するMCM (Multi Chip Module)-FCPBGAと比較し、応力と反りの検討を行った。インターポーラとしてシリコン、機械的特性の異なる2種類のガラス、有機基板のビルドアップ層のみを積層したコアレス基板の計4タイプを取り上げた。シリコンおよびガラスのインターポーラと有機材料のコアレス基板では配線の設計ルールが異なるため同じロジックチップとメモリチップを搭載する場合でも同じサイズのインターポーラを用いることができない。同一のチップサイズやI/O数などの前提条件に基づき、2.5DパッケージとMCM-FCPBGAそれぞれの代表的な設計ルールを用いてパッケージ設計を検討した。設計検討により得られたパッケージ構成を基に、シリコン、2種類のガラスおよびコアレス基板でそれぞれ異なる機械的特性を持つインターポーラを用いてFEMモデルを作成し、インターポーラの機械的特性がマイクロ接合部の応力とインターポーラの反りに与える影響を調べた。また、チップ、インターポーラ、有機基板の3層構造となる2.5Dパッケージでは、各接合の順序によってプロセス中にかかる熱応力が変化する。先にチップをインターポーラに接合する場合、先にインターポーラを有機基板に接合する場合、チップとインターポーラおよび有機基板を同時に接合する場合の3つのパターンのFEMモデルを作成し接合順序がマイクロ接合の応力と反りに与える影響を調べた。接合順序の影響の解析ではコアレス基板のインターポー

ザは除外したが、シリコンおよびガラスの各インターポーラの厚みによる影響も同時に調べた。

3D-IC パッケージではインターポーラ上に搭載されるチップは積層構造となる。チップの積層数や各チップの厚み、インターポーラの厚みはプロセスコストにも影響する重要な設計要素である。またチップ間接合には微細なピッチが必要とされるため、はんだブリッジを低減し接合部の形状安定性を高めるため Cu ピラーバンプが用いられる。Cu ピラーバンプを用いると接合部のはんだ量が少なく、接合部をすべて金属間化合物化する IMC 接合が接合部の安定性を高める有効な方法であると考えられている。しかしながら IMC 接合部は弾性率が高く接合部の応力は高くなると考えられており、はんだと Cu の間にバリアメタルを置き、CuSn の金属間化合物化を抑えて接合部に金属間化合物に比べて低弾性率のはんだを残すほうが望ましいとも考えられる。本研究では、3D-IC パッケージに搭載するチップの積層数、最上部のチップの厚み、シリコンインターポーラの厚みおよび接合部分の機械的特性を変えて、各因子がチップの反りとマイクロ接合部にかかる応力に与える影響を解析し、チップの反りとマイクロ接合部の応力を低減する条件を解明した。

## 4.2 インターポーラ上に複数チップを平面配置するパッケージと MCM FCPBGA の熱機械的解析

### 4.2.1 インターポーラ上に複数チップを平面配置するパッケージと MCM FCPBGA の設計検討前提条件

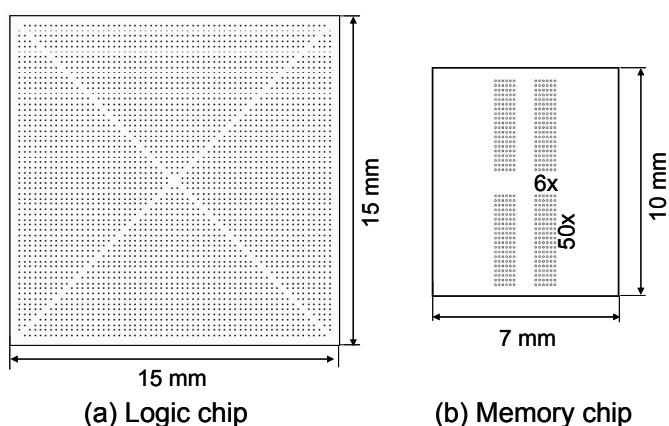

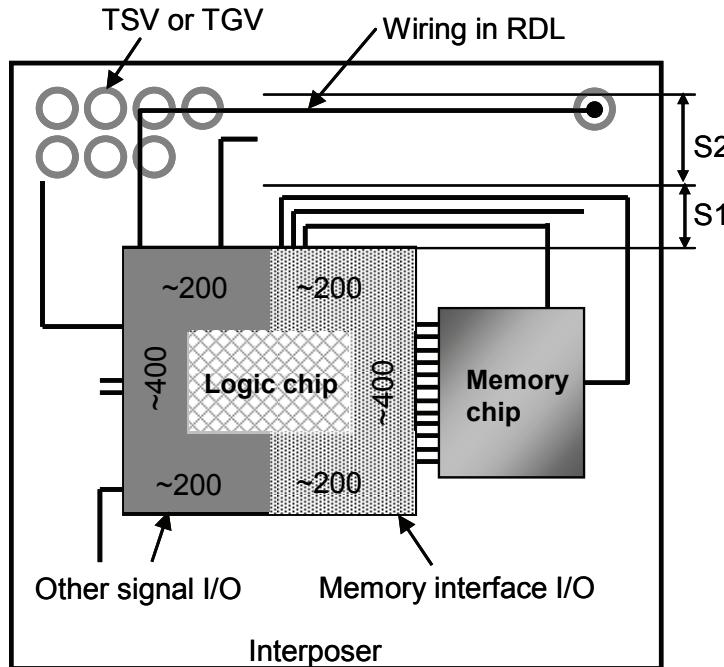

Fig. 4.1(a) にここで用いるロジックチップのバンプ配置を、Fig. 4.1(b) にメモリチップのバンプ配置を示す。また Table 4.1 にはチップとパッケージの各部の詳細な前提条件を示す。ロジックチップは 15 mm 角のチップに 150  $\mu\text{m}$  ピッチのバンプがフルアレイで配置されたとした。メモリチップは JEDEC の策定した Wide I/O メモリの MPGA の標準規格<sup>29)</sup>に基づいたバンプ配置を想定した。Fig. 4.1(b) に示すようにバンプはチップ中央に 4 つのブロックに分かれて配置され、それぞれのブロック内では 40  $\mu\text{m}$   $\times$  50  $\mu\text{m}$  のピッチで格子状に配列されている。有機基板上にチップを搭載する場合には、有機基板の配線ルールでこのピッチのバンプから引き出しを行うことができないため、メモリチップ上で再配線によってバンプを 200  $\mu\text{m}$  ピッチに再配置すると仮定した。ここではメモリの I/O 数は規格の数値を近似して 800 とした。

Fig. 4.1 Bump layout images (not to scale) for (a) logic chip and (b) memory chip.

Table 4.1 Features of chip and package.

|                                        |                                     |

|----------------------------------------|-------------------------------------|

| Chip size (logic)                      | 15 mm x 15 mm                       |

| Chip size (memory)                     | 10 mm x 7 mm                        |

| Chip thickness (logic and memory)      | 786 $\mu\text{m}$                   |

| Bump matrix (logic)                    | 94 x 94                             |

| Bump matrix (MPGA memory)              | (6 x 50) x 4                        |

| Bump matrix (custom memory)            | 30 x 40                             |

| Signal I/O count (logic)               | 1600                                |

| Signal I/O count (memory)              | 800                                 |

| Direct wiring between logic and memory | 800                                 |

| Bump pitch (logic)                     | 150 $\mu\text{m}$                   |

| Bump pitch (MPGA memory)               | 40 $\mu\text{m}$ x 50 $\mu\text{m}$ |

| Bump pitch (custom layout memory)      | 200 $\mu\text{m}$                   |

| Package size                           | 42.5 mm x 42.5 mm                   |

| Package BGA pitch                      | 1.0 mm                              |

| Package BGA ball count                 | 1600                                |

| Thickness of one build-up layer        | 45 $\mu\text{m}$ including Cu       |

### パッケージ構成と配線ルール

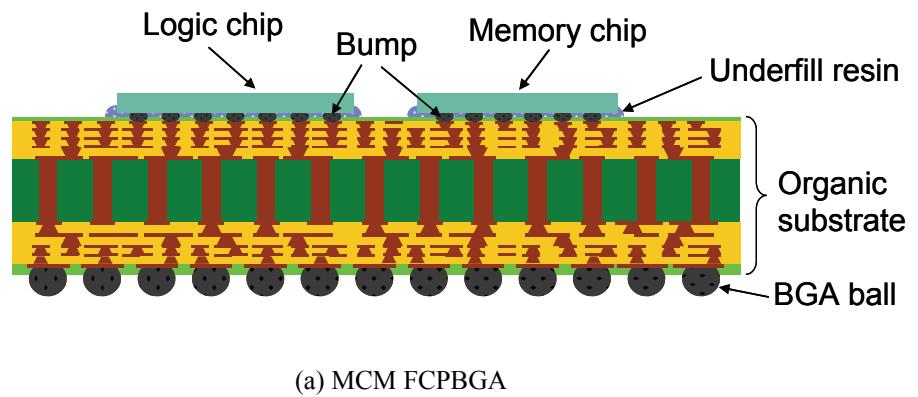

Fig 4.2 にここで用いたパッケージ構成の断面の概略図を示す。Fig 4.2(a) はビルドアップ基板を用いた MCM FCPBGA である。前述のように現行の有機基板の配線ルールでは Wide I/O メモリのバンプピッチから配線を引き出すことができないため、メモリチップ上で再配線しバンプを 200  $\mu\text{m}$  ピッチに再配置すると仮定した。Fig 4.2(b) はシリコンあるいはガラスをインターポーヴに用いた FCPBGA である。インターポーヴ上にはロジックチップおよびメモリチップからの配線を行う配線層を設け、その配線層から有機基板への伝送路として TSV (Through Silicon Via) あるいは TGV (Through Glass Via) がインターポーヴ中に形成されている。TSV および TGV はインターポーヴ全面に格子状に配置されるのが一般的である。インターポーヴと有機基板ははんだでマイクロ接合されると仮定した。Fig 4.2(c) はコアレス基板の構成を用いた有機インターポーヴを用いた FCPBGA である。ここでも MCM FCPBGA と同様にメモリ上のバンプは再配置したと仮定している。Table 4.2 にはここで用いた各パッケージのインターポーヴの厚みと設計ルールをまとめた。有機基板とシリコンおよびガラスインターポーヴそれぞれで現在適用可能な配線ルールを採用した。

(a) MCM FCPBGA

(a) Si or glass interposer FCPBGA

(a) Organic interposer FCPBGA

Fig. 4.2 Schematic cross-sections of package configurations used in this study.

Table 4.2 Design ground rules assumed in this study.

| <b>Build-up layer (FCPBGA, organic interposer)</b> |                       |

|----------------------------------------------------|-----------------------|

| Line / space                                       | 15 / 15 $\mu\text{m}$ |

| Via land diameter                                  | 85 $\mu\text{m}$      |

| <b>Si interposer</b>                               |                       |

| TSV diameter                                       | 60 $\mu\text{m}$      |

| Line / space in RDL                                | 4 / 4 $\mu\text{m}$   |

| <b>Glass interposer</b>                            |                       |

| TGV diameter                                       | 80 $\mu\text{m}$      |

| Line / space in RDL                                | 4 / 4 $\mu\text{m}$   |

### 基板とインターポーラの寸法の導出

Fig 4.3 にインターポーラ上にロジックチップとメモリチップを搭載する代表的な配置を示す。ここではシリコンおよびガラスインターポーラ上に2チップを配置した時のチップ間のクリアランスを0.375 mm, 有機インターポーラ上に2チップを配置した時のチップ間のクリアランスを3.0 mmと想定した。またメモリチップの800 I/O はすべてロジックチップのI/Oと直接配線するとし、ロジックチップの残りの800 I/O はインターポーラを介してパッケージの外部接続端子に配線されると想定した。メモリの4つのバンプブロックのうちロジックチップ側の2つのブロックはロジックチップの右面から直接配線し、メモリチップのロジックチップから見て後方の2つのブロックにはロジックチップの上面からそれぞれ200 I/Oずつ配線することになる。ロジックチップの上面からの配線に必要な領域の幅をFig 4.3中に示すようにS1と定義した。ロジックチップからTSVあるいはTGVに接続する配線のうち、同図中の右上部あるいは右下部のTSV/TGVに配線するために必要な配線領域の幅をS2と定義した。シリコンおよびガラスインターポーラの配線・スペースのルール4 / 4  $\mu\text{m}$ を用いるとS1, S2は共に約1.6 mmとなる。インターポーラの最小サイズは、ロジックチップの大きさ、S1, S2およびTSV/TGVからインターポーラ端面までの最小距離(0.5 mmと想定)により約23 mmとなる。ここではインターポーラと有機基板の接続ピッチをFBGA(Fine-pitch Ball Grid Array)等で標準的な0.65 mmピッチとして40 x 40マトリックスで1600 I/Oを確保できる27 mm角のインターポーラサイズを後の解析に用いることとした。さらに同様の検討によってコアレス基板を用いる有機インターポーラは0.8 mmの接合ピッチ33 mm角の大きさを比較対象として選択した。

Fig. 4.3 Typical layout of logic chip and memory chip.

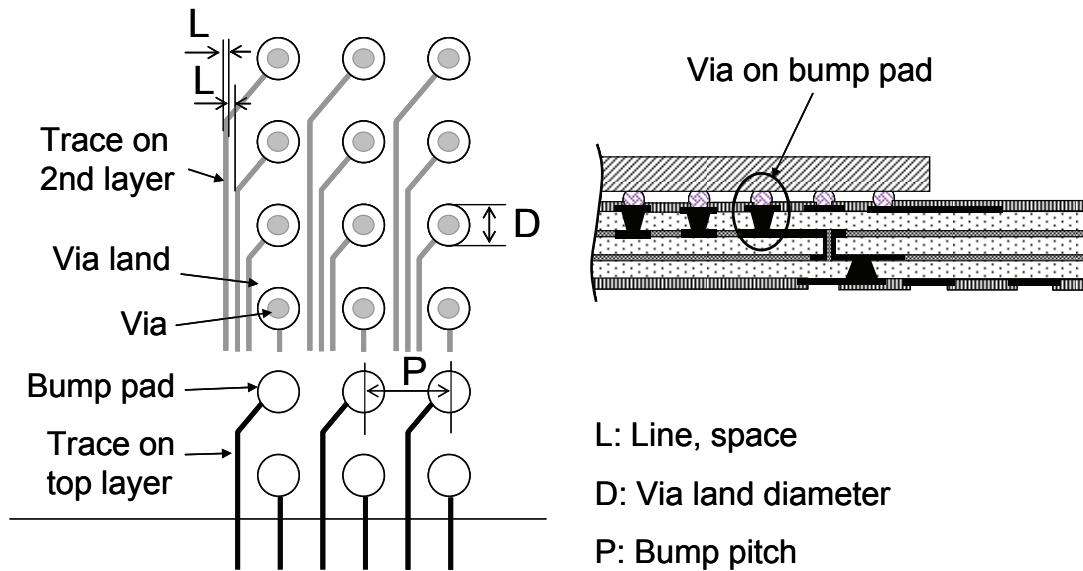

Fig. 4.4 はビルドアップ有機基板でのフリップチップ接合部からの引き出し線の代表的な設計を示す。チップ最外周部のバンプとその内側のバンプから順次ビルドアップ層の最上層で引き出し配線を配置し、バンプのランド間を抜けることができなくなった内側のバンプからは図に示すビア・オン・バンプパッドの構造により 2 層目のビルドアップ層で引き出しを行う。ビルドアップ層の 1 層で引き出せる配線数は次式で求まる。

$$EscapedTraceCount = \frac{P - D - L}{2L} \quad (4.1)$$

ここで  $P$  はバンプピッチ,  $D$  はビアランドの直径,  $L$  は配線幅あるいは配線スペース幅である。FCPBGA ではコア層よりも上側のビルドアップ層をシグナルの引き出しに使うため、ビルドアップ層の総数はコア上面のシグナル引き出しに必要な層数によって決まる。ここでの FCPBGA の場合ではシグナルの引き出しに 4 層のビルドアップ層が必要となり、ビルドアップ基板の層数の一般的な記法では 4-2-4 の構成が必要となる。コアレス基板の有機インターポーラーもシグナル引き出しに必要な層数は FCPBGA 基板と同じであり、通常電源とグラウンドに 1 層ずつのビルドアップ層を割り当て、コアレスではパッド層に 1 層用いるため、コアレス基板の一般的な記法では 6+1 の構成が必要となる。またシリコンおよびガラスインターポーラー上の RDL 層は配線ルールが  $4 / 4 \mu\text{m}$  のため 1 層ですべての引き出しが可能となり、TSV/TGV のランドを設ける層と合わせて 2 層の配線層で十分となる。

Table 4.3 にこれらの検討により得られた各基板のサイズ、構成、厚みを整理した。これらの寸法に基づいて次の解析モデルの作成を行った。

Fig. 4.4 Typical escape design from flip chip joints.

Table 4.3 Design ground rules assumed in this study.

| <b>MCM FCPBGA</b>                            |                    |

|----------------------------------------------|--------------------|

| Substrate layer stack-up                     | 4-2-4              |

| Thickness of MCM FCPBGA's substrate          | 1267 $\mu\text{m}$ |

| <b>Si/glass interposer FCPBGA</b>            |                    |

| Layer count in RDL                           | 2                  |

| TSV pitch                                    | 0.65 mm            |

| Interposer size                              | 27 mm x 27 mm      |

| Substrate layer stack-up                     | 1-2-1              |

| Thickness of base organic substrate          | 970 $\mu\text{m}$  |

| <b>Organic interposer FCPBGA</b>             |                    |

| Layer stack-up                               | 6+1                |

| Solder joint pitch (interposer to substrate) | 0.8 mm             |

| Interposer size                              | 33 mm x 33 mm      |

| Substrate layer stack-up                     | 1-2-1              |

| Thickness of organic interposer              | 285 $\mu\text{m}$  |

| Thickness of base organic substrate          | 970 $\mu\text{m}$  |

#### 4.2.2 FEM 解析モデル

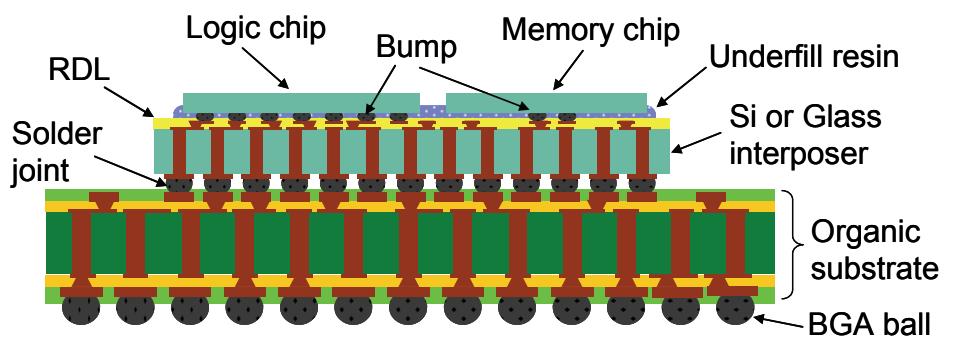

解析には Ansys Mechanical®を使用した。Fig. 4.5 に示すように、チップとインターポーラの接合とインターポーラと有機基板の接合の3つのプロセスフローを考慮して3Dのハーフモデルを作成した。Fig. 4.5(a) は先にチップをインターポーラに接合し、その後有機基板にインターポーラを接合する場合であり、これを順接続と呼ぶ。Fig. 4.5(b) は先にインターポーラを有機基板に接合し、その後チップをインターポーラに接合する場合であり、これを逆接続と呼ぶ。Fig. 4.5(c) はチップとインターポーラおよび有機基板を同時に接合する場合で、これを同時接続と呼ぶ。Fig. 4.5(a), (b) の2度の接合を解析するためにそれぞれ1度目の接合時の構成と2度目の接合時の構成のモデルを作成した。2度目の接合時の構成のモデルでは、1度目の接合部分にはアンダーフィル封止された構造とした。解析のリファレンス温度はすべて 180°C とし、25°C に冷却後の応力と反りを調べた。はんだの融点は約 220°C であるが、以前の評価で過冷却を想定した 180°C でのリファレンス温度を用いると実験との相関が高いことが分かっており、ここではこのリファレンス温度を採用した。フリップチップ接合パッドの下部配線層にかかる応力の解析には、マルチスケール解析の手法を用いた。25°C 冷却後のはんだ接合部とパッド下部の境界の歪み条件を Fig. 4.6 に示すマイクロモデルに適用し、パッド下部配線層の応力分布を求めた。

Fig. 4.5 Three different process flows of chip and interposer joining for 2.5D package.

Table 4.4 に 2.5D パッケージの解析に用いた材料特性をまとめた。2 種類のガラスは A と B で識別し、主たる特性の違いは線膨張係数である。RDL はポリイミドと Cu の複合特性、ビルドアップ層はビルドアップ材と Cu との複合特性、ガラス繊維入りビルドアップ層とコア材はそれぞれの樹脂材と Cu およびガラス繊維との複合特性であり、それぞれ複合則を用いて算出した。

シリコンとガラスのインターポーラは上面に RDL の配線層を設けた構成となる。コアレス基板を用いる有機インターポーラは 4 層をガラス繊維なしのビルドアップ材とし、残りの 3 層をガラス繊維入りのビルドアップ材とした。

Fig. 4.6 Micro model of a flip chip joint and dielectric layers.

Table 4.4 Material properties used in this analysis.

|                                                 | Elastic modulus (GPa) | Poisson's ratio | CTE (ppm/ $^{\circ}$ C) |

|-------------------------------------------------|-----------------------|-----------------|-------------------------|

| Si                                              | 165                   | 0.22            | 3.2                     |

| Glass-A                                         | 77                    | 0.22            | 3.8                     |

| Glass-B                                         | 74                    | 0.22            | 6.0                     |

| RDL <sup>*)</sup>                               | 28                    | 0.24            | 17                      |

| Build-up layer <sup>**) </sup>                  | 17                    | 0.34            | 27                      |

| Build-up layer with glass fiber <sup>***)</sup> | 20                    | 0.29            | 24                      |

| Core <sup>***)</sup>                            | 25                    | 0.33            | 15                      |

| Underfill resin                                 | 9.5                   | 0.35            | 25                      |

| Solder                                          | 27                    | 0.35            | 25                      |

<sup>\*)</sup> Composite property with Cu

<sup>\*\*)</sup> Composite property with Cu and solder resist

<sup>\*\*\*)</sup> Composite property with Cu and glass fiber

### 4.2.3 インターポーザの機械特性による応力・反りへの影響

本節では Fig. 4.5(a) の順方向接続のみを取り扱う。またインターポーザの厚みは 200  $\mu\text{m}$  とした。Table 4.5 に本節で取り上げたモデルの組み合わせをまとめた。シリコンおよびインターポーザの有機基板への接続ピッチは設計検討の結果 0.65 mm ピッチと定めた。TSV/TGV は接続パッドの直上に配置するのが一般的であり、格子状に並べられた TSV/TGV の Cu 密度を算出し、シリコンと 2 種類のガラスそれぞれのインターポーザと Cu で複合特性を求めて解析を行った。また I/O 数との整合は取れないが TSV/TGV のピッチを 0.5 mm と 0.8 mm と仮定しそれぞれの Cu 密度から複合特性を求めたケースを追加した。0.65 mm ピッチに比べると、0.5 mm ピッチの場合は Cu 密度が高く、0.65 mm ピッチの場合は Cu 密度が低くなる想定である。

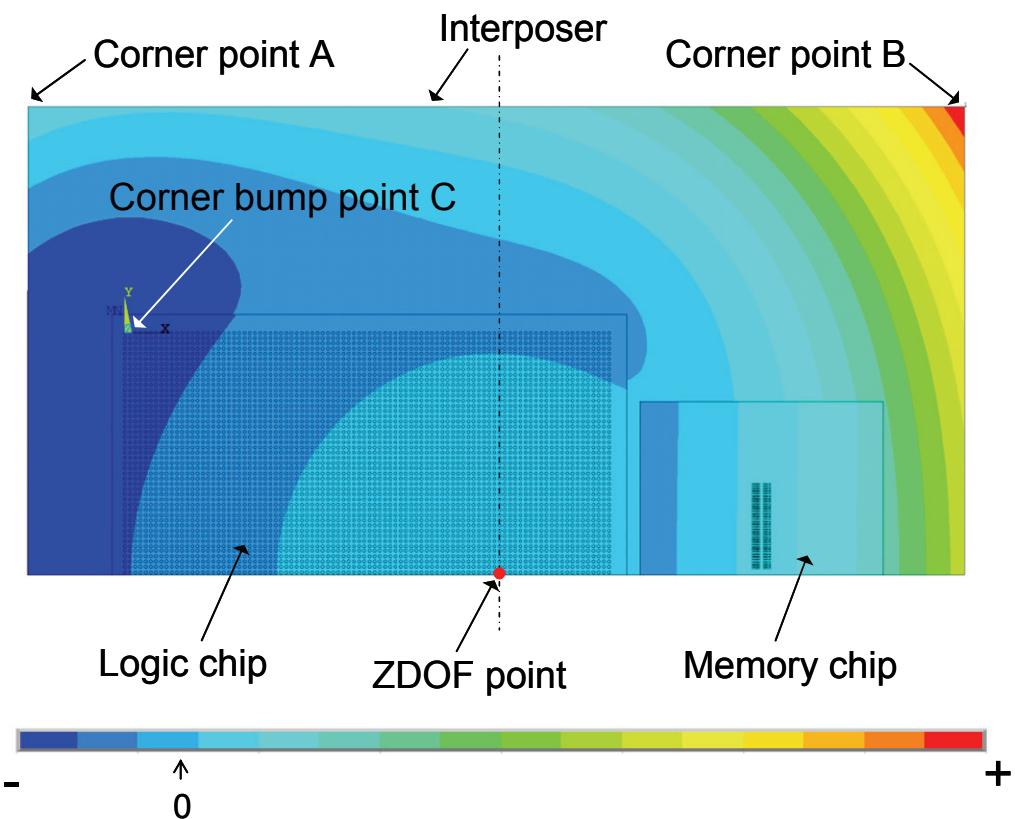

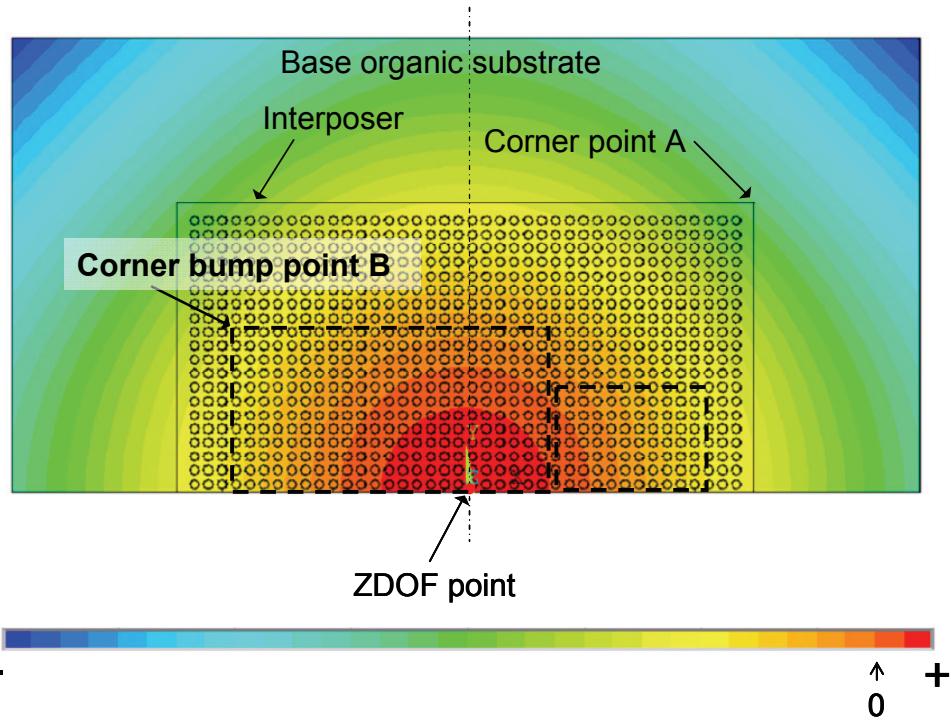

#### チップとインターポーザ接合時のインターポーザの反り

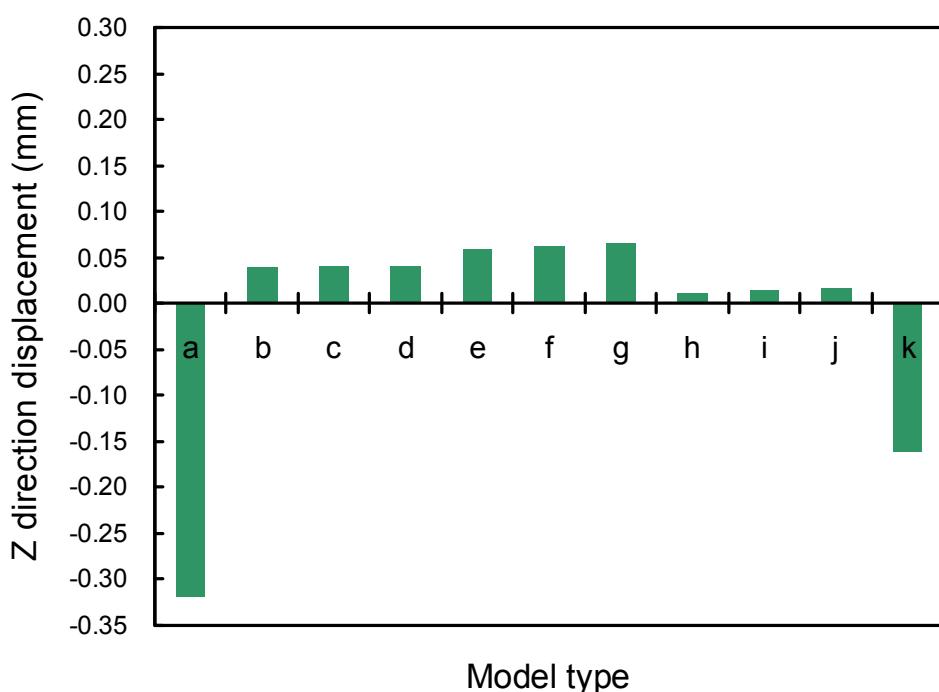

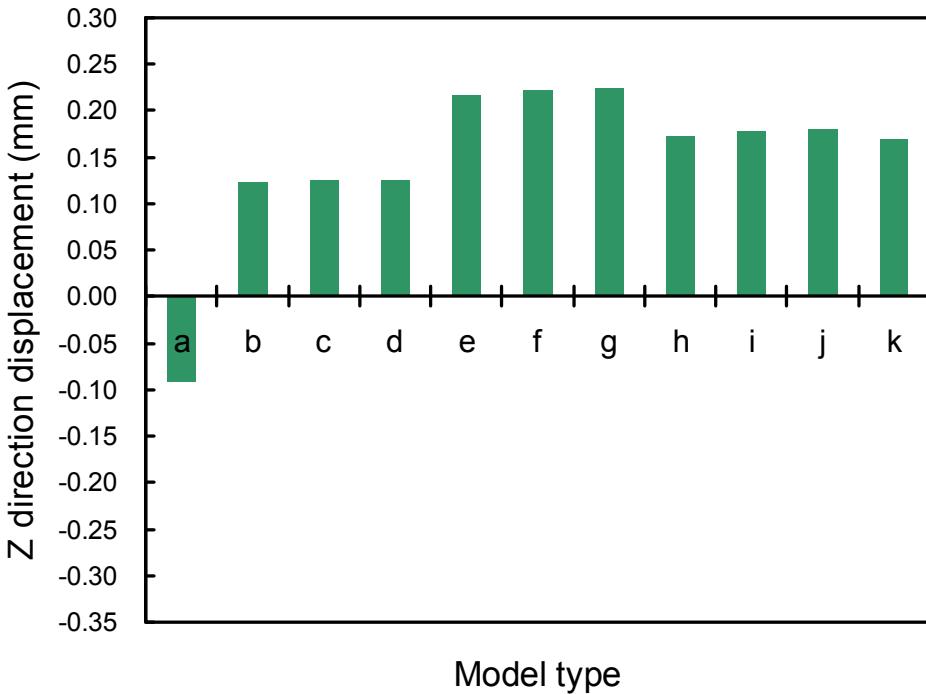

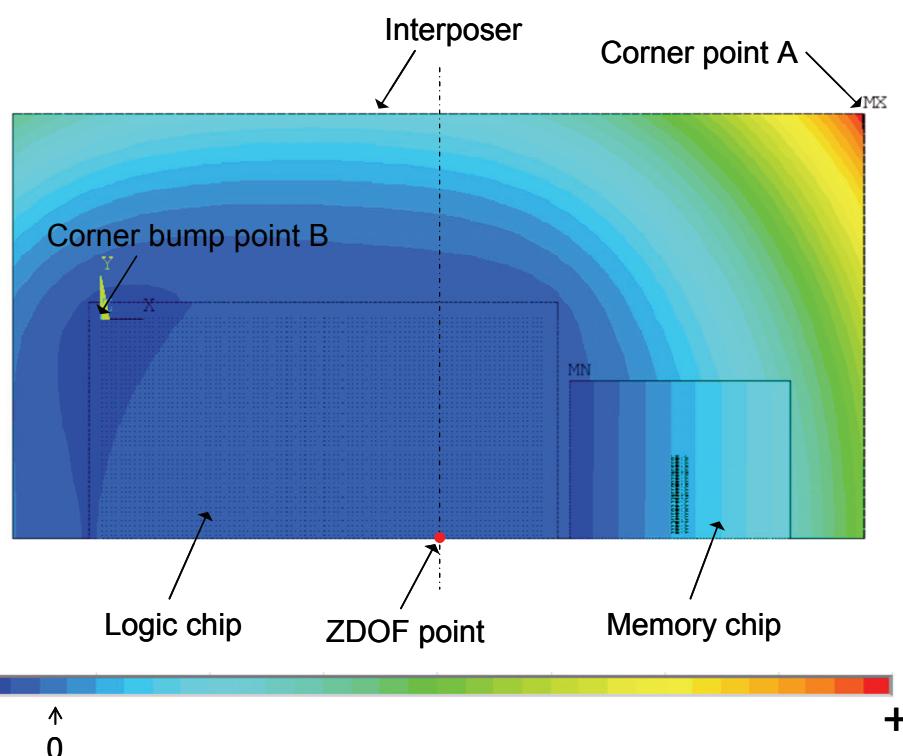

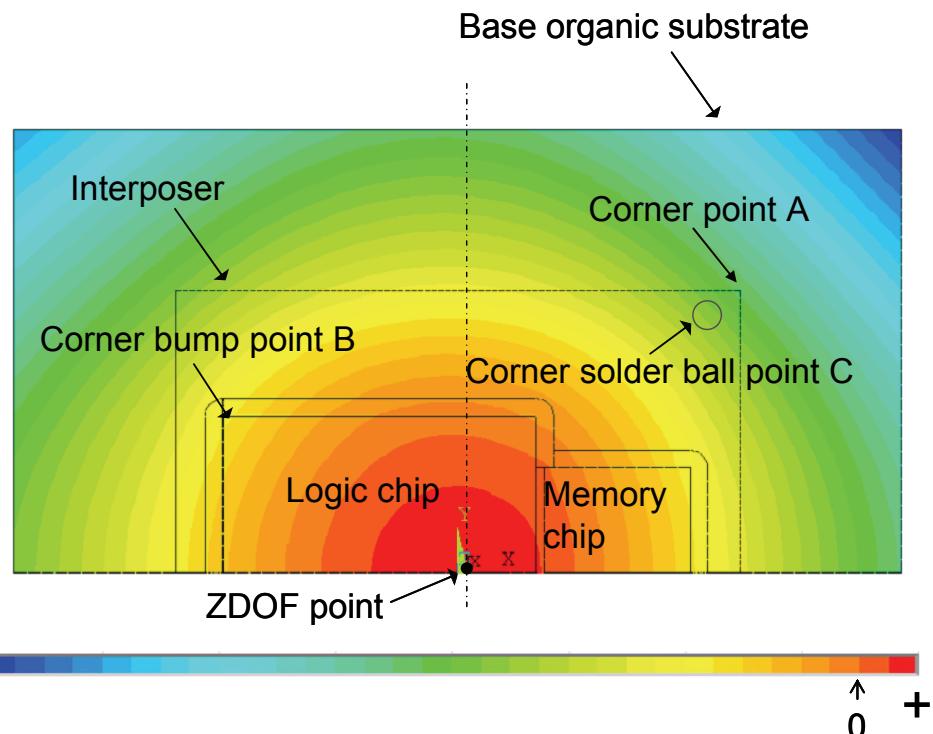

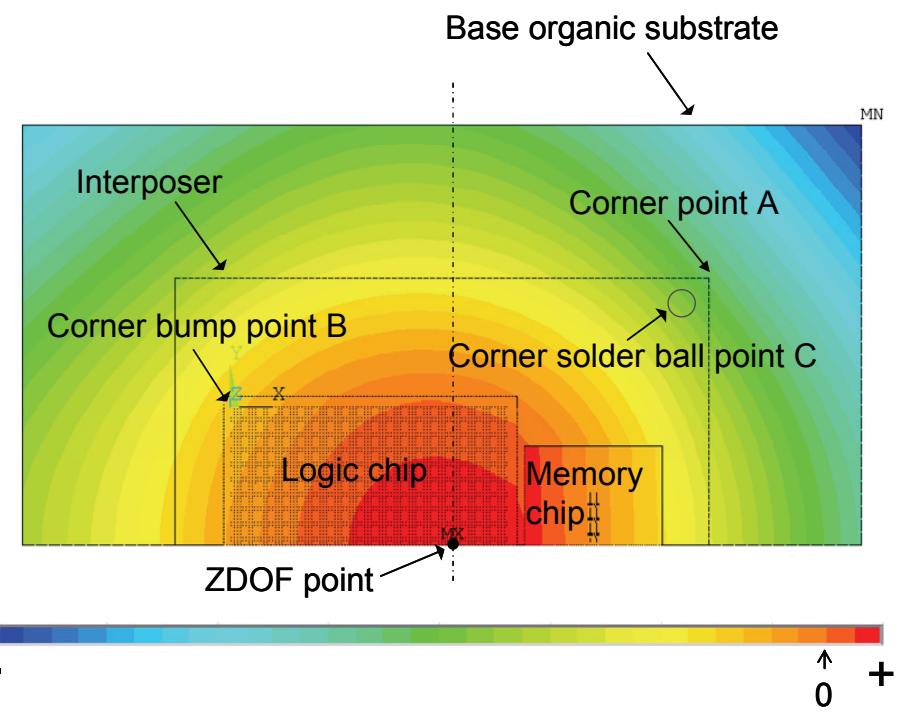

Fig. 4.7 はモデル j のチップとインターポーザ接合後の Z 方向の変位のコンター図である。1/2 モデルであるため図中の下面がパッケージ中央でのカット面である。パッケージ中央の Z 軸を固定軸として解析を行った。インターポーザのロジックチップ搭載側のコーナーをポイント A とし、メモリチップ搭載側のコーナーをポイント B とした。シリコンおよびガラスインターポーザはポイント A-B 間は 27 mm、有機インターポーザは 33 mm であり、MCM FCPBGA は有機基板のコーナーを A と B としその距離は 42.5 mm となる。

Fig. 4.8 と Fig. 4.9 は、各解析モデルのポイント A とポイント B それぞれのチップ・インターポーザ接合後の Z 方向の変位である。シリコンと 2 種類のガラスのインターポーザ（モデル b-j）はポイント A および B すべて正の変位であり、反りの形状は凹形である。これらすべてのモデルでポイント B の変位のほうが大きい。これはインターポーザ材と RDL の線膨張係数のミスマッチによるもので、

Table 4.5 Model matrix in this analysis.

| Model type | Configuration      | Equivalent via pitch |

|------------|--------------------|----------------------|

| a          | MCM FCPBGA         | -                    |

| b          | Si interposer      | 0.5 mm               |

| c          | Si interposer      | 0.65 mm              |

| d          | Si interposer      | 0.8 mm               |

| e          | Glass-A interposer | 0.5 mm               |

| f          | Glass-A interposer | 0.65 mm              |

| g          | Glass-A interposer | 0.8 mm               |

| h          | Glass-B interposer | 0.5 mm               |

| i          | Glass-B interposer | 0.65 mm              |

| j          | Glass-B interposer | 0.8 mm               |

| k          | Organic interposer | -                    |

Fig. 4.7 Contour diagram of Z-direction displacement of an interposer and chips (model-j).

Fig. 4.8 Z-direction displacement at point A after flip chip joining.

Fig. 4.9 Z-direction displacement at point B after flip chip joining.

メモリチップが小さいためチップ搭載エリアの少ない右上部に最大の変位が現れると考えられる。Fig 4.7 から見て取れるようにチップ搭載エリアは低線膨張係数のチップとインターポーラに高線膨張係数のRDLが挟まれる構造となり反りは小さくなっている。ビアピッチ 0.5 mm, 0.65 mm, 0.8 mm でのビア密度の差は 1%未満であったため、等価ビアピッチによる差は小さいがビアピッチが小さくなる、すなわちビア密度が高くなると変位が小さくなる傾向が認められる。これはビア密度が高いほどインターポーラの複合線膨張係数が大きくなり RDLとの線膨張係数のミスマッチが小さくなるためと考えられる。ガラス A インターポーラはシリコンと近い線膨張係数を持ち、弾性率はシリコンの約 1/2 であることにより、シリコンインターポーラに比べて約 2 倍の変位となると考えられる。ガラス B インターポーラは、弾性率がガラス A とほぼ同等で線膨張係数が大きくなることから RDLとの線膨張係数のミスマッチの低減により、ガラス A インターポーラよりも小さな変位となると考えられる。MCM FCPBGA（モデル a）はチップと有機基板の線膨張係数のミスマッチにより凸形の反りとなっており一般的な形状である。メモリチップよりも大きなロジックチップの搭載されたエリアのポイント A で大きな変位が現れる。ここでは 42.5 mm 角の基板のコーナーの変位であるため大きな数値となっている。有機インターポーラ（モデル k）の場合はポイント A で正、ポイント B で負の変位となる。これはコア材のない有機インターポーラは弾性率が低く、線膨張係数が大きく、2 つの異なるサイズのチップの影響による複雑な反り形状となるためと考えられる。

ここで得られたインターポーラの変位はいずれも 0.1 mm 以上であり有機基板に接合する際には、なんだの濡れ不良やブリッジの懸念が大きい。RDL や有機インターポーラの線膨張係数の低い材料を用いたり、工程中でインターポーラを平坦化して接合するなどの工夫が重要と考えられる。

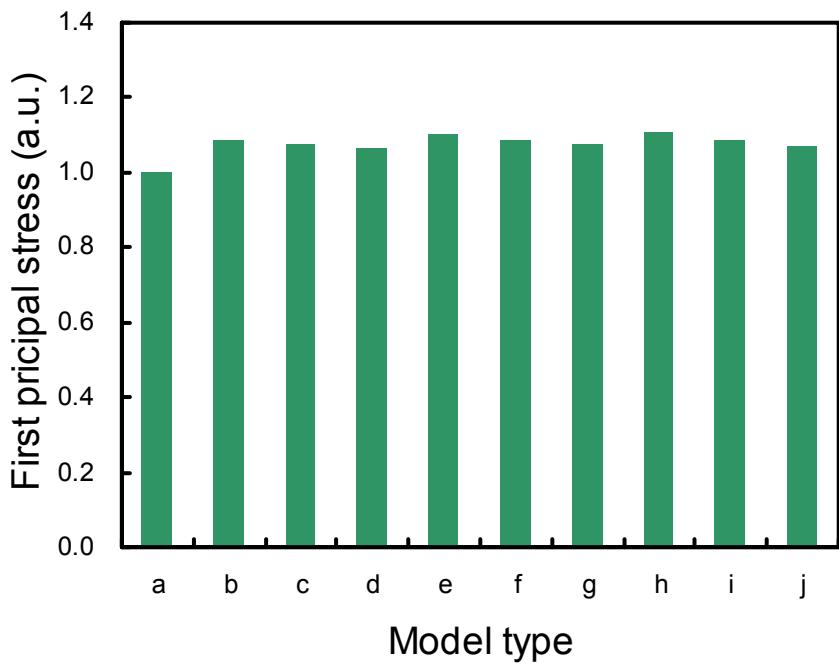

### チップとインターポーヴ接合時のフリップチップパッド下部配線層の応力

チップとインターポーヴの接合のマクロモデルの解析結果から得た接合部の歪みの境界条件を適用し、マイクロモデルの解析を行った。Fig. 4.10 は、Fig. 4.7 に示すロジックチップのコーナーバンプのポイント C におけるパッド下部配線層の第一主応力の分布を示すコンター図である。ここではモデル a, c, f および i のコンター図を示した。各図の応力のスケールは同一に揃えた。図の左上がパッケージコーナーの方向で、右下がパッケージ中心の固定点の方向である。バンプ下のパッケージ中心方向では圧縮応力が生じ、パッケージコーナー方向では引張応力が生じている。Fig. 4.11 は各モデルの最大の第一主応力を示すグラフである。MCM FCPBGA の応力を基準に任意単位で表示し、すべて圧縮応力である。ガラス A インターポーヴの応力はシリコンインターポーヴの場合の約 2 倍であり、ガラス B インターポーヴの応力はガラス A インターポーヴの約 2 倍となっている。これは各インターポーヴ材の線膨張係数とチップの線膨張係数のミスマッチが支配的要因であると考えられる。ガラスインターポーヴでは等価ビアピッチが大きくなるとわずかに応力が低下する傾向が見られる。これは Cu 密度が小さくなるとインターポーヴの複合線膨張係数が小さくなるためチップとの線膨張係数のミスマッチが低減されることによると考えられる。MCM FCPBGA と比べるとシリコンインターポーヴの場合には約 10% の応力値であり、ガラス B インターポーヴでも約 40% の応力値であるためパッド下部配線層への応力低減の効果は大きい。一方で有機インターポーヴの場合は MCM FCPBGA に比べ約 1.9 倍の応力が生じており、本研究で調べたものよりも低線膨張係数のビルドアップ材料を用いる等で応力低減を行わなければ配線層に与えるダメージが問題となりうる。

Fig. 4.10 Contour diagrams of first principal stress in the low-k dielectric layer under corner bump point C for (a) model-a, (b) model-c, (c) model-f and (d) model-i.

Fig. 4.11 First principal stress in the low-k dielectric layer under corner bump point C.

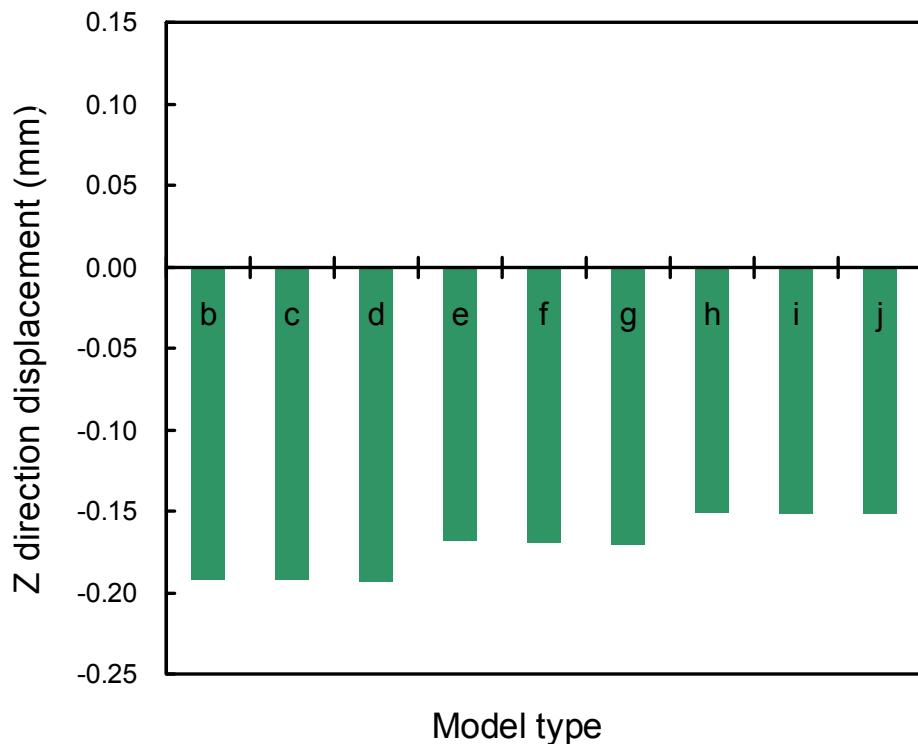

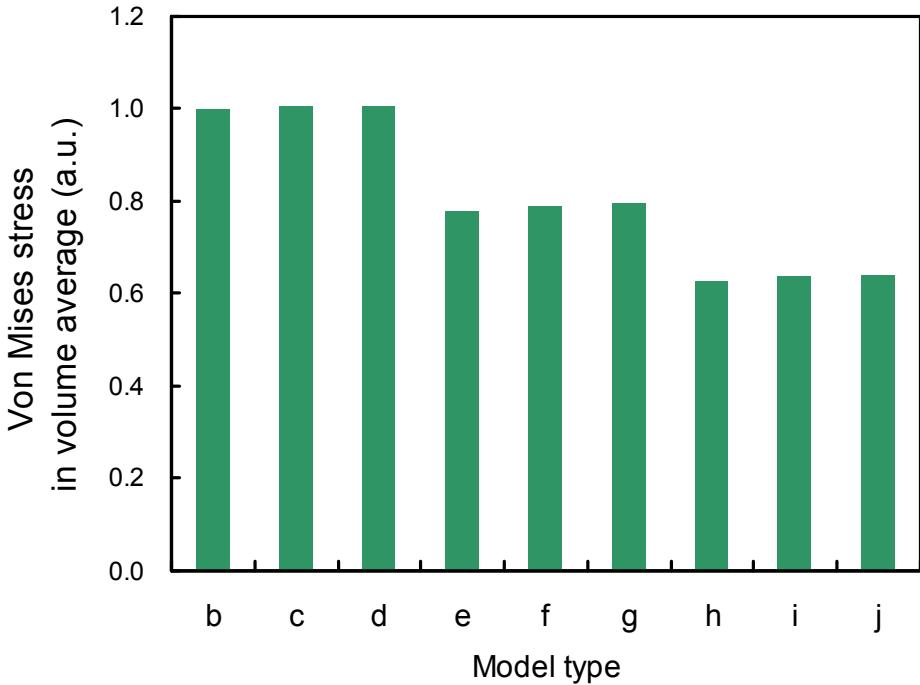

#### インターポーザと有機基板接合時のマイクロ接合部の応力

インターポーザと有機基板の接合の解析では、インターポーザ上のチップはアンダーフィルで封止されていると想定した。モデルではチップとインターポーザ間にアンダーフィルを充填した形状を作成し、アンダーフィル材とはんだの複合特性を適用した。Fig. 4.12 はモデル c の Z 方向の変位のコンター図である。インターポーザを有機基板に接合した後では、2 つのチップサイズが異なるにも関わらずパッケージ中心から同心円状に変位が変化している。Fig. 4.13 は、Fig. 4.12 に示したポイント B での Z 方向の変位である。また Fig. 4.14 は、Fig. 4.12 に示したポイント D での接合部の体積平均のフォン・ミーゼス応力である。ここでは MCM FCPBGA のモデルは検討対象から外した。Fig. 4.13 からインターポーザ接合後には有機基板の収縮によってすべてのインターポーザ材で変位が負になっている。Fig. 4.9 のチップ接合後ではすべて正の変位であったものが、インターポーザ接合後には正負が反転している。チップ接合後には一番変位の小さかったシリコンインターポーザが、インターポーザ接合後には一番大きな変位を示している。これは有機基板との線膨張係数のミスマッチがシリコンインターポーザが最も大きいことによると考えられる。ガラス B インターポーザでは線膨張係数がシリコンより大きく、有機基板の線膨張係数に近くなるため、Z 方向の変位は小さくなりシリコンインターポーザの場合よりも約 40  $\mu\text{m}$  反りを低減できる。Fig. 4.14 からはシリコンインターポーザがポイント D の接合部で最も応力が高く、次いでガラス A インターポーザが約 20% 応力が下がり、ガラス B インターポーザではシリコンインターポーザよりも約 38% 応力が下がる。これにはシリコンインターポーザとガラ

ス A インターポーザでは弾性率がおよそ 2 倍近く異なっていることが大きく寄与している。またガラス A インターポーザとガラス B インターポーザの応力の差には、線膨張係数が  $3.8 \text{ ppm}/^\circ\text{C}$  と  $6.0 \text{ ppm}/^\circ\text{C}$  の違いが大きく寄与していると考えられる。インターポーザの線膨張係数と弾性率はインターポーザの接合部にかかる応力の影響因子としてパッケージの構造設計の上で重要である。

Fig. 4.12 Contour diagram of Z-direction displacement of an organic substrate, an interposer and chips (model-c).

Fig. 4.13 Z-direction displacement at point B after interposer joining.

Fig. 4.14 Von Mises stress in volume average at the corner solder ball point D.

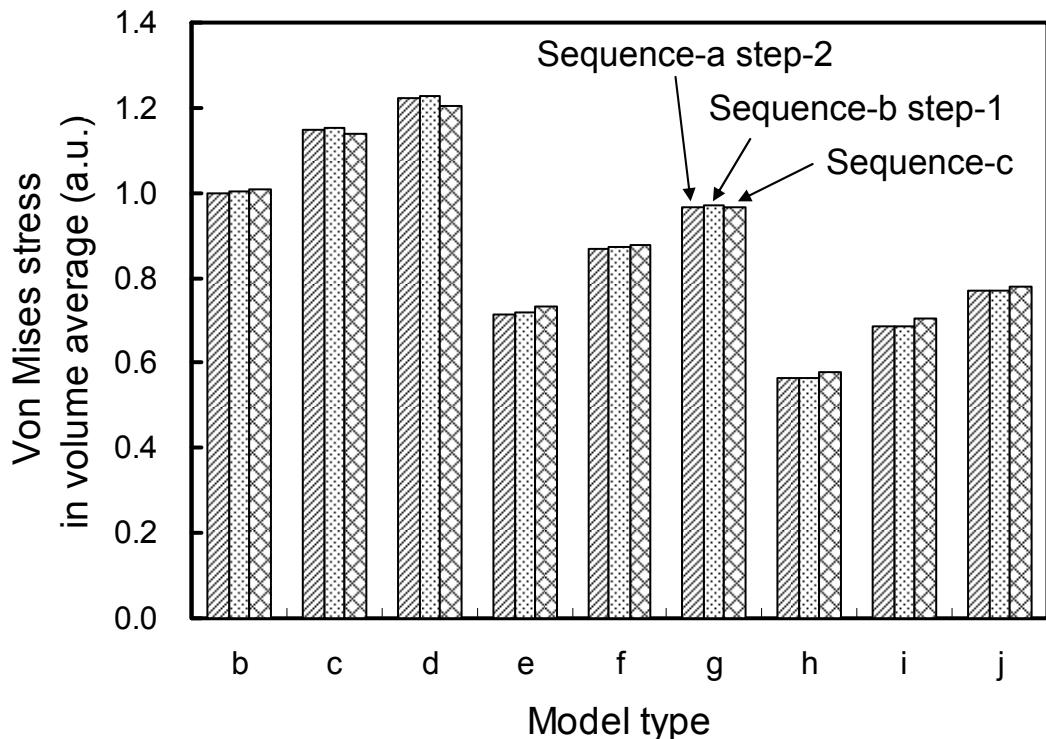

#### 4.2.4 チップ・インターポーラの接続順序とインターポーラ厚みによる応力への影響

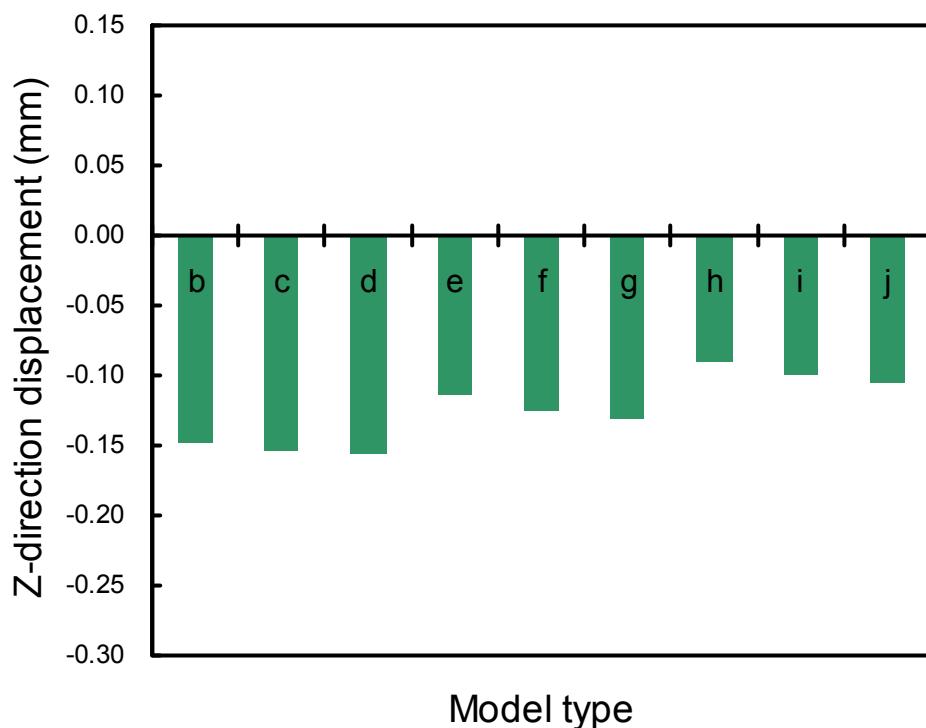

チップ・インターポーラの接続順序とインターポーラ厚みによる応力への影響を解析するため, Fig. 4.5 の(a)順接続, (b)逆接続, (c)同時接続のモデルを作成した. モデルの形状は 4.2.3 節で用いたものと同じであるが, 等価ビアピッチは 0.65 mm のみを取り上げた. 順接続のモデルでは 1 度目の接合後にチップとインターポーラ間にアンダーフィルを充填した構造で 2 度目の接合の解析モデルを作成し, 同様に逆接続のモデルではインターポーラと有機基板間にアンダーフィルを充填した構造で 2 度目の接合の解析モデルを作成した. なおここでは有機インターポーラの解析は除外した. Table 4.6 は本節の研究に用いたモデルの組み合わせである. 各インターポーラに対し 3 つの厚みを与え, インターポーラの厚みによる影響を評価した. 材料特性は Table 4.4 に挙げたものと同じである. リファレンス温度も前節と同じ 180°C とした.

#### 順接合および逆接合の 1 度目の接合後のインターポーラの反り

Fig. 4.15 は順接続の 1 度目の接合後のモデル h の Z 方向の変位のコンター図である. 前節での結果と同様にメモリチップ搭載エリアのインターポーラのコーナー部で最も大きな正の変位が見られる. Fig. 4.16 に各モデルのポイント A の Z 方向の変位を示す. 各インターポーラの線膨張係数と弾性率による変位への影響は前節の結果と同じ傾向であるが, 100 μm 厚のガラス A インターポーラとガラス B インターポーラの変位はほぼ同じ値がとなっている. インターポーラが薄くなるとガラス A インターポーラとガラス B インターポーラの変位の差は小さくなる傾向が見られる. ここで調べた範囲ではインターポーラ厚みのインターポーラの反りに与える影響は顕著である. 100 μm 厚と 150 μm 厚ではいずれもコーナー部の変位が 0.2 mm を超えており, このまま 2 度

Table 4.6 Model matrix in this analysis.

| Model type | Configuration      | Interposer thickness |

|------------|--------------------|----------------------|

| a          | MCM FCPBGA         | -                    |

| b          | Si interposer      | 100 $\mu\text{m}$    |

| c          | Si interposer      | 150 $\mu\text{m}$    |

| d          | Si interposer      | 200 $\mu\text{m}$    |

| e          | Glass-A interposer | 100 $\mu\text{m}$    |

| f          | Glass-A interposer | 150 $\mu\text{m}$    |

| g          | Glass-A interposer | 200 $\mu\text{m}$    |

| h          | Glass-B interposer | 100 $\mu\text{m}$    |

| i          | Glass-B interposer | 150 $\mu\text{m}$    |

| j          | Glass-B interposer | 200 $\mu\text{m}$    |

Fig. 4.15 Contour diagram of Z-direction displacement of an interposer and chips: sequence-a, step-1 joining, model-h.

Fig. 4.16 Z-direction displacement at point A: sequence-a step-1 joining.

目の接合を行うことは困難であると考えられる。前節で述べたように 200  $\mu\text{m}$  厚のインターポーザでも 0.1 mm 以上の反りであり、インターポーザに先にチップを搭載する場合には反りを低減する工夫は必須となると考えられる。