| Title        | Microwave high power field-effect transistors<br>amplifiers with high efficiency and low<br>distortion |

|--------------|--------------------------------------------------------------------------------------------------------|

| Author(s)    | 竹中,功                                                                                                   |

| Citation     | 大阪大学, 2014, 博士論文                                                                                       |

| Version Type | VoR                                                                                                    |

| URL          | https://doi.org/10.18910/34533                                                                         |

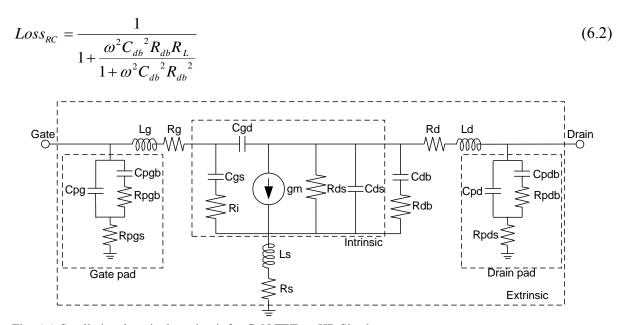

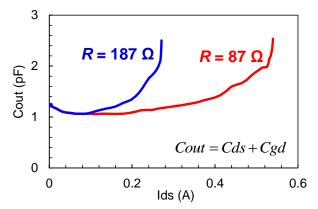

| rights       |                                                                                                        |

| Note         |                                                                                                        |

## Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

# Microwave high power field-effect transistors amplifiers with

high efficiency and low distortion

## ISAO TAKENAKA

MARCH 2014

## Microwave high power field-effect transistors amplifiers with

high efficiency and low distortion

A dissertation submitted to THE GRADUATE SCHOOL OF ENGINEERING SCIENCE OSAKA UNIVERSITY in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY IN ENGINEERING

BY

## ISAO TAKENAKA

MARCH 2014

### ABSTRACT

In recent years, the large-capacity and high-speed communication technology has accomplished rapid progress focusing on mobile communications. The microwave highpower amplifier is a key component constituting a high-speed communication system, and the performance enhancement of the high-power amplifier is connected directly with the technological advance of the system. In order to perform large-capacity and high-speed communications with a power-saving and a high quality, high efficiency and low distortion characteristics are strongly required for the high power amplifiers. This study-achievement is related to the unique and practical studies of the matching circuit and the power combining circuit which make it possible to maximize the performance of the microwave transistors used in the high power amplifiers. The results have contributed to significant improvements of the communication system.

Chapter 1 describes the history and technology trends of microwave high-power device development as a background of this study. Next, the composition of a microwave high power amplifier and the problems of the device and circuit technique in high power amplifier are described. Then, the purpose and meaning of a main subject are described and the composition of a main subject is shown.

Chapter 2 describes a study on the push-pull power combining circuit and the stability analysis under the large-signal operation for microwave high-power amplifiers.

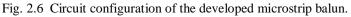

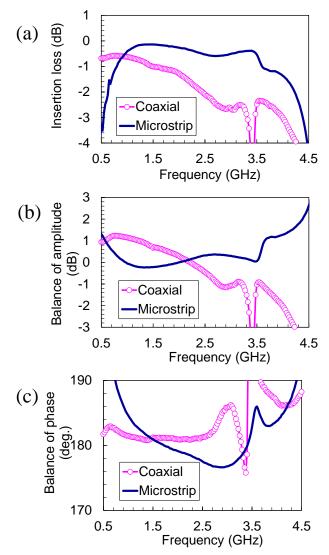

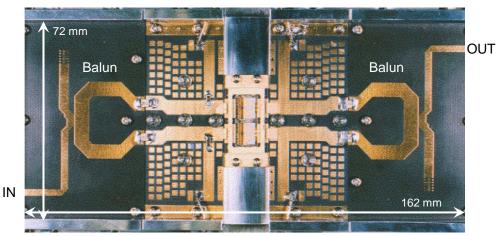

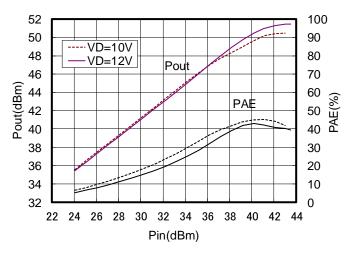

To realize low-loss power-combining circuits, a novel microstrip balun circuit was proposed and fabricated. Developed balun circuit attained low insertion loss of -0.3 dB at 2.2 GHz and the improvement of design flexibility by adopting a multi-stage configuration different from the conventional balun circuits. By applying this balun circuit, the push-pull amplifier delivered the saturated output-power ( $P_{sat}$ ) of 140 W with the power-added efficiency (PAE) of 42% at 2.2 GHz using GaAs hetero-structure FET (HFET).

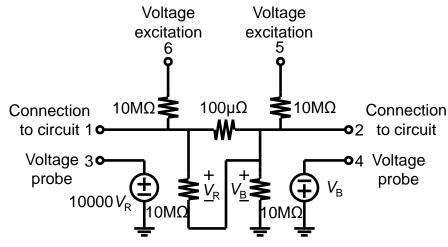

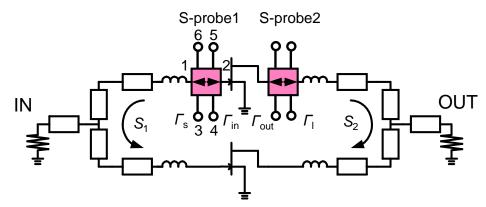

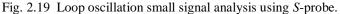

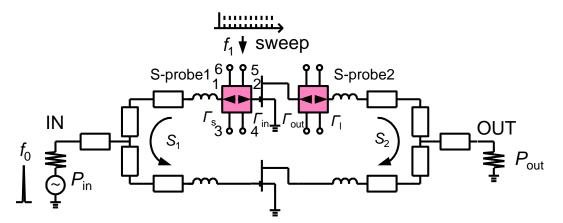

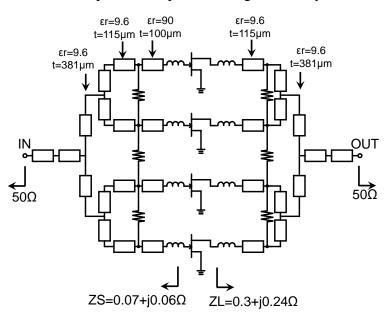

Furthermore, the *S*-probe method which can determine the reflection coefficient in arbitrary point without affecting circuit characteristics was modified so that the loop gain at the large signal operation is obtained. This method reproduced the oscillation phenomenon at the large signal operation in the C-band (5.9 GHz) 60-W power amplifier which combines four chips of AlGaAs/GaAs HFETs in parallel. It clearly showed that the cause of an oscillation is due to the increase of loop gain at the large signal operation. Furthermore, it showed the effect on the design of the balance resistance connected between the chips for the oscillation suppression, and it contributed to the stable operation of the amplifiers.

Chapter 3 describes the study on high efficiency microwave high power amplifiers.

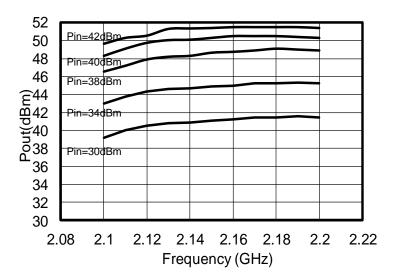

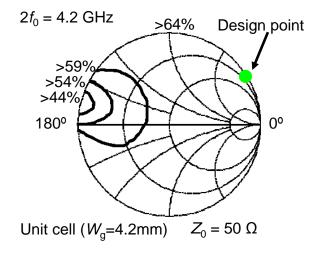

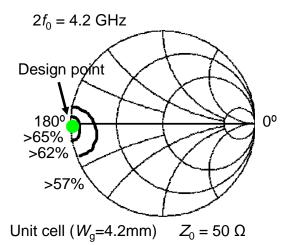

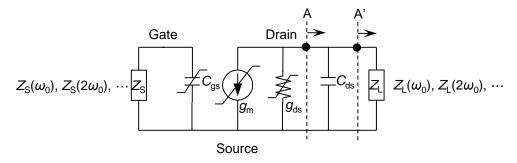

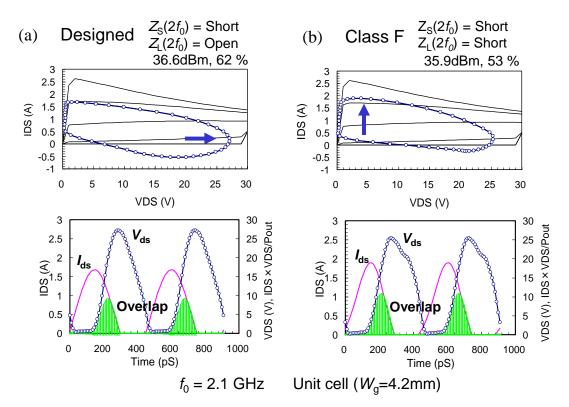

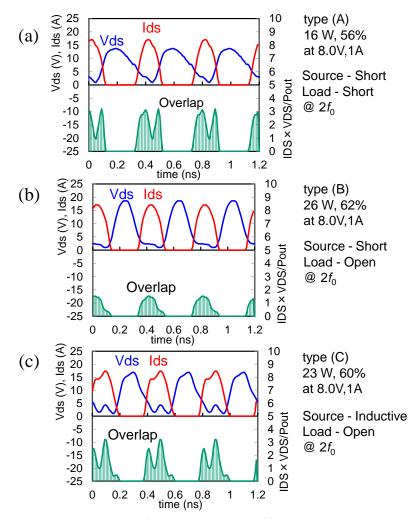

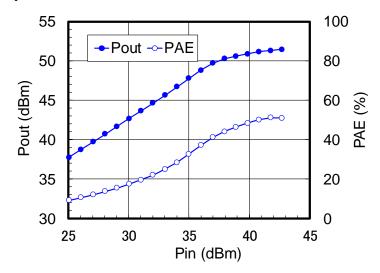

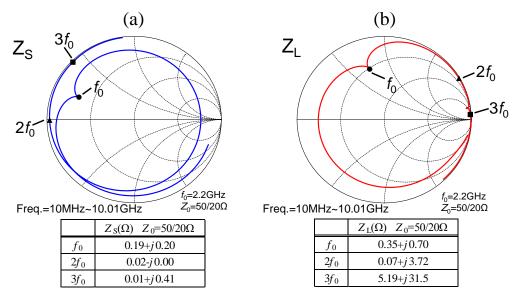

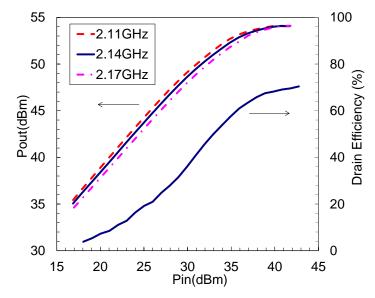

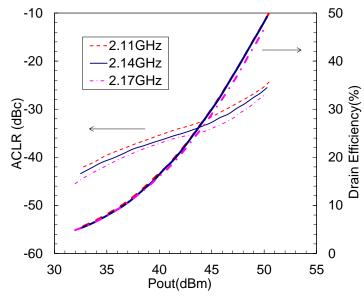

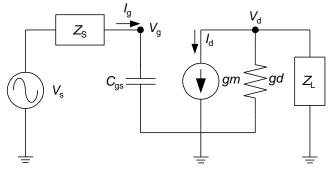

The harmonic termination techniques in the matching circuits were examined to achieve high efficiency characteristics in high power amplifiers. The voltage waveforms were observed using a large signal simulation and Electro Optical Sampling (EOS), and the high efficiency termination condition of load second harmonic was found out to be open condition opposite to conventional Class-F. Moreover, by clarifying the effect of the termination condition of source second harmonic, it was confirmed that the nonlinear gate-to-source capacitance ( $C_{\rm gs}$ ) affects the overlap of the voltage and the current waveforms. A 2.14-GHz 320-W GaAs FET amplifier with 62% drain-efficiency has been developed by employing the second-harmonic termination technique in both the input and output matching circuits.

Chapter 4 describes the study on low distortion microwave high power amplifiers.

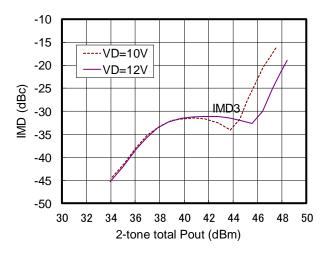

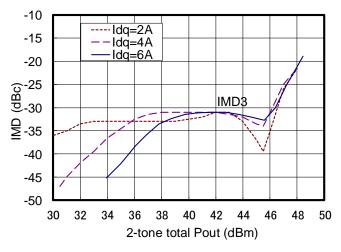

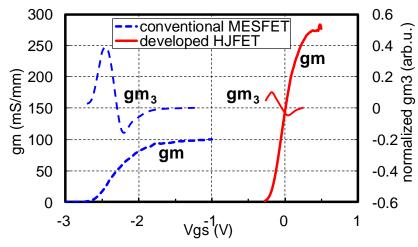

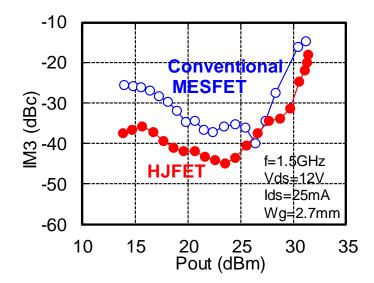

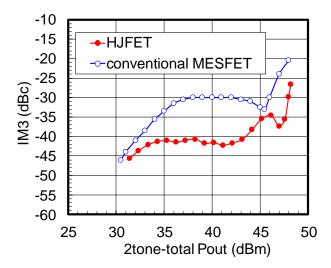

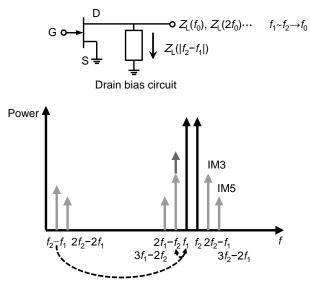

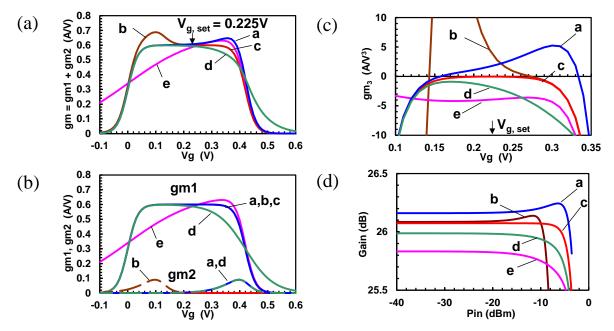

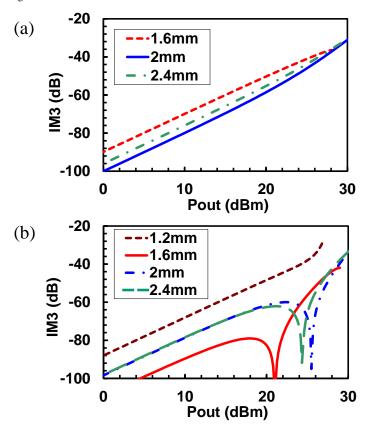

Focusing on transconductance (gm)-profile of GaAs hetero-junction (HJFET), it was found that HJFET with shallow threshold voltage ( $V_{th}$ ) and steep gm-profile has small thirdorder coefficient of gm ( $gm_3$ ) at deep Class-AB, and exhibits low distortion characteristics. Furthermore, the influence of second harmonic and difference frequency impedance on thirdorder distortion characteristics was investigated using Volterra series analysis. The circuit configuration terminating source- and load-second harmonics with short impedance was newly proposed. An L/S-band 150-W GaAs HJFET employing the second harmonic termination circuits realized low third-order intermodulation distortion (IM3) characteristics less than -40 dB.

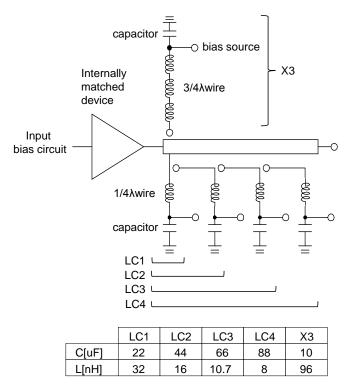

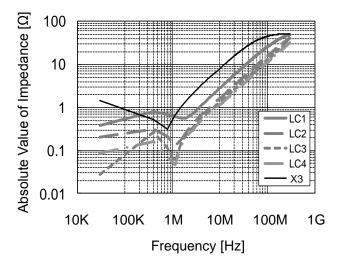

In addition, the source- and load-difference frequency termination circuits in package as well as the technique lowering drain bias circuit impedance were proposed. The proposed techniques realized low distortion characteristics without degradation over 100-MHz frequency-spacing ( $\Delta f$ ). The result is the widest bandwidth and low distortion characteristics so far, and the deployment to next-generation mobile communications such as a fourth generation (4G) can be expected.

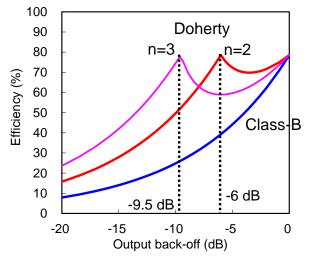

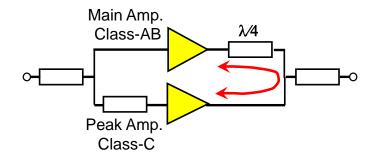

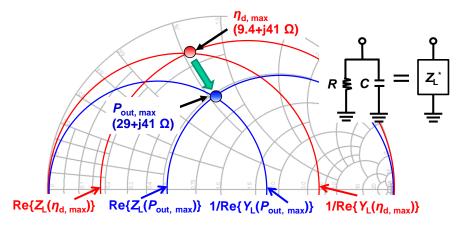

Chapter 5 describes the study on low distortion and high efficiency Doherty amplifiers.

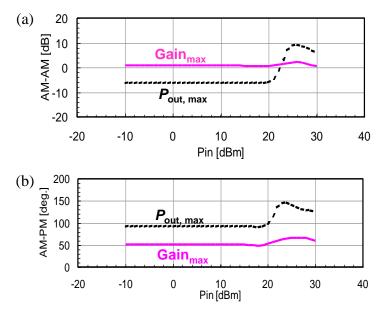

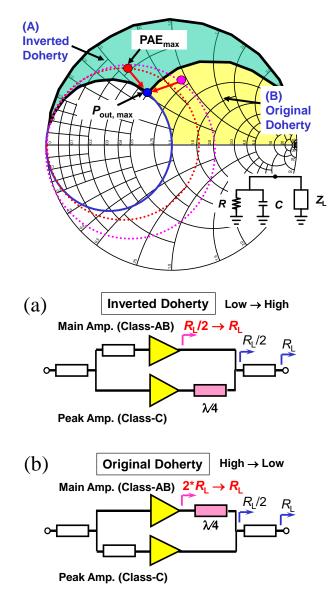

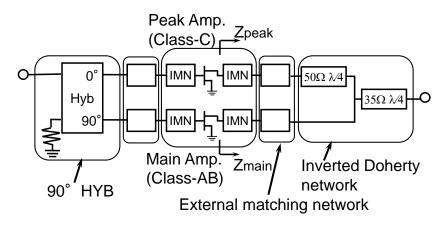

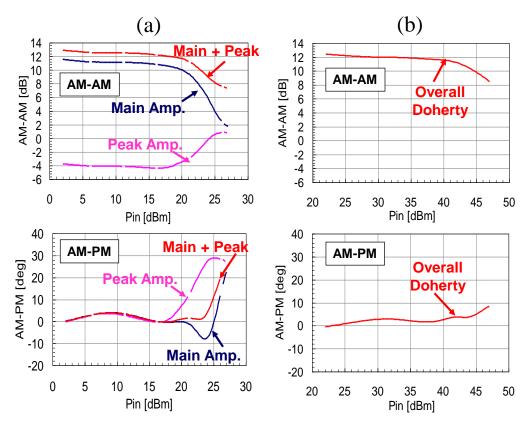

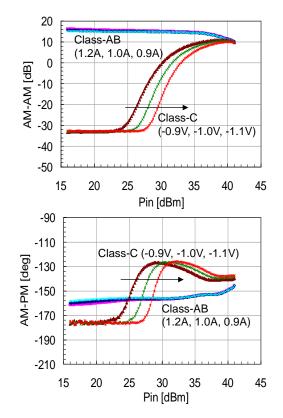

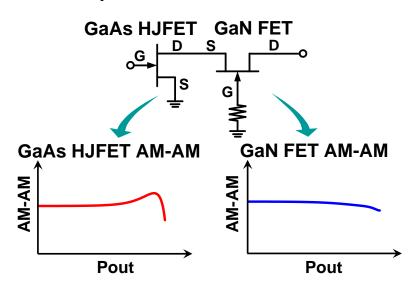

It was clarified that the optimal configuration of Doherty amplifier is present based on the impedance of the device load-pull characteristics. The design approach to perform the distortion compensation in Doherty amplifier was proposed using the distortion cancellation effect of the main and the peak amplifier in power-combining. Proposed distortion-cancelled Doherty amplifier demonstrated high efficiency of 42% and low distortion less than -35dB using 330-W GaAs HJFETs. In addition, the evaluation techniques of each AM-AM and AM-PM characteristics of the main and the peak amplifiers in an operating Doherty amplifier was proposed, and the distortion cancellation of the main and the peak amplifiers in Doherty amplifier linearity was experimentally proved for the first time.

Chapter 6 describes the study on broadband, high efficiency, and low distortion microwave high-power amplifiers using GaN FETs.

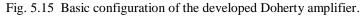

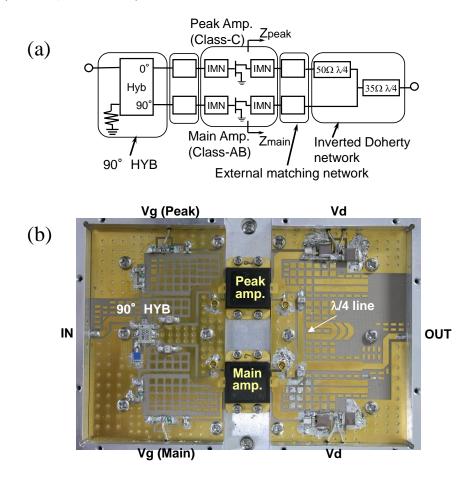

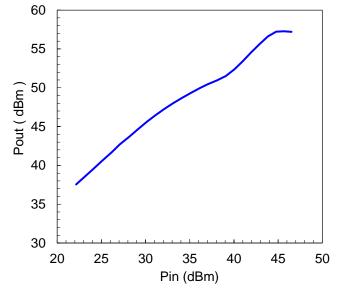

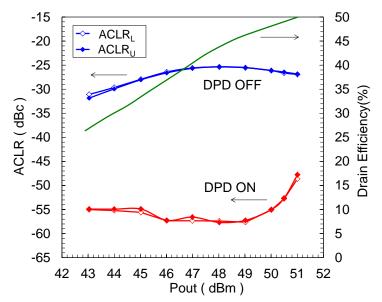

High efficiency and high-power GaN FET amplifiers were examined. The device structure was optimized for the efficiency characteristics improvement of the GaN FET on low cost Si substrate, and the Doherty amplifier was developed using the GaN FET. The developed inverted Doherty amplifier delivered the *P*sat of 537 W with the linear gain of 15.5 dB under a pulsed continuous wave signal condition of 2.14 GHz, and demonstrated the digital pre-distortion linearization characteristics with the high efficiency of 48% and the adjacent channel leakage power ratio of -55 dBc at 50 dBm. These results are state-of-the-art performance among the ever reported GaN FET high-power amplifiers.

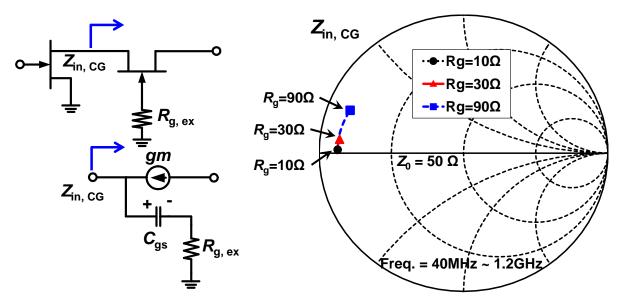

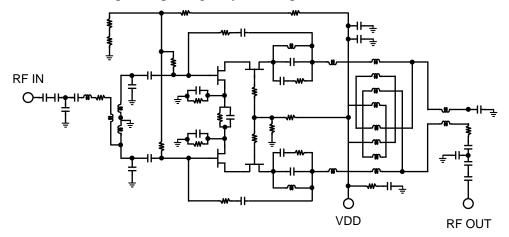

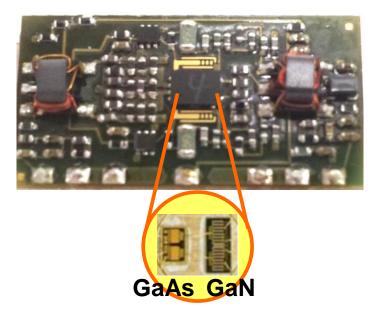

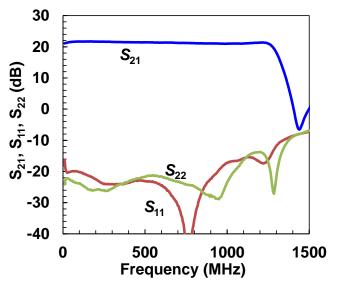

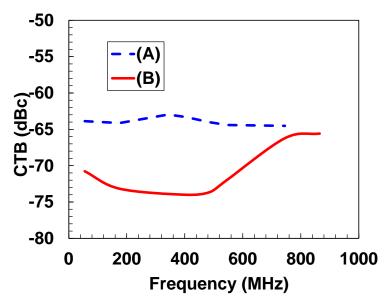

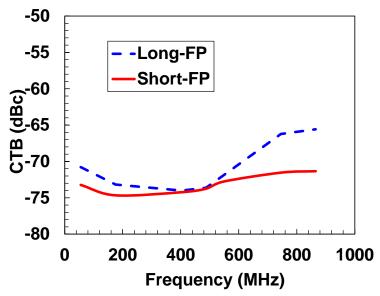

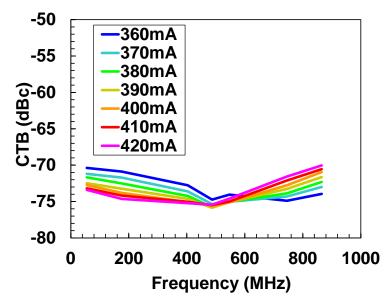

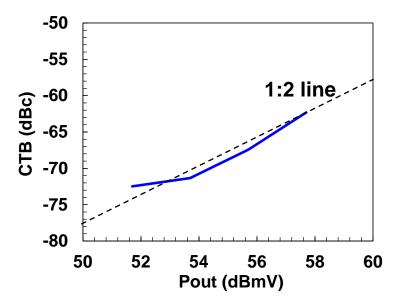

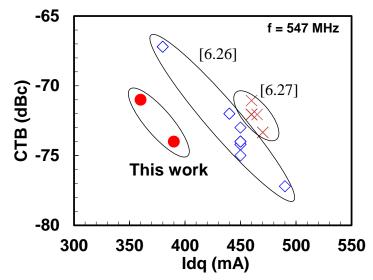

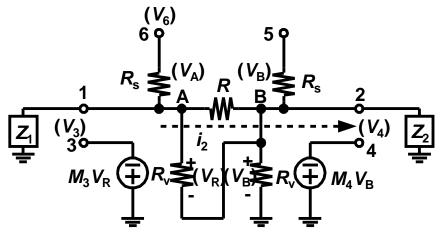

Furthermore, a broadband and low distortion amplifier module with the GaN FETs capable of high voltage operation was examined to improve output power performance. To realize low distortion characteristics required for modern cable television (CATV) system, low distortion cascode configuration composed of GaAs HJFET for first stage and GaN FET for final stage was investigated. The third-order distortion characteristics were improved by realizing distortion cancellation between GaAs HJFET and GaN FET with optimized gm-profile employing Volterra distortion analysis on load-line. The developed CATV power amplifier demonstrated the lowest composite triple beat (CTB) characteristics less than -72 dBc at low drain current condition of 380 mA from 40 MHz to 865 MHz.

Chapter 7 summarizes the conclusions of this dissertation, and describes the challenges and prospects for the future.

## TABLE OF CONTENTS

| Chapter | 1 ··· Introduction                                                                             | 1  |

|---------|------------------------------------------------------------------------------------------------|----|

| 1.1     | Research background and issues                                                                 | 1  |

| 1.1.    | 1 History and technology trends of microwave high power device development                     | t2 |

| 1.1.    | 2 Configuration of microwave high power amplifiers and issues of device and circuit techniques |    |

| 1.1.    | 2.1 Microwave high-power FET                                                                   | 6  |

| 1.1.    | 2.2 Matching circuits                                                                          | 14 |

| 1.1.    | 2.3 Power combining circuits                                                                   | 16 |

| 1.1.    | 2.4 Bias circuits                                                                              | 19 |

| 1.1.    | 2.5 Distortion compensation techniques                                                         | 20 |

| 1.2     | Purpose and significance of this dissertation                                                  | 23 |

| 1.3     | Outline of this dissertation                                                                   | 24 |

| Refere  | ences                                                                                          | 26 |

| Chapter | $\cdot2$ $\cdots$ Push-pull high power amplifiers using a microstrip balun                     | 29 |

| 2.1     | Introduction                                                                                   | 29 |

| 2.2     | Configuration of push-pull amplifier                                                           | 30 |

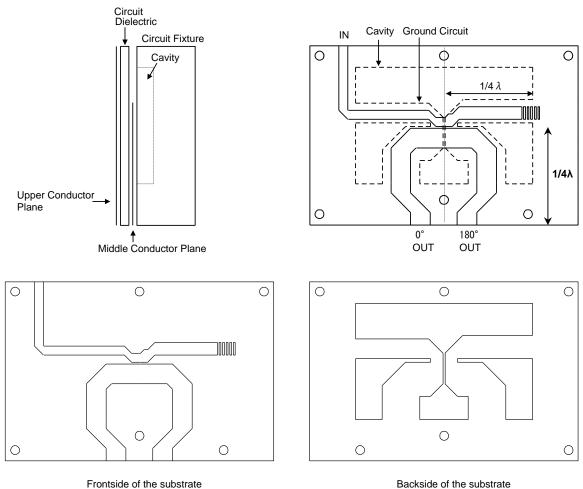

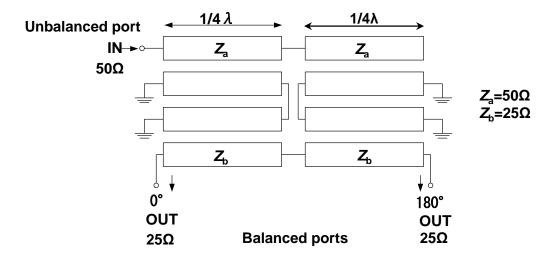

| 2.3     | Design and fabrication of a novel microstrip balun                                             | 32 |

| 2.4     | L/S-band 140-W push-pull amplifier                                                             | 36 |

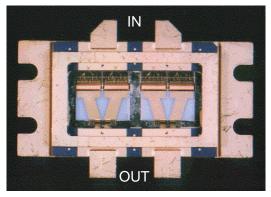

| 2.4.    | 1 Device structure                                                                             | 36 |

| 2.4.    | 2 Circuit design                                                                               | 38 |

| 2.4.    | 3 RF performance                                                                               | 40 |

| 2.5     | Stability analysis using large signal S-probe method                                           | 42 |

| 2.6     | Oscillation analysis at large signal operation in C-band 60-W AlGaAs/GaAs HFET                 | 44 |

| 2.7     | Summary                                                                                        | 48 |

| Refere  | ences                                                                                          | 50 |

| Cha | apter  | 3 High efficiency high-power amplifiers with second harmonic termination                                                | 53 |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------|----|

| 3   | .1     | Introduction                                                                                                            | 53 |

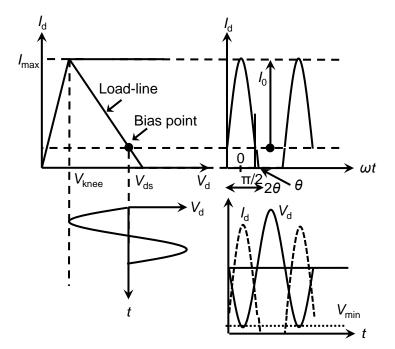

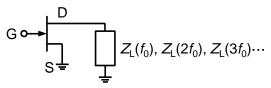

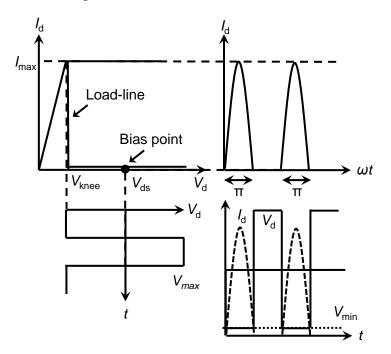

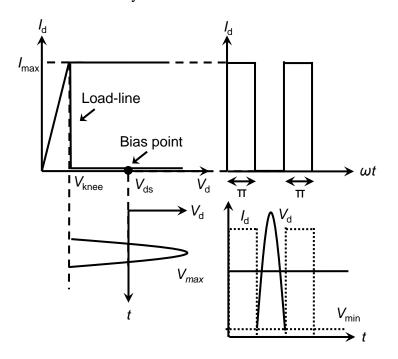

| 3   | .2     | High efficiency performance by harmonic termination                                                                     | 54 |

| 3   | .3     | Design procedure of the matching circuit with harmonic termination in high-<br>power FET                                | 58 |

| 3   | .4     | Harmonic load-pull simulation                                                                                           | 60 |

| 3   | .5     | Voltage waveform observation by Electro-Optic Sampling                                                                  | 63 |

| 3   | .6     | High efficiency 28-V-operation 320-W GaAs FP-FET amplifier                                                              | 66 |

|     | 3.6.1  | Device structure                                                                                                        | 66 |

|     | 3.6.2  | Circuit design                                                                                                          | 67 |

|     | 3.6.3  | RF performance                                                                                                          | 69 |

| 3   | .7     | Summary                                                                                                                 | 70 |

| F   | Refere | nces                                                                                                                    | 72 |

| Cha | apter  | 4 Low distortion GaAs HJFET high-power amplifiers using second harmonic and difference frequency termination techniques | 75 |

| 4   | .1     | Introduction                                                                                                            | 75 |

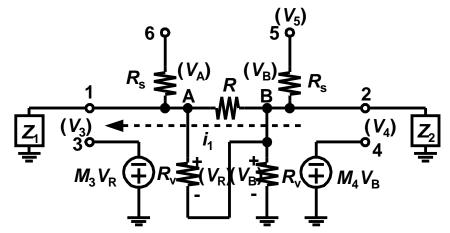

| 4   | .2     | Volterra series analysis                                                                                                | 77 |

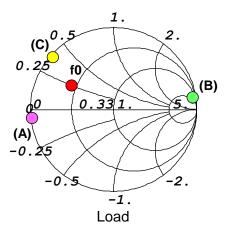

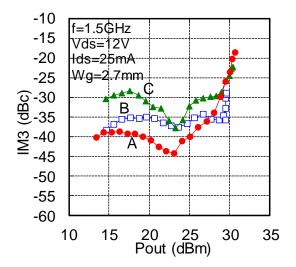

| 4   | .3     | Relation between gm-profile and third-order distortion characteristics in low distortion GaAs HJFET                     | 78 |

| 4   | .4     | Low distortion characteristics by harmonic terminations                                                                 | 80 |

| 4   | .5     | Low distortion L/S-band 150-W GaAs HJFET                                                                                | 81 |

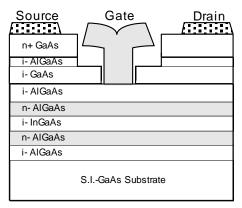

|     | 4.5.1  | Device structure                                                                                                        | 81 |

|     | 4.5.2  | Circuit design                                                                                                          | 82 |

|     | 4.5.3  | RF performance                                                                                                          | 84 |

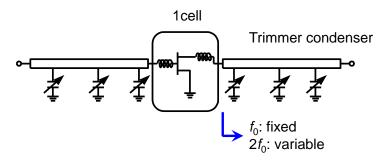

| 4   | .6     | Improvement of IMD characteristics by lowering drain bias circuit impedance                                             | 85 |

|     | 4.6.1  | Experiments of lowering drain bias circuit impedance on L/S-band 17-W GaAs FET                                          | 85 |

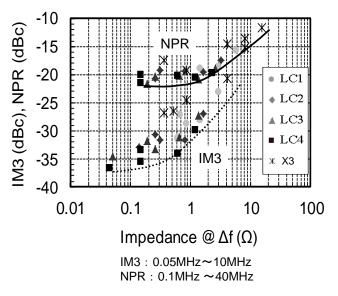

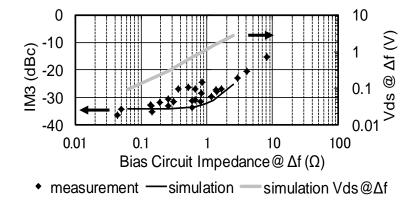

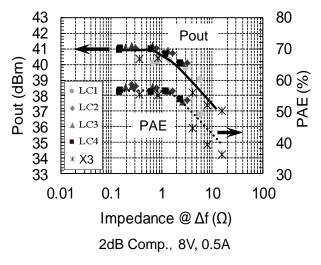

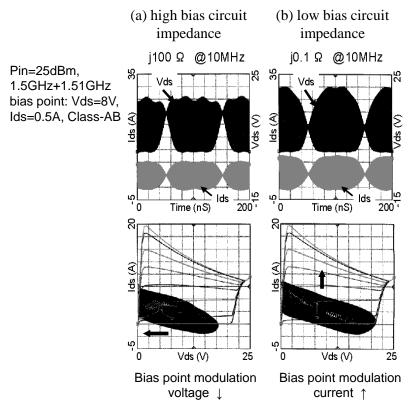

|     | 4.6.2  | Results of experiment and simulation                                                                                    | 87 |

|    | 4.6.   | 3 Drain bias circuit design                                                                | 90     |

|----|--------|--------------------------------------------------------------------------------------------|--------|

| 2  | 1.7    | Improvement technique of IMD Asymmetries caused by second-order Nonlinearity               | 92     |

|    | 4.7.   | 1 IMD3 asymmetries caused by second-order nonlinearity                                     | 92     |

|    | 4.7.2  | 2 Design of novel baseband termination circuits                                            | 93     |

|    | 4.7.   | 3 Implementation Results                                                                   | 98     |

| Z  | 1.8    | Summary                                                                                    | 101    |

| I  | Refere | nces                                                                                       | 103    |

| Ch | apter  | 5 Inverted Doherty high-power amplifiers with high efficiency and lov distortion           |        |

| 4  | 5.1    | Introduction                                                                               | 105    |

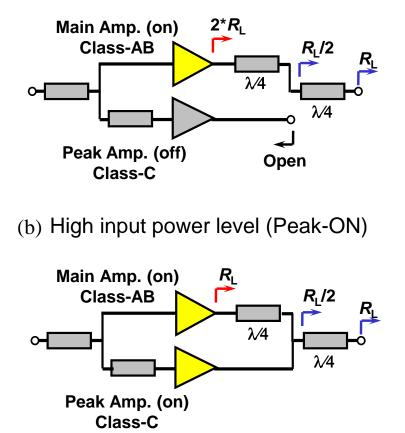

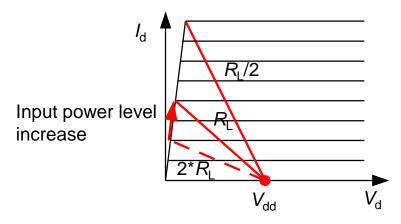

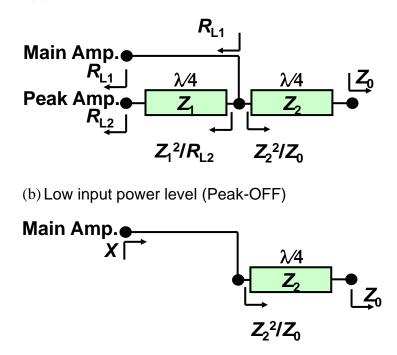

| 4  | 5.2    | Operation principle of Doherty amplifier                                                   | 106    |

|    | 5.2.   | Basic operation of a 2-way Doherty amplifier                                               | 106    |

|    | 5.2.2  | 2 Function of a Doherty network                                                            | 107    |

| 4  | 5.3    | 28-V-operation 150-W single-ended GaAs HJFETs                                              | 112    |

| 4  | 5.4    | High efficiency and low distortion circuit design of a Doherty amplifier                   | 113    |

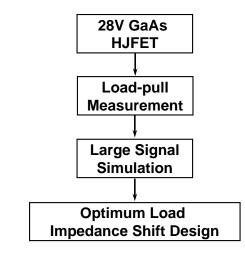

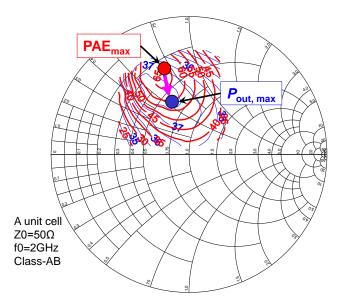

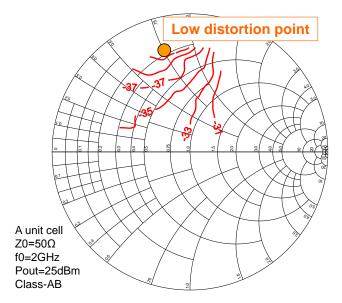

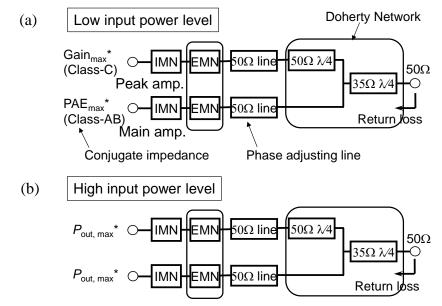

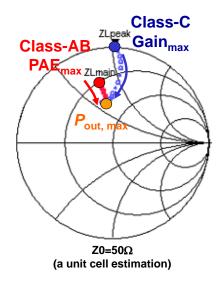

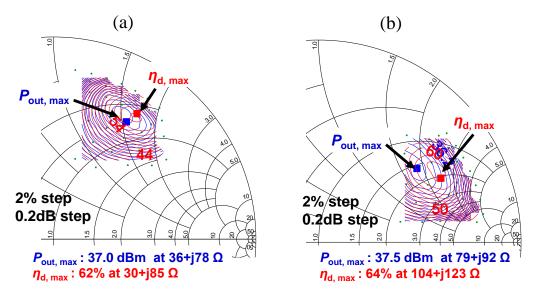

|    | 5.4.   | Circuit design strategy of Doherty amplifier                                               | 113    |

|    | 5.4.2  | 2 Main amplifier design                                                                    | 114    |

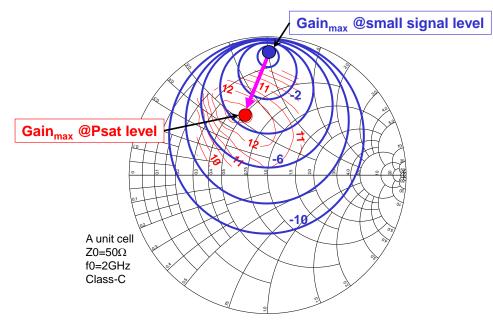

|    | 5.4.   | 3 Peak amplifier design                                                                    | 115    |

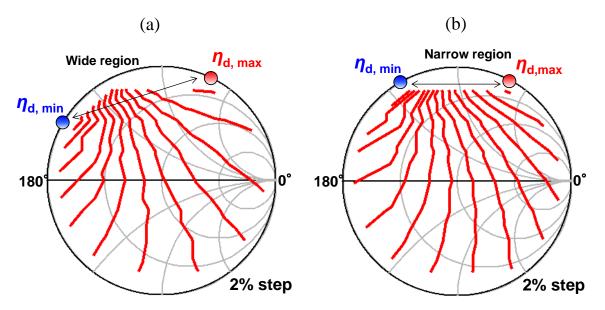

|    | 5.4.4  | 4 Selection of inverted Doherty circuit configuration                                      | 117    |

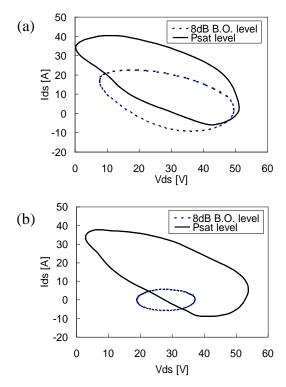

|    | 5.4.   | 5 Optimum load impedance shift design                                                      | 118    |

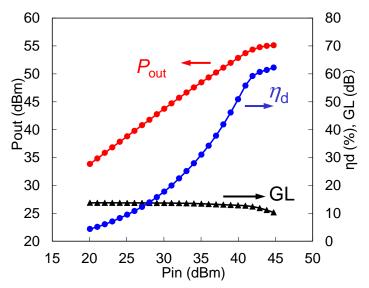

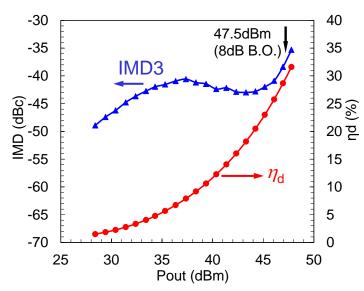

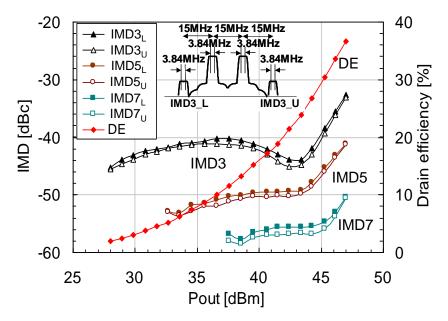

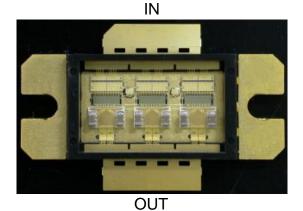

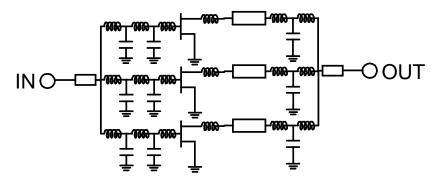

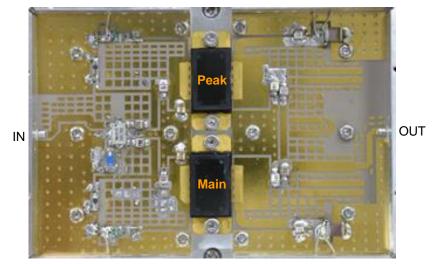

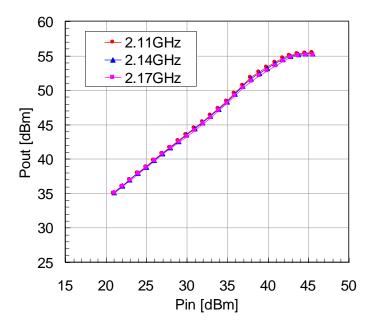

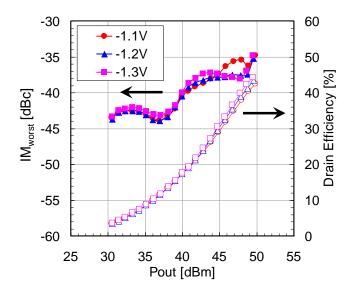

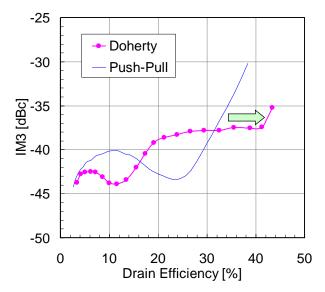

| 4  | 5.5    | Measured RF performance of distortion cancelled Doherty amplifier                          | 121    |

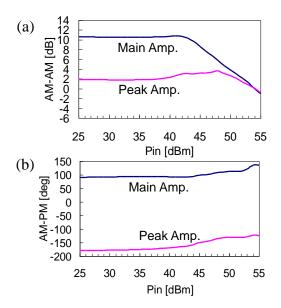

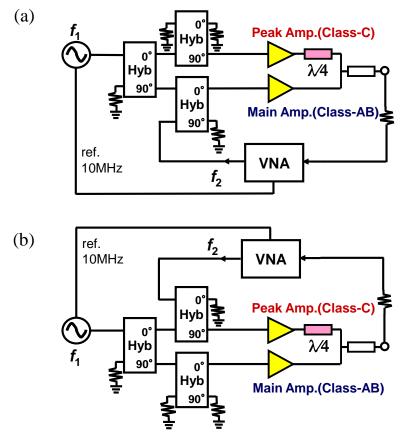

| 4  | 5.6    | Verification of the distortion improvement mechanism on a Doherty amplif                   | ier125 |

| 4  | 5.7    | IMD asymmetries of a Doherty amplifier                                                     | 129    |

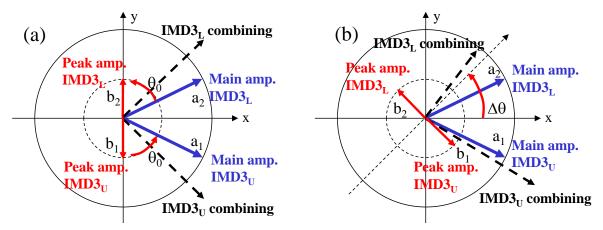

|    | 5.7.   | I IMD3 vector combination of main and peak amplifiers                                      | 129    |

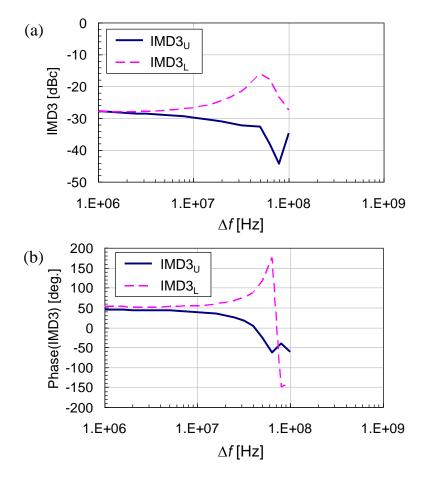

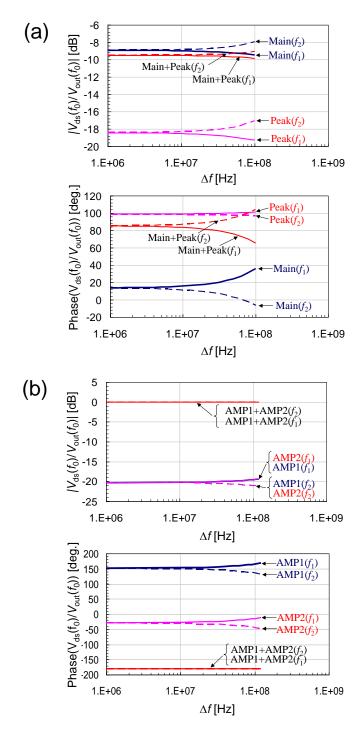

|    | 5.7.   | 2 Relationship between IMD3 asymmetries and circuit characteristics in a Doherty amplifier | 131    |

|    | 5.7.   | 3 Measured IMD versus $\Delta f$ characteristics of Doherty amplifier                      | 135    |

|    | 5.8    | Summary                                                                                  | 139 |

|----|--------|------------------------------------------------------------------------------------------|-----|

|    | Refere | ences                                                                                    | 140 |

| Ch | napter | 6 Broadband low distortion and high efficiency GaN FET high power amplifiers             | 143 |

|    | 6.1    | Introduction                                                                             | 143 |

|    | 6.2    | Potential of GaN FET                                                                     | 145 |

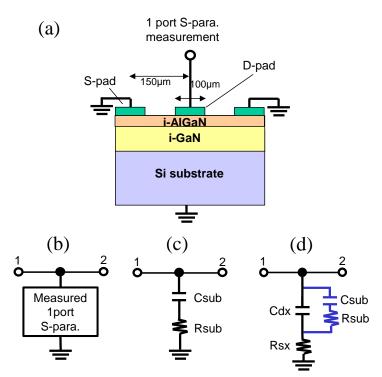

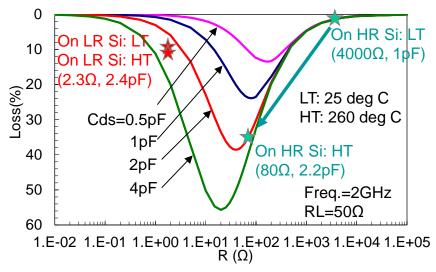

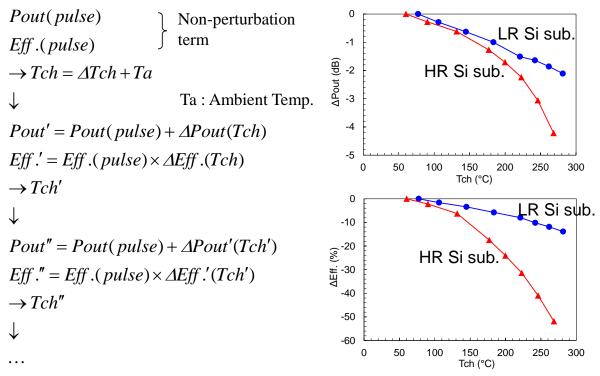

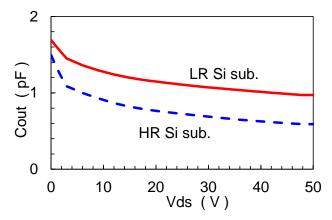

|    | 6.2.   | 1 Problems of GaN FET on HR Si substrate                                                 | 145 |

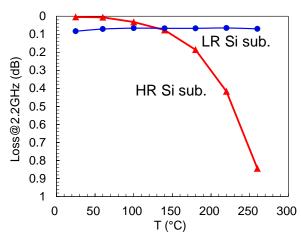

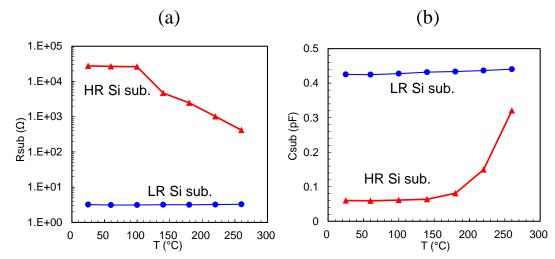

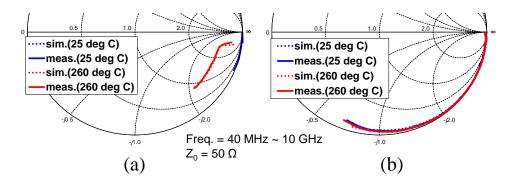

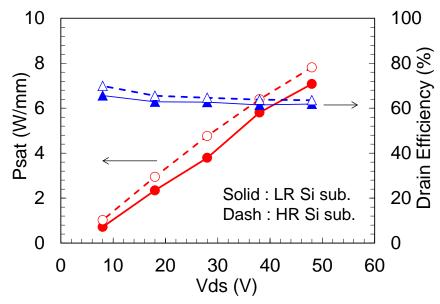

|    | 6.2.   | 1.1 Degradation of efficiency at high-voltage operation                                  | 145 |

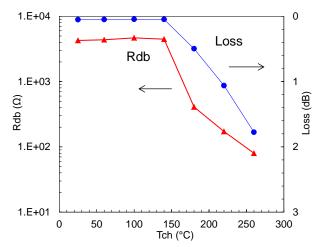

|    | 6.2.   | 1.2 Temperature dependence of substrate loss                                             | 146 |

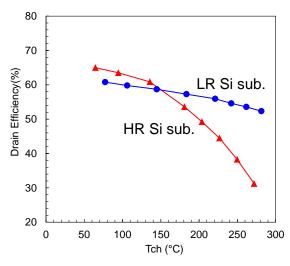

|    | 6.2.   | 1.3 Temperature dependence of device efficiency                                          | 149 |

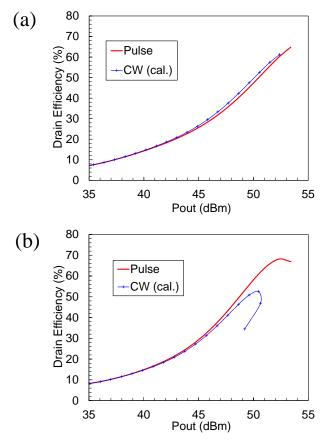

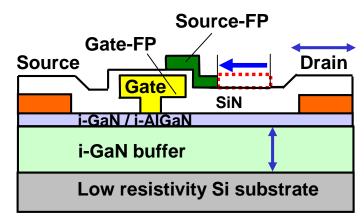

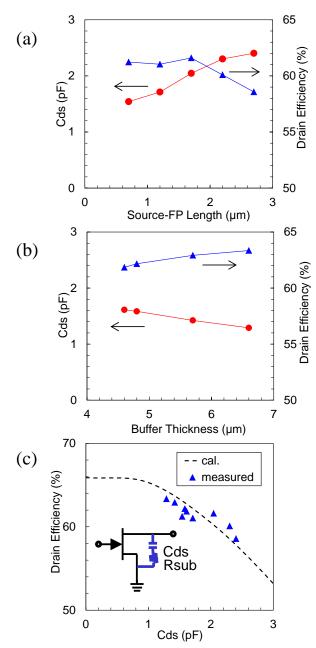

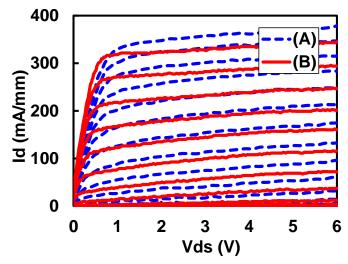

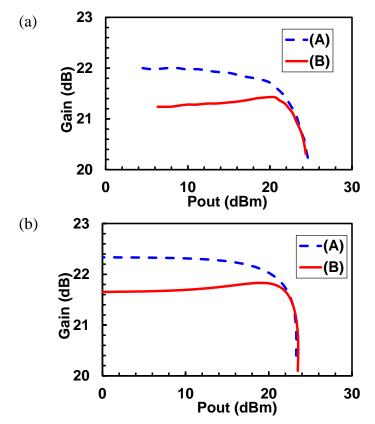

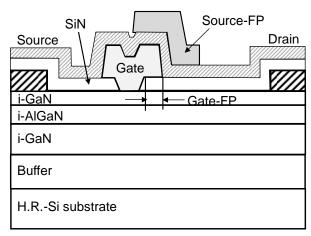

|    | 6.2.   | 2 Device structure optimization of GaN on LR Si                                          | 153 |

|    | 6.3    | L/S-band GaN on Si FET high power amplifiers                                             | 157 |

|    | 6.3.   | 1 250-W GaN FET on LR Si substrate amplifier                                             | 157 |

|    | 6.3.   | 2 537-W two-way inverted Doherty amplifier                                               | 161 |

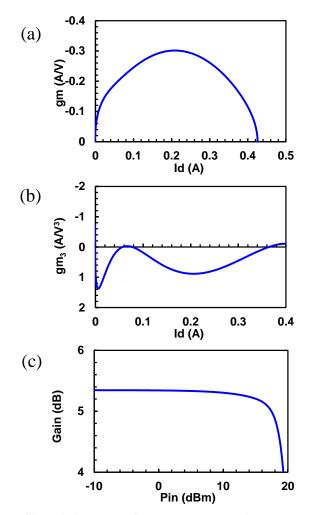

|    | 6.4    | Broadband low distortion GaAs HJ and GaN FET cascode amplifier                           | 165 |

|    | 6.4.   | 1 Distortion cancellation technique in device level                                      | 165 |

|    | 6.4.   | 2 Volterra distortion analysis on load-line                                              | 166 |

|    | 6.4.   | 3 Investigation of relationship between gm-profile on load-line and gain characteristics | 168 |

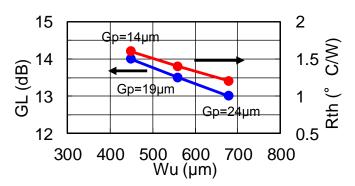

|    | 6.4.   | 4 Optimization of device structure                                                       | 169 |

|    | 6.4.   | 4.1 GaAs HJFET for first stage of cascode configuration                                  | 169 |

|    | 6.4.   | 4.2 GaN FET for final stage of cascode configuration                                     | 173 |

|    | 6.4.   | 5 Circuit optimization                                                                   | 174 |

|    | 6.4.   | 5.1 $W_{\rm g}$ design of cascode configuration                                          | 175 |

|    | 6.4.   | 5.2 Inter-stage impedance design of cascode configuration                                | 176 |

|    | 6.4.   | 6 Amplifier performance                                                                  | 177 |

|    | 6.5    | Summary                                                                                  | 181 |

|    | Refere | ences                                                                                    | 183 |

| Chapte          | Chapter 7 ··· Conclusions                                                                                               |                   |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------|-------------------|--|

| 7.1             | Summary of this dissertation                                                                                            | 187               |  |

| 7.2             | Future issues and prospects                                                                                             | 191               |  |

| Refe            | ences                                                                                                                   | 193               |  |

| Acknow          | vledgements                                                                                                             | 195               |  |

|                 |                                                                                                                         | 107               |  |

| Append          | lix A. <i>S</i> -probe circuit                                                                                          | 197               |  |

|                 | ix A. S-probe circuit<br>lix B. IMD3 asymmetries analysis in consideration of source- and load-<br>difference frequency |                   |  |

| Append          | lix B. IMD3 asymmetries analysis in consideration of source- and load-                                                  | 201               |  |

| Append<br>Refer | lix B. IMD3 asymmetries analysis in consideration of source- and load-<br>difference frequency                          | <b>201</b><br>207 |  |

| Append<br>Refer | lix B. IMD3 asymmetries analysis in consideration of source- and load-<br>difference frequency                          | 201<br>207<br>209 |  |

## **Chapter 1**

## Introduction

### 1.1 Research background and issues

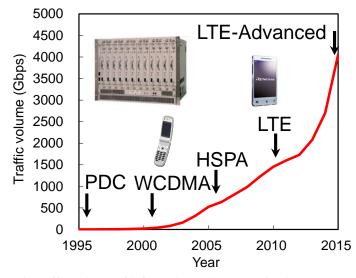

In recent years, the large-capacity and high-speed communication technology has accomplished rapid progress focusing on mobile communications. Figure 1.1 shows the annual changes in the traffic volume of information and communications. The volume of information is explosively increasing with the evolution of information and communication systems. In the high-speed communication systems, the microwave high-power amplifier is a key component constituting the digital cellular base station applications, and the performance enhancement of the high-power amplifier is connected directly with the technological advance of the system. So far, in the base station amplifiers, in order to expand the communication area that can be covered by one base station, higher output power has been required. In addition, in the advanced communications system of Wideband Code Division Multiple Access (WCDMA), High Speed Packet Access (HSPA) and Long Term Evolution (LTE), the multi-carrier transmission scheme is adopted for the effective use of radio wave resources. To realize the broadband multi-carrier transmission, higher output power has been required in the amplifier. Furthermore, in order to perform large-capacity and high-speed communications with a power-saving and a high quality, high efficiency and low distortion characteristics are strongly required for the high power amplifiers.

This study is related to the unique and practical developments of the matching circuit and the power combiner circuit which make it possible to maximize the performance of the microwave transistor used in the high power amplifier. This section describes the history and technology trends of microwave high-power device development as a background of this research. Next, the composition of a microwave high power amplifier and the issues of the device and circuit technique in high power amplifier are described.

Fig. 1.1 Annual changes in traffic volume of information and communications.

#### **1.1.1** History and technology trends of microwave high power device

#### development

Currently, not only is the microwave constructing the microwave communication network as the social infrastructure around the mobile phone, but also is used to the indeed wide application fields, such as terrestrial TV broadcasting, satellite broadcasting, radar, microwave plasma generator, accelerator, microwave heater, microwave medical treatment, microwave spectroscopy, microwave sensor, millimeter wave sensor, microwave power transmission and energy harvesting, and so on.

It depends on the progress of the microwave semiconductor transistor including GaAs field-effect transistor (FET), that microwaves have become widespread among the familiar apparatus, such as a mobile phone and satellite broadcasting. The traveling-wave tube (TWT) invented by Rudolf Kompfner in 1947 had been a key device of wireless communications for many years because the high output power can be obtained with broadband and high efficiency [1.1]. However, for the downsizing, high reliability, and cost-reduction of the equipment, the replacement with the semiconductor device has become an important technical issue. High-power FET developments started from the invention of multi-channel FET by S. Teszner in 1955 [1.2]. The research of Si metal oxide semiconductor (MOS) FET began in around 1969, and 10-W class output power was realized [1.3]. High-power GaAs metal semiconductor (MES) FET operating in the X-band where the Si transistor was difficult to operate appeared in 1972, and was to be used for various kinds of wireless equipment, such as the transponder for satellite communication and the amplifier for fixed

wireless access (FWA) [1.4], [1.5]. However, in the millimeter wave system and the wireless system needed for high output power more than 1 kW, the transistor is fiercely pursuing the TWT but is still slightly inferior at the point of the high-power and high-efficiency characteristics even today [1.6].

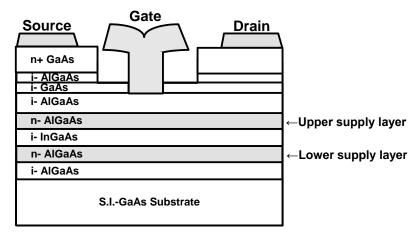

Since high electron mobility transistor (HEMT) using the high mobility twodimensional electron gas of AlGaAs/GaAs hetero-junction was invented by T. Mimura in 1980 [1.7], high performance microwave transistor development has rapidly progressed. Since HEMT was excellent in low noise characteristics, it was widely used for the satellite broadcasting receiver at first. In addition, the practical use of AlGaAs/InGaAs pseudomorphic HEMT using an InGaAs strained layer with high electron mobility to the channel layer has advanced [1.8]. Against the power amplifier used for the second-generation mobile phone terminals with personal digital cellular (PDC) started in 1993 and code division multiple access (CDMA) operated from 1998, the development of the transistors with highcurrent and low resistance became active for low voltage operation suitable for long battery life. Double-doped double-hetero AlGaAs/InGaAs/AlGaAs pHEMTs with twice current density were developed [1.9], [1.10]. In addition, the research and the development of hetero bipolar transistors (HBT) have progressed to apply the positive supply, and AlGaAs/GaAs HBT has evolved to InGaP/GaAs HBT [1.11], [1.12].

On the other hand, for mobile phone base stations, the development competition of high-power transistors more than 100 W at 2-GHz-band has begun targeting the third-generation mobile phone services start of wideband code division multiple access (W-CDMA) from 2001. The output-power more than 100 W has difficulty in achievement by improving only the transistor performance. The effort of both the devices and the circuits is required for high output power performance.

In the device, AlGaAs/GaAs hetero structure FET (HFET) of 12-V-operation [1.13], [1.14] and Si lateral diffused MOS (LDMOS) FET of 28-V-operation [1.15] were successfully developed. The optimization of epitaxial structure and electrode structure was performed for high voltage operation. Double-doped double-hetero pHEMT of 12-V-operation was also realized [1.16]. In the circuit, the push-pull amplifier was developed by combining the output power of a pair of single-ended amplifiers using the balun circuit with impedance transformation effect [1.13], [1.17]. A push-pull amplifier has larger impedance transmission ratio than a single-ended amplifier by four times.

The W-CDMA modulating signal (3GPP test model 64 ch down-link) used in the base station has large peak-to-average ratio (PAR) of 8 dB. It is necessary that the amplifier

operates taking the back-off of the PAR from the saturated output power to amplify the signal without deterioration of the signal quality. However, efficiency characteristics decrease in the back-off operation. Therefore, from system side, higher efficiency and lower distortion characteristics as well as high output power were strongly required for the amplifier. In order to meet the demand, the device aimed at high voltage operation, and to apply high efficiency and low distortion circuits was attempted.

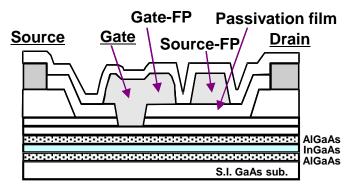

In 1998, K. Asano et al. realized GaAs HFET of 35-V-operation for the first time applying the field-plate (FP) electrode that has already been employed in the Si LDMOS FET to the gate-electrode, and achieved high power density of 1.7 W/mm [1.18]. Aiming at the higher voltage operation and the improvement of gain characteristics, dual field plate (gate and source) structure was applied to the AlGaAs/InGaAs pHEMT, and the push-pull amplifier attained the 28-V-operation and the high output power of 300 W in 2005 [1.19]. The saturation efficiency characteristic was improved by applying harmonic terminations in the internal matching circuits.

Attention was focused on the realization in the microwave band of the Doherty amplifier using a Class-AB amplifier and a Class-C amplifier which W.H. Doherty invented with a vacuum tube amplifier as a circuit technique to improve efficiency characteristics at the back-off operation in 1936 [1.20]. The concrete circuit configuration of the microwave Doherty amplifier which combines the Class-AB amplifier and the Class-C amplifier through a quarter-wave transmission line of fundamental frequency was shown by R.J. McMorrow et al. in 1994 [1.21]. Thereafter, the number of the reports of the Doherty amplifier increased at a stretch. As another method to improve the efficiency characteristics at the back-off operation, an envelope-tracking (ET) amplifier of drain voltage modulation method was proposed by P. M. Asbeck et al. in 1998 [1.22].

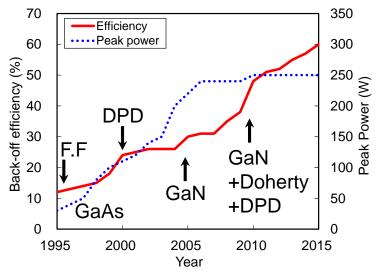

In base station amplifiers, the research and development of the distortion compensation circuits have made progress to improve the distortion characteristics. Feed-forward (F.F) distortion compensation technology was developed in the second-generation mobile phone base station system [1.23]. In the W-CDMA system of the third-generation, digital pre-distortion (DPD) technology integrated with the baseband signal processing circuits was put to practical use in 2004 [1.24]. Here, the study of so-called "memory effect" to disturb the distortion compensation has become active [1.25], [1.26].

For long term evolution of the fourth generation commercially started in 2010, the broadband performance was also demanded for the high-power amplifiers to cope with the rapid expansion of communication data volume shown in Fig. 1.1. For that, the research and

development of the high voltage, broadband, low distortion, high efficiency and high power amplifiers have become active by applying the heterostructure FET using wide bandgap semiconductor GaN whose development started in 1990s [1.27]. The performance that was not realized by the conventional device has been demonstrated by the combination of DPD, Doherty, ET, and GaN FET [1.28], [1.29].

Since low-power consumption of the base stations can be realized by these technologies, it is thought that a cooling device can be simplified, and the downsizing and weight-saving of a base station proceed further. As shown in Fig. 1.2, the peak-output power and the back-off efficiency of the 2-GHz-band high-power amplifiers have been greatly extended by the progress of the device and circuit techniques. In recent years, the pursuit of the back-off efficiency rather than the peak output power becomes the target. That is to say, in the microwave high power amplifiers, both the high efficiency and low distortion have become important issues. The estimates of KDDI say that the  $CO_2$  of 555-ton a year can be reduced deploying high efficiency base stations [1.30]. These high-performance technologies of high-power amplifier are expected to contribute to the green of information and communication technology (ICT).

Fig. 1.2 Annual changes in peak-output power and back-off efficiency of 2-GHz-band high-power amplifiers

## **1.1.2** Configuration of microwave high power amplifiers and issues of

#### device and circuit techniques

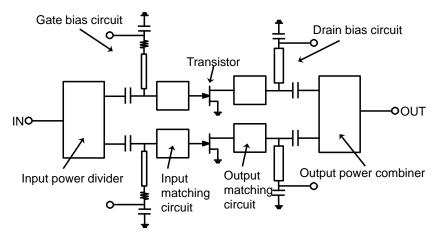

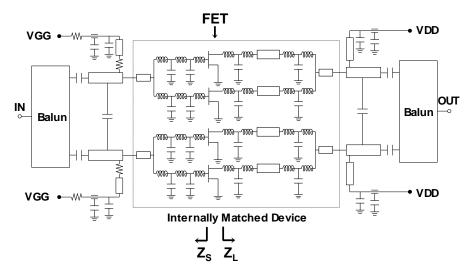

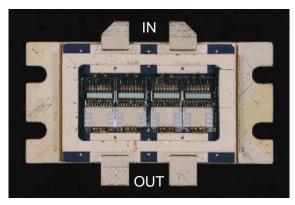

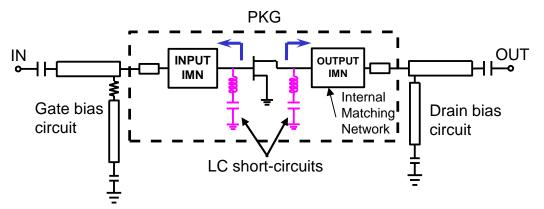

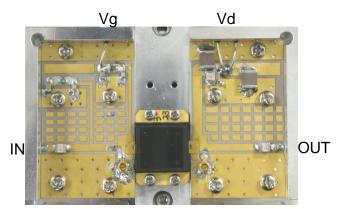

The basic configuration of microwave high-power amplifiers is shown in Fig. 1.3. The microwave high-power amplifier is composed of the microwave transistors, the input and output matching circuits to match the input and output impedance of the transistors to the system impedance of 50  $\Omega$ , the gate and drain bias circuits to supply a DC bias for the transistors, and the power-combining circuits to divide and combine the RF signals. In the microwave high-power amplifiers, since the multiple transistors are combined in parallel to achieve higher output-power, the input- and output-impedances of the high-power FETs are greatly reduced. Therefore, the matching circuit and the power-combining circuit are required for efficiently combining the microwaves.

This microwave high-power amplifier is a key component constructing a transmitter system. In order to perform large-capacity and high-speed communications with a powersaving and a high quality, high efficiency and low distortion characteristics are strongly required for the high-power amplifiers. It goes without saying that the performance enhancement of the microwave transistor itself is necessary for the technological advance of the high-power amplifiers, but the development of circuit technology to maximize the performance of the microwave transistors is also required. The technical background and issues of the devices and circuits constituting the high-power amplifiers are outlined as follows.

Fig. 1.3 Basic configuration of microwave high-power amplifiers.

#### 1.1.2.1 Microwave high-power FET

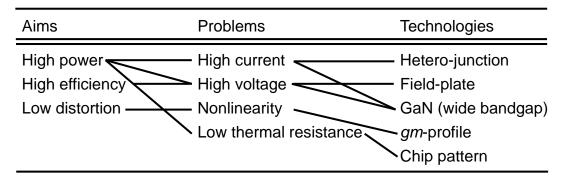

Table 1.1 shows the problems and the technologies of microwave high-power FETs against the aims of high power, high efficiency, and low distortion at power amplifier. In general, there are trade-off relations in the problems of high current, high voltage, high linearity, and low thermal resistance. They are overcome by designing the structure and the material in high-power FET.

Table 1.1 Problems and the technologies of microwave high-power FETs against the power amplifier with high power, high efficiency, and low distortion.

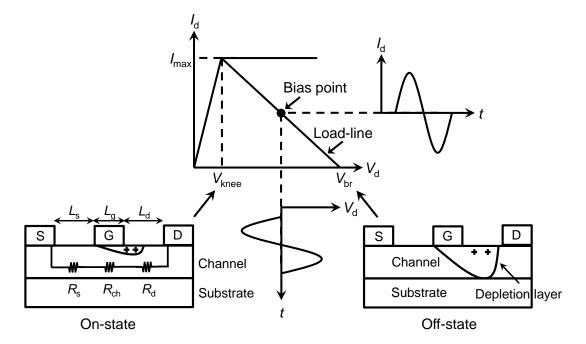

In order to make it easy to understand the RF operation of FET, ideal Class-A operation is assumed.

The condition of the load-resistance  $(R_L)$  to obtain the maximum output power in ideal Class-A operation as shown in Fig. 1.4 is the following formula (1.1).

$$R_L = \frac{V_{br} - V_{knee}}{I_{\max}} \tag{1.1}$$

where  $I_{\text{max}}$  is the maximum drain current,  $V_{\text{br}}$  is the breakdown voltage, and  $V_{\text{knee}}$  is the knee voltage. The current bias condition of Class-A operation is  $1/2 I_{\text{max}}$ .

Then, the maximum output power ( $P_{o, max}$ ) and the maximum power-added efficiency ( $\eta_{add, max}$ ) are expressed as the following formulas (1.2) and (1.3), respectively.

$$P_{o,\max} = \frac{I_{\max} \cdot (V_{br} - V_{knee})}{8} \tag{1.2}$$

$$\eta_{add,\max} = \frac{1}{2} \left( 1 - \frac{1}{G} \right) \left( \frac{V_{br} - V_{knee}}{V_{br} + V_{knee}} \right) = \frac{1}{2} \left( 1 - \frac{1}{G} \right) \frac{1}{\left( 1 + \frac{R_{on}}{R_L} \right)}$$

(1.3)

where G is the RF gain and  $R_{on}=V_{knee}/I_{max}$  shows the on-resistance which is equivalent to the resistance between the drain-electrode and the source-electrode when the FET is in on-state.

Here, it can be seen that high current and high breakdown voltage are required for high-power devices. Moreover, it is found that the devices with high breakdown and low knee voltage are suitable for high efficiency operation. Since the on-resistance is represented by the following expression (1.4), the microfabrication of the device-structure becomes important for high efficiency characteristics.

$$R_{on} = R_{ch} + R_s + R_d \propto L_g + L_s + L_d \tag{1.4}$$

where  $R_{ch}$  is channel resistance,  $R_s$  is source resistance,  $R_d$  is drain resistance,  $L_g$  is gatelength,  $L_s$  is source-gate distance, and  $L_d$  is gate-drain distance.

Fig. 1.4 Ideal Class-A operation.

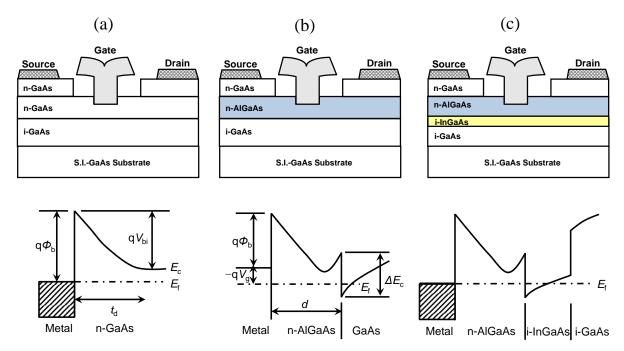

Fig. 1.5 Schematic cross-section and the energy band diagram of the typical microwave GaAs high-power FETs, (a) MESFET, (b) AlGaAs/GaAs HFET, (c) n-AlGaAs/i-InGaAs/i-GaAs pseudomorphic HEMT.

Figure 1.5 shows the schematic cross-section and the energy band diagram of the typical microwave GaAs high-power FETs used for the power amplifiers more than 1 W.

Figure 1.5 (a) shows the MESFET. MESFET uses the Schottky electrode with the rectification due to the contact of metal and semiconductor as the gate electrode. The current is controlled depleting the electron of the n-type channel layer by the gate-bias. The saturation drain current of the MESFET is represented by the following expression (1.5), assuming that all of the channel electrons under the gate transit with the saturation velocity  $v_s$  when the gate-length is sufficiently short [1.31].

$$I_{\max} = W_g (a - t_d) q N_d v_s \tag{1.5}$$

where  $W_g$  is the gate-width, *a* is the thickness of n-type semiconductor layer, *q* is elementary charge,  $N_d$  is the impurity concentration,  $v_s$  is the saturation velocity of electron, and  $t_d$  is the thickness of the depletion layer as follows (1.6).

$$t_d = \sqrt{\frac{2\varepsilon_s (V_{bi} - V_g)}{qN_d}}$$

(1.6)

where  $\varepsilon_s$  is the dielectric constant of the semiconductor and  $V_{bi}$  is the built-in potential of Schottky contact.

To increase the drain current density, the increase of impurity concentration, the increase of channel layer thickness, and the improvement of electron saturation velocity can be introduced from the above equations. However, there is a problem that the gate breakdown voltage  $V_{\rm br}$  represented by the following formula (1.7) decreases when increasing the  $N_{\rm d}$  and *a* [1.32].

$$V_{br} = \frac{\varepsilon_s F_a^2 L_{eff}}{2qN_d a} \tag{1.7}$$

where  $F_a$  is the avalanche breakdown voltage and  $L_{eff}$  is the equivalent gate-length as fitting parameter.

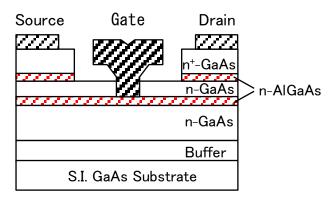

In the n-type layer in MESFET, the mobility of channel electron decreases due to the scattering caused by the donor impurity. The mobility of 8000 cm<sup>2</sup>/Vs in the intrinsic semiconductor drops to about 2000 cm<sup>2</sup>/Vs. In contrast, HFET employs GaAs for the channel layer, and AlGaAs of wider bandgap than GaAs for the Schottky layer. This is the same as the so-called HEMT. HFET is an advantageous structure to high output power performance since the gate leakage current at the large signal operation can be reduced by increasing the Schottky barrier height using AlGaAs as a barrier layer. Figure 1.5 (b) shows the schematic

cross-section and the energy band diagram of AlGaAs/GaAs HFET. In HFET, since the thickness of n-AlGaAs electron supply layer is thin enough, it is completely depleted, and free electrons are accumulated in the triangular potential formed in the interface of electron supply layer and i-GaAs channel layer. That forms the channel called two-dimensional electron gas (2DEG). GaAs can be lattice-matched with AlGaAs. Because of using a high-purity GaAs containing no impurities in the channel layer, high mobility can be obtained with almost no effect of the ionized impurity scattering. Thereby, high-speed and high-frequency operation can be realized. The two-dimensional electron gas concentration  $n_s$  is expressed as the following formula (1.8) [1.33], [1.34].

$$n_{s} = \frac{\varepsilon_{s}}{q(d+\Delta d)} \left[ V_{g} - (\phi_{b} - \frac{qN_{d}d^{2}}{2\varepsilon_{s}} - \frac{\Delta E_{c}}{q} + \frac{E_{F0}}{q}) \right] = \frac{\varepsilon_{s}}{q(d+\Delta d)} (V_{g} - V_{th})$$

(1.8)

where *d* is the thickness of AlGaAs barrier layer,  $\Delta d$  is the channel thickness of 2DEG ( $\approx$ 8nm),  $N_d$  is the donor concentration,  $\Delta E_c$  is the conduction band energy discontinuity in the heterointerface,  $E_{F0}$  is the Fermi energy at  $n_s=0$ , and Vth is the threshold voltage. The saturation drain current ( $I_{dsat}$ ) is expressed as the following formula (1.9), assuming that the electron drift velocity equals to the saturation velocity  $v_s=\mu E_s$  ( $\mu$  is the mobility and  $E_s$  is the saturation electric field).

$$I_{dsat} = \frac{\varepsilon_{s} \mu W_{g} E_{s}}{d + \Delta d} \left[ \sqrt{(V_{g} - V_{th})^{2} + E_{s}^{2} L_{g}^{2}} - E_{s} L_{q} \right]$$

(1.9)

where  $L_g$  is the gate-length. Assuming  $E_sL_g \ll V_g - V_{th}$  (supposing a short gate-length), the following formula (1.10) can be obtained.

$$I_{dsat} = \frac{\varepsilon_s W_g v_s}{d + \Delta d} (V_g - V_{th})$$

(1.10)

The current characteristics of HFET can be characterized by the value of  $d+\Delta d$  and  $N_d$ . The cut-off frequency  $f_T$  showing a high-frequency performance is the following formula (1.11).

$$f_T = \frac{g_m}{2\pi C_{gs}} = \frac{v_s}{2\pi L_g} \tag{1.11}$$

HFET can be expected to obtain high frequency characteristics improvement due to high  $v_s$ .

Figure 1.5 (c) shows the schematic cross-section and the energy band diagram of n-AlGaAs/i-InGaAs/i-GaAs pseudomorphic HEMT using InGaAs for a channel layer as a material with higher electron mobility. High current and high frequency performance can be improved than AlGaAs/GaAs HEMT by carrier confinement effect of the double heterostructure.

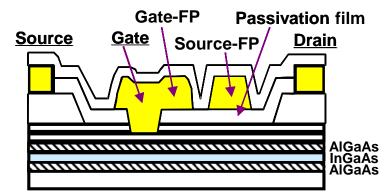

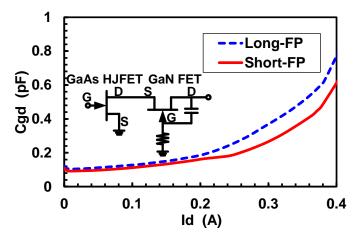

However, as mentioned above, there is a tradeoff between the increase of the carrier density and the breakdown voltage. To improve the breakdown voltage is a problem. Figure 1.6 shows the schematic cross-section of high-voltage operation AlGaAs/InGaAs heterojunction FET (HJFET) employing the dual-field plate electrode structure [1.19]. The electric field concentration to the gate-edge at high voltage operation is relaxed by the dual-field plates of gate-field plate and source-field plate. Not only can the breakdown voltage be improved by the electric field relaxation, but also the electron-capture to the trap in the semiconductor or in the interface of semiconductor and protection film can be suppressed. So-called current collapse can be improved. Thereby, high efficiency characteristics can be achieved improving the output decrease at high voltage operation. The gate-to-drain capacitance ( $C_{gd}$ ) can be greatly reduced terminating the line of electric force by the source-field-plate (SFP) connected to the ground. Therefore, high-power device with high gain and high efficiency characteristics can be realized.

Fig. 1.6 Schematic cross-section of high-voltage operation AlGaAs/InGaAs HJFET.

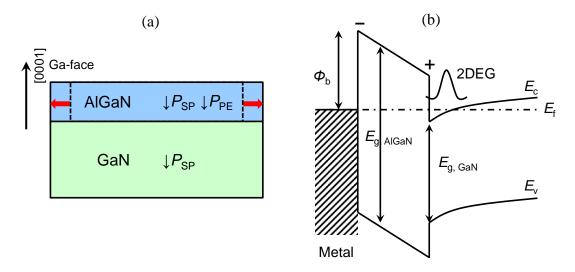

Furthermore, when paying attention to the material, a wide bandgap semiconductor, GaN has attracted attention. Figure 1.7 shows the schematic diagram and the energy band diagram of AlGaN/ GaN heterojunction. The 2DEG generation mechanism of GaN HEMT is different from GaAs HEMT. GaN has a wurtzite structure, and the spontaneous polarization  $P_{SP}$  occurs along the c-axis direction within the crystal. When AlGaN with short a-axis lattice constant is grown on the Ga-face of GaN, the tensile strain occurs in AlGaN, and piezoelectric polarization  $P_{PE}$  is added to  $P_{SP}$ . The positive fixed charge is generated in the AlGaN/GaN heterojunction interface by two polarization effect. According to the report of O. Ambacher [1.35], the relation between AlN mole fraction x and interfacial polarization charge P(x) becomes the following equation (1.12).

$$P(x) = P_{SP} + P_{PE} = (3.25x) + (1.15x^2 + 2x)$$

(10<sup>13</sup>cm<sup>-2</sup>) (1.12)

The polarization charge extends to  $1 \times 10^{13}$  cm<sup>-2</sup> at AlN mole fraction of 20%. This generates high-concentration 2DEG in the heterojunction interface. The 2DEG concentration is given by the following equation (1.13) in consideration of the influence of the interfacial polarization charge  $N_{PZ}$ .

$$n_{s} = \frac{\varepsilon_{s}}{q(d+\Delta d)} \left( V_{g} - V_{th} \right) = \frac{\varepsilon_{s}}{q(d+\Delta d)} \left( V_{g} - \Phi_{B} + \frac{qN_{PZ}d}{\varepsilon_{s}} + \frac{\Delta E_{C}}{q} - \frac{E_{F0}}{q} \right)$$

(1.13)

It can be said that GaN is suitable for the channel layer of the high-power FET because the electron saturation velocity is twice as high as GaAs, and breakdown electric field is 10 times as high as GaAs as shown in Table 1.2 [1.36].

Fig. 1.7 (a) Schematic diagram and (b) energy band diagram of AlGaN/ GaN heterojunction.

| Material             | 4H-SiC                       | GaN   | GaAs  | Si    |       |

|----------------------|------------------------------|-------|-------|-------|-------|

| Bandgap              | E <sub>g</sub> (eV)          | 3.26  | 3.39  | 1.4   | 1.1   |

| Dielectric constant  | 3                            | 10    | 9     | 12.8  | 11.8  |

| Thermal conductivity | $_{\kappa}$ (W/cm·K)         | 4.5   | 1.3   | 0.5   | 1.5   |

| Electron mobility    | $\mu$ (cm <sup>2</sup> /V·s) | 700   | 1600  | 8500  | 1350  |

| Saturation velocity  | v <sub>s</sub> (cm/s)        | 2.0E7 | 2.5E7 | 2.0E7 | 1.0E7 |

| Breakdown Field      | E <sub>b</sub> (V/cm)        | 2.0E6 | 3.3E6 | 4.0E5 | 3.0E5 |

| Johnson's FOM        | $(v_s E_b)^2$                | 180   | 760   | 7     | 1     |

Table 1.2 Comparison of material properties of SiC, GaN, GaAs, and Si.

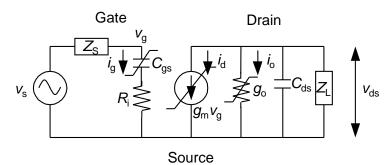

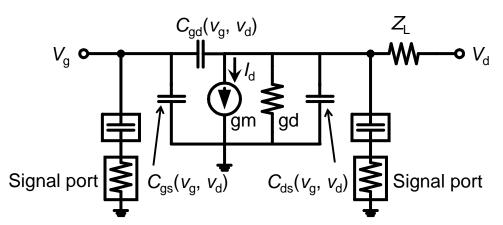

The distortion in the high-power amplifier is caused by the non-linearity of the transistor. As for the nonlinear factor of transistor, the main elements are the transconductance  $(g_m)$ , the drain conductance  $(g_d)$  of drain current, and the nonlinearity of gate capacitance  $(C_g)$ . The high frequency drain current  $(i_d)$  and gate current  $(i_g)$  at large signal operation are indicated by Taylor-series expansion with gate voltage  $(v_g)$  (1.14), (1.15) [1.37]. Here, the most important nonlinear element that dominates the third-order intermodulation distortion (IM3) is a third-order transconductance  $(g_{m3})$ . The gm-profile can be optimized by designing the epitaxial structure of FET. Nonlinearity of the gate capacitance cannot be ignored at high frequency.

$$i_d = \sum_{k=1}^n g_{mk} v_g^k$$

(1.14)

$$i_{g} = \frac{d}{dt} (\sum_{k=1}^{n} C_{gsk} v_{g}^{k})$$

(1.15)

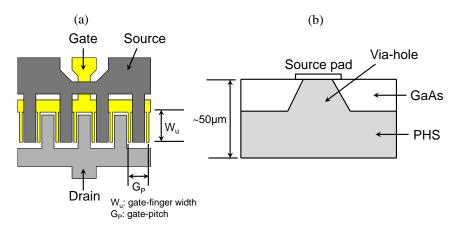

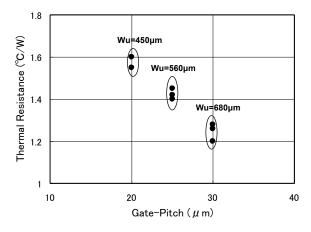

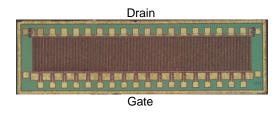

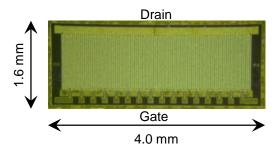

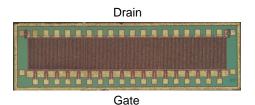

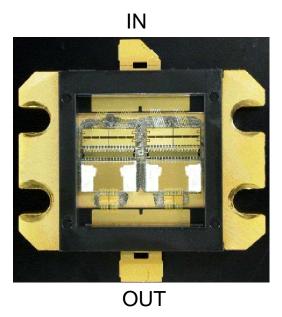

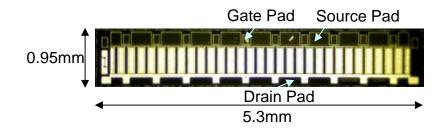

As shown in Fig. 1.8 (a), the chip pattern of the comb form electrode structure is adopted to increase the gate width in the high-power FET. In high-power FET with large power consumption ( $P_{DC}$ ), the thermal design is important. The channel temperature rise  $\Delta T_{ch}$  is expressed as the following formula (1.16) [1.37].

$$\Delta T_{ch} = R_{th} \cdot P_{dis} = R_{th} (P_{DC} + P_{in} - P_{out}) = R_{th} \cdot P_{DC} (1 - \eta_{add})$$

(1.16)

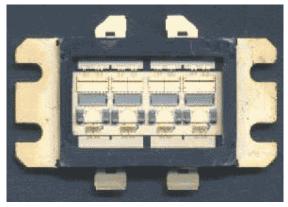

where  $R_{\text{th}}$  is the thermal resistance, and  $P_{\text{dis}}$  is the dissipation power. Although based also on the  $\eta_{\text{add}}$  at the actual high-power operation, the problem is to lower the thermal resistance. There are the thinning of the substrate and the expansion of the gate pitch (G<sub>P</sub>) as the chip design for low thermal resistance. In addition, as shown in Fig. 1.8 (b), the metal plated heat sink (PHS) is formed on the substrate backside thinned to 20~30 µm. The PHS and source electrode are connected by providing with a via-hole to the source electrode to minimize ground inductance. These high-power FET chips are mounted on the package with the metal heat sink having the high thermal conductivity and the thermal expansion coefficient close to the semiconductor such as GaAs.

Fig. 1.8 Schematic (a) chip pattern and (b) cross section of source electrode of high-power FET.

As mentioned above, various technologies have been taken against the aims of highpower, high-efficiency, and low distortion in high-power FET.

#### **1.1.2.2 Matching circuits**

The circuit techniques of high power amplifiers are outlined from here.

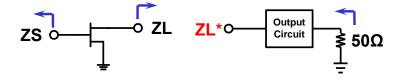

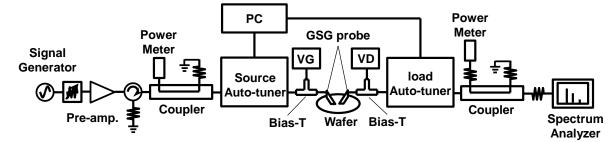

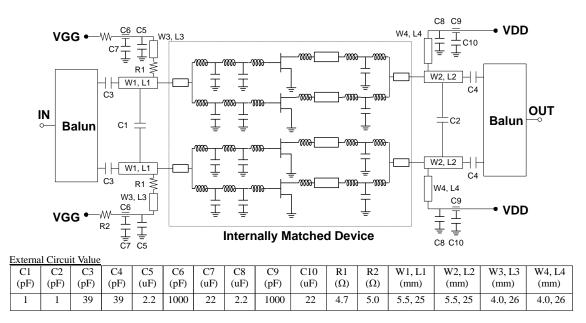

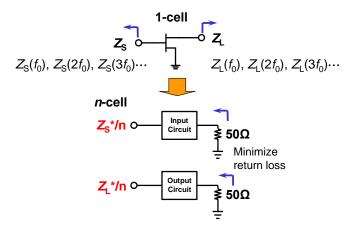

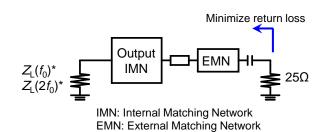

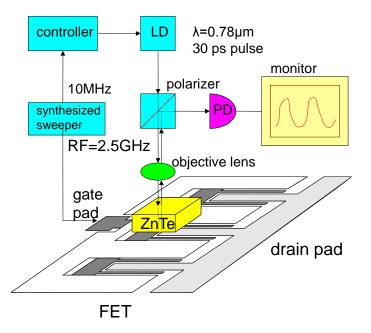

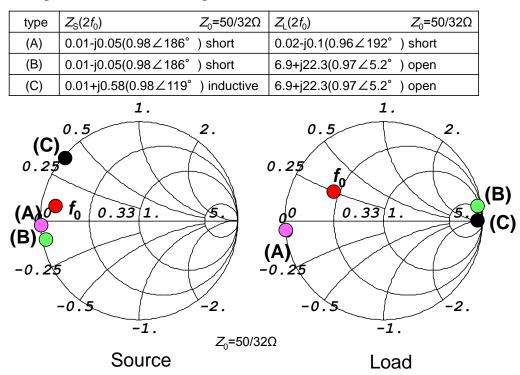

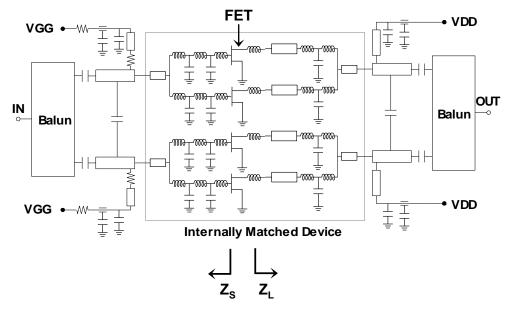

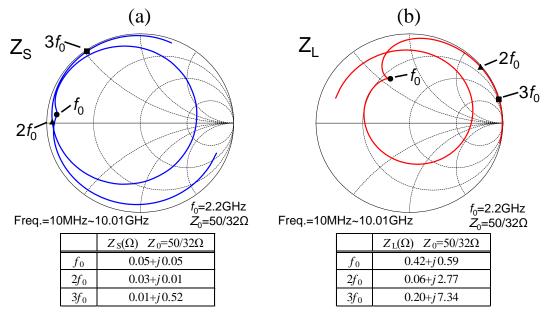

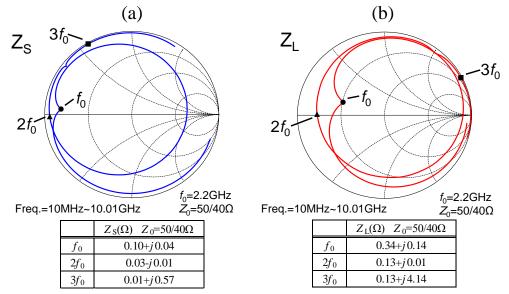

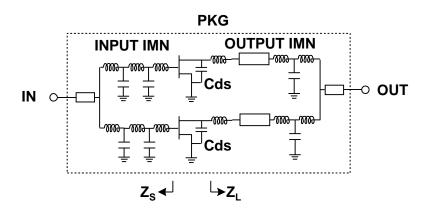

Since the large gate-width is needed to obtain higher output power in high-power FET, the input and output impedance greatly decreases compared to the system impedance of 50  $\Omega$ . Therefore, the impedance matching is performed providing the impedance matching circuits directly connected to the chips in a package (PKG). There is a problem that the matching circuits of high-power FET realize the fundamental frequency matching and the harmonic terminations with low loss. As shown in Fig. 1.9, the matching circuit parameters are optimized so as to minimize the circuit return-loss measured from the system port when the port impedance of the transistor side is to be complex conjugate of the optimum load impedance for the transistor. The optimum load impedance is determined using for example, on-wafer source- and load-pull measurement system as shown in Fig. 1.10. Thereby, the transistor can operate on the optimum load condition.

ZL\*: Complex conjugate optimum load impedance Minimize the return loss measured from system port

Fig. 1.9 Optimization of matching circuit parameters.

Fig. 1.10 Schematic of on-wafer source- and load-pull measurement system.

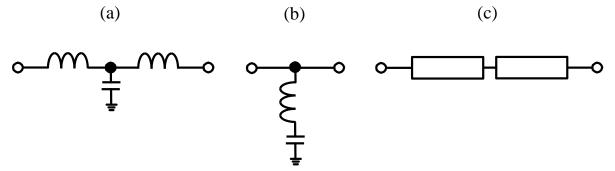

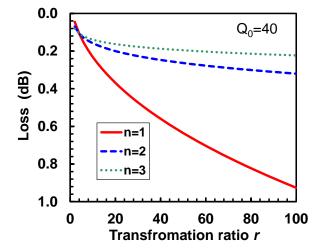

Figure 1.11 shows the typical matching circuit configuration of high-power FET. The matching circuit in high-power FET with low impedance generally takes the configuration of low-pass filter network which consists of the inductance of the bonding wires and the capacitance of the chip capacitors. When there is no room to configure the circuits in a small PKG, the high-pass filter type matching circuit composed of shunt inductor can be employed. It is also possible to configure the matching circuit using the distributed constant lines formed on the dielectric substrate. Depending on the desired circuit constant, using the impedance lines is able to set higher allowable current than bonding wires. However, since the circuit element has a loss, there is a problem that the impedance transformation loss increases, and the bandwidth becomes narrow as the impedance transformation ratio  $r (= 50/|Z_L^*|)$  in Fig. 1.9) increases. Although the bandwidth and the circuit loss can be improved by increasing the number of circuit elements, the minimum number within permission should be selected considering the complexity of circuits. The following formula (1.17) indicates the relation between the transformation ratio and the transmission loss in the *LC* low pass filter networks with the loss. Figure 1.12 shows the calculation results.

$$Loss(dB) = -20Log(1 + \frac{(r^{\frac{1}{2}} - 1)^{\frac{1}{n}}}{2Q_0})$$

(1.17)

where r is the transformation ratio,  $Q_0$  is the Q-factor of circuit element, and *n* is the stagenumber of low pass filter networks.

Fig. 1.11 Typical matching circuit configuration of high-power FET. (a) low-pass filter network type, (b) high-pass filter network type, (c) distributed constant line type.

Fig. 1.12 Calculation results of the relation between the transformation ratio and the transmission loss in the *LC* low pass filter networks with the loss.

Moreover, in the high-power FET combining the multi-chips in parallel, a loop oscillation may occur between chips. In order to suppress the oscillation, the balance resistance can be prepared between chips on the matching circuits. Even when the amplifier is stable at the DC bias setting, a loop oscillation may occur from a certain RF input power level. Therefore, the loop oscillation analysis at the large signal operation is needed for the stable operation in the wide range.

#### **1.1.2.3** Power combining circuits

The realization of the high-power amplifiers over 100W at 2-GHz-band has become challenging target for the third generation mobile phone base station. Also, the high-power amplifiers delivering the  $P_{\text{sat}}$  of from 200 W to 500 W are required for the macro-cell base station in the fourth generation system. These high-power amplifiers combine the output power of partially- or fully-matched several single-ended high-power amplifiers employing power dividing and combining circuits.

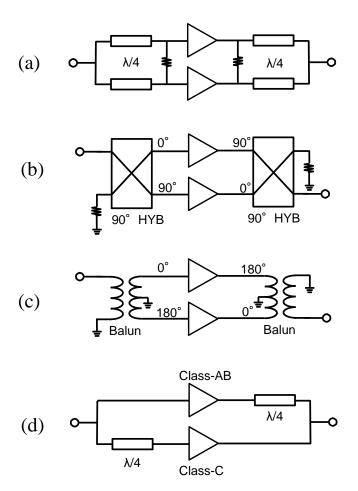

Fig. 1.13 Typical configuration of the high-power amplifiers using the typical two-branch type powercombining circuits. (a) in-phase power dividing/combining amplifier using the Wilkinson divider, (b) balance amplifier using the 3 dB-directional couplers of  $0^{\circ}-90^{\circ}$ , (c) push-pull amplifier using the balun, (d) Doherty amplifier

Figure 1.13 shows the configuration of the high-power amplifiers using the typical two-branch type power-combining circuits. Figure 1.13 (a) shows the in-phase power dividing/combining amplifier using the Wilkinson divider composed of the quarter wave transmission lines and the isolation resistor. This type is characterized by high isolation between the branches obtained by the impedance transformation effect of quarter wave ( $\lambda_g/4$ ) line and the isolation resistor. The distributed constant line with the characteristic impedance of  $Z_0$  and the line-length of l can transform the impedance of  $Z_1$  to the impedance of  $Z_2$  as follows (1.18).

$$Z_{2} = Z_{0} \frac{Z_{1} + jZ_{0} \tan(\beta l)}{Z_{0} + jZ_{1} \tan(\beta l)}$$

(1.18)

where  $\beta = 2\pi/\lambda_g$ . Especially, when  $l = \lambda_g/4$ , (1.18) becomes as follows (1.19).

$$Z_1 \cdot Z_2 = Z_0^{\ 2} \tag{1.19}$$

This quarter wave line is employed in various microwave circuits.

The balance amplifier shown in Fig. 1.13 (b) uses the 3 dB-directional couplers of  $0^{\circ}$ -90° for input/output dividing/combining circuits. Therefore, the two amplifiers composing the balance amplifier operate with a phase difference of 90° each other. The balance type not only can take the isolation between branch ports (balance ports) by a termination resistor, but also is characterized by being able to make the reflection coefficient at an input or an output signal port small even if not taking the matching at a balance port.

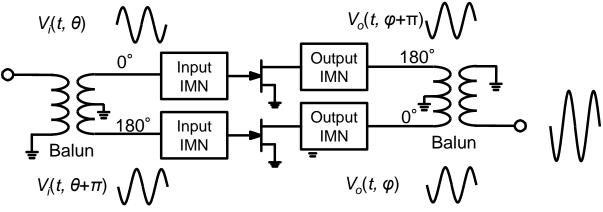

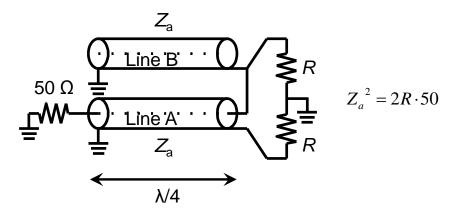

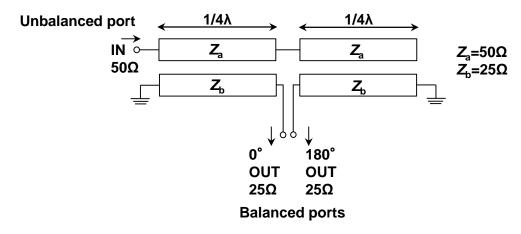

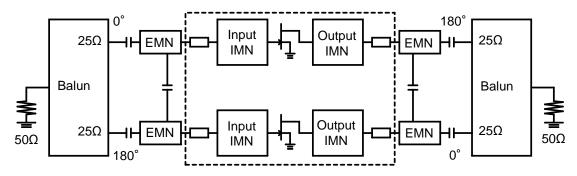

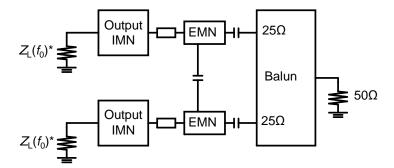

The push-pull amplifier shown in Fig. 1.13 (c) uses the  $0^{\circ}$ -180° couplers or balun (balance-unbalance) circuits for power dividing/combining circuits. The two amplifiers of push-pull configuration operate with the phase difference of 180° each other. Since the two amplifiers operate with the opposite phase, the fundamental frequency is combined in-phase at the output port through the 180° coupler, and the even order harmonics are cancelled at the output port. That is to say, in the push-pull amplifier, even-order harmonics are not generated. Furthermore, in the push-pull amplifier using the balun circuits, since balun itself has the impedance transformation effect, the two amplifiers of push-pull configuration require only to match to  $25 \Omega$ , respectively. Since the two amplifiers combined in single-end need to match to 100  $\Omega$ , respectively, a push-pull amplifier has four times merits compared with a single-ended amplifier against an impedance transformation ratio. Thus, since the push-pull amplifier is an efficient amplifier in power-combining, the examinations were promptly advanced as the configuration of the wireless base station amplifiers. Broadband and low-loss power-combining circuit becomes essential to achieve the high output power more than 100 W at 2-GHz-band. Conventionally, the balun circuits have been fabricated using coaxial lines. Newly, the balun circuits configured in microstrip coupled lines were developed by utilizing an electromagnetic field analysis [1.16].

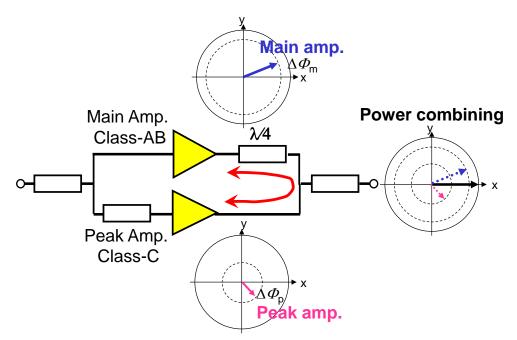

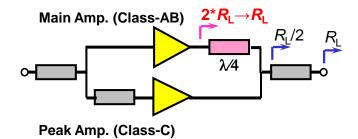

Doherty amplifier shown in Fig. 1.13 (d) combines the output power of the main amplifier biased in Class-AB and the peak amplifier biased in Class-C through a quarter wave line [1.21]. A quarter wave line is connected to the main amplifier side. Since a quarter wave line has the phase difference of 90°, the input side is constituted using a 90°-hybrid circuit, or a quarter wave line. Thereby, the output power is combined in-phase. Doherty amplifier is characterized by the efficiency characteristics improvement of 6 dB back-off due to the load impedance shift of the main amplifier caused by the impedance transformation effect of the quarter wave line at signal input. However, Doherty amplifier has a problem that the distortion characteristics deteriorate due to the distortion the peak amplifier generates in

Class-C operation. The problem is to establish the design methods of Doherty amplifier to achieve both high efficiency and low distortion characteristics.

#### **1.1.2.4 Bias circuits**

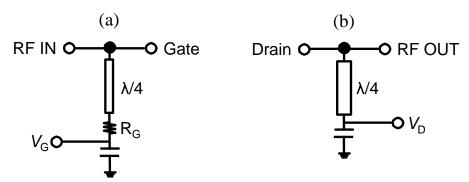

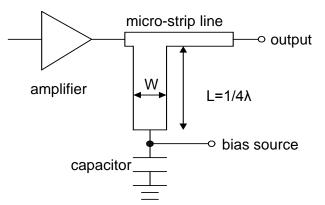

Figure 1.14 shows a typical gate bias circuit and drain bias circuit used for microwave high-power FET amplifier. It is basic to design the bias circuit of microwave amplifier so as not to generate the loss in fundamental frequency band. Therefore, the other end of the quarter wave line at fundamental frequency is short-circuited by a capacitor. This is because, as is introduced by the formula (1.19), the other end of the short-circuited quarter wave line becomes open, and does not affect the RF signal. The gate bias circuit may prepare a resistor in the line end for the stabilization of the amplifier. In the high-power amplifier with low frequency below 1 GHz, a chalk inductor may be used instead of a quarter wave line.

Fig. 1.14 Typical (a) gate bias circuit and (b) drain bias circuit used for microwave high-power FET amplifier.

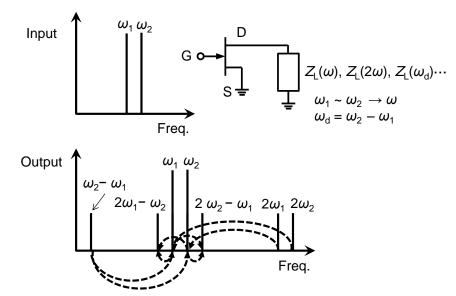

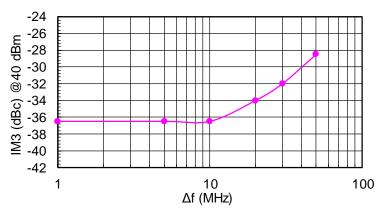

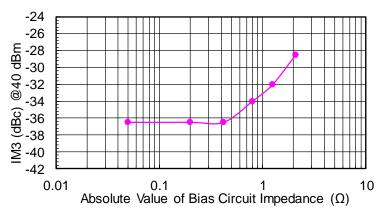

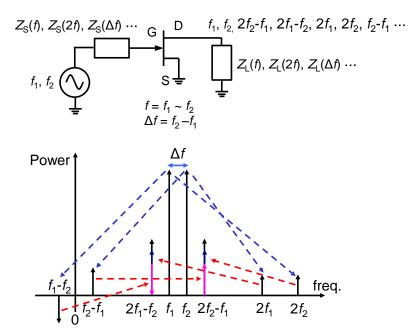

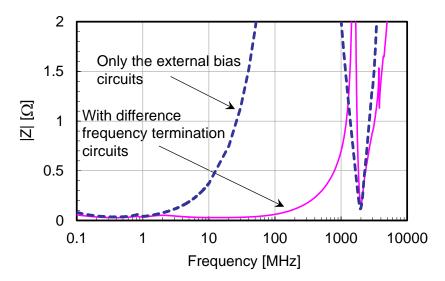

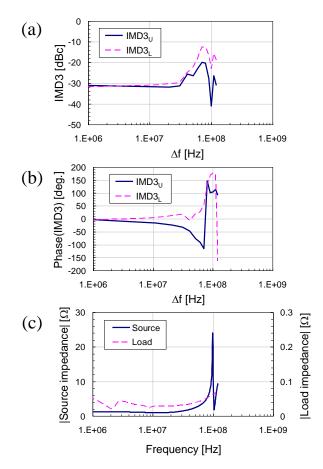

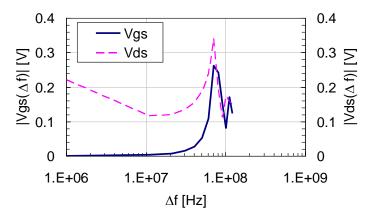

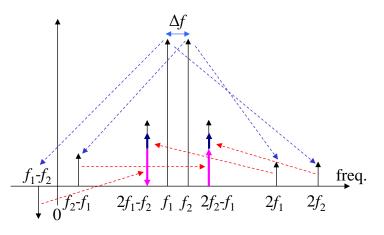

As shown in Fig. 1.15 (a), the digital modulation signals handled by modern mobile phone communication systems have the bandwidth according to the bit rate. If the signal has a bandwidth, difference frequency corresponding to the band width is caused by the second-order nonlinearity of the transistor. This difference frequency, influenced by the low-frequency impedance of the drain bias circuit, would degrade the distortion characteristics being superimposed on the third-order intermodulation when the mixing of the fundamental frequency and the difference frequency occurs. These phenomena are called the memory effect [1.25]. The main factor of low-frequency impedance increase of the drain bias circuit is the inductance component of the quarter wave line.

For simplicity, the memory effect of the amplifier is found by measuring the frequency spacing ( $\Delta f$ ) dependence on two-tone IM3 characteristics as shown in Fig. 1.15 (b). When there is a memory effect, the difference is generated in the magnitude and phase of the upper and lower IM3 components ( $2f_1-f_2$ ,  $2f_2-f_1$ ). The degradation of the distortion

characteristics by such a memory effect can be suppressed by short-circuiting the lowfrequency impedance of the drain and gate side. In the fourth generation mobile phone system of the multi-carrier signal that enables high-speed, large-capacity communication, the broadband characteristics of 100 MHz is required for the IM3- $\Delta f$  characteristics. Technical proposals for that purpose are necessary.

Fig. 1.15 Schematic output signal spectrum in high-power amplifier under (a) the digital modulation signal and (b). the two-tone CW

#### **1.1.2.5 Distortion compensation techniques**

There is a problem that the distortion characteristics deteriorate when operating in the nonlinear region where microwave amplifier can obtain high efficiency characteristics. In the high-efficiency microwave amplifier, the distortion characteristics can be improved with distortion compensation techniques. The typical distortion compensation techniques are a feedback method, a feedforward method, and a predistortion method [1.38].

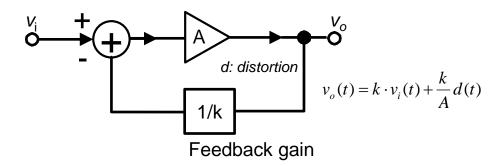

In the feedback method shown in Fig. 1.16, the distortion characteristics are improved by a loop gain at the negative feedback of a part of output power to the input side. The approach to feedback the carrier signal directly is not practical because of the stability and the small gain characteristics of the amplifier in the microwave band.

Fig. 1.16 Feedback distortion compensation method.

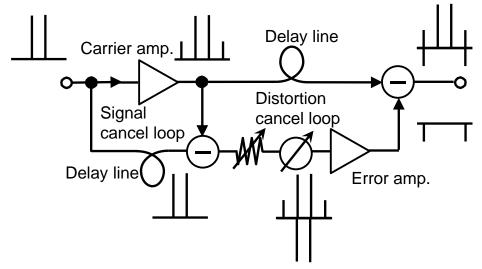

The feedforward distortion compensation amplifier shown in Fig. 1.17 is composed of a carrier amplifier, a carrier signal canceling loop for extracting the distortion component generated by the carrier amplifier, an error amplifier for amplifying the extracted distortion component, and a distortion canceling loop for canceling the distortion component included in the carrier signal using it. Large distortion compensation amount can be obtained by performing the distortion compensation using the distortion itself generated by the carrier amplifier in the feed-forward amplifier. However, since the delay lines for phase adjustment and an error amplifier are required, the circuit-size becomes large, and the power consumption also increases.

Fig. 1.17 Feedforward distortion compensation amplifier.

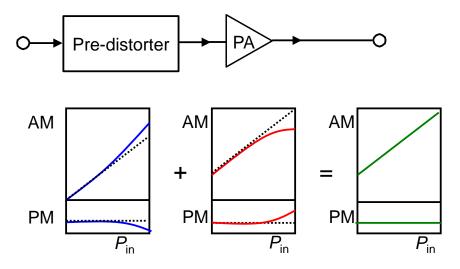

In the pre-distortion method shown in Fig. 1.18, the distortion characteristics (amplitude-to-amplitude modulation: AM-AM, and amplitude-to-phase modulation: AM-PM) of the entire amplifier can be cancelled by using the inverse characteristics of the distortion characteristics (AM-AM, AM-PM) generated by the power amplifier (PA) as the input signal. The predistortion method is advantageous in terms of the efficiency and the downsizing of the circuits.

Fig. 1.18 Predistortion method.

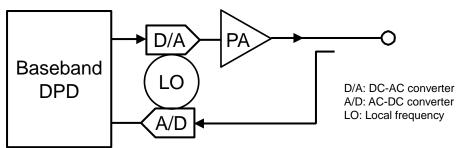

Figure 1.19 shows the baseband digital pre-distortion (DPD) amplifier making the baseband signal of the digital modulation signal an inverse characteristic. The speed improvement of the digital signal processing circuits in recent years enabled the DPD method. It is corresponding also to the expansion of the modulation signal bandwidth by the advancement of the communication system. The DPD method is becoming the mainstream of the distortion compensation techniques of the mobile phone communication system. The memory effect that occurs in the amplifier becomes a problem here. Since the DPD method creates the inverse distortion characteristics of the amplifier in advance, it is impossible to compensate the distortion if the distortion characteristics of the amplifier have differed when inputting the inverse characteristic signal. The technical proposals have been made to suppress the memory effect of the amplifier to a broadband. In recent years, low distortion and high efficiency characteristics have been demonstrated by the combination of DPD and Doherty, or ET circuits.

Fig. 1.19 Baseband digital predistortion amplifier.

### **1.2** Purpose and significance of this dissertation

This study was carried out under the above-mentioned background. The purposes of this study are as follows.

Firstly, a novel low loss broadband microwave power combining circuit is proposed, and the high-efficiency push-pull amplifier more than 100 W at an L/S-band is demonstrated using the proposed circuit. In addition, the instability analysis method at the large signal operation is established and demonstrated. This is a problem in case of the power-combining of the high-power amplifier.

Secondly, the matching circuit configuration with a new harmonic termination conditions is proposed by establishing the matching circuit design method for high-efficiency high-power amplifier. The effectiveness of the design method is verified by observing the actual voltage waveform by the EOS method. The best performance of high efficiency and high output power characteristics is demonstrated.

Thirdly, the design techniques of low distortion devices and circuits for the realization of low-distortion high-power amplifiers are established. The device structure to achieve both low distortion and high efficiency characteristics is proposed. The low distortion second harmonic termination matching circuits are proposed by investigating the effect of the second harmonic and the difference frequency impedance on the third-order distortion characteristics. In addition, to achieve low distortion characteristics without deterioration over the difference frequency spacing of 100MHz which was not be realized until now, the source- and load-difference frequency termination circuits in package as well as the technique lowering drain bias circuit impedance are proposed.

Fourthly, a new Doherty amplifier is proposed to achieve both high efficiency and low distortion characteristics. The design method of optimal Doherty amplifier based on the impedance of the load pull characteristics of the device is proposed. In order to solve the problem of the distortion characteristic degradation which exists in the Doherty amplifier, the design method for performing the distortion compensation by the distortion cancellation of the main and peak amplifiers of the Doherty amplifier is proposed. In addition, the evaluation technique of each amplitude-to-amplitude modulation (AM-AM) and amplitude-to-phase modulation (AM-PM) characteristics of the main and the peak amplifiers in an operating Doherty amplifier is proposed, and the distortion cancellation mechanism of the main and the peak amplifiers in Doherty amplifier linearity is experimentally proved for the first time. Fifthly, as a further possibility of wide bandgap semiconductor GaN, the deployment of broadband, high efficiency, and low distortion amplifier using GaN FET is demonstrated. The base station high-power amplifiers and the cable television (CATV) power amplifier modules are exemplified to achieve the realization of high performances which cannot be realized in the conventional devices, using the GaN FET of high-voltage operation and high power density. The Doherty amplifier using GaN FET is developed optimizing the device structure to improve the efficiency characteristics of the GaN FET on low cost Si substrate for base station amplifiers. The high-efficiency and low-distortion characteristics of the highest level employing the DPD techniques in the GaN FET Doherty amplifier are demonstrated. Furthermore, the distortion compensation at the device level by the distortion cancellation effect of the high *gm* GaAs HJFET and the GaN FET is demonstrated employing Volterra distortion analysis on load-line based on the pulsed-*IV* characteristics in the CATV power amplifier module. The realization of broadband and low distortion characteristics of the highest level is aimed by the techniques of the gm profile optimization.

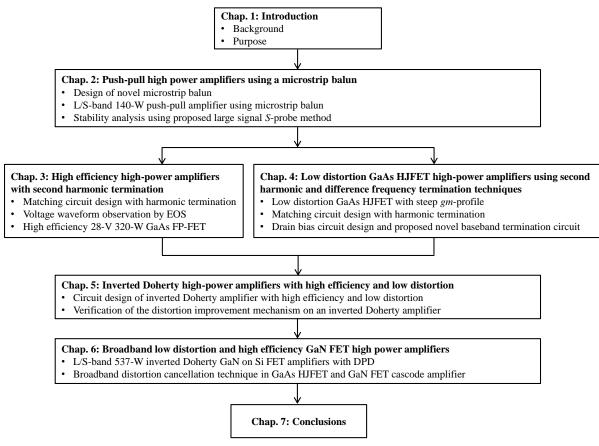

### **1.3 Outline of this dissertation**

This dissertation consists of seven chapters. The outline of this dissertation is shown in Fig. 1.20.

**Chapter 1 "Introduction"** describes the history and technology trends of microwave high-power device development as a background of this study. Next, the composition of a microwave high power amplifier and the problem of the device and circuit technique in high power amplifier are described. Then, the purpose and meaning of a main subject are described and the composition of a main subject is shown.

**Chapter 2 "Push-pull high power amplifiers using a microstrip balun"** describes the study results on the push-pull power combining circuit and the stability analysis under the large-signal operation for microwave high-power amplifiers.

**Chapter 3 "High efficiency high-power amplifiers with second harmonic termination**" describes the study results on high efficiency microwave high power amplifiers.

Chapter 4 "Low distortion GaAs HJFET high-power amplifiers using second harmonic and difference frequency termination techniques" describes the study results on low distortion microwave high power amplifiers. Chapter 5 "Inverted Doherty high-power amplifiers with high efficiency and low distortion" describes the study results on low distortion and high efficiency Doherty amplifiers.

Chapter 6 "Broadband low distortion and high efficiency GaN FET high power amplifiers" describes the study results on broadband, high efficiency, and low distortion microwave high-power amplifiers using GaN FETs.

Chapter 7 "Conclusions" summarizes this dissertation, and describes the challenges and prospects for the future.

Fig. 1.20 Outline of this dissertation.

## References

- [1.1] R. Kompfner, "The invention of the traveling-wave tube," San Francisco Press, 1964.

- [1.2] S. Teszner, "High power field effect transistor," U.S. patent 2930950 (Mar. 1960), France Application Field (Dec. 1955).

- [1.3] Y. Morita, H. Takahashi, H. Matayoshi, and M. Fukuta, "Si UHF MOS high-power FET," IEEE Trans. Electron Devices, ED-21, 11, pp. 733-734 (Nov.1974).

- [1.4] W. Beachtold, W. Walter, and P. Wolf, "X and Ku band GaAs M.E.S.F.E.T.," Electron Lett., vol. 8, pp. 35-37, Jan. 1972.

- [1.5] C. A. Liechti, E. Gowen, and J. Cohen, "GaAs microwave Schottky-gate FET," 1972 ISSCC, pp. 158–159, Feb. 1972.

- [1.6] C.K. Chong and W.L. Menniger, "Latest advancements in high-power millimeterwave helix TWTs," Plasma Science, IEEE Transactions on, vol. 38, Issue 6, pp. 1227-1238, Mar. 2010.

- [1.7] T. Mimura, S. Hiyamizu, T. Fujii, and K. Nanbu, "A new field-effect transistor with selectively doped GaAs/n-Al<sub>x</sub>Ga<sub>1-x</sub>As heterojunctions," Jpn. J. Appl. Phys., vol. 19, pp. L 225-L 227, 1980.

- [1.8] T. E. Zipperian, L. R. Dawson, G. C. Osbourn, and I. J. Fritz, "An  $In_{0.20}Ga_{0.80}As/GaAs$  modulatin-doped, strained-layer superlattice field-effect transistor," 1983 IEEE Int. Electron Device Meeting Tech. Dig., pp. 696-699 (Washington, DC, 1983).

- [1.9] N. Iwata, K. Inosako, and M. Kuzuhara, "High efficiency power amplifier module with novel enhancement-mode heterojunction FETs for wide-band CDMA handsets," Electronics Letters, vol. 31, Issue 25, pp. 2213-2215, 1995.

- [1.10] Y. Bito, T. Kato, and N. Iwata, "2.2 V operation power heterojunction FET for personal digital cellular telephones," GaAs IC Symposium, 2000. 22nd Annual, pp. 255-258, 2000.

- [1.11] P.M. Asbeck, A.K. Gupta, F.J. Ryan, D.L. Miller, R.J. Anderson, C.A. Liechti, and F.H. Eisen, "Microwave performance of GaAs/(Ga,Al)As heterojunction bipolar transistors," Electron Devices Meeting, 1984 International, vol. 30, pp. 864-865, 1984.

- [1.12] T. Iwai, S. Ohara, T. Miyashita, and K. Joshin, "63.2% high efficiency and high linearity two-stage InGaP/GaAs HBT power amplifier for personal digital cellular phone system," Microwave Symposium Digest, 1998 IEEE MTT-S International, vol. 2, pp. 435-438, 1998.

- [1.13] I. Takenaka, H. Takahashi, K. Asano, K. Ishikura, J. Morikawa, K. Satou, I. Takano, K. Hasegawa, K. Tokunaga, F. Emori, and M. Kuzuhara, "L/S-band 140 W push-pull power AlGaAs/GaAs HFETs for digital cellular base stations," Gallium Arsenide Integrated Circuit (GaAs IC) Symposium, 1998, Technical Digest, 20<sup>th</sup> Annual, pp. 81-85.

- [1.14] Y. Tateno, H. Takahashi, T. Igarashi and J. Fukaya, "A 150W E-mode GaAs Power FET with 35% PAE for W-CDMA Base Station", 1999 IEEE MTT-S Int. Microwave Symp. Dig., pp. 1087-1090.

- [1.15] A. Wood, W. Brakensick, C. Dragon, and W. Burger, "120 Watt, 2 GHz, Si LDMOS RF power transistor for PCS base station applications," Microwave Symposium Digest, 1998 IEEE MTT-S International, vol. 2, pp. 707-710, 1998.

- [1.16] I. Takenaka, K. Ishikura, H. Takahashi, K. Asano, and M. Kanamori, "Low distortion high power GaAs pseudomorphic heterojunction FETs for L/S-band digital cellular base stations," 2000 IEEE MTT-S Int. Microwave Symp. Dig., Vol. 3, pp. 1711-1714.

- [1.17] S. Goto, K. Fujii, H. Morishige, S. Suzuki, S. Sakamoto, N. Yoshida, N. Tanino, and K. Sato, "A 100 W S-band AlGaAs/GaAs hetero-structure FET for base stations of wireless personal communications," Gallium Arsenide Integrated Circuit (GaAs IC) Symposium, 1998. Technical Digest 1998., 20th Annual, vol. 2, pp. 77-80, 1998.

- [1.18] K. Asano, Y. Miyoshi, K. Ishikura, Y. Nashimoto, M. Kuzuhara, and M. Mizuta, "Novel high power AlGaAs/GaAs HFET with a field-modulating plate operated at 35 V drain voltage," Electron Devices Meeting, 1998. IEDM '98. Technical Digest., International, pp. 59-62, 1998.

- [1.19] K. Ishikura, I. Takenaka, H. Takahashi, M. Kanamori, K. Hasegawa, and K. Asano, "A 28V over 300-W GaAs heterojunction FET with dual field-modulating-plates for W-CDMA base stations," 2005 IEEE MTT-S Int. Microwave Symp. Dig. pp. 823-826, 2005.

- [1.20] W.H. Doherty, "A new high efficiency power amplifier for modulated waves," Proc. IRE, vol.24, no.9, pp.1163–1182, Sep. 1936.

- [1.21] R.J. McMorrow, D.M. Upton, and P.R. Maloney, "The microwave Doherty amplifier," Microwave Symposium Digest, 1994., IEEE MTT-S International., vol. 3, pp. 1653-1656, 1994.

- [1.22] P.M. Asbeck, G. Hannington, P.F. Chen, and L. Larson, "Efficiency and linearity improvement in power amplifiers for wireless communications," Gallium Arsenide Integrated Circuit (GaAs IC) Symposium, 1998. Technical Digest 1998., 20th Annual, pp. 15-18, 1998.

- [1.23] S. Narahashi and T. Nojima, "Extremely low-distortion multi-carrier amplifier-selfadjusting feed-forward (SAFF) amplifier," Communications, 1991. ICC '91, Conference, vol. 3, pp. 1485-1490, 1991.

- [1.24] B. Vassilakis, A. Cova, and W. Veitschegger, "Wireless base station technology evolution," Compound Semiconductor Integrated Circuit Symposium, 2004. IEEE, pp. 3-7, 2004.

- [1.25] J.H.K. Vuolevi, T. Rahkonen, and J.P.A. Manninen, "Measurement technique for characterizing memory effects in RF power amplifiers," IEEE Trans. Microwave Theory & Tech, vol 49, no.8, Aug. 2001, pp.1383-1389.

- [1.26] P. Draxler, J. Deng, D. Kimball, I. Langmore, and P.M. Asbeck, "Memory effect evaluation and predistortion of power amplifiers," Microwave Symposium Digest, 2005 IEEE MTT-S International, pp.1549-1552.

- [1.27] M.A. Kahn, A. Bhattarai, J.N. Kuznia, and D.T. Olson, "High electron mobility transistor based on a GaN-Al<sub>x</sub>Ga<sub>1-x</sub>N heterojunction," App. Phys. Lett., vol. 63, pp.1214-1215, 1993.

- [1.28] N. Ui, H. Sano, and S. Sano, "A 80W 2-stage GaN HEMT Doherty amplifier with 50dBc ACLR, 42% efficiency 32dB gain with DPD for W-CDMA base station," Microwave Symposium, 2007. IEEE/MTT-S International, pp.1259-1262, 2007.

- [1.29] D. Kimball, P. Draxler, J. Jeong, H. Chin, S. Lanfranco, W. Nagy, K. Linthicum, L. Larson, and P.M. Asbeck, "50% PAE WCDMA basestation amplifier implemented with GaN HFETs," Compound Semiconductor Integrated Circuit Symposium, 2005. CSIC '05. IEEE, pp.89-92, 2005.

- [1.30] Y. Yasuda. (2011, March 3). In Japanese [Online]. Available: http://www.ieice.org/cs/ns/ws/2011/pdf/27nsinws\_invited\_5.pdf

- [1.31] W. Shockley, "A unipolar "field-effect" transistor," Proc. IRE, vol. 40, pp. 1365-1376, Nov. 1952.

- [1.32] S.H. Wemple, W.C. Niehaus, H.M. Cox, J.V. Dilorenzo, and W.O. Schlosser, "Control of gate-drain avalanche in GaAs MESFET's," IEEE Trans. Electron Devices, vol. 27, pp. 1013-1018, 1980.

- [1.33] D. Delagebeaudeuf and N.T. Linh, "Metal-(n)AlGaAs-GaAs two-dimensional electron gas FET," IEEE Trans. Electron Devices, vol. ED-29, pp. 955-960, 1982.

- [1.34] T.J. Drumonnd, H, Morkoc, K. Lee, and M. Shur, "Model for modulation doped field effect transistors," IEEE Electron Device Lett., vol. EDL-3, pp. 338-341, 1982.

- [1.35] O. Ambacher, J. Smart, J.R. Shealy, N.G. Weimann, K. Chu, M. Murphy, W.J. Schaff, L.F. Eastman, R. Dimitrov, L. Wittner, M. Stutzmann, W. Rieger, and J. Hilsenbeck, "Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- and Ga-face AlGaN/GaN heterostructures," J. Appl. Phys., 85, pp. 3222-3233, 1999.

- [1.36] A. Elasser and T.P. Chow, "Silicon carbide benefits and advantages for power electronics circuits and systems," Proceedings of the IEEE vol. 90, Issue 6, pp. 969-986, 2002.

- [1.37] J.L.B. Walker, *High-Power GaAs FET Amplifiers*, Norwood, MA: Artech House, 1993.

- [1.38] S.C. Cripps, *RF Power Amplifiers for Wireless Communications*, 2<sup>nd</sup> ed. Norwood, MA: Artech House, 2006.

# Chapter 2

# Push-pull high power amplifiers using a microstrip balun

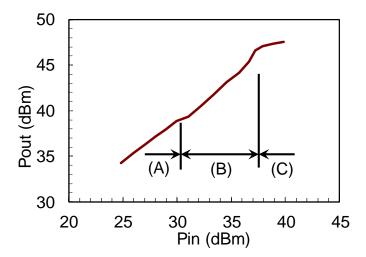

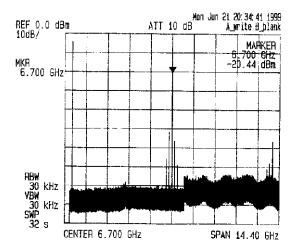

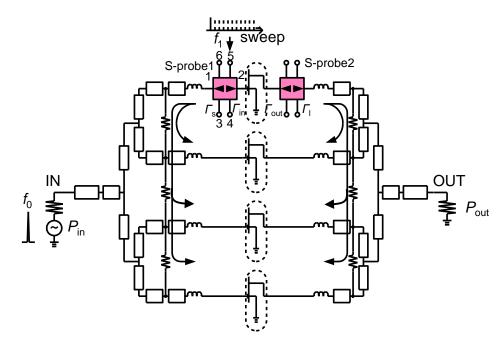

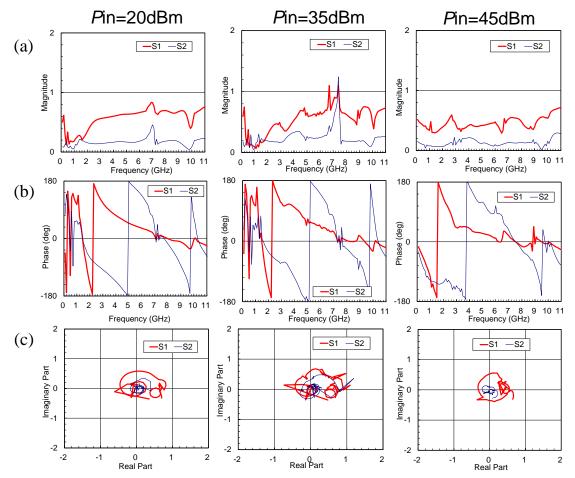

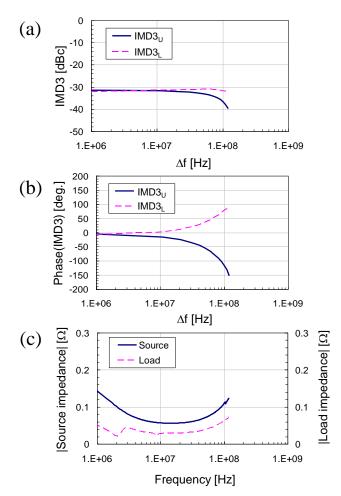

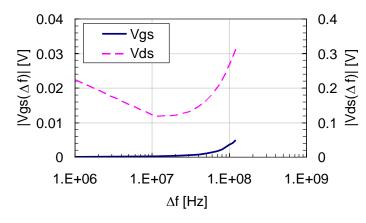

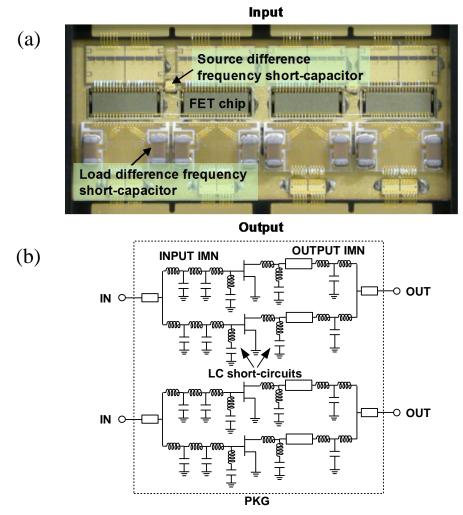

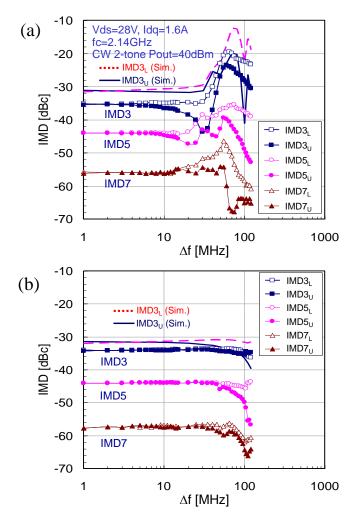

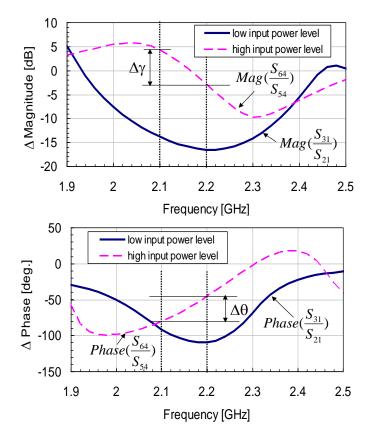

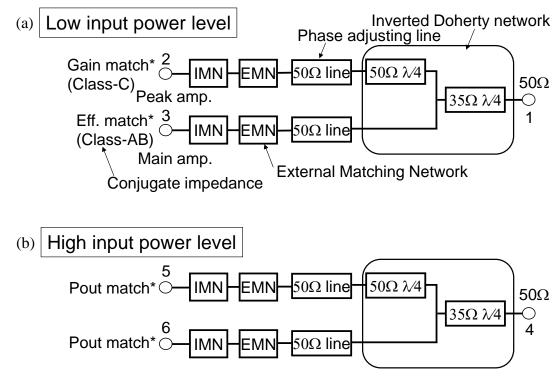

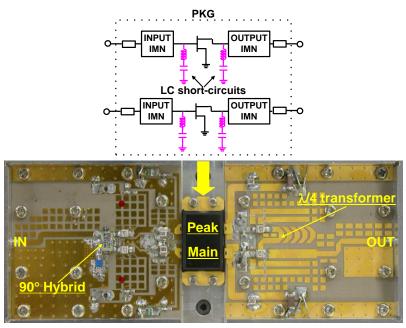

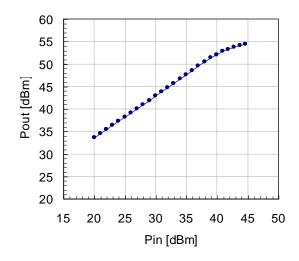

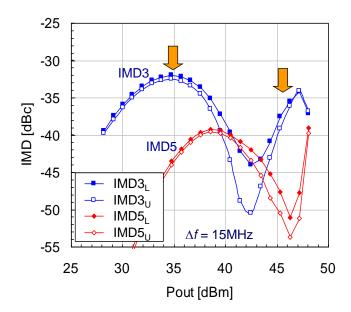

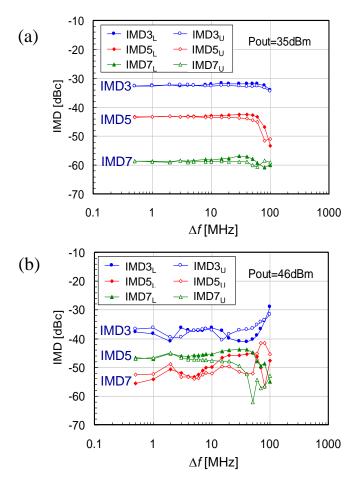

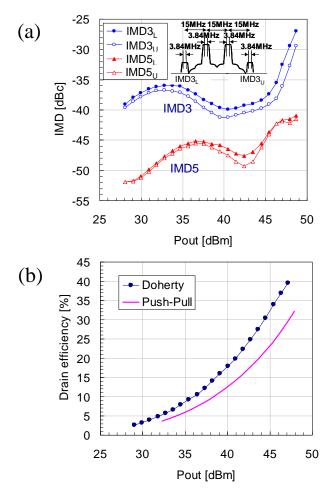

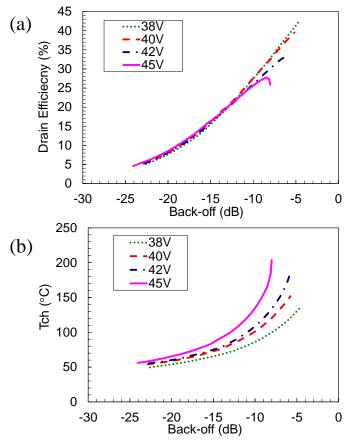

## 2.1 Introduction