|              |                                                                                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------------------|

| Title        | An Autonomous Decentralized Architecture with Agreement Protocols for Safety-Critical Embedded Distributed Control Systems |

| Author(s)    | 櫻井, 康平                                                                                                                     |

| Citation     | 大阪大学, 2014, 博士論文                                                                                                           |

| Version Type | VoR                                                                                                                        |

| URL          | <a href="https://doi.org/10.18910/34575">https://doi.org/10.18910/34575</a>                                                |

| rights       |                                                                                                                            |

| Note         |                                                                                                                            |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

# An Autonomous Decentralized Architecture with Agreement Protocols for Safety-Critical Embedded Distributed Control Systems

Submitted to

Graduate School of Information Science and Technology

Osaka University

January 2014

Kohei SAKURAI

# ABSTRACT

Embedded control systems are widely equipped in current industrial products such as home appliances, automobiles, trains, and power plants. They need to have hard real-time and mission-critical capabilities, and to be more severely restricted in cost and available hardware resources than computer systems in the information technology industry.

Automotive control systems, out of the various embedded control systems, impose particularly severe restrictions on the cost because of the scale of mass production, while recent advances in electronic control using embedded controllers should enable more sophisticated vehicle control systems that are aimed toward autonomous driving. One of the emerging systems is an X-by-Wire system, where driving, steering, and braking are electrically and electronically controlled synthetically, that further enhances vehicle driving performance and safety. Since control of acceleration, steering, and braking has a great influence on the safe operation of vehicles, X-by-Wire systems need to be extremely dependable. Various controllers, sensors, and actuators in this system cooperate with one another through a communication network. We take X-by-Wire systems as an example application of safety-critical embedded distributed control systems in this dissertation.

A technical challenge to X-by-Wire systems is that they are restricted by limited costs in mass production to achieve fault-tolerance. Therefore, the goal of this dissertation is to propose suitable solutions that can satisfy not only high dependability but also cost-effectiveness for automotive safety-critical distributed control systems.

We first propose a novel architecture that incorporates the concept of autonomous decentralized systems to accomplish this goal. This architecture allows all nodes in the system including sensor and actuator nodes to obtain the shared information required for vehicle control through the communication network and to autonomously execute backup control if some node in the system fails. Therefore, the proposed architecture can be fail-operational even though it does not have expensive fail-operational nodes with redundant hardware. This approach to dependability through reduced-redundancy is also applied to the node level by taking into consideration the node function. We propose a validity check method instead of dual redundancy to detect faults in actuator nodes. We demonstrate that the proposed system and node level architectures can be applied to actual automotive brake and steering control systems and that they satisfy both requirements of cost-effectiveness and dependability. Our estimation reveals that the system cost can be reduced by approximately from 20 to 30% due to the proposed autonomous decentralized architecture and optimal node hardware architecture, which contributes to a substantial cost reduction for automotive control systems.

Although the autonomous decentralized architecture satisfies competing demands, we point out that some coordination scheme in this architecture, i.e., an agreement protocol, is required to accurately identify failed nodes so that disagreements in the control mode can be avoided. To provide the coordination scheme, we propose a membership protocol as an agreement protocol for safety-critical distributed systems. In contrast to related work, our membership protocol tolerates simultaneous and non-fail-silent (Byzantine) faults and can flexibly be implemented in time-triggered systems as a middleware component. Important properties such as correctness, completeness, and consistency are defined for the proposed membership protocol and are proved by hand.

With a widely used time-triggered communication network in the automotive industry, we developed a prototype Brake-by-Wire system incorporating the proposed autonomous

---

decentralized architecture and membership middleware in a realistic hardware and software environment for automotive control systems. Although we found that the prototype system could persevere in practical use, the results from evaluating the performance of this prototype system indicated that the computation overhead for the membership middleware was prohibitively large and that the execution time required for the voting process increased along with the number of nodes in the system.

To resolve these problems, we further propose novel lightweight membership protocols, which are based on what we call voting sharing and clustering approaches. These approaches can reduce the computation overhead and the communication bandwidth for the membership protocol. Our experiments revealed that the execution time for the voting process in the voting sharing approach was reduced by approximately 60% compared with the original protocol for eight nodes. Following proofs of the same properties as the original protocol, we investigate advantages and disadvantages of the three proposed membership protocols in terms of computation and communication overhead, diagnosis latency, and fault tolerance. Our analysis shows a tradeoff between the overhead and fault tolerance. The lightweight protocols incur degradation in diagnosis accuracy in exchange for the reduction of the computational overhead. We provide additional mechanisms such as rotating voters and self-accusation to mitigate this problem.

Finally, we propose a customizable formal model of generic time-triggered systems to support key system design processes such as task scheduling, test case generation, and verification. Because the proposed formal model has a modular architecture, it can be reused and easily customized, which can reduce the model development costs for industrial practitioners. We demonstrate a prototype implementation of the formal model with the SAL (Symbolic Analysis Laboratory) language and present some use cases using the SAL tool suite. The proposed membership protocols were model-checked in a use case of verification, and the design correctness of the protocols was guaranteed.

# LIST OF MAJOR PUBLICATIONS

- (1) Kohei Sakurai, Nobuyasu Kanekawa, Kunihiko Tsunedomi, Shoji Sasaki, Katsuya Oyama, Takanori Yokoyama, and Mitsuru Watabe, High performance and cost-effective electronic controller architecture for powertrain systems, In *Proceedings of SAE 2004 World Congress: In-Vehicle Network Session*, Paper Number: 2004-01-0209, March 2004.

- (2) Kohei Sakurai, Yuichiro Morita, Kentaro Yoshimura, Nobuyasu Kanekawa, Kotaro Shimamura, Kenichi Kurosawa, and Yoshiaki Takahashi, Cost-effective and fault tolerant vehicle control architecture for X-by-Wire systems (Part 2: Implementation design), In *Proceedings of SAE 2005 World Congress: In-Vehicle Network Session*, Paper Number: 2005-01-1543, April 2005.

- (3) Kentaro Yoshimura, Kohei Sakurai, Yuichiro Morita, Nobuyasu Kanekawa, Kenichi Kurosawa, Yoshiaki Takahashi, Shigetoshi Sameshima, and Akitoshi Shimura, A dependable and cost-effective vehicle control architecture for X-by-wire systems based on autonomous decentralized concept, In *Supplemental Volume of the 2005 International Conference on Dependable Systems and Networks (DSN 2005)*, pp. 130–138, June 2005.

- (4) Kentaro Yoshimura, Kohei Sakurai, Yuichiro Morita, Kenichi Kurosawa, Yoshiaki Takahashi, Shigetoshi Sameshima, and Akitoshi Shimura, A dependable E/E ar-

chitecture for X-By-Wire systems based on autonomous decentralized concept, In *Proceedings of the 12th International Congress on Electronic Systems for Vehicles*, VDI Berichte 1907, pp. 523–534, October 2005.

(5) Kohei Sakurai, Masatoshi Hoshino, Yuichiro Morita, and Yoshiaki Takahashi, Design and implementation of middleware for network centric X-by-Wire systems, In *Proceedings of SAE 2006 World Congress: In-Vehicle Software Session*, Paper Number: 2006-01-1326, April 2006.

(6) Kohei Sakurai, Masahiro Matsubara, Marco Serafini, and Neeraj Suri, Dependable and cost-effective architecture for X-by-Wire systems with membership middleware, In *Proceedings of FISITA 2008 World Automotive Congress*, Paper Number: F2008-05-048, September 2008.

(7) Kohei Sakurai, Péter Bokor, and Neeraj Suri, Aiding modular design and verification of safety-critical time-triggered systems by use of executable formal specifications, In *Proceedings of the 11th IEEE High Assurance Systems Engineering Symposium (HASE 2008)*, pp. 261–270, December 2008.

(8) Masahiro Matsubara, Takao Kojima, Kotaro Shimamura, Nobuyasu Kanekawa, and Kohei Sakurai, Node status monitoring and state transition mechanism for network centric X-by-Wire systems, In *Proceedings of the 9th IEEE International Symposium on Autonomous Decentralized Systems (ISADS 2009)*, pp. 1–6, March 2009.

(9) Kohei Sakurai, Masahiro Matsubara, and Masatoshi Hoshino, Membership middleware for dependable and cost-effective X-by-wire systems, *SAE International Journal of Passenger Cars - Electronic and Electrical Systems*, vol. 1, no. 1, pp. 180–186, April 2009.

(10) Kohei Sakurai, Marco Serafini, Péter Bokor, and Neeraj Suri, Design and formal

verification of membership middleware for dependable automotive network systems, In *Proceedings of the 14th International Congress on Electronic Systems for Vehicles*, VDI Berichte 2075, pp. 399–410, October 2009.

(11) Masahiro Matsubara, Kohei Sakurai, Fumio Narisawa, Masushi Enshoiwa, Yoshio Yamane, and Hisamitsu Yamanaka, Model checking with program slicing based on variable dependence graphs, In *Proceedings of the 1st International Workshop on Formal Techniques for Safety-Critical Systems (FTSCS 2012)*, pp. 56–68, November 2012.

(12) Masahiro Matsubara, Kohei Sakurai, Fumio Narisawa, Masushi Enshoiwa, Yoshio Yamane, and Hisamitsu Yamanaka, Application of model checking to automotive control software with slicing technique, In *Proceedings of SAE 2013 World Congress: Model-Based Design and In-Vehicle Software Session*, Paper Number: 2013-01-0436, April 2013.

(13) Kohei Sakurai, Masahiro Matsubara, and Tatsuhiro Tsuchiya, Voting sharing: An approach to reducing computation time for fault diagnosis in time-triggered systems, *IEICE Transactions on Information and Systems*, vol. E97-D, no. 2, February 2014 (to be published).

# ACKNOWLEDGMENTS

During the course of this study, I have been fortunate to receive invaluable assistance from many individuals.

I deeply appreciate my supervisor Professor Tatsuhiro Tsuchiya, who has continuously inspired me and provided me with valuable insights and advice throughout this work. I am also grateful to Emeritus Professor Tohru Kikuno for his encouragement before I enrolled in the doctoral course at Osaka University.

I would also like to thank the members of my dissertation review committee, particularly Professor Masaharu Imai, Professor Toshimitsu Masuzawa, and Associate Professor Masanori Hashimoto for their invaluable comments and constructive criticism of this dissertation.

Furthermore, my gratitude goes to the members of Tsuchiya Laboratory, especially to Assistant Professor Hideharu Kojima for the productive discussions on this work, and Mr. Hirofumi Terada, who is also a colleague at Hitachi, Ltd., for his encouragement.

A significant part of this work has also been done with researchers of the DEEDS (Dependable Embedded Systems and Software) group in Technische Universität Darmstadt in Germany. I would like to express my sincere gratitude to Professor Dr. Neeraj Suri, Dr. Péter Bokor, and Dr. Marco Serafini for all the valuable discussions I had with them on dependable distributed systems and formal methods.

Some research work I have engaged in Hitachi, Ltd. has been helpful to me in com-

pleting this dissertation. I would therefore like to express my thanks to Dr. Takashi Hotta, Mr. Atsushi Kawabata, Dr. Toshiharu Nogi, Mr. Takaomi Nishigaito, Dr. Masahiko Amano, Mr. Yoshiaki Takahashi, and Mr. Kenichi Kurosawa for giving me the opportunity of doing research on automotive safety-critical control systems. I would also like to acknowledge Dr. Hiroyuki Mikami and Mr. Takuya Shiraishi who encouraged me while I was compiling this thesis.

This work has been done collaboratively with many colleagues at Hitachi Research Laboratory, especially Mr. Masahiro Matsubara, Dr. Kentaro Yoshimura, Dr. Nobuyasu Kanekawa, Mr. Kotaro Shimamura, Mr. Masatoshi Hoshino, and Dr. Yuichiro Morita (the last two researchers are currently with Hitachi Construction Machinery). I would like to express my deep appreciation to all of them for the valuable insights they gave me and the productive discussions from the perspectives of industry.

Finally, my sincere appreciation also goes to my family who always supported me throughout difficult times.

# CONTENTS

|                                                                |           |

|----------------------------------------------------------------|-----------|

| Abstract . . . . .                                             | i         |

| List of Major Publications . . . . .                           | v         |

| Acknowledgments . . . . .                                      | ix        |

| <b>1 Introduction</b>                                          | <b>1</b>  |

| 1.1 Scope and Background . . . . .                             | 1         |

| 1.1.1 Embedded Control Systems . . . . .                       | 1         |

| 1.1.2 Trend in Automotive Electronic Control Systems . . . . . | 2         |

| 1.1.3 Automotive X-by-Wire Systems . . . . .                   | 4         |

| 1.2 Motivation and Objective . . . . .                         | 4         |

| 1.3 Contributions . . . . .                                    | 5         |

| 1.3.1 Autonomous Decentralized Architecture . . . . .          | 5         |

| 1.3.2 Membership Protocol . . . . .                            | 7         |

| 1.3.3 Generic Formal Model of Time-Triggered Systems . . . . . | 9         |

| 1.4 Overview of Dissertation . . . . .                         | 11        |

| <b>2 Autonomous Decentralized Architecture</b>                 | <b>13</b> |

| 2.1 Reduced-Redundancy Approach . . . . .                      | 13        |

| 2.2 Autonomous Decentralized Architecture . . . . .            | 14        |

| 2.2.1 Conventional Control Systems . . . . .                   | 14        |

|          |                                                     |           |

|----------|-----------------------------------------------------|-----------|

| 2.2.2    | Autonomous Decentralized Control Systems            | 16        |

| 2.3      | Fail-Silent Node Architecture                       | 24        |

| 2.3.1    | Comparison of Fail-Silent Nodes                     | 24        |

| 2.3.2    | Node Hardware Architecture                          | 27        |

| 2.4      | Estimation of System Cost Reduction                 | 30        |

| <b>3</b> | <b>Agreement Protocol</b>                           | <b>35</b> |

| 3.1      | Challenges to Autonomous Decentralized Architecture | 35        |

| 3.2      | Model of Time-Triggered Systems                     | 36        |

| 3.2.1    | Communication Model                                 | 36        |

| 3.2.2    | Fault Model                                         | 37        |

| 3.3      | Membership Protocol                                 | 38        |

| 3.3.1    | Protocol Description                                | 38        |

| 3.3.2    | Example of Membership Protocol                      | 43        |

| 3.3.3    | Properties                                          | 45        |

| <b>4</b> | <b>Prototype Brake-by-Wire System</b>               | <b>47</b> |

| 4.1      | Introduction                                        | 47        |

| 4.2      | Software Architecture                               | 47        |

| 4.3      | Prototype Implementation and Evaluation             | 51        |

| 4.4      | Discussion                                          | 54        |

| <b>5</b> | <b>Lightweight Membership Protocol</b>              | <b>57</b> |

| 5.1      | Introduction                                        | 57        |

| 5.2      | Voting Sharing                                      | 58        |

| 5.2.1    | Protocol                                            | 58        |

| 5.2.2    | Properties                                          | 61        |

| 5.2.3    | Rotating Voters                                     | 63        |

---

|                     |                                                      |            |

|---------------------|------------------------------------------------------|------------|

| 5.2.4               | Experiment Results . . . . .                         | 65         |

| 5.3                 | Clustering . . . . .                                 | 66         |

| 5.3.1               | Protocol . . . . .                                   | 67         |

| 5.3.2               | Properties . . . . .                                 | 68         |

| 5.3.3               | Self-Accusation . . . . .                            | 71         |

| 5.4                 | Discussion . . . . .                                 | 73         |

| <b>6</b>            | <b>Formal Model of Time-Triggered Systems</b>        | <b>77</b>  |

| 6.1                 | Introduction . . . . .                               | 77         |

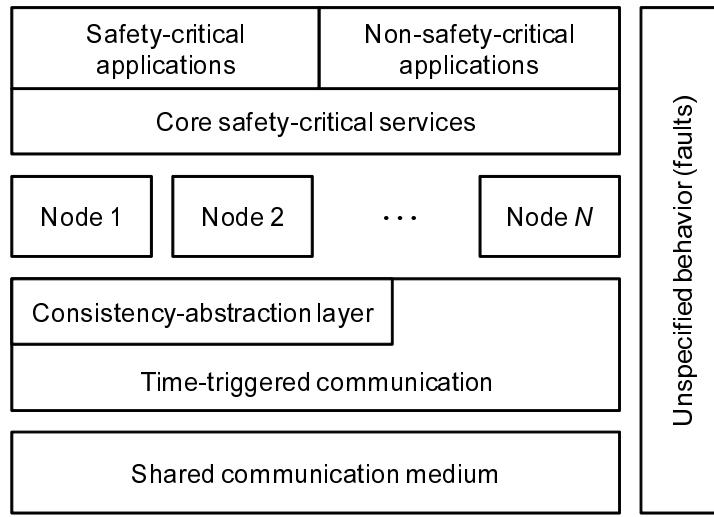

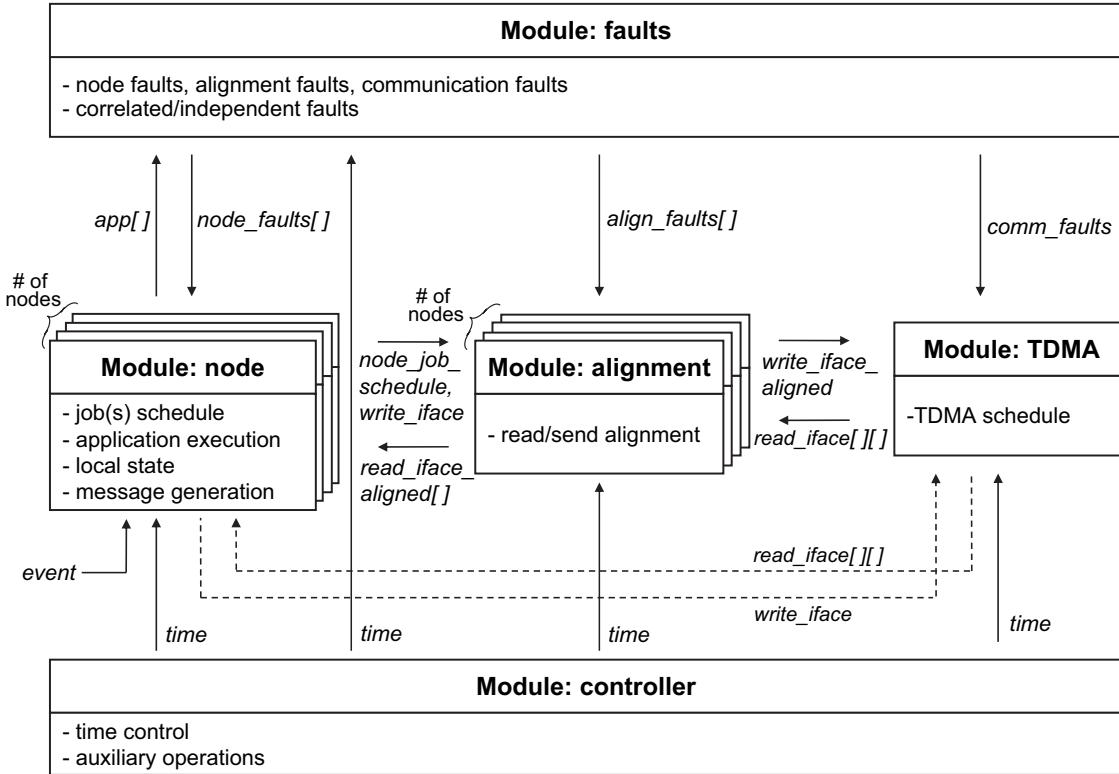

| 6.2                 | Overview of TT Systems . . . . .                     | 80         |

| 6.2.1               | Basic Concepts and Definitions . . . . .             | 80         |

| 6.2.2               | Consistency-Abstraction Layer . . . . .              | 82         |

| 6.2.3               | Characterization of Faults . . . . .                 | 83         |

| 6.3                 | Customizable Formal Model . . . . .                  | 84         |

| 6.4                 | Implementation with SAL Language . . . . .           | 87         |

| 6.5                 | Example Use Cases: Design and Verification . . . . . | 96         |

| 6.5.1               | Verification . . . . .                               | 96         |

| 6.5.2               | Scheduling of Jobs . . . . .                         | 100        |

| 6.5.3               | Test Generation . . . . .                            | 101        |

| 6.6                 | Related Work . . . . .                               | 102        |

| 6.7                 | Summary . . . . .                                    | 104        |

| <b>7</b>            | <b>Conclusion</b>                                    | <b>105</b> |

| 7.1                 | Achievements . . . . .                               | 105        |

| 7.2                 | Future Work . . . . .                                | 109        |

| <b>Bibliography</b> |                                                      | <b>111</b> |

# CHAPTER 1

## INTRODUCTION

### 1.1 Scope and Background

#### 1.1.1 Embedded Control Systems

First, we define an embedded control system, which is the scope of this dissertation.

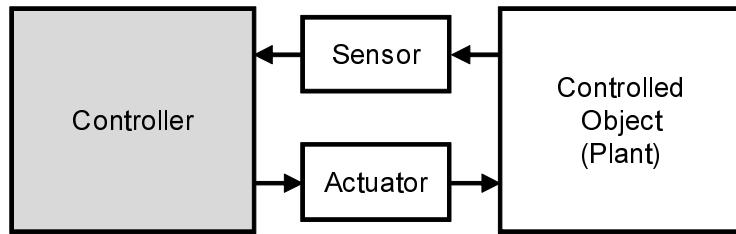

An embedded control system is a computer system integrated into some equipment and it achieves the required functionality by executing the specific control operation to the equipment. A model of embedded control systems is shown in Figure 1.1. The system consists of a controller, a controlled object that is often called a plant, sensors, and actuators. The controller is equipped with microcontrollers, on which the embedded software runs. The controller calculates control target values using information from sensors that measure the status of the plant, and drives the actuators based on the calculated control target values.

Embedded control systems are widely used in industrial products such as home appliances, automobiles, trains, and power plants. For instance, the automotive industry recently recognized that electronics and embedded software developments would represent 90% of all new-vehicle innovations. The increasing functional requirements of embedded

Figure 1.1: Embedded control systems

control systems have led to an enormous increase in software complexity and size.

Embedded control systems are required to have hard real-time and mission-critical capabilities, while they are severely restricted in cost and available hardware resources such as CPU performance, memory size, and communication bandwidth, compared with computer systems like servers and personal computers in the information technology industry.

This dissertation focuses on automotive control systems which impose one of the tightest technical restrictions in the industry due to the scale of mass production. In this dissertation, controllers will be called ECUs, or Electronic Control Units, within the context of automotive control systems.

### 1.1.2 Trend in Automotive Electronic Control Systems

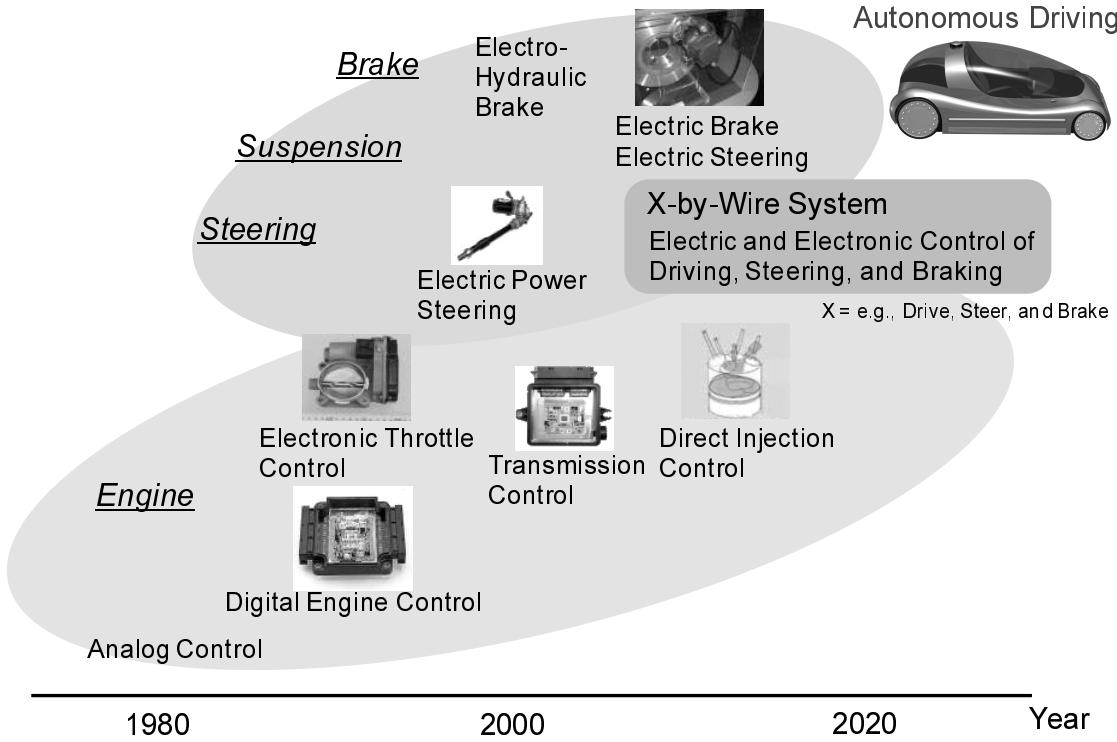

Automotive control systems have been evolving to improve environmental friendliness (i.e., better fuel efficiency, lower exhaust gas emissions), safety, and passenger comfort. Figure 1.2 outlines the trend in automotive electronic control systems. Electronic control using embedded controllers started in the 1980s for powertrain systems such as engines and transmissions. After that, electronic control was also applied to chassis systems such as brakes, suspensions, and steering in the 1990s. In addition to electronics, electric inverters and motor technologies have been used in electric powertrain and chassis systems.

Figure 1.2: Trend in automotive electronic control systems

Recent advances in automotive electronic control systems should enable more sophisticated vehicle control systems toward autonomous driving [1]. Among these systems, *X-by-Wire* systems, where driving, steering, and braking are electrically and electronically controlled synthetically are expected to further enhance vehicle driving performance and safety. The term “*X-by-Wire*” was derived from “*Fly-by-Wire*” in aircraft control systems, where “*by-Wire*” means that systems are controlled by wire, i.e., by electricity, instead of conventional mechanical devices. “*X*” corresponds to such as Drive, Brake, and Steer. *X-by-Wire* systems are expected to reduce vehicle weight and increase cabin space due to the absence of mechanical links, as well as enhance vehicle controllability.

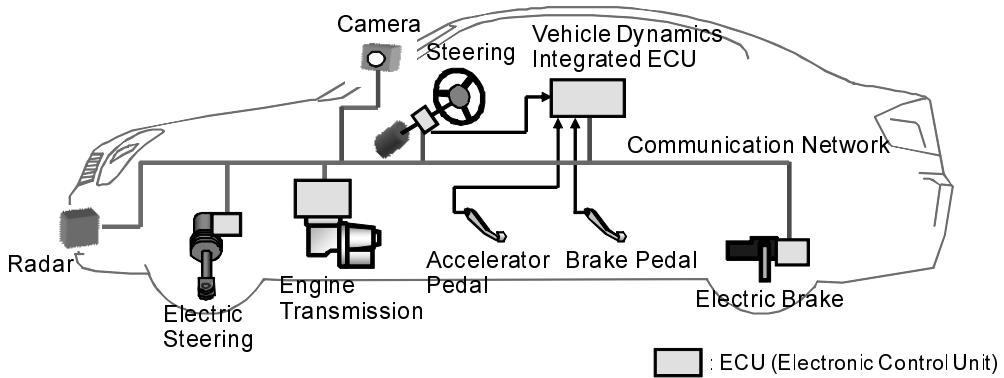

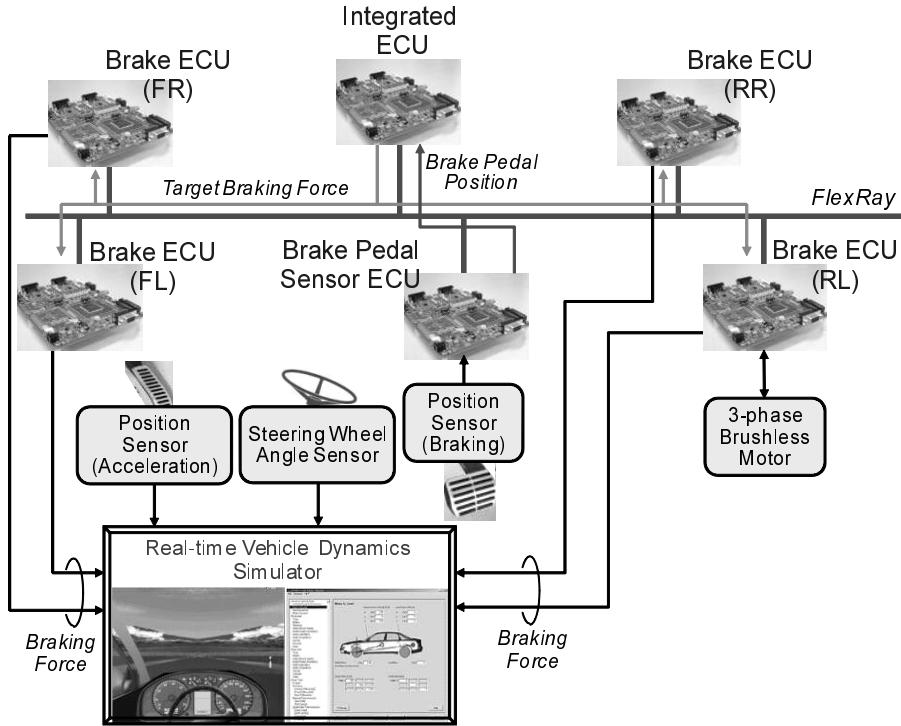

Figure 1.3: Automotive X-by-Wire system

### 1.1.3 Automotive X-by-Wire Systems

An example of the X-by-Wire system architecture is described in Figure 1.3. Various controllers (ECUs), sensors such as a camera, radar, and actuators including electric brakes and steering motors cooperate with one another through a communication network, which attains integrated control of vehicle dynamics. The vehicle dynamics integrated ECU executes integrated control using information on driver operations and the external environment, and sends control target values to the actuators. Braking and steering are electrically and electronically controlled and thus system dependability is no longer guaranteed by conventional mechanical links such as hydraulic brake hoses and steering columns to transmit driver operations to braking and steering mechanisms. Therefore, we can regard X-by-Wire systems as *safety-critical distributed control systems*. An example application in this dissertation is automotive X-by-Wire systems.

## 1.2 Motivation and Objective

X-by-Wire systems need to be highly dependable since acceleration, steering, and braking control have a great influence on the safe operation of vehicles. Several studies on the

reliability of X-by-Wire systems have been done [2, 3]. However, the cost to implement fault-tolerance is limited in mass produced X-by-Wire systems in the automotive industry. Furthermore, available hardware resources such as CPUs, memories and communication bandwidths are severely restricted. These constraints differ from those in transportation or industrial systems domains like aviation, trains, and power plant systems, where relatively expensive systems with high redundancy and sufficient hardware resources are acceptable. Therefore, the goal of this dissertation is to propose suitable solutions that can fulfill not only high levels of dependability but also cost-effectiveness for automotive safety-critical systems.

## 1.3 Contributions

### 1.3.1 Autonomous Decentralized Architecture

Because acceleration, steering, and braking control have a great influence on the safe operation of vehicles, X-by-Wire systems are required to be highly dependable. The conventional approach to improving dependability is to have component level redundancy, where nodes in the system are designed to be fail-operational with such as triple or more redundancy and to keep on operating when faults occur. Several studies on the reliability of X-by-Wire systems with this approach have been done [2, 3]. On the other hand, to mass-produce systems for various vehicle segments, the cost cannot be excessive to implement fault-tolerance.

We take a reduced-redundancy approach with system level redundancy instead of component level redundancy to balance these competing requirements of cost-effectiveness and dependability in automotive control systems. We propose a novel architecture that incorporates the concept of autonomous decentralized systems [4]. Because no general methods of applying the concept of autonomous decentralized systems have yet been

---

established, it is necessary to develop a suitable architecture for individual domains of application.

In the conventional architecture, all the control functions and information such as the sensing data from the driver's acceleration, braking, and steering operations are centralized in the controller node. In contrast, in the proposed architecture, all nodes related to vehicle control, including sensor and actuator nodes, share various data required for control through the communication network, and each node autonomously obtains or broadcasts the necessary data from or to the network. If a certain node stops operating because of some fault, the remaining normal nodes autonomously execute a backup control function to maintain at least the minimum functionality necessary for the system using the shared data. Therefore, the proposed architecture can tolerate the existence of failed nodes and thus does not need expensive fail-operational nodes with triple or more redundant architectures, which satisfies the requirements of cost-effectiveness as well as dependability. We demonstrate that the proposed architecture can be applied to actual automotive brake and steering control systems.

We apply this approach of reduced-redundancy dependability to the node level. Nodes in distributed systems need to be fail-silent so that a failed node does not interfere with communication between fully functional nodes. Conventional fail-silent nodes are designed with dual redundant architecture to detect faults. To further reduce redundancy, the concept of an output validity check is proposed for actuator control nodes. Low performance inexpensive sub-microcontrollers can be used in this concept to diagnose the main microcontrollers. The sub-microcontrollers only compare target control values and actual actuator output instead of rigidly checking the main microcontroller's execution as is done in a dual redundant architecture. The hardware architecture of individual controllers is optimized in this way according to their functions.

We estimate the system cost reduction by the proposed autonomous decentralized

architecture and optimal node hardware architecture, and show that the system cost can be reduced by approximately from 20 to 30%, which contributes to a substantial cost reduction for automotive control systems.

### 1.3.2 Membership Protocol

Autonomous backup control in the autonomous decentralized architecture is based on the accurate identification of failed nodes. However, since there is no master node to monitor the status of nodes in the system, node status monitoring or diagnosis function in each node plays a key role for fault-tolerance. Therefore, some coordination scheme, i.e., an agreement protocol, is required to accurately identify the failed nodes and ensure consistency in views on available nodes for all the normally functioning nodes so that disagreements in the control mode can be avoided. We propose a *membership protocol* as an agreement protocol for safety-critical distributed systems to resolve this issue.

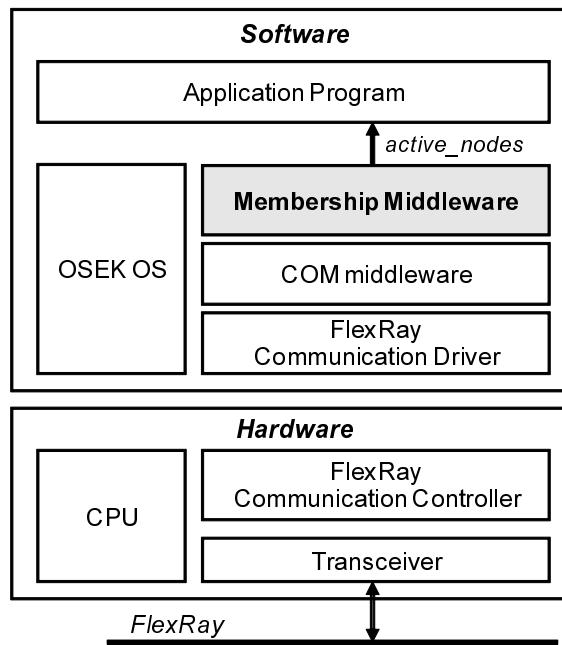

The membership protocol is a functionality that provides a consistent view of active nodes to each node. Time-triggered (TT) communication platforms such as FlexRay [5], TTP/C [6], TT-Ethernet [7], and SAFEbus [8] are increasingly being applied to safety-critical distributed control systems. Although FlexRay has widely been applied to automotive control systems, it does not specify a membership protocol in its standard specifications and this protocol remains as a user dependent functionality. The TT-Ethernet does not provide a standardized protocol either. The AUTOSAR (AUTomotive Open System ARchitecture) [9], which is a worldwide de facto standard specification for automotive electric/electronic systems, neither defines membership services. TTP/C, on the other hand, which is used in aerospace systems, has a membership protocol. However, the protocol is implemented in hardware and has been designed for dedicated applications. Furthermore, several membership protocols have been proposed [10–12], or formally verified [13, 14].

---

Many previous membership protocols for TT systems only assumed fail-silent nodes and single fault. We also assume fail-silence on the communication protocol level, as was discussed earlier. However, application programs in reality might send semantically erroneous messages because of, e.g., corrupted memory or failure in processing units, even though the messages conform to the communication protocol specifications. Several faults might also occur simultaneously. In contrast, Serafini et al. have proposed protocols that do not rely on the single-fault assumption and that can also tolerate non-fail-silent (Byzantine) faults [15]. The protocols can be added to generic TT communication protocols.

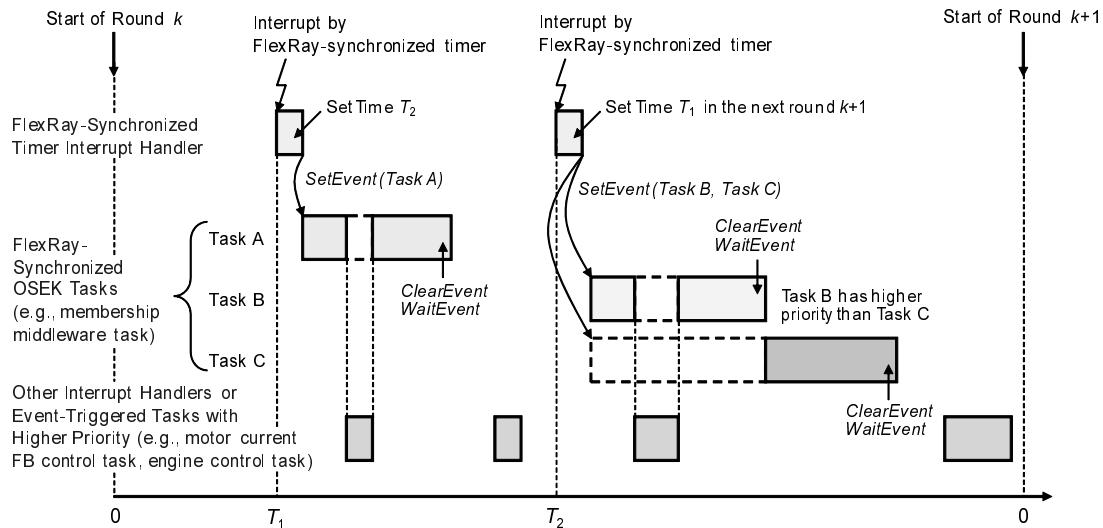

Our proposed membership protocol in this dissertation also tolerates simultaneous and Byzantine faults and can be flexibly implemented in TT systems as a middleware component [16]. We further enhance its real-time capabilities and aim at implementing the protocol in realistic automotive control systems. Each node in the membership protocol locally evaluates the status of other nodes in the system and exchanges a local view, which we call a local syndrome, with all nodes. Then, every node identifies the failed node by voting on the exchanged local syndromes. We propose a pipeline-like method of executing the protocol to improve its real-time capabilities, where a fault detected in a certain TT communication round can be identified in the next round. The membership middleware in practical X-by-Wire systems should coexist with real-time critical application programs such as motor control on microcontrollers with restricted resources. We developed a prototype Brake-by-Wire system that incorporated the proposed autonomous decentralized architecture and membership protocol, and clarified that the prototype system could persevere in practical use.

The results we obtained from evaluating the performance of this prototype system, however, revealed that the computational overhead incurred by membership functionality was unacceptably large and it increased along with the number of nodes in the system.

The membership overhead has to be small enough so that vehicle control applications can use sufficient CPU resources. Therefore, we propose novel lightweight membership protocols, which we call *voting sharing* and *clustering* in this dissertation.

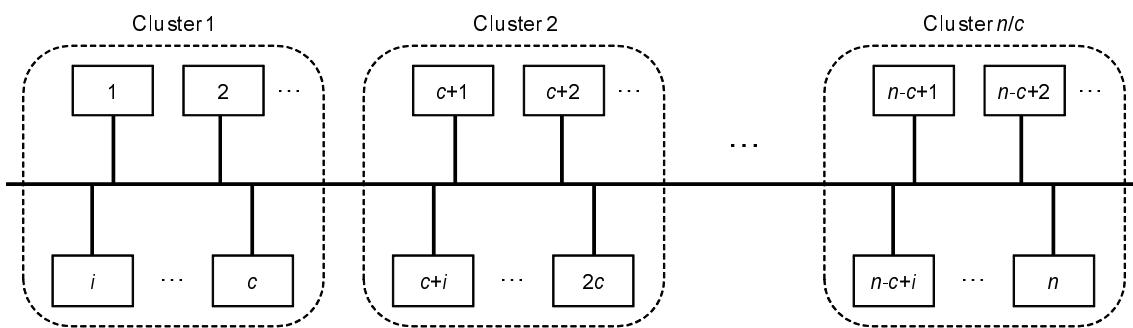

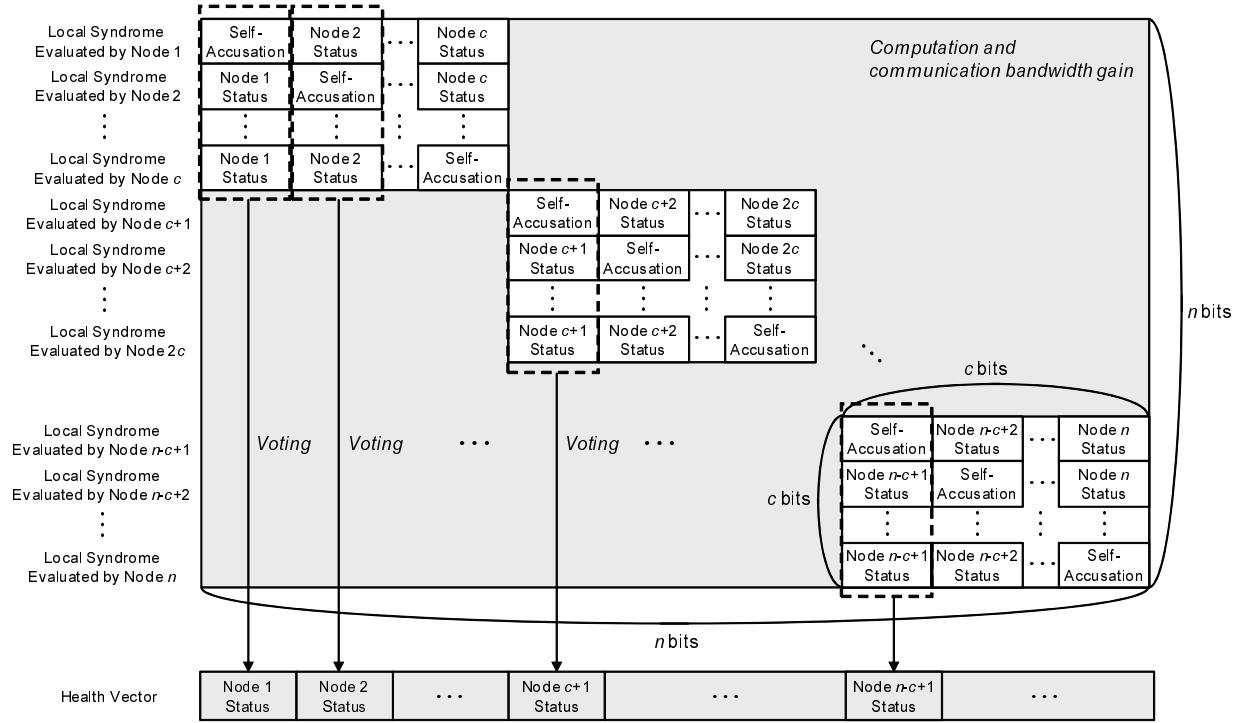

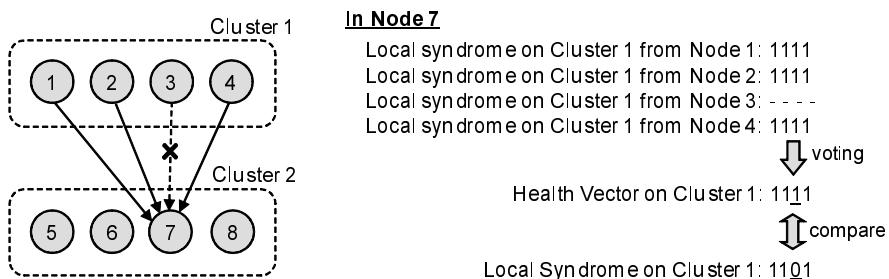

The main idea behind voting sharing is to have each node vote for only one respective node and to share the voting results with all nodes. In the clustering concept,  $n$  nodes are logically divided into  $n/c$  clusters, where each cluster consists of  $c$  nodes. Node  $p$  sends a local syndrome only with respect to nodes within the cluster to which node  $p$  belongs to all the other nodes in the system. Both approaches can reduce the computation overhead for membership, and the clustering protocol can also decrease the communication bandwidth, compared with the original protocol. The results from our experiments revealed that the execution time for the voting process in the voting sharing protocol was reduced by approximately 60% compared with the original membership protocol for eight nodes.

We investigate advantages and drawbacks of the three proposed membership protocols in terms of computation and communication overhead, diagnosis latency, and fault tolerance. Our analysis shows that there is a tradeoff between the overhead and fault tolerance. The lightweight protocols incur degradation in diagnosis accuracy in exchange for the reduction of the computational overhead. However, it can be mitigated with additional mechanisms such as rotating voters, counter update algorithm, and self-accusation. Despite the drawbacks, we point out that the clustering protocol is a well-balanced protocol among these three protocols when the system consists of large number of nodes and the fault condition is not so severe.

### 1.3.3 Generic Formal Model of Time-Triggered Systems

The use of *formal methods* is increasingly being advocated to verify general safety-critical systems, e.g., [17]. However, previous work [18, 19] has demonstrated that the correctness of high-level applications in TT systems does not directly imply the correctness of

---

implementation. Consequently, formal techniques dedicated to time-triggered systems are required, especially given their increasing deployment.

Results on the successful formal analysis of TT systems do exist; however, they present specific solutions (e.g., [18–20]), where modeling patterns can only partially be re-used in new projects. It is generally difficult in industry to apply formal methods to the development processes of mass production. Software engineers rarely design formal models of their systems or software from scratch. Therefore, we propose a generalized formal model of TT applications that can be customized, which is not restricted to any dedicated implementation and that can also easily be used by engineers who are not specialists in formal methods.

Furthermore, we seek a unified and formal treatment of general TT systems to guide key system design tasks such as task scheduling, test case generation, and verification. Although deductive reasoning (e.g., theorem proving [17]) is a powerful tool to even verify the complex properties of infinite systems, it cannot directly be used to simulate systems for finding certain execution paths (e.g., counterexamples and test cases). Consequently, we propose executable system specifications to provide further features besides verification by using model checking.

Because the proposed formal model has a modular architecture, it can be reused and easily customized, which can reduce the model development costs for practitioners in industry. Users only need to tailor the corresponding modules to customize the general model.

A prototype formal model was implemented with the SAL (Symbolic Analysis Laboratory) language [21]. We also demonstrate the usability of our prototype with the SAL tool suite by presenting use cases of verification, task scheduling, and test case generation based on an identical model. The proposed membership protocols were model-checked in a use case of verification, and we confirmed the design correctness of the protocols.

## 1.4 Overview of Dissertation

This dissertation is organized as follows:

Chapter 2 proposes an architecture that incorporates the concept of autonomous decentralized systems to satisfy both requirements of cost-effectiveness and dependability, which is in contrast to the conventional architecture. Fail-silent node architectures according to node functionalities are also discussed. We give the estimation results on the system cost reduction by the proposed autonomous decentralized architecture and optimal node hardware architecture.

Chapter 3 describes a membership protocol as an agreement protocol in distributed systems. We clarify a model of time-triggered systems including fault behaviors, following a discussion on the importance of membership services in the autonomous decentralized architecture. Then, we explain the proposed membership protocol using some examples and pseudo-codes. Important properties for distributed systems such as correctness, completeness, and consistency are defined and proved by hand.

Chapter 4 presents a prototype Brake-by-Wire system that employs the proposed autonomous decentralized architecture and membership protocol. We explain how the membership middleware is implemented on a resource-restricted microcontroller with realistic control application programs. Results obtained from evaluating the performance of the membership middleware are also provided in this chapter.

Taking into account the performance evaluation results, in Chapter 5, we propose lightweight membership protocols, voting sharing and clustering, which can reduce the computation overhead and communication bandwidth. We explain both protocols in detail by using pseudo-codes and prove the same properties as the original protocol. This chapter also compares three types of membership protocols, i.e., original, voting sharing, and clustering, in terms of various aspects and discusses a tradeoff between the computational

---

overhead and fault tolerance.

Chapter 6 proposes a modular formal model of generic time-triggered systems. We demonstrate a prototype implementation of the formal model with the SAL language and provide example use cases of system design such as task scheduling, verification, and test case generation based on the same model in the SAL tool suite environment. The proposed membership protocols are also model-checked in a verification use case.

Finally, we conclude this dissertation in Chapter 7 with achievements and directions for future work.

# CHAPTER 2

## AUTONOMOUS DECENTRALIZED ARCHITECTURE

### 2.1 Reduced-Redundancy Approach

We take a reduced-redundancy approach to satisfy both dependability and cost-effectiveness requirements for automotive control systems.

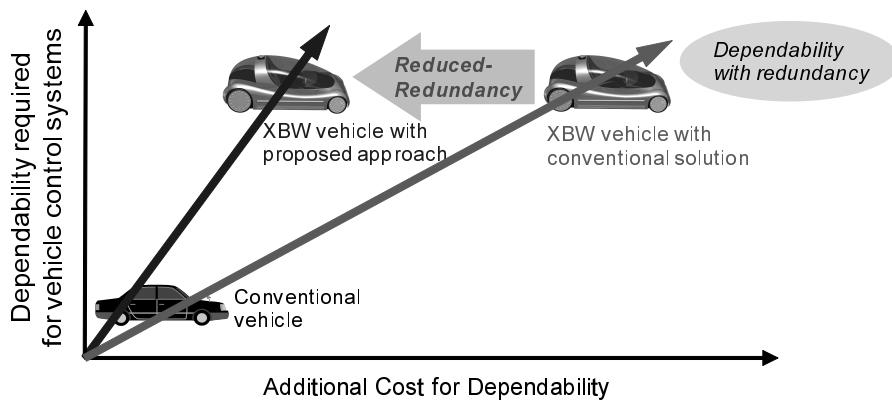

In systems where system fault-tolerance is achieved by improving fault-tolerance of each component that makes up the system, components are designed to be fail-operational, e.g., triple redundant, which will increase the cost of the components. Our basic concept to balance dependability and cost-effectiveness is *reduced-redundancy dependability*. As can be seen in Figure 2.1, this approach tries to reduce redundancy as much as possible and to accomplish equivalent dependability with lower additional cost than the conventional solution. Because we cannot rely on the redundancy, we design the system such that it can keep on operating without the functions of failed components if some components should fail. Consequently, the component cost can be reduced as each component does not necessarily need to be fail-operational.

Figure 2.1: Reduced-redundancy approach

We have developed technologies for reduced-redundancy dependability in several layers at the system level, node (ECU) level, and chip (microcontroller) level. This dissertation focuses on the system and the node levels. We propose an autonomous decentralized architecture for the system level, and optimal hardware architectures in fail-silent nodes appropriate to their functions for the node level, which will be discussed in Sections 2.2 and 2.3 respectively.

## 2.2 Autonomous Decentralized Architecture

### 2.2.1 Conventional Control Systems

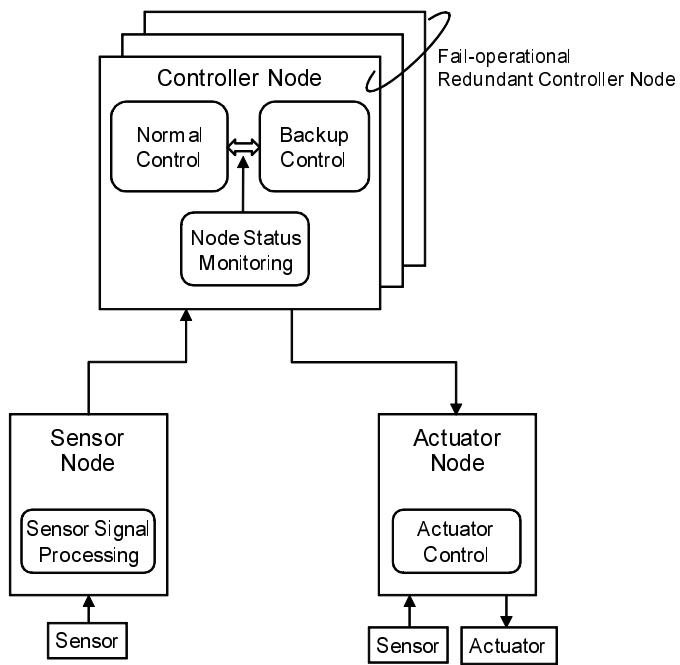

Figure 2.2 outlines the architecture for a conventional control system. The system consists of sensor nodes, controller nodes, and actuator nodes. The controller nodes execute the control functions based on sensor signals received from the sensor nodes, and send control commands to the actuator nodes. The controller nodes also monitor the status of the sensor/actuator nodes and if failure in a certain node is detected, the controller nodes change the normal control function to a backup control function. The actuator nodes

Figure 2.2: Conventional control system architecture

receive the control command for backup control\*.

However, all the control functions in the conventional architecture are centralized in the controller node, which means that this architecture is essentially equivalent to a master-slave architecture. The actuator node (slave) only executes actuator control as the controller node (master) orders. It follows that a failure in the controller node will easily lead to system failure due to centralization of the control functions. To avoid this problem, the controller node should be fail-operational, i.e., it should keep operating even if one or possibly multiple faults have occurred in the node. A triple or more redundant architecture is commonly used for fail-operational nodes, but this solution tends to increase node costs, and consequently system costs.

\*Each node actually has a self-diagnosis function and a node-level backup function based on the self-diagnosis results, which are not specifically described in Figure 2.2.

## 2.2.2 Autonomous Decentralized Control Systems

### Basic Idea

We propose an architecture based on the concept of *autonomous decentralized systems* [4] to balance the competing requirements of cost-effectiveness and dependability for automotive control systems.

Autonomous decentralized systems represent one type of distributed control systems, that are used in industrial systems such as factory and train control systems required to be highly efficient and dependable. For example, the ATOS (Autonomous decentralized Transport Operation Control System) has been developed for the train traffic control system in the Tokyo metropolitan area [22].

The concept is derived from an analogy of living organisms that consist of *autonomous* and *decentralized* cells. Elements called *nodes* are loosely connected through a *data field*, where the data required for control are shared. We can achieve a fault-tolerant and scalable system with this concept, where every node is autonomous and independent. The system will not fail when nodes malfunction and improve scalability because of communication based on a standardized data interface. It is necessary to develop a suitable architecture for each application domain to apply the concept based on a biological model to real systems because no general methods of application have yet been established.

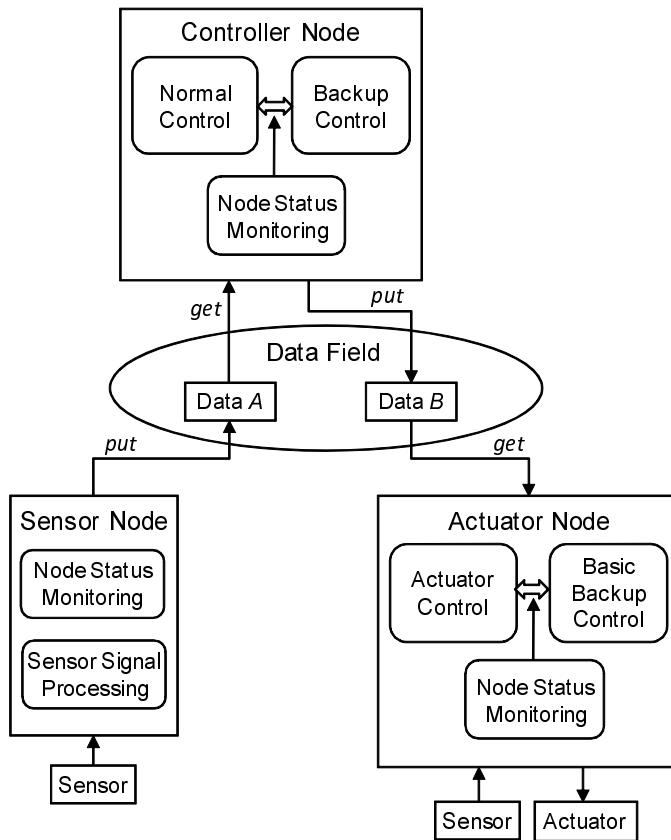

We propose the autonomous decentralized architecture for automotive control systems outlined in Figure 2.3. Although the normal vehicle control function is centralized in the controller node in this architecture, the backup control function and the node status monitoring function are decentralized in all nodes<sup>†</sup>. All nodes share various data required to control the vehicle through the data field, equivalent to a virtual shared memory. Each node autonomously *gets* or *puts* data from or to the data field and executes its functions,

---

<sup>†</sup>Sensor nodes do not have backup control functions.

Figure 2.3: Architecture for autonomous decentralized control system

which are triggered by conditions in the time and state transitions of the node without receiving processing demands from the control nodes.

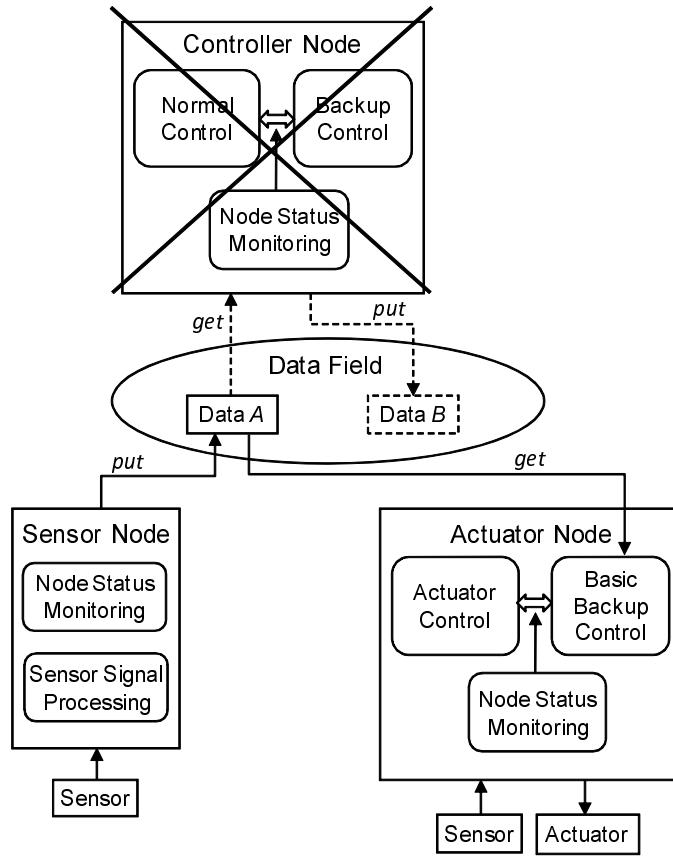

Every node, including the sensor/actuator nodes, can monitor the status of the other nodes in the system to ensure fault-tolerance. Figure 2.4 shows how the system operates when the controller node has failed. If the actuator node has diagnosed the controller node as faulty, it autonomously gets shared Data A that is put by the sensor node because the control target, Data B, from the controller node can no longer be used for actuator control. Then, the actuator node executes the backup control function by using shared Data A.

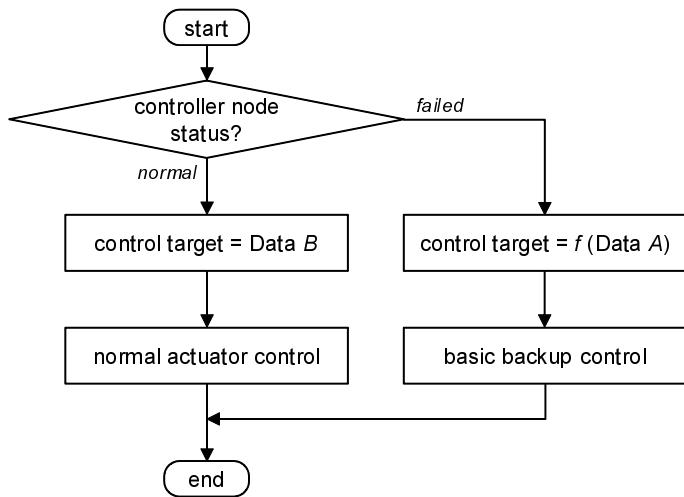

Figure 2.5 summarizes a process flow in actuator nodes. The actuator node periodi-

Figure 2.4: Autonomous backup control when controller node has failed

cially monitors the status of the controller node. If the actuator node diagnoses that the controller node normally functions, it uses Data *B* as the control target. Otherwise, the actuator node itself calculates the control target by  $f(\text{DataA})$  and controls actuators with this target value. Although sensor/actuator nodes in the autonomous decentralized architecture are required to be more intelligent than those in the conventional architecture, the increase in computational overhead in actuator nodes can be suppressed by limiting the backup control function to a minimum necessary function for safe vehicle operation, which we call a *basic backup control* function.

Therefore, as the proposed architecture can tolerate the existence of failed nodes and does not require expensive redundant fail-operational nodes, we can reduce system costs.

Figure 2.5: Process flow in actuator nodes

In other words, the system with the proposed autonomous decentralized architecture can be fail-operational although the system consists of only inexpensive fail-silent components.

### Actual Vehicle Control Systems

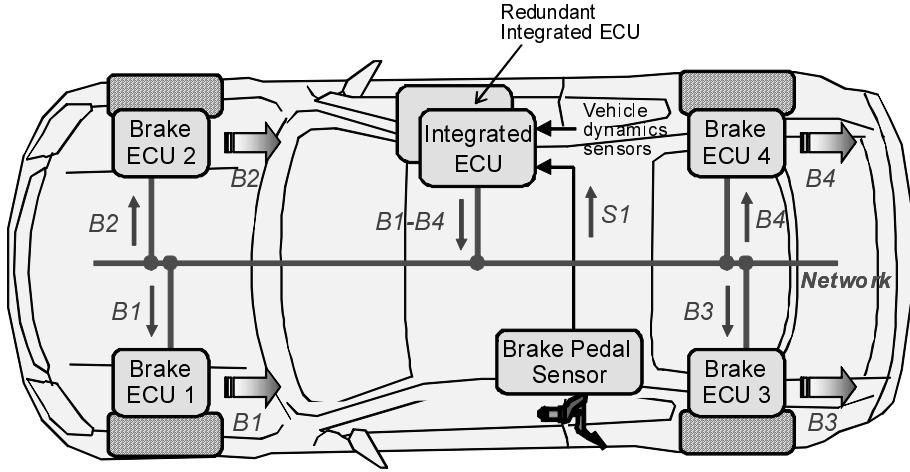

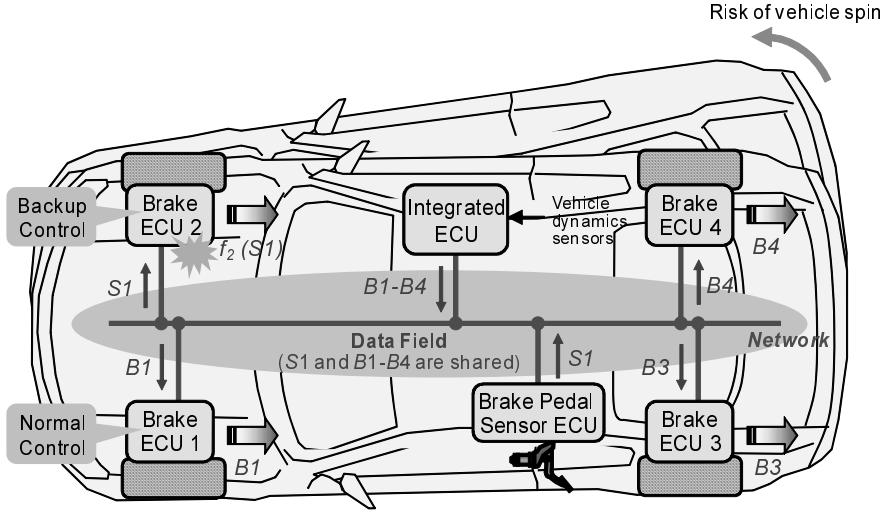

Figure 2.6 shows a brake-by-wire system with the conventional control architecture. The system consists of a vehicle dynamics integrated ECU (Electronic Control Unit), four brake ECUs that actuate braking motors, and a brake pedal sensor. The brake pedal position signal,  $S1$ , from the brake pedal sensor is directly input only to the integrated ECU. The integrated ECU calculates the target braking force values,  $B1$  to  $B4$ , for the four brake ECUs, using  $S1$  as well as the signals from vehicle dynamics sensors such as yaw rate and acceleration sensors. Each brake ECU receives the target braking force values and controls a braking motor so that the actual braking force becomes the target value.

In this architecture, however, if the integrated ECU fails, it becomes impossible to control the vehicle dynamics because each brake ECU cannot receive the target braking

Figure 2.6: Brake-by-wire system with conventional control architecture

force values. Therefore, the integrated ECU should be redundant to be fail-operational, which increases the system cost.

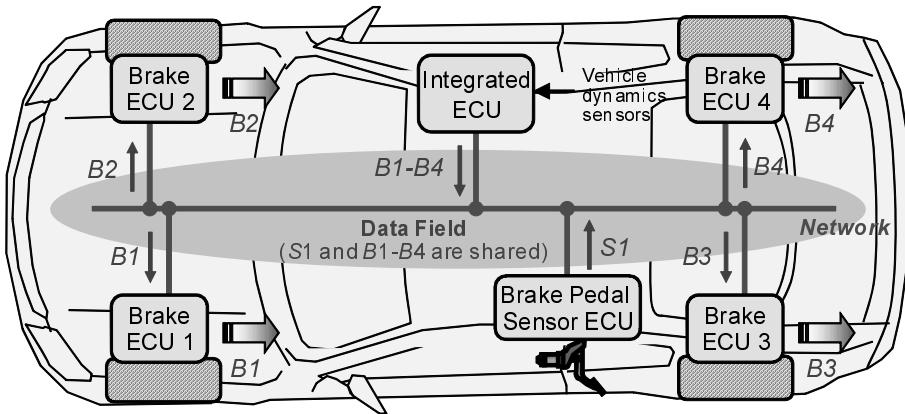

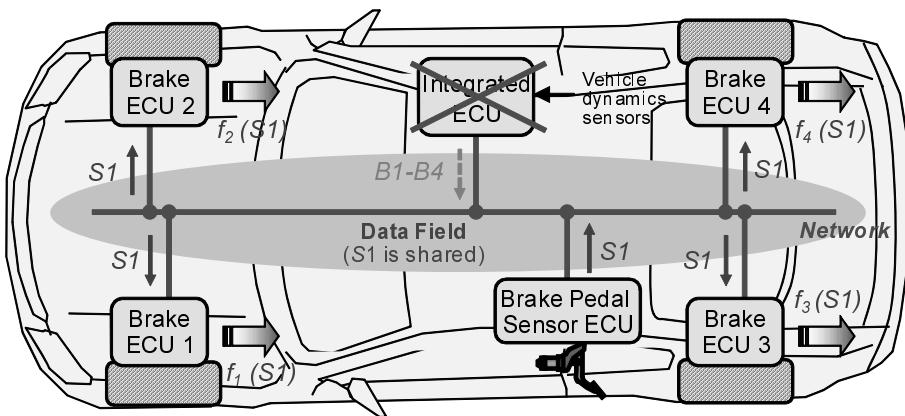

In contrast to the conventional architecture, all the ECUs share the information required for brake control throughout the data field in the autonomous decentralized brake-by-wire system. The data field is implemented with a communication network. As shown in Figure 2.7, the brake pedal sensor is connected to the network and thus becomes more intelligent node, i.e., brake pedal sensor ECU, so that driver demand can be shared.

When the system normally operates, as indicated in Figure 2.7 (a), the control operation is logically the same as one in the conventional architecture. If the integrated ECU should fail, its sophisticated braking control function would be suspended. However, the vehicle can maintain the minimal necessary braking functionality for safe vehicle operation thanks to the autonomous backup control mechanism shown in Figure 2.7 (b). After recognizing the integrated ECU has failed, each brake ECU gets shared brake pedal position signal  $S1$  in autonomous backup control. The brake ECU independently calculates the target braking force value,  $f_i(S1)$  ( $1 \leq i \leq 4$ ), with the basic backup control function implemented in each brake ECU by using data  $S1$ . Therefore, we can eliminate

(a) Normal operation

(b) When integrated ECU has failed

Figure 2.7: Autonomous decentralized brake-by-wire system

redundancy from the integrated ECU because it does not need to be fail-operational.

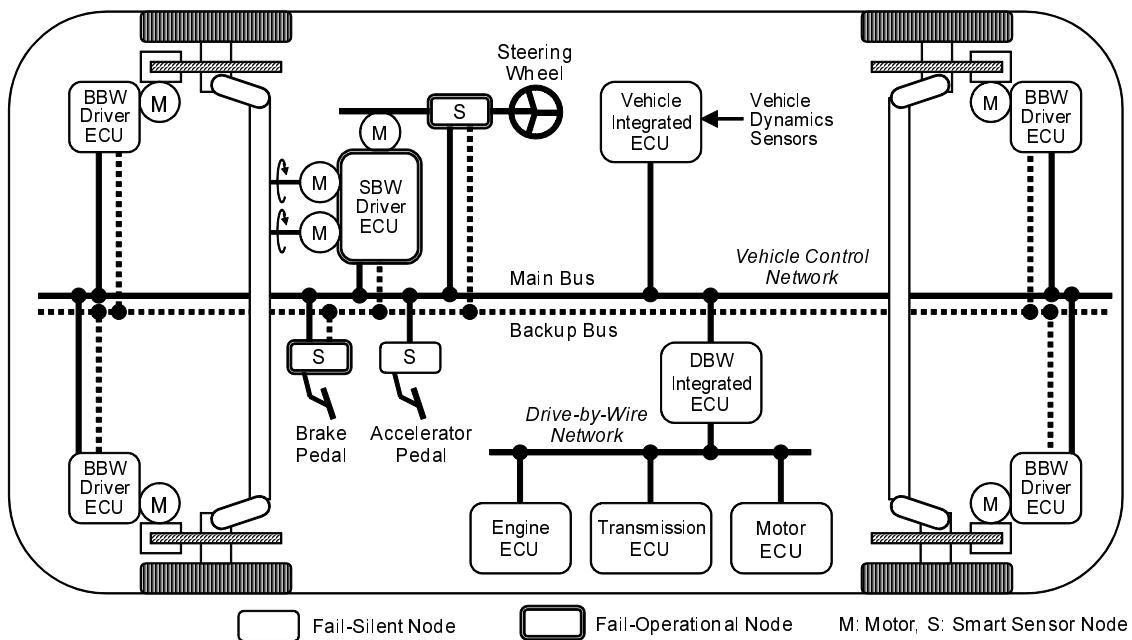

Figure 2.8 outlines the entire architecture for vehicle dynamics control with the concept of autonomous decentralized systems. This figure focuses on the components that are related to vehicle fundamental functions of driving, steering, and braking. The data field is implemented by the communication network, which we call a vehicle control network. The integrated ECUs, motor driver ECUs, and sensor nodes communicate with one another through the vehicle control network. For example, FlexRay is utilized for the vehicle control network due to its high bandwidth and deterministic features.

Figure 2.8: Vehicle dynamics control system with autonomous decentralized architecture

The vehicle integrated ECU synthetically controls the vehicle dynamics by interpreting driver demand from the signals received from the accelerator pedal sensor, brake pedal sensor, and steering wheel angle sensor, and also by recognizing the vehicle's motion status from the acceleration sensor, yaw rate sensor, and wheel rotation sensor. It is essential in the autonomous decentralized architecture to connect sensors to measure driver demand, i.e., the accelerator pedal sensor, brake pedal sensor, and steering wheel angle sensor, to the vehicle control network so that this information can be shared among all ECUs. On the other hand, these sensors are not connected to the network in the conventional architecture, but directly to the vehicle integrated ECU.

The vehicle integrated ECU calculates the target values for each actuator, such as those for the engine, steering, and braking, and transmits these target values to the vehicle control network. The Drive-by-Wire (DBW) integrated ECU receives the target driving force value, the Steer-by-Wire (SBW) driver ECU receives the target steering angle value,

and the Brake-by-Wire (BBW) driver ECU receives the target braking force value. The SBW/BBW driver ECU controls a motor by calculating the motor torque required to achieve these target values. The SBW driver ECU also controls a motor for actuating a variable gear ratio (VGR) mechanism that is installed on the steering column to generate a virtual reactive force for vehicle drivers. The DBW integrated ECU is a master controller for the powertrain system. This ECU executes the driving force distribution to the engine and motor to improve energy efficiency. The calculated target driving torque and gear ratio values are transmitted to the engine ECU, motor ECU, and transmission ECU through the drive-by-wire network, e.g., CAN (Controller Area Network).

The vehicle control network has redundant buses for fault-tolerance, i.e., main and backup buses. The vehicle integrated ECU, DBW integrated ECU, SBW driver ECU, BBW driver ECUs, and three sensor nodes are connected to the main bus. In contrast, only the minimum necessary nodes for safe vehicle operation, viz., the SBW driver ECU, BBW driver ECUs, brake pedal sensor, and steering wheel angle sensor, are connected to the backup bus to decrease network costs. Since a loss of function to generate driving force does not cause fatal accidents, the accelerator pedal sensor is not connected to the backup bus and the drive-by-wire network is not redundant. If the main bus of the vehicle control network should fail, as described in the autonomous backup function, the BBW Driver ECU autonomously obtains data from the brake pedal sensor and the SBW driver ECU autonomously obtains those from the steering wheel angle sensor, and they control the motors with the control target values calculated in the basic braking/steering backup control functions.

Furthermore, the SBW driver ECU, brake pedal sensor, and steering wheel angle sensor should be fail-operational nodes as shown in Figure 2.8 to maintain the functions for safe vehicle operation. It is also necessary to make the steering motor dual-redundant. A fail-operational SBW driver ECU consists of two fail-silent nodes and each fail-silent

node independently controls one steering motor. Although some nodes and motors have to be fail-operational, the number of fail-operational nodes can be minimized and thus the system cost can be reduced due to the autonomous decentralized architecture.

The autonomous decentralized architecture also improves system scalability and thus simplifies the development process because the data on the vehicle control network have a high degree of abstraction. For example, the target values for each actuator are defined so that the vehicle control logic in the vehicle integrated ECU can be developed without any knowledge of actuator variety or characteristics. Sensor nodes broadcast physical values that are meaningful to control logic after processing of sensor signal filtering and conversion of voltage to a physical value.

Various functions can easily be extended in the proposed architecture due to high levels of scalability by connecting the required components to the vehicle control network. Moreover, integrating a gateway function into the vehicle integrated ECU enables cooperative control with the components connected to other networks, such as information, body, and safety networks.

## 2.3 Fail-Silent Node Architecture

### 2.3.1 Comparison of Fail-Silent Nodes

The proposed X-by-Wire systems can be mostly implemented with inexpensive fail-silent ECUs, as shown in Figure 2.8, i.e., they do not interfere with communication between other ECUs even if they have failed. Although the SBW driver ECU, brake pedal sensor, and steering wheel angle sensor have to be fail-operational, a fail-silent node is essential for safety-critical distributed systems since a fail-operational node can be composed of two fail-silent nodes.

The fail-silent nodes of three redundancy types are compared in Table 2.1 in terms of

Table 2.1: Comparison of fail-silent nodes

| Redundancy Type          | Q&A        | Validity Check     | Dual Redundancy            |

|--------------------------|------------|--------------------|----------------------------|

| Node Architecture        |            |                    |                            |

| Fault Detection Coverage | Low        | Middle-High*       | High                       |

| Cost                     | Low        | Low                | Low**-Middle               |

| ECU Type                 | Engine ECU | BBW/SBW Driver ECU | Integrated ECU Sensor Node |

\* Coverage for fatal fault, \*\* Where dual CPU LSI is applied

cost and coverage of fault detection. The fault detection coverage has a great influence on system reliability, although it is difficult to precisely estimate its value. A node is not guaranteed to be fail-silent if a fault is not detected, and this fatal event occurs with a rate of  $(1 - C) \times \lambda$ , where  $C$  is the fault detection coverage and  $\lambda$  is the failure rate of the node. The fatal event rate decreases as  $C$  approaches one. However, because there is a tradeoff between node cost and coverage, we have to apply a suitable architecture to each node depending on node function to optimize costs.

A node in the *question and answer* (*Q&A*) method consists of a main microcontroller and a sub-microcontroller (a microcontroller is called a micro after this). The sub-micro transmits an appropriate calculation problem to the main micro, and the main micro calculates the answer and returns it to the sub-micro. The sub-micro compares the returned answer with a predetermined answer. If the two values differ, the sub-micro determines that the main micro has failed, and stops the node function. Conversely, the state of health of the sub-micro is monitored by the main micro. The main micro also diagnoses I/O

circuits and related sensors/actuators. Although this structure is inexpensive, its fault detection coverage is the lowest at around 90% [23] among the three types because it is unsure whether the calculation problems are designed such that all faults can be completely detected. This architecture has been applied to conventional ECUs, such as engine and transmission ECUs.

We found that while the hardware architecture was similar to the question and answer method, i.e., without cost increases, a method of *validity check* could improve the fault detection coverage. The sub-micro monitors not only the returned answer from the main micro, but also the actuation output result. The sub-micro compares the actuator output with the target value for actuation and determines the validity of the actuation. Although a rigid check of the main microcontroller's execution result is not carried out, a fatal fault generated in the path from the main micro to the actuator can reliably be detected by monitoring the final actuation status. This architecture is suitable for the motor driver ECU. It is essential to design the node such that the execution load to compare these two values in the sub-micro can be reduced to utilize inexpensive sub-micros.

Rigid checks of the microcontroller execution result are required in the node that calculates the control target value based on control logic and outputs the calculated value to the other nodes. Therefore, not the validity check method but a *dual redundancy* architecture is applied to nodes such as vehicle integrated ECUs. The nodes are composed of two equivalent microcontrollers and a comparator. The comparator confirms whether the execution results of the main and reference micros coincide. A self-checking type comparator has to be used to detect faults in the comparator itself, which will be discussed later. The coverage in this architecture exceeds 99% [23]. The cost of dual redundancy is higher than that of the other two types, but it is still lower than that of a fail-operational architecture like triple redundancy. Moreover, the cost can be reduced where the two micros and the self-checking comparator are integrated into one LSI chip.

### 2.3.2 Node Hardware Architecture

#### Motor Driver ECU

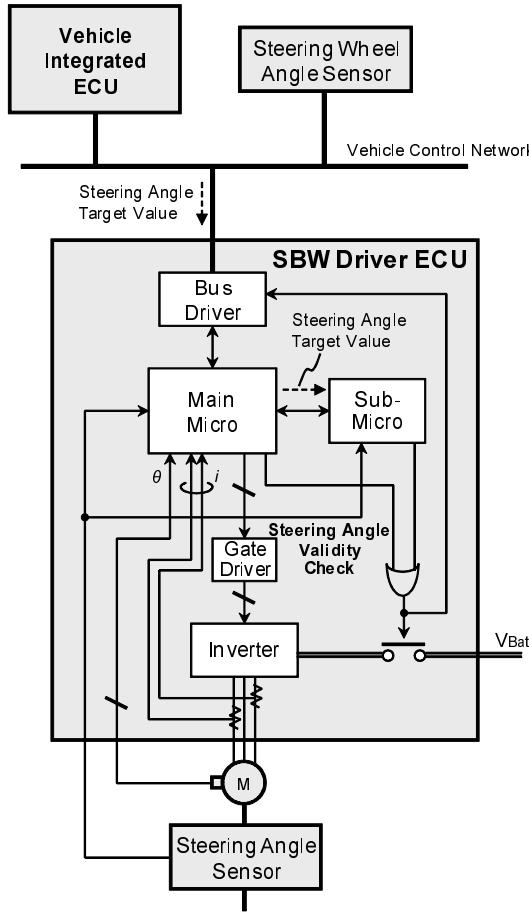

The hardware architecture for the fail-silent SBW driver ECU<sup>‡</sup> is shown in Figure 2.9 as an example of the method of validity check. The SBW driver ECU obtains the target steering angle value calculated by the vehicle integrated ECU. The main micro calculates the required target motor torque and current to attain this target steering angle, and performs vector control of the three phase motor. The sub-micro compares the steering angle target value with the actual steering angle that is measured by a steering angle sensor. When the sub-micro detects that these values are different, it disables access to the communication network and shuts down the power supply for the steering motor.

It is important to determine the timing in this architecture to compare the target and the actual steering angle by taking into account the response delay time of the mechanical system. Because the sub-micro is not connected to the network to reduce the cost of the communication interface, it cannot receive the target value directly from the network. Consequently, if the main micro fails and sends an incorrect target value to the sub-micro, failure in the main micro may not be able to be detected since the main micro controls the motor and the sub-micro executes the validity check based on this incorrect target value. The vehicle integrated ECU adds a data check code to the target value data to prevent this problem. After the frame from the vehicle integrated ECU is received, the main micro sends it to the sub-micro without processing. The sub-micro can determine whether the data are correct or not by checking this data check code.

---

<sup>‡</sup>Two fail-silent ECUs form fail-operational SBW driver ECU described in Subsection 2.2.2.

Figure 2.9: Validity check architecture for SBW driver ECU

### Integrated ECU

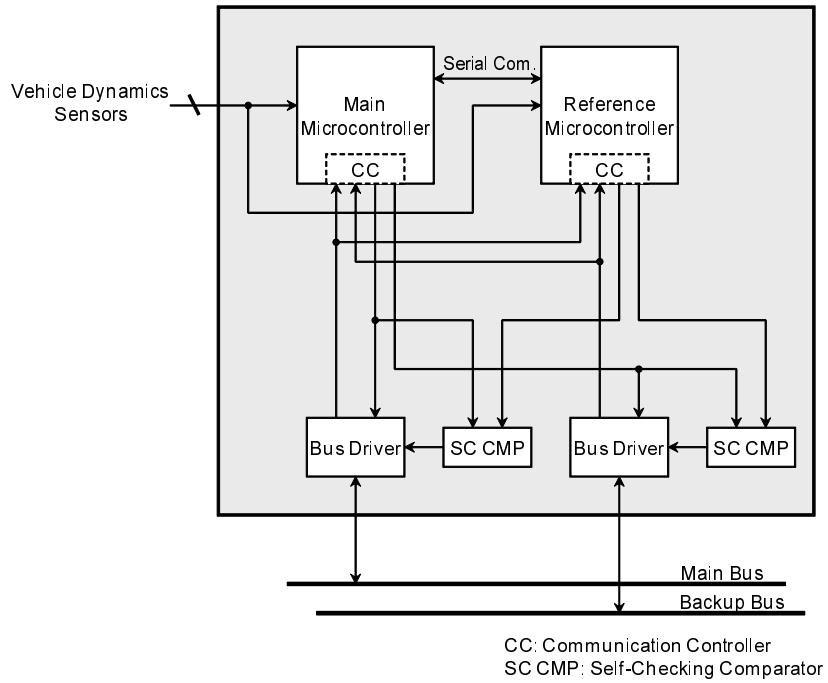

Figure 2.10 indicates the hardware architecture for the vehicle integrated ECU to which dual redundancy architecture is applied. Signals from vehicle dynamics sensors, such as the acceleration and yaw rate sensors are input to both the main and the reference micros. The main and reference micros communicate with each other via the serial communication to synchronize the analog-to-digital (A/D) conversion and make the conversion values coincide. The calculated values in both microcontrollers are compared by self-checking comparators. If the self-checking comparators detect disagreements in both values, they disable the bus driver to stop network access.

Figure 2.10: Dual redundancy architecture for integrated vehicle ECU

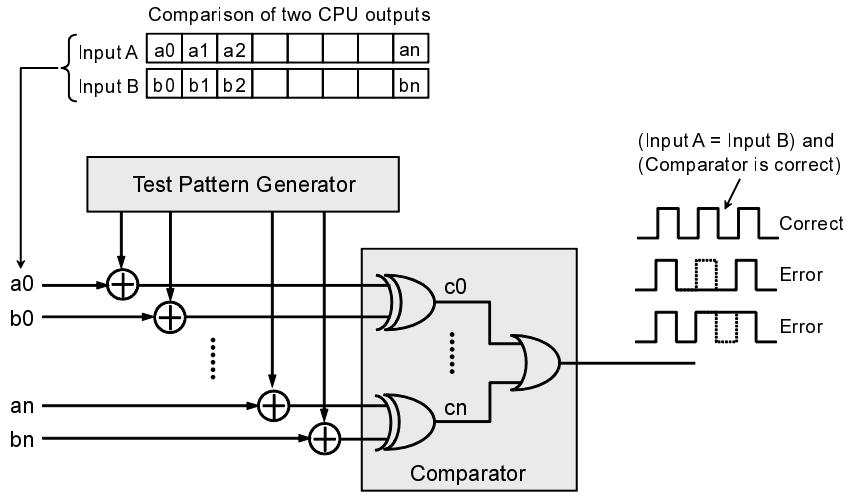

A self-checking comparator consists of the test pattern generator and comparator as shown in Figure 2.11 [24]. The test pattern generator periodically injects a test pattern and “00..00” (all bits are 0) to each bit of the input data. When inputs A and B are equal, and the self-checking comparator is operating correctly, it outputs a rectangular wave with a period that is identical to the test pattern injection period. If the comparator does not output a rectangular wave with this predetermined period, it means either “input A and input B are not equal” or “the self-checking comparator itself is faulty”. Thus, the self-checking comparator can not only detect faults in the input data, but also in the comparator itself, which improves the reliability of the dual redundancy node.

### Sensor ECU

The autonomous decentralized architecture requires fail-silent sensor ECUs that can directly broadcast the sensing data to the vehicle control network, as was explained in Sub-

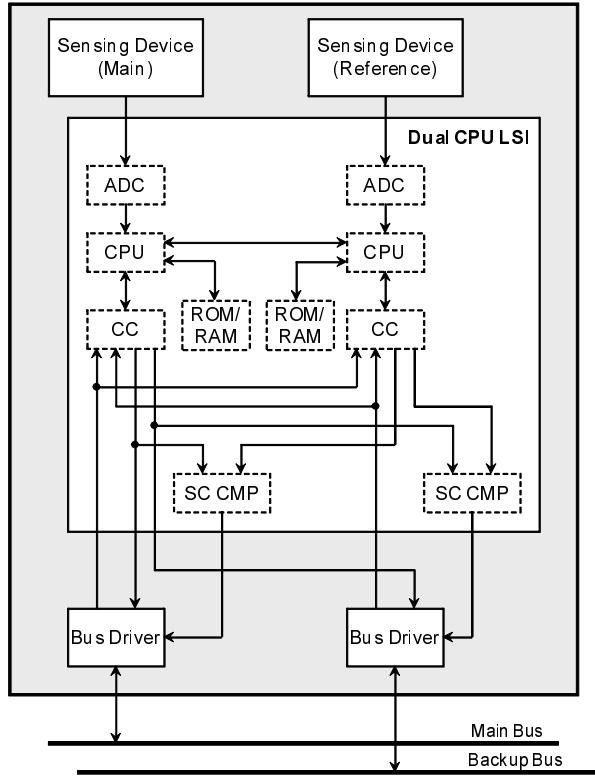

Figure 2.11: Configuration of self-checking comparator

section 2.2.2. The hardware block diagram of a smart sensor node that employs the dual redundancy architecture is shown in Figure 2.12. The sensor node consists of two sensing devices and a dual CPU LSI chip that integrates dual CPU cores, A/D converters, communication controllers, self-checking comparators, and ROMs/RAMs with ECC (Error Correcting Code). This LSI contributes to size reduction in the sensor node. The two CPUs communicate with each other to synchronize the A/D conversion and make the A/D conversion values of the sensor signals coincide. The CPUs execute the appropriate signal processing for each sensing device, such as sensor signal filtering and conversion of voltage to physical values to improve system scalability.

## 2.4 Estimation of System Cost Reduction

We estimate the effect of the system cost reduction due to the proposed autonomous decentralized architecture and optimal node hardware architecture. A brake-by-wire system with the conventional architecture (Figure 2.6) is compared with one incorporating the autonomous decentralized architecture (Figure 2.7). We focus on electronic components,

Figure 2.12: Hardware architecture for smart sensor node

i.e., ECUs to estimate the system cost. The system cost for the conventional architecture,  $C_{\text{sys}}^{\text{conve}}$ , is as follows:

$$C_{\text{sys}}^{\text{conve}} = 2C_C + 4C_A \quad (2.1)$$

where  $C_C$  is the cost of a fail-silent integrated ECU, and  $C_A$  is the cost of a fail-silent brake ECU that employs the conventional dual redundancy architecture shown in Table 2.1. Note that the fail-operational integrated ECU consists of two fail-silent integrated ECUs as discussed in Section 2.2. The cost of a sensing device of the brake pedal sensor is assumed to be negligible small compared with that of an ECU.

The increase of the system cost,  $C_{\text{sys}}^+$ , for the autonomous decentralized architecture is as follows:

$$C_{\text{sys}}^+ = C_S + \frac{C_{\text{dev}}}{N_{\text{pro}}} \quad (2.2)$$

where  $C_S$  is the cost of the intelligent brake pedal sensor ECU that can communicate with the other ECUs through the control network,  $C_{\text{dev}}$  is the additional software development cost for the node status monitoring and the backup control functions, and  $N_{\text{pro}}$  is the production volume of the system. We assume that  $N_{\text{pro}}$  is large enough to make the second term in Equation (2.2) negligible because of the mass-production scale in the automotive industry. Although the autonomous decentralized architecture requires the node status monitoring and the backup control functions even for sensor and actuator nodes, a microcontroller with equivalent performance as one equipped with the conventional architecture can be applied. This is because only the basic function is required for the autonomous backup control and the CPU computational overhead for the node status monitoring can be sufficiently reduced, which will be discussed in Chapter 5. Thus, the cost increase of the microcontroller in each ECU is not included in Equation (2.2).

Equation (2.3) expresses the cost decrease,  $C_{\text{sys}}^-$ , by the proposed autonomous decentralized architecture and optimal node hardware architecture:

$$C_{\text{sys}}^- = C_C + 4\Delta C_A = C_C + 2C_{\text{mc}} \quad (2.3)$$

where  $\Delta C_A$  is the cost reduction per one fail-silent brake ECU. Because we can apply less expensive validity check architecture to fail-silent brake ECUs as indicated in Table 2.1,  $\Delta C_A$  can approximately be estimated as  $2C_{\text{mc}} - 1.5C_{\text{mc}}$ , where  $C_{\text{mc}}$  is the cost of a main microcontroller which is assumed to be double compared with the cost of a sub-microcontroller. Furthermore, as discussed in Section 2.2, since the integrated ECU can be fail-silent due to the system-level redundancy in the autonomous decentralized architecture, we can eliminate one fail-silent integrated ECU.

Therefore, with Equations (2.1), (2.2), and (2.3), we can calculate a ratio of the reduced system cost,  $\Delta C_{\text{sys}}$ , to the system cost for the conventional architecture as follows:

$$\frac{\Delta C_{\text{sys}}}{C_{\text{sys}}^{\text{conve}}} = \frac{C_{\text{sys}}^- - C_{\text{sys}}^+}{2C_C + 4C_A} \simeq \frac{C_C + 2C_{\text{mc}} - C_S}{2C_C + 4C_A} \simeq \frac{C_C + 2\alpha C_C - \beta C_C}{6C_C} \quad (2.4)$$

where  $\alpha$  is a ratio of the cost of a microcontroller to that of a fail-silent integrated ECU ( $\alpha = C_{mc}/C_C < 1$ ), and  $\beta$  is a ratio of the cost of a sensor ECU to that of a fail-silent integrated ECU ( $\beta = C_S/C_C < 1$ ). In Equation (2.4), we assume that  $C_A$  is almost the same as  $C_C$ .

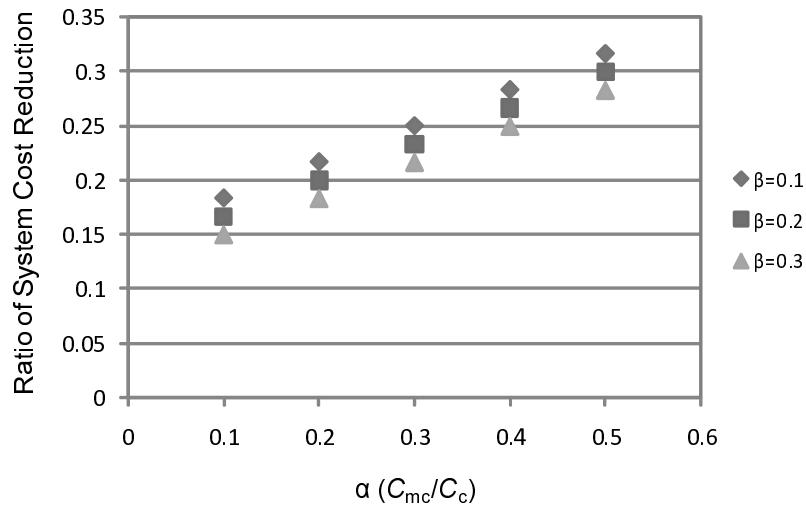

Figure 2.13 shows the estimation results on the system cost reduction. Although parameters  $\alpha$  and  $\beta$  depend on the actual hardware implementation, we conclude that approximately from 20 to 30% cost reduction can be achieved with practically possible combinations of parameters  $\alpha$  and  $\beta$ , which contributes to a substantial cost reduction for automotive control systems.

Figure 2.13: Cost reduction in autonomous decentralized brake-by-wire system

# CHAPTER 3

## AGREEMENT PROTOCOL

### 3.1 Challenges to Autonomous Decentralized Architecture

The autonomous backup control is an essential feature in the autonomous decentralized architecture as was discussed in the previous chapter. Backup control should be based on the accurate identification of failed nodes. However, as there is no master node for monitoring the status of nodes in the system, the node status monitoring function in each node plays a key role for fault-tolerance.

For example, as shown in Figure 3.1, suppose that the brake ECU 2 has not received braking control target value  $B2$  from the integrated ECU because of failure in the receiver, i.e., brake ECU 2. In this case, only the brake ECU 2 autonomously changes the control mode to the backup control mode because it cannot determine by itself whether the sender (integrated ECU) or the receiver (brake ECU 2) is faulty, which might lead to vehicle spin due to braking imbalances.

Therefore, some coordination scheme, i.e., an agreement protocol, is required to accurately identify the failed node and ensure consistency of the information on which nodes

Figure 3.1: Disagreements in control mode in autonomous decentralized architecture

are available among all remaining normal nodes so that disagreements in the control mode can be avoided. We propose a membership protocol as an agreement protocol for safety-critical distributed systems to address this issue, which will be discussed in this chapter.

## 3.2 Model of Time-Triggered Systems

### 3.2.1 Communication Model

Before we discuss the proposed membership protocol, let us first define a generic time-triggered (TT) system including a FlexRay communication system, which will be used in X-by-Wire systems.

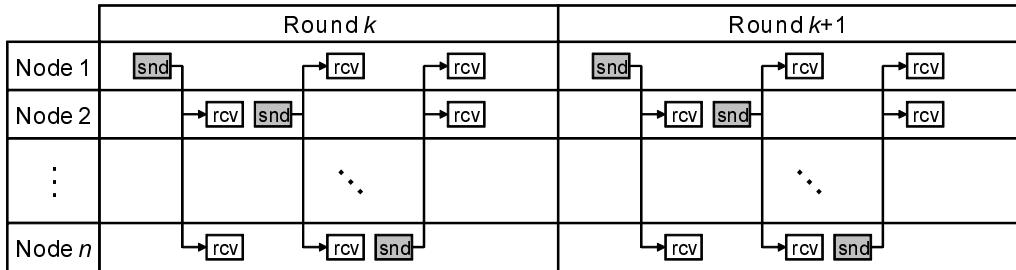

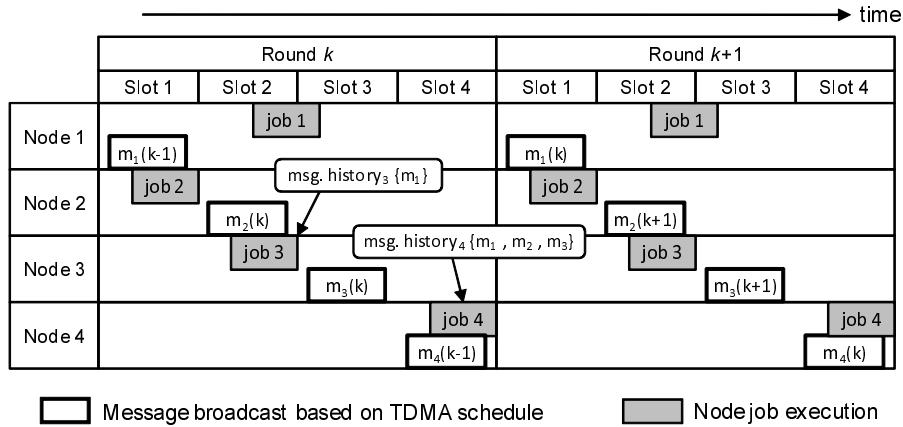

The system consists of  $n$  nodes having unique IDs  $1, 2, \dots, n$ . The communication network is the bus type with TDMA (Time Division Multiple Access). As we can see from Figure 3.2, the system runs by consecutively executing synchronous rounds, starting from round 1. A node is assigned its own sending slots as to where it can send a message frame. A frame sent by a node is received by all the other nodes. All sending slots are

statically scheduled in the design time and thus never overlap. Every node sends a frame at least once in one round.

Figure 3.2: Communication in time-triggered systems

### 3.2.2 Fault Model

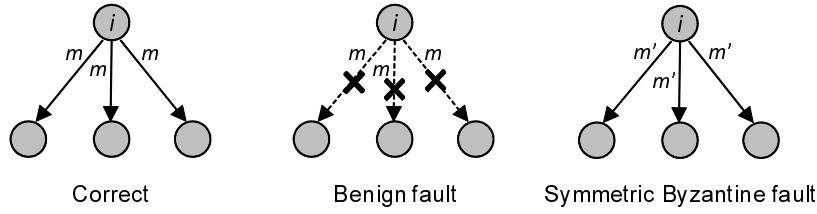

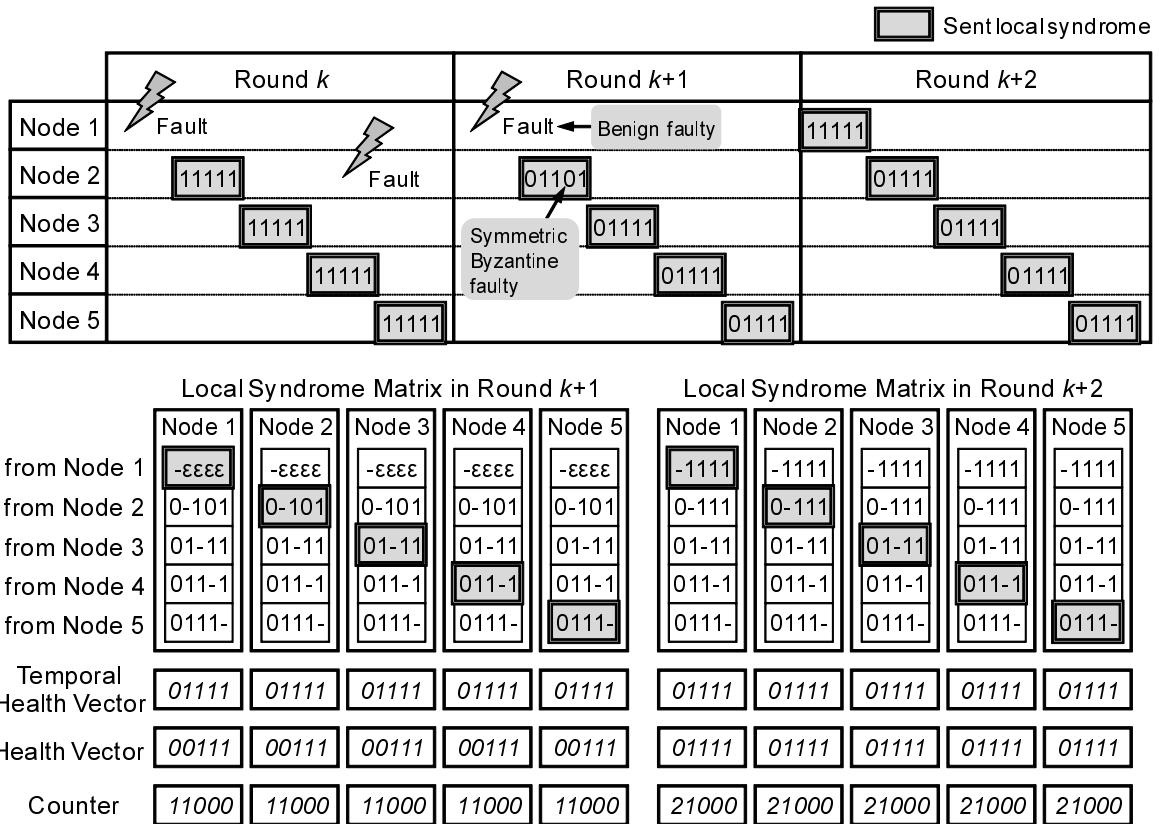

Faults in nodes are observed as communication errors. Figure 3.3 illustrates three fault types: *correct*, *benign fault*, and *symmetric Byzantine fault*. If node  $i$  suffers neither benign fault nor symmetric Byzantine fault, the node correctly sends the message frame  $m$ . If node  $i$  suffers a benign fault in round  $k$ , then the message frame  $m$  sent by the node in the round is lost. Hence, all nodes can locally detect it in round  $k$ . A benign fault arises from a transmission error due to e.g., a node crash. If node  $i$  suffers a symmetric Byzantine fault in round  $k$ , then, all nodes in the same round receive the same erroneous message  $m'$  from the faulty node, which does not conform to the protocol specifications. In this dissertation, we assume that a reception error in a certain node can be seen as a symmetric Byzantine fault, as discussed in detail later.

We take account of intermittent faults as well as permanent faults, and also assume that the fault types, either benign or symmetric Byzantine, never change along with communication rounds in one node.

Our fault model does not include faults in terms of timing violation in communication, where a node sends message frames at the sending slots disallowed for the node.

This is because we assume that each node is equipped with so called *bus guardians* that physically prevent a faulty node from accessing the bus at the sending slots assigned to the other nodes [25].

Figure 3.3: Fault types

Nodes are *correct*, *obedient*, or *symmetric Byzantine faulty*. Correct nodes follow the protocol specifications and suffer no faults. Obedient nodes follow the specifications but they may or may not suffer benign faults. Correct nodes are thus also obedient. Symmetric Byzantine faulty nodes do not follow the specifications and suffer symmetric Byzantine faults. We assume:

$$2s + b + 1 < n \quad (3.1)$$

where  $s$  is the number of symmetric Byzantine faulty nodes and  $b$  is the number of benign faulty nodes.

## 3.3 Membership Protocol

### 3.3.1 Protocol Description

We propose a membership protocol for TT systems as an agreement protocol to solve these problems in the autonomous decentralized architecture [16]. It provides information on the availability of all nodes in the system by exchanging a local view of the status of other nodes with all nodes.

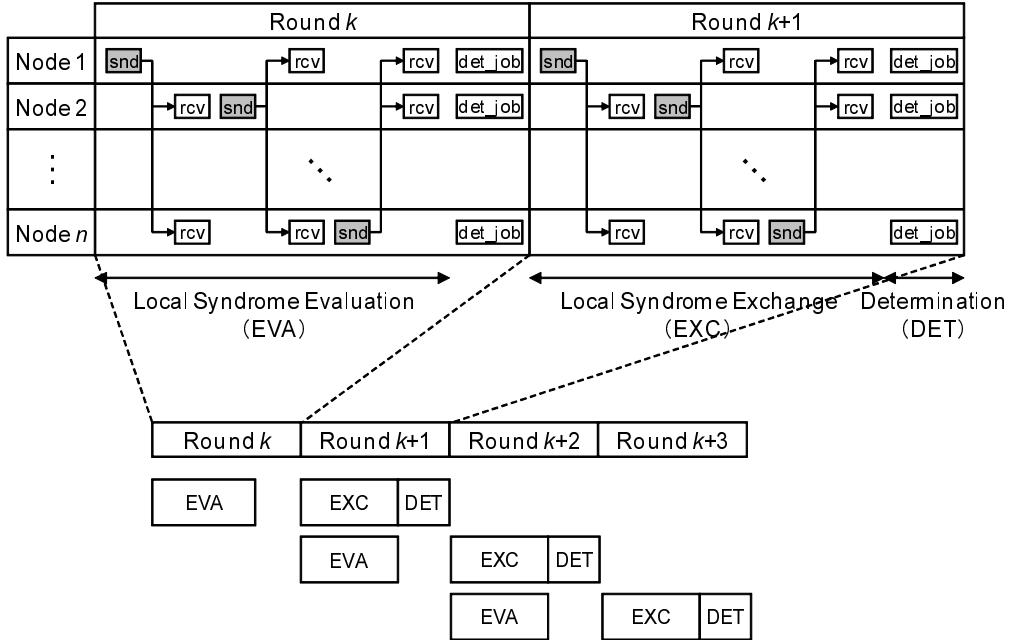

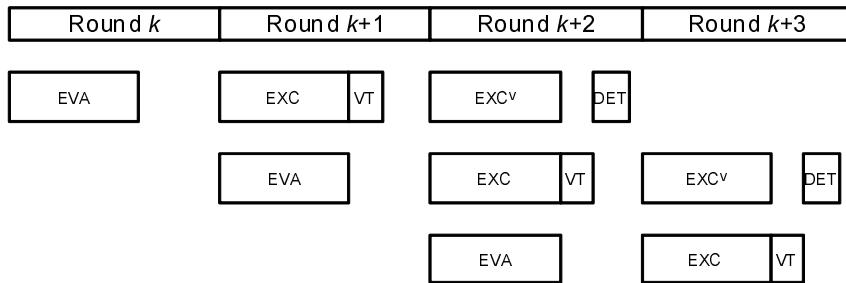

Figure 3.4: Overview of execution sequence in membership protocol

An execution sequence of the protocol in the TT system is outlined in Figure 3.4. In every round  $k$ , the membership protocol starts the sequence of three phases, which spans two consecutive rounds, viz., rounds  $k$  and  $k + 1$ . The pseudo-code of the membership process of three phases executed in each node  $p$  in round  $k$  is also presented in Algorithm 1. In the pseudo-code, hereinafter,  $information_{k-p}[i, \dots, j]$  denotes  $information$  on statuses with respect to from node  $i$  to node  $j$  in round  $k$  computed by node  $p$ .

In round  $k$ , each node evaluates other nodes' statuses locally by receiving frames sent by the other nodes ( $receive\_ls_{k-1\_msg\_i}[\cdot]$ ) and evaluating them (EVA phase). The evaluation result, which we call a *local syndrome*, represents the local view of other nodes' statuses that was evaluated in round  $k$ . A local syndrome evaluated in node  $p$ , i.e.,  $ls_{k-p}[\cdot]$ , is a binary  $n$ -tuple  $\langle s_1, s_2, \dots, s_n \rangle$  where  $s_i = 1$  if  $p$  evaluates node  $i$  as non-faulty and  $s_i = 0$  otherwise (Algorithm 1, lines 5-8). In the pseudo-code,  $\emptyset$  denotes no received message (line 5). Note that  $ls_{k-p}[\cdot]$  has to be buffered in  $send\_ls_{k\_msg\_p}[\cdot]$  because it is

not sent in the current round, but in the next round, i.e., round  $k + 1$  (line 12).

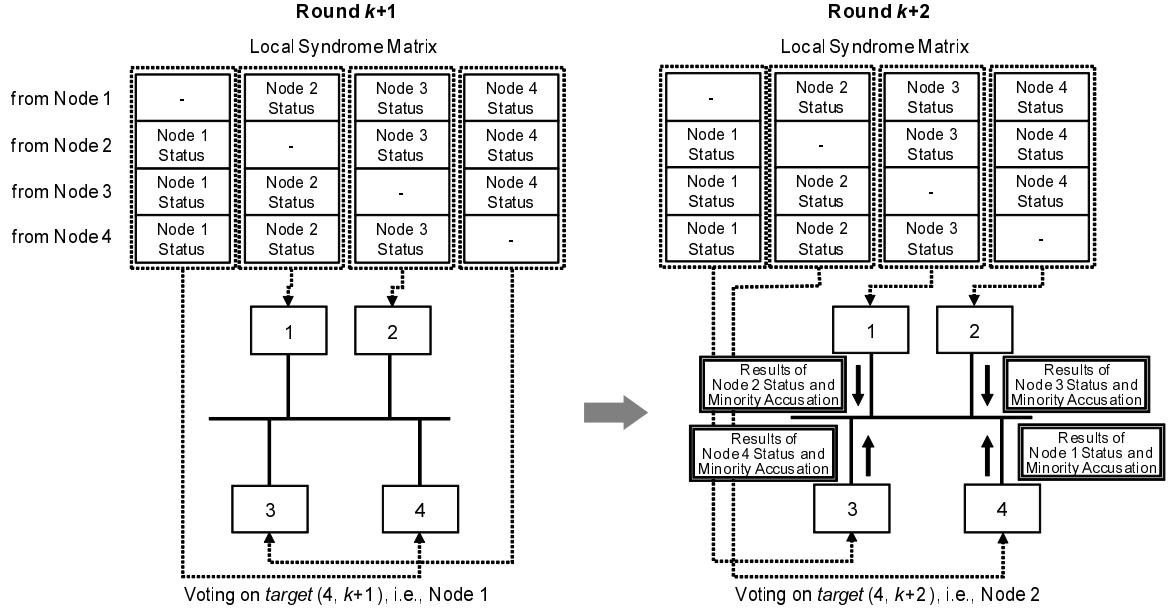

In the following round, round  $k + 1$ , the local syndromes evaluated in round  $k$  are exchanged by all nodes and node  $p$  constructs a local syndrome matrix,  $ls_k\text{-matrix}[][],$  where the  $i$ th row is the local syndrome received from node  $i$  and the  $j$ th column is a vector representing the evaluation for node  $j$  from all nodes (EXC phase). An element,  $e_{i,j}$ , is either 1, 0,  $\varepsilon$ , or  $-$ . The case,  $e_{i,j} = \varepsilon, i \neq j$ , occurs if node  $i$  failed to send its local syndrome in round  $k + 1$  because of its benign fault (lines 17-18). In line 18,  $[\varepsilon, \dots, \varepsilon]_n$  is a vector that has  $n$  elements of  $\varepsilon$ . The opinion of a node about itself, i.e.,  $e_{i,i}, 1 \leq i \leq n$ , is considered unreliable and thus is assigned special value  $-$ , which specifies that it is to be discarded in voting (line 22).

Each node determines node status in the same round (i.e., round  $k + 1$ ) by voting on the local syndrome matrix (DET phase). Each node obtains a binary  $n$ -tuple called a *temporal health vector*,  $\hat{hv}$ , where the  $i$ th element represents whether node  $i$  is non-faulty or faulty by hybrid voting [26] over each of the columns (line 27). Hybrid voting is specifically defined as:

$$H\text{-maj}(V) = \begin{cases} 0 & N_0(V) > N_1(V) \\ 1 & N_0(V) \leq N_1(V) \end{cases}$$

where  $V$  is the column that is voted on, and  $N_0(V)$  and  $N_1(V)$  are the number of occurrences of 0 and 1 in  $V$ .

The temporal health vector is then updated to accuse symmetric Byzantine faulty nodes, which we call a *minority accusation*. If the temporal health vector,  $\hat{hv}$ , and the local syndrome sent from node  $i$  respectively have 0 and 1 or 1 and 0 in the same position, then node  $i$  is identified as a faulty node (lines 31-32). The final health vector,  $hv$ , is obtained from  $\hat{hv}$  by setting the value in the  $i$ th position to 0 for all such nodes  $i^*$ .

---

\*We regard benign and symmetric Byzantine faulty nodes as equally serious because the potential causes of these faults are all physical [27]. This is in contrast to systems deployed in open networks, where intrusion is the main cause of Byzantine faults.

Finally, a node updates counters associated with nodes based on the health vector and possibly eliminates faulty nodes from active ones. For example, one can eliminate a node by counting the number of times when the node is diagnosed as faulty and by deciding to eliminate it when the counter exceeds a predefined threshold. The process of updating the counters can be regarded as executing a stateful function that takes a health vector,  $hv$ , as input and produces a set of active nodes as output. We denote this counter updating function by  $updateCounter(hv)$ . Thus, the output of the membership protocol is obtained by executing the following operation in each node (lines 38 and 40):

$$active\_nodes \leftarrow updateCounter(hv)$$

We emphasize that multiple instances of this sequence of phases are executed concurrently, as shown in Figure 3.4. The node status evaluation process (EVA) can be done concurrently in the status data exchanging phase (EXC) by evaluating the exchanged status data. The node status, correct or faulty, in a certain round can be identified in the next round, which can enhance real-time capabilities for diagnosing faults, due to this pipeline-like process execution.

---

**Algorithm 1:** Node  $p$  membership process in round  $k$

---

```

1 // EVA Phase

2 // local syndrome evaluation

3 for  $i \leftarrow 1, \dots, n$  do