|              |                                                                                 |

|--------------|---------------------------------------------------------------------------------|

| Title        | スパッタリングによる薄膜の形成とシリコンMOS半導体素子への応用に関する研究                                          |

| Author(s)    | 芹川, 正                                                                           |

| Citation     | 大阪大学, 1984, 博士論文                                                                |

| Version Type | VoR                                                                             |

| URL          | <a href="https://hdl.handle.net/11094/389">https://hdl.handle.net/11094/389</a> |

| rights       |                                                                                 |

| Note         |                                                                                 |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

スパッタリングによる薄膜の形成と

シリコンMOS半導体素子への応用に関する研究

著者

井上　正一

監修

田中　義和

監修

大庭　義和

スパッタリングによる薄膜の形成と

シリコン MOS 半導体素子への応用に関する研究

昭和59年 4 月

芹 川 正

# 内 容 梗 概

本論文は、著者が行ってきた「スパッタリングによる薄膜の形成とシリコンMOS半導体素子への応用に関する研究」をまとめたもので、本文8章から構成されている。

以下、その各章について、内容の梗概を述べる。

## 第1章 序論

本章では、本研究の目的と意義、および本研究の背景を述べ、さらに、本論文の概要と構成を示す。

## 第2章 反応性スパッタリング法による窒化シリコン膜の形成

本章では、ターゲットとしてSiを用いてAr-N<sub>2</sub>混合ガス中で窒化シリコン膜を形成する際のスパッタリングガス圧や膜形成速度等のスパッタリング特性、および、膜の特性について述べる。スパッタリング特性の変化は、Siターゲット表面での窒化反応とスパッタエッチングとを考慮することにより定性的に説明できること、および、適正なスパッタリング条件の下では、ち密でストキオメトリの窒化シリコン膜が得られることを示す。さらに、この膜は酸素の拡散を阻止することが実験から明らかとなり、この膜が半導体素子製作用選択酸化マスクとして有用なことを述べる。

## 第3章 スパッタリング法によるSiO<sub>2</sub>膜の形成と特性

本章では、マグネットロン型装置により形成にしたSiO<sub>2</sub>膜の特性は、スパッタリングガス圧に著しく依存し、適正な条件では、ち密でストキオメトリのSiO<sub>2</sub>膜が得れること、および、スパッタリングガス中に水素を混合することにより、膜特性が著しく改善されることを示す。さらに、これらの方法によって形成したSiO<sub>2</sub>膜の特性を詳細に述べる。

## 第4章 スパッタリング法によるSiO<sub>2</sub>膜およびAl膜のステップカバレジ

本章では、SiO<sub>2</sub>膜のステップカバレジと膜形成条件との関連を述べ、ステップカバレジの形状は、入射粒子の段差による陰影効果によって定性的に説明できることを記述する。さらに、スパッタリングガス中に水素を混合することにより、ステップカバレジが著しく改善されることを示す。

## 第5章 スパッタリング法によるSiO<sub>2</sub>膜およびAl膜のリフトオフ加工

本章では、従来困難とされていた、スパッタリング法によるSiO<sub>2</sub>膜およびAl膜のリフトオフ加工が行えることを明らかにし、本リフトオフ加工の詳細な方法と特徴を述べる。

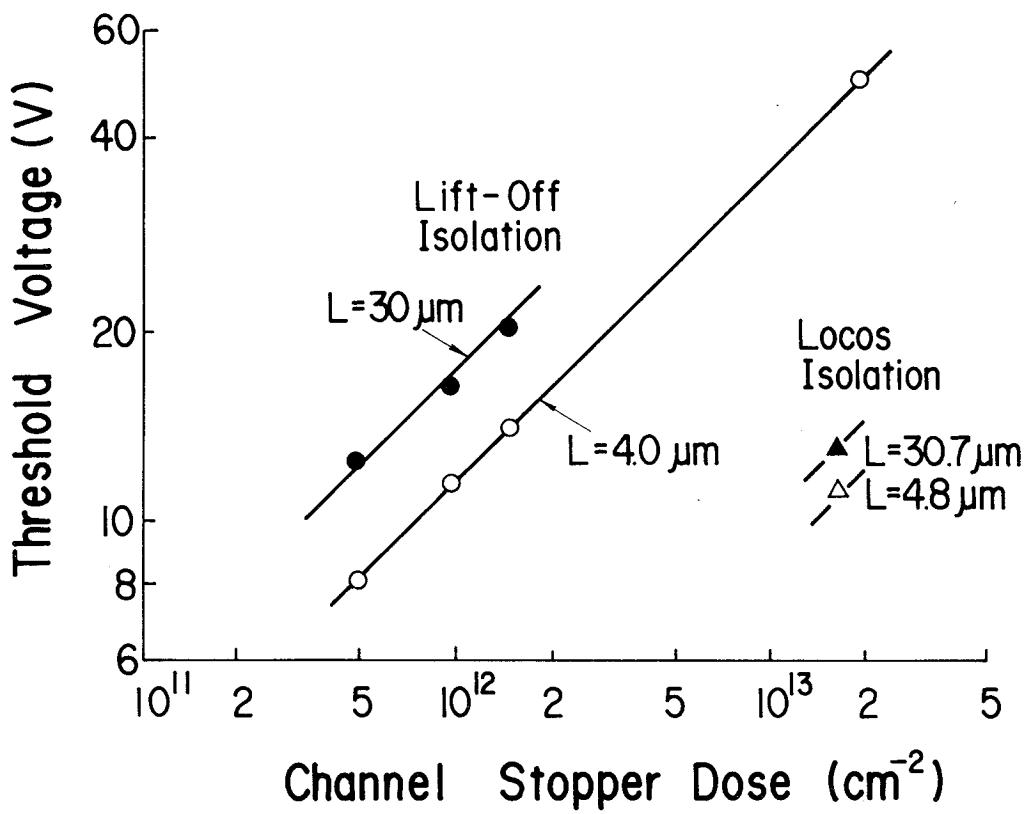

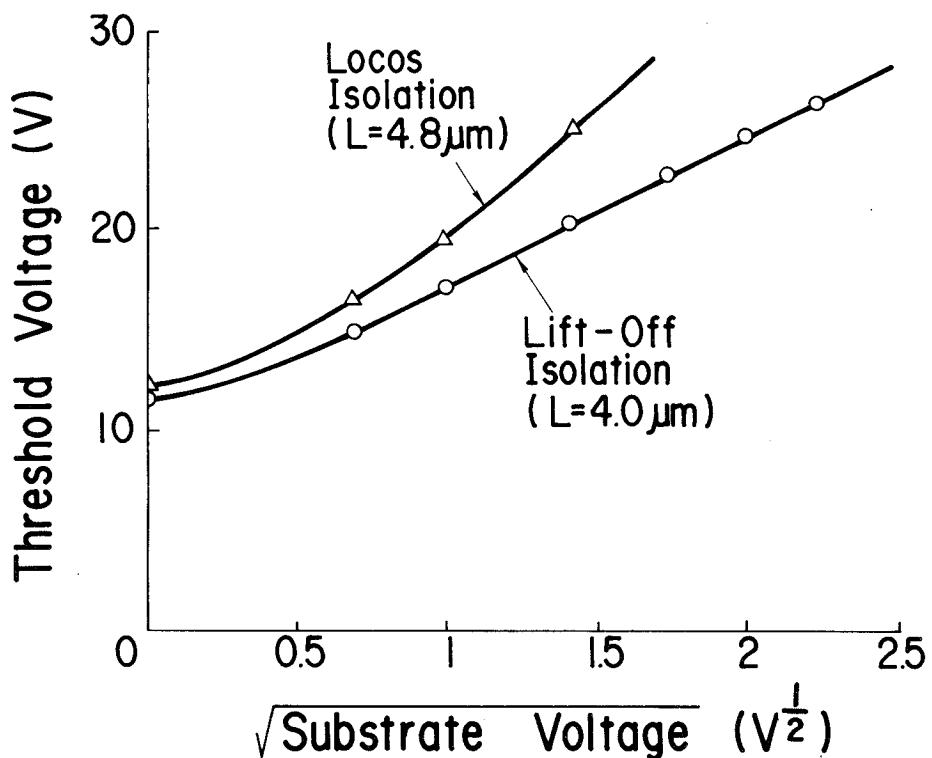

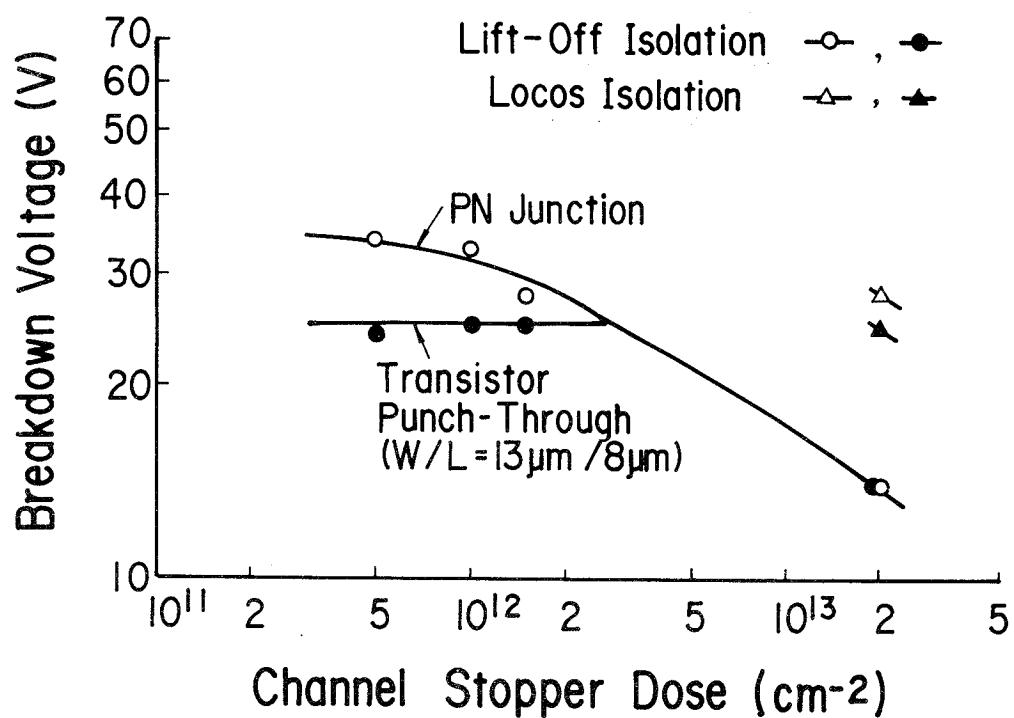

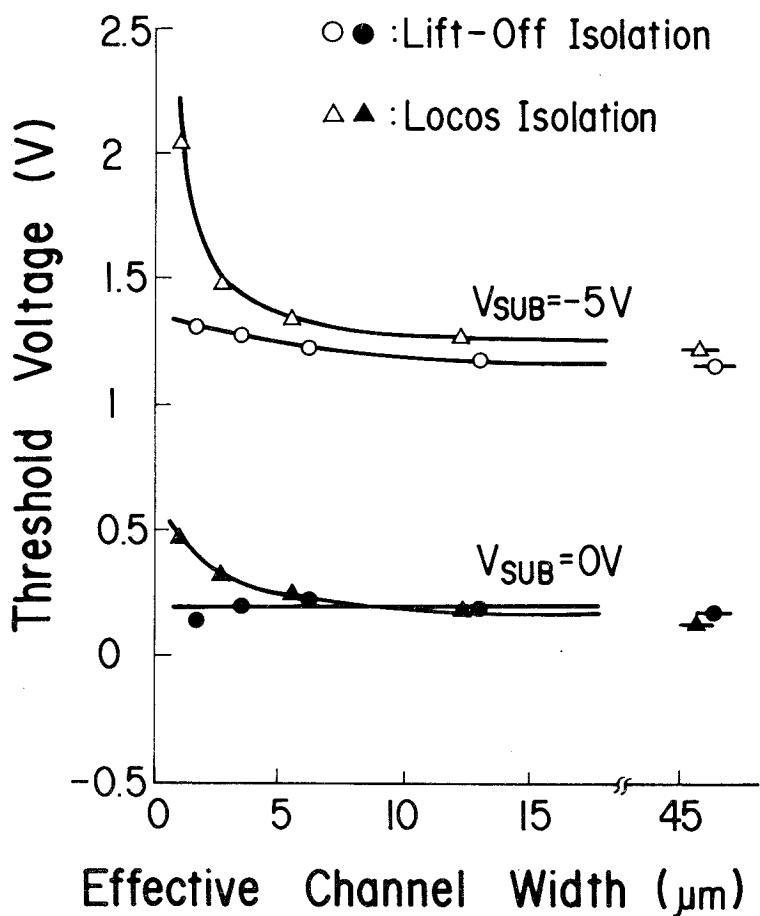

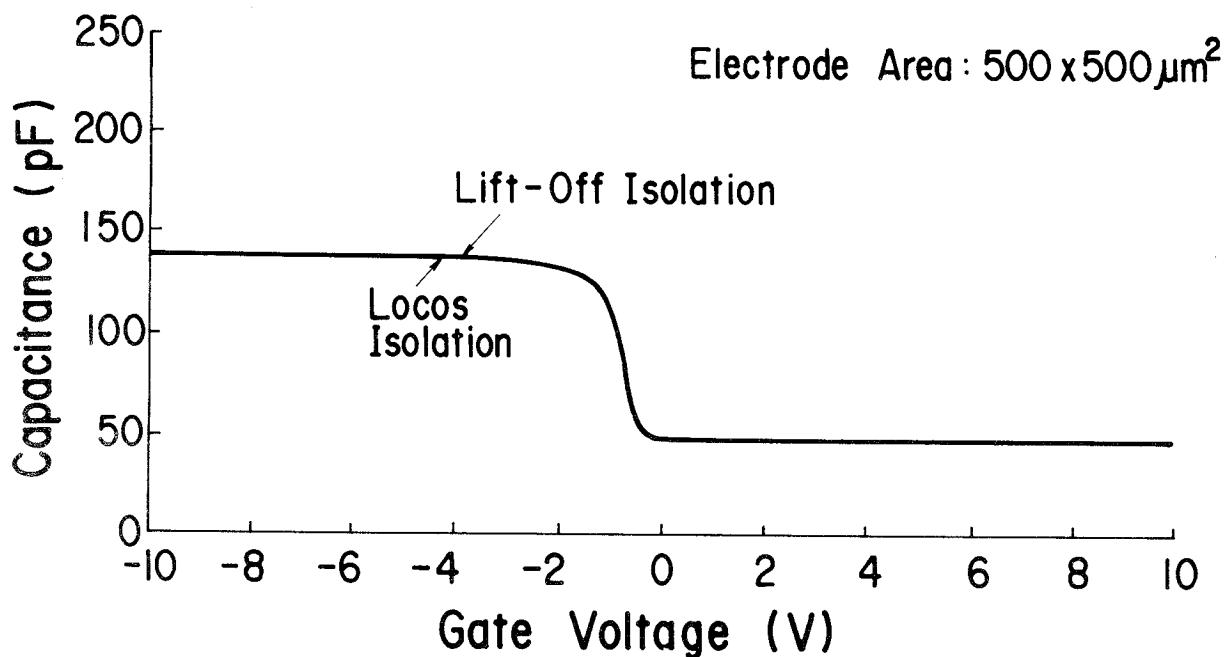

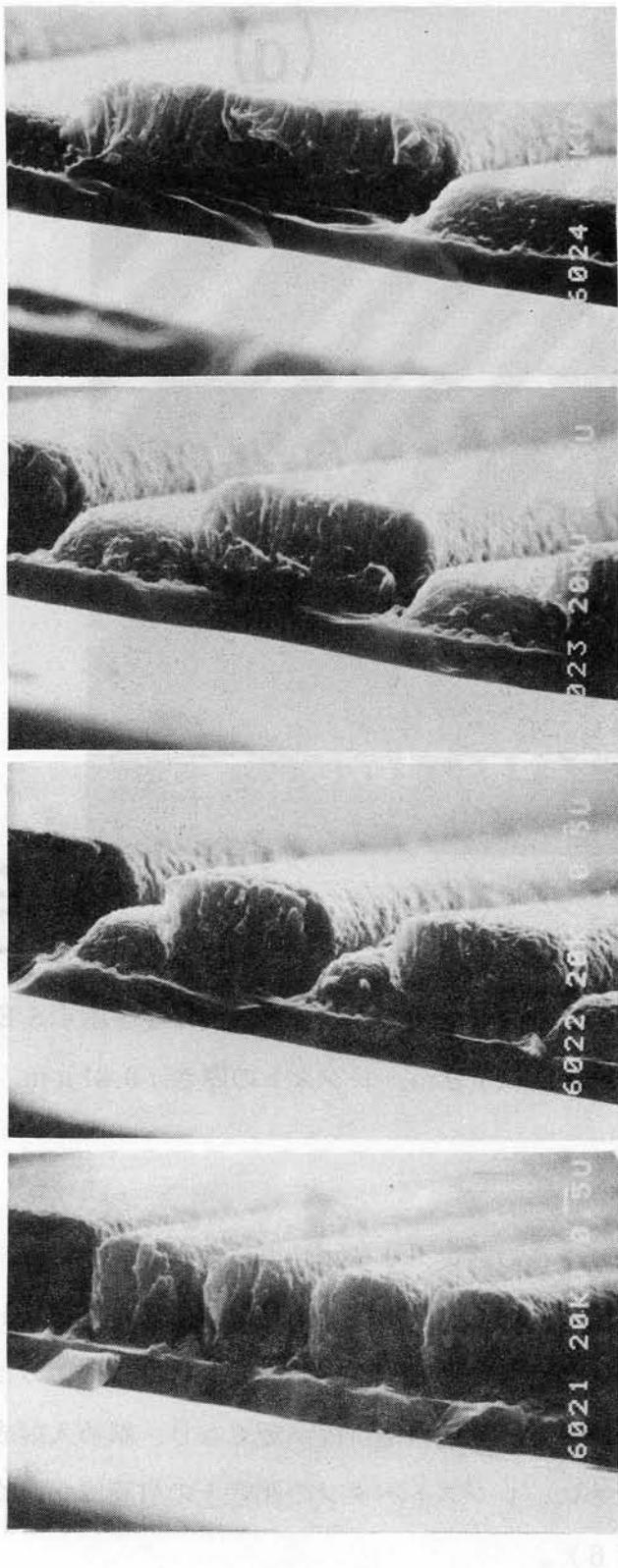

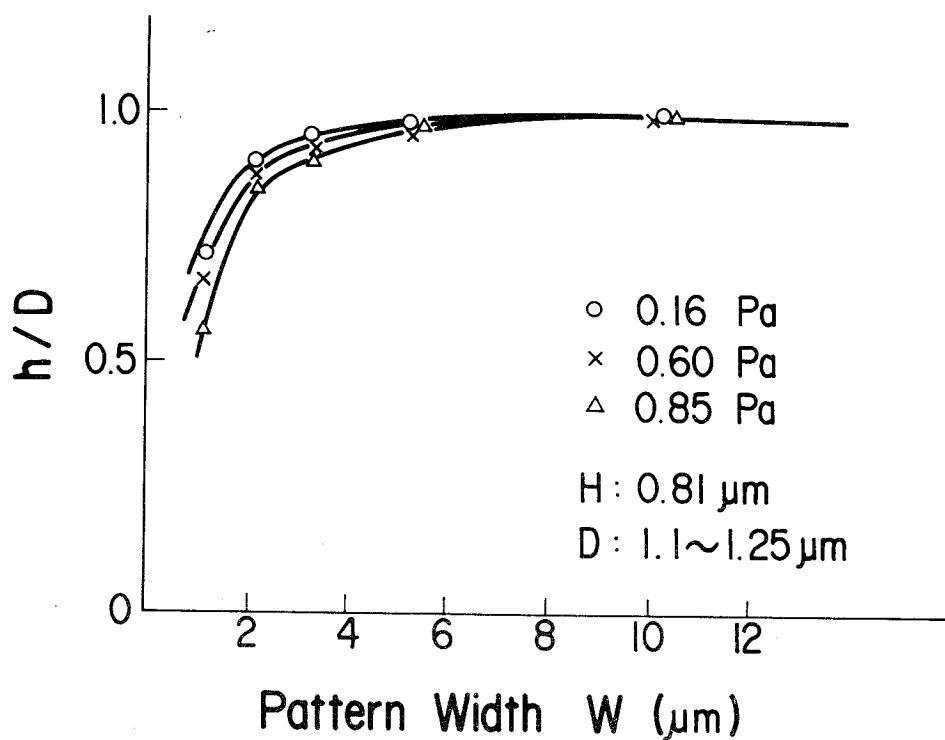

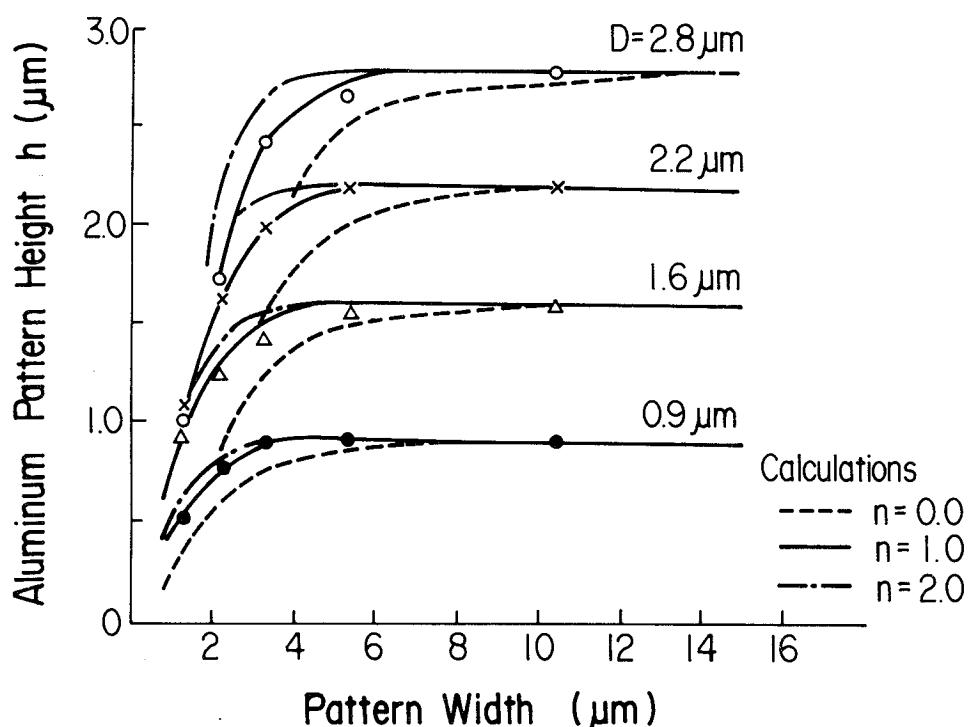

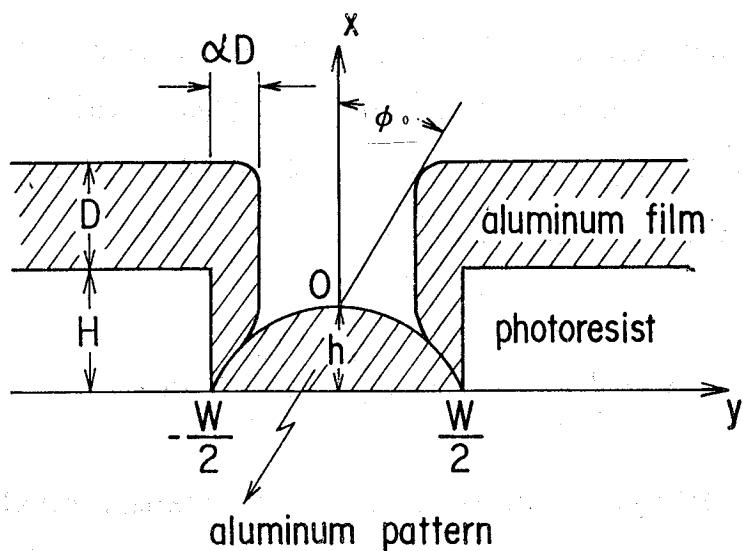

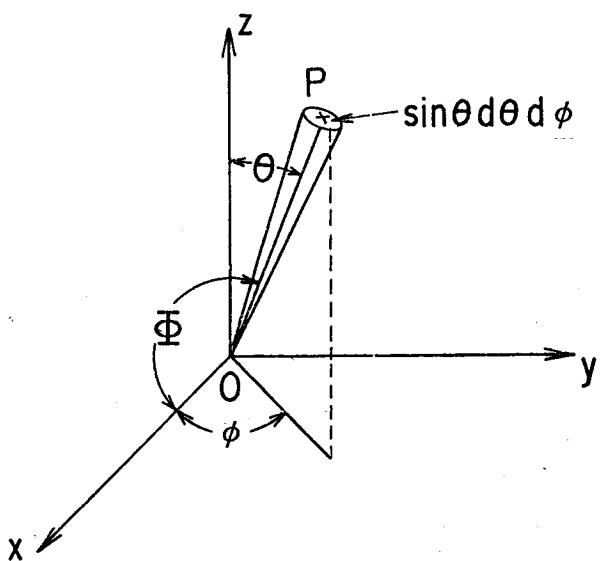

さらに、本加工法により形成したSiO<sub>2</sub>膜を、シリコンMOS半導体素子間分離に応用し、従来から広く使用されている選択酸化分離法に比べて、著しく優れた分離特性を示すことを記述する。一方、Al膜のリフトオフ加工において見い出された、Alパタンの高さが幅に依存する、サイズ効果について述べ、このサイズ効果を定量的に解析し、さらに、このサイズ効果の抑制法を、解析結果と実験結果の両面から明らかにする。

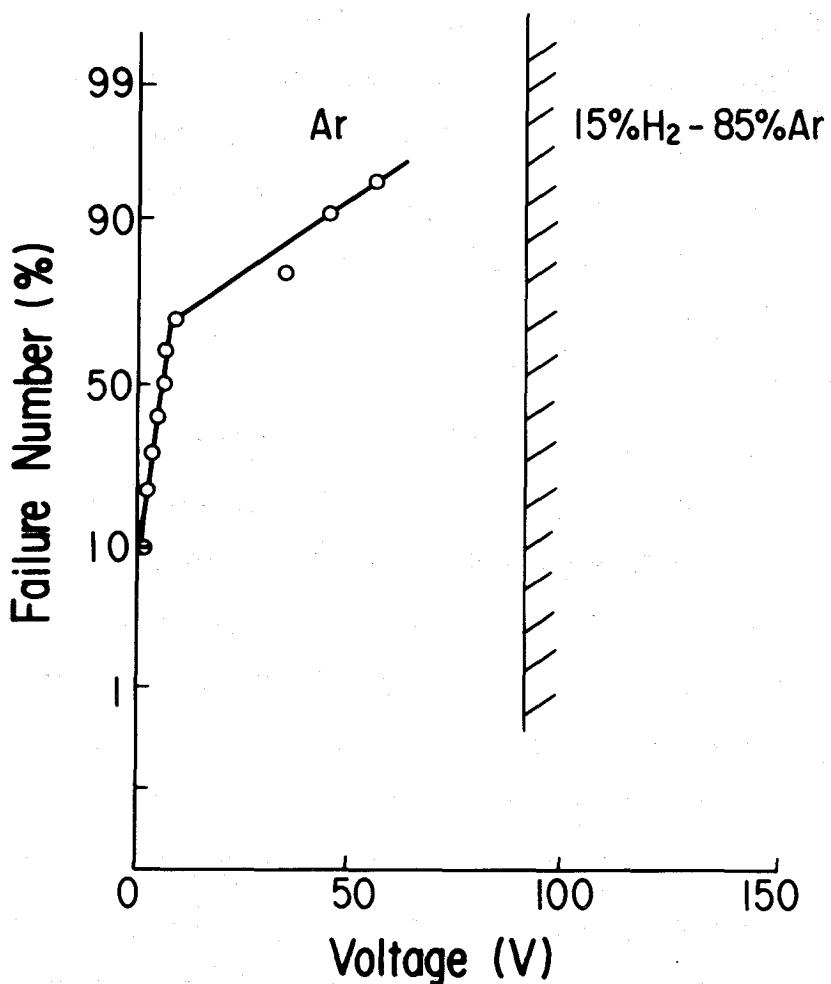

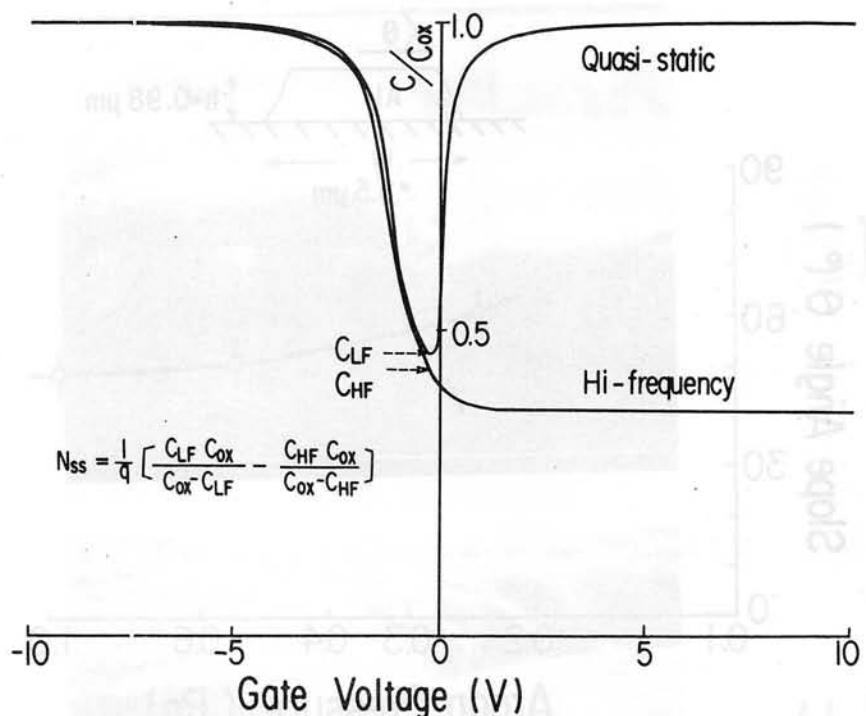

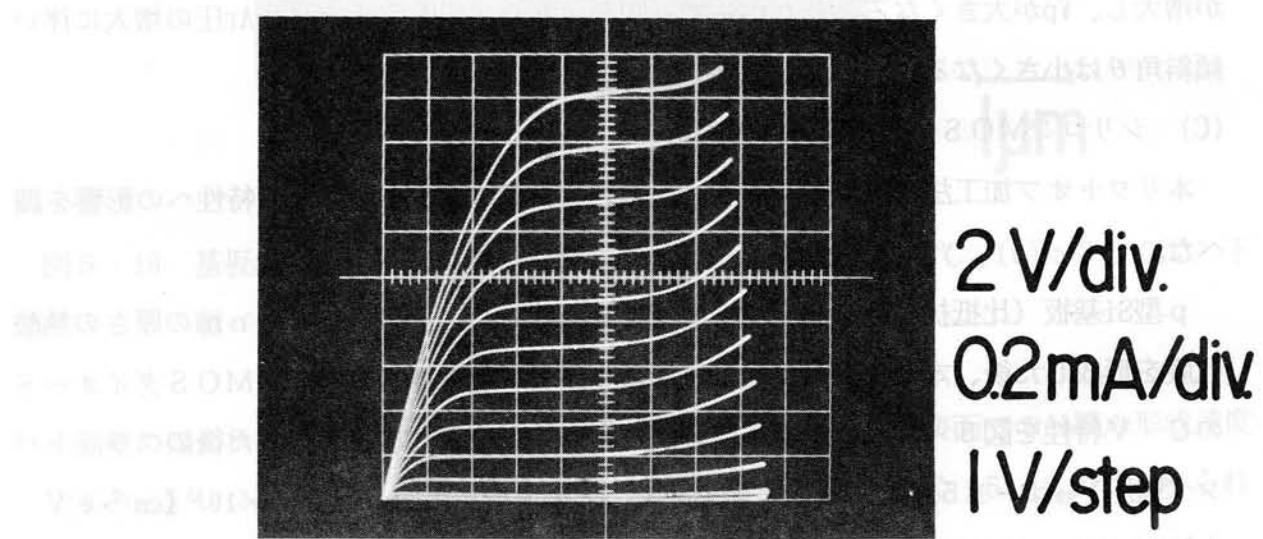

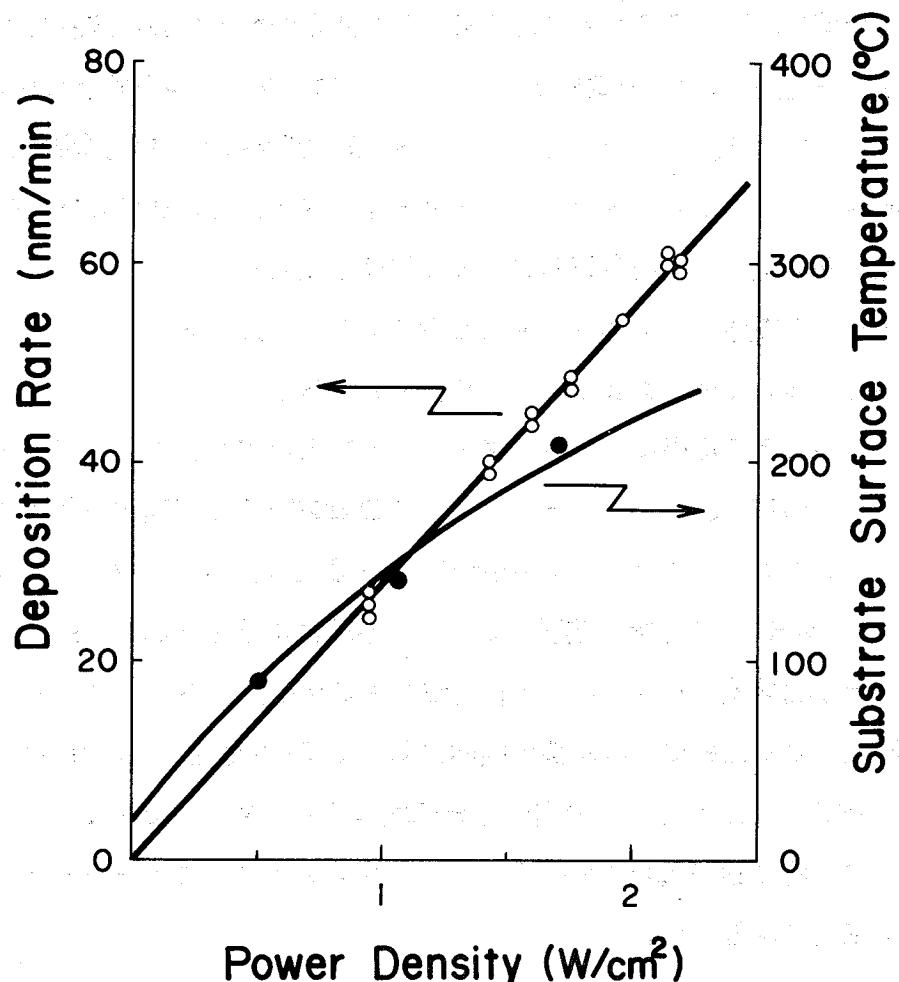

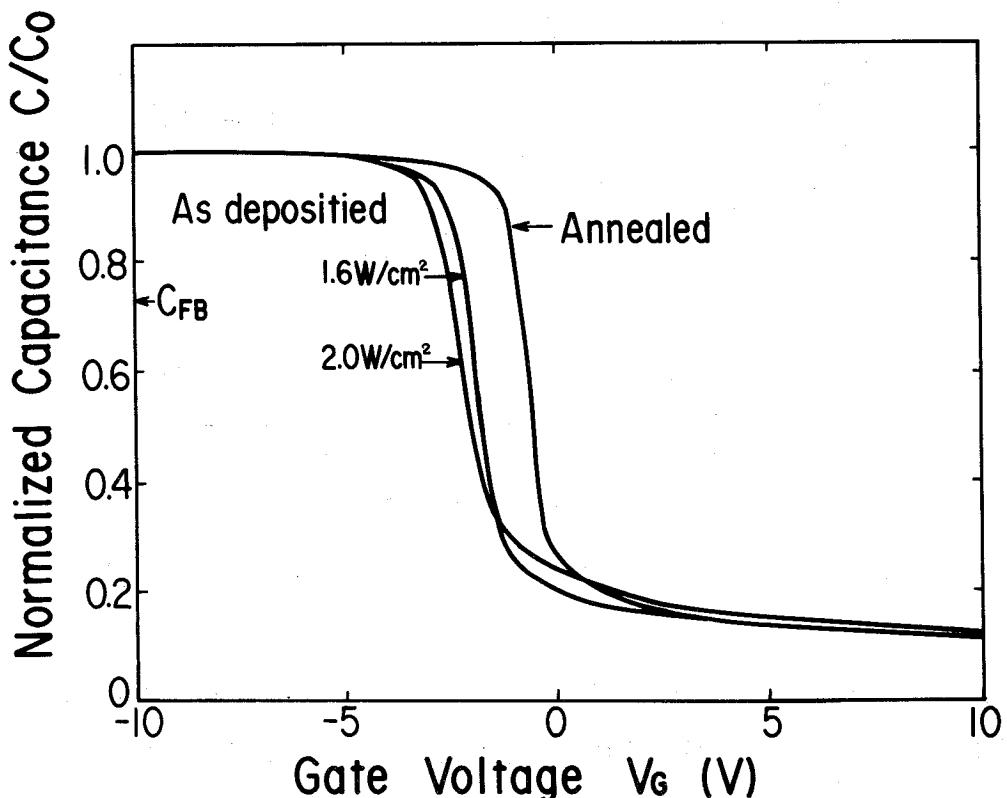

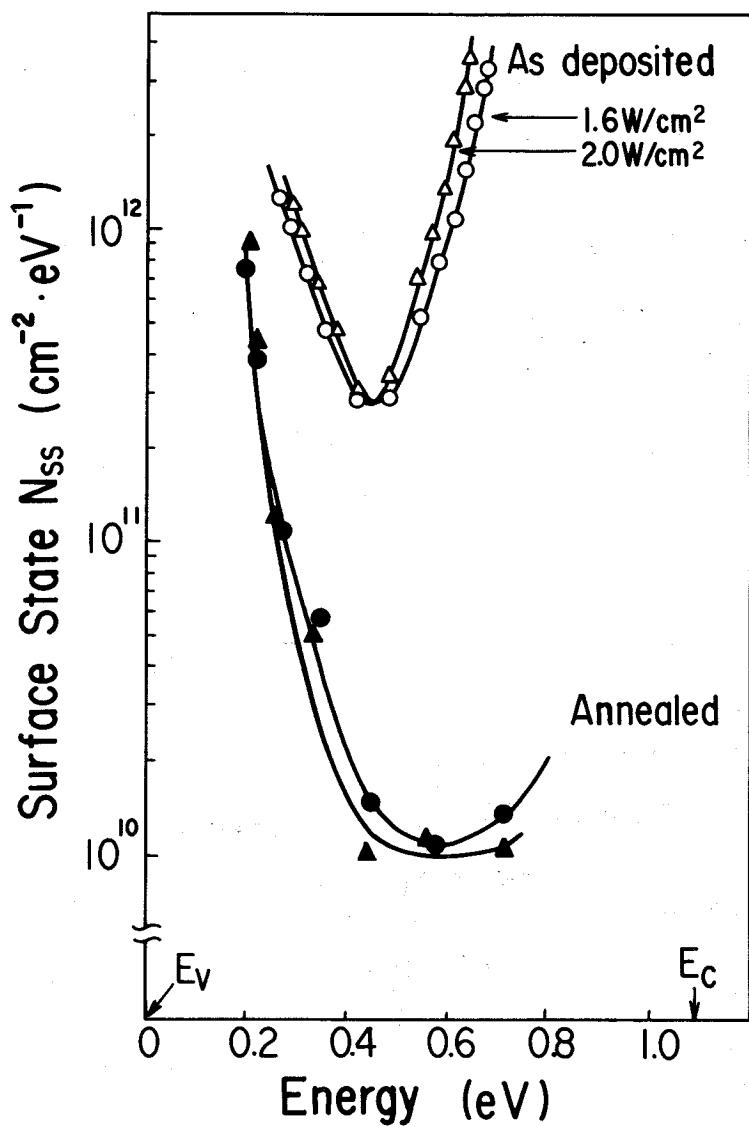

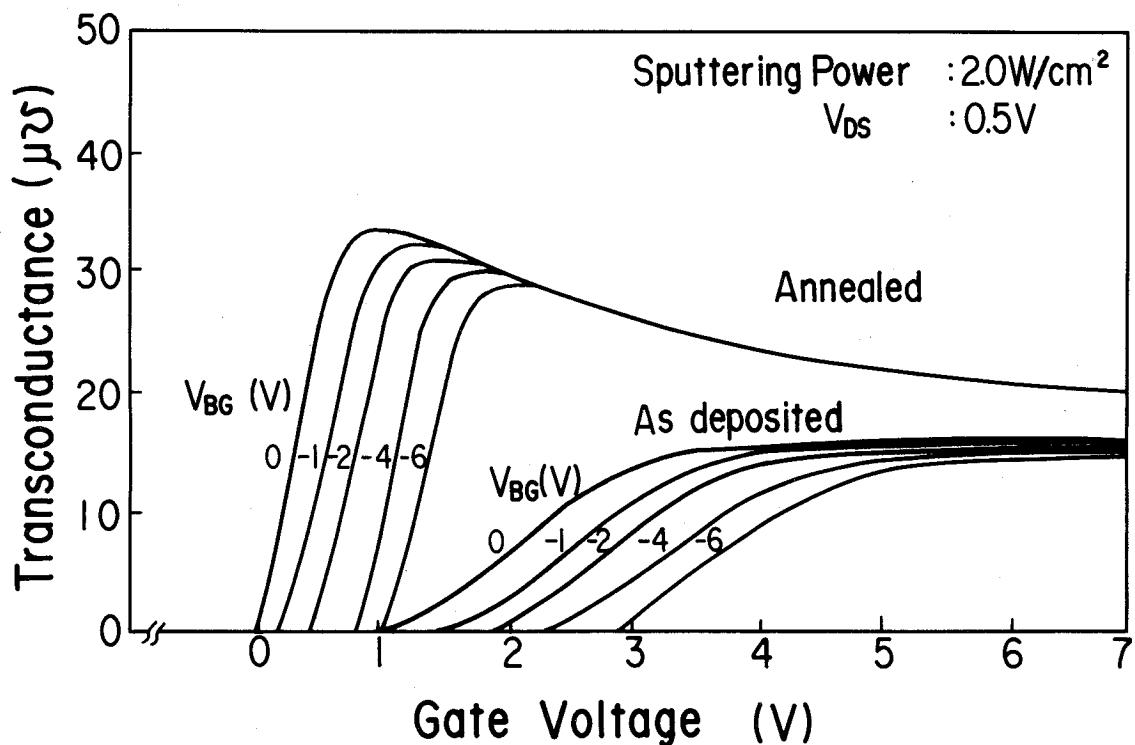

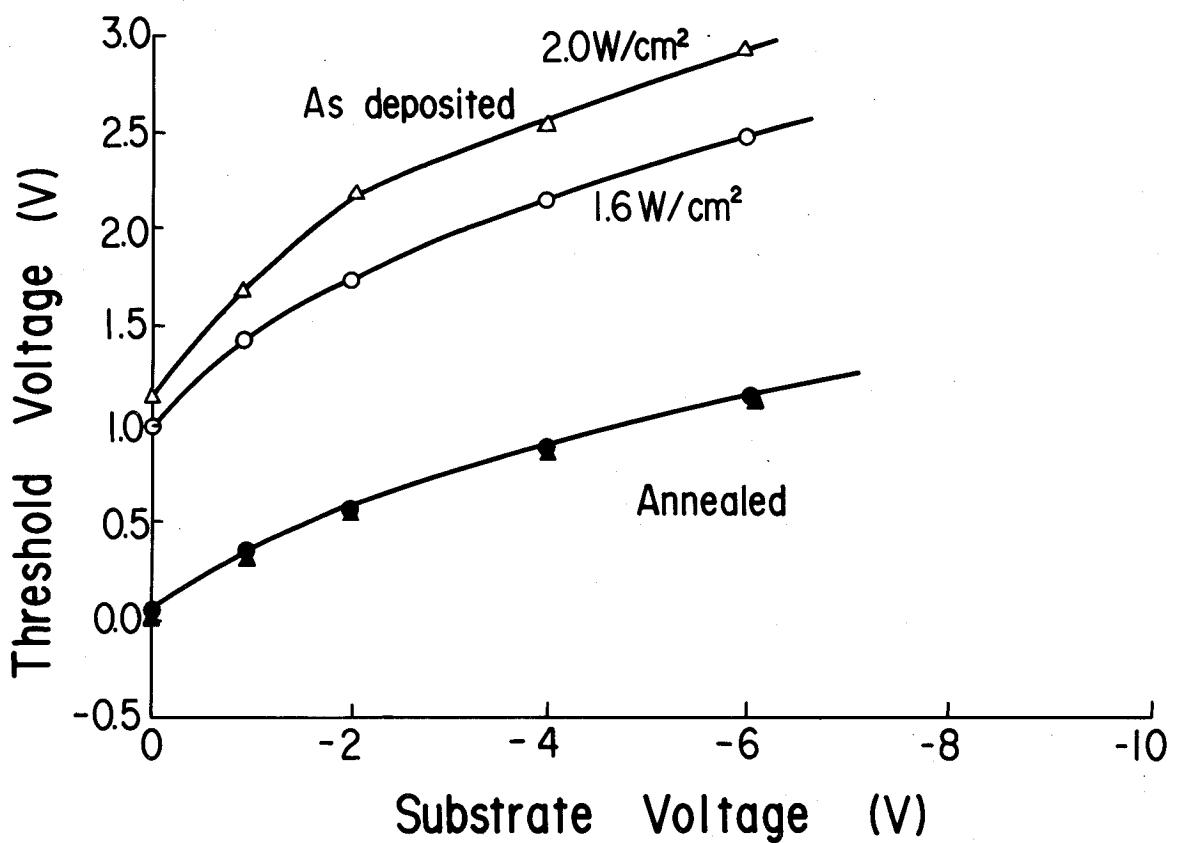

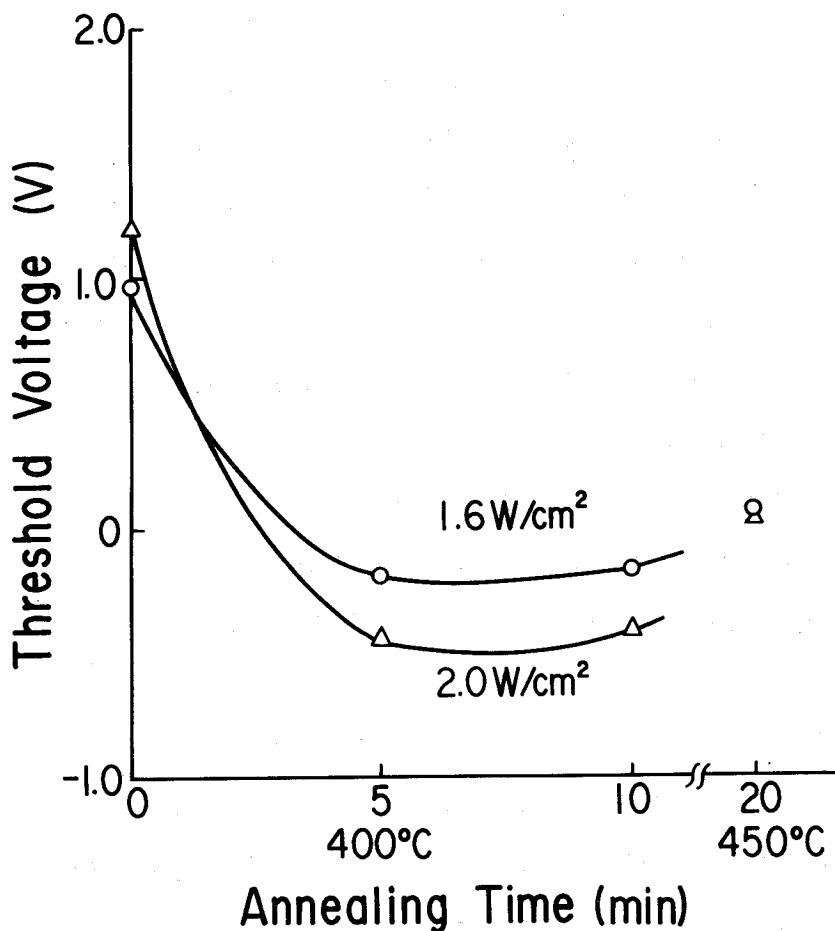

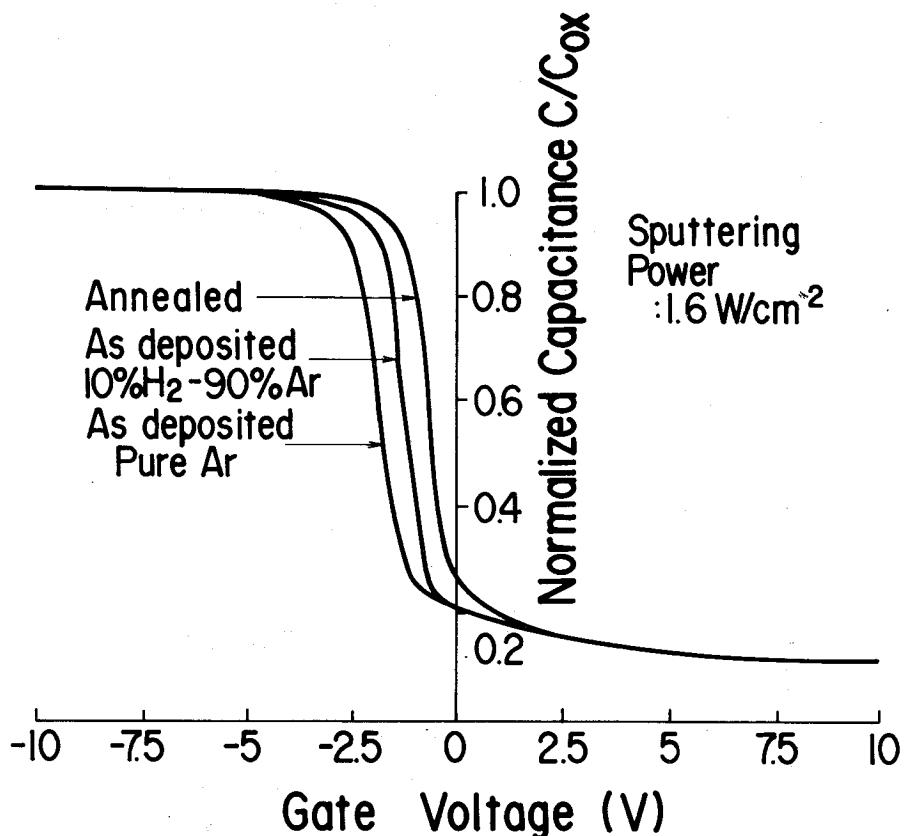

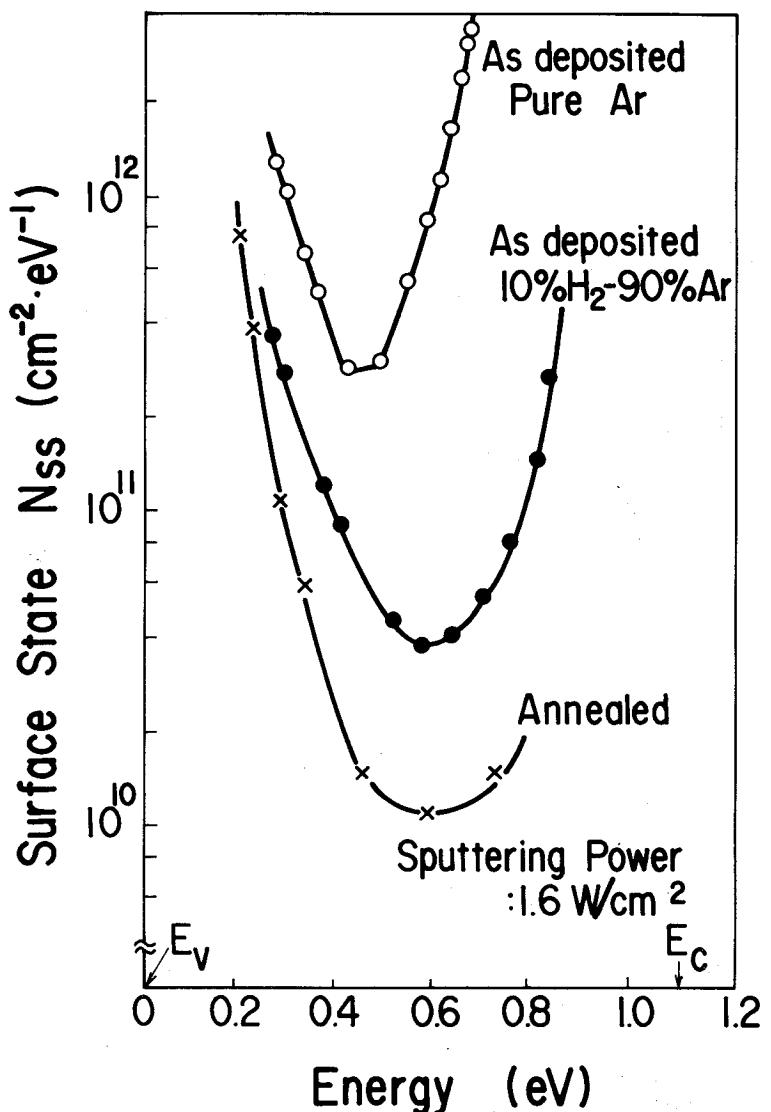

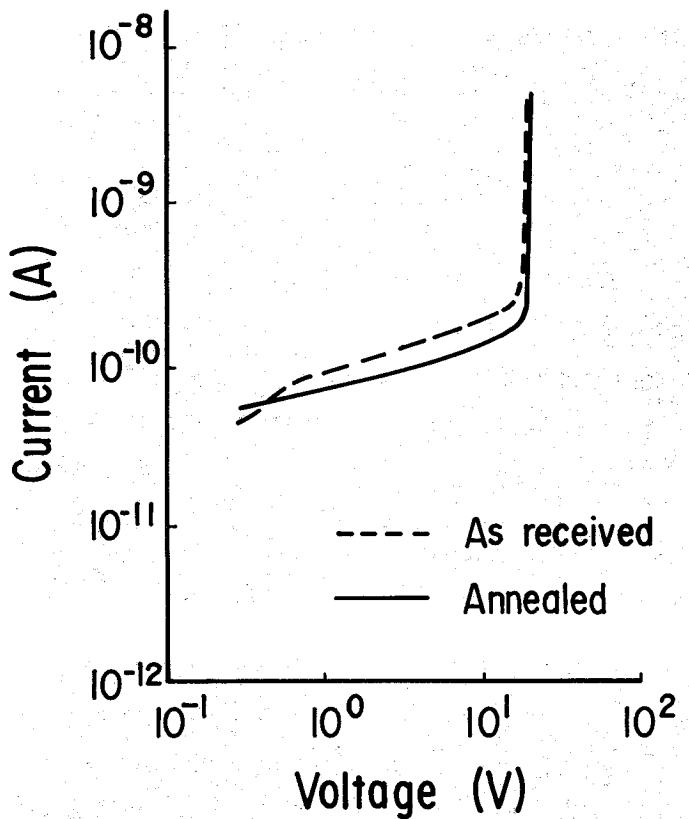

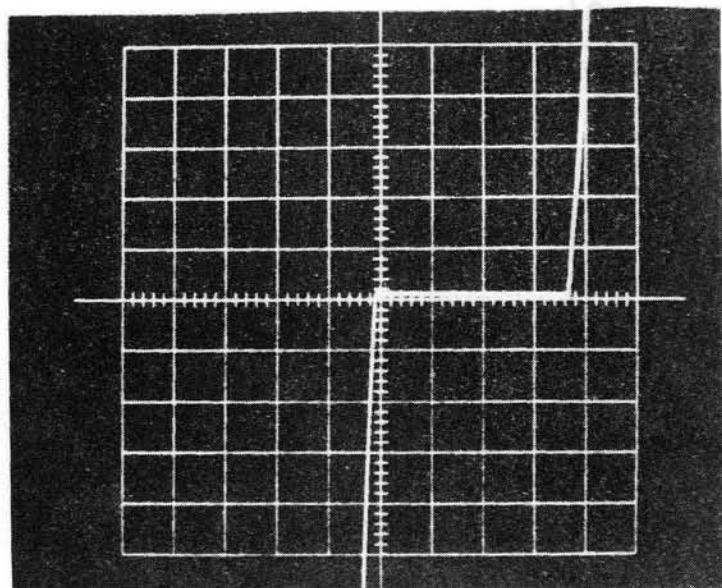

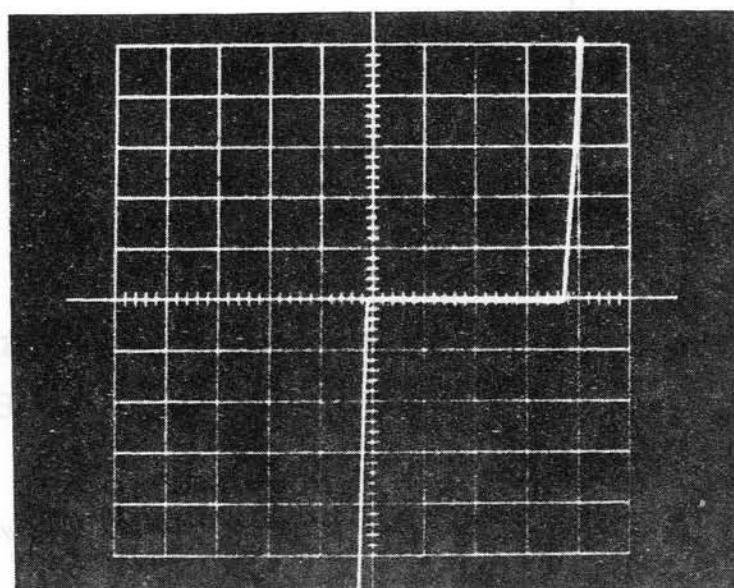

## 第6章 スパッタリング法のシリコンMOS半導体素子特性への影響と損傷改善法

本章では、スパッタリング法によりシリコンMOS半導体素子配線用Al膜を形成する際の、素子特性に与える影響を詳細に述べる。さらに、スパッタリング法による照射損傷は、水素雰囲気中熱処理により消滅すること、および、スパッタリングガス中に水素を混合することによって、この損傷を改善できることを示す。

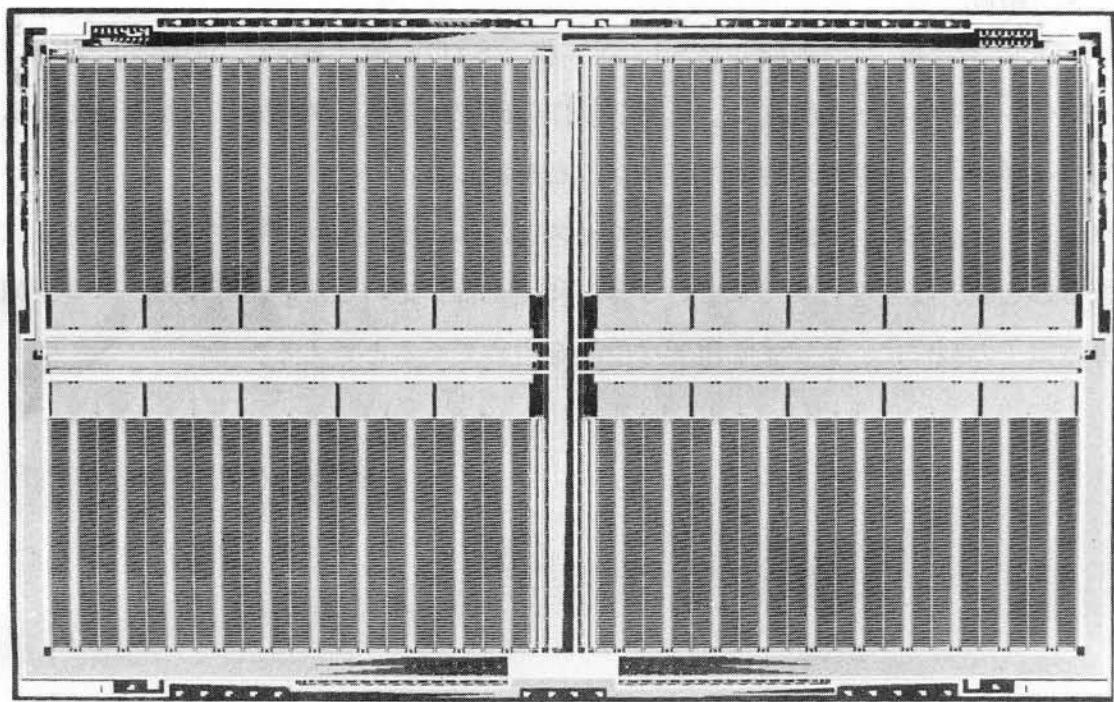

## 第7章 スパッタリング法による薄膜のシリコンMOS半導体素子への応用

本章では、本研究において明らかになった結果をもとに、窒化シリコン膜、SiO<sub>2</sub>膜、およびAl膜を一貫して用いて、シリコンMOS半導体素子を製作し、スパッタリングによる薄膜の形成がシリコンMOS半導体素子の製作に極めて有効なことを実証する。

## 第8章 結論

本章では、以上の各章で得た結果を総括する。

## 目 次

|                                                   |    |

|---------------------------------------------------|----|

| 第1章 序論 .....                                      | 1  |

| 1 - 1 研究の目的と意義 .....                              | 1  |

| 1 - 2 研究の背景 .....                                 | 1  |

| 1 - 2 - 1 シリコンMOS半導体素子の概略と製作上の問題点 .....           | 1  |

| 1 - 2 - 2 スパッタリングによる薄膜の形成の概要と特徴 .....             | 5  |

| 1 - 2 - 3 本研究の位置と要求条件 .....                       | 9  |

| 1 - 3 本論文の概要と構成 .....                             | 10 |

| 参考文献 .....                                        | 12 |

| 第2章 反応性スパッタリング法による窒化シリコン膜の形成 .....                | 14 |

| 2 - 1 緒言 .....                                    | 14 |

| 2 - 2 Ar - N <sub>2</sub> 混合ガス中反応性スパッタリング特性 ..... | 15 |

| 2 - 2 - 1 装置と実験方法 .....                           | 15 |

| 2 - 2 - 2 結果と考察 .....                             | 15 |

| 2 - 3 反応性スパッタリング法による窒化シリコン膜の特性 .....              | 32 |

| 2 - 3 - 1 試料作製と測定 .....                           | 32 |

| 2 - 3 - 2 結果と考察 .....                             | 33 |

| 2 - 4 反応性スパッタリング法による窒化シリコン膜の選択酸化マスクへの応用 .....     | 44 |

| 2 - 4 - 1 シリコンMOS半導体素子の製作と特性測定 .....              | 45 |

| 2 - 4 - 2 測定結果と考察 .....                           | 46 |

| 2 - 5 結言 .....                                    | 48 |

| 参考文献 .....                                        | 49 |

| 第3章 スパッタリング法によるSiO <sub>2</sub> 膜の形成と特性 .....     | 52 |

| 3 - 1 緒言 .....                                    | 52 |

| 3 - 2 実験方法 .....                                  | 52 |

| 3 - 2 - 1 装置と試料作製 .....                           | 52 |

|                                                     |                                                             |     |

|-----------------------------------------------------|-------------------------------------------------------------|-----|

| 3 - 2 - 2                                           | 測定方法                                                        | 53  |

| 3 - 3                                               | Ar中スパッタリング法によるSiO <sub>2</sub> 膜の特性                         | 55  |

| 3 - 3 - 1                                           | 測定結果                                                        | 55  |

| 3 - 3 - 2                                           | 膜特性に対する考察                                                   | 62  |

| 3 - 4                                               | Ar - H <sub>2</sub> 混合ガス中スパッタリング法によるSiO <sub>2</sub> 膜特性の改善 | 64  |

| 3 - 4 - 1                                           | 測定結果                                                        | 65  |

| 3 - 4 - 2                                           | H <sub>2</sub> 混合効果の考察                                      | 77  |

| 3 - 5                                               | 結言                                                          | 79  |

|                                                     | 参考文献                                                        | 81  |

| <br>第4章 スパッタリング法によるSiO <sub>2</sub> 膜のステップカバレジ      |                                                             | 83  |

| 4 - 1                                               | 緒言                                                          | 83  |

| 4 - 2                                               | ステップカバレジに関する一般的考察                                           | 84  |

| 4 - 3                                               | 装置と実験方法                                                     | 86  |

| 4 - 4                                               | ステップカバレジの形状                                                 | 89  |

| 4 - 5                                               | Ar - H <sub>2</sub> 混合ガス中スパッタリング法によるステップカバレジの改善             | 96  |

| 4 - 6                                               | 結言                                                          | 100 |

|                                                     | 参考文献                                                        | 102 |

| <br>第5章 スパッタリング法によるSiO <sub>2</sub> 膜およびAl膜のリフトオフ加工 |                                                             | 104 |

| 5 - 1                                               | 緒言                                                          | 104 |

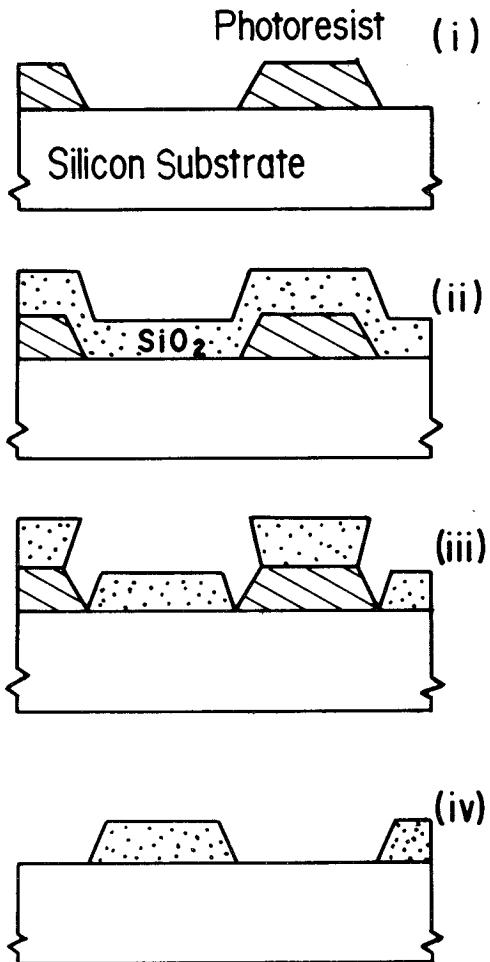

| 5 - 2                                               | スパッタリング法によるSiO <sub>2</sub> 膜のリフトオフ加工                       | 105 |

| 5 - 2 - 1                                           | 試料およびシリコンMOS半導体素子の製作と測定                                     | 105 |

| 5 - 2 - 2                                           | リフトオフ加工特性                                                   | 107 |

| 5 - 2 - 3                                           | シリコンMOS半導体素子分離への応用                                          | 111 |

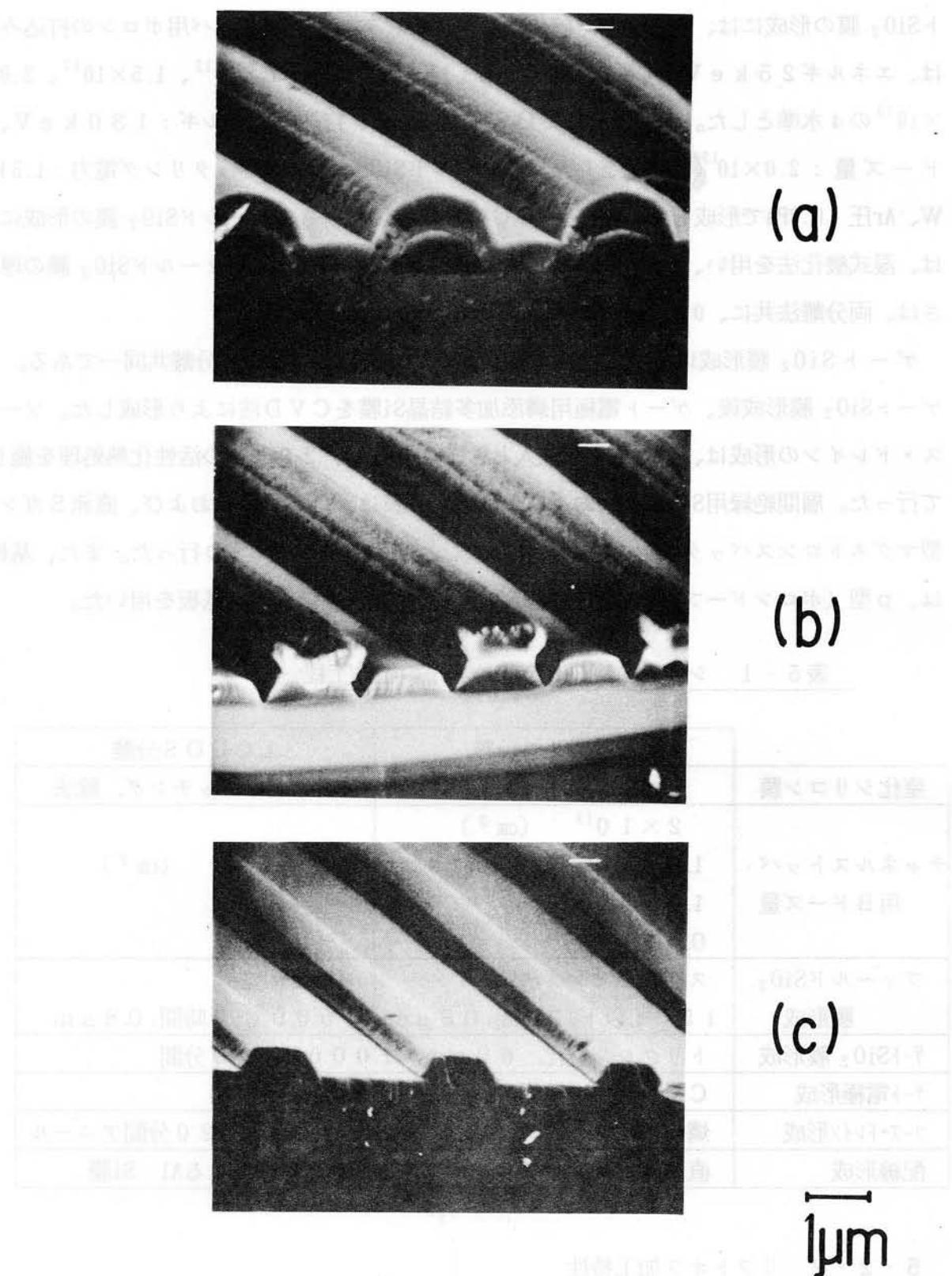

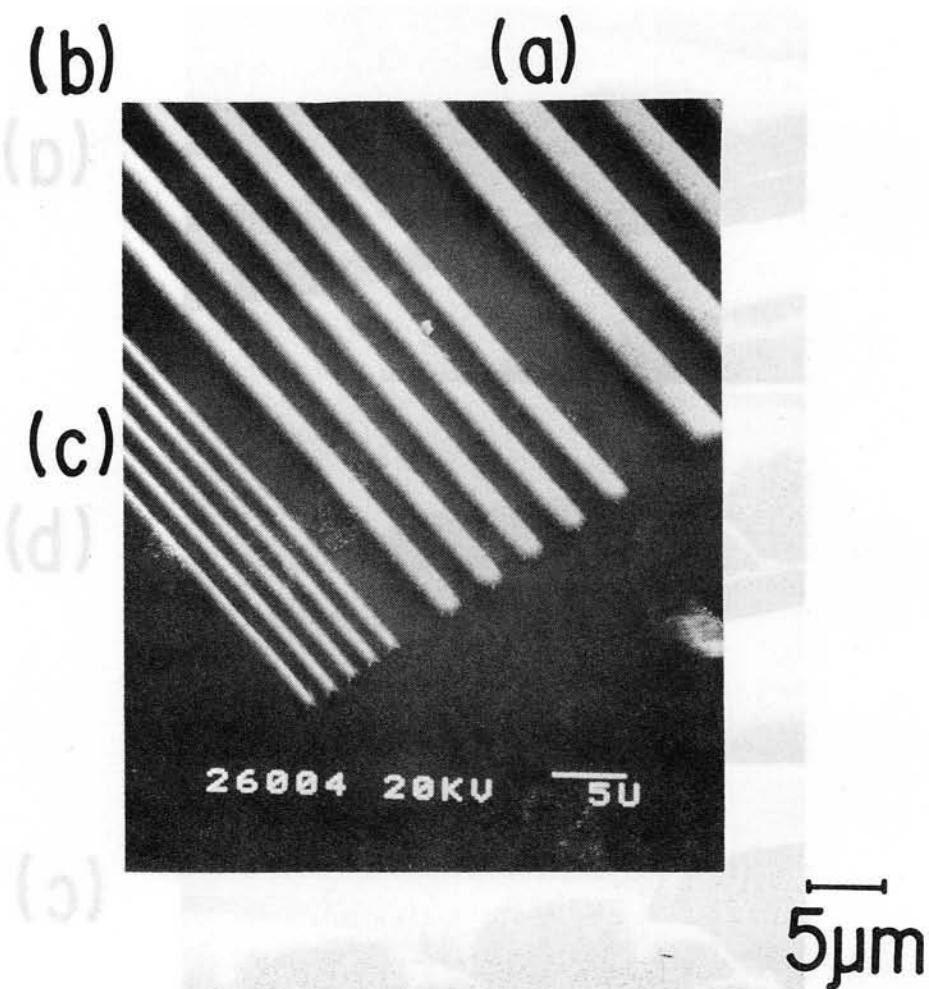

| 5 - 3                                               | スパッタリング法によるAl膜のリフトオフ加工                                      | 121 |

| 5 - 3 - 1                                           | 試料作製と測定                                                     | 121 |

| 5 - 3 - 2                                           | 結果と考察                                                       | 121 |

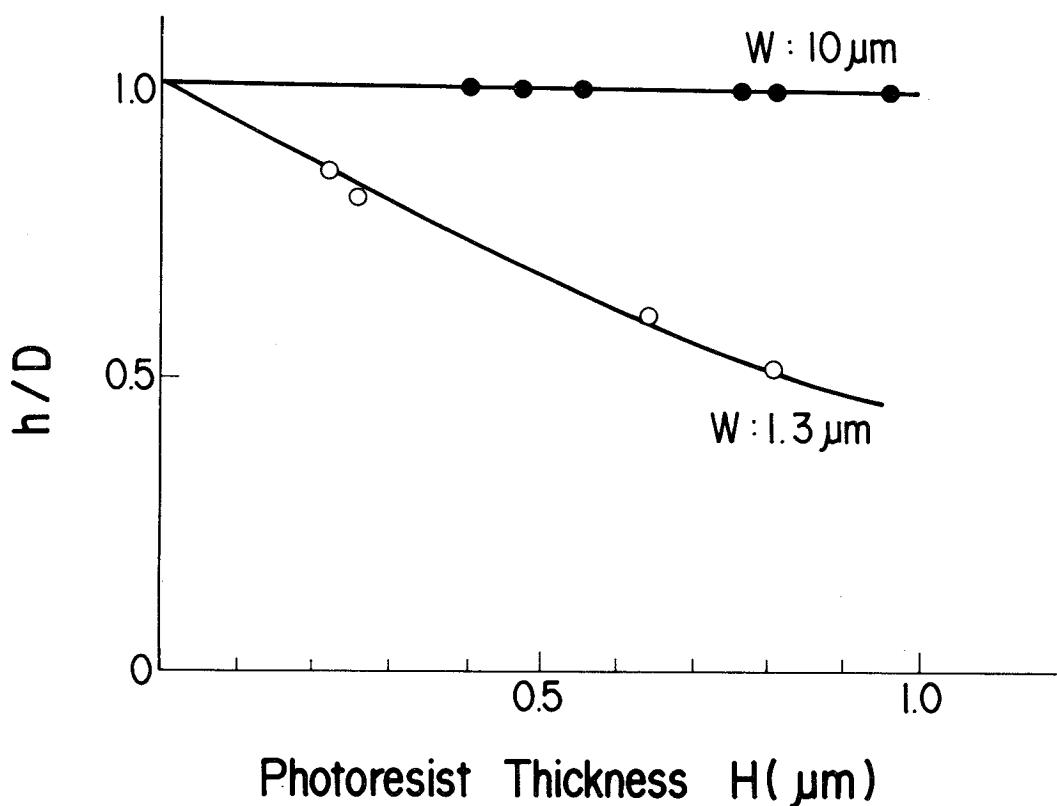

| 5 - 3 - 3                                           | リフトオフ加工におけるサイズ効果                                            | 129 |

|                                       |                                           |     |

|---------------------------------------|-------------------------------------------|-----|

| 5 - 4                                 | 結言                                        | 136 |

|                                       | 付録                                        | 137 |

|                                       | 参考文献                                      | 140 |

| 第6章 スパッタリング法のシリコンMOS半導体素子特性への影響と損傷改善法 |                                           | 142 |

| 6 - 1                                 | 緒言                                        | 142 |

| 6 - 2                                 | 実験方法                                      | 143 |

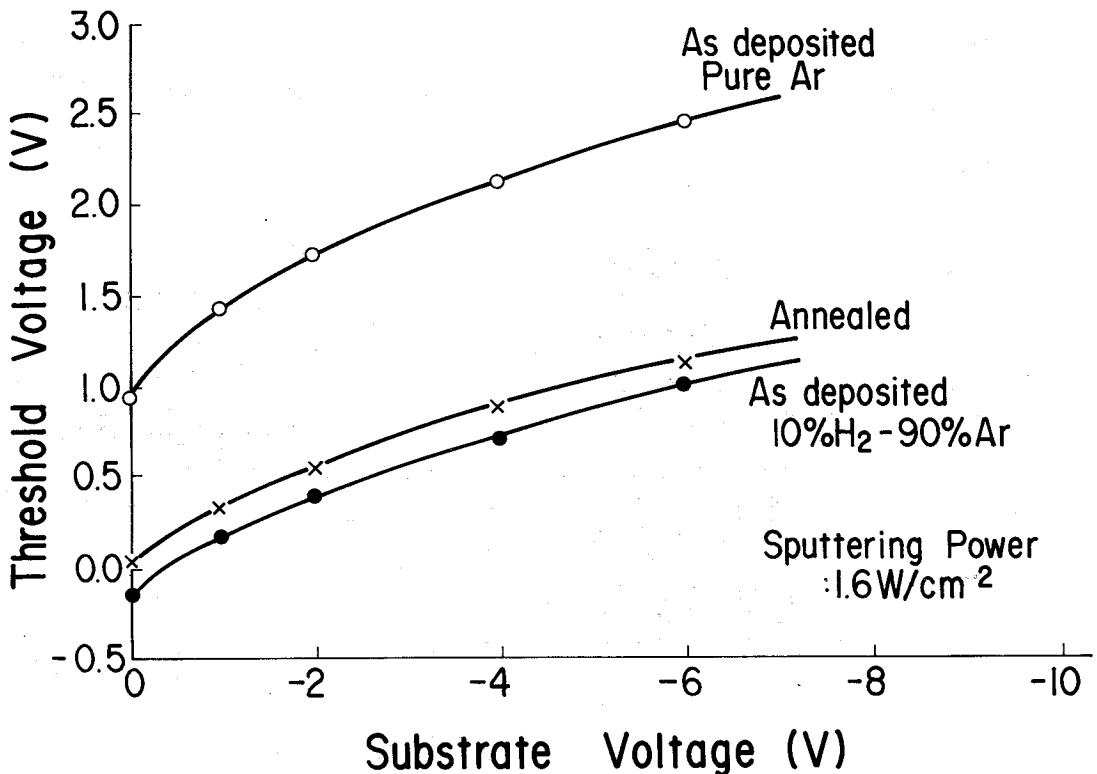

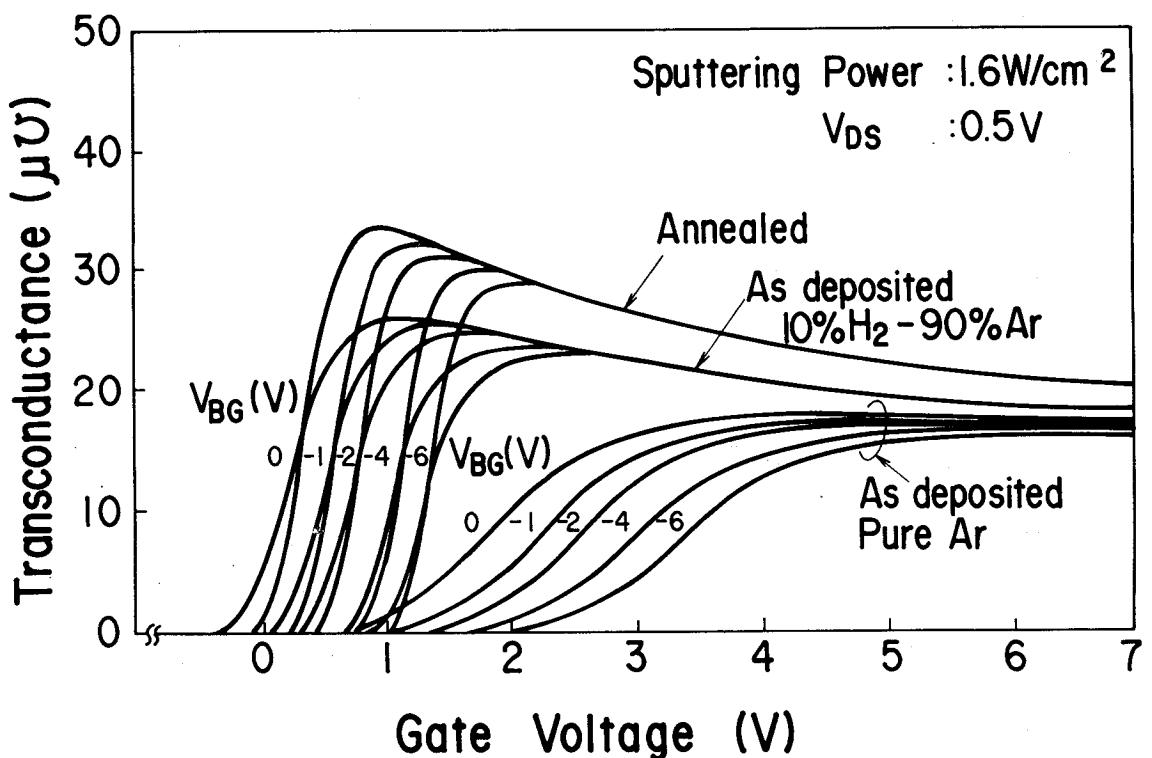

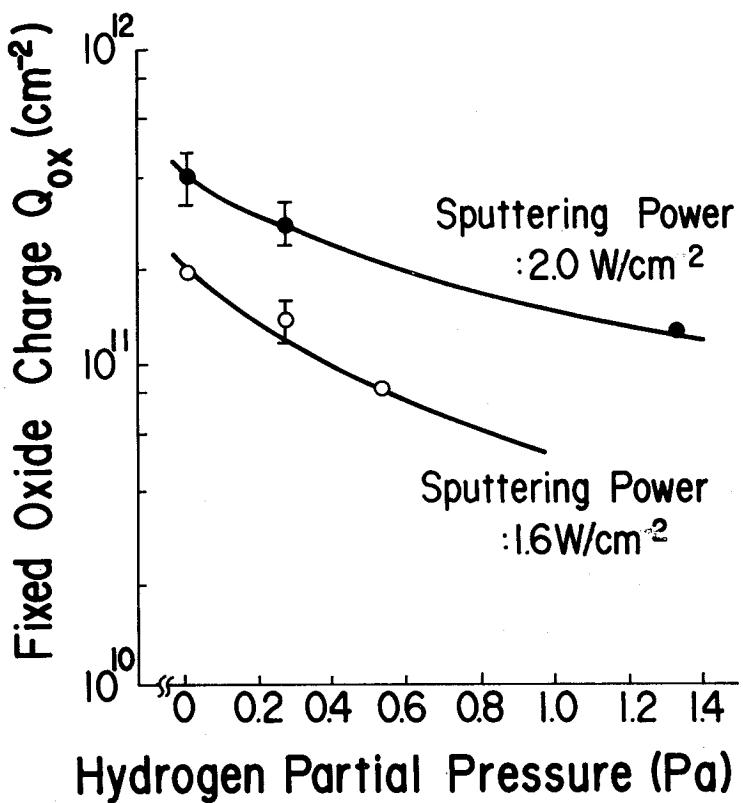

| 6 - 3                                 | スパッタリング法のシリコンMOS半導体素子特性への影響               | 144 |

| 6 - 4                                 | 水素混合ガス中スパッタリング法による損傷改善法                   | 150 |

| 6 - 5                                 | 結言                                        | 154 |

|                                       | 参考文献                                      | 156 |

| 第7章 スパッタリング法による薄膜のシリコンMOS半導体素子への応用    |                                           | 158 |

| 7 - 1                                 | 緒言                                        | 158 |

| 7 - 2                                 | シリコンMOS半導体素子の製作と測定                        | 158 |

| 7 - 3                                 | 結果と考察                                     | 159 |

| 7 - 4                                 | 結言                                        | 164 |

|                                       | 参考文献                                      | 165 |

| 第8章 結論                                |                                           | 166 |

|                                       | 謝辞                                        | 169 |

|                                       | スパッタリングによる薄膜の形成とシリコンMOS半導体素子への応用に関する論文リスト | 170 |

# 第1章 序論

## 1 - 1 研究の目的と意義

近年における、シリコンを中心とする半導体素子の発展は急激であり、大規模・高密度な半導体素子や高速な半導体素子が実現している。これらの半導体素子の製作に必要とされる薄膜の形成には、真空蒸着法や気相成長法が一般に用いられている。

本論文では、シリコン半導体素子、特に、シリコンMOS半導体素子の、一層の大規模・高密度化を図るために、従来からの薄膜形成法に代る方法を実現することを目的とし、スパッタリング法による窒化シリコン膜、 $\text{SiO}_2$  膜、および、Al膜の形成とシリコンMOS半導体素子への応用に関して行った研究の結果について述べる。

本研究の意義は、従来法に代って、スパッタリングによる薄膜の形成を実現することにより、シリコンMOS半導体素子の一層の発展に寄与し、さらに、将来における半導体素子の開発に新たな進展と指針を与えることである。

## 1 - 2 研究の背景

### 1 - 2 - 1 シリコンMOS半導体素子の概略と製作上の問題点

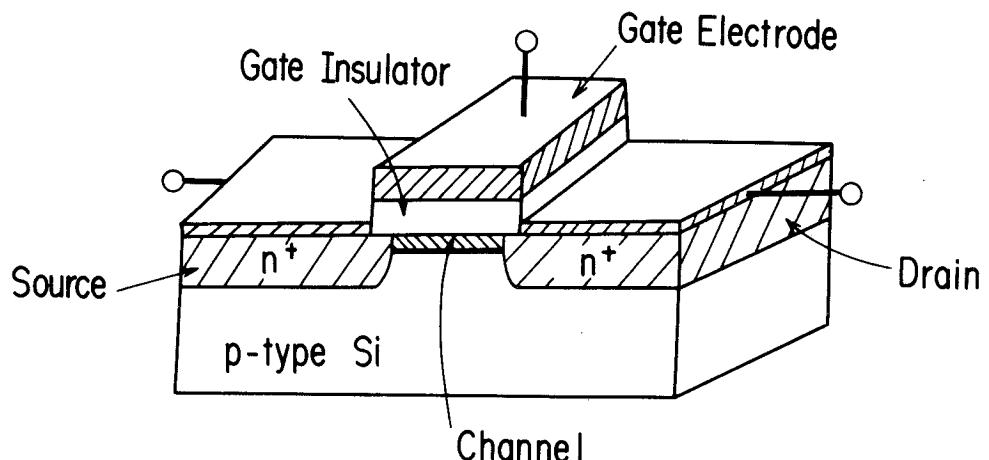

近年、シリコンを中心とする半導体素子の発展は急激であり、その代表的なものとして、シリコンMOS(Metal-Oxide-Semiconductor)半導体素子が挙られる。この素子は、MOSトランジスタを基本とし、多数のトランジスタを配線により結線する構造を成している。図1-1に、このMOSトランジスタの構造を示す。半導体基板（この図では、p型Si基板）上に、ソース電極やドレイン電極となる不純物拡散層（この図では、n<sup>+</sup>拡散領域）を有し、これらの電極の間に、ゲート電極、ゲート絶縁膜、ならびに半導体基板から成るMOSダイオードが形成されている。

MOSトランジスタは、図1-1に示すように、ソース電極、ドレイン電極、および、ゲート電極がほぼ同一平面上に形成されたプレーナ構造を成し、さらに、ソース電極とドレイン電極が対称に形成され、極めて簡単な構造を成している。一方、MOSトランジスタの基本動作は、ゲート電極と基板との間に電圧を印加し、ゲート絶縁膜と半導体基板との界面に、チャネルと呼れる反転層を形成し、この反転層の電気伝導度を制御して、ソース電極とドレイン電極間の電流を変化させることにもとづく。このように、MOSトラン

図1 - 1 シリコンMOSトランジスタの構造図

ジスタは、構造や動作原理が簡単で、かつ、プレーナ構造を成している特徴を有している。この結果、シリコンMOS半導体素子は高密度化、高集積化に適し、記憶素子においては、ゲート長（ソース電極とドレイン電極間の間隔）が $1\text{ }\mu\text{m}$ を切り、記憶容量が1Mビット／チップのものも実現されようとしている<sup>1)</sup>。

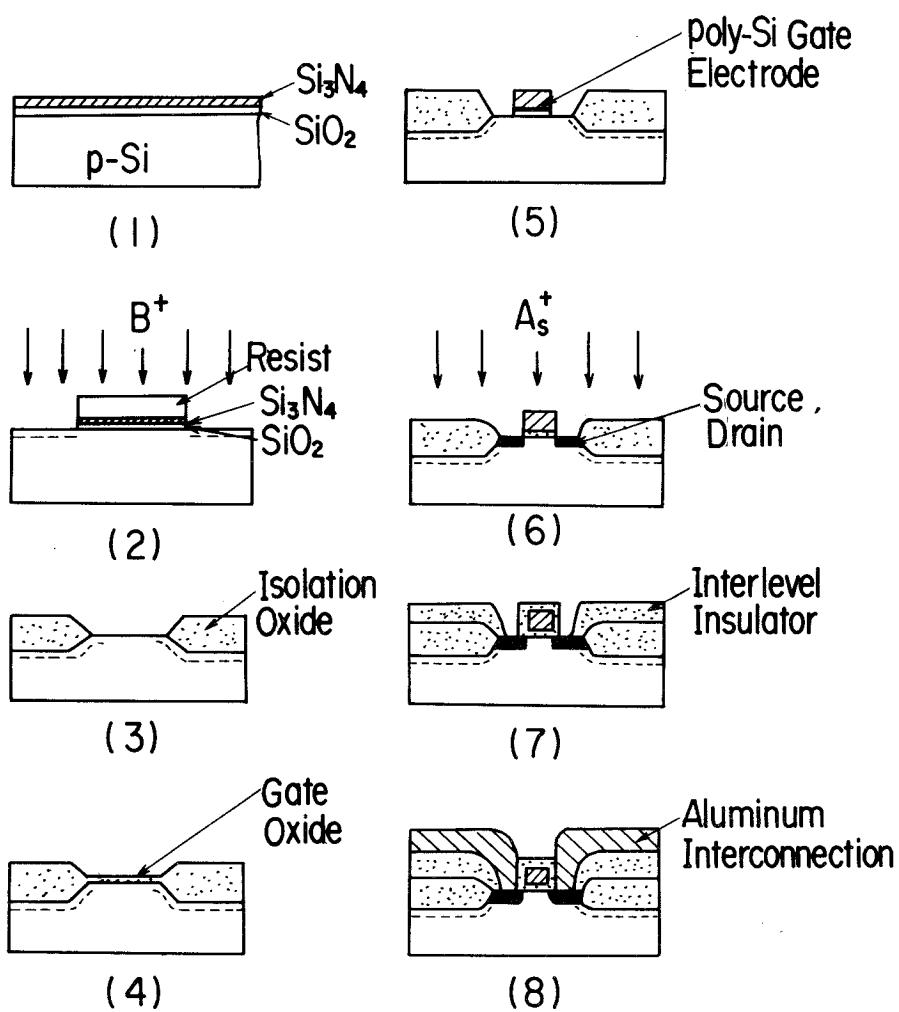

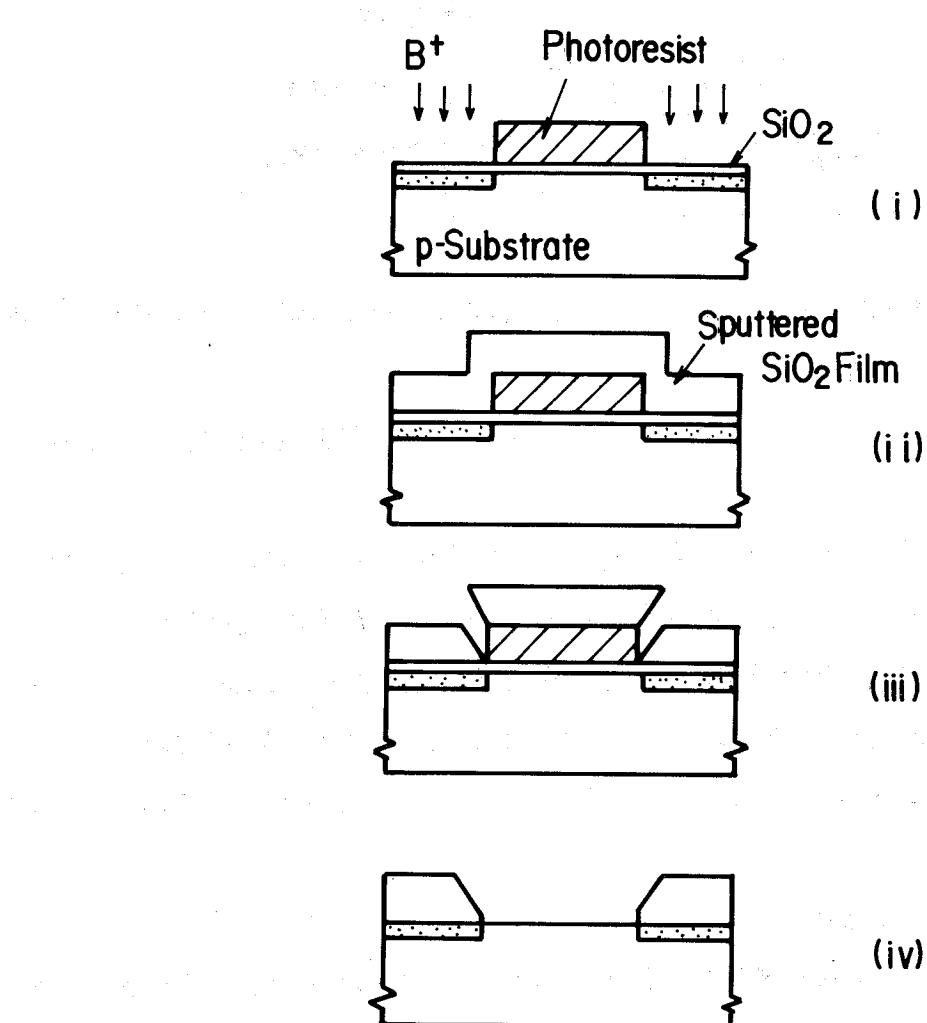

シリコンMOS半導体素子の製作には、通常、ボロン（B）を添加したp型Si基板が用いられている。現在一般に使用されているMOS半導体素子製作工程の概略を図1 - 2に示す<sup>2)3)</sup>。以下、図に示す工程に従って要点を述べる。

工程(1)：面方位（100）、p型Si基板（比抵抗： $1\sim10\text{ }\Omega\cdot\text{cm}$ ）を洗浄した後、厚さ約 $50\text{ nm}$ の酸化膜を熱酸化法により、続いて、約 $150\text{ nm}$ の厚さの窒化シリコン膜を形成する。

工程(2)：トランジスタ形成領域にレジストパタンを形成する。このパタンをマスクとして、プラズマエッティング法により窒化シリコン膜の加工を行う。その後、このレジスタパタンをマスクとして、 $2\times10^{13}\text{ cm}^{-2}$  程度のp型不純物であるボロン（B）を基板にイオン注入する。

工程(3)：レジストパタンを除去し、基板洗浄後、約 $1000\text{ }^{\circ}\text{C}$ の水蒸気雰囲気中で数時間酸化し、約 $1\text{ }\mu\text{m}$ のフィールド酸化膜を形成する<sup>4)</sup>。その後、窒化シリコン膜、ならびに、その下の酸化膜を除去する。

工程(4)：塩素（Cl）を含む雰囲気中でゲート酸化膜を、 $50\sim100\text{ nm}$ 厚形成する。

図1-2 シリコンMOS半導体素子の製作工程の概略図

工程(5)：磷添加多結晶シリコン膜を形成した後、ホトリソグラフィ、および、プラズマエッティングにより、ゲート電極を形成する。

工程(6)：n型不純物（磷やヒ素）をイオン注入し、活性化熱処理を施し、ソースおよびドレイン不純物拡散領域を形成する。この際、n型不純物は、ゲート電極とフィールド酸化膜によりさえぎられ、自己整合的に上記不純物拡散領域が形成できる。

工程(7)と(8)：これらの工程は配線形成のために行う。まず、層間絶縁膜として、約0.5  $\mu\text{m}$  の $\text{SiO}_2$ 膜を形成した後、スルホールを開口し、次に、配線用Al合金（2%Si-Al）膜を堆積し、エッティングする。最後に、水素を含む雰囲気中、400～500°Cでの熱処理を施す。

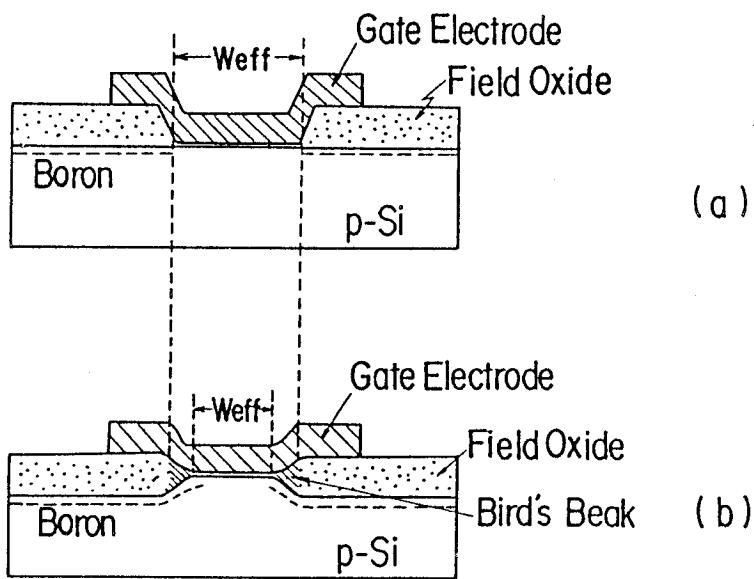

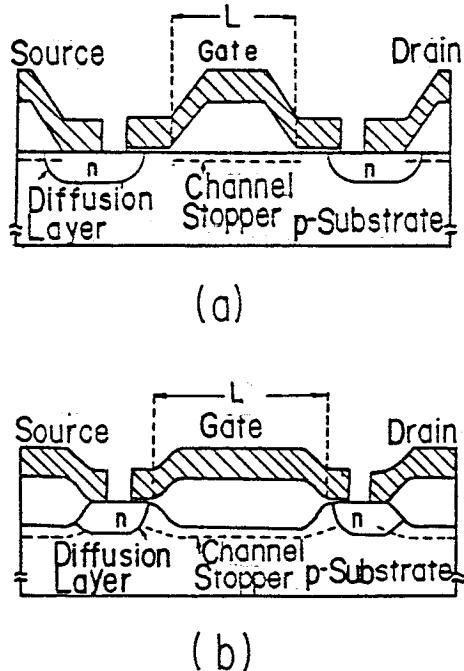

上記工程(2)におけるp型不純物の注入、ならびに、工程(3)における、厚いフィールド酸

化膜の形成の目的は、隣接したトランジスタ間のリーク電流を低減し、トランジスタ間を分離することである。隣接するトランジスタ間では、フィールド酸化膜をゲート絶縁膜とするMOSトランジスタ（フィールドトランジスタ、または、寄生トランジスタと称されている）が形成される。このトランジスタのリーク電流を小さくするには、フィールド酸化膜による容量を小さくし、さらに、不純物濃度を高くし、フィールドトランジスタの閾値電圧を大きくすればよい。

最後の工程(8)での熱処理は、不純物拡散層と配線とのコンタクト抵抗を小さくし、かつ、ゲート酸化膜とSi基板との界面の特性を改善するために行う。

シリコンMOS半導体素子の製作工程は、窒化シリコン膜、 $\text{SiO}_2$ 膜やAl膜等の薄膜の形成工程、これらの薄膜を微細加工するエッティング工程、ならびに、不純物の導入と熱処理を行う工程とに大別される。

前述したように、近年のシリコンMOS半導体素子の発展は急激であり、その高密度化・微細化は著しい。このために、従来からの製作技術には限界が見えてきた。その主要な問題点と現状を次に示す。

(1)微細加工技術：エッティングマスクを形成するためのリソグラフィ技術には、紫外線照射法が用いられ、一方、薄膜のエッティング技術には湿式法が用いられてきた。しかし、さらに微細な寸法で設計されている半導体素子を製作するために、紫外線照射法に代って、電子線やイオンを用いる方法が研究され、一部実用に供されている<sup>5)6)</sup>。一方、薄膜の微細加工には、プラズマやイオンを用いる乾式法が急速にとり入れられつつある<sup>7)8)</sup>。さらに、他の微細なパタンの形成法として、リフトオフ法も検討されている<sup>9)</sup>。この方法は、ドライエッティング装置等の高価な装置を必要としない簡単な方法であり、さらに、プラズマエッティング等によるような損傷がない利点を有している。

(2)薄膜の形成技術：従来からの半導体素子におけるAl膜、窒化シリコン( $\text{Si}_3\text{N}_4$ )膜や酸化シリコン( $\text{SiO}_2$ )膜の形成には、真空蒸着法、気相成長法や、Si基板を熱酸化する方法が広く用いられている<sup>2)3)</sup>。

微細な寸法で設計された半導体素子の基板上には、高さ $1 \mu\text{m}$ 程度の凹凸が多く生じている。素子の信頼性を確保し、かつ、製作工程における良品率を向上するには、この表面の凹凸を出来る限り均一な厚さのAl膜や $\text{SiO}_2$ 膜でおおわなければならない。しかし、従来からの、真空蒸着法によるAl膜や、気相成長法による $\text{SiO}_2$ 膜では、微細なパタンになったシリコンMOS半導体素子での上記問題には、もはや対処できなくなっている。—

方、 $\text{Si}_3\text{N}_4$ 膜の形成にも、 $\text{SiO}_2$ 膜と同様、気相成長法が用いられている。しかし、この膜の形成には、750°C以上の高温を必要とし、さらにその制御性が困難な問題もある。このため、従来からの方法に代り、低温度で、ステップカバレジにすぐれ、さらに、制御性にすぐれた方法が要求されている。

(3) 不純物導入ならびに熱処理技術：図1-2の工程(2)および(6)における不純物導入には、現在、イオン注入法が用いられている。これは、熱拡散法に比べて、不純物の濃度や分布の制御が極めて容易なためである。しかし、イオン注入法により導入した不純物の濃度や分布は、後に行う熱処理により変動する。例えば、工程(2)において導入したp型不純物原子Bは、素子間分離用フィールド酸化膜形成のための熱処理時に、素子形成領域に拡散し、この結果、MOSトランジスタの閾値電圧や移動度が設計値と異ってくる<sup>12)</sup>。このことは、微細なパターンの場合には特に顕著となる。このために、工程中に受ける熱処理を出来るだけ低温化する必要がある。この低温化法として、フィールド酸化膜の形成に高圧酸化法を用いる等の対策がとられている。しかし、この方法でも不充分であり、抜本的な対策が求められている。

上記技術に関する問題点の外に、基板の取扱いを含む製作工程の自動化の問題も重要である。同一品質の素子を製作するために、多くの細分化された製作工程から、出来るだけ作業者的人間的要因を除去しなければならない。微細なパターンの素子を製作する場合程、その必要性は強く、製作工程を自動化して、製作工程の信頼性を向上させることが広く行っている。この自動化は、製作工程が低温である程、さらに、制御性にすぐれた製作工程程容易である。中でも、作業者がピンセットで基板を取扱う薄膜の形成工程においては、工程の自動化が切望されている。

今後のシリコンMOS半導体素子のさらに一層の大規模化・高密度化を図るには、その製作工程の低温化・自動化をはじめ、従来までは問題とされなかった多くのことがらを解決しなければならない。

### 1 - 2 - 2 スパッタリングによる薄膜の形成の概要と特徴

固体の表面に、数100eVから数keVの高エネルギー粒子を衝突させると、固体を構成している原子が、高エネルギー粒子と運動量を交換して固体表面から放出される。この現象はスパッタリング(sputtering)と呼ばれ、古く前世紀の半頃には、すでに知られていた<sup>11)</sup>。この現象を利用した薄膜形成法の有効性も明らかにされ、現在、薄膜コンデンサや

薄膜抵抗等の電子部品、ならびに、光学部品の製作に広く用いられている<sup>12)13)</sup>。しかしながら、近年著しい発展を遂げている半導体素子の製作に一般に使用されているとは言い難い。その理由としては、次の二点が考えられる。(1)半導体素子に必要な導体膜から絶縁膜までの薄膜を形成できるスパッタリング法が存在しなかった。(2)高品質な薄膜を、高速度で形成できる装置がなかった。しかし、1965年に、高周波スパッタリング法が発明されるによんで第1の問題点が解決された<sup>14)</sup>。次に、第2の問題点は、マグネットロン方式スパッタリング法の開発により解決され、スパッタリング法の欠点が除かれた<sup>15)</sup>。

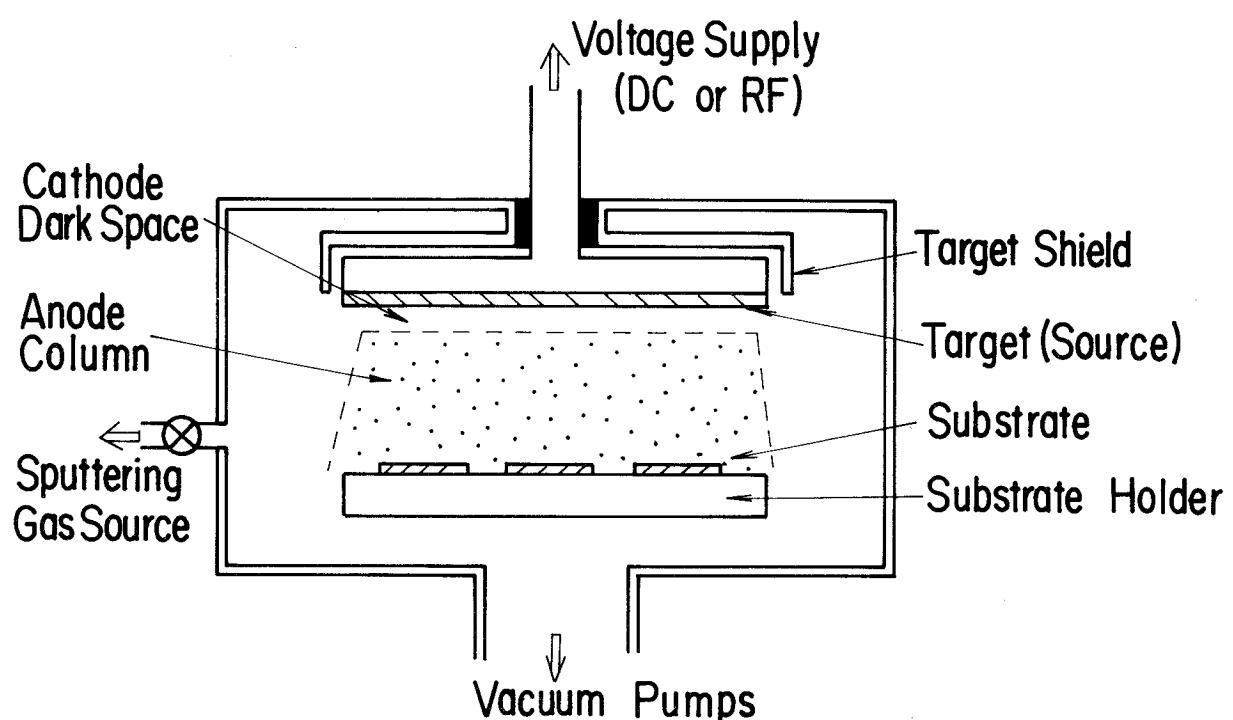

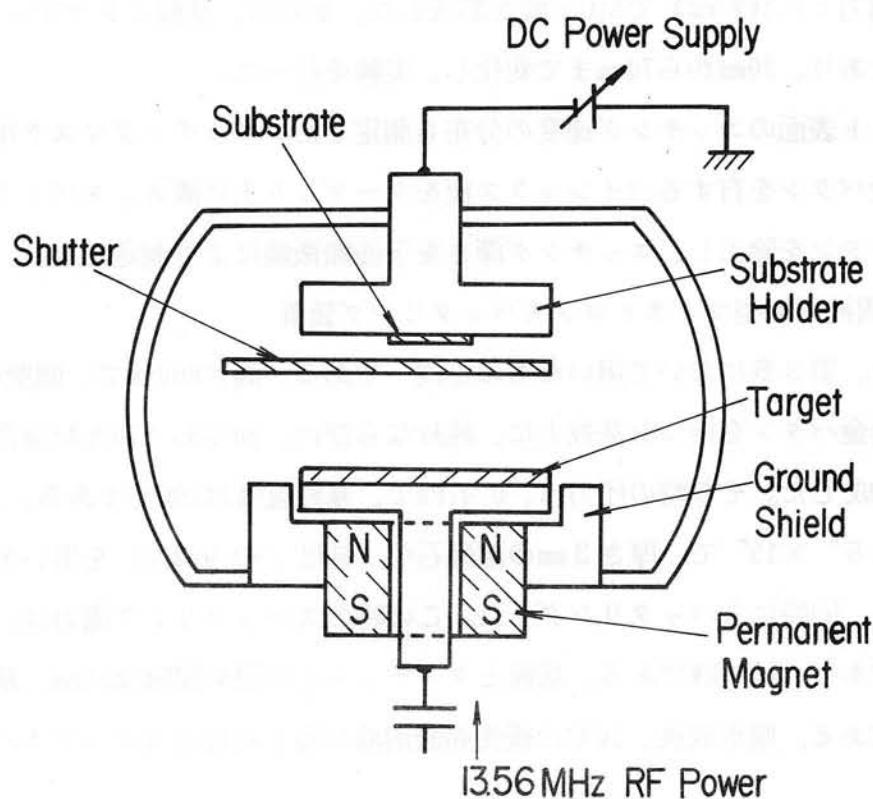

図1-3は、広く用いられているスパッタリング装置の概略図である。薄膜の源となる

図1-3 スパッタリング装置の概略図

ターゲットは陰極に設置され、このターゲットと対向して基板が置れる。スパッタリング槽内に、 $10^{-1} \sim 10^2$  Paのガスを導入し、陰極に負電圧あるいは高周波電圧を印加すると、グロー放電が起る。この際に形成された正のイオンが陰極暗部で加速され、数100 eV～数keVのエネルギーを有してターゲットに衝突する。この衝突した正イオンとターゲット原子との間での運動量の交換によって、ターゲット原子が叩き出される<sup>16)17)</sup>。この原子が基板上に堆積し、薄膜が形成される。

グロー放電を用いたスパッタリング法には、放電法、磁界印加法、および、使用するガ

スの種類により、種々の方法がある。以下に、各方法の概略と特徴について述べる。

### (1) 直流スパッタリング法と高周波スパッタリング法

陰極に負の直流電圧を印加するスパッタリング法が直流スパッタリング法である。その方法では絶縁物から成るターゲットを用いることは出来ない。しかしながら、50 kHz以上の高周波電圧（通常は13.56MHz）を印加すると、絶縁物のターゲットのスパッタリングが可能となる。これが高周波スパッタリング法である<sup>14)18)</sup>。

コンデンサを直列に接続した電極に高周波電圧を印加する場合を考える。電界の時間的变化に応じて振動する電子が気体原子と衝突し、イオン化を促進する。放電気体中のイオンと電子とでは、それらの移動度の差が著しいために、グロー放電の電流・電圧特性に整流特性が現われる。高周波電圧の正の半周期においては、多量の電子が電極に流れる。一方、他の半周期においては、少量のイオンしか流入しない。コンデンサが直列に接続されているために、電荷の流出は起らず、電極表面の電圧は、一周期あたりの平均電流値が零となるまで、負に自己バイアスされる。その結果、パルス状の負電圧が誘起される<sup>19)</sup>。この負電圧の直流値により、イオンが加速されてターゲット表面に衝突し、スパッタリングが起る。さらに、ターゲットのみがスパッタリングされる様に、装置が設計されている。すなわち、ターゲットが設置されている電極の面積が、真空槽や基板支持台から成る、他の電極の面積よりも小さくしてある。このようにすることにより、ターゲットと真空槽との間に印加する電圧は、プラズマとターゲットとの間の電圧にはほぼ等しくなり、プラズマと真空槽との間の電圧は小さくできる<sup>20)</sup>。このために、真空槽内壁や基板がスペッタされることなく、薄膜の形成が行れる。

以上のように、直流スパッタリング法は、金属ターゲットのみに適用されるのに対して、高周波スパッタリング法では、ターゲットの材質を選ばない。

### (2) ダイオードスパッタリング法とマグнетロンスパッタリング法

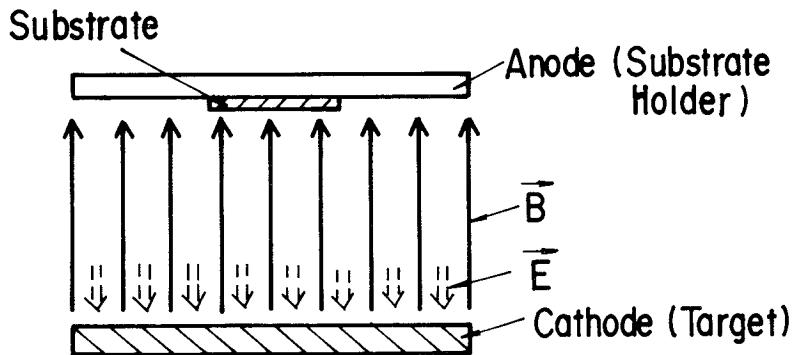

グロー放電時のイオン化率を高め、グロー放電を安定化するために、外部から数百Gの磁界を印加する。この磁界の印加法としては、ターゲット表面に垂直に印加する方法と平行に印加する方法がある。図1-4には、ターゲット表面に垂直に磁界を印加するダイオード方式における磁界分布と電界分布とを示す。スパッタリングガスがイオン化される際に生じた電子や、ターゲット表面からの二次電子は、サイクロトロン運動を行いつつイオン化を促進する。さらに、この磁界の印加により、プラズマはターゲット・基板間領域に集束する。この結果、カソード電流が増大し、薄膜の形成速度を向上できる。

図1-4 ダイオードスパッタリング方式における磁界分布と電界分布

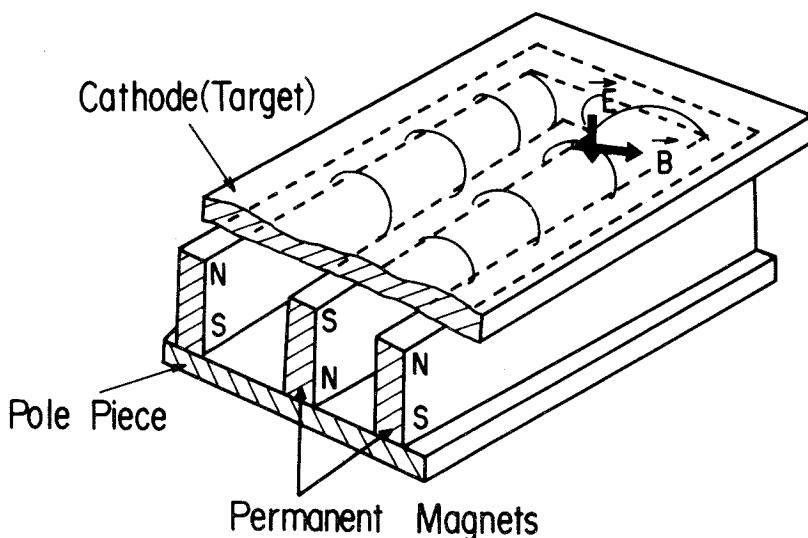

一方、図1-5には、ターゲット表面と平行な磁界成分を有するマグネトロン方式における磁界分布と電界分布とを示す<sup>7)21)</sup>。磁石を、図1-5に示すように設けることにより、電界Eは磁界Bと直交する。このために、電子はターゲット表面に押し留められ、ターゲット表面をトロコイダル運動を行いつつイオン化を行う。この方式では、ダイオード方式に比較して、ターゲット近傍に高密度なプラズマが形成される。この結果、非常に大きな膜形成速度が得られる。さらに、基板へのプラズマ照射を押えることができ、基板温度の上昇やプラズマ損傷を抑制できる。

図1-5 マグネトロンスパッタリング方式における磁界分布と電界分布

マグネトロンスパッタリング法は、ターゲット形状により種々のものに分類される<sup>7)24)</sup>。スパッタガン（通称Sガン）型マグネトロン方式、平板型マグネトロン方式や同軸型マグネトロン方式が広く用いられている。

### (3)直接スパッタリング法と反応性スパッタリング法

不活性ガスをスパッタリングガスとして使用すると、ターゲットとほぼ同一組成の薄膜が、ターゲットから直接に形成できる。これに対して、反応性ガスを混合すると、ターゲット原子との化合物膜が得られる。この方法は反応性スパッタリング法と呼ばれ、化合物から成るターゲットの作製が困難な場合などに適する<sup>22)</sup>。

以上に述べたように、使用目的に応じて、各種の組み合せによるスパッタリング法を用いることが出来る。表1-1に、各種組合せによるスパッタリング法の分類を示す。

表1-1 スパッタリング法の分類

|                                              |

|----------------------------------------------|

| (1)放電法による分類： 直流スパッタリング法、高周波スパッタリング法          |

| (2)磁界印加法による分類： ダイオードスパッタリング法、マグネットロンスパッタリング法 |

| (3)スパッタリングガス種による分類： (直接)スパッタリング法、反応性スパッタリング法 |

スパッタリング法は、半導体素子製作に広く用いられている真空蒸着法や気相成長法と比較して、プラズマを用い、高エネルギー粒子を利用する物理的方法であり、さらに、低温プロセスである。このために、スパッタリング法は制御性に富み、すぐれた薄膜を低温で形成できる特長を有している。

半導体素子の急激な発展に伴い生じた製作上の問題点とスパッタリング法の上記特長とが相まって、スパッタリング法を半導体素子の製作に応用する気運が急激に高まりつつある。この結果、配線用Al膜の形成にスパッタリング法がすでに実用化されている<sup>23)</sup>。しかし、シリコンMOS半導体素子へ応用する観点から、スパッタリングによる薄膜の形成、MOS素子特性への影響、ならびにスパッタリング法の特長を考慮した新規使用法に関する研究を系統的に行った例はみられない。

### 1 - 2 - 3 本研究の位置と要求条件

スパッタリング法は、真空蒸着法や気相成長法とは、次の点で異なる。

(1)ターゲット表面からの原子が、スパッタリングガスとの衝突を繰り返しながら基板に到達するため、基板での入射角分布やエネルギー分布は、スパッタリング特有のものとな

る。

(2)薄膜形成時に、高エネルギーを有する原子、電子やX線が基板表面に照射される。

(3)低基板温度で種々の薄膜を形成できる。

本研究では上記項目に注目し、シリコンMOS半導体素子製作に用いられる窒化シリコン膜、 $\text{SiO}_2$ 膜および、Al膜を製作し、これらの薄膜の評価・適正化を図る。さらに、スパッタリング法の新規利用法を提案する。

スパッタリング法による薄膜をシリコンMOS半導体素子に応用する際の要求条件としては、次のことが挙られる。

(1)シリコンMOS半導体素子を汚染せず、清浄な薄膜もしくはプロセスであること。

(2)シリコンMOS半導体素子の特性に損傷を与えないか、あるいは、その損傷が容易に除去できること。

(3)ステップカバレジにすぐれ、微細化が容易など、半導体素子への応用が容易なこと。

表1-2に、本研究でとりあげた薄膜、すなわち、窒化シリコン膜、 $\text{SiO}_2$ 膜、およびAl膜の形成のためのスパッタリング法と、本論文での関連章をまとめて示す。

表1-2 膜種、スパッタリング法ならびに関連章節

| 膜種               | スパッタリング法                     | 関連章節                        |

|------------------|------------------------------|-----------------------------|

| 窒化シリコン膜          | 高周波平板型マグнетロン<br>反応性スパッタリング法 | 第2章<br>第7章                  |

| $\text{SiO}_2$ 膜 | 高周波平板型マグネットロン<br>スパッタリング法    | 第3章, 第4章第5節,<br>第5章第2節, 第7章 |

|                  | 高周波ダイオードスパッタ<br>リング法         | 第4章第4節                      |

| Al膜              | 直流Sガン型マグネットロン<br>スパッタリング法    | 第5章第3節,<br>第7章              |

|                  | 高周波ダイオードスパッタ<br>リング法         | 第6章                         |

### 1-3 本論文の概要と構成

本論文は、スパッタリング法による窒化シリコン膜、 $\text{SiO}_2$ 膜、およびAl膜の形成とシ

リコンMOS半導体素子への応用について述べ、本章を含めて8章から構成されている。

第2章では、ターゲットとしてSiを用い、Ar-N<sub>2</sub>混合ガス中反応性スパッタリング法により、窒化シリコン膜を形成する際の、反応性スパッタリング特性ならびにその機構を明らかにする<sup>24)</sup>。さらに、反応性スパッタリング法により形成した窒化シリコン膜の特性を評価し、ち密でストキオメトリの膜が低基板温度で得られることを示し、また、この膜はMOS半導体素子製作時の選択酸化マスク用として有用なことを明らかにする<sup>25)</sup>。

第3章では、マグネットロン方式スパッタリング法によるSiO<sub>2</sub>膜の形成と特性を詳細に述べ、さらに、スパッタリングガス中に水素を混合することにより、SiO<sub>2</sub>膜が著しくち密となることを初めて明らかにする<sup>26)</sup>。

第4章では、スパッタリング法によるSiO<sub>2</sub>膜のステップカバレジについて述べ、この膜のステップカバレジの形状は、入射粒子の段差による陰影効果によって説明できることを記述する<sup>27)</sup>。さらに、スパッタリングガス中に水素を混合することによって、すぐれたステップカバレジが得られることを示す<sup>28)</sup>。

第5章では、スパッタリング法によるSiO<sub>2</sub>膜およびAl膜は、リフトオフ法により微細加工が行えることを明らかにし、本リフトオフ加工法の詳細と特徴を述べる<sup>29)30)</sup>。さらに、本加工法によるSiO<sub>2</sub>膜を、シリコンMOS半導体素子間の分離に応用し、特性評価の結果、従来から広く使用されている選択酸化分離法に比べて、著しくすぐれた分離特性を示すことを記述する<sup>31)</sup>。一方、Al膜の場合において見い出された、Alパタンの厚さが幅に依存する、サイズ効果を定量的に解析し、その原因と抑制法を明らかにする<sup>32)</sup>。

第6章では、配線用Al膜を形成する際の、シリコンMOS半導体素子特性に与える影響を明らかにし、さらに、この損傷は、スパッタリングガス中に水素を混合することによって改善できることを示す<sup>33)34)</sup>。

第7章において、本研究で得た結果をもとに、スパッタリング法により形成した窒化シリコン膜、SiO<sub>2</sub>膜、およびAl膜を一貫して用いてシリコンMOS半導体素子を製作し、スパッタリングによる薄膜の形成がシリコンMOS半導体素子製作に極めて有効なことを実証する。

第8章では、以上の各章で得た結果を総括する。

## 第1章参考文献

- 1) 例えば、Proceedings of the 14th Conference on Solid State Devices (Tokyo, 1982) P. 3.

- 2) 徳山：MOSデバイス（工業調査会、1975）。

- 3) 原、鈴木、柏木、前田：超LSIプロセスデータハンドブック（サイエンスフォーラム、1982）。

- 4) J. A. Appels, E. Kooi, M. M. Paffen, J. J. H. Schatroeje and W. H. C. G. Wevkuulen : Philips Res. Rept., 25 (1970) 118.

- 5) W. D. Grobman, H. E. Luhn, T. P. Donohue, A. J. Speth, A. Wilson, M. Hatzakis and T. H. Chang : I E E E J. Solid - S tate Circuits S C - 14 (1979) 282.

- 6) 難波：応用物理 51 (1982) 166.

- 7) J. L. Vossen and W. Kern : Thin Film Processes (Academic Press, New York, San Francisco, London, 1978) .

- 8) B. Chapman : Glow Discharge Processes - S P U T T E R I N G AND PLASMA E T C H I N G - (John Wiley& Sons, New York, Chichester, Brisbane, Toronto, Singapore, 1980) .

- 9) H. I. Smith : Proc. I E E E. 62 (1974) 1361.

- 10) K. E. Kroell and G. K. Ackermann : Solid - S tate Electronics 19 (1976) 77.

- 11) W. R. Grove : Phil. Trans. Roy. Soc. London 142 (1852) 87.

- 12) 神山、菅田：薄膜工学ハンドブック（オーム社、1968）。

- 13) L. I. Maissel and R. Glang : Handbook of Thin Film Technology (McGraw - Hill, New York, 1970) .

- 14) P. D. Davidse and L. I. Maissel : Trans. 3rd Intern. Vacuum Congr. (Stuttgart, 1965) .

- 15) S. D. Dahlgren and E. D. McClanahan : Proc. Symp. Deposition

- Thin Film, 3rd, (Rochester Univ. 1969).

- 16) M. W. Thompson : Phil. Mag. 18 (1968) 377.

- 17) P. Sigmund : Phys. Rev. 184 (1969) 383.

- 18) P. D. Davidse and L. I. Maissel : J. Appl. Phys. 37 (1966) 574.

- 19) H. S. Butcher and G. S. Kino : Phys. Fluids. 6 (1963) 1346.

- 20) H. R. Koenig and L. I. Maissel : IBM J. Res. Dev. 14 (1970) 168.

- 21) P. J. Clarke : U. S. Patent 3,616,450 (1971).

- 22) S. Schiller, U. Heisig and K. Goedike : Thin Solid Film 64 (1979) 455.

- 23) D. W. Wilson and L. E. Terry : J. Vac. Sci. Technol. 13 (1976) 157.

- 24) T. Serikawa and A. Okamoto : Thin Solid Film 101 (1983) 1.

- 25) T. Serikawa and A. Okamoto : submitted to J. Electrochem. Soc.

- 26) T. Serikawa and T. Yachi : Jpn. J. Appl. Phys. 20 (1981) L 111.

- 27) T. Serikawa : J. Vac. Sci. Technol. 17 (1980) 582.

- 28) T. Serikawa : Jpn. J. Appl. Phys. 19 (1980) L 259.

- 29) T. Sakurai and T. Serikawa : J. Electrochem. Soc. 126 (1979) 1257.

- 30) T. Serikawa and T. Yachi : J. Electrochem. Soc. 128 (1981) 918.

- 31) 谷内, 芹川, 和田 : 信学会半導体トランジスタ研究会技報 (1981) SSD 80 - 41.

- 32) T. Serikawa and T. Sakurai : IEEE Trans. Electron Devices ED - 29 (1982) 834.

- 33) T. Serikawa and T. Yachi : IEEE Trans. Electron Devices ED - 28 (1981) 882.

- 34) T. Serikawa and T. Yachi : IEEE Trans. Electron Devices ED - 28 (1981) 1187.

## 第2章 反応性スパッタリング法による 窒化シリコン膜の形成

### 2 - 1 緒言

窒化シリコン膜（以下、SiN膜と略記する）は、ち密性に富むために、半導体素子の製造や保護膜として、その応用範囲は極めて広い<sup>1)</sup>。SiN膜の形成法としては、気相成長法（CVD法）、プラズマCVD法、およびスパッタリング法が一般に知られている<sup>1)2)</sup>。CVD法による膜は、選択酸化マスク用として広く使用されているが、750°C以上の高温度処理を必要とするため、半導体素子の保護膜や層間絶縁膜としては使用できない。一方、プラズマCVD法は、比較的低温度で膜形成が可能なため、保護膜や層間絶縁膜として多くの研究がなされている<sup>3)4)</sup>。しかし、この方法は、CVD法と同様に、SiH<sub>4</sub>とNH<sub>3</sub>との混合ガスを用いる。このために、膜中にN-H基やSi-H基が残り、膜特性の劣化が懸念される<sup>4)5)</sup>。さらに、この方法による膜のち密さも十分ではない<sup>3)4)5)</sup>。これらの方法に対して、スパッタリング法は、ターゲット表面から叩き出された原子が基板に堆積する原理に基づくために、N-H基やSi-H基の混入はなく、ち密な膜が、低温度で形成できる<sup>6)</sup>。

スパッタリング法によるSiN膜の形成法としては、窒化シリコンのターゲットから直接に、SiN膜を得る方法と、Siをターゲットとして、窒素混合ガス中で形成する反応性スパッタリング法とがある。後者の方法は、前者の方法に比べて、高純度の膜が得れる利点を有している。このために、SiN膜の形成には、この反応性スパッタリング法が広く用いられている<sup>7)11)</sup>。しかしながら、反応性スパッタリング法は、ターゲット表面での反応とスパッタエッチングとが同時に起るために、化合物から成るターゲットを使用する方法に比べて複雑な現象を呈する<sup>12)16)</sup>。

反応性スパッタリング法によるSiN膜の形成には、従来からダイオード方式が広く用いられている<sup>7)~11)</sup>。しかしながら、種々の特徴を有するマグネットロン方式を用いた報告はない。このマグネットロン方式は、ダイオード方式に比べて、膜の形成速度が著しく大きく、また、基板表面へのプラズマ照射を抑制できる利点を有している。このために、マグネットロン方式による膜は、ダイオード方式による膜とは異なる特性を示すと考えられる。さ

らに、膜形成時の反応性スパッタリング特性にも不明な点が多い。

本研究の目的は、マグнетロン方式反応性スパッタリング特性とその機構を明らかにし、ち密な窒化シリコン膜を得ることである。本章では、反応性スパッタリング特性とその機構、膜特性の形成条件依存性を詳論し、さらに、適正条件の下で形成した窒化シリコン膜は、選択酸化マスク用として有用なことを明らかにする。

## 2 - 2 Ar - N<sub>2</sub> 混合ガス中反応性スパッタリング特性

本節では、スパッタリング装置の特徴を考慮したマグネットロン方式反応性スパッタリング特性を明らかにし、その機構を解明する。具体的には、ターゲットにはSiを、スパッタリングガスにはAr - N<sub>2</sub> 混合ガスを使用し、スパッタリング条件による、スパッタリングガス圧、膜の形成速度や膜組成等のスパッタリング特性の変化とその機構を明らかにする。

### 2 - 2 - 1 装置と実験方法

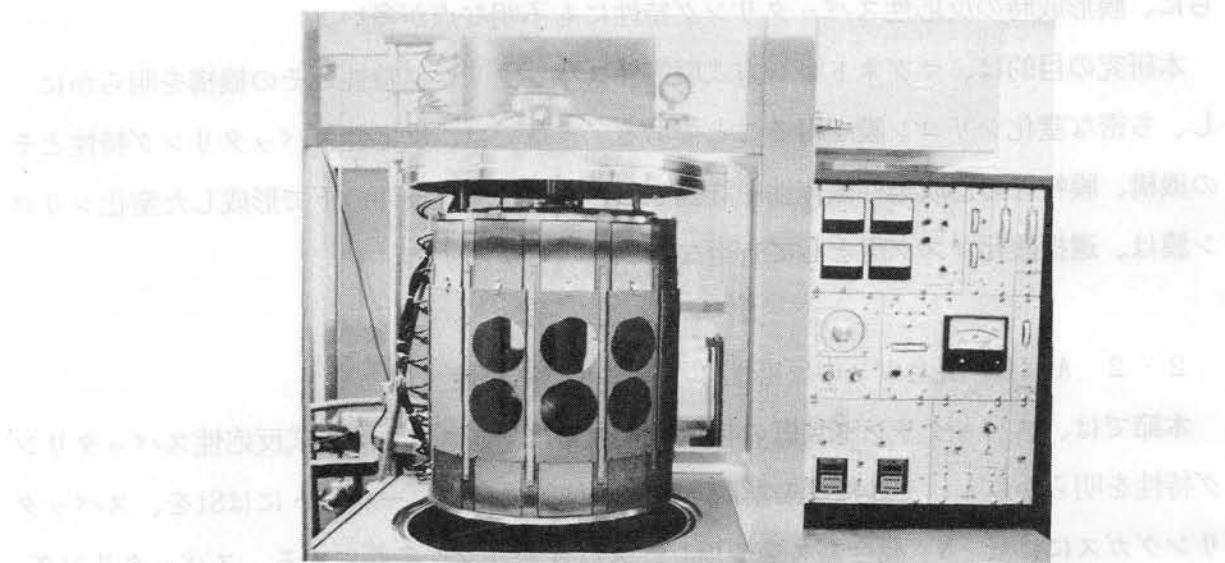

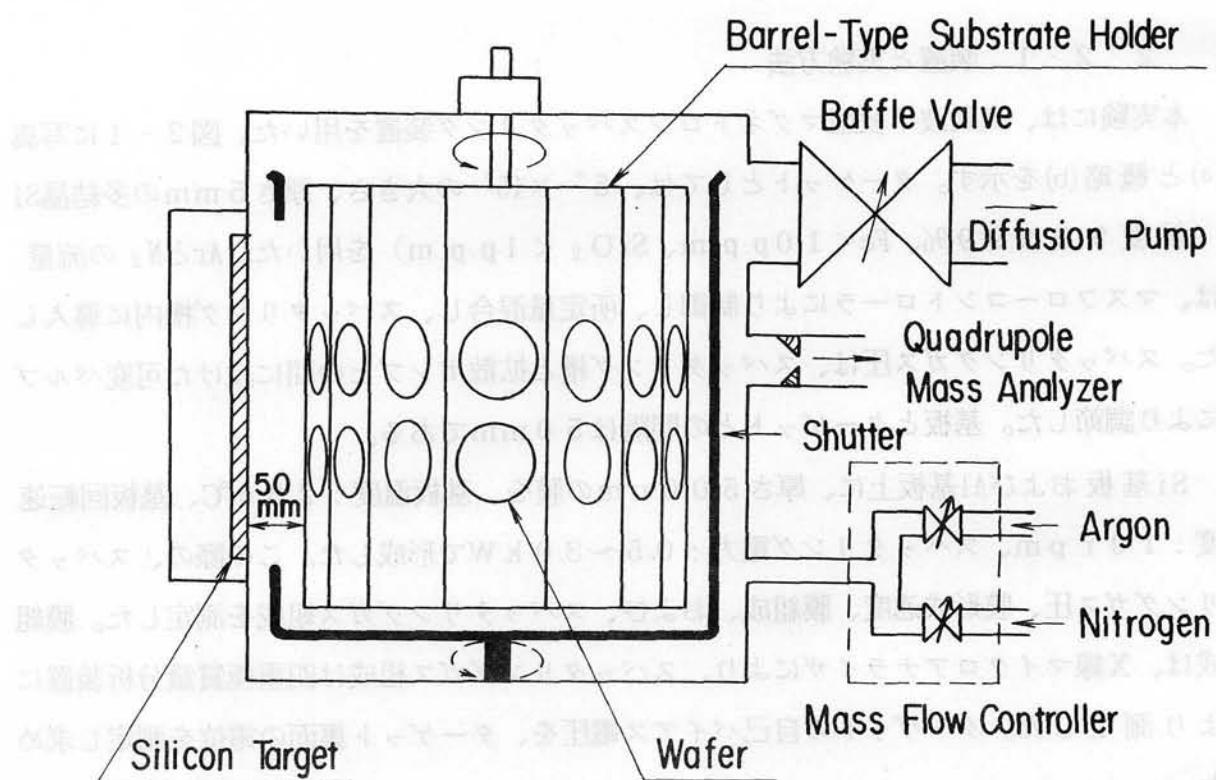

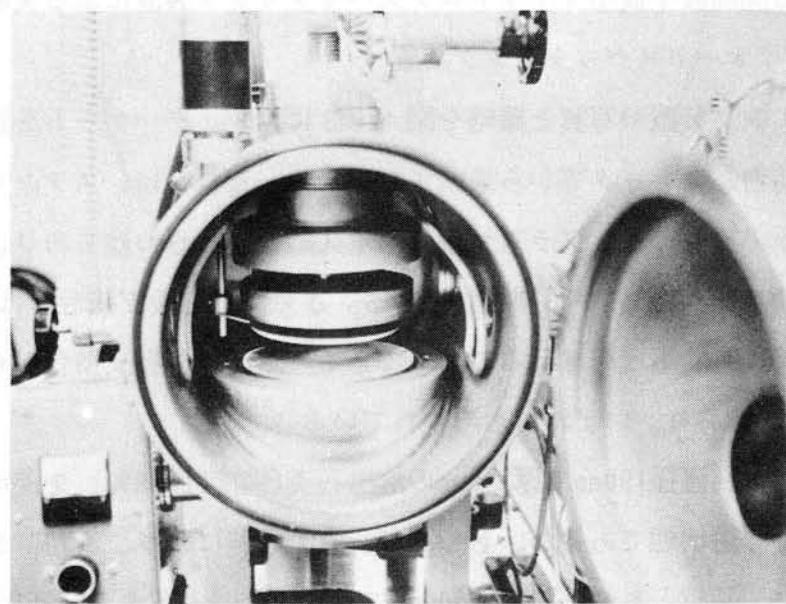

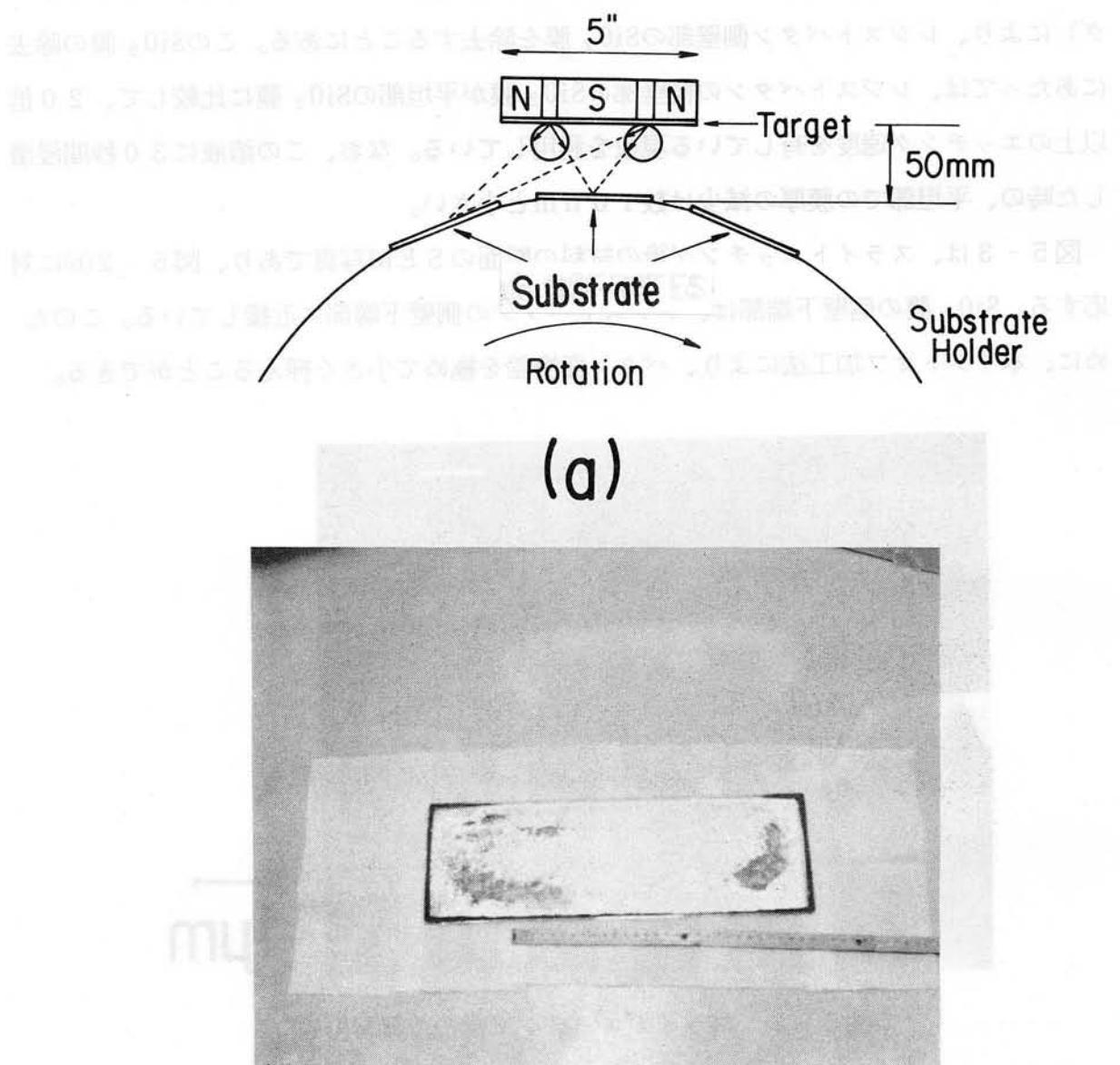

本実験には、高周波平板型マグネットロൺスパッタリング装置を用いた。図2 - 1に写真(a)と概略(b)を示す。ターゲットとしては、5" × 15" の大きさ、厚さ5 mmの多結晶Si(純度 9 9 9 9 %、Fe < 10 ppm、SiO<sub>2</sub> < 1 ppm)を用いた。ArとN<sub>2</sub>の流量は、マスフローコントローラにより制御し、所定量混合し、スパッタリング槽内に導入した。スパッタリングガス圧は、スパッタリング槽と拡散ポンプとの間に設けた可変バルブにより調節した。基板とターゲットとの間隔は50 mmである。

Si基板およびAl基板上に、厚さ500 nmの膜を、基板温度：200 °C、基板回転速度：10 rpm、スパッタリング電力：0.5～3.0 kWで形成した。この際の、スパッタリングガス圧、膜形成速度、膜組成、および、スパッタリングガス組成を測定した。膜組成は、X線マイクロアナライザにより、スパッタリングガス組成は四重極質量分析装置により測定した。ターゲットの自己バイアス電圧を、ターゲット裏面の電位を測定し求めた。

### 2 - 2 - 2 結果と考察

以下に、N<sub>2</sub> 分圧の影響、および、Ar - N<sub>2</sub> 混合法の効果に分けて述べる。

#### (A) N<sub>2</sub> 分圧の影響

図2-1 (a) 高周波平板型マグнетロンスパッタリング装置の写真

図2-1 (b) 高周波平板型マグネットロンスパッタリング装置の概略図

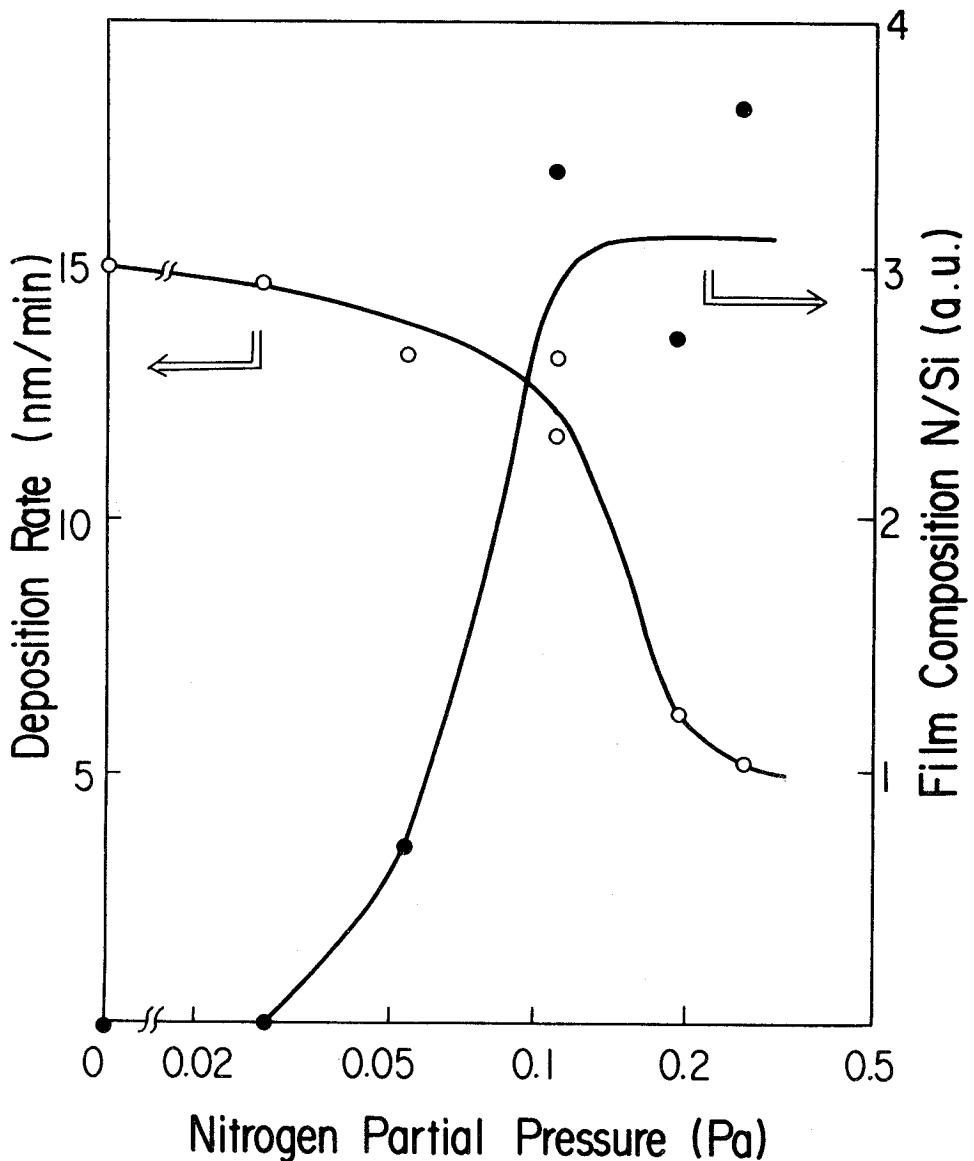

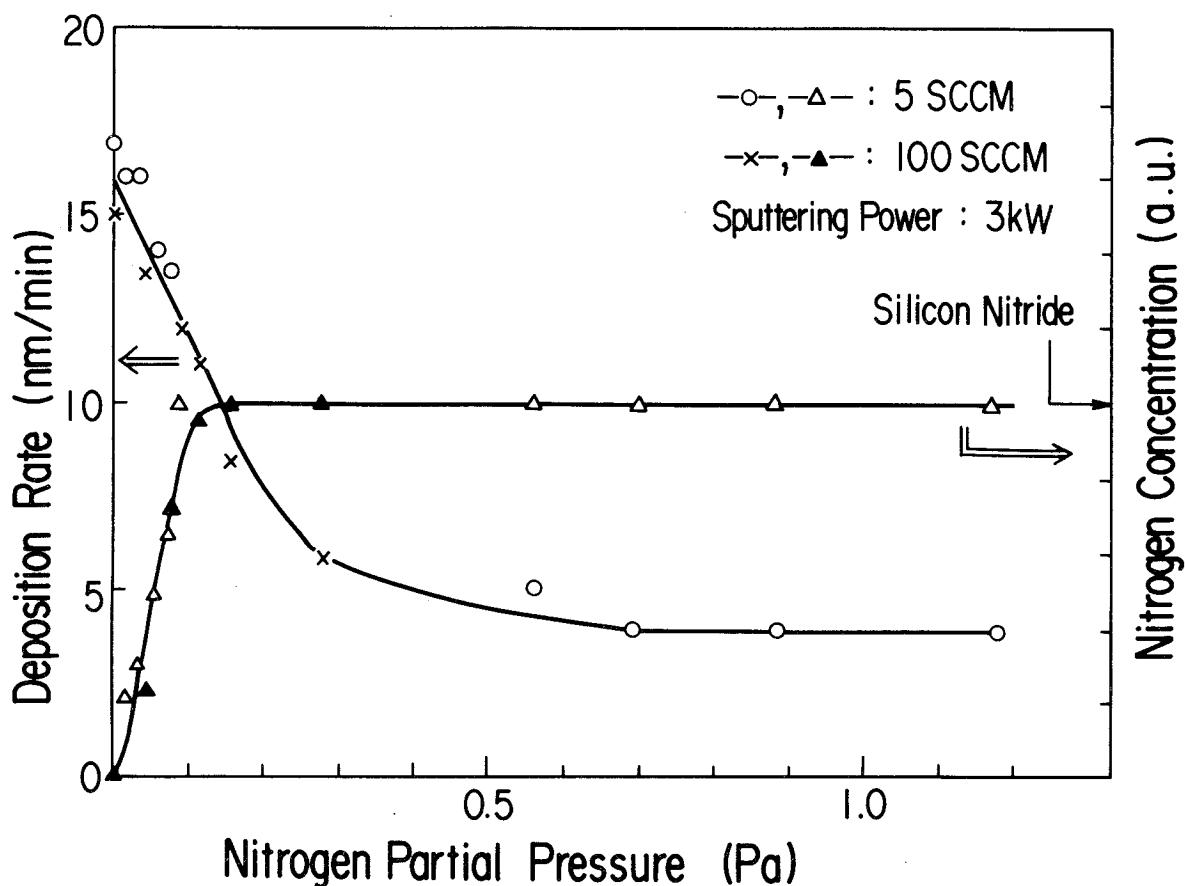

図2-2は、 $N_2$ 分圧による膜の形成速度、および、膜の窒素含有量の変化である。

Arと $N_2$ との総流量は100 SCCMであり、スパッタリングガス圧は0.56 Paである。

図2-2 膜の形成速度および膜中の窒素含有量の窒素分圧依存性

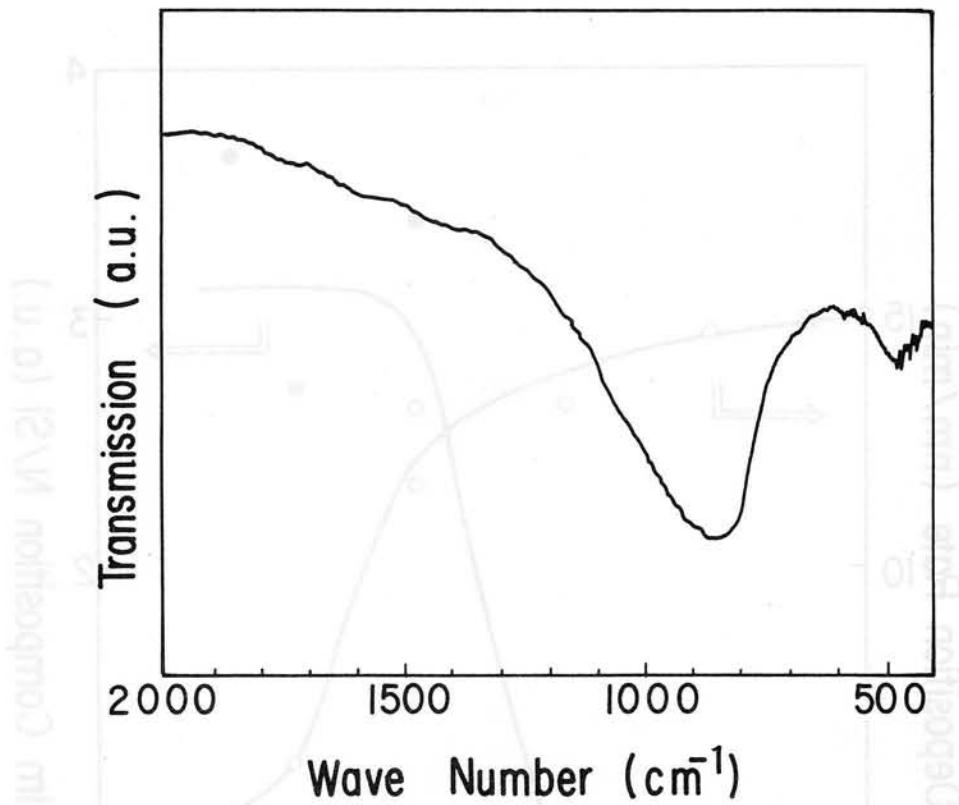

$N_2$  分圧が 0.1 2 Paまで増大しても、膜形成速度の変化は小さい。しかし、この圧力以上になると、膜の形成速度は急激に小さくなる。一方、膜中の窒素含有量は、 $N_2$  分圧 0.1 2 Pa以上で飽和する。図2-3ならびに図2-4は、 $N_2$  分圧：0.2 8 Paで形成した膜の赤外吸収特性ならびに電子線回折パタンである。SiとNとの結合を示す吸収ピークが、波数  $8\ 4\ 0\ cm^{-1}$  と  $4\ 6\ 0\ cm^{-1}$  に現われている<sup>17</sup>。この吸収ピークの位置は、CVD法による窒化シリコン膜とほぼ同じ位置にある。図2-4の回折パタンにはハローがみられ、アモルファス状態の膜が得られる。

図2-3 赤外吸収特性 スパッタリングガス圧：0.56Pa

図2-4 電子線回折パタン スパッタリングガス圧：0.56Pa

反応性スパッタリング法における、SiとNとの反応可能な場所としては、次の場所が考えられる<sup>18</sup>。(1) ターゲット表面、(2) 基板表面、および(3) ターゲットと基板との間の空間、である。最後の(3)の場所での反応は無視できる。なぜならば、スパッタされたSi原

子が基板に到達するまでの間に窒素と衝突する回数が高々1回のN<sub>2</sub>分圧: 0.12Paにおいて、すでに窒化シリコン膜が得られているからである。一方、マグネットロン方式においては、高密度なプラズマがターゲット近傍に局在する。このため、基板表面よりもターゲット表面での反応がより活発である。

Siターゲット表面では、窒化反応とスパッタエッチングとが同時に進行している<sup>16)19)~21)</sup>。N<sub>2</sub>分圧が小さい場合には、窒化反応速度が小さく、スパッタエッチング速度を下回る<sup>15)</sup>。このために、ターゲット表面は、Siの状態になっている。一方、N<sub>2</sub>分圧を大きくし、反応速度がスパッタエッチング速度以上になると、ターゲット表面は、窒化物でおおわれる。窒化物等の化合物のスパッタエッチング速度は、Si等の金属における速度よりも、一般に小さい<sup>2)</sup>。また、化合物の、高エネルギーイオンの衝突による二次電子放出係数は、金属よりも大きい<sup>2)</sup>。すなわち、入射イオンのエネルギーの内、二次電子の放出に費す割合が増大する。これらの理由から、N<sub>2</sub>分圧を0.1~2Pa以上にすると、膜の形成速度が急激に減少する。さらに、N<sub>2</sub>分圧が小さい場合の膜は、膜中の窒素が欠乏し、一方、N<sub>2</sub>分圧を大きくすると、膜中の窒素含有量が増大し、飽和する。

以上に述べたように、N<sub>2</sub>分圧の増大に伴う膜形成速度、および、膜組成の変化は、Siターゲット表面での、窒化反応とスパッタエッチングとから説明できる。

#### (B) Ar-N<sub>2</sub>混合法の効果

##### (i) 反応性スパッタリング特性

本節での実験は、表2-1に示す工程に従って行った。この方法では、ArとN<sub>2</sub>とを混合した後に放電を開始する、従来からの方法とは異り、Ar中で放電を開始した後、N<sub>2</sub>を導入する。実験パラメータは、N<sub>2</sub>流量、Ar流量、Ar圧やスパッタリング電力である。さらに、N<sub>2</sub>流量の設定法としては、徐々に増加し所定の値にする方法と、N<sub>2</sub>流量を一旦大きくした後、徐々に減少する方法とを用いた。

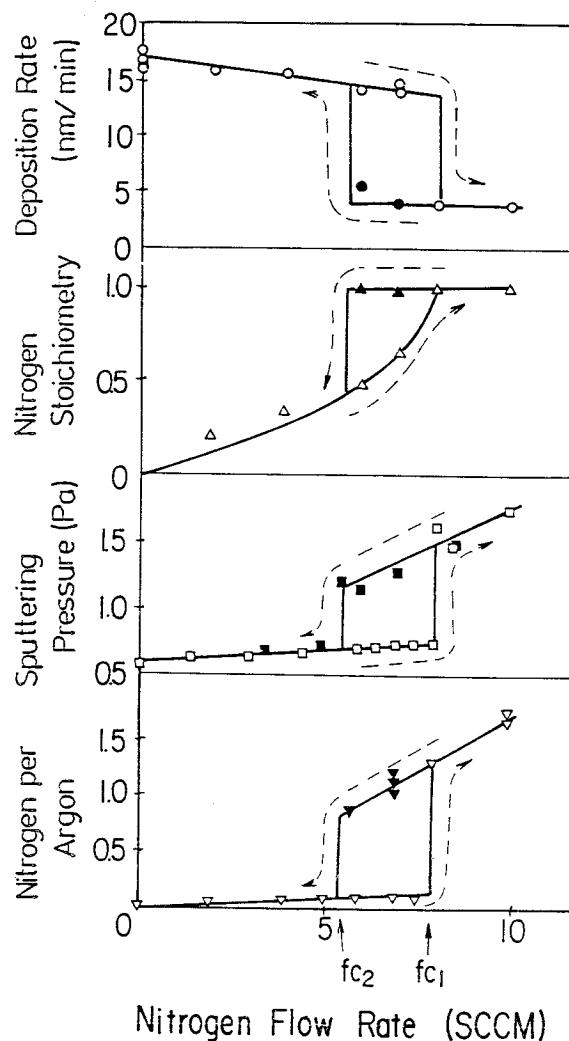

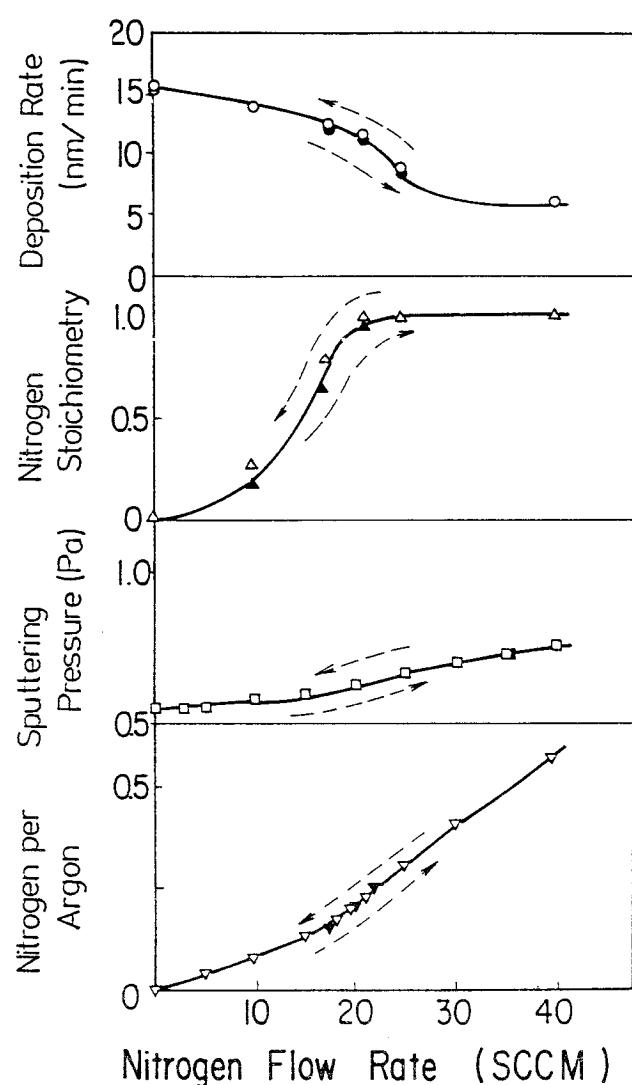

図2-5は、Ar流量が5 SCCMの時の、膜の形成速度、膜中の窒素含有量、スパッタリング槽内の圧力、および、ガス組成の、N<sub>2</sub>流量、および、その増減による変化である。このときのAr圧は0.5~6Paである。膜形成速度は、N<sub>2</sub>流量を増大すると徐々に変化し、臨界流量f<sub>C1</sub>で急激に減少し、初期の値の約25%になる。しかし、さらにN<sub>2</sub>流量を増し、f<sub>C1</sub>以上にしても膜形成速度の変化はない。反対に、N<sub>2</sub>流量を減少していくと、上記臨界流量f<sub>C1</sub>を過ぎても膜形成速度は増大せず、f<sub>C1</sub>よりも小さな臨界流量f<sub>C2</sub>で急増し、流量を増大した場合の値に戻る。すなわち、N<sub>2</sub>流量の増減に対して、ヒステ

リシス現象が現われる。

表2 - 1 膜形成工程

| 手 順                             |

|---------------------------------|

| (1) Arを所定の流量、スパッタ槽内に導入する。       |

| (2) 所定の圧力に設定する。                 |

| (3) 放電を開始し、所定のスパッタリング電力をとする。    |

| (4) 所定の流量のN <sub>2</sub> を導入する。 |

| (5) シャッタを開いて、膜形成を行う。            |

図2 - 5 N<sub>2</sub> 流量に対する、膜の形成速度、膜中の窒素含有量、スパッタリングガス圧、およびガス組成の変化 Ar流量：5 SCCM, Ar圧：0.56Pa, スパッタリング電力：3 kW

膜中の窒素含有量は、 $N_2$  流量の増大に伴い増加し、臨界流量  $f c_1$  以上では変化しない。 $N_2$  流量を減少すると、流量  $f c_2$  までは一定値を示す。しかし、この流量以下にすると、増大した場合の値になる。スパッタリングガス圧やガス組成も、膜形成速度と同様に、臨界流量  $f c_1$  、および、  $f c_2$  で急激に変化し、さらに  $N_2$  流量の増減に対してヒステリシス現象を示す。

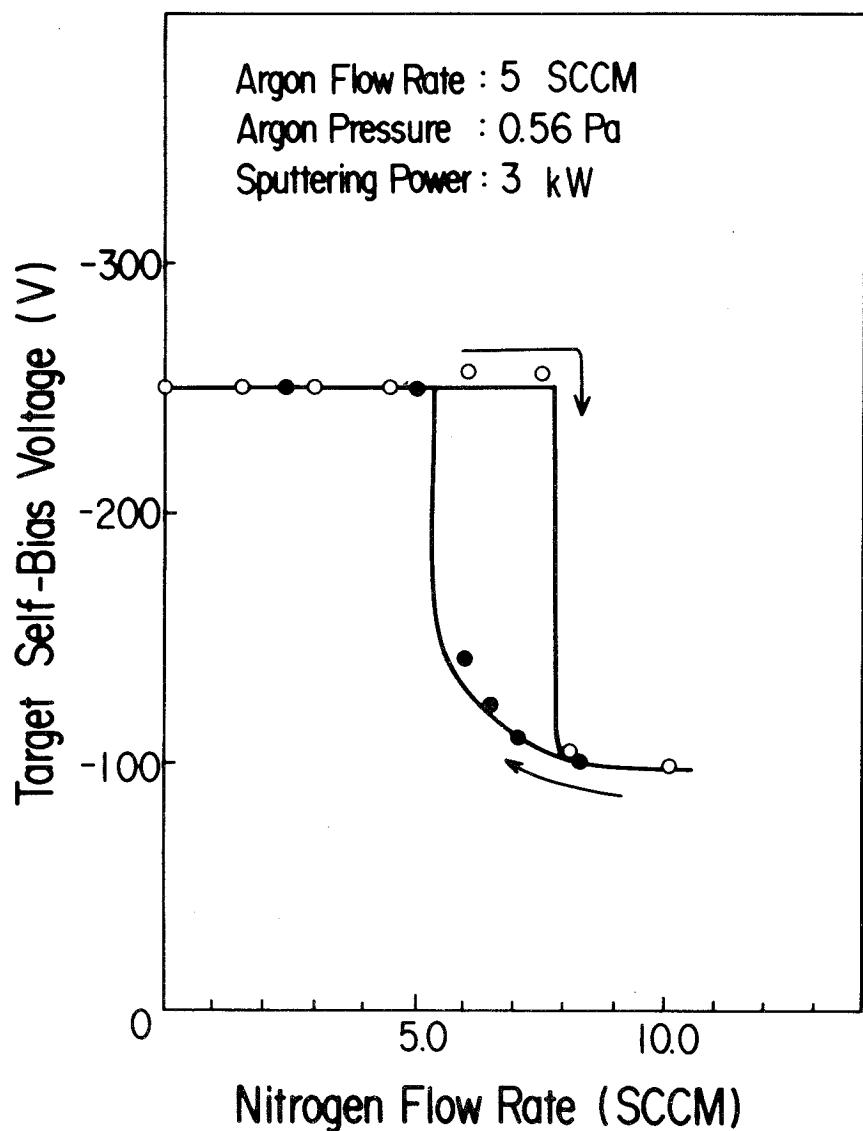

図2-6は、 $N_2$  流量の増減に伴う、ターゲットに誘起される自己バイアス電圧  $V_{sb}$  の変化である。スパッタリング条件は、図2-5と同じである。 $V_{sb}$  は、ターゲット裏面の電圧を測定した。 $N_2$  流量を 7.8 SCCM (図2-5の  $f c_1$ ) まで増大しても、 $V_{sb}$  は

図2-6  $N_2$  流量によるターゲット自己バイアス電圧の変化 スパッタ条件は

図2-5と同じ

-250Vと一定である。しかし、これ以上の流量にすると、-250Vから約-100Vに急激に減少し、その後は、一定となる。一方、N<sub>2</sub>流量を減らすと、5.6 SCCM（図2-5のfc<sub>2</sub>）までの変化は小さいが、この流量以下になると再び-250Vに戻る。このように、自己バイアス電圧V<sub>sb</sub>も、図2-5におけるスパッタリング特性と同様に、臨界流量で急激に変化し、また、ヒステリシス現象を示す。

Siターゲット表面では、窒化物の形成とスパッタエッチングが同時に起っている。N<sub>2</sub>流量が小さい場合、ターゲット表面を窒化物でおおうには、窒素が不充分であり、ターゲット表面は金属Si状態である<sup>16)～19)</sup>。このために、膜形成速度の変化は小さい。さらに、N<sub>2</sub>流量が、図2-5における臨界流量fc<sub>1</sub>よりも小さい領域では、導入されたN<sub>2</sub>は膜中に効率良く含有される。このために、N<sub>2</sub>をスパッタリング槽に導入しているにもかかわらず、圧力の増大やガス組成の変化は小さく、また、膜中に含有される窒素量は、N<sub>2</sub>流量の増大と共に大きくなる。

N<sub>2</sub>流量が臨界流量fc<sub>1</sub>に達した時に、ターゲット表面を窒化物でおおうに充分なN<sub>2</sub>流量となる。この臨界流量において、スパッタリング特性が急激に変化する。この理由として、次のことが挙げられる。まず、(1) ターゲット表面が窒化物でおおわれ、スパッタリング率（入射イオン1個当たりのスパッタ原子数）が低下すること、次に、(2) ターゲット表面が窒化物でおおわれ、二次電子放出係数が大きくなること。第二の事項は、図2-6に示したように、スパッタリング電力を一定としているために、ターゲットとプラズマとの間の電圧、すなわち、自己バイアス電圧V<sub>sb</sub>を小さくする。このように、ターゲットに入射するイオンのエネルギーが小さくなり、さらに、第1の事項のスパッタリング率が減少することから、臨界流量fc<sub>1</sub>で膜形成速度が急激に小さくなる。N<sub>2</sub>流量がfc<sub>1</sub>以上になり、膜形成速度が小さくなると、膜中に含有されて消費される窒素量も少なくなる。導入した窒素の一部が膜中に含有され、残りは不用となるため、スパッタリングガス圧は急激に大きくなり、また、スパッタリングガス中の窒素量も増大する。さらに、この状態では、ターゲット表面は窒化されているために、膜中の窒素含有量は一定となる。膜中に含有されずに不用となつた窒素は、スパッタリング系外に排気される。

一方、N<sub>2</sub>流量を減少しても、臨界流量fc<sub>1</sub>では、N<sub>2</sub>流量を増大した場合のスパッタリング特性に戻らない。これは、ターゲット表面がすでに窒化物でおおわれ、スパッタエッチング速度が小さくなるために、ターゲット表面を窒化物でおおうに必要な窒素流量は、fc<sub>1</sub>よりも少なくてもよいからである。fc<sub>1</sub>よりも小さな臨界流量fc<sub>2</sub>において

て、ターゲット表面を窒化物でおおっておくことが最早出来なくなり、 $N_2$  流量を増大した場合の値に戻る。

図2-6における自己バイアス電圧 $V_{sb}$ の変化も、図2-5と同様に説明できる。Siターゲットの表面が窒化物でおおわれると、高エネルギーイオンの衝突による二次電子放出係数が増大する<sup>2)8)</sup>。スペッタリング電力を一定に保持しているために、自己バイアス電圧 $V_{sb}$ は急激に小さくなる。一方、 $N_2$  流量が減少し、ターゲット表面が金属Si状態に戻ると、二次電子放出係数が小さくなり、 $V_{sb}$ は大きくなる。この自己バイアス電圧 $V_{sb}$ の変化が、ターゲット表面での窒化物と共に、図2-5でのスペッタリング特性に変化をもたらすことは前述した。

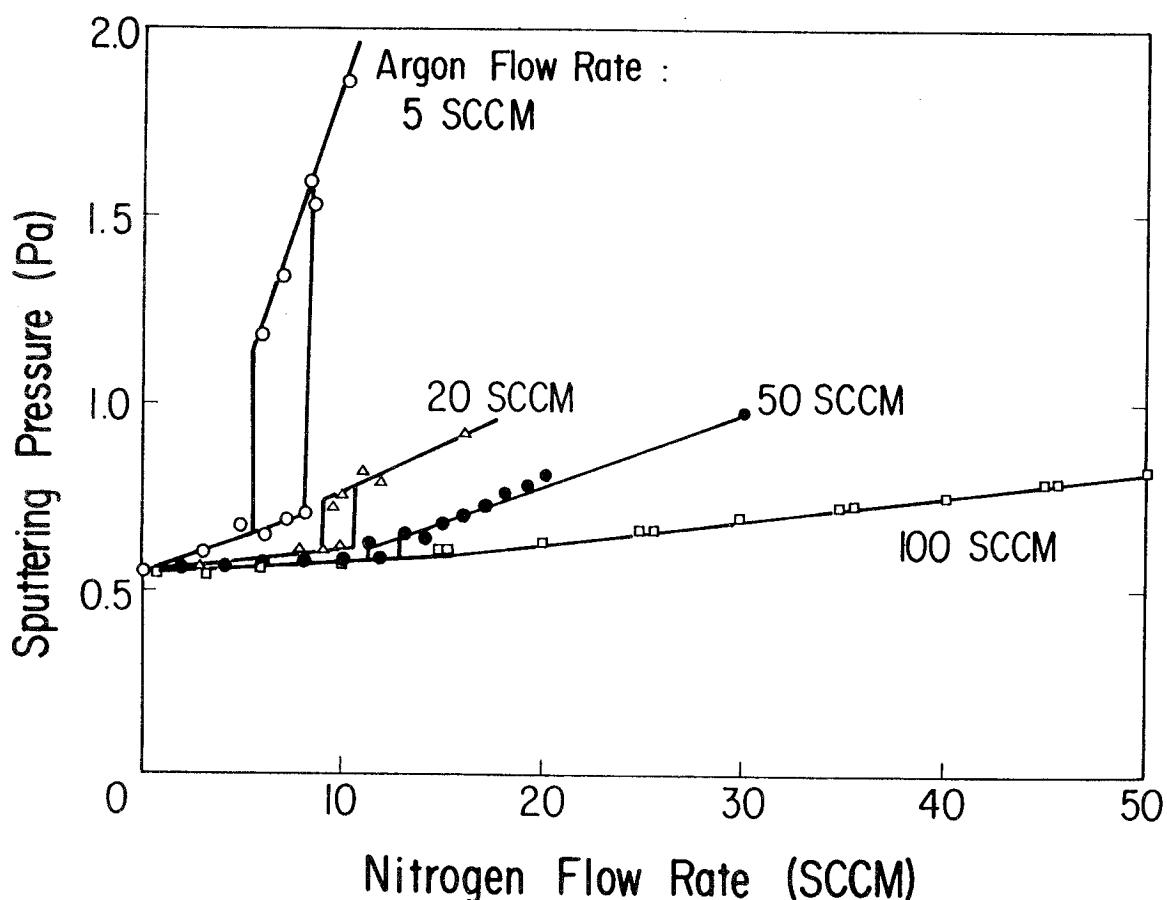

図2-7は、Ar流量をパラメータとした時の、 $N_2$  流量によるスペッタリング時の圧力変化である。 $N_2$  導入前のAr圧は、バッフルバルブのコンダクタンスを調節して、すべての場合、0.56Paとした。Ar流量が小さい場合（これは図2-5に対応する）、圧力は急

図2-7 Ar流量をパラメータとした時の、 $N_2$  流量によるスペッタリングガス圧の変化 Ar圧：0.56Pa，スペッタリング電力：3 kW

激な変化を示し、 $N_2$  流量の増減に伴うヒステリシス現象は顕著である。しかし、Ar流量を大きくし、100 SCCMでは、ヒステリシス現象は現れない。図2-8は、Ar流量が100 SCCMの場合の、膜の形成速度、膜中の窒素含有量やスパッタリング時の圧力、および、ガス組成の、 $N_2$  流量とその増減による変化である。いずれの特性の変化も滑らかであり、ヒステリシス現象は現れない。

スパッタリング槽内に導入される窒素の一部は、ターゲット表面での窒化反応に消費され、膜中に含有される。残りの窒素はバッフルバルブを通じて排気される。Ar流量を増大した場合、所定のAr圧に設定するために、バッフルバルブのコンダクタンスを大きくす

図2-8  $N_2$  流量に対する、膜の形成速度、膜中の窒素含有量、スパッタリングガス圧、および、ガス組成の変化 Ar流量：100 SCCM, Ar圧：0.56Pa、スパッタリング電力：3 kW

る。したがって、Ar流量の増大と共に、スパッタリング槽から排気される $N_2$ 流量も増大する。このため、図2-7に示したように、Ar流量の増大に伴い、臨界流量 $f_{c1}$ は大きくなり、この $f_{c1}$ での圧力の変化は小さくなる。さらに、Ar流量が大きくなり、100 SCCMになると、ヒステリシスは認められなくなり、図2-8に示した結果となる。

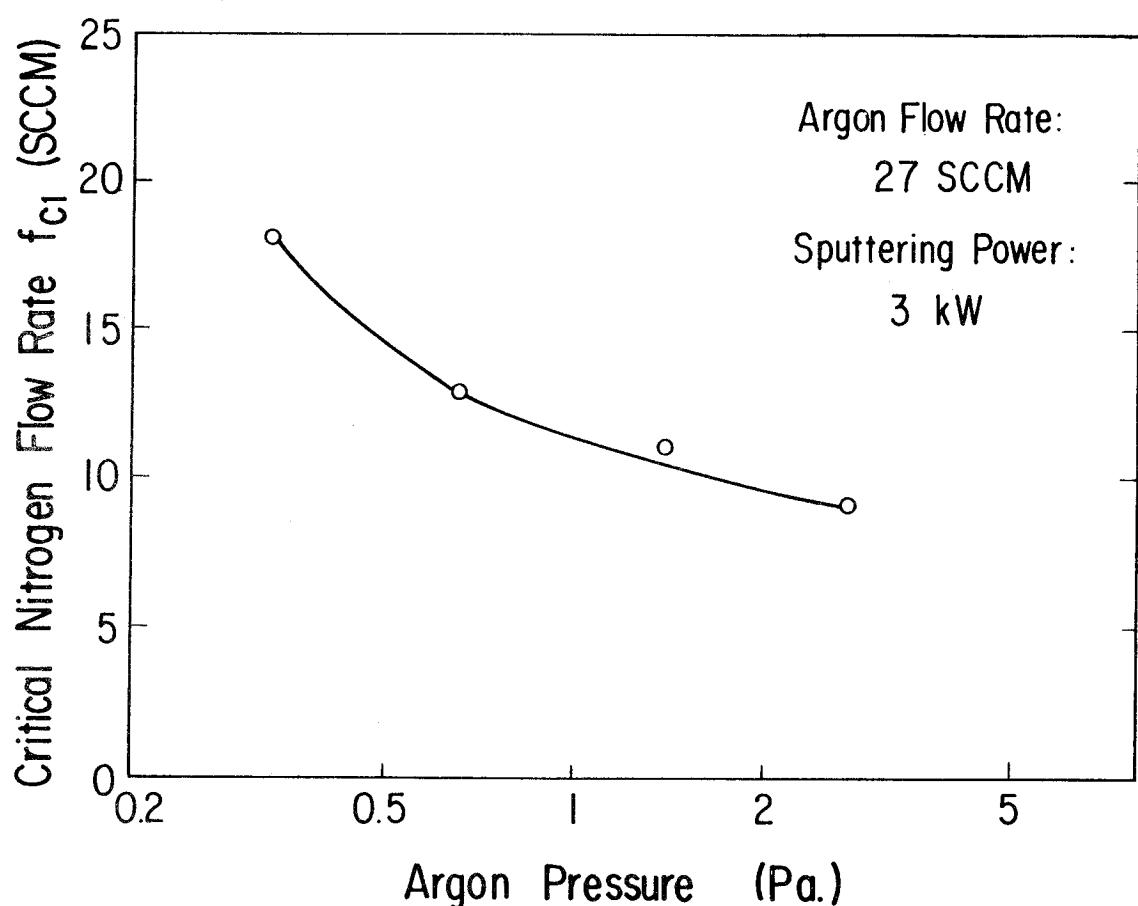

図2-9は、Ar流量が27SCCMでの、Ar圧による臨界流量 $f_{c1}$ の変化である。Ar圧の増大と共に、 $f_{c1}$ は減少する。すでに述べたように、Ar圧はバッフルバリブのコンダクタンスにより調節する。Ar圧を小さくする、すなわち、コンダクタンスを大きくすると、スパッタリング槽から排気される窒素流量が増大し、この結果、臨界流量 $f_{c1}$ が大きくなる。

図2-9 Ar圧による臨界窒素流量 $f_{c1}$ の変化

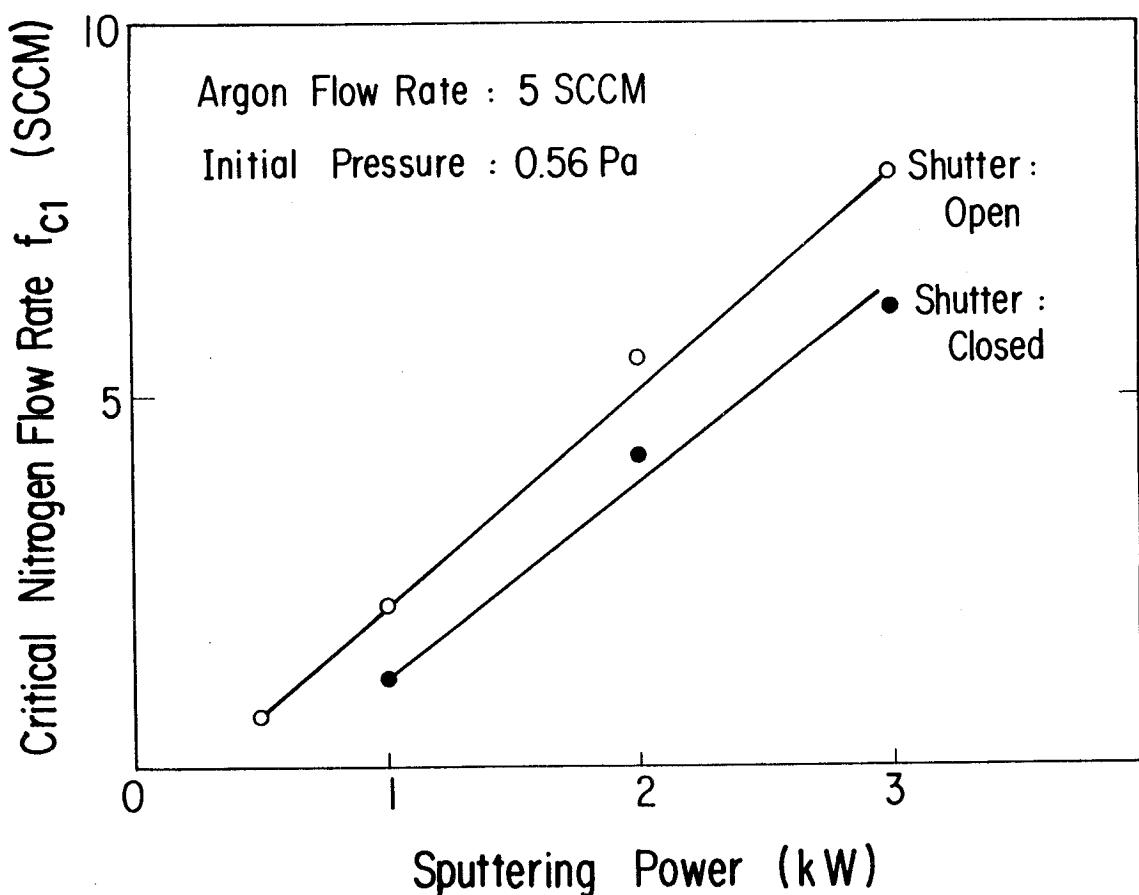

図2-10には、臨界流量 $f_{c1}$ のスパッタリング電力による変化が、シャッタ開閉の場合について示してある。 $f_{c1}$ は、スパッタリング電力と共に、線型に増大する。また、この $f_{c1}$ は、シャッタを開いている方が閉じている場合よりも大きい。スパッタリ

ング電力を大きくすると、スパッタエッチング速度が大きくなる。このため、ターゲット表面を窒化物でおおっておくに必要な臨界流量  $f c_1$  は大きくなる。一方、シャッタを開じると、この臨界流量  $f c_1$  は小さくなる。しかし、この機構の詳細は不明である。

図2-10 スパッタリング電力による臨界窒素流量  $f c_1$  の変化

以上のように、反応性スパッタリングの諸特性は、Siターゲット表面での窒化反応、スパッタエッチング、および、スパッタリング槽からの窒素の排気特性を考慮することにより説明できることが明らかとなった。

#### (ii) 反応性スパッタリング特性のモデル設定

以下では、反応性スパッタリング特性をモデル化し、考察する。

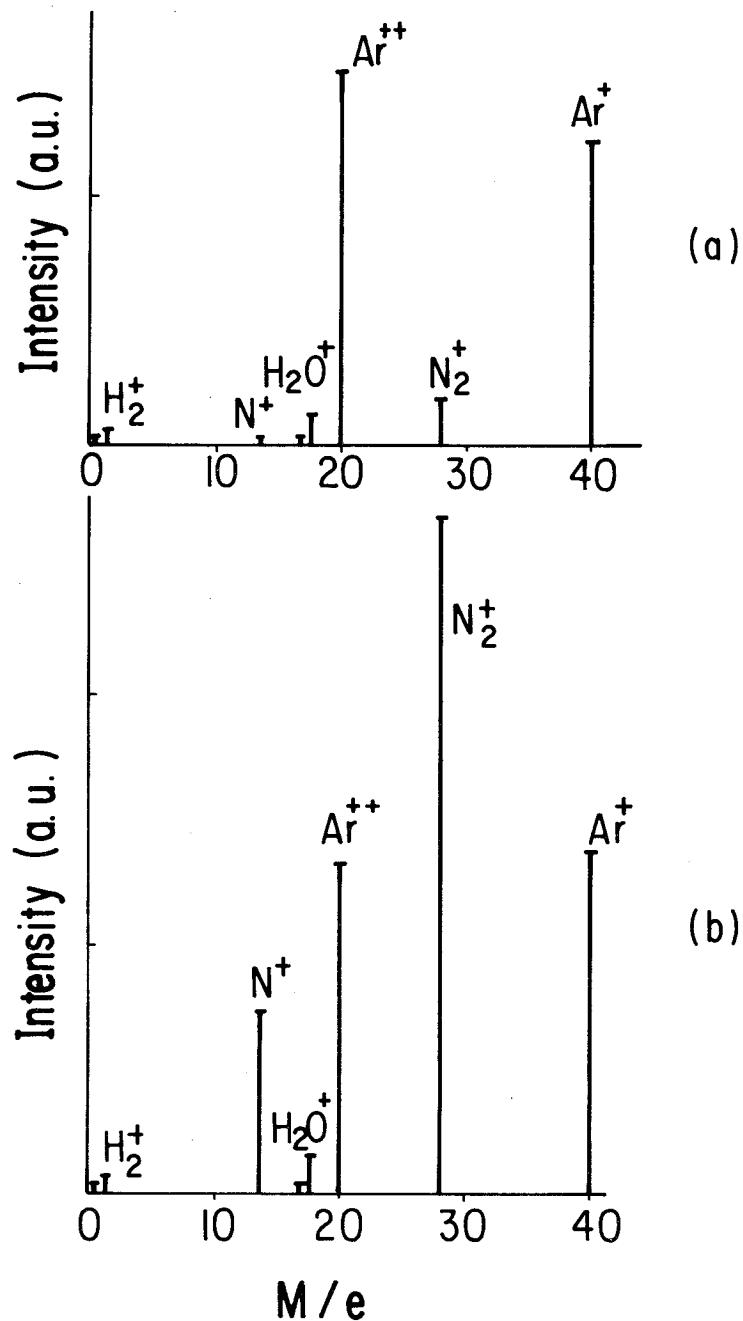

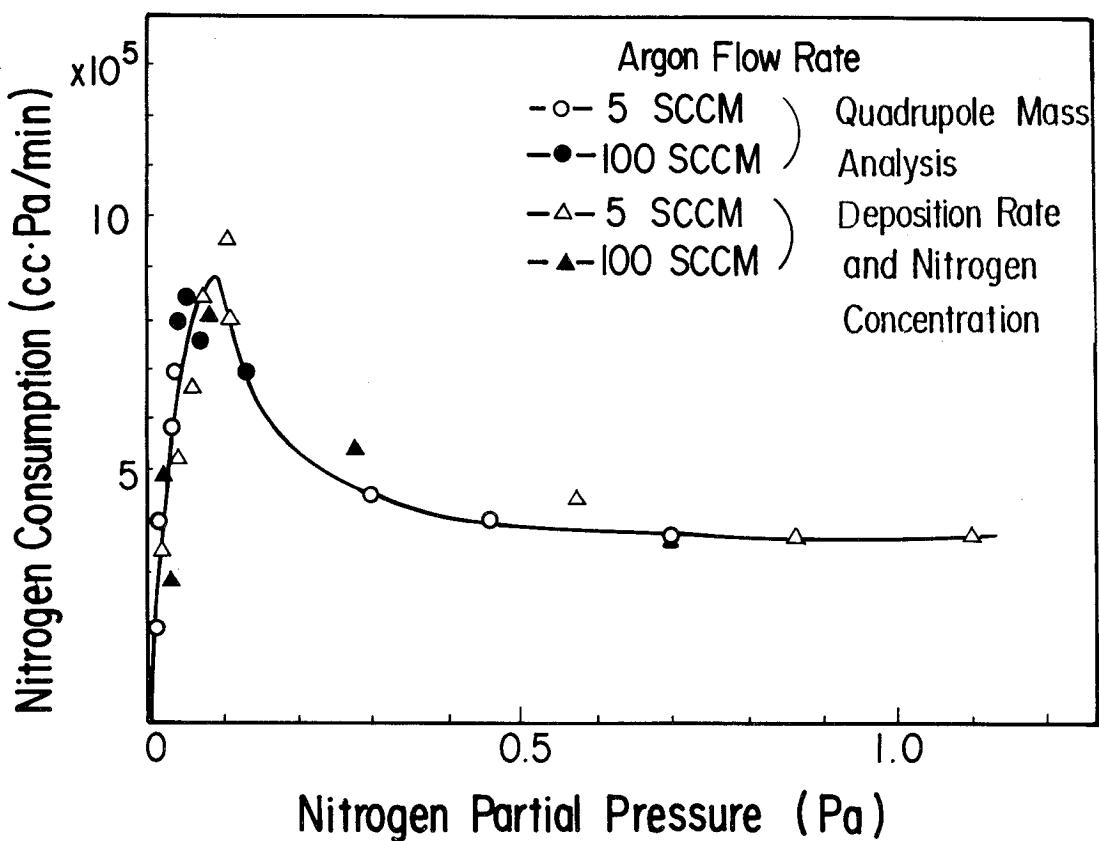

図2-11は、窒素分圧に対する、膜の形成速度と膜中の窒素含有量の変化であり、図2-2における実験を、さらに高分圧にまで拡張したものである。膜の形成速度と窒素含有量との積から、膜中に含有されて消費される窒素量が求まる。図2-12は、スパッタリング槽内の四重極質量分析スペクトルであり、スパッタリング電力がON(a)、およびO

図2-11 膜の形成速度および膜中の窒素含有量の窒素分圧による変化

FF(b)の時を比較して示す。 $N^+$  や  $N_2^+$  による窒素のピークは、ONからOFFになると高くなる。これは、スパッタリング槽内に導入した窒素の一部が、スパッタリング時に膜中に含有されるからである。この $N^+$  や  $N_2^+$  のピーク高さの変化と  $N_2$  流量から求めた、膜中に含有されて消費される窒素量の窒素分圧依存性が、図2-13に示してある。同図には、図2-11から求めたデータも併記してある。このデータは、四重極質量分析から求めた消費量と、窒素分圧 0.7 Paで一致するように規格した。両データは、低い窒素分圧領域でも良く一致する。図2-13から、窒素分圧が小さい領域では、分圧に比例して消費量は増大する。しかし、窒素分圧 0.1 Pa近傍に鋭いピークを成した後、急激に減少し、一定となる。このピークよりも低分圧側では、スパッタエッチング速度が窒化速度を上回る。一方、高分圧側では、反対となり、ターゲット表面が窒化物でおおわれる。

スパッタリング槽内に導入した窒素の一部は、図2-13に示した窒素分圧依存性に従って膜中に含有されて消費されるが、残りは排気される。窒素分圧を  $P_{N_2}$  [Pa]、導入される  $N_2$  流量を  $J$  [SCCM]、窒素消費量を  $N_c(P_{N_2})$  [ccPa/min]、バッフルバル

図2-12 スパッタリング電力ON(a)、およびOFF(b)時の四重極質量分析スペクトル

のコンダクタンスをC [SCCM/Pa] とすると、これらの間には次式が成り立つ。

$$J = Nc (PN_2) + C \cdot PN_2 \dots \dots \dots \quad (2-1)$$

上式の第2項は、スパッタリング槽外に排気されるN<sub>2</sub>流量である。コンダクタンスCは、Ar流量 J<sub>Ar</sub> [SCCM] やAr圧 P<sub>in</sub> [Pa] と次式で関連している。

$$J_{Ar} = C \cdot P_{in} \dots \dots \dots \quad (2-2)$$

図 2 - 13 窒素分圧による窒素消費量の変化

式(2-1)、および、式(2-2)から、 $N_2$  流量  $J$ 、Ar流量  $J_{Ar}$ 、および、Ar压  $P_{in}$  が与えられると、窒素分圧  $P_{N_2}$  の変化を求めることができる。具体的には、式(2-1)を、

$$Nc(P_{N_2}) = J - C \cdot P_{N_2} \dots \dots \dots \quad (2-3)$$

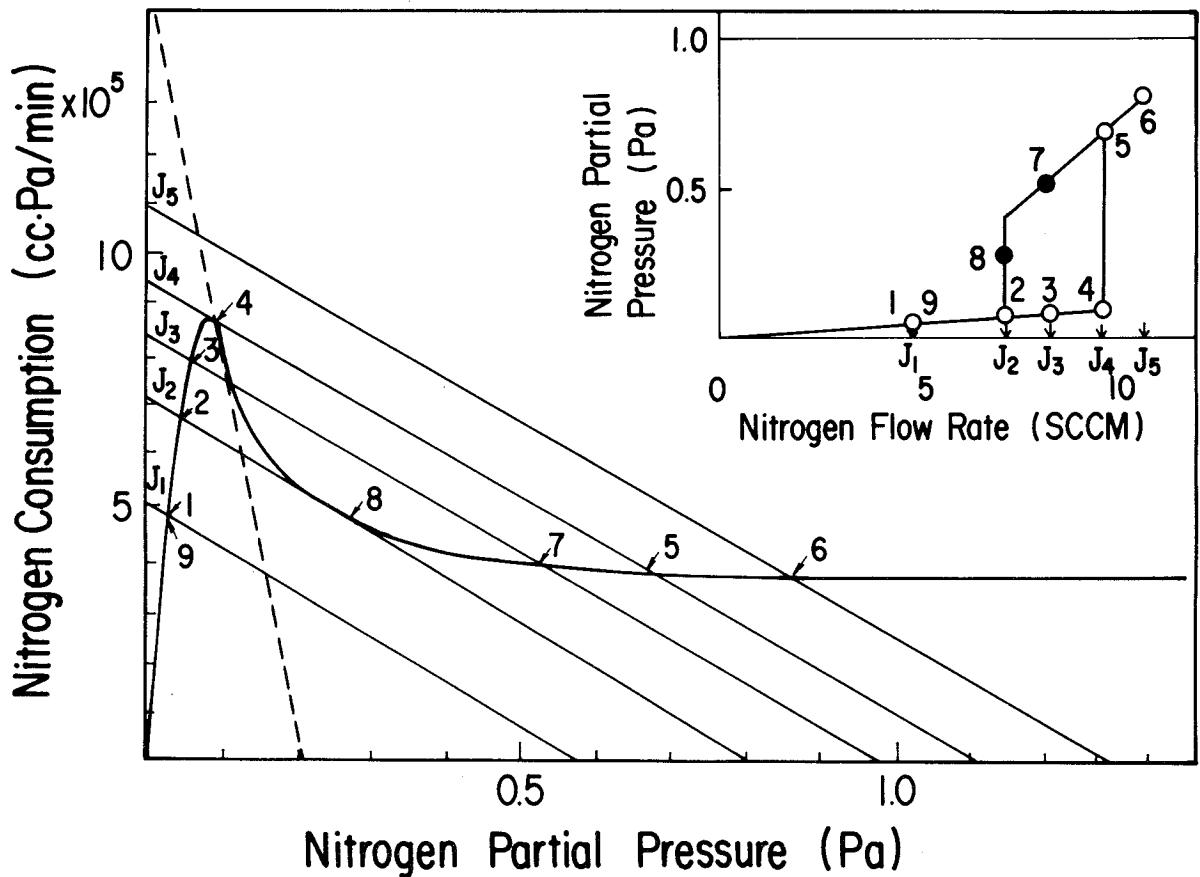

のように変形し、式(2-3)の右辺と左辺の窒素分圧依存性を同一図面上に図示することにより、曲線  $Nc(P_{N_2})$  と、直線  $J - C \cdot P_{N_2}$  との交点から窒素分圧  $P_{N_2}$  が求められる。直線  $J - C \cdot P_{N_2}$  の、縦軸との切片は  $N_2$  流量  $J$  で、傾きはバッフルバルブコンダクタンス  $C$  である。

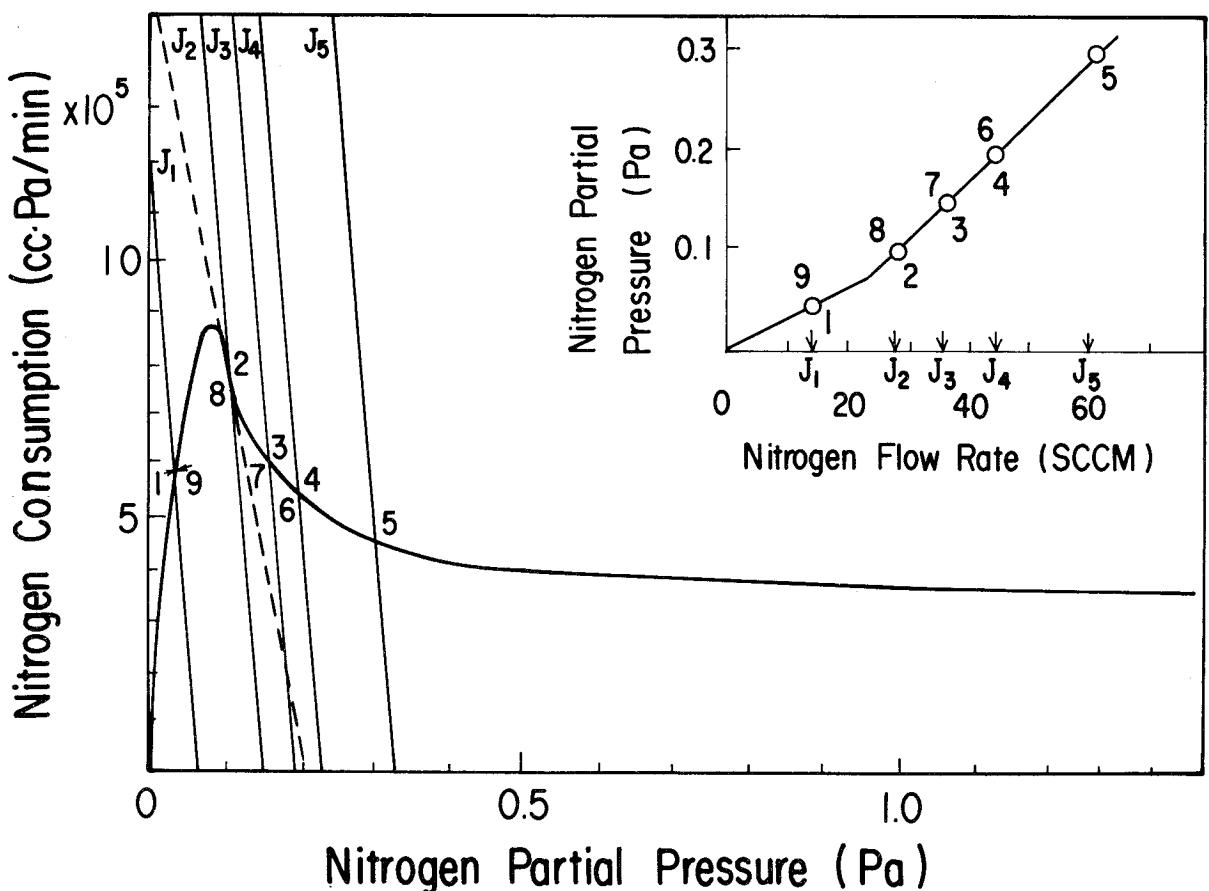

上記方法による、 $N_2$  流量による窒素分圧の変化を図 2-14 に示す。同図には、窒素分圧対窒素消費量曲線の外に、その曲線の最大傾斜が破線で示されている。この図は、Ar流量が 5 SCCM とし、コンダクタンス  $C$  を破線の傾斜  $C_0$  よりも小さくした場合のものである。 $N_2$  流量が  $J_1$ 、 $J_2$ 、 $J_3$ 、 $J_4$  と増加すると、交点は 1、2、3、4 と移動し、窒素分圧は徐々に大きくなる。しかし、 $J_4$  から  $J_5$  に増大すると、交点は 4 から 5

図2-14 Ar流量が小さい場合の、窒素消費曲線Ncと直線J-C・PN<sub>2</sub>、および、N<sub>2</sub>流量による窒素分圧の変化

の位置に飛び、窒素分圧は急激に増大する。逆に、N<sub>2</sub>流量がJ<sub>5</sub>から減少すると、J<sub>4</sub>を過ぎても、7、8と分圧の大きい所に交点があるため、窒素分圧は連続的に変化する。しかしながら、J<sub>2</sub>より小さくすると、交点は8から2の位置に飛び、窒素分圧は急減し、N<sub>2</sub>流量を増加した場合の値に戻る。同図右上には、上述の方法により求めた、N<sub>2</sub>流量による窒素分圧の変化が示してある。窒素分圧は急激な変化を示し、また、ヒステリシス現象がみられる。

これに対して、図2-15は、Ar流量を100SCCMと大きくし、コンダクタンスCが破線の傾斜Coよりも大きい場合の、N<sub>2</sub>流量によるN<sub>2</sub>分圧の変化を示す。この場合、コンダクタンスCが小さな図2-14の場合と異り、N<sub>2</sub>流量をJ<sub>1</sub>からJ<sub>5</sub>まで増加し、再びJ<sub>1</sub>まで減少しても、交点は1から9まで連続的に変化する。同図右上には、N<sub>2</sub>流量による窒素分圧の変化が示してある。N<sub>2</sub>流量の増減に伴う窒素分圧の変化は滑らかであり、ヒステリシスも現われない。また、上述の議論から、コンダクタンスCが傾斜Coよ

りも小さいか否かで、ヒステリシスが現れるか否かが定まる。例えば、傾斜C<sub>0</sub>に対応するAr流量は62 SCCMであり、図2-7に示すように、これ以上の流量では、ヒステリシスは現れない。

Ar圧による臨界流量 $f_{C_1}$ の変化(図2-9)は、図2-14や図2-15における直線： $N_c(PN_2) = J - C \cdot PN_2$ の傾きCを変化させることにより求めることができる。Ar圧を大きくする、すなわち、コンダクタンスCを小さくすると、臨界流量 $f_{C_1}$ は小さくなり、図2-9の結果となる。

以上述べたように、Ar-N<sub>2</sub>混合法による反応性スパッタリング特性の変化に対して、膜中に含有され消費される窒素量、N<sub>2</sub>流量、および、排気特性を考慮したモデルを提案し、これにより、実験結果を良く説明できた。さらに窒化シリコン特有のC<sub>0</sub>(図2-14や図2-15における最大傾斜)と、スパッタリング装置のコンダクタンスCとの間の大・小関係により、反応性スパッタリング特性に上記ヒステリシスが現れるか否かが定まるこ

図2-15 Ar流量が大きい場合の、窒素消費曲線 $N_c$ と直線 $J - C \cdot PN_2$ 、および、N<sub>2</sub>流量による窒素分圧の変化

とを明らかにできた。

反応性スパッタリング法による化合物薄膜形成の利点は、本章緒言で述べたことの外に、化合物の組成を任意に制御できることである。この利点を考慮して、電子部品として、Al、Ti、ZnとOやNから成る任意の組成を有する化合物薄膜の形成が、本研究と同様な方法により行なわれている<sup>20)～24)</sup>。これらの化合物薄膜形成の機構に対する考察は、すべて、ターゲット表面での反応速度とスパッタエッチング速度とから行なわれていた。さらに、このヒステリシスが現れるか否かの判定は、試行錯誤的に行なわれていた。これに対して、本研究では、反応速度とスパッタエッチング速度の外に、スパッタリング装置の特性をも考慮したモデルを提案し、実験結果を良く説明できた。さらに、ここで提案したモデルは、他のスパッタリング装置を用い、他の化合物薄膜を、反応性スパッタリング法により形成する際の良い指針となる。

### 2 - 3 反応性スパッタリング法による窒化シリコン膜の特性

本節では、スパッタリング条件による膜特性を詳細に述べ、適正条件の下では、ち密でストキオメトリの窒化シリコン膜が得られることを述べる。

#### 2 - 3 - 1 試料作製と測定

##### (A) 試料作製

本実験に用いた窒化シリコン膜は、図2 - 1に示した装置を用い、反応性スパッタリング法により製作した。

Siターゲット（純度：99.999%、大きさ15" × 5"）を用い、50%Ar - 50% N<sub>2</sub>混合ガス中で、厚さ100～200 nmの膜を、Si基板、および、Al基板上に形成した。本研究での主な実験パラメータは、スパッタリングガス圧であり、0.3 Paから6.7 Paの範囲で変化した。他の条件は、表2 - 2に示す値に固定した。

表2 - 2 膜形成条件

|                 |            |                  |                             |

|-----------------|------------|------------------|-----------------------------|

| (1) スパッタリング電力   | : 3 kW     | (4) 基板支持台回転速度    | : 10 rpm                    |

| (2) 基板温度        | : 200 °C   | (5) 背圧           | : < 2 × 10 <sup>-4</sup> Pa |

| (3) スパッタリングガス流量 | : 100 SCCM | (6) 基板とターゲットとの間隔 | : 50 mm                     |

## (B) 測定

形成した窒化シリコン膜について、次の項目を測定した。(1) 形成速度、(2) エッティング速度、(3) 赤外吸収特性、(4) 組成、(5) 密度、(6) 表面状態、(7) 屈折率、(8) 比抵抗、(9) 絶縁耐圧、(10) 内部応力。

エッティング速度の測定には、30°Cの緩衝弗酸溶液 [100ml (50%HF) + 860ml (40%NH<sub>4</sub>F)] を用いた。

赤外吸収特性は、透過法により求めた。

膜の組成は、オージェ電子分光法、および、測定した屈折率と密度とを用いて Lorentz - Lorenz の関係式から求めた<sup>25)</sup>。なお、膜の密度は重量法により測定した。

膜の表面状態は、カーボンレプリカ法透過電子顕微鏡写真により、膜堆積後、ならびに、上記緩衝弗酸溶液に約5秒間浸した後の試料について評価した。

膜の比抵抗と絶縁耐圧は、MIS (Al電極 - SiN膜 - Si基板) ダイオードを作製し、Al電極に負電圧を印加して測定した。

膜の内部応力は、ニュートンリング法により測定し、計算により求めた<sup>26)</sup>。計算の詳細は、第3章に記述してある。

さらに、窒化シリコン膜の、酸素の拡散に対する阻止能を求めた。この膜を、1000°Cの湿式雰囲気中に370分間晒し、表面酸化膜の厚さを測定して求めた。上記条件下でのSi基板上の酸化膜の厚さを、SiN膜上の酸化膜厚で割った値として、上記阻止能を定義した。

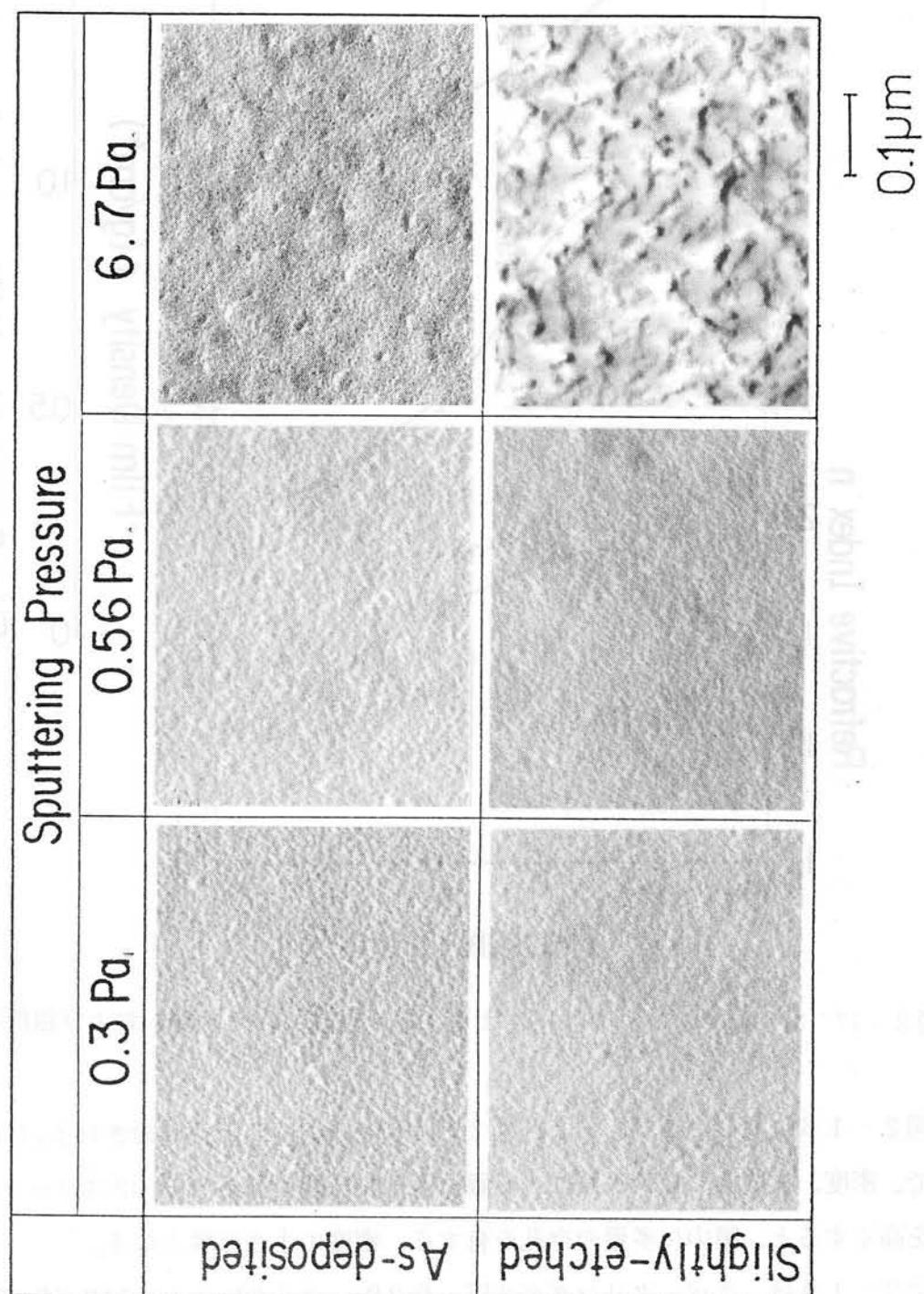

### 2 - 3 - 2 結果と考察

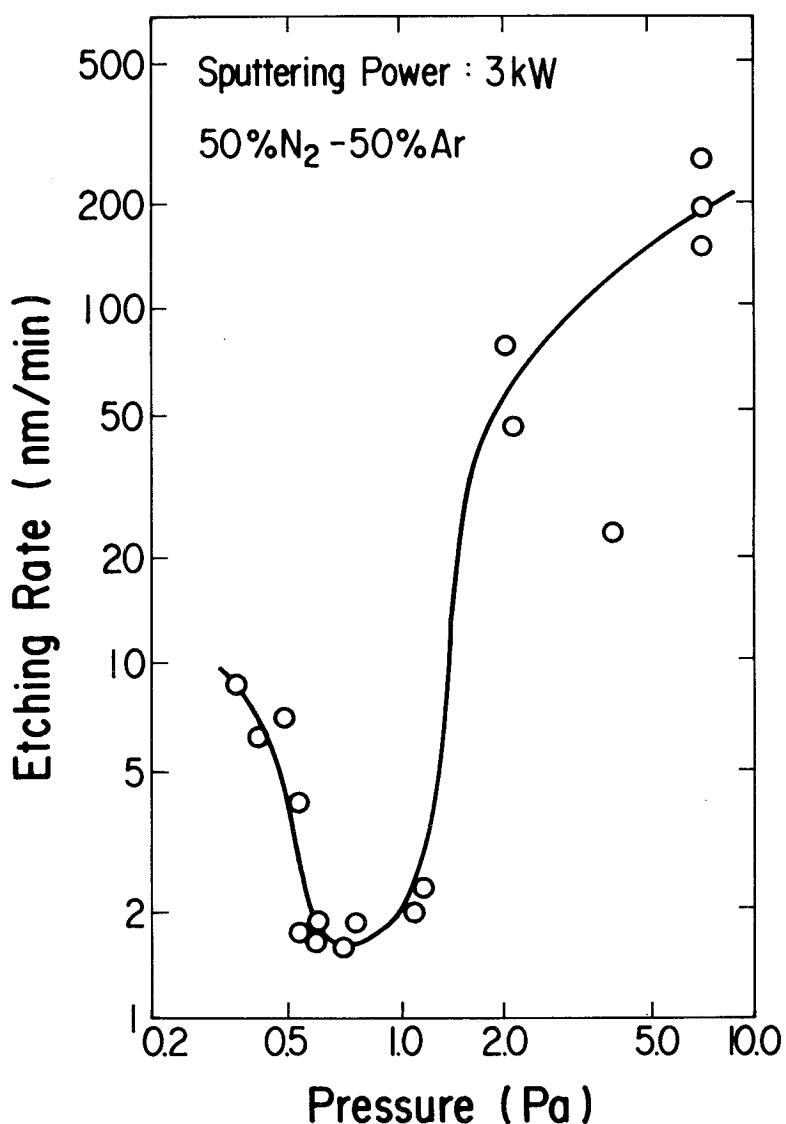

50%Ar - 50%N<sub>2</sub> 混合ガスでは、アモルファス状の窒化シリコン膜が得られることは、前節において明らかにした。図2-16は、緩衝弗酸溶液中エッティング速度に与えるスパッタリングガス圧の影響を示す。エッティング速度は、圧力：0.56Pa近くで最小値を示し、また、圧力：1.5Paで急激に大きくなる。図2-17は、膜の組成、膜の密度、および、屈折率のスパッタリングガス圧による変化である。膜の組成は、同図中に示した屈折率と密度とを用い、Lorentz - Lorenz の関係式により求めた。膜の密度、および、屈折率は、エッティング速度が最小となる0.56Paにおいて、最大となり、2.97 g/cm<sup>3</sup>、および、1.97を示す。また、この圧力での膜の組成N/Siは1.42と、ストキオメトリの値1.33に近い。また、組成N/Siは、圧力の増大と共に、Nが欠乏する傾向を示す。

図2-16 スパッタリングガス圧による膜のエッチング速度の変化

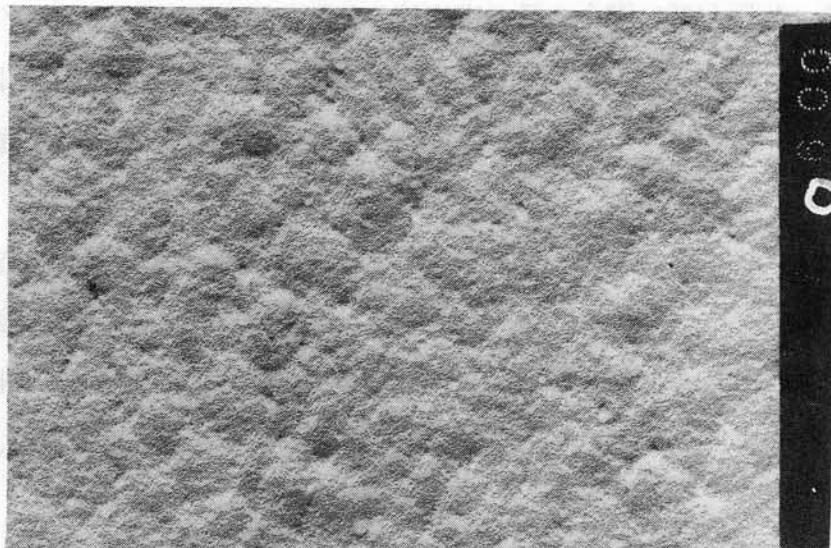

図2-18は、スパッタリングガス圧が0.3 Pa、0.56 Pa、および、6.7 Paで形成した膜の、形成した後、および、30℃の緩衝弗酸溶液により極く短時間エッチング（スライト・エッチング）を施した後の、膜表面のレプリカ写真である。形成した直後での膜の表面は、0.56 Paのものが最も滑らかであり、一方、6.7 Paでの膜には約100 nmの周期の起伏が見られる。スライトエッチングを施すと、いずれの膜の表面も荒れてくる。この表面の荒れは、0.56 Paでの膜が最も小さく、6.7 Paでの膜が最も顕著である。6.7 Paでの膜には、直径数nmの微小な空孔が多数観察され、この空孔のために、膜の密度が小さくなる。

図2-17 スパッタリングガス圧による、膜の組成、膜の密度、および屈折率の変化

図2-16、図2-17、および図2-18から次のことが結論される。(1)0.56 Pa近傍で、密度、組成共にCVD法による膜に匹敵する膜が得られる。(2)スパッタリングガス圧を高くすると、膜中に多量の空孔を有する、密度の小さな膜となる。

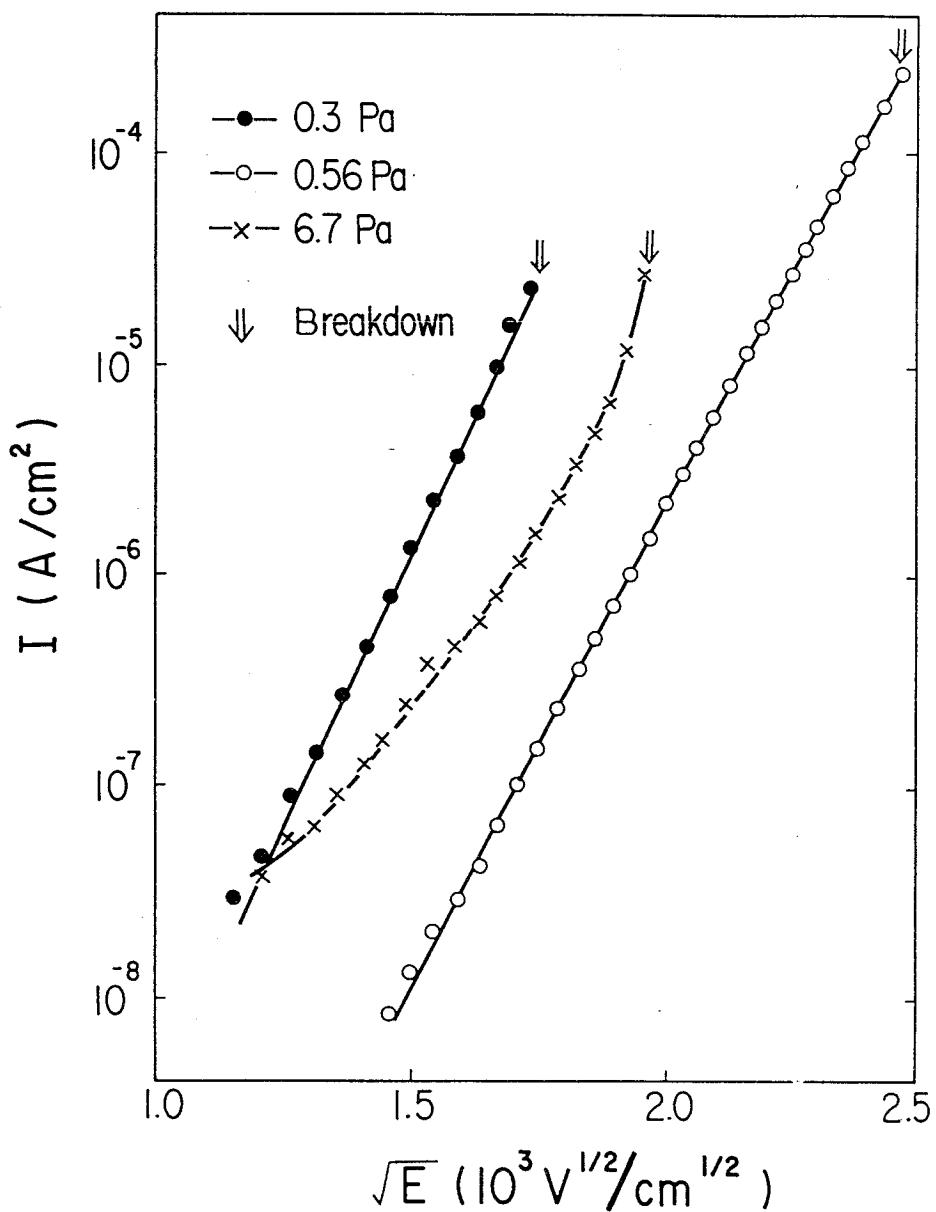

図2-19は、スパッタリングガス圧: 0.3 Pa、0.56 Pa、および6.7 Paで形成した膜の電流-電圧特性を示す。試料は、Al ( $500 \mu\text{m}\phi$ ) 電極 - SiN膜 - (100) p型Si基板の構造を成し、Al電極に負電圧を印加して測定した。圧力: 0.3 Paと0.56 Paでの膜は、 $\ln I$  対  $\sqrt{E}$  の関係が線形となり、Pool-Frenkel伝導機構を示す<sup>11)</sup>。一方、圧力が大きい場合の膜は、湾曲した関係を示す。同図には、絶縁耐圧が矢印で示してある。圧力が0.56 Paでの膜が最大の絶縁耐圧と比抵抗を示す。反対に、0.3 Paで形成した膜は最も小

図2-18 SiN膜表面のスパッタリングガス圧による変化を示すレプリカ写真

さな値となる。

スパッタリング時には、ターゲット表面は窒化シリコンによっておおわれている。この窒化シリコンは、ArイオンやNイオンの衝突によって、平均値が10 eVのエネルギー分布を

図2-19 SiN膜の電流-電圧特性 膜厚:  $0.15 \mu\text{m}$

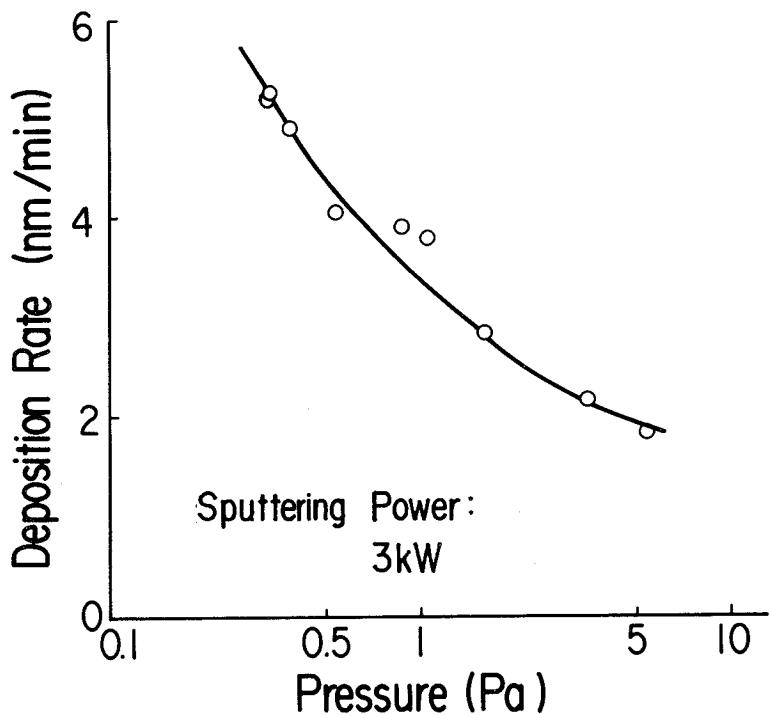

有して、ターゲット表面から叩き出される<sup>27)</sup>。この窒化シリコンは、Ar原子やN原子との衝突を繰り返しながら飛行する。この衝突によって、ターゲット表面で得たエネルギーや方向性を失う。図2-20は、スパッタリングガス圧による膜の形成速度の変化である。膜の形成速度は、スパッタリングガス圧の増大に伴い減少する。この減少は、スパッタされた粒子が、Ar原子やN原子との衝突により、スパッタ時の方向を失うためである<sup>28)</sup>。さらに、この時の基板面での入射角分布は、垂直成分だけでなく、斜め成分や水平成分を有していく<sup>29)30)</sup>。

図2-20 スパッタリングガス圧による膜の形成速度の変化

図2-16に示したように、スパッタリングガス圧：1.5 Paでエッチング速度は急激に増大する。この圧力での、スパッタ粒子が平均熱エネルギーになるまでに飛行する距離は、スパッタ粒子を  $\text{Si}_3\text{N}_4$  と仮定すると、35 mmとなる<sup>29)</sup>。しかし、本実験におけるスパッタリングガス中には、Arよりも質量の小さなNが50%混合してあるため、さらにこの距離は大きくなる。すなわち、圧力：1.5 Paでは、ターゲットから50 mm隔った基板上では、ほぼ平均熱エネルギーを有していると考えられる。

スパッタされた粒子がエネルギーを失うと、基板上での次の効果が抑制される<sup>11)</sup>。(1) 基板面での表面拡散と、(2) 弱く結合した粒子の、基板面からの再放出、である。さらに、エネルギーを失うと同時に、基板面へのスパッタ粒子の入射角もランダムになってくる。このために、基板面に入射する粒子の入射角分布には、垂直だけでなく、斜め方向や水平方向の成分が混ってくる。この斜め方向成分や水平方向成分を持つ入射粒子は、基板面や形成しつつある膜の表面の凹凸により遮られる。さらに、表面拡散が抑制されているために、凹凸により遮られた領域は、微小な空孔として残る<sup>2)31)</sup>。その結果、図2-18に示したように、スパッタリングガス圧を大きくすると、多量の微小空孔を含む膜構造となる。さらに、スパッタリングガス圧が大きい場合、弱く結合した粒子の再放出が抑えられ

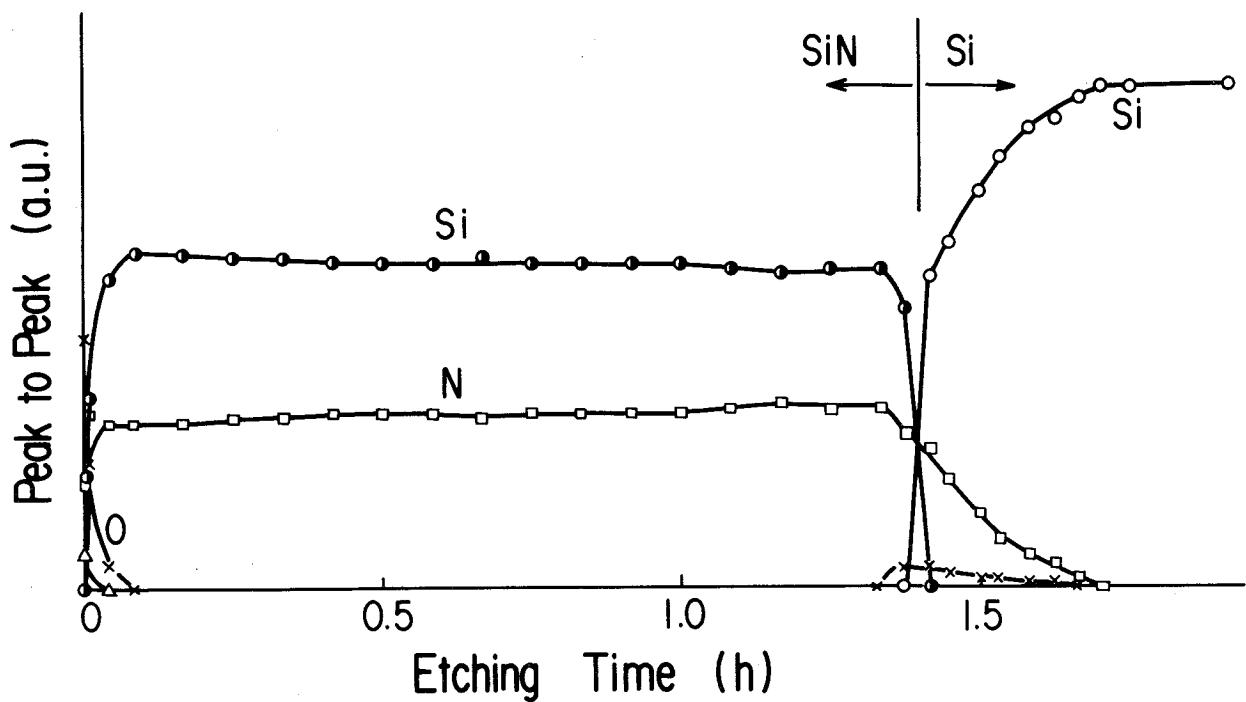

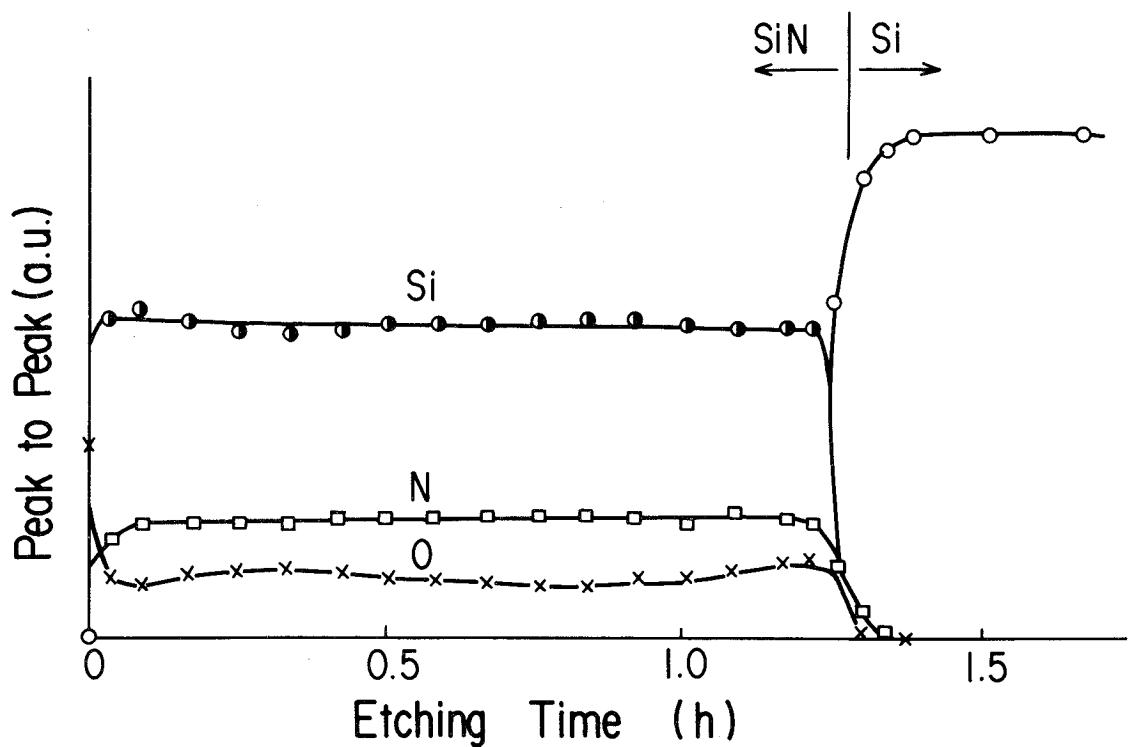

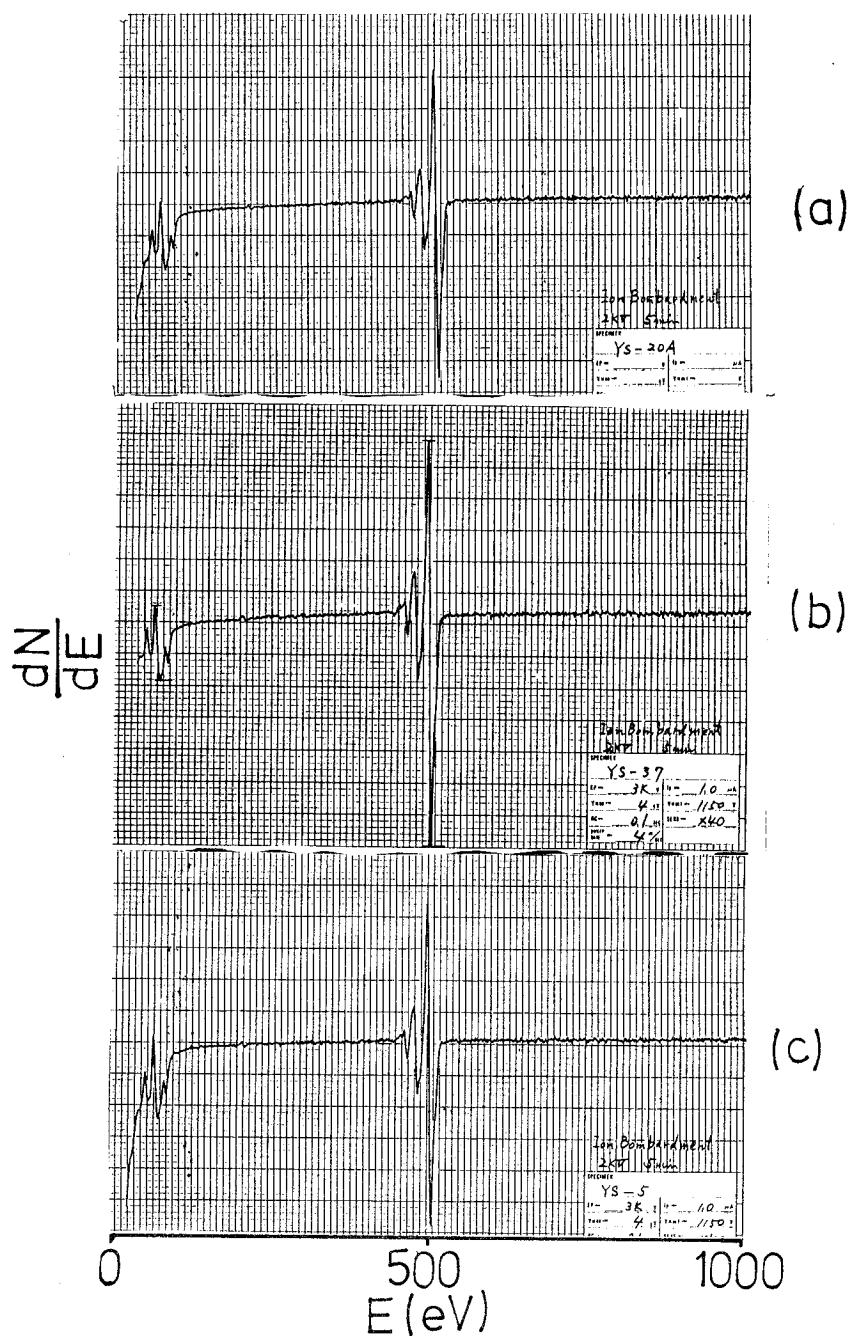

図2-21 オージュ電子分光法による膜組成分布 (a) : 0.56Pa

図2-21 オージュ電子分光法による膜組成分布 (b) : 6.7Pa

る。これらの原因により、スパッタリングガス圧が 1.5 Pa 以上の圧力で形成した膜のエッチング速度は、異常に大きくなり、比抵抗や絶縁耐圧は小さくなる。

図 2 - 21 は、オージェ電子分光法により測定した膜組成の厚さ方向分布である。0.5~6 Pa で形成した膜(a)では、膜は Si と N とから構成されおり、膜表面ならびに基板との界面にのみ酸素が検出される。しかし、6.7 Pa での膜(b)では、膜中に多量の酸素が検出される。これは、この圧力で形成した膜が多量の空孔を有する膜構造となっているため、大気中の酸素と容易に反応したからと考えられる。

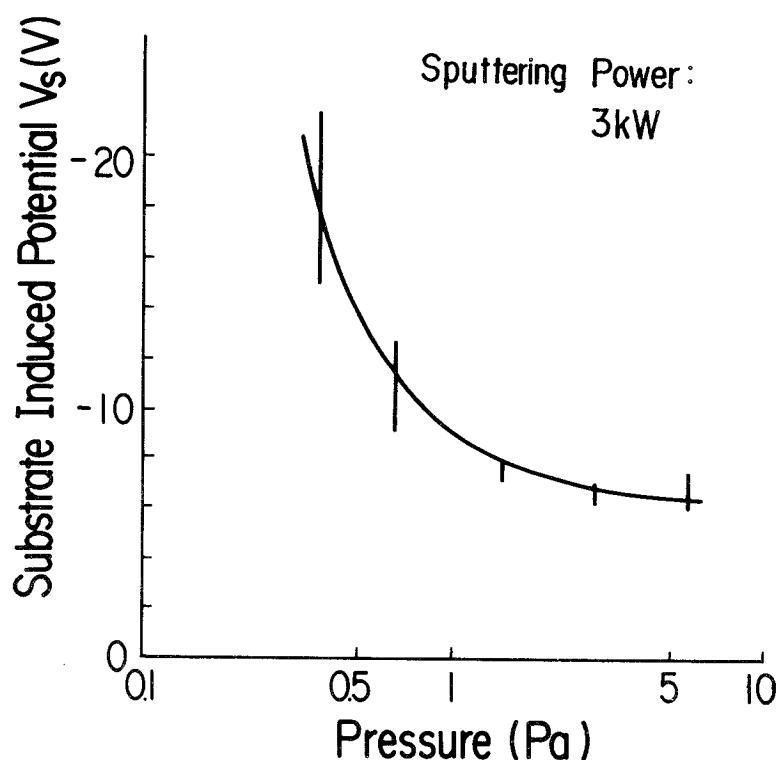

図 2 - 16 と 17 に示したように、スパッタリングガス圧をさらに小さくすると、エッチング速度は大きくなり、屈折率は小さくなる。図 2 - 22 は、アース電位に対する基板支持台の電位の、スパッタリングガス圧による変化である。基板支持台は負電位を示し、圧力が 1 Pa 以下になると急激に大きくなる<sup>32)33)</sup>。プラズマの電位は、スパッタリング槽の電位すなわちアース電位とほぼ一致するため、ここに示した電位はプラズマに対する値である<sup>34)</sup>。スパッタリングガス圧を小さくすると、膜の形成途中に膜の表面がイオンの衝突をより多く受け、この結果、膜特性が劣化したと考えられる。このことは、外部から高周波電圧を印加すると、膜のエッチング速度が大きくなり、また、膜の表面が荒れてしまうことからも確認されている<sup>35)</sup>。

図 2 - 22 スパッタリングガス圧による基板支持台電位の変化

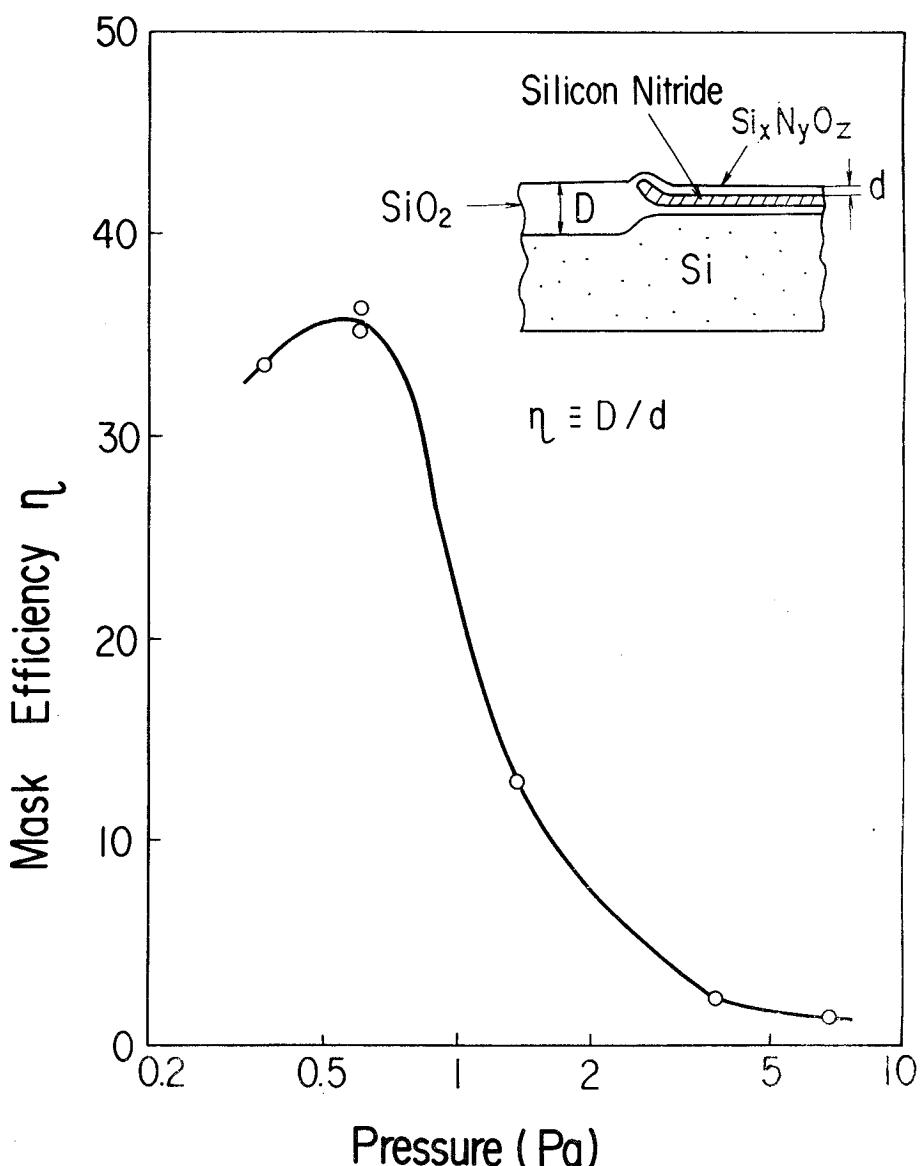

図2-23は、1000°Cの湿式雰囲気中に370分間晒した時の、酸素の拡散に対する阻止能 $\eta$ の、スパッタリングガス圧による変化を示す。阻止能 $\eta$ は、図中に示すように、(100)面のSi基板上に形成された酸化膜厚を、窒化シリコン膜上の酸化膜厚で割った値である。この阻止能 $\eta$ は、スパッタリングガス圧に顕著に依存し、0.56Paで最大

図2-23 スパッタリングガス圧による阻止能 $\eta$ の変化

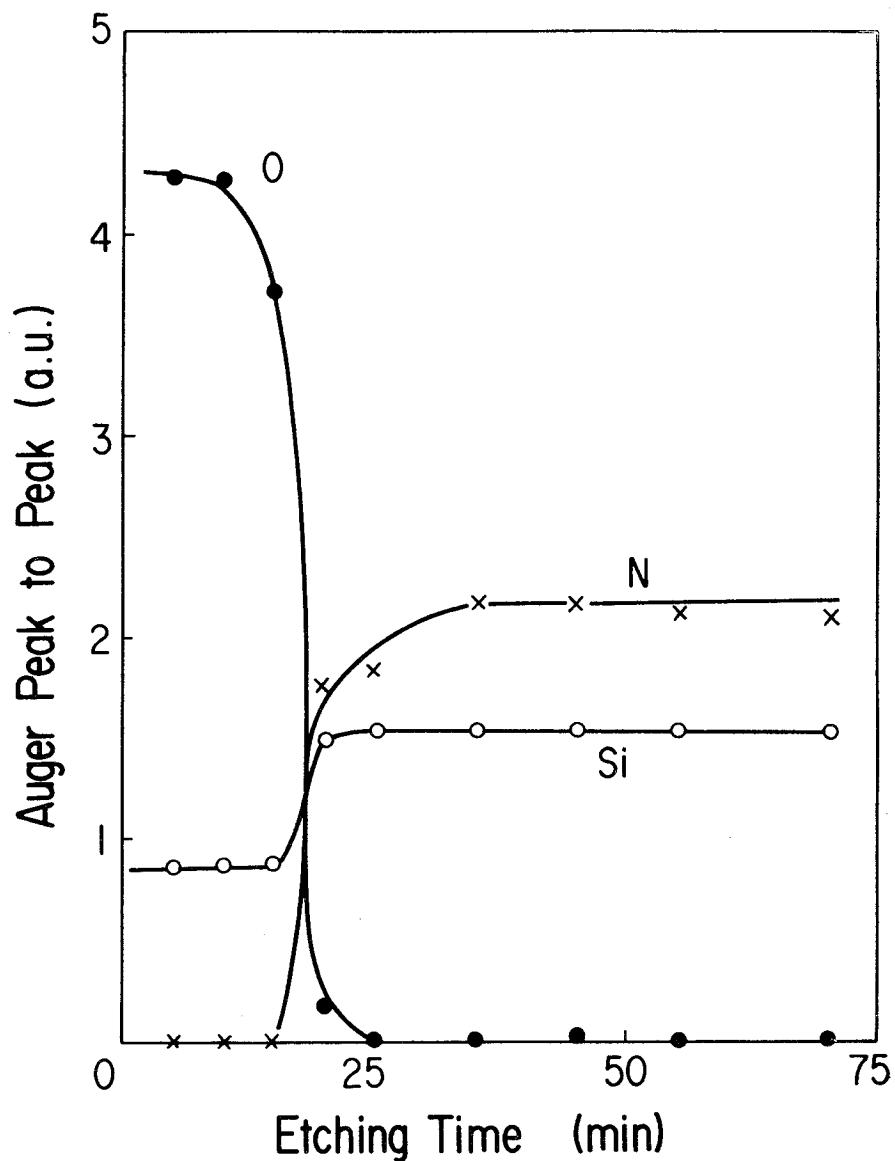

となる。図2-24は、熱処理を施したこの膜を、オージェ電子分光法により組成分析した時の、表面からの組成変化である。酸素Oは、スパッタエッチング時間25分間のところまでに存在し、それよりも深い位置には認められない。図2-25は、熱処理を施した膜の表面状態であり、(a)は $\eta$ が最大となる0.56Paでのものを、(b)は $\eta$ が小さな5.6

図2-24 热処理を施した膜の組成分布

热処理条件：1000°C湿式雰囲気中370分，スパッタリングガス圧：

0.56Pa

Paでのものである。0.56Paでの膜(a)は、膜形成直後(図2-18)におけると同様に平滑な表面状態を示している。しかし、5.6Paでの膜(b)は、(a)に比べて、表面の凹凸が激しいばかりでなく、膜形成直後(図2-18)よりも荒れてくる。

図2-17に示したように、0.56Paで形成した膜はち密するために、高温度・長時間の热処理においても、酸素Oの拡散を良く阻止し、阻止能ηとして35が得られる。このことは、Si基板を1μm厚酸化する場合には、選択酸化用マスクとしてのSiN膜の厚さ

(a)

(b)

0.2 $\mu$ m

図2-25 热処理を施した膜の表面状態 (a) : 0.56Pa , (b) : 5.6Pa<sub>o</sub>

热処理条件は図2-24と同じ

は 30 nm で良いことを意味する。この高い阻止能のために、図2-24に示したように、酸素は表面近傍に局在し、また、平滑な表面状態となる。これに対して、高いスペッタリングガス圧での膜は、ち密さに欠け、膜中に多量の微小空孔を有する。このために、酸素の拡散が容易となり、酸化速度が大きくなる。この結果、阻止能  $\eta$  は、圧力と共に急激に小さくなり、図2-25(b)に示すように表面荒れが顕著となる。

本反応性スパッタリング法により形成した窒化シリコン膜は、すべて、圧縮応力を示した。この応力は、スパッタリングガス圧の増大に伴い小さくなる。

以上述べたように、マグネットロン方式反応性スパッタリング法により形成した窒化シリコン膜は、その形成条件、特に、スパッタリングガス圧に著しく依存することを明らかにした。さらに、適正圧力での膜は、CVD法による膜に匹敵する、ち密で、酸素の阻止能にすぐれた特性を示す膜が低基板温度で初めて得られた。表2-3に、スパッタリングガス圧が0.56Pa、および、6.7Paで形成した膜の特性をまとめて示す。

表2-3 膜の特性の比較

| Pressure                               | 0.56 Pa                                                | 6.7 Pa                                                 |

|----------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| Film Density                           | 2.97 g/cm <sup>3</sup>                                 | 2.28 g/cm <sup>3</sup>                                 |

| Refractive Index                       | 1.97                                                   | 1.82                                                   |

| Composition N/Si by L-L<br>Correlation | 1.42                                                   | 1.15                                                   |

| Infrared Absorption Peak               | 840 cm <sup>-1</sup> , 460 cm <sup>-1</sup>            | 900 cm <sup>-1</sup> , 460 cm <sup>-1</sup>            |

| Etching Rate(30°C BHF)                 | 1.7 nm/min                                             | 200 nm/min                                             |

| Dielectric Strength                    | 5.5 × 10 <sup>6</sup> V/cm                             | 3.5 × 10 <sup>6</sup> V/cm                             |

| Resistivity(E=3×10 <sup>6</sup> V/cm)  | 3×10 <sup>11</sup> Ω·cm                                | 3×10 <sup>10</sup> Ω·cm                                |

| Stress                                 | 5×10 <sup>9</sup> dyn/cm <sup>2</sup><br>(Compressive) | 1×10 <sup>9</sup> dyn/cm <sup>2</sup><br>(Compressive) |

| $\eta$                                 | 35                                                     | 1.5                                                    |

#### 2-4 反応性スパッタリング法による窒化シリコン膜の選択酸化マスクへの応用

前節において、適正条件のもとで形成した窒化シリコン膜は、ち密で、酸素の拡散に対する阻止能が十分大きいことを明らかにした。本節では、この窒化シリコン膜がMOS半導体素子製作作用として有用なことを明らかにする。

## 2 - 4 - 1 シリコンMOS半導体素子の製作と特性測定

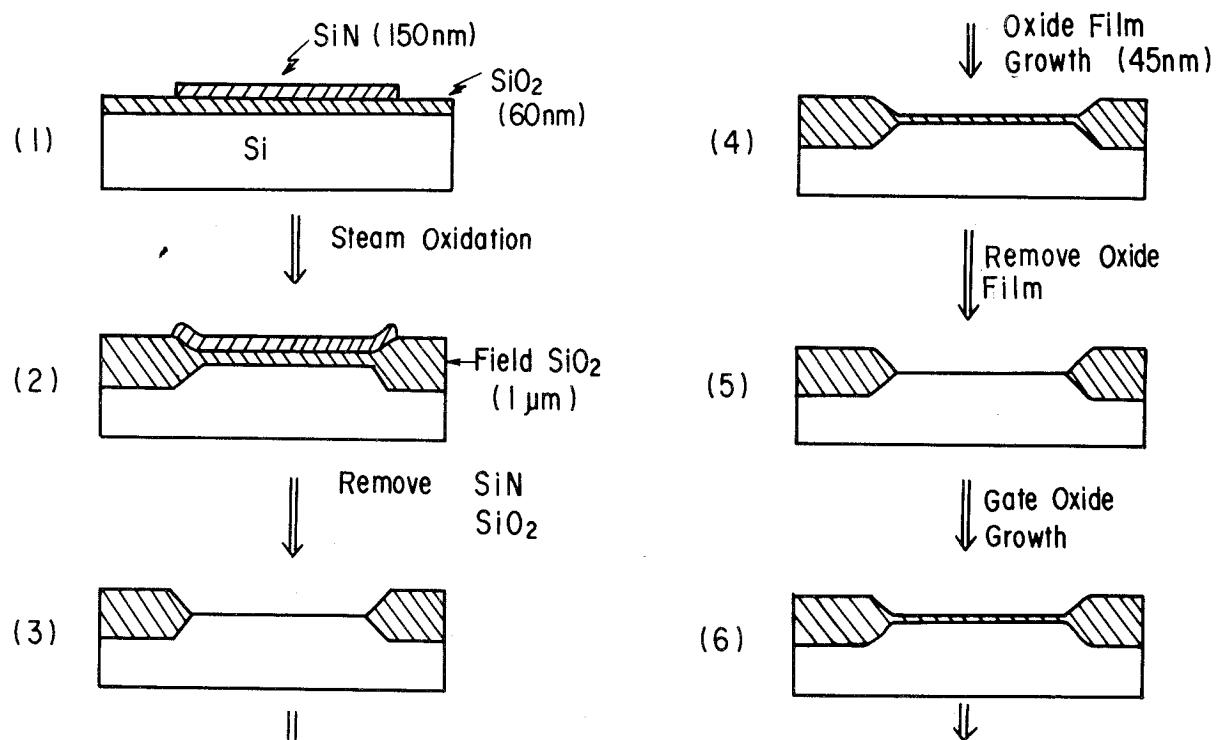

本窒化シリコン膜を選択酸化マスクに応用し、シリコンMOS半導体素子を製作した。その工程を図2-26に示す<sup>36)37)</sup>。Si基板（B添加p型、比抵抗3～5Ω·cm、(100)面）表面を、厚さ60nm熱酸化した後、本SiN膜を150nm厚形成し、パターン形成を行う（工程1）。これをマスクとして、1000°Cの湿式雰囲気中で370分間熱酸化し、素子間分離用フィールドSiO<sub>2</sub>膜を形成する（工程2）。その後、工程1でのSiN膜と、その下の熱酸化膜を除去し、再度、酸化膜の形成と除去を行う（工程3、4および5）。工程6で、ゲートSiO<sub>2</sub>膜を形成した後、多結晶シリコン電極やソース、ドレイン拡散層の形成等の工程を経て半導体素子が形成される。工程4と5を行う理由は、工程2のフィールドSiO<sub>2</sub>膜の形成中に、SiN膜のN原子が下層のSiO<sub>2</sub>膜を貫通し、Si-SiO<sub>2</sub>界面に、SiNが新たに形成されることが考えられるからである。この状態でゲートSiO<sub>2</sub>膜を形成すると、SiNが存在する場所では、ゲートSiO<sub>2</sub>膜の成長が阻止され、絶縁耐圧に乏しいゲートSiO<sub>2</sub>膜となる。したがって、工程4により、このSiNを酸化物に一度変え、工程5によりこれを除去する<sup>38)</sup>。

半導体素子製作に用いた窒化シリコン膜は、50%Ar-50%N<sub>2</sub>混合ガス中で、スパッタリングガス圧：0.56Pa、基板温度：200°Cで形成した。このようにして形成した

図2-26 MOS半導体素子の製作工程

シリコンMOSトランジスタの閾値電圧および移動度、さらに、ゲートSiO<sub>2</sub>膜の絶縁耐圧特性を測定した。

#### 2 - 4 - 2 測定結果と考察

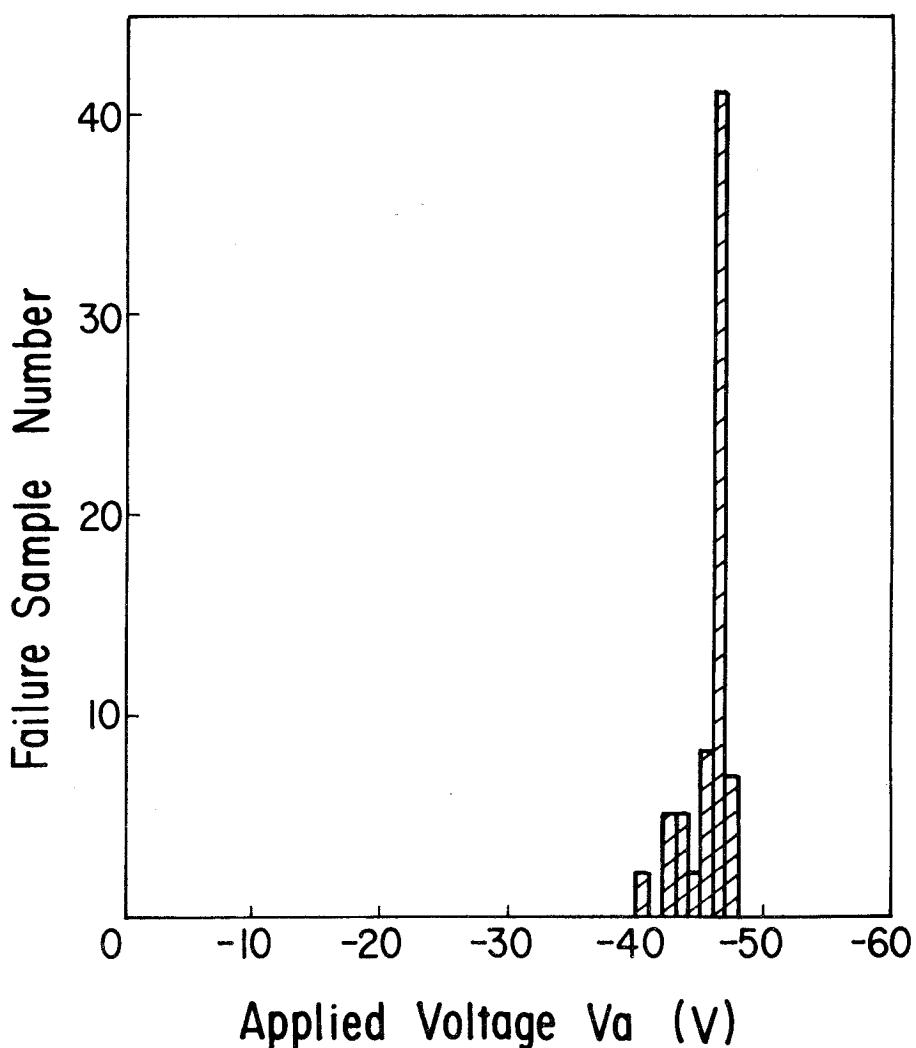

SiN膜パタンの部分に、ゲートSiO<sub>2</sub>膜が形成され、能動領域となることは、図2-26において説明した。したがって、このSiN膜パタンが大きな阻止能を有するだけでは不充分であり、ゲートSiO<sub>2</sub>膜の特性を損ってはならない。このゲートSiO<sub>2</sub>膜は、フィールドSiO<sub>2</sub>膜形成後、SiN膜とその下層のSiO<sub>2</sub>膜を除去し、再度、薄い酸化膜を形成し、再びこれを除去した後に形成される。この余計とも考えられるSiO<sub>2</sub>膜の形成と除去の工程は、ホワイトリボン効果によるといわれているゲートSiO<sub>2</sub>膜の耐圧劣化を阻止する目的で行われる<sup>37)</sup>。図2-27には、本SiN膜(0.56Paで、厚さ150nm形成)を用い、図

図2-27 ゲートSiO<sub>2</sub>膜の絶縁耐圧分布 ゲートSiO<sub>2</sub>膜の厚さ：60nm

2-26に示した工程を経て、トリクロレン酸化法により形成したゲート $\text{SiO}_2$ 膜の絶縁耐圧特性を示す。このゲート $\text{SiO}_2$ 膜の厚さは60 nmである。7.8 MV/cmにピークを有する分布となり、すべての試料で6.6 MV/cm以上の耐圧が得られる。

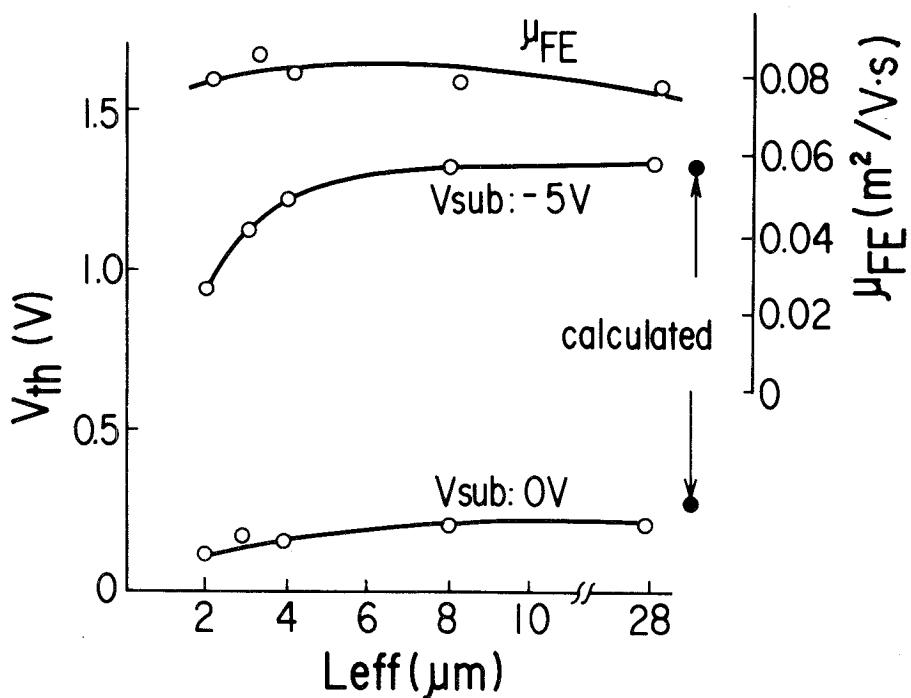

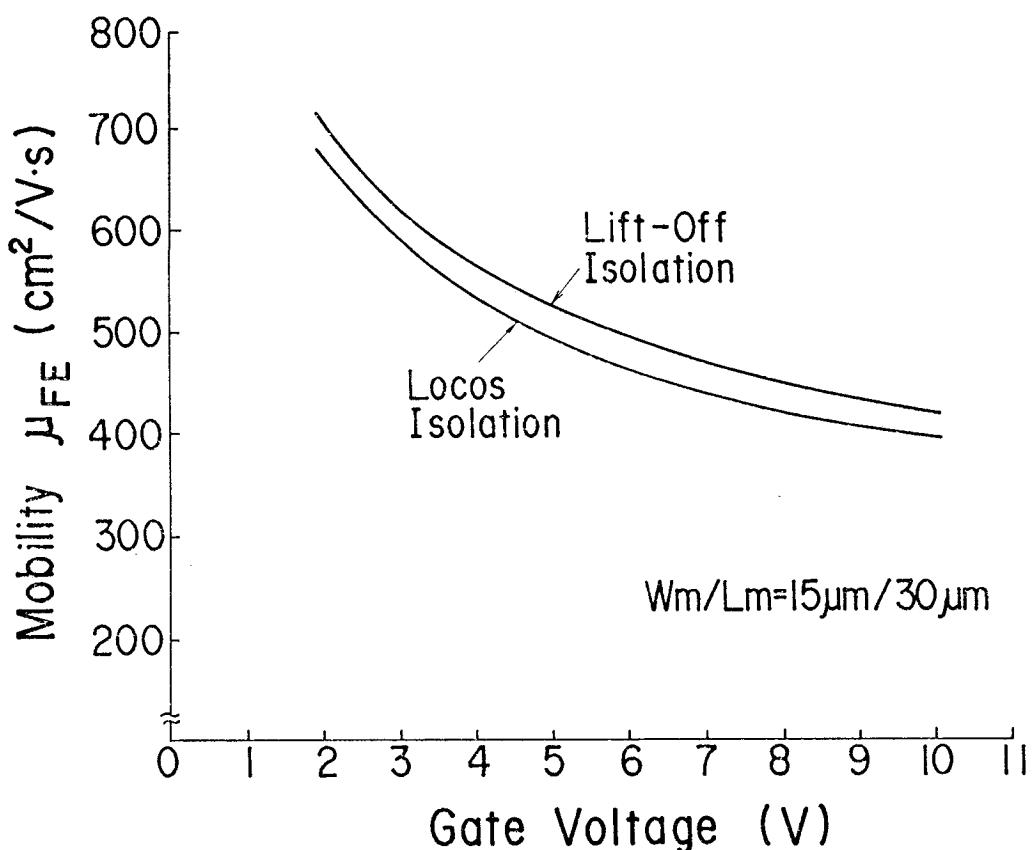

図2-28は、図2-26に示した工程に従って形成したMOSトランジスタの閾値電圧、および、移動度のチャネル長依存性である。この時のゲート $\text{SiO}_2$ 膜の厚さは66 nmである。閾値電圧は、基板のアクセプタ濃度 $NA : 3.5 \times 10^{15} \text{ cm}^{-3}$ 、界面電荷密度 $Q_{ss}$ が存在しないとした時の計算値と良く一致する。さらに、移動度 $\mu_{FE}$ は、 $0.07 \text{ m}^2/\text{V}\cdot\text{s}$ 以上である。これらの結果より、スパッタリング法によるSiN膜を用いたことによる、基板表面の汚染や基板への欠陥の導入が無いことが明らかとなった。ちなみに、同一工程を経て形成した1トランジスタダイナミックメモリセルの情報保持特性も良好であった。

図2-28 MOSトランジスタにおけるチャネル長による閾値電圧および移動度の変化

従来、シリコンMOS半導体素子製作のための選択酸化マスク用窒化シリコン膜は、専ら、気相成長法により形成されていた。しかし、本研究の結果から、マグネットロン方式反応性スパッタリング法により、選択酸化マスクとして有用な窒化シリコン膜が低基板温度で形成できることが初めて示された。

## 2 - 5 結言

SiのAr-N<sub>2</sub>混合ガス中マグнетロン方式反応性スパッタリング法による窒化シリコン膜の形成の研究を行った。結言として、反応性スパッタリング特性に関することと、膜特性、ならびに、選択酸化マスクへの応用に関する二つに分けてまとめる。

### 2 - 5 - 1 反応性スパッタリング特性について

- (1) スパッタリング時の窒素分圧により、膜形成速度、および、膜組成が著しく変化し、分圧0.12Pa以上では、アモルファス状の窒化シリコン膜が得られる。これらの変化は、Siターゲット表面での、窒化速度とスパッタエッチング速度とから説明できる。

- (2) Ar中で放電を開始した後、N<sub>2</sub>を導入する方法において、膜の形成速度、膜中の窒素含有量、スパッタリングガス圧やガス組成は、N<sub>2</sub>流量に対して急激に変化し、さらに、N<sub>2</sub>流量の増減に伴いヒステリシス現象を示す。また、このヒステリシス現象の現わられないスパッタリング条件も明らかにした。

- (3) 上記(2)の変化に対し、膜中含有による窒素消費量の窒素分圧依存性、N<sub>2</sub>流量、および、スパッタリング装置の排気特性を考慮したモデルを提案した。さらに、このモデルにより実験結果を良く説明できることを示した。

以上の結果は、本研究での窒化シリコン膜以外の他の化合物薄膜を反応性スパッタリング法により形成する場合の有益な指針となると考える。

### 2 - 5 - 2 窒化シリコン膜の特性と選択酸化マスクへの応用について

- (1) 窒化シリコン膜の特性は、スパッタリングガス圧に著しく依存して変化し、ち密でストキオメトリの膜形成に適正な圧力が依存することを明らかにした。

- (2) 上記適正条件で形成した膜は、低基板温度形成にもかかわらず気相成長法による膜に匹敵する、ち密で、酸素の拡散に対する阻止能にすぐれた特性を示すことを明らかにした。

- (3) 本方法で得た窒化シリコン膜は、選択酸化マスク用として、Si基板への汚染を伴うことなく、半導体素子製作に応用できることを実証した。

以上のように、本方法による窒化シリコン膜は、低基板温度で極めて良質な特性を示すため、ここで述べた用途だけでなく、層間絶縁膜や保護膜としても有用であると考える。

## 第2章参考文献

- 1) C. E. Morosanu : Thin Solid Films 65 (1980) 171.

- 2) J. L. Vossen and W. Kern : Thin Film Processes (Academic Press, New York, San Francisco, London, 1979) P P. 1 - 137.

- 3) A. K. Sinha, H. I. Levinstein, T. E. Smith, G. Quintana and S. E. Haszko : J. Electrochem. Soc. 125 (1978) 601.

- 4) R. S. Rosler, W. C. Benzing and J. Baldo : Solid State Technol. June (1976) 45.

- 5) E. A. Taft : J. Electrochem. Soc. 118 (1971) 1341.

- 6) H. J. Erler, G. Reisse and C. Weissmantel : Thin Solid Films 65 (1980) 233.

- 7) S. M. Hu : J. Electrochem. Soc. 113 (1966) 693.

- 8) S. M. Hu and L. V. Gregar : J. Electrochem. Soc. 114 (1967) 826.

- 9) A. W. Stephens, J. L. Vossen and W. Kern : J. Electrochem. Soc. 123 (1976) 303.

- 10) C. J. Mogab and E. Lugujjo : J. Appl. Phys. 47 (1976) 1302.

- 11) C. J. Mogab, P. M. Petroff and T. T. Sheng : J. Electrochem. Soc. 122 (1975) 815.

- 12) R. E. Jones, H. F. Winters and L. I. Maissel : J. Vac. Sci. Technol. 5 (1968) 84.

- 13) E. Holland and D. S. Campbell : J. Mat. Sci. 3 (1968) 544.

- 14) A. T. Stirling and W. D. Westwood : Thin Solid Films 7 (1971) 1.

- 15) J. Heller : Thin Solid Films 17 (1973) 163.

- 16) S. Maniv and W. D. Westwood : J. Appl. Phys. 51 (1980) 718.

- 17) E. A. Taft : J. Electrochem. Soc. 118 (1971) 1341.

- 18) S. Maniv and W. D. Westwood : J. Vac. Sci. Technol. 17

(1980) 743.

- 19) J. Heller : I E E E Trans. Magn. MAG - 12 (1976) 396.

- 20) J. H. Greiner : J. Appl. Phys. 45 (1974) 32.

- 21) K. G. Geraghty and L. F. Donaghey : J. Electrochem. Soc. 123

(1976) 1201.

- 22) S. Maniv, W. D. Westwood and E. Colombini : J. Vac. Sci.

Technol. 20 (1982) 162.

- 23) R. McMahon, J. Affinito and R. R. Parsons : J. Vac. Sci.

Technol. 20 (1982) 376.

- 24) A. R. Nyairesh and L. Holland : J. Vac. Sci. Technol. 20

(1982) 1389.

- 25) A. K. Sinha and E. Lugujjo : Appl. Phys. Lett. 32 (1978) 245.

- 26) R. Glang, R. A. Holmwood and R. L. Rosenfeld : Rev. Sci.

Inst. 36 (1965) 7.

- 27) M. W. Thompson : Philos. Mag. 18 (1968) 377.

- 28) J. H. Keller and R. G. Simmons : IBM J. Res. Develop. 23

(1979) 24.

- 29) W. D. Westwood : J. Vac. Sci. Technol. 15 (1978) 1.

- 30) T. Serikawa and T. Sakurai : I E E E Trans. Electron Devices.

ED - 29 (1982) 834.

- 31) T. Serikawa and T. Yachi : Jpn. J. Appl. Phys. 20 (1981)

L111.

- 32) J. S. Logan, F. S. Maddocks and P. D. Davidse. IBM J.

Res. Develop. 14 (1970) 182.

- 33) J. W. Cobarn and Evic Kay : J. Appl. Phys. 43 (1972) 4965.

- 34) H. R. Koenig and L. I. Maissel : IBM J. Res. Develop. 14

(1970) 168.

- 35) 岡本、芹川 : 第29回応用物理学関係連合講演会 4 a - C - 3 (1982)

- 36) J. A. Appels, E. Kooi, M. M. Paffen, J. J. Schatroe and

- W. C. G. Wavkuylen : Philips. Res. Rept. 25 (1970) 118.

- 37) E. Kooi, J. G. van Lierop and J. A. Appels : J. Electrochem. Soc. 123 (1976) 1117.

- 38) P. B. Ghate and Lou. H. Hall : J. Electrochem. Soc. 119 (1972) 491.

## 第3章 スパッタリング法による $\text{SiO}_2$ 膜の形成と特性

### 3-1 緒言

$\text{SiO}_2$  膜は、半導体素子やLSIの製作作用として、また、それらの構成要素として不可欠である。この絶縁膜の形成にどのような方法を用いるかは、半導体素子やLSIの製作における重要な鍵の一つである。近年における半導体素子やLSIの著しい進歩に伴い、絶縁膜に対する要求も厳しくなっている。この要求の一つとして、より低温で良質な膜の形成が行えることが挙られる。この低温プロセスには、半導体素子やLSIの製作の制御や製作が容易となる利点がある。

低温での絶縁膜の形成には、スパッタリング法が適している<sup>1)～4)</sup>。その理由としては、スパッタリング法では、低温においても膜形成が容易であることの外に、内部応力が小さい等、膜特性にすぐれている利点を有しているからである。しかしながら、従来からのダイオードスパッタリング法では、基板表面がプラズマに晒されるために、半導体素子、特に、シリコンMOS半導体素子の特性が損われる懼れがあり、また、膜の形成速度が小さい欠点があった<sup>5)～7)</sup>。このために、ダイオードスパッタリング法の適用対象は限定されていた。ところが、近年、プラズマをターゲット近傍に閉じ込めるマグネットロンスパッタリング法が開発され、上記ダイオードスパッタリング法の欠点が一挙に解決された。このために、スパッタリング法の適用範囲が著しく拡大し、スパッタリング法による  $\text{SiO}_2$  膜の半導体素子製作への応用に関する研究が各所で開始されている<sup>8)～10)</sup>。しかし、マグネットロンスパッタリング法により形成した  $\text{SiO}_2$  膜の特性は、ほとんど明らかにされていない。

本研究では、マグネットロンスパッタリング法により形成した  $\text{SiO}_2$  膜の特性を詳細に評価し、さらに、スパッタリングガス中に  $\text{H}_2$  を混合することにより、  $\text{SiO}_2$  膜を著しくち密にできることを示す。

### 3-2 実験方法

#### 3-2-1 装置と試料作製

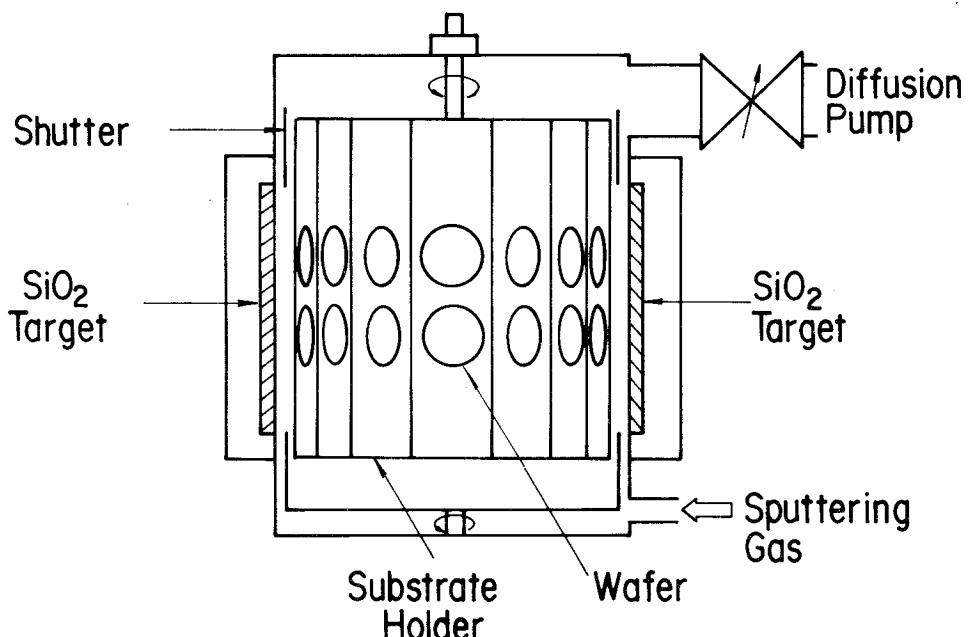

$\text{SiO}_2$  膜の形成には、高周波平板型マグネットロンスパッタリング装置を用いた。図3-1には、装置の概略図を示す。本装置は、2個の高周波電極、0～10 rpmで回転するドラム状基板支持台、回転式シャッタ、基板を裏面から加熱する赤外線ランプ、および、排気系から構成されている。ターゲットは、5" × 15" の大きさの溶融石英（純度：99.999%）である。ターゲットと基板との間隔は50 mmである。排気系は、油拡散ポンプと油回転ポンプとから成っている。

図3-1 スパッタリング装置の概略図

膜の形成は、次に示す手順で行った。面方位(100)の3"  $\phi$  Si基板を基板支持台上に設置した後、真空度  $1 \times 10^{-4}$  Paまで排気し、次に、基板の加熱を行う。その後、Ar（純度99.999%）あるいはH<sub>2</sub>との混合ガスを導入し、プリスパッタリングを行う。その後に、シャッタを開き、所定のスパッタリング条件で  $\text{SiO}_2$  膜を堆積する。本実験における主なパラメータはAr圧とH<sub>2</sub>混合量である。基板温度は、特に断りのない限り、200°Cである。また、基板回転速度は10 rpmでスパッタ電力は4 kW（但し、ターゲット2個）である。

### 3-2-2 測定方法

厚さ0.2～2.5  $\mu\text{m}$ の  $\text{SiO}_2$  膜を形成し、次に示す膜の特性を調べた。すなわち、(1) 形成速度、(2) エッチング速度、(3) 赤外吸収特性、(4) 表面状態、(5) 密度、

(6) 組成、(7) 比抵抗、および、(8) 応力、ある。

エッティング速度、赤外吸収特性、表面状態、および、密度の測定は、第2章第3節で述べた方法により行った。

比抵抗は、膜形成後、 $0.25\text{ mm}^2$  の面積のA1電極を形成し、チップ状に切断した後、TO-5にカン封じし測定した。

応力はニュートンリング法を用い、 $\text{SiO}_2$  膜形成後の基板の曲率半径を測定して算出した。応力  $\sigma_f$  は次式で表わせる<sup>11)</sup>。

$$\sigma_f = \frac{E_s}{6(1-\nu_s)} \cdot \frac{d_s}{d_f} \cdot \frac{1}{R_s} \quad \dots \quad (3-1)$$

ここに、 $E_s$ 、 $\nu_s$ 、 $d_s$ は、基板のヤング率、ポアソン比、厚さを示し、 $d_f$ は $\text{SiO}_2$  膜の厚さを、 $R_s$ は基板の曲率半径を示す。面方位(100)を有するSi基板では、上式(3-1)の  $E_s / (1 - \nu_s)$  は、 $1.81 \times 10^{12} \text{ dyne/cm}^2$  となる<sup>12)</sup>。また、本Si基板の厚さは0.38mmである。

次に、真性応力  $\sigma_i$  は次式から求まる。

$$\sigma_i = \sigma_f - \sigma_{th} \quad \dots \quad (3-2)$$

ここに、 $\sigma_{th}$ は、膜形成時と測定時との温度差  $\Delta T$ に基づいて発生した応力であり、次の式で計算できる<sup>13)</sup>。

$$\sigma_{th} = \frac{E_f}{1 - \nu_f} \cdot (\alpha_s - \alpha_f) \cdot \Delta T \quad \dots \quad (3-3)$$

$E_f$ 、 $\nu_f$ は $\text{SiO}_2$  膜のヤング率とポアソン比であり、各々、 $6 \times 10^{11} \text{ dyne/cm}^2$ 、<sup>14)</sup> 0.17、<sup>15)</sup> である。また、 $\alpha_s$ 、 $\alpha_f$ は、Si基板および $\text{SiO}_2$  膜の熱膨張係数であり、各々、 $2.5 \times 10^{-6} \text{ deg}^{-1}$ 、 $0.35 \times 10^{-6} \text{ deg}^{-1}$  である<sup>16)</sup>。

さらに、H<sub>2</sub>混合ガス中で形成した $\text{SiO}_2$  膜のH<sub>2</sub>含有量を、二次イオン質量分析法(SIMS)により測定した。

なお、実験に用いたSi基板は、直徑3"、比抵抗3~5Ω·cm、p型、面方位(100)であり、厚さ0.38mmのものである。Si基板は、アンモニア水と過酸化水素水との混合溶液ならびに、弗酸、塩酸と過酸化水素水との混合溶液を用いて洗浄し、スピンドライ法により乾燥した後、膜を形成した。

### 3-3 Ar中スパッタリング法によるSiO<sub>2</sub>膜の特性

#### 3-3-1 測定結果

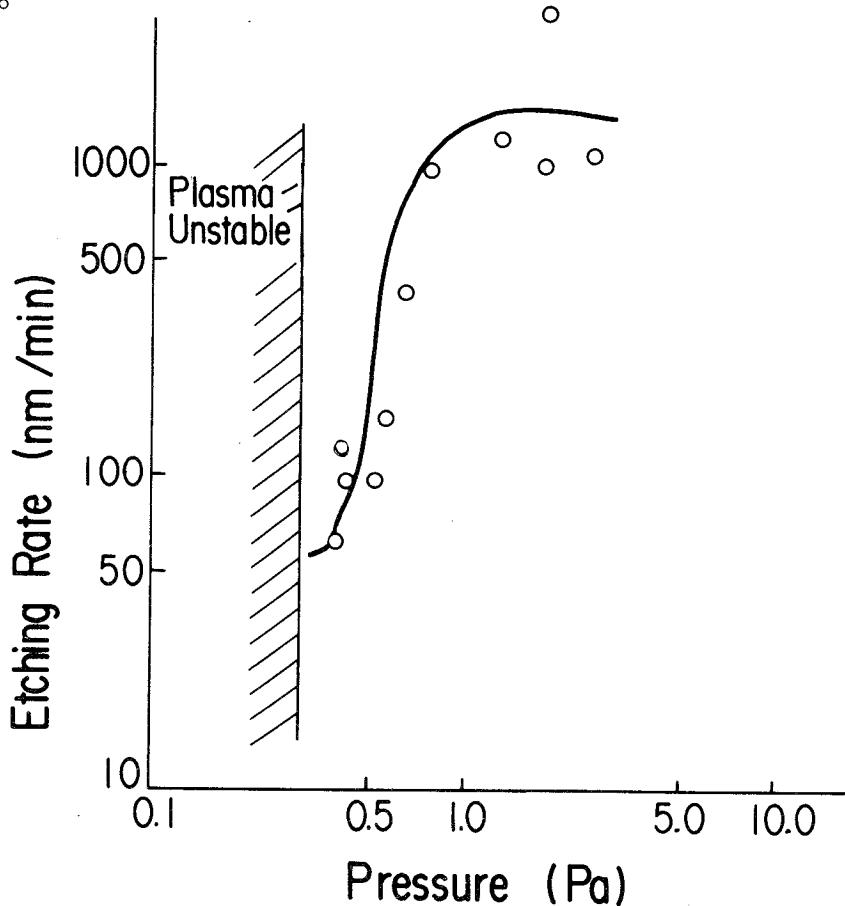

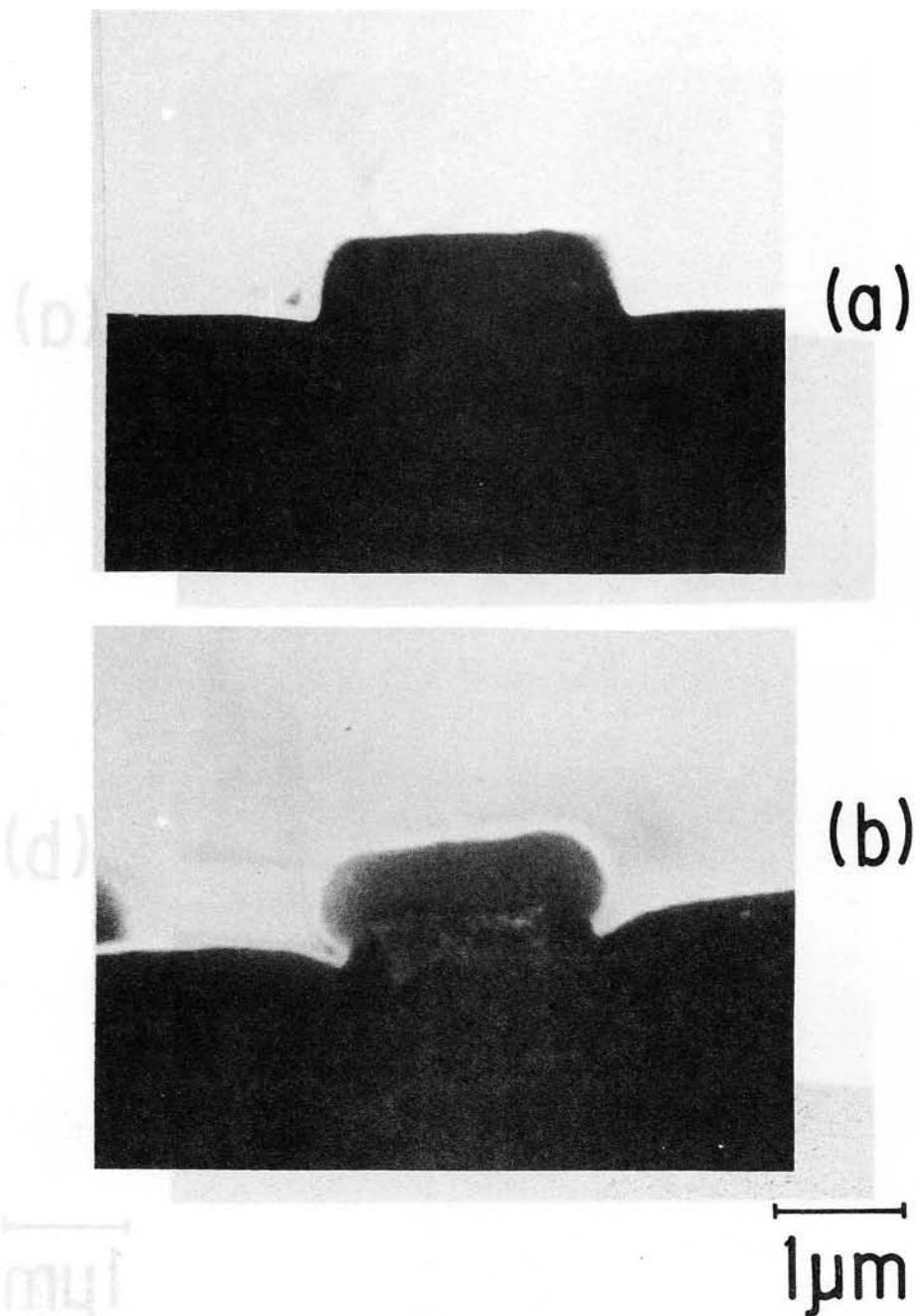

図3-2は、SiO<sub>2</sub>膜のエッチング速度のAr圧依存性を示す。圧力0.40Paでは60nm/分のエッチング速度となる。この値は、最も良質なSiO<sub>2</sub>膜といわれている熱酸化膜に匹敵する。しかし、圧力が臨界Ar圧0.46Pa以上で、エッチング速度は著しく増大し、飽和する。

図3-2 SiO<sub>2</sub>膜のエッチング速度のAr圧依存性

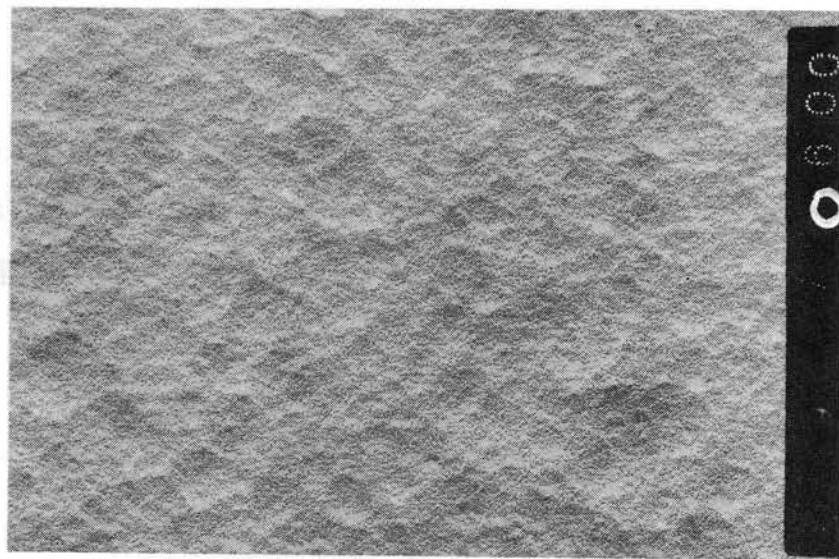

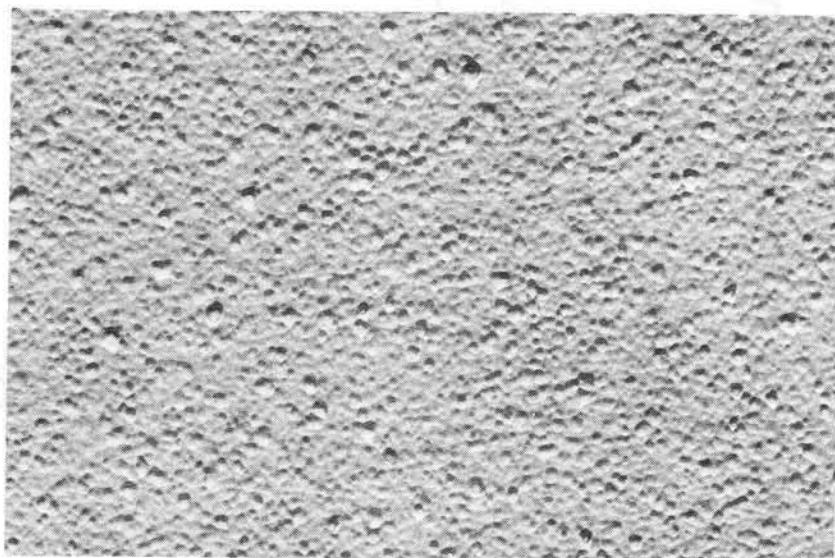

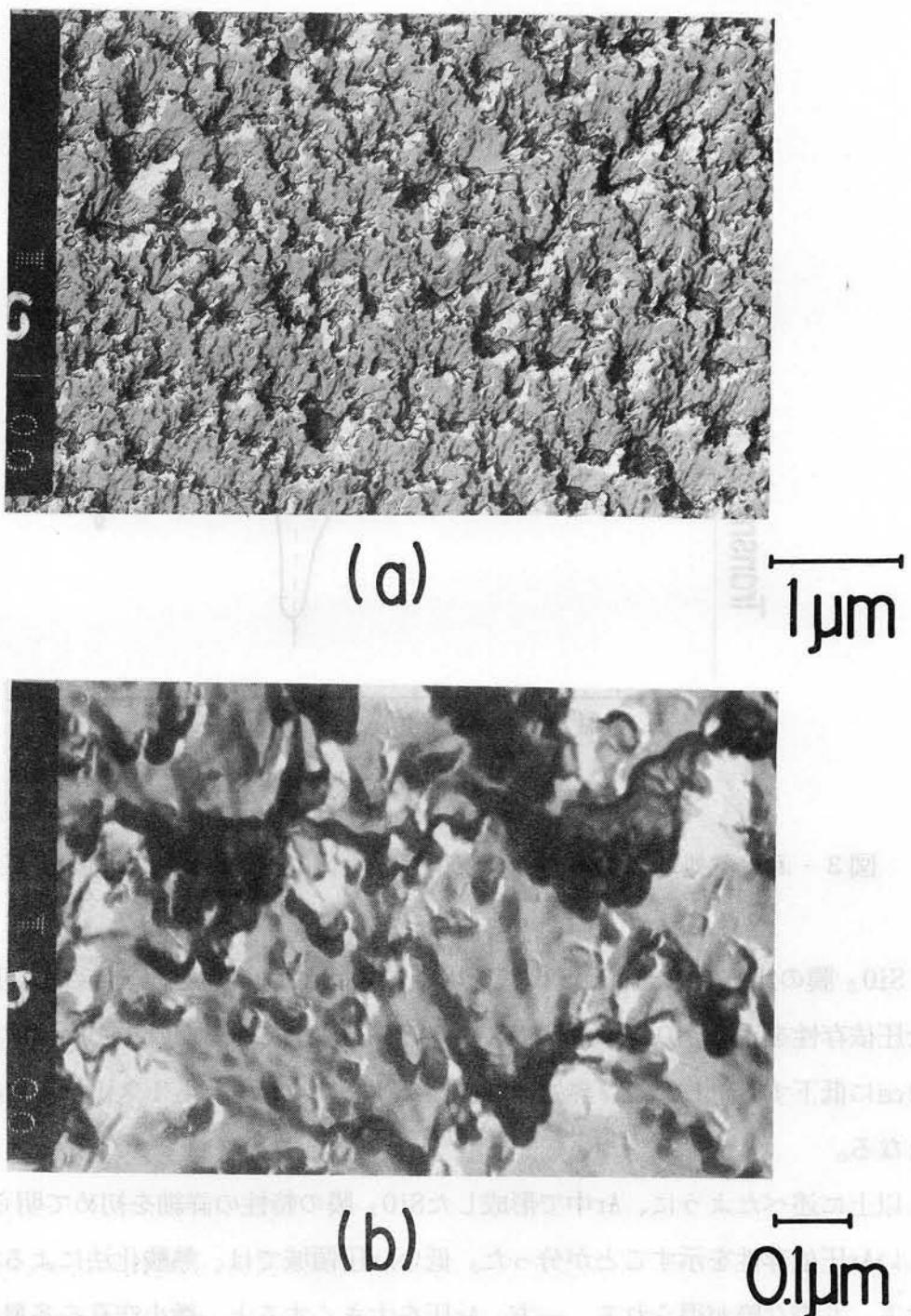

図3-3は、臨界Ar圧0.46Paよりも低いAr圧0.4Pa(a)、および、高いAr圧1.1Pa(b)で形成した、1μmの厚さのSiO<sub>2</sub>膜の、形成後と表面をわずかにエッチングした後における表面状態の電子顕微鏡写真である。圧力の低い膜の表面が高いものよりも平滑である。また、極くわずかにエッチングを施した膜では、直径0.2μm程度の球面状の表面状態を呈している。しかし、Ar圧を高めた膜(b)では、表面の荒れが著しく、鱗状を呈し、数nmの大きさの微小な空孔が多数見られる。Ar圧が0.46Pa、および2.0Paで形成した膜の密度は、2.22 g/cm<sup>3</sup> および、2.10 g/cm<sup>3</sup> であり、Ar圧の増大と共に

As deposited

Slightly etched

1 μm

(a)

図3-3 Ar圧0.4Pa(a)および1.1Pa(b)で形成した膜の形成後、およびスライトエッティング後における電子顕微鏡写真

As deposited

Slightly etched

1 μm

(b)

図3-3 Ar圧: 0.4Pa(a)および1.1Pa(b)で形成した膜の形成後、およびスライトエッチング後における電子顕微鏡写真

小さくなる。Ar圧が低い場合の膜の密度は、熱酸化膜の値  $2.25 \text{ g/cm}^3$  にほぼ等しい<sup>17)</sup>。Ar圧が臨界値以上になると、微小空孔を含む多孔質な膜となり、同図(b)に示す表面状態となる。このように、臨界Ar圧よりも低い圧力領域と高い圧力領域とでは、 $\text{SiO}_2$  膜の特性が著しく異なる。

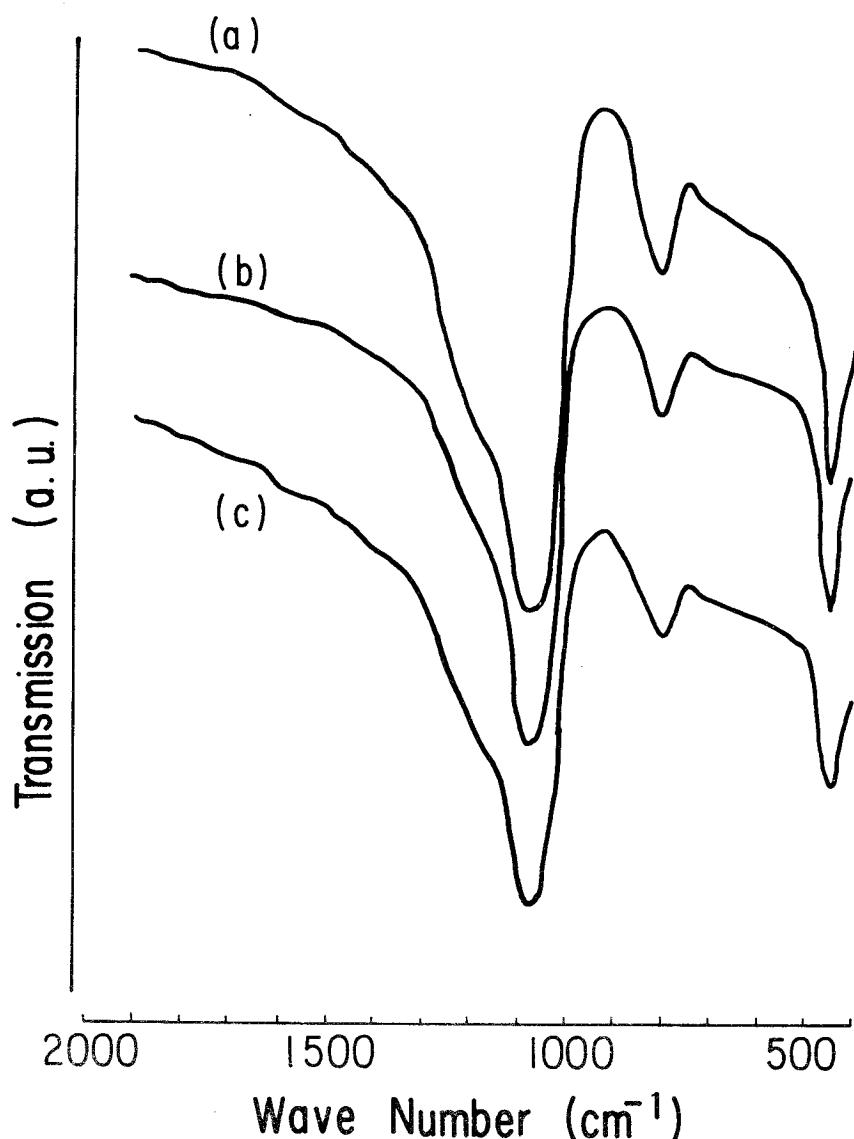

図3-4および図3-5は、異なるAr圧力領域で形成した $\text{SiO}_2$  膜の赤外吸収特性およびオージェ電子分光スペクトルを、熱酸化膜と比較して示す。いずれのAr圧の膜の赤外吸収特性も、熱酸化膜と同様に、 $\text{Si}-\text{O}$ の伸縮運動に基づく $\text{SiO}_2$  膜の吸収ピークが  $1050 \text{ cm}^{-1}$  (波長:  $9.5 \mu\text{m}$ ) と  $800 \text{ cm}^{-1}$  (波長:  $12.5 \mu\text{m}$ ) に現われ、 $\text{Si}_2\text{O}_3$  による

図3-4  $\text{SiO}_2$  膜の赤外吸収特性 (a)Ar :  $0.4\text{Pa}$ , (b)Ar压 :  $1.0\text{Pa}$ , (c)熱酸化膜

図3・5 SiO<sub>2</sub>膜のオージェ電子分光スペクトル (a)Ar圧 : 0.4Pa,(b)Ar圧 : 1.0Pa,(c)

熱酸化膜

吸収ピーク ( $880\text{ cm}^{-1}$ ) やSiOによる吸収ピーク ( $1000\text{ cm}^{-1}$ ) は見られない<sup>18</sup>。さらに、オージェ電子分光スペクトルの間の差もない。これらのこととは、マグネットロンスパッタリング法によりSiO<sub>2</sub>膜が形成できることを示している。Maissel等は、高周波ダイオードスパッタリング法によるSiO<sub>2</sub>膜の組成を調べ、その膜の組成はSiO<sub>x</sub> ( $x \geq 1.9$

4)であることを明らかにしている<sup>19)</sup>。この結果は、マグネットロン方式による本実験結果と矛盾しない。

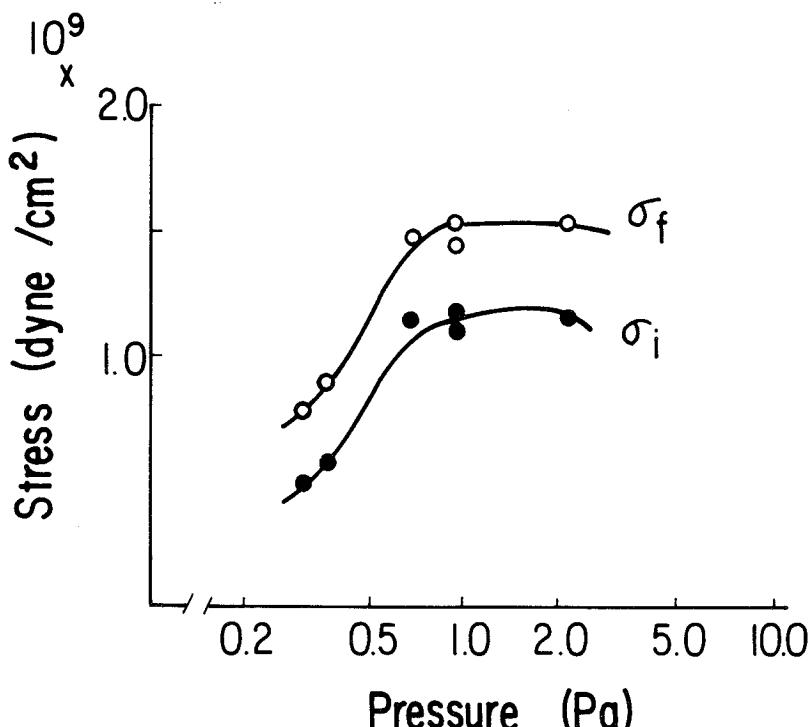

図3-6は、 $\text{SiO}_2$ 膜の応力 $\sigma_f$ と、膜の真性応力 $\sigma_i$ のAr圧による変化である。 $\sigma_f$ および $\sigma_i$ は、前述の式(3-1)、(3-2)および(3-3)を用いて計算した値である。 $\text{SiO}_2$ 膜は、いずれのAr圧でも圧縮応力を示す。さらに、 $\sigma_f$ 、 $\sigma_i$ は、図3-2におけるエッティング特性と同様に、臨界Ar圧0.4~6Pa以上になると急激に大きくなる。この変化は、Ar圧の増大と共に膜中に多量の空孔等の欠陥が形成されるためと考えられる。

図3-6  $\sigma_f$ および $\sigma_i$ のAr圧依存性

$\text{SiO}_2$ 膜を半導体素子に使用する場合、この膜は高温度での熱処理を受けることが多い。900°C 20分間の窒素雰囲気中の熱処理により $\text{SiO}_2$ 膜のエッティング速度を小さくできる。この減少量は、高Ar圧領域で特に著しい。しかし、Ar圧が0.5Pa以上のエッティング速度の異常は残っている。

図3-7(b)は、熱処理を施した $\text{SiO}_2$ 膜の表面を極くわずかにエッティングした後の膜表面の電子顕微鏡写真である。同図(a)の熱処理を施さない場合に比べて滑らかになっている。高Ar圧で見られた鱗状組織も不鮮明となり、さらに、微小空孔は無くなっている。しかし、鱗状組織の痕跡は残っている。

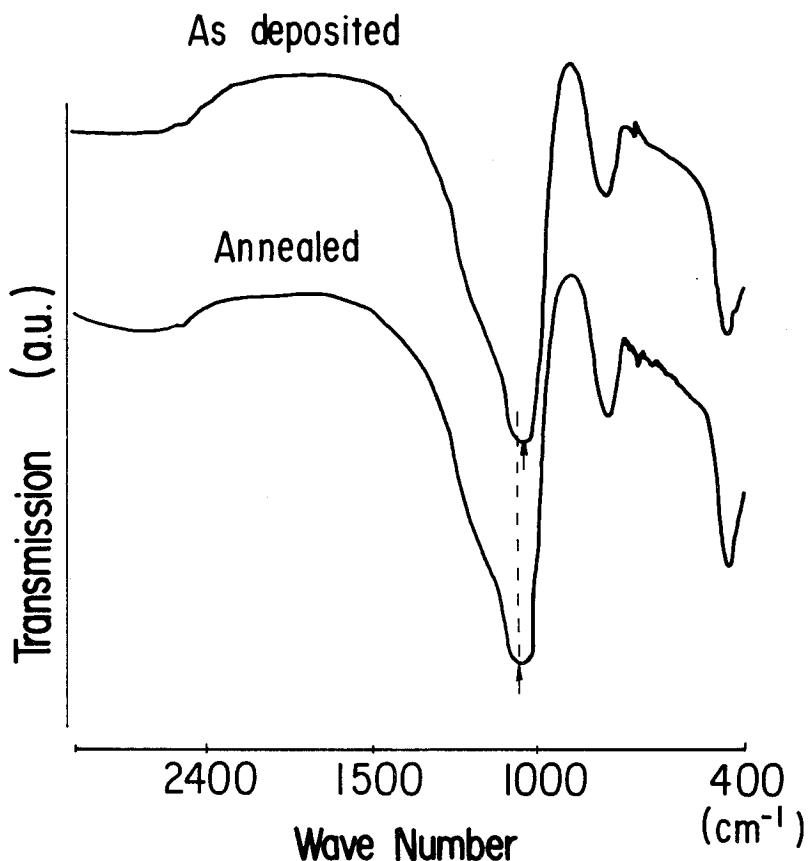

図3-8は、熱処理による赤外吸収特性の変化である。 $\text{Si}-\text{O}$ の伸縮振動に基づく

図3-7 热処理を施した $\text{SiO}_2$ 膜表面の電子顕微鏡写真 (a)热処理前, (b)热処理後

(900°Cで20分間), 膜形成条件: Ar压1.0Pa

$9\ \mu\text{m}$ 帯吸収ピークが、热処理により、 $9.5\ \mu\text{m}$ に移動し、热酸化膜の位置 $9.3\ \mu\text{m}$ に近く。この短波長に移動する原因是、热処理を施すことにより、膜中の微小空孔等の欠陥が減少したためである。

図3-8 热処理による赤外吸収特性の変化 热処理条件は図3-7と同じ

$\text{SiO}_2$  膜の比抵抗を、MOS構造を用いて測定した。热処理を施さない膜の比抵抗は、Ar圧依存性を示し、 $0.4 \text{ Pa}$ では $1 \times 10^{14} \Omega \cdot \text{cm}$ 以上であるが、 $1.1 \text{ Pa}$ にすると $1 \times 10^{13} \Omega \cdot \text{cm}$ に低下する。しかし、热処理を施した膜では、いずれも $1 \times 10^{14} \Omega \cdot \text{cm}$ 以上の比抵抗となる。

以上に述べたように、Ar中で形成した $\text{SiO}_2$  膜の特性の詳細を初めて明らかにでき、著しいAr圧依存性を示すことが分った。低いAr圧領域では、熱酸化法による $\text{SiO}_2$  膜に匹敵する、ち密な膜が得られる。一方、Ar圧を大きくすると、微小空孔を多量に含む、密度の小さな膜となる。

### 3-3-2 膜特性に対する考察

スパッタリング法においては、ターゲット構成原子あるいは分子は、数eVにピークを持つエネルギー分布を有してターゲット表面からスパッタされる。スパッタされた粒子は、Ar原子との衝突を繰り返しながら飛行し、基板に到達する。そのために、ターゲット表面

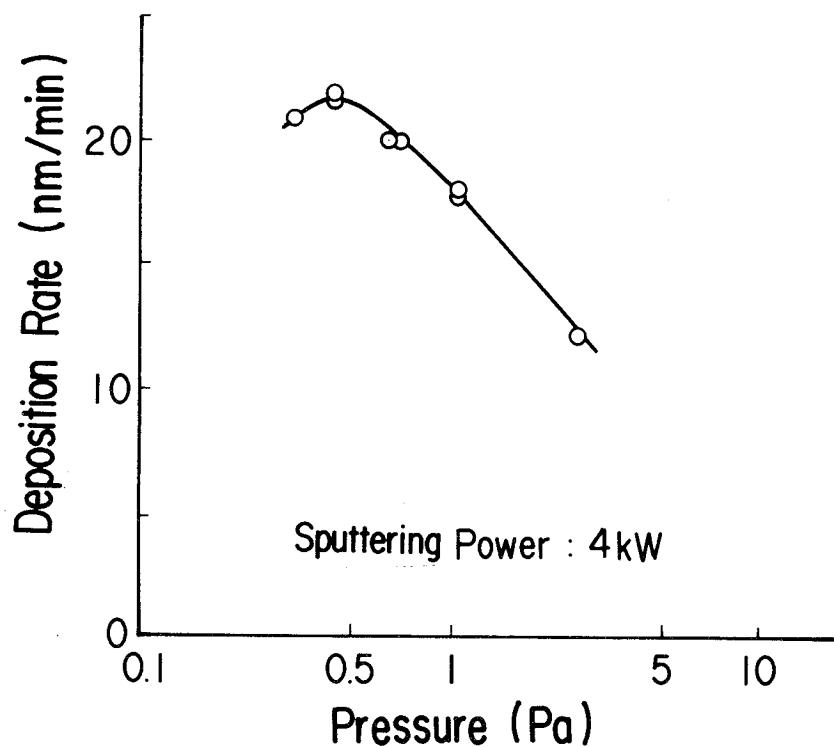

で得たエネルギーと方向を失う。図3-9は、Ar圧による膜形成速度の変化である。膜の

図3-9 膜形成速度のAr依存性 スパッタリング電力：4 kW

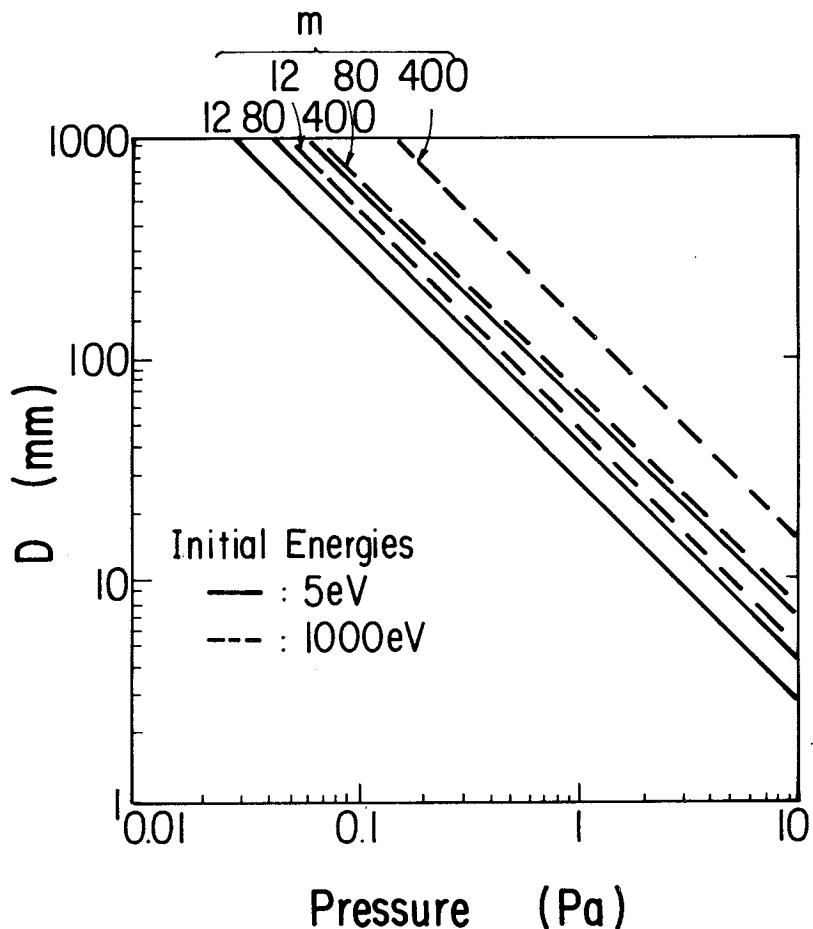

形成速度は、Ar圧の増大に伴い減少する。これは、Ar圧の増大に伴い、衝突回数が増し、スパッタ時の方向性が徐々に失れるからである<sup>20)</sup>。Ar原子との衝突により、スパッタ時のエネルギーを失い、最終的には熱エネルギーとなる。W. D. Westwoodは、スパッタされた粒子が熱エネルギーになるまでの間に飛行する距離D (thermalization distance) を計算している<sup>21)</sup>。図3-10は、このDのAr圧依存性を、スパッタ時のエネルギーとスパッタされた粒子の質量をパラメータとして示してある。スパッタされる粒子としてSiO<sub>2</sub>を仮定し、その初期のエネルギーが5 eVおよび1 0 0 0 eVの場合の、0.46 PaでのDは、6.5 mm、および10.0 mmとなる。このDの値は、ターゲットと基板との間の距離5.0 mmに近い。従って、Ar圧0.46 Pa以上においては、基板表面に到達する粒子は大部分熱エネルギーを有していると考えてよい。さらに、到達粒子の入射角分布には、垂直成分の外に、斜め成分や水平成分が多く混ってくる<sup>22)</sup>。この斜め成分や水平成分を持つ入射粒子は、基板表面や形成されている膜の表面に存在する微小な凹凸により遮られる。さらに、この入射粒子のエネルギーが小さいために、表面拡散や再放出が抑制され、微小な凹凸に遮られた領域は微小な空孔として残る<sup>23)</sup>。このために、図3-3(b)に示すように、微小な空孔を

図3-10 Ar圧と、熱化するまでに飛行する距離Dとの関係

多量に含む $\text{SiO}_2$ 膜となり、この結果、異常に大きなエッチング速度を示す。

ここで述べた、膜特性の顕著なAr圧依存性は、前章での窒化シリコン膜でも観察されている。ただし、エッチング速度が急激に大きくなる臨界Ar圧は1.5 Paと、 $\text{SiO}_2$ 膜での値0.46 Paよりも大きい。これは、窒化シリコン $\text{Si}_3\text{N}_4$ の質量が、 $\text{SiO}_2$ よりも大きく、高Ar圧領域まで、スパッタ時のエネルギーと方向性を保持できるためである。このように、スパッタリング法による膜の特性の顕著なAr圧依存性は、スパッタされた粒子とスパッタリングガス原子との衝突により、初期のエネルギーと方向性が失なわれることによる。低Ar圧領域では良質な膜が、一方、高Ar圧領域では極めて多孔質な膜となる。このことは、ここで述べた以外の膜を、スパッタリング法により形成する場合にも有益である。

### 3-4 Ar-H<sub>2</sub>混合ガス中スパッタリング法による $\text{SiO}_2$ 膜特性の改善

前節では、マグネットロンスパッタリング法により形成した $\text{SiO}_2$ 膜の特性は、Ar圧に

より著しく変化し、ち密な膜から多孔質な膜までが得られることを明らかにした。本節では、この $\text{SiO}_2$  膜をさらに改善する方法を述べる。現在までに明らかにされている改善法としては、バイアス・スパッタリング法と<sup>24)</sup>、スパッタリングガス中に少量の $\text{O}_2$  を混合する方法とが提案されている<sup>25)</sup>。本研究において、スパッタリングガス中に $\text{H}_2$  を混合する、新たな改善法を見い出すことができた。

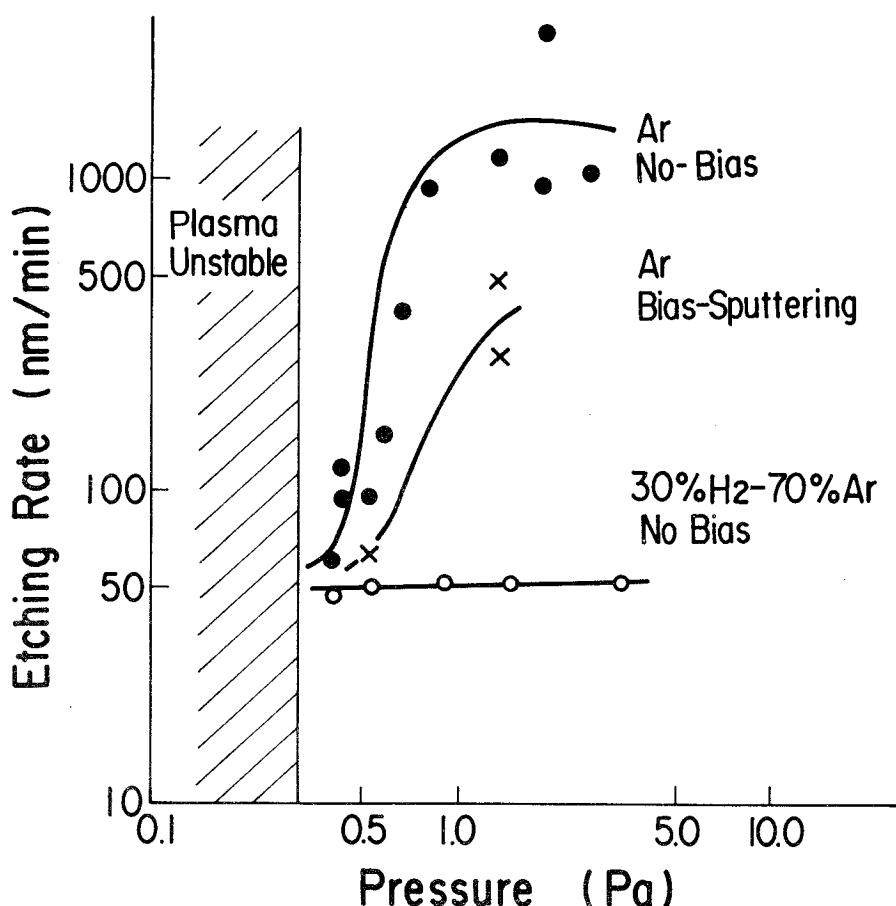

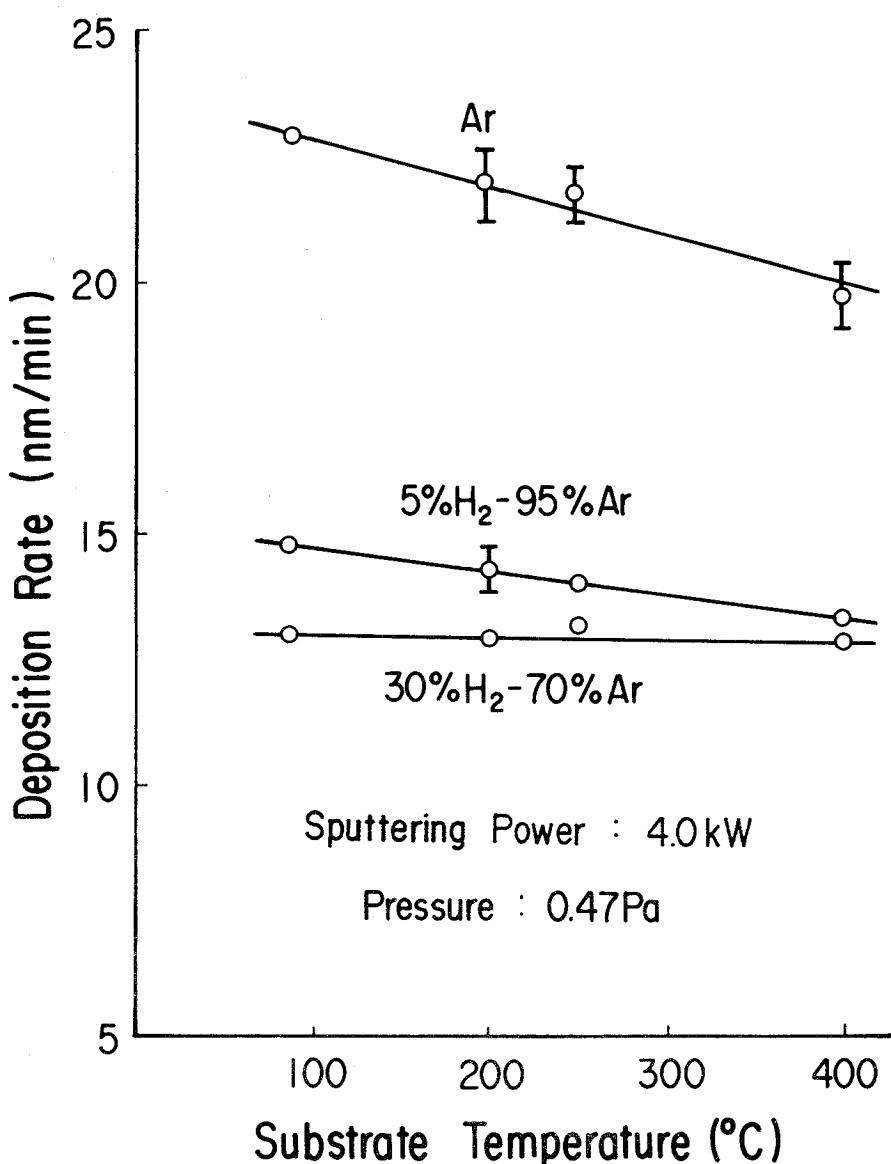

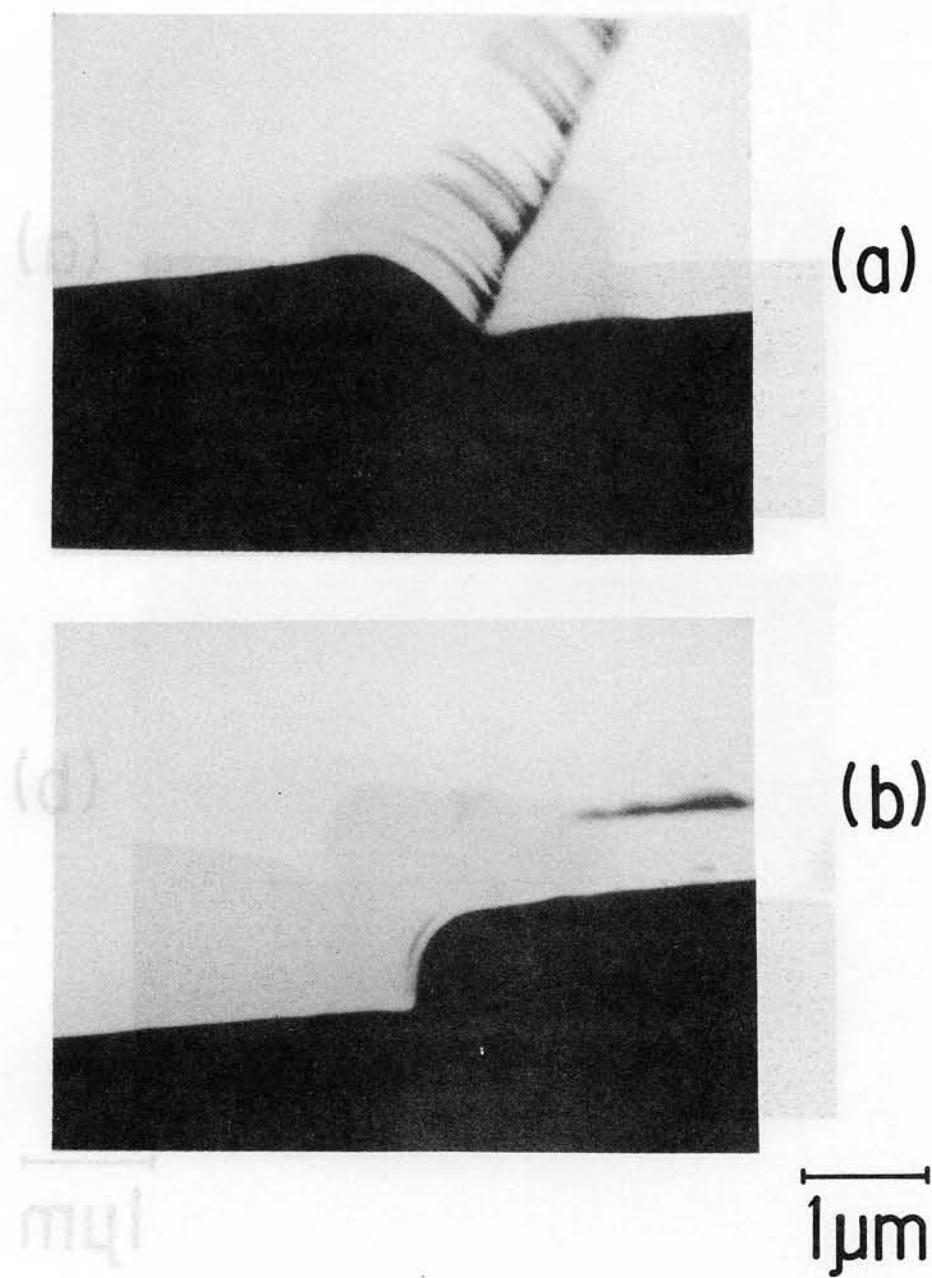

### 3 - 4 - 1 測定結果

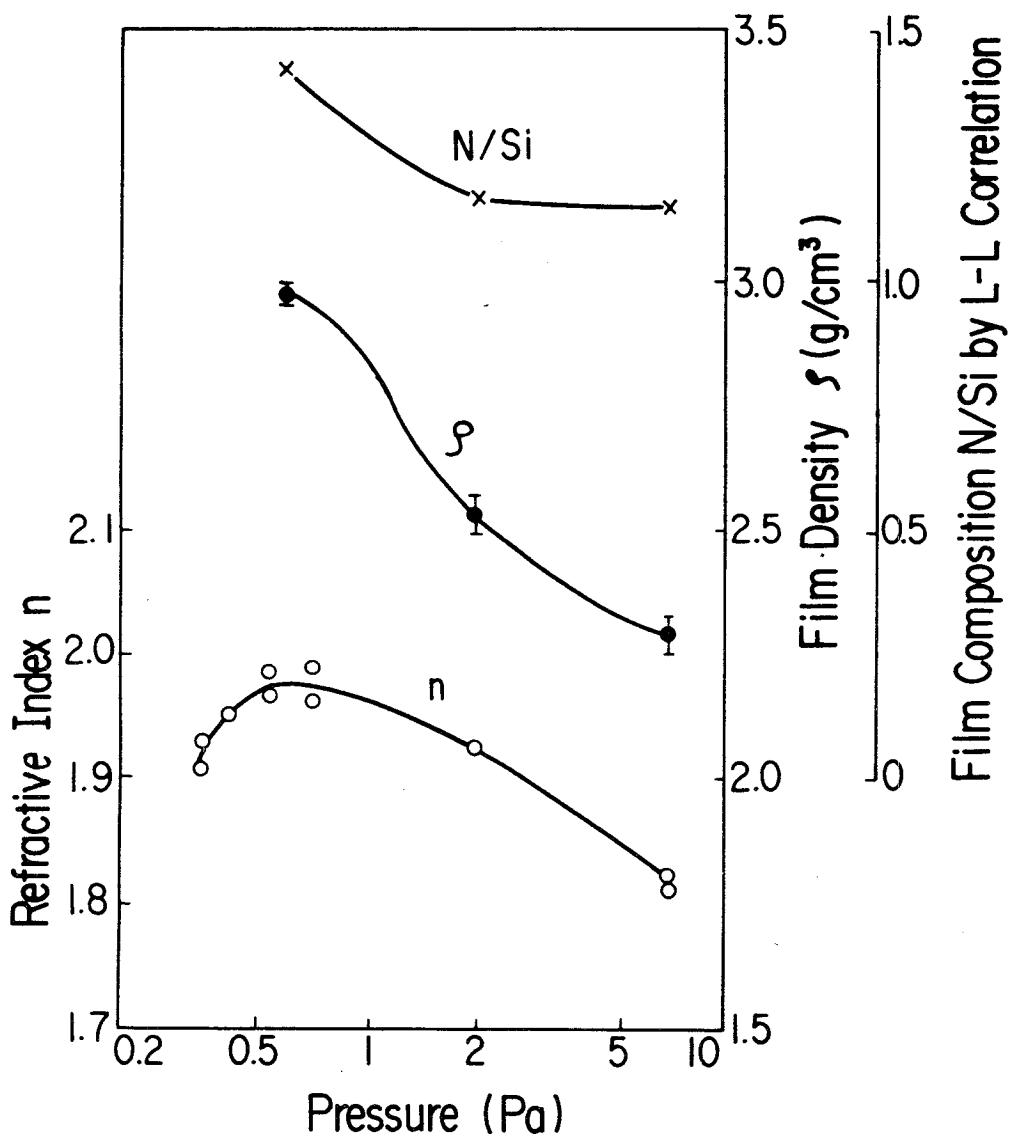

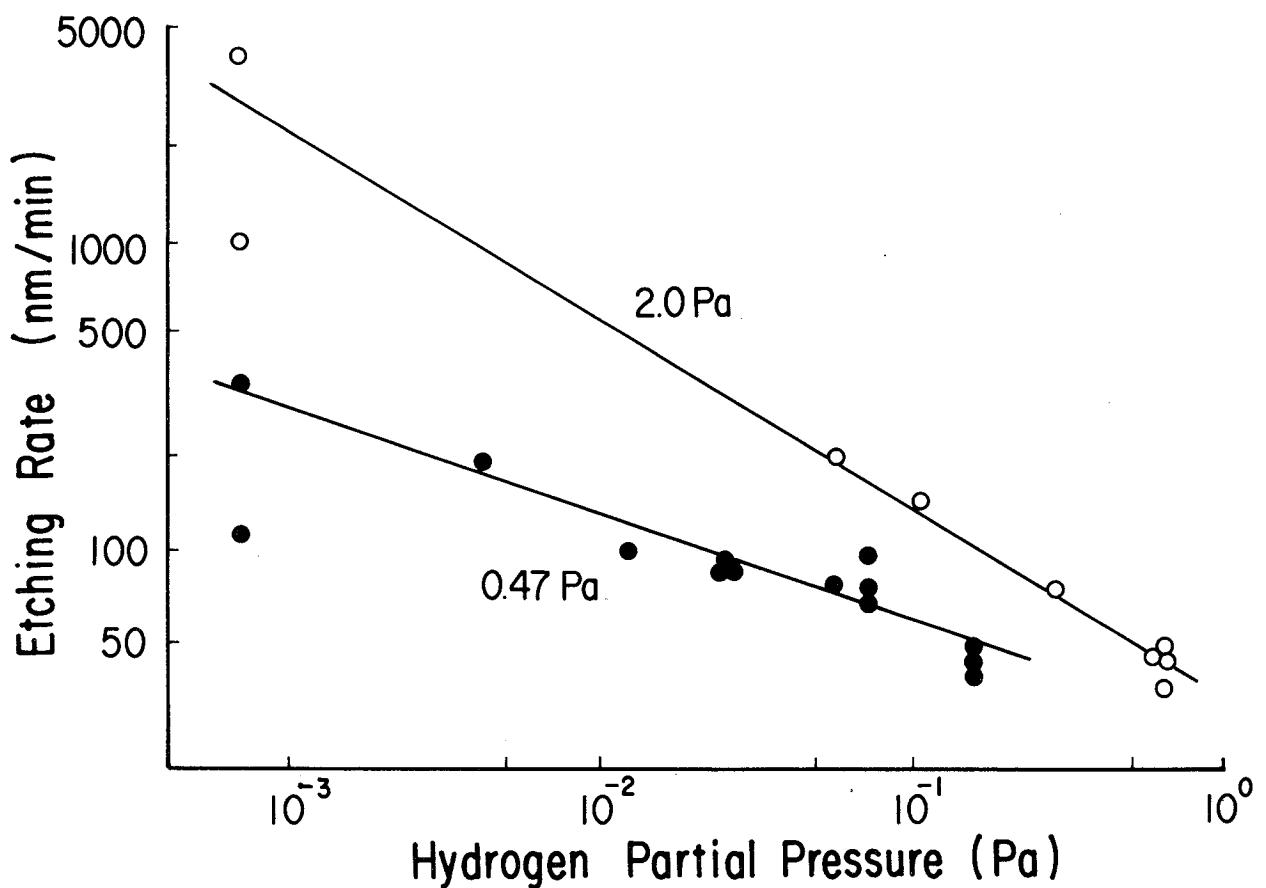

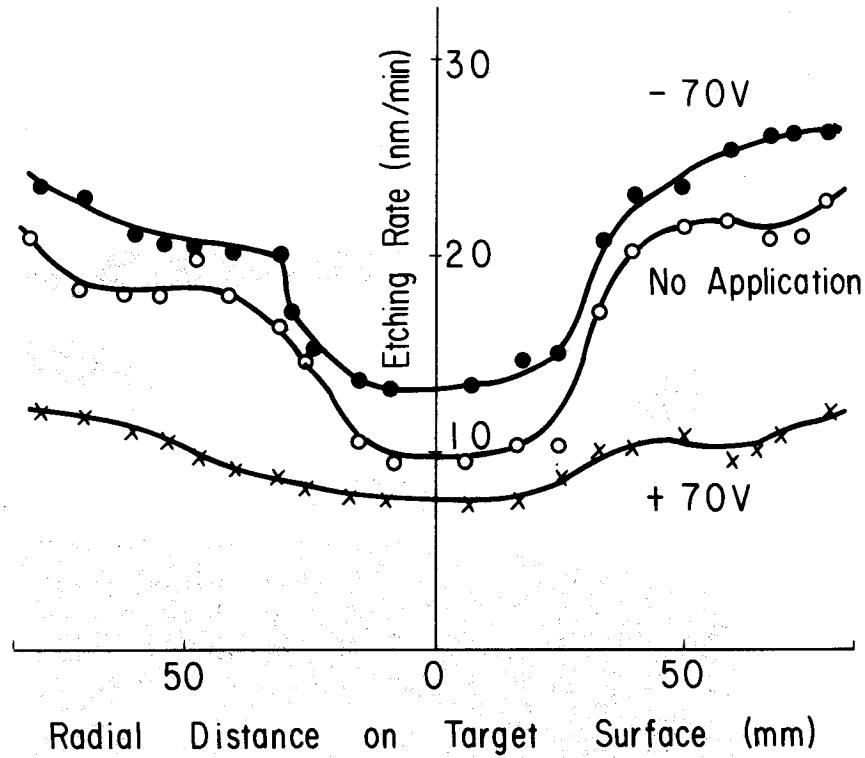

図3-11には、30°C緩衝弗酸溶液によるエッチング速度の、スパッタリングガス圧による変化が示されている。図中には、バイアス・スパッタリング法によるデータを、無バイアス状態でのArおよび30% $\text{H}_2$ -70%Ar混合ガス中の結果と比較して示す。 $\text{H}_2$  混合法は、他の方法に比べて、膜のエッチング速度を小さくでき、さらに、Ar圧依存性を無くすることができる。

図3-11  $\text{H}_2$  混合ガス中で形成した $\text{SiO}_2$  膜のエッチング速度のスパッタリングガス圧依存性

Ar中スパッタリング法では、ち密な膜形成のためのスパッタリングガス圧領域は、Ar圧が0.4~6Pa以下で、かつ、プラズマが安定に形成できる極く狭い領域に限定されている。一方、バイアス・スパッタリング法によって、この圧力領域を0.6Paまで拡大することができても、顕著な圧力依存性は依然として残っている。これらの方法に対して、H<sub>2</sub>混合法では、上記圧力依存性を無くすことができ、さらに、全圧力領域において、熱酸化膜のエッチング速度105nm／分よりも小さな膜が形成できる。H<sub>2</sub>混合法の、SiO<sub>2</sub>膜特性への影響を、以下の各項目にわたり述べる。

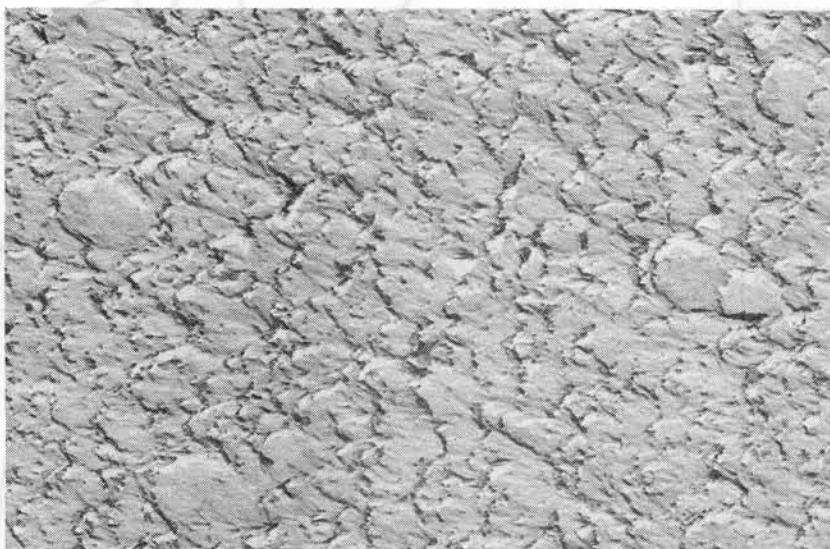

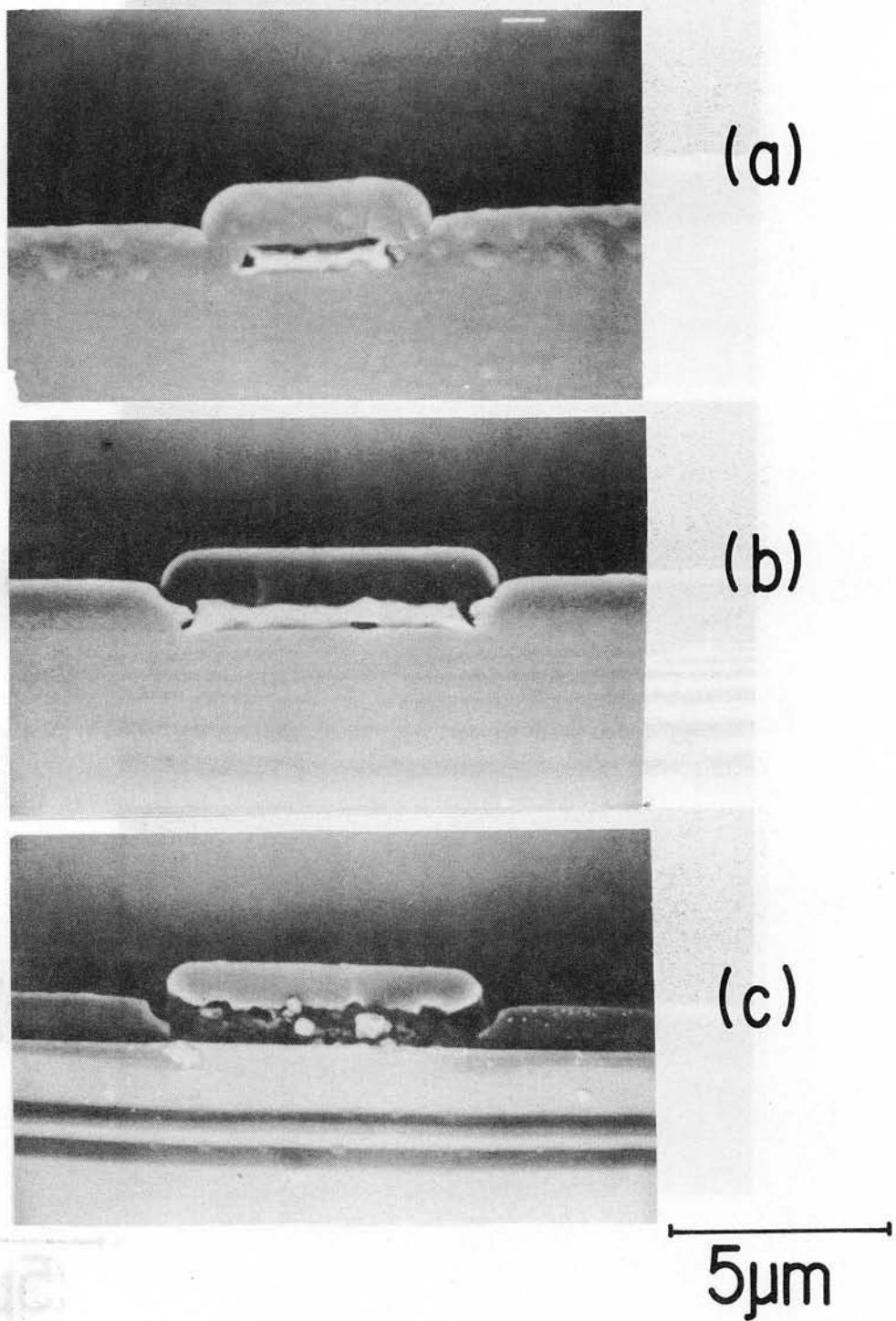

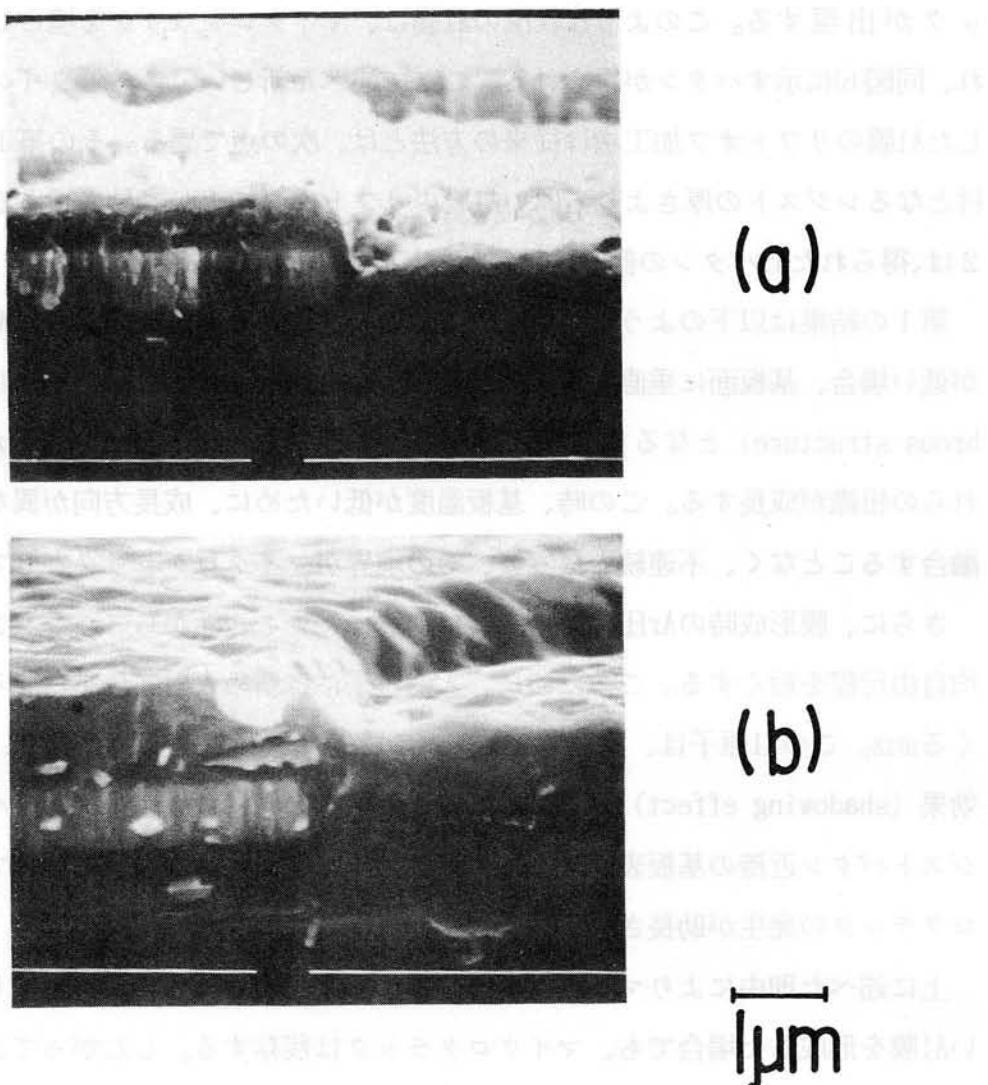

#### (A) エッチング速度、組織および密度

図3-12に、30%H<sub>2</sub>-70%Ar混合ガス中で形成したSiO<sub>2</sub>膜の表面状態のスパッタリングガス圧による変化が、熱酸化SiO<sub>2</sub>膜と比較して示してある。同図(a)および(b)は、圧力0.47Paおよび1.0Paで形成した膜であり、(c)は熱酸化法によるものである。いずれの試料も、30°Cの緩衝弗酸溶液に数秒間浸した後のものである。H<sub>2</sub>を混合すると、Arだけの場合に見られた、表面荒れや微小空孔(図3-3)は無くなり、スパッタリングガス圧が高い場合(同図(b))でも、極めて平滑となる。さらに、H<sub>2</sub>を混合した膜は、熱酸化法により形成した膜(同図(c))よりも平滑になっている。一方、膜の密度は、Arの場合、スパッタリングガス圧が0.47Paから2.0Paに変化するに伴い、2.22g/cm<sup>3</sup>から2.11g/cm<sup>3</sup>に減少する。しかしながら、30%H<sub>2</sub>-70%Ar混合ガスの場合には、全スパッタリングガス圧において、2.33g/cm<sup>3</sup>と、Arの場合は勿論のこと、熱酸化SiO<sub>2</sub>膜の値2.25g/cm<sup>3</sup>よりも大きくなる。このように、H<sub>2</sub>を混合すると、膜中における微小空孔は除去され、著しく膜のち密化が図れる。

図3-13は、H<sub>2</sub>分圧によるエッチング速度の変化である。H<sub>2</sub>分圧の増大に伴い、エッチング速度は徐々に小さくなる。図3-14は、H<sub>2</sub>濃度によるSiO<sub>2</sub>膜表面状態の変化である。H<sub>2</sub>濃度が0.8%でも、Arだけの場合に存在した微小空孔は無くなっている。しかし、表面凹凸の痕跡は残っている。H<sub>2</sub>濃度を5%に増加すると、この痕跡も消えて極めて平滑な表面となり、この時のエッチング速度は105nm／分と、小さくなる。

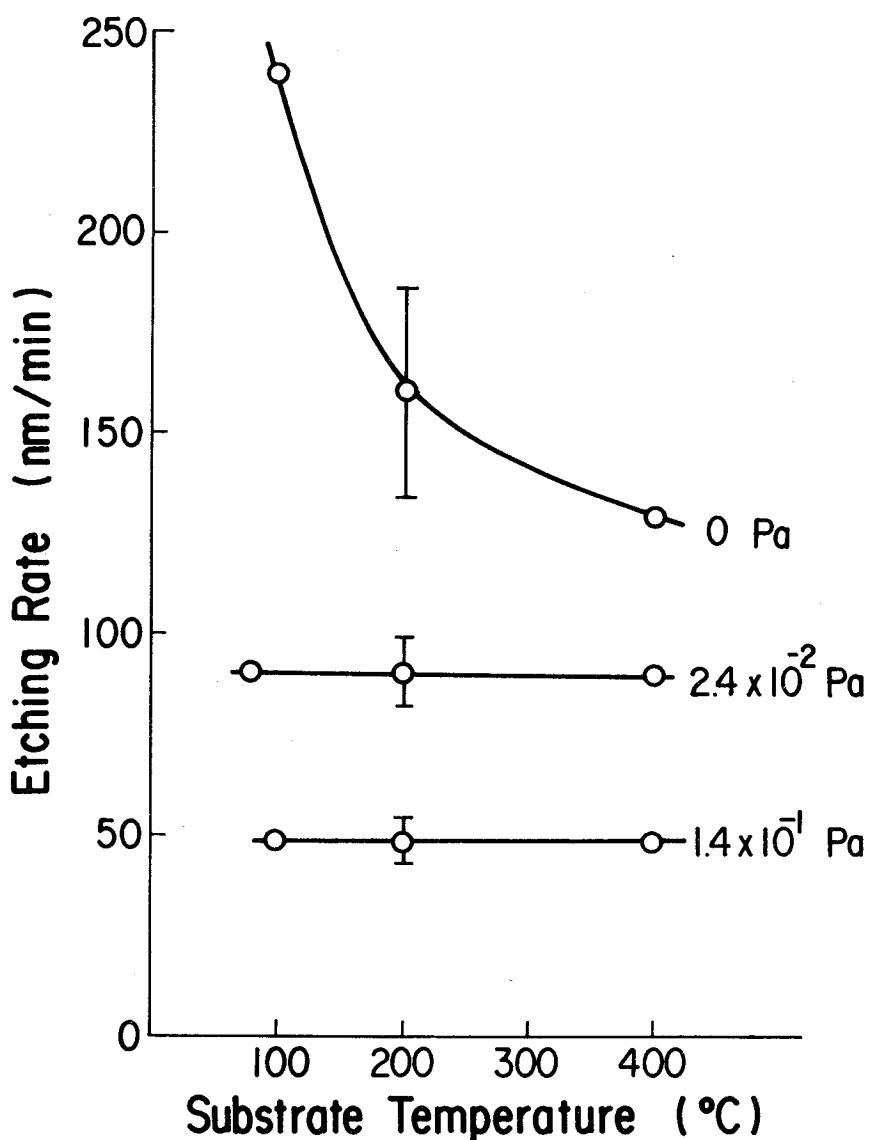

図3-15は、H<sub>2</sub>混合ガス中で形成したSiO<sub>2</sub>膜のエッチング速度の基板温度依存性である。パラメータはH<sub>2</sub>混合量である。Ar単独の場合には顕著な基板温度依存性を示す。しかし、H<sub>2</sub>を5%以上混合すると、エッチング速度を小さくでき、さらに、この依存性が無くなる。

(a)

0.1μm

(b)

0.1μm

(c)

0.1μm

図3-12 H<sub>2</sub>混合ガス中で形成したSiO<sub>2</sub>膜表面の電子顕微鏡写真

(a)30%H<sub>2</sub>-70%Ar混合ガス, 0.47Pa, (b)30%H<sub>2</sub>-70%Ar混合ガス, 1.0Pa, (c)熱酸化法によるSiO<sub>2</sub>膜

図3-13 H<sub>2</sub> 分圧によるエッチング速度の変化

#### (B) 赤外吸収特性、オージェ電子分光分析、および、二次イオン質量分析

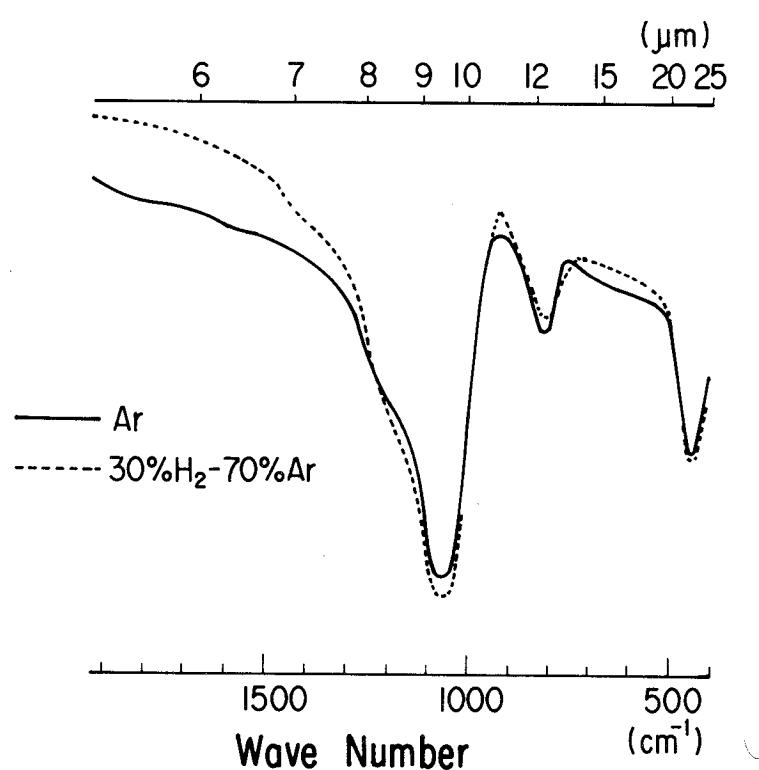

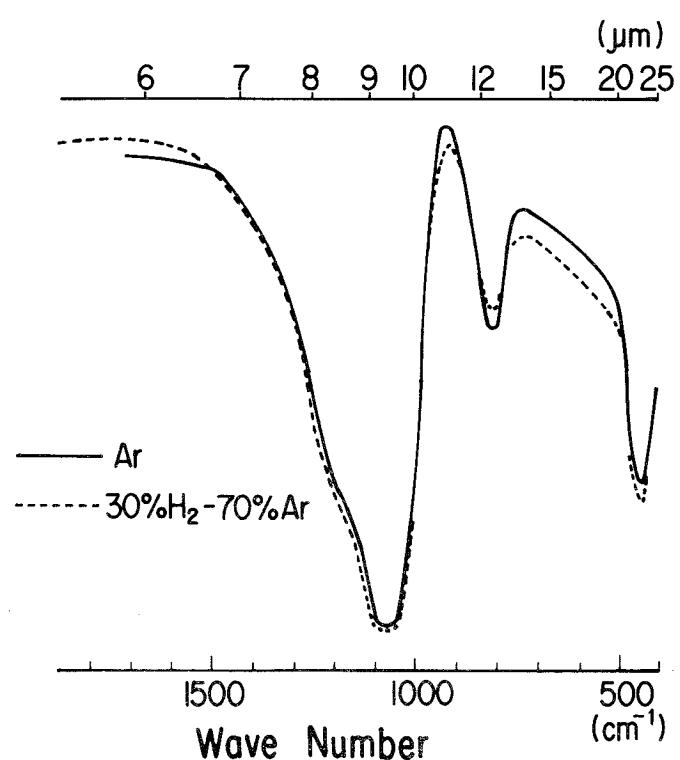

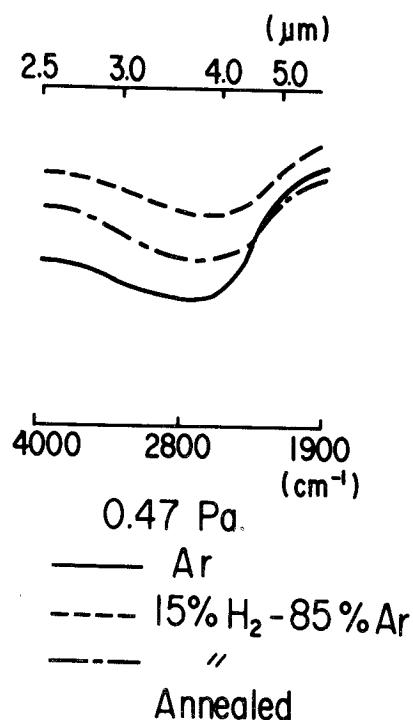

図3-16は、本方法による膜の赤外吸収特性である。H<sub>2</sub>を混合しても、SiO<sub>2</sub>特有のピーク（1080 cm<sup>-1</sup>と800 cm<sup>-1</sup>近傍のピーク）のみが現われ、Si<sub>2</sub>O<sub>3</sub>やSiOによる吸収ピークは認められない<sup>18</sup>。また、1080 cm<sup>-1</sup>でのピークの位置および半値幅共に、Arだけの場合と大差はない。

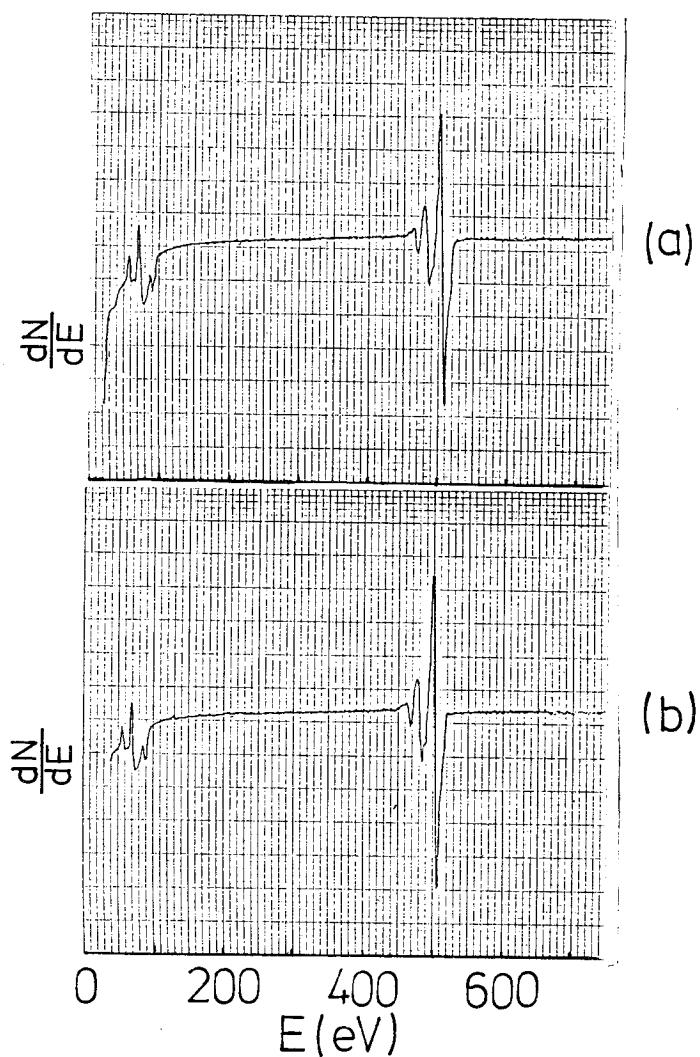

図3-17は、水素混合ガス中で形成した膜の、オージェ電子分光法によるオージェスペクトルである。試料は表面を極くわずかイオンエッチング法により除去してある。いずれのデータも、SiO<sub>2</sub>によるSiおよびOのオージェピークが78 eVおよび500 eVに現れ、金属Siによる92 eVでのピークは見られない<sup>26</sup>。また、SiとOのピークの高さの比 I<sub>Si</sub>/I<sub>O</sub>は、熱酸化SiO<sub>2</sub>膜では0.25である（図3-5(c)）。これに対して、H<sub>2</sub>混合法による膜のピークの高さの比は、0.47 Paでは0.22であり、2.0 Paでは0.27と、熱酸化法によるSiO<sub>2</sub>膜と大差はない。このように、オージェ電子分光法による結果も、

図3-14 H<sub>2</sub>濃度によるSiO<sub>2</sub>膜表面状態の変化 (a)0.8%, (b)5% スパッタリング

図3-15 エッティング速度の基板温度による変化 スパッタリングガス圧: 0.47Pa

H<sub>2</sub> 混合法によるSiO<sub>2</sub> 膜の組成変化がないことを示している。

表3-1には、二次イオン質量分析法 (S I M S) によるH<sub>2</sub> 含有量の分析結果を、純Ar中で形成した膜の結果と比較して示す。H单独では勿論のこと、SiHやOHとしての含有量も、純Arの場合と大差ない。すなわち、H<sub>2</sub> 混合ガス中で形成したSiO<sub>2</sub> 膜中へのH<sub>2</sub> 含有量は少ない。

さらに、SiO<sub>2</sub> 膜中の水素の含有状態を知るために、波数4000～2000cm<sup>-1</sup> の範囲の赤外吸収特性を調べた。その結果を図3-18に示す。いずれのデータも、膜形成後あるいは熱処理後、湿度50%の室温に約1週間放置したものである。Arだけの場合に

図3-16 30% $\text{H}_2$ -70%Ar混合ガス中で形成した $\text{SiO}_2$ 膜の赤外吸収特性 (a)0.47Pa

図3-16 30% $\text{H}_2$ -70%Ar混合ガス中で形成した $\text{SiO}_2$ 膜の赤外吸収特性 (b)2.0Pa

図3-17 30%H<sub>2</sub>-70%Ar混合ガス中で形成したSiO<sub>2</sub>膜のオージェ電子分光スペクトル

ル (a)0.47Pa, (b)2.0Pa

表3-1 水素関連二次イオンのSIMSによる測定結果

| 試料製作条件                                  | I <sup>1</sup> H <sup>+</sup> /I <sup>28</sup> Si <sup>+</sup> | I <sup>17</sup> (OH) <sup>+</sup> /I <sup>16</sup> O <sup>+</sup> | I <sup>29</sup> M <sup>+</sup> /I <sup>28</sup> Si <sup>+</sup> |

|-----------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------|

| 30%H <sub>2</sub> -70%混合ガス中形成、<br>200°C | 5.0~5.4×10 <sup>-3</sup>                                       | 2.7~3.0×10 <sup>-2</sup>                                          | 5.5×10 <sup>-2</sup>                                            |

| Ar中形成、200°C                             | 4.5×10 <sup>-3</sup>                                           | 3.3~3.4×10 <sup>-2</sup>                                          | 5.2×10 <sup>-2</sup>                                            |

注1) M = <sup>29</sup>Si + <sup>28</sup>(<sup>28</sup>SiH)

2) (i) 1次イオンビーム : Ar<sup>+</sup> 10 kV 1.2 μA (110 μmφ)

(ii) 試料室真空度 : 5.3×10<sup>-5</sup> Pa

比べて、 $\text{SiOH}$  ( $3650\text{cm}^{-1}$ ) や  $\text{H}_2\text{O}$  ( $3330\text{cm}^{-1}$ ) による吸収は少なく<sup>18</sup>、 $\text{H}_2$  混合ガス中形成膜の水素含有量は小さい。これは、 $\text{H}_2$  混合ガス中形成膜は、著しくち密であるために、大気に晒した時の外部からの水分の貫通が阻止されるためと考えられる。一方、本  $\text{SiO}_2$  膜を熱処理しても、水素の含有量の変化は小さい。この原因は、膜形成直後における膜が十分にち密であるために、その後に施される熱処理によるち密化作用があまり有効に作用しないからと考える。このように、 $\text{H}_2$  混合ガス中スパッタリング法による  $\text{SiO}_2$  膜中への水素含有量を小さく押えることができる。

図3-18 波数 $4000\sim2000\text{cm}^{-1}$ での赤外吸収特性

### (C) 膜の形成速度と均一性

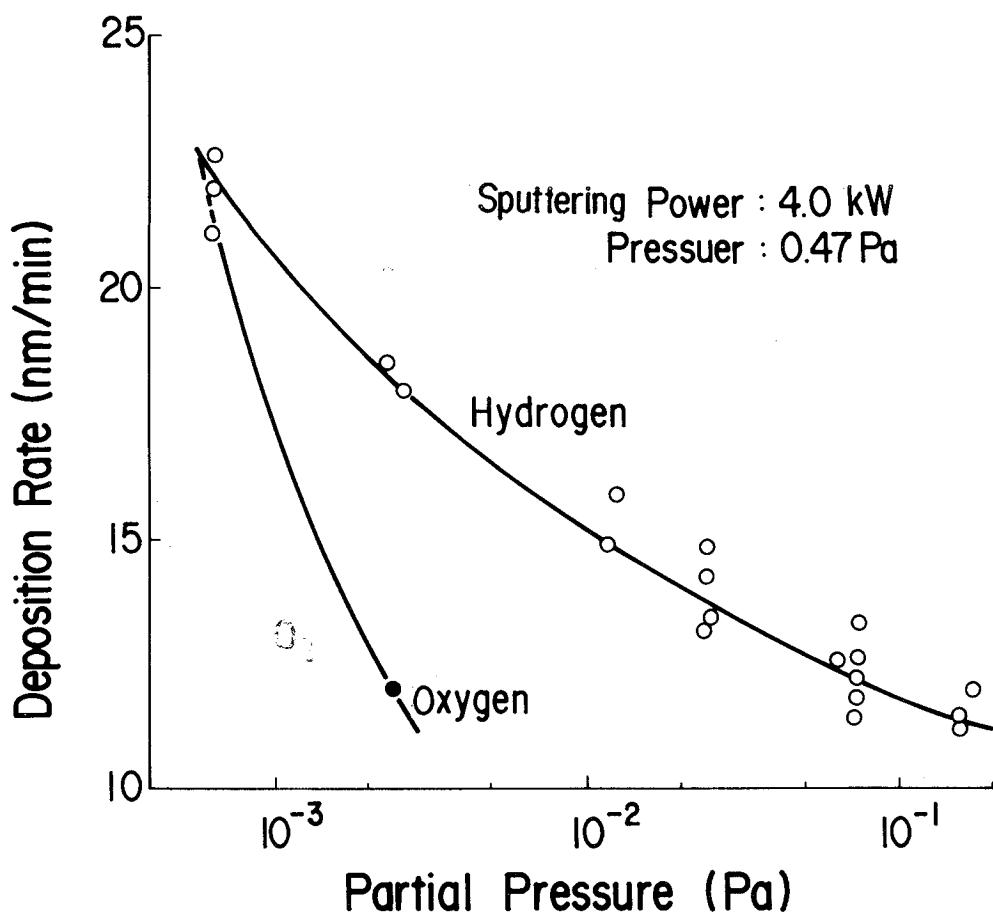

図3-19は、 $\text{H}_2$  分圧による  $\text{SiO}_2$  膜の形成速度の変化を示す。同図には、 $\text{SiO}_2$  膜の膜特性を改善する目的で広く行われている、 $\text{Ar}-\text{O}_2$  混合法における結果を比較してある。 $\text{H}_2$  分圧の増大に伴い、膜の形成速度は減少する。 $\text{H}_2$  分圧が  $2.3 \times 10^{-2}\text{Pa}$  (5% 混合) および  $1.4 \times 10^{-1}\text{Pa}$  (30% 混合) の時の減少率は、18% および 48% である。これに対して、酸素  $\text{O}_2$  の場合は、分圧  $2.3 \times 10^{-2}\text{Pa}$  (5% 混合) においても、すでに 45% に達する。このように、膜形成速度の面からも、本方法は、従来から広く用いられている  $\text{O}_2$  混合法よりもすぐれている。

図3-19 H<sub>2</sub> 分圧による膜形成速度の変化 スパッタリング電力：4 kW

(ターゲット2個),スパッタリングガス圧：0.47Pa

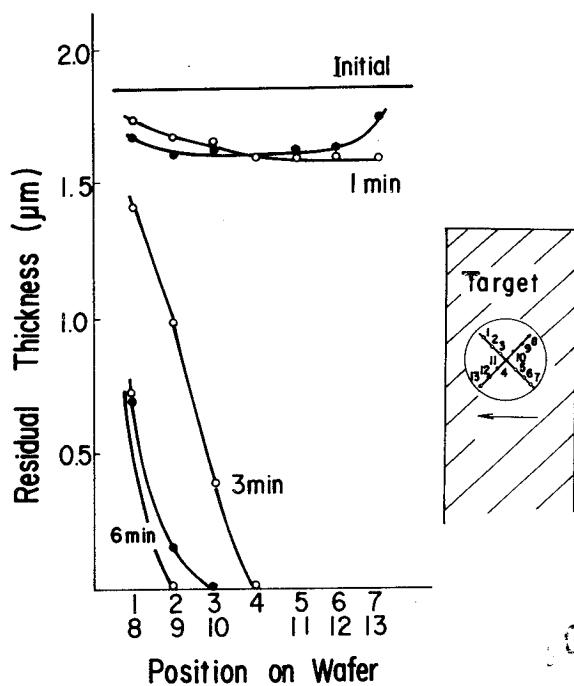

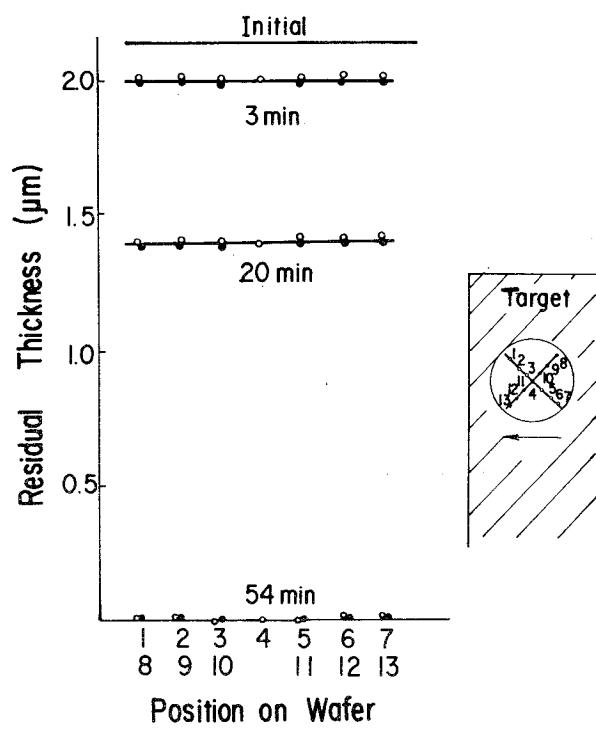

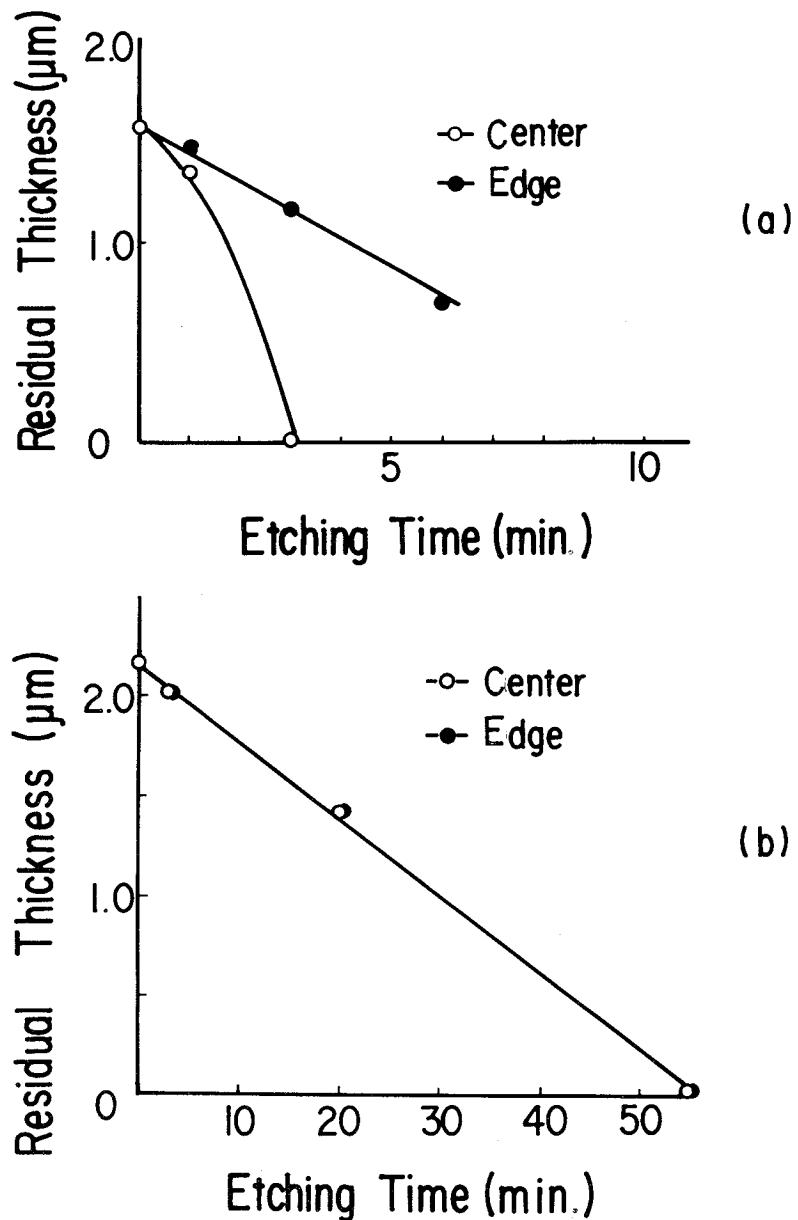

図3-20は、3インチ基板上における、エッチング時間による残留膜厚の分布の変化である。図中に示した図は、測定した位置を、また、図中の矢印は、ターゲットに対する基板の運動方向を示す。Ar単独の場合(a)、残留膜厚は不均一であり、基板下部ではエッチング速度の大きな膜となっている。これに対して、H<sub>2</sub>を30%混合した膜(b)では、基板全面にわたって極めて均一である。

図3-21は、エッチング時間による残留膜厚の変化である。図には、基板中央部(図3-20における位置4)と基板端部(図3-20における位置1)での変化が示してある。Ar単独の場合(a)、残留膜厚は、エッチング時間と共に線型には減少しない。これは、SiO<sub>2</sub>膜の特性が厚さ方向でも不均一となっているためである。これに対して、Ar-H<sub>2</sub>混合法(b)では、残留膜厚は、エッチング時間と共に線型に減少し、また、その減少速度の基板内分布も非常に均一である。

図3-20 エッチング時間による残留膜厚の分布の変化 (a)Ar

図3-20 エッチング時間による残留膜厚の分布の変化 (b)30%  $\text{H}_2$  - 70% Ar

図3-21 エッチング時間による残留膜厚の変化 (a)Ar, (b)30%  $\text{H}_2$  - 70% Ar

本研究に用いたスパッタリング装置では、図3-1に示したように、膜形成途中、基板支持台は回転している。膜表面は、ターゲット前面に発生したプラズマの照射を受ける。さらに、この照射が断続的に行なわれる。このために、基板の上下、左右で異なる膜組織となり、特性の不均一性が生じる。しかし、 $\text{H}_2$ を混合すると、微小空孔等の欠陥が除去でき、膜の著しい密化が図れるため、基板面だけでなく、厚さ方向の特性が著しく均一となる。このように、Ar- $\text{H}_2$ 混合法は、膜特性の著しい均一化が図るために、半導体素子製造歩留りの向上が図れる利点を有している。

以上に述べたように、スパッタリングガス中にH<sub>2</sub>を混合すると、低基板温度において、極めてち密なSiO<sub>2</sub>膜が形成できることを明らかにした。さらにこのすぐれたSiO<sub>2</sub>膜を、基板全面にわたり均一に形成できることも分った。

### 3 - 4 - 2 H<sub>2</sub> 混合効果の考察

スパッタリング法によるSiO<sub>2</sub>膜の特性については、L. I. Maissel等が詳細に調べている<sup>27)</sup>。彼等は、不適正なスパッタリング条件の下では、SiO<sub>2</sub>膜中にピンホール（本研究における微小空孔に相当すると考えられる）が形成され、このピンホールが膜の特性を損うことを指摘している。このピンホールの形成は、基板上に到達したSiO<sub>2</sub>が再び基板から放出される、再放出効果（re-emission）に原因している。すなわち、再放出効果が著しいと、堆積したSiO<sub>2</sub>とルーズに結合したSiO<sub>2</sub>は、基板表面から容易に放出され、ピンホールが少なく、ち密な膜となる。反対に、基板温度が低いなどの理由で、再放出効果が小さい場合には、ルーズな結合状態で膜が形成され、その結果、ピンホールが形成される。さらに、純Ar中における再放出係数R. E.（入射粒子数に対する再放出粒子数の割合）を測定し、基板温度T(°C)との間に、次の関係式が成り立つことを明らかにした<sup>27)</sup>。

$$R. E. = 0.2 + 0.00058 T \quad \dots \quad (3-1)$$

本研究においても、再放出係数を測定した。図3-22は、基板温度T(°C)によるSiO<sub>2</sub>膜の形成速度の変化である。基板温度の上昇に伴い膜形成速度は線型的に減少する。この関係から、Ar中ならびに5%H<sub>2</sub>混合ガス中の再放出係数R. E.の基板温度T(°C)依存性を求めるとき、次式となる。

$$R. E. (\text{Ar中}) = 0.12 + 0.00044 T \quad \dots \quad (3-2)$$

および

$$R. E. (5\%H_2 \text{混合ガス中}) = 0.08 + 0.00029 T \quad \dots \quad (3-3)$$

Ar中での値（3-2）は、ダイオードスパッタリングにおける値（3-1）にはほぼ等しい。H<sub>2</sub>を混合すると、（3-3）に示すように、小さなR. E.となる。さらに同図には、30%H<sub>2</sub>混合の場合のデータが示されている。膜の形成速度の基板温度依存性はほとんど無くなり、R. E.はさらに小さくなる。

図3-15に示したように、Ar中で形成したSiO<sub>2</sub>膜のエッチング速度は、基板温度に著しく依存する。これはMaissel等が主張するように、基板温度と共に再放出係数が大き

くなり、その結果、膜中の欠陥が減少したためである。しかしながら、 $H_2$ を混合する方法では、再放出係数が小さいにもかかわらず、膜特性が著しく改善されている。このことから、 $H_2$ 混合による $SiO_2$ 膜のち密化作用は、再放出効果によるのではなく、他の理由によると考える。

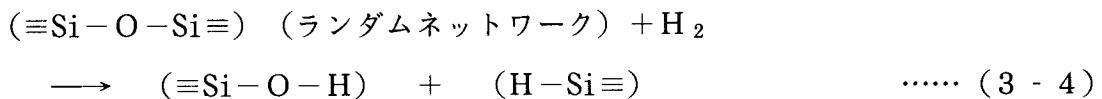

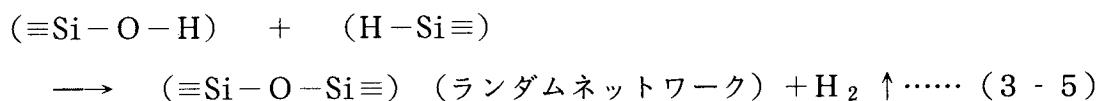

水素原子は、SiやO原子と水素化結合し、それらの活性度を減じる作用があることは広く知られている<sup>28)</sup>。ここでは、この水素化結合に基づく、ち密化の機構を提案し、考察する。

ターゲット表面から叩き出され、基板上に堆積した $SiO_2$ は、SiとOとがランダムネットワークを形成し、アモルファス状態の膜となる。スペッタリングガス中に水素を混合す

図3-22 基板温度による膜形成速度の変化

ると、この水素はイオン化されたり励起され、高エネルギーを有して膜表面に衝突する。この際、次式（3-4）で示すように、上記ランダムネットワークの結合（bond）が破壊され、水素化結合する。

ランダムネットワークの結合の破壊と水素化結合の結果、 $(\equiv \text{Si}-\text{O}-\text{H})$  や  $(\text{H}-\text{Si}\equiv)$  の膜表面での拡散が容易となる。拡散が容易となった  $(\equiv \text{Si}-\text{O}-\text{H})$  や  $(\text{H}-\text{Si}\equiv)$  は、膜表面における微小窪みや結合の弱い位置において、次式（3-5）に示すように、再度ランダムネットワークを形成し、 $\text{SiO}_2$  となる。

この際に水素は、再び、スパッタリングガス中に放出される。この結果、膜はち密となり、エッチング速度が小さく、さらに、極めて均一な表面の $\text{SiO}_2$  膜が得られる。さらにこの $\text{SiO}_2$  膜中への H の含有も小さく押えることができる。

グロー放電を利用するスパッタリング法においては、膜表面だけでなく、ターゲットの表面にも高エネルギーの水素が衝突する。この結果、ターゲット表面においても、式（3-4）と同様な水素化結合が起ると考えられる。水素化結合した  $(\equiv \text{Si}-\text{O}-\text{H})$  や  $(\text{H}-\text{Si}\equiv)$  がターゲット表面から叩き出されて基板表面に到達し、式（3-5）に従ってち密な $\text{SiO}_2$  膜が形成される過程も、同時に起っていると思われる。

上記の水素化反応や表面拡散に必要なエネルギーは、プラズマから容易に得られる。このために、図3-15に示したように、低基板温度においても、著しくち密な $\text{SiO}_2$  膜となる。

以上のように、水素化結合に基づく機構により、ち密な $\text{SiO}_2$  膜が得られると考える。

### 3-5 結言

高周波平板型マグネトロンスパッタリング法を用いて $\text{SiO}_2$  膜を形成し、膜特性、ならびに膜特性の改善法を研究し、以下のことを明らかにした。

- (1) 本スパッタリング法により、低基板温度で、組成ずれの少ない、ち密な $\text{SiO}_2$  膜を得ることができる。

- (2)  $\text{SiO}_2$  膜の特性は、Ar圧に著しく依存し、臨界圧力以上では、従来得られなかった

多量の微小空孔を含む、密度の小さな膜となる。すなわち、Ar圧を制御することにより、熱酸化SiO<sub>2</sub> 膜に匹敵する膜から、ち密性に欠ける膜まで、種々の特性の膜を形成できる。

- (3) SiO<sub>2</sub> 膜の特性の改善法として、スパッタリングガス中にH<sub>2</sub> を混合する方法を新たに明らかにした。この方法により、膜特性の著しい改善が図られ、熱酸化SiO<sub>2</sub> 膜よりもち密な膜が、低基板温度で得られる。

- (4) 上記Ar-H<sub>2</sub> 混合法により、基板上での均一性ばかりでなく、膜厚方向の均一性も著しく改善できる。

以上のように、スパッタリング法によって種々の特性のSiO<sub>2</sub> 膜を、低基板温度で容易に形成でき、本方法によるSiO<sub>2</sub> 膜は、半導体L S Iにおける絶縁膜として極めて有効である。さらに、H<sub>2</sub> 混合によるち密化作用に対しては、水素化結合に基づく機構を提案し、考察した。

### 第3章参考文献

- 1) J. L. Vossen and W. Kern : Thin Film Processes (Academic Press, New York, San Francisco, London, 1978) P. 11-173.

- 2) R. E. Jones, C. L. Standley and L. I. Maissel : J. Appl. Phys. 38 (1967) 4656.

- 3) J. S. Logan, F. S. Maddocks and P. D. Davidse : IBM J. Res. Develop. 14 (1970) 182.

- 4) T. Kubota : Jpn. J. Appl. Phys. 11 (1972) 1413.

- 5) D. V. McCaughan and R. A. Kushner : Proc. IEEE 62 (1974) 1236.

- 6) J. M. Aikten : IEEE Trans. Electron Devices ED - 26 (1979) 372.

- 7) T. Serikawa and T. Yachi : IEEE Trans. Electron Devices ED - 28 (1981) 882.

- 8) K. Urbanek : Solid State Technol. 20 (1977) 87.

- 9) K. Hara, Y. Suzuki and Y. Taga : Jpn. J. Appl. Phys. 18 (1979) 2027.

- 10) R. A. Larsen : IBM J. Res. Develop. 24 (1980) 268.

- 11) R. Glang, R. Holmund and R. Rosenberg : Rev. Sci. Inst. 36 (1965) 7.

- 12) W. A. Brantley : J. Appl. Phys. 44 (1973) 534.

- 13) A. K. Sinha and T. T. Sheng : Thin Solid Films 48 (1978) 117.

- 14) 菅野・小野・垂井 : MOS電界効果トランジスタ (日刊工業新聞社、1969) P201.

- 15) 飯田 : 物理定数表 (朝倉書店、1969) P77.

- 16) 飯田 : 物理定数表 (朝倉書店、1969) P93.

- 17) A. S. Grove : Physics and Technology of Semiconductor Devices (John Wiley and Sons, Inc, New York, London and Sydney, 1967) Chap 2.

- 18) W. A. Pliskin : J. Vac. Sci. Technol. 14 (1977) 1064.

- 19) W. A. Pliskin, P. D. Dawidse, H. S. Lehman and L. I. Maissel :

- I BM J. Res. Develop. 11 (1967) 461.

- 20) J. H. Keller and R. G. Simmons : I BM J. Res. Develop. 23 (1979) 24.

- 21) W. D. Westwood : J. Vac. Sci. Technol. 15 (1978) 1.

- 22) J. Serikawa : J. Vac. Sci. Technol. 17 (1980) 582.

- 23) C. J. Mogab, P. M. Petroff and T. T. Sheng : J. Electrochem. Soc. 122 (1975) 815.

- 24) T. N. Kennedy : J. Vac. Sci. Technol. 13 (1976) 1135.

- 25) R. E. Jones, H. F. Winters and L. I. Maissel : J. Vac. Sci. Technol. 5 (1968) 84.

- 26) 菅野、御子柴、平木：表面電子工学（コロナ社 1979年）P 71.

- 27) L. I. Maissel, R. E. Jones and G. L. Standly : I BM J. Res. Develop. 14 (1970) 176.

- 28) 例えば、菊池監修／田中編著：アモルファス半導体の基礎（オーム社，1982年）。

## 第4章 スパッタリング法によるSiO<sub>2</sub>膜の ステップカバレジ

### 4 - 1 緒言

半導体LSIは、導電膜と絶縁膜とを交互に積層することによって形成されている。通常、半導体LSIの表面は平坦でなく、多くの段差が存在する。導電膜が段差を横切る際に、この段差の部分で断線したり、あるいは、薄くなることがある<sup>1)2)</sup>。一方、絶縁膜が段差の部分に不均一に形成されると、上層の導電膜が断線したり、または、下層の導電膜と短絡する<sup>3)4)</sup>。このように、導電膜や絶縁膜の段差被覆性、すなわち、ステップカバレジ (step coverage) の良否は、半導体LSIの製造歩留りや信頼性に著しい影響を及ぼす。従来、導電膜の形成には電子ビーム真空蒸着法が、SiO<sub>2</sub>膜などの絶縁膜の形成には、気相成長(CVD)法が広く用いられている。真空蒸着法では、ステップカバレジを良くする目的で、基板に極めて複雑な運動を与えていた<sup>5)6)</sup>。一方、気相成長法は、高温度で膜の形成を行うために、配線用Al膜上への絶縁膜の形成には不適である<sup>7)</sup>。これらの方針に対して、スパッタリング法は、大きな面積を有するターゲットを用いているため、真空蒸着法に比べて、極めて装置が簡単となる。さらに、スパッタリング法は、低基板温度で膜形成が行える特徴を有している<sup>7)</sup>。これらの理由により、導電膜の形成に真空蒸着法に代ってスパッタリング法が導入され、実用化されている。

スパッタリング法により形成した膜のステップカバレジに関しては多くの報告がある<sup>3)4)8)~11)</sup>。これらの研究では、スパッタされたターゲット原子の平均自由行程を無限大と仮定したり、または、装置の幾何学的側面のみから、実験結果の解析や説明を行っている。しかし、実際の膜形成条件の下での平均自由行程は10mm程度であり、ターゲット原子とスパッタリングガスとの衝突を無視できない。以上の理由から、スパッタリング法による膜のステップカバレジは、幾何学的要因だけでなく、膜形成条件によっても変化すると考えられる。しかしながら、膜形成条件を考慮した研究は少ない。さらに、段差部での膜特性をも含めたステップカバレジの改善法に関する研究はない。

本研究では、まず、陰影効果に基づいて、ステップカバレジに関する一般的な考察を行い、次に、SiO<sub>2</sub>膜のステップカバレジの膜形成条件依存性を実験した。その結果、すぐ

れたステップカバレジが得られる適正条件を明らかにでき、また、実験結果は上記陰影効果により定性的に説明できることを明らかにした。さらに、 $\text{SiO}_2$  膜のステップカバレジに対しては、スパッタリングガス中に  $\text{H}_2$  を混合することにより、著しく改善できることを新たに見い出した。

#### 4 - 2 ステップカバレジに関する一般的考察

スパッタリング法の特徴は、膜の源となるターゲットの面積が大きく、さらにスパッタされたターゲット原子が Ar 等のスパッタリングガスと衝突を繰り返しながら基板に到着することである<sup>8)11)12)</sup>。この結果、スパッタされたターゲット原子は、種々の方向から基板面に飛来する。このことが、基板面上の段差の形状と、膜のステップカバレジの形状とが異なる主な原因である。いま、基板表面での再放出や表面拡散が起らないと仮定すると、段差の側壁や段差近傍には、膜が形成されなかったり、薄くしか形成しない。これは、基板上の段差や、その上に形成された膜自身によって、入射するターゲット原子が遮られるからである。この現象は、陰影効果 (shadowing effect) と呼れている<sup>4)5)13)</sup>。

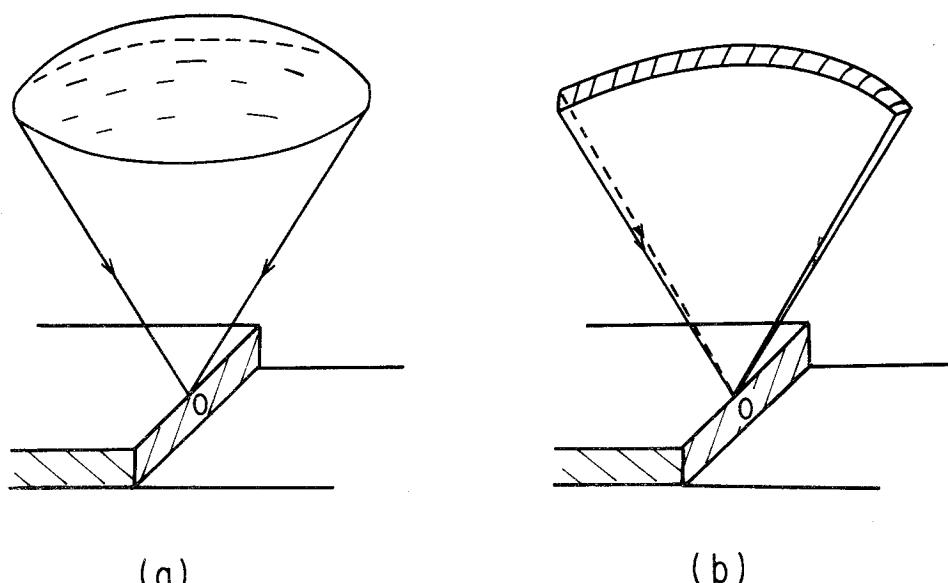

スパッタされたターゲット原子は、図 4 - 1(a) に示すように、ある立体角を持つ円錐内の方向から飛来する。この円錐を薄片に切り、同図(b) に示すように、この問題を二次元の問題に置き換えることができる<sup>2)</sup>。さらに、この入射角分布は、基板面に垂直な成分の外に、斜め成分や水平成分から成り立っていると考えても一般性を失うことではないと考える。

図 4 - 1 段差部への入射角分布 (a): 円錐状入射角分布, (b): 平板状入射角分布

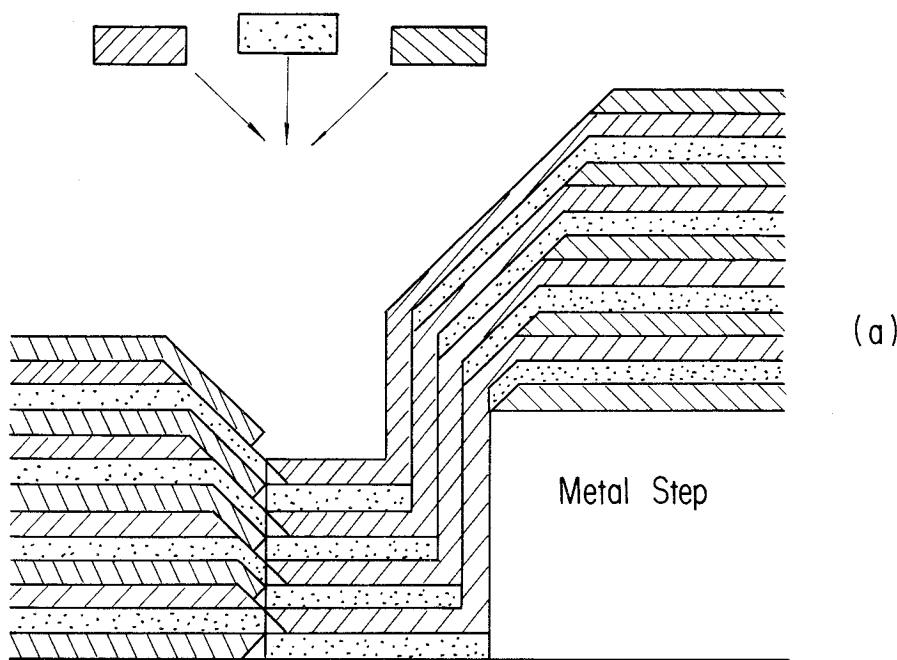

図4-2は、ステップ・バイ・ステップ方式により構成した、垂直な段差でのステップカバレジの形状である<sup>2)</sup>。同図(a)は、入射成分が垂直成分と斜め成分とから成る場合である。図中右からの斜め成分を持つターゲット原子は、段差や、段差上に形成されたターゲット原子自身によって遮られる。このために、段差の近傍に窪みを有し、垂直な傾斜を持つステップカバレジとなる。この窪みの底部から段差上の膜表面までの高さは、元の段差よりも高くなっている。

図4-2 ステップ・バイ・ステップ法により構成したステップカバレジの形状

(a): 垂直成分と斜め成分の場合

図4-2(b)は、同図(a)の場合に、さらに、水平成分が混った時のステップカバレジである。左側から飛來した水平成分のターゲット原子は、段差前面に形成された膜に遮られる。このために、この水平成分のターゲット原子は、段差側壁の上側のみに形成され、下側には形成されない。この結果、異常な窪みを有し、負の傾斜角を持つステップカバレジとなる。この場合のステップカバレジの形状は、半球面状の入射角分布の場合とほぼ同形となる<sup>2)</sup>。上記議論から、窪みが形成される理由は、斜め成分や水平成分が入射成分に混り、これらの成分を有するターゲット原子が段差や膜自身により遮られるからである。

実際の膜形成時には、上述した場合よりもさらに多くの成分が混り、また、それらの混合比も異ってくる。このために、図4-2に示した形状を修正したステップカバレジとな

図4-2 ステップ・バイ・ステップ法により構成したステップカバレジの形状

(b):垂直成分、斜め成分、および、水平成分が混った場合

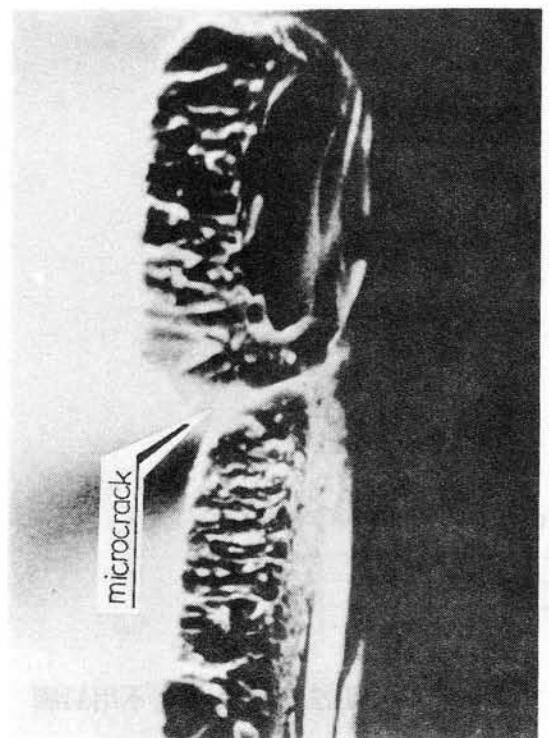

る。例えば、図4-2(b)における異常窪みの幅が狭まり、マイクロクラックになるなどである。一方、段差側壁上での膜の厚さは、斜め成分や水平成分の増大に伴い大きくなることは、図4-2の説明から分る。このように、入射角分布が種々の入射成分を有していく理由としては、装置の幾何学的要因の外に、スパッタされたターゲット原子とAr原子との衝突等のスパッタリング条件が挙られる。半導体LSIの製造歩留りや信頼性を向上するには、段差側壁部に厚く膜を形成し、その膜のステップカバレジの傾斜を正にすることが重要である。この正の傾斜角を有するステップカバレジは、上述の説明から明らかのように、入射角分布を制御することだけからは得ることができない。しかしながら、図4-2に示した窪みを小さくし、さらに、スパッタされた原子の基板表面での表面拡散を助長することによって、ステップカバレジを改善できる。次章以降では、本節での議論をもとにして、実験結果を述べ、考察する。

#### 4-3 装置と実験方法

まず、高周波ダイオードスパッタリング装置を用いて、 $\text{SiO}_2$ 膜のステップカバレジに

与える諸条件を明らかにし、次に、これらの条件を考慮して、低基板温度・高膜形成速度の特長を有する高周波平板型マグネットロンスパッタリング装置による実験を行った。

#### (A) 高周波ダイオードスパッタリング装置

スパッタリング装置の写真と概略を図4-3に示す。ターゲットを設置する高周波電極、基板支持台、シャッタ等から構成されている。これらは、ステンレスから出来ている。高周波電極の裏側には、プラズマ集束用永久磁石がとりつけてあり、ターゲット表面に垂直に、約200Gの磁界が印加されている。さらに、基板支持台には、直流電源により、スパッタ時に直流電圧を加えることができる。上記の基板支持台ならびに高周波電極は、直径が170mmであり、いずれも水冷されている。

ターゲットには、直径190mmで厚さ5mmの溶融石英(純度99.99%)を使用した。基板支持台は、電気的に浮遊状態であるか、もしくは、直流電源により、+70Vまたは、-70Vの電圧を印加した。基板としては、高さ600nmで垂直な側壁を有するFe-Ni合金パタン、もしくは、M<sub>0</sub>パタンを搭載したパイレックス基板(厚さ：0.3mm)を用いた。このパイレックス基板を、基板支持台の中心から半径20mm以内の領域に設置した。この基板上に、スパッタリング電力：2.5W/cm<sup>2</sup>でSiO<sub>2</sub>膜を形成した。さらに、基板とターゲットとの間の間隔は可変であり、20mmから70mmまで変化し、実験を行った。

ターゲット表面のエッチング速度の分布も測定した。エッチングマスク用、1μm厚のFe-Ni合金パタンを有するパイレックス板をターゲット上に置き、スパッタリング工程後、このパタンを除去し、エッチング深さを干渉顕微鏡により測定した。

#### (B) 高周波平板型マグネットロンスパッタリング装置

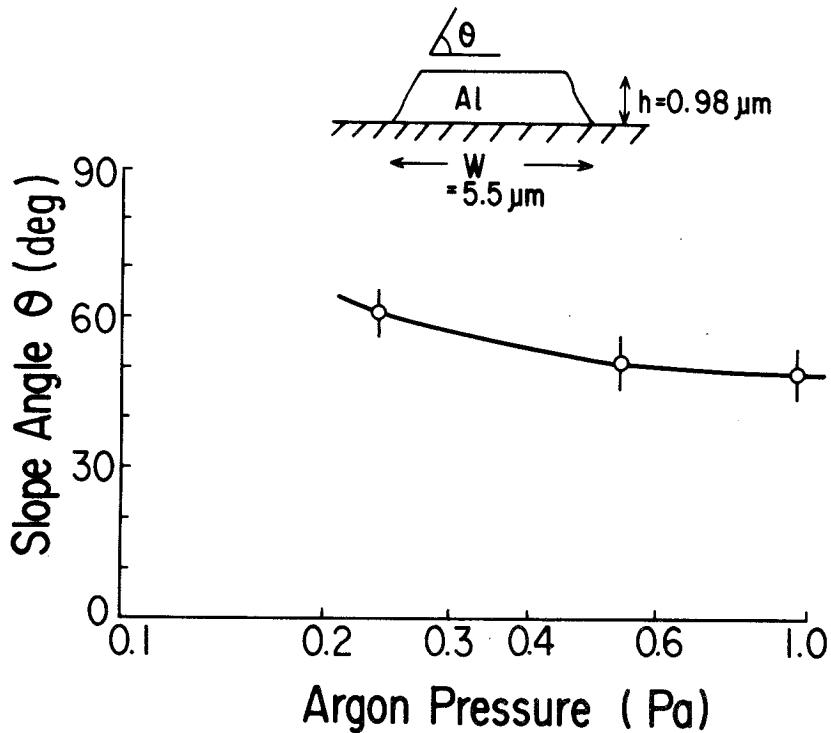

本装置は、第3章において用いたものと同一である。高さ800nmで、側壁傾斜角70°を有するAl合金パタンを持つSi基板上に、純Arならびに、30%H<sub>2</sub>-70%Ar混合ガス中でSiO<sub>2</sub>膜を形成した。その時の圧力は、0.47Paで、基板温度は200°Cである。ターゲットには、大きさ5"×15"で、厚さ3mmの溶融石英(純度：99.999%)を用いた。このターゲット2個を、同時にスパッタリングした。この時のスパッタリング電力は、各ターゲット当たり2kWであり、計4kWである。基板とターゲットとの間の間隔は50mm、基板の回転速度は10rpmである。膜形成後、30°Cの緩衝弗酸溶液に浸した後のステップカバレジも調べた。

上記いずれの装置を用いた場合のステップカバレジも、走査型電子顕微鏡により調べた。

図4-3 高周波ダイオードスパッタリング装置の写真(a)

図4-3 高周波ダイオードスパッタリング装置の概略図(b)

#### 4 - 4 ステップカバレジの形状

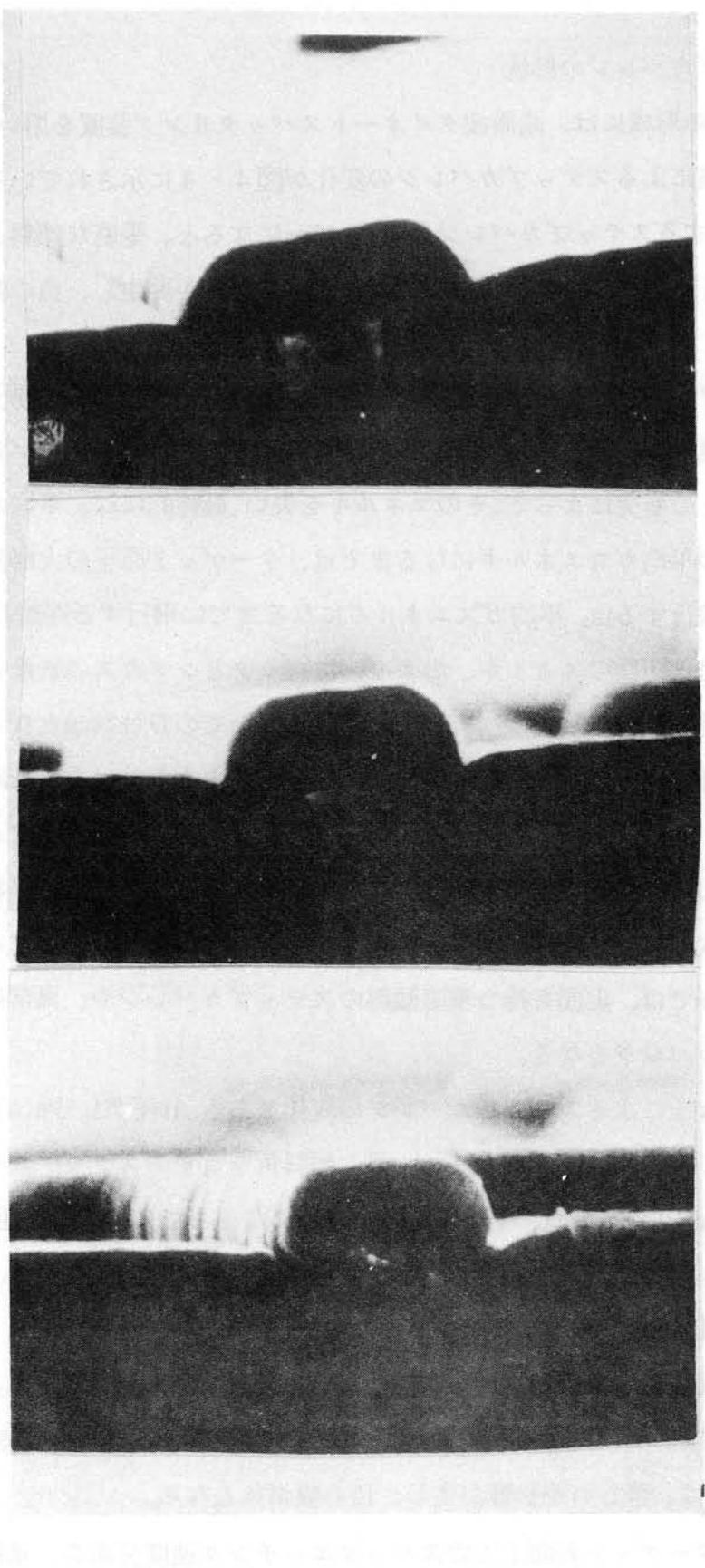

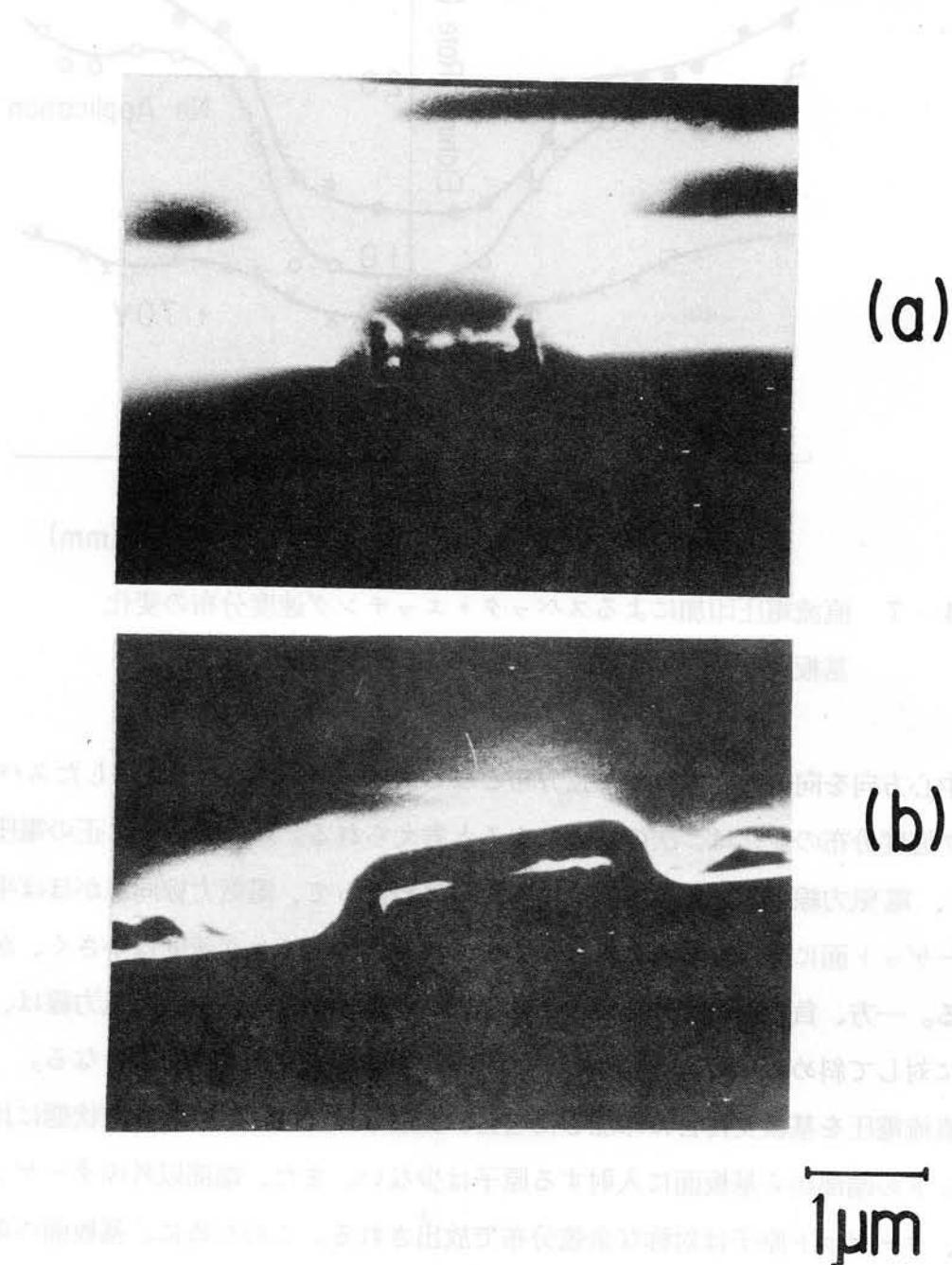

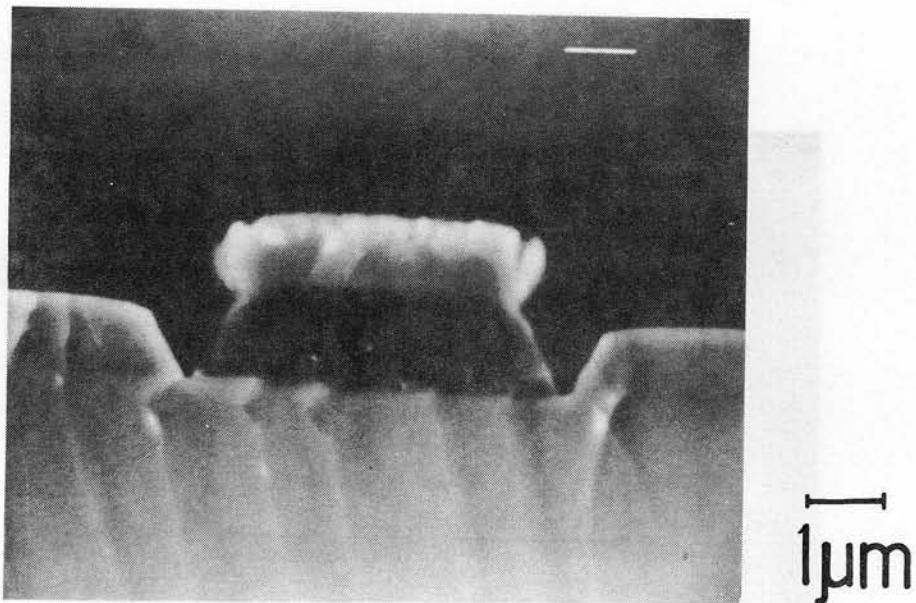

本節での $\text{SiO}_2$  膜の形成には、高周波ダイオートスパッタリング装置を用いた。基板とターゲットとの間隔によるステップカバレジの変化が図4-4に示されている。間隔20mmでは、正の傾斜を有するステップカバレジとなる。40mmになると、垂直な傾斜となり、側壁部に尖頭が生じてくる。さらに、70mmにすると、異常な窪みが発生し、負の傾斜のステップカバレジとなる。

端部以外のターゲット表面からは、余弦則に従う角度分布でターゲット原子はスパッタされる。それらの原子は、数eVに鋭いピークを有するエネルギー分布を示す。このスパッタされた原子は、Arとの衝突によって、そのエネルギーを失い、最終的には、平均ガスエネルギーまで減少する。この平均ガスエネルギーになるまでは、ターゲット原子の大部分は、ターゲット表面に垂直に飛行する<sup>12)</sup>。平均ガスエネルギーになるまでに飛行する距離Dは、スパッタされた原子の質量と初期のエネルギー、および、スパッタリングガスの質量と圧力によって定まる。 $\text{SiO}_2$  の状態でスパッタされると、Ar圧が3.4PaでのDは20mmとなる<sup>12)</sup>。ターゲットと基板との間隔が20mmでは、基板へのターゲット原子の大部分は垂直方向から入射する。このために、前節の議論から、正の傾斜を持つステップカバレジとなる。しかし、ターゲットと基板との間隔を上記の距離Dよりも大きくすると、スパッタされた時の方向性が失われ、斜め入射成分や水平入射成分が増してくる。その結果、図4-4に示すように、間隔40mmや70mmでは、尖頭を持つ垂直傾斜のステップカバレジや、異常窪みを伴う負の傾斜のステップカバレジとなる。

図4-5は、Ar圧によるステップカバレジの変化である。Ar圧が1.7Pa(a)では、3.4Pa(図4-4)に於てみられた窪みは消滅し、正の傾斜角を有するステップカバレジに改善される。これはAr圧1.7Paでの、平均ガスエネルギーになるまでに飛行する距離Dが30mmと、20mmより大きくなり、その結果、3.4Paの場合よりも垂直成分が増加したためである。一方、Ar圧7.9Paでは、垂直なステップカバレジとなる。

図4-6は、基板支持台に直流電圧を印加した時のステップカバレジである。 $+70\text{ V}$ を印加する(a)と、側壁部での尖頭は除去され、ステップカバレジは改善される。反対に、 $-70\text{ V}$ の場合(b)には、著しい悪影響が生じ、負の傾斜角となる。

図4-7には、ターゲット表面上でのスパッタエッチング速度分布を、基板支持台の電位状態をパラメータとして示してある。スパッタリング条件は、図4-6と同じである。正の電圧を印加した場合、スパッタエッチング速度が最も小さく、かつ、最も均一であ

図4-4 基板とターゲットとの間隔によるステップカバレジの変化 (a):20mm,

(b):40mm, (c):70mm Ar圧:3.4Pa, 基板電位:浮遊状態

図4-5 Ar圧によるステップカバレジの変化 (a):1.7Pa, (b):7.9Pa 基板ターゲット間隔:40mm, 基板電位:浮遊状態

る。一方、負の電圧の場合、このエッティング速度は最大となる。しかし、すべての場合、ターゲットの端部で過度なエッティングが起っている。

上述した、ターゲット端部での過度なエッティングの原因は、次の機構による。その一つは、イオン化を促進するために印加した垂直磁界の効果である。すなわち、電子の横方向

図4-6 基板支持台への直流電圧印加によるステップカバレジの変化

(a): +70V, (b): -70V 基板・ターゲット間隔: 40mm, Ar圧: 3.4Pa

拡散が抑制され、ターゲットの端部付近でのArイオン電流密度が増大するからである<sup>14)</sup>。他の原因是、ターゲット外周部におけるシールドの存在により、ターゲット端部での電気力線が平行でなくなるからである<sup>14)15)</sup>。ターゲット端部においては、Arイオンは斜め方向から入射し、垂直に入射するターゲット中央部よりも、スパッタリング率が大きくなる。さらに、ターゲット端部での、スパッタされた原子の放出分布は、対称な余弦分布とはな

図4-7 直流電圧印加によるスパッタ・エッチング速度分布の変化

基板・ターゲット間隔：40mm, Ar圧：3.4Pa

らず、中心方向を向いた非対称な余弦分布となる<sup>15)</sup>。一方、図4-7に示したスパッタエッチング速度分布の変化は、次の原因によると考えられる。基板支持台に正の電圧を印加すると、電気力線はターゲット表面の大部分にわたって、電気力線同志がほぼ平行となり、ターゲット面に垂直となる。この結果、スパッタエッチング速度は小さく、かつ、均一となる。一方、負の電圧を印加すると、ターゲットの中央部まで、電気力線は、ターゲット面に対して斜めとなる。このため、スパッタエッチング速度は最大となる。

正の直流電圧を基板支持台に印加した場合、上述した理由により、浮遊状態に比べて、ターゲットの端部から基板面に入射する原子は少ない。また、端部以外のターゲット表面からは、ターゲット原子は対称な余弦分布で放出される。このために、基板面への、ターゲット原子の入射角分布における斜め成分や水平成分が小さくなり、側壁近くでの尖頭が除去され、ステップカバレジは改善される。反対に、負の直流電圧を印加した場合、中心部を向いた非対称分布で放出される原子が多くなる。このために、斜めや水平の入射角成 分が大きくなり、この結果、負の傾斜を有するステップカバレジとなる。

上述した実験から、斜めや水平の入射成分を少なくすることにより、ステップカバレジの傾斜角を正にすることができます。このことは、シールドリングを用いる、次の実験により、さらに明確になる。図4-8は、基板上に、高さ15mmで直径30mmのAl製のリングを置いた時のステップカバレジの走査型電子顕微鏡写真である。このリング

図4-8 高さ15mmで直径30mmのシールドリングを使用した時のステップカバレジ

(a) : 基板電位が浮遊状態のとき, (b) : 基板支持台に+70Vを印加したとき

基板・ターゲット間隔 : 40mm, Ar圧 : 3.4Pa

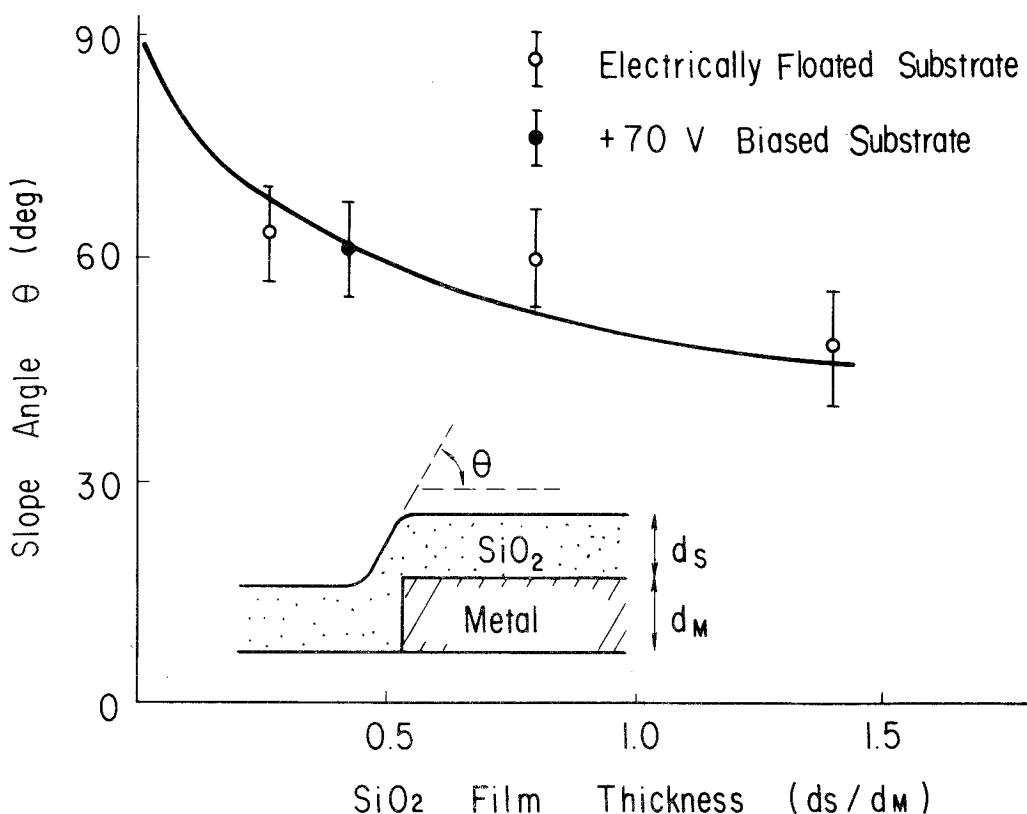

により、斜め成分や水平成分が除去され、著しくすぐれたステップカバレジとなる。また、基板支持台に正に電圧を印加すると、ステップカバレジの形状は滑らかとなる。図4-9は、 $\text{SiO}_2$  膜厚によるステップカバレジの傾斜角の変化である。 $\text{SiO}_2$  膜が厚くなるに伴い、傾斜は緩やかとなる。

高周波ダイオードスパッタリング法による $\text{SiO}_2$  膜のステップカバレジの実験から、次の点を明らかにできた。(1)基板への入射角分布によって、ステップカバレジの形状は著しく変化する。斜め入射成分や水平入射成分が増すと、垂直あるいは負の傾斜を有するステップカバレジとなり、これらの入射成分を少なくすると、正の傾斜に改善される。(2)基板への入射角分布は、装置の幾何学要因の外に、スパッタリング条件によって著しく変化する。正の傾斜を有するステップカバレジは、ターゲットと基板との間隔やAr圧を小さくするか、あるいは、基板支持台に正の直流電圧を印加することによって得れる。

以上のように、スパッタリング法による $\text{SiO}_2$  膜のステップカバレジの形状は、装置の幾何学的要因と共に、膜形成条件によって制御できる。したがって、ここで得られた知見

図4-9 シールドリングを用いた時の、 $\text{SiO}_2$  膜厚による傾斜角の変化 スパッタリング条件は図4-8と同じ

は、半導体LSIの層間絶縁膜をスパッタリング法によって形成する場合だけでなく、スパッタリング装置の設計にも有益である。

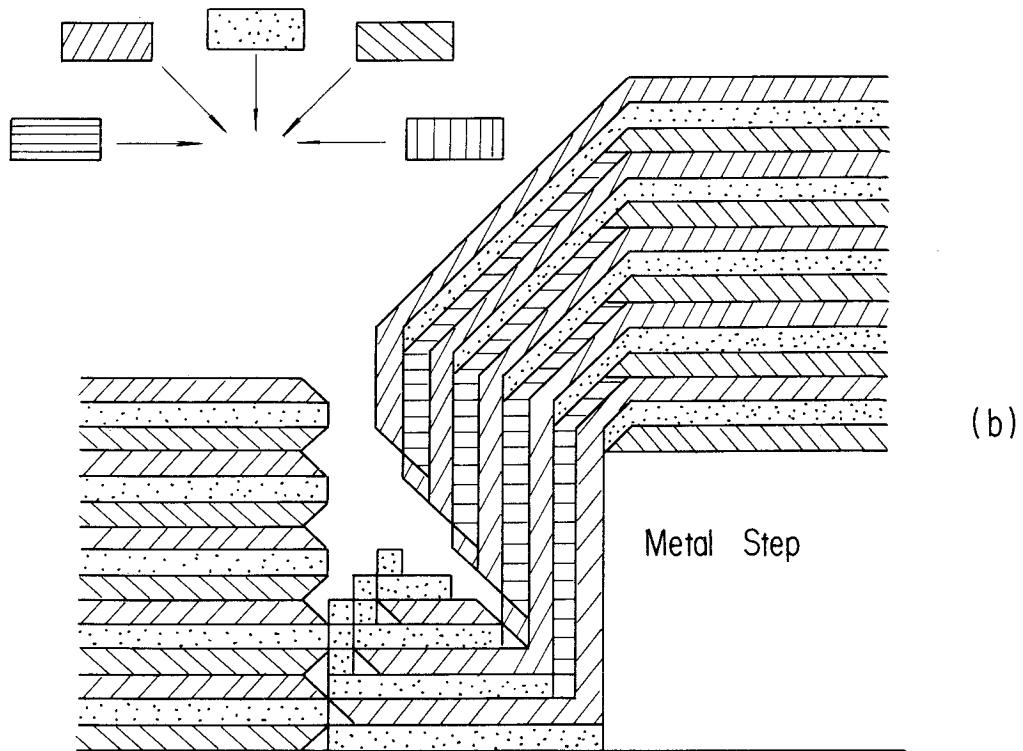

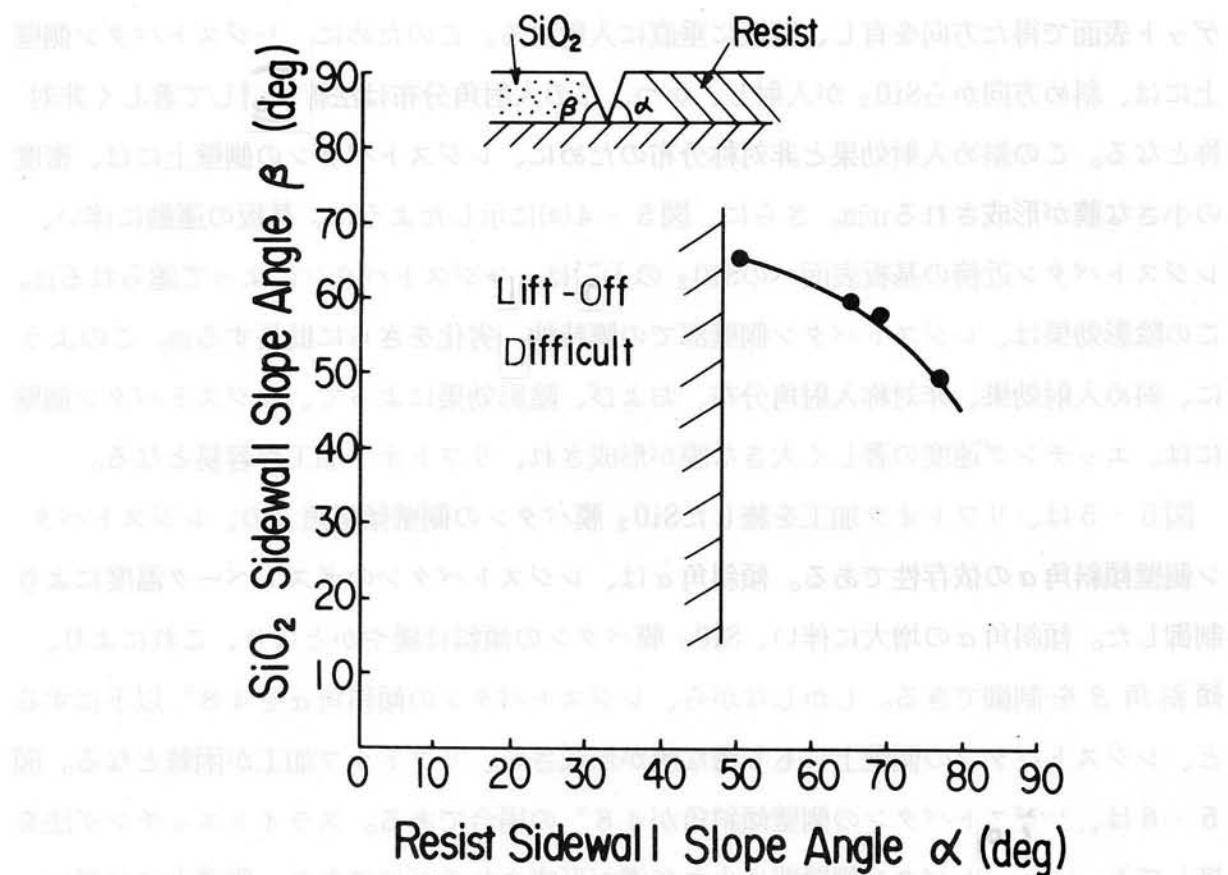

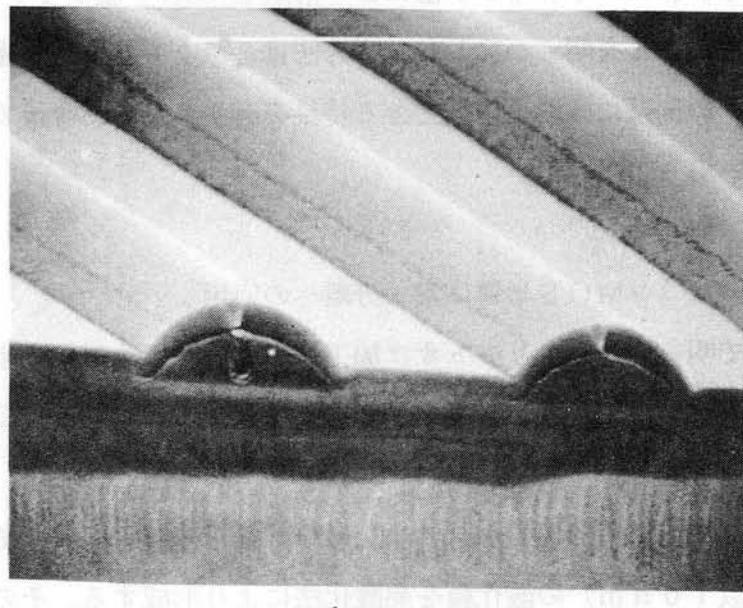

#### 4 - 5 Ar-H<sub>2</sub>混合ガス中スパッタリング法によるステップカバレジの改善

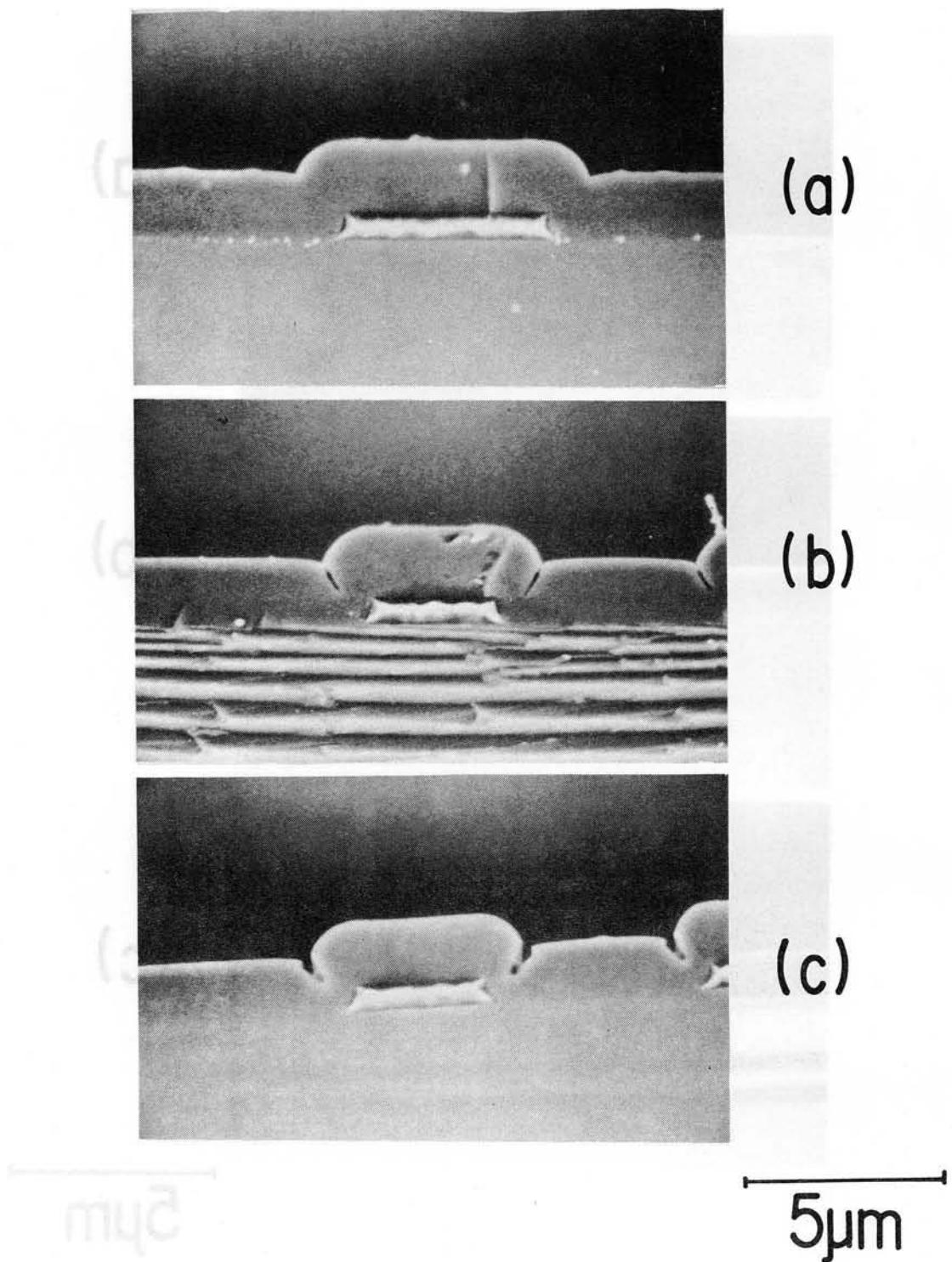

ここでの実験は、高周波平板型マグネットロンスパッタリング装置を用いて行った。