| Title        | Pipelined Processor Synthesis from Micro-<br>operation Level Specification |

|--------------|----------------------------------------------------------------------------|

| Author(s)    | Itoh, Makiko                                                               |

| Citation     | 大阪大学, 2001, 博士論文                                                           |

| Version Type | VoR                                                                        |

| URL          | https://doi.org/10.11501/3184179                                           |

| rights       |                                                                            |

| Note         |                                                                            |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

Pipelined Processor Synthesis from Micro-operation Level Specification

Makiko Itoh

January, 2001

0 Pipelined Processor Synthesis from Micro-operation Level Specification Doctoral Dissertation by Makiko Itoh Department of Informatics and Mathematical Science Graduate School of Engineering Science Osaka University

# Contents

## 1 Introduction

- 1.1 Background . . .

- ASIP Development

Objective . . . .

- 1.4 Approach . . . .

- 1.5 Contribution of the

- 1.6 Organization of the

## 2 Related Work

- 2.1 HW/SW co-design

- 2.2 Recent ASIP Devel

- 2.2.1 Prepared Pr

- 2.2.2 Software De

- 2.2.3 Processor Sy

- 2.3 Problems of Existin

# 3 PEAS-III: Processor

- 3.1 Characteristics of M

- 3.2 Design Methodolog

- 3.2.1 Flexible Har

- 3.3 Micro-operation Le

- 3.3.1 Design Goal

- 3.3.2 Resource De

- 3.3.3 Instruction

- 3.3.4 Interrupt Co

- 3.3.5 Interface De

- 3.3.6 Micro Opera

# 4 Processor Model

- 4.1 Processor Class .

- 4.2 Processor organizat

- 4.3 Datapath Model.

- 4.4 Controller Model

|                                      | T  |

|--------------------------------------|----|

|                                      | 1  |

|                                      | 2  |

|                                      | 4  |

|                                      | 4  |

| e Research                           | 6  |

| e Thesis                             | 6  |

|                                      |    |

|                                      | 9  |

| in early years                       | 9  |

| lopment System                       | 9  |

| rocessor based Approach              | 10 |

| evelopment Tool Generation Systems   | 11 |

| ynthesis Systems                     | 12 |

| ng Processor Descriptions            | 13 |

|                                      |    |

| 0                                    | 15 |

| Modern Processor Architecture        | 15 |

| y                                    | 18 |

| rdware Model                         | 21 |

| evel Processor Specification         | 22 |

| l and Architecture Parameter Setting | 22 |

| eclarations                          | 24 |

| Format Definitions                   | 24 |

|                                      | 28 |

| efinitions                           | 28 |

|                                      | 29 |

|                                      |    |

|                                      | 33 |

|                                      | 33 |

| tion                                 | 34 |

|                                      | 38 |

|                                      | 38 |

i

|   |     | 4.4.1   | Instruction Decoder                                         |

|---|-----|---------|-------------------------------------------------------------|

|   |     | 4.4.2   | Pipeline Stage Controller                                   |

|   |     | 4.4.3   | Interrupt Controller                                        |

|   |     |         |                                                             |

| 5 | Pro | cessor  | Synthesis 53                                                |

|   | 5.1 | Datap   | oath Synthesis                                              |

|   |     | 5.1.1   | DFG generation                                              |

|   |     | 5.1.2   | Basic Datapath Synthesis                                    |

|   |     | 5.1.3   | Signal Conflicts Resolution                                 |

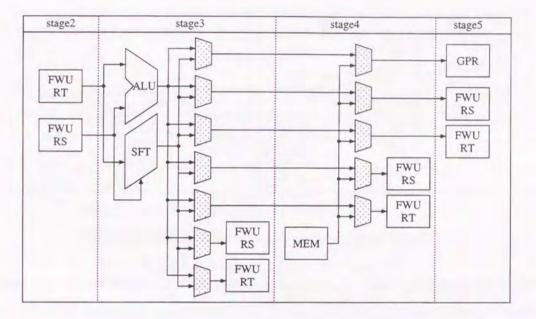

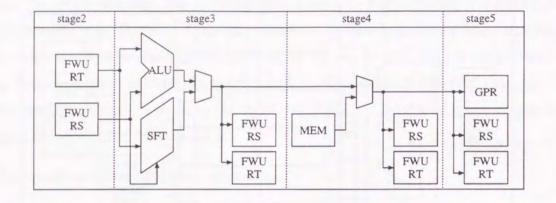

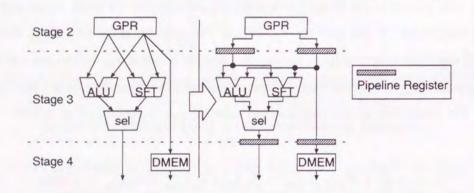

|   |     | 5.1.4   | Pipelining                                                  |

|   | 5.2 | Contro  | oller Synthesis                                             |

|   |     | 5.2.1   | Control Signal Extraction                                   |

|   |     | 5.2.2   | Interlock Condition Extraction                              |

|   |     | 5.2.3   | Branch Condition Extraction                                 |

|   |     | 5.2.4   | Instruction Decoder Synthesis                               |

|   |     | 5.2.5   | Stage Controller Synthesis                                  |

|   |     | 5.2.6   | Interrupt Controller Synthesis                              |

|   |     | 0.110   |                                                             |

| 6 | Exp | erime   | nts 77                                                      |

|   | 6.1 | Object  | tive of the Experiments                                     |

|   | 6.2 | Basic   | RISC Processor                                              |

|   | 6.3 |         | -I Processor Core                                           |

|   | 6.4 |         | dded RISC Controller                                        |

|   | 6.5 |         | ne Stage Tuning                                             |

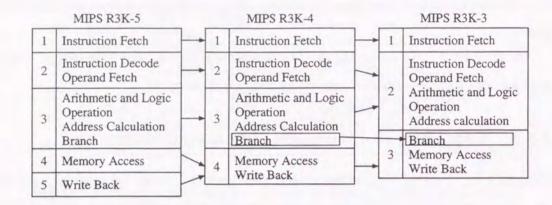

|   |     | 6.5.1   | Changing the Number of Pipeline Stages                      |

|   |     | 6.5.2   | Clock Frequency Improvement                                 |

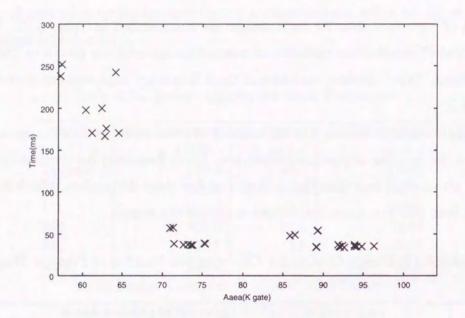

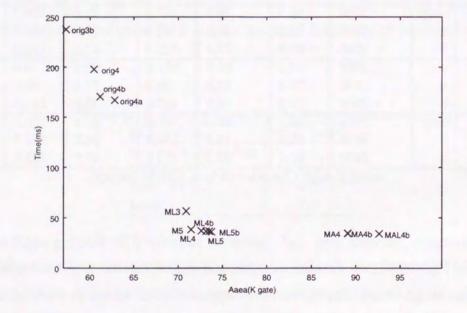

|   | 6.6 |         | 1 Space Exploration for DSP Application                     |

|   |     | 6.6.1   | Customization of PEAS R3K                                   |

|   |     | 6.6.2   | Pipeline Stage Tuning for Derivative Processors 91          |

|   |     | 6.6.3   | Results of Design Space Exploration for DSP Applications 91 |

|   |     |         |                                                             |

| 7 | Dis | cussion | 97                                                          |

|   | 7.1 | Design  | 1 Space                                                     |

|   | 7.2 | Design  | a Time and Design Space Exploration Time                    |

|   |     | 7.2.1   | Design Time for New Processors                              |

|   |     | 7.2.2   | Design Time for Derivative Processors                       |

|   | 7.3 | Design  | Quality                                                     |

|   |     | 0       |                                                             |

| 8 | Con |         | ns and Future Work 103                                      |

|   | 8.1 | Conclu  | usion                                                       |

|   | 8.2 |         | e Work                                                      |

|   |     | 8.2.1   | Design Space Expansion                                      |

|   |     | 8.2.2   | Design Exploration Time Reduction                           |

|   |     | 8.2.3   | Improvement of the Design Quality                           |

- A Grammar of Micro-o

- A.1 Organization of Mi

- A.2 Architecture Paran

- A.2.1 Design Goa

- A.2.2 Pipeline Pro A.3 Interface Definition

- A.4 Instruction Format

- A.4.1 Instruction

- A.4.2 Instruction

- A.5 Resource Declarati

- A.6 Interrupt Definition

- A.7 Micro-operation De

- A.7.1 Variable .

- A.7.2 Constant.

- A.7.3 Storage .

- A.7.4 Operands

- A.7.5 Function .

- A.7.6 Assignment

- A.7.7 If-statement A.7.8 Decode stat

- A.I.o Decode sta

# **B** Processor Specification

- C Synthesis Result of P

- C.1 VHDL Descriptionf C.2 VHDL Descriptionf

| eration Level Processor Specification 113                                                                                | 3 |

|--------------------------------------------------------------------------------------------------------------------------|---|

| ro-operation Level Specification                                                                                         | 3 |

| eter                                                                                                                     | 1 |

|                                                                                                                          | 4 |

| cessor Parameters                                                                                                        | 5 |

|                                                                                                                          | 5 |

| Definition                                                                                                               | 6 |

| Type Definition                                                                                                          | 6 |

| Definition                                                                                                               |   |

| n                                                                                                                        |   |

|                                                                                                                          |   |

| scription $\ldots \ldots 119$ |   |

|                                                                                                                          |   |

|                                                                                                                          |   |

|                                                                                                                          |   |

|                                                                                                                          |   |

|                                                                                                                          |   |

| statement                                                                                                                |   |

|                                                                                                                          |   |

| ement                                                                                                                    | 2 |

| n of PEAS R3K 123                                                                                                        | 3 |

| EAS R3K Processor 133                                                                                                    | 9 |

| f | of | PEAS | R3K | Datapath   |  |  |  |  |  |  |  | 139 |

|---|----|------|-----|------------|--|--|--|--|--|--|--|-----|

| f | of | PEAS | R3K | Controller |  |  |  |  |  |  |  | 150 |

# Abstract

In an embedded system area, application specific instruction set processors (ASIPs) provide better performance, lower power consumption and a smaller chip area than general purpose processors. However, the design time of ASIPs becomes longer with the growth of the design scale. Higher abstraction level processor design method is required more than a traditional register transfer level (RTL) processor design method. The processor designs at RTL require a long design time because the designer has to design datapath and controller structures while considering the assignment of registers, functional units, interconnects among them, and the organization of the finite state machine of the controller. Designing processor organization at RTL from instruction set architecture level processor specification is an error-prone and time-consuming task. In addition, the modification of the processor specification requires a long time for re-design of datapath and controller at RT level. Therefore, comparing with several design candidates for specific application in a short design time is difficult.

In this thesis, micro-operation level pipelined processor specification and a processor synthesis method from a micro-operation level processor description are proposed for the improvement of design productivity of the ASIP development. The higher abstraction level than RTL contributes to the easiness of design and design modification for ASIP design. The ease of specification and modification of processor architecture enables architectural exploration of a large design space in a short design time. The designer only specified clock based instruction behavior in micro-operation level specifications. Datapath and controller of the processor are synthesized from the behavioral description of instructions.

The design space of micro-operation level processor specification is large enough

for practical straightforward pipelined processors. Exploration of larger design space enables the designer to select a more suitable architecture for the target application. The target architecture of micro-operation level processor specification includes the following features: user-defined pipeline organization in terms of the number of pipeline stages, the number of delayed branch slots and the role of each pipeline stage; clock based behavioral representation of instructions and interrupts; utilization of parameterized hardware modules; and user-defined instruction format, processor interface ports and external interrupt conditions.

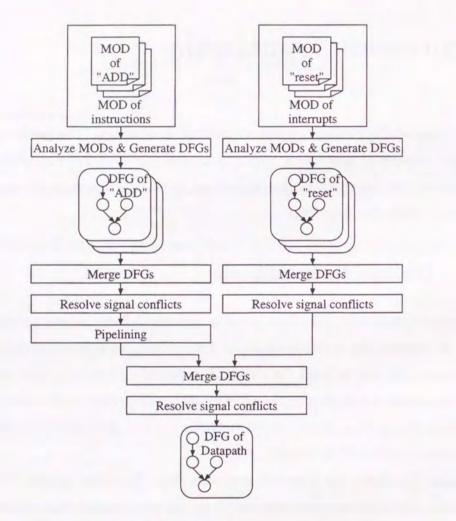

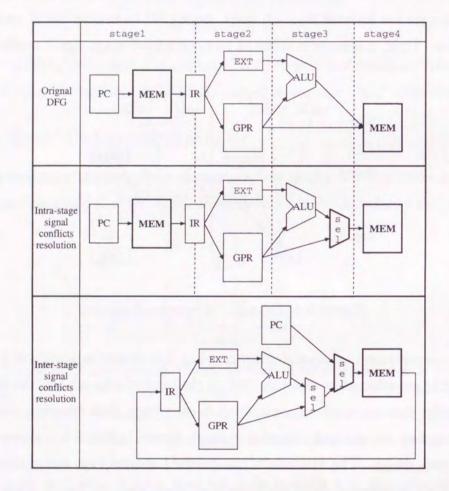

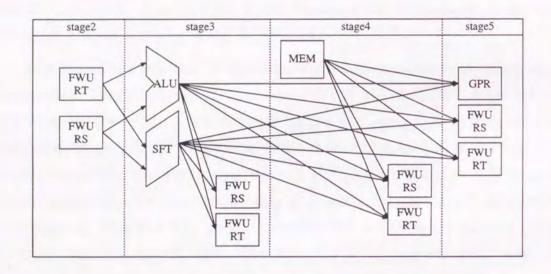

Processor synthesis from the micro-operation level processor specification includes datapath synthesis and controller synthesis. The synthesis of datapath and controller allows the designer to concentrate on instruction set design and evaluate various architecture candidates in a short time. In datapath synthesis, data flow graph generation from micro-operation description, signal conflicts resolution and insertion of pipeline registers are performed. In controller synthesis, instruction decoder, pipeline control logic such as pipeline stall and pipeline flush, and external interrupt control are synthesized.

From experimental results, the effectiveness and feasibility of the proposed processor synthesis method were evaluated. Examples in experiments are a MIPS R3000 compatible processor, DLX, PEAS-I core, a simple RISC controller, and a customized MIPS R3000 processor for DSP application. The amounts of processor design time and design modification time were drastically reduced compared with that of conventional RT level manual design. Processor synthesis time was about two minutes for the processor, which has 52 instructions. The design space of practical processors was explored at an architecture level in a short design time. In the design quality of synthesized processors and manually design processors, the clock frequencies are almost the same. The area of synthesized processors is about 20% larger than that of manually designed processors. Though the area is inferior to manual design, the advantage of effective design space exploration has an impact on the total design quality. The effectiveness of the micro-operation level processor specification and processor synthesis for architectural design space exploration is confirmed. The proposed processor synthesis method enables the designer to explore a large design space at an architectural level. By the architectural exploration of a large design space, design productivity for application specific processors is drastically improved.

# Acknowledgments

I would like to express my deepest gratitude to my supervisor Prof. Masaharu Imai, Osaka University, for introducing me to this research area and guiding this work, for providing all the facilities to carry it out, and for continuous support, help and encouragement.

I would also like to express my thanks to Prof. Ken-ichi Taniguchi and Prof. Teruo Higashino for helpful suggestions and comments in writing this thesis. I wish to express my thanks to the professors and staff of the Department of Informatics and Mathematical Science, Graduate School of Engineering Science, Osaka University, for their guidance, especially the late Prof. Seishi Nishikawa, and the late Prof. Mamoru Fujii, and Prof. Masaru Sudo, Prof. Nobuki Tokura, Prof. Akihiro Hashimoto, Prof. Toru Kikuno, Prof. Hideo Miyahara, Prof. Toshinobu Kashiwabara, Prof. Toru Fujiwara, Prof. Katsuro Inoue, Prof. Kenichi Hagihara, Prof. Masayuki Murata, Prof. Toshimitsu Masuzawa, Prof. Tadahiro Kitahashi and Prof. Shinichi Tamura.

The author is extremely thankful to Prof. Yoshinori Takeuchi, Prof. Akira Kitajima from Osaka University, Prof. Jun Sato from Tsuruoka National College of Technology and Prof. Akichika Shiomi from Shizuoka University for their continuous support, help and encouragement, and many thanks to all members of the PEAS project for their kind assistance, especially, Dr. N. N. Binh, Mr. Yoshimichi Homma, Prof. Takumi Nakano, Prof. Tsutomu Kimura, Mr. Nobuyuki Hikichi from Software Research Associates, Inc., and to the members of the VLSI System Design Laboratory at Osaka University, especially, Ms. Akiko Fujii, Ms. Ranko Morimoto, Mr. Takafumi Morifuji, Mr. Norimasa Ohtsuki, Mr. Shigeaki Higaki, Mr. Shinsuke Kobayashi, Mr. Yoshiharu Watanabe, Mr. Tomohide Maeda and Mr. Naoki Morita.

The author would like to express her special thanks to Dr. Tokinori Kozawa, Mr. Michiaki Muraoka and Dr. Eiji Masuda from STARC (Semiconductor Technology Academic Research Center), Dr. Masao Hotta, Mr. Mitsuho Seki, Mr. Yoshio Takamine from Hitachi Limited, and Mr. Masanobu Mizuno from Matsushita Electric Industry Corporation.

This research was supported in part by STARC.

# Chapter 1 Introduction

### Background 1.1

With advancements in semiconductor technology, chip complexity, that is, the number of transistors on a silicon chip, is doubling every three years. In the near future, it is estimated that over 10 million transistor circuits will be realized on a silicon chip of only 1 cm<sup>2</sup>. From the technology innovation, System-on-a-Chip (SoC) with compound functionalities integrated on a single chip tends to be widely used in electronic equipment [1]. Figure 1.1 shows a typical organization of SoC. SoC usually consists of a combination of the following components: processors such as CPU core, digital signal processor (DSP) and specific processors; ASICs such as signal processing hardware, control hardware and other specific hardware; memories like flash and DRAM; and analog circuits. LSI designs are moved from the individual design of microprocessors and application-specific integrated circuits (ASICs) to a whole system design on a chip.

In SoC design, design productivity is a key issue. The roadmap of SEMAT-ECH [2] indicates the growing productivity gap between available transistors and those that can be designed in microprocessors. The growth of transistor density is 58% per year. On the other hand, the growth of design productivity is only 21% per year. In addition, the rapidly changing technological environment shrinks product life cycles and shortens time-to-market.

| CPU<br>Core                | DRAM                                  |

|----------------------------|---------------------------------------|

| Signal<br>Processing<br>HW | Specific<br>Processor                 |

| Control<br>HW              | Analog                                |

|                            | Signal<br>Processing<br>HW<br>Control |

Figure 1.1: Typical Organization of System-On-a-Chip.

### **ASIP** Development 1.2

Focusing on the design of application specific instruction set processors (ASIPs) that are integrated to the SoC, Hardware/Software co-design [3] environment with architectural design space exploration is considered to be key to design productivity improvement. For the ASIP design, it is important to explore suitable processor architecture for the target application. The HW/SW co-design environment enables the designer to design and evaluate the processor while considering target application and suggests the direction for design improvement. Using the HW/SW co-design environment, the designer is able to design and evaluate various architecture candidates at instruction set architecture level easily. As a consequence, the designer is able to choose the most suitable architecture for the target application in a short design time.

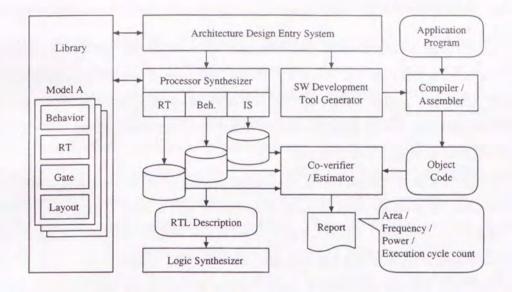

Figure 1.2 shows one HW/SW co-design framework for effective design space exploration. The designer specifies processor architecture with entry system at instruction set architecture level. Processor components such as registers, memory access units, functional units and so on are instantiated from a module library. The module library provides instances at various abstraction levels. A processor synthesizer generates a simulation model and a synthesizable model of the designed

processor. The processor synthesizer receives instances used in the processor from the database manager of the library. Software development tools such as a compiler and an assembler are also generated from the same processor description as processor synthesis. The synthesized instruction set simulation model and SW development tools enable co-verification and performance evaluation of the designed processor. A generated RT level processor model is used to estimate area, clock frequency and power consumption. Estimation and verification results suggest the direction for improvement of the processor design. Using a HW/SW co-design framework like this, exploration of large design space becomes possible because the turn-around time of the ASIP is drastically reduced.

The following techniques are required to implement a HW/SW co-design framework: instruction set level processor specification, processor synthesis and software development tool synthesis method from the same processor description, and fast estimation of designed processor. The processor synthesis method of the HW/SW co-design system often limits the design space of the system. In the recent research, several HW/SW co-design methods and processor synthesis methods are proposed, but their design space is very small in regard to pipeline organization.

Figure 1.2: HW/SW Co-design Framework

# 1.3 Objective

The aim of this research is an investigation of a processor synthesis method for exploration of a large design space for ASIPs. Because processor synthesis methods usually limit the design space of the HW/SW co-design environment, processor synthesis methods should support various other architecture candidates of the ASIPs for architectural design exploration.

To explore a large design space, two requirements must be satisfied: a short turnaround time for evaluation of various candidates, and a large design space. Even if the design space is large enough, the design space cannot be fully explored in the restricted design time if the turn-around time for the design is too long. There is a tradeoff between the easiness of the processor specification and the design space. An appropriate abstraction level for processor specification should be considered.

# 1.4 Approach

Considering the tradeoff between the easiness of the processor specification and the design space of the specification language, micro-operation level processor specification for processor synthesis and a processor synthesis method for micro-operation level specification are proposed in this thesis.

Micro-operation level processor specification is based on a clock base behavioral description of instructions. With the abstraction level processor specification higher than the RT level, the design time and design modification time of the ASIPs are drastically reduced. Despite the easiness of the specification, the design space of micro-operation level processor specification enables the designer to specify practical straightforward pipelined processors. The designer can specify the pipeline organization, hardware module configuration and external interrupts. From these points, a micro-operation level is appropriate for a straightforward pipelined processor in terms of the easiness of the design and design space.

At a micro-operation level processor design, datapath structure and controller are synthesized from behavioral description of instructions and hardware module configuration. The designer is free from tedious, error-prone datapath and controller design. Therefore the designer can design various ASIPs in a short design time.

The target processor architecture is straightforward pipelined architecture that includes basic functionality of embedded microprocessors [4, 5, 6, 7, 8, 9] such as multi-cycle operation, delayed branch and external interrupts. Micro-operation level processor specification includes: the number of pipeline stages and the number of delayed branch slots; utilization of parameterized hardware modules; user-defined instruction format, processor interface ports and external interrupt conditions; and clock-based behavioral representation of instructions and interrupts. Operations of each pipeline stage are specified by the designer with micro-operation description of instructions. The pipeline depth, role of each pipeline stage and hardware modules have an impact on clock frequency and area. The number of delayed branch slots affects code size and execution cycles. Therefore, flexibility in the processor architecture, such as the number of pipeline stages and delayed branch slot and the role of pipeline stages, and in the configuration of hardware modules, allows exploration of a large design space.

For the processor synthesis method from a micro-operation level processor specification, datapath and controller synthesis is required for user-defined pipeline organization in terms of the number of pipeline stages, the number of delayed branch slot and role of each pipeline stage. The controller synthesis includes pipeline control logic synthesis for pipeline hazards, interrupt controller synthesis, and instruction decoder synthesis. Structural hazards are caused by multi-cycle operations and resource conflicts from multiple stages. Hence generation of the hazard detection logic and pipeline interlock logic is required. To deal with the specified number of delayed branch slots, generation of branch control and pipeline flush control logic are also required.

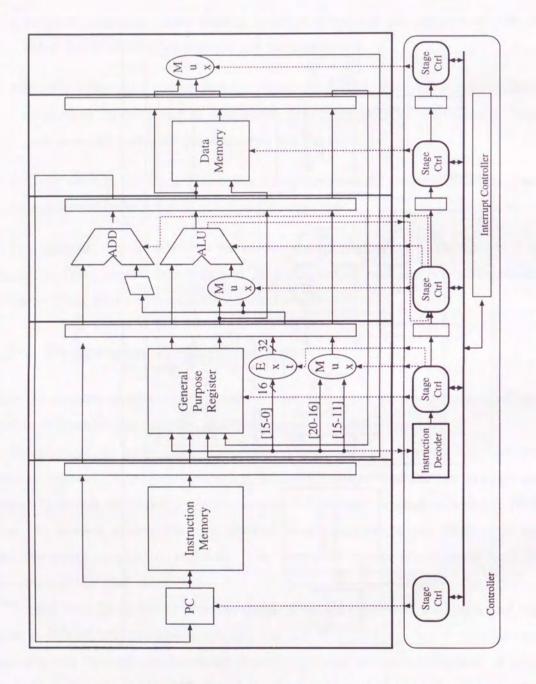

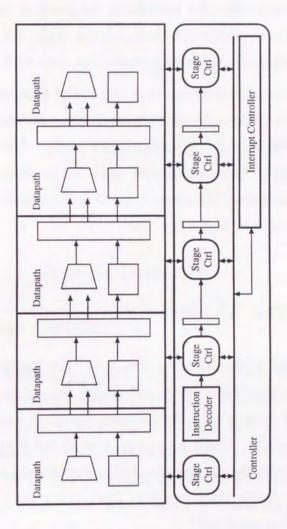

In this thesis, to deal with user-defined pipeline organization, a flexible pipelined processor model is proposed. The model has flexibility regarding the number of pipeline stages and pipeline control logic. The model consists of datapath and controller of each pipeline stage, instruction decoder and external interrupt controller. The pipeline control mechanism using the model for pipeline interlock and pipeline flush is discussed. The processor model and pipeline control mechanism supports the processor synthesis from the micro-operation level processor specification.

Finally, the processor synthesis method based on the processor model is proposed. Processor synthesis from the micro-operation level processor specification includes datapath structure synthesis and controller synthesis. Synthesis of datapath and controller allows the designer to concentrate on instruction set design and evaluate various architecture candidates in a short time. In datapath synthesis, data flow graph generation from micro-operation description, signal conflicts resolution and insertion of pipeline registers are performed. In controller synthesis, instruction decoder, pipeline control logic such as pipeline stall and pipeline flush, and external interrupt control are synthesized.

# 1.5 Contribution of the Research

The effectiveness of architectural design space exploration using the proposed processor design method and synthesis method is known from the experimental results. Design and design modification time is reduced compared with the RT level processor design. Processor design space was successfully explored at an architecture level in a short design time. Processor synthesis time was about two minutes for the processor, which has 52 instructions.

In the design quality of synthesized processors and manually design processors, the clock frequencies are almost the same. The area of synthesized processors is about 20% larger than those of manually designed processors. Though the area is inferior to manual design, the advantage of effective design space exploration has an impact on the total design quality.

Consequently, the effectiveness of the micro-operation level processor specification and processor synthesis for architectural design space exploration is confirmed. By the architectural exploration of a large design space, design productivity for application specific processors is improved drastically.

# 1.6 Organization of the Thesis

This thesis is organized as follows.

In Chapter 2, existing HW/SW co-design environments, customizable processor cores and processor synthesis methods are reviewed. Problems of existing methods are discussed.

Chapter 3 describes micro-operation level processor specification and processor design environment PEAS-III. To determine parameters and user-definable parts of target processors, the characteristics of processor architecture are classified and evaluated in view of their impacts on performance and area on the processor.

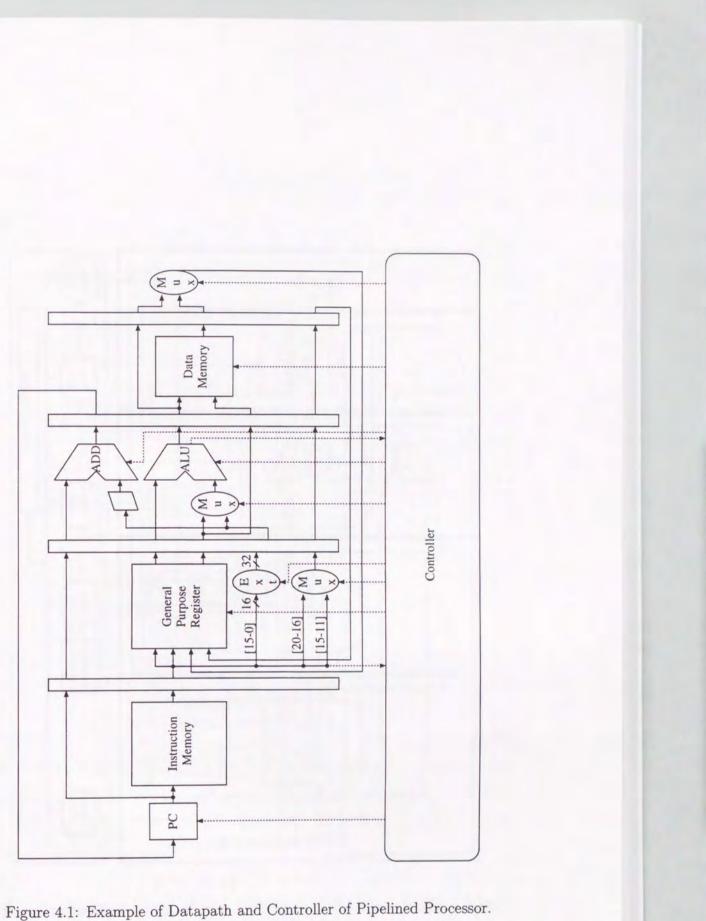

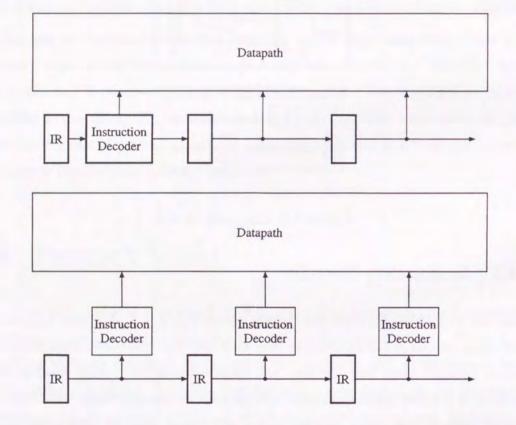

In Chapter 4, the pipelined processor model for processor synthesis is illustrated. The model consists of datapath, an instruction decoder, a pipeline controller and an external interrupt controller. The conditions of pipeline interlock and pipeline flush are considered. The pipeline controller mechanism using these conditions is explained.

Chapter 5 is devoted to the processor synthesis method. The datapath and controller synthesis methods are described. The datapath synthesis includes data flow graph generation, signal conflicts resolution, and pipeline register insertion. The controller synthesis includes instruction decoder synthesis, pipeline control logic synthesis and interrupt controller synthesis.

In Chapter 6, the effectiveness of the method is evaluated through several experiments and architectural design space exploration is demonstrated. Examples in experiments are a MIPS R3000 compatible processor, DLX, a simple RISC controller, PEAS-I core, and a customized MIPS R3000 processor for DSP application. The amount of processor design time was drastically reduced compared with that of conventional RT level manual design in HDL. The processor design space was successfully explored at an architecture level in a short design time.

Chapter 7 presents the discussion of this thesis. The design space, design productivity and design quality of the proposed processor synthesis method are evaluated. The direction of further expansion of design space, reduction of turn-around time and improvement of the design quality are discussed. The last chapter discusses the research results and concludes with future work.

# Chapter 2 **Related Work**

design is reviewed.

# 2.1 HW/SW co-design in early years

HW/SW co-design systems in early years are closely connected to the base processor of the system. The system adopts parameterized processor cores. However, datapath structure and pipeline organization are almost restricted. PEAS-I [10], Satsuki [11] and ARC [12] are classified to this approach. In these systems, the given configurable architecture is tuned to specific application by changing some architectural parameters such as bit width of hardware functional blocks, register file size, memory size, etc. The super set of instructions that can be executed on adopted processor architecture for the system is restricted. The system does not allow the user-defined extension instructions, so that the system cannot always fully satisfy the demand of diverse applications. User-defined instructions for extension are required to gain high performance.

### 2.2**Recent ASIP Development System**

In the recent research, several ASIP development systems, which permit user-defined application specific instructions to be equipped with the target processor, have been proposed. These systems use their original processor description language to describe the target processor's instruction set and the hardware structure. From the

In this chapter, related work for application specific instruction set processors (ASIPs)

processor description, a code generator, an instruction set simulator and HDL description of the target processor are generated.

ISPS [13] is a common processor description for code generation, simulation and processor synthesis in 1980's. While it incorporates a rich set of control mechanisms to describe parallelism and synchronization of processes, the synchronization mechanisms are inadequate to model pipeline operations and hazards for modern pipeline processors.

The other processor description based ASIP design systems for pipelined processors are classified into three types.

- Adding several dedicated instructions to already designed processors. This approach includes FLEXWARE [14], Xtensa [15], Trimaran [16], CASTLE [17] and MetaCore [18].

- Software development tool generation and performance evaluation system for its original processor specification language. This approach includes ISDL [19] based system, Expression [20] based system and LISA [21] based system.

- RT level processor HDL description synthesis system for its original processor specification language. This approach includes MIMOLA [22] based system, nML [23] based system, AIDL [24] based system, and [25].

# 2.2.1 Prepared Processor based Approach

Processor descriptions in the first approach describe instruction set and portion of the datapath structure. In the approach, their pipeline organizations are fixed, so that modification of pipeline control does not allowed.

In the FLEXWARE [14], user-defined instructions can be described by the combination of generic instructions. The generic instructions are supported by instruction set simulator model of the FLEXWARE in VHDL. The designer can specify execution cycles for each instruction, but cannot specify pipeline organization. While FLEXWARE supports the retargetable code generator CodeSyn and the instruction set simulator Insulin, it doesn't support processor synthesis. Xtensa [15] uses a customizable processor core. Xtensa permits some user-defined instructions using Tensilica Instruction Extension Language (TIE). While Xtensa supports both processor synthesis and software development tool generation, user-defined instructions must be executed in restricted cycles. The designer can only describe behavior of the instructions and the structure of "execution" stage, but he/she cannot change the number of pipeline stages and other pipeline stages.

Trimaran uses processor description language MDes [26], which describes both behavior/structure of the target processor. Trimaran allows only a restricted retargetability of the simulator to the HPL-PD [27] processor family.

CASTLE [17] specifies target processor's datapath in block diagram and generates VHDL description of a processor. The target architecture of CASTLE is VLIW. The feature of CASTLE includes: instantiation of VHDL descriptions for functional units from a module library, automatic input signal conflict resolution by selector insertion, and generation of VLIW control word for specified datapath. However, CASTLE assumes a basic VLIW architecture and cannot change pipeline stages.

MetaCore [18] is an application specific DSP development system. MetaCore prepares basic and extended instruction set, and additional user-defined instructions are permitted. Net-list level description of the datapath structure and behavioral description of instructions are described as a specification of a target processor. From these descriptions, software development tools and an HDL description of the target processor are synthesized. However, additional execution units are specified only for the "execution" stage. Additional execution units for other stages and changing the number of pipeline stages are not permitted.

# 2.2.2 Software Development Tool Generation Systems

Processor descriptions in the second approach describe an instruction set and structure of datapath. The designer can define pipeline structure of the target processor in terms of the number of pipeline stages and operations in each pipeline stage.

ISDL [19] [28] is one of such approach that describes an instruction set and datapath structure. In ISDL, constraints of pipeline execution are explicitly specified through illegal operation groupings. This is tedious for complex architectures like

DSPs that permit operation parallelism.

EXPRESSION [20] specifies an instruction set and datapath structure. A Pipeline description provides a mechanism to specify the order of pipeline stages. Accurate reservation tables can be generated from the description. While EXPRESSION supports cycle-accurate instruction set simulation by SIMPLESS [29], processor synthesis has not been supported.

LISA [21] [30] describes the datapath structure and operation-level description of the pipeline. LISA describes activation relationship among pipeline stages, pipeline stalls and pipeline flushes. However, LISA is used for retargetable simulators [31]. Processor synthesis has not been supported, either. Furthermore, description of pipeline control is tedious to design and to modify branch instructions and multicycle operations.

# 2.2.3 Processor Synthesis Systems

In the last approach, both behavior and datapath structure of the target processor are described. Synthesizable processor HDL descriptions are generated.

MIMOLA [22] describes behavior and structure of the target processor and generates RT level processor description. However, pipeline control is not supported since MIMOLA is micro-code based approach.

nML [23] describes behavior of instructions and datapath structure. From nML description, an instruction set simulator is generated [32]. nML is used by the retargetable code generation environment CHESS [33] to describe DSPs and ASIPs. Processor synthesis tool "Go" is also developed for nML processor description. However, nML does not directly support complex pipeline control such as pipeline interlock.

AIDL [24] specifies operations of each pipeline stage and timing relations and cause/effect relations among pipeline stages. Using AIDL, various kinds of processors can be represented including processors with out-of-order completion. However, the modification of the design is difficult for complicated architecture because the designer have to consider various kinds of dependency in the inter-instruction behavior.

Hamabe, et al. [25] proposed a description of clock based instruction behavior

and pipeline stage information includes the correspondence of hardware units to the stage that contains their operations. However, designers must describe instruction behaviors considering with pipeline registers. Furthermore, pipeline control is not directly described.

### **Problems of Existing Processor Descriptions** 2.3

Existing processor development systems have some problems.

- long design time.

For the more effective architectural design space exploration, synthesis of datapath from behavioral description of instructions and pipeline control logic synthesis for user-defined pipeline organization are required. The ability of dealing with the user-defined pipeline organization is essential to evaluate various pipelined processor architectures. Datapath synthesis and pipeline control logic synthesis for user-defined pipeline organization and instructions can reduce the design time and design modification time drastically. Consequently, large design space for ASIPs can be explored in a short design time.

1. Existing processor development systems need both structural and behavior description of the target processor in order to generate the processor. Describing a datapath structure wastes design time. Furthermore, for design space exploration it is tedious to describe datapath structure in consideration of consistency between behavior/structural descriptions.

2. Most systems do not support specification of pipeline organization. The pipeline model of such languages is restricted. The designer cannot change the number of pipeline stages and role of each stage. Several systems support pipeline control synthesis, but explicit definition of the pipeline control is needed. Pipeline control definition is error-prone task and design of it takes

# Chapter 3 **PEAS-III:** Processor Design Environment

This chapter describes micro-operation level processor specification and application specific instruction set processor (ASIP) design environment PEAS-III based on micro-operation level processor specification. First of all, characteristics of processor architecture are classified. Then, their impacts on performance and cost on the processor are evaluated for decision of flexibility on micro-operation level processor specification.

# tecture

points:

- architectural features described below.

# 3.1 Characteristics of Modern Processor Archi-

Architectural characteristics of modern processors are classified into the following

• instruction set architecture: Instruction set architecture is an interface between software and hardware. Instruction set is influenced by many other

• configuration of functional units: Performance of the functional unit affects execution time of application program. Hardware cost of the function unit affects total chip area. The functionality of the units and connectivity among them, in other words "datapath structure," restricts instruction set. The number of functional units determines how many operations are executed at the

same time.

• storage units' organization: Storage units' organization includes location of operands, the number of operands, size of register-file and memory, memory hierarchy and so on.

The operands can be located in accumulators, special registers, general-purpose registers and memories. When operands are located in the accumulators or special registers, location of them are implicitly appointed by an instruction. Using implicit operands, the designer can reduce the instruction word length. However, load and store overhead from memory or register to accumulator or special registers makes execution time long. On the other hand, locations of operands are explicitly declared in an instruction when operands are located in a general-purpose register or in a memory.

Furthermore, the processor architecture is classified to register-register architecture, register-memory architecture and memory-memory architecture whether operands are located in a general-purpose register or memory. Addressing modes for operands affect various fields such as instruction bit width, execution cycles, the number of address generation units and memory access units, pipeline organization and structural hazards.

In general, register-register architecture and harvard architecture are preferred for the design of general purpose RISC processor. Complex memory architecture and memory-accumulator architecture are often preferred for data intensive digital signal processor design. For ASIP design, decision of suitable memory organization for applications is required.

• pipeline organization and pipeline hazard resolution policy: Clock frequency and pipeline hazard occurrence are influenced by pipeline organization in terms of the number of pipeline stages and role of each pipeline stage. The deep pipeline makes clock frequency high, but hardware cost of it also increases. Scheduled operations of each pipeline stage decide clock frequency of the processor. Specifying the operations of each pipeline stage also decides clock frequency, area, and condition of pipeline hazard occurrence and penalties of

## them.

The penalty of pipeline hazards increases execution time of application program. Several techniques to decrease penalty of pipeline hazards are proposed. Data forwarding, re-order buffer reduces data hazards. Delaved branch, branch prediction and non-overhead loop reduce the penalty of control hazards. Additional functional units for the division of the operations of conflicted resource resolve structural hazards. Selection of those techniques makes trade-off between performance and hardware cost.

- becomes high, too.

- exception.

These characteristics are not orthogonal and influenced each other. The designer has to decide processor architecture in considering with these architecture characteristics and feature of target applications. To overcome the difficulty of architecture exploration, pipeline stage level processor design system is indispensable. PEAS-III is proposed as one of pipeline stage level processor design system.

For the architectural design space exploration in consideration of target application, micro-operation level processor specification and design system PEAS-III is proposed [34, 35]. PEAS-III enables the designer to do architectural design space exploration in a short design time. The designer can try various architecture candidates including following architecture variations: configuration of hardware modules,

• instruction issue and completion policy: The policies of instruction issue and completion are classified into in-order and out-of-order. Complex issue and completion mechanism make processor performance high but hardware cost

• exception and interrupts: Exception and interrupt handling manner has some variations especially for architectures with out-of-order instruction completion. One of the exception mechanisms is to use history file or future file to keep original register values. Another approach is to store status of each pipeline stage in detail and let the interrupt handling routine to recover the pipeline status. The other is a technique that stops the instruction issue while it is

uncertain that all the execution instructions will complete without causing an

specification of application specific instructions which include multi-cycle operations, user-defined external interrupts, the number of branch delay slots, and the number of pipeline stages.

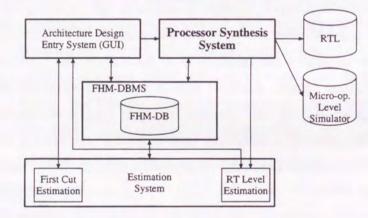

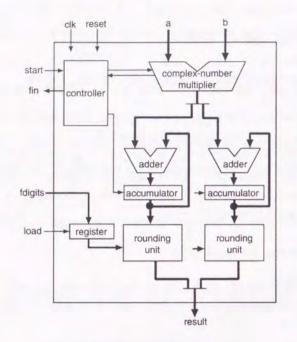

Figure 3.1 shows the organization of PEAS-III. The designer entries processor specification using GUI, "Architecture Design Entry System," and processor synthesis system generates micro-operation level simulation model and RT level processor description for logic synthesis in VHDL [36]. The designer selects resources from flexible hardware model database (FHM-DB) [37] and the processor synthesis system receives HDL descriptions of selected resources from FHM-DBMS. Estimation is also performed at each design step, architecture design phase and micro-operation specification phase. Estimation system also accesses to FHM-DBMS to get estimation results of selected resources. This thesis describes architecture level processor specification and processor synthesis.

Figure 3.1: PEAS-III System.

### Design Methodology 3.2

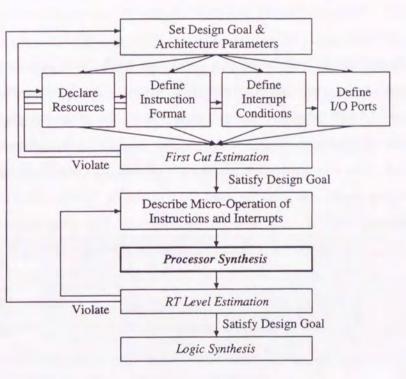

Figure 3.2 shows a design flow of PEAS-III. With PEAS-III, processor is designed design step by step. Firstly, design goal and processor architecture type are set. Secondly, outline of the processor is specified. Specification in the second step includes declarations of resources, which are used in the processor, definition of instruction format and conditions of external interrupts, and definition of interface

Figure 3.2: PEAS-III Design Flow.

ports. In the resource declaration, hardware modules are selected with appropriate parameters from parameterized hardware library FHM-DB. The designer can specify application specific interface between the processor core and other modules on SoC by specifying the external interrupt condition and specific processor interface ports. Then, area, clock frequency and power consumption of designed processor are estimated at the first cut estimation. When the estimation results do not satisfy the design goal, the designer changes architecture parameters, resources, instruction formats and so on to satisfy design constraint.

After the estimation results satisfy the design goal, clock based micro-operation description of instructions and interrupts is defined. Simulation model and synthesizable model of the processor are generated from the processor description. The functionality of the designed processor can be validated using the generated simulation model. The simulation model consists of behavior level instances in VHDL. The simulation model can also be used for evaluation of execution cycles of application programs, and for cycle based co-verification. The area, clock frequency and power consumption of the designed processor are evaluated from synthesized datapath and controller. When estimation results do not satisfy the design goal, the designer improves the processor design by re-scheduling operations of instructions to the pipeline stages or changing the number of pipeline stages. Re-scheduling may improve clock frequency and the number of pipeline stages improve area and clock frequency.

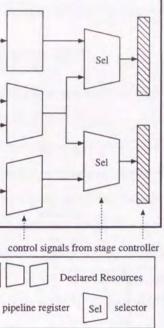

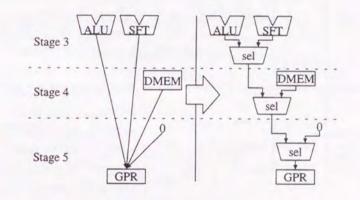

Description and modification time of micro-operation level processor specification is shorter than other existing processor description for synthesis because datapath and pipeline control logic are automatically generated. To generate datapath of designed processor, "Processor Synthesis System" inserts selectors for signal conflicts and pipeline registers for pipeline execution. The pipeline hazard detection and pipeline control logic for pipeline interlock and pipeline flush are also synthesized. The designer can concentrate on instruction set design.

# 3.2.1 Flexible Hardware Model

For architectural design space exploration, effective design reuse of hardware modules and frequent cut and try of them are required. For that purpose, flexible hardware model [38] is utilized. FHM is parameterized with various characteristics such as bit width, algorithm of the operation, etc., and various design instances can be generated according to the given parameter values. Since instances can be generated with various combinations of parameter values, the designer is able to evaluate many kinds of resources only by changing parameter values of FHM.

Several instances of different abstraction levels can be generated from an FHM. The processor synthesis system uses behavioral level instances to synthesis microoperation level simulation model and gate level instances to generate RT level processor HDL description for logic synthesis. FHM provides estimation results of instances for various combinations of parameter values. The estimation results of FHMs are also used for estimation of the designed processor.

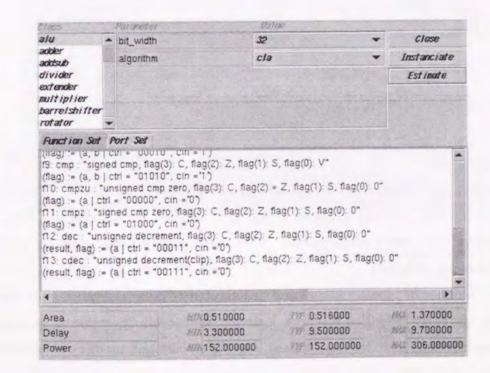

Figure 3.3: Flexible Hardware Model Browser View.

Figure 3.3 shows an FHM browser. FHMs in FHM-DB are displayed in the left box. FHM parameters are shown in the upper-central box and the designer can select candidates of parameter values from the pull down menu on the right. Functionality of the selected FHM is shown in the central box. Estimation results of the FHM with selected parameters are shown at the bottom of the window. An FHM "alu" has a two parameters "bit\_width" and "algorithm." "32" and "carry look ahead (cla)" are selected for the parameter value of "alu" respectively.

# 3.3 Micro-operation Level Processor Specification

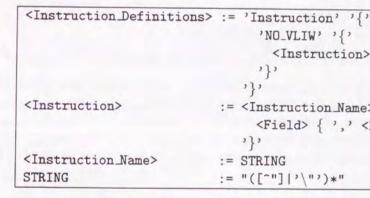

The micro-operation level processor description consists of six major parts as follows:

- 1. Design Goal and Architecture Parameter Setting

- 2. Resource Declarations

- 3. Instruction Format Definition

- 4. Interrupt Condition Definitions

- 5. Interface Definitions

- 6. Micro-operation Descriptions of instructions and interrupts

In this section, details of each part are described.

## 3.3.1 Design Goal and Architecture Parameter Setting

Figure 3.4 shows a portion of design goal and architecture parameter setting window. In this step, the designer specifies design goal of area, clock frequency, execution cycle count and power consumption. Then, architecture parameters for pipelined processors are specified.

The number of pipeline stages and the number of delayed branch slots are supported, currently. Pipeline interlock logic for multi-cycle operation is synthesized. Pipeline interlock logic for data hazard, register bypass and memory bypass are not synthesized. These parameters are prepared for future extension of PEAS-III. Figure 3.5 shows a portion of processor description, which is output from architecture

| Annual cake | 1100 23  | A VETROLA       |

|-------------|----------|-----------------|

| Complete    |          |                 |

| CPU TYPE    | Non-p    | oipeline •      |

| Prpetinc    | FOFS     | Y age 5         |

|             | 1 31 2   | onnon Stage (   |

|             | tain o   | t phose par s   |

|             | 51390    | 7 IF            |

|             |          | 2 ID            |

|             |          | 3 EXE           |

|             |          | 4 MEM           |

|             |          | 5 WB            |

|             | Milti    | ocle interit    |

|             | Data I   | azard interh    |

|             |          |                 |

|             | 1.NDG131 | ter Byganss (3) |

|             | Herson   | Bypass 🔿 🕼      |

|             | Delan    | d branch 🔶 🛛    |

|             | 105      | the of delay    |

Figure 3.4: Architecture Parameter Setting Window.

|                |                |                              | Help           |

|----------------|----------------|------------------------------|----------------|

| 3.53 V 4.54    |                |                              |                |

| Pipeline UL    | IW             |                              |                |

| (stages)       |                |                              |                |

| ) (Istage      | 5)             |                              |                |

| tuge 1         | ljuhasse/stage | 2                            |                |

|                | 1              | (phase)                      |                |

|                | 1              | (c)c.te)                     |                |

|                | 1              | [cycle]                      |                |

|                | 1              | [cucle]                      |                |

|                | 1              | [cycle]                      |                |

| ict 🖲 Use 🖂 U  | huse           |                              |                |

| d use • l      | huse           | Concerning of the            |                |

| Use • Unuse    |                | the support of the second of |                |

| e e Unuse      |                |                              | aller Property |

| les Alo        | and the second |                              |                |

| ed stat 1      | (instruct      | (orl)                        |                |

| Charles States | 1000000        |                              |                |

entry system (GUI). In the example the number of pipeline stages is five and delayed branch architecture is selected. The number of delayed branch slots is specified to '1'. It indicates that synthesized execute one succeeding instruction to the branch instruction whether branch is taken or not.

Abstract\_level\_architecture{ Pipeline\_architecture{ Number\_of\_stages{"5"} Delayed\_branch{"Yes"}, Number\_of\_exec\_delayed\_slot{number{"1"}}}

Figure 3.5: Example of Architecture Parameter Settings.

# 3.3.2 Resource Declarations

Figure 3.6 shows a resource declaration window. Flexible hardware models are selected from FHM-DB, and instance names and parameter values for them are specified. Abstraction levels of resources are specified for micro-operation level simulation model and for RT level synthesizable model, respectively. To synthesize simulation model, "Behavior" is more preferable than "RT" and "Gate" for simulation. On the other hand, "Gate" level is frequently used for synthesizable model generation.

Figure 3.7 shows a portion of a resource declaration description. The processor synthesis system instantiates HDL descriptions of declared resources from resource declarations.

In an example shown in Fig. 3.7, instruction register "IR" is declared. "IR" is a positive edge trigger type register and its bit width is "32." "Behavior" level instance is used for micro-operation level simulation model generation and "Gate" level instance is used for logic synthesizable model generation.

## 3.3.3 Instruction Format Definitions

Figure 3.8 shows an instruction format definition window. Bit fields, field type, field name, and binary value of it are defined for each instruction type. Field type is

| File Edit Se                                                                                                                              | arch                                                                | and the second                        | and the state of the                   | Help                      |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------|----------------------------------------|---------------------------|--|--|

| Complete                                                                                                                                  |                                                                     |                                       |                                        |                           |  |  |

| lestance.                                                                                                                                 | Instance lis                                                        | Ne Th                                 | Class Mare and and                     |                           |  |  |

| Z IR                                                                                                                                      | Paraneter                                                           | Mar/de                                |                                        |                           |  |  |

| A HI<br>A LO                                                                                                                              | bit width                                                           | 32                                    | -for Steaded int                       |                           |  |  |

| STANDO                                                                                                                                    | edge_trigger                                                        | positive                              |                                        | RT Gate                   |  |  |

|                                                                                                                                           |                                                                     |                                       | for Syndhesis                          |                           |  |  |

| ALUO                                                                                                                                      |                                                                     |                                       | Behavior RT                            | • Gate                    |  |  |

| Z DIVO<br>Z SFTO                                                                                                                          | 19 20 20                                                            |                                       |                                        |                           |  |  |

| Function Set Por                                                                                                                          | A Cod Annual                                                        |                                       |                                        |                           |  |  |

| f0: nop : "No opera                                                                                                                       | ation"                                                              |                                       |                                        |                           |  |  |

| 0 = (  enb = '0', r<br>1 reset "reset"<br>0 = (  rst = "1')<br>12 write "register<br>0 = (data_in   enb                                   | write"<br>o = '1') after 1/1 cycle                                  | when positive_edg                     | ge(Clk)                                | ,                         |  |  |

| 0 = (  enb = '0', r<br>1 reset "reset"<br>0 = (  rst = '1')<br>12 write "register<br>0 = (data_in   enb<br>13 read "register<br>4         | write"<br>b = "1") after 1/1 cycle<br>read"                         |                                       |                                        | .120000                   |  |  |

| 0 = (  enb = '0', r<br>1 reset "reset"<br>0 = (  rst = '1')<br>12 write "register<br>0 = (data_in   enb<br>13 read "redister<br>4<br>Area | write"<br>o = "1") after 1/1 cycle<br>read"<br>#//A.0.1             | when positive_edg<br>120000<br>700000 | FIP 0.120000 MAR                       | •<br>0.120000<br>0.700000 |  |  |

| 0 := (  enb = '0', r<br>f1: reset: "reset"<br>0 := (  rst = '1')<br>f2: write: "register<br>0 := (data_in   ent<br>f3: read: "register    | write"<br>o = '1') after 1/1 cycle<br>read"<br>#//k 0.1<br>#//k 0.1 | 120000                                | 717 0.120000 /848<br>715 0.700000 /848 | and the second second     |  |  |

Resource{ "IR" { class{"register"}, classpath{""}, parameter{ abstraction\_level{ for\_simulation{"Behavior"} for\_synthesis{"Gate"}}, bit\_width{"32"}, edge\_trigger{"positive"}}}

Figure 3.6: Resource Declaration Window.

Figure 3.7: Example of Resource Declarations.

| Edit           |         |         |      |      |               |        |        |            |              |

|----------------|---------|---------|------|------|---------------|--------|--------|------------|--------------|

| last ru        | ct ium  | 739至 13 | xic. | R1   | type          |        |        |            | STAN ALSO    |

| 156 1          | 50 F    | ield M  | ġe:  | F.)  | leta l        | Atti   | Vatue  |            |              |

| 31             | 26      | 00-00   | de   | -    | bin           | ary -  | 0000   | 00         |              |

| 25             | 21      | Opera   | nd   | •    | nam           | e 🔻    | rs     |            |              |

| 20             | 16      | Opera   | nd   | *    | nam           | e 👻    | rt     |            |              |

| 15             | 11      | Opera   | nd   | •    | <i>1</i> 7309 | e 👻    | rd     |            |              |

| 10             | 6       | Reser   | ved  | -    | bin           | ary -  | 0000   | D          |              |

| 5              | 0       | OP-con  | de   | •    | nam           | e 🔻    | rfunct |            |              |

|                |         |         |      |      |               |        |        |            |              |

|                | 22      | OK      |      |      | Canc          | æ/     |        |            | Carles and a |

| nstru          | clion   | Inereni | ic.  | ADD  | )             |        |        | 1.5.2      |              |

| nstra          | ct i on | Pype .  |      | 1000 | 1.55          | Field  | Type   | Field Atts | Value        |

| type           |         |         |      | 31   | 26            | OP-CO  | de     | binary     | 000000       |

| type<br>type   |         |         |      | 25   | 21            | Operar | nd     | name       | rs           |

| 11 ype         |         |         |      | 20   | 16            | Operar | nd     | name       | rt           |

| type           |         |         |      | 15   | 11            | Operar | nd     | name       | rd           |

| Stype          | -       |         |      | 10   | 6             | Reserv | ed     | binary     | 00000        |

| 211000         | #1      |         | 1    | 5    | 0             | OP-co  | de     | binary     | 100000       |

|                |         |         |      |      |               |        |        |            |              |

| Ftype<br>Ttype |         |         | +    |      | 2             |        |        |            |              |

Figure 3.8: Instruction Format Definition Window.

selected among "op-code," "operand" and "reserved." "op-code" means operation code and "reserved" indicates that the field is reserved for extension in the future. Operation code value is specified when the value is constant for all instructions belongs to that type, and the value for reserved field is also specified.

Then, for each instruction, instruction type is selected among defined instruction types and operation code value is decided.

# Instruction\_type{ "R1type"{ "OP-code" {"binary" {"000000"}, width {"31", "26"}}, "Operand" {"name" {"rs"}, width {"25", "21"}}, "Operand" {"name" {"rt"}, width {"20", "16"}}, "Operand" {"name" {"rd" }, width {"15", "11" }}, "Reserved" {"binary" {"00000"}, width {"10", "6"}}, "OP-code" {"name" {"rfunct" }, width {"5", "0" } } } Instruction{ "Operand" {"name" {"rs"}, width {"25", "21"}}, "Operand" {"name" {"rt"}, width {"20", "16"}}, "Operand" {"name" {"rd" }, width {"15", "11" } }, "Reserved" {"binary" {"00000"}, width {"10", "6"}}, "OP-code" {"binary" {"100000"}, width {"5", "0"}}}

In micro-operation descriptions, bit field of the instruction is referred by the field name that is defined in instruction format definition phase. Modification of instruction format which includes varying instruction bit width, re-ordering instruction fields, changing operation code and so on do not require modification of microoperation description of instructions. When bit width, name and role of the field are not changed, there is no need to modify micro-operation description. Instruction code definition is used to generate instruction decoder, which is mentioned in Section 4.4.1 and Section 5.2.4.

In an example shown in Fig. 3.9, an instruction type "R1type" and an instruction "ADD" which belongs to "R1type" are defined. The instruction type "R1type" has

"ADD" {type{"R1type"}," OP-code" {"binary" {"000000"}, width {"31", "26"}},

Figure 3.9: Example of Instruction Format Definitions.

six instruction fields. The range of the first field is from "31" to "26." The type of the first field is "OP-code" and its value is constant "000000." The second and the third fields indicate register address of source operands and the forth field indicates destination register address. The fifth field is reserved for future extension. The last filed is an operation code for R1type instructions. The operation code for "ADD" is "100000."

## 3.3.4 Interrupt Condition Definitions

Figure 3.10 shows an interrupt condition definition window. Interrupt definitions include interrupt conditions and the number of execution cycles of the interrupt. In the example of interrupt "int0." Processor receives interrupt "int0" when external input port "INT" received '1', and needs one cycle to process the interrupt "int0."

| Exception       | Internal • External                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reset<br>init 0 | F of Execution cycles 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 | Behavior Description Constraint, assertion Compent Cause condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |