|              |                                                                                   |

|--------------|-----------------------------------------------------------------------------------|

| Title        | 電子1個の流れを制御するデバイス                                                                  |

| Author(s)    | 谷口, 研二; 桑村, 信博; 浜口, 智尋                                                            |

| Citation     | 大阪大学低温センターだより. 1994, 86, p. 6-9                                                   |

| Version Type | VoR                                                                               |

| URL          | <a href="https://hdl.handle.net/11094/4215">https://hdl.handle.net/11094/4215</a> |

| rights       |                                                                                   |

| Note         |                                                                                   |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

# 電子1個の流れを制御するデバイス

工学部 谷口研二、桑村信博、浜口智尋（吹田5012）

## 1. はじめに

今日の情報化社会を支えるコンピュータの心臓部はシリコン集積回路でできている。1チップに含まれる素子の数は加工技術の進歩によって過去15年間に100倍以上にもなり、シリコン集積回路に搭載されている素子の数は爆発的に増加している。この調子でシリコン集積回路が進歩するとその将来は極めて明るいはずであるが、21世紀頃にはチャネル長 $0.1\mu\text{m}$ のMOS型電界効果トランジスタが原理的限界に突き当たってしまうという暗い予測もある。本研究ノートではこのようなMOS素子の原理限界を打破する有望な候補として注目されている単一電子トンネル素子を取り上げる。

## 2. 単一電子トンネル素子の動作原理

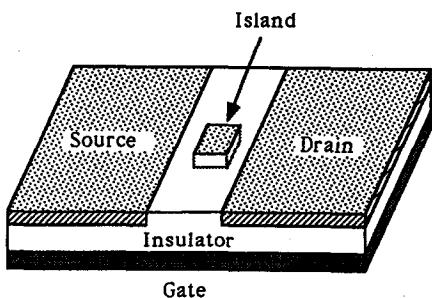

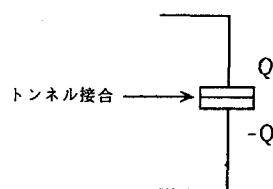

高校時代に習った物理の教科書には「キャパシタCの電極に電荷Qを載せると電極間には $V=Q/C$ の電圧が現れる」という記述がある。もしキャパシタの容量Cが $0.1\text{ aF}$  ( $1 \times 10^{-19}\text{ F}$ ) 程度の小さな値であると仮定すれば、たった1個の電子をキャパシタ電極に載せただけで1V以上の電圧が電極の間に現れる。さらに、このキャパシタの絶縁膜がトンネル酸化膜であるならば、構造に特有な電気的特性を持つ素子ができる可能性がある。Likharevはこのように考えて単一電子トンネル素子なるものを提案した<sup>1)</sup>。図1に示す単一電子トンネル素子は従来のMOS型素子と構造的に類似しているが、(1)2個のトンネル接合と(2)その間に挟まれた島部分のあることが相違点である。この素子のドレインに正電圧を印加しゲート電圧を適当に選べば、電子がソース側からトンネル接合を通り抜けて中央の島に入り、その後ドレイン側へ抜けてゆくように調整することができる。このようにソース電極から出た電子が1個ずつ中央の島に立ち寄り、最終的にドレイン電極に抜けてゆく過程は、小学校の遠足で児童が一人一人飛び石を通りながら川を渡る様子に似ている。この電子を一つ一つ流す機構はクーロンブロックエイドとよばれる現象に基づいている。図2に示すように微小なキャパシタ（電子がトンネルできる程度

図1 単一電子トンネル素子の基本構造

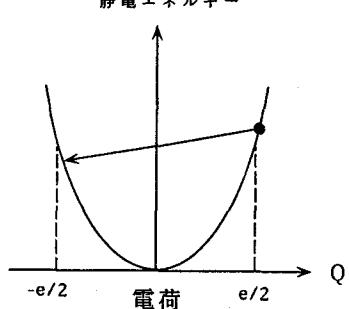

図2 単一電子トンネル素子の基本動作原理

の薄い絶縁膜が電極間に挟まれている)に蓄えられた静電エネルギーは電荷量の2乗に比例して大きくなる。蓄積電荷がある程度大きくなると電子が1個トンネルしてキャパシタ電極上の電荷量を減らした方が静電エネルギーは得をする。ただし、トンネルする電子の電荷  $e$  が  $1.6 \times 10^{-19} \text{ C}$  で量子化されることを考慮すると、蓄積電荷量  $Q$  が  $\pm e / 2$  の間にあるときにはトンネルしない方が安定である。すなわち、印加電圧が  $\pm e / 2 \text{ C}$  の間では電子のトンネルが起こらない(電流が流れない)。このように電子の固有の電荷量が原因で微小キャパシタを電子がトンネルできなくなる現象をクーロンブロックエフェクトとよんでいる。

### 3. 回路シミュレーションによる疑似 CMOS 回路解析

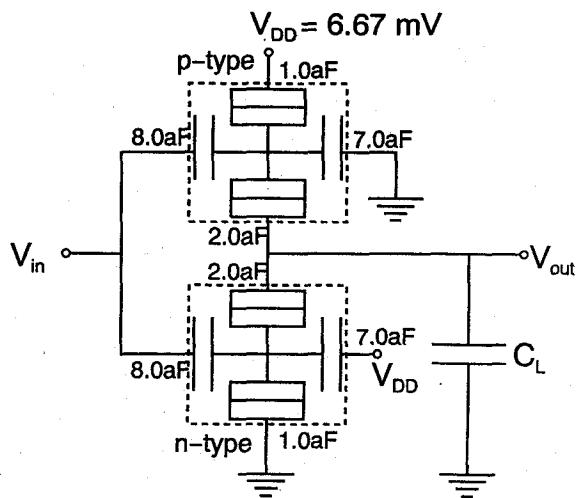

図3はイリノイ大学で考案された単一電子トンネル素子を使った疑似 CMOS インバータの構造である<sup>2)</sup>。我々はこのインバータの動作を確認するために、モンテカルロ法による単一電子トンネル回路シミュレータを作成して回路特性の解析をおこなった。疑似 MOSFET の基本構造は点線で囲まれた2個のトンネル接合と2個の通常キャパシタから成る4個のキャパシタの組で構成される。

今回のシミュレーションではキャパシタンスの容量は図3に示した値を用い、電源電圧は  $V_{DD} = e / 24aF \sim 6.67 \text{ mV}$  とした。トンネル接合のトンネル抵抗はす

図3 単一電子トンネル素子を組み合わせた疑似 CMOS インバータ

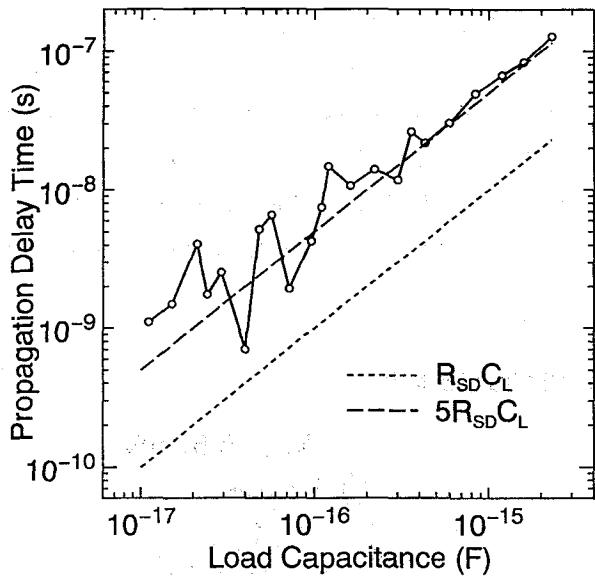

べて  $5 \text{ M}\Omega$  で動作温度は  $51.6 \text{ mK}$  (静電エネルギーの  $1/1000$ ) である。図4にインバータ回路のゲート遅延時間を負荷容量の関数として示した。ソース・ドレイン間の抵抗を  $R_{SD}$  ( $= 2R_T$ ) とすると、図よりインバータのスイッチング時間は従来のゲート回路で予測される時定数  $R_{SD}C_L$  より大きいことが分かる。これは、素子の寸法が極端に小さくなるとクーロンブロックエフェクトの発現によってソースードレイン間の実効的な抵抗がトンネル抵抗  $R_{SD}$  より大きくなるからである。シミュレーションによるトンネル頻度からソースードレイン間の実効的な抵抗を見積もると  $R_{SD}$  の約5倍となる。今回の計算ではトンネル抵抗として  $5 \text{ M}\Omega$  を用いたが、実際には数百  $\text{k}\Omega$  のトンネル抵抗でクーロンブロックエフェクト現象が観測されていることを考慮すると、スイッチング時間は図に示された値より1桁以上短くすることは可能である。さらに負荷容量を小さくして電子1個の有無で1ビットを表すことにすれば、疑似 CMOS インバータ回路で約  $10 \text{ ps}$  のゲート遅延時間を得ることができる。

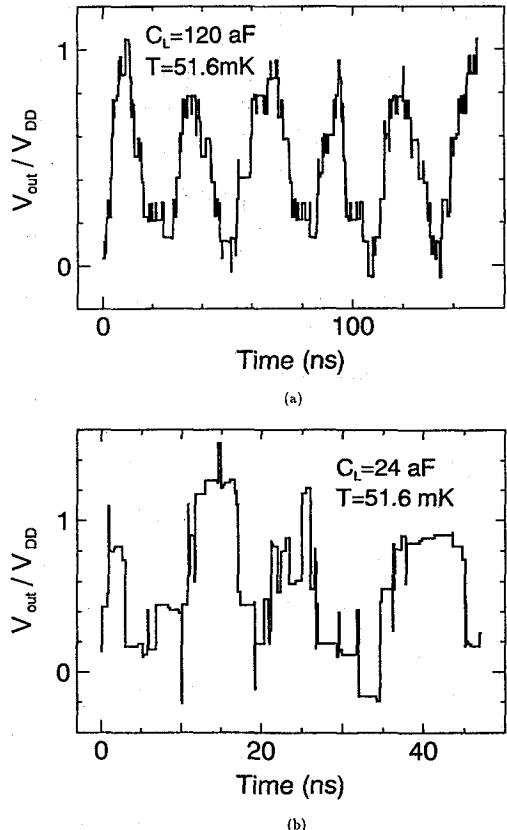

図5は疑似 CMOS インバータ回路を3段接続したリングオシレータの出力を示す。図5(a)、(b)はそれぞれ負荷容量として  $120 \text{ aF}$ 、 $24 \text{ aF}$  を用いたものである。図5(a)は電子5個で1ビットを表す回路である。インバータ出力の論理振幅はフルスイシングしないものの、何段つないでも振幅の減少はある程度

図4 負荷容量の関数として示した疑似インバータ回路のゲート遅延時間

図5 疑似 CMOS インバータを 3段接続したリングオシレータの出力波形。(a)、(b)はそれぞれ負荷容量が 120 aF、24 aF

で抑えられることが分かる。図5(b)で発振周期にムラが目立つのは(1)1ビットを1個の電子で表しているために、個々の電子のトンネル時間のばらつきが周期ムラとなって現れるためと(2)小さな負荷容量の場合には次段ゲートの各節点における電子配置がトンネル頻度に影響を及ぼすからである。

この他、限界動作温度についても考察をおこなった。その結果、 $k_B T$ が  $e^2 / 2C_T$  のおよそ 1/20 以下となる温度にしなければならないことが分かった。すなわち上述の超高密度の集積回路が 300 K で安定した動作を行うためには  $C_T / 0.16 \text{ aF}$  という小さな単一電子素子が必要であることが分かる。

以上の回路シミュレーションの結果から疑似 CMOS 回路の特徴として、(1)微細化すれば雑音に対する耐性は高い、(2)CMOS 論理回路で培ってきた設計論の延長で単一電子によるデジタル回路を構成することができる、(3)ゲート当たりの遅延時間・消費電力積は従来の CMOS 回路の 5 倍以上小さくできるなどが分かった。

## 5. むすび

たった 1 個 1 個の電子を操作しながら情報処理をする夢の単一電子トンネル電子回路も数 nm オーダーの超微細加工ができるはじめて本格的な研究開発の段階に移ることができる。このためには現在の微細加工技

術をさらに1～2桁進めることができる画期的な技術の開発が不可欠である。数nmレベルの微細加工が可能になると1チップ当たり100Gゲートもの超高集積システムができることになるが、これだけのゲートが全て満足に動作することはあり得ず、適当な割合で不良素子があることを前提とした回路設計を行わなければならない。このように単一電子トンネル素子のネガティブな側面は幾つか考えられるが、それ以上に素子がもつ良い側面もある。単一電子トンネル素子で不良ゲートが不可避なら、従来の決定論的な論理回路から飛躍してニューラルネットワークなどのあいまいな論理への応用を考えることも一法である。また、従来の素子と動作原理が違っているだけに、全く新しい電子回路が実現できる可能性がある。

### 参考文献

- 1) K. K. Likharev: "Correlated discrete transfer of single electrons in ultrasmall tunnel junctions," IBM J. Res. & Dev. 32, pp. 144-158 (1988).

- 2) J. R. Tucker: "Complementary digital logic based on the Coulomb Blockade", J. Appl. Lett., 72, 4399 (1992).