|              |                                                                                 |

|--------------|---------------------------------------------------------------------------------|

| Title        | 光・電子融合型マルチプロセッサシステムに関する研究                                                       |

| Author(s)    | 香川, 景一郎                                                                         |

| Citation     | 大阪大学, 2001, 博士論文                                                                |

| Version Type | VoR                                                                             |

| URL          | <a href="https://doi.org/10.11501/3184224">https://doi.org/10.11501/3184224</a> |

| rights       |                                                                                 |

| Note         |                                                                                 |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

光・電子融合型マルチプロセッサ

システムに関する研究

2000年

香川景一郎

## 略語対応表

|         |                                                         |

|---------|---------------------------------------------------------|

| AOD     | acousto-optic beam deflector                            |

| BER     | bit error rate                                          |

| bps     | bit per second                                          |

| BS      | beam splitter                                           |

| CAD     | computer-assisted design                                |

| CAM     | computer-assisted manufacturing                         |

| CGH     | computer generated hologram                             |

| CMOS    | complementary metal oxide semiconductor                 |

| CMOS-PD | complementary metal-oxide-semiconductor photodetector   |

| CPLD    | complex programmable logic device                       |

| DCP     | discrete correlation processor                          |

| FLC-SLM | ferro-electric liquid crystal spatial light modulator   |

| I/O     | input/output                                            |

| IT      | information technology                                  |

| LIGA    | lithographie galvanoformung abformung                   |

| LED     | light emitting diode                                    |

| MEMS    | micro-electro-mechanical systems                        |

| ML      | microlens                                               |

| MOEMS   | micro-opto-electro-mechanical systems                   |

| MSM-PD  | metal-semiconductor-metal photodetector                 |

| MQW     | multiple quantum well                                   |

| OE-VLSI | optoelectronic very large scale integration             |

| PAL-SLM | parallel-aligned liquid crystal spatial light modulator |

| PBS     | polarized beam splitter                                 |

| PD      | photodetector                                           |

| PE      | processing element                                      |

| PM      | parallel matching                                       |

| PMA     | parallel matching architecture                          |

| PML     | planar microlens                                        |

| PM-SPA  | parallel matching smart-pixel array                     |

| SEED    | self-electro-optic effect device                        |

| SOI     | silicon on insulator                                    |

| SLM     | spatial light modulator                                 |

| SON     | silicon on nothing                                      |

| SPA     | smart-pixel array                                       |

| ULSI    | ultra large scale integration                           |

| VCSEL   | vertical-cavity surface-emitting laser                  |

| VLSI    | very large scale integration                            |

---

## 目 次

|                                             |           |

|---------------------------------------------|-----------|

| 緒論                                          | 1         |

| <b>1 光・電子融合型マルチプロセッサシステムアーキテクチャ</b>         | <b>4</b>  |

| 1.1 緒言 . . . . .                            | 4         |

| 1.2 光・電子融合型コンピュータ . . . . .                 | 4         |

| 1.2.1 OE-VLSI を用いたチップ間光接続 . . . . .         | 4         |

| 1.2.2 マルチプロセッサシステムにおける光接続の利用 . . . . .      | 6         |

| 1.2.3 自由空間光接続 . . . . .                     | 6         |

| 1.2.4 自由空間光学系の実装技術 . . . . .                | 6         |

| 1.2.5 自由空間光接続を用いたマルチプロセッサシステム . . . . .     | 8         |

| 1.3 大域処理指向光・電子融合型マルチプロセッサシステム . . . . .     | 9         |

| 1.3.1 大域処理と帯域幅不整合 . . . . .                 | 9         |

| 1.3.2 自由空間光接続を利用した大域処理の高速化アーキテクチャ . . . . . | 10        |

| 1.4 技術課題と本研究との対応 . . . . .                  | 12        |

| 1.5 結言 . . . . .                            | 12        |

| <b>2 離散相関プロセッサ DCP-1</b>                    | <b>14</b> |

| 2.1 緒言 . . . . .                            | 14        |

| 2.2 離散相関プロセッサ . . . . .                     | 14        |

| 2.2.1 アーキテクチャ . . . . .                     | 14        |

| 2.2.2 離散相関演算への符号化の導入 . . . . .              | 16        |

| 2.3 DCP-1 プロトタイプ . . . . .                  | 17        |

| 2.3.1 DCP-1S と DCP-1D . . . . .             | 17        |

| 2.3.2 デバイス . . . . .                        | 18        |

| 2.3.3 CGH フィルタ . . . . .                    | 19        |

| 2.3.4 VCSEL の駆動 . . . . .                   | 21        |

| 2.3.5 光学系の光量効率 . . . . .                    | 21        |

| 2.4 実験結果 . . . . .                          | 23        |

---

|          |                                          |           |

|----------|------------------------------------------|-----------|

| 2.4.1    | 静的特性 . . . . .                           | 23        |

| 2.4.2    | 動的特性 . . . . .                           | 24        |

| 2.5      | 考察 . . . . .                             | 25        |

| 2.6      | 結言 . . . . .                             | 25        |

| <b>3</b> | <b>離散相関プロセッサ DCP-2</b>                   | <b>26</b> |

| 3.1      | 緒言 . . . . .                             | 26        |

| 3.2      | DCP-2 . . . . .                          | 26        |

| 3.2.1    | アーキテクチャ . . . . .                        | 26        |

| 3.2.2    | プロトタイプに用いたデバイス . . . . .                 | 28        |

| 3.3      | 光学系の構成 . . . . .                         | 28        |

| 3.3.1    | 光学系設計 . . . . .                          | 30        |

| 3.3.2    | 最大入力点数 . . . . .                         | 31        |

| 3.4      | プロトタイプ . . . . .                         | 32        |

| 3.4.1    | AOD . . . . .                            | 32        |

| 3.4.2    | VCSEL 放射角の低減 . . . . .                   | 33        |

| 3.4.3    | プロトタイプのシステムパラメータ . . . . .               | 34        |

| 3.5      | 実験結果 . . . . .                           | 35        |

| 3.5.1    | 光学系 . . . . .                            | 35        |

| 3.5.2    | 静的特性 . . . . .                           | 35        |

| 3.5.3    | 動的特性 . . . . .                           | 37        |

| 3.6      | 考察 . . . . .                             | 39        |

| 3.7      | 結言 . . . . .                             | 40        |

| <b>4</b> | <b>並列マッチングアーキテクチャ</b>                    | <b>41</b> |

| 4.1      | 緒言 . . . . .                             | 41        |

| 4.2      | 並列マッチングアーキテクチャ . . . . .                 | 41        |

| 4.2.1    | 分散最適化アルゴリズム . . . . .                    | 41        |

| 4.2.2    | 分散最適化アルゴリズムに適したマルチプロセッサアーキテクチャ . . . . . | 43        |

---

|                                  |           |

|----------------------------------|-----------|

| 4.2.3 並列マッチング処理                  | 44        |

| 4.2.4 光・電子融合型マルチプロセッサシステムの構成     | 47        |

| 4.3 光・電子融合型並列マッチング処理             | 48        |

| 4.4 性能評価                         | 52        |

| 4.4.1 評価モデル                      | 52        |

| 4.4.2 通信帯域                       | 54        |

| 4.4.3 基本大域処理の評価                  | 56        |

| 4.4.4 比較                         | 58        |

| 4.5 プロトタイプによるアーキテクチャのデモストレーション   | 60        |

| 4.5.1 並列マッチングの方式                 | 60        |

| 4.5.2 システム構成                     | 60        |

| 4.5.3 並列マッチングクラスタ                | 62        |

| 4.5.4 CGH フィルタの設計・作製             | 64        |

| 4.6 プロトタイプの動作実験結果                | 65        |

| 4.6.1 VCSEL と CMOS 受光素子の駆動       | 65        |

| 4.6.2 並列マッチング処理                  | 67        |

| 4.7 考察                           | 69        |

| 4.8 結言                           | 70        |

| <b>5 光造形技術を用いた光学系実装技術</b>        | <b>72</b> |

| 5.1 緒言                           | 72        |

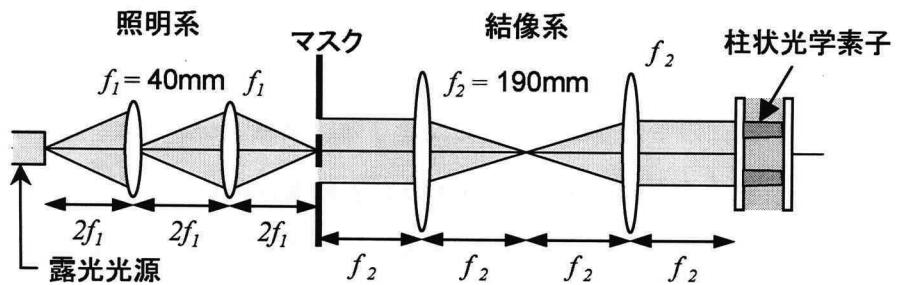

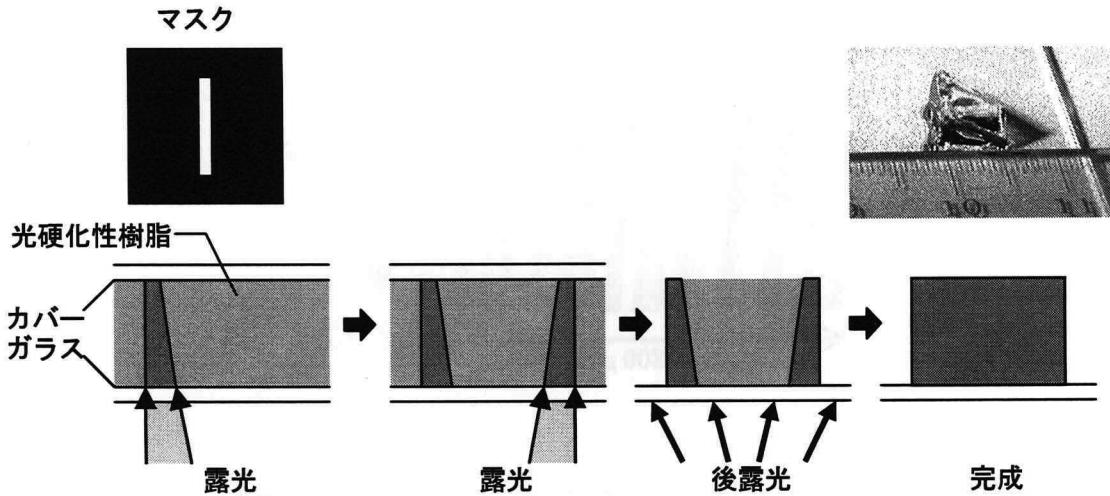

| 5.2 光造形技術を応用した光学系の作製             | 72        |

| 5.2.1 光造形技術                      | 72        |

| 5.2.2 光造形装置への光学素子作製機能の組み込み       | 74        |

| 5.3 光ベースプレート                     | 76        |

| 5.3.1 マイケルソン干渉計用光ベースプレート         | 77        |

| 5.3.2 考察                         | 78        |

| 5.4 2.5 次元光学系の作製                 | 80        |

| 5.4.1 積層型マスク露光法を用いた 2.5 次元光学系の作製 | 80        |

---

|                                          |            |

|------------------------------------------|------------|

| 5.4.2 実験                                 | 81         |

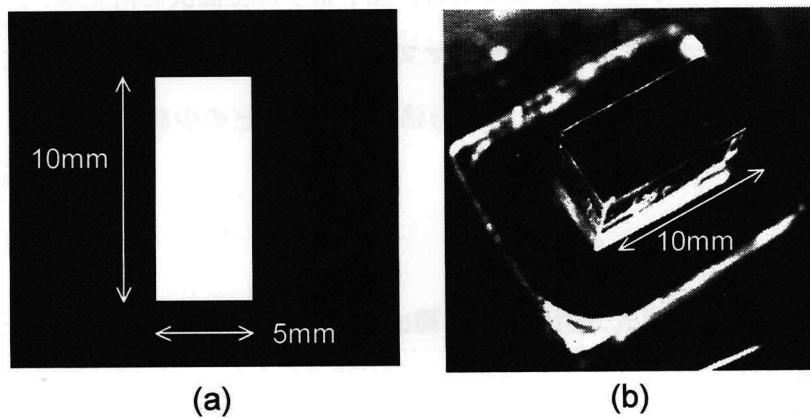

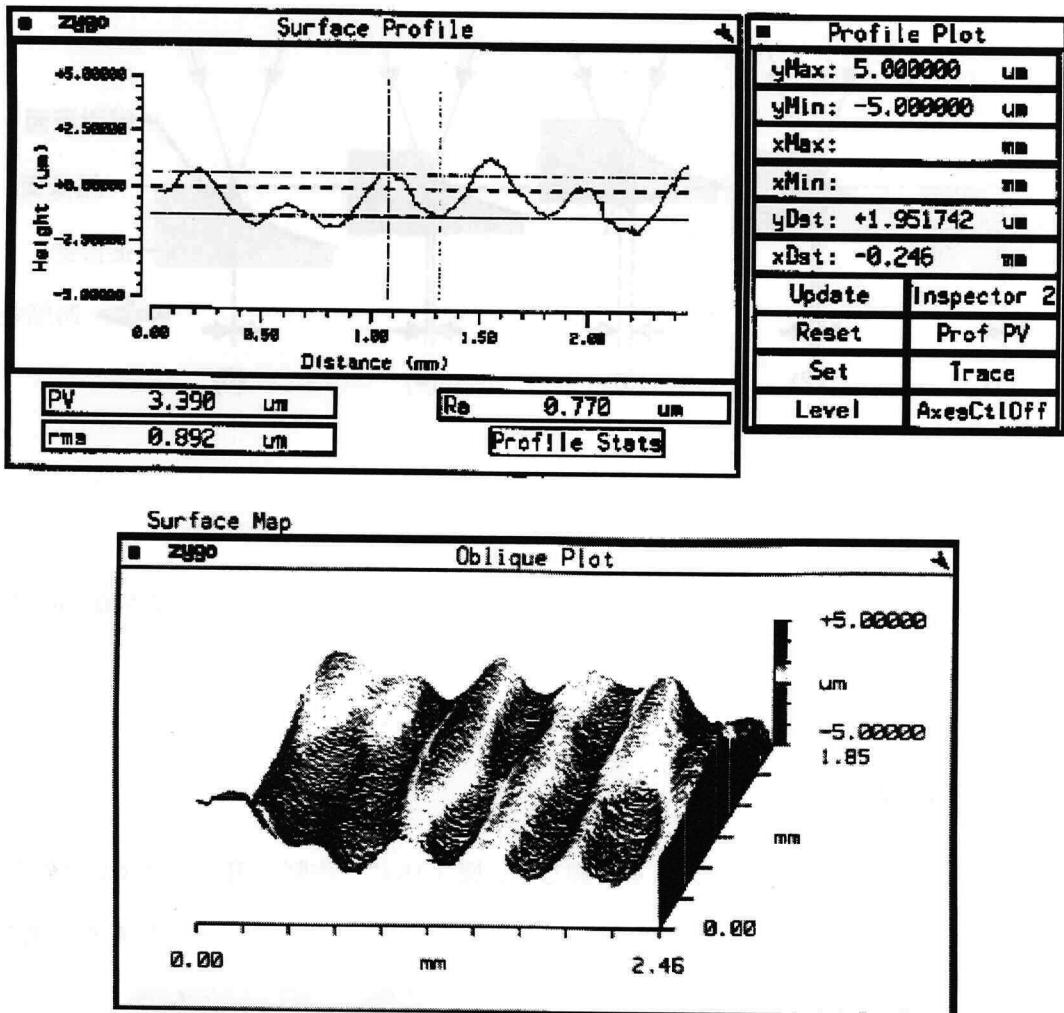

| 5.4.3 表面精度                               | 82         |

| 5.4.4 直角プリズム                             | 84         |

| 5.4.5 プリズムビームエキスパンダー                     | 85         |

| 5.4.6 考察                                 | 87         |

| 5.5 結言                                   | 88         |

| <b>6 総括</b>                              | <b>90</b>  |

| <b>謝辞</b>                                | <b>93</b>  |

| <b>参考文献</b>                              | <b>95</b>  |

| <b>付録 A. VLSI の現状</b>                    | <b>102</b> |

| <b>付録 B. フーリエ変換レンズの設計</b>                | <b>104</b> |

| <b>付録 C. CGH フィルタの設計</b>                 | <b>107</b> |

| <b>付録 D. DCP-2 光学系パラメータの設計</b>           | <b>109</b> |

| <b>付録 E. 並列マッチングアーキテクチャの基本大域処理アルゴリズム</b> | <b>113</b> |

| <b>発表論文一覧</b>                            | <b>115</b> |

---

## 緒論

インターネットは、商用目的の利用が認められると同時に爆発的に普及し、IT (information technology) 革命と呼ばれる未曾有の一大社会現象が起こった。金融・流通などの商業システムは変貌し、政治・経済を含めた社会システムにも大変革が起こりつつある。IT 革命は、シリコン VLSI (very large scale integration) 技術とソフトウェア技術を基盤としたパーソナルコンピュータの進歩と、広域ネットワークの進歩によりもたらされた。高度情報化の流れは、インターネットの普及により個人レベルまで浸透し、社会に対する個人の価値観が大きく変わりつつある。多様な個性と嗜好をもった個人が無数のコミュニティを形成し、強い発言力と存在感を示すようになる。その結果、個人が社会を動かす時代が到来すると予想される。一方で、個人が扱わなければならぬ情報量は肥大化を続け、近い将来、人間の能力の限界を超える。パーソナルコンピュータは、情報にアクセスするための端末としての存在から、全世界に散在する膨大な情報を管理・解釈し、必要なデータを抽出するための第 2 の脳としての役割を強くして行くものと思われる。その結果、ネットワーク負荷は増加し続け、コンピュータに要求される処理能力も増加の一途を辿ると予想される。インターネットのコンテンツ提供側は、質の高い情報サービスを提供する上で、大容量高速処理を可能にするマルチプロセッサシステム [1-6] の重要性が、現在以上に高まって行くだろう。

今日の情報処理の担い手は、汎用電子プロセッサである。その一方で、1970 年代から研究されてきた光コンピューティング [7-11] は、レンズのフーリエ変換作用と結像を基本とした自由空間光学系の超高速・超並列情報処理を特徴とし、潜在的な情報処理能力の高さから、精力的に研究がなされてきた [12]。近年、光コンピューティングにおけるデバイス研究が結実し始め、半導体や有機非線型デバイスなどの高性能光デバイスを利用できるようになってきた [13, 14]。また、小型の超短光パルスレーザや、高性能な非線型光学結晶も開発されている [15]。このような状況は、光コンピューティングシステムの実現に対する力強い支援となっている。

光コンピュータ研究の中で、最も実用化に近い技術が、光接続である [16]。今日までの汎用電子プロセッサ進化の歴史を振り返ると、幾度となく限界が指摘されながらも [17-19]、ムーアの法則に従い着実に性能を向上させてきた [20]。今後も VLSI は、微細化によるトランジスタの動作限界に達するまで集積度は高まり、動作速度は高速化し続けると予想される。しかし、残念ながらそれは集積回路上 (オンチップ) に限った話であり、集積回路の外 (オフチップ) に対しては集積化の恩恵が得られない。オフチップに関する問題は、VLSI の I/O ボトルネックとして、広く認識され

---

ている。オフチップ信号の周波数は、オンチップ信号の数分の1にすぎず、チップから入出力できる信号数も限られている。この問題を解決するのが、チップ間光接続である。光は電気信号とは異なり、配線の時定数の影響を受けない。そのため、自由空間・光導波路などのいずれの伝送路に対しても、高速に信号を伝送できる。光接続のキーデバイスは OE-VLSI (optoelectronic VLSI) またはスマートピクセルとよばれる光・電子融合型デバイスである [21]。OE-VLSI は、VLSI チップ上に発光素子（または光変調素子）と受光素子を集積したデバイスである。OE-VLSI を用いることにより、オフチップ性能を飛躍的に向上できる。システム実装性の点から、実用化に向けた光接続の主流は、光導波路を用いた方式である。その一方で、自由空間方式のもつ大きな情報処理能力に着目した研究が、盛んになされている。

自由空間光接続特有の利点は、大きい空間帯域幅積、大ファンアウト性 [22–24]，信号の並列組み換え性である。空間帯域幅積が大きいことは、多数の光信号を並列的に扱えることを意味し、この特長を利用したマルチプロセッサシステム向けの光ネットワークシステムが多く試作されている [25–29]。また、大ファンアウト性を利用し、電子技術では実装の難しい大規模な光クロスバーネットワーク [30] や、並列的組み替え可能性を利用したソーティングシステム [31] が試作されている。

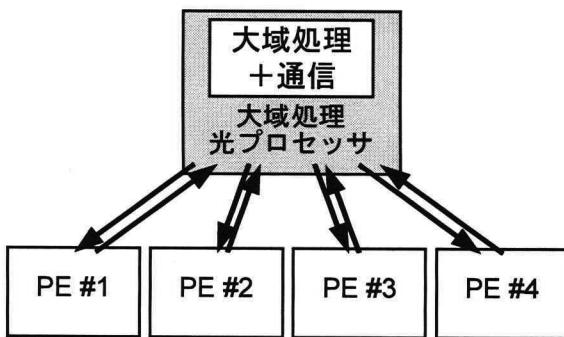

自由空間光接続はその独特な特長故に、マルチプロセッサシステムのアーキテクチャ自体を革新し、従来アーキテクチャでは到達し得ない高速演算を実現する能力をもっている。大阪大学の谷田らにより、局所的処理を行う並列電子プロセッサと、大域処理を行う光プロセッサから構成される協調的マルチプロセッサシステムアーキテクチャが提案されている [32–34]。このアーキテクチャは、電子プロセッサと光プロセッサを、局所処理と大域処理のそれぞれに特化し、協調的に処理を行うことにより、大きな性能を生み出す。

本研究の目的は、大域処理光プロセッサを中心とした光・電子融合型マルチプロセッサシステムアーキテクチャを開発し、最新の光・電子デバイスを利用したプロトタイプの構築を通して、アーキテクチャの有効性を実証することである。自由空間光接続の特長を活用したマルチプロセッサシステムアーキテクチャとして、並列マッチングアーキテクチャを提案する。このアーキテクチャは、分散最適化アルゴリズムの実行を高速化する。光・電子融合型マルチプロセッサシステムの中心的な構成要素として、汎用的な光プロセッサを作製する。光プロセッサのアーキテクチャとして、離散相関プロセッサ (DCP) アーキテクチャと、それを改良した DCP-2 アーキテクチャを

---

提案し，プロトタイプを試作する。DCP プロトタイプを利用し，並列マッチングアーキテクチャのプロトタイプシステムを構築する。また，自由空間光接続システムの実装問題を解決する方法として，光造形技術 [35-39] を応用した光学系作製技術を提案し，基礎実験を示す。

第 1 章では，OE-VLSI を用いた光・電子融合型コンピュータの特長を述べる。大域処理プロセッサを中心としたマルチプロセッサシステムアーキテクチャの有効性を述べ，自由空間光接続を用いた大域処理光プロセッサについて述べる。

第 2 章では，自由空間光接続を用いた光・電子融合型マルチプロセッサシステムの基本モジュールである光プロセッサのアーキテクチャとして，DCP アーキテクチャを提案する。このアーキテクチャに基づき，DCP-1 プロトタイプを試作する。

第 3 章では，DCP アーキテクチャを改良した DCP-2 アーキテクチャを提案する。プロトタイプを試作し，提案アーキテクチャの有効性を示す。

第 4 章では，自由空間光接続を用いた光・電子融合型マルチプロセッサアーキテクチャとして，並列マッチングアーキテクチャを提案する。提案アーキテクチャをモデル化し，性能評価を行う。また，DCP-1 プロトタイプを応用したプロトタイプシステムを試作し，動作確認を行う。

第 5 章では，自由空間光接続の実用化に不可欠な光学系実装技術として，光造形技術を応用した光学系作製技術を提案し，基礎実験を行う。

## 1. 光・電子融合型マルチプロセッサシステムアーキテクチャ

### 1 光・電子融合型マルチプロセッサシステムアーキテクチャ

#### 1.1 緒言

本章では、自由空間光接続を利用した光・電子融合型マルチプロセッサアーキテクチャについて述べる。このアーキテクチャは、局所処理を行う複数の電子プロセッサと大域処理を行う光プロセッサの協調処理により、従来の電子マルチプロセッサシステムを超える処理性能の実現を目指す。

光接続は、シリコン VLSI 間のデータ伝送帯域を飛躍的に向上する技術として期待されている。自由空間光接続は、大きい空間帯域幅積、非干渉性、大ファンアウト性、並列的な信号組み換え性などをもち、高速光ネットワークの実現に有望視されている。さらに、自由空間光接続はその優れた特長から、コンピュータシステムのアーキテクチャを革新し、光技術と電子技術を融合した高性能マルチプロセッサシステムを実現する潜在能力を有している。

1.2 節では、VLSI のオフチップ性能を向上する技術として、OE-VLSI を用いたチップ間光接続について述べ、これを用いた光・電子融合型コンピュータを示す。1.3 節では、大域処理光プロセッサを利用した光・電子融合型マルチプロセッサシステムアーキテクチャについて述べる。1.4 節では、自由空間光接続を用いた光・電子融合型システムを実現するために必要となる要素技術について述べる。

#### 1.2 光・電子融合型コンピュータ

##### 1.2.1 OE-VLSI を用いたチップ間光接続

VLSI または ULSI (ultra large scale integration) チップ間の接続に光を利用する光接続は、チップ間接続のデータ伝送帯域を飛躍的に向上する技術として、精力的に研究されている。チップ間光接続では、スマートピクセルと呼ぶ光・電子融合型 VLSI (OE-VLSI: optoelectronic VLSI) を用いる [16, 21, 40]。OE-VLSI は、半導体集積回路上に発光素子（または光変調素子）と受光素子を複合集積したデバイスである。チップ間接続に光を導入することにより、次の利点がもたらされる。光接続では電気配線の時定数に相当するものが存在しないため、配線長に依存せず数 GHz を超える信号を扱える。また、電磁的な輻射の問題がなく、電磁ノイズの影響もうけにくい。数 GHz 以上の高周波領域では、電気配線と比較して光接続の方が消費電力が少なくなる [41]。従来

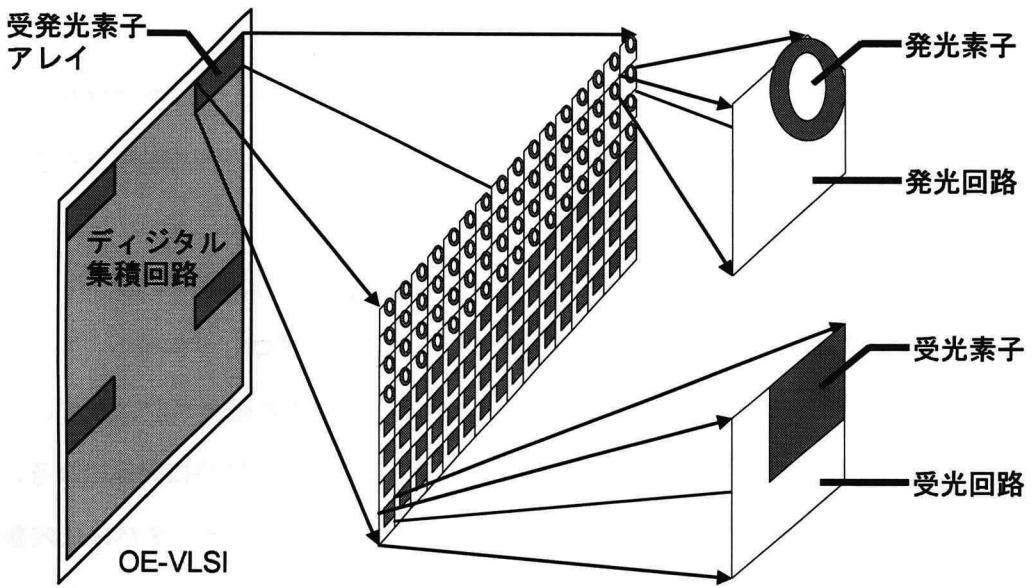

図 1.1: OE-VLSI の構造の例。

の VLSI では、OE-VLSI では光入出力ポートを VLSI 面上に 2 次元的に高密度に配置できるため、数 1,000 を超える I/O 数を実現できる [28] .

現在、OE-VLSI に用いられている代表的な発光・変調・受光素子をとして次が挙げられる。発光素子としては、面発光レーザ (VCSEL: vertical-cavity surface-emitting laser) [42, 43] や、LED (light emitting diode) [44, 45] などがある。VCSEL は使用する波長に応じて、GaN 系 ( $0.3\mu\text{m}$ - $0.6\mu\text{m}$ )、GaAs 系 ( $0.78\mu\text{m}$ - $1.3\mu\text{m}$ )、InP 系 ( $1.2\mu\text{m}$ - $1.6\mu\text{m}$ ) の材料が用いられており、広い波長域に対応できる。VCSEL は、動作速度として 7.8GHz [46]、ピクセル数は並列アクセス方式で  $16 \times 16$  画素 [47]、マトリックスアクセス方式で  $64 \times 64$  画素 [48] が報告されている。光変調素子としては、SEED (self-electro-optic effect device) [49, 50] や偏光回転型素子 [51] がある。SEED を用いたスマートピクセル作製技術は成熟しており、シリコン CMOS VLSI に複合集積した場合で、チャネル密度  $28,000$  チャネル/ $\text{cm}^2$ 、動作速度 500MHz が報告されている。この動作速度は、CMOS トランジスタの動作速度の限界によるものである。また、受光デバイスとして、MSM (metal semiconductor metal) 受光素子 [52] が広く用いられている。一方、通常のシリコン CMOS プロセスによりディジタル回路と同時に作製できることから、寄生 pn 接合を用いた MOS (metal oxide semiconductor) 型受光素子も利用されるが、受光感度が悪く、高速通信には向いていない。そのため、主にイメージセンサー応用に用いられている [53, 54] .

## 1. 光・電子融合型マルチプロセッサシステムアーキテクチャ

---

### 1.2.2 マルチプロセッサシステムにおける光接続の利用

光接続は、マルチプロセッサシステムを高速化するために有効である。マルチプロセッサシステムは、ネットワークを介して接続した複数の汎用プロセッサを用いて並列処理を行うことにより、高い処理性能を実現する [1-6]。マルチプロセッサシステムの性能は、ネットワークトポロジー、ネットワークの通信帯域幅、タスクスケジューリング方式、メモリアーキテクチャなど多くの要素から決まるが、特にネットワークの通信帯域幅は重要である。プロセッサ間の通信速度を飛躍的に向上するために、マルチプロセッサシステムに光接続を導入する研究がなされている [32, 55-57]。VLSI の I/O ボトルネックは、マルチプロセッサシステムにおいて特に問題になる。マルチプロセッサシステムに光接続を導入することにより、プロセッサの外部データバスに内部データバスと同等の性能をもたせることが可能になり、劇的な処理性能の改善が期待される。

### 1.2.3 自由空間光接続

OE-VLSI 間の接続には、自由空間光学系、光導波路、光ファイバなどが用いられる。自由空間光学系は、他の方式にはない高速情報処理に有望な特長をもっている [58]。自由空間光学系に特有な特長として、大きい空間帯域幅積、大ファンアウト性 [22-24]、光信号の並列的組み換え性がある。結像系などの自由空間光学系は大きい空間帯域幅積をもち、理想的には光の回折限界により規定される高密度接続を可能にする。ホログラム、プリズムやレンズアレイなどの微小光学素子 [59]などを用いることにより、1 点からの光信号を多点に分岐することができる。これは、ファンアウトとよばれる。逆に、多点からの光信号を 1 点に集中することもでき、これはファンインとよばれる。自由空間光接続は、他の方式のように物理的な配線を必要とせず、自由空間中の光伝播を利用して OE-VLSI 間の接続を行う。光導波路などの場合、複数の配線を交差させることは困難であるが、自由空間光接続の場合、原理的にはどれだけ多くの光信号が交差しても問題は生じない。したがって、多数の光信号の配列を組み替えることができる。

### 1.2.4 自由空間光学系の実装技術

自由空間光接続では、多数の光学素子に対して、3 次元的な精密位置合わせが必要である。そのため、自由空間光接続に特化した光学システム実装技術の研究が、多くなされている。特に、回

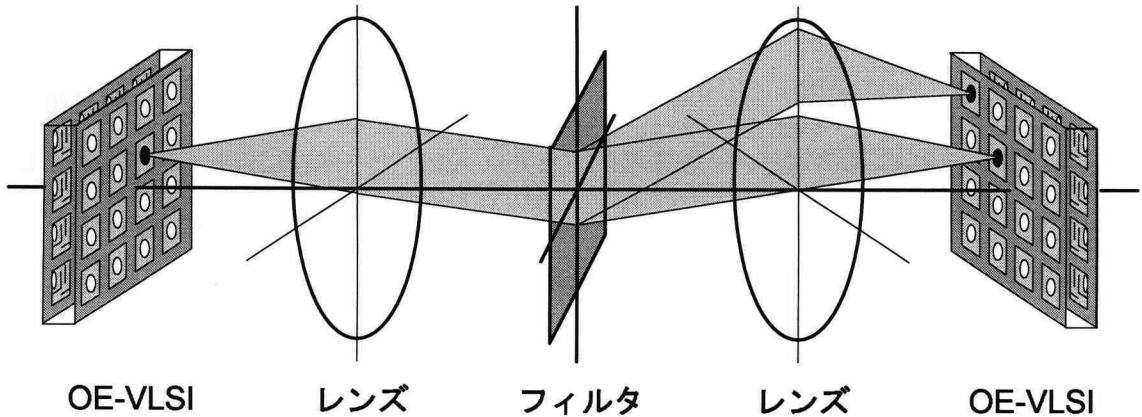

図 1.2:  $4f$  相関光学系を用いた自由空間光接続システムの例.

折光学素子 [60, 61] , 屈折率分布型光学素子 [62] , 光マイクロマシン [63–68] などに代表される近年の微小光学 [69, 70] の発展は, 自由空間光学系の実装技術の向上に大きく貢献した. 実用化に向けて特に有望な自由空間光学系の実装技術に, プレーナ光学系 [71, 72] がある. これは, 自由空間光学系を反射型にして折りたたむことにより, ガラス板内部に自由空間光学系を作製する技術である. 光学素子は, 半導体リソグラフィ技術を用い, 回折光学素子としてガラス板表面に作り込む. 可動部がなく, 光学系を完全に固体化するため, 機械的安定性に優れている. 実用化を考えると, 量産性が高いことも重要な特長である. その他の光学系実装技術として, 反射型ブロック光学系 [73] , スロット光学系 [74] , アクリルブロック光学系 [75] などがある. また, 受・発光素子と光学素子のカップリングのために, 様々な精密位置決め手法が提案されている [76–83] .

自由空間光接続システムの例を図 1.2 に示す. これは  $4f$  相関光学系を用いた例である [12] . OE-VLSI から出力した光を, フーリエ面に配置した回折光学素子で波面を操作してファンアウトし, 反対側に配置した異なる OE-VLSI で受光する. 回折光学素子のかわりに, 位相分布を変更できる空間光変調器 (SLM: spatial light modulator) を利用すると, 光接続パターンを動的に変更でき, 自由度の高いシステムを構築できる. 現在よく用いられている SLM には, ネマティック液晶 [84] , 強誘電性液晶 (FLC: ferroelectric liquid crystal), 半導体量子井戸型 (MQW: multiple quantum well) 変調器 [85] , MEMS (micro-electro-mechanical systems) ミラーなどを用いたものがある. SLM には, 高光量効率, 高コントラスト, 高速動作などが要求されるが, 現状ではこれらすべての条件を満たすものはなく, 用途に応じて使い分けられている.

## 1. 光・電子融合型マルチプロセッサシステムアーキテクチャ

### 1.2.5 自由空間光接続を用いたマルチプロセッサシステム

自由空間光接続の特長は、マルチプロセッサシステムにおける通信ネットワークの高速化に有用である。自由空間光接続の大きい空間帯域幅積と大ファンアウト性を利用して、多数のプロセッサからのデータを高速に切り換えるネットワークスイッチを実現できる。光導波路や光ファイバを用いた場合には、ネットワークを実現するために多数の配線や、多段光スイッチを用いた大規模なシステムが必要となるが、自由空間光接続によりネットワークスイッチを単純な構成で実装できると考えられている。自由空間光接続を用いた試作システムとして、光バックプレーン [26]、光クロスバネットワーク [30]、光マルチメッシュハイパキューブ (OMMH) [25]、FAST-Net [29]などがあり、自由空間光接続の有効性がデモストレーションされている。

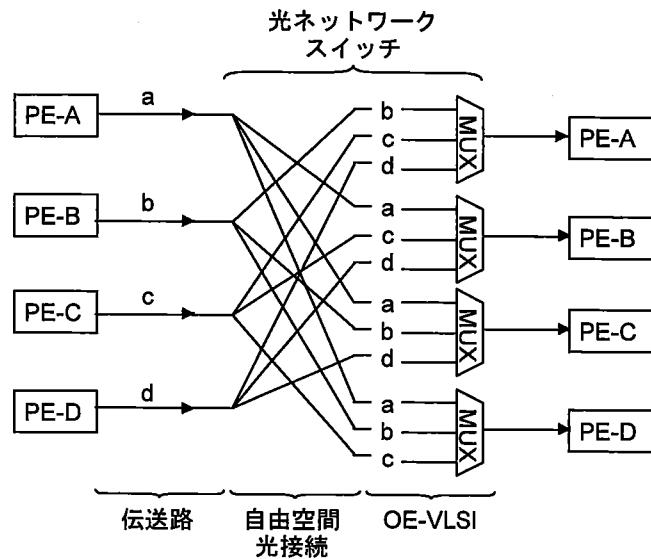

光クロスバネットワークは自由空間光接続の大ファンアウト性を活用したマルチプロセッサシステム用光ネットワークである。高速スイッチングを実現するために、図 1.3 に示す機構を用いている。各プロセッサからの光信号を、回折光学素子を用いて光学的にファンアウトし、配列を組み換える。全プロセッサからの光信号を、ネットワークスイッチ用 OE-VLSI 上の複数の受光素子で受信し、電気信号に変換する。受信した光信号の中から、通信相手であるプロセッサからのデータを、OE-VLSI 上で電気的に選択する。光マルチメッシュハイパキューブでも、同様の方式が用

図 1.3: 光クロスバネットワークの実現例 (4 プロセッサの場合)。PE はプロセッサ、

a-d は PE-A から PE-D が出力するデータ、MUX はマルチプレクサを意味する。

### 1.3. 大域処理指向光・電子融合型マルチプロセッサシステム いられている。

## 1.3 大域処理指向光・電子融合型マルチプロセッサシステム

自由空間光接続の優れた特長を利用すると、処理アルゴリズムの特性を反映したマルチプロセッサシステムアーキテクチャの新規開発が可能になる。本節では、大域処理指向の新しい光・電子融合型マルチプロセッサシステムアーキテクチャについて述べる。このアーキテクチャは、局所処理に特化した光・電子プロセッサと、大域処理に特化した光プロセッサ（大域処理光プロセッサ）から構成される協調的アーキテクチャである。

### 1.3.1 大域処理と帯域幅不整合

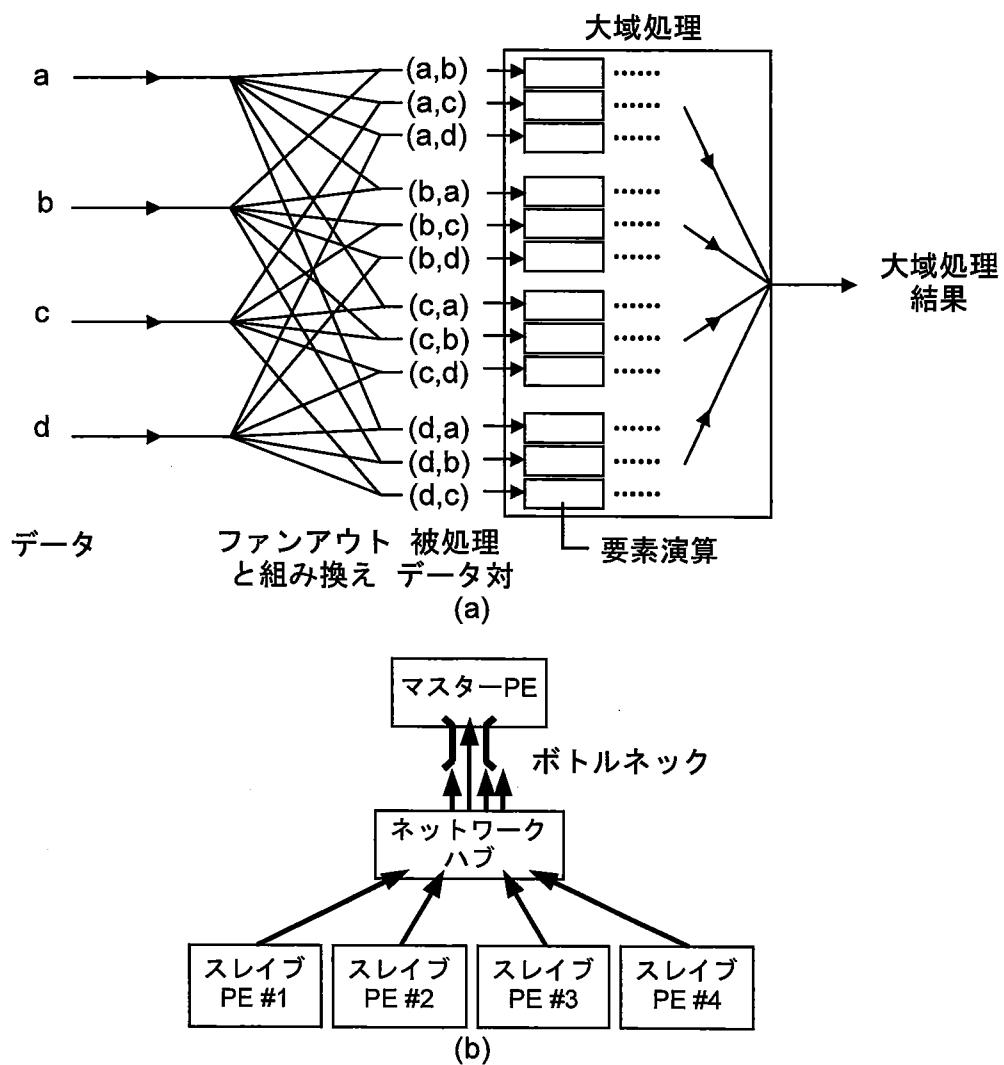

本論文では、複数のプロセッサからの複数データに対する処理として、大域処理を定義する。例えば、複数プロセッサに分散したデータのソーティング、総和演算、データ検索などがある。一般に、大域処理におけるデータの流れは以下のようになる。1) プロセッサからのデータをファンアウトして組み換え、被処理データ対を生成する。2) 各被処理データ対に対して、処理を実行する。3) 処理結果を各プロセッサに返す。大域処理は、並列性をもっていることが多く、大域処理を効率的に実行できる並列アーキテクチャであれば、高速処理が可能である。しかし、既存のマルチプロセッサシステムは大域処理に適した機構をもっていないため、帯域幅不整合の問題が生じて処理速度が低下する。

大域処理において帯域幅不整合が生じる理由を、図1.4を用いて述べる。従来のマルチプロセッサシステムアーキテクチャの構組みでは、プロセッサ間通信とプロセッサでの処理は別々に実装される。実質的な処理はプロセッサが行い、ネットワークはプロセッサ間のデータ転送だけを担当する。このため、大域処理を行う場合、アーキテクチャを2層化して、大域処理を実行するマスター・プロセッサと、それ以外のスレイブ・プロセッサに役割分担する。複数のスレイブ・プロセッサからのデータをマスター・プロセッサに転送し、そこで処理を行う。大域処理において、 $N$ 個のスレイブ・プロセッサからの $N$ 個のデータを、ネットワークハブを介してマスター・プロセッサに転送する場合を考える。データ転送において、マスター・プロセッサとスレイブ・プロセッサ間の通信経路を流れるデータ量は、常にネットワークハブとプロセッサ間の通信帯域の $N$ 倍になる。本論文では、このような状況を帯域幅不整合と呼ぶ。帯域幅不整合が生じると、マルチプロセッサシス

## 1. 光・電子融合型マルチプロセッサシステムアーキテクチャ

システムのスループットが低下する。帯域幅不整合によるボトルネックは、単純にネットワークの通信帯域幅を広げるだけでは解決できないため、既存の光ネットワークにおいても同様のボトルネックが存在する。この問題を解決するには、システムアーキテクチャそのものを変える必要がある。

### 1.3.2 自由空間光接続を利用した大域処理の高速化アーキテクチャ

帯域幅不整合によるボトルネックを解消するためには、従来システムにおけるネットワークハブとマスター・プロセッサを1つに集積化する方法が有効である。このような大域処理機能を融合

図 1.4: (a) 大域処理におけるデータの流れ, (b) 従来のマルチプロセッサアーキテクチャにおけるデータの流れ。

### 1.3. 大域処理指向光・電子融合型マルチプロセッサシステム

したネットワークハブを，大域処理プロセッサとよぶ。大域処理プロセッサは，OE-VLSI と自由空間光接続を用いることで初めて実装できる。これを，大域処理光プロセッサとよぶ。

ネットワークハブには全プロセッサからのデータが集中するため，大域処理をハブで行えば，プロセッサにはデータ量の減った処理結果だけを送信すれば良いことになる。そのため，1つのプロセッサに大量のデータを送信する必要がなくなり，帯域幅不整合は解消される。このような大域処理光プロセッサに基づくマルチプロセッサアーキテクチャの原型は，谷田らによって提案されており，光コンピューネクション (optical connection: optical computing + interconnection からの造語) とよばれている [32–34]。図 1.5 に，大域処理光プロセッサを用いたマルチプロセッサシステムアーキテクチャの構成を示す。このマルチプロセッサアーキテクチャは，局所処理を行う複数の光・電子並列プロセッサと，光・電子プロセッサ間の接続と大域処理を行う大域処理光プロセッサから成る。光・電子並列プロセッサは，プロセッサ上に受・発光素子をもち，大域処理光プロセッサを介して相互接続されている。プロセッサは，大域処理光プロセッサを介して，通信と大域処理を行う。

大域処理プロセッサは，膨大な処理能力が要求されるため，VLSI だけでは実装できない。帯域幅不整合を完全に解消するには，大域処理プロセッサが，通信速度に同期して全プロセッサからのデータを遅延なく処理する必要がある。つまり，プロセッサ間の通信路の幅を  $w$  [bit]，通信の同期周波数を  $r$  [Hz]，大域処理に要する 2 項演算の数を  $m$  とすると， $2mwr$  [bit per second (bps)] の処理能力が必要である。プロセッサ数を  $N$  とすると，例えば，全プロセッサが出力するデータの総和をとる大域処理は  $2Nwr$  [bps]，データの大小関係を完全比較するには，最も単純な方法を

図 1.5: 大域処理光プロセッサに基づいた光・電子融合型マルチプロセッサシステムアーキテクチャ。

## 1. 光・電子融合型マルチプロセッサシステムアーキテクチャ

---

用いた場合で  $N^2wr$ [bps] の処理能力が必要になる。 $N = 64, w = 64, r = 1\text{GHz}$  を仮定すると、総和演算で約 8Tbps、完全比較では約 260Pbps の処理能力が要求される。このように、大域処理プロセッサには、汎用プロセッサ以上の処理能力が要求される。

大域処理光プロセッサは、自由空間光接続の大ファンアウト性と並列組み換え性を用いることにより、大域処理における並列的なデータの流れを、忠実に実行できる。その結果、大域処理のもつ並列性を完全に利用することができ、高速処理が可能になる。

### 1.4 技術課題と本研究との対応

本章で述べた光・電子融合型マルチプロセッサアーキテクチャを実践するには、システムの用途を明確にした上でアーキテクチャ設計を行い、アーキテクチャの性能を定量的に把握する必要がある。また、アーキテクチャの有効性を示すには、プロトタイプシステムを試作し、デモストレーションを行うことが不可欠である。光・電子融合型マルチプロセッサシステムのコアモジュールは、大域処理光プロセッサである。本研究では、システム開発の効率化と他のシステムへの応用性を考慮し、汎用的な光プロセッサを開発し、これをプロトタイプシステムに利用する。現在、プロトタイプ試作に大して、決め手となる光学系実装技術は存在しない。試作には、光学系の様々な仕様に適合した実装が要求されるため、そのような用途に合致した光学系実装技術の開発が必要である。

これらの技術課題に対して、第 2, 3 章では 2 種類の光プロセッサアーキテクチャの提案とプロトタイプの試作について述べる。第 4 章では光・電子融合型マルチプロセッサシステムアーキテクチャの提案、評価、プロトタイプシステムの試作についてまとめ、第 5 章では光学系実装技術の提案と原理確認実験について述べる。

### 1.5 結言

本章では、VLSI チップ間のデータ伝送帯域を飛躍的に向上する技術として、OE-VLSI を用いたチップ間光接続について述べた。自由空間光接続の大きい空間帯域幅積、大ファンアウト性、信号の並列組み換え性が、マルチプロセッサシステムにおける高速ネットワークスイッチの実現に効果的であることを示した。大域処理に有効な光・電子融合型マルチプロセッサアーキテクチャ

## 1.5. 結言

---

の方式として、光・電子プロセッサと大域処理光プロセッサを用いた協調処理アーキテクチャを示し、これが帯域幅不整合の問題を解決できることを述べた。

## 2. 離散相関プロセッサ DCP-1

### 2 離散相関プロセッサ DCP-1

#### 2.1 緒言

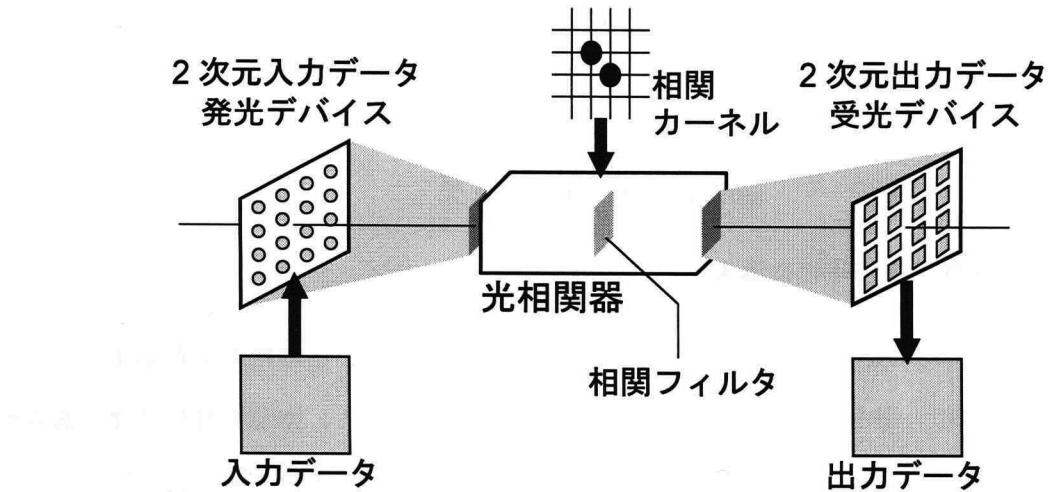

離散相関演算は、自由空間光接続を用いた光・電子融合型情報処理システムにおける光学系の基本処理である。本論文では、離散相関演算を光学的に高速実行する光・電子融合システムの中核モジュールを光プロセッサとよぶ。汎用的な光プロセッサを作製することにより、光接続をはじめとして、様々な光・電子融合型アーキテクチャの実証プロトタイプシステムの構築が可能になる。本章では、光プロセッサの基本アーキテクチャとして、離散相関プロセッサ (DCP) アーキテクチャを提案する。また、DCP アーキテクチャに基づくプロトタイプとして、DCP-1 を作製する。DCP-1 では、VCSEL アレイを光源として用いることによりデータを 2 次元的に並列に出力し、光相関器の相関出力を CMOS-PD で並列に受光する。離散相関における相関カーネルの実装方式に対応して、2 つのプロトタイプ DCP-1S, DCP-1D を作製する。DCP-1S では、レーザビームリソグラフィ技術により作製した固定カーネルパターンの位相型 CGH フィルタを用いる。DCP-1D では、強誘電性 (FLC) SLM を用いることにより、相関カーネルパターンを可変とする。離散相関演算に符号化を導入することにより、光接続に演算機能を追加できる。本章では、DCP-1 に光演算手法である光アレイロジックを導入し、処理能力の拡張を行う。

2.2 節では、DCP アーキテクチャを定義する。2.3 節では、2 種類の DCP-1 プロトタイプの実装について述べる。2.4 節では、プロトタイプの静的特性・動的特性を測定し、性能を示す。

#### 2.2 離散相関プロセッサ

##### 2.2.1 アーキテクチャ

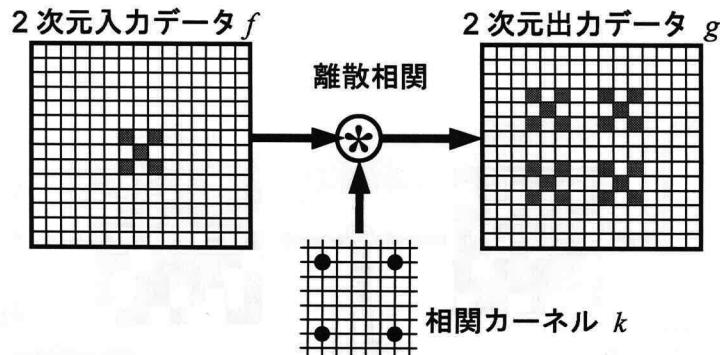

離散相関演算は光プロセッサの基本処理の 1 つであり、次式で定義される。

$$g_{i,j} = \sum_m \sum_n k_{m,n} f_{i-m, j-n}. \quad (2.1)$$

ここで、 $f, g$  はそれぞれ 2 次元入力データ、出力データ（離散相関演算の結果）である。 $k$  は相関カーネルとよばれ、離散相関演算の内容を記述する。これは、自由空間光接続では、光接続パターンに対応する。離散相関演算では、図 2.1 に示すように、入力画像を  $(m, n)$  画素平行移動した複製画像を生成し、異なる平行移動量に対する複製画像を重ね合わせる処理を行う。 $k_{m,n}$  は重ね合

図 2.1: 離散相関演算.

図 2.2: 離散相関プロセッサ (DCP) アーキテクチャ.

わせの重みを表し, 光接続の場合は 0 または 1 の値をとる. 1 は, 平行移動量  $(m, n)$  の複製画像を生成することを意味する. 0 の場合は, その複製画像は出力されない.

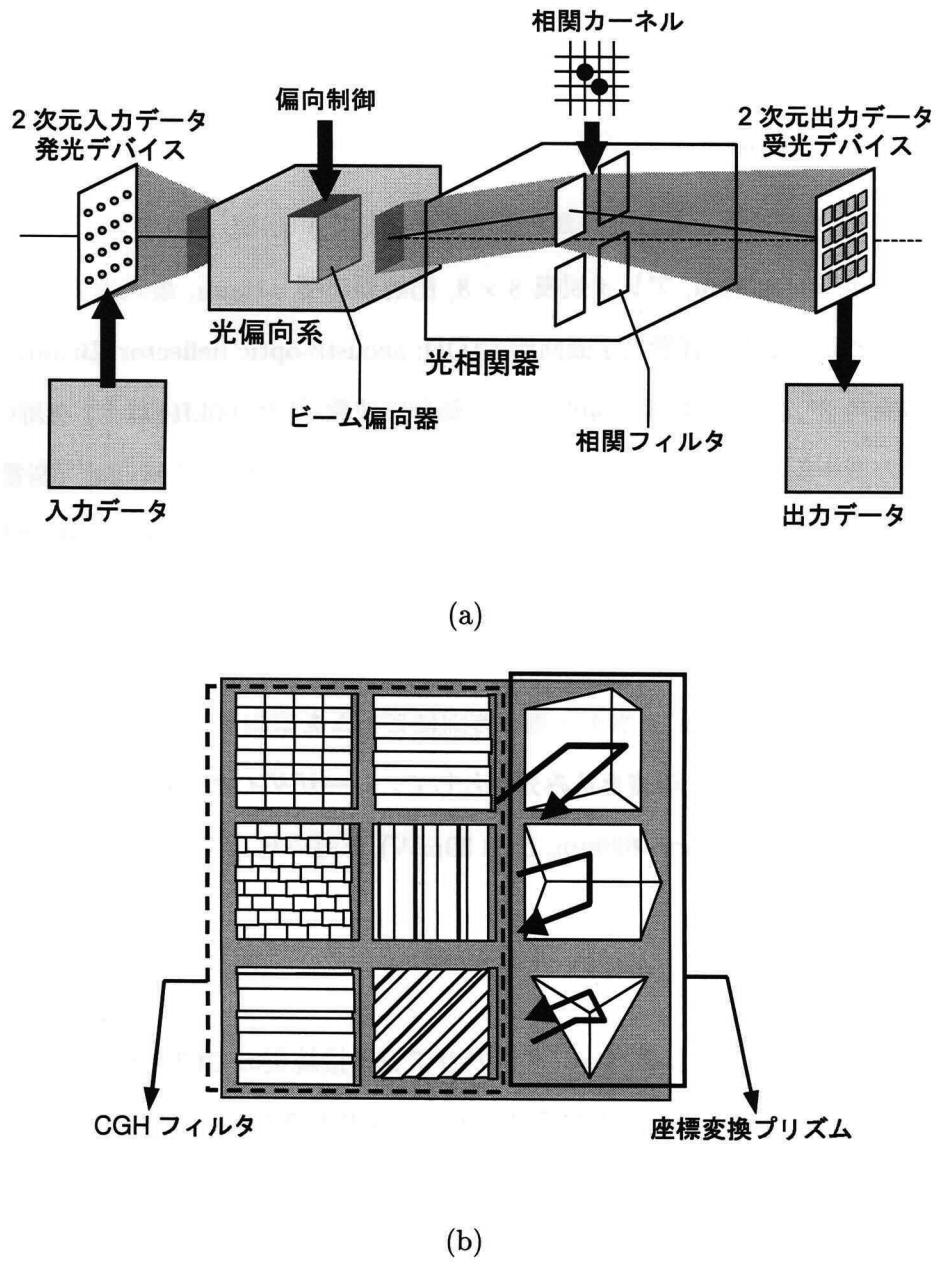

式 (2.1) を, 光・電子デバイスを用いて実装するための光プロセッサアーキテクチャとして, 離散相関プロセッサ (DCP) アーキテクチャを提案する. 図 2.2 に, DCP プロセッサアーキテクチャのブロック図を示す. DCP アーキテクチャは, 2 次元入力データ発光デバイス・光相関器・2 次元出力データ受光デバイスから構成する. 2 次元発光デバイス・2 次元受光デバイスとして, VCSEL アレイなどの点光源アレイ・高速半導体受光素子アレイを用いる. 光相関器の相関カーネルを可変にする場合, SLM を光相関器内部で用いる.

## 2. 離散相関プロセッサ DCP-1

図 2.3: 光アレイロジック.

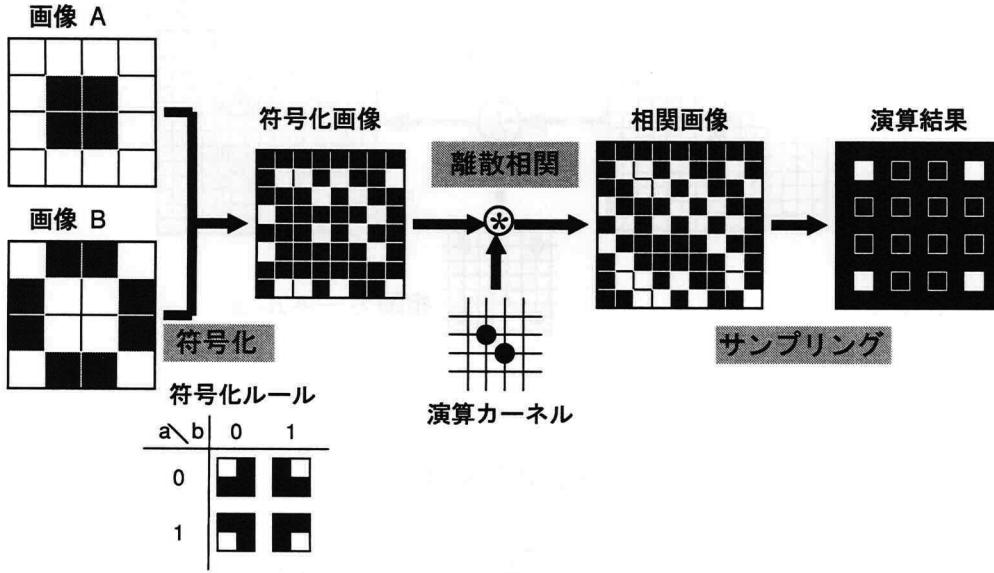

### 2.2.2 離散相関演算への符号化の導入

空間符号化は、離散相関の処理能力を拡張する重要な技術である。この技術を利用することにより、離散相関演算に、論理演算や数値演算などの処理を付加できる。空間符号化では、あらかじめ定義した符号化ルールに従い、複数の2次元データを1つの2次元データ  $f$  に変換する。相関カーネル  $k$  に演算内容を記述し、これを演算カーネルとよぶ。

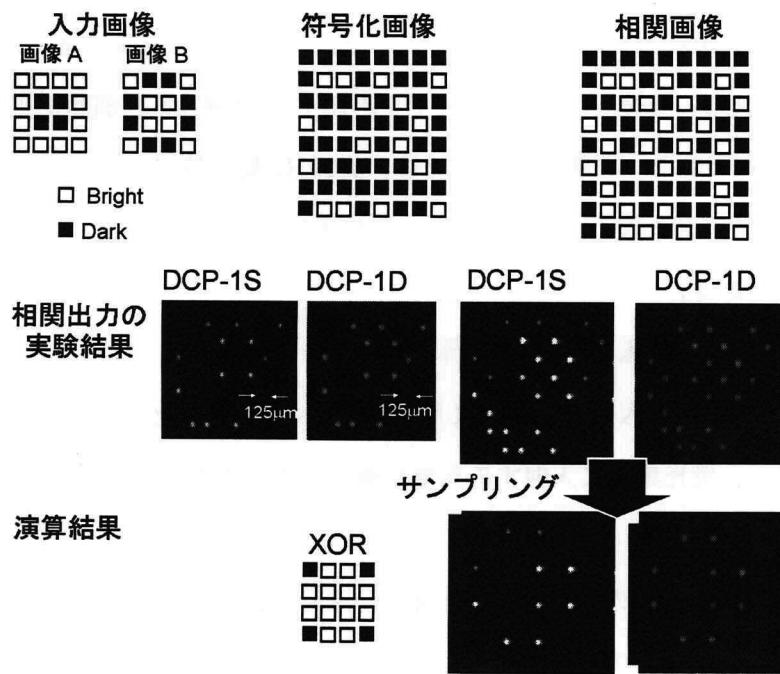

空間符号化法の例として、光アレイロジックがある [86]。図 2.3 は光アレイロジックの手順を示している。2つの2値画像を、符号化ルールにしたがって1つの画像に変換する。符号化前の  $N \times N$  画素のオリジナル画像を、符号化によって  $2N \times 2N$  画素の画像に拡張する。光アレイロジックでは、 $2 \times 2$  の相関カーネルにより、1ビット2入力データに対して16種類の基本論理演算を実行できる。相関出力を1画素おきにサンプリングし反転処理を施し、最終的な論理演算結果を得る。

## 2.3 DCP-1 プロトタイプ

### 2.3.1 DCP-1S と DCP-1D

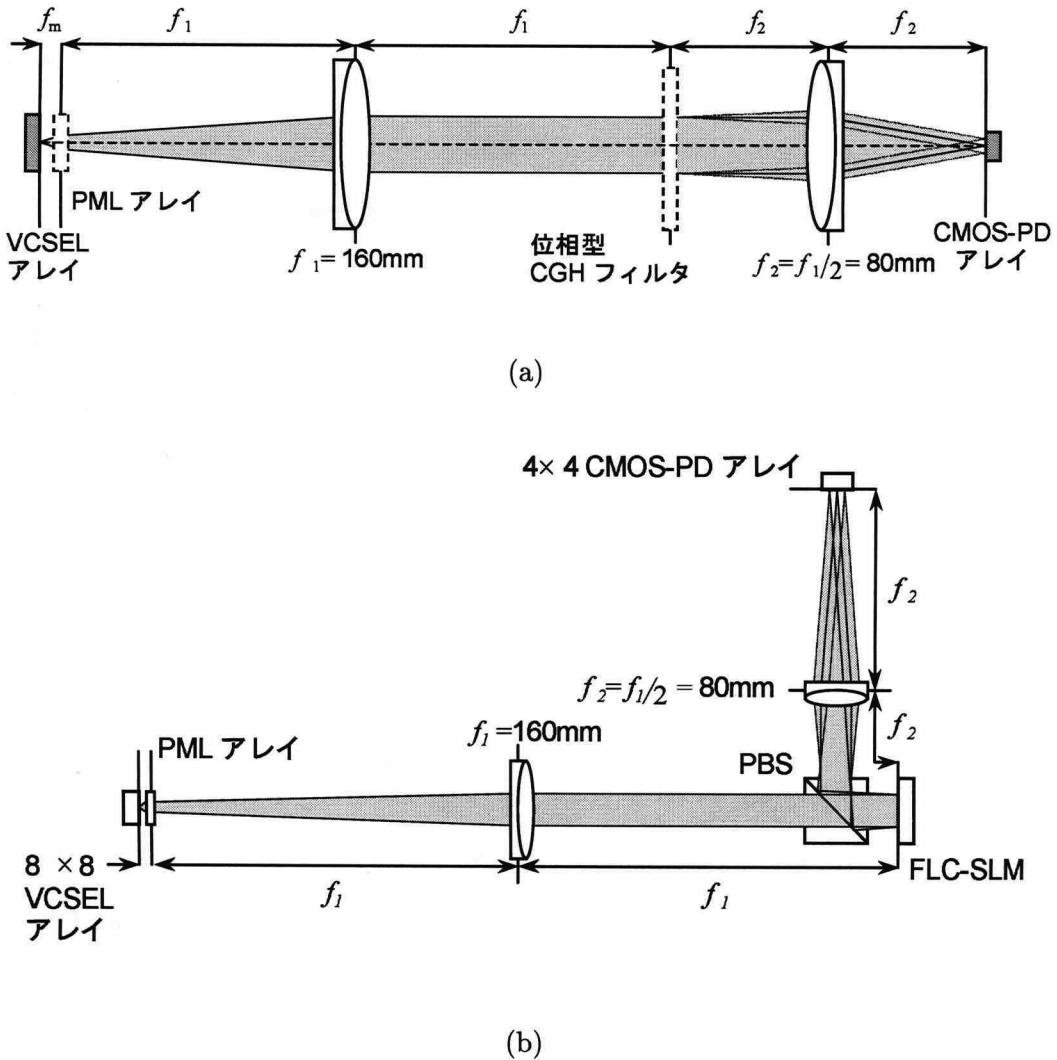

DCP アーキテクチャに基づき、DCP-1 プロトタイプを作製した。プロトタイプでは、光相関器として  $4f$  相関光学系を用いた。この光学系では、フーリエ面に、相関カーネルのフーリエ変換像を記録した計算機ホログラム (CGH: computer-generated hologram) フィルタ [61] を配置する。空間光変調器の実装により、固定フィルタ方式 (DCP-1S) と可変フィルタ方式 (DCP-1D) の 2 種類のプロトタイプを作製した。それぞれの光学系の構成を、図 2.4(a), (b) に示す。光学系に用いるレンズの仕様は、2 つのプロトタイプで共通とした。

図 2.4: DCP-1 プロトタイプ: (a) DCP-1S, (b) DCP-1D.

## 2. 離散相関プロセッサ DCP-1

---

表 2.1: DCP-1 に用いたデバイス。

| 製品名                                     | 提供元                   | アレイサイズ            | ピクセル<br>ピッチ ( $\mu\text{m}$ ) | ピクセル<br>サイズ ( $\mu\text{m}$ ) | 動作速度             | その他                     |

|-----------------------------------------|-----------------------|-------------------|-------------------------------|-------------------------------|------------------|-------------------------|

| VCSEL アレイ<br>( <i>Gigalase</i> )        | Micro Optical Devices | 8×8               | 250                           | φ8                            | -                | -                       |

| VCSEL ドライバ<br>(N73BAC)                  | JOP                   | 16 I/O            | -                             | -                             | >100MHz          | -                       |

| FLC-SLM<br>( <i>SLM Developer Kit</i> ) | Displaytech           | 256×256           | 15                            | 14                            | 2.5kHz<br>(25°C) | 反射率 <20%,<br>最適波長 633nm |

| CMOS 受光素子<br>(N73CGD)                   | JOP                   | 4×4               | 250                           | 110                           | 15MHz            | -                       |

| 平板マイクロレンズ<br>(PML-FW0250S0096S-NC)      | Micro-Opt             | 0.96mm<br>×0.96mm | 250                           | φ250                          | -                | 焦点距離<br>720μm (850nm)   |

SLM の性能は年々向上しているが、光波面を高速・高光量効率・高コントラストで変調できるデバイスは存在しない。そこで、異なる応用に適用できるように、2種類のプロトタイプを構築した。固定フィルタ方式は、表面にレリーフ構造をもつ石英ガラス基板などの受動光学素子で実現できる。この場合、相関カーネルは固定であるが、高い光量効率が得られ、高速光信号を低いエラー率で扱える信頼性の高いシステムを構築できる。可変フィルタ方式は、SLM に表示する相関フィルタを書き換えることにより、複数の相関カーネルを切り換えて利用できる。そのため、複数の相関カーネルを利用する応用には不可欠である。

### 2.3.2 デバイス

DCP-1 に用いたデバイスを、表 2.1 にまとめる。2 次元入力データ発光デバイスには、 $8 \times 8$  の VCSEL (製品名 Gigalase, Micro Optical Devices 製, 発振波長 850nm, ピクセルピッチ  $250\mu\text{m}$ ) を用いた。VCSEL の制御には、JOP (United States-Japan Joint Optoelectronics Project) が提供する VCSEL ドライバ (型番 N73BAC, 動作速度 100MHz 以上 (SPICE シミュレーションによる)) を用いた。VCSEL 駆動電流の振幅・バイアスは、VCSEL ドライバに与える変調電圧  $V_{SS}$  とバイアス電圧  $V_{bias}$  により制御する。相関出力は、JOP が提供する  $4 \times 4$  画素の CMOS 受光素子 (型番 N73CGD, 画素ピッチ  $250\mu\text{m}$ , 受光部面積  $110\mu\text{m} \times 110\mu\text{m}$ , 最大動作速度 15MHz (入力光

### 2.3. DCP-1 プロトタイプ

量  $100\mu\text{W}$  時)) で受信した。この受光デバイスは、受光部で光電変換した光電流を、直列接続した 2 段のコンパレータにより増幅・2 値化して出力する。2 値化の閾値電圧は、外部信号  $V_{t1}, V_{t2}$  で制御する。これらの電圧信号は、1 段目・2 段目のコンパレータに対する閾値である。

プロトタイプに用いた VCSEL は、放射角が  $15^\circ$  と大きい。そのため、レンズ・SLM などの開口内に光が収まらず、光量損失が生じる。放射角を小さくするために、VCSEL の直後に平板マイクロレンズ (PML: planar microlens, 型番 PML-FW0250S0096S-NC, Micro-Opt 製, 焦点距離  $720\mu\text{m}$  (波長  $850\text{nm}$  に対して)) を配置した。また、DCP-1 に光アレイロジックを適用した場合、相関結果を 1 つおきにサンプリングする必要があるため、光学系の倍率  $f_2/f_1$  を 0.5 に設定した。

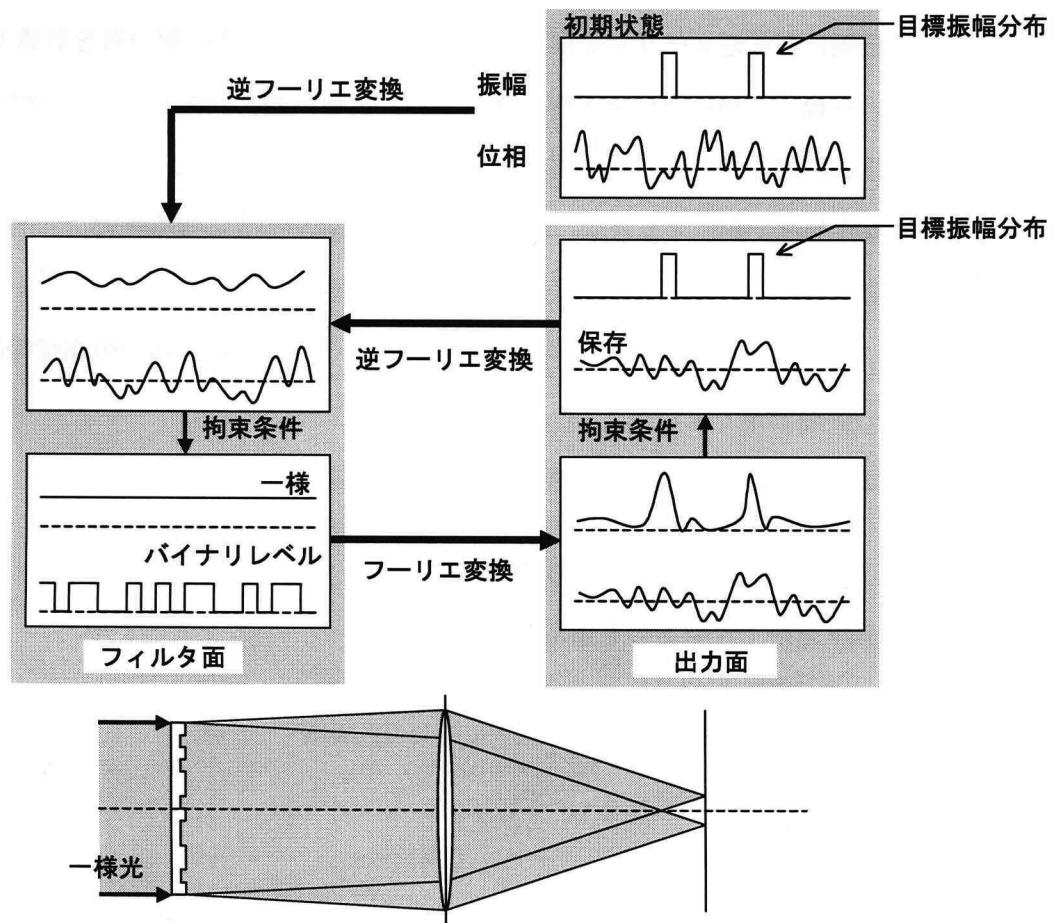

#### 2.3.3 CGH フィルタ

DCP-1S の CGH フィルタとして、2 レベル位相型フィルタを用いた [87]。石英基板にフォトレジスト (型番 AZ1500, Hoechst Industry Ltd. 製, ネガ型) をスピンドルコートし、フィルタパターンをレーザビーム描画装置で描画した [87]。フォトレジストを現像した後、 $\text{CF}_4$  ガスにより石英基板を反応性エッチングし、レジストパターンを石英基板に転写した。DCP-1D では、フィルタパターンを FLC-SLM (製品名 SLM Developer Kit, Displaytech 製, 強度変調型, 最適波長  $633\text{nm}$ , 画素数  $256 \times 256$ , 画素サイズ  $15\mu\text{m} \times 15\mu\text{m}$ , コントラスト 100:1 以上 (波長  $633\text{nm}$ ), 動作速度  $2.5\text{kHz}$  ( $25^\circ\text{C}$ )) に表示した。

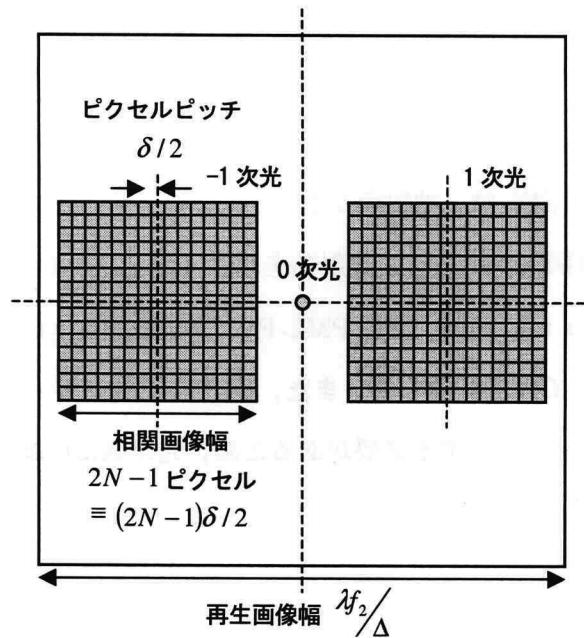

図 2.5 に、離散相関出力像の配置を示す。図 2.5(a) に、単一光源に対する離散相関出力の配置、図 2.5(b) に、VCSEL アレイ全体に対する離散相関出力の配置を示す。設計のパラメータとして、VCSEL アレイのピクセルピッチ  $\delta$ , アレイサイズ  $N \times N$ , 発振波長  $\lambda$ , CGH フィルタのピクセルピッチ  $\Delta$ , レンズ 2 の焦点距離  $f_2$  を考慮した。出力面では、-1 次回折像が相関出力となり、その中心  $N \times N$  画素が有効な演算結果になる。全画素間の相関をとるには、 $(2N - 1) \times (2N - 1)$  の相関カーネルが必要である。0 次回折像が有効演算結果と重ならない条件から、 $f_2$  の最小値が決まる。用いたデバイスの仕様として、 $\delta = 250\mu\text{m}$ ,  $\lambda = 850\text{nm}$ ,  $\Delta = 15\mu\text{m}$ ,  $N = 8$  から、 $f_2$  を  $80.0\text{mm}$  とした。この場合、0 次回折光と有効な演算結果領域の間隔は  $133\mu\text{m}$  となる。

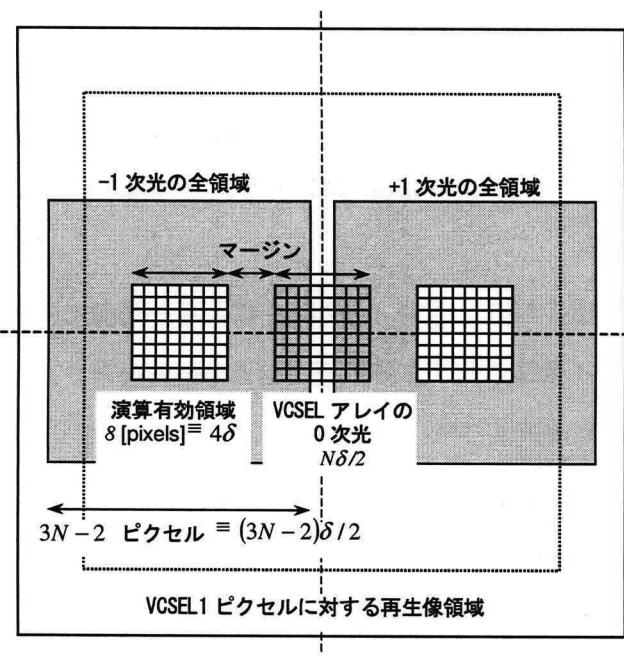

以上のパラメータに対して、Gerchberg-Saxton アルゴリズムにより、光アレイロジックで XOR 演算を実行するフィルタを設計した (付録 C 参照)。このフィルタのファンアウト数は 2 である。DCP-1S と DCP-1D で、ピクセルサイズおよびピクセル数は同一とし、それぞれ  $15\mu\text{m} \times 15\mu\text{m}$ ,

## 2. 離散相関プロセッサ DCP-1

(a)

(b)

図 2.5: CGH フィルタ再生像面の出力像の配置: (a) VCSEL1 ピクセル, (b) VCSEL アレイ全体。

図 2.6: XOR 演算用 CGH フィルタ.

$256 \times 256$  とした。図 2.6 に、相関カーネルの形状、設計したフィルタパターン、作製した DCP-1 用 CGH フィルタの光学顕微鏡写真を示す。

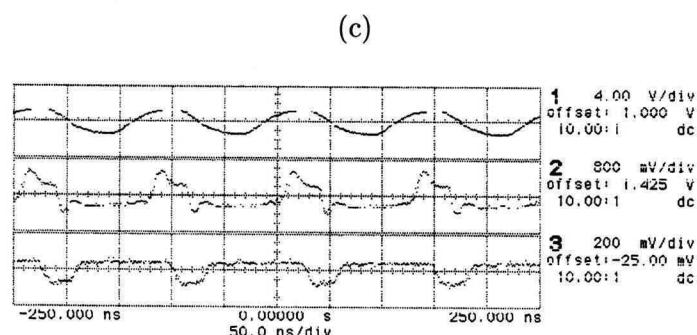

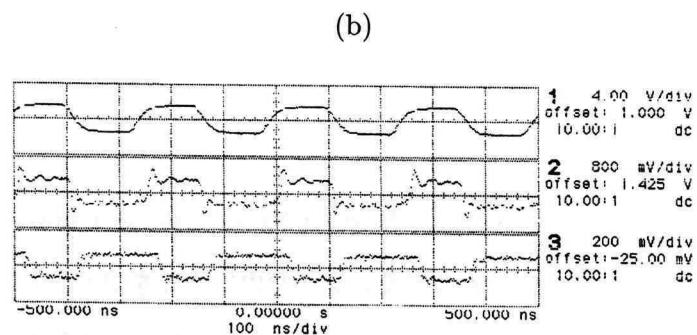

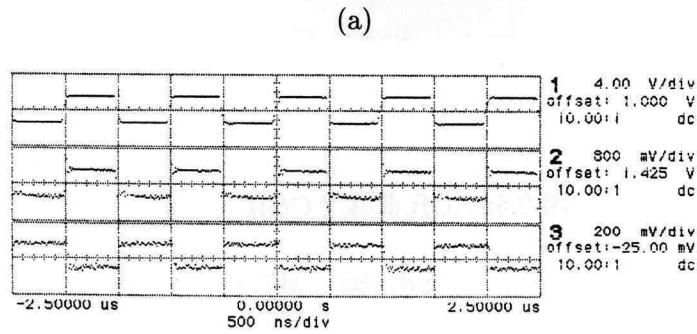

#### 2.3.4 VCSEL の駆動

図 2.7 に、VCSEL を強度変調して発光させた場合の、時間的な光強度波形を示す。図 2.7(a) に示すように、波形ジェネレータ (型番 33120A, Hewlett Packard 製、最大周波数 15MHz) の発生する繰り返し矩形波を VCSEL ドライバに入力する。レーザの出力光をアバランシェ方式受光モジュール (型番 S5331-01, 浜松ホトニクス製、帯域 100MHz) により電気信号に変換し、オシロスコープ (型番 54503A, Hewlett Packard 製、最大周波数 500MHz) により測定した。異なる周波数に対する出力波形を図 2.7(b)～(d) に示す。測定において、VCSEL ドライバの制御電圧は  $V_{bias} = 4.95V$ ,  $V_{ss} = 6.1V$  とした。このときの、1 画素の発光強度は  $22\mu W$ 、オン時とオフ時のコントラストは 100:1 以上であった。この測定結果から、8MHz で光信号を出力できることを確認した。

#### 2.3.5 光学系の光量効率

VCSEL に平板マイクロレンズを組み合わせて放射角を小さくし、光学系の光量効率を向上した。光量効率の測定結果を表 2.2 にまとめる。平板マイクロレンズにより、放射角が  $15^\circ$  から  $1.8^\circ$  に低減された。その結果、平板マイクロレンズを用いない場合と比べて、光量効率が 4.3 倍の 13.75% に上昇した。86.25% の光量損失は、VCSEL のビーム NA が、マイクロレンズの NA よりも大きいために生じていると考えられる。

## 2. 離散相関プロセッサ DCP-1

(d)

図 2.7: VCSEL 駆動の実験結果: (a) 測定系, (b) 1MHz, (c) 4MHz, (d) 8MHz. チャンネル 1~3 は、それぞれ VCSEL ドライバの入力波形、VCSEL ドライバの出力電圧波形、VCSEL の光強度波形を示す。

## 2.4 実験結果

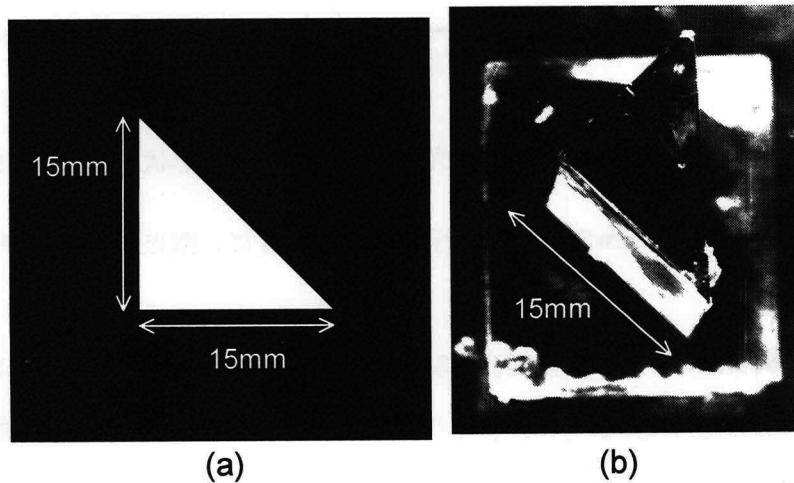

### 2.4.1 静的特性

DCP-1S, DCP-1D に CGH フィルタを挿入し, 出力像の静的特性を測定した。XOR 演算に対する相関出力像を, 図 2.8 に示す。光アレイロジックの符号化ルールにより, 2つの入力画像を符号化したデータを VCSEL アレイに表示し, 光相関器の離散相関出力を CCD カメラにより観測し

表 2.2: DCP-1 の光量効率。

| システム                       | レンズ<br>透過率 (%) | フィルタ<br>透過率 (%) | 回折効率<br>(%) | ファンアウト数 | その他<br>(%) | 全効率<br>(%)         |

|----------------------------|----------------|-----------------|-------------|---------|------------|--------------------|

| DCP-1S<br>(フィルタ・PML なし)    | 3.2            | -               | -           | 1       | -          | 3.2                |

| DCP-1S<br>(フィルタなし, PML あり) | 13.75          | -               | -           | 1       | -          | 13.75              |

| DCP-1S<br>(フィルタ・PML あり)    | 13.75          | 63.34           | 31.74       | 2       | -          | 1.62               |

| DCP-1D<br>(フィルタ・PML あり)    | 13.75          | -               | 5.2         | 2       | 8.4        | 0.03<br>(PBS, SLM) |

図 2.8: DCP-1 プロトタイプの静的特性。

## 2. 離散相関プロセッサ DCP-1

---

た. 相関出力において, スポット径  $60\mu\text{m}$  (DCP-1S),  $115\mu\text{m}$  (DCP-1D) を得た. これは, 受光素子の開口と同程度以下の大きさであり, ほぼすべての光エネルギーを受信できる. また, 図 2.8 に示されている理想的な符号化像と実験結果が異なっているのは, VCSEL アレイとドライバに欠陥画素があったためである. この実験において, 回折効率は DCP-1S で 37.74%, DCP-1D で 5.2% であった. DCP-1D で回折効率が低いのは, 用いた SLM が強度変調型であり, 最適波長が VCSEL の発振波長とは異なるためであると考えられる.

### 2.4.2 動的特性

プロトタイプの動的特性として, 光アレイロジックを適用した DCP-1S において, 演算時のビットエラー率 (BER: bit error rate) を測定した. ここで, 演算の BER を, 入力データ対の数に対する演算エラー発生率で定義する. 光アレイロジックの 2 入力として擬似ランダム信号を与え, 演算  $A \text{ XOR } B$  と  $A \cdot \overline{B}$  を実行した. ここで,  $A, B$  は 2 値画像を意味する.  $A \cdot \overline{B}$  は, ファンアウト数 1 の相関カーネルにより実行できる. そのため, CGH フィルタを用いずに, CMOS 受光素子を平行移動することにより演算を実行した. この場合, 光量効率は最大, 出力像のスポットサイズは最小になるため, システムは最大速度で動作する. 計測では, パーソナルコンピュータ (PC) により  $10^9$  ビット長の擬似ランダム信号を発生し, 光学系の離散相関出力を CMOS 受光素子で受信して, PC のメモリ上に蓄積した. その後, DCP-1S により得られた演算結果を正しい演算結果と照合し, BER を算出した. 実験システムでは, 500kHz 動作時にエラーは発生しなかった. この結果,  $\text{BER} < 10^{-9}$  (500kHz 動作時) を得た. 動作速度 500kHz は, パーソナルコンピュータの入出力速度の限界である.

続いて CGH フィルタを挿入し, XOR 演算を実行した. その結果,  $\text{BER} \sim 10^{-5}$  (25kHz 動作時) を得た. CGH フィルタを挿入したことにより, 演算  $A \cdot \overline{B}$  の場合と比較して光学系の出力像のコントラストが低下し, 受光素子に入射する光量が減少した. そのため動作速度が低下し, BER が悪くなつたと考えられる.

DCP-1D では, 光学系全体の光量効率が 0.03% と非常に低かった. そのため, 相関出力を CCD カメラでは観察できたが, CMOS 受光素子では受信できなかつた.

## 2.5 考察

DCP-1 プロトタイプの動作速度は、主に受光素子によって制限されている。受光素子の感度が低いため、プロトタイプの光学系の光量効率では、十分な動作速度が得られなかつた。この問題を改善するには、光学系の光量効率を上げ、高速な受光素子を利用する必要がある。表 2.2 から、DCP-1S において最も光量損失が大きいのは、平板マイクロレンズであることがわかる。平板マイクロレンズを用いた場合、フーリエ変換レンズには全光束が損失なく入射していた。したがつて、VCSEL の放射角に適合した NA をもつマイクロレンズを用いることにより、光量効率を大きく改善できると考えられる。また、CMOS-PD の代わりに、MSM-PD などの高感度な受光素子を用いることにより、少ない光量でも高速に光信号を受信できる。

DCP-1D における光量損失は、大部分が FLC-SLM で生じている。これは、FLC-SLM が VCSEL 発振波長に適合していないことと、強度変調型であるため回折効率が低いことが原因である。この問題は、PAL-SLM などの位相変調型 SLM を VCSEL の発振波長に最適化して用いることにより解決できると考えられる。

## 2.6 結言

本章では、自由空間光接続を用いた光・電子融合型情報処理システムに利用する光プロセッサの基本アーキテクチャとして、離散相関プロセッサ (DCP) アーキテクチャを提案した。最新の光・電子デバイスを用いて、2 種類の DCP-1 プロトタイプを試作した。DCP-1 プロトタイプに光アレイロジックを適用し、光論理演算が実行できることを確認した。固定フィルタ型の DCP-1S では、ファンアウト数 1 の論理演算 ( $A \cdot \bar{B}$ ) で  $BER < 10^{-9}$  (500kHz 動作時)、ファンアウト数 2 の論理演算 ( $A \text{ XOR } B$ ) では  $BER \sim 10^{-5}$  (25kHz 動作時) を得た。

### 3. 離散相関プロセッサ DCP-2

## 3 離散相関プロセッサ DCP-2

### 3.1 緒言

本章では、高速パターン変更、高光量効率、高コントラストなどの特長を兼ね備えた理想的な光プロセッサを実現するために、光プロセッサの基本アーキテクチャとして、DCP アーキテクチャを改良した DCP-2 アーキテクチャを提案する。DCP-2 アーキテクチャでは、理想的な SLM を実現するために、SLM を単体で用いるのではなく、高速ビーム偏向器と組み合わせる。SLM に複数のパターンを表示し、これらのうち 1 つをビーム偏向器で選択する。この方式により、SLM のパターン変更速度に依存せず、光接続パターンを変更できる。ビーム偏向器での光量損失と引き換えに、低速な（または固定の）SLM の実効速度をビーム偏向器の速度まで向上させることができ、高性能な光プロセッサを実現できる。

3.2 節では、DCP-2 アーキテクチャを定義する。3.3 節では、2 次元音響光学偏向器 (AOD: acousto-optic beam deflector) を用いた DCP-2 プロトタイプの設計について述べる。3.4 節では、DCP-2 プロトタイプの構成要素の特性の測定結果と、それらから決定したシステムパラメータを示す。3.5 節では、DCP-2 プロトタイプの静的特性と動的特性を測定し、提案アーキテクチャの原理確認を行う。

### 3.2 DCP-2

#### 3.2.1 アーキテクチャ

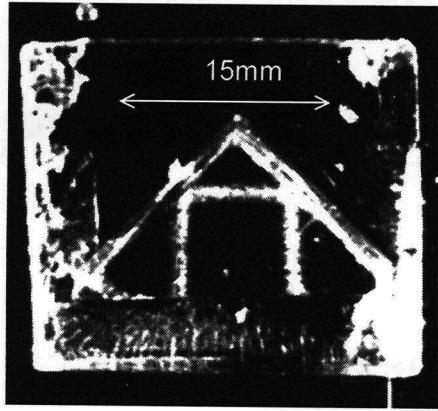

DCP-2 アーキテクチャは、理想的な光プロセッサを実現するための拡張アーキテクチャである。図 3.1(a) に、DCP-2 アーキテクチャを示す。DCP-2 アーキテクチャは、光接続パターンの高速切換、高光量効率、高コントラストを実現するために、SLM をビーム偏向器と組み合わせて用いる。光プロセッサは、2 次元入力データ発光デバイス、光偏向系、光相関系、2 次元出力データ受光デバイス、偏向角制御信号、相関カーネル制御信号から成る。光相関器の相関フィルタ面には、複数の光機能フィルタをアレイ状に配置する（図 3.1(b)）。ビーム偏向器により、発光デバイスからの光の進行方向を変え、相関フィルタのうち 1 つを選択的に照明する。選択したフィルタとの光学的相関結果が、出力画像となる。この方式により、低速な SLM の見かけ上のパターン切り換え速度を、ビーム偏向器の偏向切り換え速度まで向上させることができる。ただし、ビーム偏向器

### 3.2. DCP-2

図 3.1: (a) DCP-2 アーキテクチャ, (b) 光機能フィルタアレイ。

における光量損失の分だけ全体の光量効率は低下する。

図 3.1(b) に示すように, DCP-2 アーキテクチャでは, 光機能フィルタとして相関フィルタだけでなく, 直角プリズムなどの画像反転・回転子などを利用できる。そのため, 式 (2.1) で定義される演算だけでなく, 座標変換などの処理も可能である。従来の光プロセッサでは, 利用できる光機能フィルタは相関フィルタに限られていたが, DCP-2 アーキテクチャは利用できる光機能素子

### 3. 離散相関プロセッサ DCP-2

---

に制限がなく、複数の異なる機能をもつ光学素子を配置できる。

#### 3.2.2 プロトタイプに用いたデバイス

DCP-2 プロトタイプでは、入力画像表示デバイスとして VCSEL (NTT エレクトロニクス研究所提供, 発振波長  $854 \pm 5\text{nm}$ , アレイ規模  $8 \times 8$ , 出射開口径  $\phi 15\mu\text{m}$ , 最大出力  $3\text{mW}$ , p 型基板) , ビーム偏向器として 2 次元音響光学偏向器 (AOD: acousto-optic deflector, Brimrose 製, 最適波長  $850\text{nm}$ , 偏向角  $3^\circ$ , 回折効率 最大 40%以上, 動作周波数 最大  $100\text{kHz}$  以上) を用いた。動的に相関カーネルパターンを変更するために、液晶ディスプレイ付 PAL-SLM [84] (型番 X7550-850, 浜松ホトニクス製, 最適波長  $850\text{nm}$ , 画素ピッチ  $41.4\mu\text{m}$ , 有効画素数  $480 \times 480$  ピクセル, 位相変調量  $2\pi$  以上, 反射読み出し型) を用いた。また, 固定パターンの SLM として, 電子ビームリソグラフィ技術を用いて作製した表面レリーフ型の位相型フィルタを用いた。2 次元 AOD は, 奥行き  $77\text{mm}$  の金属モールド内に, 水平・垂直方向にビームを偏向するための 2 つの音響光学結晶が配置されている。PAL-SLM の書き込み光源として, レーザダイオードモジュール (型番 L7666, 浜松ホトニクス製, 波長  $650\text{nm} \sim 690\text{nm}$ , 出力  $30\text{mW}$ ) を用いた。

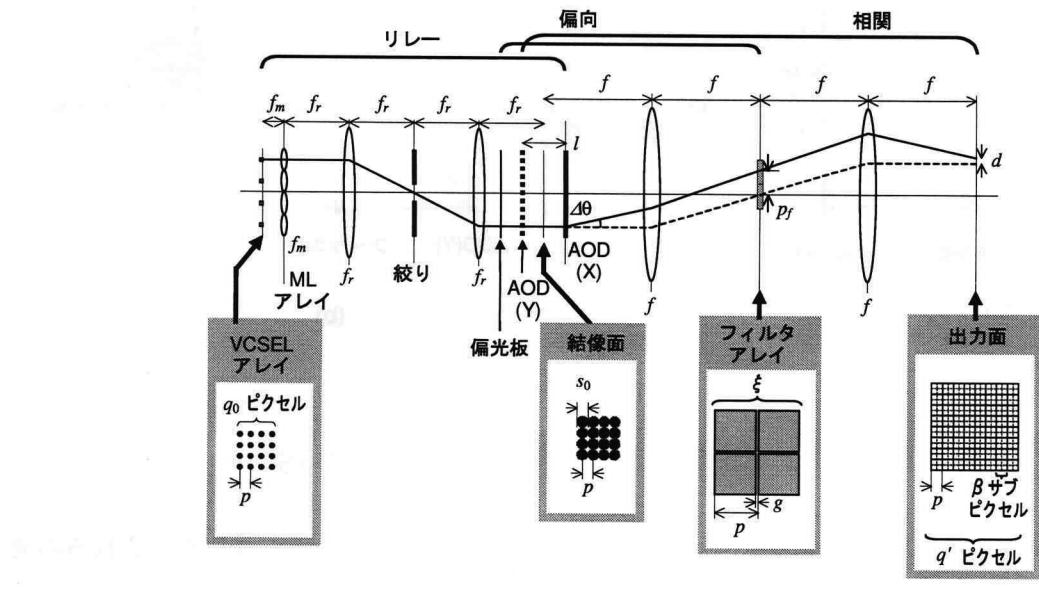

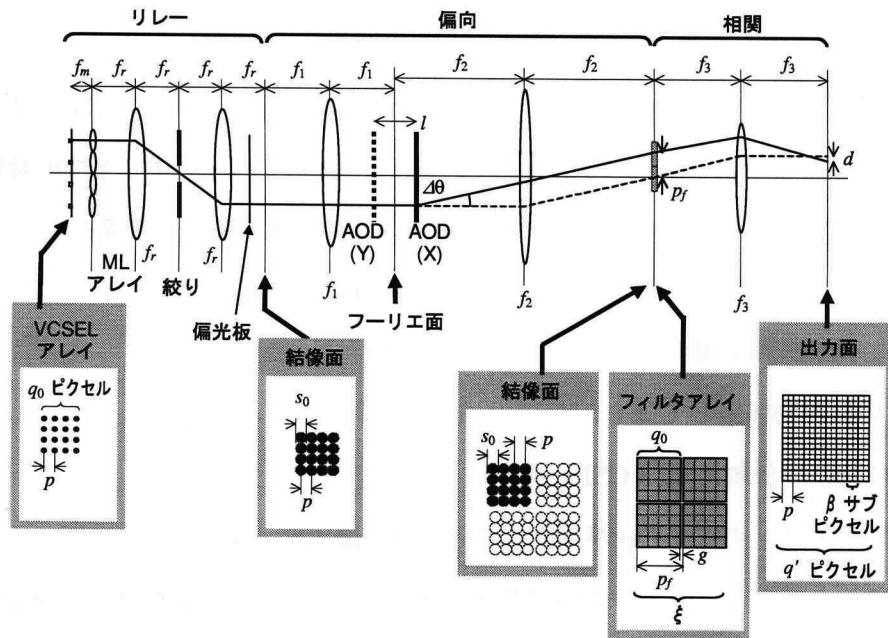

### 3.3 光学系の構成

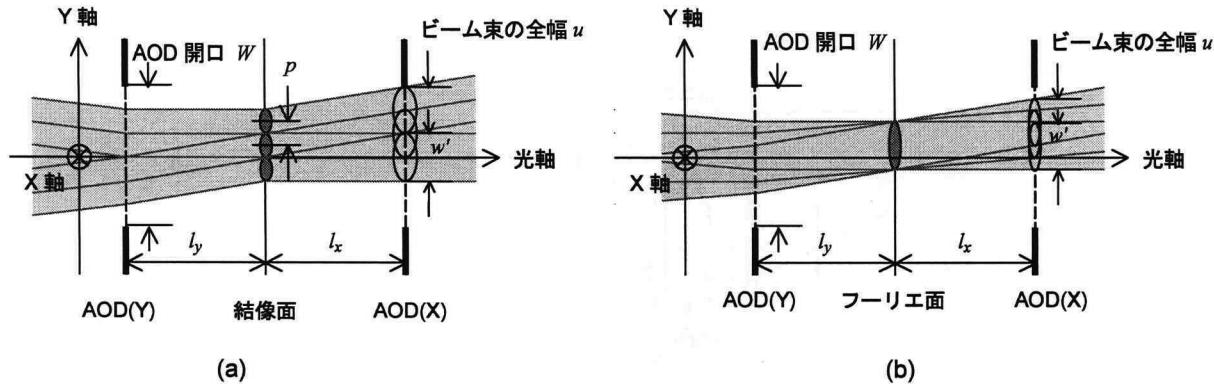

DCP-2 プロトタイプとして, スペースインバリアント接続型の DCP-2SI とスペースバリアント接続型の DCP-2SV を試作した。光学系はハイブリッド光学系 [88] を基本としており, リレー系, 偏向系, 相関系から構成する。リレー系では, VCSEL アレイの直後にマイクロレンズアレイを置き, 各光源の放射角を小さくする。このとき, ガウスビームの特徴として, ビームウェスト径は逆に大きくなる。光学系の迷光を除去するために, リレー系のフーリエ面には絞りを配置する。スペースインバリアント型では, 偏向系の入力面に AOD を配置し, 相関系のフーリエ面を空間分割で用いる(図 3.2(a))。実際のプロトタイプでは反射型 SLM を用いるが, 図 3.2(a) では簡単のため透過型として図示している。2 次元 AOD は, 光源アレイからの光束をすべて同じ角度に偏向し, フーリエ面にある 1 つのフィルタを照明する。光源アレイ全体に対し, 同一の離散相関演算や座標変換を実行する。

スペースバリアント型では, 2 次元 AOD を偏向系のフーリエ面に配置し, 偏向系の出力面(実面)を空間分割してフィルタアレイを配置する(図 3.2(b))。偏向系の出力面は, 相関系のフーリ

(a)

(b)

図 3.2: (a) DCP-2SI, (b) DCP-2SV の構成.

### 3. 離散相関プロセッサ DCP-2

図 3.3: 最大入力点数の評価: (a) DCP-2SI, (b) DCP-2SV.

エ面と一致する。出力面には、偏向量に応じて平行移動した光源アレイ像が現れる。これらの光源の1つ1つに異なるCGHフィルタ(サブフィルタと)を対応させる。この方式により、スペースインвариантな任意の接続パターンを実現できる。

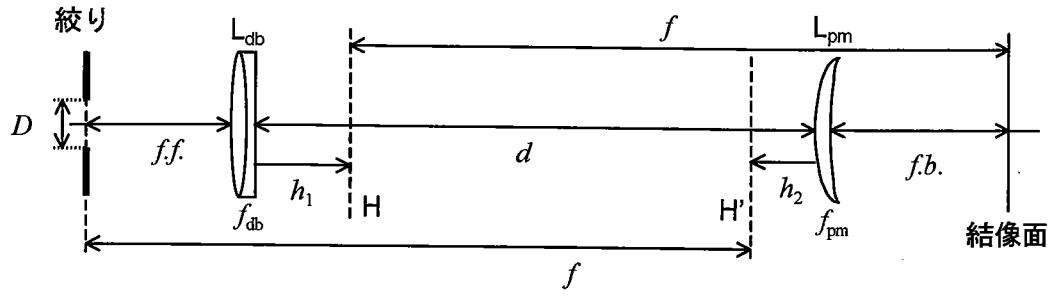

### 3.3.1 光学系設計

DCP-2 プロトタイプでは、入射ビーム束を X, Y 軸の 2 方向に偏向するために、2 個の音響光学結晶を用いる。これらの結晶は 1 つの金属モールド内に固定されているが、2 つの音響光学結晶が離れているため、偏向系の出力像の原点が偏向量に応じて変化する。光学系のパラメータが適切に設定されているとき、出力像位置の変位は相関系の CGH フィルタで補正できる。出力像位置の補正を考慮し、近軸光線追跡に基づいた光学系設計を行う。設計では、レンズ、音響光学素子は厚さをもたない薄肉物体として扱う。VCSEL、受光素子アレイのピッチ  $p$ , VCSEL のアレイサイズ  $q_0 \times q_0$ , VCSEL の放射角  $\phi$ , VCSEL 発振波長  $\lambda$ , AOD の最大変調角  $\theta_{\max}$ , 出力面のピクセル数  $q' \times q'$  (受光素子アレイピッチ  $p$  が単位), フィルタの最大サイズ  $\zeta \times \zeta$  から、フィルタアレイ数  $\xi \times \xi$ , フィルタサイズ  $s \times s$ , フィルタのピクセルサイズ  $\Delta \times \Delta$ , フィルタのピクセル数  $N \times N$ , 偏向角のスキャンピッチ  $\Delta\theta$ , 出力面での CGH 再生像のピクセルサイズ  $\delta \times \delta$  を決定する。詳細は、付録 D に記述する。

### 3.3.2 最大入力点数

光学系が扱える最大入力点数は、2次元 AOD の開口や最大変調量により制限を受ける。これらの影響を考慮し、光プロセッサの最大入力点数を求める。以下、X, Y 軸方向に偏向する AOD を、それぞれ X-AOD, Y-AOD と表記する。

DCP-2SI の場合、VCSEL アレイ像が 2 次元 AOD の開口に入りきらないことから、最大入力点数が制限される(図 3.3(a))。VCSEL の結像面の手前  $l_y$  の位置に Y-AOD、後方  $l_x$  に X-AOD があるとする( $l_x + l_y = l$ )。各 AOD の開口は  $W \times W$  の矩形とする。X-AOD 上において、VCSEL アレイからのビーム束の全幅  $u$  は次式で表される。

$$u = l_x \theta_{\max} + (q_0 - 1)p + \gamma w'. \quad (3.1)$$

VCSEL ビームはガウスビームとし、 $w'$  は X-AOD 面上での VCSEL ビームのビーム径とする。また、ビーム径の  $\gamma$  倍を VCSEL ビームのスポット径として扱う。ただし、VCSEL ビームはマイクロレンズでコリメートされていることに注意する。X-AOD における VCSEL ビーム径  $w'$  は次式で表される。

$$w' = (s_0/\gamma) \sqrt{1 + \left( \frac{\gamma^2 \lambda (l_x + l_y)}{\pi s_0^2} \right)^2}. \quad (3.2)$$

全光束が 2 次元 AOD の開口に入るには、 $u \leq W$  を満たす必要がある。これより、 $q_0$  は次の不等式を満たす最大の整数で与えられる。ただし、 $q_0$  は一軸方向に関する値であることに注意する。2 次元データに対しては、 $q_0^2$  が最大入力点数となる。

$$q_0 \leq 1 + \frac{W - l_x \theta_{\max}}{p} - \frac{\gamma w'}{p}. \quad (3.3)$$

DCP-2SI の最大入力点数を示す。音響光学結晶を薄いフィルムと考えたとき、2 次元 AOD の光学的な結晶間隔は実験的に 29.27mm と決まる(3.4.1 節参照)。音響光学結晶の位置  $l_x = l_y = 29.27/2$  mm, AOD の開口径  $W = 3.0$  mm, フィルタアレイ数  $\xi = 2$ , 最大変調角  $\theta_{\max} = 26$  mrad, VCSEL 発振波長  $\lambda = 850$  nm とする。また、VCSEL ピッチとスポットサイズが等しいとし( $p = s_0$ ),  $\gamma = 1.2$  とする。このとき、最大入力点数は 11 である。また、 $p$  を  $62.5\mu\text{m}$  に縮小した場合、最大入力点数は 42 になる。

DCP-2SV の最大入力点数を求める(図 3.3(b))。X-AOD 面上での全ビーム幅  $u$  は、

$$u = (l_x + l_y) \theta_{\max} + \frac{(q_0 - 1)p l_x}{f_1} + \gamma w', \quad (3.4)$$

### 3. 離散相関プロセッサ DCP-2

---

で与えられる。ここで、レンズ1の焦点距離  $f_1$  が VCSEL の発振波長  $\lambda$  よりも十分長いことから、レンズ1によりコリメートした VCSEL 光のビーム径を次式で与える。

$$w' = \frac{\gamma\lambda f_1}{\pi s_0}. \quad (3.5)$$

また、 $f_1$  を不等式 (D.22) の下限で定義する。全ビーム幅が AOD 開口に入る条件  $u \leq W$  から、次の不等式を得る。

$$\left( \frac{p\sqrt{\alpha\lambda l_x}}{s_0} + \frac{\gamma^2\lambda}{\pi}\sqrt{l_x}\alpha\lambda \right) q_0 + \{(l_x + l_y)\theta_{\max} - W\}\sqrt{q_0} - \frac{p\sqrt{\alpha\lambda l_x}}{s_0} \leq 0. \quad (3.6)$$

また、最大入力点数はフィルタアレイ数  $\xi$  によっても制限される。式 (D.21) より、

$$q_0 \leq \frac{\theta_{\max}^2 l_x}{\alpha(\xi - 1)^2 \lambda}. \quad (3.7)$$

これら 2 つの不等式を満たす最大の  $q_0$  が最大入力点数になる。

VCSEL アレイ結像面からの音響光学結晶の位置  $l_x = 0, l_y = 29.27\text{mm}$ , 最大変調量  $\theta_{\max} = 50\text{mrad}$ ,  $\alpha = 1, \xi = 2$ , それ以外の条件は DCP-2SI の場合と同じとし, 最大入力点数を求める。このとき, 最大入力点数は 18 となる。 $p$  を  $62.5\mu\text{m}$  に縮小した場合, 最大入力点数は 75 になる。

## 3.4 プロトタイプ

付録 D に示す設計手法に従い, DCP-2 プロトタイプのシステムパラメータを決定する。パラメータの決定のために, AOD の  $V - \theta$  特性と, AOD 間隔  $l$ , マイクロレンズと結合した場合の VCSEL の放射角を測定する。

### 3.4.1 AOD

AOD ドライバへの印可電圧と偏向角の関係を測定し, 直線近似すると, 次式を得た。

$$\theta_X = 0.0065V_X - 0.00040, \quad (3.8)$$

$$\theta_Y = 0.0059V_Y + 0.00050. \quad (3.9)$$

ただし,  $V_X, V_Y$  はそれぞれ, X, Y 軸に印可した電圧 (V),  $\theta_X, \theta_Y$  は X, Y 軸方向の偏向角 (rad) を示す。

図 3.4: 平板マイクロレンズ透過後の VCSEL ビーム強度分布の断面図。

偏向角と回折効率の依存性を測定した結果、回折効率 40%以上が得られる変調範囲は、X 軸では 25mrad, Y 軸では 15mrad であった。用いた 2 次元 AOD は、Y 軸のトランスデューサに問題があると思われ、変調範囲が狭くなっている。

また、図 3.2(a) に示す光学系で、 $f_r = 80.0\text{mm}$ ,  $f = 100.0\text{mm}$  とし、フーリエ面に CCD を配置して、絞り像位置の変化量から結晶間隔  $l$  を計測した。その結果、 $l = 29.27\text{mm}$  を得た。

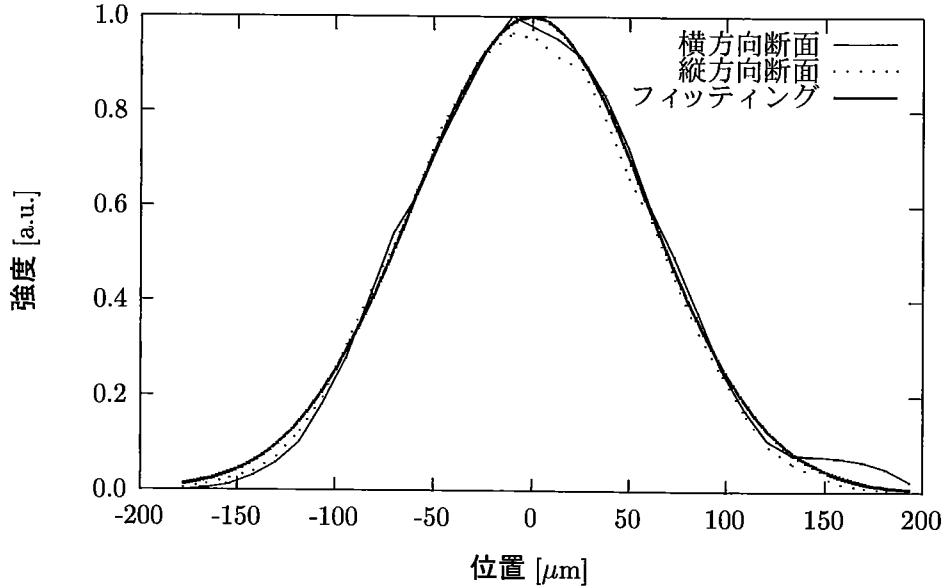

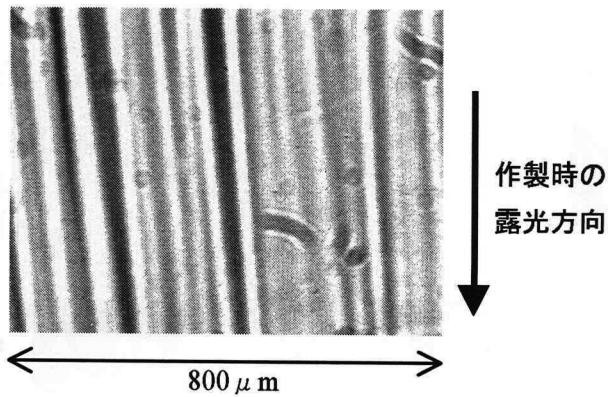

### 3.4.2 VCSEL 放射角の低減

VCSEL の放射角を小さくするために、平板マイクロレンズ (型番 PML-FW0250S0096S-NC, マイクロオプト製、焦点距離  $720\mu\text{m}$  (波長  $850\text{nm}$  に対する)) を用いた。ビームプロファイラ (製品名 ビームアライザ, Melles Griot 製) を用いて、マイクロレンズ面における光強度分布を測定した結果を図 3.4 に示す。ビームはほぼガウス分布をしており、ビーム径は約  $240\mu\text{m}$  であった。また、ビームの放射角は 25mrad であった。ガウスビームを仮定した場合、このビームウェスト径に対する放射角は  $1.13\text{mrad}$  である。この値と比較すると、実測値はかなり大きい。これは、用いた VCSEL は横多モード発振であることが主な原因であると考えられる。

より詳しく調べるために、図 3.2(b) に示す光学系において、リレー結像系のフーリエ面を結像した。その結果、光強度が強い中心部分を取り巻くように、周辺にドーナツ状の強度分布が見ら

### 3. 離散相関プロセッサ DCP-2

---

表 3.1: DCP-2 のシステムパラメータ。特に表記がない限り X 軸, Y 軸ともに同じ値。

|                | DCP-2SI                                                                      | DCP-2SV                                          |

|----------------|------------------------------------------------------------------------------|--------------------------------------------------|

| $q'_0$         | 4                                                                            | 4                                                |

| $q'$           | 32                                                                           | 32                                               |

| $\xi$          | 2                                                                            | X:3, Y:2                                         |

| $f$            | $f_1 = 389.65\text{mm}$<br>$f_2 = 389.65\text{mm}$<br>$f_3 = 27.29\text{mm}$ | $f_1 = 100.0\text{mm}$<br>$f_2 = 300.0\text{mm}$ |

| $\Delta$       | $41.4\mu\text{m}$                                                            | $2.9\mu\text{m}$                                 |

| $\alpha$       | 24                                                                           | 1                                                |

| $\beta$        | 8                                                                            | 8                                                |

| $\Delta\theta$ | 25.62mrad                                                                    | 11.62mrad                                        |

| $d$            | X:750 $\mu\text{m}$<br>Y:0 $\mu\text{m}$                                     | X:31.25 $\mu\text{m}$<br>Y:0 $\mu\text{m}$       |

| $\delta$       | 31.25 $\mu\text{m}$                                                          | 31.25 $\mu\text{m}$                              |

れた。これは、リレー結像系のフーリエ面が VCSEL の結像面になっていることから、VCSEL の電極構造による散乱光であると考えられる。測定の結果、ビームの全光強度のうち中心部に 93%, ドーナツ状部分に 7% が分布していることがわかった。周辺光は迷光の原因となるため、リレー系の絞りで除去するようにした。

#### 3.4.3 プロトタイプのシステムパラメータ

DCP-2SI, SVにおいて、2次元 AOD の最大変調角  $\theta_{\max}$  を、26mrad (X 軸方向), 15mrad (Y 軸方向), VCSEL の発振波長  $\lambda = 850\text{nm}$ , 2次元 AOD の結晶間隔  $l = 29.27\text{mm}$  とした場合、VCSEL アレイサイズ  $q'_0$ , 出力アレイ数  $q'$  を与え、プロトタイプのシステムパラメータを決めた。DCP-2SIにおいて Y 軸方向のアレイ数を X 軸と同じにとると変調角が不足する。プロトタイプではフィルタアレイサイズを優先し、回折効率を犠牲にして最大変調量を X 軸と同じ値として設計した。設計結果を表 3.1 に示す。

### 3.5 実験結果

#### 3.5.1 光学系

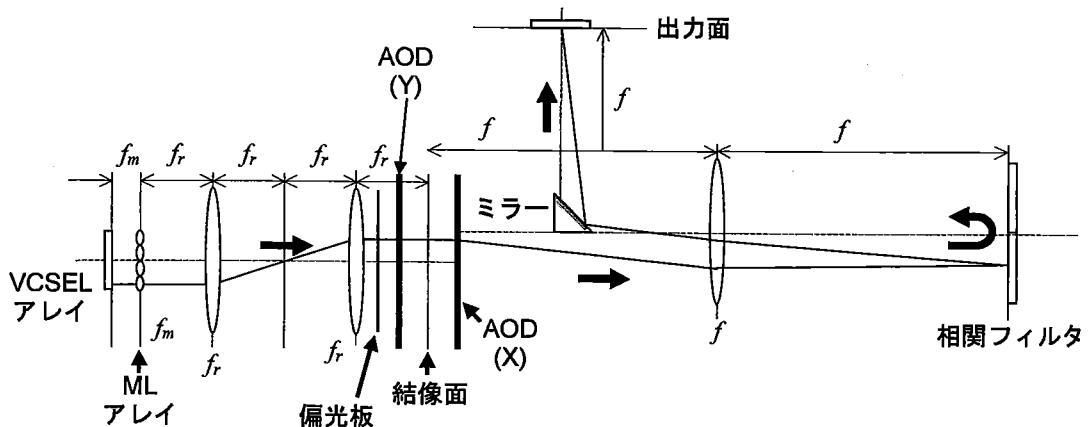

PAL-SLM が反射型であることから、DCP-2SI のプロトタイプでは、図 3.5 に示す折りたたみ光学系を用いた。図において、相関光学系の下半分を往路、上半分を復路として用いた。復路には稜面をアルミ反射コートした直角プリズムを配置し、進行方向を 90 度変えて受光素子に入射した。DCP-2SV は偏向系の中心に 2 次元 AOD があるため反射型の構成にしにくい。そのため、図 3.2(b) の光学系をそのまま用いた。

相関フィルタは、付録 C に示すアルゴリズムを利用して設計した。固定フィルタの作製には、電子ビームリソグラフィを用いた。フォトレジスト（型番 ZEP-520-22, NIPPON ZEON 製、ポジ型）を石英基板上に 5,000Å の厚さでスピンドルコートし、電子ビーム描画装置（型番 JBX-5000SI, 日本電子製）でパターンを描画した。現像後、プラズマドライエッチング装置（型番 NLD-800, ULVAC Japan 製）を用いて、フォトレジストのレリーフ形状を石英基板に転写した。エッチングには、 $\text{CH}_2\text{F}_2$  と  $\text{C}_4\text{F}_8$  の混合ガスを用いた。

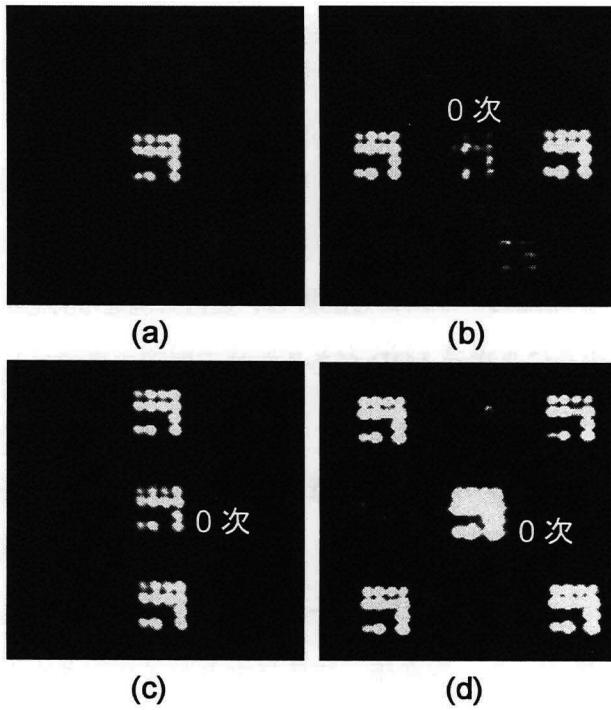

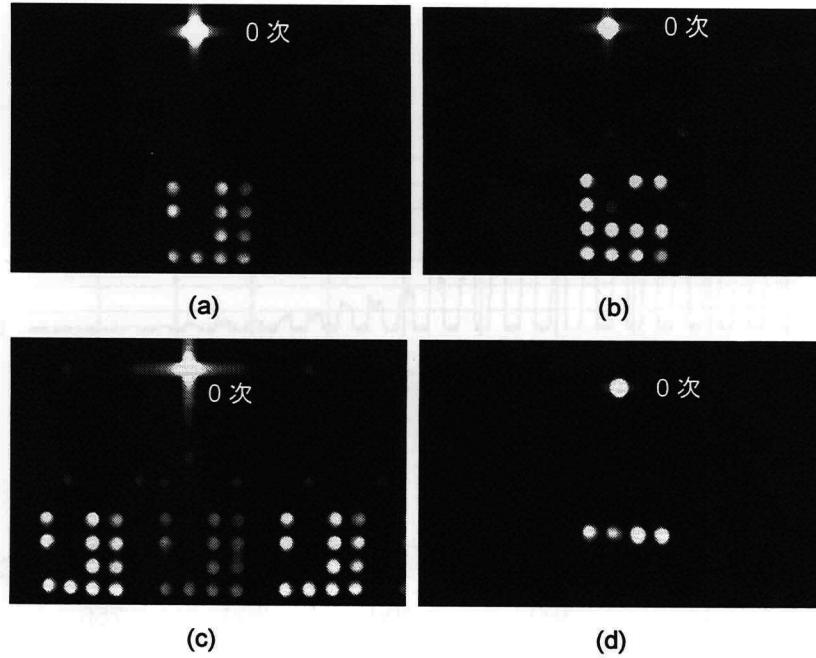

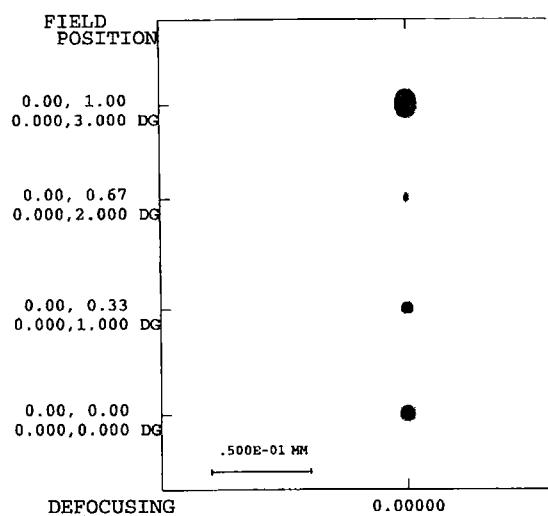

#### 3.5.2 静的特性

図 3.6, 図 3.7 に DCP-2SI, DCP-2SV の静的な相関出力像を示す。ただし、DCP-2SV では Y-AOD の動作不良の影響が強く、VCSEL 像の一部しか透過しなかった。そのため、図 3.7 は AOD を

図 3.5: DCP-2SI プロトタイプの光学系の構成。

### 3. 離散相関プロセッサ DCP-2

図 3.6: DCP-2SI の静的相関出力: (a) VCSEL 像, (b) 横 2 つにファンアウト, (c) 縦 2 つにファンアウト, (d) 正方形の 4 つの頂点上にファンアウト.

用いない場合の実験結果になっている。また、表 3.2 にプロトタイプの光量効率を示す。DCP-2SI と SV では共通のリレー系を用いた。リレー系において、VCSEL とマイクロレンズの結合効率は 73%，偏光ビームスプリッタの透過率は 94% であった。DCP-2SI, SV における CGH フィルタの反射率・透過率は、それぞれ 88.5%, 93.5% であった。

DCP-2SI におけるコントラストは 100:1 以上であった。また、図 3.6(c), (d) に示す出力像の回折効率が低いのは、Y-AOD の回折効率が低い領域を使っているためである。この領域では、AOD からの出射ビームの均一性が悪いため、0 次光が増加している。高い回折効率をもつ変調範囲でもビームはガウス形状から少し崩れており、それがゴーストの原因になっていると考えられる。

図 3.7(d) は、図 3.7(a) に示す VCSEL 出力データの縦 1 列分を、1 点にファンインした結果である。図 3.7(a) において、それぞれの列で点灯している VCSEL の個数は 3, 1, 4, 4 である。図 3.7(d) の 4 つのスポットの明るさは、明点の個数を反映していることがわかる。図 3.7 に示されるように、多くのゴーストスポットが生じている。信号光に対するゴーストの強度比は、約 2.5:1 であった。

図 3.7: DCP-2SV の静的特性: (a) VCSEL 像, (b) 時計回りに 90 度回転, (c) 横 3 つにファンアウト, (d) 縦方向にファンイン.

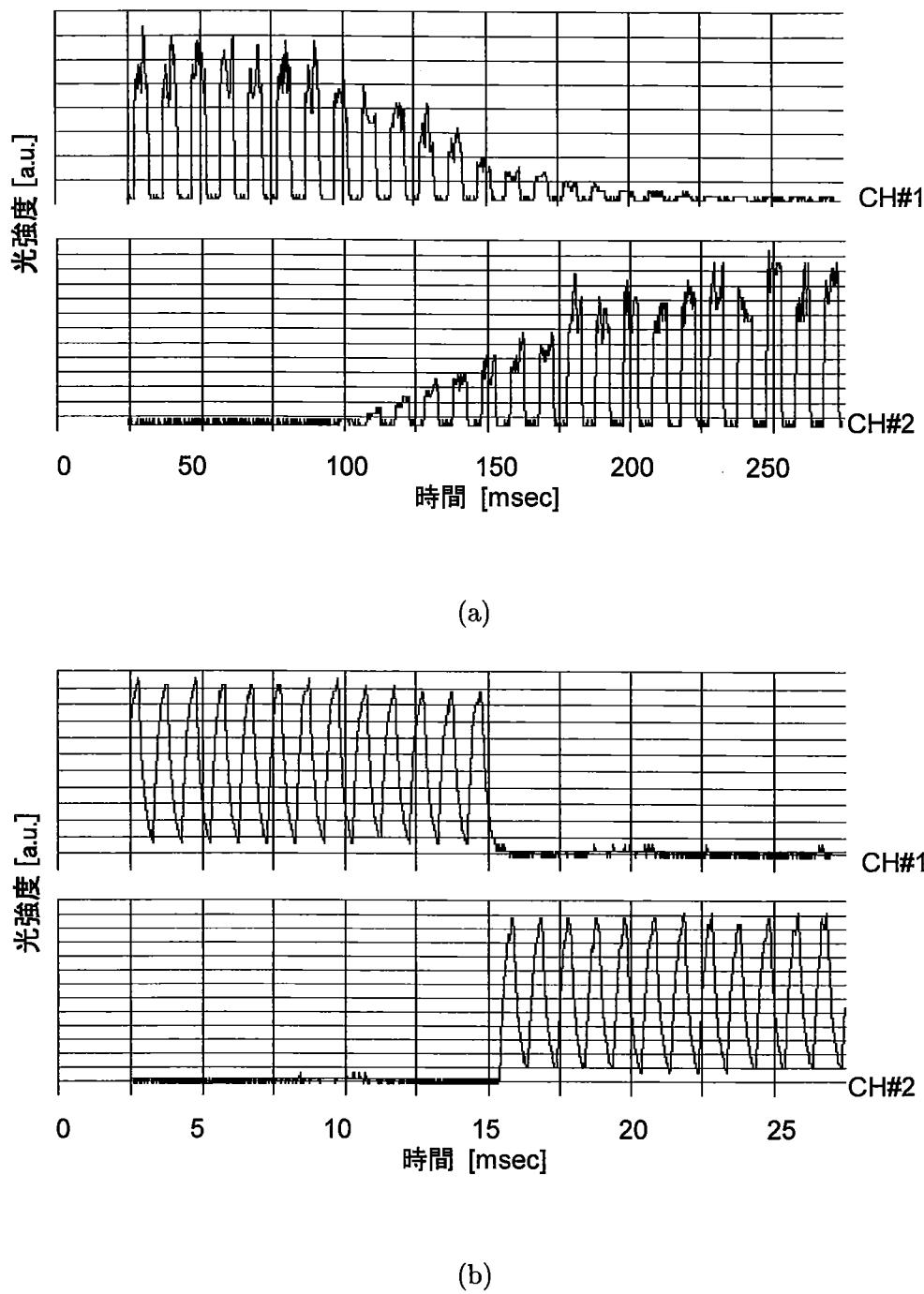

### 3.5.3 動的特性

DCP-2SIにおいて、PAL-SLM 単体で用いた場合と、AODと組み合わせて用いた場合の動的特性を測定した。実験では、VCSELから繰り返し矩形波の光信号を出力しながら、2つの異なる接続パターンをもつ CGH フィルタを切り換える、出力面における光強度の時間変化を測定した。PAL-SLM 単体の場合、フィルタをトリガ信号に同期して書き換えた。DCP-2SIでは、PAL-SLM に2つの光接続パターンを表示した。トリガ信号に同期して AOD の偏向角を変化させ、選択するフィルタを切り換えた。測定には、受光素子としてシリコン PIN フォトディテクタ (型番 ET-4000, Electro-Optics Technology 製) を用いた。測定結果を図 3.8 に示す。図 3.8(a) のタイムスケールは、図 3.8(b) の 10 倍であることに注意する。ここで、信号の立ち上がり時間を、接続パターンを切り換えてから光強度が 90% になるまでの時間で定義する。PAL-SLM の場合、立ち上り時間は 107 msec であった (図 3.8(a))。一方、DCP-2SI における立ち上がり時間は図 3.8(b) からわかるように、シリコン PIN フォトディテクタでは確認できないほど短かった。高速なアバランシェ方式受光モジュール (型番 S5331-01, 浜松ホトニクス製, 検出信号帯域 100MHz) を用いて測定した結

### 3. 離散相関プロセッサ DCP-2

図 3.8: DCP-2SI の動的特性: (a) PAL-SLM 単体, (b) DCP-2SI.

表 3.2: DCP-2 回折効率・光量効率.

|            | 0 次<br>(%) | 高次<br>(%) | ±1 次<br>(%) | AOD の回折効率<br>(%) | 全透過率<br>(%) |

|------------|------------|-----------|-------------|------------------|-------------|

| DCP-2SI(a) | -          | -         | -           | 46.2             | 29.8        |

| DCP-2SI(b) | 9.60       | 36.6      | 53.8        | 44.8             | 15.6        |

| DCP-2SI(c) | 13.9       | 38.1      | 47.9        | 9.00             | 2.80        |

| DCP-2SI(d) | 41.4       | 50.0      | 8.60        | 9.90             | 0.550       |

| DCP-2SV    | 13.4       | 12.2      | 74.4        | -                | 50.8        |

果、DCP-2SI における立ち上がり時間は  $4.1\mu\text{sec}$  であった。この実験結果から、光接続パターン変更速度を見かけ上 26,097 倍に高速化できたことを確認した。

### 3.6 考察

今後、AOD の改善により、フィルタアレイ全体に対して高い光量効率を保ったまま、高速な光接続パターン切り換えが可能になると期待できる。プロトタイプに使用した VCSEL は横多モード発振であったため、放射角が大きかった。そのため、十分なフィルタアレイ数が得られず、実際の入力点数も少なかった。また、VCSEL は偏光制御されていないため、偏光デバイスを用いる場合、損失が無視できなかった。これらの問題は、ピクセルピッチの狭い偏光制御した横单一モード VCSEL を用いることにより、改善できる [89]。

AOD は現在容易に入手可能なビーム偏向器ではあるが、開口が小さく、偏向切り換え速度も VCSEL の変調速度と比較するとさほど速くない。MEMS デバイス [63] は、大口径と高光量効率が見込めるところから有望である。ただし、変調速度は高々  $\mu\text{sec}$  オーダであり、AOD とあまり変わらない。光接続パターン切り換え時に生じる無駄時間は、システム性能に大きな制限を与えることになる。接続パターン切換速度を、信号の変調周波数に近づけるためには、超高速光学現象を用いた高速・高光量効率のビーム偏向機構を探る必要がある [90]。

DCP-2SV の相関出力において、ゴーストが多く見られたのは、CGH フィルタの設計アルゴリズムの問題であると考えられる。ダイレクトバイナリサーチ [91]、シミュレーテッドアニーリング [92] などのアルゴリズムを用いることにより、解決できると考えられる。

### 3. 離散相關プロセッサ DCP-2

#### 3.7 結言

本章では、大ファンアウト光接続システムの構築に不可欠な高性能光プロセッサの基本アーキテクチャとして、高速ビーム偏向器と空間光変調器を組み合わせた DCP-2 アーキテクチャを提案した。提案アーキテクチャを利用すると、2つのデバイスが相補的に働くことにより、高速パターン切換・高光量効率・高コントラストを兼ね備えた理想的な光プロセッサを実現できる。2次元 AOD を利用した DCP-2 プロトタイプの光学系設計と、プロトタイプで扱える最大入力点数を示した。DCP-2 プロトタイプシステムとして、スペースインвариант型の DCP-2SI と、スペースвариант方の DCP-2SV を試作し、アーキテクチャの原理を実証した。DCP-2SI では、空間光変調器に PAL-SLM、DCP-2SV ではガラスレリーフ基板を用いた。これらのプロトタイプの静的特性と動的特性を測定した。動的特性の測定結果から、PAL-SLM を単体で用いた場合と比較して、DCP-2SI では、接続パターンの切り換え速度を約 26,000 倍に向上できることを確認した。このとき、AOD を挿入することによる光量損失は、約 50% であった。

---

## 4 並列マッチングアーキテクチャ

### 4.1 緒言

本章では、第1章で述べた大域処理光プロセッサを利用した光・電子融合型マルチプロセッサシステムアーキテクチャの具体例として、並列マッチングアーキテクチャ (PMA: parallel matching architecture) を提案する。また、光プロセッサ DCP-1S を応用した実証プロトタイプシステムを試作し、基本機能を検証する。PMA は、専用の大域プロセッサである並列マッチング (PM) モジュールをもち、大域処理を高速実行する。各プロセッサは、PM モジュールを通して通信・大域処理を行う。PM モジュールは、基本大域演算として、複数プロセッサ間におけるデータの大小関係検出・絶対差分和演算を行う。これらを並列マッチング処理とよぶ。PM モジュールを利用し、大域データ比較・最大(小)値検出・データのランク付けなどを高速実行できる。PM モジュールが要求する大きな処理帯域を実現するために、大ファンアウト自由空間光接続光学系と、並列マッチングスマートピクセルアレイ (PM-SPA) を利用する。

4.2節では、PMA の概念と、PM-SPA の機能を述べる。4.3節では、PM モジュールの光・電子融合型実装方式を示す。4.4節では、マルチプロセッサシステムアーキテクチャをモデル化し、他の光ネットワークを用いた既存アーキテクチャと大域処理性能を比較する。4.5節では、プロトタイプシステムの構成要素について述べる。4.6節では、プロトタイプシステムの実験結果を示す。4.7節では、PMA の課題を述べる。

### 4.2 並列マッチングアーキテクチャ

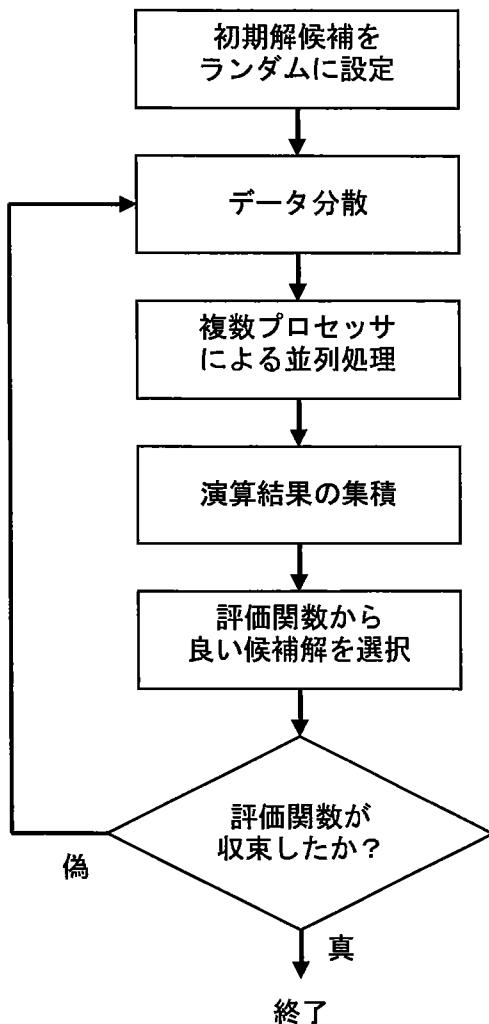

#### 4.2.1 分散最適化アルゴリズム

$N$  個のプロセッサ (PE: processing element) で構成する MIMD (multiple-instruction multiple-data stream) 型マルチプロセッサシステムを考える。プロセッサは、OE-VLSI により実装されており、広い通信大域幅をもつ光ネットワークにより相互接続されているとする。この場合、プロセッサは、プロセッサ内の局所的処理帯域幅と同等のオフチップ通信帯域幅をもっているとみなす。発見的手法に基づく分散最適化アルゴリズムは、マルチプロセッサシステムにより高速実行できる良い例である [93, 94]。例えば、代表的な分散最適化アルゴリズムとして、遺伝的アルゴリズム (GA: genetic algorithm) [95] がある。このアルゴリズムは、必ずしも厳密解法が存在し

#### 4. 並列マッチングアーキテクチャ

図 4.1: 分散最適化アルゴリズムのフローチャート。

ない広範な問題に適用でき、近似解を求めることができる。複数のプロセッサを用いて、解空間の複数の座標を並列探索し、求解を高速化できる。処理速度と解の正確性は、プロセッサ数を増やすことにより改善できる。

図 4.1 に、分散最適化アルゴリズムの一般的な処理手順を示す。分散最適化アルゴリズムは、データの分散・並列処理(局所処理)・計算結果の統合(大域処理)から成る。最初に、得られる近似解が局所解に陥ることを避けるために、解空間の全域を覆うように候補解の初期値をランダムに設定する。候補解をプロセッサに分散した後、あらかじめ決めた手順にしたがい、各プロセッサは候補解の内容を更新する。候補解の最適性を判断するためには、評価関数を用いる。評価関数

図 4.2: 並列マッチングアーキテクチャと従来アーキテクチャのシステム構成: (a) 従来のマスター・スレイブ型アーキテクチャ, (b) 並列マッチングアーキテクチャ.

の大きい (定義によっては小さい) 候補解を選び、その他の解を捨てる。この手順を、評価関数が収束するまで繰り返す。

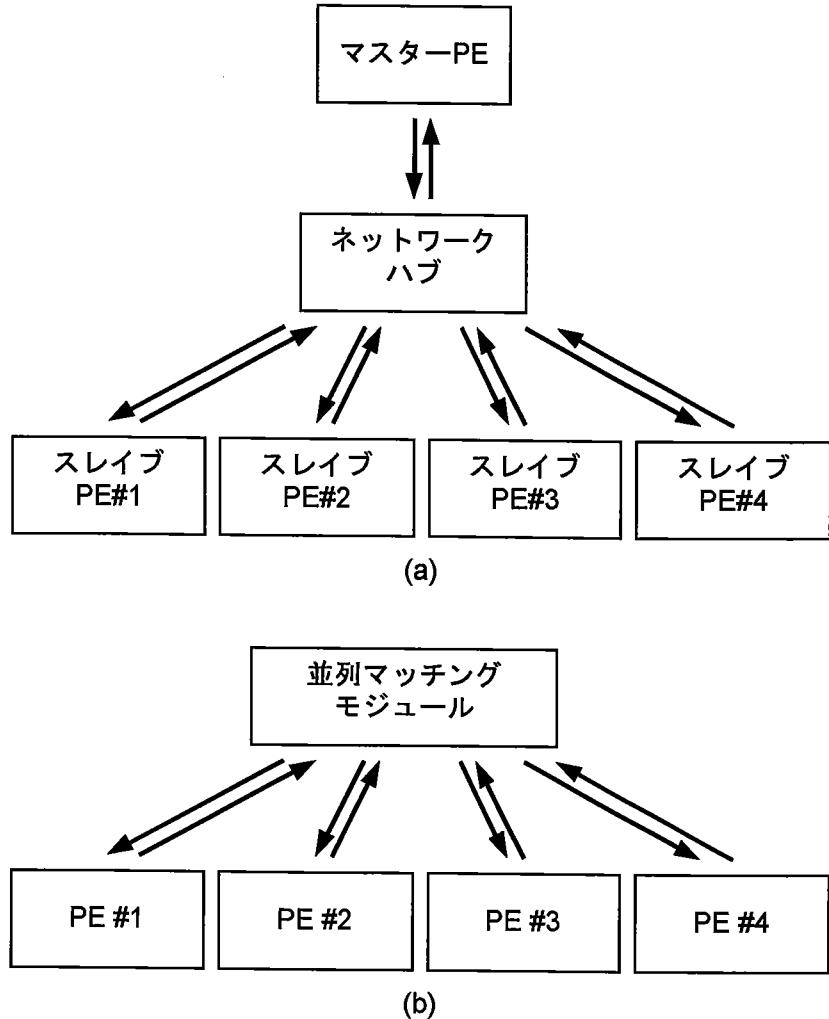

#### 4.2.2 分散最適化アルゴリズムに適したマルチプロセッサアーキテクチャ

図 4.2(a) に、従来のマルチプロセッサシステムの構成を示す。分散最適化アルゴリズムを実行する場合、従来のアーキテクチャでは、マスタープロセッサが複数のスレイブプロセッサを管理する階層構造を用いる。マスタープロセッサの役割は、スレイブプロセッサへのデータ分散・処理

#### 4. 並列マッチングアーキテクチャ

結果の統合(大域処理)である。大域処理において、アルゴリズムが要求するデータ処理帯域は、プロセッサのデータ処理帯域の約  $N$  倍に達する。そのため、アルゴリズムの要求する処理帯域とハードウェアの処理帯域の間に帯域幅不整合が生じる。その結果、従来のマルチプロセッサシステムアーキテクチャでは、大域処理がボトルネックになる。

帯域幅不整合を解決するマルチプロセッサシステムアーキテクチャとして、第1章で述べた大域処理光プロセッサに基づく並列マッチングアーキテクチャ(PMA: parallel matching architecture)を提案する。PMAの構成を図4.2(b)に示す。PMAでは、プロセッサ同士を並列マッチング(PM: parallel matching)モジュールを介して接続する。PMAは、プロセッサ同士が階層構造をもたない平坦なアーキテクチャである。全プロセッサが同じ優先順位をもつ点が、従来のアーキテクチャと異なる。PMモジュールは、プロセッサ間通信に加えて、専用の大域処理機構をもつ。大域処理は大きなデータ処理帯域を要求するが、PMモジュールの内部で大域処理を実行するため、プロセッサにはその結果だけが転送される。大域処理結果のデータ転送帯域幅は、プロセッサの処理帯域幅程度に削減できるため、帯域幅不整合は生じない。分散最適化アルゴリズムでは、PMモジュールの大域処理機能を利用することにより、あるプロセッサのもつ候補解の評価関数を、他のプロセッサの候補解の評価関数と並列に比較できる。その結果、提案するアーキテクチャでは大域処理はボトルネックにならない。

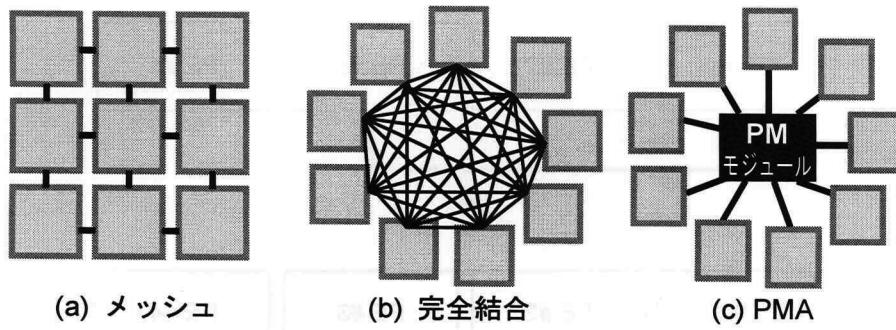

PMAには、任意のネットワークトポロジを適用できる。このため、PMAシステムの設計において、用途に特化した最適なネットワークトポロジを選択できる。以下では、PMAのネットワークトポロジとして完全結合ネットワークを考える。完全結合ネットワークはネットワーク直径が1であるため、パケットをリレーすることなく、プロセッサ同士が直接通信できる利点をもっている。しかし、ネットワークに繋がるノード数が多くなると、配線数が急激に増加する。このため、大規模な完全結合ネットワークを、電気的に実装することは困難であった。近年の光・電子融合型デモストレーションシステムにより、光の大ファンアウト性を用いて、大規模な完全結合ネットワークを実装できることが示されている[30]。このことは、PMAでも有効である。

##### **4.2.3 並列マッチング処理**

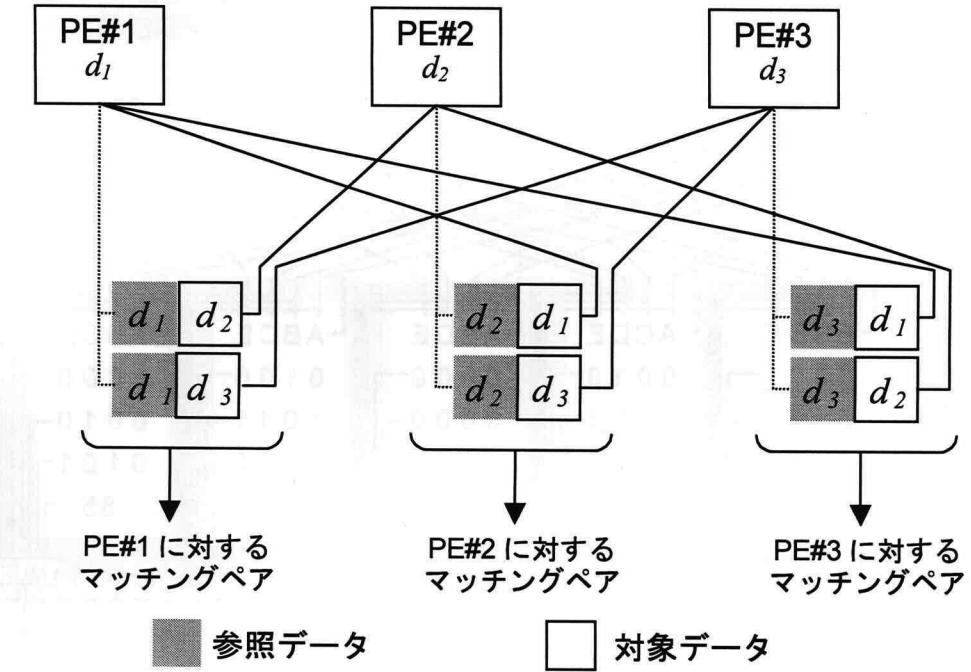

PMモジュールが実行する大域処理として、並列マッチング処理を定義する。図4.3に、並列マッチング処理におけるデータの流れを示す。並列マッチング処理は全プロセッサで共通している

図 4.3: 並列マッチングにおけるデータの流れ.  $d_1, d_2, d_3$  はそれぞれ PE#1-#3 の出力データを意味する。

ため, 1つのプロセッサについて述べる。プロセッサの出力するデータを参照データ（図中で網掛けたデータ），他のプロセッサのデータを対象データ（無地のデータ），参照データと対象データの対を，マッチングペアとよぶ。マッチングペアは，比較対象となるプロセッサと同数存在する。図 4.3 では，3つのプロセッサがデータ  $d_1, d_2, d_3$  を出力し，各プロセッサに対して 2 つのマッチングペアを生成している。1 つのマッチングペアに対する比較演算が，マッチング演算である。マッチング演算は，並列マッチング処理の要素演算である。1 つのプロセッサに対する並列マッチング処理は，そのプロセッサに属する全マッチングペアに対するマッチング演算の集合で与えられる。

マッチング演算として，マッチングペアに対する次の条件判断を定義する。1) 参照データと対象データが等しい。2) 参照データは対象データよりも小さい。3) 参照データは対象データよりも大きい。1 つのマッチングペアに対する条件判断の結果を，1 ビットの論理値で表す。条件が満たされる場合は 1，満たされない場合は 0 とする。これら 3 種類のマッチング演算を，それぞれ識別子 EQU, MORETHAN, LESSTHAN と表記する。1 つのプロセッサに属する全マッチングペアに対するマッチング演算結果の集合が，並列マッチング処理結果となり，2 値の数列で表される。1

#### 4. 並列マッチングアーキテクチャ

図 4.4: PMA の基本処理. MUX はマルチプレクサを意味する.

~3 の条件に対する並列マッチング処理を，それぞれ pEQU, pMORETHAN, pLESSTHAN で表記する。並列マッチング処理を，要素演算であるマッチング演算と区別するために，識別子に p を付加して表記する。プロセッサが  $m$  ビットのデータフォーマットを扱えるとすると， $(m + 1)$  個のプロセッサの大域比較処理を一度に行える。

並列マッチング処理として，さらに絶対差分和を定義し，pDIFF で表記する。pDIFF の要素演算は，絶対差分演算 DIFF である。DIFF は，参照データと対象データの差の絶対値を与える。全ての対象データに対する DIFF 演算結果の総和が pDIFF であり，正の整数となる。この処理を用いると，各プロセッサが出力するデータと他の複数のプロセッサのデータの差異を，定量的に得ることができる。

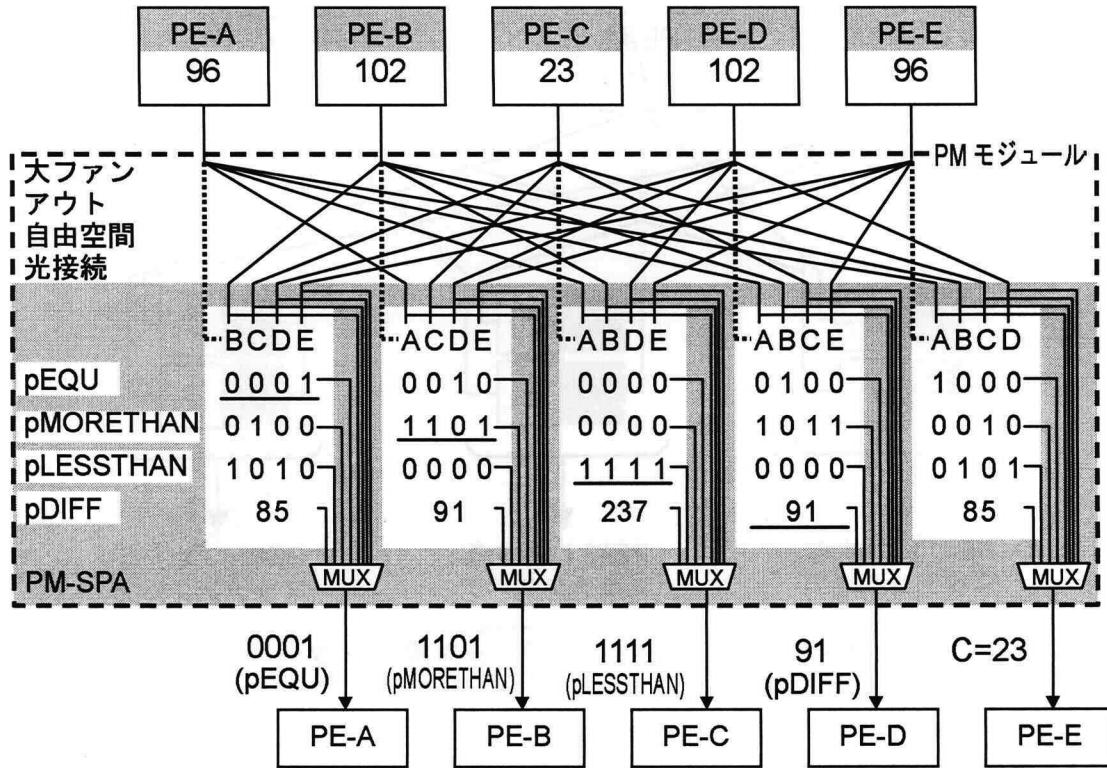

図 4.4 は，5 プロセッサから成るマルチプロセッサシステムにおける並列マッチング手順を示している。プロセッサの枠内の数字は，各プロセッサが出力しているデータを表している。図中で，プロセッサ A, B, C, D は並列マッチング処理 (pEQU, pMOREHTAN, pLESSSTHAN, pDIFF) を行い，E はプロセッサ間通信をしている。例の場合，pDIFF を除く並列マッチング処理の結果

## 4.2. 並列マッチングアーキテクチャ

は、4ビットの論理値の集合で表される。並列マッチング処理では、各プロセッサからのデータをファンアウトして並べ換え、マッチングペアを生成する。実線は、対象データを生成するためのファンアウトを示しており、完全結合の場合、プロセッサ数から1を引いたファンアウト数をもつ。参照データのファンアウト数も対象データと同数であるが、同一プロセッサに対しては共通であるため、省略して1本の破線で示している。PMモジュールは、プロセッサからの要求に応じて4種類の並列マッチング結果と全対象データの中から1つをマルチプレクサで抽出し、プロセッサに返す。対象データを選択することは、プロセッサ間通信により、送信元プロセッサからのデータを受信することに対応する。図4.4の例では、プロセッサCのデータがプロセッサEに転送されている。

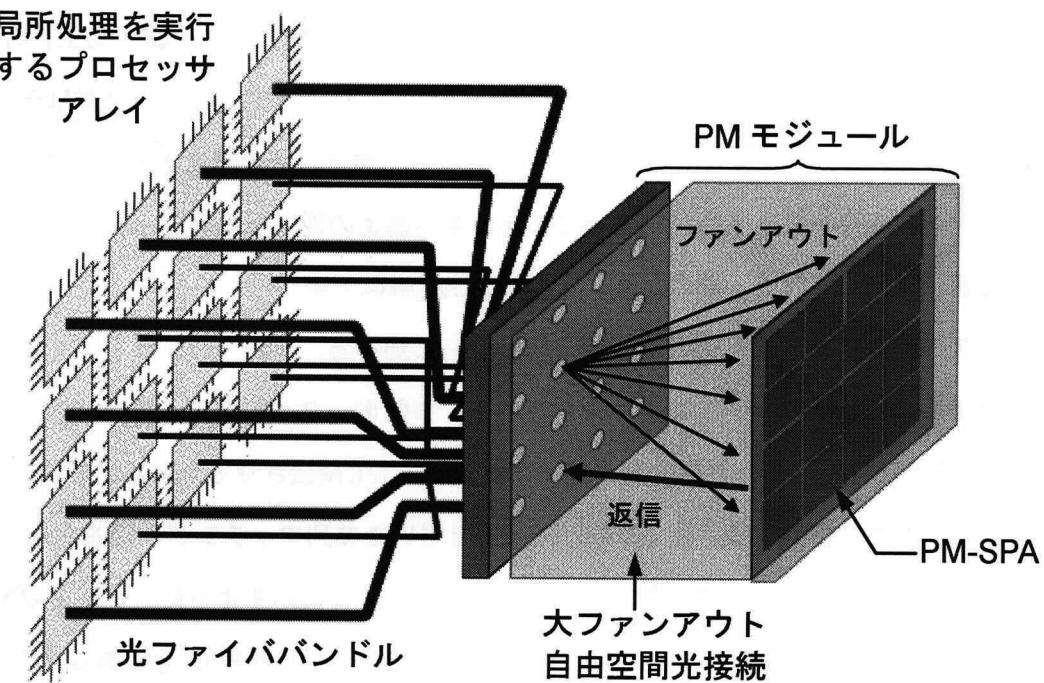

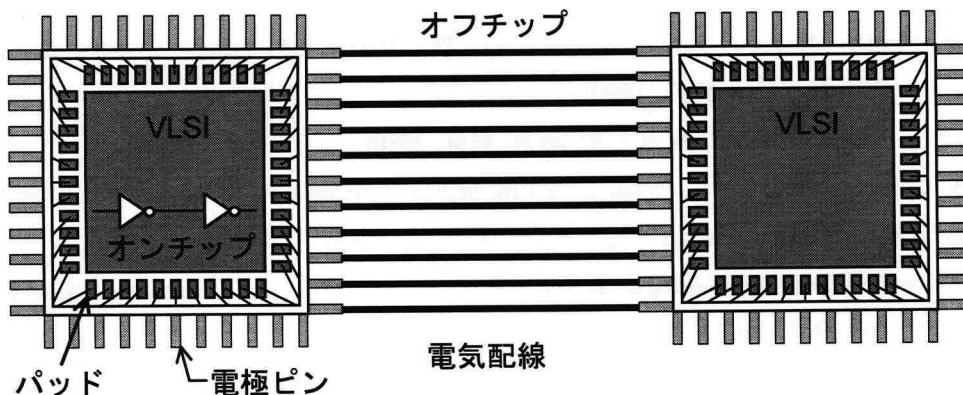

### 4.2.4 光・電子融合型マルチプロセッサシステムの構成

図4.5に、 $4 \times 4$ プロセッサから構成されるPMAシステムの実装例を示す。各プロセッサは、PMモジュールを介して他のプロセッサと接続される。プロセッサは2次元メッシュ上に配置し、

図4.5: PMAシステムの実装例。

#### 4. 並列マッチングアーキテクチャ

---

光ファイババンドルにより並列マッチングモジュールと接続される。PM モジュールは、高密度・高速接続と大規模並列演算を必要とするため、大ファンアウト光接続と並列マッチングスマートピクセルアレイ (PM-SPA: parallel-matching smart pixel array) により実装する。プロセッサは OE-VLSI により実装し、光ファイババンドルを介して多ビットデータを PM モジュールとやりとりする。

### 4.3 光・電子融合型並列マッチング処理

PM モジュールを、以下の指針で光・電子デバイスを用いて実装する。大域処理 (並列マッチング処理) を、並列実行可能な複数の要素処理 (マッチング演算) に分解する。要素処理を実行するハードウェアとして、マッチングノード (後述) とよぶスマートピクセルを 2 次元平面上にアレイ状に配置する。自由空間光接続の大ファンアウト性を利用して、入力データから 2 次元平面上に、要素処理に必要なデータ対を生成する。これらをスマートピクセルアレイで受信し、多数のマッチング演算を並列に実行する。これにより、大域処理を高速に実行できる。

PM-SPA の設計は、VLSI 作製上の様々な拘束条件により制限される。その中でも、VLSI のデバイスレイアウトは重要である。VLSI 上では、複雑な配線はチップ面積を消費する上、信号遅延・スキューの原因になる。したがって、複雑な配線を避けるために、被処理データ対はチップ上に近接して存在していることが望ましい。OE-VLSI を用いる場合、光接続によるデータの並べ換えは、レイアウトの条件を満たすために有効である。並べ換えの後、被処理データはチップ上の近接した受光素子で受信される。そのため、複雑な電気配線は不要である。

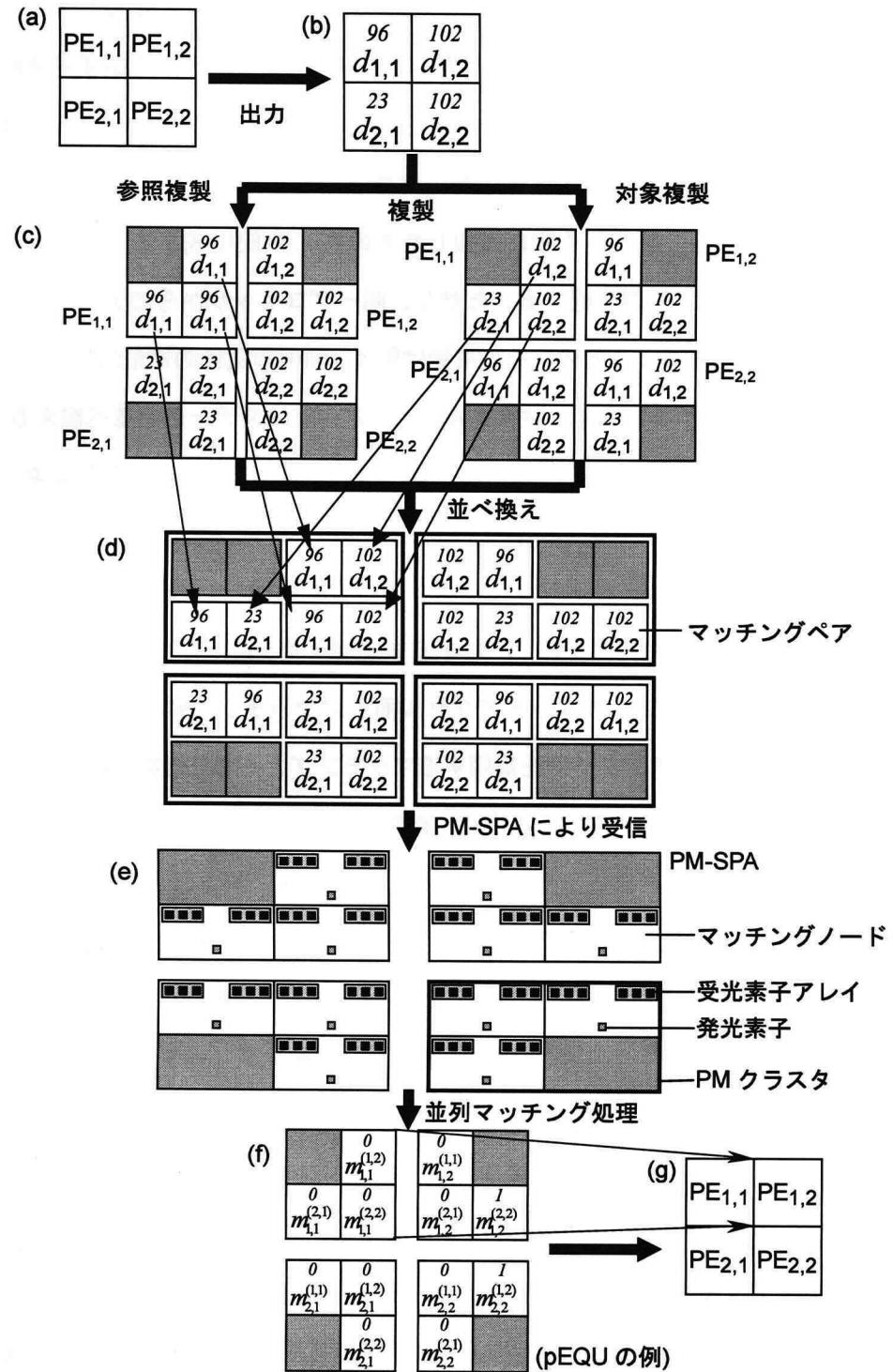

マッチングペアを生成するための光接続方式について述べる。この方式では、プロセッサの出力データを 2 種類の接続パターンでファンアウトし、参照データと対象データを生成する。その際、マッチングペアになるデータ同士をスマートピクセル上で隣接させるために、参照データと対象データを並べ換えて合成する。図 4.6 に、光接続を用いた並列マッチング手法を示す。図中で、斜体の数字は並列マッチング処理の例を示している。図 4.6(a) に示すように、 $\sqrt{N} \times \sqrt{N}$  個のプロセッサが 2 次元メッシュ上に並んでいるとする。ここで、 $PE_{i,j}$  は座標  $[i, j]$  にあるプロセッサを表す。各プロセッサは、他の全てのプロセッサと完全結合している。このとき、1 つのプロセッサと接続されるプロセッサ数は  $N - 1$  となる。図 4.6 は  $N = 4$  の場合を示しており、接続プロセッサ数は 3 である。

### 4.3. 光・電子融合型並列マッチング処理

図 4.6: 光・電子並列マッチング手順: (a) 2次元メッシュ上に配置したプロセッサ (PE), (b) 発光素子アレイに表示した出力データ, (c) 参照複製と対象複製, (d) データを入れ換えてマッチングペアを生成, (e) 並列マッチングスマートピクセルアレイ (PM-SPA), (f) 並列マッチング結果, (g) データを受信するプロセッサ.

#### 4. 並列マッチングアーキテクチャ

$\text{PE}_{i,j}$  が output するデータを  $d_{i,j}$  とする。プロセッサからのデータを、PM モジュールの入力面で 2 次元格子上に配置する(図 4.6(b))。ここで、参照データ・対象データを生成する手続きを、それぞれ参照複製、対象複製と呼ぶ。完全結合ネットワークでは、1 つのプロセッサに対する並列マッチング処理には、 $N - 1$  組のマッチングペアが必要である。したがって、参照複製はそれぞれのプロセッサの出力データ  $d_{i,j}$  を  $N - 1$  個に複製したものを、 $N$  組生成する。対象複製では、入力データ(図 4.6(b)) の複製を  $N$  組生成する。ただし、同一プロセッサからのデータ同士を比較しても必ず一致し、処理に意味がないため、その複製は除く(図中の灰色の矩形)。

次に、マッチングペアを作るために、参照複製データと対象複製データを並べ換える(図 4.6(d))。1 つのマッチングペアを処理する単位スマートピクセルを、マッチングノードとよぶ。スマートピクセル面上では、図 4.6(e) に示すように、生成したマッチングペアと同数のマッチングノードを配置する。マッチングノードは、受信したマッチングペアを処理し、1 ビットのマッチング結果を発光素子から出力する。プロセッサ  $\text{PE}_{i,j}$  に対するプロセッサ  $\text{PE}_{k,l}$  のマッチング結果を  $m_{i,j}^{(k,l)}$  で表すと、図 4.6(f) に示すように、スマートピクセル面上にマッチング結果が並ぶ。

同じ参照データをもつマッチングペアを処理するマッチングノードの組を、並列マッチング(PM)クラスタとよぶ。PM クラスタは、互いに独立に動作する。1 プロセッサに対する並列マッチング結果は、PM クラスタの出力するマッチング結果の集合になる。例えば、 $\text{PE}_{1,1}$  に対する並列マッチング結果は、 $m_{1,1}^{(1,2)}, m_{1,1}^{(2,1)}, m_{1,1}^{(2,2)}$  の 3 ビットから成る。これらの結果は、光通信チャネルを通じてプロセッサに返される(図 4.6(g))。

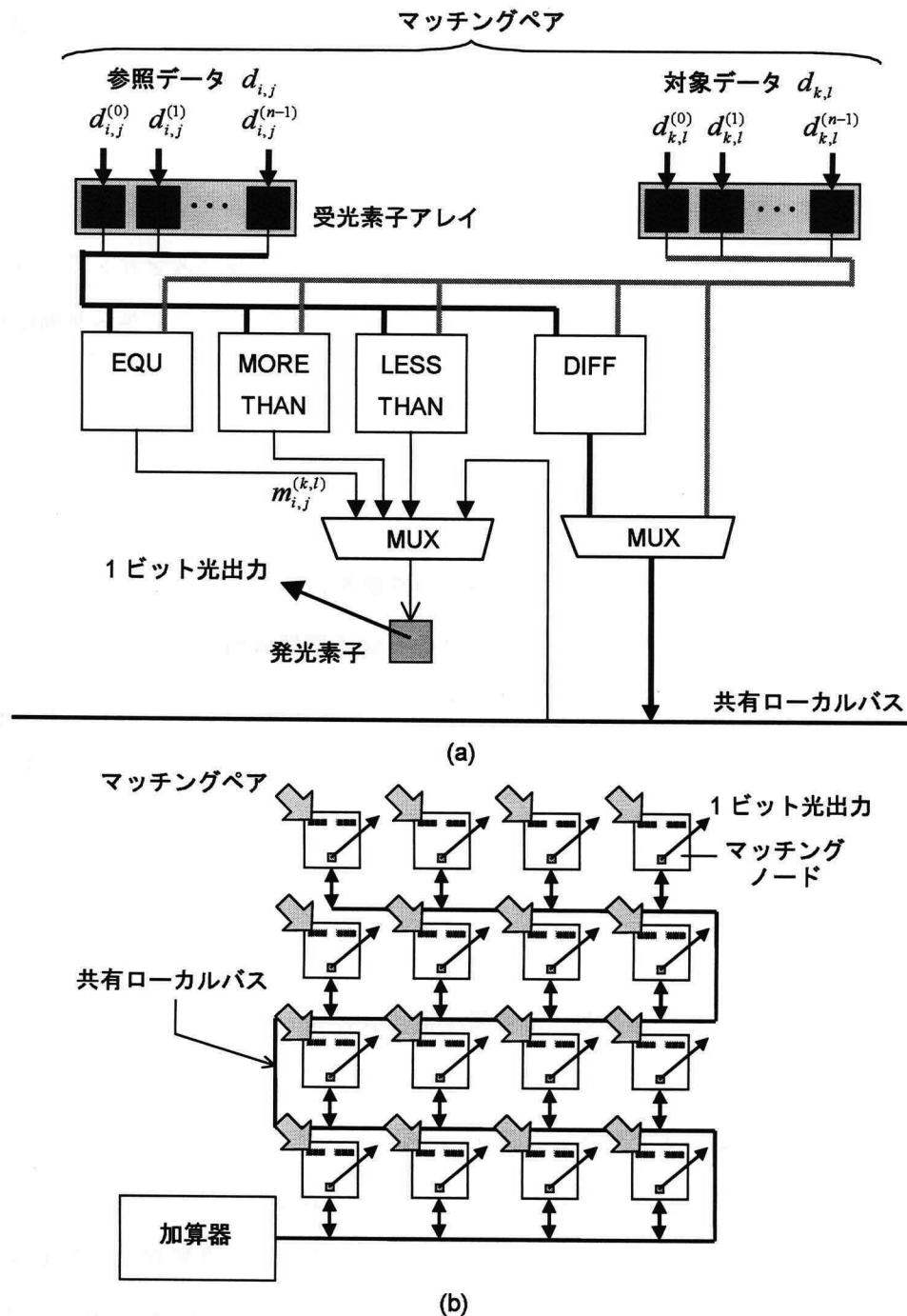

図 4.7(a) にマッチングノードのブロック図を示す。マッチングノードは 4 種類のマッチング演算を実行するために、4 つのマッチングユニットをもつ。マッチングユニットは、参照データ  $d_{i,j}$ 、対象データ  $d_{k,l}$  から成るマッチングペアを入力として、マッチング演算を実行する。マッチングノードは、入力データのビット長と同数の受光素子を 2 組と、1 つの発光素子をもつ。図 4.7(a) では、入力データ  $d_{i,j}$  を 2 値表現した  $p$  番目のビットを  $d_{i,j}^{(p)}$  で表す。マッチング結果のビット長の違いにより、2 種類のデータ経路を用いる。EQU, MORETHAN, LESSTHAN 演算の結果は 1 ビットである。マルチプレクサにより、これらの演算結果から 1 つを選択し、 $m_{i,j}^{(k,l)}$  として出力する。

pDIFF 演算を実行するために、PM クラスタに 1 つの加算器を用意する。図 4.7(b) に示すように、共有ローカルバスを介して、PM クラスタの全マッチングノードを加算器に接続する。加算器では、各マッチングノードから集めた DIFF 演算結果の総和を計算し、ローカル共有バスを通

図 4.7: (a) マッチングノード, (b) 1 プロセッサに対するマッチングノードの構造。

#### 4. 並列マッチングアーキテクチャ

じてマッチングノードに結果を返す。pDIFF 演算の結果は多ビットである。マッチングノードは 1 つの発光素子しかももたないため、1 つのマッチングノードから演算結果を出力すると時間がかかる。そこで、pDIFF 結果の各ビットを異なるマッチングノードに対応させる。例えば、図 4.7において、加算器に近いマッチングノードから順に、pDIFF 結果の最上位ビットから最下位ビットまでを 1 ビットずつを割り当てて転送する。その後、複数のマッチングノードから並列にデータを出力して、プロセッサに返す。プロセッサ間通信処理の場合も、多ビットデータをプロセッサに返す必要がある。そのため、pDIFF の場合と同様に、共有ローカルバスを介して対象データの各ビットをマッチングノードに対応付けて転送し、複数のマッチングノードから並列にデータを出力する。

### 4.4 性能評価

評価モデルに基づき、大域処理における PMA の性能を、他のマルチプロセッサシステムアーキテクチャと比較する。評価では、ネットワークの実効通信帯域幅とプロセッサの処理帯域幅から処理時間を求める。このような評価モデルは単純ではあるが、アーキテクチャの性能を定量化できる。分散最適化アルゴリズムで用いられる基本大域処理として、大域データ比較、最大(小)値検出、データのランク付けについて評価する。

#### 4.4.1 評価モデル

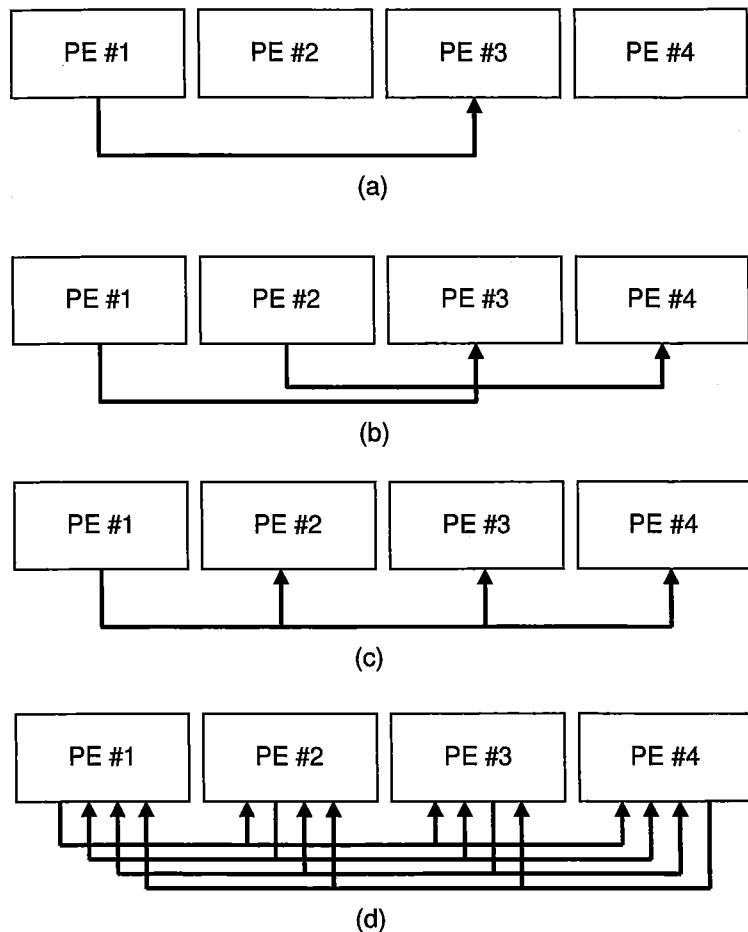

マルチプロセッサシステムの性能を、処理帯域幅  $\alpha$  [bit per second (bps)] と被処理データ量  $\beta$  [bit] で評価する。このとき、処理時間  $\tau$  [sec] は  $\beta/\alpha$  で表される。簡単のため、メモリアクセスやネットワークアクセスなどのオーバヘッドは無視する。 $\alpha$  をネットワークの通信帯域幅、 $\beta$  を被通信データ量とすると、通信時間も処理時間と同様に  $\beta/\alpha$  で表される。したがって、以下では、処理時間と通信時間を等価に扱う。評価では、プロセッサにおける局所処理とプロセッサ間通信を考える。プロセッサ間通信の形態として、図 4.9 に示す单一通信・多重通信・単一ブロードキャスト・多重ブロードキャストを考える。

コスト関数として処理時間  $\tau$  を用い、システム性能を評価する。被処理データ量は、プロセッサのデータ幅  $w$  と、アルゴリズムのステップ数  $s$  の積で与えられる。“job” が通信または処理を指す

図 4.8: 性能評価に用いるマルチプロセッサシステムアーキテクチャ: (a) メッシュネットワーク, (b) 完全結合ネットワーク, (c) 並列マッチングアーキテクチャ (PMA).

とするとき、ある処理に対するコスト関数を次式で表す。ただし、 $w$  は全ての処理で共通とする。

$$\text{Cost}(\text{job}; s_{\text{job}}) = \frac{w s_{\text{job}}}{\alpha_{\text{job}}}. \quad (4.1)$$

$\alpha_{\text{job}}$  は第 1 パラメータ “*job*” が決まれば一意に決まるので、簡単のため引き数には記述しない。あるアルゴリズムに対する全コスト  $T$  を、コストの総和で定義する。

$$T = \sum_{\text{job}} \text{Cost}(\text{job}; s_{\text{job}}). \quad (4.2)$$

メッシュネットワーク、完全結合ネットワークをもつマルチプロセッサシステムと、完全結合ネットワークをもつPMAの性能を比較する(図4.8)。これらの通信・処理帯域幅を、 $\alpha_{\text{job}}^{(\text{mesh})}$ 、 $\alpha_{\text{job}}^{(\text{cc})}$ 、 $\alpha_{\text{job}}^{(\text{pma})}$ で表す。ここで、上付きの添え字はネットワークアーキテクチャ、下付きの添え字は処理を表す。プロセッサは、光・電子融合実装した光ネットワークにより接続されているとする。したがって、プロセッサの処理帯域幅とネットワークの通信帯域幅は等しいと考える。

議論を簡単化するために、次の仮定を設ける。

- マルチプロセッサシステムは、 $N$  個のプロセッサから成る。

- 各プロセッサは、1 つのプロセスを実行する。

- プロセッサのデータ幅を  $w$  ビットとする。 $(w \geq N)$

- プロセッサは十分な数のレジスタをもつ。

- 光通信の入出力ポートをレジスタとして扱う。

#### 4. 並列マッチングアーキテクチャ

図 4.9: 通信形態: (a) 単一通信, (b) 多重通信, (c) 単一ブロードキャスト, (d) 多重ブロードキャスト。

- プロセッサが基本命令の実行に要するステップ数を, ジャンプは 2, それ以外は 1 とする。

- メモリとネットワークのアクセスに伴うオーバヘッドは無視する。

- プロセッサの動作周波数と, プロセッサとネットワークハブ間におけるデータ転送のクロック周波数を  $r$  とする。

#### 4.4.2 通信帯域

单一通信・多重通信・単一ブロードキャスト・多重ブロードキャストの有効通信帯域幅 ( $\alpha_{s.comm}$ ,  $\alpha_{m.comm}$ ,  $\alpha_{s.bcast}$ ,  $\alpha_{m.bcast}$ ) を考える。通信路の実効的な通信帯域幅は、複数のプロセッサで共有

表 4.1: ネットワークのスループット。

| ネットワークトポジ | $\alpha_{s.\text{comm}}$ | $\alpha_{m.\text{comm}}$ | $\alpha_{s.\text{bcast}}$ | $\alpha_{m.\text{bcast}}$ |

|-----------|--------------------------|--------------------------|---------------------------|---------------------------|

| メッシュ      | $wr$                     | $wr/\sqrt{N}$            | $wr/\sqrt{N}$             | $wr/(N-1)\sqrt{N}$        |

| 完全結合      | $wr$                     | $wr$                     | $wr$                      | $wr/(N-1)$                |

| PMA       | $wr$                     | $wr$                     | $wr$                      | $wr/(N-1)$                |

されるなどの理由から、最大通信帯域幅（本評価では  $wr$ ）から低下する。そこで、帯域幅の低下を考慮した有効通信帯域幅を考える。单一通信では、並列システムの中で唯一のプロセッサが、他の1つのプロセッサにデータを転送する（図 4.9(a)）。单一通信の例として、スレイブプロセッサからマスタープロセッサへのデータ転送がある。多重通信では、複数のプロセッサが同時に他のプロセッサにデータを転送する（図 4.9(b)）。ただし、転送先のプロセッサは1つに限定し、プロセッサはデータの発信・受信を同時には行えない。また、通信先のプロセッサは1つに限る。单一ブロードキャストでは、並列システム中で唯一のプロセッサが、他の全プロセッサに同じデータを転送する（図 4.9(c)）。一方、多重ブロードキャストでは、複数のプロセッサが同時に他の全プロセッサにデータをブロードキャストする（図 4.9(d)）。このような通信は、各プロセッサが他の全プロセッサのデータを取得する場合に生じる。

まず、完全結合ネットワークと PMA の有効通信帯域を考える。单一通信において、プロセッサは通信路の帯域を占有できるため、 $\alpha_{s.\text{comm}}^{(cc)}$  と  $\alpha_{s.\text{comm}}^{(pma)}$  は  $wr$  になる。多重通信・单一ブロードキャストにおいても、各通信路は1つのプロセッサが占有できるため、 $\alpha_{m.\text{comm}}^{(cc)}$ ,  $\alpha_{m.\text{comm}}^{(pma)}$ ,  $\alpha_{s.\text{bcast}}^{(cc)}$ ,  $\alpha_{s.\text{bcast}}^{(pma)}$  は  $wr$  で表される。多重ブロードキャストでは、複数のプロセッサが1つのデータ経路を共有する。このため、有効通信帯域幅は、最大通信帯域幅を通信路を共有するプロセッサ数で割った値になる。したがって、 $\alpha_{m.\text{bcast}}^{(cc)}$  と  $\alpha_{m.\text{bcast}}^{(pma)}$  は  $wr/(N-1)$  となる。

メッシュネットワークの有効通信帯域幅を、平均通信帯域幅  $\alpha_{m.\text{comm}}^{(\text{mesh})}$  から算出する。文献 [45] より、 $\alpha_{m.\text{comm}}^{(\text{mesh})}$  は次式で与えられる。

$$\alpha_{m.\text{comm}}^{(\text{mesh})} = \frac{wr}{\sqrt{N}}. \quad (4.3)$$

ただし、パケットサイズは通信路のデータ幅に等しいとし、パケットの衝突を無視する。多重通信におけるデータ流量は、单一ブロードキャストで生じるデータ流量と等しいため、 $\alpha_{s.\text{bcast}}^{(\text{mesh})}$  は

## 4. 並列マッチングアーキテクチャ

---

表 4.2: 基本大域処理のコスト。

|                | 非 PMA                                                                  | PMA                                                     |

|----------------|------------------------------------------------------------------------|---------------------------------------------------------|

| 大域データ<br>マッチング | Cost(local; $5N - 4$ )<br>+Cost(m.bcast; 1)                            | Cost(m.comm; 1)                                         |

| 最大 (小) 値<br>検出 | Cost(local; $6N - 4$ )<br>+Cost(s.comm; $N - 1$ )<br>+Cost(s.bcast; 1) | Cost(local; 4)<br>+Cost(m.comm; 1)<br>+Cost(s.bcast; 1) |

| ランク付け          | Cost(local; $S(N)$ )<br>+Cost(s.comm; $2N - 2$ )                       | Cost(local; 1)<br>+Cost(m.comm; 1)                      |

$\alpha_{m.comm}^{(mesh)}$  と等しい。しかし、これはパケット衝突を無視しているためであり、実際には  $\alpha_{m.comm}^{(mesh)}$  は  $\alpha_{s.bcast}^{(mesh)}$  よりも小さいと考えられる。パケット衝突を無視していることから、単一通信の有効通信帯域も式 (4.3) で与えられる。多重ブロードキャストでは、多重通信の場合の  $(N - 1)$  倍の量のデータが流れる。したがって、 $\alpha_{m.bcast}^{(mesh)}$  は  $wr / \{(N - 1)\sqrt{N}\}$  となる。表 4.1 に、各アーキテクチャの有効通信帯域をまとめる。

### 4.4.3 基本大域処理の評価

3 種類の基本大域処理について、処理コストを評価する。PMA は他のアーキテクチャと構成が大きく異なるため、以下の評価ではアルゴリズムを分けて考える。大域データ比較、最大 (小) 値検出、データのランク付けについて評価する。処理アルゴリズムの詳細は付録 E に記し、以下では概要を述べる。表 4.2 に、各アルゴリズムの処理コストをまとめる。

#### i. 大域データ比較

大域データ比較は、各プロセッサのデータを他の全プロセッサのデータと比較する処理である。分散最適化アルゴリズムでは、同じ、小さい、大きい評価値をもつ候補解を探すために用いる。また、同じ内容の候補解の存在を検出する場合にも用いる。

- 非 PMA

従来の電子マルチプロセッサシステムのように、プロセッサの処理帯域幅よりも通信帯域幅

#### 4.4. 性能評価

が狭い場合、全てのスレイブプロセッサ上にあるデータをマスタープロセッサに集める方法が効率的である。しかし、広帯域の光ネットワークを用いる場合、分散的手法が有効である。分散的手法では、各プロセッサは多重ブロードキャストを用いて他の全プロセッサ上のデータを取得する。この手順により、各プロセッサは全プロセッサのデータの複製をもつことになる。それらをプロセッサ内部の参照データと比較し、大域データ比較の結果を得る。

- PMA

PMA は大域データ比較の機構をもっているため、プロセッサでの局所処理なしに、この大域処理を実行できる。この場合、通信形態は多重通信と同一である。したがって、ネットワークの 1 フレームサイクルで大域データ比較を実行できる。

#### ii. 最大 (小) 値検出

この大域処理は、最大 (小) の評価値をもつ候補解の検出に用いる。

- 非 PMA

マスタープロセッサを用いるのが有効である。全スレイブプロセッサのデータを、マスター プロセッサに転送する。その後、マスター プロセッサは受け取ったデータを順番に検索し、最大 (小) 値を検出する。最後に、単一ブロードキャストを用い、スレイブプロセッサに結果を返す。

図 4.10: PMA によるランク付けの手順。

#### 4. 並列マッチングアーキテクチャ

---

- PMA

各プロセッサは、 pLESSTHAN (pMORETHAN) を用いて、それぞれのデータが最大 (小) であることを検出する。最大値検出の場合、最大値をもつプロセッサの pLESSTHAN 結果は、全ビットが 0 になる。最大値を検出したプロセッサは、他のプロセッサに対して最大値を单一プロードキャストする。最小値検出も、 pMOREHTAN を用いて同様に実行できる。

##### iii. ランク付け

分散最適化アルゴリズムにおいて、ランク付けは候補解の最適性を比較するために用いられる。

- 非 PMA

最大値検出の場合と同様に、マスタープロセッサを用いてランク付けを行う。マスター プロセッサに集めたスレイブプロセッサのデータを並べ換え、ランク付けする。その結果を、 単一プロードキャストを用いてスレイブプロセッサに返す。ソートアルゴリズムとして、クイックソート・マージソート・ヒープソートなどが利用できる [31, 96, 97]。被処理データ数を  $N$  とすると、これらのアルゴリズムの平均命令数は、 $N \log_2 N$  のオーダであることが知られている。

- PMA

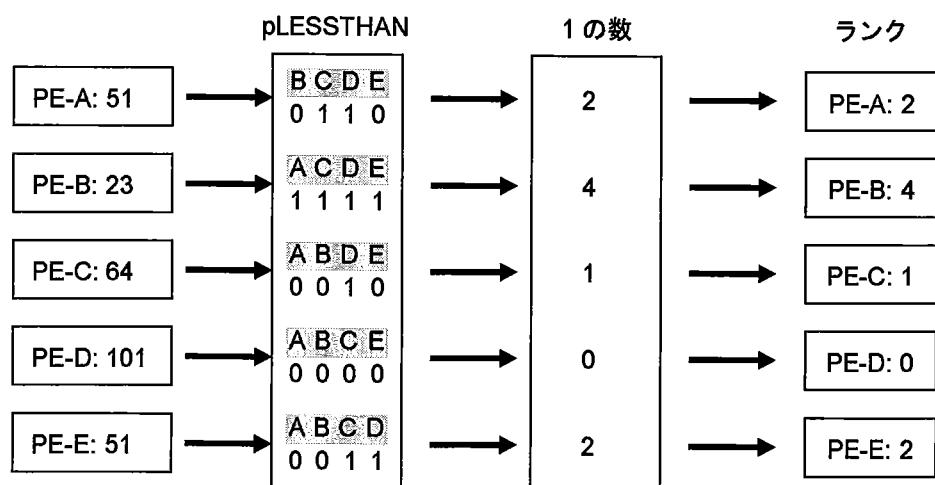

図4.10に、ランク付けの手順を示す。データのランクは、 pLESSTHAN または pMORETHAN により求められる。データを昇順にランク付けする場合には pMORETHAN、降順の場合には pLESSTHAN を用いる。pLESSTHAN (pMORETHAN) の結果は、プロセッサのデータよりも大きい (小さい) データをもつプロセッサの数に対応している。したがって、並列マッチング結果に含まれる 1 の数は、データのランクを示している。ただし、ランク値は 0 から始まる。

##### 4.4.4 比較

表4.3は、3種類の大域処理の処理時間のオーダを示している。この結果から、大域プロセッサをもたない従来型アーキテクチャと比較して、PMA は高い性能をもっていることがわかる。従来アーキテクチャでは、プロセッサ数が増えるとともに処理時間が急激に増加する。PMA では、処理時間が  $N$  によらず一定である。完全結合ネットワークは、PMA とネットワークトポロジが同

表 4.3: 基本大域処理の処理時間のオーダ.

| 大域処理       | メッシュ      | 完全結合       | PMA |

|------------|-----------|------------|-----|

| 大域データ比較    | $N^{3/2}$ | $N$        | 1   |

| 最大 (小) 値検出 | $N^{3/2}$ | $N$        | 1   |

| ランク付け      | $N^{3/2}$ | $N \log N$ | 1   |

表 4.4: 大きい  $N$  に対する通信率の近似値.

| 大域処理        | メッシュ                                                 | 完全結合                                         | PMA   |

|-------------|------------------------------------------------------|----------------------------------------------|-------|

| 大域データ比較     | $1 - 5/\sqrt{N}$                                     | $1/6$                                        | 1     |

| 最大 (最小) 値検出 | $1 - 6/\sqrt{N}$                                     | $1/7$                                        | $1/3$ |

| ランク付け       | $1/\left(1 + \frac{\gamma \log N}{2\sqrt{N}}\right)$ | $1/\left(1 + \frac{\gamma \log N}{2}\right)$ | $1/2$ |

じであるため、提案アーキテクチャを採用することによる性能向上が直接現れる。完全結合ネットワークと比較して、PMA の処理コストが非常に小さいことから、提案アーキテクチャの有効性が確認できる。

性能向上比を、非 PMA に対する PMA のコストの比で定義する。また、ランク付けにおいて、非 PMA がソートに要するステップ数を  $2N \log_2 N$  クロックとする。プロセッサの動作クロック  $\gamma$  を 1GHz と仮定し、データ幅としてプロセッサでよく用いられる 64 ビット、128 ビットを想定した場合、性能向上比は数 100 から数 1,000 倍に達する。

通信率を、全処理コストにおける通信コストの割合で定義する。通信率から、ネットワーク負荷を評価できる。表 4.4 に、 $N$  が大きい場合に対して、基本大域処理における通信率の近似式を示す。PMA の通信率は、 $N$  によらない。メッシュネットワークでは、 $N$  が大きくなるにしたがって、最大 (小) 値検出とランク付けの通信時間比が増加する。これは、有効通信帯域幅が狭いため、処理時間の大部分が通信に費やされることを示している。一方、PMA の全基本大域処理と、完全結合ネットワークにおける大域データ比較・最大 (小) 値検出は、 $N$  が大きくなるにしたがって、1 未満の定数に収束する。このことは、これらの処理に対して通信能力が釣り合っていることを示している。

#### 4. 並列マッチングアーキテクチャ

##### 4.5 プロトタイプによるアーキテクチャのデモストレーション

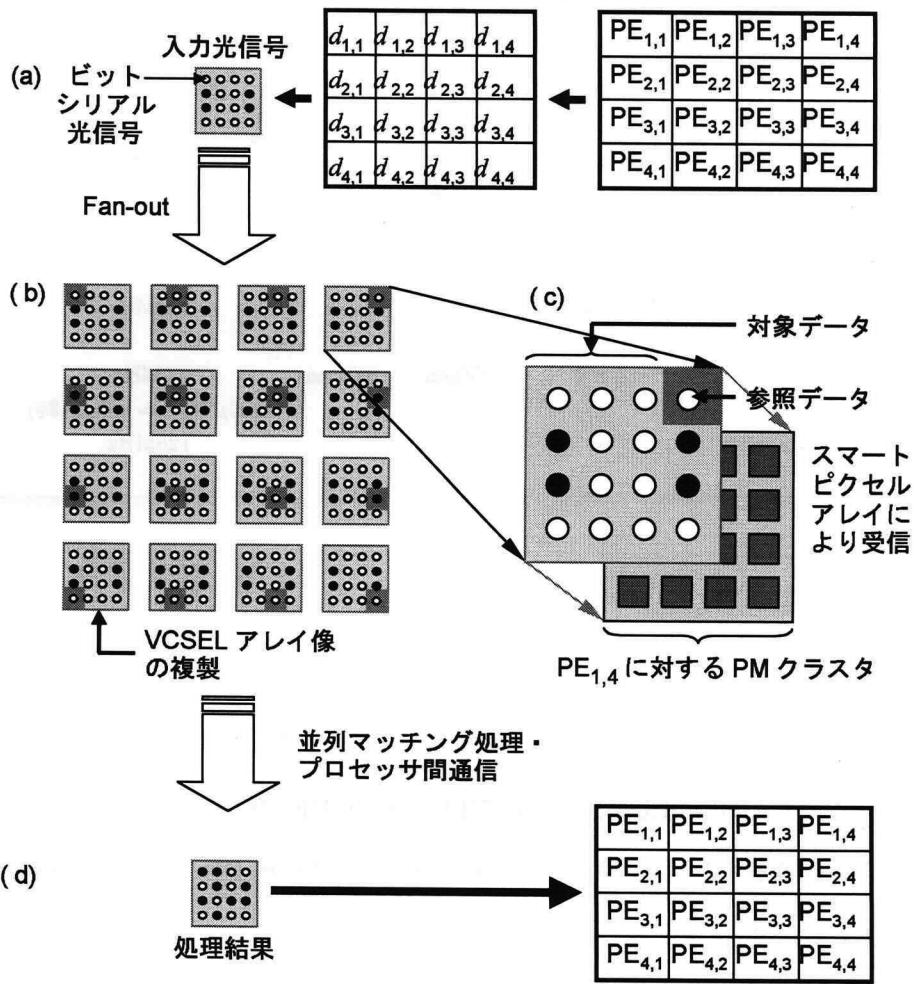

PMA の基本機能を実証するために、PM モジュールのプロトタイプを構築した。プロトタイプの設計において、図 4.5 に基づいたマルチプロセッサシステムを仮定した。システムは  $4 \times 4$  プロセッサから成り、これらを PM モジュールを介して完全結合するとした。利用可能な光・電子デバイスの制約から、図 4.5 から仕様を一部変更した。プロセッサと PM モジュールの間は、1 ビットシリアル光通信で結んだ。PM モジュールの入力面には、ファイバアレイの代わりに VCSEL を直接配置した。受光素子のピクセル数が少ないため、対象複製を光学系では行わず、PM-SPA 上で受信した参照複製データから対象複製データを生成した。このプロトタイプでは、結果をプロセッサに返す経路は実装しなかった。

###### 4.5.1 並列マッチングの方式

図 4.11 に、PMA プロトタイプシステムの光・電子デバイスを用いた実装方式を示す。図 4.11(a) に示すように、 $4 \times 4$  プロセッサからの光信号を PM モジュールの入力面にアレイ状に並べる。1 つのプロセッサに対する大域処理とプロセッサ間通信を実行するには、他の全プロセッサからのデータが必要である。したがって、図 4.11(b) に示すように、図 4.11(a) の VCSEL 像を  $4 \times 4$  個に複製する。図 4.11(c) は、 $PE_{1,4}$  に対する複製画像を拡大したものである。複製画像を  $4 \times 4$  個の受光素子をもつ PM クラスタで受信し、電気信号に変換する。PM クラスタでは、参照データを全マッチングノードに電気的にファンアウトする。プロトタイプでは、データをビット単位でシリアル転送するため、マッチング結果は各マッチングノードから 1 ビットずつ読み出す。PM クラスタは 1 個の発光素子をもち、読み出した処理結果をビット単位で出力する。図 4.11(d) に示すように、全 PM クラスタからの出力データは  $4 \times 4$  個のアレイになる。

###### 4.5.2 システム構成

表 4.5 に、プロトタイプに用いたデバイスをまとめる。光源として VCSEL アレイ (品名 Gigalase<sup>TM</sup>, Micro Optical Devices 製、発振波長 854nm, アレイ規模  $8 \times 8$ ) を用いた。プロトタイプでは、PM-SPA を CPLD (complex programmable logic device, 型番 FLASH374i, Cypress 製、最大動作周波数 100MHz) と CMOS-PD アレイ (型番 N73CGD, JOP 提供、アレイ規模  $4 \times 4$ ) を組み

#### 4.5. プロトタイプによるアーキテクチャのデモストレーション

図 4.11: プロトタイプシステムにおける光・電子並列マッチング手順: (a) VCSEL アレイ上に表示するデータ, (b) 4 × 4 プロセッサの完全結合を行うために VCSEL 像を 4 × 4 個に複製, (c) PE<sub>1,4</sub> に対する VCSEL 複製像, (d) 出力データ.

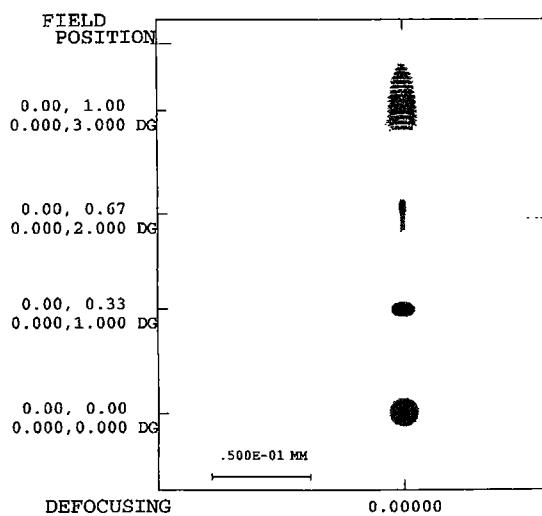

合わせて実装した。受光素子のピクセル数が少ないため、VCSEL アレイの有効ピクセル数は 4 × 4 に限られる。大ファンアウト接続光学系として、DCP-1S プロトタイプのレンズ構成を改良したものを用いた。2 つのフーリエ変換レンズの焦点距離は 160.0mm で、光学系の倍率は 1.0 である。前側のフーリエ変換レンズには、ダブルレットレンズを用いた。後側のフーリエ変換レンズにはファンアウトした光線が入射するため、前側レンズよりも広い画角が必要である。そこで、付録 B に示す方法で設計した組み合わせレンズを用いた。図 4.11(b) に示す接続パターンを生成する光ファンアウト素子として、2 レベル位相型 CGH フィルタを設計し、電子ビームリソグラフィを用いて

## 4. 並列マッチングアーキテクチャ

表 4.5: プロトタイプシステムに用いるデバイス。

| デバイス                     | 提供元                      | アレイ<br>サイズ | ピクセル<br>ピッチ | ピクセル<br>サイズ | 最大動作<br>速度                                    | その他                                |

|--------------------------|--------------------------|------------|-------------|-------------|-----------------------------------------------|------------------------------------|

| VCSEL アレイ<br>(Gigalase™) | Micro Optical<br>Devices | 8 × 8      | 250 μm      | φ15 μm      | -                                             | 最大 3mW<br>$\lambda = 854\text{nm}$ |

| VCSEL ドライバ<br>(CLDA2)    | JOP                      | 32 チャンネル   | -           | -           | 150MHz                                        | -                                  |

| CMOS-PD アレイ              | JOP                      | 4 × 4      | 250 μm      | 120 μm      | 15MHz<br>(100 μW, $\lambda = 850\text{nm}$ 時) | -                                  |

| CPLD<br>(FLASH374i)      | Cypress                  | -          | -           | -           | 125MHz                                        | 128<br>マクロセル                       |

作製した。

### 4.5.3 並列マッチングクラスタ

プロトタイプシステムでは, pEQU, pLESSTHAN, pMORETHAN 演算とプロセッサ間通信などの PM クラスタの機能を CPLD に実装した。CPLD は, CMOS-PD アレイの受信した光信号と制御信号を入力とし, 処理結果を出力する。実際のシステムでは, プロセッサからの通信パケットに対して非同期に対応する必要がある。このため, クロック信号・処理結果の読み出しタイミング信号, 動作モードなどの制御信号は, 参照データと対象データから CPLD 内で生成するべきである。しかし, プロトタイプシステムでは回路を簡略化するために, 外部から独立に与える構成にした。PM クラスタは 15 個のマッチングノード (MN#0~#14) と 1 個の参照ノードから成り, 並列マッチングモード・通信モードの 2 種類の動作モードをもつ。これらのモードは, 専用の制御信号を用いて選択する。参照ノードは, 受信したデータを他のマッチングノードにブロードキャストする。

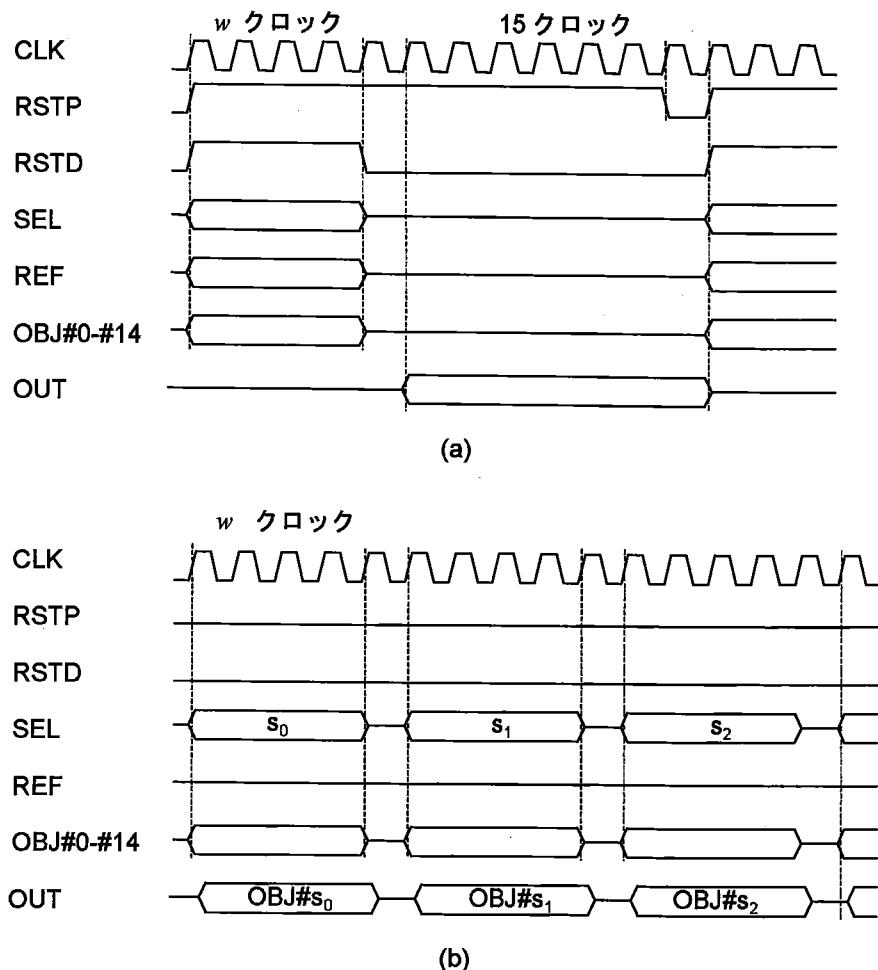

図 4.12(a) に, 並列マッチング処理のタイミングチャートを示す。CPLD は, クロック信号 (CLK) に同期して動作する。参照データと対象データを, REF, OBJ#0~#14 で表す。CPLD からの並列マッチング結果または通信データの出力信号を, OUT で表す。RSTP, RSTD の 2 つのタイミング信号は, 並列マッチング結果のリセットと読み出しに用いる。入力データのビット長  $w$  は可変で, これらのタイミング信号によって決める。並列マッチングモードでは, 実行する並列マッ

#### 4.5. プロトタイプによるアーキテクチャのデモストレーション

図 4.12: (a) 並列マッチング処理, (b) プロセッサ間通信のタイミングチャート。 $s_i$  はデータ送信元プロセッサの識別番号を意味する。

チング処理の種類を SEL 信号で指定する。並列マッチング結果は、MN#0 から MN#14 まで逐次的に OUT 信号に出力する。

通信モードのタイミングチャートを図 4.12(b) に示す。このモードでは、通信元プロセッサを SEL 信号で指定し、その対象データを OUT 信号に出力する。

#### 4. 並列マッチングアーキテクチャ

図 4.13: (a)  $4 \times 4$  プロセッサ間完全結合のための光接続パターン, (b) 設計した 2 レベル位相単独 CGH フィルタパターンの一部, (c) 作製した CGH フィルタの再生像.

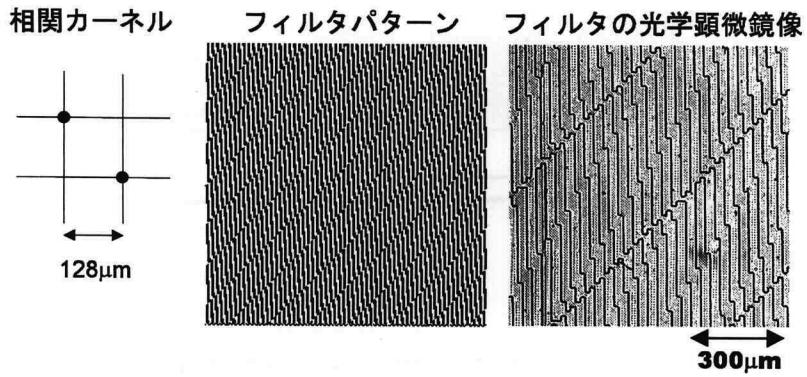

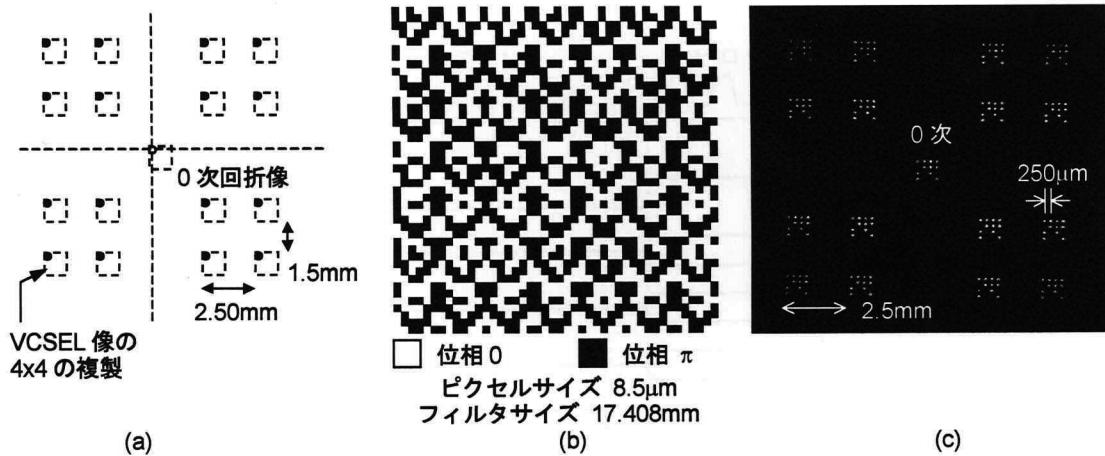

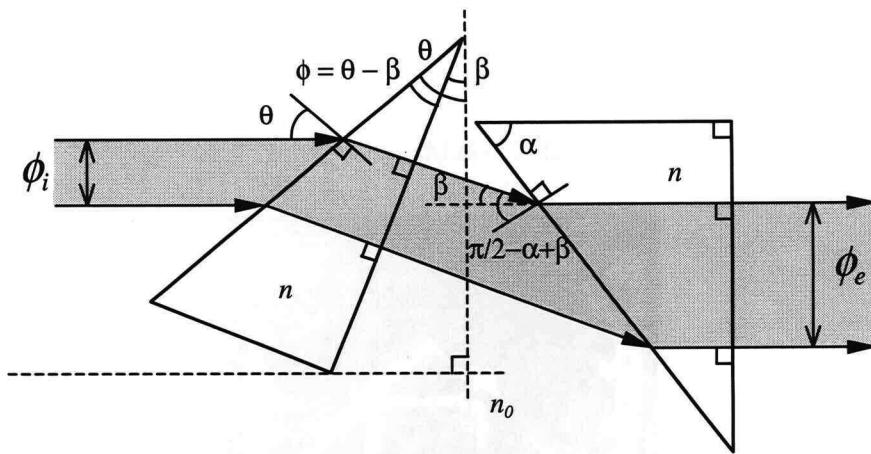

#### 4.5.4 CGH フィルタの設計・作製

プロトタイプシステムの光接続を実現する CGH フィルタを設計した。図 4.13(a) に、光プロセッサの出力面におけるデータの配置を示す。出力パターンは、 $4 \times 4$  個の VCSEL アレイ像の複製である。エッチング量の制御精度が十分ではないため、0 次回折光が現れることが予想された。そのため、0 次回折像と複製像が重ならないようにフィルタを設計した。図 4.13(a) に示すように、各象限には  $2 \times 2$  個の VCSEL アレイ複製像を配置する。現プロトタイプでは、VCSEL アレイのうち  $4 \times 4$  だけが有効であるが、将来ピクセル数の多い受光素子アレイが利用できるようになることを期待し、 $8 \times 8$  ピクセルの入力データに対応した設計を行った。そのため、VCSEL アレイ複製像のピッチを  $2.5\text{mm}$  とした。隣接する複製像の間隔は、 $8 \times 8$  ピクセルの場合  $0.5\text{mm}$ 、 $4 \times 4$  ピクセルの場合  $1.5\text{mm}$  である。

フィルタの設計には、付録 C に示す手法を用いた。設計では、CGH のピクセルサイズ、ピクセル数、パターンサイズを  $8.5\mu\text{m} \times 8.5\mu\text{m}$ ,  $2048 \times 2048$ ,  $17\text{mm} \times 17\text{mm}$  とした。フィルタにおける光量損失を低減するために、フィルタは第 2 フーリエ変換レンズの入射瞳と同程度の大きさとした。前述のピクセルサイズに対して、出力像面の大きさは  $16\text{mm} \times 16\text{mm}$  になる。これは、プロトタイプの光接続には十分な大きさである。図 4.13(b) に、設計したフィルタパターンの一部を示す。

設計したフィルタを、電子ビームリソグラフィにより作製した。作製条件は、第 3 章で述べた

## 4.6. プロトタイプの動作実験結果

DCP-2SV 用固定フィルタと同様である。位相変調量  $\pi$  を得るには、850nm のエッティング量が必要である。白色干渉計 (型番 New-View5020, ZYGO 製) を用いてフィルタの表面形状を測定したところ、エッティング量は 864nm であった。作製した CGH を光学系に挿入し、出力パターンを観察した。図 4.13(c) に、VCSEL の  $4 \times 4$  ピクセルを用いた場合の出力パターンを示す。回折効率は 68% であった。また、0 次回折光、高次回折光はそれぞれ、6%, 26% であった。0 次回折光はエッティング誤差によるものであると考えられる。

## 4.6 プロトタイプの動作実験結果

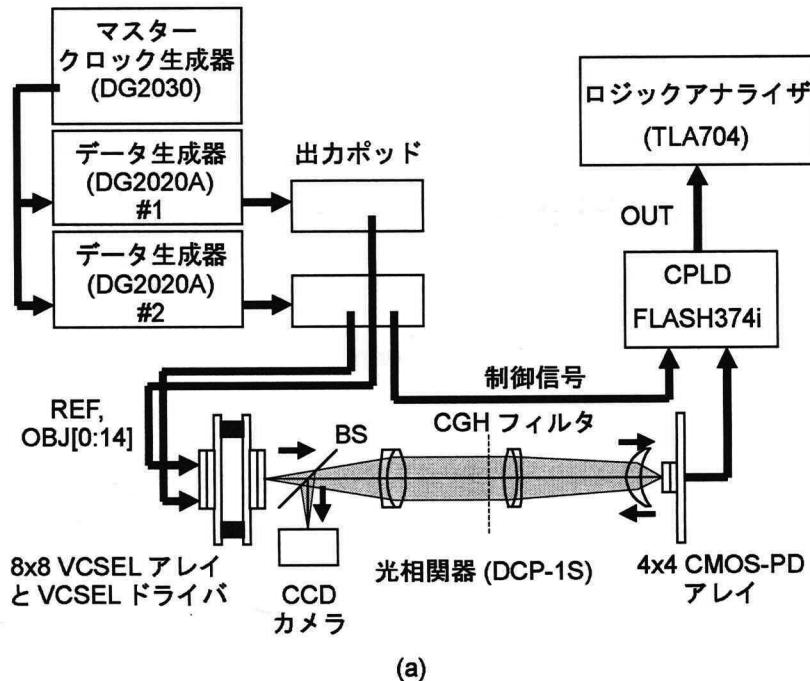

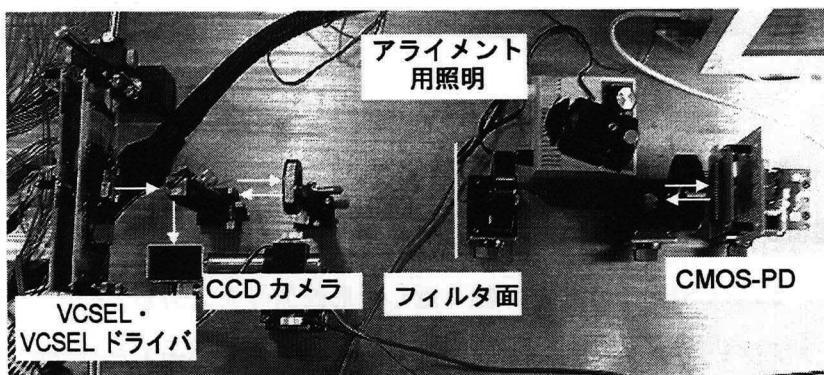

図 4.14 に示す実験システムを用いて、プロトタイプシステムの動作を確認した。信号源として、1 台のデータジェネレータ (型番 DG2030, Tektronix 製、出力信号の同期クロック 400MHz、出力チャネル数 4) をマスタークロック源とし、2 台のデータジェネレータ (型番 DG2020A, Tektronix 製、出力信号の同期クロック 200MHz、出力チャネル数 36) を同期して用いた。CPLD の動作を測定するために、ロジックアナライザ (型番 TLA704, Tektronix 製、最大データ取込み同期クロック 500MHz、入力チャネル数 68) を用いた。

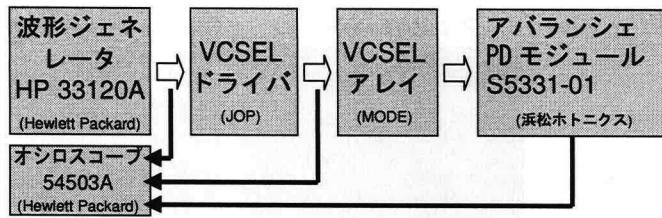

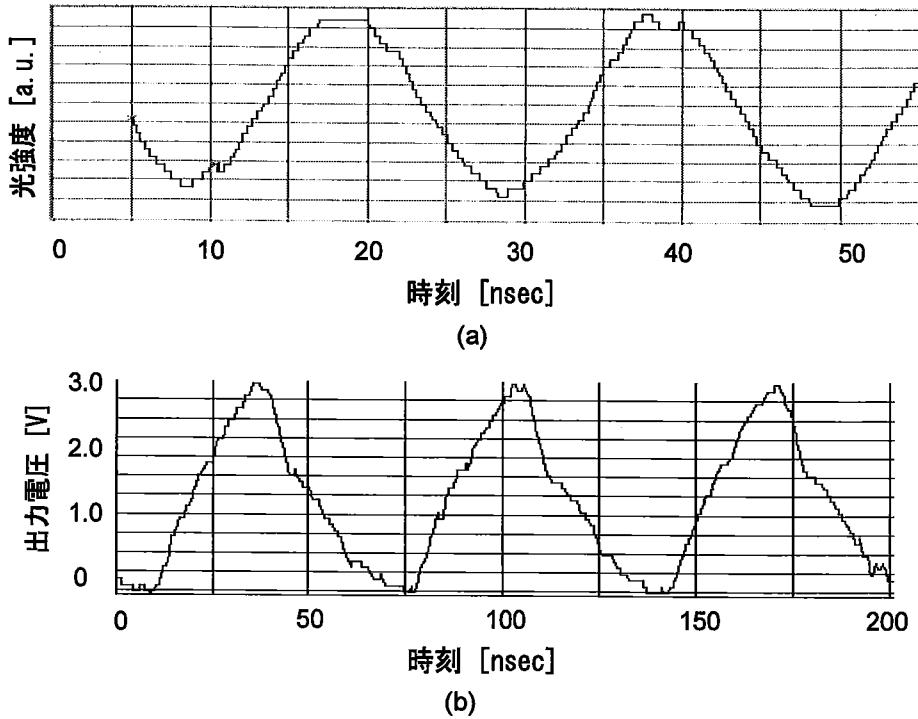

### 4.6.1 VCSEL と CMOS 受光素子の駆動

プロトタイプシステムの動作速度を決めるために、VCSEL アレイと CMOS-PD アレイの最大動作速度を測定した。VCSEL ドライバチップ (型番 CLDA2, JOP 提供、最大動作速度 500MHz) は、VCSEL を電流駆動する。VCSEL ドライバの出力電流の振幅は、変調電圧  $V_{MOD}$  とバイアス電圧  $V_{BIAS}$  で制御する。VCSEL ドライバに繰り返し矩形波信号を入力し、結像系を介して VCSEL の出力光をアバランシェ方式受光モジュール (型番 S5331-01, 浜松ホトニクス製、検出光信号帯域 100MHz) で測定した。その結果、50MHz での動作を確認した。図 4.15(a) に、50MHz に対する VCSEL の光強度波形を示す。このとき、 $V_{MOD}, V_{BIAS}$  はそれぞれ 3.146V, 2.495V であった。結像系の出力面における光強度は、1 ピクセルあたり約  $700\mu\text{W}$  であった。結像系の開口によるけられとレンズ面での反射による光量損失の合計は 42% であった。

CMOS-PD の動作速度の測定では、光学系にビームスプリッタを挿入し、CCD で CMOS-PD 面を観察しながら VCSEL 像と CMOS-PD のピクセルを一致させた。ビームスプリッタでの光量損失により、結像系の出力面における VCSEL の光強度は約  $350\mu\text{W}$  に半減した。この光強度に

#### 4. 並列マッチングアーキテクチャ

(a)

(b)

図 4.14: (a) プロトタイプシステムの構成, (b) 光学系の構成.

#### 4.6. プロトタイプの動作実験結果

対して、CMOS-PD が正しく受信できる光信号の最大周波数は 15MHz であった。図 4.15(b) は、VCSEL からの 15MHz の光信号に対して、CMOS-PD が output した電圧波形である。CMOS-PD に与えた閾値電圧  $V_{t1}, V_{t2}$  は、それぞれ 1.825V, 1.833V、電源電圧は 3V とした。15MHz 以上の光信号に対しては、すべての光チャネルに対して共通の閾値電圧が得られなかった。これは、VCSEL の光強度がピクセルごとに異なるためであると考えられる。

##### 4.6.2 並列マッチング処理

プロトタイプシステムを 15MHz で動作させ、1 つの PM クラスタの動作確認を行った。図 4.16 に、並列マッチング処理とプロセッサ間通信の実験結果をまとめる。データ転送はビットシリアルであるため、データは横軸に展開して表されている。VCSEL ドライバと CMOS-PD アレイに印可した電圧は、前述の実験と同じである。データのビット長は 4 とした。

並列マッチング処理が正しく行われていることをわかりやすく表現するために、OBJ#0 から

図 4.15: 測定波形: (a) 50MHz の矩形波入力に対する VCSEL の出力光, (b) 15MHz の VCSEL 出力光に対する CMOS-PD の出力信号。

#### 4. 並列マッチングアーキテクチャ

#14 に 1 (バイナリ表現で 0001) から 15 (1111) までの値を順に与えた。並列マッチングモードにおける参照データは 5 (0101) とした。OBJ#4 だけが参照データと等しいため、pEQU 演算において、OBJ#4 に対する OUT 信号が 1 となり、それ以外は 0 となった。この場合、並列マッチング結果は 00001000000000 で表される。ただし、最上位ビットは OBJ#0 に対応する。OBJ#0 から #3 は参照データよりも小さいため、pMORETHAN に対する OUT 信号は 11110000000000 となった。逆に、pLESSTHAN 演算の結果は 00000111111111 となった。通信モードでは、参照プロセッサは PE#8 とした。その結果、OBJ#8 の 9 (1001) が OUT 信号に出力されていることがわかる。

図 4.16: 並列マッチング処理とプロセッサ間通信の実験結果。個別に測定したデータを 1 つの図にまとめた。

これらの結果から、プロトタイプでは 15MHz で並列マッチング処理が正しく実行できたことを確認した。1 プロセッサ当たりとプロトタイプシステム全体での通信ビットレートは、それぞれ 15Mbps (bit per second), 240Mbps であった。この場合、ネットワークのスイッチング周波数は 3MHz である。1 プロセッサ当たり、およびプロトタイプシステム全体に対する並列マッチング処理速度はそれぞれ 0.68M operations/sec, 11M operations/sec であった。

#### 4.7 考察

スケーラビリティは、マルチプロセッサシステムに求められる重要な特徴である。本章では、PMA のネットワークトポロジーとして完全結合を仮定したが、このネットワークはスケーラビリティをもたない。したがって、ネットワークに接続できるプロセッサ数の最大値は変更できない。 $N$  プロセッサ構成用の PM モジュールに  $(N + 1)$  番目の PE を追加するには、PM モジュール自体を再設計しなければならない。この問題を解決するには、メッシュ、バス、リングネットワークなどのスケーラブルなネットワークトポロジーに、非スケーラブルなネットワークを埋め込む手法が有効である [3]。PMA は任意のネットワークトポロジーをとることができるために、PMA にトポロジー埋め込みの手法を適用することにより、スケーラビリティをもつマルチプロセッサシステムを構築できる。

提案アーキテクチャの演算能力を改善する方法の 1 つに、大域処理の演算種を増やすことが考えられる。例えば、データの総和演算・積和演算などが挙げられる。演算種を増やす場合、トランジスタの微細化によりもたらされるトランジスタ数の増加分を演算種の増加に割り当て、バランスのとれた設計をしなければならない。演算種を増やすと、より大きい OE-VLSI のチップ面積が必要になる。その結果、光学系の体積が増加し、設計・作製が困難になる。そのため、むやみに演算種を増やすことは避けるべきである。演算種を増やす場合、以下の条件を考慮することにより、設計指針が得られる。1) プロセッサのデータ幅は動作クロック周波数ほど急激には増加しない。2) PMA において、効率よく他のプロセッサを監視するには、ネットワークに接続されるプロセッサ数はデータ幅程度であることが望ましい。3) OE-VLSI において、デジタル回路の面積は、受・発光回路の利用する面積によって制約される。発光回路を構成するトランジスタは、必要な発光強度を得るために、出力電流をある一定以上に確保しなければならない。そのため、半導体プロセスの微細化が進んでも、トランジスタサイズをあまり小さくできない。受光回路では、

#### 4. 並列マッチングアーキテクチャ

---

ノイズレベルを抑えるために、トランジスタサイズを極端に小さくすることはできない。これらのことから、受・発光回路の消費する面積は、トランジスタの微細化が進んでもあまり変化しないことがわかる。その結果、ディジタル回路に利用できる面積も変わらないため、半導体集積回路の微細化が進むにつれて、ディジタル回路に利用できるトランジスタ数は着実に増加する。

また、並列アーキテクチャの評価に用いたモデルは、メモリアクセス、パイプライン・スーパースカラなどのプロセッサの内部構造を考慮していない。実際にアルゴリズムを実行するときには、これらの要素が複合的に絡み合う。現実のシステムに即したシミュレーションによる評価が必要である。また、本章で示したプロトタイプは、ごく基本的なものである。実際のシステムに適用可能な PM モジュールを実現するためには、エラー訂正機構、プロセッサ間調停機構などの制御回路を組み込み、スマートピクセル化することが必要である。PM モジュールプロトタイプの性能は、CMOS-PD アレイの動作速度により制限されている。これは、MSM 受光素子などの高速・高感度受光素子に、トランスインピーダンス光增幅回路を組み合わせて用いることで改善できる。VCSEL ドライバ (CLDA2) は、データシートによると、最大 150MHz で動くことが実験的に検証されている。8 × 8 画素の高速受光素子アレイを用いた PM クラスタを作製し、VCSEL を最大速度で駆動した場合、プロトタイプシステム全体でのプロセッサ間通信幅、マッチング周波数は 9.6Gbps, 2.4G operations/sec になる。

### 4.8 結言

本章では、大域プロセッサを利用した光・電子融合型並列マッチングアーキテクチャ (PMA) を提案し、性能評価とプロトタイプによる実証を行った。PMA は、複数のプロセッサと並列マッチング (PM) モジュールから構成される。PM モジュールは、通常のプロセッサ間通信に加え、複数プロセッサが出力するデータを並列比較する専用の機構をもつ。PMA の基本大域処理として、分散最適化アルゴリズムに有効な 4 種類の並列マッチング処理 (pEQU, pMORETHAN, pLESSTHAN, pDIFF) を定義した。性能評価により、提案アーキテクチャが大域データ比較・最大 (小) 値検出・データのランク付けなどの基本大域処理を飛躍的に高速化し、光ネットワークを適用した従来アーキテクチャのマルチプロセッサシステムよりも高い性能をもつことを明らかにした。

DCP-1S プロトタイプを応用し、光・電子デバイスと位相型 CGH フィルタを用いた PM モジュールのプロトタイプを構築した。プロトタイプは、ビットシリアル光通信ポートをもつ  $4 \times 4$  のプロ

#### 4.8. 結言

---

セッサを完全結合ネットワークにより接続する場合を想定した。プロトタイプでは、PMモジュールのコアデバイスであるPM-SPAを、CPLDとCMOS-PDアレイを用いて実装し、PMAの基本大域処理をデモストレーションした。実験から、プロトタイプを用いて基本並列マッチング処理・プロセッサ間通信を15MHzで実行できることを確認した。

## 5. 光造形技術を用いた光学系実装技術

# 5 光造形技術を用いた光学系実装技術

## 5.1 緒言

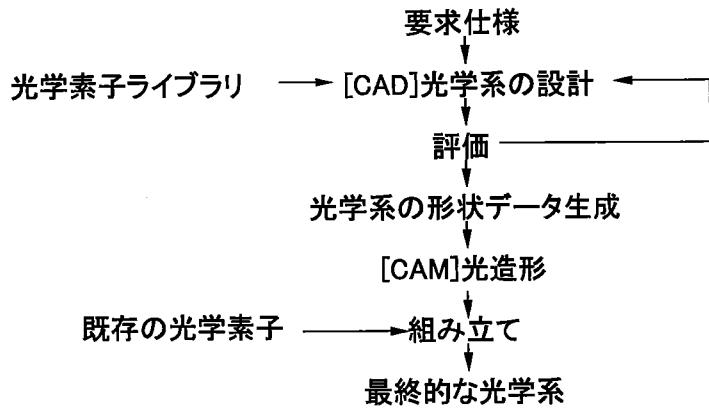

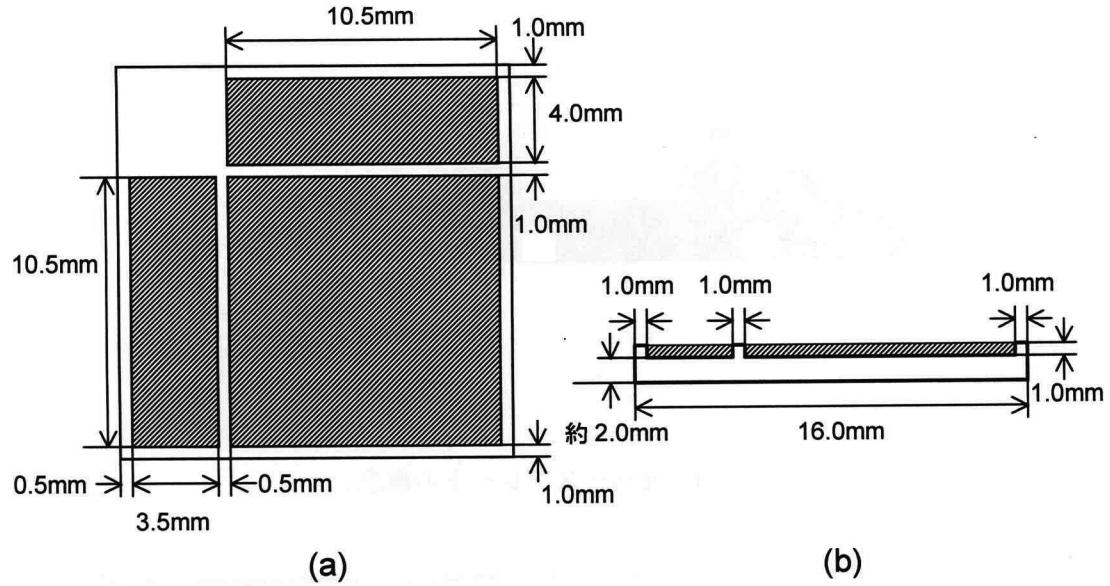

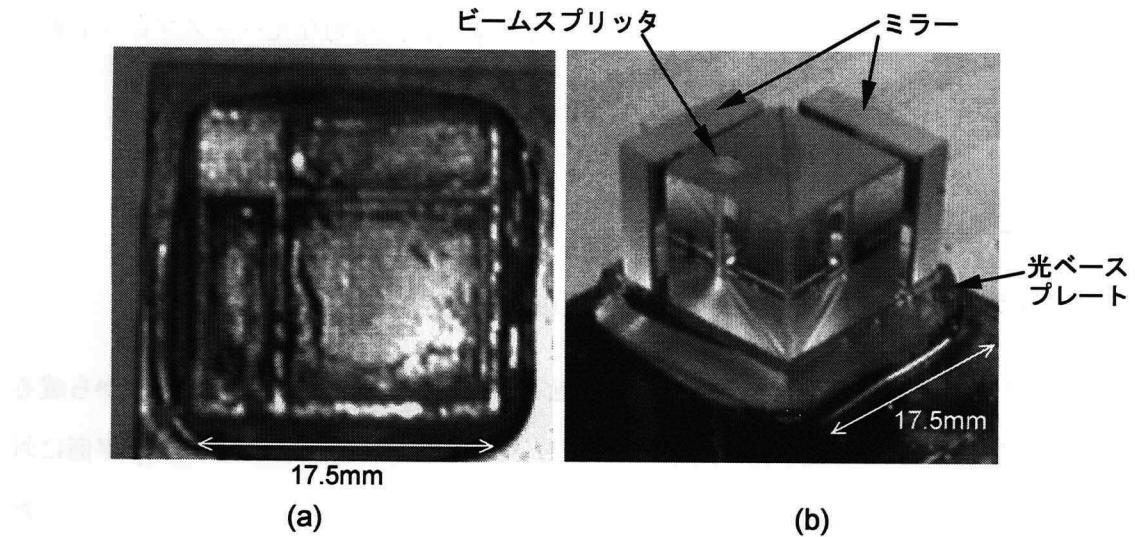

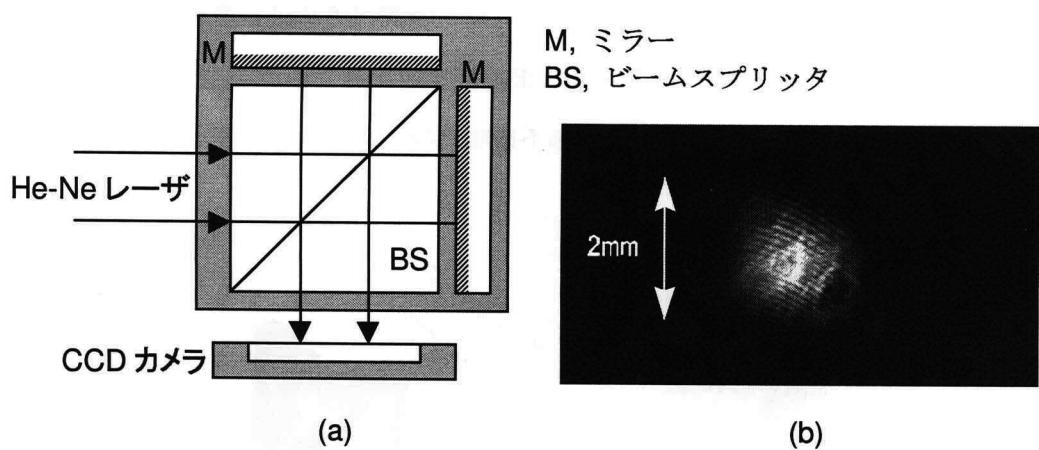

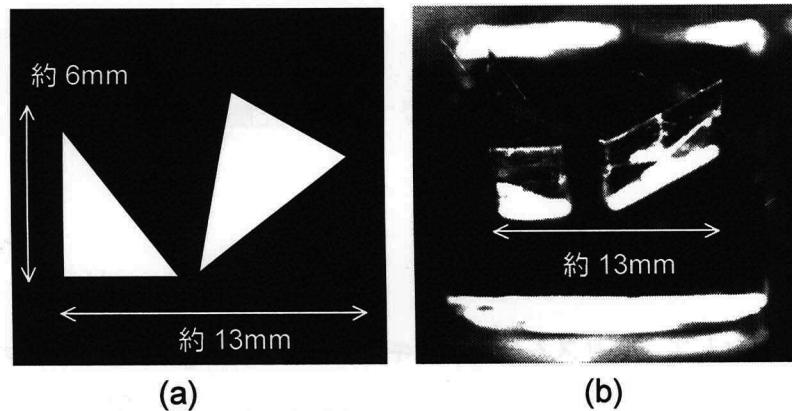

光・電子融合型情報処理システムは多数の光学素子から構成され、精密な位置決めと機械的な安定性が要求される。そのため、光学系の実装技術は重要な課題となっている。本章では、光学系の実装手法として、光造形技術を応用した光ベースプレートと2.5次元光学系の作製手法を提案する。光造形技術は、光硬化性樹脂を用い、任意の形状をもつ立体物を作製する技術である。作製原理が単純であるため、コンピュータ制御による立体物の自動作製に適している。光造形技術を光学系の作製に応用し、光学系の作製・組み立てを容易にする柔軟性に富んだ実装技術の開発する。

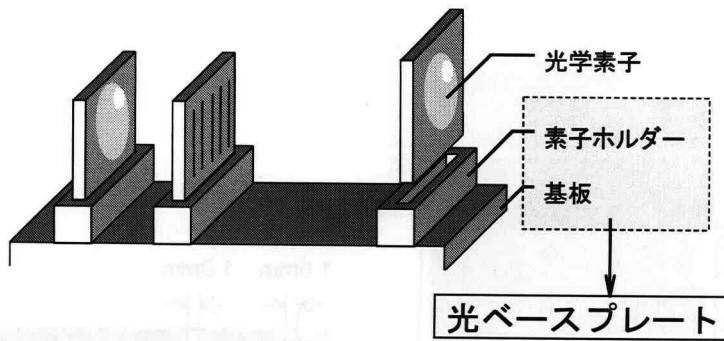

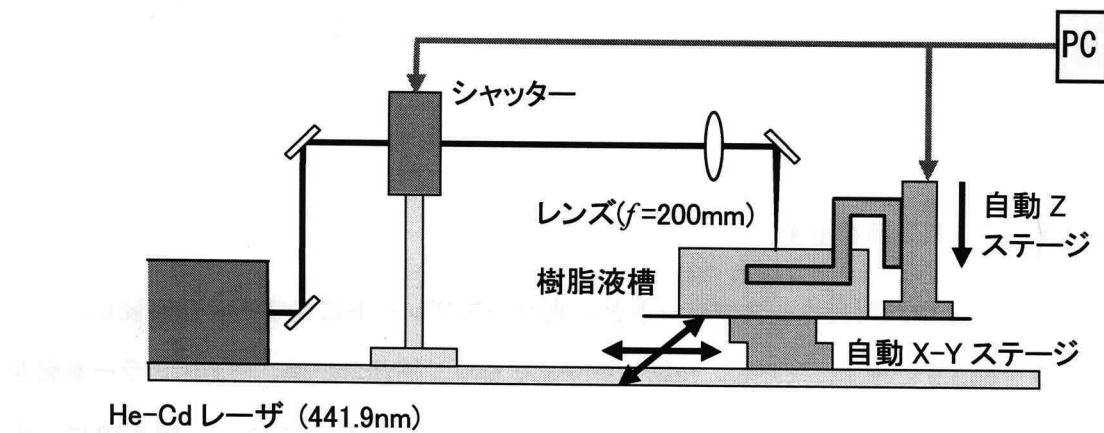

光ベースプレートは、電子技術で用いられるプリント基板に相当する。光ベースプレートは、光学素子を実装する素子ホルダーとホルダーを固定する基板から成り、既製の光学素子を素子ホルダーに実装する。ビーム露光方式の光造形装置を用いて作製したマイケルソン干渉計用光ベースプレートの実験結果を示す。

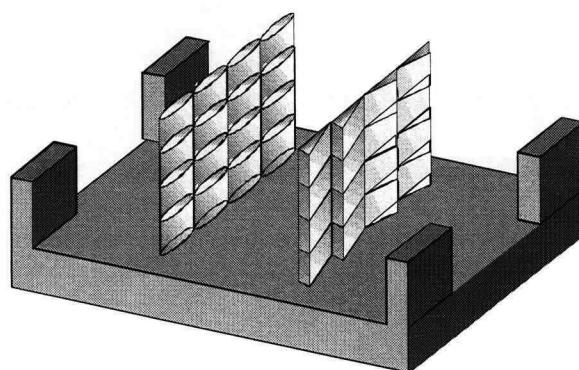

2.5次元光学系は、2.5次元光学素子とよばれる柱状の光学素子から成る光学系である。2.5次元光学素子には、プリズム・シリンドリカルレンズなどがある。これらの光学素子は、マスク露光方式の光造形装置により、单一マスクを用いて作製することができる。光学系の要素素子の例として直角プリズムを作製する。また、光学系の例としてプリズムビームエキスパンダーを作製する。

5.2節では、光造形技術を応用した光学系作製手法を述べる。5.3節では、レーザビームスキャン方式の光造形装置を利用した光ベースプレートの作製について述べる。5.4節では、マスク露光積層方式を利用した2.5次元光学系の作製手法を述べる。

## 5.2 光造形技術を応用した光学系の作製

### 5.2.1 光造形技術

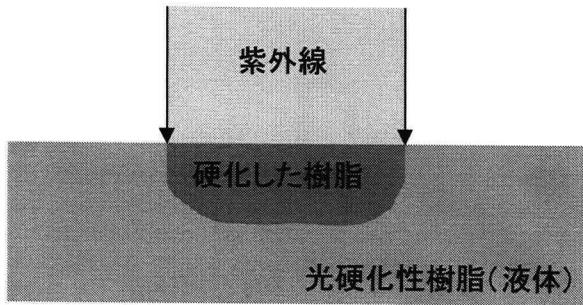

光造形技術は、光硬化性樹脂に光を照射して硬化させることにより、任意形状の立体物を作製する技術である[35-39]。従来の機械加工技術では、作製する物体よりも大きい材料から、切削により目的物体の形状を作製する。加工装置の機構によって作製できる形状に制限があり、粉塵・切削屑などの環境的な問題もある。一方、光造形技術では、液状の光硬化性樹脂から立体物を作製する。光硬化性樹脂は、光重合性のモノマー・オリゴマーを主成分とする液体であり、主に紫

図 5.1: 光硬化性樹脂。

外光を吸収して重合反応を起こし硬化する（図 5.1）。光を照射した部分の樹脂液が選択的に硬化するため、光照射の位置を制御することにより、任意形状の硬化物が作製できる。作製原理が単純なため装置が簡潔で、コンピュータ制御による自動化に適している。既に多数の商用光造形装置が発表されており、製品の RP/M (rapid prototyping and manufacturing) などに広く用いられている。これらの装置は、コンピュータで設計した立体物の実物を、短時間で得ることができる。大きいものでは、1m程度の構造物などを迅速に自動作製できる。研究レベルでは、ミクロンからサブミクロンの精度をもつ微小構造も作製され、マイクロマシンの作製などに応用されている [98–100]。また、造形物の大量生産を狙い、レプリカ技術なども研究されている [101]。

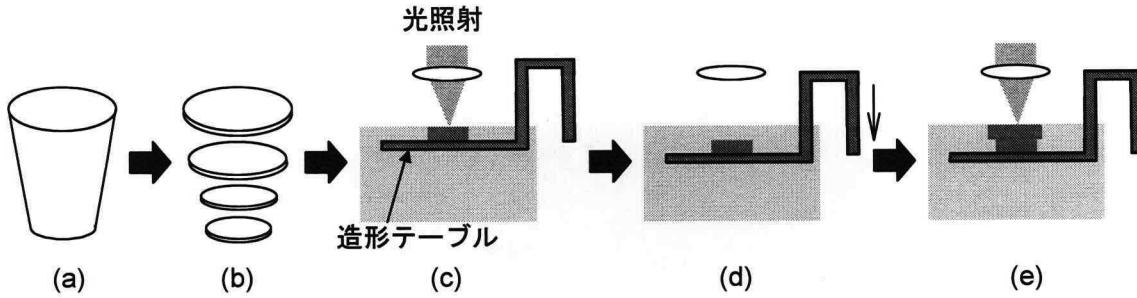

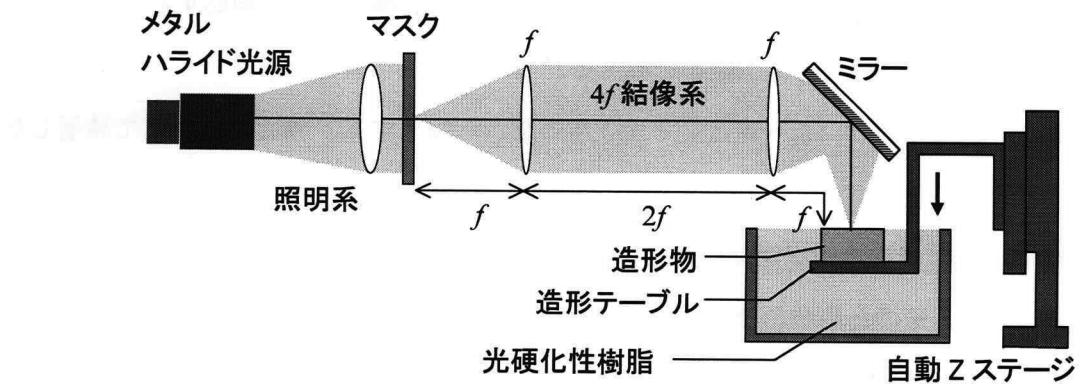

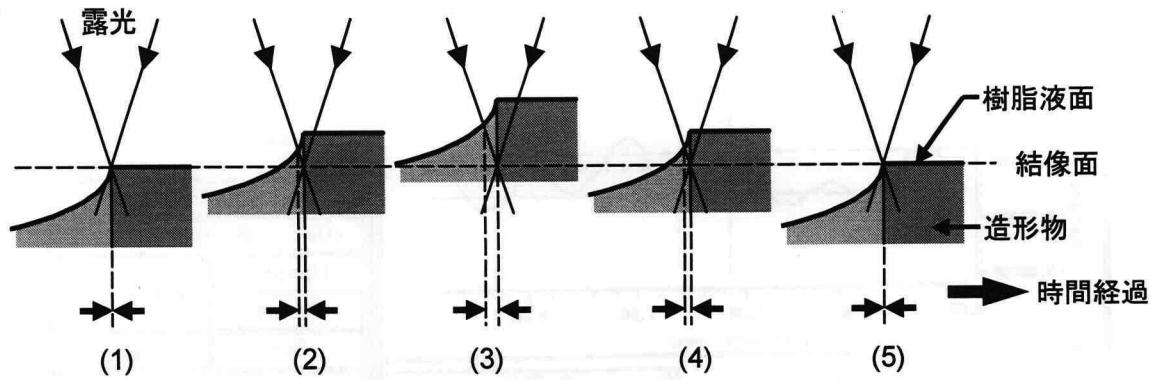

図 5.2 に、一般的な積層方式の光造形の手順を示す。積層方式の光造形では、まず作製する立体物をコンピュータ内で水平方向に切断し、多数のスライスに分割する。露光装置を用いて、スライス形状と同じ光強度分布を液槽内の樹脂液表面につくる。すると光の当たった部分が硬化し、1 層分のスライスが形成される。次に、造形テーブルをスライスの厚さ程度下げ、新しい液面を作る。この手順を繰り返すことにより、スライスの積み重ねとして、目的とする立体物が得られる。

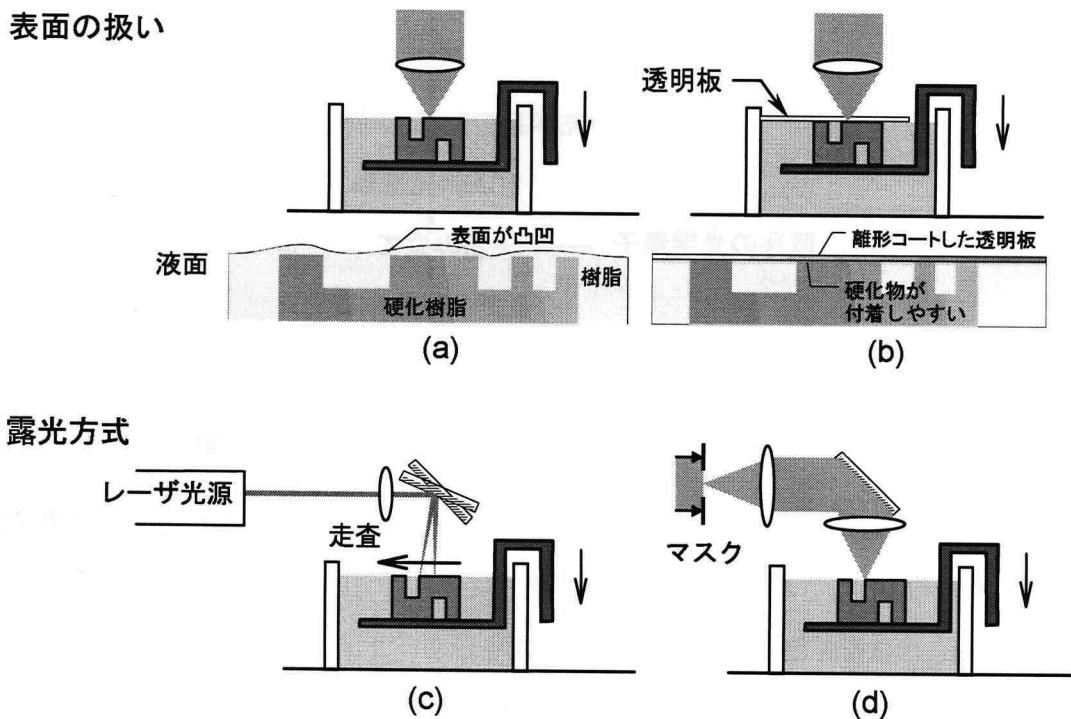

光造形の方式は、光硬化性樹脂液面の扱い・露光方式によって分類できる（図 5.3）。樹脂液面の扱いには、自由液面方式と規制液面方式がある。自由液面方式では、光硬化性樹脂の液面を空気にさらし、液表面に光を当てて硬化させる。それに対して、規制液面方式では液面を透明板で覆い、透明板と接する付近の樹脂を硬化させる。透明板の樹脂と接する面には離形コートを施し、硬化物が付着しないように加工しておく。高さ方向の造形精度は、自由液面方式よりも規制液面方式の方が高い。しかし、離形コートは繰り返し利用すると次第に劣化するため、硬化物の一部が透明板に付着して造形物が壊れことがある。

## 5. 光造形技術を用いた光学系実装技術

図 5.2: 光造形の手順: (a) 作製する立体物, (b) コンピュータ内でスライスに分割, (c) 最初の 1 層分のスライスを作製, (d) 次の 1 層分造形テーブルを下げる, (e) 次の 1 層を作製。

露光方式には、ビーム露光方式とマスク露光方式がある。ビーム露光方式では、レーザビームを光変調器や機械式シャッターでオン・オフしながら液面上を 2 次元的に走査し、スライスを作製する。走査には、ガルバノミラーや機械式自動ステージを用いる。光学系が単純で、大きい物体の作製に向いているため、ほとんどの商用光造形装置がこの方式を採用している。マスク露光方式では、液晶ディスプレイなどの SLM にスライス形状を表示する。SLM を光源で照明し、SLM に表示したパターンを液表面に結像してスライスを作製する [102]。スライスを一度の露光で作製できる利点があるが、大きい物体の作製には向かない。

### 5.2.2 光造形装置への光学素子作製機能の組み込み

既存の光造形装置を用いた場合、作製した立体物は不透明になり、そのまま光学素子として使うことはできない。これは、ビーム露光方式を用いると、硬化物にはビームの光強度分布を反映した屈折率分布が生じ、光を散乱するためである。マスク露光の場合には、SLM の画素構造が硬化物に転写され不透明になる。また、造形物の表面は光学素子に利用できるほど平坦ではない。一方、今までに光硬化性樹脂を用いて光学素子を作る試みがいくつかなされている [103–105]。したがって、既存の光造形装置を改良し、光学素子作製能力を付加することが可能であると考えられる。

一般に、光学系は、フレーム・光学素子ホルダー・光学素子から構成される。光学素子ホルダーは光学素子を固定するために用い、フレームは光学素子ホルダー間の位置関係を固定し、光学系全体をモジュール化するために用いる。光造形装置に光学素子作製機能を追加することにより、これ

図 5.3: 光造形の方式: (a) 自由液面方式, (b) 規制液面方式, (c) ビーム露光方式, (d) マスク露光方式.

図 5.4: 光造形技術を応用した光学系の自動作製.

## 5. 光造形技術を用いた光学系実装技術

図 5.5: 光造形技術を応用した光学系の設計・作製手順.

らすべてを同時に作製できるようになる。ただし現状では、光造形で作製できる光学素子は、レンズ・プリズム・回折光学素子などの受動光学素子に限られている。