| Title        | GaAs電界効果トランジスタの高周波特性および雑音特性の向上に関する研究 |

|--------------|--------------------------------------|

| Author(s)    | 中島,成                                 |

| Citation     | 大阪大学, 1996, 博士論文                     |

| Version Type | VoR                                  |

| URL          | https://doi.org/10.11501/3110214     |

| rights       |                                      |

| Note         |                                      |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

GaAs 電界効果トランジスタの高周波特性 および雑音特性の向上に関する研究

1995年11月

中 島 成

GaAs 電界効果トランジスタの高周波特性 および雑音特性の向上に関する研究

1995年11月

中 島 成

### 内容要旨

本研究は、GaAs 集積回路(IC)の基本素子となるショットキーゲート型電界効果トランジスタ(MESFET)の高周波特性、低雑音性向上のために必要な素子作製技術、素子構造を検討し、これまで必ずしも明らかにされていなかったGaAs MESFETの高速性、低雑音性の起因を明らかにするとともに、量産性に優れたGaAs ICへの展開を図ることを目的としている。

第1章では、序論としてGaAs電子デバイスの開発の歴史と電子デバイス産業における 位置づけを概観する。その中でGaAs電子デバイスの社会普及に向けての問題点と MESFETの特性決定要因に関して未解明であった点を要約し、本研究の目的と必要性を 明らかにした。

第2章では、GaAs MESFETの基本的な作製方法の改良結果について述べる。単層レジストをダミーゲートとしてソースおよびドレインの低抵抗領域をゲートに対して自己整合的に形成するプロセスは、表面準位に起因するチャンネル領域の寄生抵抗の低減に有効であることを示すとともに、従来プロセスに比べ工程数が少なく素子各部の寸法を正確に制御できる特徴を持っていることを明らかにした。また、この新しいプロセスを用いて0.5 μmゲートGaAs MESFETをウェハ面内に均一にかつ再現性よく形成できることを実証した。

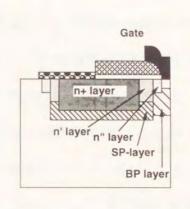

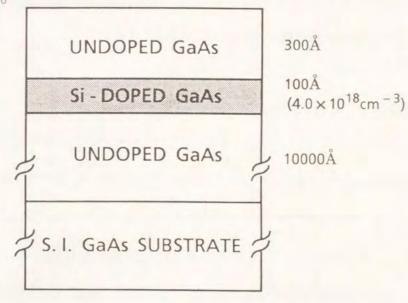

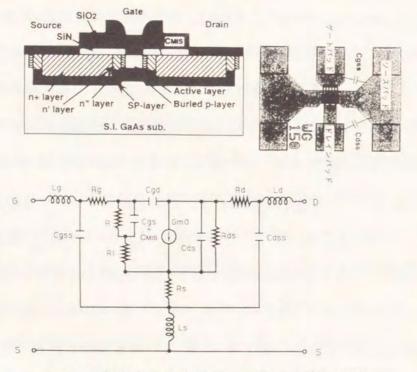

第3章では、素子の微細化を進めて行く際に問題となる「短チャンネル」効果の抑制 法について述べる。短チャンネル効果の発生要因は、チャンネルの2次元効果によるキャ リアの基板への漏れ電流と、対峙する高不純物濃度ソース/ドレイン低抵抗領域から基 板への漏れ電流の2つに大別できる。前者に対してはパルスドープ活性層を、後者に対 してはソース/ドレイン領域をn+, n', n"と多段階に形成した上、n+, n'層の下にp型層を 設ける新LDD(Lightly Doped Drain)構造を採用することにより、短チャンネル効果を抑制 できることを明らかにした。その結果、実用上問題のないゲート長0.3 μmのGaAs MESFETが作製できることを確認した。 第4章では、パルスドープ高濃度不純物層の電子輸送特性を述べる。有機金属気相成長法で作製した100Å厚のパルスドープ層を持つ試料についてシュブニコフ・ド・ハース振動、電流一電圧特性、ホール効果の測定を行った結果、V型ポテンシャル内に2次元電子ガスが形成されており、同一キャリア濃度のバルクに比べ優れた高電界輸送特性を有することを示した。

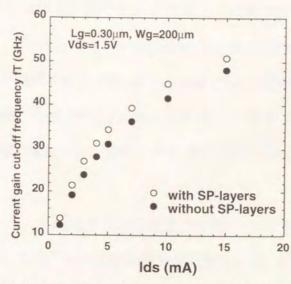

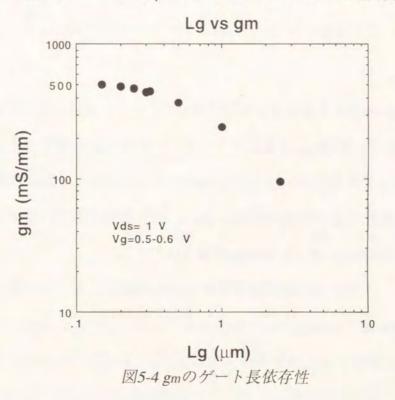

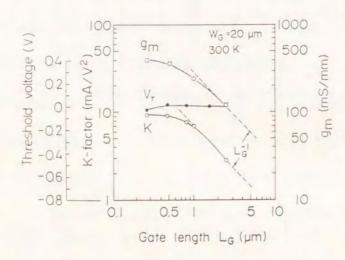

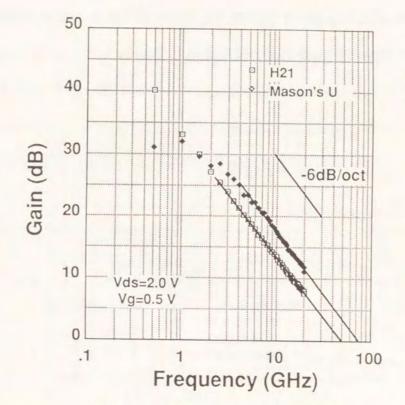

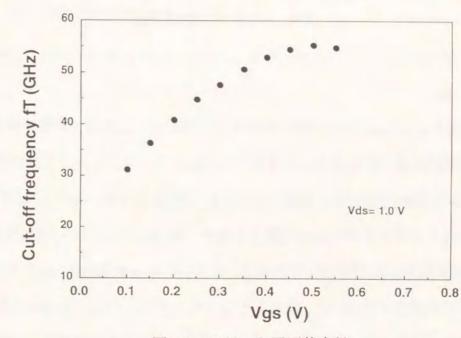

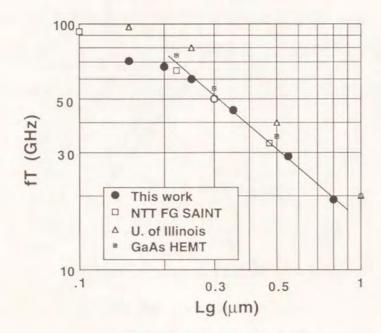

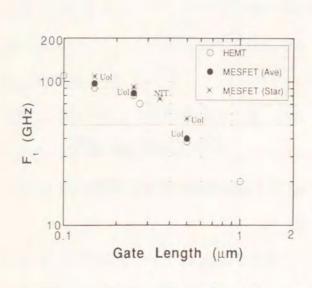

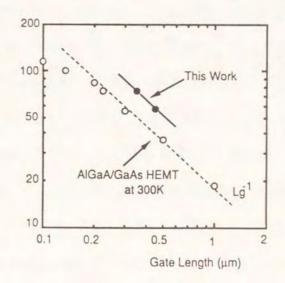

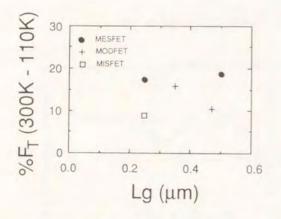

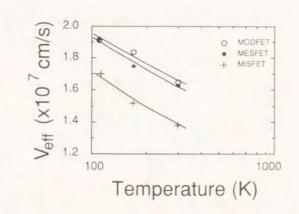

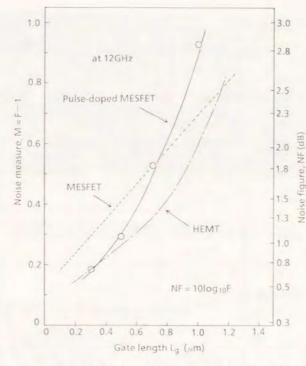

第5章では、本研究で開発したプロセスおよび素子構造を適用したGaAs MESFETの高速/高周波特性を調べ、HEMT (High Electron Mobility Transistor)を含む様々な素子の特性と比較検討することによりMESFETの高速性を決める要因の解明を試みている。作製されたゲート長0.3 μmのGaAs MESFETでは、450 mS/mmの伝達コンダクタンスと52 GHzの電流遮断周波数を得ることができた。これらの結果はHEMTの特性と同等であり、MESFETの高速/高周波特性は低電界移動度よりはむしろ電子飽和速度によって支配されていることが明らかとなった。

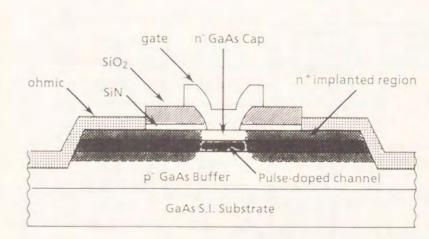

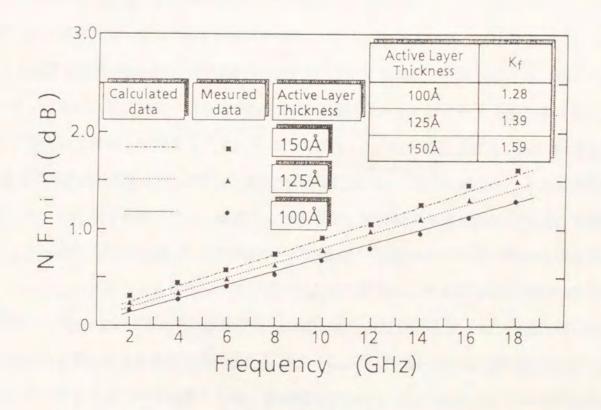

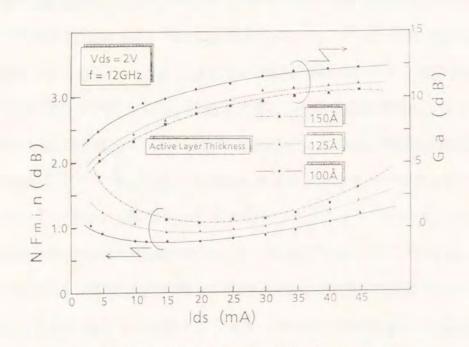

第6章では、GaAs MESFETの雑音特性の向上手法について述べる。パルスドープ構造 MESFETの高濃度不純物層の厚みと雑音特性との関係を調べ、不純物層厚を薄くすると 雑音特性が向上することを見い出した。パルスドープ高濃度不純物層厚をHEMTの2次 元電子ガス厚と同等の100 Åにすることにより、ゲート長0.3 μmのGaAs MESFETで12 GHzでの雑音指数が0.72 dBとHEMTと同等の性能が得られた。

第7章では、以上の研究結果を総括し本研究の結論を述べるとともに、今後の問題点 および残された課題について言及する。

### 目 次

# 第1章序 論 1-1 本研究の背景・・・・・・・・ 1 1-2 本研究の目的・・・・・・・・ 4 1-3 本論文の構成・・・・・・・・・・・・・6 1-4 参考文献 · · · · · · · · · · · · · · · · · · 8 第2章 ダミーゲート法による自己整合型MESFETの作製 2-1 緒 言・・・・・・・・・・・・・ 11 2-2 GaAs MESFETの構造と動作原理 · · · · · · · · · · · 12 2-3 寄生抵抗低減のための構造 ......... 14 2-3-2 ダミーゲートを用いた自己整合プロセス・・・・・・ 17 2-4 生産性、制御性に優れた自己整合プロセス・・・・・・ 19 2-4-2 イオン注入に対する阻止能 ・・・・・・・・ 20 2-4-3 ダミーゲートの加工 ・・・・・・・・・・ 20 2-4-4 パターン反転工程 ・・・・・・・・・ 22 2-5 MESFET作製プロセス · · · · · · · · · · · · · · · · 24 2-6 結 言 · · · · · · · · · · · · 29 2-7 参考文献 · · · · · · · · · · · · · · · · · 30 第3章 短チャンネル効果の抑制 3-1 緒 言 · · · · · · · · · · · · · · · · · 34 3-2 短チャンネル効果とは・・・・・・・・・・・ 34

| 3-2-1 短チャンネル効果の要因とこれまでの対策 ・・・・・・ 36                    |

|--------------------------------------------------------|

| 3-3 パルスドープ構造による短チャンネル効果の抑制・・・・・ 37                     |

| 3-3-1 パルスドープ構造 ・・・・・・・・・ 37                            |

| 3-3-2 有機金属気相成長法によるパルスドープ構造の形成 ・・・・ 40                  |

| 3-3-3 素子の作製(Rapid Thermal Annealを用いた活性化 · · · · · · 41 |

| 3-3-4 短チャンネル効果の高濃度層厚依存性 ・・・・・・・ 46                     |

| 3-4 新LDD構造による短チャンネル効果の抑制 · · · · · · · 48              |

| 3-4-1 p層埋め込み構造とは・・・・・・・・・ 48                           |

| 3-4-2 LDD構造とは · · · · · · · · · · · · · · · 49         |

| 3-4-3 新LDD構造の提案 · · · · · · · · · · · · · · · 50       |

| 3-4-4 新LDD構造の作製方法 · · · · · · · · · · · · · 51         |

| 3-4-5 新LDD構造による短チャンネル効果の抑制 · · · · · · · 53            |

| 3-5. 結 言 · · · · · · · · · · · · · · · · · 55          |

| 3-6. 参考文献 · · · · · · · · · · · · · · · · · 57         |

|                                                        |

| 第4章 パルスドープ構造による電子輸送特性の改善                               |

| 4-1 緒 言 60                                             |

| 4-2 高濃度薄層半導体におけるバンド構造・・・・・・・・ 61                       |

| 4-2-1 パルスドープ構造 GaAs · · · · · · · · · · · · 62         |

| 4-2-2 シュブニコフ・ド・ハース(SdH)振動 · · · · · · · · 62           |

| 4-2-3 パルスドープ構造GaAs のSdH振動 · · · · · · · · 63           |

| 4-3 半導体中の電子移動度と飽和速度 ・・・・・・・・ 66                        |

| 4-3-1 パルスドープ構造の電子移動度・・・・・・・ 67                         |

| 4-3-2 パルスホール効果による高電界輸送特性評価・・・・・ 70                     |

| 4-3-3 パルスI-V測定による高電界輸送特性評価 · · · · · · · 72            |

| 4-4 ダブルパルスドープ構造による電子輸送特性の改善・・・・・ 73                    |

| 4-4-1 ダブルパルスドープ構造・・・・・・・ 73                      |

|--------------------------------------------------|

| 4-4-2 ダブルパルスドープ構造GaAs MESFET・・・・・・ 75            |

| 4-5 結 言 ・・・・・・・・・・ 78                            |

| 4-6 参考文献 · · · · · · · · · · · · 80              |

|                                                  |

| 第5章 GaAs MESFETの高速、高周波特性                         |

| 5-1 緒 言 · · · · · · · · · · · · · · · 84         |

| 5-2 素子の高速動作、高周波特性を表す指標・・・・・・・ 84                 |

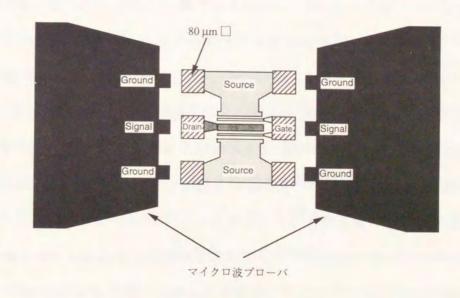

| 5-3 素子の評価技術 ・・・・・・・・・・ 87                        |

| 5-4 素子の評価結果 ・・・・・・・・・・ 89                        |

| 5-4-1 DC特性 · · · · · · · · · · · · · · · 89      |

| 5-4-2 高周波特性 · · · · · · · · · · · · · · · 91     |

| 5-4-3 考 察 · · · · · · · · · · · · · · 93         |

| 5-5 サブ0.25 μm以下での特性解析 · · · · · · · · · · · · 96 |

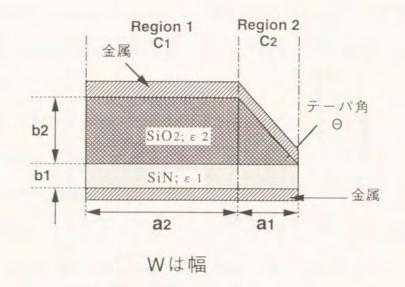

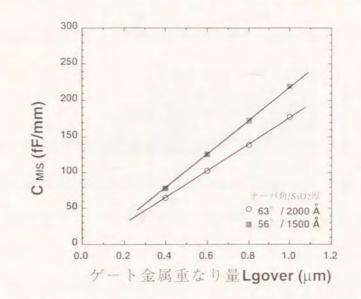

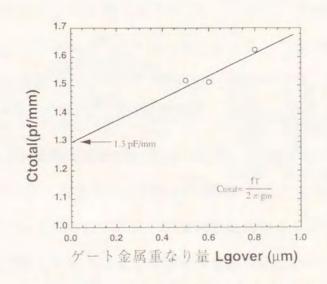

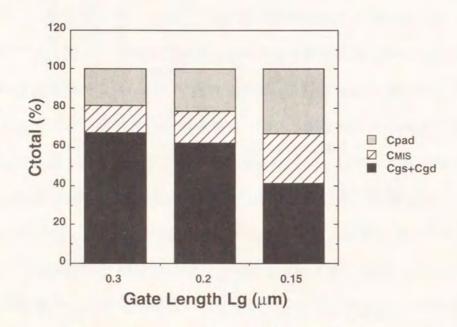

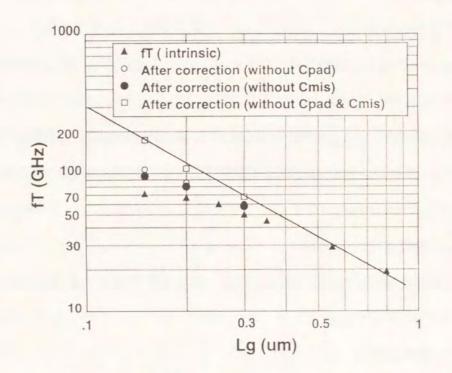

| 5-5-1 GaAs MESFETの寄生容量 ・・・・・・・・ 97               |

| 5-5-2 寄生容量の影響 ・・・・・・・・・・ 101                     |

| 5-6 電子速度のオーバシュート効果 ・・・・・・・ 102                   |

| 5-7 高速化、高周波化への方針 ・・・・・・・ 103                     |

| 5-7-1 ゲート長の短縮 ・・・・・・・・・ 103                      |

| 5-7-2 短ゲート長での素子構造の最適化 ・・・・・・ 103                 |

| 5-7-3 寄生抵抗の低減 ・・・・・・・・・ 104                      |

| 5-7-4 寄生容量の低減 ・・・・・・・・・・ 104                     |

| 5-7-5 材料の選択 ・・・・・・・・・・・・ 105                     |

| 5-8 結 言 · · · · · · · · · · · · · · · · · ·      |

| 5-9 参考文献 · · · · · · · · · · · · · · · · · · ·   |

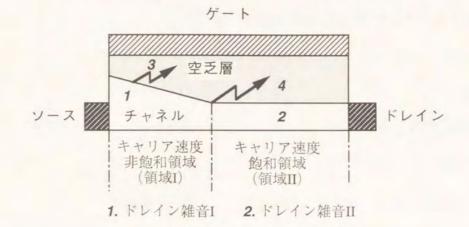

| 第6章 GaAs MESFETの雑音特性                                  |

|-------------------------------------------------------|

| 6-1緒 言 · · · · · · · · · · · · · · · · · ·            |

| 6-2 雑音指数とは ・・・・・・・・・ 113                              |

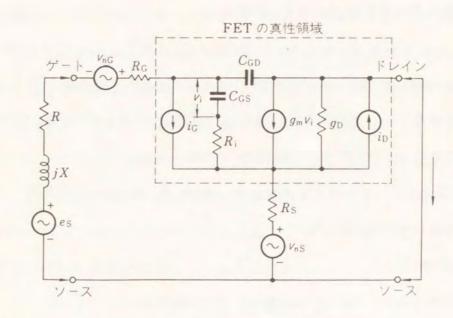

| 6-2-1 雑音指数を決める要因 ・・・・・・・・ 115                         |

| 6-2-2 Rs, Rgの低減方法 · · · · · · · · · · · · · · · · 118 |

| 6-2-3 Kfの低減方法 · · · · · · · · · · · · · · 120         |

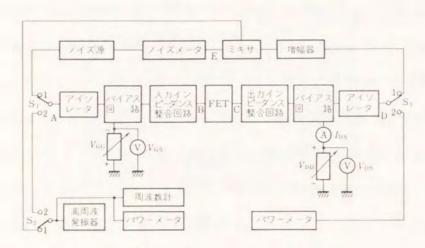

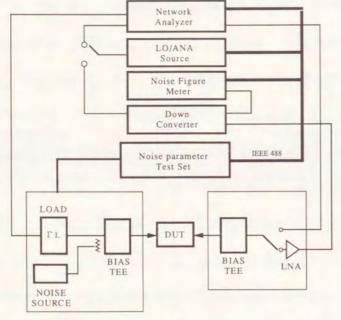

| 6-3 雑音指数の評価方法 ・・・・・・・・・ 120                           |

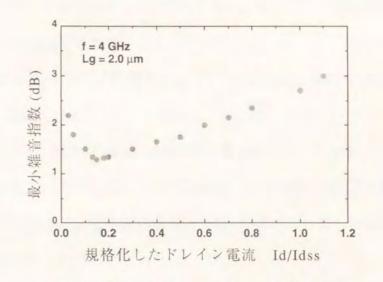

| 6-4 パルスドープ構造による低雑音化 ・・・・・・・ 122                       |

| 6-4-1 素子の作製方法・・・・・・・・・・ 122                           |

| 6-4-2 雑音特性のチャンネル厚依存性・・・・・・・ 123                       |

| 6-4-3 チャンネル層の薄層化の効果・・・・・・・ 126                        |

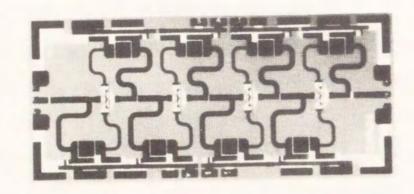

| 6-5 12 GHz帯低雑音MMICへの応用・・・・・・・ 128                     |

| 6-6 低雑音化への方針 ・・・・・・・・・ 130                            |

| 6-6-1 ゲート長の短縮 ・・・・・・・・・ 130                           |

| 6-6-2 寄生抵抗、寄生容量の低減 ・・・・・・・ 131                        |

| 6-6-3 素子構造の最適化 ・・・・・・・・・ 131                          |

| 6-6-4 材料の選択 ・・・・・・・・・・・ 132                           |

| 6-7 結 言 · · · · · · · · · · · · 132                   |

| 6-8 参考文献 · · · · · · · · · · · · · · · · 134          |

|                                                       |

| 第7章結論                                                 |

| 7-1 本研究の総括 ・・・・・・・・・・ 140                             |

| 7-2 今後の課題 ・・・・・・・・・・ 140                              |

| 7-3 参考文献 · · · · · · · · · · · · · · · · 143          |

|                                                       |

| 謝 辞 · · · · · · · · · · · · · · · · · ·               |

# 関連発表論文

| 本論文内容に直接関わる著者発表論文                          |   |  |  |  |  |  | 147 |

|--------------------------------------------|---|--|--|--|--|--|-----|

| その他論文 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |   |  |  |  |  |  | 148 |

| 本論文内容に直接関わる国際会議発表                          |   |  |  |  |  |  | 149 |

| その他国際会議発表・・・・・・                            | , |  |  |  |  |  | 151 |

### 第1章 序 論

#### 1-1 本研究の背景

半導体電子デバイスは、1947年にBardeenらにより発明されたGe点接触トランジスタによって開発の幕が開いた。その直後、接合型トランジスタが開発、製造され、1960年には後の集積回路(IC)の基盤となるプレーナプロセスが発表された。その後半導体デバイスの進歩は目覚ましく、Si MOSFET (Metal Oxide Semiconductor Field Effect Transistor)を中心にして、今日の情報化社会を築く礎として必要不可欠な存在に成長した1)。この間のICの集積度の進歩も著しく、1960年から1980年にかけては年率2倍の速度で進み、1995年のIEEE International Solid-State Circuits Conference (ISSCC)ではついに1Gbitの DRAM (Dynamic Random Access Memory)が発表されるに至った2,3)。

現在のICはそのほとんどがSiを素材として構成されている。これはICの基本素子であるトランジスタが、安定な表面酸化膜をゲート酸化膜とするMOSFETで構成されるという優位性に負うところが大きい4)。

一方、化合物半導体とりわけGaAsは、その優れた電子物性によりポストSi材料として 古くから注目され研究が進められてきた。

GaAsの特長を挙げると以下のようになる。

- 1) Siは共有結合性結晶であるが、GaAsはイオン結合性が強い結晶である。

- 2) バンド構造もSiが間接遷移型であるのに対して直接遷移型であり、このことは発 光素子と電子素子を集積化したOEIC (Opto-Electric IC)の実現をも可能にする。

- 3) 電子移動度がSi の約6倍の4000cm<sup>2</sup>/Vsec(ドーピング濃度1×10<sup>17</sup>/cm<sup>3</sup>の時) を示す。このことが低消費電力化や高速化に優位に働く。

- 4) エネルギーギャップが1.42 eV とSiの1.12 eVに比べて広いため、深い準位を利用することで抵抗率107~108 Ωcmの半絶縁性の基板が得られる。このことは集積化の際の素子間分離を容易にするとともに、配線容量の低減にも寄与している。またSiより高温動作が可能である。

- 5) 伝導帯バンド構造に起因して負の微分移動度を生じる。この効果を利用してGunn 発振器などのTELD (Transferred Electron Logic Device)が実現可能である。

- 6) 3元あるいは4元の混晶の組成比を変えることにより、基板と格子整合を取りつつ ヘテロ接合(異種間半導体接合)を作ることができる。この特長は半導体レーザな どの光デバイスやHEMT(High Electron Mobility Transistor)やHBT(Heterojunction Bipolar Transistor)などの電子デバイスやいわゆるエネルギーギャップ工学(gap engineering)に利用されている。

- 7) 耐放射線特性に優れる。このことは宇宙や原子炉などの環境下での使用を可能にしている。

GaAsの電子デバイスとしての利用は、マイクロ波帯から始まった。電子の谷間遷移効果を用いたGunn発振器5)や、低雑音および高出力特性を活かせるショットキーゲート型電界効果トランジスタ(MESFET)である。最初のGaAs MESFETは、1966年カリフォルニア工科大のMeadにより報告された6)。そして早くも1970年代にはマイクロ波帯の増幅器として実用化された。GaAs MESFETは主に軍事用/宇宙用として米国を中心に開発が進み、現在では60 GHzを越えるミリ波帯まで適応できる素子が実現されている7)。

一方、集積回路としては1974年にはHewlett-Packard社より最初のGaAs MESFET論理ゲートICが報告された8)。続いて集積度向上を目指した選択イオン注入技術とプレーナ技術の開発が行われ、この技術にはRockwell社が先導的役割りを果たした9)。選択イオン注入による動作層の形成は、エピタキシャル動作層に比べ均一性に優れ、数種類のしきい値電圧が同一基板上に実現できること、素子間分離の容易さ、プレーナ化による配線の段差切れ防止に有効であることより、今日のGaAs ICの基本技術となっている。

さらにこの技術はMESFETの高性能化、高均一化を目指したソース/ドレイン領域の 自己整合(セルフアライン)技術に発展していく10,11)。セルフアライン技術は特にノー マリオフ型(またはエンハンスメント型とも言う)のMESFETの特性向上に有効であり、 これによりDCFL(Direct Coupled FET Logic)型LSI回路が実現された。そして日本を中心に Si ICの置き換えを目的として高速メモリICの開発が盛んに行われた。GaAsの場合には 半絶縁性基板を使うために、SiのようなDRAMは実現が困難でありSRAM(Static Random Access Memory)を中心に開発が進められた。GaAsの高速性/低消費電力性を保ち集積度を上げるために回路形式にはDCFLが採用された。そして試作レベルでは16K SRAMまでが実現されたが12,13)、集積度、コスト、平均したアクセス時間などの点でSi ICとの明確な優位性を示すことができなかった。GaAsの場合、Siのような安定な自然酸化膜が得られないためMOS構造が実現できず、MESFETでは論理振幅が大きく取れない。そのため回路の動作余裕度は、しきい値電圧(Vth)のばらつきに弱い。これが後のICの集積度に大きな差を産み出した一因である。これ以外にもウェハの結晶としての不完全さに基づくMESFETの特性ばらつきやSiウェハとの口径差も原因である。

GaAs電子デバイスが一般の民生機器に広く使われるようになったのは衛星放送 (DBS:Direct Broadcast Satellite)受信用のコンバータとしてであろう。12 GHzという高周波 帯を使用するDBSにはGaAs MESFETの持つ高速性と低雑音性がいかんなく発揮された。 特に1980年に発明されたAlGaAs/GaAsへテロ接合を利用したHEMT(High Electron Mobility Transistor)14)は、当時のMESFETよりもはるかに優れた低雑音性を示し、月産数百万チップのオーダで出荷されてきた。

さらに最近では、TVチューナ、ファイバを使った光通信分野(155 Mbps-2.48 Gbps)、移動体通信/携帯電話(800 MHz-1.9 GHz)に代表される無線通信分野においてもGaAsデバイスは注目を集めている15-17)。 TVチューナ部では低雑音/低歪み用のデュアル・ゲートFETにGaAsが採用されたのを始め、光通信では、大量の情報を高速で処理することが必要なため発光素子である半導体レーザの駆動回路や、受光素子であるフォトダイオードの増幅回路や、信号処理を行うための各種回路にGaAs ICが採用されている。無線通信においても、出力段のパワー増幅器にGaAs MESFETが採用され低電圧駆動/低消費電力の特長を活かしバッテリーの寿命の向上に大きく寄与しており、受信部においては低雑音特性を活かしてRF増幅部にGaAs ICが採用されて始めている。これらの分野ではメモリのような大規模な集積回路は必要でなく、中/小規模な集積回路で十分である。しかしながらSiデバイスもバイポーラトランジスタによる高速化/低雑音化、

MOSFETによる高効率化を進めており性能面、価格面での競争が激化していくものと予想される。GaAsデバイスを広く世の中に浸透させるためには、GaAsデバイスが持つ高周波特性、低雑音特性、低電圧駆動/低消費電力特性を活かしつつSiを凌駕する高機能化、低価格化が必要と考えられる。

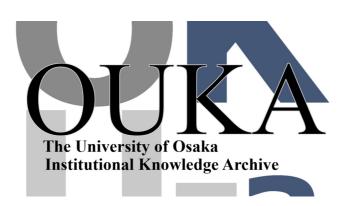

図1-1にGaAs MESFET/ICの開発の経緯を示す。

なお、詳細は次の参考文献に詳しい18-22)。

図 1-1 GaAs MESFET/ICの開発の経緯

#### 1-2 本研究の目的

GaAs ICの市場はSi ICの置き換えというより、Si ICでは実現困難と考えられる領域を補完する領域にある。GaAs ICが広く世の中に浸透し産業の柱に成長するためには、その特性を活かし安価で安定に生産できる体制が求められる。そのためには最適な作製技術、素子構造の選択が必要である。

セルフアライン技術は、GaAs LSI実現のために必須の技術であったがMESFET単体や

Small Scale IC (SSI)/Medium Scale IC (MSI)クラスのICにとっても歩留り向上のために必要な技術である。 またGaAsデバイスの高速/高周波特性向上のためにはゲート長の短縮が必須である。しかし現在のリソグラフィ技術では0.5 μm以下のパターンを得るためには、電子ビーム露光や位相シフト法などの特殊な技術23)を必要としコストやスループットの面で問題が残されている。

また、GaAs MESFETではゲート長を短縮していく際に「短チャンネル効果」が素子特性の向上、均一性を妨げる要因となっている。これらの問題を解決し、GaAs デバイスが安定に生産できる生産技術を確立することが必須である。

一方、特性の向上のためには電子が走行するチャンネルの最適設計も重要である。チャンネルの構造としては、MESFETはn型不純物をドープしたGaAs層を用いる。しかし低雑音素子や超高速素子として期待されてきたHEMTは、選択ドープしたAlGaAs/GaAsまたはAlGaAs/InGaAs などのヘテロ接合を用いて、不純物が存在しない層をチャンネルに用いている。確かにHEMTの高速性、低雑音性は優れたものではあるが、何がこの特性をもたらしているのであろうか。HEMTが開発された当時は、選択ドープ構造による電子移動度の向上がその大きな理由とされてきた。しかし筑波大学の長谷川は、HEMTがMESFETよりも優れた特性を示す理由は、高電子移動度よりも空乏層の厚みの差によるものでないかと指摘した24)。この論文をきっかけに応用物理学会誌でも、討論の広場で"高速電子デバイスのスイッチング速度の決定機構"という企画がなされたが、その当時は明確な結論を得るに至らなかった25)。

「デバイス特性を決定している物理的機構」という基本問題を明確にすることは、 GaAsを用いた電子デバイスの特性向上の設計指針になるはずである。

以上のことを踏まえ、本研究はGaAs電子デバイスの適応分野である高周波領域と低 雑音領域に最適なデバイス構造を研究する。そのため基本素子となるMESFETの作製技 術、素子構造を開発し、作製された素子を評価、解析することによりこれまで必ずしも 明らかにされていなかったGaAs MESFETの高速性、低雑音性の起因を明らかする。

#### 1-3 本論文の構成

本論文は第1章から第7章までで構成されている。

第2章では、GaAs MESFETの作製方法について述べる。GaAsは表面準位が多いために MESFETを形成した場合、表面空乏層の影響を受けソース領域/ドレイン領域での寄生 抵抗が増加する。そのために寄生抵抗を低減するためのさまざまな構造および作製方法 が開発されてきた。本論文では、再現性、均一性に優れたプレーナ型のデバイス構造作 製を目的にして、ソース/ドレイン低抵抗領域をゲートに対して自己整合的に形成する 自己整合プロセスの開発26)を中心に述べる。

第3章では、素子の微細化を進めて行く際に問題となる「短チャンネル効果」の抑制について述べる。ゲート長の短縮化に伴い、「短チャンネル効果」によりFETのしきい値電圧が負側にシフトしピンチオフ特性が劣化すると共に、伝達コンダクタンス(gm)の低下などの特性劣化、しきい値電圧(Vth)のばらつき増大などの特性ばらつきを招く。本章では「短チャンネル効果」発生の要因を分析し、その抑制のため不純物濃度を深さ方向にパルス状に変化させた「パルスドープ」構造と呼ぶチャンネル構造採用による改善27)と、新しいLDD(Lightly Doped Drain)構造によるソース/ドレイン領域の改善28)について述べる。

第4章では、第3章で提案した高濃度薄層をパルス状に配した「パルスドープ」構造の電子輸送特性を述べる。高濃度層をMESFETのチャンネルに採用することは、不純物散乱による電子移動度の低下やドリフト速度の低下のため素子特性の劣化が懸念される。本章ではまず、シュブニコフ・ド・ハース振動測定により「パルスドープ」構造のバンド構造を調べた結果29)を述べる。次にパルスI-V、パルスホール効果の測定により「パルスドープ」構造の高電界輸送特性を調べ、バルクに比べ優れた特性を示すことを明らかにした30)。最後にこの良好な電子輸送特性が、パルスドープ構造特有のV型ポテンシャルを有するバンド構造に起因していることを述べる。

第5章では、製作したGaAs MESFETの高速/高周波特性について述べる。さらに本研究で開発された素子の特性を、MESFETに対して2~3倍高い電子移動度を有するHEMT

素子の特性と比較、解析することにより電界効果トランジスタの高速性を決める要因を明らかにする。さらに、微細素子で問題となる寄生容量について解析を行い、最後に高速、高周波化の指針について述べる。

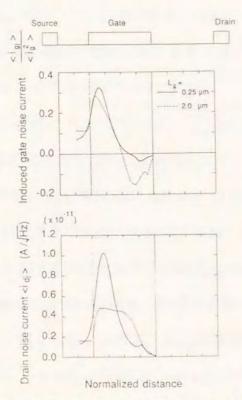

第6章では、GaAs MESFETの雑音特性について述べる。本研究で提案したプロセスおよび「パルスドープ」構造を用いて作製したGaAs MESFETの雑音特性を解析した。高電子移動度を有するHEMTと従来のMESFETのチャンネルの厚みの差に着目して実験を行い、これまで必ずしも明らかでなかった電界効果トランジスタの雑音特性を決める要因について実験的に得た知見を述べる31)。さらに素子の低雑音化の指針についても述べる。第7章ではこれらの研究結果を総括し本研究の結論を述べるとともに、今後の問題点および残された課題について言及する。

#### 1-4 参考文献

- 1) A. Toffler: "The Third Wave", William Collins Sons & Co Ltd, 1980

- 2) M. Horiguchi et al., "An Experimental 220 MHz 1 Gb DRAM", 1995 IEEE International Solid-State Circuits Conference, 14.5

- 3) H. Mori et al., "A 1 Gb DRAM for File Applications", 1995 IEEE International Solid-State Circuits Conference, 14.6

- 4) 例えば 徳山 巍著 "MOSデバイス",(株) 工業調査会

- 5) J.B. Gunn, "Microwave Oscillations of Current in III-V Semiconductors", Solid State Comm., 1, No.4, pp.595-598, 1963

- 6) C.A. Mead, "Schottky Barrier Gate Field Effect Transistor", Proc. IEEE, 54, No.2, pp. 307-308, 1966

- 7) Milton Feng, and Joy Laskar, "On the Speed and Noise Performance of Direct Ion-Implanted GaAs MESFET's", IEEE Trans. on Electron Devices, Vol. 40, No.1, pp.9-17, 1993

- 8) R. Van Tuyl, and C.A. Liechti, "High-Speed Integrated Logic with GaAs MESFETs", ISSCC Dig. Tech. Paper, pp.114-115, 237, 1974

- 9) B.M. Welch and R.C. Eden, "Planar GaAs Integrated Circuits Fabricated by Ion Implantation", IEDM Tech. Dig., pp.205-208, 1977

- 10) N. Yokoyama, T. Mimura, M. Fukuta, and H. Ishikawa, "A Self-Aligned Source/Drain Planar Device for Ultla-High-Speed GaAs MESFET VLSI's", ISSCC Dig. Tech, Paper, pp.218-219, 1981

- 11) K. Yamasaki, K. Asai, and K.Kurumada, "GaAs LSI-Directed MESFET's with Self-Aligned Implantation for n+-Layer Technology (SAINT)", IEEE Trans., ED-29, No.11, pp.1772-1777, 1982

- 12) M. Hirayama, M. Togashi, N. Kato, M. Suzuki, Y. Matsuoka, and Y. Kawasaki, "A GaAs 16-kbit Static RAM Using Dislocation-Free Crystal", IEEE Trans. ED-33, No.1, pp.104-110, 1986

- 13) H. Nakano, M. Noda, M. Sakai, S. Matsue, T. Oku, K. Sumitani, H. Makino, H. Takano, and K. Nishitani, "A high-speed GaAs 16Kb SRAM of 4.4 ns/2 W using triple-level metal interconnection", Techinical Digest in IEEE GaAs IC Symp., pp.151-154, 1990

- 14) T. Mimura, S. Hiyamizu, T. Fujii, and K. Nanbu, "A New Field-Effect Transistor with Selectively Doped GaAs/AlxGa1-xAs Heterojuctions", Jpn. J. Appl. Phys., 19, No.5, pp. L225-227, 1980

- 15) H. Mizukami, H. Ikedo, K. Ideno, T. Nagashima, and S. Yamada, "Low supply voltage GaAs ICs for a TV tuner," Inst. Phys. Conf. Ser., No.129: Chapter 11, pp.863-868, 1993

- 16) 多良 勝司, "移動体通信機器用 MMIC", 電子技術、1995-2, pp.29-34, 1995

- 17) 宮垣 克則、"通信用高周波デバイス、新素子で、ひたすら低雑音、高出力へ、" 日経エレクトロニクス 1990. 6.4. pp.189-201

- 18)Paul Greiling, "The Histrical Development of GaAs FET Digital IC Technology", IEEE Trans. MTT-32, No.9, pp.1144-1155, 1984

- 19) "実用期に突入するGaAs LSIの技術", 日経マイクロデバイス、1985年春号 特別編集版、pp.25-34

- 20) Charles A. Liechti, "GaAs IC技術"、Semiconductor World, 1985, 5, pp.149-155

- 21) "新製品ラッシュのGaAs IC", 日経マイクロデバイス、1985年10月号 pp.154-159

- 22) "GaAsデジタルICの開発、SSIは市場へ、LSIは難題と格闘中", 日経エレクトロニクス、1987. 5.4. (no.420), pp.99-115

- 23) L.G. Studebaker, "Sub-0.2 Micron Gate Lithography Using E-Beam, X-Ray and Optical Technologies-An Overview", Technical Digest in IEEE GaAs IC Symp., pp.321-324, 1994 24) 長谷川 文夫、"HEMTはほんとうに高電子移動度トランジスタか?", 電子通信学会研究会、ED85-73, pp.25-32, 1985

- F. Hasegawa, "Is HEMT really a high electron mobility transistor?", IEEE Trans. Electron Devices, Vol. ED-32, No.11, p. 2528, 1985

- 25) 長谷川、浜口、石橋、三村、長谷川、"高速電子デバイスのスイッチング速度の

-9-

決定機構"、応用物理 pp.359-385, 1988年

- 26) S. Nakajima, G. Ishii, Y. Saito, N. Kuwata, T. Fukuzawa, K. Koike, and H. Nishizawa, "Manufacturability of Dummy-gate Self-aligned LDD GaAs MESFETs for High Volume Production", Technical Digists of IEEE GaAs IC Symposium, pp.119-122, 1994

- 27) S. Nakajima, K. Otobe, T. Katsuyama, N. Shiga, and H. Hayashi, "OMVPE grown GaAs MESFETs with step-doped channel for MMICs," Technical Digest in IEEE GaAs IC Symposium, pp.297-300, 1988

- 28) S. Nakajima, K. Matsuzaki, K. Otobe, H. Nishizawa, and N. Shiga, "Enhancement-mode GaAs MESFET Technology for Low Consumption Power and Low Noise Application", IEEE Trans, Microwave Theory and Tech., Vol.42, No.12, pp.2517-2524, 1994

- 29) S. Nakajima, N. Kuwata, N. Nishiyama, N. Shiga, and H. Hayashi, "Hot electron transport in a pulse-doped GaAs structure", Semiconductor Science Technologies, Vol.7, pp.B372-274, 1992

- 30) S. Nakajima, N. Kuwata, N. Nishiyama, N. Shiga, and H. Hayashi, "Electronic properties of a pulse-doped GaAs structure grown by organometallic vapor phase epitaxy", Applied Physics Letters, vol.57, No.13, pp.1316-1317, 1990

- 31) S. Nakajima, K. Otobe, N. Shiga, N. Kuwata, K.Matsuzaki, T. Sekiguchi, and H. Hayashi, "Low-Noise Characteristics of Pulse-Doped GaAs MESFET's with planar Self-Aligned Gates", IEEE Trans. Electron Devices, Vol.39, No.4, pp.771-776, 1992

### 第2章 ダミーゲート法による自己整合型MESFETの作製

#### 2-1 緒 言

GaAs MESFETはSiの高速デバイスと比較すると、ユニポーラでかつショットキーゲート型デバイスという点で製造工程が簡単である。そのためマスク枚数が少なくて済むという利点がある。表2-IにGaAs IC, Si CMOS IC, Si Bipolar ICの典型的なプロセスを比較した。

ウェハの口径ではSi0150 mm(6")  $\Phi$  に対して100 mm(4")  $\Phi$  と小さいが、同じ多層配線 を用いてもマスクは $3\sim7$  枚も少ない。そのため製造日数はSi デバイスに比べて短い。

| GaAs MESFET      | Si Bipolar       | Si Bi-CMOS       |  |  |  |  |  |  |

|------------------|------------------|------------------|--|--|--|--|--|--|

| 100 mm S.I. Sub. | 150 mm S.C. Sub. | 150 mm S.C. Sub. |  |  |  |  |  |  |

| 2-3 Metal Layers | 2-3 Metal Layers | 2-3 Metal Layers |  |  |  |  |  |  |

| 13 Mask Layers   | 16 Mask Layers   | 20 Mask Layers   |  |  |  |  |  |  |

表2-1 各デバイスを用いた場合のプロセス比較

S.I.: Semi-Insulating, S.C.: Semi-Conductive

一方、GaAs デバイスはSiデバイスに比べて

- ・結晶自体にストイキオメトリに関する問題がある。

- ・プロセス中の熱処理で蒸気圧の高いAsが解離しやすい。

- ・結晶が極性を有しているためへき開性が強い。

- ・現在実用化されている結晶の口径が4" Φと小さい。

などの製造上の問題がある。GaAsは電気的特性、光学的特性の面でSiに対して様々な 利点を持つが、化合物半導体であるが故に結晶性自体は不完全であり、まずこの点がデ バイスを作製する上で均一性や再現性の問題となっている。

1985年頃から結晶を引き上げる際に入る転位とMESFETのしきい値電圧(Vth)の関係が

取りざたされ1,2)、結晶の無転位技術が進んだ3,4)。しかしその後の研究により転位そのものはVthと相関がなく、転位によって引き起こされるストイキオメトリのずれの方が影響することが明らかになってきた5)。そして結晶引き上げ後のインゴットアニールという手法により転位を均一化することで、デバイス作製に適したウェハ作製技術が1980年代後半より確立されてきた6,7)。

一方、デバイス作製技術の方も導電層の形成技術にイオン注入法が導入され、デバイス構造もプレーナ型の自己整合構造が開発された。また注入されたイオンを活性化するためのアニール技術(保護膜やアニール条件)の開発も進んだ。デバイスを作製する場合は生産性に優れたプロセスにより、優れた特性のデバイスを再現性よく均一に作り出すことが重要である。

本章では、まずMESFETの動作原理を概説しデバイス特性に影響を与える要因を分析する。次にこれまでに開発されてきた自己整合プロセスを概略し、それらの問題点を述べる。そして新たに開発した単層レジストをダミーゲートに用いた自己整合プロセスとその利点について述べる。

#### 2-2 GaAs MESFETの構造と動作原理

GaAs の場合、Si の場合のSiO2ような良質で安定な自然酸化膜が得られない。そのためSi MOSFETのように反転モードで動作するMOSFETやMISFET(Metal Insulator Semiconductor Field Effect Transistor)デバイスは実現されていない。またディプレッションモードで動作するMISFETでは、酸化膜とGaAs 界面に存在する多数の界面準位のためドレイン電流のドリフトやヒステリシスなどの問題があり8,9)、現在では構造が単純なMESFETに主役が移っている。

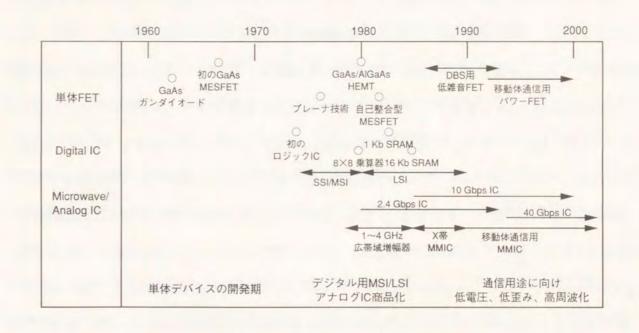

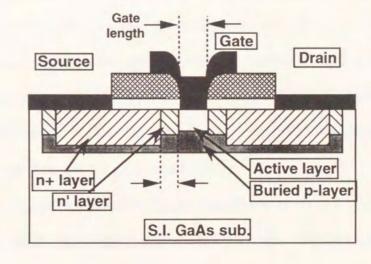

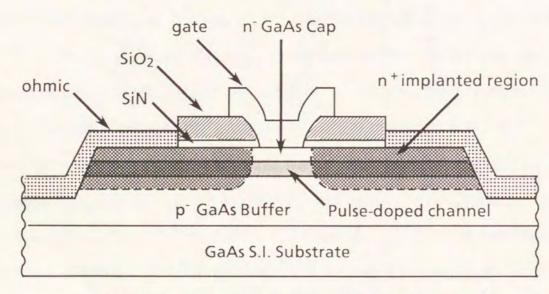

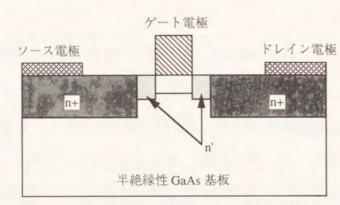

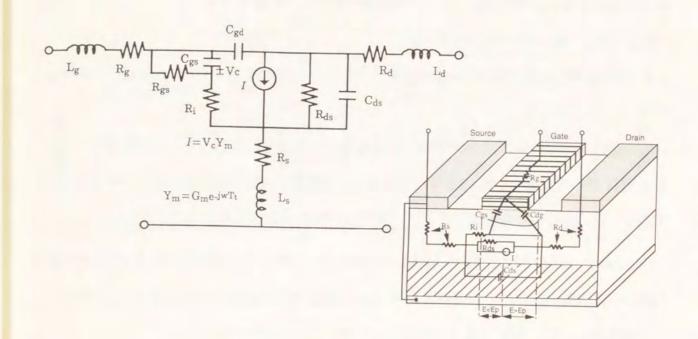

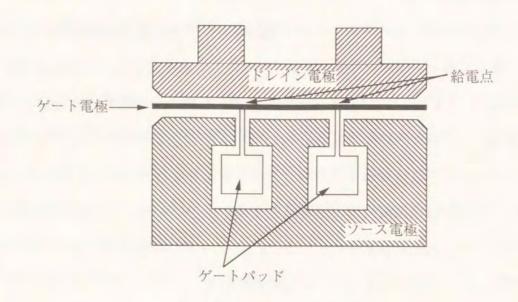

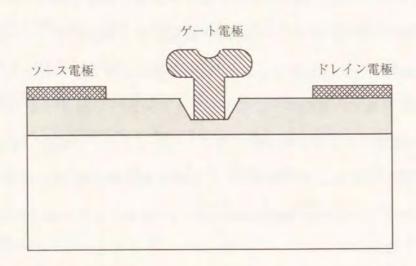

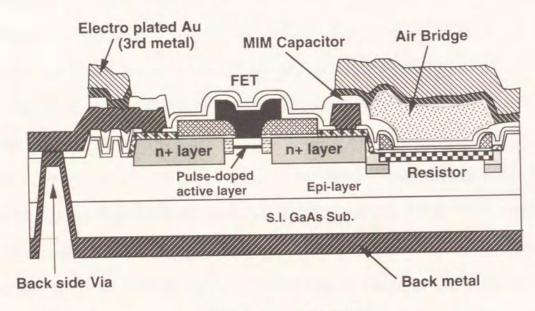

図2-1にGaAs MESFETの模擬的断面構造を示す。半絶縁性基板上にイオン注入やエピタキシャル法によりチャンネルを形成し、その表面にはオーミック接合からなるソース/ドレイン電極、ショットキー接合からなるゲート電極が形成されている。ソース電極に対してドレイン電極に正の電圧を印加すると、電子がソースからドレインに向かって

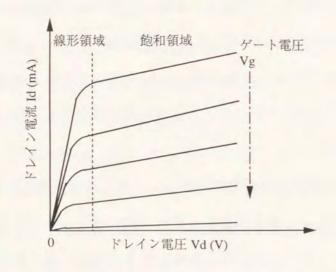

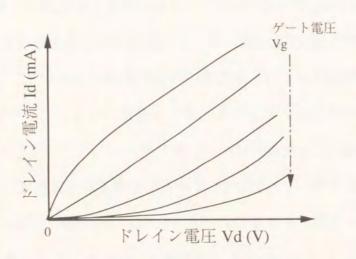

流れる。ゲート電極の電圧を変化させることで、ゲートから延びる空乏層の厚みが変化しソース/ドレイン間電流を変調することができる。典型的なMESFETの電流/電圧特性を図2-2に示す。ドレイン電流(Id)がドレイン電圧(Vd)に対して増加する線形領域とVdにほとんど依存しない飽和領域に分けることができる。Vdを一定にして、ゲートに負の電圧を印加していくとチャンネルが狭まり、ついにはドレイン電流が流れなくなる。その時のゲート電圧をMESFETのしきい値電圧(Vth)と言う。

図2-1 GaAs MESFETの模擬的断面構造

図2-2 代表的なGaAs MESFETの電流/電圧特性

MESFETの特性を表す重要なパラメータであるVthは次式で与えられる。

Vth=Vbi  $-(qN_Da^2/2 \epsilon * \epsilon_0)$

ここでVbiは金属/半導体の接触電位差、NDはキャリア密度、 $\epsilon$ \*は半導体の比誘電率、 $\epsilon$ 0は真空の誘電率、aはチャンネル厚みである。高精度のVth制御のためにはキャリアプロファイルの正確な制御が重要である。このためエピタキシャル成長により導電層を形成する場合は厚みと不純物のドーピング量制御が、イオン注入法の場合は注入条件や注入後の活性化アニール条件の制御が重要である。

GaAs MESFETでは、表面準位の影響のために生じるソース/ゲート間あるいはゲート /ドレイン間の寄生抵抗低減も重要である。これは表面準位のため表面空乏層が導電層 に拡がり電流通路を狭めるため、チャンネルとの間に直列抵抗が入ったのと等価になり +分な特性を引き出せなくなるからである。そのために表面準位の影響をなくす様々な 構造が考えられた。

#### 2-3 寄生抵抗低減のための構造

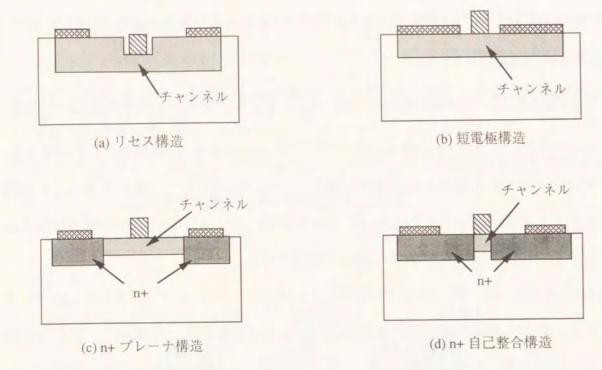

図2-3に寄生抵抗低減のために開発された代表的な構造を示す。

まず(a)は、ゲート電極近傍のチャンネル部を掘り下げ寄生領域を厚く保ったリセス構造である10)。(b)は、ソース/ドレイン電極をゲート電極の際まで近接させ、寄生抵抗部分を可能な限り低減した短電極間構造である11,12)。(c)は、高濃度で深いn+領域をソース/ドレイン電極の下に形成した構造である13)。(d)は(c)の構造をさらに改良し、ゲート電極に対して高濃度で深いn+領域を自己整合的に形成した構造である14,15)。自己整合とは、それ以前の工程で形成したパターン構造を用いて自己のパターン構造を形成することをいう。MESFET特性のウェハ面内での均一性やウェハ間での再現性は、デバイスの高性能化や歩留り向上のために重要である。(a)のリセス構造では、リセス領域形成の際のエッチングばらつきによりチャンネル厚にばらつきが生じ、均一性や再現性に優れた素子を実現することは困難である。

図2-3 寄生抵抗低減のための各種構造

そのためイオン注入を用いたプレナー型の構造が注目されるようになった。この構造では、(d)のような寄生抵抗低減のためソース側、ドレイン側のイオン注入領域をゲートに対して自己整合的に形成する構造が理想的である。この構造の実現のため大別して2種類のプロセスが提案されている。

# 2-3-1 耐熱ゲートを用いた自己整合プロセス

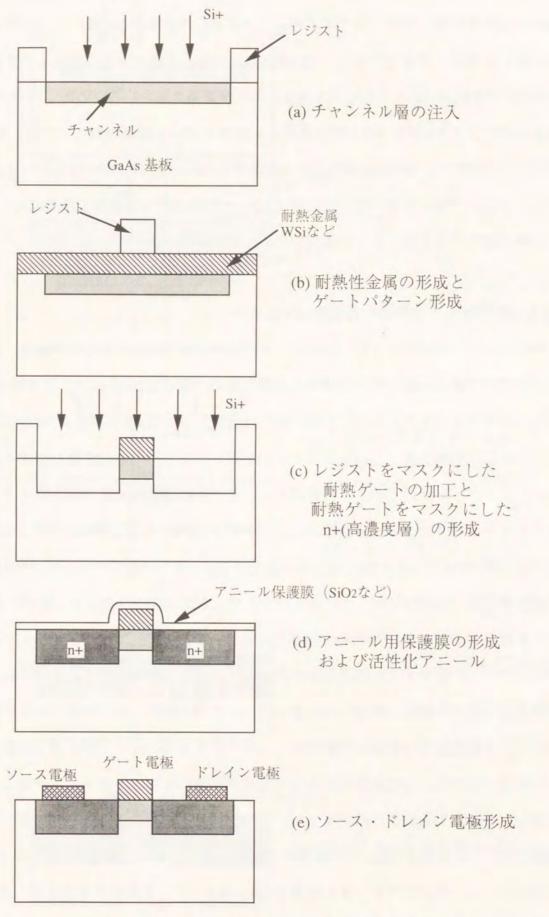

ひとつは高温でもGaAsと反応しないWSiなどの耐熱金属をゲート電極として用い、それをマスクにイオン注入を行いソース/ドレイン高濃度領域を形成するプロセスである 14)。このプロセスの作製工程を図2-4に示す。まず選択イオン注入によりチャンネルを 形成する。次にWSiなどの耐熱性の金属をスパッタ法によりウェハ全面に形成し、ゲートパターンをフォトリソグラフィにて形成する。このパターンをマスクに反応性イオン エッチ(Reactive Ion Etch: RIE)にて耐熱性金属を加工する。加工後の耐熱金属をマスクに 高濃度領域形成のためのイオン注入を行う。そしてSiO2やSiONなどの絶縁膜でウェハ全面を覆い、注入されたイオンの活性化のためのアニールを行う。アニール温度としては

図2-4 耐熱ゲートによるGaAs MESFETの作製フロー

800~850℃である。最後にソース/ドレイン領域のパターンを形成し、AuGe系のオーミック金属を蒸着し合金化することでFETが完成する。耐熱ゲートの材料としては、WSiの他にWN16)、WAl17)、TiWN18)、WSiN19)などが開発されている。このプロセスは簡便さからディジタルLSIを中心に採用された。しかしゲート金属材料としては、注入されたイオンの活性化に必要な800℃付近の高温でもGaAsと反応しない材料という限定がありゲート抵抗の増大を招いていた。またGaAsと耐熱金属との熱膨張係数の大きな差もアニールの際に歪みを起こし、活性化率の不安定要素の一因となっていた20)。

#### 2-3-2 ダミーゲートを用いた自己整合プロセス

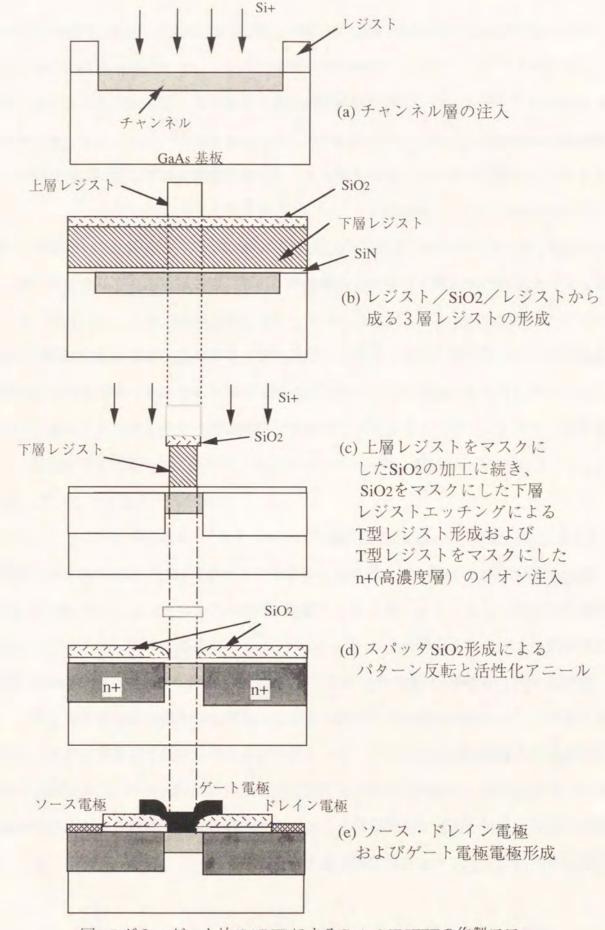

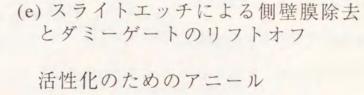

もうひとつは、ダミーゲート(置換ゲート)プロセスと呼ばれるものである。このプ ロセスの代表であるSAINT15)と呼ばれる作製工程の一例を図2-5に示す。まず選択イオ ン注入によりチャンネルを形成した後、表面保護膜としてSiN膜をプラズマCVD法によ りウェハ全面に形成する。次にレジスト/SiO2/レジストからなる3層レジストを形成 する。ダミーゲートは以下のように形成する。まず中間層のSiO2膜を最上層のフォトレ ジストパターンをマスクに反応性イオンエッチング(RIE)にて加工する。さらに最下層の フォトレジストをSiO2をマスクにRIEにて加工する。この時RIEでのエッチング条件/時 間を制御することでSiO2に対して下層レジストにアンダーカットを入れ、T型のダミー ゲートを形成する。上層レジストはこの工程で消失する。T型に加工されたパターン (ダミーゲート)をマスクに高濃度層形成のためのイオン注入を行う。この時SiO2がイ オン注入のマスクとなる。次にスパッター法によりSiO2膜をウェハ全面に形成する。ダ ミーゲート上に形成されたSiO2の膜質は、レジスト側壁部に付いた部分が多孔質(ポー ラス)になっている。この性質を利用して緩衝フッ酸によるスライトエッチにより側壁 部のSiO2のみ除去する。さらにダミーゲートをリフトオフにより除去してダミーゲート 部に開口パターンを形成する。この状態にて注入されたイオンの活性化アニールを行う。 ソース/ドレイン領域のパターンを形成しAuGe系オーミック金属を形成する。最後に ゲートパターンをSiO2に重なるように形成し、Ti/Pt/Auのゲート金属を形成することで

図2-5 ダミーゲート法(SAINT)によるGaAs MESFETの作製フロー

FETが完成する。ダミーゲート部に真のゲート電極が形成されていることがわかる。このプロセスではダミーゲート形成時に下層レジストにアンダーカットを入れるが、これは活性化アニールの際に高濃度領域が熱拡散によりゲート領域にまで拡がりゲート容量の増加を招くことを防ぐためである。ダミーゲートのプロセスとしては、他にSiO2をダミーゲートとしてフォトレジストでパターン反転を行うもの21)、SiN膜をダミーゲートとしてCVDで形成したSiO2膜でパターン反転を行うものなど22)がある。

SAINTプロセスの特長は、RIEにて下層レジストにアンダーカットを入れることである。そのため横方向拡散による容量の増加を招かず、かつ初期パターンをさらに短縮するので光学露光を用いても0.5 μm以下のゲート長が得られる。またアニール時にゲート金属が形成されていないため、耐熱性には優れないが低抵抗であるAu系の金属を選択できることなどがある。以上の特徴によりデジタル応用のみならず、ゲート抵抗の低減が要求されるアナログやマイクロ波の分野への応用にも適していると考えられる。

しかしこのプロセスは3層レジストを用いる複雑な工程のため生産性に問題があった。

#### 2-4 生産性、制御性に優れた自己整合プロセス

特性の優れたGaAs MESFETを均一にかつ再現性よく作製するには、自己整合プロセスが必須である。本研究では前述した2つのプロセスからダミーゲート法を選択し、更に工程を簡略化することを考えた。

これは、GaAs MESFET, ICの今後の応用分野はSiのようなディジタルLSIではなく、アナログやマイクロ波の分野になると考えたからである。このような分野では、ゲート抵抗の低減化が必要であるが、ダミーゲート法の場合は耐熱ゲート法と異なりゲート金属の選択が自由である。さらにマイクロ波帯での特性向上には、ゲート長の短縮が必須であるが、ダミーゲート法では光学露光とエッチング技術を組み合わせることで、短ゲート長化を容易に実現できる可能性があるからである。

#### 2-4-1 単層レジストを用いたダミーゲートプロセス

工程の簡便化のためにダミーゲートとしては、SAINTの3層構造T型レジストに替えてフォトレジスト単層を用いることを考えた。

この場合、次の点を考慮しなければならない。

- 1) ソース/ドレイン領域形成の際、イオン注入に対して十分な阻止能を有すること。

- 2) SAINTの3層レジストのアンダーカットに相当するレジストの短縮工程を行えること。

- 3) ダミーゲートを真のゲートと置き換えるためダミーゲートパターンを反転させなければならないが、その際に反転させる材料と十分なエッチング選択比があること。

フォトレジストは、ある厚み以上では注入イオンに対して十分な阻止能を有し、酸素 プラズマにより容易にエッチング可能である。またパターン反転にSiO2を用いた場合、 緩衝フッ酸に対してエッチングの選択性が大きくとれる。

#### 2-4-2 イオン注入に対する阻止能

注入イオンの不純物分布は、LSS理論をもとに深さ方向にはガウス分布で近似しピーク位置(Rp)と標準偏差( $\Delta$ Rp)で決定できる曲線で表される。各種イオンのRpや $\Delta$ RpはGibbonsらの「Projected Range Statistics」に記載されている23)。

選択注入マスクに用いる被膜の厚さは、 $(Rp+3\Delta Rp)$ 以上が目安となる。フォトレジストの200 KeVの加速エネルギのSiイオンに対するRpは0.9082  $\mu m$ ,  $\Delta Rp$ は0.1339  $\mu m$ であるから、フォトレジストの厚みを1.31  $\mu m$ 以上に設定することでSiイオンに対しては200 KeVの加速エネルギまで阻止することができる。フォトレジストの厚みは、フォトレジストの粘度(Cpで表される)と塗布時の回転数を調整することで所望の値が得られる。

本研究ではヘキスト社のAZ-5214を4100rpmで塗布することにより、1.60  $\mu$ mの厚みを得ている。

2-4-3 ダミーゲートの加工

フォトレジストは、酸素プラズマによりエッチングできる。レジスト膜をCxHyと表すと反応式は次のようになる。

$$CxHy + O \rightarrow CO_2 + H_2O$$

そのためエッチングを組み合わせることにより光学露光で得たパターンをさらに短縮でき、光学露光の限界を越えた微細パターンの形成が可能になる。ここで重要なことはレジストの縦方向、横方向をできる限り同じ速度(等方性)でエッチングすることである。縦方向(つまり厚み)はイオン注入の阻止能に関係し、横方向は後のゲート長に関係する。

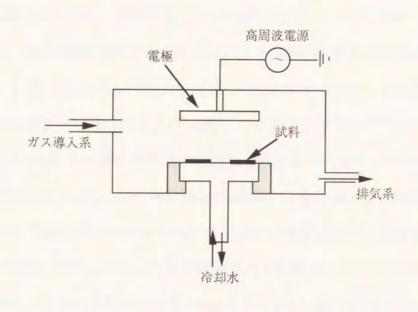

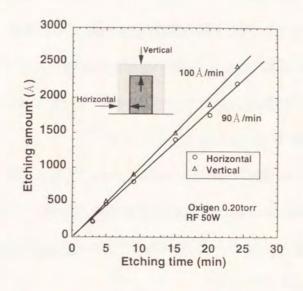

そのため、制御性に優れた平行平板型プラズマ装置を用いた。装置の概略を図2-6に示す。酸素ガスの圧力を最適化することにより等方性エッチングの条件が得られ、RFパワーを最適化することにより制御性のよいエッチング特性が得られた。図2-7にエッチング時間とレジストの縦/横方向のエッチング量の関係を示す。縦/横方向共100Å/minの速度でエッチングされ、制御性も±10%以内である。

図2-6 平行平板型プラズマエッチング装置の概略

図2-7 フォトレジストのエッチング特性

#### 2-4-4 パターン反転工程

ダミーゲートパターンを反転する絶縁膜はSiO2が適している。これは後工程(ゲートの窓開け)で下地のSiN膜(アニールの際の保護膜)をCF4ガスでエッチングする場合、エッチングの選択比が大きく取れるためである。なおダミーゲートのフォトレジストは熱に弱いために、SiO2の堆積には通常の熱CVDやPE-CVDなどの方法は使用できない。一方、スパッタ法24)やECR(Electron Cyclotron Resonance)-CVD法25)は比較的低温で良質な絶縁膜が形成でき、膜質に方向性を有するためフォトレジストなどのパターン上にデポした際、側壁と平面部分の膜質差をつけることができる。パターン反転では緩衝フッ酸でのスライトエッチにより側壁の膜のみを除去し、ダミーゲートをリフトオフするが、この時に十分な選択比が必要となる。もし十分な選択比が取れなければ、残るべき絶縁膜の膜厚が薄くなったりリフトオフした部分にバリが生じる。膜厚が薄くなると、後のFETの作製工程で述べるが、ゲート金属がパターン反転に用いた絶縁膜に重なることにより生ずるMIS容量の増大を招く。またバリが生じると金属膜の付きまわりが悪くなり断線が生じる場合がある。

パターン反転を良好に行うため、ダミーゲートとして用いたレジストに対しては露光

条件、現像条件などを最適化することにより、側面をできる限り垂直にして矩形に近い 形状に制御した。またレジスト側壁部とウェハ面上での膜質の差を大きくするために、 SiO2の形成には基板側にもRFバイアスを印加するバイアススパッタ法を用いた。このた め、側壁部と平面部に形成されたSiO2膜の緩衝フッ酸(NH4F:HF=120:1)に対するエッ チングレートは10倍以上の差がある。

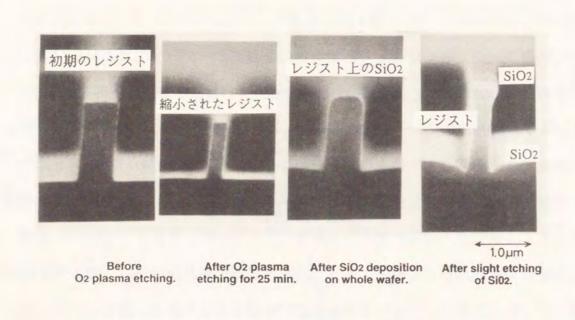

図2-8にn+工程での、初期パターンからパターン反転までのダミーゲートの走査電子顕 微鏡(Scanning Electron Microscope: SEM)による断面写真を示す。初期のパターンは矩形を示し、酸素プラズマエッチングによりパターンが縮小され、最後はSiO2膜により正確に反転されている様子がわかる。

図2-8パターン反転工程でのダミーゲートの断面写真

#### 2-5 MESFET作製プロセス

以上の技術を組み合わせたプロセスをGaAs MESFETの作製に適応した。

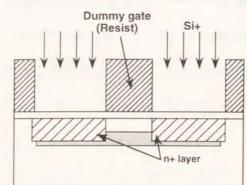

図2-9に主要な工程図を示す。「短チャンネル効果」抑制のため、チャンネルは次章で述べるp層埋め込み構造を、ソース/ドレイン領域はLightly Doped Drain (LDD)構造を採用している。

ウェハを洗浄し、まずフォトリソグラフィーのための合わせマークを基板中に作り込んだ後、フォトレジストをマスクに半絶縁性基板に選択イオン注入によりチャンネルを形成する。さらにGaAsの表面保護のためにPE-CVD法によりSiN膜 800 Åを形成する(図 2-9-a)。

次にSiN膜の上にダミーゲートとなる厚さ1.6  $\mu$ mのフォトレジストパターンを形成する。このフォトレジストをマスクに高濃度層(n+層)形成のためのイオン注入を行う(図 2-9-b)。

次に先程述べた酸素プラズマによるエッチングにより、フォトレジスト(ダミーゲート)パターンの短縮を行う。その後中間濃度層(n'層)形成のためのイオン注入を行う (図2-9-c)。

ダミーゲートのパターンを正規のゲート電極と置換するためにダミーゲートの位置に 開口部を形成する(これをパターン反転と呼ぶ)。パターン反転は以下の手順で行う。 ダミーゲートが形成されているウェハ全体にスパッター法でSiO2膜を3000 Å形成する (図2-9-d)。スパッター法では段差被覆性(ステップカバレージ)に優れた膜が形成で きるが、基板側にもバイアスを印加すること(バイアススパッタ法)で段差の側壁に形 成される膜質と平面上に形成される膜質を大きく違えることができる。つまり側壁部は 非常に多孔性(ポーラス)な膜になり、平面上では緻密な膜が得られる。この性質を利 用することでダミーゲートの側壁に付いた膜のみを除去する。緩衝フッ酸(HF:NH4F = 1:120)によりウェハ全体に形成したSiO2膜をわずかにエッチングすれば、側壁のSiO2は エッチング速度が早いため完全に除去され平面上のSiO2のみが残ることになる。この状 態でウェハをフォトレジストの溶剤であるアセトンに浸ければ、不要なフォトレジスト とその上のSiO2を除去することができる(図2-9-e)。

その後、注入されたイオンを活性化するための熱処理(800℃、20分、N2雰囲気中)を 行う。耐熱ゲートの様なGaAsと熱膨張係数が大きく異なる材料が存在しないため、安定 した活性化が行える。

次にフォトリソグラフィによりソース/ドレイン電極パターンを形成して、反応性イオンエッチング(RIE)にてSiO2/SiN膜をエッチングした後、AuGe/Niを蒸着しリフトオフにより不要な部分を取り除く。 そして合金化のために450℃、1分の熱処理を行う。

ゲート電極の形成には先ずフォトリソグラフィによりゲート電極パターンを形成する。この時、露光時の合わせ余裕を見込んでSiO2の開口部より広いパターンを形成する必要がある。パターン形成後、CF4を用いたRIEにて反転パターンを形成したSiO2をマスクにSiN膜をエッチングする。この時にはRIEでのダメージによりGaAs表面が損傷を受け、ショットキー特性が劣化しないようエッチング条件を最適化することも必要である26)。GaAs表面が露出した後、低抵抗金属であるTi/Pt/Auを順次蒸着し不要な部分をリフトオフすることでLDD構造を有するMESFETが完成する(図2-9-f)。

ダミーゲートの位置に正確に真のゲート電極が形成されているので、n+,n'層をゲート電極に対して自己整合的に形成することができる。

SAINT工程のT型ダミーゲートでは、工程上LDD構造を得ることは困難である。また耐熱ゲートプロセスでは、LDD構造を得るには耐熱ゲートを加工した後にn'層の注入を行い、さらに絶縁膜により側壁を形成してn+層のイオン注入を行う必要がある<sup>27)</sup>。そのため工程数が増加するという欠点がある。その点、本研究で開発したプロセスでは、初期のパターンを酸素プラズマエッチングで短縮することによりLDD構造を形成できるため単純である。

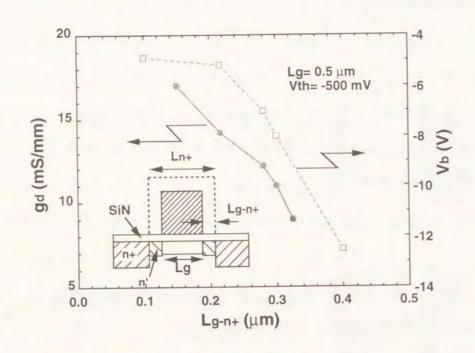

またこのプロセスではダミーゲート(フォトレジスト)の短縮量(Lg-n+)やn+,n'の形成条件は、MESFETの伝達コンダクタンスgm,ドレインコンダクタンスgd,ゲート/ドレイン間耐圧Vbなどの値が用途に応じて最適になるように考慮して設定する。例えばアナログ用にはLg-n+間を $0.3~\mu m$ とし、gmは少し低いがVbが高くなるように設定している。

(a) 選択イオン注入によるチャンネル 形成とPE-CVD SIN膜の形成

(b) フォトレジストによるダミーゲート の形成とn+領域のイオン注入

(c) 酸素プラズマによるダミーゲート のエッチングとn'領域のイオン注入

(d) スパッター法によるSiO2膜 の形成

(f) ソース/ドレイン電極の形成 ゲート電極の形成

図2-9 単層レジストをダミーゲートに用いたGaAs MESFETの作製フロー

特に短縮量(Lg-n+)は、これらパラメータに影響を与えると考えられる。図2-10にはLgを一定にして実験的にLg-n+を変えて、Lg-n+がVbやgdに及ぼす影響を示した。ここでgdは図2-2において、任意のゲート電圧におけるドレイン電流のドレイン電圧に対する傾きであり(図2-10でのgdはVg=0 V、Vd=2.0 Vの条件)、Vbはゲート/ドレイン間に逆方向に電圧を印加していった場合にゲートに $1\mu$ A/ $1\mu$ mの電流が流れるゲート電圧である。gdはFETの利得(gm/gd)を決定し、VbはFETに印加できる最大電圧を決定する。

図2-10 Lg-n+がgdとVbに与える影響

VbやgdはLg-n+に大きく依存していることがわかる。これらパラメータは特にアナログ 回路の特性に影響を与えるものである。従って、Lg-n+は正確に制御する必要がある。 本プロセスでは、工程中にウェハ状態のままでレジストパターンをSEMによりモニタで きるため常にこの寸法を正確に制御することができる28)。

このことはT型のダミーゲートプロセスや絶縁膜側壁を用いる耐熱ゲートプロセスに 比べて大きな利点となる。

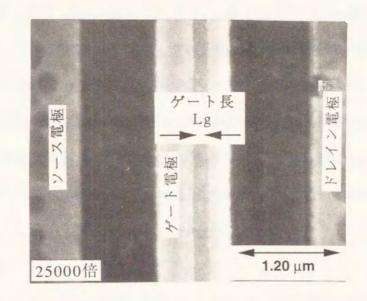

またフォトレジストの短縮量(Lg-n+)を片側 $0.3 \mu m$ に選べば、 $0.3 \mu m$ のゲート長は初期のレジストパターンが $0.9 \mu m$ から得ることができ、光学露光を用いても光学露光の限界

を越えた微細なゲート長を実現することができる。このことは、 $GaAs\ MESFET$ の高速性向上に不可欠である。実際に作製した $0.3\ \mu m$ ゲート長を有するMESFETのSEM写真を図 2-11に示す。

本プロセスはサブ $0.5 \mu m$ のMESFETのゲート長までも再現性/均一性よく作製するのに適している。実際に $0.5 \mu m$ のゲート長を有するMESFETは、Vthの面内ばらつきが20 mV以下、ウェハ間でのばらつきも30 mV以下という優れた均一性と再現性を有し、5Gbpsクラスの光通信に対応できる各種ICの生産に実用されている。

図2-11 0.3 μmゲートを有するGaAs MESETのSEM写真

#### 2-6 結 言

寄生抵抗の低減とIC実現に不可欠であるプレーナ型のGaAs MESFETを作製するため、 改良ダミーゲート法による自己整合プロセスを開発した。

従来のダミーゲート法に比べフォトレジスト単層をダミーゲートに選択することにより、加工精度、プロセスの簡便さの点で優位であることが分かった。

平行平板型ドライエッチング装置を用いた酸素プラズマによるエッチングによりダミ ーゲートの精密な加工が可能となった。

バイアススパッタ法により形成したSiO2によりダミーゲートパターンを正確に反転することで高濃度層(n+)/中間濃度層(n')をゲート電極に対して自己整合的に形成し、LDD 構造GaAs MESFETを実現することができた。

このプロセスはn+やn'層の幅、ゲート長を正確に制御することが可能なため、従来から問題になっていたMESFETの特性ばらつきを著しく低減することも成功した。さらに、素子特性の向上に必須なゲート長の短縮に関しても、通常の光学露光を用いて光学露光の限界を越える0.5 μm以下の微細ゲートを形成できることを実証することができた。

#### 2-7 参考文献

- 1) S. Miyazawa and Y. Ishii, "Dislocations as the Origin of Threshold Voltage Scattering for GaAs MESFET on LEC-Grown Semi-Insulating GaAs Substrate", IEEE Trans. Electron Devices, ED-31, pp.1057-, 1984

- 2) 宮澤、笠原、佐野、江川、中村、上西、長谷川、"討論の広場、GaAs FET しきい値電圧を支配するもの", 応用物理、第56巻、第1号、pp.19-44, 1987年

- 3) K. Tada, S. Murai, S. Akai, and T. Suzuki, "Growth and Characterization of Dislocation-Free GaAs Mixed Cristal for IC Substrate", Technical Digest in IEEE GaAs IC Symposium, pp.49-52, 1984

- 4) 宮澤 信太郎、千川 圭吾、"FEC法によるGaAs無転位結晶成長技術", Semiconductor World 1985. 6, pp. 101-109

- 5) J. Kasahara, M. Arai, and N. Watanabe, "Extremely uniform threshold voltage distribution of GaAs FET made on LEC-grown crystals," Electron. Lett., Vol.21, No.22, pp.1040-1042, 1985

6) S. Miyazawa, T. Honda, Y. Ishii, and S. Ishida, "Improvement of crystal homogeneities in

- liquid-encapsulated Czochralski grown semi-insulating GaAs by heat treatment," Appl. Phys. Lett., 44 (4), pp.410-412, 1984

- 7) J. Kasahara, M. Arai, and N. Watanabe, "Threshold Voltage Uniformity of GaAs-FETs on Ingot-Annealed Substrates," Jpn. J. Appl. Phys., 25, pp.L85-86, 1986

- 8) T. Sugano, F. Koshiga, K. Yamasaki, and S. Takahashi, "Application of anodization in oxgine plasma to fabrication of GaAs IGFET's", IEEE Trans. ED, ED-27, pp.449-, 1980

- 9) N. Yokoyama, T. Mimura, and M. Fukuta, "Planar GaAs MOSFET integrated logic", IEEE Trans. Electron Devices, Vol. ED-27, pp.1124-, 1980

- 10) K. Ohata, K. Itoh, F. Hasegawa, and Y. Fujiki, "Super low noise GaAs MESFET's with a deep-recess structure, IEEE Trans. Electron Devices, ED-27, pp.1029-1034, 1980

- 11) M. Berth, M. Cathelin, and G. Durand, "Self-Aligned Planar Technology for GaAs Integrated Circuits", IEDM Tech. Dig., 1977, pp.493-496

- 12) T. Furutsuka, K. Takahashi, M. Ishikawa, S. Sano, and A. Higashisaka, "A GaAs 12×12 Bit Expandable Parallel Multiplier LSI using Sidewall-Assisted Closely-Spaced Electrode Technology", IEDM Tech. Dig., pp.344-347, 1984

- 13) F.S. Lee, R.C. Eden, S.I. Long, B.M. Welch, and R. Zucca, "High Speed LSI GaAs Integrated Circuits", Proc. IEEE Int. Conf. Circuits and Computers, pp.697-700, 1980

14) N. Yokoyama, T. Mimura, M. Fukuta, and H. Ishikawa, "A Self-Aligned Source/Drain Planar Device for Ultra-High-Speed GaAs MESFET VLSI's", ISSCC Dig. Tech. Papers, pp.218-219, 1981

- N. Yokoyama, T. Ohnishi, K. Odani, H. Onodera, and M. Abe, "TiW Silicide Gate Self-Alignment Technology for Ultra-High-Speed GaAs MESFET LSI/VLSI's", IEEE Trans. Electron Devices, Vol.ED-29, No.10, pp.1541-1547, 1982

- 15) K. Yamasaki, K. Asai, and K.Kurumada, "GaAs LSI directed MESFET's with self-aligned implantation for N+ layer technology (SAINT)", IEEE Trans. Electron Devices, Vol.ED-29, pp.1772-1777, 1982

- 16) N. Uchitomi, Y. Kitaura, T. Mizoguchi, Y. Ikawa, N. Toyoda, and A. Hojo, "Refractory WN Gate Self-Aligned GaAs MESFET Technology and Its Application to Gate Array IC's", Extended Abstract of the 16th Conference on Solid State Devices and Materials, pp.383-386, 1984

- N. Uchitomi, M. Nagaoka, K. Shimada, T. Mizoguchi, and N. Toyoda, "Characterization of reactive sputtered WNx films as a gate metal for self-alignment GaAs metal-semiconductor field effect transistors," J. Vac. Sci. Technol., vol. B4, no.6, pp.1392-1397, 1986

17) H. Nakamura, Y. Sano, T. Nonaka, T. Ishida, and K.Kaminishi, "A Self-Aligned GaAs MESFET with W-Al Gate", Techical Digest in 1983 IEEE GaAs IC Symposium, pp.134-137

- 18) A.E. Geissberger, R.A. Sadler, M.L. Balzan, and J.W. Crites, "TiW nitride thermally stable Schottky contacts to GaAs: Characterization and application to self-aligned gate field-effect transistor fabrication", J. Vac.Sci. Technol. B5 (6), pp.1701-1706, 1987

- A.E. Geissberger, I.J. Bahl, E.L. Griffin, and R.A. Sadler, "A new refractory self-aligned gate technology for GaAs microwave power FET's and MMIC's, "IEEE Trans. Electron Devices, Vol.35, pp.615-622, 1988

- 19) K. Onodera, M. Tokumitsu, S. Sugitani, Y. Yamane, and K. Asai, "A 630-mS/mm GaAs MESFET with Au/WSiN Refractory Metal Gate", IEEE Trans. Electron Device Lett. vol.9, No.8, pp.417-418, 1988

- K. Asai, H. Sugawara, Y. Matsuoka, and M. Tokumitsu, "Refractory sputtered WSiN films suppresses As and Ga out-diffusion", J. Vac. Sci. Technol., vol.B6, pp.1526-, 1988

20) T. Otsuki, "Annealing behavior of implanted Si in semi-insulating GaAs in the presence of stress", J. Appl. Phys. 61(3), pp.928-932, 1987

- 21) M. Hagio, S. Katsu, M. Kazumura, and G. Kano, "A New Self-Align Technology for GaAs Analog MMIC's", IEEE Trans. Electron Devices, vol.ED-33, No.6, pp.754-758, 1986

22) T. Tambo, O.Ishikawa, H. Yagita, K. Inoue, T. Onuma, "Low-Noise GaAs MESFET by

- Dummy-Gate Self-Alignment Technology for MMIC", Technical Digest in IEEE GaAs IC

Symposium, pp.49-52, 1987

- 23) J.F. Gibbons, W. S. Johnson, S. W. Mylroie, "Projected Range Statistics", Semiconductors and Related Materials 2nd edition, Halsted Press, Dowden, Hutchinson & Ross, Inc.

- 24) T. Serikawa and T. Yachi, "Lift-off Patterning of Sputtered SiO2 Films," J. Electrochem.

- Soc.: Solid-State Science and Technology, Vol.128, No.4, pp.918-919, 1981

- 25) S.Shikata, H. Hayashi, H. Takahashi, and K. Yoshida, "Formation of Submicron Silicon-nitride pattern by lift-off method using ECR-CVD," Proceeding of the SPIE-The International Society for Optical Enginnering, Vol.797, pp.126-129, 1987

- 26) S.W. Pang, G.A. Lincoln, R.W. McClelland, P.D. DeGraff, M.W. Geis, and W.J. Piacentini, "Effect of dry etching on GaAs," J. Vac. Sci. Technol., B 1 (4), pp.1334-1337, 1983 Y. Yamane, K. Yamasaki, and T. Mizutani, "Annealing Behavior of Damage Introduced in GaAs by Reactive Ion Beam Etching," Jpn. J. Appl. Phys., Vol.21, No.9, pp. L537-538, 1982

27) S. Asai, N. Goto, M. Kanamori, Y. Tanaka, and T. Furutsuka, "A High Performance LDD GaAs MESFET with a Refractory Metal Gate", Extended Abstracts of the 18th Conference on

Solid State Device and Materials, pp.383-386, 1986

28) S. Nakajima, G. Ishii, Y Saito, N. Kuwata, T. Fukuzawa, K.Koike, and H. Nishizawa, "Manufacturability of Dummy-gate Self-aligned LDD GaAs MESFETs for High Volume Production", Technical Digest in IEEE GaAs IC Symposium, pp.119-122, 1994

### 第3章 短チャンネル効果の抑制

#### 3-1 緒 言

電子デバイスの特性向上のためにはデバイスの微細化が必須条件である。ゲート長が短かくなるとチャンネル内の電界が高くなり、電子はほぼ飽和速度で走行するようになる。最近では電子の走行距離が短い場合、電子が数多くの散乱を受ける前にチャンネル内を走行してしまうことにより、定常状態よりも早い速度で走行する「速度オーバシュート」を起こす可能性が指摘されている1)。この現象は散乱緩和時間の短いSiより、散乱緩和時間の長いGaAsに顕著に現われデバイスの性能をさらに向上させるのに役立つ2)。また電子の有効質量がGaAsの方が軽いことも、高電界の速度を高めることに寄与する。さらにデバイスの微細化はデバイス自体の容量の低減につながり、デバイス自身のスイッチング速度を高めることに寄与する。ゲート端部のフリンジング容量のような寄生容量を除いて、MESFETの真性容量はゲート長に反比例して小さくなるからである。

しかしながら、単にデバイスを微細化していっても素子特性は思うように向上しない。 これは「短チャンネル効果」によるためであり、GaAs MESFETのみならずSi MOSFETに おいても問題になっている。GaAs MESFETの場合、短チャンネル効果は半絶縁性基板へ 流れる漏れ電流が原因である。

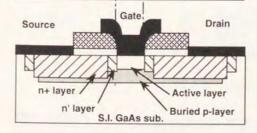

本章ではまず、GaAs MESFETでの短チャンネル効果とその要因について述べる。次に短チャンネル効果抑制のためこれまで試みられてきた方法を概説する。そして本論文の目的である高周波特性と雑音特性向上のために短ゲートデバイスの構造として、高濃度薄層(4×1018/cm³, 100Å)をパルス状に配したパルスドープ構造とソース/ドレイン低抵抗層を多段にすると共に、この低抵抗層を囲い込むような反対の導電型を有する導電層を形成する新しいLDD (Lightly Doped Drain) 構造を提案し、その効果を実証する。

#### 3-2 短チャンネル効果とは

GaAs MESFETにおいてゲート長を短縮していくと次のような現象が現われる。

- ・しきい値電圧(Vth)が負側にシフトする。

- ・ピンチオフ特性が悪くなりサブスレッショルド電流が増加する。

- ・伝達コンダクタンス(gm)が低下する。

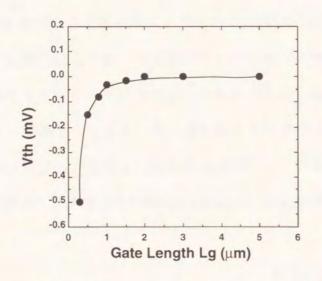

この現象を「短チャンネル効果」と呼び、素子の微細化を阻む一因となっている。 図3-1に短ゲート長を有するGaAs MESFETの静特性を、図3-2にはVthのゲート長依存性 の一例を示す。ゲート長が1.0 μmを切るあたりから負側へのシフトが顕著になっている。 また短チャンネル効果のため、ゲート長のばらつきに対応してVthもばらつくので素子 特性の均一性を要求されるIC実現にも大きな障害となる。

図3-1 短ゲートを有するGaAs MESFETの電圧/電流特性

図3-2 GaAs MESFETのゲート長とVthの関係

### 3-2-1 短チャンネル効果の要因とこれまでの対策

短チャンネル効果の要因には次の2つが挙げられている。

### 1) チャンネルの2次元効果

ゲート長の短縮に伴い空乏層の形は矩形より半円に近づいてくる。空乏層の形が矩形の場合は、ソースからドレインに向かう水平方向の電界のみを考えればよい(グラジュアルチャンネル近似)。この近似が成り立つためには、チャンネル厚み(a)とゲート長(Lg)の比(a/Lg)は1/5より十分小さくする必要がある3,4)。

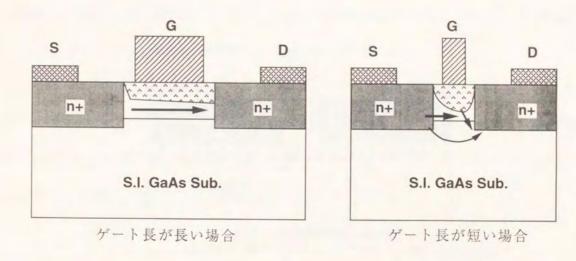

この近似が成り立たなくなれば、空乏層の中では水平方向のみならず垂直方向の電界を考慮せねばならず、この垂直方向の電界によりチャンネル内の電子が基板側に流れ出し、Vthのシフト、ピンチオフ特性の劣化といった問題を引き起こす。この様子を図3-3に示した。

図3-3 短チャンネル効果の一要因である空乏層の変形 (2次元効果)

この対策としてはチャンネルの薄層化が有効である。

UenoらはMBEにより形成した200 Å, 3.6×10<sup>18</sup>/cm³のGaAs層をMESFETのチャンネルに使用した5)。Kuzuharaらは、SiF2+分子イオン注入により極浅チャネルを形成した<sup>6)</sup>。 またYamaneらは、Si+の10 KeV注入にRTA(Rapid Thermal Anneal)による活性化アニールを 組み合わせることで極浅チャネルを形成した7)。いずれの報告も短チャンネル効果が抑制され、サブ0.5 μm領域で良好な特性を得ている。

### 2) 対峙するn+領域からの基板リーク電流

短チャンネル効果は、基板内部にn+層を形成した自己整合型のMESFETにおいて特に 顕著である。これはゲート長の短縮と共に対峙するn+間隔も短縮され、n+領域から半絶 縁性基板を伝わってリーク電流が流れるためである8)。

このリーク電流を抑制するためにはn+層を浅くする構造が提案されたが、表面準位の影響を受けやすくなり寄生抵抗の増大を招きgmの低下につながる9)。そのためにn+層の深さは変えずにn+層の導電型とは反対の導電型を示す層(n型に対してはp型)を埋め込むことで、p-n接合による電位障壁を設けることが提案された10,11)。

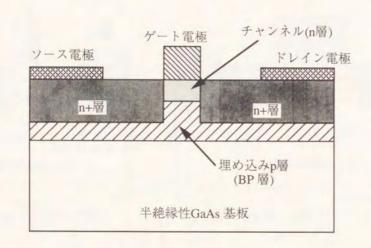

この構造を図3-4に示す。この構造では、p層の形成は活性層と同時に行われるためチャンネルの下にもp層が形成され、チャンネルの薄層化にも有効である。

図3-4 埋め込みp層を有するGaAs MESFETの断面構造

3-3 パルスドープ構造による短チャンネル効果の抑制方法

#### 3-3-1 パルスドープ構造

チャンネルの2次元効果が現われないようにするためにはa/Lg<1/5の関係を保てばよい。

これにはチャンネルを高濃度薄層化することが有効であるとされてきた12)。

a/Lg=1/10としてゲート長 $0.25 \, \mu m$ のMESFETを考えた場合、チャンネルの厚みは $250 \, A$  以下にしなければならない。この場合MESFETを動作させるために最低必要な不純物濃度(Ndmin)は、MESFETのショットキ障壁高( $\Phi$ )を0.7Vと仮定すると

Ndmin=2  $\varepsilon * \varepsilon 0 \Phi / qa^2 = 1.62 \times 10^{18} / cm^3$

となる。ここで  $\varepsilon$  \*は半導体の比誘電率、  $\varepsilon$  0は真空の誘電率、 q は電荷、 aはチャンネル厚である。

ただしこの場合のVthは0 Vとなり、実際には電流密度がもっと要求される場合にはこれ以上の不純物濃度が必要となる。高濃度層をチャンネルに用いることはショットキー特性を劣化させゲート耐圧の低下も招く13)。この様な現象はマイクロ波の応用ではゲートリーク電流増加によるノイズ特性の劣化、耐圧の低下による高出力特性の劣化を招き、またデジタルの応用では論理振幅が低下し回路の動作余裕が減少することが考えられる14)。実際、これまでの薄層チャンネルを用いたGaAs MESFETはショットキー障壁高が低くゲート耐圧も低いため、その応用分野は限られている。

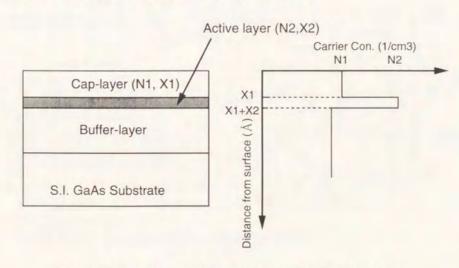

そこで本研究では短チャンネル効果低減のために高濃度で薄層化したチャンネルを用いると共に、ショットキー特性を劣化させないために高濃度層の表面側に低濃度層を設ける「パルスドープ」構造を採用した。

パルスドープ構造の断面図と不純物分布を図3-5に示す。

図3-5パルスドープ構造の断面とその不純物分布

パルスドープ構造ではしきい値電圧Vthは1次元のポアッソン方程式を解くことにより 次の様に与えられる。

$$\frac{d^2\Phi}{dx^2} = -\frac{qN1}{\epsilon s} \qquad 0 \le x \le X1$$

$$\frac{d^2\Phi}{dx^2} = -\frac{qN2}{\epsilon s} \qquad X1 \le x \le (X1+X2)$$

境界条件x=X1+d で $\frac{d\Phi}{dx}=0$  とx=X1で $\frac{d\Phi}{dx}$  が連続であることを用いて

Vth = Vbi-

$$\frac{qN2}{2 \varepsilon s} X2^2 - \frac{qN2}{\varepsilon s} X1X2 - \frac{qN1}{2 \varepsilon s} X1^2$$

ここで、Vbiは金属/半導体の接触電位差、N1,X1は表面側の低濃度層のキャリア濃度と厚みで、N2,X2は高濃度層のキャリア濃度と厚みである。また  $\varepsilon$  sは半導体の誘電率である。

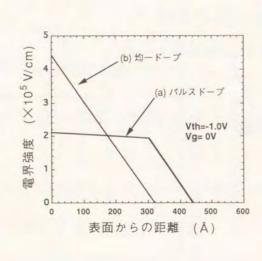

さらに高濃度層を均一にドープした構造とパルス状にドープした構造の表面電界強度 を比較したものが図3-6である。ここではVthとして-1.0 Vを、不純物濃度として

$1\times10^{18}$ /cm³ を仮定している。パルスドープ構造の場合、最大電界強度が $2.1\times10^5$  V/cmであるのに対し、均一ドープの場合 $4.4\times10^5$  V/cmと2 倍以上になることがわかる。 ショットキー効果による障壁高低下( $\Delta$   $\Phi$ =(q  $\epsilon$   $m/4\pi$   $\epsilon$  s)1/2)を計算するとパルスドープ 構造の場合0.048 Vであるのに対して、均一ドープの場合は0.070 Vとなりパルスドープ 構造のショットキー特性に対する有効性がわかる。

図3-6パルスドープ構造と均一ドープ構造の電界強度分布の比較

# 3-3-2 有機金属気相成長(OMVPE)法によるパルスドープ構造の形成

高濃度薄層化は最近の優れた結晶成長法により容易に実現可能となった。本研究では有機金属気相エピタキシャル(Organometallic Vapar Phase Epitaxy: OMVPE)法によりパルスドープ構造を成長した。OMVPE(MO-CVDとも言う)技術は、III族元素の有機化合物とV族元素の水素化合物を原材料として用いる気相エピタキシャル結晶成長法である。この技術は、従来技術であるLPE(Liquid Phase Epitaxy: 液相エピタキシャル)やVPE (Vapar Phase Epitaxy: 気相エピタキシャル)と比較して次のような優れた特徴を有する。

- 1)極限としては、単分子層程度の薄膜成長が可能

- 2) 多元混晶の組成制御が可能

- 3) 薄膜(~10 Å)、多元混晶の多層へテロエピタキシャル層の形成が可能

- 4) ウェハ面内エピタキシャル層特性の均一性が良好

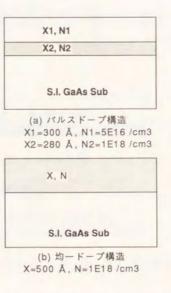

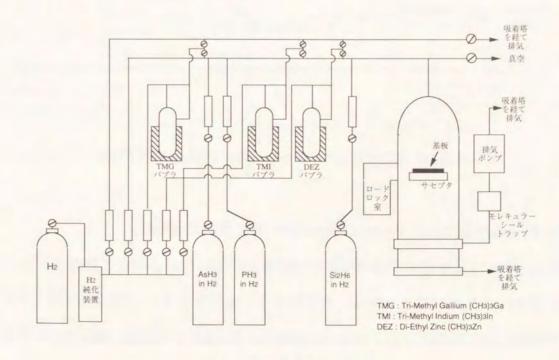

ここで使用したOMVPEの成長装置は縦型炉の減圧タイプである。装置の概略図を図 3-7に示す。原料ガスとしてはトリメチルガリウム(TMG)とアルシン(AsH3)をGaAsの成長に、ジシラン(Si2H6)をn型のドーパントとして用いた。

図3-7 OMVPE装置の概略

有機化合物および水素化合物は室温近傍では安定であるが、結晶成長温度ではいずれも分解し元素を解離する。TMGとAsH3を原料として用いたGaAsの生成は次のように表される。

#### (CH3)3Ga + AsH3→GaAs + 3CH4

本研究で用いた成長温度は650℃、成長圧力は60 Torr, である。

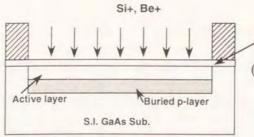

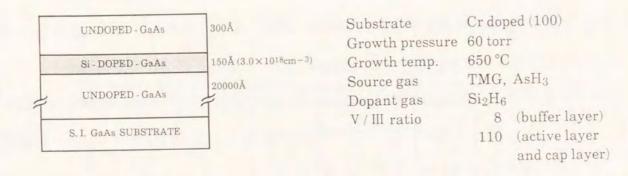

V族とIII族の流量比を変える(これはV族源の有機金属中のCの成長層中への取り込み量を制御する)ことによって、バッファー層をp型に表面アンドープ層をn型にしている。バッファー層をp型にすることにより、対峙するn+からの基板リーク電流を抑制することができるからである。実際に成長した断面構造を図3-8に示す。

またGaAs層のドーピング/厚みの面内均一性も2"Φにて5%と3%と良好である15)。

# Growth Condition

図3-8 実際に成長したパルスドープ構造の断面構造

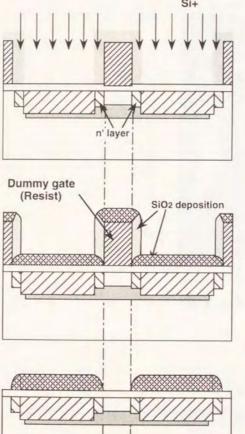

# 3-3-3 素子の作製(Rapid thermal Anneal (RTA)を用いた活性化)

素子の作製方法は第2章で述べたダミーゲートを用いた自己整合プロセスである16)。 n+層の活性化のためのアニールは、超薄層を有するパルスドープ構造を維持するため熱による不純物拡散を最小に押さえる必要がある。熱源にランプを用いるランプアニール (一般にはラピッドサーマルアニール(RTA)) は、数秒~数十秒の短時間に $800 \sim 1000$  の高温でアニールするため高活性化率を保ちつつ、不純物拡散を押さえることが知られ

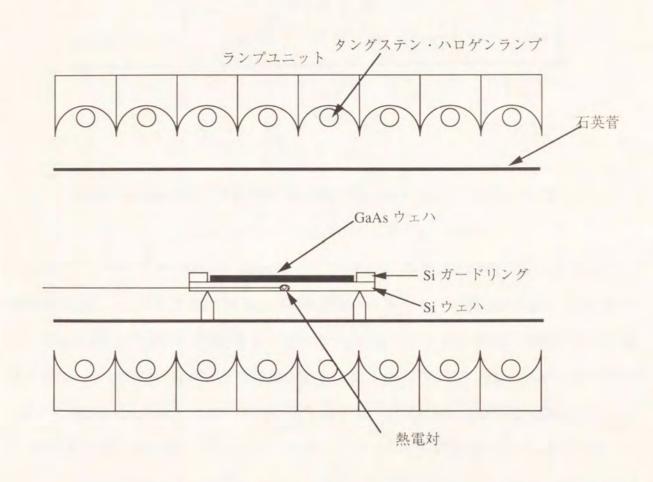

ている17,18)。そのためパルスドープ構造GaAs MESFETの作製には、RTAによる活性化を用いた。本研究でのRTAは、タングステン/ハロゲンの光源を用いている。

RTA装置の概観を図3-9に示す。RTAでは短時間に昇温/降温が行われるため、ウェハ中心部と周辺部での温度差が大きくなり、熱応力によるウェハ周辺でのスリップラインの発生やウェハのそりが問題となる。そのためウェハ周辺にSiウェハをくり抜いたガードリングを設置し、ウェハ面内の均熱性を向上させている。

図3-9 RTA装置の概略

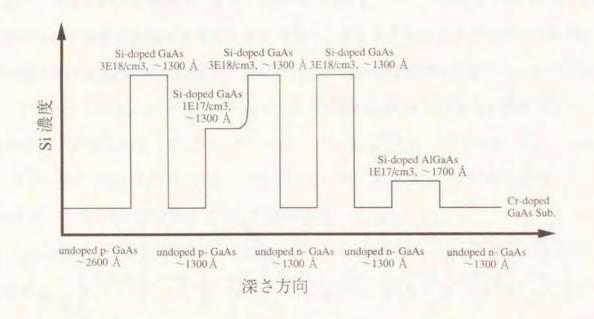

次にRTAにて不純物拡散が抑制されているかを調べるため、GaAs中にSiを周期的にドープした試料を用意しアニール前後の拡散の様子をSIMS (Secondary Ion Mass Spectroscopy)にて調べた。図3-10に試料のドーピングプロファイルを示す。

図3-10 RTAによる不純物拡散を調べるためのSIMS分析用試料の構造

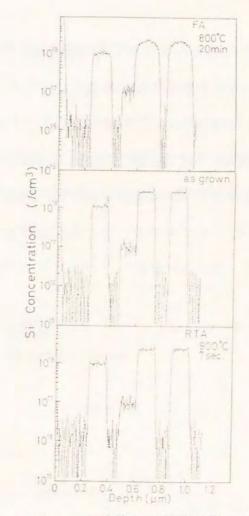

この試料を、通常の抵抗加熱による炉アニール(Furnace Anneal: FA)した場合と、RTA アニールした場合のSi のプロファイルの比較を図3-11示す。FAでのアニール条件は窒素 雰囲気中で800  $\mathbb C$ 、20分であり、一方RTAでの条件は窒素雰囲気中860  $\mathbb C$ 、7秒である。FAでアニールした試料では、明らかにSi イオンの拡散が見られるのに対して、RTAでアニールした試料では as grownの試料とほとんど変わりないプロファイルが得られていることがわかる。温度や時間などのアニール条件は、パルスドープ構造の急峻性を保持すること共にn+層の活性化を+分行うことが満足するように設定する必要がある。

図3-12にRTAでのアニール温度を変えた時のドーピングプロファイルの変化をC-V (Capacitance-Voltage)測定より求めた結果を示す。容量測定は1 MHzの周波数で行った。 アニール温度が900  $\mathbb{C}$ 以上では表面のキャリア密度が減少し、テイル側の急峻性も失われていることがわかる。アニール時間に関しては、どの温度においても2秒以上では拡散度合いは変わらなかった。つまり時間よりもむしろ温度の方が拡散には影響を及ぼす。

図3-11 アニール前後の不純物拡散の比較

Depth from surface (μm) 図3-12 C-V法より求めた電子濃度分布

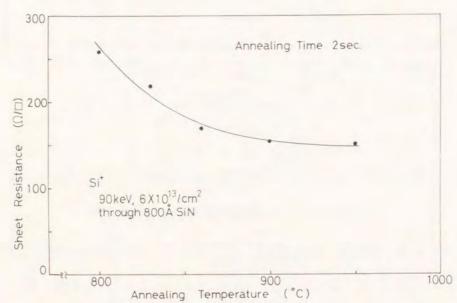

そのためアニール時間は、2秒として温度を最適化した。

アニール温度とn+領域のシート抵抗の関係を図3-13に示す。アニール温度が860 $\mathbb{C}$ 以上でシート抵抗はほぼ飽和しており $160\Omega$ / $\square$ が得られた。この値はFAアニールした場合の値 $180\Omega$ / $\square$ よりも低く、RTAが不純物拡散を抑制しかつ高活性化を得る方法であることを示している。以上の結果よりアニール条件は $860\mathbb{C}$ 、2 secと設定した19)。

この条件では結晶成長後のキャリアプロファイルがほぼ保たれ、チャンネル層薄層化の効果が十分に期待できる。図3-14に作製したパルスドープ構造MESFETの断面図を示す。

図3-13 アニール温度とn+領域のシート抵抗の関係

図3-14 作製したパルスドープ構造GaAs MESFETの断面構造

#### 3-3-4 短チャンネル効果の高濃度層厚依存性

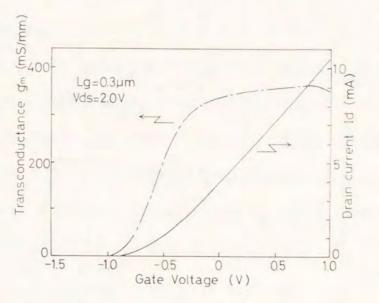

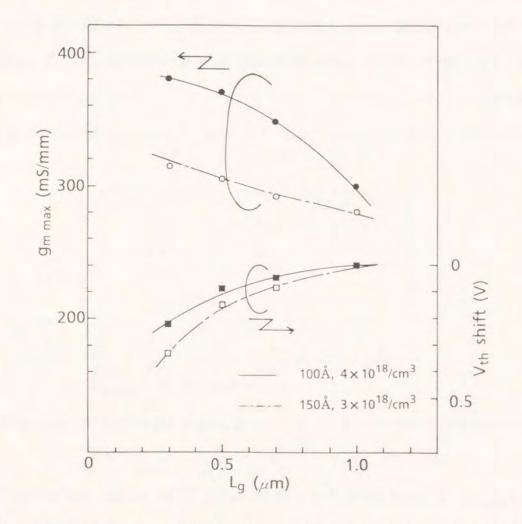

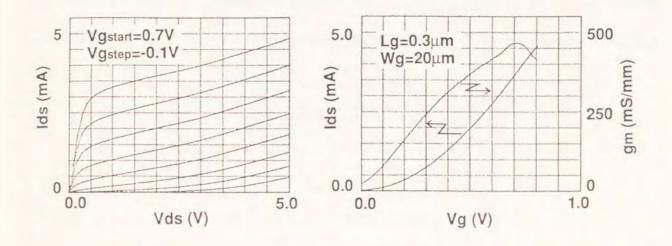

高濃度薄層化の効果を調べるため、高濃度層厚が150 Åでキャリア濃度が3×1018/cm3 と、高濃度層厚が100 Åでキャリア濃度が4×1018/cm<sup>3</sup>のパルスドープ構造をMESFETのチャンネルに用いて比較した(両者のVthを合わすためドーピング濃度を変えている)。 図3-15に活性層厚100 Åの場合のMESFETのVgとgm, Idsの関係を示す。ゲート長は0.3  $\mu m$ である。

図3-15 ゲート長0.3 μmのパルスドープ構造GaAs MESFETのVgとgm, Idsの関係

gmはVgに対してピンチオフ近傍から急激に立ち上がり、その後は広い範囲に渡ってほぼ一定の値を示している。この特性はパルスドープ構造MESFETではホモ接合でも電子が狭い領域に閉じ込められいることの証拠であり、gmがVgに対してピークを持つHEMTや通常のMESFETと異なっている。この特性は大振幅の入力に対する出力の歪みを押さえる上で大きな利点であり20)、近年低歪み特性を必要とする高出力FETの構造としても期待されている21-23)。

図3-16ゲート長に対するVthのシフト量とgmの変化を示す。ゲート長に対するVthのシフト量は高濃度薄層化することにより、ゲート長1.2 μmから0.3 μmにて210 mVと100 mV程度小さくなっている。gmの向上も高濃度薄層化することにより大きくなり、ゲート長0.3 μmにて380 mS/mmが得られている。またショットキー特性に関してもショットキー

障壁高0.65 V, n値1.3と良好な値が得られている。これは表面アンドープ層を有するパルスドープ構造の利点である。

図3-16パルスドープ構造GaAs MESFETにおけるgmとVthのゲート長依存性

以上のことから、パルスドープ構造を活性層に採用することによりショットキー特性 を劣化させずに、短チャンネル効果を低減できることを確認した。

なお本構造では100 Åの厚みのチャンネルを用いたが、原子層ドーピング( $\delta$ ドーピング) を用いて極限の厚みを有するGaAs MESFETも開発されている24,25)。 $\delta$ ドーピング を用いた場合は、SiOドーピングは $3\times10^{12}$ /cm<sup>2</sup>で飽和してしまう。そのため所望のドレイン電流値が制限されてしまう。また熱処理による不純物の拡散やキャリアの大幅な減少も報告されており26)、実用上は解決すべき問題が残っている。

# 3-4 新LDD構造による短チャンネル効果の抑制

これまではチャンネルの構造を改良することで、短チャンネル効果を抑制する方法を 提案してきた。これはチャンネルの2次元効果を抑制するためであった。本節では短チャ ンネル効果のもうひとつの要因である対峙するn+層からの基板リーク電流を、ソース/ ドレイン領域構造の改良によって抑制する方法について述べる。

#### 3-4-1 p層埋め込み構造とは

図3-4に示したp層を埋め込む構造では、活性層下にもp層が形成されるためp層から延びる空乏層にてチャンネルを薄層化して、2次元効果を抑制することにも有効である。しかしながら、このp層はゲート寄生容量を増加させないために活性層により空乏化していなければならない4,5)。これによりp層濃度の上限が決定される。一方、p/n 界面に生じる障壁高は次式で表されるように、p層の濃度が高い程大きくなり、その分n+層から基板へのリーク電流が抑制されることが予想される。

Vbi=(kBT/q)ln(nnoppo/ni<sup>2</sup>)=(kBT/q)ln(NAND/ni<sup>2</sup>)

ここでkBはボルツマン定数、Tは温度、qは電子の電荷、nnoはn型領域の電子濃度、ppo はp型領域の電子濃度、NAはアクセプタ濃度、NDはドナー濃度である。

素子単体の容量より配線容量の方がはるかに大きいLSIには、素子の容量はそれほど 影響せずむしろ駆動能力、言い換えればgmが性能を決める。そのためLSI用MESFETと して短チャンネル効果を抑制し素子特性の均一性を図るため、完全空乏化条件以上の濃 度の埋め込みp層が使用された例はあり、p層の高濃度化による「短チャンネル効果」の 抑制を示している27,28)。

そこで本研究では、MESFET単体の容量を増加させずに短チャンネル効果を抑制するため、活性層下のp層(BP層)とは独立にn+, n'層の下にBP層よりも濃度の濃いp層(Surrounding p-layer: SP層)を形成する新しいLDD構造を提案する。

#### 3-4-2 LDD構造とは

通常のn+自己整合型FETでは、チャンネルとドレイン領域ではキャリア濃度に大きな差があるためチャンネルのドレイン端で高電界領域が生じる。この高電界領域のため電子はホットとなり本来のチャンネルより飛び出す。Si MOSFETにおいては、ホットエレクトロンがゲート酸化膜中に注入され素子特性の変動を起こすことが問題となった。そのためドレイン側のキャリアプロファイルの水平方向の傾斜を緩やかにして、電界集中を緩和する構造が発明された29,30)。その中でもLightly Doped Drain (LDD)構造は、1 μm以下のデバイスにもっともよく使用される構造である。従来の高濃度領域(n+)をゲートから離し、その間にチャンネルと高濃度層との中間的な濃度領域(n)を形成している。中間濃度領域を設けることでドレイン端でのピーク電界強度を緩和することができる。この構造は1986年にGaAs MESFETにも初めて適用された31)。

図3-17にその断面構造図を示す。

n'の濃度はn+とチャンネルの中間程度

図3-17 LDD構造を有するGaAs MESFETの断面構造

作製方法はSi MOSFETとほぼ同じで、ゲート金属をマスクにn'領域のイオン注入を行った後、CVD法による絶縁膜形成とRIEによる異方性エッチングにより、ゲート金属の側壁にのみ絶縁膜を形成する。そして側壁絶縁膜とゲート金属をマスクにしてn+領域のイ

オン注入を行う。n+とゲートの間隔は側壁絶縁膜の厚みにより制御する。この構造は GaAs MESFETの短チャンネル効果を抑制し、同時に高gm化と高耐圧化を図ることに成 功した。しかしながら、この構造でもゲート長が0.5 μm以下になると十分に短チャンネル効果は抑制できていない。

そのため本研究ではゲート長は $0.5 \mu m$ 以下の $GaAs\ MESFET$ に対するLDD構造としてn+/n'/n''と3段階にキャリア濃度/厚みを変化させたLDD構造を提案する。

#### 3-4-3 新LDD構造の提案

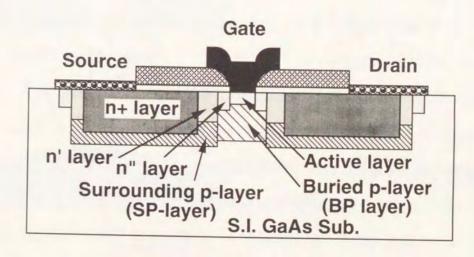

図3-18に本研究で提案する新LDD 構造を採用したGaAs MESFETの断面構造を示す。 ソース/ドレイン領域はn+/n'/n"とステップ状にキャリア濃度と厚みを変化させた。

キャリア濃度はn+からn"に向かって薄くなり、厚みはn+からn"に向かって浅くなっている。活性層下に形成する埋め込みp層は完全空乏化の条件で形成されている。n+/n'領域からのリーク電流をさらに抑制するため、n+/n'領域の下に濃度の濃いp層(SP層)を形成している。このSP層はゲートの寄生容量を増加させないように、不純物の横方向拡散を考慮して、ゲート電極からはわずかに距離をおいて形成されている。

図3-18 新LDD構造の断面構造

次にこの新LDD構造の作製方法について述べる。

#### 3-4-4 新LDD構造の作製方法

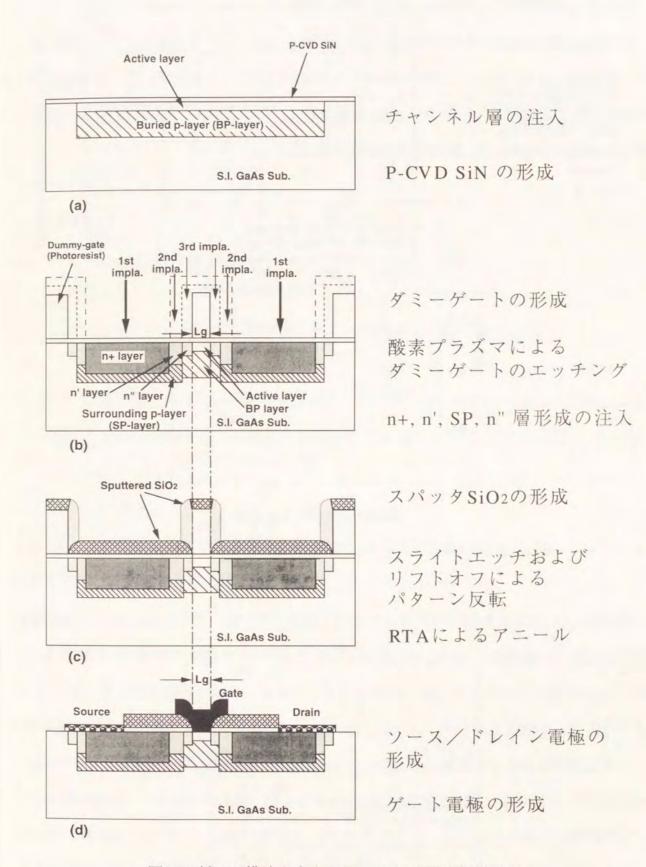

作製プロセスは第2章で説明した工程にダミーゲートのエッチングを1回加えることと、n'の注入の際にSP層形成の注入を追加することで実現できる。作製プロセスの主要断面図を図3-19に示す。新LDD構造形成の部分だけを詳細に述べる(b 参照)。活性層/埋め込みp層(BP層)を形成しPE-CVD SiN膜をGaAs表面に形成した後、フォトレジストによりダミーゲートを形成する。BP層の形成条件は、Beイオンを70 KeV,  $4.5 \times 10^{11}$ /cm2で注入している。次に初期のダミーゲートパターンをマスクにn+領域形成のためSi イオンを注入する。注入条件は120 KeV,  $4 \times 10^{13}$ /cm2である。次に酸素プラズマによりダミーゲートの短縮を行う。そしてSP領域形成のためにBe イオンを90 KeV,  $4.5 \times 10^{11}$ /cm2で注入し、続いてn'領域形成のためSi イオンを80 KeV,  $6 \times 10^{12}$  /cm2で注入する。さらに酸素プラズマによりダミーゲートの短縮を行った後、n''領域形成のためSi イオンを50 KeV,  $4 \times 10^{12}$  /cm2で注入する。図3-19でわかるようにSP領域は、BP層が重なって形成されておりBP層よりも高濃度になっている。

なお、SP層の濃度をこれ以上高めても「短チャンネル効果」はそれほど抑制されず、逆にソース/ドレイン領域の抵抗増加を招いた。そのためSP層の注入条件はこの濃度が適切と考える。SP層をn"領域の下まで形成せずn'領域の下までにした理由は、前述したようにBeイオンの横方向拡散を考慮したためである。Beイオンの横方向拡散は定量的には調べられていないが、SP層をn"の下(つまりゲートに隣接する)まで形成した場合は、しきい値電圧が長ゲート長のMESFETにおいても浅くなった。これはBeイオンが横方向拡散によりチャンネル領域に侵入しSiイオンを補償したためと考えられる。そのため本研究ではSP層とゲート端に0.1 μmの間隔を設けた。

本プロセスは、提案した新LDD構造GaAs MESFETを実現することに対して、他の自己整合プロセスより簡便である。例えば耐ゲートを用いた自己整合プロセスの場合は、絶縁膜形成とRIEによる側壁形成を繰り返す必要がある32)。またSAINTのようにT字型のダミーゲートを有するプロセスでは多段階層によるソース/ドレイン領域の形成は不可能である。

図3-19 新LDD構造を有するGaAs MESFETの作製フロー

#### 3-4-5 新LDD構造による短チャンネル効果の抑制

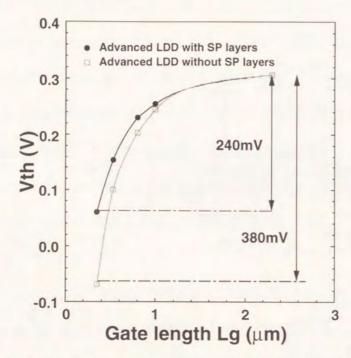

図3-20に新LDD構造を有するMESFETのVthのゲート長に対する変化を示す。比較のためにSP層を持たない従来のLDD構造を有するMESFETのデータを併記した。従来のLDD構造ではゲート長が2.3  $\mu$ mから0.3  $\mu$ mに短縮されるに伴い、Vthは380 mV変化するのに対してSP構造を有する新LDD構造では240 mVに低減されている。

図3-20 新LDD構造を有するGaAs MESFETのVthのゲート長依存性

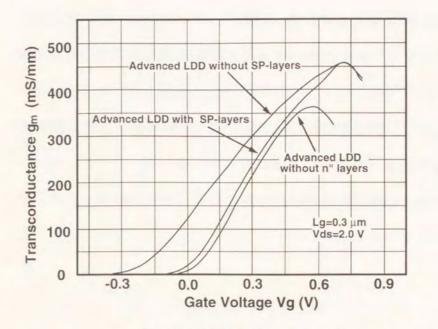

また図3-21には新LDD構造での各層の役割を確認するため、ゲート長 $0.3\,\mu m$ のMESFET のgm-Vg特性を3種類のLDD構造間で比較した結果を示す。本研究で採用したLDD構造と比べるとSP層のない構造は、最大gmは同等であるがピンチオフ特性が悪くまたピンチオフ近傍でgmが低下している。一方、n"層のない構造はピンチオフ特性は良好であるがソース抵抗の増大により最大gmは低下している。ソース抵抗は新LDD構造では $0.78\,\Omega$ ・mmであり、n"層のない構造では $0.99\,\Omega$ ・mmであった。なお最大gmとして $460\,m S/mm$ という良好な値が得られている。また短チャンネル効果が抑制されたため、Vthの面内均一性も向上し、3"Φ面内に配置された40個のMESFETの標準偏差で $12.5\,m V$ とSP層を有さない構造の半分になっている。

図3-21 各種LDD構造を有するGaAs MESFETの特性比較

さらにSP層が空乏化しない中性領域を形成して、ゲート寄生容量の増加を招かないことを調べるため、SP層を有する構造とSP層を有さない構造の電流遮断周波数(fT)を比較した。fTは以下の式で表される。

#### $f_T=g_m/2\pi Cg$

Cgはゲート容量であり、この容量が大きいとgmが同じでもfTは低くなる。 図3-22にfTのドレイン電流依存性を示す。

図3-22 SP層の有無によるGaAs MESFETの電流遮断周波数(fT)の比較

すべてのドレイン電流の範囲でSP層を有するMESFETのfrは、SPを有さないMESFET のfrと同等かそれ以上であることがわかる。この結果よりSP層はゲート容量の増加を招いていないと言える。

以上のことより新LDD構造では、寄生容量の増加を招くことなく寄生抵抗の低減と短チャンネル効果の抑制の両方が実現されていることが明らかになった。

また、パルスドープ構造と新LDD構造を組み合わせることで、さらに短チャンネル効果を抑制できることが実証されている33)。

#### 3-5 結 言

GaAs MESFETの短ゲート化に伴って発生する「短チャンネル効果」を抑制する以下のような手段を提案した。

(1) 活性層を高濃度薄層化してチャンネルの2次元効果を低減する方法

短にチャンネルを高濃度化するだけではショットキー特性の劣化の問題が避けられない。この問題を解決するために、高濃度薄層チャネルを埋め込み型にし、表面側に低濃度層を設ける「パルスドープ」構造を提案した。この構造に対してポアソンの方程式を解くことで、所望のしきい値電圧(Vth)を得るための各層の厚みとドーピング濃度を設計した。表面のキャップ層を400 Å,チャンネル厚みを100 Åにまで薄層化することにより、良好なショットキー特性を維持し、短チャンネル効果が抑制されゲート長0.3 μmでも実使用上問題のない特性が得られることがわかった。

(2) n+自己整合型MESFETにおける対峙するn+層からの基板リーク電流を低減する方法 これには従来のチャンネル下にBP層を有するLDD構造に、新たにn' 層をゲート直近に 加えると共に、n+層/n'層を囲い込むような濃度の高いp層 (SP層) を形成する新LDD構造を提案した。

n"層を加えることはドレイン端での電界緩和につながり、ホットエレクトロンによる 基板リーク電流を抑制する。BP層濃度は完全空乏化を保ったまま、SP層は対峙するn+, n'層からの基板リーク電流をより高い電位障壁により抑制する。 各層の効果を実験的に調べ、新LDD構造の有効性を実証した。つまり、本構造では寄 生抵抗や寄生容量の増大を招くことなく短チャンネル効果を有効に抑制できる。

第2章で述べた作製技術と本章で述べたデバイス構造により0.3 μm程度までは実使用 上問題のないGaAs MESFETが実現可能となった。

#### 3-6 参考文献

- 1) J.G. Ruch, IEEE Trans. Electron Devices, ED-19, pp.652-, 1972

- 2) 菅野 卓雄 監修、"超高速化合物半導体デバイス", 2章、培風館

- 3) J.R. Hauser, "Characteristics of junction field effect devices with small channel length-to-width ratios", Solid State Electronics, vol.10, pp.577-587, 1967

- 4) H.T. Daembkes, W.Brockerfoff, K. Heime, and A. Cappy, "Improved short-channel GaAs MESFETs by use of higher doping concentration", IEEE Trans. Electron Devices, Vol. ED-31, pp. 1032-, 1984

- 5) K. Ueno et al., "A High Transconductance GaAs MESFET with Reduced Short Channel Effect Characteristics", Technical Digest of IEDM 85, pp.82-85,

- 6) M. Kuzuhara et al., "High Performance LDD GaAs MESFETs With SiF2+ Implanted Extremely Shallow Channels", Technical Digest of IEDM 86, pp.763-766

- 7) Y. Yamane et al., "5.9 ps/gate operation with 0.1 μm gate-length GaAs MESFET's", Technical Digest of IEDM 88, pp.894-896

- 8) 山崎 王義他、昭和58年電子通信学会半導体·材料部門全国大会 p.67

- 9) N. Kato, K. Yamasaki, K. Asai, and K. Ohwada, "Electron-Beam Lithography in n+ Self-Aligned Gate MESFET Fabrication", IEEE Trans. Electron Devices, Vol. ED-30, pp. 663-668, 1983

- 10) K. Matsumoto, et al., "Sub-Micron-Gate Self-Aligned GaAs FET with P-type Barrier Layer Fabricated by Ion Implantation", 42nd Annual Device Research Conference VI B-5, 1984

11) K. Yamasaki, N. Kato, and M.Hirayama, "Buried P-layer SAINT for Very High-Speed GaAs LSI's with Submicrometer Gate Length", IEEE Trans. Electron Devices, Vol.ED-32, pp.2420-2425, 1985

- 12) H. Dambkes, W. Brockerhoff, and K. Heime, "GaAs MESFET's with highly doped (10<sup>18</sup> cm<sup>-3</sup>) channels An experimental and numerical investigation", Tech. Dig. of IEDM, pp.621-624, 1983

- 13) R.F. Broom, H.P. Meier, and W. Walter, "Doping dependence of the Schottky-barrier height of Ti-Pt contacts to n-gallium arsenide," J. Appl. Phys. 60 (5), pp.1832-1833, 1986 14) M. Suzuki, K. Murase, N. Kato, M. Togashi, and M. Hirayama, "Advantages of Metallic-Amorphous-Silicon-Gate FET's in GaAs LSI Applications", IEEE Trans. Electron Devices, Vol. ED-33, pp.919-924, 1986

- 15) S. Nakajima, K. Otobe, T. katsuyama, N. Shiga, and H. Hayashi, "OMVPE grown GaAs MESFETs with step-doped channel for MMICs", Tech. Digest of IEEE GaAs IC Symp., pp.297-300, 1988

- 16) S. Nakajima, G. Ishii, Y. Saito, N. Kuwata, T. Fukuzawa, K. Koike, and H. Nishizawa, "Manufacturability of Dummy-gate Self-aligned LDD GaAs MESFETs for High Volume Production", Tech. Digest of IEEE GaAs IC Symp., pp.119-122, 1994

- 17) M. Kuzuhara et al., Appl. Phy. Lett., 41, pp.755-758, 1982

- 18) T. Ohnishi et al., "Experimantal and Theoretical Studies on Short Channel Effects in Lamp-Annealed WSix-Gate Self-Aligned GaAs MESFET's", Extended Abstract of the 16th Conference on Solid State Devices and Materials, pp.391-394, 1984

- 19) S. Nakajima, K. Otobe, N. Kuwata, N. Shiga, K. Matsuzaki, and H. Hayashi,

"Pulse-doped GaAs MESFETs with planar self-aligned gate for MMIC", Tech. Digest of IEEE

MTT-S 1990 International Microwave Symposium, pp.1081-1084, 1990

- 20) R.A. Pucel, "Profile Design for Distortion Reduction in Microwave Field-Effect Transistors," Electron. Lett., 14, p.204, 1978

- 21) T.S. Tan, et al., "A Low-Distortion K-Band GaAs Power FET," IEEE Trans. Microwave Theory and Tech., Vol.30, No.6, pp.1023-1032, 1988

- 22) K. Otobe, N. Kuwata, N. Shiga, S. Nakajima, K. Matsuzaki, T. Sekiguchi, and H. Hayashi, "Low-distortion MESFET with advanced pulse-doped structure for power applications," Inst. Phys. Conf. Ser., No.129: Chaper 6, pp.761-766, 1993

- 23) S.L. G. Chu, J. Huang, W. Struble, G. Jackson, N. Pan, M.J. Schindler, and Y. Tajima,

"A Highly Linear MESFET," Technical Digest in IEEE MTT-S 1991 International Microwave Symposium, pp.725-728, 1991

24) E.F. Shubert, A. Fischer, and K. Ploog, "The Delta-Doped Field-Effect Transistor

(δ FET)," IEEE Trans. Electron Devices, Vol. ED-33, No.5, pp.625-623, 1986

25) W.P. Hong, J. Harbison, L. Florez, and J.H. Abeles, "DC and AC Chanracteristics of Delta-Doped GaAs FET," IEEE Electron Device Lett., Vol. 10, No.7, pp.310-312, 1989

26) Y. Yamauchi, T. Makimoto, and Y. Horikoshi, "Annealing Properties of

Si-Atomoic-Layer-Doped GaAs," Jpn. J. Appl. Phys., Vol. 28, No.10, pp. L1689-L1692, 1989

27) R.A. Sadler, G.D. Studtmann, A.E. Geissberger, and H.P. Singh, "A High Yield Buried p-layer Fabrication Process for GaAs LSI Circuits," IEEE Trans. Electron Devices, Vol.38,

28) M. Noda, K. Hosogi, T. Oku, K. Nishitani, and M. Otsubo, "A High-Speed and Highly Uniform Submicronmeter-Gate BPLDD GaAs MESFET for GaAs LSI's," IEEE Trans. Electron Devices, Vol.39, No.4, pp.757-765, 1992

29) S. Ogura et al., "Design and Characteristics of the Lightly Doped Drain-Source (LDD)

Insulated Gate Field Effect Transistor", IEEE Trans. Electron Devices, ED-27, p.1359, 1980

30) E. Takeda et al., "Submicrometer MOS FET Structure for Minimizing Hot-Carrier

Generation", IEEE Trans.Electron Devices, ED-29, p.611, 1982

No.6, pp.1271-1279, 1991

31) S. Asai et al., "A High Performance LDD GaAs MESFET with a Refractory Metal Gate", Extended Abstracts of the 18th Conference on SSDM, pp.383-386, 1986

32) M. Tsunotani et al., "Advanced Self-Alignment Process Technique With Very Thick Sidewall for High Speed GaAs LSIs", Tchnical Digest of IEDM, pp.700-703, 1988

33) K. Matsuzaki, N. Kuwata, S. Nakajima, K. Otobe, N. Shiga, and H. Nishizawa, "Low Noise MMIC Technology with Pulse-doped GaAs MESFET," Proceeding in 1994 Asia Pacif Microwave Conference, pp.283-286, 1994

# 第4章 パルスドープ構造による電子輸送特性の改善

## 4-1 緒 言

GaAsは、同一キャリア濃度で比べるとSiより電子移動度が約6倍大きい。 また高電界特性においてもSiより高いピーク速度を示すことが知られているり。

また、近年ではヘテロ接合を用いてイオン化不純物散乱を増やさずにキャリア濃度の みを増加させる変調ドープ構造が実現され、高電子移動度が得られている2)。

一方、第3章で提案した高濃度薄層チャンネルを有するパルスドープ構造では、不純 物散乱による電子移動度の低下とそれに伴うデバイス特性の劣化が懸念される。

微細化が進んだ段階では、低電界の輸送特性よりも高電界の輸送特性の方がデバイス特性の決定には重要と言われている。このような理由から半導体中の電子の高電界輸送特性に関しては、シミュレーションと実験の両面より研究がなされている3-5)。最近では変調ドープされたAlGaAs/GaAs ヘテロ接合において、「GaAsからAlGaAs中への実空間遷移により高電界での電子速度は高純度GaAs中よりも遅くなる」という結果も報告されている6.7)。逆にInP/InGaAs ヘテロ接合ではInGaAs中の電子がInPの下点に遷移することによりInGaAsより1.5~2倍高い飽和速度を示すことが示唆されており8)、実際にこの系のデバイスが試作され、InGaAsをチャンネルとするデバイス以上の特性が得られている9.10)。このように電子輸送特性は、バンド構造とも密接に関係している。

本章ではパルスドープ構造のデバイス特性を予想するため、そのバンド構造と電子輸送特性を調べた。

まず高濃度薄層でのバンド構造をシュブニコフ・ド・ハース振動により調べ、パルスドープ構造内では電子は2次元性を有していることを示す11)。次に低電界/高電界での電子輸送特性を評価し、同じキャリア濃度を有するバルクと比較して高い電子速度を有していることを示す。さらにこの高い電子速度は量子井戸構造を有するパルスドープ構造特有の効果であることを述べる12)。

## 4-2 高濃度薄層半導体におけるバンド構造

近年、MBEやOMVPEに代表される結晶成長技術の目覚ましい進歩により原子層オーダーの半導体層も容易に形成できるようになった。この技術により電子デバイスではヘテロ接合を用いたHEMTやHBTといった超高速デバイスが、光デバイスではMQW(Multi Quantum Well)を利用した低しきい値のレーザが生み出された。また不純物のドーピングに関しても、原子層ドーピング(Atomic Layer Doping または Planar Doping、さらに不純物分布の形状より &-ドーピングとも言う)技術により局所的に不純物層を形成することができるようになった「3」。例えばMBEにおいてGaAs中にSiを原子層ドーピングする場合は、GaAsの成長中に一旦Ga分子を止めてAs雰囲気下でSiフラックスを飛ばす。同じようにOMVPEでは、Flow-rate Modulation Epitaxy (FME)という方法で原子層ドーピングが実現されている「4」。これらの技術は、HEMTの電子供給層「5-17)やトンネル効果を利用したノンアロイコンタクト18)やFETのチャンネル19,20)に適用され、さらに鋸波状にドーピングした構造は光学素子への応用も検討されている。&ドーピングのデバイス応用は次の文献に詳しい21」。

高濃度に原子層ドーピングしたGaAsのバンド構造(ドーピングが $\delta$  関数的であるから  $\delta$  ドーピングとも言う)は、Zrennarらにより初めて報告された。彼らはシュブニコフ・ド・ハース効果により 2 次元電子ガスの存在とサブバンド構造を明らかにした $^{22}$ )。変調(選択)ドーピングしたヘテロ接合では、伝導帯のエネルギー差により電子が電子親和力の小さい半導体側に移り 2 次元電子ガスを形成する。これに対し、 $\delta$  ドープ GaAs ではドーピング面が縮退しており両側の伝導帯を下方に曲げることにより2 次元電子ガス状態が得られる。しかし原子層ドーピングでは真に $\delta$  関数的な電子濃度プロファイルが実現されているのであろうか? ドーピングでは真に $\delta$  関数的な電子濃度プロファイルがまりるがあるであろう。Fernarとに疑問を抱き、さらに詳細な解析よりfernalとれた層でもfernalとの拡がりを持つと報告しているfernal23)。

本研究では、OMVPE法において特別なドーピング方法を用いずに形成した、100 Aの 高濃度不純物層を有するパルスドープ構造のバンド構造を探求した。

## 4-2-1 パルスドープ構造GaAs

評価に用いた試料の構造を図4-1に示す。半絶縁性GaAs 基板上にOMVPE法により、アンドープGaAsバッファー層を10000 Å, SiドープのGaAs層( $4\times10^{18}$ /cm³, 100 Å)、アンドープのGaAsキャップ層を300 Å成長させた。成長温度は $650^{\circ}$ C、成長圧力は60 Torrである。成長時のV族原料とIII族原料の流量比を制御することによって、バッファー層はp-型にキャップ層はp-型にしている。またGaAsの成長にはtrimethylgallium(TMG)とarsine(AsH3)をp-型のドーパントにはdisilane(Si2H6)を使用している。

ホール効果による測定でのシート電子濃度は4.5×10<sup>12</sup>/cm<sup>2</sup>, 電子移動度は1800 cm<sup>2</sup>/Vs (室温での値)である。

図4-1評価に用いたパルスドープ構造GaAs

# 4-2-2 シュブニコフ・ド・ハース(SdH)振動

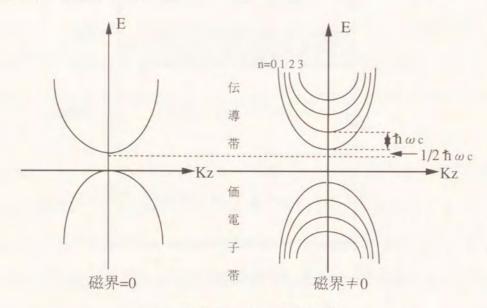

電子が半導体表面反転層、あるいは変調ドーピングされたヘテロ界面で2次元電子ガス状態を示すことは、シュブニコフ・ド・ハース効果の測定によって明らかにされている24)。

定数、kBはボルツマン定数、 $\tau$ は緩和時間)では、磁界中の電子の運動は量子化され離散的なエネルギー準位をとる。この離散的なエネルギー準位をランダウ準位と呼びその間隔は $\hbar\omega$ cとなる(図4-2参照)。通常の3次元結晶では、磁界の強さを増加させるとランダウ準位がフェルミ準位を通過するたびに導電率が周期的に変化する。この量子的振動をシュブニコフ・ド・ハース効果という。2次元電子系では、電子は界面に平行方向には自由に運動できるが、垂直方向に対してはポテンシャルに邪魔されて自由に運動ができない。そのため、2次元電子系での磁場強度に対する導電率の変化は、印加する磁場の向きに依存することになる。つまり界面に対して垂直に磁場を印加した時は、電子は界面に対して平行にサイクロトロン運動をするためSdH振動が得られ、逆に平行に印加した場合はSdH振動は得られない。

図4-2 磁界中のランダウ準位

### 4-2-3 パルスドープ構造GaAsのSdH振動

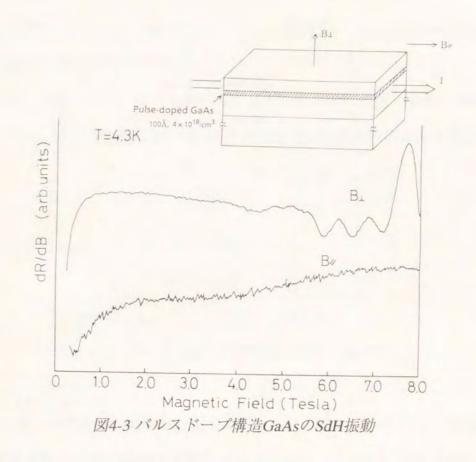

試料をフォトリソグラフィとメサエッチによりホールブリッジに加工し、4.3 Kの極低温下でSdH振動測定を行った。図4-3にその結果を示す。横軸は磁場強度、縦軸は磁気抵抗を磁場強度で1回微分した結果である。ドーピング界面に垂直に磁場を加えた時のみSdH振動が観測されており、本研究で用いた試料でも電子は2次元性を有することが明らかになった。図4-3からは、振動はいくつかの周期より成り立っていることがわかる。

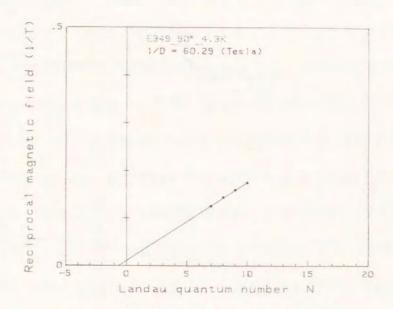

周期の一番短い山のランダウ数を、磁場の逆数に対してプロット (ランダウプロット) した結果を図4-4に示す。得られる直線はn=-1/2で横軸を切っている。このことは

$\hbar\omega c(n+1/2)=\varepsilon$  Fに対応する磁場で、磁気抵抗が極大値をとっていることを示している。この結果は、一番短い周期に対応するエネルギー準位の状態密度の最大値は、2次元電子ガスのランダウ準位の位置にあることを示している。またこの直線の傾きよりこの振動に対応した電子密度Ns1は、電子の有効質量を0.067mと仮定するとNs1=2.9×1012/cm2と計算され、その準位のフェルミエネルギーからの間隔  $\varepsilon$  FI は  $\varepsilon$  FI = 103 mVと計算される。

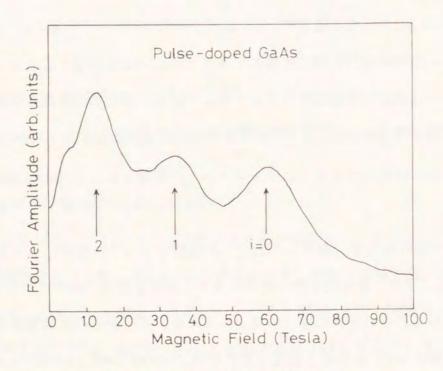

次に、いくつかの周期を分離するためにこの振動をフーリエ変換により分離した。その結果を図4-5に示す。本研究で用いたパルスドープ構造は3つのサブバンドを有していることがわかる。それぞれの準位のフェルミエネルギーからの間隔を求めると、103 mV、58.5 mV、20.7 mVとなり電子濃度はそれぞれ2.9×10<sup>12</sup>/cm²、1.6×10<sup>12</sup>/cm²、0.6×10<sup>12</sup>/cm²と計算された。

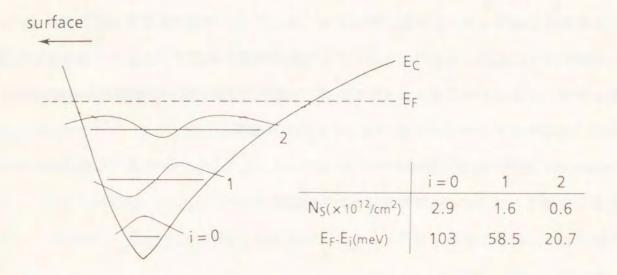

図4-4 一番短い周期に対するランダウプロット

総電子密度は5.1×10<sup>12</sup>/cm<sup>2</sup>となりホール測定より得られた値とほぼ一致する。これらの結果より得られたパルスドープ構造のバンド構造を図4-6に示す。表面側のアンドープ層は表面準位により空乏化しているため、ポテンシャルが持ち上がりV型ポテンシャルを示す。

図4-5 フーリエ変換による結果

GaAs中へのSiの δ ドーピングの場合も、ドーピング濃度に依存するがほぼ同様なサブバンド構造が観測されている13,25,26)。

以上の結果よりるドーピングという特別な成長方法を用いずとも、通常のOMVPE法により成長した100点の高濃度層においても量子井戸構造が形成されることが確認された。

図4-6パルスドープ構造GaAsのバンド図

## 4-3 半導体中の電子移動度と飽和速度

一般に半導体中の電子は、主に音響フォノンと不純物により散乱を受ける。音響フォノンは温度による格子振動に由来するものでその温度依存性はT-3/2となる。

一方、不純物散乱のなかでもっとも影響が大きいものは、イオン化不純物散乱である。 イオン化不純物散乱は、イオン化した不純物が電子に対してクーロンポテンシャルを及 ぼすことが要因である。この散乱の温度依存性はT3/2であり音響フォノン散乱の場合と 逆である。つまり低温領域ではイオン化不純物散乱が、高温領域では音響フォノン散乱 が支配的である。

選択ドープ構造を有するn-AlGaAs/GaAs ヘテロ界面に形成される 2 次元電子ガスは、電子とイオン化ドーナが空間的に分離されているため不純物散乱の影響が少なく、特に

低温で移動度が大きく向上する2)。

ところでGaAsのような半導体にさらに電界を印加していくと、電子は低い谷 (Γ点) から高い谷 (L点) に遷移する。これを谷間電子遷移効果という。高い谷では低い谷よりも電子の有効質量が大きい(つまり移動度が低い)ために、高い谷での電子占有確率が増すと負性微分移動度を示すようになる。

さらに電界が高くなり、電子のエネルギーが光学フォノンのエネルギーよりも大きくなると電子は光学フォノンと強く結合する。光学フォノンのエネルギーは音響フォノンのエネルギーに比べて非常に大きい。 そのため、電子が光学フォノンを放出すると電界から得たエネルギーはほとんど0になってしまう。つまり電子の運動エネルギーの最大値は光学フォノンのエネルギーħωορによって決まる。

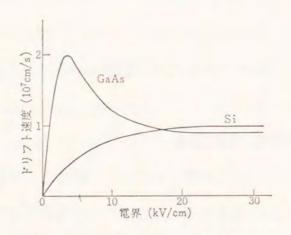

GaAs の代表的な速度ー電界特性を図4-7に示す。このような特性は、高電子移動度を 有する変調ドープされたヘテロ接合系でも同様である27)。

図4-7 GaAsの代表的な速度-電界特性

# 4-3-1 パルスドープ構造の電子移動度

第3章で述べたパルスドープ構造は、チャンネルに高濃度層を有するために不純物散 乱による電子輸送特性の劣化が懸念される。電子輸送特性の劣化はMESFETの特性にも 影響を与えることが考えられる。

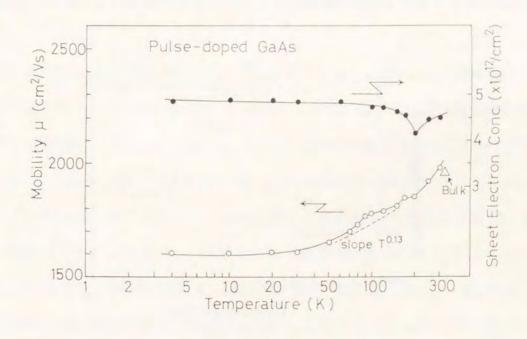

まずホール測定により、パルスドープ構造のホール移動度の温度依存性を調べた。そ

の結果を図4-8に示す。電子移動度は、あまり温度に依存しないことがわかる。もし本 試料でも不純物散乱が支配的であるなら、低温領域では移動度はT<sup>3/2</sup>の依存性を示すは ずである。しかしながら、本試料の移動度の温度依存性はT<sup>0.13</sup>であった。これはパルス ドープ構造では不純物散乱が低減されていること、フェルミエネルギーが縮退している こと、高濃度化により不純物イオンをスクリーニングしていることによるものと考えられる。

一方、電子濃度は温度に依存し、約200 Kあたりで極小値を示している。またさらに低温領域では、室温よりも高い電子濃度を示している。これらの結果は、4-1章で述べたパルスドープ構造のバンド構造に起因すると考えられる。すなわち、パルスドープ構造ではV型ポテンシャルを有するため低温領域では電子は3つのサブバンドに量子化され分布している。基底サブバンドより上のサブバンドでは、電子の存在確率は不純物中心よりずれた所で高くなる。このような状態では、電子移動度が高くなることが予想される。そのため、移動度の異なる3つのサブバンドの並行電子伝導を考慮しなければならない。

図4-8パルスドープ構造GaAsの移動度と電子濃度の温度依存性

Makimotoらは、 $\delta$ ドープ構造GaAsでも同様な電子濃度の温度依存性を観測し、電子濃度が温度に対して極小値を示す理由を移動度の異なる2つのバンドの並行電子伝導を仮定することで説明している28)。

2つのバンドの並行電子伝導では、ホール効果より得られるシート電子濃度Nhは次のように表される。

Nh= $(n_1 \mu_1 + n_2 \mu_2)^2 / (n_1 \mu_1 \mu_1 + n_2 \mu_2 \mu_2 h)$  (1)

ここで $n_1$ ,  $\mu_1$ ,  $\mu_1$ hはそれぞれ低いエネルギーレベルのバンドのキャリア密度、ドリフト移動度、ホール移動度である。 $n_2$ ,  $\mu_2$ ,  $\mu_2$ hは高いエネルギーレベルのバンドのそれである。ここで $\mu_1$ h= $\mu_1$ と仮定する。

$\pm t \mu 2/\mu 1=b>1$

n1+n2=n0 (総電子数)、

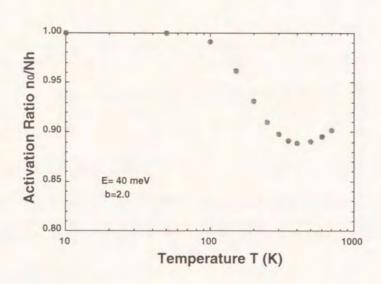

$n_2=n_0\exp(-qE/kT)$ , Eは電子が下のレベルから上のレベルに上がるための活性化エネルギーとする。式(1)を書き直すと次のようになる。

Nh=[ $(b-1)n_2+n_0$ ]<sup>2</sup> / [ $(b^2-1)n_2+n_0$ ] (2)

E=40 meV, b=2.0と仮定して、この式に従って計算された結果を図4-9に示す。電子濃度が極小値を示し、低温側では室温付近よりも高い濃度が得られていることがわかる。

図4-92つのサブバンドを考慮した場合の電子濃度の温度依存性(計算結果)

極小値を示す温度が、測定値とずれているのは計算では2つのサブバンドしか考慮しなかったが、実際は3つのサブバンドが存在するためと考えられる。

さらに、量子振動を起こす必要条件  $\mu$  B>1 ( $\mu$  は電子移動度)を満たすことより図4-3 のSdH振動からは  $\mu$  =2500 cm²/Vsが計算される。この値はホール効果で得られる4.3 Kの  $\mu$  =1600 cm²/Vsよりも大きい。この結果もパルスドープ構造中の電子は、異なる移動度 を有するサブバンドに分布していることを示している。

## 4-3-2 パルスホール効果による高電界輸送特性評価

ホール効果で得られた電子移動度1800 cm2/Vsという値は、同じ濃度を持つバルクでの値よりも高い。Schubertらは、分子線エピタシャル法にて原子層オーダのドーピングプロファイルを持つるドープ構造を作製し、バルクよりも高い移動度を得ている29)。この現象も前節で述べたパルスドープ構造のバンド構造に起因する。すでに示したようにパルスドープ構造は3つのサブバンドを形成している。基底サブバンドの電子は不純物分布の中心部に位置することになるが、第1、第2サブバンドの電子は不純物分布の中心よりずれた所に位置する。そのためこれらのサブバンドに属する電子は不純物散乱の影響を受けにくくなる。つまりこれらのサブバンドの電子は高い移動度を有することになる。

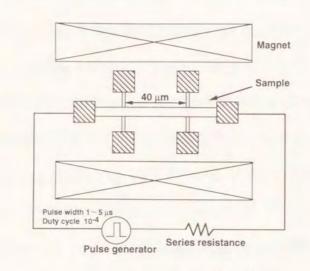

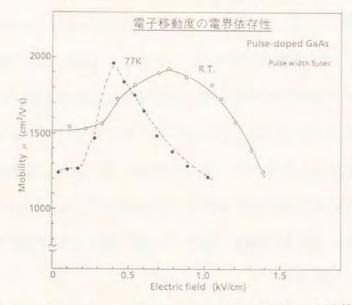

電子の分布状態は電子が受けるエネルギーにより変化し、それに伴い移動度も変化することが予想される。そこでパルスホール効果により電子移動度の電界依存性を調べた。 測定のため試料は、ホールブリッジに加工され発熱の影響を避けるためパルス幅5 μsec, デューティ比10-4のパルス電圧を印加した。各端子の電位はオシロスコープにより測定した。図4-10に測定系の概略を示す。測定は室温(25℃)と液体窒素温度(77K)にて行った。図4-11にその結果を示す。低電界では移動度は通常のホール測定より得た値とほど同じであるが、電界強度が0.2-0.3 kV/cmの付近で増加していることがわかる。電子移動度は室温では1500 cm²/Vsより1800 cm²/Vsに、77Kでは1200 cm²/Vsより2000 cm²/Vsにまで増加している。

図4-10パルスホール測定系の概略

図4-11パルスホール測定による電子移動度の電界依存性

このことは、基底準位の電子が電界よりエネルギーを得て電子移動度の高い上のサブバンドに移ることより説明できる。77 Kでの方が室温よりも低い電界で増加傾向を示し増加率も大きいのは、77 Kの方がエネルギー状態が低いためより多くの電子が基底準位に存在するためと考えられる。基底準位とフェルミレベルのエネルギー差は100 mV程度しかないので、さらに高電界になると電子はV型ポテンシャルより飛び出し両側のアンドープ層に遷移すると考えられる。そこでホットになった電子は光学フォノンと結合してエネルギーを放出し、一定の速度(飽和速度)に達する。これが電界強度がさらに強

くなった時の移動度が減少する理由である。

このようにパルスドープ構造は、通常のバルクとは異なった電子輸送現象を示すこと が明らかになった。

## 4-3-3 パルスI-V測定による高電界輸送特性評価

短ゲートの素子において実際に素子の性能を支配するのは、低電界の移動度よりむしろ高電界での電子移動度、電子ピーク速度、電子飽和速度ではないかと言われている。 実際の素子を考えてみると、ゲート長が1 µmの素子の空乏層に1 Vの電界が印加されたとすれば電界強度は10 kV/cmにも達することがわかる。このような高電界でのパルスドープ構造中の電子の振る舞いを調べることは、素子特性への影響を考えるためにも重要である。

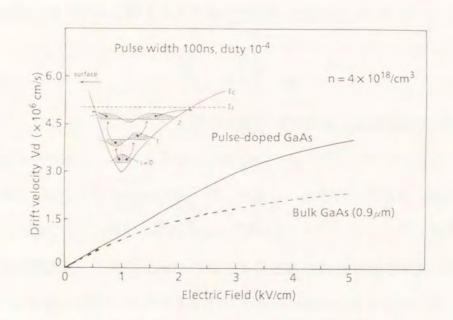

そこでパルス電圧印加による電流ー電圧特性を測定した。この測定のための試料は、2端子素子で電極間隔は10 μmである。測定は、発熱の影響を除くためパルス幅100 ns, デューティ比10-4を用いた。電流値より電子ドリフト速度Vdは次式で与えられる。

## Vd=J/qns

ここで、Jは電流密度、qは電荷量、nsはシートキャリア密度である。

比較のために同じキャリア濃度を持つバルク (厚み0.9 µm) の特性も評価した。

図4-12にその結果を示す。低電界領域では両者には大差は見られないが、1 kV/cmを越える高電界領域からはパルスドープ構造の方が高い電子速度を示している。電子ピーク速度は、不純物散乱の少ないアンドープの材料の方が不純物散乱の大きい高濃度な材料より高い5)。そのため、高電界になると電子がアンドープ層に遷移してしまうパルスドープ構造の方が電子ドリフト速度が高くなると考えられる。 さらに高電界での電子飽和速度Vsatは、不純物散乱よりむしろ光学フォノン散乱が支配的となるので不純物濃度に依存せずほぼ同じ値(室温で1.2×107 cm/sec)を示すと考えられる。低電界から高電界領域に推移する際の移動度の増加やドリフト速度の増加は、デバイスの空乏層内の電界強度分布を考えれば電子の平均した速度を高めることに寄与すると考えられる。

図4-12 パルスI-V測定によるドリフト速度の電界依存性

以上の結果よりパルスドープ構造は高濃度層を有するが、通常のバルクとは異なりV型のポテンシャルに起因する電子遷移効果のために良好な輸送特性を示すことが明らかになった。なおパルスドープ(あるいは $\delta$ ードープ)構造の高電界輸送特性は、最近他の研究機関でも調べられ、本研究同様にバルクの特性より優れていることが報告されている30,31)。

#### 4-4 ダブルパルスドープ構造による電子輸送特性の改善

#### 4-4-1 ダブルパルスドープ構造

GaAs MESFETの高出力応用を考えた場合、ドレイン電流を増加させなければならない。この場合不純物濃度を増加させるか、不純物層の厚みを増加させることが必要である。パルスドープ構造の場合、不純物濃度が1×1018/cm3台とかなり高くこれ以上濃度を増やすことは困難である。一方、不純物層の厚みを増加させた場合は、前節で述べた量子井戸の形成が崩れ、電子の多くは高電界下で不純物層中を走行しなければならず、ドリフト速度の低下や結果的に素子特性の劣化が懸念される。

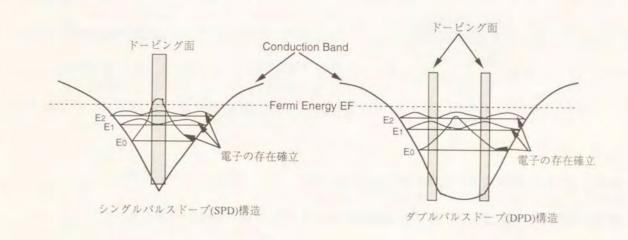

そこでパルスドープ層を電子の平均自由行程内に2層配したダブルパルスドープ構造を提案した32,33)。ダブルパルスドープ構造におけるエネルギーバンド図を図4-13に示す。各々のパルスドープ層での電子の波動関数が重なり合うことで、両パルスドープ層間にあるアンドープ層での電子存在確率が増加し電子輸送特性の改善が期待できる。

図4-13 ダブルパルスドープ構造GaAs内の電子分布

実際に、この効果を確かめるためにOMVPE法により各種構造を作製して評価した。シングルパルスドープ構造では、ドーピング層の厚みを100 Åとし、ダブルパルスドープ構造では50 Åのドーピング層を50 Å離して形成した。表4-1にドーピング濃度を同じにした各種構造(バルク、パルスドープ、ダブルパルスドープ)のホール測定より得た電子移動度とシートキャリア濃度の比較を示す。パルスドープ構造を2層配することで1層の場合に比べて電子移動度が増加していることがわかる。このことはアンドープ層での電子存在確率が増加したためであり、高電界輸送特性の改善にもつながると考えられる。ダブルパルスドープ構造では、77 Kにおいて移動度の増加を期待したが見られなかった。これはドーピング層の間隔が狭いため、電子がドーピング面からのクーロン散乱を十分受けにくい距離に存在できなかったためと考えられる。

表4-1 各種構造の電子移動度と電子濃度の比較

|                      | 300K                         |                                     | 77K                          |                                     |

|----------------------|------------------------------|-------------------------------------|------------------------------|-------------------------------------|

|                      | $\mu$ (cm <sup>2</sup> /V·s) | N <sub>s</sub> (1/cm <sup>2</sup> ) | $\mu$ (cm <sup>2</sup> /V·s) | N <sub>s</sub> (1/cm <sup>2</sup> ) |

| Bulk                 | 1800                         | $3.7 \times 10^{14}$                | ******                       |                                     |

| Pulse-dope           | 1800                         | $4.5 \times 10^{12}$                | 1500                         | $4.7 \times 10^{12}$                |

| Double<br>Pulse-dope | 2750                         | $2.4 \times 10^{12}$                | 2730                         | 2.8 × 10 <sup>12</sup>              |

## 4-4-2 ダブルパルスドープ構造GaAs MESFET

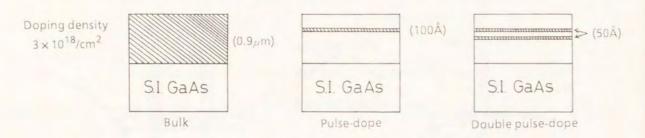

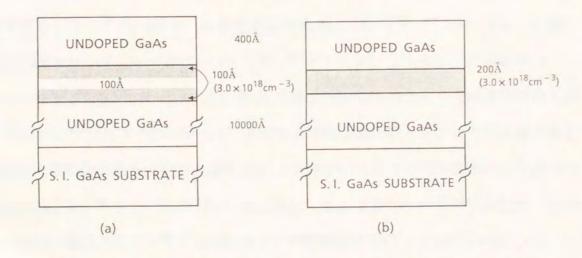

前述の結果を確かめるために、通常のパルスドープ(PD)構造とダブルパルスドープ (DPD)構造によるMESFETを試作して比較した。通常のPD構造ではドーピング層を200 Å として、DPD構造では100 Å のドーピング層を100 Å 離して形成した。活性層のドーピング濃度は両者とも $3\times10^{18}$ /cm $^3$ である。図4-14に両者のエピタキシャル構造断面図を示す。

図4-14 ダブルパルスドープ構造とシングルパルスドープ構造の断面図

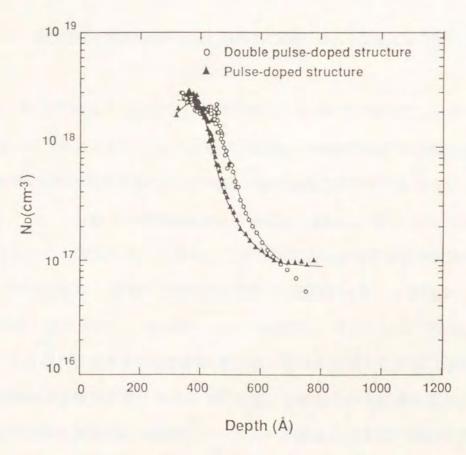

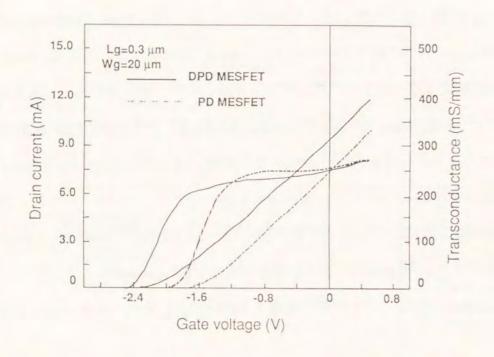

MESFETの作製プロセスは、第2章で提案したダミーゲート法を用いたn+自己整合プロセスである。n+層形成のために注入したSi+イオンは、RTA(Rapid Thermal Anneal)にて活性化している。この活性化アニールによってもDPD層が崩れないことは、Capacitance - Voltage (C-V)法より求めたキャリアプロファイル分布から明らかである(図4-15参照)。図4-16にゲート長0.3 μmの両素子のVgとgm,Idsの関係を示す。DPD構造MESFETの方が、Vthが少し深くなっているが両者ともVgの広い範囲に渡って一定のgm特性を示している。DPD構造においてgmに2つのピークが現われないことは、2つのパルスドープ層がひとつのチャネルとして働いていることを示唆している。最大gmは両者とも265 mS/mmが得られている。またVg=0 V時のドレイン電流密度は、350 mA/mm以上と図3-15に示した高濃度層厚が100 Åのパルスドープ構造を有するMESFETに比べて大きくなっている。

図4-15 C-V法より求めたRTA後の電子濃度分布

図4-16 DPD GaAs MESFETとPD GaAs MESFETの特性比較

電子輸送特性は、第5章で述べるように高周波特性の測定より評価できる。図4-17には電流利得(H21)と最大安定利得(MSG)の周波数依存性を示す。ダブルパルスドープ構造の方がより高い値を示していることがわかる。H21が1となる周波数が電流遮断周波数fTと定義され、PD構造では35 GHz, DPD構造では40 GHzが得られる。

短チャネル近似のもとではfTは次式にて与えられる。

fT = Vave/2πLg ; Vaveは電子の平均したドリフト速度、Lgはゲート長

この結果は、ダブルパルスドープ構造の方がより高いドリフト速度で走行していることを示している。即ち、チャンネル厚を増し電流密度を増加させたい場合は、単にパルスドープ構造の厚みを増すのではなく、薄いパルスドープ構造を電子の波動関数の拡がり程度の間隔で多層に配することが、パルスドープ構造の良好な電子輸送特性を活かすことができるのである。

このようなパルスドープ層を2層にした素子特性の改善は、最近ではSi MESFETにも 適応されている34-36)。

-77-

図4-17 DPD GaAs MESFETとPD GaAs MESFETのH21とMSGの周波数依存性

## 4-5 結 言

本章では、パルスドープ構造の高濃度層がGaAs MESFETの特性に与える影響を調べる ため、パルスドープ構造GaAsのバンド構造と電子輸送特性を解明した。

シュブニコフ・ド・ハース効果の測定より本研究で用いたパルスドープ構造は100 Å の厚みを有するにも関わらず、δドーピングで形成したGaAs同様に2次元電子ガスを有し、そのバンド構造は3つのサブバンドを有するV型ポテンシャルを示すことがわかった。

そのため、電子の分布は不純物散乱の中心からずれた位置にも存在し、同じキャリア 濃度を有するバルク材料よりも高い電子移動度を示すことが明らかになった。

素子特性に重要な高電界輸送特性をパルスホール効果、パルスI-V測定により調べた結果、V型ポテンシャルに起因する電子移動度の増加が観測され、また高電界での電子速度は同じ濃度を有するバルク材料のそれよりも高いことが観測された。これはパルスドープ構造内でホットになった電子がV型ポテンシャル内の基底準位より上の準位へ、さ

らには両側のアンドープ層に遷移するためと考えられる。その結果として、高電界では 低不純物濃度層と同等な速度を有する。

また量子井戸構造による電子輸送特性の改善に着目して、パルスドープ構造を電子の 波動関数の拡がり程度の間隔に2層配したダブルパルスドープ構造を提案し、素子特性 の改善効果を明らかにした。

以上のことより、パルスドープ構造は高濃度不純物層を有するが、電子輸送特性は良好で素子特性の劣化を引き起こさないと言える。

## 4-6 参考文献

- 1) P. Smith, M. Inoue, and J. Frey, "Electron Velocity in Si and GaAs at Very High Electric Fields", Appl. Phys. Lett., 37, p.797, 1980

- 2) R. Dingle, H. Stormer, A.C. Gossard, and W. Wiegman, "Electron mobilities in modulation-doped semiconductor heterojunction superlattices", Appl. Phys. Lett., pp.665-667, 1978

- 3) K. Hirakawa and H. Sakaki, "Hot-electron transport in selectivery doped n-type AlGaAs/GaAs heterojunctions", J. Appl. Phys. 63 (3), pp.803-808, 1988

- 4) K. Yokoyama, "Drift velocity comparison between high-electron mobility transistors and doped-channel field-effect transistors at very small dimensions", J. Appl. Phys. 63 (3), pp.938-943, 1988

- 5) W.T. Masselink and T. F. Kuech, "Velocity-Field Characteristics of Electrons in Doped GaAs", J. of Electronic Materials, Vol.18, No.5, pp.579-584, 1989

- 6) W.T. Masselink, N. Braslau, W.I. Wang, and S.L. Wright, "Electron velocity and negative differential mobility in AlGaAs/GaAs modulation-doped heterostrictures", Appl. Phys. Lett., 51, (19) PP.1533-1535, 1987

- 7) R.Sakamoto, K. Akai, and M. Inoue, "Real Space Transfer and Hot Electron Transport Properties in III-V Semiconductor Heterostructures," IEEE Trans. Electron Devices, Vol.36, pp.2344-2352, 1989

- 8) W.T. Masselink, N. Braslau, D. LaTulipe, W.I. Wang, and S.L. Wright, "Electron Velocity at High Electric Fields in AlGaAs/GaAs Modulation-Doped Heterostructures", Solid-State Electronics Vol.31, No.3/4, pp.337-340, 1988

- 9) T. Enoki, A. Kunihiro, A. Kohzen, and Y. Ishii, "InGaAs/InP double channel HEMT on InP," Fourth Int'l Conf. on InP and Related Mater. Conf. Proc., p.15, 1992

- 10) S. Strahle, B. Henle, and E. Kohn, "Low voltage characteristics of InGaAs/InP composite channel HEMT structure fabricated by optical lithography," Electron. Lett., Vol. 30, No. 23,

pp.1989-1991, 1994

- 11) S. Nakajima, N. kuwata, N. Nishiyama, N. Shiga, and H. Hayashi, "Electronic properties of a pulse-doped GaAs structure grown by organometallic vapor phase epitaxy", Appl. Phys. Lett. 57 (13), pp.1316-1317, 1990

- 12) S. Nakajima, N. Kuwata, N. Nishiyama, N. Shiga, and H. Hayashi, "Hot electron transport in a pulse-doped GaAs structure", Semicond. Sci. Technol., 7, pp.B372-374, 1992

- 13) C.F.C. Wood, G. Metze, J. Berry, and L.F.Easrman, Appl.Phys.Lett., 51 p.383, 1980

- 14)N. Kobayashi, T. Makimoto, and Y. Horikoshi, Jpn. J. Appl. Phys. 24 p.L962, 1985

- 15) N. Moll, M.R. Hueschen, and A. Fischer-Colbrie, "Pulse-Doped AlGaAs/InGaAs Psedomorphic MODFET's," IEEE Trans. Electron Devices, Vol. 35, No. 7, pp.879-885, 1988

- 16) J.C. Huang, M. Zaitlin, W. Hoke, M.Adlerstein, P. Lyman, P.Saledas, G. Jackson, E. Tong, and G. Flynn, "A High-Gain, Low-Noise, 1/2-μm Pulse-Doped Pseudomorphic HEMT," IEEE Electron Device Letters, Vol. 10, No. 11, pp.511-513, 1989

- 17) P.C. Chao, M.S. Shur, R.C. Tiberio, K.H. George Duh, P.M. Smith, J.M. Ballingall, Pin Ho, and A.A. Jabra, "DC and Microwave Characteristics of Sub-0.1-μm Gate-Length Planar-Doped Pseudomorphic HEMT's," IEEE Trans. Electron Devices, Vol. 36, No. 3, pp.461-473, 1989

- 18) E.F. Schubert, J.E. Cunningham, W.T. Tsang, and T.H. Chiu, "Delta-doped ohmic contacts to n-GaAs," Appl. Phys. Lett., 49 (5), pp.292-294, 1986

- 19) E. F. Schubert, A. Fischer, and K. Ploog, "The Delta-Doped Field-Effect Transistor

(δ FET), "IEEE Trans. Electron Devices, Vol. ED-33, No.5, pp.625-632, 1986

- 20) E.F. Schubert, J.E. Cunnimgham, and W.T. Tsang, "Self-aligned enhancement-mode and depletion-mode GaAs field-effect transistors employing the  $\,\delta$ -doping technique," Appl. Phys. Lett., 49 (25), pp.1729-1731, 1986

- 21) K. Ploog, "Delta-(δ-) Doping in MBE-Grown GaAs: Concept and Device Application," J. Crystal Growth 81, pp.304-313, 1987

22) A. Zrenner, H. Reisinger, F. Koch, and K. Ploog, "Electron Subband Structure of a  $\delta$  (z)-Doping Layer in n-GaAs", Proc. of the 17th Int. Conf. on the Physics of Semiconductors,

pp.325-328, 1985

- 23) A.Zrenner, F. Koch, and K. Ploog, "Facts and fancies about the δ -doping layer of Si in MBE-grown GaAs", Inst. Phys. Conf. Ser. No. 91, pp.171-174, 1988 (Paper presented at Int. Symp. GaAs and Related Compounds, Heraklion, Greece, 1987)

- 24) L.L. Chang, H. Sakaki, C.A. Chang, and L. Esaki, Phys. Rev. Lett. 38, p.1489, 1977

- 25) S. Yamada and T. Makimoto, "Subband mobility of quasi-two-dimensional electrons in Si atomic layer doped GaAs", Appl. Phys. Lett. 57 (10), pp.1022-1024

- 26) N. Pan, J. Carter, G.S. Jackson, H.Hendriks, and X.L. Zheng, "Si delta-doped field-effect transisors by atmospheric pressure metalorganic chemical vapor deposition", Appl. Phys. Lett. 59 (4), pp.458-460, 1991

- 27) M. Inoue, M. Inayama, S. Shirafuji, and Y. Inuishi, "Parallel Electron Transport and Field Effects of Electron Distributions in Selectively-Doped GaAs/n-AlGaAs", Jpn. J. Appl. Phys, Vol.22, No.4, pp.L213-215, 1983

- 28) T. Makimoto, N. Kobayashi, and Y. Horikoshi, "Electron conduction in GaAs atomic layer doped with Si", J. Appl. Phys., 63 (10), pp.5023-5026, 1988

- 29) E.F. Schubert, J.E. Cunningham, and W.T. Tsang, "Electron-Mobility Enhancement and Electron-Concentration Enhancement in δ-doped n-GaAs at T=300K", Solid State Comm., Vol.63, No.7, pp.591-594, 1987

- 30) Y. Balynas, A. Krotkus, T. Lideikis, A. Stalnionis, and G. Treideris, "Electro-optical Measurement of High-field Conductivity in  $\delta$ -doped GaAs Epitaxial Layers", Electronics Lett., Vol.27, No.1, pp.2-3, 1991

- 31) W.T. Masselink, "High differential mobility of hot electrons in delta-doped quantum wells", Appl. Phys. Lett. 59 (6), pp.694-696, 1991

- 32) 中島 成、林 秀樹、「電界効果トランジスタ」、特願平 3-10870

" Field Effect Transistor having a double pulse-doped structure,"

United States Patent- 540811

- 33) S. Nakajima, N. Kuwata, N. Shiga, K. Otobe, K. Matsuzaki, T. Sekiguchi, and H. Hayashi, "Characterization of Double Pulse-Doped Channel GaAs MESFET's", IEEE Electron Device Lett., Vol.14, No.3, pp.146-148, 1993

- 34) S.J. Wang, S.L. Wu, H.D. Chung, T.K. Carns, X.Zheng, and K.L. Wang, "A p-Channel Coupled Delta-Doped Silicon MESFET Grown by Molecular Beam Epitaxy", IEEE Electron Device Lett., Vol.15, No.6, pp.206-208, 1994

- 35) S.L. Wu, S.J. Wang, and C.C. Liu, "High-Performance Double δ-Doped Channel Si Metal Semiconductor Field-Effect Transistors", Jpn. J. Appl. Phys., Vol.33, pp.L1195-L1197, 1994

36) X. Xheng, T.K. Carns, K.L. Wang, and B. Wu, "Electron mobility enhancement from coupled wells in delta-doped GaAs," Appl. Phys. Lett., 62 (5), pp.504-506, 1993

# 第5章 GaAs MESFETの高周波特性

## 5-1緒言

ない。

GaAsをデバイス材料として用いる利点はその優れた高速動作、高周波特性にある。 近年Si バイポラートランジスタの性能が向上してきたとはいえ、比較的電流容量の大 きなもの、また低電圧駆動応用ではGaAs系デバイスの優位は動かない。高速動作や高周 波特性の良さは、電子デバイスの特性を評価する上で重要である。しかしながら「デバ イス特性を決定している物理機構は何か」という基本問題は必ずしも明確にはなってい

1980年に開発された高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor) は、その高い電子移動度ゆえにMESFETよりも優れた特性を示すと言われてきた。しかしながら、デバイスの動作を考えた場合、チャンネルには高電界が印加されているので低電界の移動度は素子特性に大きな影響を与えないとも考えられる。筑波大学の長谷川は、この観点からHEMTの動作原理を見直しHEMTの特性には高電子移動度はほとんど寄与していないことを指摘した1)。一方、ゲート長が短縮されてきた場合、電子輸送に非定常的つまり電子速度のオーバーシュート効果が見えるため低電界での移動度の高いHEMTがやはり有利ではないかという意見もある2)。

本章では、本研究で作製したMESFETとこれまでに他研究期間で開発されたHEMTを 比較することにより、デバイスの高速性/高周波特性を決める要因を明らかにする。

## 5-2 素子の高速動作、高周波特性を表す指標

GaAs MESFETの高速動作を表す指標には伝達コンダクタンス gmが用いられる。また 高周波特性を表す指標としては電流遮断周波数 frが用いられる。

MESFETのドレイン電流(Ids)はポアソン方程式を解くことで求められる。

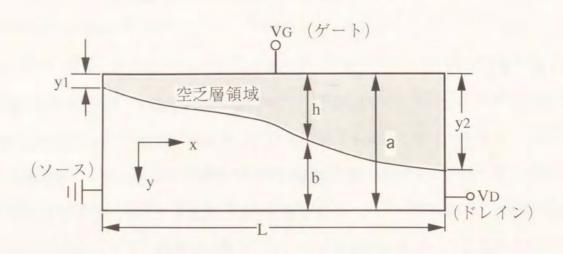

計算のために図5-1のようにx,y 座標の向きを取る。今、グラジュアル近似が成り立つ時には一次元のポアソン方程式は次のようになる。

図 5-1 チャンネル内の空乏層の模式図

$-d^2V/dy^2=dEy/dy=\rho(y)/\epsilon s$   $\pm t^2V^2=qNd/\epsilon s$  (1)

Eyはy方向の電界強度である。

ソース側からxだけ離れた場所での空乏層幅hは

$h=\{2 \in s[V(x)+Vg+Vbi]/qNd\}^{1/2}$  であるので

$dh=\{2 \in s[V(x)+Vg+Vbi]/qNd\}^{-1/2} \cdot (\epsilon s/qNd) dV$  (2)

ソース端、ドレイン端での空乏層幅はそれぞれ次のようになる。

$y_1=[2 \epsilon s(Vg+Vbi)/qNd]^{1/2}$  ソース端 (x=0) (3)

y2=[2 ε s(Vd+Vg+Vbi)/qNd]<sup>1/2</sup> ドレイン端 (x=L)

$y_2$ の最大値はチャネル厚(a)に等しく、それに対応する電圧をピンチオフ電圧(Vp)と呼ぶ。

$V_p=V(y_2=a)=qN_da^2/2 \in s$  (4)

x方向の電流密度Jxは

$Jx=qN_d \mu Ex$  (5)

Exはx方向の電界強度(Ex=-dV/dx)、 $\mu$ は移動度である。

ドレイン電流(Id)は次のように与えられる。

$Id=qN_d \mu (dV/dx)(a-h)Z$  (

Id ·  $dx=Z \mu qN_d(a-h)dV$  (6a)

ここで式(2)を用いて dV=(qNd/εs)·h·dh (7)

(7)式を(6)式に代入してx=0からx=Lまで積分すると

$$Id = \frac{1}{L} \int_{y_1}^{y_2} Z \mu q N_D(a-h) \frac{q N_D}{\varepsilon_s} h dh$$

$$= \frac{Z \mu q^2 N_D^2 a^3}{6 \varepsilon_s L} \left[ \frac{3}{a^2} (y_2^2 - y_1^2) - \frac{2}{a^3} (y_2^3 - y_1^3) \right]$$

(8)

ゲート長が短くなると電子は飽和速度で走行する。つまり  $\mu$  (dV/dx)=Vs よって(6)式はId=qVsZ(a-h)Ndと表される。この場合は均一ドープの場合であるが 一般的なドーピングプロファイル  $\rho$  (y)の場合は、

$$I = VsZ \int_{0}^{a-h} \rho(y) dy \qquad (9)$$

$dI/dh=VsZ \rho (h), dV/dh=h \rho (h)/ \varepsilon s$