| Title        | Study on Model Abstraction for Model Checking of<br>Real-time Systems |

|--------------|-----------------------------------------------------------------------|

| Author(s)    | Nagaoka, Takeshi                                                      |

| Citation     | 大阪大学, 2011, 博士論文                                                      |

| Version Type | VoR                                                                   |

| URL          | https://hdl.handle.net/11094/482                                      |

| rights       |                                                                       |

| Note         |                                                                       |

### Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

Study on Model Abstraction for Model Checking of Real-time Systems

January 2011

Takeshi NAGAOKA

Study on Model Abstraction for Model Checking of Real-time Systems

Submitted to Graduate School of Information Science and Technology Osaka University

January 2011

Takeshi NAGAOKA

### Abstract

Model checking techniques are considered as promising techniques for information system verification due to their ability of exhaustive checking. In addition, diagnostic information of model checking, which is provided as a counter example, is thought to be useful for error correction. In recent years, model checking supports more complicated analysis such as verification of real-time requirements, performance evaluation for systems with random behavior, and so on. It is difficult, however, to apply such analysis into large systems because of the well-known state explosion problem.

Timed automata, which can model real-time behavior of systems, are used to verify real-time requirements. The timed automata are finite automata with real-time constraints described by real-valued variables called clocks. Therefore the timed automata theoretically have infinite state space. Almost all verification techniques for the timed automata use the fact that the infinite state space can be approximated to finite one. However, the size of the approximated state space increases exponentially with the number of clock variables. For verification of systems with random behavior, probabilistic model checking techniques are developed, where probabilistic models such as Markov chains, Markov decision processes are used. In these days, probabilistic timed automata, which can model real-time and probabilistic behavior of systems, are proposed.

To reduce the state space of timed automata, we propose an abstraction technique for timed automata. The proposed technique is based on a well-organized abstraction framework, CounterExample-Guided Abstraction Refinement (CEGAR), in which we use a counter example as a guide to refine an abstracted model. In this technique, we generate an abstract model by removing all of the clock variables from given timed automata. Then, we refine the abstract model repeatedly to generate an appropriate abstract model for checking a given property. Although, in general, the refinement operation is applied to an abstract model directly, the proposed technique modifies the original timed automata, and next generates refined abstract models from the modified automata. Experimental results show the abstraction algorithm can reduce the total memory consumption by at most 80 percent compared to applying model checking without abstraction.

We extend the abstraction technique into abstraction for probabilistic timed automata. In the technique, we remove clock variables from given probabilistic timed automata as well as the original one. Then, we apply probabilistic model checking to the generated abstract model which is just a Markov decision process (MDP) with no time attributes. In general, probabilistic model checking does not produce concrete paths as a counter example which are required for abstraction refinement. Therefore, we also perform k-shortest paths search to obtain the concrete paths. Experimental results show that the proposed technique reduces state space of probabilistic timed automata compared to an existing approach. Also, the contribution of this study includes generation of concrete paths as a counter example while other related works cannot generate them.

In this study, we propose a QoS analysis technique of real-time distributed systems based on hybrid analysis of probabilistic model checking and simulation. For the Internet, system developers often have to estimate the QoS by simulation techniques or mathematical analysis. Probabilistic model checking can evaluate performance, dependability and stability of information processing systems with random behavior. We apply a hybrid analysis approach onto real-time distributed systems. In the hybrid analysis approach, we perform stepwise analysis using probabilistic models of target systems in different abstract levels. First, we create a probabilistic model with detailed behavior of the system (called detailed model), and apply simulation on the detailed model. Next, based on the simulation results, we create a probabilistic model in an abstract level (called simplified model). Then, we verify qualitative properties using the probabilistic model checking techniques. This prevents from state-explosion. We evaluate the validity of our approach by comparing to simulation results of NS-2 using a case study of a video data streaming system. The experiments show that the result of the proposed approach is very close to that of NS-2 simulation. The result encourages the approach is useful for the performance analysis on various domain.

Finally, we propose a stepwise method to verify consistency of timeliness QoS of component-based designed real-time systems. In the proposed method, the system components are designed using UML diagrams and are provided with the timeliness QoS annotated with OCL. The basis of this technique is to formally ensure that the required timeliness QoS is satisfied under the provided timeliness QoS, given the network property and the UML diagrams. In order to avoid the state-explosion problem during model checking, we separate the model checking problem into two steps. The first step checks the satisfiability using an abstract model of each of the components derived automatically from the provided QoS. The second step independently performs model checking for each of the component.

Such an approach reduces the number of total states to check. Furthermore, the approach can be extended into hierarchical design, which leads to good scalability.

### **List of Publications**

#### **Major Publications**

- [1-1] Takeshi Nagaoka, Eigo Nagai, Kozo Okano, and Shinji Kusumoto: "Stepwise Approach to Design of Real-Time Systems based UML/OCL with Formal Verification," International Journal of Informatics Society (IJIS), Informatics Society, Vol.1, No.2, pp37-44, Sep.2009.

- [1-2] Takeshi Nagaoka, Akihiko Ito, Kozo Okano, and Shinji Kusumoto: "Qos Evaluation for Real-Time Distributed Systems Using the Probabilistic Model Checker Prism," In Proceedings of International Workshop on INformatics, IWIN 2009, pp.60-66, Sep.2009.

- [1-3] Takeshi Nagaoka, Akihiko Ito, Kozo Okano, and Shinji Kusumoto: "Qualitative Analysis of Real-time Distributed Systems Considering Network Congestion by Probabilistic Model Checker PRISM," In Proceedings of International Workshop on Empirical Software Engineering in Practice 2009, IWE-SEP2009, Oct.2009.

- [1-4] Takeshi Nagaoka, Kozo Okano, and Shinji Kusumoto: "An Abstraction Refinement Technique for Timed Automata Based on Counterexample-Guided Abstraction Refinement Loop," IEICE Transactions on Information and Systems, IEICE, Vol.E93-D, No.5, pp.994-1005, 2010.

- [1-5] Takeshi Nagaoka, Akihiko Ito, Toshiaki Tanaka, Kozo Okano, and Shinji Kusumoto: "Reachability Analysis of Probabilistic Real-Time Systems Based on CEGAR for Timed Automata," In Proceedings of International Workshop on INformatics, IWIN 2010, pp.18-26, Sep.2010.

- [1-6] Takeshi Nagaoka, Akihiko Ito, Toshiaki Tanaka, Kozo Okano, Shinji Kusumoto: "Reachability Analysis of Probabilistic Timed Automata Based on an Abstraction Refinement Technique," In Proceedings of International Workshop

on Empirical Software Engineering in Practice 2010, IWESEP2010, pp.33-38, Dec.2010.

[1-7] Takeshi Nagaoka, Akihiko Ito, Kozo Okano, and Shinji Kusumoto: "QoS Analysis of Real-time Distributed Systems Based on Hybrid Analysis of Probabilistic Model Checking Technique and Simulation," IEICE Transactions on Information and Systems, accepted.

### Acknowledgements

This work could be achieved owing to a great deal of help of many individuals.

First, I would like to thank my supervisor Professor Shinji Kusumoto of Osaka University, for his continuous support, encouragement and guidance of the work.

I would like to express my gratitude to Professor Toshimitsu Masuzawa, and Professor Katsuro Inoue for their valuable comments and helpful suggestions and questions on this thesis.

I would like to express my sincere gratitude to Associate Professor Kozo Okano of Osaka University for his adequate guidance, valuable suggestions and discussions throughout this work.

I'm grateful to Assistant Professor Yoshiki Higo of Osaka University for his helpful comments and suggestions.

Many of courses that I have taken during my graduate career have been helpful in preparing this thesis. I would especially like to acknowledge the guidance of Professor Ken-ichi Hagihara and Professor Yasushi Yagi.

Finally, I would like to thank the all members of Kusumoto Laboratory of Osaka University for their helpful advice.

## Contents

| 1 | Intr           | oductio                                                                   | n                                                                                                                                                                                                                                                                                                                                                                 |

|---|----------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1            | Forma                                                                     | l Verification of Information Systems                                                                                                                                                                                                                                                                                                                             |

|   | 1.2            | Model                                                                     | Checking                                                                                                                                                                                                                                                                                                                                                          |

|   |                | 1.2.1                                                                     | Models                                                                                                                                                                                                                                                                                                                                                            |

|   |                | 1.2.2                                                                     | Properties to be Checked                                                                                                                                                                                                                                                                                                                                          |

|   | 1.3            | Appro                                                                     | aches to Avoid State Explosion                                                                                                                                                                                                                                                                                                                                    |

|   |                | 1.3.1                                                                     | Counterexample Guided Abstraction Refinement                                                                                                                                                                                                                                                                                                                      |

|   |                | 1.3.2                                                                     | Predicate Abstraction                                                                                                                                                                                                                                                                                                                                             |

|   |                | 1.3.3                                                                     | Partial Order Reduction                                                                                                                                                                                                                                                                                                                                           |

|   |                | 1.3.4                                                                     | Symmetry Reduction                                                                                                                                                                                                                                                                                                                                                |

|   | 1.4            | Resear                                                                    | rch Overview                                                                                                                                                                                                                                                                                                                                                      |

|   |                | 1.4.1                                                                     | Abstraction Refinement for Timed Automata based on CE-                                                                                                                                                                                                                                                                                                            |

|   |                |                                                                           | GAR                                                                                                                                                                                                                                                                                                                                                               |

|   |                | 1.4.2                                                                     | Abstraction Refinement for Probabilistic Timed Automata                                                                                                                                                                                                                                                                                                           |

|   |                |                                                                           |                                                                                                                                                                                                                                                                                                                                                                   |

|   |                |                                                                           | based on CEGAR                                                                                                                                                                                                                                                                                                                                                    |

|   |                | 1.4.3                                                                     | Qualitative Analysis of Real-time Distributed Systems Us-                                                                                                                                                                                                                                                                                                         |

|   |                | 1.4.3                                                                     | Qualitative Analysis of Real-time Distributed Systems Us-<br>ing the Probabilistic Model Checker PRISM                                                                                                                                                                                                                                                            |

|   |                | 1.4.3<br>1.4.4                                                            | Qualitative Analysis of Real-time Distributed Systems Us-<br>ing the Probabilistic Model Checker PRISM Formal Verification with a Stepwise Abstraction Approach                                                                                                                                                                                                   |

|   |                |                                                                           | Qualitative Analysis of Real-time Distributed Systems Us-<br>ing the Probabilistic Model Checker PRISM                                                                                                                                                                                                                                                            |

| 2 | Abs            | 1.4.4                                                                     | Qualitative Analysis of Real-time Distributed Systems Us-<br>ing the Probabilistic Model Checker PRISM Formal Verification with a Stepwise Abstraction Approach                                                                                                                                                                                                   |

| 2 | <b>Abs</b> 2.1 | 1.4.4<br>traction                                                         | Qualitative Analysis of Real-time Distributed Systems Us-<br>ing the Probabilistic Model Checker PRISM<br>Formal Verification with a Stepwise Abstraction Approach<br>for UML/OCL Based Design of Real-time Systems                                                                                                                                               |

| 2 |                | 1.4.4<br>traction<br>Introd                                               | Qualitative Analysis of Real-time Distributed Systems Us-<br>ing the Probabilistic Model Checker PRISM<br>Formal Verification with a Stepwise Abstraction Approach<br>for UML/OCL Based Design of Real-time Systems                                                                                                                                               |

| 2 | 2.1            | 1.4.4<br>traction<br>Introd                                               | Qualitative Analysis of Real-time Distributed Systems Us-<br>ing the Probabilistic Model Checker PRISM Formal Verification with a Stepwise Abstraction Approach<br>for UML/OCL Based Design of Real-time Systems <b>A Refinement for Timed Automata based on CEGAR</b><br>uction                                                                                  |

| 2 | 2.1            | 1.4.4<br><b>tractio</b> r<br>Introd<br>Prelim                             | Qualitative Analysis of Real-time Distributed Systems Us-<br>ing the Probabilistic Model Checker PRISM Formal Verification with a Stepwise Abstraction Approach<br>for UML/OCL Based Design of Real-time Systems<br><b>Refinement for Timed Automata based on CEGAR</b><br>uction                                                                                 |

| 2 | 2.1            | 1.4.4<br>traction<br>Introd<br>Prelim<br>2.2.1                            | Qualitative Analysis of Real-time Distributed Systems Using the Probabilistic Model Checker PRISM          Formal Verification with a Stepwise Abstraction Approach for UML/OCL Based Design of Real-time Systems          Refinement for Timed Automata based on CEGAR          uction           Name           Clock and Zone                                   |

| 2 | 2.1            | 1.4.4<br>traction<br>Introd<br>Prelim<br>2.2.1<br>2.2.2                   | Qualitative Analysis of Real-time Distributed Systems Using the Probabilistic Model Checker PRISM          Formal Verification with a Stepwise Abstraction Approach for UML/OCL Based Design of Real-time Systems <b>Refinement for Timed Automata based on CEGAR</b> uction          tinary          Clock and Zone          Timed Automaton                     |

| 2 | 2.1            | 1.4.4<br>traction<br>Introd<br>Prelim<br>2.2.1<br>2.2.2<br>2.2.3          | Qualitative Analysis of Real-time Distributed Systems Using the Probabilistic Model Checker PRISM          Formal Verification with a Stepwise Abstraction Approach for UML/OCL Based Design of Real-time Systems <b>Refinement for Timed Automata based on CEGAR</b> uction          Clock and Zone          Timed Automaton          Region Automaton           |

| 2 | 2.1            | 1.4.4<br>traction<br>Introd<br>Prelim<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4 | Qualitative Analysis of Real-time Distributed Systems Using the Probabilistic Model Checker PRISM          Formal Verification with a Stepwise Abstraction Approach for UML/OCL Based Design of Real-time Systems <b>Refinement for Timed Automata based on CEGAR</b> uction          inary          Clock and Zone          Region Automaton          Zone Graph |

|   |     | 2.2.7    | CounterExample-Guided Abstraction Refinement 21      |

|---|-----|----------|------------------------------------------------------|

|   | 2.3 | Propos   | sed Algorithm                                        |

|   |     | 2.3.1    | Abstract Model                                       |

|   |     | 2.3.2    | Initial Abstraction                                  |

|   |     | 2.3.3    | Simulation                                           |

|   |     | 2.3.4    | Abstraction Refinement                               |

|   |     | 2.3.5    | Example                                              |

|   | 2.4 | Correc   | ztness Proof                                         |

|   | 2.5 | Experi   | ment                                                 |

|   |     | 2.5.1    | goals of the Experiments                             |

|   |     | 2.5.2    | Example                                              |

|   |     | 2.5.3    | Procedure of the Experiments                         |

|   |     | 2.5.4    | Results of Experiments                               |

|   |     | 2.5.5    | Discussion                                           |

|   |     | 2.5.6    | Complexity                                           |

|   | 2.6 | Summ     | ary                                                  |

| 3 | Abs | traction | Refinement for Probabilistic Timed Automata based on |

| 5 |     | GAR      | 45                                                   |

|   | 3.1 | Introdu  | uction                                               |

|   | 3.2 | Prelim   | inary                                                |

|   |     | 3.2.1    | Probability Distribution                             |

|   |     | 3.2.2    | Markov Decision Process                              |

|   |     | 3.2.3    | Probabilistic Timed Automaton                        |

|   |     | 3.2.4    | Probabilistic CTL                                    |

|   | 3.3 | Propos   | sed Approach                                         |

|   |     | 3.3.1    | Initial Abstraction                                  |

|   |     | 3.3.2    | Model Checking                                       |

|   |     | 3.3.3    | Simulation                                           |

|   |     | 3.3.4    | Abstraction Refinement 54                            |

|   |     | 3.3.5    | Compatibility Checking                               |

|   |     | 3.3.6    | Model Transformation                                 |

|   | 3.4 | Correc   | ctness Proof                                         |

|   | 3.5 | Experi   | ments                                                |

|   |     | 3.5.1    | Goals of the Experiments                             |

|   |     | 3.5.2    | Example                                              |

|   |     | 3.5.3    | Procedure of the Experiments                         |

|   |     | 3.5.4    | Results of the Experiments                           |

|   |     | 3.5.5    | Discussion                                           |

|   | 3.6 | Summ     | ary                                                  |

| 4 | Qua   | itative Analysis of Real-time Distributed Systems Using the Prob- |          |

|---|-------|-------------------------------------------------------------------|----------|

|   | abili | stic Model Checker PRISM                                          | 69       |

|   | 4.1   | Introduction                                                      | 69       |

|   | 4.2   | Preliminary                                                       | 70       |

|   |       | 4.2.1 Probabilistic Model Checker PRISM                           | 70       |

|   |       | 4.2.2 Protocols for Net-streaming                                 | 71       |

|   | 4.3   |                                                                   | 73       |

|   |       | 4.3.1 Target System                                               | 73       |

|   |       | 4.3.2 The Detailed Model                                          | 73       |

|   |       |                                                                   | 77       |

|   | 4.4   | Experiments                                                       | 81       |

|   |       | 4.4.1 Analysis of the Correctness                                 | 81       |

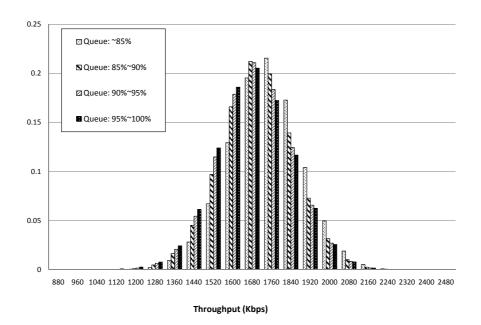

|   |       | 4.4.2 Verification results for the simplified model               | 84       |

|   |       | -                                                                 | 85       |

|   | 4.5   | Summary                                                           | 85       |

| 5 | For   | al Verification with a Stepwise Abstraction Approach for UML/OC   | T.       |

| 5 |       |                                                                   | 12<br>87 |

|   | 5.1   | 8                                                                 | 87       |

|   | 5.2   |                                                                   | 88       |

|   | 5.2   | 5                                                                 | 88       |

|   |       | e                                                                 | 88       |

|   | 5.3   | Ç ,                                                               | 90       |

|   | 5.5   |                                                                   | 91       |

|   |       | · · · · · · · · · · · · · · · · · · ·                             | 95       |

|   | 5.4   | 1                                                                 | 97       |

|   | 5.4   | 1                                                                 | 97       |

|   |       | 1                                                                 | 97       |

|   |       | ······                                                            | 97<br>00 |

|   |       | 1                                                                 | 00       |

|   | 5.5   |                                                                   | 01       |

|   |       |                                                                   | 02       |

| 6 |       |                                                                   | 03       |

|   | 6.1   | 5                                                                 | 03       |

|   | 6.2   | Directions of Future Research                                     | 04       |

# **List of Figures**

| 1.1 | The Light User Model                                                                                    | 3  |

|-----|---------------------------------------------------------------------------------------------------------|----|

| 1.2 | The Randomised Self-Stabilizing Algorithms Model                                                        | 4  |

| 1.3 | The FireWire Root Contention Protocol Model                                                             | 5  |

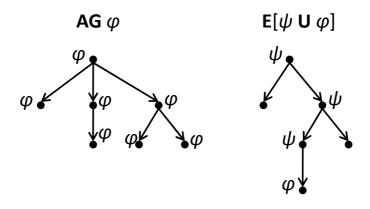

| 1.4 | Examples of Semantics of LTL                                                                            | 6  |

| 1.5 | Examples of Semantics of CTL                                                                            | 7  |

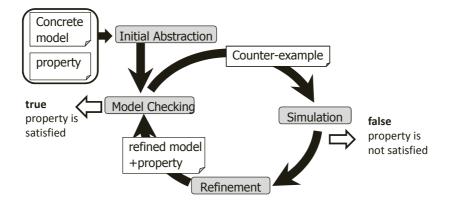

| 1.6 | A General CEGAR Technique                                                                               | 8  |

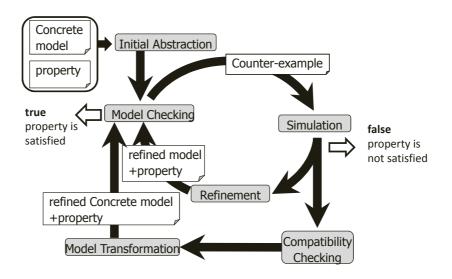

| 1.7 | Our CEGAR Technique for Reachability Analysis of a Probabilis-                                          |    |

|     | tic Timed Automaton                                                                                     | 11 |

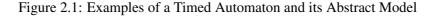

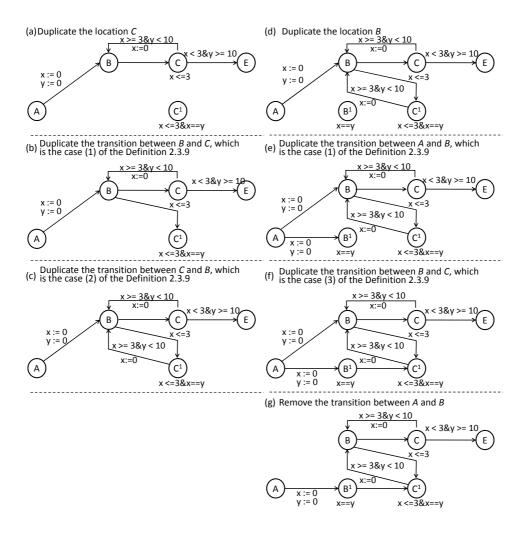

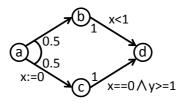

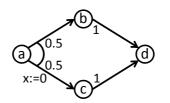

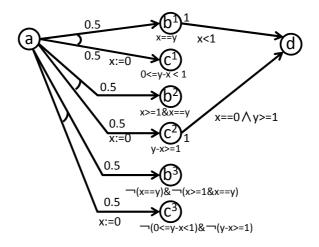

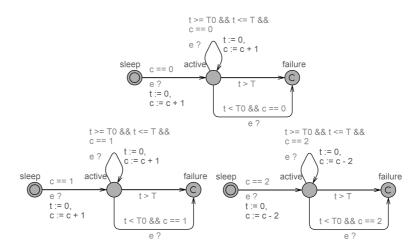

| 2.1 | Examples of a Timed Automaton and its Abstract Model                                                    | 24 |

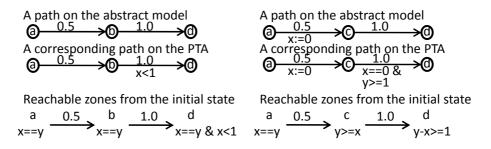

| 2.2 | A Simulation Process                                                                                    | 27 |

| 2.3 | An Example of the Algorithm Reaches to the Initial Location                                             | 29 |

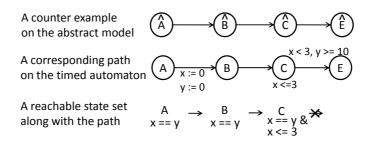

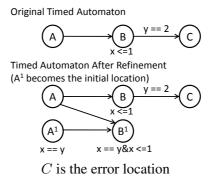

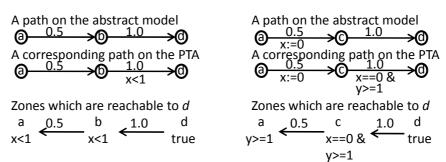

| 2.4 | The Refinement Process for the Path in Fig.2.2                                                          | 36 |

| 2.5 | The Timed Automata After the Second ((a) of the Figure) and                                             |    |

|     | Third ((b) of the Figure) Refinement Steps Respectively                                                 | 37 |

| 2.6 | An Example of the Case When $s_1 \stackrel{a}{\Rightarrow} s_2 \notin \Rightarrow'$ in the Proof (i) of |    |

|     | Lemma 2.4.1                                                                                             | 38 |

| 2.7 | An Overview of the Timed Automaton After the Refinement Step                                            |    |

|     | with the Path $\pi$                                                                                     | 41 |

| 3.1 | An Example of an MDP                                                                                    | 46 |

| 3.2 | Examples of Adversaries                                                                                 | 47 |

| 3.3 | An Example of a PTA                                                                                     | 48 |

| 3.4 | An Initial Abstract Model                                                                               | 53 |

| 3.5 | Simulation Results for a Set of Paths                                                                   | 55 |

| 3.6 | Results of Backward Simulation for a Set of Paths                                                       | 57 |

| 3.7 | The Transformed PTA                                                                                     | 63 |

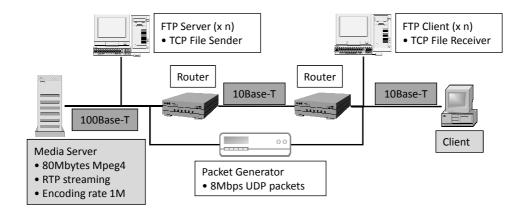

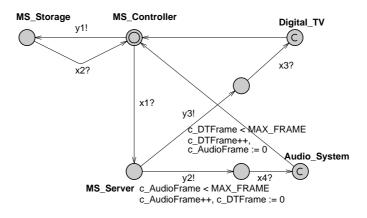

| 4.1 | A Configuration of Experimental System                                                                  | 74 |

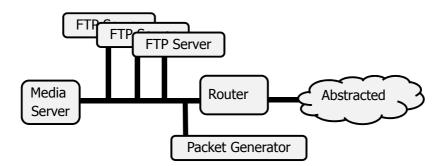

| 4.2 | An Abstract Outline of the Detailed Model                                                               | 74 |

| 4.3  | The Module of Router Described with PRISM Language             | 76  |

|------|----------------------------------------------------------------|-----|

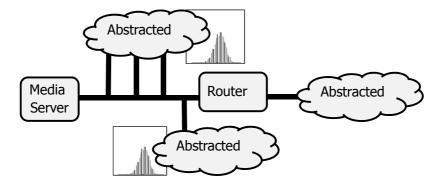

| 4.4  | An Abstract Outline of the Simplified Model                    | 78  |

| 4.5  | A Part of Reward Descriptions for Analysis of the Distribution | 79  |

| 4.6  | The Abstracted Module for four FTP servers                     | 80  |

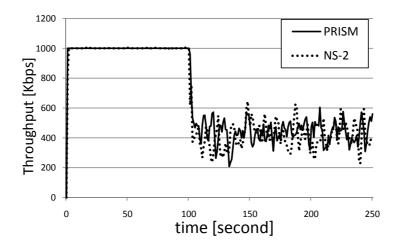

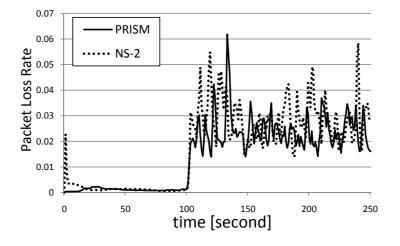

| 4.7  | Comparison of the Throughput                                   | 82  |

| 4.8  | Comparison of Packet Loss Rates                                | 82  |

| 4.9  | The Discrete Probability Distribution of Throughput of the FTP |     |

|      | Servers                                                        | 84  |

| 5.1  | A Configuration of Components in UML Class Diagram             | 89  |

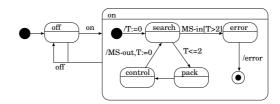

| 5.2  | An Abstract QoS automaton for Anchored Throughput              | 92  |

| 5.3  | An Abstract QoS automaton for Non-Anchored Jitter              | 92  |

| 5.4  | An Abstract QoS automaton for Latency                          | 93  |

| 5.5  | A Test Automaton for Throughput                                | 94  |

| 5.6  | A Test Automaton for Jitter                                    | 95  |

| 5.7  | A Test Automaton for Latency                                   | 96  |

| 5.8  | Verification on UPPAAL Based on Test Automata                  | 97  |

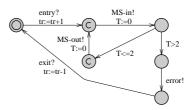

| 5.9  | The Class Diagram of Media Server                              | 98  |

| 5.10 | The Configuration Automaton                                    | 99  |

| 5.11 | The network of test automata for the given required QoS        | 99  |

| 5.12 | The UML Statechart Diagram of Component MS-Storage             | 101 |

| 5.13 | The UPPAAL Timed Automaton of Component MS-Storage             | 101 |

|      |                                                                |     |

## **List of Tables**

| 2.1 | The Experimental Results                        | 43  |

|-----|-------------------------------------------------|-----|

| 3.1 | The Experimental Results                        | 66  |

| 3.2 | Analysis of Counter Example Paths               | 67  |

| 4.1 | Parameters of the Throughput Estimation Formula | 72  |

| 4.2 | Summary of the Analyzed Data (3 FTP servers)    | 83  |

| 4.3 | Summary of the Analyzed Data (4 FTP servers)    | 83  |

| 4.4 | Summary of the Analyzed Data (5 FTP servers)    | 83  |

| 5.1 | The Result (1) of the First Step                | 100 |

| 5.2 | _                                               |     |

### **Chapter 1**

### Introduction

#### **1.1** Formal Verification of Information Systems

In recent years, though information systems play an important role in social activities, defects on the systems may cause serious loss to society. As the systems become larger and more complicated, it is difficult to assure the reliability of the systems. In order to develop reliable systems, it is important to verify designs of the systems at an early phase of their development. Such verification avoids us to regress the development steps.

Formal methods are considered as promising techniques for reliable systems development. The formal methods can automatically prove the correctness of the systems using formal descriptions of the system designs and mathematical theories in order to analyse the systems. Using the formal methods, we can also obtain reliable proofs based on the mathematical theories.

In general, the formal methods are classified into two kinds of approaches, model checking[1] and automated theorem proving[2]. In the model checking technique, information systems are modeled as finite state machines. Model checkers[3, 4, 5, 6] decide whether the model satisfies given requirements or not by searching state space exhaustively. On the other hand, in the automated theorem proving technique, systems and requirements are described in logical forms. Theorem provers[7, 8, 9] prove whether the system satisfies the requirements in mathematical ways. Usually, theorem provers only check if proofs, which are human constructed manually, are correct or not. Conventional theorem provers are not full automatic. The proofs are constructed interactively. A simple theory, such as inequalities on integer arithmetic, can be automatically proved. For example, x > y implies x + 2y > 3y, can be proved by most of automated theorem provers. However, some of them cannot automatically prove a tautology x = y and  $\forall x.f(x) = g(x)$  imply f(x) = g(y). Thus, each theorem prover only supports its own limited class of theories. Though some of modern theorem provers also support for engineers to construct their proofs and have facilities to enhance several non-standard logics, and domain specific axioms and inference rules, the essential of the theorem provers is not to provide proofs but to check proofs. In general, theorem proving approaches can deal with a wide range of information systems according to their basis theories and mathematic abilities of the users. In contrast, model checking approaches are easy to use but the target domain is limited. They are suitable to check behaviour of the systems rather than check correctness of calculation. Some methods are hybrid. For example, B Method[10] supports both of a theorem prover and a model checker in order to resolve "proof obligations" which are automatically derived from specifications described in B Method syntax. Although formal verification has merits with automated and reliable verification, there are several problems such as difficulty of formal descriptions, limitation of its scalability. In this study, we propose techniques to improve the limitation of scalability of model checking using model abstraction techniques.

#### 1.2 Model Checking

A model checker checks if a given system modeled in a finite automaton satisfies given specifications by searching the finite transition system exhaustively. It sometimes has, however, limitation in scalability. In order to improve the scalability, a model abstraction technique is important[11, 12, 13, 14, 15].

For verification of real-time systems such as embedded systems, timed automata[16, 17, 18] are usually used. On the other hand, probabilistic model checking can evaluate performance, dependability and stability of information processing systems with random behaviors[19]. Probabilistic model checking handles several probabilistic models such as discrete-time Markov chains (DTMC), continuoustime Markov chains (CTMC), Markov decision processes (MDP), and so on. In recent years, probabilistic models with real-time behaviors, called probabilistic timed automata[20] are used to evaluate dependability of real-time systems based on the probabilistic model checking technique.

#### 1.2.1 Models

This research mainly focuses on timed automata and probabilistic models including probabilistic timed automata as models for model checking.

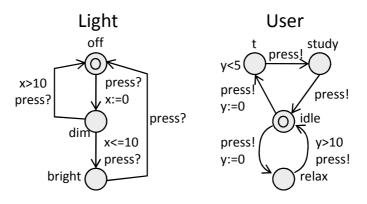

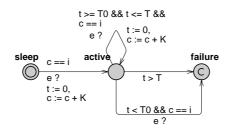

Figure 1.1: The Light User Model

#### **Timed Automata**

Timed automata are finite state automata with real-time constraints described with real-valued variables called clocks. In timed automata, real-valued clock constraints are assigned to their control state (called a location) and transitions. Therefore, they have infinite state space represented in a product of discrete state space made by locations and continuous state space made by clock variables. In traditional model checking for timed automata, using the property that we can treat the state space of clock variables as a finite set of regions, we can perform model checking on timed automata models. However, the size of such regions increases exponentially with the number of clock variables, Thus an abstraction technique is also needed. For verification of timed automata, several tools such as UPPAAL[5, 21, 22], KRONOS[23, 24] are developed.

Figure 1.1 is an example of timed automata, the Light User model[16]. The model is composed of two timed automata, a light model (left side of the figure) and a user model (right side of the model). Each model has one clock variable and communicates with the other model through the channel *press*.

#### **Probabilistic Models**

Probabilistic models[25] can describe behavior of stochastic systems such as network protocols which decide next behavior stochastically, randomised distributed algorithms, and so on. In the probabilistic models, transitions between states are labeled by the probability to fire the transitions.

In general, the probabilistic models are classified into discrete-time Markov chains (DTMCs), continuous-time Markov chains (CTMCs), and Markov decision

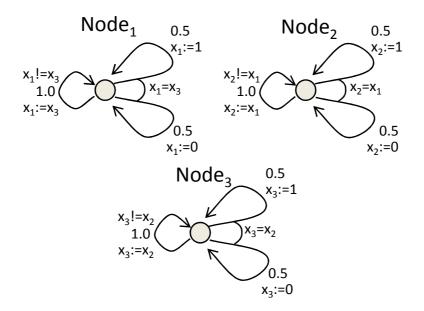

Figure 1.2: The Randomised Self-Stabilizing Algorithms Model

processes (MDPs). In the DTMCs, the label of probability is assigned discretely for each transition. In the CTMCs, transitions between states occur in a real time step while transitions of DTMCs occur in a discrete time step. MDPs can be seen as a generalisation of DTMCs. MDPs can describe both non-deterministic and probabilistic behavior.

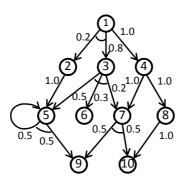

Figure 1.2 shows an example of the DTMCs, the Randomised Self-Stabilizing Algorithms[26] model. In the model, each node has one integer variable  $x_i$ . The stable configurations are those where exactly one node has a token. In this model, the *node<sub>i</sub>* has a token if  $x_i = x_{i-1}$  holds. Each node changes the value of  $x_i$  randomly, and this finally makes the configuration stable.

One of probabilistic model checkers PRISM[6, 27] can handle DTMCs, CTMCs, and MDPs.

#### **Probabilistic Timed Automata**

Probabilistic timed automata are kinds of timed automata extended with probabilistic behavior. Therefore, state space of probabilistic timed automata is same as that of timed automata. Since the probabilistic timed automata accept nondeterministic transitions, they are also considered as kinds of Markov decision processes. Using the probabilistic timed automata, several case studies were intro-

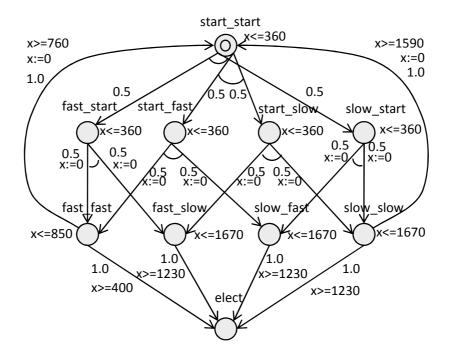

Figure 1.3: The FireWire Root Contention Protocol Model

duced. For example, Papers[28, 29] performed performance analysis of protocols for wireless networks.

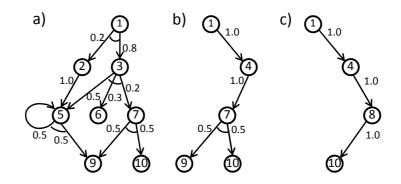

Figure 1.3 shows an example of a probabilistic timed automaton, the FireWire root contention protocol model[29]. In the figure, transitions which belong to the same distribution are connected with a small arc at their source points. For example, at the location *start\_start*, there are two probability distributions. In one of them, the control moves to the location *fast\_start* with the probability 0.5 and to the location *start\_fast* with 0.5 as well. In the other one, the control moves to the location *start\_fast* with 0.5 and to the location *start\_fast* with 0.5 as well. These distributions are selected non-deterministically.

#### 1.2.2 Properties to be Checked

If we model behavior of systems, we should formally describe properties to be checked. In formal verification, the properties are described with temporal logic[1] such as liner temporal logic (LTL)[30] and computational tree logic (CTL)[31]. The temporal logic can describe properties quantified in terms of time. In formulae

Figure 1.4: Examples of Semantics of LTL

described with temporal logic, we can use temporal operators such as  $\mathbf{F}$  which means the property will hold in the future,  $\mathbf{A}$  which means that the property always holds, and so on.

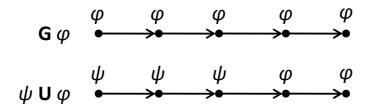

#### LTL

LTL can represent properties related to a path on a target model. For example, properties such as 'for some state on the path' or 'for every two consecutive states' can be expressed. LTL accepts temporal operators **F** (in the future), **G** (globally), **X** (next) and **U** (until) as well as general logical operators such as conjunction ( $\land$ ), disjunction ( $\lor$ ), implication ( $\rightarrow$ ), and so on. For example, the LTL formula '**G**  $\phi$ ' means that the property  $\phi$  holds at all states along the path, and ' $\psi$  **U**  $\phi$ ' means that there is a state on the path at which  $\phi$  holds, and  $\psi$  holds at every state before  $\phi$ . Figure 1.4 shows examples of semantics of LTL. The dots in the figure show states. The states where some LTL formulae such as  $\phi$  and  $\psi$  are associated show that the associated formulae hold at the states.

The model checker SPIN[3] supports LTL model checking. In the LTL model checking, the property described with LTL is translated into a Büchi automaton[32]. SPIN computes the synchronous product of this Büchi automaton and the automaton describing target system's behavior, and checks whether there exists the language accepted by the product automaton.

#### CTL

CTL can represent properties with tree like structures which have several branches. CTL accepts quantifiers over paths such as **A**, which means that the property holds for all paths starting from the current state, and **E**, which means that the there exists at least one path starting from the current state where the property holds, as well as temporal operators **F**, **G**, **X** and **U**. In the CTL formula, these quantifiers and temporal operators are combined. For example, the CTL property 'AG  $\phi$ '

Figure 1.5: Examples of Semantics of CTL

means that for all paths starting from the current state the property  $\phi$  holds at all states along the paths. Figure 1.5 shows examples of semantics of CTL.

The model checker NuSMV[4] supports CTL model checking. In the CTL model checking, the model checker inductively computes a set of states which satisfy the given CTL formula. If the set of states obtained by CTL model checking includes initial states, the model checker concludes that the model satisfies the given CTL property. If the model is finite, such computation converges within finite time. Therefore, the CTL model checking terminates.

There are several extensions of CTL to represent real-time properties, probabilistic properties, and so on.

Timed CTL (TCTL)[33, 34] extends CTL with clock variables. Therefore, TCTL accepts atomic formulae about clock variables, which are restricted by differential inequalities between two clock variables in general. TCTL is used to describe properties on timed automata and probabilistic timed automata.

Probabilistic CTL (PCTL)[35] extends CTL with probability. In the PCTL properties, the operator  $\mathbf{P}$ , which indicates probability over an associated computation tree, is provided. For example, PCTL can describe the property of 'what is the probability to reach a given error state.' PCTL is used to describe properties on discrete-time Markov chains, Markov decision processes, and probabilistic timed automata. On the other hand, for continuous-timed Markov chains, continuous stochastic logic (CSL)[36], which is inspired by the logic CTL, PCTL, and TCTL, is mainly used.

Probabilistic timed CTL (PTCTL)[20] is proposed to combine the probabilistic operator of the PCTL and timing constraints of the TCTL. PTCTL is used to describe properties of probabilistic timed automata.

Figure 1.6: A General CEGAR Technique

#### **1.3** Approaches to Avoid State Explosion

In model checking, explosion of state space or execution time is a major problem. In general, such problem is caused by increasing of size of target systems or complexity of properties to be checked. In recent years, there are several studies which tackle this problem.

#### 1.3.1 Counterexample Guided Abstraction Refinement

Clarke *et al.* proposed an abstraction technique called CEGAR (CounterExample-Guided Abstraction Refinement)[11] shown in Fig.1.6. The technique is used for abstraction of finite models[11, 12], hybrid systems[13], timed automata[37, 38, 39], and other models. In the CEGAR technique, we use a counter example produced by a model checker as a guide to refine excessively abstracted models.

A general CEGAR technique consists of several steps. First, we abstract an original model and generate an initial abstract model. Next we perform model checking on the abstract model. In this step, if a counter example is detected by a model checker, we check the counter example on the original model. If we find that the counter example is spurious, we have to refine the abstract model. The last step is repeated until the valid output is obtained. In the CEGAR loop, an abstract model must satisfy the following property; if the abstract model satisfies a given specification, the concrete model also satisfies it.

#### 1.3.2 Predicate Abstraction

Predicate abstraction[14, 15] abstracts state space using a given finite set of predicates. For the set of predicates, predicate abstraction defines an equivalence relation over a set of states with regard to the truth of every predicate. In the predicate abstraction, how to choose such a set of predicates is one of major problems. Some works use the framework of CEGAR, i.e. if abstraction generates spurious behavior, they refine an abstract model by adding other predicates into the set.

#### 1.3.3 Partial Order Reduction

Partial order reduction[40, 41] mainly reduces state space search for a model described as a set of concurrent processes. An execution of such a concurrent model is represented as a sequence of events where events of concurrent processes are interleaved. Concrete orders of such events, however, have little effect on the truth of properties to be checked in general, if the events are independent each other. Partial order reduction defines partial orders over such interleaves and reduces state space search which is seems to be equivalent.

#### 1.3.4 Symmetry Reduction

Symmetry Reduction[42, 43, 44] exploits symmetry of a concurrent process model. Then it reduce state space of the model into that of its quotient model, where symmetric states are identified. For model checking of timed automata[43] and probabilistic models[44], the symmetry reduction is adopted.

#### 1.4 Research Overview

In this study, we propose techniques to avoid state explosion for model checking of real-time systems. First, we propose an abstraction refinement technique for timed automata using the CEGAR framework. Next, we extend the technique into abstraction for probabilistic timed automata. On the other hand, for model checking of distributed systems, we propose a hybrid approach of probabilistic model checking and simulation techniques.

#### 1.4.1 Abstraction Refinement for Timed Automata based on CEGAR

Chapter 2 describes the abstraction refinement technique for timed automata using the CEGAR framework. The first step of the technique is abstraction, in which we delete all of time attributes from the given timed automaton. The obtained automaton is just a finite automaton preserving the transition relations of the original timed automaton; therefore the obtained finite automaton is, in general, an over-approximation of the original one. We restrict the class of the verification properties into reachability; thus if an abstract model satisfies a given property then the concrete model also satisfies the property. The reachability analysis is the primitive procedure for safety checking. This means that model checking problems on several important properties could be reduced into the reachability analysis problem.

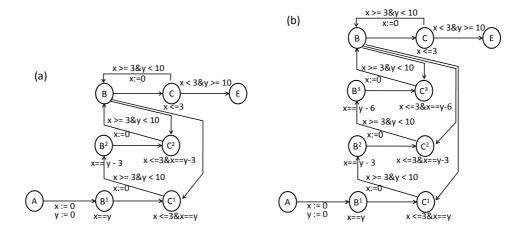

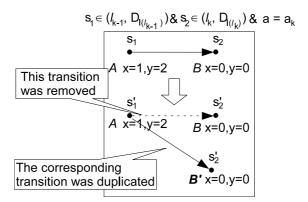

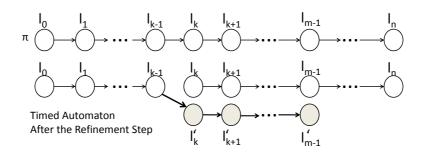

In general, CEGAR techniques[11, 12, 13, 37, 38, 39] directly transforms an abstract model using counter examples in the refinement step. Our proposed method, however, doesn't directly transform the abstract model. It first transforms the original model using counter examples and then it creates a new abstract model from it by removing clock attributes; thus our algorithm indirectly refines the abstract model. The algorithm transforms the original timed automaton by adding extra transitions and removing some transitions but it preserves the behavioral equivalence of the timed automaton and prevents the spurious counter examples. More concretely, it duplicates locations and transitions so that its abstract model can tell behavioral difference caused by clock values which affects the counter examples. Consequently the obtained new abstract model does not accept the spurious counter example.

Related works [37, 38, 39] have proposed CEGAR based abstraction techniques for timed automata. Although these techniques mainly refine the abstract models by adding clock variables which have been removed by initial abstraction, our refinement method modifies the original timed automata and produces the refined abstract model from the modified models, instead of adding clock variables.

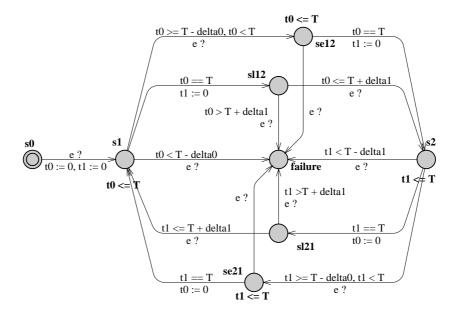

### 1.4.2 Abstraction Refinement for Probabilistic Timed Automata based on CEGAR

Chapter 3 describes the extension of our CEGAR technique into abstraction for probabilistic timed automata. In this study, we propose a reachability analysis technique for probabilistic timed automata. The abstraction technique abstracts time attributes of probabilistic timed automata by applying our abstraction technique for timed automata. Then, we apply probabilistic model checking to the generated abstract model which is just a Markov decision process (MDP) with no time attributes. The probabilistic model checking algorithm calculates a summation of occurrence probabilistic timed automata, however, we have to consider required clock constraints for such paths, and choose the paths whose required constraints are compatible. Since our abstract model does not consider the clock constraints, we add a new flow where we check whether all paths used for probability calcu-

Figure 1.7: Our CEGAR Technique for Reachability Analysis of a Probabilistic Timed Automaton

lation are compatible. Also, if they are not compatible, we transform the model so that we do not accept such incompatible paths simultaneously. The proposed procedure for the probabilistic timed automata is shown in Fig.1.7.

Several papers including Paper[45] have proposed probabilistic model checking algorithms. These algorithms, however, don't provide counter examples when properties are not satisfied. Our proposed method provides a counter example as a set of paths based on k-shortest paths search. This is a major contribution of our method. The proposed method also performs model checking considering compatibility problem. Few approaches resolve the compatibility problem. Our approach also shows the efficiency via performing experiments.

### **1.4.3** Qualitative Analysis of Real-time Distributed Systems Using the Probabilistic Model Checker PRISM

Chapter 4 describes a qualitative analysis technique for Real-time Distributed Systems.

Probabilistic model checking can evaluate performance, dependability and stability of information processing systems with random behaviors[19]. PRISM[6] is one of the probabilistic model checkers. It handles automata with probabilities (discrete and continuous time Markov chains) and time elapse. Therefore, it is suitable for modeling the network systems. One of the approaches, which overcomes drawbacks of simulation approach and model checking approach, seems to be a kind of a hybrid approach.

In order to find if the hybrid approach is applicable to real systems, we apply a hybrid analysis technique onto real-time distributed systems, which uses both of simulation and model checking techniques. In our approach, we perform a stepwise analysis using probabilistic models of target systems in different abstract levels. First, we create a probabilistic model with detailed behavior of the system (called detailed model), and apply simulation on the detailed model. Next, based on the simulation results, we create a probabilistic model in an abstract level (called simplified model). Then, we verify qualitative properties using the probabilistic model checking techniques.

As related works, several case studies are performed using PRISM[45, 28, 20]. For example, Paper[28] deals with a network protocol. Few works, however, concern the QoS analysis of the whole system. Papers[46] and [47] propose abstraction methods for probabilistic systems based on an abstraction refinement approach. Papers[48] and [49] propose verification approach based on the simulation technique. Paper[46] extracts a number of representative sample paths on a probabilistic model and decides if the model satisfies a given property using such paths. In Paper[49], they model a biomedical sensor network as timed automata, and use the simulation technique to adjust some parameters.

The contribution of this research includes that we present a technique to guarantee the QoS of real-time distributed systems. Our experimental results show the correctness of our detailed model at least for all of nine scenarios. Also, we can apply probabilistic model checking on the simplified model within realistic time without state explosion. It shows that the proposed method is useful to analyze the network performance. We believe that such analysis is useful for other kind of network analysis.

#### 1.4.4 Formal Verification with a Stepwise Abstraction Approach for UML/OCL Based Design of Real-time Systems

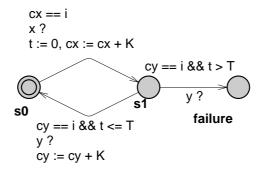

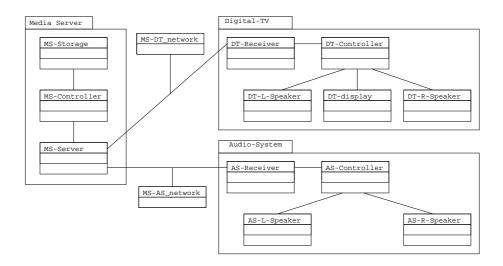

Chapter 5 describes a technique to verify consistency of timeliness QoS of component-based design for real-time systems.

Nowadays, most real-time systems are designed with help of UML diagrams[50]. Especially components and their relation through signal communication can be represented in a class diagram of UML. In UML based design, such timeliness QoS can be annotated in OCL[51]. The annotation is associated to each of components as a provided QoS and also to a network link as a network property.

This study proposes a new method to verify consistency of timeliness QoS of component-based real-time systems. We assume that timeliness QoS is not only

given to a whole system (Required QoS) but also associated with each component of a given system (Provided QoS). Timeliness QoS is a time aspect of QoS (Quality of Service) features[52]. In this study, we treat jitter, latency and throughput as timeliness QoS.

The proposed method is revised version of paper [53]. The method in [53] uses Linear Programming (LP) for some of verification. The approach has a disadvantage that connection among components has to be acyclic, and it cannot be applied to hierarchical design. The proposed method uses abstract QoS automata instead of using LP; thus it improves the former disadvantage. The heart of the technique is formally to ensure that the required timeliness QoS is satisfied under the provided timeliness QoS, given network property and the class diagram.

In order to check the satisfiability, there are several approaches. Model checking is one of such approaches. Notion of Test Automata[54, 55] and its application is also useful. However, one of disadvantage of the method is the state-explosion problem. In order to avoid state-explosion while performing model checking, we separate the problem into two steps. The first step checks the satisfiability using abstract model of each of components derived automatically from the provided QoS. The second step performs model checking each of components independently using more detailed version of behavioral model of a component. Such an approach efficiently reduces the number of total states to check. Moreover the approach can be extended into hierarchical design; therefore it has good scalability.

### **Chapter 2**

## Abstraction Refinement for Timed Automata based on CEGAR

#### 2.1 Introduction

In verification of real time systems, timed automata have widely been used[16, 17, 18], which can describe behavior of real-time systems. In timed automata, real-valued clock constraints are assigned to its control state (called a location). Therefore, it has an infinite state space represented in a product of discrete state space made by locations and continuous state space made by clock variables. In traditional model checking for a timed automaton, using the property that we can treat the state space of clock variables as a finite set of regions; we can perform model checking on timed automata models. However, the size of such regions increases exponentially with the number of clock variables; thus an abstraction technique is also needed. One of the approaches to avoid explosion of the state space is a model abstraction approach. Especially, the CEGAR (CounterExample-Guided Abstraction Refinement)[11] technique proposed by Clarke *et al.* is considered as the promising technique for model abstraction.

This chapter describes a CEGAR technique for timed automata. This technique removes all of the clock variables from the timed automata, which means that the obtained abstract model is just a finite automaton with no clock constraints. Therefore, applying model checking into the abstract model may generate spurious counter examples which do not occur on the original timed automata. If such spurious counter example is detected, we transform the transition relation on the original timed automata so that the model behaves correctly even if we don't consider the clock constraints. Such transformation obviously represents the difference of behavior caused by the clock attributes. Therefore, the finite number of application of the refinement algorithm enables us to check the given property without the clock attributes.

In this chapter, we show concrete algorithm of abstraction refinement for timed automata, and prove its correctness. Also, experimental results indicate our abstraction can reduce state space of timed automata.

# 2.2 Preliminary

#### 2.2.1 Clock and Zone

Let C be a finite set of clock variables which take non-negative real values  $(\mathbb{R}_{\geq 0})$ . A map  $\nu : C \to \mathbb{R}_{\geq 0}$  is called a clock assignment. The set of all clock assignments is denoted by  $\mathbb{R}_{\geq 0}^C$ . For any  $\nu \in \mathbb{R}_{\geq 0}^C$  and  $d \in \mathbb{R}_{\geq 0}$  we use  $(\nu + d)$  to denote the clock assignment defined as  $(\nu + d)(x) = \nu(x) + d$  for all  $x \in C$ . Also, we use  $r(\nu)$  to denote the clock assignment obtained from  $\nu$  by resetting all of the clocks in  $r \subseteq C$  to zero.

**Definition 2.2.1** (Differential Inequalities on *C*). Syntax and semantics of a differential inequality *E* on a finite set *C* of clocks is given as follows:  $E ::= x - y \sim a \mid x \sim a$ , where  $x, y \in C$ , a is a literal of a real number constant, and  $\sim \in \{\leq, \geq, <, >\}$ . Semantics of a differential inequality is the same as the ordinal inequality.

**Definition 2.2.2** (Clock Constraints on C). A set of clock constraints c(C) on a finite set C of clocks is defined as follows: A differential inequality  $in_1$  on C is an element of c(C). Let  $in_1$  and  $in_2$  be elements of c(C),  $in_1 \wedge in_2$  is also an element of c(C).

A zone  $D \in c(C)$  is described as a product of finite differential inequalities on clock set C, which represents a set of clock assignments that satisfy all the inequalities.

# 2.2.2 Timed Automaton

**Definition 2.2.3** (Timed Automaton). A timed automaton  $\mathscr{A}$  is a 6-tuple  $(A, L, l_0, C, I, T)$ , where A: a finite set of actions; L: a finite set of locations;  $l_0 \in L$ : an initial location; C: a finite set of clocks;

$I \subset (L \rightarrow c(C))$ : a mapping from locations to clock constraints, called a location invariant; and

$T \subset L \times A \times c(C) \times \mathscr{R} \times L$ , where c(C) is a clock constraint, called guards;  $\mathscr{R} = 2^C$ : a set of clocks to reset.

A transition  $t = (l_1, a, g, r, l_2) \in T$  is denoted by  $l_1 \xrightarrow{a, g, r} l_2$ . A map  $\nu : C \to \mathbb{R}_{\geq 0}$  is called a clock assignment. We define  $(\nu + d)(x) = \nu(x) + d$  for  $d \in \mathbb{R}_{\geq 0}$ .  $r(\nu) = \nu[x \mapsto 0], x \in r$ , where  $\nu[x \mapsto 0]$  means the valuation that maps x into zero, is also defined for  $r \in 2^C$ .

**Definition 2.2.4** (Semantics of a Timed Automaton). Given a timed automaton  $\mathscr{A} = (A, L, l_0, C, I, T)$ , let  $S \subseteq L \times \mathbb{R}^C_{\geq 0}$  be a set of whole states of  $\mathscr{A}$ . The initial state of  $\mathscr{A}$  shall be given as  $(l_0, 0^C) \in S$ . For a transition  $l_1 \stackrel{a,g,r}{\longrightarrow} l_2 \ (\in T)$ , the following two transitions are semantically

For a transition  $l_1 \xrightarrow{a.g.} l_2 \ (\in T)$ , the following two transitions are semantically defined. The former one is called an action transition, while the latter one is called a delay transition.

$$\frac{l_1 \xrightarrow{a,g,r} l_2, g(\nu), I(l_2)(r(\nu))}{(l_1, \nu) \xrightarrow{a} (l_2, r(\nu))}, \qquad \frac{\forall d' \le d \quad I(l_1)(\nu + d')}{(l_1, \nu) \xrightarrow{d} (l_1, \nu + d)}$$

**Definition 2.2.5** (A Semantic Model of a Timed Automaton). For timed automaton  $\mathscr{A} = (A, L, l_0, C, I, T)$ , an infinite transition system is defined according to the semantics of  $\mathscr{A}$ , where the model begins with the initial state.

#### 2.2.3 Region Automaton

For a given timed automaton  $\mathscr{A}$ , we can introduce a corresponding clock region  $CR(\mathscr{A})[56, 33]$ . In general, a clock region divides a |C|-dimensional Euclidean space into finite points, segments, and faces. By [u], an element (a region) in  $CR(\mathscr{A})$  is denoted. For  $[u] \in CR(\mathscr{A})$ , g([u]) and I([u]) represent that any point in [u] satisfies a guard g and invariant I, respectively. Also by r([u]), applying clock resetting r onto [u] is denoted, where  $r([u]) = [u][x \mapsto 0]$ , and  $x \in r$ .

**Definition 2.2.6** (Region Automaton). A region automaton  $\mathscr{A}_r = (A, L_r, l_r_0, T_r)$ of a given timed automaton  $\mathscr{A} = (A, L, l_0, C, I, T)$  is defined as follows.  $L_r \subset L \times CR(\mathscr{A}),$

$L_r \subset L \times OI(\mathcal{A}),$   $l_r = (l_0, [0^C]), \text{ where } [0^C] \text{ satisfies } I(l_0),$  $T_r \subset L_r \times A \times L_r,$

$T_r$  consists of the transitions which satisfy the following property.

$$(l, [u]) \stackrel{a}{\Rightarrow} (l', [v]) \iff \exists d \in \mathbb{R}_{\geq 0}. \ (l, u) \stackrel{a}{\Rightarrow} (l, u') \in \mathscr{T}(\mathscr{A})$$

$$\land (l, u') \stackrel{a}{\Rightarrow} (l', v) \in \mathscr{T}(\mathscr{A}) \land u \in [u] \land v \in [v].$$

There is bi-simulation equivalence between a timed automaton  $\mathscr{A}$  and its region automaton  $\mathscr{A}_r$  [1].

#### 2.2.4 Zone Graph

In [16], a state space of timed automata, which has infinite semantic states, is represented as a finite state transition system called a zone graph. In this study, we treat a zone D as a set of clock assignments  $\nu \in \mathbb{R}_{\geq 0}^C$  (For a zone  $D, \nu \in D$ means the assignment  $\nu$  satisfies all the inequalities in D). In addition to this, using a location l and a zone D, we describe a set of semantic states as (l, D) = $\{(l, \nu) | \nu \in D\}$ . Also, for an initial location  $l_0$ , a set of initial states is denoted by  $(l_0, D_0) = \{(l_0, 0^C + d) | (l_0, 0^C) \stackrel{d}{\Rightarrow} (l_0, 0^C + d) \in \Rightarrow\}$ .

Paper[16] also gives operation functions on zones, such as up, and and so on, which represent elapsing time, intersection of time spaces and so on, respectively. For a given zone D, there is a minimal set of differential inequalities which is enough to represent D [16]. We use Ineqset(D) to denote such a minimal set for D. Ineqset(D) can be obtained by reduction operations on zones. A set of every state which satisfies an invariant I(l) of location l is denoted by  $(l, D_{I(l)})$  $(= \{(l, \nu) | I(l)(\nu)\}).$

When we create a zone graph from a timed automaton, we perform zone normalization called k-normalization[16], where  $k : C \to \mathbb{N}$  is a clock ceiling, to prevent zones from increasing infinitely. The clock ceiling k is given by the maximal clock constants appearing in the automaton. In k-normalization, we represent zones that may contain arbitrarily large constants as a single representative zone. The details are given as follows; we remove the constraints of the form x < m,  $x \le m, x - y < m, x - y \le m$  from the given zone, and also we replace the constraints of the form  $x > m, x \ge m, x - y > m, x - y \ge m$  with x > k(x),  $x \ge k(x), x - y > k(x), x - y \ge k(x)$ , where  $x, y \in C$  and m > k(x), respectively.

#### 2.2.5 DBM (Difference Bound Matrix)

In [16, 57], a data structure DBM is introduced to represent a convex space in |C| -dimensional Euclidean space, where C is a set of clock variables. DBM is a set of differential inequalities on two clock variables, and represents a state space which satisfies all inequalities over it (the state space is called a zone). DBM represents these set of inequalities as a  $|C_0| \times |C_0|$  matrix, where  $C_0 = C \cup \{0\}$ , and **0** is a special variable which means a constant value 0. The (i, j)-th entry  $(D_{i j})$  of the matrix means a differential inequality of  $x_i - x_j$  for  $x_i, x_j \in C_0$ . Suppose there is an inequality  $x_i - x_j \preceq n$  for  $\preceq \in \{< . \le \}$ , the (i, j)-th entry  $D_{i j}$  is represented by  $(n, \preceq)$ . Also, when  $x_i - x_j$  is unbounded, the entry  $D_{i j}$  is represented by  $\infty$ . In addition, the upper bound and lower bound of  $x_i$  itself are indicated by  $D_{0,i}$  and  $D_{i,0}$  respectively.

As an example of DBM, let's consider a zone which satisfies following constraint.

$$x - 0 < 20 \land y - 0 \le 20 \land x - y \le -10 \land y - x \le 10 \land 0 - z < 5.$$

When we represent this zone as DBM, variables 0, x, y, z are numbered with 0, 1, 2, 3 respectively in the matrix. DBM which represents the zone of the constraint is given by (2.1).

$$D = \begin{pmatrix} (0, \le) & (0, \le) & (0, \le) & (5, <) \\ (20, <) & (0, \le) & (-10, \le) & \infty \\ (20, \le) & (10, \le) & (0, \le) & \infty \\ \infty & \infty & \infty & (0, \le) \end{pmatrix}.$$

(2.1)

DBM is also represented as a set of some elements in the clock region  $CR(\mathscr{A})$ . Therefore a state set of states of a region automaton  $\mathscr{A}_r = (L_r, l_r_0, T_r, A)$ , can be represented in  $(l, D) = \{(l, [u]) \mid [u] \in D\}$  using the corresponding DBM D. Paper[16] gives operation functions on DBM, such as up, and and other functions, which represent elapsing time, intersection of time spaces and so on, respectively. There is a minimum set of differential inequalities which can represents DBM D[16]. Such a set is denoted by c(D). c(D) can be obtained by reduction operations on DBM. A set of every region which satisfies an invariant I(l) of location l is denoted by  $(l, D_{Inv})$ .

#### 2.2.6 Temporal Logic

Here, we give formal descriptions for temporal logic LTL and CTL.

# LTL

LTL represents properties related to a path on a target model. The syntax of LTL is given as follows.

**Definition 2.2.7** (Liner Temporal Logic). *Syntax of LTL formulae is given as follows,*

where p is an arbitrary atomic proposition.

Also, we can interpret the semantics of LTL as follows.

**Definition 2.2.8** (Semantics of LTL). For a transition system TS = (S, R, L)where S is a set of states,  $R: S \times S$  is transition relation on S, and  $L: S \rightarrow 2^{AP}$ is function labeling states with atomic propositions, and for a path  $\pi$  on TS, the semantics of LTL is given as follows.

$$\begin{split} \pi \models p &\iff p \in L(\pi(0)) \\ \pi \models \neg \phi &\iff not \pi \models \phi \\ \pi \models \phi_1 \land \phi_2 &\iff \pi \models \phi_1 \text{ and } \pi \models \phi_2 \\ \pi \models \phi_1 \lor \phi_2 &\iff \pi \models \phi_1 \text{ or } \pi \models \phi_2 \\ \pi \models \phi_1 \to \phi_2 &\iff \pi \models \phi_1 \text{ implies } \pi \models \phi_2 \\ \pi \models F[\phi] &\iff \exists i.\pi^i \models \phi \\ \pi \models G[\phi] &\iff \forall i.\pi^i \models \phi \\ \pi \models X\phi &\iff \pi^1 \models \phi \\ \pi \models [\phi_1 U \phi_2] &\iff \exists i.(\pi^i \models \phi_2 \land \forall j.(0 \le j < i \to \pi^j \models \phi_1))) \\ \pi \models [\phi_1 R \phi_2] &\iff \forall i.(\pi^i \models \phi_2 \lor \exists j.(0 \le j < i \to \pi^j \models \phi_1))), \end{split}$$

where p is an arbitrary atomic proposition,  $\phi$ ,  $\phi_1$  and  $\phi_2$  are arbitrary LTL formulae,  $\pi(i)$  is *i*-th state in the path  $\pi$ , and  $\pi^i$  is the suffix of  $\pi$  after the *i*-th state.

# CTL

CTL represents properties with tree like structures which have several branches. The syntax of CTL is given as follows.

**Definition 2.2.9** (Computational Tree Logic). *Syntax of CTL formulae is given as follows*,

where *p* is an arbitrary atomic proposition.

**Definition 2.2.10** (Semantics of CTL). For a transition system TS = (S, R, L)where S is a set of states,  $R: S \times S$  is transition relation on S, and  $L: S \rightarrow 2^{AP}$ is function labeling states with atomic propositions, and for a state  $s \in S$ , the semantics of CTL is given as follows.

$$\begin{split} s &\models p \iff p \in L(s) \\ s &\models \neg \phi \iff not s \models \phi \\ s &\models \phi_1 \land \phi_2 \iff s \models \phi_1 and s \models \phi_2 \\ s &\models \phi_1 \lor \phi_2 \iff s \models \phi_1 or s \models \phi_2 \\ s &\models \phi_1 \rightarrow \phi_2 \iff s \models \phi_1 implies s \models \phi_2 \\ s &\models AF[\phi] \iff for all paths (s_0, s_1, \ldots), \\ &\exists i.(i \ge 0 \land s_i \models \phi) \\ s &\models EF[\phi] \iff for some paths (s_0, s_1, \ldots), \\ &\exists i.(i \ge 0 \land s_i \models \phi) \\ s &\models AG[\phi] \iff for all paths (s_0, s_1, \ldots), \\ &\forall i.(i \ge 0 \land s_i \models \phi) \\ s &\models EG[\phi] \iff for some paths (s_0, s_1, \ldots), \\ &\forall i.(i \ge 0 \land s_i \models \phi) \\ s &\models EX\phi \iff for all states t such that(s, t) \in R, t \models \phi \\ s &\models EX\phi \iff for all paths (s_0, s_1, \ldots), \\ &\exists i.(i \ge 0 \land s_i \models \phi) \\ s &\models E[\phi_1 U\phi_2] \iff for all paths (s_0, s_1, \ldots), \\ &\exists i.(i \ge 0 \land s_i \models \phi_2 \land \forall j.(0 \le j < i \rightarrow s_j \models \phi_1)) \\ s &\models E[\phi_1 U\phi_2] \iff for some paths (s_0, s_1, \ldots), \\ &\exists i.(i \ge 0 \land s_i \models \phi_2 \land \forall j.(0 \le j < i \rightarrow s_j \models \phi_1)) \\ \end{cases}$$

where p is an arbitrary atomic proposition,  $\phi$ ,  $\phi_1$  and  $\phi_2$  are arbitrary CTL formulae.

The CTL formulae  $AF\phi$  and  $EF\phi$  can be replaced by  $A[true U\phi]$  and  $E[true U\phi]$ , respectively. Also  $AG\phi$  and  $EG\phi$  can be replaced by  $\neg EF \neg \phi$  and  $\neg AF \neg \phi$ , respectively.

#### 2.2.7 CounterExample-Guided Abstraction Refinement

Since model abstraction sometimes over-approximates an original model, we may obtain spurious CEs which are infeasible on the original model. Paper [11] gives an abstraction refinement framework called CEGAR (CounterExample-Guided Abstraction Refinement) (Fig.1.6).

In the algorithm, at the first step (called Initial Abstraction), it generates an initial abstract model. Next, it performs model checking on the abstract model. In this step, if the model checker reports that the model satisfies a given specification, we can conclude that the original model also satisfies the specification, because the abstract model is an over-approximation of the original model. If the model checker reports that the model does not satisfy the specification, however, we have to check whether the CE detected is spurious or not in the next step (called Simulation). In the Simulation step, if we find that the CE is valid, we stop the loop. Otherwise, we have to refine the abstract model to eliminate the spurious CE, and repeat these steps until valid output is obtained.

# 2.3 Proposed Algorithm

Our proposed algorithm generates an abstract model  $\hat{M}$  from a given timed automaton  $\mathscr{A}$ , and performs model checking on  $\hat{M}$ .  $\hat{M}$  is in fact a finite automaton. If a counter example  $\hat{\rho}$  (represented as a sequence of states and labels on  $\hat{M}$ ) is detected by model checking, we check whether  $\hat{\rho}$  is feasible on the concrete model  $\mathscr{T}(\mathscr{A})$  or not at the simulation step (In this study, for an abstract model  $\hat{M}$  obtained from a timed automaton  $\mathscr{A}$ , we call the semantic model  $\mathscr{T}(\mathscr{A})$  a concrete model of  $\hat{M}$ ). In this step, we obtain a set  $\Pi$  of sequences of transitions on  $\mathscr{A}$  corresponding to  $\hat{\rho}$ , and check whether each path in  $\Pi$  is feasible on  $\mathscr{T}(\mathscr{A})$  or not. If every path in  $\Pi$  is infeasible, the next step shall refine the model so that the counter example  $\hat{\rho}$  becomes infeasible. Our algorithm does not directly refine  $\hat{M}$  but it modifies  $\mathscr{A}$ and then obtains a new abstract model from the modified timed automaton  $\mathscr{A}$ .