| Title        | A New Analog Correlator Circuit for DS-CDMA<br>Wireless Applications            |

|--------------|---------------------------------------------------------------------------------|

| Author(s)    | Eltokhy, Mostafa A. R.; Tan, Boon-Keat;<br>Matsuoka, Toshimasa et al.           |

| Citation     | IEICE Transactions on Fundamentals of Electronics. 2003, E86-A(5), p. 1294-1301 |

| Version Type | VoR                                                                             |

| URL          | https://hdl.handle.net/11094/51658                                              |

| rights       | copyright@2003 IEICE                                                            |

| Note         |                                                                                 |

## The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

#### PAPER

# A New Analog Correlator Circuit for DS-CDMA Wireless Applications

Mostafa A.R. ELTOKHY $^{\dagger a}$ , Boon-Keat TAN $^{\dagger}$ , Nonmembers, Toshimasa MATSUOKA $^{\dagger}$ , and Kenji TANIGUCHI $^{\dagger}$ , Regular Members

SUMMARY A new analog correlator circuit is proposed for direct sequence code division multiple access (DS-CDMA) demodulator. The circuit consists of only 16 switches, 4 capacitors and 2 level shifters. Control sequence requires only three clock phases. Simulation with code length of 127 reveals that the proposed circuit has a good ability to cancel off the charge error and dissipates 3.4 mW at 128 MHz. The circuit had been designed using a 0.6  $\mu m$  CMOS process. The area of  $256\,\mu m \times 245\,\mu m$  is estimated to be 9 times smaller compared to other reported equivalent analog correlators.

key words: code division multiple access, analog correlator, demodulation process, switched-capacitor circuits, spread spectrum

#### 1. Introduction

Direct Sequence Code Division Multiple Access (DS-CDMA) has been studied as a major system for future generation mobile phones because of its high capacity and robustness against interference and noise [1], [2]. In DS-CDMA, all users share the same carrier frequency, but are assigned unique Pseudo Noise (PN) codes for spreading. The desired user's signal is separated from those of other users after performing despreading process using the same PN code as a transmitter sending the desired signal [3]. Using digital domain in recovering the information requires highspeed analog-to-digital converter (ADC) to digitize the received signal [4], [5]. This leads to high dissipation power at high-speed applications. An alternative approach would be to avoid the power consumption of a high-speed ADC and to perform the despreading in the analog domain [6]–[8]. Then, if needed a slower ADC can follow the analog correlator leading to a low power solution since the recovered signal has a lower bandwidth. A CMOS switched capacitor analog correlator has been demonstrated in [6], which describes DS-CDMA correlators operating at 128 MHz dissipates 4 mW using code length of 64 and requires more than 64 non-overlapping clocks to drive the switches. This is achieved only at the expense of chip area because a large number of capacitors and switches are used.

Manuscript received April 22, 2002.

Manuscript revised December 25, 2002.

Final manuscript received February 6, 2003.

a) E-mail: mostafa@eie.eng.osaka-u.ac.jp

This paper seeks to extend the performance of these approaches considering different circuit topology but with a small number of devices. The proposed circuit in this paper operates at 128 MHz while dissipating  $3.4\,\mathrm{mW}$  using code length (N) of 127, but consists of only 4 capacitors, 16 switches and 2 level-shifters. The level shifter is introduced to provide good linearity. Digitizing the output of the proposed analog correlator requires sampling rate of only 1 Ms/s with a 7-bit of ADC compared to the sampling rate of 128 Ms/s with a 10-bit ADC for digital domain correlator. The remainder of the paper is organized into five sections. Section 2 gives an overview of DS-CDMA and describes how correlation is used in despreading process. Section 3 introduces the proposed circuit principle of operation. In Sect. 4 design considerations for the proposed circuit are discussed. Section 5 shows physical layout and simulation results of the proposed circuit. In Sect. 6 we summarize the main results.

### 2. DS-CDMA System Overview

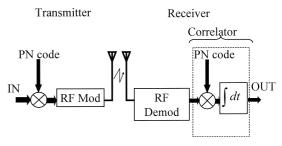

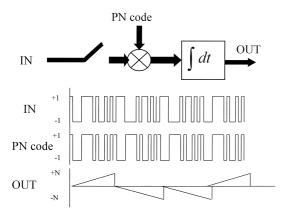

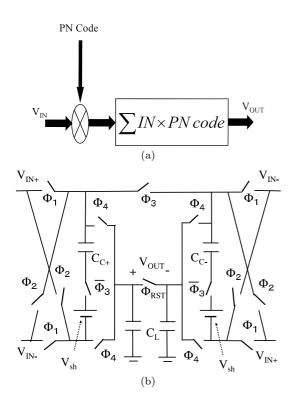

Figure 1 depicts a simplified wireless DS-CDMA system. In the transmitter the serial data bit stream is spreaded by a PN sequence code. Because of the random nature and high frequency content of the PN code, the spectrum of spreaded data is relatively flat and much wider in bandwidth. In the receiver, despreading is accomplished by performing a correlation between the received signal and the PN code, i.e., multiplying the received signal by the PN code followed by integration. Figure 2 shows a more detailed despreading process, which is accomplished by performing a discrete-time correlation of the baseband-received

Fig. 1 Simplified wireless DS-CDMA system.

<sup>&</sup>lt;sup>†</sup>The authors are with the Department of Electronics and Information Systems, Osaka University, Suita-shi, 565-0871 Japan.

Fig. 2  $\,$  DS-CDMA demodulation process using discrete time correlation.

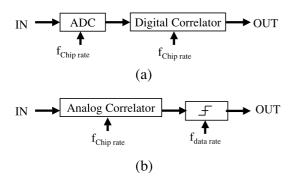

Fig. 3 (a) Digital and (b) analog correlator block diagram.

signal with the PN code using discrete-time correlation. This discrete-time correlation  $(C_{DT})$  is defined as shown in Eq. (1)

$$C_{DT} = \sum_{i=1}^{N} S_R(i).PN(i)$$

(1)

where  $S_R(i)$  is the chip-rate sampled value of the received input signal, PN(i) is the N-length PN code. If the input sampled values and PN codes are normalized to 1, the output of the correlator equals +N when the two signals are in-phase and -N when they are out-of-phase. Thus, the original data bits are contained in the sign of the correlator output but not in the magnitude, permitting data recovery by employing a simple slicer.

There are two types of correlators which are used in demodulation process as shown in Fig. 3, digital correlator and analog correlator. The digital correlator consumes more power because high speed analog-to-digital converter (ADC) is needed to digitize the received signal waveform to perform despreading process operating at a high clock rate (chip rate). By using analog architecture, power consumption required for a front-end ADC sampling at the chip rate can be significantly reduced. The resolution of ADC required after analog correlator also decreases comparing to the digital counterpart one.

The first step in performing the analog correlation

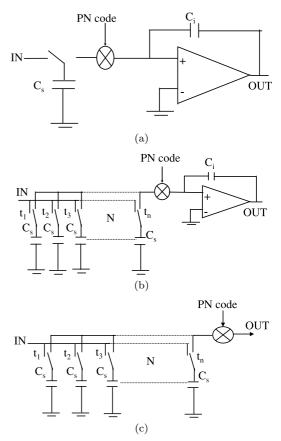

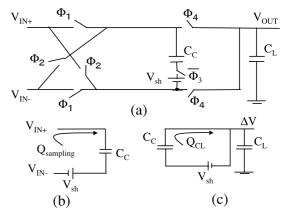

${\bf Fig.\,4}$  (a) Active chip rate correlation, (b) active data rate correlation and (c) passive data rate correlation.

is multiplying the input sample with the PN code. The PN code values are  $\pm 1$ , so PN code multiplication is simply sign modulation of the input samples prior to integration/summation. Three possible approaches for implementing an analog correlator as shown in Fig. 4 have been reported in [6]. Figure 4(a) shows an active chip rate correlator circuit, which operates at chip rate to take a sample and integrate it. This architecture has disadvantages. Its opamp settling time must be very fast and hence opamp static power will be large. Although Fig. 4(b), which shows an active data rate correlator, modified the opamp settling time and static power dissipation by a factor of N (code length), this achieved at the expense of chip area. Figure 4(c) shows a passive data rate correlator. This architecture cancels all static power but still requires large chip area because large number of sampling capacitors and switches are used. Implementation of fully differential passive data rate correlator requires 9N switches, and 2N sampling capacitors. It was reported that the circuit operating at 128 MHz dissipates 4 mW by the use of Walsh code of length 64 together with more than 64 non-overlapping clocks to sequence the switches.

### 3. Circuit Principle of Operation

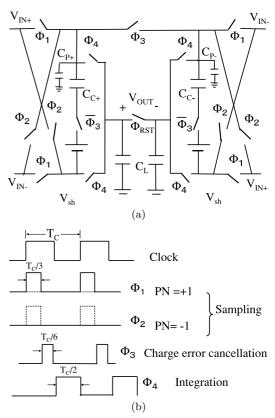

We proposed a new architecture to implement analog correlator, which only consists of four capacitors, (two sampling capacitors  $C_C$ , two load capacitors  $C_L$ ), two level shifters  $V_{sh}$ , and sixteen switches which are implemented by transmission gates as shown in Fig. 5. The specifications of the proposed circuit are shown in Table 1.

For simplicity and clarity, a single-ended representation is used as shown in Fig. 6(a). The level shifter is introduced to decouple the output node from the correlator circuit. Theoretically, the level shifter is ideal, i.e. its gain equals unity. During the sampling phase  $(\phi_1$  and  $\bar{\phi}_3)$ , electric charge is stored at the sampling capacitor,  $C_C$  as shown in Fig. 6(b). At the integrating phase  $(\phi_4$  and  $\bar{\phi}_3)$ , the storage charge is then injected into the load capacitance  $C_L$  as shown in Fig. 6(c). The charge stored during sampling phase,  $Q_{sampling}$  and the charge remained at the  $C_C$  during integrating phase,  $Q_{remain}$

Fig. 5 Proposed analog correlator circuit.

Table 1 Analog correlator circuit specifications.

| Power supply            | 5 V                                        |

|-------------------------|--------------------------------------------|

| Resolution              | 10 bits                                    |

| PN code length          | 127                                        |

| Maximum clock frequency | $128\mathrm{MHz}$                          |

| Output signal format    | Analog                                     |

| Power dissipation       | $3.4\mathrm{mW}$                           |

| Process                 | CMOS $0.6 \mu\mathrm{m}$                   |

| Chip size               | $256\mu\mathrm{m} \times 245\mu\mathrm{m}$ |

are given by Eqs. (2) and (3) respectively.

$$Q_{sampling} = C_C \{ V_{IN+} - (V_{IN-} + V_{sh}) \}$$

(2)

$$Q_{remain} = C_C \{ V_{OUT} - (V_{OUT} + V_{sh}) \}$$

(3)

The amount of electric charge injected to the load capacitance is the difference of  $Q_{sampling}$  and  $Q_{remain}$  as shown in Eq. (5).

$$Q_{CL} = Q_{sampling} - Q_{remain} \tag{4}$$

$$= C_C(V_{IN+} - V_{IN-}) (5)$$

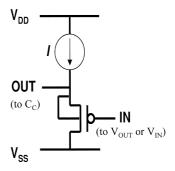

Due to the level shifter, the amount of charge is independent of the output voltage  $V_{OUT}$ . Because the level shifter shown in Fig. 7, has low output resistance, the switch  $\bar{\phi}_3$  is added to protect the signal charge during zero charge cancellation phase as described in Sect. 4. Signal voltage swing  $\Delta V$  for one charging cycle resulted from the charge injecting is given by

$$\Delta V = \frac{C_C(V_{IN+} - V_{IN-})}{C_L} \tag{6}$$

Discharging the same amount of charge from  $C_L$  is simple by just interchanging  $V_{IN+}$  and  $V_{IN-}$  ( $\phi_2$ ), i.e. injecting the same amount of negative charge into  $C_L$ . At the end of each cycle, the output nodes of the correlator ( $V_{OUT+}$  and  $V_{OUT-}$ ) will be shorted ( $\phi_{RST}$ ) to

Fig. 6 (a) Single-ended analog correlator, (b) sampling phase and (c) integrating phase.

Fig. 7 Level shifter circuit.

Fig. 8 Behavior of ideal correlator circuit without mismatch or parasitic capacitance. Correlated signals are summed up while non-correlated signal is rejected (curve A).

distribute electric charges and set the output nodes of the correlator back to reference point.

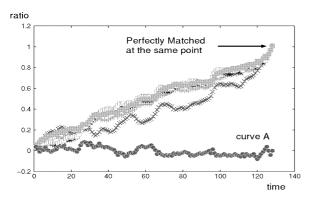

In addition, the proposed circuit requires only three non-overlapping clocks, which reduces the complexity of the control sequence. Eventually, this leads to less switching and low power consumption. When the PN code matched the input signal, every signal transmitted would be summed up as shown in Fig. 8, where all curves terminate at the same point except curve A. If the codes do not match, the correlator circuit gives no output because all the signals would cancel off each other as shown by curve A.

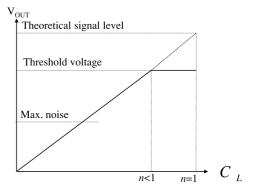

The size of charging capacitor,  $C_C$  should be related to load capacitor  $C_L$  as

$$C_L = C_C \times \frac{n \times N}{\lambda} \tag{7}$$

where n is multiplication factor between 0.7 and 1, and  $\lambda$  is the ratio of output voltage range to input voltage range. Although theoretically n should be one, a smaller number of n would make the output node,  $V_{out}$  saturates before the final output is obtained at the end of the clock cycles (N-th sampling for PN codes). Theoretical threshold voltage (n=1) is not required and can be chosen smaller (n<1) to reduce power consumption as shown in Fig. 9. The minimum value of n is limited by the maximum of the interference level due to other channels. We have calculated the interference due to 10 channels using the same taps for N=127. The value of this interference which is only 7% is acceptable for using n=0.7 to realize the correlator circuit.

In practical case, due to the level shifter channel length modulation (the level shifter's gain < 1). Equation (6) can be rewritten as follows

$$\Delta V = \frac{C_C(V_{IN+} - V_{IN-})}{C_L} + \frac{C_C(G-1)(V_{OUT} - V_{IN-})}{C_L}$$

(8)

where G is the level shifter's gain. Taking the channel

Fig. 9 An example of choosing the load capacitance value.

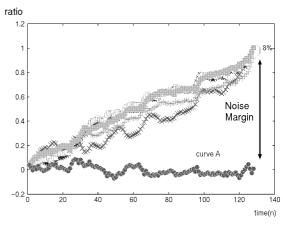

Fig. 10 Behavior of ideal correlator circuit considering the effect of channel length modulation. Noise margin remains high.

length modulation effect into consideration using transistor size of  $W/L=16.5\,\mu\mathrm{m}/0.9\,\mu\mathrm{m}$  in  $0.6\,\mu\mathrm{m}$  CMOS technology, the output deviated but at a range of less than 8% although every signals swing varied at maximum 10% as shown in Fig. 10.

#### 4. Design Considerations

Theoretically, the proposed circuit is able to charge and discharge precise amount of electronic charge. However, in reality, the circuit is not completely balanced due to charge injection of the switches, clock feedthrough, parasitic capacitance and mismatch. We will discuss these effects on the proposed analog correlator circuit.

#### 4.1 Charge Error

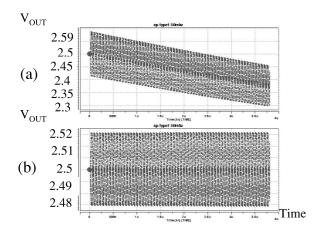

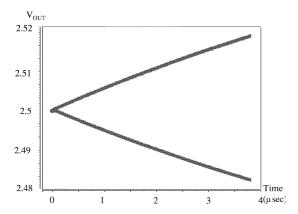

Figure 11(a) shows simulation results of the proposed circuit with initial output of 2.5 V for 127 cycle of charging and discharging in alternative period. Although theoretically net charge injection is zero, the output node voltage of the circuit gradually changes. We can conclude from the simulation results that the amount of charge injection depends on the load capacitance voltage. The behavior of the load can be explained by

**Fig. 11** Simulation with  $V_{in}=4\,\mathrm{mV},\,\lambda=2,\,n=0.7$  initial output at 2.5 V and  $C_L=44C_C$  for 127 cycles (a) without cancellation technique and (b) with cancellation technique.

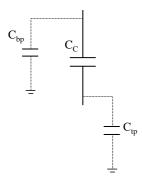

Fig. 12 Sampling capacitor with parasitic capacitance. Parasitic capacitors exist at both bottom and top plates.

taking into account the parasitic capacitance of the circuit. Actually, in a switched capacitor sampling circuit, charge errors can be caused by switch charge injection, clock feedthrough, and charge transfer on parasitic capacitance. The first two errors can be solved by using bottom-plate sampling and fully differential circuitry [9]. Figure 12 depicts the equivalent circuit when parasitic capacitance is taken into account. The value of parasitic capacitance varies depending on how the capacitor is implemented [10]. Top-plate parasitic capacitance  $(C_{tp})$  due to interconnect at capacitor is usually small, i.e., at the order of 1/100 of  $C_C$ . The effect of  $(C_{tp})$  is negligible small. Bottom-plate parasitic capacitance  $(C_{bp})$  is usually larger than top-plate capacitance. The charge error gets stored on the parasitic capacitances  $(C_P)$  (bottom-plate parasitic capacitance of  $C_C$ , junction capacitances of the switching circuit, and the wiring capacitances of the metal lines).

In order to cancel off the charge transfer due to the parasitic capacitance, charge cancellation technique as shown in Fig. 13(a) is applied. The sequence of canceling the effect of parasitic capacitance is shown in Fig. 13(b).

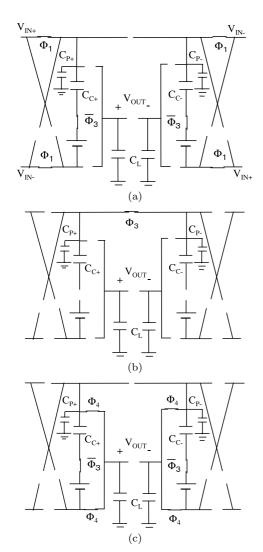

Initially the sampling switches  $(\phi_1 \text{ or } \phi_2)$  and  $\bar{\phi}_3$

Fig. 13 (a) Fully differential correlator circuit and (b) switching sequence.

are closed for  $T_C/3$  ( $T_C$  is chip period), connecting the sampling capacitance to the input [Fig. 14(a)]. Next, the charge pump capacitances are disconnected from the input by opening the  $(\phi_1 \text{ or } \phi_2)$  and  $\phi_3$  switches. This creates charge error from the signal dependent charge injection from the  $(\phi_1 \text{ or } \phi_2)$  switches onto  $C_P$ . To cancel off the charge error due to the bottom plate parasitic capacitance and the junction capacitance of switching circuit, the switch  $(\phi_3)$  is momentarily closed for  $T_C/6$  converting the differential charge on  $C_{P+}$  and  $C_{P-}$  to a common-mode charge effectively eliminating it [Fig. 14(b)]. Then the integration step can be done by closing switches ( $\phi_4$  and  $\bar{\phi}_3$ ) for  $T_C/2$  [Fig. 14(c)] (note that  $\phi_4$  has longer time period for integration step that is because  $C_L$  is greater than  $C_C$ ). With the parasitic charge cancellation circuitry, the simulation reveals the results as shown in Fig. 11(b), indicating that parasitic capacitance effect is well taken care of.

The nonlinearity of the source and drain junction capacitances associated with the transistor switches, which are voltage dependence as follows,

$$C_P = \frac{C_{Po}}{\sqrt{1 + \frac{V_P}{\phi_o}}}\tag{9}$$

where  $C_{Po}$  is the depletion capacitance at  $V_P$ =0. These capacitance nonlinearity can introduce errors in the sampling process that generate an extra noise compo-

Fig. 14 The sequence of canceling the effect of parasitic capacitance, (a) sampling, (b) charge error cancellation and (c) integrating phases.

nent to the correlation process. To minimize this effect, the sampling capacitor can be increased and/or the switch sizes decreased. Doing either of these increases the settling time constant ( $\tau = R_{ON} \times [C_C + C_L]$ ), where  $R_{ON}$  is the on-resistance of the integration switch, so there is a trade off between operating bandwidth and nonlinearity error. The switch sizes ( $W/L = 1.2\,\mu\text{m}/0.6\,\mu\text{m}$ ) and sampling capacitors ( $C_C = 140\,\text{fF}$ ) are used in  $0.6\,\mu\text{m}$  CMOS technology.

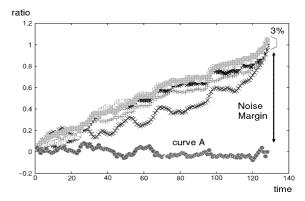

#### 4.2 Capacitance Mismatch

As shown in Eq. (5), the charge injected into the load capacitance depends on  $C_C$  and  $V_{IN+}-V_{IN-}$ . Mismatch between  $C_{C+}$  and  $C_{C-}$  can be kept under 2% by applying layout technique such as using unit square capacitor [11]. Depending on its implementation, mismatch of  $(V_{IN+})-(V_{IN-})$  may range from 0.2–5%. However, due to the noise rejection ability of the

Fig. 15 Behavior of ideal correlator circuit considering the effect of capacitance mismatch. Noise margin remains large.

correlation circuit, the effect of mismatch is tolerable. This is verified through simulation result as shown in Fig. 15 in which the output of analog correlator fluctuates in less than 3% range. Due to its large noise margin, the effect due to capacitance mismatch can be easily eliminated.

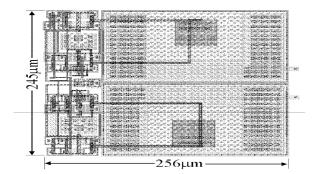

#### 5. Physical Layout and Simulation

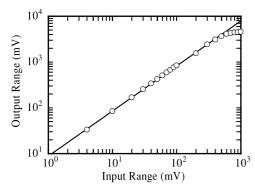

The proposed analog correlator circuit had been designed using a  $0.6 \,\mu \mathrm{m}$  triple-metal double polysilicon CMOS process. The designed circuit contains a clock generator for three phases (sampling, charge error cancellation, and integration). The physical layout of the correlator circuit is shown in Fig. 16. The layout size of  $256 \,\mu\mathrm{m} \times 245 \,\mu\mathrm{m}$  is sufficiently small. This layout has symmetry, considering wiring capacitance matching. The circuit dissipates 3.4 mW (this includes all clock power to sequence the switches and parasitic wiring capacitance) with code length of 127 at voltage supply of 5 V and operational clock frequency of 128 MHz. As the power is estimated from circuit simulations including parasitic capacitances based on the layout. The PN code used in this simulation is M-sequence with 127 code length. Figure 17 shows the simulation results of charging up the load capacitance for 127 cycles with parasitic wiring capacitance, sampling capacitor  $C_C$ =140 fF, load capacitor  $C_L$ =44 $C_C$  and input range of 4 mV. The output shows sign of saturation toward the threshold voltage because a smaller number of n(n=0.7) is used. Even though the input voltage amplitude is only 4 mV (the minimum input value which is limited by level shifer mismatch), which requires 10-bit resolution at the input, the output of the correlator becomes 35 mV, indicating that the resolution required after the analog correlator is 7 bit. In addition, the ADC after analog correlation is done with the data rate instead of chip rate. Figure 18 shows the linear behavior of the analog correlator, which is a plot of its transfer charactersitics. The maximum input range is limited by output saturation toward voltage supply of 5 V.

Fig. 16 Physical layout of analog correlator circuit.

Fig. 17 Simulation results of charging up  $C_L$  with  $V_{in}=4$  mV,  $\lambda=2,\ n=0.7$  and  $C_L=44C_C$  for 127 cycle.

Fig. 18 Simulation results of analog correlator transfer characteristics with  $\lambda$ =2, n=0.7 and  $C_L$  = 44 $C_C$ .

#### 6. Conclusion

An analog correlator circuit for DS-CDMA wireless communication had been proposed. The circuit consists of only sixteen switches, four capacitors and two level shifters. Control sequence for the proposed circuit is simple, as it requires only three clock phases. Simulation results verified that the charge error due to parasitic capacitance is canceled off and the integration phase can be processed in free of charge error. The proposed circuit dissipates 3.4 mW (including all

clock power to sequence the switches) at 128 MHz. The output of analog correlator requires 7-bit ADC at the sampling rate of only 1 Ms/s to convert its output to digital format, which relaxes the design constraints of analog correlator circuit compared to 10-bit resolution with sampling rate of 128 Ms/s of digital correlator.

#### Acknowledgement

The VLSI chip used in this study was fabricated under the chip fabrication program of the VLSI Design and Education Center (VDEC) of the University of Tokyo with the collaboration of the Rohm Corporation and the Toppan Printing Corporation. This work is supported by the Japan Society for the Promotion of Science (JSPS) as part of the Research for the Future Program.

#### References

- W.C. Lee, "Overview of cellular CDMA," IEEE Trans. Veh. Technol., vol.40, no.2, pp.291–302, May 1991.

- [2] K.S. Gilhousen, I.M. Jacobs, R. Padovani, A.J. Viterbi, L.A. Weaver, Jr., and C.E. Wheatley, III, "On the capacity of a cellular CDMA system," IEEE Trans. Veh. Technol., vol.40, no.2, pp.303–312, May 1991.

- [3] J. Chen, G. Shou, and C. Zhou, "High-speed low-power complex matched filter for W-CDMA: Algorithm and VLSI-architecture," IEICE Trans. Fundamentals, vol.E83-A, no.1, pp.150–157, Jan. 2000.

- [4] Y. Ogawa, Y. Kinugasa, M. Tanaka, K. Nagi, and T. Takei, "Development of 1 chip SS communication LSI using digital matched filters," IEICE Technical Report, SST94-65, Dec. 1994.

- [5] M.D. Hahm, E.G. Friedman, and E.L. Titlebaum, "A comparison of analog and digital circuit implementations of low power matched filters for use in portable wireless communication terminals," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process, vol.44, no.6, pp.498–506, June 1997.

- [6] K.K. Onodera and P.R. Gray, "A 75-mW 128-MHz DS-CDMA baseband demodulator for High-speed wireless applications," IEEE J. Solid State Circuits, vol.33, no.5, pp.753-761, May 1998.

- [7] M. Sawahashi, F. Adachi, and C. Zhou, "Low power consuming analog-type matched filter for DS-CDMA mobile radio," IEICE Trans. Fundamentals, vol.E79-A, no.12, pp.2071–2077, Dec. 1996.

- [8] T. Shibano, K. Iizuka, M. Miyamoto, M. Osaka, R. Miyama, and A. Kito, "Matched filter for DS-CDMA of up to 50MChips/s based on sampled analog signal processing," ISSCC Dig. Tech. Papers, pp.100–101, Feb. 1997.

- [9] K. Lee and R.G. Meyer, "Low-distortion switched-capacitor filter design techniques," IEEE J. Solid-State Circuits, vol.20, no.6, pp.1103–1113, Dec. 1985.

- [10] D. Slater and J. Paulos, "Low voltage coefficient capacitor for VLSI processes," IEEE J. Solid-State Circuits, vol.24, no.1, pp.165–173, Feb. 1989.

- [11] D.A. Johns and K. Martin, Analog Integrated Circuit Design, John Wiley & Sons, 1997.

Mostafa A.R. Eltokhy was born in Kaluobia, Egypt in 1970. He received his B.S. from Zagazig University, Banha branch, Egypt and M.S. degree from Technical University, Eindhoven, The Netherlands in 1993 and 1998 respectively. He is currently Ph.D. student at Osaka University, Osaka, Japan. His current research interests are analog circuits for wireless applications. He is a student member of the IEEE.

Boon-Keat Tan was born in Penang, Malaysia in 1972. He received his M.S. and Ph.D. degrees from Osaka University, Osaka, Japan in 1999. He is now working for Agilent Technologies Corporation. His current research interests are reconfigurable processors, high performance digital circuits and analog circuits. He is a member of the IEEE.

Toshimasa Matsuoka received the B.S., M.S. and Ph.D. degrees in electronic engineering from Osaka University, Osaka, Japan, in 1989, 1991 and 1996, respectively. During 1991–1998, he worked for the Central Research Laboratories, Sharp Corporation, Nara, Japan, where he was engaged in the research and development of deep submicron CMOS devices and ultra thin gate oxides. Since 1999, he has been worked with Osaka University.

His current research includes CMOS RF circuits and analog circuits. Dr. Matsuoka is a member of the Japan Society of Applied Physics and the IEEE.

Kenji Taniguchi received the B.S., M.S. and Ph.D. degrees from Osaka University, Osaka, Japan, in 1971, 1973 and 1986 respectively. From 1973 to 1986, he worked for Toshiba Research and Development Center, Kawasaki, Japan where he was engaged in process modeling and the design of MOS LSI fabrication technology. He was a Visiting Scientist at Massachusetts Institute of Technology, Cambridge, from July 1982 to November

1983. Presently, he is a Professor of Electronics Engineering at Osaka University. His current research interests are in analog circuits, radio frequency circuits, device physics and process technology. Prof. Taniguchi is a member of the Japan Society of Applied Physics. He is a fellow of the IEEE.