| Title        | 低電源電圧動作可能な高速 CMOS デマルチプレクサ             |

|--------------|----------------------------------------|

| Author(s)    | 清水,新策;田中,智之;井田,司他                      |

| Citation     | 電子情報通信学会論文誌C. 2005, J88-C(1), p. 66-67 |

| Version Type | VoR                                    |

| URL          | https://hdl.handle.net/11094/51659     |

| rights       | copyright@2005 IEICE                   |

| Note         |                                        |

# The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

## 低電源電圧動作可能な高速 CMOS デマルチプレクサ

清水 新策 $^{\dagger}$  田中 智之 $^{\dagger}$  井田 司 $^{\dagger}$  宮本 潤 $^{\dagger}$

High Speed CMOS DEMUX at Low Power Supply Voltage

Shinsaku SHIMIZU<sup>†</sup>, Tomoyuki TANAKA<sup>†</sup>, Tsukasa IDA<sup>†</sup>, Jun MIYAMOTO<sup>†</sup>, Toshimasa MATSUOKA<sup>†</sup>, and Kenji TANIGUCHI<sup>†</sup>

あらまし 抵抗とトランジスタ 1 段のみで構成する低電源電圧動作 CSL (Current Switched Logic) ラッチを用いた高速 CMOS 1:8 デマルチプレクサを提案した .  $0.25\,\mu\mathrm{m}$  の CMOS プロセスパラメータを用いた回路シミュレーションより , デマルチプレクサの消費電力は電源電圧  $1\,\mathrm{V}$  ,  $4\mathrm{-Gbit/s}$  の伝送速度において  $6.2\,\mathrm{mW}$  であることを確認した .

キーワード デマルチプレクサ,低電源電圧,高速動作,CMOS

### 1. まえがき

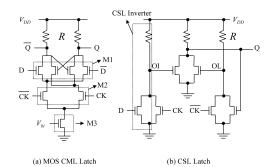

低消費電力化,低コスト化のために,高速シリアル 伝送インタフェース用デマルチプレクサを  $\mathrm{CMOS}$  プロ セスを用いて設計する方法が研究されている  $[1] \sim [3]$  . しかしデマルチプレクサを構成するラッチ回路は電源 電圧とグランド電圧間に縦積み 3 段のトランジスタと 抵抗によって構成されているため低電源動作が困難である(図 1 (a)). そのため低電源  $\mathrm{CMOS}$  ディジタル 回路と混載する場合は別電源を用意する必要がある.本論文では低電源電圧動作が可能なラッチ回路を提案 し,提案型ラッチによる低消費電力  $\mathrm{CMOS}$  1:8 デマルチプレクサを検討した.

#### 2. 低電源電圧動作 CSL ラッチ

CMOS プロセスにおいて,低電源電圧下でも高速動作可能な CSL (Current Switched Logic) ラッチを図 1 (b) に示す.CSL ラッチは,電源電圧からグランド電圧間に存在する素子が抵抗と 1 段の縦積みMOSFET であるため低電源動作が可能である.CSLラッチは論理 "H"を示す電圧を $V_{DD}$ ,論理 "L"の電圧は電流値を最小とするためにn チャネル MOSFETのしきい値電圧 $V_{thn}$  と同じにする.CK が "L"のとき,OL が "L"となるため,入力信号 D と同じ論理値が Q に出力される.一方 CK が "H"のときは OIが "L"となり,入力にかかわらず前状態のデータが保持される.振幅  $\Delta V$  は抵抗 R 及び MOSFET の

しきい値,移動度ばらつきによって変動する.しかし,想定するばらつきにおいて最低の R 値及び最も電流量が少なくなるしきい値,移動度において  $IR=\Delta V$  となるように設定することで,そこから素子がばらついても論理 "L" を表す電圧がしきい値以下になるだけで,論理判定に問題はない.

$\mathrm{CSL}$  ラッチを用いた分周回路の負荷容量  $C_o$  は自身の出力  $\mathrm{MOSFET}$  のドレーン容量及び次段のゲート容量である .  $C_o$  の大部分が  $\mathrm{MOSFET}$  のゲート幅に比例することから ,  $C_o = \alpha W$  とすると ,  $\mathrm{CSL}$  ラッチを用いた分周回路の出力端子の時定数  $\tau$  及び電源電圧は ,

$$\tau = \frac{2\alpha L}{\mu C_{ox} \Delta V} \tag{1}$$

$$V_{thn} < V_{DD} = \Delta V + V_{thn} < 2 V_{thn} \tag{2}$$

となる.ここで  $\Delta V$  ,  $C_{ox}$  はそれぞれ信号振幅 , ゲート酸化膜容量である.式 (2) の上限は MOSFET が飽和領域で動作することを保障するためである.したがって  $\mathrm{CSL}$  ラッチの最高動作速度は  $\Delta V = V_{thn}$  のときであり ,  $V_{thn}$  によって制限される.

#### 3. MOS-CML との比較

CMOS プロセスを用いたデマルチプレクサの設計には、図 1 (a) に示すような MOS-CML (MOS Current Mode Logic) が用いられている [2], [3].

MOS-CML における差動入力トランジスタ対はスイッチング動作 (スルー領域で動作) する必要があることから,

<sup>†</sup> 大阪大学大学院工学研究科電子情報エネルギー工学専攻,吹田市 Department of Electronics and Information Systems, Osaka University, 2-1 Yamada-oka, Suita-shi, 565-0871 Japan

図 1 (a) MOS CML ラッチ, (b) CSL ラッチ Fig. 1 (a) MOS CML latch, (b) CSL latch.

$$\Delta V > \sqrt{\frac{2I}{\mu C_{ox}(W/L)}} \tag{3}$$

となる. したがって MOS-CML ラッチによって構成される分周回路の出力端子の時定数,電源電圧は,

$$\tau = \frac{4\alpha L}{\mu C_{\alpha x} \Delta V} \tag{4}$$

$$V_{DD} = \Delta V + V_{thn} + V_{ov} \tag{5}$$

である.ここで  $V_{ov}$  は  $\mathrm{M3}$  のオーバドライブ電圧である.式 (4) の係数が式 (1) の 2 倍であるのは, $\mathrm{M2}$  が線形領域で動作するため  $\mathrm{CSL}$  と同じ電流を流すためには  $\mathrm{M1}$ , $\mathrm{M2}$  のゲート幅を 2 倍以上にする必要があるからである.

以上のことから,CSL ラッチは MOS-CML ラッチと比べて,低電源下で高速動作が可能である.p-基板,n-well プロセスでは基板バイアス効果により M1,M2 のしきい値電圧が上昇することから CSL のメリットは更に大きくなる.

#### 4. CSL 1:8 デマルチプレクサ

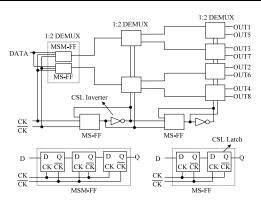

$\mathrm{CSL}$  ラッチを用いた 1:8 デマルチプレクサ回路を図 2 に示す 1:2 DEMUX は  $\mathrm{CSL}$  ラッチを用いた MS-FF (master-slave flip flop) 及び MSM-FF (master-slave-master filp flop) を用いる  $0.25~\mu\mathrm{m}$  CMOS プロセスを用いて 1:8 デマルチプレクサのシミュレーションを行ったところ 1:8 ボマルチプレクサのシミュレータ 1:8 電源電圧 1:8 1:8 で 1:8 で

図 2 1:8 デマルチプレクサのブロック図 Fig. 2 Block diagram of the 1:8 DEMUX.

#### 5. む す び

抵抗及び 1 段の MOSFET によって構成される低電源動作 CSL ラッチ回路を提案した.CSL ラッチ回路は従来の MOS-CML によるラッチに比べて,電流源 MOSFET のオーバドライブ電圧だけ低い電源電圧で動作可能でありながら,高速動作を実現する.CSL ラッチによって構成される 1:8 デマルチプレクサのシミュレーションを行ったところ, $0.25\,\mu\mathrm{m}$  CMOS プロセス,電源電圧  $1\,\mathrm{V}$ , $4\mathrm{-Gbit/s}$  の伝送速度, $6.2\,\mathrm{mW}$  の消費電力が確認された.

謝辞 本研究は,東京大学大規模集積システム設計 教育研究センターの協力により行われたものである. また,独立行政法人科学技術振興機構先端計測分析技術・機器開発事業の援助により行われたものである.

#### 文 献

- M. Fukaishi, K. Nakamura, M. Sato, Y. Tsutui, S. Kishi, and M. Yotsuyanagi, "A 4.25-Gb/s CMOS fiber channel tranceiver with asynchronous tree-type demultiplexer and frequency conversion architecture," IEEE J. Solid-State Circuits, vol.33, no.12, pp.2139-2147, Dec. 1998.

- [2] A. Tanabe, M. Umetani, I. Fujiwara, T. Ogura, K. Kataoka, M. Okihara, H. Sakuraba, T. Endoh, and F. Masuoka, "0.18-\(\mu\)m CMOS 10-Gb/s multiplexer/demultiplexer ICs using current mode logic with tolerance to threshold voltage fluctuation," IEEE J. Solid-State Circuits, vol.36, no.6, pp.988-996, June 2001.

- [3] J. E. Rogers, and J. R. Long, "A 10-Gbs/CDR/DEMUX with LC delay line VCO in 0.18- $\mu$ m CMOS," IEEE J. Solid-State Circuits, vol.37, no.12, pp.1781–1789, Dec. 2002.

(平成16年9月16日受付)