|              |                                                                                     |

|--------------|-------------------------------------------------------------------------------------|

| Title        | 広い入力ビットレート範囲をもつクロックリカバリ回路                                                           |

| Author(s)    | 井田, 司; 田中, 智之; 中尾, 賢他                                                               |

| Citation     | 電子情報通信学会論文誌C. 2008, J91-C(6), p. 349-356                                            |

| Version Type | VoR                                                                                 |

| URL          | <a href="https://hdl.handle.net/11094/51666">https://hdl.handle.net/11094/51666</a> |

| rights       | copyright©2008 IEICE                                                                |

| Note         |                                                                                     |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

## 広い入力ビットレート範囲をもつクロックリカバリ回路

井田 司<sup>†a)</sup>田中 智之<sup>†</sup>中尾 賢<sup>†</sup>松岡 俊匡<sup>†</sup>谷口 研二<sup>†</sup>

Clock Recovery Circuit with Wideband Input Bitrate Range

Tsukasa IDA<sup>†a)</sup>, Tomoyuki TANAKA<sup>†</sup>, Satoshi NAKAO<sup>†</sup>, Toshimasa MATSUOKA<sup>†</sup>, and Kenji TANIGUCHI<sup>†</sup>

あらまし PFD ( Phase/Frequency Detector ) を VCO の出力クロックで駆動させ , VCO の出力周波数が入力ビットレートの一定倍率となるように制御する広帯域のクロックリカバリ回路を提案する . 最大連続同符号長が既知の信号列において , PFD では入力信号の連続同符号長を検知して , 擬似ロックの発生を抑止する . 提案回路の非理想性は OSR ( Over-Sampling Ratio ) と最大連続同符号長で決定され , OSR が高いほど絶対位相誤差が改善され , 最大連続同符号長が大きいほど正常通信のために許容されるジッタ生成の条件は厳しくなる . 数値シミュレーションの結果 , OSR=10 のとき , ビットレートが 100 k~10 Mbit/s の入力信号に対して , VCO の初期周波数が 10 kHz , 200 MHz のそれぞれにおいて , 擬似ロックを生じることなく正常にロックすることを確認した .

キーワード クロックリカバリ回路 , オーバサンプリング , PFD

## 1. まえがき

近年 , 集積回路の高機能化とともに , 様々なインターフェースが使用されている . シリアル通信では受信側で受信信号からクロックを復元する CDR ( Clock and Data Recovery ) 回路 [1] が用いられる . 汎用性の高い CDR 回路として , FPGA やマイクロコンピュータの入力 IP ( Intellectual Property ) に利用するには , 広い入力ビットレート範囲に対応する必要がある . また , 広い入力ビットレート範囲に対応することで , 新しいインターフェース規格への対応も容易になる . しかし , CDR 回路で広い入力ビットレート範囲を実現するには所望クロック周波数の遙倍の周波数におけるロック ( 擬似ロック ) に対する対策が必要である . そのため , 実際の回路では擬似ロックを防ぐため , それぞれのアプリケーションに応じて狭帯域の CDR 回路をカスタム設計することが多い .

一般的な CDR 回路には , PLL ( Phase Locked

Loop ) 回路と同様 , 位相検出器 ( PD ) に周波数検出器 ( FD ) を加えた回路構成 [2] が用いられる . しかし , PD や FD は信号とクロックのエッジをもとに動作するため , 厳密に 1 データ当りの長さを知ることができず , 広帯域化を行った場合 , 擬似ロックが生じる . また , マルチフェーズ出力の VCO [3] を用いた位相補間方式 [4] の CDR 回路も報告されているが , 外部のリファレンスクロックで駆動するため , 位相精度がリファレンスクロックの周波数で決まる . この方式に基づく広帯域の CDR 回路では , 想定される最大の入力ビットレートのリファレンスクロック周波数を使用するため , 低いビットレートの信号を入力したときにはリファレンスクロック発生回路部で無駄に電力が消費される .

本研究の目的は , 最大連続同符号長が既知の信号に対して , リファレンス回路を用いず小規模の回路で広帯域でロックできる手法を提案し , その動作をシミュレーションで確認することである . 最大連続同符号長が既知の信号を用いることで , 1 データ当りの長さが厳密に求められ , 擬似ロックを生じず CDR を動作させることができる .

<sup>†</sup> 大阪大学大学院工学研究科 , 吹田市

Graduate School of Engineering, Osaka University, 2-1

Yamadaoka, Suita-shi, 565-0871 Japan

a) E-mail: ida@si.eei.eng.osaka-u.ac.jp

## 2. 提案手法

### 2.1 回路構成

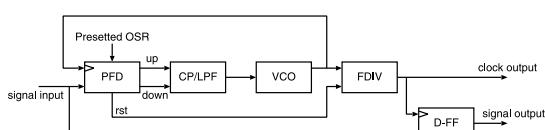

提案する CDR 回路のブロック図を図 1 に示す。この図において、PFD (Phase/Frequency Detector) は VCO の出力クロックで動作するカウンタを含むデジタル回路である。VCO は入力ビットレートよりも速い周波数で動作し、ロック時には入力信号を一定の倍率でオーバサンプリングする。なお、入力信号には 8b/10b 符号 [5] のような最大連続同符号長が決められている信号を用いる。

また、CP (Charge Pump) と LPF (Low-Pass Filter) はそれぞれチャージポンプと低域フィルタの略で、通常の CDR や PLL と同様、PFD で出力された信号を VCO の制御電圧に変換する。この回路の VCO が所望の出力クロックの数倍～数十倍の周波数で発振するように、入力ビットレートと VCO の出力周波数の比 (OSR) を設定する。FDIV は分周器で、VCO の出力信号を分周し、信号ビットレートに対応した周波数にまでクロック周波数を落として出力する。また、分周器は入力信号と位相を合わせるための非同期のリセット入力をもつ。フリップフロップ D-FF は、FDIV から出力されたクロックで入力信号をサンプリングして出力する。

このような回路構成をとることで、単一の回路で広い帯域の信号に対応した CDR 回路ができる。

### 2.2 回路動作

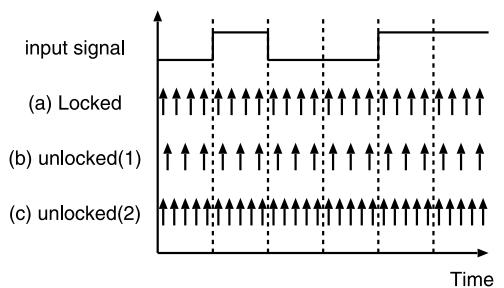

本構成は図 1 に示すように、通常の PLL 型の CDR 回路と同様、入力信号と VCO の出力クロックを比較し、その誤差を VCO の制御電圧にフィードバックする。このとき、VCO の出力クロック周波数が正確に入力ビットレートの一定倍率 (OSR 倍) となるまで VCO の制御電圧が調整される。そのため、図 2(a) に示すように、ロックしたときには 1 データ長につき VCO の出力パルス数が OSR 回になる。一方、図 2(b), (c) のようにカウント数に過不足がある場合は、それを誤差として検知し、設定値へとフィードバックして、

図 1 提案する CDR 回路のブロック図

Fig. 1 Block diagram of proposed CDR circuit.

図 2(a) の状態に近づける。したがって、上記の動作を実行する PFD では 1 データ長当りの VCO の出力パルス数を得る必要がある。

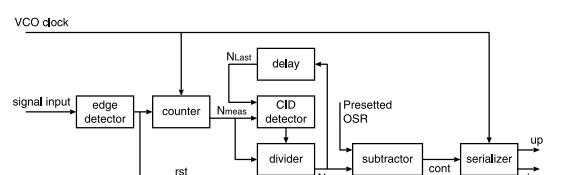

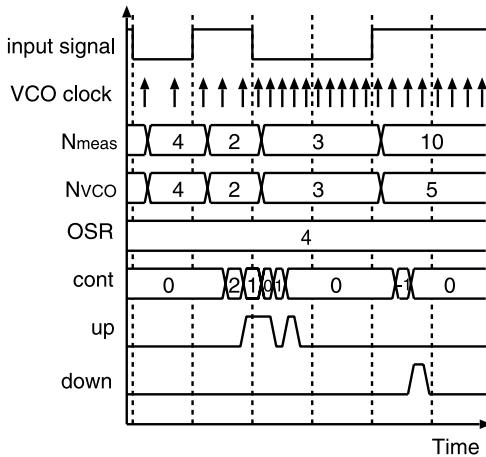

図 3 に示すように、エッジ検出器、カウンタ、連続同符号長検出器、除算器、減算器、シリアルライザから構成される PFD は、1 データ長当りの VCO の出力パルス数を検出し、OSR との差を出力のパルス数の形で出力する。また、差分器に入力される OSR はあらかじめ設定しておく。カウンタとシリアルライザは VCO のクロックに同期して動作するが、それ以外はすべて入力信号のエッジを検出したタイミングでのみ動作する。一例として、OSR=4 のときの PFD の動作波形を図 4 に示す。その動作について以下に述べる。

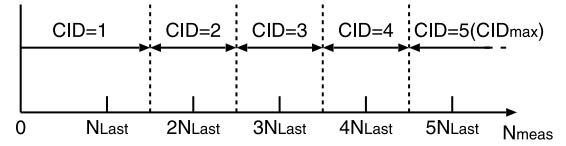

カウンタでは VCO の出力パルス数を計数し、エッジ検出器で入力信号の論理が変化したタイミングでカウンタのリセットを行う。こうして、入力信号の論理が変化してから再び論理が変化するまでの VCO の出力パルス数を得る。このときの 1 データ長当りの VCO の出力パルス数を  $N_{VCO}$  とすると、実際に測定される駆動回数  $N_{meas}$  は入力信号の連続同符号長によって異なり、 $CID \cdot N_{VCO}$  ( $CID = 1 \sim CID_{max}$  ( $CID_{max}$  は入力信号列の最大連続同符号長))、若しくはクロックのタイミングによっては、それに近い値となる。次に、連続同符号長検出器において、後述するアルゴリ

図 2 入力信号と VCO 出力との関係 (OSR=4)

Fig. 2 Relations between input signals and VCO outputs. (OSR=4)

図 3 PFD の構成

Fig. 3 Block diagram of PFD.

図 4 PFD の動作波形 (OSR=4)

Fig. 4 Waveform of PFD. (OSR=4)

ズムで  $N_{meas}$  の値から連続同符号長 CID を求め、これらの値から除算器で  $N_{VCO}$  を求める。

減算器では  $N_{VCO}$  とあらかじめ設定した OSR の値を比較し、その差分値  $cont$  を出力する。

シリアルライザでは  $cont$  の値を CP の入力に適した形式に変換する。 $up$ ,  $down$  とも 1 bit 出力である。 $cont$  の値の符号をもとに、 $up$  若しくは  $down$  にパルスを出力すると同時に、 $cont$  をカウントアップ/ダウンし、 $cont$  の値が 0 になるまでパルスを出力する。本 CDR では、 $up$ ,  $down$  を各 1 bit の出力にし、それを CP, LPF で処理することで、VCO に入力される制御電圧の変化を緩やかにすると同時に CP, LPF 回路の単純化を図っている。

PFD の出力をもとに、1 データ長当たりの VCO の出力パルス数が正確に OSR 倍となるよう VCO の出力周波数が制御されるという点で PFD は周波数検出器として動作している。また、ロックした時点で VCO の出力周波数は入力ビットレートの OSR 倍となり、PFD 内のカウンタは  $nOSR$  ( $n = 1 \sim CID_{max}$ ) のいずれかの値でリセットされる。したがって、FDIV の分周比を OSR とすると、このカウンタのリセットに同期して FDIV もリセットされることで、 $nOSR$  及び  $(n + 0.5)OSR$  のカウンタ値で出力のクロックの相が変化する。クロックの相がデータの中心部で変化するため、PFD が位相検出器としても機能していることが分かる。

例として、OSR=10,  $CID_{max}=5$  の PFD を Verilog で実装し、論理合成したところ、ゲート数は 708

図 5 連続同符号長の決定 ( $CID_{max} = 5$ )

Fig. 5 Consecutive identical digits decision.

( $CID_{max} = 5$ )

図 6  $N_{Last}$  が本来の値と違うときの連続同符号長の決定

( $CID_{max} = 5$ )

Fig. 6 Consecutive identical digits decision when

$N_{Last}$  is different from the actual value.

( $CID_{max} = 5$ )

となり、図 3 に示す回路のディジタル部は比較的少ないゲート数で実装が可能であることを確認した。

### 2.3 連続同符号長検出器の動作

連続同符号長検出器 (CID detector) では直前に連続同符号長を求めたときの  $N_{VCO}$  の値を  $N_{Last}$  とすると、連続同符号長 CID を次のようにして検出する。

- $0 < N_{meas} < 1.5N_{Last}$  のとき ,

$$N_{VCO} = N_{meas} \quad (1)$$

- $(n - 0.5)N_{Last} < N_{meas} < (n + 0.5)N_{Last}$  ( $n = 2, \dots, CID_{max} - 1$ ) のとき ,

$$N_{VCO} = N_{meas}/n \quad (2)$$

- $(CID_{max} - 0.5)N_{Last} < N_{meas}$  のとき ,

$$N_{VCO} = N_{meas}/CID_{max} \quad (3)$$

例として  $CID_{max} = 5$  のときの様子を図 5 に示す。ただし、 $N_{Last}$  の値が不定である電源投入時などの初期状態における  $N_{Last}$  の値は次のように決定される。

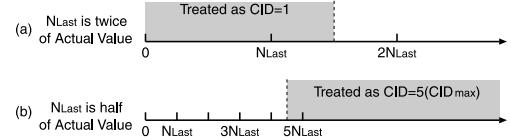

- (1)  $N_{Last}$  が本来の値より大きい場合

例として、 $N_{Last}$  が本来の値の 2 倍のときの  $N_{meas}$  の連続同符号長の判別を図 6(a) に示す。このとき、連続同符号長が 2 のデータは連続同符号長が 1 と誤認識されて、VCO は信号ビットレートの  $OSR/2$  倍の周波数で擬似ロックする。しかし、 $CID = 1$  のデータ

が入力されると、 $N_{meas} < N_{Last}$  となり、式(1)より  $N_{VCO}$  の値は  $N_{meas}$  に変更されて、 $N_{Last}$  の値は正常な値になる。

#### (2) $N_{Last}$ の値が本来の値より小さい場合

例として、 $N_{Last}$  が本来の値の  $1/2$  倍のときの  $N_{meas}$  の連続同符号長の判別を図 6(b) に示す。このとき、連続同符号長が 1 のデータは連続同符号長が 2 と誤認識されて、VCO は信号ビットレートの  $2OSR$  倍の周波数で擬似ロックする。しかし、 $CID = CID_{max}$  のデータが入力されると、 $N_{meas} > N_{Last} \cdot CID_{max}$  となり、式(3)より  $N_{VCO}$  の値は  $N_{meas}/CID_{max}$  と変更されて、 $N_{Last}$  の値は正常な値になる。

以上の考察から分かるように、 $N_{Last}$  の初期値にかかわらず、 $CID = 1$  と  $CID = CID_{max}$  のデータが入力されると、 $N_{Last}$  には正確な 1 データ長当たりの VCO の出力パルス数が格納される。一般的 CDR では  $N_{Last}$  が本来の値の  $n$  倍、若しくは  $1/n$  倍 ( $n$  は 2 以上の整数) となると擬似ロックが生じるが、本構成では 1 データ当たりの VCO の出力パルス数を正確に得られるため、擬似ロックは生じない。 $N_{Last}$  の値を決定した後、急激な VCO の出力周波数や入力ビットレートの変化がなければ、1 データ長当たりの VCO の出力パルス数は  $N_{Last}$  と比較して大幅には変化しない。したがって、図 5 のように、 $N_{Last}$  を用いて  $N_{meas}$  の連続同符号長を得ることができる。

### 3. 特性検討

本構成における非理想性の発生要因として、絶対位相誤差とジッタが考えられる。

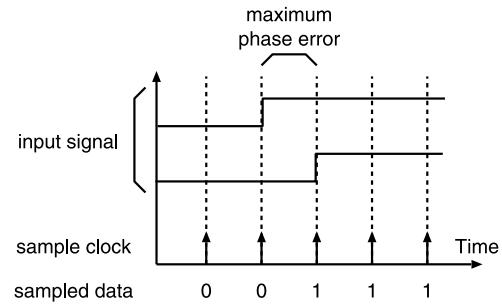

#### (1) 絶対位相誤差

CDR 回路がロックすると、VCO の出力周波数は信号ビットレートの正確に OSR 倍となる。入力論理の変化点でのサンプリング誤差は図 7 のように入力信号周期に対して最大で  $\frac{2\pi}{OSR}$  (rad) であり、この位相のずれがそのまま絶対位相誤差となる。したがって、絶対位相誤差の最大値は OSR を調節すれば制御可能であるが、その値は入力信号周期に対して一定の割合となる。

#### (2) ジッタ

最大連続同符号長が増加すると入力信号の変化的頻度が少なくなるため、VCO の出力周波数はより正確でなければならない。ここでは、信号を復元する際にエラーフリーとなる VCO の動作周期範囲から許容される位相差を算出し、それを PFD に起因する許容

図 7 サンプリング時に生じる位相誤差

Fig. 7 Phase error on sampling.

ジッタ生成とする。許容ジッタ生成が小さいと、許容される VCO の出力周波数範囲は狭くなるため、収束の過程で、正常なデータとクロックの復元ができるまでに時間がかかる。

提案回路では入力信号のエッジを検出して FDIV のカウンタがリセットされるため、下記の二つの条件を満たせば受信時にエラーを生じない。

(a)  $CID = CID_{max}$  のデータを受信したとき、 $CID_{max}$  番目のデータを正確に取得できること

(b)  $CID = CID_{max}$  のデータを受信したとき、 $CID_{max} + 1$  番目のデータの取得までに入力の信号論理が変化すること

ここで、完全にロックしたときの VCO の動作周期を  $T_{ideal}$ 、実回路の VCO の動作周期を  $T_{real}$  とすると、条件(a)は  $T_{real} > T_{ideal}$  のとき、条件(b)は  $T_{real} < T_{ideal}$  のときに適用される。また、信号論理は PFD と FDIV のカウンタが  $T_{real} \cdot OSR \cdot (n - 0.5)$  ( $n = 1 \sim CID_{max}$ ) となるときに取得される。したがって、条件(a)から次式が得られる。

$$\begin{aligned} & T_{real}(CID_{max} - 0.5)OSR + T_{real} \\ & < T_{ideal}CID_{max}OSR \end{aligned} \quad (4)$$

なお、式(4)の左辺で  $T_{real}$  が加算されている理由は入力信号論理が変化して PFD と FDIV のカウンタがリセットされてから VCO の出力パルスが入力されるまでの時間差が最大で  $T_{real}$  であることによる。

また、条件(b)から次式が得られる。

$$\begin{aligned} & T_{ideal}CID_{max}OSR \\ & < T_{real}(CID_{max} + 0.5)OSR \end{aligned} \quad (5)$$

式(4), (5)より、

$$\frac{CID_{max}}{CID_{max} + 0.5}T_{ideal} < T_{real}$$

図 8  $CID_{max}$  を変化させたときの許容ジッタ生成

Fig. 8 Allowable jitter generation characteristics as a parameter of  $CID_{max}$ .

$$< \frac{CID_{max}OSR}{(CID_{max}-0.5)OSR+1} T_{ideal} \quad (6)$$

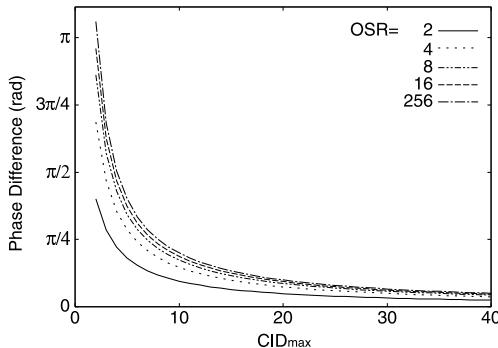

の関係が得られる。式(6)より、正常に信号を復元するために許容されるジッタ生成を位相差で表すと、

$$\begin{aligned} & 2\pi \left( \frac{CID_{max}OSR}{(CID_{max}-0.5)OSR+1} - \frac{CID_{max}}{CID_{max}+0.5} \right) \\ &= 2\pi \frac{CID_{max}(OSR-1)}{CID_{max}^2 OSR + CID_{max} - 0.25 OSR + 0.5} \end{aligned} \quad (7)$$

となる。式(7)において、 $CID_{max}$  と許容ジッタ生成との関係を図 8 に示す。この図より、最大連続同符号長が増加すると、許容ジッタ生成は小さくなる。また、OSR が極めて小さいときは OSR が増加すると許容ジッタ生成は大きく改善されるが、OSR が増加するにつれて、許容ジッタ生成の改善幅は急激に減少する。

#### 4. シミュレーション結果

提案回路の有効性を示すため、数値シミュレーションを行った。シミュレーションを簡略化するため、オシレータは NCO ( numeric controlled oscillator ) として実装した。また、PFD 出力の up, down のパルス数を累算する NCO は CP, LPF の機能も内包している。NCO の精度は 1 Hz, OSR 設定値は 10 とした。また、本シミュレーションでは入力信号として長さ  $2^8 - 1$  の LFSR によるランダムデータを用いた。このとき、 $CID_{max} = 8$  である。

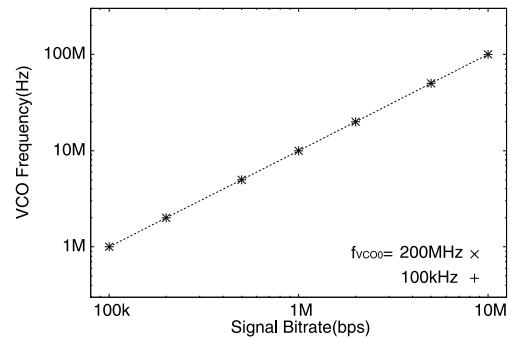

図 9 に入力ビットレートに対する VCO 出力周波数の収束値を示す。高い周波数側からと低い周波数側からの両方で正常にロックすることを確認するため、100 kbit/s の信号ビットレートに対して、VCO

図 9 入力ビットレートをパラメータとしたときの出力クロック周波数

Fig. 9 Output clock frequency as a parameter of input bitrate.

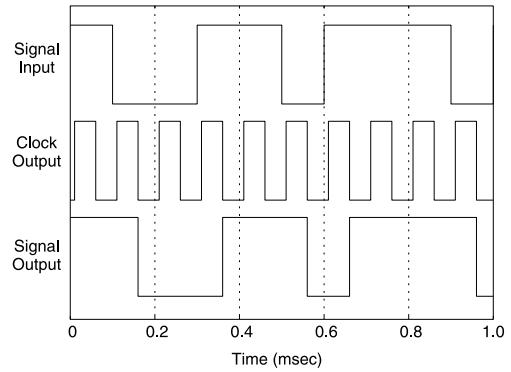

図 10 CDR 回路の入出力波形

Fig. 10 Input and output waves of CDR circuit.

の初期周波数  $f_{VCO0}$  を 10 kHz と 200 MHz で行った。この結果、入力ビットレートの全域において、VCO の初期周波数が信号ビットレートの高低にかかわらず、VCO が正常に信号ビットレートの 10 倍 (OSR 倍) の周波数でロックしていることが確認できる。

入力ビットレートが 100 kbit/s のとき、完全にロックしたときの入力信号、出力クロック、出力信号のシミュレーション結果を図 10 に示す。この図より、出力クロックは入力信号に対して、一定の絶対位相誤差を保ちつつ出力され、それに同期して出力信号が得られていることが確認できる。

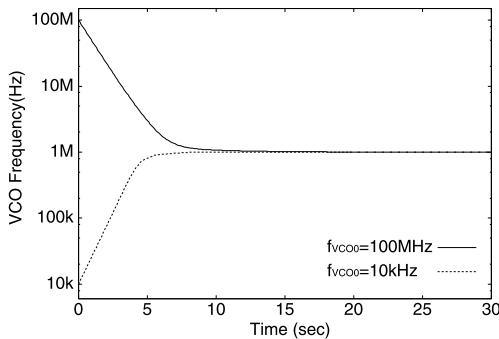

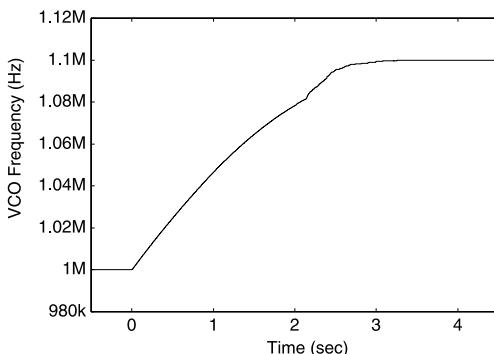

図 11 は、入力ビットレートを 100 kbit/s, VCO の初期周波数  $f_{VCO0}$  を 10 kHz, 100 MHz としたときの VCO 周波数の収束過程を示している。この図からも提案回路が擬似ロックせず、所望の周波数にロックしていることが確認できる。周波数誤差が最終値の 1% になるまでの時間はそれぞれ、8.1 s, 17.5 s である。

図 11 VCO の発振周波数の時間変化

Fig. 11 Time transition of VCO output frequency.

表 1 最大/最小エラー発生周波数を求めるためのシミュレーション条件

Table 1 Simulation condition of detecting maximum/minimum error occurrence frequency.

| OSR             | 10          |

|-----------------|-------------|

| 入力ビットレート        | 100 kbit/s  |

| VCO 初期周波数 (高域側) | 1.2~1.5 MHz |

| VCO 初期周波数 (低域側) | 500~800 kHz |

| 試行回数            | 各 10000 回   |

が、以下の方法で収束時間の短縮を図ることは可能である。例えば、

- (1) NCO の精度を落とす、

- (2)  $N_{VCO}$  と OSR の差が大きいときには出力周波数の変化幅を大きくとる、

- (3) Dual-Loop 構成の CDR [6] を用い、本回路で擬似ロックが生じない周波数にまで VCO の制御電圧を制御し、その後の調整を収束時間の速い別の CDR で行う

- などの例が考えられる。

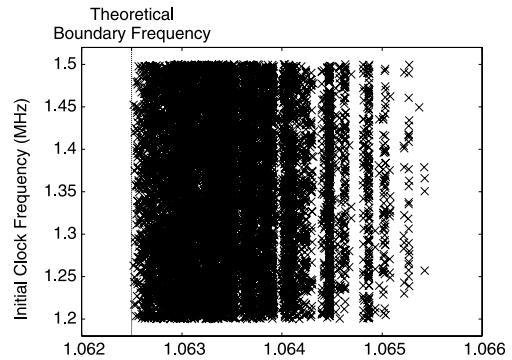

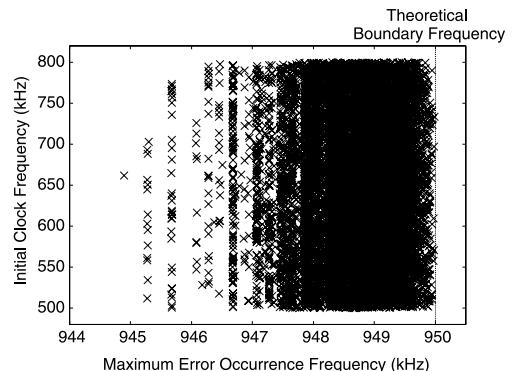

式 (6) の検証を目的として、収束時にエラーフリーとなる境界周波数について、ロック周波数に対して高域側と低域側のそれぞれから表 1 に示す条件でシミュレーションを行った。VCO の初期周波数を表 1 に示した範囲内でランダムに設定したときの収束時にエラーフリーとなる境界周波数について、高域側からロックさせたときの結果を図 12 に、低域側からロックさせたときの結果を図 13 に示す。また、図 12、図 13 のそれぞれに式 (6) から得られた理論境界周波数を点線でプロットした。これらの図より、シミュレーションで得られた境界周波数は初期周波数にかかわらず、式 (6) で得られる理論境界周波数よりもロック周波数に近い側には存在しないことが確認でき、式 (6) の条件を満たすことでエラーフリーとなることが確認できる。

図 12 高域側よりロックさせたときのエラー発生周波数の最小値

Fig. 12 Minimum error occurrence frequency when initial frequency is higher than lock frequency.

図 13 低域側よりロックさせたときのエラー発生周波数の最大値

Fig. 13 Maximum error occurrence frequency when initial frequency is lower than lock frequency.

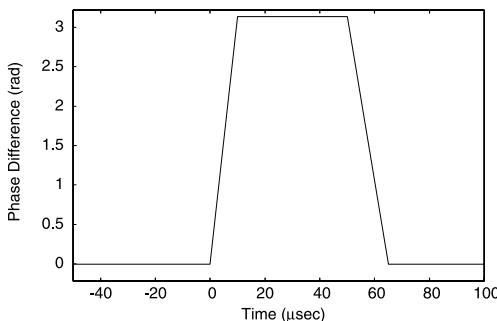

提案回路の過渡応答特性を確認するため、入力信号のビットレートと位相をロック後に変化させた例をシミュレーションした。計算例として入力ビットレートは 100 kbit/s, OSR=10 を用いた。まず、入力ビットレートを瞬時に 110 kbit/s に変化させたときの VCO の周波数の経時変化を図 14 に示す。図 11 と同様、入力ビットレートを変化させても所望の周波数へ収束している。図 15 は入力信号の位相を  $\pi$  進めたときの入力信号と出力クロックの位相差を示している。この結果より、数データ長で出力の位相が追従していることが確認できる。これは入力信号のエッジが検出されると FDIV のカウンタがリセットされて位相が調節されることによる。また、入力信号の位相変化に起因する

図 14 入力信号のビットレートを変化させたときの VCO の周波数の変化

Fig. 14 Time transition of VCO output frequency when input bitrate is changed.

図 15 入力信号の位相を変化させたときの位相差の変化

Fig. 15 Time transition of phase difference with input signal and output clock when input phase is changed.

出力周波数の変化は見られなかった。

## 5. むすび

最大連続同符号長が既知の入力信号に対して、擬似ロックを生じない広帯域 CDR 回路を提案した。本回路では VCO の発振周波数を入力ビットレートより高くし、入力信号をオーバサンプリングすることで、VCO の発振周波数と入力ビットレートの比があらかじめ指定した値と等しくなるよう、VCO の発振周波数を制御する。本構成における非理想性については、絶対位相誤差が OSR に依存する。また、正常通信のために許容されるジッタ生成は位相で表され、OSR と最大連続同符号長に依存する。提案構成について、数值シミュレーションを行ったところ、2 けたにわたる広い入力ビットレートの範囲で正常にロックすることを確認した。

謝辞 本研究は文部科学省グローバル COE プログ

ラム「次世代電子デバイス教育研究開発拠点」の助成を受けて行われたものである。

## 文 献

- [1] B. Razavi, "Challenges in the design of high-speed clock and data recovery circuits," IEEE Commun. Mag., vol.40, no.8, pp.94–101, Aug. 2002.

- [2] R.J. Yang, S.P. Chen, and S.I. Liu, "A 3.125Gb/s clock and data recovery circuit for the 10-Gbase-LX4 ethernet," IEEE J. Solid-State Circuits, vol.39, no.8, pp.1356–1360, Aug. 2004.

- [3] L.M. Lee, D. Weinlader, and C.K.K. Yang, "A sub-10-ps multiphase sampling system using redundancy," IEEE J. Solid-State Circuits, vol.41, no.1, pp.265–273, Jan. 2006.

- [4] J. Kim, J. Yang, S. Byun, H. Jun, J. Park, C.S.G. Conroy, and B. Kim, "A four-channel 3.125-Gb/s/ch CMOS serial-link transceiver with a mixed-mode adaptive equalizer," IEEE J. Solid-State Circuits, vol.40, no.2, pp.462–471, Feb. 2005.

- [5] A.X. Widmer and P.A. Franaszek, "A DC-balanced, partitioned-block, 8b/10b transmission code," IBM J. Research and Development, vol.27, no.5, pp.440–451, Sept. 1983.

- [6] M. Meghelli, B. Parker, H. Ainspan, and M. Soyuer, "SiGe BiCMOS 3.3-v clock and data recovery circuits for 10-GB/s serial transmission systems," IEEE J. Solid-State Circuits, vol.35, no.12, pp.1992–1995, Dec. 2000.

(平成 19 年 8 月 28 日受付, 11 月 5 日再受付)

井田 司 (学生員)

平 15 阪大・工・電子卒。平 17 同大学院博士前期課程了。現在、同大学院工学研究科博士後期課程在学中。CMOS 回路の研究に従事。

田中 智之 (学生員)

平 11 関西大・工・応用化学卒。平 13 阪大大学院工学研究科物質・生命工学専攻博士前期課程了。現在、同大学院工学研究科電気電子情報工学専攻博士後期課程在学中。CMOS アナログ回路の研究開発に従事。

中尾 賢

平 19 阪大・工・電子卒。現在、同大大学院工学研究科博士前期課程在学中。クロックリカバリ回路の研究に従事。

松岡 俊匡（正員）

平元阪大・工・電子卒。平 3 同大大学院博士前期課程了。平 3 シャープ（株）入社。平 11 阪大大学院工学研究科電子情報エネルギー工学専攻リサーチ・アソシエイト（日本学术振興会研究員）。平 12 同大大学院工学研究科電子情報エネルギー工学専攻講師。平 16 同大大学院工学研究科電子情報エネルギー工学専攻助教授。CMOS RF 回路の研究に従事。工博。応用物理学会、電気学会、IEEE 各会員。

谷口 研二（正員）

昭 46 阪大・工・電子卒。昭 48 同大大学院修士課程了。昭 50 東芝（株）入社。昭 57 より 1 年間マサチューセッツ工科大学客員研究員。昭 61 阪大工学部電子工学科助教授。平 8 同大大学院工学研究科電子情報エネルギー工学専攻教授。現在まで Si の酸化・拡散プロセス、半導体デバイスの物理、半導体シミュレーション技術、アナログ集積回路の研究に従事。工博。応用物理学会、電気学会、IEEE 各会員。