|              |                                                                                     |

|--------------|-------------------------------------------------------------------------------------|

| Title        | 入出力相互コンダクタンス及び位相補償容量を可変とする可変利得増幅器の低消費電力化に関する検討                                      |

| Author(s)    | 大倉, 鉄郎; 大倉, 俊介; 松岡, 俊匡 他                                                            |

| Citation     | 電子情報通信学会論文誌C. 2012, J95-C(7), p. 131-138                                            |

| Version Type | VoR                                                                                 |

| URL          | <a href="https://hdl.handle.net/11094/51668">https://hdl.handle.net/11094/51668</a> |

| rights       | copyright©2012 IEICE                                                                |

| Note         |                                                                                     |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

# 入出力相互コンダクタンス及び位相補償容量を可変とする可変利得増幅器の低消費電力化に関する検討

大倉 鉄郎<sup>†a)</sup>

大倉 俊介

松岡 俊匡<sup>†</sup>

谷口 研二<sup>†</sup>

A Low Power Technique for Programmable Gain Amplifier with Controllable input/output Transconductance and Compensation Capacitor

Tetsuro OKURA<sup>†a)</sup>, Shunsuke OKURA, Toshimasa MATSUOKA<sup>†</sup>,

and Kenji TANIGUCHI<sup>†</sup>

あらまし 2段構成演算増幅器を用いたスイッチトキャパシタ型可変利得増幅器 (PGA: Programmable Gain Amplifier) の低消費電力化手法を提案する。演算増幅器の入力相互コンダクタンスと位相補償容量を PGA の利得に応じて制御し、更に、出力相互コンダクタンスも可変にすることで、高い電力効率で全利得に対して帯域と安定性を満たす可変利得増幅器を実現した。0.25  $\mu\text{m}$  CMOS プロセスを用い動作速度が 40 MSps、利得幅が 0~30 dB の PGA を設計した。シミュレーション結果より、可変利得増幅器の消費電流は PGA の利得に応じて、最大で 28.6 mA、最小で 11.0 mA となった。また、出力換算ノイズの二乗平均平方根 (RMS) は同様に最大で 2.2 mVrms、最小で 133.6  $\mu\text{Vrms}$  となった。

キーワード 可変利得増幅器、可変相互コンダクタンス、可変位相補償容量、スイッチトキャパシタ、低消費電力

## 1. まえがき

可変利得増幅器 (PGA: Programmable Gain Amplifier) はイメージングシステムや、通信システム等で信号振幅を適切に制御するために広く用いられている。ディジタル制御 PGA としては、オペアンプの帰還率を制御するスイッチトキャパシタ方式 [1] や、バイアスオフセットテクニック方式 [2] が提案されている。スイッチトキャパシタ型 PGA は、高精度な可変利得を実現可能であるが、帰還率を制御すると帯域と位相余裕が帰還率によって変わることを抱えている [3]。一般に PGA では帰還率を指数関数的に変化させ利得を制御するため、電力効率を下げずに帯域と安定性を両立させることは困難である。帰還率に応じた帯域及び位相余裕の変動を抑えるため、位相補償容量可変 PGA ( $C_c$ -PGA) [4]、入力相互コンダクタンス可変 PGA ( $g_m$ -PGA) [5] が提案されている。 $C_c$ -PGA

では、帰還率に比例した位相補償容量を使用することで、帰還率の変化に起因する一次極の変動を抑えていくが、位相補償容量に依存する二次極とゼロ点の変動を抑えることができない。そのため、位相余裕を帰還率によらず一定にすることが難しく、電力効率が低下する。また、位相補償容量を指数関数的に可変にするため使用する容量値が大きく、チップ面積が大きいという欠点がある。一方、 $g_m$ -PGA は、帰還率に反比例して入力相互コンダクタンスを制御して一次極の変動を抑えている。二次極とゼロ点は入力相互コンダクタンスに依存しないことから、帰還率にかかわらず帯域と位相余裕が一定となる。しかし、低利得時に入力段の相互コンダクタンスを指数関数的に小さくするため、低利得時の出力換算ノイズは、 $C_c$ -PGA に比べて悪くなる。

本論文では、従来の PGA の問題点を解決するため、帰還率に応じて入力相互コンダクタンスと位相補償容量を同時に制御し、更に出力相互コンダクタンスも制御する低消費電力可変利得増幅器を提案する。提案する PGA は入力相互コンダクタンス、位相補償容量を同時に制御することで、それぞれの制御幅を小さ

<sup>†</sup> 大阪大学大学院工学研究科、吹田市

Graduate School of Engineering, Osaka University, Suita-shi, 565-0871 Japan

a) E-mail: [ohkura@si.eei.eng.osaka-u.ac.jp](mailto:ohkura@si.eei.eng.osaka-u.ac.jp)

くことが可能であり、 $C_c$ -PGA に比べて小面積、 $g_m$ -PGA に比べて低ノイズで実現することができる。また、二次極を考慮して出力相互コンダクタンスを制御することで、更なる消費電力の削減を実現している。以下では、シミュレーションにより本方式の有用性を明かにし、また、各方式の面積の比較を行った。

## 2. PGA 回路の動作原理

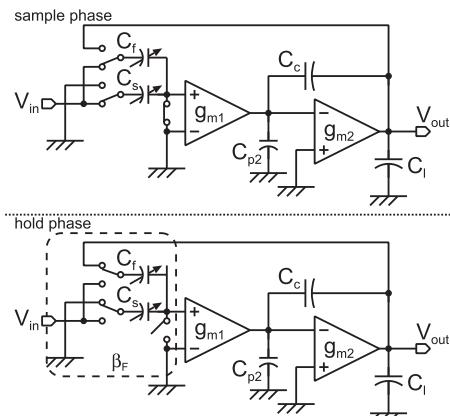

図 1 に PGA 回路のブロック図を示す。PGA 回路は帰還率  $\beta_F$  の負帰還を有した 2 段オペアンプで構成される。サンプリング相において入力信号 ( $V_{in}$ ) はキャパシタ  $C_f$ 、 $C_s$  にサンプリングされる。ホールド相で  $C_f$  がフィードバックキャパシタとして出力端子に接続され、 $C_s$  は信号グランドに接続される。これにより、PGA 回路の利得は、

$$\begin{aligned} V_{out} &= \frac{C_s + C_f}{C_f} V_{in} = \frac{1}{\beta_F} V_{in} \\ &= 2^x \cdot V_{in} \quad (x = 0, 1, \dots, n) \end{aligned} \quad (1)$$

で表される。 $C_s$  と  $C_f$  の和を常に一定とし、 $C_f$  の値を指数関数的に制御することで可変利得を実現している。また、PGA 回路のホールド時における周波数特性は、

$$\frac{V_{out}(s)}{V_{in}}(s) = \frac{1 - \frac{s}{z}}{\beta_F + s \left( \frac{1}{\omega_1} + \frac{1}{A_0 \omega_2} \right) + \frac{s^2}{\omega_1 \omega_2}} \quad (2)$$

で表される。 $\omega_1$ 、 $\omega_2$  及び  $z$  は式 (3)、(4)、(5) で与えられる。

$$\omega_1 = \frac{g_{m1}}{C_c} \quad (3)$$

図 1 PGA 回路ブロック図

Fig. 1 Block diagram of PGA.

$$\omega_2 = \frac{g_{m2}}{C_L + C_{p2} + C_L C_{p2}/C_c} \quad (4)$$

$$z = \frac{g_{m2}}{C_c} \quad (5)$$

ここで、 $g_{m1}$ 、 $g_{m2}$ 、 $A_0$  はそれぞれ入力段、出力段の相互コンダクタンス及び 2 段オペアンプの DC 利得である。また、 $C_c$ 、 $C_{p2}$  はそれぞれ位相補償容量、出力段の入力寄生容量である。 $C_L$  はオペアンプの負荷容量  $C_l$  と帰還容量の並列接続であり、 $C_L = C_l + C_s C_f / (C_s + C_f)$  で表される。 $z$  が  $\omega_2$  より十分に高周波側に存在し、かつ  $\omega_2$  が  $\omega_1/A_0$  よりも十分に高周波側に存在する場合 ( $z \gg \omega_2 \gg \omega_1/A_0$ )、PGA 回路の帯域 ( $\omega_c$ ) と位相余裕 ( $\phi_m$ ) はそれぞれ、

$$\omega_c = \omega_2 \left[ \sqrt{\frac{1}{4} + \left( \frac{\beta_F \omega_1}{\omega_2} \right)^2} - \frac{1}{2} \right]^{\frac{1}{2}} \quad (6)$$

$$\phi_m = \tan^{-1} \left[ \sqrt{\frac{1}{4} + \left( \frac{\beta_F \omega_1}{\omega_2} \right)^2} - \frac{1}{2} \right]^{-\frac{1}{2}} \quad (7)$$

と表すことができる。式 (6)、(7) より、 $\beta_F$  に対して  $\beta_F \omega_1$  と  $\omega_2$  の変動量を抑えることで、帰還率によらず帯域と安定性の両立が可能となる。 $C_c$ -PGA では、帰還率  $\beta_F$  に比例して  $C_c$  を制御することで  $\beta_F \omega_1$  を一定にしているが、 $C_c$  による  $\omega_2$  の変動量が大きいため電力効率が悪い。また、PGA 特有の指数関数的な制御に起因して非常に大きな  $C_c$  が必要となり、回路面積が増大する。 $g_m$ -PGA では、 $g_{m1}$  を帰還率  $\beta_F$  に反比例するよう制御することで  $\beta_F \omega_1$  は一定となる。しかし、 $g_{m1}$  を指数関数的に制御すると、高い帰還率において  $g_{m1}$  が非常に小さくなり、 $C_c$ -PGA に比べて出力換算ノイズが増大する。

## 3. 提案回路構成

提案する PGA 回路では、指数関数的に変化する帰還率  $\beta_F$  に応じて、 $g_{m1}$  と  $C_c$  の双方を同時に制御することでそれぞれの指数関数的な変動を抑え、小面積と低ノイズを両立している。また、 $g_{m2}$  を制御することにより高い電力効率を実現している。 $\beta_F$  は  $x = b$  近傍におけるテイラー展開を用いると、

$$\beta_F = \frac{1}{2^x} \approx 2^{-b} \frac{1 - (1-a)(x-b) \ln 2}{1 + a(x-b) \ln 2} \quad (8)$$

と近似することができる。ここで、 $a$ 、 $b$  は  $|x-b| \ll (\ln 2)^{-1}$ 、 $0 < a < 1$  を満たす定数とする。 $g_{m1}$  と  $C_c$

を式(9)のように  $\beta_F$  の近似式の逆関数に比例するよう制御することで、線形制御のみを用いて近似的に指数関数制御を行い  $\beta_F\omega_1$  を  $\beta_F$  によらず一定にしている。

$$\omega_1 = \frac{g_{m1}}{C_c} \propto \frac{1 + a(x-b) \ln 2}{1 - (1-a)(x-b) \ln 2} \quad (9)$$

また、 $g_{m2}$  を制御することにより  $C_c$  の変化に応じた  $\omega_2$  の変動量を抑え(式(4))、更に低利得時における電力効率を上げている。

#### 4. 比較検討

ここでは、表1に示す提案PGAと従来PGAの主要パラメータの例から、それぞれの方式を電力、ノイズ、面積から比較する。

PGA利得を0dBから30dBまで可変にするために、帰還率  $\beta_F$  を1から1/32まで指数関数的に制御する。 $g_{m10}$ 、 $g_{m20}$ 、 $C_{c0}$  はそれぞれ  $\beta_F = 1/32$ において従来PGAで要求仕様を満たす入力相互コンダクタンス、出力相互コンダクタンス、位相補償容量である。

提案PGA回路では、 $g_{m1}$ を線形的に制御する。その際、近似式(9)のずれを補い、 $\beta_F\omega_1$ が一定となるように  $C_c$  の値を制御する。更に、PGA利得24dB未満では出力相互コンダクタンス  $g_{m2}$  を30dBにおける値の0.7倍に変更する。位相補償容量の増加によって、 $\omega_2$  が高周波側にシフトするが、 $g_{m2}$  を低下させて  $\omega_2$  の変動量を抑制し、電力効率を向上させている。

表1 PGA回路の主要パラメータ

Table 1 Key parameters of PGA circuits.

(a) 提案 PGA 回路

| 利得        | 0 dB                 | 6 dB                 | 12 dB                | 18 dB                | 24 dB                | 30 dB     |

|-----------|----------------------|----------------------|----------------------|----------------------|----------------------|-----------|

| $\beta_F$ | 1                    | 1/2                  | 1/4                  | 1/8                  | 1/16                 | 1/32      |

| $g_{m1}$  | $\frac{1}{6}g_{m10}$ | $\frac{2}{6}g_{m10}$ | $\frac{3}{6}g_{m10}$ | $\frac{4}{6}g_{m10}$ | $\frac{5}{6}g_{m10}$ | $g_{m10}$ |

| $g_{m2}$  | $0.7g_{m20}$         | $0.7g_{m20}$         | $0.7g_{m20}$         | $0.7g_{m20}$         | $0.7g_{m20}$         | $g_{m20}$ |

| $C_c$     | $\frac{16}{3}C_{c0}$ | $\frac{16}{3}C_{c0}$ | $\frac{12}{3}C_{c0}$ | $\frac{8}{3}C_{c0}$  | $\frac{5}{3}C_{c0}$  | $C_{c0}$  |

(b)  $C_c$ -PGA回路[4]

| 利得        | 0 dB       | 6 dB       | 12 dB     | 18 dB     | 24 dB     | 30 dB     |

|-----------|------------|------------|-----------|-----------|-----------|-----------|

| $\beta_F$ | 1          | 1/2        | 1/4       | 1/8       | 1/16      | 1/32      |

| $g_{m1}$  | $g_{m10}$  | $g_{m10}$  | $g_{m10}$ | $g_{m10}$ | $g_{m10}$ | $g_{m10}$ |

| $g_{m2}$  | $g_{m20}$  | $g_{m20}$  | $g_{m20}$ | $g_{m20}$ | $g_{m20}$ | $g_{m20}$ |

| $C_c$     | $32C_{c0}$ | $16C_{c0}$ | $8C_{c0}$ | $4C_{c0}$ | $2C_{c0}$ | $C_{c0}$  |

(c)  $g_m$ -PGA回路[5]

| 利得        | 0 dB                  | 6 dB                  | 12 dB                | 18 dB                | 24 dB                | 30 dB     |

|-----------|-----------------------|-----------------------|----------------------|----------------------|----------------------|-----------|

| $\beta_F$ | 1                     | 1/2                   | 1/4                  | 1/8                  | 1/16                 | 1/32      |

| $g_{m1}$  | $\frac{1}{32}g_{m10}$ | $\frac{1}{16}g_{m10}$ | $\frac{1}{8}g_{m10}$ | $\frac{1}{4}g_{m10}$ | $\frac{1}{2}g_{m10}$ | $g_{m10}$ |

| $g_{m2}$  | $g_{m20}$             | $g_{m20}$             | $g_{m20}$            | $g_{m20}$            | $g_{m20}$            | $g_{m20}$ |

| $C_c$     | $C_{c0}$              | $C_{c0}$              | $C_{c0}$             | $C_{c0}$             | $C_{c0}$             | $C_{c0}$  |

なお、この0.7の因子は、本研究で100MHz以上の帯域を想定し、 $C_{p2}$ や負荷容量を考慮したものであり、具体的な設計目標値により多少変動するものである。一方、 $C_c$ -PGA回路では帰還率  $\beta_F$  に比例して  $C_c$  を指数関数的に制御する。 $g_m$ -PGA回路では  $g_{m1}$  を帰還率  $\beta_F$  に反比例した指数関数的な制御を行っている。これらの制御方式により、提案、従来PGAは帰還率によらず帯域と安定性の両立を実現している。

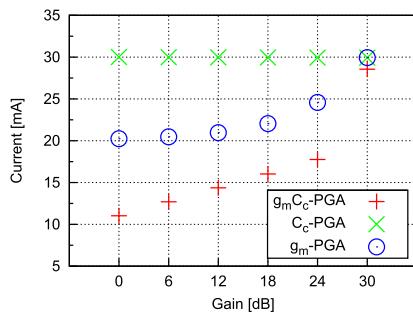

#### 4.1 消費電流

PGA回路の消費電流は入力段、出力段アンプのドレーン電流の和に比例する。トランジスタのドレーン電流( $I_D$ )及び相互コンダクタンス( $g_m$ )は、

$$I_D = \frac{W}{2L} \mu_0 C_{ox} (V_{GS} - V_{TH})^2 \quad (10)$$

$$g_m = \frac{W}{L} \mu_0 C_{ox} (V_{GS} - V_{TH}) \quad (11)$$

で表される。ここで、 $W$ 、 $L$ 、 $\mu$ 、 $C_{ox}$ 、 $V_{GS}$ 及び $V_{TH}$ はそれぞれチャネル幅、チャネル長、移動度、単位面積当たりのゲート酸化膜容量、ゲートソース間電圧及びしきい値である。入力段では相互コンダクタンスの制御幅が大きいため  $W$  の制御を用いて  $g_{m1}$  を可変している。これにより、入力段アンプの消費電流は  $g_{m1}$  に比例する。チャネル幅  $W$  が固定の出力段アンプの消費電流は  $g_{m2}^2$  に比例する。提案PGA回路ではPGA利得の低下に伴い入力段のみならず出力段の相互コンダクタンスも同時に下げるため、相互コンダクタンスを制御しない  $C_c$ -PGAや、入力相互コンダクタンスのみを制御する  $g_m$ -PGAよりも低消費電力となる。表1より、提案PGA回路は利得0dBでは30dB時と比べて入力段のドレーン電流が1/6、出力段のドレーン電流が1/2になる。利得30dBにおける入出力段のドレーン電流の比を  $I_{D10}:I_{D20} = 1:2$  とすると、利得0dBにおいて、提案PGAは、 $g_m$ -PGAより40%、 $C_c$ -PGAより60%、消費電流が小さくなる。

#### 4.2 面積

$C_c$ -PGA回路では、低利得時に安定性を保つために必要な  $C_c$  が指数関数的に大きくなるため、 $C_c$  の面積はサンプリング容量やアンプの面積に比べ非常に大きく、チップ面積の大きな比率を占める。一方、提案PGAの  $C_c$  の面積は  $C_c$ -PGAのおよそ1/6程度と十分小さくすることができる。また、提案PGAは  $g_m$ -PGAよりも大きな位相補償容量を用いるものの、サンプリング容量やトランジスタの面積の占める比率が大きくなるため、全体面積に与える影響は小さい。

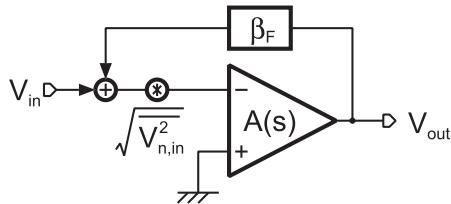

図 2 PGA 回路のノイズモデル

Fig. 2 Model of PGA circuits.

#### 4.3 出力換算ノイズ

PGA 回路の主なノイズ源としてサンプリング容量の  $kT/C$  ノイズとオペアンプの熱ノイズがある。各 PGA のサンプリング容量値は同じであるため、ここでは各 PGA で差異が生じるオペアンプノイズについて比較検討を行う。簡略化のため、PGA 回路を伝達関数  $A(s)$  をもったオペアンプに帰還率  $\beta_F$  の負帰還をかけた回路として考える（図 2）。オペアンプの入力換算熱ノイズを  $\sqrt{V_{n,in}^2}$  とすると、PGA 回路の出力換算ノイズの二乗平均平方根 (RMS)  $V_{n,rms}$  は、

$$V_{n,rms} = \sqrt{V_{n,in}^2} \sqrt{\int_0^\infty \left| \frac{A(s)}{1 + \beta_F A(s)} \right|^2 df} \quad (12)$$

で表される。 $g_m C_c$ -PGA,  $g_m$ -PGA,  $C_c$ -PGA は、それぞれ、同等の伝達関数  $A(s)$  になるよう設計するため、各 PGA の出力換算ノイズは  $\sqrt{V_{n,in}^2}$  で比較可能である。 $\sqrt{V_{n,in}^2}$  は、

$$\sqrt{V_{n,in}^2} = \sqrt{\frac{8}{3} kT \left( \frac{1}{g_{m1}} + \frac{1}{A_{o1}^2} \cdot \frac{1}{g_{m2}} \right)} \quad (13)$$

で表される。 $k$ ,  $T$ ,  $A_{o1}$  はそれぞれボルツマン定数、絶対温度、入力段 DC 利得である。 $A_{o1}$  が十分大きければ  $\sqrt{V_{n,in}^2}$  は入力相互コンダクタンスの平方根に反比例する。 $C_c$ -PGA 回路では PGA 利得によらず  $g_{m1}$  が常に一定であることから、 $\sqrt{V_{n,in}^2}$  は PGA 利得に依存しない。 $g_m$ -PGA 回路では  $g_{m1}$  が非常に小さくなる利得 0 dB において  $C_c$ -PGA と比較して出力換算ノイズが増大する。提案 PGA 回路 ( $g_m C_c$ -PGA)においては、 $g_{m1}$  の変化量を  $g_m$ -PGA より小さく抑えることで、低 PGA 利得におけるノイズ性能の悪化を低く抑えることができる。

#### 4.4 比較のまとめ

以上の比較検討を表 2 にまとめる。電力は  $g_m C_c$ -PGA における最小値を、 $C_c$  面積は  $g_m C_c$ -PGA にお

表 2 各 PGA の比較結果

Table 2 Comparison results about each PGAs.

|                | 電力  | $C_c$ 面積 | ノイズ |

|----------------|-----|----------|-----|

| $g_m C_c$ -PGA | 1.0 | 1.0      | 1.0 |

| $C_c$ -PGA     | 2.6 | 6.0      | 0.4 |

| $g_m$ -PGA     | 1.7 | 0.2      | 2.3 |

ける位相補償容量サイズの最大値を、ノイズは  $g_m C_c$ -PGA の 0 dB における出力換算ノイズを 1 と規格化している。提案 PGA 回路は、 $g_m$ -PGA 及び  $C_c$ -PGA と比べて、低電力で小面積と低ノイズが両立できる。

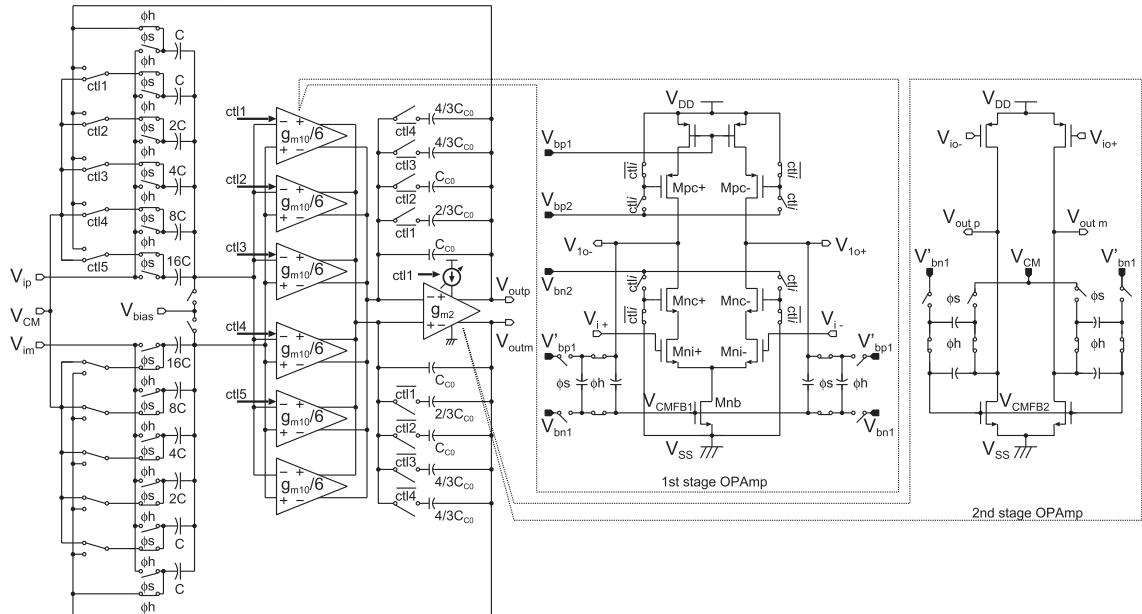

#### 5. 設計回路

提案 PGA 回路の回路図を図 3 に示す。制御信号  $ctl_i$  ( $i = 1, 2, \dots, 5$ ) によって帰還容量として出力端子に接続されるキャパシタ数を制御することで可変利得を実現している。 $ctl_i = "Low"$  で対応するキャパシタが出力端子に接続され、 $ctl_i = "High"$  では差動間グランド電圧 ( $V_{CM}$ ) に接続される。例として、全制御信号  $ctl_1$  から  $ctl_5$  が "Low" のとき、サンプリング容量 32C に対して帰還容量は 32C であり、利得は 0 dB となる。 $ctl_1$  から  $ctl_5$  が全て "High" のとき、サンプリング容量 32C に対して帰還容量は C であり、利得は 30 dB となる。

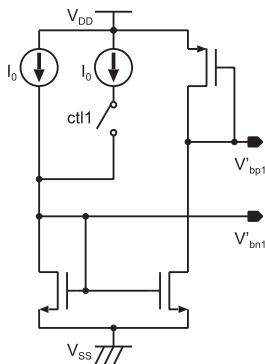

オペアンプの入力段はキャパシタを用いた離散時間コモンモードフィードバック回路を有したカスコードオペアンプを並列に接続した構成をとる。カスコードトランジスタのゲート電圧を制御信号 ( $ctl_i$ ) によってバイアス電圧 ( $V_{bn2}$  または  $V_{bp2}$ ) かグランドまたは電源電圧に接続し、動作するオペアンプの数を制御することで可変入力相互コンダクタンスを実現している。トランジスタ  $M_{nc+}$ ,  $M_{nc-}$ ,  $M_{pc+}$  及び  $M_{pc-}$  は  $ctl_i$  が "High" のときカスコードトランジスタとして動作する。 $ctl_i$  が "Low" のときにはそれぞれのトランジスタがオフし、電流は流れない。PGA 利得 30 dB において  $g_{m1} = g_{m10}$  となり、0 dB 時に  $g_{m1} = g_{m10}/6$  となる。出力相互コンダクタンスは、 $V_{io+}$  と  $V_{io-}$  の同相レベル  $V'_{bp1}$  及びバイアス電圧  $V'_{bn1}$  によって制御する。 $V_{io+}$  と  $V_{io-}$  の同相レベルは入力段コモンモードフィードバック回路で決定される。 $V'_{bn1}$  と  $V'_{bp1}$  を可変にする出力相互コンダクタンス制御回路を図 4 に示す。制御回路に流れる電流量は、 $ctl_1 = "High"$  のとき  $I_d (= 2I_0)$  とすると、 $ctl_1 = "Low"$  のとき  $0.5I_d$  となる。したがって、PGA 利得 30 dB において  $g_{m2} = g_{m20} (= \sqrt{2\beta_0 I_d})$  とすると、0 dB 時におい

図 3 提案 PGA の回路図

Fig. 3 Schematic of proposed PGA.

図 4 出力相互コンダクタンス制御回路

Fig. 4 Control circuit for transconductance of output stage.

て  $g_{m2} = 0.7g_{m20} (= \sqrt{\beta_0}I_d)$  となる。並列に配置した  $C_{c0}$  を制御することで位相補償容量  $C_c$  を可変にしていく。PGA 利得 30 dB 時において、 $ctl_i$  ( $i = 1, \dots, 5$ ) は "High" とし、 $C_c = C_{c0}$  となる。0 dB 時には、 $ctl_i$  ( $i = 1, \dots, 5$ ) は "Low" とし、 $C_c = 16C_{c0}/3$  となる。 $g_mC_c$ -PGA,  $C_c$ -PGA,  $g_m$ -PGA の各設計回路で用いた全キャパシタの面積（位相補償容量、サンプリング容量及びコモンモードフィードバック容量の和）とトランジスタサイズについて表 3 に示す。 $g_mC_c$ -PGA 設計回路で使用した全キャパシタの面積

表 3 各 PGA のトランジスタ、キャパシタ設計サイズ

Table 3 Transistors and capacitors sizes of each PGA.

|                                | $g_mC_c$ -PGA         | $C_c$ -PGA            | $g_m$ -PGA           |

|--------------------------------|-----------------------|-----------------------|----------------------|

| 全キャパシタ面積<br>[mm <sup>2</sup> ] | $16.0 \times 10^{-3}$ | $43.4 \times 10^{-3}$ | $8.7 \times 10^{-3}$ |

| トランジスタ面積<br>[mm <sup>2</sup> ] | $7.0 \times 10^{-3}$  | $7.0 \times 10^{-3}$  | $7.0 \times 10^{-3}$ |

とトランジスタ面積の和は、 $g_m$ -PGA に比べて 1.4 倍となり、 $C_c$ -PGA の 1/2 倍以下となることが分かった。

## 6. シミュレーション結果

0.25  $\mu$ mCMOS プロセスを用いて  $g_mC_c$ -PGA,  $C_c$ -PGA,  $g_m$ -PGA を設計した。設計には 3 V 耐圧トランジスタ及び MIM 容量を用いた。動作電源電圧は 3.3 V とした。 $C_c$ -PGA,  $g_m$ -PGA は図 3 と同様の回路構成を用い、それぞれ  $C_c$  のみを制御する回路と  $g_m$  のみを制御する回路とし、表 1 に記載されているパラメータに基づいて設計を行った。負荷容量は 4 pF、帰還回路の単位容量 ( $C_u$ ) は 100 fF とした。サンプリングレートは 40 MSps に対して、セトリング誤差を最大で 0.1% とした。

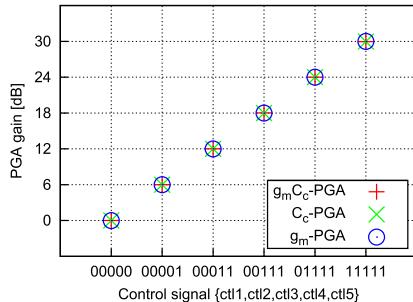

制御信号 ( $ctl_i$ ) に対する各 PGA 利得のシミュレーション結果を図 5 に示す。それぞれの PGA において利得幅が 6 dB ステップの 0~30 dB となることが確認

図 5 制御信号と PGA 利得の関係

Fig. 5 Control signal v.s. Gain of PGA.

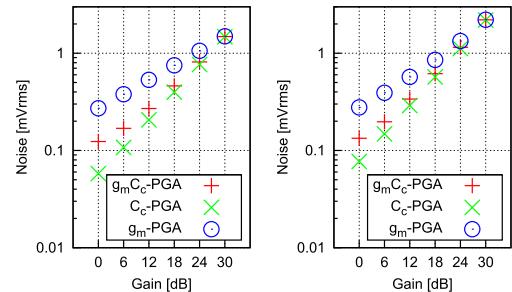

(a) without sampling noise (b) with sampling noise

Fig. 8 Gain of PGA v.s. Output RMS noise.

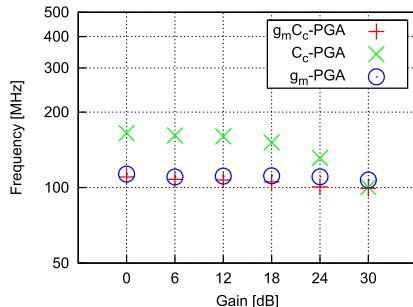

図 6 PGA 利得と帯域の関係

Fig. 6 Gain of PGA v.s. OPamp bandwidth.

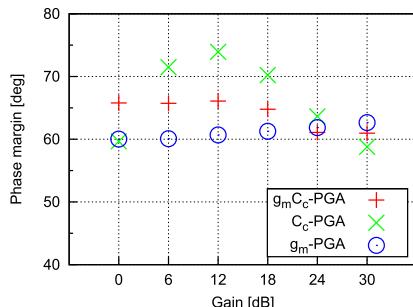

図 7 PGA 利得と位相余裕の関係

Fig. 7 Gain of PGA v.s. OPamp phase margin.

できる。各 PGA 利得に対する帯域のシミュレーション結果を図 6 に示す。 $g_mC_c$ -PGA と  $g_m$ -PGA では、全利得において帯域がほぼ 100 MHz で一定となっていることが確認できる。また、 $C_c$ -PGA では低利得において帯域が高周波側に移動していることが確認できる。これは、低 PGA 利得時に  $C_c$  が非常に大きくなることで、ゼロ点が低周波側に移動し、その影響で帯域が延びるためである。

位相余裕のシミュレーション結果を図 7 に示す。 $g_mC_c$ -PGA 及び  $g_m$ -PGA では全利得において位相

余裕が  $60^\circ$  以上となることが確認できる。PGA 利得 30 dB 時において、 $C_c$ -PGA で位相余裕が  $60^\circ$  以下になるのは、指数関数的に  $C_c$  を制御するため、制御用スイッチが大きくなり、その寄生容量の影響が見えるためである。また、位相余裕が利得により大きく変化するのは、ゼロ点が指数関数的に変化し、その影響が出てくるためである。

オペアンプのノイズシミュレーションより、PGA 回路の出力換算ノイズの RMS 値を算出した結果を図 8 に示す。図 8(a) は、PGA 回路の出力換算ノイズの RMS 値を示し、図 8(b) はサンプリング容量による  $kT/C$  ノイズとの二乗和平方根を示す。ここで、PGA 回路の出力換算ノイズは 1 kHz から 10 GHz までを考慮している。PGA 利得が 30 dB においては、各 PGA の入力相互コンダクタンスが同じであるため、出力換算ノイズに差異は現れず、1.5 mVrms である。また、 $kT/C$  ノイズとの二乗和平方根は 2.2 mVrms である。利得の低下に伴い、各 PGA 共にノイズ量は低下するが、 $g_m$ -PGA では利得の低下に伴い入力相互コンダクタンスが対数スケールで小さくなるため  $C_c$ -PGA よりもノイズ性能が悪くなる。 $g_mC_c$ -PGA においても利得の低下に伴い入力相互コンダクタンスが小さくなるため  $C_c$ -PGA よりもノイズ性能は劣化するが、その影響は  $g_m$ -PGA より低く抑えられている。0 dB における出力換算ノイズは、 $123.5 \mu\text{Vrms}$  で、 $g_m$ -PGA に対して 55% の低減となった。また、 $kT/C$  ノイズとの二乗和平方根では、0 dB において  $133.6 \mu\text{Vrms}$  となり、 $g_m$ -PGA に対して 52% の低減となった。これは、 $g_mC_c$ -PGA の方が  $g_m$ -PGA に対してノイズ性能に大きく寄与する入力相互コンダクタンスの変化量が抑えられるためである。

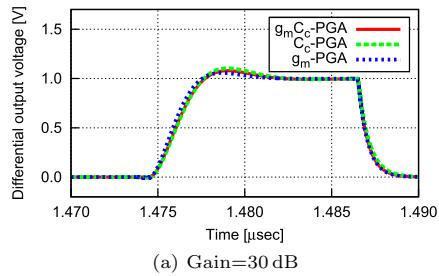

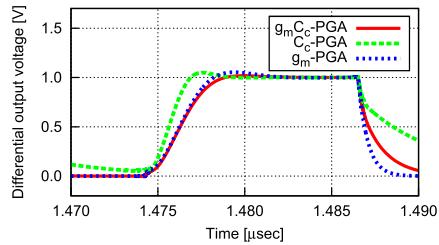

各 PGA 回路の過渡応答特性を図 9 に示す。PGA

(a) Gain=30 dB

(b) Gain=0 dB

図 9 過渡応答特性

Fig. 9 Transient response.

図 10 PGA 利得と消費電流の関係

Fig. 10 Gain of PGA v.s. Current consumption.

利得 30 dB における過渡応答特性は、各 PGA 間で同等のセトリング特性を示す。0 dB では  $C_c$ -PGA の帯域が伸び位相余裕が小さくなるため、立上りが速くなりオーバーシュートしている。セトリング時間 11.6 nsec に対して各 PGA 共に 0.1%以下のセトリング誤差であった。スルーレートは入力段のテイル電流と位相補償容量で決まるため、各 PGA 間においてスルーレートに差異は現れない。

各 PGA 回路における消費電流のシミュレーション結果を図 10 に示す。PGA 利得 30 dB において、提案方式の消費電流は 28.9 mA となった。利得の低下につれて消費電流は低下し、0 dB において消費電流は 11.0 mA となった。 $g_m$ -PGA に対して 40%、 $C_c$ -PGA に対して 60% 消費電流が低くなった。

## 7. む す び

本論文では、入出力相互コンダクタンス及び位相補償容量を可変とする可変利得増幅器の低消費電力化について述べた。この技術は、可変利得増幅器の利得に応じて線形的に入力相互コンダクタンスと位相補償容量を制御することで、低ノイズ性能と小面積を両立する。更に、出力相互コンダクタンスも制御することで、低利得動作時における消費電力を削減し、高い電力効率を実現している。0.25  $\mu$ m CMOS プロセスを用いた設計において、利得 30 dB での消費電流が 28.85 mA、利得 0 dB での消費電流が 11.0 mA となった。また、出力換算ノイズは利得 30 dB において 2.2 mVrms、0 dB において 133.6  $\mu$ Vrms であった。入力相互コンダクタンス制御のみを用いた従来の可変利得増幅器と比べて、消費電流が最大で 40%、0 dB における出力換算ノイズは 52% 低減された。また、位相補償容量制御のみを用いた可変利得増幅器と比べて、消費電流は最大で 60%、必要な容量面積は 60% 低減された。

**謝辞** 本研究は、文部科学省グローバル COE プログラム「次世代電子デバイス教育研究開発拠点」の協力のもとで行われたものである。また、本設計は、東京大学大規模集積システム設計教育研究センターを通じ、日本ケイデンス（株）の協力を受けたものである。

## 文 献

- [1] Y. Fujimoto, H. Tani, M. Maruyama, H. Ogawa, and M. Miyamoto, "A low-power switched-capacitor variable gain amplifier," IEEE J. Solid-State Circuits, vol.39, no.7, pp.1213–1216, July 2004.

- [2] C.W. Mangelsdorf, "A variable gain CMOS amplifier with exponential gain control," Digest of Technical Papers. 2000 Symposium on VLSI Circuits, 2000, pp.146–149, 2000.

- [3] C.C. Hsu and J.T. Wu, "A highly linear 125-MHz CMOS switched-resistor programmable-gain amplifier," IEEE J. Solid-State Circuits, vol.38, no.10, pp.1663–1670, Oct. 2003.

- [4] M.T. Sanz, S. Celma, and B. Calvo, "High linear digitally programmable gain amplifier," IEEE International Symposium on Circuits and Systems, vol.1, pp.208–211, May 2005.

- [5] T. Okura, S. Okura, T. Ido, and K. Taniguchi, "A high efficiency variable gain amplifier circuit with controllable transconductance AMP," IEEJ Trans. EIS, vol.129, no.10, pp.1968–1969, Oct. 2009.

（平成 23 年 8 月 2 日受付、12 月 24 日再受付）

大倉 鉄郎

平 18 阪大・工・電子卒、平 20 同大大学院博士前期課程了。CMOS アナログ回路の研究に従事。

大倉 俊介

平 15 阪大・工・電子卒、平 17 同大大学院博士前期課程了。平 19 (株) Rosnes 入社。平 20 阪大・工・特任研究員。CMOS アナログ回路の研究開発に従事。工博。

松岡 俊匡 (正員)

平元阪大・工・電子卒。平 3 同大大学院博士前期課程了。平 3 シャープ(株)入社。平 11 阪大大学院工学研究科電子情報エネルギー工学専攻リサーチ・アソシエイト(日本学術振興会研究員)。平 12 同大学院工学研究科電子情報エネルギー工学専攻講師。平 16 同大学院工学研究科電子情報エネルギー工学専攻助教授。CMOS RF 回路の研究に従事。工博。応用物理学会、電気学会、IEEE 各会員。

谷口 研二 (正員)

昭 46 阪大・工・電子卒。昭 48 同大大学院修士課程了。昭 50 東芝(株)入社。昭 57 より 1 年間マサチューセッツ工科大学客員研究員。昭 61 阪大工学部電子工学科助教授。平 8 同大学院工学研究科電子情報エネルギー工学専攻教授。現在まで Si 酸化・拡散プロセス、半導体デバイスの物理、半導体シミュレーション技術、アナログ集積回路の研究に従事。工博。応用物理学会、電気学会、IEEE 各会員。