|              |                                                                                     |

|--------------|-------------------------------------------------------------------------------------|

| Title        | 低消費電力1 V動作 630 MHz周波数分周器                                                            |

| Author(s)    | 山本, 泰子; 松岡, 俊匡; 谷口, 研二                                                              |

| Citation     | 電子情報通信学会論文誌C. 2004, J87-C(1), p. 192-194                                            |

| Version Type | VoR                                                                                 |

| URL          | <a href="https://hdl.handle.net/11094/51680">https://hdl.handle.net/11094/51680</a> |

| rights       | copyright©2004 IEICE                                                                |

| Note         |                                                                                     |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

## 低消費電力 1 V 動作 630 MHz 周波数分周器

山本 泰子<sup>†,††</sup>(学生員) 松岡 俊匡<sup>†</sup>(正員)谷口 研二<sup>†</sup>(正員)

Low Power 1 V-Operation 630 MHz Frequency Divider Circuits

Yasuko YAMAMOTO<sup>†,††</sup>, Student Member,

Toshimasa MATSUOKA<sup>†</sup>, and Kenji TANIGUCHI<sup>†</sup>, Members<sup>†</sup> 大阪大学大学院工学研究科, 吹田市

Department of Electronics and Information Systems, Osaka University, Suita-shi, 565-0871 Japan

<sup>††</sup> 松下電工株式会社, 門真市

Matsushita Electric Works, Ltd., Kadoma-shi, 571-8686 Japan

あらまし 630 MHz 動作の分周比切換付周波数分周器において, 0.35  $\mu$ m CMOS プロセスを利用して 1 V 動作を実現した。消費電力は 2.1 mW であった。この回路の特徴は低電圧動作用 D-Flip Flop (D-FF) と NAND 結合型 D-FF 回路を組み込んだことにある。

**キーワード** 周波数分周器, 低消費電力, 低電圧動作, Source Coupled Logic, D-Flip Flop

## 1. まえがき

近年, 携帯端末やワイヤレスセンサの分野では, 電池寿命が主要な課題となっている。本論文では, 無線 IC の主要ブロックである Phase-Locked Loop (PLL) 方式周波数シンセサイザを低消費電力で動作させるための低電圧動作周波数分周器を提案する。2 の階乗で分周する分周器は, D-FlipFlop (D-FF) 回路で構成される二分周器を直列接続することで得られる。このため, 周波数分周器の低電圧低消費電力化を実現するには D-FF 回路の低電圧化が鍵となる。

動作速度と消費電力はトレードオフの関係にある。高速動作が可能な D-FF 回路としては, True Single Phase Clock (TSPC) 回路 [1] や, Source Coupled Logic (SCL) 回路を用いたマスタースレーブラッチで構成される差動型回路 [2], [3] が知られている。電源電圧 1 V での 0.35  $\mu$ m CMOS TSPC 回路動作を考えると, 入力信号に Rail-to-Rail の振幅を与えて, PMOS のオーバードライブ電圧が小さくなり, 駆動電流を確保するにはデバイスサイズを大きくせざるを得ない。この結果, ドレイン容量が大きくなり, 動作速度が制限される。一方, 図 1 に示す SCL 回路では最大動作周波数とバイアス電流の関係は, 式 (1) で表される [4]。

$$I_{SS} = 4(\ln 2)f_{max}C_{LOAD}\Delta V \quad (1)$$

ここで,  $I_{SS}$ ,  $f_{max}$ ,  $C_{LOAD}$ ,  $\Delta V$  は各々バイアス電

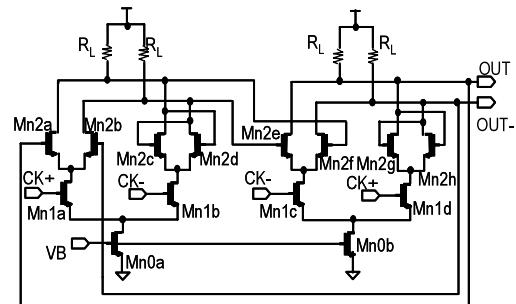

図 1 SCL 回路による D-FlipFlop

Fig. 1 D-FlipFlop using SCL.

図 2 低電圧動作に適した SCL 回路による D-FlipFlop

Fig. 2 D-FlipFlop using SCL for low supply voltage.

流, 最大動作周波数, 負荷容量, 入出力信号の振幅である。デバイスサイズが同じであれば, 動作周波数によらず消費電流は一定である。しかし, 図 1 の回路では定電流源の NMOS (Mn0a, Mn0b) を飽和領域で動作させるため, 電源電圧 1 V で高速動作させることは困難である。

本研究では, 1 V 動作 630 MHz の周波数分周器を NMOS トランジスタのしきい値電圧  $V_{TH0}$  が 0.47 V の 0.35  $\mu$ m CMOS プロセスで実現する手法を検討し, 設計, 試作を行った。

## 2. 低電圧 D-FF 回路方式

SCL 回路を 1 V で動作させるために, 図 1 の定電流源の NMOS を取り除き, クロックが入力される NMOS のソースを直接接地した構成 [5] を採用した(図 2)。消費電流は, 入力段の NMOS と負荷抵抗  $R$  のサイズ及びクロック入力の DC レベルにより決定される。しきい値ばらつきを考慮し, この低電圧動作 SCL D-FF 回路の最大動作周波数を 630 MHz, 入出力信号の DC レベルを同一とし, 利得が 1 以上になるように最適化した結果,

回路シミュレーションでの消費電力は,  $0.35\text{ }\mu\text{mCMOS}$  プロセス Typical 条件で  $223\text{ }\mu\text{A}$  である。

なお, 比較のため, TSPC 回路を用いた D-FF 回路の電源電圧  $1\text{ V}$  での回路シミュレーションを行った。消費電流はわずか  $21\text{ }\mu\text{A}$  であったが, しきい値ばらつきを考慮すると, 最高  $150\text{ MHz}$  程度でしか動作しなかった。この結果と低電圧動作 SCL 回路でのシミュレーション結果とを比較すると, 図 2 の低電圧動作 SCL 回路が低電圧高速動作に長けていることが分かる。

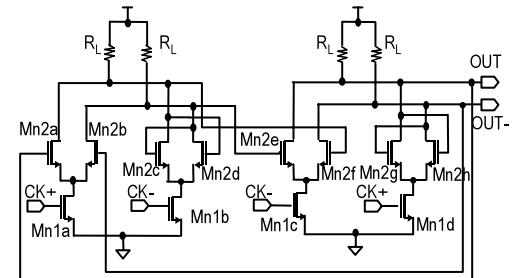

### 3. NAND 結合型分周比切換回路

周波数分周器の動作周波数と消費電流に大きな影響を与えるもう一つの回路は, 分周比切換回路である。 $\div 2$  と  $\div 3$  の切換を実現する回路の論理ゲートでの遅延を補うために, D-FF 回路は通常の二分周機能 ( $\div 2$ ) を実現する場合と比較して, 倍程度の高速動作が必要である。電流を増やすことなく最大動作速度を上げるために, ゲートでの遅延をできる限り小さくする回路構成が必要である。

そこで, 図 3(a) に示すように, DFF 回路の初段のラッチ回路に NAND 機能をもたせる回路構成とした。このラッチ付き NAND 回路は, 低電圧動作のために, 文献 [6] の回路を図 3(b) のように改良した。NAND を付加した部分では, トランジスタが 3 段に積まれることとなるが, SEL 入力を受ける 2 段目のトランジスタは常に飽和状態で動作する必要はなく, 低電圧動作への影響は少ない。

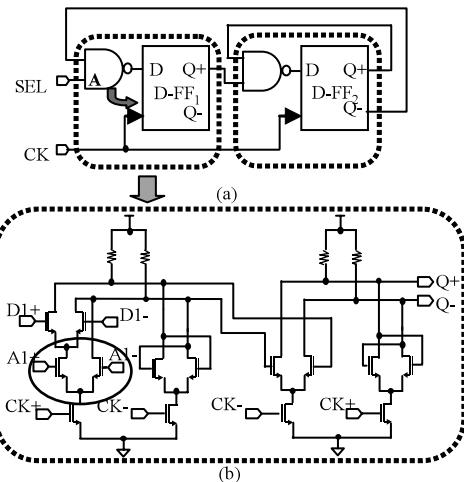

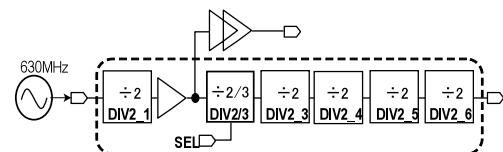

### 4. 周波数分周器

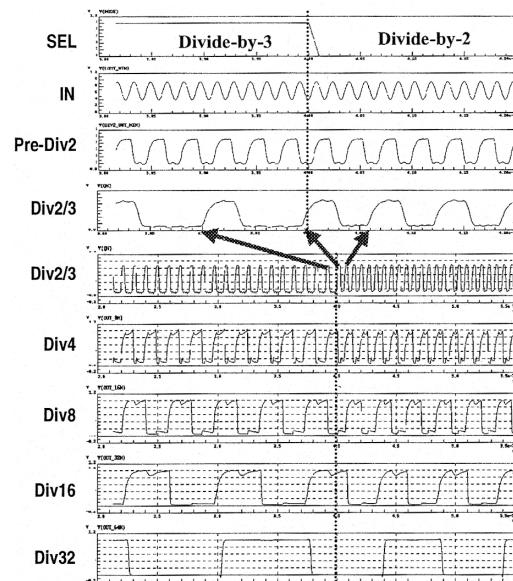

周波数切換回路を含めた周波数分周器全体 (図 4) を動作させるには, それぞれ次段の分周器を正しく動作させる必要がある。各分周器の入出力のコモンモード電圧を適切に設定することにより, 各分周器を直接直列接続した。周波数分周器の各段の入出力波形 (シミュレーション) を図 5 に示す。SEL は分周比切換信号である。最終段を除き, SCL 回路を用いた D-FF 回路で構成し, 動作周波数に応じてデバイスサイズを最適化した。最終段は, 周波数が十分低いえ, その出力は PLL 回路において位相比較器の入力となり, Rail-to-Rail の振幅が必要とされるため, デジタルロジック回路の D-FF 回路を用いた。ここでは, 前置分周器と  $\div 2/3$  分周器の間に周波数シンセサイザの出力信号用のバッファを挿入している。また, レイアウトの簡略化のため図 4 の DIV2\_3 と DIV2\_4 は同一サイズの分周器を用いた。前置分周器の消費電流を 1 とした場合, 二つの D-FF 回路で構成される DIV2/3 の

図 3 (a)  $\div 2/3$  回路 (b) SCL 回路による NAND 機能付き D-FlipFlop

Fig. 3 (a) Block diagram of divide- by -2/3. (b) D-FlipFlop combined NAND circuit using SCL.

図 4 周波数分周器の構成

Fig. 4 Frequency divider block diagram.

図 5 シミュレーション結果

Fig. 5 Waveforms of the frequency divider.

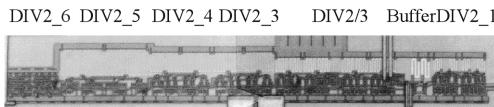

図6 チップ写真

Fig. 6 Microphotograph of the frequency divider.

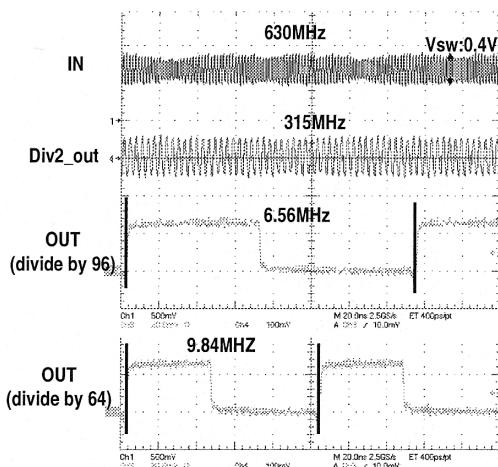

図7 測定波形

Fig. 7 Measured waveforms of the frequency divider.

消費電流は約1.25倍、後段の二分周器は、それぞれ約0.25, 0.25, 0.125, 0.01倍となるように設計した。

チップ写真を図6に示す。ゲート長0.35μm, 3層メタル標準CMOSプロセスを用い、抵抗はポリシリコン抵抗を使用した。周波数分周器の面積は55μm×460μmと小さい。

## 5. 評価結果

630MHzの前置分周器と周波数切換回路を含む周波数分周器において、0.35μmCMOSプロセスを利用して1V動作を実現した。図7にオシロスコープでの測定結果を示す。電源電圧1Vのときの消費電流は2.1mAであった。この消費電流は、worst power条

件時の回路シミュレーション結果の1.2倍程度である。入力感度は入力信号のDCレベルを0.6Vとしたとき、50mVRMSであった。

## 6. むすび

0.35μmCMOSプロセスを用いて、電源電圧1Vで、630MHz動作の周波数分周器を実現した。定電流源MOSトランジスタを除去したSource Coupled Logic D-FF回路とNAND結合型D-FF回路により低電圧化と低消費電力化を併せて実現し、消費電力は2.1mWであった。

謝辞 本研究の一部は、日本学術振興会未来開拓学術研究推進事業の援助を受けて行われたものであり、関係者の方々には大変感謝致します。

## 文 献

- [1] Q. Huang and R. Rogenmoser, "Speed optimization of edge-triggered CMOS circuits for gigahertz single-phase clocks," IEEE J. Solid-State Circuits, vol.31, pp.456-465, March 1996.

- [2] H. Darabi and A. Abidi, "A 4.5 mW 900-MHz CMOS receiver for wireless paging," IEEE J. Solid-State Circuits, vol.35, pp.1085-1096, Aug. 2000.

- [3] M. Mizuno, M. Yamashina, K. Furuta, H. Igura, H. Abiko, K. Okabe, A. Ono, and H. Yamada, "A GHz MOS adaptive pipeline technique using MOS current-mode logic," IEEE J. Solid-State Circuits, vol.31, pp.784-791, June 1996.

- [4] 清水新策, Tan Boon Keat, 小川徹, 吉村隆治, 富中信吾, 松岡俊匡, 谷口研二, "MOS電流モードロジックを用いた拡散符号生成器," 電学研資, ECT-01-15, pp.27-31, Jan. 2001.

- [5] B. De Muer and M. Steyaert, "A 12GHz/128 frequency divider in 0.25μm CMOS," European Solid-State Circuits Conference (ESSCIRC), pp.220-223, Stockholm, Sweden, Sept. 2000.

- [6] C. S. Vaucher, I. Ferencic, M. Locher, S. Sedvallson, U. Voegeli, and Z. Wang, "A family of low-power truly modular programmable dividers in standard 0.35-μm CMOS technology," IEEE J. Solid-State Circuits, vol.35, pp.1039-1045, July 2000.

(平成15年4月28日受付, 7月18日再受付)