|              |                                                                                           |

|--------------|-------------------------------------------------------------------------------------------|

| Title        | Thickness Dependence of Furnace N20-Oxynitridation Effects on Breakdown of Thermal Oxides |

| Author(s)    | Matsuoka, Toshimasa; Taguchi, Shigenari; Taniguchi, Kenji et al.                          |

| Citation     | IEICE Transactions on Electronics. 1995, E78-C(3), p. 248-254                             |

| Version Type | VoR                                                                                       |

| URL          | <a href="https://hdl.handle.net/11094/51686">https://hdl.handle.net/11094/51686</a>       |

| rights       | copyright©1995 IEICE                                                                      |

| Note         |                                                                                           |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

**PAPER** *Special Issue on Sub-1/4 Micron Device and Process Technologies*

# Thickness Dependence of Furnace N<sub>2</sub>O-Oxynitridation Effects on Breakdown of Thermal Oxides

Toshimasa MATSUOKA<sup>†</sup>, Shigenari TAGUCHI<sup>†</sup>, *Nonmembers*,

Kenji TANIGUCHI<sup>†</sup>, Chihiro HAMAGUCHI<sup>†</sup>, *Members*,

Seizo KAKIMOTO<sup>††</sup> and Junkou TAKAGI<sup>††</sup>, *Nonmembers*

**SUMMARY** Thickness dependence of breakdown properties in control and N<sub>2</sub>O-oxynitrided oxides was investigated. Nitrogen atoms piled up at the Si/SiO<sub>2</sub> interface increase charge-to-breakdown ( $Q_{BD}$ ) under substrate injection conditions for oxide thickness below 10 nm, while no meaningful improvement is observed above 10 nm. This thickness dependence is explained by the fact that N<sub>2</sub>O-oxynitridation reduces oxide defects near the Si/SiO<sub>2</sub> interface. N<sub>2</sub>O-oxynitridation of the oxides reduces the number of neutral electron traps due to the chemical reaction of oxide defect with nitrogen atoms. Electron trapping of N<sub>2</sub>O-oxynitrided oxides is significantly suppressed; the reduction of electron trapping events into neutral electron traps increases  $Q_{BD}$  under substrate injection. On the other hand, under gate injection, N<sub>2</sub>O-oxynitrided oxides show low rate of hole trapping during the initial stress period. However, in heavily injected condition, electron trapping is not suppressed, resulting in little improvement of  $Q_{BD}$ . In addition, the control and N<sub>2</sub>O-oxynitrided oxides show quite similar dependence of  $Q_{BD}$  on stress current density, which is related primarily to the carrier transport phenomena (tunneling, traveling, impact ionization and hole injection).

**key words:** *N<sub>2</sub>O-oxynitridation, charge-to-breakdown, thin dielectrics, MOS structure, dielectric reliability*

## 1. Introduction

For the past decade, considerable works on oxynitrides [1]–[11] have been reported as alternative gate dielectrics for deep submicrometer MOS devices. The high reliability of oxynitrides originates from rigid Si–N bonds at the Si/SiO<sub>2</sub> interface [3]–[5], [11], [12]. It has been reported that N<sub>2</sub>O-based oxidation process is more promising than NH<sub>3</sub>-nitridation of SiO<sub>2</sub> due to the hydrogen-free nature of the processing [4]. Incorporation of hydrogen in gate oxide during NH<sub>3</sub>-nitridation requires light nitridation and/or an additional reoxidation or N<sub>2</sub> annealing with rapid thermal processing (RTP) to reduce electron traps in nitrided oxides [8], [11]. Simultaneous oxidation and nitridation occurred during N<sub>2</sub>O-oxynitridation result in the increase of the oxide thickness and the decrease of the oxide defect density.

Manuscript received September 13, 1994.

Manuscript revised October 28, 1994.

<sup>†</sup>The authors are with the Faculty of Engineering, Osaka University, Suita-shi, 565 Japan.

<sup>††</sup>The authors are with the Central Research Laboratories, Sharp Corporation, Tenri-shi, 632 Japan.

N<sub>2</sub>O-oxynitridation processing is classified into two categories such as resistance-heated furnace processing and RTP. Although RTP is a promising alternative to a conventional resistance-heated furnace, the latter is still the dominant process equipment in today's LSI fabrication lines. Chu et al. showed that N<sub>2</sub>O-oxynitrides grown by RTP exhibit both thickness and compositional nonuniformities [13] though the process controllability and dielectric integrity of N<sub>2</sub>O-based dielectrics are important issues. In addition, the growth of oxynitrides in pure N<sub>2</sub>O ambient requires unacceptable long oxynitridation time because the oxynitridation in N<sub>2</sub>O ambient shows significantly lower growth rate. Therefore, the conventional thermal oxidation followed by furnace N<sub>2</sub>O-oxynitridation is a promising process [6], [9].

Ahn et al. reported that the furnace N<sub>2</sub>O-oxynitrided oxides show higher endurance in time-to-breakdown under substrate electron injection compared to those of control oxides with the thickness of 8.5 nm [6]. Joshi et al. reported the breakdown properties of oxynitrides grown directly in N<sub>2</sub>O ambient with thickness range from 4.7 to 12 nm [10]. However, no literatures have been reported on the thickness dependence of the breakdown properties of oxynitrides formed by the furnace N<sub>2</sub>O-oxynitridation of the conventional thermal oxides.

In this study, we have investigated the breakdown properties of the N<sub>2</sub>O-oxynitrided oxides with various thicknesses formed by the furnace processing. The aim of this study is to clarify mechanisms of improvement of breakdown properties in N<sub>2</sub>O-oxynitrided oxides.

## 2. Sample Preparation

The samples used in this study were MOS capacitors with n<sup>+</sup> and p<sup>+</sup> poly-Si gate electrodes fabricated on p and n-type (100)-oriented Si wafers, respectively. The capacitors were isolated using standard LOCOS process. Electrons are injected into the gate oxides using constant Fowler-Nordheim (F-N) tunneling current stress method. In the above two sample structures, the total energy losses of the injected electrons are quite similar [14], meaning that carrier transport in the two

structures are similar regardless of the oxide field polarity.

The wafers were oxidized at 800°C in dry O<sub>2</sub>/HCl ambient. Some of the wafers were followed by the oxynitridation of the control oxides at 950°C for 20 min in N<sub>2</sub>O ambient to form N<sub>2</sub>O-oxynitrided oxides. During the N<sub>2</sub>O-oxynitridation process, oxide thickness increases about 2 nm regardless of pure oxide thickness. This indicates that the oxynitridation process is limited by the chemical reaction at the Si/SiO<sub>2</sub> interface. After the gate oxidation, a poly-Si gate with 150-nm thickness was deposited by low-pressure chemical-vapor-deposition (LPCVD). The n<sup>+</sup> and p<sup>+</sup> poly-Si gate electrodes were doped by phosphorus diffusion and boron ion implantation, respectively. The boron ion implantation (<sup>11</sup>B<sup>+</sup>, 15 keV,  $3 \times 10^{15} \text{ cm}^{-2}$ ) was implemented after silicon ion implantation for an amorphous layer formation. After delineating the gate electrodes by optical lithography and reactive ion etching, the wafers were annealed at 900°C for 10 min in N<sub>2</sub> ambient. The capacitor area used was 0.44 mm<sup>2</sup>. The oxide thickness was measured with a well-calibrated automatic ellipsometer with the refractive index of 1.46, and was evaluated after averaging five measurements within an area of the wafer.

Using high-frequency C-V measurements, we confirmed that boron penetration was suppressed sufficiently for p<sup>+</sup> poly-Si gate samples in this process. This is due to the fact that boron ions are implanted into the oxides without fluorine incorporation [15]. In addition, using quasi-static C-V measurements, we also confirmed that the depletion near the poly-Si/SiO<sub>2</sub> interface was suppressed for the p<sup>+</sup> poly-Si gate samples.

### 3. Results and Discussion

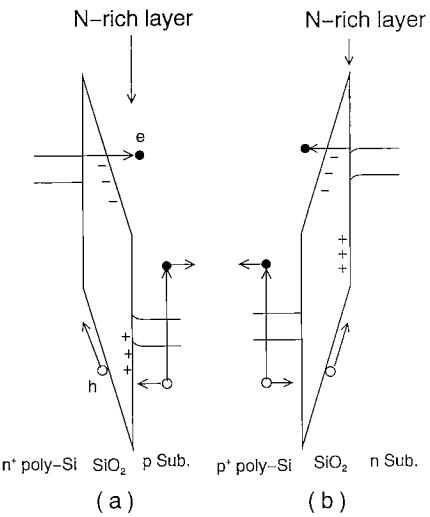

We studied breakdown properties of the control and the N<sub>2</sub>O-oxynitrided oxide films under the F-N electron injection from either the gate electrodes (gate injection,  $-V_G$ ) or the substrates (substrate injection,  $+V_G$ ). Figures 1 (a) and 1 (b) show band diagrams under gate injection in n<sup>+</sup> poly-Si gate MOS capacitors and under substrate injection in p<sup>+</sup> poly-Si gate MOS capacitors, respectively.

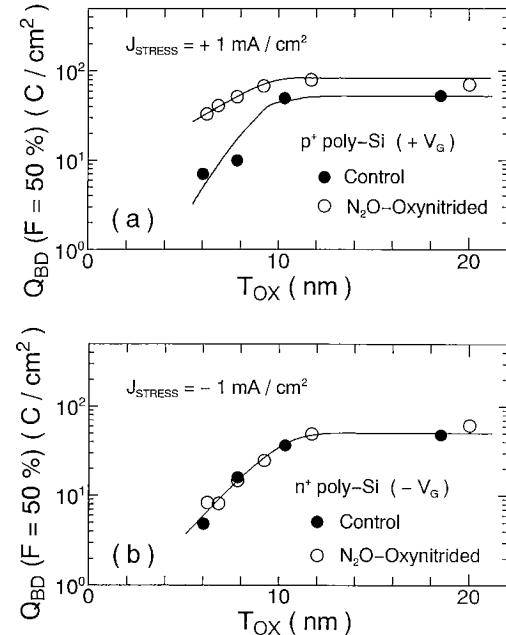

Figures 2 (a) and 2 (b) show charge-to-breakdown ( $Q_{BD}$ ) in the control and the N<sub>2</sub>O-oxynitrided oxides as a function of oxide thickness ( $T_{OX}$ ) for the substrate injection in the p<sup>+</sup> poly-Si gate samples and the gate injection in the n<sup>+</sup> poly-Si gate samples, respectively. Figure 2 (a) demonstrates that under the substrate injection for the p<sup>+</sup> poly-Si gate samples,  $Q_{BD}$  values in the N<sub>2</sub>O-oxynitrided oxides show excellent improvement for thicknesses below 10 nm. Above 10 nm, slight improvement of  $Q_{BD}$  values over the control oxides is observed. On the other hand, as is shown in Fig. 2 (b), under the gate injection for n<sup>+</sup> poly-Si gate samples, no meaningful difference between the control and the

Fig. 1 Energy band diagrams of MOS capacitors (a) under gate injection in n<sup>+</sup> poly-Si gate MOS capacitors and (b) under substrate injection in p<sup>+</sup> poly-Si gate MOS capacitors.

Fig. 2 Oxide thickness ( $T_{OX}$ ) dependence of charge-to-breakdown ( $Q_{BD}$ ) for 50% failure (a) under the substrate injection in the p<sup>+</sup> poly-Si gate samples and (b) under the gate injection in the n<sup>+</sup> poly-Si gate samples.

N<sub>2</sub>O-oxynitrided oxides is observed in terms of  $Q_{BD}$ .

As can be seen in Figs. 2 (a) and 2 (b), the oxide thickness dependences of  $Q_{BD}$  in control oxides are similar for the substrate injection and the gate injections. This is attributed to the similar total energy loss of injected electrons between p<sup>+</sup> poly-Si gate samples and n<sup>+</sup> poly-Si gate samples at a constant F-N tunneling current density [14]. Fukuda observed that  $Q_{BD}$  in gate injection decreases with decreasing oxide thickness, while increases in substrate injection [16]. One of the

reasons of this discrepancy is that his samples used for substrate injection have  $n^+$  poly-Si gate, resulting in the lower average total energy loss of the injected electrons than that for gate injection in  $n^+$  poly-Si gate samples on p-type wafers.

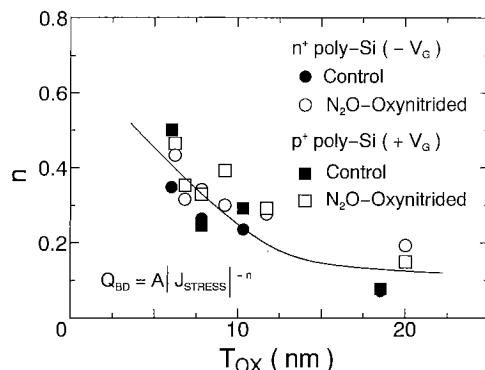

In addition, Liang and Choi observed that as stress current increases,  $Q_{BD}$  behavior with reduction in oxide thickness changes from increasing to decreasing for the both gate and substrate injection [17]. However, we cannot also observed this tendency for  $|J_{STRESS}| = 1 - 100 \text{ mA/cm}^2$ . The reason is that the capacitor area of our samples ( $0.44 \text{ mm}^2$ ) is larger than that of theirs ( $1 \times 10^{-3} \text{ mm}^2$ ). As described latter, the power exponent,  $n$  of  $Q_{BD} \propto J_{STRESS}^{-n}$  increases with reduction in oxide thickness. Therefore, thickness dependence of  $Q_{BD}$  at a fixed stress current density is thought to be decided by the compensation between the increase of  $n$  and the variation of oxide defect number (oxide defect density times capacitor area) with reduction in thickness. If we use lower stress current densities and longer measurement time, the above tendencies may be observed for our samples.

The excellent  $Q_{BD}$  improvement below 10 nm under the substrate injection may be caused by thickness dependence of oxide defects:  $N_2O$ -oxynitridation reduces the number of oxide defects in the transition layer. No improvement under the gate injection condition is attributed to the fact that electron trapping is not reduced under gate injection, while trapping events into neutral electron trap centers are reduced under substrate injection, as discussed in what follows.

The breakdown properties are associated primarily with the carrier trapping characteristic. To investigate the effect of nitrogen atoms piled up near the  $\text{Si}/\text{SiO}_2$  interface on carrier trapping behavior, we studied carrier trapping behavior at high oxide field by taking account of the field polarity.

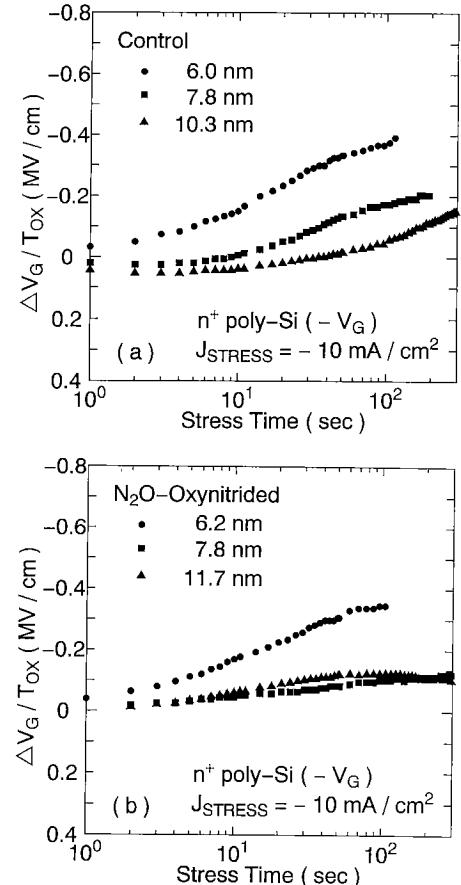

Figures 3 (a) and 3 (b) show the oxide thickness dependence of charge trapping properties under the gate injection for the control and the  $N_2O$ -oxynitrided oxides: The figures demonstrate the relative shift of the applied oxide field under a constant F-N tunneling current condition  $\Delta V_G/T_{\text{OX}}$  as a function of stress time. The thicker control oxides ( $T_{\text{OX}} = 7.8, 10.3 \text{ nm}$ ) exhibit a small net positive charge trapping during the initial stress period, which is attributed to the existence of hole traps near the  $\text{Si}/\text{SiO}_2$  interface. The hole trapping strongly depends on  $T_{\text{OX}}$ : the thinner oxide has lower hole trapping rate. Lo et al. also found similar phenomenon under gate injection for thermal oxides grown by RTP [18]. According to their model, the electrons in thicker oxide without suffering the trapping events gain higher energy from the applied field, which leads to higher rate of hole generation in the oxide bulk through impact ionization. As electron injection from the gate electrode continues, electron trapping becomes dominant in the thicker control oxides as seen

Fig. 3 Stress time dependence of the shift of the applied oxide field  $\Delta V_G/T_{\text{OX}}$  in the  $n^+$  poly-Si gate samples with (a) the control and (b) the  $N_2O$ -oxynitrided oxides as a function of stress time under the gate injection at  $-10 \text{ mA/cm}^2$ .

in Fig. 3 (a). Thinnest oxide ( $T_{\text{OX}} = 6.0 \text{ nm}$ ) shows a significant electron trapping, which differs from the result of Lo et al. [18]. The difference of the gate oxidation methods would be a main reason for the discrepancy. Lo et al. used RTP in dry  $O_2$  ambient, while we used the furnace oxidation in dry  $O_2/\text{HCl}$  ambient. Fukuda et al. confirmed that a 10 nm-thick oxide grown by RTP is superior to conventional furnace-grown oxides in breakdown and  $\text{Si}/\text{SiO}_2$  interface characteristics [19]. According to their explanation, the reason is that the RTP oxide is formed at high temperature ( $> 1000^\circ\text{C}$ ), resulting in an automatically flat  $\text{Si}/\text{SiO}_2$  interface and improvement in the weak  $\text{Si}-\text{O}-\text{Si}$  network. Therefore, electron trapping center density in our samples seems to be higher compared with the sample of Lo et al.

On the other hand, compared with the control oxides, all the  $N_2O$ -oxynitrided oxides show little net positive charge trapping as seen in Fig. 3 (b), while similar negative charge trapping behaviors with the control oxides. The negative gate voltage shift is primarily related to the electron trap centers near the poly-Si/ $\text{SiO}_2$

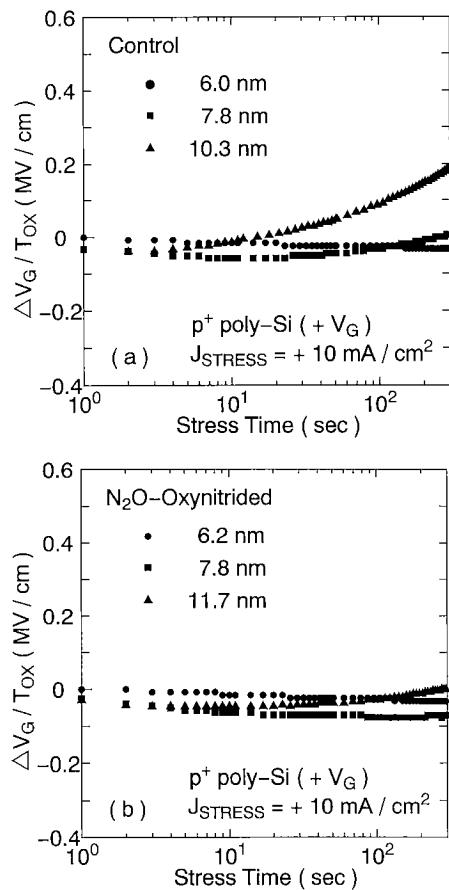

Fig. 4 Stress time dependence of the shift of the applied oxide field  $\Delta V_G/T_{OX}$  in the  $p^+$  poly-Si gate samples with (a) the control and (b) the  $N_2O$ -oxynitrided oxides as a function of stress time under the substrate injection at  $+10 \text{ mA}/\text{cm}^2$ .

interfaces as seen in Fig. 1 (a). This means that  $N_2O$ -oxynitridation has no effect on electron trapping under the gate injection. Reduction of the positive charge trapping by  $N_2O$ -oxynitridation is attributed to the decrease of hole trap density due to the existence of nitrogen atoms near the  $\text{Si}/\text{SiO}_2$  interface. On the basis of the broken bond model [20], trivalent silicon defects  $\text{Si}^*$  ( $\text{O}_3 \equiv \text{Si}^*$  and/or  $\text{Si}_3 \equiv \text{Si}^*$ ) play a significant role of hole trap centers such as  $\text{O}_3 \equiv \text{Si}^* + \text{h}^+ \rightarrow \text{O}_3 \equiv \text{Si}^+$ . Fukuda et al. pointed out that the trivalent silicon defects  $\text{Si}^*$  are annihilated after the formation of rigid  $\text{Si}-\text{N}$  bonds near the  $\text{Si}/\text{SiO}_2$  interface [3].

Figures 4 (a) and 4 (b) show the oxide thickness dependence of the charge trapping properties of the control and the  $N_2O$ -oxynitrided oxides under the substrate injection. Figure 4 (a) shows that the thicker control oxides ( $T_{OX} = 7.8, 10.3 \text{ nm}$ ) exhibit a slight net positive charge trapping during the initial stress period, and then a significant negative charge trapping during the following stress. The thinnest control oxide ( $T_{OX} = 6.0 \text{ nm}$ ) exhibits a slow positive charge trapping. These experimental results indicate that for the thicker oxides, the

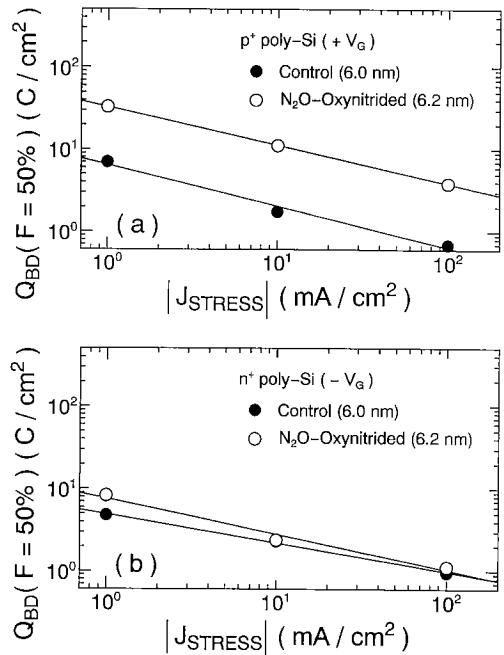

Fig. 5 Charge-to-breakdown ( $Q_{BD}$ ) as a function of stress current density ( $J_{STRESS}$ ) (a) under the substrate injection in the  $p^+$  poly-Si gate samples and (b) under the gate injection in the  $n^+$  poly-Si gate samples.

hole generation due to high energy electrons and the electron trapping occur simultaneously. Figure 4 (b) shows that the positive charge trapping behavior during the initial stress period seems to have no difference with that of the control oxides. However, it is shown that the electron trapping rate during the following stress is reduced. This behavior differs from that under the gate injection. Uchida et al. pointed out that trapped holes near the  $\text{Si}/\text{SiO}_2$  interface generate neutral electron traps [21], which originate from the relaxation of strained bonds near the interface due to hole trapping. Since nitrogen incorporation by  $N_2O$ -oxynitridation reduces strained bonds near the  $\text{Si}/\text{SiO}_2$  interface, one can simply expect the reduction of the neutral electron traps in  $N_2O$ -oxynitrided oxides.

Figure 5 (a) shows  $Q_{BD}$  values of the  $p^+$  poly-Si gate MOS capacitors as a function of stress current  $J_{STRESS}$  under the substrate injection condition. The power exponents,  $n$  of  $Q_{BD} \propto J_{STRESS}^{-n}$  for the control oxides is the same as that of  $N_2O$ -oxynitrided oxides. Figure 5 (b) shows  $Q_{BD}$  versus current density of the  $n^+$  poly-Si gate capacitors for the gate injection condition. There exists no significant difference between the control and the  $N_2O$ -oxynitrided oxides. Figure 6 shows  $n$  value as a function of oxide thickness,  $T_{OX}$ . The value  $n$  increases with decreasing  $T_{OX}$ . This is attributed to the effective traveling distance of electrons in the oxides (the oxide thickness minus the tunneling distance) [17]. As the electron traveling distance in the oxides nearly equals to the energy relaxation length, the

Fig. 6 The power exponent  $n$  as a function of oxide thickness ( $T_{\text{OX}}$ ) in the form  $Q_{\text{BD}} \propto J_{\text{STRESS}}^{-n}$ .

nonstationary electron transport in the oxides becomes significant, resulting in the large dependence of the electron energy on the traveling distance. The traveling distance increases with increasing the oxide field due to the decrease of the tunneling distance. This results in the large influence of the oxide field on the breakdown. Scarce dependence of the stress current polarity on  $n$  reflects the similarity of the average energy of the injected electrons between  $p^+$  poly-Si gate and  $n^+$  poly-Si gate MOS capacitors at constant F-N tunneling current densities [14]. The power exponent  $n$  is directly related to the physical mechanisms of carrier transport in the oxides; tunneling, traveling, impact ionization and hole injection, as shown in Figs. 1 (a) and (b).

#### 4. Conclusions

We have investigated thickness dependence of breakdown properties in the control and the  $N_2O$ -oxynitrided oxides. Nitrogen atoms piled up at the  $\text{Si}/\text{SiO}_2$  interface increases  $Q_{\text{BD}}$  under substrates injection for oxide thickness below 10 nm, while only slight increase is observed for the oxide above 10 nm. This thickness dependence is explained by the fact that  $N_2O$ -oxynitridation reduces oxide defects whose fraction is larger in thinner control oxides due to the existence of the transition layer. Under heavily injected condition from the substrate, the rate of electron trapping into neutral electron traps is smaller for the  $N_2O$ -oxynitrided oxides than for the control oxides. The dynamical carrier trapping behaviors reflect the breakdown properties; the reduction of electron trapping centers near the  $\text{Si}/\text{SiO}_2$  interface after  $N_2O$ -oxynitridation increases  $Q_{\text{BD}}$  under substrate injection. On the other hand, under gate injection condition,  $N_2O$ -oxynitrided oxides show the reduction of hole trapping during the initial stress period but no meaningful difference on electron trapping in heavily injected conditions. This results in little improvement on  $Q_{\text{BD}}$ . In addition, the control and the  $N_2O$ -oxynitrided oxides show quite similar dependence of  $Q_{\text{BD}}$  on stress current density, which is related pri-

marily to the carrier transport phenomena (tunneling, traveling, impact ionization and hole injection).

#### References

- [1] Suzuki, E., Schroder, K. and Hayashi, Y., "Carrier conduction in ultrathin nitrided oxide films," *J. Appl. Phys.*, vol.60, no.10, pp.3616-3621, Nov. 1986.

- [2] Cheng, X.R., Cheng, Y.C. and Liu, B.Y., "Nitridation-enhanced conductivity behavior and current transport mechanism in thin thermally nitrided  $\text{SiO}_2$ ," *J. Appl. Phys.*, vol.63, no.3, pp.797-802, Feb. 1988.

- [3] Fukuda, H., Arakawa, T. and Ohno, S., "Highly reliable thin nitrided  $\text{SiO}_2$  films formed by rapid thermal processing in an  $N_2O$  ambient," *Jpn. J. Appl. Phys.*, vol.29, no.12, pp.L2333-L2336, Dec. 1990.

- [4] Uchiyama, A., Fukuda, H., Hayashi, T., Iwabuchi, T. and Ohno, S., "High performance dual-gate sub-halfmicron CMOSFETs with 6nm-thick nitrided  $\text{SiO}_2$  films in an  $N_2O$  ambient," in *IEDM Tech. Dig.*, pp.425-428, 1990.

- [5] Ahn, J., Ting, W., Chu, T., Lin, S.N. and Kwong, L., "High quality ultrathin gate dielectrics formation by thermal oxidation of Si in  $N_2O$ ," *J. Electrochem. Soc.*, vol.138, no.9, pp.L39-L41, Sep. 1991.

- [6] Ahn, J., Ting, W. and Kwong, D.L., "Furnace nitridation of thermal  $\text{SiO}_2$  in pure  $N_2O$  ambient for ULSI MOS application," *IEEE Electron Device Lett.*, vol.13, no.2, pp.117-119, Feb. 1992.

- [7] Hori, T., Yasui, T. and Akamatsu, S., "Hot-carrier effects in MOSFET's with nitrided-oxide gate-dielectrics prepared by rapid thermal processing," *IEEE Trans. Electron Devices*, vol.39, no.1, pp.134-147, Jan. 1992.

- [8] Hori, T., Akamatsu, S. and Odake, Y., "Deep-submicrometer CMOS technology with reoxidized or annealed nitrided-oxide gate dielectrics prepared by rapid thermal processing," *IEEE Trans. Electron Devices*, vol.39, no.1, pp.118-126, Jan. 1992.

- [9] Hwang, H., Hao, M.Y., Lee, J., Mathews, V., Fazan, P.C. and Dennison, C., "Furnace  $N_2O$  oxidation process for submicron MOSFET device applications," *Solid State Electron.*, vol.36, no.5, pp.749-751, May 1993.

- [10] Joshi, A.B., Yoon, G., Kim, J., Lo, G.Q. and Kwong, D.L., "High-field breakdown in thin oxides grown in  $N_2O$  ambient," *IEEE Trans. Electron Devices*, vol.40, no.8, pp.1437-1445, Aug. 1993.

- [11] Momose, H.S., Morimoto, T., Ozawa, Y., Yamabe, K. and Iwai, H., "Electrical characteristics of rapid thermal nitrided-oxide gate n- and p-MOSFET's with less than 1 atom% nitrogen concentration," *IEEE Trans. Electron Devices*, vol.41, no.4, pp.546-552, Apr. 1994.

- [12] Carr, E.C. and Buhrman, R.A., "Role of interfacial nitrogen in improving thin silicon oxides grown in  $N_2O$ ," *Appl. Phys. Lett.*, vol.63, no.1, pp.54-56, Jul. 1993.

- [13] Chu, T.Y., Ting, W.T., Ahn, J. and Kwong, D.L., "Thickness and compositional nonuniformities of ultrathin oxides grown by rapid thermal oxidation of silicon in  $N_2O$ ," *J. Electrochem. Soc.*, vol.138, no.6, pp.L13-L16, Jun. 1991.

- [14] Yamada, H. and Makino, T., "Correlations between stress-induced positive charges and time-dependent dielectric breakdown in ultrathin silicon oxide films," *Appl. Phys. Lett.*, vol.59, no.17, pp.2159-2161, Oct. 1991.

- [15] Sung, J.M., Lu, C.Y., Chen, M.L., Hillenius, S.J., Lindenberger, W.S., Manchanda, L., Smith, T.E. and Wang, S.J., "Fluorine effect on boron diffusion of  $p^+$  gate Devices," in *IEDM Tech. Dig.*, pp.447-450, 1989.

- [16] Fukuda, H., "A comparative study of high-field endurance for NH<sub>3</sub>-nitrided and N<sub>2</sub>O-oxynitrided ultrathin SiO<sub>2</sub> films," *IEICE Trans. Electron.*, vol.E76-C, no.4, pp.511-518, Apr. 1993.

- [17] Liang, M.S. and Choi, J.Y., "Thickness dependence of oxide breakdown under high field and current stress," *Appl. Phys. Lett.*, vol.50, no.2, pp.104-106, Jan. 1987.

- [18] Lo, G.Q., Kwong, D.L., Abbott, K.J. and Nazarian, D., "Thickness dependence of charge-trapping properties in ultrathin thermal oxides prepared by rapid thermal oxidation," *J. Electrochem. Soc.*, vol.140, no.2, pp.L16-L19, Feb. 1993.

- [19] Fukuda, H., Iwabuchi, T. and Ohno, S., "The dielectric reliability of very thin SiO<sub>2</sub> films grown by rapid thermal processing," *Jpn. J. Appl. Phys.*, vol.27, no.11, pp.L2164-L2167, Nov. 1988.

- [20] Witham, H.S. and Lenahan, P.M., "Nature of the E' deep hole trap in metal-oxide-semiconductor oxides," *Appl. Phys. Lett.*, vol.51, no.13, pp.1007-1009, Sep. 1987.

- [21] Uchida, H. and Ajioka, T., "Electron trap center generation due to hole trapping in SiO<sub>2</sub> under Fowler-Nordheim tunneling stress," *Appl. Phys. Lett.*, vol.51, no.6, pp.433-435, Aug. 1987.

**Toshimasa Matsuoka** was born in Osaka, Japan, on November 29, 1966. He received the B.S. and M.S. degrees in electronic engineering from Osaka University, Osaka, Japan, in 1989 and 1991, respectively. During 1988-1991, he was engaged in the research of heterostructures and superlattices of GaAs and related compounds. Since 1991, he has been working for the Central Research Laboratories, Sharp Corporation, Nara, Japan, where he has been engaged in the research and development of deep submicron CMOS devices and ultra thin gate oxides. Since 1993, he has been also working toward the Ph.D. degree in electronic engineering at Osaka University, where he has been engaged in the research of hot carrier degradation of MOS devices and dielectric breakdown of gate oxides. Mr. Matsuoka is a member of the Japan Society of Applied Physics.

**Shigenari Taguchi** was born in Toyama, Japan, on July 5, 1971. He received the B.S. degree in electronic engineering from Osaka University, Osaka, in 1993. He is currently working toward the M.S. degree in electronic engineering at Osaka University. His current research interests are in hot carrier degradation of MOS devices and dielectric breakdown of gate oxides. Mr. Taguchi is a member of the Japan Society of Applied Physics.

**Kenji Taniguchi** received the B.S., M.S. and Ph.D. degrees from Osaka University, Osaka, Japan, in 1971, 1973, and 1986, respectively. From 1973 to 1986, he worked for the Toshiba Research and Development Center, Kawasaki, Japan, where he was engaged in process modeling and the design of MOS LSI fabrication technology. He was a Visiting Scientist at MIT from July 1982 to November 1983. Presently, he is an Associate Professor of Electronic Engineering at Osaka University. His current research interests are in device physics and process technology. Dr. Taniguchi is a senior member of IEEE and a member of the Japan Society of Applied Physics. He is now serving as Treasurer of the IEEE Electron Device Society, Tokyo Chapter.

**Chihiro Hamaguchi** received the B.S., M.S. and Ph.D. degrees in electrical engineering from Osaka University, in 1961, 1963, and 1966, respectively. During 1966-1967, he was a Research Associate of the Electrical Engineering Department, Faculty of Engineering Science, Osaka University. In 1967, he joined the Faculty in Electronic Engineering, Faculty of Engineering, at Osaka University, where he is presently a Professor. He has made significant contributions in the field of semiconductor physics, publishing many papers in the areas of hot electron effects, acoustoelectric instabilities, Brillouin scattering, resonant Brillouin scattering, modulation spectroscopy, and magnetotransport in semiconductors. His present research areas include the physics of small devices and heterostructure devices, hot electron effects, magnetophonon resonance effects, and modulation spectroscopy. Dr. Hamaguchi is a member of the Physical Society of Japan, the Japan Society of Applied Physics, a Fellow of IEEE, and a Fellow of the American Physical Society. He is now serving as Vice Chairman of the IEEE Electron Device Society, Tokyo Chapter.

**Seizo Kakimoto** was born in Nara, Japan, on October 8, 1957. He received the B.E. and M.E. degrees from Kyoto University in 1980 and 1982, respectively. In 1982, he joined the Semiconductor Research Laboratories, Sharp Corporation. He is currently engaged in research on deep submicron MOSFET at the Central Research Laboratories. His research interests include device structures and properties of ultra thin gate oxides. He is a member of the Japan Society of Applied Physics.

**Junkou Takagi** was born in Isikawa, Japan, on February 14, 1945. He received B.S. and M.S. degrees from Kanazawa University, Isikawa, Japan, in 1967 and 1969, respectively, and Dr. degree from the University of Tokyo, Tokyo, Japan, in 1972, all in mineralogical science. In 1972, he joined Sharp Corporation, Nara, Japan, where he was involved in the research of opto-electronic, magnetic, and microwave devices of GaAs and related compounds. Since 1985 he has been engaged in the research and development of process technology for submicron CMOS memories. He is a member of the Institute of Electrical Engineers of Japan.