|              |                                                                                     |

|--------------|-------------------------------------------------------------------------------------|

| Title        | 0.5 Vボディ入力コンパレータの特性補償に関する検討                                                         |

| Author(s)    | 王, 軍; 松岡, 俊匡; 谷口, 研二                                                                |

| Citation     | 電子情報通信学会論文誌C. 2010, J93-C(9), p. 326-327                                            |

| Version Type | VoR                                                                                 |

| URL          | <a href="https://hdl.handle.net/11094/51687">https://hdl.handle.net/11094/51687</a> |

| rights       | copyright©2010 IEICE                                                                |

| Note         |                                                                                     |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

## 0.5 V ボディ入力コンパレータの特性補償に関する検討

王 軍<sup>a)</sup> 松岡 俊匡<sup>b)</sup> 谷口 研二<sup>†</sup>

Process Variation Compensation Technique for 0.5 V Body-Input Comparator

Jun WANG<sup>a)</sup>, Toshimasa MATSUOKA<sup>b)</sup>, and Kenji TANIGUCHI<sup>†</sup>

あらまし 0.5 V 程度の低電源電圧で動作するボディ入力コンパレータの製造プロセスばらつきに対する特性劣化を改善するために、製造プロセスばらつきを補償する方法を提案し、コンパレータの動作安定性に対する改善効果を回路シミュレーションにより確認した。

キーワード ボディ入力、コンパレータ、プロセスばらつき補償

## 1. まえがき

ボディ入力コンパレータは 0.5 V 低電源電圧下で MOSFET の弱反転領域での動作を避けて高速及び高分解能を実現できる [1]。しかし、このような超低電源電圧で製造プロセスでの素子特性ばらつきの影響が顕著となり、これに応じてコンパレータの性能も劣化する。

本研究では、MOSFET のボディ効果を用いることで、0.5 V 低電源電圧での動作で顕著となる MOSFET の素子特性ばらつきを低減するための手法を提案する。本提案方法により、素子特性ばらつきで生じる回路の特性変動を抑え、コンパレータの精度を維持できる。

## 2. 提案回路構成

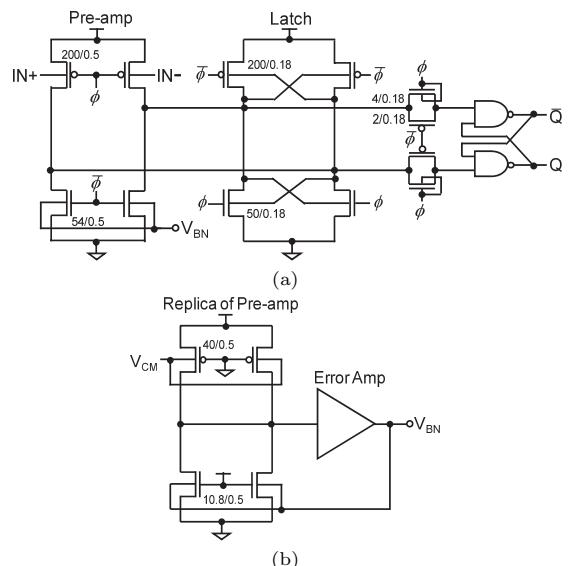

提案回路を図 1 に示す。ボディ入力コンパレータに補償回路を追加する構成となっている。なお、トリプルウェル構造を用いる CMOS プロセスを想定している。Pre-amp とラッチの各 MOSFET のゲートにクロック信号が入力される。入力信号が Pre-amp のボディ・トランスクンダクタンスで増幅されて出力データが 2 段のクロスカッピングインバータにラッチされる。

補償回路ではレプリカの Pre-amp と誤差アンプ [2], [3] が使用されている。レプリカの Pre-amp の入力電圧  $V_{CM}$  は  $V_{DD}/2$  にする。誤差アンプを利用して NMOS のボディ電位  $V_{BN}$  を調節し、出力の同相

図 1 (a) ボディ入力コンパレータと (b) プロセスばらつき補償回路。数値は MOSFET のゲート幅/ゲート長(単位:  $\mu\text{m}$ )を示す。

Fig. 1 (a) Body-input comparator (b) process variation compensation circuit. Gate width/gate length of MOSFETs in  $\mu\text{m}$  are shown.

レベルを  $V_{DD}/2$  程度に保持できる。この  $V_{BN}$  はコンパレータの Pre-amp を制御する。これにより、製造プロセスばらつきに対する NMOS と PMOS の特性バランスが補償され、コンパレータの特性変動がある範囲に抑えられる。その上、Pre-amp のレプリカのトランジスタのサイズが元回路の 1/5 として回路全体の消費電力を低減している。

製造プロセスばらつきのほかに、出力段の負荷容量はコンパレータの精度にも大きく影響しているので、できるだけ大容量の負荷を避ける。また、後段に

<sup>†</sup> 大阪大学大学院工学研究科、吹田市

Graduate School of Engineering, Osaka University, Suita-shi, 565-0871 Japan

a) E-mail: wang@eei.eng.osaka-u.ac.jp

b) E-mail: matsuoka@eei.eng.osaka-u.ac.jp

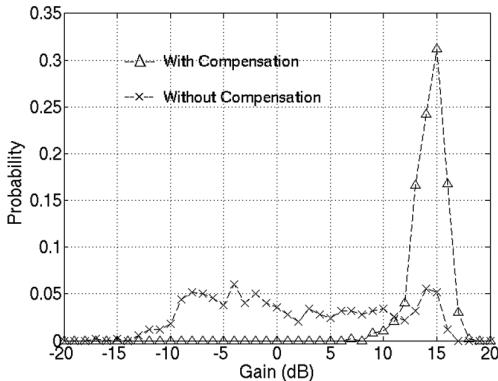

図 2 補償回路付きとない場合の Pre-amp の利得特性の Monte-Carlo シミュレーション結果（試行回数 500 回）

Fig. 2 Gain characteristics' Monte-Carlo simulation results of the pre-amp with/without process variation compensation circuit. (500 trials)

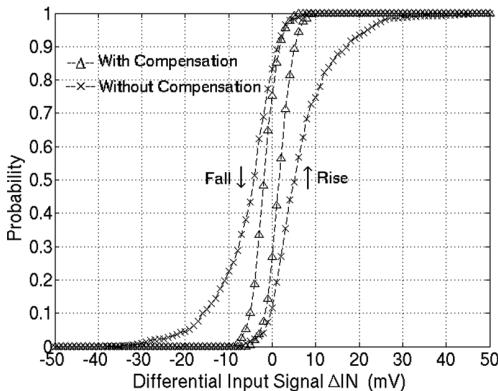

図 3 コンパレータの Monte-Carlo シミュレーション結果（試行回数 500 回）

Fig. 3 Monte-Carlo simulation result of comparator. (500 trials)

NAND 構成の SR ラッチなどのロジック回路を使う場合に、サンプリング時におけるコンパレータの出力の影響により、 $Q/\bar{Q}$  のデータは保持されない可能性がある。そこで、スイッチを使うことでサンプリング時でのコンパレータの出力を遮断している。

### 3. 回路シミュレーション結果

回路シミュレーションには、 $0.18\text{ }\mu\text{m}$  CMOS プロセスのデバイス・パラメータを使用した。電源電圧は  $0.5\text{ V}$  とした。NMOS, PMOS のしきい値電圧は  $\pm 0.45\text{ V}$  程度である。

Pre-amp 単体利得特性の Monte-Carlo シミュレーション結果を図 2 に示す。製造プロセスでの素子特性

変動により NMOS と PMOS の特性バランスが大幅に変動するが、これは特に低電圧で動作する Pre-amp 特性に大きく影響する。図 2 に補償回路付きの場合とない場合の利得分布を示す。製造プロセスばらつきに対する補償回路は Pre-amp の NMOS のボディ電圧を制御することで、Pre-amp の利得を  $11\text{ dB} \sim 18\text{ dB}$  までの範囲に抑えられる。これにより、コンパレータを超低電源電圧でもより高精度かつ安定な動作が可能となる。

コンパレータの Monte-Carlo シミュレーション結果を図 3 に示す。同相入力電圧  $V_{CM}$  は  $V_{DD}/2$  にしている。横軸が差動入力信号の振幅  $\Delta IN$ 、縦軸が正しい判定出力が得られる確率を示す。図より、補償回路による NMOS と PMOS の特性バランスの補償により、精度が向上することが分かる。また、詳細な計算により、標準偏差値  $\sigma$  は  $8.3\text{ mV}$  から  $2.7\text{ mV}$  に改善できることが分かった。

### 4. む す び

素子特性の製造プロセス上のはらつきに対するボディ入力コンパレータの特性変動を解析した。補償回路で NMOS と PMOS の特性バランスを補償することで、コンパレータを  $0.5\text{ V}$  低電源電圧でもより安定した動作が可能となる。

謝辞 本研究を遂行するにあたり（株）半導体理工学研究センターの協力、及び文部科学省グローバル COE プログラム「次世代電子デバイス教育研究開発拠点」（大阪大学）の助成を得たことに深謝します。また、本研究の設計は東京大学大規模集積システム設計教育研究センターを通じ、シノブシス（株）及び日本ケイデンス（株）の協力で行われたものである。

### 文 献

- [1] K.P. Pun, S. Chatterjee, and P. Kinget, "A 0.5-V 74-dB SNDR 25-kHz continuous-time Delta-Sigma modulator with a return-to-open DAC," IEEE J. Solid-State Circuits, vol.42, no.3, pp.496–507, March 2007.

- [2] S. Chatterjee, Y. Tsividis, and P. Kinget, "A 0.5-V analog circuit techniques and their application in OTA and filter design," IEEE J. Solid-State Circuits, vol.40, no.12, pp.2373–2387, Dec. 2005.

- [3] J. Wang, T-Y Lee, D-G Kim, T. Matsuoka, and K. Taniguchi, "Design of a 0.5 V Op-Amp based on CMOS inverter using floating voltage sources," IEICE Trans. Electron., vol. E91-C, no.8, pp.1375–1378, Aug. 2008.

（平成 22 年 6 月 8 日受付）