|              |                                                                                     |

|--------------|-------------------------------------------------------------------------------------|

| Title        | CMOSプロセスを用いたプレディストータの検討                                                             |

| Author(s)    | 車, 承佑; 松岡, 俊匡; 谷口, 研二                                                               |

| Citation     | 電子情報通信学会論文誌C. 2004, J87-C(10), p. 777-779                                           |

| Version Type | VoR                                                                                 |

| URL          | <a href="https://hdl.handle.net/11094/51692">https://hdl.handle.net/11094/51692</a> |

| rights       | copyright©2004 IEICE                                                                |

| Note         |                                                                                     |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

CMOSプロセスを用いたプレディストーターの検討

車 承佑<sup>†</sup> 松岡 俊匡<sup>†</sup>(正員)

谷口 研二<sup>†</sup>(正員)

A Study on Predistorter Using CMOS Process Technology

Sungwoo CHA<sup>†</sup>, Nonmember, Toshimasa MATSUOKA<sup>†</sup>,

and Kenji TANIGUCHI<sup>†</sup>, Members

<sup>†</sup> 大阪大学大学院工学研究科, 吹田市

Graduate School of Engineering, Osaka University, 2-1 Yamadaoka, Suita-shi, 565-0871 Japan

あらまし バイアスフィード抵抗とp+/nウェル接合ダイオードを用いたプレディストーターを0.35-μmCMOSプロセスで試作及び評価した。また、外部増幅器を用いて3次相互変調ひずみ特性を評価し、提案したCMOSプレディストーターのCMOS電力増幅器への線形化器としての可能性を検討した。

キーワード CMOS, プレディストーター, p+/nウェル接合ダイオード

### 1. まえがき

近年、CMOSプロセスを利用した高周波無線通信システムの研究が活発になり、高効率で線形性の優れたCMOS電力増幅器への要求が高まりつつある[1], [2]。電力増幅器の非線形性を改善するために、これまでフィードフォワード方式、フィードバック方式、プレディストーション方式等を利用して線形化回路が開発されてきた[3], [4]。その中でも、プレディストーション方式の線形化技術はその低消費電力とコンパクトな回路構成から集積回路に最も適した方式である。

ショットキーダイオードやMESFETを用いたプレディストーター[5]~[8]は既に報告されているが、CMOSプロセスに適していないため、オンチップCMOSRFICの基本回路として使うには余分なプロセスを必要とする。本研究ではショットキーダイオードに代わり、CMOSプロセスで作製可能なp+/nウェル接合ダイオードを用いたプレディストーターを検討した。

### 2. CMOS プレディストーター

バイアスフィード抵抗とp+/nウェル接合ダイオードを用いたCMOSプレディストーターの基本動作原理は、ショットキーダイオードを用いたプレディストーター[5]のそれと同様である。

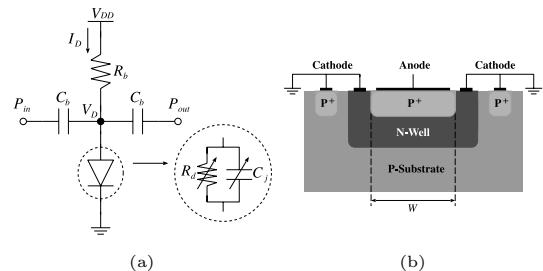

図1はプレディストーターの回路図と1辺Wの正方形p+/nウェル接合ダイオードの断面図を示している。p+/nウェル接合ダイオードの等価回路は等価抵抗R<sub>d</sub>

図1 (a) プレディストーターの回路図 (b)p+/nウェル接合ダイオードの断面図

Fig. 1 (a)Schematic of a CMOS predistorter and (b)Cross-section of a p<sup>+</sup>/n-well junction diode.

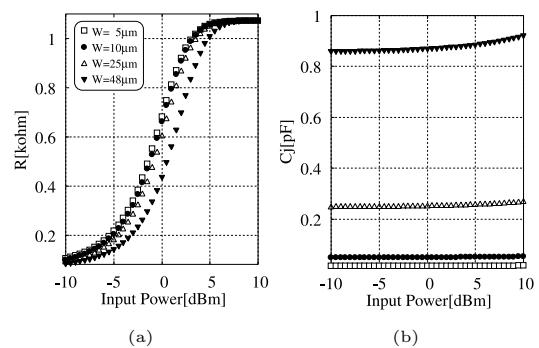

図2 V<sub>DD</sub> = 1.5 V での入力電力による (a)R, (b)C<sub>j</sub> の計算結果

Fig. 2 Calculated results of (a)R, (b)C<sub>j</sub> at V<sub>DD</sub> = 1.5 V with input power.

と等価容量C<sub>j</sub>で表せる。V<sub>D</sub>とI<sub>D</sub>はそれぞれダイオードのアノード電圧とダイオードに流れるDC電流である。ダイオードのI-V特性は次式で表される。

$$I_D = I_s \left( e^{\frac{V_D}{V_T}} - 1 \right) \quad (2)$$

ここで、I<sub>s</sub>は飽和電流( $\propto W^2$ )、V<sub>T</sub>は熱電圧である。小信号での動作点にバイアスされたダイオードは入力信号の増加に伴い(小信号→大信号)、整流作用によるクリッピングを起こしてI<sub>D</sub>が増える。その結果、バイアスフィード抵抗間電圧が増加し、V<sub>D</sub>が減少する。これにより、等価抵抗は指数関数的に、そして等価容量は徐々に増加する。図2は入力電力に対する総抵抗R (=R<sub>b</sub>||R<sub>d</sub>)とC<sub>j</sub>の計算結果である。その条件はバイアスフィード抵抗R<sub>b</sub>≈1kΩ、DCブロック容量C<sub>b</sub>=7.4pF、電源電圧V<sub>DD</sub>=1.5Vである。総抵抗RはR<sub>d</sub>が支配的な低入力電力では指数関数的に増加し、ある入力電力以上では、R<sub>b</sub>に漸近する。一方、ダ

$$|S_{21}| = \frac{2\omega^2 C_b^2 Z_0}{\sqrt{\left(\frac{\omega^2 C_b^2 Z_0^2 - 1}{R} + 2\omega^2 C_b C_j Z_0 + 2\omega^2 C_b^2 Z_0\right)^2 + \left(\frac{2\omega C_b Z_0}{R} - \omega^3 C_b^2 C_j Z_0^2 + \omega C_j + 2\omega C_b\right)^2}}$$

$$\angle S_{21} = -\tan^{-1} \frac{\omega^3 C_b^2 C_j Z_0^2 - \frac{2\omega C_b Z_0}{R} - \omega C_j - 2\omega C_b}{\frac{\omega^2 C_b^2 Z_0^2 - 1}{R} + 2\omega^2 C_b C_j Z_0 + 2\omega^2 C_b^2 Z_0} \quad Z_0: \text{特性インピーダンス}$$

(1)

イオードの等価容量  $C_j$  は、入力電力にはほとんど依存しないが、その絶対値はダイオードサイズにほぼ比例する。

プレディストータの等価回路から求めた挿入損 ( $|S_{21}|$ ) と位相 ( $\angle S_{21}$ ) は式(2)で与えられる。ここでは、文献[5]と異なり、面積の小さいダイオードでは  $C_j$  が非常に小さいため、 $C_b$  を考慮している。式(2)はこの p<sup>+</sup>/n ウェル接合ダイオードを用いたプレディストータが入力電力の増加、すなわち総抵抗の増加により、正の挿入損偏差・負の位相偏差特性をもつことを示している。

プレディストータを電力増幅器の前段に設け、総ひずみを減らすためにダイオードアノード電圧  $V_{DD}$ 、すなわち、 $V_{DD}$  を変えながらプレディストータの伝達特性の傾きを電力増幅器の A.M./A.M., A.M./P.M. 特性に合わせて調節することができる。挿入損・位相偏差の傾きの変化範囲が広いと電力増幅器の A.M./A.M., A.M./P.M. 特性にその傾きを合わせることが容易となる。ダイオードのサイズが大きくなるほど入力電力による抵抗変化量の  $V_{DD}$  依存性が小さくなり、挿入損・位相偏差の傾きの変化範囲が狭くなる。

大面積ダイオードを有するプレディストータは小面積のそれに比べ  $C_j$  が大きいため挿入損が大きい。これは電力増幅器の駆動に必要な入力電力の増加を意味する。一方、挿入損の小さい小面積ダイオードを有するプレディストータはより高電力で特性が現れる。実用化に際しては、以上の特性を考慮してダイオードのサイズを選択する必要がある。

### 3. 評価結果

#### 3.1 プレディストータの伝達特性

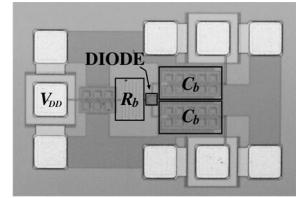

我々はサイズと  $C_j$  の関係、総抵抗の  $V_{DD}$  依存性を考慮した挿入損・位相偏差の特性に着目し、アノード幅  $W = 10, 25\mu\text{m}$  の 2 種類のダイオードを有するプレディストータを 3 層メタルダブルポリシリコン 0.35- $\mu\text{m}$  CMOS プロセスで試作し、その伝達特性を評価した。図 3 は  $W = 25\mu\text{m}$  のダイオードを用いたプレディストータの写真である。そのチップ面積はプロービング

図 3  $W = 25\mu\text{m}$  のプレディストータの写真

Fig. 3 Photomicrograph of a  $W = 25\mu\text{m}$  predistorter.

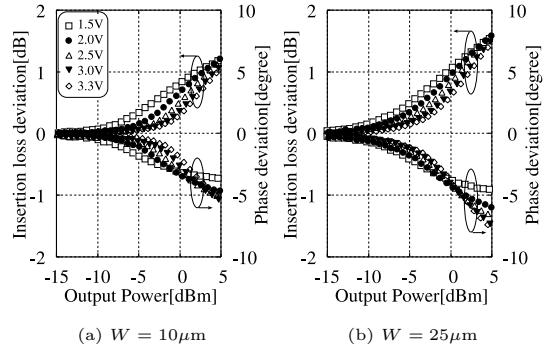

図 4 CMOS プレディストータの挿入損・位相偏差の測定結果

Fig. 4 Measured gain and phase deviations of CMOS PDs at different  $V_{DD}$ .

グ用パッドを含めて  $500\mu\text{m} \times 760\mu\text{m}$  である。

図 4 は動作周波数 2.4 GHz における、出力電力に対する  $W = 10, 25\mu\text{m}$  のプレディストータの伝達特性を  $V_{DD}$  をパラメータとして測定した結果である。なお、実測値はそれぞれの出力電力が最も小さいときの挿入損を 0 dB、位相を 0 度に正規化している。測定に使用した測定器はベクトルネットワークアナライザ Agilent 8722ES である。これらのプレディストータは希望出力電力範囲内で、大きい挿入損・位相偏差をもしながらその傾きの変化範囲も広い特性を示している。

#### 3.2 外部増幅器を用いた 2 周波 3 次相互変調ひずみ特性

CMOS プレディストータの CMOS 電力増幅器用線形化器としての可能性を検討するために、外部増幅器

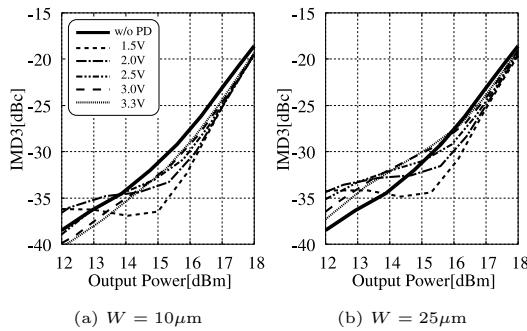

図5 プレディストータ付外部増幅器の3次相互変調ひずみ特性

Fig.5 Measured IMD3's of the amplifier with CMOS predistorters at different  $V_{DD}$ .

(Mini-Circuits ZRON-8G) を用いて2周波相互変調テストを行い3次相互変調ひずみ特性を評価した。

信号発生器 Agilent E4437B からの周波数 2.3995 GHz と 2.4005 GHz(周波数オフセット 1 MHz) の信号をプレディストータに入力し、次段の外部増幅器の出力をスペクトルアナライザ Agilent E4448 A で観測した。外部増幅器のゲインは 22 dB, 出力 P1 dB は 20 dBm である。図 5 に  $W = 10, 25 \mu\text{m}$  のプレディストータを用いた測定結果を示す。

$W = 10 \mu\text{m}$  のプレディストータを前段に設けた外部増幅器の3次相互変調ひずみ特性の場合、外部増幅器のみに比べて出力電力 15 dBm で約 6 dB 改善している。 $W = 25 \mu\text{m}$  のプレディストータでは、出力電力 15.3 dBm で約 5 dB の改善ができた。図 5 から、 $V_{DD} = 1.5 \text{ V}$  時のプレディストータの伝達特性の傾きが外部増幅器の A.M./A.M., A.M./P.M. 特性に最も合っていることが分かる。ひずみ特性の最適値を得る出力電力が存在するのは、最適出力電力以上では増幅器の飽和が進みすぎプレディストータの制御範囲から外れる [8] ため、それ以下の出力電力ではプレディストータの伝達特性が増幅器の飽和前に働き、ひずみ特性の改善が抑えられるためである。

#### 4. む す び

バイアスフィード抵抗と  $p^+/n$  ウェル接合ダイオード

を用いたプレディストータを  $0.35-\mu\text{m}$  CMOS プロセスで試作及び評価した。CMOS RF IC にこのプレディストータを実装するためには、等価容量  $C_j$  と抵抗の  $V_{DD}$  依存性を考慮したダイオードサイズの選択が重要である。適切なサイズのプレディストータを外部増幅器の前段に設け 3 次相互変調ひずみ特性を評価した結果、最大 6 dB の改善ができ、提案した CMOS プレディストータが CMOS 電力増幅器の非線形特性を改善できる線形化器として使えることが明らかとなった。

謝辞 本研究は日本学術振興会未来開拓学術研究推進事業の援助のもとで行われたものである。また、本チップ試作は東京大学大規模集積システム設計教育研究センターを通じローム(株)及び凸版印刷(株)の協力で行われたものである。

#### 文 献

- [1] C. Yen, C. Liao, and H. Chuang, "A 2.4 GHz CMOS power amplifier with output power 20 dBm for Bluetooth and WLAN applications," APMC2002, pp.697–700, 2002.

- [2] D. Leenaerts, J. V. D. Tang, and C. Vaucher, Circuit Design for RF Transceivers, Kluwer Academic Publishers, 2001.

- [3] P. B. Kenington, High-linearity RF Amplifier Design, Artech House, 2000.

- [4] 高木 直, 森 一富, “低歪み増幅器設計の基礎,” MWE 2000 Microwave Workshop Digest, pp.471–484, 2000.

- [5] K. Yamauchi, K. Mori, M. Nakayama, Y. Mitsui, and T. Takagi, "A microwave miniaturized linearizer using a parallel diode with a bias feed resistance," IEEE Trans. Microw. Theory Tech., vol.45, no.12, pp.2431–2435, Dec. 1997.

- [6] M. Nakayama, K. Mori, K. Yamauchi, Y. Itoh, and T. Takagi, "A novel amplitude and phase linearizing technique for microwave power amplifiers," IEEE MTT-S Digest, pp.1451–1454, 1995.

- [7] K. Yamauchi, K. Mori, M. Nakayama, Y. Itoh, Y. Mitsui, and O. Ishida, "A novel series diode linearizer for mobile radio power amplifiers," IEEE MTT-S Digest, pp.831–834, 1996.

- [8] C. Haskins, T. Winslow, and S. Raman, "FET diode linearizer optimization for amplifier predistortion in digital radios," IEEE Microw. Guided Wave Lett., vol.10, no.1, pp.21–23, Jan. 2000.

(平成 16 年 4 月 28 日受付)