|              |                                                                                     |

|--------------|-------------------------------------------------------------------------------------|

| Title        | MOSFETのマッチング特性の高精度評価のためのテスト回路                                                       |

| Author(s)    | 清水, 由幸; 中村, 光男; 松岡, 俊匡 他                                                            |

| Citation     | 電子情報通信学会論文誌C. 2003, J86-C(7), p. 726-733                                            |

| Version Type | VoR                                                                                 |

| URL          | <a href="https://hdl.handle.net/11094/51698">https://hdl.handle.net/11094/51698</a> |

| rights       | copyright©2003 IEICE                                                                |

| Note         |                                                                                     |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

# 論 文

## MOSFET のマッチング特性の高精度評価のためのテスト回路

清水 由幸<sup>†</sup>

中村 光男<sup>†</sup>

松岡 俊匡<sup>†</sup>

谷口 研二<sup>†</sup>

Test Structure for Precise Measurement of MOSFET's Matching Properties

Yoshiyuki SHIMIZU<sup>†</sup>, Mitsuo NAKAMURA<sup>†</sup>, Toshimasa MATSUOKA<sup>†</sup>,

and Kenji TANIGUCHI<sup>†</sup>

あらまし チップ内における MOSFET のマッチング特性を高精度に評価する回路を設計した。この回路は、アレー状に配置された測定対象となる 10,000 個以上の MOSFET と、測定時にその中から任意の 1 素子を選択するための周辺回路とから構成されている。アレー内のすべての MOSFET に同一バイアスを与えることを可能にするために、電極と測定対象の MOSFET 間に存在するスイッチ抵抗、配線抵抗などの回路の寄生抵抗の影響を、ケルビン法による測定を回路内に組み込むことで除去している。この回路により、1 チップ内における MOSFET のしきい値電圧とトランスコンダクタンスのばらつきに関して統計的なデータを得ることに成功した。

キーワード MOSFET, チップ内ばらつき, しきい値電圧, トランスコンダクタンス, ケルビン法

### 1. まえがき

集積回路、特にアナログ CMOS 回路では、回路内の MOSFET のしきい値電圧 ( $V_{th}$ ) やトランスコンダクタンス ( $g_m$ ) など、その特性値にはばらつきがあると、回路の動作や性能に影響を与える。アナログ回路で問題となるのは、ウェーハ間、ウェーハ内のような広範囲におけるゲート絶縁膜厚やドーパント濃度の不均一性による特性ばらつきだけでなく、チップ内で近接、密集した MOSFET の集合における特性ばらつきが大きな問題となる。これをマッチング特性という。この MOSFET のマッチング特性は、イオン注入や熱拡散などの LSI 製造プロセスで必然的に引き起こされるドーパント原子数の揺らぎ、多結晶ポリシリコン粒によるゲート形状の揺らぎによると考えられ、プロセス装置の性能に対する依存性は小さいことが報告されている [1], [2]。

MOSFET のマッチング特性は、コンパレータや差動增幅回路など、複数の MOSFET 特性のマッチングが必要な回路で大きな影響を及ぼす。また、電流セルマトリックス型 D-A コンバータの出力の線形性も

MOSFET で構成される電流源のマッチングに大きく依存する [3], [4]。このため、アナログ CMOS 回路設計者にとって MOSFET の特性ばらつきを考慮することは非常に重要なことである [5], [6]。特に、MOSFET の微細化、低電圧化に伴い、マッチング特性がアナログ回路のダイナミックレンジを決定する要因の一つにもなっている [7]。そこで、本論文では、チップ内での MOSFET の特性のばらつきを、統計的に高精度に評価できる回路方式を提案する。これにより、MOSFET の  $V_{th}$  や  $g_m$  のマッチング特性を評価することが可能となる。

### 2. 評価回路の構成

#### 2.1 評価回路の小面積化と寄生抵抗の影響

単純に多数の MOSFET を測定するには、被測定 MOSFET の数以上のパッド数が要求され、必然的に大きな占有面積のテストチップが必要となる。プロセスの微細化が進んでも、パッド面積とパッド間の距離はプロービング装置との兼合いがあるために小さくすることはできず、限られた面積中に配置可能な被測定 MOSFET の数は限られてしまう。例えば  $100 \mu\text{m} \times 100 \mu\text{m}$  のパッドを用いる場合、 $4 \text{ mm} \times 4 \text{ mm}$  の面積には 200 個程度の MOSFET しか配置できず、これではチップレベルで統計的なデータをとるには不十分である。こ

<sup>†</sup> 大阪大学大学院工学研究科、吹田市

Graduate School of Engineering, Osaka University, 2-1 Yamadaoka, Suita-shi, 565-0871 Japan

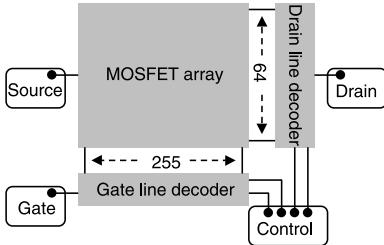

図 1 MOSFET 特性の評価回路全体のブロック図。デジタル制御信号によりドレーン線とゲート線をそれぞれ 1 本選択し、MOS アレー中の被測定素子を指定する。

Fig. 1 Block diagram of the statistical data acquisition circuit for MOSFET characteristics.

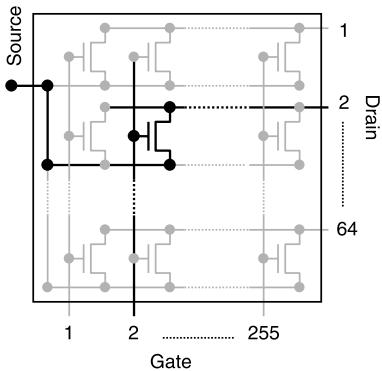

図 2 64×255 個の MOSFET アレー。ドレーン線とゲート線の選択により、一つの MOSFET が被測定素子として選び出される。

Fig. 2 255-row 64-column MOSFETs array. Any MOSFET in the array can be chosen by selecting a pair of the drain and gate lines.

れに対して、MOSFET をアレー状に集積化することで面積効率を大幅に改善する評価回路が報告されている [2], [8]。

図 1 は、我々が既に提案した回路全体のブロック図である [8]。MOS アレーブロック (MOSFET array), ドレーン選択回路ブロック (Drain line decoder), ゲート選択回路ブロック (Gate line decoder) の三つのブロックで構成されている。MOS アレーブロックは、縦 64 個、横 255 個並んだ被測定 N 型 MOSFET で構成されている (図 2)。MOS アレーブロックの各 MOSFET のソース端子はすべて同一配線に接続されている。また、縦方向の 64 個の MOSFET はゲート端子が同一配線に接続され、横方向の 255 個の MOSFET はドレン端子が同一配線に接続されている。これらがそれぞれゲート配線、ドレーン配線となる。測定時には、縦

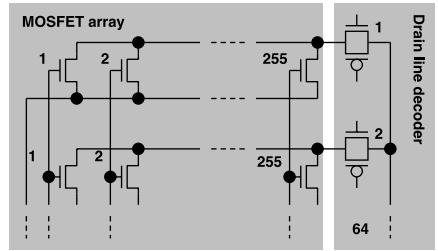

図 3 測定回路における寄生抵抗。選択スイッチ、配線などに寄生抵抗が存在しており、被測定 MOSFET の電極電位はパッドに印加した電圧とは異なる。

Fig. 3 Parasitic resistance in the circuit. The source and drain voltages of a selected MOSFET slightly differ from those applied to the pads due to the resistance of selector switches and metal wirings.

に伸びる 255 本のゲート配線、横に伸びる 64 本のドレーン配線から各々 1 本をゲート選択回路ブロック、ドレーン選択回路ブロックにより選択し、交点に当たる一つの MOSFET を選び出す。ここでゲート選択回路ブロック、ドレーン選択回路ブロックは、MOS アレーブロックから伸びるゲート、ドレーン配線からそれぞれ 1 本を選択してそれぞれの入力パッドと接続するスイッチの役割を果たしている。この回路を利用することで、 $2 \text{ mm} \times 4 \text{ mm}$  の面積にパッドと周辺回路、そして被測定 MOSFET を  $64 \times 255$  個配置できる。

しかし、この回路には被測定 MOSFET と各端子への入力パッドとの間に、図 3 に示す MOS アレーブロック内の長い配線による配線抵抗、ドレーン選択ブロックのスイッチ抵抗などの寄生抵抗が存在する。そのため、MOSFET にドレーン電流 ( $I_D$ ) が流れると寄生抵抗による電圧降下が生じ、MOSFET の各端子に実際にかかる電圧とパッド印加電圧とが異なる。また、配線抵抗は被測定 MOSFET の位置によって異なるので、MOSFET の各端子に印加される電圧を制御することは難しく、すべての MOSFET を同一印加電圧下で測定することは困難である。

Chou らの計算方法 [9] によると、ソース側に  $R_S$ 、ドレーン側に  $R_D$  の寄生抵抗をもつ素子の相互コンダクタンス  $g_m$  は、寄生抵抗のない素子の相互コンダクタンス  $g_{m,i}$  と以下のよう関係にある。

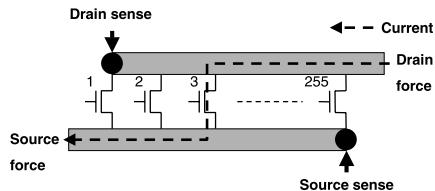

図4 被測定MOSFETのドレーン/ソース電圧の参照方法

Fig. 4 Technique to monitor intrinsic drain/source voltages of a selected MOSFET. Solid circles represent the points where voltages applied to the MOSFET are monitored.

$$g_m = \frac{g_{m,i}}{1 + g_{m,i}R_S + g_{d,i}(R_S + R_D)} \quad (1)$$

ここで、 $g_{d,i}$ は、寄生抵抗のない素子のドレーンコンダクタンスである。この式で  $g_{m,i} \gg g_{d,i}$  として、 $g_{m,i}$  のばらつきによる  $g_m$  のばらつきを求めるとき、以下のようになる。

$$\frac{\Delta g_m}{g_m} = \frac{\sqrt{(\Delta g_{m,i}/g_{m,i})^2 + (g_{m,i}\Delta R_S)^2}}{1 + g_{m,i}R_S} \quad (2)$$

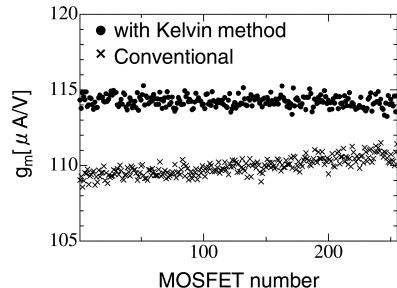

この式よりわかるように、 $g_m$  のマッチングを評価する場合、ソース側の寄生抵抗が評価結果に大きく影響する。更に、線形領域での  $g_m$  はドレーン電圧  $V_{DS}$  に比例して小さくなるため、寄生抵抗の影響は更に大きくなる。図5 (Conventional) は、1本のドレーン配線に接続されている 255 個の MOSFET ( $W/L=10.0\mu\text{m}/0.8\mu\text{m}$ ) の線形領域測定から求めた  $g_m$  をプロットしたものである。ドレーン入力端から離れるにつれて (255 → 1), 配線抵抗による  $V_{DS}$  の電圧降下の影響 ( $g_m$  の低下) が現れている。このように、この評価回路は MOSFET の選択に用いるスイッチ回路の抵抗や、被測定 MOSFET までの配線抵抗などの寄生抵抗をもち、微少ドレーン電流領域で求められる  $V_{th}$  については評価できるが、 $V_{DS}$  が大きく影響する  $g_m$  やドレーン電流値自体を正確に評価できない。このような寄生抵抗の影響を避けるために、我々はケルビン法 [10] を用いた。

## 2.2 ケルビン法の評価回路への適用

ケルビン法では任意の点への電圧印加に、電圧参照端子 (sense) と電圧印加端子 (force) の二つの端子を用いる。電圧値を測る電圧参照端子は高いインピーダンスをもち、計測時にも電流を流さない。よって、測定点と端子間の経路にケーブル等による抵抗が存在しても電流による電圧降下がなく、経路の寄生抵抗と無関係に測定点の正確な電圧を測ることができる。測定点への電圧印加は電圧印加端子によって行う。ここで、

図5 寄生配線抵抗による  $g_m$  の低減。 $W/L=10.0\mu\text{m}/0.8\mu\text{m}$ ,  $V_{DS}=50\text{mV}$ 。ケルビン法による電圧参照を行うと  $g_m$  の低減は回避される。

Fig. 5 Reduction of  $g_m$  ( $\times$ ) due to parasitic resistance of the wires connecting to the MOSFETs with  $W/L=10.0\mu\text{m}/0.8\mu\text{m}$  measured at  $V_{DS}=50\text{mV}$ . The  $g_m$  reduction can be avoided by using Kelvin method ( ).

電圧印加端子と測定点の間には寄生抵抗による電圧降下が生じるが、電圧参照端子によって測定点の電圧を直接に参照できるために、寄生抵抗の影響に関係なく電圧を任意の値に調節できる。このように、ケルビン法の測定では電圧参照端子と電流印加端子を用いることで、経路の寄生抵抗に関係なく任意の点に任意の電位を正確に与えることができる。

前述した回路にドレーン、ソース電圧の参照点 (Drain sense, Source sense) を加えた回路を図4に示す。ドレーン電圧参照点と被測定 MOSFET のドレーンの間には電流は流れないので、この区間では電圧降下が生じず、参照点の電位は実際に MOSFET のドレーンに印加されている電圧となる。また、この電位をモニタしながら、ドレーン電圧を正確に制御することも可能となる。ソース側についても同様である。この参照点を追加した回路で  $g_m$  の測定を行った結果を図5 (with Kelvin method) に示す。図より、測定結果が配線抵抗の影響を受けていないことがわかる。また、全体的に値が増しているのは、ドレーン選択回路内のスイッチ抵抗の影響が消えたためである。

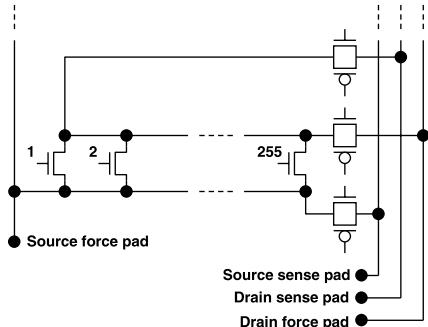

電圧参照回路を加えた全体の回路を図6に示す。参照点からの配線はドレーン選択回路ブロック内で、ドレーン配線と同様、スイッチ回路で外部に取り出している。ケルビン法を採用しているため、ここで挿入されるスイッチ抵抗はばらつきも含めて測定に影響しない。この方式を採用することにより回路規模をほとんど変えることなく、正確に MOSFET のマッチング特性を評価できる回路が実現できる。測定回路の寄生抵

図 6 ドレーン/ソース電圧参照回路を加えた全体の回路構成

Fig. 6 Auxiliary circuit to monitor the drain and source terminal voltages.

抗は、ドレーン/ソース側以外にゲート側にも存在するが、ゲート電極には電流が流れないと、その影響は無視できる。

なお、本方法は回路上のスイッチ抵抗と配線抵抗の影響の除去が目的であり、コンタクト抵抗、ドレーン/ソース拡散層抵抗、広がり抵抗など素子自体に関連する寄生抵抗[11]の影響は除去しない。マッチング評価では、実際の回路での使用において避けることのできないこれらの抵抗は、素子の特性に含まれる。

以上の回路構成を用いることで、被測定 MOSFET ごとに測定用パッドをもつ従来のレイアウトでは 100 個程度しか配置できない  $2\text{ mm} \times 4\text{ mm}$  の面積内に、 $64 \times 255$  個の MOSFET を配置できる。測定時にはケルビン法によって、すべての MOSFET に任意の印加条件を高い精度で与えることが可能である。また、すべての被測定 MOSFET が測定用パッドを共有し、測定素子の選択はドレーン選択回路、ゲート選択回路の制御によって行われる。よって、測定素子の選択にプローブ針の移動の必要がなく、二つの選択回路の制御もプログラムによって簡単に行うことができるため、多数の MOSFET を測定する時間は短縮される。

### 3. 評価回路の設計・作製

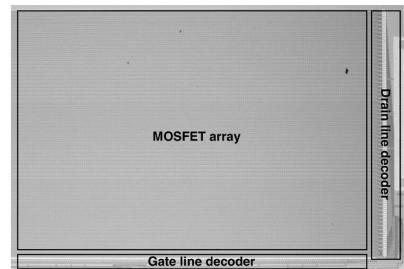

#### 3.1 レイアウト

$0.35\text{ }\mu\text{mCMOS}$  プロセスを用いて本マッチング評価回路の設計、試作を行った(図 7)。回路の MOSFET アレープロック内には 16 種類のゲート寸法の N-MOSFET を各々の寸法につき  $4 \times 255$  個ずつ、全部で  $64 \times 255$  個配置した。

MOSFET アレープロック内の被測定 MOSFET をレイアウトするにあたっては、ドレーン/ソース領域

図 7 試作チップ写真

Fig. 7 Photograph of the fabricated test chip.

形成の際の不純物イオン注入で起こり得る素子の非対称性[12]を考慮し、素子及び素子を流れる電流の向きに注意したレイアウトを行った。また、パターンの密集により生じる製造プロセスの不均一を回避するため、MOSFET 間に  $20\text{ }\mu\text{m}$  程度の素子分離領域を設けている。

#### 3.2 リーク電流

本回路では、1 本のドレーン配線に対して 255 個の MOSFET が並列に接続される。測定時には、測定を行う 1 個の MOSFET 以外に電流が流れないよう、ゲートを接地することでオフ状態にする。しかし、MOSFET はオフ状態でも電流を完全に遮断せず、実際には微小なオフ電流( $I_{off}$ )が存在し、測定に誤差を生じさせる。よって、本回路の設計では、このリーク電流の影響を考慮する必要がある。

1 本のドレーン配線に接続された 255 個の MOSFET の中の 1 個を測定するとき、 $I_D$  の測定値には、他の 254 個の MOSFET の  $I_{off}$  が誤差として加算される。その和  $I_{leak}$  は、次の式で見積もることができる。

$$I_{leak} = (N - 1)I_{off} \quad (3)$$

ここで  $N$  は 1 本のドレーン配線に接続された MOSFET の数であり、本回路では 255 である。

次に、リーク電流によりケルビン法測定に生じる誤差を見積もる。この測定では測定点と電圧参照点の間にリーク電流が流れると、配線抵抗による電圧降下が生じ、参照点から取り出す電圧値に誤差が生じてしまう。この誤差は、すべての非選択 MOSFET が測定点と参照点の間に接続される、参照点から最も遠い MOSFET を測定するときに最大となり、その大きさ  $V_{err}$  は、 $I_{leak}$  とドレーン配線の配線抵抗  $R_w$  から次の式で見積もられる。

$$V_{err} = \frac{1}{2} R_w I_{leak} \quad (4)$$

係数  $1/2$  は、 $I_{leak}$  がドレーン配線を流れるにつれて、途中に接続された非選択 MOSFET から少しづつ流れ出し減少していく効果を表したものである。

以上の手順により、リーク電流による測定値への誤差を具体的に見積もることができる。これらが測定値に対して十分に小さい値であれば無視できる。また、これらは MOSFET の数を減らす、配線幅を増やす、ゲート選択回路のローレベル出力を低くする等により改善が可能である。

試作回路では、 $I_{leak}$  は測定値で  $V_{DS}=1.0\text{ V}$  時で約  $120\text{nA}$ 、ドレーン電圧による変動は  $7.8\text{nA/V}$  程度であり、これにより見積もられる  $V_{err}$  は  $1.8\mu\text{V}$  である。測定ではどちらも無視できることを確認している。

#### 4. 測 定 方 法

本評価回路の MOS アレー上の全 MOSFET の  $V_{th}$ 、 $g_m$  を求めるために、ミクストシグナル LSI テストシステム HP94000 を用いて、ドレーン選択回路とゲート選択回路の制御による測定素子の選択、及び  $V_{GS}-I_D$  特性の測定を行った。

線形領域においては、 $V_{GS}-I_D$  特性から  $g_m$  の最

図 8 同一 MOSFET に対する 1000 回の繰返し測定における  $V_{th}$  及び  $g_m$  の再現性

Fig. 8 The reproducibility of  $V_{th}$  and  $g_m$  from 1,000 times measurement at one MOSFET.

大値を求め、そのときの  $V_{GS}$  での接線から  $V_{th}$  を求めた。飽和領域では、 $V_{GS} - \sqrt{I_D}$  曲線から、同様な方法を用いて  $V_{th}$  を求める [13]。飽和領域での  $g_m$  の算出については、 $V_{th}$  の算出方法との整合性を考慮して、 $\partial\sqrt{I_D}/\partial V_{GS}$  が最大値になる点について、以下の式を用いて求めた。

$$g_m = 2\sqrt{I_D} \frac{\partial \sqrt{I_D}}{\partial V_{GS}} \quad (5)$$

本手法は、 $I_D$  が微小な規定値に達したときの  $V_{GS}$  を  $V_{th}$  に定める手法と比較して、測定環境（プローブカード等）のリーク電流による影響を少なくすることができます。測定精度を調べるために、回路内の 1 個の被測定素子に対して線形領域 ( $V_{DS}=50\text{ mV}$ ) で 1000 回測定を繰り返し、その再現性を確認した。図 8 は測定結果から得た  $V_{th}$ 、 $g_m$  の度数分布である。それぞれの標準偏差は  $\sigma(V_{th})=0.10\text{ mV}$ 、 $g_m$  は絶対値に対して  $(\sigma(g_m)/g_m)=\pm 0.05\%$  である。

#### 5. 測 定 結 果

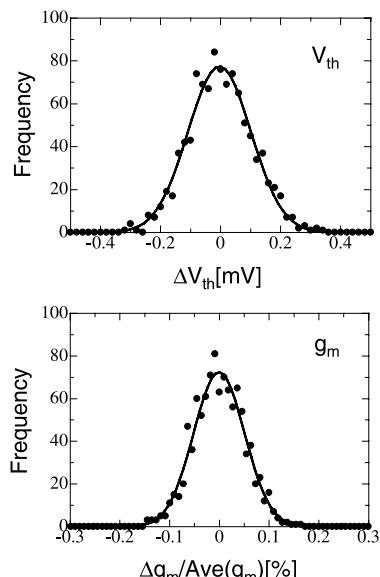

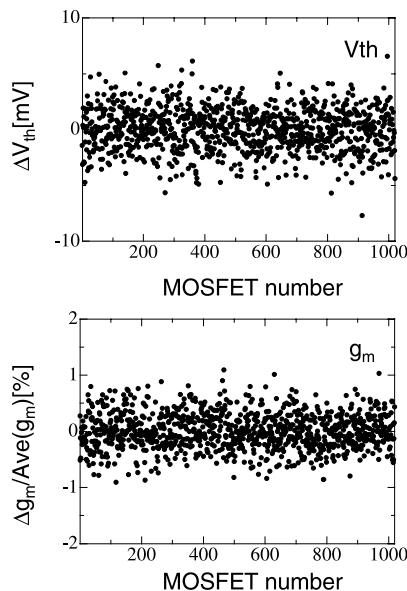

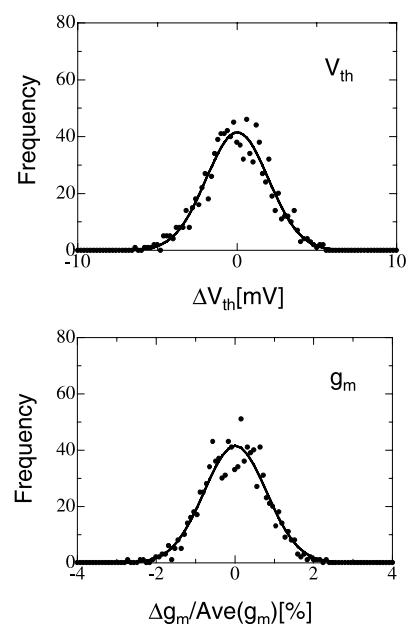

MOSFET アレーブロック内のすべての MOSFET に対して  $V_{DS}=50\text{ mV}$  の線形領域測定を行った。測定結果の中から、ゲート寸法  $W/L = 10.0\mu\text{m}/0.8\mu\text{m}$  である  $4 \times 255$  個の MOSFET について  $V_{th}$  と  $g_m$  の平均値からのはらつきを図 9 に示す。 $V_{th}$ 、 $g_m$  とともに、MOSFET の位置には依存しない不規則なはらつきをもっていることがわかる。また、1, 255, 256, 510, 511, 765, 766, 1020 番目の MOSFET はそれぞれ MOSFET アレーブロックの両端に位置しているが、MOSFET 同士の間隔を十分に設けているため、それら及び、その周辺の MOSFET と MOSFET アレーブロック内部の MOSFET との間に特性の大きな違いは見られない。

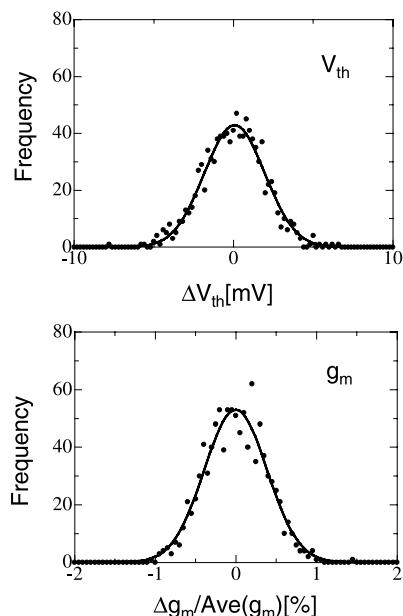

図 10 には、これらのはらつきを度数分布で表した。 $V_{th}$ 、 $g_m$  のはらつきは、ともにガウス分布を示す。他の 15 種類のゲート寸法の MOSFET についても、 $4 \times 255$  個の MOSFET の測定から  $V_{th}$ 、 $g_m$  のはらつきの分布を同様に得ることができた。

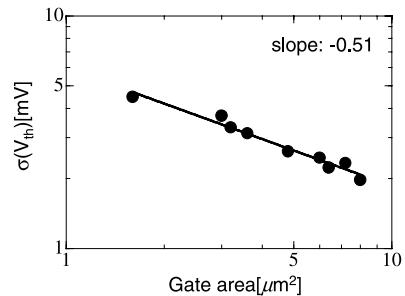

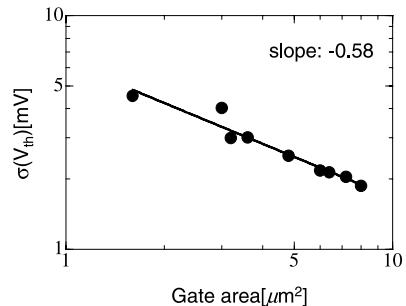

更に、この 16 種類のゲート寸法のうち、ゲート面積が同じもの（ $W/L$  比は異なる）及び、短チャネル効果の影響が現れるプロセス最小ゲート長をもつものを除いた 9 種類のゲート寸法について  $V_{th}$  の度数分布から標準偏差を取り出し、ゲート面積との関係をグラフに示した（図 11）。 $V_{th}$  はらつきの標準偏差  $\sigma(V_{th})$  とゲート面積  $LW$  の間には次の関係がある [2], [6]。

図 9 線形領域の測定によって得られた MOSFET の  $V_{th}$  と  $g_m$  の平均値からのずれ。測定は  $W/L=10.0\mu\text{m}/0.8\mu\text{m}$  の  $4 \times 255$  個の試料について行った。 $V_{DS}=50\text{mV}$

Fig. 9 Fluctuation of  $V_{th}$  and  $g_m$  from their averages from the data measured in linear region. The measurements were performed for  $4 \times 255$  MOSFETs with  $W/L=10.0\mu\text{m}/0.8\mu\text{m}$  at  $V_{DS}=50\text{mV}$ .

図 10 図 9 の度数分布

Fig. 10 Frequency distribution of  $V_{th}$  and  $g_m$  shown in Fig. 9.

図 11  $V_{th}$  ばらつきの標準偏差とゲート面積の関係（線形領域測定）

Fig. 11 Standard deviation of  $V_{th}$  as a function of gate area, which were measured in the linear region.

$$\sigma(V_{th}) \propto \frac{1}{\sqrt{LW}} \quad (6)$$

図 11 のグラフの傾きは両 log 表示で  $-0.51$  であり、ほぼ、式 (6) の関係を満たしている。この関係式は、個々の MOSFET のゲート酸化膜厚や不純物濃度に差がない、若しくは無視できるほど小さく、 $V_{th}$  ばらつきは、MOSFET ごとのチャネル空乏層中に含まれるアクセプタ不純物の個数のランダムな揺らぎにのみ起因するという議論から求められている [2]。すなわち、本回路の測定範囲においても、MOSFET 間のゲート酸化膜厚や不純物濃度の違いは無視でき、得られたばらつきは、MOSFET アレーブロック内の位置に依存しないランダムなものである。よって、これをそのままマッチング特性とみなしている。このグラフに加えていないが、最小ゲート長をもつ素子は、短チャネル効果の影響によってばらつきが大きくなるため、ゲート面積に関係なくこの傾向から外れる。

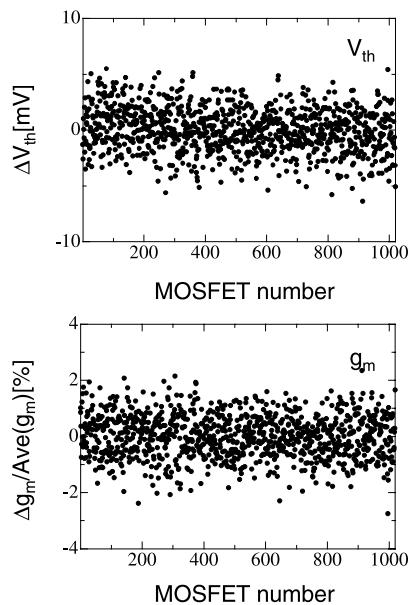

同じく MOSFET アレーブロック内のすべての MOSFET に対して  $V_{DS}=1.0\text{V}$  の飽和領域測定を行った。測定結果の中から、ゲート寸法  $W/L = 10.0\mu\text{m}/0.8\mu\text{m}$  である  $4 \times 255$  個の MOSFET について、 $V_{th}$  と  $g_m$  の平均値との差を図 12 に示す。図 13 はそれらを度数分布で表したものである。更に、 $V_{th}$  の標準偏差と面積の関係を図 14 に示す。 $I_D$  が大きな飽和特性領域においても寄生抵抗による電圧降下の影響が抑えられ、 $V_{th}$ 、 $g_m$  のばらつき、及び式 (6) に示す  $V_{th}$  ばらつきとゲート面積の関係が線形領域測定と同様に得られていることがわかる。他の 15 種類のゲート寸法についても同様の測定結果を得ることができた。

図 12 飽和領域の測定により MOSFET から求めた  $V_{th}$  と  $g_m$  のばらつき。測定には  $4 \times 255$  個の素子 ( $W/L=10.0 \mu\text{m}/0.8 \mu\text{m}$ ) を用い、 $V_{DS}=1.0 \text{ V}$  とした。

Fig. 12 Fluctuation of  $V_{th}$  and  $g_m$  in saturation region from their averages. The measurements were performed for  $4 \times 255$  MOSFETs with  $W/L=10.0 \mu\text{m}/0.8 \mu\text{m}$  at  $V_{DS}=1.0 \text{ V}$ .

図 13 図 12 の度数分布

Fig. 13 Frequency distribution of  $V_{th}$  and  $g_m$  shown in Fig. 12.

図 14  $V_{th}$  ばらつきの標準偏差とゲート面積の関係(飽和領域測定)

Fig. 14 Standard deviation of  $V_{th}$  as a function of gate area, which were measured in saturation region.

## 6. むすび

MOSFET の特性のマッチングを調べるための評価回路を提案した。1 チップという限られた面積内に測定対象となる MOSFET をできるだけ多く配置するために、被測定 MOSFET をアレー状に配置し、測定時にその中から 1 個の MOSFET を任意に選択するための周辺回路を加えてパッドの共有化を図った。今回設計した回路には  $2 \text{ mm} \times 4 \text{ mm}$  の面積に、 $64 \times 255$  個の被測定 MOSFET を配置した。

また、本回路ではケルビン法を用いることで、MOSFET の選択に用いるスイッチ回路素子の抵抗や長い配線による配線抵抗など、測定の妨げとなる回路の寄生抵抗の影響を取り除いている。この方式により、従来、寄生抵抗の影響で測ることができなかつた  $g_m$  の値とそのばらつきを正確に測定することが可能となった。

試作した評価回路を用い、16 種類のゲート寸法について、それぞれ  $4 \times 255$  個の MOSFET を測定することによってチップ内の  $V_{th}$ 、 $g_m$  のランダムなばらつきに関するデータを得た。また、これらのばらつきは測定範囲において MOSFET の位置に依存しないため、このデータを隣接 MOSFET のマッチング特性とみなすことができる。更に、これらをもとにして、測定対象にないゲート寸法をもつ MOSFET の特性ばらつきに対する推定値を得ることができ、アナログ回路の設計に役立てることができる。

謝辞 本研究は東京大学大規模集積システム設計教育研究センターの協力と日本学術振興会未来開拓学術研究推進事業の援助のもとで行われたものである。

## 文 献

- [1] M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G.

- Welbers, "Matching properties of MOS transistors," IEEE J. Solid-State Circuits, vol.24, no.5, pp.1433–1440, 1989.

- [2] T. Mizuno, J. Okamura, and A. Toriumi, "Experimental study of threshold voltage fluctuation due to statistical variation of channel dopant number in MOSFET's," IEEE Trans. Electron Devices, vol.41, no.11, pp.2216–2221, 1994.

- [3] Y. Nakamura, T. Miki, A. Maeda, H. Kondoh, and N. Yazawa, "A 10-b 70-MS/s CMOS D/A converter," IEEE J. Solid-State Circuits, vol.26, no.4, pp.637–642, 1991.

- [4] C-H. Lin and K. Bult, "A 10-b, 500-MSamples/s CMOS DAC in 0.6 mm<sup>2</sup>," IEEE J. Solid-State Circuits, vol.33, no.12, pp.1948–1958, 1998.

- [5] K. R. Lakshmikumar, R. A. Hadaway, and M. A. Copeland, "Characterisation and modeling of mismatch in MOS transistors for precision analog design," IEEE J. Solid-State Circuits, vol.21, no.6, pp.1057–1066, 1986.

- [6] F. Forti and M.E. Wright, "Measurement of MOS current mismatch in the weak inversion region," IEEE J. Solid-State Circuits, vol.29, no.2, pp.138–142, 1994.

- [7] K. Bult, "Analog design in deep sub-micron CMOS," Proc. 26th European Solid-State Circuits Conference, pp.11–17, 2000.

- [8] 清水由幸, 中村光男, 松岡俊匡, 谷口研二, "しきい値のばらつきの統計に見るMOSFETの特性の研究," 電気学会研究会資料, pp.83–87, June 2000.

- [9] S. Y. Chou and D. A. Antoniadis, "Relationship between measured and intrinsic transconductances of FET's," IEEE Trans. Electron Devices, vol.34, no.2, pp.448–450, 1987.

- [10] A. Hastings, The Art of Analog Layout, pp.503–504, Prentice-Hall, 2001.

- [11] 原 央, MOS集積回路の基礎, pp.231–237, 近代科学社, 1992.

- [12] B. Razavi, Design of Analog CMOS Integrated Circuits, pp.637–639, McGraw-Hill, 2001.

- [13] N. Arora, MOSFET Models for VLSI Circuit Simulation, pp.438–443, Springer Verlag, 1993.

(平成14年10月2日受付, 15年1月17日再受付)

中村 光男 (学生員)

平9東北大・工・電子卒。平11阪大大学院博士前期課程了。現在、同大学院工学研究科博士後期課程在学中。CMOS RF回路の研究に従事。IEEE会員。

松岡 俊匡 (正員)

平元阪大・工・電子卒。平3同大大学院博士前期課程了。平3シャープ(株)入社。平11阪大大学院工学研究科電子情報エネルギー工学専攻リサーチ・アソシエイト(日本学術振興会研究員)。平12同大大学院工学研究科電子情報エネルギー工学専攻講師。CMOS RF回路の研究に従事。工博。応用物理学会, IEEE各会員。

谷口 研二 (正員)

昭46阪大・工・電子卒。昭48同大大学院修士課程了。昭50東芝(株)入社。昭57より1年間マサチューセッツ工科大学客員研究员。昭61阪大工学部電子工学科助教授。平8同大大学院工学研究科電子情報エネルギー工学専攻教授。今までSiの酸化・拡散プロセス, 半導体デバイスの物理, 半導体シミュレーション技術, アナログ集積回路の研究に従事。工博。応用物理学会, 電気学会, IEEE各会員。

清水 由幸 (学生員)

平12阪大・工・電情卒。平14同大大学院博士前期課程了。現在、同大学院博士後期課程在学中。MOSFETの特性の研究に従事。