|              |                                                                                     |

|--------------|-------------------------------------------------------------------------------------|

| Title        | Adaptive Bias回路を用いたスイッチトキャパシタ回路用省電力演算増幅器                                            |

| Author(s)    | 井田, 司; 田中, 智之; 石原, 寛明 他                                                             |

| Citation     | 電子情報通信学会論文誌C. 2006, J89-C(10), p. 645-647                                           |

| Version Type | VoR                                                                                 |

| URL          | <a href="https://hdl.handle.net/11094/51700">https://hdl.handle.net/11094/51700</a> |

| rights       | copyright©2006 IEICE                                                                |

| Note         |                                                                                     |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

## ショートノート

## Adaptive Bias 回路を用いたスイッチトキャパシタ回路用省電力演算増幅器

井田 司<sup>a)</sup>(学生員)田中 智之<sup>†</sup>(学生員)石原 寛明<sup>†</sup>松岡 俊匡<sup>†</sup>(正員)谷口 研二<sup>†</sup>(正員)

Low Power-Consumption OP-Amp Using Adaptive Biasing for Switched Capacitor Circuit

Tsukasa IDA<sup>a)</sup>, Tomoyuki TANAKA<sup>†</sup>, Student Members,

Hiroaki ISHIHARA<sup>†</sup>, Nonmember, Toshimasa MATSUOKA<sup>†</sup>,

and Kenji TANIGUCHI<sup>†</sup>, Members<sup>a)</sup> 大阪大学大学院工学研究科, 吹田市Graduate School of Engineering, Osaka University, 2-1

Yamadaoka Suita-shi, 565-0871 Japan

a) E-mail: ida@si.eei.eng.osaka-u.ac.jp

あらまし 弱反転動作による省電力スイッチトキャパシタ用オペアンプを提案する。バイアス電流を入力振幅に応じて動的に変更することで動作速度を向上させた。スイッチトキャパシタ回路のシミュレーションにおいて通常のオペアンプと比較してセトリング時間が約10倍改善することを確認した。

**キーワード** CMOS アナログ回路, 弱反転領域動作, スイッチトキャパシタ回路, オペアンプ

## 1. まえがき

現在, 携帯機器に使用される回路は電池による長時間動作を実現するため, 省電力化が要求されている。省電力化の手法の一つとして, CMOS アナログ回路では素子を弱反転領域で駆動させて大幅に消費電力を減少させることが可能となる[1], [2]。しかし, 消費電流の減少はオペアンプにおいて, 帯域の減少, スルーレートの悪化を招き, 所望の特性を得ることが困難となる。そこで, 本論文では MOS トランジスタの弱反転領域で動作するオペアンプのスルーレート特性を改善するための Adaptive Bias 回路を提案し, その動作をシミュレーションにおいて確認した。

## 2. Bias 調整の方法

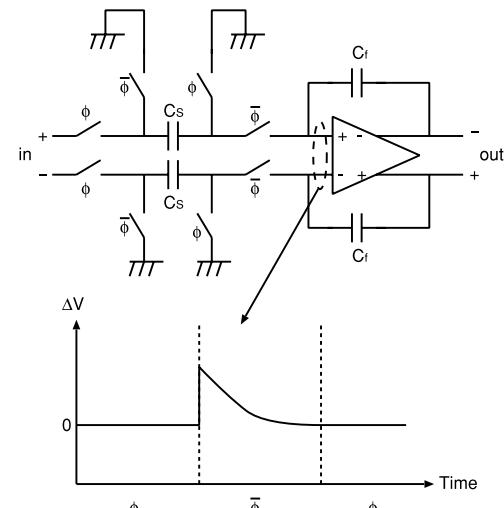

図 1 にスイッチトキャパシタ回路を示す。この図において, オペアンプの入力  $in_p$ ,  $in_n$  はクロックの相が  $\phi$  のとき, 同電位である。クロックの相が  $\bar{\phi}$  に変化したとき, サンプリングキャパシタ  $C_s$  に蓄積された電荷が  $C_f$  に移動する。このとき, オペアンプの入力は図 1 に示すように,  $\bar{\phi}$  になった瞬間に電圧が発生し, 次第に仮想接地へと収束する。仮想接地になるまでの速度はオペアンプのスルーレートと帯域に依存し, 入力された電荷が大きい場合には, スルーレートの影響

図 1 スイッチトキャパシタ回路とスイッチ切換時の入力端子電圧の過渡特性

Fig. 1 Schematic of switched-capacitor circuit and transient characteristics of input voltage.

が, また小さい場合には帯域が支配的となる。そこで, オペアンプの入力をモニタリングし, 入力振幅に対応した電流をアンプに流して, スルーレートを改善し, 低消費電力のスイッチトキャパシタ回路を実現することが可能となる。

## 3. 提案回路

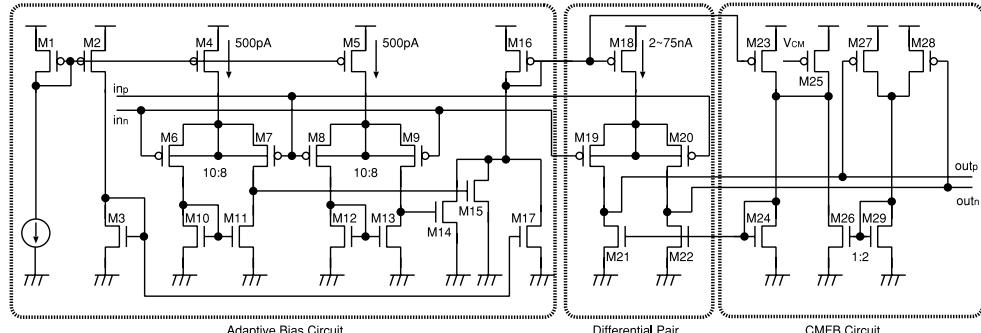

図 2 にオペアンプの回路図を示す。オペアンプは差動対, CMFB (Common Mode FeedBack) 回路, Adaptive Bias 回路から構成される。シミュレーションには  $0.25 \mu\text{m}$  CMOS プロセスのデバイスマネージャーを用いた。弱反転領域動作で消費電力を抑えるために, 電源電圧は  $500 \text{ mV}$  として設計を行った。

## 3.1 差動対

差動対はカスコード等の特殊な構成を一切用いず, 通常の差動対で設計を行った。その理由として, 低電源電圧が挙げられる。通常, MOSFET を弱反転領域の飽和特性で動作させるには, ドレーン・ソース電圧を  $75 \text{ mV}$  以上確保すればよい[3]ことが知られている。そこで, 広い出力レンジを確保するため, 図 2 の Differential Pair 構成を採用した。

テール電流源  $2 \text{ nA}$ , 負荷容量  $3 \text{ pF}$  のとき, 設計した差動対のゲインは  $36 \text{ dB}$ , 位相余裕は  $92^\circ$ , ユニティゲイン周波数は  $0.6 \text{ kHz}$  となった。

## 3.2 Adaptive Bias 回路

Adaptive Bias 回路は入力振幅の絶対値をもとに電

図 2 適応型バイアス回路、入力差動対、コモンモードフィードバック回路で構成されたオペアンプの回路図

Fig. 2 Schematic of proposed OP-amp composed of adaptive bias circuit, differential pair, and CMFB circuit.

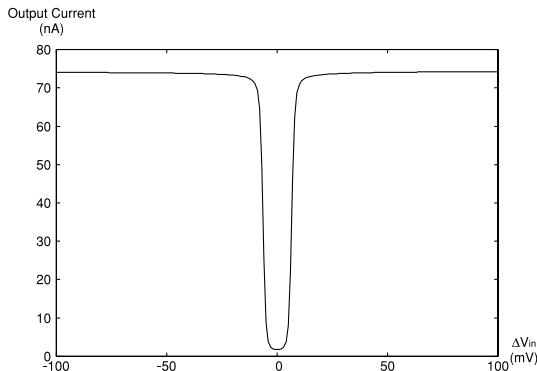

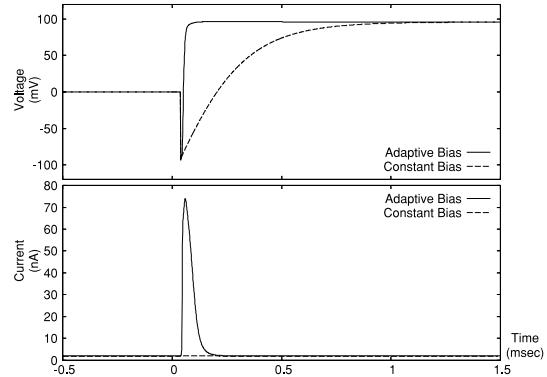

図 3 Adaptive Bias 回路のシミュレーション結果

Fig. 3 Simulation result of Adaptive bias circuit.

流の制御を行う。図 2 の M6–M9 で入力振幅をモニタし、M14, M15 で電流に変換する。M14, M15 のサイズを調整してオペアンプの負荷よりも十分に軽くすることで、モニタリング用差動対をスイッチトキャパシタ回路の帯域よりも十分に高い周波数まで動作させることができるとなる。また、入力振幅の感度を調整するため、モニタリング回路の M6–M7 と M8–M9 の二組の差動対の MOS トランジスタのサイズ比を変更し、故意にサイズオフセットをもたせ、入力振幅が小さいときには定電流バイアスのオペアンプとして動作するようにした。

回路シミュレーションを用いて横軸に差動入力電圧、縦軸に Adaptive Bias 回路の出力電流をプロットしたグラフを図 3 に示す。この図より、入力振幅に応じて、2~75 nA の範囲で変化することが確認できる。

### 3.3 CMFB 回路

通常、スイッチトキャパシタ回路では離散時間型の CMFB 回路 [4] が多く用いられるが、バイアス電流が

動的に変化する Adaptive Bias には、連続時間型の CMFB 回路を使用した。しかし、差動対構成の連続時間型 CMFB 回路 [5] は出力可能範囲が狭い。また、線形領域で MOS トランジスタを動作させる手法 [6] はバイアス電流が変化すると動作点も変化するため、常に線形領域で動作させることは困難である。そこで、図 2 に示すカレントミラーを用いて動的にバイアスを変化させる CMFB 回路を提案する。すべての MOS トランジスタは弱反転領域の飽和特性で動作する。通常、強反転動作を前提とした CMFB 回路では

$$V(out_p) + V(out_n) - 2V_{CM} = 0 \quad (1)$$

となるようにバイアス電流を調整するが、本回路ではコモンモード電圧の誤差の検出を電流の加減算によって実現する。M24 に流れるドレーン電流  $I_{D,M24}$  は

$$I_{D,M24} = I_{D,M23} + I_{D,M25} - \frac{1}{2}(I_{D,M27} + I_{D,M28}) \quad (2)$$

と表せる。入力振幅と  $V_{CM}$  の差が十分に小さいとき、飽和領域の弱反転動作 MOSFET のドレーン電流は

$$I_D = I_{S0} \exp\left(\frac{V_{GS} - V_{th}}{nv_t}\right) \quad (3)$$

で表される。 $I_{S0}, n$  は定数、 $v_t$  は熱電圧、 $V_{th}$  はしきい値電圧である。式 (3) をテイラー展開し、オーダーを考慮して近似すると

$$I_{D,M24} = I_{D,M23} + \frac{I_{S0}}{nv_t} (V_{av} - V_{CM}) \exp\left(\frac{V_{av} - V_{th}}{nv_t}\right) \quad (4)$$

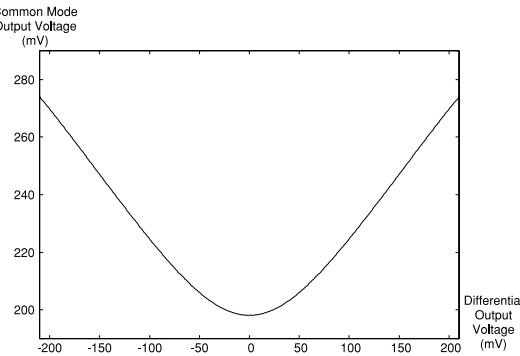

図 4 オペアンプの差動出力-同相出力特性

Fig. 4 Common mode output voltage characteristics versus differential output voltage.

と表せる。ただし、 $V_{av} = \frac{V(out_p) + V(out_n)}{2}$  である。第 2 項がコモンモード電圧の誤差の補正項となり、 $V_{av} - V_{CM}$  が 0 となるように  $I_{D,M24}$  が調整され、CMFB 回路が動作する。

図 2 に示した回路構成で  $V_{CM} = 0.2\text{ V}$  のときの差動出力電圧と同相出力電圧の関係をプロットしたグラフを図 4 に示す。この図より、同相出力電圧が  $V_{CM}$  付近となり、CMFB 回路が正常に動作することが確認できる。また、差動出力電圧が増加するにつれ、同相出力電圧が設定値から乖離する原因是式 (4) の近似による誤差が増加することによる。

#### 4. むすび

Adaptive Bias 回路を使用したオペアンプと定電流バイアスを使用したオペアンプのそれぞれにおいて、表 1 に示す条件で回路シミュレーションを用いて理想スイッチを用いたスイッチトキャパシタ回路のシミュレーションを行った。図 5 に出力波形と差動対のテール電流値を示す。この図より、Adaptive Bias を使用し、スルーレートを改善することで、より高い周波数でスイッチトキャパシタ回路が動作することが分かる。出力が最終値の 99% になるまでのセトリング時間は Adaptive Bias 回路を用いた場合と用いない場合でそれぞれ、 $100.0\text{ }\mu\text{s}$ 、 $1074\text{ }\mu\text{s}$  となり、Adaptive Bias 回路を導入することで、セトリング時間が約 10 倍改善された。また、消費電力は定電流バイアスのときに  $4\text{ nW}$ 、Adaptive Bias 回路を使用した場合、 $5\text{ nW}$  であり、20% 程度の電力増加で Adaptive Bias を実現できた。

謝辞 本研究は東京大学大規模集積システム設計教育研究センターを通じ、シノプシス株式会社の協力で

表 1 シミュレーション条件

Table 1 Simulation condition.

|                 |       |

|-----------------|-------|

| 電源電圧            | 0.5 V |

| コモンモード電圧        | 0.2 V |

| 差動信号振幅          | 0.1 V |

| サンプリングキャパシタ容量   | 5 pF  |

| フィードバックキャパシタ容量  | 5 pF  |

| 定常状態での差動対のテール電流 | 2 nA  |

図 5 出力波形と消費電流のシミュレーション結果

Fig. 5 Simulation results of output voltage and current waveforms.

行われたものである。

#### 文 献

- [1] E. Vittoz and J. Fellrath, "CMOS analog integrated circuits based on weak inversion operation," IEEE J. Solid-State Circuits, vol.SC-12, no.3, pp.224–231, 1977.

- [2] R.R. Harrison and C. Charles, "A low-power low-noise CMOS amplifier for neural recording applications," IEEE J. Solid-State Circuits, vol.38, no.6, pp.958–965, 2003.

- [3] D.A. Johns and K. Martin, Analog integrated circuit design, New York, 1996.

- [4] D. Senderowicz, S.F. Dreyer, J.H. Huggins, C.F. Rahim, and C.A. Laber, "A family of differential NMOS analog circuits for a PCM codec filter chip," IEEE J. Solid-State Circuits, vol.SC-17, no.6, pp.1014–1023, 1982.

- [5] T. Kwan and K. Martin, "An adaptive analog continuous-time CMOS biquadratic filter," IEEE J. Solid-State Circuits, vol.26, no.6, pp.859–867, 1991.

- [6] T.C. Choi, R.T. KaneShiro, R.W. Brodersen, P.R. Gray, W.B. Jett, and M. Wilcox, "High-frequency CMOS switched-capacitor filters for communications application," IEEE J. Solid-State Circuits, vol.SC-18, no.6, pp.652–664, 1983.

(平成 18 年 1 月 30 日受付, 5 月 2 日再受付)