|              |                                                                                     |

|--------------|-------------------------------------------------------------------------------------|

| Title        | 短距離無線通信用電圧制御CMOS移相発振回路に関する研究                                                        |

| Author(s)    | 中村, 光男; 松岡, 俊匡; 谷口, 研二                                                              |

| Citation     | 電子情報通信学会論文誌C. 2002, J85-C(6), p. 449-454                                            |

| Version Type | VoR                                                                                 |

| URL          | <a href="https://hdl.handle.net/11094/51709">https://hdl.handle.net/11094/51709</a> |

| rights       | copyright©2002 IEICE                                                                |

| Note         |                                                                                     |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

## 短距離無線通信用電圧制御CMOS移相発振回路に関する研究

中村 光男<sup>†a)</sup> 松岡 俊匡<sup>†</sup> 谷口 研二<sup>†</sup>

Voltage Controlled CMOS Phase-Shift Oscillator for Short-Range Wireless Communication

Mitsuo NAKAMURA<sup>†a)</sup>, Toshimasa MATSUOKA<sup>†</sup>, and Kenji TANIGUCHI<sup>†</sup>

あらまし チップ間無線通信インターフェース等の短距離無線通信への応用を目的としてオンチップインダクタを用いずに、簡単な回路構成で正弦波信号を出力する電圧制御CMOS移相発振回路を提案する。0.6  $\mu$ m CMOSプロセスで試作したCMOS移相発振回路の発振周波数は600 MHz程度である。その他、高調波、発振周波数のチューニングレンジ、位相雑音等の項目について測定した結果、短距離無線通信に電圧制御CMOS移相発振回路が使用でき、回路規模の大幅な小型化が可能であることがわかった。

キーワード 短距離無線通信、RF回路、電圧制御発振器、CMOS、位相雑音

### 1. まえがき

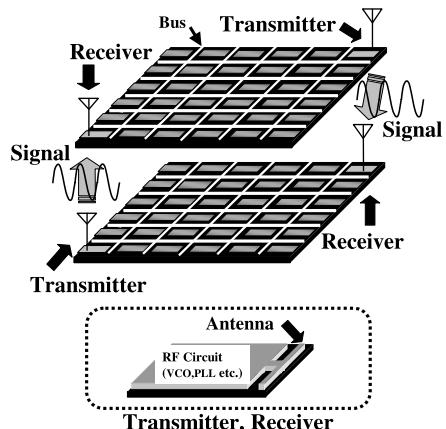

集積回路技術の進歩により、多数の電子回路を一つのシリコンチップに集積したシステムLSIが実現する時代になってきた。しかし、設計されるシステムLSIの規模が大きくなり、情報処理の複雑さが増すと、チップの内外での配線数が必然的に増加する。このような多入出力・多層配線を前提とした将来のLSIでは、(1)プロセス工程の増加によるチップコストの増大、(2)プロセス歩留りの低下、(3)配線駆動用電力の増大、(4)プリント基板への実装コストの増大などの問題が表面化すると予想される。このような問題を解決する手段の一つとして、我々は無線通信を用いてチップ間でデータ転送を行うインターフェース回路の研究開発を行っている。空間を1本のバスラインとしてとらえ無線データ通信を介してLSIチップの3次元的な実装を行うことにより、大規模システムの小型実装の実現が期待される(図1)。

このようなチップ間無線データ通信インターフェース回路においては、その回路規模がコアの回路ブロックに比べて極めて小型であることが求められる。無線通

図1 チップ間無線通信インターフェース概念図。3次元的にアンテナを通してデータ転送を行っている

Fig. 1 Concept of short-range wireless chip-to-chip communication interface. Data are transferred through the on-chip antenna.

信システムにおいて重要な回路ブロックの一つとして、位相雑音が小さいLC発振回路が多用される[1]。しかし、オンチップインダクタを用いたLC発振回路を用いると、占有面積が大きくなる欠点がある。チップ間無線データ通信インターフェース回路では、小面積化が要求される一方、短距離無線通信のため、携帯電話等に比べて、位相雑音等の仕様をより軽減することが可能となる。以上のことから、今回、チップ間無線データ

<sup>†</sup> 大阪大学大学院工学研究科電子情報エネルギー工学専攻、吹田市

Department of Electronics and Information Systems, Osaka

University, 2-1 Yamada-oka, Suita-shi, 565-0871 Japan

a) E-mail: nakamura@eie.eng.osaka-u.ac.jp

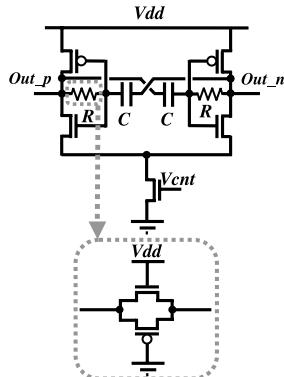

図2 電圧制御CMOS移相発振回路構成図。二つの出力から逆相信号が outputされる差動発振回路構成となっている

Fig. 2 Schematic of voltage-controlled differential CMOS phase-shift oscillator with output phase-shift of 180 degree.

タ通信インターフェース用に回路規模の小型化を目的とした電圧制御発振回路の試作、評価を行った。

## 2. 提案回路

高周波回路で正弦波を発生させる場合、オンチップインダクタを用いた発振回路がよく用いられている。しかしながら、この回路はオンチップインダクタが大きな面積を占有する。更に、インダクタと基板との間に大きな寄生容量を生じ、インダクタ自身が高い寄生抵抗をもつため、Q値の劣化の問題が存在する[2]。そこで、インダクタを用いずにキャパシタとMOSFETのみで正弦波発振を行う図2に示す電圧制御CMOS移相発振回路を提案する。

### 2.1 発振原理

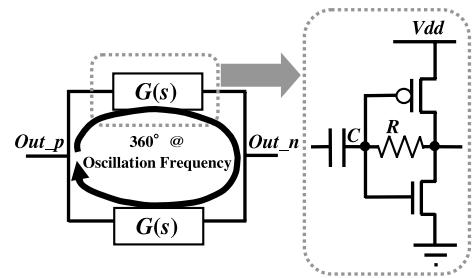

図2に示す電圧制御CMOS移相発振回路では、CMOS増幅回路[3]を2段つなげることにより図3に示す閉ループが形成されている。ある特定の周波数でのみ、入力された信号との位相差が360度となる信号がoutputされ、ゲインが1以上であれば、発振条件を満たす。

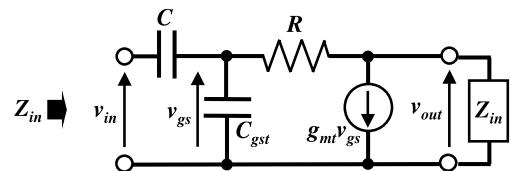

以下、この発振回路を解析する。利得段1段の回路に對して図4の等価回路を用いる。ここで、 $r_{ds} \gg 1/\omega C$ としており、 $C_{gst} = C_{gsn} + C_{gsp}$ 、 $g_{mt} = g_{mn} + g_{mp}$ である。この等価回路の入力インピーダンスは、近似的に次のようになる。

$$Z_{in} = \frac{s(C + C_{gst}) + g_{mt}}{sC(sC_{gst} + g_{mt})} \quad (1)$$

図3 電圧制御CMOS移相発振回路概念図。伝達関数  $G(s)$  で表される回路2段により閉ループを構成している

Fig. 3 Conceptual schematic of CMOS phase-shift VCO with closed-loop composed of two  $G(s)$  transfer functions.

図4 閉ループ1段当たりの等価回路。 $Z_{in}$  は入力インピーダンス、 $C_{gst} = C_{gsn} + C_{gsp}$ 、 $g_{mt} = g_{mn} + g_{mp}$  である

Fig. 4 Equivalent circuit of  $G(s)$ .  $Z_{in}$  is input impedance.  $C_{gst} = C_{gsn} + C_{gsp}$ ,  $g_{mt} = g_{mn} + g_{mp}$ .

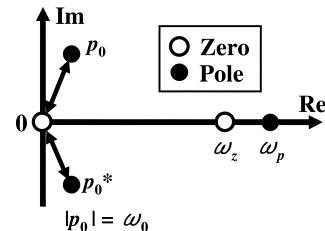

図5 伝達関数  $G(s)$  の極、零点の配置

Fig. 5 Coordinates of  $G(s)$ 's poles and zero.

閉ループ構成での利得段1段の伝達関数を求める場合、図4の回路の出力ポートに  $Z_{in}$  を接続して計算する。その結果、閉ループ構成での利得段1段の伝達関数は、次式で表される。

$$G(s) = \frac{v_{out}(s)}{v_{in}(s)} = \frac{-K(s + \omega_z)s}{[s^2 + (\omega_0/Q)s + \omega_0^2](s + \omega_p)} \quad (2)$$

次に、式(2)の伝達関数の零点や極を図5のような配置にする。このとき、式(2)の各パラメータは、各々

図 6 零点と極の配置から、利得段 1 段当たりの伝達関数  $G(s)$  について予想されるボード線図のイメージ図

Fig. 6 Bode plot of  $G(s)$  function derived from  $G(s)$ 's poles and zero.

以下の式で表される。

$$\omega_0 \approx \frac{\omega_T}{\sqrt{1 + (3 + g_{mt}R)\eta + (1 + g_{mt}R)\eta^2}} \quad (3)$$

$$\omega_z \approx \frac{\omega_T}{1 + \eta} \quad (4)$$

$$\omega_p \approx \frac{1 + (3 + g_{mt}R)\eta + (1 + g_{mt}R)\eta^2}{RC_{gst}\eta(1 + \eta)} \quad (5)$$

$$K = \frac{g_{mt}R - 1}{RC_{gst}} > 0 \quad (6)$$

$$Q \approx [1 + (3 + g_{mt}R)\eta + (1 + g_{mt}R)\eta^2]^{3/2} / [2 + (9 + g_{mt}R)\eta + 5(2 + g_{mt}R)\eta^2 + 3(1 + g_{mt}R)\eta^3] \quad (7)$$

ここで、 $\eta = C/C_{gst}$ 、 $\omega_T = g_{mt}/C_{gst}$  である。 $\omega_T$  は遮断周波数を表している。このような零点や極の配置では、式 (2) の伝達関数は、図 6 に示すボード線図で表される。このボード線図から、 $\omega_0$  で位相差が 180 度になり、ゲインがピーク値をとる。利得段 2 段をカスケード接続すると、 $\omega_0$  で位相差が 360 度になる。したがって、ゲインのピーク値が 1 より大きくなれば  $\omega_0$  で発振条件を満たす。このように、電圧制御 CMOS 移相発振回路では、マルチバイブレータ等の  $RC$  の時定数で周波数が決まる発振回路と異なり、ループゲインの調整により発振周波数の選択を行っている。

式 (3) を見てわかるように、 $g_{mt}$  により、発振周波数  $\omega_0$  をチューニングすることが可能である。飽和領域では、 $g_{mt}$  は  $\sqrt{I_d}$  に比例するため、図 2 の制御電圧  $V_{cnt}$  で  $I_d$  を調節して発振周波数  $\omega_0$  のチューニングを行っている。

## 2.2 設計指針

発振周波数  $\omega_0$  でのゲインは、近似的に次のようになる。

$$\begin{aligned} |G(j\omega_0)| &\approx KQ/\omega_0 \\ &\approx (\omega_T/\omega_0)^4 / [2 + (9 + g_{mt}R)\eta \\ &\quad + 5g_{mt}R\eta^2 + 3g_{mt}R\eta^3] \end{aligned} \quad (8)$$

最後の式では、 $g_{mt}R \gg 1$  として近似している。また、 $\omega_T$  は MOSFET のゲート幅には依存せず、ゲート長にのみ依存するため、製造プロセスでほぼ決まる。発振周波数  $\omega_0$  が与えられると、発振周波数でのゲイン  $|G(j\omega_0)|$  が 1 以上になる  $g_{mt}R$  及び  $\eta$  の範囲が決定される。今回の設計では、 $g_{mt}R \sim 10$  及び  $\eta \sim 1$  としている。この場合、式 (4), (5) より、 $\omega_p \approx \omega_T$ 、 $\omega_z \approx \omega_T/2$  となり、 $\omega_p$ 、 $\omega_z$  ともに遮断周波数に近い値となる。

次に、抵抗  $R$  について検討する。抵抗  $R$  をポリシリコンで実現した場合、抵抗値が大きくばらつき [4]、発振回路の特性がばらつく。式 (3) からわかるように、 $\omega_0$  が  $g_{mt}R$  によって記述されているため、抵抗  $R$  をトランスマッシュゲート [5] で実現することにより、ゲート酸化膜厚や移動度などのばらつきに対して、 $g_{mt}R$  の変動を抑制することができる。このため、今回、抵抗  $R$  をトランスマッシュゲートで実現した。

## 2.3 シミュレーション

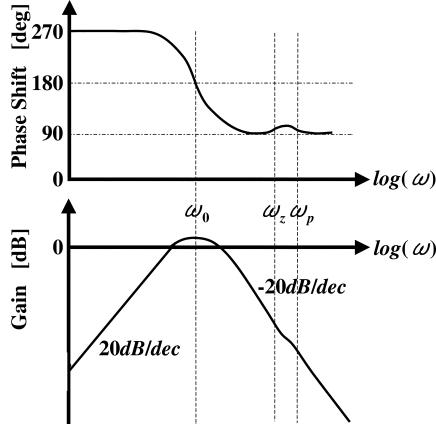

図 4 の回路を 2 段で構成したものの伝達関数について、回路シミュレーションを行った結果、図 7 に示す位相変化及びゲインの周波数特性が得られた。この結果、 $\omega_0$  付近で、

$$\angle G(\omega)^2 = 360^\circ, |G(\omega)^2| > 1$$

なる発振条件を満たすことが確かめられる。

## 3. 測定結果

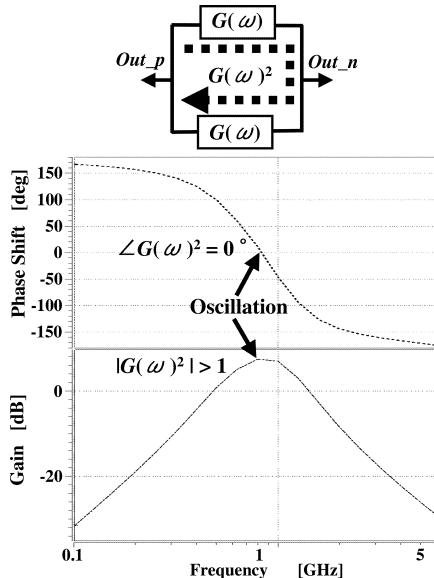

2 層ポリシリコン・3 層メタル  $0.6 \mu\text{m}$  CMOS プロセスを用いて、提案する電圧制御 CMOS 移相発振回路を設計、試作した。

### 3.1 回路面積

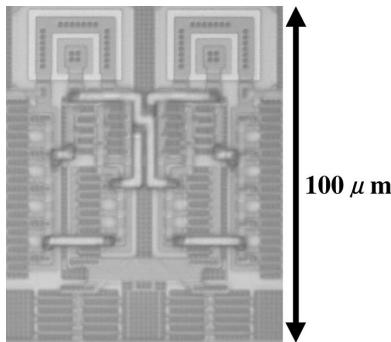

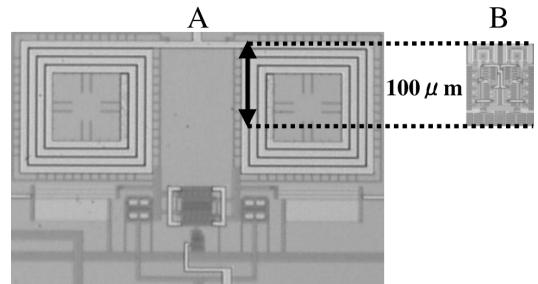

図 8 に、試作した CMOS 移相発振回路のチップ写真を示す。逆相の出力信号を得られるように、軸対称

図 7  $G(\omega)$  を 2 段カスケード接続した発振回路のボード線図

Fig. 7 Simulated bode plot of  $G(\omega)^2$ .

図 8 電圧制御 CMOS 移相発振回路チップ写真

Fig. 8 Chip photograph of fabricated CMOS phase-shift VCO.

性を考慮したレイアウトを行っている。参考のために、LC 発振回路のチップ写真と CMOS 移相発振回路を同じ縮尺にして大きさを比較したものを図 9 に示す。LC 発振回路は、 $0.35 \mu\text{m}$  CMOS プロセスで試作している。この写真を見てわかるように、CMOS 移相発振回路は LC 発振回路の  $1/10$  程度の面積に収まり、大幅に小型化されていることがわかる。図 9 に示す LC 発振回路が  $0.35 \mu\text{m}$  プロセスであるのに対して、CMOS 移相発振回路が  $0.6 \mu\text{m}$  プロセスで面積が  $1/10$  であることも考慮すると、同じルールのプロセスでは更に小さくなる。従来の LC 発振回路では、その回路面積がインダクタによってほとんど占有されることを考える

図 9 LC 発振回路チップ写真と CMOS 移相発振回路のチップサイズ比較。A:LC 発振回路、B:CMOS 移相発振回路

Fig. 9 Comparison of chip sizes, LC VCO and CMOS phase-shift VCO. A:LC VCO, B:CMOS phase-shift VCO.

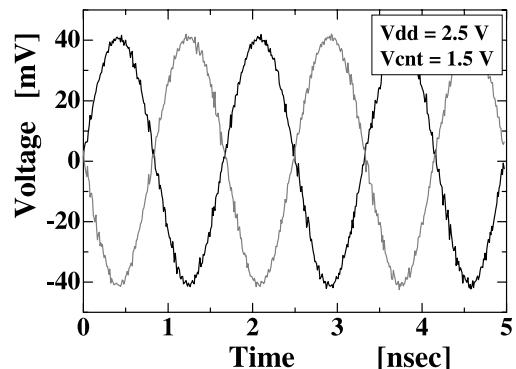

図 10 電圧制御 CMOS 移相発振回路における時間波形の実測値。バッファ回路を通して得た出力をオシロスコープで測定した。約 600 MHz で発振している

Fig. 10 Wave forms of CMOS phase-shift VCO with oscillation frequency of about 600 MHz measured using an oscilloscope.

と、インダクタを用いず、簡便な回路構成で高周波インターフェース回路を作り上げることはインターフェース回路の小型化に向けて重要なかぎとなる。

### 3.2 発振周波数及び高調波

CMOS 移相発振回路のバッファ回路を通して得られた時間波形をオシロスコープで測定した結果を図 10 に示す。二つの出力ポートから互いに逆相の出力信号が得られ、600 MHz 程度で発振している。正相と逆相波形の間では、8 度以下の範囲内で差動性が確認できる。

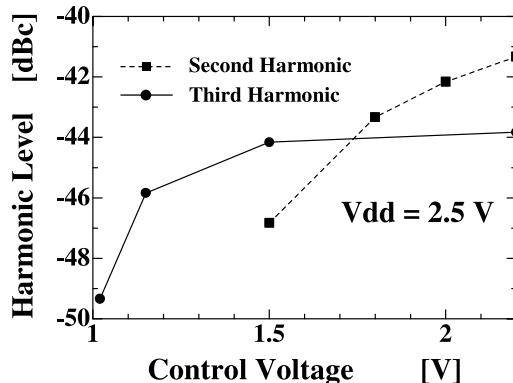

また、2 次と 3 次の高調波を図 11 に示す。制御電圧  $V_{cnt}$  を上げるとともに増加し、一定値に近づく様子がうかがえる。これは、グラウンドと発振部を結んでいる電流源回路の動作領域が制御電圧  $V_{cnt}$  を上げることにより飽和領域から外れていくためと考えられる。2

図 11 電圧制御 CMOS 移相発振回路における 2 次，3 次高調波の制御電圧依存性

Fig. 11 Harmonics/carrier vs. control voltage of CMOS phase-shift VCO.

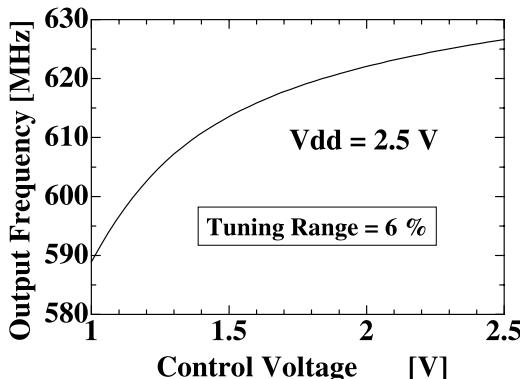

図 12 電圧制御 CMOS 移相発振回路における発振周波数の制御電圧依存性

Fig. 12 Output frequency vs. control voltage of CMOS phase-shift VCO with tuning range of 6%.

次高調波は出力の差動成分をとることにより低減可能である。

### 3.3 発振周波数のチューニングレンジ

電圧制御 CMOS 移相発振回路における発振周波数の制御電圧依存性を図 12 に示す。制御電圧に対して、CMOS 移相発振回路の周波数は約 6% 变化している。なお、消費電流は約 2 mA である。

### 3.4 位相雑音

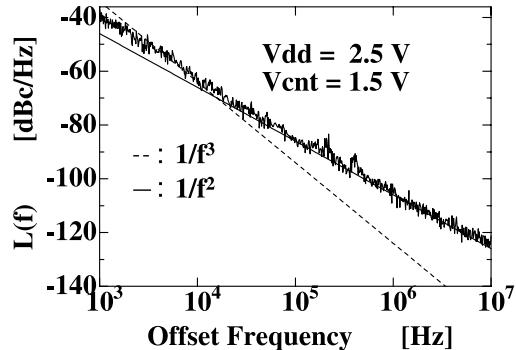

位相雑音測定には、VCO/PLL シグナルアナライザ Agilent 4352B を使用した。位相雑音の測定結果を図 13 に示す。ここで、 $1/f^2$  と  $1/f^3$  によるフィッティングを行っている。位相雑音の雑音源が熱雑音であれば  $L(f)$  は  $1/f^2$  に比例し、その雑音源が  $1/f$  雜音であれば  $L(f)$  は  $1/f^3$  に比例する [6]。CMOS 移相発振回路

図 13 CMOS 移相発振回路の位相雑音特性

Fig. 13 Phase noise characteristic of CMOS phase-shift VCO.

ではその位相雑音特性がほぼ  $1/f^2$  で決まっている。つまり、CMOS 移相発振回路では、 $1/f$  雜音に比べて熱雑音が支配的である。オフセット周波数 1 MHz における位相雑音が  $-105$  dBc/MHz であることは、チップ間インターフェースのような短距離無線通信という軽減された仕様の下では十分に適用可能であることを示している。ただし、式(3)から、抵抗を下げるに発振周波数が上るので、より高周波では熱雑音による位相雑音の影響が低減されることが期待される。

## 4. むすび

本論文では、高周波においてインダクタを用いず、かつ回路構成を簡便にすることにより、小型化が可能な電圧制御 CMOS 移相発振回路の提案を行った。また、実際の試作回路に対して発振周波数、高調波、チューニングレンジ、位相雑音等の測定及び評価を行った。その結果 CMOS 移相発振回路は、その性能においてインターフェースとしての短距離無線通信に用いる上で遜色なく、更に回路規模の大幅な小型化が可能となった。

謝辞 本チップ試作は東京大学大規模集積システム設計教育センターを通しローム(株)及び凸版印刷(株)の協力で行われたものである。また、本研究は日本学術振興会未来開拓学術研究推進事業の援助のもとで行われた。

## 文 献

- [1] A. Hajimiri and T. H. Lee, *The Design of Low Noise Oscillators*, Kluwer Academic Publishers, Boston Dordrecht London, 1999.

- [2] C. P. Yue and S. S. Wong, "On-chip spiral inductors with patterned ground shields for Si-based RF IC's," *IEEE J. Solid-State Circuits*, vol.33, no.5, pp.743-752, May 1998.

- [3] 原 央, 超 LSI 入門シリーズ⑤: MOS 集積回路の基礎, pp.145-147, 近代科学社, 東京, 1980.

- [4] A. Hastings, The Art of Analog Layout, pp.214-259, Prentice-Hall, Upper Saddle River, 2001.

- [5] R. J. Baker, H. W. Li, and D. E. Boyce, CMOS Circuit Design, Layout, and Simulation, pp.255-259, The Institute of Electrical and Electronics Engineers, New York, 1998.

- [6] U. L. Rohde, Microwave and Wireless Synthesizer: Theory and Design, John Wiley and Sons, New York, 1997.

(平成 13 年 6 月 27 日受付, 11 月 26 日再受付)

中村 光男 (学生員)

平9東北大・工・電子卒. 平11阪大大学院博士前期課程了. 現在, 同大学院工学研究科博士後期課程在学中. CMOS RF回路の研究に従事. IEEE会員.

松岡 俊匡 (正員)

平1阪大・工・電子卒. 平3同大大学院博士前期課程了. 平3シャープ(株)入社. 平11阪大大学院工学研究科電子情報エネルギー工学専攻リサーチ・アソシエイト(日本学術振興会研究員). 平12同大大学院工学研究科電子情報エネルギー工学専攻講師. CMOS RF回路の研究に従事. 工博. 応用物理学会, IEEE各会員.

谷口 研二 (正員)

昭46阪大・工・電子卒. 昭48同大大学院修士課程了. 昭50東芝(株)入社. 昭57より1年間マサチューセッツ工科大学客員研究員. 昭61阪大工学部電子工学科助教授. 平8同大大学院工学研究科電子情報エネルギー工学専攻教授. 現在までSiの酸化・拡散プロセス, 半導体デバイスの物理, 半導体シミュレーション技術, アナログ集積回路の研究に従事. 工博. 応用物理学会, 電気学会, IEEE各会員.