| Title        | CMOS Front-end Circuits of Dual-band GPS<br>Receiver                |

|--------------|---------------------------------------------------------------------|

| Author(s)    | Utsurogi, Yoshihiro; Haruoka, Masaki; Matsuoka,<br>Toshimasa et al. |

| Citation     | IEICE Transactions on Electronics. 2005, E88-<br>C(6), p. 1275-1279 |

| Version Type | VoR                                                                 |

| URL          | https://hdl.handle.net/11094/51717                                  |

| rights       | copyright©2005 IEICE                                                |

| Note         |                                                                     |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

# **CMOS Front-End Circuits of Dual-Band GPS Receiver**

Yoshihiro UTSUROGI<sup>†a)</sup>, Nonmember, Masaki HARUOKA<sup>†,††</sup>, Toshimasa MATSUOKA<sup>†</sup>, and Kenji TANIGUCHI<sup>†</sup>, Members

**SUMMARY** A RF front-end chip for a dual-band Global Positioning System (GPS) receiver for L1 and L2 bands is designed using  $0.25 \,\mu\text{m}$ CMOS technology. All function blocks of the GPS front-end are integrated onto one chip. The low noise amplifier has input matching over a wide frequency range to handle the L1 and L2 bands. This receiver uses a dualband image-reject mixer with the quadrature mixer sharing a transconductor stage. This configuration enables the RF blocks to be shared with the L1 and L2 bands. The receiver has a chip area of  $3.16 \,\text{mm} \times 3.16 \,\text{mm}$ , and consumes  $35 \,\text{mA}$  at  $2.5 \,\text{V}$ .

key words: dual-band GPS receiver, L1/L2, LNA, image-reject mixer, image-rejection ratio (IMRR)

## 1. Introduction

The Global Positioning System (GPS) has been widely used for applications which require position information such as car navigation systems and cellular phones. Although it was originally only a satellite-based survey system of global time based on atomic clocks, it is becoming important as an infrastructure which offers globally precise positioning and time information. A GPS satellite sends RF signals in two frequency bands, the L1 and L2 bands. The L1 (1.58 GHz) band carries the P code, which is limited to military use, together with the civil C/A-code, while the L2 (1.23 GHz) band is for military use only. However, launch of a satellite that will provide the C/A code for both the L1 and L2 bands is scheduled in the near future. Such a policy of GPS modernization gives rise to a new demand for simultaneous L1/L2 dual-band receivability, which can realize more precise positioning.

To meet such demand, we designed the front-end circuits of a dual-band GPS receiver using  $0.25 \,\mu$ m CMOS technology, which can receive the L1 and L2 bands simultaneously. The receiver uses a dual-band image-reject mixer based on the Hartley architecture [1], which can handle two frequency bands and outputs each demodulated signal. The designed receiver shares a quadrature mixer for down-conversion of L1 and L2 signals, which is useful for reduction of power consumption and occupied area.

#### 2. Receiver Architecture

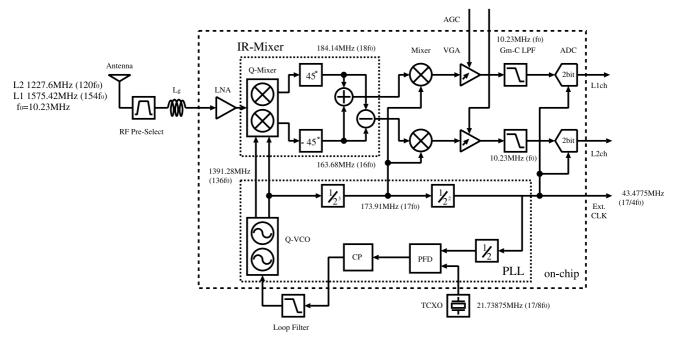

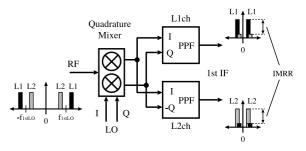

Figure 1 shows the block diagram of the designed front-end chip of the L1/L2 dual-band GPS receiver. All functional blocks for the GPS front-end circuits are integrated onto one chip. The down-converter is a double conversion system, consisting of a low noise amplifier (LNA), a Hartley-type image-reject mixer, a second mixer, and IF blocks including a variable gain amplifier (VGA), a Gm-C low-pass filter and a two-bit A/D converter. We used identical IF blocks for the L1 and L2 channels. The PLL synthesizer consists of a quadrature voltage-controlled oscillator (Q-VCO), frequency dividers, a phase frequency detector (PFD), a charge pump (CP), and a off-chip PLL loop filter.

The L1/L2 GPS signals from the external antenna are fed into the LNA, which handles the dual-band as described in Sect. 2.1. The first LO frequency is assigned to a position near the middle of the L1 and L2 bands, so that each of the bands becomes a complementary image of the other band. Thus, the image-reject (IR) mixer down-converts the L1/L2 signals to the first IF frequency signals [2]–[4]. The analog adder and subtracter in the IR mixer separate the L1/L2 signals. The IR mixer has a high image rejection ratio (IMRR), even without an external image-reject filter. The amplitude error of the first LO signals primarily deteriorates the IMRR in this architecture. Note that the Weaver architecture used in our previous works [2], [3] has additional IMRR deterioration caused by phase error in the second LO signals.

Moreover, the second mixer down-converts each of the separated signals to a second IF signal. The VGA in the IF blocks adjusts the voltage swing within a given range through the external auto gain control (AGC) loop, and the subsequent Gm-C low-pass filter eliminates out-of-band signals from the IF signal to avoid the occurrence of aliasing.

As shown in Fig. 1, this architecture can realize a dualband GPS receiver with both low power consumption and small occupied area, because of the use of a shared quadrature mixer for down-conversion of L1 and L2 signals.

The first and second LO frequencies are 1391 MHz and 174 MHz, respectively. In this frequency plan, the second IF frequency for the L1/L2 signals is 10.23 MHz. Such high a second IF frequency is suitable for both C/A and P codes, although only C/A code main lobe is of concern in consumer low-power GPS CMOS receivers [5], [6]. This is another promising feature for the wide application of this front-end

Manuscript received October 30, 2004.

Manuscript revised January 13, 2005.

<sup>&</sup>lt;sup>†</sup>The authors are with the Graduate School of Engineering, Osaka University, Suita-shi, 565-0871 Japan.

<sup>&</sup>lt;sup>††</sup>The author is with FURUNO ELECTRIC CO.,LTD., Nishinomiya-shi, 662-8580 Japan.

a) E-mail: utsurogi@qd.eie.eng.osaka-u.ac.jp

DOI: 10.1093/ietele/e88-c.6.1275

Fig. 1 Block diagram of dual-band GPS receiver ( $f_0$ : standard frequency of atomic clock in GPS satellite).

chip. The two-bit A/D converters sample the second IF signals at the rate of 43.4 MHz, which is greater than twice the upper bound of the second IF band (20.46 MHz).

## 2.1 LNA

Dual-band capability can be realized using an off-chip passive input matching network [7]. However, the L1/L2 dualband LNA does not necessarily require this technique, because the desired signals are relatively close in frequency, which is useful for reducing the number of passive components.

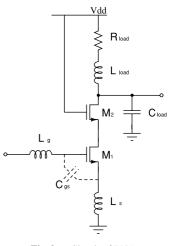

Figure 2 shows the LNA used for the dual-band GPS receiver, which is based on an inductively degenerated common-source amplifier. The input impedance  $Z_{in}$  of the LNA is given by

$$Z_{in} = \frac{g_{m1}}{C_{gs}} L_s + j \left[ \omega \left( L_s + L_g \right) - \frac{1}{\omega C_{gs}} \right],\tag{1}$$

where  $g_{m1}$  and  $C_{gs}$  are the transconductance and the gatesource capacitance of the transistor M<sub>1</sub>, respectively. Since the input reactance becomes zero at  $\omega_0 = 1/\sqrt{C_{gs}(L_s + L_g)}$ , the resistance at  $\omega_0$  must equal  $R_s$  for input impedance matching. The input Q factor is given by the following equation.

$$Q_{in} = \frac{1}{\omega_0 R_s C_{gs}} \tag{2}$$

The magnitude of the input reflection coefficient  $|S_{11}|$  is derived from Eqs. (1) and (2) as follows.

$$S_{11}| = \left| \frac{jQ_{in} \left( \frac{\omega}{\omega_0} - \frac{\omega_0}{\omega} \right)}{2 + jQ_{in} \left( \frac{\omega}{\omega_0} - \frac{\omega_0}{\omega} \right)} \right|$$

(3)

Fig. 2 Circuit of LNA.

$Q_{in}$  must satisfy the following condition to keep  $|S_{11}|$  below  $\Gamma$  [dB] in the frequency range from the L1 band to the L2 band.

$$Q_{in} < \frac{2 \times 10^{\frac{1}{20}}}{\sqrt{1 - 10^{\frac{\Gamma}{10}} \cdot \left|\frac{\omega_{1,2}}{\omega_0} - \frac{\omega_0}{\omega_{1,2}}\right|}}$$

(4)

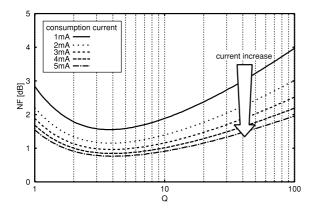

Here,  $\omega_{1,2}$  is the frequency of the L1 and L2 bands, and  $\omega_0$  is their geometric mean. Figure 3 shows the *NF* calculated with the following relation [8].

$$NF \approx 1 + \frac{\gamma}{\alpha} \frac{\chi}{Q_{in}} \left( \frac{\omega_0}{\omega_T} \right),$$

(5)

$$\chi = 1 + 2|c| \sqrt{\frac{\delta\alpha^2}{\kappa\gamma} + \frac{\delta\alpha^2}{\kappa\gamma} \left(1 + Q_{in}^2\right)} \tag{6}$$

**Fig.3** Analytical calculation of NF versus  $Q_{in}$  in LNA as a function of current consumption.

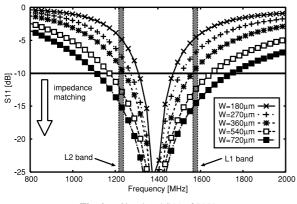

Fig. 4 Simulated S11 of LNA.

The  $Q_{in}$  of the dual-band LNA must be chosen so as to minimize NF under the constraint given by Eq. (4). Eq. (2) suggests that an increase in  $C_{gs}$  leads to a low  $Q_{in}$ , resulting in impedance matching over a wide frequency range [9]. Figure 4 shows the calculated  $|S_{11}|$  as a function of the gate width W of M<sub>1</sub> under the L1/L2 geometric mean  $f_0$  of 1391 MHz. It turns out that a value of W over 540  $\mu$ m results in  $|S_{11}| < -10$  dB in the frequency range from the L1 band to the L2 band. Thus, both low NF and dual-band capability are realized under the condition of input impedance matching. In addition, the quality factor of the load tank circuit is reduced by placing  $R_{load}$  in series with  $L_{load}$  as shown in Fig. 2.

## 2.2 Image-Reject Mixer and VCO

The Hartley-type image-reject mixer shown in Fig. 5 consists of a quadrature mixer and two poly phase filters [10] for L1 and L2 channels. The poly phase filter acts as either an adder or a subtracter depending on the phase of the input signal. As shown in Fig. 5, the I-phase of L1 inputs in the poly phase filters is in phase with that of the L2 channel, while the Q-phase inputs have the opposite phase to derive the L1 and L2 channels. In the output stage, for example, the desired and the image signals in the L1 channel are L1 and L2 signals, respectively. The IMRR is limited by the

Fig. 5 Block diagram of image-reject mixer.

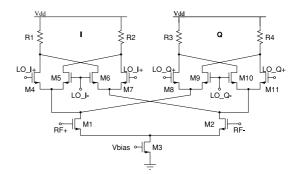

Fig. 6 Quadrature mixer with shared transconductor.

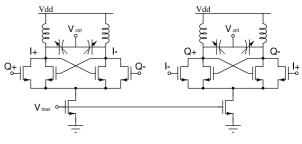

Fig. 7 Quadrature-coupled LC-VCO.

mismatch of the quadrature mixer, polyphase filter, and IQ accuracy of the LO signal.

Figure 6 shows the quadrature mixer with a shared transconductor for the I and Q phases [2], [3], [11]–[13]. Both the conversion gain and noise figure are improved by 3 dB at a given bias current due to the different switching characteristic compared with a conventional Gilbert mixer. Moreover, the quadrature mixer compensates the phase error of LO.

Figure 7 shows a quadrature-coupled-type LC VCO (Q-VCO) [14]–[17] for generating IQ LO signals. Although mismatch in physical layout and process variation in the load impedance deteriorates the IQ accuracy of the Q-VCO, the circuit simulation proves that an IMRR of over 30 dB is achievable even in the case of 5% mismatch of capacitances in the tank circuit at the output terminals.

# 1278

# 2.3 IF Blocks

A VGA composed of two-stage differential amplifiers is used to achieve gain control in the range over 60 dB, which compensates for temperature and process variations in the receiver. A second-order Gm-C low-pass filter [18] is used for band limitation of the second IF. In this design, the bias current of the transconductor is controlled using the band gap reference circuit, which reduces the temperature dependence of the transconductance. The circuit simulation confirmed that variation of the cut-off frequency is reduced within 1.2% over the temperature range of  $-45-85^{\circ}$ C, while the influence of process variation is approximately 9%.

## 3. Experimental Results

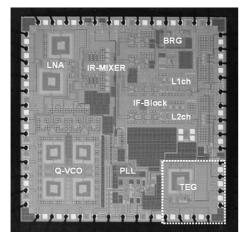

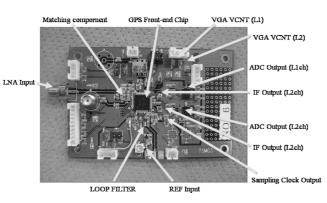

The front-end chip of a dual-band GPS receiver was fabricated using  $0.25 \,\mu\text{m}$  CMOS technology. A photograph of the chip is shown in Fig. 8. The chip area is  $3.16 \,\text{mm} \times 3.16 \,\text{mm}$ , and current consumption is  $35 \,\text{mA}$  at  $2.5 \,\text{V}$ . Figure 9 shows a printed circuit board using a 52-pin LCC package that was used to measure the RF characteristics of the chip.

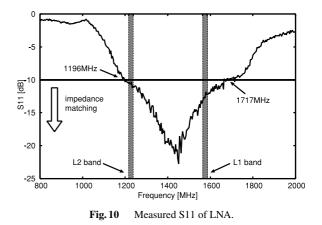

The measured S<sub>11</sub> of LNA with an off-chip surface-

mount-type inductor for input impedance matching is shown in Fig. 10. The return loss less than  $-10 \,\text{dB}$  is achieved in the L1/L2 frequency range. The LNA has a voltage gain of 25 dB for both L1 and L2 bands with a current of 5 mA. The noise figures are 4.0 dB and 5.8 dB for the L1 and L2 bands, respectively.

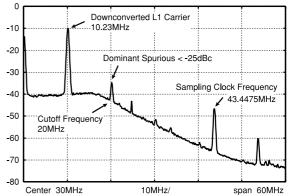

Figure 11 shows the second IF signal spectrum at the output terminal (L1ch) of the Gm-C low-pass-filter. The RF carrier signal (L1:1575.42 MHz) fed into the dual-band GPS front-end chip is down-converted to 10.23 MHz, where the A/D converter is turned off. The dominant spurious level is less than -25 dBc. Moreover, the noise floor observed in the figure reflects the frequency characteristic of receiver gain.

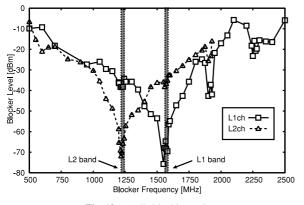

Figure 12 shows the blocking characteristics of the front-end chip at the receiver gain of 68.5 dB without an external filter. The blocking level is measured by evaluating the power of the interference CW signal which decreases the desired signal level by 1 dB at an RF input signal of -84 dBm. The blocking characteristics deteriorate for the blocker signal near 1900 MHz. This is attributed to the down-conversion of the third harmonics in the second LO signal to the second IF band. Figure 12 shows that the interference wave of the L1/L2 band does not affect either channel up to -40 dBm. This feature reflects the high IMRR (>

**Fig. 8** Photograph of fabricated chip.

Fig. 9 Printed circuit board for evaluation.

**Fig. 11** Spectrum of second IF signal at output terminal (L1ch) of Gm-C low-pass-filter.

Fig. 12 1 dB blocking point.

Table 1

Receiver performance summary.

| Supply Voltage               | 2.5 V                   |

|------------------------------|-------------------------|

| Supply Current               | 35 mA                   |

| Maximum Gain                 | 85 dB                   |

| VGA range                    | 65 dB                   |

| Input S11                    | < -10 dB                |

| $NF_{DSB}$ (L1ch / L2ch)     | 7 dB / 8 dB             |

| $P_{1\mathrm{dB}}$           | -35 dB@Min Gain         |

| Image Rejection Ratio        | 32 dB                   |

| Filter Cutoff Frequency      | 20 MHz                  |

| Filter Stopband Attenuation  | -30 dB@50 MHz           |

| Spurious Level @ADC OFF / ON | < -25  dBc / < -23  dBc |

| LO leakage to RF             | -63 dBm                 |

| PLL In-band Phase Noise      | < -77.7 dBc/Hz          |

| PLL spurs                    | -58 dBc                 |

| 1st LO Frequency             | 1391.28 MHz             |

| 2nd LO Frequency             | 173.91 MHz              |

| Baseband Frequency           | 10.23 MHz               |

| Sampling Clock Frequency     | 43.44775 MHz            |

|                              |                         |

#### 30 dB).

The measured characteristics of the GPS receiver frontend chip are summarized in Table 1.

## 4. Conclusions

The front-end chip of a dual-band GPS receiver for the L1 and L2 bands is designed using  $0.25 \,\mu\text{m}$  CMOS technology. The RF block is characterized with the first Hartley-type image-rejection mixer shared by the L1 and L2 channels. The proposed dual-band receiver shares a quadrature mixer for down-conversion of L1 and L2 signals, which is useful for reducing the power consumption and occupied area. The occupied area of the fabricated chip is  $3.16 \,\text{mm} \times 3.16 \,\text{mm}$ , and the current consumption is  $35 \,\text{mA}$  at  $2.5 \,\text{V}$ . The fabricated dual-band GPS front-end chip has a maximum voltage gain of 85 dB, a variable range of 65 dB, a NF of 8 dB, and a IMRR of 32 dB.

# Acknowledgments

Support for the present study is provided by the Japan Soci-

ety for the Promotion of Science (JSPS) research for future program. This work is also supported by the VLSI Design and Education Center (VDEC), the University of Tokyo, in collaboration with Cadence Design Systems, Inc. and Synopsys, Inc.

#### References

- [1] R. Hartley, "Modulation system," U.S. Patent 1 666 206, April 1928.

- [2] M. Haruoka, Y. Utsurogi, T. Matsuoka, and K. Taniguchi, "A dualband image-reject mixer for GPS with 64 dB image rejection," Proc. IEEE Topical Conference on Wireless Communication Technology, pp.168–169, Oct. 2003.

- [3] M. Haruoka, Y. Utsurogi, T. Matsuoka, and K. Taniguchi, "A study on the LO phase error compensation of GPS dual-band image-reject mixer," IEICE Trans. Electron. (Japanese Edition), vol.J86-C, no.11, pp.1177–1183, Nov. 2003.

- [4] S. Wu and B. Razavi, "A 900 MHz/1.8 GHz CMOS receiver for dual band applications," Proc. Int. Solid-State Circuits Conf., pp.124– 125, Feb. 1998.

- [5] D.K. Shaeffer, A.R. Shahani, S.S. Mohan, H. Samavati, H.R. Rategh, M. del M. Hershenson, M. Xu, P. Yue, D.J. Eddleman, and T.H. Lee, "A 115-mW, 0.5-μm CMOS GPS receiver with wide dynamic-range active filters," IEEE J. Solid-State Circuits, vol.33, no.12, pp.2219–2231, Dec. 1998.

- [6] T. Kadoyama, N. Suzuki, N. Sasho, H. Iizuka, I. Nagase, H. Usukubo, and M. Katakura, "A complete single-chip GPS receiver with 1.6-V 24-mW radio in 0.18-μm CMOS," IEEE J. Solid-State Circuits, vol.39, no.4, pp.562–568, April 2004.

- [7] H. Hashemi and A. Hajimiri, "Concurrent multiband low-noise amplifiers—Theory, design, and applications," IEEE Trans. Microw. Theory Tech., vol.50, no.1, pp.288–301, Jan. 2002.

- [8] D.K. Shaeffer and T.H. Lee, Low-Power CMOS Radio Receivers, Kluwer Academic Publishers, 1999.

- [9] K.K. O, "Design and analyses of tuned RF circuits including the effects of process and component variations," Tutorial of 2003 Asia-Pacific Microwave Conference, TUTORIAL3, Nov. 2003.

- [10] J. Crols and M.S.J. Steyaert, "A single-chip 900 MHz CMOS receiver front-end with a high performance low-IF topology," IEEE J. Solid-State Circuits, vol.30, no.12, pp.1483–1492, Dec. 1995.

- [11] J. Harvey and R. Harjani, "An integrated quadrature mixer with improved image rejection at low voltage," 14th International Conference on VLSI Design, pp.269–273, Jan. 2001.

- [12] J. Harvey and R. Harjani, "Analysis and design of an integrated quadrature mixer with improved noise, gain and image rejection," Proc. IEEE Int. Symp. Circuits and Systems, vol.IV, pp.786–789, May 2001.

- [13] M. Ugajin, J. Kodate, and T. Tsukahara, "A 1-V 2-GHz RF receiver with 49 dB of image rejection in CMOS/SIMOX," IEICE Trans. Fundamentals, vol.E85-A, no.2 pp.293–299, Feb. 2002.

- [14] P. Andreani, A. Bonfanti, L. Romano, and C. Samori, "Analysis and design of a 1.8-GHz CMOS LC quadrature VCO," IEEE J. Solid-State Circuits, vol.37, no.12, pp.1737–1740, Dec. 2002.

- [15] R. Aparicio and A. Hajimiri, "A noise-shifting differential colpitts VCO," IEEE J. Solid-State Circuits, vol.37, no.12, pp.1728–1736, Dec. 2002.

- [16] A. Rofougaran, J. Rael, M. Rofougaran, and A. Abidi, "A 900 MHz CMOS LC-oscillator with quadrature outputs," Proc. Int. Solid-State Circuits Conf., pp.392–393, Feb. 1996.

- [17] M. Tiebout, "Low-power low-phase-noise differentially tuned quadrature VCO design in standard CMOS," IEEE J. Solid-State Circuits, vol.36, no.7, pp.1018–1024, July 2001.

- [18] S. Pavan and Y. Tsividis, High Frequency Continuous Time Filters in Digital CMOS Process, Kluwer Academic Pubulishers, 2000.