|              |                                                                                     |

|--------------|-------------------------------------------------------------------------------------|

| Title        | 入力周波数レンジ可変型CMOS電圧制御プリスケーラ                                                           |

| Author(s)    | 春岡, 正起; 洞木, 吉博; 山本, 泰子 他                                                            |

| Citation     | 電子情報通信学会論文誌C. 2004, J87-C(9), p. 732-733                                            |

| Version Type | VoR                                                                                 |

| URL          | <a href="https://hdl.handle.net/11094/51721">https://hdl.handle.net/11094/51721</a> |

| rights       | copyright©2004 IEICE                                                                |

| Note         |                                                                                     |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

## 入力周波数レンジ可変型 CMOS 電圧制御プリスケーラ

春岡 正起<sup>†,††</sup>洞木 吉博<sup>†</sup>山本 泰子<sup>†,†††</sup>松岡 俊匡<sup>†</sup>谷口 研二<sup>†</sup>

Wide Tuning Range CMOS Voltage-Controlled Prescaler

Masaki HARUOKA<sup>†,††</sup>, Yoshihiro UTSUROGI<sup>†</sup>, Yasuko YAMAMOTO<sup>†,†††</sup>,

Toshimasa MATSUOKA<sup>†</sup>, and Kenji TANIGUCHI<sup>†</sup>

あらまし MS-DFF(Master-Slave D-Type Flip-Flop)の自走発振周波数を可変にし、広帯域の入力周波数レンジをカバーした電圧制御プリスケーラを提案する。0.25 μm CMOS プロセスを用いて設計を行い 100 MHz から 3.5 GHz の動作をシミュレーションにより確認した。

キーワード MS-DFF, Source Coupled Logic, プリスケーラ, 入力感度

## 1. まえがき

最近の高周波通信機器では PLL 周波数シンセサイザや Quadrature 生成のために周波数分周器(プリスケーラ)が必要となる。一般に高速の周波数分周器として SCL (Source Coupled Logic) 回路で構成された MS-DFF(Master-Slave D-Type Flip-Flop)が広く利用されている[1],[2]。この自走発振を行う MS-DFF は、発振周波数のおよそ 2 倍の入力信号にロックさせることで入力信号を 2 分周した出力信号が得られる。入力感度は自走発振周波数の 2 倍の周波数で最も高くなり、その周波数から離れると入力感度は大きく劣化する。本研究では、MS-DFF の自走発振周波数を可変にし、入力周波数レンジを広帯域化した電圧制御プリスケーラを新規に提案する。

## 2. 回路構成

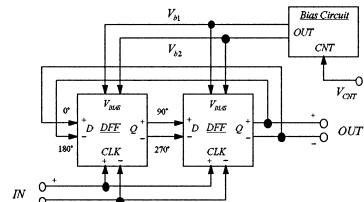

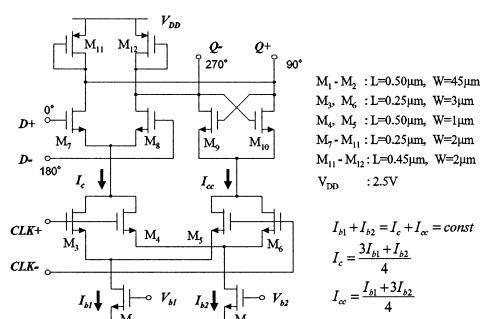

提案する電圧制御プリスケーラは、図 1 に示すように MS-DFF と周波数制御用のバイアス回路により構成される。MS-DFF を構成する DFF はそれぞれ図 2 に示す SCL 回路により構成される。この回路の特徴は CLK 入力部のトランジスタの差動入力のペアを 2 系統に分離し ( $M_3-M_6$ )、トランジスタサイズを非対称

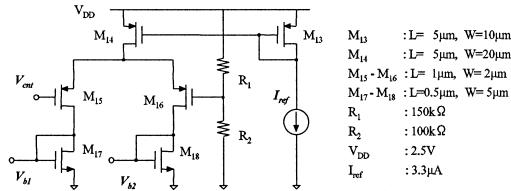

に組み合わせたことにある。これにより  $I_{b1}$ ,  $I_{b2}$  の比率を変化させれば、負性抵抗生成用トランジスタ  $M_9$ ,  $M_{10}$  と結合用トランジスタ  $M_7$ ,  $M_8$  に流れるバイアス電流  $I_{cc}$ ,  $I_c$  の比率を制御することができる。 $M_1$ ,  $M_2$  のゲート電圧  $V_{b1}$ ,  $V_{b2}$  は図 3 のバイアス回路より加えられ、 $V_{cnt}$  により  $I_{b1}$ ,  $I_{b2}$  の比率を制御し、トータルの電流は一定に保たれる。

図 1 電圧制御プリスケーラの構成

Fig. 1 Voltage-controlled prescaler architecture.

図 2 DFF の回路図

Fig. 2 Schematic of the DFF circuit.

† 大阪大学大学院工学研究科電子情報エネルギー工学専攻、吹田市

Department of Electronics and Information Systems, Graduate School of Engineering, Osaka University, Suita-shi, 565-0871 Japan

†† 古野電気株式会社、西宮市

Furuno Electric CO., LTD., Nishinomiya-shi, 662-8580 Japan

††† 松下電工株式会社、門真市

Matsushita Electric Works, LTD., Kadoma-shi, 571-8686 Japan

図 3 バイアス回路

Fig. 3 Schematic of bias circuit.

### 3. 動作原理

MS-DFF は出力端子 Q の電圧位相が入力端子 D に対して  $90^\circ$  となる条件で自走発振する。このとき、出力端子 Q における出力インピーダンス  $Z_{out}$  と出力負荷に流れる電流  $i_{load}$  には次式の関係が成り立つ。

$$\angle Z_{out} + \angle i_{load} = 90^\circ \quad (1)$$

ここで  $\angle i_{load}$  は入力端子 D の電圧位相を基準とした値を示し、次式で表すことができる。

$$\angle i_{load} = \tan^{-1} \left( \frac{-I_{cc}}{I_c} \right) \quad (2)$$

また  $Z_{out}$  の位相は  $M_{11}(M_{12})$  の  $g_m$  と寄生容量成分  $C_{load}$  より次式で表すことができる。

$$\angle Z_{out} = -\tan^{-1} \left( \frac{\omega C_{load}}{g_m} \right) \quad (3)$$

式 (1) ~ (3) より自走発振周波数  $\omega_{osc}$  は次式のように、バイアス電流の比  $I_c/I_{cc}$  に比例する。

$$\omega_{osc} = \frac{g_m}{C_{load}} \frac{I_c}{I_{cc}} \quad (4)$$

### 4. シミュレーション結果

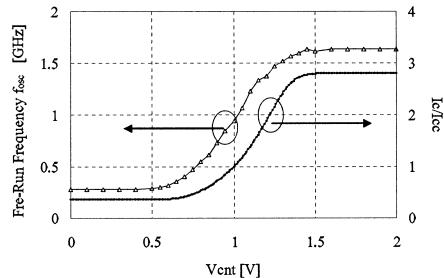

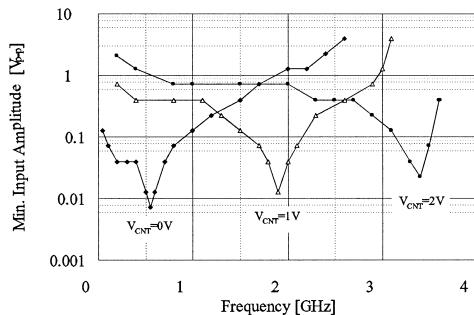

0.25  $\mu m$  CMOS プロセスを用いてプリスケーラの設計を行いシミュレーションにより動作の確認を行った。電源電圧は 2.5 V、消費電流 140  $\mu A$  であった。図 4 にコントロール電圧  $V_{cnt}$  に対する自走発振周波数  $f_{osc}$  と  $I_c/I_{cc}$  の関係を示す。 $V_{cnt}$  で  $I_c/I_{cc}$  を制御することにより、自走発振周波数が 276 MHz から 1.63 GHz まで変化している。図 5 に  $V_{cnt} = 0, 1, 2$  V における入力感度の周波数特性を示す。図 4 と比較すると自走発振周波数の 2 倍の周波数において感度が最も高くなることが分かる。自走発振周波数を制御することにより 100 MHz から 3.5 GHz において 0.1  $V_{p-p}$  以下の振幅の入力感度が得られている。

図 4  $V_{cnt}$  に対する自走発振周波数と  $I_c/I_{cc}$  の関係

Fig. 4 Free-run frequency and  $I_c/I_{cc}$  versus  $V_{cnt}$ .

図 5 入力感度の周波数特性

Fig. 5 Input sensitivity versus frequency.

### 5. む す び

MS-DFF の自走発振周波数を可変にし、広帯域の入力周波数をカバーできる電圧制御プリスケーラを提案した。0.25  $\mu m$  CMOS プロセスを用いて設計を行い 100 MHz から 3.5 GHz において 0.1  $V_{p-p}$  以下の振幅の入力感度が得られることをシミュレーションにより確認した。

謝辞 本研究は日本学術振興会未来開拓学術研究推進事業の援助のもとで行われた。

### 文 献

- [1] M.Mizuno, M.Yamashina, K.Furuta, H.Igura, H.Abiiko, K.Okabe, A.Ono, and H.Yamada, "A GHz MOS adaptive pipeline technique using MOS current-mode logic," IEEE J. Solid-State Circuits, vol.31, pp.784–791, June 1996.

- [2] 山本泰子, 松岡俊匡, 谷口研二, “低消費電力 1 V 動作 630 MHz 周波数分周器,” 信学論 (C), vol.J87-C, no.1, pp.192–194, Jan. 2004.

(平成 16 年 6 月 21 日受付)