| Title        | ANALYSIS OF A CONTROLLER-BASED ALL-DIGITAL<br>PHASE-LOCKED LOOP              |

|--------------|------------------------------------------------------------------------------|

| Author(s)    | Radhapuram, Saichandrateja; Bae, Jungnam; Jo,<br>Ikkyun et al.               |

| Citation     | Far East Journal of Electronics and<br>Communications. 2015, 15(1), p. 57–73 |

| Version Type | VoR                                                                          |

| URL          | https://hdl.handle.net/11094/52099                                           |

| rights       | © 2015 Pushpa Publishing House                                               |

| Note         |                                                                              |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

## ERRATUM: ANALYSIS OF A CONTROLLER-BASED ALL-DIGITAL PHASE-LOCKED LOOP

[Published in Volume 15, Number 1 (2015) Pages 57-73 of the Far East Journal of Electronics and Communications]

## Saichandrateja Radhapuram, Jungnam Bae, Ikkyun Jo, Weimin Wang and Toshimasa Matsuoka

Graduate School of Engineering Osaka University 2-1 Yamada-oka, Suita-shi Osaka 565-0871, Japan e-mail: teja@si.eei.eng.osaka-u.ac.jp matsuoka@eei.eng.osaka-u.ac.jp

This paper was published online in July, 2015 [Volume 15, Number 1, Pages 57-73]. In this paper, we performed modeling and analysis of a controller-based all-digital phase-locked loop (ADPLL). However, we made a mistake in the calculation of the step response of the ADPLL to validate the model using behavior-level simulation.

The following sentences in the pages 69, 70, 71 should be corrected and Figure 5 should be replaced as follows.

Page 69, line 1: "... with tuning range of 393MHz to 418MHz."

Page 69, line 10: "The DCO integer and fractional bit code changes for a power-up condition are shown in Figures 4(a) and 4(b) as decimal value variations."

## 200 S. Radhapuram, J. Bae, I. Jo, W. Wang and T. Matsuoka

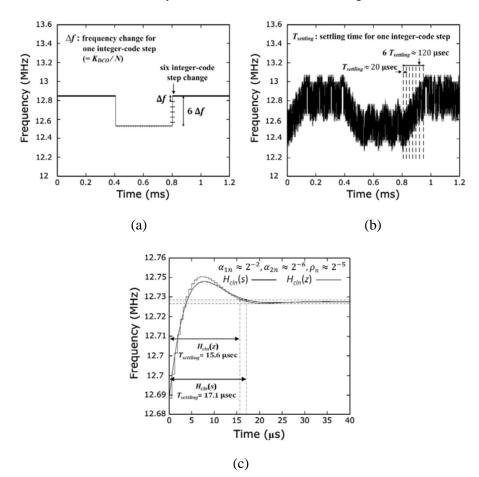

Page 70, line 1: "... code with time to reduce the phase error is shown in Figure 4(c) as decimal variation. Figure 5(a) shows the frequency step of the reference clock corresponding to a step change of six DCO integer-code, which can show enough change in ADPLL output frequency over frequency variation. By considering this large frequency step as combination of small one integer-code step, the small-signal approximation used in equations (3) and (4) can still be validated. As shown in Figure 5(b), the output frequency settling to a step change of one integer-code is around 20µsec. The  $K_{DCO}$  from simulations is about 1.6MHz/code change (=  $3.2\pi$  Mrps/code change), and the  $K_{PPF+PI}$  is  $2\pi/64$  for the 64-phase..."

Page 71, line 7: "... $\rho_n \approx 2^{-5}$ ".

Page 71, line 10: "... settling times of 15.6µsec and 17.1µsec which are close to the settling time simulated using the behavior-level simulation  $(T_{\text{setting}} \approx 20 \mu \text{sec})$ ".

The corrected Figure 5 is shown as below.

**Figure 5.** (a) Frequency step of the reference clock, (b) ADPLL output frequency response with frequency division (N = 32) for the reference frequency step, and (c) step responses of  $H_{cln}(z)$  and  $H_{cln}(s)$  with the extracted simulation parameters.

The correction does not affect the other parts. We express our apology for confusing the readers and the editors.