|              | A Study on Handware Anabitecture for H OCE /HEVO                                    |

|--------------|-------------------------------------------------------------------------------------|

| Title        | A Study on Hardware Architecture for H.265/HEVC<br>Fast Mode Decision and Transform |

| Author(s)    | 趙, 文軍                                                                               |

| Citation     | 大阪大学, 2015, 博士論文                                                                    |

| Version Type | VoR                                                                                 |

| URL          | https://doi.org/10.18910/53943                                                      |

| rights       |                                                                                     |

| Note         |                                                                                     |

## Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

# A Study on Hardware Architecture for H.265/HEVC Fast Mode Decision and Transform

January 2015

Wenjun ZHAO

## **Publication list**

#### **Transactions**

1. W. Zhao, T. Onoye, and T. Song, "Hierarchical structure based fast mode decision for H.265/HEVC," *IEEE Transactions on Circuits and Systems for Video Technology*, (in press).

## Conference papers with referee

- 1. W. Zhao, T. Onoye, and T. Song, "Hardware architecture of the fast mode decision algorithm for H.265/HEVC," In *Proc. of IEEE International Conference on Image Processing (ICIP)*, Oct. 2014.

- 2. W. Zhao, T. Onoye, and T. Song, "Hardware-oriented fast mode decision algorithm for intra prediction in HEVC," In *Proc. of Picture Coding Symposium (PCS)*, pp. 109 112, Dec. 2013.

- 3. W. Zhao, T. Onoye, and T. Song, "High-performance multiplierless transform architecture for HEVC," In *Proc. of IEEE International Symposium on Circuits and Systems (ISCAS)*, pp. 1668 1671, May 2013.

## Conference papers without referee

1. W. Zhao, and T. Onoye, "A high-performance multiplierless hardware architecture of the transform applied to H.265/HEVC emerging video coding standard," *IEICE Technical Report*, vol. 112, no. 207, SIS2012-18, pp. 11 - 16, Sep. 2012.

## **Abstract**

This thesis mainly discusses the fast mode decision algorithms for the H.265/HEVC (high efficiency video coding). HEVC has incorporated a series of the state-of-the-art technologies and algorithms. These features help HEVC to achieve significantly high compression efficiency. However, these features also increase the computational complexity. In order to find the best encoding parameters (e.g. coding mode) for a certain block (comprised of luma and chroma components), a huge number of combinations of block sizes and candidate modes have to be checked, which is very time-consuming. Hence, in this work, a course of fast mode decision algorithms are proposed to accelerate the mode decision process. Moreover, the corresponding hardware architecture of the proposed fast decision algorithms as well as the hardware design of the transform of H.265/HEVC are proposed.

First, this thesis gives a brief introduction about the H.265/HEVC. The HEVC codec employs the well-known hybrid block-based coding framework, including advanced intra prediction with 35 modes, improved motion-compensation prediction with merge technique, newly added large-sized transform engine, and high-efficiency entropy coding tool. Moreover, the reconstructed pixels are filtered by the similar de-blocking and newly adopt sample adaptive offset filters before sent to the decoded picture buffer. Unlike the previous video coding standards, the HEVC adopts a flexible quadtree structure based block partition scheme that enables effective use of different block sizes during the prediction and transform coding processes. Two strategies aiming at overcoming the limitations of the parallelization approaches employed in H.264/AVC have been included in the HEVC, namely Tiles and wavefront parallel processing.

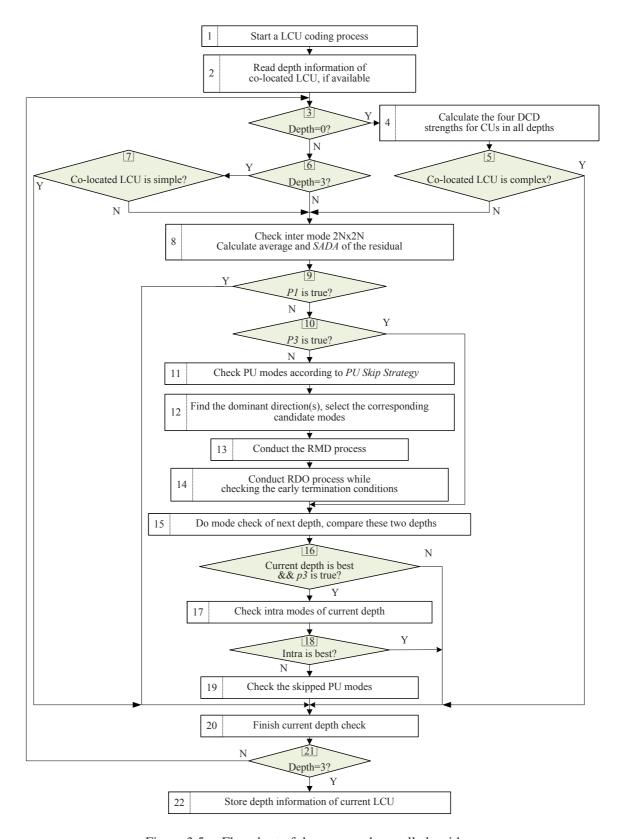

Second, this dissertation presents a course of low complexity fast mode decision algorithms. In order to skip some unlikely depths, the maximum depth information of a co-located block is referred to predict the depth of current block. To make a prediction, after encoding one frame, the depth information is saved, in order to enable later coded frames to refer to these data. In order to reduce the complexity introduced by saving the depth information, it is proposed in this dissertation that co-located LCU from the previous frame in encoding order will be used. Next, for a certain sized block, the motion character of inter prediction residual is analyzed to determine whether to terminate the current check or to skip over unnecessary modes and split the block into smaller sizes. In order to detect the motion character of each portion inside a block, we propose to divide the residual block and calculate the average and the sum of absolute difference over average. Two conditions are defined to terminate the mode check process or to skip current depth mode check process and move on to the next depth. Moreover, in order to skip some unlikely partition modes, a skip strategy is also proposed. To make compensation to a wrong split condition, a novel remedy process is introduced. After inter prediction, a hardware-oriented low complexity fast intra prediction algorithm is presented. The proposed algorithm adopts a fast discrete cross differences (DCD) to detect the dominate direction of the coding unit. Based on DCD information, only a subset of the 35 iv Abstract

candidate modes are selected for the rough mode decision process. Moreover, four simple but efficient early termination strategies are proposed to terminate the RDO process properly.

Third, in this thesis, the corresponding hardware architectures of the proposed fast mode decision algorithms are proposed. In order to achieve a better compatibility, the proposed fast mode decision architectures are designed as an individual module that can be easily embedded into a common video codec for H.265/HEVC. A state machine based mode dispatch module for the depth prediction combined with the residual check algorithm is described. In this mode dispatch module, mainly 4 kinds of elements are contained according to its functional definition: information recording element, controlling and decision making element, interface element, and the core mode dispatcher. For the proposed state machine, there are 13 states are defined. Then, the hardware implementation of the proposed fast DCD algorithm and two previous works are discussed. Moreover, the complexity and performance of the proposed DCD algorithm is compared with previous works.

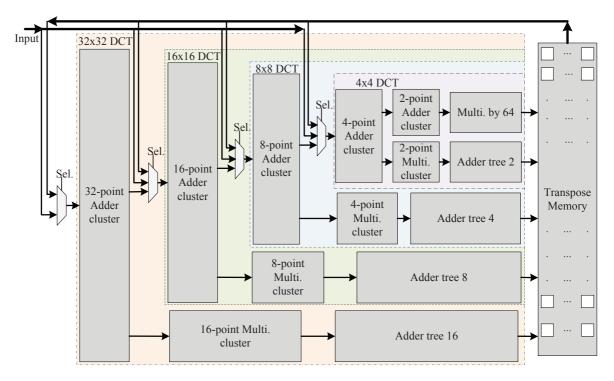

Finally, this dissertation describes a hardware architecture of the transform applied in HEVC. The proposed architecture can support a variety of transform sizes from 4x4 to 32x32. The hardware design proposed in this work focuses on low cost and high throughput. To achieve such objectives, some simplification strategies are adopted during the implementation, such as reusing part of the structure of the larger sized transform for smaller sized transform, and turning multiplication by constant into shift and sum operations. The transform architecture proposed in this dissertation is implemented in the form of pipeline structure. Moreover, a high-performance transposition memory is proposed to store and transpose the intermediate data between the 1-D and 2-D transform.

As a conclusion, in this thesis, a course of fast mode decision algorithms and its corresponding hardware architectures as well as the hardware design of the transform of H.265/HEVC are proposed.

## Acknowledgments

First of all, I would like to express my deepest gratitude to Professor Takao Onoye in Osaka University for providing me a precious opportunity and an excellent environment to study as a doctoral student in his laboratory. All of my productive researches are credited to none other than him. His advanced perspective and thoughtful advises led me to successful achievements.

I would like to demonstrate my gratitude to Associate Professor Tian Song in Tokushima University for giving so much help from both research and daily life.

My appreciation also goes to Professor Masaharu Imai, and Associate Professor Masanori Hashimoto in Osaka University for detailed review and insightful suggestions.

I am deeply grateful to Professor Tatsuhiro Tsuchiya, Professor Koji Nakamae, Professor Haruo Takemura, Professor Makoto Nakamura, Associate Professor Yoshinori Takeuchi, Associate Professor Nakagawa Hiroyuki, Associate Professor Katsuyoshi Miura, Associate Professor Yoshihiro Kuroda, and Associate Professor Kiyoshi Kiyokawa in Osaka University for useful advices.

I would like to express my sincere appreciation to Assistant Professor Masahide Hatanaka, and Assistant Professor Constantin Siriteanu in Osaka University for technical and other supports in laboratory.

I also appreciate Professor Isao Shirakawa, Mr. Shozo Tsukahara, Mr. Hiroyuki Okuhata, Dr. Masanao Ise and Dr. Kenji Watanabe in Synthesis Corporation for providing me a chance to engage on jobs with regard to VLSI design.

I would like to thank Dr. Takehiko Amaki, Dr. Igors Homjakovs, Dr. Masashi Okada, Dr. Dawood Alnajjar, Dr. Jaehoon Yu, Dr. Hiroaki Konoura, Dr. Kosuke Nakajima, and Dr. Ryo Harada for fruitful discussions and advices.

I would like to thank my closest colleagues Ms. Twe Ta Oo and Mr. Younghun Ko for helpful discussions.

I express my appreciation to all the members of Onoye Lab in Osaka University for all kinds of supports in laboratory.

I would like to thank Mrs. Mayuko Nakamura, Ms. Tomomi Kondo and Ms. Yuki Yoshida for their various supports throughout my student life.

I would like to express my sincere appreciation to all the members of Osaka Chinese Presbyterian Church who have accompanied me during these three years. I also would like to thank all of my friends for having good times.

I want to give my sincerely thanks to my family, my father and my mother, thanks for your always supporting in my study. Without you, it would be impossible for me to gain these achievements. I wish you all a healthy body.

I owe my most sincere gratitude to my wife and her parents for everything. Thanks GOD!

# Contents

| 1   | Introduction                                                   | 1  |

|-----|----------------------------------------------------------------|----|

| 1.1 | Background and motivation                                      | 1  |

| 1.2 | Previous researches                                            | 2  |

|     | 1.2.1 Fast mode decision algorithms for H.264/AVC              | 3  |

|     | 1.2.2 Fast mode decision algorithms for H.265/HEVC             | 5  |

|     | 1.2.3 Hardware architecture of the transform for H.265/HEVC    | 7  |

| 1.3 | Objective and outline of this thesis                           | 8  |

| 2   | High efficiency video coding                                   | 11 |

| 2.1 | Introduction                                                   | 11 |

| 2.2 | Block partition structure and parallel scalability             | 11 |

|     | 2.2.1 Block partition structure                                | 11 |

|     | 2.2.2 Parallel scalability                                     | 12 |

| 2.3 | HEVC video coding technology                                   | 13 |

|     | 2.3.1 Prediction coding                                        | 13 |

|     | 2.3.2 Transform coding                                         | 14 |

|     | 2.3.3 Pixel reconstruction                                     | 16 |

| 2.4 | Prediction structure                                           | 16 |

| 2.5 | Conclusion                                                     | 18 |

| 3   | Hierarchical structure based fast mode decision for H.265/HEVC | 19 |

| 3.1 | Introduction                                                   | 19 |

| 3.2 | Depth prediction                                               | 19 |

|     | 3.2.1 Correlation between co-located LCU and current LCU       | 19 |

|     | 3.2.2 Complexity reduction                                     | 23 |

|     | 3.2.3 Implementation of depth prediction algorithm             | 23 |

| 3.3 | Residual check                                                 | 24 |

|     | 3.3.1 Residual characteristic analysis                         | 24 |

|     | 3.3.2 CU termination and split conditions                      | 25 |

|     | 3.3.3 PU skip strategy                                         | 27 |

|     | 3.3.4 Implementation of residual check algorithm               | 28 |

| 3.4 | Fast intra mode decision                                       | 29 |

|     | 3.4.1 Proposed discrete cross difference                       | 29 |

|     | 3.4.2 Candidate mode selection                                 | 30 |

|     | 3.4.3 Early RDO termination strategy                           | 31 |

| 3.5 |                                                                | 32 |

| 3.6 | Simulation results                                             | 35 |

<u>viii</u> Contents

|          | 3.6.1 Performance of depth prediction                                      | 35       |

|----------|----------------------------------------------------------------------------|----------|

|          | 3.6.2 Performance of depth prediction combined with residual check         | 37       |

|          | 3.6.3 Performance of fast intra mode decision                              | 40       |

|          | 3.6.4 Performance of overall algorithm                                     | 40       |

|          | 3.6.5 Performance compared with previous works                             | 43       |

| 3.7      | Conclusion                                                                 | 43       |

| 4        | Hardware architecture of the fast mode decision algorithm for              | 47       |

| 4.1      | H.265/HEVC                                                                 | 47       |

| 4.1      | Introduction                                                               | 47       |

| 4.2      | Hardware architecture of the depth prediction combined with residual check | 47       |

|          | 4.2.1 Proposed mode dispatch system                                        | 47<br>53 |

| 4.3      | 4.2.2 Proposed state machine based fast mode decision architecture         | 55<br>57 |

| 4.3      | Hardware implementation of the proposed fast DCD algorithm                 | 61       |

| 4.4      | 4.4.1 Synthesis results for the proposed mode dispatch module              | 61       |

|          | 4.4.2 Synthesis results for the proposed fast DCD algorithm                | 63       |

| 4.5      | Conclusion                                                                 | 64       |

| 1.5      | Conclusion                                                                 | 01       |

| 5        | High-performance transform architecture for H.265/HEVC                     | 65       |

| 5.1      | Introduction                                                               | 65       |

| 5.2      | Algorithm for hardware implementation                                      | 65       |

|          | 5.2.1 Review of the transform of HEVC                                      | 65       |

|          | 5.2.2 Hardware-oriented algorithm                                          | 67       |

| 5.3      | Hardware Architecture design                                               | 72       |

|          | 5.3.1 Hardware reuse                                                       | 72       |

| ~ .      | 5.3.2 Transposition memory design                                          | 74       |

| 5.4      | Synthesis results                                                          | 77       |

| 5.5      | Conclusion                                                                 | 79       |

| 6        | Conclusion                                                                 | 81       |

| Bibliogr | aphy                                                                       | 83       |

## List of tables

| 3.1  | Distribution (%) of the ratios of simple, complex, and medial LCUs             | 21 |

|------|--------------------------------------------------------------------------------|----|

| 3.2  | Correctness (%) of prediction from co-located LCU to current LCU               | 22 |

| 3.3  | Accuracy (%) of termination and split over current depth based on residual     |    |

|      | check                                                                          | 27 |

| 3.4  | Candidate modes corresponding to the estimated dominate direction(s)           | 31 |

| 3.5  | Simulation results for the proposed depth prediction algorithm                 | 36 |

| 3.6  | Impact of the selection of $ThS mooth$ and $ThAvg$                             | 37 |

| 3.7  | Simulation results for the proposed depth prediction combined with residual    |    |

|      | check algorithm                                                                | 39 |

| 3.8  | Simulation results for the proposed fast intra mode decision algorithm         | 41 |

| 3.9  | Simulation results for the proposed overall algorithm                          | 42 |

| 3.10 | Performance of the depth prediction compared with previous works               | 44 |

| 3.11 | Performance of the residual check                                              | 45 |

| 4.1  | The overall state transition                                                   | 58 |

| 4.2  | The number of states checked in each transition                                | 58 |

| 4.3  | Synthesis results of the proposed mode dispatch module on FPGA                 | 62 |

| 4.4  | Total memory bits consumed by the proposed local buffer on FPGA                | 62 |

| 4.5  | Number of arithmetic operations used to derive the dominant direction          | 63 |

| 4.6  | Synthesis results of the three fast intra mode decision algorithms on FPGA     | 63 |

| 4.7  | Estimated throughput of the proposed fast DCD algorithm                        | 63 |

| 4.8  | Performance of fast intra decision algorithm compared with previous works.     | 64 |

| 5.1  | Operations in the first stage                                                  | 69 |

| 5.2  | Demonstration of the constants in multiplication converted into shift and sum. | 70 |

| 5.3  | Number of arithmetic operations used to perform the transform                  | 77 |

| 5.4  | Synthesis results on FPGA                                                      | 77 |

| 5.5  | Estimated throughput (Msamlpes/s) at 125 MHz on FPGA                           | 78 |

| 5.6  | Performance comparison with previous work on FPGA                              | 78 |

| 5.7  | Efficiency comparison with previous work on ASIC platform                      | 79 |

| 5.8  | Transpose memory comparison with previous work on ASIC platform                | 79 |

| 5.9  | Estimated throughput (Msamlpes/s) at 333MHz on ASIC platform                   | 79 |

# List of figures

| 1.1  | Simplified block diagram of HM encoder                                   | 2  |

|------|--------------------------------------------------------------------------|----|

| 1.2  | The mode decision process for a block                                    | 2  |

| 1.3  | Classification tree of proposals on fast mode decision algorithms for    |    |

|      | H.264/AVC                                                                | 3  |

| 1.4  | Classification tree of proposals on fast mode decision algorithms for    |    |

|      | H.265/HEVC                                                               | 5  |

| 1.5  | The proposed mode decision process for a block                           | 9  |

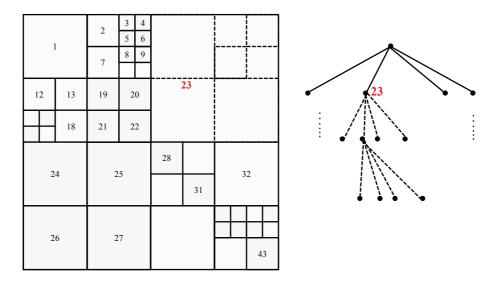

| 2.1  | Example of CU partition scheme                                           | 12 |

| 2.2  | Example of dividing a frame into nine Tiles                              | 13 |

| 2.3  | Parallel processing of each LCU row in WPP                               | 13 |

| 2.4  | Intra prediction mode directions                                         | 14 |

| 2.5  | Partition modes for inter PU                                             | 15 |

| 2.6  | Example of TU splitting structure                                        | 15 |

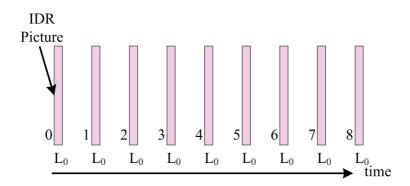

| 2.7  | Graphical presentation of intra-only prediction structure                | 17 |

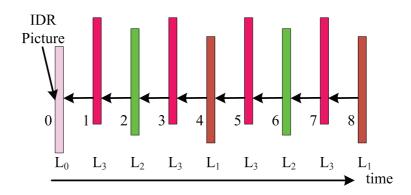

| 2.8  | Graphical presentation of low-delay P prediction structure               | 17 |

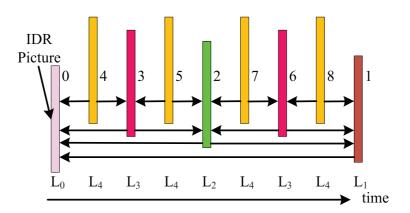

| 2.9  | Graphical presentation of random access prediction structure             | 17 |

| 3.1  | Example of LCU partition for two consecutive frames                      | 20 |

| 3.2  | Division a CU into 16 sub-blocks                                         | 25 |

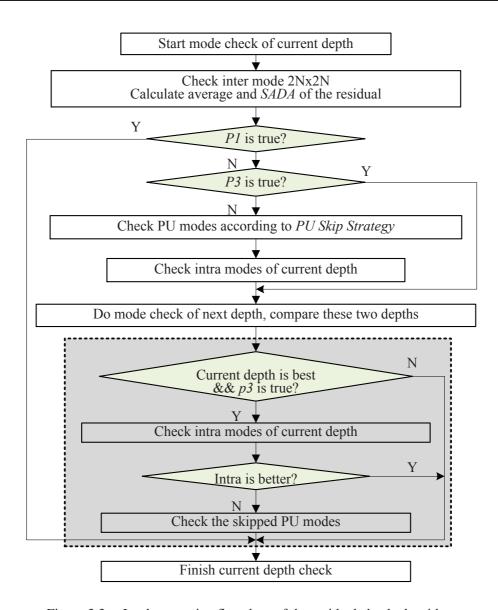

| 3.3  | Implementation flowchart of the residual check algorithm                 | 28 |

| 3.4  | Discrete cross difference calculation pattern                            | 30 |

| 3.5  | Flowchart of the proposed overall algorithm                              | 34 |

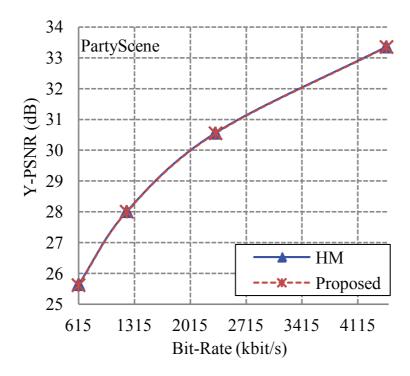

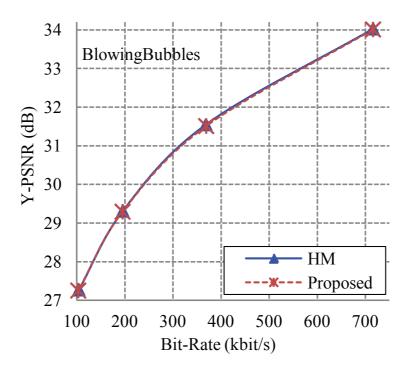

| 3.6  | RD curve of PartyScene                                                   | 37 |

| 3.7  | RD curve of BlowingBubbles                                               | 38 |

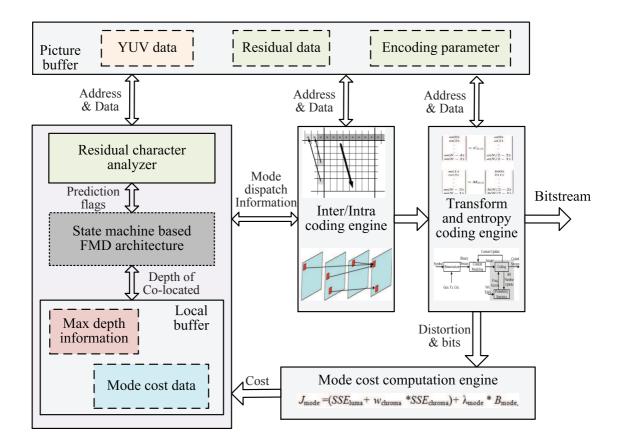

| 4.1  | The framework of video codec where the mode dispatch module is embedded. | 48 |

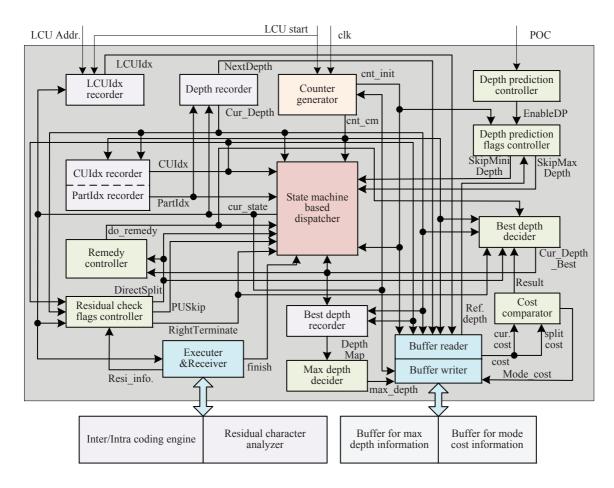

| 4.2  | The proposed hardware architecture for the mode dispatch module          | 49 |

| 4.3  | The index of the CUs                                                     | 50 |

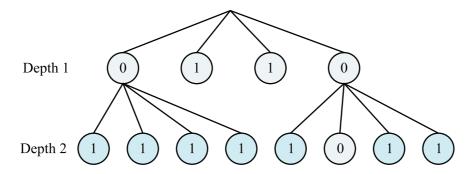

| 4.4  | An example of the depth map                                              | 51 |

| 4.5  | The implementation logic of the depth prediction controller              | 51 |

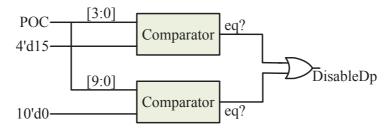

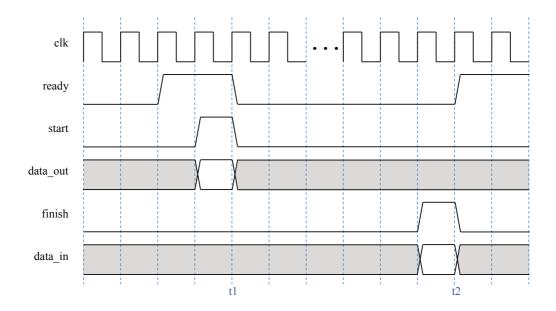

| 4.6  | The simple handshake based protocol for the executer & receiver          | 52 |

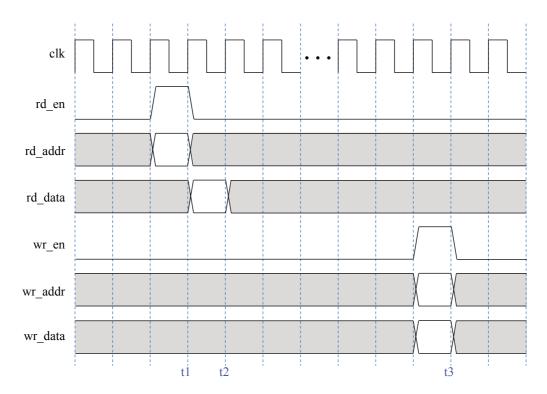

| 4.7  | The standard read/write protocol for the buffer reader & writer          | 53 |

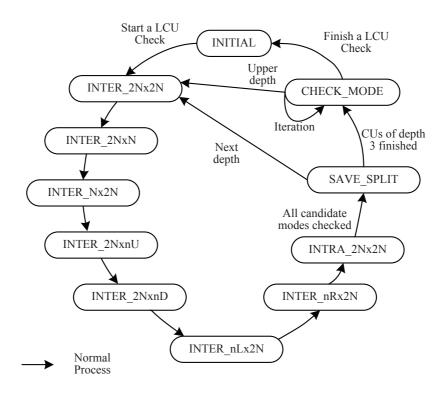

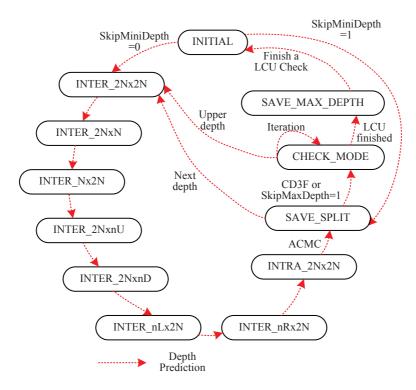

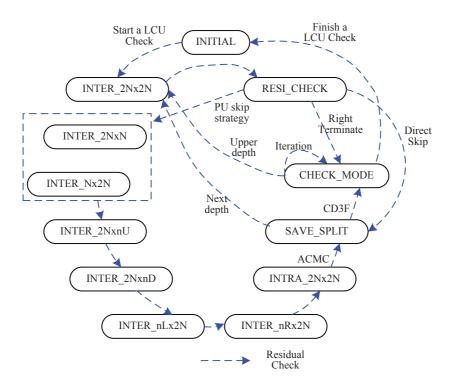

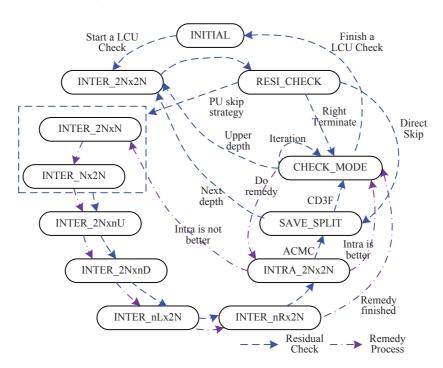

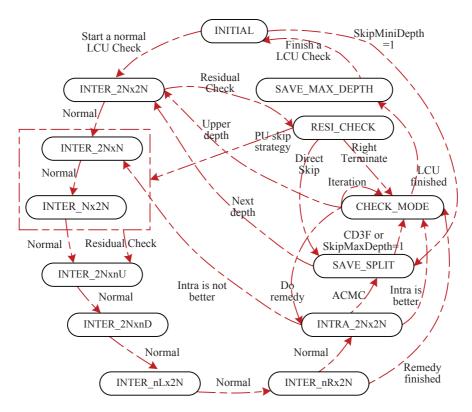

| 4.8  | The normal state transition diagram                                      | 54 |

| 4.9  | The state transition diagram for depth prediction algorithm              | 55 |

| 4.10 | The state transition diagram for residual check algorithm                | 55 |

| 4.11 | The state transition diagram for remedy process                          | 56 |

**xii** List of figures

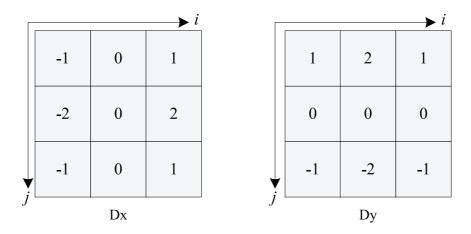

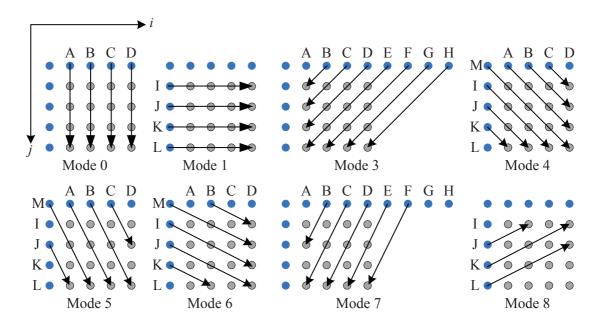

| 4.12<br>4.13<br>4.14 | The overall state transition diagram.  Sobel masks for gradients calculation.  The directional intra modes in H.264/AVC. | 59 |

|----------------------|--------------------------------------------------------------------------------------------------------------------------|----|

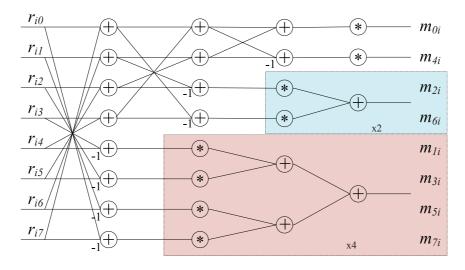

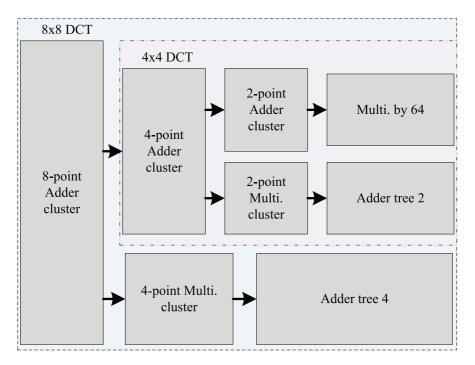

| 5.1                  | Flow-chart of the 1-D 8x8 transform                                                                                      | 69 |

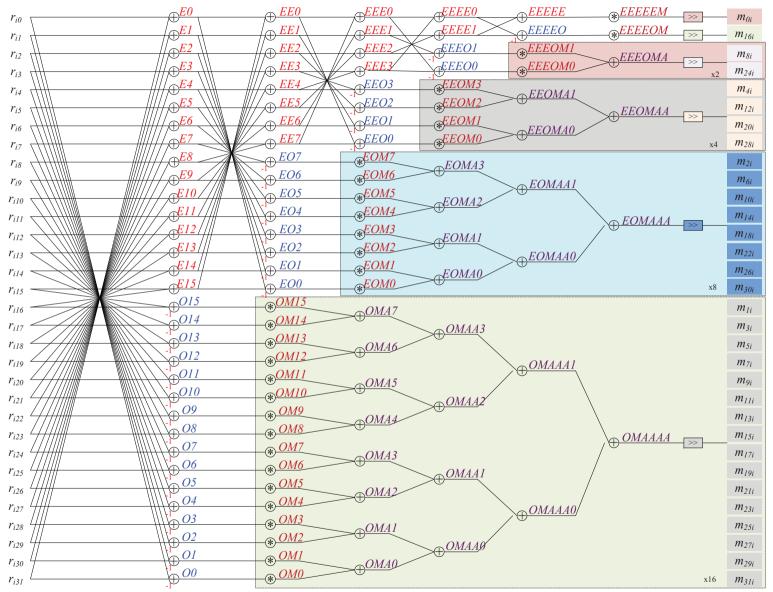

| 5.2                  | Flow-chart of the 1-D 32x32 transform                                                                                    | 71 |

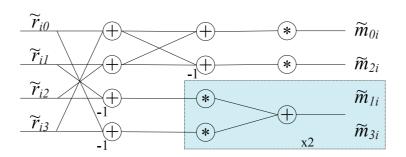

| 5.3                  | Flow-chart of the 1-D 4x4 transform                                                                                      | 73 |

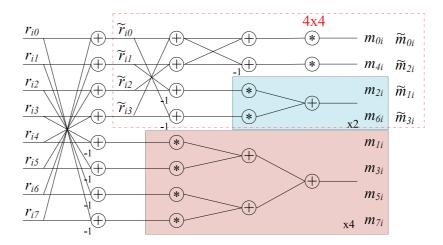

| 5.4                  | Combined flow-chart of the 1-D 8x8 and 4x4 transform                                                                     | 74 |

| 5.5                  | Hardware architecture for the 8x8 transform in HEVC                                                                      | 74 |

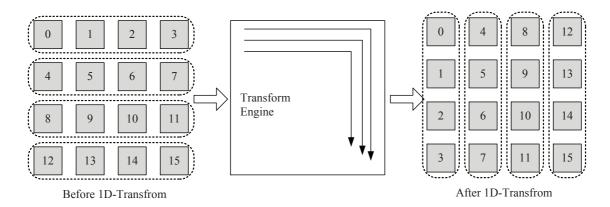

| 5.6                  | The order of the pixels during transform process                                                                         | 75 |

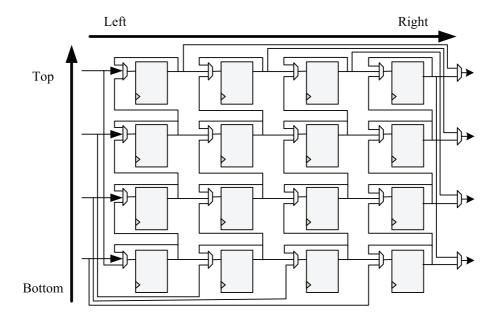

| 5.7                  | 4x4 transposition memory architecture                                                                                    | 75 |

| 5.8                  | Whole architecture for transform in HEVC                                                                                 | 76 |

## Chapter 1

## Introduction

This chapter describes the background and the objectives of this thesis. This thesis focuses on the fast mode decision algorithms for the H.265/HEVC. HEVC has incorporated a series of technologies and algorithms. These algorithms help HEVC to achieve a high compression efficiency. However, these technologies also increase the complexity. In order to find the best encoding mode for a block, a huge number of combinations of block sizes and modes will be checked exhaustively. Moreover, larger sized transform is a newly-added feature in HEVC and the traditional design of this part cannot be directly reused. Also, the transform of HEVC involves heavy computations and the hardware allocation for this part should be considered carefully. Therefore, in this work, a course of fast mode decision algorithms and its corresponding hardware architectures as well as the hardware design of the transform of H.265/HEVC are proposed.

## 1.1 Background and motivation

For the past several years, the great achievement in video compression area is the creation of the H.264/MPEG-4 advanced video coding (AVC) standard [1], which has been world-widely used in a variety of applications.

As technology advances, the definition and the quality of the digital video materials have improved fast and steadily. More and more electronic terminals become capable to support high resolution video capture and display. Therefore, studies on performance improvement of video codec are becoming common concerns. The standardization of the next generation video coding standard, i.e. high efficiency video coding (HEVC), was formally launched by the same video compression standardization organizations, named ITU-T video coding experts group (VCEG) and the ISO/IEC moving picture experts group (MPEG), in January 2010, and the first edition of the H.265/HEVC standard [2] was finalized in January 2013.

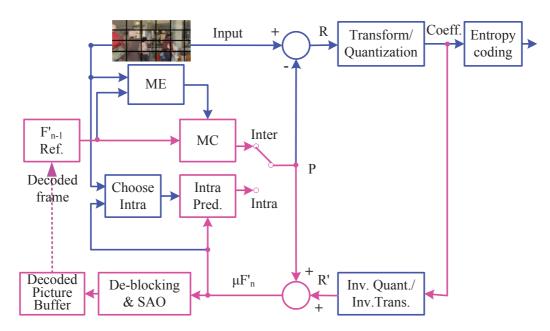

As a successor, the design of HEVC codec [3] has incorporated state-of-the-art technologies and algorithms, as shown in Figure 1.1. Following features are contained: intra prediction with 35 modes, inter prediction with merge technique, large-sized transform coding, high-efficiency entropy coding, de-blocking and sample adaptive offset (SAO) filters.

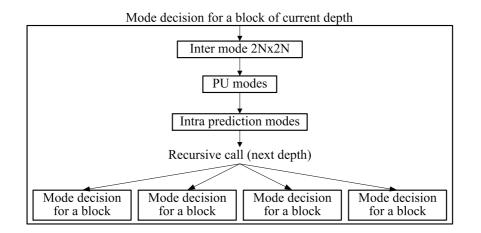

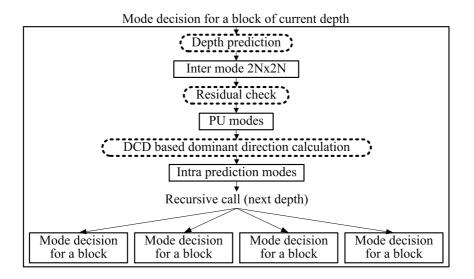

These features help HEVC to achieve significantly high compression efficiency. However, these features also increase the computational complexity. As is depicted in Figure 1.2, the blocks with solid lines denote the mode decision process in HEVC. In this process, first, the size of a block is decided according to its depth. Second, the inter and intra prediction modes are checked to find the best one for this block. Third, this block is split into the next depth

Figure 1.1: Simplified block diagram of HM encoder.

Figure 1.2: The mode decision process for a block.

and the first two steps are repeated to find the best modes for the blocks in the next depth. Finally, these two depths are compared to determine the better depth and mode.

On the basis of the above analysis, in order to find the best encoding mode for a certain block, a huge number of combinations of block sizes and candidate modes have to be checked, which is very time-consuming.

#### 1.2 Previous researches

As stated, the complexity of HEVC has increased a lot, compared with the previous standards. In references [4–7], a series of simulations of complexity analysis have been conducted. According to the results of complexity analysis of HEVC reference encoder [4, 5],

1.2 Previous researches 3

Figure 1.3: Classification tree of proposals on fast mode decision algorithms for H.264/AVC.

the rate\_distortion optimization (RDO) [8, 9] based mode decision encoding stage always holds a high percentage of the encoding time.

Therefore, a lot of research works have been proposed to reduce the computational complexity caused by the exhaustive mode decision process adopted in the encoder of HEVC.

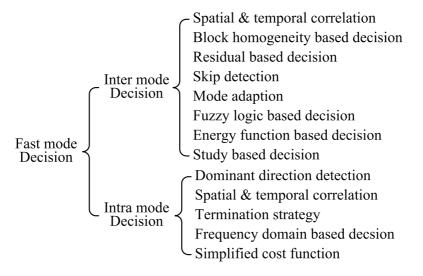

## 1.2.1 Fast mode decision algorithms for H.264/AVC

Since both the newly H.265/HEVC and the previous H.264/AVC adopt the well-known hybrid block- based coding framework, most of the fast mode decision algorithms proposed for H.265/HEVC can trace back to the fast mode decision researches for H.264/AVC. Hence, we first make a summary of the fast mode decision algorithms for H.264/AVC. Since the beginning of the standardization of H.264/AVC, how to make a fast and accurate mode prediction has been an important research topic and lots of research works have been proposed. These previous algorithms are categorized according to decision stage and criteria, as shown in the classification tree in Figure 1.3.

There are roughly two categories of algorithms: fast inter mode decision and fast intra mode decision algorithms. References [10–16] propose to reduce the computational complexity of the variable block-size motion estimation based on the temporal and spatial correlation in a video sequence. C. Duanmu *et al.* [10] present an early detection of the 16x16 block or SKIP mode according to the condition that the sum of absolute difference corresponding to the (0,0) motion vector is less than a predetermined threshold, and one of the chosen modes of the spatially neighboring is SKIP or 16x16. K. Chang *et al.* [11] use the best modes of the spatial neighboring blocks and the most correlated block from the previous frame as prediction candidates. In reference [12], the mode decision process can be terminated by referring the lowest RD\_Cost among the co-located blocks of the previous encoded frames. Authors of [13] propose to classify the blocks into three sub-sets on the basis of the luminance difference between current block and its collocated block in previous frame, and then check some certain modes for each sub-set. References [14, 15] propose novel intra prediction mode selection schemes in P-frames by using the temporal correlation between the

intra predicted block in the current frame and the corresponding block in its reference frame. B. Hilmi *et al.* [16] propose reducing the number of candidate modes using direct information of the co-located blocks from previous frames.

Authors of references [17, 18] propose using homogeneous character of a block to avoid splitting into smaller blocks. In [17], the homogeneity of the block is evaluated based on the edge information calculated by Sobel operator, while in [18], a fast hierarchal cross differences algorithm is proposed to estimate the homogeneity of the block.

References [19–21] propose some fast inter mode selection algorithms according to the homogeneity of the residual block. A. Yu *et al.* [19] evaluate the homogeneity of the residual block by comparing the difference between current and co-located residual blocks. In [20,21], the homogeneity of each portion of the current residual block is used to decide whether this block needs to be split into smaller blocks.

In [22], I. Choi *et al.* propose a fast SKIP mode detection algorithm on the basis of block size, reference frame, motion vector, and the transformed coefficients. Authors of [23] propose to construct a priority-based mode candidate list by adaptively projecting the modes as points onto a 2-D map, and perform mode decision of the modes from this list with early termination conditions.

Reference [24] presents a mode classification strategy that fuzzy logic technique is used to determine the possible candidate modes for a certain block. On the other hand, in work [25], it is proposed that the energy function of the transformed coefficients is adopted to sort the blocks to certain categories. Moreover, a learning based algorithm is proposed in [26], where the number of candidate inter modes is reduced according to the statistical data obtained from the previously encoded frames.

For the fast intra mode decision algorithms, in references [27–30], some fast algorithms are proposed based on the local edge information of the block, e.g. dominant direction. F. Pan *et al.* [27] advocate using Sobel operator to create a local edge direction histogram and a small part of intra prediction modes are chosen for RDO calculation based on the distribution of this histogram. In [28], the dominant direction is estimated based on the sum of absolute error of the sub-sampled block. C. Miao *et al.* [29] propose an extensive pixel-based algorithm that the direction strength of a certain mode i is calculated based on the differences between every two neighboring pixels located along the direction defined by the mode i. In reference [30], the same edge detection strategy is proposed and variance of current block is calculated to decide whether smaller blocks should be checked or not.

References [31–33] exploit the correlation between optimal coding modes of temporal and spatial adjacent blocks to reduce the computational complexity of the encoding. J. Xin *et al.* [31] propose to measure the difference between current block and its co-located block in the previous frame. If they are close enough, the current block will reuse the mode of its co-located block and the entire mode decision process is skipped. Authors of [32, 33] present a method based on the statistical properties (e.g. mode information and block size) of references pixels and adjacent blocks.

Some early termination strategies are given in [34–36]. An early termination method with adaptive threshold is developed by H. Zeng *et al.* [34], and the candidate modes are selected according to their Hadamard distances and prediction directions. The authors of [35] exploit the correlation between the sum of absolute transform difference and rate distortion to terminate or skip some unlikely prediction modes efficiently. Reference [36] proposes to construct a priority-based mode candidate list, and perform mode decision of the modes from this list

1.2 Previous researches 5

Figure 1.4: Classification tree of proposals on fast mode decision algorithms for H.265/HEVC.

with early termination conditions.

In reference [37], the proposed algorithm finds the candidate modes by analyzing the transformed coefficients of its neighboring blocks. This method modifies the mode decision scheme, which estimates the direction of current block in frequency domain. C. Tseng *et al.* [38] propose a simplified rate-distortion cost function to reduce the calculation complexity.

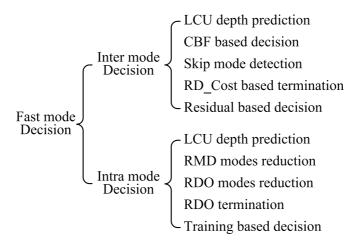

## 1.2.2 Fast mode decision algorithms for H.265/HEVC

On the basis of the fast mode decision algorithms proposed for H.264/AVC, a lot of researches have been conducted to accelerate the mode decision process for H.265/HEVC. These previous algorithms are also classified according to decision stage and criteria, as shown in the classification tree in Figure 1.4.

There are also roughly two categories of algorithms: fast inter mode decision and fast intra mode decision algorithms. The large coding unit (LCU) depth prediction schemes of both categories deliver a suitable prediction of the depth of current block. References [39–43] propose using the depth information of LCUs from reference frames and/or neighboring LCUs to predict the suitable depth range for current LCU, in order to skip unnecessary depths and/or terminate current depth check. S. Tai *et al.* [44] suggest that some specific depths of a coding unit (CU) quadtree can be eliminated by referring to the coding information of the co-located CUs and CUs adjacent to the co-located CUs. M. Cassa *et al.* [45] present a Top Skip technique in which the larger CU sizes are avoided by selecting a starting LCU depth based on an observation that there exists a high correlation between the minimum depth of the current LCU and that of the co-located LCU in the previous frame. In reference [46], proposes to skip some unlikely depth based on the texture complexity of the down-sampled LCU. Authors of [47] propose an algorithm that collects relevant and computational-friendly features to assist decision of the depth of LCU on the basis of a predefined Bayesian decision rule.

The algorithms of the coded block flag (CBF) based decision are designed to seek an early detection of the SKIP mode. In references [48, 49], the difference motion vector (DMV) and

CBF after searching the mode 2Nx2N are simply checked to detect the SKIP mode. Reference [50] introduces a method to reduce the encoding complexity by simply investigating the CBF. For the SKIP mode decision scheme, the authors of [51] propose a simple tree-pruning algorithm to exploit the observation that sub-tree computations can be skipped if the coding mode of current block is SKIP. All the mentioned proposals from the above two sub-categories have been adopted in the HEVC test model HM10 [3]. Moreover, the authors of references [52,53] present a depth range selection mechanism according to the location of a depth with SKIP mode.

As for the algorithms of RD\_Cost based termination, some proposals advocate terminating the mode decision process by comparing the RD\_Cost of current CU with pre-defined thresholds. Reference [54] presents a strategy that if the current best RD\_Cost is less than a threshold, the mode decision process will stop. Authors of [55,56] investigate a strategy that no further splitting process is necessary when the RD\_Cost of current CU is lower than the cost obtained from the modes already coded with SKIP mode. Work [57] proposes to terminate the estimation of all the RD\_Costs of the merge candidates when for any candidate of the list, the cost of the SKIP mode is inferior to the minimum of any previous RD\_Costs already computed for previous candidates.

For the residual based decision proposals, authors of [58] propose terminating the splitting process of LCU if the average and variance of the best residual of current CU are less than a pre-defined threshold. The authors of reference [59] design a fast algorithm for residual quadtree coding that replaces the original depth-first residual transform process by a merge-and-split transform process. K. Choi *et al.* [60] propose to prune a residual quadtree in the early stage based on the number of nonzero transformed coefficients. P. Chiang *et al.* [61] investigate to reduce the computational complexity of residual coding according to a fast zero block detection scheme based on the sum of absolute difference value which is available in the inter prediction computation.

In HEVC, the number of modes for intra prediction has been increased to 35, which will lead to a higher computational complexity when exhaustively checking over all candidate modes. Therefore, intra mode decision algorithms have been proposed to reduce the number of modes to be checked. Some authors propose reducing the number of modes checked by the rough mode decision (RMD) process. A. Motra et al. [62] propose to use the direction information of the co-located block of a previous frame along with the neighboring blocks of current frame as candidates to reduce the number of intra prediction modes in the RMD process. The work in [63] presents an intra mode decision algorithm that reduces the complexity by taking into account the dominant edge orientation of the current and previous depths and then calculating the dominant edge based on the differences between neighboring sub-sampled pixels along a certain direction. W. Jiang et al. [64] use the Sobel edge operators to detect the gradient of a block to accelerate the intra prediction process in HEVC, while in reference [65], the gradient of the block is calculated by summing the absolute differences between neighboring pixels located along some pre-defined directions. G. Chen et al. [66] propose a fix-point arithmetic based edge detector to analyze the textures of the source image block and select a small set of possible modes to send to the RMD process.

Algorithms that reduce the number of modes checked by the RDO process have also been proposed. Reference [67] proposes to use the mode information from spatial neighbors to reduce the number of candidates checked by the RDO process, ensuring that the most probable mode (MPM) is always checked in the RDO. This method had been added into the HM [3].

1.2 Previous researches 7

Reference [68] proposes a fast intra prediction mode decision based on estimating the rate distortion cost using Hadamard transform to reduce the number of modes sent to the RDO process. References [69, 70] propose analyzing the statistics generated by the RMD process to select a smaller set of modes output from RMD process and then send it to the RDO process combined with DC mode and MPM. The authors of [71, 72] propose to determine the best prediction mode of a CU by referring to the mode of a parent CU in the previous depth. In the technique in reference [73], a mode output from RMD can be selected as the best mode when it is similar to modes from a co-located CU in a previous frame and spatial CUs in the current fame. Various RDO termination strategies have been presented in [74] and [75].

In the last sub-category, another group of studies have been conducted based on various training methods [76–79]. Information (such as threshold) obtained from the study process can be used to stop the mode decision process of current CU if necessary or to skip modes that are thought to be unlikely.

#### 1.2.3 Hardware architecture of the transform for H.265/HEVC

Same as the previous video coding standard, an encoder can be decomposed into a series of coding stages, and each stage is conducted on the basis of different compression norm. Among these coding stages, transform coding stage plays a relatively important role. Generally, transform coding is achieved by discrete cosine transform (DCT), and the purpose of this stage is to concentrate the energy of a residual block generated from the prediction stage to the first few numerical coefficients, enabling the following quantization and entropy coding stages to be performed more efficiently.

In order to decrease the computational complexity and solve the mismatch problem between forward and inverse transforms, integer DCT rather than floating DCT is used. The largest transform size adopted in H.264/AVC is 8x8, while in HEVC, even larger sized DCT including 16x16 and 32x32 is provided, since larger sized transform could achieve higher compression ratio.

The theory of the transform for HEVC is proposed in [80–83]. The transform size is ranging from 4x4 to 32x32, and the computational complexity of which is much higher than that of H.264/AVC (transform size is 4x4 or 8x8). The corresponding transform matrixes are also given in [80–83]. The transform of HEVC is implemented on the basis of transform unit (TU) in the HM [3] using butterfly combined with multipliers method. However, the matrix multiplication is inevitable based on this method. Hence, in reference [84], it is proposed to decompose the transform matrixes into orthogonal matrixes and general matrixes with smaller elements. The number of different elements in these matrixes can be reduced after decomposing, so that the number of multiplication can be reduced.

Since the development of H.264/AVC, a variety of researches [85–90] have been proposed about the hardware implementation of its transform. Authors of [85–87] propose a direct 2-D forward transform architecture according to the symmetry properties of the transform matrixes, while taking account of eliminating drift effects, multiplying free, and reducing memory bandwidth. In [88, 89], a separate 1-D forward transform architecture with a transposition memory, realized by parallel register array, are proposed. K. Chen *et al.* [90] present a high-performance direct 2-D transform coding IP.

However, larger sized transforms used in HEVC increase the computational complexity in two aspects. One aspect is the computation logic of the transform. For larger sized transform logics need more multipliers and adders, so that more hardware resource will be consumed.

The other problem is the cost of the transpose memory. In order to store more intermediate results, more areas will be consumed by the transpose architecture. To solve the above two problems, several latest researches [91–94] about the HEVC transform have been reported.

The authors of reference [91] present area- and power-efficient architectures for the transform of HEVC. The proposed structures could be reusable for DCT of all sizes, and power-efficient structures for folded and full-parallel implementations of 2-D DCT are proposed. R. Jeske *et al.* [92] provide a 16-point 1-D transform architecture used by a 16x16 2-D transform, and this design is conducted in a fully combinational way. In reference [93], a fully pipeline based 2-D transform engine supporting variable block sizes with the efficient hardware utilization is proposed. A unified architecture for inverse transform and forward transform is devised through the algorithm optimization. S. Park *et al.* [94] present high throughput and power-efficient architectures with efficient matrix multiplication schemes.

Moreover, some works [95–97] propose combined transform architectures that supporting several popular video coding standards. In references [95, 96], unified transform architectures are investigated, which can support both the existing video coding standards like H.264/AVC [1], MPEG-2/4 [98, 99], AVS [100], VC-1 [101], and the HEVC [2]. M. Martuza *et al.* [97] present a shared architecture which can compute the 8x8 inverse transform of the HEVC from that of the H.264/AVC using a new mapping technique.

## 1.3 Objective and outline of this thesis

For the LCU depth prediction algorithm proposed in previous works, the depth information of a co-located LCU from a reference frame is used to make a prediction. Hence, the depth information of all possible reference frames needs to be stored, and this of course results in the consumption of a large amount of memory. Therefore, in this dissertation, we propose using the co-located LCU from the previous frame in an encoding order. This means that the depth information of only one frame needs to be saved while still maintaining a better performance. In the residual based decision algorithm mentioned above, the residual information is only used to terminate the current depth mode decision, but in our proposal, this obtained information is used not only to terminate but also to skip over unlikely modes and directly split current CU into the next depth. We also propose a remedy strategy to prevent prediction error propagation. For the RMD modes reduction algorithms for intra prediction, such as those using the Sobel operator, the algorithm itself is very complex, and thus we also propose a low complexity hardware-oriented fast intra prediction algorithm. Hardware synthesis results show that only 1/9 of the resources are consumed compared with previous works.

The purpose of this work is to reduce the computational complexity of the HEVC encoder without causing any noticeable performance degradation. First, in order to determine the size of current block, the depth information of a co-located block from the previous frame is used to predict the proper block size. Then, for a certain sized block, the residual generated by inter prediction is analyzed to determine whether to terminate current check or to skip over unnecessary modes and split into smaller sizes. Finally, after inter prediction, a hardware-oriented low complexity fast intra prediction algorithm is proposed. Our algorithm adopts a fast discrete cross difference (DCD) to detect the dominant direction of the coding unit. Based on DCD information, only a subset of the 35 candidate modes are selected for the RMD process. We also propose four simple but efficient early termination strategies for

Figure 1.5: The proposed mode decision process for a block.

terminating the RDO process properly. As shown in Figure 1.5, the blocks marked by dotted lines are the added processes we propose in this work.

The rest of this thesis is organized as follows. Chapter 2 gives a brief introduction about the H.265/HEVC, including the quadtree structure based block partition scheme, advanced prediction and transform coding tools, improved in-loop reconstruction filters, and three prediction structures. Chapter 3 proposes a course of low complexity fast mode decision algorithms, namely depth prediction, residual check, and fast intra mode decision algorithm. The performances of individual or combined algorithms are also analyzed. Chapter 4 presents the corresponding hardware architectures of the proposed fast mode decision algorithms in Chapter 3, and the synthesis results of each architecture are also provided. Chapter 5 describes a low cost and high throughput transform architecture for 1-D and 2-D transform in HEVC. This architecture supports a transform size ranging from 4x4 to 32x32. Chapter 6 makes a conclusion about this thesis.

## Chapter 2

## High efficiency video coding

#### 2.1 Introduction

High efficiency video coding (HEVC) is the video coding standard of the VCEG and MPEG. The main goal of the HEVC standardization effort is to enable significantly improved compression performance relative to existing standards – in the range of 50% bit-rate reduction for equal perceptual video quality.

The HEVC standard adopts the well-known hybrid block-based coding framework, containing advanced intra prediction with 35 modes, advanced motion-compensation prediction with merge technique and large-sized transform coding followed by high-efficiency entropy coding. Moreover, the reconstructed pixels will be processed by de-blocking and SAO filters before sent to the decoded picture buffer. For special case, the lossless coding [102] is also supported in the HEVC.

In the following sections, a brief introduction about the key technologies of HEVC is presented, and more detail information about HEVC is provided in references [103, 104].

## 2.2 Block partition structure and parallel scalability

## 2.2.1 Block partition structure

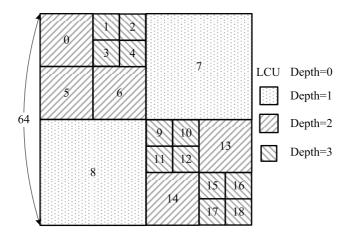

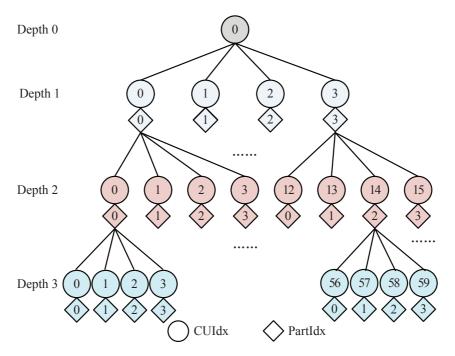

Other than the previous video coding standards, this HEVC uses a flexible quadtree block partition structure [105, 106] that enables effective use of different block sizes during the prediction and transform coding processes. As depicted in Figure 1.1, an input video image is first divided into a sequence of LCUs. An LCU, comprised of a 2Nx2N block of luma samples, can be part of a slice or a tile defined by the configuration file. LCU is broadly analogous to the concept of macroblock in H.264/AVC and an index is allocated to each LCU in raster-scanning order. All encoding procedures are conducted on the basis of LCU. Each LCU can be recursively split into four smaller blocks with the same size, called CUs. One possible way to split an LCU into CUs is illustrated in Figure 2.1.

Each CU located inside an LCU is indexed in a Z-scanning order. The CU is the basic coding region used in the intra/inter prediction coding procedure. The shape of an CU is always square and may take a block size starting from the size of the LCU going all the way down to a minimum size of 8x8 luma samples. This recursive CU splitting process can generate a content-adaptive quadtree structure, providing a flexible partition scheme and enabling efficient use of large and multiple block sizes.

Figure 2.1: Example of CU partition scheme.

As shown in Figure 2.1, different sized CUs are given different depth indexes. For example, the 1<sup>st</sup> CU with a size of 16x16 is indexed by depth 2, while the depth of 2<sup>nd</sup> CU sized by 8x8 is 3, and the whole LCU with a size of 64x64 is indexed by depth 0. Therefore, the size of CU is expressed in terms of depth. There are totally four depths from 0 to 3 defined in HEVC.

### 2.2.2 Parallel scalability

For the sake of overcoming the limitations of the parallelization approaches employed in H.264/AVC, two strategies aiming at enhancing the parallel scalability [107] of the HEVC, have been included in the HEVC, namely Tiles and wavefront parallel processing (WPP). Both of these two approaches propose to divide each frame of the video sequence into multiple partitions that can be processed in parallel. An integer number of LCUs are contained in each partition.

When the Tiles strategy is enabled during encoding process, a picture will be divided into rectangular groups of LCUs separated by vertical and horizontal boundaries, as shown in Figure 2.2. The thick lines in this figure represent the Tile boundaries. The number of tiles and the location of the corresponding boundaries can be controlled by the configuration command. The scanning order of each LCU will be also changed according to the Tiles, where LCUs will be scanned from tile to tile. An example is given in Figure 2.2. To facilitate high level parallel processing, each tile can be processed independently.

When the WPP strategy is used in the codec, each LCU row of a frame is recognized as a separated partition, and can be processed independently. An example of the WPP approach is illustrated in Figure 2.3. In this example, the LCU rows indexed by 1, 2, 3, 4 can be encoded in parallel by the corresponding threads 1, 2, 3, 4. So that, several LCU rows can be encoded in parallel. When the encoding of the LCU rows 1, 2, 3 finishes, that of the LCU rows 5, 6, 7 starts in parallel. Additionally, in order to further reduce the coding losses, the coding information, e.g. probabilities, from the second LCU of the previous LCU row, can be taken as reference when encoding current LCU row. For example, when thread 2 starts to encode LCU 8 in LCU row 2, the coding information of LCU 1 will be used as reference. So, each thread starts only when the first two LCUs are encoded in the previous thread.

| 0  | 1  | 2  | 3  | 12 | 13 | 14 | 21 | 22 | 23 |

|----|----|----|----|----|----|----|----|----|----|

| 4  | 5  | 6  | 7  | 15 | 16 | 17 | 24 | 25 | 26 |

| 8  | 9  | 10 | 11 | 18 | 19 | 20 | 27 | 28 | 29 |

| 30 | 31 | 32 | 33 | 38 | 39 | 40 | 44 | 45 | 46 |

| 34 | 35 | 36 | 37 | 41 | 42 | 43 | 47 | 48 | 49 |

| 50 | 51 | 52 | 53 | 58 | 59 | 60 | 64 | 65 | 66 |

| 54 | 55 | 56 | 57 | 61 | 62 | 63 | 67 | 68 | 69 |

Figure 2.2: Example of dividing a frame into nine Tiles.

| Thread 1 | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | LCU Row 1 |

|----------|----|----|----|----|----|----|----|----|-----------|

| Thread 2 | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | LCU Row 2 |

| Thread 3 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | LCU Row 3 |

| Thread 4 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | LCU Row 4 |

| Thread 1 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | LCU Row 5 |

| Thread 2 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | LCU Row 6 |

| Thread 3 | 48 | 49 | 50 | 51 | 52 | 53 | 54 | 55 | LCU Row 7 |

Figure 2.3: Parallel processing of each LCU row in WPP.

## 2.3 HEVC video coding technology

## 2.3.1 Prediction coding

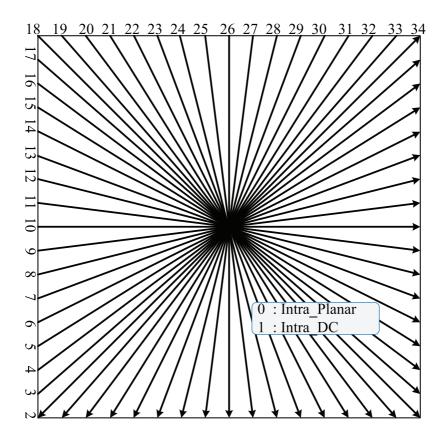

As is stated, there are 35 intra prediction candidate modes [108] for each CU for all permissible sizes, as shown in Figure 2.4. The mode indexed by 0 is called Intra\_Planar [109], which assumes the current block as an amplitude surface with horizontal and vertical slopes derived from the boundaries. The mode 1 is defined as Intra\_DC, which is similar as the DC mode defined in H.264/AVC. Other directional modes indexed by 2...34 are Intra\_Angular modes.

In practice, the intra prediction process is generally divided into two steps. Firstly, a rough

Figure 2.4: Intra prediction mode directions.

mode decision is conducted over the 35 candidate modes to select a number of sub-optimal modes based on the Hadamard transform results and estimated mode bits. Then, the chosen subset of modes are sent to the RDO process one by one to find out the best mode with lowest cost, denoted as RD\_Cost, evaluated by the distortion and the encoded mode bits. Based on the two-step search strategy, the complexity can be relatively reduced without decreasing the quality remarkably. However, there still exits a high computational complexity.

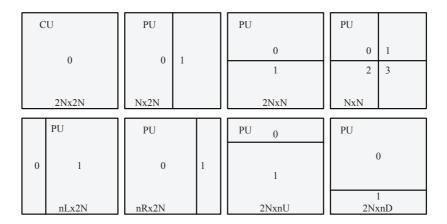

For inter prediction, in order to match the boundary of real objects, a CU can be go on divided into smaller blocks, called prediction units (PUs), as depicted in Figure 2.5. In general, the PU is not restricted to be square in shape, and can be divided into asymmetric rectangle blocks. Basically, all the possible PU partition modes should be checked to find the best one for current CU. Even though a high degree of adaptability is achieved by this PU partitioning scheme, this strategy has certain intrinsic drawbacks, that is, it may result in redundant sets of motion parameters being encoded and transmitted. Hence, a block merging technique [110] has been included in the HEVC.

#### 2.3.2 Transform coding

The transform of HEVC is implemented on the basis of transform unit (TU), which is also the basic unit for quantization. TUs are also formed in a quadtree structure with a root located in residual CU, which means that a residual CU can be recursively divided into four blocks with a size starting from that of residual CU down to a certain size, which is derived from

Figure 2.5: Partition modes for inter PU.

Figure 2.6: Example of TU splitting structure.

the parameter – maximum quadtree depth – specified in the slice header syntax. In HEVC, a TU may take the size from 4x4 up to 32x32 luma samples. Therefore, each residual CU may contain one or more TUs, in which the multiple TUs are arranged in a quadtree structure. As the dashed line illustrated in Figure 2.6, the residual CU indexed by 23 is divided into smaller blocks to transform. This division of residual CU 23 can be converted into tree structure as the quadtree depicted on the right part.

To encode the transformed coefficients, a unique entropy coding tool is used in all configurations of HEVC, i.e. context adaptive binary arithmetic coding (CABAC) [111, 112], compared with H.264/AVC. The core of the CABAC coding engine of HEVC is essentially the same as the CABAC used in H.264/AVC, other than some improvements in the details of practice implementation. For example, relatively fewer contexts are used in HEVC compared with H.264/AVC standard, and also the memory requirements are reduced to benefit both throughput and implementation costs. Moreover, in reference [113], a method for analyzing the dynamic range along the data-path of the residual encoding and reconstruction is

presented.

#### 2.3.3 Pixel reconstruction

In HEVC, two filters are designed for the reconstructed pixels, namely de-blocking filter and SAO filter. The de-blocking filter [114] is used to reduce visible artifacts at block boundaries, which are due to the usage of a series of block-based coding tools. The de-blocking process is applied to all samples adjacent to each CU boundary in the same order as the reconstruction process, except following cases when the CU boundary is also the boundary of a frame, or when de-blocking process is not permitted across slice or tiles boundaries. In this process, vertical edges are first filtered by using the horizontal filter, and then horizontal edges are filtered by vertical filter. The minimum CU with a size of 8x8 is the filtering unit, for both luma and chroma components. Hence, the boundaries aligned on a 4x4 block are not filtered, so as to reduce the complexity, which is different from H.264/AVC.

The SAO [115] is a process which modifies the values of the reconstructed pixels after the de-blocking filter through look-up tables. The SAO filter aims to improve the accuracy of the amplitudes of the reconstructed pixels compared with the original pixels. The SAO is applied adaptively to all the pixels, by conditionally adding an offset value to each pixel based on the information from look-up tables defined by the encoder. That is, depending on the local gradient at the position of a certain pixel, a corresponding offset value picked up from a look-up table is added to this reconstructed pixel. The SAO is designed to improve the subjective performance of the codec, and this filter can be selectively turned on or turned off in the configuration file.

### 2.4 Prediction structure

The HM encoder [3] defines three kinds of temporal prediction structures as test conditions for simulation: intra-only, low-delay, and random access. The management of the reference picture list(s) corresponding to each prediction structure is given in [116, 117].

For the intra-only prediction structure, all the frames of a video sequence are encoded as instantaneous decoding refresh (IDR) pictures. Inter prediction between pictures is not used. Coding parameters for a picture, such as Qp, do not change during the encoding process of the whole sequence, and all the pictures belong to the same layer  $L_0$ . Layer is used to describe a group of pictures that are encoded with the same parameters. Layer is also used to denote the importance of this group of pictures. The smaller the index of layer is, the more importance it is. Figure 2.7 gives a graphical illustration of the intra-only prediction structure, where the number assigned to each frame represents the encoding order.

In the test case of low-delay coding, as a normal coding configuration, only the first frame of a video sequence is encoded as an IDR picture. All other pictures are coded as P pictures using inter prediction. These P pictures are classified to different layers, from  $L_1$  to  $L_3$ , according to the encoding order. Coding parameters for a frame, such as Qp, will also change as the layer index. Figure 2.8 shows a graphical presentation of this low-delay P configuration. The number associated with each frame represents the encoding order. The arrow in this figure points to the reference picture.

For the random access test condition, a so-called hierarchical B structure is adopted for encoding. Figure 2.9 gives a graphical explanation of a random access prediction structure,

2.4 Prediction structure 17

Figure 2.7: Graphical presentation of intra-only prediction structure.

Figure 2.8: Graphical presentation of low-delay P prediction structure.

Figure 2.9: Graphical presentation of random access prediction structure.

where the index of each picture denotes the encoding order. Unlike the low-delay coding, an intra picture is encoded at regular intervals defined in the configuration file. Among them, the first intra picture of a video sequence is encoded as an IDR picture while others are non-IDR intra pictures. The remaining pictures located between two intra pictures are encoded as P or B pictures. That is, the picture belong to layer  $L_1$  is a P picture, and others associated with

layers from  $L_2$  to  $L_4$ , are encoded as B pictures.

#### 2.5 Conclusion

In this chapter, a brief introduction about the H.265/HEVC was presented. In order to achieve a better performance, a course of state-of-the-art techniques had been adopted in HEVC. First, during the prediction and transform coding processes, a flexible quadtree based block partition scheme was supported. Approaches, such as Tiles and WPP, were taken in to enhance the parallel scalability. Then, for the prediction coding, an enhanced intra prediction with 35 candidate modes as well as a flexible motion-compensation prediction with merging technology were employed. Next, larger sized transform and advanced CABAC engine were applied to encode the residual, and a de-blocking filter along with a newly SAO filter were used to filter the reconstructed samples. Finally, three common used test conditions were introduced.

## Chapter 3

# Hierarchical structure based fast mode decision for H.265/HEVC

#### 3.1 Introduction

In this chapter, a course of low complexity fast mode decision algorithms [118] are presented. First, the depth information of a co-located block from a previous frame is used to predict the size of current block. Next, for a certain sized block, the inter prediction residual is analyzed to determine whether to terminate the current check or to skip over unnecessary modes and split the block into smaller sizes. After inter prediction, a hardware-oriented low complexity fast intra prediction algorithm is proposed. A fast DCD is adopted to detect the dominant direction of the block. In addition, four simple but efficient early termination strategies are proposed to terminate the RDO process properly.

## 3.2 Depth prediction

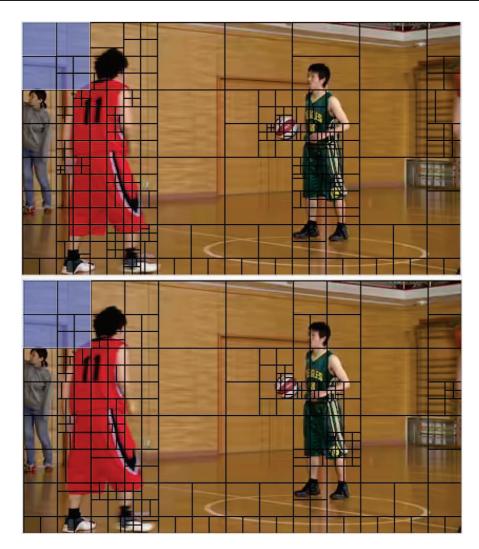

It is well-known that, the consecutive frames from nature video sequence tend to be similar, for the objects in the video always moving continuously. As is shown in Figure 3.1, the contents of the two successive frames are almost same, and the partition structure of LCUs located in the same position is also similar to each other. The partition structure is generated using the HEVC reference software HM. Such as the first LCU in both frames, they split in the same way, and generate same sized CUs in the same place.

As stated, the size of CU is expressed in terms of depth, which means that if the depth of current CU can be predicted, its size will also be known. While other impossible sizes (depths) can be directly skipped to reduce the complexity. Based on these analysises, maybe the partition structure of the co-located LCU, which has already been encoded, can be used to predict the depth of current LCU. To achieve this, the relationship between current LCU and co-located one should be made clear first.

#### 3.2.1 Correlation between co-located LCU and current LCU

Generally, an LCU with a larger depth means that there is detail texture inside this block, and hence, smaller CU sizes such as 8x8, are preferred to encode this LCU. Whereas, for LCU within a homogeneous region, large block partition will be better. Therefore, in this work,

Figure 3.1: Example of LCU partition for two consecutive frames.

we proposed to classify different LCUs into different categories corresponding to different texture characters. There are three categories defined: simple, complex, medial. An LCU will be classified as complex when at least one of the CUs inside this LCU takes the maximum depth, 3 as defined. On the other hand, when all the CUs takes the depth not larger than 1, this LCU will be seen as simple. The rest LCUs will be defined as medial.

The distributions of the occurrence ratios of these three kinds LCUs are estimated over some video sequences, under three different coding structures (Section 2.4), and other configurations are defined in [123]. A single Qp value of 32 is used for this simulation. The results are shown in Table 3.1. From this table, we can see that the distributions of the ratios under different coding structures are different from each other. But for all these three coding structures, the sum of the ratios of simple and complex LCUs always holds a high percentage, while the ratio of medial LCU is around 10%.

Based on Table 3.1, the relationship of the depths of the current LCU and the co-located LCU from the previous frame is analyzed, and the results are given in Table 3.2. A single Qp value of 32 is used for this simulation. In this table, the "NoMaxDepth" column shows the occurrence ratio of such LCU that no CUs inside it takes the maximum depth when the

|--|

| Sequence |                 | All intra |         |        | Low-delay P |         |        | Random access |         |        |

|----------|-----------------|-----------|---------|--------|-------------|---------|--------|---------------|---------|--------|

|          |                 | Simple    | Complex | Medial | Simple      | Complex | Medial | Simple        | Complex | Medial |

| Class A  | Traffic         | 10.8      | 81.7    | 7.5    | 67.7        | 21.1    | 11.2   | 77.0          | 15.5    | 7.5    |

|          | PeopleOnStreet  | 6.1       | 91.3    | 2.7    | 24.4        | 64.0    | 11.6   | 31.4          | 54.4    | 14.2   |

| Class B  | Kimono          | 61.9      | 18.8    | 19.3   | 59.4        | 15.5    | 25.1   | 71.7          | 11.5    | 16.8   |

|          | ParkScene       | 17.7      | 78.4    | 3.9    | 55.6        | 34.1    | 10.3   | 68.1          | 24.7    | 7.2    |

|          | Cactus          | 14.0      | 77.7    | 8.3    | 63.1        | 25.8    | 11.1   | 71.1          | 20.6    | 8.3    |

|          | BQTerrace       | 20.6      | 76.5    | 2.8    | 65.8        | 25.9    | 8.3    | 79.5          | 16.3    | 4.3    |

|          | BasketballDrive | 35.2      | 48.9    | 15.9   | 67.8        | 20.1    | 12.0   | 73.5          | 16.8    | 9.7    |

| Class C  | RaceHorsesC     | 5.1       | 90.5    | 4.3    | 22.0        | 63.1    | 14.9   | 33.2          | 50.5    | 16.4   |

|          | BQMall          | 4.8       | 90.9    | 4.3    | 45.0        | 45.2    | 9.8    | 54.4          | 34.5    | 11.1   |

|          | PartyScene      | 0.4       | 99.2    | 0.4    | 31.2        | 56.0    | 12.8   | 48.7          | 42.2    | 9.1    |

|          | BasketballDrill | 1.4       | 96.0    | 2.6    | 52.5        | 36.2    | 11.3   | 58.9          | 28.9    | 12.2   |

| Class D  | RaceHorses      | 0.6       | 98.4    | 1.0    | 4.0         | 81.6    | 14.4   | 11.0          | 64.5    | 24.5   |

|          | BQSquare        | 0.0       | 97.7    | 2.3    | 26.8        | 45.2    | 28.0   | 52.6          | 23.6    | 23.8   |

|          | BlowingBubbles  | 0.1       | 99.8    | 0.1    | 19.8        | 57.2    | 23.0   | 36.5          | 38.9    | 24.6   |

|          | BasketballPass  | 11.4      | 83.0    | 5.6    | 42.6        | 34.4    | 23.0   | 50.4          | 24.8    | 24.8   |

| Class E  | Vidyo1          | 18.5      | 61.2    | 20.3   | 81.1        | 5.5     | 13.4   | 83.7          | 4.8     | 11.5   |

|          | Vidyo3          | 26.8      | 61.1    | 12.1   | 75.8        | 10.2    | 14.1   | 81.1          | 6.8     | 12.1   |

|          | Vidyo4          | 23.6      | 60.3    | 16.1   | 79.8        | 7.3     | 12.9   | 82.6          | 6.0     | 11.4   |

| AVG      |                 | 14.4      | 78.4    | 7.2    | 49.1        | 36.0    | 14.8   | 59.2          | 27.0    | 13.9   |

Table 3.2: Correctness (%) of prediction from co-located LCU to current LCU.

|         | Saguanaa        | All        | intra       | Low-c      | lelay P     | Randon     | n access    |

|---------|-----------------|------------|-------------|------------|-------------|------------|-------------|

|         | Sequence        | NoMaxDepth | NoMiniDepth | NoMaxDepth | NoMiniDepth | NoMaxDepth | NoMiniDepth |

| Class A | Traffic         | 84.1       | 99.0        | 90.5       | 76.4        | 91.3       | 68.7        |

| Class A | PeopleOnStreet  | 86.7       | 99.5        | 88.9       | 98.2        | 84.2       | 96.3        |

|         | Kimono          | 97.2       | 96.4        | 94.6       | 91.7        | 96.3       | 89.7        |

|         | ParkScene       | 91.9       | 99.1        | 84.2       | 78.4        | 87.9       | 76.5        |

| Class B | Cactus          | 90.2       | 99.2        | 93.7       | 90.3        | 92.4       | 85.1        |

|         | BQTerrace       | 92.1       | 98.6        | 85.2       | 68.0        | 93.0       | 72.6        |

|         | BasketballDrive | 91.2       | 97.7        | 95.4       | 90.2        | 94.6       | 86.7        |

|         | RaceHorsesC     | 75.9       | 99.6        | 76.3       | 96.7        | 74.0       | 94.9        |

| Class C | BQMall          | 81.0       | 99.7        | 87.3       | 90.5        | 87.9       | 89.9        |

| Class C | PartyScene      | 73.9       | 100.0       | 70.1       | 87.8        | 82.5       | 89.2        |

|         | BasketballDrill | 59.5       | 99.8        | 90.2       | 90.9        | 88.3       | 86.6        |

|         | RaceHorses      | 60.0       | 99.9        | 49.2       | 99.8        | 53.6       | 97.9        |

| Class D | BQSquare        | -          | 100.0       | 60.8       | 85.7        | 84.3       | 79.8        |

| Class D | BlowingBubbles  | -          | 99.9        | 66.8       | 94.3        | 77.2       | 92.0        |

|         | BasketballPass  | 86.2       | 99.9        | 92.1       | 93.8        | 90.4       | 90.2        |

|         | Vidyo1          | 96.8       | 99.5        | 97.4       | 58.2        | 97.0       | 56.5        |

| Class E | Vidyo3          | 93.4       | 98.4        | 97.1       | 78.0        | 96.2       | 66.0        |

|         | Vidyo4          | 92.0       | 98.5        | 97.1       | 68.2        | 96.7       | 64.5        |

|         | AVG             | 84.5       | 99.1        | 84.3       | 85.4        | 87.1       | 82.4        |

co-located LCU is classified as simple. The average value of "NoMaxDepth" is around 85%. In other words, if co-located LCU is a simple one, large sized CUs are coded inside it. Hence there will also be a high probability that current LCU will be coded using large sized CUs, and then maximum depth will not appear. While "NoMiniDepth" is equal to the occurrence ratio of such LCU that the minimum depth is not suitable for it when the co-located LCU is tested as complex. The value of "NoMiniDepth" is around 90%.

#### 3.2.2 Complexity reduction

To make a prediction, after encoding one frame, the depth information has to be saved, so that later coded frames can refer to these data. In reference [41], co-located LCUs from reference frames are used, in this case, depth information of all the possible reference frames has to be stored. This will cause a large memory cost, when implemented on hardware platform. In order to reduce the complexity introduced by saving the depth information of co-located LCU, it is proposed in this chapter that co-located LCU from the previous frame in encoding order will be used so that depth information of only one frame needs to be saved.

Based on the definition of LCU classification, to classify one LCU, only the maximum depth of the CUs inside it will be needed. Compared with [39, 42], in which the depth range of current LCU is predicted using minimum and maximum depth information of co-located or spatial neighboring LCUs, in our proposal only the maximum depth information needs to store.

#### 3.2.3 Implementation of depth prediction algorithm

As we can see from Table 3.2, the depth prediction is not always 100% accurate. The optimal depth of an LCU might be skipped due to a wrong prediction, and such prediction errors can accumulate during the encoding process. Therefore, we propose that for the last frame of every N frames, all possible sized CUs corresponding to the whole depth range will be checked in order to maintain the performance. That is, depth prediction is turned off for the last one of every N frames. The number N is selected by taking account of the GOP size and many simulation results.

The proposed depth prediction algorithm is explained by pseudo codes as:

```

Algorithm Depth Prediction

while current LCU != last LCU do

if (depth information of co-located LCU is available

&& mod(POC 	ext{ of current picture}, N) != 0) then

for depth = 0 to 3 do

if (co-located LCU is complex && depth == 0) then

skip check on current depth;

depth ++;

else if (co-located LCU is simple && depth == 3) then

terminate check on current depth;

break:

else

check current depth;

depth ++;

end if

end for

else

test all CU sizes according to the whole depth range;

store maximum depth information of current LCU;

end while

```

#### 3.3 Residual check

In this section, we will analyze the motion character of each portion of a CU based on its residual information to decide the following encoding flow.

#### 3.3.1 Residual characteristic analysis

After motion estimation, there may be some portions, whose motion compensation residuals may contain a significant amount of energy if motion estimation mismatches these regions. Whereas energy will tend to be lower in matched area. If the mismatched energy is too high, the movement of objects inside this CU is inconformity.

Therefore, a different motion estimation, motion vector to be exact, is needed for the mismatched region. Consequently, current CU will possibly need to split into PUs or smaller sized CUs to match the movement of each small portion.

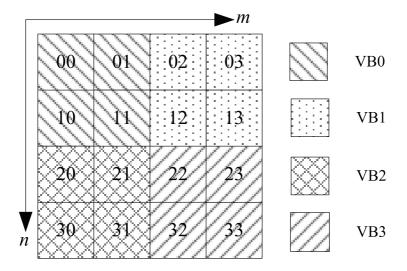

In order to detect the motion character of each portion inside a CU, we propose to divide the residual block, generated by inter prediction with 2Nx2N partition mode, into sixteen sub-blocks (four, when depth is maximum), as depicted in Figure 3.2. The sizes of these sub-blocks are 16x16, 8x8, 4x4, 4x4 corresponding to the depth 0 to 3, respectively.

Then, the average and sum of absolute difference over average (SADA) of each sub residual block are calculated. The average and SADA are calculated by

$$Avg = \frac{1}{S * S} \sum_{m=0}^{S-1} \sum_{n=0}^{S-1} p(m, n),$$

(3.1)

3.3 Residual check 25

Figure 3.2: Division a CU into 16 sub-blocks.

$$SADA_{ij} = \sum_{m=0}^{S-1} \sum_{n=0}^{S-1} |p(m,n) - Avg_{ij}|,$$

(3.2)

where (i, j) is the index of sub-blocks; p(m, n) is the value of the residual pixel in position (m, n) inside the sub-block indexed by (i, j) and  $Avg_{ij}$  is the average of this sub-block. S is the size of current sub-block.

Since *SADA* is broadly analogous to the concept of variance, it can be used to reflect the character of a block. If the *SADA* is lower than a threshold, noted as *ThS mooth*, current sub residual block can be recognized as a smooth or homogeneous region.

ThS mooth is defined as

$$ThS \, mooth = \begin{cases} (d + uiDepth) * ((1 << 2) << 2), & uiDepth = 3 \\ (d + uiDepth) * ((1 << (4 - uiDepth)) << (4 - uiDepth)), & otherwise \end{cases}$$

(3.3)