| Title                                       | A Study on Modeling and Mitigating Wire Shape<br>Variation with Measurement Data Analysis |

|---------------------------------------------|-------------------------------------------------------------------------------------------|

| Author(s) 福田, 大輔  Citation 大阪大学, 2015, 博士論文 |                                                                                           |

|                                             |                                                                                           |

| URL                                         | https://doi.org/10.18910/53944                                                            |

| rights                                      |                                                                                           |

| Note                                        |                                                                                           |

### Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

# A Study on Modeling and Mitigating Wire Shape Variation with Measurement Data Analysis

# Submitted to Graduate School of Information Science and Technology Osaka University

July 2015

Daisuke FUKUDA

## **Publication list**

#### Journal papers

- 1. D. Fukuda, K. Watanabe, N. Idani, Y. Kanazawa, and M. Hashimoto, "Edge-over-Erosion Error Prediction Method Based on Multi-Level Machine Learning Algorithm," *IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences*, vol. E97-A, no. 12, pp. 2373-2382, Dec. 2014.

- 2. D. Fukuda, K. Watanabe, Y. Kanazawa, and M. Hashimoto, "Modeling the Effect of Global Layout Pattern on Wire Width Variation for On-the-Fly Etching Process Modification," *IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences*, vol. E98-A, no. 07, pp. 1467-1474, Jul. 2015.

#### Conference papers with referee

1. D. Fukuda, T. Shibuya, N. Idani, and T. Karasawa, "Full-Chip CMP Simulation System," In *International Conference on Planarization/CMP Technology (ICPT)*, pp. 187-194, Oct. 2007.

#### Conference papers without referee

- 1. D. Fukuda, I. Nitta, Y. Kanazawa, T. Shibuya, N. Idani, T. Karasawa, O. Yamasaki, and M. Ito, "Yield Enhance Technique Using CMP Simulation in Design and Manufacturing Process," In *Proceedings of IPSJ DA Symposium*, pp. 271-276, Aug. 2008 (in Japanese)

- 2. D. Fukuda, H. Matsuoka, and T. Shibuya, "Modeling of Layout Dependent Copper Electrochemical Plating," In *IEICE Technical Report*, VLD2006-15, vol. 106, no. 113, pp.7-12, Jun. 2006 (in Japanese)

## **Abstract**

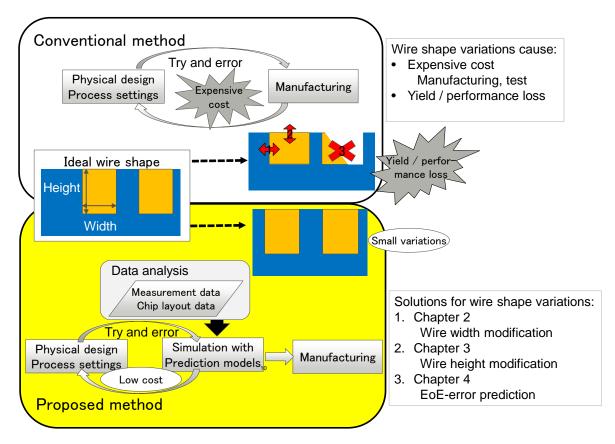

This thesis discusses prediction and mitigation methods of wire shape variation. Wire shape variations have a large impact on chip performance and yield, but they are found after manufacturing process. Once unacceptable wire shape variation is detected from fabricated chips, process or chip layout tunings are launched. Hence, this conventional countermeasure costs a huge amount of time and money. In addition, this conventional countermeasure may be applied iteratively in trial-and-error manner because the effect of tunings cannot be estimated correctly before fabrication. In the worst case, the iteration does not converge and acceptable shape cannot be obtained.

In nano-scale processes, copper interconnect is mainly adopted and formed with damascene fabrication process. Wire shape variations of copper interconnect consist of wire width variation and wire height variation. Additionally, in recent advanced technologies, irregular open / short error called Edge-over-Erosion error (EoE-error) occurs frequently. This error is hardly predicted in conventional simulation models. The purpose of this thesis is to predict wire shape variations accurately and to mitigate its impact before manufacturing for improving yield and productivity. For this purpose, the main causes of each variation need to be identified first. Then, an accurate prediction model for each variation is constructed with analysis of measurement data obtained from manufacturing process and chip layout characteristics extracted from chip design data.

This thesis firstly presents a prediction model of wire width variation. The main cause of unexpected wire width variations originates from etching process. The analysis of measurement data and chip layout characteristics reveals that wire width variation heavily depends on the chip layout even distant from a wire of interest. From this fact and qualitative properties of etching process, this thesis proposes a prediction model. This thesis also proposes a wire width adjustment method that tunes the etching process on the fly using the proposed prediction model. Experimental results show that the proposed wire width adjustment method reduces the gap between target value and real value by 68.9% in a test case.

This thesis secondly presents a mitigation method of wire height variation with ECP (Electro-Chemical Plating) and CMP (Chemical Mechanical Planarization) prediction models. ECP is a copper deposition process to fill up wire trenches and CMP is a technique to remove redundant copper after ECP process. In this thesis, three problems which the mitigation method faces for the practical use are discussed: how to efficiently handle huge chip data, insufficient accuracy of ECP model, and how to predict hard-to-detect errors effectively. To solve these problems, this thesis develops an efficient data extraction tool from GDSII data format. In addition, this tool extracts necessary data quickly from the information on dummy fill modification without updating GDSII file. Therefore, this tool can reduce large processing cost of layout characteristics extraction and dummy fill modification. This study then improves an ECP process prediction model. Although ECP process strongly affects the final chip surface topography, the accuracy of existing ECP prediction model is not sufficient.

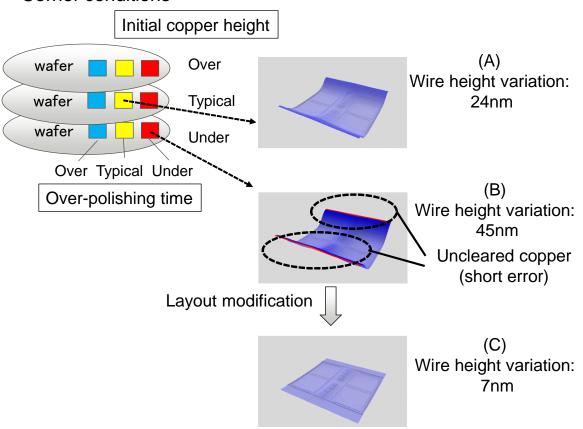

iv Abstract

The improved model can reduce the error of initial copper shape by 51.1% - 68.2%. Based on these methods, an effective hot-spot detection method considering die-to-die variations is devised, where a hot-spot is defined as the point which may degrade timing or manufacturing yield due to the wire height variations occurred in ECP and CMP processes. Die-to-die variations have a great impact on final wire height variations, but ECP and CMP prediction models cannot take care of die-to-die variations directly. Thus, this work defines corner conditions of ECP and CMP process variations, and finds the short-error in those corner conditions. By performing the model-guided layout modification to eliminate these error, wire height variations of chip surface is reduced by 84.4% and these short-errors are avoided before manufacturing.

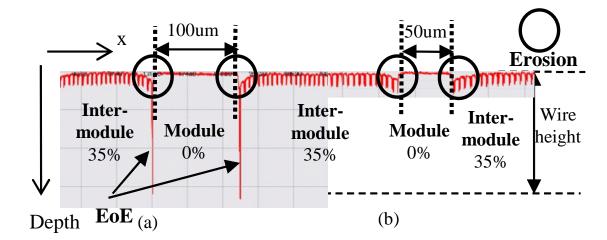

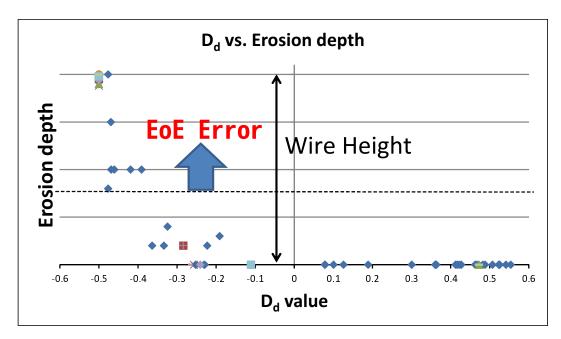

Finally, this thesis proposes an EoE-error prediction method in CMP process with a novel multi-level machine learning technique. EoE-errors occur at copper removal stage of CMP process at which multiple materials are polished simultaneously. The cause of this error is unexpected over-polishing with more than ten times larger removal rate of copper than ordinary rate, which leads to open errors. On the other hand, the mechanism of EoE-error occurrence is complicated and is not understood well enough. Therefore, to find parameters which affect EoE-error, data analysis is executed with error measurement data of a test chip and its layout characteristics. An EoE-error prediction model is constructed from these parameters using the proposed multi-level machine learning method. Experimental results show that the proposed method can predict EoE-errors with 89.6-89.7% accuracy.

With utilizing these proposed methods, wire shape variations occurred in manufacturing process can be estimated before fabrication, and the risk of chip performance reduction and yield loss can be mitigated in design time.

# Acknowledgments

First of all, I would like to express my deepest gratitude to Professor Takao Onoye in Osaka University for providing me a precious opportunity and an excellent environment to study as a doctoral student in his laboratory.

I have no adequate words to express my heartfelt appreciation to Associate Professor Masanori Hashimoto in Osaka University. All of my productive researches are credited to none other than him. His advanced perspective and thoughtful advises led me to successful achievements.

I would like to express my appreciation to Professor Kouji Nakamae in Osaka University for detailed review and insightful suggestions.

I am deeply grateful to Professor Masaharu Imai, Professor Tatsuhiro Tsuchiya, Professor Haruo Takemura, Professor Makoto Nakamura, Professor Akihisa Yamada, and Professor Yasuhiro Yoshida in Osaka University for useful advices.

I would like to express my sincere appreciation to Professor Hidetoshi Onodera in Kyoto University, Professor Kazutoshi Kobayashi in Kyoto Institute of Technology, for their valuable lectures of VLSI design.

I would like to express my sincere appreciation to Mr. Shinichi Wakana, Mr. Kaoru Kawamura, and Mr. Toshiyuki Shibuya in Fujitsu Laboratories LTD. for providing me an opportunity to go to Osaka University for a doctoral course. Without their guidance and encouragement this thesis would not have been possible.

I would like to express my gratitude to Mr. Naoki Idani in Mie Fujitsu Semiconductor LTD., Mr. Kenichi Watanabe in Fujitsu Semiconductor LTD., Mr. Toshiyuki Karasawa in Fujitsu Ltd., Ms. Izumi Nitta, Mr. Yuji Kanazawa in Fujitsu Laboratories LTD., for their helpful advices, discussion, feedback, and guidance that allowed this research to progress.

I owe my deepest gratitude to Mr. Hidetoshi Matsuoka, Dr. Takahide Yoshikawa, Dr. Rafael Kazumiti Morizawa, Mr. Tatsuru Matsuo, Mr. Tsutomu, Ishida, Mr. Toshiro Uchida, Mr. Ryo Endo in Fujitsu Laboratories LTD., Mr. Masaru Ito, Mr. Osamu Yamasaki, Mr. Eizi Kondo in Socionext Inc., for their insightful comments and suggestions.

This work is supported by Fujitsu Laboratories LTD. I thank for permission to study in Osaka University. The integrated chips in this thesis has been fabricated and measured in Mie Fujitsu Semiconductor LTD.

I would like to thank Ms. Yuki Yoshida, and Ms. Tomomi Kondo for their various supports throughout my student life.

Finally I would like to thank my wife Ayumi and my son Michiyuki for their encouragements and assistance throughout my career. For their support, I dedicate this thesis to them.

# Contents

| Chapter 1 | Introduction                                                          | 1  |

|-----------|-----------------------------------------------------------------------|----|

| 1.1       | Sources of wire shape variations                                      | 1  |

|           | 1.1.1 Lithography                                                     | 2  |

|           | 1.1.2 Etching                                                         | 3  |

|           | 1.1.3 ECP and CMP                                                     | 3  |

|           | 1.1.4 Effects of each process on wire shape variation                 | 5  |

| 1.2       | Problems in manufacturing processes                                   | 6  |

|           | 1.2.1 Wire width variation                                            | 7  |

|           | 1.2.2 Wire height variation                                           | 7  |

|           | 1.2.3 EOE-error                                                       | 7  |

| 1.3       | Objective of this thesis                                              | 8  |

| Chapter 2 | Modeling the effect of global layout pattern on wire width Variation  |    |

|           | for On-the-Fly Etching Process Modification                           | 13 |

| 2.1       | Introduction                                                          | 13 |

| 2.2       | Overview of etching process                                           | 15 |

| 2.3       | Prediction and mitigation of wire width variation                     | 17 |

|           | 2.3.1 Definitions                                                     | 17 |

|           | 2.3.2 Proposed prediction model                                       | 19 |

|           | 2.3.3 On-the-fly wire width adjustment via etching process modifi-    |    |

|           | cation                                                                | 20 |

| 2.4       |                                                                       | 22 |

| 2.5       | Conclusion                                                            | 25 |

| Chapter 3 | A practical wire height mitigation method with ECP and CMP simulation | 27 |

| 3.1       |                                                                       | 27 |

| 3.2       |                                                                       | 30 |

|           | 3.2.1 Extraction                                                      | 30 |

|           |                                                                       | 31 |

|           |                                                                       | 31 |

|           |                                                                       | 32 |

|           | 3.2.5 Calibration                                                     | 32 |

| 3.3       | Issues to be solved for practical use of the proposed method          | 32 |

|           | 3.3.1 Handling huge chip data                                         | 32 |

|           | 3.3.2 Accuracy of ECP model                                           | 33 |

|           | 3.3.3 Effective methods for analysis of the results                   | 33 |

| 3.4       | Proposed approach                                                     | 33 |

<u>viii</u> Contents

|              | 3.4.1 Chip data extraction with virtual dummy filling method 3.4.2 Refined ECP model |    |

|--------------|--------------------------------------------------------------------------------------|----|

|              | 3.4.3 Effective hot-spot detection method                                            | 38 |

| 3.5          | Experimental results                                                                 | 40 |

| 3.6          | Conclusion                                                                           | 43 |

| Chapter 4    | Edge-over-Erosion error prediction based on multi-level machine                      |    |

|              | learning                                                                             | 45 |

| 4.1          | Introduction                                                                         | 45 |

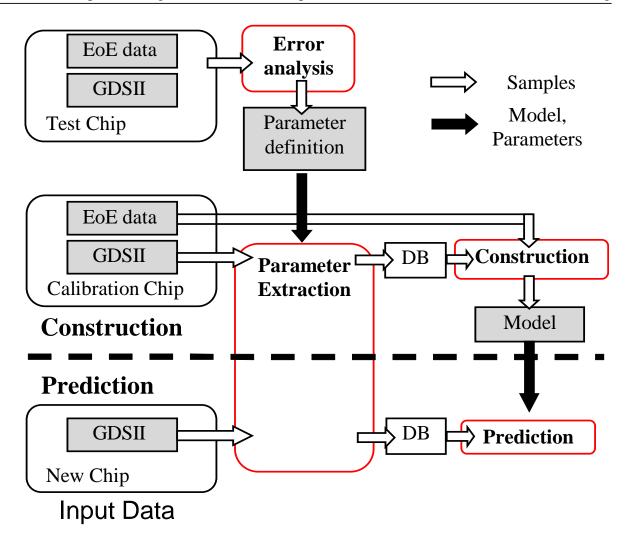

| 4.2          | Concept and overview                                                                 | 47 |

|              | 4.2.1 Concept of EoE-error prediction method                                         | 47 |

|              | 4.2.2 Overview of EoE-error prediction method                                        | 47 |

| 4.3          | Error analysis and parameter extraction stages                                       | 49 |

| 4.4          | Model construction and prediction stage                                              | 54 |

|              | 4.4.1 Machine learning algorithms                                                    |    |

|              | 4.4.2 Multi-level machine learning algorithm                                         |    |

|              | 4.4.3 Model construction and prediction flow                                         |    |

| 4.5          | Experimental results                                                                 |    |

| 4.6          | Conclusion                                                                           |    |

| Chapter 5    | Conclusion                                                                           | 65 |

| Bibliography |                                                                                      | 67 |

# List of tables

| 2.1<br>2.2 | Details of calibration / validation chip designs      |    |

|------------|-------------------------------------------------------|----|

| 3.1        | Comparison with commercial tool in extraction process | 42 |

| 4.1        | Confusion matrix                                      | 54 |

| 4.2        | Details of calibration / validation chips             | 60 |

| 4.3        | Prediction performance comparison                     | 60 |

# List of figures

| 1.1  | Manufacturing flow of wire forming                                            | 2  |

|------|-------------------------------------------------------------------------------|----|

| 1.2  | CMP process apparatus                                                         | 4  |

| 1.3  | Multi stage CMP process                                                       | 5  |

| 1.4  | Cross sectional view of interconnect layer                                    | 8  |

| 1.5  | General structure of this thesis                                              | 9  |

| 2.1  | Common test structure on a wafer                                              | 14 |

| 2.2  | Overview of RIE system                                                        | 16 |

| 2.3  | Anisotropic and isotropic etching                                             | 16 |

| 2.4  | Sidewall protection                                                           | 17 |

| 2.5  | Relationship between DICD, FICD, and target wire width                        | 18 |

| 2.6  | Region for parameter $\overline{m}$ calculation                               | 20 |

| 2.7  | Procedure of on-the-fly wire width adjustment via etching process modifi-     |    |

|      | cation                                                                        | 21 |

| 2.8  | Estimated etching vs. measured etching bias for calibration data              | 23 |

| 2.9  | Model calibration results with various effective lengths                      | 23 |

| 2.10 | Estimated etching vs. measured etching bias for validation data               | 25 |

| 2.11 | CD loss distribution of validation chips                                      | 26 |

| 3.1  | Definition of dishing and erosion                                             | 28 |

| 3.2  | Flow for mitigating wire height variation                                     | 29 |

| 3.3  | Parameters extracted from a mesh                                              | 30 |

| 3.4  | Definition of height and step height                                          | 31 |

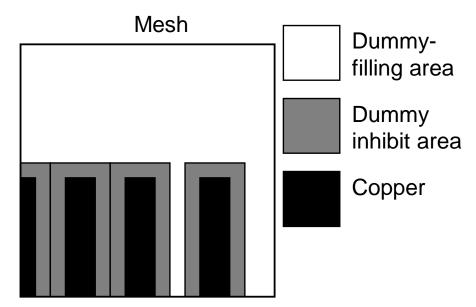

| 3.5  | Definition of dummy-filling area                                              | 34 |

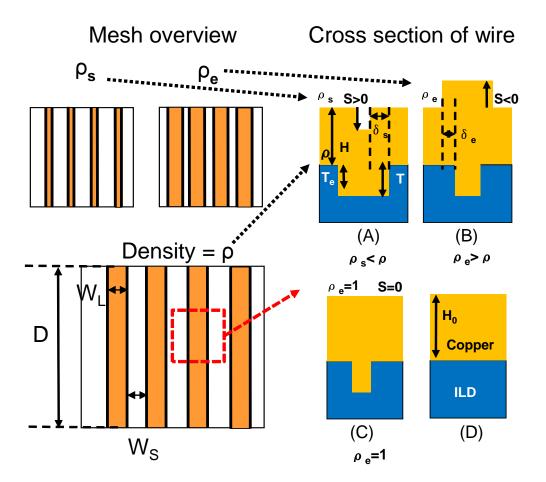

| 3.6  | 3 patterns of ECP topography                                                  | 36 |

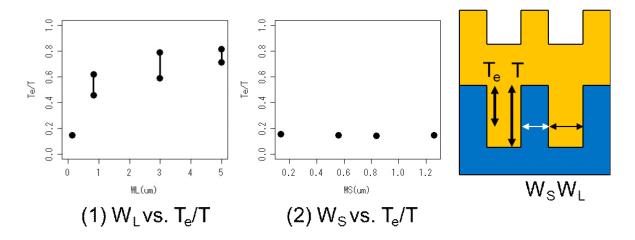

| 3.7  | Relationship between parameter $T_e$ and line width / space                   | 37 |

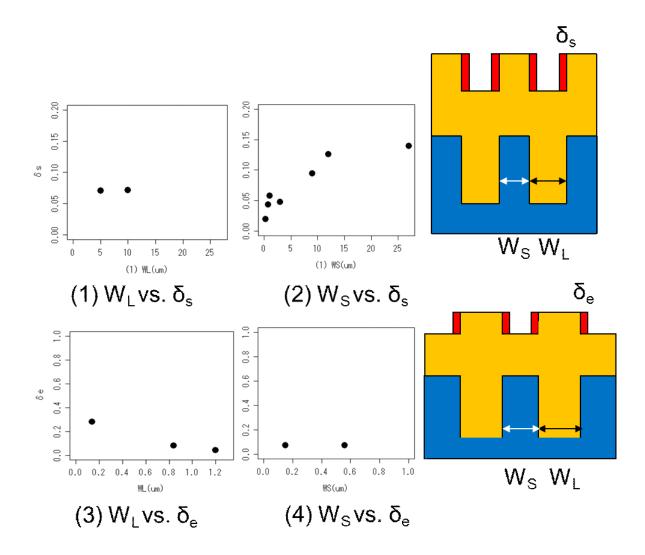

| 3.8  | Relationship between parameter $\delta_s$ , $\delta_e$ and line width / space | 38 |

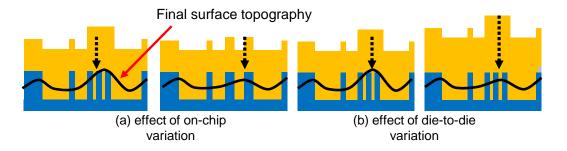

| 3.9  | Relationship between ECP topography and final surface topography              | 39 |

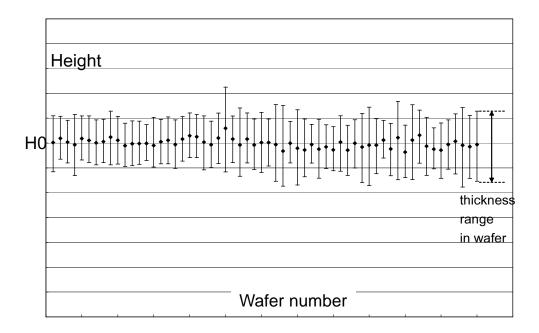

| 3.10 | Wafer-to-wafer variation of copper thickness range within a wafer             | 39 |

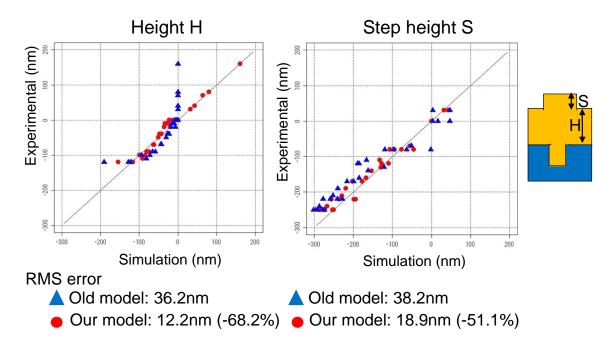

| 3.11 | Simulation vs. experimental results of ECP process                            | 41 |

| 3.12 | Chip surfaces with effective hot-spot detection method and a modification     |    |

|      | result                                                                        | 42 |

| 4.1  | Cross sectional view of interconnect layer                                    | 46 |

| 4.2  | Overview of proposed EoE-error prediction method                              | 48 |

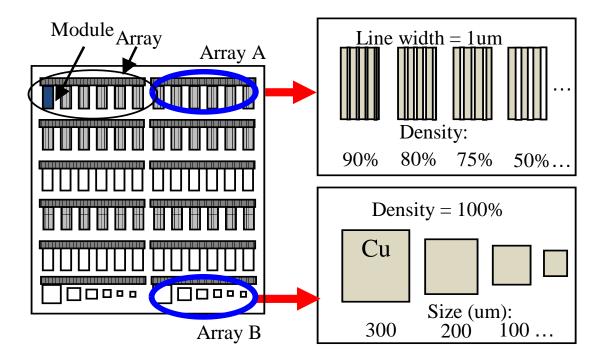

| 4.3  | Test chip structure                                                           | 49 |

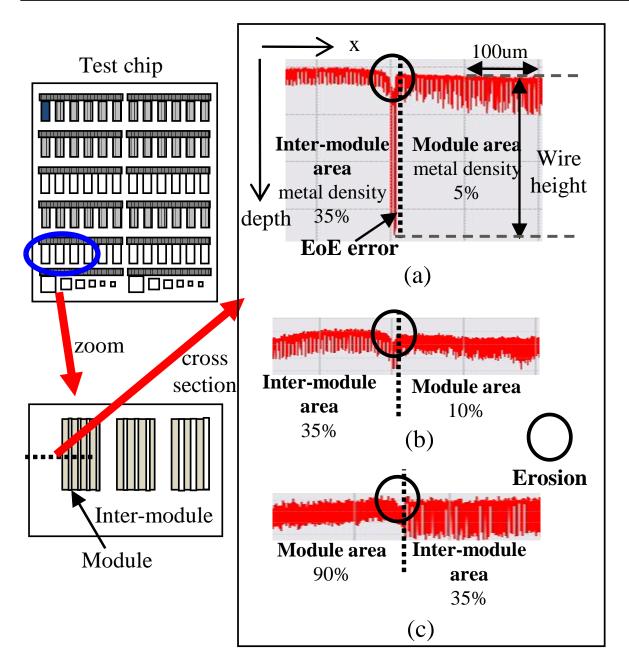

| 4.4  | Relationship between EoE and metal density of module area                     | 51 |

**xii** List of figures

| 4.5  | Relationship between EoE and module size                                     | 52 |

|------|------------------------------------------------------------------------------|----|

| 4.6  | Definition of effective length                                               | 52 |

| 4.7  | region for effective density computation                                     | 53 |

| 4.8  | Density deviation vs. EoE-error occurrence in a 65 nm process                | 53 |

| 4.9  | Detailed shapes of EoE cross section                                         | 54 |

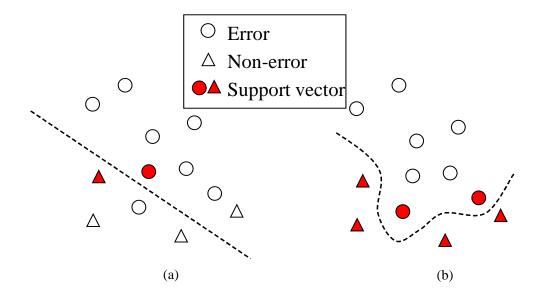

| 4.10 | Model complexity of SVM method                                               | 57 |

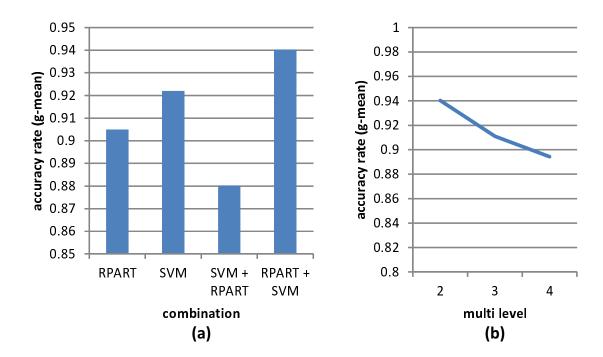

| 4.11 | Comparison of Accuracy rate of (a) combinations of learning method and       |    |

|      | (b) number of multi-level                                                    | 58 |

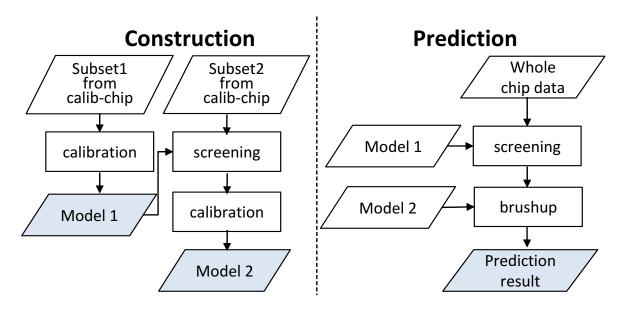

| 4.12 | Detailed flow of construction and prediction stages with multi-level machine |    |

|      | learning method                                                              | 59 |

| 4.13 | $P_{err}$ , $P_{ok}$ , and g-mean with various sampling ratio in SVM         | 61 |

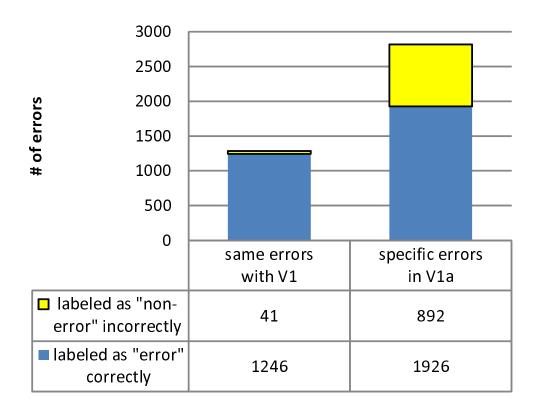

| 4.14 | Details of EoE-errors in chip V1a.                                           | 62 |

# Chapter 1

# Introduction

This chapter describes the background and the objectives of this thesis. This thesis focuses on the modeling of wire shape variations using measurement data and chip layout characteristics. The following sections describe the background of the wire shape variation problems, explain sources of the variations, and present the objective of this thesis.

#### 1.1 Sources of wire shape variations

As the technology of VLSI manufacturing process continues to shrink, it becomes a challenging problem to generate layout patterns that can satisfy performance and manufacturability requirements since design rule sets have become increasingly more complex. Technology scaling also leads interconnect delay to dominate circuit delay [1, 2]. This is because that wire resistance and capacitance increase significantly [2–4] due to the decrease in wire cross sectional area and wire pitch in advanced technologies. Furthermore, coupling capacitance of wires becomes dominant because of high aspect ratio of wire shape [5–7]. Therefore, nowadays the wire geometry has a strong impact on the wire resistance and capacitance, and consequently affects the interconnect delay significantly. On the other hand, in advanced technologies, it is getting difficult to manufacture wires as designed, and wire shape variation is inevitable. As a result, the variation of total wire capacitance can be more than 10% and the variation of wire resistance due to wire shape variation can be over 30%, which results in more than 35% delay variation on long interconnect and may cause yield loss [9–11]. Thus, the wire shape variation is one of the serious issues that degrade chip performance and yield.

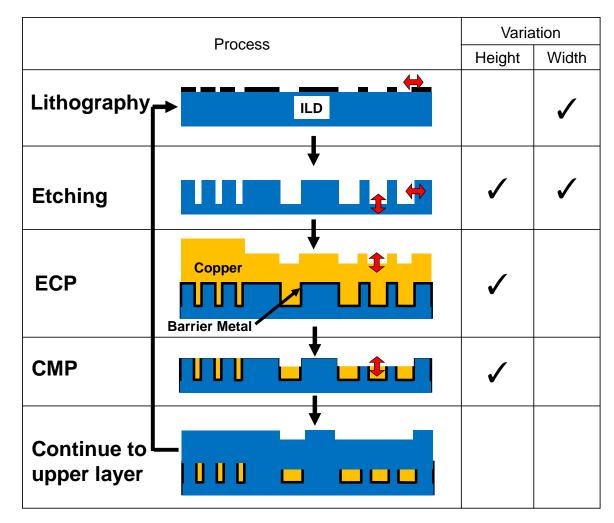

Let us review the interconnect fabrication process. Copper (Cu) interconnect is widely applied to 130 nm and below technologies, because of its smaller resistance as compared to aluminum. In the aluminum process, interconnect is patterned by dry etch process. On the other hand, copper interconnect is constructed by damascene fabrication process [12–14]. Figure 1.1 shows the manufacturing flow of copper wire forming with the damascene fabrication process. Lithography, etching, electro-chemical plating (ECP), and chemical mechanical planarization (CMP) are main processes of shaping copper metal wires. In the damascene fabrication process, interconnect trenches and via holes are printed and etched after inter-layer dielectric (ILD) material deposition. Then, a thin barrier metal layer, which facilitates copper film generation, is deposited as a seed layer [14]. Next, copper is deposited to fill up the trenches and holes on the whole wafer surface by ECP process. Finally, copper outside the trenches is removed to generate interconnect patterns. CMP process is a technique to remove redundant copper and to planarize the wafer surface. These processes iterate over layers. This

Fig. 1.1 Manufacturing flow of wire forming.

section surveys each process of interconnect manufacturing.

#### 1.1.1 Lithography

Lithography is a process to print an image of chip layout pattern on a wafer. Minimum feature size of advanced process technology has become much smaller than the lithographic wavelength (193nm), which results in unavoidable wire shape distortion and consequent wire width variations due to optical diffraction and interference. For enabling the sub-wavelength feature size manufacturing, resolution enhancement technologies (RET) have been developed, such as optical proximity correction (OPC), sub-resolution assist features (SRAF), phase-shift mask (PSM), off-axis illumination (OAI), and double patterning technology (DPT) [8, 15–25]. OPC is the most popular method, and it adds and/or subtracts features to/from the mask patterns to improve the wire shape printed on a wafer. SRAF is a feature introduced to improve the process margin of a resulting wafer pattern, where SRAF itself is not printed on a wafer. PSM controls the phase of the light between adjacent apertures. This method reduces the sensitivity to defocus conditions and achieves high-resolution imaging with good depth of focus (DOF). Here, DOF means the range of distance between

the lens and the wafer that appears acceptably sharp in an image. Large DOF value mitigates the distortion in the projected image on unflat wafer surface, where the wafer surface is not perfectly flat throughout the manufacturing process. OAI is an optical system that brings light to the mask at an oblique angle, which enables pattern printing with higher resolution. DPT decomposes a single mask pattern into two masks to increase the pitch size within each mask and improve DOF for higher resolution and better printability. The primal goal of RET techniques is to keep the feature shape printed on a wafer as close to the layout in design time as possible.

#### 1.1.2 Etching

Etching process forms interconnect trenches by removing the material from the wafer surface. Wafers are covered with photoresist except the interconnect pattern [26, 27, 29]. In the etching process, reactive-ion etching (RIE) is a popular technique, and it is a dry etching technique using plasma. Key specifications demanded in this process are high etch rate, high aspect ratio, and straight cross sectional trench sidewall profile. In RIE, free radicals and positive ions react with the wafer surface. Free radicals are electrically activated neutral species. They diffuse over the wafer and react with the surface materials. The positive ions are other reactive species in RIE. The positive ions are accelerated toward the wafer surface by electric field, and they cause both chemical and sputter etching of the surface materials.

One of the main advantages of RIE method is a high etching rate, which is achieved by the synergy between chemical reaction due to free radicals and ion bombardment due to positive ions [28]. The ion bombardment removes the reaction product on the wafer surface, which helps free radicals react with the wafer surface. The etching rate of the wafer surface using both the species simultaneously is much higher than the rate using individual species separately.

In RIE method, high selectivity and anisotropy are demanded to achieve proper wire trench shape. Selectivity is the ratio of reaction rate between the target material and the others. In etching process, wafer surface is covered with photoresist materials. To dig the trench pattern properly, high selectivity to wafer surface material compared to photoresist is required. Free radicals have high selectivity, but positive ions have low selectivity. Anisotropy is the directional dependence of etching ability. Anisotropic etching can dig the wire trench along the photoresist pattern without undercut, and mitigate wire width variations. Here, undercut means the sidewall material removal under the photoresist pattern. Positive ion drifts toward the wafer surface vertically and its etching process becomes anisotropic. On the other hand, etching mechanism of free radical is an isotropic process which has no directional dependency in etching property.

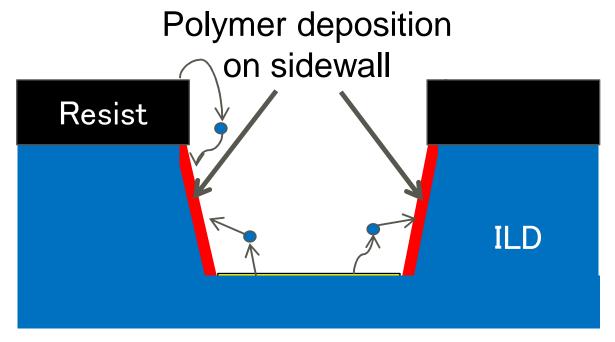

Sidewall protection mechanism also contributes to the reduction of wire width variation [29–31]. The reaction materials from the surface by etching process is deposited on the sidewall and protected from isotropic etching.

#### 1.1.3 ECP and CMP

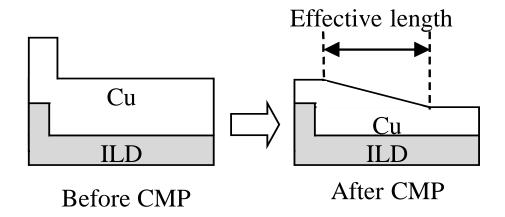

ECP is a process to deposit the copper material onto the whole wafer to fill up the trenches after barrier metal deposition, and CMP is a process to remove the copper that overflows the interconnect trenches. ECP and CMP processes have become essential techniques for enabling many-layer damascene process interconnection.

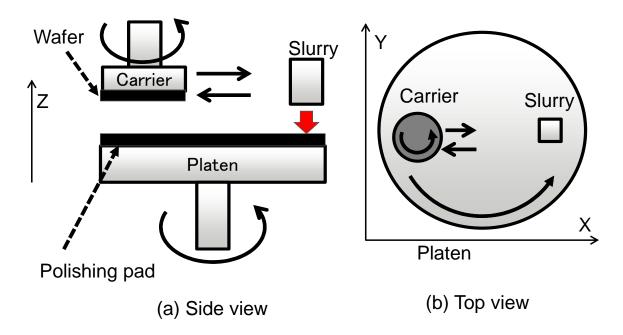

Fig. 1.2 CMP process apparatus.

ECP is the most popular method for copper deposition. Copper ions in a solution react with the wafer surface and they are deposited [32]. To achieve excellent trench filling capability, chemical additives (accelerator, suppressor, and leveler) in the plating solution play an important role [33–39]. The improvement of overall copper layer planarization benefits the subsequent copper CMP process.

Figure 1.2 shows the CMP process apparatus. In CMP process, wafer is attached to the carrier and pushed down to the platen table which is covered with the polishing pad. The wafer carrier and platen rotate in X-Y plane and the carrier is reciprocated in the radial direction of the platen. The wafer surface is polished with polishing pad in conjunction with CMP slurries. The slurries containing chemicals, fluids, and abrasives are fed on the polishing pad during polishing process. A softened surface layer is formed on a wafer thanks to chemical reactions between the wafer surface materials and slurry chemicals, and the softened layer is then removed by abrasives and polishing pad.

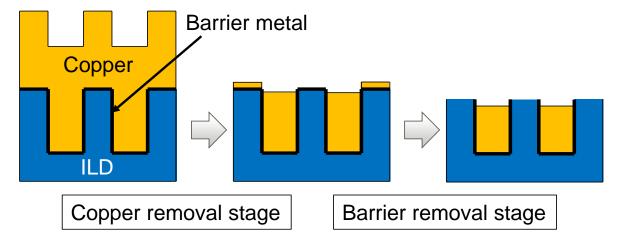

Generally, CMP process consists of multi stage polishing process because the target material in the first half is copper and that in the latter half is copper, ILD, and barrier metal [40–43,45–47]. These two stages are called copper removal stage, and barrier removal stage, respectively (figure 1.3).

The mechanism of CMP process is complicated, and hence CMP process is difficult to tune. CMP process has many parameters, such as polishing pressure, rotating speed of platen and wafer, slurry flow rate, polishing time, and consumable (polishing pad, slurry) characteristics. They all affect the wafer surface topology, and these parameters have different values in each stage. Especially barrier removal stage is very complex because multiple materials that have different polishing rate should be simultaneously polished to achieve high uniformity of wafer surface. Due to this, layout patterns affect the uniformity of wafer surface. Layout patterns include not only wire density / shape of target location but also those of its surrounding layout.

Fig. 1.3 Multi stage CMP process.

The detail of each stage of multi-stage CMP process is described in the following.

#### 1. Copper removal stage

In this stage, copper is mainly polished to reduce ECP induced height variation. To achieve good planarity, it is crucially important when the copper removal stage ends and the successive barrier removal stage starts. This stage transition is performed once barrier metal is detected at a specified wafer point by a sensor in the platen table. This barrier metal detection is called endpoint detection. After the endpoint detection, the removal process continues for a certain time to clearly remove the copper on the barrier metal across a wafer. This duration is called overpolishing time, and it adjusts the amount of copper removal to achieve the target height. In this stage, high etching rate of copper and high selectivity of copper to barrier metal are required for achieving high throughput and small surface height variation.

#### 2. Barrier removal stage

After the copper removal, the copper in the wire trench, the barrier metal on the sidewall of the wire trench and on the surface between the trenches, and the ILD below the barrier metal between the trenches are polished simultaneously. The CMP process parameters and removal selectivity between these materials are carefully selected to achieve the target height without sacrifice of surface uniformity.

#### 1.1.4 Effects of each process on wire shape variation

Wire shape variation consists of wire height variation and wire width variation. In addition, wire open / short error originating from the wire manufacturing flow is often observed in advanced technology [48]. Open / short error causes malfunctions of circuits. This phenomenon can be regarded as a result of severe wire shape variation.

Wire height variation mainly depends on ECP / CMP and etching process. Trench depth variation in etching process causes non-uniformity of the bottom of interconnect trenches, but an etch stop layer (ESL) technique provides good control of the trench depth variation. This ESL technique exploits large selectivity difference between wafer material and ESL [49].

Non-uniformity of the upper surface of wire metal is affected by the initial height of metal deposited in ECP and the amount of metal removed in CMP. To reduce the upper surface variation, several methods are proposed that restrict the acceptable metal density in a small range, where the range of acceptable metal density is one of the most effective parameter to reduce the ECP / CMP wire height variation [50–56].

Wire width variation occurs in lithography, etching, and CMP process. Wire pattern printed on a wafer in lithography process is affected by its surrounding patterns because of the diffraction effects of optical sub-wavelength lithography. Therefore, several RET, which are introduced in section 1.1.1, are adopted to reduce process variation. On the other hand, the DOF requirements of the lithography process become stringent in advanced process technology. The nonplanarity of lower layer according to CMP variation propagates to upper layer, which consumes the DOF budget and makes wire pattern printed in lithography process ambiguous [10, 51]. This printed pattern degradation results in wire width variation. Etching also influences the wire width variation because of the variation of horizontal etching performance. Both lithography and etching process are influential in wire width variation, but etching process is more influential. It is because it finalizes the variation while the variation in lithography process can be mitigated in successive etching process.

Conventional wire open / short error occurs in lithography process. Wire shape distortion in subwavelength lithography process causes bridging between wires and wire disconnection. To prevent these errors, RET techniques are widely used [8, 15–25]. On the other hand, CMP is another major factor of open / short error occurrence in advanced technologies. Improper polishing process causes over-polishing and consequent disconnection, or copper residue between wires and consequent short error. Furthermore, wafer height variation propagates to upper layer and it increases the occurrence of open / short error at upper layer [2, 32]. Recently, Edge-over-Erosion error (EoE-error), which was hardly observed in aluminum interconnect technology, occurs frequently. This is a wire defect caused by irregular over-polishing in CMP process. The detail of this error will be explained in section 1.2.3.

#### 1.2 Problems in manufacturing processes

As discussed in the previous section, wire shape variation has a large impact on chip performance. In practical manufacturing process, various countermeasures against the variation are taken.

RET techniques are adopted to reduce variation in lithography process. The wire thickness non-uniformity in CMP process is dependent on variations of layout characteristics, such as wire width and density, and hence dummy fill technique is applied [50–56], where dummy fill is a non-functional feature inserted to the layout for reducing variations in layout characteristics.

In CMP process, many process parameters and physical or chemical property values of consumable materials affect the chip surface topography [57–63, 65], and their mutual relation to the surface uniformity is complicated. Therefore, predicting thickness variations before manufacturing with CMP prediction model is becoming essential to appropriately tune the CMP process. However, it is impractical to consider all the process parameters in the prediction model because of the model complexity and exorbitant runtime. Due to this fact, CMP prediction model is often constructed with a small number of parameters which can be changed dynamically during CMP process and have a large influence on the results. CMP

prediction model also includes a few model parameters which are adjusted to improve prediction accuracy. Calibration process is executed for adjusting those model parameters with experimental data. It should be noted that the obtained CMP prediction model is effective only when other parameters that are not included in the prediction model are unchanged from the experimental data used for calibration. Hence, another calibration process using different experimental data is required once the parameters that are not included in the prediction model are changed.

In spite of these efforts against variation, there are problems in an actual wire manufacturing process. This section briefly summarizes the problems.

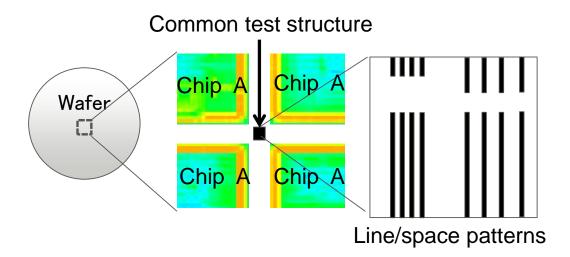

#### 1.2.1 Wire width variation

In actual manufacturing, unexpected large variation in wire width that has an impact on chip yield is observed. More specifically, such a large variation mainly originates from etching process, and hence the chip layout variation is a key contributor to the variation. Generally, common test structures to monitor the manufacturing process are placed on a wafer and wire width in these structures are measured and monitored. Reference [83] reported that the surrounding area which affected the etching process was smaller than the test structure size, and hence it was expected that the chip layout could not affect the etching process at the test structure location. However, in reality, a systematic wire width variation originating from the chip layout is observed. A prediction model of wire width variation which takes into account the surrounding layout pattern in a wider range around the test structure is needed.

#### 1.2.2 Wire height variation

Although several ECP and CMP prediction models are proposed to estimate the surface planarity of the chip, the prediction accuracy is not high enough especially in ECP prediction in practical manufacturing process, which results in a large estimation error of wire height. In addition, large variations occur only in specific regions of wafer and it is difficult to predict these errors without considering die-to-die variations in ECP and CMP processes. An effective method to identify the region of large variations in design time should be developed.

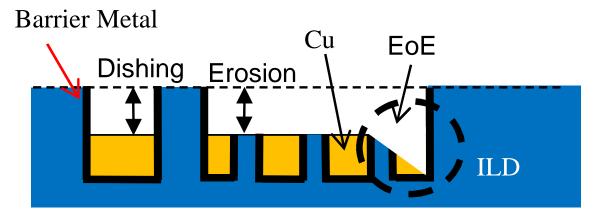

#### 1.2.3 EQE-error

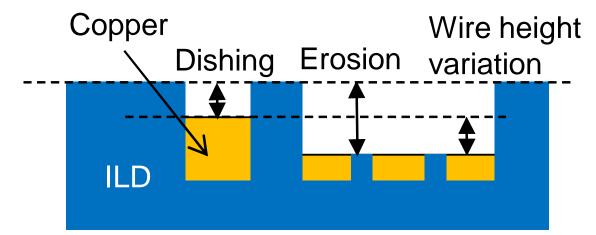

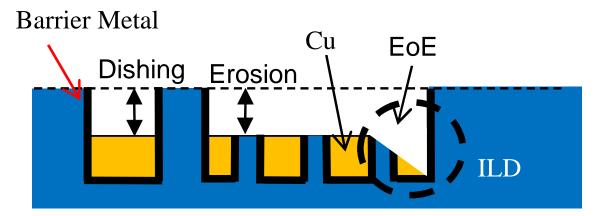

As mentioned in section 1.1.4, EoE-errors have arose in advanced technologies. Figure 1.4 shows the cross sectional view of EoE-error. Dishing is defined as the height difference between copper and ILD, and erosion is defined as the difference between initial and final ILD heights. EoE-error is the localized over-polishing error which is often seen near pattern edges. Copper metal is removed more than ten times faster than its ordinary removal rate at the place where EoE-error occurs. Empirically, EoE-error occurs under the following condition. 1) The CMP process is removing multiple materials simultaneously. 2) The removal rate of copper is much higher than other materials.

EoE-error causes not only open errors but also short errors at the upper layer due to the propagation of the surface irregularities, but its detail mechanism is still unclear. It is demanded to develop an EoE-error prediction method that can be used in design time to avoid unexpected yield loss.

Fig. 1.4 Cross sectional view of interconnect layer.

#### 1.3 Objective of this thesis

Conventionally, these problems are found after fabrication. The conventional countermeasure to these problems is illustrated in the top of figure 1.5. Once they are found, process and/or chip layout are modified to avoid the problems. However, this countermeasure to the problems is too costly and deteriorates productivity. In fact, mask set modification in nano-meter technology costs over 1 million dollars [64]. To make matters worse, this modification is often repeated through trial and error until the problems are solved, because the effect of modification cannot be estimated accurately. Therefore, to avoid such inefficient trial-and-error modification, a prediction model that reasonably reproduces these variations with acceptable modeling effort is highly demanded.

Actual manufacturing processes are usually difficult to model with "white-box" model, which is fully derived from physical laws. This is because manufacturing process may include unknown noises, unseen dynamics, and immeasurable parameters [66]. To solve this problem, "gray-box" modeling approach is widely used [67,68]. This approach combines available physical knowledge with statistical methods. This approach enables the model to take into account any unclear factors using calibration parameters, and these calibration parameters are adjusted with experimental data. In contrast, "black-box" modeling approach extracts a relation among given numerical data without understanding physical phenomenon [69–72]. This approach is effective in case that the mechanism of the target phenomenon is complicated and is not understood enough to build a physical model. Regardless of the modeling approach used to model wire shape variation, the derived model should be usable for analyzing the relationship between the target phenomenon and the characteristics of the chip layout and it should be able to guide process and chip layout modification for the problem avoidance.

The goal of this thesis is to establish a virtualization framework of wire manufacturing process with highly precise prediction models for improving yield and productivity. The contribution of this thesis is illustrated in the bottom of figure 1.5. The developed models are used to tune process parameters and modify chip layout for avoiding the problems without fabrication, which considerably reduces the turn-around-time of the process tuning and saves the

Fig. 1.5 General structure of this thesis.

mask cost. As discussed in section 1.2, there are three major variation problems in actual wire manufacturing process and they all have a serious impact on yield and productivity [73, 80]. This thesis presents accurate prediction methods for each variation problem. To achieve the goal, this thesis utilizes not only measurement data obtained in manufacturing process but also various characteristics extracted from chip layout data, and analyzes the relationship between the problems and layout characteristics. In the modeling, depending on the complexity of the target phenomenon, this thesis employs gray-box and black-box modeling approaches to build accurate prediction models that include parameters relevant to wire shape variations.

For accomplishing the goal mentioned above, the following subjects are studied in this thesis.

- To develop a prediction model of wire width variation and a wire width adjustment method that tunes the etching process.

- To develop a method to mitigate wire height variation considering die-to-die variations.

- To develop an EoE-error prediction model with machine learning techniques.

Firstly, chapter 2 proposes a prediction model of etching induced wire width variation accounting for global layout pattern variation. According to the measurement results, wire width variation heavily depends on the chip layout pattern which is far from the wire width measurement spot as well as local chip layout pattern. A prediction model is constructed from physical properties and hypotheses of etching process with data analysis of the measurement

data from many industrial chips and its layout characteristics abstracted from chip design data. This thesis then proposes a wire width adjustment method which tunes the etching process with the proposed prediction model. Then experiments verify the accuracy of the prediction model and estimates how much wire width variation can be potentially reduced with other industrial chips.

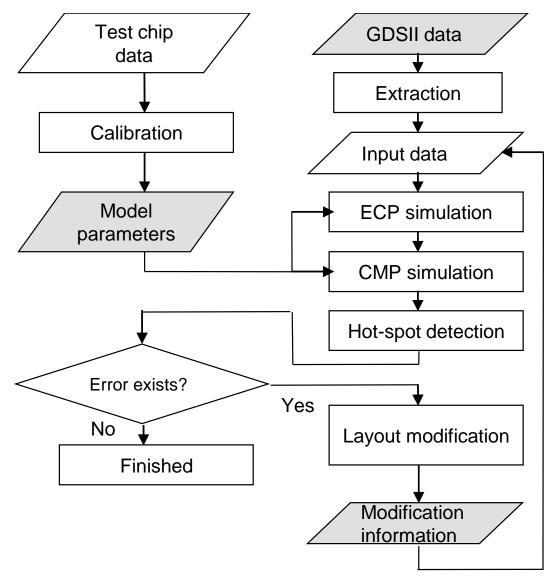

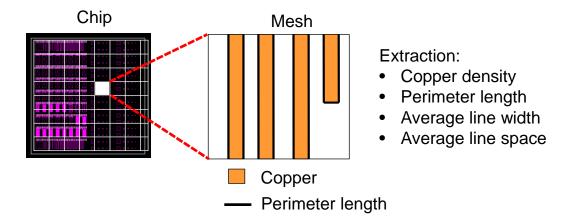

Secondly, chapter 3 discusses wire height variation and its mitigation method with ECP and CMP prediction models. In implementing the mitigation method and applying it to practical design, it is found that there are three problems to solve. The first problem is the computational time to process layout data, since layout characteristics information, wire density, perimeter length, wire width, etc. is necessary for ECP and CMP prediction models. It is too costly to handle each wire shape of the entire chip accurately. Therefore, the chip data is divided into small  $10\mu m - 40\mu m$  square meshes and average characteristic values of each mesh are stored in the database from original GDSII or OASIS format data. In addition, virtual dummy filling method is developed, which roughly calculates the wire characteristics of dummy metal without considering the exact shape and location of an enormous number of dummy fills. The reasons are as follows. 1) The amount of dummy fill features is much larger than that of other functional wires and dummy fill consumes large extraction time and data size. 2) During dummy fill optimization, dummy properties such as size and space is repeatedly varied for finding better manufacturability because dummy fill optimization does not affect the logic function and wire topology. Therefore, the virtual dummy filling method reduces the cost of iterative extraction and dummy modification drastically. The second problem is the large prediction errors of chip surface topography, and it comes from the inaccuracy of the existing ECP prediction model. This thesis then proposes a refined ECP prediction model which employs additional parameters on the basis of data analysis of measurement data and layout characteristics. The third problem is the difficulty in finding errors that occur only in a specific variation condition. To find such errors, this chapter proposes an effective hot-spot detection method which can deal with die-to-die variations, where hot-spot is defined as the point which may degrade timing or manufacturing yield. After ECP and CMP are processed, hot-spots are found in some chips on a wafer whereas other chips on the same wafer are manufactured normally. This is because die-to-die variations of ECP and CMP processes exist. The analysis of measurement data reveals that die-to-die variation heavily depends on the variations of initial copper thickness after ECP process and over-polishing time in copper removal stage of CMP process. Thus, this work solves the three problems that prevent the mitigation of wire height variation. Using these solutions, this chapter implements the proposed mitigation method that can detect hot-spots before manufacturing, and demonstrates a case study showing its efficiency.

Thirdly, chapter 4 proposes an EoE-error prediction model which can recognize unexpected yield loss before manufacturing. Though CMP process tuning, such as slurry selection, polishing pressure, etc. is an effective solution of EoE-error reduction, it may results in a significant change in chip surface topography because of complicated CMP process mechanism. It is practical to predict EoE-errors under the fixed CMP process condition with the proposed model and then to modify the chip layout using the method such as dummy fill optimization techniques. EoE occurrence mechanism is too complicated to build a physical model, and therefore the relationship between EoE-errors and chip layout characteristics is firstly analyzed with measurement data of real chips and its chip layout data. After identifying the layout characteristics that affect EoE-errors from data analysis, this chapter introduces

a black-box prediction model which judges whether EoE-error occurs or not using machine learning algorithms. Machine learning algorithms are capable of finding regularities from large data statistically, but measurement data of EoE-errors includes large amount of noise and it may cause overfitting problem. Therefore, this thesis proposes a multi-level machine learning method which can achieve high accuracy and avoid overfitting problem. The effectiveness of the proposed method is validated with industrial chips.

The rest of this thesis is organized as follows. Chapter 2 proposes a prediction model of wire width variation according to global layout pattern variation. Chapter 3 describes the issues in constructing a mitigation method of wire height variation and gives solutions to these issues. Chapter 4 proposes the EoE-error prediction method with multi-level machine learning algorithm. Finally chapter 5 concludes this thesis.

# Chapter 2

# Modeling the effect of global layout pattern on wire width Variation for On-the-Fly Etching Process Modification

This chapter describes a prediction model of etching induced wire width variation which takes into account global layout pattern variation. This chapter also presents a wire width adjustment method that modifies etching process on the fly according to the critical dimension loss estimated by the proposed prediction model and wire space measurement just before etching process.

Experimental results show that the proposed model achieved good performance in prediction, and demonstrated that the potential reduction of the gap between the target wire width and actual wire width thanks to the proposed on-the-fly etching process modification was 68.9% on an average.

#### 2.1 Introduction

Wire width and wire height control is a key factor to achieve high performance and yield enhancement as discussed in section 1.1. Chip fabrication includes manufacturing test which judges whether a chip has defects or not, and the manufacturing test occupies a considerable portion of chip fabrication cost [78]. To reduce the test cost, wafer level screening is often used in manufacturing test [79]. In this screening, a common test structure is placed on scribe lines in a wafer (figure 2.1) and electrical characteristics of the test structure are measured before all individual chips on the wafer are tested. If an outlier value is found in the measurement of the common test structure, the wafer is discarded. It is because the number of faulty chips on such a wafer is empirically much larger than those on other wafers.

For checking the result of wiring processes, wire resistance is often measured in the wafer level screening. If the systematic variation of wire resistance originated from only process conditions and local test structure layout, there should be no resistance difference regardless of the chip layout on a wafer. However, a certain difference in wire resistance value is observed in the measurement data of the test structure with various chip layouts. This means

Fig. 2.1 Common test structure on a wafer.

that the process forming wire metal pattern is affected by global layout which consists of the surrounding layout in a certain range around the test structure.

Section 1.1 described that the main processes of shaping copper metal wire were lithography, etching, electro-chemical plating (ECP), and chemical mechanical planarization (CMP). Wire height variation heavily depends on ECP and CMP processes, and chapter 3 proposed a method to mitigate wire height variation.

On the other hand, wire width variation depends on lithography and etching processes. Both the processes are affected by global layout pattern as well as local test pattern [16,29,81]. Here, local layout pattern is defined as a wire of interest and its adjacent objects, and global layout pattern is defined as features abstracted from a wire of interest and its surrounding layout within a certain range. Lithography simulation can predict the shape of interconnect accurately, but it is too costly for full chip analysis. Thus, several heuristic prediction methods whose execution time is acceptable are proposed [81–83].

To achieve desired wire widths in fabrication, etching process prediction is more important than lithography process prediction. This is because the variation occurred in lithography process can be compensated by adjusting successive etching process parameters, such as gas flow, wafer temperature, and etching time as long as etching process can be correctly simulated. For such a purpose, there are some methods that predict etching induced wire width variation in consideration of local layout pattern [84–89]. However, these do not take into account global layout pattern. Another approach is a feedback control through an iteration of fabrication, measurement and process modification [90,91], but it takes a longer time and costs wafer loss before the process is stabilized.

Aiming to mitigate wire width variation, this chapter shows a prediction model of etching induced wire width variation that considers global layout variation. In addition, this chapter propose a method that adjusts wire width through on-the-fly etching process modification [77]. Contributions of this work include the followings.

• This is the first work to develop a model that predicts etching induced wire width variation taking into account an effect of global layout pattern variation with gray-box

modeling approach. To achieve high accuracy, model parameters are calibrated with measured data of industrial chips.

- A wire width adjustment method with the prediction model is proposed. This adjustment method can reduce the wire width variation by compensating lithography and prospective etching induced variations with instant etching process alternation.

- The accuracy of the prediction model and the effectiveness of the proposed adjustment method is assessed with industrial chips.

The rest of this chapter is organized as follows. Section 2.2 reviews etching process and defines the wire width variation problem occurring in etching process. Section 2.3 introduces a prediction model for wire width variation and explain how to adjust wire width using the prediction model. Section 2.4 presents experimental results. Finally, section 2.5 concludes this chapter.

#### 2.2 Overview of etching process

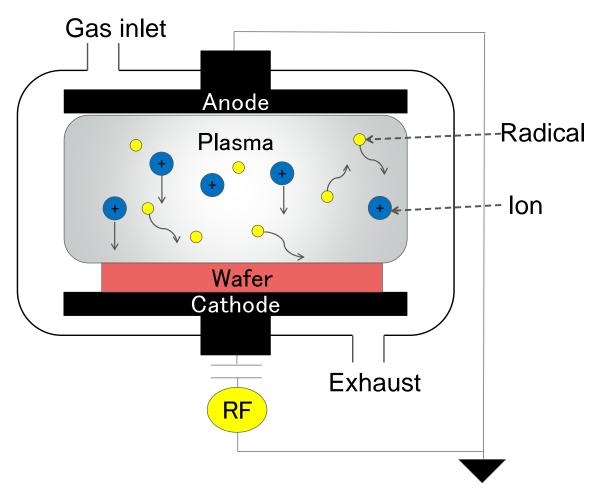

This section reviews etching process and its mechanism briefly. In the fabrication process of ultra large integrated circuits, reactive-ion etching (RIE) is widely used [26, 29] as discussed in section 1.1.2. Figure 2.2 illustrates an RIE system. RIE is a kind of dry etching method using gas glow discharge plasma, where the plasma is maintained with RF power. The plasma dissociates and ionizes feed gases (e.g. CxFy for SiO2 etching) in a vacuum system and generates free radicals and positive ions as etch species, which react with the material of the wafer surface.

Free radicals are main reactive species of etching process. Radicals, which are electrically activated neutral species, are diffused and adsorbed on the wafer surface, and they finally react with the wafer surface materials.

Energetic gas ions are other key species of etching mechanism. A wafer is located on a cathode electrode and acquires negative charge because electron mobility is higher than ion mobility. Positive ions drift toward the wafer and they collide with materials on the wafer surface. Some ions react with the materials chemically, and others cause physical sputtering.

Synergism of ion bombardment and chemical reaction gives a high etching rate [28], which is an advantage of RIE process. The etching rate of the wafer exposed to ion and radical fluxes simultaneously is much higher than that of the wafer exposed to each flux separately. Ion bombardment helps to remove reaction product of wafer surface and accelerates another surface reaction of free radicals, which results in the higher etching rate.

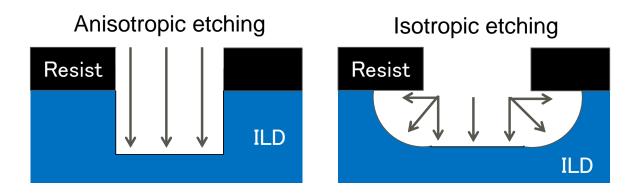

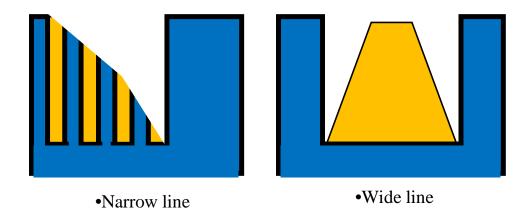

In etching process, there are two important factors to control wire trench profile. The first is selectivity, which is the etching rate ratio of a target material to other materials. In chip fabrication, wafer surface is covered by photoresist pattern, and ESL at the bottom of trench prevents over-etching. To remove only the exposed potions of SiO2 properly, high selectivity to both photoresist and ESL materials is required. Radical etching is generally more selective than ion etching because physical sputtering in ion etching process is less dependent on the materials. Secondly, anisotropy determines the shape of wire trench. Anisotropy is the directionality of etching process, and it is opposed to isotropy. Anisotropic and isotropic etching is illustrated in figure 2.3. Ion etching process is highly anisotropic because ion flux has a direction vertical to the wafer surface. Radical etching, on the other hand, is an isotropic process because free radical is electrically neutral and has the same etching rate in every direction.

In RIE process, highly anisotropic etching is accomplished thanks to sidewall protection

Fig. 2.2 Overview of RIE system.

Fig. 2.3 Anisotropic and isotropic etching.

mechanism (figure 2.4) [29,30]. SiO2 and photoresist materials output both volatile gaseous reaction products and solid polymer reaction products. The polymer products redeposit on the surface and form a polymer film layer. This polymer film plays an important role as an inhibitor to protect the surface from radical etching. Note that only sidewalls of the trench

Fig. 2.4 Sidewall protection.

are covered by the polymer film because they are not exposed to ion bombardment which can remove the polymer deposition. Thus, sidewalls are protected from etching, and RIE process becomes more anisotropic.

The sidewall protection mechanism has a great effect on the wire width variation because the horizontal etching rate heavily depends on the thickness of the sidewall polymer film. This mechanism can be related to many parameters, such as the amount of free radicals, the ratio of etchable area and photoresist area, and etching rate. An important point here is that those parameters are affected by global layout variation [27, 29]. This work focuses on the sidewall protection mechanism as a major factor of wire width variation in etching process and studies the modeling of wire width variation originating from this mechanism.

#### 2.3 Prediction and mitigation of wire width variation

This section proposes a prediction model of wire width variation, which can be applicable to a variety of chip layouts on a wafer. To achieve high accuracy of the model, the proposed model calibrates its model parameters using the measured data of various industrial chips. This section also describes a method to mitigate wire width variation with on-the-fly etching process modification.

#### 2.3.1 Definitions

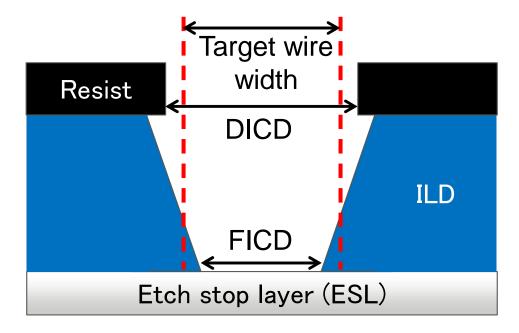

In the manufacturing process used in this study, a common test structure is placed at a fixed location on a wafer for monitoring wire width variation. Wire widths of test patterns in the structure are measured twice: before and after etching process. The former measured value is called development inspection critical dimension (DICD) and the latter is called final

Fig. 2.5 Relationship between DICD, FICD, and target wire width.

inspection critical dimension (FICD). Here, it is defined that a parameter "etching bias"  $\Delta w$  as the difference between DICD and FICD, and a parameter "Critical Dimension (CD) loss" g as the difference between target wire width  $w_t$  and FICD.

$$\Delta w = FICD - DICD, \tag{2.1}$$

$$g = FICD - w_t. (2.2)$$

CD loss g can be positive and negative according to the relationship of sizes between FICD and  $w_t$ .

Figure 2.5 shows the relationship between DICD, FICD and target wire width. To obtain a wire profile with no CD loss (g = 0), etching bias  $\Delta w$  should be equal to the difference between target wire width and DICD ( $\Delta w = w_t - DICD$ ). On the other hand, DICD varies wafer by wafer due to lithography process. If the etching process can be tuned to satisfy  $\Delta w = w_t - DICD$  for every wafer, the CD loss can be minimized.

The proposed wire width adjustment method, which will be explained in section 2.3.3, alters etching process to satisfy  $\Delta w = w_t - DICD$  aiming at g = 0. Here, DICD can be obtained by measuring the common test structure on the wafer before the etching process. The target wire width  $w_t$  is also available. On the other hand, it is difficult to obtain the tuned etching process that satisfies  $\Delta w = w_t - DICD$  directly. Therefore, the CD loss is firstly estimated if normal etching process is performed. Then, the etching process is slightly modified to eliminate the estimated CD loss, and the modified process is applied to the wafer. Note that every manufacturer empirically knows how much trench width would change when the etching process is modified. However, there are no models that estimate the absolute value of  $\Delta w$  that varies depending on global layout pattern. This is the motivation to develop a model for estimating  $\Delta w$  in case of normal etching process. This developed model will be explained in the next subsection.

#### 2.3.2 Proposed prediction model

The proposed model predicts etching bias  $\Delta w$  that occurs depending on global layout pattern. The proposed model is derived from four qualitative properties below.

#### a. Etching bias is proportional to the thickness of sidewall polymer film.

The polymer film deposited on sidewalls prevents the sidewalls from being etched by isotropic free radical etching. Therefore, the thicker the film grows, the smaller the trench width, i.e. the wire width, becomes.

#### b. Thickness of sidewall polymer film is affected by the wire area density.

The sidewall polymer is composed of the products from substrate material (e.g. Six-HyFz) and from photoresist material (e.g. CxHyFz) [29]. On the other hand, the redeposition rate to the surface and etching prevention strength are different between these materials [31]. Due to that, the etchable wire area (substrate material) to the total area (substrate and photoresist materials) has an influence on the thickness of the sidewall polymer film and the consequent etching prevention ability. The ratio of the etchable wire area to the total area is synonymous with the wire area density.

#### c. Thickness of sidewall polymer film is also affected by the total edge length.

Here, edge length is defined as the wire perimeter. Supposing the amount of generated polymer materials is fixed, the polymer film becomes thicker when the total sidewall area in which the polymer materials are redeposited is small. Besides, the sidewall area is the product of the edge length and the trench depth, and hence to the sidewall area is proportional to the edge length.

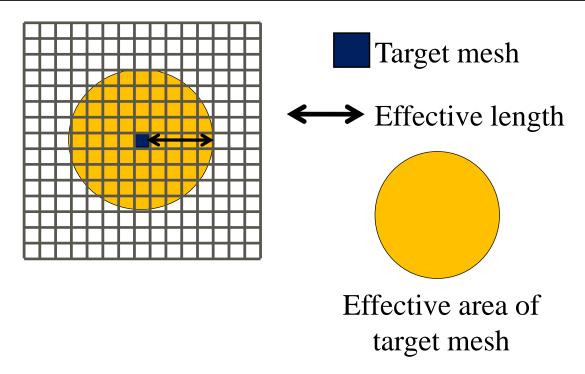

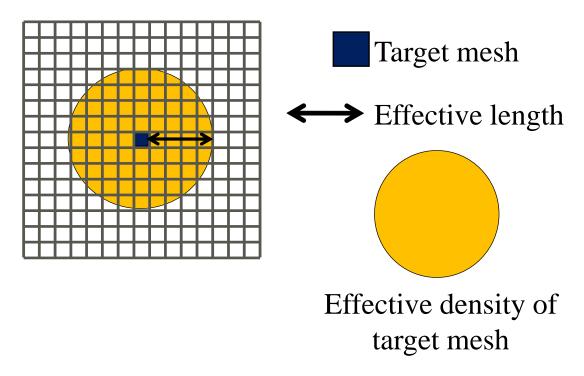

#### d. Parameters are calculated in the area within the range of effective length.

It is assumed that reaction products scattered from a certain point are redeposited within a fixed range from that point. This is reasonable since the reaction products tend to be redeposited before they are diffused distantly. As a result, the reaction products and the sidewall area out of the range have little effect on the redeposition process at the point of interest. To deal with this assumption, a parameter called "effective length" is introduced [92]. According to our preliminary evaluation, this parameter is hardly dependent on process technology size. This parameter could depend on etching process parameters, but in this chapter the etching process is assumed to be fixed.

According to the above qualitative properties, a prediction model is proposed as follows.

$$\Delta w = \alpha \cdot \overline{m},\tag{2.3}$$

$$\overline{m} = d^{\beta} \cdot e^{\gamma}, \tag{2.4}$$

where  $\Delta w$  is the etching bias at a point of interest and  $\overline{m}$  is the average of multiplication parameter m within the effective length L. d is wire area density in a mesh, e is total edge length in a mesh, and  $\alpha$ ,  $\beta$ , and  $\gamma$  are calibration parameters. Parameter  $\alpha$ ,  $\beta$ ,  $\gamma$ , and effective length L are calibrated using etching bias data of industrial chips measurement. This model employs gray-box modeling approach to integrate the both kinds of information: above physical properties and statistical information from the measurement data.

The average computation in equation 2.3 includes numerical integration. To efficiently compute equation 2.3, a whole chip is discretized into small meshes and related parameters are extracted and recorded for each mesh, which helps reduce the size of database and calcu-

Fig. 2.6 Region for parameter  $\overline{m}$  calculation.

lation cost. Namely, layout parameters necessary for the prediction of wire width variation, i.e. d and e, are extracted for every mesh from the original chip data. Consequently, wire width variation is predicted for each mesh.

Figure 2.6 illustrates  $\overline{m}$  calculation with discretized meshes. Using effective length L, the proposed model compute  $\overline{m}$  of the target mesh as an average of parameters m of the meshes within the range of effective length from the target mesh.

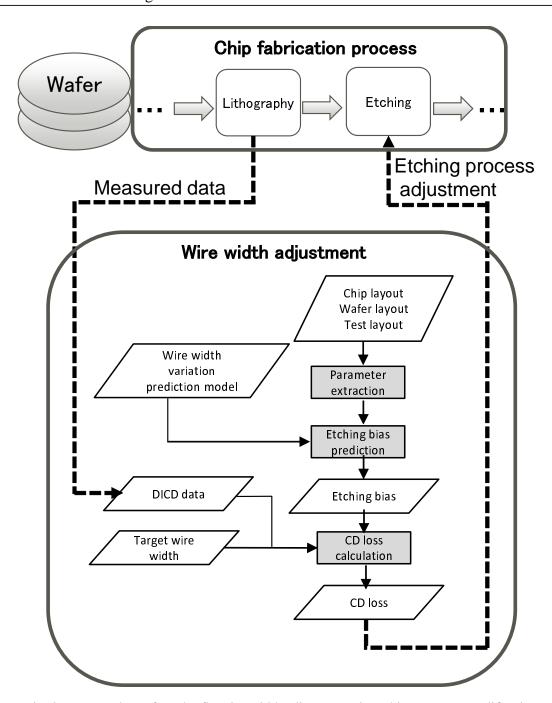

#### 2.3.3 On-the-fly wire width adjustment via etching process modification

Given the prediction model presented in the previous subsection, wire width variation that occurs depending on global layout pattern can be estimated now. This subsection explains how CD loss can be mitigated using the prediction model.

Figure 2.7 shows the procedure of wire width modification. Now, a new wafer is prepared whose lithography process is completed but whose successive etching process is not completed. This successive etching process is modified based on the CD loss estimated by the proposed prediction model of etching bias and measured DICD of the common test structure on the wafer after lithography process. This etching process modification is performed for every wire layer.

Firstly, parameters d and e are extracted from the layout data. Here, the target mesh is the mesh in which the common test structure is located, and layout parameters of each mesh within the range of effective length are extracted using layout data of chip, wafer and common test structure. Then, etching bias  $\Delta w$  is calculated with these parameters and the proposed prediction model of equations 2.3 and 2.4. Note that the prediction model has been already calibrated with calibration data. Next, CD loss g of target mesh is calculated with this pre-

Fig. 2.7 Procedure of on-the-fly wire width adjustment via etching process modification.

diction result of  $\Delta w$ , measured DICD and target wire width  $w_t$  using equations 2.1 and 2.2. In this way, CD loss g of the test pattern can be predicted in case that normal etching process is applied. Then, etching process is adjusted to eliminate the estimated CD loss of the test pattern. For example, etching time and / or gas flow can be tuned for this purpose [86]. This adjusted etching process is applied to the wafer.

| Chip name               | Chip size (mm <sup>2</sup> ) | # of layer | # of wafers | Average wire |  |  |

|-------------------------|------------------------------|------------|-------------|--------------|--|--|

|                         |                              |            |             | density (%)  |  |  |

|                         | Calibration chip designs     |            |             |              |  |  |

| A                       | $21.3 \times 20.8$           | 4          | 133         | 26.3–33.1    |  |  |

| В                       | $7.8 \times 7.8$             | 4          | 52          | 30.1–42.6    |  |  |

| С                       | $13.3 \times 10.0$           | 4          | 37          | 25.5–54.4    |  |  |

| D                       | $8.0 \times 6.4$             | 4          | 445         | 31.3–43.0    |  |  |

| Е                       | $8.5 \times 8.5$             | 4          | 67          | 31.1–50.5    |  |  |

| F                       | $7.8 \times 8.4$             | 5          | 56          | 35.3–45.1    |  |  |

| G                       | $9.4 \times 9.4$             | 6          | 42          | 26.4–32.2    |  |  |

| Н                       | $9.8 \times 8.8$             | 5          | 12          | 34.9–46.5    |  |  |

| Validation chip designs |                              |            |             |              |  |  |

| I                       | $9.9 \times 9.9$             | 4          | 200         | 32.7–46.5    |  |  |

| J                       | $6.9 \times 8.2$             | 4          | 40          | 29.8–42.6    |  |  |

| K                       | $6.9 \times 6.9$             | 4          | 30          | 30.6–43.5    |  |  |

| L                       | $9.0 \times 6.0$             | 4          | 96          | 29.0–41.4    |  |  |

| M                       | $7.9 \times 8.1$             | 4          | 72          | 29.2-41.0    |  |  |

| N                       | $18.2 \times 18.1$           | 4          | 18          | 24.9–39.7    |  |  |

| О                       | $12.1 \times 11.0$           | 5          | 14          | 35.2–46.1    |  |  |

Table 2.1 Details of calibration / validation chip designs.

# 2.4 Experimental results

This section first present experimental results to validate the accuracy of the proposed model. 36 etching bias data which are came from 8 chip designs is used for model parameter calibration. In addition, other 29 etching bias data from 7 chip designs is used for validating the efficiency of the proposed model to unknown chip data. Note that each wafer is covered by one of the 15 (= 8 + 7) chip designs and one etching bias data corresponds to a wire layer of each chip design. Each etching bias data is an average of the values measured with multiple wafers. Calibration parameters  $\alpha, \beta, \gamma$ , and effective length L in the proposed model were calibrated with these data to minimize the root mean square (RMS) value between measured data and estimated value. The mesh size has an impact on a trade-off relation between computational cost and estimation accuracy. In this work, the mesh size was set to  $10 \times 10 \mu m$ . This size was much smaller than effective length L of  $2000 \mu m$ , which will be investigated later, and numerical integration for  $\overline{m}$  is be expected to be reasonably accurate.

Table 2.1 shows an overview of all chip data. All the chips were manufactured with the same 65 nm technology node. Each layer of a chip has different average wire density values. "Average wire density" column denotes upper and lower bounds of these values. For all the wafers listed in Table 2.1, FICD and DICD of the common test structure were measured. This measurement data was used for calibration and validation purposes. Note that another calibration is needed if technology node is changed. In this chapter, the coefficient of determination  $R^2$  is used as a metric to evaluate the accuracy of the prediction model.

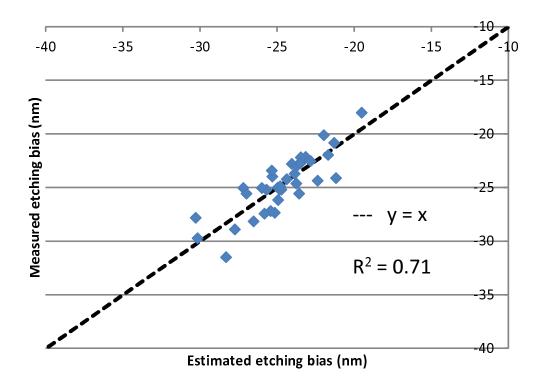

Fig. 2.8 Estimated etching vs. measured etching bias for calibration data.

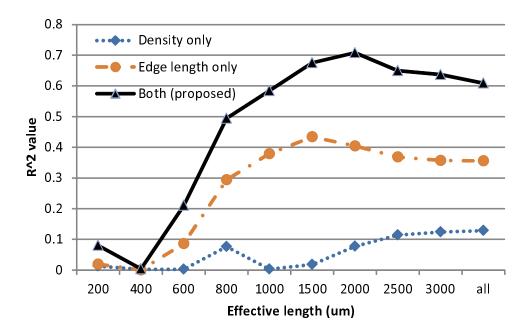

Fig. 2.9 Model calibration results with various effective lengths.

Figure 2.8 shows the accuracy of the model after the calibration process. Horizontal and vertical axes indicate estimated etching bias and measured etching bias, respectively. This

result shows that FICD value is smaller than DICD in the technology node used for this experiment since etching bias values are negative.  $R^2$  value was 0.71 and this model achieved good performance in prediction.

Besides, calibration parameters  $\alpha$ ,  $\beta$ , and  $\gamma$ , were -0.0934, -0.259, and -0.341 respectively. This calibration result indicates that CD loss value takes negative value in our 65 nm technology. Another calibration process and calibration parameter set might be required if positive CD loss value is observed in the measurement data. This calibration result also indicates that, if wire area density d increases, negative etching bias value  $\Delta w$  gets close to 0 and therefore FICD value approaches to DICD value according to equation 2.1. This means that the ability of sidewall etching prevention degrades as the rate of polymer products from substrate material to total sidewall layer component becomes higher. The calibration result also shows that an increase in edge length e results in an increase in both etching bias  $\Delta w$  and FICD. This is because sidewall thickness is inversely proportional to the sidewall area and affects the protection mechanism from isotropic etching.

Figure 2.9 shows  $R^2$  index with various effective length values. "All" in x-axis means that the calibration was carried out supposing the effective length L was infinity. In this experiment, the calibration with tree models below are performed.

- M1: Proposed (equation 2.4); both density and edge length are considered.

- M2: Density only  $(m = d^{\beta})$ ; only density is considered.

- M3: Edge length only  $(m = e^{\gamma})$ ; only edge length is considered.

First, the result of the proposed model (M1) is analyzed. The best performance was obtained in the case that L was  $2000\mu\text{m}$ . The edge bias was affected by the layout in a circle whose radius is  $2000\mu\text{m}$ , and the layout pattern in such a large area must be considered for the edge bias estimation. The effective length of  $2000\mu\text{m}$  was used for other experiments throughout this chapter. Next, the results of M1, M2 and M3 are compared for difference detection. M1 attained the highest  $R^2$ , which clarifies that both density and edge length affect the etching bias mechanism. The figure also shows that the edge length e had a stronger impact on etching bias than density d.

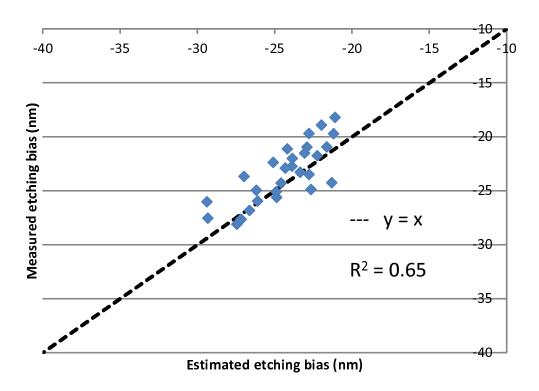

Figure 2.10 shows the prediction results for the validation chip data.  $R^2$  value of 0.65 was obtained, which confirmed that the proposed model maintained high accuracy even when unknown data was given.

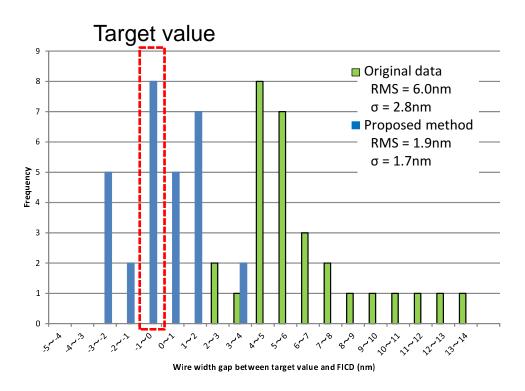

Finally, it is estimated how much the CD loss can be potentially reduced by the proposed on-the-fly wire width adjustment. In this evaluation, it is assumed that the estimated CD loss using the proposed prediction model could be completely eliminated by etching process modification. Therefore, the CD loss reduction presented in the following corresponds to the maximum value in a case that the etching process modification to increase/decrease  $\Delta w$  is perfect. Table 2.2 shows RMS values and sigma values of CD loss with and without the proposed wire width adjustment. Here, the etching bias data of validation chips was used. Figure 2.11 shows the CD loss distributions. When the proposed wire width adjustment was applied, RMS of CD loss was 1.87 nm and sigma value was 1.66 nm. Compared with the result without adjustment, the proposed method could reduce RMS of CD loss by 68.9% and sigma of CD loss by 40.9%. The CD loss distribution moved toward zero and the spread became tighter.

2.5 Conclusion 25

Fig. 2.10 Estimated etching vs. measured etching bias for validation data.

|       | Original data (nm) | Proposed    | Improvement |

|-------|--------------------|-------------|-------------|

|       | data (nm)          | method (nm) | (%)         |

| RMS   | 6.02               | 1.87        | 68.9        |

| sigma | 2.82               | 1.66        | 40.9        |

Table 2.2 CD loss value of validation chips.

# 2.5 Conclusion

This chapter proposed a model that predicted wire width variation occurring depending on global layout pattern variation. This chapter also presented a wire width adjustment method that tuned the etching process on the fly using the proposed prediction model and the measured DICD of the common test structure on the wafer. Experiments showed that the proposed model achieved good performance in prediction and could reduce the CD loss between the target wire width and FICD value by 68.9% on an average.

As the technology of VLSI manufacturing process continues to shrink, the allowable value of wire width variation becomes more stringent to satisfy performance and manufacturability requirements. A future work is to improve the accuracy of the model with further analysis of the measurement data.

Fig. 2.11 CD loss distribution of validation chips.

# Chapter 3

# A practical wire height mitigation method with ECP and CMP simulation

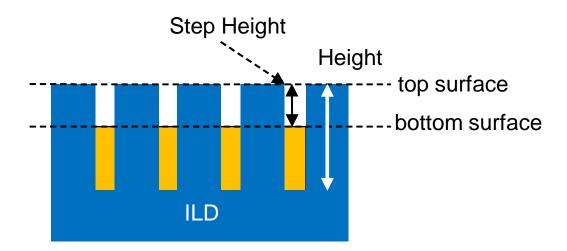

This chapter describes a mitigation method of wire height variation with ECP (Electro-Chemical Plating) and CMP (Chemical Mechanical Planarization) prediction model. In this chapter three problems are discussed in implementing the proposed mitigation method. Firstly, a fast extraction method from GDSII with virtual dummy filling method is developed to reduce large processing cost. Secondly, this study proposes a refined ECP model for improving accuracy of prediction. Finally, this chapter proposes an effective hot-spot detection method considering die-to-die variations. Experimental results show that the proposed extraction method can handle huge chip data with small processing cost. In addition, the results show that the proposed ECP model reduces an error of copper height by 68.2% and that of step height by 51.1%. This chapter also shows a case study of the proposed hot-spot detection method. This method reduced wire height variation by 84.4% and avoided short errors before manufacturing.

### 3.1 Introduction