|              |                                                                             |

|--------------|-----------------------------------------------------------------------------|

| Title        | Study on Image Rejection of GNSS CMOS Receiver for Triple-band Signal       |

| Author(s)    | Jo, Ikkyun                                                                  |

| Citation     | 大阪大学, 2015, 博士論文                                                            |

| Version Type | VoR                                                                         |

| URL          | <a href="https://doi.org/10.18910/53975">https://doi.org/10.18910/53975</a> |

| rights       |                                                                             |

| Note         |                                                                             |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

# **Doctoral Dissertation**

## **Study on Image Rejection of GNSS CMOS Receiver for Triple-band Signal**

**Ikkyun Jo**

**June 2015**

**Graduate School of Engineering,

Osaka University**

# Abstract

This thesis presents a receiver of the global navigation satellite system (GNSS) for triple-band signal, which the author studied at the Graduate School of Engineering, Osaka University.

## Chapter 1

Chapter 1 introduces the study. It explains the basic GNSS concept, motivation and main goal of the study, and organization of the thesis.

## Chapter 2

Chapter 2 describes a radio frequency (RF) characteristic of a metal-oxide semiconductor field-effect transistor (MOSFET) device. Before designing circuit blocks, the gate-region resistive features that affect input impedance are analyzed, and a high-accuracy gate-electrode resistance model is proposed. The gate-electrode resistance, including vertical resistive elements from the gate surface to the channel, is considered. By careful separation of this gate-electrode resistance and the non-quasi-static (NQS) effect, the small-signal gate/source admittance can be analyzed. The proposed model can effectively explain the small-signal gate/source resistance even for a small number of gate fingers.

## Chapter 3

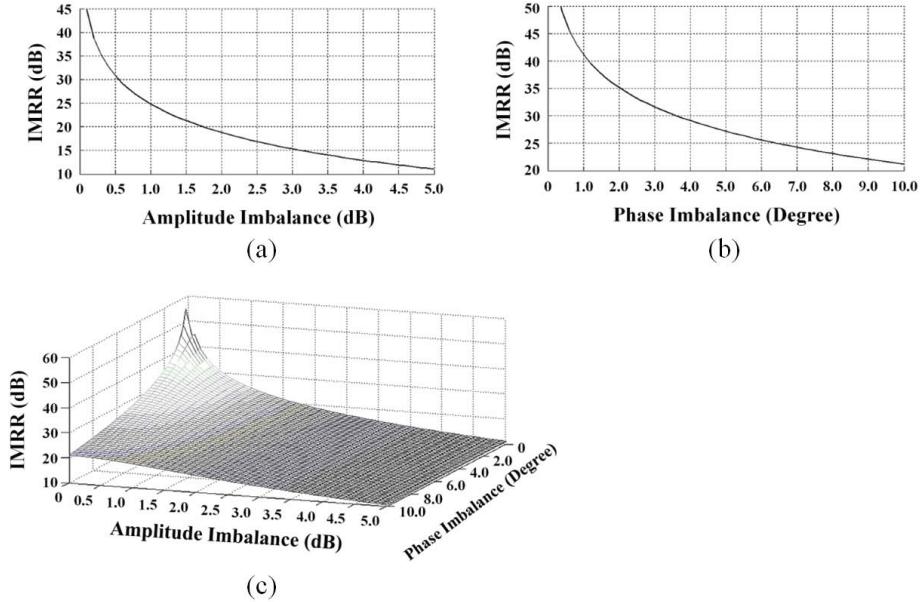

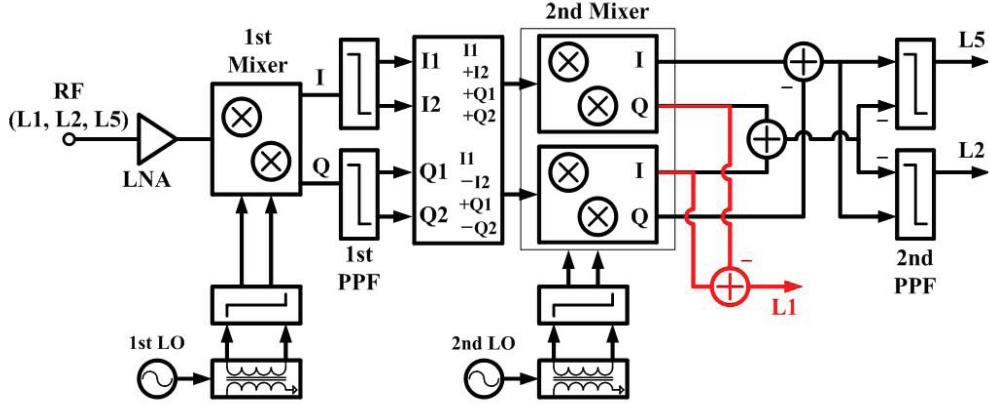

Chapter 3 explains the operation principle of the designed triple-band receiver system. It has only a RF path and separates each signal. Using fixed local oscillation (LO) signals, the triple-band signal can be simultaneously received. The signals mixed in the RF path are separated by an image rejection technique and independently obtained at each band port by the proposed receiver architecture. For

these operations, the conventional Weaver architecture is practically modified. For improvement of the image rejection ratio (IMRR), a digital compensation technique is also proposed. The behavior-level and circuit simulation results reveal the receiver system capability.

## **Chapter 4**

Chapter 4 describes the circuit blocks that compose the receiver system. A low-noise amplifier (LNA), active and passive mixers, a poly-phase filter, and an IQ generator are described. These blocks were verified through a post-layout circuit simulation. The receiver system was designed in a 130-nm CMOS process with a 1.2-V power supply. The simulation results reveal the capability of the designed receiver circuits.

## **Chapter 5**

Chapter 5 describes the measurement process and results. The measurements were obtained in three steps. Bare chips were firstly measured with a wafer probing system. A manual tuner was used to measure RF features in this step. From those results, the expected value of the external inductor for the input stage was calculated. With this value, the second process was performed. For the attachment of external components, bare chip were packaged in 24-pin QFN and a module board was designed. Using this module board, the analog features were measured and analyzed. Then, the demodulation output signals were measured with A/D converters (ADCs). In the final step, the improved IMRR of output signals was observed using a digital compensation method with ADCs output signals.

## **Chapter 6**

Finally, Chapter 6 presents the conclusions of this study.

# Contents

|                                                                   |           |

|-------------------------------------------------------------------|-----------|

| <b>Abstract</b>                                                   | <b>i</b>  |

| <b>1 Introduction</b>                                             | <b>1</b>  |

| 1.1 Overview of GNSS . . . . .                                    | 1         |

| 1.1.1 Calculation Principle of the Target's Location . . . . .    | 2         |

| 1.1.2 GNSS Species . . . . .                                      | 4         |

| 1.2 The GPS Receiver . . . . .                                    | 8         |

| 1.2.1 CMOS Integration Circuit in the Receiver . . . . .          | 8         |

| 1.2.2 General Structure of the Receiver . . . . .                 | 10        |

| 1.2.3 GPS Receiver for Multi-band Signals . . . . .               | 11        |

| 1.3 Research Purpose and Thesis Structure . . . . .               | 11        |

| 1.3.1 Research Purpose . . . . .                                  | 11        |

| 1.3.2 Thesis Structure . . . . .                                  | 13        |

| References . . . . .                                              | 15        |

| <b>2 Modeling of Effective Gate Resistance</b>                    | <b>19</b> |

| 2.1 Introduction . . . . .                                        | 19        |

| 2.2 Analysis of Gate-electrode Resistance . . . . .               | 20        |

| 2.3 Parameter Extraction for NQS Resistances . . . . .            | 22        |

| 2.4 Verification of Gate-electrode Model and NQS Effect . . . . . | 25        |

| 2.5 Conclusion . . . . .                                          | 28        |

| References . . . . .                                              | 31        |

|                                                                        |           |

|------------------------------------------------------------------------|-----------|

| <b>3 Triple-band Signal Receiver Architecture</b>                      | <b>35</b> |

| 3.1 Introduction . . . . .                                             | 35        |

| 3.2 Image Rejection Technique . . . . .                                | 36        |

| 3.2.1 Conventional Architecture of Image Rejection Technique . . . . . | 36        |

| 3.2.2 Concept of Triple-band Receiver . . . . .                        | 41        |

| 3.3 Signal Processing in Triple-band Receiver . . . . .                | 41        |

| 3.4 Simulation of Proposed Receiver Architecture . . . . .             | 46        |

| 3.5 Theory of Digital Compensation Technique . . . . .                 | 49        |

| 3.6 Conclusion . . . . .                                               | 53        |

| References . . . . .                                                   | 55        |

| <b>4 RF Front-end Circuit Design for Triple-band Receiver</b>          | <b>57</b> |

| 4.1 Introduction . . . . .                                             | 57        |

| 4.2 RF Front-end Architecture . . . . .                                | 58        |

| 4.3 CMOS LNA Stage for Triple-band . . . . .                           | 58        |

| 4.3.1 LNA Stage Outline . . . . .                                      | 58        |

| 4.3.2 LNA Stage Design Issues . . . . .                                | 59        |

| 4.3.3 LNA Design . . . . .                                             | 63        |

| 4.3.4 LNA Stage Circuit Simulation . . . . .                           | 68        |

| 4.4 Mixers . . . . .                                                   | 72        |

| 4.4.1 Outline of CMOS Doubly-Balanced Mixers . . . . .                 | 72        |

| 4.4.2 Doubly-Balanced Active Mixer . . . . .                           | 72        |

| 4.4.3 Doubly-Balanced Passive Mixer . . . . .                          | 79        |

| 4.5 PPF . . . . .                                                      | 82        |

| 4.5.1 Outline of PPF and IQ Generator . . . . .                        | 82        |

| 4.5.2 Single and Two-stage PPFs for IQ Generator . . . . .             | 84        |

| 4.5.3 Influence of PPFs Load on IMRR . . . . .                         | 88        |

| 4.6 Passive Components Consideration and Layout . . . . .              | 90        |

| 4.6.1 On-chip Passive Components . . . . .                             | 90        |

| 4.6.2 Layout of RF Front-end Architecture . . . . .                    | 95        |

---

|          |                                                                             |            |

|----------|-----------------------------------------------------------------------------|------------|

| 4.7      | Post-layout Circuit Simulation of RF Front-end Architecture                 | 97         |

| 4.8      | Conclusion                                                                  | 98         |

|          | References                                                                  | 103        |

| <b>5</b> | <b>Experimental Results and Discussion of Triple-band RF Front-end Chip</b> | <b>105</b> |

| 5.1      | Introduction                                                                | 105        |

| 5.2      | Bare Chip Measurement                                                       | 106        |

| 5.2.1    | Input Reflection Coefficient of the Bare Chip                               | 106        |

| 5.2.2    | Noise Figure of the Bare Chip                                               | 107        |

| 5.2.3    | Measurement Results of the On-wafer IC-chip                                 | 109        |

| 5.3      | Module Measurement                                                          | 110        |

| 5.4      | Discussion on the IMRR Digital Compensation                                 | 112        |

| 5.5      | Conclusion                                                                  | 116        |

|          | References                                                                  | 119        |

| <b>6</b> | <b>Conclusion</b>                                                           | <b>121</b> |

| <b>A</b> | <b>Gate Impedance of MOSFET with Vertical Current Path Elements</b>         | <b>125</b> |

| <b>B</b> | <b>NF Re-calculation with the External Inductor</b>                         | <b>127</b> |

| <b>C</b> | <b>Excess Noise Ratio with Compensation of Signal Loss</b>                  | <b>129</b> |

|          | References                                                                  | 132        |

|          | <b>Acknowledgements</b>                                                     | <b>133</b> |

|          | <b>Publications</b>                                                         | <b>135</b> |

# List of Figures

|     |                                                                                                                                                                                                                                                                                                                                                         |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

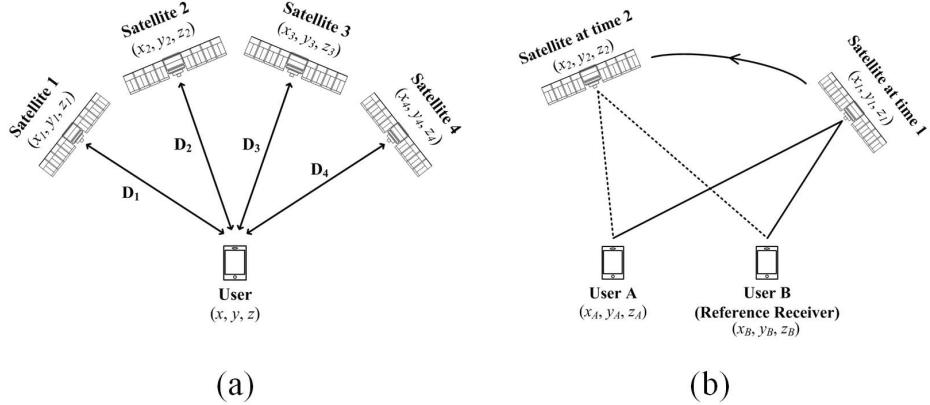

| 1.1 | Method of (a) a point positioning and (b) relative positioning. . . . .                                                                                                                                                                                                                                                                                 | 2  |

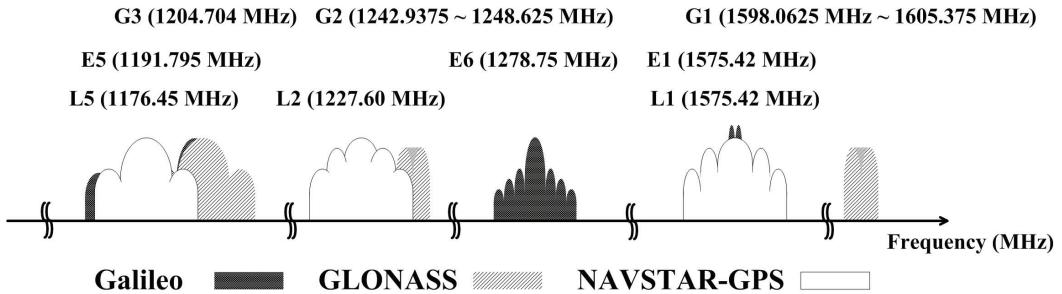

| 1.2 | GNSS frequency allocations. . . . .                                                                                                                                                                                                                                                                                                                     | 8  |

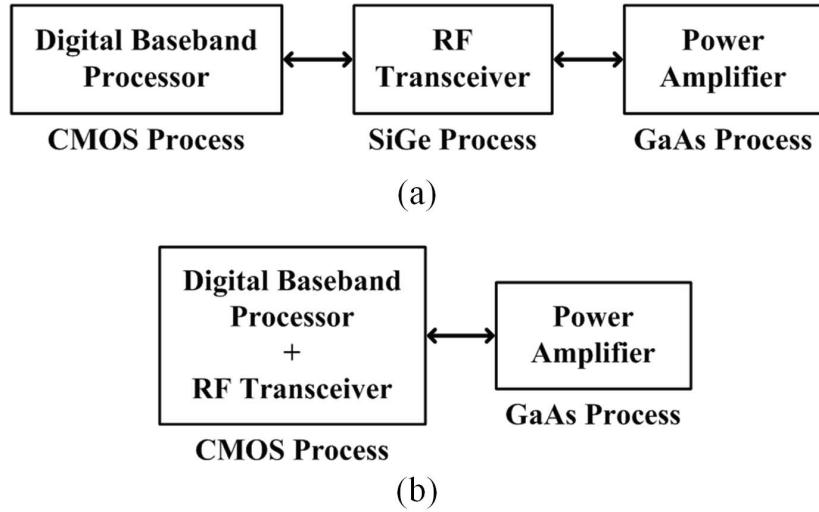

| 1.3 | Process types for RF system. . . . .                                                                                                                                                                                                                                                                                                                    | 9  |

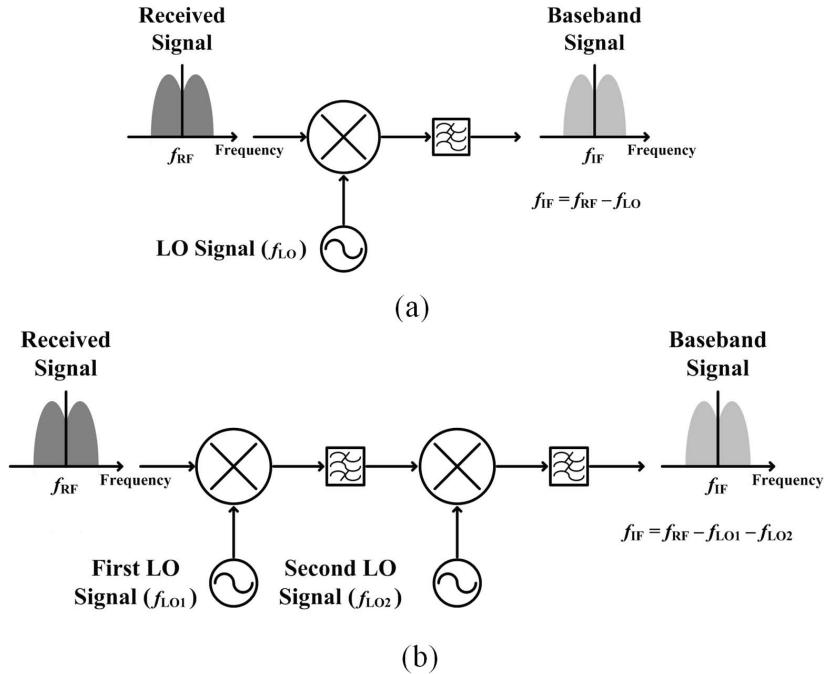

| 1.4 | Structure of (a) direct-conversion receiver and (b) double-conversion receiver. . . . .                                                                                                                                                                                                                                                                 | 10 |

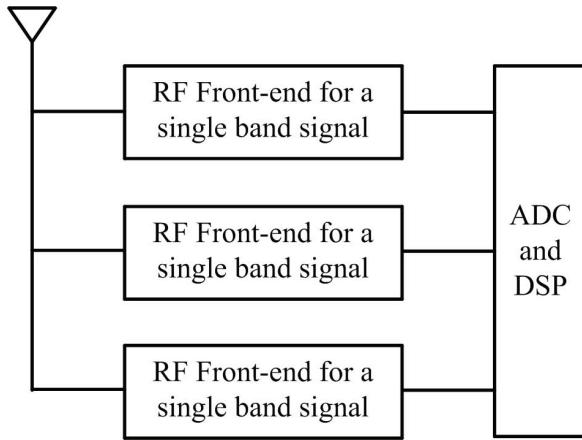

| 1.5 | Conventional GPS structure for multi-band signals. . . . .                                                                                                                                                                                                                                                                                              | 12 |

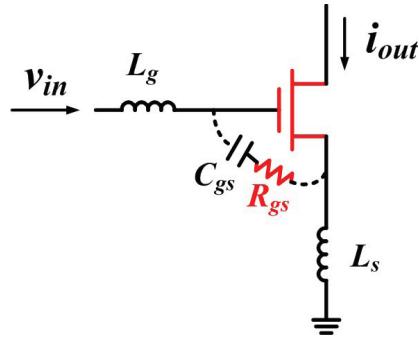

| 1.6 | Inductive-source-degeneration stage of LNA with the gate-source admittance. . . . .                                                                                                                                                                                                                                                                     | 12 |

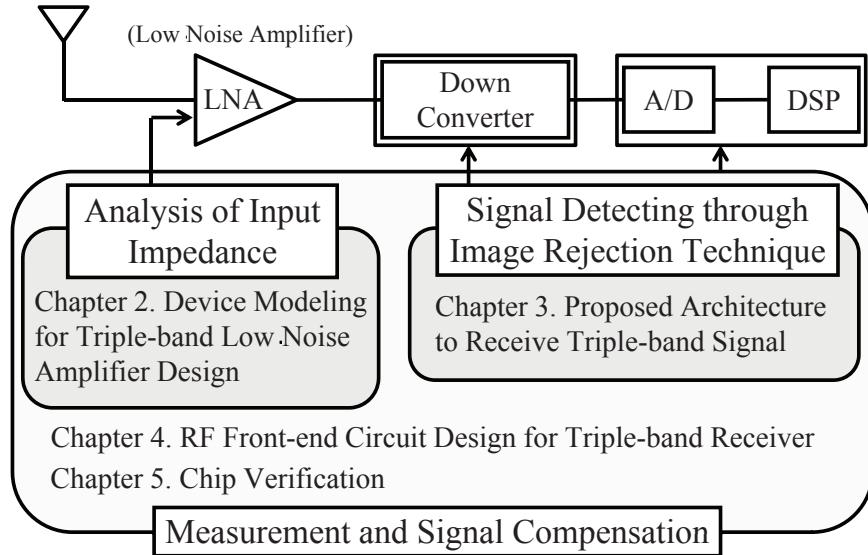

| 1.7 | Constitution of thesis. . . . .                                                                                                                                                                                                                                                                                                                         | 13 |

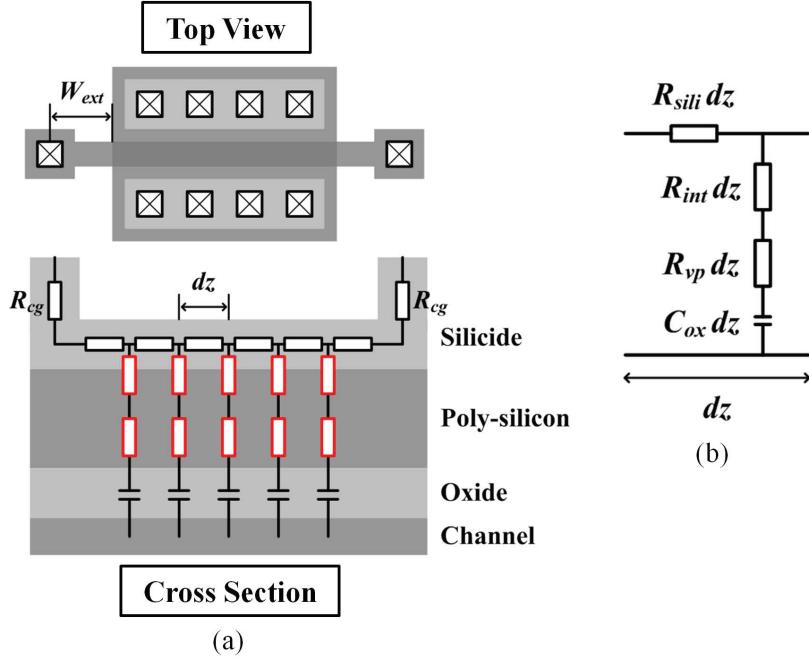

| 2.1 | (a) Top-view and cross-section of MOSFET (both-side gate connection) and (b) equivalent circuit of gate unit element. . . . .                                                                                                                                                                                                                           | 21 |

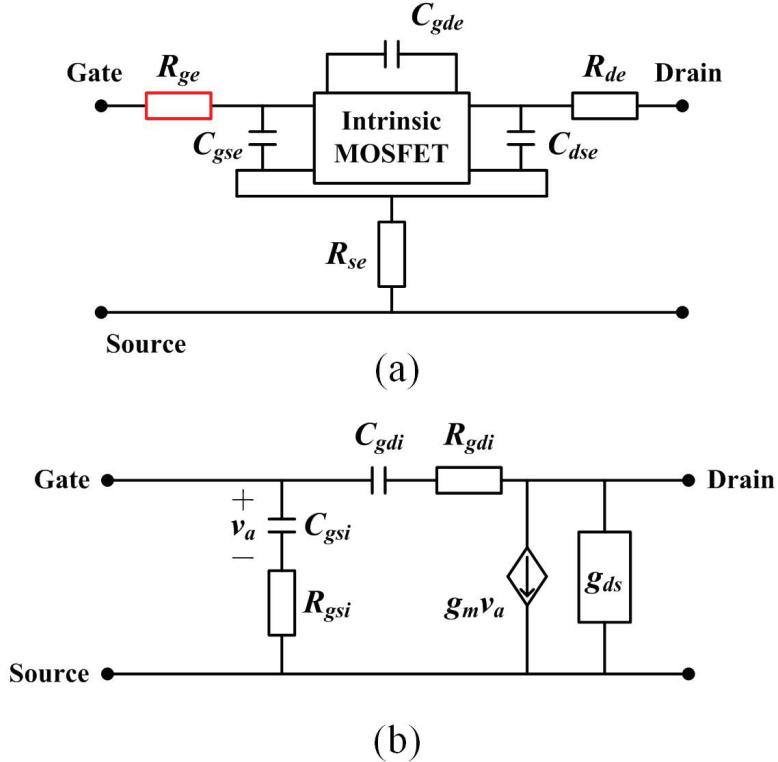

| 2.2 | (a) Small-signal equivalent circuit including external parasitic elements and (b) its intrinsic part. . . . .                                                                                                                                                                                                                                           | 23 |

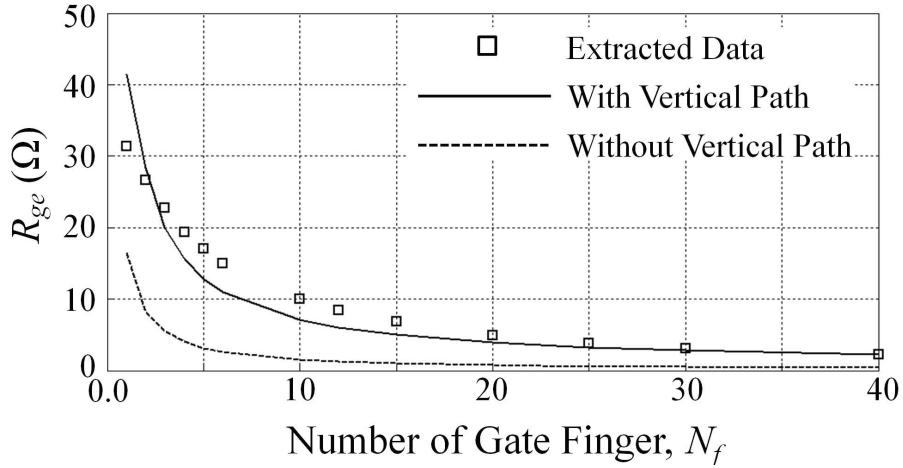

| 2.3 | Extracted and calculated values of gate-electrode resistance $R_{ge}$ versus the number of gate fingers $N_f$ ( $L = 140$ nm, $W_f = 3$ $\mu\text{m}$ , both-side gate connection). . . . .                                                                                                                                                             | 26 |

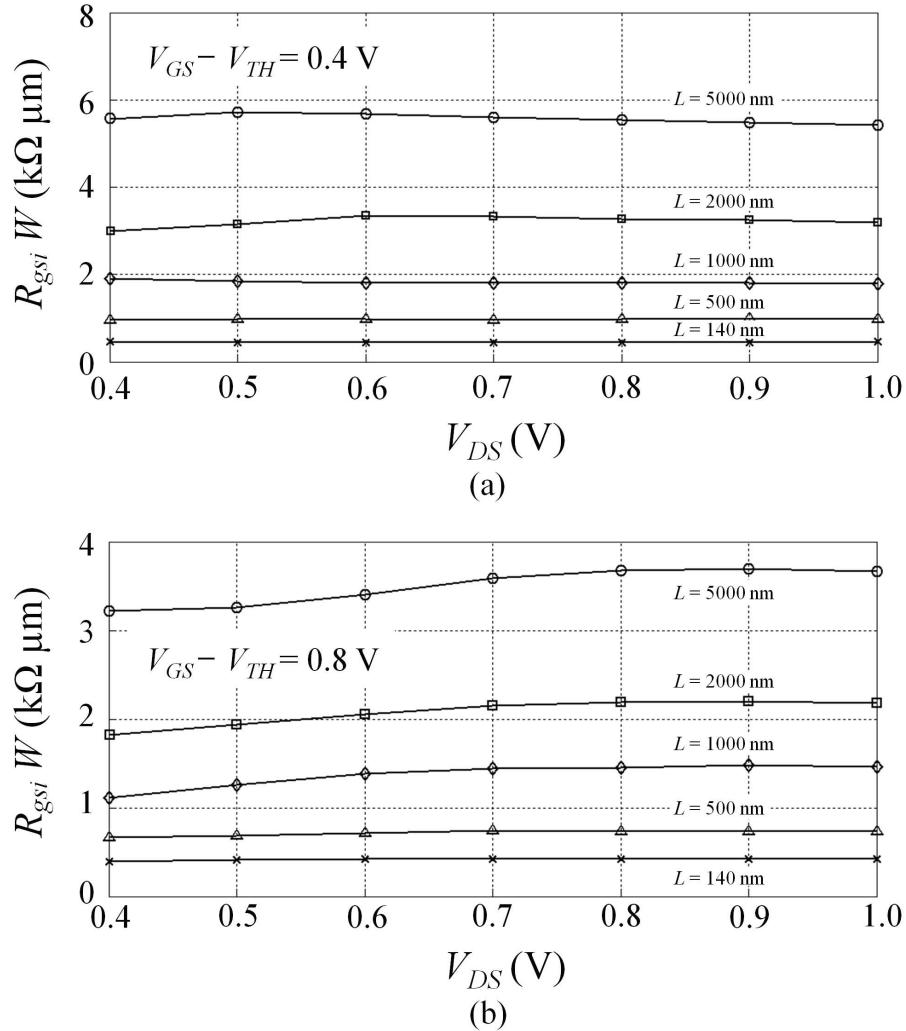

| 2.4 | Extracted values of NQS gate-source resistance $R_{gsi}$ of NMOS devices with gate length $L = 140, 500, 1000, 2000$ and $5000$ nm at gate-source overdrive voltages (a) $V_{GS} - V_{TH} = 0.4$ V and (b) $V_{GS} - V_{TH} = 0.8$ V (gate width is $120$ $\mu\text{m}$ ( $3$ $\mu\text{m}$ $\times$ $40$ fingers), both-side gate connection). . . . . | 27 |

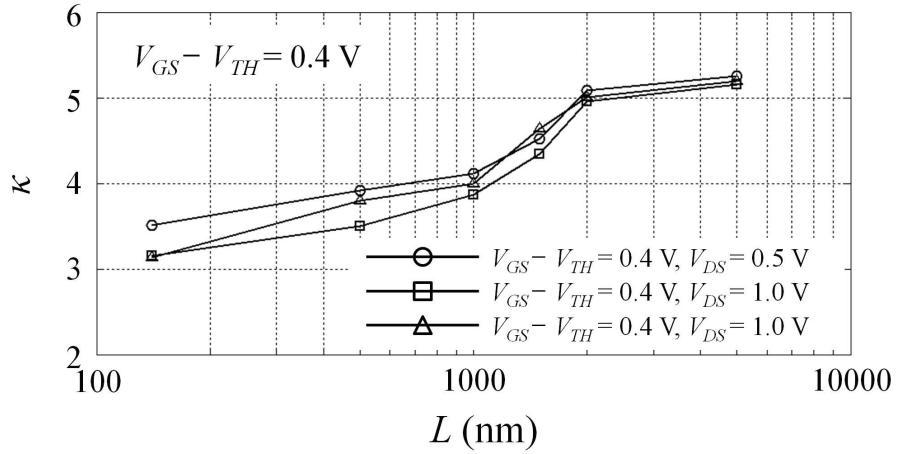

| 2.5 | Gate length dependence of extracted elmore constants $\kappa$ . . . . .                                                                                                                                                                                                                                                                                 | 28 |

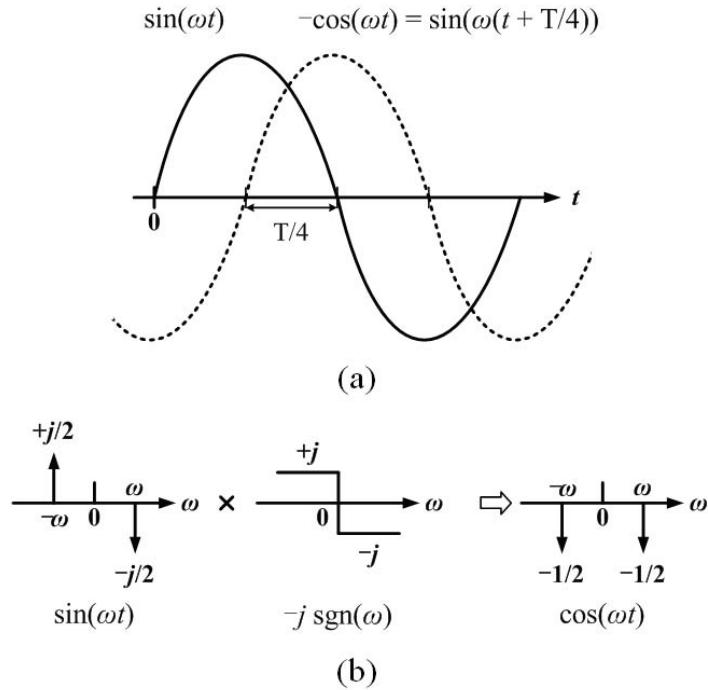

| 3.1 | $90^\circ$ phase shifting in (a) time and (b) frequency domains [11]. . . . .                                                                                                                                                                                                                                                                           | 37 |

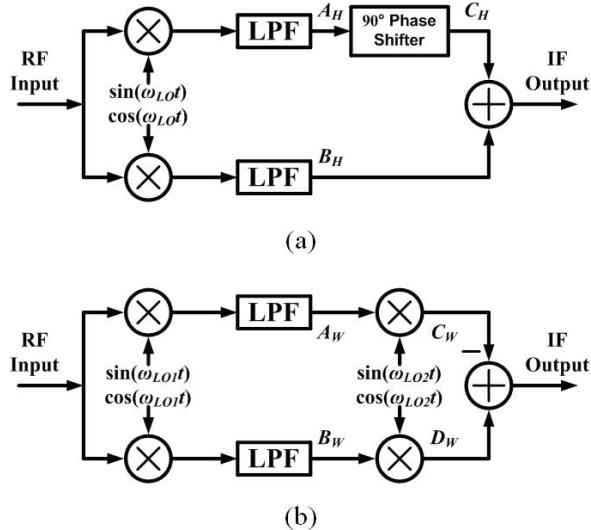

| 3.2 | (a) Hartley and (b) Weaver image rejection structures [11]. . . . .                                                                                                                                                                                                                                                                                     | 38 |

| 3.3 | Graphical signal flow of (a) Hartley and (b) Weaver image rejection structures [11]. .                                                                                                                                                                                                                                                                  | 39 |

|      |                                                                                                                                                                                                                                                                                     |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

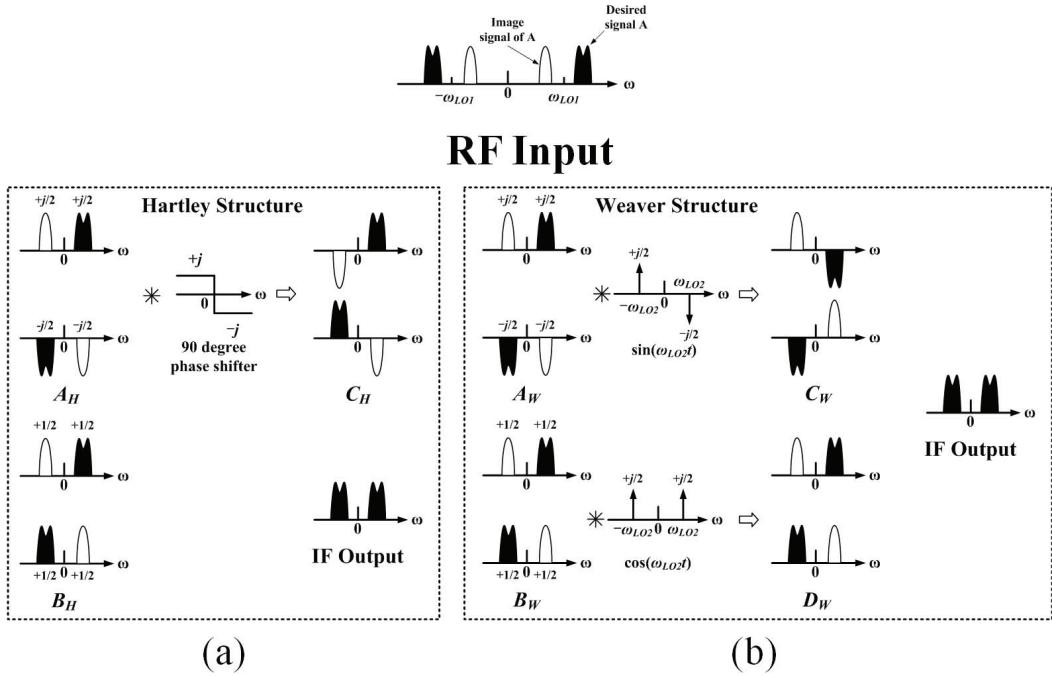

| 3.4  | IMRR with (a) amplitude, (b) phase, and (c) amplitude and phase imbalances. . . . .                                                                                                                                                                                                 | 40 |

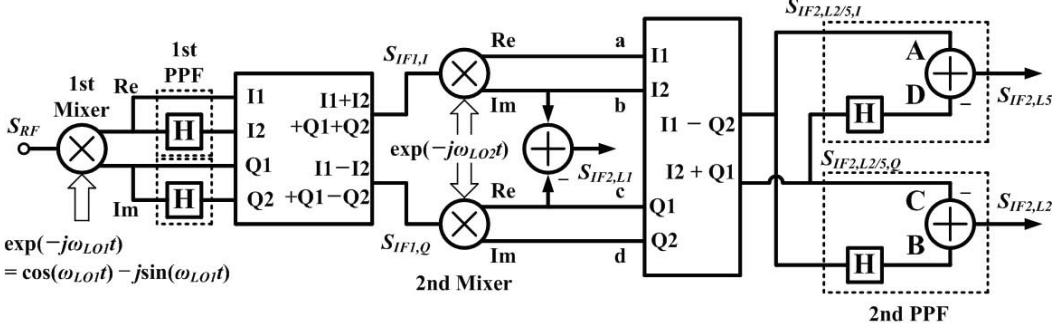

| 3.5  | Signal processing of the proposed triple-band receiver. . . . .                                                                                                                                                                                                                     | 42 |

| 3.6  | Graphical signal processing flow at the locations indicated in Fig. 3.5. . . . .                                                                                                                                                                                                    | 46 |

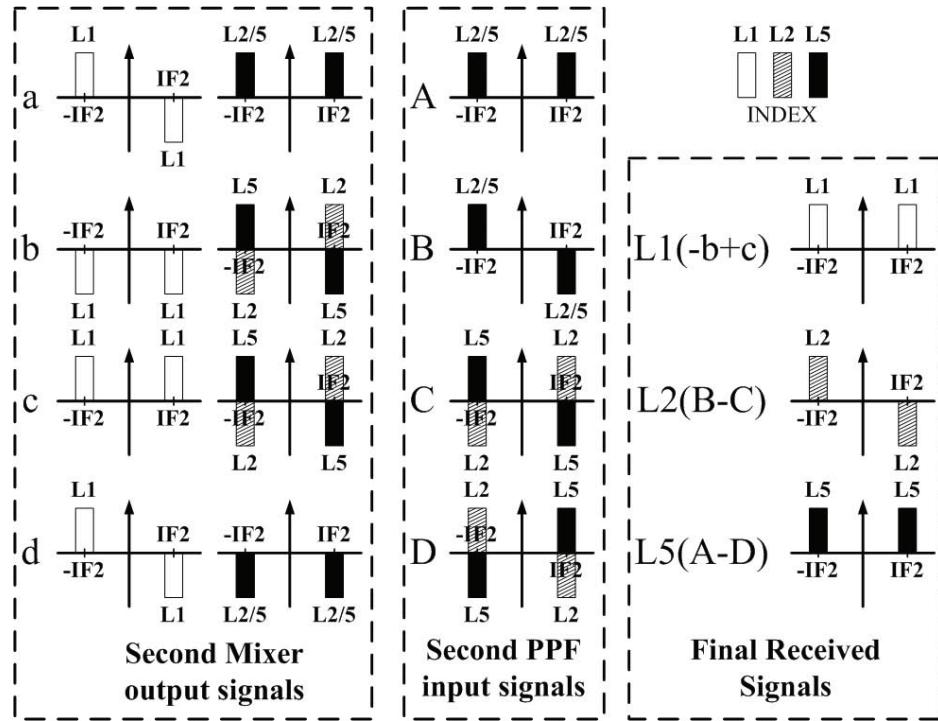

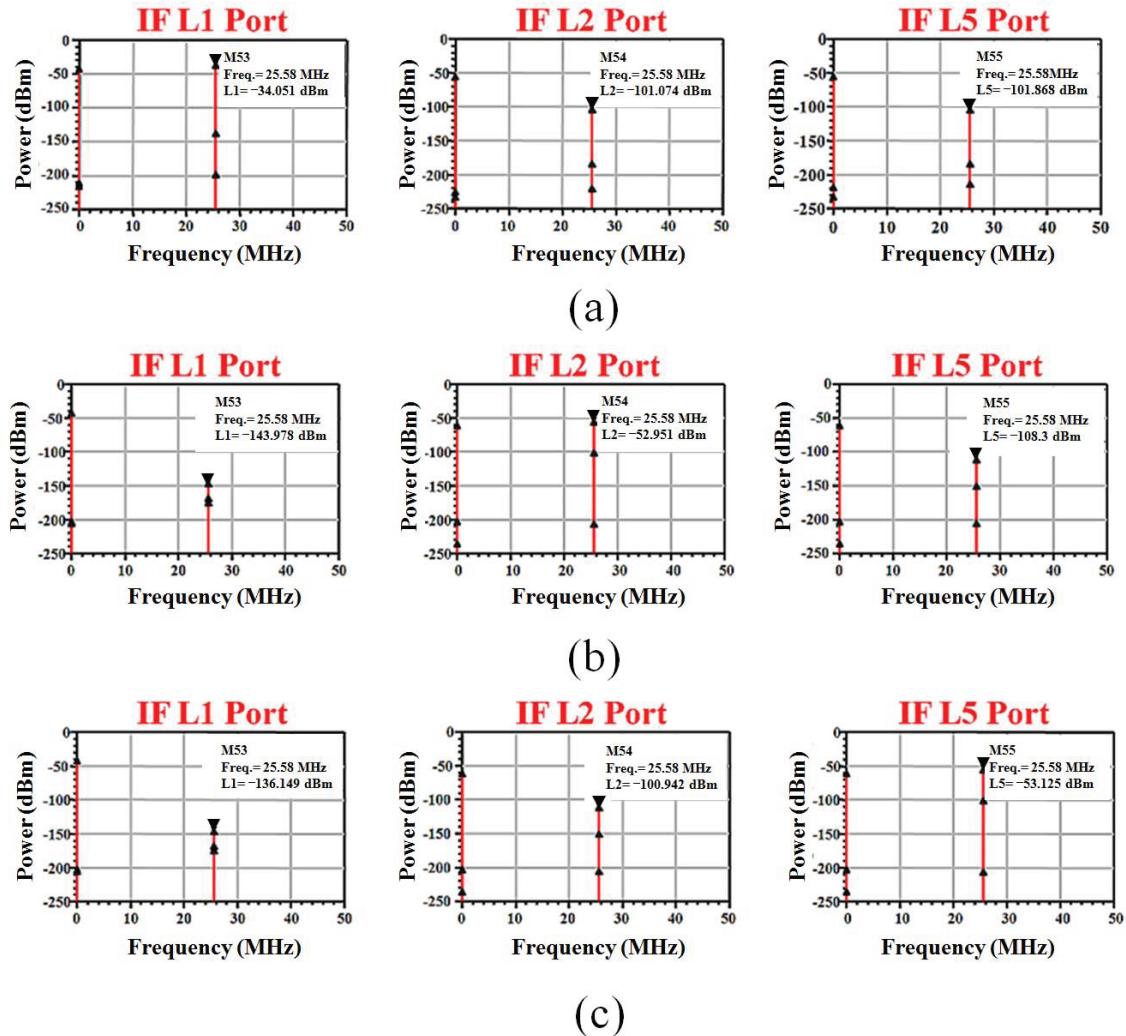

| 3.7  | Behavior-level numerical simulation results of frequency translation with only (a) L1 band signal, (b) L2 band signal, and (c) L5 band signal. . . . .                                                                                                                              | 47 |

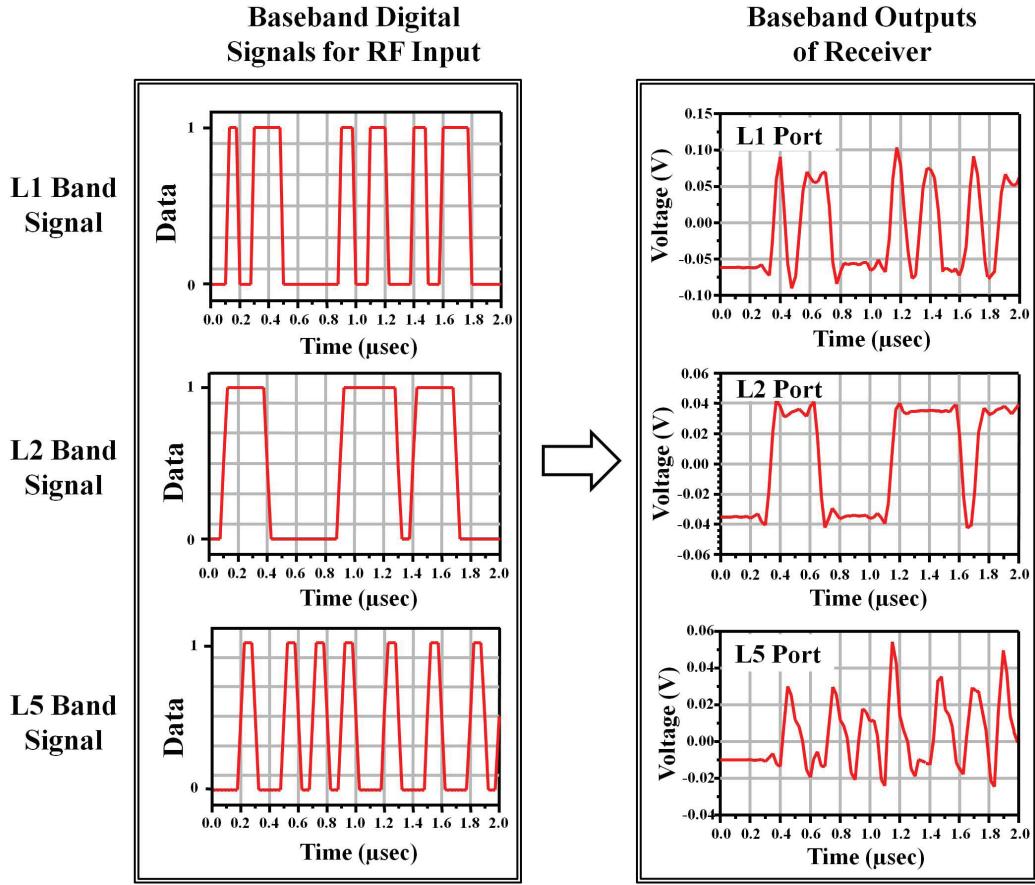

| 3.8  | Circuit simulation results of RF front-end using modulation signals. . . . .                                                                                                                                                                                                        | 48 |

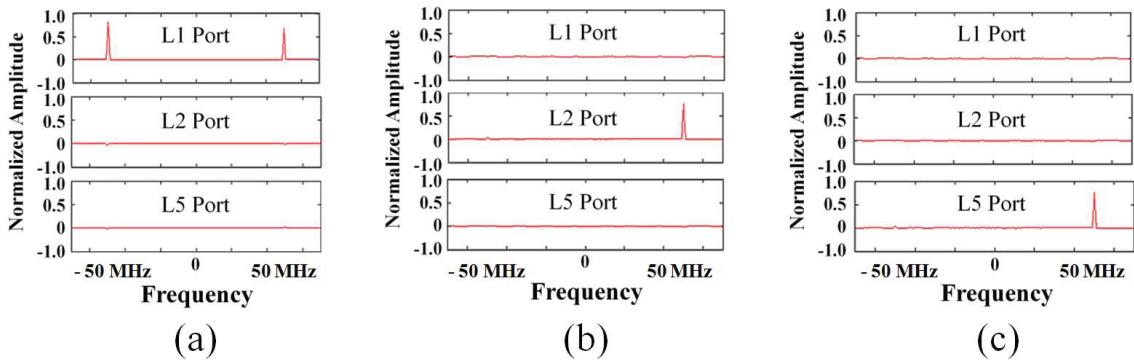

| 3.9  | Circuit simulation results of image rejection with input signal of (a) L1 band, (b) L2 band, and (c) L5 band. . . . .                                                                                                                                                               | 50 |

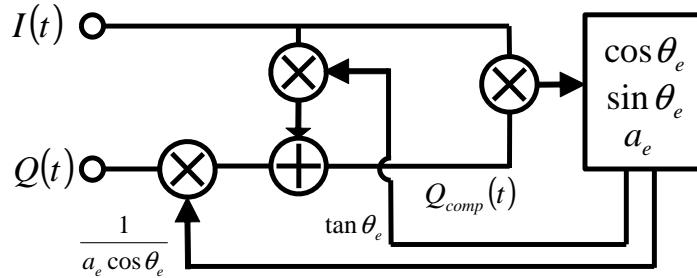

| 3.10 | Block diagram of the phase and amplitude compensation. . . . .                                                                                                                                                                                                                      | 51 |

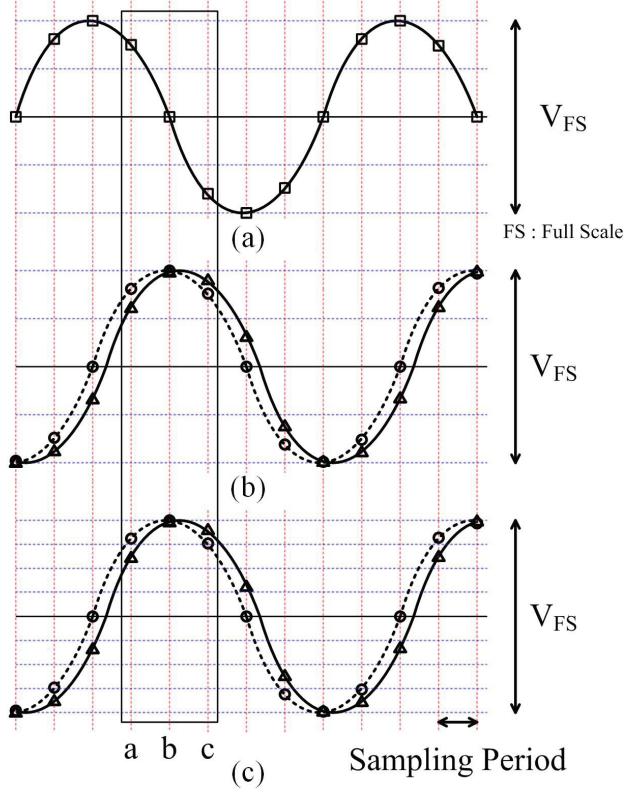

| 3.11 | (a) CW signal of in-phase reference signal, (b) quadrature signal with 2-bit ADC, and (c) quadrature signal with 3-bit ADC (The solid line and dashed line corresponds to the signals with and without $15^\circ$ phase error, respectively. Each mark is sampling point.). . . . . | 52 |

| 4.1  | RF front-end architecture for triple-band signal. . . . .                                                                                                                                                                                                                           | 58 |

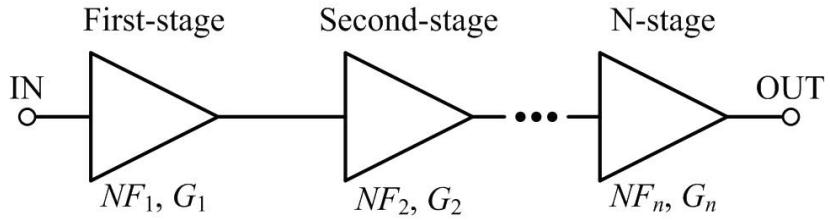

| 4.2  | Block diagram of cascaded system. . . . .                                                                                                                                                                                                                                           | 60 |

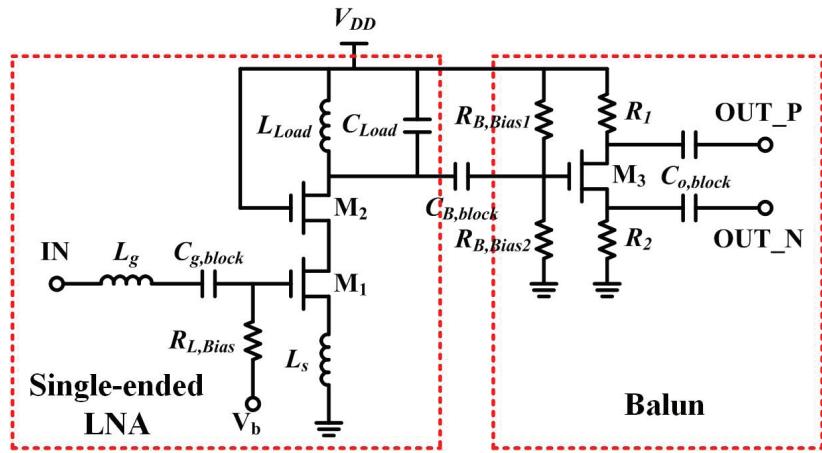

| 4.3  | Schematic of LNA stage. . . . .                                                                                                                                                                                                                                                     | 60 |

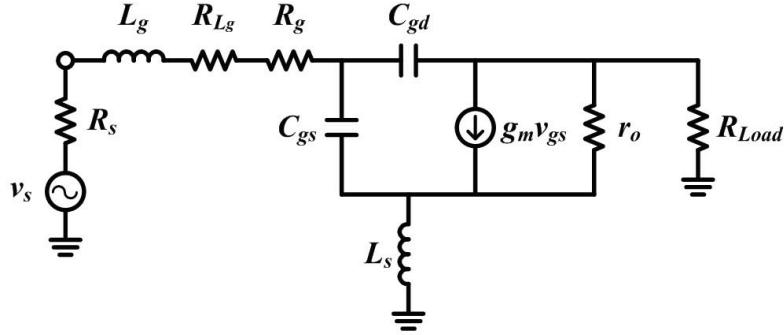

| 4.4  | Small-signal model of LNA input-stage. . . . .                                                                                                                                                                                                                                      | 62 |

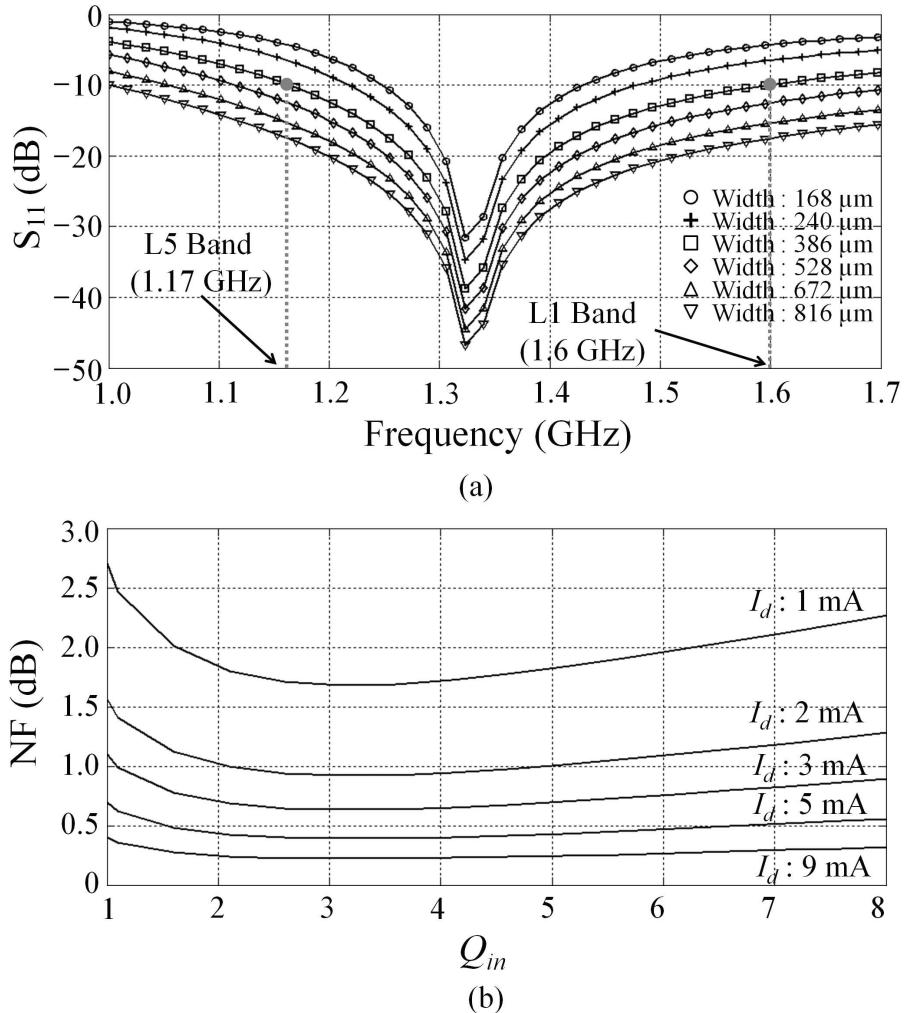

| 4.5  | Calculated (a) input coefficient and (b) NF of LNA. . . . .                                                                                                                                                                                                                         | 65 |

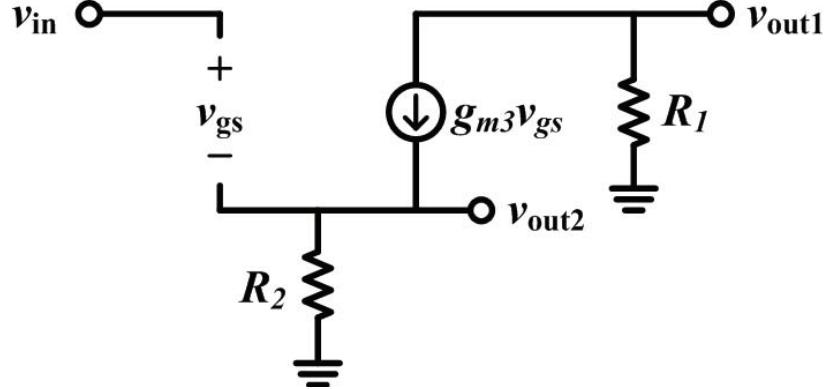

| 4.6  | Small-signal model of balun. . . . .                                                                                                                                                                                                                                                | 67 |

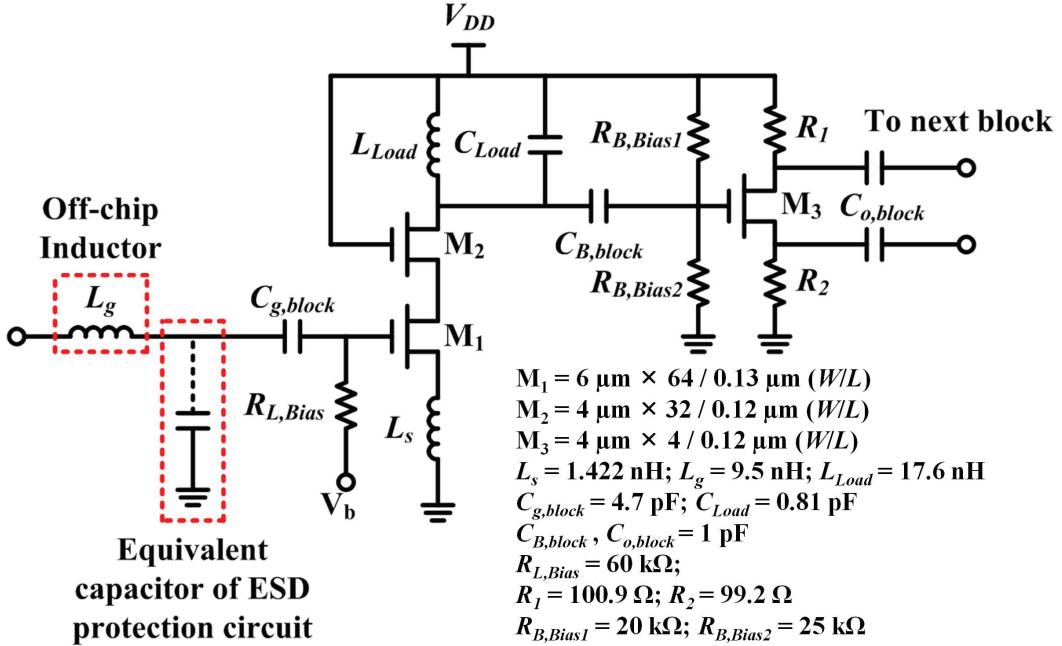

| 4.7  | Schematic of LNA stage. . . . .                                                                                                                                                                                                                                                     | 68 |

| 4.8  | LNA input device layout. . . . .                                                                                                                                                                                                                                                    | 69 |

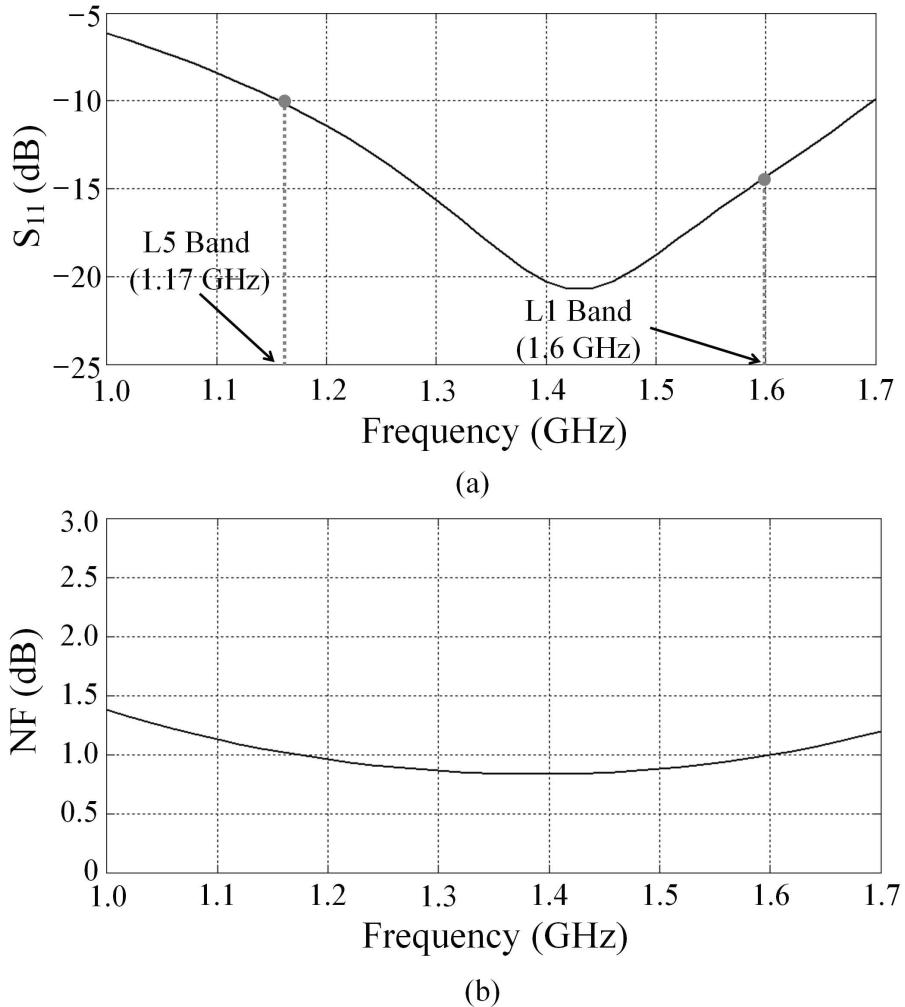

| 4.9  | (a) Input reflection coefficient ( $ S_{11} $ ) and (b) NF of LNA. . . . .                                                                                                                                                                                                          | 70 |

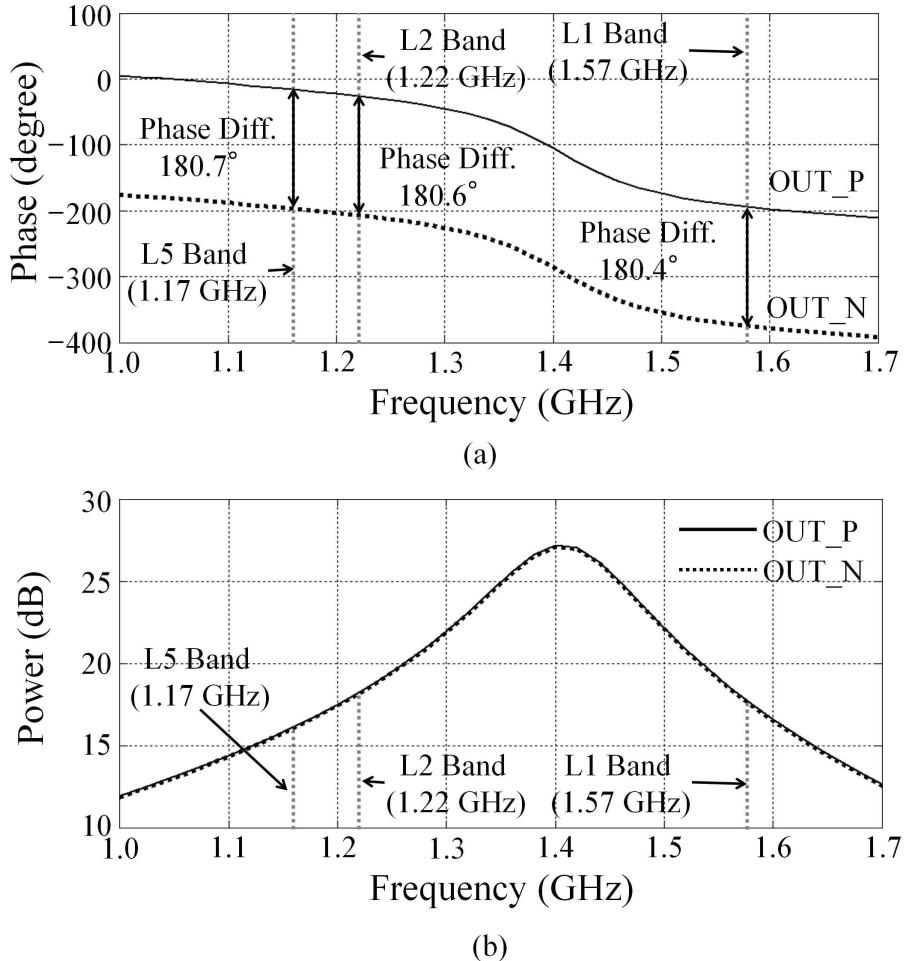

| 4.10 | (a) Phase and (b) power of LNA's differential outputs. . . . .                                                                                                                                                                                                                      | 71 |

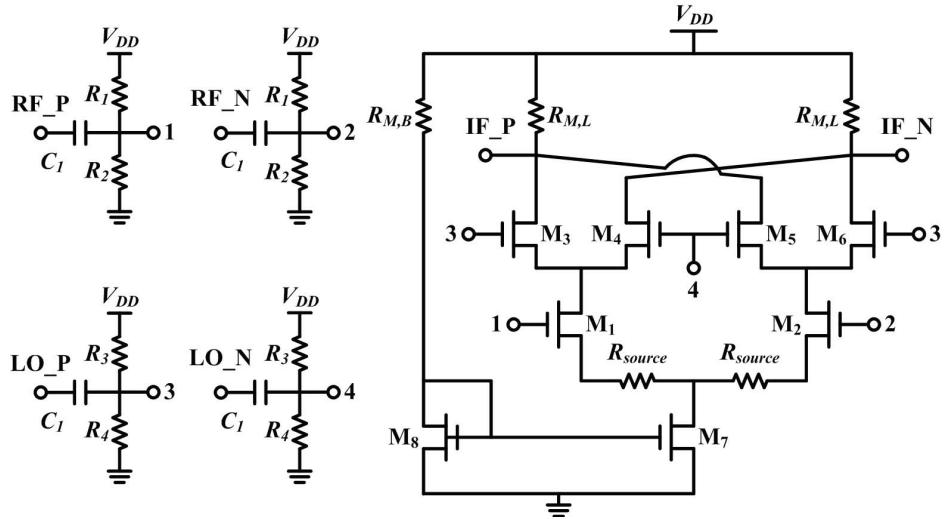

| 4.11 | Schematic of doubly-balanced active mixer. . . . .                                                                                                                                                                                                                                  | 73 |

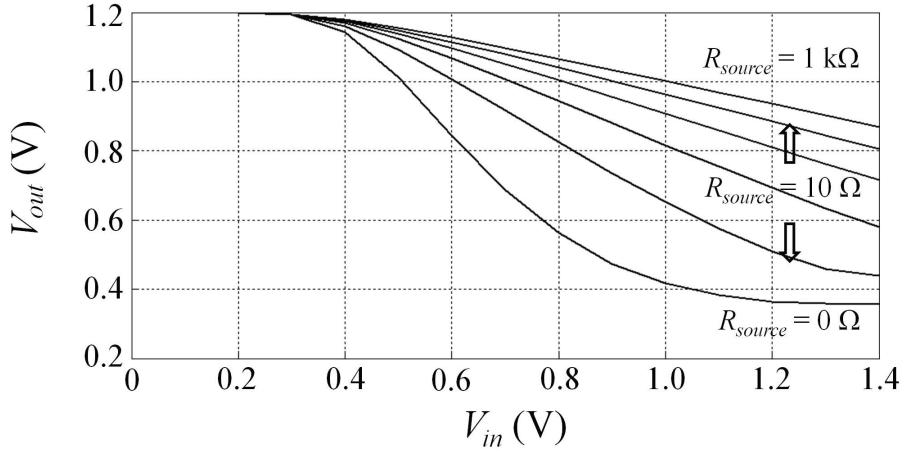

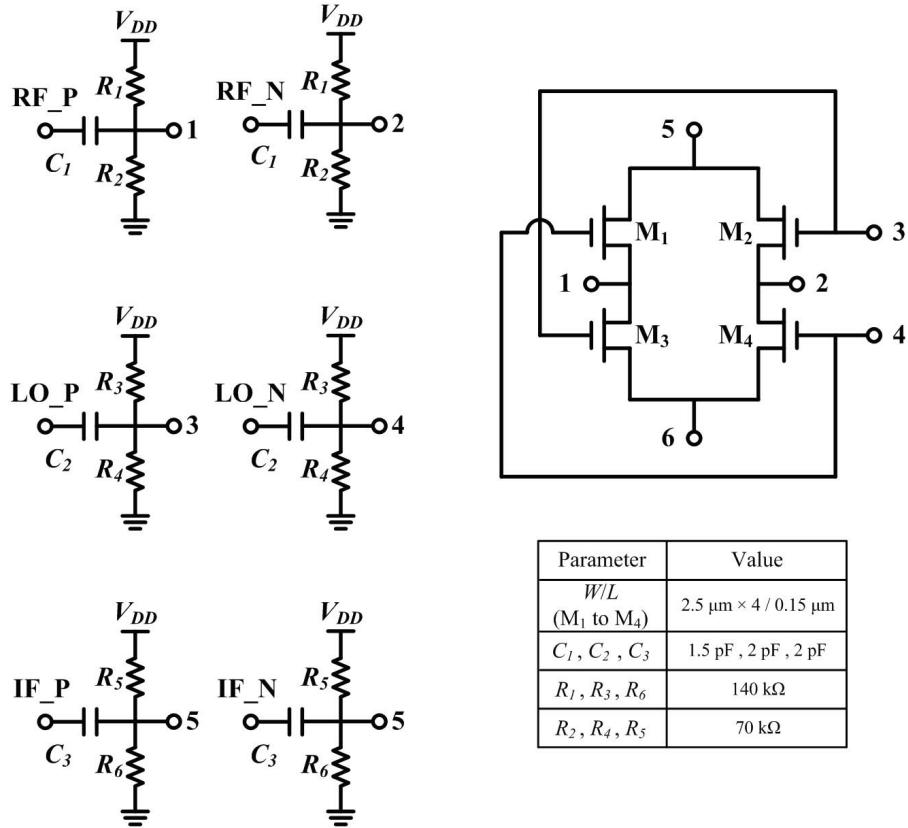

| 4.12 | DC transfer characteristic of mixer's core device ( $V_{in}$ is the voltage of Port 1 and Port 2 in Fig. 4.11. $V_{out}$ is the voltage of Port IF_P and Port IF_N in Fig. 4.11.). . . . .                                                                                          | 74 |

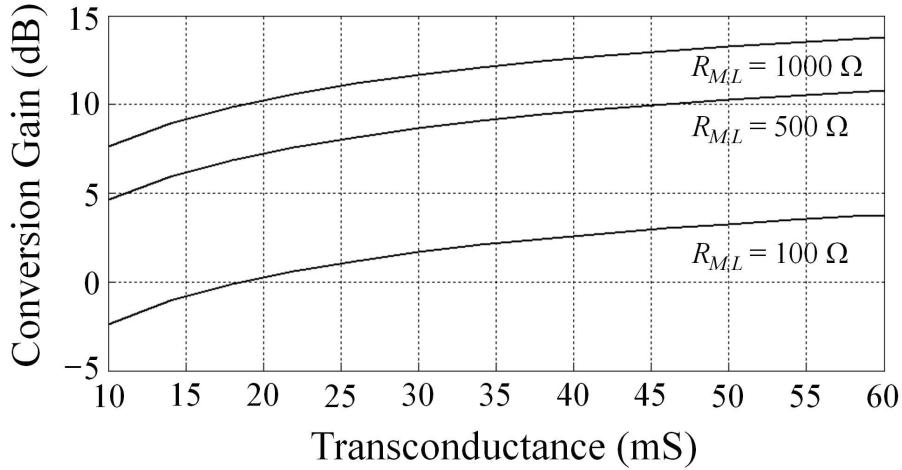

| 4.13 | Conversion gain against transconductance ( $R_{source} = 10 \Omega$ ). . . . .                                                                                                                                                                                                      | 75 |

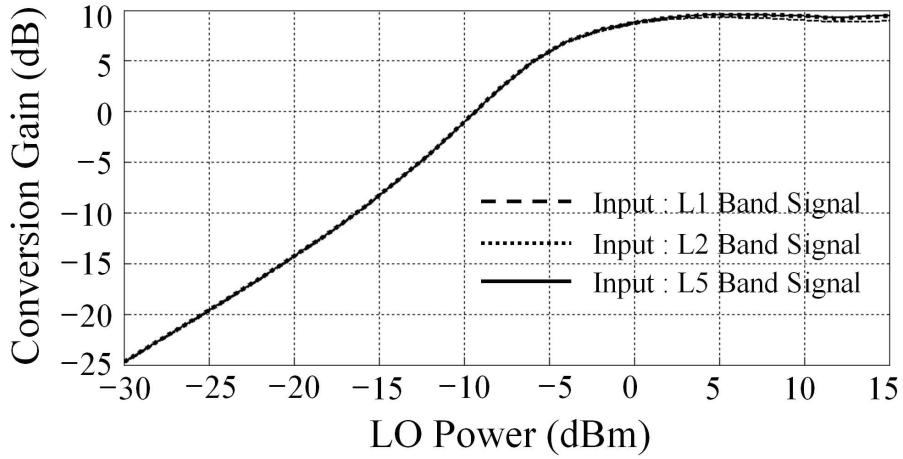

| 4.14 | Mixer's conversion gain against LO power at triple-band signal. . . . .                                                                                                                                                                                                             | 76 |

---

|                                                                                                                                                                             |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

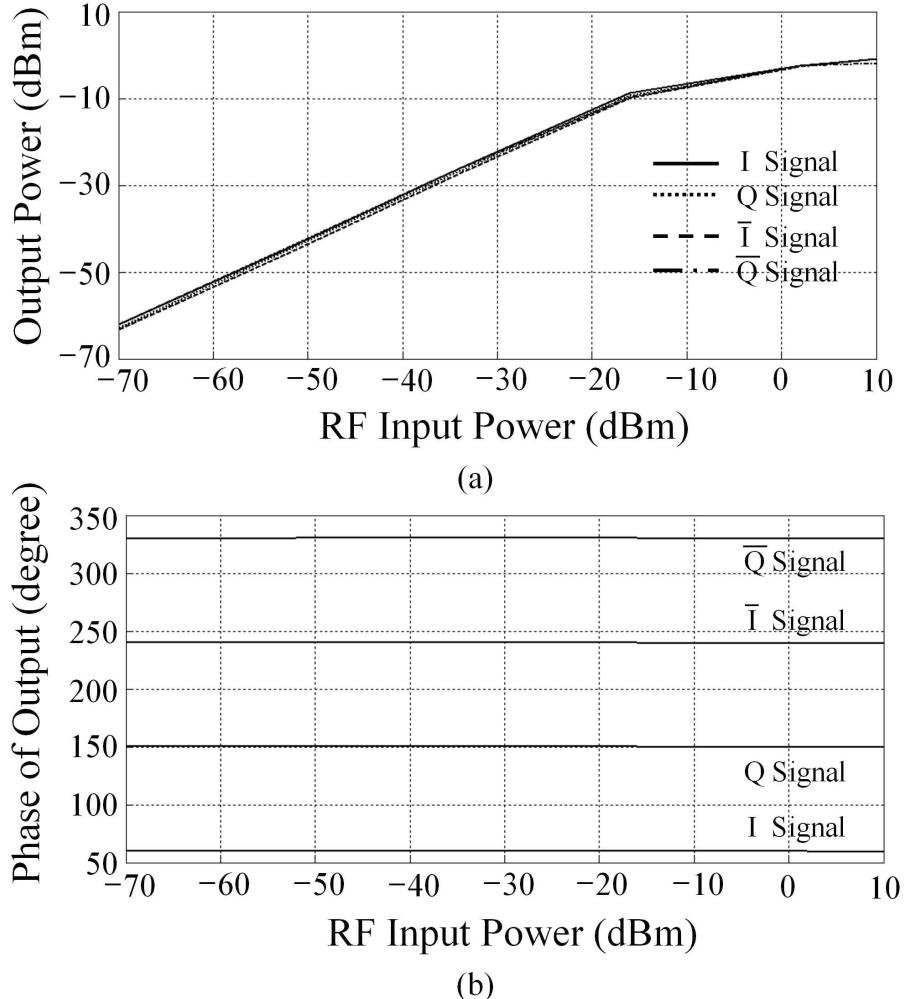

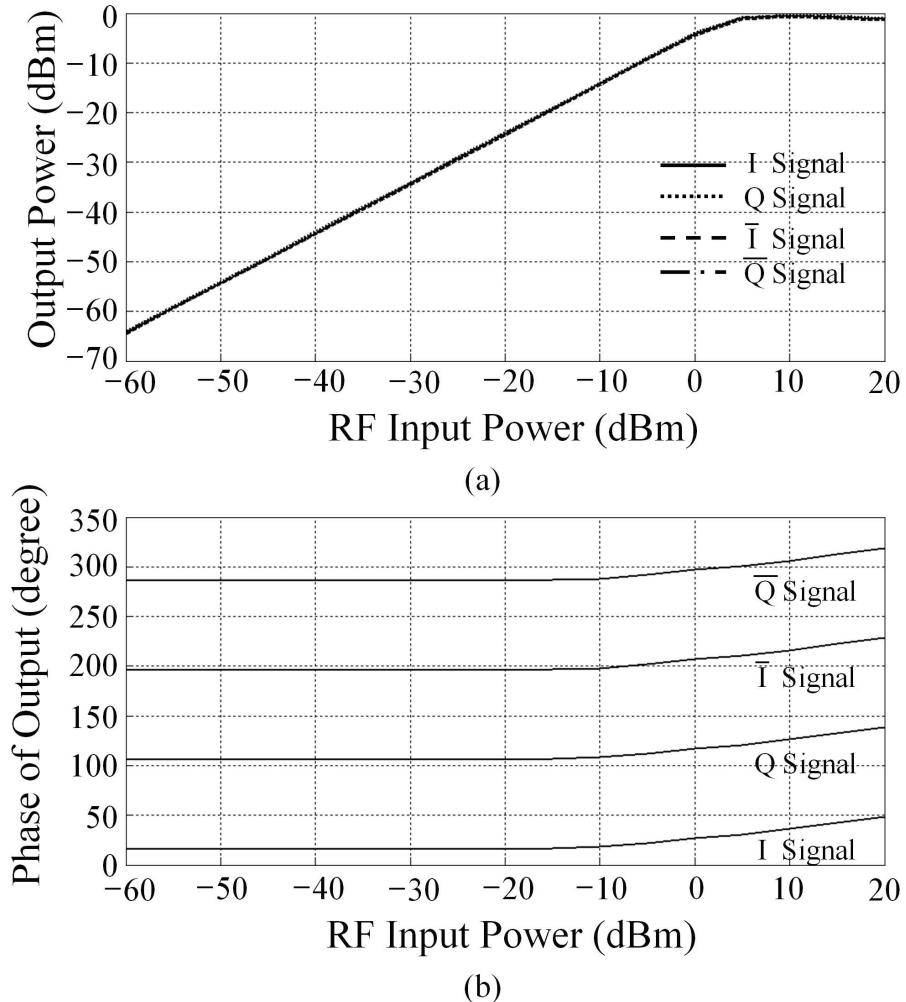

| 4.15 (a) Power and (b) phase imbalances of mixer's output signals against input signal (LO power: 5 dBm). . . . .                                                           | 77  |

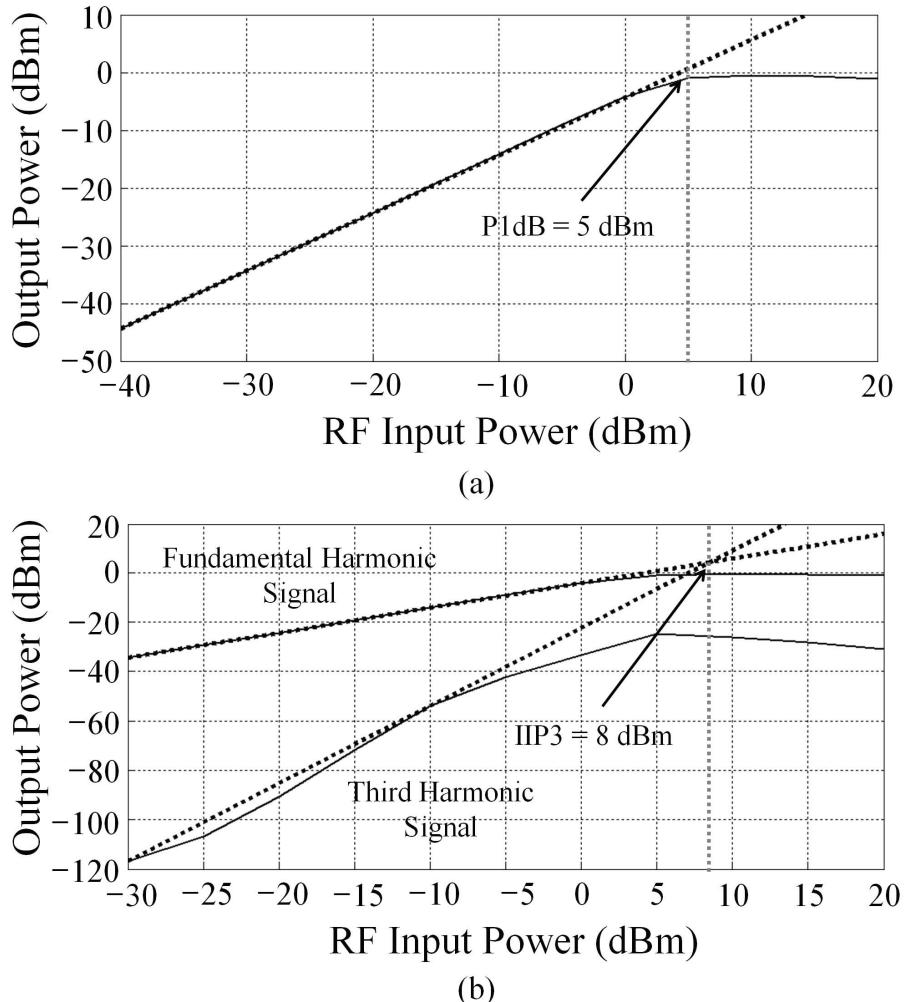

| 4.16 (a) P1dB and (b) IIP3 against mixer's input signal level (LO power: 5 dBm). . . . .                                                                                    | 78  |

| 4.17 Schematic of doubly-balanced passive mixer. . . . .                                                                                                                    | 80  |

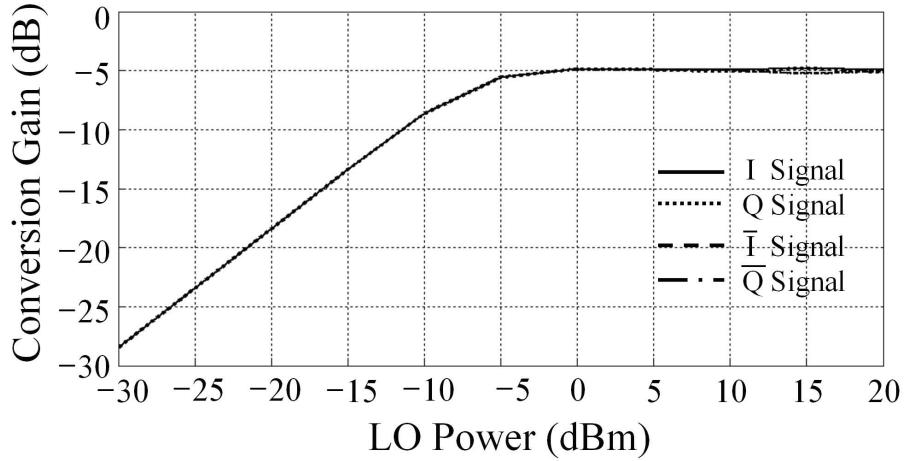

| 4.18 Conversion gain of passive mixer against LO power. . . . .                                                                                                             | 81  |

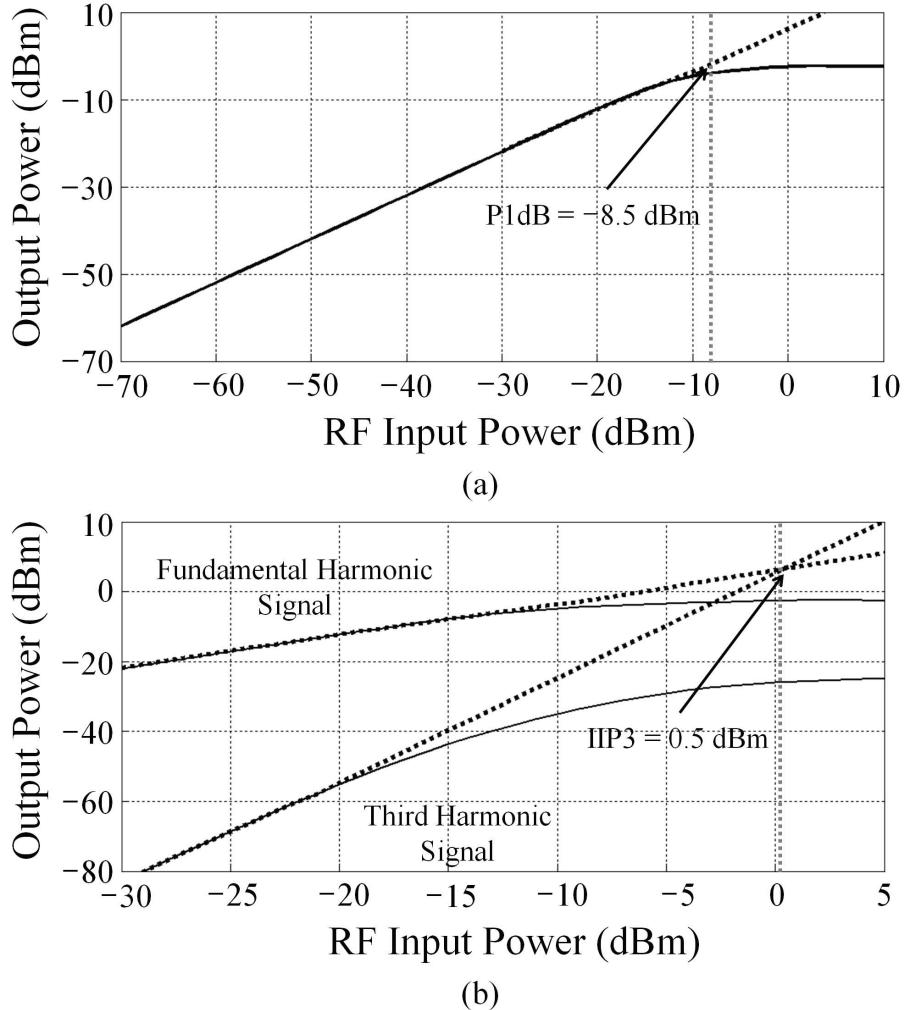

| 4.19 (a) P1dB and (b) IIP3 against passive mixer's input signal level (LO power: 0 dBm). . . . .                                                                            | 82  |

| 4.20 (a) Amplitude and (b) phase of passive mixer's outputs against input signal level (LO power: 0 dBm). . . . .                                                           | 83  |

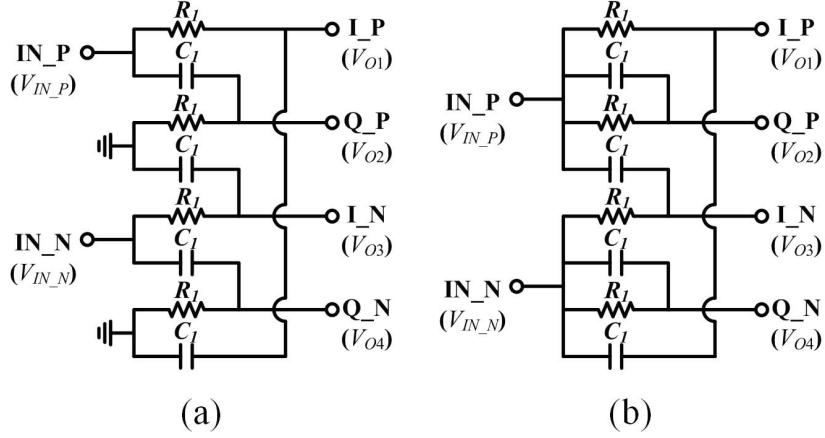

| 4.21 A single-stage PPF of (a) balanced and (b) single input type. . . . .                                                                                                  | 85  |

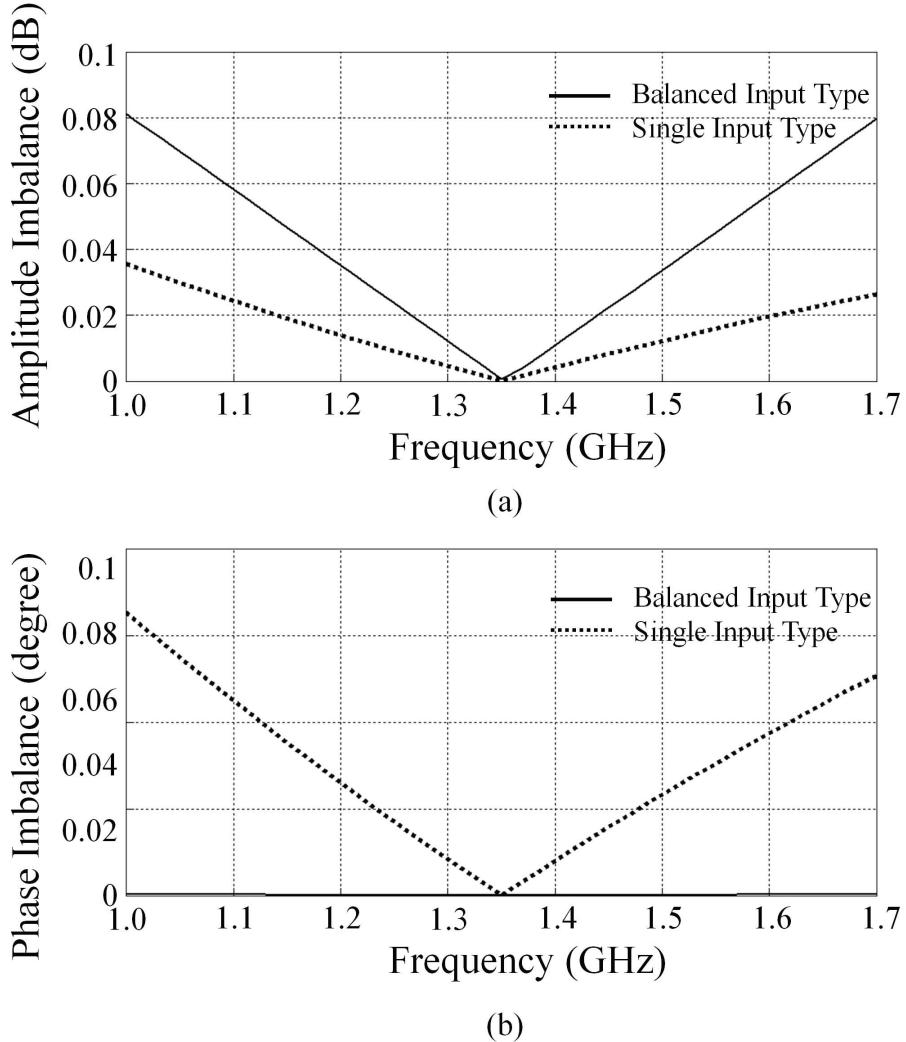

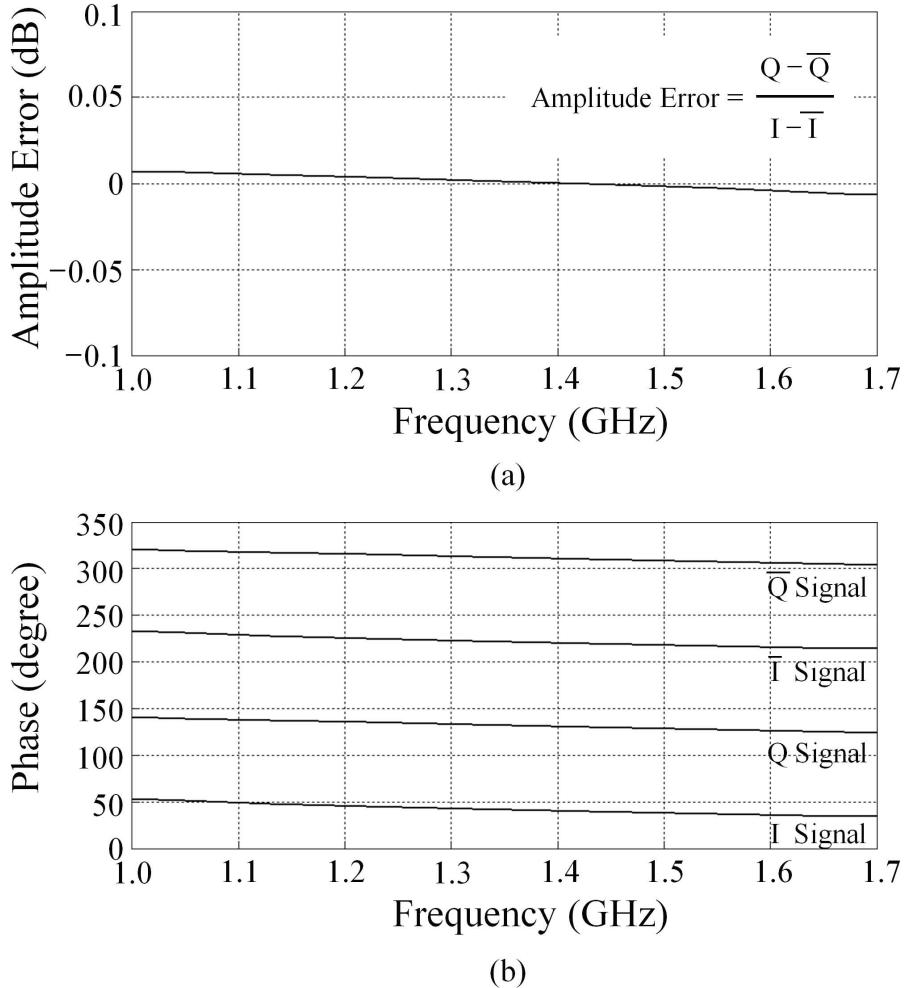

| 4.22 The output imbalance simulation results of a single-stage PPF for (a) amplitude and (B) phase according to input-stage type. . . . .                                   | 86  |

| 4.23 The two-stage PPF schematic based on single input type. . . . .                                                                                                        | 87  |

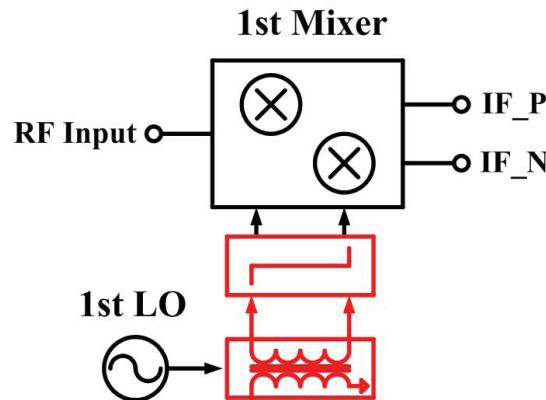

| 4.24 First mixer with IQ generator composed two-stage PPF and balun. . . . .                                                                                                | 87  |

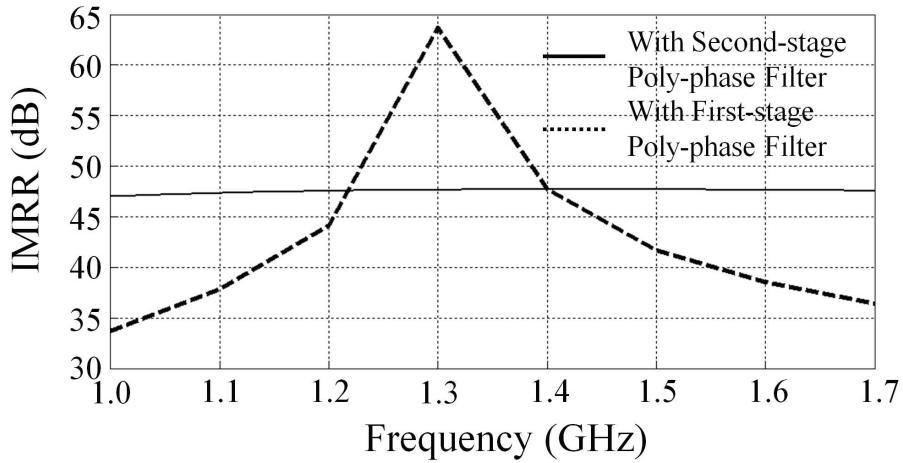

| 4.25 IMRR of first mixer with IQ generator composed two-stage PPF and balun. . . . .                                                                                        | 88  |

| 4.26 (a) Amplitude and (b) phase balance of two-stage PPF's output signals. . . . .                                                                                         | 89  |

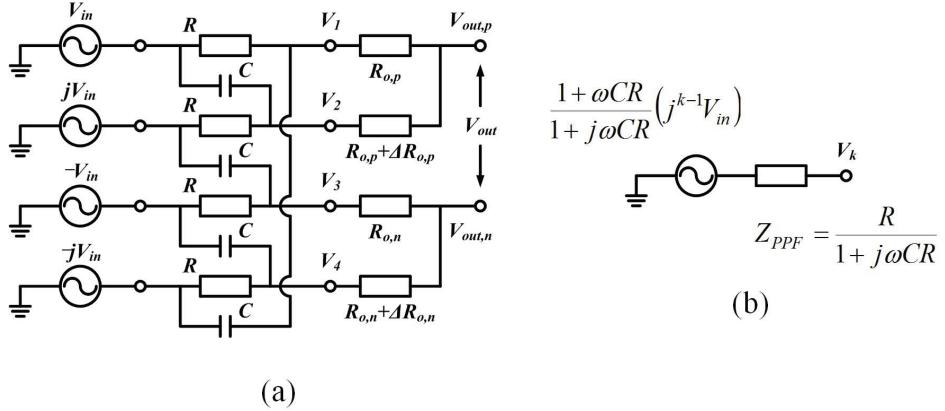

| 4.27 (a) Simple PPF with resistive adder and (b) equivalent circuit to calculate $V_k$ ( $k = 1, 2, 3, 4$ ). . . . .                                                        | 90  |

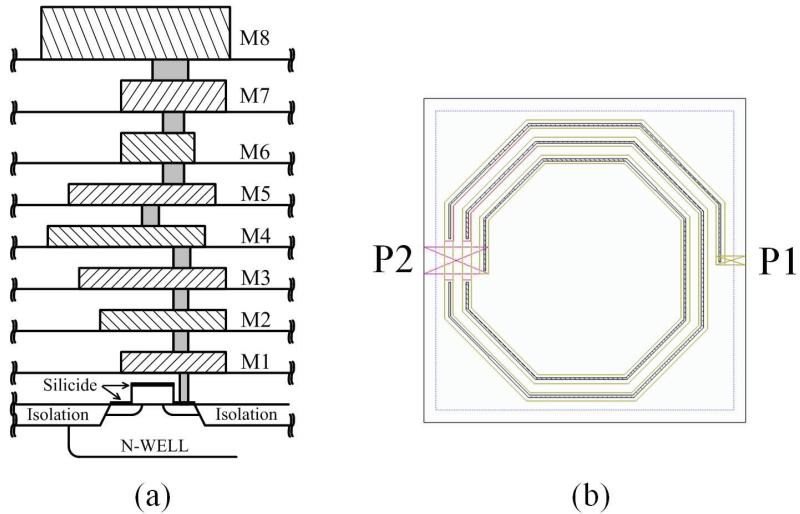

| 4.28 (a) Cross-section of used process and (b) layout structure of used inductor. . . . .                                                                                   | 91  |

| 4.29 (a) Q-factor and (b) inductance including layout condition of used inductor. . . . .                                                                                   | 92  |

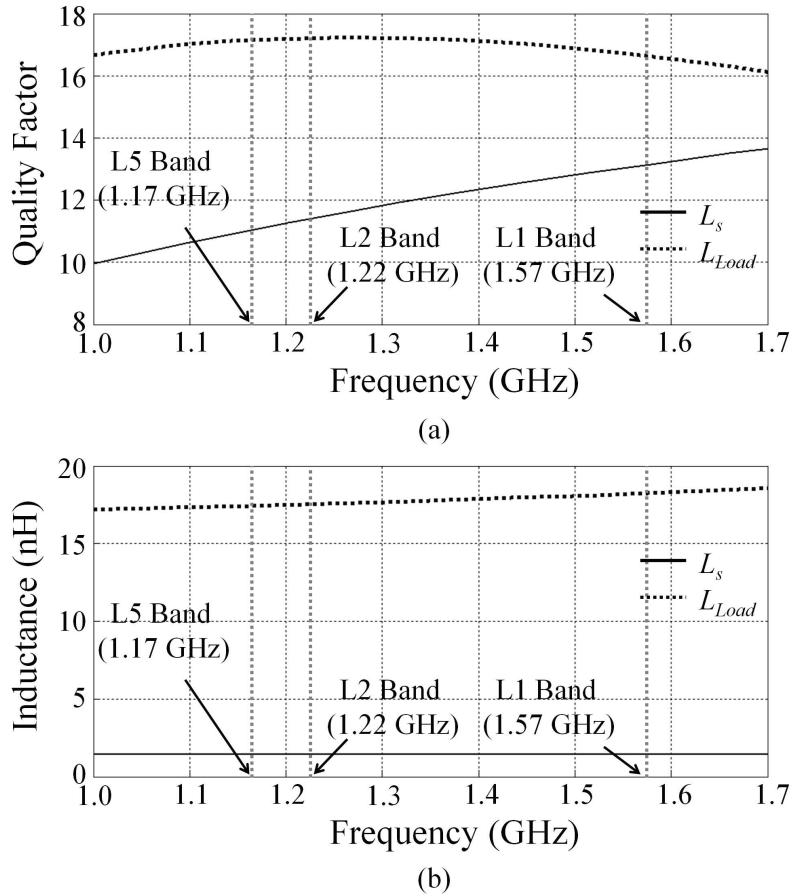

| 4.30 (a) Q-factor and (b) inductance of Murata inductor for simulation of lumped elements. . . . .                                                                          | 93  |

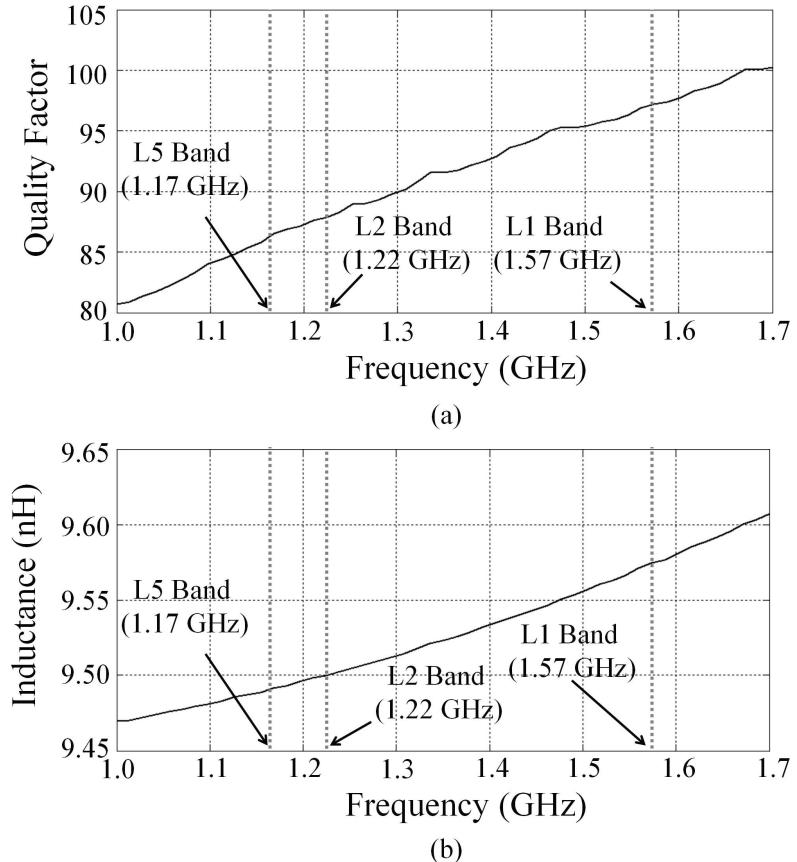

| 4.31 (a) Structure and (b) layout component of MIM capacitor. . . . .                                                                                                       | 94  |

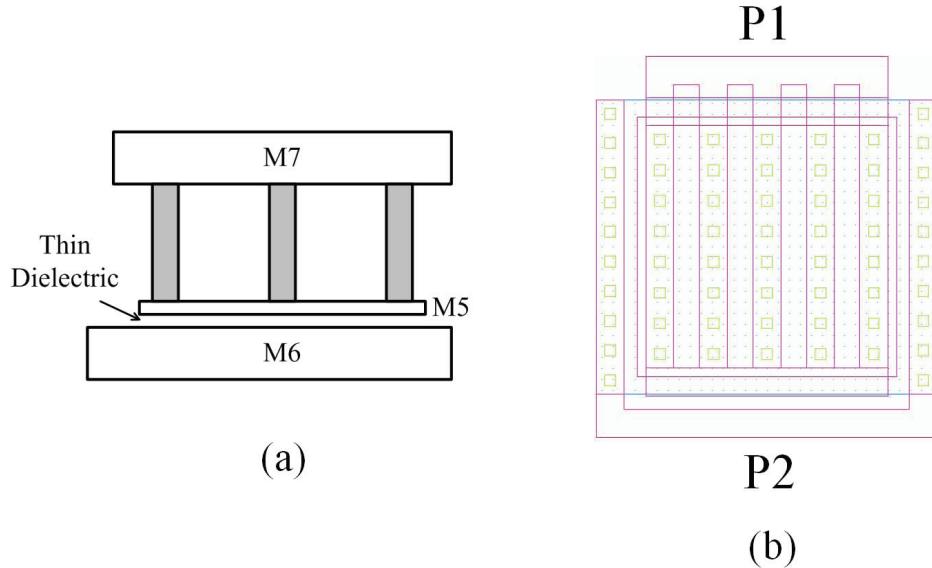

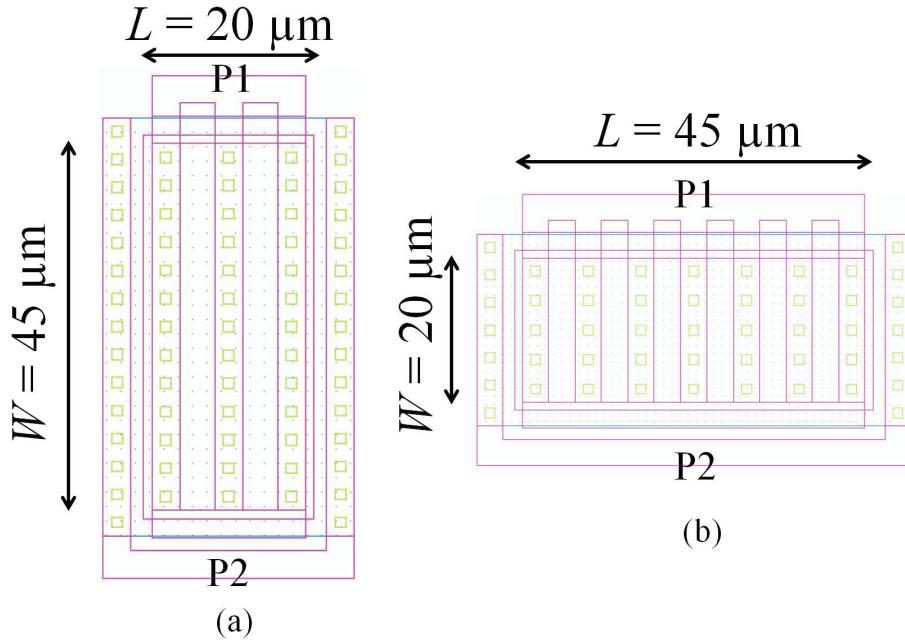

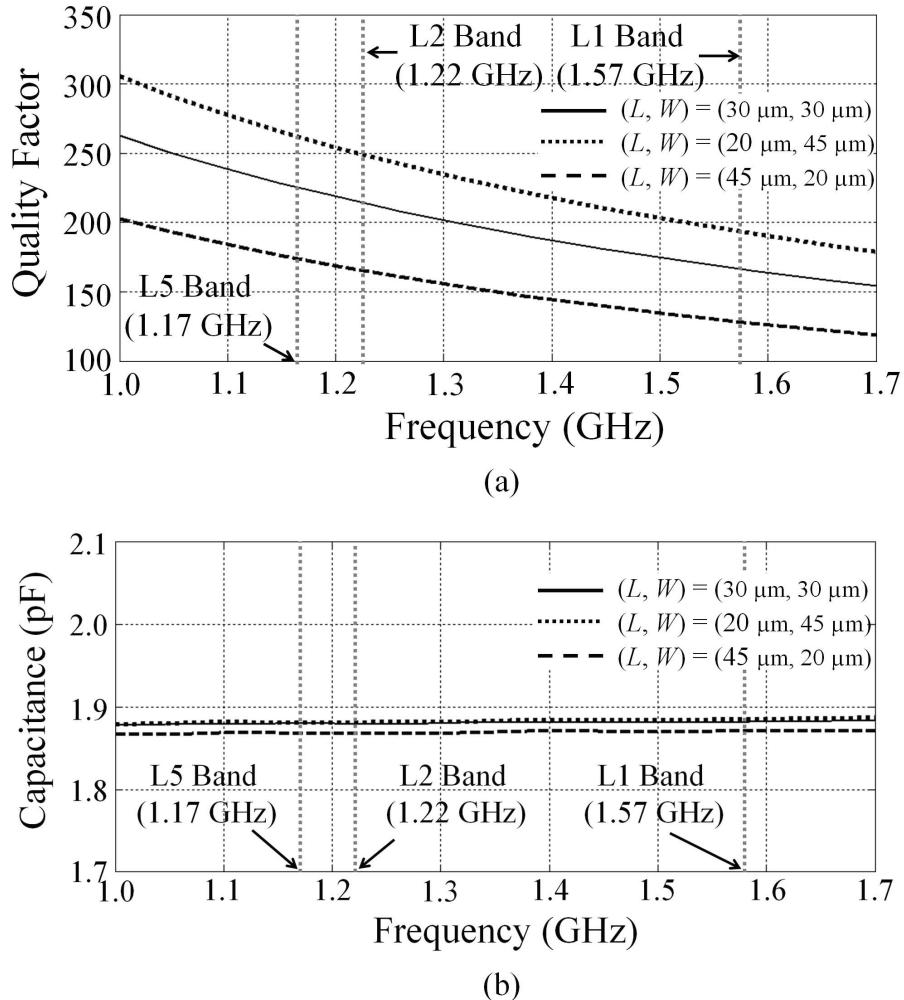

| 4.32 Differential length and width size ((a) $20 \mu\text{m} \times 45 \mu\text{m}$ and (b) $45 \mu\text{m} \times 20 \mu\text{m}$ ) of same value's MIM capacitor. . . . . | 95  |

| 4.33 (a) Q-factor and (b) capacitance of MIM capacitor. . . . .                                                                                                             | 96  |

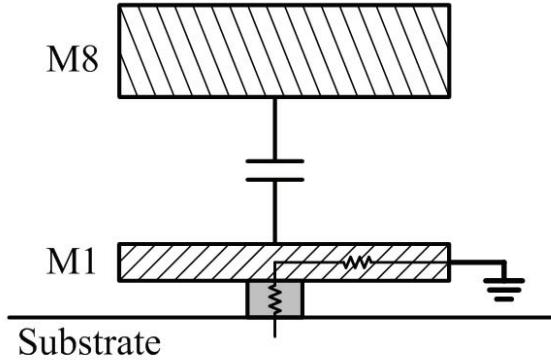

| 4.34 Cross-section of pad with ground and substrate plane. . . . .                                                                                                          | 97  |

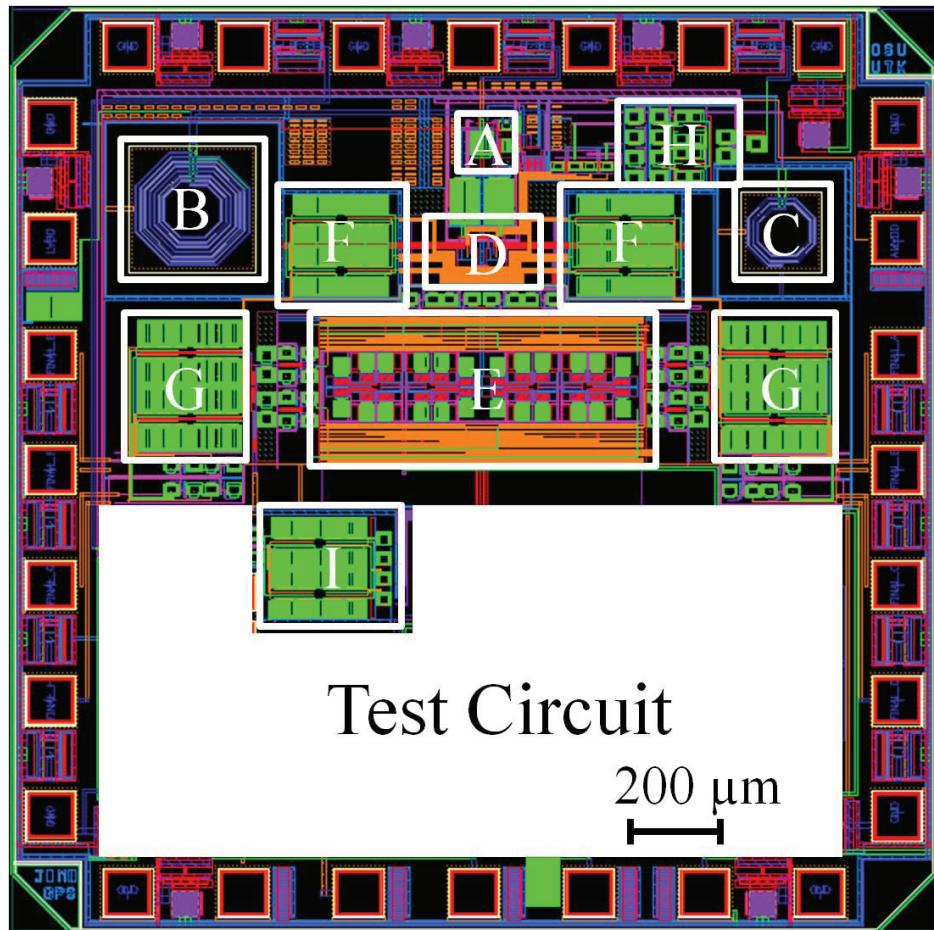

| 4.35 Designed layout of RF front-end architecture for triple-band signal. . . . .                                                                                           | 98  |

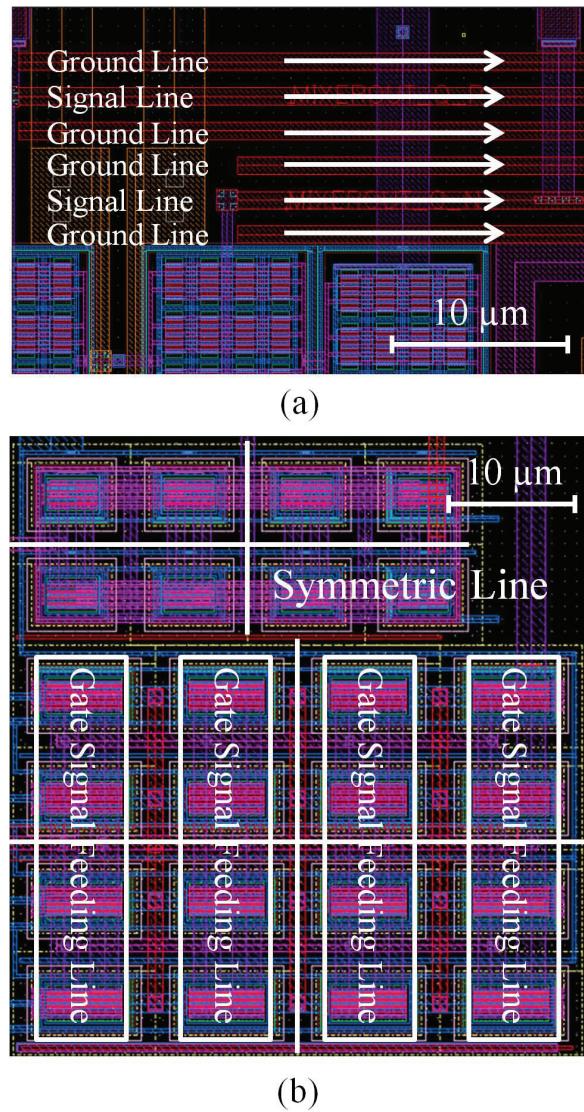

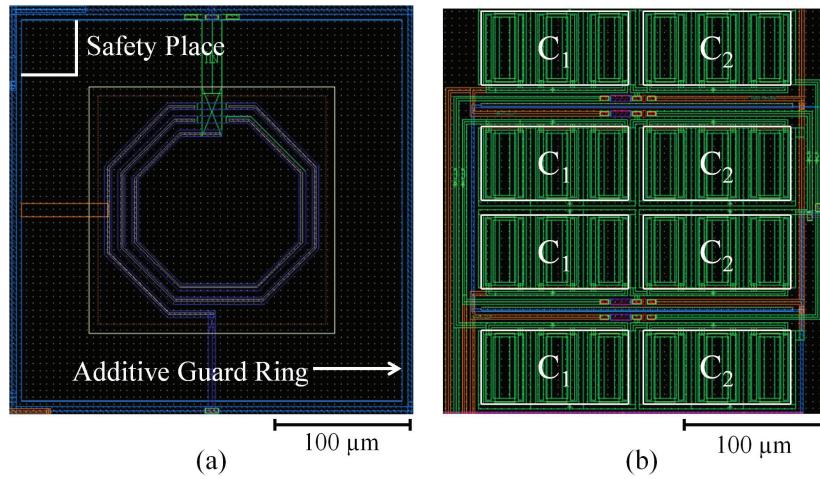

| 4.36 Layout issue point as (a) signal line and (b) MOSFET array. . . . .                                                                                                    | 99  |

| 4.37 Layout issue point as (a) inductor (1.45 nH) and (b) PPF with capacitor array ( $C_1 = C_2 = 1 \text{ pF}$ in Fig. 4.23). . . . .                                      | 100 |

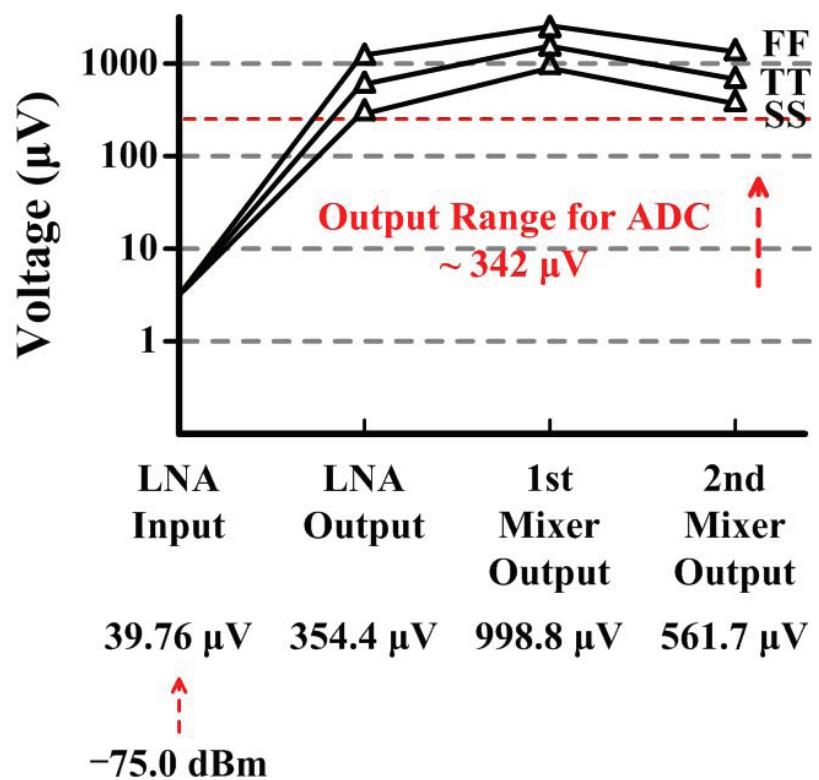

| 4.38 Process variation simulation results of RF front-end output voltage level at each block. . . . .                                                                       | 101 |

|      |                                                                                                                                                                                                                                                                                                                                           |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

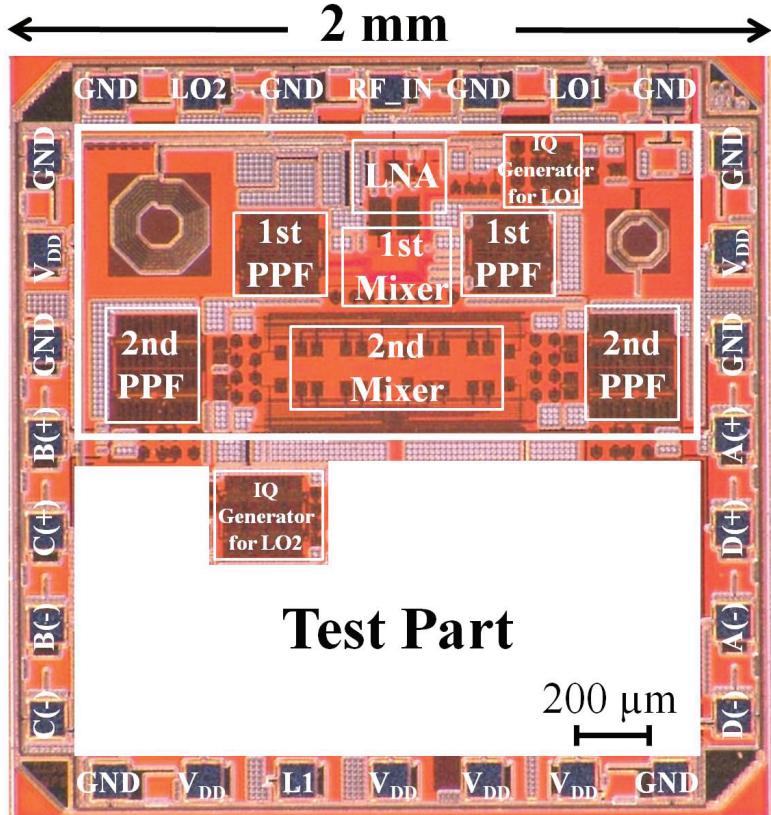

| 5.1  | Fabricated chip photo. . . . .                                                                                                                                                                                                                                                                                                            | 107 |

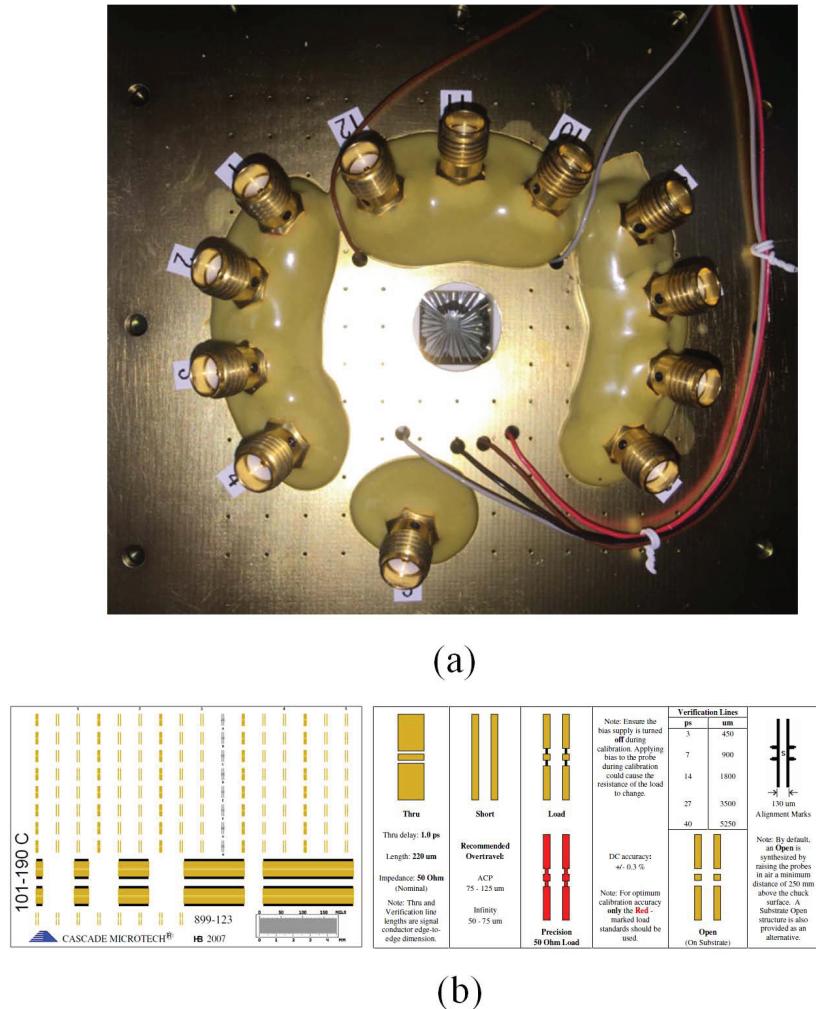

| 5.2  | (a) Probe card for high-frequency DUT measurement and (b) impedance standard substrate for calibration. . . . .                                                                                                                                                                                                                           | 108 |

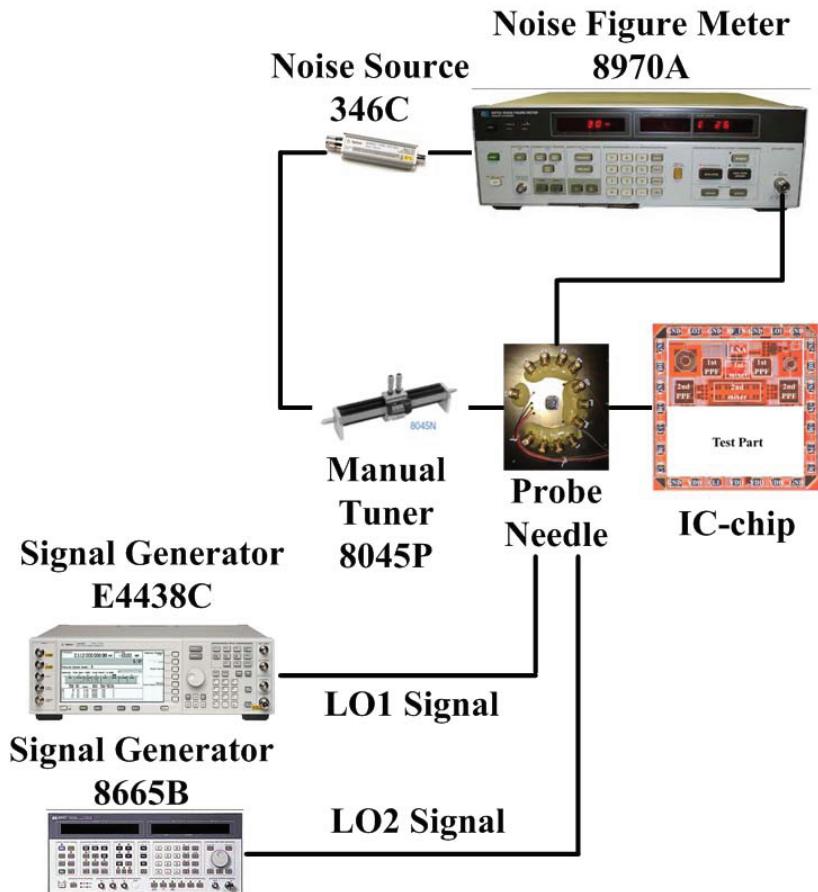

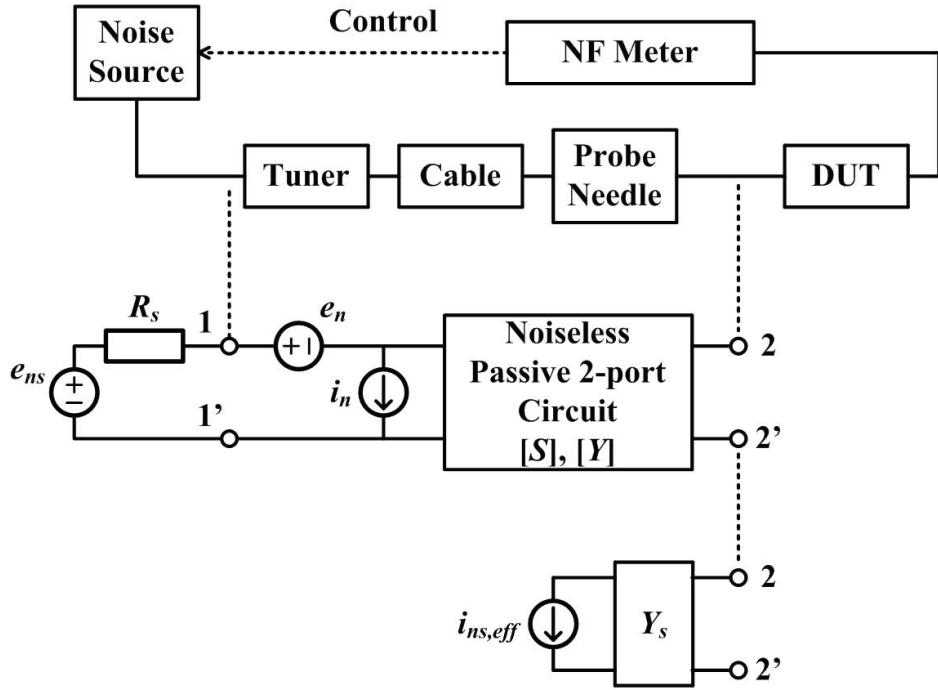

| 5.3  | Equipment set-up for NF measurement. . . . .                                                                                                                                                                                                                                                                                              | 109 |

| 5.4  | Equivalent set-up of measurement equipments for NF. . . . .                                                                                                                                                                                                                                                                               | 110 |

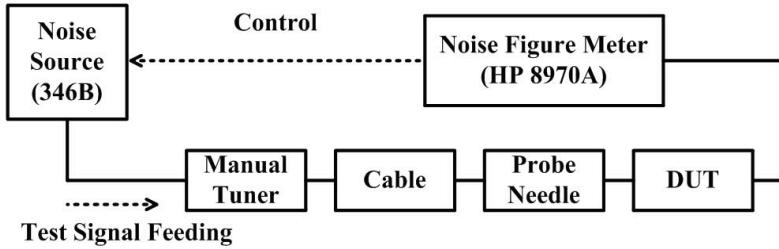

| 5.5  | Measurement results of on-wafer IC-chip: (a) input reflection coefficient and (b) NF. . . . .                                                                                                                                                                                                                                             | 110 |

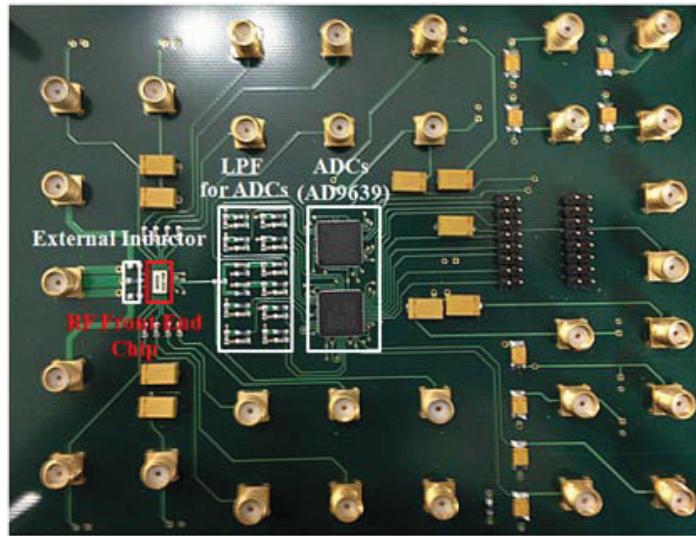

| 5.6  | Designed module PCB board. . . . .                                                                                                                                                                                                                                                                                                        | 111 |

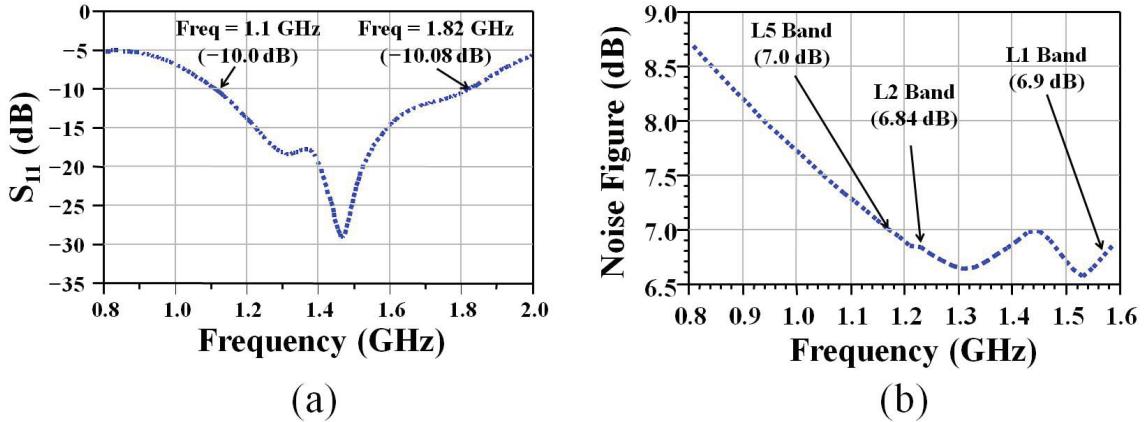

| 5.7  | Measurement results of RF front-end on module board: (a) input reflection coefficient and (b) NF. . . . .                                                                                                                                                                                                                                 | 112 |

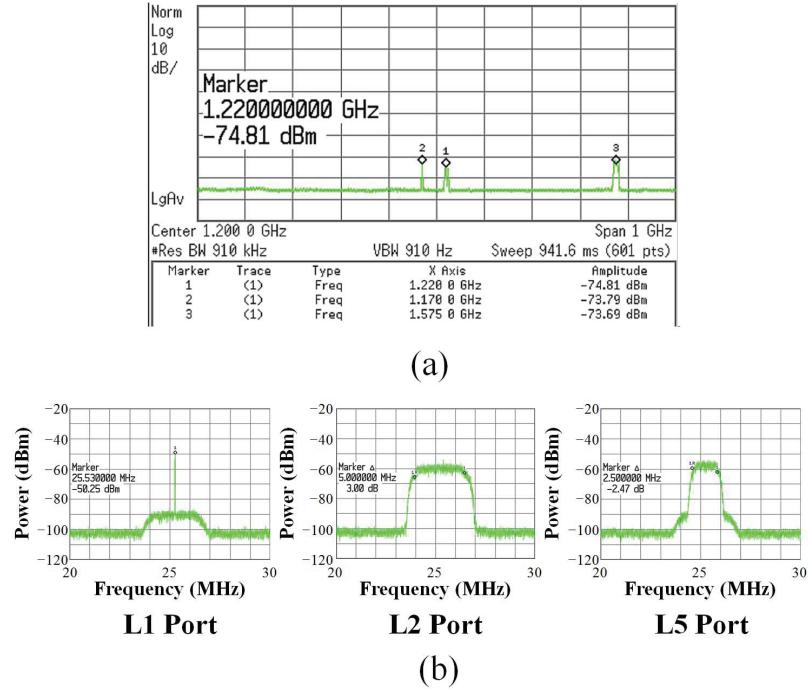

| 5.8  | (a) Triple-band RF input signals and (b) analog outputs at each band port on board. . . . .                                                                                                                                                                                                                                               | 113 |

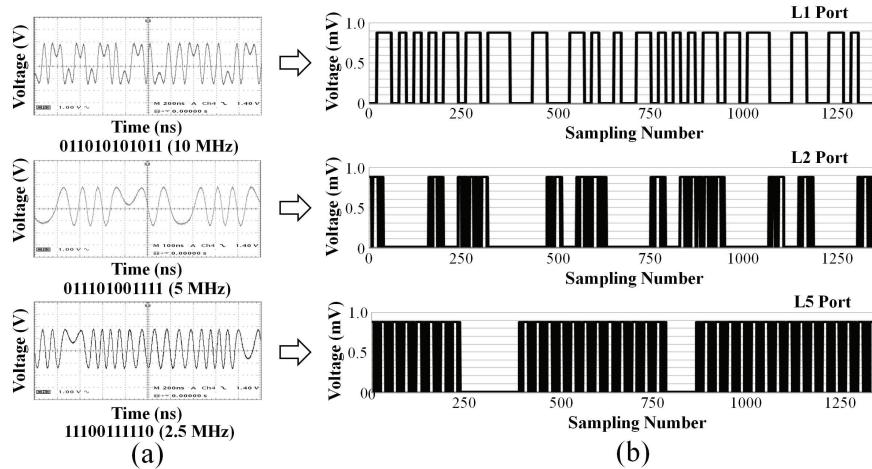

| 5.9  | (a) Modulated RF input signals (observed at low-frequency output of the signal generator) and (b) demodulation 2-bit binary output singals after ADC (LSB: $\sim 439 \mu\text{V}$ ). . . . .                                                                                                                                              | 113 |

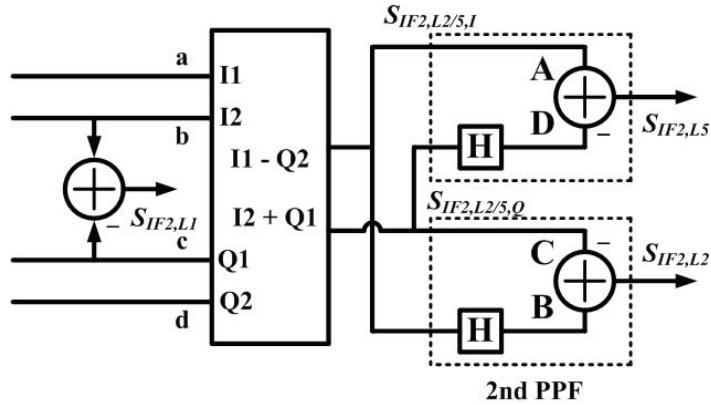

| 5.10 | End parts of proposed architecture's signal flow block. . . . .                                                                                                                                                                                                                                                                           | 114 |

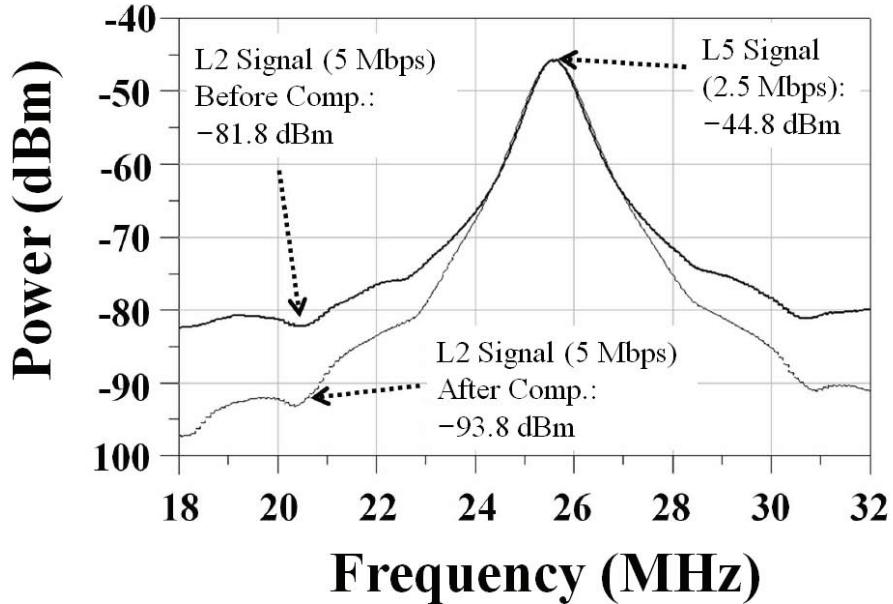

| 5.11 | Signal spectrum at the L5 port with IMRR correction (dotted line) and without IMRR correction (solid line). The obtained FFT data are processed through band-pass filtering (center frequency: 25.595 MHz, pass-band width: 10 MHz, pass-band ripple: 0.01 dB) and 61-point moving averaging. The resolution bandwidth is 50 kHz. . . . . | 116 |

| C.1  | On-wafer IC-chip NF measurement block diagram with the equivalent passive blocks. . . . .                                                                                                                                                                                                                                                 | 130 |

# List of Tables

|     |                                                                                             |     |

|-----|---------------------------------------------------------------------------------------------|-----|

| 1.1 | Comparison of survey methods using the DGPS. . . . .                                        | 4   |

| 1.2 | Features of GPS, GLONASS, and Galileo systems. . . . .                                      | 7   |

| 1.3 | Advantages and disadvantages of various process. . . . .                                    | 9   |

| 4.1 | Specification of designed RF front-end. . . . .                                             | 59  |

| 4.2 | Specification of designed LNA. . . . .                                                      | 64  |

| 4.3 | Process parameters. . . . .                                                                 | 64  |

| 4.4 | Design parameters for active mixer. . . . .                                                 | 73  |

| 4.5 | NF and IMRR results with post-layout circuit simulation (Monte-Carlo, 1000 trials). . . . . | 100 |

# Chapter 1

## Introduction

This chapter explains the necessity of the system receiving global positioning system (GPS) triple-band signal. Firstly, the global navigation satellite system (GNSS) is explained. The calculation principle of local positioning information from the satellite signal is briefly mentioned and the types of GNSS are described. The reason why the GPS system is selected as the target is explained. Some GPS RF front-end integrated circuits have been designed with the CMOS process. In this chapter, the merits of the CMOS process and conventional receiver structure are also explained. Finally, the purpose of this study and structure of this thesis are mentioned.

### 1.1 Overview of GNSS

GNSS has been steadily gaining attention since its initial development. It is the general name of the system that calculates the target's position and time using satellite signals. In particular, it is a navigation system that is available anywhere on earth regardless of the time, place, and weather conditions. Owing to the affordability, availability, and improvement of position measurement capabilities, applications are increasingly being used for geodetics and surveying in scientific areas where high-accuracy positioning is required, such as in ocean remote sensing systems [1], mobile devices, and navigational vehicle systems.

Figure 1.1: Method of (a) a point positioning and (b) relative positioning.

### 1.1.1 Calculation Principle of the Target's Location

There are generally three methods of calculating the target's location: point, relative, and differential positioning (DGPS in the GPS system) [2, 3].

#### A. Point Positioning Method

In the point positioning method, the calculation is performed by code tracking through binary pseudo-random number (PRN) codes. After comparing the synchronization of signals generated in the receiver and received from the satellite, the propagation time of the signal from the satellite is estimated. Because of analysis of signal synchronizations, a receiver requires the measurement results of a minimum of four satellites. In Fig. 1.1(a), the point positioning method is illustrated. The position coordinates of each satellite are expressed as  $(x_i, y_i, z_i)$  ( $i$  is 1 to 4 indicating each satellite). The user's coordinate is given by  $(x, y, z)$ . Then, the distance from each satellite to the user can be calculated as

$$D_i = \sqrt{(x - x_i)^2 + (y - y_i)^2 + (z - z_i)^2} + c\Delta\delta. \quad (1.1)$$

From this equation, if the simultaneous positioning information of more than four satellites can be obtained, the user's local position can be calculated [4, 5]. Here,  $c$  is a light velocity in a vacuum condition.  $\Delta\delta (= \delta_i - \delta)$  is the time error between the satellite and user.  $\delta_i$  is the time variation of the satellite, and  $\delta$  is the time variation of the user from the standard time.

### B. Relative Positioning Method

In the case of relative positioning, the location is decided from the carrier phase tracking method. The phase difference between the received signal from the satellite and synchronization signal generated in the receiver is estimated. It is used to obtain the relative local position in the survey and supports more high-accuracy positioning information than a point positioning method. As illustrated in Fig. 1.1(b), after pre-installing receivers at known points or the target's location, the distance to the baseline is obtained through simultaneous measurements at a pre-installed point (User B in Fig. 1.1(b)) and the target's location (User A in the same figure). The relative positioning method uses the following Eq. (1.2) to calculate the phases of carrier ( $\Phi_i$ ,  $i$  is 1 to 2 indicating each satellite) [4, 5].

$$\Phi_i = f \cdot \delta_i + \frac{\rho_i}{\lambda} - f \cdot \delta + N_i, \quad (1.2)$$

where  $f$ ,  $\delta_i$ ,  $\delta$ ,  $\lambda$ ,  $\rho_i$ , and  $N_i$  denote the reference frequency of the satellite, time variation at satellites and receiver, wave length of the carrier signal, geometric distance between the satellite and receiver, and an unknown factor. Through repeated measurements, the moving position (User A in Fig. 1.1(b)) is estimated and the unknown factors are obtained. Observation equations about User A and User B in Fig. 1.1(b) can be obtained according to the satellite positions. Then, from this position information of User A and User B, the displacement amount can be calculated as in Eq. (1.3).

$$\begin{aligned} x_A &= x_B + \Delta x, \\ y_A &= y_B + \Delta y, \\ z_A &= z_B + \Delta z. \end{aligned} \quad (1.3)$$

This method can support high-accuracy positioning information. However, owing to the pre-installed reference place, it is difficult to employ this method in any location. It is time-intensive to calculate the reference place positioning information. It typically takes more than 1 hour [5]; therefore, this method is used for the observation of terrain, such as altitude.

Table 1.1: Comparison of survey methods using the DGPS.

|                            | <b>Target</b>                   | <b>Survey Time</b>           | <b>Accuracy</b>   |

|----------------------------|---------------------------------|------------------------------|-------------------|

| <b>Static</b>              | Survey of reference point       | Very long (over 1 hour)      | $\pm 5$ mm        |

| <b>Rapid Static</b>        | Draw of map                     | Long                         | $\pm 10$ mm       |

| <b>Kinematic</b>           | Survey of terrain and site work | Medium (Initial set-up time) | $\pm 5$ cm        |

| <b>Pseudo Kinematic</b>    | Draw of map                     | Short (Repeated Survey)      | $\pm 5$ mm        |

| <b>Real Time Kinematic</b> | Survey of terrain and site work | Real time                    | $\pm 1 \sim 2$ cm |

### C. Differential Positioning Method

A recent positioning information calculation, the differential positioning method, is achieved by combining the two methods mentioned above. In the GPS system, this method is called differential GPS (DGPS) [4, 5]. Through a pre-installed receiver, the signal compensation information is pre-calculated. Then, when the positioning information is calculated at any moving point, the compensation information is used to obtain high-accuracy positioning. Generally, a point positioning method is used for calculation of compensation information, and the relative positioning is used as a measurement method. At this time, according to the compensation time with the calibration data, the DGPS is used in real-time as a post-processing technique. In real survey cases using DGPS, the techniques for observing the scene using GNSS signals are classified into the five methods illustrated in Table 1.1.

#### 1.1.2 GNSS Species

The first satellite launched above the Earth's orbit was Sputnik-1 of the Soviet Union in October 1957. In November of that year, after the success of the Sputnik-2 launch, the means for the space age had opened. However, these satellites were small and propagated only simple electric waves. Prompted by these events, the US began to build full-fledged satellite systems.

**A. Global Positioning System (GPS) [6]**

In the late 1950s and early 1960s, the US military began the construction of survey and navigation systems using satellites. From that point, the predecessor of the GPS system, Navistar GPS, was initiated from a multi-step project. At first, the position of an object was grasped by using aircraft instead of satellites. Then, the measurement of the time and position was introduced by observing the Doppler shift of signals transmitted from satellites, an approach that can calculate more accurate positioning information. The first satellite to operate the GNSS function, Block-I, was launched in February 1978. Until the end of the second step of this project, the nine additional Block-I satellites were launched. During these periods, the satellite system's total structure and verification were performed. By the end of 1985, the second generation satellite, Block-II, was developed. The initial satellites (Block-I) had not worked since 2003 on account of their life span. However, new satellites, such as Block-IIA and Block-IIR, were launched and operated. Today, for the GPS system, satellites operate a total of 28 and three signal bands have been used as L1, L2, and L5.

**B. Global Navigation Satellite System (GLONASS) [7]**

In the GPS system, the use of signals implies the possibility of restriction by the US, which can control the satellite positioning systems. To prevent this, some countries have been developing their own satellite positioning systems. Russia, for example, developed a satellite navigation system called Global Navigation Satellite System (GLONASS) in 1976. That country then launched satellites in 1982 and more actively developed them. In 1995, it constructed a satellite group for universal utilization. However, with the collapse of the Soviet Union and worsening of the financial situation there, the maintenance of the satellite was impossible. From the 2000s, the development of a satellite navigation systems with active involvement of the Russian government began anew, and a new version of the GLONASS-M satellite was launched in 2003. In 2008, 16 satellite groups for calculating global navigation on the whole earth was re-equipped. However, the cost of the GLONASS receiver based on frequency-division multiple-access (FDMA) was more expensive than that of the GPS receiver based on code-division multiple-access (CDMA). Unable to overcome this disadvantage, it did not succeed in the private market. Finally, a third generation satellite named GLONASS-K1 launched in 2011 began to transmit the L3OC signal based on CDMA. Russia currently intends to launch the

new satellite that can transmit L2 and L5 signals for a target GPS until 2020.

#### C. Galileo [8,9]

Another system is Galileo of the EU and European Space Agency. Since 1999, a common team for developing the satellite navigation systems was composed in the EU. That team combined the projects of each country in Europe. Galileo was also initiated to prevent a monopoly by the US. In that project, GIOVE-A in 2005 and GIOVE-E in 2008 were launched. In terms of features, they are sub-projects of GNSS-1 and GNSS-2, respectively. GNSS-1 is intended to compensate the GPS and GLONASS. GNSS-2 is intended for an independent global satellite navigation system. However, owing to the worsening of the EU financial realm and rocket launcher problems, the system's composition and operation are not yet functional.

#### D. COMPASS [10]

In Asia, China and Japan have developed satellite navigation systems. In China, the COMPASS project was undertaken. It includes a plan to launch 5 geostationary satellites and more than 30 orbit satellites for pan-global communication until 2015. The local navigation system has been operating since 2001. However, it is difficult to know the exact structural requirements because only a partial configuration of the system and signal has been released.

#### E. Quazi-Zenith Satellite System (JRANS-QZSS) [11]

In Japan, the Japanese regional advanced navigation system - the Quasi-Zenith Satellite System (JRANS-QZSS) - provides high-accuracy positioning information by 100 % coverage of the full domestic area to reinforce the positioning information in combination with the improved GPS system. The MICHIBIKI satellite was launched in 2010. JRANS is composed of three orbit satellites (QZSS), three long elliptical orbit satellites (HEO), and one geostationary satellite. In particular, more effective visual information is provided by the QZSS satellite, which is equipped with time synchronization and remote maintenance functions.

#### F. Indian Regional Navigation Satellite System (IRNSS) [12]

Otherwise, there is the Indian Regional Navigation Satellite system (IRNSS), which is developed by the Indian Space Research Organization (ISRO). It is composed of three geostationary satellites and four orbit satellites to provide India with local information.

Table 1.2: Features of GPS, GLONASS, and Galileo systems.

|                                 | <b>GPS</b>                                                                        | <b>GLONASS</b>                                  | <b>Galileo</b>                                  |

|---------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| <b>First Launch (Operation)</b> | Feb. 1978<br>(July 1995)                                                          | Oct.1982<br>(Jan. 1996)                         | Dec. 2005<br>(not yet)                          |

| <b>Number of Satellites</b>     | 24                                                                                | 24                                              | 27                                              |

| <b>Orbital Planes</b>           | 6                                                                                 | 3                                               | 3                                               |

| <b>Modulation Method</b>        | CDMA                                                                              | FDMA                                            | CDMA                                            |

| <b>Frequency (MHz)</b>          | 1575.420 (L1)<br>1227.600 (L2)<br>1381.050 (L3)<br>1379.913 (L4)<br>1176.450 (L5) | 1602.000 (G1)<br>1246.000 (G2)<br>1204.704 (G3) | 1575.420 (E1)<br>1278.750 (E6)<br>1191.795 (E5) |

A comparison of GPS, GLONASS, and Galileo is presented in Table 1.2 [3].

The GNSS frequency allocations used for global regions are illustrated in Fig. 1.2 [13]. Among these GNSS, the systems that are widely used and open the configuration and signal requirements to the public are GPS and GLONASS. However, recent studies of GLONASS are starting to compensate the GPS signals and improve the accuracy of the positioning information through the co-processing. In other words, the GPS system is still being used in the world and its application ability is seen as the most excellent. Furthermore, the US government is aware of competitors and suspended the selective availability (SA) to promote the GPS satellite navigation system with international standards. It allowed significant improvement of the performance of the GPS in May 2000. In addition, it expanded to the private sector the L5 band signal, which has been used for special purposes, such as civil aviation. It has taken great effort toward the modernization of GPS. For this reason, the GPS system is highlighted in this study.

Figure 1.2: GNSS frequency allocations.

## 1.2 The GPS Receiver

### 1.2.1 CMOS Integration Circuit in the Receiver

In the receiver design, one of the recent issues is low power consumption [14]. To integrate multi-functions in one device as a smart phone, the effects of the battery on operation time are becoming important. In addition, the signal sensitivity by the system integration is required. A compound semiconductor or superconductor has been developed and studied to minimize noise effects generated from device physics [15]. In a compound semiconductor, it is hard to integrate into a single chip and operate in low power consumption. Thus, the device designed from the CMOS process is spotlighted because of its high integration rate, low power consumption, and low cost for fabrication. In the CMOS process, it is difficult to design the circuit for operating in a high frequency because of limitations of the low unity-current-gain cut-off frequency ( $f_t$ ). To overcome these problems, some systems have been designed with a mixed process. For example, one system block diagram exists [16]. During the designing of the system, the digital stage, which has a slight noise effect, was designed in the CMOS process. The normal RF-stage was designed in SiGe BiCMOS. The power amplifier, which requires high-frequency large-output-swing operation, was designed in GaAs, as illustrated in Fig. 1.3. Recently, developing of a scaling process technique,  $f_t$  has advanced; therefore, the CMOS process has the benefit of integrating circuits for communication systems.

For development of the process, other parts can be designed with the CMOS process, as well as the digital part. Therefore, the fully integrated circuit has been widely studied to decrease loss of interconnection between the blocks. Because it still has a larger noise characteristic and long delay of

Figure 1.3: Process types for RF system.

the signal amplifier than the compound semiconductor, the integrated circuit with the CMOS process requires close attention. In particular, in the low operation voltage currently being studied, there are several physical problems, such as a high threshold voltage compared to the supply voltage. The characteristics of the process are summarized in Table 1.3.

Table 1.3: Advantages and disadvantages of various process.

| Section                | Process        | Cost | Operation Frequency | Operation Frequency | Power Consumption |

|------------------------|----------------|------|---------------------|---------------------|-------------------|

| <b>Digital Stage</b>   | CMOS           | Low  | Low                 | High                | Low               |

| <b>RF Stage</b>        | SiGe<br>BiCMOS | High | High                | Low                 | High              |

| <b>Power Amplifier</b> | GaAs           | High | High                | Low                 | High              |

Figure 1.4: Structure of (a) direct-conversion receiver and (b) double-conversion receiver.

### 1.2.2 General Structure of the Receiver

In general, the receiver structures fall into two divisions as direct-conversion receiver and double-conversion receiver according to the stage of frequency transformation. In the case of the direct-conversion receiver, the frequency of the received signal is converted to the IF frequency through the single local oscillator (LO) signal, as illustrated in Fig. 1.4(a).

It has the advantages of a simple system structure and low power consumption. However, there are some critical problems due to its simple structure as a self-mixing leakage of RF and LO signals, as well as its feed through of RF signals and DC offset. Because of the interference signal generated on account of the poor reverse isolation of the low-noise amplifier (LNA) and the poor port-to-port isolation of the mixer, the DC offset is generated at the IF-stage [17]. To solve these problems, the high-cost filter is needed as a high-performance surface-acoustic-wave (SAW) filter located at the front of the LNA [17]. On the other hand, the double-conversion structure converts the frequency

of received signals to the IF frequency through multiple stages, which can transfer the frequency as illustrated in Fig. 1.4(b). Usually, the signal located among the stages of each frequency transformation can be filtered to match the desired condition. Here, Eq. (1.4) is used to obtain the factor  $Q$ , which represents signal selectivity.

$$Q = \frac{\omega_0}{BW}. \quad (1.4)$$

The higher the  $Q$ -factor, the more the signal loss is decreased [18]. Normally, the high  $Q$ -factor can be obtained at low-frequency; however, it is difficult to obtain a high  $Q$ -factor in a high frequency. To overcome this problem, some schemes adapt filters in several stages; however, this structure increases the size and cost.

### 1.2.3 GPS Receiver for Multi-band Signals

In the current GPS environment, there are three species of signal frequency bands that can be used in a custom field. However, in the GPS receiver, which has been used until now in custom fields, there are very few multi-band GPS systems [19–24]. Some reported receivers for multi-band signals are only composed with a simple single receiver in parallel [23, 25], as illustrated in Fig. 1.5. In this structure, the system size is large and requires high power consumption. These cannot support the simultaneous reception with the same RF signal delays, which is important for some scientific applications [1].

In recent studies, some researches have addressed a dual-band receiver that has good signal isolation [21]. However, these approaches are not fitting to the development of compact low-power and low-cost devices.

## 1.3 Research Purpose and Thesis Structure

### 1.3.1 Research Purpose

Use of multi-band signals has the advantage of fast detection in the DGPS, as mentioned above. It uses the real-time kinematic (RTK) for the survey method. To realize it with high-accuracy positioning, the operation of receiving multi-band signals should be simultaneous to reduce the time delay difference between the different band signals. For these goals, this research focuses on the

Figure 1.5: Conventional GPS structure for multi-band signals.

Figure 1.6: Inductive-source-degeneration stage of LNA with the gate-source admittance.

GPS receiver, which can receive the triple-band signal through a single receiver. The proposed architecture is not composed of three individual receivers, but only a single receiver requiring an antenna. Through the single receiver, each band signal can be individually received at separate ports. To avoid the RF signal delay difference, the fixed LO signal is considered through a proper frequency arrangement. This helps the simultaneous detection of each band signal. Through this GPS receiver, the high-accuracy positioning information (through using multi-band signals) and reduction of power consumption and cost (through reducing chip size) are expected. Through the whole integration of the RF front-end, the power loss between the composed blocks can be reduced.

Figure 1.7: Constitution of thesis.

With these objectives, understanding device features is necessary. Input impedance matching can be realized by careful consideration of device's impedances. The designed receiver system includes a part of interconnecting chips and external components for the impedance matching. The separation of desired and undesired signals is an important factor that determines system capability because of the low power level of the GPS system's input signal. It is a main point of this work. Figure 1.6 shows the input impedance of the inductive-source-degeneration stage of the LNA.  $L_g$  and  $C_{gs}$  are considered in the conventional model. However,  $R_{gs}$  in the figure is more effective for input impedance as the device becomes smaller and the operation frequency increases. It is mainly handled to match the input impedance; therefore, the gate-resistance is important to the design of LNA for the triple-band signal.

### 1.3.2 Thesis Structure

The structure of this thesis is illustrated in Fig. 1.7.

Chapter 2 describes the structural characteristic of the MOSFET device and analyzes the high-accuracy gate-electrode resistance model. The signal detecting method with an image rejection technique is mentioned in Chapter 3. The theoretical background, which can make separate triple-band signal with a minimum RF path, is explained. In Chapter 4, the circuit level implementation of the receiver system is described including the device features explained in Chapter 2 and the system architecture mentioned in Chapter 3. For this work, element circuits, a proper signal line for signal balance, and layout features are considered. Experimental results of the designed chip are shown in Chapter 5. Finally, the conclusions are discussed in Chapter 6.

## References

- [1] T. Ebinuma and A. Yasuda, "Airborne GPS reflectometry from low altitude aircraft," *SICE Journal of Control, Measurement, and System Integration*, vol. 3, no. 6, pp. 429–434, Nov. 2010.

- [2] A. Leick, *GPS Satellite Surveying*, 3rd ed., New York:John Wiley and Sons, 2003.

- [3] W. Hofmann, Bernhard, Lichtenegger, Herbert, Wasle, and Elmar, *GNSS - Global Navigation Satellite Systems*, Springer Wien NewYork, 2008.

- [4] G. Nawrocki, *NAVSTAR GPS User Equipment: Introduction*, NATO, 1991.

- [5] T. B. James, *Fundamentals of Global Positioning System Receivers: A Software Approach*, 2nd ed., John Wiley and Sons, 2005.

- [6] G. Scott and G. Demoz, *GNSS Applications and Methods*, Artech House, 2009.

- [7] O. Phillip, *Commerce in Space: Infrastructures, Technologies, and Applications*, IGI Global, 2008.

- [8] O. Phillip, *Space Technologies for the Benefit of Human Society and Earth*, Springer, 2009.

- [9] N. Jari, L. S. Elena, S. Stephan, and H. Heikki, *GALILEO Positioning Technology*, Springer, 2015.

- [10] G. S. Rao, *Global Navigation Satellite Systems with Essentials of Satellite Communications*, Tata McGraw-Hill, 2010.

- [11] S. G. Mohinder, P. A. Angus, and G. B. Chris, *Global Navigation Satellite Systems, Inertial Navigation, and Integration*, 3rd ed., John Wiley and Sons, 2013.

- [12] L. Ajey, *Asian Space Race: Rhetoric or Reality?*, Springer, 2013.

- [13] K. M. Anil and A. Varsha, *Satellite Technology: Principles and Applications*, John Wiley and Sons, 2007.

- [14] A. P. Chandrakasan and R. W. Brodersen, “Minimizing power consumption in digital CMOS circuits,” *Proc. IEEE*, vol. 83, no. 4, pp. 498–523, Apr. 1995.

- [15] A. Rofougaran, J. Y. C. Chang, M. Rofougaran, and A. A. Abidi, “A 1 GHz CMOS RF front-end IC for a direct-conversion wireless receiver,” *IEEE J. Solid-State Circuits*, vol. 31, no. 7, pp. 880–889, July 1996.

- [16] H. S. Bennett, R. Brederlow, J. C. Costa, P. E. Cottrell, W. M. Huang, A. A. Immorlica, J. E. Mueller, M. Racanelli, H. Shichijo, C. E. Weitzel, and B. Zhao, “Device and technology evolution for Si-based RF integrated circuits,” *IEEE Trans. Electron Devices*, vol. 52, no. 7, pp. 1235–1258, July 2005.

- [17] B. Razavi, *RF Microelectronics*, Prentice Hall PTR, 1998.

- [18] J. Hong and M. J. Lancaster, *Microstrip Filter for RF/Microwave Application*, John Wiley and Sons, 2001.

- [19] J. Ko, J. Kim, S. Cho, and K. Lee, “A 19 mW 2.6 mm<sup>2</sup> L1/L2 dual band CMOS GPS receiver,” *IEEE J. Solid-State Circuits*, vol. 40, no. 7, pp. 1414–1424, July 2005.

- [20] Y. Utsurogi, M. Haruoka, T. Matsuoka, and K. Taniguchi, “CMOS front-end circuits of dual-band GPS receiver,” *IEICE Trans. Electron.*, vol. E88-C, no. 6, pp. 1275–1279, June 2005.

- [21] J. Wu, P. Jiang, D. Chen, and J. Zhou, “A dual-band GNSS RF front end with a pseudo-differential LNA,” *IEEE Trans. Circuits Syst. II*, vol. 58, no. 3, pp. 134–138, Mar. 2011.

- [22] D. Chen, W. Pan, P. Jiang, J. Jin, T. Mo, and J. Zhou, “Reconfigurable dual-channel multiband RF receiver for GPS/Galileo/BD-2 systems,” *IEEE Trans. Microw. Theory Tech.*, vol. 60, no. 11, pp. 3491–3501, Nov. 2012.

- [23] T. Elesseily, T. Ali, and K. Sharaf, “A crystal-tolerant fully integrated CMOS low-IF dual-band GPS receiver,” *Analog Integrated Circuits and Signal Processing*, vol. 63, no. 2, pp. 143–159, May 2010.

- [24] M. Detratti, E. López, E. Pérez, and R. Palacio, “Dual-band RF front-end solution for hybrid Galileo/GPS mass market receivers,” *IEEE Consumer Communications and Networking Conference*, pp. 603–607, Jan. 2008.

- [25] Z. Gradincic, R. Materni, P. Orsatti, and F. Piazza, “Multiband GNSS receiver,” US Patent App. 11/589,607, May 2007.

## Chapter 2

# Modeling of Effective Gate Resistance

In this chapter, the gate-electrode resistance of MOSFET and effect of non-quasi-static (NQS) for RF operation are analyzed. The gate-electrode resistance is more precisely analyzed through consideration of the vertical current paths located between the silicide and poly-silicon layers. These elements located there are not effective at long-channel devices, however more significant in short-channel devices. So, in practical RF CMOS circuit design, it occupies the important part. This analysis is undergone by careful separation of the above gate-electrode resistance and NQS effect. To verify it, the extraction method for de-embedded MOS parameters from a 130-nm CMOS process is used. Through these values, the Elmore constant ( $\kappa$ ) of NQS gate-source resistance is calculated and compared with semi-empirical model.

### 2.1 Introduction

CMOS technology realizing a low-power, large-scale integration, and low cost for manufacture are recently matching demands for miniaturization, low-power operation, and low cost in wireless communication system [1–4].

Scaling CMOS devices also are overwhelming the device performance, such as unity-current-gain-cut-off frequency  $f_t$ , against bipolar junction transistors and compound semiconductor devices, which were popular in RF circuits [5]. So, RF system on chip (SoC) integration from digital domain to RF analog domain can be realized. Although complexity of such a RF SoC increases, its short development time is always forced. In such a situation, precise simulations of analog/RF circuits are

important, and more accurate MOS device model and analysis of parasitic elements are needed for their implementations [6–8]. One of important issues in the MOSFET model in RF region is about the effective gate resistance. It influences the input impedance, maximum oscillation frequency  $f_{max}$ , and noise performance [9–11]. Especially, these features are affected in the design of multi-band and wide-band CMOS low-noise amplifiers (LNAs) [12–15]. The RF input resistance in common-source MOSFET has two factors [8, 16–18]. The first is related to the physical gate-electrode. The second originates from the channel itself in the intrinsic MOSFET region and its coupling with the gate-source capacitance  $C_{gs}$ , which causes a relaxation-time dependent phenomenon of channel charge response for a time-varying input signal, so called non-quasi-static (NQS) effect [19, 20]. As semi-empirical model, the NQS gate-source resistance  $R_{gsi}$  of the MOSFET operating in saturation region is approximately given by

$$R_{gsi} \approx \frac{1}{\kappa g_m}, \quad (2.1)$$

where  $g_m$  is the transconductance, and the Elmore constant  $\kappa$  is five for long-channel and is reported to be as small as one for short-channel devices [17]. Because the above two resistance factors have a different gate size dependence [18], their separate analysis is important in scalable MOSFET model and is also useful in RF circuit design [8]. Therefore, the accurate resistance model of extrinsic gate-electrode is required in advanced short-channel devices as well as the accurate prediction of  $\kappa$ . The accurate value of  $\kappa$  can be useful in some analytical design approaches of LNA [15, 21].

In this chapter, high-accuracy gate-electrode resistance model is mentioned. The model includes the vertical current paths between the silicide and poly-silicon layers in MOSFET. Through the separation between the gate-electrode resistance and NQS effect, the small-signal gate-source admittance is analyzed. Some parameters extracted in a 130-nm CMOS process such as  $\kappa$  are derived, verified and discussed.

## 2.2 Analysis of Gate-electrode Resistance

The gate of conventional MOSFET model is composed of gate insulator, poly-silicon, silicide and metal. Figure 2.1(a) illustrates top-view and cross section of n-channel MOSFET with a gate length  $L$  and gate width  $W$  in the silicided poly-silicon gate technology. When feeding the signal to gate, it propagates in horizontal direction of the silicide on the gate-electrode surface, and then in

Figure 2.1: (a) Top-view and cross-section of MOSFET (both-side gate connection) and (b) equivalent circuit of gate unit element.

vertical direction of poly-silicon and gate insulator to effect channel. Gate resistance of MOSFET is composed with gate contact resistance between the metal and silicide, resistance of the silicide itself, the interface resistance between the silicide and poly-silicon, and the vertical resistance of the poly-silicon itself [22]. The interface resistance is important in the vertical signal propagation [11], and its typical values are about  $25 \Omega \mu\text{m}^2$  ( $\text{TiSi}_2$ ) [11] and about  $2 \sim 3 \Omega \mu\text{m}^2$  ( $\text{NiSi}$ ) [23]. In long channel MOSFET, vertical elements of the gate-electrode are less effective than gate contact and silicide resistance. However, as gate length decreases, the influence of vertical elements is becoming more important. As gate width decreases, the horizontal resistance decreases, while the vertical resistance increases inversely proportional to the gate width.

Each part of gate-electrode resistance can be expressed with lumped elements for the signal path length in a horizontal gate width direction  $dz$  using a transmission line model as illustrated in Fig. 2.1(b), which is similar to that in silicided diffusion region [24]. Here,  $R_{cg}$  is unit gate con-

tact resistance between the silicide and poly-silicon,  $\rho_{sili}$  is the sheet resistivity of the silicide,  $\rho_{int}$  is an interface resistivity between the silicide and poly-silicon,  $\rho_{vp}$  is the vertical resistivity of poly-silicon layer per unit dimension.  $C_{ox}$  is unit capacitance of the gate insulator. For simplification in mathematical expression, let  $R_{sili} = \rho_{sili}/L$ ,  $R_{int} = \rho_{int}/L$ ,  $R_{vp} = \rho_{vp}/L$ . When  $C_{gc}$  is defined as the capacitance between the gate and channel, it can be considered as  $C_{gc}/W \propto C_{ox}L$ .

Considering the steady state at the angular frequency  $\omega$  in Fig. 2.1(b), the total admittance of vertical current path elements for unit signal propagation length on the gate-electrode surface,  $Y_{vp}$ , is given by

$$Y_{vp} = \frac{j\omega C_{gc}/W}{1 + j\omega C_{gc}(R_{int} + R_{vp})/W}. \quad (2.2)$$

From the manipulation described in Appendix A, the gate-electrode resistance seen from the gate contact position for unit gate finger with length  $W_f$  is expressed as

$$R_{g,ele} = \frac{k}{3} \rho_{sili} \frac{W_f}{L} + \frac{\rho_{int} + \rho_{vp}}{LW_f}, \quad (2.3)$$

where  $k$  is 1 and 1/4 for a single-side and a both-side gate connections, respectively.

Additionally, considering the gate contact between the silicide and metal as well as the gate extension to the channel area in a similar way based on the previous work [7], the gate-electrode resistance for the number of gate finger  $N_f$  is expressed as

$$R_{ge} = \frac{k}{3} \rho_{sili} \frac{W_f + W_{ext}/\sqrt{k}}{LN_f} + \frac{\rho_{int} + \rho_{vp}}{LN_f W_f} + \frac{R_{cg}}{N_{cg} N_f}, \quad (2.4)$$

where  $W_{ext}$  is the distance between the channel area edge and gate contact, and  $N_{cg}$  is the number of gate contacts per finger [7]. Capacitive coupling of the gate extension to the substrate is also considered in the above equation by using a factor 1/3. Compared to the previous works [7, 8], Eq. (2.4) has the second term inversely proportional to the channel area  $LN_f W_f$ , which originates from the vertical resistance elements. As the channel area decreases, this influence increases.

### 2.3 Parameter Extraction for NQS Resistances

In low-frequency operation, carriers in the channel can respond immediately to the applied terminal voltages, which corresponds to charging and discharging of the gate-source capacitance  $C_{gs}$ .

Figure 2.2: (a) Small-signal equivalent circuit including external parasitic elements and (b) its intrinsic part.

This is considered as quasi-static operation. On the other hand, as the operation frequency gets much higher, the channel resistance influences response time of the carriers, which is NQS operation. Although the transconductance, drain conductance and large-signal operation are influenced by the NQS effect, the influence of the small-signal gate-source admittance  $y_{gs}$  is crucial in the multi-band and wide-band LNA designs. This work focuses on the small-signal gate-source admittance.

To estimate the NQS effect, the careful parameter extraction for MOSFET model is required. Figure 2.2(a) shows the small-signal equivalent circuit which includes external parasitic elements. In this work, the body is connected to the source, resulting in no body effect.  $R_{gsi}$  and  $R_{gdi}$  in Fig. 2.2(b) give NQS effect.  $R_{ge}$  is a gate-electrode resistance,  $R_{de}$  and  $R_{se}$  are series resistances of drain and

source, and  $C_{gse}$  and  $C_{gde}$  are overlap capacitances between the gate and source/drain.  $C_{dse}$  is the external capacitance between the drain and source (body in this case). Extraction method separates extrinsic and intrinsic parameters from two-port parameters of the MOSFET. In the first step, the external resistances ( $R_{ge}$ ,  $R_{de}$ , and  $R_{se}$ ) and the external capacitances ( $C_{gde}$ ,  $C_{gse}$ , and  $C_{dse}$ ) are de-embedded from the two-port parameters of the MOSFET, using the de-embedding technique [8]. The estimation techniques of the external resistances and capacitances are described later. In the second step, the equivalent circuit including only intrinsic parameters can be obtained.

To estimate the external parameters, the cold biasing ( $V_{GS} = V_{DS} = 0$  V) is utilized. It is assumed that the intrinsic parameters except for drain-source conductance  $g_{ds}$  are not presented in cold bias. External parameters are nearly independent of  $V_{GS}$ . Thus the  $Z$ -parameters of the MOSFET in the cold biasing can be obtained as follows:

$$Z_{11} = R_{ge} + R_{se} - \frac{g_{ds} C_{gde}^2}{A(\omega)} - j \cdot \frac{g_{ds}^2 (C_{gse} + C_{gde})/\omega + \omega B (C_{gde} + C_{dse})}{A(\omega)}, \quad (2.5)$$

$$Z_{12} = Z_{21} = R_{se} + \frac{g_{ds} (C_{gse} + C_{gde}) C_{gde}}{A(\omega)} - j \cdot \frac{\omega B C_{gde}}{A(\omega)}, \quad (2.6)$$

$$Z_{22} = R_{de} + R_{se} + \frac{g_{ds} (C_{gse} + C_{gde})^2}{A(\omega)} - j \cdot \frac{\omega B (C_{gde} + C_{gse})}{A(\omega)}, \quad (2.7)$$

$$A(\omega) = \omega^2 (C_{gde} C_{dse} + C_{gse} C_{gde} + C_{gse} C_{dse})^2 + g_{ds}^2 (C_{gse} + C_{gde})^2,$$

$$B = C_{gde} C_{dse} + C_{gse} C_{gde} + C_{gse} C_{dse}.$$

In the cold bias condition,  $g_{ds}$  is negligibly small. Assuming it, real parts of the  $Z$ -parameters in high frequency can be approximated as

$$\Re[Z_{11}] = R_{ge} + R_{se}, \quad (2.8)$$

$$\Re[Z_{12}] = \Re[Z_{21}] = R_{se}, \quad (2.9)$$

$$\Re[Z_{22}] = R_{de} + R_{se}. \quad (2.10)$$

From these equations,  $R_{ge}$ ,  $R_{de}$ , and  $R_{se}$  can be estimated. In addition, Using Eqs. (2.5)-(2.10) with

the same assumption of small  $g_{ds}$ , imaginary parts of the  $Z$ -parameters can be approximated as.

$$\Im[Z_{11}] = -\frac{C_{gde} + C_{dse}}{\omega B}, \quad (2.11)$$

$$\Im[Z_{12}] = \Im[Z_{21}] = -\frac{C_{gde}}{\omega B}, \quad (2.12)$$

$$\Im[Z_{22}] = -\frac{C_{gde} + C_{gse}}{\omega B}. \quad (2.13)$$

From these equations,  $C_{gse}$ ,  $C_{gde}$ , and  $C_{dse}$  can be estimated.

The intrinsic  $Y$ -parameter matrix  $[Y_{int}]$  can be obtained from the embedded  $Z$ -parameter  $[Z_{em}]$  matrix of the MOSFET model shown in Fig. 2.2 by using the following equations.

$$[Z_{ext}] = \begin{bmatrix} R_{ge} + R_{se} & R_{se} \\ R_{se} & R_{de} + R_{se} \end{bmatrix}, \quad (2.14)$$

$$[Y_{ext}] = j\omega \begin{bmatrix} C_{gse} + C_{gde} & -C_{gde} \\ -C_{gde} & C_{gde} + C_{dse} \end{bmatrix}, \quad (2.15)$$

$$[Y_{int}] = [Z_{em} - Z_{ext}]^{-1} - [Y_{ext}]. \quad (2.16)$$

Based on the equivalent circuit shown in Fig. 2.2(b), the parameters of MOSFET's intrinsic parts can be calculated from relations of real and imaginary parts of Eq. (2.16) as following equations.

$$C_{gsi} = \frac{\Im[Y_{11,int}] + \Im[Y_{12,int}]}{\omega}, \quad (2.17)$$

$$C_{gdi} = -\frac{\Im[Y_{12,int}]}{\omega}, \quad (2.18)$$

$$R_{gsi} = \Re\left[\frac{1}{Y_{11,int} + Y_{12,int}}\right], \quad (2.19)$$

$$R_{gdi} = -\Re\left[\frac{1}{Y_{12,int}}\right], \quad (2.20)$$

$$g_m = \Re[Y_{21,int}]_{\omega=0}, \quad (2.21)$$

$$g_{ds} = \Re[Y_{22,int}]_{\omega=0}. \quad (2.22)$$

## 2.4 Verification of Gate-electrode Model and NQS Effect

In this work, instead of on-chip high-frequency  $S$ -parameter measurement, simulated small-signal  $S$ -parameters are used with a RF MOSFET model (BSIM4 with GATEMOD=3 [25]), which can

Figure 2.3: Extracted and calculated values of gate-electrode resistance  $R_{ge}$  versus the number of gate fingers  $N_f$  ( $L = 140$  nm,  $W_f = 3$   $\mu\text{m}$ , both-side gate connection).

reproduce RF and DC characteristics well with many parameters for a commercial 130-nm CMOS process. This can realize cost-effective verification of device models. As narrow gate width under 3  $\mu\text{m}$  has an effect of the interface resistance on the gate resistance, NMOS devices with single finger width of 3  $\mu\text{m}$  and both-side gate connection are used in this work. The embedded  $Z$ -parameter [ $Z_{em}$ ] matrix can be obtained from the simulated  $S$ -parameters of the device for the maximum frequency of 50 GHz.

The external gate-electrode resistance  $R_{ge}$  is extracted by using Eqs. (2.5)–(2.10), and is compared with calculated ones by using Eq. (2.4). The results are illustrated in Fig. 2.3. The second term of Eq. (2.4) originates from the vertical current paths. To confirm the influence of the vertical current path in Fig. 2.1,  $R_{ge}$  with and without the second term (solid and dotted lines in Fig. 2.3, respectively) was calculated. The value of  $R_{int} + R_{vpoly}$  is determined by curve fitting as  $12.5 \Omega\mu\text{m}^2$  which is reasonable value considering the reported typical values [11, 23]. From this figure, consideration of the vertical current path becomes significant for small gate finger numbers. It is more effective for short-channel devices.

Based on the extracted external parameters, NQS gate-source resistance  $R_{gsi}$  and transconductance  $g_m$  are extracted by using Eqs. (2.19) and (2.21). In this parameter extraction, to neglect

Figure 2.4: Extracted values of NQS gate-source resistance  $R_{gsi}$  of NMOS devices with gate length  $L = 140, 500, 1000, 2000$  and  $5000$  nm at gate-source overdrive voltages (a)  $V_{GS} - V_{TH} = 0.4$  V and (b)  $V_{GS} - V_{TH} = 0.8$  V (gate width is  $120$  μm ( $3$  μm ×  $40$  fingers), both-side gate connection).

high-order NQS effect [26] and delays in transconductance and drain conductance [8], the maximum frequency is set to 6.5 GHz. Figure 2.4 shows the dependence of  $R_{gsi}$  on drain-source voltage  $V_{DS}$  at the gate-source overdrive voltages  $V_{GS} - V_{TH} = 0.4$  V and 0.8 V for various gate lengths. In

Figure 2.5: Gate length dependence of extracted Elmore constants  $\kappa$ .

saturation region ( $V_{DS} > V_{GS} - V_{TH}$ ),  $R_{gsi}$  has little  $V_{DS}$  dependence.