| Title        | A Design of 0.7-V 400-MHz All-Digital Phase-<br>Locked Loop for Implantable Biomedical Devices |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------|--|--|--|--|

| Author(s)    | Bae, Jungnam; Radhapuram, Saichandrateja; Jo,<br>Ikkyun et al.                                 |  |  |  |  |

| Citation     | IEICE TRANSACTIONS on Electronics. 2016, 99-C(4), p. 431-439                                   |  |  |  |  |

| Version Type | VoR                                                                                            |  |  |  |  |

| URL          | https://hdl.handle.net/11094/55420                                                             |  |  |  |  |

| rights       | Copyright © 2016 by The Institute of Electronics, Information and Communication Engineers      |  |  |  |  |

| Note         |                                                                                                |  |  |  |  |

# The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

PAPER Special Section on Solid-State Circuit Design—Architecture, Circuit, Device and Design Methodology

# A Design of 0.7-V 400-MHz All-Digital Phase-Locked Loop for Implantable Biomedical Devices

Jungnam BAE<sup>†a)</sup>, Saichandrateja RADHAPURAM<sup>†</sup>, Ikkyun JO<sup>†</sup>, Weimin WANG<sup>†</sup>, Nonmembers, Takao KIHARA<sup>††</sup>, Member, and Toshimasa MATSUOKA<sup>†</sup>, Senior Member

SUMMARY A low-voltage controller-based all-digital phase-locked loop (ADPLL) utilized in the medical implant communication service (MICS) frequency band was designed in this study. In the proposed design, controller-based loop topology is used to control the phase and frequency to ensure the reliable handling of the ADPLL output signal. A digitally-controlled oscillator with a delta-sigma modulator was employed to achieve high frequency resolution. The phase error was reduced by a phase selector with a 64-phase signal from the phase interpolator. Fabricated using a 130-nm CMOS process, the ADPLL has an active area of 0.64 mm², consumes 840  $\mu$ W from a 0.7-V supply voltage, and has a settling time of 80  $\mu$ s. The phase noise was measured to be -114 dBc/Hz at an offset frequency of 200 kHz.

key words: all-digital phase-locked loop, controller, digitally-controlled oscillator, phase interpolator, CMOS, MICS

#### 1. Introduction

Biomedical radio-frequency (RF) transceivers require miniaturized forms with a long battery life and low power consumption. It is usually preferable for implantable medical devices to be fully-integrated on a single chip to realize easier surgery and encapsulation for high biocompatibility. The medical implant communication service (MICS) band in the frequency range of 402 to 405 MHz is widely used for medical RF transceivers because MICS band signals have reasonable propagation characteristics in the human body and are well suited to achieve a good trade-off between size and power [1], [2].

There are many challenges associated with the implementation of the RF front-end in implantable medical devices such as pacemakers, implantable cardioverter defibrillators, and neurostimulators because their application requires extremely low power consumption, minimal external components, and high reliability. The basic system requirements of RF transceivers for medical implantable devices are as follows [2]. To increase battery life, the current of RF transceivers should be limited to below 6 mA during MICS band communication. The use of few external components provides a higher reliability, lower cost, and smaller size. RF modules for pacemakers must be no more than approximately 3 mm × 5 mm × 10 mm. Pacemaker applications

Manuscript received July 31, 2015.

Manuscript revised November 20, 2015.

a) E-mail: bae@si.eei.eng.osaka-u.ac.jp DOI: 10.1587/transele.E99.C.431 currently demand a reasonable data rate of over 20 kbps with higher data rates projected for the future. Their operating range is typically over 2 m because the MICS band is designed to improve upon the very-short-range inductive link.

In particular, the frequency synthesizer is one of the most critical building blocks of the RF front-end. Phaselocked loops (PLLs) are widely used in many communication systems to perform frequency synthesis or clock and data recovery. Analog PLLs based on charge-pumps are still widely used, but all-digital PLLs (ADPLLs) have been attracting more attention because of their significant advantages over their analog counterparts. ADPLLs, which interface to allow peripheral circuitry to be digitally implemented, provide low-voltage operation compatibility under process and temperature variations with a shorter system turnaround-time [3]. Hence, ADPLLs provide several benefits to duty-cycled battery-operated systems, including MICS transceivers, wireless sensor nodes, and wireless telemetry devices. In the design of an ADPLL, realizing a low level of spurs and high resolution are challenges to achieving fully-integrated high-performance ADPLL architecture.

In ADPLLs, time-to-digital converters (TDCs) have been replacing conventional phase-frequency detectors (PFDs) and charge-pumps [4]. The resolution of the TDC is very important in the performance of the ADPLL because low resolution causes in-band phase noise. TDCs require advanced CMOS technology and additional system complexity to achieve high resolution and thereby have high power consumption. Additionally, TDCs are sensitive to process, voltage, and temperature variation. Such high sensitivity can cause poor linearity and non-uniform phase detector gain, resulting in widespread spur generation. Hence, we consider a TDC-less controller-based ADPLL for high performance and low complexity. The digital implementation of a controller reduces the silicon die area and eliminates external loop filter components.

This paper describes the proposed controller-based ADPLL, which is fabricated using a 130-nm CMOS process. The circuit is intended for medical implantable transceivers operating in the MICS band and is based on a programmable integer-*N* PLL. In our previous studies [5], [6], we confirmed the system stability and functionality of controller-based ADPLL through phase-domain modeling. In this paper, we focus on circuit design and implementa-

<sup>&</sup>lt;sup>†</sup>The authors are with the Graduate School of Engineering, Osaka University, Suita-shi, 565–0871 Japan.

<sup>&</sup>lt;sup>††</sup>The author is with the Faculty of Engineering, Osaka Institute of Technology, Osaka-shi, 535–8585 Japan.

tion details as well as measurement results in the MICS frequency band for medical applications. Section 2 presents the controller-based ADPLL architecture. Section 3 describes the circuit design and implementation. The measurement results are presented in Sect. 4, and the performance of the proposed ADPLL is compared with that of related devices previously reported in the literature. Finally, conclusions are drawn in Sect. 5.

## 2. Architecture of All-Digital Phase-Locked Loop

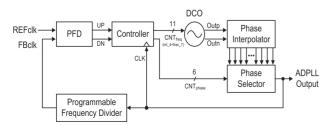

Figure 1 shows the top-level architecture of the designed ADPLL. It consists of a PFD, a controller, a digitallycontrolled oscillator (DCO), a phase interpolator (PI), a phase selector (PS), and a programmable frequency divider. The proposed ADPLL has a secondary phase selection path to select the phase with the least error from the phases generated by the PI. Furthermore, the phase of the ADPLL output signal is pre-settled by the phase selection, thereby reducing the phase acquisition time of the ADPLL. The feedback path includes a programmable frequency divider that divides the output signal for comparison with a reference signal. The PFD detects both the phase and frequency differences between the reference and feedback signals (REFclk and FBclk, respectively, in Fig. 1). The pulse widths of the PFD outputs (UP and DN) indicate the phase difference. The controller then measures the UP and DN pulses to digitize the phase differences. The accumulator in the controller counts the phase error using the time resolution of the CLK of the controller. Based on the phase and frequency errors, the controller adjusts the digital control words. The frequency and phase control words are generated by the division (/) and modulo (%) operations, respectively. The DCO generates a signal whose output frequency is tuned with the digital control word  $CNT_{freq}$  from the controller. Based on the phase control word  $CNT_{phase}$ , the PS selects one of the multiphase signal generated by the PI with the least phase error. The phase of the output signal is pre-settled by phase selection, as described above.

# 2.1 Phase-Domain ADPLL Model

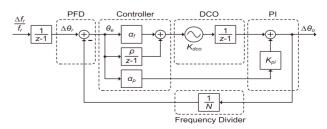

The controller-based ADPLL is a discrete-time sampled system implemented with all digital components. Therefore, the *z*-domain representation is the most accurate without requiring approximations [7]. Figure 2 shows the discrete-

Fig. 1 Architecture of the controller-based ADPLL.

time z-domain model of the ADPLL, where  $K_{dco}$  is the gain of the DCO and  $K_{pi}$  is the gain factor from the PS. The variables  $\Delta\theta_r$  and  $\Delta\theta_0$  are the excess reference and feedback phases, respectively, and the sampling rate is the reference frequency  $f_r$ .

The controller has two types of digital control words based on the counter operation, and its two transfer functions  $K_{cnt,dco}$  and  $K_{cnt,ps}$  for the DCO and PS in discrete-time *z*-domain are respectively given by [5], [6]

$$K_{cnt,dco}(z)\theta_e(z) = 2^{-b_{frac}} \left[ \frac{1}{M_{PI}} \frac{1}{z - 1} \left[ \frac{N \cdot \theta_e(z)}{2\pi} \right] \right], \quad (1)$$

$$K_{cnt,ps}(z)\theta_{e}(z) = \frac{1}{M_{PI}} \frac{1}{z-1} \left\lfloor \frac{N \cdot \theta_{e}(z)}{2\pi} \right\rfloor - \left\lfloor \frac{1}{M_{PI}} \frac{1}{z-1} \left\lfloor \frac{N \cdot \theta_{e}(z)}{2\pi} \right\rfloor \right\rfloor, \tag{2}$$

where  $\lfloor x \rfloor$  is the floor function, and yields the largest integer not greater than x,  $\theta_e$  is the phase error,  $b_{frac}$  is the number of digits of a fractional part of the DCO input, N is the frequency division ratio,  $M_{Pl}$  is the number of phases generated through the PI, and  $z = \exp(s/f_r)$ . The expressions on the right-hand sides of Eqs. (1) and (2) correspond to the Verilog-hardware description language (HDL) description of the controller in this study. Within a small-signal analysis, to simplify the ADPLL analysis,  $K_{cnt,dco}(z)$  and  $K_{cnt,ps}(z)$  are approximated as  $\alpha_f + \rho/(z-1)$  and  $\alpha_p$ , respectively. The multiplication factors  $\alpha_f$  and  $\rho$  are the loop parameters, and  $\alpha_p$  is the phase compensation factor. To simplify the mathematical expressions, the scaled factors are given as  $\alpha_{fn} = K_{dco}\alpha_f/N$ ,  $\rho_n = K_{dco}\rho/N$ , and  $\alpha_{pn} = K_{pi}\alpha_p/N$ .

The ADPLL has been mathematically analyzed as z-domain and linearly approximated s-domain models in [5], [6], [8]. It is common to approximate the z-transform as a linear continuous-time system in the s-domain. The sampling rate  $f_r$  must be at least 10 times the PLL bandwidth [9], such that the approximation  $z = \exp(s/f_r) \approx 1 + s/f_r$  is vaild. From Appendix, the phase selection path generates additional zero, and it affects the system parameters. As a result, the phase selection can enhance the tunability of zero in the open-loop transfer function. Generally, the closed-loop function of the ADPLL exhibits classical two-pole system behavior. For this phase model to be compared with the classical two-pole system transfer function, the phase error transfer function is expressed as

**Fig. 2** z-domain model of the controller-based ADPLL.

**Fig. 3** (a) Magnitude response  $H_{cl}(s)/N$  and (b) frequency jitter response for one-integer frequency step in the behavior-level simulation.

$$H_e(s) = 1 - \frac{H_{cl}(s)}{N} = \frac{1}{1 + \alpha_{pn}} \cdot \frac{s^2}{s^2 + 2\zeta\omega_n s + \omega_n^2},$$

(3)

where  $f_n = \omega_n/2\pi = \sqrt{\rho_n/(1+\alpha_{pn})}f_r/2\pi$  is the natural frequency and  $\zeta = \alpha_{fn}/2\sqrt{(1+\alpha_{pn})\cdot\rho_n}$  is the damping factor. The additional phase compensation factor  $\alpha_{pn}$  affects factors  $\zeta$  and  $f_n$ . The phase and frequency errors are eliminated by the closed-loop system. The inclusion of the phase compensation factor reduces the residual phase error of the system.

Figure 3 shows the simulation results of the phasedomain model for the s-domain approximation and the behavior model based on Verilog-HDL. The modeling parameters  $\alpha_f$ ,  $\rho$ , and  $\alpha_p$  can be approximately expressed using  $M_{PI}$ ,  $b_{frac}$ , and N. In this simulation, the gains  $K_{dco}$  and  $K_{pi}$  are 2 MHz/code-change (= $4\pi$  Mrps/code-change) and  $2\pi/M_{PI}$  rad/code-change, respectively. From Fig. 3 (a), as  $M_{PI}$  increases, the phase domain model simulation of the ADPLL shows that the loop bandwidth increases. The sdomain model has been validated against Verilog-HDL simulations in the previous studies [5], [6]. From the behaviorlevel simulation shown in Fig. 3 (b), as  $M_{PI}$  increases, the settling time and frequency jitter variation both decrease. In this study, with  $f_r$ =150 kHz, N=2700,  $b_{frac}$ =7, and  $M_{PI}$ =2<sup>6</sup>  $(\alpha_f = 2^{-10}, \rho = 2^{-12}, \text{ and } \alpha_p = 2^{-6}), f_n \text{ and } \zeta \text{ are } 10 \text{ kHz and}$ 0.85, respectively. Note that  $f_n \ll f_r$ . The settling time  $(=4/\zeta\omega_n)$  is less than 70  $\mu$ s.

From similar behavior-level simulation results for N=27-2700 and  $M_{PI}=2^4$ ,  $2^5$ , and  $2^6$  and their comparison with the s-domain analytical model, the empirical approximations for  $\alpha_f$ ,  $\rho$ , and  $\alpha_p$  were obtained in this study as

$$\alpha_f \approx 4 \, \rho \approx \frac{1}{5} \cdot \frac{2^{-b_{frac}}}{2\pi} \cdot \frac{N^{1.25}}{M_{Pl}^2},\tag{4}$$

Table 1

Design considerations

| Technology           | 130-nm CMOS process            |  |  |

|----------------------|--------------------------------|--|--|

| Supply voltage       | 0.7 V                          |  |  |

| Power consumption    | < 1 mW                         |  |  |

| Operating frequency  | 402 ~ 405 MHz (MICS band)      |  |  |

| Tuning range         | > 3 MHz                        |  |  |

| Frequency resolution | < 30 kHz                       |  |  |

| Phase noise          | < -100 dBc/Hz @ 200 kHz offset |  |  |

| Settling time        | < 100 μs                       |  |  |

$$\alpha_p \approx \frac{1}{2} \cdot \frac{1}{2\pi} \cdot \frac{M_{PI}^2}{N^{1.25}}.\tag{5}$$

The variables  $\alpha_f$  and  $\rho$  depend on the maximum number of digitized phase differences (N) and the phase resolution  $(\propto 1/M_{PI})$ . Equation (5) implies that  $\alpha_p$  depends on the range of the modulo of  $M_{PI}$   $(0, 1, \dots, M_{PI}-1)$  and the time resolution of the CLK  $(\propto 1/N)$ .

#### 2.2 Design Considerations

Table 1 shows the design considerations of the ADPLL based on the MICS band requirements. In this ADPLL, digital circuits are implemented based on the standard-cell library. To ensure low power consumption, a supply voltage of 0.7 V, which is the minimum voltage for the stable operation of the employed digital standard-cell circuits, is applied. The phase noise requirement for the MICS band is less than -100 dBc/Hz at an offset frequency of 200 kHz. Additionally, the frequency tuning specifications for the DCO are derived from the intended application with a periodic calibration, where the MICS reference tolerance is 100 ppm [1]. Accordingly, the target frequency resolution considering the margin is set to less than 30 kHz. The settling time is set to less than 100  $\mu$ s for low start-up energy. From behaviorlevel simulations, the phase interpolation technique with 64 phases is used considering the margin, and it yields a phase deviation of  $2\pi/64$ .

#### 3. Circuit Design and Implementation

# 3.1 Phase Frequency Detector and Controller

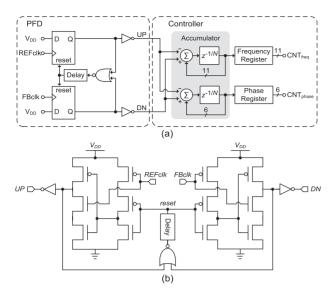

Figure 4 (a) shows the combination of the PFD and the controller used to convert the phase difference between the reference and feedback signals from the frequency divider to digital data. The employed PFD consists of D-flip-flops (DFFs), a NOR gate, and a delay element. As shown in Fig. 4 (b), the DFFs are implemented by the true-single-phase-clock (TSPC) [10] for low-voltage operation. This structure has low power consumption and a large operating frequency range because of short gate delays in the critical reset path. Furthermore, the added delay element is helpful in preventing the dead-zone problem. It improves the phase adjustment and reduces the phase noise of the oscillator. The controller consists of an accumulator and registers to measure the PFD outputs and generates the control words. It uses a high CLK frequency to achieve high resolution. The

**Fig. 4** (a) Structure of the PFD and controller and (b) schematic of the TSPC DFF-based PFD.

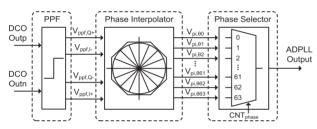

Fig. 5 Structure of the PI.

delay element in the accumulator in Fig. 4 (a) is expressed as  $z^{-1/N}$ . In this study, Verilog-HDL is used to design the controller. The logic-synthesizer is used to synthesize the module for gate-level circuits with a standard-cell library following a digital design flow.

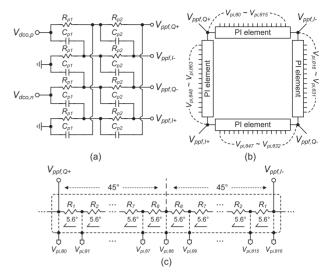

#### 3.2 Phase Interpolator

Figure 5 shows the structure of the PI. It consists of a polyphase filter (PPF), a resistive PI, and a PS. A combination of the PPF and PI is used to generate the 64-phase signal. First, quadrature signals are generated by the PPF from the DCO differential outputs. In this study, as shown in Fig. 6(a), a two-stage RC network PPF was employed because of the wide bandwidth [11]. A two-stage PPF is useful to enhance the robustness of the process variations in passive elements [12]. Furthermore, high load impedances can reduce component mismatch. The resistor and capacitor values of the two-stage PPF are  $R_{p1}$ =100  $\Omega$ ,  $R_{p2}$ =82  $\Omega$ , and  $C_{p1}$ = $C_{p2}$ =4.42 pF. The designed PPF has a bandwidth of 350 to 450 MHz and a phase error of 0.1°. Second, an additional 15 signals are generated by the PI element, which consists of a resistor ladder between quadrature signals, as shown in Fig. 6 (b), resulting in the 64-phase signal. The resistive voltage-mode interpolator generates the interpolation outputs with a symmetric zero-crossing [13], [14]. More-

**Fig. 6** Schematics of (a) the two-stage PPF, (b) the PI, and (c) a PI element  $(M_{PI}=2^6)$ .

over, the resistive interpolator reduces the power consumption in comparison with a current-mode interpolator [15].

Nonlinear resistor values were used to achieve equal phase differences. Figure 6 (c) shows a schematic of the resistor ladder-based PI element. The interpolated signals are defined by the resistance ratio. The resistance ratio  $k_i$  (= $R_i/\sum_{k=1}^{M_{PI}/8} R_k$ , i=1, ···,  $M_{PI}/8$ ) of the resistor ladder can be obtained from the following equation:

$$\sum_{i=1}^{i} k_j = 1 - \tan\{(M_{PI}/8 - i) \phi\},$$

(6)

where  $\phi$ =45°/( $M_{PI}/8$ ) is the phase difference. In the 64-phase interpolator ( $M_{PI}$ =26),  $\phi$ =5.625°. In this study, a resistance scale on the order of  $k\Omega$  was used for the actual implementation of the resistor ladders. Based on the resistance ratio, the resistance of each branch resistor is  $R_1$ =1.8  $k\Omega$ ,  $R_2$ =1.53  $k\Omega$ ,  $R_3$ =1.34  $k\Omega$ ,  $R_4$ =1.2  $k\Omega$ ,  $R_5$ =1.1  $k\Omega$ ,  $R_6$ =1.04  $k\Omega$ ,  $R_7$ =1  $k\Omega$ , and  $R_8$ =985  $\Omega$ .

The PS selects one of them as an output signal based on the 64-phase signal according to the phase control word from the controller. This scheme ensures reliable operation and always presents 64 stabilized interpolated signals after the phase interpolation is settled. Because the output signal lock is selected among the 64 pre-settled signals generated by the PI, the output signal is always stabilized for small reference phase fluctuation.

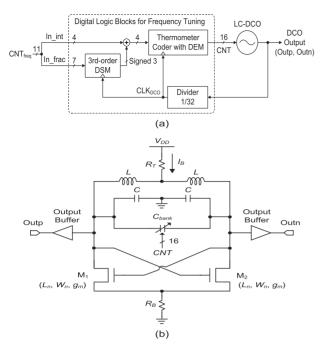

#### 3.3 Digitally-Controlled Oscillator

Figure 7(a) shows the structure of the DCO, which consists of an LC-DCO core and digital logic blocks with two types of digital words (In\_int and In\_frac) for frequency tuning [16]. A thermometer coder employing dynamic element matching (DEM) is used to convert the input digital bit. DEM effectively eliminates component mismatches [17]. Thus, the influence of capacitor mismatch can be reduced

Fig. 7 (a) Structure of the DCO and (b) schematic of the LC-DCO.

by changing the capacitor selection [18]. In this study, dataweighted averaging (DWA) is considered as the DEM technique because it requires less hardware complexity and the distortion is at a higher frequency. Additionally, a thirdorder feedforward delta-sigma modulator (DSM) [19] is utilized to achieve precise frequency resolution. Digital tuning circuits are clocked with the high-frequency signal derived from the DCO output using a divide-by-32 circuit.

A schematic of the differential LC-DCO is shown in Fig. 7 (b). An NMOS cross-coupled pair is chosen for the oscillator core, which operates with a supply voltage of 0.7 V, because it has the advantage of common-mode noise suppression and low-voltage operation. The DCO oscillation frequency is determined by the tank inductance and capacitance. In this study, a dual-layer spiral inductor and switchable capacitor bank were used for the LC tank circuit. The inductance and Q factor of the spiral inductor L at 400 MHz were 8.18 nH and approximately 8, respectively. For low-voltage operation, a switchable capacitor bank [20] was utilized instead of a MOS varactor because it has a high Q factor, linear characteristics, and low temperature coefficients. The oscillation frequency was determined by integer and fractional frequency tuning steps. To achieve high frequency resolution (under 30 kHz), the control codes have 4-bit integer and 7-bit fractional steps. The main capacitance C corresponding to the inductance is 14.3 pF, and the tuning capacitance  $C_{bank}$  is in the range of 0.1 to 1.6 pF to span the MICS band.

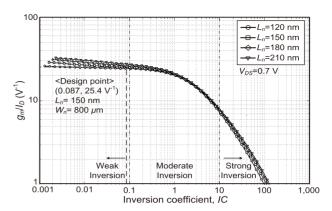

The CMOS devices operating in the weak-inversion region provide high transconductance for the given bias conditions. The required NMOS device transconductance  $g_m$  that satisfies the unity loop gain at the oscillation frequency is set to 12 mS with a safety factor of 2 for stable oscillation.

**Fig. 8** Plot of  $g_m/I_D$  versus *IC* for difference channel lengths.

The NMOS devices were designed in the weak-inversion region to satisfy the required transconductance specification at a supply voltage of 0.7 V. The inversion coefficient *IC* provides a measure of the level of inversion for a given set of bias conditions and is given by [21]

$$IC = \frac{I_D}{I_0 \cdot (W_n / L_n)},\tag{7}$$

where  $I_D$  is the drain current,  $I_0$  is the technology current, and  $W_n/L_n$  is the device aspect ratio. Weak, moderate, and strong inversion correspond to IC < 0.1, 0.1 < IC < 10, and IC > 10, respectively. The weak-inversion operation is especially useful because  $g_m/I_D$  is nearly constant.

Figure 8 shows the simulated value of  $g_m/I_D$  plotted against the IC ratio for different channel lengths. This plot demonstrates that  $g_m/I_D$  increases with decreasing IC. In weak-inversion regions, the longer channel lengths yield higher values of  $g_m$  because longer devices have more ideal subthreshold slope factors. However, longer devices under weak-inversion would more likely result in impractically large device aspect ratios, resulting in the degradation of the unity-current-gain cut-off frequency  $f_T$ . Considering the required  $g_m$ , a channel with a length  $L_n$  of 150 nm and a width  $W_n$  of 800  $\mu$ m was used for the NMOS pair transistors. Regarding this design point,  $g_m$  is approximately 12 mS, and  $f_T$  is 8.5 GHz, which is sufficient for operation in the MICS frequency band.

For the current biasing, resistive biasing with a top resistor  $R_T$  with a resistance of approximately 380  $\Omega$  is utilized because of the inherent advantage of the low noise and large voltage output swing [22]. In addition, a bottom resistor  $R_B$  with a low resistance of 10  $\Omega$  is utilized to obtain the common-mode rejection.

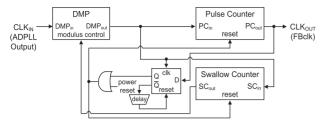

# 3.4 Programmable Frequency Divider

The employed programmable frequency divider is a pulse-swallow type system based on a dual-modulus prescaler (DMP), as shown in Fig. 9. It consists of a DMP (M/(M+1)), a pulse counter (P), and a swallow counter (S). The division ratio is determined by changing the control words of either P or S. The fundamental speed limitation of this structure

Fig. 9 Structure of the programmable frequency divider.

| T 11 4  | D        | . •    | c   | 11100  |      |         | 4         |  |

|---------|----------|--------|-----|--------|------|---------|-----------|--|

| Table 2 | Division | ratios | tor | MILES. | nana | channei | selection |  |

| Channel | CLKin  | P code    | S code    | Division ratio |

|---------|--------|-----------|-----------|----------------|

|         | (MHz)  | (decimal) | (decimal) | D=MP+S, M=32   |

| 1       | 402.15 | 83        | 25        | 2681           |

| 2       | 402.45 | 83        | 27        | 2683           |

| 3       | 402.75 | 83        | 29        | 2685           |

| 4       | 403.05 | 83        | 31        | 2687           |

| 5       | 403.35 | 83        | 33        | 2689           |

| 6       | 403.65 | 83        | 35        | 2691           |

| 7       | 403.95 | 83        | 37        | 2693           |

| 8       | 404.25 | 83        | 39        | 2695           |

| 9       | 404.55 | 83        | 41        | 2697           |

| 10      | 404.85 | 83        | 43        | 2699           |

usually arises from the critical delay path of the modulus control (MC) signal. This structure adopts the MC retiming scheme using a DFF [23]. The gate count and critical delay path of the MC signal extending the timing margin are reduced, which provides a low-power and high-frequency operating range in low-voltage operation. Moreover, unlike conventional complex reset circuitry with a set-reset latch and FF, the MC signal is set and reset by a single triggering signal to eliminate the unwanted offset of the total division ratio. As a result, the division ratio of the first half of each period is given by S(M+1), and the second half of each period has a division ratio of (P-S)M. Thus, the total division ratio is simply MP+S. The reset circuitry is designed by tapping the divider output CLK<sub>OUt</sub> and feeding it as an input to the DFF clocked with DMP<sub>out</sub>. An OR gate is used to turn off the entire divider as an external power reset. Usually, the P code is fixed, and the S code is varied to allow the selection of successive channel values. In this study, M, P, and S are set to 32, 83, 25–43, respectively, to select the 10 channels of the MICS band. Therefore, the total division ratio is 2681-2699 for the reference CLK of 150 kHz. Table 2 summarizes the required division ratios for MICS band channel selection.

#### 4. Experimental Results and Comparison

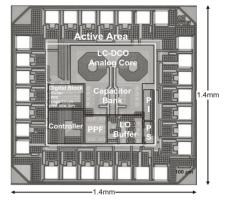

Figure 10 shows a die photograph of the ADPLL fabricated in a 130-nm CMOS process with a supply voltage of 0.7 V. The total chip area including pads is 1.96 mm<sup>2</sup>, and the active chip area is approximately 0.64 mm<sup>2</sup>. The total power consumption of the fabricated ADPLL is 840  $\mu$ W, where the DCO including the frequency-tuning and other digital blocks consume 700 and 140  $\mu$ W, respectively.

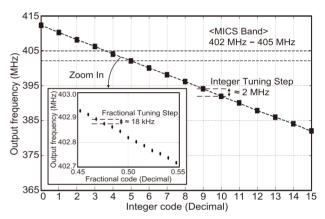

Figure 11 shows the measured DCO frequency tuning

**Fig. 10** Die photograph (active area of  $0.8 \text{ mm} \times 0.8 \text{ mm}$ ).

Fig. 11 Measured frequency tuning range of the DCO.

range. The fabricated LC-DCO has a wide integer frequency tuning range of 382 to 412 MHz that covers the MICS frequency band. The frequency resolution of integer tuning by 4-bit is approximately 2 MHz. The fractional frequency tuning range is achieved by using DSM. To obtain the precise fractional tuning range, data measured with the same codes are averaged. The fractional frequency resolution is approximately 18 kHz, which satisfies the target of the MICS band frequency tolerance.

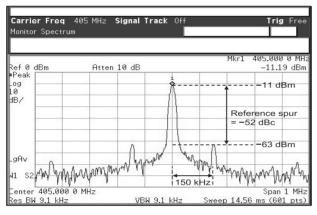

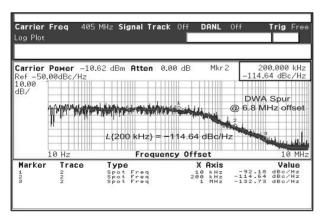

Figure 12 shows the output spectrum of the ADPLL. The measured reference spur is approximately -52 dBc at an offset frequency of 150 kHz from the carrier frequency; this obtained value is similar to those obtained in related studies. As many medical applications typically operate in isolated and protected environments with relatively short communication distances, the requirement for the reference spurs is less stringent than other requirements. Figure 13 shows the measured phase noise of the ADPLL at an operating frequency of 405 MHz. Digital blocks for frequency tuning introduce a spurious tone based on the quantization noise. A DWA spur with a -120 dBc/Hz is generated at an offset frequency of 6.8 MHz. Furthermore, the DSM generates a spur at a large offset of 12.5 MHz, which is nearly equal to the clock frequency. However, the generated spur has no influence on the phase noise because it is generated at

|                     | This work            | [25]                 | [26]                | [27]                 | [28]                  |

|---------------------|----------------------|----------------------|---------------------|----------------------|-----------------------|

| Technology          | 130-nm               | 65-nm                | 130-nm              | 130-nm               | 180-nm                |

| Supply voltage      | 0.7 V                | 1.0 V                | 1.2 V               | 0.5 V                | 1.8 V                 |

| PLL Type            | Integer-N            | Integer-N            | Integer-N           | Integer-N            | Fractional-N          |

| VCO Type            | LC-DCO               | LC-VCO               | LC-VCO              | Ring oscillator      | Ring oscillator       |

| Operating frequency | 382 MHz~412 MHz      | 400 MHz~405 MHz      | 640 MHz~650 MHz     | 400 MHz~433 MHz      | 400 MHz~410 MHz       |

| Phase noise         | -114 dBc/Hz          | -102 dBc/Hz          | −99 dBc/Hz          | −92 dBc/Hz           | -84 dBc/Hz            |

| Filase noise        | @ 200 kHz offset     | @ 200 kHz offset     | @ 100 kHz offset    | @ 1 MHz offset       | @ 300 kHz offset      |

| Settling time       | 80 μs                | $350 \mu \mathrm{s}$ | $500 \mu\mathrm{s}$ | 90 μs                | 110 μs                |

| Reference spur      | -52 dBc              | -45 dBc              | -52 dBc             | -38 dBc              | -55 dBc               |

| Area                | 0.64 mm <sup>2</sup> | $0.54 \text{ mm}^2$  | 1.0 mm <sup>2</sup> | $0.072 \text{ mm}^2$ | 0.135 mm <sup>2</sup> |

| Power dissipation   | $840 \mu\mathrm{W}$  | $430 \mu\mathrm{W}$  | 1.2 mW              | $440 \mu\mathrm{W}$  | 1.26 mW               |

| FoM                 | -181.4 dBc/Hz        | -171.8 dBc/Hz        | -174.4 dBc/Hz       | -147.5 dBc/Hz        | -145.2 dBc/Hz         |

Table 3

Performance summary and comparison

Fig. 12 Measured output spectrum of the ADPLL.

Fig. 13 Measured phase noise of the ADPLL.

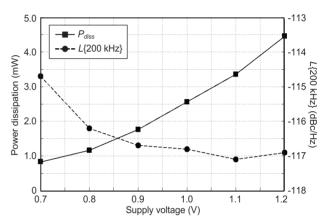

a large offset frequency outside of the MICS channel bandwidth. The measured phase noise at an offset frequency of 200 kHz is -114 dBc/Hz, and it satisfies the MICS band requirement. The phase noise is suppressed at a loop bandwidth of less than approximately 15 kHz and has an in-band noise of -90 dBc/Hz. Figure 14 shows the measured power consumption and phase noise for different supply voltages. The fabricated ADPLL has a wide supply voltage operating range (0.7–1.2 V).

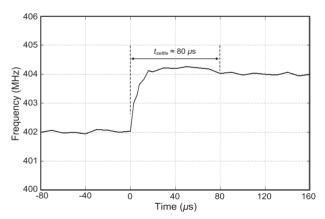

Figure 15 shows the settling time response of the AD-PLL from one locked state to another, which was taken from

Fig. 14 Measured power dissipation and phase noise for supply voltages.

Fig. 15 Measured settling time of the ADPLL.

the integer tuning of the DCO. The settling time is approximately  $80 \mu s$  with  $\pm 1\%$  accuracy.

To evaluate the ADPLL designed in this study, the well-known figure-of-merit (FoM) is employed [24]:

$$\text{FoM} = L\{\Delta f\} - 20\log_{10}\left(\frac{f_c}{\Delta f}\right) + 10\log_{10}\left(\frac{P_{diss}}{1\text{ mW}}\right), (8)$$

where  $L\{\Delta f\}$  is the phase noise at an offset frequency of  $\Delta f$ ,  $f_c$  is the oscillation frequency, and  $P_{diss}$  is the power dissipation. Table 3 summarizes the performance of the proposed ADPLL and compares this device with other PLLs

in the MICS frequency band that have been reported in the existing literature. In comparison with the devices in such related works, the proposed ADPLL demonstrates better phase noise performance and faster settling time. Low phase noise is realized by weak-inversion operation and a resistive biasing technique. The wide frequency tuning range is achieved through the switchable capacitor bank controlled by digital logic blocks. The DSM is adopted to achieve precise frequency resolution with a small number of capacitors. Additionally, the ADPLL is rapidly settled through phase selection with the PI.

#### 5. Conclusion

A low-voltage ADPLL design for use in biomedical RF transceivers was presented in this paper. In the proposed ADPLL, controller-based loop topology is used to control the phase and frequency to yield a stable ADPLL output signal. A DSM-based DCO is employed to achieve high frequency resolution, and low phase noise is achieved through weak-inversion operation and a resistive biasing technique. Moreover, the phase error is decreased by the PS with a 64-phase signal from the PI. The ADPLL fabricated in a 130-nm CMOS process achieves good phase noise performance, a wide frequency tuning range with precise frequency resolution, and rapid settling time for MICS band applications.

#### Acknowledgments

The IC in this study was designed as part of the chip fabrication program of the VDEC at the University of Tokyo in collaboration with Cadence Design Systems, Inc. In addition, the authors would like to thank SPChange, LLC for their technical support.

#### References

- [1] FCC Rules and Regulations, "MICS band plan," Part 95, Jan. 2003.

- [2] P.D. Bradley, "An ultra low power, high performance medical implant communication system (MICS) transceiver for implantable devices," in Proc. IEEE Biomed. Circuits and Syst. Conf., pp.158–161, Dec. 2006

- [3] R.B. Staszewski and P.T. Balsara, "All-digital PLL with ultra fast settling," IEEE Trans. Circuits Syst. II, vol.54, no.2, pp.181–185, Feb. 2007.

- [4] R.B. Staszewski, S. Vemulapalli, P. Vallur, J. Wallberg, and P.T. Balsara, "1.3 V 20 ps time-to-digital converter for frequency synthesis in 90-nm CMOS," IEEE Trans. Circuits Syst. II, vol.53, no.3, pp.220–224, March 2006.

- [5] S. Radhapuram, J. Bae, I. Jo, W. Wang, and T. Matsuoka, "Analysis of a controller-based all-digital phase-locked loop," Far East J. Electronics and Communications, vol.15, no.1, pp.57–73, Sept. 2015.

- [6] S. Radhapuram, J. Bae, I. Jo, W. Wang, and T. Matsuoka, "Erratum: Analysis of a controller-based all-digital phase-locked loop," Far East J. Electronics and Communications, vol.16, no.1, pp.199–201, March 2016.

- [7] J.P. Hein and J.W. Scott, "z-domain model for discrete-time PLLs," IEEE Trans. Circuits Syst., vol.35, no.11, pp.1393–1400, Nov. 1988.

- [8] R.B. Staszewski and P.T. Balsara, "Phase-domain all-digital phase-locked loop," IEEE Trans. Circuits Syst. II, vol.52, no.3, pp.159–163, March 2005.

- [9] F.M. Gardner, "Charge-pump phase-lock loops," IEEE Trans. Commun., vol.28, no.11, pp.1849–1858, Nov. 1980.

- [10] Q. Huang and R. Rogenmoser, "Speed optimization of edge-triggered CMOS circuits for gigahertz single-phase clocks," IEEE J. Solid-State Circuits, vol.31, no.3, pp.456–465, March 1996.

- [11] J. Kaukovuori, K. Stadius, J. Ryynänen, and K.A.I. Halonen, "Analysis and design of passive polyphase filters," IEEE Trans. Circuits Syst. I, vol.55, no.10, pp.3023–3037, Nov. 2008.

- [12] F. Behbahani, Y. Kishigami, J. Leete, and A.A. Abidi, "CMOS mixers and polyphase filters for large image rejection," IEEE J. Solid-State Circuits, vol.36, no.6, pp.873–887, June 2001.

- [13] E.M. Martins and E.C. Ferreira, "An 8-bit folding A/D converter with a new interpolation technique," Analog Integr. Circuits Signal Process., vol.41, no.2/3, pp.237–252, Dec. 2004.

- [14] A. Maxim, "A 0.16-2.55-GHz CMOS active clock deskewing PLL using analog phase interpolation," IEEE J. Solid-State Circuits, vol.40, no.1, pp.110–131, Jan. 2005.

- [15] D. Miyashita, H. Kobayashi, J. Deguchi, S. Kousai, M. Hamada, and R. Fujimoto, "A -104dBc/Hz in-band phase noise 3GHz all digital PLL with phase interpolation based hierarchical time to digital converter," IEICE Trans. Electron., vol.E95-C, no.6, pp.1008-1016, June 2012

- [16] J. Bae, S. Radhapuram, I. Jo, T. Kihara, and T. Matsuoka, "A design of 0.7-V 400-MHz digitally-controlled oscillator," IEICE Trans. Electron., vol.E98-C, no.12, pp.1179–1186, Dec. 2015.

- [17] J. Wang, T. Matsuoka, and K. Taniguchi, "A switched-capacitor programmable gain amplifier using dynamic element matching," IEEJ Trans. Electrical and Electronic Engineering, vol.2, no.6, pp.600–607, Nov. 2007.

- [18] G. Tsuruyama, H. Ham, J. Wang, T. Matsuoka, and K. Taniguchi, "Analysis on influence of capacitor switching in digitally-controlled oscillator using behavior-level simulation," IEICE Trans. Fundamentals (Japanese Edition), vol.J94-A, no.2, pp.145–148, Feb. 2011.

- [19] W. Rhee, B.-S. Song, and A. Ali, "A 1.1-GHz CMOS fractional-N frequency synthesizer with a 3-b third-order ΣΔ modulator," IEEE J. Solid-State Circuits, vol.35, no.10, pp.1453–1460, Oct. 2000.

- [20] T. Kamata, T. Matsuoka, and K. Taniguchi, "RF front-end design for CMOS terrestrial wideband TV tuner IC," IEEE Trans. Consum. Electron., vol.56, no.3, pp.1340–1348, Aug. 2010.

- [21] D.M. Binkley, C.E. Hopper, S.D. Tucker, B.C. Moss, J.M. Rochelle, and D.P. Foty, "A CAD methodology for optimizing transistor current and sizing in analog CMOS design," IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst., vol.22, no.2, pp.225–237, Feb. 2003.

- [22] J. Bae, S. Radhapuram, I. Jo, T. Kihara, and T. Matsuoka, "A sub-threshold low-voltage low-phase noise CMOS LC-VCO with resistive biasing," Circuits and Systems, vol.6, no.5, pp.136–142, May 2015.

- [23] S. Radhapuram, J. Bae, I. Jo, T. Kihara, and T. Matsuoka, "A low-power CMOS programmable frequency divider with novel retiming scheme," IEICE Electron. Express, vol.12, no.6, pp.20141233, March 2015.

- [24] H.-Y. Chang and Y.-T. Chiu, "K-band CMOS differential and quadrature voltage-controlled oscillators for low phase-noise and low-power applications," IEEE Trans. Microw. Theory Tech., vol.60, no.1, pp.46–59, Jan. 2012.

- [25] J. Yang and E. Skafidas, "A low power MICS band phase-locked loop for high resolution retinal prosthesis," IEEE Trans. Biomed. Circuits Syst., vol.7, no.4, pp.513–525, Aug. 2013.

- [26] A. Italia and G. Palmisano, "A 1.2-mW CMOS frequency synthesizer with fully-integrated LC VCO for 400-MHz medical implantable transceivers," in Proc. IEEE Radio Frequency Integrated Circuits Symp., pp.333–336, June 2009.

- [27] W.-H. Chen, W.-F. Loke, and B. Jung, "A 0.5-V, 440-µW frequency synthesizer for implantable medical devices," IEEE J. Solid-State Circuits, vol.47, no.8, pp.1896–1907, Aug. 2012.

- [28] W. Khalil, S. Shashidharan, T. Copani, S. Chakraborty, S. Kiaei,

and B. Bakkaloglu, "A 700-µA 405-MHz all-digital fractional-*N* frequency-locked loop for ISM band applications," IEEE Trans. Microw. Theory Tech., vol.59, no.5, pp.1319–1326, May 2011.

## Appendix: Open Loop Analysis

The open-loop transfer function of controller-based ADPLL is expressed as

$$H_{ol}(s) = \frac{\alpha_{pn}}{s^2} \left[ s^2 + 2\left(1 + \frac{1}{\alpha_{pn}}\right) \zeta \omega_n s + \left(1 + \frac{1}{\alpha_{pn}}\right) \omega_n^2 \right],$$

$$= \frac{\left(1 + \alpha_{pn}\right) \omega_n^2}{s^2} \left(1 + \frac{s}{\omega_{z1}}\right) \left(1 + \frac{s}{\omega_{z2}}\right). \tag{A·1}$$

The open-loop transfer function shows two poles at origin and two zeros at  $\omega_{z1}$  and  $\omega_{z2}$ , which are expressed as

$$\omega_{z1} = \left(1 + \frac{1}{\alpha_{pn}}\right) \zeta \omega_n \left[1 - \sqrt{1 - \frac{4\alpha_{pn}\rho_n}{\alpha_{fn}^2}}\right],$$

$$\omega_{z2} = \left(1 + \frac{1}{\alpha_{pn}}\right) \zeta \omega_n \left[1 + \sqrt{1 - \frac{4\alpha_{pn}\rho_n}{\alpha_{fn}^2}}\right]. \tag{A·2}$$

The controller-based ADPLL has an additional zero from the phase selection path. So, the system parameters depend on the phase compensation factor  $\alpha_{pn}$ . In this model, the system characteristics can be controlled by adjusting the phase compensation factor  $\alpha_{pn}$ .

For the case where  $\alpha_{pn}$ =0, the open-loop transfer function is obtained as follows:

$$H_{ol}(s) = \frac{\omega_n^2}{s^2} \left( 1 + \frac{2\zeta}{\omega_n} s \right) = \frac{\omega_n^2}{s^2} \left( 1 + \frac{s}{\omega_z} \right), \tag{A-3}$$

where  $\omega_z = \omega_n/2\zeta$ . This open-loop expression follows the general second-order PLL system. Comparison shows that the phase compensation factor  $\alpha_{pn}$  can enhance tunability of zero in the open-loop transfer function.

Jungnam Bae received B.S. and M.S. degrees in electronic engineering from Kwangwoon University, Seoul, Korea, in 2009 and 2011, respectively. He is currently working toward the Ph.D. degree at Osaka University, Osaka, Japan. His current research interests include digitally-assisted analog circuits, VLSI computer-aided design, and low-voltage RF circuits

Saichandrateja Radhapuram received B.Tech. degree in electronics and communications engineering from JNTU College of Engineering, Pulivendula, India in 2010 and M.Tech. degree in micro-electronics and VLSI from Indian Institute of Technology, Hyderabad, India, in 2012. He is currently working toward Ph.D. degree at Osaka University, Osaka, Japan. His current research interests focus on low-power, high performance CMOS analog and digital integrated circuits.

Ikkyun Jo received B.S. and M.S. degrees in electrical, electronic engineering from University of Seoul, Seoul, Korea, in 2007 and 2009, respectively. He is currently working toward the Ph.D. degree at Osaka University, Osaka, Japan. His current research interests are in RF integrated circuits design and RF system design for GPS.

Weimin Wang received B.S. degree in information engineering from Shanghai Jiao Tong University, Shanghai, China in 2009 and M.S. degree in electronic engineering from Osaka University, Osaka, Japan in 2012. He worked on digital and analog circuit design for measurement instruments since 2012.

Takao Kihara received B.S., M.S., and Ph.D. degrees in electronic engineering from Osaka University, Osaka, Japan, in 2005, 2006, and 2009, respectively. He was working from 2009 to 2014 at Renesas Electronics Corp., Japan, where he was developing LTE/WCDMA CMOS transmitters and Bluetooth Low Energy (BLE) CMOS receivers. Since 2014, he has been Assistant Professor at Osaka Institute of Technology, Japan. He received the 2010 IEICE Best Paper Award.

Toshimasa Matsuoka received B.S., M.S. and Ph.D. degrees in electronic engineering from Osaka University, Osaka, Japan, in 1989, 1991 and 1996, respectively. During 1991-1998, he worked for the Central Research Laboratories, Sharp Corporation, Nara, Japan, where he was engaged in the research and development of deep submicron CMOS devices and ultra thin gate oxides. Since 1999, he has been working at Osaka University, where he is presently Associate Professor. His current research includes

CMOS analog and RF circuits, and device modeling. Dr. Matsuoka is a member of the Japan Society of Applied Physics, the IEEE, and the IEEJ.