| Title        | Studies on Thermal Characterization and Analysis<br>of Packaged SiC Power Devices for High<br>Temperature Applications |

|--------------|------------------------------------------------------------------------------------------------------------------------|

| Author(s)    | 金, 泰華                                                                                                                  |

| Citation     | 大阪大学, 2016, 博士論文                                                                                                       |

| Version Type | VoR                                                                                                                    |

| URL          | https://doi.org/10.18910/59582                                                                                         |

| rights       |                                                                                                                        |

| Note         |                                                                                                                        |

### Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

## **Doctoral Dissertation**

# Studies on Thermal Characterization and Analysis of Packaged SiC Devices for High Temperature Applications

Taehwa Kim

May 2016

Graduate School of Engineering, Osaka University Dedicated to my wife Yunhee

### Abstract

Recently, silicon carbide (SiC) semiconductors, one of the wide band gap semiconductors, have received a great attention as a promising device to replace Si power devices in power conversion systems due to their superior material properties. The SiC devices offer high temperature operation capability of 200°C that is higher than the limitation temperature of the general Si devices, and it is expected to increase power density and to reduce a size of power conversion systems. In high temperature operation of the SiC devices, the thermal management is important, because the thermal margin of the packaged devices is shrunk. In addition, the thermal properties of the package materials such as thermal conductivity and specific heat are affected by temperature, and this effect results in variation of the thermal performance of the packaged semiconductor. In order to operate the SiC devices, stably, at high temperature environment, the accurate thermal analysis of the packaged devices is introduced for high temperature applications. This dissertation is organized as follows:

In chapter 1, background and related trend of research are reviewed. In addition, objectives and outline on this research are introduced.

In chapter 2, the fundamental theories for the thermal analysis of packaged SiC devices are presented. The heat transfer mechanism, the finite difference method (FDM), the compact thermal model, and the thermal measurement and characterization methods are described.

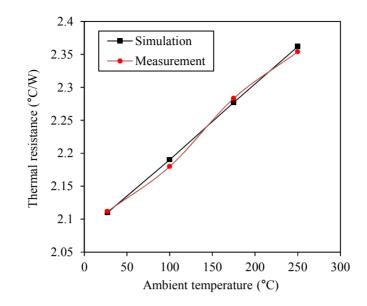

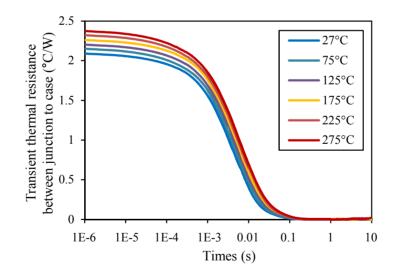

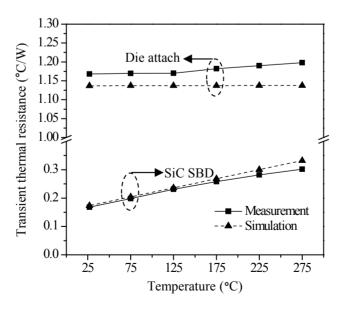

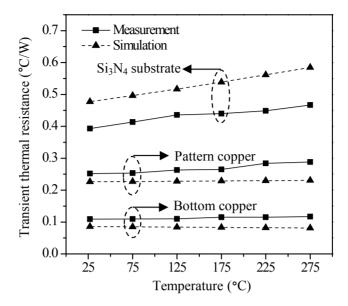

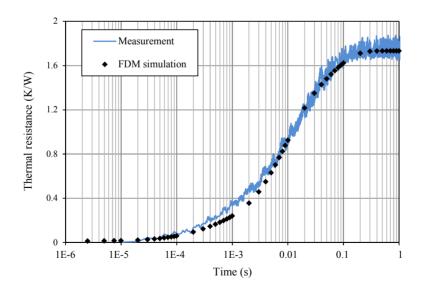

In chapter 3, thermal characteristics of a packaged SiC device for high temperature operation is investigated. The numerical thermal simulation of the packaged SiC SBD using finite difference method (FDM) is carried out considering the nonlinear thermal properties of the package materials. The transient thermal resistances of the packaged SiC SBD are experimentally measured, and compared with the simulated results. It is observed that the time constant of the transient thermal resistance and the steady state thermal resistance of the packaged SiC SBD are prolonged and increased for the temperature rise, respectively.

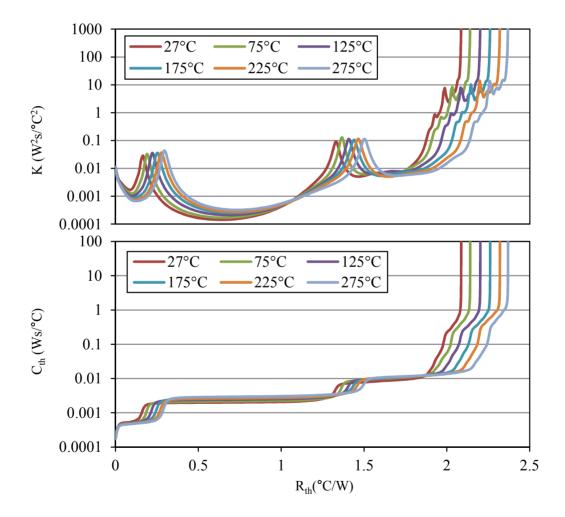

In chapter 4, the temperature dependence of partial thermal resistances of a packaged SiC SBD is analyzed at elevated temperature environment. The partial thermal resistances of the packaged SiC SBD are extracted from the transient thermal resistances using the cumulative and differential thermal structure functions. The extracted partial thermal resistances are compared to the results from the numerical simulation model, and the comparison results show good agreement. The temperature dependence of the partial thermal resistances of the SiC device and the Si<sub>3</sub>N<sub>4</sub> substrate contribute to the overall thermal resistance variation of the packaged SiC SBD.

In chapter 5, new approach for the thermal measurement of a packaged SiC MOSFET is introduced.

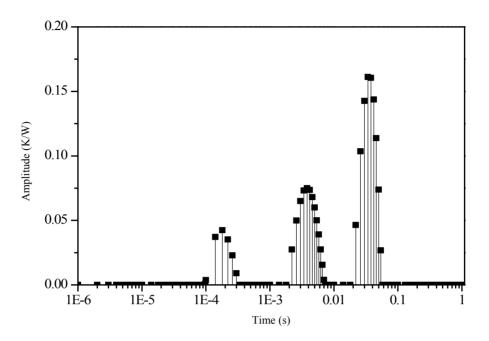

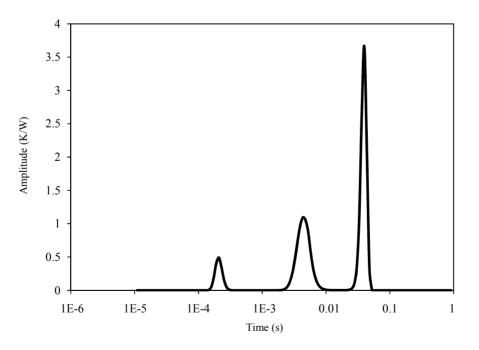

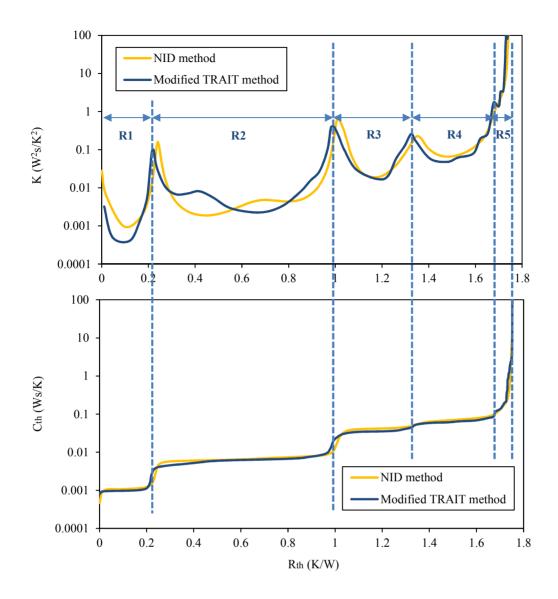

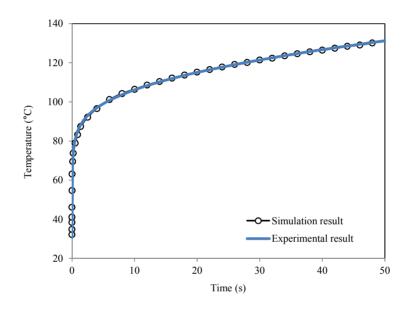

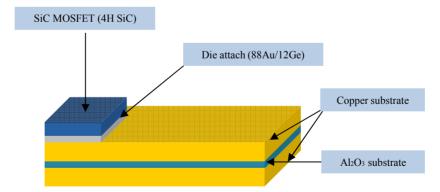

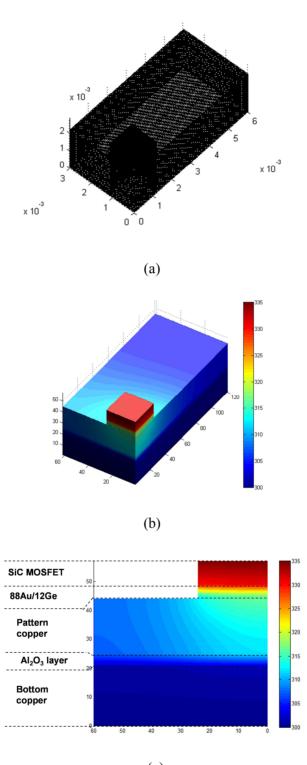

In the thermal measurement, a relationship of gate-source voltage and temperature of the SiC MOSFET measured using constant current pulses is employed to measure junction temperature. The transient thermal resistance of the packaged SiC MOSFET is measured with the constant power injection in heating condition. A modified thermal resistance analysis by an induced transient (TRAIT) method is suggested for the thermal characterization of the packaged SiC MOSFET. The modified TRAIT method characterizes the measured transient thermal resistance with the discrete time constant spectrum and the thermal structure functions. The results from the modified TRAIT method showed good consistency with that of the network identification by deconvolution (NID) method. The thermal compact model of the packaged SiC MOSFET based on a Cauer equivalent thermal network is extracted and validated using the experimentally measured results in transient temperature response of the device. The partial thermal resistances of the packaged SiC MOSFET are compared and analyzed with results from the conventional NID and the numerical FDM simulation.

Chapter 6 concludes this dissertation with the achieved results, and future tasks are discussed.

**Keywords**: SiC, SBD, MOSFET, Thermal analysis, Finite difference method, TRAIT, Partial thermal resistance, Thermal structure function.

## Contents

| Abstract                                                                                         | i   |

|--------------------------------------------------------------------------------------------------|-----|

| Contents                                                                                         | iii |

| Chapter 1: Introduction                                                                          | 1   |

| 1.1 SiC power devices                                                                            | 1   |

| 1.2 Thermal analysis of packaged SiC devices                                                     | 2   |

| 1.2.1 Researches of thermal analysis of packaged SiC devices                                     | 2   |

| 1.2.2 The thermal properties of packaged SiC devices for high temperature operation              | 4   |

| 1.3 Research objectives and outline                                                              | 5   |

| References                                                                                       | 6   |

| Chapter 2: Fundamentals of thermal analysis for packaged SiC devices                             | 10  |

| 2.1 Fundamentals of heat transfer theories                                                       | 10  |

| 2.2 Finite difference method                                                                     | 11  |

| 2.3 Thermal compact model network                                                                | 13  |

| 2.3.1 Transient thermal resistance of packaged semiconductor device                              | 13  |

| 2.3.2 Foster and Cauer equivalent thermal network                                                | 15  |

| 2.3.3 Transient thermal characterization procedure                                               | 18  |

| 2.3.4 TRAIT method                                                                               | 19  |

| 2.3.5 NID method                                                                                 | 20  |

| 2.4 Conclusion                                                                                   | 22  |

| References                                                                                       | 22  |

| Chapter 3: Analysis on transient and steady state thermal characteristics of packaged SiC SBDs . | 25  |

| 3.1 Introduction                                                                                 | 25  |

| 3.2 Structure of packaged SiC SBD                                                                | 26  |

| 3.3 Finite difference thermal modeling                                                           | 26  |

| 3.3.1 Finite difference equation                                                                 | 26  |

| 3.3.2 Thermal model of packaged SiC SBD                                                          | 30  |

| 3.3.3 Simulation                                                                                 | 31  |

| 3.4 Experimental thermal measurement                                                             | 35  |

| 3.4.1 Thermal sensitive electrical parameter                                                     | 35  |

| 3.4.2 Transient thermal measurement                                                              | 36  |

| 3.5 Comparison and discussion                                                                | 42 |

|----------------------------------------------------------------------------------------------|----|

| 3.6 Conclusion                                                                               | 44 |

| References                                                                                   | 44 |

| Chapter 4: Characterization and analysis of partial thermal resistances of packaged SiC SBDs | 47 |

| 4.1 Introduction                                                                             | 47 |

| 4.2 Partial thermal resistance network of packaged SiC SBD                                   | 48 |

| 4.3 Thermal characterization of packaged SiC SBD                                             | 49 |

| 4.3.1 Experimental thermal measurement                                                       | 49 |

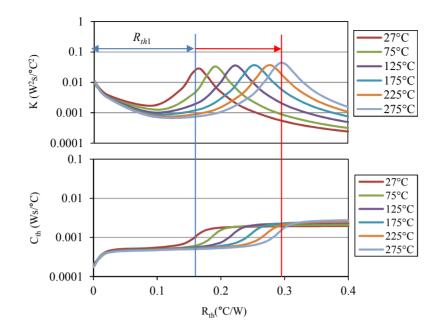

| 4.3.2 Thermal structure functions                                                            | 50 |

| 4.4 Partial thermal resistance analysis of packaged SiC SBD                                  | 52 |

| 4.4.1 Partial thermal resistance with FDM                                                    | 52 |

| 4.4.2 Comparison and discussion                                                              | 54 |

| 4.5 Conclusion                                                                               | 56 |

| References                                                                                   | 56 |

| Chapter 5: Thermal measurement and characterization of packaged SiC MOSFETs                  | 58 |

| 5.1 Introduction                                                                             | 58 |

| 5.2 Thermal measurement of packaged SiC MOSFET                                               | 59 |

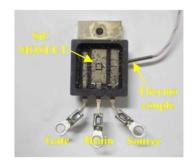

| 5.2.1 Structure of packaged SiC MOSFET                                                       | 59 |

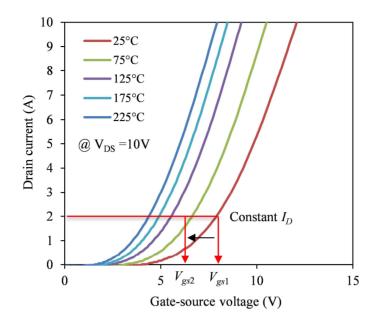

| 5.2.2 Thermal sensitivity electrical parameter for SiC MOSFETs                               | 59 |

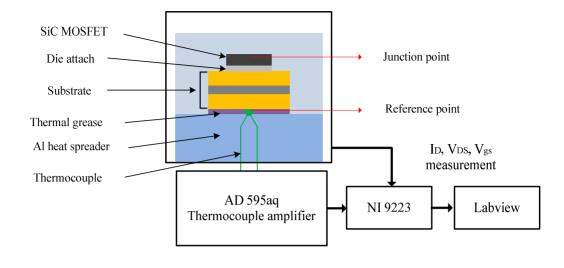

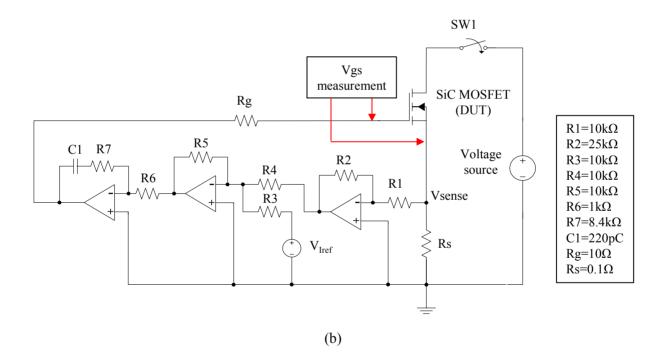

| 5.2.3 Measurement system for thermal measurement of packaged SiC MOSFETs                     | 60 |

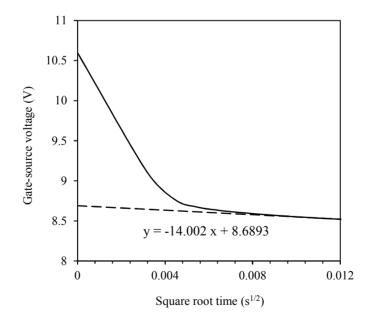

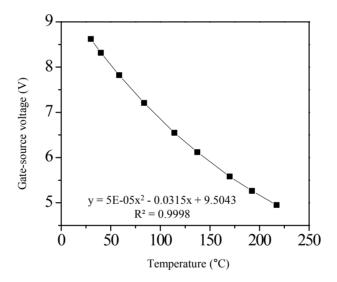

| 5.2.4 Measurement of temperature dependence of gate-source voltage                           | 63 |

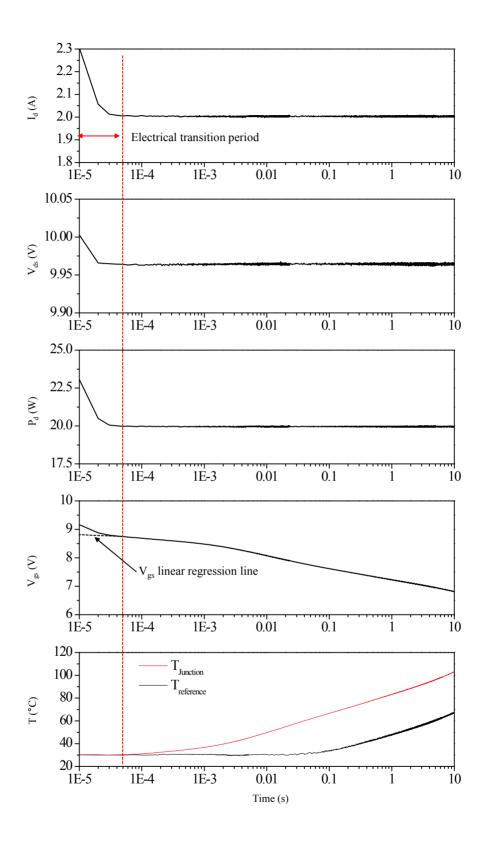

| 5.2.5 Transient thermal resistance measurement                                               | 64 |

| 5.3 Thermal characterization and modelling of packaged SiC MOSFET                            | 67 |

| 5.3.1 Characterization of transient thermal resistance                                       | 67 |

| 5.3.2 Thermal model and validation                                                           | 70 |

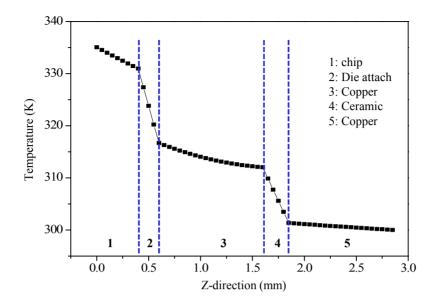

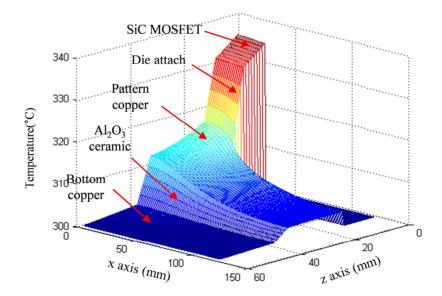

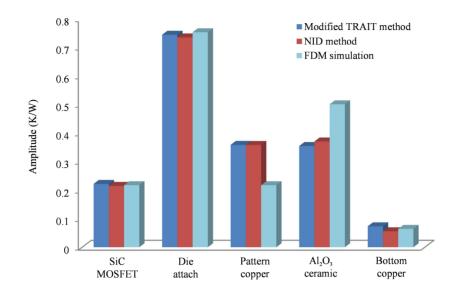

| 5.3.3 Thermal analysis of partial thermal resistance                                         | 72 |

| 5.4 Conclusion                                                                               | 77 |

| References                                                                                   | 77 |

| Chapter 6: Conclusion                                                                        | 80 |

| Acknowledgments                                                                              | 83 |

| Publications                                                                                 | 85 |

## Chapter 1: Introduction

#### 1.1 SiC power devices

In recent years, the power conversion systems to increase the energy efficiency have received great attention due to environmental problems and exhaustion of fossil fuels [1],[2]. The power conversion systems such as DC-DC converters, AC-DC converters, and inverters convert the electrical power from one type into another type. In the power conversion system, one of the essential elements is power semiconductors. The power semiconductors are devices that have capability to handle the large current and high voltage to switch the high power, and the ideal power semiconductor is required to support the ability to flow the high power with zero power dissipation and fast switching speed [3].

Until recently, the main power devices are based on silicon (Si) technology. The Si based power devices have covered requirements of power conversion systems up to now, satisfactorily. However, the Si based power devices show limitation of technical development due to its physical limitations [4]. The Si based power devices are shown to not meet requirements for future power conversion systems that require fast switching and low power loss such as electric and hybrid vehicles, high power conversion systems for wind and photovoltaic power generation.

Silicon carbide (SiC) is one of the wide bandgap semiconductors, and is the most promising alternatives to Si in power devices due to its superior electrical, mechanical and thermal characteristic [5]-[7]. Among the SiC semiconductors, 4H-SiC has received the most attraction compared to other SiC materials due to their inherent material properties, quality of the crystal growth, and the maturity of manufacturing process [8],[9]. The 4H-SiC semiconductor exhibits about 10 times higher breakdown electric field strength, 3 times higher band gap, and 3 times higher thermal conductivity than Si. Table I shows the comparison of the electrical, material, and thermal properties between Si and 4H-SiC materials [7]-[10].

Currently, SiC schottky barrier diodes (SBDs), SiC junction field effect transistors (JFETs) and SiC metal oxide field effect transistors (MOSFETs) have been researched actively, and several SiC devices are commercially released by some manufactures. The SiC SBDs have ability of much lower reverse recovery current and recovery time compared to Si diodes, and the SiC SBDs have been employed in several power conversion system such as switch-mode power supplies, photovoltaic power conversion system, and electric, hybrid vehicles [11-13]. As the switching power devices, SiC JFETs have been introduced, primarily, due to simple device structures [14],[15]. Although SiC JFET shows the fast switching speed, low power loss and high temperature operation capability, it is shown the limitation of the acceptance from the power conversion system due to the normally on characteristics. It has been reported that the research results about the SiC JFET with normally off characteristics [16-18].

SiC MOSFETs have been received attention as a promising device to replace Si IGBTs used for high voltage, high current power conversion applications in an industrial, consumer and automotive system, prevalently. Development of SiC MOSFETs has been reported through the several research results [19-22]. The SiC MOSFET have shown the various advantages such as high voltage, low on-resistance, fast switching speed, and high temperature operation compared to Si IGBTs. We expect to develop the power conversion system with improved efficiency, high reliability, and shrunk size with SiC devices.

| Parameters                                                | Si                   | 4H-SiC                |

|-----------------------------------------------------------|----------------------|-----------------------|

| Energy band gap $E_{\rm G}({\rm eV})$                     | 1.11                 | 3.26                  |

| Intrinsic carrier concentration $n_i$ (cm <sup>-3</sup> ) | $1.4 \times 10^{10}$ | 6.7×10 <sup>-11</sup> |

| Electron affinity $X_s$ (eV)                              | 4.05                 | 3.7                   |

| Saturation drift velocity $v_{sat}$ (cm/s)                | 1×10 <sup>7</sup>    | 2.1×10 <sup>7</sup>   |

| Break down electric field $E_{\rm B}$ (V/cm)              | 2.5×10 <sup>5</sup>  | $2.2 \times 10^{6}$   |

| Relative dielectric constant ( $\varepsilon_s$ )          | 11.7                 | 9.7                   |

| Thermal conductivity (W/cm·K)                             | 1.5                  | 3.7                   |

Table 1.1 Comparison of the material properties between Si and 4H-SiC materials at room temperature.

#### 1.2 Thermal analysis of packaged SiC devices

#### 1.2.1 Researches of thermal analysis of packaged SiC devices

In operation of the SiC devices, the static (conduction) and dynamic (switching) losses increase the device temperature due to the self-heating effect. The self-heating effect is well-known concern for the SiC devices, because the device temperature affects the electrical characteristic, life time, and reliability. The carrier mobility of the SiC semiconductor decreases with temperature rise, and it results in the increase of the drift region resistance required to support the blocking voltage [5]. The forward voltage drops in p-n junction and schottky junction of SiC diodes and the threshold voltage of the SiC MOSFETs decrease with the temperature rise [14],[22]. The reverse leakage currents of the SiC devices increase with temperature rise [5]. These effects result in the variation of the electrical performance of the power conversion system such as the efficiency and noise characteristics. Furthermore, the operation of the semiconductors over the safe temperature range results in permanent damage or destruction [23],[24].

The temperature changes the mechanical characteristics of the package component materials. The variation of the temperature induces the mechanical stress of the package components such as the semiconductor devices, the solder, the bonding wires, and the substrates due to their different thermal coefficients [26],[27]. The cracks in interface parts inside the package are the typical example of such mechanical stress.

In order to operate the packaged SiC device, safely, the junction or device temperature must be managed under the safe operation region. Under the appreciated thermal management, the generated heat from the operation of the SiC devices can be transferred through the package and removed by the heat dissipation system such as a heat sink or the convection mechanism. The thermal characteristics of the packaged SiC devices such as the transient or static thermal resistances are very useful in the design of the thermal management system by providing the information on the thermal description inside the assembled package. Therefore, the analysis on the thermal characteristics of the packaged SiC devices is a fundamental issue in development of the power conversion system using the SiC devices.

Due to these reasons, the research on the thermal analysis for the packaged SiC devices has been carried out. Many researches have focused on the electro-thermal effect of the SiC devices. These researches have introduced the physical and analytical models of the electrical characteristics of the SiC devices that are combined with the thermal models that have the numerical type or the compact type that consist of the linear passive resistance-capacitance elements. They have tried to describe the electrical behavior variation of the SiC devices due to the self-heating in the device operation [28]-[30].

On the other hand, there are few researches that deal with nonlinear thermal characteristics of the SiC devices. The nonlinear thermal model of the SiC SBDs has been developed based on the temperature dependence in thermal conductivity and specific heat which have been extracted from the measured transient thermal responses in [31]. The nonlinear thermal compact models considering the dissipated power of the SiC devices have been introduced, and verified experimentally in [32]. Both research results have shown the significant differences in thermal responses between the linear and nonlinear models, and the nonlinearity should be considered to estimate the exact junction temperature of the SiC devices.

Since the SiC power devices in the mentioned researches have been packaged with a commercial transfer molding and can't be operated in high temperature environment. Currently, packaging technologies have been developed for high temperature operation of SiC power devices [33],[34]. These technologies include a copper bonded substrate with low thermal resistance, bonding materials and encapsulation materials with high temperature withstanding capability. In [35], the comparison of the static thermal performance of the packaged SiC SBD with the high temperature solders has been carried out with the experiment and numerically simulated results with finite element method (FEM). In addition, the evaluation on the electro-thermal responses of the SiC modules in high temperature environment has been carried out with comparison between the measured and numerically simulated results with finite difference method (FDM) [36].

#### 1.2.2 The thermal properties of packaged SiC devices for high temperature operation

As previously mentioned, the generated heat from the power loss of the semiconductor device transfers through the package, and thermal properties are important factors to determine the heat transfer ability of the package: heat capacity and thermal conductivity. The solid substance is composed of free electrons and atoms bound in periodic structures termed lattice. The atoms bound in the lattices vibrate with frequencies and amplitudes, and these vibrations are coupled with that of adjacent atoms. Where, the vibrations of the atoms are termed with phonon. The vibrational movements of the atoms produce elastic waves that propagate though the lattices, and it results in atomic displacement.

The thermal properties are dependent on the energies of the free electrons and atoms. The thermal energy is represented by the energy of all phonons and all free electrons at given temperature. When heat is supplied into the substance, then the temperature of the substance increases with the rise of the internal thermal energy. Heat capacity means the ability of the material to store the thermal energy as it changes in temperature. The heat capacity is often replaced by the specific heat, the heat capacity per unit mass of a material [37].

The heat transfer is mainly carried out by the migration of the free electron and the phonon. In the solid substance that has temperature gradient, the net movement of phonons transfers the thermal energy from high to low temperature regions, and also, the free electrons gained a kinetic energy in high temperature region, migrate to the low temperature regions where, the free electrons transfer their kinetic energy to atoms through collision with phonons. Thermal conductivity is ability to transfer the thermal energy by both phonons and free electrons. For the conductors, the thermal conductivity is dominated by the effect of the migration of free electrons, because there are large number of the electrons participated in the transportation, while the heat conductivity of the

nonconductor is mainly depended on the phonon effects, because they are absence of the numbers of free electrons. Generally, the migration of the free electrons is much more efficient than phonons in thermal energy transportation because the free electrons have higher velocities and is less affected by phonons scattering by lattice imperfections, so that the thermal conductivities of the conductor have higher values than that of the nonconductor.

In temperature ranges of the semiconductor operation, for the package component materials such as the copper, the ceramics, and Si or SiC materials, the phonon scatterings increase with temperature so that the migration of the free electrons is interrupted. It results in the variation of their thermal conductivity [38]. The average thermal energy of the phonons and free electrons increases with the temperature rise, and it results in the increase of the heat capacity. The temperature dependence of the heat capacity can be represented by the Debye model [39].

The effect of the temperature dependent thermal properties may be particularly critical for the SiC devices compared to the Si devices, because the SiC device has the operation capability in the wide temperature range. The conventional Si devices have limitation operation temperature about  $150^{\circ}$ C ~  $170^{\circ}$ C, but The SiC devices shows the operation ability in high temperature environment over 200°C [7],[36]. The wider temperature change induces the larger thermal properties variation. Consequently, the variation of the thermal properties of the package materials results in change of thermal characteristics of the packaged device such as thermal resistance and capacitance. Therefore, thermal characteristics analysis considering temperature effects is required for high temperature operation of the packaged SiC devices.

#### 1.3 Research objectives and outline

This dissertation focuses on the thermal measurement and analysis of the packaged SiC devices for high temperature applications. The main objectives of this dissertation are transient and steady state thermal analysis on the packaged SiC SBD with temperature dependent thermal properties, and investigation of the temperature dependence of partial thermal resistances of the packaged SiC SBD for high temperature applications. In addition, new methodology for thermal measurement and characterization for the packaged SiC MOSFET is proposed. This dissertation is structured as follows:

Chapter 1 gives a background on this research. The electrical, material, and thermal properties of SiC materials are presented. In addition, researches on the thermal analysis of the SiC devices are briefly reviewed, and the research objectives and outline are described.

In chapter 2, the fundamentals for the thermal analysis of the packaged SiC devices are presented. The heat transfer mechanism, the finite difference method (FDM), the compact thermal model, and the thermal measurement and characterization method are explained. In chapter 3, it is described that analysis of thermal characteristics of the packaged SiC SBD for high temperature operation. The finite difference thermal model considering the temperature dependent thermal properties is introduced. The measurement procedure for the transient thermal resistances of the packaged SiC SBDs is described, precisely. The comparisons between the numerically simulated and experimentally measured results are carried out, and the thermal performances of the packaged SiC SBD are discussed.

In chapter 4, the temperature dependence of partial thermal resistances of the packaged SiC SBD is investigated. The transient thermal resistances are measured at elevated temperature conditions and characterized using the cumulative and differential thermal structure functions. The extracted partial thermal resistances of the packaged SiC SBD are compared to the results from the finite difference thermal model. Finally, the partial thermal resistances of the packaged SiC SBD are analyzed and discussed.

In chapter 5, the new thermal measurement and characterization method for the packaged SiC MOSFET is introduced. The transient thermal resistance of the packaged SiC MOSFET are measured and compared with the results from the FDM numerical thermal simulation. Transient thermal characteristic of the packaged SiC MOSFET is modelled based on a Cauer network and validated with experimentally measured results. The analysis on partial thermal resistance of the packaged SiC MOSFET is carried out using the modified thermal resistance analysis by an induced transient (TRAIT) method, the network identification by deconvolution (NID) method, and the FDM thermal simulation.

Chapter 6 concludes this dissertation and the achieved results of the research are summarized.

#### References

- B. Bose, "Global energy scenario and impact of power electronics in 21st century", *IEEE Trans. Ind. Electron.*, vol. 60, no. 7, pp. 2638-2651, Jul. 2013.

- [2] O. Ellabban, AR. Haitham, and B. Frede, "Renewable energy resources: Current status, future prospects and their enabling technology", *Renewable Sustainable Energy Rev.*, vol. 39, pp. 748-764, Nov. 2014.

- [3] B. J. Baliga, *Fundamentals of power semiconductor devices*, Springer Science & Business Media, 2010.

- [4] J. L. Hudgins, G. S. Simin, E. Santi, and M. A. Khan, "An assessment of wide bandgap semiconductors for power devices", *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 907-914, May 2003.

- [5] B. J. Baliga, Silicon carbide power devices, World scientific: Singapore, 2005.

- [6] B. J. Baliga, "Trends in power semiconductor devices", *IEEE Trans. Electron Devices*, vol. 43, no. 10, pp. 1717-1731, Oct.1996.

- [7] J. B. Casady and R. W. Johnson, "Status of silicon carbide (SiC) as a wide-bandgap semiconductor for high-temperature applications: A review", *Solid-State Electron*, vol. 39, no.10, pp. 1409-1422, Oct. 1996.

- [8] C. H. Park, B. H. Cheong, K. H. Lee, and K. J. Chang, "Structural and electronic properties of cubic, 2H, 4H, and 6H SiC", *Phys. Rev. B: Condens. Matter*, vol. 49, no. 7, pp. 4498-4493, Feb. 1994.

- [9] W. J. Choyke and G. Pensl, "Physical properties of SiC", Mrs Bull., vol. 22, no. 3, pp. 25-29, Mar.1997.

- [10] S. M. Sze and K. K. Ng, Physics of semiconductor devices, John wiley & sons, 2006.

- [11] K. Takao, Y. Tsutomu, and A. Kazuo, "High di/dt switching characteristics of a SiC Schottky barrier diode", *IEEJ Trans. IA.*, vol. 124, no. 9, pp. 917-923, Dec. 2004.

- [12] J. H. Zhao, P. Alexandrov, and X. Li, "Demonstration of the first 10-kV 4H-SiC Schottky barrier diodes", *IEEE Electron Device Lett.*, vol. 24, no.6, pp. 402-404, Jun. 2003.

- [13] D. Han, J. Noppakunkajorn, and B. Sarlioglu, "Comprehensive Efficiency, Weight, and Volume Comparison of SiC-and Si-Based Bidirectional DC–DC Converters for Hybrid Electric Vehicles", *IEEE Trans. Veh. Technol.*, vol. 63, no. 7, pp. 3001-3010, Sep. 2014.

- [14] D. Jiang, R. Burgos, F. Wang, and D. Boroyevich, "Temperature-dependent characteristics of SiC devices: performance evaluation and loss calculation", *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 1013-1024, Feb. 2012.

- [15] V. Veliadis, E. J. Stewart, H. Hearne, M. Snook, A. Lelis, and C. Scozzie, "A 9-kV normally-on vertical-channel SiC JFET for unipolar operation", *IEEE Electron Device Lett.*, vol. 31, no. 5, pp. 470-472, May 2010.

- [16] C. Cai, W. Zhou, and K. Sheng, "Characteristics and application of normally-off SiC-JFETs in converters without antiparallel diodes", *IEEE Trans. Power Electron.*, vol. 28, no. 10, pp. 4850-4860, Oct. 2013.

- [17] K. Tone, J. H. Zhao, L. Fursin, P. Alexandrov, and M. Weiner, "4H-SiC normally-off vertical junction field-effect transistor with high current density", *IEEE Electron Device Lett.*, vol. 24 no. 7, pp. 463-465, Jul. 2002.

- [18] A. Rodriguez Alonso, M. Fernandez Diaz, D. G. Lamar, M. Arias Perez de Azpeitia, M. M. Hernando, and J. Sebastian, "Switching performance comparison of the SiC JFET and SiC JFET/Si MOSFET cascode configuration", *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2428-2440, May 2014.

- [19] J. Spitz, M. R. Melloch, J. A. Cooper Jr, and M. A. Capano, "2.6 kV 4H-SiC lateral DMOSFETs", *IEEE Electron Device Lett.*, vol.19, no.4, pp. 100-102, Apr. 1998.

- [20] D. M. Brown, E. Downey, M. Ghezzo, J. Kretchmer, V. Krishnamurthy, W. Hennessy, and G. Michon, "Silicon carbide MOSFET technology", *Solid-State Electron.*, vol. 39, no.11 pp. 1531-1542, Nov. 1996.

- [21] D. Okamoto, H. Yano, K. Hirata, T. Hatayama, and T. Fuyuki, "Improved inversion channel mobility in 4H-SiC MOSFETs on Si face utilizing phosphorus-doped gate oxide", *IEEE Electron Device Lett.*, vol. 31, no.7, pp. 710-712, Jul. 2012.

- [22] L. Cheng, A. K. Agarwal, S. Dhar, S. H. Ryu, and J. W. Palmour, "Static performance of 20 A, 1200 V 4H-SiC power MOSFETs at temperatures of -87°C to 300°C", *J. Electron. Mater.*, vol. 41, no.5, pp. 910-914, Mar. 2012.

- [23] X. Huang, G. Wang, Y. Li, A. Q. Huang, and B. J. Baliga, "Short-circuit capability of 1200V SiC MOSFET and JFET for fault protection", 2013 28<sup>th</sup> Annual IEEE Applied. Power Electronics Conf. and Expo. (APEC), IEEE, pp. 197-200, Mar. 2013.

- [24] M. Riccio, A. Castellazzi, G. De Falco, and A. Irace, "Experimental analysis of electro-thermal instability in SiC Power MOSFETs", *Microelectron. Reliab.*, vol. 53, no.9 pp. 1739-1744, Sep./Nov. 2013.

- [25] T. Y. Hung, S. Y. Chiang, C. J. Huang, C. C. Lee, and K. N. Chiang, "Thermal-mechanical behavior of the bonding wire for a power module subjected to the power cycling test", *Microelectron. Reliab.*, vol. 51, no.9, pp. 1819-1823, Sep./Nov. 2012.

- [26] A. Morozumi, K. Yamada, T. Miyasaka, S. Sumi, and Y. Seki, "Reliability of power cycling for IGBT power semiconductor modules", *IEEE Trans. Ind. Appl.*, vol. 39, no.3 pp. 665-671, May/Jun. 2013.

- [27] P. Alexakis, O. Alatise, J. Hu, S. Jahdi, L. Ran, and P. A. Mawby, "Improved electrothermal ruggedness in SiC MOSFETs compared with silicon IGBTs", *IEEE Trans. on Electron Devices*, vol. 61, no.7, pp. 2278-2286, Jul. 2014.

- [28] L. Starzak, M. Zubert, M. Janicki, T. Torzewicz, M. Napieralska, G. Jablonski, and A. Napieralski, "Behavioral approach to SiC MPS diode electrothermal model generation", *IEEE Trans. Electron Devices*, vol. 60, no. 2, pp. 630-638, Feb. 2013.

- [29] J. M. Ortiz-Rodriguez, M. Hernandez-Mora, T. H. Duong, S. G. Leslie, and A. R. Hefner, "Thermal network component models for 10 kV SiC power module packages", 2008 IEEE Power Electronics. Specialists. Conf. (2008 PESC), IEEE, pp. 4470-4475, Jun. 2008.

- [30] M. Zubert, L. Starzak, G. Jablonski, M. Napieralska, M. Janicki, T. Pozniak, and A. Napieralski,

"An accurate electro-thermal model for merged SiC PiN Schottky diodes", *Microelectron. J.*, vol. 43, no.5 pp.312-320, May 2012.

- [31] W. Janke and A. Hapka, "Nonlinear thermal characteristics of silicon carbide devices", *Mater. Sci. Eng.*, *B*, vol. 176, no. 4, pp. 289-292, Mar. 2011.

- [32] K. Górecki, J. Zarębski, D. Bisewski, and J. Dąbrowski, "Nonlinear compact thermal model of SiC power semiconductor devices", Proc. of the 17th Int. conf. Mixed Design of Integrated Circuits and Systems 2010, pp. 365-370, Jun. 2010.

- [33] M. Horio, Y. Iizuka, and Y. Ikeda, "Packaging Technologies for SiC Power Modules", *Fuji Electric Review*, vol. 58, no. 2, pp. 75-78, May. 2002.

- [34] R. Kisiel and Z. Szczepański, "Die-attachment solutions for SiC power devices", *Microelectron. Reliab.*, vol. 49, no. 6, pp. 627-629, Jun. 2009.

- [35] A. Gracia, S. Azzopardi, and E. Woirgard, "Thermal performance evaluation of SiC power devices packaging", 2012 13th Int. Conf. on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE), IEEE, Feb. 2012.

- [36] T. Funaki, A. Nishio, T. Kimoto, and T. Hikihara, "A study on electro thermal response of SiC power module during high temperature operation", *IEICE Electron. Exp.*, vol. 5, no.16, pp. 597-602, Aug. 2002.

- [37] T. L. Bergman, F. P. Incropera, and A. S. Lavine, *Fundamentals of heat and mass transfer*, John Wiley & Sons, 2011.

- [38] M. N. Ozisik, Heat conduction, John Wiley & Sons, 1993.

- [39] C. Kittel, Introduction to solid state physics, Wiley, 2005.

# Chapter 2: Fundamentals of thermal analysis for packaged SiC devices

#### 2.1 Fundamentals of heat transfer theories

In the packaged semiconductor device, three heat transfer mechanisms play a role to determine the temperature of the package, namely, conduction, convection, and radiation [1],[2]. The heat from the power loss of the semiconductor device transfers through the package component materials by the conduction. The conduction is thermal energy transfer due to the temperature gradient by microscopic collision of particles and movement of electrons in the substance. The governing equation of the heat conduction is defined by:

$$\ddot{q}_{\rm cond} = -\lambda \cdot \nabla T \tag{2.1}$$

where  $\ddot{q}_{cond}$  is the heat flux (W/m<sup>2</sup>), and  $\lambda$  is the material property known as the thermal conductivity of the substance (W/m·K), respectively.  $\nabla T$  is the three-dimensional temperature gradient, and the negative sign means that the heat transfers is directed from high to low temperature, respectively.

The transferred heat that reaches the surface of the package is dissipated by the convection. The convection is the thermal energy transfer as a result of random motion of fluids from one place to another. The natural convection is caused by buoyancy forces due to the density variations that result from the temperature variation within the fluid. The forced convection results from the movement of the fluid forced by external sources such as fans, pumps, or atmospheric winds. The governing equation of the convection is defined by:

$$\ddot{q}_{\rm conv} = h(T_s - T_{\infty}) \tag{2.2}$$

where  $\ddot{q}_{conv}$  is the convective heat flux (W/m<sup>2</sup>), and *h* is convective heat transfer coefficient (W/m<sup>2</sup>·K).  $T_s$  and  $T_{\infty}$  are the surface temperature of the substance and the fluid temperature, respectively. The convective heat transfer coefficient is depended on the physical properties of the fluid and physical condition between the substance and the fluid.

All substances with temperature above absolute zero radiate the energy, and the heated semiconductor package transfers heat by the thermal radiation, too. The thermal radiation is the

energy transmission in the form of waves or particle from the surface of these substances. The heat flux ( $\ddot{q}_{rad}$ ) emitted by the substance is defied by:

$$\ddot{q}_{\rm rad} = \varepsilon \sigma (T_s^4 - T_\infty^4) \tag{2.3}$$

where  $\epsilon$  is the radiative properties of the substance known as emissivity, and  $\sigma$  is the Stefan-Baltzmann constant ( $\sigma$ =5.67×10<sup>-8</sup>W/m<sup>2</sup>·K<sup>2</sup>).

#### 2.2 Finite difference method

It is very difficult to solve the partial differential equations of the mathematical physic, directly, for most real cases that deal with nonlinearities, complicated geometries, and complex boundary conditions. Presently, the numerical methods are very frequently used to solve the partial differential equations for many real cases. Finite difference method (FDM) is one of the simplest methods to solve partial differential equations [3]. In FDM, the partial differential equations are replaced with the approximated discrete algebraic equation near the node, and are solved through analytical calculation. The FDM is easy to structure the formulation and has less computational work than other numerical analysis method such as finite element method (FEM), and can be helpfully applicable to solve the engineering and scientific problems that have partial differential equations with simple geometric models [4].

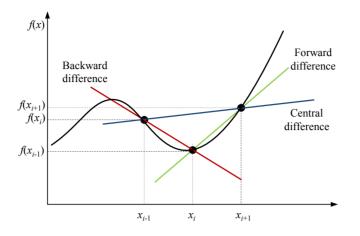

Generally, there are three types of the finite difference approximation: forward, backward, and central difference, and these approximations can be induced from Taylor's theorem. Figure 2.1 shows the finite difference approximation related to forward, backward, and central difference approximation at point  $x_i$ . Using the Taylor series expansion, the function f(x) at  $x_i$  is expressed as follows:

$$f(x) = f(x_i) + f'(x_i)(x - x_i) + \frac{f''(x_i)}{2}(x - x_i)^2 + \frac{f'''(x_i)}{3!}(x - x_i)^3 + \dots + \frac{f^n(x_i)}{n!}(x - x_i)^n + \dots = \sum_{n=0}^{\infty} \frac{f^n(x_i)}{n!}(x - x_i)^n$$

(2.4)

By expanding the function f(x) at  $x_{i+1}$  about the point  $x_i$ :

$$f(x_i + \Delta x) = f(x_i) + f'(x_i)\Delta x + \frac{f''(x_i)}{2}\Delta x^2 + \frac{f'''(x_i)}{3!}\Delta x^3 + \dots$$

(2.5)

Equation (2.5) can be rearranged as follows:

$$f'(x_i) = \frac{f(x_i + \Delta x) - f(x_i)}{\Delta x} - \underbrace{\frac{f''(x_i)}{2} \Delta x - \frac{f'''(x_i)}{3!} \Delta x^2 + \cdots}_{\text{TruncationError}}$$

(2.6)

where the first term of the right hand side is definition of the first order derivate of the function f(x) at the point  $x_i$ . If  $\Delta x$  is a sufficiently small quantity, then remaining of the series expansion after the first term in the right hand side of eq. (2.6) can be neglected in the calculation of the  $f'(x_i)$ , and this is referred to as the discretization error or the truncation error. This is known as a **forward difference** approximation because the derivate uses  $x_{i+1}$  that is a forwarded point from  $x_i$  by an increment  $\Delta x$ .

If the function f(x) is expanded at  $x_{i-1}$  about the point  $x_i$ , then the derivate function  $f'(x_i)$  can be written as:

$$f'(x_i) = \frac{f(x_i) - f(x_i - \Delta x)}{\Delta x} + \underbrace{\frac{f''(x_i)}{2} \Delta x - \frac{f'''(x_i)}{3!} \Delta x^2 + \cdots}_{\text{Truncation Error}}$$

(2.7)

The first term of the right hand side of the Eq. (2.7) is called by the **backward difference** approximation.

The **central difference** approximation for the first derivative is obtained by combining eq. (2.7) and eq. (2.6), and it is expressed as follows:

$$f'(x_i) = \frac{f(x_i + \Delta x) - f(x_i - \Delta x)}{2\Delta x} + \underbrace{\frac{f'''(x_i)}{3!} \Delta x^2 - \frac{f^5(x_i)}{5!} \Delta x^4 + \cdots}_{\text{TruncationError}}$$

(2.8)

The orders of the first term in the truncation errors represent the order of the error magnitude. The forward and backward difference approximations have the error of the first order, while the central difference approximation has the error of the second order. Considering the order of the error magnitude, the central difference approximation has the better approximated result in the first derivative than the forward and backward difference approximations.

Based on the upper three approximations, the heat transfer partial thermal equation for the packaged SiC devices can be discretized. The heat transfer governing equation inside the packaged device, the discretized process, FDM equations, and thermal analysis are introduced in chapter 3.

Fig. 2.1 Finite difference approximation related to forward, backward, and central difference approximation.

#### 2.3 Compact thermal network model

#### 2.3.1 Transient thermal resistance of packaged semiconductor device

Usually, transient thermal characteristics of the packaged semiconductor device are expressed by the transient thermal resistance [5],[6]. The transient thermal resistance of the packaged semiconductor device is defined as a ratio of the temperature difference between the junction and reference point to the dissipated power as a function of time, and means the one dimensional thermal characteristic of the package materials to oppose the generated heat flow from the device. The mathematical expression of the transient thermal resistance ( $Z_{th}$ ) is represented as follows:

$$Z_{th}(t) = \frac{T_j(t) - T_r(t)}{P_d}$$

(2.9)

where  $T_j$  is the junction temperature of the semiconductor device,  $T_r$  is the reference temperature, and  $P_d$  is the dissipated power in the device, respectively. Generally, there are two reference points. One is a case that is the interface point between package and ambient, and another is ambient whose temperature is not affected by the semiconductor heating. The transient thermal resistance between the junction and case can be used to design a heat sink for a power electronics application, and can be used in thermal analysis on the inside of the package according to the heat path [7],[8]. While the transient thermal resistance between the junction and ambient can be used in operation of the power devices without any heat sink [9].

Traditionally, the junction temperature of the packaged semiconductor device can be calculated

using the estimated power from the electrical characteristics of the device and the transient thermal resistance between the junction and case, and the heat dissipation system can be designed considering the desired junction temperature. The measurement and analysis for transient thermal resistance is one of very interesting areas for the thermal and package engineer, and the many researches have been carried out [10]-[14].

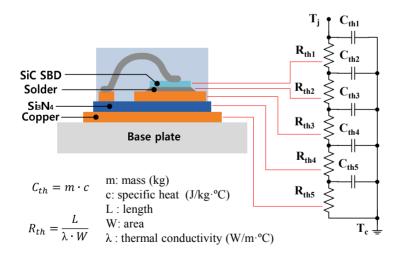

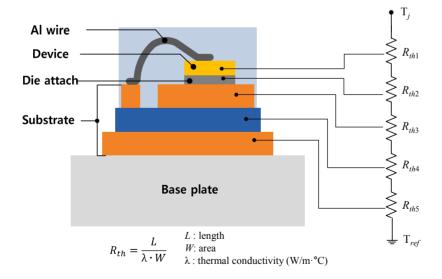

Figure 2.2 shows the compact thermal network with the thermal resistances and capacitances to express the transient thermal behavior of the packaged semiconductor device between the junction and reference point. As described the previous chapter, the materials for the package components have the thermal properties: the thermal conductivity and specific heat, and the thermal characteristics of the packaged device are determined by these properties and the geometrical structure of the package for the heat flow path from the semiconductor.

The thermal resistance  $(R_{th})$  and capacitance  $(C_{th})$  are defined by:

$$R_{th} = \frac{L}{\lambda \cdot W} \tag{2.10}$$

$$C_{th} = m \cdot c = \rho \cdot V \cdot c \tag{2.11}$$

where  $\lambda$ ,  $\rho$ , and *c* are the thermal conductivity, the density, and the specific heat of the package materials, respectively. *L*, *W*, *m*, and *V* are the length, the area, the mass and the volume of the package materials for heat flow path, respectively.

Fig. 2.2 The cross sectional view of the packaged semiconductor devices and the compact thermal network with the thermal resistances and capacitances.

Because the transient thermal resistance of the packaged semiconductor device between the junction and case represents a step response of the thermal characteristics including the thermal properties and the structure factors of the package, and the thermal system of the packaged semiconductor device can be obtained from the transient thermal resistance.

#### 2.3.2 Foster and Cauer equivalent thermal network

The transient thermal resistance of the packaged semiconductor device can be modelled by resistances and capacitances passive component considering the analogy between electrical and thermal domains [5],[15]. The table 2.1 shows the contrast in thermal-electrical analogy.

| Electrical domain      |        |      | Thermal domain      |          |      |

|------------------------|--------|------|---------------------|----------|------|

| Variable               | Symbol | Unit | Variable            | Symbol   | Unit |

| Current                | Ι      | А    | Power               | Р        | W    |

| Voltage                | V      | V    | Temperature         | Т        | °C   |

| Electrical resistance  | R      | Ω    | Thermal resistance  | $R_{th}$ | °C/W |

| Electrical capacitance | С      | С    | Thermal capacitance | $C_{th}$ | J/°C |

Table 2.1 Contrast in thermal-electrical analogy

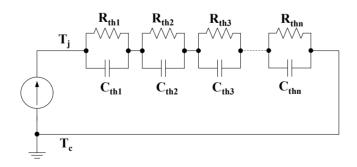

There are two canonical forms to describe the thermal system, namely, the Foster and the Cauer equivalent network [16],[17]. The Foster equivalent thermal network has a basic element that has a connection between the resistance-capacitance in parallel as shown in Fig. 2.3

Fig.2.3 Description of the Foster equivalent thermal network.

The transient thermal resistance can be described by the following transfer function considering the Foster equivalent thermal network.

$$Z_{th}(s) = \sum_{i=1}^{n} \frac{1}{C_{thi}s + 1/R_{thi}}$$

(2.12)

The Foster equivalent thermal network can express directly the exponential term that describes the transient temperature change of the substance. Using the Foster equivalent thermal network, it is easy to express the complex thermal behavior of the packaged semiconductor device. However, the elements in this thermal network have no physical signification. The heat should flow through one direction from the source to the sink. However, the configuration of the resistance-capacitance elements permits the bidirectional heat flow in this thermal equivalent network.

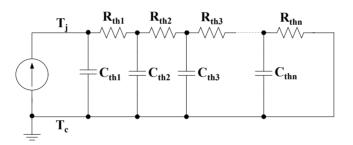

The Cauer form is used to accord the physical signification to the elements in the equivalent thermal network. The Cauer equivalent thermal network has a basic element that has the connection between the resistance and capacitance connected to ground as shown in Fig. 2.4.

Fig.2.4 Description of the Cauer equivalent thermal network.

Considering the Cauer equivalent network, the transient thermal resistance can be described by the following transfer function.

$$Z_{th}(s) = \frac{1}{C_{th1}s + \frac{1}{R_{th1} + \frac{1}{C_{th2}s + \dots + \frac{1}{R_{th,i}}}}}$$

(2.13)

In the Cauer equivalent thermal network,  $R_{thi}$  and  $C_{thi}$  represent the ability to interrupt the heat flows by the conduction and the thermal mass to store the thermal energy in the physical structures, respectively, and nodes express the interface points between the stacked structures. Using the Cauer equivalent thermal network, it is possible to monitor the thermal state of each part of the packaged device, and to express the thermal behavior variation of the device with expansion of the thermal system due to the connection of the additional physical structures such as the heat sink.

The several identification methods can extract directly the values of the elements based on the Foster equivalent thermal network, and the configuration of the Cauer equivalent thermal network can be carried out through the Foster to Cauer network conversion [18],[19]. The basic algorithm of the Foster to Cauer conversion is described below. The transfer function in the Foster equivalent thermal network shown in Eq. (2.12) is expanded as follows:

$$Z_{th}(s) = \sum_{i=1}^{n} \frac{1}{C_{thi}s + 1/R_{thi}} = \frac{a_{n-1}s^{n-1} + a_{n-2}s^{n-2} + \dots + a_{1}s + a_{0}}{b_{n}s^{n} + b_{n-1}s^{n-1} + \dots + b_{1}s + a_{0}}$$

(2.14)

Dividing the denominator by the numerator, Eq. (2.14) is expressed as follows:

$$Z_{th}(s) = \frac{1}{\frac{b_n s^n + b_{n-1} s^{n-1} + \dots + b_1 s + a_0}{a_{n-1} s^{n-1} + a_{n-2} s^{n-2} + \dots + a_1 s + a_0}} = \frac{1}{\frac{b_n}{a_{n-1}} s + \frac{b_{n-1}' s^{n-1} + b_{n-2}' s^{n-2} + \dots + b_1 s + a_0}}{a_{n-1} s^{n-1} + a_{n-2} s^{n-2} + \dots + a_1 s + a_0}}$$

(2.15)

$$= \frac{1}{C_{th1} s + Y(s)}$$

where:

$$C_{th1}s = \frac{b_n}{a_{n-1}}, \text{ and } Y(s) = \frac{b'_{n-1}s^{n-1} + b'_{n-2}s^{n-2} + \cdots + b_1s + a_0}{a_{n-1}s^{n-1} + a_{n-2}s^{n-2} + \cdots + a_1s + a_0}$$

(2.16)

From this calculation, the first capacitance of the Cauer equivalent thermal network as the quotient is obtained. The next step is dividing the denominator by the numerator of Y(s) as follows:

$$Y(s) = \frac{1}{\frac{a_{n-1}s^{n-1} + a_{n-2}s^{n-2} + \dots + a_{1}s + a_{0}}{b'_{n-1}s^{n-1} + b'_{n-2}s^{n-2} + \dots + b_{1}s + a_{0}}} = \frac{1}{\frac{a_{n-1}}{b'_{n-1}} + \frac{a'_{n-2}s^{n-2} + a'_{n-3}s^{n-3} + \dots + a_{1}s + a_{0}}{b'_{n-1}s^{n-1} + b'_{n-2}s^{n-2} + \dots + b_{1}s + a_{0}}} = \frac{1}{R_{th1} + Z'(s)}$$

(2.17)

where:

$$R_{th1} = \frac{a_{n-1}}{b_{n-1}'}, \text{ and } Z'(s) = \frac{a_{n-2}'s^{n-2} + a_{n-3}'s^{n-3} \dots + a_1s + a_0}{b_{n-1}'s^{n-1} + b_{n-2}'s^{n-2} \dots + b_1s + a_0}$$

(2.18)

As the quotient of this calculation, the first resistance of the Cauer equivalent thermal network is

obtained. After this calculation, the transfer function is expressed as follows:

$$Z_{th}(s) = \frac{1}{C_{th1}s + \frac{1}{R_{th1} + Z'(s)}} = \frac{1}{C_{th1}s + \frac{1}{R_{th1} + \frac{a'_{n-2}s^{n-2} + a'_{n-3}s^{n-3} \dots + a_{1}s + a_{0}}}$$

(2.19)

The next capacitance of the Cauer equivalent thermal network can be obtained using the repeat of the upper process, and this calculation is repeated until the remainder is zero, then elements values of the Foster equivalent thermal network turn into that of the Cauer equivalent thermal network.

#### 2.3.3 Transient thermal characterization procedure

The thermal analysis of the packaged semiconductor with a compact model based on Cauer equivalent thermal network is very attractive, because it is simple and fast to estimate the thermal behavior of the packaged devices, and it can be figured out, intuitionally, that the thermal system for the heat flow path inside the packaged device. Several researches have been carried out to identify the compact thermal model [20]-[23]. Generally, it follows the procedures below.

- (1) Obtaining the transient thermal response of the packaged device. The electrical switching method is generally used for the transient thermal response measurement [24]-[26]. This method has two phases: one is heating phase, and the other is cooling phase. In the heating phase, the high power is supplied into the device to heat up the device temperature. In cooling phase, the response of the junction temperature is measured using the temperature dependence of the electrical characteristics of the semiconductor device, namely, thermal sensitive electrical parameters (TSEPs) under low power operation. The reason that there are two phases in the measurement is difficult to measure the junction temperature using the conventional TSEPs with supplying power in the heating phase, consequently. It is challenging task to measure the junction temperature in the heating phase.

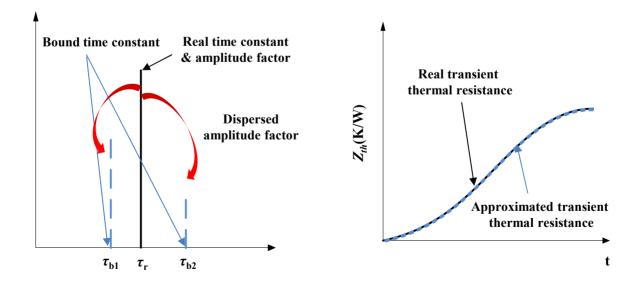

- (2) Identifying the thermal parameters for the thermal models. The several research results have been introduced to identify the thermal parameters form the measured thermal response of the packaged device. The most widely used method is network identification by deconvolution (NID) method [27],[28]. The NID method tries to identify the thermal parameters by deconvolution of the thermal response and the thermal capacitance-resistance maps. This method can be applicable to other electronic applications and support the reliable results with spatial resolution, but the procedure to identify the thermal parameter is complicate. Thermal resistance analysis by induced transient (TRAIT) method

is a well-known method for this procedure, too [29],[30]. The TRAIT method obtains the thermal parameters by the curve fitting of the thermal response to the discrete multi-exponential function. This method has a simpler procedure compared to the NID method, but the help of the numerical simulation analysis is required in the complicate packaged structure. On the other hands, the other method can be applicable in this procedure such as a genetic algorithm [31],[32].

(3) **Configuration of the equivalent thermal circuit.** The measured thermal response represents the total thermal value for the whole packaged device, but it is possible to know the contribution of each layer for the thermal response of the packaged device through the configuration of Cauer based thermal network model. This equivalent thermal model can be implemented, simply, to several simulators such as several SPICE, Matlab, and etc., and can be combined with the electrical model of the semiconductor devices for more precise analysis. The thermal response of the packaged devices can be reconstructed in various operation conditions, and the results can be used to design the power conversion applications.

#### 2.3.4 TRAIT method

The transient thermal response of the device is governed by an infinite series of exponential time constants that are affected by the thermal properties and structures of the various physical layers of the system. However, the thermal resistance analysis by induced transient (TRAIT) method has shown that the knowledge of the first *n*-terms of the time constant spectrum can express the whole transient thermal response of the device, sufficiently. In the TRAIT method, the cooling transient thermal response of the packaged semiconductor devices with a multi-layer structure after supplying a step input power can be described by a sum of exponential terms as follows [29],[30]:

$$T_{j}(0,t) = T_{r} + P_{d} \cdot \sum_{i=1}^{n} A_{i} \cdot \exp(-t/\tau_{i})$$

(2.20)

where  $T_j$  is the junction temperature,  $T_r$  is the reference temperature,  $P_d$  is the dissipated power of the heat source,  $\tau_i$  is the time constant and  $A_i$  is the corresponding amplitude factor to time constant. Eq. (2.20) can be rearranged as shown by Eq. (2.21), and transient thermal resistance at junction can be defined:

$$Z_{th}(t) = \frac{T_j(0,t) - T_r}{P_d} = \sum_{i=1}^n A_i \cdot \exp(-t/\tau_i)$$

(2.21)

In addition, the total thermal resistance of the packaged semiconductor device  $(R_{th})$  at steady state can be expressed as follows:

$$R_{th}(t) = \frac{T_j(0,0) - T_r}{P_d} = \sum_{i=1}^n A_i(0)$$

(2.22)

The identification for the thermal parameters of the Eq. (2.21) can be carried out through the several curve fitting algorithms such as Gradient descent method, Newton-Rahpson method, Gauss-Newton method, and Levenberg-Marquardt method. The most widely used algorithm is the Levenberg-Marquardt method, because it is possible to find the solution compared to other methods, rapidly, and stably.

The thermal parameters identified from Eq. (2.21) can be modelled, directly, on the Foster equivalent thermal network using the following relation.

$$R_i = A_i(0) \tag{2.23}$$

$$C_i = \frac{\tau_i}{R_i} \tag{2.24}$$

Finally, the Cauer equivalent thermal model can be obtained through the Foster to Cauer network conversion. Generally, *n*-terms represent the number of the layers, and the Foster to Cauer network conversion generated the Cauer equivalent thermal network with *n*-layer that describes the thermal system inside the packaged device.

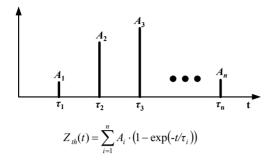

#### 2.3.5 NID method

Considering the real system, the transient thermal response of the packaged device should be expressed by the distributed or infinite discrete system. Figure 2.5 shows the discrete and distributed time constant spectrum. In the network identification by deconvolution (NID) method, the thermal system is obtained by the deconvolution with the weigh function [27],[28],[33]. If the step response of the thermal system with the multi-layers is expressed as the distributed domain, the discrete exponential function shown in Eq. (2.21) can be expressed by:

$$Z_{th}(t) = \int_0^\infty R(\tau) [1 - \exp(-t/\tau)] d\tau$$

(2.25)

where  $R(\tau)$  is the distribute time constant spectrum, and the thermal system can be known with obtaining  $R(\tau)$ . By introducing the logarithmic time variable  $z = \ln(t)$  and the logarithmic time

constant  $\zeta = \ln(\tau)$ , Eq. (2.25) is expressed as:

$$Z_{th}(t) = \int_{-\infty}^{\infty} R(\zeta) \left[ 1 - \exp(-t/\exp(\zeta)) \right] d\zeta$$

(2.26)

where the  $R(\zeta)$  is the logarithmic time constant spectrum and defined as:

$$R(\zeta) = R(\exp(\zeta)) \cdot \exp(\zeta) \tag{2.27}$$

Equation (2.27) can be changed to:

$$Z_{th}(z) = \int_{-\infty}^{\infty} R(\zeta) \left[ 1 - \exp(-\exp(z - \zeta)) \right] d\zeta$$

(2.28)

With differentiating Eq. (2.28) respect to z, Eq. (2.29) can be obtained.

$$\frac{d}{dz}Z_{th}(z) = \int_{-\infty}^{\infty} R(\zeta) \left[ \exp(z - \zeta - \exp(z - \zeta)) \right] d\zeta$$

(2.29)

By introducing the weight function  $w_z(z) = \exp(z - \exp(z))$ , Eq. (2.29) is changed to

$$\frac{d}{dz}Z_{th}(z) = \int_{-\infty}^{\infty} R(\zeta) w_z(z-\zeta) d\zeta$$

(2.30)

Equation (2.30) can be expressed by following convolution form:

$$\frac{d}{dz}a(z) = R(z) \otimes w_z(z)$$

(2.31)

where  $\otimes$  is the convolution symbol. Finally, R(z) is obtained through the deconvolution of Eq. (2.31)

$$R(z) = \left[\frac{d}{dz}a(z)\right] \otimes^{-1} w_z(z)$$

(2.32)

The convolution can be carried out using the Bayesian iteration or Fourier domain inverse filtering. The obtained distributed thermal constant spectrum should be discretized to generate the thermal model based on the Foster equivalent network. After the Foster to Cauer network conversion, the differential and cumulative structure functions based on the Cauer equivalent thermal network can be obtained. The compact thermal model of the packaged semiconductor device can be obtained from these structure functions.

(a) Discrete time constant spectrum

(b) Distributed time constant spectrum

Fig. 2.5 Discrete time constant spectrum (a) and Distributed time constant spectrum based on RC equivalent thermal system.

#### 2.4 Conclusion

In this chapter, the fundamentals for the thermal analysis of the packaged SiC devices were presented. The heat transfer mechanism for the thermal analysis of the package was described. The concept of the FDM, and the compact thermal model based on Foster and Cauer equivalent thermal network were described. The thermal measurement and characterization methods for the packaged semiconductor devices were presented and discussed.

#### References

- T. L. Bergman, F. P. Incropera, and A. S. Lavine, *Fundamentals of heat and mass transfer*, John Wiley & Sons, 2011.

- [2] M. N. Ozisik, Heat conduction, John Wiley & Sons, 1993.

- [3] G. D.Smith, *Numerical solution of partial differential equations: finite difference methods*, Oxford university press, 1985.

- [4] M. N. Ozisik, Finite difference methods in heat transfer, CRC press, 1994.

- [5] J. W. Sofia, "Analysis of thermal transient data with synthesized dynamic models for semiconductor devices", *IEEE Trans. Compon. Packag. Manuf. Technol. Part A:*, vol.18, no.1 pp. 39-47, Mar. 1995.

- [6] E. J. Diebold and L. Werner, "Transient thermal impedance of semiconductor devices", *Trans. Am. Inst. Electr. Eng. Part 1*, vol.79, no.6, pp. 719-726, Jan. 1961.

- [7] Z. Luo, H. Ahn, and M. A. E. Nokali, "A thermal model for insulated gate bipolar transistor

module", IEEE Trans. Power Electron., vol. 19, no.4, pp. 902-907, Jul. 2004.

- [8] Yun, Chan-Su, P. Malberti, M. Ciappa, W. Fichtner, "Thermal component model for electrothermal analysis of IGBT module systems, *IEEE Trans. Adv. Packag.*, vol.24, no.3, pp. 401-406, Aug. 2001.

- [9] B. Joiner, S. Neelakantan, Package Thermal Performance "What is Theta-JA?", Freescale, 2013.

- [10] J. W. Sofia, Fundamentals of Thermal Resistance Measurement, Analysis Tech, 2015.

- [11] T. L. Paoli, "A new technique for measuring the thermal impedance of junction lasers", *IEEE J. Quantum Electron.*, vol. 11, no.7, pp. 498-503, Jul. 1975.

- [12] W. Jin, W. Liu, S. K. Fung, P. C. Chan, and C. Hu, "SOI thermal impedance extraction methodology and its significance for circuit simulation", *IEEE Trans. Electron Devices*, vol. 48, no.4, pp. 730-736, Apr. 2001.

- [13] D. T. Zweidinger, R. M. Fox, J. S. Brodsky, T. Jung, and S. G. Lee, "Thermal impedance extraction for bipolar transistors", *IEEE Trans. Electron Devices*, vol.43, no. 2, pp. 342-346, Feb. 1996.

- [14] M. Busani, R. Menozzi, M. Borgarino, and F. Fantini, "Dynamic thermal characterization and modeling of packaged AlGaAs/GaAs HBTs", *IEEE Trans. Compon. Packag. Technol.*, vol. 23, no. 2, pp. 352-359, Jun. 2002.

- [15] A. F. Robertson and D. Gross, "An electrical-analog method for transient heat-flow analysis", J. Res. Nat. Bur. Stand., vol. 61, no.2, pp. 105, Aug. 1958.

- [16] M.R Foster, "Academic and theoretical aspects of circuit theory", *Proceedings of the IRE*, vol 50, no.5, pp. 866-871, May. 1962.

- [17] W. Cauer, "Die Verwirklichung von Wechselstromwiderständen vorgeschriebener Frequenzabhängigkeit", *Electr. Eng. (Archiv fur Elektrotechnik)*, vol. 17, no. 4, pp. 355-358, 1926.

- [18] K. Murthy and R. E. Bedford, "Transformation between Foster and Cauer equivalent networks", *IEEE Trans. Circuits Syst.*, vol. 25, no.4, pp.238-239, Apr. 1978.

- [19] E. A. Guillemin, "Synthesis of passive networks: theory and methods appropriate to the realization and approximation problems, RE Krieger Pub. Co., 1977.

- [20] V. Székely, "THERMODEL: a tool for compact dynamic thermal model generation", *Microelectron. J.*, vol. 29, no.4, pp. 257-267, Apr./May 1998.

- [21] M. N. Sabry, "Compact thermal models for electronic systems", *IEEE Trans. Compon. Packag. Technol.*, vol. 26, no. 1, pp. 179-185, Mar 2003.

- [22] E.G. Bosch, "Thermal compact models: An alternative approach." *IEEE Trans. Compon. Packag. Technol.*, vol. 26, no. 1, pp. 173-178, Mar. 2003.

- [23] M. Ciappa, W. Fichtner, T. Kojima, Y. Yamada, and Y. Nishibe, "Extraction of accurate thermal

compact models for fast electro-thermal simulation of IGBT modules in hybrid electric vehicles", *Microelectron. Reliab.*, vol. 45, no.9, pp. 694-1699, Sep./Nov. 2005

- [24] F. F. Oettinger, D. L Blackburn, and S. Rubin, "Thermal characterization of power transistors", *IEEE Trans. Electron Devices*, vol. 23, no. 8, pp. 831-838, Aug. 1976.

- [25] D. L Blackburn and F. F. Oettinger, "Transient thermal response measurements of power transistors", *IEEE Trans. Ind. Electron. Contr. Instrum.*, vol. 2 pp. 134-141, May 1975.

- [26] EIA/JESD 51-1 JEDEC Solid State Technology Association, 1995.

- [27] V. Székely, "A new evaluation method of thermal transient measurement results", *Microelectron. J.*, vol. 28, no.3, pp. 277-292, Mar. 1997.

- [28] V. Székely, and T. Van Bien, "Fine structure of heat flow path in semiconductor devices: a measurement and identification method", *Solid-State Electron.*, vol. 31, no.9, pp. 1363-1368, Sep. 1988.

- [29] P. E. Bagnoli, C. Casarosa, M. Ciampi, E. Dallago, "Thermal resistance analysis by induced transient (TRAIT) method for power electronic devices thermal characterization. I. Fundamentals and theory", *IEEE Trans. Power Electron.*, vol. 13, no.6, pp. 1208-1219, Nov. 1998.

- [30] P. E. Bagnoli, C. Casarosa, E. Dallago, and M. Nardoni, "Thermal resistance analysis by induced transient (TRAIT) method for power electronic devices thermal characterization. II. Practice and experiments", *IEEE Trans. Power Electron.*, vol. 13, no.6, pp. 1220-1228, Nov. 1998.

- [31] P. Arunasalam, K. N. Seetharamu, and I. A. Azid, "Determination of thermal compact model via evolutionary genetic optimization method", *IEEE Trans. Compon. Packag. Technol.*, vol. 28, no.2, pp. 345-352, Jun. 2005.

- [32] A. Aranyoshi, A. Ortega, R. A. Griffin, S. West, and D. R. Edwards, "Compact thermal models of packages used in conduction cooled applications", *IEEE Trans. Compon. Packag. Technol.*, vol. 23, no.3, pp. 470-480, Sep. 2000.

- [33] R. M. Rencz and V. Székely, "Measuring partial thermal resistances in a heat-flow path", *IEEE Trans. Compon. Packag. Technol.*, vol. 25, no.4, pp. 547-553, Dec. 2002.

### **Chapter 3:**

## Analysis on steady state and transient thermal characteristics of packaged SiC SBDs

#### **3.1 Introduction**

As described in chapter 1, the thermal properties of the package materials for the SiC semiconductor devices change with temperature due to the variation of the lattice vibration waves and the movement of electrons in materials with temperature [1],[2]. The thermal conductivity of the 4H-SiC material is decreased from 350.88 to 174.93 W/m·°C in the temperature rise from 27 to 300°C. In case of the specific heat of 4H-SiC material, the increasing trend is shown from 676.71 to 1018.45 J/kg·°C within the same temperature variation range [3]. In addition, the temperature dependence of the thermal properties of the other package materials such as the copper, the aluminum, and the ceramics (Al<sub>2</sub>O<sub>3</sub>, AlN and Si<sub>3</sub>N<sub>4</sub>) has been reported in several research results [4]-[6].

In the high temperature operation of the SiC devices, the thermal management is important, because the temperature margin to guarantee the electrical and physical performance of the packaged SiC devices is reduced [7],[8]. The thermal management allows the temperature of the SiC semiconductor device to be controlled under the safe operation condition. In the design of the thermal management of the packaged SiC devices for the high temperature operation, the accurate thermal information of the packaged devices considering the thermal characteristics variation with temperature is necessary.

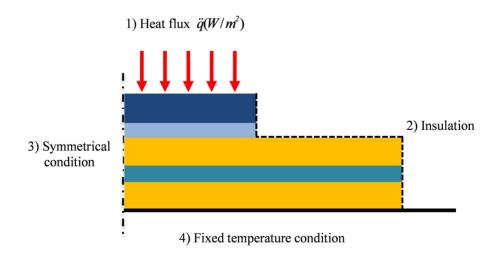

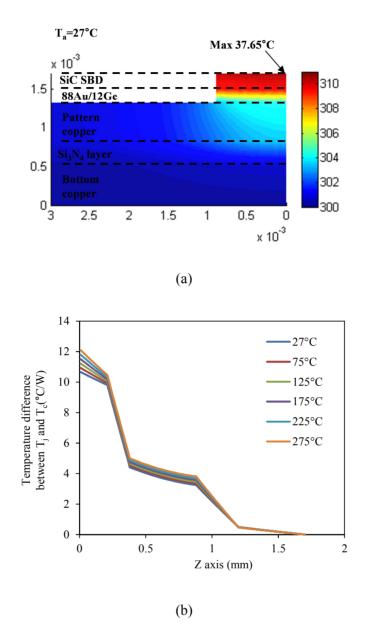

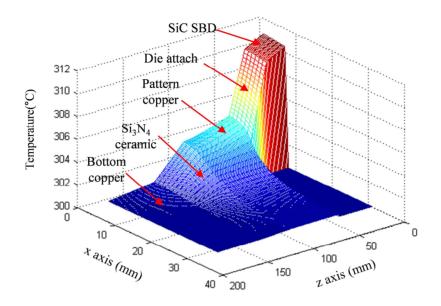

This chapter presents the thermal analysis of the packaged SiC SBD for high temperature operation based on the experimental and numerical simulation results. The packaged SiC SBD for high temperature operation is introduced in section 3.2. The thermal modelling for the packaged SiC SBD with finite difference method considering the temperature dependence of the thermal properties, and the numerical simulation procedure are explained in section 3.3. The transient thermal resistance measurement of the packaged SiC SBD was carried out to validate the numerically simulated results. This experimental measurement details and results are shown in section 3.4. Then, the measured and simulated results are compared and analyzed through section 3.5. Finally, this chapter is concluded with a summary of the achieved results.

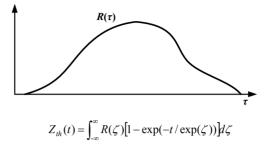

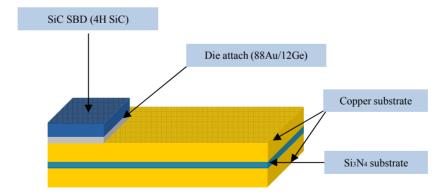

#### 3.2 Structure of packaged SiC SBD

A  $1.8 \times 1.8 \text{mm}^2$  SiC SBD manufactured by "Rohm" was used as a DUT. The SiC SBD was soldered with 88Au/12Ge on an active metal brazed (AMB) Si<sub>3</sub>N<sub>4</sub> substrate manufactured by "KYOCERA". The size of the AMB substrate, thickness of the wiring copper, the Si<sub>3</sub>N<sub>4</sub> substrate and the backside copper metal were  $20 \times 20 \text{mm}^2$ , 0.5mm, 0.35mm and 0.5mm, respectively. The anode of the SiC SBD was bonded with an Al wire (diameter of 300um), and the substrate was covered with a high temperature resin manufactured by "ADEKA". The packaged SiC SBD was attached on an Al heat-sink, and a thermal grease ("SUNHAYTO" SCH-30) was used to reduce the contact resistance between the package and the heat-sink. A K-type thermocouple was attached to the center position of the SiC SBD device in the bottom side of the packaged SiC SBD with the soldering contact to measure the temperature of the bottom copper layer. The overview and schematic cross sectional structure of the packaged SiC SBD is shown in Fig. 3.1.

Fig. 3.1 Overview of the packaged SiC SBD (a) and schematic cross sectional structure view of the packaged SiC SBD

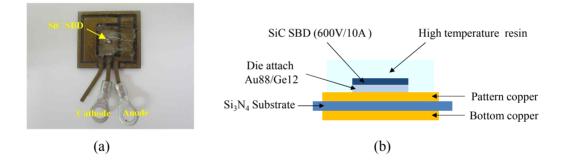

#### 3.3 Finite difference thermal modeling

#### 3.3.1 Finite difference equation

Although the three mechanisms described in chapter 2 affect the whole heat transfer of the packaged semiconductor device, the heat transfer inside the packaged devices is dominated by the heat conduction so that it can be assumed that the effects of the convection and radiation are negligible [9]. Therefore, the heat transfer inside the packaged SiC SBD can be expressed by the governing partial difference equation as follows:

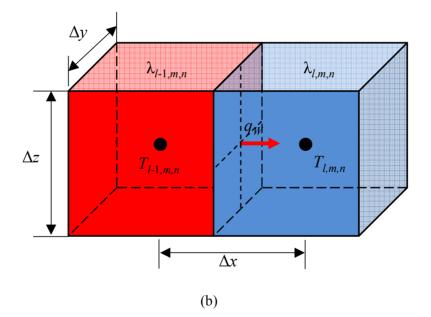

Fig. 3.2. Thermal network with thermal resistance and capacitance (a), and the heat flow between (l-1, m, n) and (l, m, n) with the different thermal conductivities (b).

$$\rho c(T) \frac{\partial T(x, y, z, t)}{\partial t} = \nabla \cdot \left[ \lambda(T) \nabla T(x, y, z, t) \right] + g(x, y, z, t)$$

(3.1)

where  $\rho$  is the density, c(T) and  $\lambda(T)$  are the specific heat and the thermal conductivity with temperature dependency, and g is the power density of the heat source.

As described in chapter 2, the finite difference method (FDM) is a widely used method to solve the partial difference equations, and it can be used for solving the heat conduction equation as shown in Eq. (3.1) [10]. In this research, the governing equation for Eq. (3.1) is changed into the explicit finite difference equation based on the forward approximation, and the energy balance method for each node.

Figure 3.2(a) shows the thermal network with the thermal resistance and capacitance in the three dimensional orthogonal coordinate for the finite difference method. The thermal network has a control volume that has the node (l, m, n) in the center, and has the lengths  $\Delta x$ ,  $\Delta y$ ,  $\Delta z$ . There are six adjacent nodes  $(l\pm 1, m, n)$ ,  $(l, m\pm 1, n)$ , and  $(l, m, n\pm 1)$  around the node (l, m, n), and the distances between the node (l, m, n) and the adjacent nodes are  $\Delta x$ ,  $\Delta y$ ,  $\Delta z$ , respectively. Assuming that all the heat flow goes into the node (l, m, n), the general energy conservation equation for the control volume  $\Delta V = \Delta x \cdot \Delta y \cdot \Delta z$  is expressed as follows:

$$\sum_{i=1}^{n} E_{in,i} = E_{stored} - E_{generaged}$$

(3.2)

where  $E_{in}$  is the input energy,  $E_{stored}$  is the stored energy, and  $E_{generated}$  is the generated energy. The energy exchange is affected by the heat generation in the control volume, and by conduction between the node (l, m, n) and the adjacent nodes. The heat conduction can be represented by the heat flow q so that Eq. (3.2) is can be expressed:

$$\sum_{i=1}^{6} q_{(i)\to(l,m,n)} + \dot{g}\Delta V_{l,m,n} = E_{stored}$$

(3.3)

where  $\dot{g}$  is the rate of the heat generation per unit volume, and the subscripts *l*, *m*, *n* denote the grid point. As described in chapter 2, the heat flow can be expressed by Fourier's heat conduction equation. Considering the temperature dependence of the thermal conductivities, even if the nodes are in the same material, the thermal conductivities of each node change with the temperature variation of the nodes. Figure 3.2(b) shows the schematic heat flow from the node (*l*-1, *m*, *n*) to (*l*, *m*, *n*) with the different thermal conductivities. In Fig. 3.2(b), the heat flow  $q_W$  through the area  $\Delta A = \Delta y \cdot \Delta z$  can be expressed as follows:

$$q_{W} = -\lambda_{W} \Delta A \frac{\partial T}{\partial x}$$

$$\approx \frac{\lambda_{l-1,m,n} + \lambda_{l,m,n}}{2} \left( \frac{\Delta y \Delta z}{\Delta x} \right) \left( T_{l-1,m,n} - T_{l,m,n} \right)$$

$$\approx \lambda_{l-1/2,m,n} \left( \frac{\Delta y \Delta z}{\Delta x} \right) \left( T_{l-1,m,n} - T_{l,m,n} \right)$$

(3.4)

where

$$\lambda_{l-1/2,m,n} = \frac{\lambda_{l-1,m,n} + \lambda_{l,m,n}}{2}$$

(3.5)

where  $\lambda_{l-1,m,n}$ ,  $\lambda_{l,m,n}$  are the thermal conductivities of the control volume with the node (*l*-1, *m*, *n*) and (*l*, *m*, *n*), respectively. A similar expression can be written for the other heat flows into the node (*l*, *m*, *n*).

The stored energy for the control volume is represented as follows:

$$\dot{E}_{stored} = (\rho c)_{l,m,n} \Delta V_{l,m,n} \frac{\partial T}{\partial t} \approx (\rho c)_{l,m,n} (\Delta x \cdot \Delta y \cdot \Delta z) \frac{T_{l,m,n}^{p+1} - T_{l,m,n}^{p}}{\Delta t}$$

(3.6)

where the superscript *p* represents the current time step, and  $\Delta t$  identifies the time interval between the current time *p* and the next time *p*+1.

It is required to discretize the temperature dependent thermal properties for the thermal simulation. Thermal conductivity  $\lambda^{p+1}$  at the time level p+1 can be expressed as follows:

$$\lambda^{p+1} \cong \lambda^p + \left(\frac{\partial\lambda}{\partial t}\right)^p \Delta t \cong \lambda^p + \left(\frac{\partial\lambda}{\partial T}\right)^p \left(\frac{\partial T}{\partial t}\right)^p \Delta t$$

(3.7)

where the term of the time derivative of the temperature is approximated by:

$$\left(\frac{\partial T}{\partial t}\right)^{p} \cong \frac{T^{l} - T^{p-l}}{\Delta t}$$

(3.8)

Substituting Eq. (3.8) into (3.7), the thermal conductivity with temperature dependence at the time level p+1 is determined as:

$$\lambda^{p+1} = \lambda^p + \left(\frac{\partial \lambda}{\partial T}\right)^p \left(T^p - T^{p-1}\right)$$

(3.9)

Using the similar procedure, the specific heat can be obtained as follows:

$$c^{p+1} = c^{p} + (\partial c/\partial T)^{p} (T^{p} - T^{p-1})$$

(3.10)

Based on the equations of (3.4)-(3.10), the finite difference equation for the thermal simulation of the packaged SiC SBD at the internal node (l, m, n) is obtained as follows:

$$(\rho c)_{l,m,n} \Delta x \Delta y \Delta z \frac{T_{l,m,n}^{p+1} - T_{l,m,n}^{p}}{\Delta t} \\ = \left[ \lambda_{l-1/2,m,n} \frac{\Delta y \Delta z}{\Delta x} \left( T_{l-1,m,n}^{p} - T_{l,m,n}^{p} \right) + \lambda_{l+1/2,m,n} \frac{\Delta y \Delta z}{\Delta x} \left( T_{l+1,j,k}^{p} - T_{l,m,n}^{p} \right) \right] \\ + \left[ \lambda_{l,m-1/2,n} \frac{\Delta x \Delta z}{\Delta y} \left( T_{l,m-1,n}^{p} - T_{l,m,n}^{p} \right) + \lambda_{l,m+1/2,n} \frac{\Delta x \Delta z}{\Delta y} \left( T_{l,m+1,n}^{p} - T_{l,m,n}^{p} \right) \right] \\ + \left[ \lambda_{l,m,n-1/2} \frac{\Delta x \Delta y}{\Delta z} \left( T_{l,m,n-1}^{p} - T_{l,m,n}^{p} \right) + \lambda_{l,m,n+1/2} \frac{\Delta x \Delta y}{\Delta z} \left( T_{l,m,n+1}^{p} - T_{l,m,n}^{p} \right) \right]$$

(3.11)

$$+ g(x_{l}, y_{m}, z_{n}, t)$$

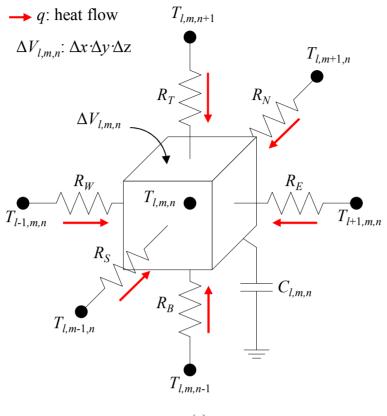

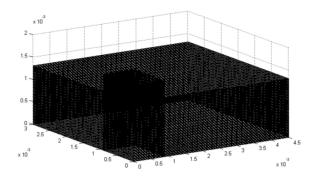

#### 3.3.2 Thermal model of packaged SiC SBD

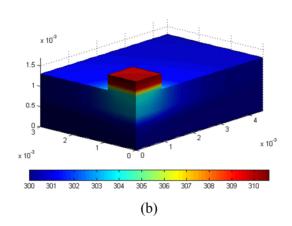

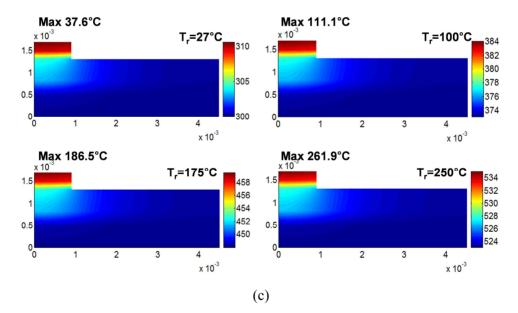

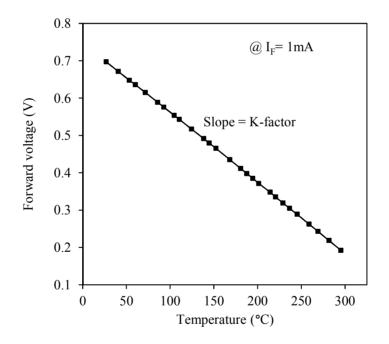

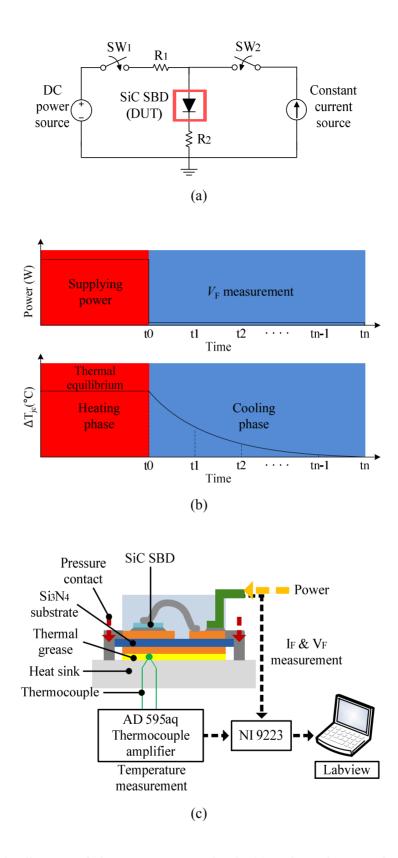

Because the most of the heat generated from the SiC SBD flows through the center copper pattern inside the package, thermal model was built considering it. The schematic thermal simulation model and the dimensions of the packaged SiC SBD structure are shown in Fig. 3.3, and Table 3.1, respectively. The dimensions for the thermal simulation are accordance with the experimented real package structure.

Fig. 3.3 Description of schematic thermal model for transient thermal response simulation of the packaged SiC SBD.

| Component        |                                | Surface area(mm <sup>2</sup> ) | Thickness (mm) |

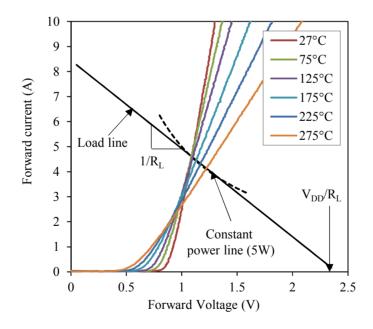

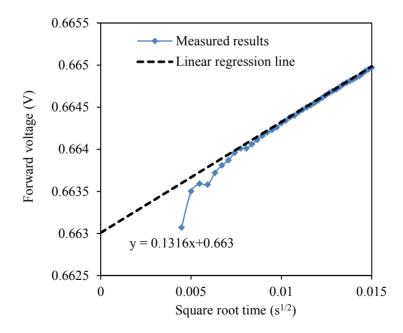

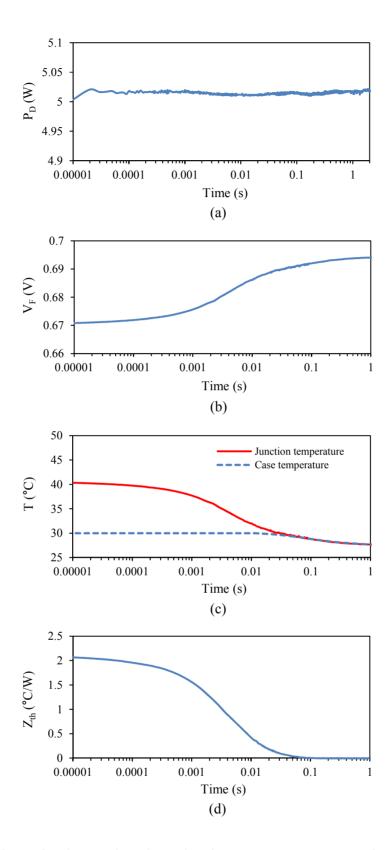

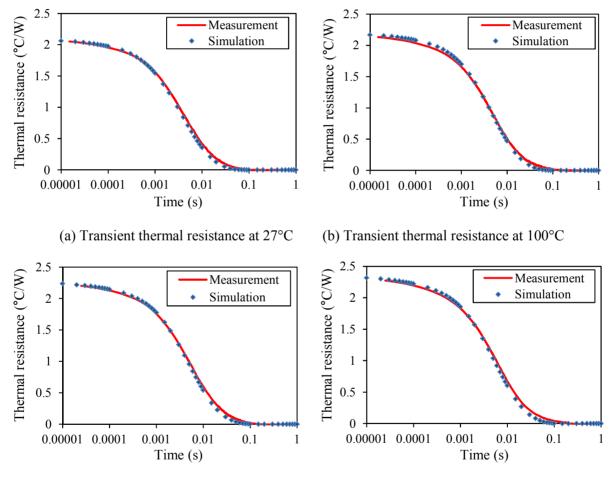

|------------------|--------------------------------|--------------------------------|----------------|