| Title        | A Study on All-Digital Phase-Locked Loop for Biomedical RF Transceivers |

|--------------|-------------------------------------------------------------------------|

| Author(s)    | Bae, Jungnam                                                            |

| Citation     | 大阪大学, 2016, 博士論文                                                        |

| Version Type | VoR                                                                     |

| URL          | https://doi.org/10.18910/59590                                          |

| rights       |                                                                         |

| Note         |                                                                         |

## Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

## **Doctoral Dissertation**

## A Study on All-Digital Phase-Locked Loop for Biomedical RF Transceivers

Jungnam Bae

**July 2016**

Division of Electrical, Electronic and Information Engineering, Graduate School of Engineering, Osaka University

## **Abstract**

This dissertation addresses low-voltage and low-complexity design and implementation of fully integrated all-digital phase-locked loop (ADPLL) for biomedical radio frequency (RF) transceivers. It is organized into five chapters. The summary of each chapter is as follows:

#### Chapter 1

The background for this work and fundamentals of PLLs and the medical implant communication service (MICS) band are described.

#### Chapter 2

A phase noise reduction technique for low-voltage oscillator design is demonstrated. Phase noise is a key parameter for the design of RF transceivers and depends on many factors. In addition, the current biasing technique affects the phase noise. In this study, MOS current source and resistive biasing were considered as current biasing techniques. The current biasing technique, which has less noise contribution, was analyzed for low-voltage oscillators in terms of phase noise, and it was confirmed that top resistive biasing has good compatibility between phase noise and low-voltage operation. In addition, an LC oscillator with resistive biasing is presented to verify the implementation feasibility.

#### Chapter 3

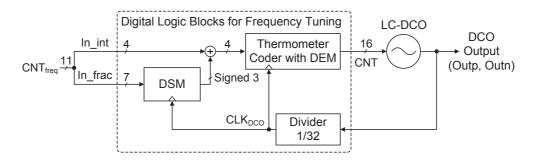

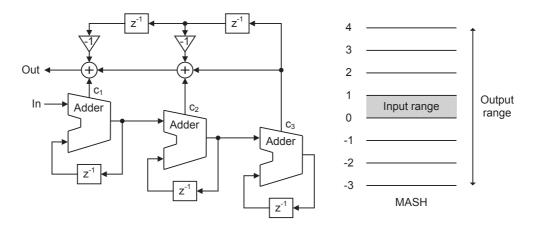

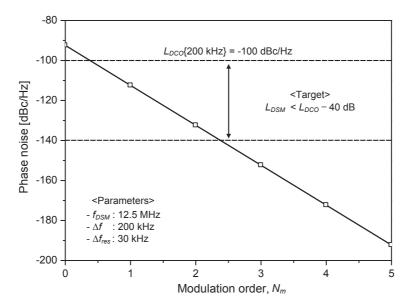

A low-voltage design of a delta-sigma digitally controlled oscillator (DCO) for biomedical applications is demonstrated. The analog type of frequency tuning by voltage control has a limitation because of voltage scaling and linearity. Therefore, the digital approach is more suitable for low-voltage

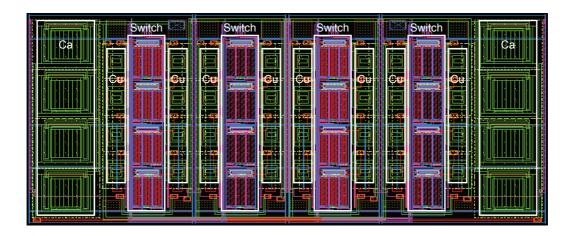

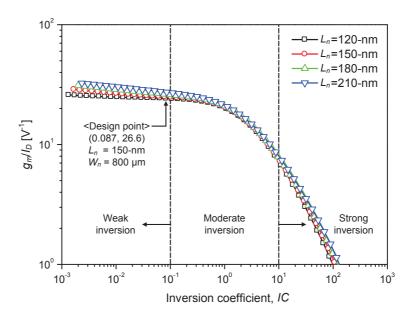

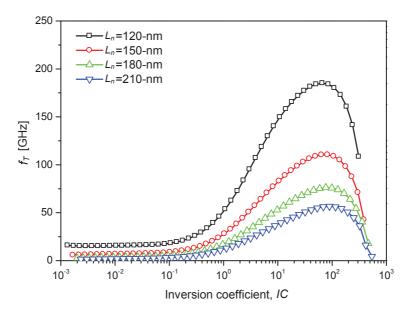

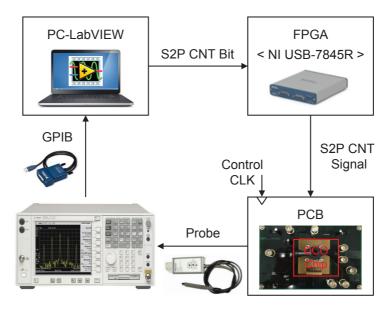

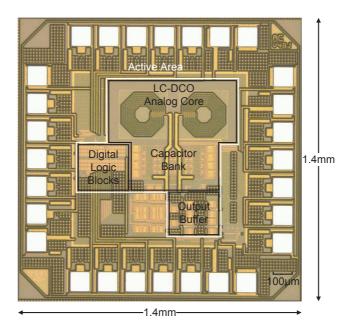

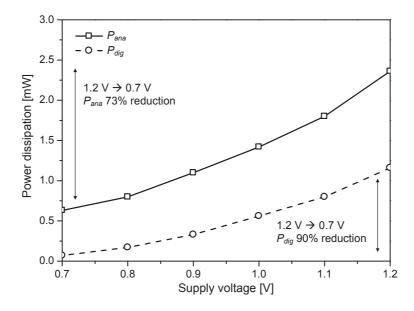

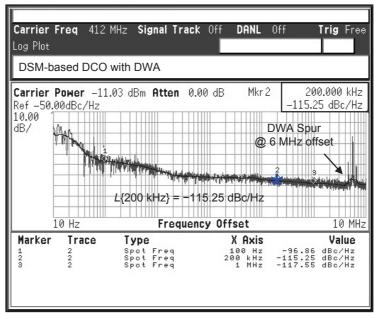

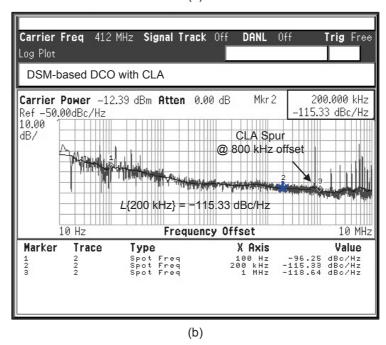

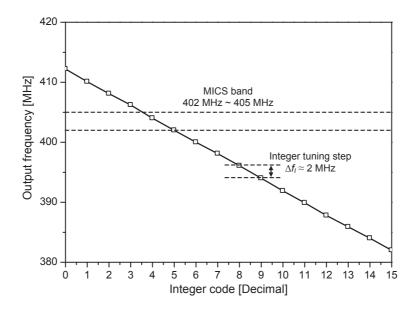

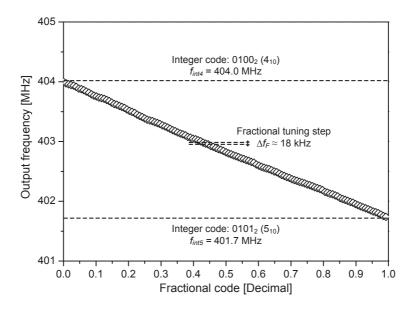

operation because of its robustness and programmability. In this study, an 11-bit DCO controlled by digital logic blocks was designed. This architecture has fully digital control and a fractional tuning range using the delta-sigma modulator. In addition, dynamic element matching was used to reduce the capacitor mismatch. In the DCO core design, for low-voltage operation, the  $g_m/I_D$  methodology was used for optimizing the MOS size. For current biasing, top resistive biasing was applied for low voltage and low phase noise. The DCO was fabricated in a 130-nm CMOS process for a 0.7-V supply voltage. The fabricated DCO is controlled in a fully digital manner and has an active area of 0.41 mm<sup>2</sup>. The total power consumption of the fabricated DCO is 740  $\mu$ W. The fabricated chip was evaluated via a field-programmable gate array (FPGA)-based test bench. This DCO exhibited a phase noise of -115 dBc/Hz at an offset frequency of 200 kHz and a wide frequency tuning range with precise resolution of 18 kHz. Through chip evaluation, it has been demonstrated that the fabricated DCO satisfies the MICS band requirements and exhibits good performance compared with related works.

#### Chapter 4

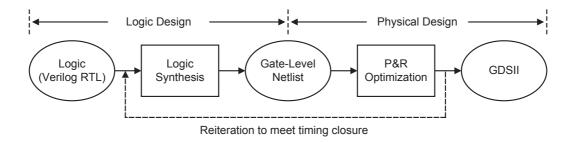

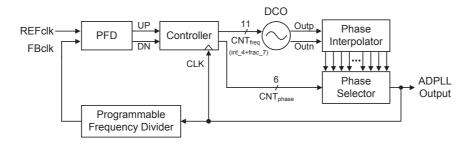

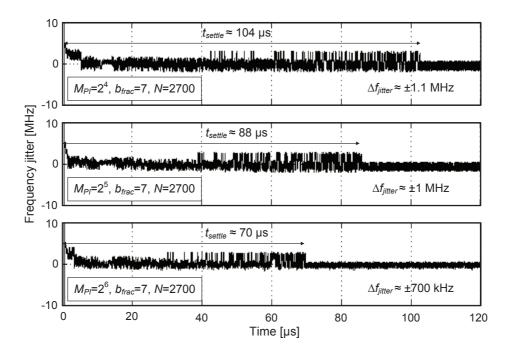

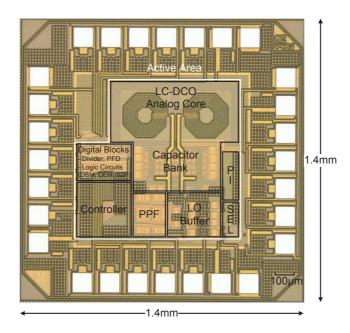

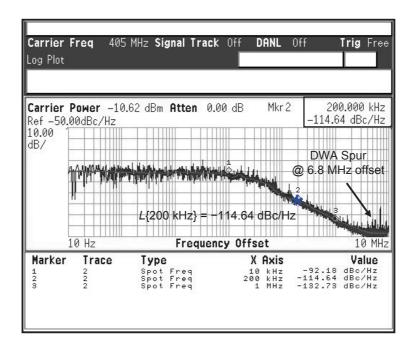

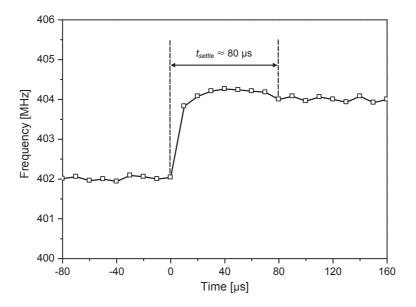

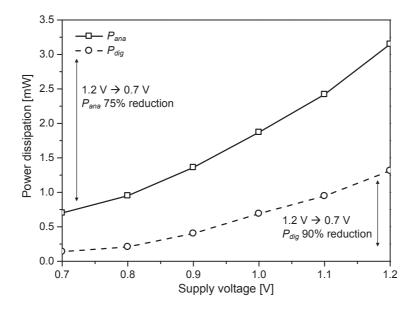

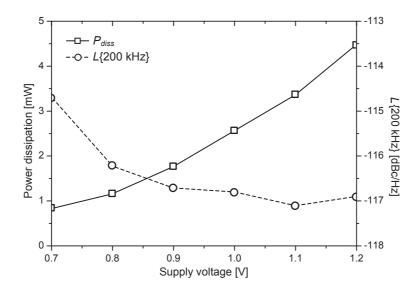

A low-complexity ADPLL for biomedical RF transceivers is demonstrated. General time-to-digital converter (TDC)-based ADPLLs require highly complex systems to achieve high resolution, and thus have large power requirements. In this study, a TDC-less controller-based architecture was employed for a low-complexity ADPLL. In addition, to improve the phase acquisition performance, a phase selection scheme was applied that provided pre-settled operation of the phase of the ADPLL output signals. Through phase domain model analysis, it was confirmed that this architecture performs the PLL functionality, and its functionality was validated through the behavior model simulations. ADPLL circuits were implemented with a focus on low-voltage operation and high performance. Digital circuits were synthesized and implemented by using the standard cell library. This ADPLL was fabricated in a 130-nm CMOS process for a 0.7-V supply voltage. The fabricated ADPLL is controlled in a fully digital manner, and has an active area of 0.64 mm $^2$ . During operation, the total power consumption of the fabricated ADPLL is 840  $\mu$ W. In this study, the FPGA-based test bench was used to evaluate the chip performance. This ADPLL exhibited a settling time of 80  $\mu$ s and phase noise of -114 dBc/Hz at an offset frequency of 200 kHz. In addition, it has precise channel selection based on the precise frequency resolution from the delta-sigma DCO. Through chip eval-

uation, it has been demonstrated that the fabricated ADPLL satisfies all MICS band requirements and shows better performance compared with related works. In addition, it is compatible with the various CMOS processes and supply voltages, and thus can be utilized in various fields that require high-performance, fully integrated RF transceivers with a low-voltage and advanced CMOS process.

#### Chapter 5

The achievements obtained in this study are summarized and this dissertation is concluded.

## **Acknowledgements**

First and foremost I would like to express my sincere gratitude to my advisor Associate Professor Toshimasa Matsuoka (Division of Electrical, Electronic and Information Engineering, Graduate School of Engineering, Osaka University) for the continuous support of my Ph.D. study and related research, for his patience, motivation, and immense knowledge. His appropriate and critical advice always lead to successful research.

Besides my advisor, I am very grateful to Professor Nobuya Mori and Professor Tetsuya Yagi (Division of Electrical, Electronic and Information Engineering, Graduate School of Engineering, Osaka University) for their insightful comments and encouragement.

I would like to thank the rest of my thesis committee: Professor Toshimichi Ito, Professor Yusuke Mori, Professor Mitsuhiro Katayama, Professor Masanori Ozaki, Professor Ryuji Katayama, and Professor Masahiko Kondow (Division of Electrical, Electronic and Information Engineering, Graduate School of Engineering, Osaka University) for their helpful suggestions on the dissertation.

I am also highly thankful to Associate Professor Yoshinari Kamakura (Division of Electrical, Electronic and Information Engineering, Graduate School of Engineering, Osaka University) and Emeritus Professor Kenji Taniguchi for their precious supports.

My sincere thanks also go to Assistant Professor Takao Kihara (Department of Electrical and Electronic Systems Engineering, Graduate School of Engineering, Osaka Institute of Technology) and Dr. Takatsugu Kamata (SPChange, LLC) for his technical suggestions and helpful advice on my research.

I would like to acknowledge my fellow labmates Dr. Ikkyun Jo and Mr. Saichandrateja Radhapuram for their supports and discussions on RF integrated circuits. Also, I am very grateful to my seniors Mr. Donggyu Kim and Dr. Hyunju Ham for their valuable comments. I would like to thank secretaries Ms. Noriko Furuta and Ms. Kayoko Iwahara (Osaka University) for their various supports.

Lastly, I would like to thank all my family for their lasting love and encouragement. Especially, I sincerely express my deepest love and gratitude to my wife Choyoun Lee and most precious my children Yeonwoo Bae and Yeona Bae.

# **Contents**

| Al | ostrac | t        |                                                      | i  |

|----|--------|----------|------------------------------------------------------|----|

| Ac | know   | ledgem   | ents                                                 | v  |

| 1  | Intr   | oductio  | n                                                    | 1  |

|    | 1.1    | Backg    | round                                                | 1  |

|    | 1.2    | Funda    | mentals of Phase-Locked Loops                        | 3  |

|    |        | 1.2.1    | Analog PLL                                           | 3  |

|    |        | 1.2.2    | All-Digital PLL                                      | 6  |

|    |        | 1.2.3    | Performance Metrics                                  | 7  |

|    | 1.3    | Power    | Consumption in CMOS Digital Circuits                 | 11 |

|    | 1.4    | Medica   | al Frequency Band                                    | 13 |

|    | 1.5    | Motiva   | ition                                                | 15 |

|    | 1.6    | Outline  | e of This Dissertation                               | 17 |

|    | Bibl   | iography | ·                                                    | 19 |

| 2  | Resi   | stive Bi | asing Technique for Oscillator Phase Noise Reduction | 23 |

|    | 2.1    | Introdu  | action                                               | 23 |

|    | 2.2    | Resisti  | ve Biasing Technique                                 | 24 |

|    | 2.3    | Phase    | Noise Analysis of Biasing Techniques                 | 25 |

|    |        | 2.3.1    | Effective Noise                                      | 27 |

|    |        | 2.3.2    | Oscillation Amplitude                                | 29 |

|    |        | 233      | Comparison and Discussion                            | 30 |

|   | 2.4  | Circuit Design and Simulation Results         | 2  |

|---|------|-----------------------------------------------|----|

|   | 2.5  | Conclusion                                    | 3  |

|   | Bibl | liography                                     | 7  |

| 3 | Delt | ta-Sigma Digitally Controlled Oscillator 3    | 9  |

|   | 3.1  | Introduction                                  |    |

|   | 3.2  | Phase Noise Analysis                          | -1 |

|   |      | 3.2.1 Influence of DSM on Phase Noise         | -1 |

|   |      | 3.2.2 Employed 3rd-Order DSM                  | 2  |

|   | 3.3  | Digital Frequency Tuning                      | 4  |

|   |      | 3.3.1 Dynamic Element Matching                | 6  |

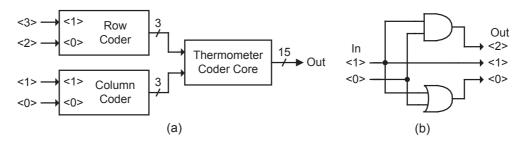

|   |      | 3.3.2 Thermometer Coder                       | .7 |

|   | 3.4  | Circuit Design and Implementation             | 8  |

|   |      | 3.4.1 LC-Tank                                 | 0  |

|   |      | 3.4.2 Oscillator Core                         | 4  |

|   |      | 3.4.3 Digital Logic Blocks                    | 7  |

|   | 3.5  | Measurement Results and Discussion            | 8  |

|   |      | 3.5.1 LabVIEW-Based Test Bench                | 8  |

|   |      | 3.5.2 Measurement Results                     | 0  |

|   |      | 3.5.3 Comparison and Discussion               | 2  |

|   | 3.6  | Conclusion                                    | 4  |

|   | Bibl | liography                                     | 7  |

|   |      |                                               |    |

| 4 | Con  | troller-Based All-Digital Phase-Locked Loop 7 | 1  |

|   | 4.1  | Introduction                                  |    |

|   | 4.2  | Architecture of All-Digital Phase-Locked Loop | 2  |

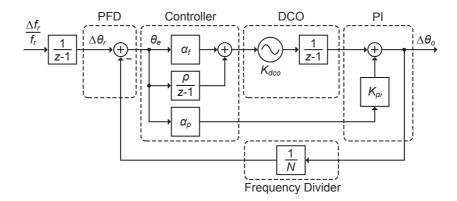

|   |      | 4.2.1 Discrete Time z-Domain Model            | 3  |

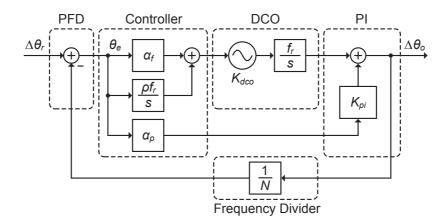

|   |      | 4.2.2 Linear s-Domain Approximation           | 5  |

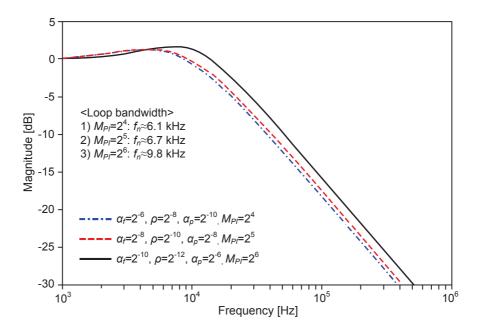

|   |      | 4.2.3 Behavior Model Simulation               | 8  |

|   |      | 4.2.4 Design Considerations                   | 9  |

|   | 4.3  | Circuit Design and Implementation 8           | 0  |

|     |        | 4.3.1    | Phase Frequency Detector and Controller | 80  |

|-----|--------|----------|-----------------------------------------|-----|

|     |        | 4.3.2    | Phase Interpolator                      | 81  |

|     |        | 4.3.3    | Programmable Frequency Divider          | 85  |

|     | 4.4    | Measu    | rement Results and Discussion           | 86  |

|     |        | 4.4.1    | Measurement Results                     | 86  |

|     |        | 4.4.2    | Comparison and Discussion               | 90  |

|     | 4.5    | Conclu   | asion                                   | 94  |

|     | Bibli  | iography | y                                       | 97  |

| 5   | Con    | clusion  |                                         | 101 |

| A   | Veri   | log HDl  | L Codes: Delta-Sigma DCO                | 105 |

|     | A.1    | 3rd-Or   | der DSM                                 | 105 |

|     | A.2    | Dynan    | nic Element Matching                    | 107 |

|     |        | A.2.1    | DWA/CLA Integration                     | 107 |

|     |        | A.2.2    | Bitwise AND/OR                          | 108 |

|     |        | A.2.3    | DEM Switch                              | 109 |

|     |        | A.2.4    | Row/Column Coder                        | 110 |

|     |        | A.2.5    | Thermometer Coder Element               | 110 |

|     | A.3    | Adder    |                                         | 111 |

| В   | Veri   | log HDl  | L Codes: ADPLL                          | 113 |

|     | B.1    | Contro   | oller                                   | 113 |

|     | B.2    | Phase S  | Selector                                | 114 |

|     | B.3    | Serial-  | to-Parallel Converter                   | 115 |

| Pıı | blicat | tions    |                                         | 117 |

# **List of Figures**

| 1.1  | Structure of RF front-end for biomedical applications                                       | 2  |

|------|---------------------------------------------------------------------------------------------|----|

| 1.2  | Block diagram of analog PLL                                                                 | 4  |

| 1.3  | Linear s-domain model of analog PLL                                                         | 4  |

| 1.4  | Structure of the LF based on charge-pump                                                    | 5  |

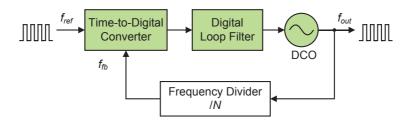

| 1.5  | Block diagram of digital PLL                                                                | 6  |

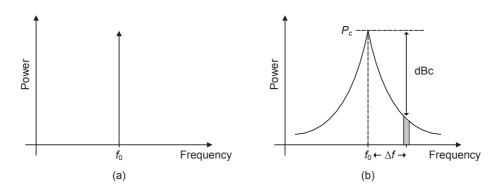

| 1.6  | Frequency spectrum of (a) an ideal and (b) a practical oscillators                          | 8  |

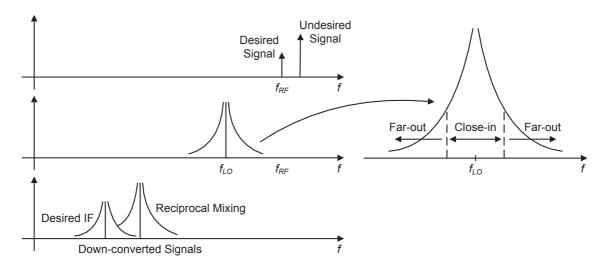

| 1.7  | Influence of LO phase noise on RF receiver reciprocal mixing                                | 9  |

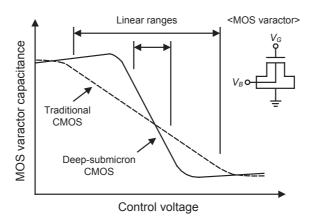

| 1.8  | MOS varactor characteristic for both a traditional and a deep-submicron CMOS pro-           |    |

|      | cess                                                                                        | 10 |

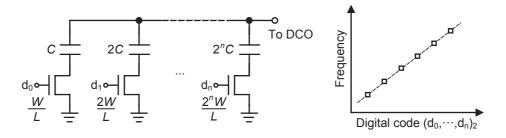

| 1.9  | Discrete frequency tuning technique                                                         | 11 |

| 1.10 | Frequency spectrum of MICS band.                                                            | 14 |

| 1.11 | The effect of phase noise and interference on RF receiver reciprocal mixing                 | 14 |

| 1.12 | Structure of this dissertation                                                              | 16 |

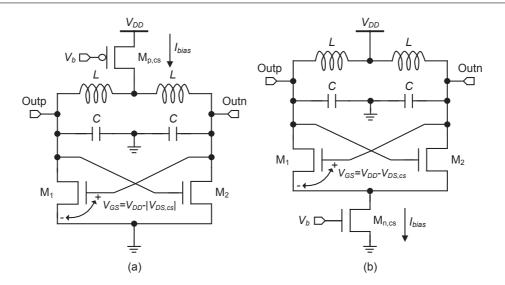

| 2.1  | Active current biasing technique by (a) PMOS current source and (b) NMOS current            |    |

|      | source                                                                                      | 24 |

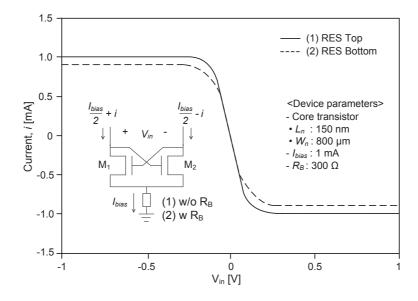

| 2.2  | Passive current biasing technique by (a) top resistive biasing and (b) bottom resistive     |    |

|      | biasing                                                                                     | 25 |

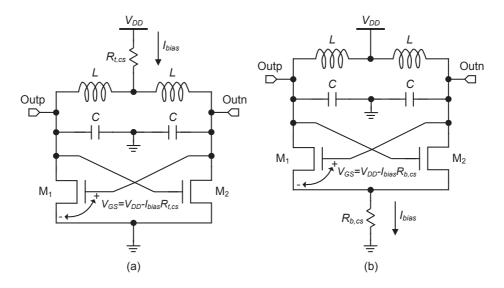

| 2.3  | Effective noise contribution in current sources ("NMOS CS" and "PMOS CS") and               |    |

|      | resistive ("RES Top" and "RES Bottom") biasing techniques                                   | 28 |

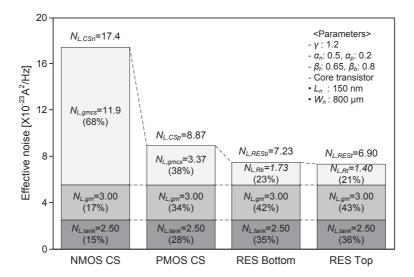

| 2.4  | Characteristics of current $i$ and different voltage $V_{in}$ in the differential-pair part | 29 |

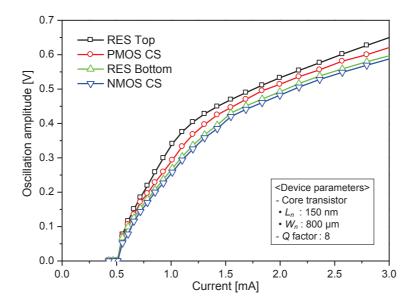

| 2.5  | Oscillation amplitude                                                                       | 31 |

| 2.6  | Phase noise comparison                                                                      | 31 |

|------|---------------------------------------------------------------------------------------------|----|

| 2.7  | Schematic of LC-VCO with top resistive biasing.                                             | 32 |

| 2.8  | Phase noise and current consumption in accordance with top resistance                       | 34 |

| 2.9  | Phase noise performance                                                                     | 34 |

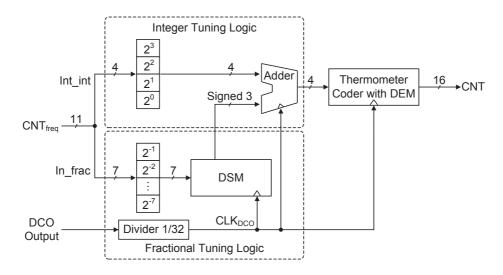

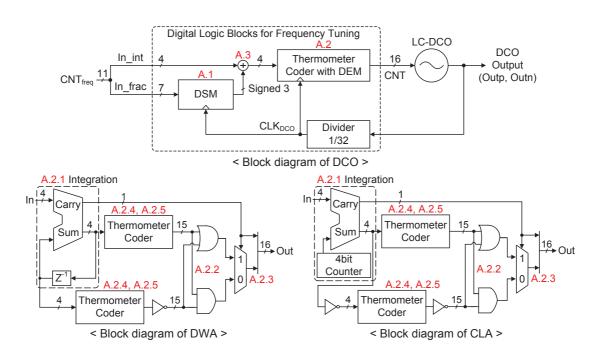

| 3.1  | Architecture of the DCO with digital logic blocks                                           | 40 |

| 3.2  | Structure of the 3rd-order MASH DSM                                                         | 41 |

| 3.3  | Phase noise due to a modulation order                                                       | 42 |

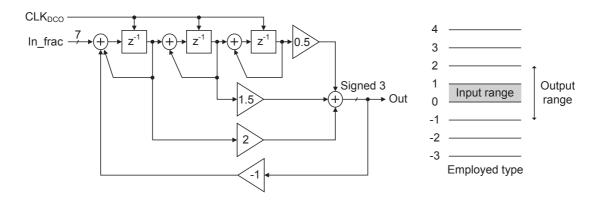

| 3.4  | Structure and output range of the 3rd-order DSM                                             | 43 |

| 3.5  | Structure of digital logic blocks                                                           | 44 |

| 3.6  | Block diagram of (a) DWA and (b) CLA                                                        | 45 |

| 3.7  | Bit-shift operation of (a) DWA and (b) CLA (Input: 3 <sub>10</sub> )                        | 45 |

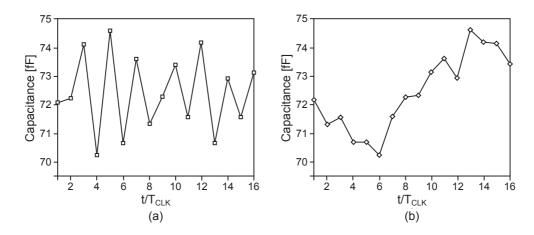

| 3.8  | Capacitor variation of (a) DWA and (b) CLA                                                  | 46 |

| 3.9  | (a) Structure of 4-bit thermometer coder and (b) equivalent circuit of 2-bit row/column     |    |

|      | coder                                                                                       | 47 |

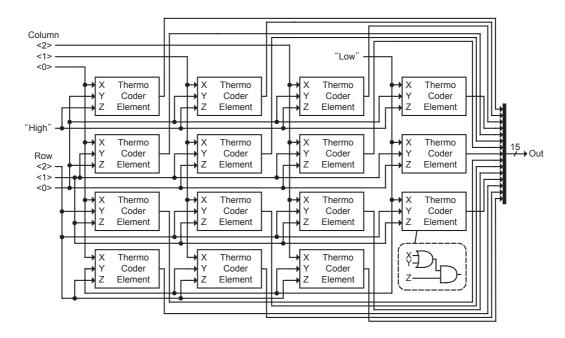

| 3.10 | Structure of thermometer coder core                                                         | 48 |

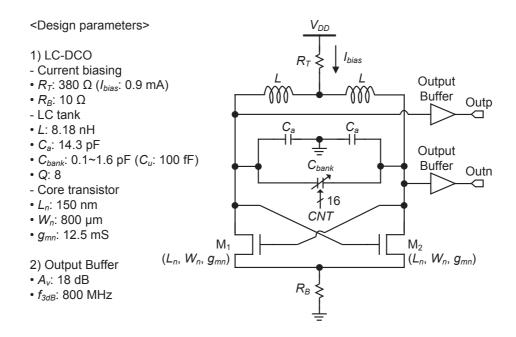

| 3.11 | Schematic of the LC-DCO                                                                     | 49 |

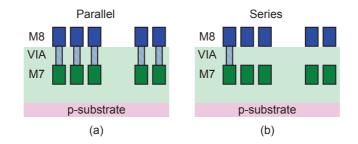

| 3.12 | Structure of (a) parallel and (b)series inductors                                           | 51 |

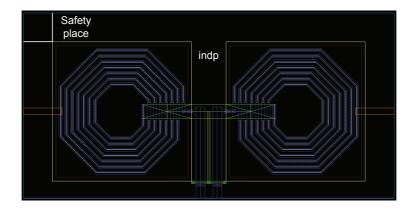

| 3.13 | Layout of integrated inductor                                                               | 51 |

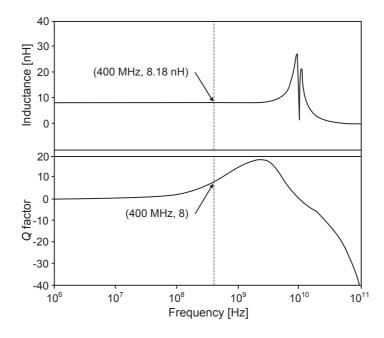

| 3.14 | Simulated inductance and $Q$ factor                                                         | 52 |

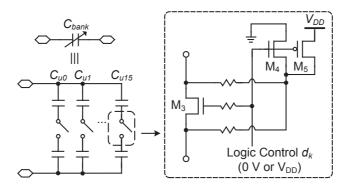

| 3.15 | Schematic of the switchable capacitor bank                                                  | 53 |

| 3.16 | Layout of switchable capacitor back                                                         | 53 |

| 3.17 | Plot of $g_m/I_D$ versus $IC$ for difference channel lengths                                | 55 |

| 3.18 | Unity-current-gain cut-off frequency $f_T$ versus $IC$ ratio for different channel lengths. | 56 |

| 3.19 | The digital design flow for fully synthesizable digital blocks                              | 58 |

| 3.20 | FPGA-based DCO chip evaluation environment                                                  | 59 |

| 3.21 | Die micrograph (active area of $0.41~\text{mm}^2$ )                                         | 60 |

| 3.22 | Measured power dissipation of each part for different supply voltages                       | 61 |

| 3.23 | Measured phase noise of DSM-based DCO with (a) DWA and (b) CLA                              | 65 |

| 3.24 | Measured DCO frequency range of integer tuning.                                             | 66 |

| 3.25 | Measured DCO frequency range of fractional tuning                                    | 66  |

|------|--------------------------------------------------------------------------------------|-----|

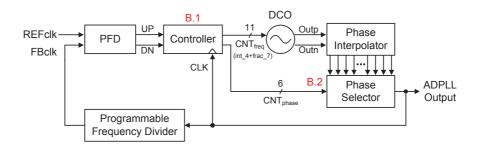

| 4.1  | Architecture of the controller-based ADPLL                                           | 73  |

| 4.2  | z-domain model of the controller-based ADPLL                                         | 74  |

| 4.3  | Linear s-domain model of the controller-based ADPLL                                  | 76  |

| 4.4  | Magnitude response $H_{cl}(s)/N$                                                     | 77  |

| 4.5  | Frequency jitter response for one-integer frequency step in the behavior-level simu- |     |

|      | lation                                                                               | 78  |

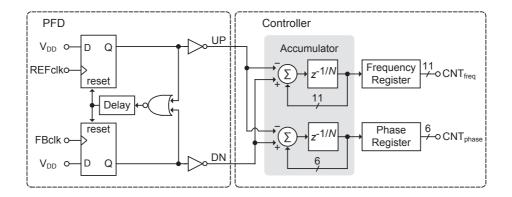

| 4.6  | Structure of the PFD and controller                                                  | 80  |

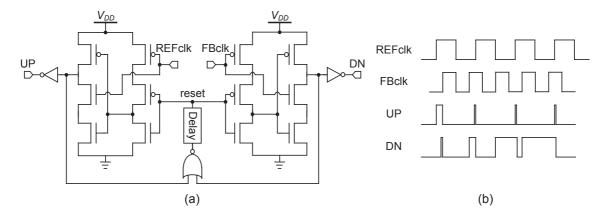

| 4.7  | (a) Schematic of TSPC DFF-based PFD and (b) its timing diagram                       | 80  |

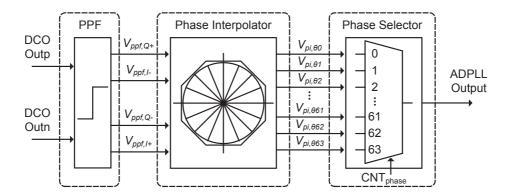

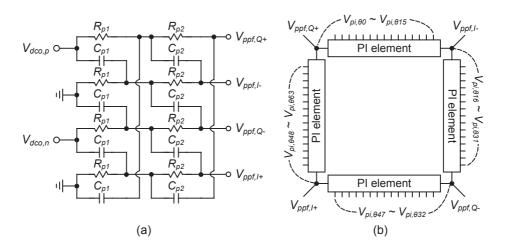

| 4.8  | Structure of the PI                                                                  | 82  |

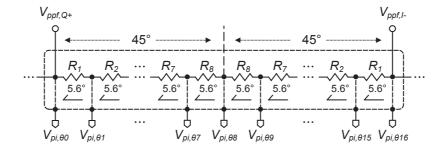

| 4.9  | Schematic of (a) the two-stage PPF and (b) the PI                                    | 83  |

| 4.10 | PI element $(M_{PI}=2^6)$                                                            | 83  |

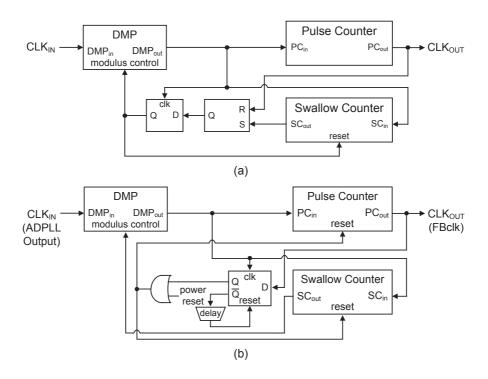

| 4.11 | Structure of (a) conventional pulse-swallow divider and (b) programmable frequency   |     |

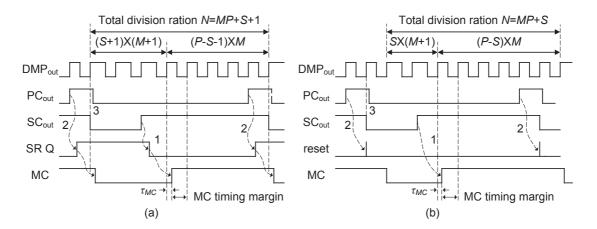

|      | divider with modified MC re-timing                                                   | 84  |

| 4.12 | Timing diagram of (a) conventional and (b) modified types                            | 85  |

| 4.13 | Die micrograph (active area of 0.64 mm <sup>2</sup> )                                | 87  |

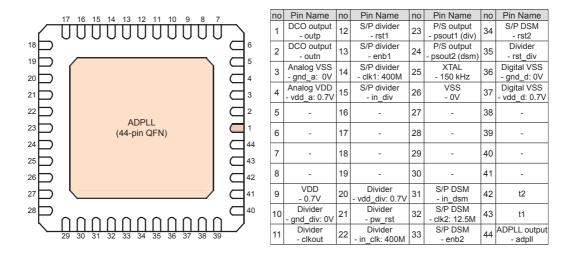

| 4.14 | Package pin assignments (44-pin QFN)                                                 | 88  |

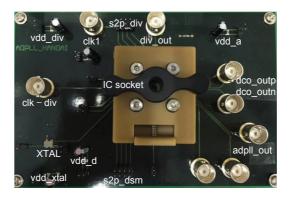

| 4.15 | Evaluation PCB board (Size of 15 cm × 10 cm)                                         | 88  |

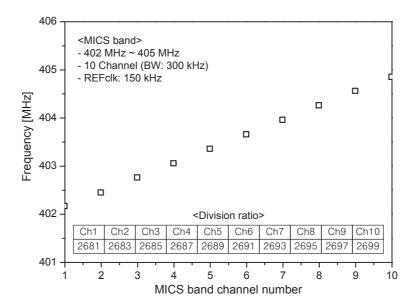

| 4.16 | Measured MICS band channel selection                                                 | 89  |

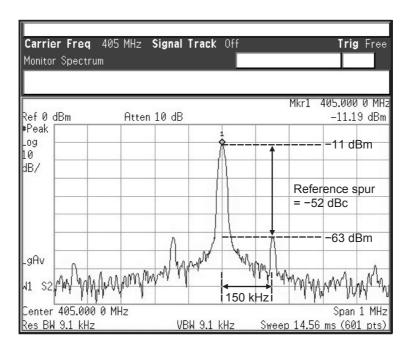

| 4.17 | Measured output spectrum of the ADPLL                                                | 90  |

| 4.18 | Measured phase noise of the ADPLL                                                    | 91  |

| 4.19 | Measured settling time of the ADPLL                                                  | 92  |

| 4.20 | Measured power dissipation of each part for different supply voltages                | 92  |

| 4.21 | Measured power dissipation and phase noise for different supply voltages             | 93  |

| A.1  | Block diagram of digital logic blocks for DCO corresponding to Appendix codes        | 111 |

| B.1  | Block diagram of digital logic blocks for ADPLL corresponding to Appendix codes.     | 115 |

# **List of Tables**

| 3.1 | 4-Bit Binary to Thermometer Coder Logic Truth Table          | 48 |

|-----|--------------------------------------------------------------|----|

| 3.2 | DCO Design Considerations                                    | 50 |

| 3.3 | Measured Performance and Comparison of MICS Band Oscillators | 63 |

| 4.1 | ADPLL Design Considerations                                  | 79 |

| 4.2 | Division Ratios for MICS Band Channel Selection              | 86 |

| 4.3 | Measured Performance and Comparison of MICS Band PLLs        | 94 |

## Chapter 1

## Introduction

#### 1.1 Background

Biomedical radio frequency (RF) transceivers require miniaturized forms with a long battery life and low power consumption. It is usually preferable for implantable medical devices to be fully integrated on a single chip to realize easier surgery and encapsulation for high biocompatibility. The medical implant communication service (MICS) band in the frequency range of 402 MHz to 405 MHz is widely used for supporting biomedical RF transceivers because of its reasonable signal propagation characteristics in the human body and its suitability to achieve a favorable trade-off between chip size and power dissipation [1,2]. There are many challenges associated with the implementation of the RF front-end in implantable medical devices such as pacemakers, implantable cardioverter defibrillators, and neurostimulators because their application requires extremely low power consumption, small size, minimal external components, and high reliability. The basic system requirements of RF transceivers for medical implantable devices are as follows [2]: To increase battery life, the RF transceiver current should be limited to below 6 mA during MICS band communication. The use of few external components provides higher reliability, lower cost, and smaller size. RF modules for pacemakers must be no more than approximately  $3 \text{ mm} \times 5 \text{ mm} \times 10 \text{ mm}$ . Pacemaker applications currently demand a reasonable data rate of over 20 kbps with higher data rates projected for the future. Their operating range is typically over 2 m because the MICS band is designed to improve upon the very short-range inductive link.

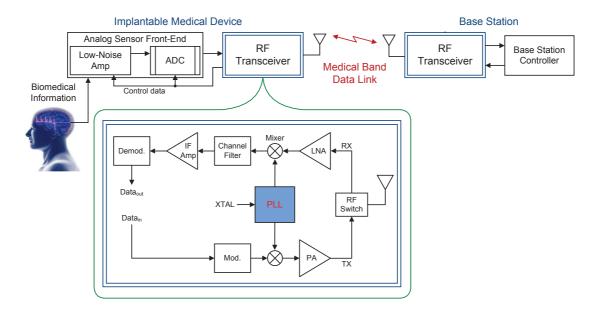

Figure 1.1 shows an example of the RF front-end structure for implantable biomedical applica-

Figure 1.1: Structure of RF front-end for biomedical applications.

tions. The biomedical information in implantable devices is sensed through the analog sensor frontend and transmitted by RF transceivers. The modulated baseband signal is up-converted by the mixer using an RF frequency. The RF signal is amplified by a power amplifier (PA) to the required power level before transmission through the antenna. In the RF transceiver, the RF signal is received by the antenna and processed through a low-noise amplifier (LNA). After the LNA, the amplified RF signal is down-converted to an intermediate frequency (IF) by the mixer. The local oscillator (LO) generates the reference frequency necessary for the mixer, and the LO frequency is tuned to select the desired channel by using a frequency synthesizer. The IF signal is filtered to pass a specific frequency by using a channel selection filter and once more amplified by the IF amplifier. The channel select filter reduces interference from adjacent channels and spurious signals. Finally, the signal is demodulated in the digital domain before signal processing. The demodulated signal is used to control the analog sensor front-end.

In particular, the frequency synthesizer is one of the most important building blocks of the RF front-end because the quality of the LO signal plays a key role in the overall performance. Low power consumption and full integration are the most critical challenges for the design of implantable

RF transceivers. After rapid growth over a decade in CMOS technology scaling, digital circuits have become more preferable compared to analog circuits because of the aggressive improvements in cost, size, flexibility, and repeatability. The high level of integration demanded in wireless communication systems can be achieved with digital or digital-intensive approaches. Phase-locked loops (PLLs) are widely used in many wireless communication systems to perform frequency synthesis or clock and data recovery. The conventional PLLs are often designed using analog approaches, which usually consist of a phase and frequency detector (PFD), charge-pump, loop filter (LF), and voltage-controlled oscillator (VCO). However, analog PLLs are highly sensitive to process parameters and should be redesigned when a process is changed or the design migrates to the latest CMOS process.

Analog PLLs based on charge-pumps are still widely used, but all-digital PLLs (ADPLLs) have been attracting more attention because of their significant advantages over their analog counterparts. ADPLLs, which interface to enable peripheral circuitry to be digitally implemented, provide low-voltage operation compatibility under process and temperature variations with a shorter system turnaround time [3]. Therefore, ADPLLs provide several benefits to duty-cycled battery-operated systems, including MICS transceivers, wireless sensor nodes, and wireless telemetry devices. Realizing a low level of spurs and high-resolution is a challenge to achieve a fully integrated high-performance ADPLL architecture.

This chapter presents the fundamentals of PLLs and medical frequency band for a better understanding of the study and it also describes the motivation and structure of this dissertation. This chapter is organized as follows. Section 1.2 presents the fundamentals of PLLs and performance metrics. Section 1.3 explains the power consumption in CMOS digital circuits. Section 1.4 describes the medical frequency band and phase noise requirements for implantable biomedical RF transceivers. Section 1.5 presents the motivation of this study, and then Section 1.6 describes the structure of this dissertation.

#### 1.2 Fundamentals of Phase-Locked Loops

#### 1.2.1 Analog PLL

Analog PLLs have been investigated for the past several decades. As a result, various types of analog PLLs have been analyzed, and design procedures have been developed. Several references

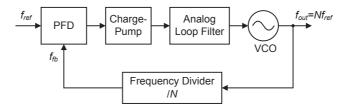

Figure 1.2: Block diagram of analog PLL.

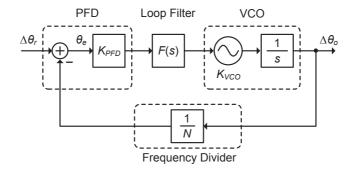

Figure 1.3: Linear s-domain model of analog PLL.

provide an analysis and design procedure for analog PLLs [4–7]. A PLL is a negative feedback system that aligns the phases of the input and output signals. In an analog PLL, as shown in Fig. 1.2, a PFD compares the phases between the reference signal frequency  $(f_{ref})$  and feedback signal frequency  $(f_{fb})$  from the divider and generates an output signal that includes the phase difference. The output signal of the PFD is converted to current by a charge-pump, and filtered by the analog LF and then used to control the frequency of a VCO. A divider is used in the feedback path for frequency multiplication. The negative feedback loop is needed to correct any phase misalignment resulting from internal or external noise sources. If the input and output phases match, the PLL is in a phase lock state (output frequency  $f_{out} = Nf_{ref}$ ).

The block diagram of an analog PLL for linear s-domain phase model is shown in Fig. 1.3, where  $K_{PFD}$  is the gain of the PFD and charge-pump, F(s) is the transfer function of the LF, and  $K_{VCO}$

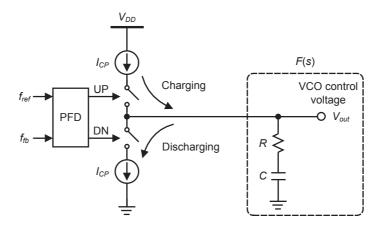

Figure 1.4: Structure of the LF based on charge-pump.

is the gain of the VCO. The open- and closed-loop transfer functions are given by

$$H_{ol}(s) = \frac{\Delta\theta_o(s)/N}{\theta_e(s)} = \frac{K_{PFD}F(s)K_{VCO}}{Ns},$$

(1.1)

$$H_{cl}(s) = \frac{\Delta\theta_o(s)}{\Delta\theta_r(s)} = \frac{NH_{ol}(s)}{1 + H_{ol}(s)}$$

$$= \frac{K_{PFD}F(s)K_{VCO}}{s + K_{PFD}F(s)K_{VCO}/N}.$$

(1.2)

The phase error transfer function is expressed as

$$H_e(s) = \frac{\theta_r(s)}{\Delta \theta_r(s)} = 1 - \frac{H_{cl}(s)}{N}.$$

(1.3)

The PLL order is defined by the number of poles of the open-loop transfer function and equals the loop filter order plus one. The closed-loop stability can be obtained by analyzing the open-loop frequency response  $H_{ol}(s)$ . For this purpose, the open-loop gain information for amplitude and phase is needed.

Simple passive LFs can be used to implement a second-order PLL with zero static phase error. Figure 1.4 shows the second-order passive LF structure based on a charge-pump. In this case,  $K_{PFD} = I_{cp}/2\pi$ . The transfer function of the second-order passive LF is given by

$$F(s) = \frac{1 + sRC}{sC}. ag{1.4}$$

Figure 1.5: Block diagram of digital PLL.

From, Eq. (1.1), the open-loop transfer function of a second-order PLL with this loop filter is expressed as:

$$H_{ol}(s) = \frac{K_{PFD}K_{VCO}}{Ns} \cdot \frac{1 + sRC}{sC}.$$

(1.5)

By using the final value theorem, the steady state phase error of this second-order PLL is zero when a step phase input is applied.

The closed-loop transfer function of this second-order PLL is:

$$H_{cl}(s) = \frac{\frac{K_{PFD}K_{VCO}}{C}(1 + sRC)}{s^2 + \frac{K_{PFD}K_{VCO}R}{N}s + \frac{K_{PFD}K_{VCO}}{NC}}$$

$$= \frac{N\omega_n^2 (1 + 2\zeta s/\omega_n)}{s^2 + 2\zeta\omega_n s + \omega_n^2}, \tag{1.6}$$

where

$$\omega_n = \sqrt{\frac{K_{PFD}K_{VCO}}{NC}},$$

$$\zeta = \frac{\omega_n}{2}RC.$$

(1.7)

This type is a popular structure for LF design because a second-order PLL may converge to zero phase error even with a frequency offset. It requires a zero in the loop filter for stability. This zero can cause extra peaking in the frequency response. Although it is an analog type PLLs, the PFD and divider can be implemented by using digital circuits.

#### 1.2.2 All-Digital PLL

In the deep-submicron CMOS process, RF transceivers are adapted in order to reduce the cost, power consumption, and die area of the system. With the scaling of MOS device to submicron fea-

ture size, the supply voltage will also decrease. Analog PLLs are more sensitive to noise and process variations in low supply voltage. Although analog PLLs need to be redesigned as the process is changed, digital PLLs can be more easily changed for a new process. The power consumption of a digital circuit depends on the supply voltage. In voltage scaling, digital-based circuits can more efficiently reduce power consumption. Therefore, digital circuits are less susceptible to process and voltage variations. ADPLL is realized mostly from digital-intensive circuits. The components and functionality are similar to the analog PLL, but the implementation consists of digital components. ADPLLs consist of a time-to-digital converter (TDC), a digital LF, and a digitally controlled oscillator (DCO). A general block diagram of the ADPLL is shown in Fig. 1.5. The TDC measures the time difference between the reference and feedback clocks and converts it to a digital code. This digital code is filtered by the digital LF and then is used to control the DCO frequency. Recently, several digital PLLs for different applications have been reported [8–10]. They demonstrate the ability of a digital implementation by outperforming analog PLLs. The ADPLL has better portability, which can be used in fully integrated applications, and is independent of process variations. It also minimizes the design cost and time.

#### 1.2.3 Performance Metrics

#### **Phase Noise**

Practical oscillators consist of both passive and active components, which cause noise in the system. This noise takes various forms, including shot noise, flicker noise, and thermal noise [11]. With regard to the frequency domain, the existence of phase noise in oscillators causes the output signals to contain significant energy at other frequencies. Considering the output signal of an ideal sinusoidal oscillator, shown in Fig. 1.6(a), operating at a given frequency  $f_0$ , the spectrum shape is characterized as an impulse. However, in a practical oscillator, the spectrum has power distributed around the desired oscillation frequency in addition to power located at harmonic frequencies. This undesired power distribution around the oscillation frequency is phase noise, and is depicted in Fig. 1.6(b).

Phase noise is expressed as the ratio of power at a specific offset frequency  $(\Delta f)$  from the carrier to the power at the center frequency. This power is measured in a unit bandwidth at a certain  $\Delta f$ .

Figure 1.6: Frequency spectrum of (a) an ideal and (b) a practical oscillators.

The oscillator phase noise ( $L\{\Delta f\}$ ) is mathematically defined by

$$L\{\Delta f\} = \frac{P_{sideband}(f_0 + \Delta f, 1\text{Hz})}{P_c},$$

(1.8)

where  $P_c$  is the power in the fundamental carrier  $f_0$  and  $P_{sideband}$  is the power distributed around the carrier. From this simple definition, it may be confirmed that phase noise may be improved by increasing  $P_c$  at the cost of increased power dissipation.

The Leeson's semi-empirical phase noise model proposed in [12] is based on a linear time-invariant (LTI) assumption for the LC-tank oscillator. It quantitatively predicts the following behavior:

$$L\left\{\Delta f\right\} = \frac{2Fk_BT}{P_c} \left[ 1 + \left(\frac{f_0}{2Q\Delta f}\right)^2 \right] \left( 1 + \frac{\Delta f_{1/f^3}}{|\Delta f|} \right),\tag{1.9}$$

where F is a fitting parameter describing the noise of the circuit,  $k_B$  is the Boltzmann constant, T is the absolute temperature, and  $\Delta f_{1/f^3}$  is the corner frequency between  $1/f^3$  and  $1/f^2$  regions. It is important that the empirical fitting parameter must be determined from measurements. Because Leeson's phase noise model is an LTI system, properties of the oscillator such as signal power, resonator Q factor, and noise factor, which do not change with time, are used to obtain an estimation of phase noise. In summary, the dominating phase noise in the  $1/f^2$  region is improved by increasing the resonator Q factor or  $P_c$ . The main bottleneck of Leeson's model is the lack of knowledge about the fitting parameter F. The fitting parameter related to the noise remains as an unspecified value and strongly depends on the oscillator topology.

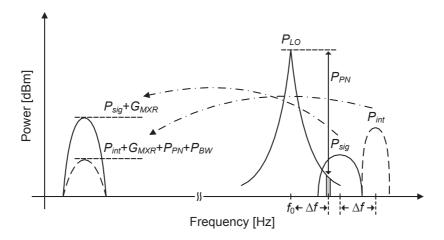

Figure 1.7: Influence of LO phase noise on RF receiver reciprocal mixing.

Phase noise degrades different aspects of the system depending on its applications. In RF transceivers, the LO phase noise degrades the received signal-to-noise ratio (SNR) by a reciprocal mixing. This effect is illustrated in Fig. 1.7. In addition to the direct superposition of the LO phase noise on the down-converted channel, the presence of a nearby interferer further degrades the SNR of the desired signal. Therefore, although close-in phase noise at offsets within the channel bandwidth is obviously important, far-out phase noise can also have a significant impact on system performance. In some applications, the LO phase noise specifications are the most difficult to meet at offsets far away from the carrier. Although close-in phase noise can be reduced to some extent by increasing the PLL loop bandwidth, far-out phase noise is typically dominated by the oscillator. Hence, the design of low-phase-noise oscillators is important for high-performance RF transceivers.

#### **Settling Time**

Settling time is the time interval to move from one frequency to another and settle on the new frequency. It depends on the frequency step and the PLL loop dynamics characteristics. The settling time is improved by using a wide LF bandwidth. If too wide an LF is used, it may cause degradation of phase noise and reference spurs because there is a trade-off between fast settling time and good spectrum performance. Because lock time often is a bottleneck in PLL implementations, various ap-

Figure 1.8: MOS varactor characteristic for both a traditional and a deep-submicron CMOS process.

proaches exist to improve the settling time. One method is to dynamically adapt the PLL bandwidth. Using a wide bandwidth during PLL lock results in a fast settling time. Once the PLL is locked to the correct frequency, a narrow bandwidth is used to provide good phase noise and spur performance.

#### **Spurious Level**

The undesired frequency components generated in the operating band of a device at some discrete frequency points are called spurs. Their power levels are described in a way similar to the phase noise power levels, namely by comparison with carrier power. Reference spurious signals are generated in a PLL system by a charge pump or amplifier leakage current. The spur generally can be reduced by using a high reference frequency and minimizing the charge-pump current mismatch.

#### **Frequency Tuning Range**

The operating frequency range is generally limited by the tuning range of the oscillators. Achieving high performance over a wide tuning range is challenging because the oscillator tuning range is always designed to have some margin in order to allow correct operation with noise and process variations. Frequency tuning of a low-voltage and deep-submicron CMOS oscillator is quite a difficult task because of its high non-linear characteristics and lack of low-voltage headroom. The oscillation frequency may be changed by using a varactor in the resonator. The capacitance of the varactor is

Figure 1.9: Discrete frequency tuning technique.

changed by controlling an external DC voltage that is applied to the varactor, and thus the oscillation frequency can be selected by changing the natural frequency of oscillation in the resonator. Figure 1.8 shows normalized curves of a MOS varactor capacitance versus control voltage (C-V) for both a traditional and a deep-submicron CMOS process. Obviously, a large linear range of the C-V curve can be applied for a precise and wide operational control of frequency. With a deep-submicron process, the linear range is quite narrow. This makes the operating point shifts because of its undesirable high gain. One technique is to use digitally controlled fixed capacitors to cover a larger frequency range, as conceptually shown in Fig. 1.9. The frequency range has linear trends, and the performance depends on the tuning capacitors and switch design. The digital-approach frequency tuning is more suitable for a low-voltage and deep-submicron CMOS process because of its inherent advantages of digital control.

### 1.3 Power Consumption in CMOS Digital Circuits

The power consumption of a CMOS circuit usually can be divided into three different components: dynamic ( $P_{dynamic}$ ), short-circuit ( $P_{short-circuit}$ ), and leakage ( $P_{leakage}$ ) power consumption. Switching power, which includes both dynamic power and short-circuit power, is consumed when signals through CMOS digital circuits change their logic state. Leakage power is primarily due to the subthreshold currents in a CMOS transistor. Therefore, total power consumption is given by

$$P_{total} = P_{dynamic} + P_{short-circuit} + P_{leakage}. {(1.10)}$$

#### **Dynamic Power**

The dynamic power consumption in CMOS digital circuits is due to the charging and discharging of load capacitance. The dynamic power consumption can be calculated by [13]

$$P_{dynamic} = \alpha C_L V_{DD}^2 f_{CLK}, \tag{1.11}$$

where  $\alpha$  is the switching activity,  $C_L$  is the load capacitance,  $V_{DD}$  is the supply voltage, and  $f_{CLK}$  is the operating clock frequency. In CMOS digital circuits with high switching activity, the dynamic power accounts for most of the power used by CMOS circuits. Therefore, the dynamic power is dominant to the total power consumption. A simple way to reduce the dynamic power is by decreasing  $V_{DD}$ , because reducing  $V_{DD}$  causes a quadratic reduction.

#### **Short-Circuit Power**

Short-circuit power consumption occurs when a digital circuit switches [14]. During the transition, there is a short time when both the NMOS and PMOS transistor conduct. It is equivalent to shorting the supply and ground rails for a brief period time. Thus, this current flow consumes power. The short-circuit power consumption is simply given by

$$P_{short-circuit} = I_{sc}V_{DD}, (1.12)$$

where  $I_{sc}$  is the short circuit current. The short-circuit power is proportional to the gate rise time and fall time. Therefore, reducing the input transition times will decrease the short-circuit current component.

#### **Leakage Current Power**

In deep-submicron CMOS, even though a transistor is in a stable logic state, it continues to leak small amounts of power, primarily because of subthreshold currents. The subthreshold leakage is the current between the drain and source of a transistor operating in the weak-inversion region [15]. The leakage current power consumption is simply given by

$$P_{leakage} = I_{leakage} V_{DD}, (1.13)$$

where  $I_{leakage}$  is the leakage current. Along with reducing  $V_{DD}$ , threshold voltage also must be scaled down, which results in an exponential increase in leakage power. As a result, leakage power has become a significant contributor in the total chip power dissipation according to the voltage and MOS scaling.

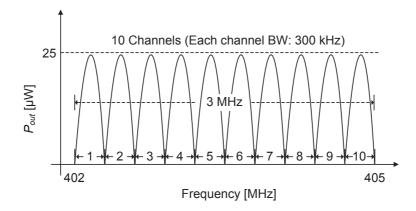

#### 1.4 Medical Frequency Band

For implantable medical devices, full integration on a single chip is usually preferred to realize easier surgery and encapsulation for better biocompatibility. Many biomedical telemetry systems have used very short-range magnetic (inductive) links [16,17]. These systems require close coupling between the external unit and implanted device and can be easily affected by electromagnetic interference, which presents a risk to patient safety and medical effectiveness due to the increasing usage of electromagnetic energy radiating devices such as cell phones and security systems. To address these limitations, the Federal Communications Commission (FCC) allocated the MICS band in the frequency range of 402 MHz to 405 MHz with 10 channels in 1999 [1], as shown in Fig. 1.10. In the MICS band, each channel bandwidth is 300 kHz and located very close. In the transmit path, the phase noise will make the transmitter emit signals outside the allowed frequency band. So, the analysis of adjacent channel power ratio (ACPR) is important. ACPR covers all signal emission in adjacent bands, including phase noise and spurious tones. This band's signals have reasonable propagation characteristics in the human body and are well suited for achieving a good trade-off between size and power [2]. Furthermore, the use of the MICS band does not pose a significant risk of interference to other radio frequencies within or close to this band [1].

Extending battery lifetime without recharging is a challenge. Medical implantable devices must be optimized to consume as little energy as possible while achieving acceptable levels of performance. With the advance of CMOS technology, this frequency band promises high-level integration compared to inductive link designs, which results in miniaturization and low power consumption. In addition, penetration loss at these frequencies is relatively insignificant and is therefore suitable for implantable medical device applications.

Figure 1.11 shows the concept of the effect of phase noise and interference on an RF receiver reciprocal mixing [18]. Although the RF signal with power  $P_{sig}$  (dBm) is down-converted to an IF

Figure 1.10: Frequency spectrum of MICS band.

Figure 1.11: The effect of phase noise and interference on RF receiver reciprocal mixing.

by the LO with power  $P_{LO}$  (dBm), interference with power  $P_{int}$  (dBm) from adjacent channels is also down-converted to the same IF with the phase noise that has power  $P_{PN}$  (dBc/Hz).  $G_{MXR}$  (dB) is the conversion gain of switching mixing for sufficient large  $P_{LO}$  [19]. Because the phase noise is a random process, the effective bandwidth with power  $P_{BW}$  (dB) is considered in the total noise power calculation. The minimum SNR (dB) requirement that the IF signal should satisfy is given by

$$SNR = (P_{sig} + G_{MXR}) - (P_{int} + G_{MXR} + P_{PN} + P_{BW}) > SNR_{min}.$$

(1.14)

1.5. MOTIVATION 15

After re-arrangement focusing on the phase noise,

$$P_{PN} < P_{siq} - P_{int} - P_{BW} - SNR_{min}. \tag{1.15}$$

The phase noise requirement for an MICS-band oscillator that has been locked by PLL is relatively relaxed. For MICS-band receivers, because of the limited distance and upper bound of the equivalent isotropically radiated power, the dynamic range ( $|(P_{sig} - P_{int})|$ ) is not too high and is determined by a path loss of approximately 30 dB at 2 m [1]. For this reason, the down-conversion of the phase noise in the adjacent channel is not a serious problem. The MICS band has 10 channels, and each channel occupies up to 300 kHz bandwidth [20]. If frequency shift keying (FSK) modulation is used, and the deviation of the two FSK tones is 50 kHz, then the closest adjacent-channel interferer is at 200 kHz away from the carrier. Assuming a SNR of 15 dB is required by the FSK demodulation [21] to obtain a bit error rate of  $10^{-3}$ , the required phase noise at 200 kHz offset can be estimated by [22]

$$L \{200 \text{ kHz}\} = -15 \text{ dB} - 30 \text{ dB} - 10 \log_{10}(300 \text{ kHz})$$

$$= -100 \text{ dBc/Hz}. \tag{1.16}$$

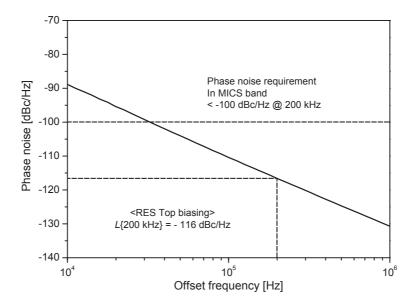

The local oscillator signal should achieve a phase noise under -100 dBc/Hz at an offset frequency of 200 kHz while suffering from adjacent-channel interference. This value is the target phase noise requirement in the oscillator design.

#### 1.5 Motivation

In ADPLLs, TDCs have been replacing conventional PFDs and charge-pumps [23]. The resolution of the TDC is critical to the performance of the ADPLL because low resolution causes in-band phase noise. TDCs require advanced CMOS technology and additional system complexity to achieve high-resolution and thereby have large power consumption. Additionally, TDCs are sensitive to process, voltage, and temperature variation. Such high sensitivity can cause poor linearity and non-uniform phase detector gain, resulting in widespread spur generation. Hence, a TDC-less controller-based ADPLL [24, 25] for high performance and low complexity is considered. The digital implementation of a controller reduces the silicon die area and eliminates external loop filter components. RF oscillators, which traditionally use an analog approach for frequency tuning, now have digital interfaces to allow the peripheral circuitry to be implemented in a digital manner. A DCO, which was

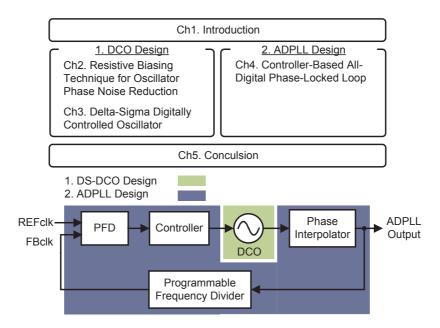

Figure 1.12: Structure of this dissertation.

proposed for wireless applications in [26], generates a signal whose frequency can be controlled with digital words. The DCO enables efficient implementation of the direct frequency modulation in an ADPLL. In the design of DCO, the low level of spurs and high resolution are challenges for implementations of the ADPLL. Low phase noise and precise frequency resolution are desirable for the high-performance fully integrated ADPLL architecture for wireless communications.

The goal of this study is to address and demonstrate a low-voltage and low-complexity fully integrated ADPLL for biomedical RF transceivers. ADPLLs are essential building blocks for biomedical RF transceivers, which require relatively high compatibility between complexity and performance. This causes difficulties in implementing low-voltage and low-complexity RF front-end chips. In addition, the conventional circuit topologies of fully integrated ADPLLs are quite complex, which implies that different topologies suitable for RF transceivers are required. Therefore, low-voltage and low-complexity ADPLLs can contribute to the implementation of biomedical RF transceivers.

#### 1.6 Outline of This Dissertation

This dissertation describes a low-voltage and low-complexity fully integrated ADPLL for supporting biomedical RF transceivers. The structure of this dissertation is depicted in Fig. 1.12, and the dissertation is organized as follows:

Chapter 2 presents a phase noise reduction technique with top resistive biasing for low-voltage oscillator design. Phase noise analysis for current biasing methods is presented and an LC oscillator circuit design is described.

Chapter 3 presents the low-voltage design of a delta-sigma DCO, which is controlled in a fully digital manner. The circuit implementations for low-voltage operation are described and the chip evaluation results are presented.

Chapter 4 presents a low-complexity ADPLL for biomedical RF transceivers. The functionality of the considered ADPLL is analyzed and circuit implementations for low-voltage operation are described. The chip evaluation results are also presented.

Chapter 5 concludes the dissertation.

BIBLIOGRAPHY 19

## **Bibliography**

[1] FCC Rules and Regulations, "MICS band plan," Part 95, Jan. 2003.

- [2] P. D. Bradley, "An ultra low power, high performance medical implant communication system (MICS) transceiver for implantable devices," *Proc. IEEE Biomed. Circuits and Syst. Conf.*, pp. 158–161, Dec. 2006.

- [3] R. B. Staszewski and P. T. Balsara, "All-digital PLL with ultra fast settling," *IEEE Trans. Circuits Syst. II*, vol. 54, no. 2, pp. 181–185, Feb. 2007.

- [4] J. Hein and J. W. Scott, "z-domain model for discrete-time PLL's," *IEEE Trans. Circuits Syst.*, vol. 35, no. 11, pp. 1393–1400, Nov. 1988.

- [5] I. I. Novof, J. Austin, R. Kelkar, D. Strayer, and S. Wyatt, "Fully integrated CMOS phase-locked loop with 15 to 240 MHz locking range and ±50 ps jitter," *IEEE J. Solid-State Circuits*, vol. 30, no. 11, pp. 1259–1266, Nov. 1995.

- [6] J. G. Maneatis, "Low-jitter process-independent DLL and PLL based on self-biased techniques," *IEEE J. Solid-State Circuits*, vol. 31, no. 11, pp. 1723–1732, Nov. 1996.

- [7] P. K. Hanumolu, M. Brownlee, K. Mayaram, and U.-K. Moon, "Analysis of charge-pump phase-locked loops," *IEEE Trans. Circuits Syst. I*, vol. 51, no. 9, pp. 1665–1674, Sep. 2004.

- [8] R. B. Staszewski, D. Leipold, K. Muhammad, and P. T. Balsara, "Digitally controlled oscillator (DCO)-based architecture for RF frequency synthesis in a deep-submicrometer CMOS process," *IEEE Trans. Circuits Syst. II*, vol. 50, no. 11, pp. 815–828, Nov. 2003.

- [9] R. B. Staszewski, J. L. Wallberg, S. Rezeq, C.-M. Hung, O. E. Eliezer, S. K. Vemulapalli, C. Fernando, K. Maggio, R. Staszewski, N. Barton, M.-C. Lee, P. Cruise, M. Entezari, K. Muhammad, and D. Leipold, "All-digital PLL and transmitter for mobile phones," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2469–2482, Dec. 2005.

- [10] N. D. Dalt, E. Thaller, P. Gregorius, and L. Gazsi, "A compact triple-band low-jitter digital LC PLL with programmable coil in 130-nm CMOS," IEEE J. Solid-State Circuits, vol. 40, no. 7, pp. 1482–1490, Jul. 2005.

- [11] P. R. Gray, P. J. Hurst, S. H. Lewis, and R. G. Meyer, *Analysis and Design of Analog Integrated Circuits*. John Wiley & Sons, 2001.

- [12] D. B. Leeson, "A simple model of feedback oscillator noise spectrum," *Proc. IEEE*, vol. 54, no. 2, pp. 329–330, Feb. 1996.

- [13] J. M. Rabaey, A. P. Chandrakasan, and B. Nikolic, *Digital Integrated Circuits: A Design Perspective*. Prentice-Halle, 2006.

- [14] L. Bisdounis and O. Koufopavlou, "Short-circuit energy dissipation modeling for submicrometer CMOS gates," *IEEE Trans. Circuits Syst. I*, vol. 47, no. 9, pp. 1350–1361, Sep. 2000.

- [15] R. Rao, A. Srivastava, D. Blaauw, and D. Sylvester, "Statistical analysis of subthreshold leakage current for VLSI circuits," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 12, no. 2, pp. 131–139, Feb. 2004.

- [16] G. Simard, M. Sawan, and D. Massicotte, "High-speed OQPSK and efficient power transfer through inductive link for biomedical implants," *IEEE Trans. Biomed. Circuits Syst.*, vol. 4, no. 3, pp. 192–200, Jun. 2010.

- [17] G. Wang, P. Wang, Y. Tang, and W. Liu, "Analysis of dual band power and data telemetry for biomedical implants," *IEEE Trans. Biomed. Circuits Syst.*, vol. 6, no. 3, pp. 208–215, Jun. 2012.

- [18] R. Harjani, Design of High-Speed Communication Circuits. World Scientific, 2006.

- [19] C. Nguyen, Radio-Frequency Integrated-Circuit Engineering. John Wiley & Sons, 2015.

- [20] H. S. Savci, A. Sula, Z. Wang, N. S. Dogan, and E. Arvas, "MICS transceivers: regulatory standards and applications," *Proc. IEEE Int. Southeast Conf.*, pp. 179–182, Apr. 2005.

- [21] B. Sklar, Digital Communications: Fundamentals and Applications. Prentice-Hall, 2001.

- [22] B. Razavi, RF Microelectronics. Prentice-Hall, 1998.

- [23] R. B. Staszewski, S. Vemulapalli, P. Vallur, J. Wallberg, and P. T. Balsara, "1.3 V 20 ps time-to-digital converter for frequency synthesis in 90-nm CMOS," *IEEE Trans. Circuits Syst. II*, vol. 53, no. 3, pp. 220–224, Mar. 2006.

BIBLIOGRAPHY 21

[24] S. Radhapuram, J. Bae, I. Jo, W. Wang, and T. Matsuoka, "Analysis of a controller-based all-digital phase-locked loop," *Far East J. Electronics and Communications*, vol. 15, no. 1, pp. 57–73, Sep. 2015.

- [25] —, "Erratum: analysis of a controller-based all-digital phase-locked loop," *Far East J. Electronics and Communications*, vol. 16, no. 1, pp. 199–201, Mar. 2016.

- [26] R. B. Staszewski, C.-M. Hung, D. Leipold, and P. T. Balsara, "A first multigigahertz digitally controlled oscillator for wireless applications," *IEEE Trans. Microw. Theory Tech.*, vol. 51, no. 11, pp. 2154–2164, Nov. 2003.

# **Chapter 2**

# Resistive Biasing Technique for Oscillator Phase Noise Reduction

#### 2.1 Introduction

One of the major challenges in the design of RF front-end modules is the implementation of fully integrated low-power, low-phase noise voltage-controlled oscillators (VCOs). CMOS devices operating in the weak-inversion region have the advantage of a higher transconductance to power dissipation ratio with satisfactory noise performance in comparison with the strong inversion region. Therefore, the subthreshold-biased VCO achieves low-power and low-phase-noise characteristics. The circuits designed with MOS transistors biased in the subthreshold region operate with reduced voltage headroom, resulting in lower supply voltage. However, the phase noise performance is degraded because of the small amplitude at low supply voltages, and it is recognized that the active current source for biasing purposes introduces noise performance degradation [1,2]. There have been many efforts to improve the phase noise performance by improving the quality (Q) factor of the resonator or reducing the noise power [3,4]. This study focuses on the current biasing technique in the weak-inversion region for better performance. The subthreshold-biased LC-VCO and resistive biasing technique are employed to achieve low-voltage operation and low phase noise.

This chapter presents the analysis of phase noise performance through various biasing techniques, and a low phase noise LC-VCO is designed using resistive biasing instead of the active current source scheme. Top resistive biasing is employed for low phase noise and low-voltage operation because of its inherent advantage of low effective noise and large voltage swing.

Figure 2.1: Active current biasing technique by (a) PMOS current source and (b) NMOS current source.

This chapter is organized as follows. Section 2.2 presents the resistive current biasing technique for low-voltage operation. Section 2.3 describes the analytical phase noise analysis for current biasing techniques. Section 2.4 presents the actual circuit design based on this analysis and describes its simulation results, and then Section 2.5 concludes the chapter.

## 2.2 Resistive Biasing Technique

Transistor biasing is the process of setting a transistor's DC operating voltage or current conditions to the correct level so that any AC input signal can be amplified correctly by the transistor. Figures 2.1 and 2.2 show the biasing techniques in oscillator design. In this study, MOS current source and resistive biasing techniques are considered to provide the current of the core MOS devices. The active current source technique is widely used to supply current in integrated circuit technology. A current mirror is a circuit block that functions to produce a copy of the current in one active device by replicating the current in a second active device. Thus, it needs a reference circuit block to supply the constant current. In typical oscillators operating at high current levels with moderate-to-high resonator Q factors, the current source contribution dominates other sources of phase noise.

Figure 2.2: Passive current biasing technique by (a) top resistive biasing and (b) bottom resistive biasing.

In addition, it reduces voltage headroom, which is not suitable for low-voltage applications. There have been many efforts to improve phase noise performance by reducing the noise contribution from the current source [2, 5]. Resistive biasing is another approach to improve the phase noise and directly provides the current without extra reference circuits. The resistive biasing is simple and has a smaller noise contribution than active current source because of its low thermal noise. In this study, the mathematical analysis of phase noise according to biasing techniques is presented.

## 2.3 Phase Noise Analysis of Biasing Techniques

There are many ways to realize integrated LC-VCOs. For the analysis of the current biasing techniques, an NMOS cross-coupled differential pair is used for the core oscillator design, which has the advantages of common-mode noise suppression and low-voltage operation. The different cases of current biasing techniques in differential LC-VCO are shown in Figs. 2.1 and 2.2. In general, the active biasing with MOS current sources,  $M_{p,cs}$  and  $M_{n,cs}$  (Fig. 2.1), and passive biasing with resistors,  $R_{t,cs}$  and  $R_{b,cs}$  (Fig. 2.2), are used to supply the bias current.

The lack of completeness concerning the noise factor in Leeson's model still remains as the chal-

lenge of phase noise in oscillator design. A more accurate linear time-variant (LTV) model was developed by Hajimiri and Lee [6, 7]. The essential and key idea in this LTV approach is the introduction of a sensitivity function called the impulse sensitive function (ISF with symbol  $\Gamma$ ). In [6], it was shown that the impact of stationary and cyclostationary noise sources on phase noise conversion varies across the oscillation period, and the ISF quantitatively exhibits these effects. ISF is a dimensionless, frequency- and amplitude-independent periodic function, and encodes information about the sensitivity of the oscillator to an injected impulse [6]. The detailed derivation of LTV phase noise is described in [6,7], and the phase noise in harmonic oscillators based on the LTV analysis approach is expressed as [6–8]

$$L\{\Delta f\} = \frac{1}{8\pi^2 \Delta f^2 C_{tot}^2 A_T^2} \cdot \sum_{i} N_{L,i},$$

(2.1)

where  $\Delta f$  is the offset requency,  $C_{tot}(=C/2)$  is the total capacitance of LC resonator,  $A_T$  is the oscillation amplitude across the LC resonator, and the effective noise power  $N_{L,i}$  is given by [8]

$$N_{L,i} = \frac{\overline{|i_{n,i}(\Delta f)|^2}}{\Delta f} \cdot \frac{1}{T_p} \int_0^{T_p} \Gamma_i^2(t) dt, \tag{2.2}$$

where  $T_p$  is the oscillation time period,  $\overline{|i_{n,i}(\Delta f)|^2}/\Delta f$  is the noise current power spectral density per unit frequency generated by the i-th device, and  $\Gamma_i(t)$  is the ISF representing the time-varying sensitivity of the oscillator phase to perturbations. ISF describes how much phase shift occurs from applying a unit impulse at any point in time. The phase noise depends on the reciprocal of the oscillation amplitude. On the basis of a simple analytical model similar to [9], the oscillation amplitude  $A_T$  is given by

$$A_T \propto I_{bias} R_p,$$

(2.3)

where  $I_{bias}$  is the bias current and  $R_p$  is the equivalent parallel resistance of the LC resonator. Among the components of an LC resonator, the Q factor of the inductor is usually more dominant than that of the capacitor because the inductor has a lower Q factor than the capacitor. Thus,  $R_p$  can be calculated as

$$R_n \approx 2\pi f_0 L_{tot} Q_L,\tag{2.4}$$

where  $f_0$  is the oscillation frequency,  $L_{tot}(=2L)$  is the total inductance, and  $Q_L$  is the Q factor of inductor. This is the reason that the usual design practices try to maximize both the available

oscillation amplitude and the Q factor in order to reduce the phase noise. In addition, the effective noise power proportionally links the phase noise performance and has relevance to the noise source, which depends on the biasing techniques.

#### 2.3.1 Effective Noise

Lower effective noise improves phase noise performance, and it depends on the noise source. The total effective noise of LC-VCO using MOS current source (Fig. 2.1),  $N_{L,CS}$ , is expressed as [10]

$$N_{L,CS} = N_{L,tank} + N_{L,gm} + N_{L,gmcs}$$

$$= \frac{2k_BT}{R_p} \left( 1 + \gamma + \alpha_{n/p} \gamma g_{mn/p,cs} R_p \right), \qquad (2.5)$$

where  $N_{L,tank}$ ,  $N_{L,gm}$ , and  $N_{L,gmcs}$  are the effective noise of LC resonator, differential-pair MOS devices, and n/p-channel MOS current source, respectively.  $k_B$  is the Boltzmann's constant, T is the absolute temperature,  $g_{mn/p,cs}$  is the transconductance of MOS current source,  $\gamma$  is the channel noise coefficient of MOS device, and  $\alpha_{n/p}$  is a parameter related to the transition time interval between the switching action of differential-pair devices M<sub>1</sub> and M<sub>2</sub> in the case of n/p-channel MOS current source. In this work,  $\alpha_{n/p}$  is different from the 4/9 value in the literature [5] because of the weakinversion region operation. The value of  $\alpha_{n/p}$  is determined from the circuit simulation results of phase noise. From the circuit simulation results,  $\alpha_n$  and  $\alpha_p$  are obtained as 0.5 and 0.2, respectively. This equation describes three noise contributions. The first and second terms describe the noise contribution from the LC resonator loss and the differential-pair MOS devices, respectively. The third term describes the noise from the MOS current source. In typical LC-VCOs operating at high current levels with a moderate-to-high Q factor, the MOS current source noise dominates phase noise over other noise sources [1]. There have been many efforts to reduce the phase noise by using a highvalue inductor in series with the current source in order to isolate the source node of differential-pair devices and the current source, thus obtaining a composite current generator [5, 11]. In such an approach, however, the noise of the tail transistor still affects at the source node of differential-pair MOS devices in spite of wasting the area for the added inductor.

To reduce the noise from the MOS current source, a low-value resistor is employed as a practical biasing technique for LC-VCOs. In the case of using a resistor as a current source, the thermal noise caused by the MOS current source can be replaced by the thermal noise of the bias-feeding resistor.

Figure 2.3: Effective noise contribution in current sources ("NMOS CS" and "PMOS CS") and resistive ("RES Top" and "RES Bottom") biasing techniques.

Here, considering the differential-pair MOS switching action in the resistive biasing case, the total effective noise for LC-VCO using resistive biasing (Fig. 2.2),  $N_{L,RES}$ , can be expressed as

$$N_{L,RES} = N_{L,tank} + N_{L,gm} + N_{L,R_{t/b,cs}} = \frac{2k_BT}{R_p} \left( 1 + \gamma + \beta_{t/b} \frac{R_p}{R_{t/b,cs}} \right),$$

(2.6)

where  $N_{L,R_{t/b,cs}}$  is the effective noise of bias feeding resistor,  $R_{t/b,cs}$  is the bias feeding resistance for each biasing position (top and bottom), and  $\beta_{t/b}$  is a parameter related to the transition time interval between the switching action of differential-pair devices  $M_1$  and  $M_2$  in the case of resistive biasing. The value of  $\beta_{t/b}$  is determined from the circuit simulation results of phase noise. From the circuit simulation results,  $\beta_t$  and  $\beta_b$  are obtained as 0.65 and 0.8, respectively. Similar to the MOS current source case, in the above equation the first and second terms of noise contribution are from the LC resonator loss and the differential-pair MOS devices, respectively. The third term indicates the contribution from the thermal noise of the bias-feeding resistor.

Figure 2.3 represents the simulated effective noise contribution for different biasing techniques. Typically, an NMOS transistor has a larger drain noise current than a PMOS transistor under the

Figure 2.4: Characteristics of current i and different voltage  $V_{in}$  in the differential-pair part.

same drain current. Thus, the choice of using PMOS transistors as a current source reduces the effective noise. However, a PMOS current source case still has a large effective noise. Contrarily, resistive biasing techniques show low effective noise because they avoid the use of a noisy MOS current source. Thermal noise from the bias feeding resistor as a current source is low, and therefore it has a small influence on phase noise.

#### 2.3.2 Oscillation Amplitude

From the preceding discussion, increasing oscillation amplitude reduces the phase noise. In Eq. (2.1), the oscillation amplitude in LC-VCO is proportional to the equivalent parallel resistance of the LC resonator  $R_p$  and bias current  $I_{bias}$ . Because the LC-VCOs shown in Figs. 2.1 and 2.2 have the same LC resonator, the current in each VCO dominates the improvement of oscillation amplitude.

Figure 2.4 shows the I-V characteristic of the differential-pair part of the LC-VCO, which realizes small-signal negative resistance. In the bottom resistive biasing, this part is equivalent to a couple of common-source MOS devices with a source degeneration resistor. The instantaneous gate-source voltage of the common-source MOS devices for bottom and top resistive biasing techniques ( $V_{GS,b}$

and  $V_{GS,t}$ ) have a relationship as follows:

$$V_{GS,b} = V_{GS,t} - \Delta V_{R_B},\tag{2.7}$$

where  $\Delta V_{R_B}$  is the voltage change of bottom resistor from a biasing point.  $V_{GS,t}$  and  $V_{GS,b}$  are the instantaneous gate-source voltage of top biasing and bottom biasing, respectively. MOS drain current in the weak-inversion region is proportional to the exponential of the gate-source voltage. The gate-source voltage in bottom biasing is attenuated by the voltage drop across the bottom resistor. The subthreshold drain currents for the two resistive biasing techniques have the following relationship:

$$I_{D,b} \approx I_0 \frac{W}{L} e^{\frac{V_{GS,b} - V_{TH}}{nU_T}}$$

$$= I_{D,t} e^{-\frac{\Delta V_{R_B}}{nU_T}}, \qquad (2.8)$$

where  $I_{D,t}$  and  $I_{D,b}$  are the drain current of top biasing and bottom biasing, respectively.  $I_0$  is the technology current factor, L and W are the effective channel length and width,  $V_{TH}$  is the threshold voltage, n is the substrate factor,  $U_T = k_B T/q$  is the thermal voltage, and q is the electronic charge ( $U_T = 25.9 \text{ mV}$  at room temperature). This equation explains that top biasing has more current than bottom biasing as shown in Fig. 2.4. Considering this phenomenon, instead of Eq. (2.3), the oscillation amplitude can be modified as  $A_T \propto iR_p$ , where i is the instantaneous current in the differential-pair part. The simulated oscillation amplitude by biasing technique is shown in Fig. 2.5. Top biasing has a larger oscillation amplitude than bottom biasing according to the current at the peak of the differential oscillation voltage characteristics of the differential-pair, and thereby improves the phase noise performance.

#### 2.3.3 Comparison and Discussion

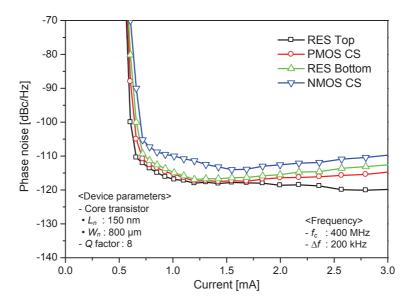

Figure 2.6 shows the simulated phase noise comparison for different biasing techniques. The phase noise results are obtained from the periodic steady-state circuit simulation with various current conditions. In the aspect of a biasing source, through the effective noise analysis, the resistive biasing techniques, which do not use a noisy MOS current source, have 60% less effective noise than the NMOS current source case. The low thermal noise introduced by a biasing resistance lower than nearly 1 k $\Omega$  does not influence the oscillator's spectral purity. In the aspect of a biasing position, the

Figure 2.5: Oscillation amplitude.

Figure 2.6: Phase noise comparison.

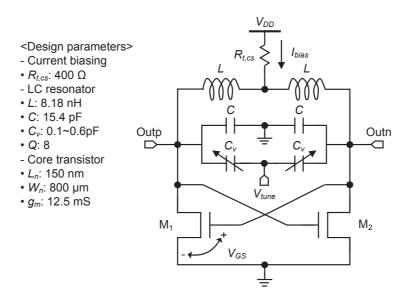

Figure 2.7: Schematic of LC-VCO with top resistive biasing.

bottom biasing technique degrades the oscillation amplitude because of the degradation of drain current. As a result, the top position biasing technique has a higher oscillation amplitude of 1.15 to 1.35 times that of the other biasing techniques. All things considered, the top resistive biasing technique has better phase noise performance because of its smaller effective noise and large output swing. In low-voltage and deep-submicron CMOS technologies, achieving low phase noise is becoming more difficult. In spite of supplying stable current, the MOS current source is not appropriate as current biasing for applications requiring high signal purity, because it operates as a high noise source and needs extra circuits for the reference stable current. In the case of requiring low phase noise, the resistive biasing technique may be efficiently utilized to supply the current in oscillator designs. It is a passive type and thus does not require extra reference circuits. Therefore, this technique has good compatibility in terms of phase noise and implementation complexity.

# 2.4 Circuit Design and Simulation Results

In this study, the top resistive biasing is applied to design the LC-VCO operating at a 0.7-V supply for the medical implant communication service (MICS) band. The structure of the NMOS cross-

2.5. CONCLUSION 33

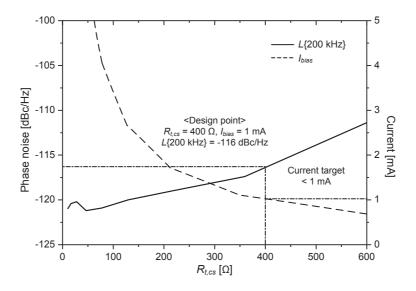

coupled differential LC-VCO with top resistive biasing is shown in Fig. 2.7. The MOS transistors optimally biased in the weak-inversion region  $(V_{GS}-V_{TH}\approx -80\,\mathrm{mV})$  are utilized to provide enough transconductance for a given bias condition, resulting in a reduction of the power dissipation of the LC-VCO. Additionally, a lower gate bias voltage would increase the maximum achievable oscillation amplitude [8] and thereby improves the phase noise performance. The dual-layer spiral inductor and varactor are used for the LC resonator. A dual-layer spiral inductor has a high Q factor value because of its lower series resistance [12]. The inductance of the spiral inductor is 8.18 nH. The capacitance corresponding to inductance is 15.4 pF, and the varactors have a capacitance range of 0.1 pF to 0.6 pF. The Q factor value of the LC resonator is approximately 8 at 400 MHz. Figure 2.8 shows the phase noise and current consumption in accordance with top biasing resistance. With the increase in current consumption, the phase noise performance is improved. However, it is a trade-off between power consumption and performance. For low power consumption, the target of current consumption is set under 1 mA, and the top bias-feeding resistance is approximately 400  $\Omega$ , which has a small influence on the phase noise performance. The power consumption of the designed LC-VCO is 700 µW with a 0.7-V supply voltage. Figure 2.9 shows the phase noise performance. The designed LC-VCO using top resistive biasing oscillating near 400 MHz has a phase noise of -116 dBc/Hz at 200 kHz offset frequency, meeting the MICS band phase noise requirement of less than -100 dBc/Hz at 200 kHz offset frequency. The tuning range of the designed LC-VCO is 398 MHz to 408 MHz, covering the MICS band (402 MHz~405 MHz).

#### 2.5 Conclusion

A phase noise reduction technique using resistive biasing in a low-voltage oscillator design is presented. Phase noise is a key parameter for RF transceivers, and it demands the low-phase noise condition for better spectral purity. Oscillator phase noise is affected by many factors, and the current source is one of the main parameters. In typical oscillators, the current source contribution dominates other sources of phase noise. In this chapter, the phase noise by current biasing techniques is analyzed, and a low-voltage design of LC-VCO using a phase noise reduction technique is presented. Through the phase noise analysis by various current biasing techniques, resistive biasing has the smallest effective noise power because of the elimination of the noisy MOS current source, and

Figure 2.8: Phase noise and current consumption in accordance with top resistance.

Figure 2.9: Phase noise performance.

2.5. CONCLUSION 35

top position basing has a large output swing because it has no current degradation. Therefore, the top resistive biased LC-VCO realizes low-voltage operation with better phase noise performance. The designed LC-VCO using top resistive biasing operates from 398 MHz to 408 MHz and exhibits a phase noise of -116 dBc/Hz at 200 kHz offset frequency with an improvement of 1 dB to 6 dB compared to other biasing techniques at similar conditions. In addition, it consumes 700  $\mu$ W from a 0.7-V supply. From this result, it is confirmed that the top resistive biasing provides a good phase noise performance, and is more proper to low-voltage oscillator designs.

BIBLIOGRAPHY 37

## **Bibliography**

[1] A. Hajimiri and T. H. Lee, "Design issues in CMOS differential *LC* oscillators," *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 717–724, May 1999.

- [2] B. Soltanian and P. R. Kinget, "Tail current-shaping to improve phase noise in *LC* voltage-controlled oscillators," *IEEE J. Solid-State Circuits*, vol. 41, no. 8, pp. 1792–1802, Aug. 2006.

- [3] F. Svelto, S. Deantoni, and R. Castello, "A 1.3 GHz low-phase noise fully tunable CMOS LC VCO," *IEEE J. Solid-State Circuits*, vol. 35, no. 3, pp. 356–361, Mar. 2000.

- [4] G. D. Astis, D. Cordeau, J.-M. Paillot, and L. Dascalescu, "A 5-GHz fully integrated full PMOS low-phase-noise LC VCO," *IEEE J. Solid-State Circuits*, vol. 40, no. 10, pp. 2087–2091, Oct. 2005.

- [5] E. Hegazi, H. Sjöland, and A. A. Abidi, "A filtering technique to lower *LC* oscillator phase noise," *IEEE J. Solid-State Circuits*, vol. 36, no. 12, pp. 1921–1930, Dec. 2001.

- [6] A. Hajimiri and T. H. Lee, "A general theory of phase noise in electrical oscillators," *IEEE J. Solid-State Circuits*, vol. 33, no. 2, pp. 179–194, Feb. 1998.

- [7] T. H. Lee and A. Hajimiri, "Oscillator phase noise: a tutorial," *IEEE J. Solid-State Circuits*, vol. 35, no. 3, pp. 326–336, Mar. 2000.

- [8] A. Mazzanti and P. Andreani, "Class-C harmonic CMOS VCOs, with a general result on phase noise," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2716–2729, Dec. 2008.

- [9] F. Yamashita, T. Matsuoka, T. Kihara, I. Takobe, H.-J. Park, and K. Taniguchi, "Analytical design of a 0.5V 5GHz CMOS LC-VCO," *IEICE Electron. Express*, vol. 6, no. 14, pp. 1025–1031, Jul. 2009.

- [10] P. Andreani, X. Wang, L. Vandi, and A. Fard, "A study of phase noise in colpitts and LC-Tank CMOS oscillators," IEEE J. Solid-State Circuits, vol. 40, no. 5, pp. 1107–1118, May 2005.

- [11] P. Andreani and H. Sjöland, "Tail current noise suppression in RF CMOS VCOs," *IEEE J. Solid-State Circuits*, vol. 37, no. 3, pp. 342–348, Mar. 2002.

- [12] J. N. Burghartz, K. A. Jenkins, and M. Soyuer, "Multilevel-spiral inductors using VLSI interconnect technology," *IEEE Electron Device Lett.*, vol. 17, no. 9, pp. 428–430, Sep. 1996.

# **Chapter 3**

# **Delta-Sigma Digitally Controlled Oscillator**

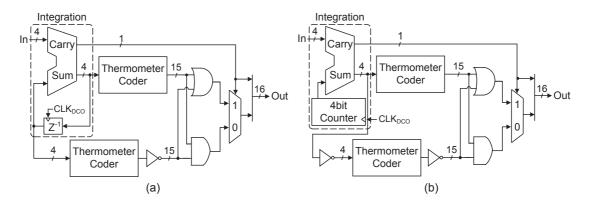

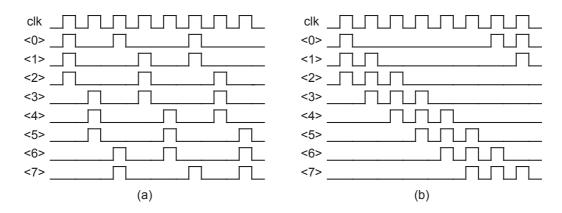

#### 3.1 Introduction