| Title        | 実時間マルチスケール空間フィルタ処理機能を有する<br>知能視覚センサの開発と応用 |

|--------------|-------------------------------------------|

| Author(s)    | 安川, 真輔                                    |

| Citation     | 大阪大学, 2017, 博士論文                          |

| Version Type | VoR                                       |

| URL          | https://doi.org/10.18910/61748            |

| rights       |                                           |

| Note         |                                           |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

## 博士学位論文

実時間マルチスケール空間フィルタ処理機能を 有する知能視覚センサの開発と応用

安川 真輔

2016年 1月

大阪大学大学院工学研究科 電気電子情報工学専攻

# 目次

| 目次                                  | i     |

|-------------------------------------|-------|

| 内容梗概                                | iv    |

| 表記法                                 | vi    |

| 第1章 序論                              | 1     |

| 1.1 複数のスケールで視覚情報を解釈する生物の視覚系         | 1     |

| 1.2 マルチスケール解析の有用性                   | 2     |

| 1.3 生体の視覚神経回路に学んだセンシング技術とその応用       | 4     |

| 1.4 研究目的                            | 5     |

| 第2章 空間フィルタ処理とその高速化に関する先行研究          | 7     |

| 2.1 緒言                              | 7     |

| 2.2 逐次型演算による空間フィルタ処理                | 7     |

| 2.2.1 空間フィルタ処理                      | 7     |

| 2.2.2 逐次型演算器による空間フィルタ処理の問題点         | 9     |

| 2.3 低域通過型空間フィルタと帯域通過型空間フィルタ         | 11    |

| 2.3.1 ガウシアンフィルタの空間特性と周波数特性          | 11    |

| 2.3.2 DoG フィルタの空間特性と空間周波数特性         | 13    |

| 2.3.3 実空間と周波数空間                     | 14    |

| 2.4 スケーラブルフィルタ                      | 15    |

| 2.5 ソフトウェア・アルゴリズムの工夫による高速化          | 17    |

| 2.6 ハードウェアシステムによる高速化                | 17    |

| 2.7 生体の外網膜とアナログ抵抗回路網                | 18    |

| 2.8 シリコン網膜                          | 22    |

| 2.8.1 内部構成と動作原理                     | 22    |

| 2.8.2 FPGA によるシリコン網膜の制御             | 25    |

| 2.8.3 MOS 抵抗回路網と MOS 抵抗             | 27    |

| 2.9 結言                              | 31    |

| 第3章 複数の帯域通過型空間フィルタ処理機能を有する知能視覚センサの関 | 開発 32 |

| 3.1 緒言                              | 32    |

| 3.2 知能視覚センサの構成と処理の流れ                | 33    |

| 3.3 MOS 抵抗回路網の空間特性の測定               | 36    |

| 3.4 MOS 抵抗回路網の空間周波数応答の測定            | 38    |

| 3.5 画像に対するセンサの出力応答の測定               | 40    |

| 3.6 考察                               | 40 |

|--------------------------------------|----|

| 3.6.1 提案するアーキテクチャの利点                 | 40 |

| 3.6.2 単一フレーム内に適用できる空間フィルタの数について      | 42 |

| 3.6.3 MOS 抵抗の入力電圧レベルの依存性             | 42 |

| 3.7 結言                               | 46 |

| 第4章 実時間マルチスケールエッジ検出機能を有する知能視覚センサの開発  | 47 |

| 4.1 緒言                               | 47 |

| 4.2 ゼロ交差法によるエッジ検出                    | 47 |

| 4.3 ゼロ交差検出回路                         | 49 |

| 4.4 FPGA 上での差分画像とエッジ画像の並列処理          | 50 |

| 4.5 システムの出力応答の測定                     | 51 |

| 4.5.1 単純な視覚対象に対する応答                  | 51 |

| 4.5.2 複雑な視覚対象に対する応答                  | 51 |

| 4.6 考察                               | 54 |

| 4.7 結言                               | 56 |

| 第5章 抵抗回路網を用いたスケール不変特徴量抽出の解析とシミュレーション | 57 |

| 5.1 緒言                               | 57 |

| 5.2 SIFT アルゴリズムとその関連研究               | 57 |

| 5.2.1 スケーラブルフィルタによるキーポイント検出          | 57 |

| 5.2.2 特徴量記述                          | 59 |

| 5.2.3 キーポイントマッチング                    | 60 |

| 5.2.4 関連研究                           | 61 |

| 5.3 抵抗回路網フィルタとガウシアンフィルタの比較           | 61 |

| 5.4 DoG フィルタ処理画像と DoR フィルタ処理画像の比較    | 62 |

| 5.5 シミュレーション解析によるキーポイント検出の検討         | 66 |

| 5.6 シミュレーションによる特徴量記述の検討              | 68 |

| 5.7 考察                               | 70 |

| 5.8 結言                               | 71 |

| 第6章 実時間スケール不変特徴量抽出機能を有する知能視覚センサシステム  |    |

| 6.1 緒言                               | 72 |

| 6.2 抵抗回路網による実時間スケーラブルフィルタ処理          | 73 |

| 6.2.1 実時間マルチスケールフィルタ処理               | 73 |

| 6.2.2 MOS 抵抗回路網によるスケーラブルフィルタ処理       | 73 |

| 6.3 FPGA によるキーポイント検出及び勾配ベクトル演算       | 75 |

| 6.3.1 FPGA による並列処理                   | 75 |

| 6.3.2 SIFT キーポイント検出                  | 77 |

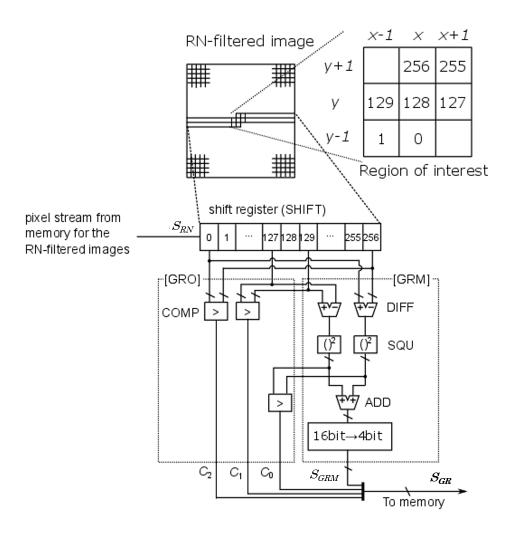

| 6.3.3 勾配ベクトル画像の生成回路         | 79 |

|-----------------------------|----|

| 6.4 ソフトウェアによる特徴ベクトル記述と対応点探索 | 81 |

| 6.5 評価実験                    | 82 |

| 6.6 考察                      | 85 |

| 6.6.1 アーキテクチャに対する考察         | 85 |

| 6.6.2 実環境への応用に対する考察         | 86 |

| 6.7 結言                      | 87 |

| 第 7 章 結論                    | 88 |

| 参考文献                        | 90 |

| 謝辞                          | 98 |

| 業績一覧                        | 99 |

## 内容梗概

本論文は、筆者が主に大阪大学大学院工学研究科博士後期課程在学中に行った実時間マルチスケール空間フィルタ処理機能を有する知能視覚センサの開発と応用に関する研究をまとめたものであり、全7章から構成されている.

#### 第1章 序論

本章では、本論文の目的と意義を述べた。視覚情報は様々なスケールの構造が組み合わされて構成されている。生体の視覚系はその並列階層的な構造により、視覚情報を効率的にマルチスケールで解析していると考えられている。従来の汎用イメージセンサと逐次演算型コンピュータとを組み合わせた画像センシングシステムでは、実時間で効率よく画像をマルチスケール解析することは難しい。従って、生体の視覚系に学び、アーキテクチャレベルからセンサシステム全体を見直すことが必要であることを論じた。

#### 第2章 空間フィルタ処理とその高速化に関する先行研究

マルチスケール解析法の初段にはマルチスケール空間フィルタ処理がある。本章では、空間フィルタ処理と、その高速化の試みについての先行研究を述べた。まず逐次型演算による空間フィルタ処理とその問題点について述べた。次に、低域通過型及び帯域通過型空間フィルタの特性について述べた。また複数の空間フィルタ処理は多大な計算コストを要し、汎用コンピュータでは実時間処理が困難であることを述べた。これまでの空間フィルタ処理の高速化の手法について、先行研究を紹介した。最後に、本研究における高速化の鍵となる技術である生体網膜神経回路を模擬したアナログ抵抗回路網とそれを内蔵する知能視覚センサについて述べた。

#### 第3章 複数の帯域通過型空間フィルタ処理機能を有する知能視覚センサの開発

本章では、複数の空間フィルタ処理の実行に適したハードウェア・アーキテクチャを提案し、試作した知能視覚センサの動作とその有用性について述べた。まず、本視覚センサが空間フィルタ処理を瞬時に実行するアナログ抵抗回路網と FPGA (Field-Programmable Gate Array)を有しており、このアナログ回路とデジタル回路の双方の利点を生かし、小型かつ低消費電力で実時間処理を実現していることを説明した。アナログ抵抗回路網は、その抵抗値によって空間特性が決定される。また本研究で用いる抵抗回路網の抵抗は MOS (Metal-Oxide-Semiconductor)抵抗で構成されており、その抵抗値を外部信号により容易に制御できる。そこで、実機実験によって MOS 抵抗回路網の空間特性及び空間周波数特性が制御できることを示した。また FPGA からの制御信号により、取得画像に対して一フレーム取得

時間内に複数の空間フィルタを適用する手法を提案した. 最後に試験画像を用いて, 提案する知能視覚センサが実時間で複数の空間フィルタ処理を実行し, マルチスケール処理画像を取得できることを示した.

### 第4章 実時間マルチスケールエッジ検出機能を有する知能視覚センサの開発

本章では、第3章で述べた知能視覚センサの後段にデジタル演算回路を追加することで、マルチスケールの輪郭検出機能を有する知能視覚センサを構築したことについて述べた.まず帯域通過型空間フィルタ処理画像からエッジを検出する手法とその回路について述べた.次に、知能視覚センサからの画像を FPGA 内のメモリに記録する際、画像読み出しと同時に FPGA 上のデジタル回路で演算することで、フレームの遅れがなく、輪郭検出を実行する手法について述べた.最後に、複数の試験画像を用いて、提案する知能視覚センサが画像内の大まかな構造から細やかな構造まで抽出する、マルチスケール輪郭検出画像群が実時間で取得できることを示した.

#### 第5章 抵抗回路網を用いたスケール不変特徴量抽出の解析とシミュレーション

本章では、マルチスケール解析で多く用いられているガウシアンフィルタの代わりに抵抗回路網フィルタを用いた、スケール不変特徴量の抽出についての解析とシミュレーションについて述べた。まず、従来のスケール不変特徴量抽出手法について簡潔に述べた。次に、スケール不変特徴量を抽出するために必要な空間フィルタのフィルタサイズの設定について述べた。また、ガウシアンフィルタと抵抗回路網フィルタの空間特性の違いが、スケール不変な特徴点の検出に与える影響をソフトウェア・シミュレーションで比較・検討した。最後に、異なる大きさのテスト画像群を用いて、二次元抵抗回路網によるスケール不変特徴量の抽出について検証した結果を述べた。

#### 第6章 実時間スケール不変特徴量抽出機能を有する知能視覚センサシステム

本章では、画像からスケール不変特徴量を実時間で抽出する知能視覚センサシステムについて述べた、次いで、実時間スケール不変特徴量抽出を実現するためのシステム構成と、その動作について述べた。その中で特徴量抽出の高速化を図るために、視覚センサ内のFPGA上に新たに実装した並列演算モジュールについて述べた。実機においても、第5章で述べたようにスケール不変特徴量を抽出するために要求される抵抗回路網のフィルタサイズの設定ができることを示した。最後に、試験動画を視覚システムに提示し、本システムが実時間でスケール不変な特徴量を抽出できることを示した。

#### 第7章 結論

本章では、本研究で得られた結果を総括した.

# 表記法

以下の表1に、本文中で各章を横断して用いられる主な記号をまとめる.

表1 表記法リスト

| 表記                                | 意味・説明                                                                         |  |

|-----------------------------------|-------------------------------------------------------------------------------|--|

| E(X)                              | 抵抗回路網の入力端子に印加される光センサの画素電圧.                                                    |  |

| $V(X, \lambda)$                   | 抵抗回路網の出力端子電圧.                                                                 |  |

| V                                 | 画素位置 (x, y) を要素にもつベクトル. フレーム t 及び t+1 を更                                      |  |

| X                                 | に要素として持つ時, <b>X</b> t及び <b>Xh1</b> と表記する.                                     |  |

| $f_{RN}(\lambda)$                 | スケールパラメータ $\lambda$ をもつ RN (Resistive Network)フィルタ.                           |  |

|                                   | スケールパラメータ $\lambda_1$ , $\lambda_2$ をもつ DoR (Difference of Resistive          |  |

| $f_{DR}(\lambda_1,\lambda_2)$     | $network)$ フィルタ. $\lambda_1$ と $\lambda_2$ の大きさの比が決まる時, $f_{DR}(\lambda_1)$ と |  |

|                                   | 略記.                                                                           |  |

| λ                                 | 抵抗回路網フィルタのスケールパラメータ.                                                          |  |

| L                                 | $R_s$ と $R_m$ の比の平方根.                                                         |  |

| $R_s$                             | 抵抗回路網の側方抵抗.                                                                   |  |

| $R_m$                             | 抵抗回路網の縦方向抵抗.                                                                  |  |

| D                                 | 抵抗回路網のノード間距離.                                                                 |  |

| $V_{rsbn}$                        | $R_s$ の nMOS 側バイアス電圧.                                                         |  |

| $V_{rsbp}$                        | $R_s$ の p $	ext{MOS}$ 側バイアス電圧.                                                |  |

| $V_{rmbn}$                        | $R_m$ の nMOS 側バイアス電圧.                                                         |  |

| $V_{rmbp}$                        | $R_m$ の pMOS 側バイアス電圧.                                                         |  |

| $S_{RN}(X,\lambda)$               | RN フィルタ処理画像.                                                                  |  |

| $C_{}(\mathbf{V} \mid 1 \mid 1)$  | $DoR$ フィルタ処理画像. $\lambda_1$ と $\lambda_2$ の大きさの比が決まる時, $S_{DR}$               |  |

| $S_{DR}(X, \lambda_1, \lambda_2)$ | (X, 1)と略記.                                                                    |  |

| $f_G(o)$                          | スケールパラメータ $\sigma$ をもつガウシアンフィルタ.                                              |  |

| $f_{DG}(\sigma_1, \sigma_2)$      | スケールパラメータ σ <sub>1</sub> , σ <sub>2</sub> をもつ DoG フィルタ.                       |  |

| σ                                 | ガウシアンフィルタのスケールパラメータ.                                                          |  |

|                                   |                                                                               |  |

## 第1章 序論

## 1.1 複数のスケールで視覚情報を解釈する生物の視覚系

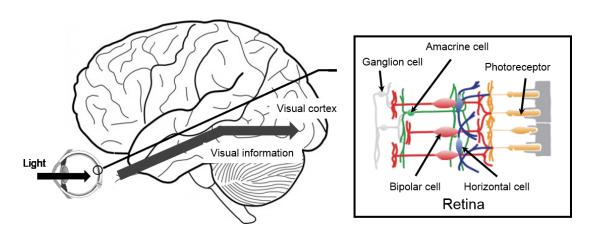

生体の網膜には外界の三次元構造を反映した二次元像が投影される. 視覚とは, 眼底に投影された二次元網膜像から目の前の三次元世界を解釈する情報処理過程である. 図 1.1 に生体の視覚情報処理の流れの模式図を示す. 視覚情報は網膜神経細胞内の初段の視細胞(図 1.1 内の Photoreceptor)により電気信号に変換され, 出力段の神経節細胞((図 1.1 内の Ganglion cell)を介して, 脳の視覚野(図 1.1 内の Visual cortex)へと送られる. この過程において並列階層的に配された様々な神経細胞群が, 電気信号をやり取りすることで, 視対象の大きさや動きや色, 奥行きといった特徴の抽出から個体認識まで様々な視覚的な情報処理課題を解決している. 網膜の段階から既に特徴抽出過程は始まっており, 近年の研究では従来考えられていたよりも網膜神経回路は多くの機能を担っているという議論もある(総説として[1]). この意味で, 生体の視覚系は, 外界の様子をきめ細かく, 色再現性が高く切り出すことのできるデジタルカメラ等の撮像装置とは, 目的が異なる情報処理装置であり, その設計原理も異なる. 多くの視覚的課題は三次元世界から投影され, 奥行き情報の欠落した二次元網膜像から推定することとなるため, 解が一つに定まらない不良設定問題となる. 生体の視覚系では(例えば, 太陽のような光源が頭上にある等といった) 物理的な仮説を有しており, これを拘束条件として, 視覚的課題を解いていると考えられる[2].

図 1.1 視覚の情報処理過程. まず外界からの光が網膜内の視細胞 (Photoreceptor) で電気信号に変換される. その電気信号が網膜神経回路網でやり取りされることで, エッジや動き情報が抽出される. それらの視覚情報は神経節細胞 (Ganglion cell) を介して視覚野に送られる. 視覚野 (Visual cortex) 内において, 更に高次な視覚的課題 (形状認識等) が実行される.

三次元世界には様々な大きさの物体がある。従って、その様子が投影された二次元網膜像上には様々な大きさの幾何学的な特徴が表現されている。更に、眼と視対象との位置関係で対象の投影像が網膜を覆う領域の大きさ、すなわち対象の見えの大きさが変化する。生体の視覚神経回路では、このような様々な大きさの物体が表現されている像を解釈するために、視覚情報をあるスケールのみで処理せず、異なるスケールで並列に処理する仕組みを有していると考えられている[2]。ある神経細胞の応答に変化を生じさせる入力の空間的な範囲を受容野と呼ぶが、その大きさは網膜神経細胞の段階から複数に分類されることが知られている[3]。視覚心理学の先行研究においても、生体の視覚系が視覚情報を空間周波数帯域ごとに分割し、その帯域ごとに、すなわちマルチスケールで処理することを示唆する実験結果が得られている[4]。更にマルチスケールで視野内の状況を解釈する生体の視覚系の計算原理に基づいた視覚情報処理モデルもまた提案されている[5,6]。

上記の視覚情報のマルチスケール解析は有用なアプローチであるため、コンピュータビジョン分野のアルゴリズムにも広く利用されている[2,7,8].この情報処理過程については、次節でその詳細を述べる.

## 1.2 マルチスケール解析の有用性

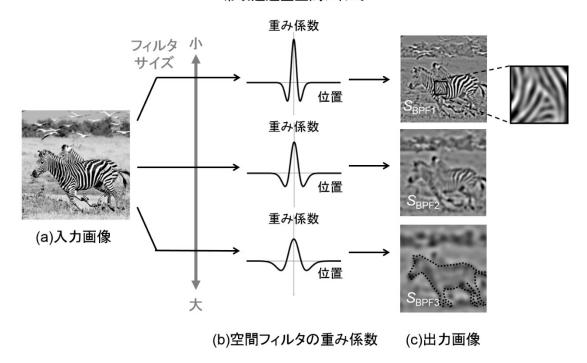

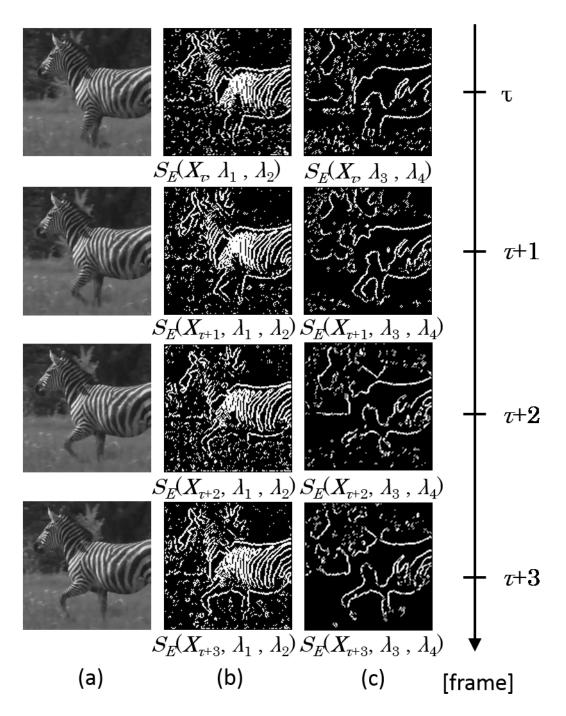

自然画像上には,物体の輪郭といった大局的な構造から,物体表面の模様といった局所的 な構造まで,様々なスケールの様々な幾何学的特徴を持つ物体が表現されている[9]. そし て,自然画像には様々な空間周波数成分が含まれている[10].一般的に画像から情報を抽出 する際, 前処理として, 着目した画像上の構造に応じたスケールに設定された空間フィルタ を画像に適用することで、そのスケールの構造のみを強調する.この処理は、画像上のある 空間周波数帯域の成分のみを強調することを意味する. マルチスケール画像解析では, 複数 の異なるスケールの空間フィルタを画像に適用することで、まず空間周波数帯域ごとに画 像を分離する. これらの処理画像では, 物体の輪郭や模様といった, それぞれ異なるスケー ルの構造が強調されている.マルチスケール画像解析ではそれらの画像群を個別に解析す ることで,入力画像上の局所的な構造から大局的な構造まで解析することができる.図 1.2(a) のシマウマの画像を用いてマルチスケールで二次元像を解析する有用性を論じる. マルチスケール解析では、その初段で異なる複数の大きさの空間フィルタを入力画像に適 用する (図 1.2(b)) . 図 1.2(b) は (一次元) 空間フィルタの重み係数を表す. このマルチス ケール空間フィルタ処理によって、細かい特徴を強調した画像から、粗い特徴を強調した画 像まで複数の画像が生成される. この処理についての詳細は第 2 章で説明する. 高周波帯 域信号を通過させる小さなスケールの空間フィルタ (図 1.2(b)上段) が適用された画像はシ マウマの縞のような細かい構造が強調される (図 1.2(c)上段). 一方で, 低周波帯域信号を通 過させる大きなスケールの空間フィルタ (図 1.2(b)下段) が適用された画像は比較的細かい 構造が除去され、シマウマの輪郭のみ強調される(図1.2(c)下段).このようにマルチス

#### 帯域通過型空間フィルタ

図 1.2 マルチスケール解析. (a) 入力画像. (b) 帯域通過特性を有する DoG (Difference of Gaussian) フィルタ群の重み係数 (一次元). 下のフィルタほどスケールが大きく, より低周波帯域の信号を通過させる. (c) 帯域通過型空間フィルタ処理画像. 入力画像 にそれぞれ左に示される空間フィルタを適用することで得られる. 小さいスケールのフィルタでは細かい構造が, 大きいスケールのフィルタでは粗い構造がそれぞれ強調されている.

ケール画像解析は、幅広い周波数帯域を含んだ画像情報から、特定の周波数帯域のテクスチャやエッジのような画像特徴の抽出をする時に役立つとされている[2,8]. マルチスケール画像解析は、コンピュータビジョン分野において、エッジ検出[11]、ステレオマッチング[12]、スケール不変特徴記述[13,14]のような様々な応用[15-21]で利用されており、その有用性が示されている.

画像センシングシステムでは、ここで例に挙げたシマウマのように動く対象を解析する場合、センサと対象物の間の相対的な距離が変化し、像上での対象の見えの大きさも刻一刻と変化する. 従って、画像センシングシステムには単一フレーム内に処理を完了させる実時間性が求められる. しかしながら、複数の大きなサイズの空間フィルタを画像に適用する処理は、計算コストが非常に高いため、画像の実時間マルチスケール解析は難しい課題である. この点については 2.2.2 節でその詳細を述べる.

## 1.3 生体の視覚神経回路に学んだセンシング技術とその応用

視覚は外界の空間的な情報を一度に受容するため、生物が自己の置かれた状況を効率的に把握し、適切な行動を選択する上で重要な感覚情報である。外界の状況を効率よく解釈する画像センシングシステムを工学的に実現する上で、生体の視覚神経回路の計算原理や設計指針を手本とする研究がなされてきた。生物は自律行動という側面から、現状の工学的なシステムに比べて、非常に効率よく合理的な情報処理システムである。例えば国防高等研究計画局 (DARPA) によるロボットカーレース (DARPA グランド・チャレンジ) に参加した自律型ロボットカーは約 1kW のエネルギーが計算にかかること[22]に比べて、ハチは数 $10\mu W$  のエネルギーで視覚ナビゲーションを実現していると言われている[23]。

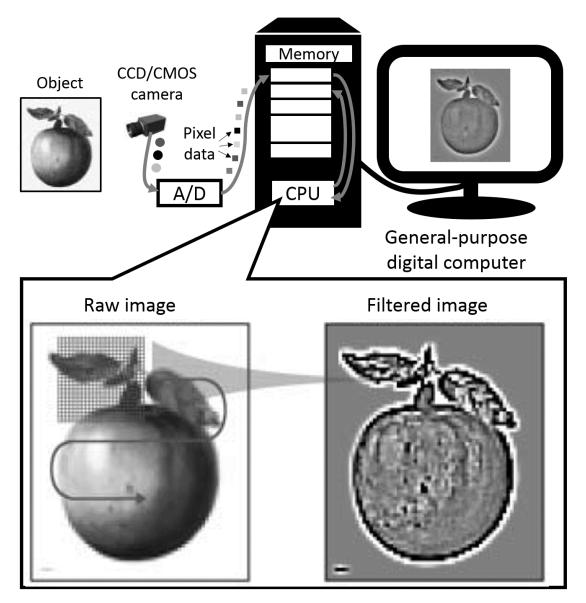

従来の画像センシングシステムの多くが、画像センサとマイクロコントローラのような汎用デジタルコンピュータから構成されている。近年の半導体プロセス技術や回路技術の発展に伴い、CMOS (Complementary Metal—Oxide—Semiconductor) イメージセンサに代表される画像センサの解像度や感度の向上が目覚ましい[24]。従来から用いられてきたCCD (Charge Coupled Device) イメージセンサと比較して、CMOS イメージセンサは安価であることや、低消費電力であること、また受光部の他に CMOS 回路が LSI に内蔵できることを理由に、現在では主流の画像センサとなり、携帯電話のカメラ等に広く採用されている。画像センシングシステムでは、この画像センサで取得された画像を汎用コンピュータ上のメモリに転送し、その中でデジタル画像処理が実行される。デジタル画像処理は一画素一画素、逐次的に情報を処理するために、処理が完了するまで次のフレームの画像を処理することができない。実時間処理が要求される応用の場合、一枚の画像に対する全ての処理を通常ビデオレート(33ms)程度の時間内に完了させる必要がある。処理の高速化のために、CPU のクロックを高速にすると、それに伴う消費電力が上昇し、冷却用装置や大容量バッテリー等のハードウェアの規模の拡大を余儀なくさせる。

一方で、生体の神経回路の形態や計算原理の合理性に学び、それを電気電子回路で模倣し、システムを設計するニューロモフィック・エンジニアリング(Neuromorphic Engineering)と呼ばれる分野が 1980 年頃に創成された[25]. 初期の研究では、MOS トランジスタ回路によって、ワンチップ上に神経回路の電気的接続と演算機能を再現し、物理現象をそのまま演算に利用することで、最小のエネルギーで処理を実行するアナログ集積回路チップの開発が行われた。そこでは視覚や聴覚などの感覚系の神経回路や無脊椎動物が有する単純な神経回路を模倣したアナログ集積回路チップが複数の研究室で開発された(総説として[25-28])が、中でも大きな成功をおさめた研究の一つとして、シリコン網膜[29-36]の開発が挙げられる。シリコン網膜は、生体の網膜の合理的な構造に学んで、非常に効率よく空間フィルタ処理画像を取得できる画像センサである。ここで、本論文では情報処理機能を内蔵する画像センサを視覚センサと呼ぶこととする。この成功は、それまでに積み上げられてきた生体の網膜の構造やその電気的特性に関する生理学的研究[37-42]の知見に基づいて達成

された.シリコン網膜についての詳細はその基礎となった生理学的知見を 2.6 節で,技術的な内容を 2.7 節で述べる.

本グループで開発されたシリコン網膜はその後,後段に追加のアナログ回路,制御用・処理用デジタル回路を配することで,視細胞の受光特性を模した順応型視覚センサ[43]や,後段の視覚野の神経回路を模した方位選択性チップ[44]や色恒常機能の実現[45],そして二つのカメラを用いた両眼視差検出システム[46]へと発展した.一方で,スイス連邦工科大学やスタンフォード大学を中心とした欧米のグループでは従来のデジタル画像の中には空間的・時間的に冗長な情報が含まれているとし,その変化分だけをアドレス・イベント表現(Address-Event Representation; AER)と呼ばれる手法で受け手側の計算機システムに送信するベースの視覚センサを開発してきた[28, 47].

生体模倣型視覚センサを用いた応用もまた提案されており、例えばロボットの両眼システムによるナビゲーション[48]、行動モニタリング[49]、転倒検出[50]、ペン立て制御[51]、ゴールキーパーロボット[52]、神経補綴のための実時間シミュレータ[53]などのセンサシステムが研究・開発されてきた。

## 1.4 研究目的

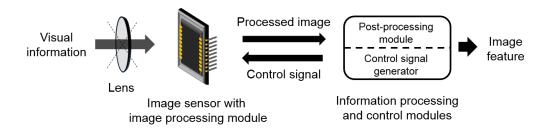

本論文では、内蔵された専用の画像処理回路によって決められた簡易な前処理のみを実行する視覚センサに対して、より高度な画像処理機能を有するセンサである知能視覚センサを提案する。図 1.3 に知能視覚センサのコンセプト図を示す。本センサでは前段にレンズから入ってきた視覚情報を、受光と同時に画像処理する視覚センサを配し、後段に視覚センサ内への制御信号を生成するモジュールと、画像特徴を抽出する後処理モジュールを配する。知能視覚センサではセンサ内の画像処理回路の特性を動的に制御し、かつ後処理モジュールで更に情報処理を実行することで、より高度な画像処理機能を実現できる。

生物が外界の状況を把握するために、マルチスケール解析がその視覚系の神経回路内でなされていると考えられている[2].本研究の目的は、生体の視覚系に学ぶことで、単一フ

図 1.3 知能視覚センサのコンセプト図. 知能視覚センサは画像処理機能を有する視覚センサと後処理及び制御機能を有するモジュールで構成される.

レーム内に効率よくマルチスケール空間フィルタ処理を実行できる視覚センサのアーキテクチャを提案し、それに基づく知能視覚センサを開発することである。提案する知能視覚センサは情報処理を実行するアナログ集積回路チップの他に、その特性を制御する信号を生成するデジタル回路を有している。上記の構成をとることで、本知能視覚センサはコンパクトでありながら、マルチスケール空間フィルタ処理のような高度な処理を実行する。更に、本論文では、この知能視覚センサの応用として実時間マルチスケール輪郭検出機能を有するセンサや、実時間でスケール不変特徴量抽出機能を有するセンサシステムを開発し、その有用性を示す。

# 第2章 空間フィルタ処理とその高速化に 関する先行研究

## 2.1 緒言

空間フィルタ処理は、画像の認識過程における前処理の一つである.この処理は、演算を空間的に広範囲にわたって実行するため、逐次型演算器が不得意とする処理である.更にマルチスケール空間フィルタ処理では、空間フィルタ処理を複数回実行するため、逐次型演算器にとって非常に計算負荷が高い.

本章では、空間フィルタ処理について、ガウシアンフィルタを代表例として用いて説明する。また逐次型演算器における空間フィルタの計算コストについて述べる。次いで、空間フィルタ処理を高速化するためのソフトウェア・アルゴリズムやハードウェアの工夫についての先行研究をまとめる。最後に、本研究で鍵となる生体の網膜にある抵抗回路網と呼ばれる神経回路の構造と、網膜の構造を模したシリコン網膜と呼ばれるアナログ VLSI についての詳細を述べる。

## 2.2 逐次型演算による空間フィルタ処理

#### 2.2.1 空間フィルタ処理

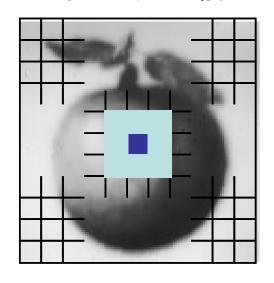

空間フィルタ処理は、画像内のノイズ除去や、ある大きさの特徴を選択的に強調する機能を持つ画像処理技術の一種である。デジタルコンピュータ上での空間フィルタ処理を、図 2.1、図 2.2 を用いて説明する。この処理では、図 2.1 の画像内にある格子状で示されるマスクと呼ばれる重み係数配列(フィルタカーネルともいう)を全画面にわたって、左上から右下まで一画素ずつ走査していく。画像配列とマスクが重なった部分(注目領域)において、要素ごとに重みを掛け合わせ、それらの合計を取ることで、マスク中心の画素の出力値が計算される。以上の計算は入力画像に対してフィルタの重み係数の畳み込み演算を実行したことを意味する。例えば図 2.2 のような重み係数配列(カーネル)と画像配列の注目領域を考える。このときの注目画素(中央の  $b_{22}$ )の位置における畳み込み演算の結果  $b_{22}$  は次のようになる。

$$b_{22}' = \sum_{i=1}^{3} \sum_{j=1}^{3} a_{ij} b_{ij}$$

(2.1)

# フィルタ処理前

# フィルタ処理後

図 2.1 逐次型演算による空間フィルタ処理の例. 空間フィルタでは下の図内の矢印のように右上の画素から左下の画素まで重み係数配列を一画素ずつ走査していき, 重み付き加算平均を実行していく.

図 2.1, 図 2.2 の例では 3 × 3 画素のフィルタカーネルを用いて説明したが、このフィルタカーネルの大きさ(以下、フィルタサイズ)は、強調したい特徴の大きさに応じて設定される. 例えば、画像内における大局的な変化を強調したい場合は、大きなフィルタサイズの空間フィルタを入力画像に適用する必要がある.

| a <sub>11</sub> | a <sub>12</sub> | a <sub>13</sub> |

|-----------------|-----------------|-----------------|

| a <sub>21</sub> | a <sub>22</sub> | a <sub>23</sub> |

| a <sub>31</sub> | a <sub>32</sub> | a <sub>33</sub> |

| $b_{11}$        | b <sub>12</sub> | b <sub>13</sub> |

|-----------------|-----------------|-----------------|

| b <sub>21</sub> | b <sub>22</sub> | b <sub>23</sub> |

| b <sub>31</sub> | b <sub>32</sub> | b <sub>33</sub> |

重み係数配列

画像配列の注目領域の ピクセル値

図 2.2 重み係数配列と注目領域.

## 2.2.2 逐次型演算器による空間フィルタ処理の問題点

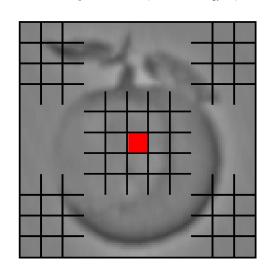

図 2.3 を用いて、従来の画像センシングシステムによる空間フィルタ処理の問題点を説明する. このシステムは汎用の CCD/CMOS イメージセンサを内蔵したカメラと、メモリと CPU を内蔵した汎用デジタルコンピュータで構成されている. CCD/CMOS イメージセンサは各画素のフォトセンサによって外界からの光を受け、画像を生成する. その画像データは一画素ずつ走査的に読み出され、A/D (Analog-to-Digital) 変換器によってデジタル信号に変換後、画像保存用のメモリに転送される. その後、CPU はそのメモリにアクセスし、逐次的に処理を実行する.

空間フィルタ処理は、画像と空間フィルタの畳み込み演算である。従来のシステムによって、この処理を実行する場合、最も左上の画素から右下の画素まで順に注目画素と周辺の画素を読み出し、これらの重み付け加算を逐次的に実行することとなる。この空間フィルタ処理の積和演算(Multiply-Accumulation;MAC)数はそのフィルタサイズが大きくなるに従い、莫大な数に膨れ上がる。空間フィルタ処理において、積和演算の数  $N_{ps}$ はフィルタ幅の二乗に比例する。従って、複数回空間フィルタ処理の計算量  $N_{ps}$ は次の式で表現される。

$$N_{ps} = N_i \sum_{n=1}^{N_f} w_n^2.$$

(2.2)

ここで、 $N_i$ は入力画像の画素数を表す。 $w_n$ ( $1 < n < N_i$ ) は空間フィルタの幅を、 $N_i$ は適用するフィルタの数をそれぞれ表している。この式から、二次元空間フィルタの計算コストは、画像サイズに比例して増加するのに加えて、フィルタ幅の二乗に比例して増加することが分かる。

従来のシステムのアーキテクチャが、空間フィルタ処理の実行に不向きな理由は次の二つである。一つはメモリアクセス、もう一つは汎用 CPU に内蔵されている演算器である。

図 2.3 従来の逐次型演算を実行する視覚センシングシステムにおける空間フィルタ処理. CCD イメージセンサに代表される汎用イメージセンサとデジタルコンピュータで構成される. カメラで撮像された画像が一画素ずつメモリに保存される. CPU がメモリ内の画像に一画素ずつアクセスし,処理を実行する.

まずメモリへのアクセスの問題について述べる. 逐次演算器によって画像処理をする場合,外部メモリから CPU 内の一時メモリに画素情報,フィルタカーネル情報を読み込んで演算することとなる. この時, CPU がメモリにアドレスを指定して,メモリがそのアドレスからデータを出力するまでに一定の時間がかかる. このメモリへのアクセス時間は扱うデータが多いとその分だけ長くかかることになる. この問題はノイマンボトルネックといい,逐次直列的に演算する方式では避けられない問題である.

また汎用 CPU には積和演算器が少ないため、膨大な数の積和演算処理は不得意である. ハードウェア的な工夫についての先行研究は 2.5 節でその詳細を扱う.

上記の理由から、大きなサイズの空間フィルタを複数回、画像に適用するとなると、計算 コストが深刻な問題となる.

## 2.3 低域通過型空間フィルタと帯域通過型空間フィルタ

#### 2.3.1 ガウシアンフィルタの空間特性と周波数特性

ガウシアンフィルタ (Gaussian filter) は、中央値フィルタや平均化フィルタ等のフィルタと同様に、画像の平滑化やノイズ除去を目的として画像に適用される空間フィルタの一つである。 ガウシアンフィルタという名称は重み付けの分布をガウス分布に則って生成している所に由来する。一次元ガウス関数  $f_G(x,\sigma)$  を式(2.3)に示す。

$$f_G(x, o) = A_G \exp\left(-\frac{x^2}{2\sigma^2}\right). \tag{2.3}$$

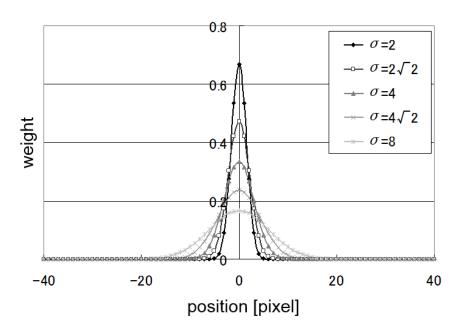

ここで、x は位置、 $A_G=1/\sqrt{2\pi\sigma^2}$  は正規化係数、 $\sigma$  はガウス関数の形状を決めるパラメータである標準偏差である。図 2.4 に一次元ガウス関数を示す。図中  $\sigma$  はガウス関数の標準偏差であり、標準偏差が大きいほどガウス分布の広がりが大きくなる。そのため  $\sigma$  はスケールパラメータとも呼ばれる。画像は二次元であるため、画像処理に通常用いられるガウシアンフィルタのカーネルは式(2.4)で示される二次元ガウス関数である。

$$f_{2G}(x, y, o) = A_{2G} \exp\left(-\frac{x^2 + y^2}{2o^2}\right).$$

(2.4)

ここで、x,yは位置、 $A_{2G}=1/2\pi\sigma^2$ は正規化係数である.

ガウシアンフィルタの処理結果を図 2.5 に示す。図 2.5(a)は入力画像であり,図 2.5(b)-(f)がガウシアンフィルタ処理画像である。図 2.5(a)に比べ,その他のガウシアンフィルタ処理画像は平滑され,円の輪郭部がぼけていることがわかる。また  $\sigma$ の大きなフィルタの方が, $\sigma$ の小さいフィルタよりも空間的に広い範囲で平滑化がなされていることがわかる。ガウシアンフィルタは注目画素の周囲の平均を計算する平均化フィルタに比べ,自然な平滑化がなされる。これは中央付近に大きな重みをもち,周辺に向かうにつれてなだらかに重みが小さくなるガウス関数の形状に起因している。ここで図 2.5 の出力画像の端はフィルタが処理できないため,黒く塗りつぶして表現している。

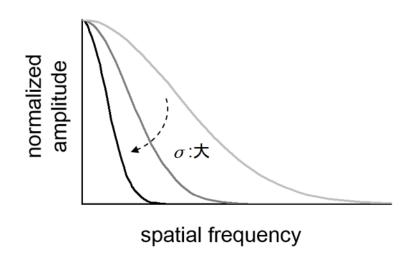

次にガウシアンフィルタの空間周波数特性について述べる. ガウシアンフィルタの空間 周波数特性を図 2.6 に示す. 図から平滑化フィルタは高周波数成分のみを遮断する低域通過

図 2.4 ガウシアンフィルタのフィルタカーネル (一次元) .  $\sigma$ が小さいほど鋭い形状をし、 $\sigma$ が大きいほど広範囲に広がる.

図 2.5 ガウシアンフィルタ処理結果.  $\sigma$ が大きいほど、平滑化度合が強い. 画像の境界領域の黒色領域は入力画素がなく、演算できない領域を表す.

特性を有していることがわかる。実空間において空間フィルタのフィルタサイズが小さい時、すなわち $\sigma$ が小さい時ほど、画像上で表現されている大まかな構造を残し、細やかな構造のみを除去する。すなわちカットオフ周波数が高域側にあり、高周波成分を多く含む細かい構造のみが除去される。一方、フィルタサイズと $\sigma$ が大きい時、図2.6の矢印で示されるように、空間フィルタの周波数成分のカットオフ周波数はより低域側になり、細やかな構造は除去され、より大きく粗い構造のみが抽出される。

図 2.6 ガウシアンフィルタの空間周波数特性.  $\sigma$ が大きいほど, カットオフ周波数が低くなる.

### 2.3.2 DoG フィルタの空間特性と空間周波数特性

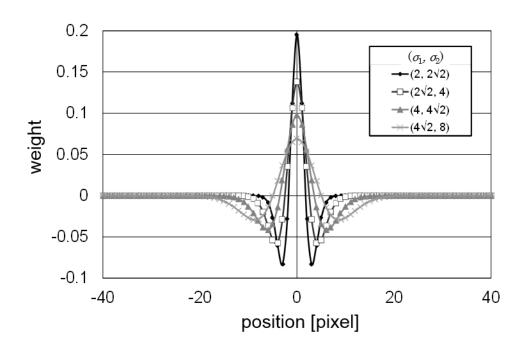

DoG (Difference of Gaussian) フィルタは異なる標準偏差の二つのガウス関数の差分のことであり、LoG (Laplacian of Gaussian) フィルタの近似として用いられることがある [13]. 一次元 DoG 関数を式 (2.5) に示す.

$$f_{DG}(x, \sigma_1, \sigma_2) = A_{GI} \exp\left(-\frac{1}{2} \frac{x^2}{\sigma_1^2}\right) - A_{G2} \exp\left(-\frac{1}{2} \frac{x^2}{\sigma_2^2}\right).$$

(2.5)

ここで  $\sigma_1$  及び  $\sigma_2$  はそれぞれのガウス関数の標準偏差であり, $A_{G1}=1\sqrt{2\pi\sigma_1^2}$ , $A_{G2}=1\sqrt{2\pi\sigma_2^2}$  は正規化係数である.次に様々なスケールの一次元  $\operatorname{DoG}$  フィルタのフィルタカーネルを図 2.7 に示す.ここで,二つの標準偏差の関係は  $\sigma_2=\sqrt{2}\sigma_1$  として  $\sigma_1$  を 2 から4 $\sqrt{2}$ まで変更した. $\sigma_2$ を大きくするとフィルタカーネルの中心の重みが低くなり,周辺に重みが広がることがわかる.ガウシアンフィルタと同様に,画像処理に通常用いられる  $\operatorname{DoG}$  フィルタのカーネルは式(2.6)で示される二次元  $\operatorname{DoG}$  関数である.

$$f_{2DG}(x, y, \sigma_1, \sigma_2) = A_{2GI} \exp\left(-\frac{1}{2} \frac{x^2 + y^2}{\sigma_1^2}\right) - A_{2G2} \exp\left(-\frac{1}{2} \frac{x^2 + y^2}{\sigma_2^2}\right).$$

(2.6)

ここで, $A_{2G1}=1/2\pi\sigma_1^2$ , $A_{2G2}=1/2\pi\sigma_2^2$  は正規化係数である.

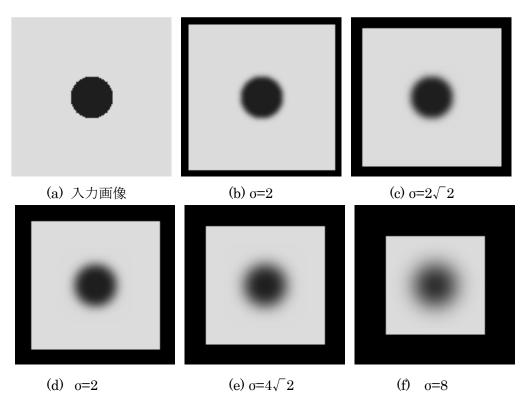

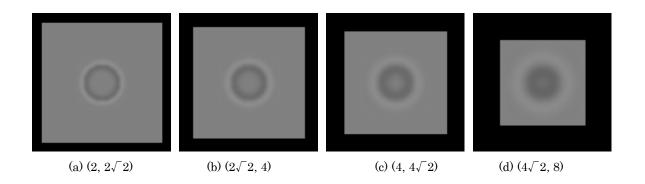

DoG フィルタは輪郭強調や特定の大きさの特徴を選択的に強調することを目的として画像に適用される. 先ほどと同様の入力画像 (図 2.5(a)) に DoG フィルタを適用した場合の出力画像を図 2.8(a)-(d)に示す.  $\sigma$ が小さいほど輪郭で鋭敏に応答しており、逆に  $\sigma$ が大きいほど輪郭で粗く応答していることが確認できる.

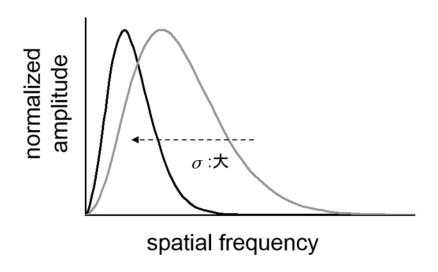

次に DoG フィルタの空間周波数特性の模式図を図 2.9 に示す。DoG フィルタの空間周波数特性はある特性の周波数帯域を通過させる特性をもつ。また DoG フィルタは  $\sigma$ が大きくなるとより低い帯域を通過させる特性となる。上記のように低域通過型空間フィルタであるガウシアンフィルタの差分は帯域通過型空間フィルタと数学的に等価となり,そのフィルタサイズを変更することで,異なる帯域通過特性が実現できる。

#### 2.3.3 実空間と周波数空間

2.3.1 節と 2.3.2 節でガウシアンフィルタ及び DoG フィルタについて, それぞれ実空間 における空間フィルタのフィルタカーネルの形状及び機能について説明した. 実空間における画像と空間フィルタの畳み込み演算は,空間周波数領域では,画像の振幅スペクトルと

図 2.7 DoG フィルタのカーネル (一次元).

図 2.8 DoG フィルタ処理. (ơ1, ơ2) は DoG のスケールを表す.

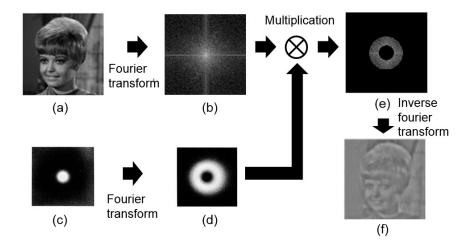

空間フィルタの空間周波数特性の掛け算となる. 図 2.10 を用いてフーリエ変換を用いたフィルタ処理について説明する. 入力画像 (図 2.10(a)) をフーリエ変換し、周波数空間で表現した結果が図 2.10(b) (振幅特性)である. また DoG フィルタ (図 2.10(c)) をフーリエ変換し、周波数空間で表現した結果が図 2.10(d)である. これらを周波数空間上で掛け算し、逆フーリエ変換することで図 2.10(f)に示されるように、空間フィルタ処理を実行することが出来る. しかし、フーリエ変換は計算コストが高いため、今回はこの方法を採用しない.

図 2.9 DOG フィルタの帯域通過特性.  $\sigma$ が大きいと, 通過帯域が低域側に移る.

## 2.4 スケーラブルフィルタ

マルチスケール解析では処理の初段で、異なるフィルタサイズの複数の空間フィルタを画像に適用する。マルチスケール解析の技術の一つに本論文の5章、6章で対象となるスケール不変特徴量[13,14]の抽出がある。この特徴量抽出のためには、初段で適用する帯域通過型空間フィルタ群がスケーラブルと呼ばれる特性を有していることが要求される。ここ

図 2.10 周波数空間でのフィルタ処理. (a) 入力画像を (b) フーリエ変換した結果と, (c) 二次元帯域通過型空間フィルタを (d) フーリエ変換した結果の掛け算した結果が (e) である. この (e) を (f) 逆フーリエ変換することで, 空間フィルタ処理が実行できる.

で、フィルタの重み関数の横方向の拡がり度合が、あるパラメータで決定される時、そのフィルタはスケーラブル性を備えているといい、このパラメータをフィルタのスケールもしくはスケールパラメータという。すなわち、スケーラブル性を備えたフィルタ(以降、スケーラブルフィルタ)とは、重み関数であるフィルタカーネルが、中心位置からの距離  $d_s$ とスケールパラメータ  $a_s$  の比の関数  $f_s$  ( $d_s$   $a_s$ )であり、かつ正規化されたフィルタと定義される。スケール不変特徴量を抽出する手法の代表である SIFT (Scale-Invariant Feature Transform) アルゴリズム[13, 14]では、スケーラブル性を備えるように標準偏差が設定された DoG (difference-of-Gaussian) 関数  $f_{DGn}(o_n)$  を採用している。そこで、DoG フィルタがスケーラブル性を備える条件を述べる。

問題を簡略化するために一次元で考える.マルチスケール解析における n 番目のガウシアンフィルタのカーネルは式 (2.3) からガウス関数は一次元において,次の式で表される.

$$f_{Gn}(x|\sigma_n) = A_G \exp\left(-\frac{1}{2}\left(\frac{x}{\sigma_n}\right)^2\right). \tag{2.7}$$

式 (2.7) からガウシアンフィルタは  $xl\sigma_n$  の関数であるため,スケーラブルフィルタである.次に二つのガウシアンフィルタの小さいスケール,大きいスケールの標準偏差をそれぞれ $\sigma_n$ と $\sigma_{n+1}$ である $\sigma_n$ 0の関係をもつとする.

$$\sigma_{n+1} = K\sigma_n (K: 正の整数).$$

(2.8)

n番目の一次元DoG 関数は式(2.5)と式(2.8)から次のように表される.

$$f_{DG_n}(x/\sigma_n) = A_{GI} \exp\left(-\frac{1}{2} \left(\frac{x}{\sigma_n}\right)^2\right) - A_{G2} \exp\left(-\frac{1}{2 \cdot K^2} \left(\frac{x}{\sigma_n}\right)^2\right).$$

(2.9)

式 (2.9) から、DoG 関数  $f_{DG}$ は  $xlo_n$ の関数であるため、スケーラブルである.

## 2.5 ソフトウェア・アルゴリズムの工夫による高速化

2.2.2 節で述べたように、空間フィルタ処理は従来の逐次型演算では非常に計算コストが高く、複数回の空間フィルタ処理を画像に実行するとなると、その計算量は膨大なものとなる。この処理を高速化するために、ソフトウェア・アルゴリズムや専用ハードウェアが開発されてきた。本節ではまずソフトウェア・アルゴリズムの先行研究をまとめる。

空間フィルタ処理を高速化するソフトウェア手法として、主に処理の範囲を限定するこ とで高速化する手法と、空間フィルタ処理自体の処理速度を向上させる手法とに分類でき る. 前者は空間フィルタに限らず一般的に画像処理を高速化する手法としてよく知られて いる. この手法ではコンピュータが事前知識をもっていない, 最初のフレームのみ画像内の 全ての画素を対象に演算を実行し, 注目領域を抽出する. 次のフレームから, コンピュータ はその領域のみ空間フィルタ処理を実行する. しかしながら, この手法は注目領域が移動す る場合,一度見失うと事前知識となる注目領域抽出処理からやり直すこととなる. また,解 析対象が画像全体でとらえている場合など,画像内を大局的に解析したい場合,この手法は 使うことができない. 後者は定時間空間フィルタ処理と呼ばれるソフトウェア・アルゴリズ ムである. 2.2.2 節で説明した通り、畳み込み演算はフィルタ幅が大きくなればなるほど、 長い計算時間が要求される.一方で、ここで紹介する手法はフィルタ幅に依存せずに、ガウ シアンフィルタ処理を定時間で適用できる. これらの定時間空間フィルタ処理は Sugimoto らの研究[54]に詳しくまとめられているため、ここでは簡略化して述べる. 定時間空間フィ ルタ処理はフィルタの重ね掛け[55,56]と再帰型フィルタ[57,58], そして拡張積分画像によ るフィルタ[59-61]の三つタイプに大別される.しかしながら入力画像のサイズが特に多い とき、これらのアルゴリズムであっても、マルチスケール画像を生成することは非常に計算 時間がかかる.

## 2.6 ハードウェアシステムによる高速化

汎用CPUには積和演算器が少ないため、膨大な積和演算処理は不得意である.そのため、

近年,汎用 GPU (General-purpose graphics processing unit) [62],DSP (Digital signal processor),FPGA (Field-programmable gate array) (例えば[63]),そして ASIC (application specific integrated circuit) [64-67]といった専用プロセッサで画像処理を実行する研究がされており,それらが比較されている[68, 69].以下に,各ハードウェアでの空間フィルタ処理についてまとめる. 汎用 GPU を採用する場合,高速に演算は実行されるが,消費電力とシステムの規模が問題となる。またコンピュータ上のメモリから GPU 側のメモリへの画像転送速度もまた一定のボトルネックとなる.DSP を採用したとしても,DSP 内に用意されている積和演算命令に対応する演算器の数に比べて,非常にフィルタサイズが大きい空間フィルタを画像に適用する場合,複数の空間フィルタ処理を高速に実行することは困難である.FPGA は組み込み画像処理システムへの搭載が進んでおり,その開発の進展は目覚ましいものがあるが,複数回空間フィルタ処理を数十 ms オーダー内で計算するには,FPGA に多くの内部ロジックを必要とする.ASIC は非常に小型・低消費電力ではあるが,特定用途に特化しており,例えばマルチスケール画像を解析することで,注目領域の抽出と,そのテクスチャの解析を同時に抽出するなど様々な応用に利用していくための拡張性を備えることは難しい.

これらのデジタルベースのハードウェア高速化手法は処理時間と消費電力を、CPU ベースの画像処理システムに比べて削減できるが、それらとシステム規模は画像の入力サイズとフィルタ幅に強く依存する.従って、画像処理システムのフロントエンドにおいて、空間フィルタ処理を行う演算器として、最善の選択とはいえない.

## 2.7 生体の外網膜とアナログ抵抗回路網

生体の視覚神経回路で実行されている計算原理を学ぶことは、情報処理機能を有する知能視覚センサのアーキテクチャを設計する上で有用である. なぜならば、生体の神経回路内の計算は、並列処理を基本としており、空間的に広がりをもった情報である視覚情報を処理するためには並列処理が本来向いているためである. 一方、現在多くの画像処理システムが逐次的に演算を実行するコンピュータで計算しているため、効率化の向上にはアーキテクチャ的な限界がある.

これまでの研究で、生体の視覚システムが多くの画像処理タスクをロバストに行うことが示されてきた。生体の視覚系は周波数帯域ごとに画像を分離した後で、各周波数に関して画像を処理する[4,70]。生物学的に合理的な視覚処理モデルがいくつか提案されており[5,6]、これらの前段の処理としても帯域分離処理が採用されている。本研究では、画像情報の帯域分離を目的に画像上の全画素並列に広域の空間フィルタを適用するにあたって、生体の網膜の構造を模倣したアナログ抵抗回路網[37,39]に着目する。抵抗回路網による空間フィルタ処理は消費電力を最小化するために最適な解決法であると考えられている[71,72]。

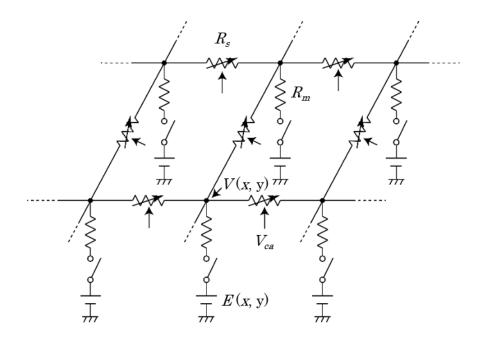

図 2.10 に二次元抵抗回路網の回路図を示す. 抵抗回路網の各ノード (x, y) は画像上の画

図 2.11 アナログ抵抗回路網. 抵抗回路網は入力ノードと出力ノード間を接続する  $R_m$  とノード間を接続する  $R_s$  とで構成される. 入力ノードには画素電圧 E(x, y)が印加される. 画素信号は  $R_s$ を介して,側方向に拡がり,出力ノードには V(x, y)が生成される.  $R_s$ の抵抗値の大きさで信号の拡がる度合が変わる.  $V_{ca}$ によって  $R_s$ の抵抗値の大きさを変更できる.

素に対応するように正方格子状に接続されている. 抵抗回路網は入力ノードと出力ノードを接続する抵抗  $R_m$  と、隣接するノードを接続する  $R_s$  で構成されている. 入力ノードには 画素値に対応する電圧源 E(x,y)が接続されており、画素信号が側方に接続された抵抗  $R_s$  を介して、隣接するノードに拡がる. その結果、出力ノードの画素電圧 V(x,y)が生成される.  $R_s$  の抵抗値の大きさによって画素信号の拡がる度合が変わる. ここでは  $V_{ca}$  によって  $R_s$  の抵抗値の大きさを変更できるとする (後述).

図 2.11 のノード (x, y) においてキルヒホッフの電流則から、次の式が得られる.

$$I_m(x, y) + \sum I_{adi}(x, y) = 0.$$

(2.10)

ここで、電流  $I_m(x, y)$ はノード(x, y)における  $R_m$ を通る電流であり、

$$I_m(x, y) = (E(x, y) - V(x, y))/R_m.$$

(2.11)

と表現できる. また  $I_{adj}(x, y)$ は  $R_s$ を流れる電流であり、次のように表現される.

$$I_{adj}(x, y) = (E(x+i, y+j) - V(x, y))/R_s,$$

(2.12)

$\geq t$ 3.  $\leq t$ 5.  $\leq t$ 6.  $\leq t$ 7.  $\leq t$ 8.  $\leq t$ 9.  $\leq t$

問題を簡略化するために、一次元抵抗回路網を考える.一次元抵抗回路網のノード上でx=0でインパルス入力を与えた時、インパルス応答は式(2.13)のように記述される[39].

$$V_{ir}(n/\lambda) = A \exp\left(-D\frac{|\mathbf{n}|}{\lambda}\right) \tag{2.13}$$

$$2\cosh\left(\frac{D}{\lambda}-1\right) = \sqrt{\frac{R_s}{R_m}} = L \tag{2.14}$$

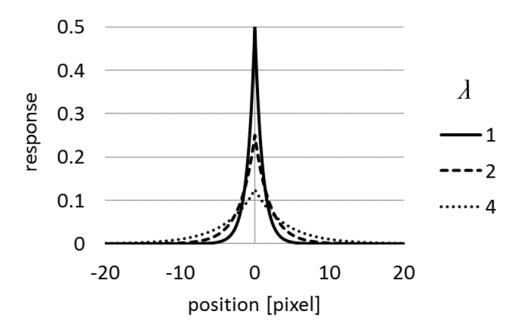

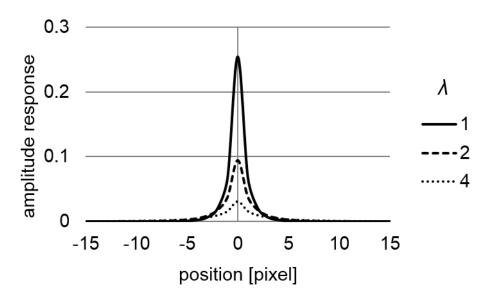

Dは二つの隣接ノードの間の距離を表現し、ここで A はインパルス入力の振幅に比例する 応答をとる。図 2.12 に  $\lambda$  が 1,2,4 の場合の応答の分布を示す。ここで  $\lambda$  の値が増加する時 により多くの距離までの信号が広がる。抵抗回路網を構成する抵抗  $R_s$  と  $R_m$  が理想的であるとき、抵抗回路網は線形である。従って、出力ノードには入力ノードの電圧に対して、インパルス応答  $V_{ir}$  を畳み込んだ出力値の電圧分布が生成される。すなわち抵抗回路網は式 (2.13) のカーネルをもつ空間フィルタ処理を実行する。この空間フィルタを抵抗回路網フ

図 2.12 一次元抵抗回路網の空間インパルス応答. 応答はインパルスの入力位置から離れるほど指数的に減衰する.  $\lambda$  によって減衰の度合が変わり、大きいほど側方向に広く信号が流れる.

ィルタ (RN フィルタ) と呼び、 $\Lambda$  はそのスケールパラメータである。また $\Lambda$  は  $R_s$  と  $R_m$  を用いて式(2.14)のようにして表される。

これらの結果から、抵抗回路網のフィルタサイズは抵抗値  $R_s$  と  $R_m$  の比を変更することで制御できることがわかる. 抵抗回路網のインパルス応答、すなわち RN フィルタの重み係数は空間的に等方的であり、そして中心からの距離が増加すると、その重みが減衰する. このことから RN フィルタはガウシアンフィルタと同様に低域通過型空間フィルタとして機能することがわかる. また RN フィルタは中心からのノード番号 n とスケールパラメータ  $\lambda$  との比の関数となっている. 従って、RN フィルタはスケーラブル性を備えている. 抵抗回路網による空間フィルタ処理は抵抗回路網の回路の時定数に基づいた時間内(数マイクロ秒(ns)オーダー)に完了する[36].

抵抗回路網は外網膜の視細胞層や水平細胞層を模擬した構造である.この細胞層は視覚入力に対して平滑化フィルタ,すなわち低周波通過型空間フィルタとして働く.ここで,同じく外網膜内にある双極細胞層は視覚入力に対して帯域通過型空間フィルタとして働くことが知られている[38].この帯域通過型空間フィルタ処理を視覚入力に適用する神経回路のアーキテクチャは二つの抵抗回路網の出力の間の差としてモデル化されている[42].本論文では,この帯域通過型空間フィルタを DoR (Difference of Resistive network) フィルタと呼ぶ.

次に、DoR フィルタのスケーラブル性を考える。DoR フィルタ処理画像は二つの RN フィルタ処理画像の差によって生成される。DoR フィルタでは差をとる二つの RN フィルタのスケールパラメータを DoG フィルタの場合と同様に適切に設定することでスケーラブル性を備えた帯域通過型空間フィルタ群を用意できる。すなわち、一つ目の RN フィルタのスケールパラメータ  $\Lambda_1$  と二つ目の RN フィルタのスケールパラメータ  $\Lambda_2$  の関係を  $\Lambda_2=K\lambda_1$  とする。スケーラブル性を有する一次元 DoR フィルタの重み関数は次のように表現される。

$$f_{DR}(\mathbf{n}/\lambda) = A_{RI} \exp\left(-D\frac{|\mathbf{n}|}{\lambda}\right) - A_{R2} \exp\left(-D\frac{|\mathbf{n}|}{K\lambda}\right),$$

(2.15)

ここで、 $A_{RI}$ と  $A_{R2}$ は正規化定数である.パラメータ  $\Lambda$ と  $K\!\Lambda$  はそれぞれ抵抗回路網フィルタの比較的小さいスケールと比較的大きいスケールをもつ抵抗回路網フィルタの空間定数である.パラメータ n は中心からのノード番号である.この式(2.15)で示される DoR フィルタのカーネルは中心からのノード番号とスケールパラメータの比となっており,スケーラブル性を有している.このフィルタを活かすことで,デジタルマスクによる DoG フィルタ処理を,アナログ抵抗回路網の物理特性を活かした高速演算に置き換えることができ,非常に低消費電力に瞬時にマルチスケール画像を生成できると考えられる.

## 2.8 シリコン網膜

生体の外網膜神経回路網の構造を模倣したアナログ抵抗回路網[37,39]は、全ての画素に対して瞬時に低消費電力で大きなサイズの低域通過型空間フィルタ処理を入力画像に適用できる.特筆する性質として、抵抗回路網によるフィルタ処理の時間はフィルタの大きさと入力画像の大きさのどちらにも依存しない. Mead と Mahowald は小型なハードウェア構成で画像取得・フィルタ処理を同時に達成するためにアナログ集積回路技術によって、シリコン網膜と呼ばれる抵抗回路網を含む視覚センサを設計・製作した[25,29]. しかしながら、従来のチップは、アナログ回路特有の素子特性のばらつきに起因する計算精度の低さにより、実際の応用に適用することは困難であった.

Mead らの先駆的な仕事に続いて、抵抗回路網を含んだ様々な小型・エネルギー効率の良い空間フィルタ処理機能を有する視覚センサが設計・製作されてきた[29-36]. これらのセンサのアーキテクチャは更に MOS トランジスタで構成された二層の抵抗回路網を含むように発展した[30,31,34,35]. これらの二つの層の出力の差をとることで帯域通過型空間フィルタ処理画像を生成する. この画像の通過帯域は二つの層の空間周波数特性によって決まる. ガウシアンフィルタに近似的なカーネルの空間フィルタを適用できるスイットドキャパシタで構成された抵抗回路網[73]や、スイッチドレジスタ型の抵抗回路網[74]もまた開発されてきた. MOS 抵抗で構成された抵抗回路網の特筆すべき利点として、μs オーダーでフィルタサイズが設定可能であることが挙げられる.

Kameda らによって開発されたシリコン網膜は自然照明下において比較的高い出力精度を持つことが確認されており、実用に近い性能が実現されている[35].この集積回路はその後改良され、ニューラルイメージ社によって製品化された("ASPECTUS-U"). 本研究ではマルチスケール空間フィルタ処理機能を有する知能視覚センサの一部として、このシリコン網膜チップを用いた.

#### 2.8.1 内部構成と動作原理

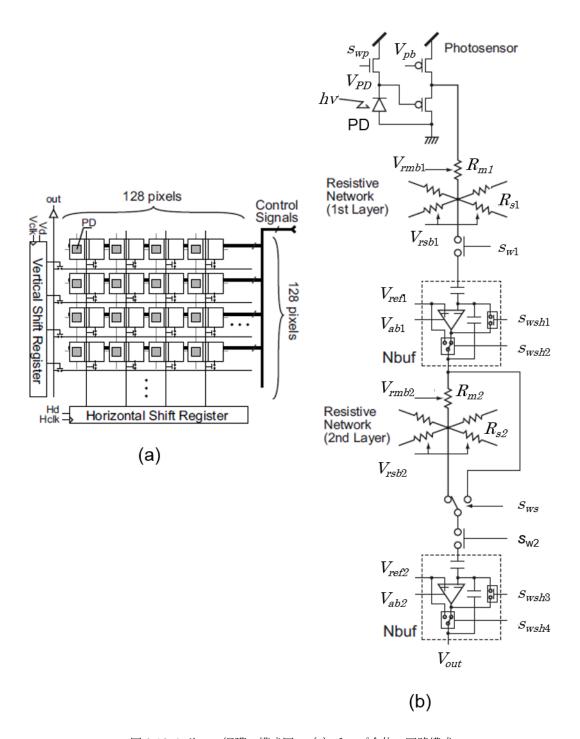

本節ではチップの内部構成と動作原理を説明する.シリコン網膜チップの回路構成を図 2.13(a)に示す.受光部 (フォトダイオード:図中 PD) と処理回路からなる画素回路が、水平および垂直方向に  $128 \times 128$  画素分並べられている.各画素は、受光面が正方格子上に配置されるように並べられている (Kameda らのチップでは  $40 \times 46$  画素が六方格子上に配置されていた[35]).チップ出力は、垂直方向、水平方向それぞれに用意されたシフトレジスタからのデータ信号により、一画素ずつ出力線(図中 out)に接続され、順に読み出される、シリコン網膜の一画素分の回路構造を図 2.13(b) に示す.

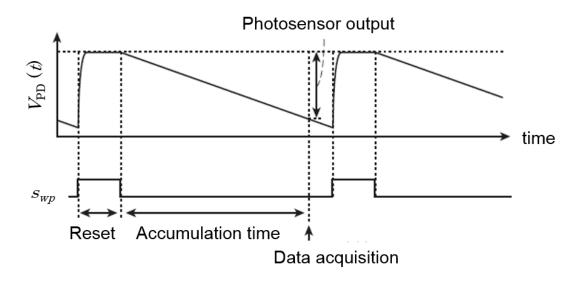

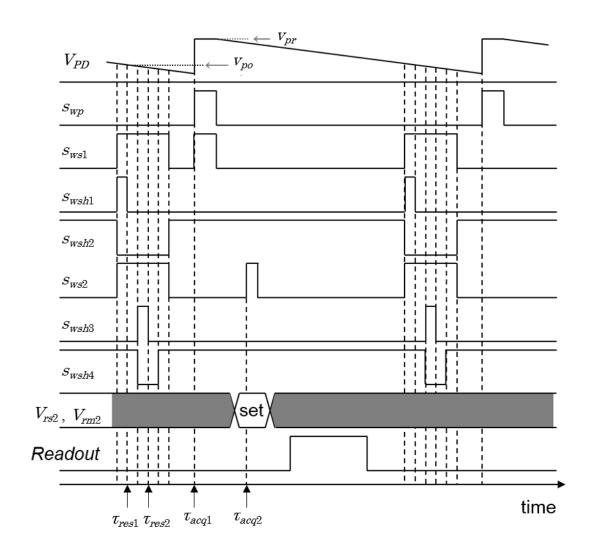

光センサ部は、フォトダイオード (PD) の寄生容量成分を利用する電荷蓄積型の光センサを採用している。この光センサ部の動作のタイミングチャートを、図 2.14 に示す。まず、nMOSFET スイッチ (制御信号を  $s_{wp}$  と表記) を ON することで、PD に逆バイアスを印

加し、その寄生容量を充電する。これを光センサ部のリセット動作(Reset)と呼ぶ。その後、*swp*によりスイッチを OFF し、PD に光が当たると、その強度に応じて寄生容量に蓄えられた電荷が放電し、PD の電位が降下する。この電位降下の大きさが光センサ出力 (Photosensor output) となる。リセット動作を終えてから、光センサ出力値が確定するまでの時間を蓄積時間 (Accumulation time) と呼ぶ。この蓄積時間を長くすることで、光強度が弱い場合でも、出力ゲインを大きくすることができる。出力ゲインが高いこの方式を採用することにより、日常の自然照明下におけるような、照度の低い環境においても十分な感度が得られる。光センサの出力電圧は、二つの pMOSFET で構成されたソースフォロア回路を介して処理回路へと出力される。このような画素構造をもつ光センサを APS (Active pixel sensor) と呼ぶため、以降の光センサ部は APS と記述する。

本センサには二つの抵抗回路網が内蔵されている. 一層目の抵抗回路網( $R_{m1}$ ,  $R_{s1}$ ), 二層目の抵抗回路網 ( $R_{m2}$ ,  $R_{s2}$ ) は,それぞれ近傍 4 画素と接続され,光センサの出力を空間的に平滑化する. 本研究では一層目の抵抗回路網は用いないため,各画素間の接続をスイッチでオフしており,二層目の抵抗回路網は用いるため,接続スイッチをオンしている. まず画素情報は固定パターンノイズ[24] をキャンセルする機能をもったノイズ補償バッファ(Nbuf)[75] に保存される. その出力が二層目の抵抗回路網 ( $R_{m2}$ ,  $R_{s2}$ ) で平滑化される. 出力段のノイズ補償バッファは,一層目,二層目それぞれの抵抗回路網のノードの値がスイッチで切り替えられて入力,差分するように設計されているが,本研究では出力段の切り替えスイッチ ((制御信号を  $s_{ws}$  と表記)) は常に二層目側に接続し,二層目の電圧応答をそのまま出力する. 抵抗回路網は,MOS 抵抗器により構成されており,図 2.13(b)の抵抗回路網に外部から印加するバイアス電圧 ( $V_{rmb2}$ ,  $V_{rsb2}$ ) によって,その抵抗値が変更できる.

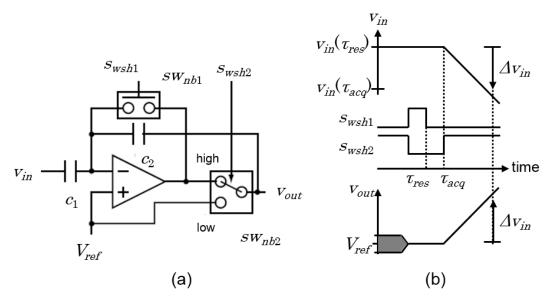

ノイズ補償バッファの動作について、簡単に説明を行う (動作の詳細は[35] 参照). ノイズ補償バッファでは、図 2.15(a) の二つのスイッチ ( $sw_{sh1}$ ,  $sw_{sh2}$ ) を、図 2.15(b) に示すように制御する事により、リセット時刻 ( $\tau_{res}$ ) における入力電圧 ( $v_{in}(\tau_{res})$ ) と、リセット後の任意のデータ取得時刻 ( $\tau_{acq}$ ) における入力電圧 ( $v_{in}(\tau_{act})$ ) の差  $\Delta v_{in}$  に応じた電圧が出力される. 出力電圧  $v_{out}$  は、以下の式で表される.

$$v_{out} = -\frac{C_1}{C_2} \left( v_{in} (\tau_{acq}) - v_{in} (\tau_{res}) \right) + V_{ref}.$$

(2.16)

このノイズ補償バッファの動作では、トランジスタのミスマッチによるオフセット電圧がキャンセルされる。このため、出力電圧における固定パターンノイズは $5\,\mathrm{mV}$ 以下となる [39]. また、光ショットノイズを始めとしたランダムノイズ[24] の影響も $5\,\mathrm{mV}$  以下である。通常の入力条件では、数 $100\,\mathrm{mV}$  の出力電圧範囲で使用できるため、ノイズは数%のオーダーとなり、大きな問題とはならない。

図 2.13 シリコン網膜の模式図. (a) チップ全体の回路構成. (b) 一画素分の回路構成.

図 2.14 光センサ部の動作のタイミングチャート.

図 2.15 ノイズ補償バッファ. (a) 回路図. (b) 制御信号のタイミングチャート.

#### 2.8.2 FPGA によるシリコン網膜の制御

シリコン網膜を用いて画像取得・空間フィルタ処理出力を得るために用いた制御信号を図 2.16 に示す. チャート左に記された信号名は、シリコン網膜の回路図 (図 2.13) に記された信号名と対応する. 最上段はフォトダイオードの出力電圧を示し、次段から八段目までのタイミングチャートはノイズ補償バッファのスイッチを制御する信号を示している. APS とノイズ補償バッファの動作については図 2.14, 図 2.15 で詳しく述べた. ノイズ補償

図 2.16 シリコン網膜の制御信号のタイミングチャート. 最上段はフォトダイオード の出力電圧 *Vpo*を, 次段から八段目まではノイズ補償バッファのスイッチを制御する 信号のタイミングチャートを示す.

バッファはサンプルアンドホールド (S/H) 回路としての機能もまた果たしている. ここでは、本研究で用いたシリコン網膜の持つ二つの S/H 回路 (S/H1, S/H2) を用いて APS の蓄積動作を途切れなく実行し、二層目の抵抗回路網の出力画像を取得する制御手法を述べる.

二層目の抵抗回路網出力を取得する手法として、前節と述べた APS 及び S/H 回路による 画像取得と異なる部分は APS の蓄積動作終了時に S/H1、S/H2 のリセット時間  $\tau_{res1}$ 、 $\tau_{res2}$  を設定することである.  $\tau_{res1}$ 時の S/H1 の出力  $v_{out1}$  は式 (2.16)に従い、

$$v_{out1} = -\frac{C_1}{C_2} \left( v_{in1} \left( \tau_{acq1} \right) - v_{in1} \left( \tau_{res1} \right) \right) + V_{ref1}. \tag{2.17}$$

となる. この時刻では、 $v_{in1}(\tau_{acq1})=v_{po}$ 、 $v_{in1}(\tau_{res1})=v_{po}$ が等しいため、 $v_{out1}=V_{ref1}$ となる. 従って、 $\tau_{res2}$ 時のS/H2 のリセット時の電圧  $v_{in2}(\tau_{res2})$ は、以下のようになる.

$$V_{in2}(\tau_{res2}) = V_{ref1}. \tag{2.18}$$

次に, tacq1 時の S/H1 の出力は,

$$v_{out1} = -\frac{C_1}{C_2} (v_{pr} - v_{po}) + V_{ref1},$$

(2.19)

となり、最終的に  $\tau_{acq2}$  時の S/H2 の出力は、次式で表わされる.

$$v_{out2} = \frac{C_3}{C_4} \times G\left(\frac{C_1}{C_2}(v_{pr} - v_{po})\right) + V_{ref2}.$$

(2.20)

ここで、 $G(\cdot)$ は二層目の抵抗回路網による変換(平滑化処理)を表現している。式(2.20)から、 $v_{pr}$ より  $v_{po}$ の方が電圧の値が大きいため、 $V_{ref2}$ を基準としてマイナス方向に信号応答が出力されるため、画素応答として正の値の方向でより明るい画素を表現するならば、A/D変換後、外部メモリに保存する際、正負の反転処理が必要となる。また式(2.19)は二層目の MOS 抵抗回路網への入力レベルと関係するため、次節で述べられる MOS 抵抗の動作域と関係する.

#### 2.8.3 MOS 抵抗回路網と MOS 抵抗

シリコン網膜に内蔵する抵抗回路網の抵抗器は MOS 抵抗により実現されている[34]. MOS 抵抗は抵抗値を高く、消費電力を低く設定でき、回路構成も単純なので高集積化に適している。また外部から与えるバイアス電圧によりその抵抗値を変化させることが可能であり、抵抗回路網の空間フィルタ特性の変更の実現に重要な役割を果たす。まず最も単純化した MOS 抵抗について説明した後に ASPECTUS-U で用いられている MOS 抵抗回路の説明を行う.

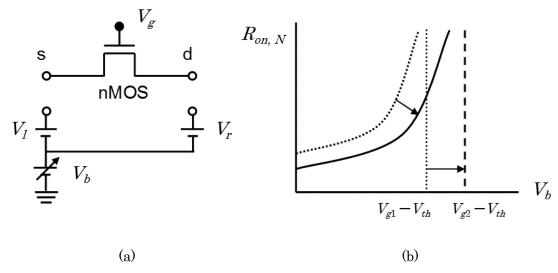

MOS 抵抗回路の最小の構成単位である MOSFET (nMOS で説明)を図 2.17(a)に、その  $V_{in}$ - $R_{ds}$ 特性を図 2.17(b)に示す[76]。MOS 抵抗は両端の電圧  $V_{ds}$ と  $V_{gs}$ によって、抵抗値が 定まる。MOS の構造は対称的であるため、nMOS の場合、ドレイン、ソースの高い電圧が 印加した方がドレイン、もう一方がソースとなる。説明のため左側をドレインとし、入力電

圧を加え、右側をソースとする.ゲート電圧  $V_g$ を一定  $V_{dd}$ とし、 $V_{in}$ を徐々に大きくする. $V_{in}$ が小さい時、 $V_g$ の方が  $V_s$ より  $V_{th}$ 以上高くなり、MOS は非飽和領域で動作する.さらに  $V_{in}$ を大きくし、 $V_{dd}$   $V_{th}$ に近づくと  $V_{gs}$  が小さくなり、図のようにオン抵抗は急激に大きくなる.ここで抵抗の線形性が保たれた動作範囲として、 $V_{ds}$  が  $V_{dd}$  -  $V_{th}$  より十分小さいという条件が成り立つ場合、抵抗値は下式のようになる.

$$R_{on} = -\frac{1}{\mu_n C_{ox} \frac{W}{I} (V_g - V_{in} - V_{th})}.$$

(2.21)

例として  $R_{on}$ の変化を 1/4 に制限するときは入力レベルの最大値は下式で与えられる. この数式内の Wはチャネル幅,Lはチャネル長を示す.

$$V_{in,max} = -\frac{3}{4} (V_g - V_{th}).$$

(2.22)

この値は  $V_{dd}/2$  程度まで劣化するため、入力振幅が極端に制限されることになる。またトランジスタのしきい値電圧は直接的に入力振幅を制限する。

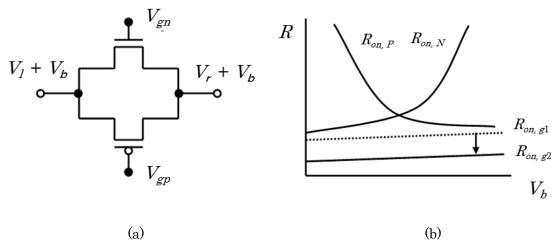

次に線形性を高め、入力振幅範囲を広げるため、図 2.18(a)に示すような CMOS 構成による MOS 抵抗について考える。NMOS と PMOS のオン抵抗の増加特性が入力電圧レベルに対し、反対の特性を有することを利用する。この MOS 抵抗はグランドから  $V_{dd}$  までのレールツーレール動作が可能であるが、相補的な制御電圧( $V_{gn}$ ,  $V_{gp}$ )が必要となる。図 2.18(b)に一般的な  $R_{on}$  の挙動を示す。オン抵抗の変動は各々単独の場合より非常に小さく、入力依存性が小さくなっていることがわかる。

本研究で用いた抵抗器の特性は抵抗回路網の空間周波数特性に影響を与えるため、画像 処理として利用できるように、抵抗値を制御できなければならない。単独の MOSFET では、実現できる抵抗値に限界があるため、通常 MOS 抵抗は、複数の MOSFET により構成されている[34]. ここで Kameda らの提案したシリコン網膜に使用されている MOS 抵抗が nMOS ベースで構成されているのに対して[35]、その線形性を上げ、動作範囲を広げるため、本研究で採用する ASPECTUS-U の抵抗回路網では CMOS 構成に改善されている[36]. 以下でその特性を説明する.

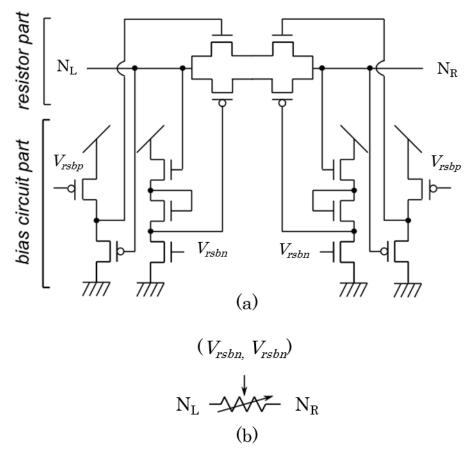

本研究では、二次元抵抗回路網の  $R_s$ の値を変更することによって、その空間特性を制御する。その MOS 抵抗回路の回路図、対応する回路記号とその特性の模式図をそれぞれ図 2.19(a)-(c)に示す。 MOS 抵抗回路は抵抗部とバイアス電圧生成回路部の二部により構成される。各 MOS 抵抗はノード  $N_L$ と  $N_R$ で隣り合う抵抗に接続される。 MOS 抵抗の抵抗値は ソース-ゲート間の電圧に強く依存する。図 2.19(c)に示すように抵抗部は PMOS トランジスタと PMOS トランジスタで構成されており、その相補性から入力電圧依存性を抑える構

図 2.17 MOS 抵抗. (a) nMOSFET. (b) 可変抵抗特性.

#### 成をとっている.

バイアス回路部は  $V_{rsbn}$  と  $V_{rsbp}$  の電圧によって決定される電圧を PMOS トランジスタと NMOS トランジスタにそれぞれ適用する. バイアス電圧  $V_{rsbn}$  を高くすることで抵抗部の PMOS の抵抗値を下げることができ、 $V_{rsbp}$  を低くすることでも、NMOS の抵抗値を下げることができる. 電流の通り道となる PMOS と NMOS の両方の抵抗値が増加,もしくは減少するように  $V_{rsbn}$  と  $V_{rsbp}$  を同時に制御することによって, $R_s$  の抵抗値を制御することができる. バイアス電圧によって制御される MOS 抵抗回路の抵抗値を変化させるためにかかる時間は非常に短く,本研究で用いた抵抗回路網の場合, $\mu$ s オーダーである. また研究段階ではあるが,更に抵抗値の精度の良い,抵抗回路網もまた提案されている [74].

図 2.18 CMOS 構成の MOS 抵抗. (a) CMOS 回路. (b) 可変抵抗特性.

図 2.19 (a) MOS 抵抗回路  $R_s$ の回路図[40]. (b) MOS 抵抗回路に対応する回路記号. 各 MOS 抵抗はノード  $N_L$  と  $N_R$  で隣り合う抵抗と接続されている. MOS 抵抗  $R_s$  の抵抗値は外部制御電圧の組み合わせ ( $V_{rsbn}$ ,  $V_{rsbp}$ ) で決定される. (c) バイアス電圧に対する抵抗値の変化.

#### 2.9 結言

本章では、逐次型演算による空間フィルタ処理について述べた後に、マルチスケール空間フィルタ処理の計算コストに関する問題点を述べた。空間フィルタ処理の高速化についてソフトウェアとハードウェアのそれぞれの観点から、これまで行なわれてきた高速化手法について紹介した。

本研究では、従来のデジタル演算器ではなく、生体網膜の神経回路の構造に学んだアナログ抵抗回路網に着目する。この抵抗回路網では全画素並列に効率的に空間フィルタ処理を実行できる。また構成している抵抗の値を変更することで、適用する空間フィルタの空間特性を制御できる。これまでの研究では、光センサと二層の抵抗回路網で構成されるシリコン網膜と呼ばれる知能視覚センサが提案されており、これは効率よく、ある一つの周波数帯域を通過させる帯域通過型空間フィルタ画像を取得できるものであった。

上記で述べたシリコン網膜は、CMOS集積回路技術で実現されており、その抵抗はMOSトランジスタで構成されている。MOS抵抗は外部からの制御電圧により、抵抗値を制御できる。次章からは、このMOS抵抗の抵抗値を制御することで、様々な空間特性の空間フィルタ処理を実時間で実行する知能視覚センサの開発について述べる。

# 第3章 複数の帯域通過型空間フィルタ処理 機能を有する知能視覚センサの開発

#### 3.1 緒言

自然画像上には、様々なスケールの様々な幾何学的特徴を持つ物体が表現されている. そのような画像には様々な空間周波数成分が含まれている[10]. 画像から情報を抽出するためには、複数の異なる帯域通過特性を持つ空間フィルタを用いて、空間周波数帯域ごとに画像を分割し、様々なスケールで特徴を解析することが有効である[2,7,8]. マルチスケール解析や周波数分離画像処理には多くの利点があることが先行研究によって示され、コンピュータビジョン分野の研究者に注目されてきた[13-21]. 例えば、マルチスケール解析はステレオマッチング[12,15]、オプティカルフロー推定[17]など幅広く利用されている. しかしながら、デジタル画像処理システム上での逐次計算によるアルゴリズムを採用した場合、積和演算の多い空間フィルタ処理を複数回画像に適用しなければならないため、この処理は非常に高い計算量となる. そのため実時間で画像を空間周波数帯域ごとに分離することは難しい.

第2章で述べたように、ソフトウェア[54-61]及びハードウェア[62-67]の工夫による画像センシングシステムの高速化の研究が行われてきた。本研究では網膜の構造を模した集積回路である、シリコン網膜と呼ばれる視覚センサに着目する。この視覚センサは全画素同時に瞬時に空間フィルタが実行できる抵抗回路網を有する。過去の研究では、異なる抵抗値の二層の抵抗回路網を用いて、固定の帯域通過特性を有する空間フィルタ、すなわちシングルスケールの空間フィルタを画像に適用するシリコン網膜が提案されている[35]。本研究では、単一フレーム内で異なる通過帯域をもつ複数の空間フィルタを画像に適用することにより、空間周波数帯域ごとに画像を分離することのできる知能視覚センサのアーキテクチャを提案する。更にそのアーキテクチャに基づいて新しい知能視覚センサを構築し、そのセンサに対してテスト画像を提示し、センサの出力画像を評価した。実験の結果から、本システムの有用性を示すことができた[77,78]。本章では、その知能視覚センサの開発に関する研究内容をまとめる。

更に次節では、提案する知能視覚センサのアーキテクチャと処理の流れについて述べる. 次いで、提案システムの空間特性と空間周波数特性を測定し、評価した結果について述べる. その後、センサの有用性を実証するため、開発した知能視覚センサにテスト画像を提示し、 その出力を評価した結果を述べる. 最後に本センサで単一フレーム内に適用できる空間フィルタ処理の数と、抵抗回路網の入力依存性について考察し、本章をまとめる.

## 3.2 知能視覚センサの構成と処理の流れ

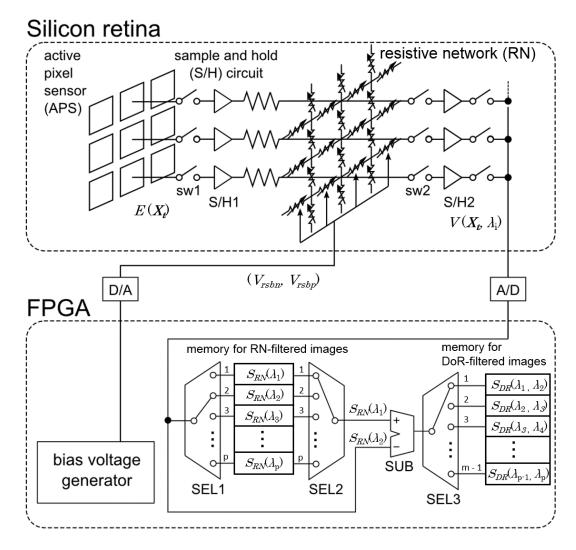

図 3.1 に本研究で提案された知能視覚センサの構成を示す。本センサはシリコン網膜  $(128 \times 128 \text{ 画素})$ , FPGA (XC3S400, Xilinx), A/D 変換器, そして USB インターフェース で構成されている。このシリコン網膜は APS, 二つのサンプルアンドホールド回路 (図中

図 3.1 提案した知能視覚センサの構成. 本センサはシステム網膜と FPGA で構成される. このシリコン網膜は APS と抵抗回路網で構成されている. 抵抗回路網の抵抗値はバイアス電圧  $V_{rsbn}$ と  $V_{rsbp}$ によって制御される. バイアス電圧は FPGA から D/A 変換器を介して抵抗回路網に与えられる. FPGA 内の  $S_{RN}(\lambda_n)$ と  $S_{DR}(\lambda_n)$ のブロックはそれぞれ RN フィルタ処理画像と DoR フィルタ処理画像を記録するためのメモリを表現している. SEL1, SEL2, そして SEL3 はセレクタを表現している. 図 3.2 にこれらのセレクタによって選択された接続に関するタイミングチャートを示す.

S/H1, S/H2), 抵抗回路網 (図中 RN), そして読み出し回路で構成されている. FPGA 内には APS, S/H 回路と読み出し回路のための制御信号を生成するデジタル回路, 抵抗回路網へのバイアス電圧を指定するためのコマンド信号を生成するデジタル回路, そして画像処理のためのデジタル回路が実装されている. 図 3.2 に画像取得, RN フィルタの適用, FPGA上での演算に関するタイミングチャートを示す. ここでは t フレーム目に実行される処理の流れが示されている.

まず図 3.2 内の時刻  $t_s$ に一つ目のスイッチ(図 3.1 内の sw1) が閉じ,  $x \cdot y$  平面に配置された t フレーム目の APS の出力  $E(X_t)$  が S/H1 に保持される. ここで,  $X_t = (x, y, t)$  であり、x = 1, 2, ... 128 と y = 1, 2, ... 128 はそれぞれ画像の横方向と縦方向の画素の位置である. また t = 1, 2, ...はフレーム数である. S/H1 への保持動作が終了後, sw1 を開き, APS が次のフレームの蓄積動作を始める. この動作により, 蓄積動作と後段の処理を切り離すことができ、途切れなく画像取得・画像処理ができる.

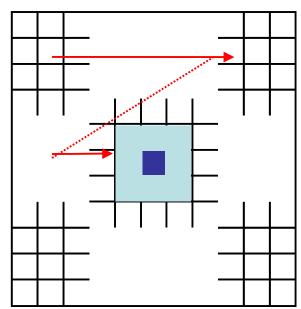

S/H1 に保存された E(X)は、抵抗回路網によって瞬時にフィルタ処理され、その出力応答  $V(X_t, \lambda)$  が S/H2 に保持される。2.6 節で述べたように、RN フィルタのスケールパラメータ  $\lambda$  の値は抵抗回路網を構成する抵抗器の抵抗値の比によって決定される。FPGA から送られた外部バイアス電圧  $V_{rsbn}$ 、  $V_{rsbp}$  の組み合わせによって、まず最もスケールパラメータが小さくなるように、すなわちカットオフ周波数が最も高くなるように、抵抗回路網の側方抵抗  $R_s$  の抵抗値が最も高い値に設定される。この時の抵抗回路網のスケールパラメータ  $\lambda_1$  とし、空間フィルタを  $f_{RN}(\lambda_1)$ と表現する。sw2 が閉じ、S/H2 には  $f_{RN}(\lambda_1)$ でフィルタ処理された画像  $S_{RN}(\lambda_1)$ が保存される。sw2 が開かれた後、フィルタ処理画像  $S_{RN}(\lambda_1)$ が A/D 変換器によって、Sbit に変換後、 $S_{RN}(\lambda_1)$  に送られ、 $S_{RN}(\lambda_1)$  用のメモリ領域に保存される。次に、ある一定の値分  $S_{RN}(\lambda_2)$  に設定する。図  $S_{RN}(\lambda_1)$  ののサイミングで、空間フィルタ  $S_{RN}(\lambda_2)$  を  $S_{RN}(\lambda_2)$  に適用する。その後  $S_{RN}(\lambda_2)$  は  $S_{RN}(\lambda_2)$  に  $S_{R$

次のサンプル時間(図 3.2 内  $\tau$ )まで,この手順の繰り返すことで,様々なカットオフ周波数の RN フィルタで処理された低域通過処理画像群が生成される. tフレーム目と同様に,t+1番目のフレームの APS 出力  $E(X_{t+1})$ が,時刻  $\tau$ 。で sw1 が再度閉じ,S/H1 に保存される.抵抗回路網の処理時間は画像の読み出し時間と比較して十分短いため,一フレームの中で適用できるフィルタの最大の数 m は読み出し時間によって制限される.このフィルタ処理画像の数 m については考察で議論する.本研究では m の値は 4 とした.

保存される.

取得された RN フィルタ処理画像群を FPGA 上の回路で差を取ることで帯域ごとに画像を分離する処理が実行される. 異なる低域通過特性を有する RN フィルタ処理画像間の差を取る処理は生画像に帯域通過型空間フィルタを適用することと等価である. この帯域通過型空間フィルタ処理を DoR フィルタ処理と呼び, 処理画像を DoR フィルタ処理画像と

図 3.2 画像取得と抵抗回路網によるフィルタ適用についてのタイミングチャート. 最上段の行は画像取得と APS の蓄積開始の時刻を示す. 二番目の行は様々なカットオフ周波数で空間フィルタの適用の時刻. 三番目と最下段の行は, 個々の空間フィルタ適用とフィルタ処理画像の取得のためのセレクタ SEL1, SEL2, そして SEL3 の時刻をそれぞれ示す.

呼ぶ. n番目の  $\mathrm{DoR}$  フィルタ処理画像  $S_{DR}(\lambda_{\mathrm{n}})$ は, シリコン網膜部から  $S_{RN}(\lambda_{(\mathrm{n+1})})$ が読み出 される区間に、並列に生成される. この処理について図 3.1 の記号を用い、図 3.2 内の  $\pi$ - $\mathbb{Z}_2$  の区間を例に説明する. 時刻  $\mathbb{Z}_1$  において既に  $S_{RN}(\lambda_1)$ は RN フィルタ処理画像を保存す るメモリ領域 (図 3.1 中の memory for RN-filtered images ブロック. 以下, RN 用メモリ) に保存されており、次の  $v_2$ までの区間で  $S_{RN}(\lambda_2)$ が一画素ずつ読み出され、  $S_{RN}(\lambda_1)$ とは異 なるメモリ番地に保存される.メモリの書き込み番地はセレクタ SEL1 によって指定され、  $\tau_1$ - $\tau_2$ 区間では SEL1 は端子 2 に接続されている.  $S_{RN}(\lambda_2)$ は RN 用メモリへ保存されると同 時に,差分器 SUB に入力される.SEL2 は RN 用メモリの読み出し番地を指定するための セレクタである.一つ前の区間に保存された画像  $S_{RN}(\lambda_1)$ を読み出すために,SEL2 は端子 1 に接続される. 読み出された  $S_{RN}(\lambda_1)$ は SUB のもう一端に入力される. SUB で  $S_{RN}(\lambda_1)$ と  $S_{RN}(\lambda_2)$ の差が取られ、得られた  $S_{DR}(\lambda_1)$ の画素値がセレクタ SEL3 を介して DoR フィ ルタ処理画像を保存するメモリ領域(図 3.1 中の memory for DoR-filtered images ブロッ ク. 以下, $\mathrm{DoR}$  用メモリ)に保存される. $\mathit{Sor}(\lambda_{\mathrm{n}})$ の  $\lambda_{\mathrm{n}}$  の添え字  $\mathrm{n}$  が小さいほど,帯域が より高い周波数であることを表しており、より詳細な構造を表現している画像となる. 最終 的に,これらのフィルタ処理画像は,USB インターフェースを介して,デジタルコンピュ ータのような後処理用の画像処理装置に転送される. 以上の仕組みにより, この知能視覚セ ンサは単一フレーム (20ms) の間に複数の空間フィルタ処理とフィルタ処理画像の読み出 しを完了できる.

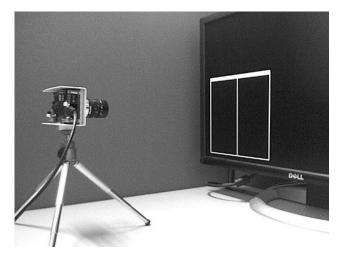

#### 3.3 MOS 抵抗回路網の空間特性の測定

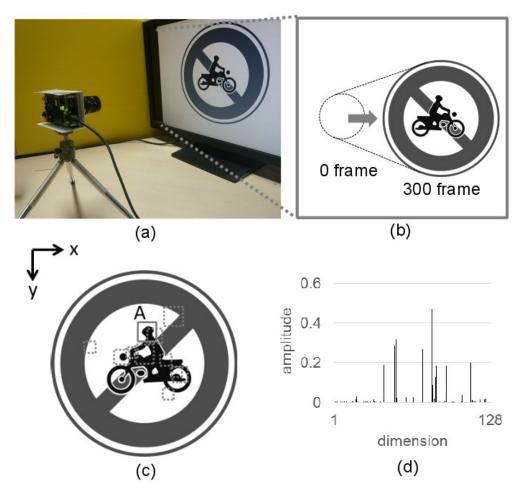

提案した知能視覚センサを用いて、内蔵されている MOS 抵抗回路網の空間特性の測定を行った。図 3.3 に示すように、50cm の距離でセンサ前方に置かれた液晶ディスプレイ (Liquid Crystal Display; LCD) 上に視覚刺激を提示することによって評価を行った。視覚刺激にスリット光のパターンを用いることで、抵抗回路網の線拡がり関数 (line spread function)を測定した。光パターンは搭載されたレンズ(最大 f値:4) を介してセンサ受光面に投射される。抵抗回路網の空間特性は MOS 抵抗  $R_s$  への電圧  $V_{rsbn}$  と  $V_{rsbp}$  の両方を変更することで制御できる(2.6 節,2.7.3 節を参照)。以下、バイアス電圧は( $V_{rsbn}$ 、 $V_{rsbp}$ )と表現する。まず四つの異なる低域通過特性をもつ RN フィルタ  $f_{RN}(\lambda_1)$ 、 $f_{RN}(\lambda_2)$ 、 $f_{RN}(\lambda_3)$ 、 $f_{RN}(\lambda_4)$ の空間特性を測定した。これらのフィルタのスケールパラメータ  $\lambda_1$ 、 $\lambda_2$ 、 $\lambda_3$ 、 $\lambda_4$  に対応するバイアス電圧の組み合わせは、それぞれ(0.50V, 2.75V)、(0.60V, 2.40V)、(0.73 V, 2.20 V)、そして(1.25V, 1.43V)である。またこの時の各空間フィルタの  $R_s$ の関係を以下に示す。

$$R_s \text{ of } f_{RN}(\lambda_1) > R_s \text{ of } f_{RN}(\lambda_2) > R_s \text{ of } f_{RN}(\lambda_3) > R_s \text{ of } f_{RN}(\lambda_4).$$

(3.1)

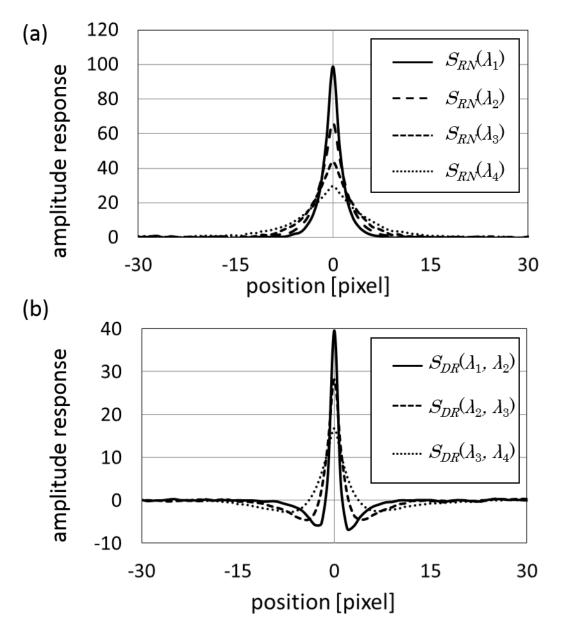

図 3.4(a)にスリット光を視覚刺激とした時の抵抗回路網による低域通過型空間フィルタ処理画像  $S_{RN}(\lambda_n)$  (n=1,2,3,4)の水平方向の応答振幅の分布を示す.これはフィルタ処理画像の 44 番目から 84 番目までの水平方向 40 行の応答の平均である.この図が示すように,信号は  $R_s$  がより低い値の時ほど,側方向により長く拡がる.これは,2 章で示したシミュレーションと同様の結果である(図 2.12 参照).

図 3.3 実験環境. 知能視覚センサは LCD に描画された視覚刺激(ここでは縦のスリット光)を受け取り、USB インターフェースに介して PC に帯域通過型空間フィルタ処理画像を転送する.

図 3.4 提案した知能視覚センサの空間特性. (a) 抵抗回路網による低域通過型空間フィルタの線拡がり関数. 凡例の  $\lambda$  の添え字 n は抵抗回路網フィルタの各スケールパラメータの番号を示す. この番号は図 3.2 と対応している. n がより大きいとき,よりスケールパラメータ  $\lambda$  も大きくなり,抵抗回路網フィルタがより低いカットオフ周波数を持つことを表している.  $\lambda$  の値はバイアス電圧の組み合わせ( $V_{rsbn}$ ,  $V_{rsbp}$ )V で設定する. 四つの低域通過型空間フィルタ  $f_{RN}(\lambda_1)$ ,  $f_{RN}(\lambda_2)$ ,  $f_{RN}(\lambda_3)$ ,  $f_{RN}(\lambda_4)$ に与えられたバイアス電圧はそれぞれ(0.50, 2.75)V,(0.60, 2.40) V,(0.73, 2.20) V,(1.25, 1.43)V である. (b) 知能視覚センサによる帯域通過型空間フィルタの線拡がり関数. 三つのサイズの帯域通過型空間フィルタが実現できている.

次に知能視覚センサによって適用できる帯域通過特性を持つ DoR フィルタ foR の空間特性を同様の手法で測定した. 図 3.4(b)にスリット光を視覚刺激として提示した時に得られた三つの DoR フィルタ処理画像  $SoR(A_1, A_2)$ ,  $SoR(A_2, A_3)$ ,  $SoR(A_3, A_4)$ の水平方向の応答振幅の分布を示す. RN フィルタ処理画像の場合と同様に、この応答振幅は 44 番目から 88 番目までの水平方向の応答振幅の平均である.  $SoR(A_n, A_{n+1})$ は図 3.4(a)に示される異なるカットオフ周波数で低域通過処理をされた RN フィルタ処理画像  $SRN(A_n)$ と  $SRN(A_{n+1})$ の間の差を取ることによって得られた. 各応答は、他の帯域通過型空間フィルタの線拡がり関数と同様に、中心で正に、周辺で負に応答していることがわかる. この結果から、開発した知能視覚センサにより三つのサイズの帯域通過型空間フィルタが適用できることを実証できた.

## 3.4 MOS 抵抗回路網の空間周波数応答の測定

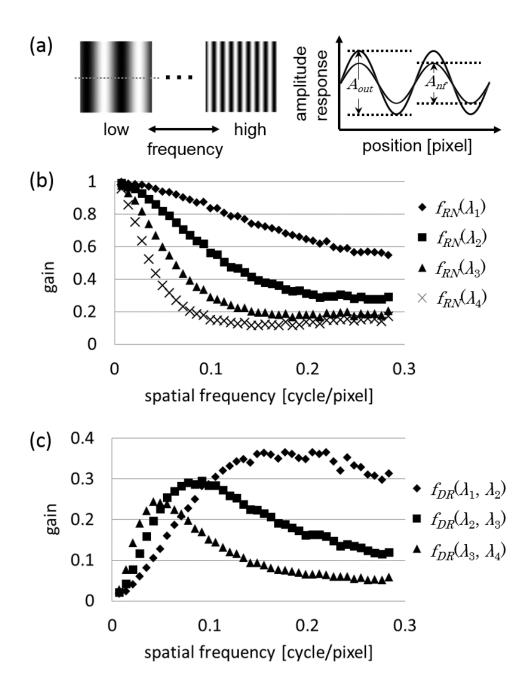

LCD に様々な空間周波数の正弦波パターン(図 3.5(a))を提示することによって、MOS 抵抗回路網の空間周波数特性を測定した. 前節で述べた四つの RN フィルタ  $f_{RN}(\Lambda_1)$ ,  $f_{RN}(\Lambda_2)$ ,  $f_{RN}(\Lambda_3)$ ,  $f_{RN}(\Lambda_4)$ の特性を測定対象とし、抵抗回路網を構成する MOS 抵抗  $R_s$ へのバイアス電圧は前節と同様とした.空間周波数応答は各空間周波数の正弦波パターンに対する抵抗回路網のゲインである.抵抗回路網のゲインは  $A_{out}/A_{nf}$ の式で計算された.ここで  $A_{out}$  は RN フィルタ処理画像  $S_{RN}(\Lambda_n)$ の正弦波(図 3.5(a)右図の灰色の実線)の振幅応答である. $A_{nf}$ はスケールパラメータ  $\Lambda$  を最小に設定した場合の RN フィルタ処理画像  $S_{RN}(\Lambda_0)$ の正弦波(図 3.5(a)右図の黒色の実線)の振幅応答である.ここで  $R_s$ へのバイアス電圧を制御し,その抵抗値を最大にした時のスケールパラメータを  $\Lambda_0$  とする.

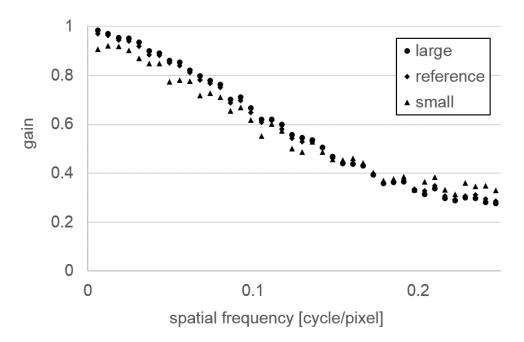

図 3.5(b)にこうして求めた RN フィルタ  $f_{RN}(\lambda_1)$ ,  $f_{RN}(\lambda_2)$ ,  $f_{RN}(\lambda_3)$ ,  $f_{RN}(\lambda_4)$ の空間周波数 応答を示す。この結果は抵抗回路網が低域通過型空間フィルタとして動作し, $R_s$  の抵抗を変更することで,そのカットオフ周波数が制御できるということを示している。四つの抵抗回路網フィルタ  $f_{RN}(\lambda_1)$ ,  $f_{RN}(\lambda_2)$ ,  $f_{RN}(\lambda_3)$ ,  $f_{RN}(\lambda_4)$ の  $R_s$  の抵抗値は式(3.1)で述べた関係を持つ。従って,図から  $\lambda_n$  の添え字 n が小さいほど,すなわち  $R_s$  の抵抗値が増加するほどカットオフ周波数が増加していることがわかる。

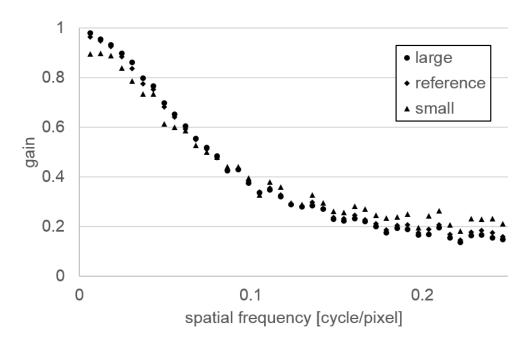

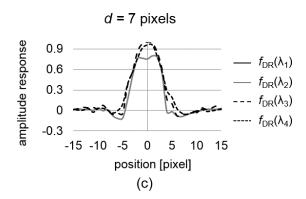

次に、知能視覚センサによって適用できる DoR フィルタ  $f_{DR}(\lambda_1, \lambda_2)$ ,  $f_{DR}(\lambda_2, \lambda_3)$ ,  $f_{DR}(\lambda_3, \lambda_4)$ の空間周波数応答を測定した。 測定手法は DoR フィルタ処理画像  $S_{DR}(\lambda_n, \lambda_{n+1})$ の出力振幅を  $A_{out}$  とした点以外は RN フィルタを測定した場合と同様である。 測定結果を図 3.5(c) に示す。この結果は  $f_{DR}(\lambda_1, \lambda_2)$ ,  $f_{DR}(\lambda_2, \lambda_3)$ ,  $f_{DR}(\lambda_3, \lambda_4)$ が,それぞれ画像中で 6.4 画素,10.9 画素,28.2 画素程度の大きさの周期構造を主に強調できるフィルタであると示している。 上記より,開発した知能視覚センサが  $R_s$  を制御することで,異なる通過帯域を有する空間フィルタを適用できることを実証できた.

図 3.5 視覚センサの空間周波数応答. (a) 視覚刺激として用いられた正弦波グレーティングパターン (左). 正弦波グレーティングの灰色点線上の水平振幅応答 (右).  $A_{out}$ は RN フィルタ処理信号の振幅応答を、 $A_{nf}$ は  $\lambda$  を最小に設定した場合 ( $\lambda_0$ ) のフィルタ処理信号の正弦波の振幅応答をそれぞれ示す. (b) 低域通過特性を持つ RN フィルタ  $f_{RN}(\Lambda_1)$ ,  $f_{RN}(\Lambda_2)$ ,  $f_{RN}(\Lambda_3)$ ,  $f_{RN}(\Lambda_4)$ の空間周波数応答. バイアス電圧 ( $V_{rsbn}$ ,  $V_{rsbp}$ ) は図 3.4 に示した値と同じである. (c) 帯域通過特性を持つ DoR フィルタ  $f_{DR}(\Lambda_1, \Lambda_2)$ ,  $f_{DR}(\Lambda_2, \Lambda_3)$ ,  $f_{DR}(\Lambda_3, \Lambda_4)$ の空間周波数応答. 帯域通過処理画像は二つの RN フィルタ処理画像の差をとることで得られた.

## 3.5 画像に対するセンサの出力応答の測定

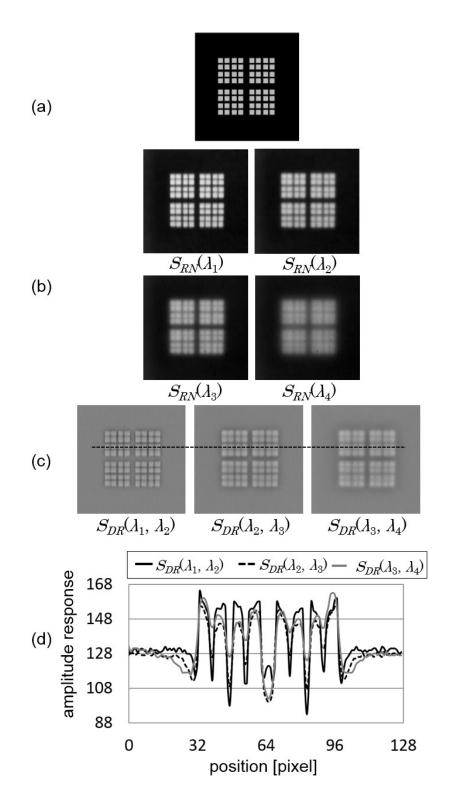

最後に,LCD に画像を表示し,それを知能視覚センサに提示することで,センサの応答 を評価する. 視覚刺激として、図 3.6(a)に示す大きさの異なる複数の四角形を組み合わせた 画像を用いた. 図 3.6(b)に RN フィルタ  $f_{RN}(\lambda_1)$ ,  $f_{RN}(\lambda_2)$ ,  $f_{RN}(\lambda_3)$ ,  $f_{RN}(\lambda_4)$ によって, フィ ルタ処理された画像  $S_{RN}(\lambda_1),~S_{RN}(\lambda_2),~S_{RN}(\lambda_3),~S_{RN}(\lambda_4)$ を示す.図 3.6(c)に  $\operatorname{DoR}$  フィル  $\mathcal{F}_{FDR}(\lambda_1, \lambda_2), f_{DR}(\lambda_2, \lambda_3), f_{DR}(\lambda_3, \lambda_4)$ によってフィルタ処理された画像  $S_{DR}(\lambda_1), S_{DR}(\lambda_2),$  $S_{DR}(\lambda_3)$ を示す. これらのフィルタの空間周波数特性は図 3.5 で示したものと同様である. 図 3.6(d)に,図 3.6(c)の点線上の行の応答振幅の空間分布を示す. $\mathrm{DoR}$  フィルタ  $\mathit{for}(\lambda_1,\lambda_2)$ を用いて,フィルタ処理された画像の信号 (図 3.6(d)内の黒色の実線) は他のフィルタ処理 信号に比べ、より入力信号の細やかなテクスチャ構造を強調して表現していることがわか る. これは DoR フィルタ  $f_{DR}(\lambda_1, \lambda_2)$ の通過帯域が適用した空間フィルタの間で最も高いた めである. 一方で、DoR フィルタ  $f_{DR}(\lambda_3, \lambda_4)$ によってフィルタ処理された信号は低周波帯 域を通過させるため,細やかなテクスチャ構造が抑制され,四角形のグループ全体の輪郭, すなわち大まかな構造を強調して表現していることがわかる (図 3.6(d)の灰色の実線). こ れらの帯域通過処理画像は 20ms 内にフレーム落ちなく取得できた. 以上の結果から, 提案 した知能視覚センサによって、異なる帯域通過特性を有する複数の空間フィルタ処理画像 が実時間で取得できることが確認できた.

## 3.6 考察

#### 3.6.1 提案するアーキテクチャの利点

我々は単一フレーム内に複数の空間フィルタを効率よく実行できる,新しい知能視覚センサのアーキテクチャを提案した.アーキテクチャに基づいて構築した試作機は複数回の空間フィルタ処理を実時間で実行できた.このアーキテクチャは高速で画像取得・フィルタ処理を実行するシリコン網膜とそれを制御するデジタル回路で構成されている.本アーキテクチャを採用した知能視覚センサは,抵抗回路網の空間特性を制御信号で動的に変更することで,コンパクトな構成でかつ,低消費電力で,実時間処理が実現できた.本知能視覚センサと,逐次型演算を実行する従来の画像センシングシステムとの主な違いは、センサのフロントエンドにある,全画素同時並列演算を実行するアナログ抵抗回路網と,次段にある画像情報の並列演算回路が実装できる FPGA で構成されている点である.本章では、FPGAは抵抗回路網の制御信号生成と差分演算の目的のみで利用したが,次章から詳細を述べるように本アーキテクチャは FPGA 内にミッションに応じた画像処理モジュール群を並列に配置することで,様々な画像特徴量を抽出できる拡張性を備えている.

提案したアーキテクチャに基づいて構築された試作機は USB バスパワー (2.5 ワット)で動作する. これは現在の一般的なデスクトップ・コンピュータが演算のために数十ワット

図 3.6 四角形のグループの画像への応答. (a) 入力画像. (b) RN フィルタ  $f_{RN}(\lambda_1)$ ,  $f_{RN}(\lambda_2)$ ,  $f_{RN}(\lambda_3)$ ,  $f_{RN}(\lambda_3)$ の出力画像. バイアス電圧は図 3.4 と同様である. (c) 帯域 通過型空間フィルタ  $f_{DR}(\lambda_1, \lambda_2)$ ,  $f_{DR}(\lambda_2, \lambda_3)$ ,  $f_{DR}(\lambda_3, \lambda_4)$ の出力画像. (d) カラム(c)の 点線によって示された行の応答プロファイル.

かかることに比べて、非常に低消費電力である.

汎用デジタルコンピュータ上で複数回の空間フィルタ処理を実行するとなると、それにかかる計算時間は画像サイズや空間フィルタのサイズに、式(2.2)に示すように非常に強く依存するのに対して、本アーキテクチャを採用したセンサではほぼ影響しない。これは汎用デジタルコンピュータ上では、空間フィルタ処理のための積和演算を一画素一画素、逐次的に実行しているためである。一方で、抵抗回路網による空間フィルタ処理の計算コストは画像サイズにも空間フィルタのサイズにもほぼ依存せず、空間フィルタ処理は µs オーダーで実行できる。

#### 3.6.2 単一フレーム内に適用できる空間フィルタの数について

本研究で提案した戦略の場合,空間フィルタ処理を複数回適用するために,単一フレーム内に適用できる帯域通過フィルタの最大の数は抵抗回路網の処理時間,画像の読み出し時間,蓄積時間の三つの要素で決定される.本研究で構築した試作機では画素数が128×128画素であり,その一画素を読み出すために約200nsかかる.従って,試作したセンサでは全画像データを逐次的に読み出すため,画像の読み出しに約3.3msほど必要である.抵抗回路網による処理と空間特性の変更に必要な時間は双方ともアナログ回路の整定時間に達するまでに要する時間となる.これらの期間は本研究で用いられた抵抗回路網ではμsオーダーである.抵抗回路網による空間フィルタ処理に要する時間は画像の読み出しに比べて非常に短いため,蓄積時間内に帯域通過型空間フィルタの適用できる数は,読み出し時間によって決定される.従って,単一フレーム内に空間フィルタを適用できる数を増やすことを考えた場合,読み出し速度が現段階におけるボトルネックとなる.この問題の解決方法の一つとして列並列型のA/D変換器の採用が挙げられる[79].列並列型A/D変換は高速度での画像読み出しを達成できる.この技術を採用することで,提案したセンサは非常に高速に帯域通過型空間フィルタを適用でき,数百のフィルタ処理画像を実時間で得る見込みがある.

#### 3.6.3 MOS 抵抗の入力電圧レベルの依存性

提案した知能視覚センサで採用した抵抗回路網内の MOS 抵抗は, 2.7.3 節で述べたように, 入力電圧レベルの依存性を抑えるために CMOS 抵抗の構成をとっている. しかしながら, CMOS 抵抗の構成をとっていてもなお, 抵抗回路網の空間特性は入力電圧レベル, すなわち入力光の強度に依存する. 本節では, その入力電圧レベルに対する依存性について実験し, 結果を考察したことをまとめる. 入力電圧レベル依存性は, 屋外から屋内にカメラが移動する場合など, 視覚環境が時々刻々と変化する応用において問題となる. この問題は, シリコン網膜がレベルシフト機能を有するために, 抵抗回路網への入力信号のレベルを適応的にシフトすることによって解決できる見込みがある. 以下にその詳細を述べる.

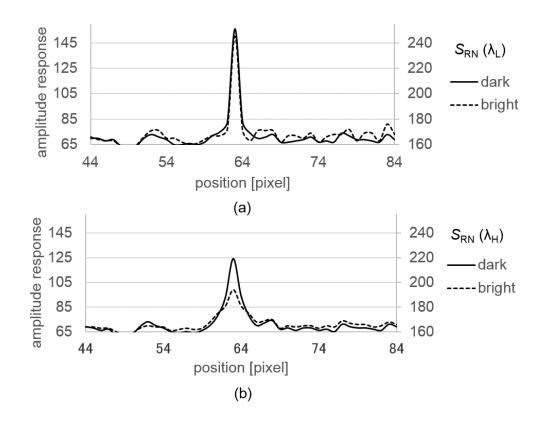

MOS 抵抗回路網の入力光依存性を検証した. まず 3.3 節で述べたように, MOS 抵抗回路網の線拡がり関数を測定した. ここでは小さなスケールパラメータ AL と大きなスケール

パラメータ  $\Lambda_H$  に設定した二つの抵抗回路網フィルタ  $f_{RN}(\Lambda_L)$ と  $f_{RN}(\Lambda_H)$ を用いた. フィルタ 特性を  $f_{RN}(\Lambda_L)$ と  $f_{RN}(\Lambda_H)$ に設定するために用いたバイアス電圧の組み合わせはそれぞれ, (0.36V, 2.69V)と(0.45V, 2.40V) とした. LCD からの光刺激はスリット光の強度を一定とし, 背景光を明るくした場合(平均画素値:約 168)と暗くした場合(平均画素値:約 68)の二パターンを用意した. 図 3.7 に実験結果を示す.  $f_{RN}(\Lambda_H)$ に比べ  $f_{RN}(\Lambda_L)$ に顕著であるが, 双方とも背景光が明るい場合の方が暗い場合に比べて応答が側方向に拡がる傾向があることがわかる. ここで,3.3 節に比べ,どちらの線拡がり関数の振幅応答もノイズの影響が強い理由は水平方向の振幅応答の平均をとっていないためである.

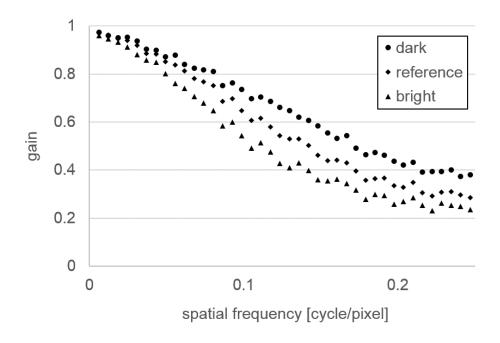

次に  $f_{RN}(\lambda_I)$ と  $f_{RN}(\lambda_H)$ が入力光のレベルが変化した時,空間周波数特性がどのように変化するか検討した. 測定は 3.3 節と同様の手法で行った. 正弦波の振幅は一定 (平均画素値:約 128)とし、背景光を基準の明るさに対して、明るい場合 (平均画素値:約 158)と暗い場合 (平均画素値:約 98)の結果を比較した.  $f_{RN}(\lambda_H)$ と  $f_{RN}(\lambda_H)$ の結果をそれぞれ図 3.8 と図 3.9 に示す. この結果から抵抗比に関わらず入力光が明るくなるとカットオフ周波数が低くなることがわかる.

図 3.7 背景光を変化させた時の線拡がり関数. (a)  $S_{RN}(\Lambda_L)$ の場合. (b)  $S_{RN}(\Lambda_L)$ の場合. 左は背景光が暗い場合の応答のための目盛であり、右の目盛は明るい場合の応答のための目盛である.

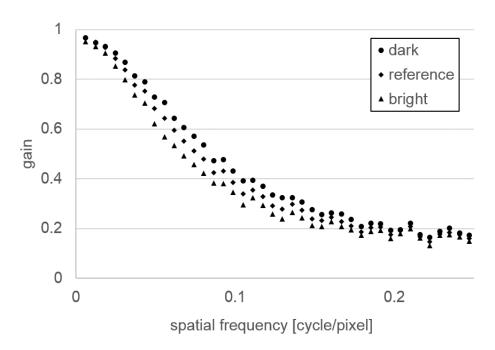

次に入力光の振幅を変化させて同様の実験を行った. 背景光は一定として,正弦波信号を基準の振幅に対して,大きい時と小さい時の結果を比較した. 背景光の時と同様に抵抗比  $\lambda$ が低い場合の空間フィルタ  $f_{RN}(\lambda L)$ と,高い場合の空間フィルタ  $f_{RN}(\lambda L)$ において調べた. 図 3.10,図 3.11 にそれぞれの結果を示す.この結果から振幅依存性は図 3.8,図 3.9 に示した入力光レベルの依存性に比べ,比較的低いということがわかる.

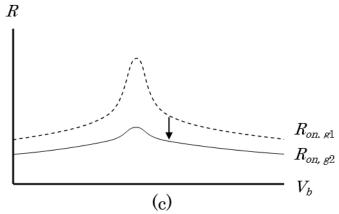

本センサが刻一刻と環境光のレベルが変化する場面で用いられる場合,この入力光レベルの依存性は改善しなければならない問題である。抵抗回路網への入力光レベルが影響する理由は 2.7 節で述べた通りである。入力光レベルが低い場合は図 2.18(c)内の  $V_6$ が中間辺りの動作域で MOS 抵抗が動作しており,各  $R_s$ の抵抗値が低くなり,スケールパラメータが小さくなる。一方で,入力光レベルが高い場合は  $R_s$ の抵抗値が先ほどより小さくなる領域で MOS 抵抗が動作しており,その結果スケールパラメータが比較的大きくなる。この説明は実験結果と一致する。さて本研究で用いたシリコン網膜では抵抗回路網への画素入力は式 (2.19) で表される。問題は背景が明るいと,各画素での信号値  $v_{po}-v_{pr}$  が高くなり,各画素入力  $v_{in}$  の値が高くなるということになる。従って,この問題は  $v_{po}-v_{pr}$  の平均的な値に応じて,その DC 成分を打ち消すように S/H1 のリファレンス電圧  $V_{reft}$  の値を制御し, $v_{in}$ を一定の範囲内に収めることによって緩和されると考えられる。

図 3.8 入力光レベルを変化させた場合の  $f_{RN}(\lambda_I)$ の空間周波数特性への影響. 暗く入力電圧レベルが低い場合に比べ、明るく入力電圧レベルが高い場合の方が抵抗回路網のカットオフ周波数が低くなる.

図 3.9 入力光レベルを変化させた場合の  $f_{RN}(\lambda_H)$ の空間周波数特性への影響.  $f_{RN}(\lambda_H)$ の場合と同様に、より明るく入力電圧レベルが高い場合の方が、抵抗回路網のカットオフ周波数が低くなる.

図 3.10 正弦波パターンの振幅強度を変化させた場合の  $f_{RN}(\lambda_D)$ の空間周波数特性への影響. 振幅強度が大きい場合と小さい場合で、抵抗回路網の空間周波数特性はほぼ変化がない.

図 3.11 正弦波パターンの振幅強度を変化させた場合の  $f_{RN}(\lambda_H)$ の空間周波数特性への影響.  $f_{RN}(\lambda_L)$ の場合と同様に、振幅強度が大きい場合と小さい場合で、抵抗回路網の空間周波数特性はほぼ変化がない.

## 3.7 結言

本章では、抵抗回路網を活用することで、実時間で複数の空間フィルタ処理を効率よく適用できる知能視覚センサについて述べた。我々の知能視覚センサは、コンパクトでかつ低電力で実時間演算を実現するために、アナログ/デジタル混合型のアーキテクチャ構成を採用した。知能視覚センサは APS、S/H 回路、アナログ抵抗回路網、そして FPGA で構成される。我々は、抵抗回路網による低域通過型空間フィルタ及び知能視覚センサによる帯域通過型空間フィルタの空間特性と空間周波数特性を測定し、それらが外部制御信号によって制御できることを確認した。次に、テスト画像をセンサに提示することで、画像中にある複数の異なるスケールの構造が強調されている出力画像群をセンサが抽出できていることを示した。

この研究は低消費電力でかつ実時間で帯域分離処理を実行するシステムの実現に向けた 第一歩である. 続く四章から六章までは帯域分離処理の例として実時間マルチスケールエッジ抽出と,スケール不変特徴量抽出の機能を有する知能視覚システムを構築したことについて述べる.

# 第4章 実時間マルチスケールエッジ検出機能 を有する知能視覚センサの開発

#### 4.1 緒言

前章ではマルチスケール空間フィルタ処理機能を有する知能視覚センサの開発について述べた.マルチスケール画像は、様々な特徴抽出の前段の処理として多く利用されている[13-21].しかしながら、取得された出力画像群は非常にデータ量が多く、従来の逐次処理型デジタル画像処理システムで画像を処理する場合、多くの計算時間を要する.そこで、本章では前章で論じた知能視覚センサの後段に並列デジタル演算回路を配し、センサからの画素読み出しと同時に画像を処理することで、フレーム落ちを生じず、後段の処理を実行できるアーキテクチャを構築した[78].まず特徴抽出機能として、画像処理の様々なタスクで利用されているエッジ検出を対象とした。本章では、提案したアーキテクチャに基づき、実時間マルチスケールエッジ検出機能を有する知能視覚センサのアルゴリズムを開発し、その出力を評価した.

## 4.2 ゼロ交差法によるエッジ検出

エッジ検出は画像理解において基本となる処理の一つであり、物体認識や領域分割などのタスクの前に実行される。エッジ検出のための基本的な戦略として、Marrらのゼロ交差法を採用した[2,11]。この手法では、光学的な特性から、エッジがある位置では画素値の強度が空間的に急激に変化していると仮定し、その応答変化の位置を検出することでエッジを検出する。Marrと Hildrith は強度変化を効率よく検出するために、ラプラシアンガウシアンフィルタを演算子として採用した[80]。応答強度の急激な変化は二次の導関数においてはゼロ交差を引き起こす。ラプラシアン演算子は二次の空間微分演算子として採用されており、ガウシアンフィルタはそのスケールパラメータによって、対象となる構造の大きさに同調させるために採用されている。例えば大きなスケールのフィルタを採用すれば、大まかな構造やぼやけた影のエッジを検出でき、小さなスケールのフィルタを採用すれば、画像中の鋭く焦点が合った微細な部分を検出できる[2]。ラプラシアンガウシアンフィルタがゼロ交差法で用いることのできる唯一の演算子ではなく、同じく帯域通過特性を有する DoG フィルタや DoR フィルタもまた演算子として用いることができる。

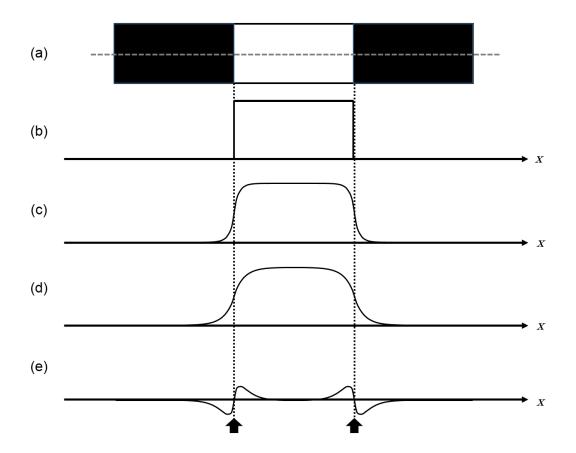

図 4.1 にゼロ交差法によるエッジ検出の概念図を示す. 図 4.1(a)に示す明暗パターンの点

図 4.1 ゼロ交差法によるエッジ検出. (a) 明暗パターン. (b) (a)の点線上のラインプロファイル. (c) 小さなスケールの RN フィルタによる処理結果. (d) (c)に比べて大きなスケールの RN フィルタによる処理結果. (e) 二つの RN フィルタ処理信号の差を取ることによって得られた DoR フィルタ処理信号.

線上のラインプロファイル (図 4.1(b)) を入力信号とし、DoR フィルタをゼロ交差法に用いる演算子として用いた場合のエッジ検出の処理過程について述べる。図 4.1(c)(d)は入力信号に RN フィルタを適用して得られたフィルタ処理信号である。図 4.1(c)は大きなスケールの RN フィルタを,図 4.1(d)は大きなスケールの RN フィルタを適用した結果である。図 4.1(c)に比べて図 4.1(d)はより信号が側方向に拡がっていることがわかる。図 4.1(c)はそれらの差を取ることで得られた DoR フィルタ処理信号である。図中矢印で示すように入力信号で応答強度の変化が強い付近で強く応答し、そのエッジ部分でゼロレベルを横切っていることがわかる。

## 4.3 ゼロ交差検出回路

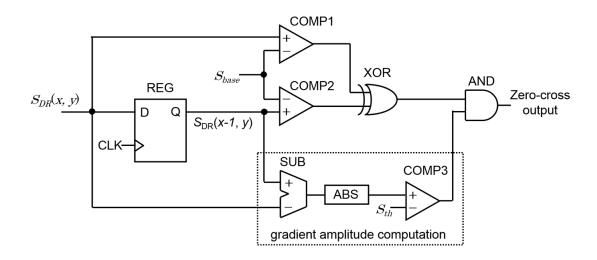

本節では、4.2 節で述べたゼロ交差法を実行するデジタル回路について述べる. FPGA 上にゼロ交差検出回路を配することで、知能視覚センサの応用として実時間マルチスケールエッジ検出機能の実装を試みた. ゼロ交差検出回路は井上ら[81]の研究を参考に開発した.

一次元ゼロ交差検出回路の構成を図 4.2 に示す。図 4.2 の例は画像内の x 方向のゼロ交差を検出する回路である。本回路は主にレジスタ(図中 REG),比較器(図中 COMP),および論理ゲート(図中 XOR,AND)によって構成される。まず DoR フィルタ処理画像の画素 SDR (x-1, y)がレジスタに保存される。画像内の横方向に隣り合う画素がゼロレベルを交差しているかを比較器 COMP1,COMP2 と XOR 回路により,次式の演算を実行することで検出する。ここで, $S_{base}$  はゼロレベルを表す。

$$(S_{DR}(x, y) > S_{base}) \text{ xor } (S_{DR}(x-1, y) > S_{base}).$$

(4.1)

次に、エッジ由来のゼロ交差点とノイズによるゼロ交差点を分離するために、隣り合う画素間で大きく応答が変化している位置を検出する勾配検出器(図中点線内の回路)を用いた.この勾配検出器の出力を以下に示す.ここで、 $S_{th}$ は応答変化の閾値を表す.

$$|S_{DR}(x-1, y) - S_{DR}(x, y)| > S_{th}.$$

(4.2)

最後に XOR 回路と勾配検出器の出力の AND を取ることで、ゼロ交差点を検出する.

図 4.2 一次元ゼロ交差検出回路. 上部のゼロ交差検出器と下部の勾配検出器で構成される. 勾配検出器の出力は信号とノイズとを区別するために用いられる.

提案した知能視覚センサには上記で述べた回路を二次元に拡張した回路を実装した。画像のx方向だけでなく,y方向の回路を実装し,それらのORを取った出力をエッジ検出回路の出力とした。

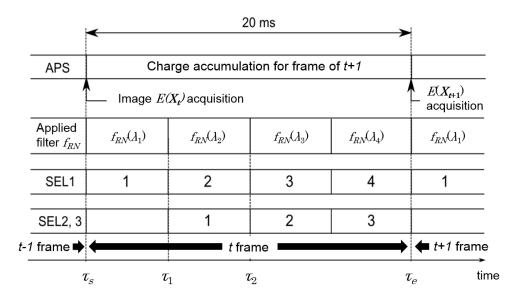

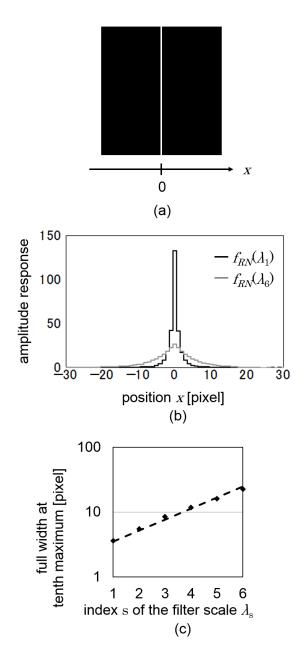

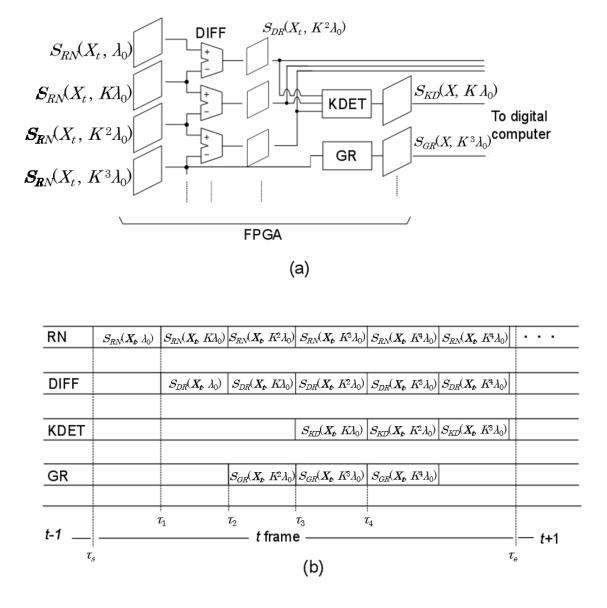

## 4.4 FPGA 上での差分画像とエッジ画像の並列処理

図 4.3 に示すタイミングチャートを用いて、実時間マルチスケールエッジ検出の流れを説明する. 第 3 章で述べたように、4 つの異なるスケールの RN フィルタ処理画像  $S_{RN}(X_t, \lambda_1)$ ,  $S_{RN}(X_t, \lambda_2)$ ,  $S_{RN}(X_t, \lambda_3)$ ,  $S_{RN}(X_t, \lambda_4)$ が A/D 変換器を介して FPGA 内のメモリに保存される. ここで、 $X_t=(x,y,t)$ は画像の位置と時刻を表現するベクトルである. この RN フィルタ処理画像の読み出しと同時並列的に DoR フィルタ処理画像  $S_{DR}(X_t, \lambda_1, \lambda_2)$ ,  $S_{DR}(X_t, \lambda_2, \lambda_3)$ ,  $S_{DR}(X_t, \lambda_3, \lambda_4)$ とエッジ画像  $S_E(X_t, \lambda_1, \lambda_2)$ ,  $S_E(X_t, \lambda_2, \lambda_3)$ ,  $S_E(X_t, \lambda_3, \lambda_4)$ が生成される. ここで、エッジ要素がある画素位置に 1 の値をもつ画像をエッジ画像とする.

図 4.3 内の時刻  $\tau_1$  における FPGA 上での処理を考える。  $\tau_1$  において,すでに RN フィルタ処理画像  $S_{RN}(X_t, \lambda_1)$ がメモリに保存されている。  $\tau_1$  から  $\tau_2$  までの区間で  $S_{RN}(X_t, \lambda_2)$ が一画素ずつ読み出される。 すでに 3.2 節で説明をしたように  $S_{RN}(X_t, \lambda_2)$ の画素読み出しと同時にメモリから読み出された  $S_{RN}(X_t, \lambda_1)$ が一画素ずつ順に読み出され,共に差分器に入力されることで差分画像,すなわち DoR フィルタ処理画像  $S_{DR}(X_t, \lambda_1, \lambda_2)$ が生成される。  $S_{DR}(X_t, \lambda_1, \lambda_2)$ はメモリに保存される一方で,前節で述べたゼロ交差検出回路に入力される。このようにしてエッジ画像  $S_E(X_t, \lambda_1, \lambda_2)$ の画素出力も FPGA 内で同時並列的に演算され,エッジ画像用メモリに順次に保存されていく。この処理を各 RN フィルタ処理画像の読み出し時に実行することで,三つの異なるスケールのエッジ画像を取得できる。

| $	au_{_{S}} \hspace{1cm} 	au_{_{1}} \hspace{1cm} 	au_{_{2}}$ |                          |                                          |                                          |                                          | $	au_e$ t | ime |

|--------------------------------------------------------------|--------------------------|------------------------------------------|------------------------------------------|------------------------------------------|-----------|-----|

| <i>t</i> -1                                                  |                          |                                          | t frame                                  |                                          |           | _   |

| Zero-cross                                                   |                          | $S_{E}(X_{t}, \lambda_{1}, \lambda_{2})$ | $S_{E}(X_{t}, \lambda_{2}, \lambda_{3})$ | $S_{E}(X_{t}, \lambda_{3}, \lambda_{4})$ |           |     |

|                                                              |                          |                                          |                                          |                                          |           |     |

| DIFF                                                         |                          | $S_{DR}(X_t, \lambda_1, \lambda_2)$      | $S_{DR}(X_t, \lambda_2, \lambda_3)$      | $S_{DR}(X_t, \lambda_3, \lambda_4)$      |           | _   |

|                                                              |                          |                                          |                                          |                                          |           |     |

| RN                                                           | $S_{RN}(X_t, \lambda_1)$ | $S_{RN}(X_t, \lambda_2)$                 | $S_{RN}(X_t, \lambda_3)$                 | $S_{RN}(X_t, \lambda_4)$                 |           | _   |

図 4.3 FPGA 上でのエッジ画像の演算についてのタイミングチャート. 本知能視覚センサでは、FPGA 上で RN フィルタ処理画像  $S_{RN}$ (一段目)と DoR フィルタ処理画像  $S_{DR}$ (二段目), そしてエッジ画像(三段目)を同時並行的に取得する.

## 4.5 システムの出力応答の測定

#### 4.5.1 単純な視覚対象に対する応答

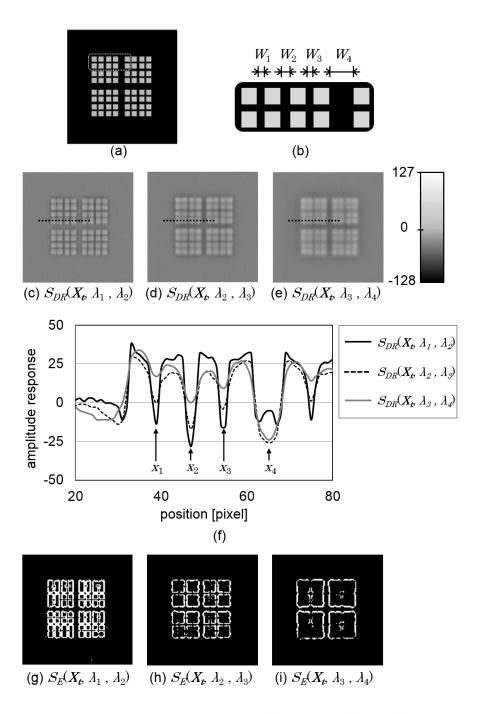

我々は図 3.6 と同様に図 4.4(a)に示す四角形のグループの画像を知能視覚センサに提示し、その出力画像を検討した。四角形の間の幅は図 4.4(b)に示されるようにそれぞれ異なるように配置している。図 4.4(c)-(e)に t フレーム目の三つの DoR フィルタ処理画像  $S_{DR}$  ( $X_t$ ,  $A_1$ ,  $A_2$ ),  $S_{DR}$  ( $X_t$ ,  $A_2$ ,  $A_3$ ),  $S_{DR}$  ( $X_t$ ,  $A_3$ ,  $A_4$ )を示す。本実験で用いた空間フィルタ群は図 3.5(c)に示された空間周波数特性を持つ。右側のグレースケールの階調を示すバーが帯域通過信号の応答振幅を表現する。DoR フィルタによって帯域通過処理された三つの画像の全てにおいて、四角形のない周辺領域の応答はゼロレベルを示す均一な灰色で表現されている。一方、四角形のグループの周辺と内部は正もしくは負の値をとる。図 4.4(f)は図 4.4(c)-(e)の黒色の点線によって指定された線上の応答を示している。

最も通過帯域が高い、 $f_{DR}(\mathbf{X}, \lambda_1, \lambda_2)$ によってフィルタ処理された信号(図 4.4(f)中の黒色の実線)は小さい四角形のそれぞれのエッジで鋭く変化している( $\mathbf{x}_1, \mathbf{x}_2, \mathbf{x}_3, \mathbf{x}_4$ ). 一方で最も通過帯域が低い、 $f_{DR}(\mathbf{X}, \lambda_3, \lambda_4)$ によってフィルタ処理された信号(図 4.4(f)中の灰色の実線)は四角形間の隙間の距離が狭い点( $\mathbf{x}_1, \mathbf{x}_2, \mathbf{x}_3$ )で大きい変化を示さず、 $\mathbf{x}_4$  でのみ大きく変化を示した.

図 4.4(g)-(i)に画像(c)-(e)からそれぞれ抽出されたエッジ画像  $S_E(X_1, \lambda_1, \lambda_2)$ ,  $S_E(X_1, \lambda_2, \lambda_3)$ ,  $S_E(X_1, \lambda_3, \lambda_4)$ を示す。これらの図の白色の点群は信号がゼロに交差する,ゼロ交差点を表現する。図 4.4(g)に示すように, $S_E(X_1, \lambda_1, \lambda_2)$ ではゼロ交差点が小さな四角形のそれぞれのエッジ  $(x_1, x_2, x_3, x_4)$  で抽出されていることがわかる。一方で, $S_{DR}(X_1, \lambda_3, \lambda_4)$ の場合は,四角形間の距離が広い  $x_4$  の位置でのみエッジが現れる。従って,図 4.4(g)の白色の点群が小さな四角形の輪郭を表現する。一方で,図 4.4(i)のそれは四角形の四つのグループのエッジが表現する。

#### 4.5.2 複雑な視覚対象に対する応答

複雑な視覚対象として二つの自然画像を知能視覚センサに提示し、出力画像群とその時系列データを検討した.

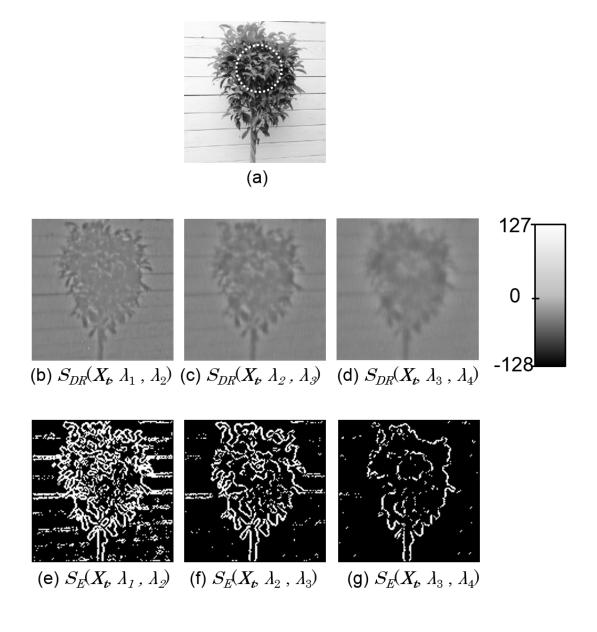

まず知能視覚センサによって図 4.5(a)に示す植物の写真に対する出力画像群を取得した. 図 4.5(b)-(d)に t フレーム目の出力画像群である三つの DoR フィルタ処理画像  $S_{DR}(X_t, \Lambda_1, \Lambda_2)$ ,  $S_{DR}(X_t, \Lambda_2, \Lambda_3)$ ,  $S_{DR}(X_t, \Lambda_3, \Lambda_4)$ を示す。  $S_{DR}(X_t, \Lambda_1, \Lambda_2)$ では葉の形状のような細かいテクスチャパターンを表現されている(図 4.5(b)). 一方で, $S_{DR}(X_t, \Lambda_3, \Lambda_4)$ ではこれらのパターンが平滑化されて除去されている(図 4.5(d)). 図 4.5(e)-(g)は図 4.5(b)-(d)からそれぞれ抽出されたエッジ画像を示している。これらの図の白色の点群はエッジを表現する。図 4.5(e) において,葉の形や背景の壁の水平の線が表現されている。他方,植物の外郭や葉の固まりと

図 4.4 四角形のグループの画像に対する応答. (a) 入力画像. (b) 図 4.3(a)の白色の点線によって囲まれた領域の拡大図. 四角形の間の距離は次の関係を持つ:  $W_1 = W_3 < W_2 < W_4$ . (c) (d) (e) それぞれ  $S_{DR}(X_4, \lambda_1, \lambda_2)$ ,  $S_{DR}(X_4, \lambda_2, \lambda_3)$ ,  $S_{DR}(X_4, \lambda_3, \lambda_4)$ を示す. 右側のグレースケールの階調を持つバーは帯域通過処理信号の応答のレベルを示す. (f) 図 4.3(c)-(e)の黒色の点線上の応答. (g) (h) (i) 図 4.3(c)-(e)から抽出されたエッジ画像  $S_E(X_4, \lambda_1, \lambda_2)$ ,  $S_E(X_4, \lambda_2, \lambda_3)$ ,  $S_E(X_4, \lambda_3, \lambda_4)$ . これらの図の白色の点群はゼロ交差点を表現している.

図 4.5 自然画像(植物の写真)に対する応答. (a) 入力画像. (b) (c) (d) DoR フィルタ 処理  $S_{DR}(X_1, \lambda_1, \lambda_2)$ ,  $S_{DR}(X_1, \lambda_2, \lambda_3)$ ,  $S_{DR}(X_1, \lambda_3, \lambda_4)$ . (e) (f) (g) 画像(b)(c)(d)からそれ ぞれ抽出されたエッジ画像  $S_E(X_1, \lambda_1, \lambda_2)$ ,  $S_E(X_1, \lambda_2, \lambda_3)$ ,  $S_E(X_1, \lambda_3, \lambda_4)$ .

いった粗い構造が、図 4.5(a)で点線の円によって指定された図 4.5(g)が表現された.

次いで我々はシマウマが歩いているシーンの動画を提示し、知能視覚センサの出力画像の時系列データを検証した. 図 4.6 は出力画像の四つの連続するフレームを示す. 図 4.6 (b) (c) に帯域通過処理画像  $S_{DR}(\textbf{X}, \lambda_1, \lambda_2)$ と  $S_{DR}(\textbf{X}, \lambda_3, \lambda_4)$ から抽出されたエッジ画像  $S_E(\textbf{X}, \lambda_1, \lambda_2)$ と  $S_E(\textbf{X}, \lambda_3, \lambda_4)$ を示す. 図 4.6 (b) において、細かいテクスチャパターンの輪郭とシマウマや他の物体の外郭の両方が表現されている.一方で、図 4.6 (c) において、シマウマの縞のよう

な細かいテクスチャパターンが除去され、シマウマと他の物体の外郭線などの大まかな構造のみが表現されている。図 4.6(b)(c)の画像は全フレームで視覚センサが複数の大きさで輪郭を抽出できていることを示している。例えば、シマウマの前足に着目すると、その動きが時系列データとして適切に表現されている。これらの結果から本研究で提案された知能視覚センサの有用性が示された。

## 4.6 考察

我々は実時間マルチスケールエッジ検出機能を有する知能視覚センサを開発した.本知能視覚センサはマルチスケール空間フィルタ処理機能を有する視覚センサと後段の FPGA 上のゼロ交差検出回路とを組み合わせることで、効率的に粗い構造から細かい構造までの輪郭情報を抽出できた.高周波数成分から構成された帯域通過型空間フィルタ処理画像から抽出された輪郭抽出画像は、物体のテクスチャや輪郭のパターンを両方表現しているため、主に物体認識において利用できると考えられる.他方、低周波成分から構成された帯域通過型空間フィルタ処理画像から抽出された輪郭抽出画像は、細かい構造は除去され、物体の輪郭が主に表現されているために、物体の領域分離に利用できると考えられる.

シリコン網膜から FPGA 上のメモリへの画素読み出しには一定の時間を要する. 一般的に、FPGA 上において、マルチスケール解析をする際も同様に逐次的に画像が保存されているメモリにアクセスし、画素情報を読み出し、処理を実行後、メモリ上の異なるアドレスに画素情報を書き込む. 3.7.1 節で議論したように、この読み出し時間は本視覚センサのフレームレートのボトルネックとなるが、画素の読み出しとメモリへの書き込み時間は必ず必要な工程であるため、時間短縮には限界がある. 本知能視覚センサのアーキテクチャではFPGA 上の読み出し信号線の途中に画像処理回路を配することで、計算時間増大の原因となるメモリへのアクセスの回数を減らしている. 本知能視覚センサは、すでにフィルタ処理済みの画像を読み出す上、画素を読み出し時に、FPGA 上の画像処理回路でパイプライン処理を実行するため、処理のための回路面積・効率の面で非常に優れた構成であると考えられる.

図 4.6 シマウマが歩いている動画に対する出力画像の時系列データ. (a) 入力画像の時刻  $\tau$  から  $\tau$ +3 までの連続する四フレーム分の入力画像. (b)(c) 帯域通過フィルタ  $f_{DR}(\lambda_1, \lambda_2)$ と  $f_{DR}(\lambda_3, \lambda_4)$ による帯域通過処理画像から抽出されたエッジ画像. 時刻  $\tau$  のエッジ画像を  $S_E(X_t, \lambda_1, \lambda_2)$ ,  $S_E(X_t, \lambda_3, \lambda_4)$ とする. (b)には細かい構造の動きが表現されており, (c)には粗い構造の動きが表現されている.

## 4.7 結言

本章では、実時間マルチスケールエッジ検出機能を有する知能視覚システムの開発と構築について述べた。開発した知能視覚センサでは、フィルタ処理画像の読み出しと同時に FPGA による並列処理を実行することで、実時間処理を実現した。実時間マルチスケールエッジ画像は粗い構造から細かい構造までの同時形状解析に利用できる他、これまでコンピュータビジョンの分野で研究されてきたマルチスケール画像を用いたエッジ検出法[11] や輪郭特徴ベースのステレオビジョンの粗密法[12]にも発展できる.

次章で構築されたスケール不変特徴量抽出機能を有する知能視覚センサシステムもまた、 第三章で述べた複数回フィルタ処理機能を有する知能視覚センサと、本章で述べた FPGA による並列処理を活用することで実現されている.

# 第5章 抵抗回路網を用いたスケール不変特徴 量抽出の解析とシミュレーション

## 5.1 緒言

画像情報による物体の認識は、画像処理の中心的課題の一つである. 近年の画像認識システムの多くは探索画像から特徴点を抽出し、予め抽出しておいたテンプレート特徴点との特徴量同士との対応付けを用いる. この物体認識で用いられる特徴点が備えているべき重要な特性は、その特徴量が画像上での物体の見えの変化に対して不変性を有していることである.

本研究では、開発した知能視覚センサの一応用として、スケール不変特徴量の一つである SIFT 特徴量を実時間で抽出するハードウェアの構築を試みた. SIFT 特徴量とは、画像か 抽出されるスケール変化や回転変化に不変な局所特徴量の一種である[13, 14]. しかしながら SIFT アルゴリズムは、前段にマルチスケール画像を生成する処理が必要であり、非常に計算コストが高く、実時間で実行することが難しい.

本研究ではマルチスケール画像を高速に生成するために、抵抗回路網(図 2.11 参照)を用いる[82]. 一方で、従来の SIFT アルゴリズムでは、マルチスケール画像生成のためにガウシアンフィルタが採用されている。そこで本章では、抵抗回路網 (RN) フィルタが SIFT アルゴリズムに用いることができるかを検討する。まずコンピュータ・シミュレーションにより、ガウシアンフィルタとの空間特性の違いが特徴点検出にどのように影響するか検討した。次に、様々なサイズのテストパターンを入力として、画像サイズによらず同じ場所で特徴点が検出できること、また画像サイズに応じたスケールで SIFT キーポイントと呼ばれる特徴点が検出できることを示す。

## 5.2 SIFT アルゴリズムとその関連研究

#### 5.2.1 スケーラブルフィルタによるキーポイント検出

本研究では、入力画像から局所特徴量を抽出するために SIFT アルゴリズムを採用する. SIFT アルゴリズムについての詳細は Lowe の原著論文に記述されているため[14], 本節ではその概要を簡単に説明する.

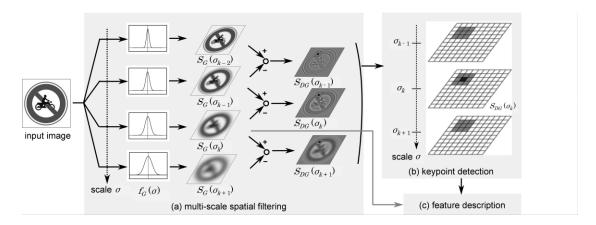

図 5.1 に SIFT アルゴリズムの処理の流れを示す。SIFT アルゴリズムは主に、マルチスケール (図 5.1(a))、SIFT キーポイント検出 (図 5.1(b))、そして特徴量記述 (図 5.1(c)) の三つの処理で構成されている。

SIFT キーポイントとは画像の並進移動,スケール変化,回転変化に対して不変であり,かつ小さなノイズや画像の歪みに対しても影響を受け難い画像上の位置のことを指す[13]. SIFT キーポイントは次のように検出される.

図 5.1(a)に示すように、最初に、マルチスケールの帯域通過型空間フィルタ群が入力画像に適用される。この帯域通過型空間フィルタ群はスケーラブル性を備えている必要がある。 Lowe の提案した SIFT アルゴリズムでは、 式(2.8)を満たすスケーラブル性を備えた DoG 関数 (式(2.9)) が帯域通過型空間フィルタとして採用されている。

次に、隣り合う三つのスケール  $Spd(o_{k-1})$ 、 $Spd(o_k)$ 、 $Spd(o_{k+1})$ の DoG フィルタ処理画像間の画素値を比較することによって SIFT キーポイント候補点が探索される. ここで、 $o_k$  はキーポイント探索スケールとする. 注目画像に隣り合う三つのスケールの画像上で、注目画素(図 5.1(b)の黒色のセル)の周辺  $3\times 3$  画素の領域中の画素間((図 5.1(b)の灰色の 26 個のセル))で、注目画素の応答が最大値か最小値であるならば、この画素は SIFT キーポイント候補点として選択される. 各候補点群に対して安定性についての検査をし、それを通過した点を最終的な SIFT キーポイントとする. この検査では、低コントラストである点と輪郭周辺の候補点が除去される. ここで、スケール  $o_k$  の帯域通過型処理画像上でキーポイントが検出された時、この  $o_k$ をキーポイントのスケールと定義する.

最後に、SIFT キーポイント周辺の特徴ベクトルが記述される。この特徴ベクトルはスケール及び方位の両方に不変である。SIFT キーポイントの特徴ベクトルはガウシアンフィルタ処理画像  $S_{c}(o_{k})$ から演算される。特徴ベクトル記述についての詳細は次の節で述べる。

図 5.1 SIFT アルゴリズムにおける処理の流れ. SIFT アルゴリズムは (a) マルチスケール空間フィルタ, (b) SIFT キーポイント検出, そして (c) 特徴抽出で構成されている. この画像で,  $S_{cl}(o_k)$ は入力画像にガウシアンフィルタ  $f_{G}(o_k)$ を適用することで得られたガウシアンフィルタ処理画像を示す. 更に,  $S_{DG(o_k)}$ は DoG フィルタ処理画像を表現し,  $o_k$ はキーポイントが検出されるフィルタのスケールパラメータを表現する.

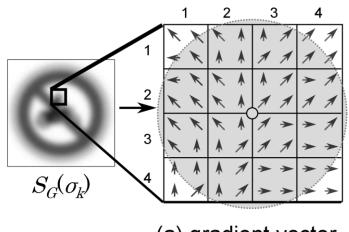

#### 5.2.2 特徴量記述

各 SIFT キーポイント位置の周辺で、キーポイントのスケールをもつ勾配ベクトル画像から 128 次元の特徴量 (特徴ベクトル)  $F = (F_1, F_2..., F_{128})$  が記述される.ここで勾配ベクトル画像  $S_{GR} = (S_{GRM}, S_{GRO})$  は勾配強度  $S_{GRM}$ と勾配方向  $S_{GRO}$ から構成される.勾配強度  $S_{GRM}$ と勾配方向  $S_{GRO}$ はそれぞれ次の式に従って計算できる.

$$S_{GRM}(\boldsymbol{X}, \sigma_{k}) = \left\{ S_{Gx}(\boldsymbol{X}, \sigma_{k})^{2} + S_{Gy}(\boldsymbol{X}, \sigma_{k})^{2} \right\}^{1/2}. \tag{5.1}$$

$$S_{GRO}(\mathbf{X}, \sigma_{k}) = \tan^{-1} \{ S_{GV}(\mathbf{X}, \sigma_{k}) / S_{GX}(\mathbf{X}, \sigma_{k}) \}. \tag{5.2}$$

図 5.2 を用いながら更に特徴量の記述についての詳細を説明する. キーポイントの特徴ベクトルは勾配ベクトル画像  $S_{GR}$ から計算される. 式(5.2)によって求められた勾配方向  $S_{GRO}$ は  $0^\circ$  から  $360^\circ$  までの連続的な値をもつが,その後の処理で離散化される(本研究では図5.2(a)に示すように 8 方位に離散化する). キーポイントの特徴ベクトルを記述するために,まずキーポイント位置の周辺のベクトル  $S_{GR}$  がガウシアンフィルタで重みづけられる. そのスケールは図 5.1 (a)内の灰色の円に示すように, $S_{Cl}$ ( $O_{Cl}$ )のスケール  $O_{Cl}$  の三倍大きくなるように設定される.

特徴ベクトルは SIFT キーポイント周辺の勾配ベクトルから形成される. まず勾配ベクトルから方位ヒストグラム  $H_{pq}$  を計算する. 図 5.2(a)に示すようにキーポイント周辺を  $4\times 4$  のサブ領域に分割する. 方位ヒストグラムはサブ領域内の全画素の勾配ベクトルのベクトル和をとることで求める. 勾配ベクトルは 8 方位に分類されるために, サブ領域でそれぞれ 8 方位のヒストグラム  $H_{pq}$  が得られる. ここで, 添え字  $p(1 \le p \le 4)$  と  $q(1 \le q \le 4)$  はサブ領域の位置を意味する. これらの 16 個のサブ領域の中の 8 方位のビンから図 5.2(b)に示される特徴ベクトル Fが形成される. Fと  $H_{pq}$  はそれぞれ次式のように表現される.

$$\mathbf{F} = (F_1, F_2, ..., F_{128}),$$

$$= (H_{11}, H_{12}, ..., H_{44}),$$

(5.3)

$$H_{11} = (F_1, F_2, \dots, F_8),$$

(5.4)

$$H_{12} = (F_9, F_{10}, \dots, F_{16}),$$

(5.5)

• • •

$$H_{44} = (F_{121}, F_{122}, ..., F_{128}).$$

(5.6)

特徴記述の領域の広さは検出スケールに従って変更する.図 5.2(a)において、8 つの矢印は画素の勾配方位を指し、サブ領域は 2×2 画素のサイズである.図 5.2(b)の垂直方向のバーの長さは特徴ベクトルの各要素の値の大きさを示す.

図 5.2 ベクトルの記述. (a) 現在のスケール  $\alpha$  の三倍のスケールを有するガウス関数で重みづけられた, $SG(\alpha)$ のキーポイント周辺での勾配ベクトル. 点線の円によって示された領域がそのガウス関数を示す. キーポイントの周りの領域は特徴ベクトルを記述するために  $4\times 4$  のサブ領域に分割される. (b) 128 次元の特徴ベクトル. サブ領域内の勾配ベクトルから 8 方位のヒストグラム H が生成される. 各方位は 45 度ごとに離散化されている. バーの長さはサブ領域内の各方位の勾配ベクトルを加算することで求められた特徴ベクトルの各次元の値を示す.

#### 5.2.3 キーポイントマッチング

物体認識のためには入力画像から抽出したキーポイントの特徴ベクトル  $F=(F_1, F_2, ..., F_{128})$  と予め用意したテンプレートキーポイントの特徴ベクトル  $T=(T_1, T_2, ..., T_{128})$ とを比較することでキーポイントマッチング (対応点探索) を実行する必要がある. 本研究ではキーポイントの類似度は式 (5.3) に示すユークリッド距離 Eを用いて評価した.

$$E = \sqrt{\sum_{l=1}^{128} (F_l - T_l)^2}.$$

(5.7)

もし、入力画像から抽出されたキーポイントとテンプレートキーポイントとの間の類似度 が閾値  $E_{th}$  より小さく、かつすべてのキーポイントの間で最小となる時、キーポイントがテンプレートとの対応点として選択される。

#### 5.2.4 関連研究

物体認識[13,83]や分類[84],歩行者トラッキング[85],ロボットの位置推定[86],そしてパノラマ画像生成[87]など,SIFT 特徴量を用いた様々な応用やその改良アルゴリズムが研究されてきた[88-97].局所特徴量の高速抽出が組み込み画像処理システムで実現されると、更に様々な応用範囲が広がると考えられるため、SIFT アルゴリズムの効率化のためにソフトウェア及びハードウェア的工夫が提案されてきた.

ソフトウェアベースのアプローチとしては、例えば Fast approximated SIFT [88], SURF (Speeded Up Robust Features) [89], BRISK (Binary Robust Invariant Scalable Keypoints) [90], そして ORB (Oriented FAST and Rotated BRIEF) [91]といった高速に抽出できる特徴点に関するアルゴリズムが挙げられる。これらの方法は抽出された特徴の質を犠牲にすることによって、計算時間を減少することを狙いとしている。2.4 節、2.5 節で述べたように、先行研究としてガウシアンフィルタ処理の高速化技術もまた開発されている。これらの手法はSIFT の計算コストを減少することに成功しているが、特に画像入力が高解像度である場合、依然として計算コストは高くなる。

SIFT アルゴリズムを高速化するための専用ハードウェアもまた設計されてきた.これらのシステムは GPU, FPGA, そして ASIC を用いることによって高速化を試みている. GPU ベースのシステムは SIFT アルゴリズムを用いて三次元物体認識に適用されている[62]. GPU はその並列性から高い処理速度を提供するが, GPU ベースのシステムでは, 非常に消費電力が高いため, 携帯性の高い応用には不向きである等, 用途に限りがある. 複数の計算機コアによって, 関心領域を抽出し, その領域のみ選択的に SIFT アルゴリズムを適用する物体認識を実行する ASIC もまた開発されてきた. その他の先行研究として FPGA (例えば [63]) や ASIC[98, 99] 上で実装されてきた. これらの専用ハードウェアでは計算速度は向上するものの回路規模やメモリ容量を増加させるなど, 空間フィルタの本質的な計算コストが依然として問題となる.

## 5.3 抵抗回路網フィルタとガウシアンフィルタの比較

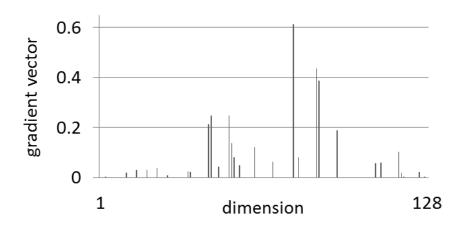

Lowe の提案した SIFT アルゴリズムでは DoG フィルタにスケーラブル性を持たせるために、フィルタサイズを決定する  $\sigma$  を等比的に増加させたガウシアンフィルタ群が要求さ

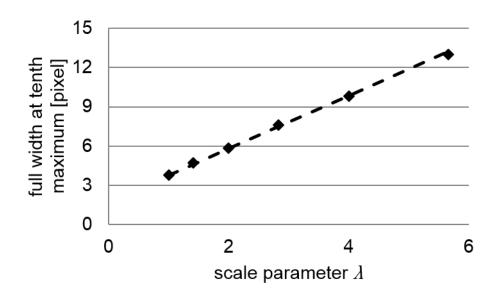

れる. 本研究では RN フィルタによってガウシアンフィルタを置き換えるために、これら の空間特性を比較する必要がある. そこで, 我々は MATLAB 上で二次元抵抗回路網の空間 インパルス応答をシミュレーション解析した.図 5.3 は様々な λ の場合の二次元の正方格 子抵抗回路網の単一インパルス応答を示す。各プロットは入力を受け取った画素を通る水 平方向の振幅応答を示す. 水平軸のゼロは入力位置を示し、図の凡例は A の値を示してい る. 信号は A の大きい値においてより広く拡がっている. 抵抗回路網フィルタの中央近く の応答での減衰はガウシアンフィルタに比べて急激である一方で、抵抗回路網の中心から 離れた位置での応答はガウシアンフィルタに比べてより大きい. 図 5.4 は図 5.3 の抵抗回路 網の $\lambda$ とフィルタサイズの間の関係を示す。ここで、抵抗回路網のフィルタサイズは1/10値幅 (FWTM: full width at one tenth of the maximum), すなわち, 抵抗回路網のノード 上の応答振幅が最大値の 1/10 になる値の間のピクセル数として定義した. 点線は FWTM= 2.03  $\lambda + 1.74$  を描画したものであり、図 5.4 はフィルタサイズが  $\lambda$  に比例して増加するこ とを示している. 一次元抵抗回路網の場合,式(2.7)から振幅応答がxと $\lambda$ の比の関数と なっているため、フィルタサイズが $\lambda$ に比例することは明らかである。図 5.4の結果は解析 的に解くことが難しい離散二次元抵抗回路網においても、スケールパラメータ A とフィル タサイズがほぼ比例することを示している.この結果から、DoR フィルタを入力画像に適 用するためには、 *A*を次のように等比的に設定すればよいことがわかる.

$$\lambda_{s} = K^{s-1} \lambda_{o}(s=1,2,3,...),$$

(5.8)

ここで  $\lambda_0$  は  $\lambda$  の最小値であり、s はフィルタの番号である.次の節からの画像処理シミュレーションでは、上記のインパルス応答を抵抗回路網フィルタのカーネルとして採用した.

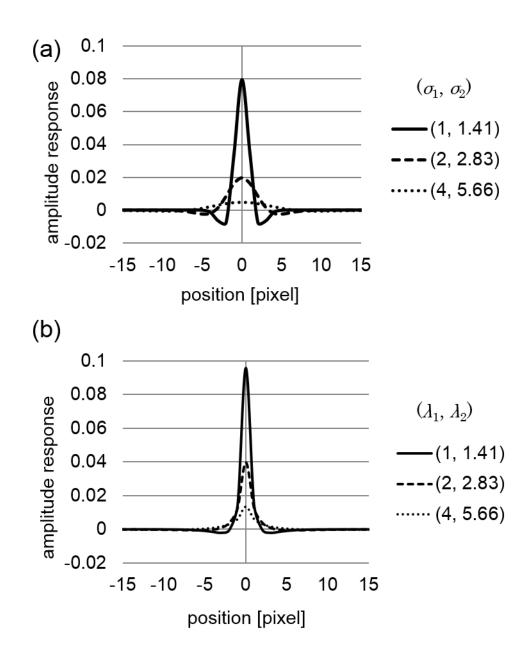

### 5.4 DoG フィルタ処理画像と DoR フィルタ処理画像の比較

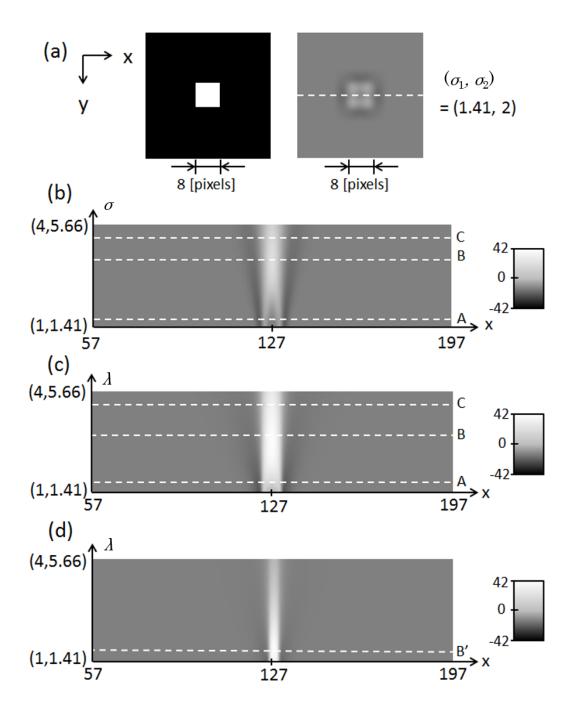

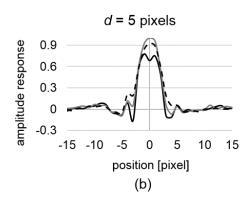

我々は 2.3 節で述べた DoG フィルタ処理画像と DoR フィルタ処理画像をシミュレーションにより比較した. 図 5.5(a)(b)に DoG フィルタと DoR フィルタの単位インパルス応答をそれぞれ示す. DoG フィルタと DoR フィルタの両方が中心周辺拮抗型の空間特性を有している. それらの応答は  $\sigma$ や  $\lambda$  の値が大きいほど、広く拡がる. 次に我々はフィルタサイズがどのようにフィルタ信号に影響を与えるかを検討した. 試験画像として、背景が黒く、中央部に 8 画素幅の白い四角形がある画像( $256 \times 256$  画素)を用いた(図 5.6(a)左). この入力に対して DoG フィルタ  $f_{DG}(\sigma_1,\sigma_2) = f_{DG}(1.41,2)$ を適用した画像を図 5.6(a)右に示す. このフィルタ処理画像の白色の点線上の水平方向の応答振幅に着目する. 図 5.6(b)(c)に様々なスケールにおける DoG フィルタ処理画像と DoR フィルタ処理画像の水平方向の応答振幅を示す. 横軸は画素位置であり、縦軸の値の組はフィルタのスケールパラメータの組であ

図 5.3 2 次元正方格子抵抗回路網の空間インパルス応答. インパルス入力を受け取った画素を通る水平方向の振幅応答を示す.

図  $5.4~\rm RN$  フィルタのフィルタサイズと  $\lambda$  との間の関係. ここでは 1/10 値幅をフィルタサイズとしている. 離散二次元抵抗回路網においてもフィルタサイズは  $\lambda$  に比例して増加していることがわかる.

る. DoG フィルタのスケールパラメータの組  $(o_1, o_2)$  の関係は  $o_2 = Ko_1$  であり,DoR フィルタのスケールパラメータの組  $(\lambda_1, \lambda_2)$  の関係は  $\lambda_2 = K\lambda_1$  である. ここでシミュレーションのパラメータとして,Kは $\sqrt{2}$ で固定し, $o_1$ と  $\lambda_1$  の値は 1.0 から 0.1 ずつ 4.0 まで 30 ステップほど変更した.

図 5.5 様々なスケールにおける (a) DoG フィルタと(b) DoR フィルタの空間インパルス応答. シミュレーションによって二次元空間インパルス応答を求めたが,ここではインパルス入力が入った画素を通る位置の水平方向の振幅応答を示す.

DoG フィルタと DoR フィルタは双方、中心周辺拮抗型の空間フィルタを有するため、それらの出力画像が近い空間特性を持つ。四角形の幅に比べて、それぞれのフィルタのフィルタサイズが小さい時(図 5.6 (b)(c)の点線 A)、四角形の輪郭が大きく強調され、中心の応答が輪郭部周辺より小さくなる。フィルタサイズが四角形の幅に合っている時(図 5.6(b)(c)の点線 B)、四角形の中央が極値をとり、そしてこの画素がキーポイントとして選択される。

図 5.6 (a) DoG フィルタと DoR フィルタのサイズの変化に対する出力応答への影響を検討するために用いた 256 画素幅の入力画像 (左). 画像の中央には 8 画素の幅の四角形がある. DoG フィルタ  $f_{DG}(o_1, o_2) = f_{DG}(1.41, 2)$ による処理画像 (右). (b) 様々なスケールにおける DoG フィルタ処理信号. (c) 様々なスケールにおける DoR フィルタ処理信号. (b)と(c)の各行は(a)の点線上のフィルタ処理信号を示す. また縦軸はスケールパラメータを示し、横軸は画素位置を示す. (d) 4 画素幅の四角形を入力とした時の DoR フィルタ処理信号.

フィルタサイズは四角形を覆うほど十分に大きい場合 (図 5.6 (b)(c)の点線 C), 四角形の中心の応答は減衰する.

次に DoR フィルタを用いたキーポイント検出においても,入力パターンのサイズの変更に応じて,SIFT キーポイントの検出スケールが適切に変化するか確認をした.図 5.6(d)は中央部に4 画素幅の四角形がある入力画像に対する DoR フィルタ処理信号を示す. 結果として,上記の場合と比較して半分のスケールで極値が検出された(図 5.8(d)の点線 B).

図 5.6(b)(c)に示される二つのフィルタ処理信号の差は二つのフィルタの空間特性の差に起因する. キーポイント検出された周辺のフィルタ処理信号の応答に着目すると,空間方向に対する DoR フィルタ信号の勾配は DoG フィルタ処理信号の勾配よりも大きい. 一方で,スケール方向に対する DoR フィルタの勾配は DoG フィルタ処理信号の勾配よりも小さい.図 5.6 から, DoR フィルタの空間特性とスケール特性との間のバランスは DoG フィルタのそれとは異なるが,キーポイント検出は DoR フィルタを用いても可能であることを示すことができた.

## 5.5 シミュレーション解析によるキーポイント検出の検討

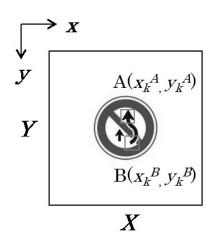

DoR フィルタを用いて視対象のサイズによらず同じ位置で SIFT キーポイントが検出されるかどうかを検討した. 図 5.7 にシミュレーション解析で用いたテスト画像のパターン (標識)を示す. 本実験では、三つの異なるサイズの画像(128×128、181×181、256×256 画素)を入力画像として用いた. SIFT キーポイントが検出された位置を表 5.1 に示す. 画像上でのキーポイントの相対位置  $(x_r, y_r)$  は $(x_t/X, y_t/Y)$ として表現した.  $(x_k, y_k)$  はキーポ

図 5.7 抵抗回路網フィルタによる SIFT アルゴリズムを評価するために使われた入力 画像. 灰色の四角形は, 画像から検出された多くのキーポイントから抽出された二つ のキーポイント  $(A(x_k^A,y_k^A), B(x_k^B,y_k^B))$  の位置を示す. 三つの画像のサイズは 128 × 128, 181 × 181, そして 256 × 256 画素である.

表 5.1 キーポイント A の相対的な位置 T

| Image size | Location $(x_k, y_k)$ | Relative position |

|------------|-----------------------|-------------------|

| [pixels]   | [pixels]              | $(x_r, y_r)$      |

| 128 × 128  | (66, 53)              | (0.516, 0.414)    |

| 181 × 181  | (93, 76)              | (0.514, 0.420)    |

| 256 × 256  | (132, 107)            | (0.514, 0.418)    |

図  $5.8\,256$  画素幅の画像を入力として用いた時の様々なスケールにおける DoR フィルタのフィルタ処理信号. 水平及び垂直な点線はキーポイント A の位置及びスケールをそれぞれ示す.

イントの位置を表現し、X、Yは画像の幅と高さを表現する.三つのキーポイント相対位置  $(x_r, y_r)$  の平均値は (0.5153, 0.4173)であり,三つのキーポイントのどれもがこの位置から 1%以下のずれの範囲に収まる.従って,DoR フィルタを用いて画像サイズによらず,ほぼ 同じ位置でキーポイントが検出されたといえる.

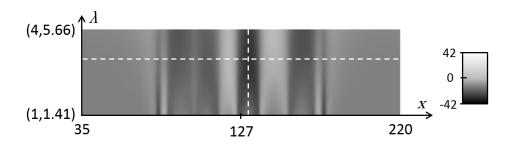

図 5.8 に 256 画素幅の画像の場合における様々なスケールでの DoR フィルタ処理信号を示す. 図 5.8 の行は図 5.7 のキーポイント A 上の水平ラインのフィルタ処理信号を示す. 垂直方向の白い点線はキーポイント A が検出された位置を示しており、x=132 番目の画素で負の極値をとっていることがわかる. 次に、水平方向の白い点線はキーポイント A が検出されたスケールを表しており、x=132 番目の画素位置でスケール方向の変化に着目すると、A1=2.83 で負の極値をとっていることがわかる.

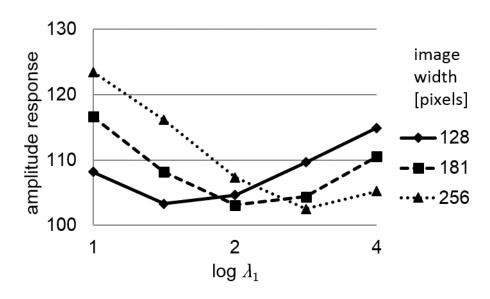

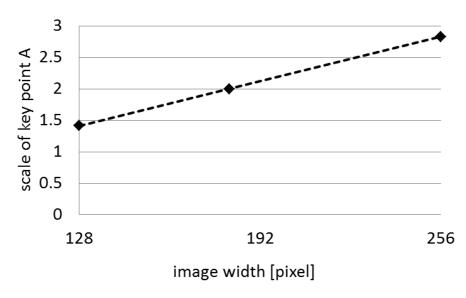

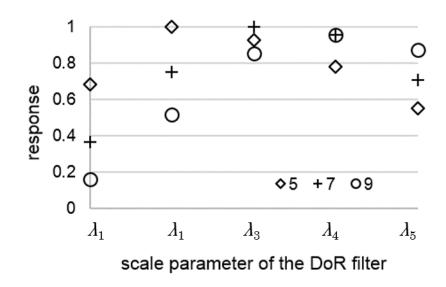

図 5.9 はキーポイント A におけるスケールパラメータ  $\Lambda_1$  と画素値の間の関係を示す. 図 5.9 に示すように、キーポイント A の検出された位置の画素値は画像が小さいサイズでは小さなスケールで最小値となり、画像が大きいサイズでは大きいスケールで最小値となる. すなわち、画像サイズに応じて適切なスケールで極値をとり、これがキーポイントのスケールとして選出された. 図 5.10 は画像サイズとキーポイントの検出スケールとの間の関係を示す. 画像サイズの大きさに応じて同じ位置で検出されるキーポイントのスケールが線形的に変化することがわかる. この結果から DoR フィルタを用いてキーポイントが適切なスケールで検出できることが示された.

図 5.9 キーポイント A でスケールパラメータ  $\lambda_1$  と画素値との間の関係.

図 5.10 キーポイント A のスケールと画像の幅との間の関係. スケールは画像幅で線形的に増加する.

# 5.6 シミュレーションによる特徴量記述の検討

5.5 節において、DoR フィルタに用いてスケール不変な特徴点の検出が可能であることが示された. 次に 5.2.2 節で説明した特徴量記述の手法に基づいて、スケール不変特徴量のシミュレーションを行った. 従来の SIFT アルゴリズムとの違いはガウシアンフィルタの代わりに RN フィルタ処理画像の勾配画像から特徴ベクトルを求める点である. 入力画像には

三つの画像サイズの図 5.7 に示すパターンを用いた.

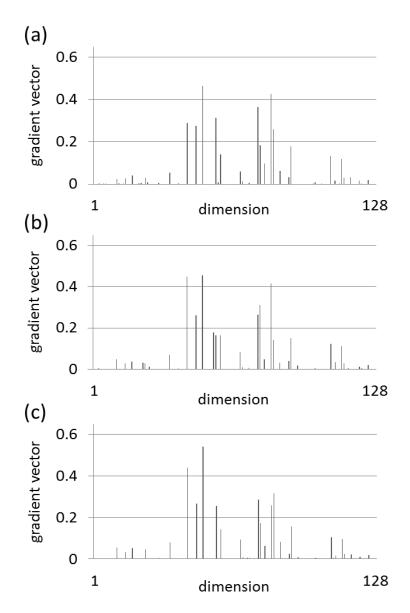

図 5.11 に、図 5.7 のキーポイント A の特徴ベクトルを示す。図 5.12 は 256 画素幅の画像上で検出されたキーポイント B で記述された特徴ベクトルを示す。128 次元の特徴ベクトルはキーポイント周辺の画像勾配から計算された。

図 5.11 異なる画像サイズで検出されたキーポイント A の特徴ベクトル. (a) 128 × 128 画素. (b) 181 × 181 画素. (c)  $256 \times 256$  画素.

図  $5.12~256 \times 256$  画素の画像から検出されたキーポイント B の特徴ベクトル.

表 5.2 キーポイントの間のユークリッド距離.

| Key point | Image size       | Euclidean |

|-----------|------------------|-----------|

| location  | [pixels]         | distance  |

| A         | 128 × 128        | 0.077     |

| A         | 181 × 181        | 0.128     |

| В         | $256 \times 256$ | 1.464     |

画像サイズ 256×256 画素におけるキーポイント A の特徴ベクトルと

他のキーポイントの特徴ベクトルとの間のユークリッド距離

同じ位置から抽出された特徴点がスケール不変な特徴量を有しているか検討するために、キーポイント間の類似性をユークリッド距離によって評価した. ユークリッド距離は式(5.7)を用いて計算した. 表 5.2 に 256 画素幅の画像で検出されたキーポイント A の特徴ベクトルと他のキーポイントの特徴ベクトルとの間のユークリッド距離を示す. 異なる画像サイズで検出されたキーポイント A の特徴ベクトル間のユークリッド距離に対して、同じ画像サイズから検出されたキーポイント A と B の間のユークリッド距離が 10 倍以上、大きいことがわかる.

## 5.7 考察

前節までのシミュレーション結果から、正方格子の二次元抵抗回路網によって、スケール不変特徴量を抽出することが可能であると考えられる. DoR フィルタ処理信号と DoG フィルタ処理信号との違いは空間方向の勾配の強さとスケール方向の勾配の強さのバランスのみであり、これは特徴点検出において大きな問題にはならない.

非常にスケールパラメータが小さい場合,離散抵抗回路網のフィルタカーネルの形状がスケーラブル性を備えなくなるという問題が考えられる.しかしながら,画像内で数画素の領域で小さく写っている対象はそもそも入力の段階で,そのパターンがうまく表現できていない可能性が高く,実用上問題がないと考えられる.一方,スケールパラメータが大きい場合はフィルタの形状に関して問題がなく,むしろ計算コストの面で抵抗回路網を採用した利点が発揮される.

#### 5.8 結言

スケール不変な特徴量は様々な画像処理応用に用いられている技術である. その特徴を 抽出する手法の代表例として SIFT アルゴリズムがあるが, その中でのマルチスケール空 間フィルタ処理の計算コストが高く, 高速化は困難であった.

本研究では抵抗回路網を採用することが、マルチスケール空間フィルタ処理の高速化を実現する上で、非常に効果的な手法であると提案した。このマルチスケール空間フィルタ処理に用いられる低域通過型空間フィルタと帯域通過型空間フィルタにはスケーラブル性が要求されていることを述べた。まず、一次元抵抗回路網モデルにおいて、スケールパラメータの値が等比的になるように設定することで、RNフィルタと DoR フィルタによってスケーラブル性をもたせることができることを示した。また、それは二次元正方格子抵抗回路網においてもシミュレーション実験を行うことで検討された。

様々なスケールにおける DoG フィルタ処理画像と DoR フィルタ処理画像の比較により、これらの出力が中心周辺拮抗型の空間特性を持ち、キーポイントの検出スケールが両方のフィルタにおいて同じように対象のサイズに応じて変化することが示された. DoR フィルタを用いた SIFT アルゴリズムのシミュレーションから、画像サイズに依らず、同じ場所でキーポイントが検出されること、そしてキーポイントのスケールが適切に検出されることが示された. 更に表 5.2 は抵抗回路網フィルタから記述された特徴がスケール不変性を有していることを示唆させる結果であった.

本章で述べた研究は次章に議論する実時間・低消費電力で SIFT 特徴量を記述することができる知能視覚センサシステムに向けた第一歩となった. 次章では、これを発展させ、第3章で提案した抵抗回路網の時分割制御と第4章で提案した FPGA による並列処理機構のアイデアに基づき、実時間スケール不変特徴量抽出機構を有する知能視覚センサの開発したことを論じる.

# 第6章 実時間スケール不変特徴量抽出機能を有する知能視覚センサシステム

#### 6.1 緒言

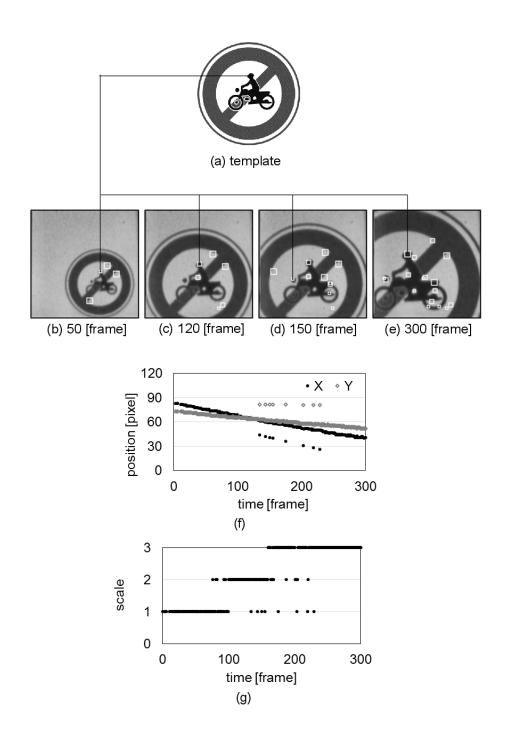

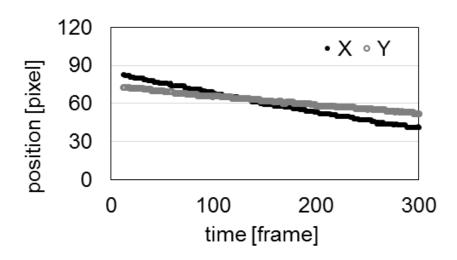

実時間物体追跡は定点カメラによる人流監視から移動カメラによるロボットの制御まで様々な応用に期待される画像処理技術の一つである。視覚情報に基づく物体追跡では対象物の画像特徴量に基づいて、各画像フレーム内の対象物を探索・追従する。これらのタスクには特徴点検出器や特徴量抽出器(記述子)を使うことが効果的であることが知られている(総説として[96, 97]).

特徴点ベースの物体追跡手法ではまず画像から特徴点を検出し、各特徴点において特徴ベクトルを記述する。例えば移動ロボットなど絶え間なく対象と搭載されたカメラとの距離が変化する場合、画像上での見えの大きさが時々刻々と変化する。従って、物体追跡に適した特徴点にはスケール不変性が要求される。このような特徴点を高速に抽出する必要があることに加えて、移動ロボットに使われる画像センシングシステムはコンパクトでかつ低消費電力であることが要求される。