|              |                                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------|

| Title        | Germanium-Tin-Based Optoelectronic Integration Utilizing Nucleation-Controlled Liquid-Phase Crystallization |

| Author(s)    | 岡, 博史                                                                                                       |

| Citation     | 大阪大学, 2018, 博士論文                                                                                            |

| Version Type | VoR                                                                                                         |

| URL          | <a href="https://doi.org/10.18910/69528">https://doi.org/10.18910/69528</a>                                 |

| rights       |                                                                                                             |

| Note         |                                                                                                             |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

Doctoral Dissertation

**Germanium-Tin-Based Optoelectronic Integration

Utilizing Nucleation-Controlled

Liquid-Phase Crystallization**

**Hiroshi Oka**

January 2018

Department of Material and Life Science

Graduate School of Engineering

Osaka University

# Table of Contents

|                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------|----|

| Table of Contents .....                                                                                               | 1  |

| Chapter 1 Introduction.....                                                                                           | 5  |

| 1.1 Background .....                                                                                                  | 5  |

| 1.1.1 Development of Advanced Information Society.....                                                                | 5  |

| 1.1.2 Improvement of Semiconductor Device Performance.....                                                            | 5  |

| 1.1.2.1 Scaling Limit of Silicon (Si)-based Integrated Circuit .....                                                  | 5  |

| 1.1.2.2 High-Mobility Channel.....                                                                                    | 9  |

| 1.1.2.3 Si Photonics.....                                                                                             | 10 |

| 1.2 Germanium-Tin (GeSn) Alloy.....                                                                                   | 12 |

| 1.2.1 Band Structure.....                                                                                             | 13 |

| 1.2.2 Theoretical Calculations of Electronic and Optical properties .....                                             | 13 |

| 1.3 Issues in Crystal Growth of GeSn Alloy .....                                                                      | 16 |

| 1.3.1 Epitaxial Growth on Si Substrate .....                                                                          | 16 |

| 1.3.2 Non-Epitaxial Growth on Insulating Layer .....                                                                  | 18 |

| 1.3.3 Lateral Liquid-Phase Epitaxy (LLPE) .....                                                                       | 19 |

| 1.4 Aim of This Study and Contents of Thesis .....                                                                    | 20 |

| References .....                                                                                                      | 23 |

| Chapter 2 Single-Crystalline GeSn Growth on Quartz Substrate by Nucleation-Controlled Liquid-Phase Crystallization .. | 25 |

| 2.1 Introduction .....                                                                                                | 25 |

| 2.2 Nucleation-Controlled Liquid-Phase Crystallization .....                                                          | 25 |

| 2.2.1 Concept of This Technique .....                                                                                 | 25 |

| 2.2.2 Fabrication process .....                                                                                       | 26 |

| 2.3 Physical Characterization .....                                                                                   | 27 |

| 2.3.1 Crystalline Quality and Sn Content .....                                                                        | 27 |

| 2.3.2 Determination of Strain by Synchrotron X-ray Diffraction .....                                                  | 31 |

|         |                                                               |    |

|---------|---------------------------------------------------------------|----|

| 2.4     | Optical Characterization .....                                | 32 |

| 2.5     | Evaluation of Conduction Type and Carrier Concentration ..... | 33 |

| 2.5.1   | Hall Effect Measurement .....                                 | 33 |

| 2.5.2   | Fabrication of Hall-Bar Shaped GeSn Wire .....                | 34 |

| 2.6     | N-type Doping into Liquid-Phase Grown Ge and GeSn Wires ..... | 36 |

| 2.6.1   | Issues in n-type GeSn Formation .....                         | 36 |

| 2.6.2   | LLPE-Growth of Sb-Doped Ge on Silicon Substrate .....         | 37 |

| 2.6.2.1 | Fabrication Process .....                                     | 37 |

| 2.6.2.2 | Evaluation of Sb Distribution .....                           | 37 |

| 2.6.3   | Liquid-Phase Growth of Sb-Doped GeSn on Quartz Substrate ..   | 40 |

| 2.6.3.1 | Fabrication Process .....                                     | 40 |

| 2.6.3.2 | Crystalline Quality .....                                     | 41 |

| 2.6.3.3 | Photoluminescence-Based Study .....                           | 42 |

| 2.6.3.4 | Hall Effect Measurement .....                                 | 43 |

| 2.7     | Summary .....                                                 | 44 |

|         | References .....                                              | 45 |

|           |                                                                                                                                 |    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------|----|

| Chapter 3 | High-Mobility P- and N-Channel GeSn Thin-Film Transistors .....                                                                 | 46 |

| 3.1       | Introduction .....                                                                                                              | 46 |

| 3.2       | Accumulation-Mode GeSn P-Channel Thin-Film Transistor .....                                                                     | 46 |

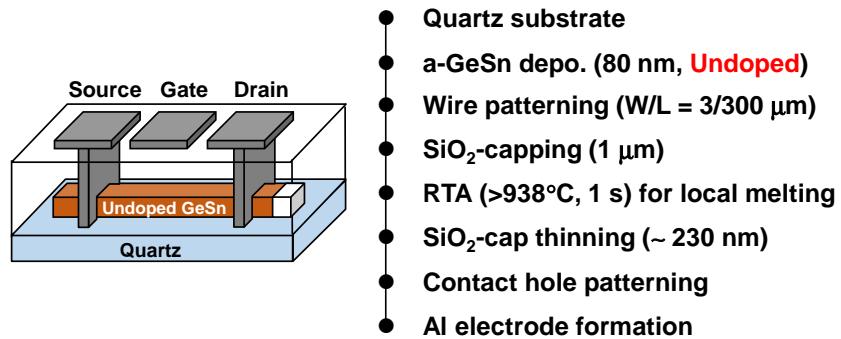

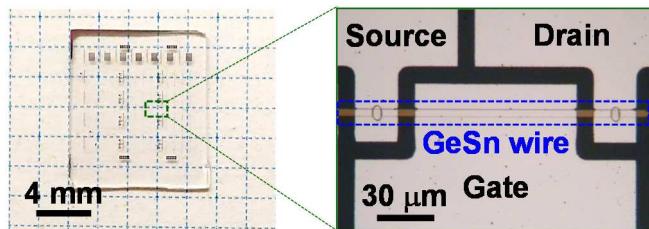

| 3.2.1     | Fabrication process .....                                                                                                       | 46 |

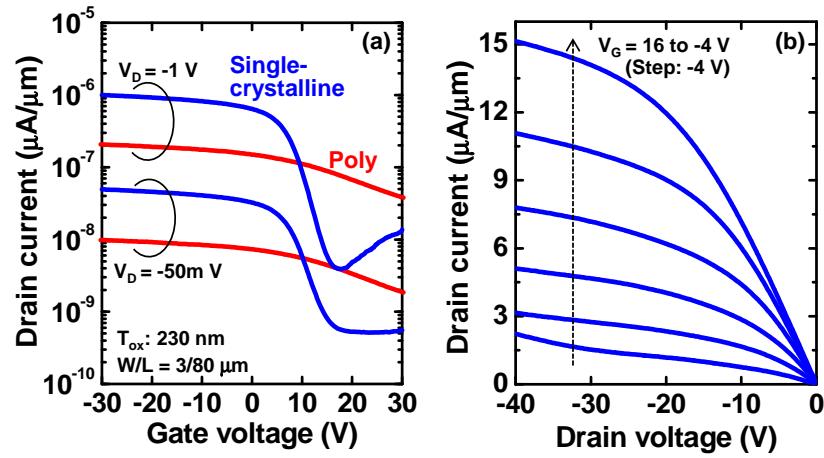

| 3.2.2     | Transistor Operation and Mobility Characterization .....                                                                        | 47 |

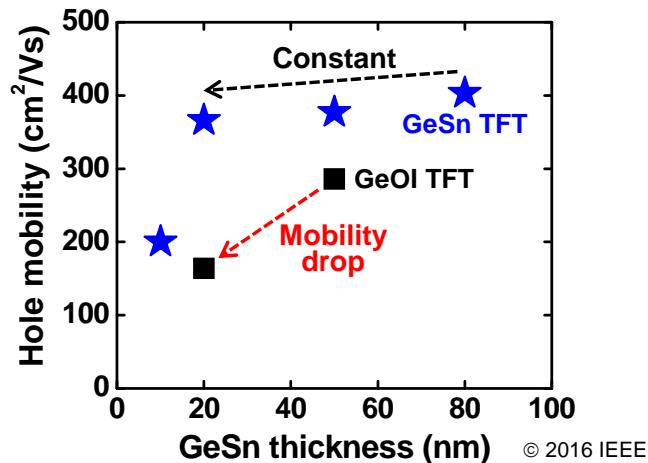

| 3.2.3     | Thickness Dependence of Mobility .....                                                                                          | 50 |

| 3.3       | Accumulation-Mode GeSn N-Channel Thin-Film Transistor .....                                                                     | 52 |

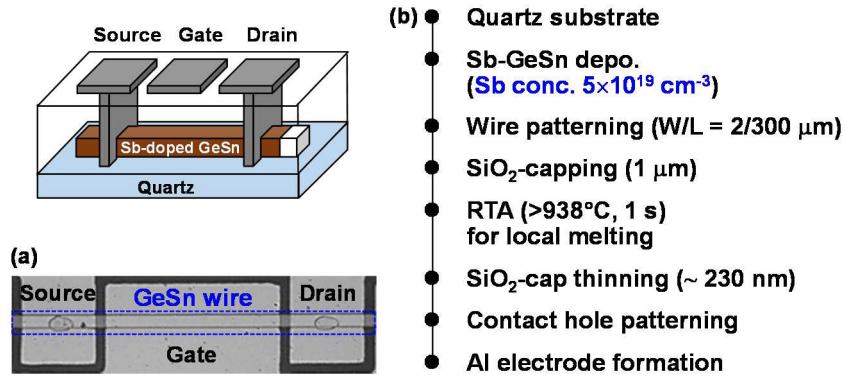

| 3.3.1     | Fabrication Process .....                                                                                                       | 52 |

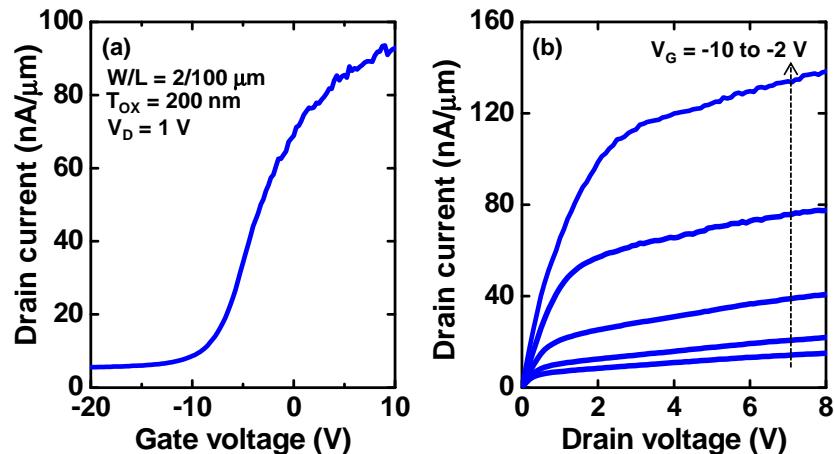

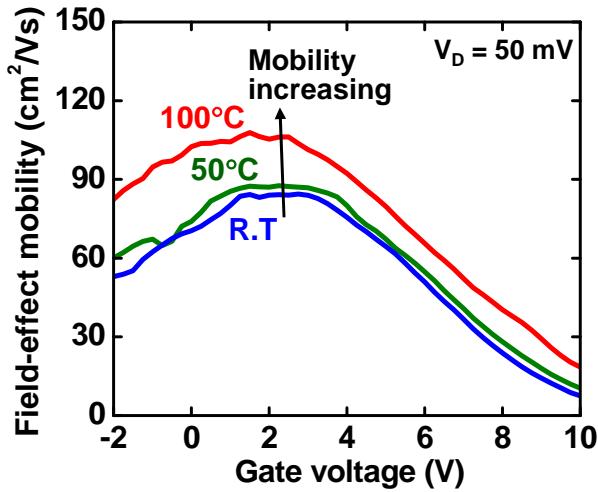

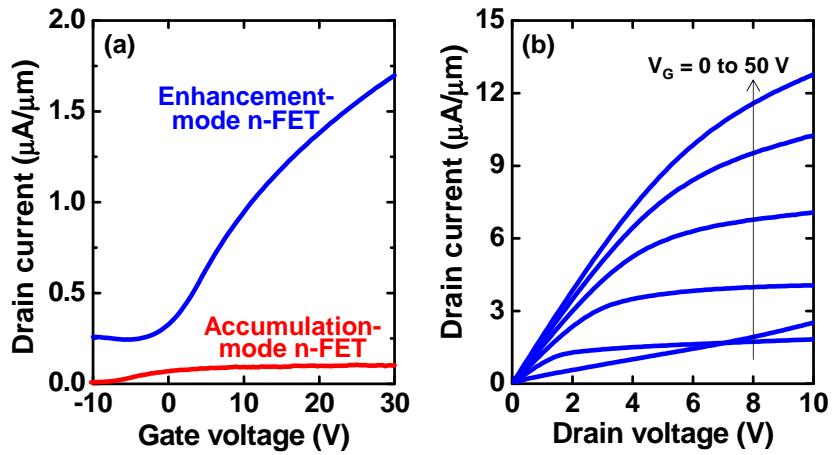

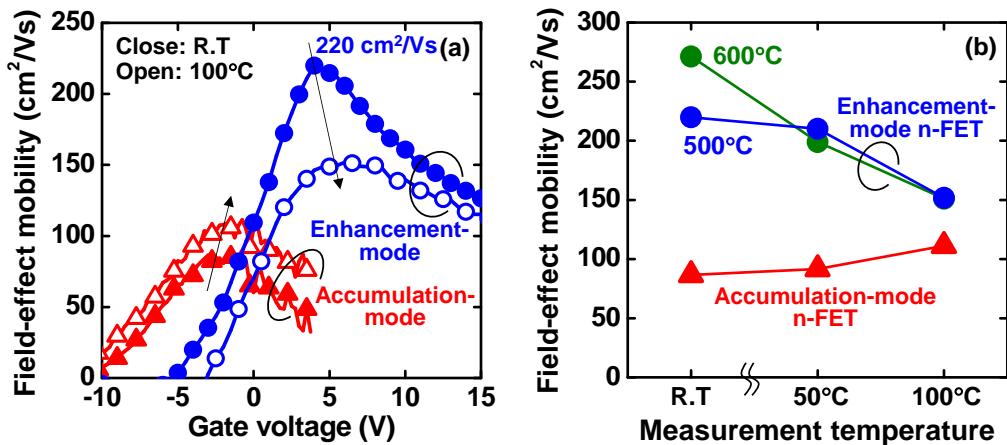

| 3.3.2     | Transistor Operation and Mobility Characterization .....                                                                        | 53 |

| 3.4       | High-Mobility Enhancement-Mode N-Channel Thin-Film Transistor Based on Single-Crystalline GeSn n <sup>+</sup> /p Junction ..... | 55 |

| 3.4.1     | Concept of This Work .....                                                                                                      | 55 |

|                                                               |    |

|---------------------------------------------------------------|----|

| 3.4.2 Single-Crystalline GeSn n <sup>+</sup> /p Junction..... | 56 |

| 3.4.2.1 Fabrication Process .....                             | 56 |

| 3.4.2.2 Activation Behavior of P <sup>+</sup> in GeSn .....   | 57 |

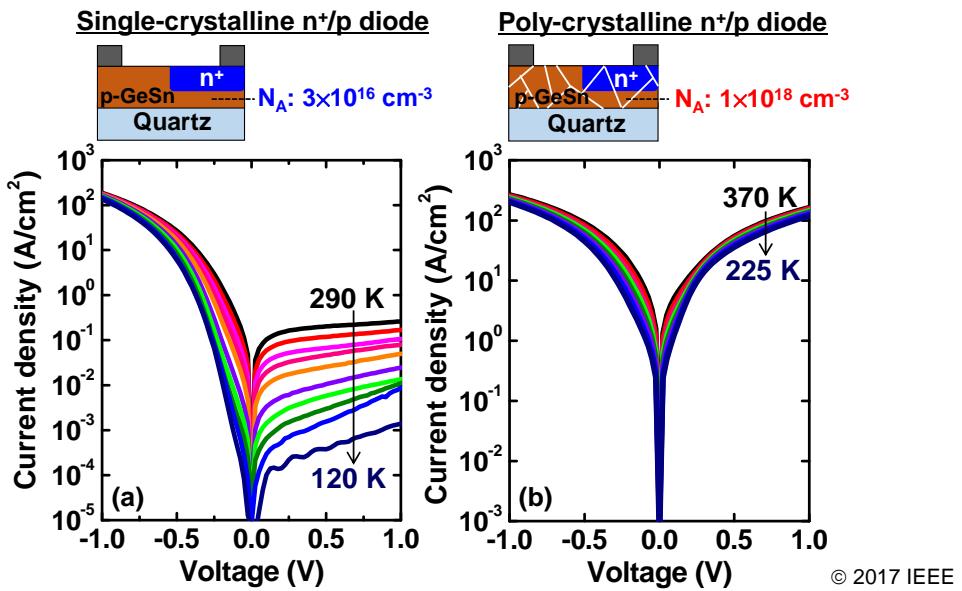

| 3.4.2.3 Current-Voltage Characteristics .....                 | 60 |

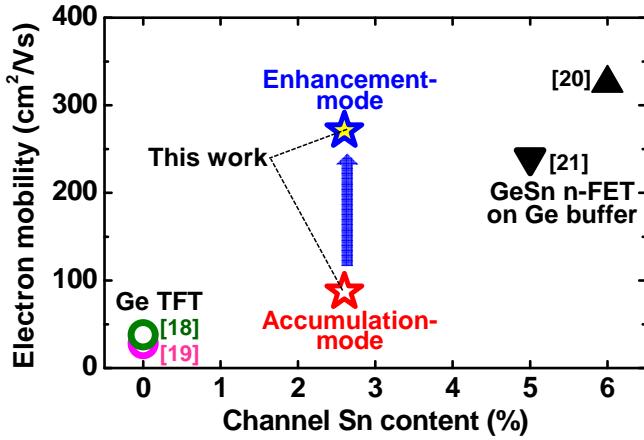

| 3.4.3 Transistor Operation and Mobility Characterization..... | 61 |

| 3.5 Summary .....                                             | 63 |

| References .....                                              | 65 |

|                                                                                                                                                    |           |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>Chapter 4 Fabrication of Back-Illuminated GeSn Photodiode Array<br/>for Monolithically-Integrated Near-Infrared (NIR) Imager<br/>Chip .....</b> | <b>66</b> |

| 4.1 Introduction .....                                                                                                                             | 66        |

| 4.2 Laser-Induced Liquid-Phase Crystallization .....                                                                                               | 68        |

| 4.2.1 Concept of This Technique .....                                                                                                              | 68        |

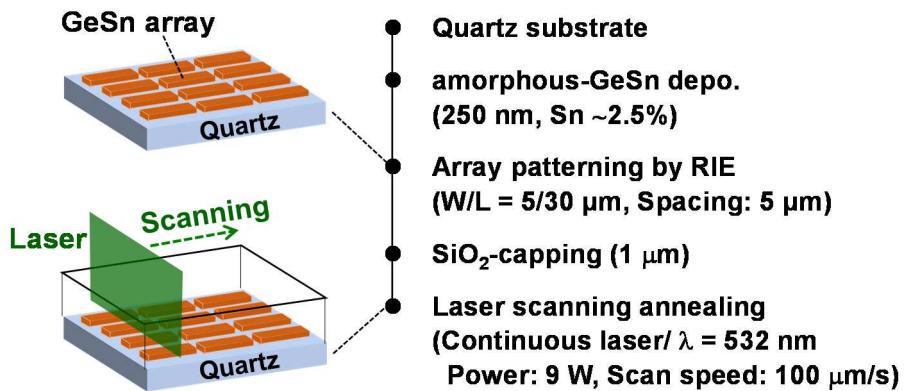

| 4.2.2 Fabrication Process .....                                                                                                                    | 70        |

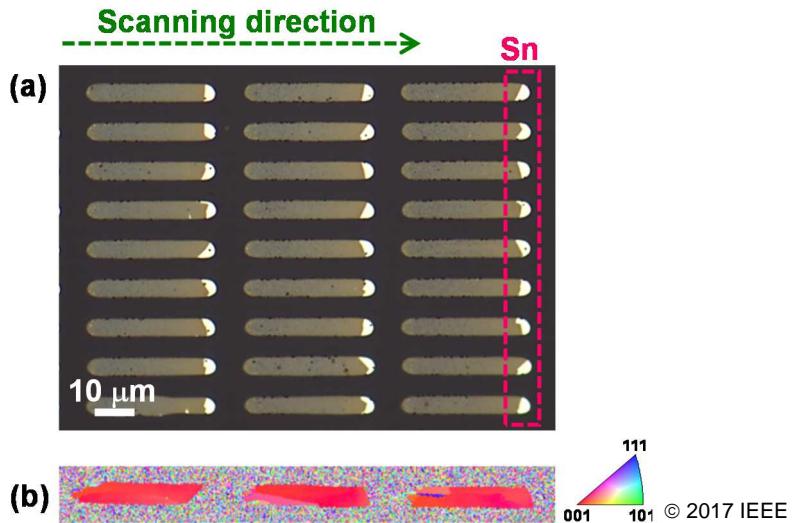

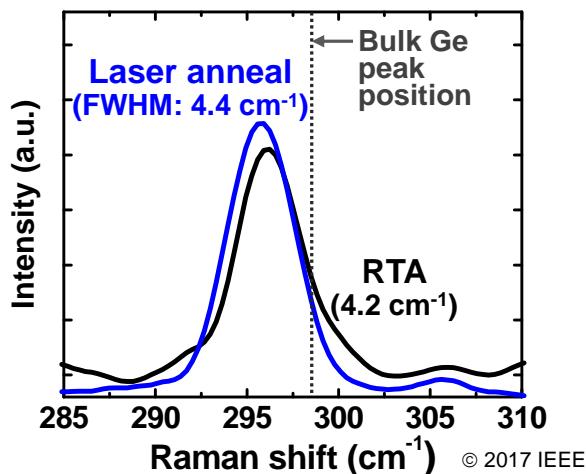

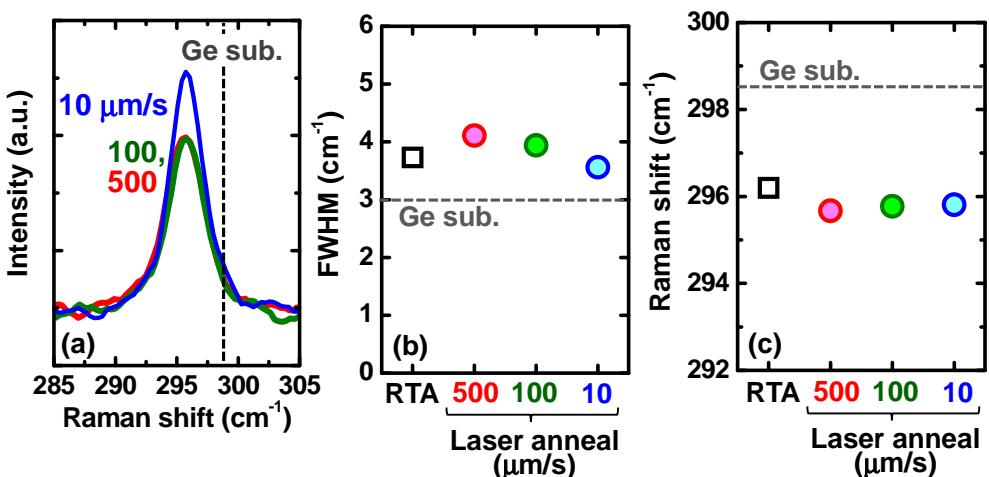

| 4.2.3 Crystallinity and Sn content .....                                                                                                           | 70        |

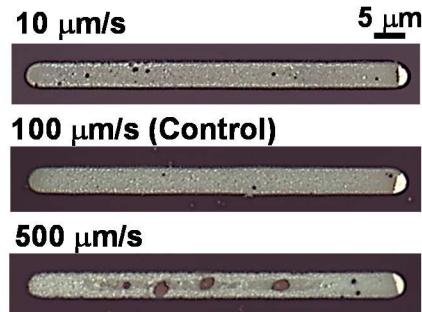

| 4.2.4 Laser Scanning Speed Dependence .....                                                                                                        | 72        |

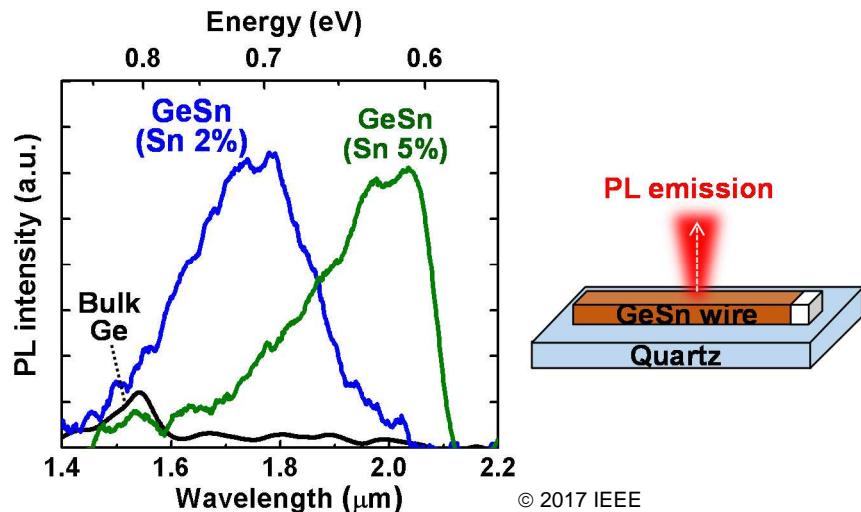

| 4.2.5 Photoluminescence Study.....                                                                                                                 | 73        |

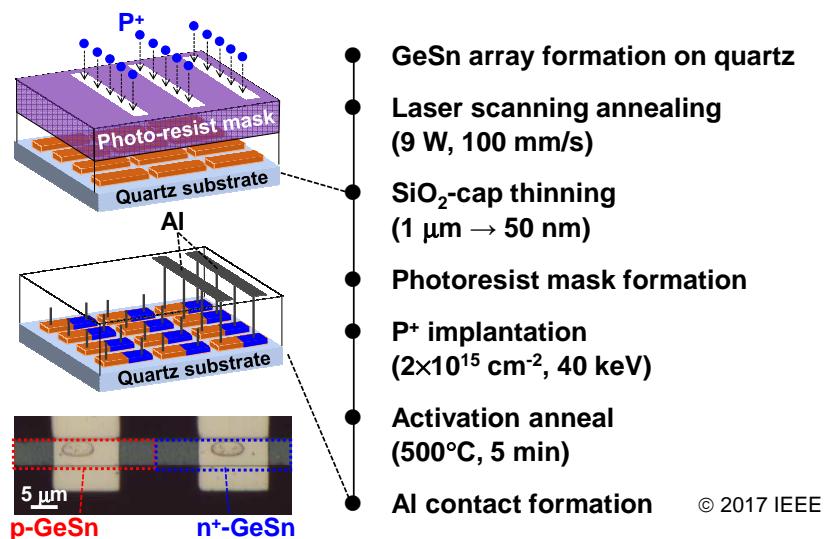

| 4.3 Single-Crystalline GeSn n <sup>+</sup> /p Photodiode Array.....                                                                                | 73        |

| 4.3.1 Fabrication process .....                                                                                                                    | 74        |

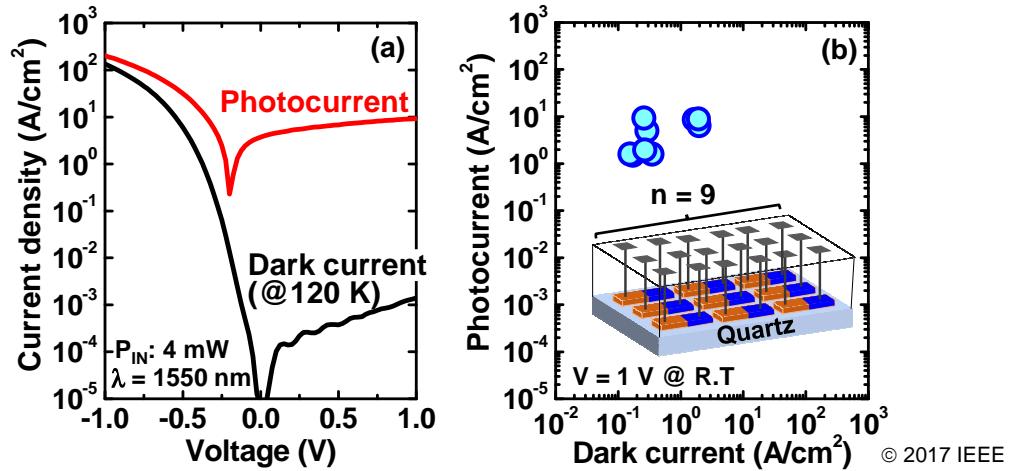

| 4.3.2 Electrical Characterization.....                                                                                                             | 75        |

| 4.4 Evaluation of NIR Optical Response of GeSn n <sup>+</sup> /p Photodiode .....                                                                  | 77        |

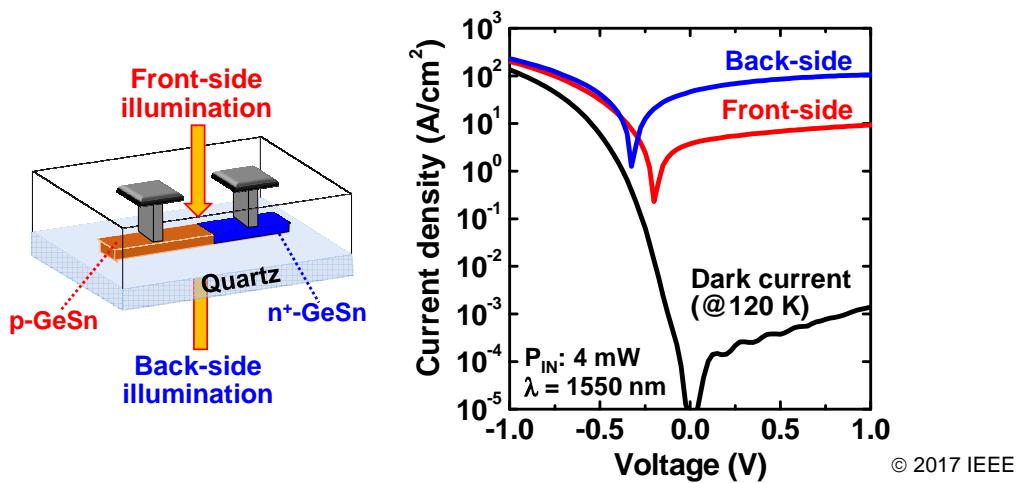

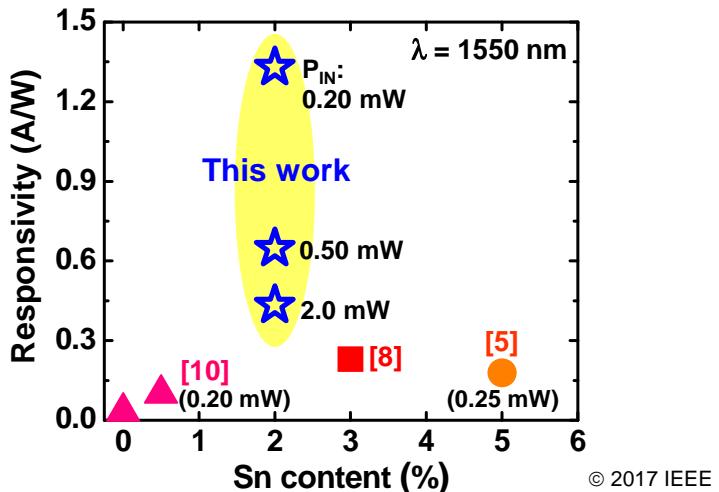

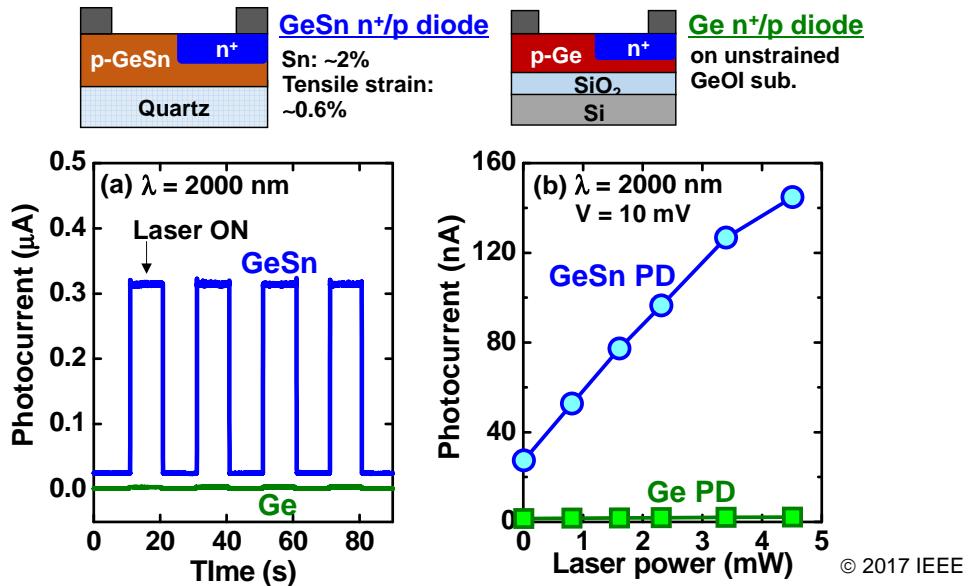

| 4.4.1 Front-Side Illuminated Photodetection .....                                                                                                  | 77        |

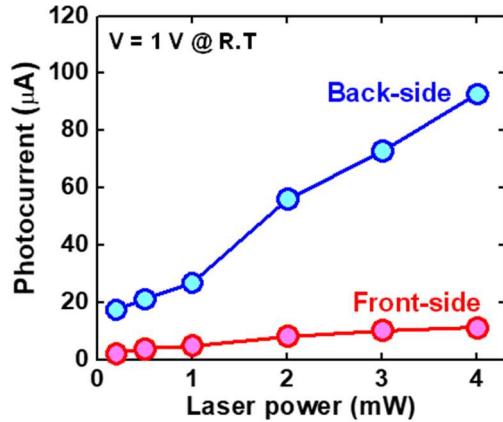

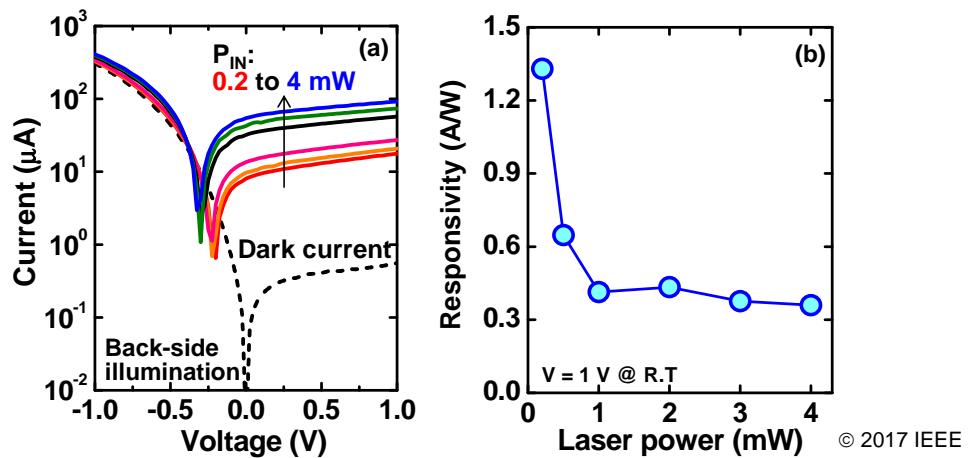

| 4.4.2 Back-Side Illuminated Photodetection.....                                                                                                    | 78        |

| 4.4.3 Extraction of Optical Responsivity .....                                                                                                     | 80        |

| 4.4.4 Optical Response in 2 μm Wavelength Range .....                                                                                              | 81        |

| 4.5 Summary .....                                                                                                                                  | 82        |

| References .....                                                                                                                                   | 84        |

|                             |    |

|-----------------------------|----|

| Chapter 5 Conclusions ..... | 85 |

| Acknowledgements.....       | 88 |

| List of Publications.....   | 89 |

# Chapter 1 Introduction

## 1.1 Background

### 1.1.1 Development of Advanced Information Society

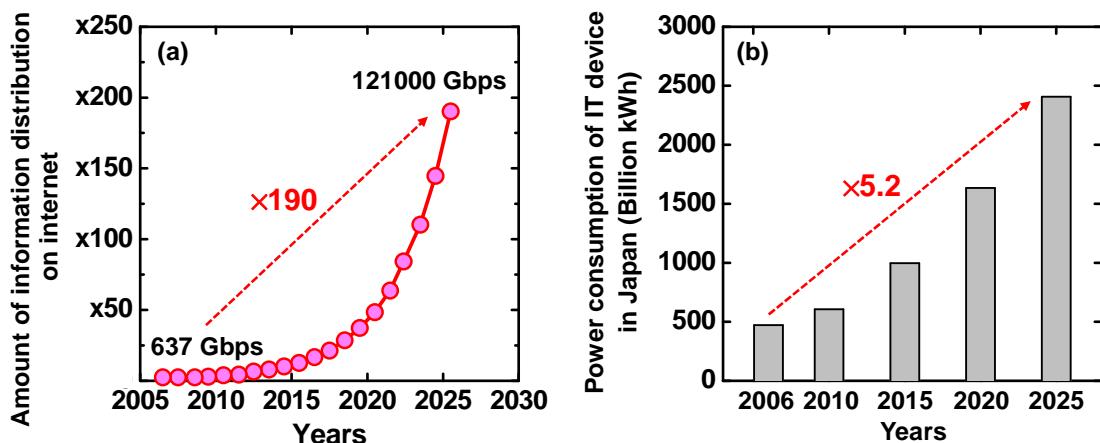

In recent years, due to the expansion of internet and spread of personal information technology (IT) devices such as computers, smartphones and tablet-type portable terminals, the amount of information distribution is now significantly increasing. It has been predicted that the internet traffic throughout the world reaches 121000 Gbps (=121 Tbps) by 2025, which is about 190 times larger than that in 2005 (Fig. 1-1(a)) [1]. With the rapid growth of information society, the power consumption of IT devices is considerably increasing. As shown in Fig. 1-1(b), the IT power consumption in Japan increased year by year and it reaches 2500 billion kWh at 2025, [1] which is 20% of the domestic electric generation amount in Japan. Under such background, sustainable development and multi-functionality is required for IT device to deal with the advanced information society.

### 1.1.2 Improvement of Semiconductor Device Performance

#### 1.1.2.1 Scaling Limit of Silicon (Si)-based Integrated Circuit

Up to this day, the growing of advanced information society is accomplished by the development of Silicon (Si)-based large-scale integrated circuit (LSI). LSI is an electronic circuit formed on semiconductor microchip that is composed of

Fig. 1-1 (a) Amount of information distribution on worldwide internet as function of years. (b) Transition of power consumption of IT devices in Japan. [1]

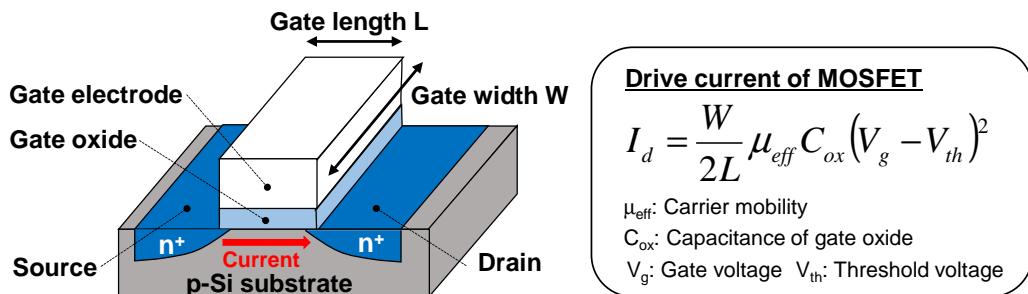

transistors. The metal-oxide-semiconductor field-effect transistor (MOSFET) is a popular type of transistor and a key component of LSI, which is now most widely used. [2]

The basic characteristics of MOSFET is switching and amplifying the electrical signals. The MOSFET is fabricated on a single-crystalline semiconductor substrate and consisted of gate electrode, gate insulator and source/drain (S/D) region with four electrical terminals as shown in Fig. 1-2. The S/D region is heavily-doped and has opposite conduction type to substrate (when substrate is p-type, S/D region should be n<sup>+</sup>-type). The gate stack has a metal-oxide-semiconductor (MOS) structure, which act as a capacitor. Since the electrical charges under the gate stack can be controlled by applying the gate voltage, the current flowing from source to drain region can be controlled and electrically switches on- and off-states of the device. The equation of drive current of MOSFET is also shown in Fig. 1-2. The drive current depends on the gate voltage, and it is proportional to gate width (W), carrier mobility ( $\mu_{eff}$ ) and capacitance of gate oxide ( $C_{ox}$ ), while inverse proportional to gate length (L). Here, the carrier mobility is the average drift velocity of hole and electron which is specific to semiconductor material (in the case of Si, mobility of hole and electrons are 1600 and 430 cm<sup>2</sup>/Vs, respectively). Therefore, scaling of the dimension of device size (gate length) is effective to increase the drive current of MOSFET and improve the performance of LSI. In the past few decades, Si-MOSFET has been aggressively scaled down and significantly increased number of transistor on a microchip. This scaling of MOSFET has been achieved with the rule generally known as Dennard scaling [3]. In the Dennard scaling, in order to keep the electric field in transistor constant, the dimension of device size

Fig. 1-2 Schematic illustration of structure and equation of drive current of MOSFET.

Fig. 1-3 Dennard scaling of MOSFET.

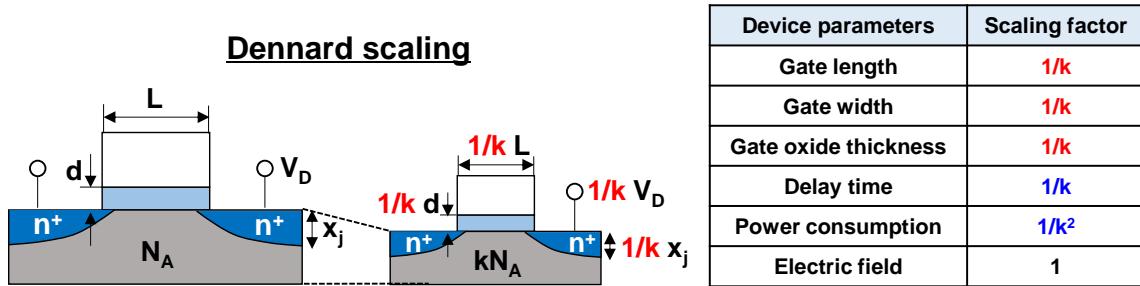

and other parameter such as a gate oxide thickness reduced by  $1/k$ , which leads to decrease in delay time and power consumption of MOSFET by  $1/k$  and  $1/k^2$ , respectively (Fig. 1-3). This is an attractive approach to improve the performance of LSI. As shown in Fig. 1-4, the minimum feature size of transistor is about 10000 nm ( $= 10 \mu\text{m}$ ) at 1970, the size scaled down exponentially year by year.

However, when the minimum feature size reached 100 nm or less around 2010, it have become difficult to improve the transistor performance with conventional scaling due to the physical limitations such as gate leakage current and the short channel effects [4]. The representative short channel effects are limitation imposed on carrier drift characteristics and the threshold voltage shift in the aggressively scaled channel. In order to deal with these problems and keeping up the performance improvement, several approaches have been explored and introduced into the scaled MOSFET, which is generally called “technology boosters”. For example, high-permittivity (high- $k$ ) gate insulator

Fig. 1-4 Scaling of Si-MOSFET (minimum feature size as function of years).

was adopted instead of silicon dioxide ( $\text{SiO}_2$ ), which can reduce the equivalent oxide thickness (EOT) and suppress the gate leakage current [5]. Also, the architecture of transistor have been also changed from the conventional planar transistor to non-planar tri-gate transistor to provide a better drivability and electrostatic control to the channel [6]. By combining above innovative technology, the performance of sub-90-nm node transistor have been enhanced until now. However, although the great effort has been paid to keeping up the scaling of MOSFET, the minimum feature size is now reaching sub-10 nm and it has become difficult to improve the performance of Si-based MOSFET.

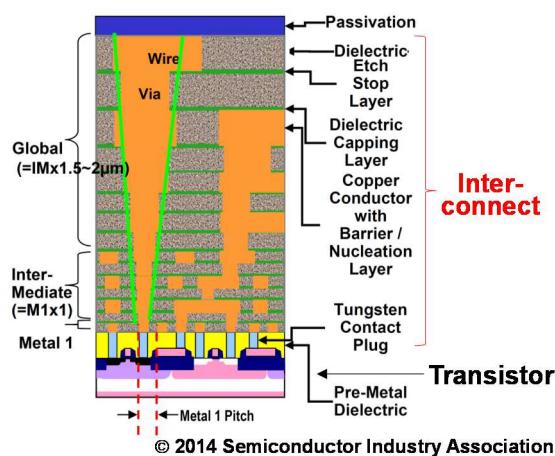

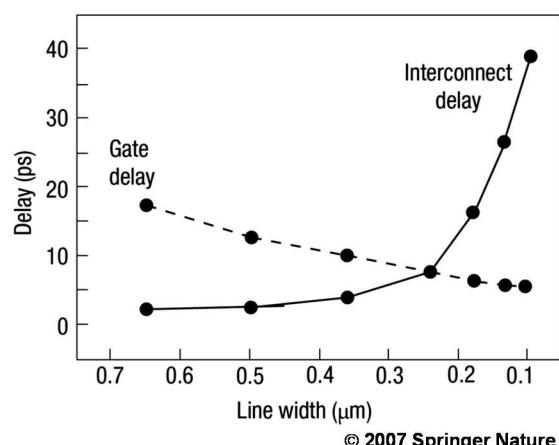

Furthermore, in addition to the scaling limit of Si-MOSFET, the interconnect delay becomes severe performance limiting factor of the LSI. In the current LSI, a copper wire has been used to transfer electrical signals which connects device to device (Fig. 1-5) [7]. In general, the processing speed of LSI is determined by transistor gate delay (switching time) and interconnect delay. With the dimension of transistor decreased and the number of transistor integrated on a chip increased, the resistance-capacitance (RC) delay of the copper interconnections has become a severe bottleneck for data processing. As shown in Fig. 1-6, while the gate delay decreased with decreasing the line width (gate length), the interconnect delay increased with decreasing the line width and crossover happened at a line width of around 0.2  $\mu\text{m}$ , and it shows rapid increase [8]. This results in degradation of processing speed and increase in power consumption.

Fig. 1-5 Cross-section illustration of LSI [7].

Fig. 1-6 Trends in gate delay and interconnect delay as function of line width. [8]

Therefore, in order to continue the development of advanced information society, alternative technological solutions that break the limitation of conventional Si-LSI are now strongly required.

### 1.1.2.2 High-Mobility Channel

As mentioned in the above session, the conventional Si-based LSI is now facing with the physical limitation in performance improvement for both device and interconnection side, and the technological breakthrough is strongly desired.

One of the promising approach is the introduction of high-mobility channel material instead of Si. As shown in Fig. 1-2, the drive current of MOSFET is proportional to carrier mobility. Thus, it has become possible to improve the device performance which does not rely only on the scaling. Table 1-1 summarizes carrier mobility for typical group-IV and III-V semiconductor materials. In order to construct a digital logic circuit, both p- and n-channel MOSFET (i.e. complementary MOSFET, CMOS) is required so that the semiconductor material which has high hole and electron mobility is desired. The III-V semiconductors such as Indium-gallium-arsenide (InGaAs) and Indium-arsenide (InAs) show a very high electron mobility. On the other hand, there is no advantage in hole mobility compared to Si. Also, in order to introduce a high-mobility channel material into advanced logic circuit seamlessly, compatibility to a mature Si-CMOS technology is required. However, III-V elements behave as impurity for group-IV semiconductor (p- or n-type dopants), which is a severe obstacle to implement III-V channel using conventional Si technology.

Germanium (Ge) is a group-IV semiconductor as in the case of Si, thus it has an advantage in process integrity with Si-CMOS technology and there are no

Table 1-1 Carrier mobility for typical group-IV and III-V semiconductors.

| Semiconductor                  | Group | Bandgap (eV) |          | Mobility (cm <sup>2</sup> /Vs) |      |

|--------------------------------|-------|--------------|----------|--------------------------------|------|

|                                |       | Direct       | Indirect | Electron                       | Hole |

| <b>Silicon (Si)</b>            | IV    | 3.4          | 1.1      | 1600                           | 430  |

| <b>Germanium (Ge)</b>          | IV    | 0.80         | 0.66     | 3900                           | 1900 |

| <b>Gallium arsenide (GaAs)</b> | III-V | 1.4          | 1.7      | 9200                           | 400  |

| <b>Indium arsenide (InAs)</b>  | III-V | 0.36         | 1.1      | 40000                          | 500  |

concern about cross contamination. Although the electron mobility is lower than that of typical III-V semiconductors, Ge has both high electron and hole mobility compared to Si, which makes it attractive material for post-Si channel material.

### 1.1.2.3 Si Photonics

Another approach to improve the performance of LSI is an electronic and photonic integration on a microchip based on group-IV semiconductors, which is generally called Si photonics. In this session, current status and technological outlook of Si photonics were described.

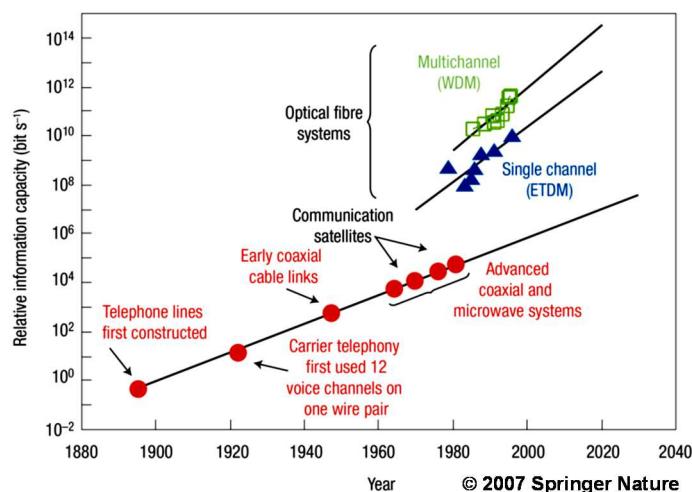

As mentioned in session 1.1.2.1, with the size of transistor decreased and number of transistor per chip increased, the interconnect delay becomes bottleneck for data transfer in the LSI due to the RC delay of copper interconnect. Thus, alternative technological solution for the massive data transfer is strongly desired in the post-scaling era. One of the most attractive approach to overcome this issue is the implementation of optical interconnect instead of conventional electrical interconnect, in which the high-density and high-speed data transmission is possible. In the long distance data transmission, the optical interconnect have been already introduced and widely used until now. Figure 1-7 shows the trend in the information-carrying capacity of a single line (metal wire or optical fiber) as a function of year [8]. The displacement of electric interconnection to optical fiber was carried out around 1990, and the information capacity was significantly increased more than three order of magnitude

Fig. 1-7 Trend in the information-carrying capacity of a single line (metal wire or optical fiber) as function of year and technology [8].

compared to conventional metal wire, which clearly indicates the advantage of optical data transmission. Therefore, realization of optical interconnection at the level of electronic microchip would be an ideal approach to break the physical limitation of processing bandwidth in the current LSI.

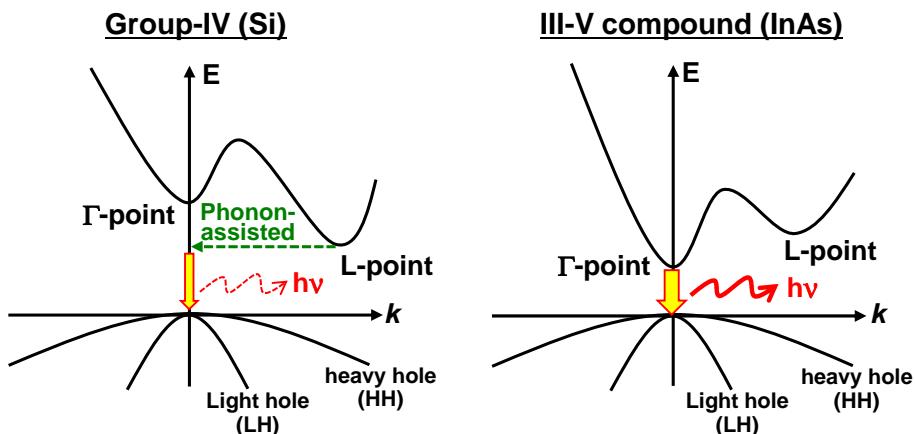

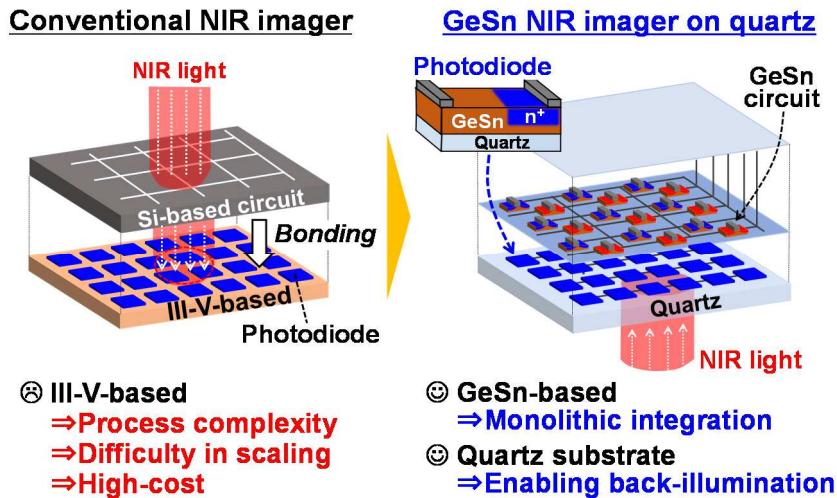

So far, photonic devices such as light emitting diode (LED) or photodetector have been developed based on III-V semiconductors such as InP or GaAs, which have a direct bandgap structure and offer highly efficient light emission/detection (Fig. 1-8). Since Si has an indirect bandgap, phonon assistance is required for carrier recombination and thus luminescence efficiency is fundamentally poor. In order to enable the optical interconnect on an electronic microchip, an integration of photonic devices on a Si-platform is required. Although heterogeneous integration of III-V-based photonic devices on Si substrate using a wafer bonding or epitaxy would be one of solutions [9], there are several disadvantages in the cost, large-volume manufacturing and process integrity to conventional Si-CMOS technology. Thus, integration of group-IV-based optical devices on Si-platform would be an ideal approach to enable the optical interconnect.

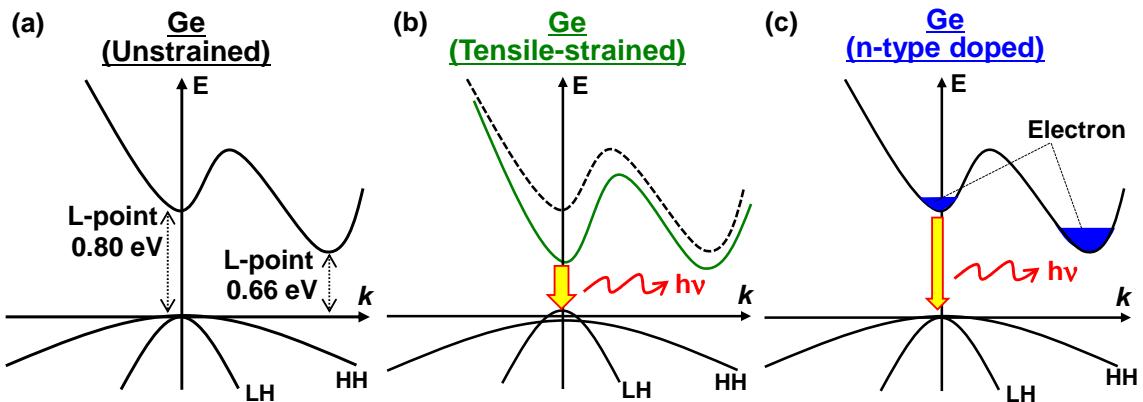

Among the group-IV material, Ge has an indirect bandgap structure, but the energy difference between  $\Gamma$  and L valleys in conduction band is only 0.14 eV ( $E_g$  Direct: 0.80 eV,  $E_g$  Indirect: 0.66 eV), which is much smaller than the energy difference of Si (2.3 eV). Since the wavelength corresponding to the direct bandgap of Ge ( $E = 0.80$  eV,  $\lambda = 1550$  nm) is within the telecom optical wavelength range currently used, it has been regarded as promising group-IV material to enable optical interconnection on the Si-platform. In order to improve

Fig. 1-8 Band structure of group-IV (Si) and III-V semiconductors (InAs).

the light emission/detection efficiency of Ge to compete with the III-V semiconductors, several approaches have been explored to modulate the band structure, such as inducing tensile strain or n-type doping [10,11]. From the theoretical calculation, by applying the tensile strain to Ge, the direct bandgap decreased faster with respect to indirect bandgap. Therefore, the energy difference between  $\Gamma$ - and L-valley reduced and thus enhancing light emission/detection efficiency (Fig. 1-9(b)). It is predicted that Ge exhibits the indirect-to-direct bandgap transition by applying biaxial tensile strain for about 1.5% [10]. Also, the increase in electron population at L-valley by n-type doping promotes the electron injection into  $\Gamma$ -valley and also improves the light emission efficiency of Ge (Fig. 1-9(c)).

Fig. 1-9 Band structure of (a) unstrained Ge, (b) tensile-strained Ge, and (c) n-type doped Ge.

As described in this session, Ge is a promising group-IV material in the post scaling era for its high carrier mobility and unique band structure, and the Ge-based technology is expected to break the physical limitation of Si-based LSI.

## 1.2 Germanium-Tin (GeSn) Alloy

As mentioned in the previous session, introduction of high-mobility channel material and implementation of Si photonics are attractive post-scaling technology, and Ge is regarded as a most promising post-Si material. So far, great efforts have been paid to modulate band structure of Ge and to exhibit enhanced electronic and photonic properties by strain engineering. However, it is quite difficult to form direct bandgap Ge since biaxial tensile strain as high as 1.5% is

required for indirect-to-direct transition [10].

Recently, group-IV mixed crystal, germanium-tin (GeSn) alloy, has gained a significant interest due to its improved electronic and photonic properties with respect to Ge thanks to its tunable band structure. In this session, the band structure, optoelectronic properties and application fields of GeSn alloy were described in detail.

### 1.2.1 Band Structure

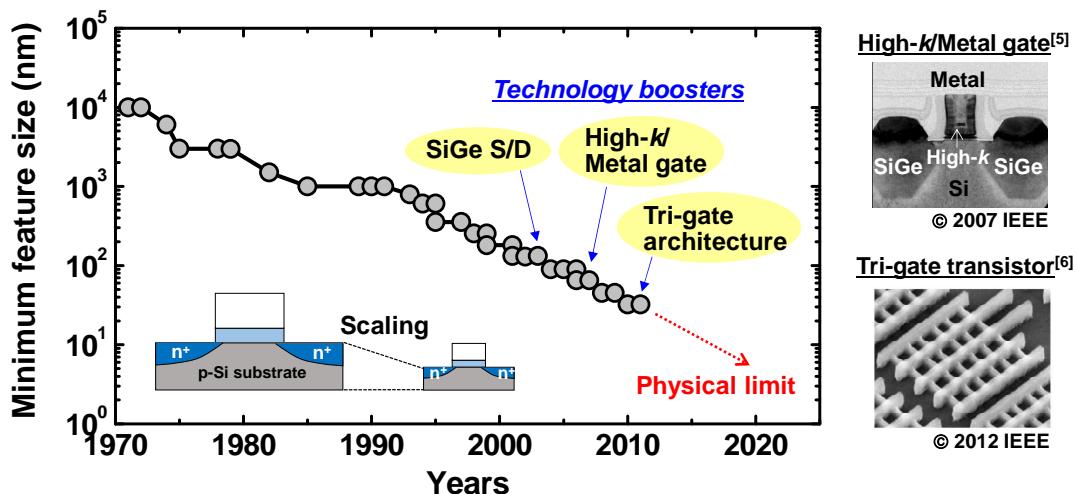

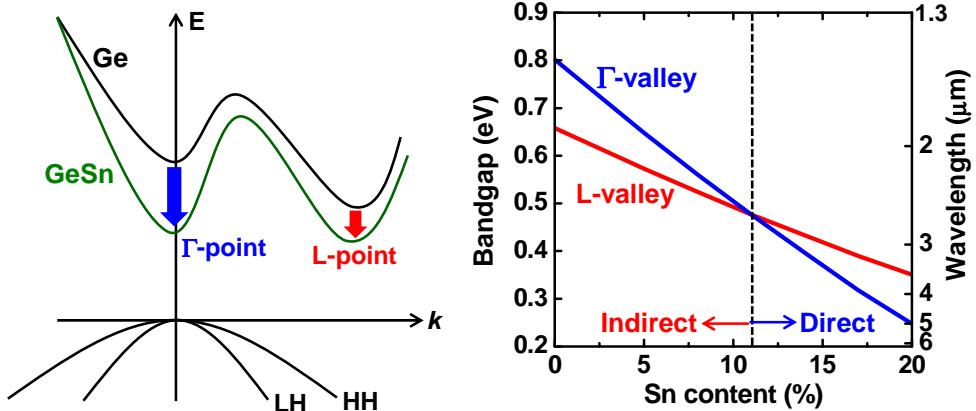

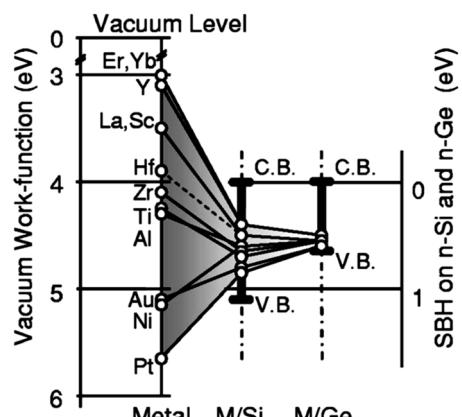

Recently, GeSn alloy has attracted a significant interest for both electronic and photonic applications due to its tunable band structure. Sn is a group-IV semi-metal element, which has a nearly zero bandgap [12]. An incorporation of Sn into Ge modulates the band structure and reduces the energy of  $\Gamma$ - and L-valleys in conduction band as illustrated in Fig. 1-10. Although Ge has an indirect band structure, GeSn alloy shows indirect-to-direct bandgap transition by incorporating certain amount of Sn because the  $\Gamma$  conduction valley decreases faster than the L valley. Recent theoretical calculations predicted incorporating

Fig. 1-10 Electronic band structures of GeSn alloy [13].

around 6-10% of Sn is required for indirect-to-direct bandgap transition (Fig. 1-10) [13,14]. Due to this bandgap modulation by GeSn alloy, significantly improved electronic and photonic properties have been expected as described in following session.

### 1.2.2 Theoretical Calculations of Electronic and Optical properties

Due to the tunable band structure of GeSn alloy, it has become possible to

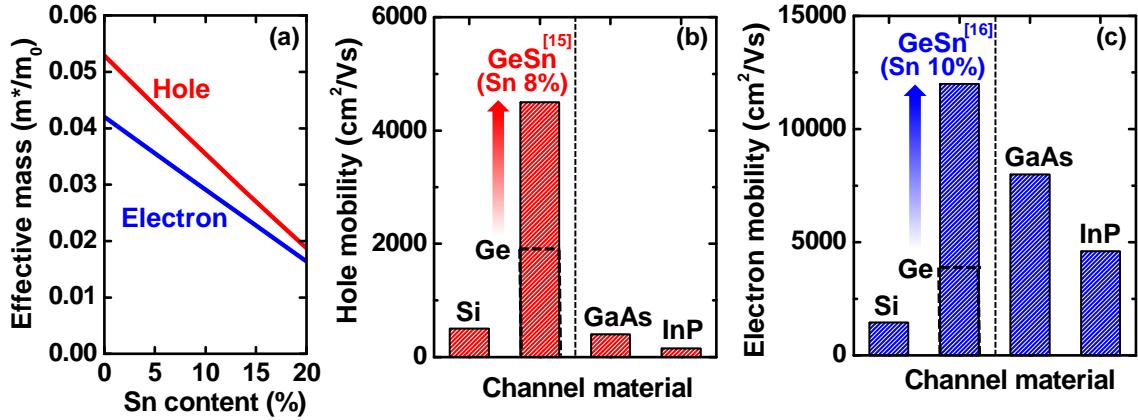

Fig. 1-11 Theoretical calculations of (a) carrier effective mass [13], (b) hole mobility [15] and (c) electron mobility [16] in GeSn alloy.

realize group-IV-based high-performance electronic and photonic devices. Theoretical calculations predict that the both hole and electron effective mass in GeSn reduce with increasing Sn content (Fig. 1-11(a)) [13]. Since carrier mobility is inverse proportional to effective mass, enhancement in both hole and electron mobility are expected. Figure 1-11(b) and 11(c) show theoretical calculation of hole and electron mobility in GeSn alloy in comparison with group-IV and III-V semiconductors, respectively [15,16]. The predicted hole mobility of GeSn is much higher than that of Si ( $1600 \text{ cm}^2/\text{Vs}$ ) or Ge ( $3900 \text{ cm}^2/\text{Vs}$ ), and it also outperform the electron mobility of III-V semiconductors. Therefore, GeSn alloy is only semiconductor material having high hole and electron mobility. Also, since GeSn alloy is a group-IV mixed material, it can be easily introduced into conventional Si technology.

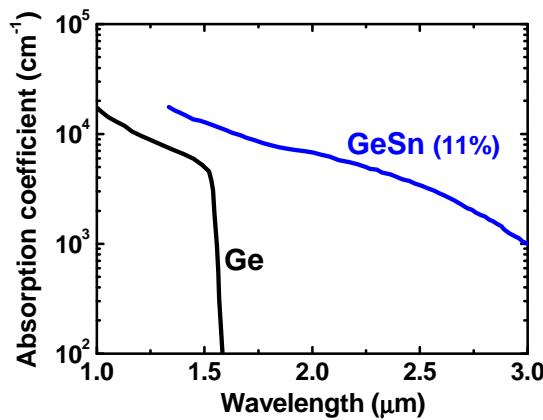

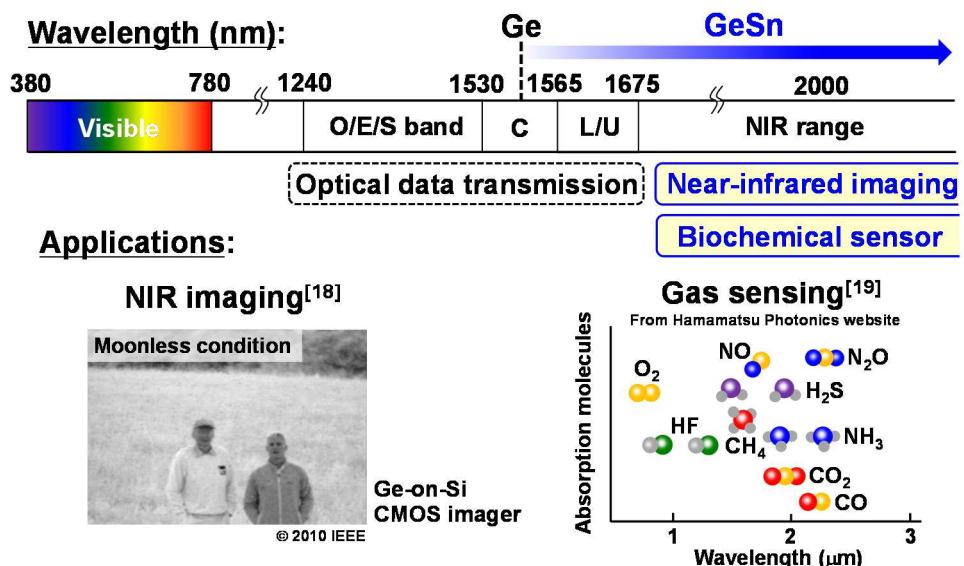

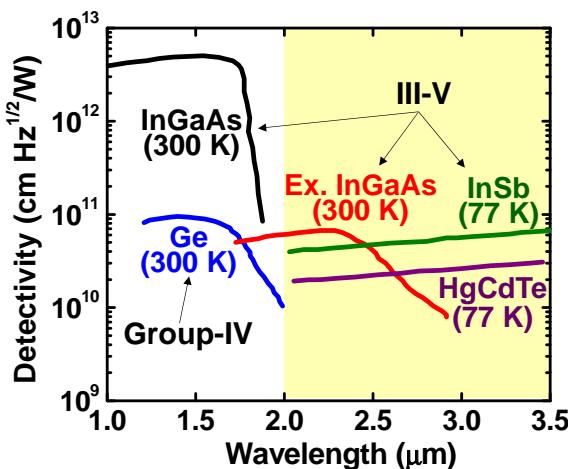

In addition to the improved electronic property, GeSn alloy is also attractive for Si photonics. With increasing Sn content, the energy difference between  $\Gamma$  and L valleys in conduction band decreases as shown in Fig. 1-10. Thus, improved light emission/detection efficiency is expected. Also, as a result of bandgap shrinkage of GeSn alloy, a corresponding cut-off wavelength extends to longer which reaches beyond  $2 \mu\text{m}$  (Fig. 1-12) [17]. Figure 1-13 shows the wavelength range and its photonic applications together with corresponding semiconductor materials. As mentioned before, Ge has a direct bandgap of  $0.80 \text{ eV}$  and corresponding cut-off wavelength is  $1550 \text{ nm}$ , which is matched to conventional optical data transmission (C-band). In the wavelength range beyond

Fig. 1-12 Absorption coefficient of Ge and GeSn [17].

1550 nm and around 2000 nm, there are many emerging applications including extended optical transmission bands, near-infrared (NIR) imaging [18] and biochemical sensing [19]. Since bandgap of GeSn alloy matches to these wavelength range, it has become possible to fabricate GeSn-based photonic components that enables not only massive and high-speed data transmission with an optical interconnect but also NIR imaging and sensing on a semiconductor microchip.

As described in this session, in addition to the superior electronic property such as high hole and electron mobility compared to other group-IV and III-V semiconductors, GeSn alloy has a great potential for NIR photonic applications. Therefore, monolithic integration of GeSn-based electronic and photonic devices is a promising post-scaling technology to break the physical limitation of Si-LSI.

Fig. 1-13 Bandgap of GeSn alloy and its photonic application fields.

## 1.3 Issues in Crystal Growth of GeSn Alloy

As described in the previous session, GeSn alloy has an excellent electronic and photonic properties and is familiar to conventional Si-CMOS process. Thus, it is considered to be one of the most attractive group-IV material for breakthrough the scaling limit of Si-LSI. It offers advanced electronic and photonic integrated circuit that would be applicable to not only optical data transfer but also imaging, environmental or medical fields.

However, it is quite difficult to obtain high-quality GeSn crystal due to the lack of suitable crystallization method, which is a severe obstacle to fabricate GeSn-based optoelectronic devices. In this session, technological outlook and key challenges of crystallizing GeSn alloy are described.

### 1.3.1 Epitaxial Growth on Si Substrate

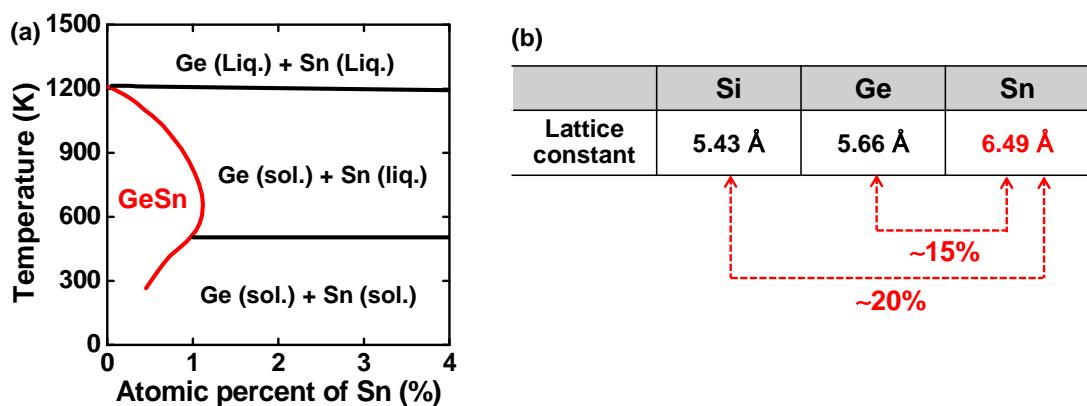

In the case of crystal growth of GeSn alloy, a low equilibrium solid solubility limit of Sn in Ge as low as 1% [20] and a large lattice mismatch between Sn and Ge or Si [21] are severe obstacles (Fig. 1-14). To deal with these issues and provide a single-crystalline GeSn layer with high Sn content, non-equilibrium low-temperature epitaxial growth technique has been widely used in recent years. “Epitaxy” means a growth of single-crystalline thin-film on top of the crystal face of another single-crystalline substrate. Thanks to the compatibility of group-IV GeSn alloy to Si process, GeSn layer can be grown on a Si substrate. A method such as molecular beam epitaxy (MBE) or chemical vapor deposition (CVD) are commonly used for epitaxial growth of GeSn layer.

Fig. 1-14 (a) equilibrium solid solubility of Sn in Ge [20]. (b) Lattice constant of Si, Ge and Sn [21].

Fig. 1-15 Schematic illustration of single-crystalline GeSn layer grown on Si substrate by CVD system [22].

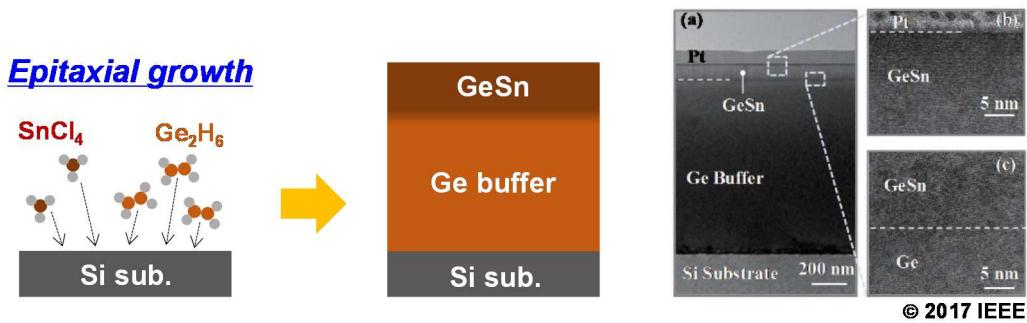

Figure 1-15 show the schematic illustration of single-crystalline GeSn layer grown by CVD system [22]. Precursors such as  $\text{Ge}_2\text{H}_6$  and  $\text{SnCl}_4$  were commonly used. By using these techniques, single-crystalline GeSn layer with a Sn content up to 12.5% has been grown via thick Ge buffer layer [23].

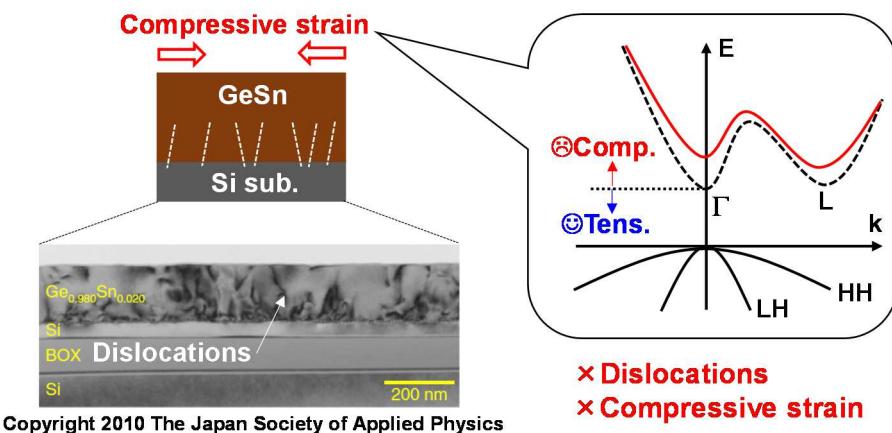

However, due to the large difference in lattice constant between GeSn and Si, dislocations are induced in epitaxially-grown GeSn layer, which deteriorate crystalline quality (Fig. 1-16) [24]. Although thick Ge buffer with a thickness of a few hundred nm to a 1  $\mu\text{m}$  can mitigate dislocations, it is not suitable for fabricating electronic and photonic devices in stacked structure or in-plane integration. Moreover, unfavorable compressive strain was inevitably induced in epitaxially-grown GeSn layer, which lifts up the both  $\Gamma$ - and L-valleys in conduction band and offset the effect of Sn alloying.

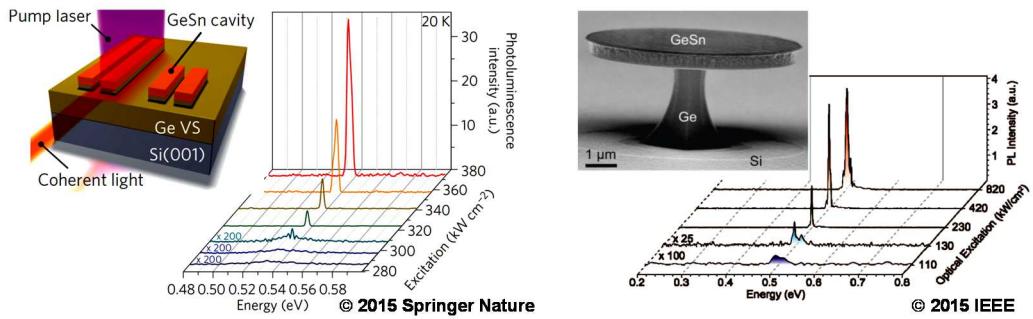

Despite the drawback of epitaxial growth methods, great effort has been paid in recent years and direct bandgap GeSn lasers have been successfully

Fig. 1-16 Issues in epitaxially-grown GeSn layer. Dislocations and compressive strain are inevitably induced due to lattice mismatch.

Fig. 1-17 Direct bandgap GeSn lasers fabricated on epitaxially-grown GeSn layer on Si substrate.

demonstrated using epitaxially-grown GeSn layer on Si substrate (Fig. 1-17) [25,26]. However, operating temperature of GeSn lasers were quite low and threshold voltage is still very high, which is originating from poor crystalline quality of compressive-strained single-crystalline GeSn layer. Thus, further improvement of crystalline quality is essential to realize high-performance GeSn-based optoelectronic devices.

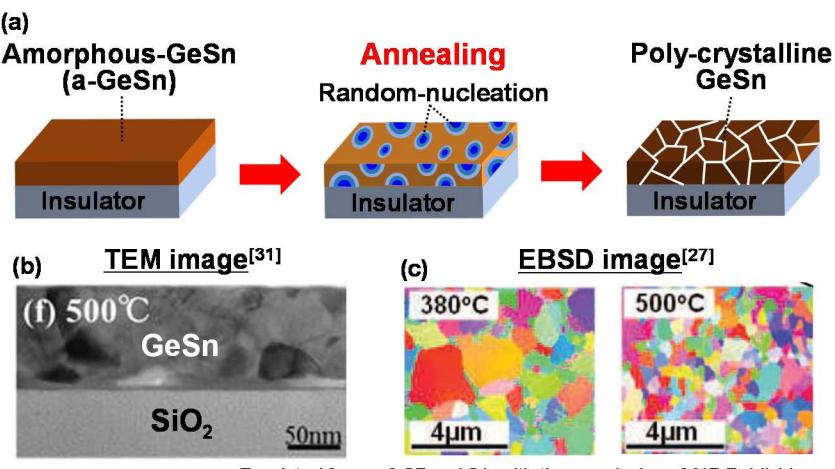

### 1.3.2 Non-Epitaxial Growth on Insulating Layer

Recently, “non-epitaxial” methods such as solid-phase crystallization [27,28] or metal-induced crystallization [29] have been developed for crystallizing GeSn alloy on insulating layers, in which an amorphous GeSn (a-GeSn) layer deposited on insulators are annealed to induce crystallization at a temperature usually below the melting point of GeSn. Figure 1-18 shows crystal orientation map of GeSn layer on quartz substrate after solid-phase

Reprinted from ref. 27 and 31, with the permission of AIP Publishing

Fig. 1-18 (a) Schematic illustration, (b) TEM [31] and (c) EBSD [27] images of solid-phase grown GeSn layer on insulator.

crystallization evaluated by electron back-scatter diffraction (EBSD) spectrometry. Various colors were observed in the EBSD image, indicating a poly-crystalline GeSn layer was formed by this method. This poly-crystallization is caused by random nucleation during the annealing process. Since crystalline quality of poly-crystalline layer is much poor than that of single-crystalline one, they exhibit significantly degraded electronic and photonic properties. For example, both hole and electron mobility in poly-crystalline GeSn layer are less than  $100 \text{ cm}^2/\text{Vs}$  [30-33], which is much lower than that of single-crystalline Ge and even single-crystalline Si.

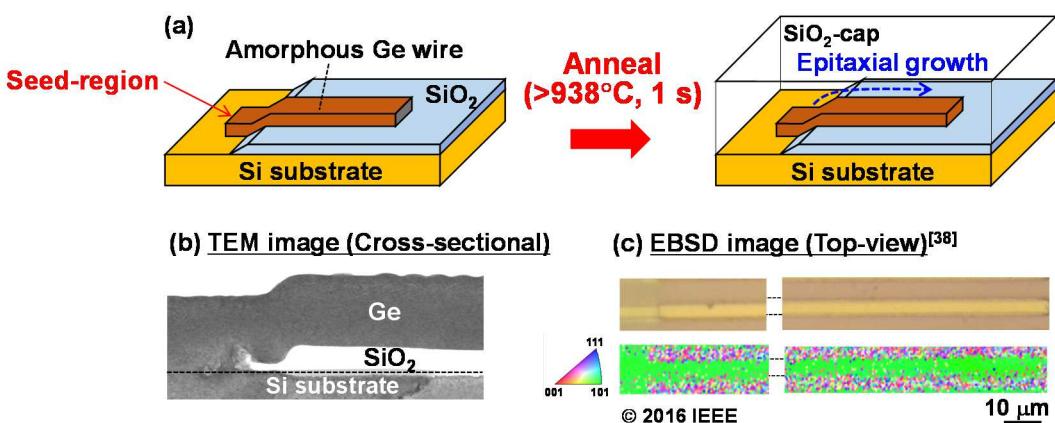

### 1.3.3 Lateral Liquid-Phase Epitaxy (LLPE)

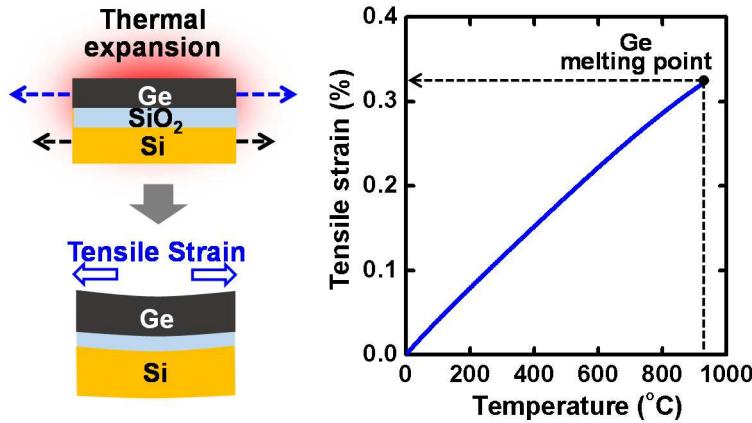

In the case of Ge, a high-quality tensile-strained single-crystalline Ge wire can be grown on an insulator by utilizing the lateral liquid-phase epitaxy (LLPE) [34-38], which is one of the most useful methods for fabricating Ge-on-insulator structure. With this method, an amorphous Ge wire, which is surrounded by  $\text{SiO}_2$  layer but partly connected to a Si substrate, is annealed above the melting point of Ge to induce lateral liquid-phase growth from the Si-seed region (Fig. 1-19). Due to the dislocation confinement at the seed region, a defect-free single-crystalline Ge wire can be obtained. In this method, tensile strain can be induced in Ge layer due to the difference in the thermal-expansion coefficients between Ge and the Si (Fig. 1-20) [39]. Here, thermally-induced strain is determined by thermal-expansion coefficients of materials and maximum crystallization temperature. In the case of LLPE, since epitaxial growth starts at

Fig. 1-19 (a) Schematic illustration, (b) TEM and (c) EBSD images of LLPE-grown GeSn wire [38].

Fig. 1-20 Thermally-induced strain in LLPE-grown Ge layer. Strain is determined by difference in thermal expansion coefficient between Ge and substrate, and crystallization temperature [39].

the melting point of Ge, tensile strain as high as 0.4% can be induced [37].

Previously, several groups have examined the LLPE-growth of GeSn alloy and obtained a tensile-strained single-crystalline GeSn wires [40-43]. Based on the liquid-phase-grown GeSn wire, a significantly enhanced photoluminescence was observed with respect to bulk Ge substrate [43], which is originating from the direct bandgap shrinkage and clearly indicates an excellent crystalline quality of single-crystalline GeSn wire formed by the LLPE.

However, with this method, crystal-seeds such as a Si substrate is required to induce the LLPE growth, which severely limits the process window and has difficulty in monolithic integration. Moreover, there is a diffusion of Si atoms into GeSn wire from seed region [43], which lifts up the energy of  $\Gamma$ -valley as in the case of inducing compressive strain.

Therefore, it has become necessary to find an alternative way to fabricate high-quality single-crystalline GeSn layer that would be applicable to electronic and photonic integrated circuit.

## 1.4 Aim of This Study and Contents of Thesis

As described in this chapter, GeSn alloy has attracted a great interest due to its enhanced electronic and photonic properties, and the monolithic integration of GeSn-based optoelectronic devices is regarded as most promising post-scaling technology that offers not only high-speed and massive data transmission, but

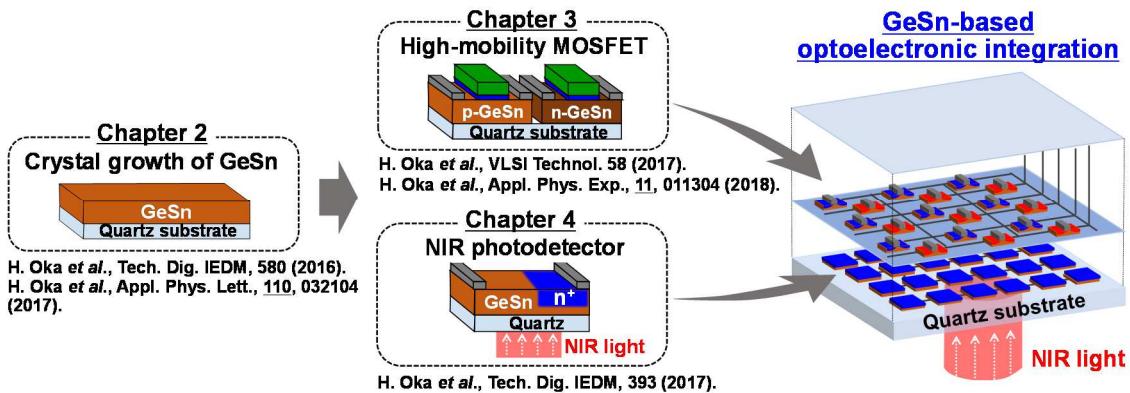

Fig. 1-21 Contents of this thesis. The aim of this study is to demonstrate GeSn-based optoelectronic integrated circuit.

also emerging NIR imaging/sensing microchip. However, due to the lack of suitable formation method of high-quality GeSn crystals, there are still difficulties in fabricating GeSn-based electronic and photonic devices, and a potential of GeSn alloy for advanced optoelectronic applications are not fully demonstrated.

The aim of this work is to provide an advanced GeSn-based optoelectronic platform that would break the physical limitation of conventional Si-based LSI and to offer emerging multi-functional devices such as NIR imaging/sensing semiconductor microchip. For this purpose, we proposed a novel crystal growth method of GeSn alloy, and fabricated high-performance GeSn devices including high-mobility CMOS and NIR photodetector. By integrating fabricated GeSn-based electronic and photonic devices, we demonstrated world's first fully-integrated group-IV-based NIR imager chip. Contents of this thesis is summarized in Fig. 1-22.

Chapter 2 focuses on crystal growth of GeSn alloy on transparent substrate. Since LLPE method requires crystal seed such as a Si substrate and thus not applicable to monolithic integration, we proposed a novel liquid-phase crystallization by controlling the nucleation during the crystallization. A crystalline quality, Sn content, and strain in fabricated GeSn layer on quartz substrate were studied in detail. Both p- and n-type single-crystalline GeSn wires

were successfully grown on a quartz substrate, which would be an ideal platform for GeSn-based electronic and photonic integration.

In order to investigate the potential of liquid-phase grown GeSn wires as a post-Si high-mobility channel material, p- and n-channel thin-film transistors (TFT) were fabricated in chapter 3. A mobility behavior in GeSn alloy is studied in detail, and revealed the mobility limiting factor in GeSn-based transistor. Based on findings, high-performance GeSn p- and n-channel TFTs were successfully demonstrated. This is the first report of GeSn-based CMOS fabricated on transparent substrate.

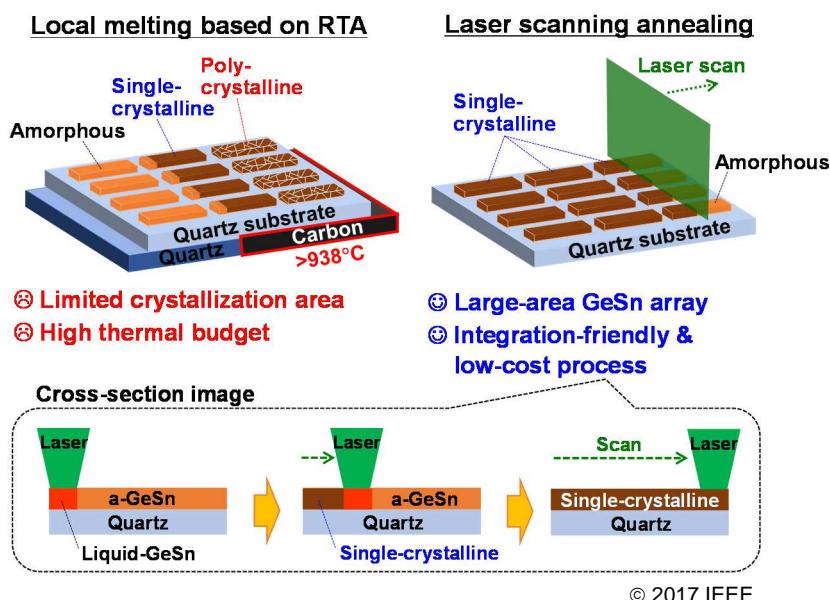

In Chapter 4, we examined the fabrication of GeSn-based photodiode array on a quartz substrate and evaluated the optical properties of GeSn alloy in the NIR wavelength range. Since GeSn alloy is expected to exhibit high light emittion/detection efficiency, it becomes possible to fabricate fully-integrated group-IV-based imager chip with low-cost and large-volume manufacturing using conventional Si-CMOS process, that would outperforms imaging device based on III-V semiconductors. For this purpose, we further developed the liquid-phase crystallization technique by utilizing laser scanning annealing, which can provide a single-crystalline GeSn array structure on quartz substrate with high-integrity with low thermal budget. The NIR optical response of GeSn photodiode array on a quartz substrate was studied in detail.

Finally, Chapter 5 provides general conclusions for GeSn-based electronic and photonic devices on a quartz substrate fabricated by liquid-phase crystallization.

## References – Chapter 1 –

- [1] From Green IT Promotion Council, Ministry of Economy, Trade and Industry (2008). Available at “<http://www.meti.go.jp/committee/materials/g80520cj.html>”.

- [2] I. Ferain *et al.*, *Nature* **479**, 310 (2011).

- [3] R.H. Dennard *et al.*, *IEEE J. Solid-State Circuits* **9**, 256 (1974).

- [4] F. D’Agostino *et al.*, *Introduction to VLSI Design* (EECS 467), (2000).

- [5] K. Mistry *et al.*, *IEDM Tech. Dig.*, p. 247 (2007).

- [6] C.-H. Jan *et al.*, *IEDM Tech. Dig.*, p. 44 (2012).

- [7] ITRS 2013 edition (Interconnect), Chapter 1, page 4, Figure 1.

- [8] R. Kirchain *et al.*, *Nature Photonics* **1**, 303 (2007).

- [9] H. Park *et al.*, *Opt. Exp.* **13**, 9460 (2005).

- [10] J. Michel *et al.*, *Nat. Photonics* **4**, 527 (2010).

- [11] X. Sun *et al.*, *Appl. Phys. Lett.* **95**, 011911 (2009).

- [12] P. Moontragoon *et al.*, *Semicond. Sci. Technol.* **22**, 742 (2007).

- [13] K. L. Low *et al.*, *J. Appl. Phys.* **112**, 103715 (2012).

- [14] S. Gupta *et al.*, *J. Appl. Phys.* **113**, 073707 (2013).

- [15] J. D. Sau *et al.*, *Phys. Rev. B* **75**, 045208 (2007).

- [16] C. Schulte-Braucks *et al.*, *Solid-State Electron.* **128**, 54 (2017).

- [17] Y. Dong *et al.*, *VLSI Tech. Symp.*, p.184 (2014).

- [18] I. Åberg *et al.*, *IEDM Tech. Dig.*, p. 344 (2010).

- [19] From Hamamatsu Photonics website. Available at “[http://www.hamamatsu.com/eu/en/community/optical\\_sensors/applications/index.html](http://www.hamamatsu.com/eu/en/community/optical_sensors/applications/index.html)”.

- [20] R. W. Olesinski *et al.*, *Bulletin of Alloy Phase Diagrams* **5**, 265 (1984).

- [21] G-E. Chang *et al.*, *IEEE J. Quantum Electron.* **46**, 1813 (2010).

- [22] D. Lei *et al.*, *VLSI Tech. Symp.*, 198 (2017).

- [23] M. Oehme *et al.*, *J. Crystal Growth* **384**, 71 (2013).

- [24] O. Nakatsuka *et al.*, *Jpn. J. Appl. Phys.* **49**, 04DA10 (2010).

- [25] S. Wirths *et al.*, *Nat. Photon.* **9**, 88 (2015).

- [26] S. Wirths *et al.*, *IEDM Tech. Dig.*, p. 36 (2015).

- [27] T. Sadoh *et al.*, *Appl. Phys. Lett.* **109**, 232106 (2016).

- [28] S. Zaima *et al.*, *Sci. Technol. Adv. Mater.* **16**, 043502 (2015).

- [29] H. Chikita *et al.*, *Appl. Phys. Lett.* **105**, 202112 (2014).

- [30] M. Kurosawa *et al.*, *SSDM*, p. 684 (2014).

- [31] N. Uchida *et al.*, *Appl. Phys. Lett.* **107**, 232105 (2015).

- [32] S. Pracnal *et al.*, *Semicond. Sci. Technol.* **31** 105012 (2016).

- [33] K. Takahashi *et al.*, *The 63<sup>rd</sup> Spring JSAP*, 16p-D61-7 (2016).

- [34] Y. Liu *et al.*, *Appl. Phys. Lett.* **84**, 2563 (2004).

- [35] M. Miyao *et al.*, *Appl. Phys. Lett.* **95**, 022115 (2009).

- [36] T. Hashimoto *et al.*, *Appl. Phys. Exp.* **2**, 066502 (2009).

- [37] M. Matsue *et al.*, *Appl. Phys. Lett.* **104**, 031106 (2014).

- [38] H. Oka *et al.*, *IEDM Tech. Dig.*, p. 580 (2016).

- [39] Y. Ishikawa *et al.*, *Appl. Phys. Lett.* **82**, 2044 (2003).

- [40] M. Kurosawa *et al.*, *Appl. Phys. Lett.* **101**, 091905 (2012).

- [41] Z. Liu *et al.*, *Sci. Rep.* **6**, 38386 (2016).

- [42] C. K. Tseng *et al.*, *Int. Symp. on IEEE Next-Generation Electronics*, p. 1 (2015).

- [43] T. Shimura *et al.*, *Appl. Phys. Lett.* **107**, 221109 (2015).

## Chapter 2

# Single-Crystalline GeSn Growth on Quartz Substrate by Nucleation-Controlled Liquid-Phase Crystallization

### 2.1 Introduction

As described in the previous chapter, formation of a high-quality single-crystalline GeSn layer is required for advanced optoelectronic integration in the post-scaling era. In this chapter, a novel crystallization technique for fabricating a tensile-strained single-crystalline GeSn layer on transparent substrate have been presented. By using this technique, both p- and n-type single-crystalline GeSn wires were successfully formed on a quartz substrate without using any crystal seed or catalyst, which enables the monolithic integration of high-mobility CMOS and highly-efficient photonic devices on a transparent substrate. The crystalline quality, Sn content and strain of fabricated single-crystalline GeSn wire were also characterized in detail in this chapter.

### 2.2 Nucleation-Controlled Liquid-Phase Crystallization

#### 2.2.1 Concept of This Technique

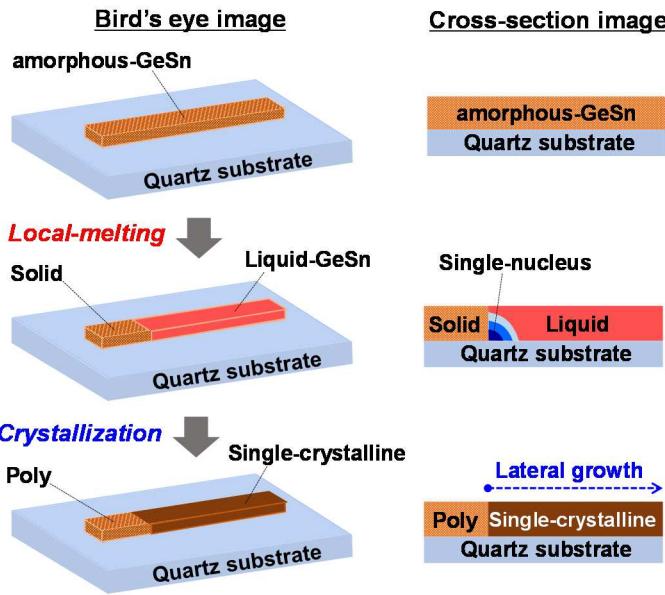

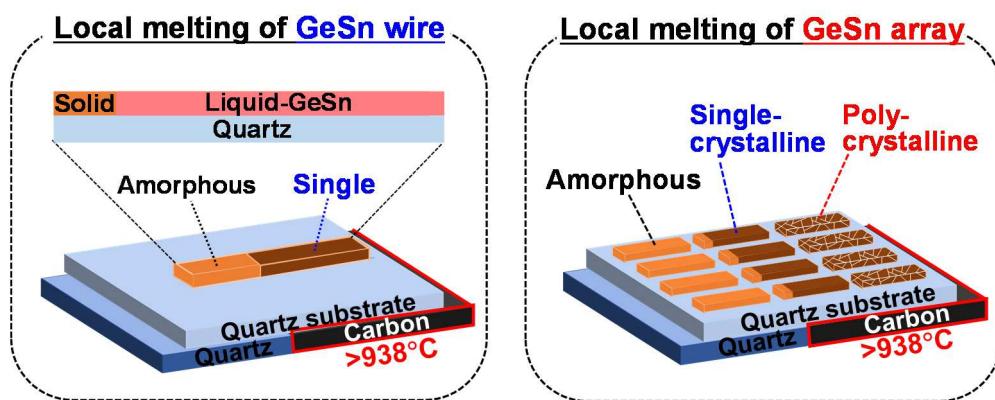

In order to provide a single-crystalline GeSn layer on a transparent substrate, we developed a novel crystallization technique based on the LLPE. In the conventional LLPE of GeSn wire, Si-seed was utilized to induce the lateral liquid-phase growth, which severely limits the process window and has disadvantage in the process integrity. Thus, we proposed an alternative method to induce the lateral liquid-phase growth without using any crystal-seed or catalyst. Figure 2-1 shows the basic concept of our proposed crystallization technique. The key is local melting of amorphous GeSn wire to control the nucleation and crystal growth in the liquid-phase GeSn. In the case of complete melting of amorphous GeSn wire, spontaneous-nucleation in the liquid-phase GeSn results in poly-crystallization. However, as for the local melting, it is expected that the solidification initiated at the single-nucleus formed at the solid/liquid interface, and lateral crystallization quickly propagated along the wire. If the lateral growth

Fig. 2-1 Schematic illustrations of nucleation-controlled liquid-phase crystallization of GeSn wire on quartz substrate. Local-melting is key to control nucleation in liquid-GeSn.

speed is enough high to prevent the spontaneous nucleation in the growth front, single-crystallization GeSn wire can be obtained on a designated area on transparent substrate without using crystal seed. This nucleation-controlled liquid-phase crystallization technique is quite simple and integration-friendly, which would be a suitable approach for fabricating a high-quality GeSn-on-insulator structure.

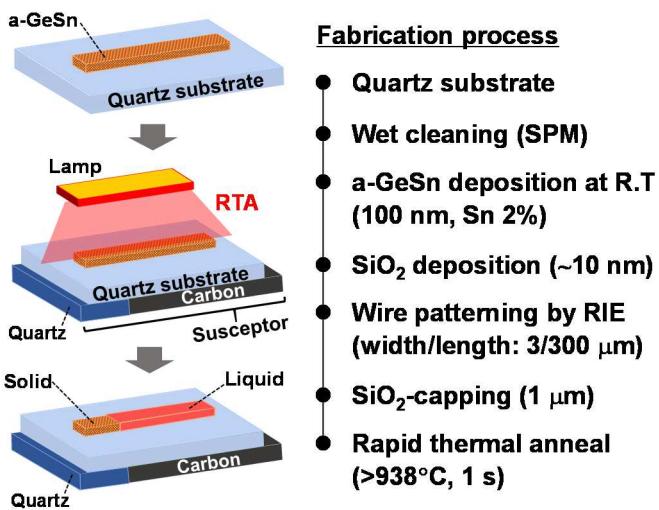

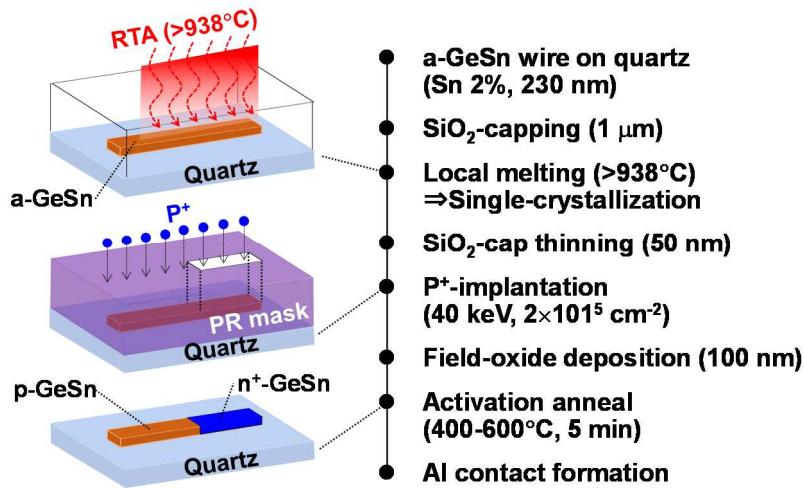

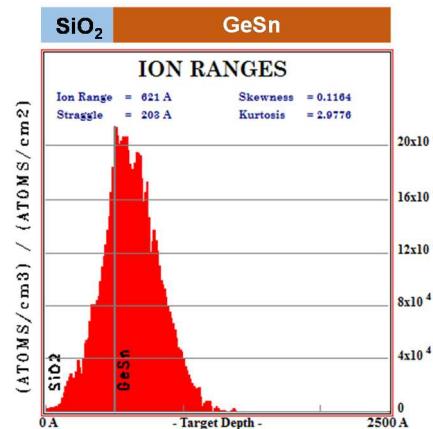

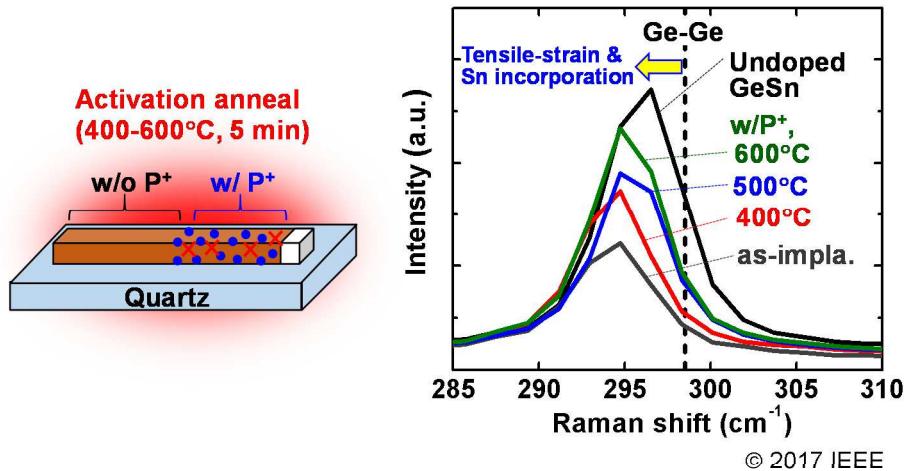

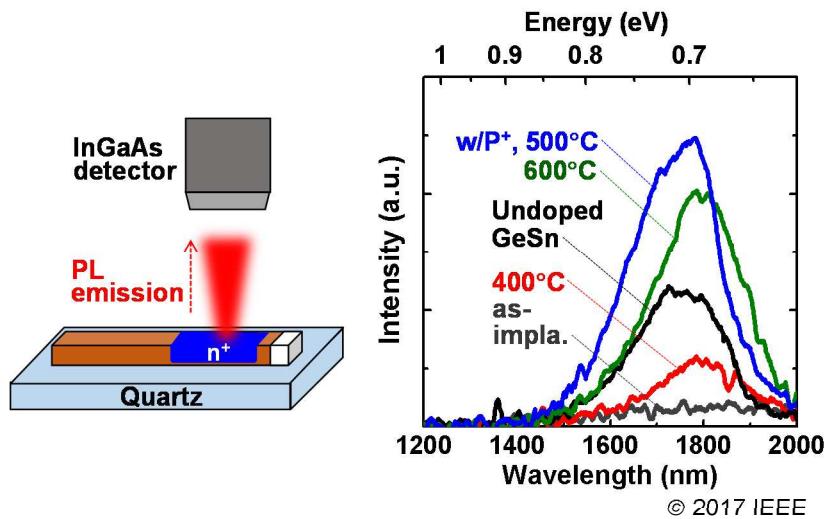

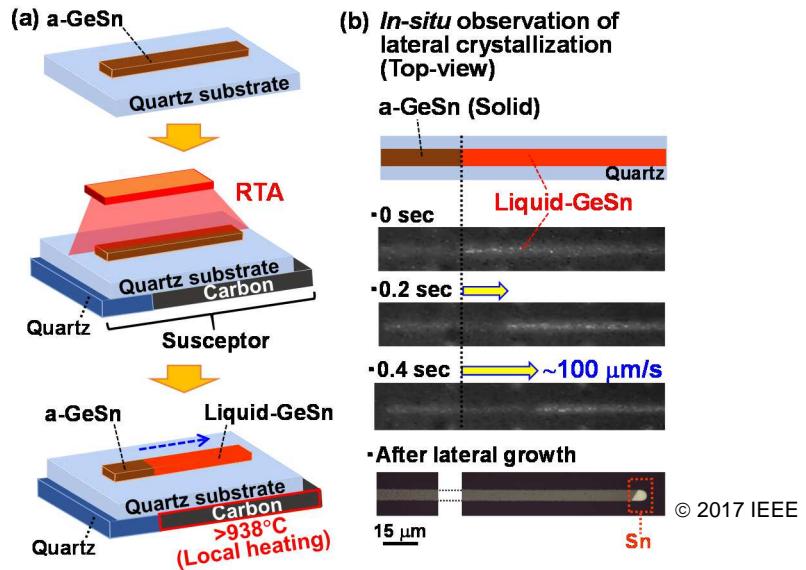

### 2.2.2 Fabrication Process

Figure 2-2 shows the fabrication process of single-crystalline GeSn wire on a quartz substrate by using the local melting process. We used a commercially available quartz substrate as a starting substrate. A 100-nm-thick amorphous GeSn layer was deposited using a molecular beam deposition system at room temperature (R.T), and patterned into narrow stripes (for example,  $W/L = 3/300 \mu\text{m}$ ) by  $\text{CF}_4$ -based reactive ion etching. The Sn content inside the amorphous GeSn layer was estimated to be around 2% through XPS measurement. It should be noted that Sn segregation at the surface of an as-deposited GeSn layer was observed due to the low solid solubility of Sn in Ge. After depositing a thick  $\text{SiO}_2$  capping layer ( $\sim 1 \mu\text{m}$ ) by RF-sputtering to prevent agglomeration of the GeSn

Fig. 2-2 Fabrication process of single-crystalline GeSn wire on quartz substrate by local-melting process.

Fig. 2-3 Simulation study of temperature gradient along the GeSn wire under the local heating condition.

alloy, rapid thermal annealing (RTA) was performed in nitrogen ( $N_2$ ) ambient above the melting point of GeSn ( $\sim 938^\circ C$ ) for 1 s. In the RTA process, in order to melt a GeSn wire locally, sample was placed on a susceptor consisting of carbon and quartz. Since a quartz is transparent to the infrared (IR) light used in this lamp annealing equipment ( $\lambda = 1.2 \mu m$ ), only the carbon part can be heated to above the melting point of GeSn. Figure 2-3 shows simulation study of temperature gradient along the 300- $\mu m$ -long GeSn wire on a quartz substrate under local heating condition, in which carbon susceptor acts as a heat source that is placed under the half area of sample. From the simulation result, it was found the temperature gradient was formed along the GeSn wire, which would be a driving force for lateral crystal growth.

## 2.3 Physical Characterization

### 2.3.1 Crystalline Quality and Sn Content

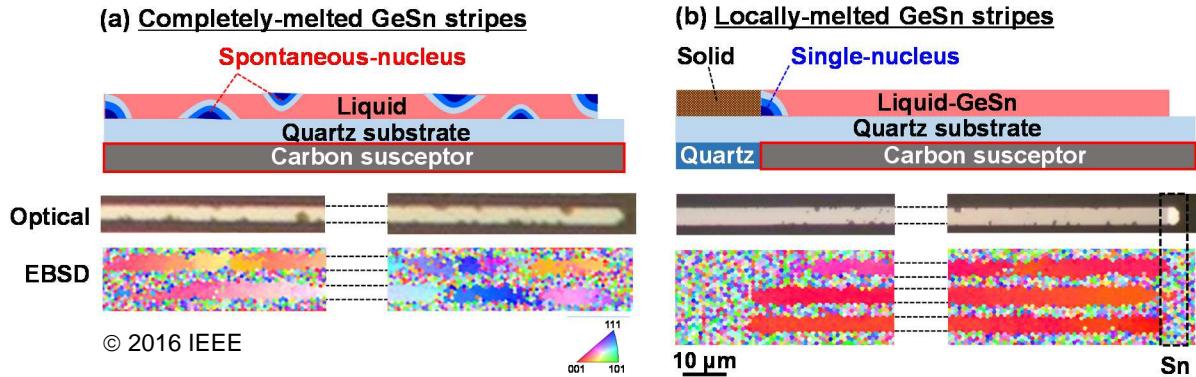

First we investigated the crystalline quality of fabricated GeSn wire on a quartz substrate by using nucleation-controlled liquid-phase crystallization. Figure 2-4 shows the optical and electron back-scatter diffraction (EBSD) images of the 300- $\mu m$ -long GeSn stripes after RTA. As shown in the EBSD image of the completely-melted GeSn stripes (Fig. 2-4(a)), the various colors were observed

Fig. 2-4 Optical and EBSD images of GeSn stripe on quartz substrate formed by (a) complete- and (b) local-melting process [1].

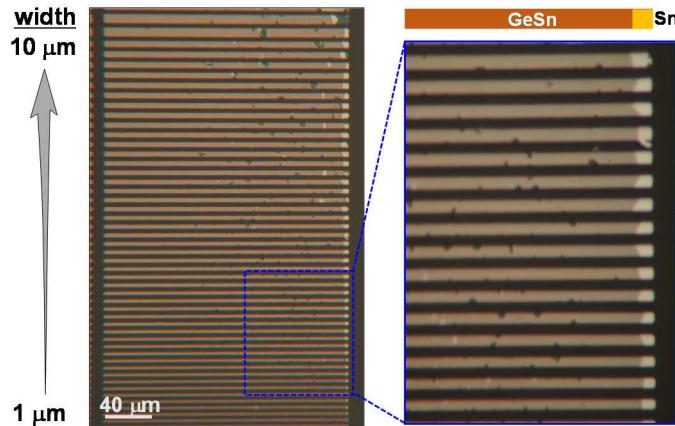

Fig. 2-5 Optical image of GeSn stripe on quartz substrate after local-melting with various width ranging from 1-10  $\mu\text{m}$ .

in each wire, which is corresponding to various crystal orientations and indicating poly-crystallization. This result indicates that it is difficult to suppress the preferential random nucleation within the complete melting process. However, for the locally-melted sample, most of the GeSn stripes appeared in the same color in the EBSD image from the middle to the end of the wire for over 250- $\mu\text{m}$ -long (Fig. 2-4(b)), which means that lateral liquid-phase crystallization was initiated from a single-nucleus formed near the solid/liquid interface. We have succeeded in fabricating a single-crystalline GeSn wire with a length up to 2 mm by this method (data not shown). Also, we confirmed that almost all of single-crystalline wires were (100)-oriented in the direction normal to the surface. This preferential orientation of GeSn wires would be determined by an interface energy between liquid GeSn and quartz. It should be noted that the bright

© 2016 IEEE

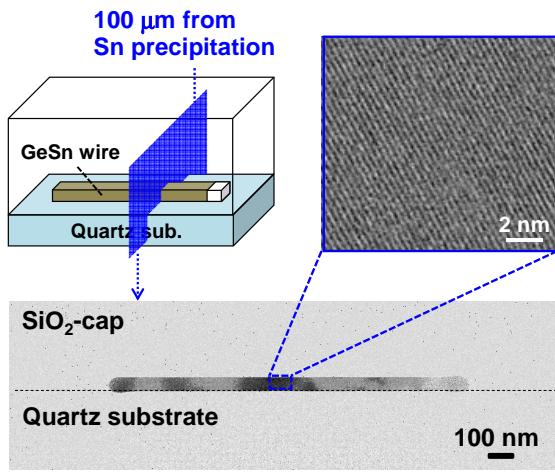

Fig. 2-6 Cross-sectional TEM images of single-crystalline GeSn wire formed on quartz substrate [1].

© 2016 IEEE

Fig. 2-7 Depth profiles of Sn and Ge composition in GeSn layer by EDX. Average Sn composition (Sn/Ge+Sn) is determined to be 2.6% [1].

contrast region in the optical image of the single-crystalline GeSn stripes is the Sn precipitation that is swept out during lateral growth due to the low solid solubility of Sn in Ge. Also, we have examined the local melting process for wide GeSn wires (width: 1-10  $\mu\text{m}$ ) to investigate the feasibility of our proposed crystallization technique. As shown in Fig. 2-5, Sn precipitation, the sign for accomplishment of lateral growth, was observed for all of GeSn wires, indicating simultaneously obtained single-crystalline wires with the widths of 1-10  $\mu\text{m}$ . This clearly indicates the advantage of our crystallization technique in terms of device fabrication.

Figures 2-6 show the cross-sectional transmission electron microscope (TEM) images of a single-crystalline GeSn wire measured 100  $\mu\text{m}$  from the Sn precipitation. It was found that a dislocation-free single-crystalline GeSn layer was grown on a quartz substrate.

Then we investigated the Sn content in the single-crystalline GeSn wire by energy dispersive X-ray spectrometry (EDX). From the EDX depth profiles of Ge and Sn shown in Fig. 2-7, over 2% of Sn uniformly distributed in the depth. The average Sn content along the depth direction was estimated to be 2.6%, which exceeds the solid solubility limit of Sn in Ge. It should be noted that the Sn content in the single-crystalline GeSn layer was higher than the initial Sn

Fig. 2-8 (a) Raman spectra obtained from single-crystalline GeSn wire and control bulk Ge substrate, (b) Position dependence of Raman shift and extracted Sn content.

content inside the amorphous GeSn layer (~2%). This can be explained by the diffusion of Sn, which was segregated at the surface of the as-deposited GeSn layer, during the melting growth process.

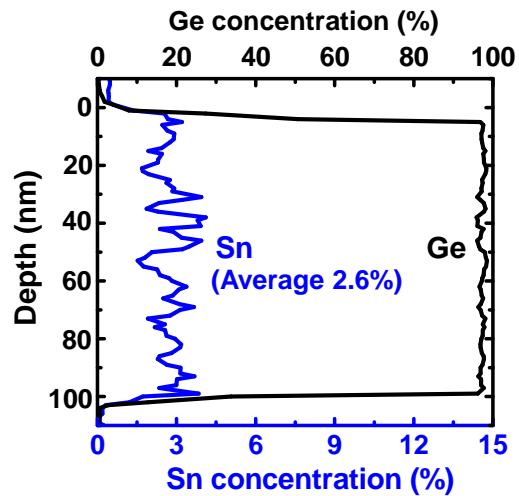

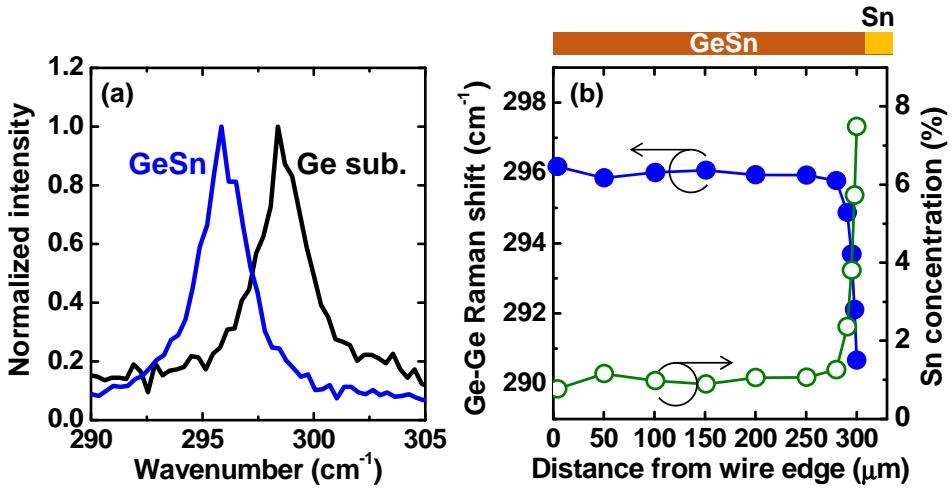

We have also confirmed Sn content along the lateral growth direction through micro-probe Raman spectroscopy. Since the excitation beam size is enough small (~1 μm) compared to the GeSn wire (~3 μm), position-dependent Raman spectra can be obtained. Figure 2-8(a) shows the normalized Raman spectra from Ge-Ge vibration mode for single-crystalline GeSn wire on quartz substrate measured 100 μm from Sn precipitation and control bulk Ge substrate. The Raman peak of GeSn wire is shifted to a lower wave number compared to that of bulk Ge substrate, which is originating from the incorporation of Sn and inducing tensile strain. According to the experimental study, the correlation between Raman shift and Sn content/strain is expressed by the following equation [2].

$$\Delta\omega = -(82 \pm 4)\chi - (563 \pm 34)\epsilon$$

( $\Delta\omega$ : Raman shift,  $\chi$ : Sn content,  $\epsilon$ : Strain,)

By assuming the strain is uniformly induced along the wire, we can evaluate the Sn distribution along the wire from Raman shift. Figure 2-8(b) shows the position dependence of Raman shift (blue line) and extracted Sn content by using the above equation (green line) for 300-μm-long GeSn wire. It was found that the Sn content in GeSn wire is almost constant for the most part of wire (0-295 μm),

which would be suitable for electronic and photonic device fabrication. It should be noted that the Sn content rapidly increased near the growth end (295–300  $\mu\text{m}$ ) and reaches as high as 8%, which is due to the Sn segregation during the lateral growth.

### 2.3.2 Determination of Strain by Synchrotron X-ray Diffraction

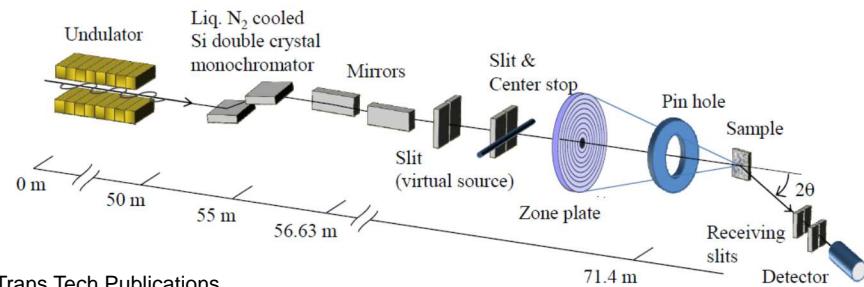

We also evaluated the strain in the GeSn stripes crystallized on a quartz substrate. For an accurate measurement of strain in the narrow GeSn stripes ( $W = 3 \mu\text{m}$ ), we employed synchrotron micro X-ray diffraction ( $\mu$ -XRD) with a beam size of  $700 \times 200 \text{ nm}^2$  and an acceleration energy of 12 keV (Fig. 2-9) [3].

© Trans Tech Publications

Fig. 2-9 Experimental setup of synchrotron  $\mu$ -XRD used in this study [3].

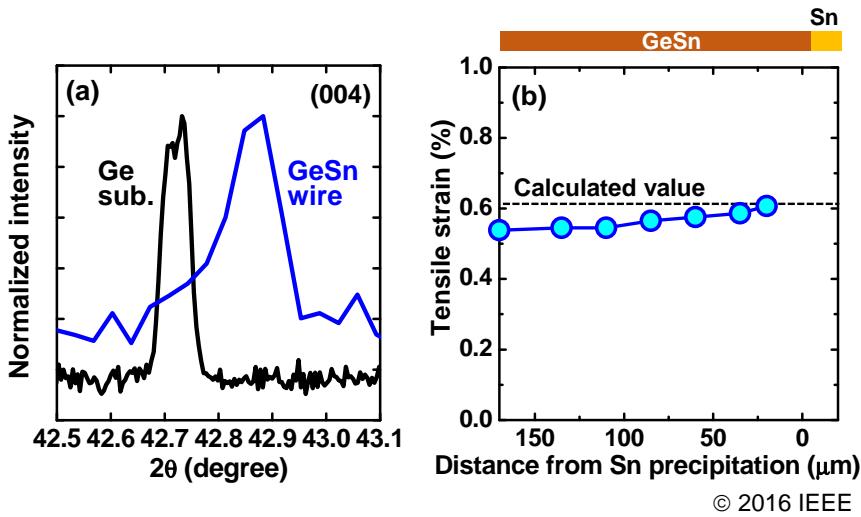

The obtained diffraction peak of (004) planes for a single-crystalline GeSn wire on a quartz substrate and a control bulk Ge substrate were shown in Fig. 2-10(a). The diffraction peak from GeSn wire was observed at a higher  $2\theta$  angle compared to that from bulk Ge substrate, indicating a decrease in lattice constant perpendicular to the planes. From the diffraction peak position of the GeSn wire and the Sn content evaluated by EDX, in-plane strain was estimated using Vegard's law for GeSn alloy [4,5]. Figure 2-10(b) shows the strain evaluated from the  $\mu$ -XRD results as a function of distance from the Sn precipitation. It was found that over 0.5% of tensile strain was induced in the GeSn wire crystallized on the quartz substrate. This tensile strain is in good agreement with the value calculated from the differences in the thermal expansion coefficient between GeSn and quartz (dashed line in Fig. 2-10(b)). From these results, we confirmed that a highly tensile-strained single-crystalline GeSn layer with a Sn content exceeding solid solubility was grown on a quartz substrate.

Fig. 2-10 (a) (004)  $\mu$ -XRD diffraction patterns of single-crystalline GeSn wire and bulk Ge substrate. (b) Strain distribution evaluated from  $\mu$ -XRD and EDX results as function of distance from Sn precipitation [1].

## 2.4 Optical Characterization

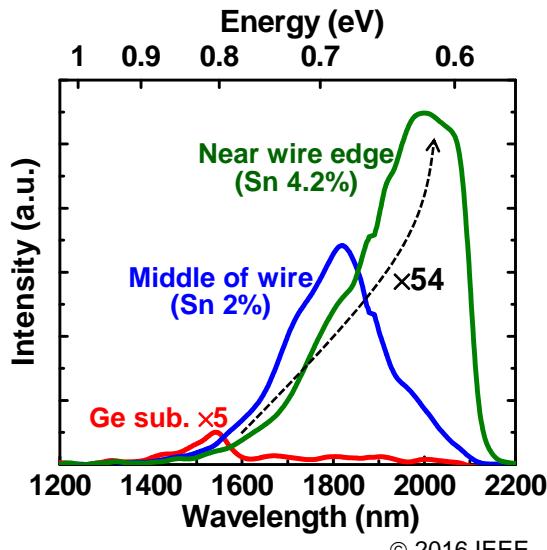

Then we investigated the luminescence property of the fabricated single-crystalline GeSn wire on a quartz substrate by micro-photoluminescence ( $\mu$ -PL) measurement. The 20-mW excited laser with a wavelength of 647 nm was focused on the sample surface through neutral density (ND) filter with a diameter of about 1  $\mu\text{m}$ . Light emission was detected from a wavelength of 1.1 to 2.2  $\mu\text{m}$  using a cooled, wavelength-extended InGaAs 1024 pixel linear photodiode array (Table 2-1, Princeton Instruments: PyLon-IR-2.2) optically coupled to a spectrograph system. In this experiment, all PL spectra were acquired at room temperature.

Figure 2-11 shows the PL spectra obtained from single-crystalline GeSn wire on a quartz substrate with different measurement position (middle and near the edge of the wire) and control bulk Ge substrate. The PL spectra from middle

Table 2-1 Specifications of photodetector used in  $\mu$ -PL system.

| Model                                                   | PyLon-IR 1023                                                             |

|---------------------------------------------------------|---------------------------------------------------------------------------|

| <b>Image sensor</b>                                     | <b>Linear InGaAs photodiode array</b>                                     |

| <b>Format</b>                                           | <b>25 <math>\mu\text{m}</math> (W) x 250 <math>\mu\text{m}</math> (H)</b> |

| <b>Spectral range</b>                                   | <b>1.0 - 2.2 <math>\mu\text{m}</math></b>                                 |

| <b>Operation temp.</b>                                  | <b>-100°C</b>                                                             |

| <b>Quantum efficiency at 2 <math>\mu\text{m}</math></b> | <b>70%</b>                                                                |

Fig. 2-11 PL spectra for middle and near edge of single-crystalline GeSn wire on quartz substrate and control bulk Ge substrate [1].

part of GeSn wire shows direct bandgap emission at the peak wavelength of around 1800 nm, which is red-shifted with respect to that from bulk Ge substrate (0.80 eV, 1550 nm) for about 0.1 eV. This bandgap shrinkage is caused by the alloying Sn and inducing biaxial tensile strain. Also, an enhanced direct bandgap emission was observed ( $\times 34$  bulk Ge), indicating an excellent crystalline quality of the fabricated single-crystalline GeSn wire. As for the near edge of GeSn wire, a significantly enhanced luminescence ( $\times 54$  bulk Ge) with a peak wavelength of about 2  $\mu$ m was observed, which is originating from the increase in Sn content due to the Sn segregation. From the theoretical calculation, the indirect-to-direct bandgap transition energy of tensile-strained GeSn alloy is predicted to be around 0.69 eV. Thus, it is expected that near the edge of GeSn wire has a direct bandgap electronic structure.

## 2.5 Evaluation of Conduction Type and Carrier Concentration

### 2.5.1 Hall Effect Measurement

As described in the previous session, we have succeeded in fabricating a high-quality tensile-strained single-crystalline GeSn wire on a quartz substrate. In order to reveal the electrical property, we have investigated the conduction type and carrier concentration of fabricated single-crystalline GeSn wire.

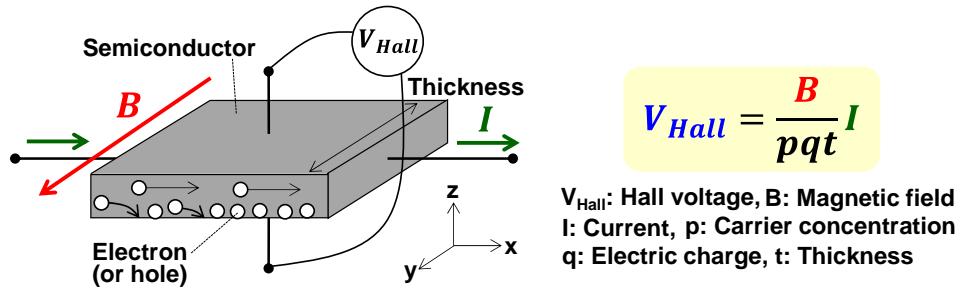

Fig. 2-12 Basic physical principle of Hall effect measurement.

One of the most popular and useful method for characterizing a conduction type is the Hall effect measurement. In this method, when the current flows in the semiconductor along a direction perpendicular to an applied magnetic field, electron (or hole) that is flowing across the semiconductor is influenced by Lorentz force, and moved toward a direction perpendicular to both current flow and magnetic field (z direction). This movement of electron to the z direction forms a positive charge on the opposite side, and thus forming an internal electric field along z direction, which is measured as Hall effect voltage and we can estimate the conduction type and carrier concentration from the equation shown in Fig. 2-12. In this method, current-voltage characteristic is measured by probing metal contact on four side on a semiconductor substrate as illustrated in Fig. 2-12.

However, the fabricated single-crystalline GeSn is a narrow stripe with a wire width of 3  $\mu\text{m}$ , and thus it has been difficult to evaluate electrical properties by Hall effect measurement.

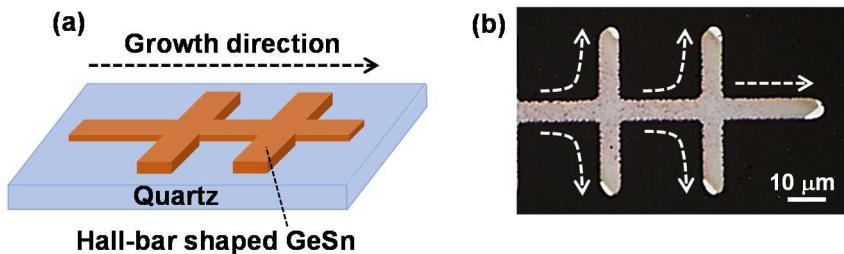

### 2.5.2 Fabrication of Hall-Bar Shaped GeSn Wire

In order to enable the Hall effect measurement and evaluate the exact carrier concentration of fabricated single-crystalline GeSn wire, we examined the liquid-phase growth of branched single-crystalline GeSn wire as shown in Fig. 2-13. Since four probes can be contacted crossover the sample, Hall voltage can be measured with this Hall-bar shaped GeSn wire. Figure 2-13(b) shows the optical image of Hall-bar shaped GeSn wire ( $T_{\text{GeSn}}$ : 200 nm) after local melting process. The Sn precipitation was clearly observed at the edge of each branch (bright contrast region), suggesting that the single-crystallization was successfully propagated. This would be beneficial not only for Hall effect

Fig. 2-13 (a) Schematic illustration of Hall-bar shaped GeSn wire on quartz substrate. (b) Optical image of Hall-bar shaped GeSn after liquid-phase growth.

measurement, but also GeSn-based optoelectronic device fabrication that requires flexibility in device structure.

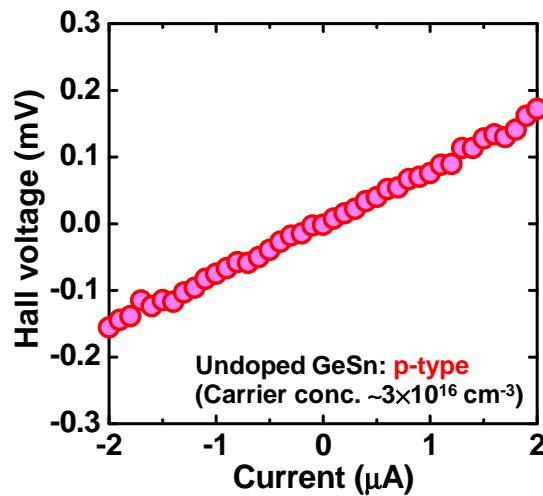

Figure 2-14 shows the Hall current-voltage characteristics of fabricated liquid-phase grown GeSn wire. In this experiment, magnetic field was set to be 0.1 T by using neodymium magnet. From positive slope of the plot, the conduction type of liquid-phase grown undoped GeSn wire was found to be p-type. This p-type conduction is typical feature of undoped GeSn layer and that is explained by the point defect in Ge or GeSn, which act as acceptor-like state. By using the equation shown in Fig. 2-12, the carrier concentration of undoped GeSn wire was estimated to be around  $3 \times 10^{16} \text{ cm}^{-3}$ , which is much smaller than that of poly-crystalline GeSn layer ( $> 10^{18} \text{ cm}^{-3}$ ) [6] or epitaxially-grown single-crystalline GeSn layer ( $10^{17}$ - $10^{18} \text{ cm}^{-3}$ ) on Si substrate [7]. This indicates the excellent crystalline quality of the fabricated liquid-phase grown GeSn wire on a quartz substrate, which would be an attractive platform for GeSn-based optoelectronic integration on a transparent substrate.

Fig. 2-14 Hall plot of fabricated liquid-phase grown undoped GeSn wire.

## 2.6 N-type Doping into Liquid-Phase Grown Ge and GeSn Wires

### 2.6.1 Issues in n-type GeSn Formation

In the previous session, we have succeeded in fabricating a single-crystalline GeSn wire on a quartz substrate by nucleation-controlled liquid-phase crystallization. The Hall effect measurement revealed that the undoped GeSn wire is p-type due to the acceptor-like point defects as in the case of Ge. Also, carrier concentration was evaluated to be around  $3 \times 10^{16} \text{ cm}^{-3}$ , indicating an excellent crystalline quality of the fabricated single-crystalline GeSn wire.

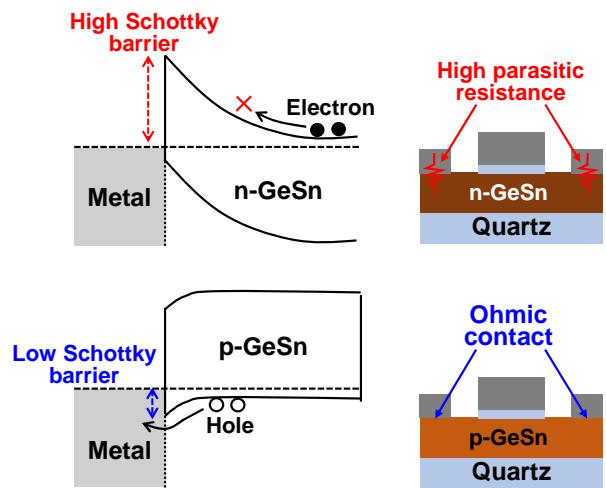

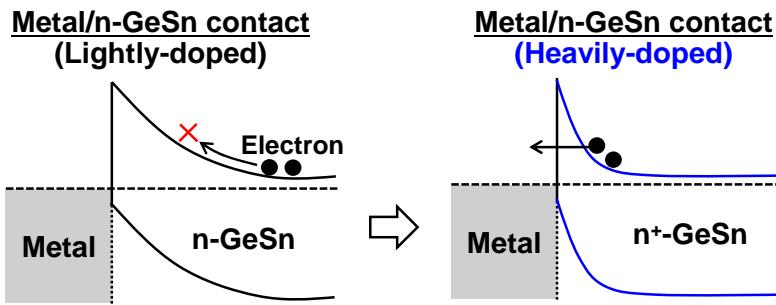

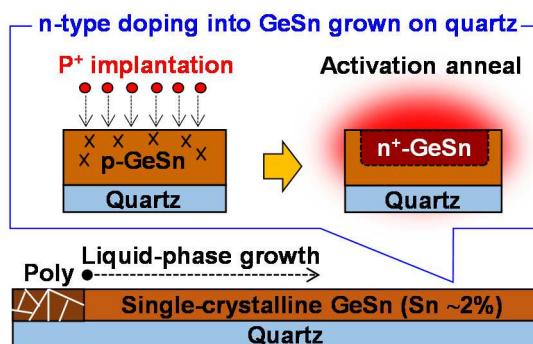

Considering the monolithic integration of CMOS and light emission/detection devices, not only p-type but also n-type GeSn layer is indispensable. In general, n-type doping of Ge is still difficult due to the high diffusivity and low solid solubility of n-type dopants in Ge [8]. In addition, in the case of GeSn, a low thermal budget is required for dopant activation annealing due to its poor thermal stability, which makes it much more challenging to form a high-quality n-type GeSn layer [9]. Previously, a unique n-type doping technique using the LLPE has been reported, in which the P ions were implanted into amorphous Ge wire followed by RTA to induce the LLPE and dopant activation simultaneously [10]. An advantage of this method is to avoid implantation damage and does not require additional activation annealing, which seems to be an attractive approach for fabricating a high-quality n-type single-crystalline GeSn wire. In recent years, the LLPE-growth of P<sup>+</sup>-implanted GeSn wire was also reported from our group and the enhanced direct bandgap PL emission was demonstrated [1,11]. However, the doping concentration and profile in liquid-phase grown Ge and GeSn wire is still unclear and the electrical properties have not been investigated in spite of its importance.

In this session, in order to provide a further insight into this n-type doping technique, we systematically investigated the diffusion and activation behaviors of n-type dopant during the liquid-phase crystallization process. In our work, Sb was selected as an n-type dopant since a high activation rate is expected during the melting and recrystallization process of Sb-doped Ge. [12] The physical,

optical and electrical properties of Sb-doped single-crystalline Ge and GeSn wires were studied in detail.

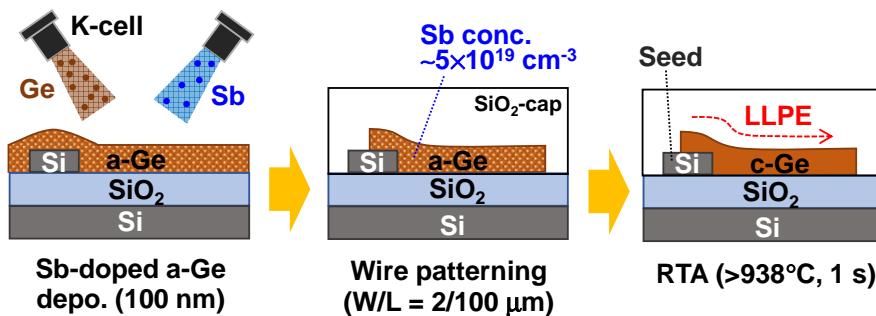

## 2.6.2 LLPE-Growth of Sb-Doped Ge on Silicon Substrate

### 2.6.2.1 Fabrication Process

Fabrication process of Sb-doped LLPE-Ge wire is illustrated in Fig. 2-15. After wet cleaning the silicon-on-insulator wafer with 50-nm-thick Si layer and 150-nm-thick buried oxide, the Si layer was patterned by tetramethyl ammonium hydroxide (TMAH) solution to define the seed region. Then, a 100-nm-thick amorphous Ge layer was deposited by molecular beam deposition system at room temperature. For the n-type doping, Sb was simultaneously evaporated during Ge deposition. From the secondary ion mass spectrometry (SIMS) measurement, the Sb concentration in the amorphous Ge layer was estimated to be around  $5 \times 10^{19} \text{ cm}^{-3}$ . After patterning the Sb-doped amorphous Ge layer into narrow stripes ( $W/L = 2/100 \mu\text{m}$ ), a thick  $\text{SiO}_2$ -capping layer ( $\sim 1 \mu\text{m}$ ) was deposited to prevent agglomeration of liquid-phase Ge. Then, RTA was performed in nitrogen ambient over  $938^\circ\text{C}$  for 1 sec to induce the LLPE-growth from the seed region.

Fig. 2-15 Schematic illustrations of LLPE-growth of Sb-doped Ge wire.

### 2.6.2.2 Evaluation of Sb Distribution

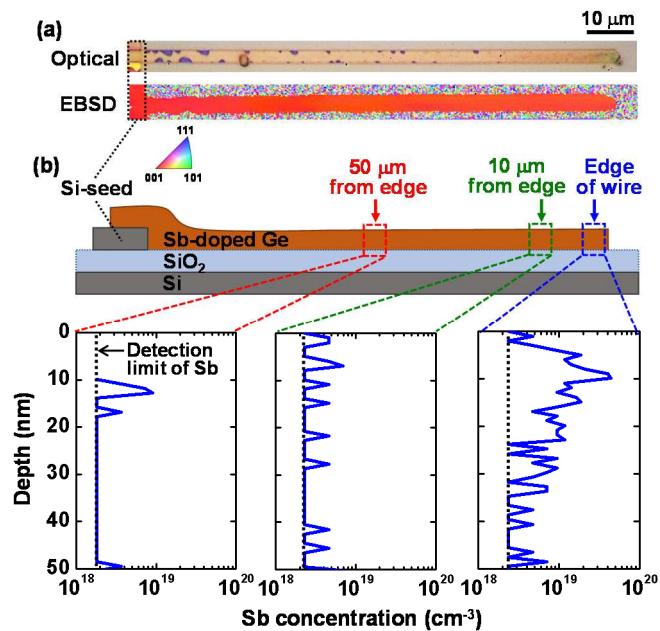

Figure 2-16(a) shows the typical optical microscope and EBSD images of the Sb-doped Ge wire after RTA. As shown in the EBSD image, the Sb-doped Ge wire exhibited a single-crystalline (001) orientation, which is identical to the Si-seed. This indicates that the LLPE-growth proceeded from the seed region and that the Sb incorporation hardly affected the lateral crystal growth of Ge.

Then we investigated the doping profile of Sb in LLPE-grown Ge wire. For an accurate measurement of Sb concentration in the narrow Ge wire ( $W = 2 \mu\text{m}$ ), micro-SIMS ( $\mu$ -SIMS) measurement with a detection area size of  $10 \times 10 \mu\text{m}^2$  was employed. Figure 2-16(b) shows the Sb depth profiles in LLPE-Ge measured at different position along the wire. Although the Sb concentration in the middle part of wire was under the detection limit ( $< 10^{18} \text{ cm}^{-3}$ ), high concentration of Sb exceeding the solid solubility ( $> 10^{19} \text{ cm}^{-3}$ ) was detected at the edge of wire. These results indicate that the Sb atoms were swept out toward the growth direction during the LLPE, resulting in a formation of highly Sb-doped region near the growth end. This would be due to the low segregation coefficient of Sb in Ge, and coincides well with the calculated profile based on Scheil's equation [13]. We also confirmed Sb precipitation at the end of wire (dark contrast region in Fig. 2-16(a)). Similar dopant segregation phenomena was reported for LLPE growth of P-doped Ge [10].

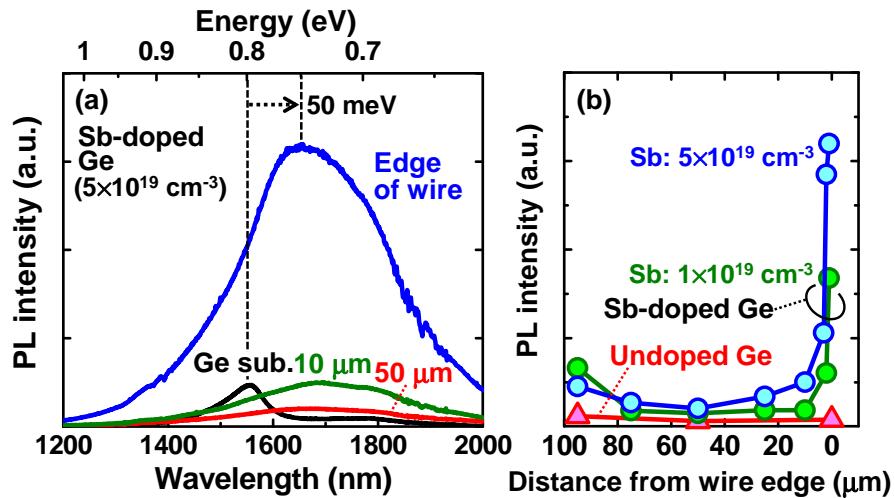

In order to provide a further insight into the activation behavior of Sb during the liquid-phase crystallization process,  $\mu$ -PL measurement was performed. In the case of Ge, it is known that the electron population at  $\Gamma$ -valley increases by n-type doping, leading to enhancement of direct bandgap emission. Since the

Fig. 2-16 (a) Optical and EBSD images of Sb-doped Ge wire after RTA. (b)  $\mu$ -SIMS depth profiles of Sb concentration in LLPE-Ge wire measured at different position along the wire (Ref. 16, Copyright 2018 The Japan Society of Applied Physics).

Fig. 2-17 (a) PL spectra of Sb-doped LLPE-Ge wire on  $\text{SiO}_2/\text{Si}$  substrate measured at different position and control bulk Ge substrate. (b) Position-dependence of peak PL intensity for Sb-doped and undoped LLPE-Ge wires (Ref. 16, Copyright 2018 The Japan Society of Applied Physics).

emission intensity increased with increasing electrically active donor concentration [14], we can estimate the active Sb distribution. The excited laser with a wavelength of 647 nm was focused on the sample surface with a diameter of about 1  $\mu\text{m}$ , enabling the evaluation of position-dependent PL spectra along the narrow Ge wire ( $W = 2 \mu\text{m}$ ).

Figure 2-17(a) shows the PL spectra obtained from Sb-doped Ge wire with different measurement position along the wire and control bulk Ge substrate. The Sb-doped Ge wire exhibits direct bandgap emission at the peak wavelength of 1660 nm, which is red-shifted with respect to that from bulk Ge substrate (0.80 eV, 1550 nm) for about 50 meV. This bandgap shrinkage is caused by the biaxial tensile strain of about 0.3%, which is originating from the large difference in thermal expansion coefficient between Ge and Si [15]. The tensile strain of about 0.3% was also estimated from Raman measurement (data not shown). Also, a significant increase in the PL intensity was observed at the edge of Sb-doped Ge wire ( $\times 7$  Ge substrate), indicating the formation of heavily n-type doped region, and this is consistent with the Sb distribution evaluated by  $\mu$ -SIMS measurement (Fig. 2-16(b)). The position-dependence of peak PL intensity for the Sb-doped and undoped LLPE-Ge wires are shown in Fig. 2-17(b). In contrast to the undoped Ge wire, the Sb-doped Ge wire shows remarkable increase in the PL

intensity near the edge of wire due to high Sb concentration. However, at the most part of Sb-doped Ge wire (20-100  $\mu\text{m}$  far from edge of wire), the PL intensity is comparable to that of undoped Ge wire and nearly constant along the wire. This indicates that the electrically active doping concentration in Sb-doped LLPE-Ge wire was low and almost uniform along the wire except for near the growth end. We have also confirmed that the PL intensity near the growth end was strongly affected by the initial Sb concentration, while negligible change was observed at the most part of wire (Fig. 2-17(b),  $1\times10^{19} \text{ cm}^{-3}$ ).

## 2.6.3 Liquid-Phase Growth of Sb-Doped GeSn on Quartz Substrate

### 2.6.3.1 Fabrication Process

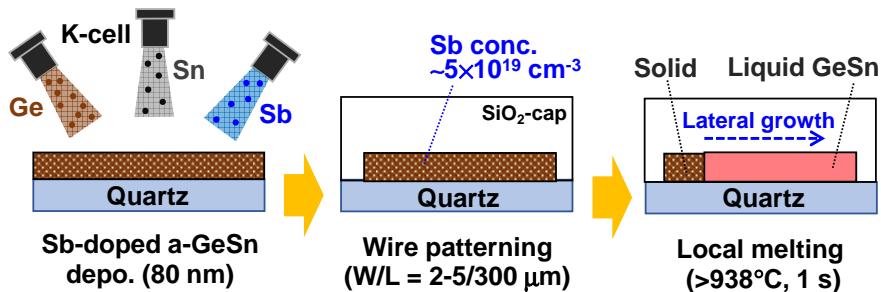

We next examined the nucleation-controlled liquid-phase growth of Sb-doped GeSn wire on a quartz substrate to obtain a high-quality single-crystalline n-type GeSn wire. In order to induce the lateral liquid-phase crystallization without using crystal-seed, the local melting process was employed (Fig. 2-18). The detail of this crystallization process is described in session 1.2. After wet cleaning a quartz substrate, a 80-nm-thick Sb-doped amorphous GeSn layer was deposited and patterned into narrow stripes ( $\text{W/L} = 2-5/300 \mu\text{m}$ ). The Sn and Sb concentrations in the amorphous GeSn wire were estimated to be 2.5% and  $5\times10^{19} \text{ cm}^{-3}$ , respectively. Then, a thick  $\text{SiO}_2$ -capping layer was deposited and RTA was performed for the local melting of amorphous GeSn wire to induce the liquid-phase growth.

Fig. 2-18 Schematic illustrations of nucleation-controlled liquid-phase growth of Sb-doped GeSn wire on quartz substrate.

### 2.6.3.2 Crystalline Quality

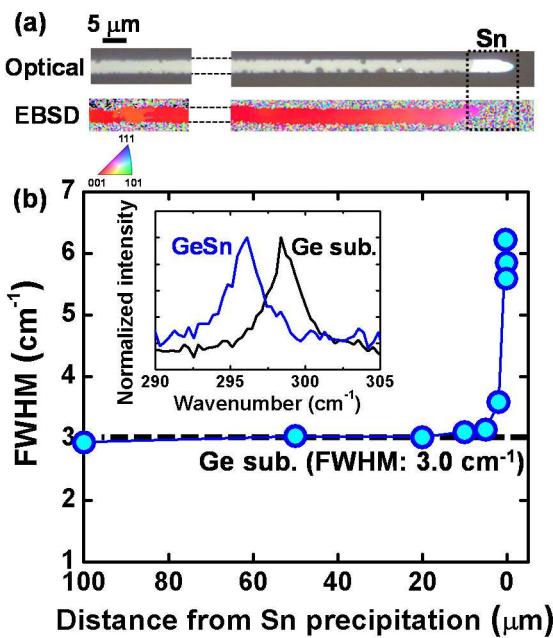

Figure 2-19(a) shows the typical optical and EBSD images of Sb-doped GeSn wire on a quartz substrate after RTA. The bright contrast region in the optical image (edge of wire) corresponds to a Sn segregation, which is the sign for accomplishment of lateral crystal growth. The identical color in EBSD image observed from the middle to end of wire for over 250- $\mu\text{m}$ -long indicates a single-crystallization propagated along the wire from a single-nucleus formed at the solid/liquid interface, which acts as a self-organized seed. It should be noted that the Sb-doped GeSn wires almost exhibited (001) orientation. This would be originating from the interface energy minimization between GeSn and  $\text{SiO}_2$ , which is in good agreement with the result of liquid-phase grown undoped GeSn wire.

The crystalline quality of fabricated Sb-doped single-crystalline GeSn wire was evaluated by the micro-probe Raman measurement (beam spot size:  $\sim 1 \mu\text{m}$ ). Since a quartz has low thermal conductivity, we carefully optimized the excitation conditions in order to avoid thermal effect during the measurement. As shown in the inset in Fig. 2-19(b), the Raman peak originating from Ge-Ge vibration mode obtained from Sb-doped GeSn wire is shifted toward lower wave number compared to that from bulk Ge substrate, which is due to the Sn incorporation and biaxial tensile strain. By combining the EDX result with Raman measurement, the Sn content and biaxial tensile strain was estimated to

Fig. 2-19 (a) Optical and EBSD images of Sb-doped GeSn wire after RTA. (b) Position-dependence of extracted FWHM from Raman peak of Sb-doped GeSn wire. Inset shows Raman peak obtained from Sb-doped GeSn wire and control bulk Ge substrate (Ref. 16, Copyright 2018 The Japan Society of Applied Physics).

be around 2% and 0.3%, respectively. The position dependence of full-width at half maximum (FWHM) extracted from Raman peak was plotted in Fig. 2-19(b). It was found that the FWHM obtained from Sb-doped GeSn wire is comparable to that from bulk Ge substrate and nearly constant along the wire, indicating an excellent crystalline quality of the Sb-doped single-crystalline GeSn wire grown on a quartz substrate. It should be noted that the drastic increase in the FWHM near the Sn precipitation is attributed to the increase in Sn content, which degraded the crystalline quality due to the large lattice mismatch between Ge and Sn.

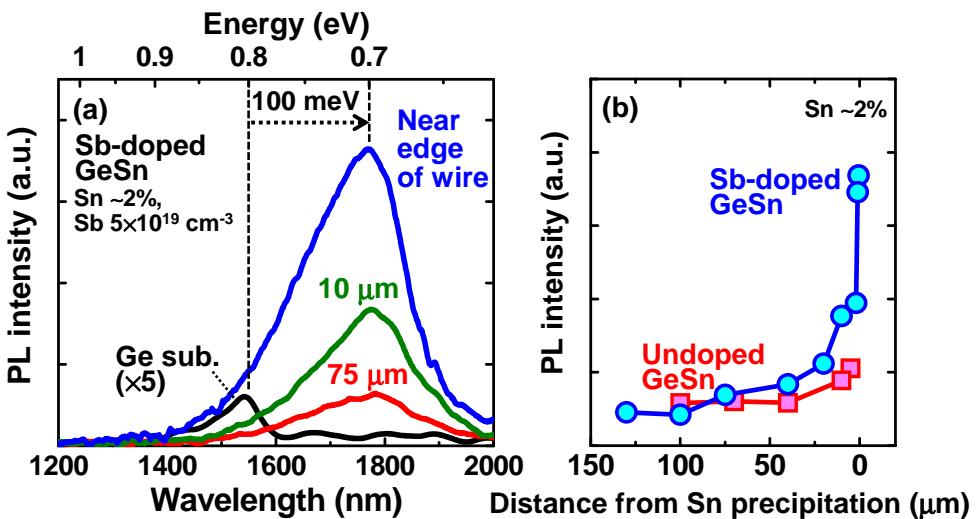

### 2.6.3.3 Photoluminescence-Based Study

The activation behavior of Sb in the liquid-phase grown GeSn wire was also evaluated by the  $\mu$ -PL measurement (Figs. 2-20(a) and 2-20(b)). Since the Sn content rapidly increased at the growth end (Fig. 2-19(b)), the PL measurement was performed at the position enough far from Sn precipitation ( $>1 \mu\text{m}$ ), where the Sn content is almost uniform (Sn  $\sim 2\%$ ). Similar to the Sb-doped Ge wire, a significant increase in the PL intensity was observed near the edge of Sb-doped GeSn wire, while the nearly constant intensity was observed at the most part of wire. This indicates that the single-crystalline GeSn wire is also uniformly-doped

Fig. 2-20 (a) PL spectra of Sb-doped liquid-phase grown GeSn wire on quartz substrate measured at different position along the wire and control bulk Ge substrate. (b) Position-dependence of peak PL intensity for Sb-doped and undoped liquid-phase grown GeSn wires (Sn  $\sim 2\%$ ) (Ref. 16, Copyright 2018 The Japan Society of Applied Physics).

along the wire. The direct bandgap emission from Sb-doped GeSn wire is red-shifted compared to that from bulk Ge substrate for about 100 meV, which is due to the biaxial tensile strain and Sn incorporation. It should be noted that the PL enhancement factor at the growth end compared to the bulk Ge substrate is much higher than that of Sb-doped Ge wire ( $\times 30$  Ge substrate). According to the theoretical calculation [17], the indirect-to-direct bandgap transition energy of GeSn alloy is around 0.69 eV when biaxial tensile strain is induced. Thus, the fabricated Sb-doped GeSn alloy would have an indirect bandgap structure, but the reduced energy difference between  $\Gamma$ - and L-valleys due to Sn alloying would be attributed to the enhancement of luminescent efficiency.

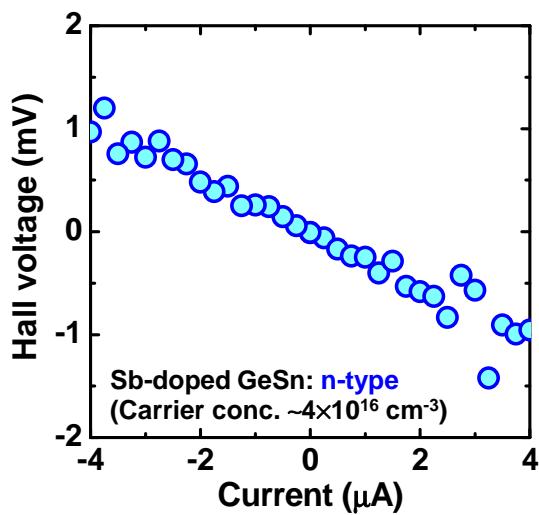

#### 2.6.3.4 Hall Effect Measurement

Then we investigated the conduction type and carrier concentration of Sb-doped GeSn wire formed on a quartz substrate. For the Hall effect measurement, Hall-bar shaped Sb-doped GeSn wire was fabricated by the liquid-phase crystallization. The detail of fabrication procedure is described in session 2.5.2. In this study, the middle part of Sb-doped GeSn wire, where Sb was uniformly doped, was used for Hall effect measurement. From the Hall voltage-current characteristic of Sb-doped GeSn wire as shown in Fig. 2-21, the Sb-doped GeSn wire was found to be n-type, and the carrier concentration was estimated to be around  $4 \times 10^{16} \text{ cm}^{-3}$ . It should be noted that the carrier

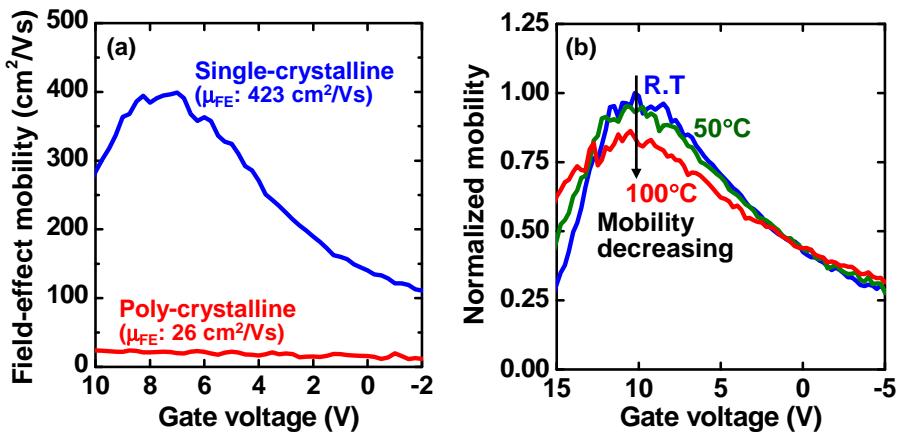

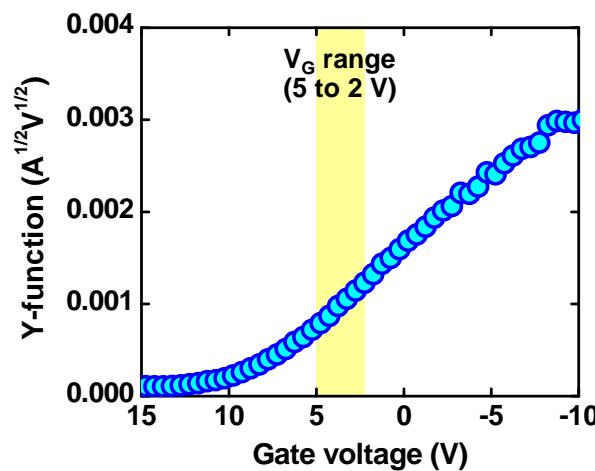

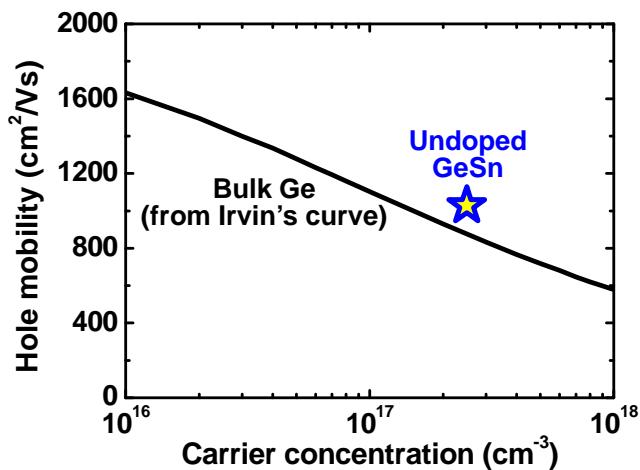

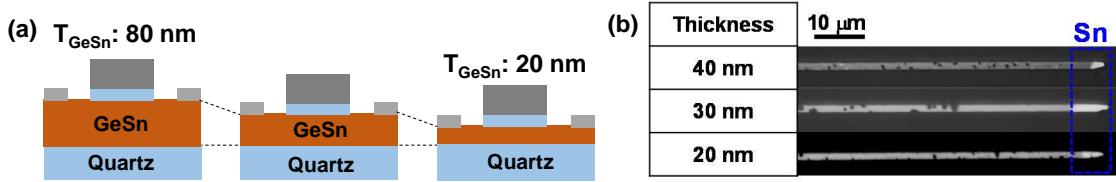

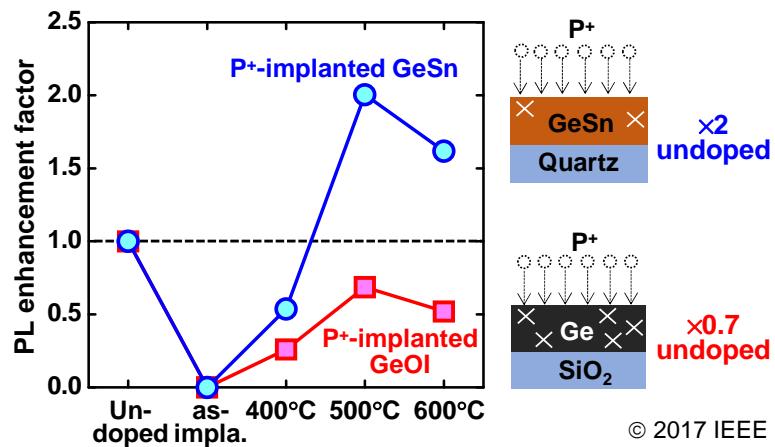

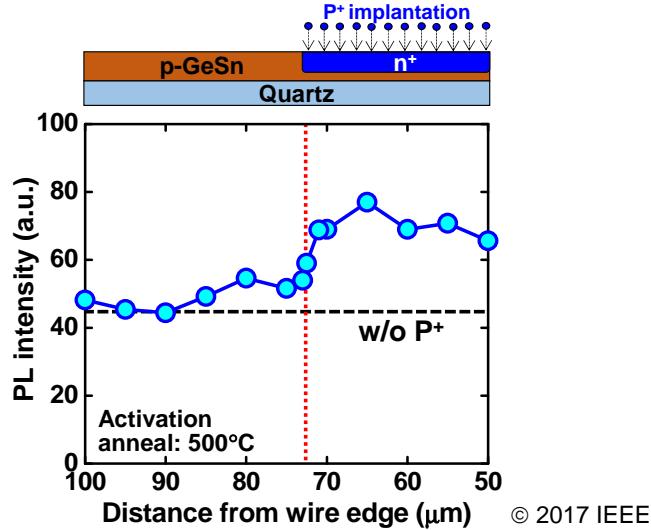

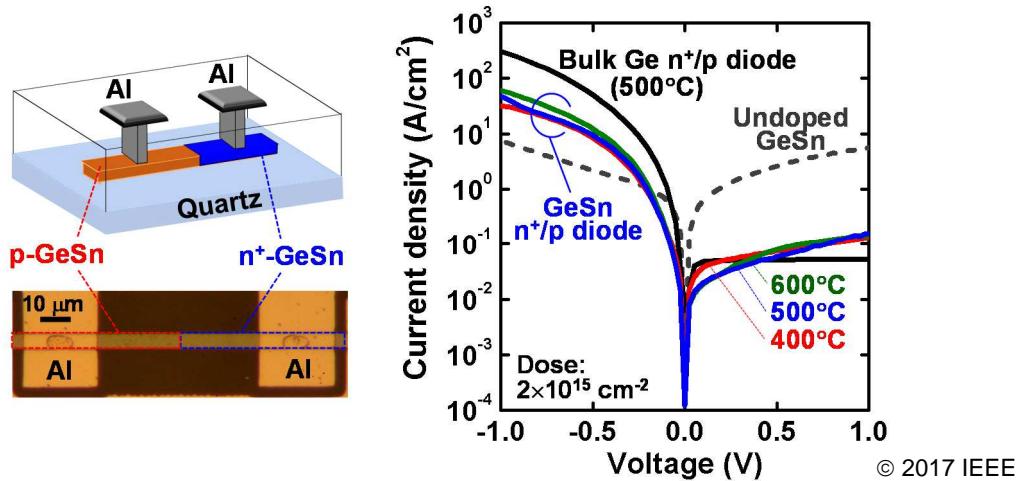

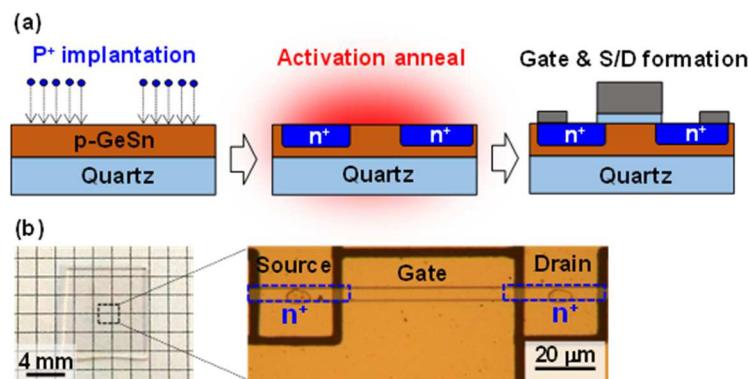

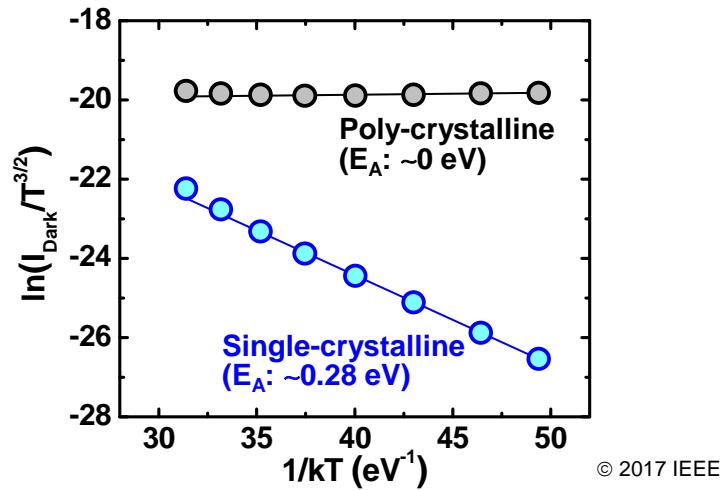

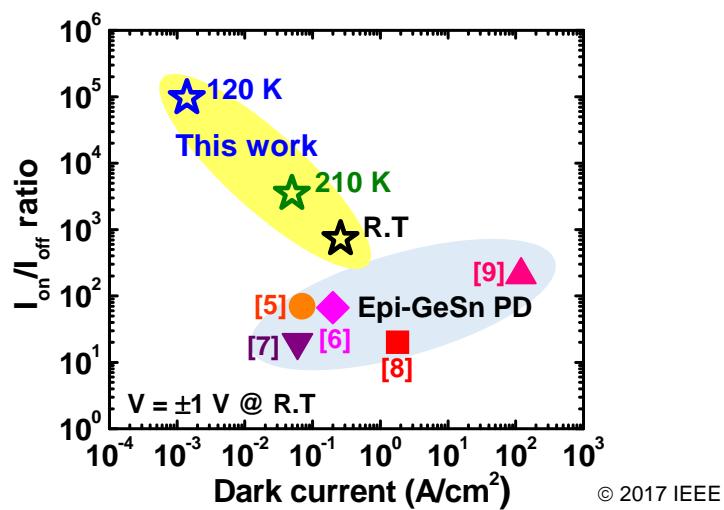

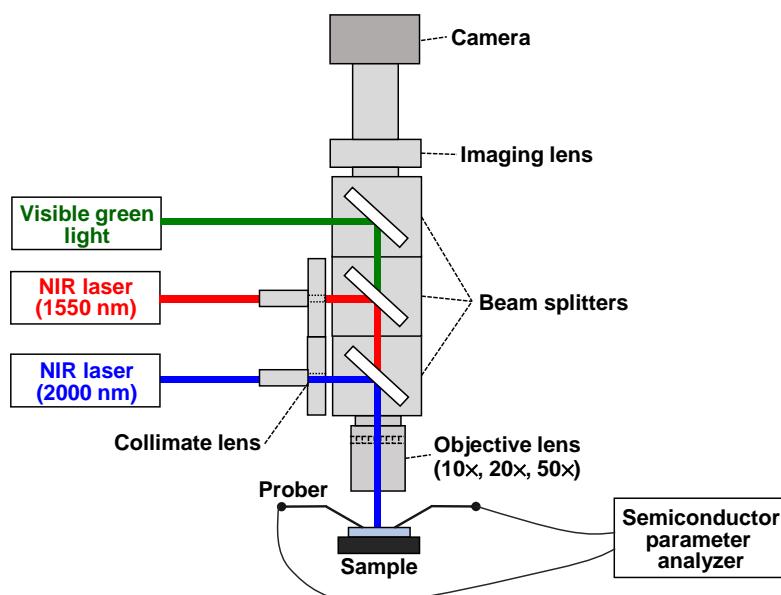

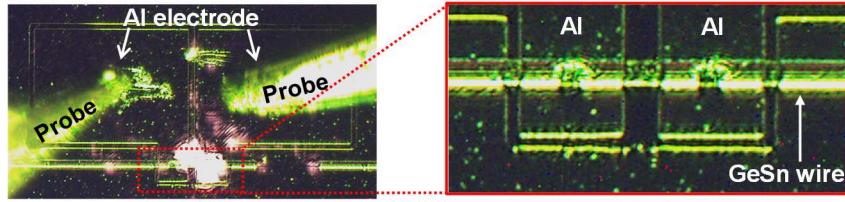

Fig. 2-21 Hall current-voltage characteristic of fabricated liquid-phase grown Sb-doped GeSn wire.