| Title                              | An Implementation of Embedded Object Detection<br>System with Information-Preserved Algorithm<br>Transformation |  |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| Author(s)                          | £成,浩一                                                                                                           |  |  |

| Citation                           | 大阪大学, 2019, 博士論文                                                                                                |  |  |

| Version Type VoR                   |                                                                                                                 |  |  |

| URL https://doi.org/10.18910/72584 |                                                                                                                 |  |  |

| rights                             |                                                                                                                 |  |  |

| Note                               |                                                                                                                 |  |  |

## Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

# An Implementation of Embedded Object Detection System with Information-Preserved Algorithm Transformation

Submitted to Graduate School of Information Science and Technology Osaka University

January 2019

Koichi MITSUNARI

## **Publications**

### **Transactions**

- K. Mitsunari, Y. Takeuchi, M. Imai, and J. Yu, "Decomposed vector histograms of oriented gradients for efficient hardware implementation," *IEICE Transactions* on Fundamentals of Electronics, Communications and Computer Sciences, vol. E101-A, no. 11, pp. 1766–1775, Nov. 2018.

- K. Mitsunari, J. Yu, T. Onoye, and M. Hashimoto, "Hardware architecture for high-speed object detection using decision tree ensemble," *IEICE Transactions* on Fundamentals of Electronics, Communications and Computer Sciences, vol. E101-A, no. 9, pp. 1298–1307, Sep. 2018.

### **International Conference Papers (Refereed)**

- 1. K. Mitsunari, J. Yu, and M. Hashimoto, "Hardware architecture for fast general object detection using aggregated channel features," in *Proceedings of IEEE Asian Solid-State Circuits Conference*, Nov. 2018, pp. 55–58.

- 2. E. Aliwarga, K. Mitsunari, J. Yu, T. Onoye, T. Azuma, and M. Koga, "System design of vision-based framework for senior driver assistance," in *Proceedings* of Workshop on Synthesis And System Integration of Mixed Information Technologies, Oct. 2016, pp. 77–80.

- 3. K. Mitsunari and J. Yu, "Influence of numerical precision on machine learning and embedded systems," in *Proceedings of International Workshop on Smart Info-Media Systems in Asia*, Sep. 2016, pp. 164–169.

- K. Mitsunari, J. Yu, Y. Takeuchi, and M. Imai, "Object tracking based on path similarity of boosted decision trees," in *Proceedings of International Technical Conference on Circuits/Systems, Computers and Communications*, Jul. 2016, pp. 563–566.

ii

## Summary

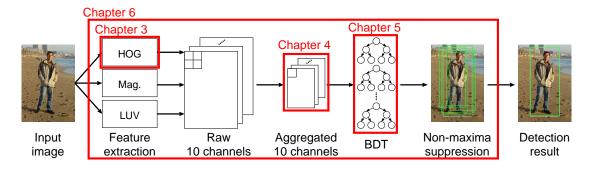

Demand for advanced driver assistance systems (ADAS) based on visual object detection is increasing for reducing deaths and economic loss due to traffic accidents. These embedded systems require fast and accurate object detection with limited power consumption. Due to the severe constraint on power consumption, hardware-oriented design optimization is a promising approach. However, it is still difficult to satisfy the above requirements simultaneously because many existing object detection algorithms are not designed considering hardware implementation. To address this issue, this dissertation proposes a hardware architecture for an object detection method with aggregated channel features (ACF). This dissertation approaches the issue through information-preserved algorithm and hardware architecture for fast classification. For improving the trade-offs, this dissertation focuses on information preservation in histograms of oriented gradients (HOG) feature descriptor and a quantization method for boosted decision trees (BDT) classifiers, and highly-parallelized hardware architecture for BDT.

For improving the trade-off between detection accuracy and power consumption of feature extraction, this dissertation proposes information-preserved HOG feature descriptor named decomposed vector HOG (DV-HOG). DV-HOG feature extraction is based on the decomposition of a gradient vector to generate a histogram. DV-HOG extracts equivalent information to the original HOG, and it can be computed only with additions and multiplications. The hardware architecture for DV-HOG utilizes the symmetry of the vectors to reduce power consumption. Experimental results show that DV-HOG achieves the equivalent or better detection accuracy to the original HOG only with one-fourteenth hardware area.

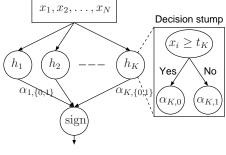

For reducing memory requirements, this dissertation proposes a quantization method for a BDT classifier, which ACF uses as a classifier. The proposed method utilizes the BDT's characteristics that BDT is based on the comparison of a pair of a feature and a threshold. Thus, the range of thresholds of a BDT classifier is narrower than that of features. The proposed quantization method focuses only on the range of thresholds for quantization. Experimental results show that the memory requirement can be reduced to one-sixteenth with 2% accuracy degradation on INRIA Person Dataset, which improves the trade-off between the detection accuracy and memory requirement.

For improving detection speed, this dissertation proposes a hardware architecture

for fast BDT classification. The fast classification is realized by hardware-software cooperative approach: highly-parallelized hardware and a software algorithm for avoiding memory access conflict from multiple hardware modules. The hardware supports 3-D parallelized classification: 2-D for images like SIMD operation and 1-D for feature channels. The hardware is designed to reduce hardware resources and connections for improving the scalability to the high degree of parallelism. The scheduling algorithm using a greedy approach determines the memory access pattern before classification. The evaluation result shows that 1,024-parallel implementation is capable of classifying pedestrian in 350 frames of Full HD images.

Based on the above three methods, this dissertation proposes an ACF object detection hardware. Thanks to the high compatibility of ACF to hardware implementation and the above hardware-oriented algorithms to overcome the challenges, the hardware achieves fast and accurate classification. An FPGA implementation result shows that the proposed system can detect pedestrians in 170 fps a Full HD image, which is 57-times faster than the existing ACF hardware implementation. As an evaluation in a practical environment, the proposed hardware can process 6-class traffic object detection in 78 fps for a Full HD image, which satisfies the requirement for the automatic braking system of ADAS.

The main contribution of this work is the improvement of trade-offs between detection accuracy, detection speed, and power consumption in object detection, which is achieved by the use of the information-preserved algorithm and hardware-oriented approaches.

## Acknowledgments

First and foremost, I would like to express my sincere gratitude to my supervisor Professor Masanori Hashimoto in Osaka University for his insightful comments and valuable advice. He carefully reviewed my papers and gave me much advice for completing this dissertation.

I would like to acknowledge Professor Takao Onoye in Osaka University for his insightful comments to this dissertation. Also, he provided me with precious opportunities to attend many research projects during my graduate studies. I would like to express my appreciation to Professor Haruo Takemura in Osaka University for reviewing my dissertation and giving me valuable suggestions to raise the quality of this dissertation as a member of my dissertation committee.

My appreciation for Assistant Professor Jaehoon Yu in Osaka University cannot be expressed in words. Without his proper guidance and continuous encouragement, this research would not have been possible.

I deeply appreciate Emeritus Professor Masaharu Imai in Osaka University and Professor Yoshinori Takeuchi in Kindai University for providing me with opportunities to study at Imai Laboratory while I was pursuing master's degree.

I would like to thank all the members of the Integrated System Design Laboratory in Osaka University for daily discussion and having a comfortable time. vi

## Contents

| 1 | Intr | oduction | n                                                         | 1  |

|---|------|----------|-----------------------------------------------------------|----|

|   | 1.1  | Backgr   | round on Object Detection                                 | 3  |

|   | 1.2  | Challer  | nges                                                      | 6  |

|   | 1.3  |          | ch Objectives                                             | 7  |

|   | 1.4  |          | e of the Dissertation                                     | 8  |

| 2 | Prel | iminari  | es of Visual Object Detection                             | 11 |

|   | 2.1  | Machin   | ne Learning Algorithms                                    | 11 |

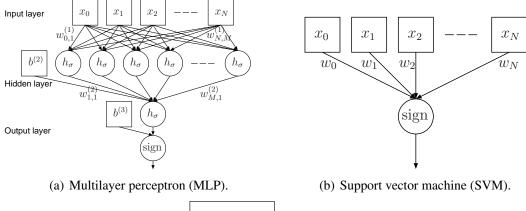

|   |      | 2.1.1    | Multilayer Perceptron                                     | 11 |

|   |      | 2.1.2    | Support Vector Machine                                    | 13 |

|   |      | 2.1.3    | Adaptive Boosting                                         | 14 |

|   | 2.2  | Aggreg   | gated Channel Features                                    | 14 |

|   | 2.3  | HOG F    | Feature Descriptors and Its Hardware Architectures        | 15 |

|   |      | 2.3.1    | HOG Feature Descriptor                                    | 15 |

|   |      | 2.3.2    | Hardware Architectures for HOG Feature Descriptors        | 18 |

|   | 2.4  | Booste   | d Decision Trees and Its Hardware Architectures           | 22 |

|   |      | 2.4.1    | Hardware Architectures for Boosted Decision Trees         | 22 |

|   | 2.5  | Pedest   | rian Detection                                            | 23 |

|   | 2.6  | Summa    | ary                                                       | 24 |

| 3 | Dec  | omposed  | d Vector Histograms of Oriented Gradients                 | 25 |

|   | 3.1  | Introdu  | action                                                    | 25 |

|   | 3.2  | Decom    | posed Vector HOG Feature Descriptor                       | 26 |

|   |      | 3.2.1    | Details of DV-HOG                                         | 26 |

|   |      | 3.2.2    | Representation Capability Analysis                        | 28 |

|   |      | 3.2.3    | Detection Accuracy Evaluation                             | 30 |

|   | 3.3  | Hardw    | are Architectures for HOG Feature Descriptors             | 33 |

|   |      | 3.3.1    | Hardware Architecture for DV-HOG                          | 34 |

|   |      | 3.3.2    | Application of Quadrant Folding to HOG-Dot                | 35 |

|   | 3.4  | Evalua   | tion                                                      | 36 |

|   |      | 3.4.1    | Detection Accuracy Evaluation with Fixed-point Arithmetic | 37 |

|   |      | 3.4.2    | Area Evaluation with Logic Synthesis                      | 39 |

|   |     | 3.4.3 FPGA Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39 |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 3.4.4 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40 |

|   | 3.5 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43 |

| 4 | Agg | ressive Quantization Method for Boosted Decision Trees                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45 |

|   | 4.1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45 |

|   | 4.2 | Influence of Numerical Precision on Classification Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46 |

|   | 4.3 | Aggressive Approximation for Fixed-Point AdaBoost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49 |

|   | 4.4 | Evaluation on Pedestrian Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51 |

|   | 4.5 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 52 |

| 5 | Har | dware Architecture for Parallel Boosted Decision Trees Classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 55 |

| U | 5.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55 |

|   | 5.2 | Parallel Implementation of BDT using Multiple Memory Banks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56 |

|   | 0.2 | 5.2.1 Architecture Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56 |

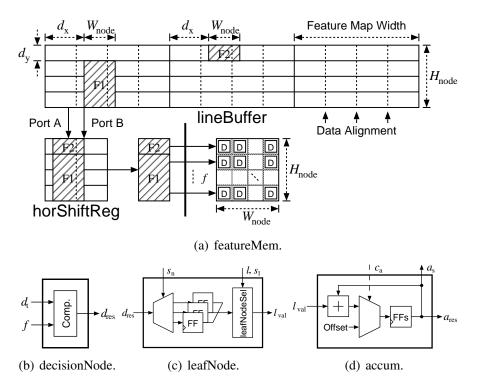

|   |     | 5.2.2 Details of Sub-modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58 |

|   | 5.3 | Task Scheduling for Parallel Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59 |

|   | 5.5 | 5.3.1 Boosted Decision Trees Scheduling Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59 |

|   |     | 5.3.2 Proposed Heuristic Scheduling Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62 |

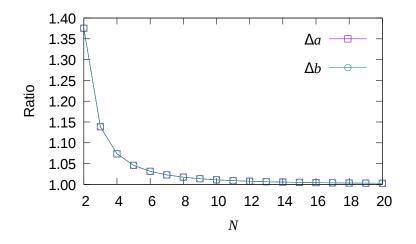

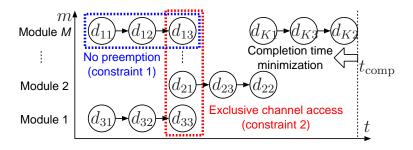

|   |     | 5.3.3 Analysis of Scheduling Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63 |

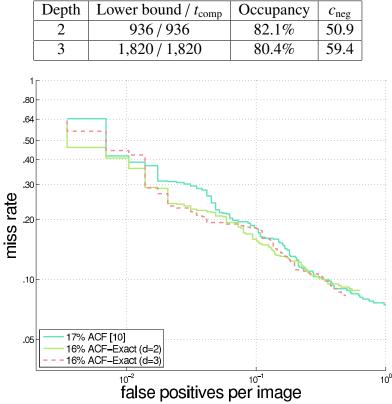

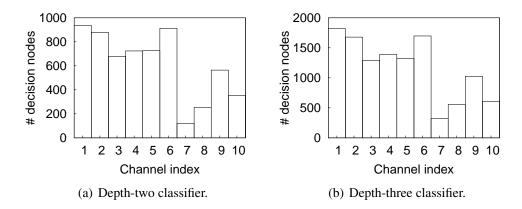

|   |     | 5.3.4 Scheduling under Deeper Boosted Decision Trees                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65 |

|   | 5.4 | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66 |

|   | 5.4 | 5.4.1 Evaluation Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66 |

|   |     | 5.4.2 Resource Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67 |

|   | 5.5 | Summary         Summary <t< th=""><th>68</th></t<> | 68 |

|   | 5.5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 00 |

| 6 |     | dware Accelerator for Aggregated Channel Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 69 |

|   | 6.1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69 |

|   | 6.2 | Proposed Hardware Accelerator Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70 |

|   | 6.3 | Evaluation using Logic Simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71 |

|   |     | 6.3.1 Processing Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72 |

|   |     | 6.3.2 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73 |

|   | 6.4 | FPGA Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74 |

|   |     | 6.4.1 Performance Evaluation on Pedestrian Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75 |

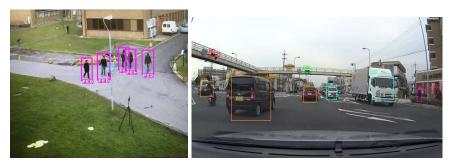

|   |     | 6.4.2 Traffic Object Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77 |

|   | 6.5 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 78 |

| 7 | Con | clusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79 |

|   | 7.1 | Summary and Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79 |

|   | 7.2 | Future Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80 |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

# **List of Figures**

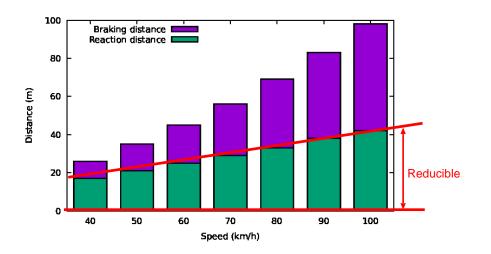

| 1.1  | Stopping distances for various running speed.                                                     | 2  |

|------|---------------------------------------------------------------------------------------------------|----|

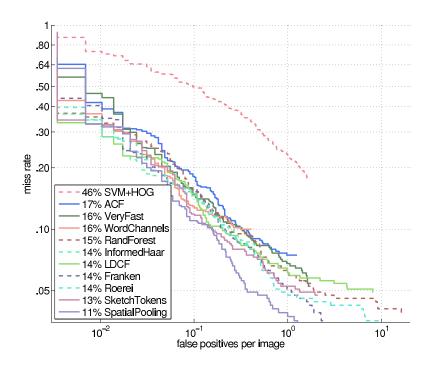

| 1.2  | Detection error trade-off (DET) curves of leading-edge algorithms and                             |    |

|      | SVM+HOG [24] from pedestrian detection benchmark [25]. The closer                                 |    |

|      | a curve gets to the bottom left corner, the better the DET is                                     | 3  |

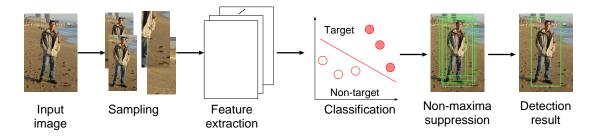

| 1.3  | Object detection flow of conventional approaches                                                  | 3  |

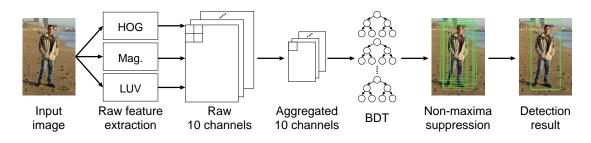

| 1.4  | ACF object detection flow.                                                                        | 5  |

| 1.5  | Boosted decision trees.                                                                           | 5  |

| 1.6  | Overview of this dissertation.                                                                    | 8  |

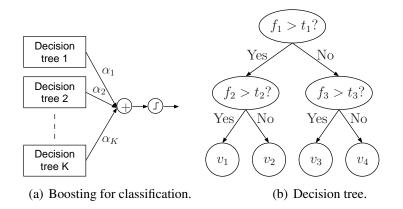

| 2.1  | Basic structure of machine learning algorithms.                                                   | 12 |

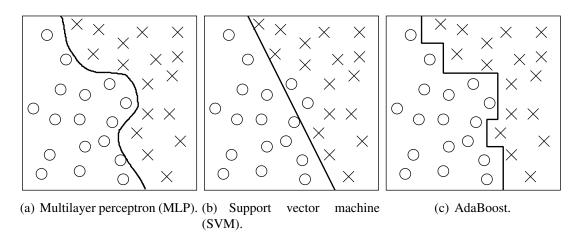

| 2.2  | Input space separation. Each classifier separates two class data: $\bigcirc$ and $\times$ .       | 13 |

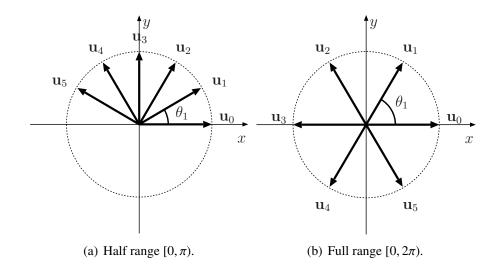

| 2.3  | Orientation unit vectors $\mathbf{u}_i$ . In this figure, six unit vectors are evenly             |    |

|      | spaced over the half range $[0, \pi)$ (a) or the full range $[0, 2\pi)$ (b)                       | 16 |

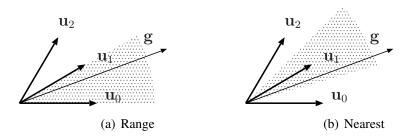

| 2.4  | Simple orientation binning methods for a gradient vector <b>g</b> . In both                       |    |

|      | methods, each gradient vector casts its magnitude for one of the                                  |    |

|      | orientations in the shadowed area including <b>g</b>                                              | 17 |

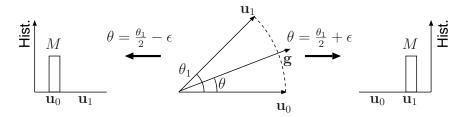

| 2.5  | Aliasing of NaiveHOG, which makes entirely different histograms from                              |    |

|      | similar gradient vectors                                                                          | 17 |

| 2.6  | Bilinearly interpolated HOG. Given a gradient vector <b>g</b> , the interpolated                  |    |

|      | HOG bilinearly decomposes its magnitude $M$ according to $\theta$                                 | 18 |

| 2.7  | Outline of InterHOG hardware                                                                      | 19 |

| 2.8  | Outline of NaiveHOG hardware                                                                      | 20 |

| 2.9  | Outline of ChenHOG hardware with sign modification.                                               | 21 |

| 2.10 | Outline of the HOG-Dot hardware proposed in [9]                                                   | 22 |

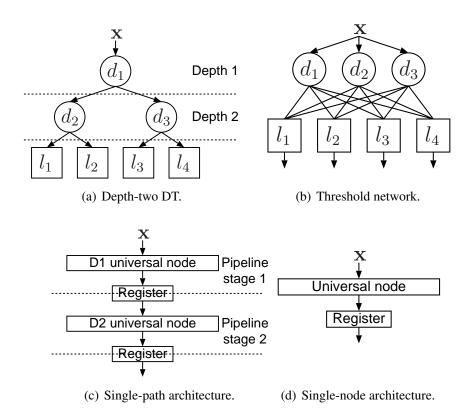

| 2.11 | BDT and available hardware architectures                                                          | 23 |

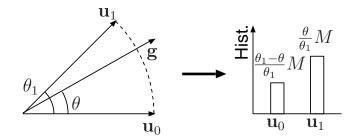

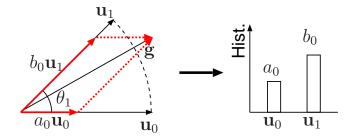

| 3.1  | Proposed DV-HOG. The proposed method decomposes a gradient                                        |    |

|      | vector $\mathbf{g}$ into two adjacent vectors with directions of a pair of $\mathbf{u}_i$ , where |    |

|      | the vectorial sum of the two decomposed vectors is equal to the gradient                          |    |

|      | vector                                                                                            | 26 |

| 3.2  | Comparison of voted weights of DV-HOG and InterHOG                                                | 29 |

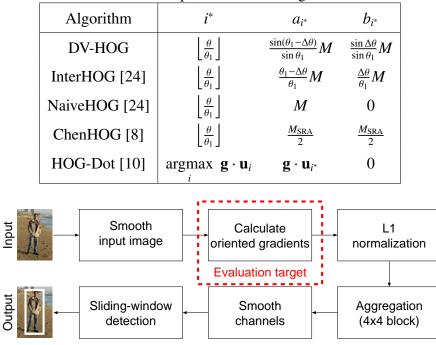

| 3.3  | Evaluation target process in ACF [36]                                                             | 30 |

|      |                                                                                                   |    |

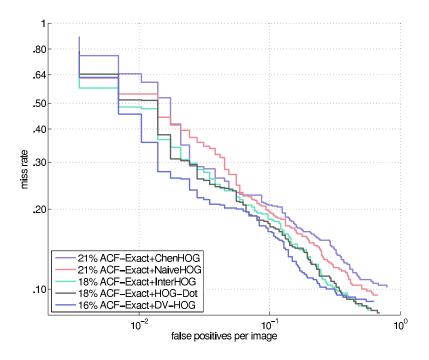

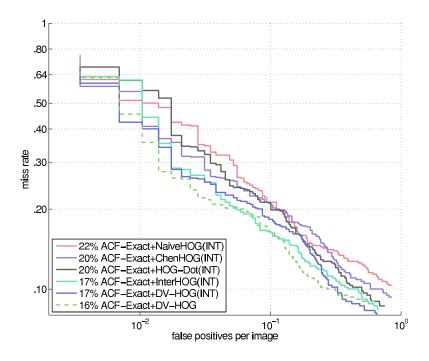

| 3.4  | DET curves of five ACF classifiers using different HOG feature                                    |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | descriptors. The closer a curve gets to the bottom left corner, the better                        | 22 |

| 2.5  | the DET is.                                                                                       | 32 |

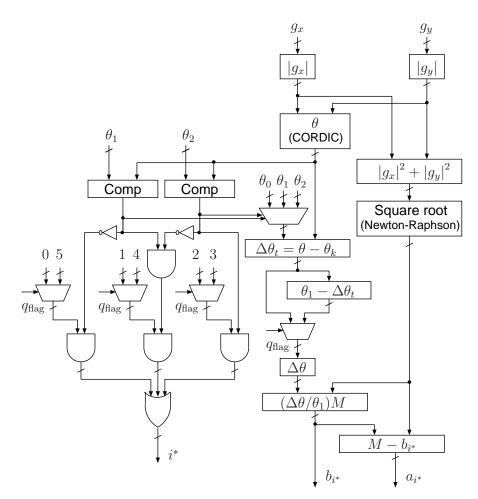

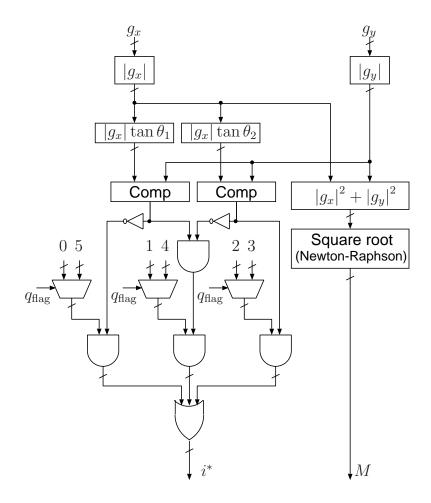

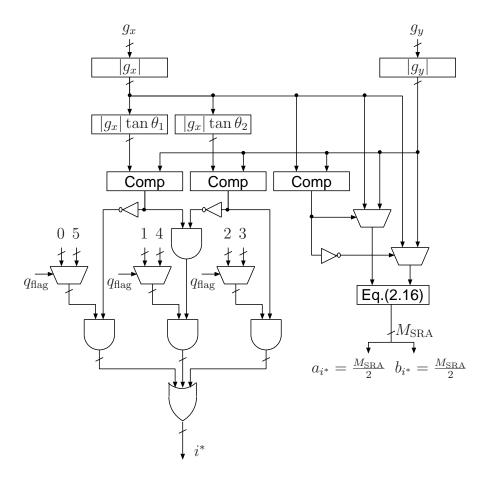

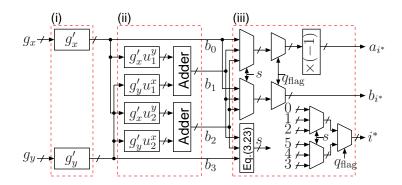

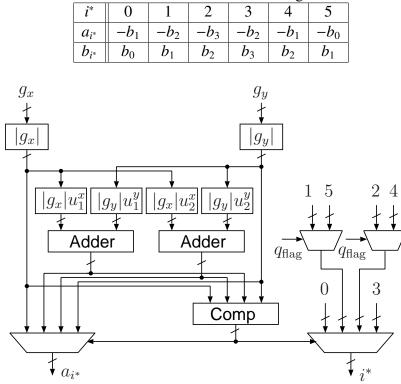

| 3.5  | Outline of DV-HOG hardware.                                                                       | 33 |

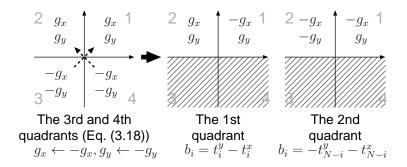

| 3.6  | Sign inversion of $g_x$ and $g_y$ for quadrant folding                                            | 34 |

| 3.7  | Outline of HOG-Dot hardware with quadrant folding                                                 | 36 |

| 3.8  | DET curves of fixed-point ACF classifiers                                                         | 37 |

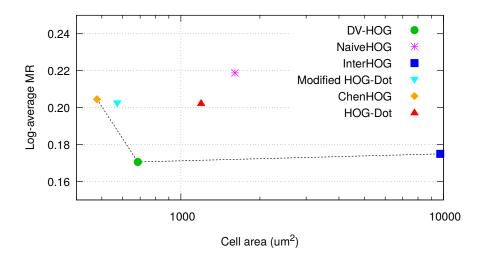

| 3.9  | Log-average MR and the circuit area of HOG algorithms                                             | 39 |

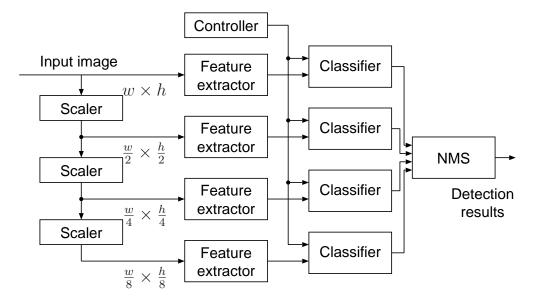

| 3.10 | Outline of hardware architecture for object detection                                             | 41 |

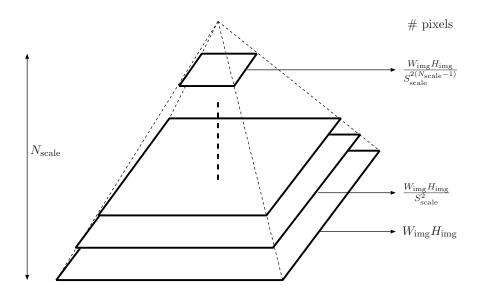

| 3.11 | The number of pixels for multi-scale object detection                                             | 42 |

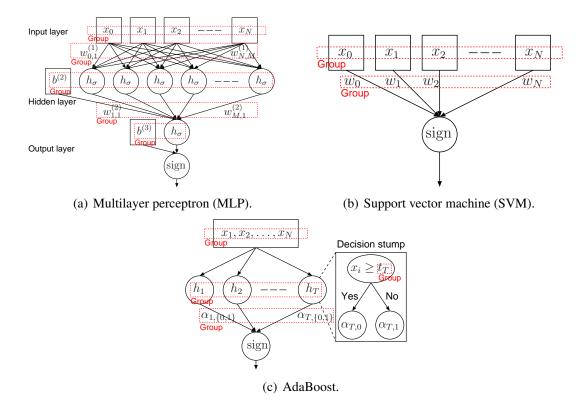

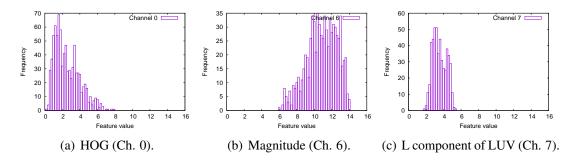

| 4.1  | Basic structure of machine learning algorithms                                                    | 47 |

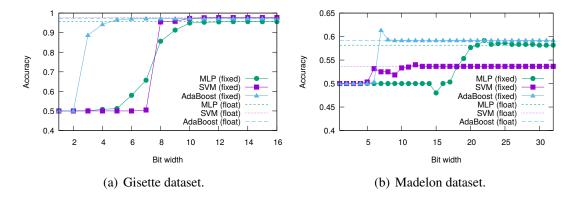

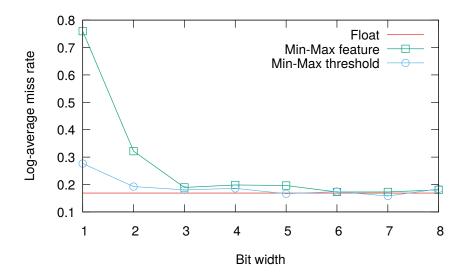

| 4.2  | Experimental results of classification accuracy with limited numerical                            | 40 |

| 4.0  | precision.                                                                                        | 48 |

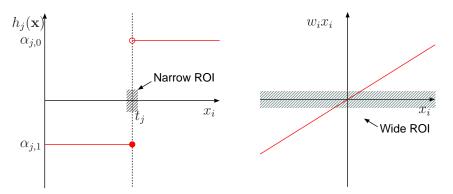

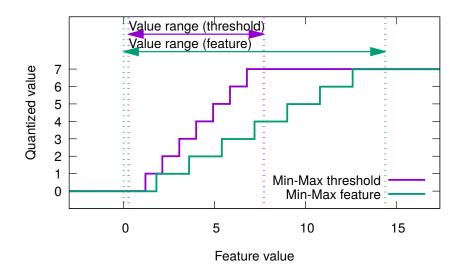

| 4.3  | Region of interest (ROI) comparison.                                                              | 49 |

| 4.4  | Histograms of thresholds.                                                                         | 50 |

| 4.5  | 3-bit quantization of features on ACF channel 0                                                   | 50 |

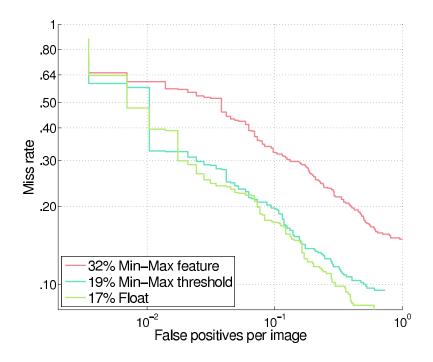

| 4.6  | Comparison of classification performances.                                                        | 51 |

| 4.7  | Comparison of DET curves.                                                                         | 52 |

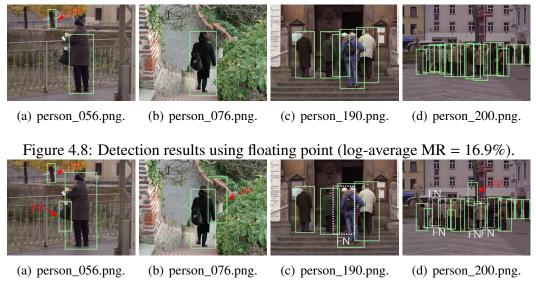

| 4.8  | Detection results using floating point (log-average MR = $16.9\%$ )                               | 53 |

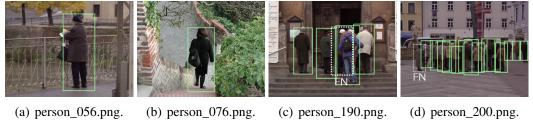

| 4.9  | Detection results using 2-bit wide fixed point (Min-Max feature, log-<br>average MR = $32.2\%$ ). | 53 |

| 4.10 | Detection results using 2-bit wide fixed point (Min-Max threshold, log-                           |    |

|      | average MR = $19.2\%$ ).                                                                          | 53 |

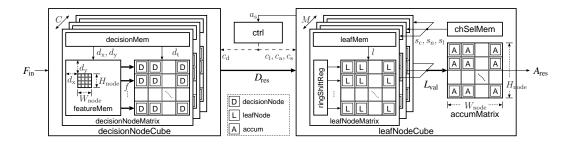

| 5.1  | Hardware architecture overview.                                                                   | 56 |

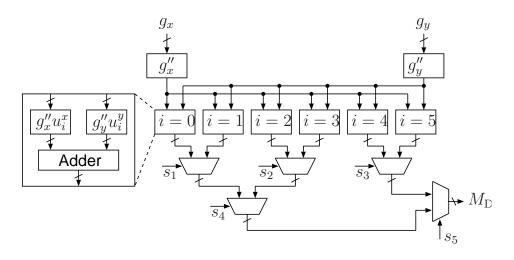

| 5.2  | Block diagrams of processing elements.                                                            | 58 |

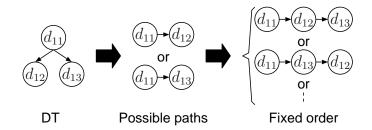

| 5.3  | Input dependency removal of DT by visiting all nodes.                                             | 60 |

| 5.4  | Target scheduling problem.                                                                        | 60 |

| 5.5  | Detection error trade-off curves on INRIA Person Dataset.                                         | 63 |

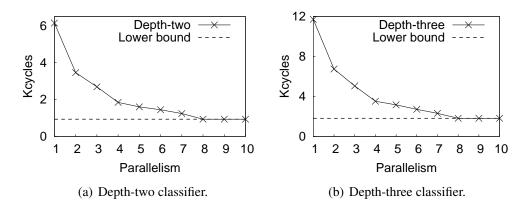

| 5.6  | Histograms of input channels.                                                                     | 64 |

| 5.7  | Scheduling results for the different number of modules.                                           | 64 |

| 5.8  | Result of depth-six ACF classifier.                                                               | 65 |

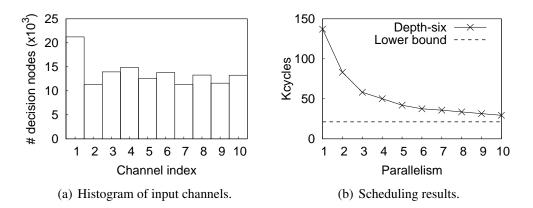

| 5.9  | Detection results from INRIA Person Dataset.                                                      | 66 |

|      |                                                                                                   |    |

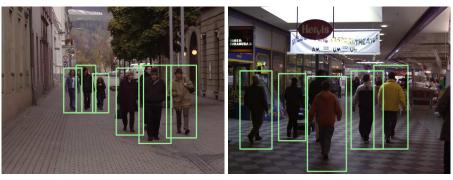

| 6.1  | Proposed object detection system overview.                                                        | 69 |

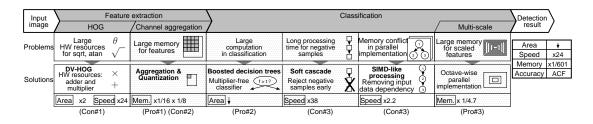

| 6.2  | Problems and solutions for ACF hardware implementation.                                           | 70 |

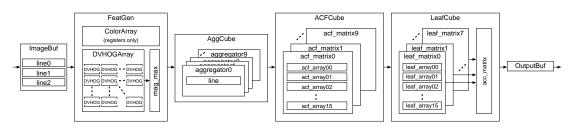

| 6.3  | ACF-Core hardware architecture.                                                                   | 70 |

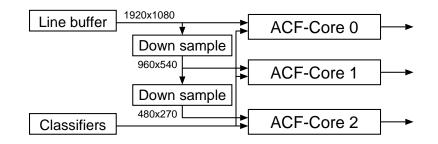

| 6.4  | Multi-scale ACF hardware architecture.                                                            | 71 |

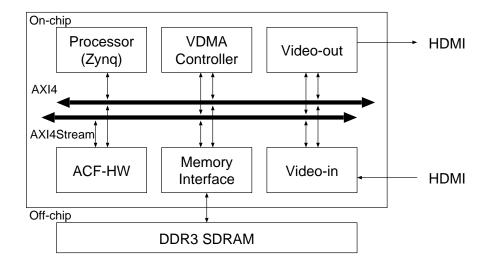

| 6.5  | FPGA implementation environment.                                                                  | 73 |

| 6.6  | FPGA implementation overview.                                                                     | 74 |

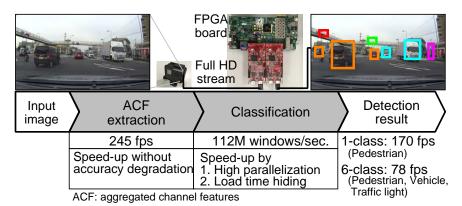

| 6.7  | Detection results.                                                                                | 76 |

| LIST O | FFIGURES                                       | xi     |

|--------|------------------------------------------------|--------|

| 6.8    | Unstable detection results of traffic objects. | <br>77 |

### LIST OF FIGURES

## **List of Tables**

| 1.1  | Comparison of existing object detection hardware implmentations      | 4  |

|------|----------------------------------------------------------------------|----|

| 1.2  | Challenges, objectives, and solutions.                               | 9  |

| 2.1  | Coordinates of six unit vectors over the half range $(N = 6)$ .      | 18 |

| 2.2  | Overview of images in INRIA Person Dataset.                          | 24 |

| 3.1  | Comparison between InterHOG and DV-HOG.                              | 28 |

| 3.2  | Comparison of HOG algorithms.                                        | 30 |

| 3.3  | Pedestrian detection parameters for the ACF classifier               | 31 |

| 3.4  | Log-average MR comparison on INRIA Person Dataset.                   | 31 |

| 3.5  | Average precision comparison on pedestrian detection using KITTI     |    |

|      | Vision Benchmark Suite.                                              | 32 |

| 3.6  | Log-average MR comparison without smoothing image on INRIA           |    |

|      | Person Dataset.                                                      | 33 |

| 3.7  | Select signals for each bin.                                         | 35 |

| 3.8  | Coefficients of DV-HOG after sign modification.                      | 36 |

| 3.9  | Log-average MR comparison with fixed-point representation            | 38 |

| 3.10 | Logic synthesis settings.                                            | 38 |

| 3.11 | Cell-based synthesis comparison of DV-HOG and conventional methods.  | 38 |

| 3.12 | FPGA implementation settings                                         | 40 |

| 3.13 | FPGA implementation results.                                         | 40 |

| 3.14 | Notation for object detection.                                       | 41 |

| 3.15 | Estimation of LUT utilization for $f = 100$ MHz, color image on FPGA |    |

|      | implementation                                                       | 42 |

| 4.1  | Format of IEEE 754 double-precision floating point.                  | 46 |

| 4.2  | Parameters and settings of each machine learning algorithm           | 48 |

| 4.3  | Details of classification datasets.                                  | 48 |

| 4.4  | Range of non-zero frequency of a pedestrian classifier for ACF       | 49 |

| 4.5  | Memory usage comparison for a Full HD image                          | 52 |

| 5.1  | Notation and description of each module.                             | 57 |

| 5.2  | Detailed scheduling result on $M = 8$                                | 63 |

#### LIST OF TABLES

| 5.3 | FPGA implementation settings.                                        | 66 |

|-----|----------------------------------------------------------------------|----|

| 5.4 | FPGA resource utilization.                                           | 67 |

| 6.1 | Processing performance comparison with conventional implementations. | 72 |

| 6.2 | Resource usage of feature extraction with 32 degrees of parallelism  | 73 |

| 6.3 | Parameters used in the evaluation.                                   | 74 |

| 6.4 | FPGA resource utilization.                                           | 75 |

| 6.5 | Detection performance comparison.                                    | 76 |

| 6.6 | Classifiers for traffic objects.                                     | 76 |

| 6.7 | Classification speed evaluation.                                     | 77 |

# Chapter 1 Introduction

The World Health Organization reported in 2018 that more than 1.25 million people died due to traffic crashes each year, and these accidents made 3% of gross domestic product loss for most countries <sup>1</sup>. In Japan, according to the National Police Agency, there exist 3,694 deaths caused by traffic accidents <sup>2</sup>, and 89% of the accidents are collisions <sup>3</sup>. For saving human lives and reducing economic loss, preventing traffic accidents is demanded as a social requirement. Of the entire traffic accidents, there exist some physically inevitable cases, but the majority originates from drivers' human errors such as operation misses and distracted driving, which is preventable with the advanced sensor technology and machine learning techniques. Advanced driver assistance system (ADAS) is a representative system developed for this purpose and provides driving assistant functionalities including collision avoidance system, driver monitoring system, automotive navigation system, etc.

Of many components composing ADAS, the collision avoidance system plays an important role in preventing traffic crashes by controlling the braking system. Figure 1.1 shows the stopping distances of human drivers at various car speeds <sup>4</sup>, where the stopping distance is a sum of reaction distance needed for driver's response and braking distance needed for deceleration to still stand. If the vehicle speed is 60 km/h, which is the speed limit of urban areas in Japan, the stopping distance is 45 meters in which 25 meters is the reaction distance. Collision avoidance system assesses collision risks of objects on the road instead of drivers and can reduce the reaction distance significantly. Although range sensors such as millimeter-wave radar provide enough information for the basic braking functionality, recent ADAS requires a more comprehensive assessment of the traffic environment, and as a result, the demand for visual object detection is

<sup>&</sup>lt;sup>1</sup>http://www.who.int/news-room/fact-sheets/detail/road-traffic-injuries

<sup>&</sup>lt;sup>2</sup>https://www.npa.go.jp/toukei/koutuu48/H29siboubunnseki.pdf

<sup>&</sup>lt;sup>3</sup>https://www.e-stat.go.jp/stat-search/file-

download?statInfId=000031674176&fileKind=2

<sup>&</sup>lt;sup>4</sup>https://www.qld.gov.au/transport/safety/road-safety/drivingsafely/stopping-distances

Figure 1.1: Stopping distances for various running speed.

increasing.

Visual object detection for embedded systems needs to satisfy the following requirements:

- 1. high detection accuracy,

- 2. real-time responsiveness, and

- 3. low power consumption.

These requirements are more stringent in ADAS than other practical applications such as surveillance systems and autonomous robots because high detection accuracy and real-time responsiveness are indispensable to guarantee the safety of ADAS. However, it is difficult to satisfy these requirements simultaneously under the constraint of low power consumption. In the case of early object detection algorithms [1–4], they require low computational cost while it is difficult to achieve high detection accuracy. Therefore, their hardware implementations operate with low power consumption but their accuracy was confined to algorithmic limitation [5-13]. On the other hand, recent object detection algorithms provide high enough detection accuracy for practical applications [14–22]. These methods require large computational cost, but thanks to advanced parallel computing devices such as GPUs, it is possible to process them in real time. A critical problem is that these devices consume more than a hundred watts, which is not affordable for the embedded systems. Dedicated hardware implementation makes it possible to reduce this power consumption, but it still does not satisfy both processing performance and power consumption for practical applications [23]. To improve the trade-off relationship between three requirements, this dissertation focuses on ADAS and will propose an object detection system focusing on information preservation,

#### 1.1. BACKGROUND ON OBJECT DETECTION

Figure 1.2: Detection error trade-off (DET) curves of leading-edge algorithms and SVM+HOG [24] from pedestrian detection benchmark [25]. The closer a curve gets to the bottom left corner, the better the DET is.